#### 64-Bit TX System RISC

# Family

The **TX49** Family of RISC microprocessors for embedded use is an original Toshiba 64-bit processor family and is based on the RISC architecture designed by the MIPS Group in the U.S.A. The **TX49** Family processors can also be used as ASSPs or as the CPU core for gate arrays and cell-based ICs, allowing you to attain a higher level of integration in your system than has ever been possible before.

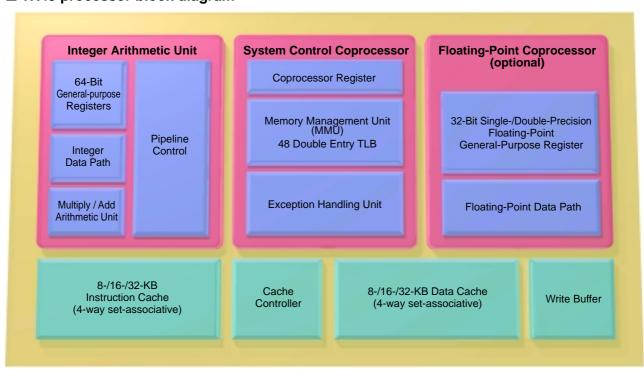

#### 64-bit RISC architecture

- 64-bit operation

- Thirty-two 64-bit general-purpose registers

- Optimized 5-stage pipelining

- Upward-compatible instruction set including MIPS I, MIPS II and MIPS III instruction set architectures (ISAs)

- Multiply/add instructions and debugging instructions added

- Built-in 48 double entry TLB

#### Useful as CPU core for gate arrays / cell-based ICs

- TX49: TC220C process technology

#### Low power consumption design

- Low power consumption modes (Doze/Halt)

- Supply voltage: 3.3 V

#### Built-in high-capacity primary cache

- Instruction cache: 8/16/32 KB (selectable)

- 4-way set-associative

- Supports lock function.

- Opata cache: 8/16/32 KB (selectable)

- 4-way set-associative

- Supports lock function.

- Write-back/write-through (every page)

- Supports snoop function.

#### Numerous optional functions

- Debug support unit

- Supports EJTAG

- Single- or double-precision floating-point unit

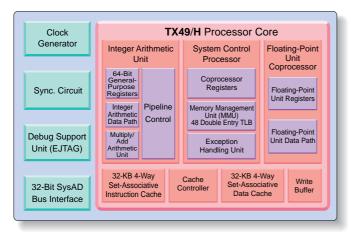

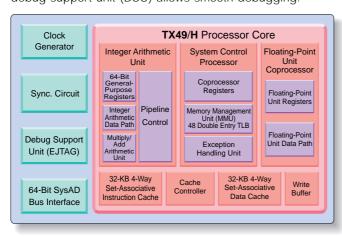

#### ■ TX49 processor block diagram

## General-purpose MPU TMPR4901F-133\* \*Under development

#### ■ 64-bit general-purpose RISC microprocessor based on the TX49 processor core

The **TMPR4901F** is the first product in the **TX49** Family. Built around the **TX49** processor core, it incorporates a clock generator and a debug support unit.

This microprocessor is not just a general-purpose MPU; it can also be used to verify functions and evaluate device performance during the development of ASICs which feature the **TX49** processor core.

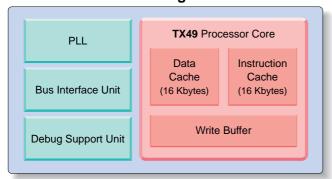

#### ■ TMPR4901F block diagram

- TX49 processor core

- Instruction cache: 16 Kbytes built in

- Data cache: 16 Kbytes built in

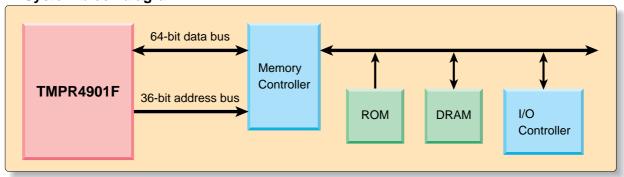

- Separate 36-bit address bus and 64-bit data bus

- Clock generator with x16 PLL

- Low power consumption modes (Doze/Halt)

- Built-in debug support unit

- Maximum internal operating frequency: 133 MHz

- Maximum external operating frequency: 66 MHz

- Supply voltage: 3.3 V

- Package: 208-pin QFP

#### ■ System block diagram

#### ■ Target applications

## EVY PRODU

#### Floating-point unit built-in

### TMPR4955F-167\*/4955F-200\* \* Under development

#### ■ 64-bit general-purpose RISC microcomputer with floating-point unit

The TMPR4955F is built around a TX49/H processor core with improved cache size and operating frequency. Incorporating a floating-point unit (FPU) and a 32-bit SysAD interface, the TMPR4955F is ideal for a wide range of applications, including laser beam printers (LBPs), network equipment and set-top boxes (STBs). In addition, a built-in debug support unit (DSU) allows smooth debugging.

- TX49/H 64-bit RISC core

- Five-stage pipeline

- On-chip caching

4-way set-associative caches Instruction cache: 32 KB built in Data cache: 32 KB built in Cache lock function

- Prefetch instruction

- 48 double entry TLB

- 32-bit system interface bus (SysAD bus)

- Single-/Double-precision FPU

- Low power consumption mode

- Supply voltage Internal: 2.5 V External: 3.3 V

- Built-in debug support unit (DSU)

- Maximum operating frequency: 167 MHz / 200 MHz

NEW

Package: 160-pin QFP

#### Floating-point unit built-in

### TMPR4956F-167\*/4956F-200\* \* Under development

#### ■ SysAD bus-extended 64-bit RISC microcomputer with floating-point unit

The TMPR4956F 64-bit microcomputer is the SysAD busextended version of the TMPR4955F. The TMPR4956F incorporates a floating-point unit (FPU) as well as a TX49/H processor core, and is ideal for a wide range of applications including laser beam printers (LBPs), network equipment and set-top boxes (STBs). In addition, a built-in debug support unit (DSU) allows smooth debugging.

- TX49/H 64-bit RISC core

- Five-stage pipeline

- On-chip caching

4-way set-associative caches Instruction cache: 32 KB built in Data cache: 32 KB built in Cache lock function

- Prefetch instruction

- 48 double entry TLB

- 64-bit system interface bus (SysAD bus)

- Single-/Double-precision FPU

- Low power consumption mode

- Supply voltage Internal: 2.5 V External: 3.3 V

- Built-in debug support unit (DSU)

- Maximum operating frequency: 167 MHz / 200 MHz

- Package: 208-pin QFP

#### 64-Bit TX System RISC

# Series

### 64-bit superscalar RISC processors for workstations and servers

- Compatible with the R10000 RISC processors available from MIPS Technologies, Inc.

- 64-bit superscalar architecture

- Capable of operating at 200 MHz

- Built-in 32-Kbyte instruction and data caches

| Pro  | duct No. | Internal Frequency | Supply Voltage | Package | Features                                                                                                  |

|------|----------|--------------------|----------------|---------|-----------------------------------------------------------------------------------------------------------|

| TC86 | R10000   | 200 MHz            | 3.3 V          | LGA 599 | Superscalar architecture Built-in primary cache memory (64 KB) Built-in secondary cache memory controller |

#### 64-Bit TX System RISC

## Series

The **TX44** Series is comprised of 64-bit RISC microprocessors that are compatible with the R4000/R4400 microprocessors from MIPS Technologies, Inc. The microprocessors in this series are suited to a wide variety of applications, ranging from personal computers to high-end workstations. In addition to the internal operating frequency of 200 MHz, 8-stage superpipeline and 32 Kbytes of primary cache memory, the microprocessors in this series contain an FPU based on the ANSI/IEEE-754-1985 standard, enhancing their integer and floating-point arithmetic capability.

- Floating-point arithmetic performance: 143 SPECfp92 (at 200 MHz)

- 8-stage super-pipeline

- Built-in secondary cache memory controller

- Multiprocessing capability

- Package: 447-pin PGA

| Product No.       | Internal Frequency | Supply Voltage | Operating Temperature Range | Package |

|-------------------|--------------------|----------------|-----------------------------|---------|

| TC86R4400-200(L)  | 200 MHz            | 3.3 V          | 0° to 70°C                  | PGA447  |

| TC86R4400-200(SB) | 200 MHz            | 3.3 V          | 0° to 85°C                  | PGA447  |

| TC86R4400-150(S)  | 150 MHz            | 3.3 V          | 0° to 85°C                  | PGA447  |

#### 64-Bit TX System RISC

| Product No.    | Internal Frequency | Supply Voltage | Operating Temperature Range | Package |

|----------------|--------------------|----------------|-----------------------------|---------|

| TC86R4300F-100 | 100 MHz            | 3.3 V          | 0° to 85°C                  | QFP120  |