#### **Preface**

Thank you for your new or continued patronage of Toshiba semiconductor products. This is the 1998 edition of the user's manual for the TX49 Family of 64-bit RISC microprocessors, entitled 64-Bit TX System RISC TX49 Family Architecture.

This manual is written so as to be accessible to engineers who may be designing a Toshiba microprocessor into their products for the first time. No prior knowledge of these devices is assumed. The manual includes a review of the architecture of the processor family, a description of the TX49 instruction set, and sections dedicated to various other relevant topics, such as the Memory Management System (MMU) and CPU exceptions.

Toshiba continually updates its technical information. Your comments and suggestions concerning this and other Toshiba documents are sincerely appreciated and may be used in subsequent editions. For updates to this document or for additional information about the product, please contact your nearest Toshiba office or authorized Toshiba dealer.

September 1998

# I□TX49 Processor Core Specification

# 1. Introduction

The TX49 Processor Core is a high performance and low-power 64-bit RISC microprocessor core developed by Toshiba which is well-suited to embedded applications such as networking, laser printer, STB (Set Top Box) and 3-D graphic.

### 2. Feature

- 64□bit operation

- 32 of 64 bit integer general purpose registers

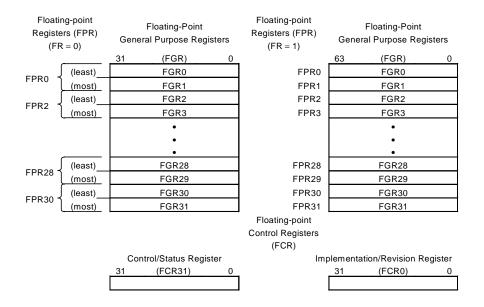

- 32 of 32 bit floating point general purpose registers: Optional

- 64 GB physical address space

- Instruction Set

- Upward compatible with MIPS I, MIPS II, and MIPS III ISA

- MAC (Multiply and Accumulate) instructions %&

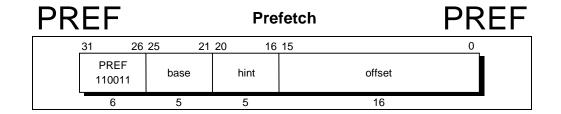

- PREF (Prefetch) instruction %

- Optimized 5 stage pipeline

- Instruction Cache

- 8□KB/□16□KB/□32KB : Selectable %

- Four-way set associative %

- Lock function support %

- Data cache

- 8 KB 16 KB 32 KB: Selectable %

- Four-way set associative %

- Lock function support %&

- Write Strategy

Write-back-Snoop

Write-through-No-Write-Allocate-Snoop %

Write-through-Write-Allocate-Snoop %

- MMU

- 48-double-entry (even/odd) Joint TLB

- 2-entry Instruction TLB

- 4-entry Data TLB

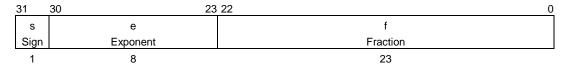

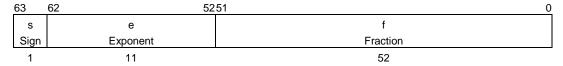

- IEEE754 compatible single and double precision FPU: Optional ('99 avairable)

- Single and double precision FPU in hardware %

- Debug support (EJTAG): Optional %&

- Debug instructions %&

- Real time debugging is supported by debug module logic %&

- Power management modes (halt, doze) %&

# 3. TX49 Block Diagram

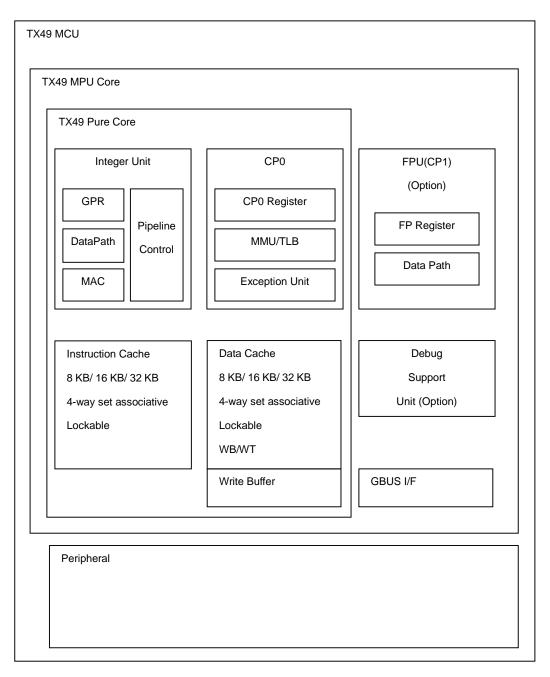

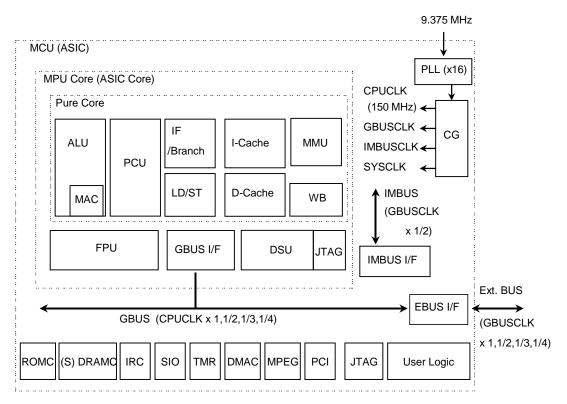

Figure 3-1 shows the block diagram of TX49 Pure Core, MPU Core and MCU. TX49 Pure Core includes an instruction cache and a data cache. These cache are selectable by user system from among a variety of possible configurations.

Figure 3-1 Block Diagram of the TX49

# 4. CPU Registers Overview

#### 4.1 Introduction

The TX49 has the CPU registers for integer operation or address calculation and the CPO registers for memory system or exception handling.

### 4.2 CPU Registers

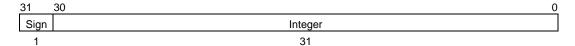

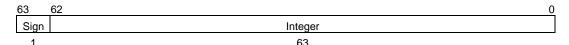

The TX49 has the 64-bit CPU registers.

- 32 general-purpose registers

- 64-bit program counters

- HI/LO register for storing the result of multiply and divide operations

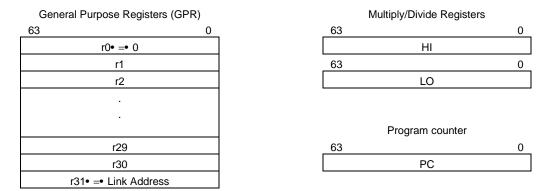

Figure 4-1 shows the configuration of these registers.

Figure 4-1 TX49 CPU registers

The r0 and r31 registers of GPR have special functions as follows.

- Register r0 always contains the value 0. It can be a target register of an instruction whose operation result is not needed. Or, it can be a source register of an instruction that requires a value of 0.

- Register r31 is the link register for the Jump and Link instruction. The address of the instruction after the delay slot is placed in r31.

The TX49 has the following some special registers that are used or modified implicitly by certain instructions.

- HI Higher result for Multiply and Divide

- LO Lower result for Multiply and Divide

These two registers are used to store that result of an integer multiplication or division. In multiplication, the 64 high-order bits of a 128-bit result are stored in the HI, and the 64 low-order bits are stored in the LO. In division, the resulting quotient is stored in the LO, and the remainder is stored in the HI.

• PC - Program Counters

The register contains the address of the currently executed instruction.

# 4.3 CP0 Registers

The TX49 has the 32-bit or 64-bit System control coprocessor(CP0) registers. These registers are used for memory system or exception handling. Table 4-1 lists the CP0 registers built into the TX49. The more detail information are described in Chapter 7.

Table 4-1 CP0 Registers

| Register Name | Reg. No. | Register Name | Reg. No. |

|---------------|----------|---------------|----------|

| Index         | Reg#0    | Config        | Reg#16   |

| Random        | Reg#1    | LLAddr        | Reg#17   |

| EntryLo0      | Reg#2    | (Reserved)    | Reg#18   |

| EntryLo1      | Reg#3    | (Reserved)    | Reg#19   |

| Context       | Reg#4    | XContext      | Reg#20   |

| PageMask      | Reg#5    | (Reserved)    | Reg#21   |

| Wired         | Reg#6    | (Reserved)    | Reg#22   |

| (Reserved)    | Reg#7    | Debug %&      | Reg#23   |

| BadVAddr      | Reg#8    | DEPC %&       | Reg#24   |

| Count         | Reg#9    | (Reserved)    | Reg#25   |

| EntryHi       | Reg#10   | (Reserved)    | Reg#26   |

| Compare       | Reg#11   | (Reserved)    | Reg#27   |

| SR            | Reg#12   | TagLo         | Reg#28   |

| Cause         | Reg#13   | TagHi         | Reg#29   |

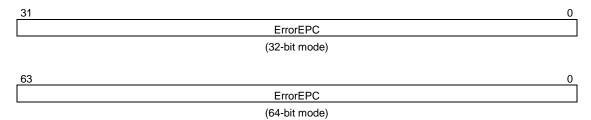

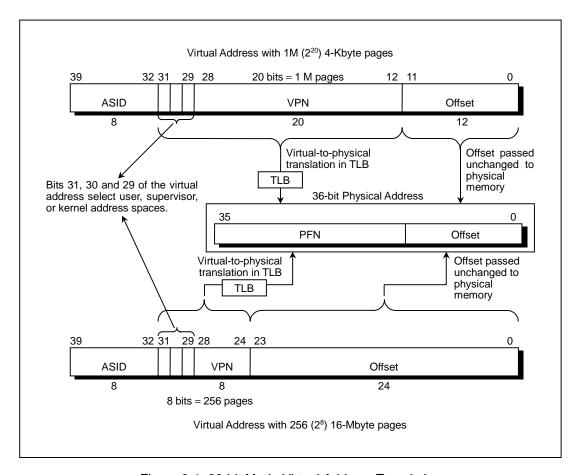

| EPC           | Reg#14   | ErrorEPC      | Reg#30   |

| PRId          | Reg#15   | DESAVE %      | Reg#31   |

# 5. CPU Instruction Set Summary

### 5.1 Introduction

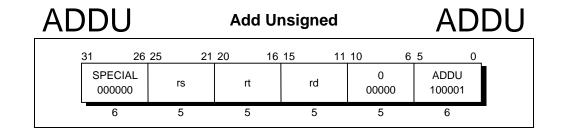

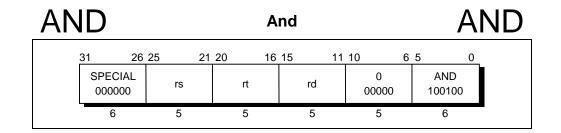

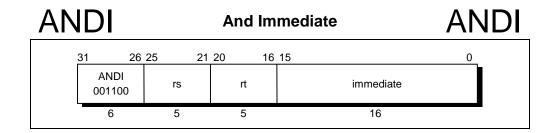

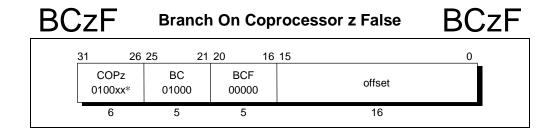

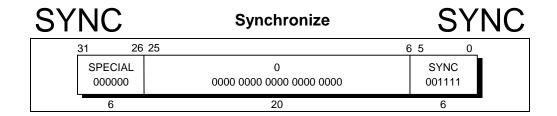

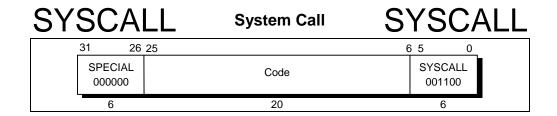

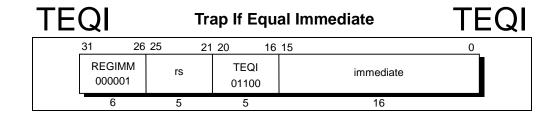

Each instruction is  $32\square$  bits long. These instructions are upward compatible with the MIPS I, II and III instruction set architecture and the TX39's instructions.

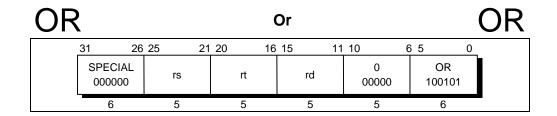

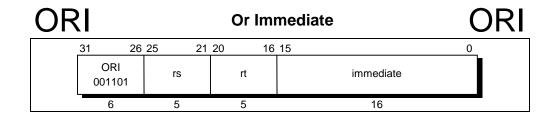

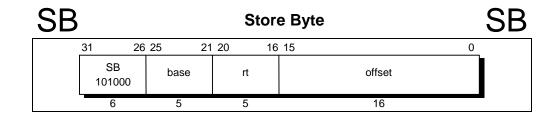

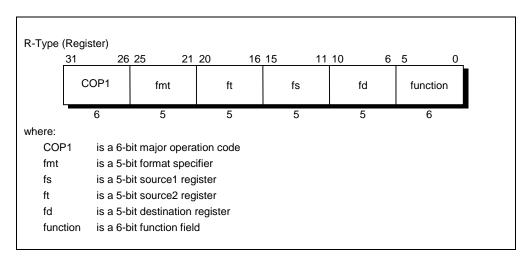

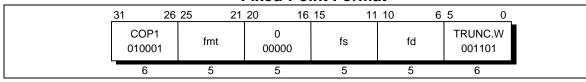

#### 5.2 Instruction Format

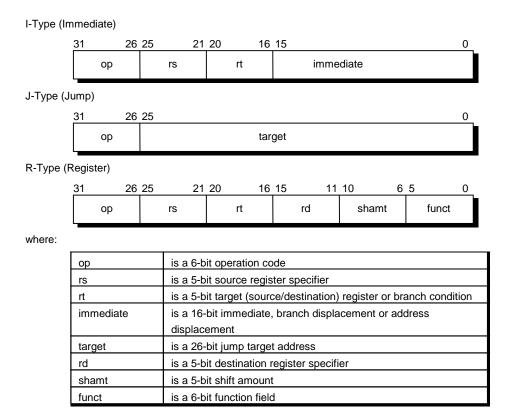

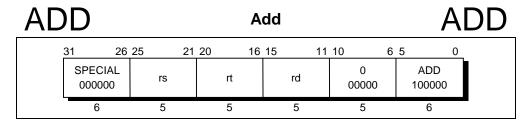

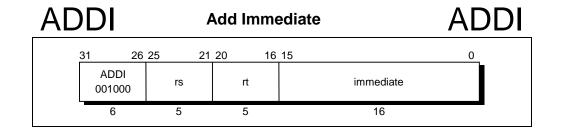

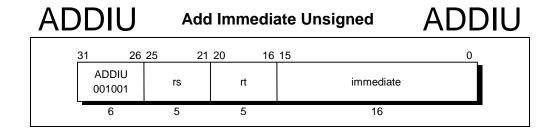

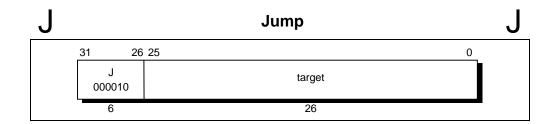

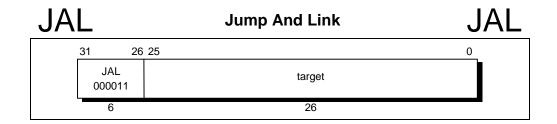

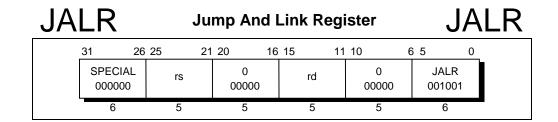

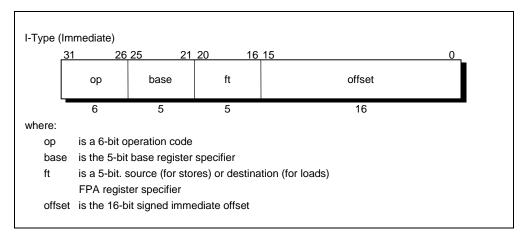

There are three instruction formats: Immediate (I-type), Jump (J-type) and Register (R-type), as shown in Figure 5-1. Having just three instruction formats simplifies instruction decoding. If more complex functions or addressing modes are required, they can be produced with the compiler using combinations of the instructions.

Figure 5-1 Instruction formats and subfield mnemonics

### 5.3 Instruction Set Overview

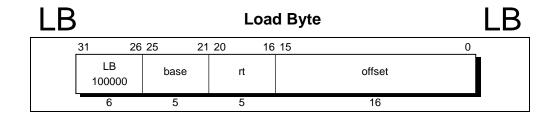

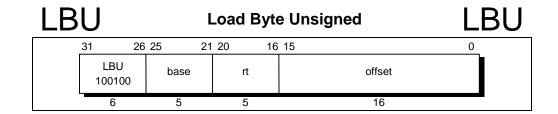

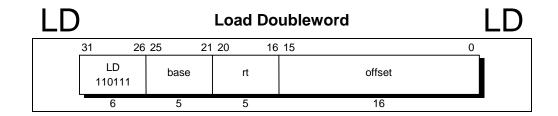

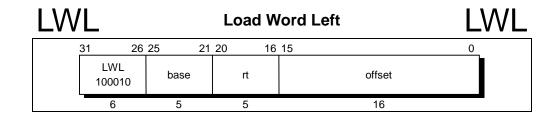

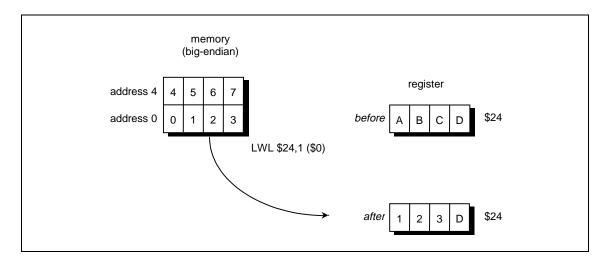

### 5.3.1 Load and Store Instructions (Table 5-1)

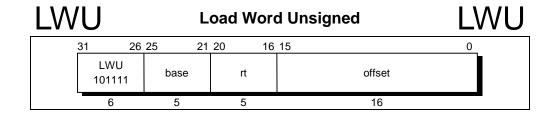

Load and Store instructions move data between memory and general purpose registers, and are all I-type instructions. The only directly supported addressing mode is "base register plus 16-bit signed immediate offset".

Table 5-1 CPU Instruction Set: Load and Store Instructions

| Instruction | Description                  | Note     |

|-------------|------------------------------|----------|

| LB          | Load Byte                    | MIPS I   |

| LBU         | Load Byte Unsigned           | MIPS I   |

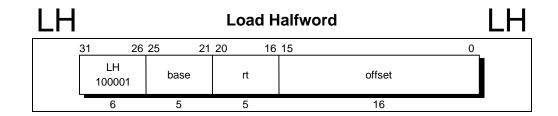

| LH          | Load Halfword                | MIPS I   |

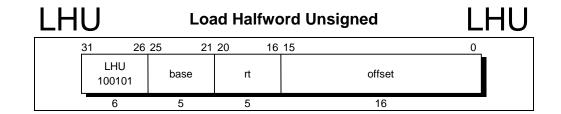

| LHU         | Load Halfword Unsigned       | MIPS I   |

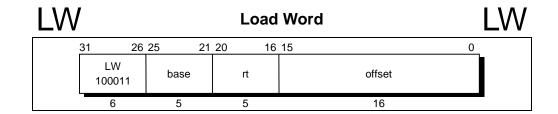

| LW          | Load Word                    | MIPS I   |

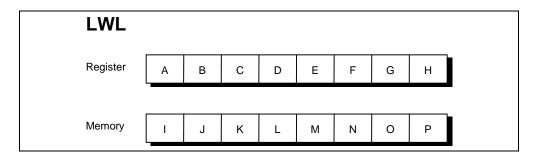

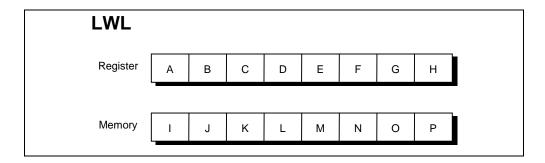

| LWL         | Load Word Left               | MIPS I   |

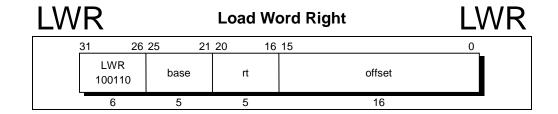

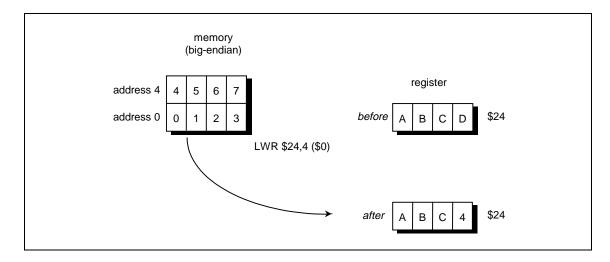

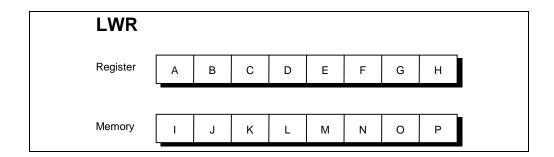

| LWR         | Load Word Right              | MIPS I   |

| SB          | Store Byte                   | MIPS I   |

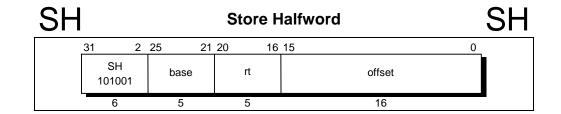

| SH          | Store Halfword               | MIPS I   |

| SW          | Store Word                   | MIPS I   |

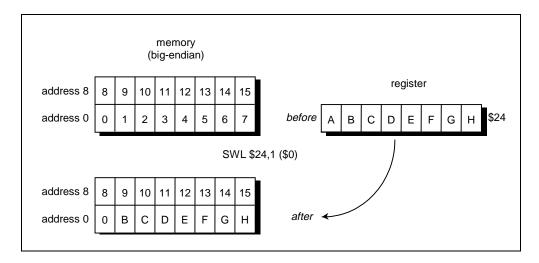

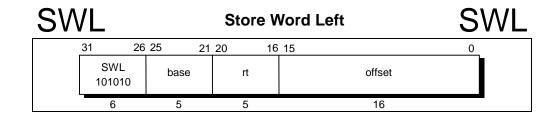

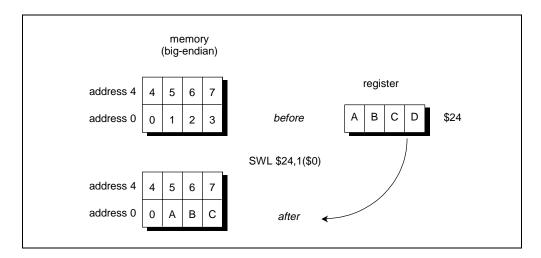

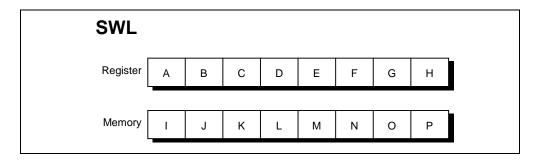

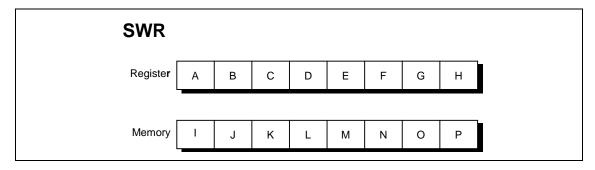

| SWL         | Store Word Left              | MIPS I   |

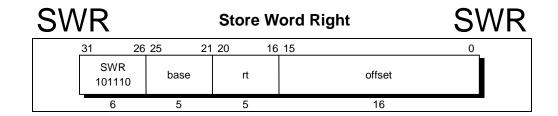

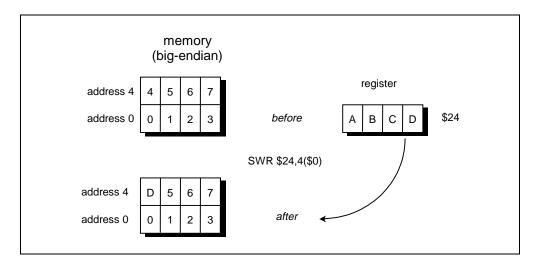

| SWR         | Store Word Right             | MIPS I   |

| LD          | Load Doubleword              | MIPS III |

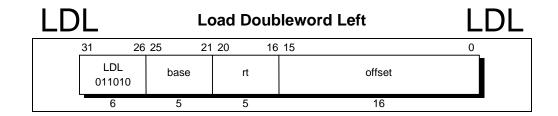

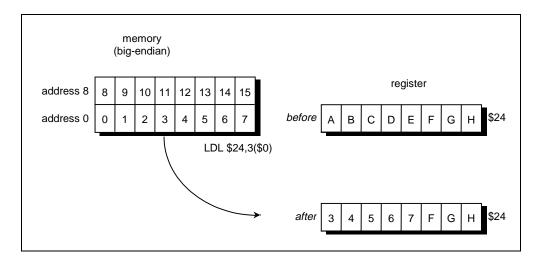

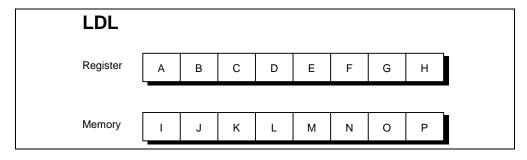

| LDL         | Load Doubleword Left         | MIPS III |

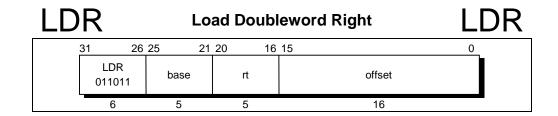

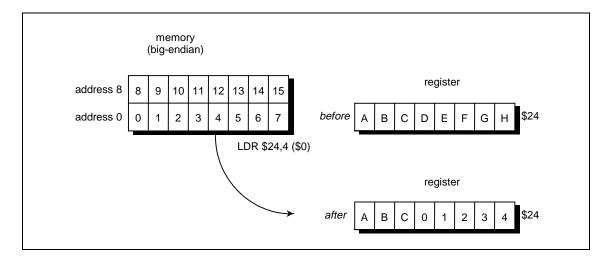

| LDR         | Load Doubleword Right        | MIPS III |

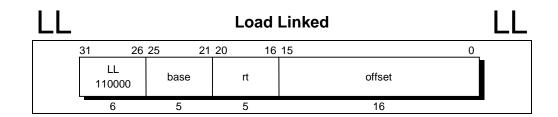

| LL          | Load Linked                  | MIPS II  |

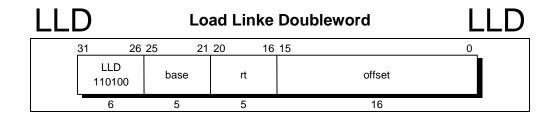

| LLD         | Load Linked Doubleword       | MIPS III |

| LWU         | Load Word Unsigned           | MIPS III |

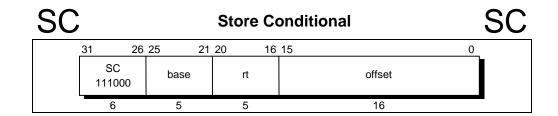

| SC          | Store Conditional            | MIPS II  |

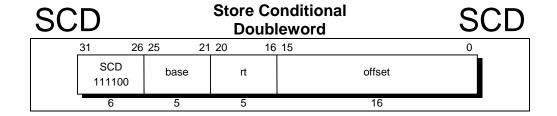

| SCD         | Store Conditional Doubleword | MIPS III |

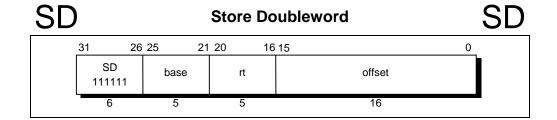

| SD          | Store Doubleword             | MIPS III |

| SDL         | Store Doubleword Left        | MIPS III |

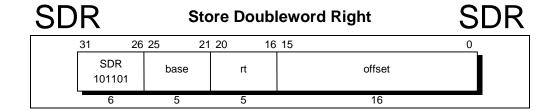

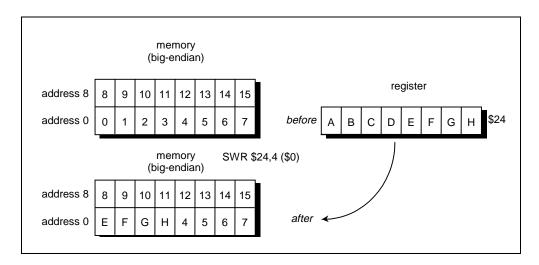

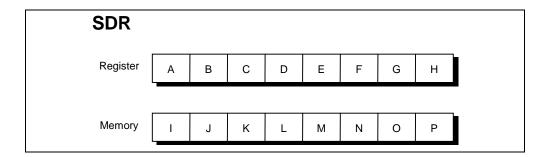

| SDR         | Store Doubleword Right       | MIPS III |

| SYNC        | Sync                         | MIPS II  |

### 5.3.2 Computational Instructions (Table 5-1)

Computational instructions perform arithmetic, logical or shift operations on values in registers. This instruction format can be R-type or I-type. With R-type instructions, the two/three operands and the result are register values. With I-type instructions, one of the operands is 16-bit immediate data. Computational instructions can be classified as follows.

- ALU immediate

- Three-operand register-type

- Shift

- Multiply/Divide

Table 5-1 CPU Instruction Set: Computational Instructions

| Instruction | Description                             | Note     |

|-------------|-----------------------------------------|----------|

|             | (ALU Immediate)                         |          |

| ADDI        | Add Immediate                           | MIPS I   |

| ADDIU       | Add Immediate Unsigned                  | MIPS I   |

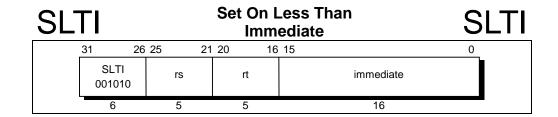

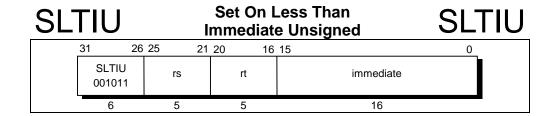

| SLTI        | Set on Less Than Immediate              | MIPS I   |

| SLTIU       | Set on Less Than Immediate Unsigned     | MIPS I   |

| ANDI        | AND Immediate                           | MIPS I   |

| ORI         | OR Immediate                            | MIPS I   |

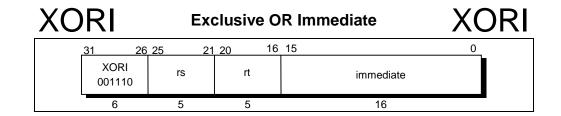

| XORI        | Exclusive OR Immediate                  | MIPS I   |

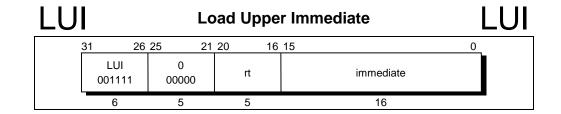

| LUI         | Load Upper Immediate                    | MIPS I   |

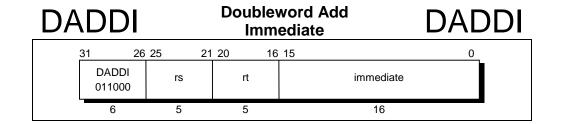

| DADDI       | Doubleword Add Immediate                | MIPS III |

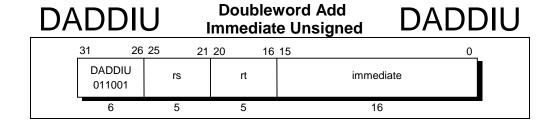

| DADDIU      | Doubleword Add Immediate Unsigned       | MIPS III |

|             | (ALU 3-Operand, register type)          |          |

| ADD         | Add                                     | MIPS I   |

| ADDU        | Add Unsigned                            | MIPS I   |

| SUB         | Subtract                                | MIPS I   |

| SUBU        | Subtract Unsigned                       | MIPS I   |

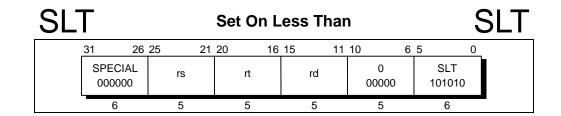

| SLT         | Set on Less Than                        | MIPS I   |

| SLTU        | Set on Less Than Unsigned               | MIPS I   |

| AND         | AND                                     | MIPS I   |

| OR          | OR                                      | MIPS I   |

| XOR         | Exclusive OR                            | MIPS I   |

| NOR         | NOR                                     | MIPS I   |

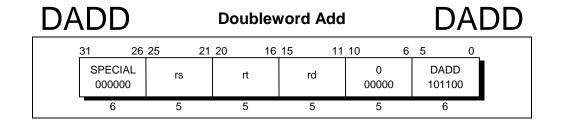

| DADD        | Doubleword Add                          | MIPS III |

| DADDU       | Doubleword Add Unsigned                 | MIPS III |

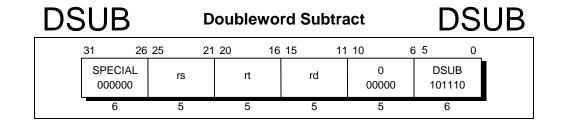

| DSUB        | Doubleword Subtract                     | MIPS III |

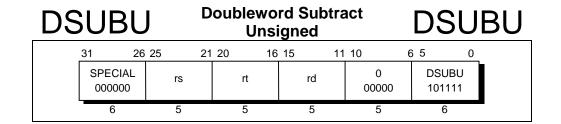

| DSUBU       | Doubleword Subtract Unsigned            | MIPS III |

|             | (Shift)                                 |          |

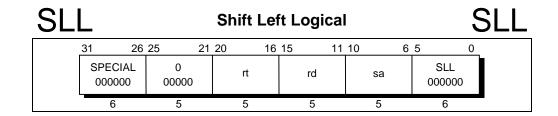

| SLL         | Shift Left Logical                      | MIPS I   |

| SRL         | Shift Right Logical                     | MIPS I   |

| SRA         | Shift Right Arithmetic                  | MIPS I   |

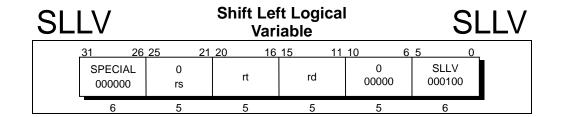

| SLLV        | Shift Left Logical Variable             | MIPS I   |

| SRLV        | Shift Right Logical Variable            | MIPS I   |

| SRAV        | Shift Right Arithmetic Variable         | MIPS I   |

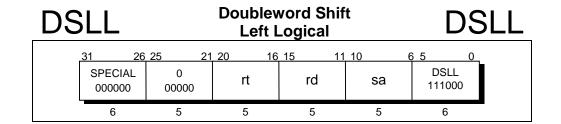

| DSLL        | Doubleword Shift Left Logical           | MIPS III |

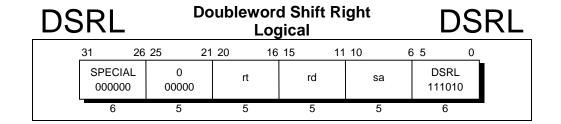

| DSRL        | Doubleword Shift Right Logical          | MIPS III |

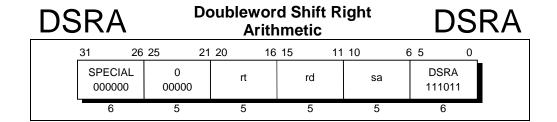

| DSRA        | Doubleword Shift Right Arithmetic       | MIPS III |

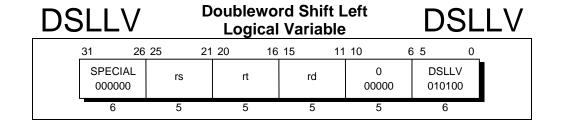

| DSLLV       | Doubleword Shift Left Logical Variable  | MIPS III |

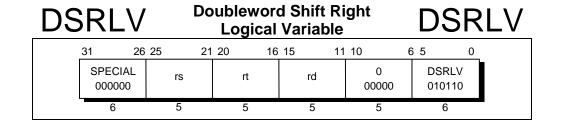

| DSRLV       | Doubleword Shift Right Logical Variable | MIPS III |

| Instruction | Description                                | Note     |

|-------------|--------------------------------------------|----------|

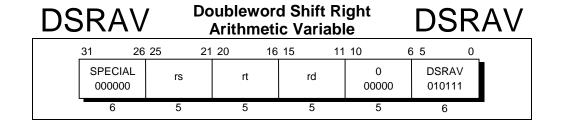

| DSRAV       | Doubleword Shift Right Arithmetic Variable | MIPS III |

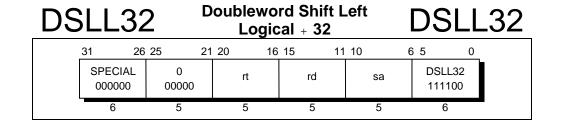

| DSLL32      | Doubleword Shift Left Logical +32          | MIPS III |

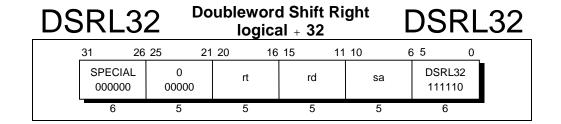

| DSRL32      | Doubleword Shift Right Logical +32         | MIPS III |

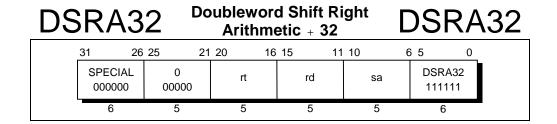

| DSRA32      | Doubleword Shift Right Arithmetic +32      | MIPS III |

|             | ( Multiply and Divide)                     |          |

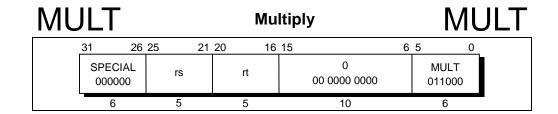

| MULT        | Multiply                                   | MIPS I   |

| MULTU       | Multiply Unsigned                          | MIPS I   |

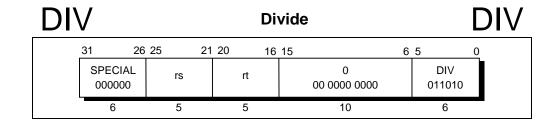

| DIV         | Divide                                     | MIPS I   |

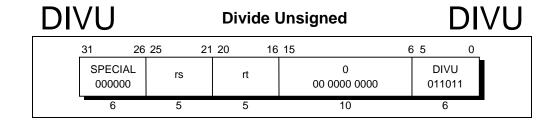

| DIVU        | Divide Unsigned                            | MIPSI    |

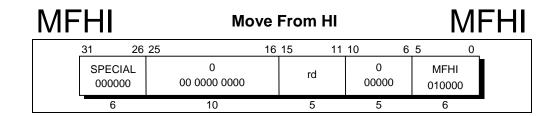

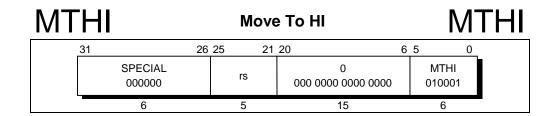

| MFHI        | Move From HI                               | MIPSI    |

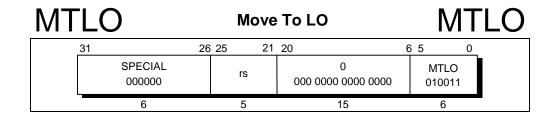

| MTHI        | Move To HI                                 | MIPS I   |

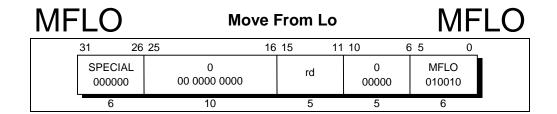

| MFLO        | Move From LO                               | MIPS I   |

| MTLO        | Move To LO                                 | MIPSI    |

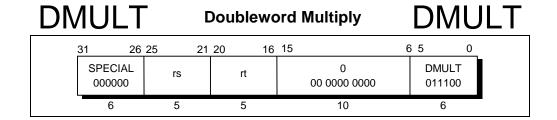

| DMULT       | Doubleword Multiply                        | MIPS III |

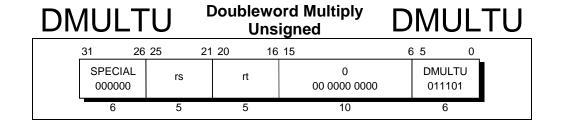

| DMULTU      | Doubleword Multiply Unsigned               | MIPS III |

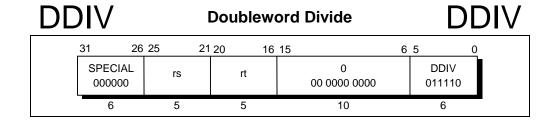

| DDIV        | Doubleword Divide                          | MIPS III |

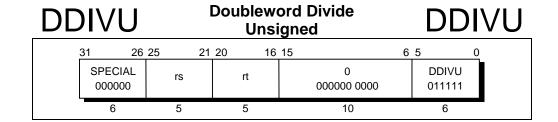

| DDIVU       | Doubleword Divide Unsigned                 | MIPS III |

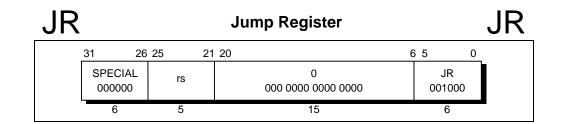

### 5.3.3 Jump and Branch Instructions (Table 5-1)

Jump/branch instructions change the program flow. A jump/branch instruction will delay the pipeline by one instruction cycle, however, an instruction inserted into the delay slot (immediately following a branch instruction) can be executed while the instruction at the branch target address is being fetched.

Table 5-1 CPU Instruction Set: Jump and Branch Instructions

| Instruction | Description                                             | Note    |

|-------------|---------------------------------------------------------|---------|

| J           | Jump                                                    | MIPS I  |

| JAL         | Jump And Link                                           | MIPS I  |

| JR          | Jump Register                                           | MIPS I  |

| JALR        | Jump And Link Register                                  | MIPS I  |

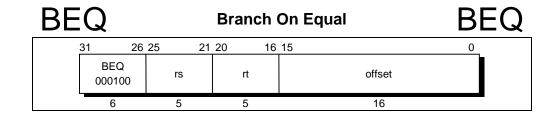

| BEQ         | Branch on Equal                                         | MIPS I  |

| BNE         | Branch on Not Equal                                     | MIPS I  |

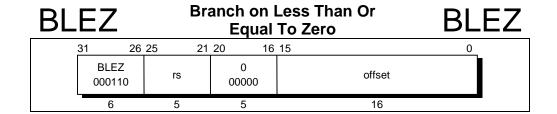

| BLEZ        | Branch on Less Than or Equal to Zero                    | MIPS I  |

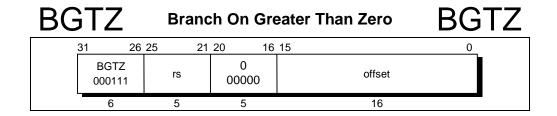

| BGTZ        | Branch on Greater Than Zero                             | MIPS I  |

| BLTZ        | Branch on Less Than Zero                                | MIPS I  |

| BGEZ        | Branch on Greater than or Equal to Zero                 | MIPS I  |

| BLTZAL      | Branch on Less Than Zero And Link                       | MIPS I  |

| BGEZAL      | Branch on Greater than or Equal to Zero And Link        | MIPS I  |

| BEQL        | Branch on Equal Likely                                  | MIPS II |

| BNEL        | Branch on Not Equal Likely                              | MIPS II |

| BLEZL       | Branch on Less Than or Equal to Zero Likely             | MIPS II |

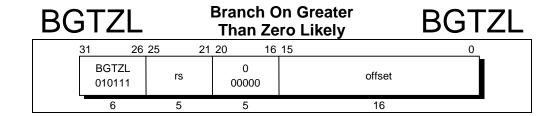

| BGTZL       | Branch on Greater Than Zero Likely                      | MIPS II |

| BLTZL       | Branch on Less Than Zero Likely                         | MIPS II |

| BGEZL       | Branch on Greater Than or Equal to Zero Likely          | MIPS II |

| BLTZALL     | Branch on Less Than Zero And Link Likely                | MIPS II |

| BGEZALL     | Branch on Greater Than or Equal to Zero And Link Likely | MIPS II |

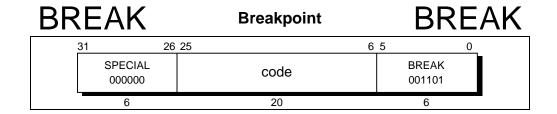

### 5.3.4 Special Instructions (Table 5-1)

There are special instructions used for software trap. The instruction format is R-type for all two.

Table 5-1 CPU Instruction Set: Special Instructions

| Instruction | Description | Note   |

|-------------|-------------|--------|

| SYSCALL     | System Call | MIPS I |

| BREAK       | Break       | MIPS I |

### 5.3.5 Exception Instructions (Table 5-1)

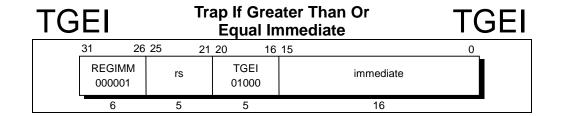

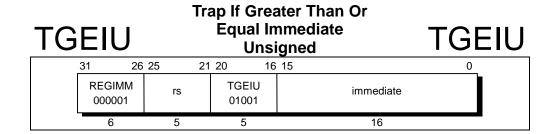

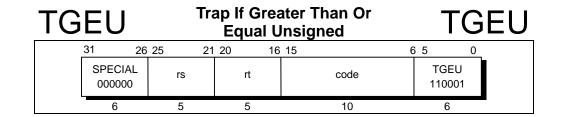

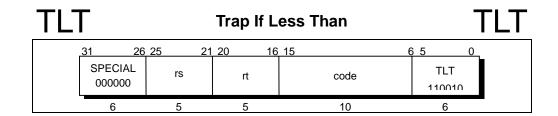

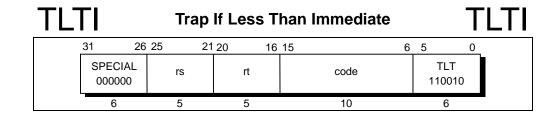

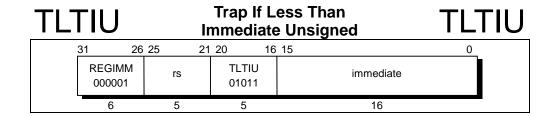

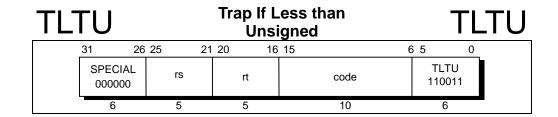

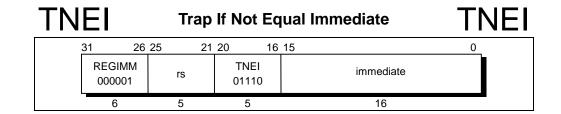

These instructions (R-type or I-type) cause a branch to the general exception handling vector based upon the result of a comparison.

Table 5-1 CPU Instruction Set: Exception Instructions

| Instruction | Description                                      | Note    |

|-------------|--------------------------------------------------|---------|

| TGE         | Trap if Greater Than or Equal                    | MIPS II |

| TGEU        | Trap if Greater Than or Equal Unsigned           | MIPS II |

| TLT         | Trap if Less Than                                | MIPS II |

| TLTU        | Trap if Less Than Unsigned                       | MIPS II |

| TEQ         | Trap if Equal                                    | MIPS II |

| TNE         | Trap if Not Equal                                | MIPS II |

| TGEI        | Trap if Greater Than or Equal Immediate          | MIPS II |

| TGEIU       | Trap if Greater Than or Equal Immediate Unsigned | MIPS II |

| TLTI        | Trap if Less Than Immediate                      | MIPS II |

| TLTIU       | Trap if Less Than Immediate Unsigned             | MIPS II |

| TEQI        | Trap if Equal Immediate                          | MIPS II |

| TNEI        | Trap if Not Equal Immediate                      | MIPS II |

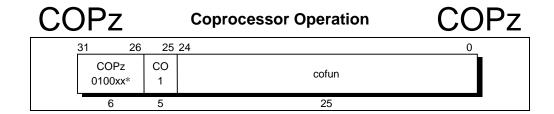

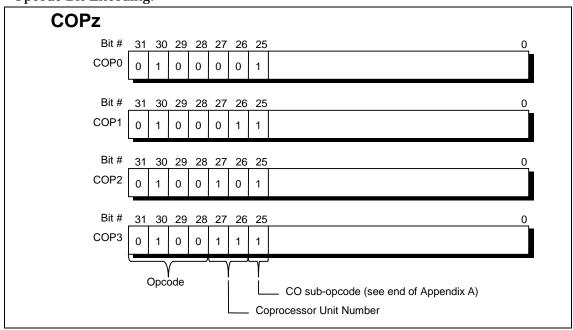

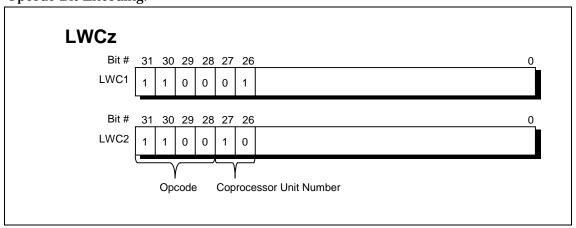

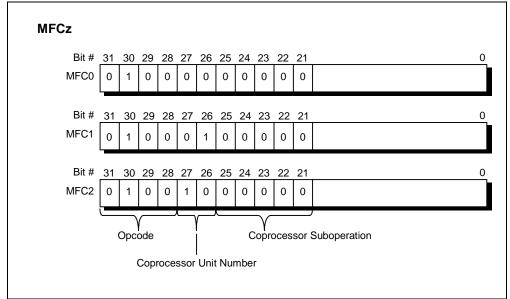

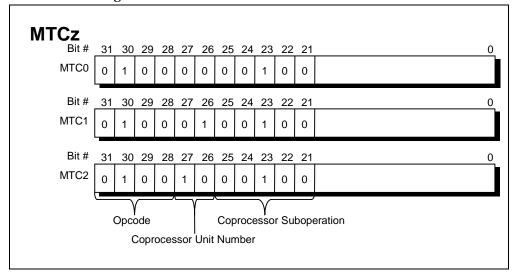

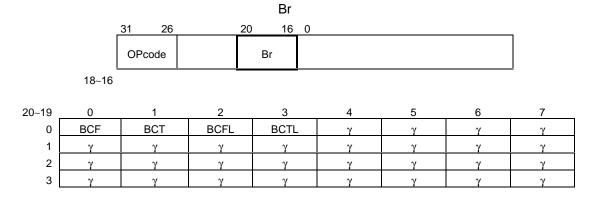

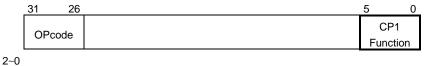

### 5.3.6 Coprocessor Instructions (Table 5-1)

Coprocessor instructions invoke coprocessor operations. The format of these instructions depends on which coprocessor is used.

Table 5-1 CPU Instruction Set: Coprocessor Instructions

| Instruction | Description                                        | Note     |

|-------------|----------------------------------------------------|----------|

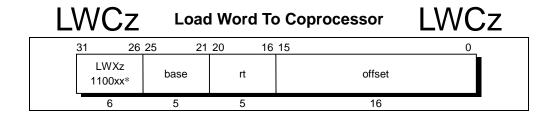

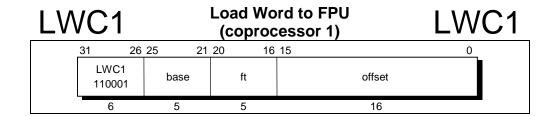

| LWCz        | Load Word to Coprocessor z (z• =• 1,2)             | MIPS I   |

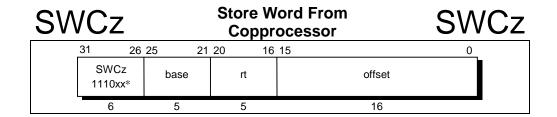

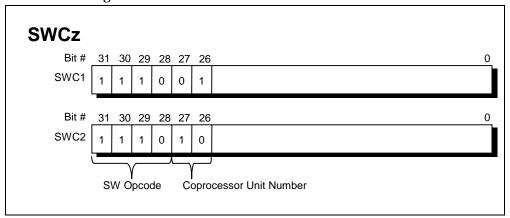

| SWCz        | Store Word from Coprocessor z (z• =• 1,2)          | MIPS I   |

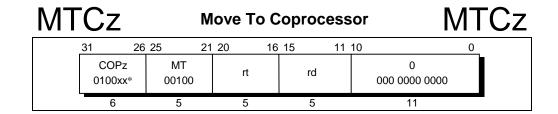

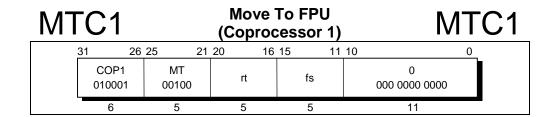

| MTCz        | Move To Coprocessor z (z• ⇒ 1,2)                   | MIPS I   |

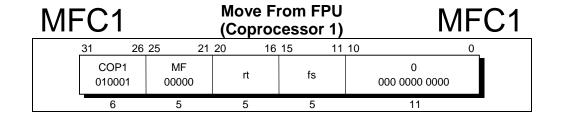

| MFCz        | Move From Coprocessor z (z• =• 1,2)                | MIPS I   |

| CTCz        | Move Control To Coprocessor z (z• =• 1,2)          | MIPS I   |

| CFCz        | Move Control From Coprocessor z (z• =• 1,2)        | MIPS I   |

| COPz        | Coprocessor Operation z ( $z^{\bullet} = 1,2$ )    | MIPS I   |

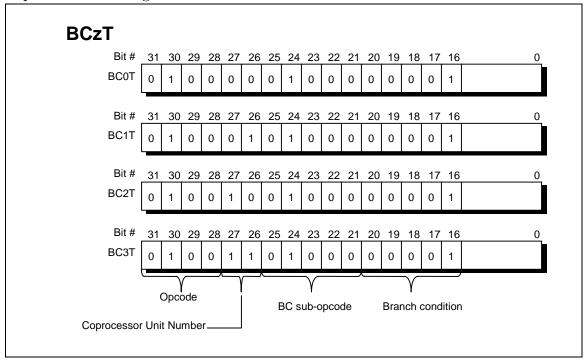

| BCzT        | Branch on Coprocessor z True (z• =• 0,1,2)         | MIPS I   |

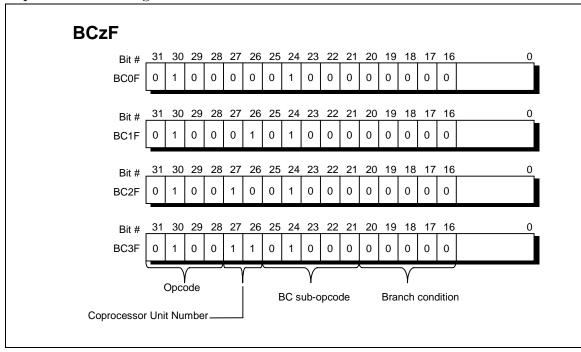

| BCzF        | Branch on Coprocessor z False (z• =• 0,1,2)        | MIPS I   |

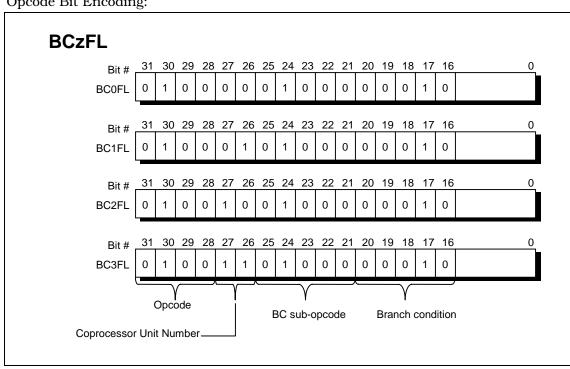

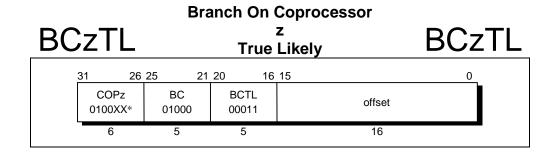

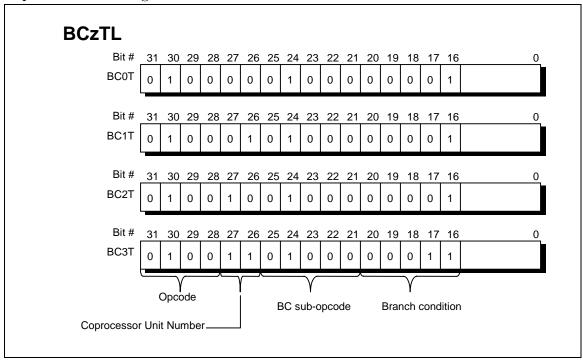

| BCzTL       | Branch on Coprocessor z True Likely (z• =• 0,1,2)  | MIPS II  |

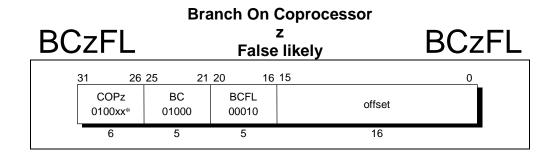

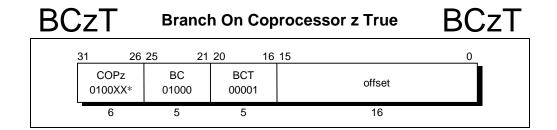

| BCzFL       | Branch on Coprocessor z False Likely (z• =• 0,1,2) | MIPS II  |

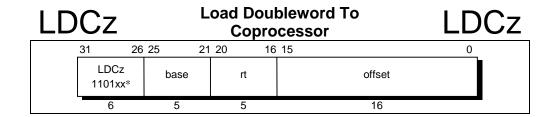

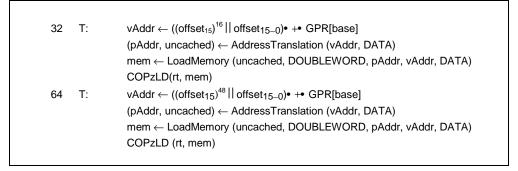

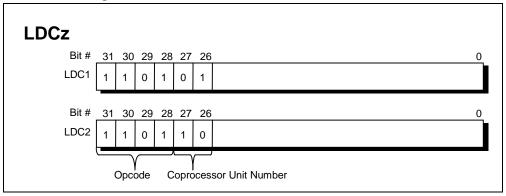

| LDCz        | Load Double Coprocessor z (z• =• 1,2)              | MIPS III |

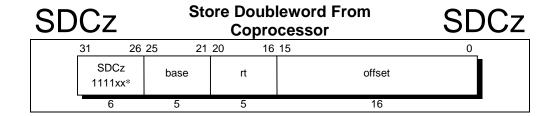

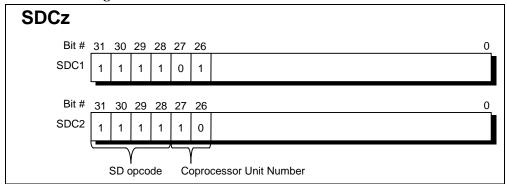

| SDCz        | Store Double Coprocessor z (z• =• 1,2)             | MIPS III |

| DMTCz       | Doubleword Move To Coprocessor z (z• =• 1,2)       | MIPS III |

| DMFCz       | Doubleword Move From Coprocessor z (z• =• 1,2)     | MIPS III |

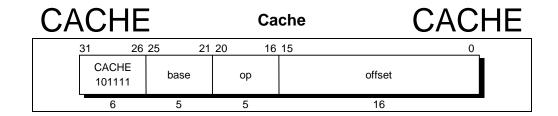

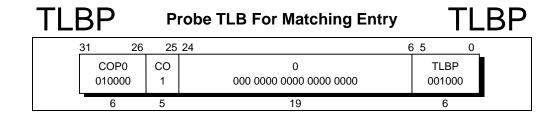

### 5.3.7 CP0 Instructions (Table 5-1)

Coprocessor 0 instructions are used for operations involving the system control coprocessor (CP0) registers, processor memory management and exception handling.

Table 5-1 Instruction Set: CP0 Instructions

| Instruction | Description                  | Note     |

|-------------|------------------------------|----------|

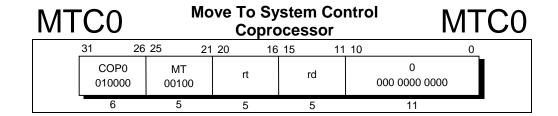

| MTC0        | Move To CP0                  | MIPS I   |

| MFC0        | Move From CP0                | MIPS I   |

| DMTC0       | Doubleword Move To CP0       | MIPS III |

| DMFC0       | Doubleword Move From CP0     | MIPS III |

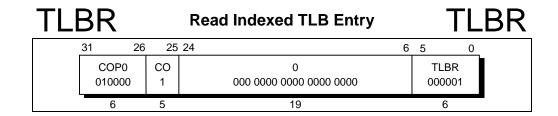

| TLBR        | Read Indexed TLB Entry       | MIPS I   |

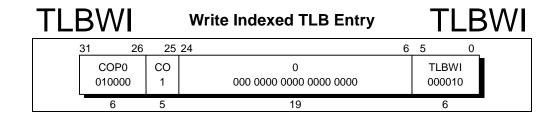

| TLBWI       | Write Indexed TLB Entry      | MIPS I   |

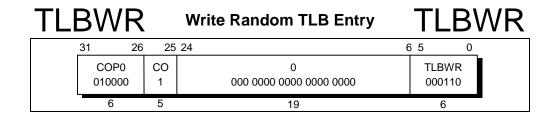

| TLBWR       | Write Random TLB Entry       | MIPS I   |

| TLBP        | Probe TLB for Matching Entry | MIPS I   |

| CACHE       | Cache                        | MIPS III |

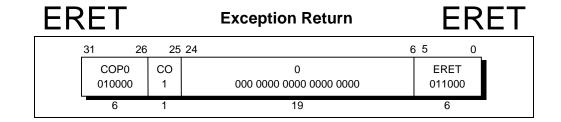

| ERET        | Exception Return             | MIPS III |

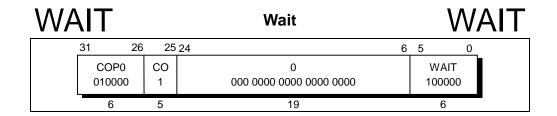

| WAIT        | Enter power management mode  |          |

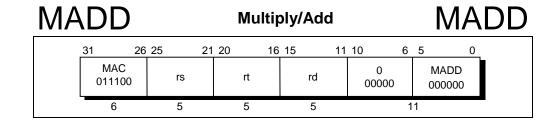

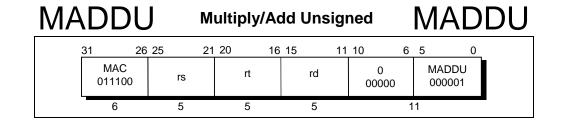

### 5.3.8 Multiply and Divide Instructions (Table 5-1) %&

Table 5-1 Extensions to the ISA: Multiply and Divide Instructions

| Instruction | Description                           | Note |

|-------------|---------------------------------------|------|

| MULT        | Multiply (3-operand)                  | % &  |

| MULTU       | Multiply Unsigned (3-operand)         | % &  |

| MADD        | Multiply and ADD (3-operand)          | % &  |

| MADDU       | Multiply and ADD Unsigned (3-operand) | % &  |

### 5.3.9 Debug Instructions (Table 5-1) %&

Table 5-1 Extensions to the ISA: Debug Instructions

| Instruction | Description                     | Note |

|-------------|---------------------------------|------|

| CTC0        | Move Control To Coprocessor 0   | %    |

| CFC0        | Move Control From Coprocessor 0 | %    |

| SDBBP       | Software Debug Breakpoint       | % &  |

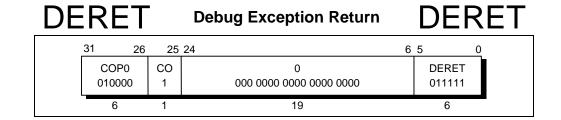

| DERET       | Debug Exception Return          | % &  |

### 5.3.10 Other Instructions (Table 5-1) %

Table 5-1 Other Instructions

| Instruction | Description | Note |

|-------------|-------------|------|

| PREF        | Prefetch    | %    |

# 5.4 Instruction Execution Cycles

Because the TX49 employs the high-speed Multiply and Add Calculator (MAC), multiply instructions, such as MULT, MULTU, DMULT and DMULTU are executed faster. And, TX49 is improved the execution of divide instructions, too.

| Instruction       | Latency | Repeat |

|-------------------|---------|--------|

| MULT 2/3 operand  | 4/4     | 1/3    |

| MADD 2/3 operand  | 4/4     | 1/3    |

| DMULT 2/3 operand | 7/7     | 6/6    |

| DIV               | 37      | 36     |

| DDIV              | 69      | 68     |

# 6. CPU Pipeline

#### 6.1 Introduction

This chapter describes the operation of the TX49 pipeline. It explains the basic operation of the pipeline. And, it explains how the TX49 handled delay instructions; these are instructions that follow a branch or load instruction in the pipeline. A later section explains interruptions to the pipeline flow caused by interlocks and exceptions.

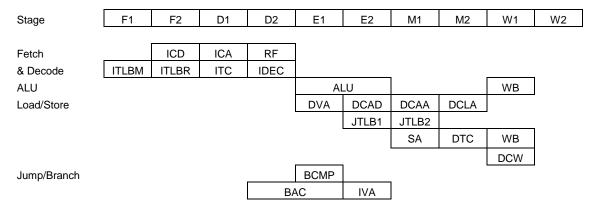

### 6.2 Basic Pipeline Operation

The TX49 executes instructions in an optimized 5 stage pipeline. Each pipeline stage is executed in one clock cycle. When the pipeline is fully utilized, five instructions are executed at the same time, resulting in an average instruction execution rate of one instruction par cycle as illustrated in Figure 6-1.

|    |    |    |    |    |    |    |    | One | cycle             | _  |    |    |    |    |    |    |    |  |

|----|----|----|----|----|----|----|----|-----|-------------------|----|----|----|----|----|----|----|----|--|

|    |    |    |    |    |    |    |    | ←   | $\longrightarrow$ |    |    |    |    |    |    |    |    |  |

| F1 | F2 | D1 | D2 | E1 | E2 | M1 | M2 | W1  | W2                |    |    | _  |    |    |    |    |    |  |

|    |    | F1 | F2 | D1 | D2 | E1 | E2 | M1  | M2                | W1 | W2 |    |    | _  |    |    |    |  |

|    |    |    |    | F1 | F2 | D1 | D2 | E1  | E2                | M1 | M2 | W1 | W2 |    |    | _  |    |  |

|    |    |    |    |    |    | F1 | F2 | D1  | D2                | E1 | E2 | M1 | M2 | W1 | W2 |    |    |  |

|    |    |    |    |    |    |    |    | F1  | F2                | D1 | D2 | E1 | E2 | M1 | M2 | W1 | W2 |  |

- F1 Instruction Fetch, Phase one

- F2 Instruction Fetch, Phase two

- D1 Instruction Decode, Phase one

- D2 Instruction Decode, Phase two

- E1 Execution. Phase one

- E2 Execution, Phase two

- M1 Memory Access, Phase one

- M2 Memory Access, Phase two

- W1 Write Back, Phase one

- W2 Write Back, Phase two

Figure 6-1 Pipeline stages for executing TX49 instructions

#### F1,F2: Instruction Fetch

During the F1 phase the ITLB begins the virtual to physical address translation. And, during the F2 phase the instruction cache fetch and the virtual to physical address translation are completed.

#### D1.D2: Instruction Decode

The instruction is decoded. Contents of the general-purpose registers are read. If the instruction involves a branch or jump, the target address is generated. The coprocessor condition signal is latched.

E1,E2: Execution

Arithmetic, logical and shift operations are performed. The execution of multiple/divide instructions is begun.

M1,M2: Memory Access

The data cache is accessed in the case of load and store instructions.

W1,W2: Write Back

The result is written to a general register.

## 6.3 TX49 Pipeline Activities

ICD: Instruction cache address decode ICA: Instruction cache array access

RF: Register fetch

ITLBM: Instruction address translation match ITLBR: Instruction address translation read

ITC: Instruction tag match IDEC: Instruction decode ALU: ALU operation

WB: Write back to register file DVA: Data virtual address calculation DCAD: Data cache address decode DCAA: Data cache array access DCLA: Data cache load align

JTLB1: Address translation in JTLB stage1 JTLB2: Address translation in JTLB stage2

SA: Store align

DTC: Data cache tag check DCW: Data cache write BCMP: Branch compare

BAC: Branch address calculation IVA: Generate instruction virtual address

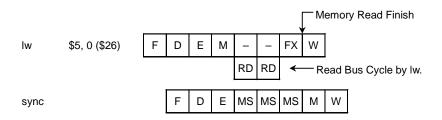

#### 6.4 Branch and Load Delay

Some TX49 instructions are executed with a delay of one instruction cycle. The cycle in which an instruction is delayed is called a delay slot. A delay occurs with load instruction and branch/jump instructions.

#### 6.4.1 Delayed load

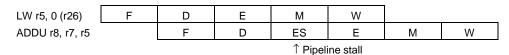

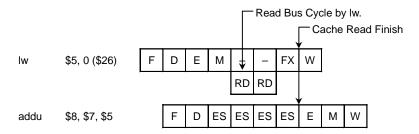

With load instructions, a one-cycle delay occurs while waiting for the data being loaded to become available for use by another instruction. The TX49 checks the instruction in the delay slot (the instruction immediately following the load instruction) to see if that instruction needs to use the load result; if so, it stalls the pipeline (see Figure 6-1).

Figure 6-1 CPU Pipeline Load Delay

#### 6.4.2 Delayed branching

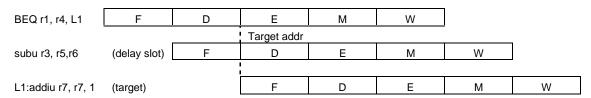

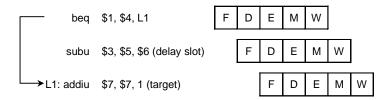

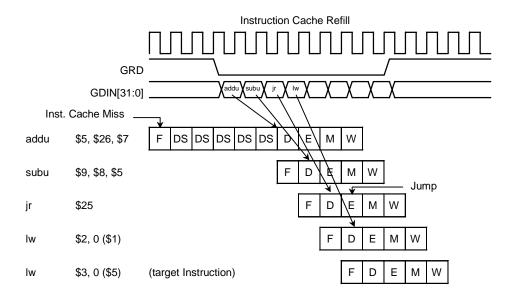

Figure 6-1 shows the pipeline flow for jump/branch instructions. The branch target address that must be generated for these type of instructions does not become available unit the E stage - too late to be used by the instruction in the branch delay slot. The branch target instruction is fetched immediately after the branch delay slot cycle.

It is, however, possible to fetch a different instruction that would normally be executed prior to the branch instruction.

Figure 6-1 CPU Pipeline Branch Delay

You can make effective use of the branch delay slot as follows.

- Since the instruction immediately following a branch instruction will be executed just prior to the branch, you can therefore place an instruction (that logically should be executed just before the branch) into delay slot following the branch instruction.

- The TX49 provides Branch Likely instructions in addition to the normal Branch instructions that allow the instruction at the target branch address to be placed in the delay slot. If the branch condition of the Branch Likely instruction is met, the instruction in the delay slot is executed and the branch is taken. If the branch is not taken, the instruction in the delay is treated as a NOP.

- If no instruction is placed in the delay slot, a NOP is placed just after the branch instruction.

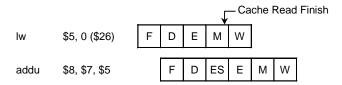

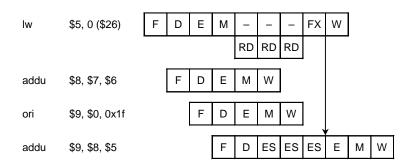

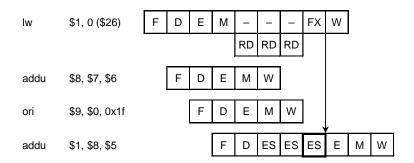

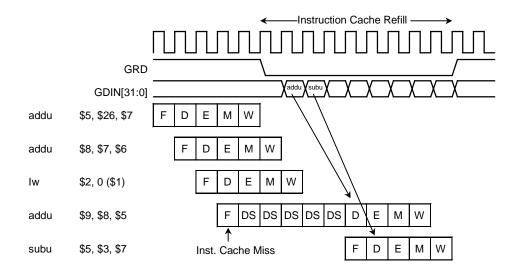

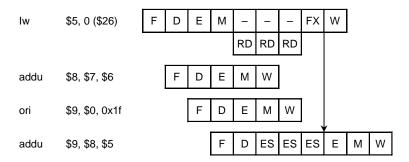

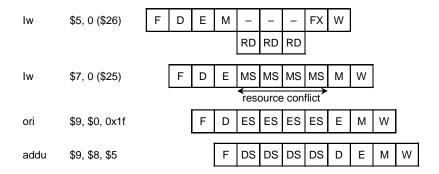

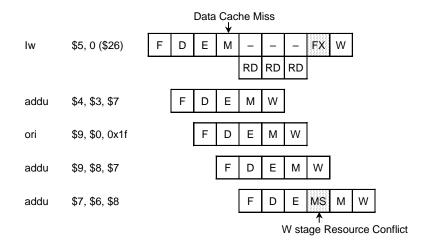

## 6.5 Non-blocking Load Function

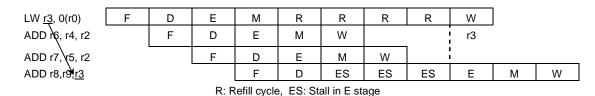

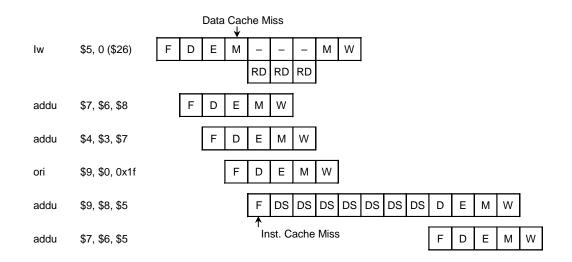

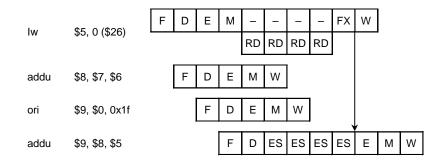

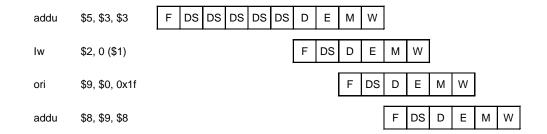

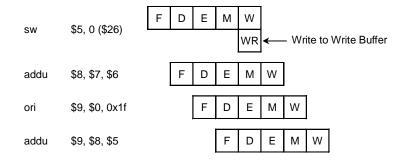

The non-blocking load function prevents the pipeline from stalling when a cache miss occurs and a refill cycle is required to refill the data cache. Instructions after the load instruction that do not use registers affected by the load will continue to be executed. An example is shown in Figure 6-1. Here a cache miss occurs with the first load instruction. The two instructions following are executed prior to the load. The fourth instruction (ADD) must use a register that will be loaded by the load instruction, therefore the pipeline is stalled until the cache data becomes valid.

Figure 6-1 Non-blocking load function

### 6.6 Interlock and Exception Handling

#### 6.6.1 Overview of Interlock and Exception Handling

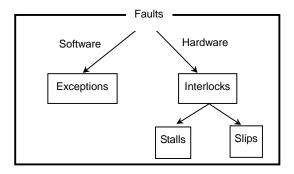

Smooth pipeline flow is interrupted when cache misses or exceptions occur, or when data dependencies are detected. Interruptions handled using hardware, such as cache misses, are referred to as interlocks, while those that are handled using software are called exceptions.

As shown in Figure 6-1, all interlock and exception conditions are collectively referred to as faults.

Figure 6-1 Interlocks, Exceptions, and Faults

These are two types of interlocks:

- stalls, which are resolved by halting the pipeline

- slips, which require one part of the pipeline to advance while another part of the pipeline is held static

At each cycle, exception and interlock condition corresponds to a particular pipeline stage, a condition can be traced to the particular instruction in the exception/interlock stage, as shown in Figure 6-2. For instance, an Illegal Instruction (II) exception is raised in the exception (EX) stage.

Table 6-1 and Table 6-2 describe the pipeline interlocks and exceptions listed in Figure 6-2.

| Otata     |      | Pipeline Stage |       |       |   |  |  |  |  |  |

|-----------|------|----------------|-------|-------|---|--|--|--|--|--|

| State     | F    | D              | Е     | М     | W |  |  |  |  |  |

| Stall     | ITM  | ICM            |       | DCM   |   |  |  |  |  |  |

| Stall     |      |                |       | CPE   |   |  |  |  |  |  |

|           |      | LDI            |       |       |   |  |  |  |  |  |

| Slip      |      | MDSt           |       |       |   |  |  |  |  |  |

|           |      | (FCBsy)        |       |       |   |  |  |  |  |  |

|           | ITLB | IBE            | RI    | DBE   |   |  |  |  |  |  |

|           |      |                | Cun   | NMI   |   |  |  |  |  |  |

|           |      |                | BP    | Reset |   |  |  |  |  |  |

| Exception |      |                | SC    | OVF   |   |  |  |  |  |  |

|           |      |                | DTLB  | Trap  |   |  |  |  |  |  |

|           |      |                | DTMod |       |   |  |  |  |  |  |

|           |      |                | Intr  |       |   |  |  |  |  |  |

Figure 6-2 Correspondence of pipeline stage to interlock condition

Table 6-1 Pipeline Interlocks

| Interlock | Description                    |

|-----------|--------------------------------|

| ITM       | Instruction TLB Miss           |

| ICM       | Instruction Cache Miss         |

| CPE       | Coprocessor Possible Exception |

| DCM       | Data Cache Miss                |

| LDI       | Load Interlock                 |

| MDSt      | Multiply / Divide Start        |

| FCBsy     | FP Coprocessor Busy            |

Table 6-2 Pipeline Exceptions

| Exception | Description                                  |

|-----------|----------------------------------------------|

| ITLB      | Instruction Translation or Address Exception |

| Intr      | External Interrupt                           |

| IBE       | Instruction Bus Error                        |

| RI        | Reserved Instruction                         |

| BP        | Breakpoint                                   |

| SC        | System Call                                  |

| Cun       | Coprocessor Unusable                         |

| OVF       | Integer Overflow                             |

| FPE       | FP Interrupt                                 |

| ExTrap    | EX Stage Traps                               |

| DTLB      | Data Translation or Address Exception        |

| TLBMod    | TLB Modified                                 |

| DBE       | Data Bus Error                               |

| NMI       | Nom-maskable Interrupt (or Soft Reset)       |

| Reset     | Reset                                        |

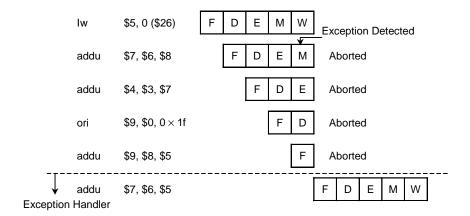

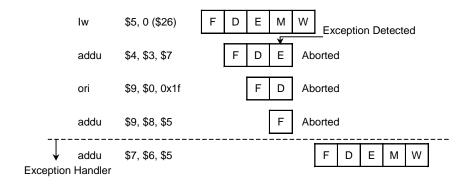

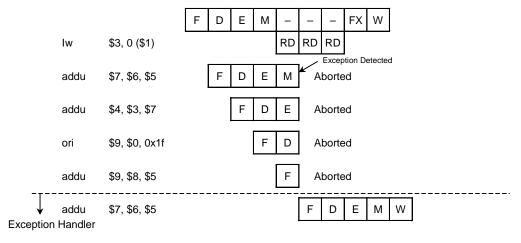

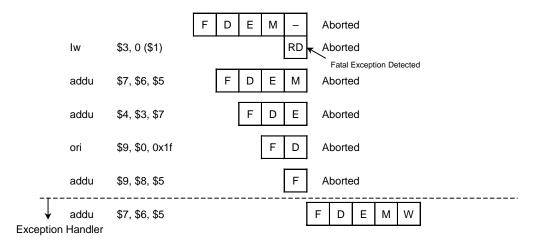

#### 6.6.2 Exception Conditions

When an exception condition occurs, the relevant instruction and all those that follow it in the pipeline are cancelled. Accordingly, any stall conditions and any later exception conditions that may have referenced this instruction are inhibited; there is no benefit in servicing stalls for a cancelled instruction.

After instruction cancellation, a new instruction stream begins, starting execution at a predefined exception vector. System Control Coprocessor registers are loaded with information that identifies the type of exception and auxiliary information such as the virtual address at which translation exceptions occur.

#### 6.6.3 Stall Conditions

Often, a stall condition is only detected after parts of the pipeline have advanced using incorrect data; this is called a pipeline overrun. When a stall condition is detected, all eight instructions-each different stage of the pipeline-are frozen at once. In this stalled state, no pipeline stages can advance until the interlock condition is resolved.

Once the interlock is removed, the restart sequence begins two cycles before the pipeline resumes execution. The restart sequence reverses the pipeline overrun by inserting the correct information into the pipeline.

#### 6.6.4 External Stalls

External stall is another class of interlocks. An external stall originates outside the processor and is not referenced to a particular pipeline stage. This interlock is not affected by exceptions.

#### 6.6.5 Interlock and Exception Timing

To prevent interlock and exception handling from adversely affecting the processor cycle time, the TX49 processor uses both logic and circuit pipeline techniques to reduce critical timing paths. Interlock and exception handling have the following effects on the pipeline:

- In some cases, the processor pipeline must be backed up (reversed and started over again from a prior stage) to recover from interlocks.

- In some cases, interlocks are serviced for instructions that will be aborted, due to an exception.

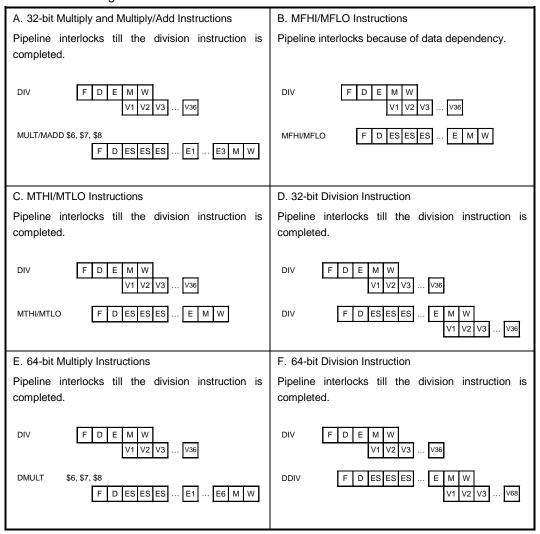

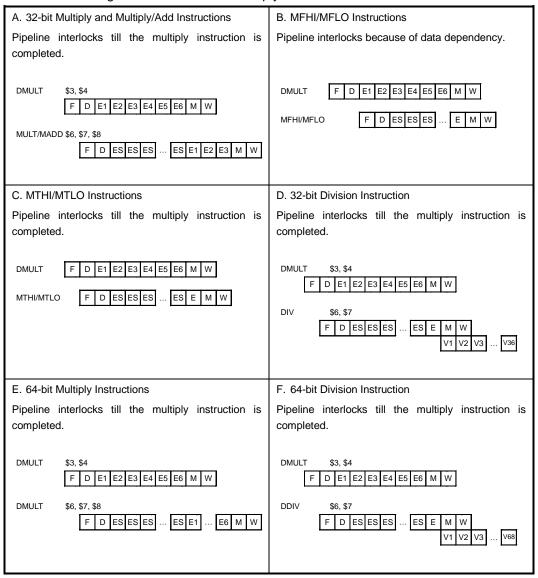

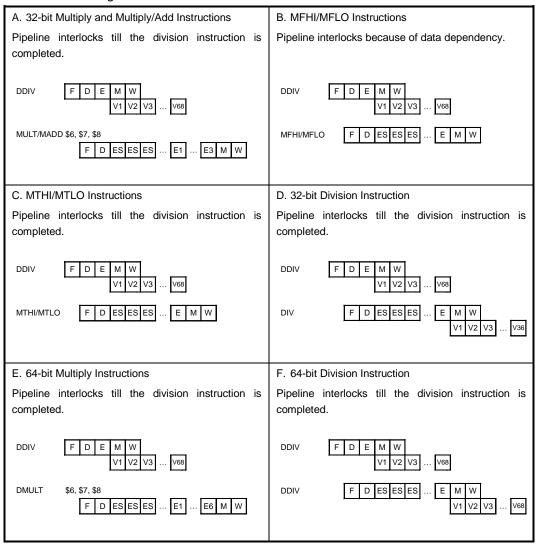

### 6.7 Multiply and Multiply/Add Instructions (MULT, MULTU, MADD, MADDU)

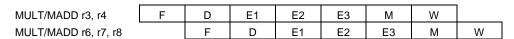

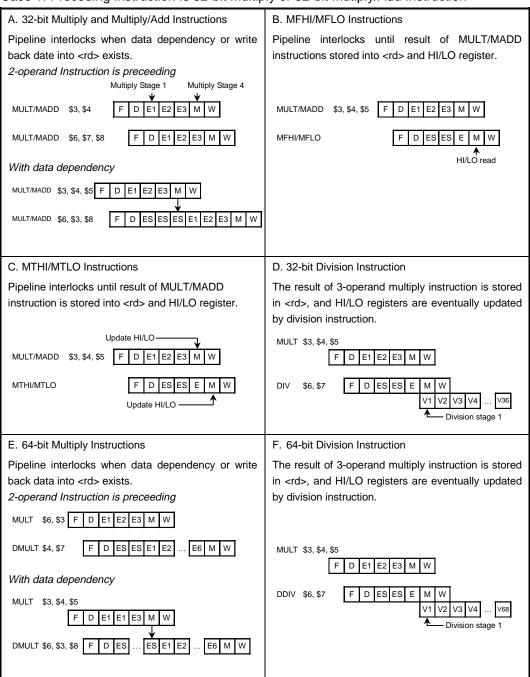

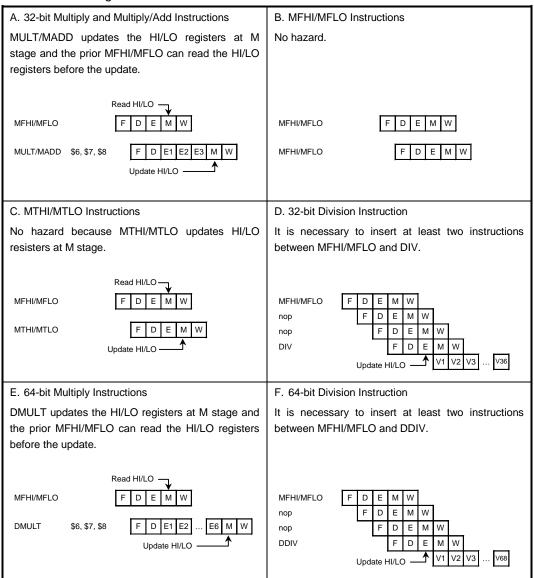

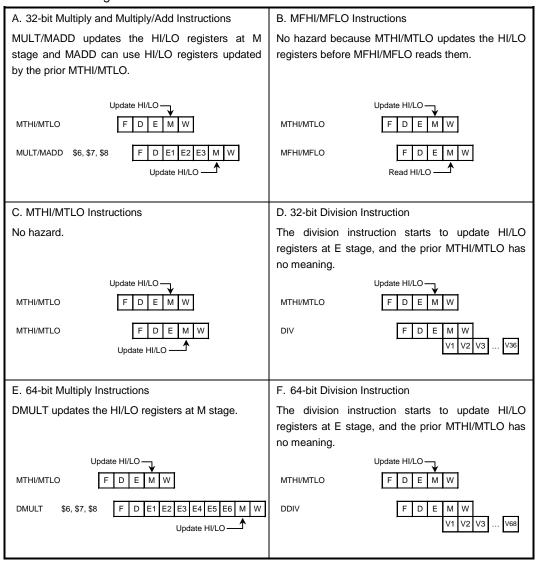

The TX49 can execute 32-bit multiply and multiply/add instructions of 2-operand continuously, and can use the results in the HI/LO registers in immediately following instructions, without pipeline stall as shown Figure 6-1. The TX49 requires three cycles to use the results of a general-purpose register as shown Figure 6-2.

Figure 6-1 MULT and MADD Instructions w/o data dependency (32-bit and 2-operand)

| MULT/MADD r3, r4, r5 | F | D | E1 | E2 | E3 | М  | W  |    |    |   |   |

|----------------------|---|---|----|----|----|----|----|----|----|---|---|

| MULT/MADD r6, r3, r8 |   | F | D  | ES | ES | ES | E1 | E2 | E3 | М | W |

Figure 6-2 MULT and MADD Instructions with data dependency (32-bit and 3-operand)

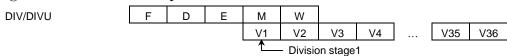

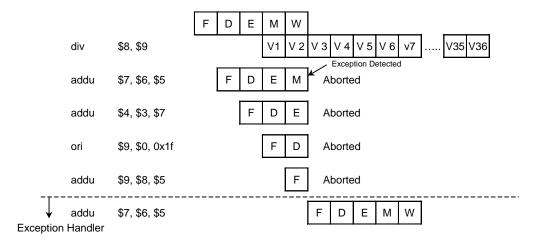

### 6.8 Divide Instructions (DIV, DIVU)

Division starts from the pipeline E stage and takes 36 cycles.

Figure 6-1 shows an example of a divide instruction.

Figure 6-1 DIV and DIVU Instructions

### 6.9 Streaming

During a cache refill operation, the TX49 can resume execution immediately after arrival of necessary data or instruction in cache even though cache refill is not

completed. This is referred to as "streaming".

# 7. System Control Coprocessor, CP0

## 7.1 Introduction

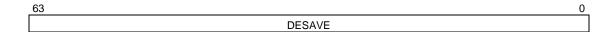

The TX49 has a System Control Co-Processor (CP0). CP0 translates virtual addresses to physical addresses. CP0 manages exceptions and transitions between kernel, supervisor, and user states. CP0 also controls the cache sub-system, as well as providing diagnostic control and error recovery facilities.

### 7.2 CP0 Registers

This section is described about the bit field of each register. The term "coldreset" of tables shows the value of each bit when GCOLDRESET\* signal is asserted. The reserved bits in description must be written the same value in reset, and return the same value when read.

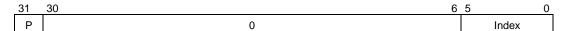

### 7.2.1 Index register (Reg#0)

The Index register is a 32-bit read/write register containing six bits to index an entry in the TLB. The P bit of the register shows the success/failure of a TLB Probe (TLBP) instruction.

The Index register also specifies the TLB entry affected by TLB Read (TLBR) or TLB Write Index (TLBWI) instructions.

Figure 7-1 shows the format of the Index register and Table 7-1 describes the Index register fields.

Figure 7-1 Index Register Format

Table 7-1 Index Register Field Descriptions

| Bit  | Field | Description                                                                               | coldreset | Read/Write |

|------|-------|-------------------------------------------------------------------------------------------|-----------|------------|

| 31   | Р     | Probe failure. Set to 1 when the previous  TLB Probe (TLBP) instruction was unsuccessful. | Undefined | Read/Write |

| 30~6 | 0     | Reserved                                                                                  | 0x0       | Read       |

| 5~0  | Index | Index to the TLB entry affected by the TLB Read and TLB Write Index instructions          | Undefined | Read/Write |

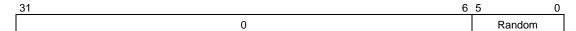

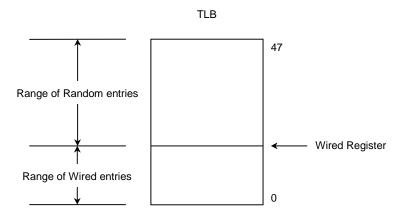

#### 7.2.2 Random register (Reg#1)

The Random register is a read only register containing six bits to index an entry in the TLB. This register decrements as each instruction executes. The values are as follows.

- A lower bound is set by the number of TLB entries reserved for exclusive use by the operating system (the contents of the Wired register).

- An upper bound is set by the total number of TLB entries (47 maximum).

The Random register specifies the TLB entry affected by TLB Write Random (TLBWR) instruction. However the register doesn't need to be read for this purpose, it is readable to verify proper operation of the processor.

To simplify testing, the Random register is set to the value of the upper bound upon system reset. This register is also set to the upper bound when the Wired register is written.

Figure 7-1 shows the format of the Random register and Table 7-1 describes the Random register fields.

Figure 7-1 Random Register Format

Table 7-1 Random Register Field Descriptions

| Bit  | Field  | Description       | coldreset        | Read/Write |

|------|--------|-------------------|------------------|------------|

| 31~6 | 0      | Reserved.         | 0x0              | Read       |

| 5~0  | Random | TLB random index. | Upper bound (47) | Read       |

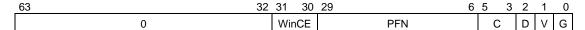

### 7.2.3 EntryLo0 register (Reg#2) and EntryLo1 register (Reg#3)

The EntryLo register consists of two registers have identical formats:

- EntryLo0 is used for even virtual pages

- EntryLo1 is used for odd virtual pages

The EntryLo0 and EntryLo1 register are read/write register. These registers hold the physical page frame number (PFN) of the TLB entry for even and odd pages, respectively, when performing TLB read and write operations.

Figure 7-1 shows the format of the EntryLo0/EntryLo1 register and Table 7-1 describes the EntryLo0/EntryLo1 register fields.

Figure 7-1 EntryLo0/EntryLo1 Register Format

Table 7-1 EntryLo0/EntryLo1 Register Field Descriptions

|       |       | , , ,                                                                                                                                                                                                          | •         |            |

|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|

| Bit   | Field | Description                                                                                                                                                                                                    | coldreset | Read/Write |

| 63~32 | 0     | Reserved                                                                                                                                                                                                       | 0x0       | Read       |

| 31~30 | WinCE | Usable for Win-CE                                                                                                                                                                                              | 0x0       | Read/Write |

| 29~6  | PFN   | Page frame number.                                                                                                                                                                                             | Undefined | Read/Write |

| 5~3   | С     | Specifies the TLB page coherency attribute.  0: Cacheable, noncoherent, write-through, no-WA  1: Cacheable, noncoherent, write-through, WA  2: Uncached  3: Cacheable,noncoherent,write-back,WA  4~7: Reserved | 0x0       | Read/Write |

| 2     | D     | Dirty                                                                                                                                                                                                          | 0         | Read/Write |

| 1     | V     | Valid.                                                                                                                                                                                                         | 0         | Read/Write |

| 0     | G     | Global                                                                                                                                                                                                         | 0         | Read/Write |

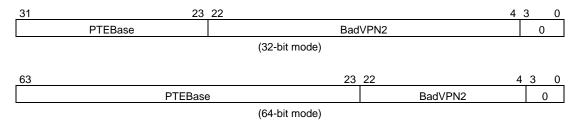

### 7.2.4 Context register (Reg#4)

The Context register is a read/write register containing the pointer to an entry in the page table entry (PTE) array. This array is an operating system data structure that stores virtual to physical address translations. When there is a TLB miss, the CPU loads the TLB with the missing translation from the PTE array. Normally, the operating system uses the Context register to address the current page map which resides in the kernel mapped segment,kseg3. However the contents of this register duplicates some information of the BadVAddr register, it is arranged in a form that is more useful for TLB exception handler by a software.

Figure 7-1 shows the formats of the Context register and Table 7-1 describes the Context register fields.

Figure 7-1 Context Register Formats

Table 7-1 Context Register Field Descriptions

#### 32-bit mode

| Bit   | Field   | Description                    | coldreset | Read/Write |

|-------|---------|--------------------------------|-----------|------------|

| 31~23 | PTEBase | Page table entry base pointer  | Undefined | Read/Write |

| 22~4  | BadVPN2 | Bad virtual address bits 31~13 | Undefined | Read       |

| 3~0   | 0       | Reserved                       | 0x0       | Read       |

#### 64-bit mode

| Bit   | Field   | Description                    | coldreset | Read/Write |

|-------|---------|--------------------------------|-----------|------------|

| 63~23 | PTEBase | Page table entry base pointer  | Undefined | Read/Write |

| 22~4  | BadVPN2 | Bad virtual address bits 31~13 | Undefined | Read       |

| 3~0   | 0       | Reserved                       | 0x0       | Read       |

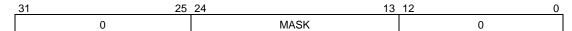

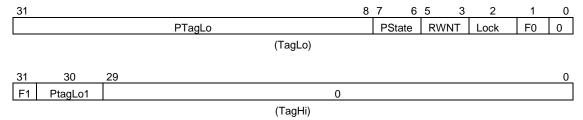

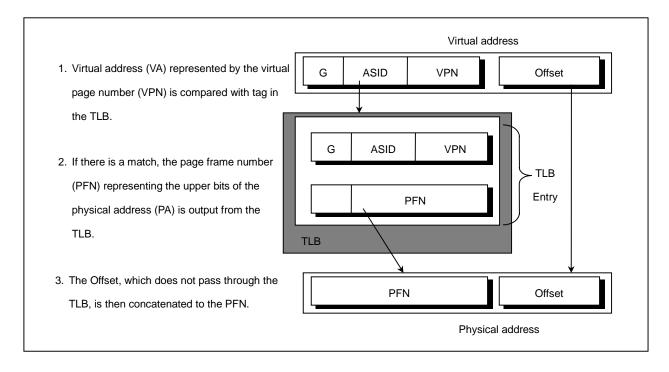

### 7.2.5 PageMask register (Reg#5)

The PageMask register is a read/write register used for reading from/writing to the TLB. This register holds a comparison mask that sets the variable page size for each TLB entry.

TLB read and write operations use this register as either a source or a destination. When virtual addresses are presented for translation into physical address, the corresponding bits in the TLB identify which virtual address bits among bits  $24\sim13$  are used in the comparison. When the Mask field is not one of the values shown in Table 7-1, the operation of the TLB is undefined.

Figure 7-1 shows the format of the PageMask register and Table 7-1 describes the PageMask register fields.

Figure 7-1 PageMask Register Format

Table 7-1 PageMask Register Field Descriptions

|       |       | rasio i i agentacit regione i iola 2 comp |           |            |

|-------|-------|-------------------------------------------|-----------|------------|

| Bit   | Field | Description                               | coldreset | Read/Write |

| 31~25 | 0     | Reserved                                  | 0x0       | Read       |

| 24~13 | MASK  | Page comparison mask                      | 0x0       | Read/Write |

|       |       | 000000000000: page size = 4• Kbytes       |           |            |

|       |       | 00000000011: page size = 16• Kbytes       |           |            |

|       |       | 00000001111: page size = 64• Kbytes       |           |            |

|       |       | 0000001111111: page size = 256• Kbytes    |           |            |

|       |       | 000011111111: page size = 1• Mbytes       |           |            |

|       |       | 001111111111: page size = 4• Mbytes       |           |            |

|       |       | 111111111111: page size = 16• Mbytes      |           |            |

| 12~0  | 0     | Reserved                                  | 0x0       | Read       |

### 7.2.6 Wired register (Reg#6)

The Wired register is a read/write register specifies the boundary between the wired and random entries of the TLB as follows. Wired entries are non-replaceable entries, which can not be overwritten by a TLB write random operation. Random entries can be overwritten.

The Wired register is set to 0 upon system reset. Writing this register also sets the Random register to the value of its upper bound.

Figure 7-1 shows the format of the Wired register and Table 7-1 describes the Wired register fields.

Figure 7-1 Wired Register

Table 7-1 Wired Register Filed Descriptions

| Bit  | Field | Description                                                         | coldreset | Read/Write |

|------|-------|---------------------------------------------------------------------|-----------|------------|

| 31~6 | 0     | Reserved (Must be written as zeroes, and returns zeroes when read.) | 0x0       | Read       |

| 5~0  | Wired | TLB Wired boundary.                                                 | 0x0       | Read/Write |

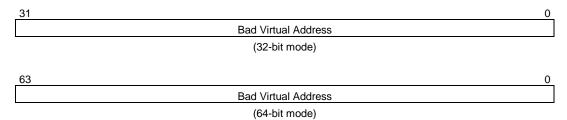

### 7.2.7 BadVAddr register (Reg#8)

The Bad Virtual Address (BadVAddr) register is a read only register that displays the most recent virtual address that cause one of the following exceptions; Address Error, TLB Invalid, TLB Modified and TLB Refill exceptions.

The processor does not write to this register when the EXL bit in the Status register is set to a 1.

Figure 7-1 shows the formats of the BadVAddr register and Table 7-1 describes the BadVAddr register fields.

Figure 7-1 BadVAddr Register Formats

Table 7-1 BadVAddr Register Field Descriptions

#### 32-bit mode

| Bit  | Field    | Description         | coldreset | Read/Write |

|------|----------|---------------------|-----------|------------|

| 31~0 | BadVAddr | Bad Virtual address | Undefined | Read       |

#### 64-bit mode

| ľ | Bit  | Field    | description         | coldreset | Read/Write |

|---|------|----------|---------------------|-----------|------------|

| Ī | 63~0 | BadVAddr | Bad Virtual address | Undefined | Read       |

### 7.2.8 Count register (Reg#9)

The Count register is a read/write register. This register acts as a timer, incrementing at a constant rate whether or not an instruction is executed, retired, or any forward progress is made through the pipeline.

This register can be also written for diagnostic purpose or system initialization.

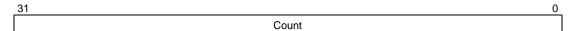

Figure 7-1 shows the format of the Count register and Table 7-1 describes the Count register field.

Figure 7-1 Count Register Format

Table 7-1 Count Register Field Description

| Bit  | Field | Description                                                | coldreset | Read/Write |

|------|-------|------------------------------------------------------------|-----------|------------|

| 31~0 | Count | 32-bit timer, incrementing at half the maximum instruction | 0x0       | Read/Write |

|      |       | issue rate.                                                |           |            |

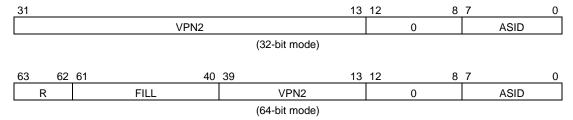

# 7.2.9 EntryHi register (Reg#10)

The EntryHi is a read/write register, and holds the high-order bits of a TLB entry for TLB read and write operations.

This register is accessed by the TLB Probe (TLBP), TLB Write Ransom (TLBWR), TLB Write Indexed (TLBWI), and TLB Read Indexed (TLBR) instructions.

When either a TLB refill, TLB invalid, or TLB modified exception occurs, this register is loaded with the virtual page number (VPN2) and the ASID of the virtual address that did not have a matching TLB entry.

Figure 7-1 shows the formats of the EntryHi register and Table 7-1 describes the EntryHi register fields.

Figure 7-1 EntryHi Register Formats

Table 7-1 EntryHi Register Field Descriptions

#### 32-bit mode

| Bit  | Field | Description                        | coldreset | Read/Write |

|------|-------|------------------------------------|-----------|------------|

| 31~1 | VPN2  | Virtual page number divided by two | Undefined | Read/Write |

| 12~8 | 0     | Reserved                           | 0x0       | Read       |

| 7~0  | ASID  | Address space ID field.            | Undefined | Read/Write |

#### 64-bit mode

| Bit   | Field | Description                            | coldreset | Read/Write |

|-------|-------|----------------------------------------|-----------|------------|

| 63~62 | R     | Region.                                | Undefined | Read/Write |

| 61~40 | Fill  | Reserved. 0 on read. Ignored on write. | Undefined | Read       |

| 39~13 | VPN2  | Virtual page number divided by two     | Undefined | Read/Write |

| 12~8  | 0     | Reserved                               | 0x0       | Read       |

| 7~0   | ASID  | Address space ID field.                | Undefined | Read/Write |

# 7.2.10 Compare register (Reg#11)

The Compare register acts as a timer. When value of the Count register equals the value of the Compare register, interrupt bit IP (7) in the Cause register is set. This causes an interrupt exception as soon as the interrupt is enabled.

Writing a value to this register, as a side effect, clears the timer interrupt.

For diagnostic purpose, this register is a read/write register. However, in normal operation this register is write only.

Figure 7-1 shows the format of the Compare register and Table 7-1 describes the Compare register field.

Figure 7-1 Compare Register Format

Table 7-1 Compare Register Field Description

| Bit  | Field   | Description                                                | coldreset | Read/Write |

|------|---------|------------------------------------------------------------|-----------|------------|

| 31~0 | Compare | Acts as a timer; it maintains a stable value that does not | 0x0       | Read/Write |

|      |         | change on its own.                                         |           |            |

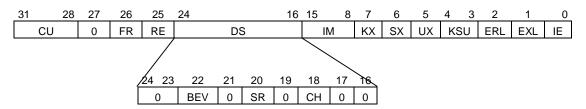

# 7.2.11 Status register (Reg#12)

The Status register is a read/write register that contains the operating mode, interrupt enabling, and diagnostic states of the processor. The more important Status register fields are as following;

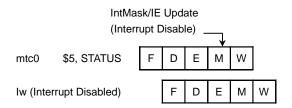

- The Interrupt Mask (IM) field of 8 bits controls the enabling of eight interrupt conditions. Interrupt must be enabled before they can be asserted, and the corresponding bits are set in both the IM field of this register and the Interrupt Pending field of the Cause register.

- The Coprocessor Usability (CU) field of 4 bits controls the usability of four possible coprocessors. Regardless of the CU0 bit setting, CP0 is always usable in Kernel mode.

- The Diagnostic Status (DS) field of 9 bits is used for self-testing, and checks the cache and virtual memory system.

- The Reverse Endian (RE) bit reverses the endianness. The processor can be configured as either little/big-endian at reset; reverse-endian selection is used in Kernel and Supervisor modes, and in the User mode when the RE bit is 0. Setting the RE bit to 1 inverts the User mode endianness.

Figure 7-1 shows the format of the Status register and Table 7-1 describes the Status register field.

Figure 7-1 Status Register Format

Table 7-1 Status Register Field Descriptions

| Bit   | Field        | Description                                                 | coldreset | Read/Write |

|-------|--------------|-------------------------------------------------------------|-----------|------------|

| 31~28 | CU (3,2,1,0) | Controls the usability of each of the four coprocessor unit | 0000      | Read/Write |

|       |              | numbers.                                                    |           |            |

|       |              | 0: unusable, 1: usable.                                     |           |            |

| 27    | 0            | Reserved                                                    | 0         | Read       |

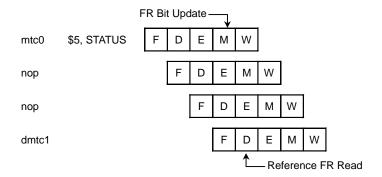

| 26    | FR           | Enables additional floating-point registers.                | 0         | Read/Write |

|       |              | 0: 16 registers, 1: 32 registers.                           |           |            |

| 25    | RE           | Reverse-Endian bit, valid in User mode.                     | 0         | Read/Write |

| 24~23 | 0            | Reserved                                                    | 0x0       | Read       |

| 22    | BEV          | Controls the location of TLB refill and general exception   | 1         | Read/Write |

|       |              | vectors.                                                    |           |            |

|       |              | 0: normal, 1: bootstrap                                     |           |            |

| Bit   | Field | Description                                                                                                                                | coldreset | Read/Write |

|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|

| 21    | 0     | Reserved                                                                                                                                   | 0         | Read       |

| 20    | SR    | 1: Indicates a soft reset or NMI has occurred.                                                                                             | 0         | Read/Write |

| 19    | 0     | Reserved                                                                                                                                   | 0         | Read       |

| 18    | СН    | "Hit" or "miss" indication for last CACHE Hit Invalidate, Hit Write Back Invalidate, Hit Write Back for a primary cache.  0: miss, 1: hit. | 0         | Read/Write |

| 17~16 | 0     | Reserved                                                                                                                                   | 0x0       | Read       |

| 15~8  | IM    | Interrupt Mask. 0: disabled, 1: enabled.                                                                                                   | 0x0       | Read/Write |

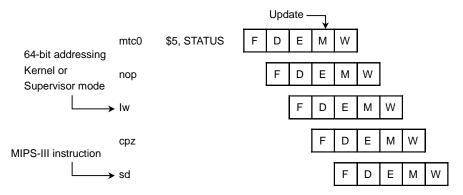

| 7     | КХ    | Enables 64-bit addressing in kernel mode. 0: 32-bit, 1: 64-bit.                                                                            | 0         | Read/Write |

| 6     | SX    | Enables 64-bit addressing and operations in supervisor mode. 0: 32-bit, 1: 64-bit.                                                         | 0         | Read/Write |

| 5     | UX    | Enables 64-bit addressing and operations in user mode. 0: 32-bit, 1: 64-bit.                                                               | 0         | Read/Write |

| 4~3   | KSU   | Mode. 10: user, 01: supervisor, 00: kernel.                                                                                                | 0x0       | Read/Write |

| 2     | ERL   | Error Level. 0: normal, 1: error.                                                                                                          | 1         | Read/Write |

| 1     | EXL   | Exception Level. 0: normal, 1: exception.                                                                                                  | 0         | Read/Write |

| 0     | IE    | Interrupt Enable. 0: disable, 1: enable.                                                                                                   | 0         | Read/Write |

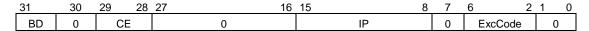

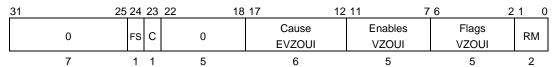

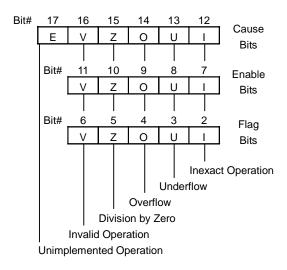

# 7.2.12 Cause register (Reg#13)

The Cause register holds the cause of the most recent exception. This register is read-only, except for the  $IP[1\sim0]$  bits.

Figure 7-1 shows the format of the Cause register and Table 7-1 describes the Cause register field.

Figure 7-1 Cause Register Format

Table 7-1 Cause Register Field Descriptions

| Bit   | Field    | Description                                                  | coldreset | Read/Write |

|-------|----------|--------------------------------------------------------------|-----------|------------|

| 31    | BD       | Indicates whether or not the last exception was taken while  | 0         | Read       |

|       |          | executing in a branch delay slot.                            |           |            |

|       |          | 0: normal, 1: delay slot.                                    |           |            |

| 30    | 0        | Reserved                                                     | 0         | Read       |

| 29~28 | CE       | Indicates the coprocessor unit number referenced when a      | 0x0       | Read       |

|       |          | coprocessor unusable exception is taken.                     |           |            |

|       |          | 00: coprocessor 0, 01: coprocessor 1,                        |           |            |

|       |          | 10: coprocessor 2, 11: coprocessor 3.                        |           |            |

| 27~16 | 0        | Reserved                                                     | 0x0       | Read       |

| 15~10 | IP [7~2] | Indicates whether an interrupt is pending.                   | INT[5:0]  | Read       |

|       |          | 0: not pending, 1: pending.                                  |           |            |

| 9~8   | IP [1~0] | Software interrupts.                                         | 0x0       | Read/Write |

|       |          | 0: reset, 1: set.                                            |           |            |

| 7     | 0        | Reserved                                                     | 0         | Read       |

| 6~2   | ExcCode  | Exception Code field.                                        | 0x0       | Read       |

|       |          | 0: Int: Interrupt.                                           |           |            |

|       |          | 1: Mod: TLB modification exception.                          |           |            |

|       |          | 2: TLBL: TLB exception (load or instruction fetch)           |           |            |

|       |          | 3: TLBS: TLB exception (Store)                               |           |            |

|       |          | 4: AdEL: Address error exception (load or instruction fetch) |           |            |

|       |          | 5: AdES: Address error exception (store)                     |           |            |

|       |          | 6: IBE: Bus error exception (instruction fetch)              |           |            |

|       |          | 7: DBE: Bus error exception (data reference: load or Store)  |           |            |

|       |          | 8: Sys: Syscall exception                                    |           |            |

|       |          | 9: Bp: Breakpoint exception                                  |           |            |

|       |          | 10: RI: Reserved instruction exception                       |           |            |

|       |          | 11: CpU: Coprocessor Unusable exception                      |           |            |

|       |          | 12: Ov: Arithmetic Overflow exception                        |           |            |

|       |          | 13: Tr: Trap exception                                       |           |            |

|       |          | 14: Reserved:                                                |           |            |

|       |          | 15: FPE: Floating-Point exception                            |           |            |

|       |          | 16-31: Reserved :                                            |           |            |

| 1~0   | 0        | Reserved                                                     | 0x0       | Read       |

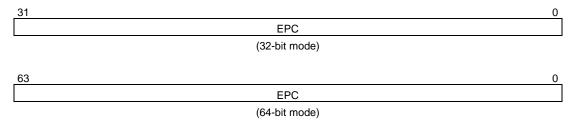

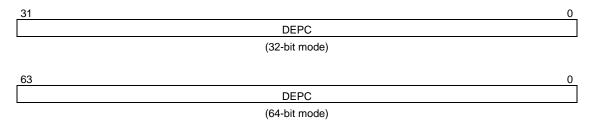

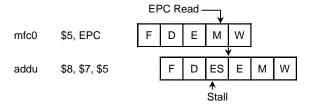

# 7.2.13 EPC register (Reg#14)

The Exception Program Counter (EPC) register is a read/write register. This register contents the address at which processing resumes after an exception has been serviced.

For synchronous exceptions, this register contains either;

- the virtual address of the instruction that was the direct cause of the exception.

- the virtual address of the immediately preceding branch or jump instruction (when the instruction is in a branch delay slot, and the Branch Delay bit in the Cause register is set).

The processor does not write to the EPC register when EXL bit in the Status register is set to 1.

Figure 7-1 shows the formats of the EPC register and Table 7-1 describes the EPC register field.

Figure 7-1 EPC Register Formats

Table 7-1 EPC Register Field Description

#### 32-bit mode

| Bit  | Field | Description               | coldreset | Read/Write |

|------|-------|---------------------------|-----------|------------|

| 31~0 | EPC   | Exception program counter | Undefined | Read/Write |

#### 64-bit mode

| Bit  | Field | Description               | coldreset | Read/Write |

|------|-------|---------------------------|-----------|------------|

| 63~0 | EPC   | Exception program counter | Undefined | Read/Write |

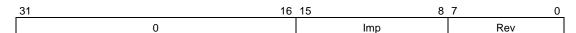

# 7.2.14 PRId register (Reg#15)

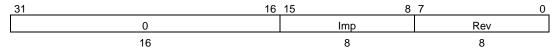

The Processor Revision Identifier (PRId) register is a read-only register. This register contents information identifying the implementation and revision level of the CPU and CPO.

Figure 7-1 shows the format of the PRId register and Table 7-1 describes the PRId register field.

Figure 7-1 PRId Register Format

Table 7-1 PRId Register Field Descriptions

| Bit   | Field | Description           | coldreset | Read/Write |

|-------|-------|-----------------------|-----------|------------|

| 31~16 | 0     | Reserved              | 0x0       | Read       |

| 15~8  | lmp   | Implementation number | 0x2d      | Read       |

| 7~0   | Rev   | Revision number +.    | +         | Read       |

<sup>+</sup> Value is shown in product sheet

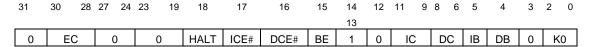

# 7.2.15 Config Register (Reg#16)

The Config register is a read-only register; except for HALT, ICE#, DCE# and K0 fields. This register specifies various configuration options selected on the TX49.

EC, BE, IC, DC, IB and DB fields are set by the hardware during reset and are included in this register as read-only status bits for the software to access.

Figure 7-1 shows the format of the Config register and Table 7-1 describes the Config register field.

Figure 7-1 Config Register Format

Table 7-1 Config Register Field Descriptions

| Bit   | Field   | Description                                                                                                                                                                                                                                                                                                                  | coldreset | Read/Write |

|-------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|

| 31    | 0       | Reserved                                                                                                                                                                                                                                                                                                                     | 0         | Read       |

| 30~28 | EC      | GBUS clock rate: 0: processor clock frequency divided by 2 1: processor clock frequency divided by 3 2: processor clock frequency divided by 4                                                                                                                                                                               | pin       | Read       |

|       |         | 7: processor clock frequency divided by 1 % 3, 4, 5, 6: reserved                                                                                                                                                                                                                                                             |           |            |

| 27~19 | 0       | Reserved                                                                                                                                                                                                                                                                                                                     | 0x0       | Read       |

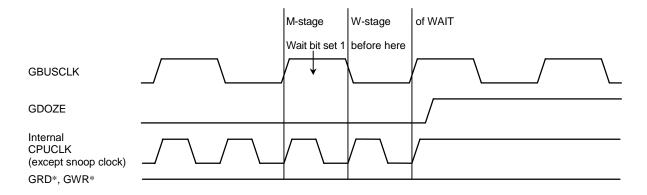

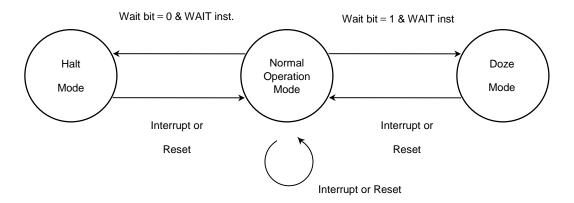

| 18    | HALT %& | Wait mode.  0: Halt  1: Doze Indicates the power-down behavior of the TX49 when WAIT instruction is executed. The TX49 stalls the pipeline both in halt and doze mode. Cache snoops are possible during Doze mode but not possible during Halt mode. Halt mode reduces power consumption to a greater extent than Doze mode. | 0         | Read/Write |

| 17    | ICE# %& | Instruction Cache Enable 0: Instruction cache enable 1: Instruction cache disable                                                                                                                                                                                                                                            | 0         | Read/Write |

| 16    | DCE# %& | Data Cache Enable 0: Data cache enable 1: Data cache disable                                                                                                                                                                                                                                                                 | 0         | Read/Write |

| 15    | BE      | Big Endian 0: Little Endian 1: Big Endian                                                                                                                                                                                                                                                                                    | pin       | Read       |

| 14~13 | 1       | Reserved                                                                                                                                                                                                                                                                                                                     | 11        | Read       |

| 12    | 0       | Reserved                                                                                                                                                                                                                                                                                                                     | 0         | Read       |

| Bit  | Field | Description                                                                                                                                                                                     | coldreset          | Read/Write |

|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------|

| 11~9 | IC    | Instruction cache size. In the TX49, this is set to 8• KB (001), 16• KB (010) or 32• KB (011).                                                                                                  | 001, 010 or<br>011 | Read       |

| 8~6  | DC    | Data cache size. In the TX49, this is set to 8• KB (001), 16• KB (010) or 32• KB (011).                                                                                                         | 001, 010 or<br>011 | Read       |

| 5    | IB    | Primary I-Cache line Size 1:32• bytes (8 words)                                                                                                                                                 | 1                  | Read       |

| 4    | DB    | Primary D-cache line Size 1:32• bytes (8 words)                                                                                                                                                 | 1                  | Read       |

| 3    | 0     | Reserved                                                                                                                                                                                        | 0                  | Read       |

| 2~0  | КО    | kseg0 coherency algorithm  0: Cacheable, noncoherent, write-through, no-WA  1: Cacheable, noncoherent, write-through, WA  2: Uncached  3: Cacheable, noncoherent, write-back, WA  4-7: Reserved | 0x0                | Read/Write |

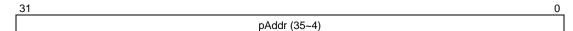

# 7.2.16 LLAddr register (Reg#17)

The Load Linked Address (LLAddr) register is a read/wirte register, and contains the physical address read by the most recent Load Linked (LL/LLD) instruction.

This register is for diagnostic purposes only, and serves no function during normal operation.

Figure 7-1 shows the format of the LLAddr register and Table 7-1 describes the LLAddr register field.

Figure 7-1 LLAddr Register Format

Table 7-1 LLAddr Register Field Description

| Bit  | Field | Description                | coldreset | Read/Write |

|------|-------|----------------------------|-----------|------------|

| 31~0 | pAddr | Physical address bits 35~4 | 0x0       | Read/Write |

## 7.2.17 XContext register (Reg#20)

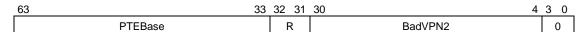

The XContext register is a read/write register, and contains a pointer to an entry in the page table entry (PTE) array, an operating system data structure that stores virtual to physical address translations. When there is a TLB miss, the operating system software loads the TLB with the missing translation from the PTE array. However the contents of this register duplicates some information of the BadVAddr register, it is arranged in a form that is more useful for TLB exception handler by a software. This register is for use with the XTLB refill handler, which loads TLB entries for references to a 64-bit address space, and is included solely for operating system use. The operating system sets the PTE base field in the register, as needed. Normally, the operating system uses this register to address the current page map which resides in the Kernel mapped segment, kseg3.

The BadVPN2 field of 27 bits has bit [39 $\sim$ 13] of the virtual address that caused the TLB miss; bit 12 is excluded because a single TLB entry maps to an even-odd page pair. For a  $4\square$ KByte page size, this format may be used directly to access the pairtable of  $8\square$ Byte PTEs. For other page sizes and PTE sizes, shifting and masking this value produces the appropriate address.

Figure 7-1 shows the format of the XContext register and Table 7-1 describes the XContext register field.

Figure 7-1 XContext Register Format

Table 7-1 XContext Register Field Description

| Bit   | Field   | Description                             | coldreset | Read/Write |

|-------|---------|-----------------------------------------|-----------|------------|

| 63~33 | PTEBase | Page table entry base pointer           | Undefined | Read/Write |

| 32~31 | R       | 00: user, 01: supervisor, 11: kernel.   | Undefined | Read/Write |

| 30~4  | BadVPN2 | Bad virtual page number divided by two. | Undefined | Read       |

| 3~0   | 0       | Reserved                                | 0x0       | Read       |

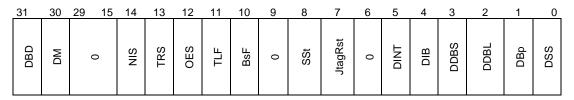

# 7.2.18 Debug register (Reg#23)

The Debug register is a read-only; except for TLF, BsF, SSt and JtagRst fields.

This register holds the information for debug handler.

Figure 7-1 shows the format of the Debug register and Table 7-1 describes the Debug register field.

Figure 7-1 Debug Register Format

Table 7-1 Debug Register Field Descriptions

| Bit   | Field | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | coldreset | Read/Write |

|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|

| 31    | DBD   | Debug Branch Delay; When a debug exception occurs while an instruction in the branch delay slot is executing, this bit is set to 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0         | Read       |

| 30    | DM    | Debug Mode; It indicates that a debug exception has taken place. This bit is set when a debug exception is taken, and is cleared upon return from the exception (DERET). While this bit is set all interrupts, including NMI, TLB exception, BUS error exception, and debug exception are masked and cache line locking function is disabled.  0: Debug handler not running.  1: Debug handler running.                                                                                                                                                                                                                                                                                                                                                   | 0         | Read       |

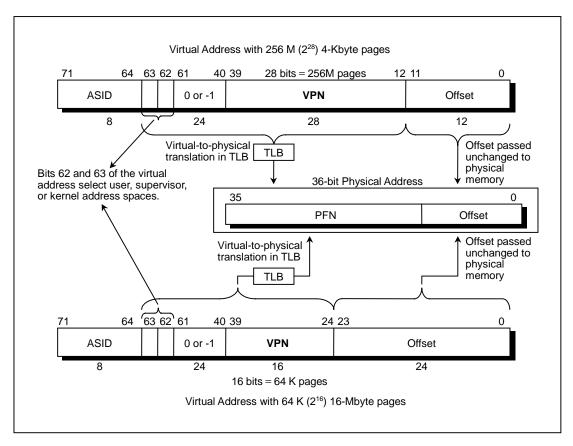

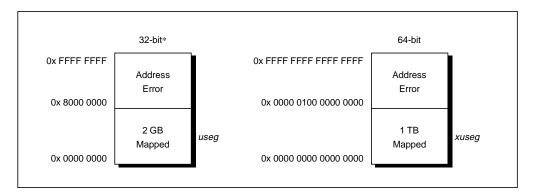

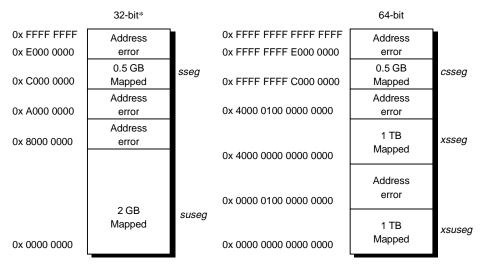

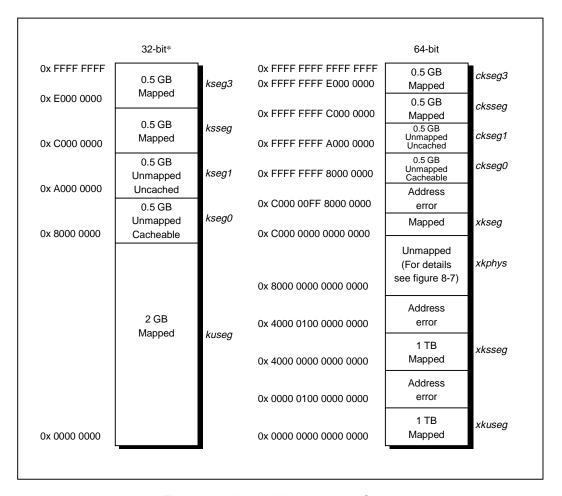

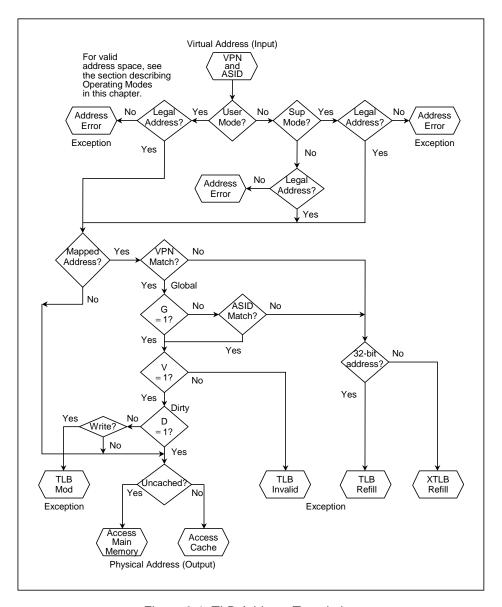

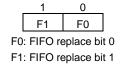

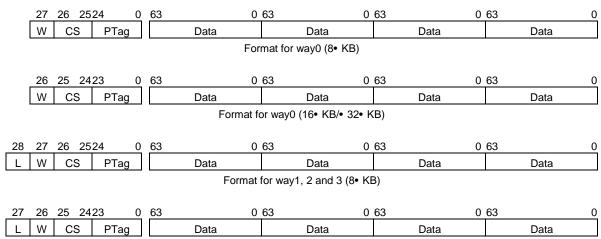

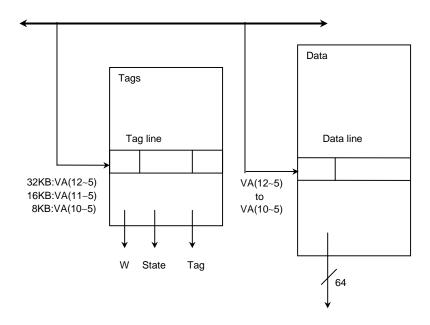

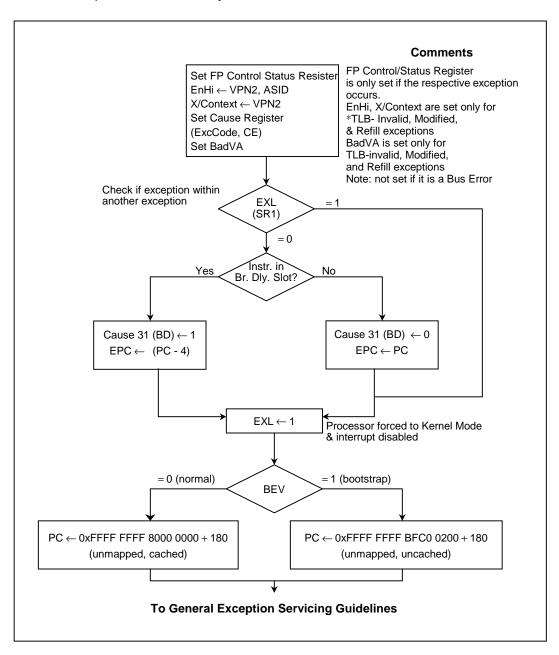

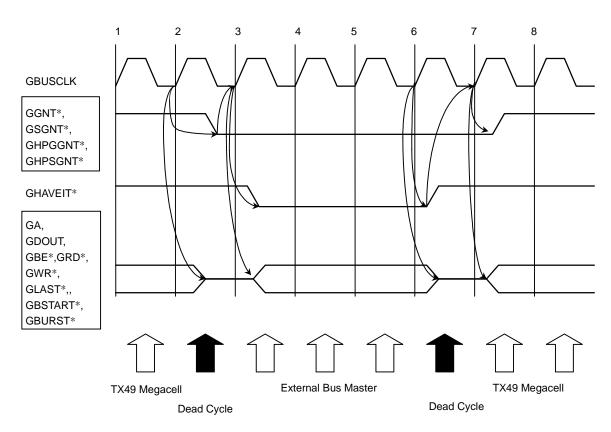

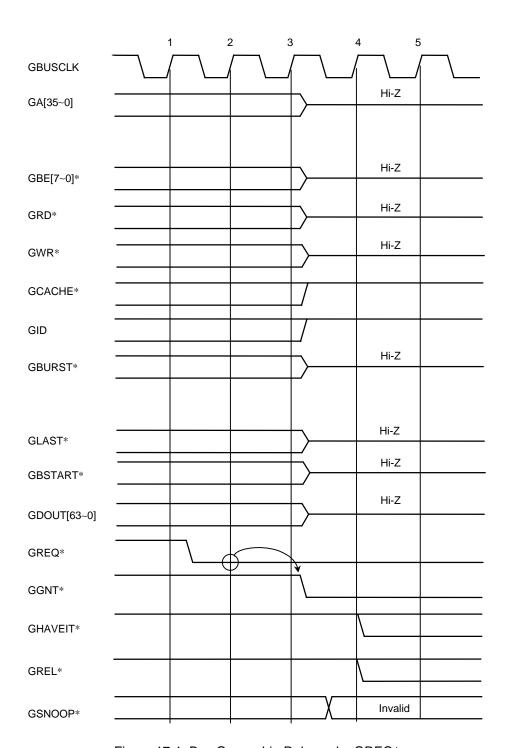

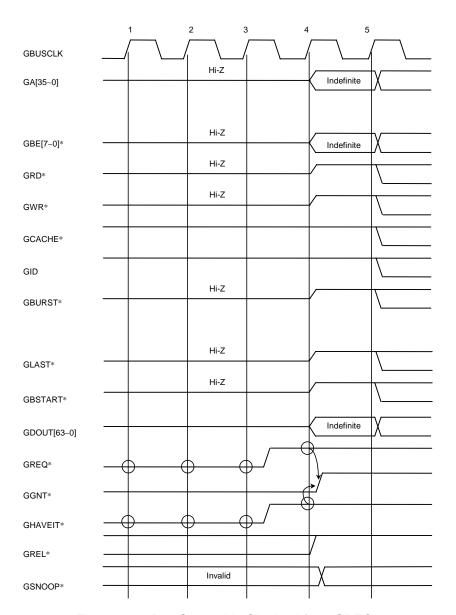

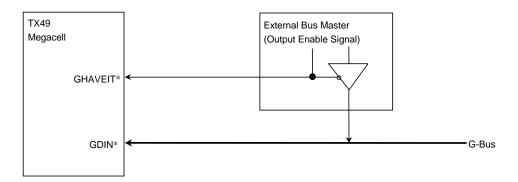

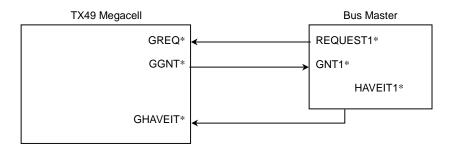

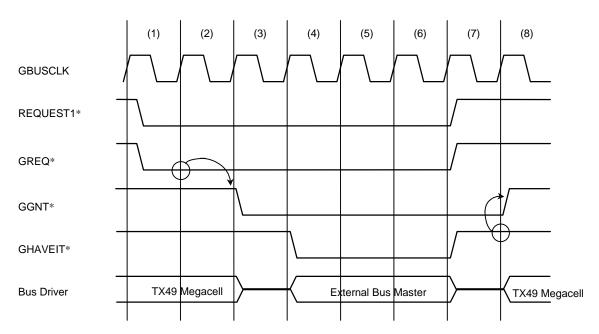

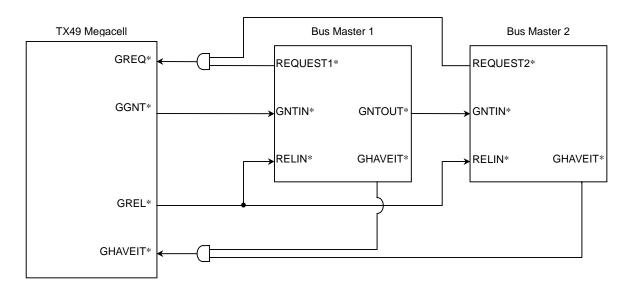

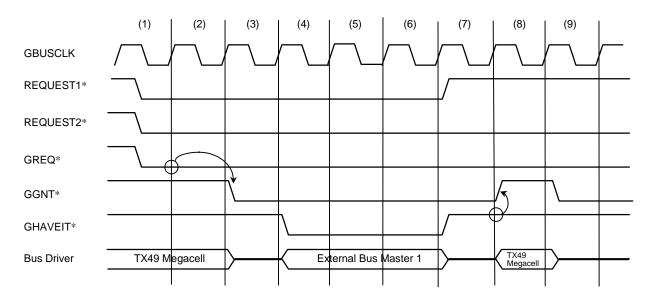

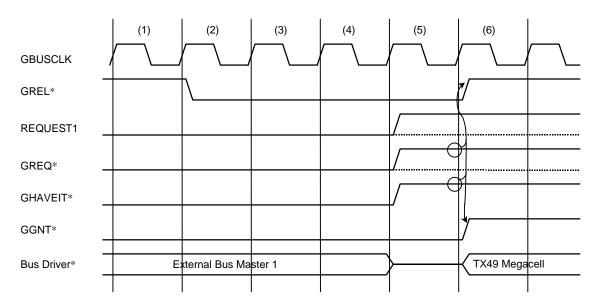

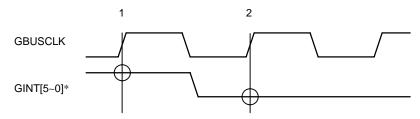

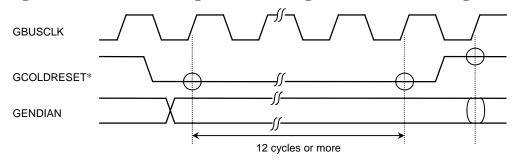

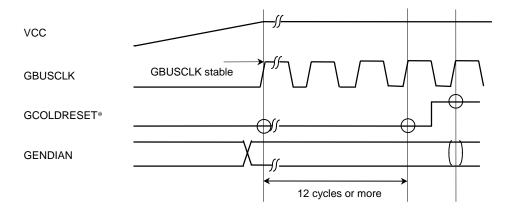

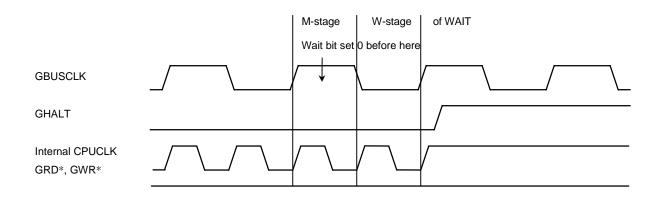

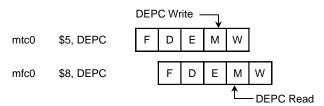

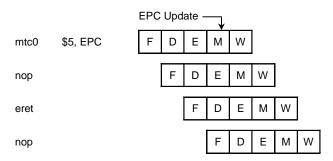

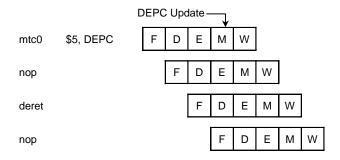

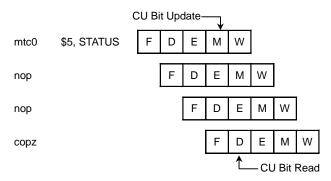

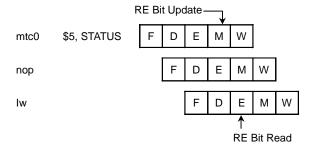

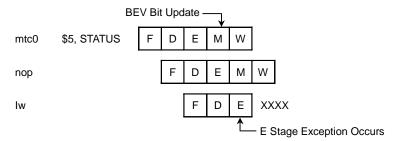

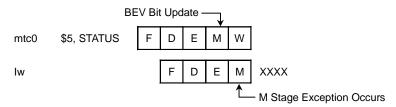

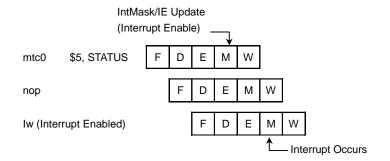

| 29~15 | 0     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0x0       | Read       |