# **General Information**

# GLOSSARY TTL TERMS AND DEFINITIONS

#### INTRODUCTION

These symbols, terms, and definitions are in accordance with those currently agreed upon by the JEDEC Council of the Electronic Industries Association (EIA) for use in the USA and by the International Electrotechnical Commission (IEC) for international use.

## PART I - OPERATING CONDITIONS AND CHARACTERISTICS (INCLUDING LETTER SYMBOLS)

#### **Clock Frequency**

#### Maximum clock frequency, fmax

The highest rate at which the clock input of a bistable circuit can be driven through its required sequence while maintaining stable transistions of logic level at the output with input conditions established that should cause changes of output logic level in accordance with the specification.

#### Current

# High-level input current, IIH

The current into\* an input when a high-level voltage is applied to that input.

-3---

# High-level output current, IOH

The current into\* an output with input conditions applied that according to the product specification will establish a high level at the output.

# Low-level input current, IIL

The current into\* an input when a low-level voltage is applied to that input.

# Low-level output current, IOL

The current into\* an output with input conditions applied that according to the product specification will establish a low level at the output.

# Off-state output current, IO(off)

The current flowing into<sup>\*</sup> an output with input conditions applied that according to the product specification will cause the output switching element to be in the off state.

Note: This parameter is usually specified for open-collector outputs intended to drive devices other than logic circuits.

#### Off-state (high-impedance-state) output current (of a three-state output), IOZ

The current into\* an output having three-state capability with input conditions applied that according to the product specification will establish the high-impedance state at the output.

#### Short-circuit output current, IOS

The current into<sup>\*</sup> an output when that output is short-circuited to ground (or other specified potential) with input conditions applied to establish the output logic level farthest from ground potential (or other specified potential).

#### Supply current, ICC

The current into\* the VCC supply terminal of an integrated circuit.

\*Current out of a terminal is given as a negative value.

TEXAS INSTRUMENTS INCORPORATED POST OFFICE BOX 5012 • DALLAS, TEXAS 75222

# GLOSSARY TTL TERMS AND DEFINITIONS

# Hold Time

# Hold time, th

The interval during which a signal is retained at a specified input terminal after an active transition occurs at another specified input terminal.

- NOTES: 1. The hold time is the actual time between two events and may be insufficient to accomplish the intended result. A minimum value is specified that is the shortest interval for which correct operation of the logic element is guaranteed.

- The hold time may have a negative value in which case the minimum limit defines the longest interval (between the release of data and the active transition) for which correct operation of the logic element is guaranteed.

#### **Output Enable and Disable Time**

## Output enable time (of a three-state output) to high level, tpZH (or low level, tpZL)<sup>†</sup>

The propagation delay time between the specified reference points on the input and output voltage waveforms with the three-state output changing from a high-impedance (off) state to the defined high (or low) level.

#### Output enable time (of a three-state output) to high or low level, tpzx<sup>†</sup>

The propagation delay time between the specified reference points on the input and output voltage waveforms with the three-state output changing from a high-impedance (off) state to either of the defined active levels (high or low).

# Output disable time (of a three-state output) from high level, tpHZ (or low level, tpLZ) $^{\dagger}$

The propagation delay time between the specified reference points on the input and output voltage waveforms with the three-state output changing from the defined high (or low) level to a high-impedance (off) state.

#### Output disable time (of a three-state output) from high or low level, tpxz<sup>†</sup>

The propagation delay time between the specified reference points on the input and output voltage waveforms with the three-state output changing from either of the defined active levels (high or low) to a high-impedance (off) state.

# **Propagation Time**

#### Propagation delay time, tPD

The time between the specified reference points on the input and output voltage waveforms with the output changing from one defined level (high or low) to the other defined level.

#### Propagation delay time, low-to-high-level output, tPLH

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined low level to the defined high level.

#### Propagation delay time, high-to-low-level output, tpHL

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined high level to the defined low level.

<sup>†</sup>On older data sheets, similar symbols without the P subscript were used; i.e. t<sub>ZH</sub>, t<sub>ZL</sub>, t<sub>HZ</sub>, and t<sub>LZ</sub>.

÷

#### Pulse Width

Pulse width, tw

The time interval between specified reference points on the leading and trailing edges of the pulse waveform.

#### **Recovery Time**

#### Sense recovery time, tSR

The time interval needed to switch a memory from a write mode to a read mode and to obtain valid data signals at the output.

#### **Release Time**

#### Release time, trelease

The time interval between the release from a specified input terminal of data intended to be recognized and the occurrence of an active transition at another specified input terminal.

Note: When specified, the interval designated "release time" falls within the setup interval and constitutes, in effect, a negative hold time.

# 3\_\_\_\_

#### Setup Time

#### Setup time, tsu

The time interval between the application of a signal that is maintained at a specified input terminal and a consecutive active transition at another specified input terminal.

- NOTES: 1. The setup time is the actual time between two events and may be insufficient to accomplish the setup. A minimum value is specified that is the shortest interval for which correct operation of the logic element is guaranteed.

- The setup time may have a negative value in which case the minimum limit defines the longest interval (between the active transition and the application of the other signal) for which correct operation of the logic element is guaranteed.

# **Transition Time**

## Transition time, low-to-high-level, tTLH

The time between a specified low-level voltage and a specified high-level voltage on a waveform that is changing from the defined low level to the defined high level.

#### Transition time, high-to-low-level, tTHL

The time between a specified high-level voltage and a specified low-level voltage on a waveform that is changing from the defined high level to the defined low level.

#### TEXAS INSTRUMENTS INCORPORATED POST OFFICE BOX 5012 • DALLAS, TEXAS 75222

# GLOSSARY TTL TERMS AND DEFINITIONS

# Voltage

# High-level input voltage, VIH

An input voltage within the more positive (less negative) of the two ranges of values used to represent the binary variables.

NOTE: A minimum is specified that is the least positive value of high-level input voltage for which operation of the logic element within specification limits is guaranteed.

#### High-level output voltage, VOH

The voltage at an output terminal with input conditions applied that according to the product specification will establish a high level at the output.

#### Input clamp voltage, VIK

An input voltage in a region of relatively low differential resistance that serves to limit the input voltage swing.

#### Low-level input voltage, VIL

An input voltage level within the less positive (more negative) of the two ranges of values used to represent the binary variables.

NOTE: A maximum is specified that is the most positive value of low-level input voltage for which operation of the logic element within specification limits is guaranteed.

#### Low-level output voltage, VOL

The voltage at an output terminal with input conditions applied that according to the product specification will establish a low level at the output.

#### Negative-going threshold voltage, VT-

The voltage level at a transition-operated input that causes operation of the logic element according to specification as the input voltage falls from a level above the positive-going threshold voltage, V<sub>T+</sub>.

#### Off-state output voltage, VO(off)

The voltage at an output terminal with input conditions applied that according to the product specification will cause the output switching element to be in the off state.

Note: This characteristic is usually specified only for outputs not having internal pull-up elements.

#### On-state output voltage, VO(on)

The voltage at an output terminal with input conditions applied that according to the product specification will cause the output switching element to be in the on state.

Note: This characteristic is usually specified only for outputs not having internal pull-up elements.

#### Positive-going threshold voltage, VT+

The voltage level at a transition-operated input that causes operation of the logic element according to specification as the input voltage rises from a level below the negative-going threshold voltage,  $V_{T-}$ .

# PART II - CLASSIFICATION OF CIRCUIT COMPLEXITY

# Gate Equivalent Circuit

A basic unit-of-measure of relative digital-circuit complexity. The number of gate equivalent circuits is that number of individual logic gates that would have to be interconnected to perform the same function.

#### Large-Scale Integration, LSI

A concept whereby a complete major subsystem or system function is fabricated as a single microcircuit. In this context a major subsystem or system, whether digital or linear, is considered to be one that contains 100 or more equivalent gates or circuitry of similar complexity.

#### Medium-Scale Integration, MSI

A concept whereby a complete subsystem or system function is fabricated as a single microcircuit. The subsystem or system is smaller than for LSI, but whether digital or linear, is considered to be one that contains 12 or more equivalent gates or circuitry of similar complexity.

### Small-Scale Integration, SSI

Integrated circuits of less complexity than medium-scale integration (MSI).

#### Very-Large-Scale Integration, VLSI

A concept whereby a complete system function is fabricated as a single microcircuit. In this context, a system, whether digital or linear, is considered to be one that contains 1000 or more gates or circuitry of similar complexity.

# TTL EXPLANATION OF FUNCTION TABLES

# **EXPLANATION OF FUNCTION TABLES**

The following symbols are now being used in function tables on TI data sheets:

| н              | = | high level (steady state)                                                                                                       |

|----------------|---|---------------------------------------------------------------------------------------------------------------------------------|

| L              | = | low level (steady state)                                                                                                        |

| ↑              | = | transition from low to high level                                                                                               |

| Ļ              | = | transition from high to low level                                                                                               |

| х              | = | irrelevant (any input, including transitions)                                                                                   |

| Z              | = | off (high-impedance) state of a 3-state output                                                                                  |

| ah             | - | the level of steady-state inputs at inputs A through H respectively                                                             |

| QO             | = | level of Q before the indicated steady-state input conditions were establsihed                                                  |

| ā <sub>0</sub> | - | complement of $\Omega_0$ or level of $\overline{\Omega}$ before the indicated steady-state input conditions were established    |

| Qn             | = | level of $\Omega$ before the most recent active transition indicated by $\downarrow$ or $\uparrow$                              |

| Л              | = | one high-level pulse                                                                                                            |

| Ţ              | = | one low-level pulse                                                                                                             |

| TOGGLE         | = | each output changes to the complement of its previous level on each active transition indicated by $\downarrow$ or $\uparrow$ . |

If, in the input columns, a row contains only the symbols H, L, and/or X, this means the indicated output is valid whenever the input configuration is achieved and regardless of the sequence in which it is achieved. The output persists so long as the input configuration is maintained.

If, in the input columns, a row contains H, L, and/or X together with  $\uparrow$  and/or  $\downarrow$ , this means the output is valid whenever the input configuration is achieved but the transition(s) must occur following the achievement of the steady-state levels. If the output is shown as a level (H, L, QQ, or QQ), it persists so long as the steady-state input levels and the levels that terminate indicated transitions are maintained. Unless otherwise indicated, input transitions in the opposite direction to those shown have no effect at the output. (If the output is shown as a pulse,  $\Box$  or  $\Box$ , the pulse follows the indicated input transition and persists for an interval dependent on the circuit.)

# TTL EXPLANATION OF FUNCTION TABLES

Amoung the most complex function tables in this book are those of the shift registers. These embody most of the symbols used in any of the function tables, plus more. Below is the function table of a 4-bit bidirectional universal shift register, e.g., type SN74194.

| INPUTS |      |    |       |        |       |          |   |   |   |                 | OUTPUTS         |                 |                 |  |

|--------|------|----|-------|--------|-------|----------|---|---|---|-----------------|-----------------|-----------------|-----------------|--|

| CLEAR  | MODE |    | сгоск | SERIAL |       | PARALLEL |   |   | 0 |                 | <u> </u>        | ~               |                 |  |

|        | S1   | SO | CLOCK | LEFT   | RIGHT | Α        | в | С | D | QA              | QB              | оc              | σD              |  |

| L      | х    | х  | х     | х      | x     | Х        | x | х | х | L               | L               | L               | L               |  |

| н      | x    | х  | L     | x      | х     | x        | х | х | х | QA0             | OB0             | QC0             | Q <sub>D0</sub> |  |

| н      | н    | н  | 1     | x      | х     | а        | b | с | d | а               | b               | с               | d               |  |

| н      | L    | н  | 1 1   | x      | н     | x        | х | х | х | н               | Q <sub>An</sub> | QBn             | QCn             |  |

| н      | L    | н  | ↑ (   | X      | L     | x        | х | х | х | L               | Q <sub>An</sub> | QBn             | QCn             |  |

| н      | н    | L  | † ↑   | н      | х     | X        | х | х | х | QBn             | QCn             | $Q_{Dn}$        | н               |  |

| н      | н    | Ľ  | † †   | L      | х     | X        | х | х | х | QBn             | QCn             | Q <sub>Dn</sub> | L               |  |

| н      | L    | L  | ×     | ×      | ×     | x        | х | х | x | Q <sub>A0</sub> | Q <sub>B0</sub> | QC0             | Q <sub>D0</sub> |  |

FUNCTION TABLE

The first line of the table represents a synchronous clearing of the register and says that if clear is low, all four outputs will be reset low regardless of the other inputs. In the following lines, clear is inactive (high) and so has no effect.

The second line shows that so long as the clock input remains low (while clear is high), no other input has any effect and the outputs maintain the levels they assumed before the steady-state combination of clear high and clock low was established. Since on other lines of the table only the rising transition of the clock is shown to be active, the second line implicitly shows that no further change in the outputs will occur while the clock remains high or on the high-to-low transition of the clock.

The third line of the table represents synchronous parallel loading of the register and says that if S1 and S0 are both high then, without regard to the serial input, the data entered at A will be at output  $\Omega_A$ , data entered at B will be at  $\Omega_B$ , and so forth, following a low-to-high clock transition.

The fourth and fifth lines represent the loading of high- and low-level data, respectively, from the shift-right serial input and the shifting of previously entered data one bit; data previously at  $Q_A$  is now at  $Q_B$ , the previous levels of  $Q_B$  and  $Q_C$  are now at  $Q_C$  and  $Q_D$  respectively, and the data previously at  $Q_D$  is no longer in the register. This entry of serial data and shift takes place on the low-to-high transition of the clock when S1 is low and S0 is high and the levels at inputs A through D have no effect.

The sixth and seventh lines represent the loading of high- and low-level data, respectively, from the shift-left serial input and the shifting of previously entered data one bit; data previously at  $Q_B$  is now at  $Q_A$ , the previous levels of  $Q_C$  and  $Q_D$  are now at  $Q_B$  and  $Q_C$ , respectively, and the data previously at  $Q_A$  is no longer in the register. This entry of serial data and shift takes place on the low-to-high transition of the clock when S1 is high and S0 is low and the levels at inputs A through D have no effect.

The last line shows that as long as both mode inputs are low, no other input has any effect and, as in the second line, the outputs maintain the levels they assumed before the steady-state combination of clear high and both mode inputs low was established.

1076

TEXAS INSTRUMENTS INCORPORATED POST OFFICE BOX 5012 • DALLAS, TEXAS 75222

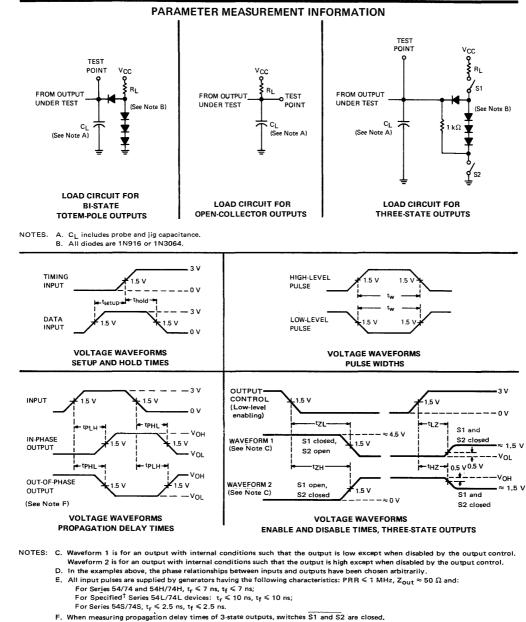

# SERIES 54/74, 54H/74H, 54S/74S, AND SPECIFIED<sup>+</sup> SERIES 54L/74L DEVICES

<sup>†</sup>'L42, 'L43, 'L44, 'L46, 'L47, 'L75, 'L77, 'L96, 'L121, 'L122, 'L123, 'L153, 'L154, 'L157, 'L164

TEXAS INSTRUMENTS OST OFFICE BOX 5012 . DALLAS, TEXAS 75222

3-10

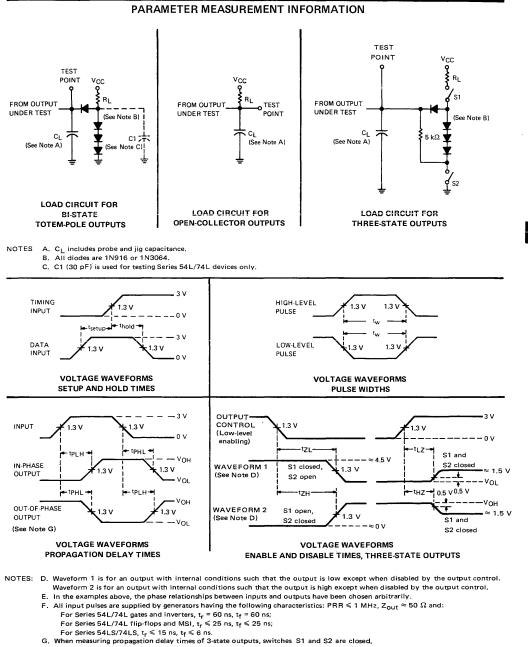

# SERIES 54LS/74LS AND MOST<sup>+</sup> SERIES 54L/74L DEVICES

<sup>+</sup>Except 'L42, 'L43, 'L44, 'L46, 'L47, 'L75, 'L77, 'L96, 'L121, 'L122, 'L123, 'L153, 'L154, 'L157, 'L164

TEXAS INSTRUMENTS INCORPORATED POST OFFICE BOX 5012 • DALLAS, TEXAS 75222

3-11