# Series 54L/74L Circuits

# Series 54L/74L Low Power TTL Integrated Circuits

- Over 14 MSI Functions

- • All Popular Package Configurations

- Fast Delivery to MIL-STD-883 for Military and Space Applications.

# SERIES 54L, 74L LOW-POWER TRANSISTOR-TRANSISTOR LOGIC

SERIES 54L, 74L REVISED JANUARY 1971

LOW-POWER TRANSISTOR-TRANSISTOR LOGIC CIRCUITS FOR AEROSPACE, MILITARY, OR INDUSTRIAL COMPUTER AND CONTROL SYSTEM APPLICATIONS

# description

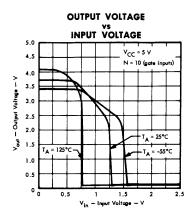

Series 54L/74L integrated circuits have been designed for aerospace, military, and industrial applications where high d-c noise margin, low power dissipation, improved speed-power relationships, and high reliability are important system considerations. This logic family includes small-scale integration (SSI) circuits and medium-scale integration (MSI) circuits needed to perform most functions of general-purpose digital systems. Definitive specifications for Series 54L/74L SSI circuits (gates and flip-flops) are provided in this section, and 54L/74L MSI circuits are included in Section 9.

Series 54L circuits are characterized for operation over the full military temperature range of -55°C to 125°C, and Series 74L circuits are characterized for operation over the temperature range of 0°C to 70°C.

### DIGITAL IC FAMILIES<sup>†</sup> 1000 Diagonal lines are lines V<sub>CC</sub> = 5 V of constant speed-power 400 T<sub>A</sub> = 25°C Average Propagation Delay Times for Logic Gates—ns product Series 100 15930 DTL C<sub>L</sub> = 30 pF 40 Series -54L TTL C<sub>L</sub> = 50 pF

10

4

0.1

Series 54 TT

0.4

C<sub>L</sub> = 15 pF

SPEED-POWER RELATIONSHIPS OF

Typical Power Dissipation-mW

<sup>†</sup>Typical saturated logic gate from the indicated families

54H TTL

= 25 pF Cı

> 40 100

# features

# **CHOICE OF PACKAGES**

- available in flat (T) and dual-in-line package (J or N)

- maximum number of circuits per package through use of 14-lead package

# **OPTIMUM CIRCUIT PERFORMANCE**

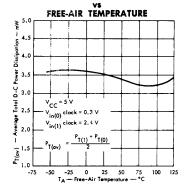

- very low power dissipation—typically 1 mW per gate at 50% duty cycle

- relatively high speed-typically gate propagation delay time of 33 ns

- high d-c noise margin-typically one volt at TA = 25°C

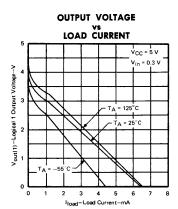

- low output impedance provides low a-c noise susceptibility

- waveform integrity over full range of loading and temperature conditions

- fan-out-10 Series 54L loads

- -1 Series 54 load and 2 Series 54L loads

- -1 Series 54H load

- a standard Series 54 output will drive 40 Series 54L loads

- logic levels are compatible with most bipolar saturated integrated circuits

# SERIES 54L/74L FEATURING 1 mW AND 33 ns PER GATE PERFORMANCE SMALL SCALE INTEGRATION (SSI)

| FUNCTION                                                                                                                                                                                                             | OPERATING TEI                                       |                                          | PA<br>Dua | CKAC        | ES*      |                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------------------|-----------|-------------|----------|--------------------------------------|

|                                                                                                                                                                                                                      | –55°C to 125°C                                      | 0°C to 70°C                              | Lii       | ne          | Flat     | SECPAGE                              |

| AND/NOR GATES                                                                                                                                                                                                        |                                                     |                                          | _         |             |          |                                      |

| Quadruple 2-Input Positive NAND Gates                                                                                                                                                                                | SN54L00                                             | SN74L00                                  | J         | N           | Т        | 8-4                                  |

| Quadruple 2-Input Positive NAND Gates                                                                                                                                                                                |                                                     |                                          |           |             |          | ,                                    |

| (with Open-Collector Output)                                                                                                                                                                                         | SN54L01                                             | SN74L01                                  | J .       | N           | T        | 8-5                                  |

| Quadruple 2-Input Positive NOR Gates                                                                                                                                                                                 | SN54L02                                             | SN74L02                                  | J         | N           | Т        | 8-6                                  |

| Quadruple 2-Input Positive NAND Gates                                                                                                                                                                                |                                                     |                                          |           |             |          |                                      |

| (with Open-Collector Output)                                                                                                                                                                                         | SN54L03                                             | SN74L03                                  | j         | N           | Т        | 8-5                                  |

| Hex Inverters                                                                                                                                                                                                        | SN54L04                                             | SN74L04                                  | J         | N           | T        | 8-9                                  |

| Triple 3-Input Positive NAND Gates                                                                                                                                                                                   | SN54L10                                             | SN74L10                                  | J         | N           | Т        | 8-10                                 |

| Dual 4-Input Positive NAND Gates                                                                                                                                                                                     | SN54L20                                             | SN74L20                                  | J         | N           | T        | 8-11                                 |

| 8-Input Positive NAND Gates                                                                                                                                                                                          | SN54L30                                             | SN74L30                                  | J         | N           | T        | 8-12                                 |

| ND-OR-INVERT GATES                                                                                                                                                                                                   | SN54L51                                             | SN74L51                                  | J         | N           | т        | T                                    |

| Dual 2-Wide AND-OR-INVERT Gates                                                                                                                                                                                      |                                                     |                                          |           |             | ı        | 8-13                                 |

|                                                                                                                                                                                                                      | SN54L54                                             | SN74L54                                  | j         | N           | <u>'</u> | 8-13<br>8-14                         |

| 4-Wide 3-2-2-3-Input AND-OR-INVERT Gates 2-Wide 4-Input AND-OR-INVERT Gates                                                                                                                                          |                                                     | SN74L54<br>SN74L55                       | J         |             |          |                                      |

| 4-Wide 3-2-2-3-Input AND-OR-INVERT Gates                                                                                                                                                                             | SN54L54                                             |                                          | +-        | N           | T        | 8-14                                 |

| 4-Wide 3-2-2-3-Input AND-OR-INVERT Gates                                                                                                                                                                             | SN54L54                                             |                                          | +-        | N           | T        | 8-14                                 |

| 4-Wide 3-2-2-3-Input AND-OR-INVERT Gates                                                                                                                                                                             | SN54L54<br>SN54L55                                  | SN74L55                                  | J         | N<br>N      | T        | 8-14<br>8-15                         |

| 4-Wide 3-2-2-3-Input AND-OR-INVERT Gates 2-Wide 4-Input AND-OR-INVERT Gates  LIP-FLOPS  R-S Master-Slave Flip-Flops                                                                                                  | SN54L54<br>SN54L55<br>SN54L71                       | SN74L55<br>SN54L71                       | J         | N<br>N      | T<br>T   | 8-14<br>8-15<br>8-16                 |

| 4-Wide 3-2-2-3-Input AND-OR-INVERT Gates 2-Wide 4-Input AND-OR-INVERT Gates  LIP-FLOPS  R-S Master-Slave Flip-Flops  J-K Master-Slave Flip-Flops                                                                     | SN54L54<br>SN54L55<br>SN54L71<br>SN54L72            | SN74L55<br>SN54L71<br>SN74L72            | J         | N<br>N      | T<br>T   | 8-14<br>8-15<br>8-16<br>8-19         |

| 4-Wide 3-2-2-3-Input AND-OR-INVERT Gates 2-Wide 4-Input AND-OR-INVERT Gates  LIP-FLOPS  R-S Master-Slave Flip-Flops  J-K Master-Slave Flip-Flops  Dual J-K Master-Slave Flip-Flops                                   | SN54L54<br>SN54L55<br>SN54L71<br>SN54L72<br>SN54L73 | SN74L55<br>SN54L71<br>SN74L72<br>SN74L73 | J         | N<br>N<br>N | T T T T  | 8-14<br>8-15<br>8-16<br>8-19<br>8-22 |

| 4-Wide 3-2-2-3-Input AND-OR-INVERT Gates 2-Wide 4-Input AND-OR-INVERT Gates LIP-FLOPS R-S Master-Slave Flip-Flops J-K Master-Slave Flip-Flops Dual J-K Master-Slave Flip-Flops Dual D-Type Edge-Triggered Flip-Flops | SN54L54<br>SN54L55<br>SN54L71<br>SN54L72<br>SN54L73 | SN74L55<br>SN54L71<br>SN74L72<br>SN74L73 | J         | N<br>N<br>N | T T T T  | 8-14<br>8-15<br>8-16<br>8-19<br>8-22 |

SEE PAGES 9-1, 9-2, AND 9-3 FOR LISTING OF TTL MSI CIRCUITS

-SEE ORDERING INSTRUCTIONS PAGE 1-1-

TEXAS INSTRUMENTS

<sup>\*</sup>For outline drawings of all packages, see Section 1.

SERIES 54L, 74L

LOW-POWER TRANSISTOR-TRANSISTOR LOGIC

| Supply Voltage V <sub>CC</sub> (See Note 1) |            |  |  |  |  |  |  |  |  |  |            |      |      |     | 8 V   |

|---------------------------------------------|------------|--|--|--|--|--|--|--|--|--|------------|------|------|-----|-------|

| Input Voltage, Vin (See Notes 1 and 2)      |            |  |  |  |  |  |  |  |  |  |            |      |      |     | 5.5 V |

| Operating Free-Air Temperature Range:       | Series 54L |  |  |  |  |  |  |  |  |  | <u>۔</u> و | 55°  | C to | o 1 | 25°C  |

|                                             | Series 74L |  |  |  |  |  |  |  |  |  |            | (    | °C   | to  | 70°C  |

| Storage Temperature Range                   |            |  |  |  |  |  |  |  |  |  | _6         | ನಿಕಂ | C +  | ຸ 1 | 50°C  |

- NOTES: 1. Voltage values are with respect to network ground terminal.

- 2. Input signals must be zero or positive with respect to network ground terminal.

### logic definition

Series 54L and 74L logic is defined in terms of standard POSITIVE LOGIC using the following definitions:

HIGH VOLTAGE = LOGICAL 1 LOW VOLTAGE = LOGICAL 0

### unused gates

Inputs of unused gates should be connected to ground. This sets the gate output to logical 1 to ensure minimum power dissipation.

### unused inputs of NAND/AND gates

Unused inputs, including preset and clear, must be maintained at a positive voltage greater than 2.4 V but not to exceed the absolute maximum rating of 5.5 V.

Some possible ways of handling unused inputs are:

- a. Connect unused inputs to an independent supply voltage. Preferably, this voltage should be between 2.4 V and 3.5 V

- b. Connect unused inputs, except preset or clear, to a used input of the same gate if maximum fan-out of the driving output will not be exceeded.

- c. Connect unused inputs to the logical 1 output of an unused gate.

- d. Connect unused inputs to VCC through a 1-k $\Omega$  resistor so that if a transient which exceeds the 5.5-V maximum rating should occur, the impedance vill be high enough to protect the input. One to 25 unused inputs may be connected to each  $1-k\Omega$  resistc .

# input-current requirements

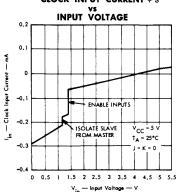

Input-current requirements reflect worst-case VCC and temperature conditions. Each input of the multiple-emitter input transistor requires no more than a 0.18-mA flow out of the input at a logical 0 voltage level; therefore, one load (N=1) is -0.18 mA maximum. Each input, except the clock inputs of the flip-flops, requires current into the terminal at a logical 1 voltage level. This current is 10 µA maximum for each. See fan-out capabilities (below) and typical characteristics (page 8-47) for flip-flop clock input current requirements. Currents into the input terminals are specified as positive values.

# fan-out capability

Fan-out (N) reflects the ability of an output to sink current from a number of Series 54L and 74L loads at a logical 0 voltage level and to supply current at a logical 1 voltage level. Each Serie, 3 to output is capable of sinking current or supplying current to 10 Series 54L loads (N=10), or one Series 54/74 load and two 54L loads. Each Series 74L output is capable of sinking current or supplying current to 20 Series 74L loads (N=20), or two Series 54/74 loads and two 74L loads. Load currents (out of the output terminal) are specified as negative values.

A Series 54 or 74 output is capable of sinking current or supplying current to 40 Series 54L or 74L loads (N=40). The Series 54/74 buffer gate circuit (SN5440/SN7440) is capable of driving 120 Series 54L/74L loads. The carry outputs of the Series 54/74 adders are capable of driving 20 Series 54L/74L loads and the A★ and B★ nodes of the SN5480/SN7480 may be used to drive 12 loads.

When fanning out into Series 54L/74L flip-flop clock inputs, no load current ( $I_{load}$ ) is drawn at  $V_{in(clock)} = 2.4 \text{ V}$ . Therefore, the fan-out limitation is the I<sub>sink</sub> capability of the driving output. A Series 54/74 output will sink sufficient current to drive 44 clock inputs (88 loads), and the SN5440/SN7440 circuit will sink sufficient current to drive 133 clock inputs (266 loads). The Series 54L output is capable of driving five 54L clock inputs and one additional load. The Series 74L output is capable of driving ten 74L clock inputs.

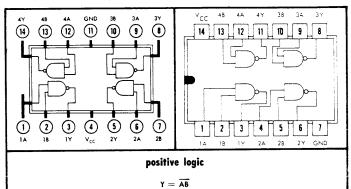

# CIRCUIT TYPES SN54L00, SN74L00 **QUADRUPLE 2-INPUT POSITIVE NAND GATES**

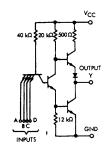

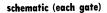

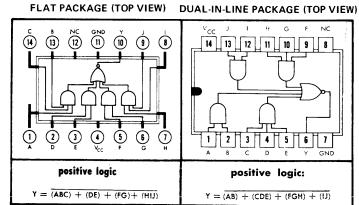

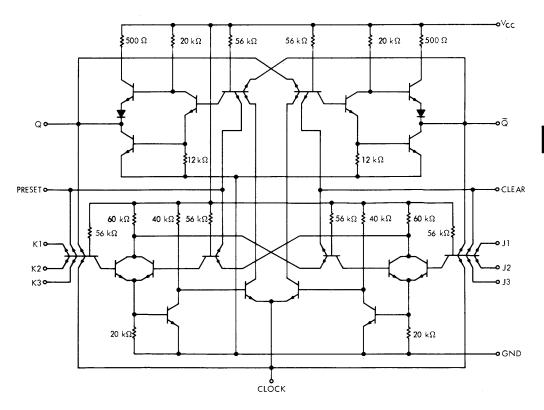

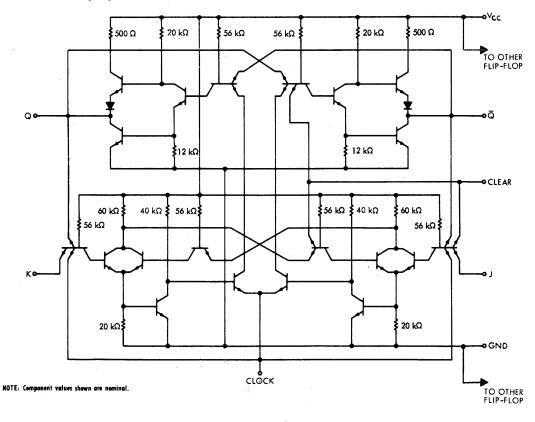

# schematic (each gate)

NOTE: Component values shown

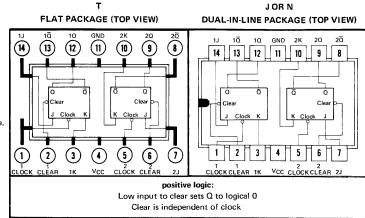

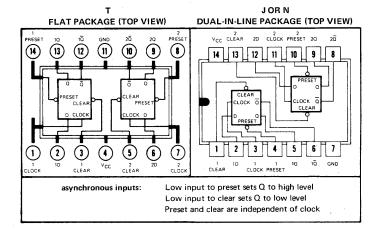

# JOR N FLAT PACKAGE (TOP VIEW) DUAL-IN-LINE PACKAGE (TOP VIEW)

recommended operating conditions

MIN NOM MAX UNIT 5.5 Supply Voltage Vcc: SN54L00 Circuits . . . . . . . . . . . . . 4.75 5 5.25 SN74L00 Circuits . . . . . . . . . . . . . . . . . Normalized Fan-Out From Each Output, N  $\cdots$   $\cdots$   $\cdots$   $\cdots$   $\cdots$ 25 125 °C Operating Free-Air Temperature Range, TA: SN54L00 Circuits . °c 70 SN74L00 Circuits . . . .

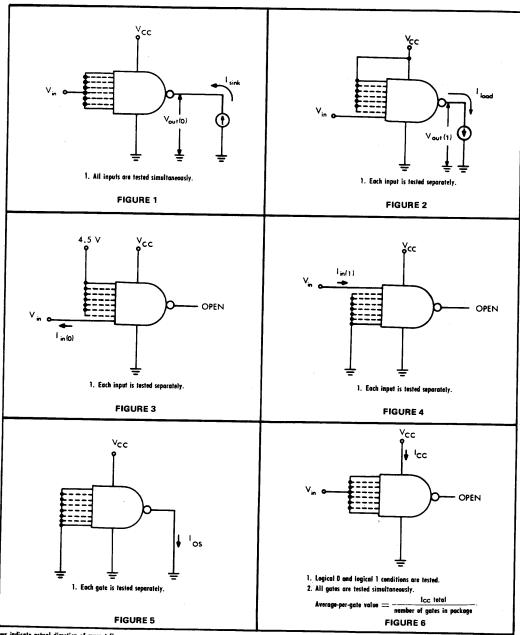

# electrical characteristics (over recommended operating free-air temperature range unless otherwise noted)

8

|                      | PARAMETER                                                                                         | TEST<br>FIGURE | TEST CONDITIONS†                                                                       | MIN | MAX       | UNIT     |

|----------------------|---------------------------------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------|-----|-----------|----------|

| V.n(3)               | Logical 1 input voltage required<br>at all input terminals to ensure<br>logical 0 level at output | 1              |                                                                                        | 2   |           | v        |

|                      | Logical 0 input voltage required<br>at any input terminal to ensure<br>logical 1 level at output  | 2              |                                                                                        |     | 0.7       | v        |

| V <sub>out[1]</sub>  | Logical 1 output voltage                                                                          | 2              | $V_{CC}=MIN$ , $V_{in}=0.7 V$ , $I_{load}=-100 \mu A$                                  | 2.4 |           | ٧        |

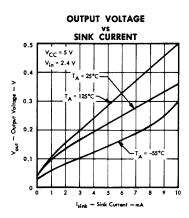

| V <sub>out [0]</sub> | Logical O output voltage                                                                          | 1              | $V_{CC} = MIN$ , $V_{in} = 2 V$ , $I_{sink} = 2 mA$                                    |     | 0.3       | ٧        |

| l <sub>infol</sub>   | Logical O level input current (each input)                                                        | 3              | $V_{cc} = MAX$ , $V_{in} = 0.3 V$                                                      |     | -0.18     | mA       |

| L <sub>in(1)</sub>   | Logical 1 level input current (each input)                                                        | 4              | $V_{CC} = MAX$ , $V_{in} = 2.4 \text{ V}$<br>$V_{CC} = MAX$ , $V_{in} = 5.5 \text{ V}$ |     | 10<br>100 | μA<br>μA |

| los                  | Short-circuit output current                                                                      | 5              | $V_{cc} = MAX$ , $V_{in} = 0$ , $V_{out} = 0$                                          | -3  | -15       | mA       |

| Icc(0)               | Logical O level supply current<br>(average per gate)                                              | 6              | $V_{CC} = MAX$ , $V_{in} = 5 V$                                                        |     | 0.51      | mA       |

| lccn                 | Logical 1 level supply current<br>(average per gate)                                              | 6              | $V_{CC} = MAX$ , $V_{in} = 0$                                                          |     | 0.2       | mA       |

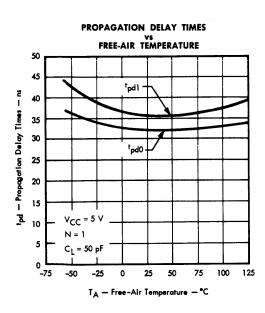

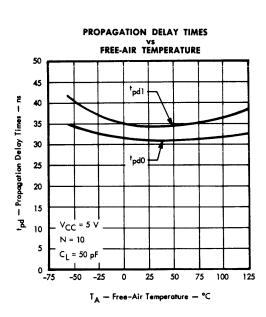

# switching characteristics, $V_{cc} = 5 \text{ V}$ , $T_A = 25 ^{\circ}\text{C}$ , N = 10

|      | PARAMETER                                 | TEST<br>FIGURE | TEST CONDITIONS                                 | MIN | TYP | MAX | UNIT |

|------|-------------------------------------------|----------------|-------------------------------------------------|-----|-----|-----|------|

| tpde | Propagation delay time to logical 0 level | 35             | $C_L = 50 \text{ pF},  R_L = 4 \text{ k}\Omega$ | 1   | 31  | 60  | ns   |

| -    | Propagation delay time to logical 1 level | 35             | $C_L=50$ pF, $R_L=4$ $k\Omega$                  |     | 35  | 60  | ns   |

<sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable circuit type.

# CIRCUIT TYPES SN54L01, SN54L03, SN74L01, SN74L03 QUADRUPLE 2-INPUT POSITIVE-NAND GATES WITH OPEN-COLLECTOR OUTPUTS

# schematic (each gate)

# SN54L01, SN74L01 T FLAT PACKAGE (TOP VIEW) J OR N DUAL-IN-LINE PACKAGE (TOP VIEW) 3Y (8) (11) (12)

SN54L03, SN74L03

# recommended operating conditions

|                                        |     | N54L0 |     | _    | N74L0 |      | UNIT |

|----------------------------------------|-----|-------|-----|------|-------|------|------|

|                                        | MIN | NOM   | MAX | MIN  | NOM   | MAX  |      |

| Supply voltage, V <sub>CC</sub>        | 4.5 | 5     | 5.5 | 4.75 | 5     | 5.25 | V    |

| Normalized fan-out from each output, N |     |       | 10  |      |       | 10   |      |

| Operating free-air temperature, TA     | -55 | 25    | 125 | 0    | 25    | 70   | °C   |

# electrical characteristics over recommended operating free-air temperature range

|      | PARAMETER                              | TEST CONDITIONS†                                | MIN | MAX   | UNIT |

|------|----------------------------------------|-------------------------------------------------|-----|-------|------|

| VIH  | High-level input voltage               |                                                 | 2   |       | V    |

| VIL  | Low-level input voltage                |                                                 |     | 0.6   | ٧    |

| lон  | High-level output current              | V <sub>CC</sub> = MIN, V <sub>IL</sub> = 0.6 V, |     | F0    |      |

| -OH  | rigit-level output current             | V <sub>OH</sub> = 5.5 V                         |     | 50    | μΑ   |

| VOL  | Low-level output voltage               | $V_{CC} = MIN$ , $V_{IH} = 2 V$ ,               |     | 0,3   | v    |

| -02  |                                        | I <sub>OL</sub> = 2 mA                          |     | 0.3   | V    |

| П    | Input current at maximum input voltage | $V_{CC} = MAX$ , $V_I = 5.5 V$                  |     | 100   | μΑ   |

| ЧН   | High-level input current               | V <sub>CC</sub> = MAX, V <sub>I</sub> = 2.4 V   |     | 10    | μΑ   |

| կլ   | Low-level input current                | V <sub>CC</sub> = MAX, V <sub>I</sub> = 0.3 V   |     | -0.18 | mA   |

| loo. | Supply current, high-level output      | V- MAY Allinoide                                | 1   |       |      |

| Іссн | (average per gate)                     | V <sub>CC</sub> = MAX, All inputs ground        | ea  | 0.2   | mA   |

|      | Supply current, low-level output       | V MAY All:                                      |     | 2.54  |      |

| ICCL | (average per gate)                     | V <sub>CC</sub> = MAX, All inputs at 5 V        |     | 0.51  | mA   |

<sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable device

# switching characteristics, $V_{CC} = 5 \text{ V}$ , $T_A = 25^{\circ}\text{C}$ , N = 10

|                  | PARAMETER                    | TEST CONDITIONS         | MIN | MAX | UNIT |

|------------------|------------------------------|-------------------------|-----|-----|------|

| *                | Propagation delay time,      |                         |     |     |      |

| <sup>‡</sup> PLH | low-to-high-level output     | C <sub>L</sub> = 50 pF, | 1   | 90  |      |

| +                | Propagation delay time,      | $R_L = 4 k\Omega$ ,     |     |     | ns   |

| <sup>t</sup> PHL | PHL high-to-low-level output | See Figure 35           | 1   | 60  |      |

# CIRCUIT TYPES SN54L02, SN74L02 QUADRUPLE 2-INPUT POSITIVE-NOR GATES

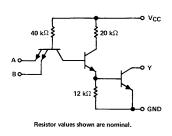

# schematic (each gate) Vcc 40 k!! 20 k!! 20 k!! O Y

# recommended operating conditions

Resistor values shown are nominal

| A STATE OF THE STA | S   | N54L | )2  | SN74L02 |     |      | UNIT |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|---------|-----|------|------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MIN | NOM  | MAX | MIN     | NOM | MAX  | ONT  |

| Supply voltage, VCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4.5 | 5    | 5.5 | 4.75    | 5   | 5.25 | V    |

| Normalized fan-out from each output, N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |      | 10  |         |     | 10   |      |

| Operating free-air temperature, TA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -55 | 25   | 125 | 0       | 25  | 70   | °C   |

# electrical characteristics over recommended operating free-air temperature range

|                  | PARAMETER                                            | TEST CONDITIONS <sup>†</sup>                                        | MIN | MAX   | UNIT |

|------------------|------------------------------------------------------|---------------------------------------------------------------------|-----|-------|------|

| VIH              | High-level input voltage                             |                                                                     | 2   |       | V    |

| VIL              | Low-level input voltage                              |                                                                     |     | 0.7   | V    |

| V <sub>OH</sub>  | High-level output current                            | $V_{CC} = MIN, V_{IL} = 0.7 \text{ V},$ $I_{OH} = -100 \mu\text{A}$ | 2.4 |       | V    |

| VOL              | Low-level output voltage                             | $V_{CC} = MIN$ , $V_{IH} = 2 V$ , $I_{OL} = 2 \text{ mA}$           |     | 0.3   | v    |

| 11               | Input current at maximum input voltage               | $V_{CC} = MAX$ , $V_1 = 5.5 V$                                      |     | 100   | μΑ   |

| ЧН               | High-level input current                             | V <sub>CC</sub> = MAX, V <sub>I</sub> = 2.4 V                       |     | 10    | μΑ   |

| 1 <sub>1</sub> L | Low-level input current                              | V <sub>CC</sub> = MAX, V <sub>1</sub> = 0.3 V                       |     | -0.18 | mA   |

| los              | Short-circuit output current                         | V <sub>CC</sub> = MAX                                               | -3  | -15   | mA   |

| Іссн             | Supply current, high-level output (average per gate) | V <sub>CC</sub> = MAX, See Note 3                                   |     | 0.4   | mA   |

| ICCL             | Supply current, low-level output (average per gate)  | V <sub>CC</sub> = MAX, See Note 4                                   |     | 0.65  | mA   |

NOTES: 3.  $I_{\mbox{\scriptsize CCH}}$  is measured with all inputs grounded and outputs open.

4. ICCL is measured with one input of each gate at 5 V, the remaining inputs grounded, and outputs open.

†For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable device type.

# switching characteristics, $V_{CC}$ = 5 V, $T_A$ = 25°C, N = 10

|                  | PARAMETER                    | TEST CONDITIONS         | MIN | TYP | MAX | UNIT |

|------------------|------------------------------|-------------------------|-----|-----|-----|------|

| *                | Propagation delay time,      | C <sub>1</sub> = 50 pF, |     | 31  | 60  |      |

| <sup>t</sup> PLH | low-to-high-level output     | $R_1 = 4 k\Omega$ ,     |     |     |     | ns   |

|                  | Propagation delay time,      | See Figure 35           |     | 35  | 60  |      |

| <sup>t</sup> PHL | PHL high-to-low-level output | See Figure 35           |     |     | 00  |      |

# **APPLICATION DATA**

# combined fan-out and wire-AND capabilities

The open-collector TTL gate, when supplied with a proper load resistor (R<sub>L</sub>), may be paralleled with other similar TTL gates to perform the wire-AND function, and simultaneously, will drive from one to nine Series 54L/74L loads. When no other open-collector gates are paralleled, this gate may be used to drive ten Series 54L/74L loads. For any of these conditions an appropriate load resistor value must be determined for the desired circuit configuration. A maximum resistor value must be determined which will ensure that sufficient load current (to TTL loads) and off current (through paralleled outputs) will be available while the output is high. A minimum resistor value must be determined which will ensure that current through this resistor and sink current from the TTL loads will not cause the output voltage to rise above the low level even if one of the paralleled outputs is sinking all the currents.

In both conditions (low and high level) the value of RL is determined by:

$$R_L = \frac{V_{RL}}{I_{RL}}$$

where VRL is the voltage drop in volts, and IRL is the current in amperes.

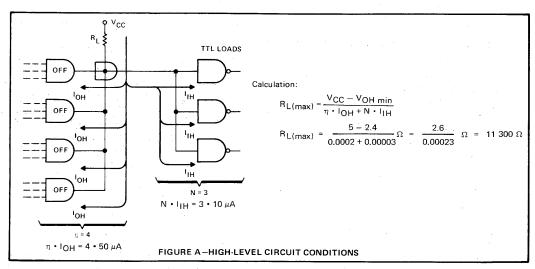

# high-level (off-state) circuit calculations (see figure A)

The allowable voltage drop across the load resistor ( $V_{RL}$ ) is the difference between  $V_{CC}$  applied and the  $V_{OH}$  level required at the load:

$$V_{RL} = V_{CC} - V_{OH min}$$

The total current through the load resistor (IRL) is the sum of the load currents (IIH) and off-state reverse currents (IOH) through each of the wire-AND-connected outputs:

$$I_{RL} = \eta \cdot I_{OH} + N \cdot I_{IH}$$

to TTL loads

Therefore, calculations for the maximum value of  $\mbox{RL}$  would be:

$$R_{L(max)} = \frac{V_{CC} - V_{OH min}}{\eta \cdot I_{OH} + N \cdot I_{JH}}$$

where  $\eta$  = number of gates wire-AND-connected, and N = number of Series 54L/74L loads.

Q

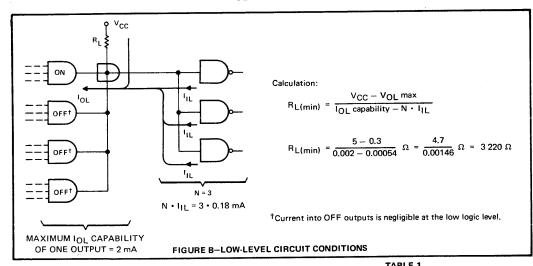

The current through the resistor must be limited to the maximum sink current of one output transistor. Note that if several output transistors are wire-AND connected, the current through RL may be shared by those paralleled transistors. However, unless it can be absolutely guaranteed that more than one transistor will be on during low-level periods, the current must be limited to 2 mA, the maximum current which will ensure a low-level maximum of 0.3 volt.

Also, fan-out must be considered. Part of the 2 mA will be supplied from the inputs which are being driven. This reduces the amount of current which can be allowed through RL.

Therefore, the equation used to determine the minimum value of RL would be:

$$R_{L(min)} = \frac{V_{CC} - V_{OL} max}{I_{OL} capability - N \cdot I_{IL}}$$

# driving series 54L/74L loads and combining outputs

Table 1 provides minimum and maximum resistor values, calculated from equations shown above, for driving one to ten Series 54L/74L loads and wire-AND connecting two to ten parallel outputs. Each value shown for one wire-AND output is determined by the fan-out plus the cutoff current of a single output transistor. Extension beyond ten wire-AND connections is permitted with fan-outs of five or less if a valid minimum and maximum R<sub>L</sub> is possible. When fanning-out to ten Series 54L/74L loads, the calculation for the minimum value of RL indicates that a value greater than the maximum value of RL should be used; however, the use of a resistor having a value between 15.6  $k\Omega$  and 17.3  $k\Omega$  in this case will satisfy the high level condition and limit the low level to less than 0.31 volt.

| 3<br>16.2<br>15.3<br>14.5<br>13.7 | 11.8<br>11.3<br>10.8 | 9.63<br>9.29<br>8.96 | 8.13<br>7.88<br>7.65                  | 7.03<br>6.85                          | 6.20<br>6.05                          | 5.53<br>5.42                          | 5.00<br>4.90                          |                                       |

|-----------------------------------|----------------------|----------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|

| 15.3<br>14.5<br>13.7              | 11.8<br>11.3<br>10.8 | 9.63<br>9.29<br>8.96 | 8.13<br>7.88<br>7.65                  | 7.03<br>6.85                          | 6.20<br>6.05                          | 5.53<br>5.42                          | 5.00<br>4.90                          | 2.87<br>3.22                          |

| 14.5<br>13.7                      | 11.3<br>10.8         | 9,29<br>8.96         | 7.88<br>7.65                          | 6.85                                  | 6.05                                  | 5.42                                  | 4,90                                  | 3.22                                  |

| 13.7                              | 10.8                 | 8.96                 | 7.65                                  |                                       |                                       |                                       |                                       |                                       |

|                                   | <u> </u>             |                      |                                       | 6.67                                  | 5.91                                  | 5.31                                  | 4.82                                  | 267                                   |

| 13.0                              | 40.4                 | Section 1            | 2000000000000                         |                                       |                                       |                                       | 5 Sec. 200                            | 3.07                                  |

| EXP. (425.4)                      | 10.4                 | 8.56                 | 7.44                                  | 6.50                                  | 5.78                                  | 5.20                                  | 4.73                                  | 4.29                                  |

| 12.4                              | 10.0                 | 8.38                 | 7.22                                  | 6.34                                  | 5.65                                  | ×                                     | X                                     | 5.20                                  |

| 11.8                              | 9.63                 | 8.13                 | 7,03                                  | Х                                     | Х                                     | ×                                     | Х                                     | 6.35                                  |

| 11.3                              | 9.29                 | Х                    | ×                                     | ×                                     | Х                                     | Х                                     | Х                                     | 8.40                                  |

| X                                 | Х                    | Х                    | Х                                     | Х                                     | Х                                     | Х                                     | Х                                     | 12:4                                  |

| Х                                 | Х                    | Х                    | Х                                     | Х                                     | Х                                     | ×                                     | ' X                                   | 15.6§                                 |

|                                   |                      | MAXI                 | MUM                                   | 4.5                                   | 111                                   |                                       | jar.                                  | MIN                                   |

|                                   | ×<br>×               | X X<br>X X           | X X X X X X X X X X X X X X X X X X X | X X X X X X X X X X X X X X X X X X X | X X X X X X X X X X X X X X X X X X X | X X X X X X X X X X X X X X X X X X X | X X X X X X X X X X X X X X X X X X X | X X X X X X X X X X X X X X X X X X X |

All values in the table are based on:

High-level condition:  $V_{CC} = 5 \text{ V}, V_{OH \text{ min}} = 2.4 \text{ V}$ Low-level condition:  $V_{CC} = 5 \text{ V}, V_{OL \text{ max}} = 0.3 \text{ V}$

X-Not recommended or not possible

$\S$  The theoretical value is 23.5 k  $\Omega.$  See explanation in text.

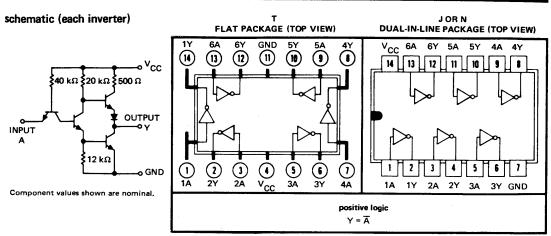

# CIRCUIT TYPES SN54L04, SN74L04 HEX INVERTERS

recommended operating conditions

MIN NOM MAX UNIT 4.5 ٧ 5 5.5 v 4.75 5.25 10 -55 25 125 °C

25

0

70

Normalized Fan-Out From Each Output, N  $\,$  Operating Free-Air Temperature Range,  $T_A$ :

SN54L04 Circuits . . . . SN74L04 Circuits . . . .

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                                                                              | TEST<br>FIGURE | TEST CONDITIONS†                                                                                 | MIN | MAX       | UNIT |

|---------------------|----------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------|-----|-----------|------|

| V <sub>in(1)</sub>  | Logical 1 input voltage required at input terminal to ensure logical 0 level at output | 7              |                                                                                                  | 2   |           | ٧    |

| V <sub>in(0)</sub>  | Logical 0 input voltage required at input terminal to ensure logical 1 level at output | 8              |                                                                                                  |     | 0.7       | ٧    |

| V <sub>out(1)</sub> | Logical 1 output voltage                                                               | 8              | $V_{CC}$ = MIN, $V_{in}$ = 0.7 V, $I_{load}$ = $-100 \mu A$                                      | 2.4 |           | ٧    |

| V <sub>out(0)</sub> | Logical 0 output voltage                                                               | 7              | V <sub>CC</sub> = MIN, V <sub>in</sub> = 2 V,<br>I <sub>sink</sub> = 2 mA                        |     | 0.3       | ٧    |

| <sup>1</sup> in(0)  | Logical 0 level input current                                                          | 9              | V <sub>CC</sub> = MAX, V <sub>in</sub> = 0.3 V                                                   |     | -0.18     | mΑ   |

| l <sub>in(1)</sub>  | Logical 1 level input current                                                          | 10             | V <sub>CC</sub> = MAX, V <sub>in</sub> = 2.4 V<br>V <sub>CC</sub> = MAX, V <sub>in</sub> = 5.5 V |     | 10<br>100 | μΑ   |

| los                 | Short-circuit output current                                                           | 11             | V <sub>CC</sub> = MAX, V <sub>in</sub> = 0<br>V <sub>out</sub> = 0                               | -3  | -15       | mA   |

| <sup>1</sup> CC(0)  | Logical 0 level supply current (Average per inverter)                                  | 12             | V <sub>CC</sub> = MAX, V <sub>in</sub> = 5 V                                                     |     | 0.51      | mA   |

| Icc(1)              | Logical 1 level supply current (Average per inverter)                                  | . 12           | V <sub>CC</sub> = MAX, V <sub>in</sub> = 0                                                       |     | 0.2       | mA   |

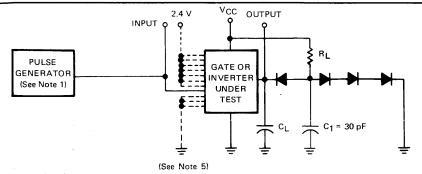

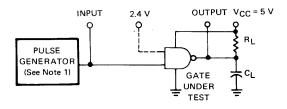

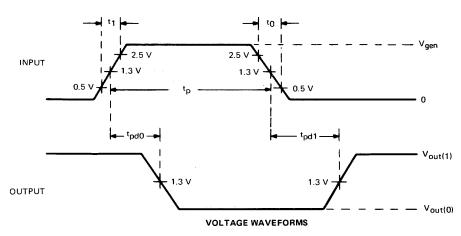

# switching characteristics, $V_{CC} = 5 \text{ V}$ , $T_{\Delta} = 25^{\circ} \text{C}$ , N = 10

|                  | PARAMETER                                 | TEST<br>FIGURE | TEST CO                 | NDITIONS <sup>†</sup> | MIN | TYP | MAX | UNIT |

|------------------|-------------------------------------------|----------------|-------------------------|-----------------------|-----|-----|-----|------|

| t <sub>pd0</sub> | Propagation delay time to logical 0 level | 35             | C <sub>L</sub> = 50 pF, | R <sub>L</sub> = 4 kΩ |     | 31  | 60  | ns   |

| tpd1             | Propagation delay time to logical 1 level | 35             | C <sub>L</sub> = 50 pF, | R <sub>L</sub> = 4 kΩ |     | 35  | 60  | ns   |

<sup>†</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable device type.

0

°C

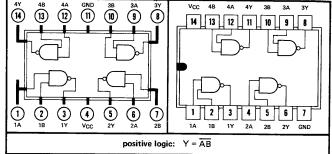

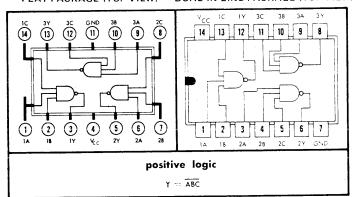

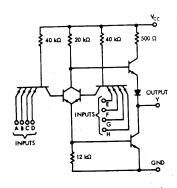

# CIRCUIT TYPES SN54L10, SN74L10 TRIPLE 3-INPUT POSITIVE NAND GATES

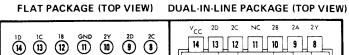

# schematic (each gate)

V<sub>C</sub>c

40 kΩ 20 kΩ 500 Ω

OUTPUT

A B C

INPUTS 12 kΩ

GND

NOTE: Component values shown are nominal.

# T JOR N FLAT PACKAGE (TOP VIEW) DUAL-IN-LINE PACKAGE (TOP VIEW)

# recommended operating conditions

|                                                            | MIN  | NOM | MAX  | UNIT |

|------------------------------------------------------------|------|-----|------|------|

| Supply Voltage Vcc: SN54L10 Circuits                       | 4.5  | 5   | 5.5  | V    |

| SN74L10 Circuits                                           | 4.75 | 5   | 5.25 | ٧    |

| Normalized Fan-Out From Each Output, N                     |      |     | 10   |      |

| Operating Free-Air Temperature Range, Ta: SN54L10 Circuits | -55  | 25  | 125  | °C   |

| SN74L10 Circuits                                           | 0    | 25  | 70   | °C   |

# electrical characteristics (over recommended operating free-air temperature range unless otherwise noted)

| PARAMETER                                                                                                      | TEST<br>FIGURE | TEST CONDITIONS†                                                                       | MIN | MAX       | UNIT       |

|----------------------------------------------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------|-----|-----------|------------|

| Logical 1 input voltage required V <sub>.n[1]</sub> at all input terminals to ensure logical 0 level at output | ī              |                                                                                        | 2   |           | V.         |

| Logical 0 input voltage required V <sub>in[0]</sub> at any input terminal to ensure logical 1 level at output  | 2              |                                                                                        |     | 0.7       | ٧          |

| V <sub>out[1]</sub> Logical 1 output voltage                                                                   | 2              | $V_{CC}=MIN$ , $V_{in}=0.7 V$ , $I_{load}=-100 \mu A$                                  | 2.4 |           | ٧          |

| V <sub>out(0)</sub> Logical 0 output voltage                                                                   | 1              | $V_{CC} = MIN$ , $V_{in} = 2 V$ , $I_{sink} = 2 mA$                                    |     | 0.3       | v          |

| lin(0) Logical O level input current (each input)                                                              | 3              | $V_{CC} = MAX$ , $V_{in} = 0.3 V$                                                      |     | -0.18     | mA         |

| l <sub>in(1)</sub> Logical 1 level input current (each input)                                                  | 4              | $V_{CC} = MAX$ , $V_{in} = 2.4 \text{ V}$<br>$V_{CC} = MAX$ , $V_{in} = 5.5 \text{ V}$ |     | 10<br>100 | μ <b>Α</b> |

| los Short-circuit output current                                                                               | 5              | $V_{CC} = MAX, \qquad V_{in} = 0, V_{out} = 0$                                         | -3  | -15       | mA         |

| Logical 0 level supply current<br>(average per gate)                                                           | 6              | $V_{cc} = MAX$ , $V_{in} = 5 V$                                                        |     | 0.51      | mA         |

| Logical 1 level supply current lcc(1) (average per gate)                                                       | 6              | $V_{CC} = MAX$ , $V_{in} = 0$                                                          |     | 0.2       | mA         |

# switching characteristics, $V_{cc} = 5 \text{ V}$ , $T_A = 25 ^{\circ}\text{C}$ , N = 10

| PARAMETER                                                  | TEST<br>FIGURE | TEST CONDITIONS                                 | MIN TY | P MAX | UNIT |  |

|------------------------------------------------------------|----------------|-------------------------------------------------|--------|-------|------|--|

| t <sub>pd0</sub> Propagation delay time to logical 0 level | 35             | $C_L = 50 \text{ pF},  R_L = 4 \text{ k}\Omega$ | 31     | 60    | ns   |  |

| t <sub>pd1</sub> Propagation delay time to logical 1 level | 35             | $C_L = 50 \text{ pF}, R_L = 4 \text{ k}\Omega$  | 35     | 60    | ns   |  |

†For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable circuit type.

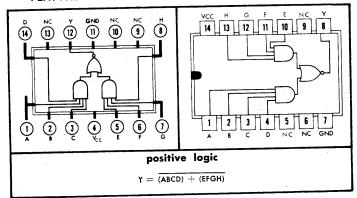

# CIRCUIT TYPES SN54L20, SN74L20 **DUAL 4-INPUT POSITIVE NAND GATES**

J OR N

# schematic (each gate)

NOTES: 1. Component values shown are nominal.

2. NC - No internal connection.

$Y = \overline{ABCD}$

# recommended operating conditions

|                                                            | MIN  | NOM | MAX  | UNIT |

|------------------------------------------------------------|------|-----|------|------|

| Supply Voltage Vcc: SN54L20 Circuits                       | 4.5  | 5   | 5.5  | V    |

| SN74L20 Circuits                                           | 4.75 | 5   | 5.25 | V    |

| Normalized Fan-Out From Each Output, N                     |      |     | 10   |      |

| Operating Free-Air Temperature Range, Tx: SN54L20 Circuits | -55  | 25  | 125  | °C   |

| SN74L20 Circuits                                           | 0    | 25  | 70   | °C   |

T

# electrical characteristics (over recommended operating free-air temperature range unless otherwise noted)

|                     | PARAMETER                                                                                             | TEST<br>FIGURE | TEST CONDITIONS†                                      | MIN    | MAX  | UNIT |

|---------------------|-------------------------------------------------------------------------------------------------------|----------------|-------------------------------------------------------|--------|------|------|

| V <sub>in{1}</sub>  | Logical 1 input voltage required<br>(1) at all input terminals to ensure<br>logical 0 level at output | 1              |                                                       | 2      |      | ٧    |

| Vin(0)              | Logical 0 input voltage required<br>at any input terminal to ensure<br>logical 1 level at output      | 2              |                                                       |        | 0.7  | ٧    |

| V <sub>out(1)</sub> | Logical 1 output voltage                                                                              | 2              | $V_{CC}=MIN$ , $V_{in}=0.7 V$ , $I_{load}=-100 \mu A$ | 2.4    |      | v    |

| Vout(0)             | Logical O output voltage                                                                              | 1              | $V_{CC} = MIN$ , $V_{in} = 2 V$ , $I_{sink} = 2 mA$   |        | 0.3  | ٧    |

| l <sub>in(0)</sub>  | Logical O level input current (each input)                                                            | 3              | $V_{CC} = MAX$ , $V_{in} = 0.3 V$                     |        | 0.18 | mA   |

| Lan                 | Logical 1 level input current (each input)                                                            | 4              | $V_{CC} = MAX$ , $V_{in} = 2.4 V$                     |        | 10   | μA   |

| **n(1)              | Logical i level input corrent (each input)                                                            | •              | $V_{CC} = MAX$ , $V_{in} = 5.5 V$                     |        | 100  | μA   |

| los                 | Short-circuit output current                                                                          | 5              | $V_{CC} = MAX$ , $V_{in} = 0$ , $V_{out}$             | = 0 -3 | -15  | mA   |

| l <sub>cc(0)</sub>  | Logical 0 level supply current<br>(average per gate)                                                  | 6              | $V_{CC} = MAX$ , $V_{in} = 5 V$                       |        | 0.51 | mA   |

| Icc(1)              | Logical 1 level supply current<br>(average per gate)                                                  | 6              | $V_{\text{cc}} = MAX$ , $V_{\text{in}} = 0$           |        | 0.2  | mA   |

# switching characteristics, $V_{cc} = 5 \text{ V}$ , $T_{A} = 25 ^{\circ}\text{C}$ , N = 10

|                  | PARAMETER                                 | TEST<br>FIGURE | TEST CONDITIONS                                 | MIN | TYP | MAX | UNIT |

|------------------|-------------------------------------------|----------------|-------------------------------------------------|-----|-----|-----|------|

| t <sub>pd0</sub> | Propagation delay time to logical 0 level | 35             | $C_L = 50 \text{ pF},  R_L = 4 \text{ k}\Omega$ |     | 31  | 60  | ns   |

| t <sub>pd1</sub> | Propagation delay time to logical 1 level | 35             | $C_L = 50 \text{ pF},  R_L = 4 \text{ k}\Omega$ |     | 35  | 60  | ns   |

<sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable circuit type.

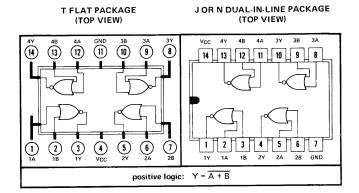

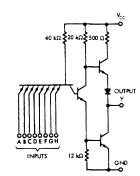

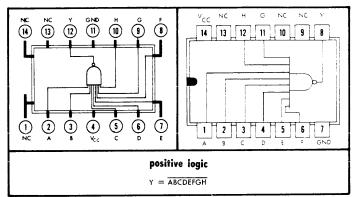

# CIRCUIT TYPES SN54L30, SN74L30 8-INPUT POSITIVE NAND GATES

# schematic

NOTES: 1. Component values shown are nominal.

2. NC — No internal connection

T JOR N

FLAT PACKAGE (TOP VIEW) DUAL-IN-LINE PACKAGE (TOP VIEW)

THE NOM MAY HAIT

# recommended operating conditions

|                                                            | WIN  | NOM | MAA  | 01411      |

|------------------------------------------------------------|------|-----|------|------------|

| Supply Voltage Vcc: SN54L30 Circuits                       | 4.5  | 5   | 5.5  | ٧          |

| SN74L30 Circuits                                           | 4.75 | 5   | 5.25 | ٧          |

| Normalized Fan-Out From Each Output, N                     |      |     | 10   |            |

| Operating Free-Air Temperature Range, TA: SN54L30 Circuits | 55   | 25  | 125  | °c         |

| SN74L30 Circuits                                           |      |     | 70   | <b>°</b> C |

# lectrical characteristics (over recommended operating free-air temperature range unless otherwise noted)

| PARAMETER                                                                                                           | TEST<br>FIGURE | TEST COM                                           | NDITIONS†               |                  | MIN | MAX   | UNIT |

|---------------------------------------------------------------------------------------------------------------------|----------------|----------------------------------------------------|-------------------------|------------------|-----|-------|------|

| Logical 1 input voltage required V <sub>in(1)</sub> at all input terminals to ensure logical 0 level at output      | 1              |                                                    |                         |                  | 2   |       | v    |

| Logical 0 input voltage required<br>V <sub>in(0)</sub> at any input terminal to ensure<br>logical 1 level at output | 2              |                                                    |                         |                  |     | 0.7   | ٧    |

| V <sub>out[1]</sub> Logical 1 output voltage                                                                        | 2              | $V_{CC} = MIN,$ $I_{load} = -100 \mu A$            | V <sub>in</sub> = 0.7 V | ,                | 2.4 |       | ٧    |

| V <sub>out(0)</sub> Logical 0 output voltage                                                                        | 1              | V <sub>CC</sub> = MIN,<br>I <sub>sink</sub> = 2 mA | $V_{in} = 2 V$ ,        |                  |     | 0.3   | ٧    |

| linto Logical O level input current (each input)                                                                    | 3              | Vcc = MAX,                                         | $V_{in} = 0.3 V$        |                  |     | -0.18 | mA   |

|                                                                                                                     |                | Vcc = MAX,                                         | $V_{in} = 2.4 V$        |                  |     | 10    | μA   |

| l <sub>in(1)</sub> Logical 1 level input current (each input)                                                       | 4              | Vcc = MAX,                                         | V <sub>in</sub> = 5.5 V |                  |     | 100   | μA   |

| los Short-circuit output current                                                                                    | 5              | V <sub>CC</sub> = MAX,                             | $V_{in} = 0, V_{ox}$    | <sub>+</sub> = 0 | -3  | -15   | mA   |

| Iccio Logical O level supply current                                                                                | 6              | Vcc = MAX,                                         | $V_{in} = 5 V$          |                  |     | 0.51  | mA   |

|                                                                                                                     | <b>-</b>       |                                                    |                         | SN54L30          |     | 0.33  | ١.   |

| locii) Logical 1 level supply current                                                                               | 6              | Vcc = MAX,                                         | $V_{in} = 0$            | SN74L30          |     | 0.2   | mA   |

# switching characteristics, $V_{\rm CC} = 5$ V, $T_{\rm A} = 25\,{\rm ^{\circ}C}$ , N = 10

| PARAMETER                                                  | TEST | TEST CONDITIONS                                 | MIN | TYP | MAX | UNIT |

|------------------------------------------------------------|------|-------------------------------------------------|-----|-----|-----|------|

| t <sub>pd0</sub> Propagation delay time to logical 0 level |      | $C_L = 50 \text{ pF},  R_L = 4 \text{ k}\Omega$ |     | 70  | 100 | ns   |

| t Propagation delay time to logical 1 level                |      | $C_L = 50 \text{ pF}, R_L = 4 \text{ k}\Omega$  |     | 35  | 60  | ns   |

<sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable circuit type.

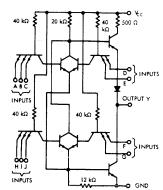

# CIRCUIT TYPES SN54L51, SN74L51 DUAL 2-WIDE AND-OR-INVERT GATES

V<sub>CC</sub>

500 Ω

OUTPUT

OUTPUT

INPUTS

NOTES: 1. Component values shown are nominal.

2. Inputs C and F are available on gate 1 only.

# recommended operating conditions MIN NOM MAX UNIT Supply Voltage Vcc: \$N54L51 Circuits 4.5 5 5.5 V SN74L51 Circuits 4.75 5 5.25 V Normalized Fan-Out From Each Output, N - 5.5 10 V Operating Free-Air Temperature Range, Ta: \$N54L51 Circuits - 5.5 25 125 °C \$N74L51 Circuits 0 25 70 °C

# electrical characteristics (over recommended operating free-air temperature range unless otherwise noted)

|         | PARAMETER                                                                                                   | TEST<br>FIGURE | TEST CO                                            | NDITIONS†                | MIN | мах   | UNIT |

|---------|-------------------------------------------------------------------------------------------------------------|----------------|----------------------------------------------------|--------------------------|-----|-------|------|

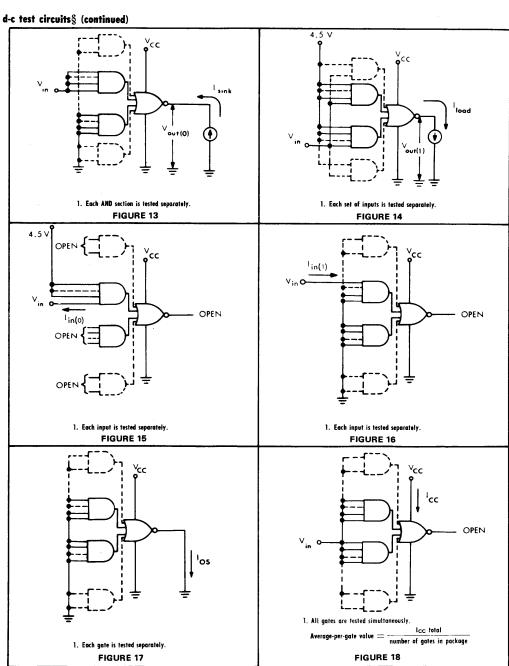

| V:n(1)  | Logical 1 input voltage required at all input terminals of either AND section to ensure logical 0 at output | 13             |                                                    |                          | 2   |       | ٧    |

| V.n(0)  | Logical 0 input voltage required at one input terminal of each AND section to ensure logical 1 at output    | 14             |                                                    |                          |     | 0.7   | v    |

| Vout(1) | Logical 1 output voltage                                                                                    | 14             | $V_{CC} = MIN,$ $I_{load} = -100 \mu A$            | V <sub>in</sub> = 0.7 V, | 2.4 |       | ٧    |

| Vout(0) | Logical 0 output voltage                                                                                    | 13             | V <sub>CC</sub> = MIN,<br>I <sub>sink</sub> = 2 mA | $V_{in} = 2 V$ ,         |     | 0.3   | ٧    |

| I.n(0)  | Logical O level input current (each input)                                                                  | 15             | Vcc = MAX,                                         | $V_{in} = 0.3 \text{ V}$ |     | -0.18 | mA   |

|         |                                                                                                             | 16             | Vcc = MAX,                                         | V <sub>in</sub> = 2.4 V  |     | 10    | μΑ   |

| Lin(1)  | Logical 1 level input current (each input)                                                                  | 10             | Vcc = MAX,                                         | $V_{in} = 5.5  V$        |     | 100   | μА   |

| los     | Short-circuit output current                                                                                | 17             | Vcc = MAX,                                         | $V_{in}=0$ , $V_{out}=0$ | -3  | -15   | mA   |

| Iccioi  | Logical O level supply current<br>(average per gate)                                                        | 18             | Vcc = MAX,                                         | V <sub>in</sub> = 5 V    |     | 0.65  | mA   |

| Icciil  | Logical 1 level supply current<br>(average per gate)                                                        | 18             | Vcc = MAX,                                         | $V_{in}=0$               |     | 0.4   | mA   |

# switching characteristics, $V_{\text{CC}} = 5 \text{ V}$ , $T_{\text{A}} = 25 ^{\circ}\text{C}$ , N = 10

| PARAMETER                                                  | TEST<br>FIGURE | TEST CONDITIONS                                 | MIN | TYP | MAX | UNIT |

|------------------------------------------------------------|----------------|-------------------------------------------------|-----|-----|-----|------|

| †pd0 Propagation delay time to logical O level             | 35             | $C_L = 50 \text{ pF, } R_L = 4 \text{ k}\Omega$ |     | 35  | 60  | ns   |

| † <sub>pd1</sub> Propagation delay time to logical 1 level | 35             | $C_L = 50$ pF, $R_L = 4$ k $\Omega$             |     | 50  | 90  | ns   |

†For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable circuit type.

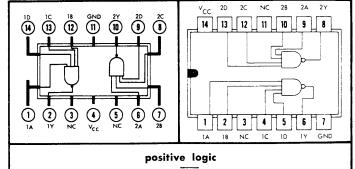

# CIRCUIT TYPES SN54L54, SN74L54 4-WIDE 3-2-2-3-INPUT AND-OR-INVERT GATES

# schematic

NOTE: 1. Component values shown are nominal.

2. NC - No internal connection

# J OR N

MIN

4.5

4.75

NOM MAX UNIT

5.5 V

# recommended operating conditions

| - •                                                        |  |  |  |  |  |  |     |

|------------------------------------------------------------|--|--|--|--|--|--|-----|

| Supply Voltage Vcc: SN54L54 Circuits                       |  |  |  |  |  |  |     |

| SN74L54 Circuits                                           |  |  |  |  |  |  |     |

| Normalized Fan-Out From Each Output, N                     |  |  |  |  |  |  |     |

| Operating Free-Air Temperature Range, TA: SN54L54 Circuits |  |  |  |  |  |  | . 1 |

| SN74L54 Circuits                                           |  |  |  |  |  |  | į   |

# electrical characteristics (over recommended operating free-air temperature range unless otherwise noted)

|                     | PARAMETER                                                                                                      | TEST<br>FIGURE | TEST CONDITIONS†                                            | MIN | MAX   | UNIT |

|---------------------|----------------------------------------------------------------------------------------------------------------|----------------|-------------------------------------------------------------|-----|-------|------|

| V:n(1)              | Logical 1 input voltage required at all input terminals of one AND section to ensure logical 0 at output       | 13             |                                                             | 2   |       | ٧    |

| V:n(0)              | Logical 0 input voltage required at<br>one input terminal of each AND<br>section to ensure logical 1 at output | 14             |                                                             |     | 0.7   | v    |

| V <sub>ouf{1</sub>  | Logical 1 output voltage                                                                                       | 14             | $V_{CC} = MIN$ , $V_{in} = 0.7 V$ , $I_{load} = -100 \mu A$ | 2.4 |       | ٧    |

| V <sub>out(0)</sub> | Logical 0 output voltage                                                                                       | 13             |                                                             |     | 0.3   | ٧    |

| 1,,,(0)             | Logical O level input current (each input)                                                                     | 15             | $V_{CC} = MAX$ , $V_{in} = 0.3 V$                           |     | -0.18 | mA   |

| tions               | Logical 1 level input current (each input)                                                                     | 16             | $V_{CC} = MAX, \qquad V_{in} = 2.4 \text{ V}$               |     | 10    | μА   |

| (.)                 | g (each input)                                                                                                 |                | $V_{CC} = MAX$ , $V_{in} = 5.5 V$                           |     | 100   | μА   |

| los                 | Short-circuit output current                                                                                   | 17             | $V_{CC} = MAX$ , $V_{in} = 0$ , $V_{out} = 0$               | -3  | -15   | mA   |

| I <sub>CC(0)</sub>  | Logical 0 level supply current                                                                                 | 18             | $V_{CC} = MAX$ , $V_{in} = 5 V$                             |     | 0.99  | mA   |

| Icc(1)              | Logical 1 level supply current                                                                                 | 18             | $V_{cc} = MAX$ , $V_{in} = 0$                               |     | 0.8   | mA   |

# switching characteristics, $V_{\text{CC}} = 5$ V, $T_{\text{A}} = 25$ °C, N = 10

|                  | PARAMETER                                 | TEST<br>FIGURE | TEST CONDITIONS                                 | MIN | TYP | MAX | UNIT |

|------------------|-------------------------------------------|----------------|-------------------------------------------------|-----|-----|-----|------|

| t <sub>pd0</sub> | Propagation delay time to logical 0 level | 35             | $C_L = 50 \text{ pF, } R_L = 4 \text{ k}\Omega$ |     | 35  | 60  | ns   |

| tpd1             | Propagation delay time to logical 1 level | 35             | $C_L = 50 \text{ pF}, R_L = 4 \text{ k}\Omega$  |     | 50  | 90  | ns   |

<sup>†</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable circuit type.

# CIRCUIT TYPES SN54L55, SN74L55 2-WIDE 4-INPUT AND-OR-INVERT GATES

### schematic

J OR N T FLAT PACKAGE (TOP VIEW) DUAL-IN-LINE PACKAGE (TOP VIEW)

NOTE: 1. Component values shown are nominal.

2. NC — No internal connection

# recommended operating conditions

Supply Voltage Vcc: SN54L55 Circuits . SN74L55 Circuits . Normalized Fan-Out From Each Output, N . . Operating Free-Air Temperature Range, TA: SN54L55 Circuits . SN74L55 Circuits .

| MIN  | NOM | MAX  | UNIT |

|------|-----|------|------|

| 4.5  | 5   | 5.5  | ٧    |

| 4.75 | 5   | 5.25 | V    |

|      |     | 10   |      |

| -55  | 25  | 125  | °C   |

| 0    | 25  | 70   | °C   |

# electrical characteristics (over recommended operating free-air temperature range unless otherwise noted)

|                     | PARAMETER                                                                                                         | TEST<br>FIGURE | TEST CO                                            | NDITIONS†                | MIN | MAX   | UNIT  |

|---------------------|-------------------------------------------------------------------------------------------------------------------|----------------|----------------------------------------------------|--------------------------|-----|-------|-------|

| Viarri              | Logical 1 input voltage required at<br>all input terminals of either AND<br>section to ensure logical 0 at output | 13             |                                                    |                          | 2   |       | ٧     |

| Vin(0)              | Logical 0 input voltage required at<br>one input terminal of each AND<br>section to ensure logical 1 at output    | 14             |                                                    | ı                        |     | 0.7   | ٧     |

| V <sub>out(1)</sub> | Logical 1 output voltage                                                                                          | 14             | $V_{CC} = MIN,$ $I_{load} = -100 \mu A$            | V <sub>in</sub> = 0.7 V, | 2.4 |       | \ \ \ |

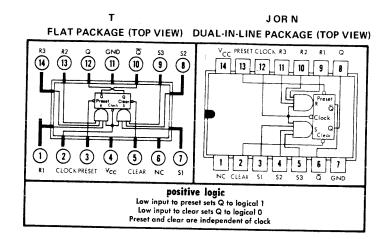

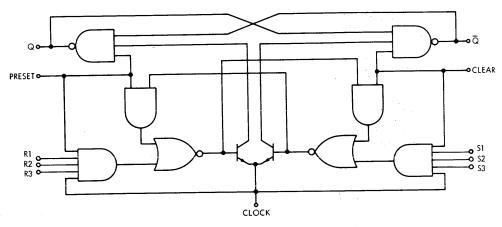

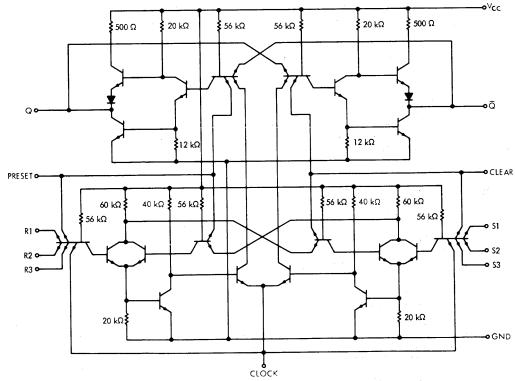

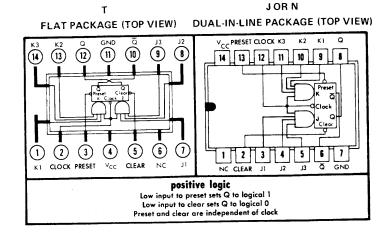

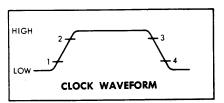

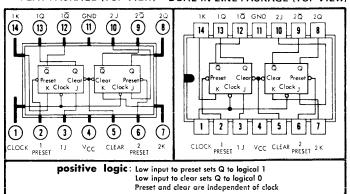

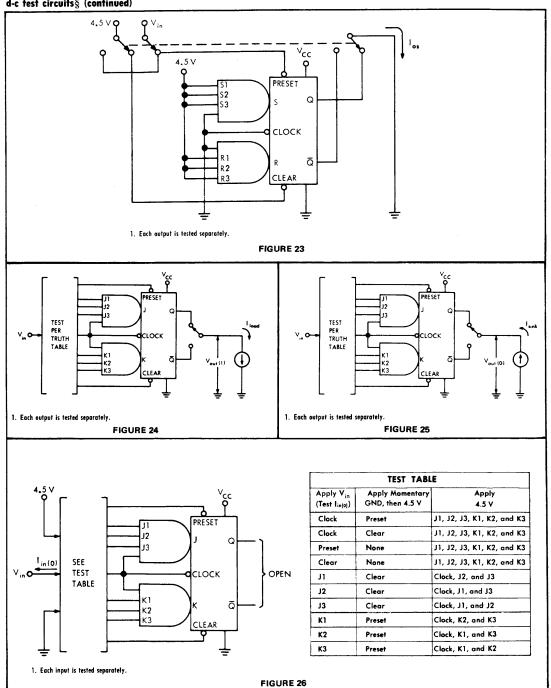

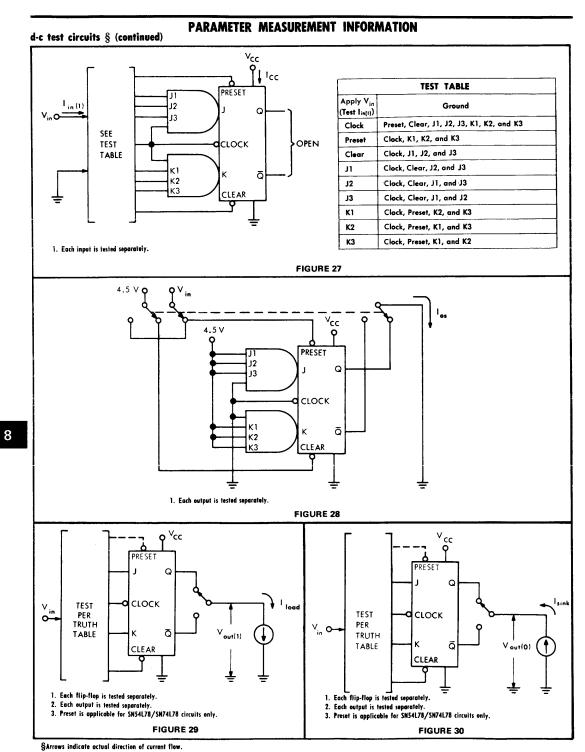

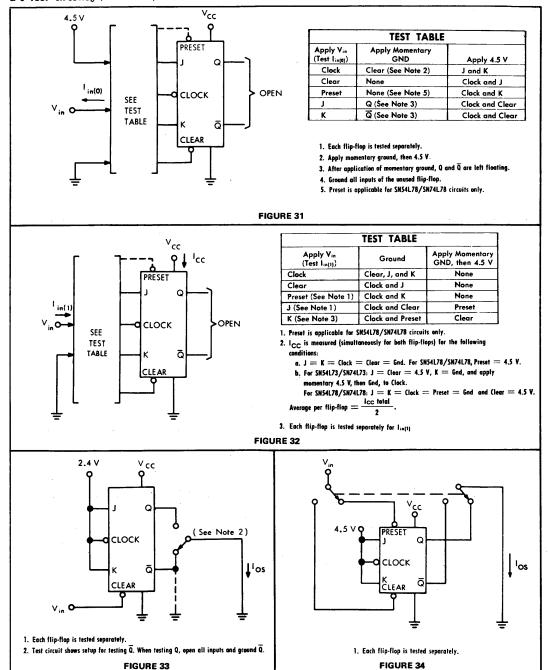

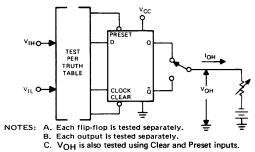

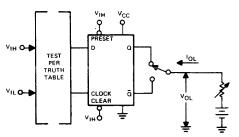

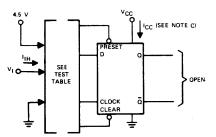

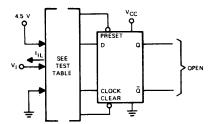

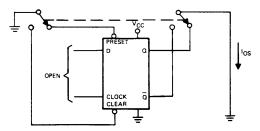

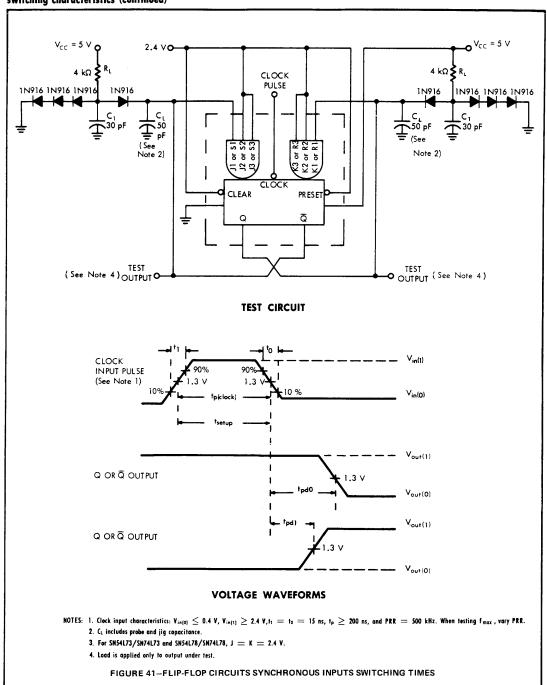

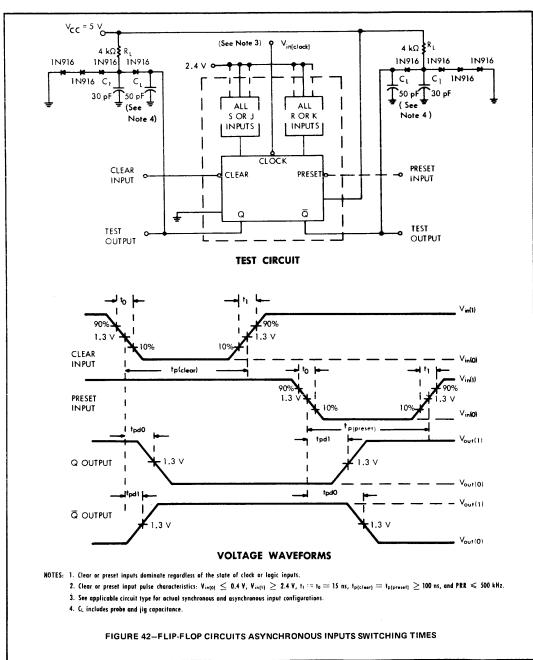

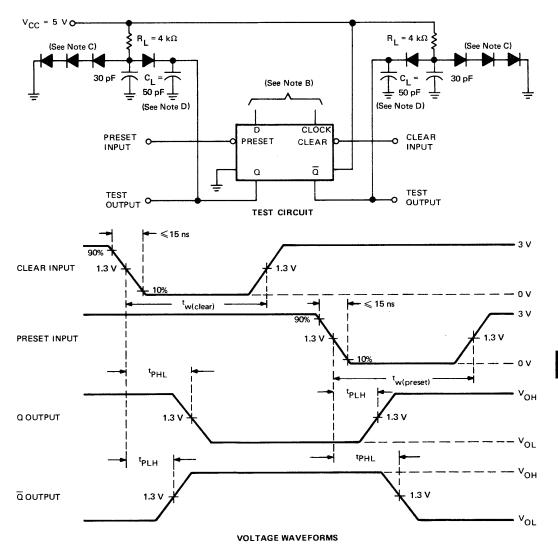

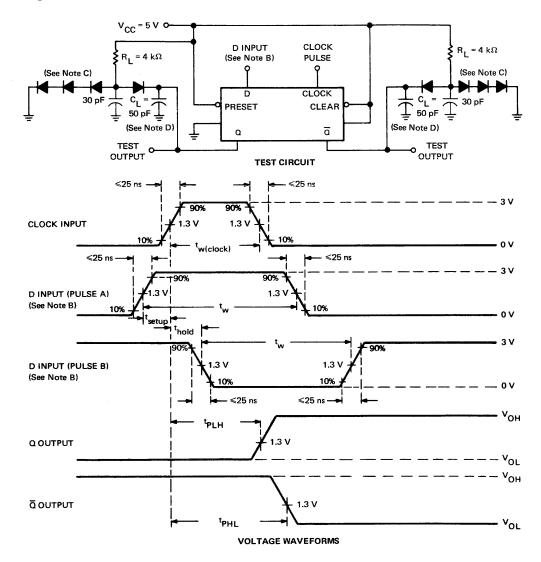

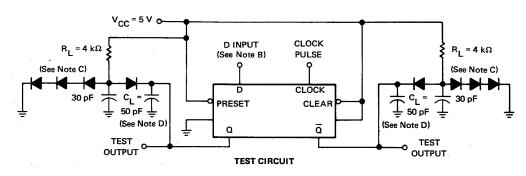

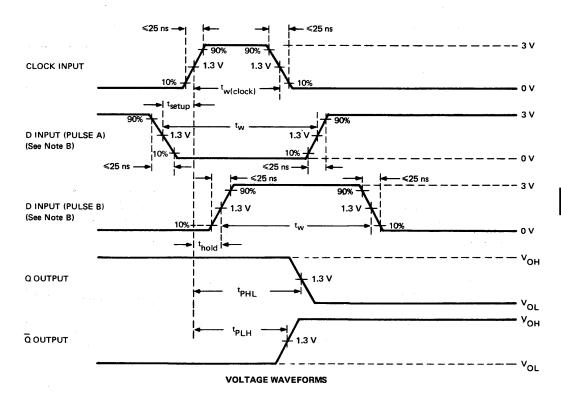

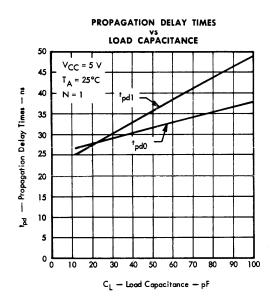

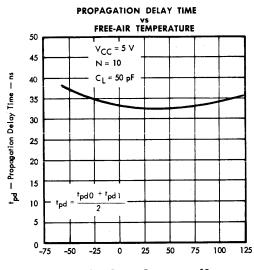

| V <sub>out[0]</sub> | Logical 0 output voltage                                                                                          | 13             | V <sub>CC</sub> = MIN,<br>I <sub>sink</sub> = 2 mA | $V_{in} = 2 V$ ,         |     | 0.3   | ٧     |