## United States Patent [19]

Robertson et al.

## [54] GRAPHICS PROCESSOR WRITING TO SHADOW REGISTER AT PREDETERMINED ADDRESS SIMULTANEOUSLY WITH WRITING TO CONTROL REGISTER

- [75] Inventors: Iain C. Robertson, Cople, England; Jeffrey L. Nye, Houston; Michael D. Asal, Sugar Land, both of Tex.; Graham B. Short, Bedford; Richard D. Simpson, Carlton, both of England; James G. Littleton, Houston, Tex.

- [73] Assignce: Texas Instruments Incorporated, Dallas, Tex.

- [21] Appl. No.: 474,863

- [22] Filed: Jun. 7, 1995

## **Related U.S. Application Data**

- [62] Division of Ser. No. 359,324, Dec. 15, 1994.

- [51] Int. Cl.<sup>6</sup> ...... G06F 9/26; G06F 9/34; G06F 12/00; G06F 12/02

- 395/427; 395/428

## [56] References Cited

### U.S. PATENT DOCUMENTS

5,129,059 7/1992 Hannah et al. ..... 395/166

## US005696923A

## [11] Patent Number: 5,696,923

## [45] Date of Patent: Dec. 9, 1997

| 5,428,754 | 6/1995 | Baldwin et al. | 395/375 |

|-----------|--------|----------------|---------|

| 5,446,904 | 8/1995 | Belt et al.    | 395/750 |

Primary Examiner-David K. Moore

Assistant Examiner-Than V. Nguyen

Attorney, Agent, or Firm-Robert D. Marshall, Jr.; James C. Kesterson; Richard L. Donadlson

## [57] ABSTRACT

A computer graphics system includes a host computer and a graphics processor. The graphics processor includes a control register. When the graphics processor writes to the control register it simultaneously generates a predetermined address on a local address bus and supplies data on a local data bus identical to data to be written into the control register. A shadow register circuit connected to both the host computer and the graphics processor includes a shadow register and first and second address decoders. The first address decoder enables a write from a local data bus into the shadow register upon detection of the predetermined address. The second address decoder enables a read from the shadow register via a host data bus upon detection of the predetermined address on a host address bus. The shadow register optionally includes a message in plurality of bits and a message out plurality of bits, the first and second address decoders enabling message passing between the host computer and the graphics processor. The shadow register circuit optionally includes a host interrupt bit and a buffer circuit. The buffer circuit generates a host interrupt signal to the host computer if either the graphics processor generates a host interrupt signal or the host interrupt bit of the shadow register has a predetermined state.

#### 5 Claims, 71 Drawing Sheets

-

FIG. 13

FIG. 20A

200 FIG.

TO FIG. 20F

| FIC OOD FROM FIG. 20A             |                          |                   |                          |

|-----------------------------------|--------------------------|-------------------|--------------------------|

| FIG. 20D FROM FIG. 20A            | <b></b>                  |                   |                          |

|                                   | REFRESHSXN               | IOMAP2SXT         | IOMAP2SXT<br>IOMAP3SXT   |

|                                   | IOMAPOSXT                | IOMAP3SXT         | ATHECUCYN                |

|                                   |                          | ATULCHSXN         | BASEOENSXN               |

| BALEADL                           | IOMAP1SXT                | BASEOENSXN        | DASETENCYN               |

| VCC                               | MCAMODESXT               | BASE1ENSXN        | BASEZENSXN               |

|                                   | M16SELSXT                | BASE2ENSXN        | BASEJENSXN               |

| MRDCMADE24                        | ULMAPSELSXT              | BASE3ENSXN        | M16ENOSXN                |

|                                   | MRDCMADE24SXN            | M16ENOSXN         | M16EN1SXN                |

| VCC MADE24SXN                     | DISABLESXN               | M16EN1SXN         | MIGENISAN                |

| TAP OT MAPSELSXT                  | MADE24SXN                | M16EN2SXN         | MIGENZSAN<br>MIGENJSXN   |

| MWTCSETUP MWTCSETUPSXN            | MAPSELSXT                | M16EN3SXN         | IOBASEOSXT               |

| BALEADLSXT                        | MWICSETUPSXN             | IOBASEOSXT        | 10BASE1SXT               |

|                                   | BALEADLSXT               | 10BASE1SXT        | IOBASE2SXT               |

|                                   | HDWRENSXT<br>SETHCSENSXT | JOBASE2SXT        | IOBASEJSXT               |

|                                   | SBHESXN                  | <b>IOBASE3SXT</b> |                          |

| NOWS NOWSSXN                      | NOWSSXN                  | PCA(21:0)         | PCA(21:0)                |

| PCINT PCINTSXT                    | PCINTSXT                 | VGASÈLSXŃ         | VGASELSXN                |

| PCIHIZENSXT                       | PCIHIZENSXT              | IOHADDLSXT        | IOHADOLSXT               |

|                                   | IO16SFDRKSXN             | IOHADDHSXT        | IOHADDHSXT               |

| 2 IO16HIZENSXT                    | IO16HIZENSXT             | IOMAPOESXT        | IOMAPOESXT               |

| M16DS16 - W16DS16SXN              | M16DS16SXN               | IOMAPENSXN        | IOMAPENSXN               |

| M16HIZENSXT                       | M16HIZENSXT              | IOMAPENSXT        | IOMAPENSXT               |

|                                   | SMWTCSOSXN               | MPBS(2:0)         | MPBS(2:0)                |

| SMRDCS1                           | SMRDCS1SXN               | W16ACTIVESXN      | MIGACTIVESXN             |

|                                   | IORCMIOSXN               | CLRCRYENSXN       | L CLIKURTENSXN 🛛 🖳       |

|                                   | IOWCCMDSXN               | CLRCHRDYSXN       | CLRCHRDYSXN              |

| AENSXI                            | AENSXT                   | HDWRITESXT        | HDWRITESXT               |

| BIOSENSXT                         | BIOSENSXT                | HDREADSXT         | HDREADSXT                |

| HINT D HINTSXN                    | HINTSXN                  | WRITESXT          | WRITESXT                 |

|                                   |                          | READSXT           | READSXT                  |

| ("IOA" & I) IOADDR(1) IOADDR(2:0) |                          | HOBYTEOSXT        | HDBYTEOSXT               |

|                                   | IOADDR(2:0)              | EMEMACSXT         | EMEMACSXT                |

| FOR 1:=0 TO 2 DOUT(15:0)          | , ,                      | MEMACSXT          | MEMACSXT                 |

|                                   | DOUT(15:0)               | IOSELSXT          | IOSELSXT                 |

| D15 - 15 - DIN(15:0)              | DIN(15:0)                | STATUSSXT         | STATUSSXT                |

|                                   | 0(.0.0)                  | IOHDATASXT        | IOHDATASXT               |

|                                   |                          | IOSHCTLSXT        | IOSHCTLSXT               |

|                                   |                          | AUTOINCSXT        | AUTOINCSXT               |

| ╘┥╱╌┼╌╌╌╍╄┥                       |                          | SBHESXT           | SBHESXT                  |

| DRIVEOUTSXN                       | DRIVEOUTSXN              | RESETS1N          | RESETSIN                 |

|                                   |                          | IOWRITESXT        | IOWRITESXT               |

|                                   |                          | IOREADSXT         | IOREADSXT                |

|                                   |                          | IOBYTEOSXT        | IOBYTEOSXT<br>IOBYTE1SXT |

| 24 DIN(I+8)                       | DEU                      | IOBYTE1SXT        |                          |

| ("0" h I) D D D D UT(I)           | DFU                      | PCO(15:0)         | PCO(15:0)                |

|                                   | <u>2031</u>              | IOBSCTLSXT        | IOBSCTLSXT               |

|                                   |                          | IOBSPRTSXT        | IOBSPRTSXT<br>UPORTSXT   |

| FOR 1:=0 TO 6                     |                          | UPORTSXT          | RESETSXT                 |

|                                   |                          | RESETSXT          |                          |

|                                   |                          |                   |                          |

TO FIG. 20E

-

FROM FIG. 20B ATULCHSXN BASEOENSXN OWRITESX **BASE1ENSXN** BASE2ENSXN **BASEJENSXN** M16ENOSXN M16EN1SXN 20EM16EN2SXN M16EN3SXN IOBASEOSXT **IOBASE1SXT** FIG.10BASE2SXT 10BASE3SXT PCA(21:0) VGASELSXN IOHADDLSXT IOHADDHSXT **IOMAPOESXT** IOMAPENSXN IOMAPENSXT MPBS(2:0) 116-M16ACTIVESXN CLRCRYENSXN **CLRCHRDYSXN** HDWRITESXT HDREADSXT WRITESXT READSXT HDBYTEOSXT EMEMACSXT MEMACSXT IOSELSXT STATUSSXT IOHDATASXT **IOSHCTLSXT** AUTOINCSXT SBHESXT **RESETSIN IOWRITESXT IOREADSXT IOBYTEOSXT** 20F **IOBYTE1SXT** TO FIG. PCO(15:0) **IOBSCTLSXT IOBSPRTSXT** UPORTSXT RESETSXT

FROM FIG. 20D

TO FIG. 21D

TO FIG. 22B

Sheet 22 of 71

TO FIG. 23B

FROM FIG. 23A

FIG. 23C

TO FIG. 23D

TO FIG. 24E

# FIG. 24E

FIG. 24F

IOBYTEOSXT > WOBASE3SXT 15 -1313  $\underline{\circ}$ IOWRITESXT C თ œ W1BASE3SXT IOBYTE1SXT D CLK **CLK** CLRZ <u>CLK</u> CLRZ **P** CLK REZ 20202  $\Box$ 0 0 ч Ч Ci R 5 0 2 S S ID D ទ័ IOBASE3SXT >> 2882 0 O o o 14 15 13 12 = 9 B3DATA(15:0) თ ω 51415  $\sim$ ഉച Ξ RBASE3SXN ω ഗ ഹ r IOREADSXT **C2Z** A44 A13 A11 G2Z A23 A23 A21 G2Z A23 A23 EN Ľ Е Y24 Y23 Y13 Y13 Y13 Y24 Y21 Y21 15 4 m 2 0 Ξ တထ ۵ ~ ۱C PCD(15:0) TO FIG. 25B PCA(21:0) ULPCA(23:17) 6 20 8 1 21 M 2 10 ę..... თ  $\infty$ 6  $\infty$ 9 5 m  $\sim$  $\simeq$ 2 = = - $\underline{\circ}$  $\circ$  $\circ$ ω ∞ 00102020240 ഹ 4 EN 23 ม่ G1Z, BASE3ENSXN D M16EN3SXN

BASE3REG

FIG. 25A

5,696,923

BASE 3REG

FIG.

5,696,923

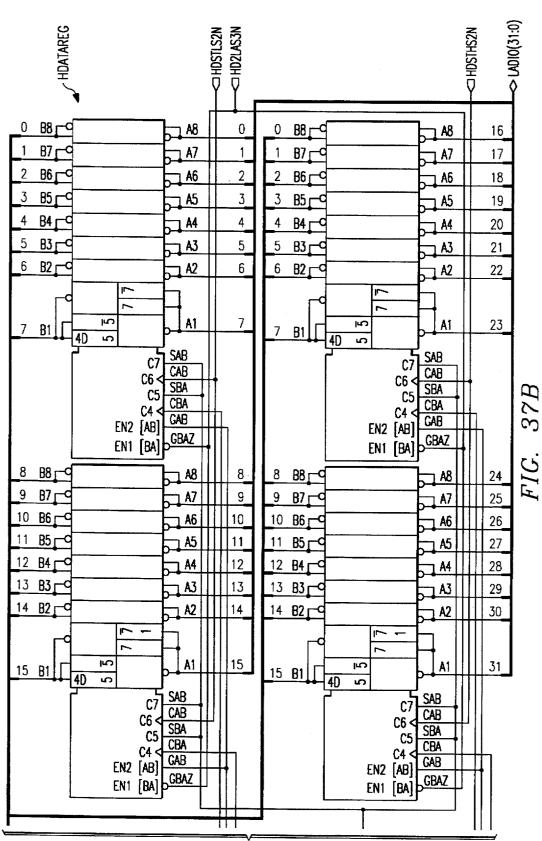

TO FIG. 37B

FROM FIG. 37A

U.S. Patent

**Sheet 53 of 71**

5,696,923

**U.S.** Patent

Sheet 54 of 71

5,696,923

**U.S. Patent**

FROM FIG. 53A

TO FIČ. 55B

S652

35

50

# **GRAPHICS PROCESSOR WRITING TO** SHADOW REGISTER AT PREDETERMINED ADDRESS SIMULTANEOUSLY WITH WRITING TO CONTROL REGISTER

This is a division of application Ser. No. 08/359,324, filed Dec. 15, 1994.

#### NOTICE

(C) Copyright, Texas Instruments Incorporated 1990. A 10 portion of the disclosure of this patent document contains material which is subject to copyright protection. The copyright owner has no objection to the facsimile reproduction by anyone of the patent document or the patent disclosure, as it appears in the Patent and Trademark Office patent file 15 or records, but otherwise reserves all copyright rights whatsoever.

# CROSS-REFERENCE TO RELATED APPLICATIONS

The following coassigned patent applications are hereby incorporated herein by reference as background and supporting information to the subject matter disclosed herein:

Ser. No. 446,019, filed Dec. 5, 1989, "Data Communications System";

Ser. No. 08/978,457, filed Nov. 19, 1992 and now abandoned, Ser. No. 798,278, filed Nov. 20, 1991 and now abandoned; a continuation of Ser. No. 408,454, filed Sep. 14, 1989 and now abandoned; a continuation of Ser. No. 256, 30 803, filed Oct. 11, 1988 and now abandoned; a continuation of Ser. No. 821,375 filed Jan. 22, 1986 and now abandoned, "Data Processing System with Variable Memory Bank Selection; and Japanese analog laid-open application No. 13275/1987;

Ser. No. 965,561 filed Oct. 23, 1992; a continuation of Ser. No. 426,480, filed Oct. 23, 1989 and now abandoned; a continuation of Ser. No. 346,388 filed Apr. 27, 1989 and now abandoned ; a continuation of Ser. No. 207,034 filed Jun. 13, 1988 and now abandoned; a continuation of Ser. No. 821, 40 641 filed Jan. 23, 1986, "Graphics Data Processor, A Data Processing System, A Graphics Processing System and a Method of Processing Graphics Data";

U.S. Pat. No. 3,161,122, "Register Write Bit Protection Apparatus and Method";

Ser. No. 387,569, filed Jul. 28, 1989 and now abandoned, "Graphics Display Split-Serial Register System";

U.S. Pat. No. 5,329,617, "Graphics Processor Nonconfined Address Calculation System";

Ser. No. 386,850, filed Jul. 28, 1989 and now abandoned, "Real Time and Slow Memory Access Mixed Bus Usage";

U.S. Pat. No. 5,341,470, "Computer Graphics Systems, Palette Device and Methods for Shift Clock Pulse Insertion During Blanking".

# BACKGROUND OF THE INVENTION

Without limiting the general scope of the invention, its background is described in connection with computer graphics, as one example only.

In computer systems, a host computer can be programmed to perform general purpose tasks including graphics routines. Greater speed and additional features are often desirable, and so a graphics coprocessor is added to supplement the capabilities of the host computer.

The graphics coprocessor is also called a graphics system processor (GSP), examples of which are the Texas Instru-

ments TMS34010 and TMS34020 GSPs. The addition of a graphics coprocessor makes the computer system a multiprocessor system which can benefit from advances in the art of multiprocessor technology. Also, different computer bus architectures are in use today such as the ISA and MCA architectures, and this situation complicates system and circuit definition. Furthermore, several different kinds of memory such as ROM, DRAM (dynamic random access memory) and VRAM (video RAM) are useful with computers that have graphics capability, and are desirably accommodated. A host computer may have one memory address space, which is an allocation of different memory addresses to different functions according to an address map, and the GSP may have another memory address space.

Any improvements in multiprocessor technology, memory and addressing management and other aspects relating to host computers and graphics system processors are desirable so that graphics and other computer and electronic systems can be made faster and more convenient <sup>20</sup> in commercial application.

# SUMMARY OF THE INVENTION

Generally, and in one form of the invention, a multifunction access circuit is provided for use with first and second digital computers each having an address bus for supplying addresses and a data bus for supplying data. The access circuit has an address decoder with inputs for the address bus from the first computer, and an address translator circuit having address inputs for addresses supplied by the address bus of the first computer and outputs for translated addresses to the address bus of the second computer. The address translator circuit also has registers selectable by the address decoder and data inputs to program the registers so selected with data from the data bus from the first computer. Also in the access circuit is a port circuit with registers controlled by the address decoder for entry of address information from the data bus of the first computer and assertion of the address information on the address bus of the second computer. Further, a mode control circuit is connected to the address decoder and connected to the data bus to program the mode control circuit to selectively establish operation of the address translator circuit and of the port circuit.

In general, another form of the invention is a multifunc-45 tion access circuit with an address decoder having inputs from the address bus from the first computer, and an address translator circuit having address inputs for addresses supplied by the address bus of the first computer and outputs for translated addresses to the address bus of the second computer. The address translator circuit also has registers selectable by the address decoder and data inputs to program the registers so selected with data from the data bus from the first computer. A bank select circuit is responsive to addresses from the address bus of the second computer to 55 supply a set of bank select outputs.

In general, a further form of the invention is a multifunction access circuit having a first address decoder with inputs for the address bus and a read line from the first computer. A second address decoder has inputs for the address bus and 60 a write line from the second computer. A logic circuit is provided with a register selectable by either of the first address decoder and the second address decoder and having data outputs for connection to the data bus from the first computer, and having data inputs for connection to the data 65 bus from the second computer.

Generally, still another form of the invention is a memory access circuit for use with a computer operative to assert

45

read and write signals and an address. The circuit has a memory accessible by asserting addresses thereto, an address translator circuit having address inputs for the address supplied by the computer and outputs for supplying a translated address, and a logic circuit connected to the 5 outputs of the address translator circuit and responsive to a write signal to automatically increment the translated address for the memory and responsive to a control signal to return to the translated address. Control circuitry connected to the logic circuit and responsive to a read signal from the 10 computer supplies the control signal to the logic circuit to return to the translated address.

In general, a yet further form of the invention is a multifunction access circuit for use with first and second digital computers each having an address bus for addresses. The access circuit has an address translator circuit with address inputs for addresses supplied by the address bus of the first computer and outputs for translated addresses to the address bus of the second computer. The address translator circuit also has registers establishing predetermined address segments, and the address translator circuit is responsive to addresse on the address inputs in the address segments. Control logic circuitry is connected to said address translator circuit and operative to supply a control signal when the address at the address inputs changes from one segment to address at the address inputs changes from one segment to address at the address inputs changes from one segment to address at the address inputs changes from one segment to address at the address inputs changes from one segment to address at the address inputs changes from one segment to address at the address inputs changes from one segment to address at the address inputs changes from one segment to address at the address inputs changes from one segment to address at the address inputs changes from one segment to address at the address inputs changes from one segment to address at the address inputs changes from one segment to address at the address inputs changes from one segment to address at the address inputs changes from one segment to address at the address inputs changes from one segment to address address at the address inputs changes from one segment to address at the address inputs changes from one segment to address at the address inputs changes from one segment to address at the address inputs changes from one segment to address at the address inputs changes from one segment to address at the address inputs changes from one segment to address at the address inputs changes from one segment to address at the address inputs changes from one s

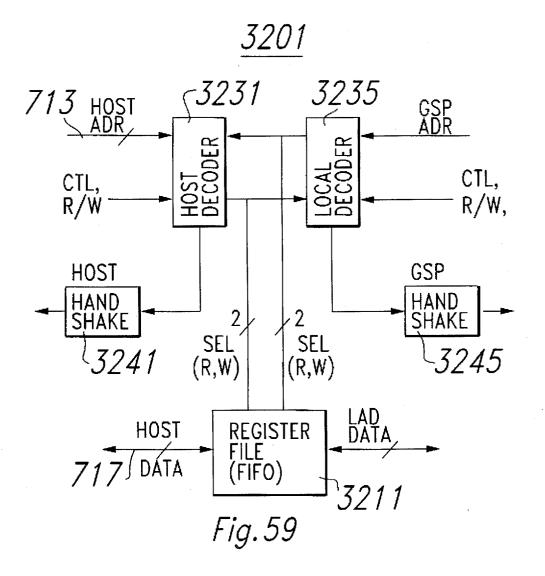

In general, a still further form of the invention is a multifunction access circuit that has a register file having data inputs and outputs connected to the data bus for each of the first and second digital computers, and a pair of address <sup>30</sup> decoders connected to the address bus for each of the first and second computers, the decoders connected to the register file to support simultaneous reads and writes.

Other circuits, devices, systems, and methods are described and claimed herein.

### BRIEF DESCRIPTION OF THE DRAWINGS

These and other features of the present invention will be readily understood from the following Description, taken in conjunction with the Drawings, in which:

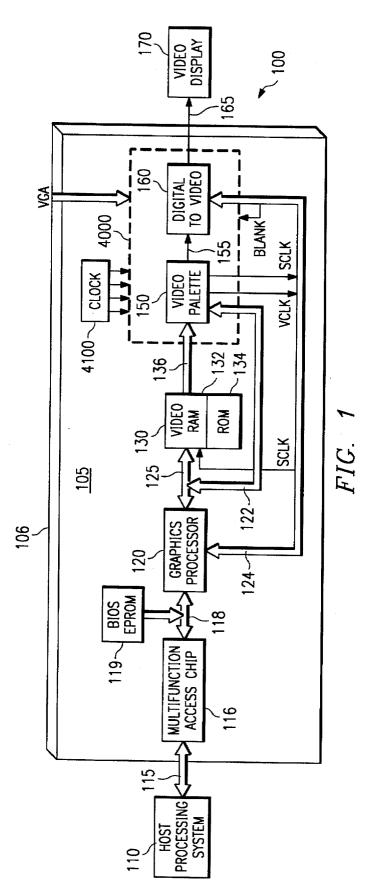

FIG. 1 is a block diagram of a computer graphics system;

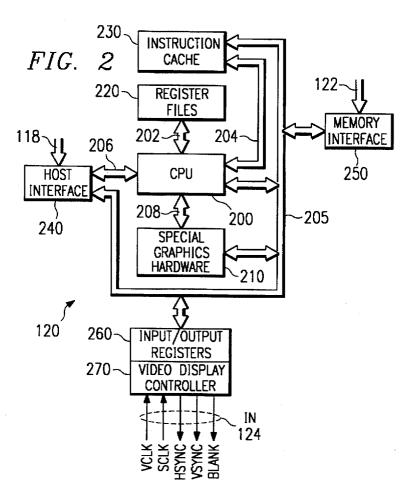

FIG. 2 is a block diagram of a graphics coprocessor;

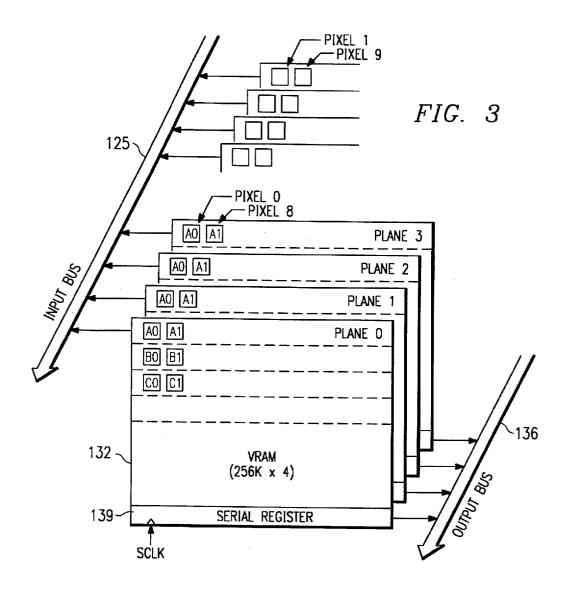

FIG. 3 is an expanded, stylized view of a video memory operating in conjunction with a split serial register;

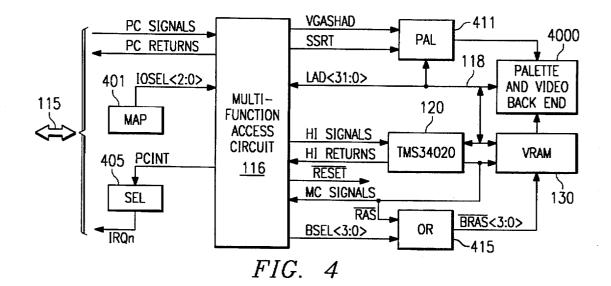

FIG. 4 is a block diagram of a computer graphics system showing a multifunctional access circuit and its signal paths in greater detail;

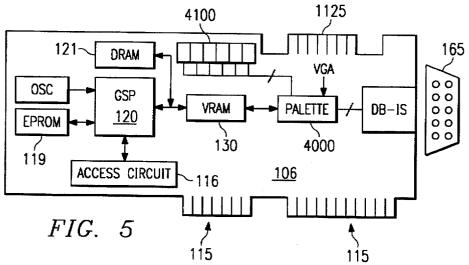

FIG. 5 is a pictorial sketch of a printed wiring board for computer graphics systems as shown in FIGS. 1 and 4;

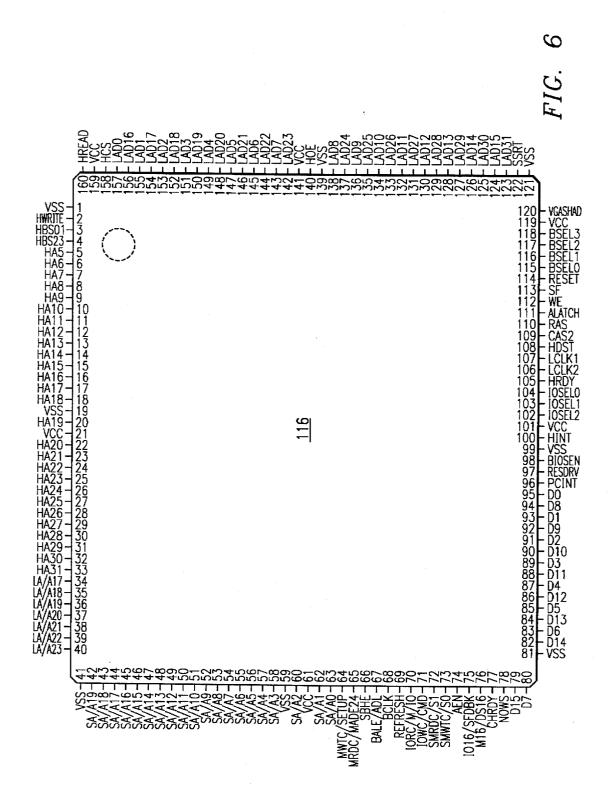

FIG. 6 is a pinout diagram of a multifunctional access circuit chip for computer graphics systems as shown in FIGS. 1 and 4;

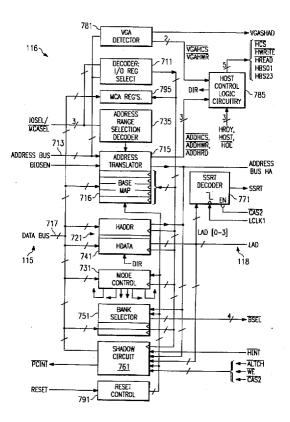

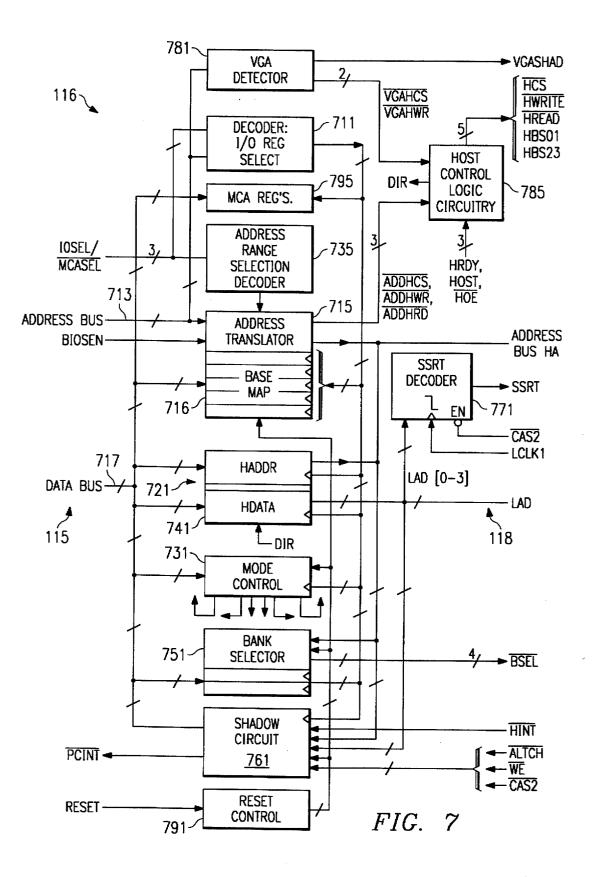

FIG. 7 is a block diagram of an multifunctional access circuit circuit of FIGS. 4 and 6 having circuits with various <sup>55</sup> registers shown in more figures hereinbelow;

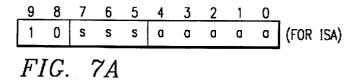

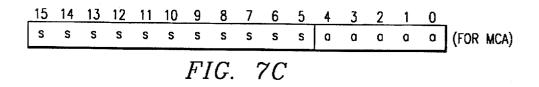

FIG. 7A is a diagram of host bus address bits according to an ISA bus architecture;

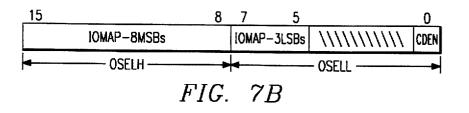

FIG. 7B is a diagram of an option select register;

FIG. 7C is a diagram of host bus address bits according to an MCA bus architecture;

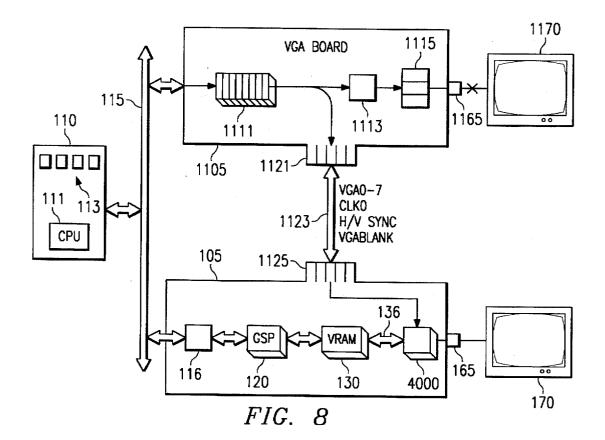

FIG. 8 is a block diagram of a computer graphics system with a VGA board and having an added printed wiring board as in FIGS. 1, 4 and 5 with VGA pass through;

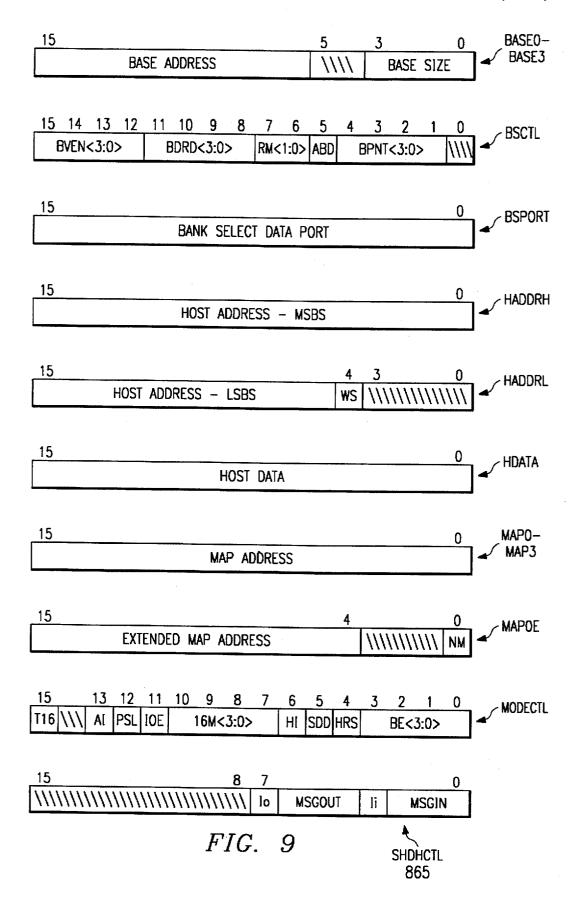

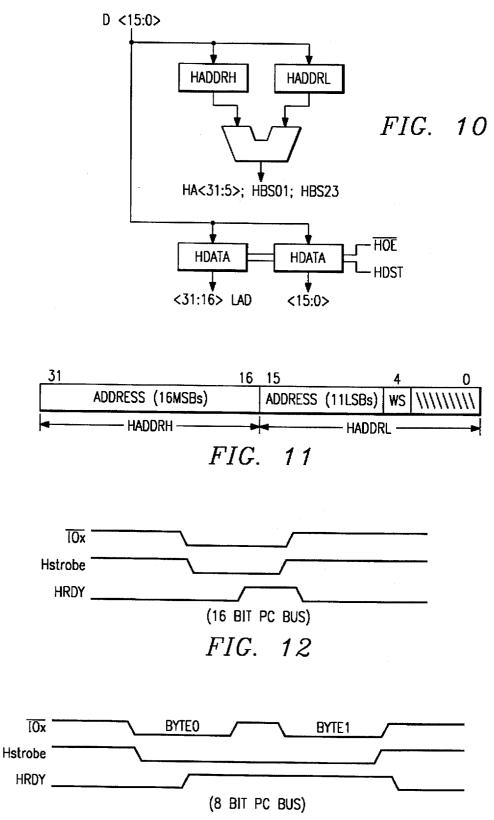

FIG. 9 is a diagram of further registers in the multifunctional access circuit of FIGS. 4, 6 and 7; FIG. 10 is a block diagram of a port circuit in the multifunctional access circuit of FIGS. 4, 6 and 7;

FIG. 11 is a diagram of a register in the circuit of FIG. 10;

FIG. 12 is a waveform diagram of voltage versus time of signals in the multifunctional access circuit of FIGS. 4 and 7;

FIG. 13 is another waveform diagram of voltage versus time of signals in the multifunctional access circuit of FIGS. 4 and 7;

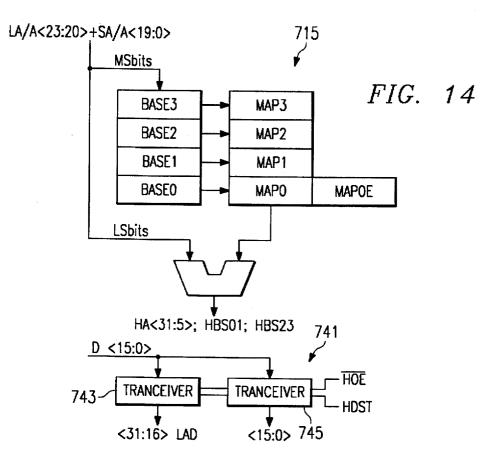

FIG. 14 is a block diagram of an address translator and a data input/output circuit in the multifunctional access circuit of FIGS. 4, 6 and 7;

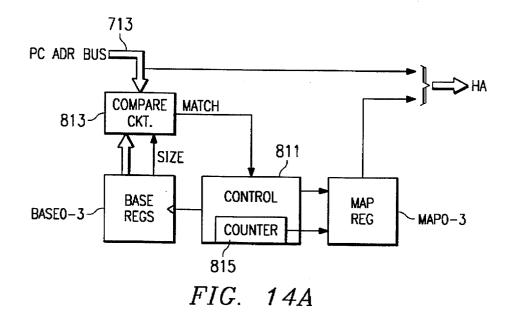

FIG. 14A is a block diagram detailing part of the address translator of FIG. 14;

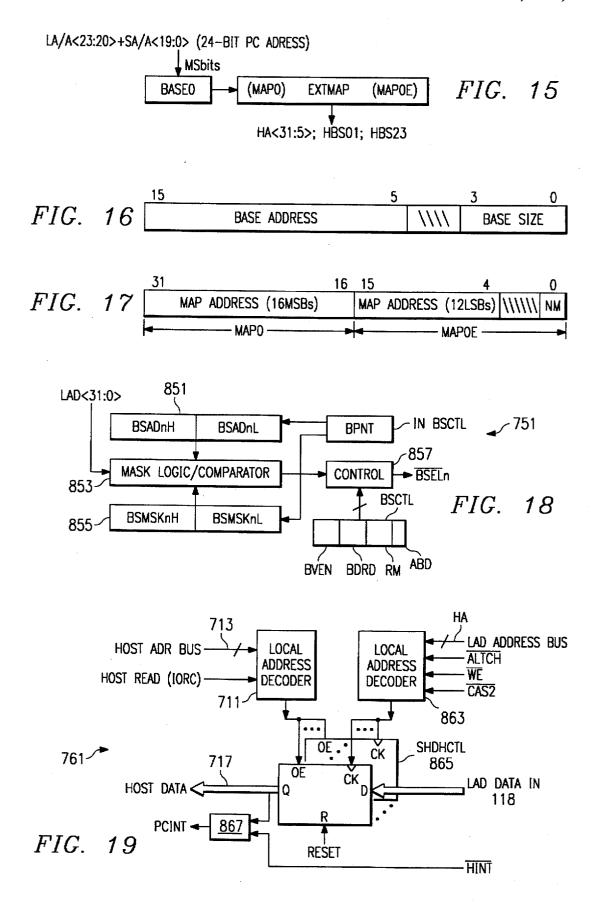

FIG. 15 is another detail of part of the circuit of FIG. 14;

FIG. 16 is a diagram of a base register of FIGS. 14 and 15;

FIG. 17 is a diagram of a map register of FIGS. 14 and 15;

FIG. 18 is a block diagram of a bank selecting circuit in the multifunctional access circuit of FIGS. 4, 6 and 7;

FIG. 19 is a block diagram of a shadow circuit in the multifunctional access circuit of FIGS. 4, 6 and 7;

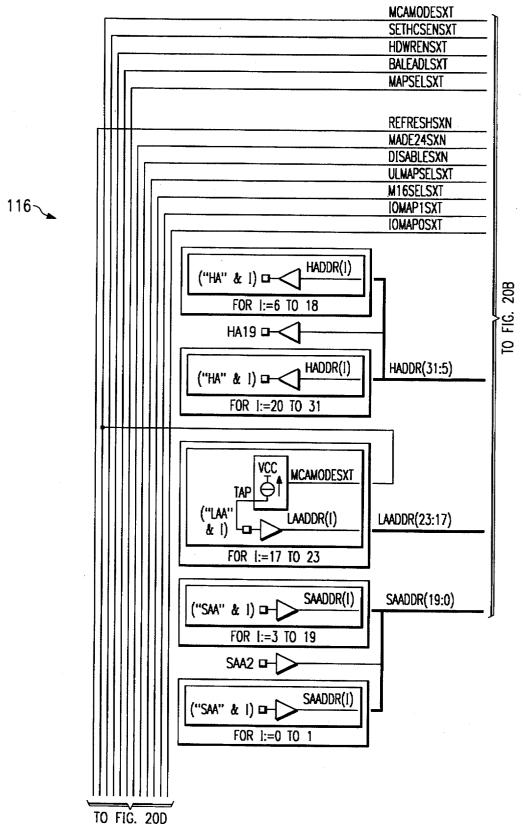

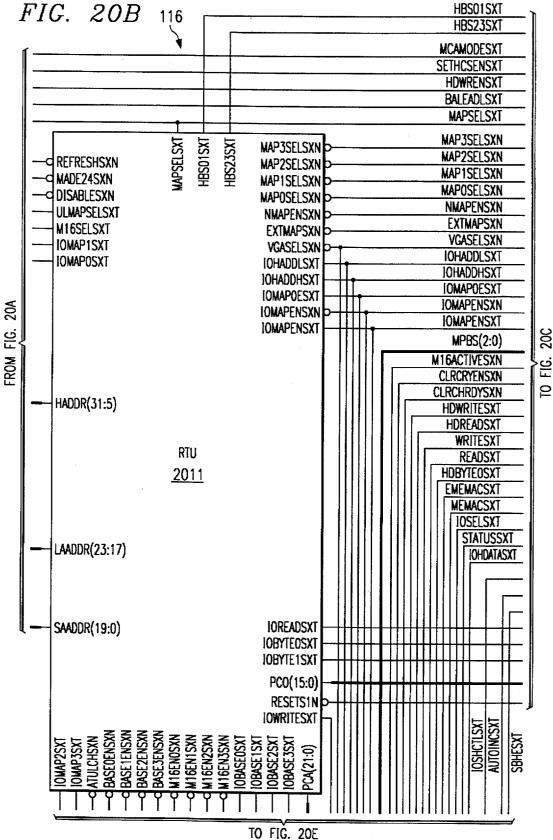

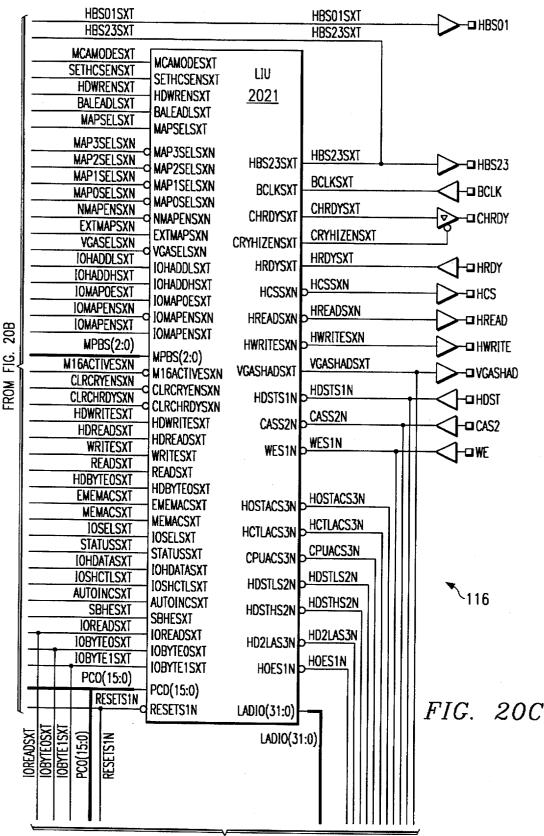

FIG. 20 is another block diagram of the multifunction access circuit of FIG. 7;

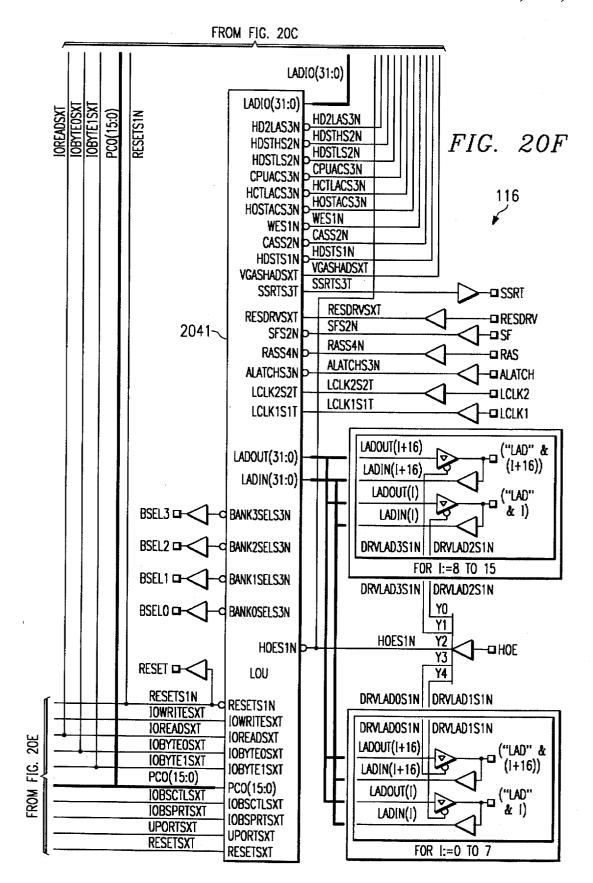

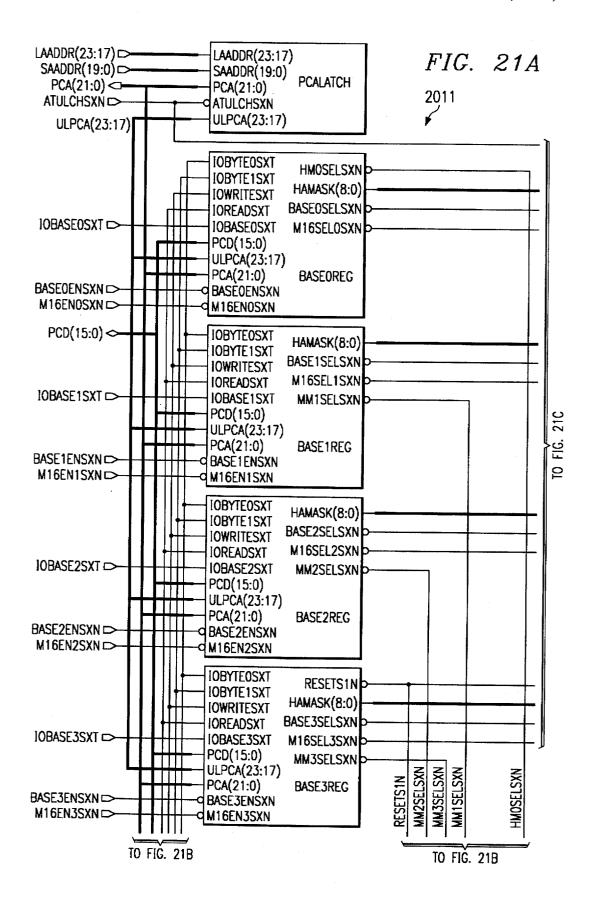

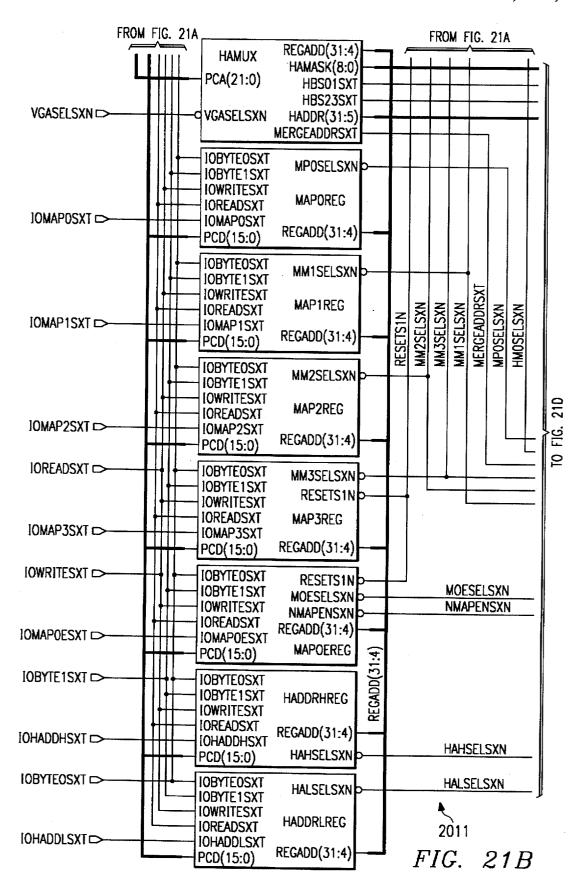

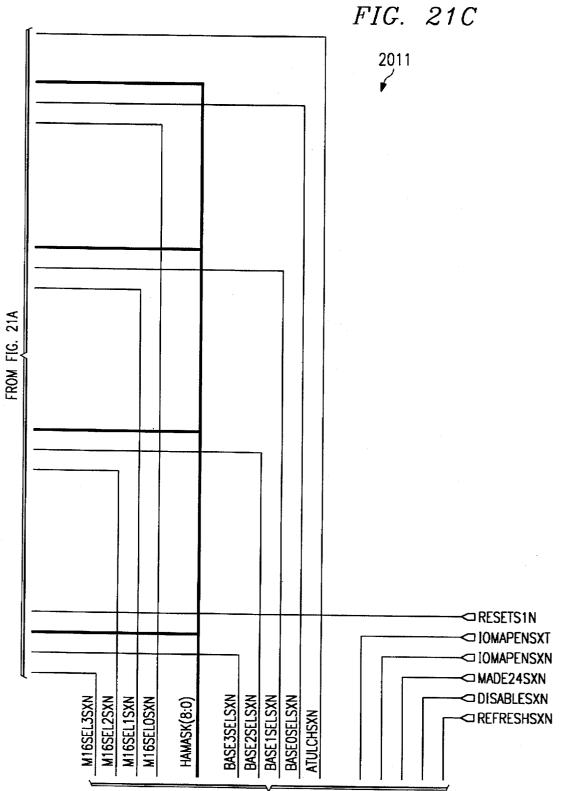

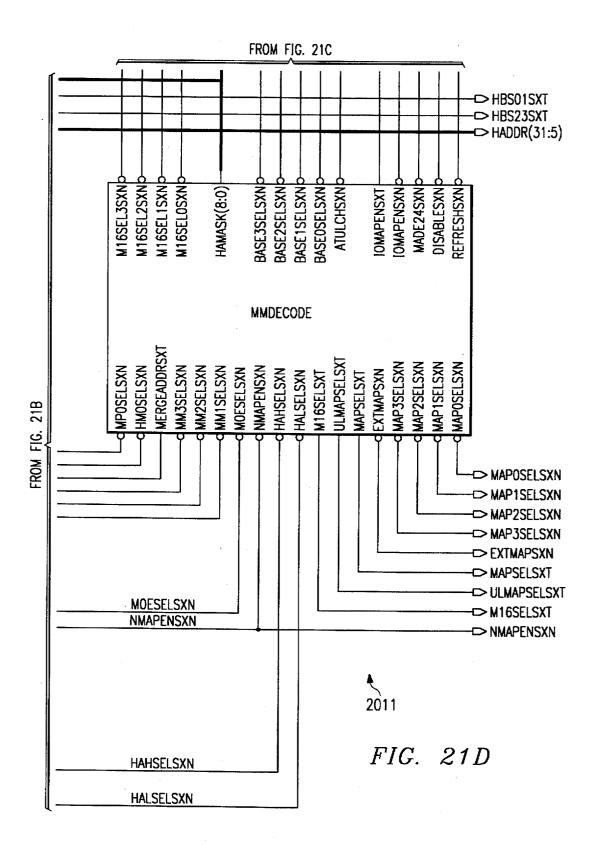

FIG. 21 is a block diagram of an Address Translation Unit block ATU of FIG. 20;

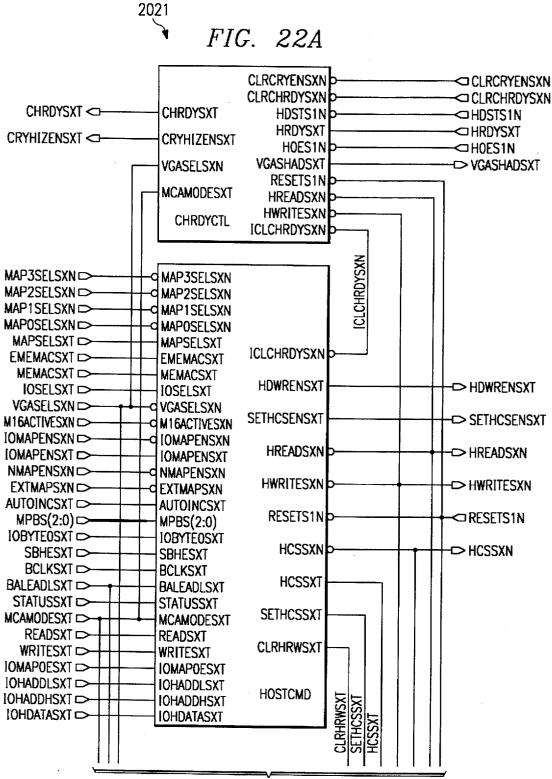

FIG. 22 is a block diagram of a Local Interface Unit block LIU of FIG. 20;

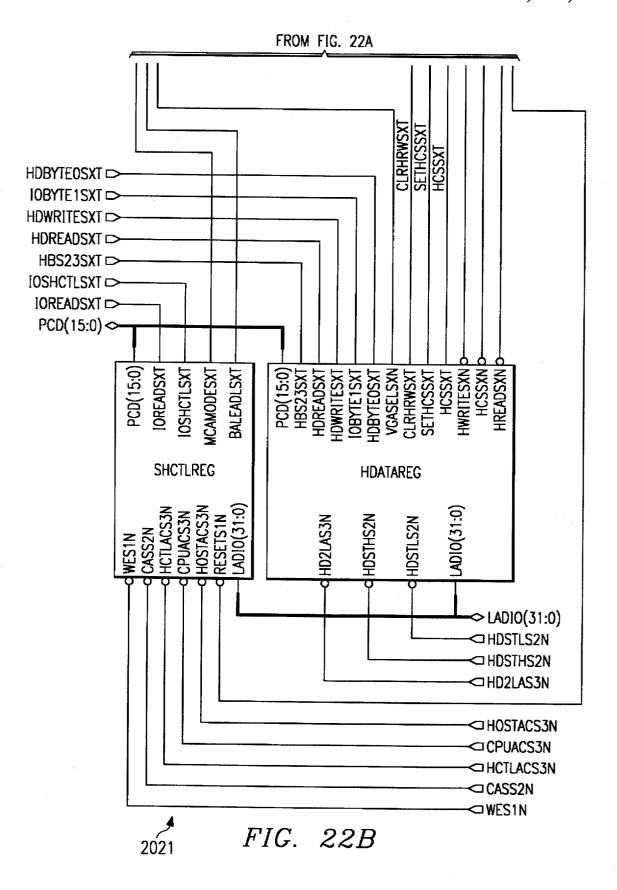

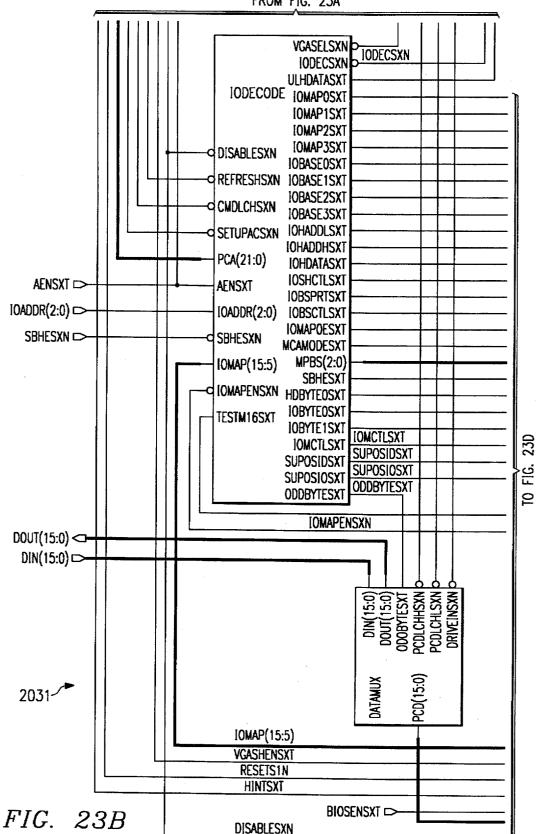

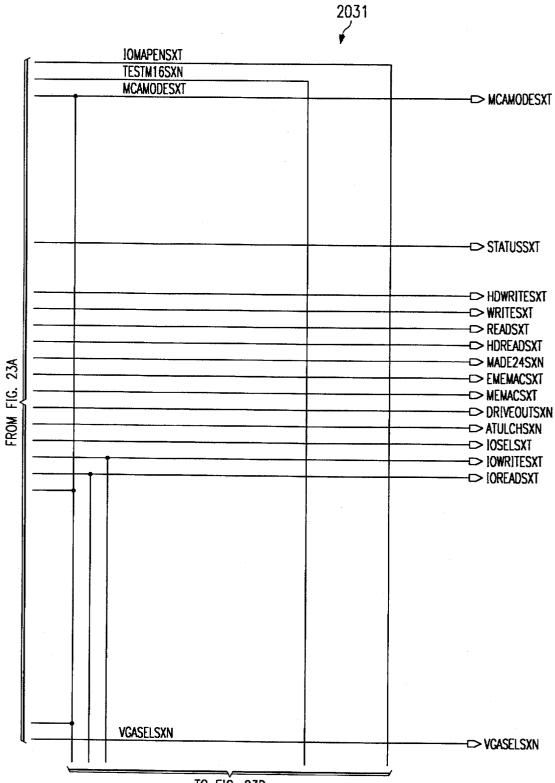

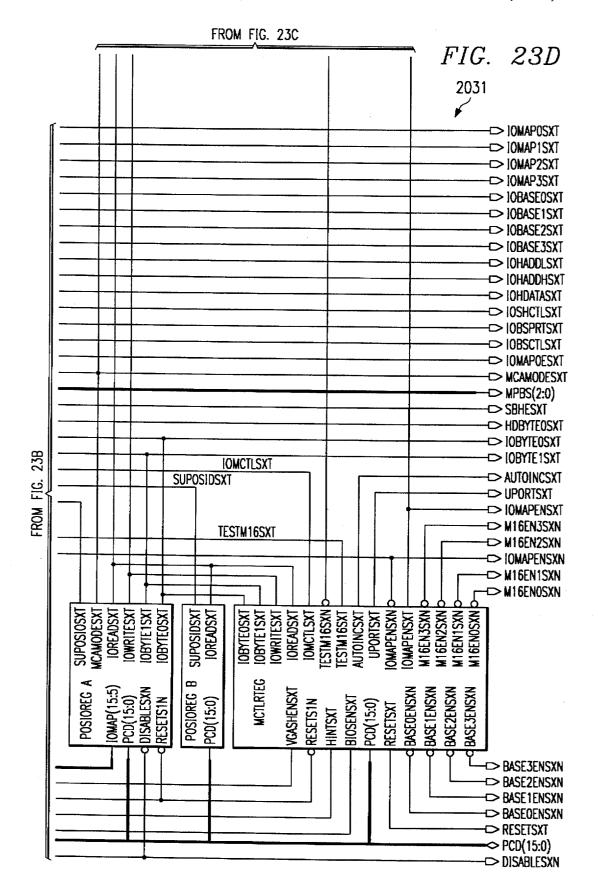

FIG. 23 is a block diagram of a Data Flow Unit block DFU of FIG. 20;

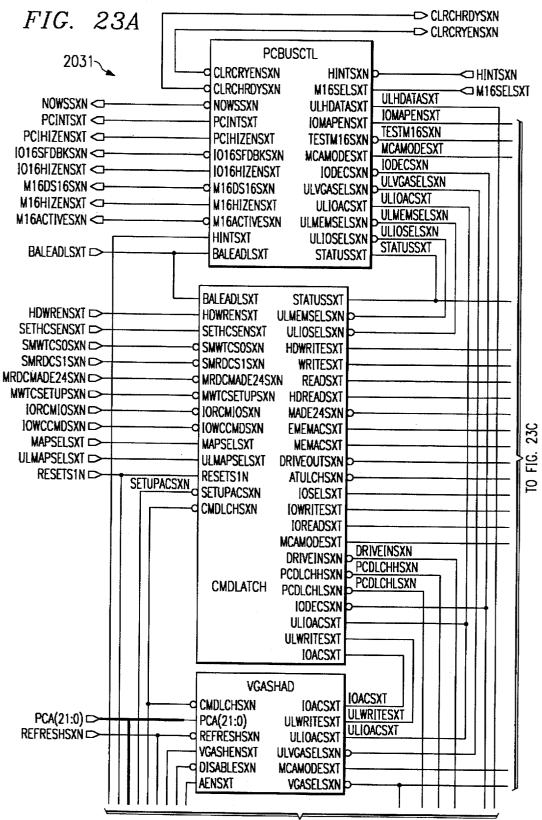

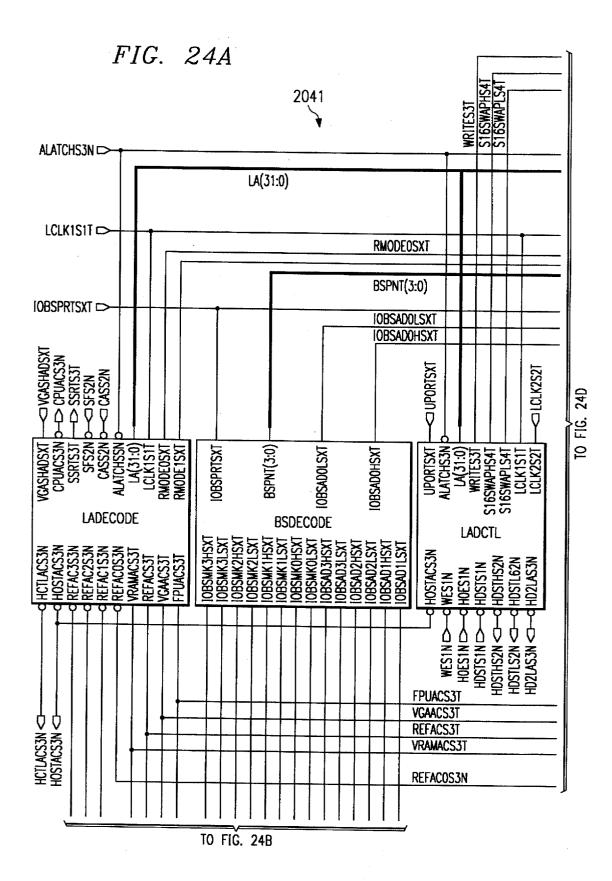

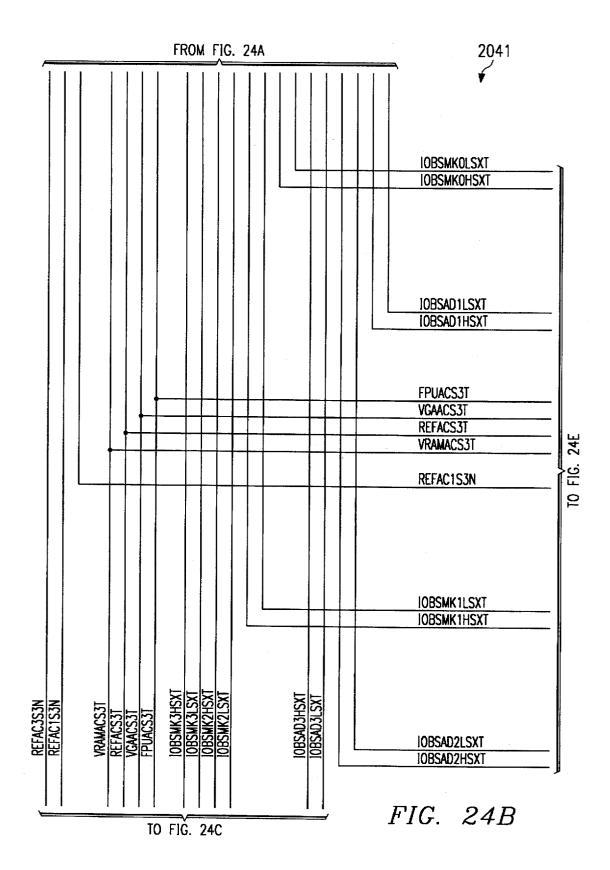

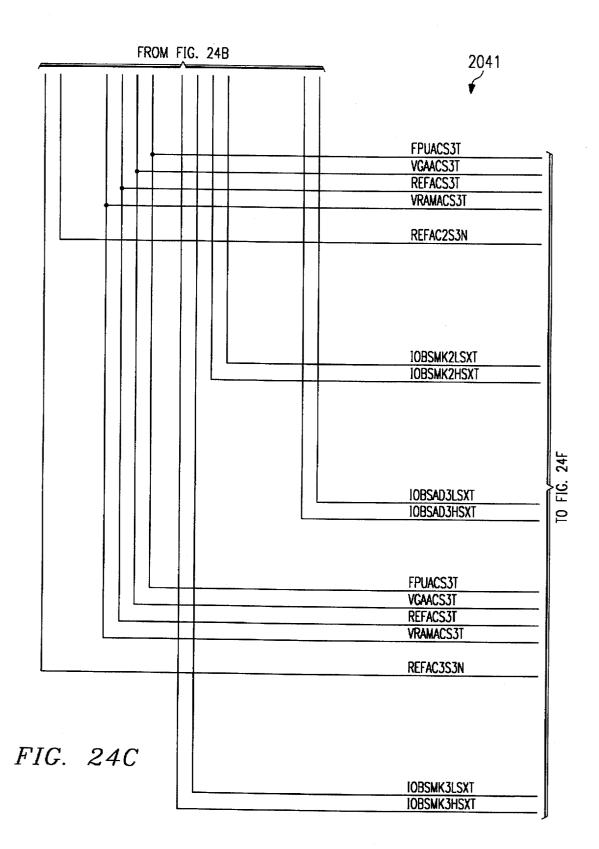

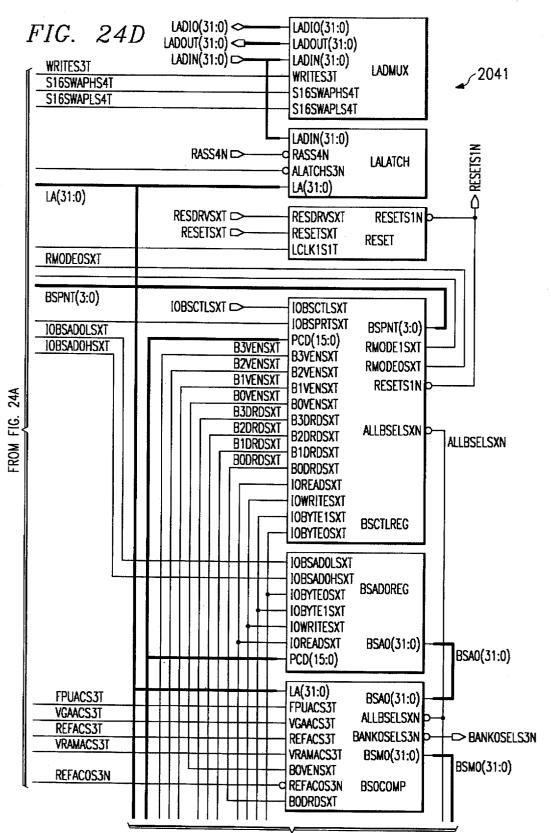

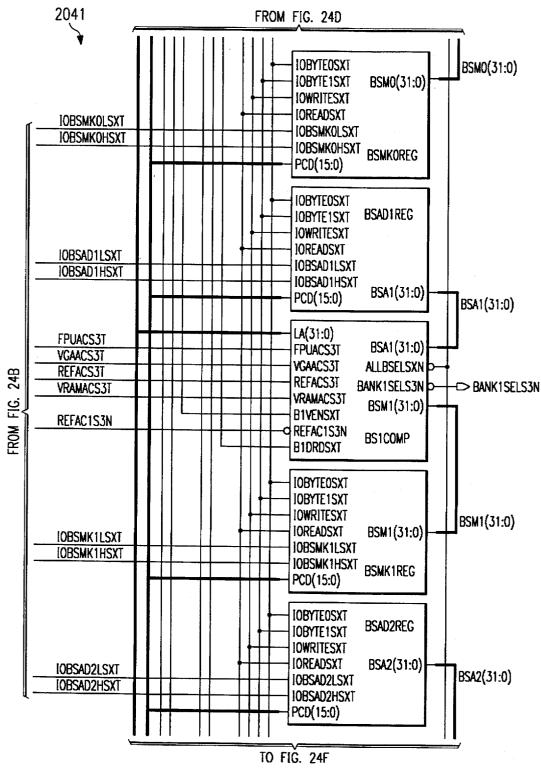

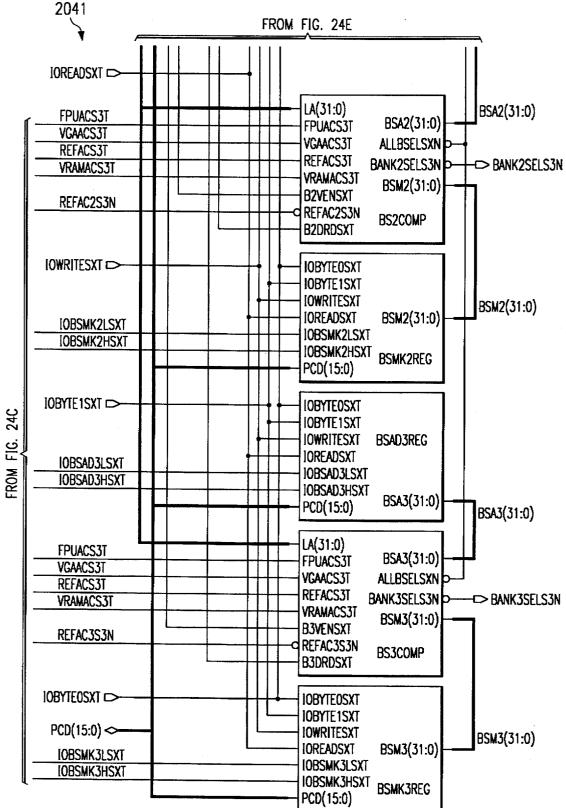

FIG. 24 is a block diagram of a block Local Decode Unit block LDU of FIG. 20;

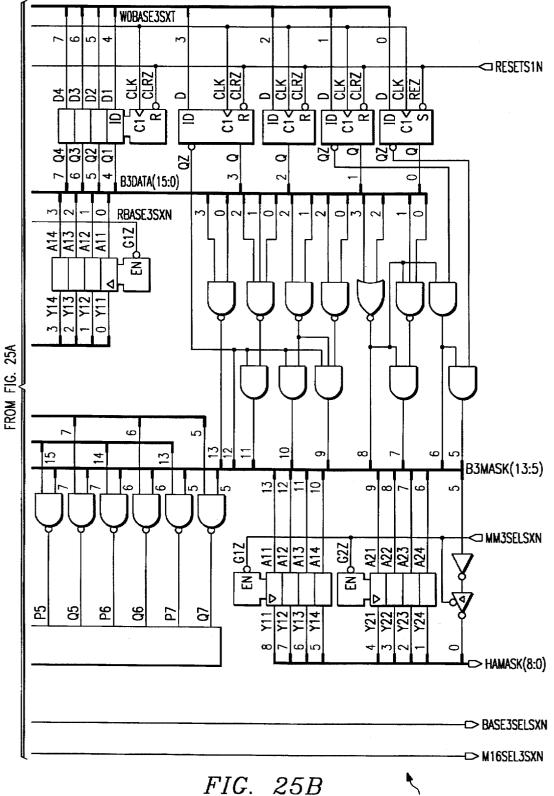

FIG. 25 is a block diagram of a base register circuit BASE3REG representative of each of four identical base register circuits BASE0REG, BASE1REG, BASE2REG, and BASE3REG in FIG. 21;

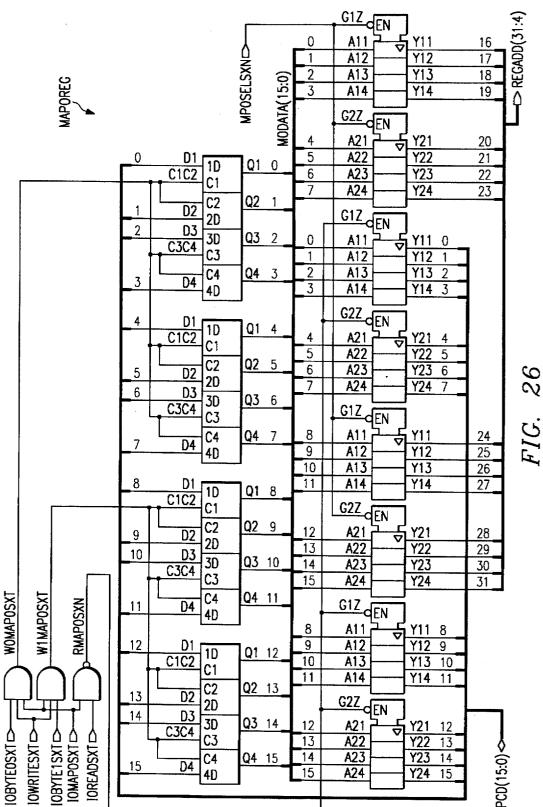

FIG. 26 is a block diagram of a map register circuit <sup>40</sup> MAP0REG in FIG. 21;

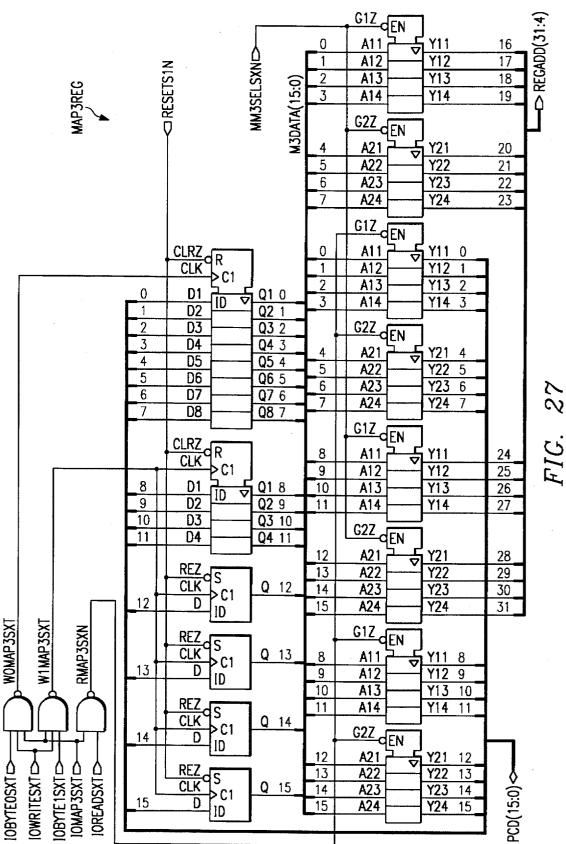

FIG. 27 is a block diagram of a map register circuit MAP3REG representative of three identical register circuits MAP1REG, MAP2REG and MAP3REG in FIG. 21;

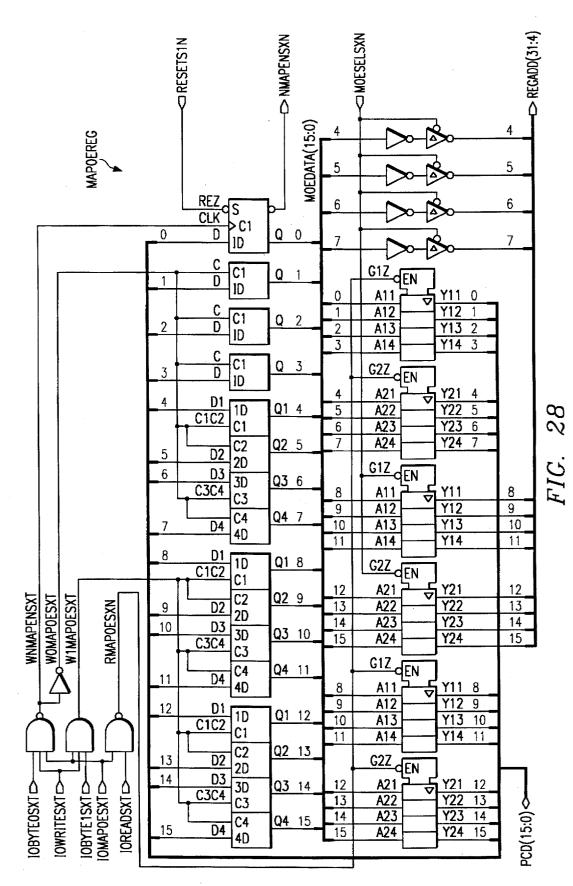

FIG. 28 is a block diagram of an extended map register circuit MAP0EREG in FIG. 21;

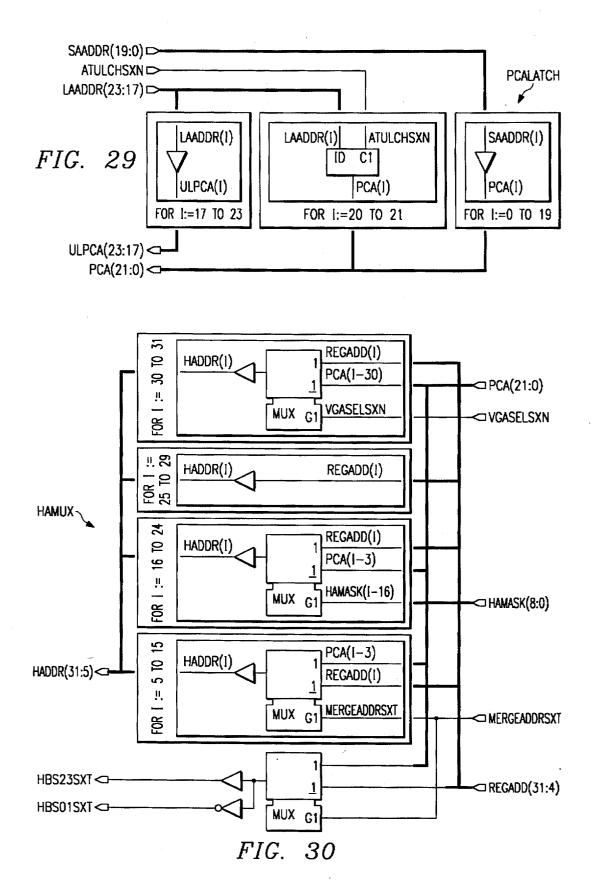

FIG. 29 is a schematic diagram of an address latch circuit PCALATCH in FIG. 21;

FIG. 30 is a schematic diagram of a circuit HAMUX of 50 FIG. 21;

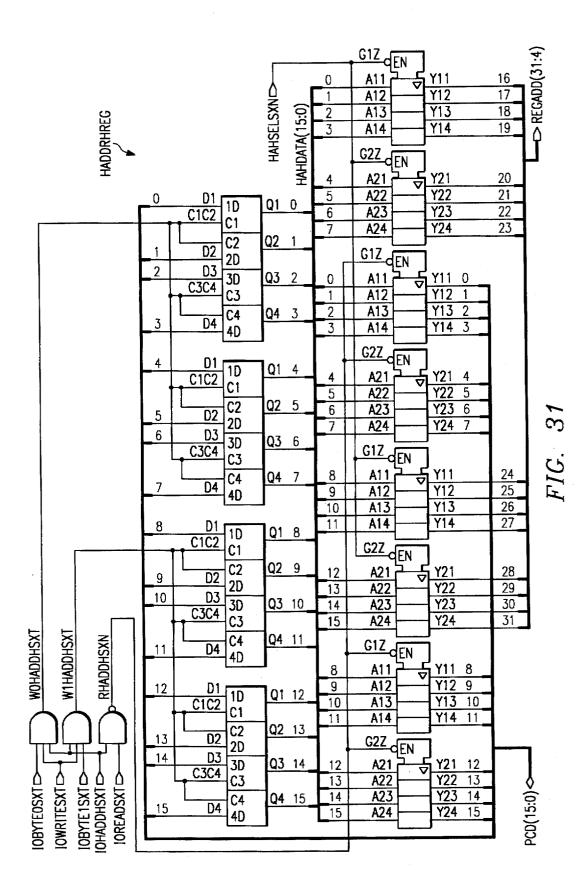

FIG. 31 is a schematic diagram of an address register circuit HADDRHREG of FIG. 21;

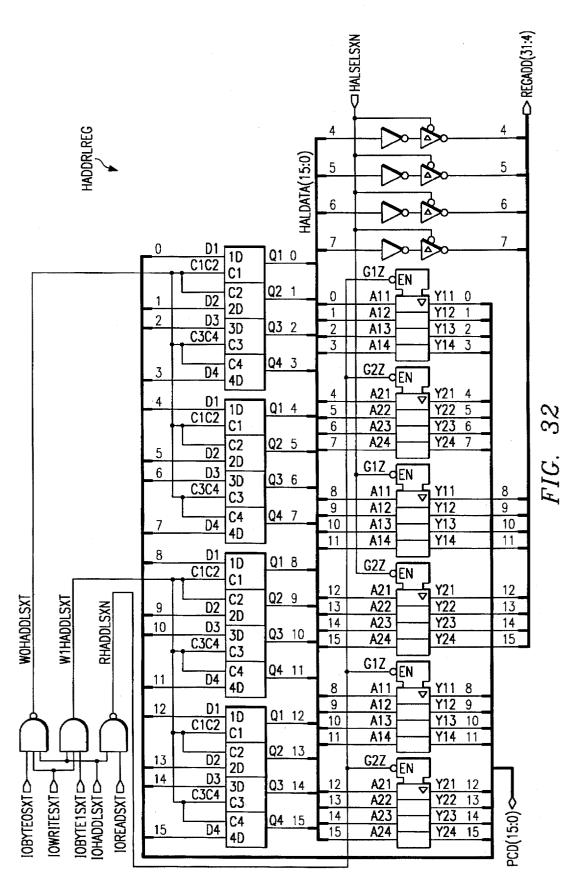

FIG. 32 is a schematic diagram of an address register circuit HADDRLREG of FIG. 21;

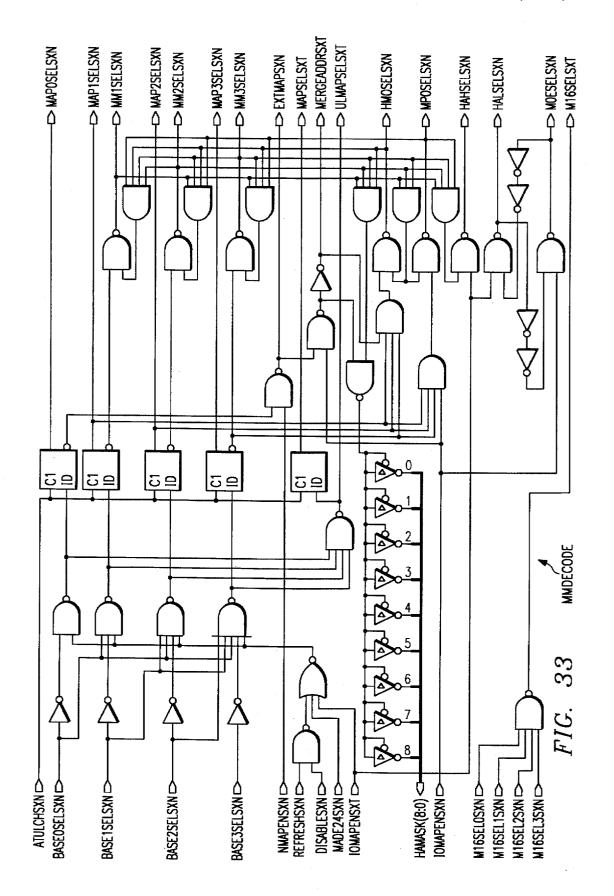

FIG. 33 is a schematic diagram of a decode circuit MMDECODE of FIG. 21;

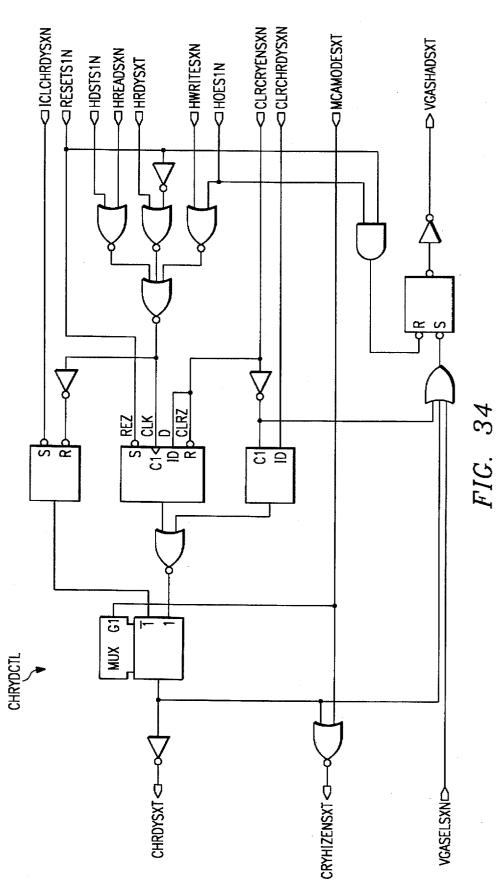

FIG. 34 is a schematic diagram of a ready control circuit CHRDYCTL of FIG. 22;

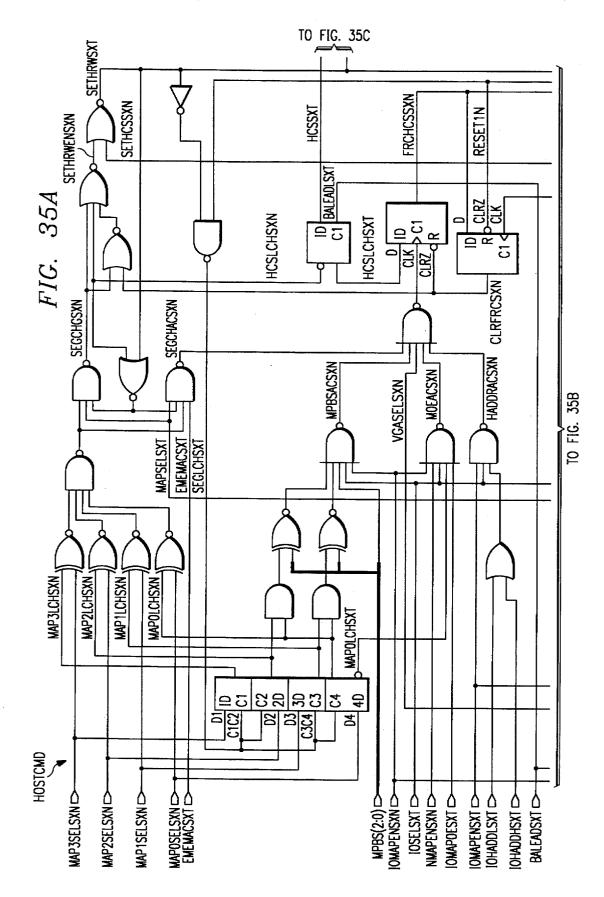

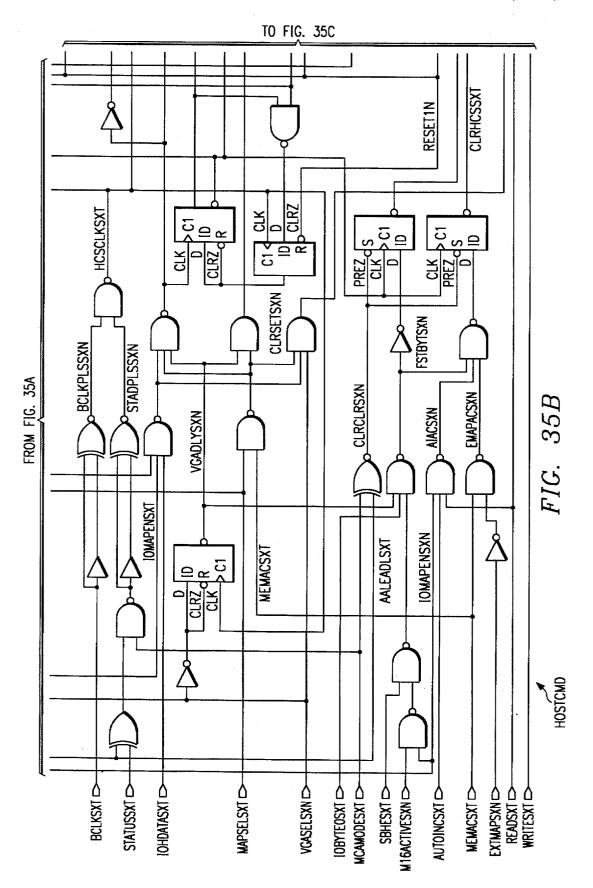

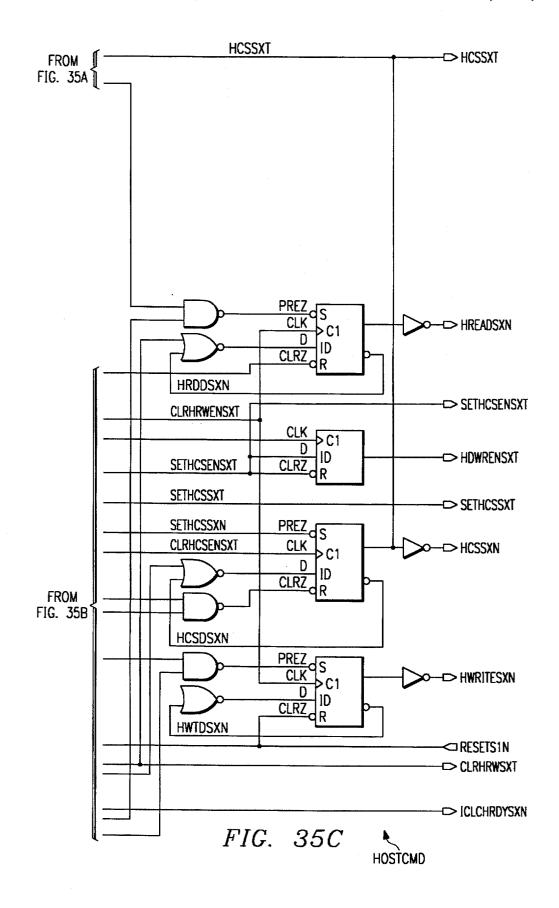

FIG. 35 is a schematic diagram of a host command circuit HOSTCMD of FIG. 22;

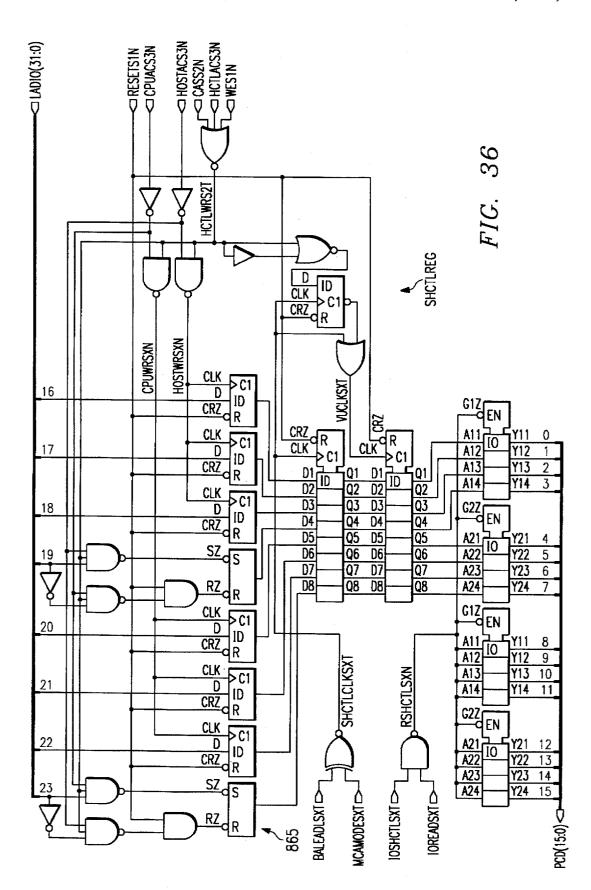

FIG. 36 is a schematic diagram of a shadow control register circuit SHCTLREG of FIG. 22;

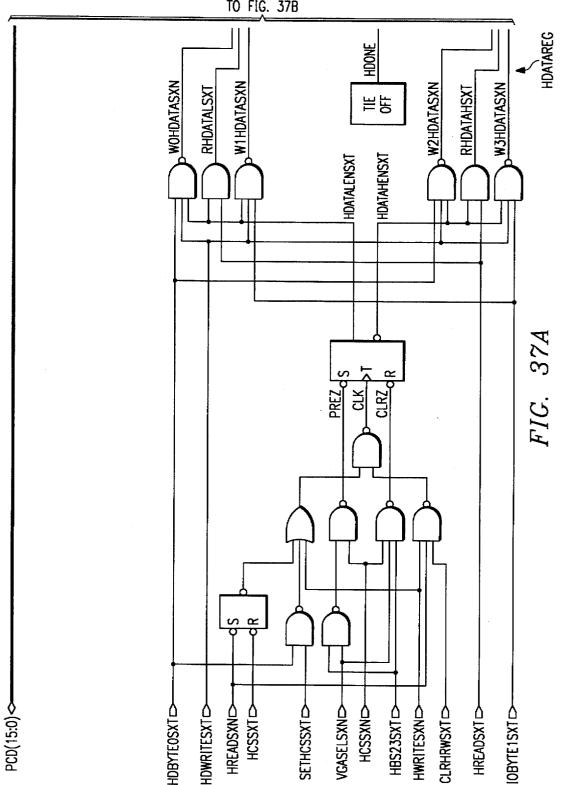

FIG. 37 is a schematic diagram of a data register circuit 65 HDATAREG of FIG. 22;

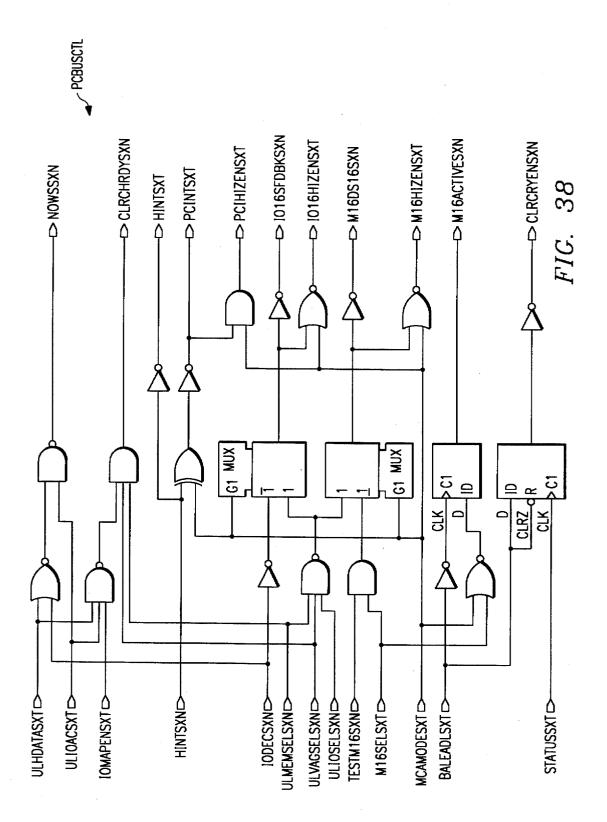

FIG. 38 is a schematic diagram of a bus control circuit PCBUSCTL of FIG. 23;

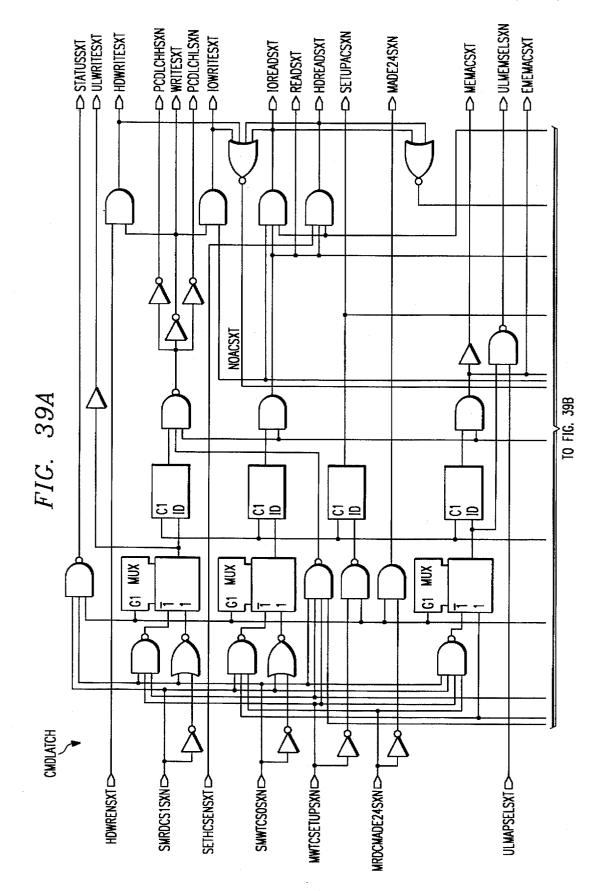

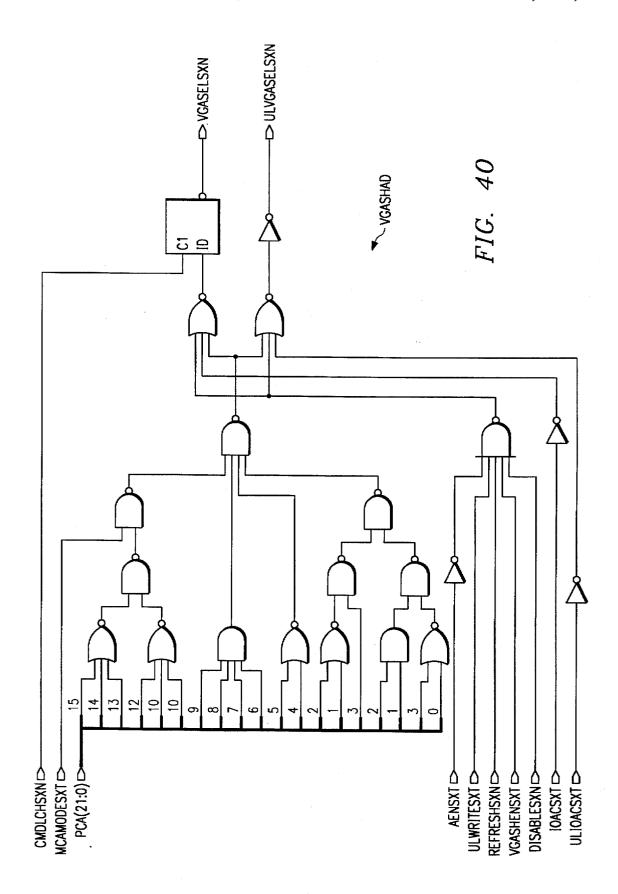

FIG. 39 is a schematic diagram of a command latch circuit CMDLATCB of FIG. 23;

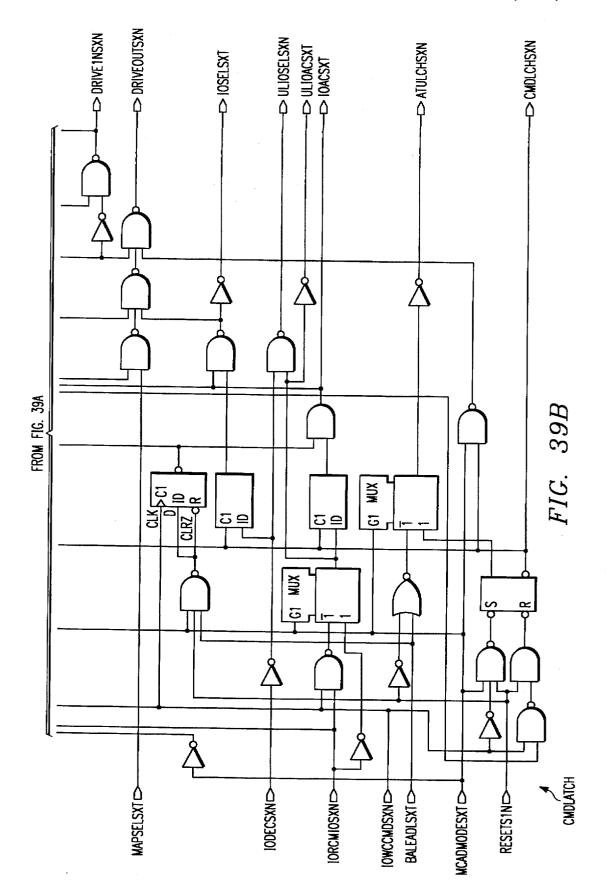

FIG. 40 is a schematic diagram of a VGA shadow circuit VGASHAD of FIG. 23;

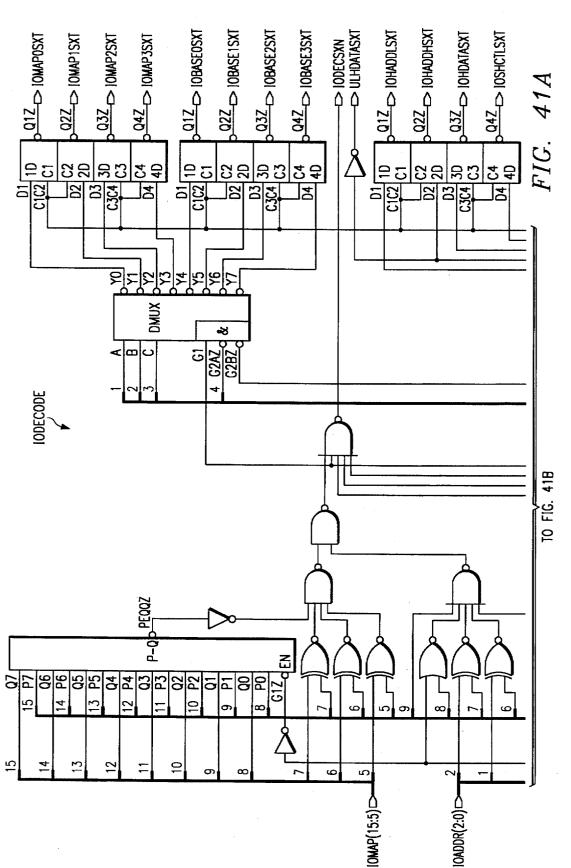

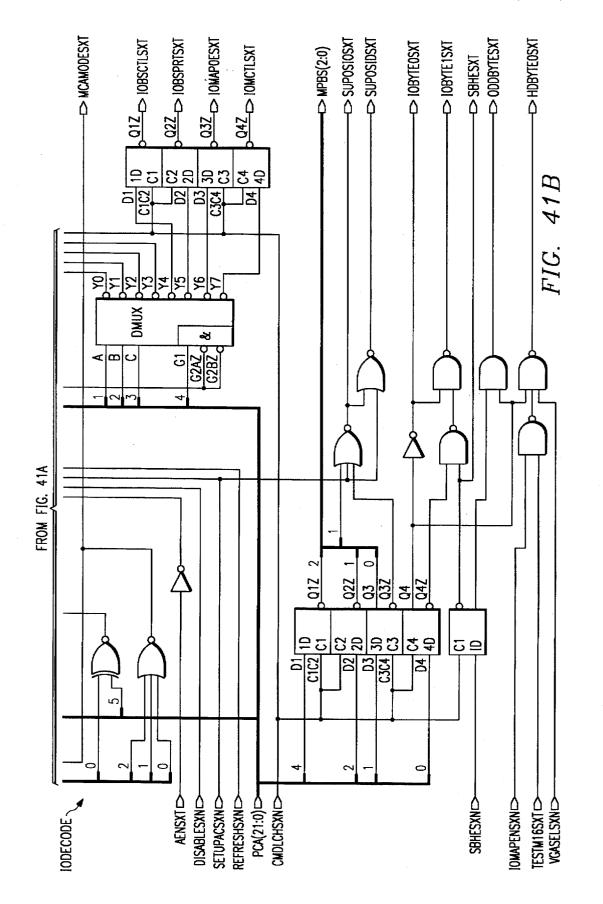

5 FIG. 41 is a schematic diagram of a decode circuit IODECODE of FIG. 23;

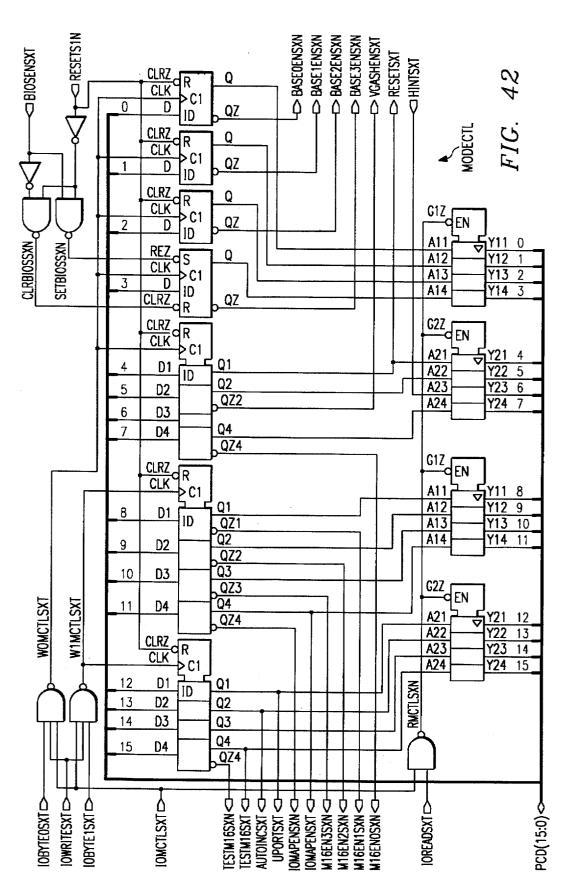

FIG. 42 is a schematic diagram of a mode control circuit MODECTL of FIG. 23;

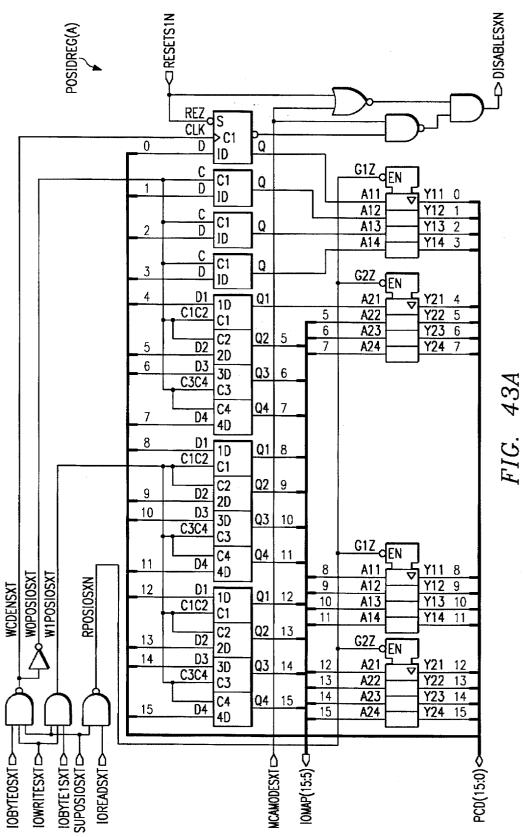

FIG. 43A is a schematic diagram of an MCA address 10 position circuit POSIDREG of FIG. 23;

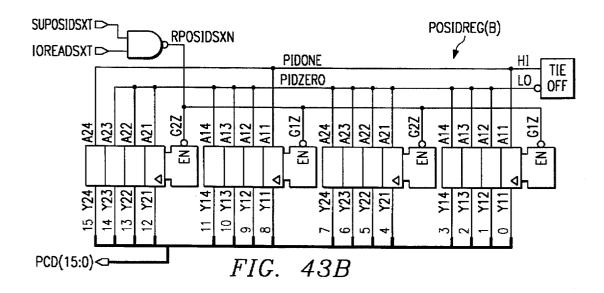

FIG. 43B is a schematic diagram of an MCA identification circuit POSIDREG of FIG. 23;

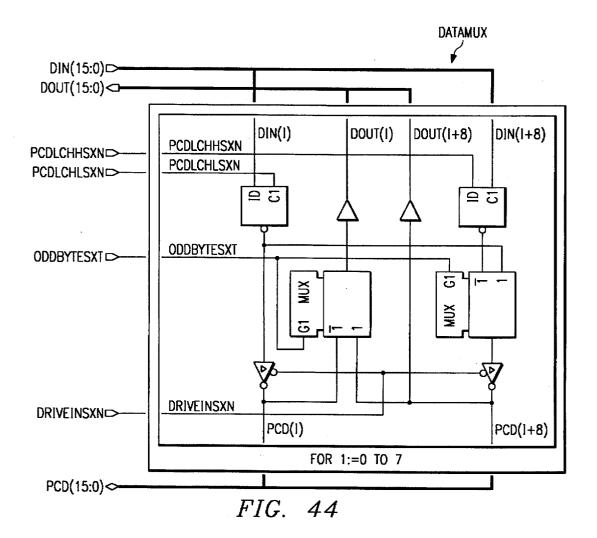

FIG. 44 is a schematic diagram of a circuit DATAMUX of 15 FIG. 23:

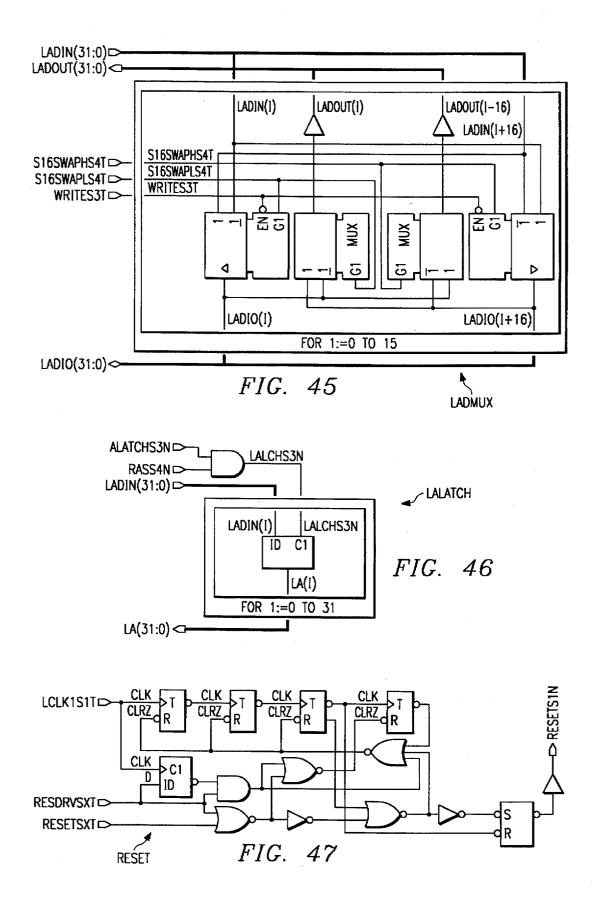

FIG. 45 is a schematic diagram of a circuit LADMUX of FIG. 24;

FIG. 46 is a schematic diagram of a latch circuit LALATCH of FIG. 24;

20 FIG. 47 is a schematic diagram of a reset circuit RESET of FIG. 24;

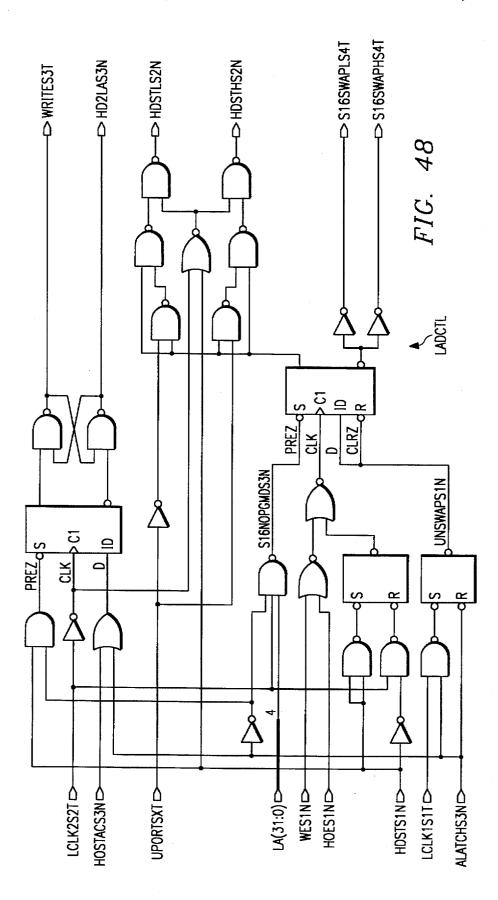

FIG. 48 is a schematic diagram of a control circuit LADCTL of FIG. 24;

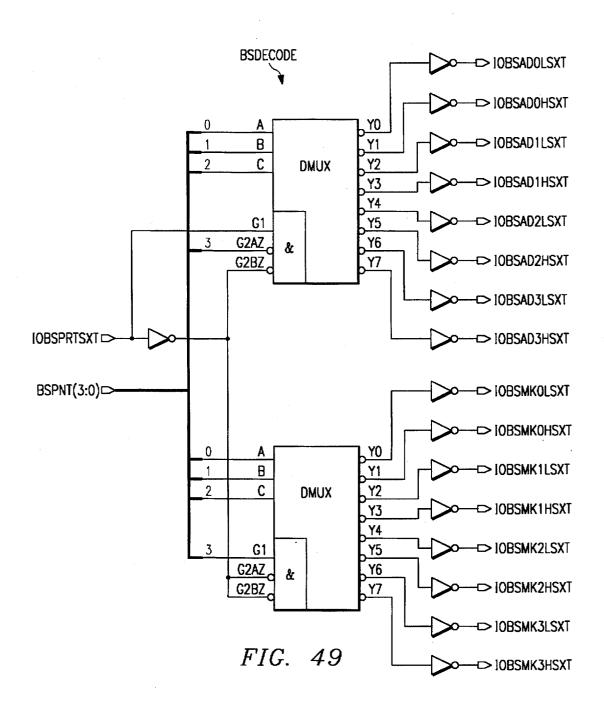

FIG. 49 is a schematic diagram of a bank select decode <sup>25</sup> circuit BSDECODE of FIG. 24;

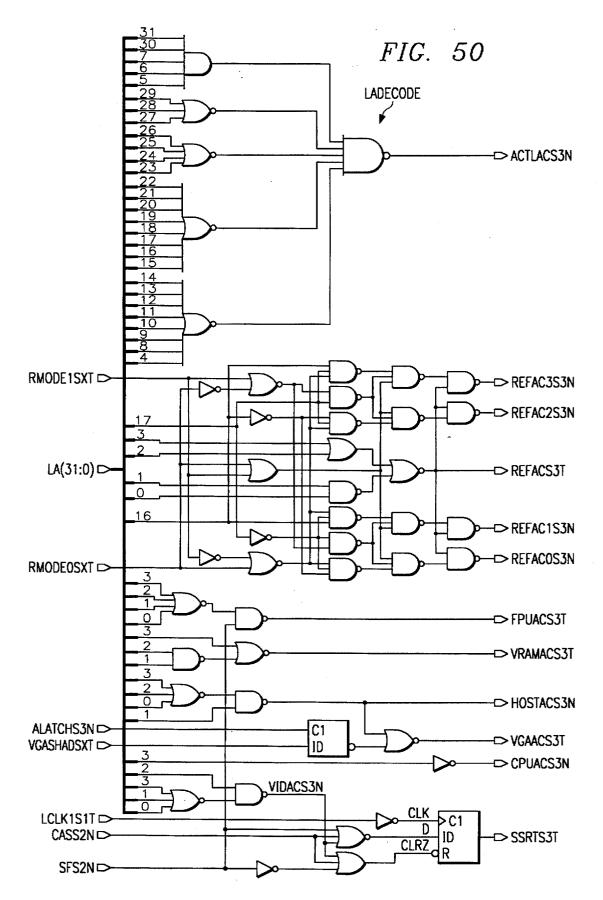

FIG. 50 is a schematic diagram of a decode circuit LADECODE of FIG. 24;

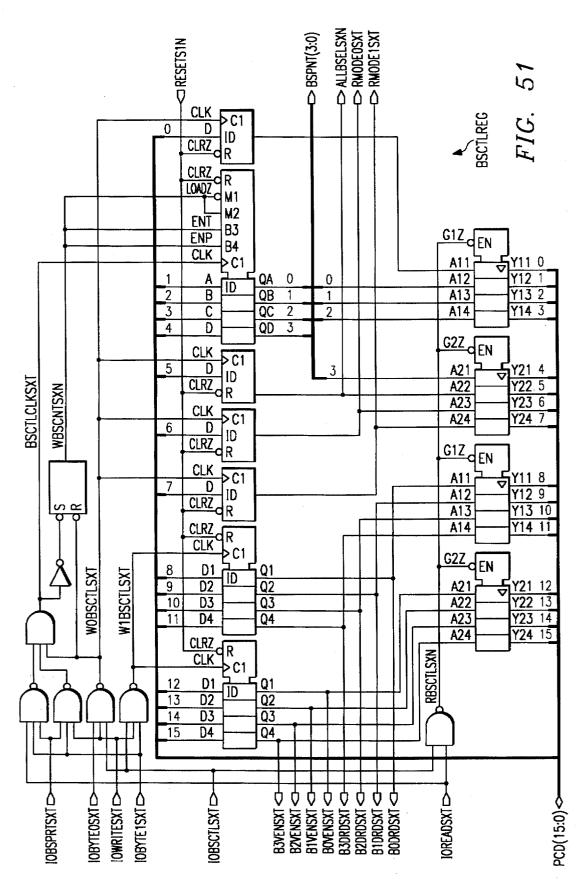

FIG. 51 is a schematic diagram of a bank select control register circuit BSCTLREG of FIG. 24;

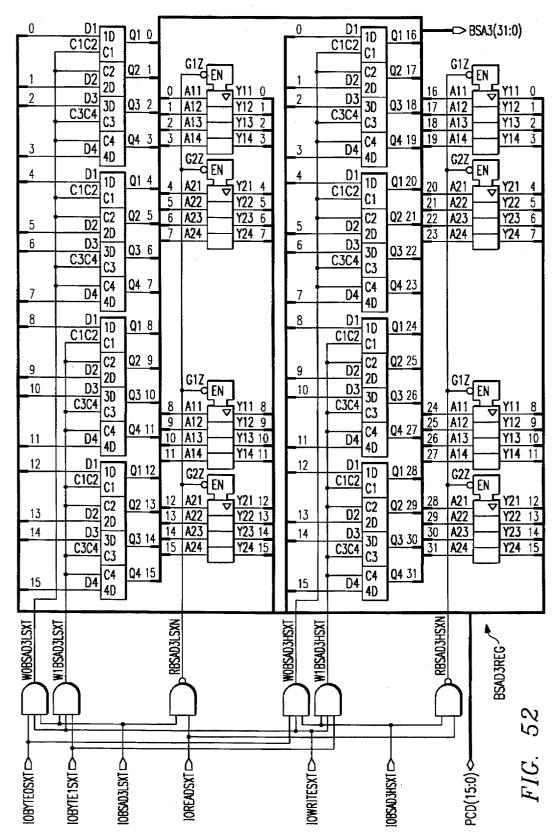

FIG. 52 is a schematic diagram of a bank select address register circuit BSAD3REG which is representative of four identical circuits BSAD0REG, BSAD1REG, BSAD2REG and BSAD3REG of FIG. 24;

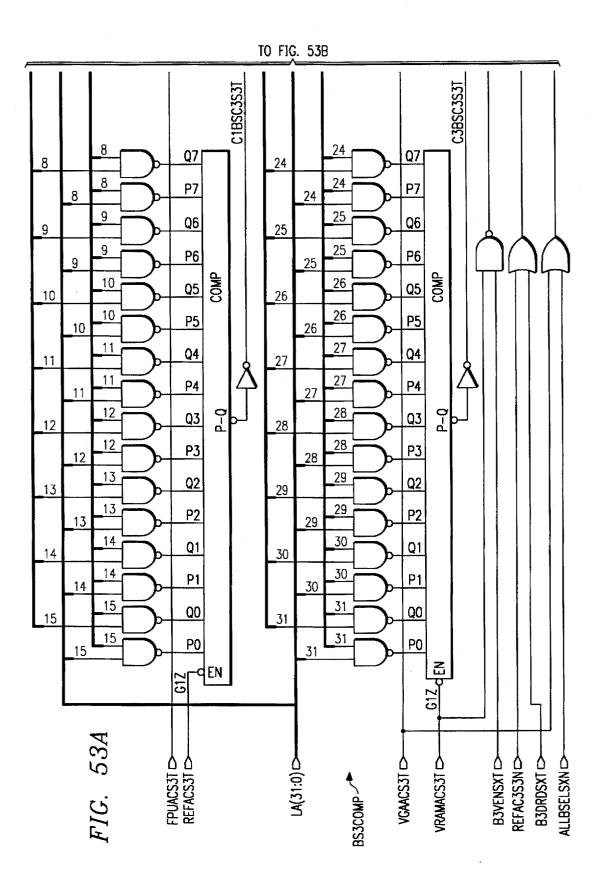

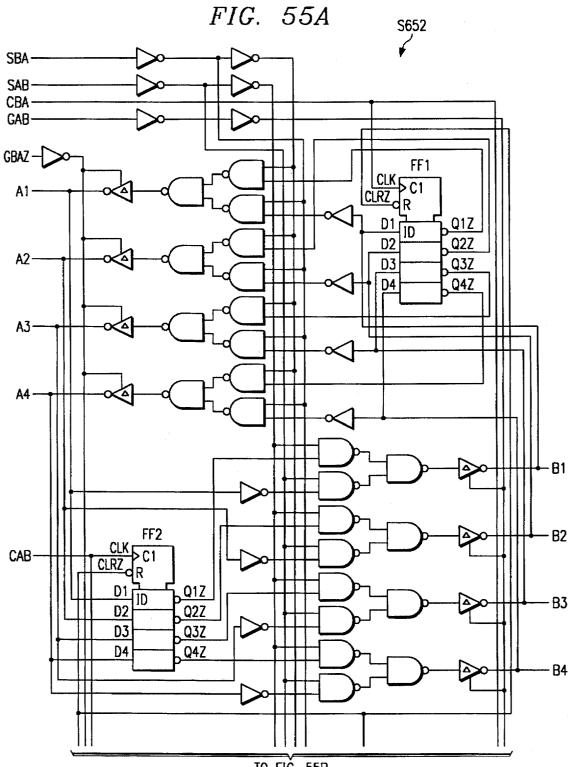

FIG. 53 is a schematic diagram of a bank select comparator circuit BS3COMP which is representative of four identical circuits BS0COMP, BS1COMP, BS2COMP and BS3COMP of FIG. 24;

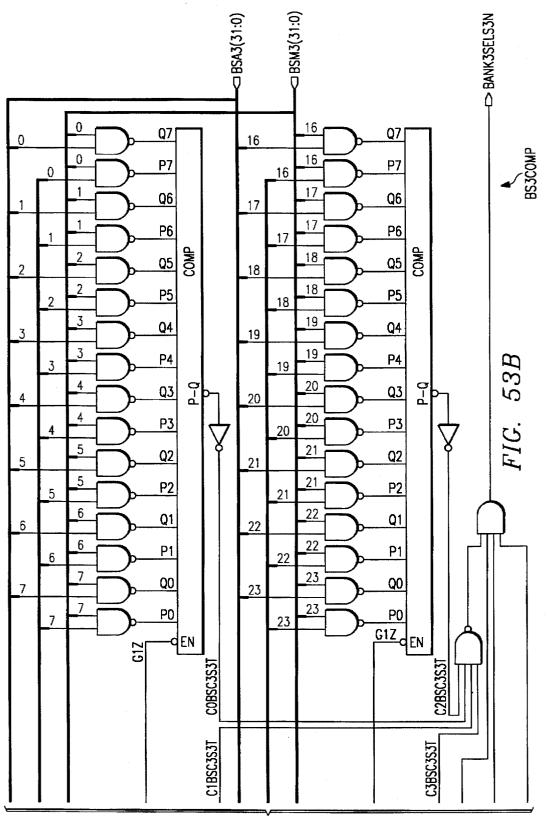

FIG. 54 is a schematic diagram of a bank select mask 40 register circuit BSMK3REG which is representative of four identical circuits BSMK0REG, BSMK1REG, BSMK2REG and BSMK3REG of FIG. 24;

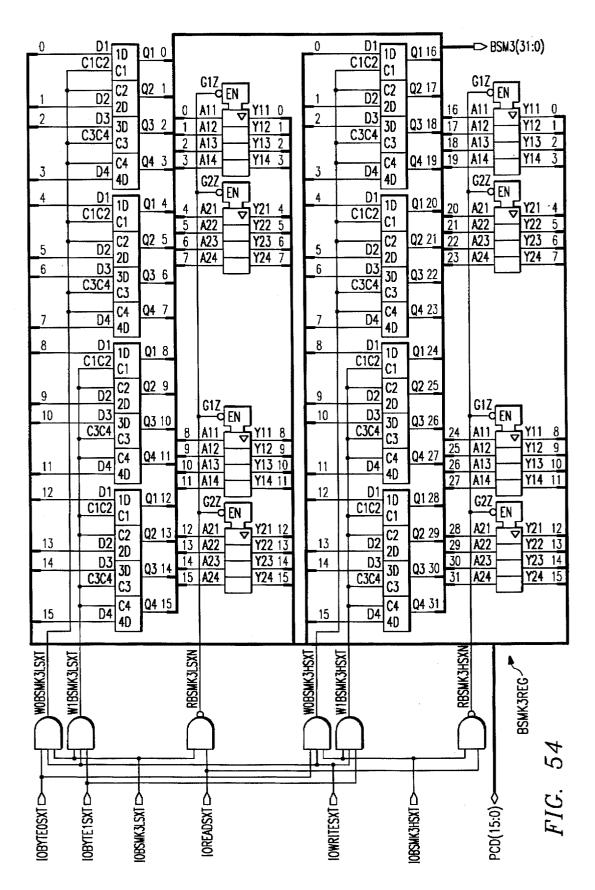

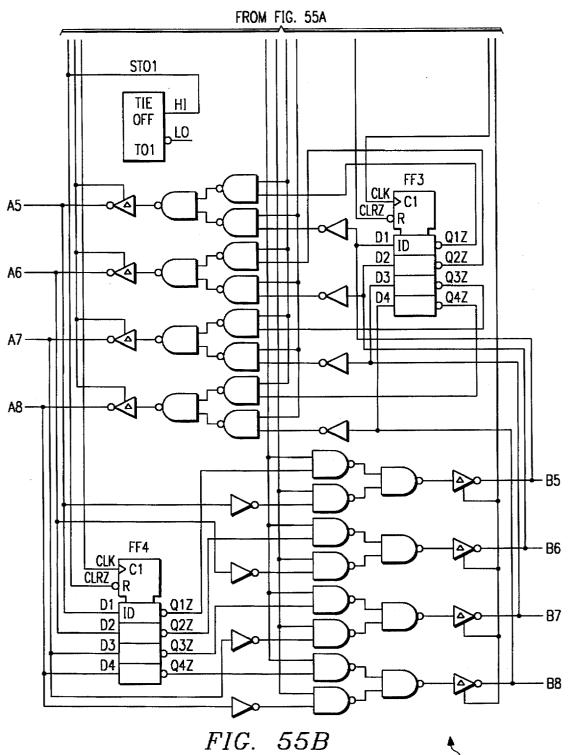

FIG. 55 is a schematic diagram of a circuit S652 of FIG. 37;

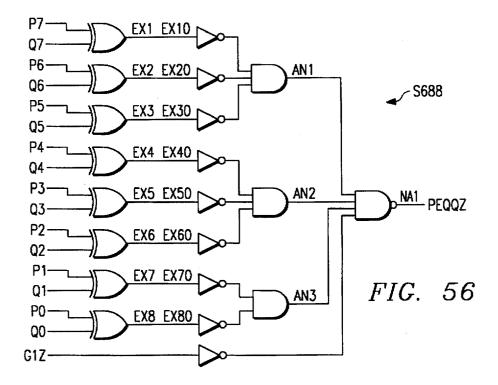

FIG. 56 is a schematic diagram of a circuit S688 of FIGS. 25 and 53;

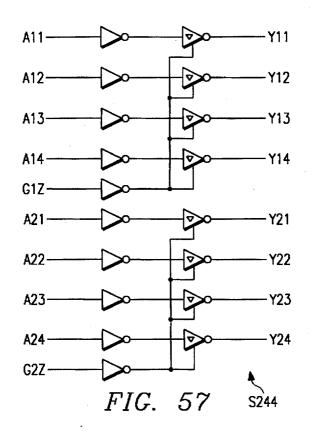

FIG. 57 is a schematic diagram of a circuit S244 of FIGS. 25-28, 31, 32, 36, 43A, 43B, 51, 52 and 54;

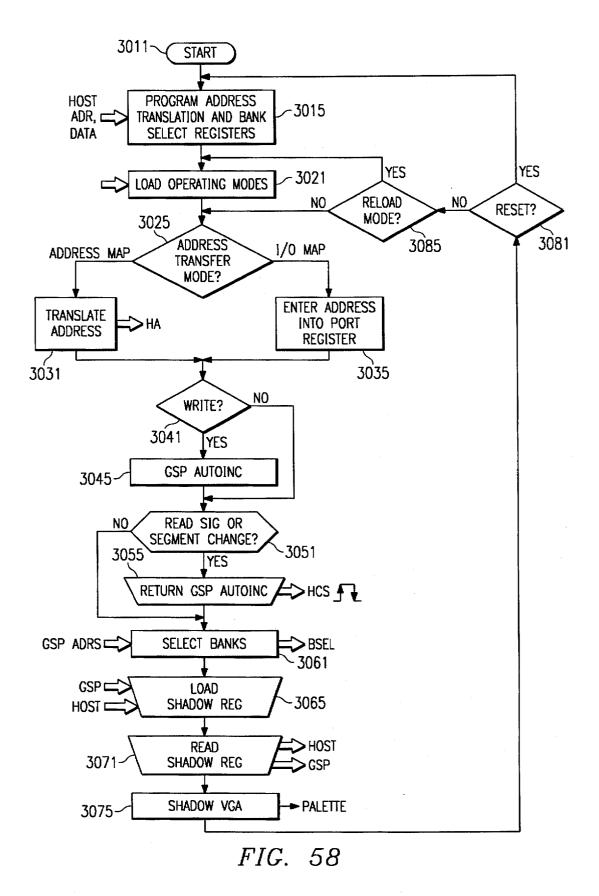

FIG. 58 is a process flow diagram of operational steps in the multifunctional access circuit of FIGS. 1, 4, 7 and 20; and

FIG. 59 is a block diagram of a FIFO register file circuit for improved data transfer between a host computer and a 55 graphics coprocessor via the access device.

Corresponding numerals and symbols in the different drawings refer to corresponding parts unless the context indicates otherwise.

# DETAILED DESCRIPTION OF PREFERRED EMBODIMENTS

FIGS. 1 and 2 illustrate a computer graphics system 100 including a graphics processing system 105 operating in conjunction with a host system 110. Supporting information 65 is provided in coassigned patent applications Ser. No. 080, 735 filed Jun. 22, 1993, a continuation of Ser. No. 544,774

filed Oct. 23, 1990 and now abandoned, entitled "PALETTE DEVICES, SYSTEMS AND METHODS FOR TRUE COLOR MODE"; U.S. Pat. No. 5,309,551 entitled "DEVICES, SYSTEMS AND METHODS FOR PALETTE PASS-THROUGH MODE"; U.S. Pat. No. 5,400,057 entitled "INTEGRATED CIRCUIT INTERNAL TEST CIR-CUITS AND METHODS"; U.S. Pat. No. 5,293,468 entitled "CONTROLLED DELAY DEVICES, SYSTEMS AND METHODS"; U.S. Pat. No. 5,327,159 entitled "PACKED BUS SELECTION OF MULTIPLE PIXEL DEPTHS IN PALEITE DEVICES, SYSTEMS AND METHODS"; U.S. Pat. No. 5,287,100 entitled "GRAPHICS SYSTEMS, PAL-ETTES AND METHODS WITH COMBINED VIDEO AND SHIFT LOCK CLOCK CONTROL"; U.S. Pat. No. 5,341,470 entitled "COMPUTER GRAPHICS SYSTEMS, PALETTE DEVICES AND METHODS FOR SHIFT CLOCK PULSE INSERTION DURING BLANKING" U.S. Pat. No. 5,270,687 entitled "PALEITE DEVICES, COMPUTER GRAPHICS SYSTEMS AND METHODS WITH PARALLEL LOOKUP AND INPUT SIGNAL SPLITTING"; Ser. No. 965,561 filed Oct. 23, 1992, a continuation of Ser. No. 426,480 filed Oct. 23, 1989 and now abandoned, a continuation of Ser. No. 346,388 filed Apr. 27, 1989 and now abandoned, a continuation of Ser. No. 207. 034 filed Jun. 13, 1988 and now abandoned, a continuation of Ser. No. 821,641 filed Jan. 23, 1986 and now abandoned, entitled "A GRAPHICS DATA PROCESSOR, A DATA PROCESSING SYSTEM, A GRAPHICS PROCESSING SYSTEM AND A METHOD OF PROCESSING GRAPH-ICS DATA", each of which is hereby incorporated by 30 reference. Also incorporated by reference herein are publications with further supporting information as follows: Texas Instruments TMS 34010 User's Guide (August 1988); TIGA-340 (TM) Interface, Texas Instruments Graphics Architecture, User's Guide, 1989, TMS 34020 User's Guide (January 1990), and TMS 44C251 Specification, all of which documents are currently available to the general public from Texas Instruments Incorporated.

FIG. 1 illustrates a block diagram of computer graphics system 100 which is constructed in accordance with the principles of a preferred embodiment of the present invention. Graphics processing system 105 includes a graphics printed wiring board 106 connected to a host processing system 110. Located on printed wiring board 106 are a graphics system processor GSP 120, a memory 130, a video 45 palette 150 and a digital to video converter 160. Elements 150 and 160 are connected by bus 155 and combined in a palette device 4000 driven by clock circuitry 41000 all as described in the incorporated patent applications such as 080,735 filed Jun. 22, 1993, continuation of Ser. No. 544, 774 filed Oct. 23, 1990 and now abandoned, entitled "PAL-50 ETTE DEVICES, SYSTEMS AND METHODS FOR TRUE COLOR MODE"; U.S. Pat. No. 5,309,551 entitled "DEVICES, SYSTEMS AND METHODS FOR PALETTE PASS-THROUGH MODE"; U.S. Pat. No. 5,400,057 entitled "INTEGRATED CIRCUIT INTERNAL TEST CIR-CUITS AND METHODS"; U.S. Pat. No. 5,293,468 entitled "CONTROLLED DELAY DEVICES, SYSTEMS AND METHODS"; U.S. Pat. No. 5,327,159 entitled "PACKED BUS SELECTION OF MULTIPLE PIXEL DEPTHS IN 60 PALETTE DEVICES, SYSTEMS AND METHODS"; U.S. Pat. No. 5,287,100 entitled "GRAPHICS SYSTEMS, PAL-ETTES AND METHODS WITH COMBINED VIDEO AND SHIFT CLOCK CONTROL". A video display 170 is driven from the video output of system 105 via connecting line 165.

Host processing system 110 provides the major computational capacity for the graphics computer system 100. Host

50

55

processing system 110 preferably includes at least one microprocessor 111 of FIG. 8, read only memory, random access memory 113 and assorted peripheral devices forming a complete computer system. Host processing system 110 of FIG. 1 preferably also includes some form of input device, 5 such as a keyboard or a mouse, and some form of long term storage device such as a disk drive. The details of the construction of host processing system 110 are conventional in nature and known in the art, therefore the present application will not further detail this element. An important 10 feature of host processing system 110, as far as the present embodiment is concerned, is that host processing system 110 determines the content of the visual display to be presented to the user by display 170.

Graphics system processor 120 provides the major data <sup>15</sup> manipulation to generate the particular video display presented to the user. Graphics processor 120 is bidirectionally coupled to host processing system 110 via a host bus 115 to a multifunction access chip or circuit 116 and a bus 118 to the GSP 120. GSP 120 operates as an independent data 20 processor from host processing system 110; however, it is expected that graphics processor 120 is responsive to requests from host processing system 110 and access circuit 116 via bus 118. Graphics processor 120 further communicates with memory 130, and video palette 4000 via video 25 memory bus 122 and palette bus 136. Graphics processor 120 controls the data stored within video RAM 132 via video memory bus 125. In addition, graphics processor 120 may be controlled by programs stored in either video RAM 132 or read only memory 134. Read only memory 134 may 30 additionally include various types of graphic image data, such as alphanumeric characters in one or more font styles and frequently used icons. In addition, graphics processor 120 controls the data stored within video palette 150. Also, graphics processor 120 controls digital to video converter 35 160 via video control bus 124. Graphics processor 120 can, for instance, control the line length and the number of lines per frame of the video image presented to the user by control of digital to video converter 160 via video control bus 124.

A preferred embodiment of multifunction access circuit <sup>40</sup> 116 (also designated by a contemplated identifier 34094) is implemented as a single chip device for interfacing the TMS 34020 GSP to either the ISA bus (Industry Standard Architecture) or MCA bus (Micro Channel Architecture) as PC (personal computer) backplane buses. The device is fabricated in a 160 pin Quad Flat Pack using Texas Instruments TSC500 Standard Cell ASIC Technology.

This single chip multifunctional access circuit 116 allows the TMS34020 to be mapped into either the memory space or the I/O space of a PC 110. I/O mapping takes advantage of the implicit addressing host interface capabilities of the TMS34020 GSP 120. Memory mapping circuitry also provided in device 116 is selectively operable to coordinate with the GSP capabilities.

Four independent sets of memory mapping hardware allow four arbitrary regions of the TMS34020 memory space to be mapped into four separate arbitrarily selected and programmable memory segments of the PC memory map. Each of these mapping regions is individually pro- 60 grammable in size from 8 Kilobytes up to 4 Megabytes.

A special arbitrary alignment mode is provided in circuitry of one or more sets of the memory mapping hardware. This alignment mode establishes a starting address from which the region size begins in a particular address region of 65 the memory map, and continues contiguously for the full region size. This is also called extended mapping mode.

Four fully programmable sets of address decoding hardware are incorporated in access circuit 116, to perform bank selecting of TMS34020 GSP 120 local memory.

VGA pass-through circuitry in access circuit 116 supports the TMS34020 subsystem in emulating VGA as one example of a resident graphics architecture to be passed through to the display as desired.

When a BIOS ROM or EPROM 119 is provided, the access device 116 is selectively preconfigurable at power-up so that GSP 120 can access the BIOS ROM 119 by asserting addresses in its own local memory space.

A shadow circuit is provided in access device 116 to shadow the HSTCTLL register of the GSP 120. In this way, interrupt polling is performed without burdening the GSP 120.

Video memory 130 includes video RAM 132 which is bidirectionally coupled to graphics processor 120 via video memory bus 125. Video RAM 130 includes bit mapped graphics data which controls the video image presented to the user. This video data may be manipulated by graphics processor 120 via video memory bus 125. In addition, the video data corresponding to the current display screen is output from video RAM 132 via video output bus 136. The data from video output bus 136 corresponds to the picture element or pixel to be presented to the user. For one example, video RAM 132 is formed of a plurality of TMS44251 256KX4 dynamic random access memory integrated circuits available from Texas Instruments Incorporated, the assignee of the present application. The TMS44251 integrated circuit includes dual ports, enabling display refresh and display update to occur concurrently.

In accordance with the typical arrangement of video random access memory 132, this memory consists of a bank of several separate random access memory integrated circuits. The output of each of these integrated circuits is typically only one or four bits wide and is output on video output bus 136.

Video palette 150 receives the high speed video data from video random access memory 132 via bus 136. Video palette 150 also receives data from graphics processor 120 via video memory bus 122. Video palette 150 converts the data received on parallel bus 136 into a video level output via bus 155. This conversion is achieved by means of a look-up table which is specified by graphics processor 120 via video memory bus 122. The output of video palette 150 may comprise color hue and saturation for each picture element or may comprise red, green and blue primary color levels for each pixel or any other suitable technique. The table of conversion from the code stored within video memory 132 and the digital levels output via bus 155 is controlled from graphics processor 120 via video memory bus 122.

FIG. 2 illustrates graphics processor 120 in further detail. Graphics processor 120 includes a central processing unit 200, special graphics hardware 210, register files 220, instruction cache 230, host interface 240, memory interface 250, input/output registers 260 and video display controller 270.

Central processing unit 200 not only does general purpose data processing and arithmetic and logic operations but also a number of special purpose graphics instructions, either alone or in conjunction with special graphics hardware 210.

Graphics processor 120 includes a major bus 205 which is connected to most parts of graphics processor 120 including the central processing unit 200. Central processing unit 200 is bidirectionally coupled to a set of register files 220 including a number of data registers, via bidirectional reg-

ister bus 202. Register files 220 serve as a depository of immediately accessible data used by central processing unit 200. Register files 220 include, in addition to general purpose registers which are employed by central processing unit 200, a number of data registers which are employed to 5 store implied operands for graphics instructions.

Central processing unit 200 is connected to instruction cache 230 via instruction cache bus 204. Instruction cache 230 is further coupled to bus 205 and is loaded with instruction words from video memory 130 (FIG. 1) via video  $^{10}$ memory bus 122 and memory interface 250. The instruction cache 230 speeds up the execution of functions that are used often within a particular portion of the program executed by central processing unit 200. Access to instruction cache 230 via instruction cache bus 204 is much faster than access to 15 video memory 130.

Host interface 240 is coupled to central processing unit 200 via host interface bus 206. Host interface 240 is further connected to host processing system 110 (FIG. 1) via access bus 118, access circuit 116 and host system bus 115. Host Interface 240 controls the timing of data transfer between host processing system 110 and graphics processor 120. In this regard, host interface 240 enables either host processing system 110 to interrupt graphics processor 120 or vice versa. 25 In addition, host interface 240 is coupled to major bus 205 enabling host processing system 110 via access circuit 116 to control directly the data stored within memory 130. Typically, host interface 240 would communicate graphics requests from host processing system 110 to graphics processor 120, enabling the host system to specify the type of display to be generated by video display 170 and causing graphic processor 120 to perform a desired graphic function.

Central processing unit 200 is coupled to special graphics hardware 210 via graphics hardware bus 208. Special graph-35 ics hardware 210 is further connected to major bus 205. Special graphics hardware 210 operates in conjunction with central processing unit 200 to perform special graphic processing operations. Central processing unit 200, in addition to its function of providing general purpose data processing, controls the application of the special graphics hardware 210 in order to perform special purpose graphics instructions. These special purpose graphics instructions concern the manipulation of data within the bit mapped portion of video RAM 132. Special graphic hardware 210 operates under the control of central processing unit 200 to enable particular advantageous data manipulations regarding the data within video RAM 132.

Memory interface 250 is coupled to bus 205 and further coupled to video memory bus 122 and 125. Memory inter-50 face 250 serves to control the communication of data and instructions between graphics processor 120 and memory 130. Memory 130 includes both the bit mapped data to be displayed via video display 170 and instructions and data necessary for the control of the operation of graphics processor 120. These functions include control of the timing of memory access, and control of data and memory multiplexing. In the preferred embodiment, video memory bus 125 includes multiplexed address and data information. Memory interface 250 enables graphics processor 120 to provide the  $_{60}$ proper output on video memory bus 125 at the appropriate time for access to memory 130.

Graphics processor 120 further includes input/output registers 260 and video display controller 270. Input/output registers 260 are bidirectionally coupled to bus 205 to enable 65 reading and writing within these registers. Input/output registers 260 are preferably within the ordinary memory

space of central processing unit 200. Input/output registers 260 include data which specifies the control parameters of video display controller 270. Video display controller 270 is clocked by a video clock signal VCLK from palette 4000. In accordance with the data stored within input/output registers 260, video display controller 270 generates the signals on video control bus 124 for the desired control of palette 4000. Data within input/output registers 260 includes data for specifying the number of pixels per horizontal line, the horizontal synchronization and blanking intervals, the number of horizontal lines per frame and the vertical synchronization and blanking intervals. Input/output registers 260 may also include data which specifies the type of frame interlace and specifies other types of video control functions. Input/output registers 260 are also a depository for other specific kinds of input and output parameter which are more fully detailed below.

Graphics processor 120 operates in two differing address modes to address memory 130. These two address modes are x y addressing and linear addressing. Because the graphics processor 120 operates on both bit mapped graphic data and upon conventional data and instructions, different portions of the memory 130 may be accessed most conveniently via differing addressing modes. Regardless of the particular addressing mode selected, memory interface 250 generates the proper physical address for the appropriate data to be accessed. In linear addressing, the start address of a field is formed of a single multibit linear address. The field size is determined by data within a status register within central processing unit 200. In x y addressing the start address is a pair of x and y coordinate values. The field size is equal to the size of a pixel, that is the number of bits required to specify the particular data at a particular pixel.

Turning to FIG. 3, the memory structure of a typical graphics memory system is illustrated. Background information on video RAM (VRAM) is found in coassigned U.S. Pat. Nos. 4,330,852; 4,639,890 and 4,683,555 which are hereby incorporated by reference. While there are many memory structures and systems which could be used, one example shown in FIG. 3 uses eight VRAM memories 132 in an array. Each VRAM memory, or unit, has four sections, or planes, 0, 1, 2 and 3. The construction of each plane is such that a single data lead is used to write information to that plane. In a system which uses a 32 bit data bus, such as data bus 125, there would be 8 VRAM memories (two of which are shown in FIG. 3) each VRAM memory having 45 four data leads connected to the input data bus.

Thus, for a 32 bit data bus, VRAM memory 132 would have its four data leads connected to data bus leads 0, 1, 2, 3 respectively. Likewise, the next VRAM memory would have its four leads 0, 1, 2, 3 connected to data bus leads 4, 5, 6, 7 respectively. This continues for the remaining six VRAM's such that the last VRAM has its leads connected to leads 28, 29, 30, 31 of bus 125.

The memories are arranged such that the pixel informa-55 tion for the graphics across the planed serially across the planes in the same row. Assuming a four bit per pixel system, then the bits for each pixel are stored in a separate VRAM memory. In such a situation, pixel 0 would be in the first VRAM and pixel 1 would be in the second VRAM. The pixel storage for pixels 2 through 7 are not shown. The pixel information for pixel 8 then would be stored in the first VRAM, still in row 0 but in column 2 thereof. The reason for this arrangement of pixel information will be more fully appreciated from an understanding of how information is retrieved from the memory.

Continuing with FIG. 3, each VRAM plane has a serial register 139 for shifting out information from a row of memory. The shifting occurs at a rate determined by shift clock signal SCLK from palette 4000. The outputs from these registers are connected to bus 136 in the same manner as the data input leads are connected to the input bus. Thus, data from a row of memory, say row  $\mathbf{0}$ , would be moved into 5 register 139 and occur serially from each register 139 and in parallel on bus 136. This would occur for each plane of the eight memory array.

Looking at data output bus 136 then at an instant of time the first bit in each shift register would be on the bus. Thus, <sup>10</sup> assuming row 0 is being outputted to the bus, the bus would have an its lead 0 the row 0, bit A0 (plane 0) of memory 130. Bus 136 lead 1 would have on it row 0, bit A0 (plane 1), while lead 2 would have row 0, bit A0 (plane 2) and lead 3 would have on it row 0, bit A0 (plane 3). These bits would <sup>15</sup> be followed by the bits from the next VRAM. Thus, at a first instant of time, data bus 136 would have on it the four bits forming pixel 0 next to the four bits forming pixel 1, next to the four bits forming pixel 2. This continues until the 32 bits forming the 8 pixels 0-7 are on the parallel leads of data bus 20 136. These bits are supplied to the graphics display and the shift registers all shift one position providing the bus with pixel information for the next 8 pixels, namely pixels 8 through 15. This shifting continues until the entire row in the VRAMs is shifted out and then a new row is selected for 25 loading into the output serial registers.

Up to this point it is assumed that the bit information per pixel is 4 bits. If the pixel information were to be, say 8 bits, then two VRAMs would have to be used per pixel. This would change the bit patterns somewhat. Also, it should be <sup>30</sup> noted that memory sizes and structures vary and the size and structure shown are only for illustrative purposes.

The serial register 139 for each memory can be 512 bits long thereby transferring 16384 bits to the display for each 35 memory-to-serial register read cycle. These 16384 bits represent data for 2048 display pixels, assuming each pixel contains 8 bits. However, assume each scan line only requires 1280 pixels. Thus, on every line of memory 768 pixels from each row of memory cannot be displayed. This 40 memory is difficult to use for other purposes and thus is effectively wasted.

To solve the problem, the serial output register 139 is split in half and each half is used to output data from the VRAM. While it is understood that 32 shift registers 139 are used, the  $_{45}$ discussion focuses on one plane of the memory with the understanding that all planes work in the same manner. The two halves of the register 139 are identified as half A and half B. Advantageously, the serial register 139 takes from memory an entire row of screen memory and presents that  $_{50}$ row to the screen pixel-by-pixel in a smooth, even flow.

As discussed above, if this were to occur with a single. unsplit serial register 139, then the information for one entire scan line of the display would have to be moved from memory 132 into the serial register 139 and then shifted onto 55 addresses supplied by the address bus 713 of the host the screen at the screen clocking rate. This, then, would require each row of memory to contain only one line (or full multiples thereof) of screen information. That is not the case with a split serial register, where bits can be shifted from the A section while other bits are loaded into the B section and 60 shifted to the screen from the B section while other bits are loaded into the A section.

In FIG. 4, multifunction access circuit 116 is connected via bus 115 to a personal computer PC 110 of FIG. 1 and receives PC signals and replies with PC returns. A MAP 65 selector 401 is a DIP switch, jumpers or other circuit that establishes a parallel digital signal for access circuit 116

activating predetermined address segments in PC address space for mapping or translation into the address space of GSP 120. An interrupt line from access circuit 116 is switched by a selector switch SEL 405 (or any suitable selector circuit) to a selected one of several interrupt lines in bus 115.

Access circuit 116 is connected to a local bus LAD connected to GSP 120 and palette and video backend 4000. A VGA control signal VGASHAD from access circuit 116 is fed to a PAL 411 which in turn supplies a VGA control output to palette chip 4000. A split shift register transfer signal SSRT is supplied to palette chip 4000 directly from access circuit 116, compare FIG. 22 and description in incorporated U.S. Pat. No. 5,341,470 entitled "COMPUTER GRAHPICS SYSTEMS, PALETTE DEVICES AND METHODS FOR SHIFT CLOCK PULSE INSERTION DURING BLANKING". Access circuit 116 also is connected to send and receive control signals and data to and from GSP 120. Bank selection of VRAM in VRAM section 130 is facilitated by bank select outputs BSEL[3:0] from access circuit 116 which are OR-ed by OR-gates 415 with RAS- (row address strobe) from GSP 120 to supply bank RAS signals BRAS-[3:0].

In the pictorial sketch of FIG. 5 multifunction access circuit 116 is provided on a graphics system board 106. The board 106 is also stuffed with a 1 Megabit VRAM 130, a TMS 34020 GSP 120, DRAM 121, EPROM 119, programmable palette 4000 and a set of clock oscillators 4100. System board 106 is advantageously provided with opposite bus connectors, one for bus 115 and a feature connector 1125 for VGA pass through respectively. Board 106 is inserted into the motherboard of its host computer by the connector for bus 115.

Further in system 105, a connector 165 supplies RS343-A video (RGB) output to a color display device 170 of FIG. 1. Sync generation is incorporated on one of the color output channels, e.g. Green.

FIG. 6 shows an exemplary pinout diagram for the multifunction access circuit 116. The designations of pins on the left and right sides of FIG. 6 are entered horizontally, and those for pins on top and bottom are entered vertically (e.g. VSS vertically in upper right corner). The functions of the pins and circuitry connected to them are described in more detail in connection with the other Figures of drawing.

In FIG. 7 multifunction access circuit 116 is used with first and second digital computers such as host PC 110 and GSP 120 of FIGS. 1 and 4. Each of the computers has an address bus for supplying addresses and a data bus for supplying data, see host bus 115 and LAD bus (including address bus HA) 118. The access circuit 116 has an address decoder 711 with inputs for the address bus 713 in bus 115 from the host computer.

An address translator circuit 715 has address inputs for computer and outputs for translated addresses to the address bus HA of the graphics coprocessor 120. The address translator circuit 715 also has base and map registers 716 selectable by the address decoder 711 and data inputs via data bus 717 to program the registers so selected with data from the data bus 717 from the host computer.

A port circuit 721 includes HADDR registers controlled by the address decoder 711 for entry of address information from the data bus 717 and assertion of the address information on the address bus HA of the second computer.

A mode control circuit 731 is connected to the address decoder 711 and connected to the data bus 717 to program

10

the mode control circuit to selectively establish operation of the address translator circuit 715 and of the port circuit 721.

An address range selection decoder 735 is fed by three lines IOSEL/MCASEL from MAP selector 401. Decoder 735 controls address translator 715. In this way selector 401 and decoder 735 act as a selection circuit feeding the address translator circuit 715 to establish a plurality of address ranges in which the address translator circuit 715 is to respond to the address bus 713 of the host computer to translate addresses.

A transceiver circuit HDATA 741 provides bidirectional communication between the data bus 717 from the host computer and the data bus [LAD 31:0] from the GSP 120.

A bank selector circuit 751 responds to addresses from the 15 address bus HA of the GSP 120 to supply a set of bank select outputs BSEL.

A shadow register circuit 761 shadows GSP 120 host control register HSTCTLL for interrupt polling and message passing as described in further detail in connection with 20 FIGS. 19 and 36.

A split shift register transfer decoder 771 is connected to the LAD data bus and responsive to control signals on LAD[0:3], local clock LCLK1 and column address strobe CAS2- from the GSP 120 to produce a flag signal on line 25 SSRT for split shift register transfer.

VGA detector 781 is an address detector circuit responsive to particular addresses on host bus 713 to produce control signals including a shadow detect signal VGASHAD, control signal VGAHCS- and read/write VGAHWR- to support VGA graphics display pass-through mode. Host control logic circuitry 785 receives both the VGA control signals and further address unit control signals ADDHCS-, ADDHWR-, ADDHRD- from address translator 715. Circuitry 785 is also responsive to 34020 control 35 signals HRDY, HOST and HOE-. Circuitry 785 feeds a communication direction control signal DIR to the transceivers in block 741. As outputs to GSP 120, the logic circuitry supplies HCS-, HWRITE-, HREAD-. and byte selects HBS01 and HBS23.

A reset control circuit 791 is responsive to a reset input RESET to establish predetermined bits in shadow circuit 761, bank selector 751, mode control 731 and address translator 715 on power up.

Viewed together, the host control logic circuitry 785 acts 45 with circuitry in the TMS34020 as a memory access circuit for use with host computer 110. Host computer 110 can assert read and write signals and an address. The circuitry of FIGS. 1-5 has memory accessible by asserting addresses thereto. Access circuit 116 has address translator circuit 715 with address inputs for the address supplied by the host computer and outputs for supplying a translated address to the address logic in host interface 240 of the TMS34020 graphics coprocessor. That address logic has an address autoincrement circuit responsive to a write signal to auto- 55 has graphics circuitry mounted on it, and produces color matically increment the translated address for the memory and responsive to a control signal HCS- to return to the translated address. Control circuitry 785 of FIG. 7 is connected to the address logic in the TMS34020 and is responsive to a read signal from the host computer 110 to supply the HCS- control signal to the logic circuit to return to the translated address. As described in the 34020 User's Guide, the TMS 34020 has an autoincrementing feature which allows a host processor 110 to address a contiguous block of local memory by specifying the address of only the first 65 word in a block. The TMS34020 in autoincrement mode automatically generates subsequent addresses and byte

selects. A host computer can access contiguous blocks of words 16 bits or 32 bits at a time.

To use autoincrementing, the host asserts HCS- active low at the beginning of the first access, providing the address and byte selects just as it does for a regular access. The host maintains HCS- active low throughout. The TMS34020 enables autoincrementing when it detects that HCS-remains low between the end of a previous access and the beginning of the current access. The host then uses HREAD-and HWRITE- as a strobe to request access to succeeding consecutive autoincremented addresses.

When autoincrementing is detected, the host interface 240 uses the value of HBS0-3 to determine whether the host is accessing the block 16 bits or 32 bits at a time. Byte select outputs HBS01 and HBS23 of the circuit 116 are fed to respective pairs of the HBS0-3 inputs of the 34020 GSP for example. If all 4 byte selects are active, the TMS34020 assumes that the host needs only one access to completely read or write a 32 bit location. If only two byte selects are active (HBS0 and HBS1, or HBS2 and HBS3), the TMS34020 assumes that the host requires two accesses to completely read or write a 32-bit location.

The TMS34020 latches the value of HBS0-3 at the falling edge of HCS-. If the next access will be made to a subsequent 16 bit or 32 bit location, the TMS34020 automatically generates the byte selects for the access by swapping its internal copy of the byte selects after each access. Thus, if the latched value of HBS0-3 is 0011, then the internal copy is swapped to 1100 at the beginning of the next access. This in turn is swapped back to 0011 at the beginning of the following access, and so on.

The TMS34020 supports autoincrementing for reads and writes when HINC=1 and HPFW=0, and it supports autoincrementing after writes only when HINC=1 and HPFW=1. HINC=0 disables the autoincrementing feature.

In a further advantageous feature, control logic circuitry 785, which is connected to address translator circuit 715, is operative to supply control signal HCS- when the hostasserted address on bus 713 changes from one address segment to another segment as defined by the base registers BASE0-3. Upon a segment change, circuit 785 generates the HCS- control signal as successive opposite transitions from low to high to low for the GSP 120. In this way, time consuming operations by the host computer 110 are eliminated by the operation of circuit 785.

VGA pass through mode provides VGA and non-VGA displays with as few as one monitor. In FIG. 8 a computer has a motherboard 110 with a microcomputer chip 111 and memory chips 113 mounted thereon. Motherboard 110 is connected to bus 115. A VGA-compatible graphics board 1105 is connected to the motherboard 110 by bus 115. If only VGA were to be used, a monitor 1170 would be connected to a DB-15 video connector 1165 on board 1105. Board 1105 code signals according to the VGA standard. The VGA circuitry has a memory buffer 1111 followed by a palette RAM 1131 and then a digital to analog converter DAC 1115. The VGA circuitry is controlled by the microcomputer chip 60 on motherboard 110.

To provide advanced non-VGA displays, a board 105 of FIG. 1 is connected to bus 115. Board 105 has multifunction access device 116 and graphics processor 120 and is responsive to control by the microprocessor 111 such as an 80386 on motherboard 110. A video memory 130 is connected to the graphics processor 120 to produce color code signals on another bus 136 according to a second graphics architecture

such as the Texas Instruments TIGA graphics architecture, for palette 4000 connected by printed wiring to the VRAM 130. A feature connector 1125 on board 105 is connected by a VGA bus 1123 to a feature connector 1121 on graphics board 1105. Feature connector 1121 provides color code signals according to the VGA standard. Feature connector 1125 on board 105 inputs the VGA color code signals.

By virtue of VGA pass-through, monitor 1170 can be dispensed with, and monitor 170 is connected to DB-15 video connector 165 to display both VGA graphics and 10 TIGA graphics as user selects.

Palette 4000 has an input register 4011 of FIG. 31 of coassigned incorporated U.S. Pat. No. 5,341,470 entitled **"COMPUTER GRAPHICS SYSTEMS, PALETTE** DEVICES AND METHODS FOR SHIFT CLOCK PULSE 15 INSERTION DURING BLANKING" with a first area connected to the video memory 130 of FIG. 8 to enter a first set of color code bits according to TIGA architecture. Input register 4011 has a second area connected to the feature connector 1125 to enter a second set of color code bits 20 according to the VGA standard. Look-up table memory 4021 of FIG. 31 in said incorporated application TI-14523 supplies color data words in response to color codes from the input register 4011. Selector circuit 4051 is connected between the input register 4011 and the look-up table 25 memory 4021. The selector circuit 4051 is connected via a control register 4371 to graphics processor 120 via bus 122 of FIG. 1 herein and is thereby controllable to transfer selected color codes on the selected bus 136 or 1123 according to the selected first or second graphics standard to 30 the look-up table memory 4021.

Because of the way the hardware and software of a typical 80386 based computer such as an IBM-compatible PC (personal computer) works, boot-up operations shortly after the PC is powered up assert a predetermined address signal 35 to "look for" the VGA graphics board 1105 of FIG. 8, which is provided as a standard board in an IBM-compatible PC. If the VGA board 1105 is connected to an IBM monitor 1170, a separate monitor 170 is needed to connect to board 105. During bootup, the PC CPU would find the VGA  $_{40}$ hardware 1105 and do the start-up sequence that would put text on the monitor 1170. Then when high resolution graphics is requested, the system would turn off the VGA monitor 1170 or not utilize it and then enable monitor 170. Since each monitor 1170 and 170 can be the same kind of device, 45 it desirable in many cases to use a single monitor. If both boards 1105 and 105 are to be used with only one monitor, the VGA pass through circuit 781 on access device 116 detects the special VGA address when the host 110 is addressing VGA board 1105. This detection, or shadowing, 50 activates the VGA pass-through circuit to allow viewing VGA data such as the initially displayed VGA prompt. VGA pass-through advantageously obviates any need to implement VGA itself on palette 4000 or anywhere on board 105. VGA board 1105 responds to the CPU on motherboard 110 55 during boot-up, provides the initial text and initial prompt directly to monitor 170 by virtue of the VGA pass-through mode provided in palette 4000, whereupon a switch can be made to the high resolution mode provided by board 105. Thus, there is no need for separate monitors for the VGA  $_{60}$ board 1105 and for high resolution board 105. Board 105 needs no VGA power up initializing software or other duplication of VGA.

In addition, the VGA pass-through mode allows VGA compatible application software to be executed by CPU 111 65 and allows VGA graphics to be created by board 110 or on the motherboard itself, whereupon the VGA graphics are

passed through board 105 in the VGA pass-through mode. When high resolution mode is called for, the graphics are controlled by the CPU on board 110 but set up by graphics processor 120 (such as TMS 34010 or 34020 GSP from Texas Instruments Incorporated using the TIGA TI Graphics Architecture), passed through the VRAM 130 and palette 4000 to monitor 170.

The pass-through improvement does not depend on particular characteristics of VGA or TIGA. Accordingly, any two or more graphics architectures, standards or methods can be accommodated.

FIGS. 7a-c and 9-13 are described elsewhere herein.

In FIG. 14 address translator circuit 715 includes base registers BASE0-3 and map registers MAP0-3. Circuit 741 of FIG. 14 has a pair of 16 bit transceivers 743 and 745 to mediate bidirectional data transfers.

In FIG. 14A a control circuit 811 cooperates with a comparing circuit 813 to present the values in base registers BASE0-3 to circuit 813 for comparison with most significant bits (MS bits) of an address value on PC address bus 713. The base registers include segment size information (see also FIG. 16) to control the number of MS bits being compared by circuit 813. If the address on bus 713 lies in the predetermined address segment of any of the BASE registers, a MATCH signal is provided to the control circuit 811. A counter 815 in control circuit 811 counts up the base registers as it accesses them, and when a match occurs, the corresponding MAP register in the set MAP0-3 is accessed by putting its map MS bits onto the address bus HA to GSP 120. In this way address translation is accomplished. Advantageously, the circuit 811 with counter 815 prevents conflicting output from a pair of the map registers if a pair of the base registers contain the same value.

An extended map register MAP0E of FIGS. 14, 15 and 17 further provides output of least significant (LS) translation bits. Advantageously the map register and extended map register are connected to supply the address bus HA to the GSP 120 with an address having a value translated from but independent of the bits of the address signal from the host computer 110.

In FIG. 18 bank selection circuit 751 of FIG. 7 has bank select address registers 851 that store a set of predetermined addresses as a basis of response to LAD bus addresses by circuit 751. The flexibility of response is enhanced by a further set of bank select mask registers 855 which establish which bits of the addresses are ignored and which are to be compared by a comparator 853. When a match occurs, comparator 853 sends a signal to a control circuit 857 which produces a bank select output appropriate to the selected bank. Thus, the comparator 853 and control 857 act as a memory strobe decoder. The mask register 855 defines which bits of an address on the LAD bus are significant for bank selection. The address register 851 holds a predetermined bank selection address, and the comparing circuit 853 is responsive to the address on the bus and mask register bits to produce a match output when the significant bits for bank selection on the address bus match the bank selection address in the address register.

The bank select circuit 751 has a programmable control register BSCTL. Control circuit 857 is responsive to bits in the control register BSCTL, such as bits indicating whether a bank consists of video RAM (VRAM) or not. The control circuitry 857 responds to the bits indicating VRAM to supply additional bank select signals. Other bits cause control circuit 857 to execute different refresh modes for dynamic random access memory (DRAM). To program load

the various registers in circuit 751 an autoincrementing pointer circuit responsive to BPNT bits in BSCTL sequentially addresses the address registers 851 and mask registers 855 in response to a single address from the host address bus 713 (FIG. 7). Successive data are thus loaded from the host data bus 717 for programming the registers respectively. In FIG. 19, shadow circuit 761 of FIG. 7 is associated with a first address decoder 711 having inputs for the host address bus 713 and a read line IORC from the host computer. A second address decoder 863 has inputs for the address bus HA, and control lines for address latch ALTCH-, column address strobe CAS2-, and write WE- from the GSP 120. A logic circuit 865 has a register selectable by either of the first address decoder 711 and the second address decoder 863. Decoder 711 initiates output enable OE from circuit 865 to activate Q data outputs for connection to the data bus 717 to the host computer. Decoder 863 clocks D data inputs of circuit 865 that connect to the LAD data bus. Write protect circuitry is suitably connected to the register in circuit 865, and the register 865 includes space for interrupt and message  $_{20}$ passing bits. Interrupt signaling to the host is suitably supplied by an interrupt bit in register 865 and directly via an interrupt output HINT of TMS34020 through logic 867 to host interrupt line PCINT, see FIG. 4.

The shadow circuit makes a local copy of the 34020 host control register. The problem solved is that if the host **110** accesses the 34020, the GSP must take a cycle for servicing the host. By shadowing, the host **110** can read-access the shadow register **865** without having to access the 34020 host control register. On write, either host **110** or GSP **120** can write to the shadow register **865**. The 34020 is connected to circuit **761** to simultaneously write to its own host control register HSTCTLL and to shadow register **865**, thereby making the contents of the two registers identical at all times. Message bits in register **865** are accessible by the 34020 and host **110**. These message bits are mailboxes respectively to the data bus of the host and to the data portion of the LAD bus.

HINT is an output signal from the 34020 and HINT is activated by the GSP writing to GSP host control register. 40 HINT is intercepted by the circuit **761** and turned into PCINT. FIG. **9** shows a detail of register **865** designated SHDHCTL. Bits Ii and Io are the images of two bits in the 34020 host control register. Ii controls the host message interrupt to the 34020 if the host **110** requested an interrupt by writing Ii. PCINT is the result of Io. The Io bit in register **865** is fed by HINT and goes from the 34020 to the circuit **761**. When bit Io in the GSP is active it makes HINT active. In circuit **867** of FIG. **19** HINT is buffered and put out as PCINT. 50

Thus in this embodiment, the Ii bit is written by a signal on the host data bus and redundantly passed through the transceiver to the Ii bit of the corresponding register in the 34020. The Io bit of host control register HSTCTLL in the 34020 is written by the 34020 and fed to the HINT output 55 of 34020 whence it is buffered in the circuit **867** and fed to the interrupt output PCINT. The Io bit of the shadow register **865** is also written in the shadowing process by the data portion of the LAD bus and fed to the interrupt output PCINT. In this way, interrupt signalling is completely 60 supported, and furthermore interrupt polling and message passing also occur with reduced burden to the 34020.

A distinct other operation herein also called shadowing involves VGA pass through mode. In VGA the host 110 does the processing work that a GSP would do. The VGA card 65 1105 (FIG. 8) has memory 1111 to buffer the graphics data coming from the host, and a palette RAM 1113 and digital

to analog converter DAC 1115. The circuits 781 and 785 of FIG. 7 operate so that access circuit 116 herein is said to shadow the VGA accesses to duplicate in palette 4000 any changes to the VGA palette 1113 entries. Different VGA 5 signals include pixel data information and address information. Host 110 using VGA might perform operations which correspond to drawing a circle. Then it would write pixel data to the VGA buffer for display of video scan lines portraying the circle. Taking the circle example a step 10 further, the color of the circle can be more efficiently changed by modifying a palette RAM entry than changing numerous VGA buffer entries. VGA detector 781 detects VGA addressing for VGA palette update by host 110 on bus 115 and simultaneously updates the palette 4000 as if it were 15 the VGA palette.

- The TMS34094 is a TSC500 standard cell ASIC

- to interface a TMS34020 to the ISA (Industry Standard Architecture) bus, or MCA (Micro Channel Architecture) bus.

MCA and ISA are both designed for the Intel  $80 \times 86$  microprocessors, and so are similar in many aspects. This makes it relatively easy to offer support for both buses within the same chip, without incurring a great overhead compared with offering support for only one bus.

The primary features are listed below.

The TMS34094 will support two methods of access:

- Memory mapped—TMS34020 memory space mapped directly into the PC memory space using mapping registers.

- I/O mapped—TMS34020 memory space accessed indirectly via ADDRESS and DATA registers in PC I/O locations.

In order to further support a TMS34010-like interface, the TMS34020's HSTCTLL I/O register will be shadowed within the TMS34094, and will be accessible from a PC bus I/O location. This will allow either of the following

handshake/interrupt schemes to be used efficiently: Direct interruption, using the IRQ pins of the PC bus with selectable priority.

Polled, without hampering TMS34020 performance by having to access the HSTCTLL register directly. The TMS34094 will also provide:

- Support for 16 Mb address range (24 bits). This is the full range available for ISA. MCA has the capability to use 32 bit addressing (4Gb),

- Full compatibility with ISA bus limitations on 16-bit transfers (minimum segment size for 16-bit transfers is 128 kb). No such restrictions exist for MCA.

- One bus wait state capability on ISA accesses. Zero wait state capability on MCA accesses.

- Shadowing of direct writes to the VGA palette to allow VGA pass-through.

- Support for power-up BIOS ROM mapped into the TMS34020's memory space on graphics subsystem.

In addition, the following features not directly related to ISA/MCA/TMS34020 interfacing will be provided, in order to further reduce the system chip count:

- A set of four fully programmable bank select signals, which can be gated, typically with  $\overline{RAS}$ , but perhaps with  $\overline{CAS}$ ,  $\overline{WE}$  or  $\overline{TR}/\overline{QE}$  from the TMS34020 to control which bank of memory is to be selected.

- A signal to the video back-end to directly support the use of VRAM split serial register transfers. This signal will indicate when to insert the required SCLK pulse between the nonsplit and split transfers, in order to ensure correct operation.

FIG. 1 shows a typical system containing the TMS34094. The TMS34094 is connected directly between the PC bus and the TMS34020. No other interface hardware is required except:

- A DIP switch package to determine the I/O address 5 mapping (not required for MCA as pins must be wired to GND).

- A DIP switch selector to determine which of the PC's IRQ lines the TMS34094's PCINT output is connected to.

- 10 A quad OR package to allow RAS to be gated with BSEL<3:0> to produce one  $\overline{RAS}$  signal for each bank.

A PAL to control access to the palette.

In order to write a single byte to the TMS34020's local memory, a read (modify) write of the word containing the 15 byte is performed.

This only applies to direct memory mapped accesses; the I/O registers on TMS34094 can be accessed as bytes or words.

| -24 | D |

|-----|---|

| -   | , |

| LCLK1     | Local clock 1.                                            |

|-----------|-----------------------------------------------------------|

| LCLK2     | Local clock 2.                                            |

| LAD<31:0> | 32-bit local address/data bus.                            |

| ALTCH     | Address latch.                                            |

| RAS       | Row address strobe.                                       |

| CAS2      | Column address strobe indicating access to the LS         |

|           | byte of HSTCTLL.                                          |

| WE        | Write enable indicating a write to HSTCTLL.               |

| SF        | VRAM special function pin, required to control SCLK       |

|           | insertion signal.                                         |

| HDST      | Host data strobe, for latching data into the TMS34094.    |

| HOE       | Host output enable for driving data out of the TMS34094.  |

| HRDY      | Host ready, indicates when a PC initiated cycle can       |

|           | complete.                                                 |

| HINT      | Host interrupt, indicates an interrupt to the PC bus from |

|           | the TMS34020.                                             |

The following pins are outputs, which either connect to the TMS34020 pins of the same name or to some other function in the TMS34020 system.

| Key: | HI signals: | HA<31:5>, HBS01, HBS23, HCS, HREAD, HWRITE                     |

|------|-------------|----------------------------------------------------------------|

|      | HI returns: | HRDY, HDST, HOE, HINT                                          |

|      | MC signals: | ALTCH, RAS, CAS2, WE, SF, LCLK1, LCLK2                         |

|      | PC signals: | All PC bus input signals that the TMS34094 has pins for.       |

|      | PC returns: | CHRDY, M16/CD DS16, IO16/CD SFDBK, NOWS.                       |

|      | OR:         | Quad OR package to gate BSEL<3:0> with RAS.                    |

|      | PAL:        | Decodes VGASHAD, WE, TR/QE and LAD<3:0> status code to control |

|      |             | accesses to the palette.                                       |

|      | SEL:        | Selector switch to determine which IRQ line PCINT connects to. |

|      | MAP:        | Selector switches to determine the value of IOSEL/MCASEL<2:0>  |

|      |             |                                                                |

A typical system containing the TMS34093 is illustrated in FIG. 4.

The TMS34094 will be packaged in a 160 pin EIAJ 35 standard Quad Flat Pack. There are 146 functional pins, which are listed below. The remaining 14 pins will be used for VCC (6) and GND (8). See FIG. 6.

Many of the pins have both ISA and MCA functions. If these cases, the pin will have two names; the first corresponding to the ISA function, the second to the MCA function, and the two will be separated by a slash (/).