SPRS030A - APRIL 1995 - REVISED APRIL 1996

- Powerful 16-Bit TMS320C5x CPU

- 20-, 25-, 35-, and 50-ns Single-Cycle Instruction Execution Time for 5-V Operation

- 25-, 40-, and 50-ns Single-Cycle Instruction Execution Time for 3-V Operation

- Single-Cycle 16 × 16-Bit Multiply/Add

- 224K × 16-Bit Maximum Addressable External Memory Space (64K Program, 64K Data, 64K I/O, and 32K Global)

- 2K, 4K, 8K, 16K, 32K × 16-Bit Single-Access On-Chip Program ROM

- 1K, 3K, 6K, 9K × 16-Bit Single-Access On-Chip Program/Data RAM (SARAM)

- 1K Dual-Access On-Chip Program/Data RAM (DARAM)

- Full-Duplex Synchronous Serial Port for Coder/Decoder Interface

- Time-Division-Multiplexed (TDM) Serial Port

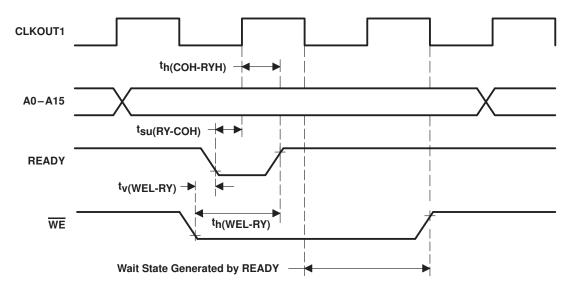

- Hardware or Software Wait-State Generation Capability

- On-Chip Timer for Control Operations

- Repeat Instructions for Efficient Use of Program Space

- Buffered Serial Port

- Host Port Interface

- Multiple Phase-Locked Loop (PLL) Clocking Options (×1, ×2, ×3, ×4, ×5, ×9 Depending on Device)

- Block Moves for Data/Program Management

- On-Chip Scan-Based Emulation Logic

- Boundary Scan

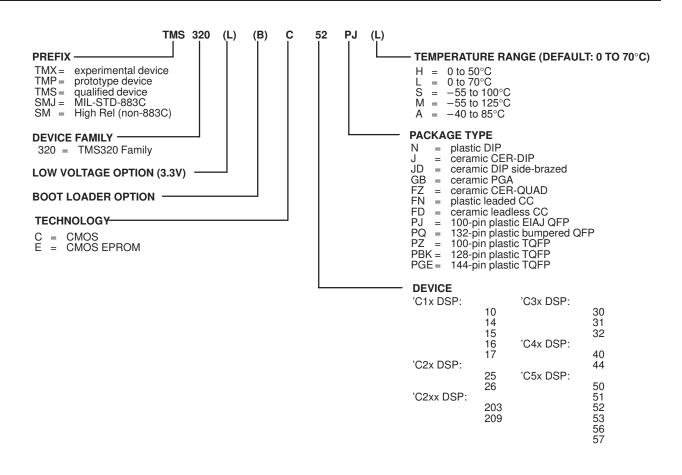

- Five Packaging Options

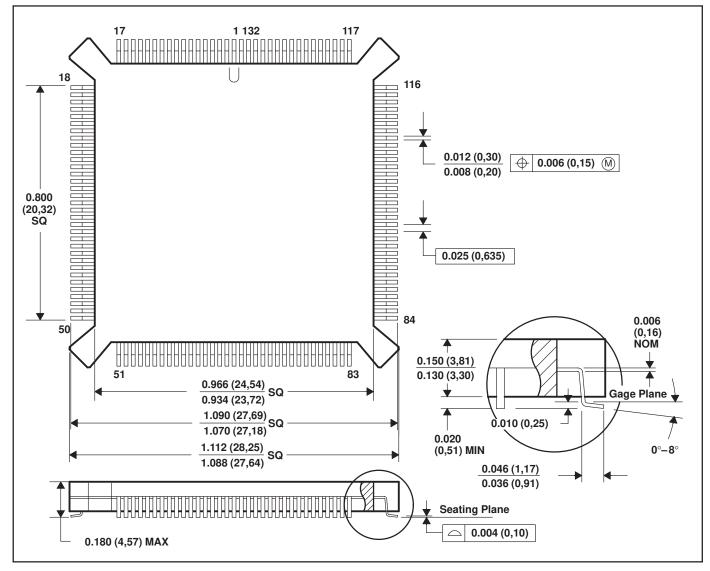

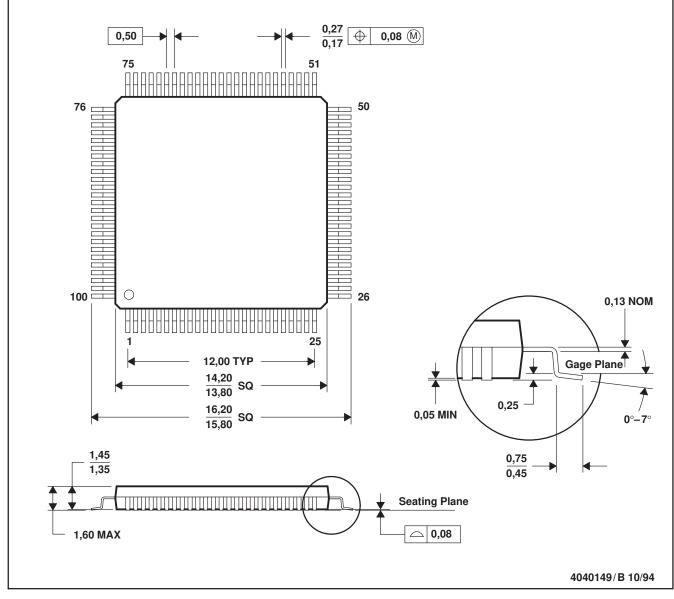

- 100-Pin Quad Flat Package (PJ Suffix)

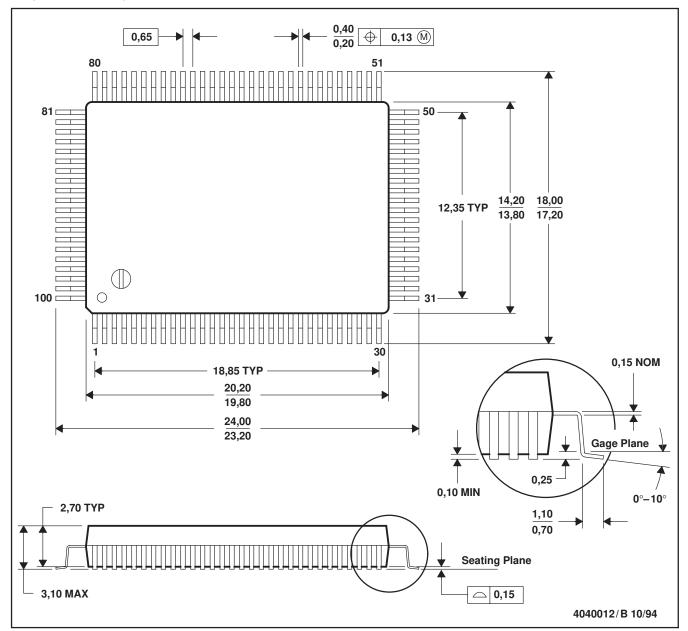

- 100-Pin Thin Quad Flat Package (PZ Suffix)

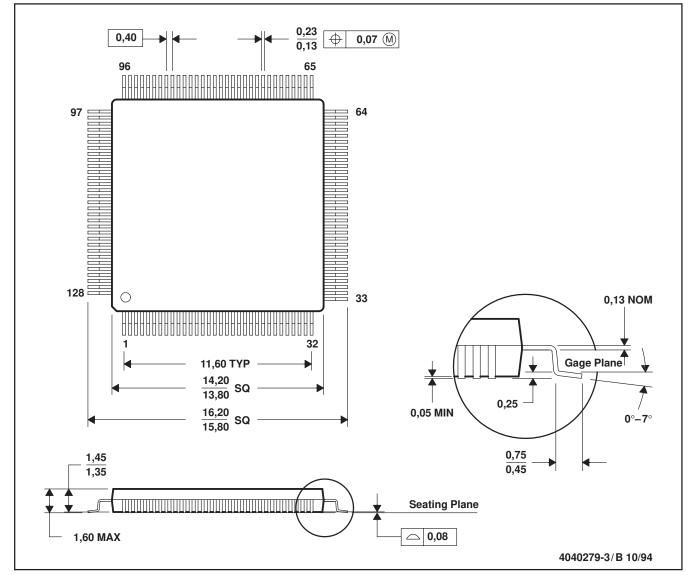

- 128-Pin Thin Quad Flat Package (PBK Suffix)

- 132-Pin Quad Flat Package (PQ Suffix)

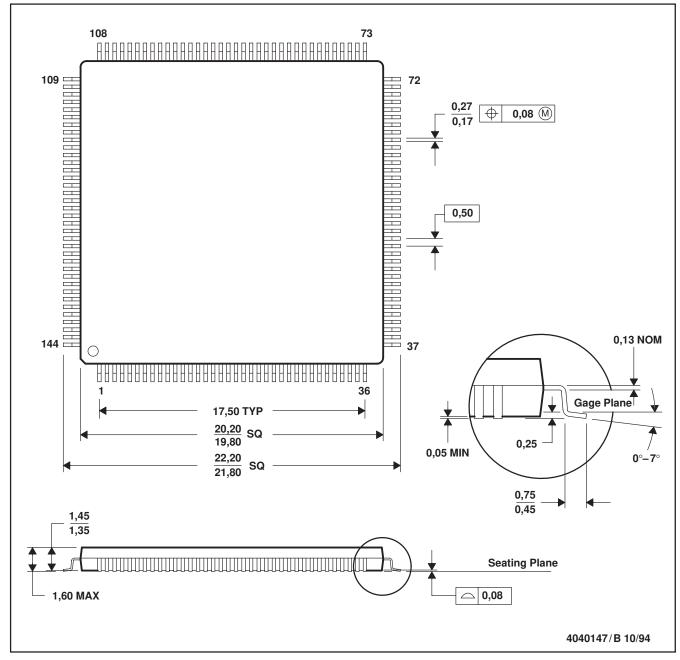

- 144-Pin Thin Quad Flat Package (PGE Suffix)

- Low Power Dissipation and Power-Down Modes:

- 47 mA (2.35 mA/MIP) at 5 V, 40-MHz Clock (Average)

- 23 mA (1.15 mA/MIP) at 3 V, 40-MHz Clock (Average)

- 10 mA at 5 V, 40-MHz Clock (IDLE1 Mode)

- 3 mA at 5 V, 40-MHz Clock (IDLE2 Mode)

- 5  $\mu\text{A}$  at 5 V, Clocks Off (IDLE2 Mode)

- High-Performance Static CMOS Technology

- IEEE Standard 1149.1<sup>†</sup> Test-Access Port (JTAG)

#### description

The TMS320C5x generation of the Texas Instruments (TI<sup>TM</sup>) TMS320 digital signal processors (DSPs) is fabricated with static CMOS integrated circuit technology; the architectural design is based upon that of an earlier TI DSP, the TMS320C25. The combination of advanced Harvard architecture, on-chip peripherals, on-chip memory, and a highly specialized instruction set is the basis of the operational flexibility and speed of the 'C5x<sup>‡</sup> devices. They execute up to 50 million instructions per second (MIPS).

The 'C5x devices offer these advantages:

- Enhanced TMS320 architectural design for increased performance and versatility

- Modular architectural design for fast development of spin-off devices

- Advanced integrated-circuit processing technology for increased performance

- Upward-compatible source code (source code for 'C1x and 'C2x DSPs is upward compatible with 'C5x DSPs.)

- Enhanced TMS320 instruction set for faster algorithms and for optimized high-level language operation

- New static-design techniques for minimizing power consumption and maximizing radiation tolerance

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

TI is a trademark of Texas Instruments Incorporated.

- <sup>†</sup> IEEE Standard 1149.1–1990, IEEE Standard Test-Access Port and Boundary-Scan Architecture

- ‡ References to 'C5x in this document include both TMS320C5x and TMS320LC5x devices unless specified otherwise.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright  $\circledast$  1996, Texas Instruments Incorporated

SPRS030A – APRIL 1995 – REVISED APRIL 1996

#### description (continued)

Table 1 provides a comparison of the devices in the 'C5x generation. It shows the capacity of on-chip RAM and ROM memories, number of serial and parallel I/O ports, execution time of one machine cycle, and type of package with total pin count.

|             | ON-C | HIP MEMOR      | Y (16-BIT W    | ORDS) | I/O PORTS |                       |                 |               |                  |

|-------------|------|----------------|----------------|-------|-----------|-----------------------|-----------------|---------------|------------------|

| TMS320      | DAF  | RAM            | SARAM          | ROM   |           | PURIS                 | POWER<br>SUPPLY | CYCLE<br>TIME | PACKAGE<br>TYPE  |

| DEVICES     | DATA | DATA +<br>PROG | DATA +<br>PROG | PROG  | SERIAL    | PARALLEL <sup>†</sup> | (V)             | (ns)          | QFP <sup>‡</sup> |

| TMS320C50   | 544  | 512            | 9K             | 2K§   | 2         | 64K                   | 5               | 50/35/25      | 132 pin          |

| TMS320LC50  | 544  | 512            | 9K             | 2K§   | 2         | 64K                   | 3.3             | 50/40/25      | 132 pin          |

| TMS320C51   | 544  | 512            | 1K             | 8K§   | 2         | 64K                   | 5               | 50/35/25/20   | 100/132 pin      |

| TMS320LC51  | 544  | 512            | 1K             | 8K§   | 2         | 64K                   | 3.3             | 50/40/25      | 100/132 pin      |

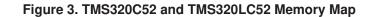

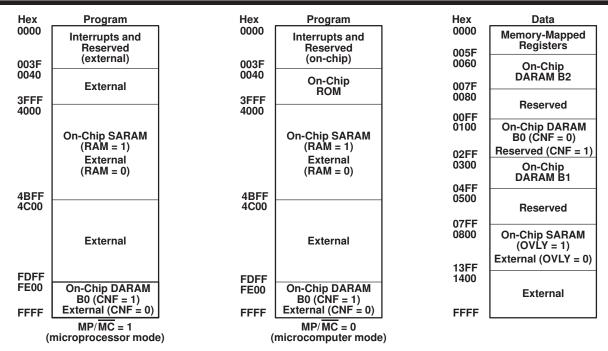

| TMS320C52   | 544  | 512            | -              | 4K§   | 1¶        | 64K                   | 5               | 50/35/25/20   | 100 pin          |

| TMS320LC52  | 544  | 512            | -              | 4K§   | 1¶        | 64K                   | 3.3             | 50/40/25      | 100 pin          |

| TMS320C53   | 544  | 512            | 3K             | 16K§  | 2         | 64K                   | 5               | 50/35/25      | 132 pin          |

| TMS320LC53  | 544  | 512            | 3K             | 16K§  | 2         | 64K                   | 3.3             | 50/40/25      | 132 pin          |

| TMS320C53S  | 544  | 512            | 3K             | 16K§  | 2¶        | 64K                   | 5               | 50/35/25      | 100 pin          |

| TMS320LC53S | 544  | 512            | 3K             | 16K§  | 2¶        | 64K                   | 3.3             | 50/40/25      | 100 pin          |

| TMS320LC56  | 544  | 512            | 6K             | 32K   | 2 #       | 64K                   | 3.3             | 35/25         | 100 pin          |

| TMS320LC57  | 544  | 512            | 6K             | 32K   | 2 #       | 64K + HPI             | 3.3             | 35/25         | 128 pin          |

| TMS320C57S  | 544  | 512            | 6K             | 2K§   | 2 #       | 64K + HPI             | 5               | 50/35/25      | 144 pin          |

| TMS320LC57S | 544  | 512            | 6K             | 2K§   | 2 #       | 64K + HPI             | 3.3             | 50/35         | 144 pin          |

Table 1. Characteristics of the 'C5x Processors

<sup>†</sup> Sixteen of the 64K parallel I/O ports are memory mapped.

‡QFP = Quad flatpack

§ ROM boot loader available

¶ TDM serial port not available

# Includes auto-buffered serial port (BSP) but TDM serial port not available

|| HPI = Host port interface

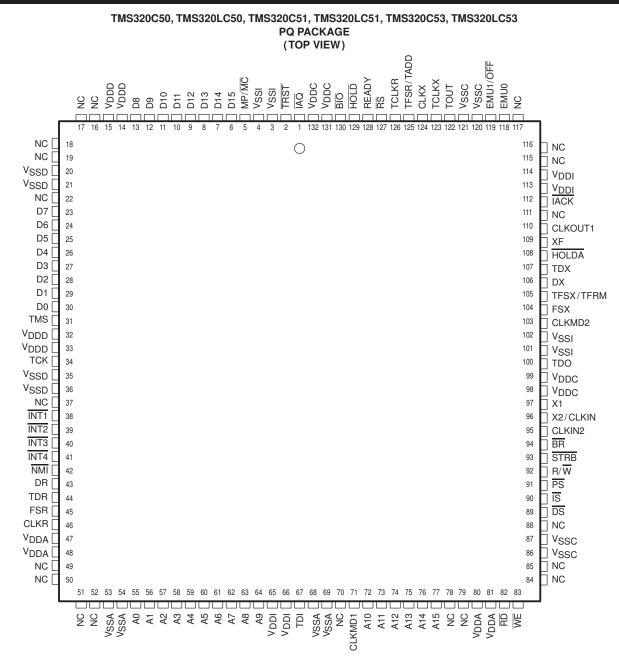

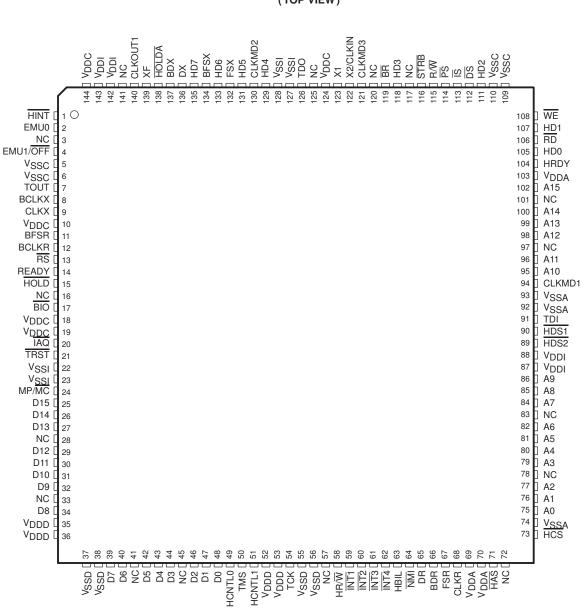

Pinouts for each package are device-specific.

NOTE: NC = No connect (These pins are reserved.)

SPRS030A - APRIL 1995 - REVISED APRIL 1996

### Pin Functions for Devices in the PQ Package

| SIGNAL      | TYPE  | DESCRIPTION                                                                                                                                            |

|-------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | •     | PARALLEL INTERFACE BUS                                                                                                                                 |

| A0-A15      | I/O/Z | 16-bit external address bus (MSB: A15, LSB: A0)                                                                                                        |

| D0-D15      | I/O/Z | 16-bit external data bus (MSB: D15, LSB: D0)                                                                                                           |

| PS, DS, IS  | O/Z   | Program, data, and I/O space select outputs, respectively                                                                                              |

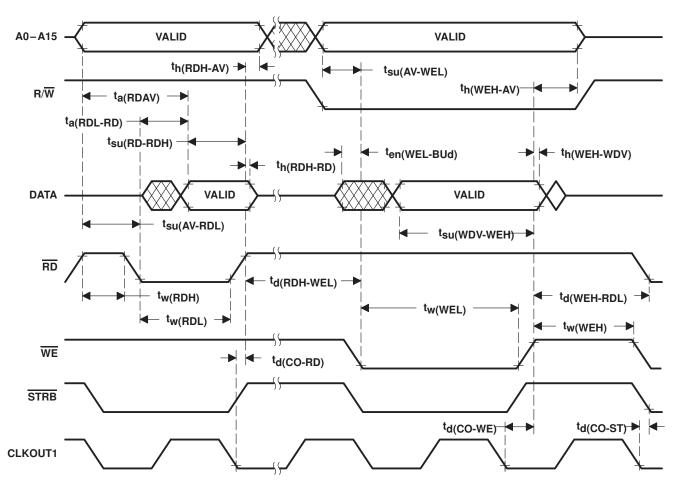

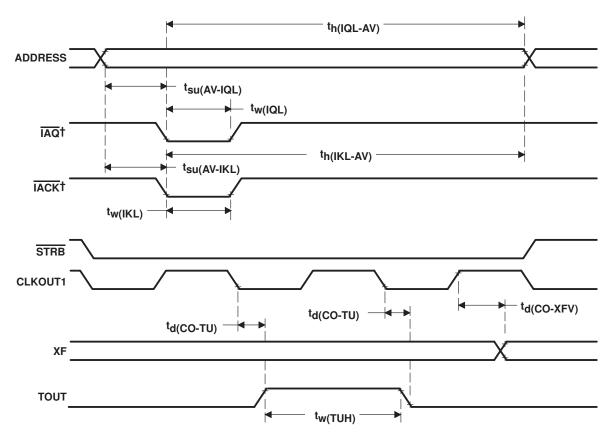

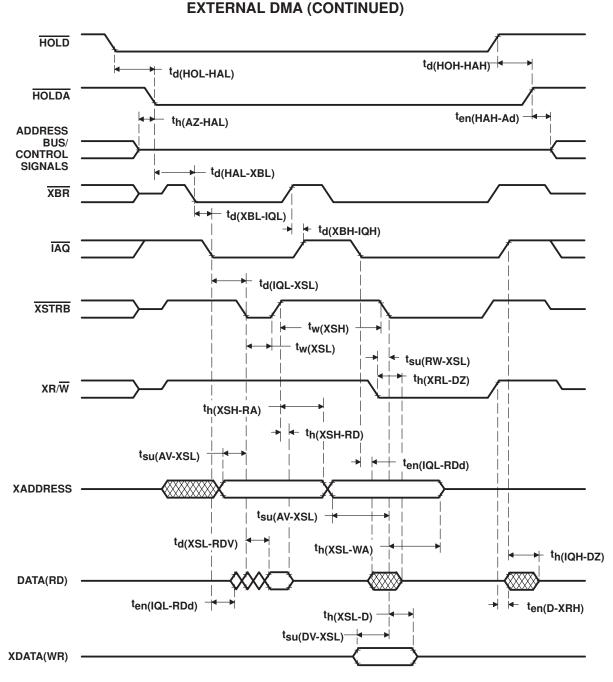

| STRB        | I/O/Z | Timing strobe for external cycles and external DMA                                                                                                     |

| R/W         | I/O/Z | Read/write select for external cycles and external DMA                                                                                                 |

| RD, WE      | O/Z   | Read and write strobes, respectively, for external cycles                                                                                              |

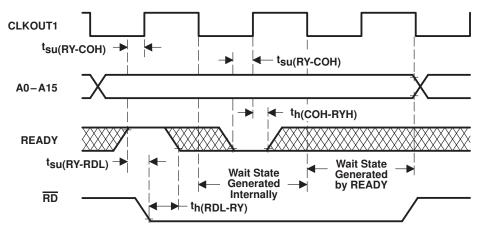

| READY       | I     | External bus ready/wait-state control input                                                                                                            |

| BR          | I/O/Z | Bus request. Arbitrates global memory and external DMA                                                                                                 |

|             |       | SYSTEM INTERFACE/CONTROL SIGNALS                                                                                                                       |

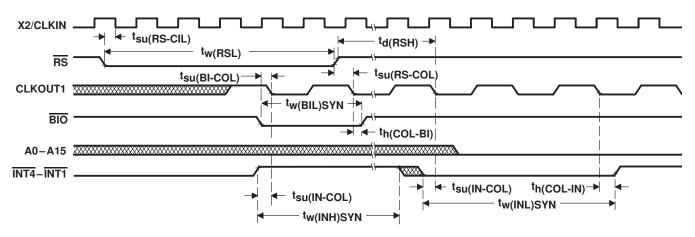

| RS          | I     | Reset. Initializes device and sets PC to zero                                                                                                          |

| MP/MC       | I     | Microprocessor/microcomputer mode select. Enables internal ROM                                                                                         |

| HOLD        | I     | Puts parallel I/F bus in high-impedance state after current cycle                                                                                      |

| HOLDA       | O/Z   | Hold acknowledge. Indicates external bus in hold state                                                                                                 |

| XF          | O/Z   | External flag output. Set/cleared through software                                                                                                     |

| BIO         | I     | I/O branch input. Implements conditional branches                                                                                                      |

| TOUT        | O/Z   | Timer output signal. Indicates output of internal timer                                                                                                |

| IAQ         | O/Z   | Instruction acquisition signal                                                                                                                         |

| IACK        | O/Z   | Interrupt acknowledge signal                                                                                                                           |

| INT1-INT4   | I     | External interrupt inputs                                                                                                                              |

| NMI         | I     | Nonmaskable external interrupt                                                                                                                         |

|             |       | SERIAL PORT INTERFACE (SPI)                                                                                                                            |

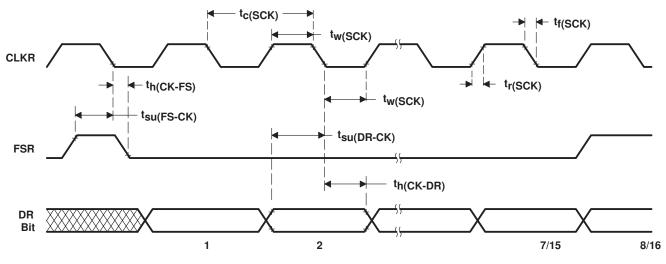

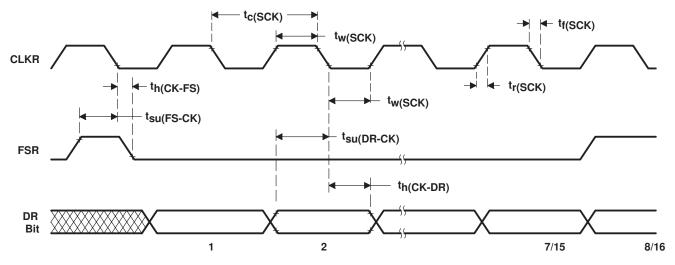

| DR          | I     | Serial receive-data input                                                                                                                              |

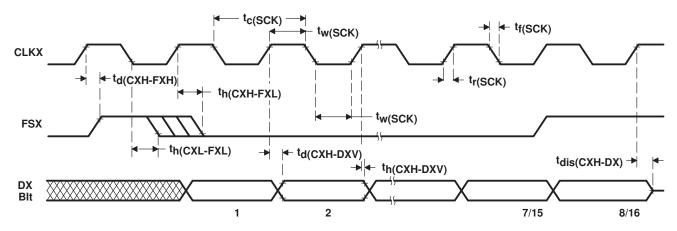

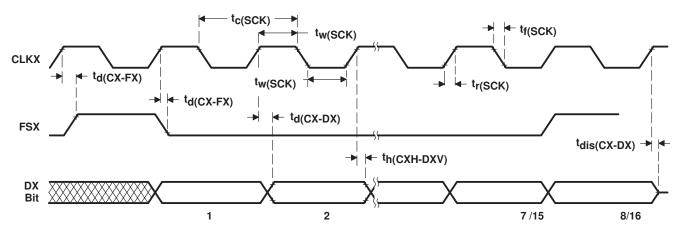

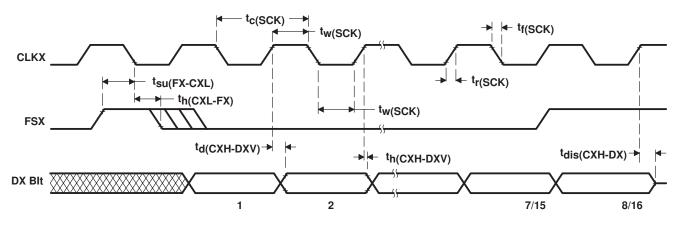

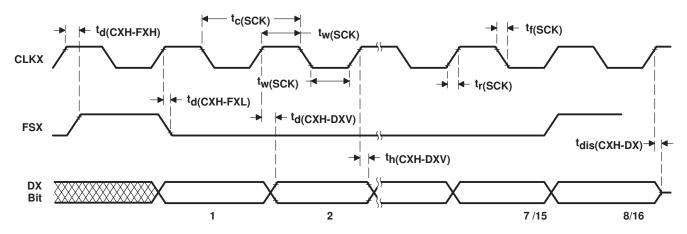

| DX          | O/Z   | Serial transmit-data output. In high-impedance state when not transmitting                                                                             |

| CLKR        | I     | Serial receive-data clock input                                                                                                                        |

| CLKX        | I/O/Z | Serial transmit-data clock. Internal or external source                                                                                                |

| FSR         | I     | Serial receive-frame-synchronization input                                                                                                             |

| FSX         | I/O/Z | Serial transmit-frame-synchronization signal. Internal or external source                                                                              |

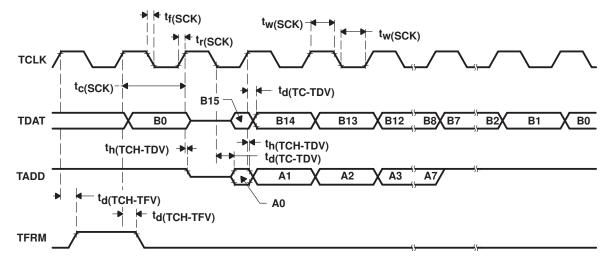

|             |       | TDM SERIAL-PORT INTERFACE                                                                                                                              |

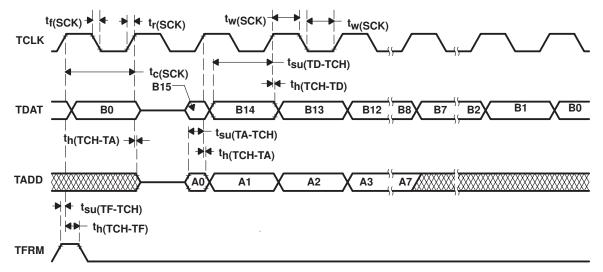

| TDR         | I     | TDM serial receive-data input                                                                                                                          |

| TDX         | O/Z   | TDM serial transmit-data output. In high-impedance state when not transmitting                                                                         |

| TCLKR       | I     | TDM serial receive-data clock input                                                                                                                    |

| TCLKX       | I/O/Z | TDM serial transmit-data clock. Internal or external source                                                                                            |

| TFSR / TADD | I/O/Z | TDM serial receive-frame-synchronization input. In the TDM mode, TFSR/TADD is used to output/ input the address of the port.                           |

| TFSX / TFRM | I     | TDM serial transmit-frame-synchronization signal. Internal or external source. In the TDM mode, TFSX/TFRM becomes TFRM, the TDM frame synchronization. |

LEGEND:

I = Input O = Output Z = High impedance

SPRS030A - APRIL 1995 - REVISED APRIL 1996

## Pin Functions for Devices in the PQ Package (Continued)

|                  | EM    | JLATION/IEEE STANDARD 1149.1 TEST ACCESS PORT (TAP)                |  |

|------------------|-------|--------------------------------------------------------------------|--|

| TDI              | I     | TAP scan data input                                                |  |

| TDO              | O/Z   | TAP scan data output                                               |  |

| TMS              | Ι     | TAP mode select input                                              |  |

| ТСК              | I     | TAP clock input                                                    |  |

| TRST             | Ι     | TAP reset (with pulldown resistor). Disables TAP when low          |  |

| EMU0             | I/O/Z | Emulation control 0. Reserved for emulation use                    |  |

| EMU1/OFF         | I/O/Z | Emulation control 1. Puts outputs in high-impedance state when low |  |

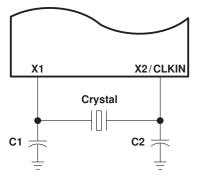

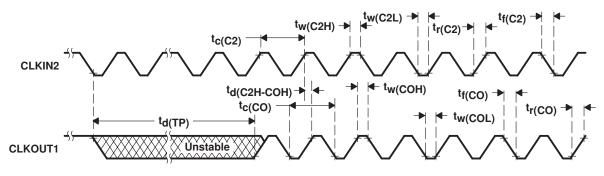

|                  |       | CLOCK GENERATION AND CONTROL                                       |  |

| X1               | 0     | Oscillator output                                                  |  |

| X2/CLKIN         | I     | Clock/oscillator input                                             |  |

| CLKIN2           | Ι     | Clock input                                                        |  |

| CLKMD1, CLKMD2   | Ι     | Clock-mode select inputs                                           |  |

| CLKOUT1          | O/Z   | Device system-clock output                                         |  |

|                  |       | POWER SUPPLY CONNECTIONS                                           |  |

| V <sub>DDA</sub> | S     | Supply connection, address-bus output                              |  |

| V <sub>DDD</sub> | S     | Supply connection, data-bus output                                 |  |

| V <sub>DDC</sub> | S     | Supply connection, control output                                  |  |

| V <sub>DDI</sub> | S     | Supply connection, internal logic                                  |  |

| V <sub>SSA</sub> | S     | Supply connection, address-bus output                              |  |

| V <sub>SSD</sub> | S     | Supply connection, data-bus output                                 |  |

| V <sub>SSC</sub> | S     | Supply connection, control output                                  |  |

| V <sub>SSI</sub> | S     | Supply connection, internal logic                                  |  |

|                  |       |                                                                    |  |

LEGEND:

I = Input O = Output

S = SupplyZ = High impedance

SPRS030A - APRIL 1995 - REVISED APRIL 1996

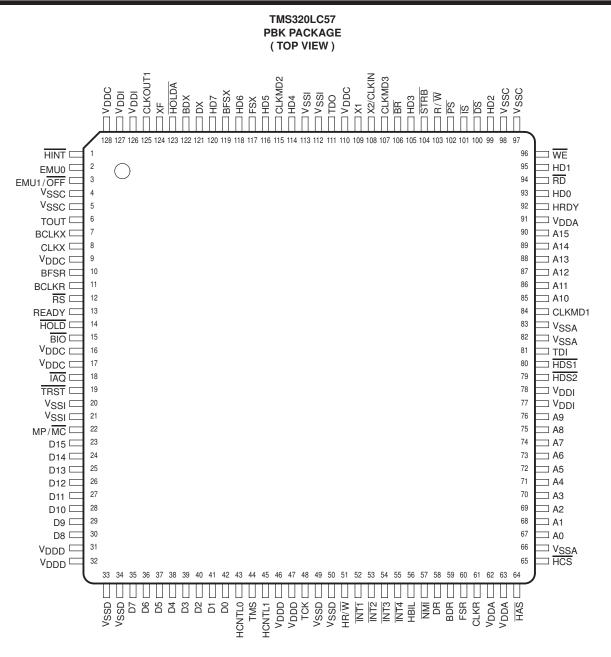

## Pin Functions for the TMS320LC57 in the PBK Package

| SIGNAL     | TYPE  | DESCRIPTION                                                                |

|------------|-------|----------------------------------------------------------------------------|

|            |       | PARALLEL INTERFACE BUS                                                     |

| A0-A15     | I/O/Z | 16-bit external address bus (MSB: A15, LSB: A0)                            |

| D0-D15     | I/O/Z | 16-bit external data bus (MSB: D15, LSB: D0)                               |

| PS, DS, IS | O/Z   | Program, data, and I/O space select outputs, respectively                  |

| STRB       | I/O/Z | Timing strobe for external cycles and external DMA                         |

| R/W        | I/O/Z | Read/write select for external cycles and external DMA                     |

| RD, WE     | O/Z   | Read and write strobes, respectively, for external cycles                  |

| READY      | I     | External bus ready/wait-state control input                                |

| BR         | I/O/Z | Bus request. Arbitrates global memory and external DMA                     |

|            | -     | SYSTEM INTERFACE/CONTROL SIGNALS                                           |

| RS         | I     | Reset. Initializes device and sets PC to zero                              |

| MP/MC      | I     | Microprocessor/microcomputer mode select. Enables internal ROM             |

| HOLD       | I     | Puts parallel I/F bus in high-impedance state after current cycle          |

| HOLDA      | O/Z   | Hold acknowledge. Indicates external bus in hold state                     |

| XF         | O/Z   | External flag output. Set/cleared through software                         |

| BIO        | I     | I/O branch input. Implements conditional branches                          |

| TOUT       | O/Z   | Timer output signal. Indicates output of internal timer                    |

| IAQ        | O/Z   | Instruction acquisition signal                                             |

| INT1-INT4  | I     | External interrupt inputs                                                  |

| NMI        | I     | Nonmaskable external interrupt                                             |

|            |       | SERIAL PORT INTERFACE                                                      |

| DR         | I     | Serial receive-data input                                                  |

| DX         | O/Z   | Serial transmit-data output. In high-impedance state when not transmitting |

| CLKR       | I     | Serial receive-data clock input                                            |

| CLKX       | I/O/Z | Serial transmit-data clock. Internal or external source                    |

| FSR        | I     | Serial receive-frame-synchronization input                                 |

| FSX        | I/O/Z | Serial transmit-frame-synchronization signal. Internal or external source  |

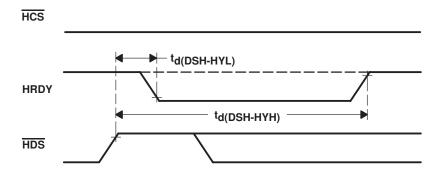

|            |       | HOST PORT INTERFACE (HPI)                                                  |

| HCNTL0     | I     | HPI mode control 1                                                         |

| HCNTL1     | 1     | HPI mode control 2                                                         |

| HINT       | O/Z   | Host interrupt                                                             |

| HDS1       | 1     | HPI data strobe 1                                                          |

| HDS2       | I     | HPI data strobe 2                                                          |

| HR/W       | I     | HPI read/write strobe                                                      |

| HAS        | I     | HPI address strobe                                                         |

| HRDY       | O/Z   | HPI ready signal                                                           |

| HCS        | 1     | HPI chip select                                                            |

| HBIL       | 1     | HPI byte identification input                                              |

| HD0-HD7    | I/O/Z | HPI data bus                                                               |

LEGEND:

I = Input O = Output

Z = High impedance

SPRS030A – APRIL 1995 – REVISED APRIL 1996

### Pin Functions for the TMS320LC57 in the PBK Package (Continued)

| SIGNAL                    | TYPE  | DESCRIPTION                                                             |  |

|---------------------------|-------|-------------------------------------------------------------------------|--|

| •                         |       | BUFFERED SERIAL PORT                                                    |  |

| BDR                       | I     | BSP receive data input                                                  |  |

| BDX                       | O/Z   | BSP transmit data output; in high-impedance state when not transmitting |  |

| BCLKR                     | I     | BSP receive-data clock input                                            |  |

| BCLKX                     | I/O/Z | BSP transmit-data clock; internal or external source                    |  |

| BFSR                      | I     | BSP receive frame-synchronization input                                 |  |

| BFSX                      | I/O/Z | BSP transmit frame-synchronization signal; internal or external source  |  |

|                           |       | EMULATION/JTAG INTERFACE                                                |  |

| TDI                       | I     | JTAG-test-port scan data input                                          |  |

| TDO                       | O/Z   | JTAG-test-port scan data output                                         |  |

| TMS                       | I     | JTAG-test-port mode select input                                        |  |

| ТСК                       | Ι     | JTAG-port clock input                                                   |  |

| TRST                      | Ι     | JTAG-port reset (with pull-down resistor). Disables JTAG when low       |  |

| EMU0                      | I/O/Z | Emulation control 0. Reserved for emulation use                         |  |

| EMU1/OFF                  | I/O/Z | Emulation control 1. Puts outputs in high-impedance state when low      |  |

|                           |       | CLOCK GENERATION AND CONTROL                                            |  |

| X1                        | 0     | Oscillator output                                                       |  |

| X2/CLKIN                  | I     | Clock input                                                             |  |

| CLKMD1, CLKMD2,<br>CLKMD3 | I     | Clock-mode select inputs                                                |  |

| CLKOUT1                   | O/Z   | Device system-clock output                                              |  |

|                           |       | POWER SUPPLY CONNECTIONS                                                |  |

| V <sub>DDA</sub>          | S     | Supply connection, address-bus output                                   |  |

| V <sub>DDD</sub>          | S     | Supply connection, data-bus output                                      |  |

| V <sub>DDC</sub>          | S     | Supply connection, control output                                       |  |

| V <sub>DDI</sub>          | S     | Supply connection, internal logic                                       |  |

| V <sub>SSA</sub>          | S     | Supply connection, address-bus output                                   |  |

| V <sub>SSD</sub>          | S     | Supply connection, data-bus output                                      |  |

| V <sub>SSC</sub>          | S     | Supply connection, control output                                       |  |

| V <sub>SSI</sub>          | S     | Supply connection, internal logic                                       |  |

LEGEND:

I = Input

O = Output

S = SupplyZ = High impedance

SPRS030A - APRIL 1995 - REVISED APRIL 1996

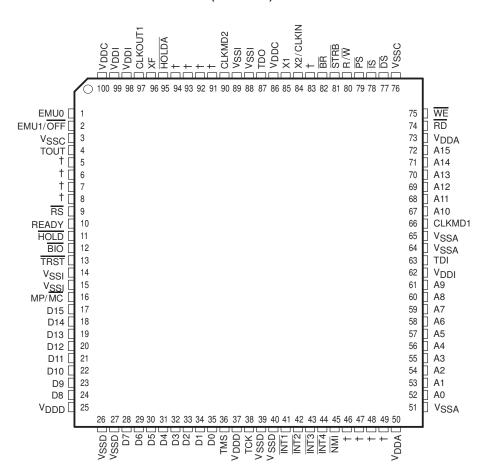

#### TMS320C51, TMS320LC51, TMS320C52, TMS320LC52, TMS320C53S, TMS320LC53S, TMS320LC56 PZ PACKAGE (TOP VIEW)

NOTE: NC = No connect (These pins are reserved.) † See Table 2 for device-specific pinouts.

| Table 2. Device-Specific | Pinouts for | the PZ Package |

|--------------------------|-------------|----------------|

|--------------------------|-------------|----------------|

| PIN | 'C51, 'LC51 | 'C52, 'LC52      | 'C53S, 'LC53S | 'LC56‡ |

|-----|-------------|------------------|---------------|--------|

| 5   | TCLKX       | VSSI             | CLKX2         | BCLKX  |

| 6§  | CLKX        | CLKX             | CLKX1         | CLKX   |

| 7   | TFSR/TADD   | VSSI             | FSR2          | BFSR   |

| 8   | TCLKR       | VSSI             | CLKR2         | BCLKR  |

| 46§ | DR          | DR               | DR1           | DR     |

| 47  | TDR         | VSSI             | DR2           | BDR    |

| 48§ | FSR         | FSR              | FSR1          | FSR    |

| 49§ | CLKR        | CLKR             | CLKR1         | CLKR   |

| 83  | CLKIN2      | CLKIN2           | CLKIN2        | CLKMD3 |

| 91§ | FSX         | FSX              | FSX1          | FSX    |

| 92  | TFSX/TFRM   | V <sub>SSI</sub> | FSX2          | BFSX   |

| 93§ | DX          | DX               | DX1           | DX     |

| 94  | TDX         | NC               | DX2           | BDX    |

<sup>‡</sup> Pin names beginning with "B" indicate signals on the buffered serial port (BSP).

§ No functional change

SPRS030A - APRIL 1995 - REVISED APRIL 1996

### Pin Functions for Devices in the PZ Package

| SIGNAL             | TYPE                   | DESCRIPTION                                                                |  |  |

|--------------------|------------------------|----------------------------------------------------------------------------|--|--|

|                    | PARALLEL INTERFACE BUS |                                                                            |  |  |

| A0-A15             | I/O/Z                  | 16-bit external address bus (MSB: A15, LSB: A0)                            |  |  |

| D0-D15             | I/O/Z                  | 16-bit external data bus (MSB: D15, LSB: D0)                               |  |  |

| PS, DS, IS         | O/Z                    | Program, data, and I/O space select outputs, respectively                  |  |  |

| STRB               | I/O/Z                  | Timing strobe for external cycles and external DMA                         |  |  |

| R/W                | I/O/Z                  | Read/write select for external cycles and external DMA                     |  |  |

| RD, WE             | O/Z                    | Read and write strobes, respectively, for external cycles                  |  |  |

| READY              |                        | External bus ready/wait-state control input                                |  |  |

| BR                 | I/O/Z                  | Bus request. Arbitrates global memory and external DMA                     |  |  |

|                    |                        | SYSTEM INTERFACE/CONTROL SIGNALS                                           |  |  |

| RS                 | I                      | Reset. Initializes device and sets PC to zero                              |  |  |

| MP/MC              |                        | Microprocessor/microcomputer mode select. Enables internal ROM             |  |  |

| HOLD               |                        | Puts parallel I/F bus in high-impedance state after current cycle          |  |  |

| HOLDA              | O/Z                    | Hold acknowledge. Indicates external bus in hold state                     |  |  |

| XF                 | O/Z                    | External flag output. Set/cleared through software                         |  |  |

| BIO                | I                      | I/O branch input. Implements conditional branches                          |  |  |

| TOUT               | O/Z                    | Timer output signal. Indicates output of internal timer                    |  |  |

| INT1-INT4          |                        | External interrupt inputs                                                  |  |  |

| NMI                | I                      | Nonmaskable external interrupt                                             |  |  |

|                    |                        | SERIAL PORT INTERFACE                                                      |  |  |

| DR, DR1, DR2       |                        | Serial receive-data input                                                  |  |  |

| DX, DX1, DX2       | O/Z                    | Serial transmit-data output. In high-impedance state when not transmitting |  |  |

| CLKR, CLKR1, CLKR2 | I                      | Serial receive-data clock input                                            |  |  |

| CLKX, CLKX1, CLKX2 | I/O/Z                  | Serial transmit-data clock. Internal or external source                    |  |  |

| FSR, FSR1, FSR2    |                        | Serial receive-frame-synchronization input                                 |  |  |

| FSX, FSX1, FSX2    | I/O/Z                  | Serial transmit-frame-synchronization signal. Internal or external source  |  |  |

|                    |                        | BUFFERED SERIAL PORT (BSP) (SEE NOTE 1)                                    |  |  |

| BDR                |                        | BSP receive data input                                                     |  |  |

| BDX                | O/Z                    | BSP transmit data output; in high-impedance state when not transmitting    |  |  |

| BCLKR              |                        | BSP receive-data clock input                                               |  |  |

| BCLKX              | I/O/Z                  | BSP transmit-data clock; internal or external source                       |  |  |

| BFSR               |                        | BSP receive frame-synchronization input                                    |  |  |

| BFSX               | I/O/Z                  | BSP transmit frame-synchronization signal; internal or external source     |  |  |

LEGEND:

NOTE 1: 'LC56 devices only

SPRS030A - APRIL 1995 - REVISED APRIL 1996

## Pin Functions for Devices in the PZ Package (Continued)

| SIGNAL                    | TYPE  | DESCRIPTION                                                                                                                                 |  |

|---------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------|--|

|                           |       | TDM SERIAL PORT INTERFACE                                                                                                                   |  |

| TDR                       | I     | TDM serial receive-data input                                                                                                               |  |

| TDX                       | O/Z   | TDM serial transmit-data output. In high-impedance state when not transmitting                                                              |  |

| TCLKR                     | I     | TDM serial receive-data clock input                                                                                                         |  |

| TCLKX                     | I/O/Z | TDM serial transmit-data clock. Internal or external source                                                                                 |  |

| TFSR / TADD               | I/O/Z | TDM serial receive-frame-synchronization input. In the TDM mode, TFSR/TADD is used to output/ input the address of the port                 |  |

| TFSX/TFRM                 | I     | TDM serial transmit-frame-synchronization signal. Internal or external source. In the TDM mode, TFSX/TFRM becomes TFRM, the TDM frame sync. |  |

|                           |       | EMULATION/JTAG INTERFACE                                                                                                                    |  |

| TDI                       | I     | JTAG-test-port scan data input                                                                                                              |  |

| TDO                       | O/Z   | JTAG-test-port scan data output                                                                                                             |  |

| TMS                       | I     | JTAG-test-port mode select input                                                                                                            |  |

| ТСК                       | I     | JTAG-port clock input                                                                                                                       |  |

| TRST                      | I     | JTAG-port reset (with pull-down resistor). Disables JTAG when low                                                                           |  |

| EMU0                      | I/O/Z | Emulation control 0. Reserved for emulation use                                                                                             |  |

| EMU1/OFF                  | I/O/Z | Emulation control 1. Puts outputs in high-impedance state when low                                                                          |  |

|                           |       | CLOCK GENERATION AND CONTROL (SEE NOTE 2)                                                                                                   |  |

| X1                        | 0     | Oscillator output                                                                                                                           |  |

| X2/CLKIN                  | I     | Clock/oscillator input (PLL clock input for 'C56)                                                                                           |  |

| CLKIN2                    | I     | Clock input (PLL clock input for 'C50, 'C51, 'C52, 'C53, 'C53S)                                                                             |  |

| CLKMD1, CLKMD2,<br>CLKMD3 | I     | Clock-mode select inputs                                                                                                                    |  |

| CLKOUT1                   | O/Z   | Device system-clock output                                                                                                                  |  |

|                           |       | POWER SUPPLY CONNECTIONS                                                                                                                    |  |

| V <sub>DDA</sub>          | S     | Supply connection, address-bus output                                                                                                       |  |

| V <sub>DDD</sub>          | S     | Supply connection, data-bus output                                                                                                          |  |

| VDDC                      | S     | Supply connection, control output                                                                                                           |  |

| V <sub>DDI</sub>          | S     | Supply connection, internal logic                                                                                                           |  |

| V <sub>SSA</sub>          | S     | Supply connection, address-bus output                                                                                                       |  |

| V <sub>SSD</sub>          | S     | Supply connection, data-bus output                                                                                                          |  |

| V <sub>SSC</sub>          | S     | Supply connection, control output                                                                                                           |  |

| V <sub>SSI</sub>          | S     | Supply connection, internal logic                                                                                                           |  |

LEGEND:

I = Input

O = Output

S = SupplyZ = High impedance

NOTE 2: CLKIN2 pin is replaced by CLKMD3 pin on 'LC56 devices.

NOTE: NC = No connect (These pins are reserved.)

SPRS030A - APRIL 1995 - REVISED APRIL 1996

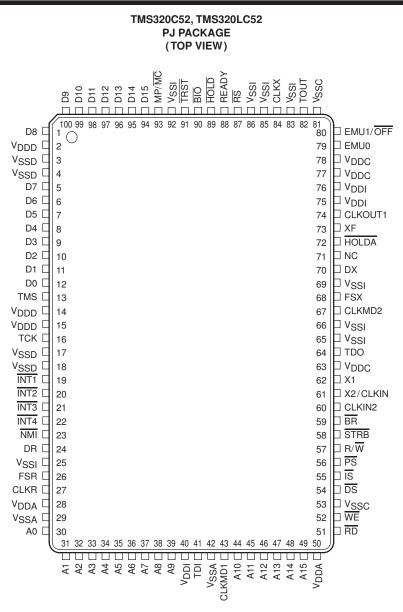

## Pin Functions for the TMS320C52, TMS320LC52 in the PJ Package

| SIGNAL     | TYPE  | DESCRIPTION                                                                |  |

|------------|-------|----------------------------------------------------------------------------|--|

|            | -     | PARALLEL INTERFACE BUS                                                     |  |

| A0-A15     | I/O/Z | 16-bit external address bus (MSB: A15, LSB: A0)                            |  |

| D0-D15     | I/O/Z | 16-bit external data bus (MSB: D15, LSB: D0)                               |  |

| PS, DS, IS | O/Z   | Program, data, and I/O space select outputs, respectively                  |  |

| STRB       | I/O/Z | Timing strobe for external cycles and external DMA                         |  |

| R/W        | I/O/Z | Read/write select for external cycles and external DMA                     |  |

| RD, WE     | O/Z   | Read and write strobes, respectively, for external cycles                  |  |

| READY      | 1     | External bus ready/wait-state control input                                |  |

| BR         | I/O/Z | Bus request. Arbitrates global memory and external DMA                     |  |

|            | •     | SYSTEM INTERFACE/CONTROL SIGNALS                                           |  |

| RS         | 1     | Reset. Initializes device and sets PC to zero                              |  |

| MP/MC      | 1     | Microprocessor/microcomputer mode select. Enables internal ROM             |  |

| HOLD       | 1     | Puts parallel I/F bus in high-impedance state after current cycle          |  |

| HOLDA      | O/Z   | Hold acknowledge. Indicates external bus in hold state                     |  |

| XF         | O/Z   | External flag output. Set/cleared through software                         |  |

| BIO        | 1     | I/O branch input. Implements conditional branches                          |  |

| TOUT       | O/Z   | Timer output signal. Indicates output of internal timer                    |  |

| INT1-INT4  | 1     | External interrupt inputs                                                  |  |

| NMI        | 1     | Nonmaskable external interrupt                                             |  |

|            | •     | SERIAL PORT INTERFACE                                                      |  |

| DR         | 1     | Serial receive-data input                                                  |  |

| DX         | O/Z   | Serial transmit-data output. In high-impedance state when not transmitting |  |

| CLKR       | 1     | Serial receive-data clock input                                            |  |

| CLKX       | I/O/Z | Serial transmit-data clock. Internal or external source                    |  |

| FSR        | 1     | Serial receive-frame-synchronization input                                 |  |

| FSX        | I/O/Z | Serial transmit-frame-synchronization signal. Internal or external source  |  |

|            | •     | EMULATION/JTAG INTERFACE                                                   |  |

| TDI        | 1     | JTAG-test-port scan data input                                             |  |

| TDO        | O/Z   | JTAG-test-port scan data output                                            |  |

| TMS        | I     | JTAG-test-port mode select input                                           |  |

| ТСК        | I     | JTAG-port clock input                                                      |  |

| TRST       | I     | JTAG-port reset (with pulldown resistor). Disables JTAG when low           |  |

| EMU0       | I/O/Z | Emulation control 0. Reserved for emulation use                            |  |

| EMU1/OFF   | I/O/Z | Emulation control 1. Puts outputs in high-impedance state when low         |  |

LEGEND:

I = Input

O = Output

Z = High impedance

SPRS030A – APRIL 1995 – REVISED APRIL 1996

## Pin Functions for the TMS320C52, TMS320LC52 in the PJ Package (Continued)

| SIGNAL           | TYPE                         | DESCRIPTION                                   |  |  |

|------------------|------------------------------|-----------------------------------------------|--|--|

|                  | CLOCK GENERATION AND CONTROL |                                               |  |  |

| X1               | 0                            | Oscillator output                             |  |  |

| X2/CLKIN         | I                            | Clock/oscillator input                        |  |  |

| CLKIN2           | I                            | Clock input (PLL clock input for 'C52, 'LC52) |  |  |

| CLKMD1, CLKMD2   | I                            | Clock-mode select inputs                      |  |  |

| CLKOUT1          | O/Z                          | Device system-clock output                    |  |  |

|                  |                              | POWER SUPPLY CONNECTIONS                      |  |  |

| V <sub>DDA</sub> | S                            | Supply connection, address-bus output         |  |  |

| V <sub>DDD</sub> | S                            | Supply connection, data-bus output            |  |  |

| V <sub>DDC</sub> | S                            | Supply connection, control output             |  |  |

| V <sub>DDI</sub> | S                            | Supply connection, internal logic             |  |  |

| V <sub>SSA</sub> | S                            | Supply connection, address-bus output         |  |  |

| V <sub>SSD</sub> | S                            | Supply connection, data-bus output            |  |  |

| V <sub>SSC</sub> | S                            | Supply connection, control output             |  |  |

| V <sub>SSI</sub> | S                            | Supply connection, internal logic             |  |  |

LEGEND:

I = Input O = Output

S = Supply

SPRS030A - APRIL 1995 - REVISED APRIL 1996

#### TMS320C57S, TMS320LC57S PGE PACKAGE (TOP VIEW)

NOTE: NC = No connect (These pins are reserved.)

SPRS030A – APRIL 1995 – REVISED APRIL 1996

## Pin Functions for the TMS320C57S, TMS320LC57S in the PGE Package

| TYPE  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •     | PARALLEL INTERFACE BUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| I/O/Z | 16-bit external address bus (MSB: A15, LSB: A0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| I/O/Z | 16-bit external data bus (MSB: D15, LSB: D0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| O/Z   | Program, data, and I/O space select outputs, respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| I/O/Z | Timing strobe for external cycles and external DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| I/O/Z | Read/write select for external cycles and external DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| O/Z   | Read and write strobes, respectively, for external cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1     | External bus ready/wait-state control input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| I/O/Z | Bus request. Arbitrates global memory and external DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | SYSTEM INTERFACE/CONTROL SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1     | Reset. Initializes device and sets PC to zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| I     | Microprocessor/microcomputer mode select. Enables internal ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1     | Puts parallel I/F bus in high-impedance state after current cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| O/Z   | Hold acknowledge. Indicates external bus in hold state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| O/Z   | External flag output. Set/cleared through software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1     | I/O branch input. Implements conditional branches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| O/Z   | Timer output signal. Indicates output of internal timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| O/Z   | Instruction acquisition signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1     | External interrupt inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1     | Nonmaskable external interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | SERIAL PORT INTERFACE (SPI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1     | Serial receive-data input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| O/Z   | Serial transmit-data output. In high-impedance state when not transmitting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1     | Serial receive-data clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| I/O/Z | Serial transmit-data clock. Internal or external source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| I     | Serial receive-frame-synchronization input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| I/O/Z | Serial transmit-frame-synchronization signal. Internal or external source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | HOST PORT INTERFACE (HPI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| I     | HPI mode control 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1     | HPI mode control 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| O/Z   | Host interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1     | HPI data strobe 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1     | HPI data strobe 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1     | HPI read/write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1     | HPI address strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| O/Z   | HPI ready signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1     | HPI chip select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1     | HPI byte identification input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1/0/7 | HPI data bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | I/O/Z         I/O/Z         O/Z         I/O/Z         O/Z         I/O/Z         O/Z         I         I/O/Z         O/Z         I         I/O/Z         O/Z         I         O/Z         O/Z         I         O/Z         I         O/Z         I         O/Z         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I |

LEGEND:

I = Input O = Output

Z = High impedance

SPRS030A - APRIL 1995 - REVISED APRIL 1996

## Pin Functions for the TMS320C57S, TMS320LC57S in the PGE Package (Continued)

| SIGNAL                    | TYPE  | DESCRIPTION                                                             |  |  |  |  |

|---------------------------|-------|-------------------------------------------------------------------------|--|--|--|--|

| BUFFERED SERIAL PORT      |       |                                                                         |  |  |  |  |

| BDR                       | I     | BSP receive data input                                                  |  |  |  |  |

| BDX                       | O/Z   | BSP transmit data output; in high-impedance state when not transmitting |  |  |  |  |

| BCLKR                     | I     | BSP receive-data clock input                                            |  |  |  |  |

| BCLKX                     | I/O/Z | BSP transmit-data clock; internal or external source                    |  |  |  |  |

| BFSR                      | I     | BSP receive frame-synchronization input                                 |  |  |  |  |

| BFSX                      | I/O/Z | BSP transmit frame-synchronization signal; internal or external source  |  |  |  |  |

| EMULATION/JTAG INTERFACE  |       |                                                                         |  |  |  |  |

| TDI                       | I     | JTAG-test-port scan data input                                          |  |  |  |  |

| TDO                       | O/Z   | JTAG-test-port scan data output                                         |  |  |  |  |

| TMS                       | I     | JTAG-test-port mode select input                                        |  |  |  |  |

| ТСК                       | I     | JTAG-port clock input                                                   |  |  |  |  |

| TRST                      | I     | JTAG-port reset (with pulldown resistor). Disables JTAG when low        |  |  |  |  |

| EMU0                      | I/O/Z | Emulation control 0. Reserved for emulation use                         |  |  |  |  |

| EMU1/OFF                  | I/O/Z | Emulation control 1. Puts outputs in high-impedance state when low      |  |  |  |  |

|                           |       | CLOCK GENERATION AND CONTROL                                            |  |  |  |  |

| X1                        | 0     | Oscillator output                                                       |  |  |  |  |

| X2/CLKIN                  | I     | PLL clock input                                                         |  |  |  |  |

| CLKMD1, CLKMD2,<br>CLKMD3 | I     | Clock-mode select inputs                                                |  |  |  |  |

| CLKOUT1                   | O/Z   | Device system-clock output                                              |  |  |  |  |

|                           |       | POWER SUPPLY CONNECTIONS                                                |  |  |  |  |

| V <sub>DDA</sub>          | S     | Supply connection, address-bus output                                   |  |  |  |  |

| V <sub>DDD</sub>          | S     | Supply connection, data-bus output                                      |  |  |  |  |

| V <sub>DDC</sub>          | S     | Supply connection, control output                                       |  |  |  |  |

| V <sub>DDI</sub>          | S     | Supply connection, internal logic                                       |  |  |  |  |

| V <sub>SSA</sub>          | S     | Supply connection, address-bus output                                   |  |  |  |  |

| V <sub>SSD</sub>          | S     | Supply connection, data-bus output                                      |  |  |  |  |

| V <sub>SSC</sub>          | S     | Supply connection, control output                                       |  |  |  |  |

| V <sub>SSI</sub>          | S     | Supply connection, internal logic                                       |  |  |  |  |

LEGEND:

I = Input

O = Output

S = Supply

Z = High impedance

#### SPRS030A – APRIL 1995 – REVISED APRIL 1996

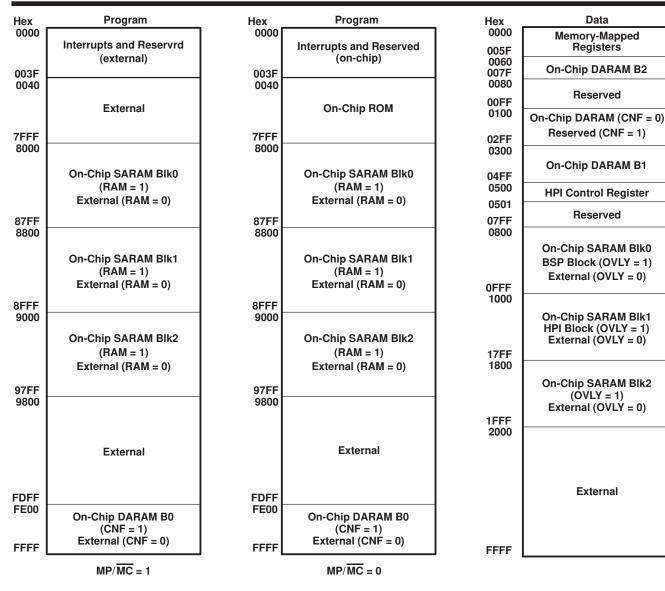

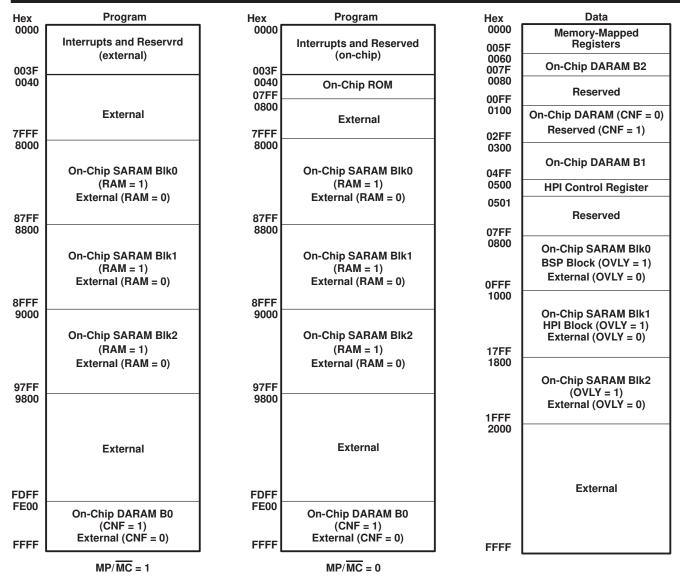

#### architecture

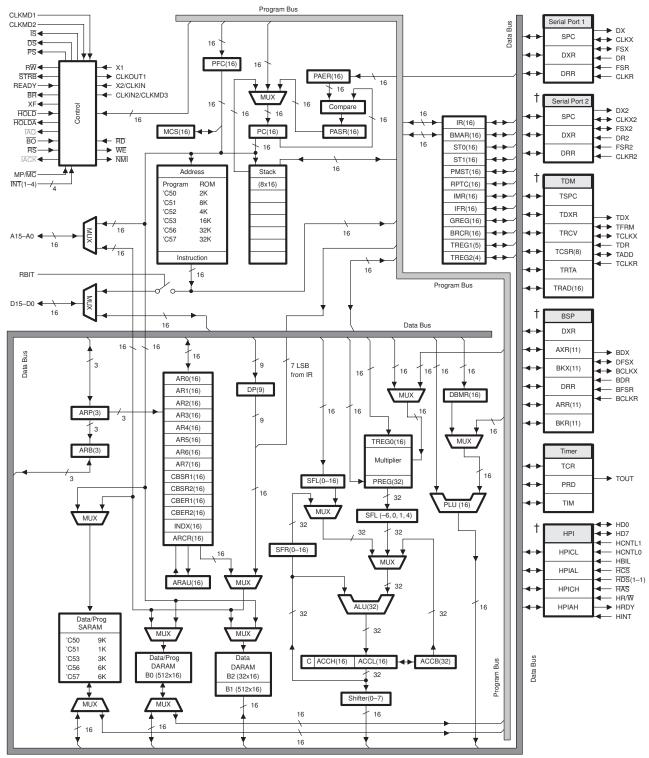

The 'C5x's advanced Harvard-type architecture maximizes the processing power by maintaining two separate memory bus structures, program and data, for full-speed execution. Instructions support data transfers between the two spaces. This architecture permits coefficients stored in program memory to be read into the RAM, eliminating the need for a separate coefficient ROM. The 'C5x architecture also makes available immediate instructions and subroutines based on computed values. Increased throughput on the 'C5x for many DSP applications is accomplished using single-cycle multiply/accumulate instructions with a data-move option, up to eight auxiliary registers with a dedicated arithmetic unit, a parallel logic unit, and faster I/O necessary for data-intensive signal processing. The architectural design emphasizes overall speed, communication, and flexibility in processor configuration. Control signals and instructions provide floating-point support, block-memory transfers, communication to slower off-chip devices, and multiprocessing implementations as shown in the functional block diagram.

Table 3 explains the symbols that are used in the functional block diagram.

| SYMBOL  | DESCRIPTION                            | SYMBOL  | DESCRIPTION                                                |  |

|---------|----------------------------------------|---------|------------------------------------------------------------|--|

| ABU     | Auto-buffering unit                    | IFR     | Interrupt-flag register                                    |  |

| ACCB    | Accumulator buffer                     | IMR     | Interrupt-mask register                                    |  |

| ACCH    | Accumulator high                       | INDX    | Indirect-addressing-index register                         |  |

| ACCL    | Accumulator low                        | IR      | Instruction register                                       |  |

| ALU     | Arithmetic logic unit                  | MCS     | Microcall stack                                            |  |

| ARAU    | Auxiliary-register arithmetic unit     | MUX     | Multiplexer                                                |  |

| ARB     | Auxiliary-register pointer buffer      | PAER    | Block-repeat-address end register                          |  |

| ARCR    | Auxiliary-register compare register    | PASR    | Block-repeat-address start register                        |  |

| ARP     | Auxiliary-register pointer             | PC      | Program counter                                            |  |

| ARR     | Address-receive register (ABU)         | PFC     | Prefetch counter                                           |  |

| AR0–AR7 | Auxiliary registers                    | PLU     | Parallel logic unit                                        |  |

| AXR     | Address-transmit register (ABU)        | PMST    | Processor-mode-status register                             |  |

| BKR     | Receive-buffer-size register (ABU)     | PRD     | Timer-period register                                      |  |

| BKX     | Transmit-buffer-size register (ABU)    | PREG    | Product register                                           |  |

| BMAR    | Block-move-address register            | RPTC    | Repeat-counter register                                    |  |

| BRCR    | Block-repeat-counter register          | SARAM   | Single-access RAM                                          |  |

| BSP     | Buffered serial port                   | SFL     | Left shifter                                               |  |

| С       | Carry bit                              | SFR     | Right shifter                                              |  |

| CBER1   | Circular buffer 1 end address          | SPC     | Serial-port interface-control register                     |  |

| CBER2   | Circular buffer 2 end address          | ST0,ST1 | Status registers                                           |  |

| CBSR1   | Circular buffer 1 start address        | TCSR    | TDM channel-select register                                |  |

| CBSR2   | Circular buffer 2 start address        | TCR     | Timer-control register                                     |  |

| DARAM   | Dual-access RAM                        | TDM     | Time-division-multiplexed serial port                      |  |

| DBMR    | Dynamic bit manipulation register      | TDXR    | TDM data transmit register                                 |  |

| DP      | Data memory page pointer               | TIM     | Timer-count register                                       |  |

| DRR     | Serial-port data receive register      | TRAD    | TDM received-address register                              |  |