### TMS320C24x DSP Controllers Evaluation Module

# Technical Reference

### TMS320C24x DSP Controllers Evaluation Module Technical Reference

Literature Number: SPRU248A August 1997

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

#### **Preface**

### **Read This First**

#### About This Manual

This manual describes the hardware and software installation and general operation of the TMS320C24x evaluation module. In this document, the TMS320C24x DSP controllers evaluation module is also referred to as the 'C24x EVM, the evaluation board included in the 'C24x EVM is the 'C24x evaluation board, and the TMS320F240 device on the evaluation board is also referred to as the 'F240 device. The TMS320C24x is a subset of the TMS320C2xx family of DSPs.

#### **Notational Conventions**

This document uses the following conventions:

Program listings and program examples are shown in a special typeface.

Here is a segment of a program listing:

```

OUTPUT LDP #6 ;select data page 6

BLDD #300, 20h ;move data at address 300h to 320h

RET

```

In syntax descriptions, **bold** portions of a syntax must be entered as shown; *italic* portions of a syntax identify information that you specify. Here is an example of an instruction syntax:

BLDD source, destination

☐ A lowercase h after a number indicates hexadecimal notation.

For example: xxxx xxxh

0000 A/11h

#### Information About Cautions

This book contains cautions.

This is an example of a caution statement.

A caution statement describes a situation that could potentially damage your software or equipment.

The information in a caution is provided for your protection. Please read each caution carefully.

#### Related Documentation From Texas Instruments

This subsection describes related TI<sup>™</sup> documents that can be ordered by calling the Texas Instruments Literature Response Center at (800) 477–8924. When ordering, please identify the book by its title and literature number.

- TMS320C24x DSP Controllers Reference Set, Volume 1: CPU, System, and Instruction Set (literature number SPRU160) describes the TMS320C24x 16-bit, fixed-point, digital signal processor controller. Covered are its architecture, internal register structure, data and program addressing, and instruction set. Also includes instruction set comparisons and design considerations for using the XDS510 emulator.

- TMS320C24x DSP Controllers Reference Set Volume 2: Peripheral Library and Specific Devices (literature number SPRU161) describes the peripherals available on the TMS320C24x digital signal processor controllers and their operation. Also described are specific device configurations of the 'C24x family.

- **TMS320C240, TMS320F240 DSP Controllers** (literature number SPRS042) data sheet contains the electrical and timing specifications for these devices, as well as signal descriptions and pinouts for all of the available packages.

- TMS320C1x/C2x/C2xx/C5x Code Generation Tools Getting Started Guide (literature number SPRU121) describes how to install the TMS320C1x, TMS320C2x, TMS320C2xx, and TMS320C5x assembly language tools and the C compiler for the 'C1x, 'C2x, 'C2xx, and 'C5x devices. The installation for MS-DOS™, OS/2™, SunOS™, and Solaris™ systems is covered.

- TMS320C1x/C2x/C2xx/C5x Assembly Language Tools User's Guide (literature number SPRU018) describes the assembly language tools (assembler, linker, and other tools used to develop assembly language code), assembler directives, macros, common object file format, and symbolic debugging directives for the 'C1x, 'C2x, 'C2xx, and 'C5x generations of devices.

- TMS320C2x/C2xx/C5x Optimizing C Compiler User's Guide (literature number SPRU024) describes the 'C2x/C2xx/C5x C compiler. This C compiler accepts ANSI standard C source code and produces TMS320 assembly language source code for the 'C2x, 'C2xx, and 'C5x generations of devices.

- TMS320C2xx C Source Debugger User's Guide (literature number SPRU151) tells you how to invoke the 'C2xx emulator and simulator versions of the C source debugger interface. This book discusses various aspects of the debugger interface, including window management, command entry, code execution, data management, and breakpoints. It also includes a tutorial that introduces basic debugger functionality.

- **TMS320C2xx** Simulator Getting Started (literature number SPRU137) describes how to install the TMS320C2xx simulator and the C source debugger for the 'C2xx. The installation for MS-DOS™, PC-DOS™, SunOS™, Solaris™, and HP-UX™ systems is covered.

- **TMS320C2xx Emulator Getting Started Guide** (literature number SPRU209) tells you how to install the Windows™ 3.1 and Windows™ 95 versions of the 'C2xx emulator and C source debugger interface.

- **XDS51x Emulator Installation Guide** (literature number SPNU070) describes the installation of the XDS510<sup>™</sup>, XDS510PP<sup>™</sup>, and XDS510WS<sup>™</sup> emulator controllers. The installation of the XDS511<sup>™</sup> emulator is also described.

- JTAG/MPSD Emulation Technical Reference (literature number SPDU079) provides the design requirements of the XDS510™ emulator controller, discusses JTAG designs (based on the IEEE 1149.1 standard), and modular port scan device (MPSD) designs.

- TMS320 DSP Development Support Reference Guide (literature number SPRU011) describes the TMS320 family of digital signal processors and the tools that support these devices. Included are code-generation tools (compilers, assemblers, linkers, etc.) and system integration and debug tools (simulators, emulators, evaluation modules, etc.). Also covered are available documentation, seminars, the university program, and factory repair and exchange.

- Digital Signal Processing Applications with the TMS320 Family, Volumes 1, 2, and 3 (literature numbers SPRA012, SPRA016, SPRA017) Volumes 1 and 2 cover applications using the 'C10 and 'C20 families of fixed-point processors. Volume 3 documents applications using both fixed-point processors, as well as the 'C30 floating-point processor.

- **TMS320 DSP Designer's Notebook: Volume 1** (literature number SPRT125) presents solutions to common design problems using 'C2x, 'C3x, 'C4x, 'C5x, and other TI DSPs.

- TMS320 Third-Party Support Reference Guide (literature number SPRU052) alphabetically lists over 100 third parties that provide various products that serve the family of TMS320 digital signal processors. A myriad of products and applications are offered—software and hardware development tools, speech recognition, image processing, noise cancellation, modems, etc.

- **TMS320C2xx Emulator Getting Started Guide** (literature number SPRU209) tells you how to install the Windows™ 3.1 and Windows™ 95 versions of the 'C2xx emulator and C source debugger interface.

- Microprocessor Development Systems Customer Support Guide (literature number SPDU08A) describes the registration, customer support services, service and warranty, and software license agreements. Precautions and safety considerations are also covered in this document.

#### Related Technical Articles

"A Greener World Through DSP Controllers", Panos Papamichalis, *DSP & Multimedia Technology*, September 1994.

"Application Guide with DSP Leading-Edge Technology", Y. Nishikori, M. Hattori, T. Fukuhara, R.Tanaka, M. Shimoda, I. Kudo, A.Yanagitani, H. Miyaguchi, et al., *Electronics Engineering*, November 1995.

"Approaching the No-Power Barrier", Jon Bradley and Gene Frantz, *Electronic Design*, January 9, 1995.

"Digital Signal Processing Solutions Target Vertical Application Markets", Ron Wages, *ECN*, September 1995.

"Digital Signal Processors Boost Drive Performance", Tim Adcock, *Data Storage*, September/October 1995.

"DSPs Advance Low-Cost 'Green' Control", Gregg Bennett, *DSP Series Part II*, *EE Times*, April 17, 1995.

"Easing JTAG Testing of Parallel-Processor Projects", Tony Coomes, Andy Fritsch, and Reid Tatge, *Asian Electronics Engineer*, Manila, Philippines, November 1995.

"Fixed or Floating? A Pointed Question in DSPs", Jim Larimer and Daniel Chen, *EDN*, August 3, 1995.

"Function-Focused Chipsets: Up the DSP Integration Core", Panos Papamichalis, *DSP & Multimedia Technology*, March/April 1995.

"Real-Time Control", Gregg Bennett, Appliance Manufacturer, May 1995.

"The Digital Signal Processor Development Environment", Greg Peake, Embedded System Engineering, United Kingdom, February 1995.

"The Growing Spectrum of Custom DSPs", Gene Frantz and Kun Lin, *DSP Series Part II*, *EE Times*, April 18, 1994.

"The Wide World of DSPs," Jim Larimer, Design News, June 27, 1994.

"Third-Party Support Drives DSP Development for Uninitiated and Experts Alike", Panos Papamichalis, *DSP & Multimedia Technology*, December 1994/January 1995.

"Toward an Era of Economical DSPs", John Cooper, *DSP Series Part I, EE Times*, Jan. 23, 1995.

#### **Trademarks**

TI, 320 Hotline On-line, XDS510, XDS510PP, XDS510WS, and XDS511 are trademarks of Texas Instruments Incorporated.

HP-UX is a trademark of Hewlett-Packard Company.

MS-DOS and Windows are registered trademarks of Microsoft Corporation.

PAL® is a registered trademark of Advanced Micro Devices, Inc.

OS/2, PC, and PC-DOS are trademarks of International Business Machines Corporation.

Solaris and SunOS are trademarks of Sun Microsystems, Inc.

GAL is a registered trademark of Lattice Semiconductor Corporation.

#### If You Need Assistance . . .

|          | World-Wide Web Sites                                         |                                    |                            |                                 |

|----------|--------------------------------------------------------------|------------------------------------|----------------------------|---------------------------------|

| 1        | TI Online                                                    | http://www.ti.con                  | า                          |                                 |

| 1        | Semiconductor Product Information Center (PIC)               | http://www.ti.con                  | n/sc/docs/pic/home.htm     |                                 |

| 1        | DSP Solutions                                                | http://www.ti.con                  | n/dsps                     |                                 |

|          | 320 Hotline On-line ™                                        | http://www.ti.con                  | n/sc/docs/dsps/support.htr | n                               |

|          | North America, South America, Cer                            | ntral America                      |                            |                                 |

| 1        | Product Information Center (PIC)                             | (972) 644-5580                     |                            |                                 |

| 1        | TI Literature Response Center U.S.A.                         | (800) 477-8924                     |                            |                                 |

| 1        | Software Registration/Upgrades                               | (214) 638-0333                     | Fax: (214) 638-7742        |                                 |

| 1        | U.S.A. Factory Repair/Hardware Upgrades                      | (281) 274-2285                     | ,                          |                                 |

| 1        | U.S. Technical Training Organization                         | (972) 644-5580                     |                            |                                 |

| 1        | DSP Hotline                                                  | (281) 274-2320                     | Fax: (281) 274-2324        | Email: dsph@ti.com              |

| 1        | DSP Modem BBS                                                | (281) 274-2323                     |                            |                                 |

|          | DSP Internet BBS via anonymous ftp to ftp://ftp              | .ti.com/pub/tms320                 | Obbs                       |                                 |

|          | Europe, Middle East, Africa                                  |                                    |                            |                                 |

| 1        | European Product Information Center (EPIC) H                 | lotlines:                          |                            |                                 |

| 1        | 3 - 3 1 - 1                                                  | 33 1 30 70 11 69                   | Fax: +33 1 30 70 10 32     | Email: epic@ti.com              |

| 1        | Deutsch +49 8161 80 33 11 or +                               |                                    |                            |                                 |

| 1        | 9 -                                                          | 33 1 30 70 11 65                   |                            |                                 |

| 1        |                                                              | 33 1 30 70 11 64                   |                            |                                 |

| 1        |                                                              | 33 1 30 70 11 67                   |                            |                                 |

| 1        |                                                              | 33 1 30 70 11 99                   |                            |                                 |

| 1        | European Factory Repair +: Europe Customer Training Helpline | 33 4 93 22 25 40                   | Fax: +49 81 61 80 40 10    | 1                               |

|          |                                                              |                                    | Fax. +49 61 61 60 40 10    |                                 |

|          | Asia-Pacific                                                 |                                    |                            |                                 |

| 1        |                                                              | +852 2 956 7288                    | Fax: +852 2 956 2200       |                                 |

| 1        | - 9 - 9                                                      | +852 2 956 7268                    | Fax: +852 2 956 1002       |                                 |

| 1        | Korea DSP Hotline                                            | +82 2 551 2804                     | Fax: +82 2 551 2828        |                                 |

| 1        | Korea DSP Modem BBS                                          | +82 2 551 2914                     |                            |                                 |

| 1        | Singapore DSP Hotline                                        | 000 0 077 4 450                    | Fax: +65 390 7179          |                                 |

| 1        |                                                              | +886 2 377 1450<br>+886 2 376 2592 | Fax: +886 2 377 2718       |                                 |

| 1        | Taiwan DSP Internet BBS via anonymous ftp to                 |                                    | ı tw/pub/TI/               |                                 |

|          |                                                              | rtp.//dap.cc.tit.cdc               | /pub/ 11/                  |                                 |

| $\Box$   | Japan                                                        |                                    | <b>-</b>                   |                                 |

| 1        |                                                              | -0026 (in Japan)                   | Fax: +0120-81-0036 (in     | . ,                             |

|          | +03-3457-0972 or (INTL                                       | ,                                  | Fax: +03-3457-1259 or      | ` ,                             |

| 1        | DSP Hotline +03-3769-8735 or (INTL DSP BBS via Nifty-Serve   | ) 813-3769-8735<br>Type "Go TIASP" | Fax: +03-3457-7071 or      | (INTL) 813-3457-7071            |

| <u> </u> |                                                              | Type GUTIAGE                       |                            |                                 |

|          |                                                              |                                    |                            |                                 |

|          | When making suggestions or reporting errors in               |                                    |                            | nformation that is on the title |

| 1        | page: the full title of the book, the publication da         | ate, and the literatu              |                            |                                 |

| 1        | Mail: Texas Instruments Incorporated                         | 10 =00                             | Email: comments@boo        | ks.sc.ti.com                    |

|          | Technical Documentation Services, N                          | /IS /02                            |                            |                                 |

| 1        | P.O. Box 1443                                                |                                    |                            |                                 |

| 1        | Houston, Texas 77251-1443                                    |                                    |                            |                                 |

**Note:** When calling a Literature Response Center to order documentation, please specify the literature number of the

# **Contents**

| 1 | 1.1<br>1.2<br>1.3<br>1.4 | BVM Contents  Features of the TMS320C24x Evaluation Board  Functional Overview of the TMS320C24x Evaluation Board  Hardware and Software Requirements  1.4.1 Hardware Requirements  1.4.2 Software Requirements | 1-2<br>1-3<br>1-4<br>1-8 |

|---|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 2 | Hard                     | ware Installation                                                                                                                                                                                               | 2-1                      |

|   | 2.1                      | Connecting the TMS320C24x Evaluation Board and XDS510PP Emulator  Supplying Power to the TMS320C24x Evaluation Board and XDS510PP Emulator                                                                      | 2-2                      |

| 3 | Ineta                    | Iling and Configuring the Code Development Tools                                                                                                                                                                | 2_1                      |

| 3 | 3.1                      | Installing the Assembly Language Tools                                                                                                                                                                          |                          |

|   | 3.2                      | Installing the TMS320C24x EVM Applications Code                                                                                                                                                                 |                          |

|   | 3.3                      | Installing the Debugger and Configuring Your System                                                                                                                                                             |                          |

|   | 0.0                      | 3.3.1 Installing the TMS320C24x EVM C Source Debugger Software                                                                                                                                                  |                          |

|   |                          | 3.3.2 Configuring Your System for the XDS510PP Emulator                                                                                                                                                         |                          |

|   |                          | 3.3.3 Verifying the Emulator Driver Installation                                                                                                                                                                |                          |

|   |                          | 3.3.4 Verifying the TMS320C24x EVM C Source Debugger Installation                                                                                                                                               |                          |

| 4 | Δ <b>9</b> 9Α            | mbling, Linking, and Running Your First Program                                                                                                                                                                 | 4-1                      |

| • | 4.1                      | Assembling the Program                                                                                                                                                                                          |                          |

|   | 4.2                      | Linking the Program                                                                                                                                                                                             |                          |

|   | 4.3                      | Running the Program                                                                                                                                                                                             |                          |

| 5 | TMS                      | 320C24x Evaluation Board Components                                                                                                                                                                             | 5-1                      |

|   | 5.1                      | External Memory                                                                                                                                                                                                 |                          |

|   |                          | 5.1.1 External Program Memory Space                                                                                                                                                                             |                          |

|   |                          | 5.1.2 External Data Memory Space                                                                                                                                                                                | 5-2                      |

|   | 5.2                      | Analog-to-Digital Converter                                                                                                                                                                                     |                          |

|   | 5.3                      | Digital-to-Analog Converter                                                                                                                                                                                     |                          |

|   | 5.4                      | RS-232 Serial Port                                                                                                                                                                                              | 5-8                      |

|   |                          | 5.4.1 Implementing a Communications Protocol with Software Handshaking                                                                                                                                          | 5-9                      |

|   |                          | 5.4.2 Implementing a Communications Protocol with Hardware Handshaking                                                                                                                                          | . 5-13                   |

|        | <ul><li>5.5</li><li>5.6</li></ul>             | Connectors 5.5.1 I/O Connector 5.5.2 Analog Connector 5.5.3 Address/Data Connector 5.5.4 Control Connector 5.5.5 Emulation Port Jumpers                                                      | 5-15<br>5-16<br>5-17<br>5-18<br>5-19 |

|--------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

|        | 5.7<br>5.8<br>5.9<br>5.10                     | LEDs                                                                                                                                                                                         | 5-24<br>5-26                         |

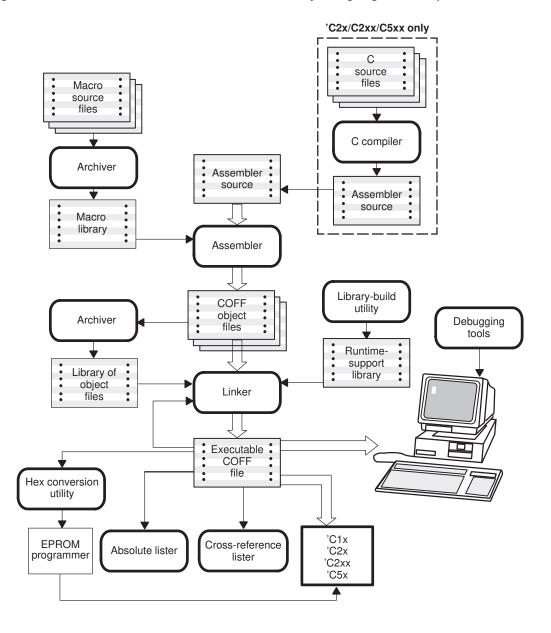

| 6      | 6.1                                           | Development Tools  Assembly Language Tools  6.1.1 Assembly Language Tools Descriptions  6.1.2 Assembly Language Tools Overview and Development Flow                                          | 6-2<br>6-2<br>6-4                    |

| Α      | 6.2<br>TMS3                                   | TMS320C24x EVM C Source Debugger                                                                                                                                                             | 6-6                                  |

| В      | Conn<br>B.1                                   | ector Signal Descriptions  I/O Connector Signal Descriptions                                                                                                                                 | B-1                                  |

|        | B.2<br>B.3<br>B.4<br>B.5                      | Analog Connector Signal Descriptions  Address/Data Connector Signal Descriptions  Control Connector Signal Descriptions  14-Pin Emulation Port Signal Descriptions                           | B-6<br>B-8                           |

| С      | B.3<br>B.4<br>B.5                             | Address/Data Connector Signal Descriptions                                                                                                                                                   | B-6 B-8 B-10 C-1                     |

| C<br>D | B.3<br>B.4<br>B.5<br><b>GAL</b><br>C.1<br>C.2 | Address/Data Connector Signal Descriptions  Control Connector Signal Descriptions  14-Pin Emulation Port Signal Descriptions  Equations  TMS320C24x Evaluation Board Peripheral Decode Logic | B-6 B-8 B-10 C-1 C-2 C-6 D-1 D-2     |

# **Figures**

| 1–1 | TMS320C24x Evaluation Board Diagram                                      | 1./  |

|-----|--------------------------------------------------------------------------|------|

| 1–2 | TMS320C24x EVM Memory Map                                                |      |

|     | · ·                                                                      |      |

| 2–1 | Connecting the TMS320C24x Evaluation Board and XDS510PP Emulator         |      |

| 3–1 | D_OPTIONS Environment Variable Dialog Box                                |      |

| 3–2 | D_SRC Environment Variable Dialog Box                                    |      |

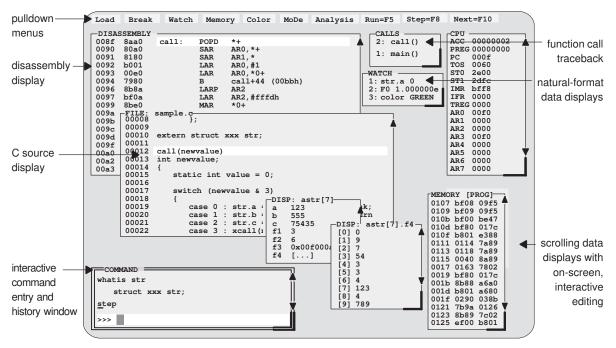

| 3–3 | TMS320C24x EVM C Source Debugger Display                                 | 3-11 |

| 4–1 | TMS320C24x EVM C Source Debugger Display                                 | 4-4  |

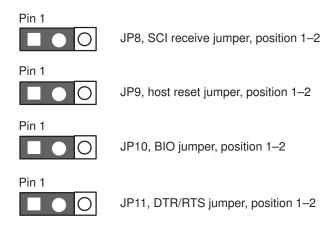

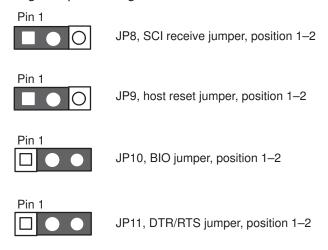

| 5–1 | Software Handshaking Jumper Configuration                                | 5-10 |

| 5–2 | Software Handshaking and Host Reset Jumper Configuration                 | 5-11 |

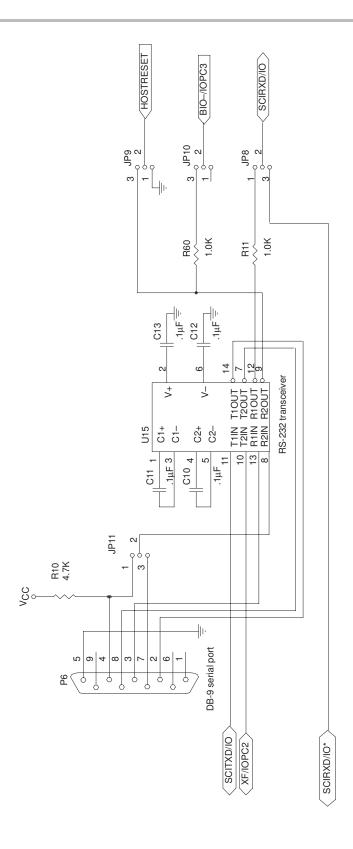

| 5–3 | RS-232 Serial Port Hardware Interface on the TMS320C24x Evaluation Board | 5-12 |

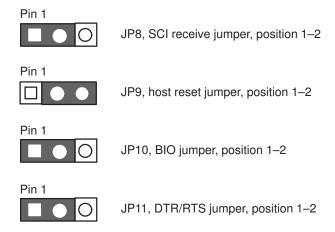

| 5–4 | Hardware Handshaking Jumper Configuration                                | 5-13 |

| 5–5 | I/O Connector (P1) Diagram                                               | 5-15 |

| 5–6 | Analog Connector (P2) Diagram                                            |      |

| 5–7 | Address/Data Connector (P3 Diagram)                                      |      |

| 5–8 | Control Connector (P4) Diagram                                           | 5-18 |

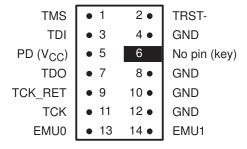

| 5–9 | 14-Pin Emulation Port Signals                                            | 5-19 |

| 6–1 | TMS320C1x/C2x/C2xx/C5x Assembly Language Development Flow                | 6-4  |

| 6–2 | The Basic Debugger Display                                               | 6-5  |

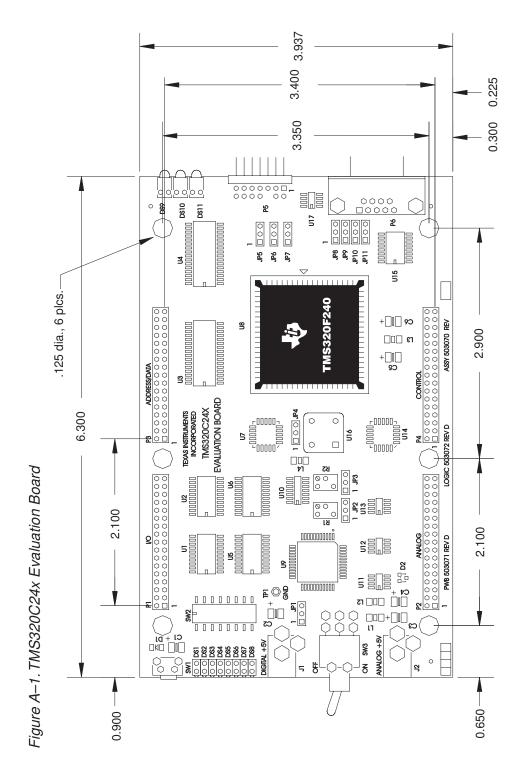

| A-1 | TMS320C24x Evaluation Board                                              | A-3  |

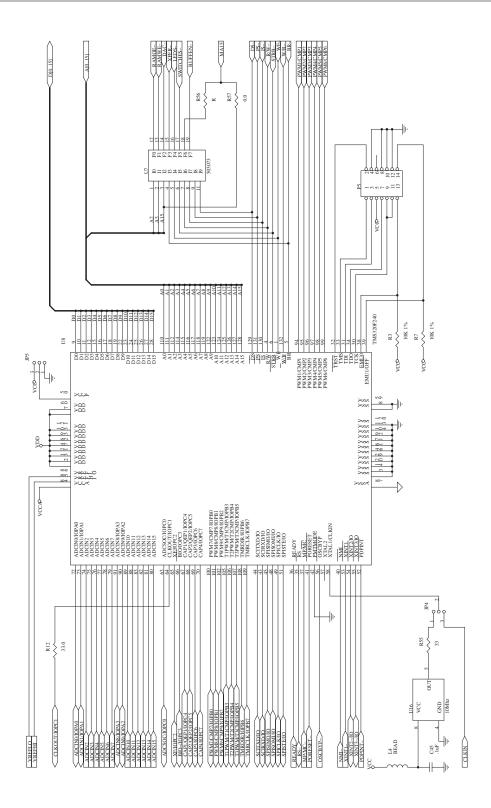

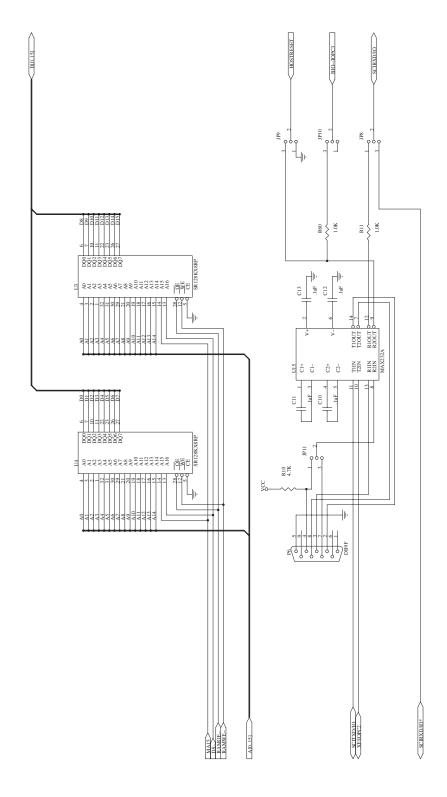

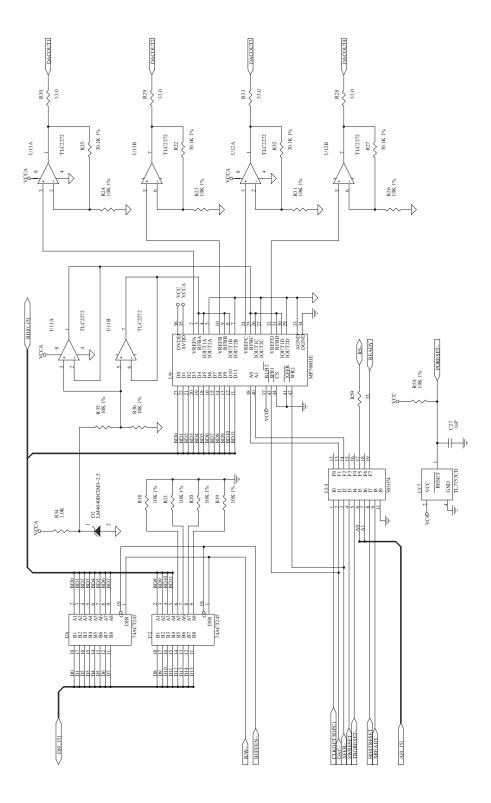

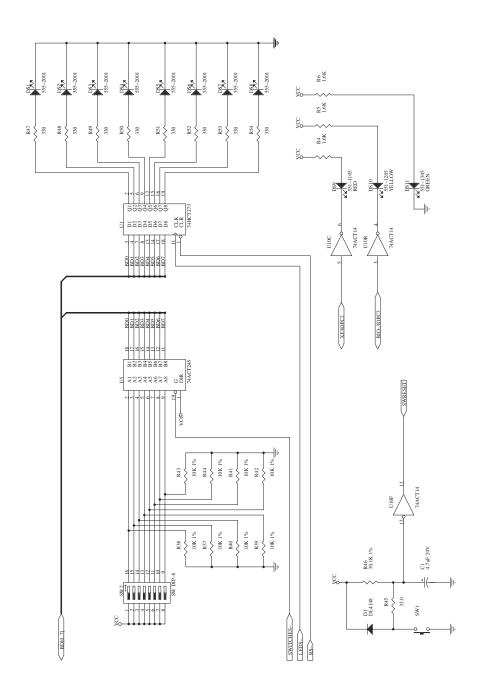

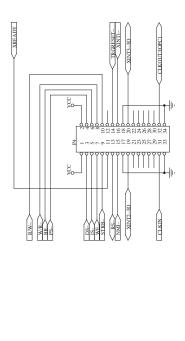

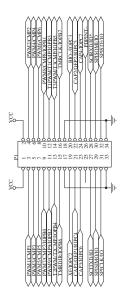

| A-2 | Schematic Diagram of the TMS320C24x Evaluation Board                     |      |

## **Tables**

| 3–1 | Options for Use With D_OPTIONS                           |      |

|-----|----------------------------------------------------------|------|

| 3–2 | XDS510PP Initialization Parameters                       | 3-7  |

| 5–1 | External Local and Global Data Memory Configurations     | 5-3  |

| 5–2 | DAC Registers                                            | 5-5  |

| 5–3 | DAC Output                                               |      |

| 5–4 | Evaluation Board and Host RS-232 Serial Port Connections |      |

| 5–5 | TMS320C24x Evaluation Board Jumpers                      | 5-20 |

| 5–6 | LEDs on the TMS320C24x Evaluation Board                  | 5-23 |

| 5–7 | Switches on the TMS320C24x Evaluation Board              | 5-25 |

| B-1 | I/O Connector Signal Descriptions                        | B-2  |

| B-2 | Analog Connector Signal Descriptions                     | B-4  |

| B-3 | Address/Data Connector Signal Descriptions               | B-6  |

| B-4 | Control Connector Signal Descriptions                    | B-8  |

| B-5 | 14-Pin Emulation Port Signal Descriptions                | B-10 |

|     |                                                          |      |

# **Examples**

| 3–1 | Sample autoexec.bat File Modified to Include the Assembly Language Tools Directory in the PATH Statement | 3-2 |

|-----|----------------------------------------------------------------------------------------------------------|-----|

| 3–2 | Sample autoexec.bat File Modified to Include the Assembly Language Tools Directory in the PATH Statement | 3-3 |

| C-1 | Peripheral Decode GAL Equation Routine                                                                   | C-3 |

| C-2 | Reset Logic and DAC Wait-State Generator GAL Equation Routine                                            | C-7 |

| D-1 | Running the portchk.exe Utility                                                                          | D-2 |

| D-2 | Running the smcmode.exe Utility                                                                          | D-3 |

| D-3 | Displaying the smcmode.exe Utility Options                                                               | D-3 |

| D-4 | Running the nscmode.exe Utility                                                                          | D-5 |

| D-5 | Displaying the nscmode.exe Utility Options                                                               | D-5 |

|     |                                                                                                          |     |

### **Chapter 1**

### Introduction

The TMS320C24x evaluation module ('C24x EVM) is a digital signal processor (DSP) development package that allows you to evaluate the 'C24x family of DSP controllers. The 'C24x EVM contains a standalone evaluation board that enables you to explore the architecture and operation of the 'C24x CPU and its peripherals. The board is built around the TMS320F240 ('F240) DSP controller, which is optimized for digital motor control and power conversion applications. The evaluation board connects to the parallel port of your PC through the XDS510PP™ emulator. The emulator and evaluation board, together with the 'C24x EVM C source debugger, allow for real-time verification of your 'C24x code. The four 34-pin connectors enable the use of expansion boards for a prototyping area or peripherals such as predrivers, power amplifiers, and user interfaces.

This chapter describes the 'C24x EVM, its features, design details, and external interfaces.

| Topic | Page |

|-------|------|

|       | •    |

| 1.1 | EVM Contents                                           | 1-2 |

|-----|--------------------------------------------------------|-----|

| 1.2 | Features of the TMS320C24x Evaluation Board            | 1-3 |

| 1.3 | Functional Overview of the TMS320C24x Evaluation Board | 1-4 |

| 1.4 | Hardware and Software Requirements                     | 1-8 |

#### 1.1 EVM Contents

There are six packages included in the 'C24x EVM. These packages contain the following hardware, software, and documentation: 'C24x evaluation board package 'C24x evaluation board 'C24x EVM software diskette (one diskette) ☐ 5-pin DIN-to-2.1-mm power supply adapter cable ☐ TMS320C24x DSP Controllers Evaluation Module Technical Reference 'C24x EVM documentation package ☐ TMS320C24x DSP Controllers Reference Set, Volume 1: CPU, System, and Instruction Set TMS320C24x DSP Controllers Reference Set, Volume 2: Peripheral Library and Specific Devices 'C24x EVM C source debugger package ☐ TMS320C2xx C source debugger software (one diskette) ☐ TMS320C2xx C Source Debugger User's Guide 'C1x/C2x/C2xx/C5x assembler package Assembly language tools software (two diskettes) ☐ TMS320C1x/C2x/C2xx/C5x Assembly Language Tools User's Guide TMS320C1x/C2x/C2xx/C5x Code Generation Tools Getting Started Guide ☐ XDS510PP emulator □ PC<sup>™</sup> parallel port cable XDS workstation power supply package Power supply (Input: 100–250 V, 50–60 Hz; Output: 5 V dc, 3.3 A)

Power cord

#### 1.2 Features of the TMS320C24x Evaluation Board

| e following features of the 'C24x evaluation board that are useful veloping digital motor control and automotive applications:                                                                                                                                                            | in |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 'F240 fixed-point DSP controller  128K words of external on-board SRAM  On-board, 4-channel, 12-bit digital-to-analog converter (DAC)  RS-232 compatible serial port  XDS510™/XDS510PP emulation port  Bank of eight I/O memory-mapped DIP switches  Bank of eight I/O memory-mapped LEDs |    |

#### 1.3 Functional Overview of the TMS320C24x Evaluation Board

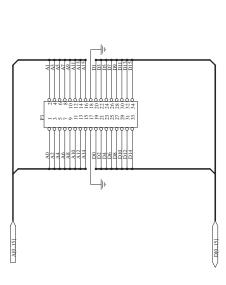

A diagram of the 'C24x evaluation board is shown in Figure 1–1. This section gives a brief overview of the major components on the 'C24x evaluation board.

DIP switch Socketed 10 MHz XDS510/XDS510PP LED bank oscillator bank emulator port 128K x 8-bit SRAMs P3 ADDRESS/DATA **VO** DS9 DS10 <u>0000000000</u> TEXAS INSTRUMENTS DS11 INCORPORATED 0000000000 TMS320C24X **0000000000 U5** 00000000000 EVALUATION BOARD 0000 JP5 □○○ DIGITAL +5V \S = JP6 □○○ GND nnni. U10 JP7 🗆 🔾 □ ○ ○ JP4 0000000 0000 0 0000 TMS320F240 0  $\bigcirc\bigcirc$ 000000000 U16  $\bigcirc\bigcirc$ JP10 1 JP2 U13 ы \_00000\_ 0000 8 U15 00000გ ¦¦¦ D2 ខ U14

OGIC 503072 REV D

Figure 1-1. TMS320C24x Evaluation Board Diagram

PWB 503071 REV D

DAC

The 'C24x evaluation board is built around the 'F240 DSP controller. This device operates at 20 MIPS with an instruction cycle time of 50 ns. It is optimized for digital motor control and power conversion applications. Some key features of the 'F240 device are listed below:

A\$SY 503070 REV

RS-232 compatible

serial port

'1 l□ o o o o o o o o o lo o o o o o o

20-MIPS

'F240 DSP

☐ The event manager (EV):

Socketed

16V8 GAL™

- Three 16-bit, 6-mode, general-purpose timers

- 12 pulse-width modulation (PWM) channels

- A quadrature encoder pulse interface (QEP)

- Four capture units

|                           | Dual 10-bit, 8-channel analog-to-digital converters (ADCs) Synchronous and asynchronous communications peripherals A programmable phase-locked-loop (PLL) clock module 544 words of dual access RAM (DARAM) 16K words of on-chip Flash memory                                                                                                                                                                               |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| iat<br>and<br>vice<br>ior | on-board, 4-channel, 12-bit DAC (U9) has been included on the 'C24x evalion board for code development purposes. The four DAC channel registers the DAC update register are mapped into the I/O space of the 'F240 dee. The DAC module requires that wait states be generated for proper operant. See section 5.3, <i>Digital-to-Analog Converter</i> on page 5-5, for more inmation on configuring the DAC for proper use. |

| 008                       | e 'C24x evaluation board supports a total of 128K words of external onard memory. The two 128K x 8 bit SRAMs (U3 and U4) on the evaluation ard are partitioned in the following manner:                                                                                                                                                                                                                                     |

|                           | 64K words external program memory<br>32K words external local data memory<br>32K words external global data memory                                                                                                                                                                                                                                                                                                          |

| Γhε                       | on-hoard SRAMs interface with the external address and data huses of                                                                                                                                                                                                                                                                                                                                                        |

to access external program and data memory spaces with zero wait states. The 'C24x evaluation board memory maps are shown in Figure 1–2.

the 'F240 device. The 15-ns access time of the SRAMs allows the 'F240 device

Figure 1–2. TMS320C24x EVM Memory Map

|        | Program                          |                 | Data                             |                 | I/O                        |

|--------|----------------------------------|-----------------|----------------------------------|-----------------|----------------------------|

| 0000h  | On-chip interrupt                | 0000h           | Managara                         | 0000h           | DAC channel 1              |

|        | ve <u>cto</u> rs<br>(MP/MC = 0)  |                 | Memory-mapped registers          | 0001h           | DAC channel 2              |

|        | External interrupt               | 005Fh           | Ŭ                                | 0002h           | DAC channel 3              |

|        | ve <u>cto</u> rs ·               | 0060h           | On-chip DARAM                    | 0003h           | DAC channel 4              |

| 003Fh  | $(MP/\overline{MC} = 1)$         | 007Fh           | B2                               | 0004h           | DAC update†                |

| 0040h  | On-chip Flash<br>EE <u>PRO</u> M | 0080h           |                                  | 0005h           | Reserved                   |

|        | (MP/MC = 0)                      |                 | Reserved                         | 0007h           | DIP switch bank†           |

|        | External SRAM                    |                 | neserveu                         | 0008h<br>0009h  | DIP SWILCH DANK!           |

| 3FFFh  | $(MP/\overline{MC} = 1)$         | 01FFh           |                                  | 000911<br>000Bh | Reserved                   |

| 4000h  |                                  | 0200h           | On-chip DARAM                    | 000BH           | LED bank†                  |

|        |                                  |                 | B0† (CNF=0)<br>Reserved          | 000Dh           |                            |

|        |                                  | 02FFh           | (CNF = 1)                        |                 |                            |

|        |                                  | 0300h           |                                  |                 |                            |

|        |                                  |                 | On-chip DARAM<br>B1 <sup>†</sup> |                 |                            |

|        |                                  | 03FFh           | ы                                |                 | Reserved                   |

|        | E                                | 0400h           |                                  |                 |                            |

|        | External SRAM                    |                 |                                  |                 |                            |

|        |                                  |                 | Reserved                         | 7FFFh           |                            |

|        |                                  | 06FFh           |                                  | 8000h           |                            |

|        |                                  | 7000h           | Peripheral                       |                 |                            |

|        |                                  | 743Fh           | memory-mapped registers          |                 |                            |

|        |                                  | 743111<br>7440h | registers                        |                 |                            |

|        |                                  |                 | Reserved                         |                 | Available<br>for off-board |

| FDFFh  |                                  | 7FFFh<br>8000h  |                                  |                 | peripherals                |

| FE00h  |                                  | 000011          |                                  |                 |                            |

| FEFFh  | Reserved                         |                 |                                  |                 |                            |

| FF00h  | Evternal CDAM                    |                 | External SRAM (local and global) |                 |                            |

| 110011 | External SRAM<br>(CNF = 0)       |                 | (100al alla global)              | FEFFh           |                            |

|        | On-chip DARAM B0                 |                 |                                  | FF00h           | Reserved                   |

| FFFh   | (CNF =1)                         | FFFh            |                                  | FFFh            | 110001100                  |

$<sup>\</sup>ensuremath{^{\dagger}}$  These registers are mapped to multiple memory locations.

The 'C24x evaluation board has an on-board, RS-232 compatible, DB-9 serial port for asynchronous communication. The DB-9 serial port (P6) interfaces to the serial communications interface (SCI) peripheral on the 'F240 device through an RS-232 transceiver. The serial port can be configured for various communications protocols with software and hardware handshaking. See section 5.4, *RS-232 Serial Port*, on page 5-8, for more information on configuring and using the on-board serial port.

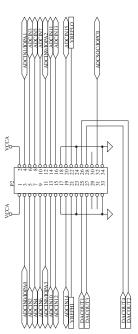

Four 34-pin connectors give access to all relevant signals on the 'C24x evaluation board. All EV, serial peripheral interface (SPI), and SCI signals are brought out to the I/O connector (P1). All analog signals, including the four DAC output channels, the 16 ADC input channels, and the ADC reference voltages, are brought out to the analog connector (P2). The external address and data bus signals can be found on the address/data connector (P3). And the external memory interface control signals are brought out to the control connector (P4).

The emulation port (P5), which is compatible with the IEEE1149.1 standard, allows the 'C24x evaluation board to act as an XDS emulator target board. The XDS510PP emulator included with the EVM operates as the main interface between the debugger and the 'C24x evaluation board.

#### 1.4 Hardware and Software Requirements

You must meet the following hardware and software requirements to use the 'C24x evaluation board.

#### 1.4.1 Hardware Requirements

In addition to the EVM contents, the following hardware is required to use the 'C24x evaluation board:

☐ Host A '386 or higher IBM PC/AT™ or 100% compatible PC, 486,

or Pentium PC with a 1.44M-byte 3.5-inch floppy disk drive

Ports Supports 4-bit standard parallel ports (SPP4s),

8-bit bidirectional standard parallel ports (SPP8s), and enhanced parallel ports (EPPs). The EVM does not sup

port extended capabilities ports (ECPs).

#### Note:

Your parallel port should be configured for EPP mode to obtain the maximum data transfer rate. Be sure to consult your PC documentation for specific instructions on configuring the parallel port.

■ Memory Minimum of 4M bytes

Monitor Color VGA

#### 1.4.2 Software Requirements

In addition to the software provided, the following applications are required to use the 'C24x evaluation board:

☐ Windows™ 3.1 or Windows 95

☐ ASCII editor

### **Chapter 2**

### **Hardware Installation**

This chapter provides instructions on how to connect the XDS510PP emulator and evaluation board to your host PC and how to supply power to the target board and emulator.

Before installing your evaluation board, verify that your PC hardware and software platforms meet the minimum requirements described in section 1.4.

#### Topic Page

| 2.1 | Connecting the TMS320C24x Evaluation Board and XDS510PP Emulator         | 2-2 |

|-----|--------------------------------------------------------------------------|-----|

| 2.2 | Supplying Power to the TMS320C24x Evaluation Board and XDS510PP Emulator | 2-3 |

#### 2.1 Connecting the TMS320C24x Evaluation Board and XDS510PP Emulator

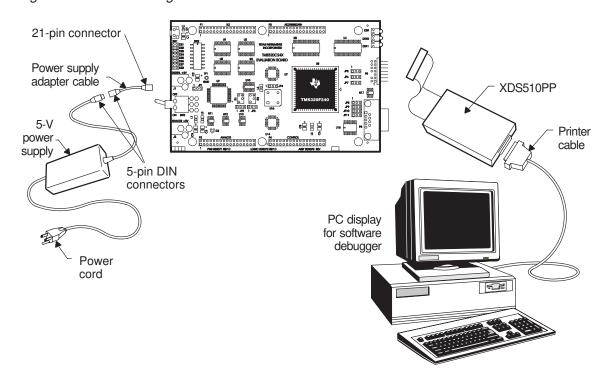

Follow the steps below to ensure proper connections among the host PC, XDS510PP emulator, and 'C24x evaluation board. See Figure 2–1 for a connection diagram.

- 1) Turn off the power to the PC.

- 2) Connect one end of the DB25 printer cable to the parallel port of your PC.

- 3) Connect the other end of the DB25 printer cable to the XDS510PP emulator.

- 4) Connect the 14-pin female header on the XDS510PP emulator to the 14-pin right-angle emulation port on the evaluation board (P5).

#### Note:

Pin 6 of the 14-pin XDS510PP emulator header is filled in and the corresponding pin 6 of the emulation port on the evaluation board is missing to ensure proper connection.

Figure 2-1. Connecting the TMS320C24x Evaluation Board and XDS510PP Emulator

### 2.2 Supplying Power to the TMS320C24x Evaluation Board and XDS510PP Emulator

Follow the steps below to supply power to the host PC and evaluation board. See Figure 2–1 for a connection diagram.

- 1) Make sure the power switch on the evaluation board is in the OFF position.

- 2) Use the black power cord to plug the power supply into the wall outlet.

- 3) Connect the 5-pin DIN end of the power supply adapter cable into the 5-pin DIN connector on the power supply.

- 4) Connect the 2.1-mm end of the power supply adapter cable into the digital power supply jack (J1) on the evaluation board.

- 5) Turn on the power to the PC and the evaluation board.

### **Chapter 3**

# Installing and Configuring the Code Development Tools

This chapter provides instructions for installing the tools code provided in the 'C24x EVM package. These include assembly language tools, C source debugger, and sample applications code. See the appropriate user's guide for complete documentation.

####

Installing the Debugger and Configuring Your System ...... 3-4

#### 3.1 Installing the Assembly Language Tools

Perform the following steps to install the assembly language tools. See the *TMS320C1x/C2x/C2xx/C5x Code Generation Tools Getting Started Guide* for additional information on installing and configuring the tools. These instructions assume that C is your fixed or hard disk and that A is your external, 3 1/2-inch drive.

- In the kit, locate the box labeled TMS320C1x/C2x/C5x Assembler, PC System. This box contains the assembly language tools. Open the box, and remove the two assembly language tools diskettes.

- Create a directory on your hard disk drive for the assembly language tools by entering the following from a system prompt.

```

MD C:\C24XTOOLS

```

3) Copy all of the files from the two diskettes to the C24XTOOLS directory on your hard disk drive. Put diskette 1 into drive A, and enter the following from a system prompt:

```

COPY A:\DOS32\*.* C:\C24XTOOLS

```

Repeat this step for disk 2 of the assembly language tools.

4) Modify the PATH statement to identify the assembly language tools directory. Edit your *autoexec.bat* file and find the line that includes PATH=. At the end of the line, type:

```

;C:\C24XTOOLS

```

See Example 3–1 for an example of how to modify your *autoexec.bat* file.

### Example 3–1. Sample autoexec.bat File Modified to Include the Assembly Language Tools Directory in the PATH Statement.

```

DATE

TIME

ECHO OFF

PATH=C:\WINDOWS;C:\C24XTOOLS

CLS

```

#### Note:

Do not copy the OS/2 tools onto your hard disk drive. These tools are contained in the os2v2 directories of the product disks. The copy command properly installs the MS-DOS tools onto your hard disk.

#### 3.2 Installing the TMS320C24x EVM Applications Code

Follow the steps below to install the sample applications code. See the *appscode.txt* file for more information on the specific applications included with your EVM. This file can be found on the *'C24x EVM Software Diskette*.

- 1) Locate the diskette labeled *'C24x EVM Software Diskette* in the 'C24x evaluation board box.

- 2) Create a directory on your hard disk for the assembly language tools by entering the following from a system prompt.

```

MD C:\C24XCODE

```

3) To install the sample applications code, copy all the files in the APPSCODE directory on the diskette to the C24XCODE directory on your hard disk. Put the 'C24x EVM Software Diskette into drive A and enter the following from a system prompt:

```

COPY A:\APPSCODE\*.* C:\C24XCODE

```

4) Modify the PATH statement to identify the assembly language tools directory. Edit your *autoexec.bat* file and find the line that includes PATH=. At the end of the line, type:

```

;C:\C24XCODE

```

See Example 3–2 for an example of how to modify your *autoexec.bat* file.

### Example 3–2. Sample autoexec.bat File Modified to Include the Assembly Language Tools Directory in the PATH Statement

```

DATE

TIME

ECHO OFF

PATH=C:\WINDOWS;C:\C24XTOOLS;C:\C24XCODE

CLS

```

#### 3.3 Installing the Debugger and Configuring Your System

This section gives you instructions on how to install the 'C24x EVM C source debugger and how to configure your system. It includes instructions on installing the debugger software, configuring your system for the XDS510PP emulator, and verifying the installation of the debugger and emulator.

#### 3.3.1 Installing the TMS320C24x EVM C Source Debugger Software

Follow the instructions below to install the 'C24x EVM C source debugger software.

- Locate the diskette labeled TMS320C24x EVM C Source Debugger in the TMS320C24x EVM C Source Debugger book. Open the box and remove the C source debugger diskette.

- 2) Insert the diskette into drive A:\, click on the *Start* button from the task bar in Windows95, select *Run...* (or in Windows 3.x.x select the *File* menu in the program manager, click *Run...*) and type:

A:\INSTALL.EXE

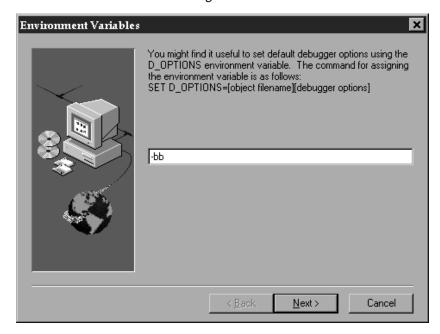

3) Follow the instructions in the installation utility until you reach the dialog box labeled *Environment Variables* shown in Figure 3–1.

Figure 3–1. D\_OPTIONS Environment Variable Dialog Box

An environment variable is a special symbol used by the debugger to find or obtain certain types of information. The D\_OPTIONS environment variable is convenient for specifying the debugger options commonly used when invoking the debugger.

SET D\_OPTIONS=[object filename] [debugger options]

For example, the -bb option can be used to increase the debugger window by two sizes. Table 3–1 lists the options that you can identify with the D\_OPTIONS environment variable.

Table 3-1. Options for Use With D\_OPTIONS

| Option            | Description                              |

|-------------------|------------------------------------------|

| -b[b]             | Increase the size of the debugger window |

| -c                | Clear the .bss section                   |

| -f filename       | Identify a new board configuration file  |

| –i pathname       | Identify additional directories          |

| -min              | Select the minimal debugging mode        |

| -n processor name | Identify processor for debugging         |

| -s                | Load the symbol table only               |

| –t filename       | Identify a new initialization file       |

| _v                | Load without the symbol table            |

See the *TMS320C2xx C Source Debugger User's Guide* for more information on debugger options and defining your target system to the debugger.

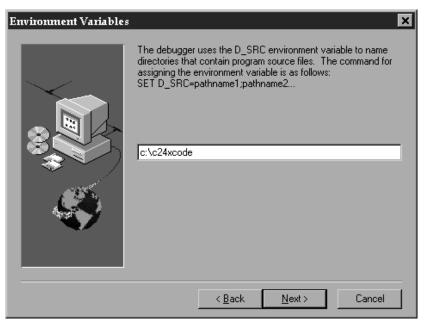

Figure 3–2. D\_SRC Environment Variable Dialog Box

- 4) Define the directories that contain program source files in the D\_SRC environment variable dialog box shown in Figure 3–2. For example, the C24XCODE directory must assigned to the D\_SRC environment variable, because this directory contains the 'C24x EVM applications programs included with the EVM.

- 5) Complete the installation utility by following the instructions listed in the remaining dialog boxes. A file folder labeled TMS320C24x EVM debugger is created by the utility and contains three icons. The 'C24x debugger icon is used to invoke the debugger. The XDS510PP reset icon resets the emulator and the readme.txt file gives additional information on configuring your system. Continue with section 3.3.2, Configuring Your System for the XDS510PP Emulator, after completing the debugger installation.

#### 3.3.2 Configuring Your System for the XDS510PP Emulator

The *xds510pp.ini* file is used to set driver parameters for the XDS510PP emulator and is located in the *C24XHLL* directory. The three parameters defined in this initialization file are *mode*, *port*, and *speed*. The following are the default values for each parameter:

port = 378 mode = spp4 speed = 10 Each parameter in the *xds510pp.ini* file must be modified to reflect the configuration your system. A brief description of each parameter is given in Table 3–2. A more detailed description of each parameter is given in the paragraphs that follow.

Table 3-2. XDS510PP Initialization Parameters

| Parameter | Description                                                                                        |

|-----------|----------------------------------------------------------------------------------------------------|

| Port      | Selects the parallel port of your PC. The default address is 378h.                                 |

| Mode      | Defines the parallel port mode. The XDS510PP emulator supports the following modes:                |

|           | SPP4 4-bit unidirectional mode<br>SPP8 8-bit bidirectional mode<br>EPP Enhanced parallel port mode |

|           | The default mode is SPP4.                                                                          |

| Speed     | Determines the amount of delay between port accesses. The default value is 10.                     |

The *port* parameter defines the address of your parallel port. The default address on most PCs is 378h. Other commonly used addresses are 278h and 3BCh. Consult your PC documentation to determine the address of your parallel port. The port detection utility included with the debugger software, *portchk.exe*, can also be used to determine the parallel port address. This utility searches for parallel ports and tries to determine if they are bidirectional. See Appendix D, *Parallel Port Utility Programs*, for more information on the *portchk.exe* utility.

The *mode* parameter defines the configuration of the parallel port for the debugger. The 4-bit unidirectional (SPP4) mode works on all machines, but is the slowest. This mode is necessary for older PCs that do not have full 8-bit bidirectional parallel port capability. Newer PCs typically have 8-bit bidirectional (SPP8) and 8-bit enhanced parallel port (EPP) capability. EPP mode is the recommended choice and provides the highest throughput.

#### Note:

Your parallel port must be configured for EPP mode to obtain the maximum data transfer rate. In many cases, this requires entering the BIOS setup utility of your PC. Consult your PC documentation for specific instructions on configuring the parallel port.

The *speed* parameter determines the amount of delay between parallel port accesses. The amount of delay increases as the parameter value increases.

Set this parameter to 10 initially. Once the XDS510PP is operating correctly, you can reduce this number.

Two utility programs, *smcmode.exe* and *nscmode.exe* are included with the debugger software. These programs may help you in setting the parallel port mode for certain PC hardware configurations. Appendix D, *Parallel Port Utility Programs*, contains instructions on their use. See the *XDS51x Emulator Installation Guide* included in the emulation controller package, or the *readme.txt* file included in the *C24XHLL* directory, for more information regarding the configuration of your system for the XDS510PP emulator.

#### 3.3.3 Verifying the Emulator Driver Installation

The emulator device driver enables the 'C24x EVM C source debugger to communicate with the XDS510PP emulator. See Appendix D, *Parallel Port Utility Programs*, for more information on this utility. Follow these steps to ensure that the emulator driver has been installed correctly:

Reset the XDS510PP emulator by double clicking on the XDS510PP Reset icon in the TMS320C24x EVM Debugger file folder. After resetting the XDS510PP emulator, you should see a message similar to the following in a system prompt window:

```

XDS510PP IS RESET, HARDWARE VERSION 1

If this message appears, continue with section 3.3.4, Verifying the Debugger and Emulator Installation.

```

If you see the following message the emulator has not been reset successfully:

```

EMURST FOR THE XDS510PP VERSION 1.0 COMMUNICATIONS ERROR, OR POD HAS NO POWER

```

Continue with step 2 to troubleshoot your system. When you see the first message in step 1, you have resolved the problem and can go to section 3.3.4, *Verifying the Debugger and Emulator Installation*.

2) Check the following items to troubleshoot your system:

EMURST FOR THE XDS510PP VERSION 1.0

| Be sure power is supplied to the 'C24x evaluation board and the power |

|-----------------------------------------------------------------------|

| switch on the board (SW3) is in the ON position.                      |

- ☐ Verify that the parallel port is firmly connected to the parallel port on your PC and to the XDS510PP emulator pod.

- ☐ Verify that the 14-pin header on the XDS510PP emulator pod is firmly connected to the emulation port (P5) on the evaluation board.

- 3) If the problem is not resolved, verify that the *xds510pp.ini* file has been configured correctly (see section 3.3.2, *Configuring Your System for the XDS510PP Emulator*, on page 3-6). Be sure that the *mode* and *port* parameters in this file match the settings of your PC. You can use the port detection utility (*portchk.exe*) to determine how your parallel port is configured.

| 4) | Run the SMC port configuration utility ( <i>smcmode.exe</i> ) to determine whether your PC uses an SMC parallel port controller device. Enter the following line at a system prompt to execute the utility:                                                                                                     |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | C:\C24XHLL\smcmode.exe                                                                                                                                                                                                                                                                                          |

|    | See Appendix D, <i>Parallel Port Utility Programs</i> , for more information on this utility.                                                                                                                                                                                                                   |

|    | If an SMC device is detected but not configured for the desired mode, then use the <i>smcmode.exe</i> utility with the –m option to configure the device for the mode desired. For example, to configure the device for mode 1, EPP and SPP mode, (the recommended mode) type the following at a system prompt: |

|    | C:\C24XHLL\smcmode.exe -m 1                                                                                                                                                                                                                                                                                     |

|    | If an SMC device is detected and configured for the desired mode, then reset the SMC device by typing the following at a system prompt:                                                                                                                                                                         |

|    | C:\C24XHLL\smcmode.exe -r                                                                                                                                                                                                                                                                                       |

|    | See Appendix D, <i>Parallel Port Utility Programs</i> for more information on how to reset an SMC device.                                                                                                                                                                                                       |

| 5) | Run the NSC port configuration utility ( <i>nscmode.exe</i> ) to determine whether your PC uses an NSC parallel port controller device. Enter the following line at a system prompt to execute the utility:                                                                                                     |

|    | C:\C24XHLL\nscmode.exe                                                                                                                                                                                                                                                                                          |

|    | If an NSC device is detected but not configured for the desired mode, then use the <i>nscmode.exe</i> utility with the –m option to configure the device for the mode desired. For example, to configure the device for mode 2, EPP mode, (the recommended mode) type the following at a system prompt:         |

|    | C:\C24XHLL\nscmode.exe -m 2                                                                                                                                                                                                                                                                                     |

#### 3.3.4 Verifying the TMS320C24x EVM C Source Debugger Installation

Follow these instructions to ensure that the debugger software and XDS510PP emulator have been installed correctly:

1) Reset the XDS510PP emulator by double clicking on the *XDS510PP Reset* icon in the *TMS320C24x EVM Debugger* file folder.

#### Note:

The XDS510PP Reset utility program only resets the XDS510PP emulator, not the 'F240 device on the evaluation board. You should reset the emulator before invoking the debugger following a PC or evaluation board power-on condition.

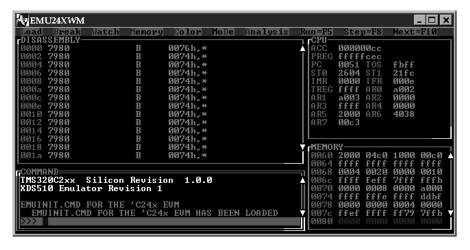

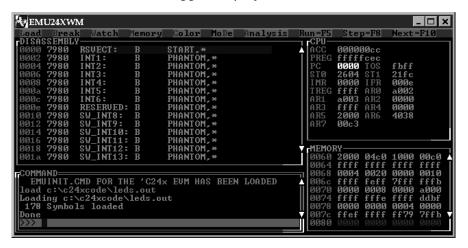

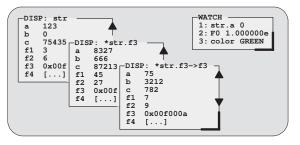

2) Invoke the debugger by double clicking on the C24x EVM Debugger icon in the TMS320C24x EVM Debugger file folder. After invoking the debugger, you should see a display similar to the display in Figure 3–3.

Figure 3–3. TMS320C24x EVM C Source Debugger Display

- ☐ If you see a display similar to this one, you have correctly installed the debugger software and XDS510PP emulator. Continue with Chapter 4, Assembling, Linking, and Running Your First Program.

- ☐ If you see a display and the lines of code say *Invalid Address* or the fields in the MEMORY window are shown in red, the debugger may not be able to find the *emuinit.cmd* file. Check for the file in the *C24XHLL* directory or verify that the file resides in a directory specified by the D\_SRC environment variable.

|       | The following message in the debugger display indicates another source:                                                            |  |  |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|       | CANNOT INITIALIZE THE TARGET !!                                                                                                    |  |  |  |  |  |  |  |

|       | - Check the I/O configuration                                                                                                      |  |  |  |  |  |  |  |

|       | - Check cabling and target power                                                                                                   |  |  |  |  |  |  |  |

| Check | Check the following items:                                                                                                         |  |  |  |  |  |  |  |

|       | Be sure power is supplied to the 'C24x evaluation board and the power switch on the board (SW3) is in the ON position.             |  |  |  |  |  |  |  |

|       | Verify that the parallel port is firmly connected to the parallel port on your PC and to the XDS510PP emulator pod.                |  |  |  |  |  |  |  |

|       | Verify that the 14-pin header on the XDS510PP emulator pod is firmly connected to the emulation port (P5) on the evaluation board. |  |  |  |  |  |  |  |

### **Chapter 4**

# Assembling, Linking, and Running Your First Program

This chapter takes you through the process of assembling, linking, and running a simple assembly source program on the 'C24x evaluation board. The chapter describes a sample program that you can run on your own. This program, *leds.asm*, causese the I/O-mapped bank of LEDs to flash sequentially, showing you the program is running. After completing this chapter, you will be able to assemble, link and run your own programs on the evaluation board.

| Topic | C                      | Page  |

|-------|------------------------|-------|

| 4.1   | Assembling the Program | . 4-2 |

| 4.2   | Linking the Program    | . 4-3 |

| 4.3   | Running the Program    | . 4-4 |

|       |                        |       |

#### 4.1 Assembling the Program

The 2-pass assembler, *dspa.exe*, translates assembly language source files into machine language object files. These translated files are in common object file format (COFF), discussed in the *TMS320C1x/C2x/C2xx/C5x Assembly Language Tools User's Guide*.

The assembly language source file, *leds.asm*, is located in the *C24XCODE* directory. Execute the following command from a system prompt in the *C24XCODE* directory to assemble *leds.asm* with the –v2xx and –s options:

```

dspa leds.asm -v2xx -s

```

#### Note:

The assembler does not execute out of the *C24XCODE* directory unless you have included the *C24XTOOLS* directory in the path statement of your *auto-exec.bat* file and have rebooted your PC.

The –v2xx option tells the assembler to produce code for the 'C2xx family of devices. The –s option puts all defined symbols, including labels, in the object file's symbol table. See the *TMS320C1x/C2x/C5x Assembly Language Tools User's Guide* for further instructions on invoking the assembler and a complete listing of all assembler options. The following message appears after successfully assembling the source file, *leds.asm*:

The assembler produces an object file, *leds.obj*, from the assembly source file, *leds.asm*. The *leds.obj* is relocatable and is used by the linker, as shown in section 4.2, *Linking the Program*.

#### 4.2 Linking the Program

The linker creates an executable COFF object module that can be downloaded to the 'F240 device on the evaluation board. The object file created by the assembler in the previous section, *leds.obj*, and the command file *f240init.cmd* are used by the linker to generate a single output file, *leds.out*. The linker, *dsplnk.exe*, accepts several types of files as input, including object files, command files, libraries, and partially linked files. The *f240init.cmd* file defines the memory map of the 'F240 device and tells the linker where certain sections of code should reside in memory.

The *leds.out* file generated by the linker can be downloaded directly to the 'F240 device. Execute the following command from a system prompt in the *C24XCODE* directory to link the *leds.obj* and *f240lnk.cmd* files:

dsplnk leds.obj f240lnk.cmd -o leds.out

#### Note:

The linker does not execute out of the *C24XCODE* directory unless you have included the *C24XTOOLS* directory in the path statement of your *autoexec.bat* file and have rebooted your PC.

The preceding command creates an output file, *leds.out*, from the *leds.obj* and *f240lnk.cmd* input files. The –o option specifies the name of the output file, *leds.out*. See the *TMS320C1x/C2x/C2xx/C5x Assembly Language Tools User's Guide* for further instructions on invoking the linker and a complete listing of all linker options. The following message appears after successfully creating the output file, *leds.out*:

TMS320C1x/C2x/C2xx/C5x COFF Linker Version 6.60 Copyright (c) 1987-1995 Texas Instruments Incorporated

#### 4.3 Running the Program

Use the C source debugger to download the *leds.out* file to the evaluation board. After invoking the debugger, type the following command at the prompt in the command window of the debugger:

load c:\C24XCODE\leds.out

#### Note:

Be sure that the  $MP/\overline{MC}$  jumper is in position 1–2 (its default position). If it is not, the debugger will unsuccessfully attempt to load the program into the internal Flash memory.

Press the F5 function key to run the program after it has been loaded. The debugger screen looks similar to the one in Figure 4–1 when the program is running. The command window indicates that the program is running and the I/O mapped bank of LEDs (DS1–DS8) on the evaluation board flashes sequentially.

Figure 4-1. TMS320C24x EVM C Source Debugger Display

## TMS320C24x Evaluation Board Components

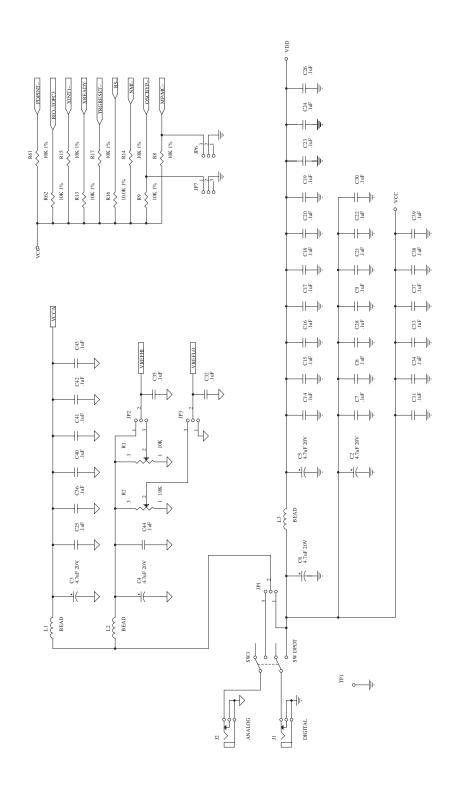

This chapter describes the major components on the 'C24x evaluation board and the hardware interfaces between the 'F240 DSP and peripherals. These include external memory, the digital-to-analog converter (DAC), LEDs, and DIP switches. This chapter also provides peripheral register definitions and discussed operation of the oscillator, DAC, LEDs, and DIP switches.

| Topic |                             | Page   |

|-------|-----------------------------|--------|

| 5.1   | External Memory             | 5-2    |

| 5.2   | Analog-to-Digital Converter | 5-4    |

| 5.3   | Digital-to-Analog Converter | 5-5    |

| 5.4   | RS-232 Serial Port          | 5-8    |

| 5.5   | Connectors                  | . 5-14 |

| 5.6   | Jumpers                     | . 5-20 |

|       | LEDs                        |        |

| 5.8   | Switches                    | . 5-24 |

| 5.9   | Oscillator                  | . 5-26 |

| 5.10  | GAL Devices                 | . 5-27 |

|       |                             |        |

#### 5.1 External Memory

The 'C24x evaluation board has a total of 128K words of external, on-board memory. The two 128K x 8-bit SRAMs (U3 and U4) are partitioned in the following manner:

| 64K words external program memory     |

|---------------------------------------|

| 32K words external local data memory  |

| 32K words external global data memory |

The on-board SRAMs interface to the external address and data buses of the 'F240 device. One of the two socketed 16V8 generic-array-logic (GAL) devices (U7) on the 'C24x evaluation board has been factory programmed to control the write-enable ( $\overline{\rm WE}$ ) and output-enable ( $\overline{\rm OE}$ ) functions of the SRAMs and the memory space decode logic. The 15-ns access time of the SRAMs allows the 'F240 device to access external program and data memory spaces with zero wait states. The 'C24x evaluation board memory maps are shown in Figure 1–2 on page 1-6.

#### 5.1.1 External Program Memory Space

The 'C24x evaluation board has 64K words of on-board external program memory. When the 'F240 device is operating in microprocessor mode, the entire program memory space of the 'F240 device resides in the 64K words of external program memory. The MP/MC jumper (JP6) must be in position 1–2 for the 'F240 device to operate in microprocessor mode.

When the 'F240 device is operating in microcomputer mode, only program memory accesses above 4000h reside in external program memory. All program memory accesses at or below 4000h reside in the 16K words of on-chip Flash memory. The MP/MC jumper (JP6) must be in position 2–3 for the 'F240 device to operate in microcomputer mode.