# Second-Generation TMS320 User's Guide

Digital Signal Processing Products

### Manual Update\_

Document Title: Second-Generation TMS320 Users Guide

Document Number: SPRU014 ECN Number: 526628

The following are changes to the Second-Generation TMS320 User's Guide. These changes will be incorporated in the next revision of the manual. Bars in the right margin indicate changes or additions to the manual.

### <u>Page</u>

Change or Add

3-25 On the top line following the words "which do not affect the accumulator" add a footnote flag (<sup>†</sup>) and, on the bottom of the page, add the following footnote:

<sup>†</sup>BIT instruction may affect the accumulator on the TMS32020 under certain circumstances. Refer to Section 4.3, Page 4-45.

4-45 Under the **Execution** heading, following the words "Affects TC", add the following warning:

### Caution: See note on next page concerning execution by TMS32020.

JMENTS

SPRZ047

| Page | Change or Add                                                                                                                                                                     |  |  |  |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

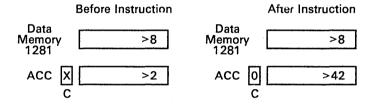

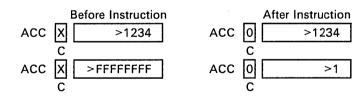

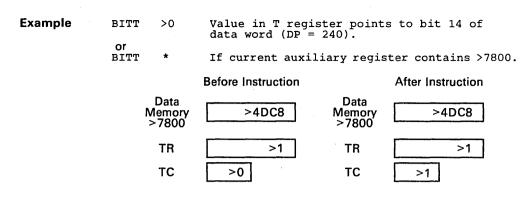

| 4-46 | Under the example given for the Test Bit instruction add the following note:                                                                                                      |  |  |  |  |  |

|      | Note:                                                                                                                                                                             |  |  |  |  |  |

|      | This instruction may affect the contents of the accumulator on the TMS32020 if the following conditions occur:                                                                    |  |  |  |  |  |

|      | 1) Overflow mode set (OVM status register bit is set).                                                                                                                            |  |  |  |  |  |

|      | 2) Two LSBs of BIT instruction opcode (bits 8 and 9 of the instruction word) are zero.                                                                                            |  |  |  |  |  |

|      | 3) Addition of accumulator contents with contents of addressed memory would cause accumulator overflow.                                                                           |  |  |  |  |  |

|      | If all of the above conditions are met, the contents of the accumulator will be replaced by the positive or negative saturation value, depending on the polarity of the overflow. |  |  |  |  |  |

|      | This situation can be avoided by any one of the following means:                                                                                                                  |  |  |  |  |  |

|      | • Precede BIT instruction with ROVM, and follow BIT with SOVM instruction.                                                                                                        |  |  |  |  |  |

|      | • If direct addressing is being used, reorganize memory so that page relative locations 0, 4, 8, C, and 10 are not used.                                                          |  |  |  |  |  |

|      | • If indirect addressing is used, select new ARP that is not AR0 or AR4, and restore code later (if necessary) with LARP AR0/4.                                                   |  |  |  |  |  |

|      | • Use BITT instead of BIT. BITT does not affect accumulator under any circumstances.                                                                                              |  |  |  |  |  |

|      | • Use TMS320C25 (pin and object code compatible) instead.                                                                                                                         |  |  |  |  |  |

|      | This situation occurs only when the BIT instruction is executed by a TMS32020 that is in the saturation mode.                                                                     |  |  |  |  |  |

### Page

### Change or Add

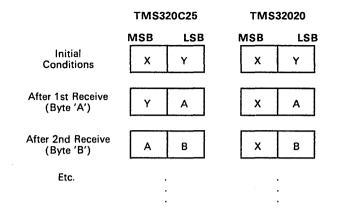

5-32 Following the last paragraph of section 5.5.2 (under the words "past processing") add the following note:

### Note:

Under certain circumstances, executing the BIT instruction may affect the contents of the accumulator on the TMS32020 device. For more information, refer to the instruction definition in Section 4.3 Page 4-45.

## Second-Generation TMS320 User's Guide

### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to or to discontinue any semiconductor product or service identified in this publication without notice. TI advises its customers to obtain the latest version of the relevant information to verify, before placing orders, that the information being relied upon is current.

TI warrants performance of its semiconductor products to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Unless mandated by government requirements, specific testing of all parameters of each device is not necessarily performed.

TI assumes no liability for TI applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1987, Texas Instruments Incorporated

### Contents

| Sect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | tion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Page                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

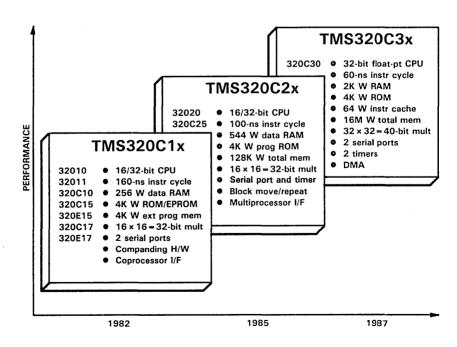

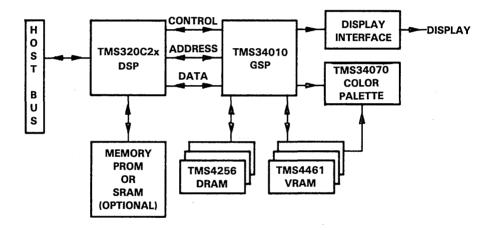

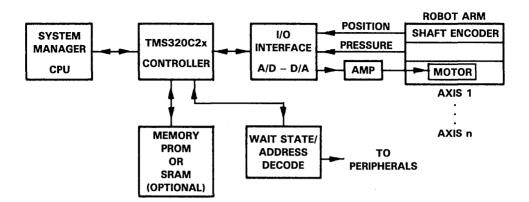

| <b>1</b><br>1.1<br>1.2<br>1.3<br>1.4<br>1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Introduction<br>General Description<br>Key Features<br>Typical Applications<br>How To Use This Manual<br>References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 1-4<br>. 1-5<br>. 1-7                              |

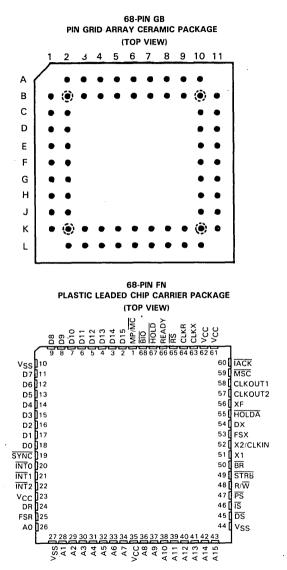

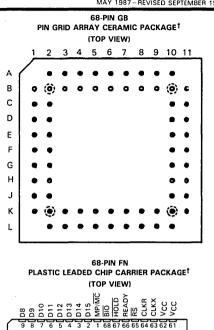

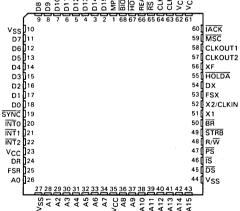

| <b>2</b><br>2.1<br>2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pinouts and Signal Descriptions<br>TMS320C2x Pinouts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>2-1</b><br>2-2<br>2-3                             |

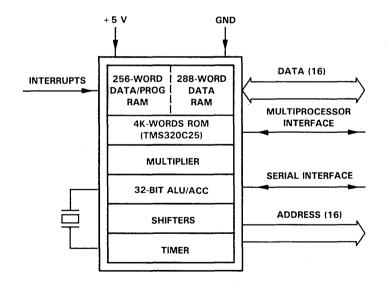

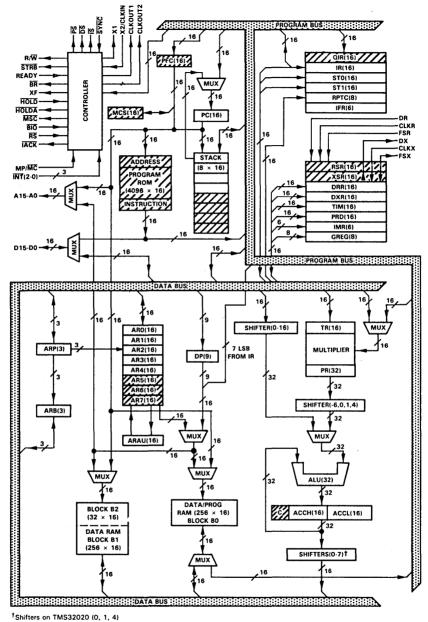

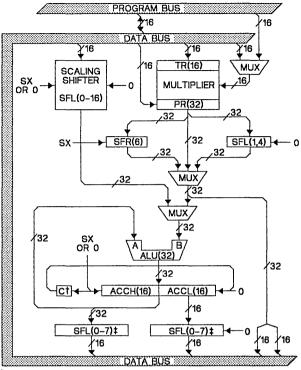

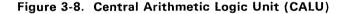

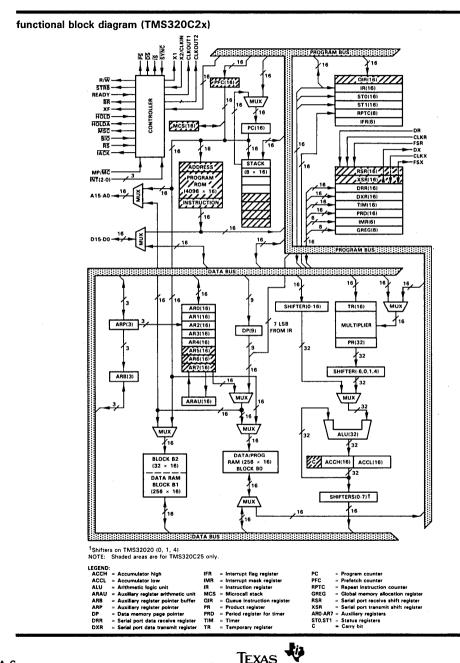

| $\begin{array}{c} \textbf{3} \\ \textbf{4} \\ \textbf{3} \\ \textbf{3} \\ \textbf{4} \\ \textbf{3} \\ \textbf{3} \\ \textbf{4} \\ \textbf{4} \\ \textbf{5} \\ \textbf{3} \\ \textbf{3} \\ \textbf{5} \\ \textbf{5} \\ \textbf{3} \\ \textbf{3} \\ \textbf{5} \\ \textbf{5} \\ \textbf{5} \\ \textbf{3} \\ \textbf{3} \\ \textbf{5} \\ \textbf{5} \\ \textbf{5} \\ \textbf{3} \\ \textbf{3} \\ \textbf{5} \\ \textbf{5} \\ \textbf{5} \\ \textbf{3} \\ \textbf{5} \\ $ | Architecture         Architectural Overview         Functional Block Diagram         Internal Hardware Summary         Memory Organization         Data Memory         Program Memory         Memory Maps         Memory Maps         Memory Addressing Modes         Memory -to-Memory Moves         Central Arithmetic Logic Unit (CALU)         Scaling Shifter         ALU and Accumulator         Multiplier, T and P Registers         System Control         Program Counter and Stack         Pipeline Operation         Reset         Status Registers         Timer Operation         Repeat Counter         Powerdown Mode (TMS320C25)         External Memory and I/O Interface         Memory Combinations         Internal Clock Timing Relationships         General-Purpose I/O Pins (BIO and XF)         Interrupt S         Interrupt Operation         External Interrupt Interface         Serial Port         Transmit and Receive Operations         Timing and Framing Control         Burst-Mode Operation         Continuous Operation | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

| 3.9.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Continuous Operation Without Frame Sync Pulses (TMS320C25)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-64                                                 |

iii

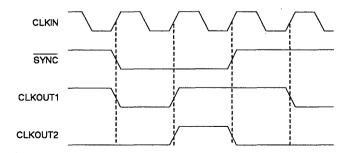

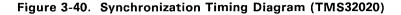

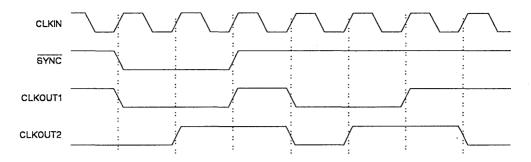

| 3.10       Multiprocessing and Direct Memory Access (DMA)       3-68         3.10.1       Synchronization       3-68         3.10.2       Global Memory       3-69         3.10.3       The Hold Function       3-71         4       Assembly Language Instructions       4-1         4.1       Memory Addressing Modes       4-2         4.1.1       Direct Addressing Mode       4-4         4.1.2       Indirect Addressing Mode       4-4         4.1.3       Immediate Addressing Mode       4-4         4.1.3       Instruction Set       4-10         4.2.1       Symbols and Abbreviations       4-10         4.2.1       Symbols and Abbreviations       4-11         4.3       Instruction Set Summary       4-12         4.3       Individual Instruction Descriptions       4-17         5       Software Applications       5-1         5.1       Processor Initialization       5-2         5.2       Program Control       5-7         5.2.1       Subroutines       5-11         5.2.2       Software Stack       5-10         5.2.3       Timer Operation       5-16         5.3.1       Context Switching       5-16 <tr< th=""><th>3.9.6</th><th></th><th>3-66</th></tr<>                | 3.9.6  |                                        | 3-66  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------|-------|

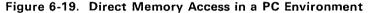

| 3.10.2       Global Memory       3-69         3.10.3       The Hold Function       3-71         4       Assembly Language Instructions       4-1         4.1       Memory Addressing Modes       4-2         4.1.1       Direct Addressing Mode       4-2         4.1.2       Indirect Addressing Mode       4-4         4.1.3       Immediate Addressing Mode       4-4         4.1.3       Inmediate Addressing Mode       4-10         4.2.1       Instruction Set       4-10         4.2.1       Symbols and Abbreviations       4-10         4.2.1       Symbols and Abbreviations       4-10         4.2.1       Instruction Set Summary       4-12         4.3       Individual Instruction Descriptions       4-17         5       Software Applications       5-1         5.1       Processor Initialization       5-2         5.2       Program Control       5-7         5.2.1       Subroutines       5-13         5.2.2       Software Stack       5-10         5.3       Timer Operation       5-11         5.4.4       Single-Instruction Loops       5-13         5.2.5       Computed GOTOs       5-22         5.3                                                                         | 3.10   |                                        | 3-68  |

| 3.10.2       Global Memory       3-69         3.10.3       The Hold Function       3-71         4       Assembly Language Instructions       4-1         4.1       Memory Addressing Modes       4-2         4.1.1       Direct Addressing Mode       4-2         4.1.2       Indirect Addressing Mode       4-4         4.1.3       Immediate Addressing Mode       4-4         4.1.3       Inmediate Addressing Mode       4-10         4.2.1       Instruction Set       4-10         4.2.1       Symbols and Abbreviations       4-10         4.2.1       Symbols and Abbreviations       4-10         4.2.1       Instruction Set Summary       4-12         4.3       Individual Instruction Descriptions       4-17         5       Software Applications       5-1         5.1       Processor Initialization       5-2         5.2       Program Control       5-7         5.2.1       Subroutines       5-13         5.2.2       Software Stack       5-10         5.3       Timer Operation       5-11         5.4.4       Single-Instruction Loops       5-13         5.2.5       Computed GOTOs       5-22         5.3                                                                         | 3.10.1 | Synchronization                        | 3-68  |

| 4       Assembly Language Instructions       4-1         4.1       Memory Addressing Mode       4-2         4.1.1       Direct Addressing Mode       4-2         4.1.2       Indirect Addressing Mode       4-4         4.1.3       Immediate Addressing Mode       4-4         4.1.3       Immediate Addressing Mode       4-9         4.1       Instruction Set       4-10         4.2.1       Instruction Set Summary       4-10         4.2.2       Instruction Set Summary       4-10         4.3       Individual Instruction Descriptions       4-17         5       Software Applications       5-1         5.2       Program Control       5-7         5.2.1       Subroutines       5-7         5.2.2       Software Stack       5-10         5.2.3       Timer Operation       5-11         5.2.4       Single-Instruction Loops       5-13         5.3.1       Contputed GOTOs       5-14         5.3.2       Interrupt Priority       5-22         5.4       Memory Management       5-23         5.4.3       Using On-Chip RAM for Program Execution       5-23         5.5.4       Jusing On-Chip RAM for Program Execution       5-24                                                       | 3.10.2 |                                        | 3-69  |

| 4.1       Memory Addressing Modes       4-2         4.1.1       Direct Addressing Mode       4-2         4.1.2       Indirect Addressing Mode       4-4         4.1.3       Immediate Addressing Mode       4-4         4.1.3       Immediate Addressing Mode       4-9         4.2.1       Symbols and Abbreviations       4-10         4.2.1       Symbols and Abbreviations       4-10         4.2.1       Instruction Set       4-10         4.2.1       Individual Instruction Descriptions       4-11         4.3       Individual Instruction Descriptions       4-11         5       Software Applications       5-1         5.1       Processor Initialization       5-2         5.2       Program Control       5-7         5.2.1       Subroutines       5-10         5.2.3       Timer Operation       5-11         5.2.4       Single-Instruction Loops       5-13         5.2.5       Computed GOTOS       5-14         5.3.1       Context Switching       5-16         5.3.2       Interrupt Priority       5-22         5.4       Memory Management       5-23         5.4.1       Block Moves       5-23                                                                                  | 3.10.3 | 3 The Hold Function                    | 3-71  |

| 4.1       Memory Addressing Modes       4-2         4.1.1       Direct Addressing Mode       4-2         4.1.2       Indirect Addressing Mode       4-4         4.1.3       Immediate Addressing Mode       4-4         4.1.3       Immediate Addressing Mode       4-9         4.2.1       Symbols and Abbreviations       4-10         4.2.1       Symbols and Abbreviations       4-10         4.2.1       Instruction Set       4-10         4.2.1       Individual Instruction Descriptions       4-11         4.3       Individual Instruction Descriptions       4-11         5       Software Applications       5-1         5.1       Processor Initialization       5-2         5.2       Program Control       5-7         5.2.1       Subroutines       5-10         5.2.3       Timer Operation       5-11         5.2.4       Single-Instruction Loops       5-13         5.2.5       Computed GOTOS       5-14         5.3.1       Context Switching       5-16         5.3.2       Interrupt Priority       5-22         5.4       Memory Management       5-23         5.4.1       Block Moves       5-23                                                                                  |        |                                        |       |

| 4.1.1       Direct Addressing Mode       4-2         4.1.2       Indirect Addressing Mode       4-4         4.1.3       Immediate Addressing Mode       4-4         4.1.4       Immediate Addressing Mode       4-9         4.2       Instruction Set       4-10         4.2.1       Symbols and Abbreviations       4-10         4.2.2       Instruction Set Summary       4-12         4.3       Individual Instruction Descriptions       4-17         5       Software Applications       5-1         5.1       Processor Initialization       5-2         5.2       Program Control       5-7         5.2.1       Subroutines       5-7         5.2.2       Software Stack       5-10         5.2.3       Timer Operation       5-11         5.2.4       Single-Instruction Loops       5-13         5.2.5       Computed GOTOs       5-14         5.3       Interrupt Service Routine       5-16         5.3.1       Context Switching       5-16         5.3.2       Interrupt Priority       5-22         5.4       Memory Management       5-23         5.4.3       Using On-Chip RAM       5-25         5.4.3                                                                                     | 4      |                                        | 4-1   |

| 4.1.2       Indirect Addressing Mode       4.4         4.1.3       Immediate Addressing Mode       4.9         4.2       Instruction Set       4-10         4.2.1       Symbols and Abbreviations       4-10         4.2.2       Instruction Set Summary       4-12         4.3       Individual Instruction Descriptions       4-17         5       Software Applications       5-1         5.1       Processor Initialization       5-2         5.2       Program Control       5-7         5.2.1       Subroutines       5-7         5.2.2       Software Stack       5-10         5.2.3       Timer Operation       5-11         5.2.4       Single-Instruction Loops       5-13         5.2.5       Computed GOTOS       5-14         5.3.1       Context Switching       5-16         5.3.2       Interrupt Priority       5-22         5.4       Memory Management       5-23         5.4.2       Configuring On-Chip RAM       5-26         5.4.3       Using On-Chip RAM       5-26         5.4.3       Using On-Chip RAM       5-23         5.5       Fundamental Logical and Arithmetic Operations       5-31         5.                                                                         | 4.1    | Memory Addressing Modes                | 4-2   |

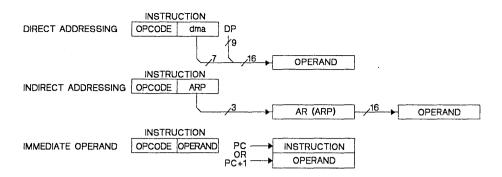

| 4.1.3       Immediate Addressing Mode       4-9         4.2       Instruction Set       4-10         4.2.1       Symbols and Abbreviations       4-10         4.2.2       Instruction Set Summary       4-12         4.3       Individual Instruction Descriptions       4-17         5       Software Applications       5-1         5.1       Processor Initialization       5-2         5.2       Program Control       5-7         5.2.1       Subroutines       5-7         5.2.2       Software Stack       5-10         5.2.3       Timer Operation       5-11         5.2.4       Software GOTOS       5-14         5.2.5       Computed GOTOS       5-14         5.3       Interrupt Service Routine       5-16         5.3.1       Context Switching       5-16         5.3.2       Interrupt Priority       5-22         5.4       Meory Management       5-23         5.4.3       Using On-Chip RAM       5-26         5.4.3       Using On-Chip RAM       5-26         5.4.4       Block Moves       5-31         5.5.1       Status Register Effect on Data Processing       5-31         5.5.1       Status                                                                                  | 4.1.1  | Direct Addressing Mode                 | 4-2   |

| 4.1.3       Immediate Addressing Mode       4-9         4.2       Instruction Set       4-10         4.2.1       Symbols and Abbreviations       4-10         4.2.2       Instruction Set Summary       4-12         4.3       Individual Instruction Descriptions       4-17         5       Software Applications       5-1         5.1       Processor Initialization       5-2         5.2       Program Control       5-7         5.2.1       Subroutines       5-7         5.2.2       Software Stack       5-10         5.2.3       Timer Operation       5-11         5.2.4       Software GOTOS       5-14         5.2.5       Computed GOTOS       5-14         5.3       Interrupt Service Routine       5-16         5.3.1       Context Switching       5-16         5.3.2       Interrupt Priority       5-22         5.4       Meory Management       5-23         5.4.3       Using On-Chip RAM       5-26         5.4.3       Using On-Chip RAM       5-26         5.4.4       Block Moves       5-31         5.5.1       Status Register Effect on Data Processing       5-31         5.5.1       Status                                                                                  | 4.1.2  | Indirect Addressing Mode               | 4-4   |

| 4.2       Instruction Set       4-10         4.2.1       Symbols and Abbreviations       4-10         4.2.2       Instruction Set Summary       4-12         4.3       Individual Instruction Descriptions       4-17         5       Software Applications       5-1         5.1       Processor Initialization       5-2         5.2       Program Control       5-7         5.2.1       Subroutines       5-7         5.2.2       Software Stack       5-10         5.2.3       Timer Operation       5-11         5.2.4       Single-Instruction Loops       5-13         5.2.5       Computed GOTOs       5-14         5.3.1       Context Switching       5-16         5.3.2       Interrupt Service Routine       5-16         5.3.1       Context Switching       5-22         5.4       Memory Management       5-23         5.4.1       Block Moves       5-23         5.4.2       Configuring On-Chip RAM       5-25         5.4.3       Using On-Chip RAM for Program Execution       5-32         5.5.1       Status Register Effect on Data Processing       5-31         5.5.2       Bit Manipulation       5-35                                                                             | 4.1.3  |                                        | 4-9   |

| 4.2.1       Symbols and Abbreviations       4-10         4.2.2       Instruction Set Summary       4-12         4.3       Individual Instruction Descriptions       4-17         5       Software Applications       5-1         5.1       Processor Initialization       5-2         5.2       Program Control       5-7         5.2.1       Subroutines       5-7         5.2.2       Software Stack       5-10         5.2.3       Timer Operation       5-11         5.2.4       Single-Instruction Loops       5-13         5.2.5       Computed GOTOs       5-14         5.3       Interrupt Service Routine       5-16         5.3.1       Context Switching       5-16         5.3.2       Interrupt Priority       5-22         5.4       Memory Management       5-23         5.4.1       Block Moves       5-23         5.4.2       Configuring On-Chip RAM       5-25         5.4.3       Using On-Chip RAM       5-25         5.4.4       Sudiamental Logical and Arithmetic Operations       5-31         5.5       Fundamental Logical and Arithmetic Operations       5-31         5.5.1       Status Register Effect on Data Processing <t< td=""><td>4.2</td><td></td><td>4-10</td></t<>  | 4.2    |                                        | 4-10  |

| 4.2.2       Instruction Set Summary       4-12         4.3       Individual Instruction Descriptions       4-17         5       Software Applications       5-1         5.1       Processor Initialization       5-2         5.2       Program Control       5-7         5.2.1       Subroutines       5-7         5.2.2       Software Stack       5-10         5.2.3       Timer Operation       5-11         5.2.4       Single-Instruction Loops       5-13         5.2.5       Computed GOTOs       5-14         5.3       Interrupt Service Routine       5-16         5.3.1       Context Switching       5-16         5.3.2       Interrupt Priority       5-22         5.4       Memory Management       5-23         5.4.1       Block Moves       5-23         5.4.2       Configuring On-Chip RAM       5-25         5.4.3       Using On-Chip RAM       5-26         5.4.4       Using On-Chip RAM       5-26         5.5       Fundamental Logical and Arithmetic Operations       5-31         5.5.1       Status Register Effect on Data Processing       5-31         5.5.2       Bit Manipulation       5-32                                                                              | 4.2.1  |                                        | 4-10  |

| 4.3       Individual Instruction Descriptions       4-17         5       Software Applications       5-1         5.1       Processor Initialization       5-2         5.2       Program Control       5-7         5.2.1       Subroutines       5-7         5.2.2       Software Stack       5-10         5.2.3       Timer Operation       5-11         5.2.4       Single-Instruction Loops       5-13         5.2.5       Computed GOTOs       5-14         5.3       Interrupt Service Routine       5-16         5.3.1       Context Switching       5-16         5.3.2       Interrupt Priority       5-22         5.4       Memory Management       5-23         5.4.1       Block Moves       5-23         5.4.2       Configuring On-Chip RAM       5-25         5.4.3       Using On-Chip RAM for Program Execution       5-28         5.5       Fundamental Logical and Arithmetic Operations       5-31         5.5.1       Status Register Effect on Data Processing       5-31         5.5.2       Bit Manipulation       5-32         5.6.3       Moving Data       5-35         5.6.4       Multiplication       5-35                                                                       | 4.2.2  |                                        | 4-12  |

| 5         Software Applications         5-1           5.1         Processor Initialization         5-2           5.2         Program Control         5-7           5.2.1         Subroutines         5-7           5.2.2         Software Stack         5-10           5.2.3         Timer Operation         5-11           5.2.4         Single-Instruction Loops         5-13           5.2.5         Computed GOTOs         5-14           5.3         Interrupt Service Routine         5-16           5.3.1         Context Switching         5-16           5.3.2         Interrupt Priority         5-22           5.4         Block Moves         5-23           5.4.2         Configuring On-Chip RAM         5-25           5.4.3         Using On-Chip RAM for Program Execution         5-28           5.4         Using On-Chip RAM for Program Execution         5-34           5.5         Fundamental Logical and Arithmetic Operations         5-31           5.5.4         Wanced Arithmetic Operations         5-34           5.6.5         Advanced Arithmetic Operations         5-34           5.6.4         Multiplication         5-37           5.6.5         Scaling         5-35 |        |                                        | • •   |

| 5.1       Processor Initialization       5-2         7.2       Program Control       5-7         5.2.1       Subroutines       5-7         5.2.2       Software Stack       5-10         5.2.3       Timer Operation       5-11         5.2.4       Single-Instruction Loops       5-13         5.2.5       Computed GOTOs       5-14         5.3       Context Switching       5-16         5.3.1       Context Switching       5-16         5.3.2       Interrupt Priority       5-22         5.4       Memory Management       5-23         5.4.1       Block Moves       5-23         5.4.2       Configuring On-Chip RAM       5-25         5.4.3       Using On-Chip RAM for Program Execution       5-28         5.5       Fundamental Logical and Arithmetic Operations       5-31         5.5.1       Status Register Effect on Data Processing       5-31         5.5.2       Bit Manipulation       5-32         5.6       Advanced Arithmetic Operations       5-34         5.6.3       Moving Data       5-35         5.6.4       Multiplication       5-35         5.6.5       Division       5-42         5.6.6                                                                              |        |                                        | • • • |

| 5.1       Processor Initialization       5-2         5.2       Program Control       5-7         5.2.1       Subroutines       5-7         5.2.2       Software Stack       5-10         5.2.3       Timer Operation       5-11         5.2.4       Single-Instruction Loops       5-13         5.2.5       Computed GOTOs       5-14         5.3       Interrupt Service Routine       5-16         5.3.1       Context Switching       5-16         5.3.2       Interrupt Priority       5-22         5.4       Memory Management       5-23         5.4.1       Block Moves       5-23         5.4.2       Configuring On-Chip RAM       5-25         5.4.3       Using On-Chip RAM for Program Execution       5-28         5.5       Fundamental Logical and Arithmetic Operations       5-31         5.5       Fundamental Logical and Arithmetic Operations       5-31         5.5.2       Bit Manipulation       5-32         5.5.2       Bit Manipulation       5-32         5.5.4       Overflow Management       5-34         5.6.3       Moving Data       5-35         5.6.4       Multiplication       5-37         5                                                                         | 5      | Software Applications                  | 5-1   |

| 5.2       Program Control       5-7         5.2.1       Subroutines       5-7         5.2.2       Software Stack       5-10         5.2.3       Timer Operation       5-11         5.2.4       Single-Instruction Loops       5-13         5.2.5       Computed GOTOs       5-14         5.3       Interrupt Service Routine       5-16         5.3.1       Context Switching       5-22         5.4       Memory Management       5-23         5.4.1       Block Moves       5-23         5.4.2       Configuring On-Chip RAM       5-25         5.4.3       Using On-Chip RAM for Program Execution       5-28         5.5       Fundamental Logical and Arithmetic Operations       5-31         5.5.1       Status Register Effect on Data Processing       5-31         5.5.2       Bit Manipulation       5-32         5.6.3       Overflow Management       5-34         5.6.4       Overflow Management       5-34         5.6.1       Overflow Management       5-34         5.6.2       Scaling       5-35         5.6.3       Moving Data       5-35         5.6.4       Multiplication       5-37         5.6.5                                                                                 |        | Processor Initialization               |       |

| 5.2.1       Subroutines       5-7         5.2.2       Software Stack       5-10         5.2.3       Timer Operation       5-11         5.2.4       Single-Instruction Loops       5-13         5.2.5       Computed GOTOs       5-14         5.3       Interrupt Service Routine       5-16         5.3.1       Context Switching       5-16         5.3.2       Interrupt Priority       5-22         5.4       Memory Management       5-23         5.4.1       Block Moves       5-23         5.4.2       Configuring On-Chip RAM       5-25         5.4.3       Using On-Chip RAM       5-25         5.4.4       Using On-Chip RAM       5-28         5.5       Fundamental Logical and Arithmetic Operations       5-31         5.5.1       Status Register Effect on Data Processing       5-31         5.5.2       Bit Manipulation       5-32         5.6.3       Moving Data       5-35         5.6.4       Multiplication       5-37         5.6.5       Division       5-42         5.6.6       Floating-Point Arithmetic       5-45         5.6.7       Indexed Addressing       5-44         5.6.8       Exte                                                                                  |        |                                        |       |

| 5.2.2       Software Stack       5-10         5.2.3       Timer Operation       5-11         5.2.4       Single-Instruction Loops       5-13         5.2.5       Computed GOTOs       5-14         5.3       Interrupt Service Routine       5-16         5.3.1       Context Switching       5-16         5.3.2       Interrupt Priority       5-22         5.4       Memory Management       5-23         5.4.1       Block Moves       5-23         5.4.3       Using On-Chip RAM       5-25         5.4.3       Using On-Chip RAM       5-25         5.4.3       Using On-Chip RAM       5-25         5.5       Fundamental Logical and Arithmetic Operations       5-31         5.5.1       Status Register Effect on Data Processing       5-31         5.5.2       Bit Manipulation       5-32         5.6       Advanced Arithmetic Operations       5-34         5.6.1       Overflow Management       5-34         5.6.2       Scaling       5-35         5.6.3       Moving Data       5-35         5.6.4       Multiplication       5-42         5.6.5       Division       5-42         5.6.6       Floating-                                                                                  |        | ······································ |       |

| 5.2.3       Timer Operation       5-11         5.2.4       Single-Instruction Loops       5-13         5.2.5       Computed GOTOs       5-14         5.3       Interrupt Service Routine       5-16         5.3.1       Context Switching       5-16         5.3.2       Interrupt Priority       5-22         5.4       Memory Management       5-23         5.4.1       Block Moves       5-23         5.4.2       Configuring On-Chip RAM       5-23         5.4.3       Using On-Chip RAM for Program Execution       5-28         5.4.3       Using On-Chip RAM for Program Execution       5-28         5.5       Fundamental Logical and Arithmetic Operations       5-31         5.5.1       Status Register Effect on Data Processing       5-31         5.5.2       Bit Manipulation       5-32         5.6       Advanced Arithmetic Operations       5-34         5.6.2       Scaling       5-35         5.6.3       Moving Data       5-35         5.6.4       Multiplication       5-34         5.6.5       Division       5-42         5.6.6       Floating-Point Arithmetic       5-45         5.6.7       Indexed Addressing       5-42                                                    |        |                                        | • •   |

| 5.2.4       Single-Instruction Loops       5-13         5.2.5       Computed GOTOs       5-14         5.3       Interrupt Service Routine       5-16         5.3.1       Context Switching       5-16         5.3.2       Interrupt Priority       5-22         5.4       Memory Management       5-23         5.4.1       Block Moves       5-23         5.4.2       Configuring On-Chip RAM       5-25         5.4.3       Using On-Chip RAM for Program Execution       5-28         5.5       Fundamental Logical and Arithmetic Operations       5-31         5.5.1       Status Register Effect on Data Processing       5-31         5.5.2       Bit Manipulation       5-32         5.6       Advanced Arithmetic Operations       5-34         5.6.3       Moving Data       5-35         5.6.4       Multiplication       5-37         5.6.5       Division       5-42         5.6.6       Floating-Point Arithmetic       5-44         5.6.4       Multiplication       5-37         5.6.5       Division       5-42         5.6.6       Floating-Point Arithmetic       5-45         5.6.7       Indexed Addressing       5-45                                                                  |        |                                        |       |

| 5.2.5       Computed GOTOs       5-14         5.3       Interrupt Service Routine       5-16         5.3.1       Context Switching       5-16         5.3.2       Interrupt Priority       5-22         5.4       Memory Management       5-23         5.4.1       Block Moves       5-23         5.4.2       Configuring On-Chip RAM       5-23         5.4.3       Using On-Chip RAM for Program Execution       5-28         5.5       Fundamental Logical and Arithmetic Operations       5-31         5.5.1       Status Register Effect on Data Processing       5-31         5.5.2       Bit Manipulation       5-32         5.6.3       Advanced Arithmetic Operations       5-34         5.6.1       Overflow Management       5-35         5.6.3       Moving Data       5-35         5.6.4       Multiplication       5-37         5.6.5       Division       5-42         5.6.6       Floating-Point Arithmetic       5-42         5.6.6       Floating-Point Arithmetic       5-45         5.6.7       Indexed Addressing       5-449         5.6.8       Extended-Precision Arithmetic       5-45         5.7.1       Companding       5-61 <td></td> <td></td> <td></td>                     |        |                                        |       |

| 5.3       Interrupt Service Routine       5-16         5.3.1       Context Switching       5-16         5.3.2       Interrupt Priority       5-22         5.4       Memory Management       5-23         5.4.1       Block Moves       5-23         5.4.2       Configuring On-Chip RAM       5-25         5.4.3       Using On-Chip RAM for Program Execution       5-28         5.5       Fundamental Logical and Arithmetic Operations       5-31         5.5.1       Status Register Effect on Data Processing       5-31         5.5.2       Bit Manipulation       5-32         5.6       Advanced Arithmetic Operations       5-34         5.6.1       Overflow Management       5-34         5.6.2       Scaling       5-35         5.6.3       Moving Data       5-35         5.6.4       Multiplication       5-37         5.6.5       Division       5-42         5.6.6       Floating-Point Arithmetic       5-49         5.6.4       Multiplication Arithmetic       5-49         5.6.5       Division       5-42         5.6.6       Floating-Point Arithmetic       5-49         5.7.1       Companding       5-60                                                                           |        |                                        |       |

| 5.3.1       Context Switching       5-16         5.3.2       Interrupt Priority       5-22         5.4       Memory Management       5-23         5.4.1       Block Moves       5-23         5.4.2       Configuring On-Chip RAM       5-25         5.4.3       Using On-Chip RAM for Program Execution       5-28         5.5       Fundamental Logical and Arithmetic Operations       5-31         5.5.1       Status Register Effect on Data Processing       5-31         5.5.2       Bit Manipulation       5-34         5.6.3       Advanced Arithmetic Operations       5-34         5.6.4       Overflow Management       5-35         5.6.3       Moving Data       5-35         5.6.4       Multiplication       5-37         5.6.5       Division       5-42         5.6.6       Floating-Point Arithmetic       5-45         5.6.7       Indexed Addressing       5-49         5.6.8       Extended-Precision Arithmetic       5-49         5.7.1       Companding       5-60         5.7.1       Companding       5-61         5.7.3       Adaptive Filtering       5-63         5.7.4       Fast Fourier Transforms (FFT)       5-68                                                         |        |                                        |       |

| 5.3.2       Interrupt Priority       5-22         5.4       Memory Management       5-23         5.4.1       Block Moves       5-23         5.4.2       Configuring On-Chip RAM       5-25         5.4.3       Using On-Chip RAM for Program Execution       5-28         5.5       Fundamental Logical and Arithmetic Operations       5-31         5.5.1       Status Register Effect on Data Processing       5-31         5.5.2       Bit Manipulation       5-32         5.6       Advanced Arithmetic Operations       5-34         5.6.1       Overflow Management       5-34         5.6.2       Scaling       5-35         5.6.3       Moving Data       5-35         5.6.4       Multiplication       5-42         5.6.5       Division       5-42         5.6.6       Floating-Point Arithmetic       5-45         5.6.7       Indexed Addressing       5-45         5.6.7       Application-Oriented Operations       5-40         5.7.1       Companding       5-60         5.7.2       FIR/IIR Filtering       5-61         5.7.3       Adaptive Filtering       5-63         5.7.4       Fast Fourier Transforms (FFT)       5-68 <td></td> <td></td> <td></td>                              |        |                                        |       |

| 5.4Memory Management5-235.4.1Block Moves5-235.4.2Configuring On-Chip RAM5-255.4.3Using On-Chip RAM for Program Execution5-285.5Fundamental Logical and Arithmetic Operations5-315.5.1Status Register Effect on Data Processing5-315.5.2Bit Manipulation5-325.6Advanced Arithmetic Operations5-345.6.1Overflow Management5-345.6.2Scaling5-355.6.3Moving Data5-355.6.4Multiplication5-425.6.5Division5-425.6.6Floating-Point Arithmetic5-455.6.7Indexed Addressing5-495.6.8Extended-Precision Arithmetic5-495.7.1Companding5-605.7.2FIR/IIR Filtering5-615.7.3Adaptive Filtering5-635.7.4Fast Fourier Transforms (FFT)5-68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |                                        |       |

| 5.4.1Block Moves5-235.4.2Configuring On-Chip RAM5-255.4.3Using On-Chip RAM for Program Execution5-285.5Fundamental Logical and Arithmetic Operations5-315.5.1Status Register Effect on Data Processing5-315.5.2Bit Manipulation5-325.6Advanced Arithmetic Operations5-345.6.1Overflow Management5-345.6.2Scaling5-355.6.3Moving Data5-355.6.4Multiplication5-375.6.5Division5-425.6.6Floating-Point Arithmetic5-495.7Application-Oriented Operations5-605.7.1Companding5-605.7.2FIR/IIR Filtering5-615.7.3Adaptive Filtering5-635.7.4Fast Fourier Transforms (FFT)5-68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |                                        |       |

| 5.4.2Configuring On-Chip RAM5-255.4.3Using On-Chip RAM for Program Execution5-285.5Fundamental Logical and Arithmetic Operations5-315.5.1Status Register Effect on Data Processing5-315.5.2Bit Manipulation5-325.6Advanced Arithmetic Operations5-345.6.1Overflow Management5-345.6.2Scaling5-355.6.3Moving Data5-355.6.4Multiplication5-375.6.5Division5-425.6.6Floating-Point Arithmetic5-455.6.7Indexed Addressing5-495.7Application-Oriented Operations5-605.7.1Companding5-615.7.2FIR/IIR Filtering5-615.7.3Adaptive Filtering5-635.7.4Fast Fourier Transforms (FFT)5-68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |                                        |       |

| 5.4.3Using On-Chip RAM for Program Execution5-285.5Fundamental Logical and Arithmetic Operations5-315.5.1Status Register Effect on Data Processing5-315.5.2Bit Manipulation5-325.6Advanced Arithmetic Operations5-345.6.1Overflow Management5-345.6.2Scaling5-355.6.3Moving Data5-355.6.4Multiplication5-375.6.5Division5-425.6.6Floating-Point Arithmetic5-455.6.7Indexed Addressing5-495.7Application-Oriented Operations5-605.7.1Companding5-605.7.2FIR/IIR Filtering5-615.7.3Adaptive Filtering5-635.7.4Fast Fourier Transforms (FFT)5-68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |                                        |       |

| 5.5Fundamental Logical and Arithmetic Operations5-315.5.1Status Register Effect on Data Processing5-315.5.2Bit Manipulation5-325.6Advanced Arithmetic Operations5-345.6.1Overflow Management5-345.6.2Scaling5-355.6.3Moving Data5-355.6.4Multiplication5-375.6.5Division5-425.6.6Floating-Point Arithmetic5-455.6.7Indexed Addressing5-495.6.8Extended-Precision Arithmetic5-495.7Application-Oriented Operations5-605.7.1Companding5-615.7.2FIR/IIR Filtering5-615.7.3Adaptive Filtering5-635.7.4Fast Fourier Transforms (FFT)5-68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |                                        |       |

| 5.5.1       Status Register Effect on Data Processing       5-31         5.5.2       Bit Manipulation       5-32         5.6       Advanced Arithmetic Operations       5-34         5.6.1       Overflow Management       5-34         5.6.2       Scaling       5-35         5.6.3       Moving Data       5-35         5.6.4       Multiplication       5-37         5.6.5       Division       5-42         5.6.6       Floating-Point Arithmetic       5-45         5.6.7       Indexed Addressing       5-49         5.6.8       Extended-Precision Arithmetic       5-49         5.7       Application-Oriented Operations       5-60         5.7.1       Companding       5-61         5.7.2       FIR/IIR Filtering       5-61         5.7.3       Adaptive Filtering       5-63         5.7.4       Fast Fourier Transforms (FFT)       5-68                                                                                                                                                                                                                                                                                                                                                      |        |                                        |       |

| 5.5.2       Bit Manipulation       5-32         5.6       Advanced Arithmetic Operations       5-34         5.6.1       Overflow Management       5-34         5.6.2       Scaling       5-35         5.6.3       Moving Data       5-35         5.6.4       Multiplication       5-37         5.6.5       Division       5-42         5.6.6       Floating-Point Arithmetic       5-45         5.6.7       Indexed Addressing       5-49         5.6.8       Extended-Precision Arithmetic       5-49         5.7       Application-Oriented Operations       5-60         5.7.1       Companding       5-60         5.7.2       FIR/IIR Filtering       5-61         5.7.3       Adaptive Filtering       5-63         5.7.4       Fast Fourier Transforms (FFT)       5-68                                                                                                                                                                                                                                                                                                                                                                                                                               |        |                                        |       |

| 5.6       Advanced Arithmetic Operations       5-34         5.6.1       Overflow Management       5-34         5.6.2       Scaling       5-35         5.6.3       Moving Data       5-35         5.6.4       Multiplication       5-37         5.6.5       Division       5-42         5.6.6       Floating-Point Arithmetic       5-45         5.6.7       Indexed Addressing       5-49         5.6.8       Extended-Precision Arithmetic       5-49         5.7       Application-Oriented Operations       5-60         5.7.1       Companding       5-60         5.7.2       FIR/IIR Filtering       5-61         5.7.3       Adaptive Filtering       5-63         5.7.4       Fast Fourier Transforms (FFT)       5-68                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |                                        |       |

| 5.6.1       Overflow Management       5-34         5.6.2       Scaling       5-35         5.6.3       Moving Data       5-35         5.6.4       Multiplication       5-37         5.6.5       Division       5-42         5.6.6       Floating-Point Arithmetic       5-45         5.6.7       Indexed Addressing       5-49         5.6.8       Extended-Precision Arithmetic       5-49         5.7       Application-Oriented Operations       5-60         5.7.1       Companding       5-60         5.7.2       FIR/IIR Filtering       5-61         5.7.3       Adaptive Filtering       5-63         5.7.4       Fast Fourier Transforms (FFT)       5-68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |                                        |       |

| 5.6.2       Scaling       5-35         5.6.3       Moving Data       5-35         5.6.4       Multiplication       5-37         5.6.5       Division       5-42         5.6.6       Floating-Point Arithmetic       5-45         5.6.7       Indexed Addressing       5-49         5.6.8       Extended-Precision Arithmetic       5-49         5.7       Application-Oriented Operations       5-60         5.7.1       Companding       5-60         5.7.2       FIR/IIR Filtering       5-61         5.7.3       Adaptive Filtering       5-63         5.7.4       Fast Fourier Transforms (FFT)       5-68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |                                        |       |