# TMS32010 Assembly Language Programmer's Guide

Digital Signal Processor Products

# TMS32010 Assembly Language Programmer's Guide

**Digital Signal Processor Products**

#### **IMPORTANT NOTICE**

Texas Instruments reserves the right to make changes at any time in order to improve design and to supply the best product possible.

Texas Instruments assumes no responsibility for infringement of patents or rights of others based on Texas Instruments applications assistance or product specifications, since TI does not possess full access to data concerning the use or applications of customer's products. TI also assumes no responsibility for customer product designs.

Copyright © 1983 by Texas Instruments Incorporated

### TABLE OF CONTENTS

| SECTIO | <b>DN</b> |             |                                           | PAGE       |

|--------|-----------|-------------|-------------------------------------------|------------|

| 1.     | INTROD    | UCTION .    |                                           | 1-1        |

|        | 1.1       | General De  | escription                                | 1-1        |

|        | 1.2       | Assembly    | Language Application                      | 1-1        |

|        | 1.3       |             | ogram Modules                             | 1-2        |

|        | 1.4       | Program R   | elocatability                             | 1-2        |

|        | 1.5       | -           | ·····                                     | 1-3        |

| 2.     | GENERA    |             | MMING INFORMATION                         | 2-1        |

|        | 2.1       |             | m                                         |            |

|        | 2.2       | Data Areas  |                                           | 2-1        |

|        | 2.3       |             | 2010 Instruction Set                      | 2-1        |

|        | 2.4       |             | atement Format                            | 2-3        |

|        | 2.1       | 2.4.1       |                                           | 2-4        |

|        |           | 2.4.2       | Command Field                             | 2-4        |

|        |           | 2.4.3       | Operand Field                             | 2-4        |

|        |           | 2.4.3       | Comment Field                             | 2-5<br>2-5 |

|        | 2.5       |             |                                           | 2-5        |

|        | 2.5       |             |                                           |            |

|        |           | 2.5.1       | Decimal Integer Constants                 | 2-5        |

|        |           | 2.5.2       | Binary Integer Constants                  | 2-5        |

|        |           | 2.5.3       | Hexadecimal Integer Constants             | 2-5        |

|        |           | 2.5.4       | Character Constants                       | 2-6        |

|        |           | 2.5.5       | Assembly-Time Constants                   | 2-6        |

|        | 2.6       | Symbols     |                                           | 2-6        |

|        |           | 2.6.1       | Predefined Symbols                        | 2-7        |

|        |           | 2.6.2       | Terms                                     | 2-7        |

|        |           | 2.6.3       | Character Strings                         | 2-7        |

|        | 2.7       | Expression  | s                                         | 2-8        |

|        |           | 2.7.1       | Arithmetic Operators in Expressions       | 2-8        |

|        |           | 2.7.2       | Parentheses in Expressions                | 2-8        |

|        |           | 2.7.3       | Well-Defined Expressions                  | 2-9        |

|        |           | 2.7.4       | Relocatable Symbols in Expressions        | 2-9        |

|        |           | 2.7.5       | Externally Defined Symbols in Expressions | 2-10       |

| 3.     | ASSEM     |             | CTIONS                                    | 3-1        |

| 0.     | 3.1       | Introductio |                                           | 3-1        |

|        | 3.2       |             | y Modes                                   | 3-1        |

|        | 0.2       | 3.2.1       | Direct Addressing Mode                    | 3-1        |

|        |           | 3.2.2       | Indirect Addressing Mode                  | 3-1<br>3-1 |

|        |           | 3.2.2       |                                           | 3-2        |

|        | 2.2       |             | Immediate Addressing Mode                 | 3-2        |

|        | 3.3       |             | Addressing Format                         |            |

|        |           | 3.3.1       | Direct Addressing Format                  | 3-2        |

|        |           | 3.3.2       | Indirect Addressing Format                | 3-2        |

|        |           | 3.3.3       | Immediate Addressing Format               | 3-2        |

|        |           | 3.3.4       | Examples of Instruction Format            | 3-3        |

|        | 3.4       |             | Set                                       | 3-3        |

|        |           | 3.4.1       | Symbols and Abbreviations                 | 3-3        |

# **TABLE OF CONTENTS (Continued)**

| SECTION | N      |               |                                                  | PAGE |

|---------|--------|---------------|--------------------------------------------------|------|

|         |        | 3.4.2         | Instruction Set Summary                          | 3-4  |

|         |        | 3.4.3         | Instruction Descriptions                         |      |

|         |        |               |                                                  |      |

| 4.      | SAMPLE | ROUTINES      | ······································           |      |

|         | 4.1    |               | n                                                |      |

|         | 4.2    | Initializing  | the TMS32010                                     | 4-1  |

|         | 4.3    | BIOZ Instru   | uction                                           |      |

|         | 4.4    | BANZ Instr    | ruction                                          | 4-3  |

|         | 4.5    | LTD Instru    | ction                                            |      |

|         | 4.6    | SUBC Instr    | ruction                                          | 4-5  |

|         | 4.7    | CALA Instr    | ruction                                          | 4-7  |

|         | 4.8    | 32-Bit Arit   | hmetic Capabilities of TMS32010                  | 4-8  |

|         | 4.9    | Table Read    | I from Program Memory Instruction                | 4-9  |

|         | 4.10   | Interrupt In  | nstruction                                       | 4-10 |

|         | 4.11   | Stack Expa    | ansion                                           | 4-11 |

|         |        |               |                                                  |      |

| 5.      | ASSEMB | LER DIREC     | TIVES                                            | 5-1  |

|         | 5.1    | Introductio   | n                                                | 5-1  |

|         | 5.2    | The TMS3      | 2010 Assembler                                   | 5-1  |

|         | 5.3    | Assembler     | Directives                                       | 5-1  |

|         |        | 5.3.1         | Directives that Affect the Location Counter      | 5-1  |

|         |        | 5.3.2         | Directives that Affect Assembler Output          | 5-17 |

|         |        | 5.3.3         | Directives that Initialize Constants             | 5-23 |

|         |        | 5.3.4         | Directives that Provide Linkage Between Programs | 5-27 |

|         |        | 5.3.5         | Miscellaneous Directives                         | 5-33 |

|         |        |               |                                                  |      |

| 6.      | PROGRA | M LINKING     |                                                  | 6-1  |

|         | 6.1    | Introductio   | n                                                | 6-1  |

|         | 6.2    | Relocation    | Capability                                       | 6-1  |

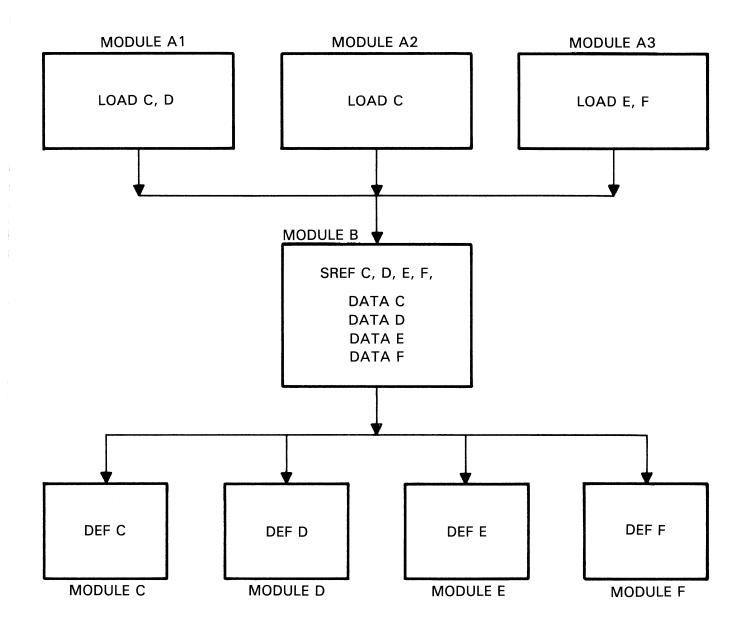

|         | 6.3    | Linking Pro   | ogram Modules                                    | 6-2  |

|         |        | 6.3.1         | External Reference Directives                    | 6-2  |

|         |        | 6.3.2         | External Definition Directive                    | 6-3  |

|         |        | 6.3.3         | Program Identifier Directive                     | 6-3  |

|         |        | 6.3.4         | Linking                                          | 6-3  |

|         |        |               |                                                  |      |

| 7.      |        | LER OUTPL     |                                                  |      |

|         | 7.1    | Introductio   | n                                                |      |

|         | 7.2    |               | ting                                             |      |

|         | 7.3    | Assembler     | Error Messages                                   | 7-2  |

|         | 7.4    | Cross-Refe    | erence Listing                                   |      |

|         | 7.5    | Object Cod    | de                                               | 7-6  |

|         |        | 7.5.1         | Object Code Format                               | 7-6  |

|         |        | 7.5.2         | External References in Object Code               | 7-10 |

|         |        | 7.5.3         | Changing Object Code                             | 7-10 |

|         |        | 0 4 D 4 D 1 - |                                                  |      |

| 8.      |        |               | Υ                                                |      |

|         | 8.1    | Introductio   | n                                                | 8-1  |

#### **TABLE OF CONTENTS (Concluded)**

| SECTION |             |                                     | PAGE |

|---------|-------------|-------------------------------------|------|

| 8.2     | Defining Ma | acros                               | 8-1  |

|         | 8.2.1       | Sample Macros                       | 8-3  |

| 8.3     | Macro Lang  | juage Elements                      | 8-4  |

|         | 8.3.1       | Strings                             | 8-4  |

|         | 8.3.2       | Constants and Operators             | 8-4  |

|         | 8.3.3       | Variables                           | 8-5  |

|         | 8.3.3.1     | Parameters                          | 8-5  |

|         | 8.3.3.2     | Macro Symbol Table                  | 8-6  |

|         | 8.3.3.3     | Variable Qualifiers                 | 8-7  |

|         | 8.3.4       | Keywords                            | 8-8  |

|         | 8.3.4.1     | Symbol Attribute Component Keywords | 8-9  |

|         | 8.3.4.2     | Parameter Attribute Keywords        | 8-9  |

|         | 8.3.5       | Verbs                               | 8-10 |

|         | 8.3.5.1     | \$MACRO Statement                   | 8-10 |

|         | 8.3.5.2     | \$VAR Statement                     | 8-13 |

|         | 8.3.5.3     | \$ASG Statement                     | 8-13 |

|         | 8.3.5.4     | \$IF Statement                      | 8-14 |

|         | 8.3.5.5     | \$ELSE Statement                    | 8-16 |

|         | 8.3.5.6     | \$ENDIF Statement                   | 8-16 |

|         | 8.3.5.7     | \$END Statement                     | 8-16 |

|         | 8.3.6       | Model Statements                    | 8-16 |

| 8.4     | Macro Exar  | nples                               | 8-17 |

|         | 8.4.1       | Macro ID                            | 8-17 |

|         | 8.4.2       | Macro GENCMT                        | 8-18 |

|         | 8.4.3       | Macro FACT                          | 8-19 |

|         | 8.4.4       | Macro FFT                           | 8-19 |

| 8.5     | Macro Erroi | Messages                            | 8-21 |

#### LIST OF APPENDICES

# APPENDIX PAGE A TMS32010 Hardware Summary ..... A-1 B Character Sets Recognized by the Assembler ..... B-1

#### LIST OF ILLUSTRATIONS

| FIGURE |                                | PAGE |

|--------|--------------------------------|------|

| 1-1    | Development Process            | 1-2  |

| 7-1    | Cross-Reference Listing Format | 7-5  |

| 7-2    | Sample Object Code             | 7-6  |

# LIST OF TABLES

#### TABLE

| 2-1 | Results of Operations on Absolute and Relocatable Items in Expressions | 2-10 |

|-----|------------------------------------------------------------------------|------|

| 3-1 | Instruction Symbols                                                    | 3-4  |

| 3-2 | Instruction Set Summary                                                | 3-5  |

| 5-1 | Assembler Directives that Affect the Location Counter                  | 5-2  |

| 5-2 | Directives that Affect Assembler Output                                | 5-17 |

| 5-3 | Directives that Initialize Constants                                   | 5-23 |

| 5-4 | Directives that Provide Linkage Between Programs                       | 5-27 |

| 5-5 | Miscellaneous Directives                                               | 5-32 |

| 7-1 | Assembly Listing Errors                                                | 7-3  |

| 7-2 | Symbol Attributes                                                      | 7-5  |

| 7-3 | Object Record Format and Tags                                          | 7-9  |

| 8-1 | Variable Qualifiers                                                    | 8-7  |

| 8-2 | Variable Qualifiers for Symbol Components                              | 8-8  |

| 8-3 | Symbol Attribute Keywords                                              | 8-9  |

| 8-4 | Parameter Attribute Keywords                                           | 8-10 |

| 8-5 | Macro Error Messages                                                   | 8-21 |

|     |                                                                        |      |

#### 1. INTRODUCTION

#### 1.1 GENERAL DESCRIPTION

An assembly language is a computer-oriented language for writing programs, consisting of symbolic instructions and assembler directives. In assembly instructions, the user assigns symbolic addresses to memory locations and specifies instructions by means of symbolic (mnemonic) operation codes. The user specifies instruction operands by means of symbolic addresses, numbers, and expressions consisting of symbolic addresses and numbers. Assembler directives control the processes of making a machine language program from the assembly language program, placing data in the program, and assigning symbols to values to be used in the program. Assembler directives that place data in memory locations allow the user to assign symbolic addresses to those locations.

Assembly language is computer-oriented in that the mnemonic operation codes correspond directly to machine instructions. The chief advantage an assembly language offers over a machine language is that the symbols of assembly language are easier to use and easier to remember than the zeros and ones of machine language. Other advantages are the use of expressions as operands and the use of decimal numbers in expressions and as operands.

This manual describes the assembly language for the TMS32010 and TMS320M10 16/32-bit high-performance digital signal processors.

#### 1.2 ASSEMBLY LANGUAGE APPLICATION

An assembly language program, called a source program, must be processed by an assembler to obtain a machine language program that can be executed by the computer. Processing of a source program is called assembling, because it consists of assembling the binary values (that correspond to the mnemonic operation code) with the binary address information to form the machine language instruction.

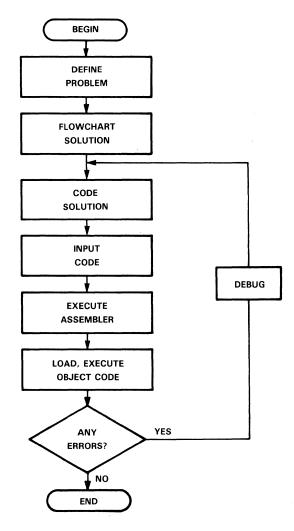

To illustrate the place of assembly language in the development of programs, consider the following steps in program development:

- 1) Define the problem.

- 2) Flowchart the solution to the problem.

- 3) Code the solution by writing assembly language statements (machine instructions and assembler directives) that correspond to the steps of the flowchart.

- 4) Prepare the source program by writing the statements on the medium appropriate to the installation; e.g., enter a file on a disk, keypunch the statements, etc.

- 5) Execute the assembler to assemble the machine language object code corresponding to the source program.

- 6) Debug the resulting object code by loading and executing the object code and making the consequent corrections indicated.

- 7) Repeat Steps 5 and 6 until no further correction is required.

The use of assembly language in program development relieves the programmer of the tedious task of writing machine language instructions and keeping track of binary machine addresses within the program. Figure 1-1 also illustrates this procedure.

#### 1.3 LINKING PROGRAM MODULES

The assembler commands include two pairs of directives, DEF/REF and SREF/LOAD, that generate the information required to link program modules, thus removing the constraint of having to assemble an entire program at once. A long program may be divided into more manageable components in order to avoid a time-consuming assembly. Also, these smaller units reduce the size of the symbol table (an entry is made in the symbol table for every symbol used in the program). Components of a large program are then linked by the link editor (also called the linker) to form a complete executable program.

#### 1.4 PROGRAM RELOCATABILITY

A major advantage of the TMS32010 Assembler is its ability to generate relocatable object code modules which can then be linked by the link editor to form an executable program. (Absolute code, on the other hand, must occupy a dedicated area of memory and cannot be moved as necessity dictates. This means that repetitive code in a program must be written into the program each time it is needed.)

The ability to relocate modules simplifies the programming task. Programs designed as a set of modules are easier to code, test, and debug, and are easier to understand and maintain. Relocatability also permits multiple programmers to work on a program's components.

FIGURE 1-1 - DEVELOPMENT PROCESS

#### 1.5 MACROS

The macro capability adds great flexibility to the assembler and provides the means to create a macro language that is capable of calling source statements from other locations within a program. A macro call statement fetches the source statements defined by the macro and substitutes them for the macro as if they had been written in that location in the program.

The obvious advantage of using macro code is that less source code must be written; this in turn means that the programs are easier to read and debug. In addition, macros usually execute faster than a comparable absolute code routine because no branching is involved. The macro capability is discussed in Section 8.

#### 2. GENERAL PROGRAMMING INFORMATION

#### 2.1 INTRODUCTION

The TMS32010 Assembly Language is a powerful set of instructions consisting of mnemonic operation codes (called mnemonics) that correspond directly to binary machine instructions. The assembly language program, as coded by the programmer, is called a source program. Before it can be executed by the computer, this source program must be processed by the assembler to obtain a machine language program. This processing of a source program is called assembling. This consists of assembling the binary values (which correspond to the mnemonic operation code) with the binary address information, to form the machine language instruction.

Assembler directives (see Section 5) control the process of making a machine language program from the assembly language program, placing data in the program, and assigning values to symbols to be used in the program.

#### 2.2 DATA AREAS

The data manipulated by the TMS32010 is organized into four areas:

- Register areas: Two 16-bit auxiliary registers, a 1-bit auxiliary register pointer, a 32-bit T register; a 32-bit P register; an accumulator, and a 4 X 12 hardware stack area. In addition, The TMS32010 CPU has access to the 12-bit program counter (PC), the 16-bit status register (ST), and the 1-bit data page pointer (DP).

- 1536 X 16-bit read-only-memory (ROM) program areas containing the main program and subroutines.

- 144 X 16-bit on-chip RAM data memory areas comprising data tables.

- Eight I/O Ports.

Detailed information and illustrations of these data areas are presented in Appendix A.

#### 2.3 THE TMS32010 INSTRUCTION SET

The TMS32010 instruction set is composed of 60 instructions that provide for the input, output, manipulation, and comparison of data. The instruction set is divided into eight functional categories. They are as follows:

1) ACCUMULATOR INSTRUCTIONS: Provide a variety of ways to add, subtract, load, and store the accumulator.

MNEMONIC

#### DESCRIPTION

| ABS  | ABSOLUTE VALUE OF ACCUMULATOR             |

|------|-------------------------------------------|

| ADD  | ADD TO ACCUMULATOR WITH SHIFT             |

| ADDH | ADD TO HIGH ACCUMULATOR                   |

| ADDS | ADD TO ACCUMULATOR WITH NO SIGN EXTENSION |

| LAC  | LOAD ACCUMULATOR WITH SHIFT               |

| LACK | LOAD ACCUMULATOR IMMEDIATE                |

| SACH | STORE HIGH ACCUMULATOR                    |

| SACL | STORE LOW ACCUMULATOR                       |

|------|---------------------------------------------|

| SUB  | SUBTRACT FROM ACCUMULATOR WITH SHIFT        |

| SUBC | CONDITIONAL SUBTRACT (FOR DIVIDE)           |

| SUBH | SUBTRACT FROM HIGH ACCUMULATOR              |

| SUBS | SUBTRACT FROM ACCUMULATOR WITH NO EXTENSION |

| ZAC  | ZERO ACCUMULATOR                            |

| ZALH | ZERO ACCUMULATOR AND LOAD HIGH              |

| ZALS | ZERO ACCUMULATOR AND LOAD LOW               |

2) AUXILIARY REGISTER AND DATA PAGE INSTRUCTION: Load, store, modify, and compare ARs and ARP.

#### **MNEMONIC**

#### DESCRIPTION

| LAR  | LOAD AUXILIARY REGISTER                   |

|------|-------------------------------------------|

| LARK | LOAD AUXILIARY REGISTER IMMEDIATE         |

| LARP | LOAD AUXILIARY REGISTER POINTER IMMEDIATE |

| LDP  | LOAD DATA PAGE MEMORY POINTER             |

| LDPK | LOAD DATA MEMORY PAGE POINTER IMMEDIATE   |

| MAR  | MODIFY AUXILIARY REGISTER AND POINTER     |

| SAR  | STORE AUXILIARY REGISTER                  |

3) T REGISTER, P REGISTER, AND MULTIPLY INSTRUCTIONS: Provide for the preparation for and execution of a multiply.

| MNEMONIC | DESCRIPTION                                         |

|----------|-----------------------------------------------------|

| APAC     | ADD P REGISTER TO ACCUMULATOR                       |

| LT       | LOAD T REGISTER                                     |

| LTA      | LOAD T REGISTER AND ACCUMULATOR PRODUCT             |

| LTD      | LOAD T REGISTER, ACCUMULATOR PRODUCT, AND MOVE DATA |

|          | IN MEMORY FORWARD ONE LOCATION                      |

| MPY      | MULTIPLY T REGISTER BY DATA MEMORY VALUE AND STORE  |

|          | THE PRODUCT IN P REGISTER                           |

| MPYK     | MULTIPLY T REGISTER BY IMMEDIATE OPERAND AND STORE  |

|          | VALUE IN P REGISTER                                 |

| PAC      | LOAD ACCUMULATOR FROM P REGISTER                    |

| SPAC     | SUBTRACT P REGISTER FROM ACCUMULATOR                |

4) BRANCH INSTRUCTIONS: Permit testing of a variety of conditions, along with subroutine calls.

#### MNEMONIC

#### DESCRIPTION

| В    | BRANCH UNCONDITIONALLY                |

|------|---------------------------------------|

| BANZ | BRANCH ON AUXILIARY REGISTER NOT ZERO |

| BGEZ | BRANCH IF ACCUMULATOR $> OR = 0$      |

| BGZ  | BRANCH IF ACCUMULATOR $> 0$           |

| BIOZ | BRANCH ON I/O STATUS = 0              |

| BLEZ | BRANCH IF ACCUMULATOR $< OR = 0$      |

| BLZ  | BRANCH IF ACCUMULATOR $< 0$           |

| BNZ  | BRANCH IF ACCUMULATOR NOT $= 0$          |

|------|------------------------------------------|

| BV   | BRANCH ON OVERFLOW                       |

| BZ   | BRANCH IF ACCUMULATOR $= 0$              |

| CALA | CALL SUBROUTINE INDIRECT VIA ACCUMULATOR |

| CALL | CALL SUBROUTINE                          |

| RET  | RETURN FROM SUBROUTINE                   |

5) CONTROL INSTRUCTIONS: Affect the overflow mode, enable and disable interrupts, and store certain registers which cannot be stored by other instructions.

#### MNEMONIC

#### DESCRIPTION

| DINT | DISABLE INTERRUPT                |

|------|----------------------------------|

| EINT | ENABLE INTERRUPT                 |

| LST  | LOAD STATUS REGISTER             |

| NOP  | NO OPERATION                     |

| POP  | TOP OF STACK TO ACCUMULATOR      |

| PUSH | PUSH ACCUMULATOR TO TOP OF STACK |

| ROVM | RESET OVERFLOW MODE              |

| SOVM | SET OVERFLOW MODE                |

| SST  | STORE STATUS REGISTER            |

6) BOOLEAN OPERATIONS: Perform logical operations between the accumulator and data memory.

#### MNEMONIC

#### DESCRIPTION

| AND | AND WITH LOW ACCUMULATOR          |

|-----|-----------------------------------|

| OR  | OR WITH LOW ACCUMULATOR           |

| XOR | EXCLUSIVE OR WITH LOW ACCUMULATOR |

7) I/O AND DATA MEMORY OPERATIONS: Allow input/output of data to external peripherals, provide for transfer of data within data memory or between program and data memory.

# MNEMONICDESCRIPTIONDMOVSHIFT CONTENTS OF DATA MEMORY ADDRESS FORWARD ONE<br/>LOCATIONININPUT DATA FROM PORTOUTOUTPUT DATA TO PORTTBLRTABLE READ FROM PROGRAM MEMORY TO DATA MEMORYTBLWTABLE WRITE FROM DATA MEMORY TO PROGRAM MEMORY

Detailed information concerning these instructions is presented in Section 3.

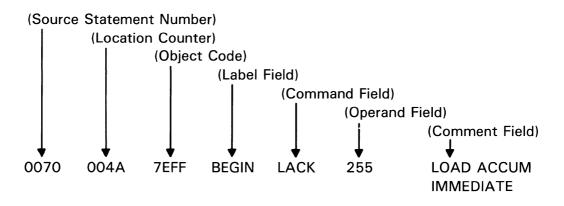

#### 2.4 SOURCE STATEMENT FORMAT

An Assembly Language source program consists of source statements that may contain assembler directives, machine instructions, or comments. Source statements scanned by the assembler may contain four ordered fields separated by one or more blanks. These fields (label, command, operand, and comment) are discussed in the following paragraphs. Source statements containing an asterisk (\*) in the first character position are comment statements, and as such, they have no effect on the assembly. The source statement line may be as long as the source file format allows; however, the assembler will truncate the source line to 60 characters without warning. The user should insure that nothing other than comments extend past column 60.

The character set accepted by the TMS32010 Assembler consists of the ASCII character set as well as special characters that are undefined in ASCII. Appendix B contains tables that list the TMS32010 Assembler character set, along with associated ASCII and Hollerith codes.

The syntax for source statements is:

| [ <label>]</label> | <mnemonic></mnemonic> | [ <operand>]</operand> | [ <comment>]</comment> |

|--------------------|-----------------------|------------------------|------------------------|

| EXAMPLE:           | LOOP IN MEM,PA0       | INPUT NEXT DA          | TA SAMPLE              |

A source statement may have a label that is defined by the user. One or more blanks separate the label from the command mnemonic. Instruction operation codes, assembler directives, and user-defined operation codes are all included in the generic term mnemonic. One or more blanks separate the mnemonic from the operand (when an operand is required). One or more blanks separate the operand(s) from the comment field. Comments are ignored by the assembler.

The last source statement of a source program, usually the END directive, is followed by the end-of-file statement for the source medium (e.g., for punched cards, a card with a slash (/) punched in column one and an asterisk (\*) in column two).

#### 2.4.1 Label Field

The label field begins in character position one of the source record, extends to the first blank, and contains a symbol of up to six significant characters. The first character of the symbol must be alphabetic. Additional characters may be any alphanumeric characters. A label is optional for machine instructions and for many assembler directives. When the label is omitted, the first character position must contain a blank. A source statement consisting of only a label field is a valid statement. It has the effect of assigning the current value of the location counter to the label; this is equivalent to the following directive statement:

< label > EQU \$ Where \$ represents the current value of the location counter at that point in the assembly.

#### 2.4.2 Command Field

The command field begins after the blank that terminates the label field, or in the first nonblank character past the first character position (which must be blank when the label is omitted). The command field is terminated by one or more blanks and may not extend past the right margin. The command field may contain one of the following opcodes:

- Assembler mnemonic of a machine instruction (e.g., IN)

- Macro directive (e.g., \$MACRO)

- Assembler directive (e.g., DATA)

#### 2.4.3 Operand Field

The operand field begins following the blank that terminates the command field and may not extend past the right margin of the source record. The operand field may contain one or more constants or expressions (described in Sections 2.5 and 2.7). The operand field is terminated by one or more blanks.

#### 2.4.4 Comment Field

The comment field begins after the blank that terminates the operand field or the blank that terminates the command field, as in the case of commands that have no operands. The comment field may extend to the end of the source record, if required, and may contain any ASCII character including blank(s). The contents of the comment field up to the end of the source record are listed in the source portion of the assembly listing and have no other effect on the assembly.

#### 2.5 CONSTANTS

The assembler recognizes the following five types of constants, each internally maintained as a 16-bit quantity:

- Decimal integer constants

- Binary integer constants

- Hexadecimal integer constants

- Character constants

- Assembly-time constants

#### 2.5.1 Decimal Integer Constants

A decimal integer constant is written as a string of decimal digits. The range of values of decimal integers is -32,768 to +65,535. Positive decimal integer constants greater than 32,767 are considered negative when interpreted as two's complement values.

The following are valid decimal constants:

1000

Constant equal to 1000 or >03E8

-32768

Constant equal to -32768 or >8000

25

Constant equal to 25 or >0019

#### 2.5.2 Binary Integer Constants

A binary integer constant is written as a string of up to 16 binary digits (0/1) preceded by a question mark, "?". If less than sixteen digits are specified, the assembler will right-justify the given bits in the resulting constant.

The following are valid binary constants:

?0000000000010011

?011111111111111111

?11110

Constant equal to 19 or >0013 Constant equal to 32767 or >7FFF Constant equal to 30 or >001E

#### 2.5.3 Hexadecimal Integer Constants

A hexadecimal integer constant is written as a string of up to four hexadecimal digits preceded by a greater than sign, '>'. If less than four hexadecimal digits are specified, the assembler will right-justify the bits which are specified in the resulting constant. Hexadecimal digits include the decimal values '0' through '9' and the letters 'A' through 'F'.

The following are valid hexadecimal constants:

| >78   | Constant equal to | 120 (or >0078)   |

|-------|-------------------|------------------|

| >F    | Constant equal to | 15 (or >000F)    |

| >37AC | Constant equal to | 14252 (or >37AC) |

#### 2.5.4 Character Constants

A character constant is written as a string of one or two alphabetic characters enclosed in single quotes. Two consecutive single quotes are required to represent each single quote contained within a character constant. If less than two characters are specified, the assembler will right-justify the given bits in the resulting constant. The characters are represented internally as 8-bit ASCII characters. A character constant consisting of only two single quotes (no character) is valid and is assigned the value 0000 (Hex).

The following are valid character constants:

| 'AB'  | Represented | internally | as | >4142 |

|-------|-------------|------------|----|-------|

| 'C'   | Represented | internally | as | >0043 |

| 'N'   | Represented | internally | as | >004E |

| '''D' | Represented | internally | as | >2744 |

#### 2.5.5 Assembly-Time Constants

An assembly-time constant is a symbol given a value by an EQU directive (see Section 2.4.1). The value of the symbol is determined at assembly time and is considered to be absolute or relocatable according to the relocatability of the expression, not according to the relocatability of the location counter value. Absolute value symbols may be assigned values with expressions using any of the above constant types.

#### 2.6 SYMBOLS

Symbols are used in the label field and the operand field. A symbol is a string of alphanumeric characters, ('A' through 'Z', '0' through '9' and '\$'). The first character in a symbol must be 'A' through 'Z' or '\$'. No character may be blank. When more than six characters are used in a symbol, the assembler prints all the characters, but accepts only the first six characters for processing (the assembler also prints a warning indicating that the symbol has been truncated). Therefore, symbols must be unique in the first six characters. User-defined symbols are valid only during the assembly in which they are defined.

Symbols used in the label field become symbolic addresses. They are associated with locations in the program and must not be used in the label field of other statements. Mnemonic operation codes and assembler directive names may also be used as valid user-defined symbols when placed in the label field.

Symbols used in the operand field must be defined in the assembly, usually by appearing in the label field of a statement or in the operand field of a REF or SREF directive. REF and SREF directives provide access to symbols defined in other programs (see Section 5.3.4).

The following are examples of valid symbols:

| START     | START is assigned the value of the location where it appears in the label field.                                                       |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------|

| ADD       | ADD is assigned the value of the location where it appears in the label field.                                                         |

| OPERATION | OPERAT (assembler recognizes only the first six characters) is assigned the value of the location where it appears in the label field. |

#### 2.6.1 **Predefined Symbols**

The predefined symbols are the dollar sign character (\$) and the register and port symbols. The dollar sign character is used to represent the current location within the program. The auxiliary register symbols are of the form "ARn," where 'n' is a constant 0 or 1.

The port addresses are of the form "PAn," where n is a constant in the range from 0 to 7.

The following are examples of valid predefined symbols:

| \$  | Represents the current location |

|-----|---------------------------------|

| ARO | Represents Auxiliary Register 0 |

| PAO | Represents Port Address 0       |

#### 2.6.2 Terms

Terms are used in the operand fields of machine instructions and assembler directives. A term may be a decimal, binary, character, or hexadecimal constant, an absolute assembly time constant, or a label having an absolute value.

#### 2.6.3 Character Strings

Several assembler directives require character strings in the operand field. A character string is written as a string of characters enclosed in single quotes. For each single quote in a character string, two consecutive single quotes are required to represent the single quote. The maximum length of the string is defined for each directive that requires a character string. The characters are represented internally as 8-bit ASCII. Appendix B gives a complete list of valid characters within character strings.

The following are valid character strings:

'SAMPLE PROGRAM'

Defines a 14-character string consisting of SAMPLE PROGRAM

'PLAN ''C'''

'OPERATOR MESSAGE : PRESS START SWITCH'

Defines a 37-character string consisting of the expression enclosed in single quotes.

#### 2.7 EXPRESSIONS

Expressions are used in the operand fields of assembler directives and machine instructions. An expression is a constant or symbol, a series of constants or symbols, or a series of constants and symbols separated by arithmetic operators. Each constant or symbol may be preceded by a minus sign (unary minus), a plus sign (unary plus), or the # symbol (unary invert). Unary minus is the same as taking the two's complement, and unary invert is the same as taking the one's complement. The # symbol causes the value of the logical complement of the following constant, symbol, or expression to be used. An expression may not contain embedded blanks. The valid range of values for an expression is -32,768 to +65,535. Symbols that are defined as external references may be operands of arithmetic instructions within certain limits, as described in Section 2.7.4.

#### 2.7.1 Arithmetic Operators in Expressions

The arithmetic operators used in expressions are as follows:

- + for addition

- for subtraction

- \* for multiplication

- / for signed division

In evaluating an expression, the assembler first negates any constant or symbol preceded by a unary minus and then performs the arithmetic operations from left to right. The unary invert will be performed last. The assembler does not assign arithmetic operation precedence to any operation other than unary plus, unary minus, or unary invert. All arithmetic operations take precedence over the unary invert (#) operation. The expression following a unary invert (i.e., ''#'') must be resolved to an absolute value. All operations are integer operations. The assembler truncates the fraction in division.

For example, the expression 4+5\*2 would be evaluated 18, not 14; and the expression 7+1/2 would be evaluated four, not seven.

The assembler checks for overflow/underflow conditions when arithmetic operations are performed at assembly time and gives the warning message "VALUE TRUNCATED" whenever an overflow/underflow occurs.; Examples of "VALUE TRUNCATED" messages are as follows:

-2\*>4001 >FFFE+2 -1\*>8001 >8000\*2 ->8000-1 -2\*>8000

#### 2.7.2 Parentheses in Expressions

The assembler supports the use of parentheses in expressions to alter the order of evaluation of the expression. Nesting of pairs of parentheses within expressions is also supported. When parentheses are used, the portion of the expression within the innermost parentheses is evaluated first; then the portion of the expression within the next innermost pair is evaluated. When evaluation of the portions of the expression within the parentheses has been completed, the evaluation is completed from left to right. Evaluation of portions of an expression within parentheses at the same nesting level is considered as simultaneous. Parenthetical expressions may not be nested more than eight deep.

For example, the use of parentheses in the expression LAB1 + ((4+3)\*7) will result in the following operation: add four to three; multiply the resulting sum by seven; and add the resulting product to the value of LAB1.

#### 2.7.3 Well-Defined Expressions

Some assembler directives require well-defined expressions in operand fields. For an expression to be well-defined, any symbols or assembly-time constants in the expression must have been previously defined. The evaluation of a well-defined expression must also be absolute, and a well-defined expression cannot contain a character constant. An example of a well-defined expression is:

>1000 + X Where X must have been previously defined

#### 2.7.4 Relocatable Symbols in Expressions

An expression that contains a relocatable symbol or constant immediately following a multiplication or division operator is illegal. When the result of evaluating an expression up to a multiplication or division operator is relocatable, the expression is also illegal.

If the current value of an expression is relocatable with respect to one relocatable section, a symbol of another section may not be included until the value of the expression becomes absolute. The following are legal expressions involving relocatable symbols:

| BLUE + 1    | The sum of the value of symbol BLUE plus 1 is legal<br>and of the same type as BLUE (BLUE can be an ab-<br>solute or a relocatable symbol).                                 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GREEN – 4   | The result of subtracting 4 from the value of symbol<br>GREEN is legal and of the same type as GREEN<br>(GREEN can be an absolute or a relocatable symbol).                 |

| 2*16+RED    | The sum of the value of symbol RED plus the product<br>of 2 times 16 is legal, and of the same type as RED<br>(RED can be an absolute or a relocatable symbol).             |

| 440/2 – RED | The result of dividing 440 by 2 and then subtracting<br>the value of symbol RED from the quotient is absolute<br>(RED must be absolute to make this a legal<br>expression). |

Table 2-1 defines the relocatability of the result for each type of operator.

#### TABLE 2-1 - RESULTS OF OPERATIONS ON ABSOLUTE AND RELOCATABLE ITEMS IN EXPRESSIONS

| IF A IS | AND B IS | RESULT OF<br>A + B | RESULT OF | RESULT OF<br>A*B | RESULT OF<br>A/B |

|---------|----------|--------------------|-----------|------------------|------------------|

| ABS     | ABS      | ABS                | ABS       | ABS              | ABS (B<>0)*      |

| ABS     | RELOC    | RELOC              | illegal   | Note 1           | illegal          |

| RELOC   | ABS      | RELOC              | RELOC     | Note 2           | Note 3           |

| RELOC   | RELOC    | illegal            | Note 4    | illegal          | illegal          |

\* <> indicates "not equal"

NOTES: 1. Illegal unless A equals zero or one. If A equals one, the result is relocatable; if A is zero, the result is an absolute zero.

2. Illegal unless B equals zero or one. If B equals one, the result is relocatable; if B is zero, the result is absolute zero.

3. Illegal unless B equals one, in which case the result is relocatable.

4. Illegal unless A and B are in the same section, in which case the result is absolute.

#### 2.7.5 Externally Defined Symbols in Expressions

The assembler allows externally defined symbols (defined in REF and SREF directives) in expressions under the following conditions:

- 1) Only one externally referenced symbol may be used in an expression.

- 2) The character preceding the referenced symbol must be a plus sign, a blank, a comma, or a unary invert. The portion of the expression preceding the symbol, if any, must be added to the symbol.

- 3) The portion of the expression following the referenced symbol must not include multiplication or division operations on the symbol (as for a relocatable symbol described in Section 2.7.4).

- 4) The remainder of the expression following the referenced symbol must be absolute.

The assembler limits the user to a total of 255 externally referenced symbols per module. Modules using more than 255 external symbols must be broken into smaller modules for assembly, and linked using the link editor.

#### 3. ASSEMBLY INSTRUCTIONS

Assembly language instructions for the TMS32010 microcomputer are described in this section. Descriptions of the addressing modes, formats for instruction addressing, and detailed instruction descriptions are included.

#### 3.1 INTRODUCTION

The instruction set contains a full set of branch instructions. Combined with the Boolean operations and shifters, these instructions permit the bit manipulation and bit test capability needed for high-speed control operations. Double-precision operations are also supported by the instruction set. Some examples are ADDH (add to high-order accumulator) and ADDS (add to accumulator with sign extension suppressed), which allow easy manipulation of 32-bit numbers.

The TMS32010's hardware multiplier allows the MPY instruction to be executed in a single cycle. The SUBC (conditional subtract for divide) instruction performs the shifting and conditional branching necessary to implement a divide efficiently and quickly.

Two special instructions, TBLR (table read) and TBLW (table write), allow crossover between data memory and program memory. The TBLR instruction transfers words stored in program memory to the data RAM. This eliminates the need for a coefficient ROM separate from the program ROM, thus permitting the user to make efficient trade-offs as to the amount of ROM dedicated to program or coefficient store. The accompanying instruction, TBLW, transfers words in internal data RAM to an external RAM. In conjunction with TBLR, this instruction allows the use of external RAM to expand the amount of data storage.

When a very large amount of external data must be addressed (i.e., >4K words), TBLR and TBLW can no longer serve as a means of expanding the data RAM. Then it becomes necessary to address external data RAM as a peripheral by using the IN and OUT instructions; these instructions permit a data word to be read into the on-chip RAM in only two cycles. This procedure requires a minimal amount of external logic and permits the accessing of almost unlimited amounts of data RAM. This is very useful for pattern recognition applications, such as speech recognition or image processing.

#### 3.2 ADDRESSING MODES

Three main addressing modes are available with the TMS32010 instruction set direct, indirect, and immediate addressing.

#### 3.2.1 Direct Addressing Mode

In direct addressing, seven bits of the instruction word concatenated with the data page pointer form the data memory address. This implements a paging scheme in which the first page contains 128 words and the second page contains 16 words. In a typical application, infrequently accessed variables, such as those used when performing an interrupt service routine, are stored on the second page.

#### 3.2.2 Indirect Addressing Mode

Indirect addressing forms the data memory address from the least significant eight bits of one of two auxiliary registers, ARO and AR1. The auxiliary register pointer (ARP) selects the current auxiliary register. The auxiliary registers can be automatically incremented or decremented in parallel with the execution of any indirect instruction to permit single-cycle manipulation of data tables.

#### 3.2.3. Immediate Addressing Mode

The TMS32010 instruction set contains special "immediate" instructions. These instructions derive data from part of the instruction word rather than from the data RAM. The constant in all immediate instructions may refer to values supplied by an external reference symbol. Some very useful immediate instructions are multiply immediate (MPYK), load accumulator immediate (LACK), and load auxiliary register immediate (LARK).

#### 3.3 INSTRUCTION ADDRESSING FORMAT

The following sections describe the opcode format for the various addressing modes of the TMS32010.

#### 3.3.1 Direct Addressing Format

| 15 | 14 | 13 | 12  | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3  | 2 | 1 | 0 |

|----|----|----|-----|----|----|---|---|---|---|---|---|----|---|---|---|

|    |    | С  | PCO | DE |    |   |   | 0 |   |   | d | ma |   |   |   |

Bit 7 = 0 defines direct addressing mode. The opcode is contained in bits 15 through 8. Bits 6 through 0 contain data memory address.

The 7 bits of the data memory address (dma) field can directly address up to 128 words (1 page) of data memory. Use of the data memory page pointer is required to address the full 144 words of data memory.

Direct addressing can be used with all instructions requiring data operands except for the immediate operand instructions.

#### 3.3.2. Indirect Addressing Format

| 15 | 14 | 13 | 12  | 11  | 10 | 9 | 8 | 7 | 6 | 5   | 4   | 3   | 2 | 1 | 0   |

|----|----|----|-----|-----|----|---|---|---|---|-----|-----|-----|---|---|-----|

|    |    |    | OPC | ODE | -  |   |   | 1 | 0 | INC | DEC | ARP | 0 | 0 | ARP |

Bit 7 = 1 defines indirect addressing mode. The opcode is contained in bits 15 through 8. Bits 6 through 0 contain indirect addressing control bits.

Bit 3 and bit 0 control the Auxiliary Register Pointer (ARP). If bit 3 = 0, then the contents of bit 0 are loaded into the ARP after execution of the current instruction. If bit 3 = 1, then the contents of the ARP remain unchanged. ARP = 0 defines the contents of ARO as a memory address. ARP = 1 defines the contents of AR1 as a memory address.

Bit 5 and bit 4 control the auxiliary registers. If bit 5 = 1, then ARP defines which auxiliary register is to be incremented by 1 after execution. If bit 4 = 1, then the ARP defines which auxiliary register is to be decremented by 1 after execution. If bit 5 and bit 4 are zero, then neither auxiliary register is incremented or decremented. Bits 6, 2, and 1 are reserved and should always be programmed to zero.

Indirect addressing can be used with all instructions requiring data operands, except for the immediate operand instructions.

#### 3.3.3 Immediate Addressing Format

Included in the TMS32010's instruction set are five immediate operand instructions (LDPK, LARK, MPYK, LACK, and LARP). In these instructions, the operand is contained within the instruction word.

#### 3.3.4 Examples of Opcode Format

| 1) | ADD | 9,5 |    |    | dd to<br>catio |    |   |   |   |   |   | nts o | of me | emo | rγ |   |

|----|-----|-----|----|----|----------------|----|---|---|---|---|---|-------|-------|-----|----|---|

|    | 15  | 14  | 13 | 12 | 11             | 10 | 9 | 8 | 7 | 6 | 5 | 4     | 3     | 2   | 1  | 0 |

|    | 0   | 0   | 0  | 0  | 0              | 1  | 0 | 1 | 0 | 0 | 0 | 0     | 1     | 0   | 0  | 1 |

Note: Opcode of the ADD instruction is 0000 and appears in bits 15 through 12. Shift code of 5 appears in bits 11 through 8. Data memory address 9 appears in bits 6 through 0.

2) ADD \*+,8 Add to accumulator the contents of data memory address defined by contents of current auxiliary register. This data is left-shifted 8 bits before being added. The current auxiliary register is auto-incremented by 1.

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| 0  | 0  | 0  | 0  | 1  | 0  | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 |

Other variations of indirect addressing are as follows:

| 3) | ADD *, 8       | As in example 2, but with no auto-increment; opcode would be > 0888                                                              |

|----|----------------|----------------------------------------------------------------------------------------------------------------------------------|

| 4) | ADD * –, 8     | As in example 2, except that current auxiliary register is decremented by 1; opcode would be > 0898                              |

| 5) | ADD * + , 8, 1 | As in example 2, except that the auxiliary register pointer is loaded with the value 1 after execution; opcode would be $> 08A1$ |

| 6) | ADD * + , 8, 0 | As in example 2, except that the auxiliary register pointer is loaded with the value 0 after execution; opcode would be $> 08A0$ |

#### 3.4 INSTRUCTION SET

The following sections include the symbols and abbreviations that are used in the instruction set summary and in the instruction descriptions, the complete instruction set summary, and a description of each instruction.

All numbers are assumed to be decimal unless otherwise indicated. Hexidecimal numbers are specified by the symbol ">" before the number.

#### 3.4.1. Symbols and Abbreviations

DATn and PRGn are assumed to have the symbolic value of n. They are used to represent any symbol with the value n.

#### TABLE 3-1 - INSTRUCTION SYMBOLS

| SYMBOL   | MEANING                                                                                            |

|----------|----------------------------------------------------------------------------------------------------|

| ACC      | Accumulator                                                                                        |

| AR       | Auxiliary register (ARO and AR1 are predefined assembler symbols equal to 0 and 1, respectively.)  |

| ARP      | Auxiliary register pointer                                                                         |

| D D      | Data memory address field                                                                          |

| DATn     | Label assigned to data memory location n                                                           |

| dma      | Data memory address                                                                                |

| DP       | Data page pointer                                                                                  |

| I        | Addressing mode bit                                                                                |

| INTM     | Interrupt mode flag bit                                                                            |

| К        | Immediate operand field                                                                            |

| °<br>≥nn | Indicates nn is a hexadecimal number. All others are assumed to be decimal values.                 |

| OVM      | Overflow (saturation) mode flag bit                                                                |

| Р        | Product (P) register                                                                               |

| ΡΑ       | Port address (PA0 through PA7 are predefined assembler symbols equal to 0 through 7, respectively) |

| PC       | Program counter                                                                                    |

| pma      | Program memory address                                                                             |

| PRGn     | Label assigned to program memory location n                                                        |

| R        | 1-bit operand field specifying auxiliary register                                                  |

| S        | 4-bit left-shift code                                                                              |

| Т        | T register                                                                                         |

| TOS      | Top of stack                                                                                       |

| X        | 3-bit accumulator left-shift field                                                                 |

| <b>→</b> | Is assigned to                                                                                     |

|          | Indicates an absolute value                                                                        |

| < >      | Items within angle brackets are defined by user.                                                   |

| []       | Items within brackets are optional.                                                                |

| ()       | Indicates "contents of"                                                                            |

| { }      | Items within braces are alternative items; one of them must be entered.                            |

| <>       | Angle brackets back-to-back indicate "not equal".                                                  |

|          | Blanks or spaces are significant.                                                                  |

Ŷ

## 3.4.2 Instruction Set Summary

The instruction set summary in the following table consists primarily of single-cycle single-word instructions. Only infrequently used branch and I/O instructions are multicycle.

|       |                                                                       | ACCU          | JMULAT       | OR I | NST | RU | СТІ | ON                | S   |    |               |   |              |     |   |   |    |   |               |

|-------|-----------------------------------------------------------------------|---------------|--------------|------|-----|----|-----|-------------------|-----|----|---------------|---|--------------|-----|---|---|----|---|---------------|

| MNEMO | NIC DESCRIPTION                                                       | NO.<br>CYCLES | NO.<br>WORDS |      |     |    |     | INS               | STR |    |               |   | EGIS         | STE | R |   |    |   |               |

|       |                                                                       |               |              | 15   | 14  | 13 | 12  | 11                | 10  | 9  | 8             | 7 | 6            | 5   | 4 | 3 | 2  | 1 | 0             |

| ABS   | Absolute value of accumulator                                         | 1             | 1            | 0    | 1   | 1  | 1   | 1                 | 1   | 1  | 1             | 1 | 0            | 0   | 0 | 1 | 0  | 0 | 0             |

| ADD   | Add to accumulator<br>with shift                                      | 1             | 1            | 0    | 0   | 0  | 0   | <                 | - S |    | $\rightarrow$ | I | $\leftarrow$ |     |   | D |    |   | $\rightarrow$ |

| ADDH  | Add to high-order<br>accumulator bits                                 | 1             | 1            | 0    | 1   | 1  | 0   | 0                 | 0   | 0  | 0             | ١ | ~            |     |   | D |    |   | $\rightarrow$ |

| ADDS  | Add to accumulator<br>with no sign extension                          | 1             | 1            | 0    | 1   | 1  | 0   | 0                 | 0   | 0  | 1             | I | ←            |     |   | D |    |   | $\rightarrow$ |

| AND   | AND with accumulator                                                  | 1             | 1            | 0    | 1   | 1  | 1   | 1                 | 0   | 0  | 1             | Т | $\leftarrow$ |     |   | D |    |   | $\rightarrow$ |

| LAC   | Load accumulator with shift                                           | 1             | 1            | 0    | 0   | 1  |     | 1                 | - S |    |               | 1 |              |     |   | D |    |   | $\rightarrow$ |

| LACK  | Load accumulator<br>immediate                                         | 1             | 1            | 0    | 1   | 1  | 1   | 1                 | 1   | 1  | 0             | < |              |     |   | K |    |   | $\rightarrow$ |

| OR    | OR with accumulator                                                   | 1             | 1            | 0    | 1   | 1  | 1   | 1                 | 0   | 1  | 0             | T | $\leftarrow$ |     |   | D |    |   | $\rightarrow$ |

| SACH  | Store high-order<br>accumulator bits with<br>shift                    | 1             | 1            | 0    | 1   | 0  | 1   | 1                 | ¢   | ×X | $\rightarrow$ | 1 | <            |     |   | D |    |   | $\rightarrow$ |

| SACL  | Store low-order<br>accumulator bits                                   | 1             | 1            | 0    | 1   | 0  | 1   | 0                 | 0   | 0  | 0             | 1 | ~            |     |   | D |    |   | $\rightarrow$ |

| SUB   | Subtract from<br>accumulator with<br>shift                            | 1             | 1            | 0    | 0   | 0  | 1   | ` <del>&lt;</del> | - S |    | $\rightarrow$ | Ι | ÷            |     |   | D |    |   | $\rightarrow$ |

| SUBC  | Conditional subtract<br>(for divide)                                  | 1             | 1            | 0    | 1   | 1  | 0   | 0                 | 1   | 0  | 0             | I | ~            |     |   | D |    |   | $\rightarrow$ |

| SUBH  | Subtract from high-<br>order accumulator bits                         | 1             | 1            | 0    | 1   | 1  | 0   | 0                 | 0   | 1  | 0             | I | $\leftarrow$ |     |   | D |    |   | $\rightarrow$ |

| SUBS  | Subtract from accumu-<br>lator with no sign<br>extension              | 1             | 1            | 0    | 1   | 1  | 0   | 0                 | 0   | 1  | 1             | l | ~            |     |   | D |    |   | $\rightarrow$ |

| XOR   | Exclusive OR with accumulator                                         | 1             | 1            | 0    | 1   | 1  | 1   | 1                 | 0   | 0  | 0             | I | <            |     |   | D | ia |   | $\rightarrow$ |

| ZAC   | Zero accumulator                                                      | 1             | 1            | 0    |     | 1  | 1   | 1                 | 1   | 1  | 1             | 1 | 0            | 0   | 0 | 1 | 0  | 0 | 1             |

| ZALH  | Zero accumulator and load high-order bits                             | 1             | 1            | 0    | 1   | 1  | 0   | 0                 | 1   | 0  | 1             | I | ~            |     |   | D |    |   | $\rightarrow$ |

| ZALS  | Zero accumulator and<br>load low-order bits<br>with no sign extension | 1             | 1            | 0    | 1   | 1  | 0   | 0                 | 1   | 1  | 0             | ١ | ~            |     |   | D |    |   | $\rightarrow$ |

#### TABLE 3-2 - INSTRUCTION SET SUMMARY

|       |                                                 | NIC           | NIC          |        |        |         |        |               |     | ~. | 200        |            |              |          |          |         |         |   |               |

|-------|-------------------------------------------------|---------------|--------------|--------|--------|---------|--------|---------------|-----|----|------------|------------|--------------|----------|----------|---------|---------|---|---------------|

| MNEMC | ONIC DESCRIPTION                                | NO.<br>CYCLES | NO.<br>WORDS |        | 2      |         |        | INS           | STR |    | PCO<br>101 |            | GI           | STE      | R        |         |         |   |               |

|       |                                                 |               |              | 15     | 14     | 13      | 12     | 11            | 10  | 9  | 8          | 7          | 6            | 5        | 4        | 3       | 2       | 1 | (             |

| LAR   | Load auxiliary<br>register                      | 1             | 1            | 0      | 0      | 1       | 1      | 1             | 0   | 0  | R          | ł          | ~            |          |          | D       |         |   | $\rightarrow$ |

| LARK  | Load auxiliary<br>register immediate            | 1             | 1            | 0      | 1      | 1       | 1      | 0             | 0   | 0  | R          | $\epsilon$ |              | · · ·    |          | к       |         |   | $\rightarrow$ |

| LARP  | Load auxiliary<br>register pointer<br>immediate | 1             | 1            | 0      | 1      | 1       | 0      | 1             | 0   | 0  | 0          | 1          | 0            | 0        | 0        | 0       | 0       | 0 | l             |

| LDP   | Load data memory<br>page pointer                | 1             | 1            | 0      | 1      | 1       | 0      | 1             | 1   | 1  | 1          | 1.         | <            |          |          | D       |         |   |               |

| LDPK  | Load data memory<br>page pointer<br>immediate   | 1             | 1            | 0      | 1      | 1       | 0      | 1             | 1   | 1  | 0          | 0          | 0            | 0        | 0        | 0       | 0       | 0 | I             |

| MAR   | Modify auxiliary<br>register and pointer        | · 1           | 1            | 0      | 1      | 1       | 0      | 1             | 0   | 0  | 0          | I          | $\leftarrow$ |          |          | D       |         |   | ->            |

| SAR   | Store auxiliary<br>register                     | 1             | 1            | 0      | 0      | 1       | 1      | 0             | 0   | 0  | R          | 1          | <            |          |          | D       |         |   | ->            |

|       |                                                 | В             | RANCH I      | NST    | RU     | сті     | ON     | S             |     |    |            |            |              |          |          |         | 1.1.1.1 |   |               |

| MNEMC | ONIC DESCRIPTION                                | NO.<br>CYCLES | NO.<br>WORDS |        |        |         |        | INS           | STR |    |            |            | GI           | STE      | R        |         |         |   |               |

|       |                                                 |               |              | 15     | 14     | 13      | 12     | 11            | 10  | 9  | 8          | 7          | 6            | 5        | 4        | 3       | 2       | 1 |               |

| В     | Branch unconditionally                          | 2             | 2            | 1<br>0 | 1<br>0 | 1<br>0  | 1<br>0 | 1<br>←        | 0   | 0  | 1<br>BR    | 0<br>AN    | 0<br>CH      | 0<br>AD[ | 0<br>DRE | 0<br>SS | 0       | 0 |               |

| BANZ  | Branch on auxiliary register not zero           | 2             | 2            | 1<br>0 | 1<br>0 | 1<br>0  | 1<br>0 | 0<br><i>←</i> | 1   | 0  | 0<br>BR    | 0<br>AN    | 0<br>CH      | 0<br>ADI | 0<br>DRE | 0<br>SS | 0       | 0 |               |

| BGEZ  | Branch if accumulator $\geqslant 0$             | 2             | 2            | 1<br>0 | 1<br>0 | 1<br>.0 | 1<br>0 | 1<br>←        | 1   | 0  | 1<br>BR    | 0<br>AN    | 0<br>СН      | 0<br>ADI | 0<br>DRE | 0<br>SS | 0       | 0 |               |

| BGZ   | Branch if accumulator $>$ 0                     | 2             | 2            | 1<br>0 | 1<br>0 | 1<br>0  | 1<br>0 | , 1<br>←      | 1   | 0  | 0<br>BR    | 0<br>ANI   | 0<br>CH      | 0<br>AD[ | 0<br>DRE | 0<br>SS | 0       | 0 |               |

| BIOZ  | Branch on $\overline{BIO} = 0$                  | 2             | 2            | 1<br>0 | 1<br>0 | 1<br>0  | 1<br>0 | 0<br>←        | 1   | 1  | 0<br>BR    | 0<br>AN    | 0<br>CH      | 0<br>AD[ | 0<br>DRE | 0<br>SS | 0       | 0 |               |

| BLEZ  | Branch if accumulator $\leqslant 0$             | 2             | 2            | 1<br>0 | 1<br>0 | 1<br>0  | 1<br>0 | 1<br>←        | -   | 1  | 1<br>BR    | 0<br>AN    | 0<br>CH      | 0<br>AD[ | 0<br>DRE | 0<br>SS | 0       | 0 |               |

| BLZ   | Branch if accumulator < 0                       | 2             | 2            | 1<br>0 | 1<br>0 | 1<br>0  | 1<br>0 | 1<br>←        | 0   | 1  | 0<br>BR    | 0<br>AN    | 0<br>CH      | 0<br>AD[ | 0<br>DRE |         | 0       | 0 | (             |

| BNZ   | Branch if accumulator<br>≠ 0                    | 2             | 2            | 1<br>0 | 1<br>0 | 1<br>0  | 1<br>0 | 1<br>←        | 1   | 1  | 0<br>BR    | 0<br>AN    |              | 0<br>ADI |          | 0<br>SS | 0       | 0 | (             |

| BV    | Branch on overflow                              | 2             | 2            | 1<br>0 | 1<br>0 | 1<br>0  | 1<br>0 | 0<br>←        | 1   | 0  | 1<br>BR    | 0<br>AN    | 0<br>CH      | 0<br>ADI | 0<br>DRE | 0<br>SS | 0       | 0 |               |

| BZ    | Branch if accumulator<br>= 0                    | 2             | 2            | 1<br>0 | 1<br>0 | 1<br>0  | 1<br>0 | 1<br>←        | 1   | 1  | 1<br>BR    | 0<br>AN    | 0<br>CH      | 0<br>AD[ | 0<br>DRE | 0<br>SS | 0       | 0 |               |

| CALA  | Call subroutine from                            | 2             | 1            | 0      | 1      | 1       | 1      | 1             | 1   | 1  | 1          | 1          | 0            | 0        | 0        | 1       | 1       | 0 |               |

| CALL  | accumulator<br>Call subroutine                  | 2             | 2            |        |        |         |        |               |     |    |            |            |              |          | Λ        |         |         |   |               |

2

2

2

1

1 1 1 1

0 0 0 0

$\leftarrow$

1 0 0 0 0 0 0 0 0 0 0 0 BRANCH ADDRESS -

0 1 1 1 1 1 1 1 1 0 0 0 1 1 0 1

$\geq$

#### TABLE 3-2 - INSTRUCTION SET SUMMARY (CONTINUED)

CALL

RET

Call subroutine

Return from sub-

immediately

routine

| MNEMO | NIC DESCRIPTION                                                                    | NO.<br>CYCLES | NO.<br>WORDS |    |    |    |    | INS | STRU |   |   |   | GIS          | STE | R |     |   |   |               |

|-------|------------------------------------------------------------------------------------|---------------|--------------|----|----|----|----|-----|------|---|---|---|--------------|-----|---|-----|---|---|---------------|

|       |                                                                                    |               |              | 15 | 14 | 13 | 12 | 11  | 10   | 9 | 8 | 7 | 6            | 5   | 4 | 3   | 2 | 1 | С             |

| APAC  | Add P register to accumulator                                                      | 1             | 1            | 0  | 1  | 1  | 1  | 1   | 1    | 1 | 1 | 1 | 0            | 0   | 0 | 1   | 1 | 1 | 1             |

| LT    | Load T register                                                                    | 1             | 1            | 0  | 1  | 1  | 0  | 1   | 0    | 1 | 0 | 1 | $\leftarrow$ |     |   | D-  |   |   | $\rightarrow$ |

| LTA   | LTA combines LT and<br>APAC into one instruc-<br>tion                              | 1             | 1            | 0  | 1  | 1  | 0  | 1   | 1    | 0 | 0 | I | <            |     |   | D-  |   |   | $\rightarrow$ |

| LTD   | LTD combines LT,<br>APAC, and DMOV into<br>one instruction                         | 1             | 1            | 0  | 1  | 1  | 0  | 1   | 0    | 1 | 1 | I | ~            |     |   | D   |   |   | $\rightarrow$ |

| MPY   | Multiply with T<br>register; store product<br>in P register                        | 1             | 1            | 0  | 1  | 1  | 0  | 1   | 1    | 0 | 1 | 1 | <            |     |   | - D |   |   | $\rightarrow$ |

| МРҮК  | Multiply T register<br>with immediate oper-<br>and; store product in<br>P register | 1             | 1            | 1  | 0  | 0  | <  |     |      |   |   |   |              | K   |   |     |   |   | $\rightarrow$ |

| PAC   | Load accumulator from<br>P register                                                | 1             | 1            | 0  | 1  | 1  | 1  | 1   | 1    | 1 | 1 | 1 | 0            | 0   | 0 | 1   | 1 | 1 | (             |

| SPAC  | Subtract P register from accumulator                                               | 1             | 1            | 0  | 1  | 1  | 1  | 1   | 1    | 1 | 1 | 1 | 0            | 0   | 1 | 0   | 0 | 0 | (             |

#### TABLE 3-2 - INSTRUCTION SET SUMMARY (CONCLUDED)

|       |                                | C             | ONTROL       | INS | TRI | JCT | ION | IS  |     |   |   |    |              |     |   |   |   |   |               |

|-------|--------------------------------|---------------|--------------|-----|-----|-----|-----|-----|-----|---|---|----|--------------|-----|---|---|---|---|---------------|

| MNEMO | NIC DESCRIPTION                | NO.<br>CYCLES | NO.<br>WORDS |     |     |     |     | INS | STR | - |   |    | EGI          | STE | R |   |   |   |               |

|       |                                |               |              | 15  | 14  | 13  | 12  | 11  | 10  | 9 | 8 | 7  | 6            | 5   | 4 | 3 | 2 | 1 | 0             |

| DINT  | Disable interrupt              | 1             | 1            | 0   | 1   | 1   | 1   | 1   | 1   | 1 | 1 | 1  | 0            | 0   | 0 | 0 | 0 | 0 | 1             |

| EINT  | Enable interrupt               | 1             | 1            | 0   | 1   | 1   | 1   | 1   | 1   | 1 | 1 | 1  | 0            | 0   | 0 | 0 | 0 | 1 | 0             |

| LST   | Load status register           | 1             | 1            | 0   | 1   | 1   | 1   | 1   | 0   | 1 | 1 | I. | $\leftarrow$ |     |   | D |   |   | $\rightarrow$ |

| NOP   | No operation                   | 1             | 1            | 0   | 1   | 1   | 1   | 1   | 1   | 1 | 1 | 1  | 0            | 0   | 0 | 0 | 0 | 0 | 0             |

| POP   | Pop stack to accumulator       | 2             | 1            | 0   | 1   | 1   | 1   | 1   | 1   | 1 | 1 | 1  | 0            | 0   | 1 | 1 | 1 | 0 | 1             |

| PUSH  | Push stack from<br>accumulator | 2             | 1            | 0   | 1   | 1   | 1   | 1   | 1   | 1 | 1 | 1  | 0            | 0   | 1 | 1 | 1 | 0 | 0             |

| ROVM  | Reset overflow mode            | 1             | 1            | 0   | 1   | 1   | 1   | 1   | 1   | 1 | 1 | 1  | 0            | 0   | 0 | 1 | 0 | 1 | 0             |

| SOVM  | Set overflow mode              | 1             | 1            | 0   | 1   | 1   | 1   | 1   | 1   | 1 | 1 | 1  | 0            | 0   | 0 | 1 | 0 | 1 | 1             |

| SST   | Store status register          | 1             | 1            | 0   | 1   | 1   | 1   | 1   | 1   | 0 | 0 | ١  | <            |     |   | D |   |   | $\rightarrow$ |

#### I/O AND DATA MEMORY OPERATIONS

| MNEMO | NIC DESCRIPTION                                                | NO.<br>CYCLES | NO.<br>WORDS |    |    |    |    | INS | STR          | -   |               |    | EGIS         | STE | R |     |   |   |               |

|-------|----------------------------------------------------------------|---------------|--------------|----|----|----|----|-----|--------------|-----|---------------|----|--------------|-----|---|-----|---|---|---------------|

|       |                                                                |               |              | 15 | 14 | 13 | 12 | 11  | 10           | 9   | 8             | 7  | 6            | 5   | 4 | 3   | 2 | 1 | 0             |

| DMOV  | Copy contents of data<br>memory location into<br>next location | 1             | 1            | 0  | 1  | 1  | 0  | 1   | 0            | 0   | 1             |    | 4            |     |   | D   |   |   | >             |

| IN    | Input data from port                                           | 2             | 1            | 0  | 1  |    | 0  | 0   | $\leftarrow$ | -PA | $\rightarrow$ | 1  | $\leftarrow$ |     |   | D   |   |   | $\rightarrow$ |

| OUT   | Output data to port                                            | 2             | 1            | 0  | 1  | 0  | 0  | 1   | $\leftarrow$ | -PA | $\rightarrow$ | 1  | $\leftarrow$ |     |   | D   |   |   | $\rightarrow$ |

| TBLR  | Table read from<br>program memory to<br>data RAM               | 3             | 1            | 0  | 1  | 1  | 0  | 0   | 1            | 1   | 1             |    | <            |     |   | D   |   |   | <b>&gt;</b>   |

| TBLW  | Table write from<br>data RAM to program<br>memory              | 3             | 1            | 0  | 1  | 1  | 1  | 1   | 1            | 0   | 1             | 1. | <            |     |   | - D |   |   | >             |

#### 3.4.3 Instruction Descriptions

Each instruction in the instruction set summary is described in the following pages. The instructions are listed in alphabetical order. An example is provided with each instruction.

Each instruction begins with an assembler syntax expression. Since the comment field which concludes the syntax is optional, it is not included in the syntax expression. A syntax example is given below that shows the spaces that are included and required in the syntax expression, and the optional comment field along with its preceding spaces that has been omitted.

[<comment>] [<label>] LACK <constant> Spaces Spaces and comment field not included in the syntax expressions for this section.

| Assembler Syr | ntax: |               | [<         | labe  | >] | A  | BS |   |   |   |   |   |   |   |   |   |

|---------------|-------|---------------|------------|-------|----|----|----|---|---|---|---|---|---|---|---|---|

| Operands:     | Nor   | ne            |            |       |    |    |    |   |   |   |   |   |   |   |   |   |

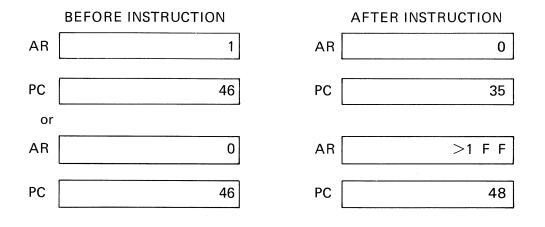

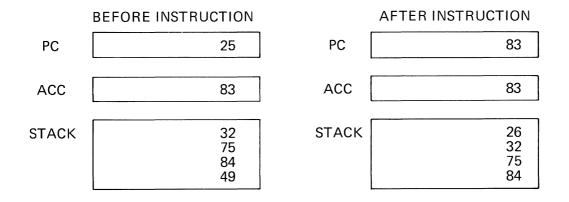

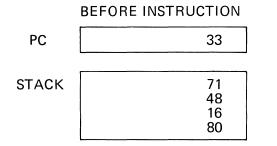

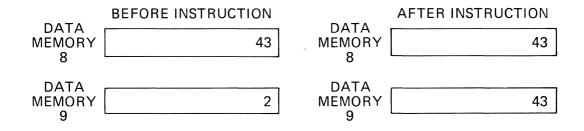

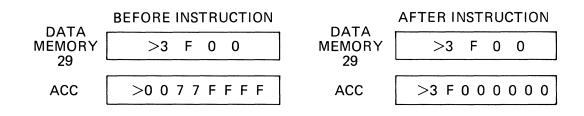

| Operation:    |       | ACC)<br>n — ( | < 0<br>ACC | ) → A | CC |    |    |   |   |   |   |   |   |   |   |   |