## DATA ACQUISITION IC HANDBOOK

## TELEDYNE SEMICONDUCTOR

## **TELEDYNE SEMICONDUCTOR**

1985 NOV 2 0

## DATA ACQUISITION IC HANDBOOK

1300 Terra Bella Avenue • P.O. Box 7267 • Mountain View, California USA 94039-7267 • Tel: 415/968-9241

Teledyne Semiconductor reserves the right to make changes in the circuitry or specifications detailed in this manual at any time without notice. Minimums and maximums are guaranteed. All other specifications are intended as guidelines only. Teledyne Semiconductor assumes no responsibility for the use of any circuits described herein and makes no representations that they are free from patent infringement.

Printed in USA/October 1985

## SECTION 1 Table of Contents

## 1986 Data and Design Manual

| Section 1<br>Table of Conte    | ents                                                                                           | 1-3          |

|--------------------------------|------------------------------------------------------------------------------------------------|--------------|

| Section 2<br>Ordering Infor    | mation/Package Drawings                                                                        | 2-3          |

| Section 3<br>Quality Assura    | nce Program                                                                                    | 3-3          |

| Section 4<br>Alphanumeric      | Product List                                                                                   | 4-3          |

| Section 5<br>Cross Referen     | ce Guide                                                                                       | 5-3          |

| Section 6                      |                                                                                                |              |

| Advance Produ                  | uct Information                                                                                | 6-3          |

| TSC04/05                       | Bandgap Voltage Reference                                                                      | 6-5          |

| TSC170/171                     | CMOS Current Mode SMPS Controller                                                              | 6-7          |

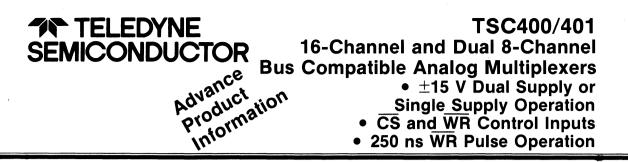

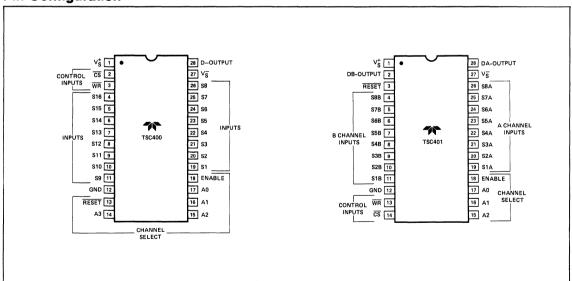

| TSC400/401<br>TSC429           | 16-Channel and Dual 8-Channel Bus Compatible Analog Multiplexers                               | 6-15<br>6-17 |

| TSC429                         | High Speed Single CMOS Power MOSFET Driver         μ-Processor Compatible CMOS Analog Switches | 6-19         |

| TSC444/445/446                 | $\mu$ -Processor Bus Compatible CMOS Quad Analog Switches                                      | 6-21         |

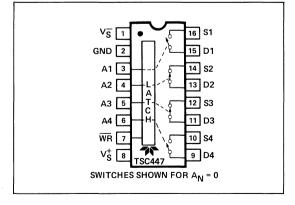

| TSC447                         | μ-Processor Compatible Quad CMOS Analog Switch                                                 | 6-23         |

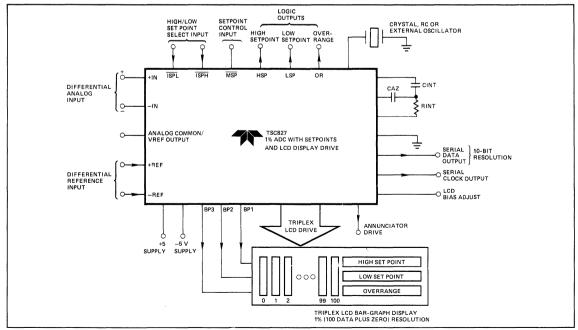

| TSC827                         | 1% ADC with LCD Bar-Graph Drive and Set Points                                                 | 6-25         |

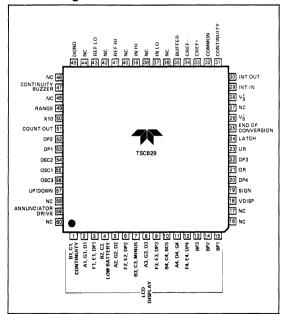

| TSC829                         | 4 1/2 Digit ADC with LCD Drive and Surface Mount Package                                       | 6-27         |

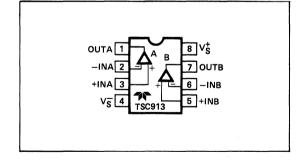

| TSC913                         | Dual Auto-Zeroed Operational Amplifier                                                         | 6-29         |

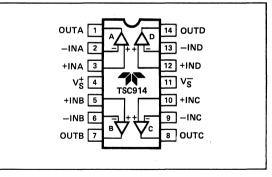

| TSC914                         | Quad Auto-Zeroed Operational Amplifier                                                         | 6-31         |

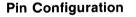

| TSC4201/4202/4203              | Low Cost CMOS Quad Analog Switches                                                             | 6-33         |

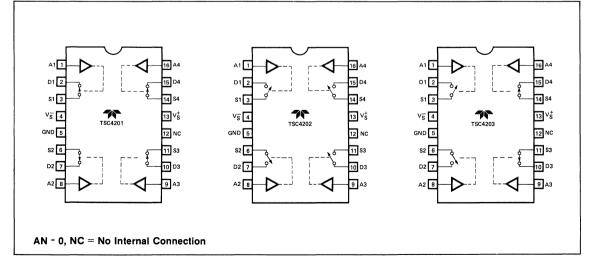

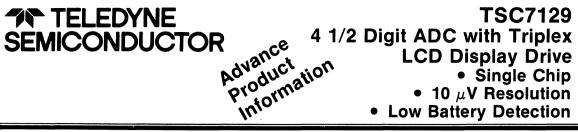

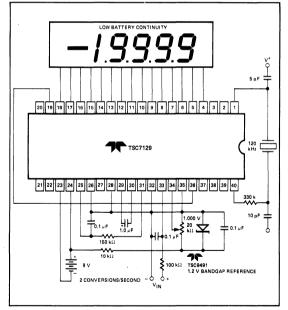

| TSC7129                        | 4 1/2 Digit ADC with Triplex LCD Display Drive                                                 | 6-35         |

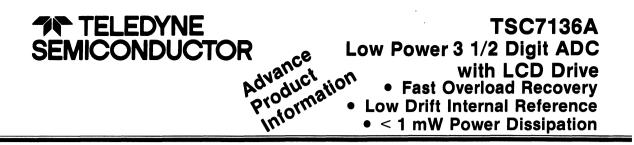

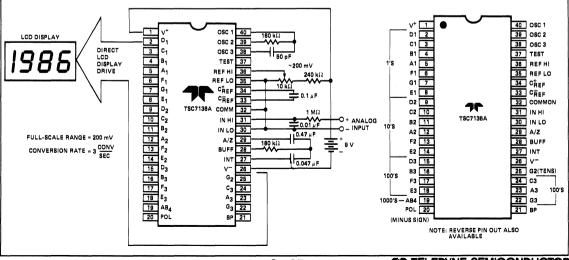

| TSC7136A                       | Low Power 3 1/2 Digit ADC with LCD Drive                                                       | 6-37         |

| Section 7                      |                                                                                                |              |

| • •                            | onverters                                                                                      | 7-3          |

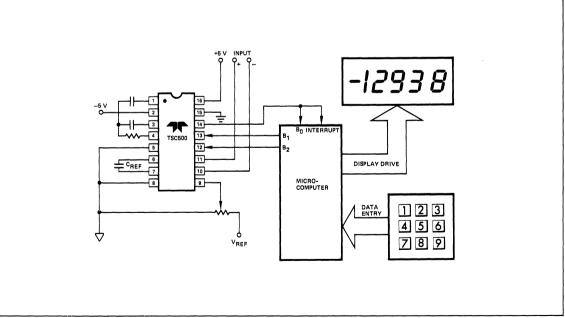

| TSC500                         | Analog Processor for Microprocessor-Based A/D Converters                                       | 7-5          |

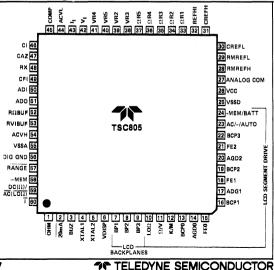

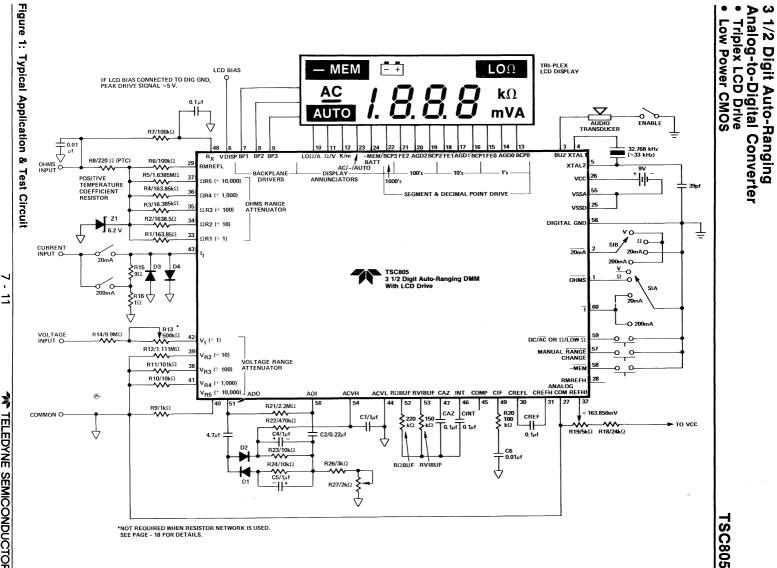

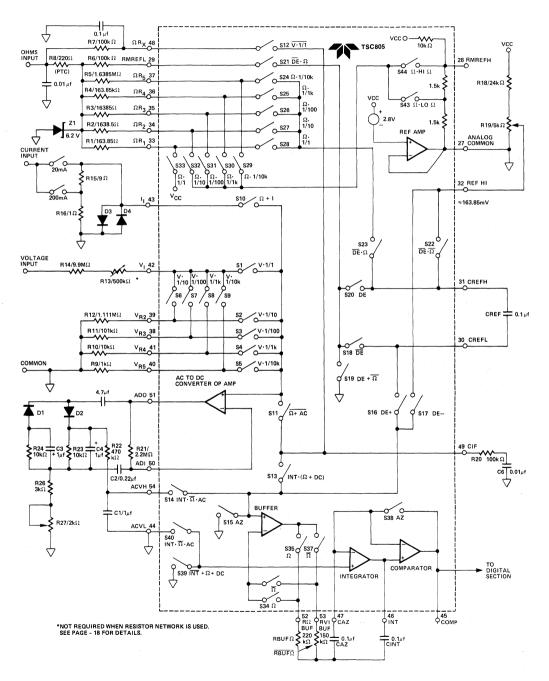

| TSC805                         | 3 1/2 Digit Auto-Ranging A/D Converter                                                         | 7-7          |

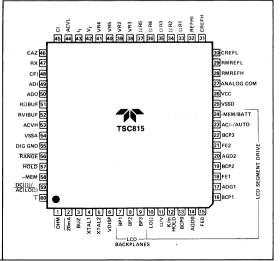

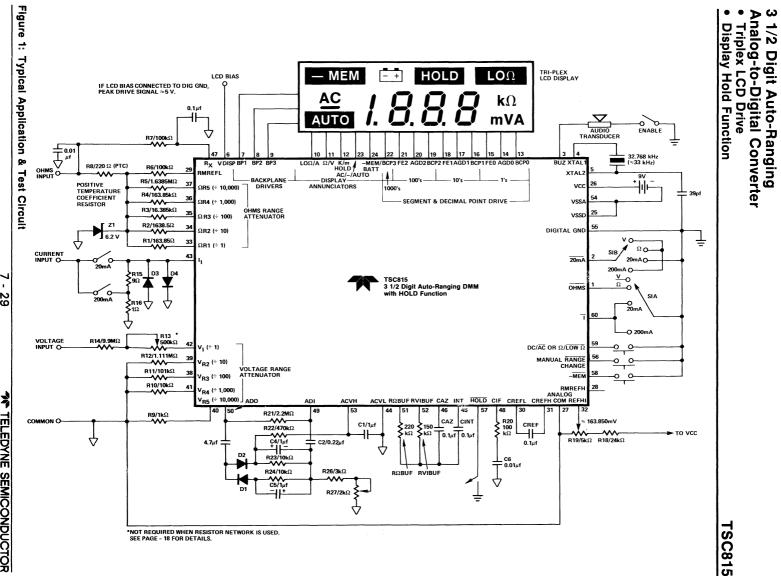

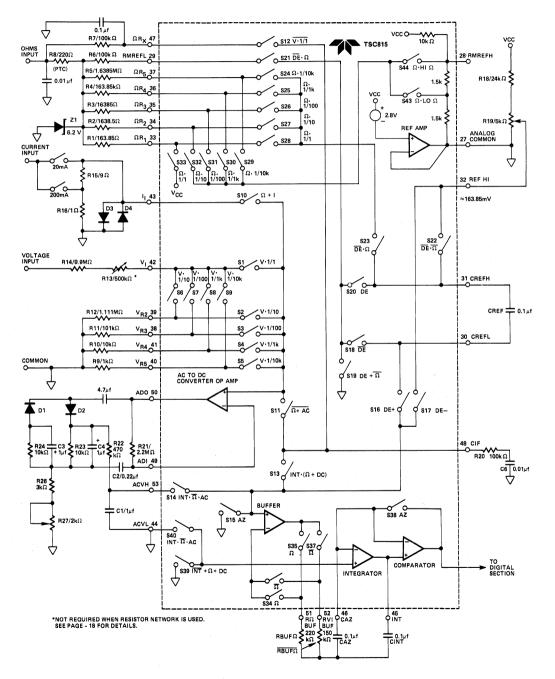

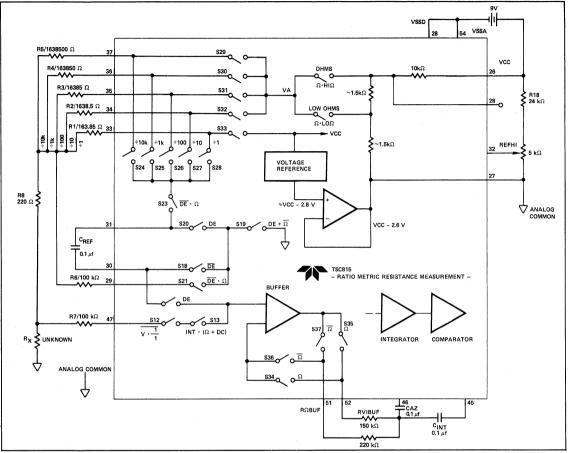

| TSC815                         | 3 1/2 Digit Auto-Ranging A/D Converter with Display Hold                                       | 7-25         |

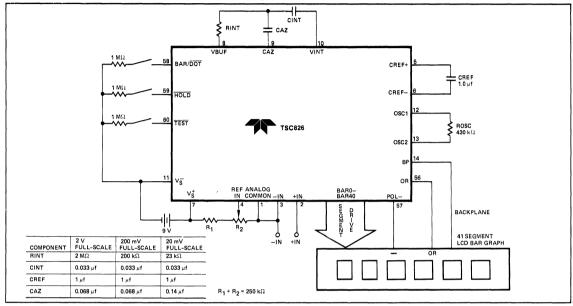

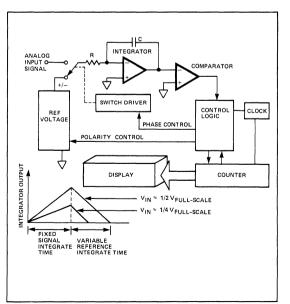

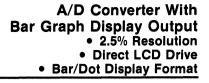

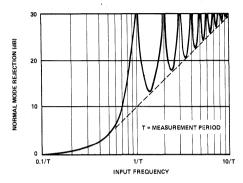

| TSC826                         | A/D Converter with Bar-Graph Display Output                                                    | 7-43<br>7-55 |

| TSC7106A/7107A<br>TSC7106/7107 | 3 1/2 Digit A/D Converter with Low Drift Reference                                             | 7-55         |

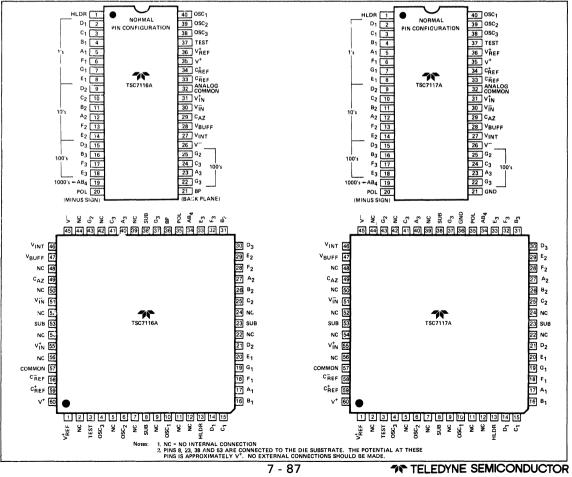

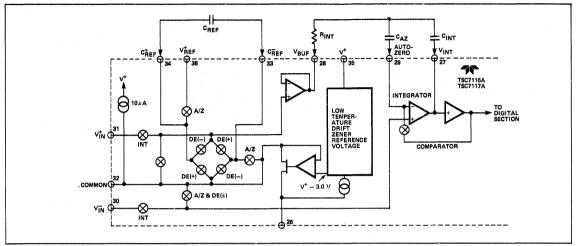

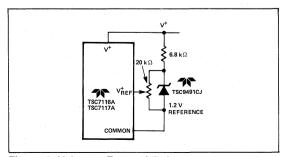

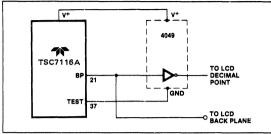

| TSC7116A/7117A                 | 3 1/2 Digit A/D Converter with Low Drift Reference and Display Hold                            | 7-85         |

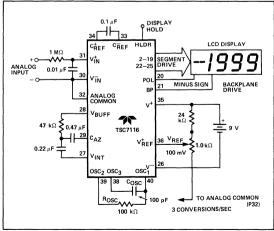

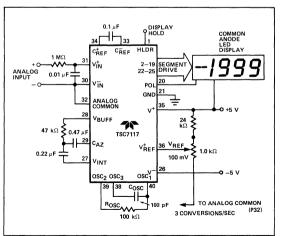

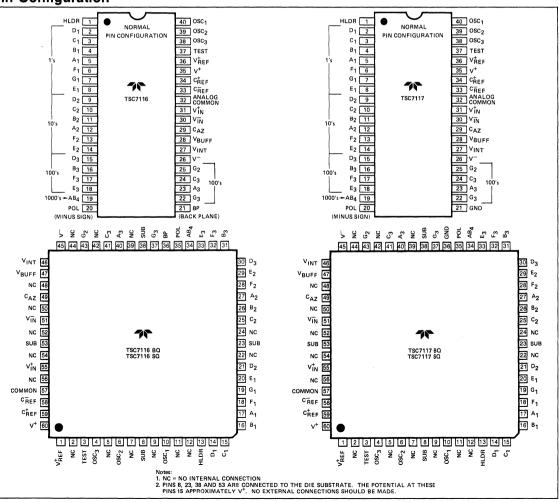

| TSC7116/7117                   | 3 1/2 Digit A/D Converter with Display Hold                                                    | 7-97         |

| TSC7126A                       | Low Power 3 1/2 Digit A/D Converter with Low Drift Reference                                   | 7-109        |

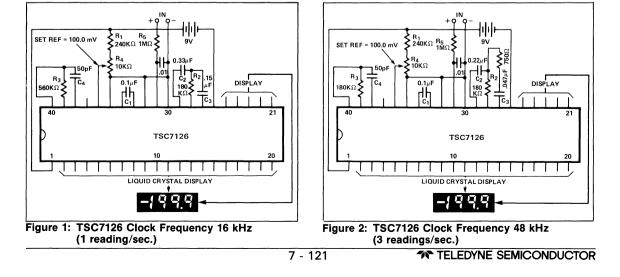

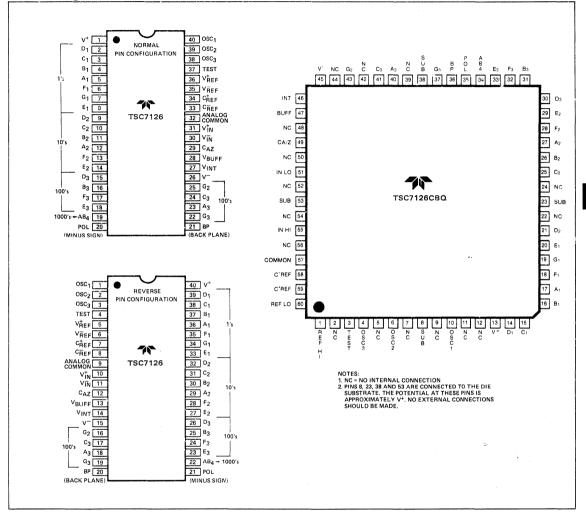

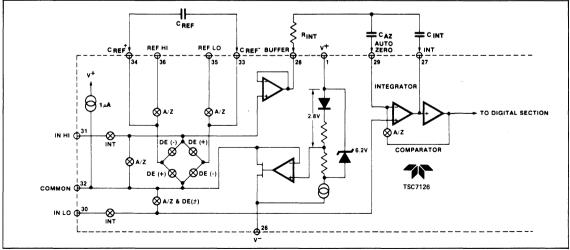

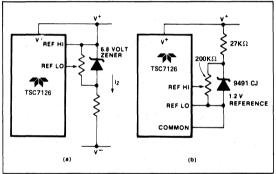

| TSC7126                        | Low Power 3 1/2 Digit A/D Converter                                                            | 7-121        |

| TSC7135                        | 4 1/2 Digit Precision A/D Converter with BCD Output                                            | 7-133        |

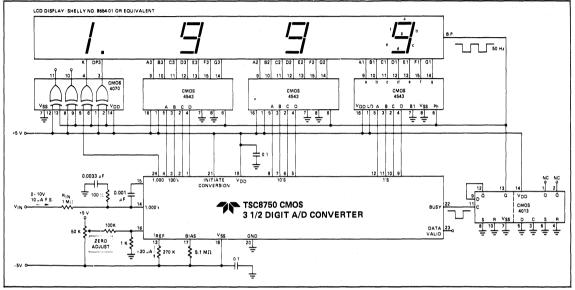

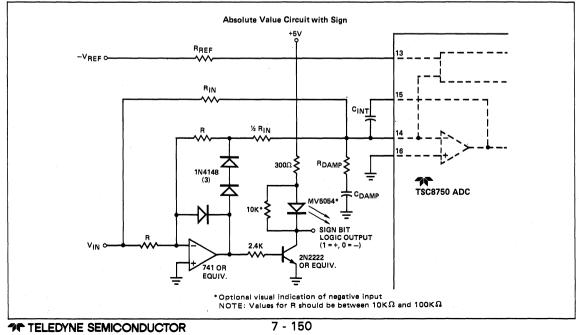

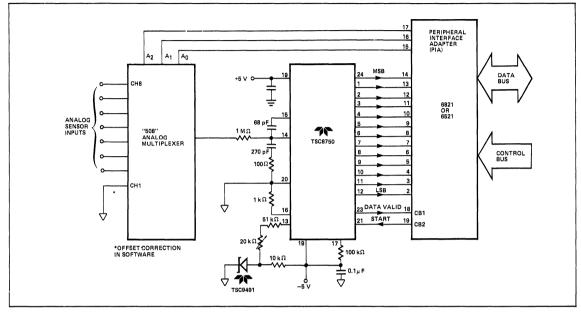

| TSC8750                        | 3 1/2 Digit ADC with Parallel BCD Output                                                       | 7-145        |

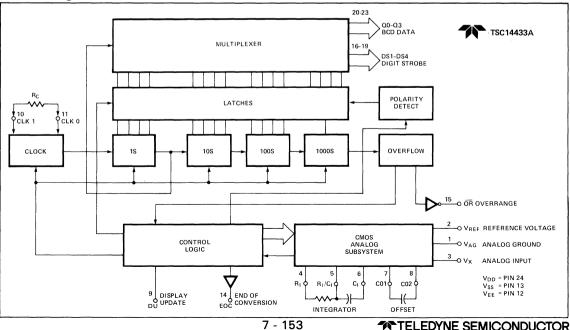

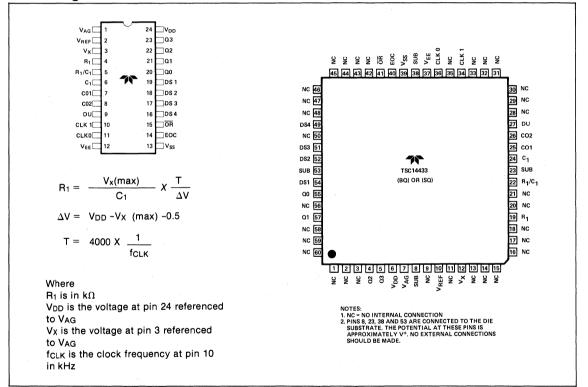

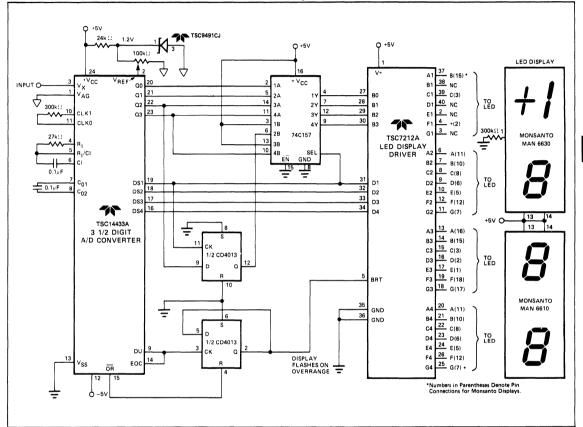

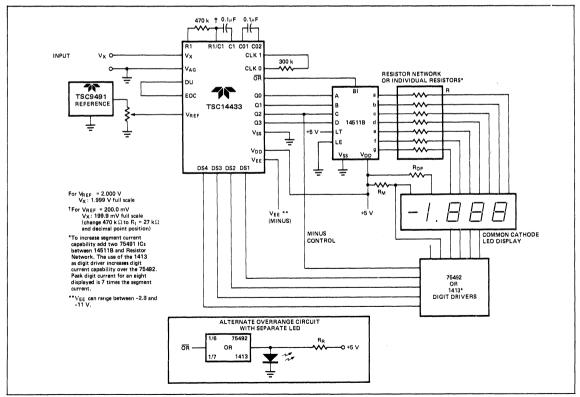

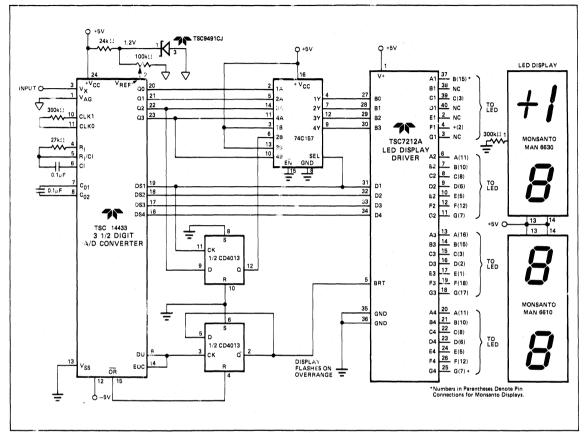

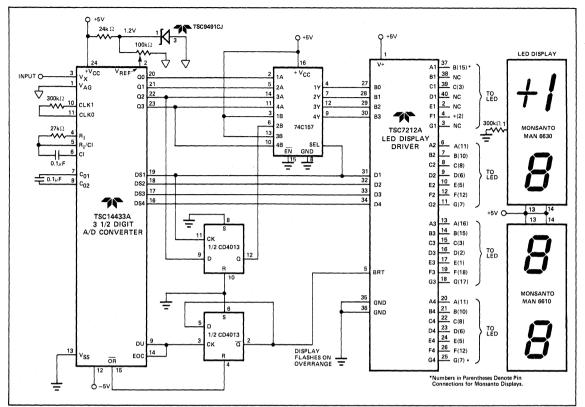

| TSC14433A                      | Precision 3 1/2 Digit ADC with Multiplexed BCD Output                                          | 7-153        |

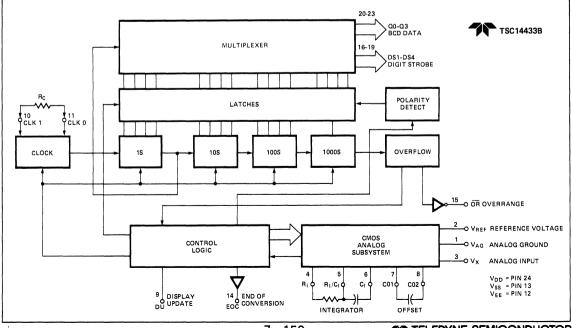

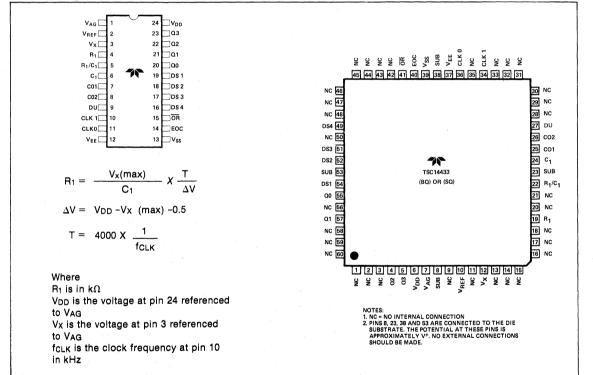

| TSC14433B                      | Low Cost 3 1/2 Digit ADC with Multiplexed BCD Output                                           | 7-159        |

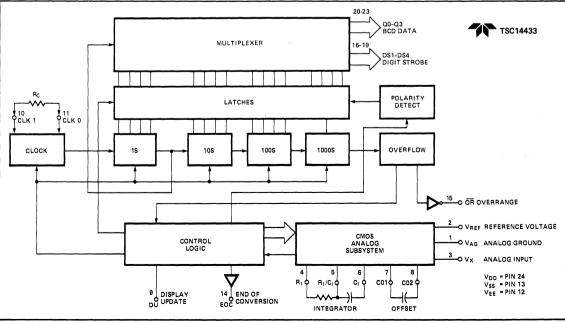

| TSC14433                       | 3 1/2 Digit ADC with Multiplexed BCD Output                                                    | 7-165        |

1

~

### Section 8

| Binary A/D Co    | nverters                                   | 8-3  |

|------------------|--------------------------------------------|------|

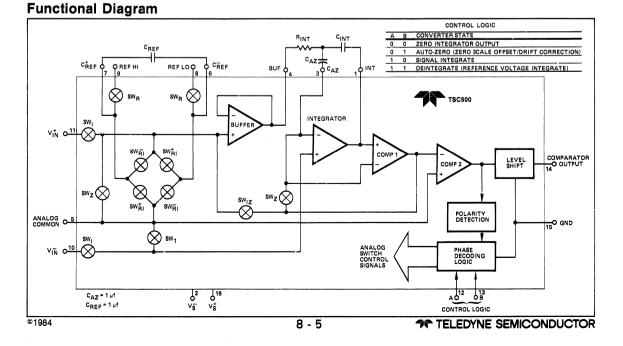

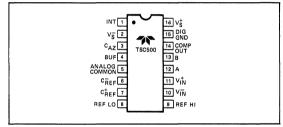

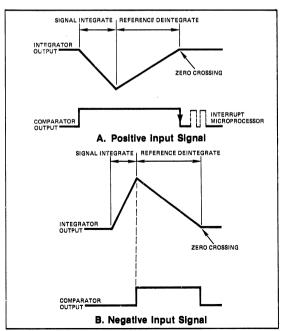

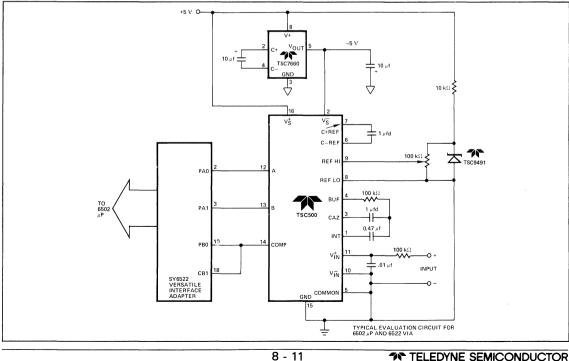

| TSC500           | Integrating Converter Analog Processor     | 8-5  |

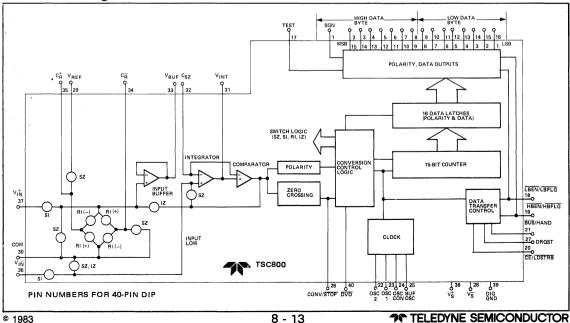

| TSC800           | 15-Bit Plus Sign Integrating A/D Converter | 8-13 |

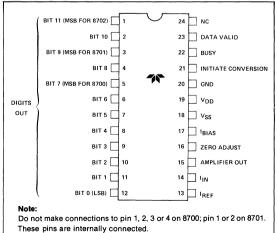

| TSC7109          | 12-Bit Plus Sign Integrating A/D Converter | 8-29 |

| TSC8700 (8-Bit)  | Binary Output ADC                          | 8-49 |

| TSC8701 (10-Bit) | Binary Output ADC                          | 8-49 |

| TSC8702 (12-Bit) | Binary Output ADC                          | 8-49 |

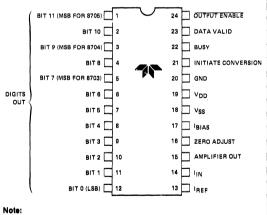

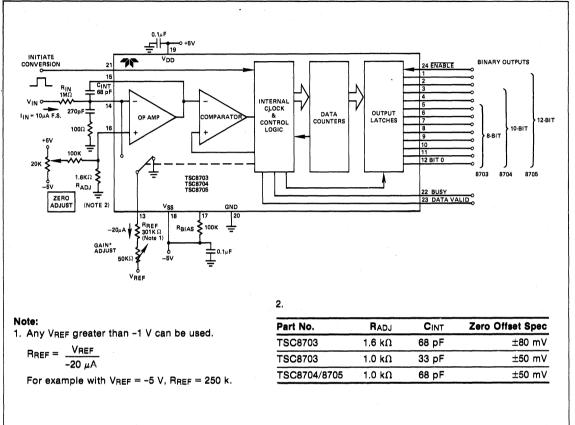

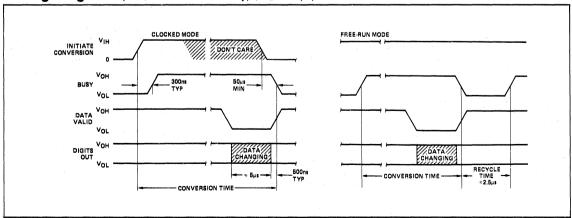

| TSC8703 (8-Bit)  | Three State Binary Output ADC              | 8-61 |

| TSC8704 (10-Bit) | Three State Binary Output ADC              | 8-61 |

| TSC8705 (12-Bit) | Three State Binary Output ADC              | 8-61 |

|                  |                                            |      |

#### Section 9

| Voltage to | Frequency/Frequency to Voltage         | Converters | 9-3 |

|------------|----------------------------------------|------------|-----|

| TSC9400    | Voltage to Frequency (0.05% Linearity) | ·          | 9-5 |

| TSC9401    | Voltage to Frequency (0.01% Linearity) |            | 9-5 |

| TSC9402    | Voltage to Frequency (0.25% Linearity) |            | 9-5 |

#### Section 10 Display Drivers

| <b>Display Drivers</b> | 3                                                 | 10-3  |

|------------------------|---------------------------------------------------|-------|

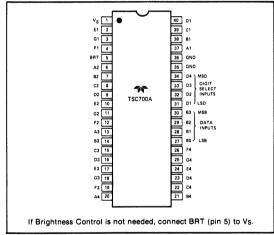

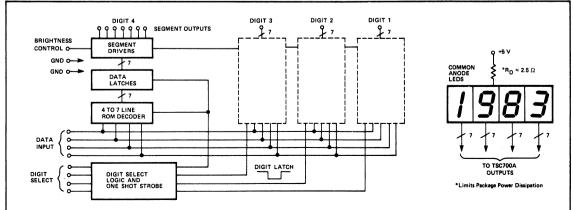

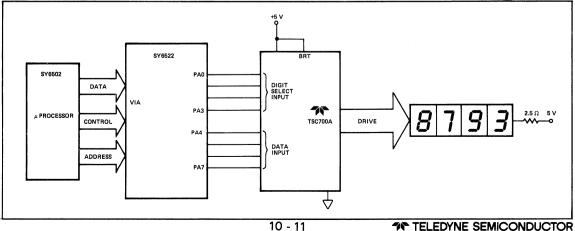

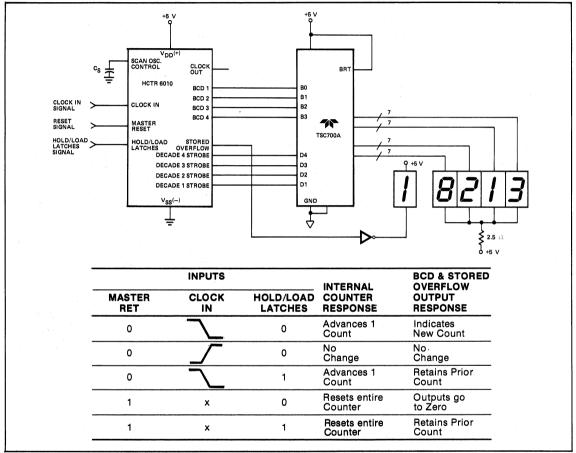

| TSC700A                | High Current Four Digit LED Driver                | 10-5  |

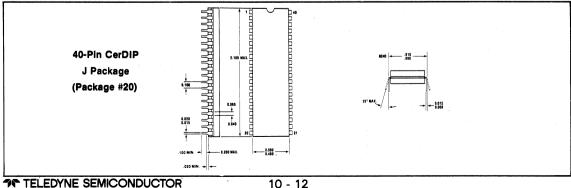

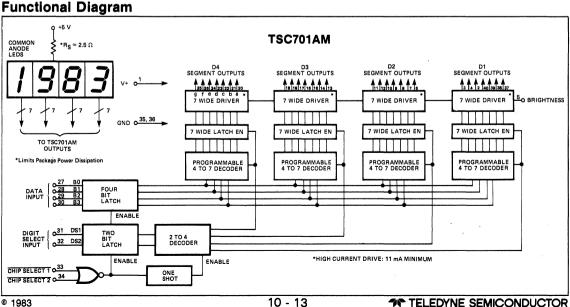

| TSC701AM               | High Current Bus Compatible Four Digit LED Driver | 10-13 |

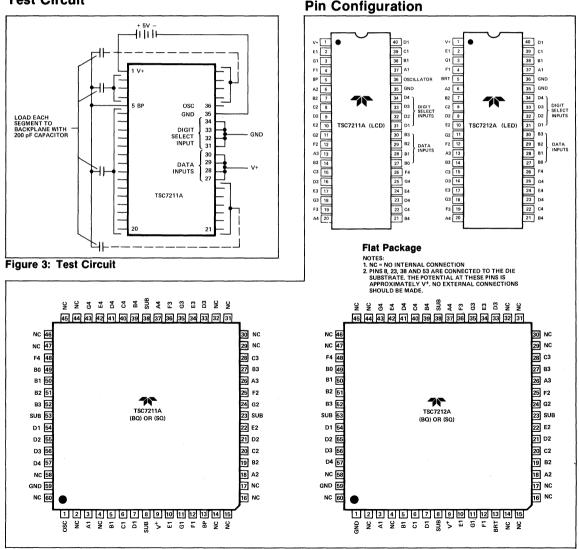

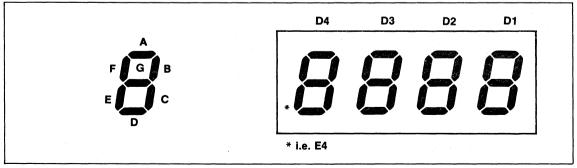

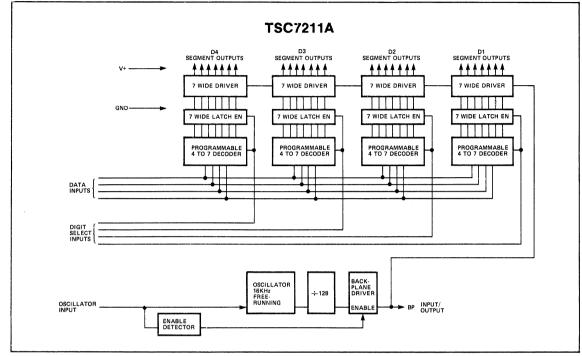

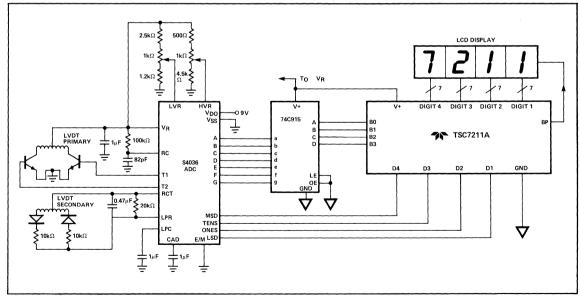

| TSC7211A               | Four Digit LCD Driver                             | 10-21 |

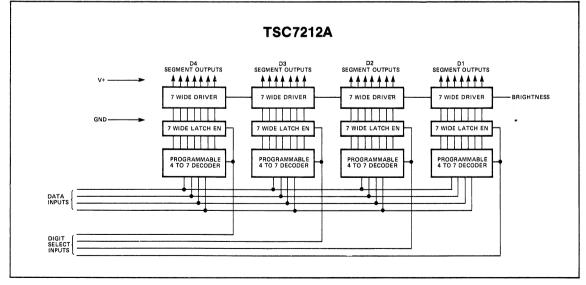

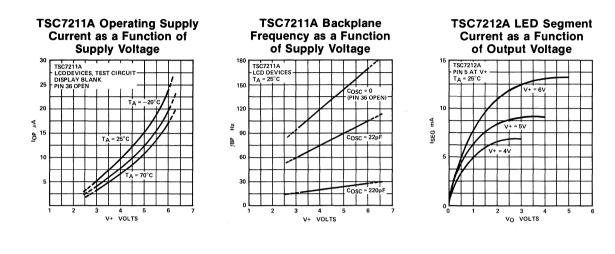

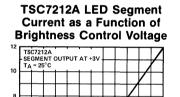

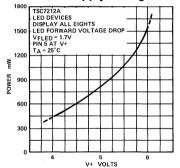

| TSC7212A               | Four Digit LED Driver                             | 10-21 |

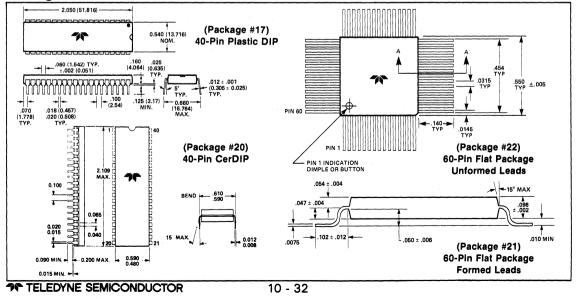

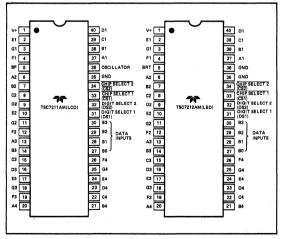

| TSC7211AM              | Bus Compatible Four Digit LCD Driver              | 10-33 |

| TSC7212AM              | Bus Compatible Four Digit LED Driver              | 10-33 |

#### Section 11 Interface ICa

| •••••••••••••••••••••••••••••••••••••••                      | 11-3                                                                                                                                                          |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dual High Speed Power MOSFET Driver                          | 11-5                                                                                                                                                          |

| Dual Power MOSFET Driver                                     | 11-15                                                                                                                                                         |

| DC to DC Voltage Converter                                   | 11-19                                                                                                                                                         |

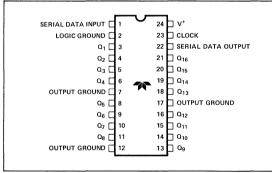

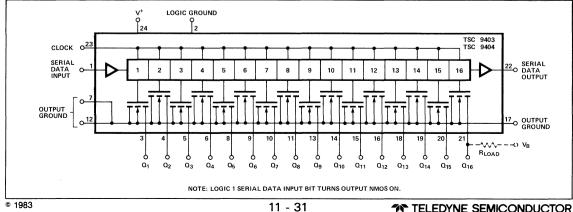

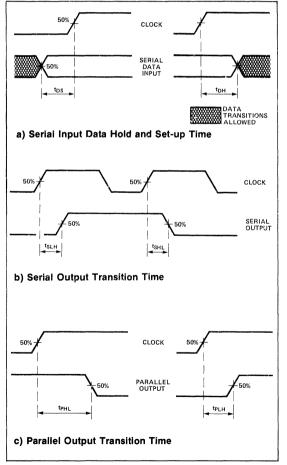

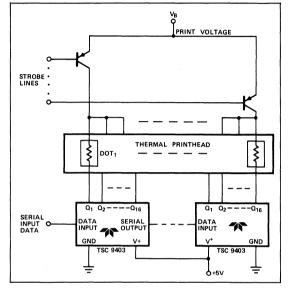

| Serial Input/16-Bit Parallel Output Peripheral Driver (20 V) | 11-31                                                                                                                                                         |

| Serial Input/16-Bit Parallel Output Peripheral Driver (15 V) | 11-31                                                                                                                                                         |

|                                                              | Dual High Speed Power MOSFET Driver<br>Dual Power MOSFET Driver<br>DC to DC Voltage Converter<br>Serial Input/16-Bit Parallel Output Peripheral Driver (20 V) |

#### Section 12

| References . |                                                       | 12-3  |

|--------------|-------------------------------------------------------|-------|

| TSC9491      | 1.22 V Bandgap Voltage Reference                      | 12-5  |

| TSC9495      | +5 V Bandgap Voltage Reference/Temperature Transducer | 12-7  |

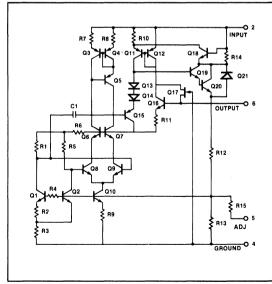

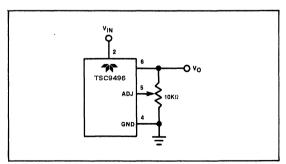

| TSC9496      | +10 V Bandgap Voltage Reference                       | 12-11 |

#### Section 13

| Operational Amplifiers |                                                    | 13-3  |

|------------------------|----------------------------------------------------|-------|

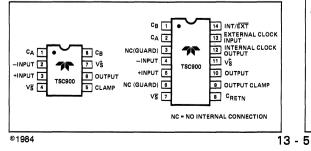

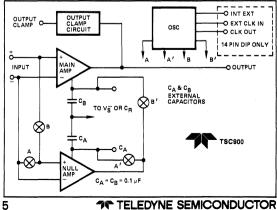

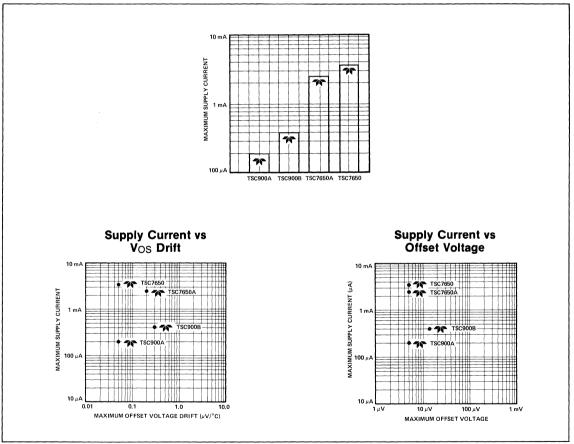

| TSC900                 | Low Power Chopper-Stabilized Operational Amplifier | 13-5  |

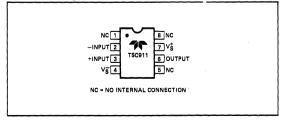

| TSC911                 | Auto-Zeroed Monolithic Operational Amplifier       | 13-13 |

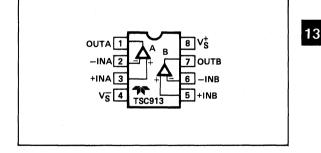

| TSC913                 | Dual Auto-Zeroed Operational Amplifier             | 13-21 |

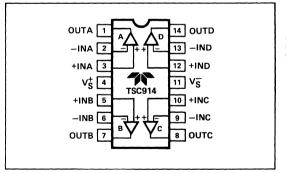

| TSC914                 | Quad Auto-Zeroed Operational Amplifier             | 13-23 |

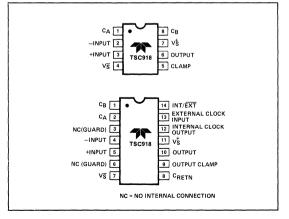

| TSC918                 | Low Cost Low Power Operational Amplifier           | 13-25 |

| TSC7650A               | Chopper-Stablilized Operational Amplifier          | 13-29 |

| TSC7650                | Precision Chopper-Stabilized Operational Amplifier | 13-37 |

1

| Section 14                                 |                                                                                 |                |

|--------------------------------------------|---------------------------------------------------------------------------------|----------------|

| Digital Logic                              |                                                                                 | 14-3           |

| 0 0                                        | Purpose of Bipolar Interface Logic                                              | 14-5           |

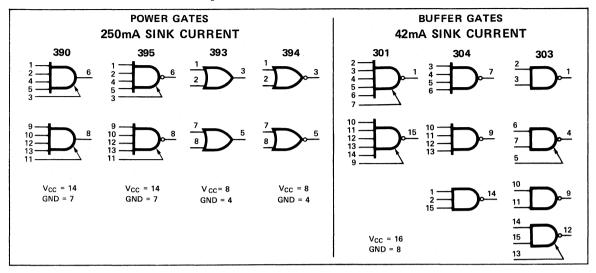

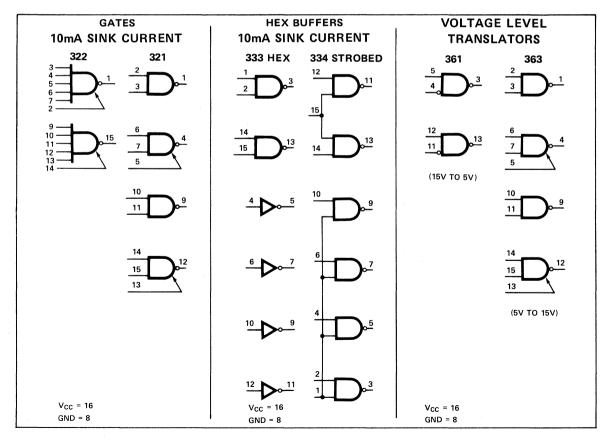

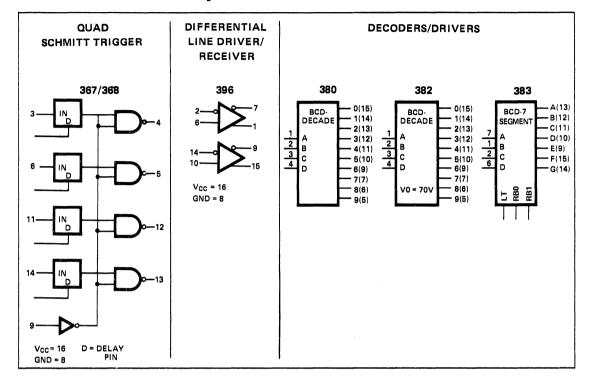

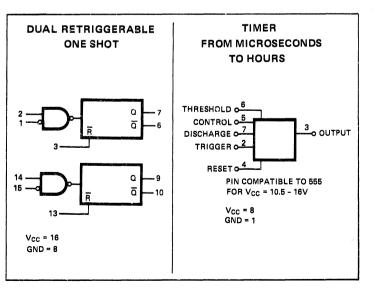

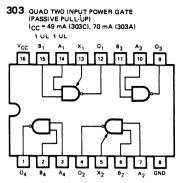

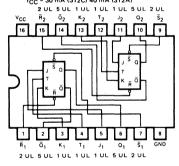

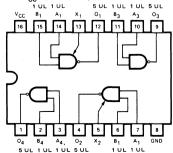

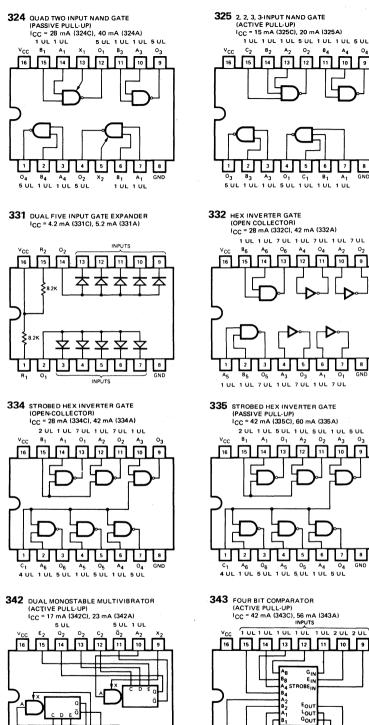

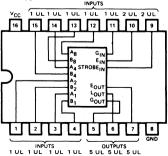

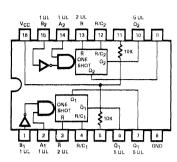

|                                            | Most Popular 300 Series Devices                                                 | 14-6           |

|                                            | Electrical Summary Data                                                         | 14-8           |

|                                            | Digital Logic — 300 Series Ordering Information                                 | 14-9           |

|                                            | Input Current Requirements                                                      | 14-10          |

|                                            | Output Sink Current vs Output Voltage                                           | 14-11          |

|                                            | Power Supply Current and Delay Times                                            | 14-12          |

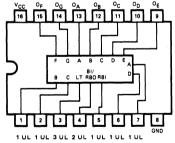

|                                            | Pin-Out Guide                                                                   | 14-13          |

| Section 15                                 |                                                                                 |                |

| Application No                             | tes                                                                             | 15-3           |

| ••                                         |                                                                                 |                |

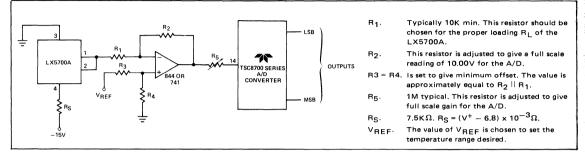

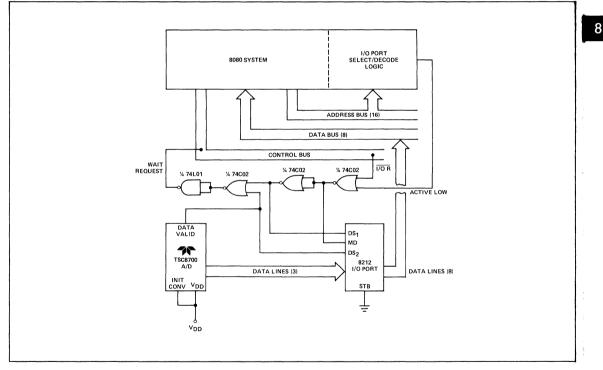

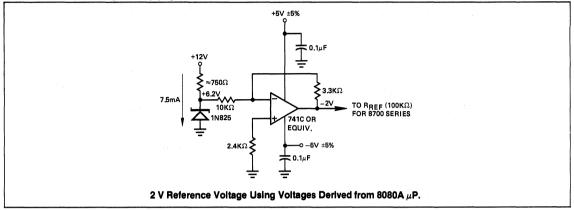

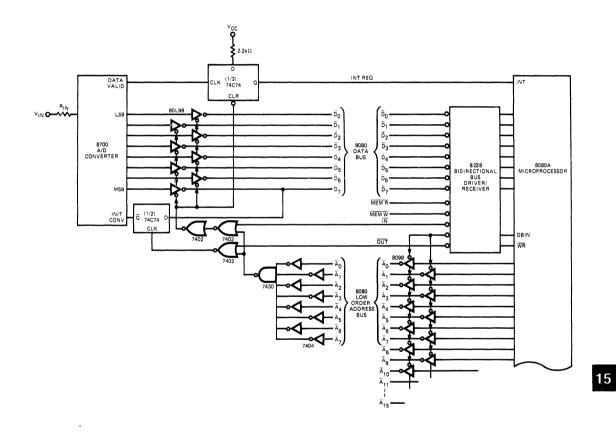

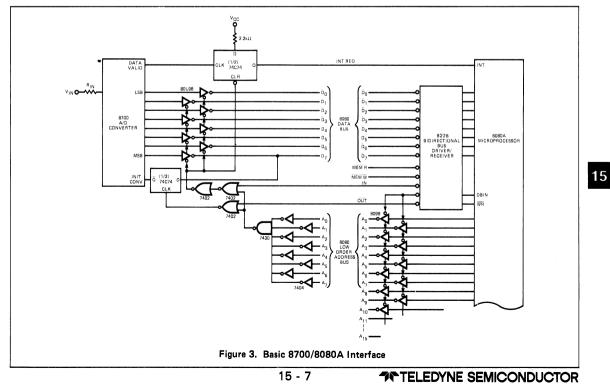

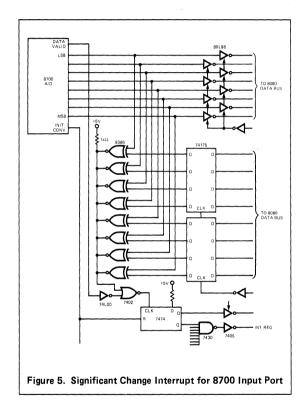

| Application Note 8                         | Interfacing the TSC8700 A/D with the 8080 µP System                             | 15-5           |

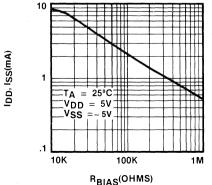

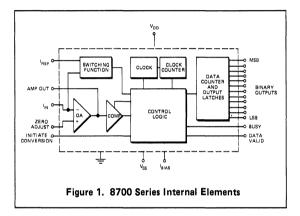

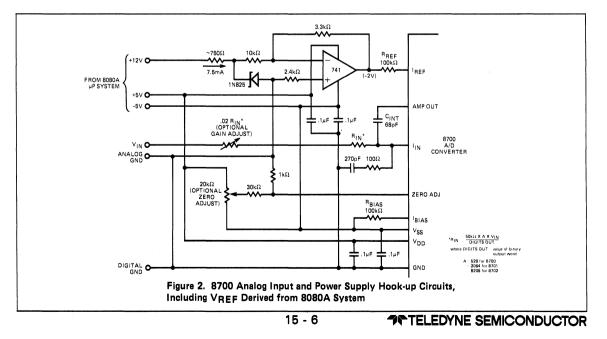

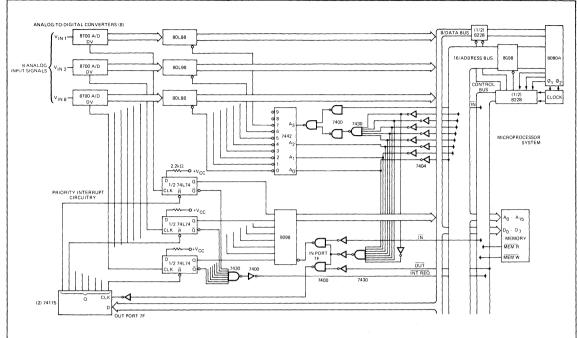

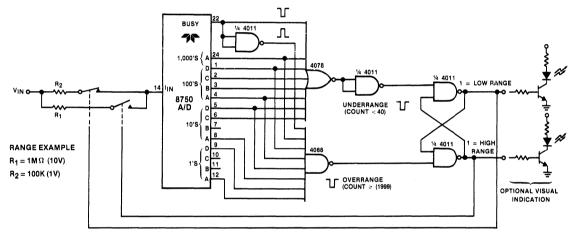

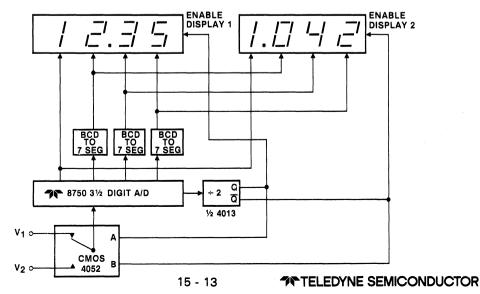

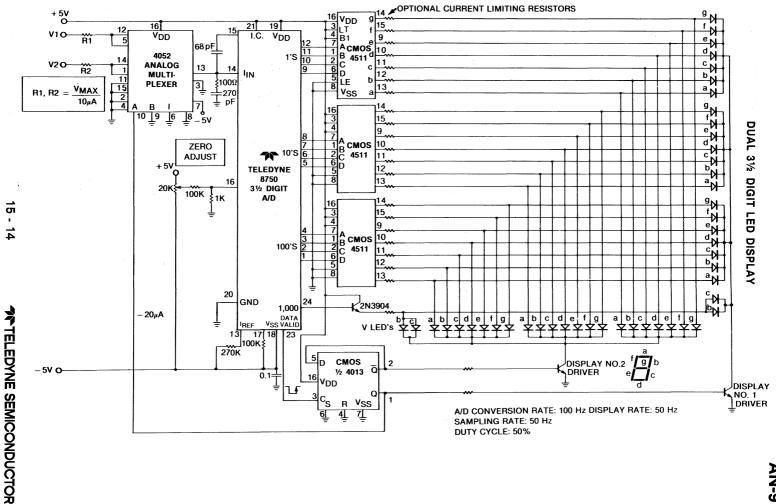

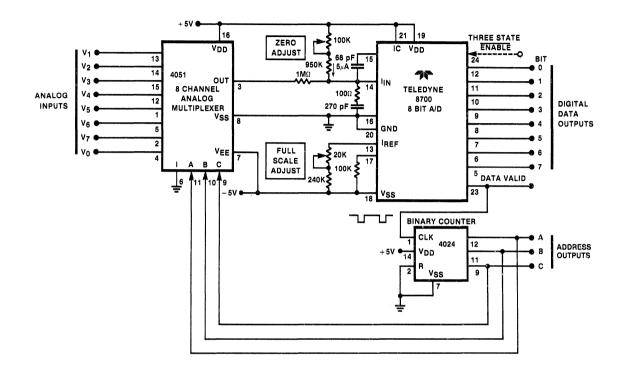

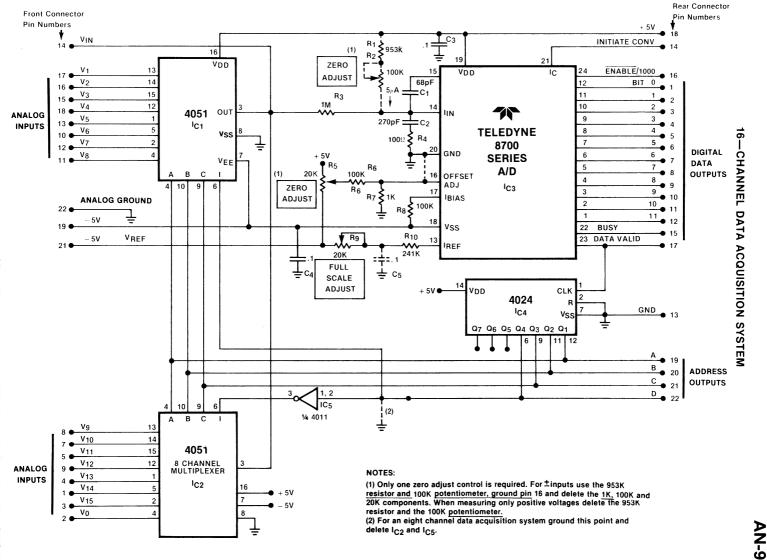

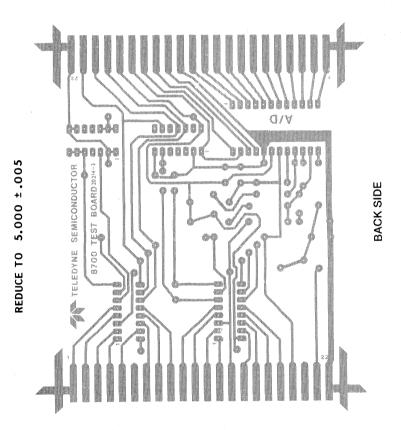

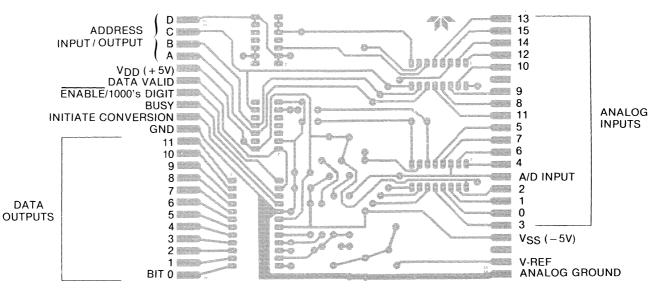

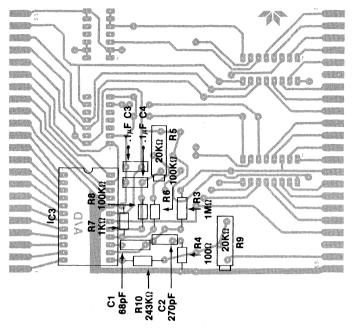

| Application Note 9                         | Applications of the TSC8700 Series A/D Converters                               | 15-11          |

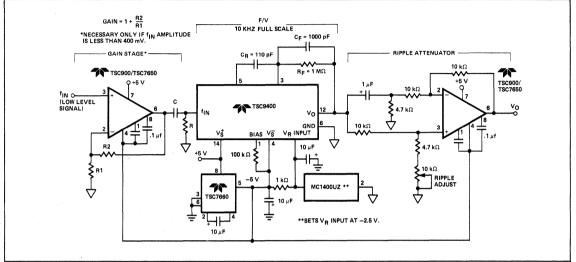

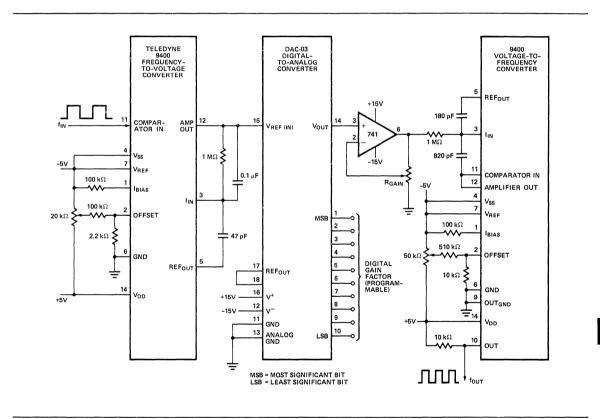

| Application Note 10                        | Applications of the TSC9400 V/F, F/V Converters                                 | 15-27          |

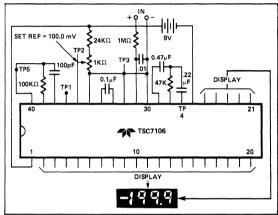

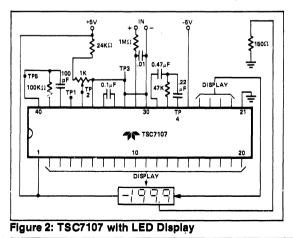

| Application Note 11                        | TSC7106/7107 Digital Meter Applications                                         | 15-37<br>15-45 |

| Application Note 12<br>Application Note 16 | A Single IC Digital Thermocouple Thermometer Using the TSC7106                  | 15-45          |

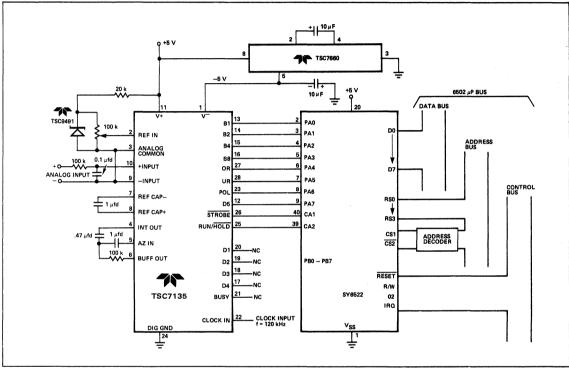

| Application Note 17                        | TSC7135 Microprocessor Interface<br>Simplify A/D Converter Interface w/Software | 15-47          |

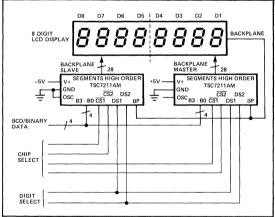

| Application Note 18                        | TSC7211AM/TSC7212AM Display Driver Microprocessor Interface                     | 15-55          |

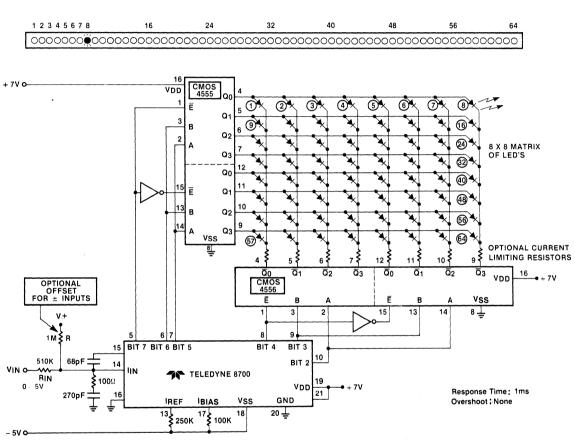

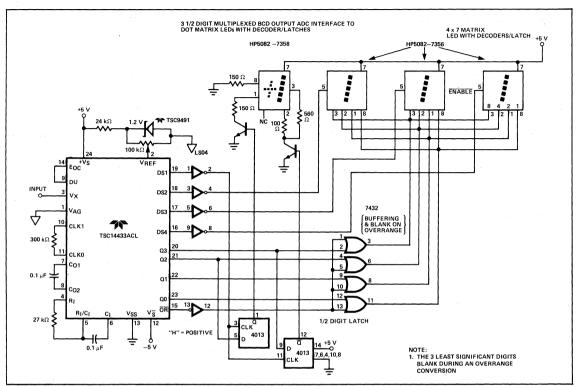

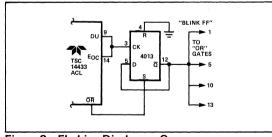

| Application Note 19                        | BCD A/D Converter Interface to Dot Matrix LEDs                                  | 15-59          |

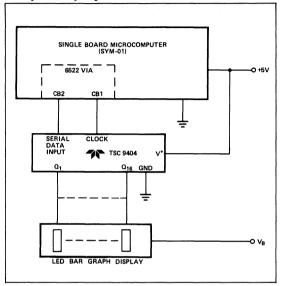

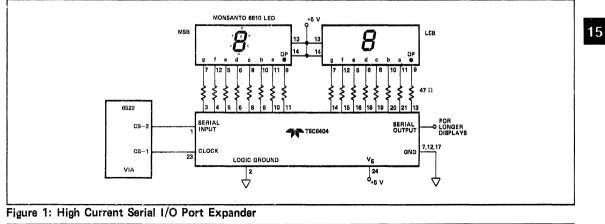

| Application Note 20                        | Two Digit Serial Input LED Display Drivers Using TSC9404                        | 15-61          |

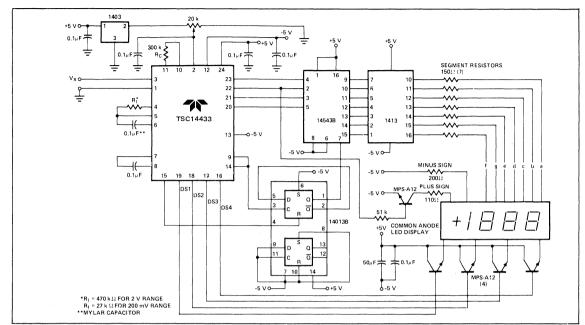

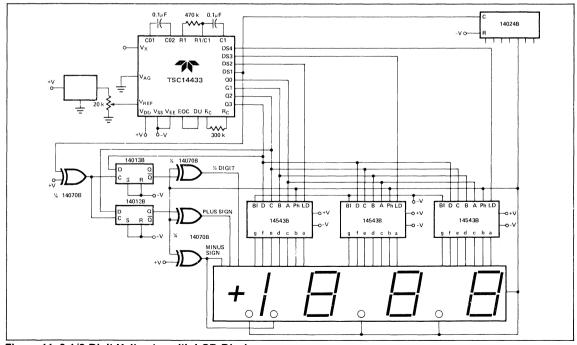

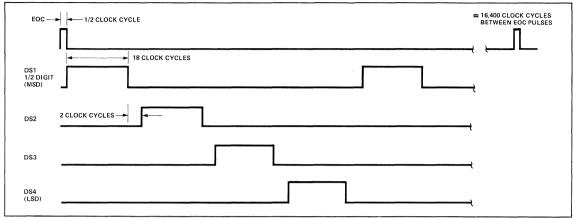

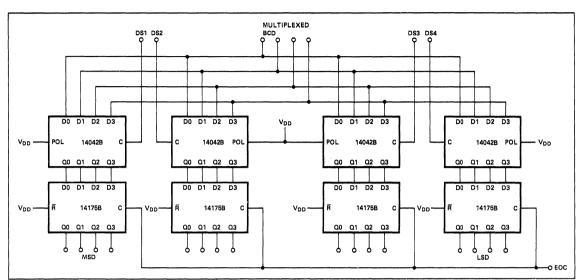

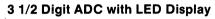

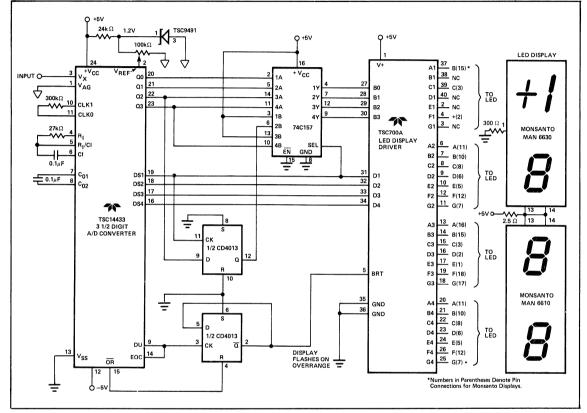

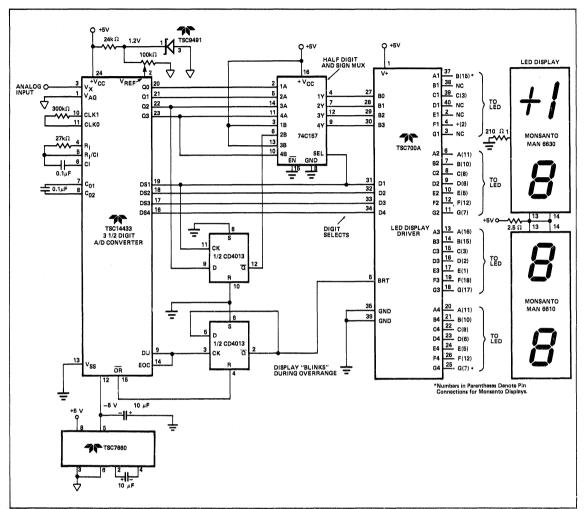

| Application Note 21                        | TSC700A Drives LED Display for TSC14433 ADC                                     | 15-63          |

| Application Note 22                        | Software Combines with CMOS LSI to Form 3 3/4 Digit DVM                         | 15-65          |

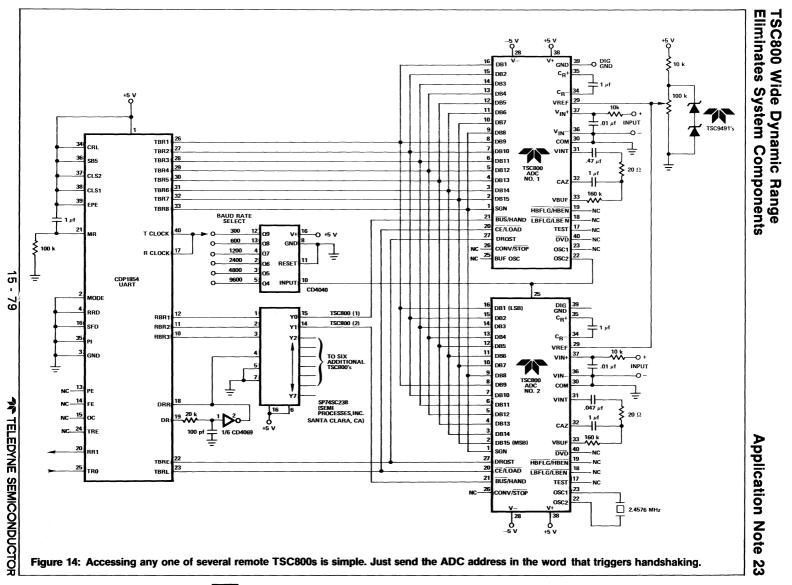

| Application Note 23                        | TSC800 Wide Dynamic Range Eliminates System Components                          | 15-69          |

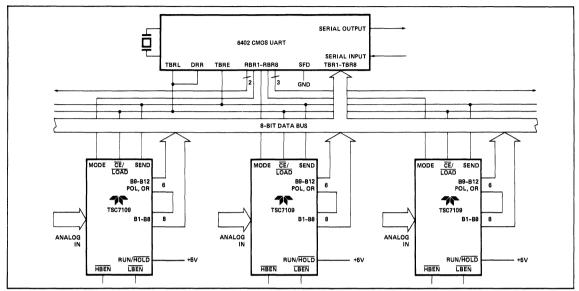

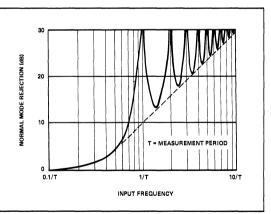

| Application Note 24                        | TSC7109 Records Remote Data Automatically                                       | 15-85          |

| Application Note 25                        | TSC426/427/428 System Design Practice                                           | 15-87          |

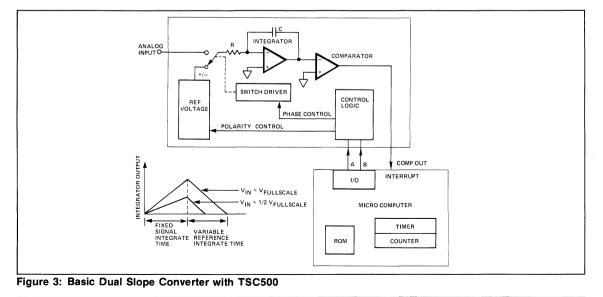

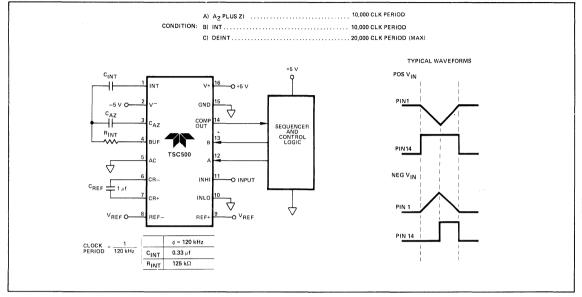

| Application Note 26                        | Flexible TSC500 ADC Simplifies Design Tradeoffs                                 | 15-91          |

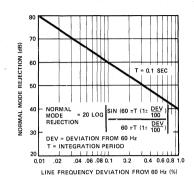

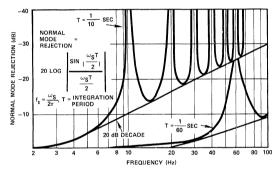

| Application Note 27                        | Numerical-Integration Techniques Speed Dual-Slope A/D Conversion                | 15-99          |

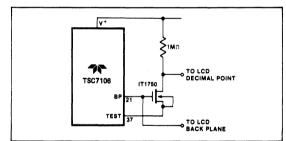

| Application Brief 7                        | Solve Sensor Offset Problems with the TSC7106                                   | 15-105         |

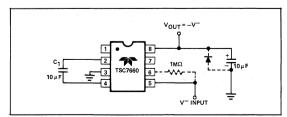

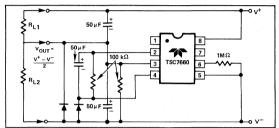

| Application Brief 8                        | TSC7660 Powers RS-232 Data Loop                                                 | 15-107         |

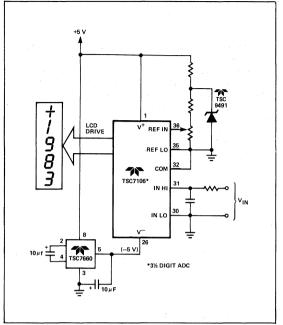

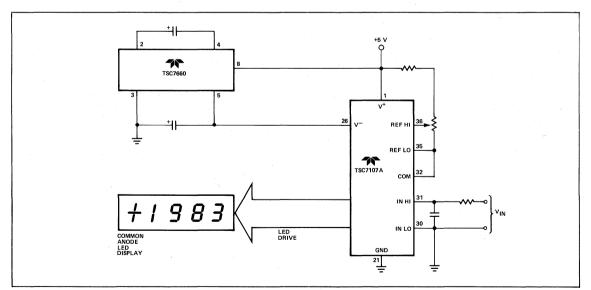

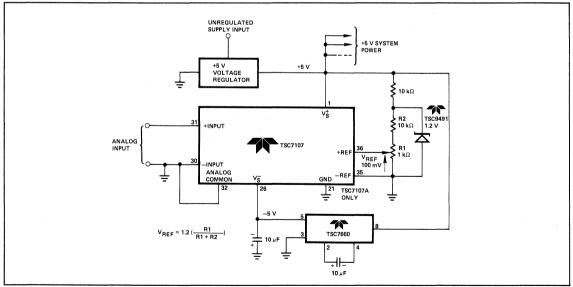

| Application Brief 9                        | ±5 V Power Supply Operation with TSC7106A/7107A                                 | 15-109         |

| Application Brief 10                       | Vendors for Support Components                                                  | 15-111         |

| Section 16                                 |                                                                                 |                |

| Glossary of Te                             | rms and Abbreviations                                                           | 16-3           |

| Section 17                                 |                                                                                 |                |

| Distributors an                            | d Representatives                                                               | 17-3           |

# **SECTION 2**

## Ordering Information Package Information

#### TSC87XX/TSC94XX/TSC14433

The Device Identification Codes for Device Numbers of TSC8700, TSC9400 and TSC14433 Family are as Follows:

| PACKAGED DEVICES                                                                                                                                                                  | TSC XXXXX X X X X |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 1. TELEDYNE SEMICONDUCTOR DEVICE                                                                                                                                                  |                   |

| 2. DEVICE NUMBER                                                                                                                                                                  |                   |

| 3. ELECTRICAL GRADE (if applicable)                                                                                                                                               |                   |

| 4. R – REVERSE LEAD CONFIGURATION (if applicable)                                                                                                                                 |                   |

| 5. OPERATING TEMPERATURE RANGE<br>C — Commercial Temperature Range (0 to 70°C)<br>E — Extended Temperature Range (-40 to +85°C)<br>B — Military Temperature Range (-55 to +125°C) |                   |

| 6. PACKAGE TYPE<br>J — Plastic Package<br>N — Ceramic Package<br>L — CerDIP<br>Y — Dice<br>E — Metal Can (TO-99)                                                                  |                   |

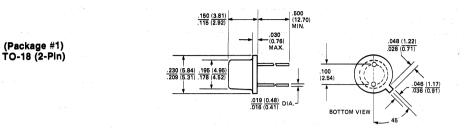

M – Metal Can (TO-18)

EXAMPLE: TSC8701CL Operates Over the Commercial Temperature Range and is a CerDIP Package

#### PRODUCT STATUS

Three Classes of Data Sheets are Shown in this Data Book. These are Identified by the Presence or Absence of a "Banner" on the First Page.

| DATA SHEET INDENTIFICATION     | PRODUCT STATUS     | COMMENTS                                                                                                                                             |

|--------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| No Identification              | Production         | Delivery Subject to Product Demand.                                                                                                                  |

| Preliminary                    | Initial Production | Data Sheet Electrical Limits<br>Established. Limited Production<br>Quantities Available. Samples<br>Available.                                       |

| Advance Product<br>Information | In Design          | Data Sheet Gives Design Goal,<br>Electrical Specifications and Major<br>Product Features. Contact Teledyne<br>Marketing for Samples and Information. |

Note: Teledyne Semiconductor Reserves the Right to Make Changes at Any Time Without Notice in Order to Improve Performance and Supply.

#### **Ordering Information**

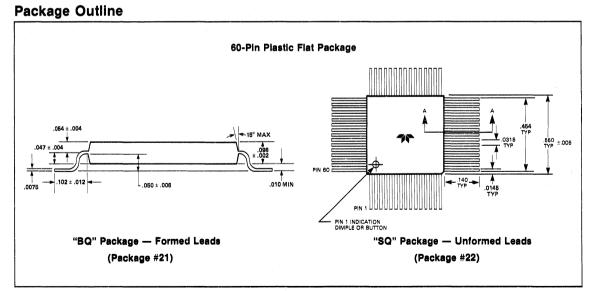

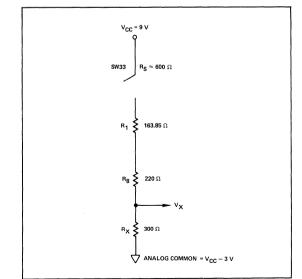

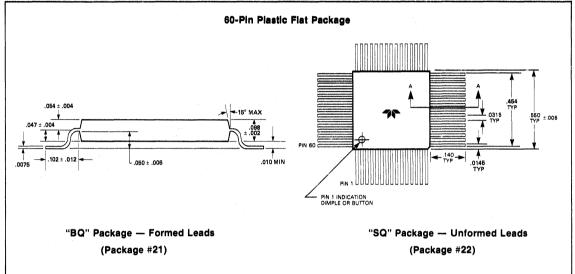

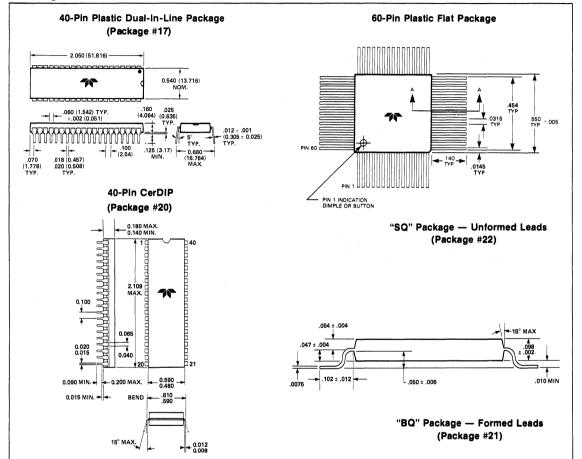

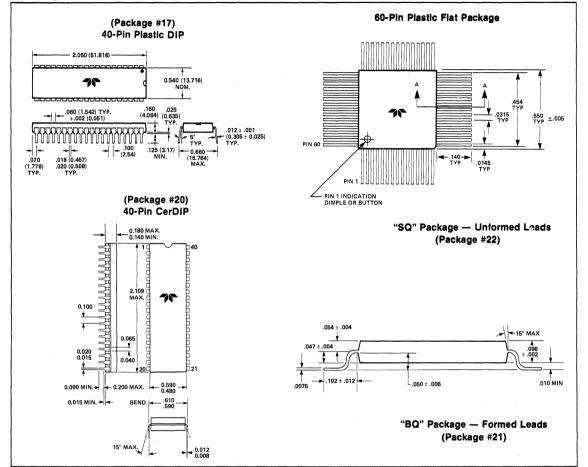

The Device Identification Codes for All Other CMOS Products and All Products in 60-Pin Flat Packages are as Follows:

| PACKAGED DEVI                                                           | CES                                                                                                                                         |                               | TSC XXXXX    | <   | X/XXX |

|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------|-----|-------|

| 1. TELEDYNE SEM                                                         |                                                                                                                                             |                               |              | TTT | TT    |

| 2. DEVICE NUMBI                                                         | ER                                                                                                                                          |                               |              |     |       |

| 3. ELECTRICAL P<br>R — Reversed Pir                                     | ERFORMANCE GRADE OP<br>ו Layout                                                                                                             | TION (if applicable)          |              | ┛║║ |       |

| M — Military Ter<br>I* — Industrial T<br>C — Commercial                 | MPERATURE RANGE<br>mperature Range (55°C to +<br>emperature Range (25°C to<br>l Temperature Range (0°C to<br>0°C to +85°C. Refer to Specifi | -125°C)<br>5 +85°C)<br>+70°C) |              |     |       |

| 5. PACKAGE TYPI                                                         | E                                                                                                                                           |                               |              |     |       |

| J — CerDIP Dua<br>P — Plastic Dual<br>T — TO—99 Typ<br>B — Plastic Flat | II-In-Line (non side brazed)                                                                                                                | L – Plastic Leaded C          |              | C)  |       |

| 6. NUMBER OF PA                                                         | ACKAGE PINS                                                                                                                                 |                               |              |     |       |

| A — 8                                                                   | N — 18                                                                                                                                      | Y – 8 (pin 4 connec           | ted to case) |     |       |

| D – 14                                                                  | G – 24                                                                                                                                      | Q — 60                        |              |     |       |

| E — 16                                                                  | I — 28                                                                                                                                      | W – 44                        |              |     |       |

| F — 22                                                                  | L — 40                                                                                                                                      | S — 68                        |              |     |       |

| 7. PROCESSING O                                                         | PTION<br>-883B, Class B Processing *                                                                                                        |                               |              |     |       |

| 005 - WIL-STD                                                           | OODD, Class D FIDUEssilly *                                                                                                                 |                               |              |     |       |

BI – 100% Burn-In at 125°C for 160 Hours

\*Contact Teledyne Semiconductor Marketing for MIL-STD 883C status.

2

####

- G Metal Can (TO-8)

- H Flatpack

- J Plastic Package

- L Ceramic Package (CerDIP)

- Y Dice

#### EXAMPLE: 303AL Operates Over an Industrial Temperature Range at 15 V and is a CerDIP Package

#### Product List — Digital Logic

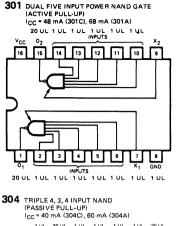

| 301 | Power NAND Gates Dual 5-Input               |

|-----|---------------------------------------------|

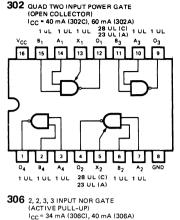

| 302 | Power NAND Gates Quad 2-Input               |

| 303 | Power NAND Gates Quad 2-Input               |

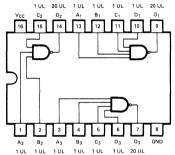

| 304 | Power NAND Gates Triple 4, 3, 4-Input       |

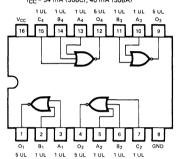

| 306 | NOR Gate Quad 2, 2, 3, 3-Input              |

| 307 | NOR Gate Quad 2, 2, 3, 3-Input              |

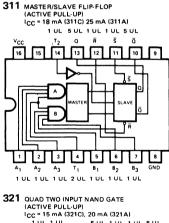

| 311 | Flip Flops Master/Slave RST                 |

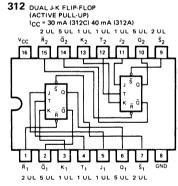

| 312 | Flip Flops Dual J-K Edge Triggered          |

| 313 | Flip Flops Dual J-K Master/Slave            |

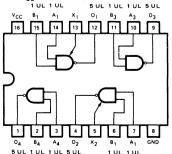

| 321 | NAND Gates Quad 2-Input                     |

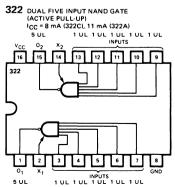

| 322 | NAND Gates Dual 5-Input                     |

| 323 | NAND Gates Quad 2-Input                     |

| 324 | NAND Gates Quad 2-Input                     |

| 325 | NAND Gates 2, 2, 3, 3-Input                 |

| 326 | NAND Gates 2, 2, 3, 3-Input                 |

| 331 | Gate Expander Dual 5-Input                  |

| 332 | Hex Inverter Gates 4-Inverter, 2-NAND       |

| 333 | Hex Inverter Gates 4-Inverter, 2-NAND       |

| 334 | Hex Inverter Gates Strobed Hex NAND         |

| 335 | Hex Inverter Gates Strobed Hex NAND         |

| 341 | Multifunction Gates Dual 2-Wide, 2-Input    |

|     | and/or Invert                               |

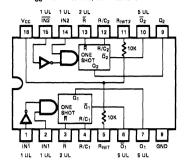

| 342 | Dual Monostable Multivibrator               |

| 343 | Digital Comparator 4-Bit                    |

| 344 | Multifunction Gates Dual Expandable AND-NOR |

| 347 | Dual Retriggerable Monostable Multivibrator |

|     |                                             |

- 349 Dual Retriggerable Pulse Stretcher

- 350 Multiplexers 8-Bit

- 351 Multiplexers Dual 4-Bit

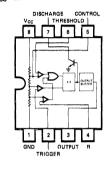

- 355 Timer

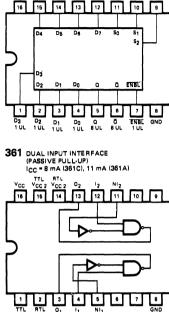

- 361 Dual 11-16V to 5V Interface Voltage Translator

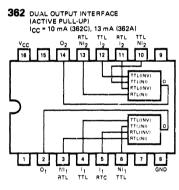

- 362 5V to 11-16V Interface Dual Translator

- 363 5V to 11-16V Interface Quad 2-Input NAND

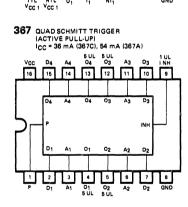

- 367 Schmitt Trigger Quad(Active Pullup)

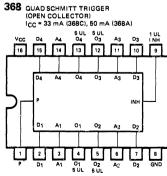

- 368 Schmitt Trigger Quad(Open Collector)

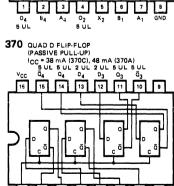

- 370 Flip Flop Quad D

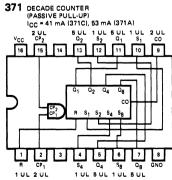

- 371 Counters Decade

- 372 Counters Hexadecimal

- 373 Up-Down Counters Decade

- 374 Up-Down Counters Hexadecimal

- 375 Shift Register 4-Bit

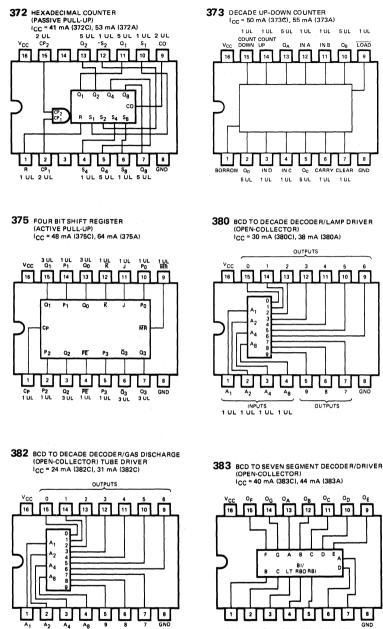

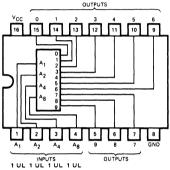

- 380 BCD-to-Decade Decoder/Drivers Lamp Driver

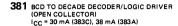

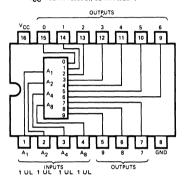

- 381 BCD-to-Decade Decoder/Drivers Logic Driver

- 382 BCD-to-Decade Decoder/Drivers Gas Tube Driver

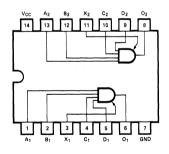

- 383 Decoder/Driver BCD-to-7 Segment

- 390 Dual Interface Buffers 4-Input Expandable AND

- 391 Dual Interface Buffers 2-Input AND

- 392 Dual Interface Buffers 2-Input NAND

- 393 Dual Interface Buffers 2-Input OR

- 394 Dual Interface Buffers 2-Input NOR

- 395 Dual Interface Buffers 4-Input Expandable NAND

- 396 Line Driver/Receiver Dual Differential

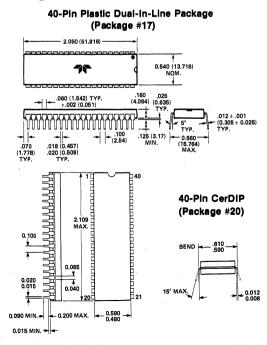

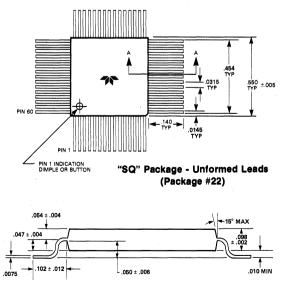

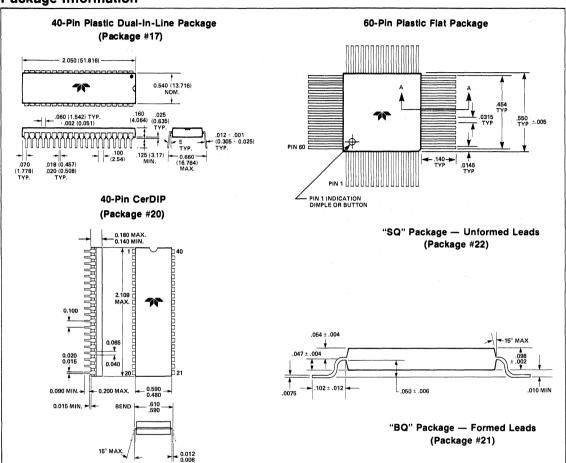

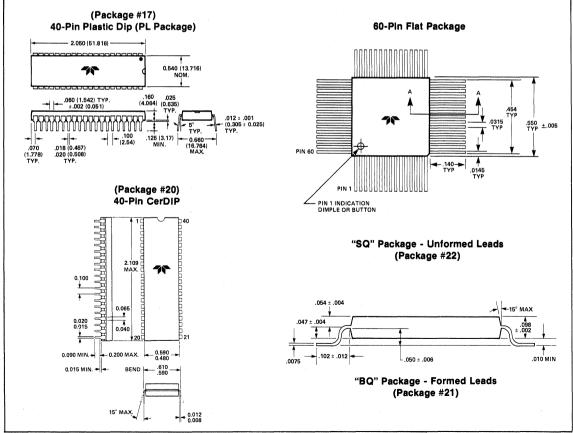

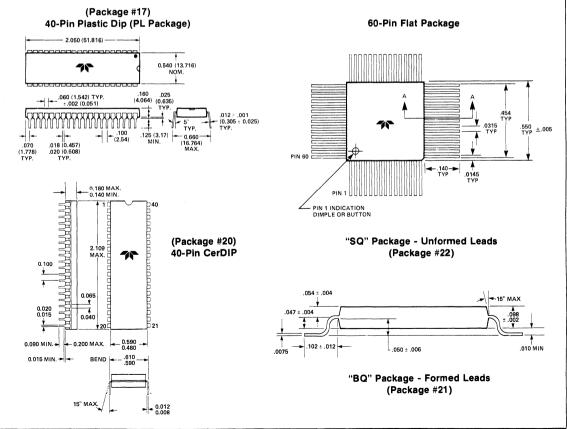

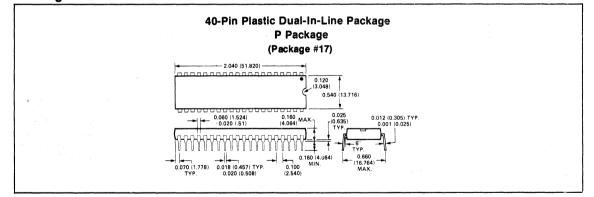

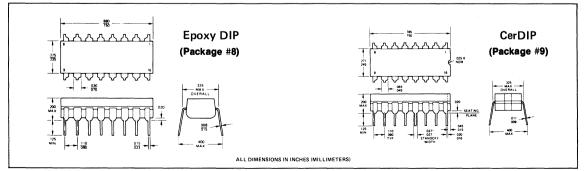

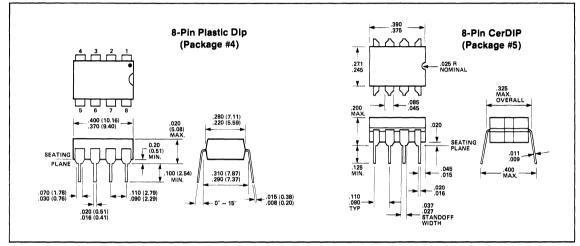

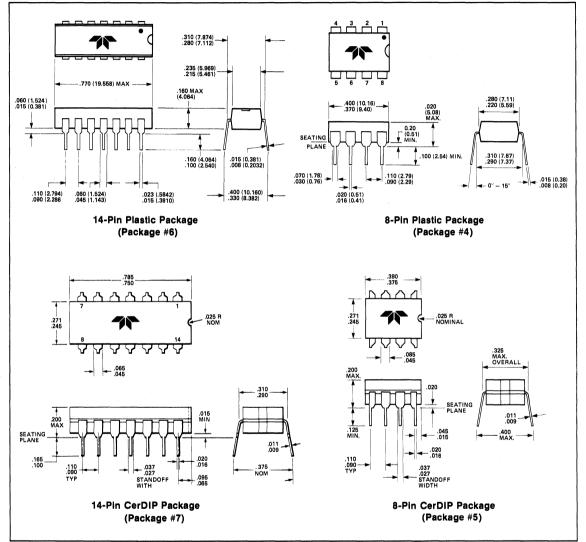

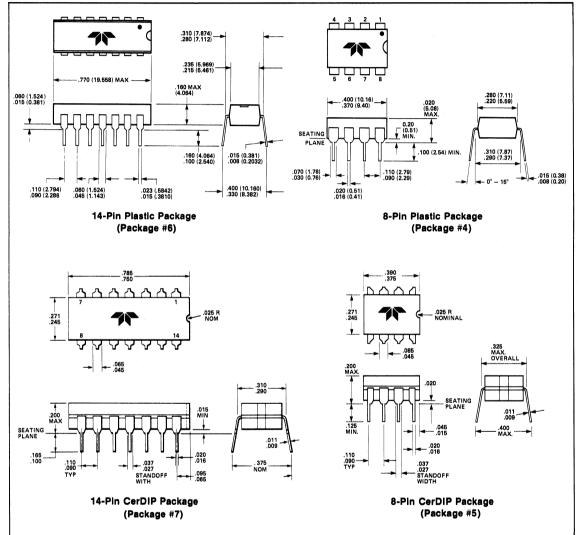

#### **Package Information**

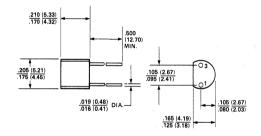

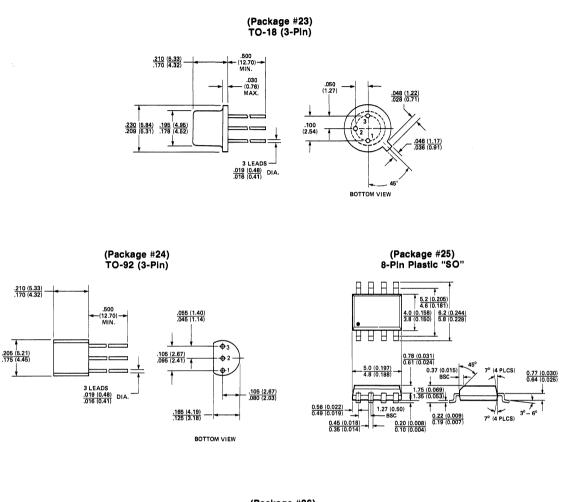

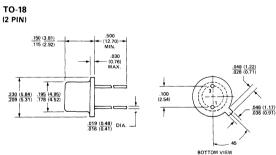

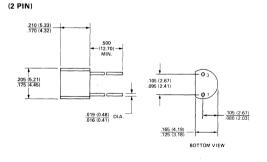

(Package #2) TO-92 (2-Pin)

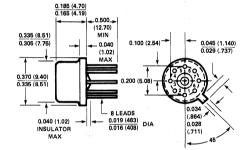

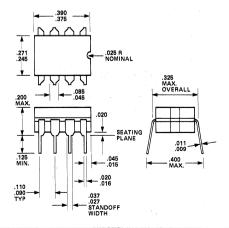

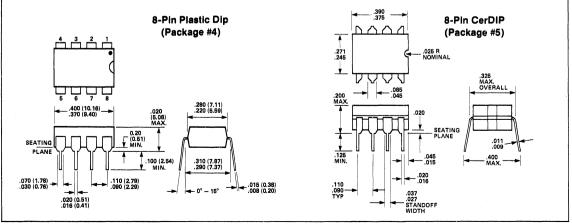

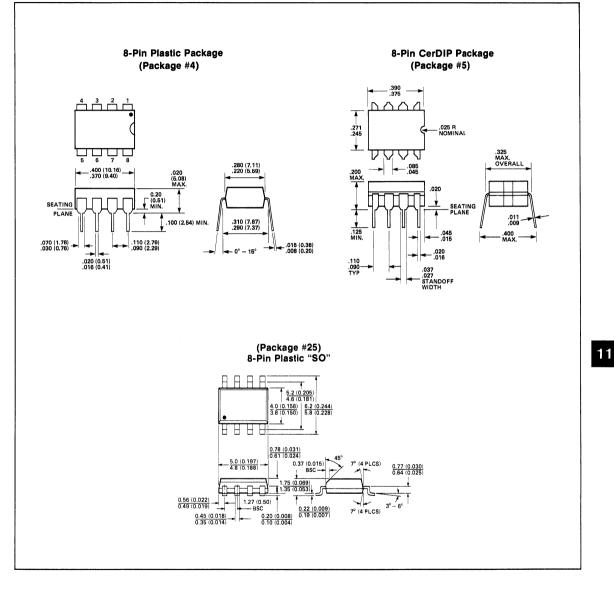

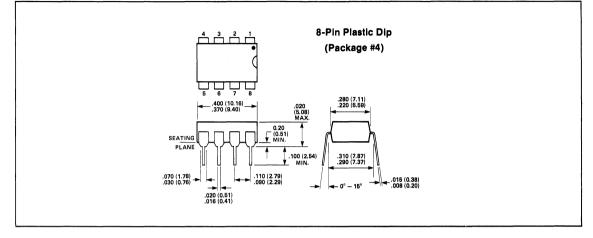

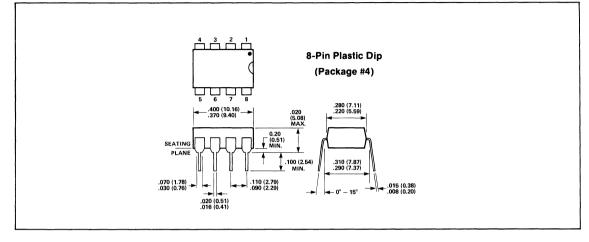

(Package #5) 8-Pin CerDIP

2

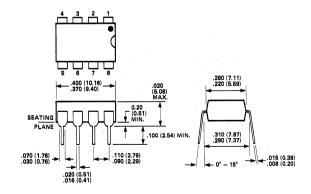

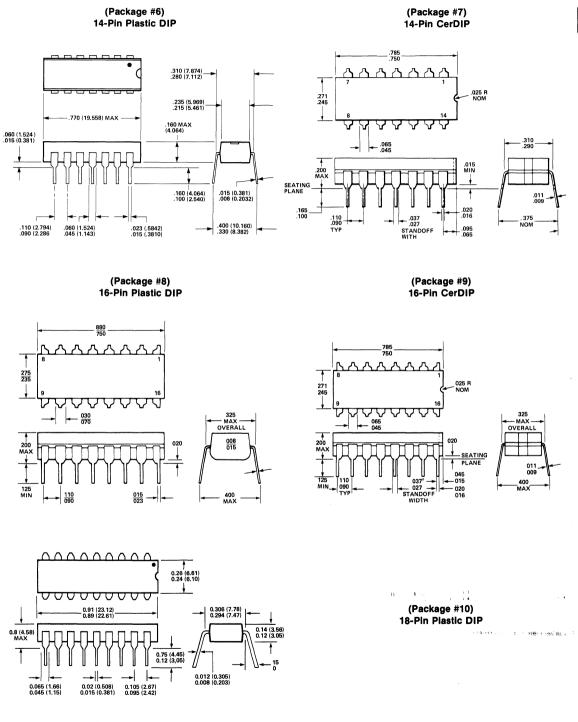

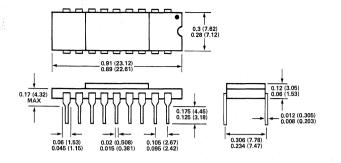

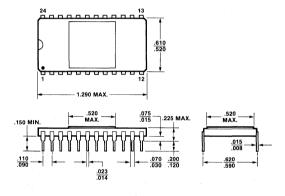

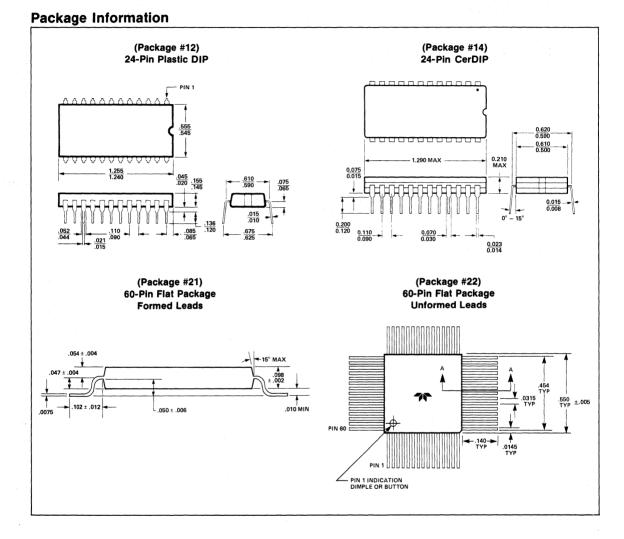

#### **Package Information**

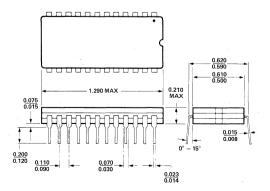

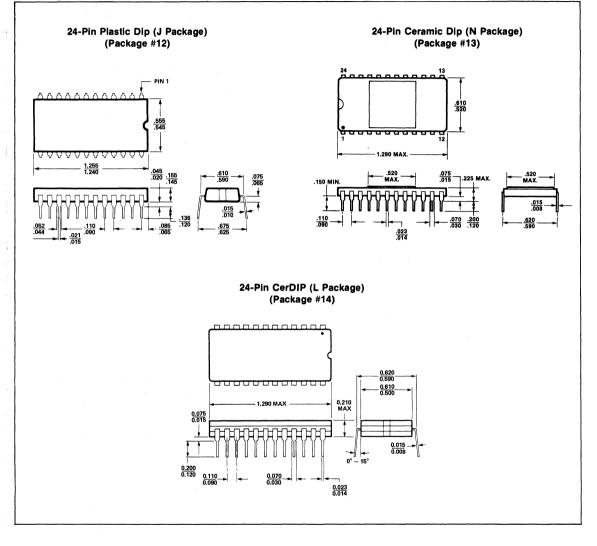

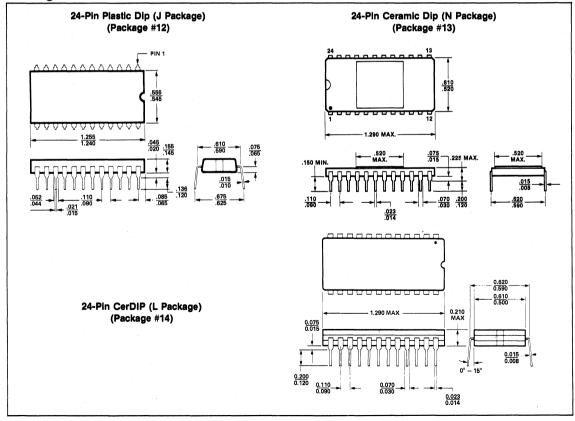

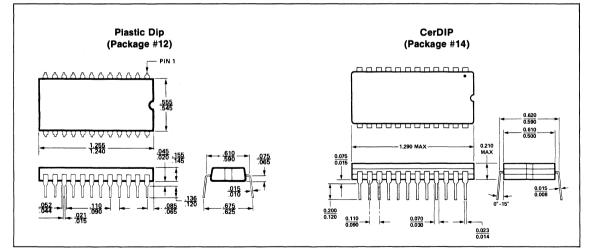

(Package #11) 18-Pin Ceramic DIP

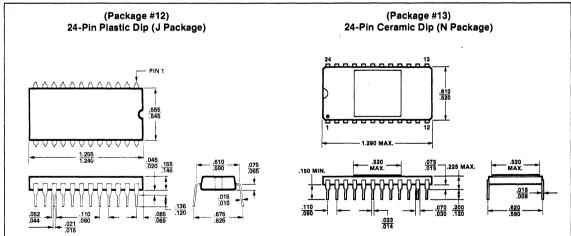

(Package #13) 24-Pin Ceramic DIP

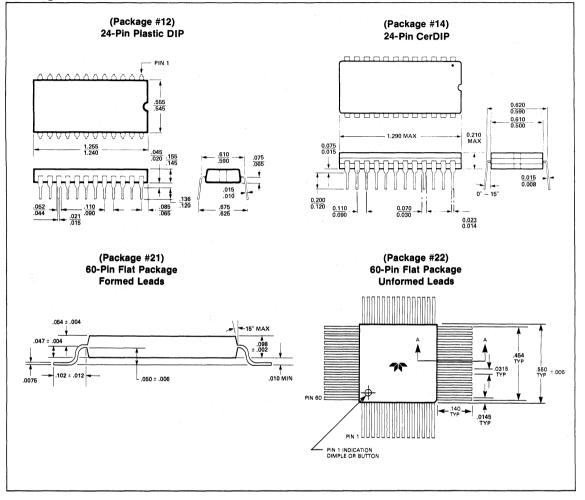

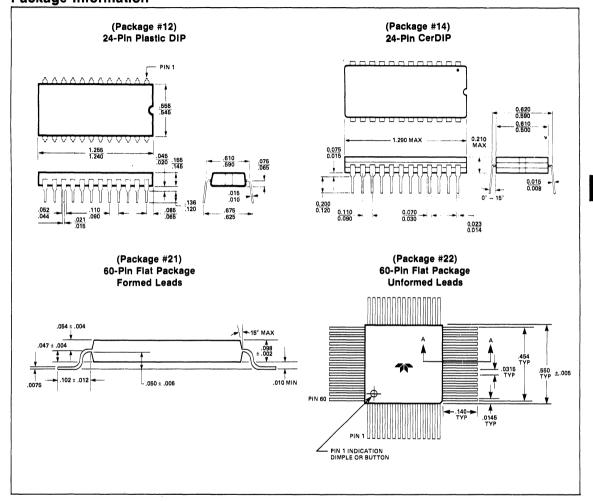

(Package #12) 24-Pin Plastic DIP

(Package #14) 24-Pin CerDIP

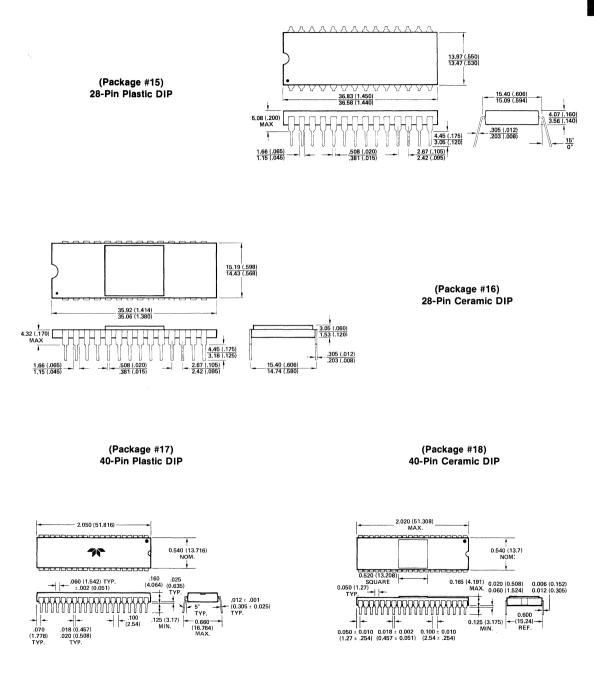

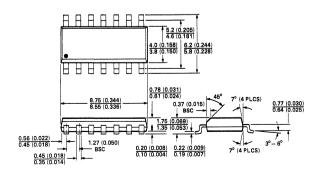

#### **Package Information**

2

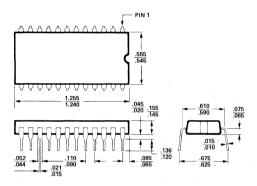

(Package #26) 14-Pin Plastic "SO"

2 - 11

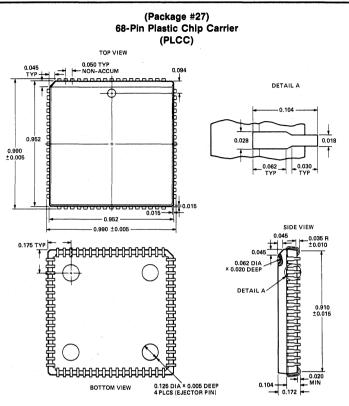

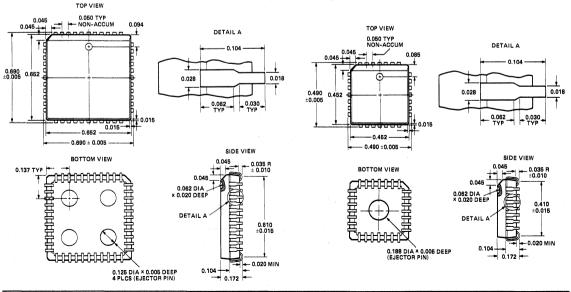

#### **Package Information**

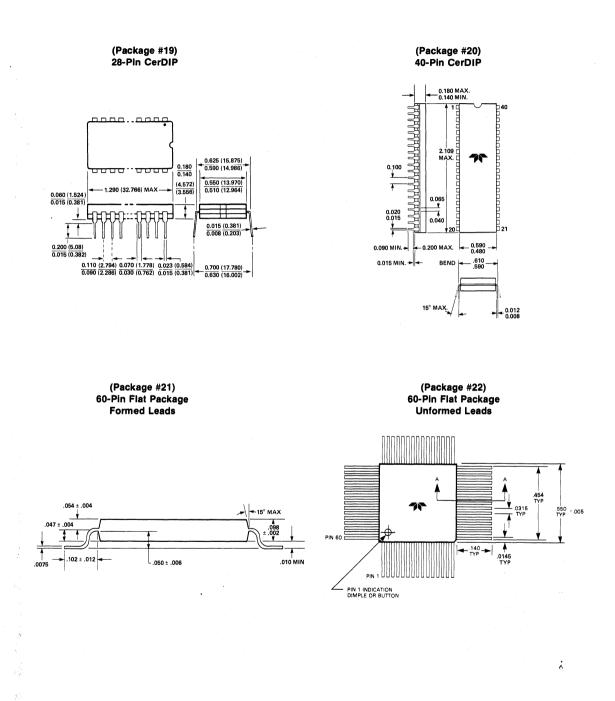

(Package #28) 44-Pin Plastic Chip Carrier (PLCC) (Package #29) 28-Pin Plastic Chip Carrier (PLCC)

TELEDYNE SEMICONDUCTOR

## SECTION 3 Quality Assurance Program

## Teledyne Semiconductor Product Assurance Program

Teledyne Semiconductor's Product Assurance Program is based on four major blocks:

- Quality Control

- Quality Assurance

- Reliability

- Quality Circles

#### **Quality Control**

The Quality Control function handles continuous monitoring of production, from incoming inspection of raw materials to wafer and assembly processing. This includes surveillance of documentation, calibration, and environmental processing.

The three major areas of Quality Control are:

- Incoming Inspection

- In-Process Control

- Operation Surveillance

- Vendor Qualification

#### Quality Assurance

After devices are subjected to 100% testing in manufacturing, they are formed into lots and submitted to Quality Assurance acceptance testing. Three types of tests are performed on samples: Visual/Mechanical, Parametric, and Functional. The sampling is based on a plan equivalent to a .07 AQL with a .5% AOQL. (All TSC sample plans are in accordance with MIL-M-38510 appendix B or MIL-HDB 105D.) Testing is done at room and elevated temperature. Lower temperature testing is performed when required by the specification, or when a potential problem is known to exist.

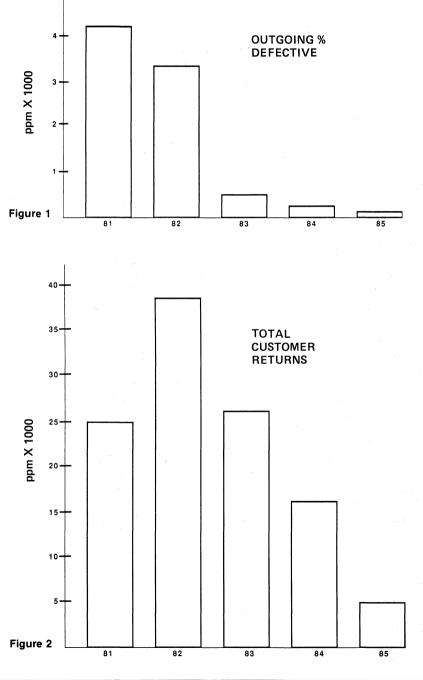

The Quality function at TSC is directed at providing a continually improving product that meets or exceeds the customer expectations. This stated goal is being achieved at Teledyne, which is evident in Figure 1 and Figure 2. These show constant improvement both in outgoing percent defective and customer return rate.

#### Reliability

The Reliability Group is responsible for the following functions:

- New Process Qualification

- Process Change Qualification

- Process Monitoring

- New Device Qualification

- Device Change Qualification

- Device Monitoring

- New Package Qualification

- Package Change Qualification

- Package Monitoring

- Failure Analysis

#### **Quality Control Circles**

Quality Control Circles are a vital part of the quality loop at Teledyne Semiconductor. The concept allows each employee directly involved in manufacturing to have a voice in how to build a quality product. Volunteers within a group meet weekly to determine and solve problems. Some solutions to problems may be implemented on the job. Others require management support, and to this end, circle members are trained in management presentation. The goal is total employee involvement with an emphasis on building-in quality.

### **Product Assurance Program**

TELEDYNE SEMICONDUCTOR

3 - 4

#### **Product Assurance Program** INCOMING QC INSPECTION MATERIALS WAFER QC AUDITS FAB QC MONITORS WAFER QC AUDITS SORT ASSEMBLY SCRIBE/BREAK 1st OPTICAL QC QC AUDITS DIE ATTACH GATES QC MONITORS BOND 2nd OPTICAL SEAL ASSEMBLY QC AUDITS ENVIRONMENTAL QC MONITORS TESTING ELECTRICAL MANUFACTURING MARK QA ACCEPTANCE **PROGRAM VERIFICATION** VISUAL/MECHANICAL TESTING FUNCTIONAL TESTING PARAMETRIC TESTING **TEMPERATURE TESTING** PACK FINAL VISUAL QA INSPECTION FINAL QA INSPECTION CLEARANCE SHIP

#### **TELEDYNE SEMICONDUCTOR**

### **Quality Conformance**

A part of the TSC Quality/Reliability program is to assure that all product lines offered meet industry accepted standards. This is done by a periodic submission of product to a conformance test program to collect generic data. All tests are done in accordance with MIL-STD 883C where applicable. (See pages 3-7/3-8) Test listings and results from submissions for a plastic encapsulated device and a CerDIP hermetic sealed device are presented in Table 1 and Table 2.

| Table 1 Plastic        |                            |                                                     |        |         |  |  |

|------------------------|----------------------------|-----------------------------------------------------|--------|---------|--|--|

| Test N                 | Ail-Std/Test Condition     | n Sample Size                                       | Qty In | Qty Out |  |  |

| Physical Dimension     | 883/2010                   | S/S = 45                                            | 45     | 45      |  |  |

| Salt Atmosphere        | 883/1009/A                 | S/S = 45                                            | 45     | 45      |  |  |

| Solderability          | 883/2003                   | S/S = 45                                            | 45     | 45      |  |  |

| Pressure Cooker        | 96 hrs.                    | S/S = 45                                            | 45     | 45      |  |  |

| 85/85°C R H (Bias)     | 1.0K hrs.                  | S/S =                                               | n/a    | n/a     |  |  |

| SSL                    | TA = 125°C t = 1,000 hrs.  | S/S = 45                                            | 45     | 45      |  |  |

| Storage                | TS = 150°C t = 1,000 hrs.  | S/S = 45                                            | 45     | 45      |  |  |

| Thermal Shock          | -55°C to +125°C 200 cycle  | S/S = 45                                            | 45     | 45      |  |  |

| Temperature Cycle      | -65°C to +150°C 1000 cycle | S/S =45                                             | 45     | 45      |  |  |

|                        | Table 2                    | CerDIP                                              |        |         |  |  |

| Group B Test           | Mil-Std                    | Sample Size                                         | Qty In | Qty Out |  |  |

|                        |                            |                                                     |        |         |  |  |

| SUBGROUP 1             |                            |                                                     |        |         |  |  |

| Physical Dimensions    | 883/2016                   | 2 devices<br>(no failures)                          | n/a    | n/a     |  |  |

| SUBGROUP 2             | 000/0015                   |                                                     |        |         |  |  |

| Resistance to Solvents | 883/2015                   | 4 devices<br>(no failures)                          | 4      | 4       |  |  |

| SUBGROUP 3             |                            |                                                     |        |         |  |  |

| Solderability          | 883/2003                   | LTPD = 15<br>3 devices min.                         | 3      | 3       |  |  |

| SUBGROUP 4             |                            | 5 devices min.                                      |        |         |  |  |

| Internal Visual        | 883/2014                   | 1 device                                            | 1      | 1       |  |  |

| And Mechanical         |                            | (no failure)                                        | •      | ·       |  |  |

| SUBGROUP 5             |                            |                                                     |        |         |  |  |

| Bond Strength          | 883/2011/D                 | LTPD =<br>4 devices                                 | 15     | 15      |  |  |

| SUBGROUP 6             |                            |                                                     |        |         |  |  |

| Internal Water Vapor   | 883/1018                   | 3 devices<br>(no failures)<br>5,000 PPM, 10,000 PPM | n/a    | n/a     |  |  |

| SUBGROUP 7<br>Seal     |                            | 0,000 1 1 11, 10,000 1 1 11                         |        |         |  |  |

| Fine leak              |                            |                                                     |        |         |  |  |

| Gross leak             | 883/1014/C                 | LTPD = 2                                            | 116    | 116     |  |  |

| SUBGROUP 8<br>NA       |                            |                                                     |        |         |  |  |

| TELEDYNE SEMIC         | ONDUCTOR 3 -               | 6                                                   |        |         |  |  |

**Conformance Flow** Generic Data is generated on a periodic basis for the following test.

| MIL-STD-883C Quality<br>Conformance Tests                                  | Method               | Test Condition                               | LTPD      |

|----------------------------------------------------------------------------|----------------------|----------------------------------------------|-----------|

| GROUP B                                                                    |                      |                                              |           |

| SUBGROUP 1<br>Physical Dimensions                                          | 2016                 |                                              | 2 Devices |

| SUBGROUP 2<br>Resistance to Solvents                                       | 2015                 |                                              | 4 Devices |

| SUBGROUP 3<br>Solderability                                                | 2022 or 2003         |                                              | 15        |

| SUBGROUP 4<br>Internal Visual: Mechanical                                  | 2014                 |                                              | 1 Device  |

| SUBGROUP 5<br>Bond Strength                                                | 2011                 | Test Condition C or D                        | 15        |

| SUBGROUP 6<br>Na                                                           |                      |                                              |           |

| SUBGROUP 7<br>Seal<br>Fine<br>Gross                                        | 1014                 |                                              | 5         |

| SUBGROUP 8<br>NA                                                           |                      |                                              |           |

| GROUP C                                                                    |                      |                                              |           |

| SUBGROUP 1<br>Steady State Life Test<br>Electrical End Points              | 1005                 | 1000 hrs. at 125°C                           | 5         |

| SUBGROUP 2<br>Temperature Cycling<br>Constant Acceleration<br>Seal<br>Fine | 1010<br>2001<br>1014 | Test Condition C<br>Test Condition E, Y only | 15        |

| Gross<br>Visual Examination<br>Electrical End Points                       | 1010 or 1011         |                                              |           |

| GROUP D                                                                    |                      |                                              |           |

| SUBGROUP 1<br>Physical Dimensions                                          | 2016                 |                                              | 15        |

| <b>SUBGROUP 2</b><br>Lead Integrity<br>Seal<br>Fine<br>Gross               | 2004<br>1014         | Test Condition B2                            | 15        |

## **Conformance Flow (Cont.)**

| MIL-STD-883C Quality<br>Conformance Tests                                               | Method                       | Test Condition                                                    | LTPD      |

|-----------------------------------------------------------------------------------------|------------------------------|-------------------------------------------------------------------|-----------|

|                                                                                         |                              |                                                                   |           |

| GROUP D (Cont.)                                                                         |                              |                                                                   |           |

| SUBGROUP 3<br>Thermal Shock<br>Temperature Cycling<br>Moisture Resistance<br>Seal       | 1011<br>1010<br>1004<br>1014 | Test Condition B, 15 Cycles<br>Test Condition C, 100 Cycles       | 15        |

| Fine<br>Gross<br>Visual Examination<br>Electrical End Points                            | 1014                         |                                                                   |           |

| SUBGROUP 4<br>Mechanical Shock<br>Vibration Variable Frequency<br>Constant Acceleration | 2002<br>2007<br>2001         | Test Condition B<br>Test Condition A<br>Test Condition E, Y1 only | 15        |

| Seal<br>Fine<br>Gross<br>Visual Examination<br>Electrical End Points                    | 1014<br>1010 or 1011         |                                                                   |           |

| SUBGROUP 5<br>Salt Atmosphere<br>Seal<br>Fine<br>Gross                                  | 1009<br>1014                 | Test Condition A                                                  | 15        |

| Visual Examination                                                                      | 1009                         |                                                                   |           |

| SUBGROUP 6<br>Internal Water-Vapor Content                                              | 1018                         | 5,000 PPM — CerDIP only                                           | 3 Devices |

| SUBGROUP 7<br>Adhesion of Lead Finish                                                   | 2025                         |                                                                   | 15        |

| SUBGROUP 8<br>Lid Torque                                                                | 2024                         |                                                                   | 5 Devices |

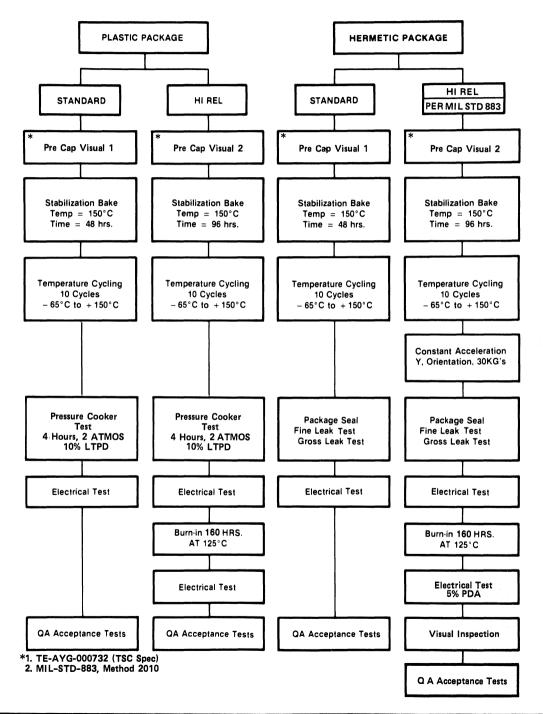

#### Quality Assurance Integrated Circuit Screening

3

#### Reliability

The work of the Reliability Group at TSC has resulted in a product which should far exceed the reliability needs of any customer. Two important measures of device failure rate are stress testing under elevated temperature and under elevated temperature in conjunction with elevated humidity.

#### **Steady State Life**

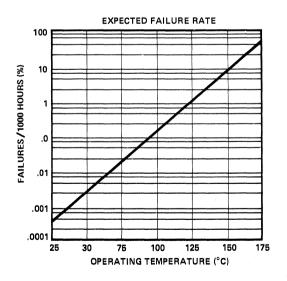

Device reliability is often measured by survival rate under high temperature operating conditions. Figure 3 illustrates expected failure rate per 1000 hrs. of operating time over a temperature range from 25° C to 175° C. This graph is for TSC CMOS integrated circuits. The data was derived from results of Dynamic high temperature stress testing at 125° C and 150° C and calculations based on MIL-HDBK 217D.

#### **Temperature and Humidity**

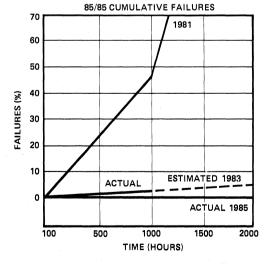

A major indicator of the reliability of a plastic encapsulated device (commercial class) is its ability to withstand temperature and humidity combined. Elevated temperature and humidity testing is routinely performed by TSC to evaluate the affect of these conditions on device reliability. The industry standard of 85°C and 85% Relative Humidity is used. Teledyne Semiconductor has a policy of using proven state-of-the-art molding compounds in its assembly process. Figure 4 illustrates the improvement this has made in TSC device reliability as measured by the 85/85 stress test.

Figure 3

Figure 4

#### Transportation

Two main concerns to be minimized during transportation are mechanical vibration and shock and Electrostatic Discharge (ESD) damage. While mechanical shock can be minimized by suitable packing and handling, ESD damage requires additional measures including:

- Use containers or jigs which will not induce static electricity as the result of vibration during transportation. It is desirable to use an electrically conductive foam or aluminum foil and static eliminating bags.

- In order to prevent device damage from clothing-induced static electricity, workers should be properly grounded with grounding straps while handling devices. A resistor of about 1 M ohm must be provided to protect from electric shock.

- When transporting the printed circuit boards on which semiconductor devices are mounted suitable preventive measures against static electricity transfer and induction must be taken. Shorting connectors should be placed on open contacts and the board transported in electrically conductive bags.

#### Storage

It is preferable to store semiconductor devices in the following ways to prevent deterioration in their electrical characteristics, solderability, and mechanical appearance.

- Store in an ambient temperature of 5 to 30° C, and in a relative humidity of 40 to 60%.

- Store in a clean air environment, free from dust and active gas.

- Store in a container which does not induce static electricity.

Store without any physical load.

If semiconductor devices are stored for a long time, store them as sent from the factory. If their lead wires are formed beforehand, they may corrode during storage.

If the chips are unsealed, store them in a cool, dry, dark, and dustless place. Assemble them within 5 days after unpacking. Storage in nitrogen gas is desirable. They can be stored for 20 days or less in dry nitrogen gas with a dew point at  $-30^{\circ}$  C or lower. Unpacked chips must not be stored for over 3 months.

Take care not to allow condensation during storage due to rapid temperature changes.

### I.C. Handling Precautions (cont.)

#### Testing

Avoid ESD, noise or voltage surges when testing ICs. The device is in its least protected state during handling, insertion and testing. Any test equipment that leaks current or is allowed to attain only a few hundred volts of ESD can destroy CMOS ICs. All equipment must be grounded and periodically tested for leakage.

#### Soldering

Semiconductor devices should not be left at high temperatures for a long time. Regardless of the soldering method, soldering must be done in a short time and at the lowest possible temperature. Soldering work must meet soldering heat test conditions, namely, 260° C for 10 seconds and 350° C for 3 seconds at a point 1 to 1.5 mm away from the end of the device package.

Use of a strong alkali or acid flux may corrode the leads, deteriorating reliability and device characteristics. The recommended soldering iron is the type that is operated with a secondary voltage supplied by a transformer and grounded to protect from lead current. Solder the leads at the farthest point from the device package.

#### Personnel

- All personnel handling or in close proximity to ICs must wear anti-static clothing and shoes.

- Handling personnel must wear grounding straps.

- Work surfaces and straps should be earth grounded through a 1 M ohm resistor.

- Floors and carpets should be treated so as not to generate static electricity.

- Unrelated sources of RF or static electrical fields (e.g., plastic boxes, plastic wrappers) should be kept away from device handling areas.

#### **Removing Residual Flux**

To insure the reliability of electronic systems, residual flux must be removed from circuit boards. Detergent or ultrasonic cleaning is usually applied. If chloric detergent is used for the plastic molded devices, package corrosion may occur. Since cleaning over extended periods or at high temperatures may cause swollen chip coating due to solvent permeation, select the type of detergent and cleaning condition carefully. Do not use trichloroethylene. For ultrasonic cleaning, the following conditions are advisable:

- Frequency: 28 to 29 kHz (to avoid device resonation)

- Ultrasonic output: 15W/L

- Keep the devices out of direct contact with the power generator.

- Cleaning time: Less than 30 seconds

- Clean Freon™ is recommended if other conditions permit.

# SECTION 4

## **Alphanumeric Product List**

## **Alphanumeric Product List**

| TSC04/05                 | 1.2 V/2.5 V Bandgap Voltage Reference                                           | 6-5          |

|--------------------------|---------------------------------------------------------------------------------|--------------|

| TSC170/171               | CMOS Current Mode SMPS Controller                                               | 6-7          |

| TSC400/401               | 16-Channel and Dual 8-Channel Bus Compatible Analog Multiplexers                | 6-15         |

| TSC426/427/428           | High Speed Dual Power MOSFET Driver                                             | 11-5         |

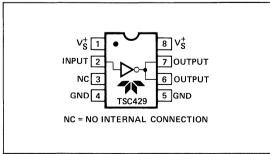

| TSC429                   | High Speed Single CMOS Power MOSFET Driver                                      | 6-17         |

| TSC441/442/443           | μ-Processor Bus Compatible CMOS Analog Switches                                 | 6-19         |

| TSC444/445/446<br>TSC447 | μ-Processor Bus Compatible CMOS Quad Analog Switches                            | 6-21<br>6-23 |

| TSC447<br>TSC450         | μ-Processor Bus Compatible Quad CMOS Analog Switch                              | 11-15        |

| TSC500                   | Integrating Converter Analog Processor                                          | 7-5/8-5      |

| TSC700A                  | High Current Four Digit LED Driver                                              | 10-5         |

| TSC701AM                 | High Current Bus Compatible Four Digit LED Driver                               | 10-13        |

| TSC800                   | 15-Bit Plus Sign Integrating A/D Converter                                      | 8-13         |

| TSC805                   | 3 1/2 Digit Auto-Ranging A/D Converter                                          | 7-7          |

| TSC815                   | 3 1/2 Digit Auto-Ranging A/D Converter with Display Hold                        | 7-25         |

| TSC826                   | A/D Converter with Bar-Graph Display Output                                     | 7-43         |

| TSC827                   | 1% ADC with LCD Bar-Graph Drive and Set Points                                  | 6-25         |

| TSC829                   | 4 1/2 Digit ADC with LCD Drive and Surface Mount Package                        | 6-27         |

| TSC900                   | Low Power Chopper-Stabilized Operational Amplifier                              | 13-5         |

| TSC911                   | Auto-Zeroed Monolithic Operational Amplifier                                    | 13-13        |

| TSC913                   | Dual Auto-Zeroed Operational Amplifier                                          | 13-21/6-29   |

| TSC914                   | Quad Auto-Zeroed Operational Amplifier                                          | 13-23/6-31   |

| TSC918                   | Low Cost, Low Power Operational Amplifier                                       | 13-25        |

| TSC4201/4202/4203        | Low Cost CMOS Quad Analog Switches                                              | 6-33         |

| TSC7106A/7107A           | 3 1/2 Digit A/D Converter with Low Drift Reference                              | 7-55         |

| TSC7106/7107             | 3 1/2 Digit A/D Converter                                                       | 7-73         |

| TSC7109                  | 12-Bit Plus Sign Integrating A/D Converter                                      | 8-29         |

| TSC7116A/7117A           | 3 1/2 Digit A/D Converter with Low Drift Reference and Display Hold             | 7-85         |

| TSC7116/7117             | 3 1/2 Digit A/D Converter with Display Hold                                     | 7-97         |

| TSC7126A                 | Low Power 3 1/2 Digit A/D Converter with Low Drift Reference                    | 7-109        |

| TSC7126                  | Low Power 3 1/2 Digit A/D Converter                                             | 7-121        |

| TSC7129                  | 4 1/2 Digit ADC with Triplex LCD Display Drive                                  | 6-35         |

| TSC7135                  | 4 1/2 Digit Precision A/D Converter with BCD Output                             | 7-133        |

| TSC7136A                 | Low Power 3 1/2 Digit ADC with LCD Drive                                        | 6-37         |

| TSC7211A/7212A           | Four Digit LCD/LED Display Drivers                                              | 10-21        |

| TSC7211AM/7212AM         | Bus Compatible Four Digit LCD/LED Display Drivers                               | 10-33        |

| TSC7650A                 | Chopper-Stabilized Operational Amplifier                                        | 13-29        |

| TSC7650                  | Precision Chopper-Stabilized Operational Amplifier                              | 13-37        |

| TSC7660                  | DC to DC Voltage Converter                                                      | 11-19        |

| TSC8700                  | Binary Output ADC (8-Bit)                                                       | 8-49         |

| TSC8701                  | Binary Output ADC (10-Bit)                                                      | 8-49<br>8-49 |

| TSC8702<br>TSC8703       | Binary Output ADC (12-Bit)                                                      | 8-61         |

| TSC8703                  | Three State Binary Output ADC (8-Bit)<br>Three State Binary Output ADC (10-Bit) | 8-61         |

| TSC8704<br>TSC8705       | Three State Binary Output ADC (10-Bit)                                          | 8-61         |

| TSC8750                  | 3 1/2 Digit ADC with Parallel BCD Output                                        | 7-145        |

| TSC9400                  | Voltage to Frequency Converter (0.05% Linearity)                                | 9-5          |

| TSC9401                  | Voltage to Frequency Converter (0.01% Linearity)                                | 9-5          |

| TSC9402                  | Voltage to Frequency Converter (0.25% Linearity)                                | 9-5          |

| TSC9403                  | Serial Input/16-Bit Parallel Output Peripheral Driver (20 V)                    | 11-31        |

| TSC9404                  | Serial Input/16-Bit Parallel Output Peripheral Driver (15 V)                    | 11-31        |

| TSC9491                  | 1.22 Bandgap Voltage Reference                                                  | 12-5         |

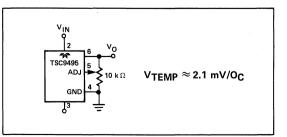

| TSC9495                  | +5 V Bandgap Voltage Reference/Temperature Transducer                           | 12-7         |

| TSC9496                  | +10 V Bandgap Voltage Reference                                                 | 12-11        |

| TSC14433A                | Precision 3 1/2 Digit ADC with Multiplexed BCD Output                           | 7-153        |

| TSC14433B                | Low Cost 3 1/2 Digit ADC with Multiplexed BCD Output                            | 7-159        |

| TSC14433                 | 3 1/2 Digit ADC with Multiplexed BCD Output                                     | 7-165        |

|                          |                                                                                 |              |

4

# SECTION 5

# **Cross Reference Guide**

#### All TSC Products Cross-Referenced Are Plug-In Replacements

| Part Number | TSC Number   | Comments                                      |

|-------------|--------------|-----------------------------------------------|

| ADC-EK10B   | TSC8701CJ    |                                               |

| ADC-EK12B   | TSC8702CN    |                                               |

| ADC-EK12DC  | TSC8750CJ    |                                               |

| ADC-EK12DM  | TSC8750BN    |                                               |

| ADC-EK12DR  | TSC8750CN    |                                               |

| ADC-EK08B   | TSC8700CJ    |                                               |

| ADC-ET10BC  | TSC8704CJ    |                                               |

| ADC-ET10BM  | TSC8704BN    |                                               |

| ADC-ET10BR  | TSC8704CN    |                                               |

| ADC-ET12BC  | TSC8705CJ    |                                               |

| ADC-ET12BM  | TSC8705BN    |                                               |

| ADC-ET12BR  | TSC8705CN    |                                               |

| ADC-ET8BC   | TSC8703CJ    |                                               |

| ADC-ET8BM   | TSC8703BL    |                                               |

| ADC-ET8BR   | TSC8703CL    |                                               |

| CD22104AE   | TSC7211AIPL  |                                               |

| CD22105AE   | TSC7211AMIPL |                                               |

| DS0026CJ-8  | TSC4261JA    | Pin Compatible, Functional Upgrade            |

| DS0026CN-8  | TSC426CPA    | Pin Compatible, Functional Upgrade            |

| DS0026J-8   | TSC426MJA    | Pin Compatible, Functional Upgrade            |

| HLCD7211-2  | TSC7211AIPL  |                                               |

| HLCD7211-4  | TSC7211AMIPL |                                               |

| ICL7106CJL  | TSC7106CJL   | TSC7106ACPL Has Improved Reference Voltage    |

| ICL7106CPL  | TSC7106CPL   | TSC7106ACPL Offers Improved Reference Tempco  |

| ICL7106RCPL | TSC7106RCPL  | TSC7106ARCPL Offers Improved Reference Tempco |

| ICL7107CJL  | TSC7107CJL   | TSC7107ACJL Offers Improved Reference Tempco  |

| ICL7107CPL  | TSC7107CPL   | TSC7107ACPL Offers Improved Reference Tempco  |

| ICL7107RCPL | TSC7107RCPL  | TSC7107ARCPL Offers Improved Reference Tempco |

| ICL7109CPL  | TSC7109CPL   | Exact Replacement. TSC7109BCPL For Lower Cost |

| ICL7109IJL  | TSC7109IJL   |                                               |

| ICL7109MJL  | TSC7109MJL   |                                               |

| ICL7116CJL  | TSC7116CJL   | TSC7116ACJL Offers Improved Reference Tempco  |

| ICL7116CPL  | TSC7116CPL   | TSC7116ACPL Offers Improved Reference Tempco  |

| ICL7117CJL  | TSC7117CJL   | TSC7117ACJL Offers Improved Reference Tempco  |

| ICL7117CPL  | TSC7117CPL   | TSC7117ACPL Offers Improved Reference Tempco  |

• •

. .

#### All TSC Products Cross-Referenced Are Plug-In Replacements (Cont.)

| Part Number  | TSC Number   | Comments                                                            |  |  |

|--------------|--------------|---------------------------------------------------------------------|--|--|

| ICL7126CJL   | TSC7126CJL   | TSC7126ACJL Offers Improved Reterence Tempco                        |  |  |

| ICL7126CPL   | TSC7126CPL   | TSC7126ACPL Offers Improved Reference Tempco                        |  |  |

| ICL7136CJL   | TSC7126CJL   | TSC7126CJL and TSC7126ACJL Are Plug-In Replacements                 |  |  |

| ICL7136CPL   | TSC7126CPL   | TSC7126CPL and TSC7126ACPL Are Plug-In Replacements                 |  |  |

| ICL7650CPA   | TSC7650CPA   | TSC900ACPA is a Low-Power Plug-In Upgrade                           |  |  |

| ICL7650CPD   | TSC7650CPD   | TSC900ACPD is a Low-Power Plug-In Upgrade                           |  |  |

| ICL7650IJA   | TSC7650IJA   | TSC900AIJA is a Low-Power Plug-In Upgrade                           |  |  |

| ICL7650IJD   | TSC7650IJD   | TSC900AIJD is a Low-Power Plug-In Upgrade                           |  |  |

| ICL7660CPA   | TSC7660CPA   |                                                                     |  |  |

| ICL7660IJA   | TSC7660IJA   |                                                                     |  |  |

| ICL7660MJA   | TSC7660MJA   |                                                                     |  |  |

| ICL8069CCZR  | TSC9491AJ    |                                                                     |  |  |

| ICL8069CMSQ  | TSC9491AM    |                                                                     |  |  |

| ICL8069DCZR  | TSC9491BJ    |                                                                     |  |  |

| ICL8069DMSQ  | TSC9491BM    |                                                                     |  |  |

| ICM7211AIPL  | TSC7211AIPL  |                                                                     |  |  |

| ICM7211AMIPL | TSC7211AMIPL |                                                                     |  |  |

| ICM7212AIJL  | TSC7212AIJL  | TSC700AIJL is a Higher LED Current Upgrade for "Brighter" Displays  |  |  |

| ICM7212AIPL  | TSC7212AIPL  | TSC700AIJL is a Higher LED Current Upgrade for "Brighter" Displays  |  |  |

| ICM7212AMIJL | TSC7212AMIJL | TSC700AMIJL is a Higher LED Current Upgrade for "Brighter" Displays |  |  |

| ICM7212AMIPL | TSC7212AMIPL | TSC701AMIJL is a Higher LED Current Upgrade for "Brighter" Displays |  |  |

| MC14433L     | TSC14433CL   | TSC14433ACL Offers Guaranteed Roll-Over Spec.                       |  |  |

| MC14433P     | TSC14433CJ   | TSC14433ACJ Offers Guaranteed Roll-Over Spec.                       |  |  |

| MMH0026CP1   | TSC426CPA    | Pin Compatible, Functional Upgrade                                  |  |  |

| MMH0026CU    | TSC426IJA    | Pin Compatible, Functional Upgrade                                  |  |  |

| MP5531C      | TSC9495CJ    |                                                                     |  |  |

| MP5532C      | TSC9496CJ    |                                                                     |  |  |

| REF01CP      | TSC9495CJ    |                                                                     |  |  |

| REF02CP      | TSC9495CJ    |                                                                     |  |  |

| TP4780       | TSC9400CJ    |                                                                     |  |  |

| TP4781       | TSC9401CJ    |                                                                     |  |  |

| VFQ-1C       | TSC9400CJ    |                                                                     |  |  |

| VFQ-1R       | TSC900CL     |                                                                     |  |  |

# SECTION 6

# **Advance Product Information**

#### Section 6 Advance Product Information 6-3 Bandgap Voltage Reference TSC04/05 6-5 TSC170/171 CMOS Current Mode SMPS Controller 6-7 16-Channel and Dual 8-Channel Bus Compatible Analog Multiplexers TSC400/401 6-15 TSC429 High Speed Single CMOS Power MOSFET Driver 6-17 TSC441/442/443 μ-Processor Compatible CMOS Analog Switches ..... 6-19 u-Processor Bus Compatible CMOS Quad Analog Switches TSC444/445/446 6-21 **TSC447** u-Processor Compatible Quad CMOS Analog Switch ..... 6-23 **TSC827** 1% ADC with LCD Bar-Graph Drive and Set Points ..... 6-25 TSC829 4 1/2 Digit ADC with LCD Drive and Surface Mount Package 6-27 **TSC913** Dual Auto-Zeroed Operational Amplifier 6-29 **TSC914** Quad Auto-Zeroed Operational Amplifier ..... 6-31 TSC4201/4202/4203 Low Cost CMOS Quad Analog Switches 6-33 TSC7129 4 1/2 Digit ADC with Triplex LCD Display Drive ..... 6-35 Low Power 3 1/2 Digit ADC with LCD Drive 6-37 TSC7136A

# TELEDYNE SEMICONDUCTOR

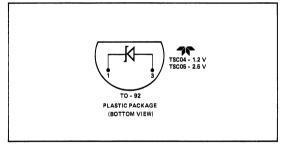

#### TSC04/1.2 V TSC05/2.5 V Band-Gap Reference

#### **General Description**

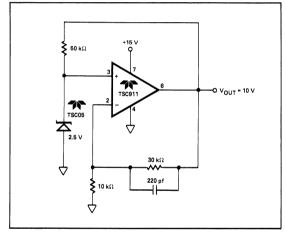

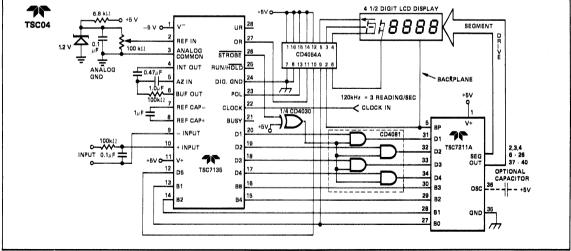

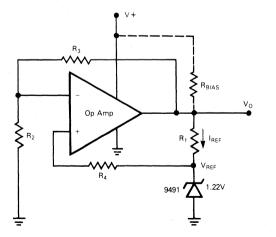

The TSC04 (1.2 V Output) and TSC05 (2.5 V Output) bipolar two terminal band-gap voltage references offer precision performance without a premium price. The TSC04/05 do not use thin film resistors. This greatly lowers manufacturing complexity and cost.

A 50 ppm/°C output temperature coefficient and 25  $\mu$ A to 10 mA operating current range make the devices attractive multimeter, data acquisition converter, and telecommunication voltage references

#### **Typical Application**

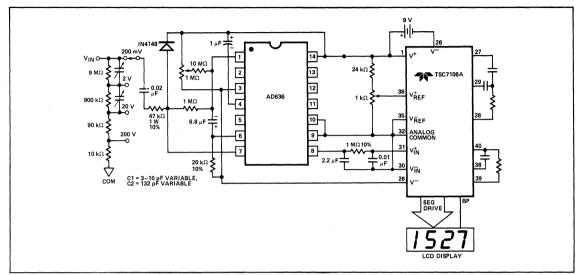

#### Typical 4 1/2 Digit DVM with LCD Display

#### Features

- 50 ppm/°C Temperature Coefficient

- 25 µA to 10 mA Operating Current Range

- 1 Ω Dynamic Impedance

- Low Cost TO-92 Plastic Package

- 1% Output Tolerance

- 1.2 V (TSC04) and 2.5 V (TSC05) Output Voltage Option

#### Applications

- ADC and DAC Reference

- Current Source Generation

- Threshold Detectors

- Power Supplies

- Multimeters

#### **Pin Configuration**

#### TELEDYNE SEMICONDUCTOR

# TELEDYNE SEMICONDUCTOR

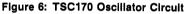

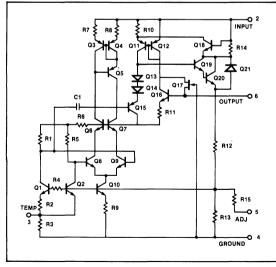

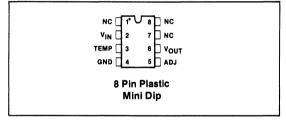

### TSC170/TSC171 CMOS Current Mode SMPS Controller • 3.8 mA Max. Supply Current Profutor • 50 ns Output Rise/Fall Time • 500 mA Output Drive

#### **General Description**

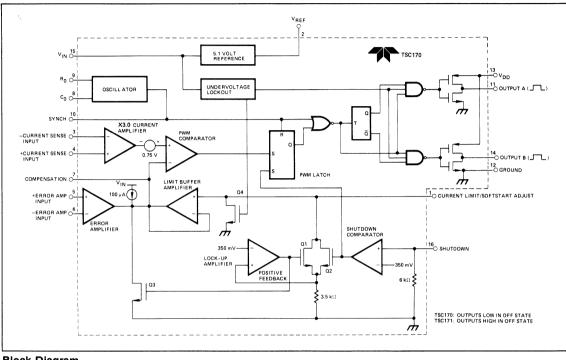

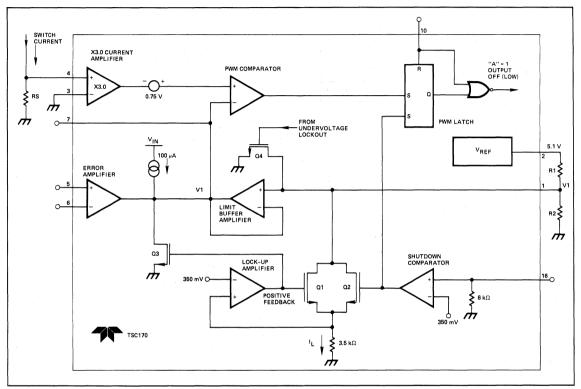

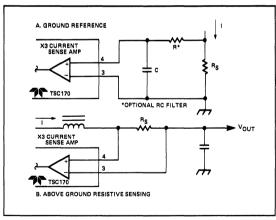

The TSC170/171 bring low power CMOS technology to the current mode switching power supply controller market. Maximum supply current is 3.8 mA. Bipolar current mode control integrated circuits require five times more operating current. Low power supply current eliminates auxiliary power transformers. In off line powering schemes where a simple zener diode circuit provides device supply voltage, power dissipation is greatly reduced. CMOS technology decreases system cost, increases power efficiency, reduces heat generation, and increases total system reliability.

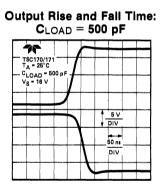

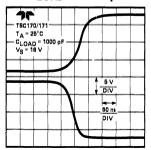

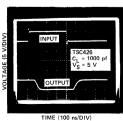

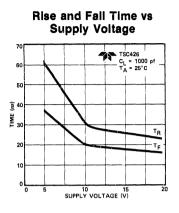

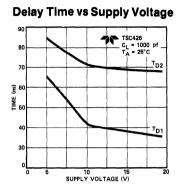

The dual totem pole CMOS outputs drive power MOSFET or bipolar transistors. The 50 ns maximum output rise and fall times with a 1000 pF capacitive load minimize power MOSFET transition power dissipation. Output peak current is 500 mA.

The TSC170/171 contain a full array of system protection circuits. The undervoltage lockout circuit forces outputs OFF if the supply voltage drops below 7.0 V. A soft start feature is also available. The soft start option forces the PWM outputs to initially operate at a minimum duty cycle and low peak output current. The TSC170/171 can be directly turned OFF through a remote shutdown control pin. The shutdown mode can be latched (power must be turned OFF to restart system) or non-latched. The soft start feature can also be used in system shutdown application. Double output pulse suppression guarantees output drive pulses always alternate from one output driver to the other. Peak current is adjustable by the user.

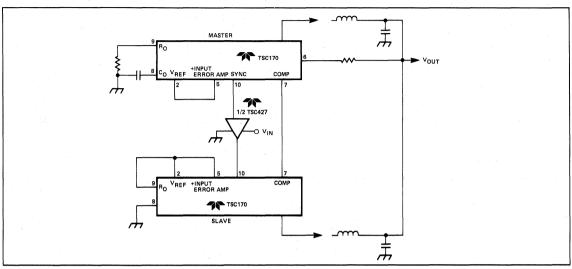

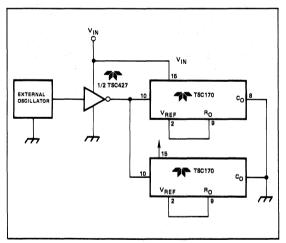

Current mode control lets users parallel power supply modules. Two or more TSC170/171 controllers can be slaved together for parallel operation. Circuits can operate from a master TSC170/171 internal oscillator or an external system oscillator.

The TSC170/171 operate from an 8 V to 16 V power supply. An internal 2% 5.1 V reference minimizes external component count. The TSC170/171 is pin compatible with the Unitrode UC1846/2846/3846 and UC1847/2847/3847 bipolar controllers.

Other advantages inherent in current mode control include superior line and load regulation and automatic symmetry correction in push-pull converters.

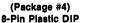

#### **Ordering Information**

| Part No.  | Package              | Operating<br>Temperature<br>Range |

|-----------|----------------------|-----------------------------------|

| TSC170CPE | 8-Pin<br>Plastic DIP | 0°C to 70°C                       |

| TSC170IJE | 8-Pin<br>CerDIP      | –25° C to 85° C                   |

#### Features

- Internal Reference ...... 5.1 V

- Fast Output Rise/Fall Time (C<sub>L</sub> = 1000 pF) ..... 50 ns

- Dual Push-Pull Outputs

- Direct Power MOSFET Drive

- High Totem Pole Output Drive ...... 500 mA

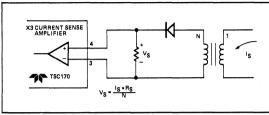

- Differential Current Sense Amplifier

- Programmable Current Limit

- Soft start Operation

- Double Pulse Suppression

- Under-Voltage Lockout

- Wide Supply Voltage Operation ...... 8 to 16 V

- High Frequency Operation ...... 200 kHz

- Plastic and CerDIP Package

- Available with Low (TSC170) or High (TSC171) "OFF" State Outputs

- Low Power, Pin Compatible Replacement for UC3846/3847

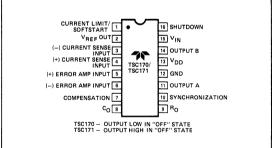

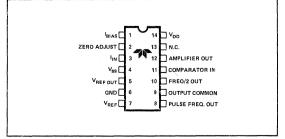

#### Pin Configuration

#### **Ordering Information Cont.**

| Part No.  | Package              | Operating<br>Temperature<br>Range |

|-----------|----------------------|-----------------------------------|

| TSC170MJE | 8-Pin<br>CerDIP      | -55°C to 125°C                    |

| TSC171CPE | 8-Pin<br>Plastic DIP | 0°C to 70°C                       |

| TSC171IJE | 8-Pin<br>CerDIP      | -25°C to 85°C                     |

| TSC171MJE | 8-Pin<br>CerDIP      | -55°C to 125°C                    |

| TSC170Y   | Chip                 |                                   |

| TSC171Y   | Chip                 |                                   |

#### TSC170/171

CMOS Current Mode SMPS Controller

• 3.8 mA Max. Supply Current

• 50 ns Output Rise/Fall Time

#### 500 mA Output Drive

#### **Absolute Maximum Ratings**

$\label{eq:linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_line$

| CerDIP Package Thermal Resistance:   |

|--------------------------------------|

| (Junction to Ambient) 105 °C/W       |

| (Junction to Case) 60 ° C/W          |

| Plasting Package Thermal Resistance: |

| (Junction to Ambient) 140 ° C/W      |

| (Junction to Case) 70 °C/W           |

| Operating Temp. Range                |

| Commercial 0 °C to +85 °C            |

| Industrial                           |

|                                      |

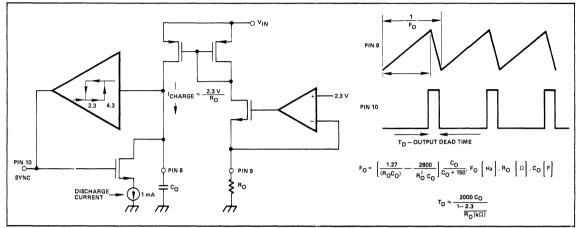

**Electrical Characteristics:**  $V_{IN} = 16 V$ ,  $R_O = 24 k\Omega$ ,  $C_O = 1 nF$ ,  $T_A = 25 °C$  Unless otherwise indicated.

|                                        |     |       |                                          |                               |              | C170/1      |                      |       |

|----------------------------------------|-----|-------|------------------------------------------|-------------------------------|--------------|-------------|----------------------|-------|

| ТҮРЕ                                   | NO. |       | PARAMETER                                | TEST CONDITION                | MIN          | ТҮР         | MAX                  | UNIT  |

|                                        | 1   | VREF  | Output Voltage                           | IOUT = 1 mA                   | 5.0          | 5.1         | 5.2                  | v     |

| REFERENCE                              | 2   |       | Line Regulation                          | V <sub>IN</sub> = 8 V to 16 V | <sup>-</sup> | 5           | 15                   | mV    |

| VOLTAGE                                | 3   |       | Load Regulation                          | IOUT = 1 mA to 10 mA          | ·····        | 3           | 15                   | mV    |

| •••••••••••••••••••••••••••••••••••••• | 4   | VRTC  | Temperature Coefficient                  | Over Operating Temp. Range    |              | 0.4         | 0.5                  | mV/°C |

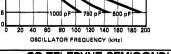

|                                        | 5   |       | Initial Frequency                        |                               | 38           | 42          | 46                   | kHz   |

| OSCILLATOR                             | 6   |       | Voltage Stability                        | V <sub>IN</sub> = 8 V to 16 V |              | 1.1         | 1.5                  | °/°/V |

|                                        | 7   |       | Temperature Stability                    | Over Operating Temp. Range    |              | 5           | 10                   | %     |

|                                        | 8   | VEOS  | Input Offset Voltage                     |                               |              |             | 20                   | mV    |

|                                        | 9   | IB    | Input Bias Current                       | · .                           |              |             | 1                    | nA    |

| ERROR                                  | 10  | VCMRR | Common-Mode Input Voltage                | V <sub>IN</sub> = 8 V to 16 V | 0            | <del></del> | V <sub>IN</sub> -2 V | v v   |

| AMPLIFIER                              | 11  | Avol  | Open-Loop Voltage Gain                   | V <sub>OUT</sub> = 1 V to 6 V | 70           |             |                      | dB    |

|                                        | 12  | BW    | Unity Gain Bandwidth                     |                               | . —          | 1.2         | -                    | MHz   |

|                                        | 13  | CMRR  | Common-Mode Rejection Ratio              | V <sub>CMV</sub> = 0 to 14 V  | 60           |             |                      | dB    |

|                                        | 14  | PSRR  | Power Supply Rejection Ratio             | VIN = 8 V to 16 V             | 60           |             |                      | dB    |

|                                        | 15  |       | Amplifier Gain                           | Pin 3 = 0 to 1.1 V            | 2.5          | 3.0         | 3.5                  | V/V   |

| CURRENT<br>SENSE<br>AMPLIFIER          | 16  |       | Maximum Differential<br>Input Signal     | Vpina - Vpin3                 | 1.1          | -           |                      | v     |

|                                        | 17  |       | Common-Mode Input Voltage                |                               | 0            |             | Vin -3 V             | V     |

| CURRENT                                | 18  |       | Current Limit<br>Offset Voltage          |                               | 0.5          |             | 1                    | v     |

| ADJUST                                 | 19  |       | Input Bias Current                       |                               | _            |             | 1                    | nA    |

|                                        | 20  | Vтв   | Threshold Voltage                        |                               | 0.3          | 0.35        | 0.4                  | V     |

| SHUTDOWN                               | 21  |       | Input Voltage Range                      |                               | 0            | _           | Vin                  | V     |

| TERMINAL                               | 22  |       | Minimum Latching<br>Current at Pin 1     |                               | 125          |             |                      | μA    |

|                                        | 23  |       | Maximum Non-Latching<br>Current at Pin 1 | ·.                            | -            |             | 50                   | μA    |

|                                        | 24  | VDD   | Output Voltage                           | Pin 13                        |              |             | Vin                  | V     |

|                                        | 25  | Vol   | Output Low Level                         | ISINK = 20 mA                 |              |             | 0.4                  | V     |

| OUTPUT                                 | 26  | Vol   | Output Low Level                         | ISINK = 100 mA                |              |             | 2.0                  | V     |

| STAGE                                  | 27  | Vон   | Output High Level                        | ISOURCE = 20 mA               | VIN - 1 V    |             |                      | v     |

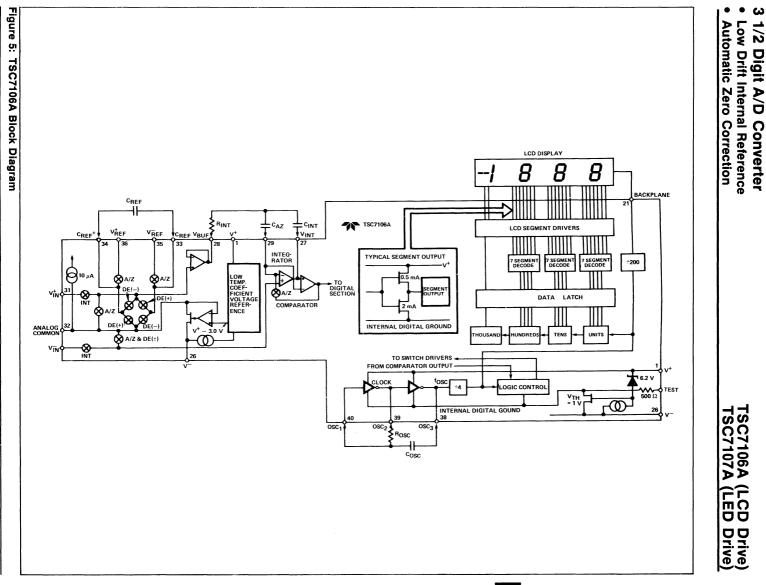

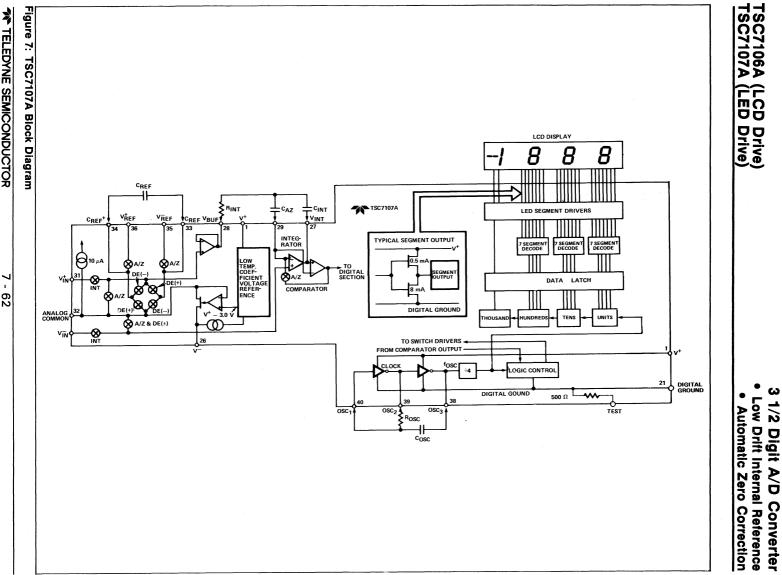

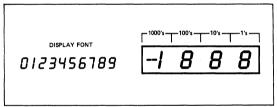

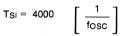

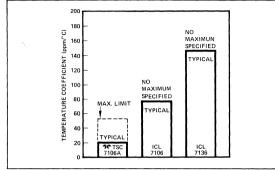

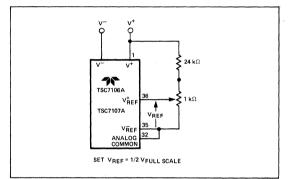

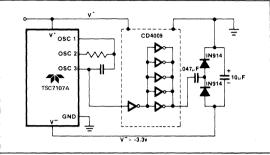

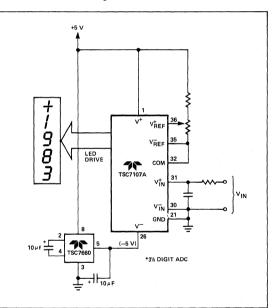

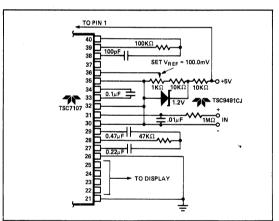

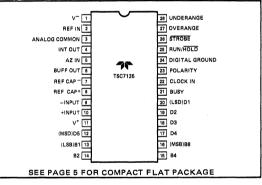

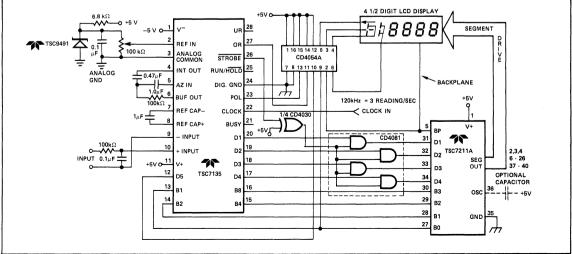

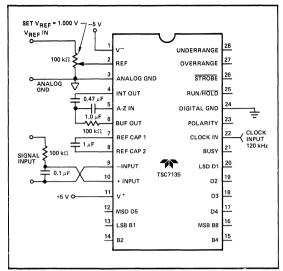

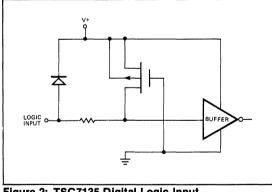

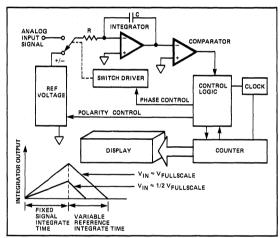

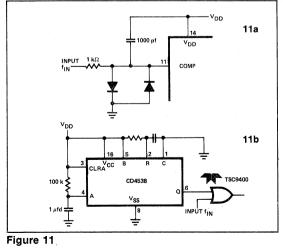

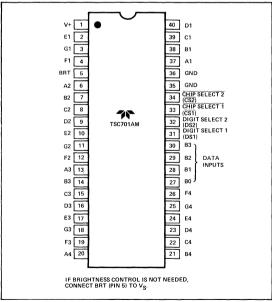

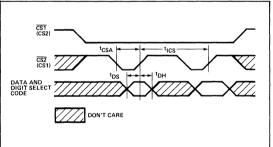

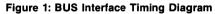

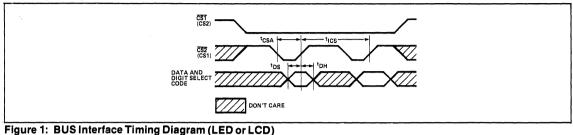

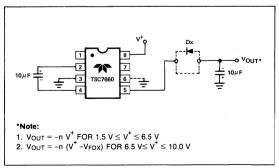

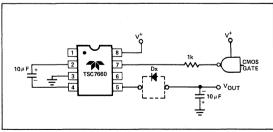

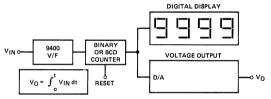

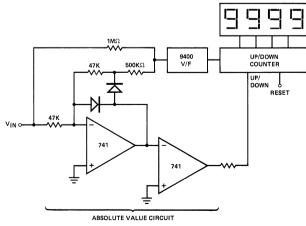

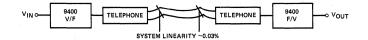

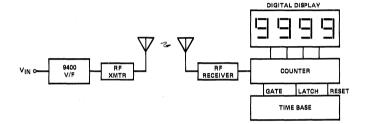

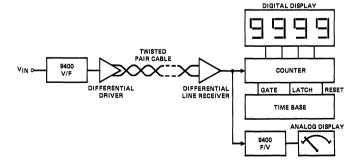

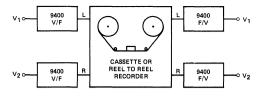

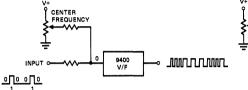

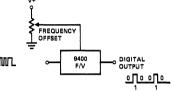

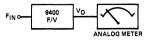

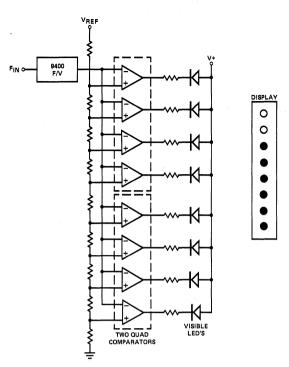

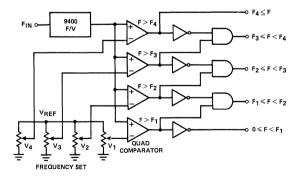

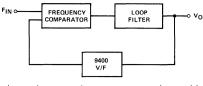

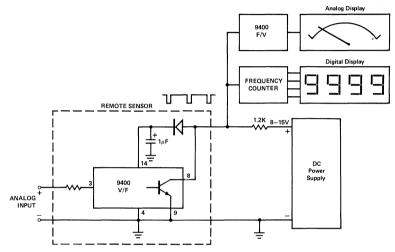

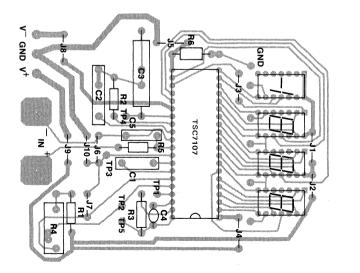

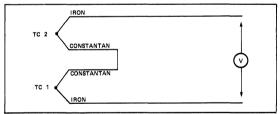

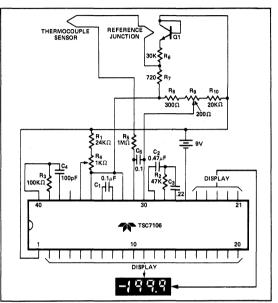

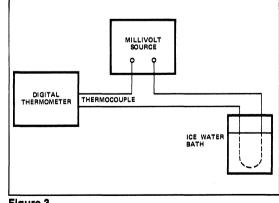

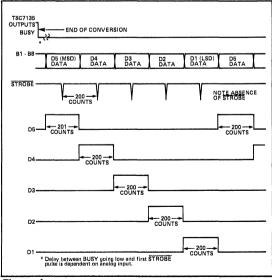

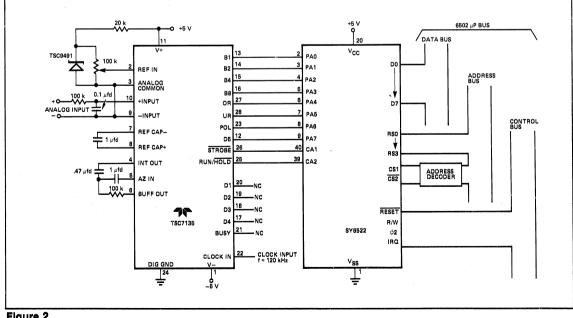

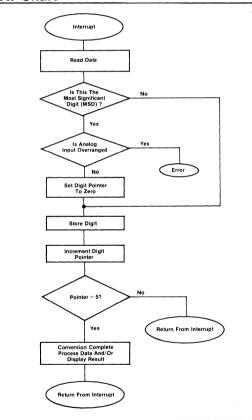

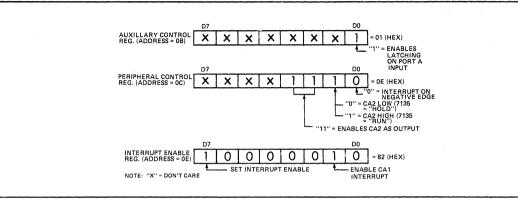

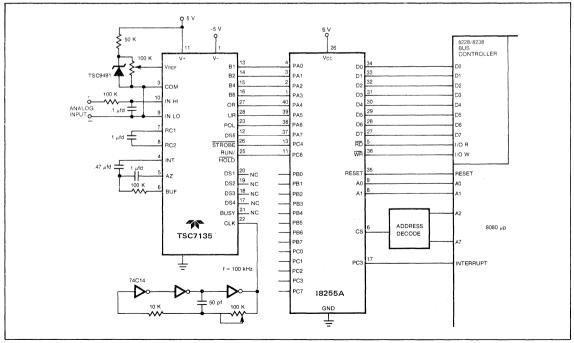

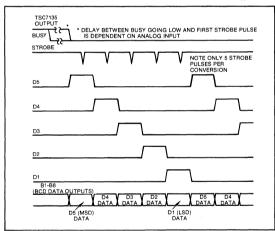

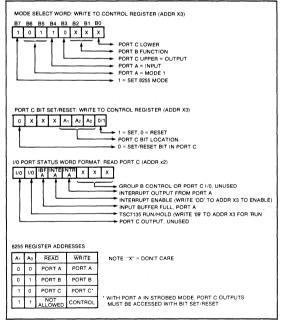

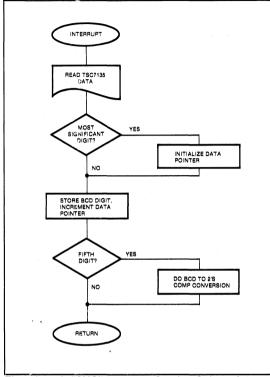

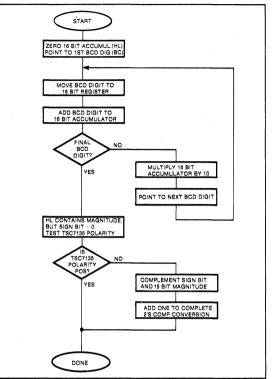

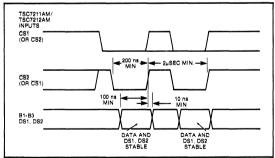

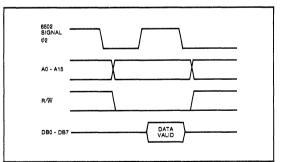

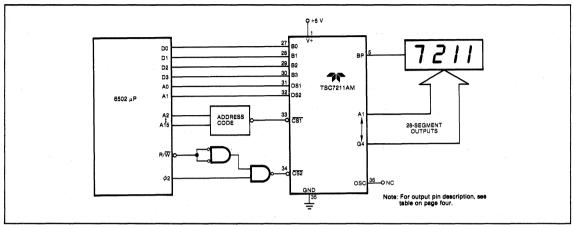

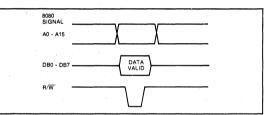

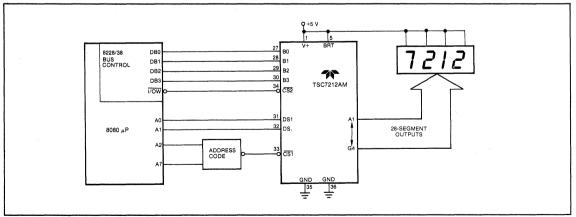

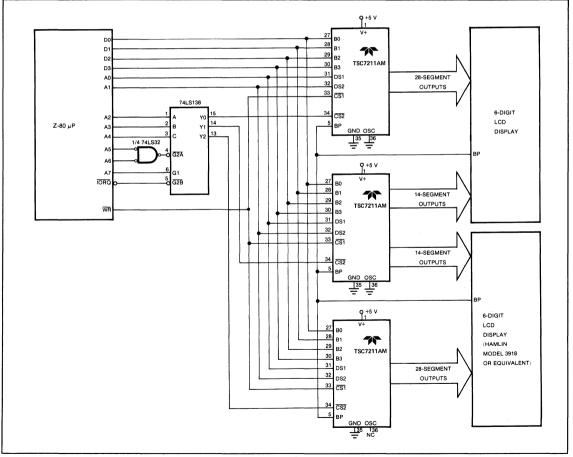

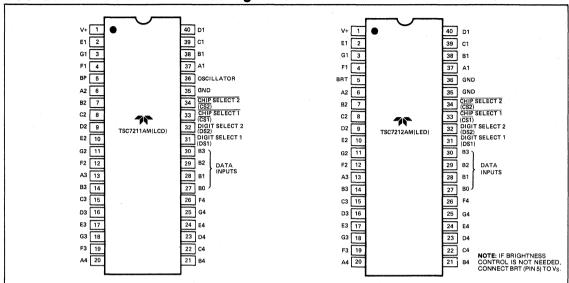

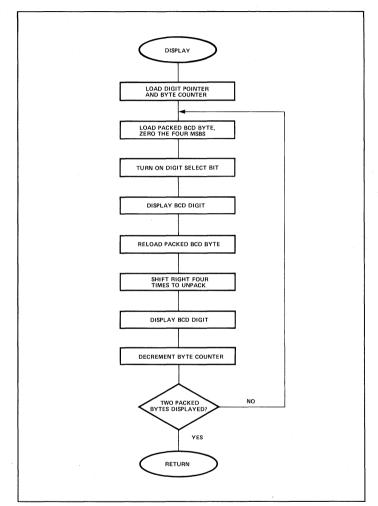

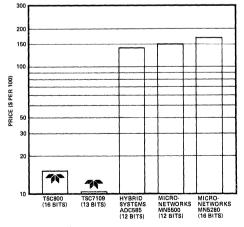

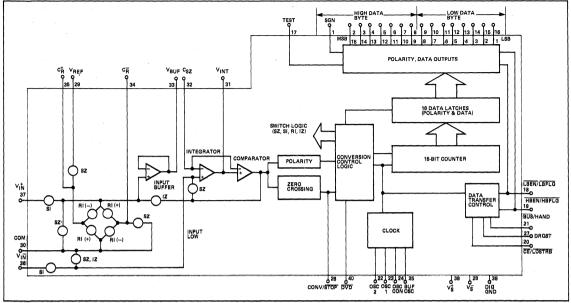

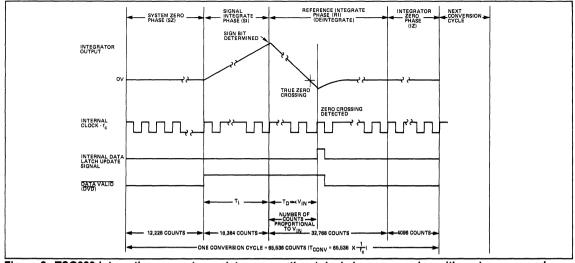

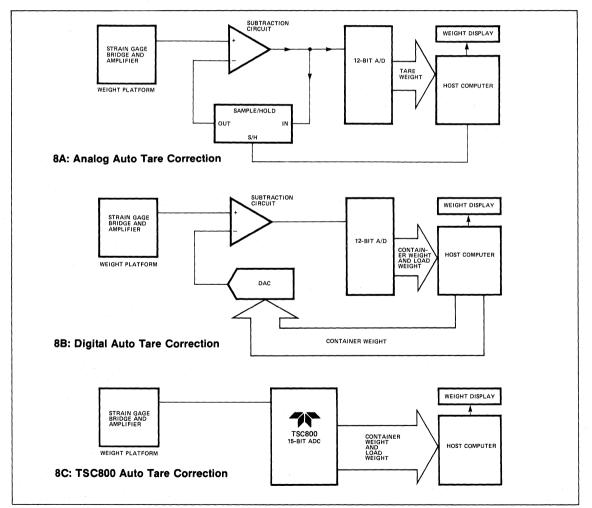

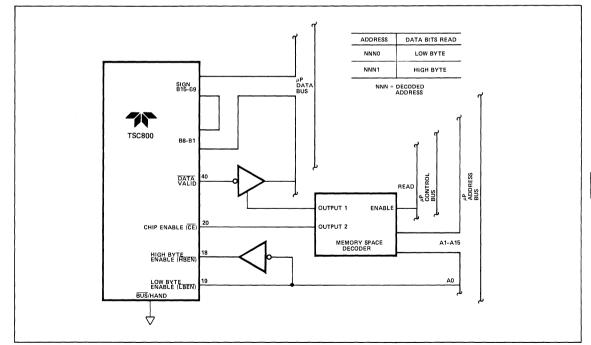

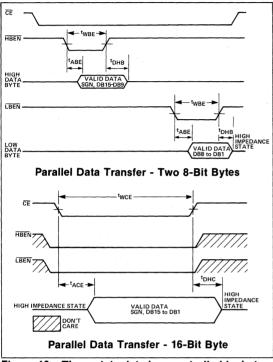

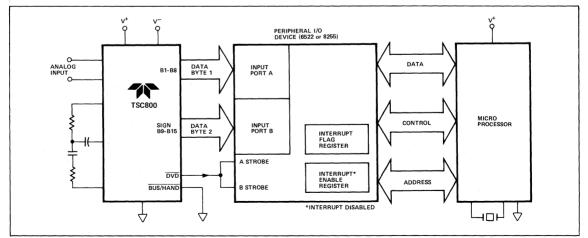

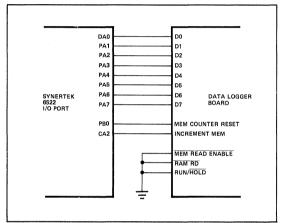

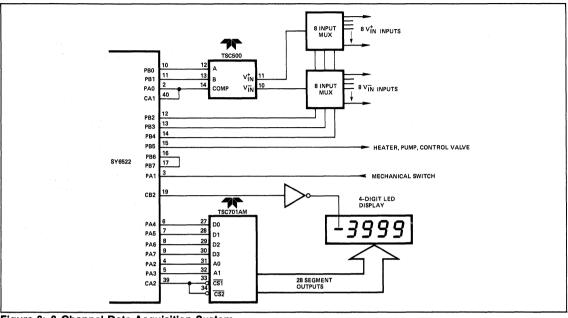

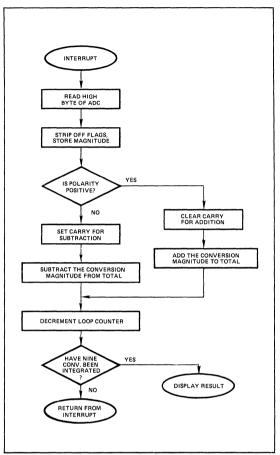

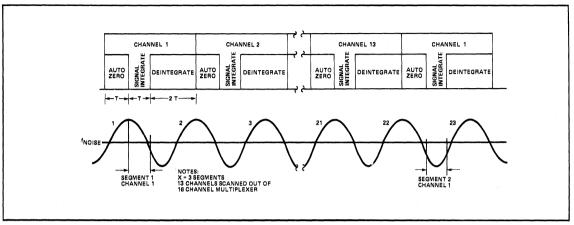

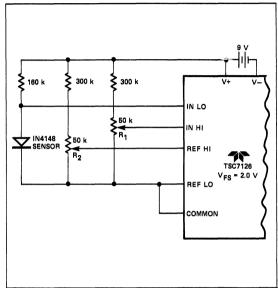

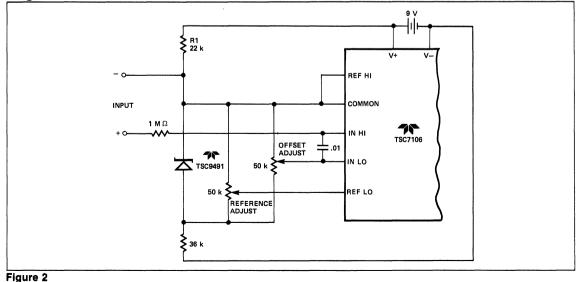

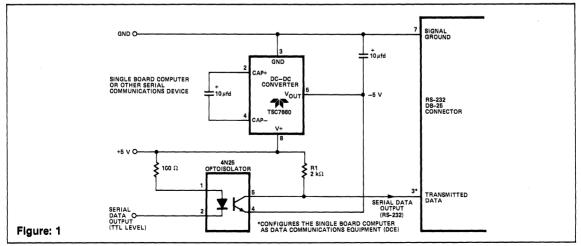

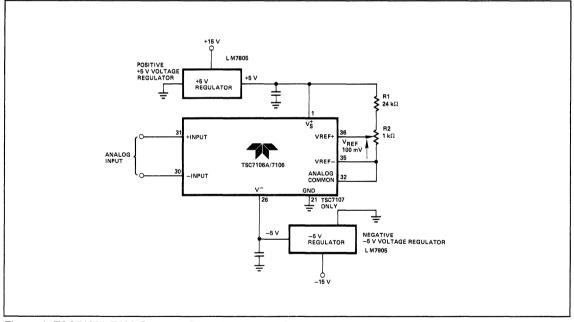

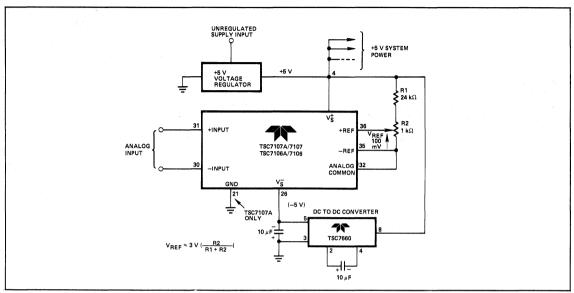

| UTAGE                                  | 28  | Vон   | Output High Level                        | ISOURCE = 100 mA              | VIN -3.5 V   | —           |                      | V     |