**Communication Solutions**

## SYM92C1000 Ethernet/IEEE 802.3 Media Access Controller with MII, 100Base-TX, and 10Base-T Interface

Copyright © 1995 by Symbios Logic, Incorporated, Fort Collins, Colorado, U.S.A. All rights reserved. ×

, č

1.1.1

¢

( ) ( )

## TABLE OF CONTENTS

| FEATURES                                   |   |

|--------------------------------------------|---|

| GENERAL DESCRIPTION                        | 7 |

| SYSTEM OVERVIEW                            |   |

| SYM92C1000 Media Access Controller         |   |

| Buffer Management Unit                     | 7 |

| Host Interface Controller                  | 7 |

| Physical Layer Device                      |   |

| PIN DESCRIPTIONS                           | 9 |

| FIXED PIN DESCRIPTIONS                     | 9 |

| MULTIPLEXED PIN DESCRIPTIONS               |   |

| MII Mode Pin Descriptions                  |   |

| TP-PMD Mode Pin Descriptions               |   |

| 10BASE-T Mode Pin Descriptions             |   |

| SYSTEM DESCRIPTION                         |   |

| HOST INTERFACE                             |   |

| I/O Register Read                          |   |

| I/O Register Write                         |   |

| HCLK Input                                 |   |

| BUFFER INTERFACE                           |   |

| Receive Interface                          |   |

| Receive Status Byte                        |   |

| Transmit Interface<br>Transmit Status Byte |   |

| JTAG INTERFACE                             |   |

| LED INTERFACE                              |   |

| CONFIGURATION INTERFACE                    |   |

| MULTIPLEXED I/O INTERFACE                  |   |

| MII Interface                              |   |

| TP-PMD Interface                           |   |

| 4B/5B Encoding                             |   |

| 100BASE-T Ciphering<br>10BASE-T Interface  |   |

|                                            |   |

| POWER SUPPLY CONSIDERATIONS                |   |

| FUNCTIONAL DESCRIPTION                     |   |

| TRANSMIT LOGIC                             |   |

| CSMA/CD PROTOCOL                           |   |

| RECEIVE LOGIC                              |   |

| ADDRESS RECOGNITION                                                       | 30         |

|---------------------------------------------------------------------------|------------|

| CYCLIC REDUNDANCY CHECK                                                   | 30         |

| FULL/HALF-DUPLEX OPERATIONS                                               | 30         |

| INTERNAL REGISTERS                                                        | 31         |

| CONFIGURATION REGISTER (00h)                                              | 31         |

| BACK-TO-BACK INTERPACKET GAP REGISTER (01h)                               | 32         |

| NON-BACK-TO-BACK INTERPACKET GAP REGISTER (02h)                           | 33         |

| MII REQUEST REGISTER (03h)                                                | 33         |

| CONTROL REGISTER ADDRESS (04h)                                            | 34         |

| MII Address Register (04h)                                                | 34         |

| TP-PMD Control Register (04h)                                             | 34         |

| 10BASE-T Control Register (04h)                                           | 35         |

| MII WRITE DATA REGISTER (05h)                                             | 35         |

| MII READ DATA REGISTER (06h)                                              | 36         |

| MII INDICATORS REGISTER (07h)                                             | 36         |

| MECHANICAL SPECIFICATIONS                                                 | 37         |

| ORDERING INFORMATION                                                      | 38         |

| ELECTRICAL SPECIFICATIONS                                                 | 39         |

| ABSOLUTE MAXIMUMS                                                         | 39         |

| DC CHARACTERISTICS                                                        | 39         |

| AC CHARACTERISTICS                                                        | 40         |

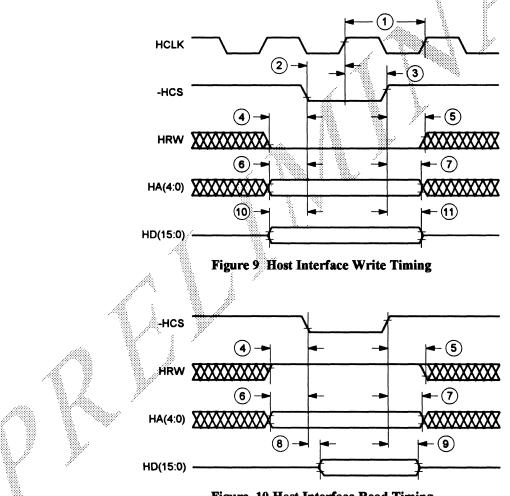

| Host Interface Read and Host Interface Write Timing                       | 40         |

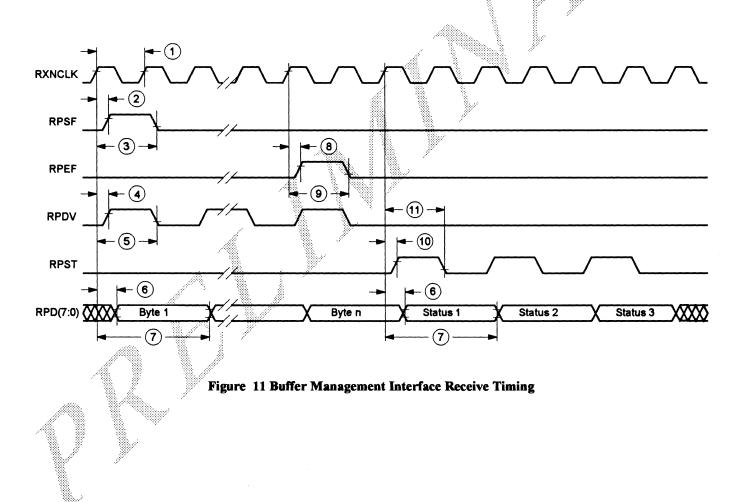

| Buffer Management Interface Receive Output Timing                         | 41         |

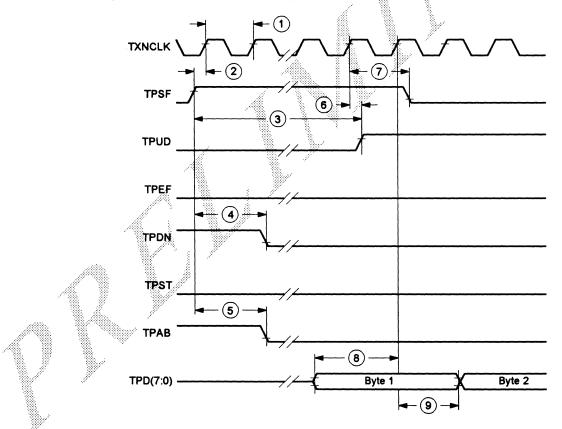

| Buffer Management Interface Begin Normal Transmit                         | 42         |

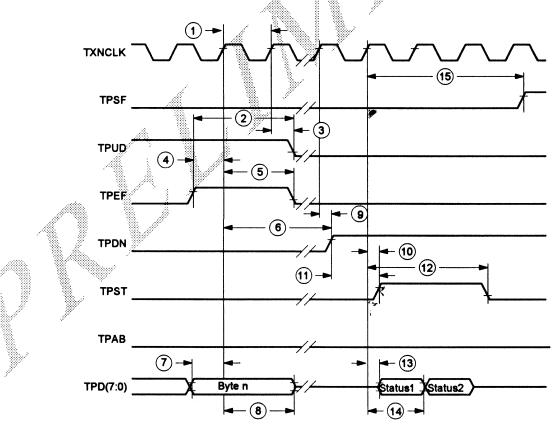

| Buffer Management Interface End Normal Transmit Timings                   | 43         |

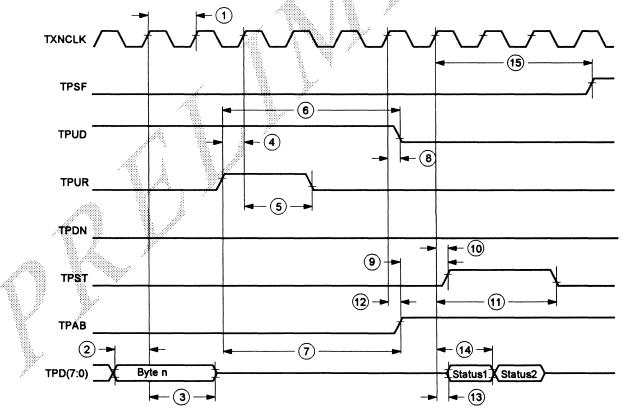

| Buffer Management Interface Transmit Underrun Abort Timing                | 44         |

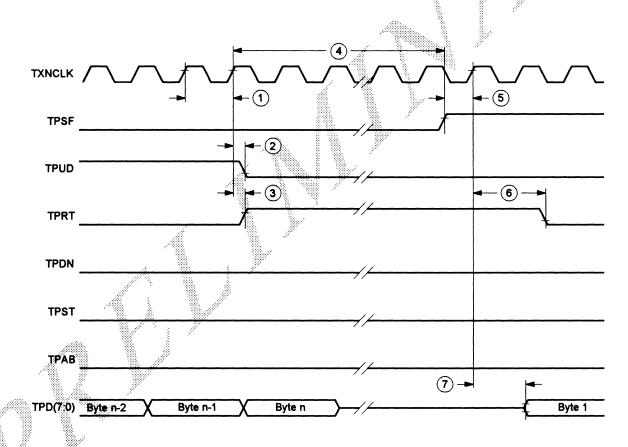

| Buffer Management Interface Transmit Retry Timing                         | 45         |

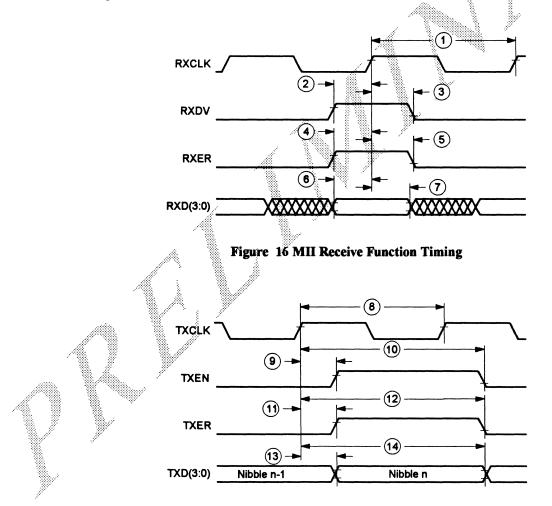

| MII Receive and MII Transmit Function Timing                              | 46         |

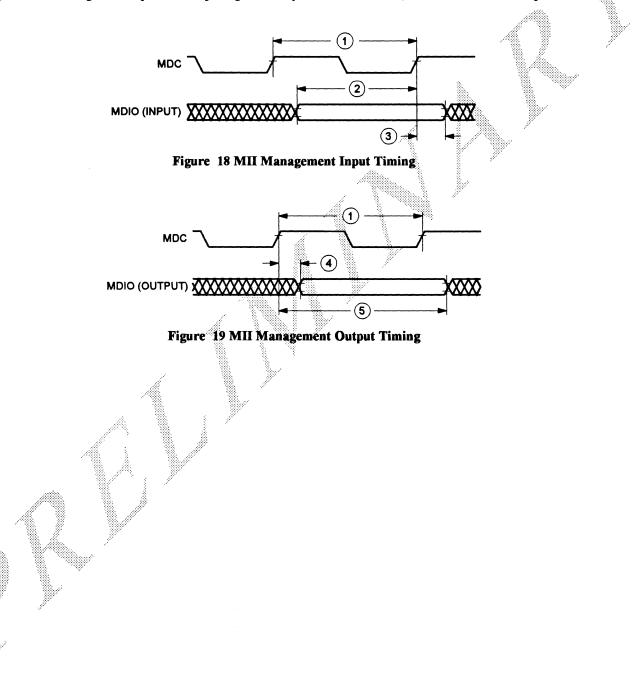

| MII Management Input and MII Management Output Timing                     | 47         |

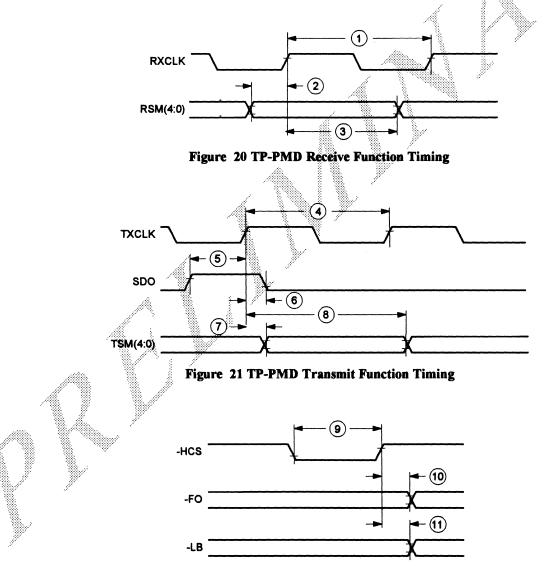

| TP-PMD Receive, TP-PMD Transmit, and TP-PMD Control Function Timing       | 48         |

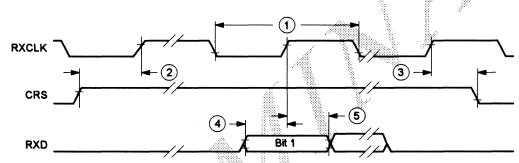

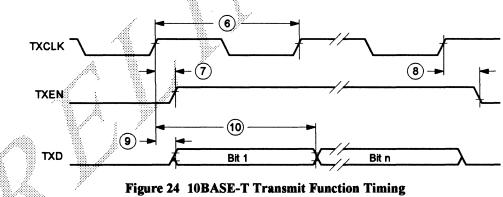

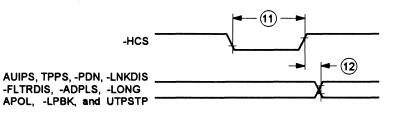

| 10BASE-T Receive, 10BASE-T Transmit, and 10BASE-T Control Function Timing | 49         |

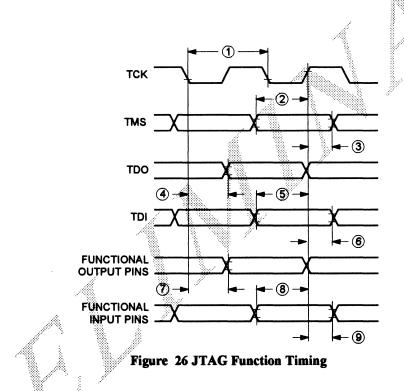

| JTAG Function Timing                                                      | 50         |

| CLOCK SPECIFICATIONS                                                      | 51         |

| HOST AND JTAG CLOCKS                                                      | 51         |

| TP-PMD CLOCKS                                                             | 51         |

| 10BASE-T CLOCKS                                                           | 51         |

| MII CLOCKS                                                                | <i>c</i> ~ |

|                                                                           | 52         |

SYMBIOS

# FAST Ethernet Media Access Controller with MII, 100BASE-TX, and 10BASE-T Interfaces

## **FEATURES**

- Supports the EtherCore<sup>™</sup> design methodology

- Supports the IEEE 802.3 standards for Media Independent Interface (MII), 100BASE-TX and 10BASE-T

- Supports IEEE 1149.1 standards for JTAG boundary-scan testing

- Accepts broadcast and multicast packets

- Supports automatic re-transmission after collisions without software intervention

- Programmable CRC generation

- Supports half- or full-duplex operation

- Provides statistics vectors for both transmit and receive modes

- 128-pin PQFP package

- Programmable pad insertion

- Programmable interframe spacing (IFS)

- Programmable huge packet support

- Supports programmable late collision retry

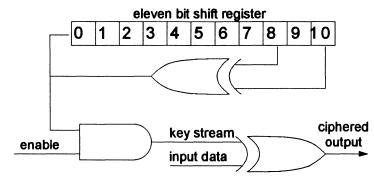

- Programmable 100BASE-TX ciphering/deciphering

- 100BASE-TX 4B/5B encoding/decoding

- 10BASE-T serializer/deserializer

- Optimized for hub and switched applications, no address comparison logic

- I/O mux for MII, TP-PMD or 10BASE-T operation

- Separate 8-bit receive and transmit ports, 16-bit host I/O port for I/O and statistics register access

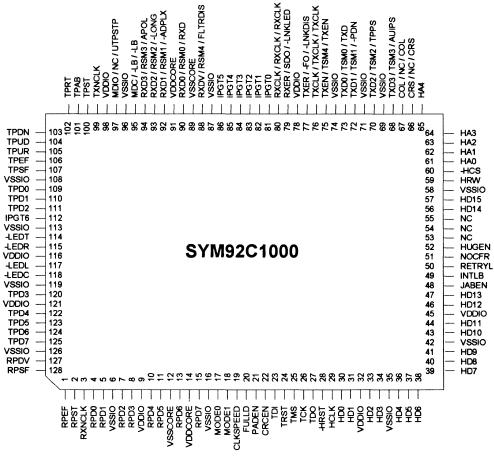

**Figure 1 Pinout Diagram**

| Pin             | Signal Name  | Туре     | Interface    | Pin Description                      |

|-----------------|--------------|----------|--------------|--------------------------------------|

| 1               | RPEF         | 0        | RX           | Receive Packet End of Frame          |

| 2               | RPST         | 0        | RX           | Receive Packet Status                |

| 3               | RXNCLK       | 0        | RX           | Receive Nibble Clock (2.5 or 25 MHz) |

| 4               | RPD0         | 0        | RX           | Receive Data Bit 0                   |

| 5               | RPD1         | 0        | RX           | Receive Data Bit 1                   |

| 6               | VSSIO        | io/gnd   | -            |                                      |

| 7               | RPD2         | 0        | RX           | Receive Data Bit 2                   |

| 8               | RPD3         | 0        | RX           | Receive Data Bit 3                   |

| 9               | VDDIO        | io/pwr   | -            |                                      |

| 10              | RPD4         | 0        | RX           | Receive Data Bit 4                   |

| 11              | RPD5         | 0        | RX           | Receive Data Bit 5                   |

| 12              | VSSCORE      | c/gnd    | -            |                                      |

| 13              | RPD6         | 0        | RX           | Receive Data Bit 6                   |

| 14              | VDDCORE      | c/pwr    | -            |                                      |

| 15              | RPD7         | 0        | RX           | Receive Data Bit 7                   |

| 16              | VSSIO        | io/gnd   | -            |                                      |

| 17              | MODE0        | i        | CONFIG       | Mode Bit 0                           |

| 18              | MODE1        | i        | CONFIG       | Mode Bit 1                           |

| 19              | CLKSPEED     | i        | CONFIG       | Host Clock Speed Select              |

| 20              | FULLD        | i        | CONFIG       | Full-Duplex Enable                   |

| 21              | PADEN        | i        | CONFIG       | Pad Enable                           |

| 22              | CRCEN        | i        | CONFIG       | CRC Enable                           |

| 23              | TDI          | i        | JTAG         | Test Data In                         |

| 24              | TRST         | i        | JTAG         | Test Reset                           |

| 25              | TMS          | i        | JTAG         | Test Mode Select                     |

| 26              | ТСК          | i        | JTAG         | Test Clock                           |

| 27              | TDO          | 0        | JTAG         | Test Data Out                        |

| 28              | -HRST        | i        | HOST         | Reset active low                     |

| 29              | HCLK         | i        | HOST         | 33 MHz maximum Host Clock            |

| 30              | HD0          | t/s      | HOST         | Host Data Bit 0                      |

| 31              | HD1          | t/s      | HOST         | Host Data Bit 1                      |

| 32              | VDDIO        | io/pwr   | -            | II - D - D' -                        |

| 33              | HD2          | t/s      | HOST         | Host Data Bit 2                      |

| 34              | HD3          | t/s      | HOST         | Host Data Bit 3                      |

| 35              | VSSIO        | io/gnd   |              | Hert Data Dit 4                      |

| 36              | HD4          | t/s      | HOST         | Host Data Bit 4                      |

| 37              | HD5          | t/s      | HOST         | Host Data Bit 5                      |

| 38              | HD6          | t/s      | HOST         | Host Data Bit 6                      |

| 39              | HD7          | t/s      | HOST         | Host Data Bit 7                      |

| 40              | HD8          | t/s      | HOST         | Host Data Bit 8                      |

| 41              | HD9          | t/s      | HOST         | Host Data Bit 9                      |

| 42              | VSSIO        | io/gnd   | LIOCT        | Uest Data Dit 10                     |

| 43              | HD10         | t/s      | HOST         | Host Data Bit 10                     |

| 44              | HD11         | t/s      | HOST         | Host Data Bit 11                     |

| <u>45</u><br>46 | VDDIO        | io/pwr   | -<br>UOST    | Uest Data Bit 12                     |

| <u>46</u><br>47 | HD12<br>HD13 | t/s      | HOST<br>HOST | Host Data Bit 12<br>Host Data Bit 13 |

| 47              |              | t/s<br>i | CONFIG       | Jabber Enable                        |

| 40              | JABEN        |          | LONLIG       |                                      |

#### **Table 1 Pinout Summary**

| Pin             | Signal Name | Туре   | Interface | Pin Description                                 |

|-----------------|-------------|--------|-----------|-------------------------------------------------|

| 49              | INTLB       | i      | CONFIG    | Internal Loopback Enable                        |

| 50              | RETRYL      | i      | CONFIG    | Late Retry Enable                               |

| 51              | NOCFR       | i      | CONFIG    | No Ciphering                                    |

| 52              | HUGEN       | i      | CONFIG    | Huge Packet Enable                              |

| 53              | NC          | -      | -         | No Connect                                      |

| 54              | NC          | -      | -         | No Connect                                      |

| 55              | NC          | -      | -         | No Connect                                      |

| 56              | HD14        | t/s    | HOST      | Host Data Bit 14                                |

| 57              | HD15        | t/s    | HOST      | Host Data Bit 15                                |

| 58              | VSSIO       | io/gnd | -         |                                                 |

| 59              | HRW         | i      | HOST      | Read Write                                      |

| 60              | -HCS        | i      | HOST      | Chip Select active low                          |

| 61              | HA0         | i      | HOST      | Host Address Bit 0                              |

| 62              | HAI         | i      | HOST      | Host Address Bit 1                              |

| 63              | HA2         | i      | HOST      | Host Address Bit 2                              |

| 64              | HA3         | i      | HOST      | Host Address Bit 3                              |

| 65              | HA4         | i      | HOST      | Host Address Bit 4                              |

| 66              | Multimode   | -      |           | Refer To Specific Mode Pin Description Table    |

| 67              | Multimode   | -      | f         | Refer To Specific Mode Pin Description Table    |

| 68              | Multimode   | -      | 1         | Refer To Specific Mode Pin Description Table    |

| 69              | VSSIO       | io/gnd | -         |                                                 |

| 70              | Multimode   | -      |           | Refer To Specific Mode Pin Description Table    |

| 71              | VSSIO       | io/gnd | -         |                                                 |

| 72              | Multimode   | -      | <u></u>   | Refer To Specific Mode Pin Description Table    |

| 73              | Multimode   | -      | <u>+</u>  | Refer To Specific Mode Pin Description Table    |

| 74              | VSSIO       | io/gnd | -         |                                                 |

| 75              | Multimode   | -      |           | Refer To Specific Mode Pin Description Table    |

| 76              | Multimode   | -      | 1         | Refer To Specific Mode Pin Description Table    |

| 77              | Multimode   | -      | 1         | Refer To Specific Mode Pin Description Table    |

| 78              | VDDIO       | io/pwr | -         |                                                 |

| 79              | Multimode   | -      |           | Refer To Specific Mode Pin Description Table    |

| 80              | Multimode   | -      |           | Refer To Specific Mode Pin Description Table    |

| 81              | IPGT0       | i      | CONFIG    | Back-to-Back IPG Bit 0                          |

| 82              | IPGT1       | i      | CONFIG    | Back-to-Back IPG Bit 1                          |

| 83              | IPGT2       | i      | CONFIG    | Back-to-Back IPG Bit 2                          |

| 84              | IPGT3       | i      | CONFIG    | Back-to-Back IPG Bit 3                          |

| 85              | IPGT4       | i      | CONFIG    | Back-to-Back IPG Bit 4                          |

| 86              | IPGT5       | i      | CONFIG    | Back-to-Back IPG Bit 5                          |

| 87              | VSSIO       | io/gnd | -         | Durk to Durk II O Dit 5                         |

| 88              | Multimode   | -      |           | Refer To Specific Mode Pin Description Table    |

| 89              | VSSCORE     | c/gnd  | <u> </u>  |                                                 |

| 90              | Multimode   | -      | <u>+</u>  | Refer To Specific Mode Pin Description Table    |

| 91              | VDDCORE     | c/pwr  |           | Refer to openie wode till Description fable     |

| 92              | Multimode   | -      | <u></u>   | Refer To Specific Mode Pin Description Table    |

| 93              | Multimode   | -      | <u> </u>  | Refer To Specific Mode Pin Description Table    |

| 94              | Multimode   | -      | +         | Refer To Specific Mode Pin Description Table    |

| 95              | Multimode   |        | <u> </u>  | Refer To Specific Mode Pin Description Table    |

| <u>93</u><br>96 | VSSIO       | io/gnd |           |                                                 |

| 90              | Multimode   |        | +         | Refer To Specific Mode Pin Description Table    |

| <u> </u>        | Imutimode   | L      | 1         | I NEICH TO Specific Mode Fill Description Table |

| Pin | Signal Name | Туре   | Interface | Pin Description                            |

|-----|-------------|--------|-----------|--------------------------------------------|

| 98  | VDDIO       | io/pwr | -         |                                            |

| 99  | TXNCLK      | 0      | TX        | Transmit Nibble Clock (2.5, 10, or 25 MHz) |

| 100 | TPST        | 0      | TX        | Transmit Packet Status                     |

| 101 | TPAB        | 0      | TX        | Transmit Packet Abort                      |

| 102 | TPRT        | 0      | TX        | Transmit Packet Retry                      |

| 103 | TPDN        | 0      | TX        | Transmit Packet Done                       |

| 104 | TPUD        | 0      | TX        | Transmit Packet Used Data                  |

| 105 | TPUR        | i      | TX        | Transmit Packet Underrun                   |

| 106 | TPEF        | i      | TX        | Transmit Packet End of Frame               |

| 107 | TPSF        | i      | TX        | Transmit Packet Start of Frame             |

| 108 | VSSIO       | io/gnd | -         |                                            |

| 109 | TPD0        | i/o    | TX        | Transmit Data bit 0                        |

| 110 | TPD1        | i/o    | TX        | Transmit Data bit 1                        |

| 111 | TPD2        | i/o    | TX        | Transmit Data bit 2                        |

| 112 | IPGT6       | i      | CONFIG    | Back-to-Back IPG Bit 6                     |

| 113 | VSSIO       | io/gnd | -         |                                            |

| 114 | -LEDT       | od     | LED       | Transmit LED                               |

| 115 | -LEDR       | od     | LED       | Receive LED                                |

| 116 | VDDIO       | io/pwr | -         |                                            |

| 117 | -LEDL       | od     | LED       | Link LED                                   |

| 118 | -LEDC       | od     | LED       | Collision LED                              |

| 119 | VSSIO       | io/gnd | -         |                                            |

| 120 | TPD3        | i/o    | TX        | Transmit Data bit 3                        |

| 121 | VDDIO       | io/pwr | -         |                                            |

| 122 | TPD4        | i/o    | TX        | Transmit Data bit 4                        |

| 123 | TPD5        | i/o    | TX        | Transmit Data bit 5                        |

| 124 | TPD6        | i/o    | TX        | Transmit Data bit 6                        |

| 125 | TPD7        | i/o    | TX        | Transmit Data bit 7                        |

| 126 | VSSIO       | io/gnd | -         |                                            |

| 127 | RPDV        | 0      | RX        | Receive Packet Data Valid                  |

| 128 | RPSF        | 0      | RX        | Receive Packet Start of Frame              |

| Pin No. | Signal Name | Туре | Pin Description       |

|---------|-------------|------|-----------------------|

| 66      | CRS         | i    | Carrier Sense         |

| 67      | COL         | i    | Collision             |

| 68      | TXD3        | 0    | Transmit Data Bit 3   |

| 70      | TXD2        | 0    | Transmit Data Bit 2   |

| 72      | TXD1        | 0    | Transmit Data Bit 1   |

| 73      | TXD0        | 0    | Transmit Data Bit 0   |

| 75      | TXEN        | 0    | Transmit Enable       |

| 76      | TXCLK       | i    | Transmit Clock        |

| 77      | TXER        | 0    | Transmit Error        |

| 79      | RXER        | i    | Receive Error         |

| 80      | RXCLK       | i    | Receive Clock         |

| 88      | RXDV        | i    | Receive Data Valid    |

| 90      | RXD0        | i    | Receive Data Bit 0    |

| 92      | RXD1        | i    | Receive Data Bit 1    |

| 93      | RXD2        | i    | Receive Data Bit 2    |

| 94      | RXD3        | i    | Receive Data Bit 3    |

| 95      | MDC         | 0    | Management Data Clock |

| 97      | MDIO        | i/o  | Management Data       |

## Table 2 MII Mode Pinout Summary

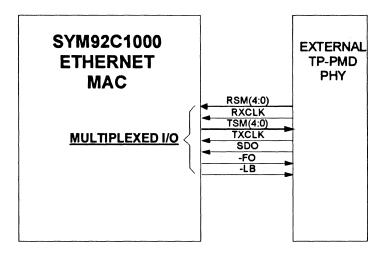

## Table 3 TP-PMD Mode Pinout Summary

| Pin No. | Signal Name | Туре | Pin Description                                         |

|---------|-------------|------|---------------------------------------------------------|

| 66      | NC          | -    | No Connect (this pin should be tied either high or low) |

| 67      | NC          | -    | No Connect (this pin should be tied either high or low) |

| 68      | TSM3        | 0    | Transmit Data Bit 3                                     |

| 70      | TSM2        | 0    | Transmit Data Bit 2                                     |

| 72      | TSM1        | 0    | Transmit Data Bit 1                                     |

| 73      | TSM0        | 0    | Transmit Data Bit 0                                     |

| 75      | TSM4        | 0    | Transmit Data Bit 4                                     |

| 76      | TXCLK       | i    | Transmit Clock                                          |

| 77      | -FO         | 0    | Fiber Optic Off (active low)                            |

| 79      | SDO         | i    | Signal Detect                                           |

| 80      | RXCLK       | i    | Receive Clock                                           |

| 88      | RSM4        | i    | Receive Data Bit 4                                      |

| 90      | RSM0        | i    | Receive Data Bit 0                                      |

| 92      | RSM1        | i    | Receive Data Bit 1                                      |

| 93      | RSM2        | i    | Receive Data Bit 2                                      |

| 94      | RSM3        | i    | Receive Data Bit 3                                      |

| 95      | -LB         | 0    | Loopback (active low)                                   |

| 97      | NC          | -    | No Connect (this pin should be tied either high or low) |

| Pin No. | Signal Name | Туре | Pin Description                |

|---------|-------------|------|--------------------------------|

| 66      | CRS         | i    | Carrier Sense                  |

| 67      | COL         | i    | Collision                      |

| 68      | AUIPS       | 0    | AUI Port Select                |

| 70      | TPPS        | 0    | TP Port Select                 |

| 72      | -PDN        | 0    | Powerdown Enable (active low)  |

| 73      | TXD         | 0    | Transmit Data                  |

| 75      | TXEN        | 0    | Transmit Enable                |

| 76      | TXCLK       | i    | Transmit Clock                 |

| 77      | -LNKDIS     | 0    | Link Disable (active low)      |

| 79      | -LNKLED     | i    | Link Pulse (active low)        |

| 80      | RXCLK       | i    | Receive Clock                  |

| 88      | FLTRDIS     | 0    | Filter Disable                 |

| 90      | RXD         | i    | Receive Data                   |

| 92      | -ADPLX      | 0    | Autoduplex Enable (active low) |

| 93      | -LONG       | 0    | Long Cable Mode (active low)   |

| 94      | APOL        | 0    | Autopolarity Enable            |

| 95      | -LB         | 0    | Loopback Enable (active low)   |

| 97      | UTPSTP      | 0    | Cable Type Select              |

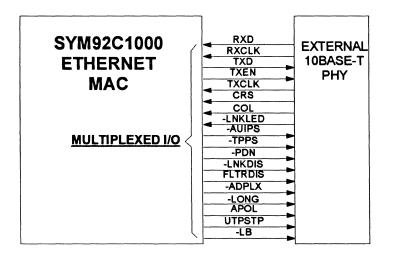

## Table 4 10BASE-T Mode Pinout Summary

## **Table 5 Pin Type Descriptions**

| Туре   | Description                                                                |

|--------|----------------------------------------------------------------------------|

| c/pwr  | Core Logic Power: a +5 V connection providing power to digital core logic. |

| c/gnd  | Core Logic Ground: a ground connection to the digital core logic.          |

| io/pwr | I/O Driver Power: a +5 V connection providing power to the I/O drivers.    |

| io/gnd | I/O Driver Ground: a ground connection to the I/O drivers.                 |

| i      | Input: a standard input signal.                                            |

| 0      | Output: a standard output signal.                                          |

| i/o    | Input/Output: a standard input/output signal.                              |

| od     | Open Drain: a switched ground connection for LEDs.                         |

| t/s    | Tristate: a bi-directional, tristate input/output signal.                  |

## **GENERAL DESCRIPTION**

The SYM92C1000 is a half- or full-duplex, highperformance Local Area Network (LAN) 10 Mbps or 100 Mbps Media Access Controller (MAC) that supports the IEEE 802.3 specifications for Ethernet LANs. The SYM92C1000 MAC controls the network parameters of an IEEE 802.3 network and supports network management with network counters and status vectors. The SYM92C1000 supports 5 volt LAN environments.

The SYM92C1000 is designed to operate in one of three physical layer (PHY) interface modes; 10-100 Mbps Media Independent Interface (MII), 100 Mbps Twisted Pair - Physical Media Dependent (TP-PMD, used for 100BASE-TX or fiber optics), or 10 Mbps 10BASE-T. The SYM92C1000 is optimized for switched applications and does not perform address comparison.

The SYM92C1000 supports a variety of programmable options including; pad insertion for small data packets, huge packet enable to allow transmission and reception of oversize packets, an Inter Packet Gap (IPG) specifier to customize system performance, late collision retry, and 100BASE-TX ciphering and deciphering.

The SYM92C1000 meets the IEEE 802.3 retransmission specifications by automatically retransmiting packets experiencing a collision up to fifteen times without software intervention. After sixteen failed attempts for a single packet the SYM92C1000 aborts the transmission and notifies the host of the failed packet transmission.

In TP-PMD mode, the SYM92C1000 supports 4-bit to 5-bit conversion to provide sufficient transition density to facilitate clock recovery when not in cipher mode. In 10BASE-T mode, the SYM92C1000 performs bit serialization and deserialization to present and receive IEEE 802.3 standard data for an external Manchester encoder/decoder (MENDEC).

The SYM92C1000 supports optional Cyclic Redundancy Checking (CRC) insertion on transmit for data verification. When the SYM92C1000 is used in a node network adapter card application, the CRC is used to ensure the transmitted and received data is valid. When the SYM92C1000 is used in either a hub or a repeater application, the CRC must be disabled, allowing the original CRC to pass through to the destination for the final data check.

The SYM92C1000 supports the Symbios Logic EtherCore design methodology. The block approach to core designs provides the flexibility to develop an Ethernet system to meet specific needs.

Symbios Logic EtherCore products are sold as standard products for quick time-to-market designs. This family of EtherCore products is developed and supported by Symbios Logic ASIC design tools for built-in cost reduction through integration.

#### SYSTEM OVERVIEW

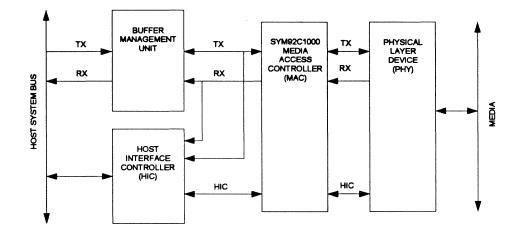

Figure 2 shows a typical system implementation using the SYM92C1000. The system is comprised of the SYM92C1000, Buffer Management Unit, Host Interface Controller (HIC), and the Physical Layer Device (PHY).

#### SYM92C1000 Media Access Controller

The SYM92C1000 performs all the MAC functions of the system, including 100 Mbps transmit and receive, 10 Mbps transmit and receive, collision monitoring and retransmission, pad insertion, CRC generation, CRC verification and IPG management.

#### **Buffer Management Unit**

The Buffer Management Unit temporarily stores the LAN data as it passes between the MAC and the Host System Bus and typically consists of a FIFO and control logic.

#### Host Interface Controller

The Host Interface Controller (HIC) is the communications port between the SYM92C1000 and the host system and receives configuration instructions from the host and returns configuration information as well as transmit and receive status upon request.

#### **Physical Layer Device**

The Physical Layer Device (PHY) has three possible configurations; MII, TP-PMD, and 10BASE-T modes. In MII mode, the PHY consists of circuitry to convert 4-bit MII frame data from the SYM92C1000 into serial data that is media-ready. In TP-PMD mode, the PHY

converts the frame data from encoded, ciphered 5-bit 25 MHz format presented by the SYM92C1000 to 125 MHz serialized 100BASE-TX data that is media-ready. In 10BASE-T mode, the PHY takes the 10 MHz serial data from the SYM92C1000, Manchester encodes it and makes it media-ready. Typically the PHY requires encoder, transceiver, filters, and magnetics.

**Figure 2** Typical System Implementation

## **PIN DESCRIPTIONS**

#### **FIXED PIN DESCRIPTIONS**

On the SYM92C1000, 110 of the 128 pins have a fixed functionality in all three modes of operation (MII, TP-PMD, or 10BASE-T), these pins are listed here. The pin descriptions for the remaining 18 pins from the multiplexed I/O have three different mode options (MII, TP-PMD, or 10BASE-T) depending on configuration and are listed in individual pin description sections related to each mode.

#### CLKSPEED: Host Clock Speed Select:

This configuration input is tied high to inform the SYM92C1000 that the host clock rate is between 25 MHz and 33 MHz, a low input indicates a clock rate less than or equal to 25 MHz. This pin is valid only in MII mode and has a weak internal pulldown, if left unconnected this function defaults to clock speed less than or equal to 25 MHz. Configuration pins are used to load startup data to the Configuration Register, the contents of the register can be overwritten at any time with new values.

#### CRCEN: Cyclic Redundancy Check Enable

This configuration input is used to enable CRC error generation. The SYM92C1000 will continuously calculate the CRC and append the result to the end of the transmit packet. If PADEN is set, CRCEN is ignored and a CRC is generated. This pin has a weak internal pulldown, if left unconnected this function is disabled at reset. Configuration pins are used to load startup data to the Configuration Register, the contents of the register can be overwritten at any time with new values.

#### FULLD: Full Duplex Enable

This configuration input is used to put the SYM92C1000 into full duplex operation. This pin has a weak internal pulldown, if left unconnected this function is disabled at reset. Configuration pins are used to load startup data to the Configuration Register, the contents of the register can be overwritten at any time with new values.

#### HA(4:0): Host Address Bus

These five input lines are used to address the internal registers of the SYM92C1000.

#### HCLK: Host Clock

This input is used as the 33 MHz maximum host interface clock.

#### -HCS: Host Chip Select

This active-low input is driven low to enable the reading and writing of data in the internal registers of the SYM92C1000 in conjunction with HRW.

#### HD(15:0): Host Data Bus

These sixteen bi-directional lines are used to transfer data between the external host and the internal registers of the SYM92C1000. HD(15:0) is in the tristate condition when not in read mode.

#### -HRST: Host Reset

This active-low asynchronous input is driven low to force the SYM92C1000 into an idle state and reset all internal registers to default values. -HRST must be held low for a minimum of 20 HCLK cycles and allowed an additional 20 cycles to complete the reset procedure before normal operations resume. For power-on reset with the configuration interface pins unconnected, -HRST must be held low for a minimum of 150 HCLK cycles and then allowed an additional 20 cycles before normal operations begin.

#### HRW: Host Read/Write Select

This input is used to select read or write operation. Driving HRW high allows read operations and driving HRW low allows write operations.

#### HUGEN: Huge Packet Enable

This configuration input is used to enable the SYM92C1000 to transmit and receive packets with more than the IEEE maximum of 1518 bytes. This pin has a weak internal pulldown, if left unconnected this function is disabled at reset. Configuration pins are used to load startup data to the Configuration Register, the contents of the register can be overwritten at any time with new values.

#### INTLB: Internal Loopback Enable

The SYM92C1000 has internal loopback capability, setting this configuration input will cause the MAC to begin internal loopback. The SYM92C1000 does not need to be in full duplex mode to perform internal loopback. This pin has a weak internal pulldown, if left unconnected this function is disabled at reset. Configuration pins are used to load startup data to the Configuration Register, the contents of the register can be overwritten at any time with new values.

#### IPGT (6:0): Back-To-Back Interpacket Gap

These configuration inputs are used to provide the reset value for the Back-to-Back Interpacket Gap register. IPGT(4:3) have weak internal pullups, the others have weak internal pulldowns. This provides a reset value of 0x18 (960 ns in 100 Mbps mode,  $2.4 \,\mu$ s in 10 Mbps mode) when left unconnected. Configuration pins are used to load startup data to the Configuration Register, the contents of the register can be overwritten at any time with new values.

#### JABEN: Jabber Enable

This configuration input is used to enable the SYM92C1000 jabber logic at reset. If the SYM92C1000 transmits continuously for 20 ms it will abort the transmission and drive TXEN low to block all transmissions for 250 ms. This configuration is valid only in 10BASE-T mode. This pin has a weak internal pulldown, if left unconnected this function is disabled at reset. Configuration pins are used to load startup data to the Configuration Register, the contents of the register can be overwritten at any time with new values.

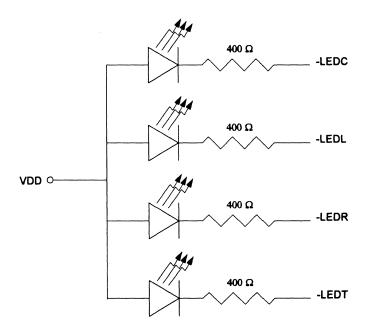

#### -LEDC: Collision LED

This open-drain output is driven low when the SYM92C1000 detects a collision. When not active it is in a high impedance state. This output is stretched to 30 ms.

#### -LEDL: Link LED

This open-drain output is driven low when the SYM92C1000 detects link. When not active it is in a high impedance state. This output is stretched to 30 ms. In MII mode the MII Request Register bit 1 (SCAN) must be set to 1 for this output to be valid.

#### -LEDR: Receive LED

This open-drain output is driven low when the SYM92C1000 is receiving. When not active it is in a high impedance state. This output is stretched to 30 ms.

#### -LEDT: Transmit LED

This open-drain output is driven low when the SYM92C1000 is transmitting. When not active it is in a high impedance state. This output is stretched to 30 ms.

#### MODE(1:0): Mode Select

This configuration input is used to select the reset configuration of the multiplexed I/O interface. 00 selects MII mode, 01 selects TP-PMD mode, and 10

selects 10BASE-T mode. These pins have a weak internal pulldown, if left unconnected the SYM92C1000 defaults to MII mode. Configuration pins are used to load startup data to the Configuration Register, the contents of the register can be overwritten at any time with new values.

#### NOCFR: No Ciphering

This configuration input disables the ciphering function in TP-PMD mode. This pin has a weak internal pulldown, if left unconnected this function is disabled at reset and ciphering will occur. Configuration pins are used to load startup data to the Configuration Register, the contents of the register can be overwritten at any time with new values.

#### PADEN: Pad Enable

This configuration input is used to instruct the SYM92C1000 to pad with zeros any short packets out to the IEEE minimum of 64 bytes after reset. It is up to the receive software to read the packet length field and strip off added padding. In the Pad Enable mode, a CRC is generated regardless of CRCEN. This pin has a weak internal pulldown, if left unconnected this function is disabled at reset. Configuration pins are used to load startup data to the Configuration Register, the contents of the register can be overwritten at any time with new values.

#### **RETRYL: Late Collision Retry**

This configuration input is used to instruct the SYM92C1000 to allow late collision retries. A late collision occurs more than 512 bit times after the start of a transmission and indicates a mis-configured network topology. This pin has a weak internal pulldown, if left unconnected this function is disabled at reset. Configuration pins are used to load startup data to the Configuration Register, the contents of the register can be overwritten at any time with new values.

#### RPD(7:0): Receive Packet Data Bus

These eight outputs are used to transfer the receive data byte and the receive status byte from the SYM92C1000 to the external buffer management unit.

#### **RPDV:** Receive Packet Data Valid

This output is driven high when a valid receive data byte is on RPD(7:0).

#### RPEF: Receive Packet End of Frame This output is driven high at the end of the receive

This output is driven high at the end of the receive packet.

#### **RPSF: Receive Packet Start of Frame**

This output is driven high at the start of the receive packet.

RPST: Receive Packet Status

This output is driven high when a valid receive status byte is on RPD(7:0).

RXNCLK: Receive Nibble Clock

This output is the 25 MHz or 2.5 MHz (depending on 100 Mbps or 10 Mbps data rate) nibble receive clock to synchronize receive data for the external buffer management unit. All receive interface signals from the SYM92C1000 to the Receive Buffer Management Unit are synchronous to RXNCLK.

#### TCK: Test Clock

This input is the JTAG clock and is limited to 10 MHz maximum. It is used to shift test data and JTAG control information into and out of the SYM92C1000 during JTAG test operations. This pin should not be left floating, if JTAG is not used tie TCK to ground.

#### TDI: Test Data In

This input is the JTAG serial data input, it is used to shift test data and instructions into the SYM92C1000 during a JTAG test. This pin has a weak internal pullup and may be left unconnected if JTAG is not used.

#### TDO: Test Data Out

This output is the JTAG serial data output, it is used to shift test data and instructions out of the SYM92C1000 during a JTAG test.

#### TMS: Test Mode Select

This input is the JTAG mode select, it is used to control the state operation of the SYM92C1000 during a JTAG test. This input has a weak internal pullup and may be left unconnected if JTAG is not used.

#### **TPAB:** Transmit Packet Abort

This output is driven high when a normal transmission is aborted due to TPUR being asserted by the buffer management unit. During a retransmit, indicated by TPRT, the transmission may still be aborted by asserting TPUR but TPAB will not be driven high and no abort will be indicated by this pin.

#### TPD(7:0): Transmit Packet Data Bus

These eight bi-directional lines are used to transfer the transmit data byte from the external buffer management unit to the SYM92C1000. After transmission these lines transfer the transmit status

bytes from the SYM92C1000 to the external buffer management unit. TPD(7:0) is in a tristate condition when not driven by the SYM92C1000 or the external buffer management unit.

#### **TPDN:** Transmit Packet Done

This output is driven high when the SYM92C1000 has finished a normal packet transmission.

#### **TPEF:** Transmit Packet End of Frame

This input is driven high coincident with data loaded into TPD(7:0) to indicate the current byte is the end of a packet.

TPRT: Transmit Packet Retry

This output is driven high when a collision has occurred and retransmission of the packet is required.

TPSF: Transmit Packet Start of Frame This input is driven high to start a packet transmission.

#### **TPST: Transmit Packet Status**

This output is driven high when valid transmit status bytes are on TPD(7:0).

#### TPUD: Transmit Packet Data Used

This output is driven high when data transmission has begun on the media.

#### TPUR: Transmit Packet Underrun

This input is driven high to abnormally end a packet transmission. This signal causes TPAB to be asserted except when TPRT is asserted.

#### -TRST: Test Reset

This active-low input is the JTAG reset. This input has a weak internal pullup, if JTAG is not used or TCK is not clocked then tie -TRST to ground. If JTAG is used then -TRST needs to be held low during chip reset.

#### TXNCLK: Transmit Nibble Clock

This output is the 25 MHz, 10 MHz, or 2.5 MHz (depending on 100 Mbps or 10 Mbps data rate) nibble transmit clock for synchronizing data from the external buffer management unit. All transmit interface signals between the Transmit Buffer Management Unit and the SYM92C1000 are synchronous to TXNCLK.

VDDCORE: Logic Core Power These pins provide +5 volts to the digital logic core.

VDDIO: IO Driver Power These pins provide +5 volts to the I/O drivers. VSSCORE: Logic Core Ground These pins provide the ground connection for the digital logic core.

VSSIO: IO Driver Ground These pins provide the ground connection for the I/O drivers.

#### MULTIPLEXED PIN DESCRIPTIONS

#### MII Mode Pin Descriptions

#### COL: MII Collision

This asynchronous input is driven high for two TXCLK periods minimum when the external MII PHY detects a collision.

#### CRS: MII Carrier Sense

This asynchronous input is driven high for two TXCLK periods minimum by the external MII PHY when either the transmit or receive medium is active.

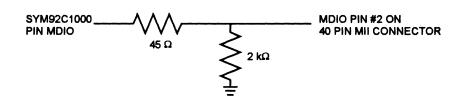

#### MDC: MII Management Clock

This output is the 2.5 MHz or less reference clock for the management data.

#### MDIO: MII Management Data

This bi-directional line is used to transfer the management data between the SYM92C1000 and the external MII PHY.

RXCLK: MII Receive Clock

This input is the 2.5-25 MHz nibble receive clock from the external MII PHY. All PHY receive signals to the SYM92C1000 are synchronous to RXCLK.

#### RXD(3:0): MII Receive Data Bus

These four inputs are used to transfer the receive data nibble from the external MII PHY to the SYM92C1000.

## RXDV: MII Receive Data Valid

This input is driven high when a valid receive data nibble is on RXD(3:0).

#### RXER: MII Receive Error This input is driven high when there is an error on the receive data stream.

#### TXCLK: MII Transmit Clock This input is the 2.5-25 MHz nibble transmit clock from the external MII PHY. All PHY transmit signals from the SYM92C1000 are synchronous to TXCLK.

#### TXD(3:0): MII Transmit Data Bus

These four outputs are used to transfer the transmit data nibble from the SYM92C1000 to the external MII PHY.

TXEN: MII Transmit Enable

This output is driven high when a valid transmit data nibble is on TXD(3:0).

TXER: MII Transmit Error

This output is driven high when there is an error on the transmit data stream.

#### **TP-PMD Mode Pin Descriptions**

#### -FO: TP-PMD Fiber Optic Off

This active-low output is driven low to turn off an external TP-PMD PHY fiber optic transmit circuit. This signal is controlled directly by the TP-PMD Control Register bit -FO.

#### -LB: TP-PMD Loopback

This active-low output is driven low to perform the loopback function in the external TP-PMD PHY. This signal is controlled directly by the TP-PMD Control Register bit -LB. External loopback can only occur when the SYM92C1000 is in full duplex mode.

#### RSM(4:0): TP-PMD Receive Data Bus These five inputs are used to transfer data from the external TP-PMD PHY to the SYM92C1000.

#### RXCLK: TP-PMD Receive Clock This input is the 25 MHz symbol receive

This input is the 25 MHz symbol receive clock from the external TP-PMD PHY. All PHY receive signals to the SYM92C1000 are synchronous to RXCLK.

#### SDO: TP-PMD Signal Detect

This input is driven high by the TP-PMD PHY when there is activity on the network.

#### TSM(4:0): TP-PMD Transmit Data Bus These five outputs are used to transfer data from the SYM92C1000 to the external TP-PMD PHY.

#### TXCLK: TP-PMD Transmit Clock

This input is the 25 MHz symbol transmit clock from the external TP-PMD PHY. All PHY transmit signals from the SYM92C1000 are synchronous to TXCLK.

#### **10BASE-T Mode Pin Descriptions**

-ADPLX: 10BASE-T Autoduplex Enable/Jabber Disable This active-low output is typically used to disable an autoduplex function and enable a jabber function on the external 10BASE-T PHY (note, the SYM92C1000 does not support autoduplex). This pin is controlled from the 10BASE-T Control Register bit -ADPLX.

APOL: 10BASE-T Autopolarity Enable

This output is typically driven high to enable an external 10BASE-T PHY autopolarity function. This pin is controlled from the 10BASE-T Control Register bit APOL.

#### AUIPS: 10BASE-T AUI Port Select

This output is typically used in conjunction with TPPS to select the output port on an external 10BASE-T PHY (see Table 6). This pin is controlled from the 10BASE-T Control Register bit AUIPS.

#### COL: 10BASE-T Collision

This asynchronuous input is driven high by the 10BASE-T PHY for two TXCLK periods minimum when a collision has been detected on the network.

#### CRS: 10BASE-T Carrier Sense

This input is driven high by the 10BASE-T PHY when there is activity on the network.

#### FLTRDIS: 10BASE-T Filter Disable

This output is typically driven high to disable an external 10BASE-T PHY transmit and receive filter function. This pin is controlled from the 10BASE-T Control Register bit -FLTRDIS.

-LB: 10BASE-T Loopback Enable/SQE Disable

This active-low output is typically used to enable the loopback or SQE functions on an external 10BASE-T PHY. This pin is controlled from the 10BASE-T Control Register bit -LB. External loopback can only occur when the SYM92C1000 is in full duplex mode.

#### -LNKDIS: 10BASE-T Link Disable

This active-low output is typically driven low to disable the external 10BASE-T PHY link pulse function. This pin is controlled from the 10BASE-T Control Register bit -LNKDIS.

-LNKLED: 10BASE-T Link Pulse

This asynchronuous input is driven low by the external 10BASE-T PHY Link LED driver for two TXCLK periods minimum when it detects a link pulse on the twisted pair receive input.

-LONG: 10BASE-T Long Cable Mode

This active-low output is typically driven low to enable a long cable mode in an external 10BASE-T PHY Long cable is defined as cable lengths in excess of 100 meters. This pin is controlled from the 10BASE-T Control Register bit -LONG.

#### -PDN: 10BASE-T Powerdown Enable

This active-low output is typically driven low to disable all PHY functions and lower power consumption to a minimum. This pin is controlled from the 10BASE-T Control Register bit -PDN.

#### RXCLK: 10BASE-T Receive Clock

This input is the 10 MHz receive clock from the external 10BASE-T PHY. This clock input must be continuous. All PHY receive signals to the SYM92C1000 are synchronous to RXCLK.

#### RXD: 10BASE-T Receive Data

This input is used to transfer received data from the external 10BASE-T PHY to the SYM92C1000.

#### TPPS: 10BASE-T TP Port Select

The outputs TPPS and AUIPS are typically used to select the output port on an external 10BASE-T device as listed in Table 6. These pins are controlled from the 10BASE-T Control Register bits AUIPS and TPPS.

#### **Table 6 Typical AUIPS/TPPS Port Selection**

| AUIPS | TPPS | Function                 |

|-------|------|--------------------------|

| 0     | 0    | Automatic port selection |

|       |      | enabled when -LNKDIS =1  |

| 0     | 1    | TP port selected         |

| 1     | 0    | AUI port selected        |

| 1     | 1    | Invalid                  |

#### TXCLK: 10BASE-T Transmit Clock

This input is the 10 MHz transmit clock from the external 10BASE-T PHY. All PHY transmit signals from the SYM92C1000 are synchronous to TXCLK.

#### TXD: 10BASE-T Transmit Data

This output is used to transfer transmit data from the SYM92C1000 to the external 10BASE-T PHY.

#### TXEN: 10BASE-T Transmit Enable

This output is driven high when valid data is on TXD.

#### UTPSTP: 10BASE-T Cable Type Select

This output is typically used to adjust the external 10BASE-T PHY transmit output current level to accommodate either 100  $\Omega$  UTP cable or 150  $\Omega$  STP cable. This signal is driven high to select UTP cable and low to select STP cable. This pin is controlled from the 10BASE-T Control Register bit UTPSTP.

## SYSTEM DESCRIPTION

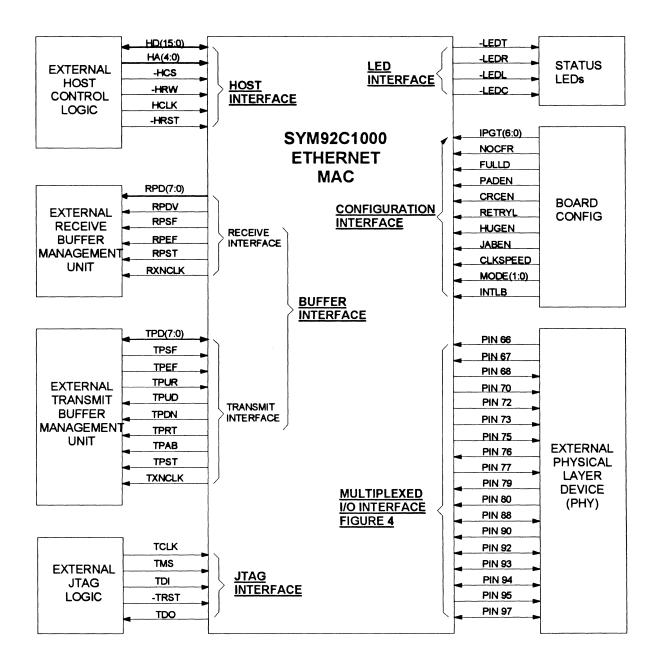

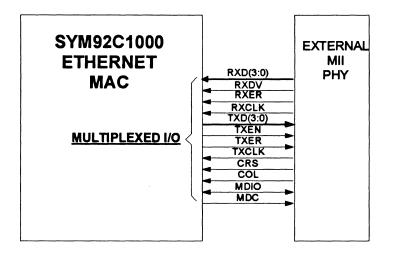

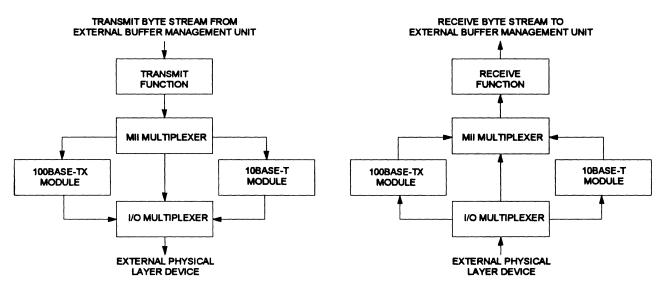

The SYM92C1000 is divided into six primary interfaces: Host Interface, Buffer Interface, JTAG Interface, Configuration Interface, LED Interface, and Multiplexed Input/Output Interface. The Buffer Interface consists of a Transmit and a Receive Interface. The Multiplexed Output interface is user configured into one of three choices: MII Interface, TP-PMD Interface, or 10BASE-T Interface. Figure 3 provides an overview of the signals associated with the six primary interfaces, and Figure 4 details the signals associated with each of the three Multiplexed Output Interface options.

Figure 3 System Block Diagram

Figure 4 Three Options for Multiplexed I/O

#### HOST INTERFACE

The following signals are used in the Host Interface

| Signal Name | Signal Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HA(4:0)     | I/O Port Address Bus: These five input lines are used to address the internal registers of the SYM92C1000.                                                                                                                                                                                                                                                                                                                                                                                                             |

| HCLK        | Host Clock: This input is used as the 25-33 MHz host interface clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| -HCS        | Host Chip Select: This active-low input is driven low to enable the transfer of data from the internal registers of the SYM92C1000 to the host when HRW is high. When HRW is low, the transition from low to high on -HCS causes the data from the host to be latched into the addressed internal register of the SYM92C1000.                                                                                                                                                                                          |

| HD(15:0)    | I/O Port Data Bus: These sixteen bi-directional lines are used to transfer data between the external host and the internal registers of the SYM92C1000. $HD(15:0)$ is in the tri-state condition when not in read mode.                                                                                                                                                                                                                                                                                                |

| -HRST       | Host Reset: This active-low asynchronous input is driven low to force the SYM92C1000 into an idle state and reset all internal registers to default valuesHRST must be held low for a minimum of 20 HCLK cycles and allowed an additional 20 cycles to complete the reset procedure before normal operations resume. For power-on reset with the configuration interface pins unconnected, -HRST must be held low for a minimum of 150 HCLK cycles and allowed an additional 20 cycles before normal operations begin. |

| HRW         | Host Read/Write Select: This input is used to select read or write operation. Driving HRW high allows read operations and driving HRW low allows write operations.                                                                                                                                                                                                                                                                                                                                                     |

The SYM92C1000 is controlled by writing to and reading from the 16 bit bi-directional data port HD(15:0). As shown in Table 7, commands, register status, and data are all issued or accessed through the port using the signals -HCS and HRW while the appropriate register address is held on HA(4:0).

Table 7 Read/Write Selection

| -HCS | HRW | Operation           |

|------|-----|---------------------|

| 0    | 0   | Write Register Port |

| 0    | 1   | Read Register Port  |

| 1    | X   | No Effect           |

#### I/O Register Read

For a register read, the External Host Control Logic must: drive the HRW pin high to enable the read function, drive the desired register address onto the HA(4:0) inputs and drive the -HCS input low to read the register contents. HRW, HA(4:0), and -HCS should

remain stable through the read cycle (refer to Read Timing Diagrams).

#### I/O Register Write

For a register write, the External Host Control Logic must: drive the HRW input low to enable the write function, drive the desired register address onto the HA(4:0) inputs, and drive the desired command onto the HD(15:0) bi-directional pins. The register write occurs on the rising transition of the -HCS input, so HRW, HA(4:0), and HD(15:0) must be stable during this transition (refer to Write Timing Diagrams).

#### **HCLK Input**

The SYM92C1000 accepts input clock rates up to 33 MHz. For proper operation the Configuration Register bit 6 (CLKSPD) must be set to 0 for HCLK input up to 25 MHz, and set to 1 for clock rate greater than 25 MHz.

#### **BUFFER INTERFACE**

The Buffer Interface is subdivided into the Receive Interface and the Transmit Interface

#### **Receive Interface**

The following signals are used in the Receive Interface.

| Signal Name     | Signal Definition                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| <b>RPD(7:0)</b> | Receive Packet Data Bus: These eight outputs are used to transfer the receive data from the                                                                                                                                                                                                                                                        |  |  |  |  |

|                 | SYM92C1000 to the external buffer management unit, and the receive status byte from the                                                                                                                                                                                                                                                            |  |  |  |  |

|                 | SYM92C1000 to the host interface controller.                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| RPDV            | Receive Packet Data Valid: This output is driven high when a valid receive data byte is on RPD(7:0).                                                                                                                                                                                                                                               |  |  |  |  |

| RPEF            | Receive Packet End of Frame: This output is driven high at the end of the receive packet                                                                                                                                                                                                                                                           |  |  |  |  |

| RPSF            | Receive Packet Start of Frame: This output is driven high at the start of the receive packet.                                                                                                                                                                                                                                                      |  |  |  |  |

| RPST            | Receive Packet Status: This output is driven high when a valid receive status byte is on RPD(7:0).                                                                                                                                                                                                                                                 |  |  |  |  |

| RXNCLK          | Receive Nibble Clock: This output is the 25/2.5 MHz nibble receive clock to the external buffer management unit. In 10BASE-T mode, RXNCLK is 2.5, in MII mode it may be either 2.5 MHz or 25 MHz, and TP-PMD modes it is a 25 MHz output. All receive signals from the SYM92C1000 to the Receive Buffer Management Unit are synchronous to RXNCLK. |  |  |  |  |

The Receive Interface transfers data and status information to the External Receive Buffer Management Unit. Received packet data is passed on to the External Receive Buffer Management Unit one byte at a time at one half the clock rate of RXNCLK. A packet transmission to the External Receive Buffer Management Unit begins when the Receive Interface asserts RPSF and RPDV along with the first byte of received packet data after the removed preamble and start of frame delimiter (SFD). Subsequent packet data bytes are accompanied by only RPDV until the last byte which is accompanied by RPDV and RPEF. A minimum of three bytes are transmitted to the External Receive Buffer Management Unit if any bytes are emitted for a packet. There is no flow control feedback from the External Receive Buffer Management Unit to the Receive Interface, the External Receive Buffer Management Unit must be able to accept all valid data passed by the SYM92C1000 MAC. Following the last byte of the packet, three bytes of status are appended with RPST asserted, RPDV is not asserted for the status bytes. The Receive Interface passes packets up to and including 1536 bytes long. Longer packets are truncated to 1536 bytes unless Configuration Register bit 5 (HUGEN) is set to one. Collision fragments and other carrier events are passed through as packets if a valid preamble is seen following a valid IPG. Other carrier events are merely noted in the status bytes.

#### **Receive Status Byte**

Immediately following the last byte of the packet, three bytes of status are appended to the packet. These bytes are used by the external host interface controller for subsequent data flow control and are detailed in Table 8.

| 23     | 22      | 21    | 20     | 19     | 18    | 17     | 16    |

|--------|---------|-------|--------|--------|-------|--------|-------|

| rsv    | CEPS    | RXOK  | BRDCST | MLTCST | CRCER | DRBNIB | RXVIO |

| 15     | 14      | 13    | 12     | 11     | 10    | 9      | 8     |

| TOOLNG | TOOSHRT | LNGTH | LNGTH  | LNGTH  | LNGTH | LNGTH  | LNGTH |

| 7      | 6       | 5     | 4      | 3      | 2     | 1      | 0     |

| LNGTH  | LNGTH   | LNGTH | LNGTH  | LNGTH  | LNGTH | LNGTH  | LNGTH |

#### **Table 8 Receive Packet Status Bytes**

| Bits | Name    | Description                                                                                                                                                                                                                                                                                                                                                                                                     |

|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-13 | LNGTH   | Packet Length: These bits indicate the length of the packet in bytes.                                                                                                                                                                                                                                                                                                                                           |

| 14   | TOOSHRT | Packet too Short: This bit is set when a received packet is less than 64 bytes long.                                                                                                                                                                                                                                                                                                                            |

| 15   | TOOLNG  | Packet Too Long: This bit is set when a received packet is greater than 1518 bytes. This bit sets regardless of HUGEN.                                                                                                                                                                                                                                                                                          |

| 16   | RXVIO   | Receive Code Violation: This bit is set when RXER is asserted.                                                                                                                                                                                                                                                                                                                                                  |

| 17   | DRBNIB  | Dribble Nibble Received: This bit is set if the received data does not end on a byte boundary.                                                                                                                                                                                                                                                                                                                  |

| 18   | CRCER   | CRC Error: This bit indicates a packet was received with an invalid Cyclic Redundancy<br>Check field. The CRC of the incoming packet is continuously calculated and checked at<br>the end of the packet. If this value does not match the CRC field of the received packet, a<br>CRC error is reported.                                                                                                         |

| 19   | MLTCST  | Multicast Packet: This bit set indicates a packet with a multicast address.                                                                                                                                                                                                                                                                                                                                     |

| 20   | BRDCST  | Broadcast Packet: This bit set indicates a packet with a broadcast address.                                                                                                                                                                                                                                                                                                                                     |

| 21   | RXOK    | Receive OK: This bit set indicates no errors occurred during the packet reception.                                                                                                                                                                                                                                                                                                                              |

| 22   | CEPS    | Carrier Event Previously Seen: This bit indicates that between the previous Receive Status Bytes and the current Receive Status Bytes a carrier event was detected, however, the reported carrier event is not associated with the packet to which the current Receive Status Byte is appended. A carrier event is activity on the receive channel that does not result in a packet receive attempt being made. |

| 23   | rsv     | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                       |

#### Transmit Interface

The following signals are used in the Transmit Interface.

| Signal Name | Signal Definition                                                                                      |

|-------------|--------------------------------------------------------------------------------------------------------|

| TPAB        | Transmit Packet Abort: This output is driven high when the transmission is aborted.                    |

| TPD(7:0)    | Transmit Packet Data Bus: These eight bi-directional lines are used to transfer the transmit data byte |

|             | from the External buffer management unit to the SYM92C1000 and to transfer the transmit status         |

| 1           | byte from the SYM92C1000 to the host interface controller. TPD(7:0) is in the tri-state condition      |

|             | with weak internal pullup when not driven by the SYM92C1000 or the External buffer management          |

|             | unit.                                                                                                  |

| TPDN        | Transmit Packet Done: This output is driven high when all packet data has been transmitted.            |

| TPEF        | Transmit Packet End of Frame: This input is driven high to end a packet transmission.                  |

| TPRT        | Transmit Packet Retry: This output is driven high when a collision has occurred and retransmission     |

|             | of the packet is required.                                                                             |

| TPSF        | Transmit Packet Start of Frame: This input is driven high to start a packet transmission.              |

| TPST        | Transmit Packet Status: This output is driven high when valid transmit status byte is on TPD(7:0).     |

| TPUD        | Transmit Packet Data Used: This output is driven high when actual data transmission has begun.         |

| TPUR        | Transmit Packet Underrun: This input is driven high to abnormally end a packet transmission.           |

| TXNCLK      | Transmit Nibble Clock: This output is the 25/10/2.5 MHz nibble transmit clock to the external buffer   |

|             | management unit. In 10BASE-T mode, TXNCLK is 2.5 MHz during transmission and 10 MHz                    |

|             | between transmissions, in MII mode it may be either 2.5 MHz or 25 MHz, and TP-PMD modes it is a        |

| 1           | 25 MHz output. All transmit signals between the SYM92C1000 and the Transmit Buffer                     |

|             | Management Unit are synchronous to TXNCLK.                                                             |

The Transmit Interface takes packet data from the External Transmit Buffer Management Unit in bytes at one half the TXNCLK clock rate and passes it on to the SYM92C1000 on TPD(7:0). A packet transmission begins when the External Transmit Buffer Management Unit asserts TPSF. The External Transmit Buffer Management Unit may also send the first data byte of the packet along with TPSF or delay supplying the first data byte for up to eight periods. The transmit function of the SYM92C1000, after any pending backoff and deference, will generate an eight byte preamble and SFD. After transmitting the SFD, the first data byte is used and TPUD is asserted. TPUD may be asserted in as few as eight byte times, but due to backoff and deferral, may not be asserted for over 500,000 bit times. After seeing TPUD, TPSF is to be dropped and the External Transmit Buffer Management Unit must hold the first packet data byte for two rising clock edges, then supply packet data bytes every other TXNCLK pulse, holding them for the full two periods. The last packet data byte must be accompanied by TPEF for both TXNCLK periods to signal an end of transmission. If the External Transmit Buffer Management Unit fails to supply the first data byte by the time SFD is transmitted, or if at any time during transmission it is unable to supply the next packet data byte, it must recognize an underrun condition and assert TPUR to abort the packet. In addition, if the buffer is overrun causing loss of data, TPUR should be asserted to abort the packet.

TPEF causes the SYM92C1000 MAC to pad a short packet, if necessary and enabled by Configuration Register bit 2 (PADEN), and append the CRC if enabled by Configuration Register bit 3 (CRCEN). With a successful packet transmission, TPDN will be asserted and beginning the following clock period two status bytes will be asserted on TPD(7:0), one period each, with TPST asserted for the two periods. The External Transmit Buffer Management Unit and Host Interface Controller must have tri-stated drivers and accept the status bytes during the time TPST is driven.

Packets longer than 1536 bytes are truncated and aborted unless Configuration Register bit 5 (HUGEN) is set. Collisions will cause the transmission to be truncated and extended with 4 jam bytes consisting of zeros. Collisions other than the sixteenth will cause TPRT to be asserted to direct the External Transmit Buffer Management Unit to restart the packet. Late collisions are treated identically when Configuration Register bit 4 (RETRYL) is set, otherwise they cause an abort, indicated by TPAB. TPAB is also asserted by sixteen collisions on the same packet, excessive deferral, or a transmission underflow. In the event of an aborted transmission, the External Transmit Buffer Management Unit must dump the aborted packet and continue to the next packet.

At the end of a transmission attempt, TPDN, TPRT, and TPAB are held in their current state until the next assertion of TPSF, at which point they are deasserted.

#### Transmit Status Byte

Immediately following the last byte of the packet, two bytes of status are presented to the External Transmit Buffer Management Unit. These bytes are used by the External Receive Buffer Management Unit for subsequent data flow control and are detailed in Table 9.

| 15      | 14    | 13   | 12   | 11   | 10   | 9    | 8  |

|---------|-------|------|------|------|------|------|----|

| LNKFAIL | NOCRS | TXOK | TALC | TAED | TAEC | TAUH | PD |

|         |       |      |      |      |      |      |    |

| _       | -     | _    | -    | -    | -    |      | -  |

| 7       | 6     | 5    | 4    | 3    | 2    | 1    | 0  |

**Table 9 Transmit Packet Status Bytes**

| Bits | Name    | Description                                                                                                                                                                                                                                                                                                                      |

|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-3  | COLCNT  | Collision Count: Bits 3 through 0 give the collision count (0-15) of any successfully transmitted packet. The maximum number of collisions before a packet is aborted is 16, so TAEC set indicates that 16 collisions have occurred.                                                                                             |

| 4    | LC      | Late Collision Seen: This bit set indicates that a late collision was seen on at least one transmission attempt. A late collision occurs more than 512 bit times after the start of the preamble. Bits 4 and 12 are mutually exclusive, this bit is valid only when Configuration Register bit RETRYL is asserted.               |

| 5    | CRCER   | CRC Error: If CRC is disabled the SYM92C1000 assumes the last four bytes of a packet are an appended CRC and it compare those bytes to its generated CRC. If the assumed CRC and the generated CRC do not match a CRC error is reported in the status bytes.                                                                     |

| 6    | MLTCST  | Multicast Packet Transmitted or Attempted: This bit is set if the preceding packet was a multicast packet.                                                                                                                                                                                                                       |

| 7    | BRDCST  | Broadcast Packet Transmitted or Attempted: This bit is set if the preceding packet was a broadcast packet.                                                                                                                                                                                                                       |