# **CXA1372Q/S**

## RF Signal Processing Servo Amplifier for CD Player

## **Description**

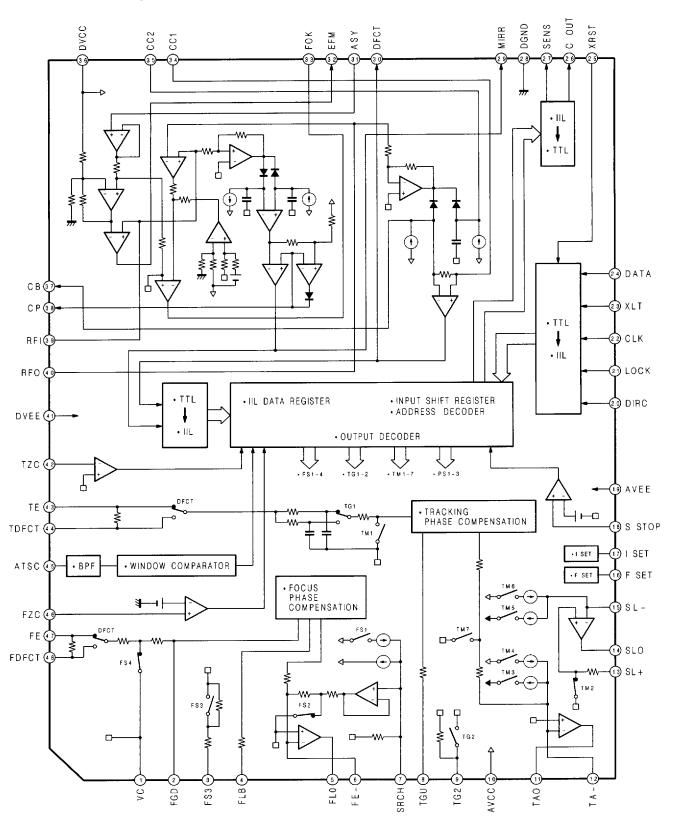

The CXA1372 is a bipolar IC developed for RF signal processing (focus OK, mirror, defect detection, EFM comparator) and servo control.

#### **Features**

- Single power supply, 5V

- Low power consumption

- · Fewer external parts

- · Built-in circuit for effective disc defect measures

- Share serial data bus from the microcomputer with CXD2500

- Fully compatible with CXA1182 for microcomputer software

#### **Functions**

- Auto asymmetry control

- Focus OK detection circuit

- Mirror detection circuit

- · Defects detection, counter measures circuit

- EFM comparator

- · Focus servo control

- · Tracking servo control

- Sled servo control

#### Structure

Silicon monolithic IC

#### Absolute Maximum Ratings (Ta = 25°C)

| • | Supply voltage              | Vcc - \ | VEE      |     | 12      | V  |

|---|-----------------------------|---------|----------|-----|---------|----|

| • | Operating temperature       | Topr    |          | -20 | to +75  | °C |

| • | Storage temperature         | Tstg    |          | -55 | to +150 | °C |

| • | Allowable power dissipation | Po      | CXA1372S |     | 833     | mW |

|   | •                           |         | CXA1372Q |     | 457     | mW |

## **Recommended Operating Conditions**

| VCC - VEE  | 3.6 to 11  | ٧ |

|------------|------------|---|

| Vcc - Dgnd | 3.6 to 5.5 | ٧ |

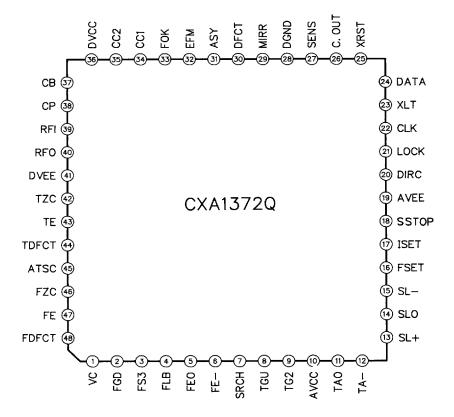

## **CXA1372Q Block Diagram**

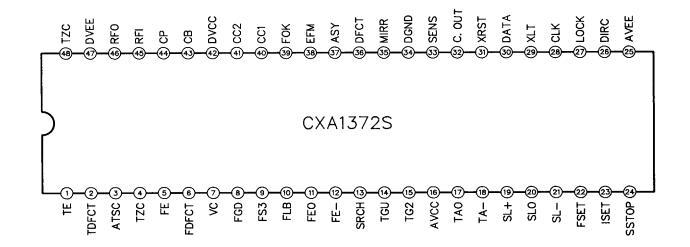

## Pin Configuration

#### **CXA1372S**

## CXA1372Q

## **Pin Description**

|     |     | iption   | ,   | T                             |                                                                                     |

|-----|-----|----------|-----|-------------------------------|-------------------------------------------------------------------------------------|

| Pin | No. | Symbol   | 1/0 | Equivolent aircuit            | Description                                                                         |

| Q   | S   | Syllibol | 1/0 | Equivalent circuit            | Description                                                                         |

| 1   | 7   | vc       | ı   |                               | Center voltage input pin For dual power: GND For single power supply: (Vcc + GND)/2 |

| 2   | 8   | FGD      | l   | 2 ¥48K<br>180<br>180<br>20 µA | Connect a capacitor between this pin and pin 3 to reduce high-frequency gain.       |

| 3   | 9   | FS3      | 1   | 3 180 46K                     | The high-frequency gain of the focus servo is switched through FS3 On and OFF.      |

| 4   | 10  | FLB      | l   | 40K \$ W-                     | Time constant external pin to raise the low bandwidth of the focus servo.           |

| 5   | 11  | FEO      | 0   |                               | Focus drive output.                                                                 |

| 11  | 17  | TAO      | 0   | (5) # (1) 250 µ A             | Tracking drive output.                                                              |

| 14  | 20  | SLO      | 0   | <b>♦</b> 12.5µA               | Sled drive output.                                                                  |

| 6   | 12  | FE-      | l   | © \$90K \$90K \$180 \$25 µA   | Inverse input pin for focus amplifier.                                              |

| Pin | No. | Symbol | I/O | Equivalent circuit                      | Description                                                              |

|-----|-----|--------|-----|-----------------------------------------|--------------------------------------------------------------------------|

| Q   | S   | Symbol | "   | Equivalent circuit                      | Description                                                              |

| 7   | 13  | SRCH   | I   | 50K ≥ 35μA ( ) (11μA                    | Time constant external pin for the formation of focus search waveforms.  |

| 8   | 14  | TGU    | ı   | 8 \$110K<br>20K<br>W \$110K<br>W \$82K  | Time constant external pin for the selection of tracking high band gain. |

| 9   | 15  | TG2    | l   | 9 180 470K\$ 124A                       | Time constant external pin for the selection of tracking high band gain. |

| 12  | 18  | TA-    | ı   | 180<br>131A (1)114A                     | Inverse input pin for tracking amplifier.                                |

| 13  | 19  | SL+    | 1   | (3)———————————————————————————————————— | Non-inverse input pin for sled amplifier.                                |

| 15  | 21  | SL-    | 1   | 180<br>180<br>13 34A 1 224A             | Inverse input pin for sled amplifier.                                    |

| Pin | No. |        |     |                                                                    |                                                                                           |

|-----|-----|--------|-----|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Q   | s   | Symbol | I/O | Equivalent circuit                                                 | Description                                                                               |

| 16  | 22  | FSET   | 1   | Vec ∆  180  180  180  180  15K  \$15K                              | Pin to set peak frequency of focus tracking phase compensation and fo of CLV LPF.         |

| 17  | 23  | ISET   | ı   | (a)                                                                | Current is input to determine focus search, track jump, and sled kick height.             |

| 18  | 24  | SSTOP  | -   | 180<br>180<br>180                                                  | Limit SW ON/OFF signal detection pin for disc inner periphery detection.                  |

| 20  | 26  | DIRC   | ŀ   |                                                                    | Pin for one-track jump. Contains a $47k\Omega$ pull-up resistor.                          |

| 21  | 27  | LOCK   | _   |                                                                    | At "L" sled runaway prevention circuit operates. Contains a $47k\Omega$ pull-up resistor. |

| 22  | 28  | CLK    | I   | ② \$\frac{1}{80}\$ \$\frac{1}{80}\$ \$\frac{1}{80}\$               | Serial data transfer clock input from CPU.                                                |

| 23  | 29  | XLT    | I   | ⊕ <b>†</b>                                                         | Latch input from CPU.                                                                     |

| 24  | 30  | DATA   | I   | <b>3</b>                                                           | Serial data input from CPU.                                                               |

| 25  | 31  | XRST   | ı   |                                                                    | Reset input pin, reset at "L".                                                            |

| 26  | 32  | SENS   | 0   | Å Å Å Å Å Å Å Å Å Å Å Å Å Å Å Å Å Å Å                              | Outputs FZC, AS, TZC and SSTOP through command from CPU.                                  |

| 27  | 33  | C. OUT | 0   | ② \$\frac{180}{\times}\$\frac{180}{\times}\$\frac{1}{\times}\$100K | Track number count signal output.                                                         |

| Pin | No. | Symbol | 1/0 | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Description                                                                       |

|-----|-----|--------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| Q   | s   | Symbol | 1/0 | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Description                                                                       |

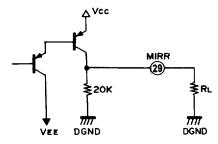

| 29  | 35  | MIRR   | 0   | (2) A (3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | MIRR comparator output pin.                                                       |

| 38  | 44  | CP     |     | ® ₹ 130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Connecting pin of MIRR hold condenser. Non-inverted input pin of MIRR comparator. |

| 34  | 40  | CC1    | 1   | \$\frac{150}{4}\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Output pin of DEFECT bottom hold.                                                 |

| 35  | 41  | CC2    | 0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Input pin for the capacitance coupled output of DEFECT bottom hold.               |

| 30  | 36  | DFCT   | 0   | <b>3</b> 180 <b>3</b> 150 <b>4</b> 30 150 <b>5</b> 30 150 5 5 30 150 5 5 30 150 5 5 30 150 5 5 30 150 5 5 30 150 5 5 30 150 5 5 30 150 5 5 30 150 5 5 30 150 5 5 30 150 5 5 30 150 5 5 30 150 5 5 30 150 5 5 30 150 5 5 30 150 5 5 30 150 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 | Output pin of DEFECT comparator.                                                  |

| 37  | 43  | СВ     | 1   | <b>† * * * * * * * * * *</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Connection pin of DEFECT bottom hold capacitor.                                   |

| 31  | 37  | ASY    | 1   | 3) \$\frac{180}{4}\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Input pin of auto asymmetry control.                                              |

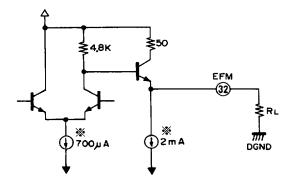

| 32  | 38  | EFM    | 0   | Depending on power supply Current source (Vcc to DGND)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Output pin of EFM comparator.                                                     |

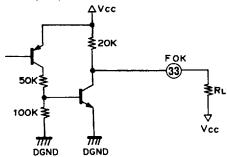

| 33  | 39  | FOK    | 0   | 3 180 20K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Output pin of FOK comparator.                                                     |

| Pin | No. | _      |     |                                         |                                                                                   |

|-----|-----|--------|-----|-----------------------------------------|-----------------------------------------------------------------------------------|

| Q   | s   | Symbol | 1/0 | Equivalent circuit                      | Description                                                                       |

| 39  | 45  | RFI    | I   | 40K | Input pin with coupling capacitor where RF summing amplifier output is connected. |

| 40  | 46  | RFO    | 0   | <b>♣</b> 180                            | Output pin of RF summing amplifier and check point of eye pattern.                |

| 42  | 48  | TZC    | ı   | 180<br>180<br>75K ≸                     | Input pin of tracking zero-cross comparator.                                      |

| 43  | 1   | TE     | 1   | @ # *********************************** | Input pin of tracking error amplifier.                                            |

| 44  | 2   | TDFCT  | I   | ⊕ ### ### ### ### ### #### ###########  | Capacitor connecting pin for time constant during defects.                        |

| 45  | 3   | ATSC   |     | Vcc                                     | Window comparator input pin for ATSC detection.                                   |

| 46  | 4   | FZC    | 1   | 180<br>180<br>W 1.2K<br>180<br>1.2K     | Pin for focus zero-cross comparator input.                                        |

| 47  | 5   | FE     | 1   | · ***                                   | Input pin of focus error.                                                         |

| 48  | 6   | FDFCT  | ı   | • • • • • • • • • • • • • • • • • • • • | Capacitor connecting pin for time constant during defect functions.               |

| m  |

|----|

| ຬ  |

| 盖  |

| .5 |

| ≅  |

| ぢ  |

| ă  |

| ĕ  |

| ۳  |

| ပ  |

| =  |

| <u></u> | ן קַל       | Electrical Characteristics |        |    |    |    |    |              |        |    |    |    |    |   |        |                | -          |        | a=z5^C, vcc=+2.5v, vee-z.5v, D.GIND=-z.5v                       | v, vee- | ֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓֓ | יים<br>מוסיים<br>מוסיים | <br>       |

|---------|-------------|----------------------------|--------|----|----|----|----|--------------|--------|----|----|----|----|---|--------|----------------|------------|--------|-----------------------------------------------------------------|---------|---------------------------------------|-------------------------|------------|

| 2       | _,          | most.                      | Sympol |    |    |    | SW | SW condition | lition |    |    |    | ç  | ä | as col | Bias condition |            | Test   | Output wafeform and                                             | Z.      | Ę                                     | May                     | <u>.</u>   |

| 2       | _           |                            | 9      | S1 | S2 | S3 | \$ | SS           | Se     | S7 | 8S | S3 | 2  | E | E2     | 8              | <b>E</b> 4 | point  | description of test method                                      |         | -<br>بع                               | Max.                    | 5          |

| -       |             | Current consumption        | cc     |    |    |    |    |              |        |    |    |    | 00 |   |        |                | •          | 10, 36 |                                                                 | 80      | 19                                    | 27                      | mA         |

| ٧       |             | Current consumption        | lee .  |    |    |    |    |              |        |    |    |    | 00 |   |        |                | ·          | 19, 41 |                                                                 | -8      | -16                                   | -22                     | ΨW         |

| က       |             | DC voltage gain            | GFEO   |    |    |    |    |              |        |    |    | _  | 90 |   |        |                |            | 2      | V <sub>1</sub> =10HZ, 100mVp-p<br>GFE0=20 log (Vout/Vin)        | 18.0    | 21.0                                  | 24.0                    | Вþ         |

| 4       |             | Field through              | VFEOF  |    |    |    |    |              |        |    |    |    | 8  |   |        |                |            | 5      | SG=10kHZ, 40mVp-p<br>Difference in gain when<br>SD=00 and SD=08 |         |                                       | -35                     | ВВ         |

| 2       |             | Max. output voltage        | VFE01  |    | 0  |    |    |              |        |    |    |    | 80 |   | ,      |                |            | 2      | V1=0.5Vpc                                                       | 2.0     |                                       |                         | ۸          |

| ဖ       | <u>`⊃v</u>  | Max. output voltage        | VFE02  |    | 0  |    |    |              |        |    |    |    | 88 |   |        |                |            | 5      | V1=-0.5Vpc                                                      |         |                                       | -2.0                    | >          |

| 7       | ဟ           | Max. output voltage        | VFE03  |    | 0  | 0  |    |              |        |    |    |    | 80 |   |        |                |            | 5      | V1=0.5Vpc                                                       | 1.2     |                                       |                         | ۸          |

| 8       | шæ:         | Max. output voltage        | VFE04  |    | 0  | 0  |    |              |        |    |    |    | 90 |   |        |                |            | 5      | V1=-0.5VDC                                                      |         |                                       | -1.2                    | ۸          |

| თ       |             | Search output voltage      | Vsясн1 | •  |    |    |    |              |        |    |    |    | 05 |   |        |                |            | 2      |                                                                 | -640    |                                       | -360                    | Λm         |

| 10      |             | Search output voltage      | Vsяснг |    |    |    |    |              |        |    |    |    | 63 |   |        |                |            | 5      |                                                                 | 360     |                                       | 640                     | ΛW         |

| Ξ       |             | FZC threshold              | VFZC   |    |    |    |    |              |        |    |    |    | 8  |   |        |                | *          | 27     | *(Vcc+DGND)/2=SENS value when E4 is varied.                     | 39      | 50                                    | 61                      | \<br>E     |

| 12      |             | DC voltage gain            | Gтео   |    |    |    |    |              |        |    |    |    | 25 |   |        |                |            | =      | V2=10Hz, 500mVp-p<br>GTE0=20 log (Vout/Vin)                     | 11.6    | 14.6                                  | 17.6                    | ЯВ         |

| 13      |             | Field through              | Vтеоя  |    |    |    |    |              |        |    |    |    | 8  |   |        |                |            | =      | V2=10kHz, 40mVp-p<br>Difference in gain when<br>SD=00 and SD=25 |         |                                       | -39                     | ф          |

| 4       | -Œ <b>⋖</b> | Max. output voltage        | Vтео1  |    |    |    |    | 0            |        |    |    |    | 52 |   |        |                |            | 1      | V2=-0.5Vpc                                                      | 2.0     |                                       |                         | >          |

| 15      |             | Max. output voltage        | Утеог  |    |    |    |    | 0            |        |    |    |    | 52 |   |        |                |            | =      | V2=0.5Vpc                                                       |         |                                       | -2.0                    | ۸          |

| 16      | -z(         | Max. output voltage        | Vте03  |    |    |    |    | 0            | 0      |    |    |    | 52 |   |        |                |            | 11     | V2=-0.5Vpc                                                      | 1.2     |                                       |                         | ۸          |

| 17      |             | Max. output voltage        | VTE04  |    |    |    |    | 0            | 0      |    |    |    | 22 |   |        |                |            | =      | V2=0.5Vpc                                                       |         |                                       | -1.2                    | ^          |

| 18      | mæ          | Jump output voltage        | VJUMP1 |    |    |    |    |              |        |    |    |    | ၃  |   |        |                |            | Ξ      |                                                                 | -640    |                                       | -360                    | ٦<br>٧     |

| 19      |             | Jump output voltage        | VJUMP2 |    |    |    |    |              |        |    |    |    | 78 |   |        |                |            | =      |                                                                 | 360     |                                       | 640                     | <b>Y</b> E |

| 8       |             | ATSC threshold             | VATSC1 |    |    |    |    |              |        |    |    |    | 8  |   |        | *              |            | 27     | *(Vcc+DGND)/2=SENS                                              | 45      | -26                                   | -7                      | λm         |

| 21      | -           | ATSC threshold             | VaTSC2 |    |    |    |    |              |        |    |    |    | 8  |   |        |                |            | 27     | value when E3 is varied.                                        | 7       | 56                                    | -45                     | Λm         |

| - 22    |             | TZC threshold              | VTZC   |    |    |    |    |              |        |    |    |    | 20 |   | *      |                |            | 27     | *(Vcc+DGND)/2 SENS value when E2 is varied.                     | -20     | 0                                     | 82                      | E<br>E     |

|         |             |                            |        |    |    |    |    |              |        |    |    |    |    |   |        |                |            |        |                                                                 |         |                                       |                         |            |

|     |      |                               |               |      |      | V    | 3W C0 | SW condition | _    |      |    |    | ā | Bias condition | dition | ۲  | Test  | Output wafeform and                                                |          |      |           |      |

|-----|------|-------------------------------|---------------|------|------|------|-------|--------------|------|------|----|----|---|----------------|--------|----|-------|--------------------------------------------------------------------|----------|------|-----------|------|

| No. |      | Item                          | Symbol        | S1 5 | S2 S | S3 S | S4 S  | S5 S6        | 6 S7 | 2 S8 | 89 | SD | E | E2             | E3     | E4 | point | description of test method                                         | <u>V</u> | Typ. | мах.      | 5    |

| ន   |      | DC voltage gain               | Osp           |      |      |      |       |              |      |      |    | 25 |   |                |        |    | 41    | V5=10Hz, 20mVp-p<br>Open loop gain                                 | 50       |      |           | В    |

| 24  | •    | Field through                 | Vs.or         |      |      |      |       |              |      |      |    | 00 |   |                |        |    | 41    | Vs=10kHz, 100mVp-p<br>Difference in gain when<br>SD=00 and SD=25   |          |      | <u>\$</u> | 8B   |

| 25  | ഗപ   | Max. output voltage           | Vs.m          |      |      |      |       |              |      |      |    | 22 |   |                |        |    | 4     | V5=1.0Vpc                                                          | 2.0      |      |           | >    |

| 56  |      | Max. output voltage           | Vs.æ          |      |      |      |       |              |      |      |    | 25 |   |                |        |    | 14    | V5=-1.0Vpc                                                         |          |      | -2.0      | >    |

| 27  | ωш   | Max. output voltage           | Va.cs         |      |      |      |       |              | 0    |      |    | 25 |   |                |        |    | 14    | V5=1.0Vpc                                                          | 2.0      |      |           | >    |

| 28  | <>   | Max. output voltage           | Vs.o4         |      |      |      |       |              | 0    |      |    | 25 |   |                |        |    | 4     | V5=-1.0Vpc                                                         |          |      | -2.0      | >    |

| 53  |      | Kick output voltage           | VKICK1        | -    |      |      |       |              |      |      |    | 22 |   |                |        |    | 14    |                                                                    | -750     |      | -450      | m\   |

| ဆ   |      | Kick output voltage           | VKICK2        |      |      |      |       |              |      |      |    | 23 |   |                |        |    | 4     |                                                                    | 450      |      | 750       | Λm   |

| 31  |      | SSTOP threshold               | Vsstop        |      |      |      |       |              |      |      |    | 30 | * |                |        |    | 27    | *(Vcc+DGND)/2=SENS value when E1 is varied.                        | -40      | -25  | -10       | ٧m   |

| 32  |      | SENS low level                | Vsevs         |      |      |      |       |              |      |      |    |    |   |                |        |    | 27    |                                                                    |          |      | -2.0      | >    |

| 33  |      | COUT low level                | Vααυτ         |      |      |      |       |              |      |      |    |    |   |                |        |    | 56    |                                                                    |          |      | -2.0      | >    |

| 34  |      | FOK threshold                 | VFOKT         |      |      |      |       |              |      |      |    |    |   |                |        |    | 33    | (Vcc+DGND)/2 the voltage between Pins 39 and 40 when V4 is varied. | -400     | -356 | -330      | Λm   |

| 35  |      | High level voltage            | VFOKH         |      |      |      |       |              |      |      |    |    |   |                |        |    | 33    |                                                                    | 2.2      |      |           | >    |

| 36  | OΥ   | Low level voitage             | VFORE         |      |      |      |       |              |      |      |    |    |   |                |        |    | 33    | V4=1Vp-p - 375mVbc                                                 |          |      | -1.8      | >    |

| 37  |      | Max. operating frequency      | Fок           |      |      |      |       |              |      |      |    |    |   |                |        |    | 33    |                                                                    | 45       |      |           | kH2  |

| 38  |      | High level voltage            | <b>Ум</b> івн |      |      |      |       |              |      |      |    |    |   |                |        |    | 83    | V4=10KHz                                                           | 1.8      |      |           | >    |

| 39  |      | Low level voltage             | VMIRL         |      |      |      |       |              |      |      |    |    |   |                |        |    | 59    | 1.0Vp-p - 0.4Vpc                                                   |          |      | -2.0      | >    |

| 40  |      | Max. operating frequency      | FMIR          |      |      |      |       |              |      |      |    |    |   |                |        |    | 83    | V4=800mVp-p - 0.4Vpc                                               | 30       |      |           | Ŧ,   |

| 4   | - co | Min. input operating volatage | Vмія1         |      |      |      |       |              |      |      |    |    |   |                |        |    | 23    | 20/10/10/10/10/10/10/10/10/10/10/10/10/10                          |          |      | 0.3       | d-d/ |

| 42  |      | Max. input operating voltage  | VMIR2         |      |      |      |       |              |      |      |    |    |   |                |        |    | 8     | 77,00                                                              | 1.8      |      |           | d-qV |

| 1  |      |                              |                            |    |    |    | SW | SW condition | ion |    |    |   | ć | ā | as co | Bias condition | _  | Test  | Output wafeform and                      | Ž   | Ş     | Ž    | <u>-</u>                  |

|----|------|------------------------------|----------------------------|----|----|----|----|--------------|-----|----|----|---|---|---|-------|----------------|----|-------|------------------------------------------|-----|-------|------|---------------------------|

| ġ  |      | Item                         | Symbol                     | S1 | S2 | SS | 8  | SS           | 98  | S7 | 88 | S | 2 | П | E2    | 8              | E4 | point | description of test method               | 3   | - yp. | Max. | 5                         |

| 53 |      | High level output voltage    | <b>V</b> <sub>D</sub> FСТН |    |    |    |    |              |     |    |    |   |   |   |       |                |    | 30    |                                          | 1.8 |       |      | >                         |

| 4  |      | Low level output voltage     | Vресть                     |    |    |    |    |              |     |    |    |   |   |   |       |                |    | 30    |                                          |     |       | -2.0 | >                         |

| 45 |      | Min. operating frequency     | FDFCT1                     |    |    |    |    |              |     |    |    |   |   |   |       |                |    | 30    | Va-AOmVa-a 15mVac                        |     |       | -    | kHz                       |

| 46 | ОШ   | Max. operating frequency     | <b>F</b> DFCT2             |    |    |    |    |              |     |    |    |   |   |   |       |                |    | 30    | 204 - 101 + d.d 104 - 144                | 2.5 |       |      | kHz                       |

| 47 | тшОІ | Min. input operating voltage | <b>V</b> рғст1             |    |    |    |    |              |     |    |    |   |   |   |       |                |    | 30    | 7/2-50H7 - 15m/75c                       |     |       | 0.5  | d-d <sub>\(\Delta\)</sub> |

| 8  | _    | Max. input operating voltage | Vоестг                     |    |    |    |    |              |     |    |    |   |   |   |       |                |    | 30    | 200-100-100-100-100-100-100-100-100-100- | 1.8 |       |      | d-d/                      |

| 64 | ,    | Duty 1                       | DEFM1                      |    |    |    |    |              |     |    | 0  |   |   |   |       |                |    | 31    | V4=750kHz, 0.7Vp-p                       | -20 | 0     | 50   | λm<br>V                   |

| S  |      | Duty 2                       | Den/2                      |    |    |    |    |              |     |    | 0  |   |   |   |       |                |    | 31    | V4=750kHz,<br>0.7Vp-p + 0.25Vbc          | 0   | 20    | 100  | Λm                        |

| 51 |      | High level output voltage    | Vеғмн                      |    |    |    |    |              |     |    | 0  | 0 |   |   |       |                |    | 32    | 2 2/2 0 -11/1035 7/                      | 1.2 |       |      | >                         |

| 22 | шш   | Low level output voltage     | VEFML                      |    |    |    |    |              |     |    | 0  | 0 |   |   |       |                |    | 32    | V4=7.30KHZ, U.7 VP-D                     |     |       | -1.2 | >                         |

| 53 | Σ    | Min. input operating voltage | Vеғм1                      |    |    |    |    |              |     |    | 0  |   |   |   |       |                |    | ¥     | V4=750kHz                                |     |       | 0.12 | νρ-p                      |

| 54 |      | Max. input operating voltage | Vеғм2                      |    |    |    |    |              |     |    | 0  |   |   |   |       |                |    | 4     |                                          | 1.8 |       |      | d-d/                      |

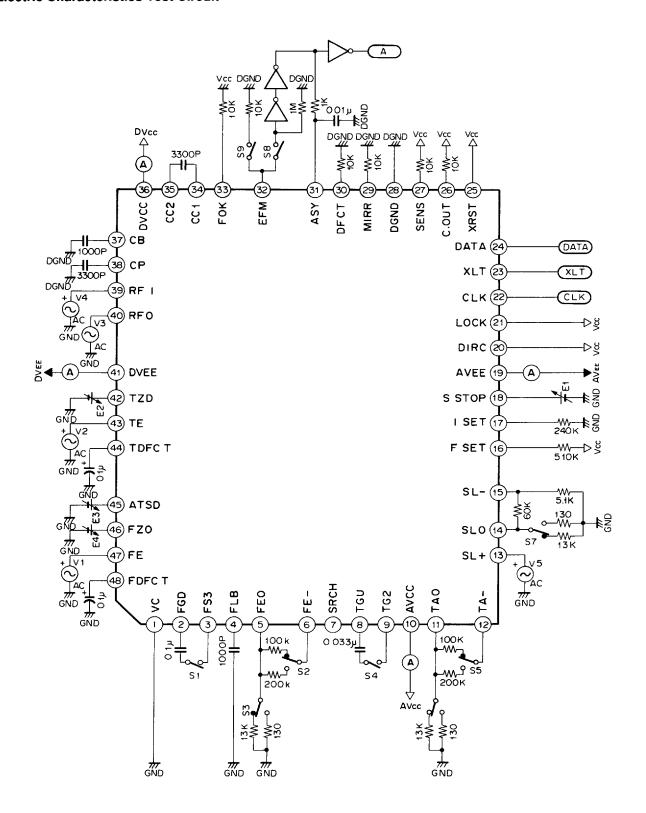

## **Electric Characteristics Test Circuit**

## **Description of Functions**

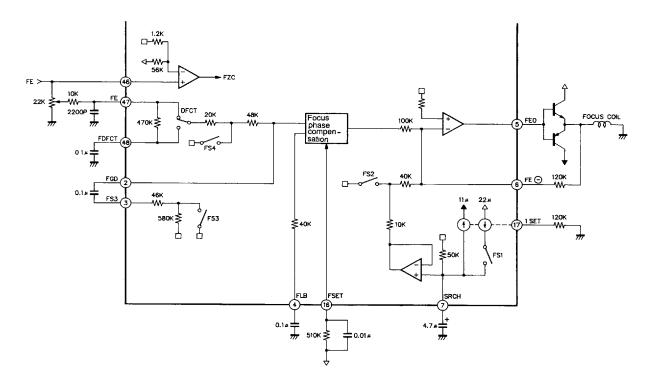

#### Focus servo system

Above is a block diagram of the focus servo system.

FE signal is gradually input to focus phase compensation circuit through  $20k\Omega$  and  $48k\Omega$  resistances. However, when DFCT is detected, FE signal is switched into the low pass filter route formed by connecting a capacitance between the built-in  $470k\Omega$  resistance and Pin 48.

When this DFCT counter measure circuit is not used, Pin 48 is left open.

When FS3 is on, the high frequency gain can be reduced by forming a low frequency time constant through a capacitor connected across Pins 2 and 3 and the internal resistor.

The capacitor across Pin 4 and GND is a time constant that raises low frequency normally in playback condition. The peak frequency of the focus phase compensation is inversely proportional to the resistor connected to Pin 16 (about 1.2kHz when the resistor is  $510k\Omega$ ).

The focus search peak becomes about  $\pm 1.1$ Vp-p with the above constant. The peak is inversely proportional to the resistor connected across Pin 17 and GND. However, when this resistor is varied, the peaks of track jump and sled kick also vary.

FZC comparator inverted input is set to 2% of the difference between the reference voltage Vcc and VC (Pin 1):  $(Vcc - VC) \times 2\%$ .

Note: For Pin 16 a 510k $\Omega$  resistor is recommended.

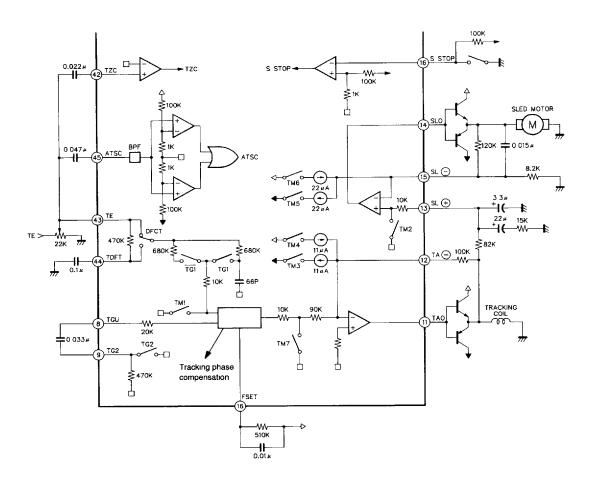

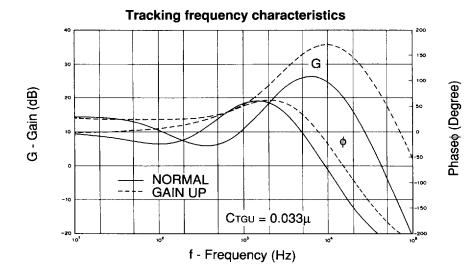

## Tracking sled servo system

Above is a block diagram of the tracking and sled servo system.

The capacitor across Pins 8 and 9 has a time constant to reduce high frequency when TG2 is switched off. The tracking phase compensation peak frequency is at about 1.2kHz when the resistor connected to Pin 16 is at  $510k\Omega$ .

For a tracking jump in FWD or REV direction, TM3 or TM4 is set on. At this time, the peak voltage fed to the tracking coil is determined by the TM3 and TM4 current values and the feedback resistor from Pin 12. That is:

Track jump peak voltage = TM3 (TM4) current value × feedback resistor value. The FWD or REV sled kick is done by setting TM5 or TM6 on. At this time, the peak voltage added to the sled motor is determined by the TM5 or TM6 current value and the feedback resistor from Pin 15.

Sled jump peak voltage = TM5 (TM6) current value  $\times$  feedback resistor value. Each SW current value is determined by the resistor connected to Pin 17 and GND when the resistor is at about 120k $\Omega$ .

TM3 or TM4 turns to  $\pm 11\mu A$  and TM5 or TM6 to  $\pm 22\mu A$ .

This current value is almost inversely proportional to the resistor, variable within a range of about 5 to  $40\mu A$  for TM3.

S STOP is the ON/OFF detection signal for the limit SW of the linear motor's innermost circumference.

TE signal is switched into low pass filter route formed by connecting a capacitance between the built-in resistance at DFCT (470k $\Omega$ ) and Pin 44 as for FE signal.

TM1 was ON at DFCT in CXA1082 and CXA1182, but it is not operational in CXA1372.

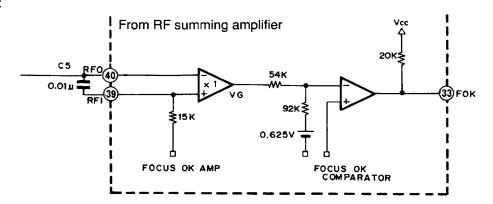

#### **Focus OK circuit**

Focus OK circuit generates a timing window to enable focus servo from a focus search condition. RF signal from Pin 46 is passed through HPF (High Pass Filter) and output from Pin 39. RF signal passed through LPF (Low Pass Filter) is output from Pin 33.

Focus OK amplifier output is inverted when VRFI-VRFO#-0.37V.

C5 determines the time constants of HPF in the EFM comparator and mirror circuits as well as that of LPF in the focus OK amplifier. Normally, when  $0.01\mu F$  is selected for C5, fc (cut-off frequency) = 1kHz. This prevents the block error rate from worsening as the result of a damaged RF envelope due to scratched disc, etc.

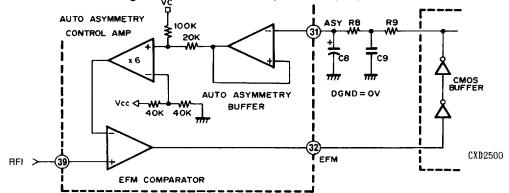

#### **EFM** comparator

EFM comparator changes RF signal a binary value. The asymmetry generated due to variations in disc manufacturing cannot be eliminated by the AC coupling alone. Therefore, the reference voltage of EFM comparator is controlled through 1 and 0 that are in approximately equal numbers in the binary EFM signals.

As this comparator is a current SW type, each of the H and L levels is not equal to the power supply voltage. A feedback has to be composed through the CMOS buffer.

R8, R9, C8, and C9 form a LPF to obtain (Vcc + DGND)/2V. When fc (cut-off frequency) exceeds 500Hz, EFM low-frequency components leak badly, and the block error rate worsens.

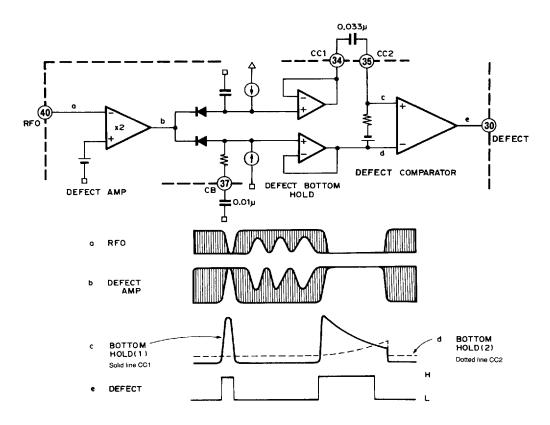

#### **DEFECT circuit**

After inversion, RFI signal is bottom held by means of one long and one short time constant. The short time-constant bottom hold responds to a disc mirror defect inexcess of 0.1 msec.

The long time-constant bottom hold keeps to the mirror level prior to the defect. By differentiating this with a capacitor coupling and shifting the level, both signals are compared to generate a mirror defect detection signal.

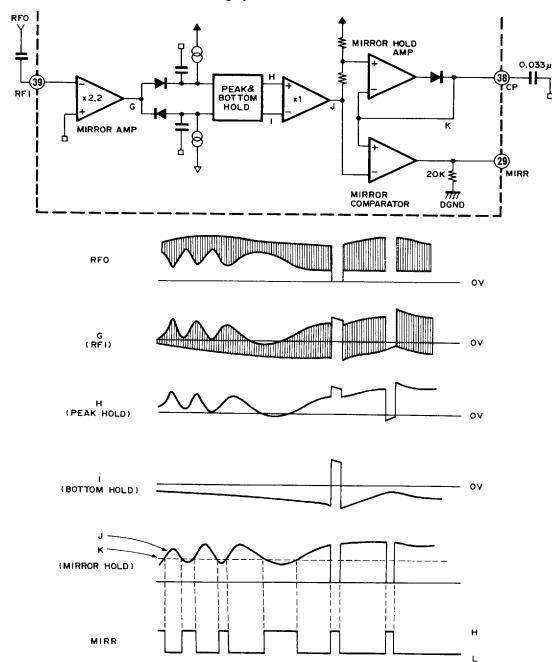

#### Mirror circuit

This circuit holds the bottom and peak (after amplifying RFI signal). Holds are performed by means of respective time constants that permit the peak hold to follow a 30kHz traverse while the bottom hold. This can follow the envelope fluctuations in the revolving cycle.

Through the differential amplification of peak and bottom hold signals, H and I, envelope signal J (demodulated to DC) is obtained. Two-thirds of the peak value of this signal J is held with a large time constant for the signal k. When k is compared with J, a mirror output is obtained by comparing signal k to signal J. Signal k equals two-thirds of J signal peak level held with a large time constant. That is, the mirror output on the disc track is at "L". Between tracks (mirror section) it is at "H". It is also at "H" when a defect is detected. The time constant for the mirror hold must be sufficiently larger than that of the traverse signal.

#### Commands

The input data that activates this IC consists of 8 bits. It is expressed hereafter as \$XX in two hexadecimal digits. (X denotes O to F). Commands for the CXA1372Q/S are classified into 4 types - \$0X to 3X.

1. At \$0X [SENSE (Pin 26) outputs "FZC" signal]

This command relates to the focus servo control.

The bit configuration is as follows:

D7 D6 D5 D4 D3 D2 D1 D0 0 0 0 FS4 FS3 FS2 FS1

Four switches, FS1 to FS4 are relate to focusing, and correspond to D0 through D3 respectively.

At \$00 FS1 = 0 and Pin 7 is charged to  $(22\mu A - 11\mu A) \times 50k\Omega = 0.55V$ ).

If FS2 = 0, this voltage is not output and the output of Pin 5 remains at 0V.

At \$02 From the above state, only FS2 turns to 1 while a negative output is output to Pin 5. This voltage level is stipulated as follows:

$$(22\mu A - 11\mu A) \times 50$$

k $\Omega \times \frac{\text{Resistance value between Pin 5 and Pin 6}}{50 \text{ k}\Omega}$  ..... (1)

At \$03 From the above state, FS1 turns to 1 and current supply to +22μA is cut off.

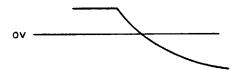

Then, CR charge/discharge circuit is formed and Pin 7 voltage decreases as time passes, as shown in Fig. 1.

Fig. 1 Voltage at Pin 7 as FS1 changes from 0 to1

The time constant is determined  $50k\Omega$  and an external capacitor.

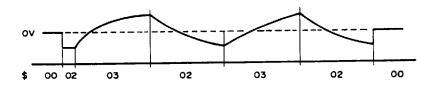

Alternating commands \$02 and \$03 provides the focus search voltage (Fig. 2).

Fig. 2 Formation of search voltage through \$02 and \$03 (Pin 5 voltage)

## 1) FS4 description

This switch is placed between focus error input 47 and the focus phase compensation to switch the focus servo on and off.

$$\$00 \rightarrow \$08$$

Focus off  $\leftarrow$  Focus on

#### 2) Focus application

For explanation sake the polarity is assumed as follows:

- a)The lens moves away or toward the disc in search.

- b)At this time, output voltage at Pin 5 varies from negative to positive.

- c)Further on, the focus S-curve changes as follows:

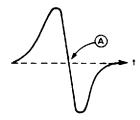

Fig. 3 S-curve

Focus servo is activated at operating point A shown in Fig. 3. Usually, focus search is performed and focus servo switch set ON when passing through A point in Fig. 3. Moreover, to prevent misoperation, a logical product (AND) is timed with the Focus-OK signal.

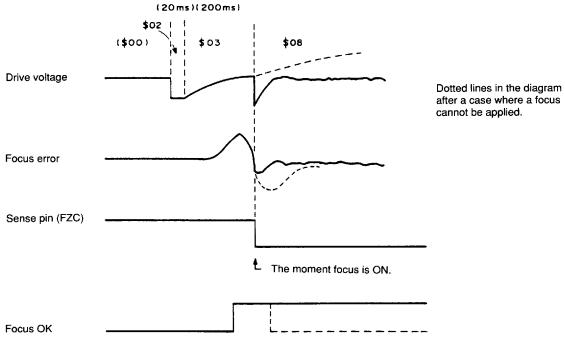

This IC is designed to output FZC (Focus Zero Cross) from Sense Pin (Pin 26), as the A point passing signal. Focus-OK signal is output to indicate focus in ON (focus is enabled in this case). The following time chart shows how to obtain the focus.

Fig. 4 Timing Chart of In-Focus

CXA1372Q/S

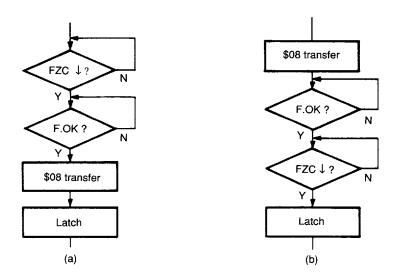

It is important here that \$08 command be transferred in the shortest possible time after FZC changes from H to L. To this effect, (b) sequence required for software is favoured over (a) sequence, shown below.

Fig. 5 Bad Sequence and Good Sequence Better case (at right) recommended over poor sequence (at left)

#### 3) Sense Pin (Pin 27)

Output at Sense Pin varies according to the input data.

That is: FZC is output with \$0X. AS is output with \$1X.

> TZC is output with \$2X. SSTOP is output with \$3X.

HIGH-Z is output with \$4X to 7X.

## 2. At \$1X SENS (Pin 27 outputs signal "AS")

This command refers to ON/OFF of TG1, TG2 and the brake circuit.

The bit configuration is as follows:

| D7 | D6 | D5 | D4 | D3     | D2     | D1  | D0  |

|----|----|----|----|--------|--------|-----|-----|

| 0  | 0  | 0  | 1  | ANTI   | Brake  | TG2 | TG1 |

|    |    |    |    | SHOCK  | Circui | t   |     |

|    |    |    |    | ON/OFF | ON/O   | FF  |     |

#### TG1, TG2

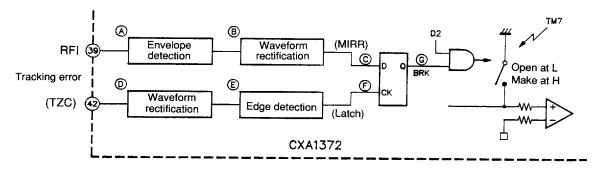

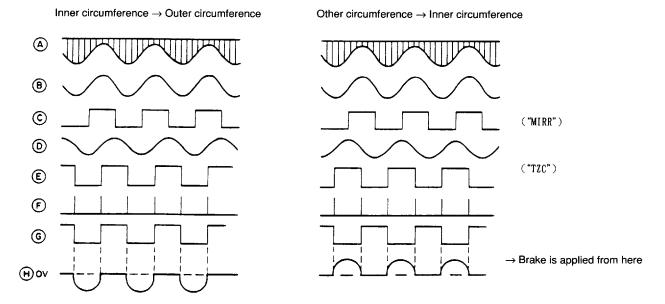

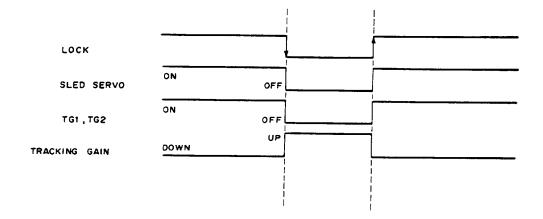

These switches select Up/Normal of the tracking servo gain. The brake circuit prevents the erratic motion of the actuator. After 100-track or 10-track jumps, the servo circuit exceeds the linear range and the actuator often sets on the wrong track. Using a feature where the RF envelope and the tracking error are out of phase by 180° braking is applied when the actuator crosses the tracks either way to cut off tracking errors and stop undesirable jumping.

Fig. 6 TM7 Movement (Brake Circuit)

Fig. 7 External Waveform

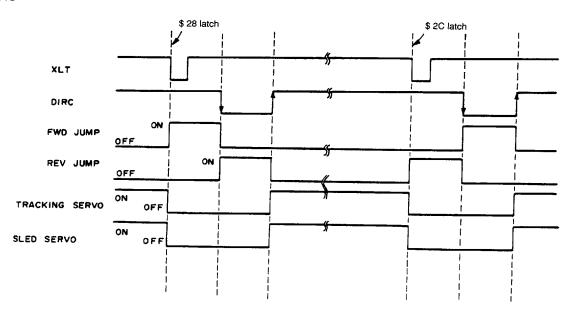

3. At \$2X SENS (Pin 27) outputs signal "TZC"

This command relates to the ON/OFF of the tracking and sled servos as well as to the formation of jump and speed feeding pulses during access.

| D7 | D6 | D5 | D4 | D3                                   | D2  | D1     |  |

|----|----|----|----|--------------------------------------|-----|--------|--|

| 0  | 0  | 1  | 0  | 00 off<br>01 Ser<br>10 F-J<br>11 R-J | UMP | 11 R-s |  |

DIRC (Pin 20) and 1 Track Jump

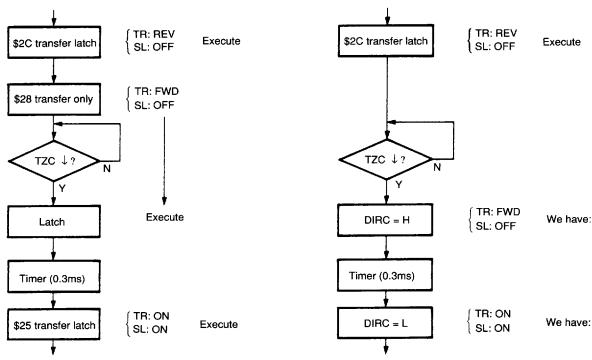

Normally, an acceleration pulse is applied for a 1-track jump. Then a deceleration pulse is given for a specified time observing the tracking error from the moment it passes point 0 tracking servo is set on again after applying a deceleration pulse for a specified time. For the 100-track jump to be explained in the next item, as long as the number of tracks is about 100 there is no problem. However for the 1-track jump it must be exactly a 1-track jump, which requires the above complicated procedure. For the 1-track jump in CD players, both the acceleration and deceleration take about 300 to 400µs. When software is used to execute this operation, it turns out as shown in the flow chart of Fig. 9. Actually, it takes time to transfer data.

Fig. 8 Pulse Waveform and Tracking Error of 1-Track Jump

Fig. 9 1-Track Jump not using DIRC 20

Fig. 10 1-Track Jump with DIRC 20

"DIRC" (Direct Control) Pin was provided in this IC to facilitate the 1-track jumping operation. That is to perform for1-track jump using DIRC, the following process takes place (DIRC = normal H).

- (a) Acceleration pulse is output. (\$2C for REV or \$28 for FWD).

- (b) With TZC ↓ (or TZC ↑), set DIRC to L. (SENS Pin 27 outputs "TZC"). As the jump pulse polarity is inverted, deceleration is applied.

- (c) Set DIRC to H for a specific time.

Both the tracking servo and sied servo are switched on automatically.

As a result, the track jump turns out as shown in the flow chart of Fig. 10 and the two serial data transfers can be omitted.

## 4. \$3X

This command selects the Focus search and Sled kick peak values.

D0, D1 ..... Sled, NORMAL feed, high-speed feed

D2, D3 ..... Focus search peak selection

|                                       | Focus sea   | arch peak   | Sled kid    | k peak      |                |

|---------------------------------------|-------------|-------------|-------------|-------------|----------------|

| D7 D6 D5 D4                           | D3<br>(PS3) | D2<br>(PS2) | D1<br>(PS1) | D0<br>(PS0) | Relative value |

| · · · · · · · · · · · · · · · · · · · | 0           | 0           | 0           | 0           | ±1             |

| 0 0 1 1                               | 0           | 1           | 0           | 1           | ±2             |

|                                       | 1           | 0           | 1           | 0           | ±3             |

|                                       | 1           | 1           | 1           | 1           | ±4             |

## **Parallel Direct Interface**

## 1. DIRC

## 2. LOCK (Sled runaway prevention circuit)

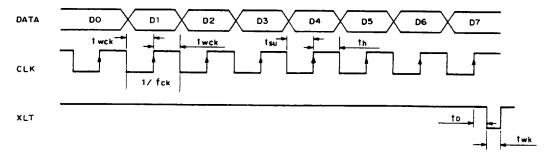

## **CPU Serial Interface Timing Chart**

DVcc - DGND = 4.5 to 5.5V

| Item              | Symbol     | Min. | Тур. | Max. | Unit |

|-------------------|------------|------|------|------|------|

| Clock frequency   | fck        |      |      | 1    | MHz  |

| Clock pulse width | fwck       | 500  |      |      | ns   |

| Setup time        | tsu        | 500  |      |      | ns   |

| Hold time         | <b>t</b> h | 500  |      |      | ns   |

| Delay time        | <b>t</b> D | 500  |      |      | ns   |

| Latch pulse width | twL        | 1000 |      |      | ns   |

## **System Control**

| مد ما            | ADDRESS     |                          | DA                       | TA                    |                       | SENS   |

|------------------|-------------|--------------------------|--------------------------|-----------------------|-----------------------|--------|

| Item             | D7 D6 D5 D4 | D3                       | D2                       | D1                    | D0                    | Output |

| Focus Control    | 0 0 0 0     | FS4<br>Focus<br>ON       | FS3<br>Gain<br>Down      | FS2<br>Search<br>ON   | FS1<br>Search<br>UP   | FZC    |

| Tracking Control | 0 0 0 1     | Anti<br>Shock            | Brake<br>ON              | TG2<br>Gain Set *     | TG1<br>1              | A.S    |

| Tracking Mode    | 0 0 1 0     | Tracking M               | ode *2                   | Sled Mode             | *3                    | TZC    |

| Select           | 0 0 1 1     | PS4<br>Focus<br>Search+2 | PS3<br>Focus<br>Search+1 | PS2<br>Sled<br>Kick+2 | PS1<br>Sled<br>Kick+1 | SSTOP  |

## Note) \*1. GAIN SET

TG1 and TG2 can be set independently.

When the anti-shock is at 1 (00011xxx), invert both TG1 and TG2 when the internal anti-shock is at H.

\*2. TRACKING MODE

|          | D3 | D2 |

|----------|----|----|

| OFF      | 0  | 0  |

| ON       | 0  | 1  |

| FWD JUMP | 1  | 0  |

| REV JUMP | 1  | 1  |

\*3. SLED MODE

|          | D1 | DO |

|----------|----|----|

| OFF      | 0  | 0  |

| ON       | 0  | 1  |

| FWD MOVE | 1  | 0  |

| REV MOVE | 1  | 1  |

## **Serial Data Truth Table**

| Serial data      | Hexa.        | Function      |

|------------------|--------------|---------------|

| FOCUS CONTROL    |              | FS = 4321     |

| 00000000         | \$00         | 0000          |

| 0000001          | \$01         | 0001          |

| 0000010          | \$02         | 0010          |

| 00000011         | \$03         | 0011          |

| 00000100         | \$04         | 0100          |

| 00000101         | \$05         | 0101          |

| 00000110         | \$06         | 0110          |

| 00000111         | \$07         | 0111          |

| 00001000         | \$08         | 1000          |

| 00001001         | \$09         | 1001          |

| 00001010         | \$0A         | 1010          |

| 00001011         | \$0B         | 1011          |

| 00001100         | \$0C         | 1100          |

| 00001101         | \$0D         | 1101          |

| 00001110         | \$0E         | 1110          |

| 00001111         | \$0F         | 1111          |

| TRACKING CONTROL |              | AS=0 AS=1     |

|                  |              | TG=2 1 TG=2 1 |

| 00010000         | \$10         | 0 0 0 0       |

| 00010001         | \$11         | 0 1 0 1       |

| 00010010         | \$12         | 1 0 1 0       |

| 00010011         | \$13         | 1 1 1 1       |

| 00010100         | \$14         | 0 0 0 0       |

| 00010101         | \$15         | 0 1 0 1       |

| 00010110         | \$16         | 1 0 1 0       |

| 00010111         | \$17         | 1 1 1 1       |

| 00011000         | \$18         | 0 0 1 1       |

| 00011001         | \$19         | 0 1 1 0       |

| 00011010         | \$1A         | 0 1 0 1       |

| 00011011         | \$1B         |               |

| 00011100         | \$1C         | 1             |

| 00011101         | \$1D<br>\$1E | 0 1 1 0 1 0 1 |

| 00011110         | \$1F         | 1 1 0 0       |

| 00011111         | фіг          | 1 1 0 0       |

| TRACKING MODE |      | DIRC=1<br>TM=654321 | DIRC=0<br>654321 | DIRC=1<br>654321 |

|---------------|------|---------------------|------------------|------------------|

| 00100000      | \$20 | 000000              | 001000           | 000011           |

| 00100001      | \$21 | 000010              | 101010           | 000011           |

| 00100010      | \$22 | 010000              | 011000           | 100001           |

| 00100011      | \$23 | 100000              | 101000           | 100001           |

| 00100100      | \$24 | 000001              | 000100           | 000011           |

| 00100101      | \$25 | 000011              | 000110           | 000011           |

| 00100110      | \$26 | 010001              | 010100           | 100001           |

| 00100111      | \$27 | 100001              | 100100           | 100001           |

| 00101000      | \$28 | 000100              | 001000           | 000011           |

| 00101001      | \$29 | 000110              | 001010           | 000011           |

| 00101010      | \$2A | 010100              | 011000           | 100001           |

| 00101011      | \$2B | 100100              | 101000           | 100001           |

| 00101100      | \$2C | 001000              | 000100           | 000011           |

| 00101101      | \$2D | 001010              | 000110           | 000011           |

| 00101110      | \$2E | 011000              | 010100           | 100001           |

| 00101111      | \$2F | 101000              | 100100           | 100001           |

#### **Others**

1. Connection of the power supply pin

|                        | Vcc | VEE | VC |

|------------------------|-----|-----|----|

| ±5V dual power supply  | +5V | -5V | 0V |

| 5V single power supply | +5V | οV  | vc |

## 2. FSET pin

FSET pin determines the high frequency phase compensation for Focus and Tracking servo, and the cut-off frequency (fc) of CLV LPF.

3. ISET pin

ISET current = 1.27V/R

= Focus search current (\$30)

= Tracking kick current

= 1/2 sled kick current (\$30)

- 4. In the tracking amplifier, input is clamped at 1 VBE to prevent over input.

- 5. How to change FE and TE gains

- (1) To increase: Pins 5 and 6, Pins 1 and 2 to more than  $100k\Omega$

- (2) To decrease: Divide FE and TE input resistance

6. Microcomputer interface 20 to 25, set input voltage of pin to

more than  $VIHVCC \times 90\%$  less than  $VILVCC \times 10\%$

- 7. Focus OK circuit

- (1) To set the time constants for the focus OK amplifier LPF and the mirror amplifier HPF refer to the paragraph on Description of Operations.

(2) The equivalent circuit of FOK output pin is as follows,

Accordingly FOK comparator output is:

Output voltage H: VFOKH = near Vcc

Output voltage L: VFOKL = Vsat (NPN) + DGND

#### 8. Mirror Circuit

(1) The equivalent circuit of MIRR output pin is as follows.

MIRR comparator output is:

Output voltage H: VMIRH = VCC - Vsat (LPNP)

Output voltage L: VMIRL = near DGND

## 9. EFM Comparator

- (1) Note that EFM duty varies when CXA1372 Vcc differs from that of DSP IC (Such as CXD2500).

- (2) The equivalent circuit of EFM output pin is as follows.

\*The power supply current is given as 5V from Vcc to DGND. Then we have EFM comparator output as follows,

Output voltage H: VEFMH = VCC - VBE (NPN)

Output voltage L: VefML =  $Vcc - 4.8 (k\Omega) \times 7 (\mu A) - VBE (NPN)$

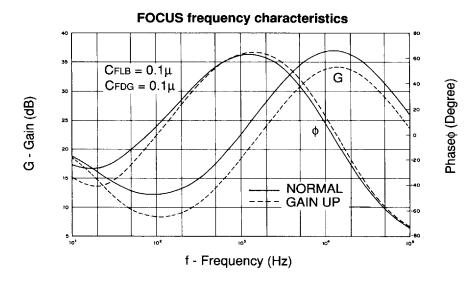

Focus Tracking Internal Phase Compensation Standard Circuit Design Data

| 4                | į      |    |       | ~• | SWa | SW condition | E    |       |    |                 | _ | Bias | Bias condition | ion | Test  | Output wafeform and        |          | •        |      | :   |

|------------------|--------|----|-------|----|-----|--------------|------|-------|----|-----------------|---|------|----------------|-----|-------|----------------------------|----------|----------|------|-----|

|                  | Symbol | Sı | S2 S3 | SS | 84  | SE S         | Se s | S7 S8 | 88 | )<br> <br> <br> |   | 1 E2 | E3             | E4  | point | description of test method | <u>.</u> | <u>.</u> | Max. |     |

| <br>1.2kHz gain  |        | 0  |       |    |     |              |      |       |    |                 |   |      |                |     | 5     | When CFLB=0.1μF            |          | 21.5     |      | дB  |

| <br>1.2kHz phase |        | 0  |       |    |     |              |      |       |    |                 |   |      |                |     | 5     |                            |          | 63       |      | geg |

| 1.2kHz gain      |        | 0  |       |    |     |              |      |       |    |                 |   |      |                |     | 5     |                            |          | 16       |      | 쁑   |

| 1.2kHz phase     |        | 0  |       |    |     |              |      |       |    |                 |   |      |                |     | 2     |                            |          | 63       |      | deg |

| 1.2kHz gain      |        |    |       |    | 0   |              |      |       |    |                 |   |      |                |     | 1     |                            |          | 5        |      | 8   |

| 1.2kHz phase     |        |    |       |    | 0   |              |      |       |    |                 |   |      |                |     | =     |                            |          | -125     |      | 6ep |

| 2.7kHz gain      |        |    |       |    | 0   |              |      |       |    |                 |   |      |                |     | Ξ     |                            |          | 265      |      | 쁑   |

| 2.7kHz phase     |        |    |       |    | 0   |              |      |       | ļ  |                 |   |      | _              |     | Ξ     |                            |          | -130     |      | geb |

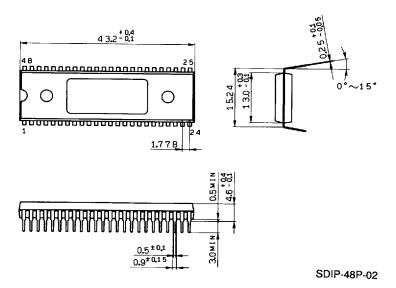

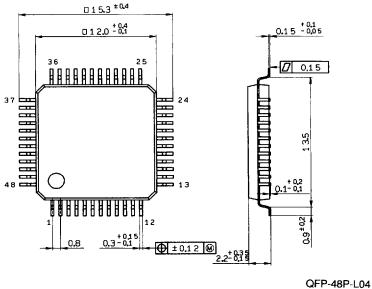

## Package Outline Unit: mm

CXA1372Q

48pin QFP (Plastic) 0.6g

CXA1372S

48pin SDIP (Plastic) 600mil 5.1g