# Data Book 1992 Computer Audio/Video

Computer Audio/Video

# Computer Audio/Video Semiconductor Data Book 1992

Numerical Index/Functional Index Description Video Processing Audio Processing CD-ROM Processing Application Notes Sales Offices

1

2

3

4

5

6

7

andre and an and a strain of the second s I and a second second

## Preface

The history of Sony Semiconductor began in 1954, with the first commercial introduction of the transistor in Japan. Since then, Sony has applied this leading edge, innovative technology in the development of the Semiconductors, currently used in most of its consumer and professional electronic products.

This Computer Audio/Video semiconductor data book has been compiled with the aim of providing the circuit designer with a reference guide describing Sony's presently available line, together with application information for each category of Computer Audio/Video Semiconductors.

#### © 1992 Sony Corporation of America.

Sony is a trademark of Sony.

The contents of this book although accurate and complete at the time of publication, are subject to incorporate improvements on the products. Circuits shown are typical examples illustrating the operation of the devices. They are not meant to convey any patents or other rights. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

# Computer Audio/Video Numerical Index

| Part Number              | Application             | Function                                       | Voltage | Package            | Page |

|--------------------------|-------------------------|------------------------------------------------|---------|--------------------|------|

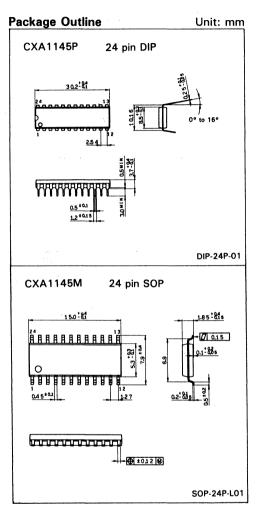

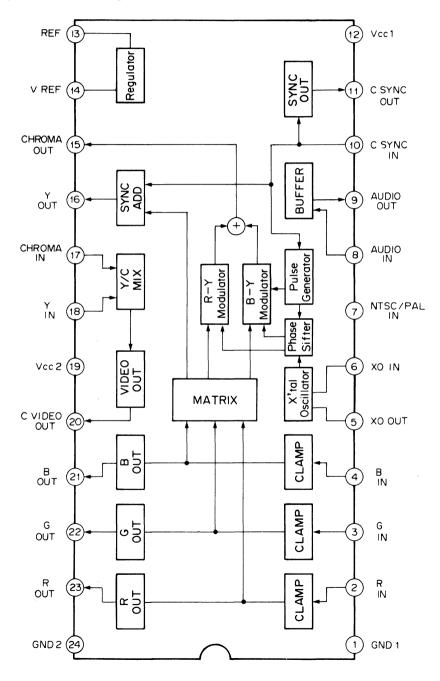

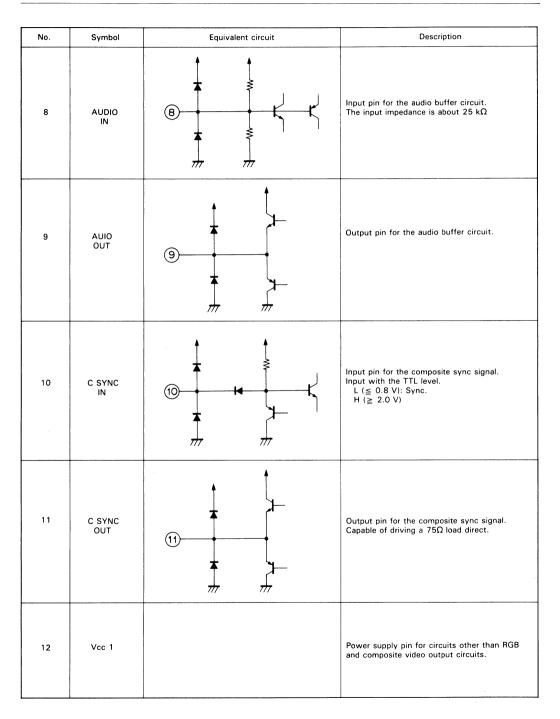

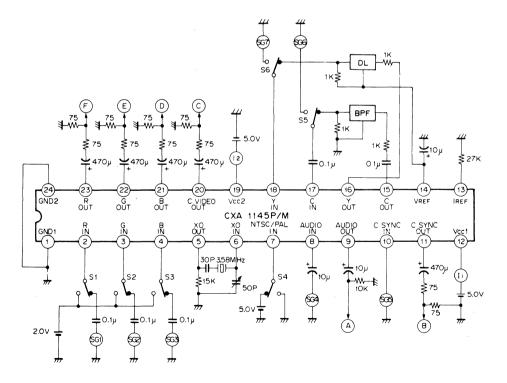

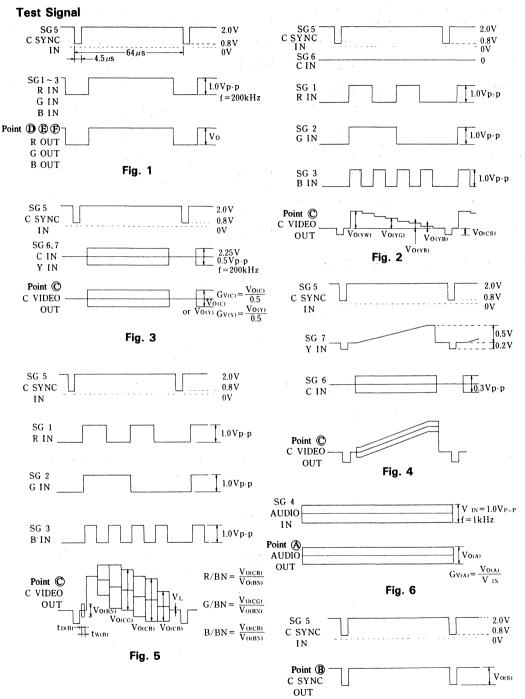

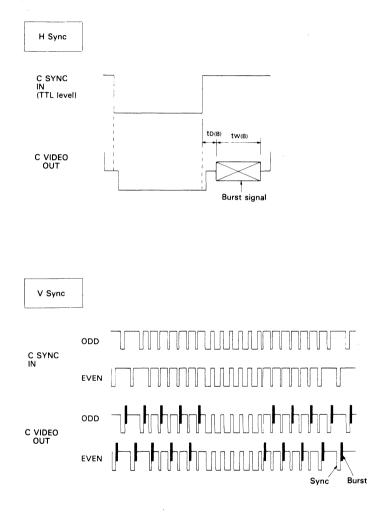

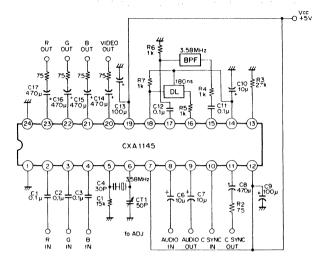

| CXA1145P/M               | Color Encoding (Analog) | RGB input, NTSC/PAL Video out                  | 5V      | 24P DIP/SOP        | 116  |

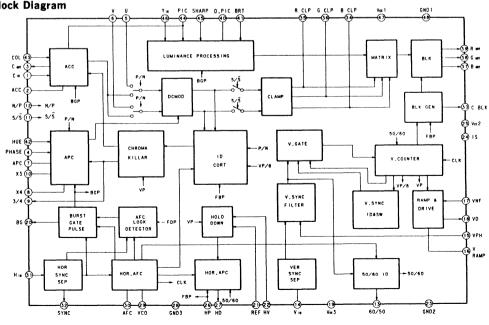

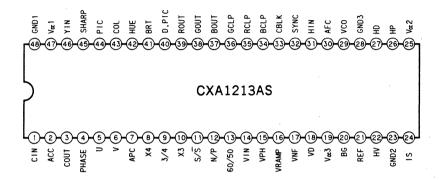

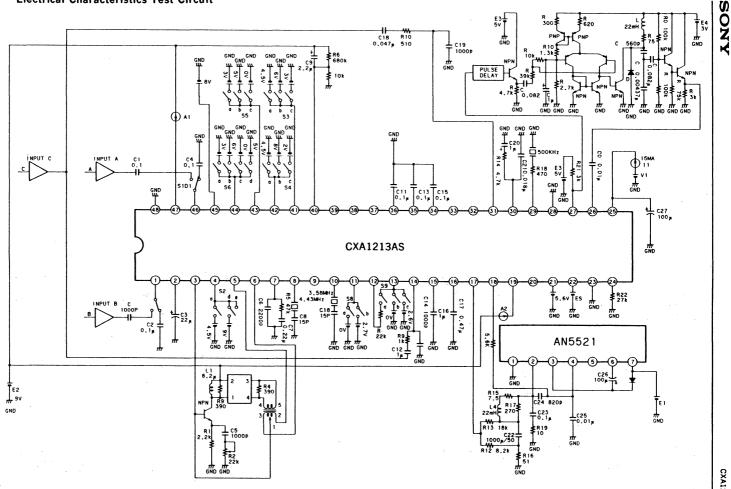

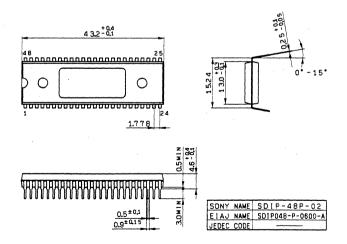

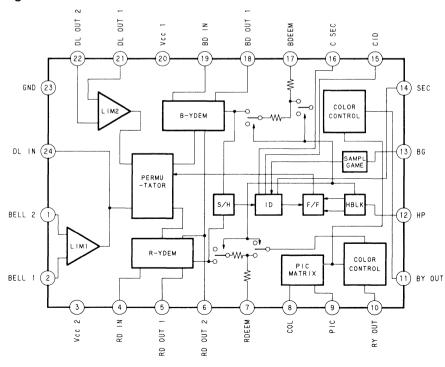

| CXA1213AS                | Color Decoding (Analog) | Chrominance Processor, RGB out                 | 9V      | 48P SDIP           | 25   |

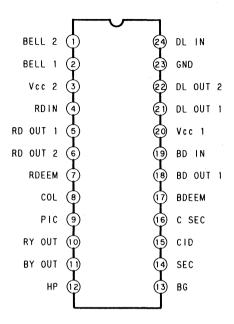

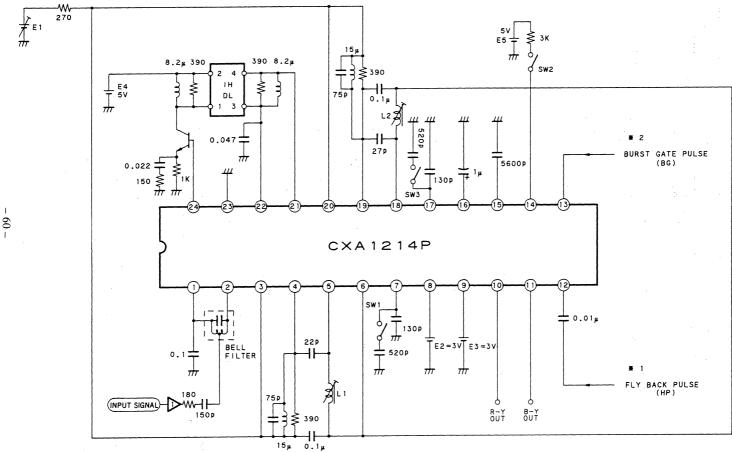

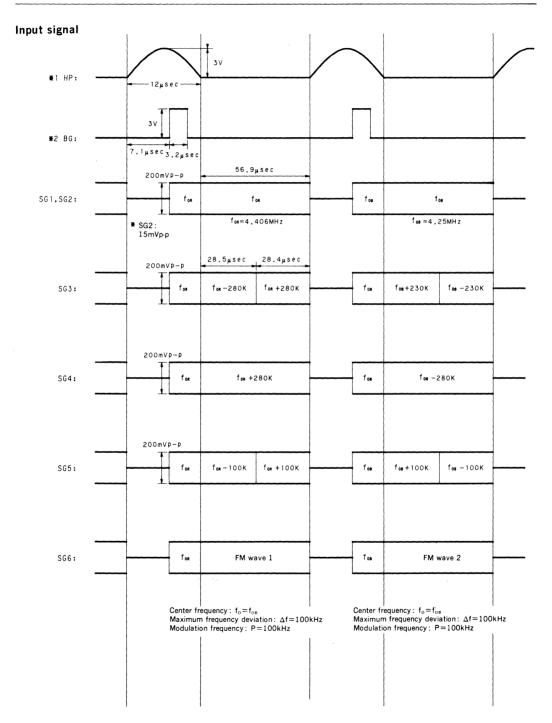

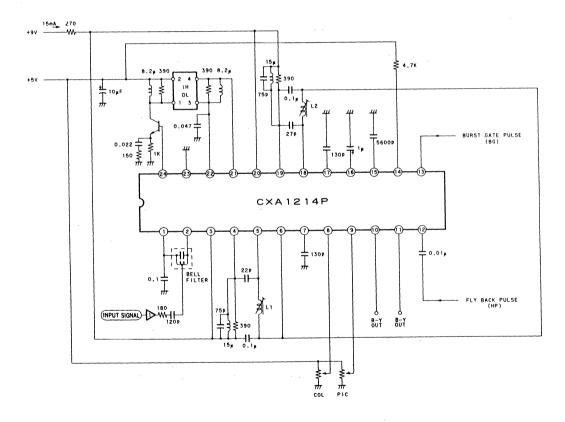

| CXA1214P                 | Color Decoding (Analog) | SECAM, Video in, UV output                     | 9V      | 24P DIP            | 51   |

| CXA1218S<br>CXA1228S     | Color Decoding (Analog) | NTSC/PAL, Video in, YUV output                 | 5V      | 28P SDIP           | 65   |

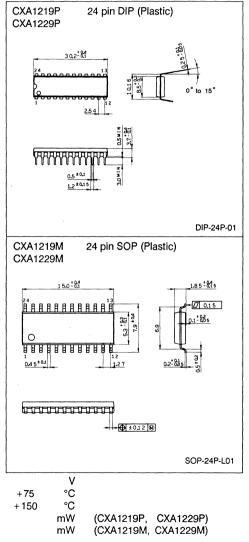

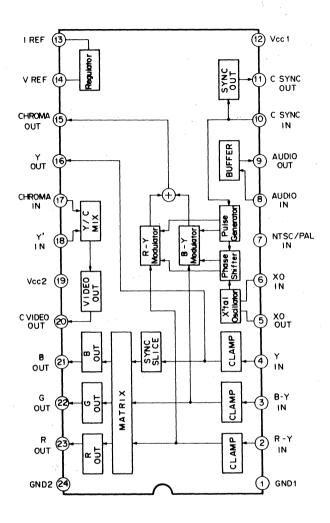

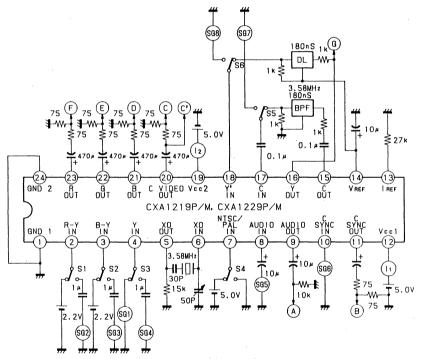

| CXA1219P/M<br>CXA1229P/M | Color Encoding (Analog) | YUV input, NTSC/PAL Video out                  | 5V      | 24P DIP/SOP        | 131  |

| CXA1236Q                 | Data Conversion; D/A    | 8bit 500MSPS Single VIDEO DAC<br>(ECL input)   | -4.5V   | 44P QFP            | 200  |

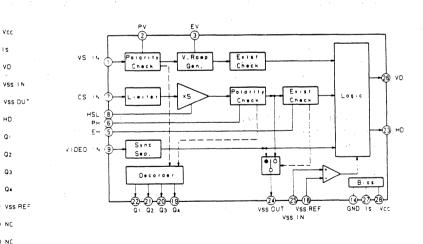

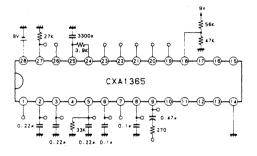

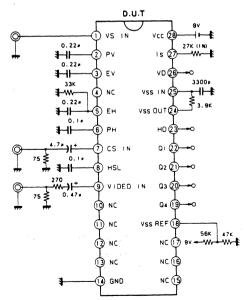

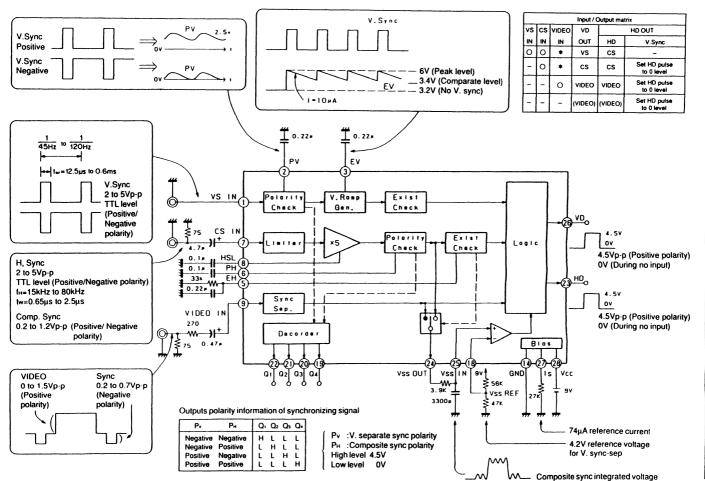

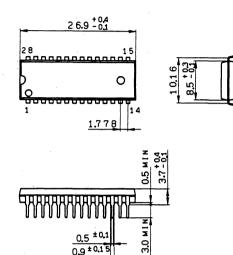

| CXA1365S                 | Synchronization/ Timing | Sync Separator for CRT                         | 9V      | 28P SDIP           | 156  |

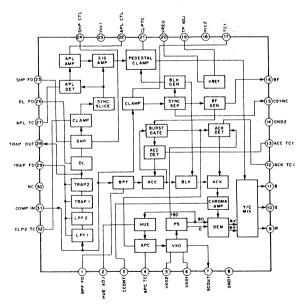

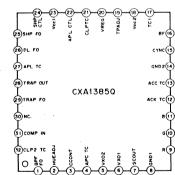

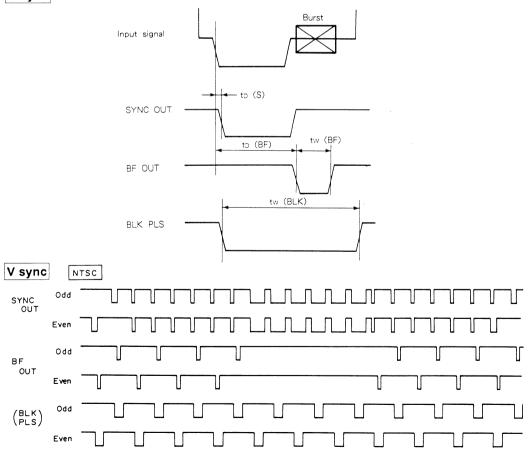

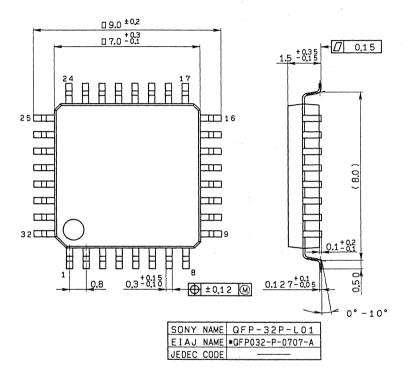

| CXA1385Q                 | Color Decoding (Analog) | NTSC, Video in, RGB output with<br>BPF & DL    | 5V      | 32P QFP            | 80   |

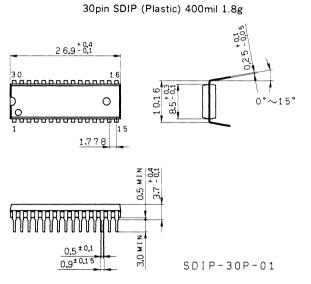

| CXA1387S                 | Miscellaneous           | Aperture Corrector                             | 9V      | 30P SDIP           | 272  |

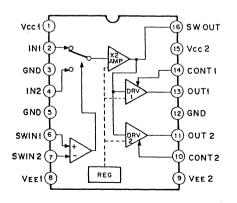

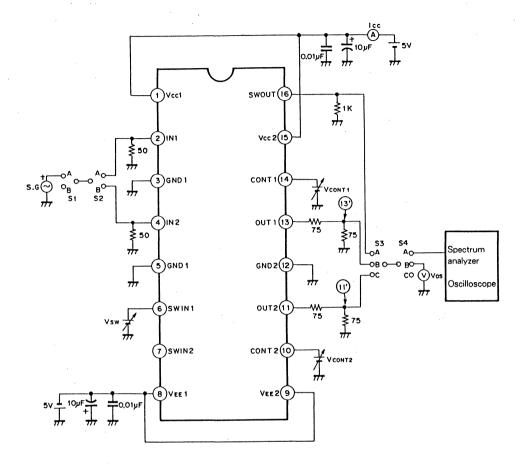

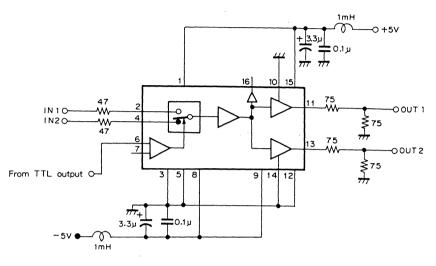

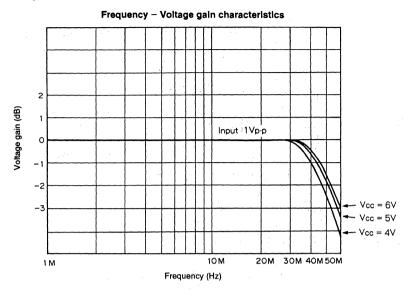

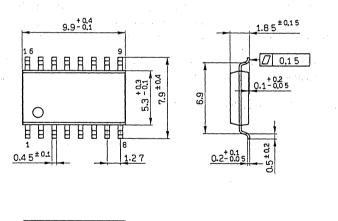

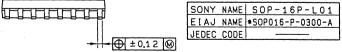

| CXA1451M                 | Miscellaneous           | Video switch with 750hm driver                 | ±5V     | 16P SOP            | 290  |

| CXA1496AQ                | Data Conversion; A/D    | 10bit 20MSPS A/D                               | ±5V     | 48P QFP            | 195  |

| CXA1693Q                 | Data Conversion; A/D    | Sample and Hold for A/D                        | ±5V     | 32P QFP            | 196  |

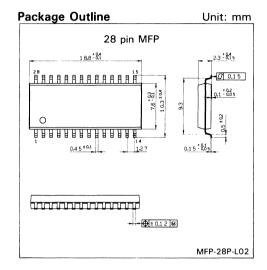

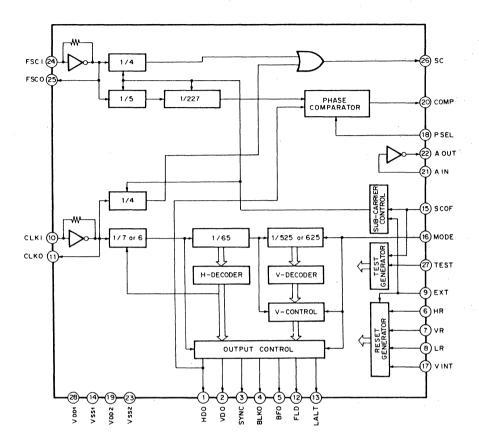

| CXD1030M                 | Synchronization/ Timing | NTSC/PAL Sync Generator                        | 5V      | 28P SOP            | 167  |

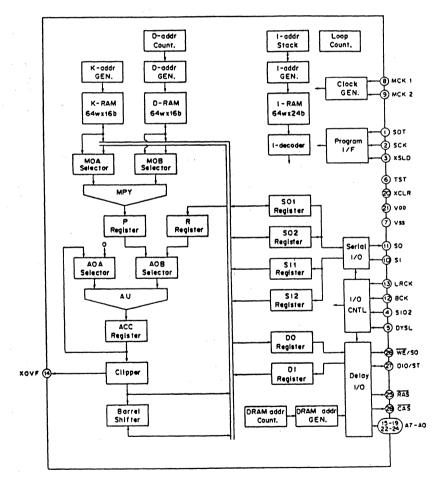

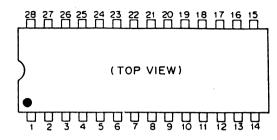

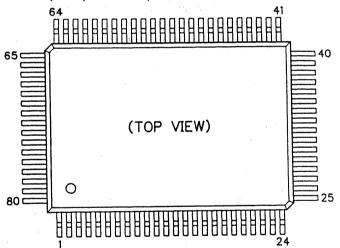

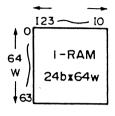

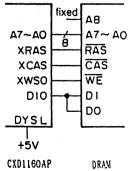

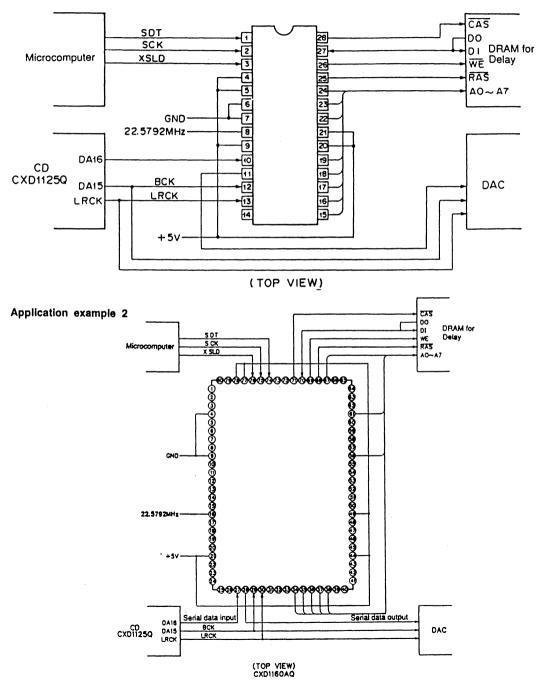

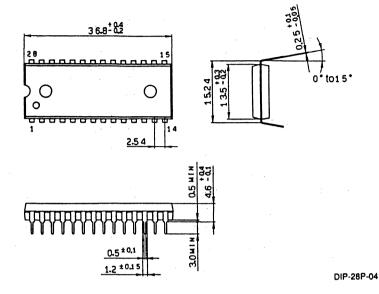

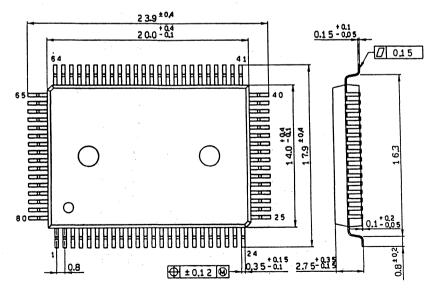

| CXD1160AP/AQ             | Audio Processing        | Digital Audio Signal Processor                 | 5V      | 28P DIP 80P<br>QFP | 299  |

| CXD1172AM/AP             | Data Conversion: A/D    | 6bit 20MSPS Video A/D                          | 5V      | 16P SOP/DIP        | 197  |

| CXD1176Q                 | Data Conversion; A/D    | 8bit 20MSPS Video Low Power                    | 5V      | 32P QFP            | 198  |

| CXD1178Q                 | Data Conversion; D/A    | 8bit 40MSPS RGB 3-Channel D/A                  | 5V      | 48P QFP            | 201  |

| CXD1179Q                 | Data Conversion; A/D    | 8bit 35MSPS Video low-power                    | 5V      | 32P QFP            | 199  |

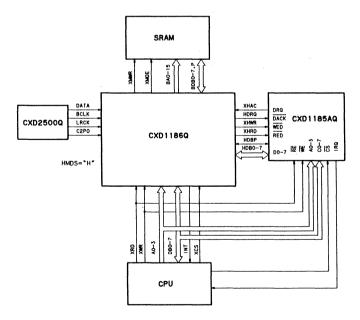

| CXD1185AQ                | CD-ROM                  | SCSI Controller Direct interface<br>w/CXD1186Q | 5V      | 64P QFP            | 383  |

| CXD1186Q                 | CD-ROM                  | CD-ROM Decoder (ECC, Buffer control)           | 5V      | 80P QFP            | 413  |

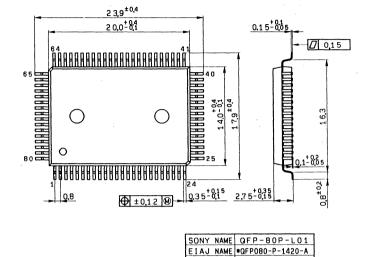

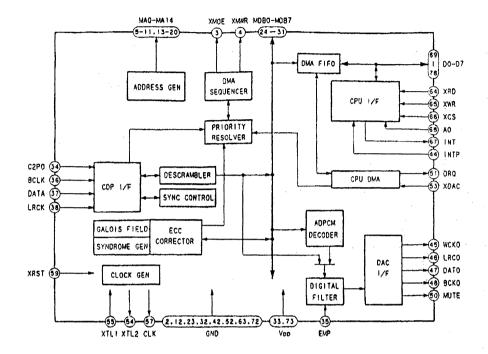

| CXD1196R                 | CD-ROM                  | CD-ROM Decoder w/ADPCM, D/F                    | 5V      | 80P VQFP           | 457  |

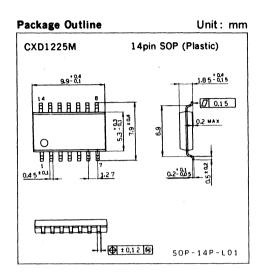

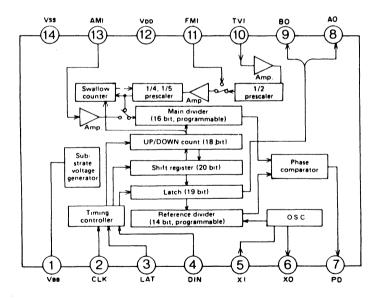

| CXD1225M                 | Synchronization/ Timing | Frequency Synthesizer                          | 5V      | 14P SOP            | 176  |

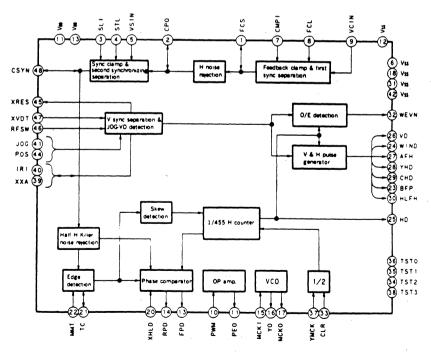

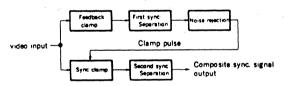

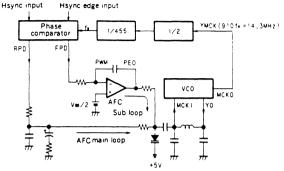

| CXD1229Q                 | Synchronization/ Timing | NTSC Sync Processor                            | 5V      | 48P QFP            | 187  |

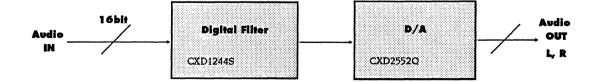

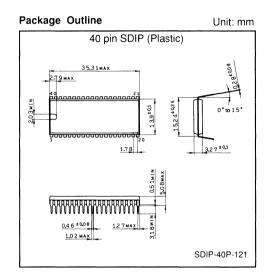

| CXD1244S                 | Audio Processing        | 100dB Attenuation Digital Filter               | 5V      | 40P SDIP           | 351  |

| CXD2011Q                 | Digital Processing      | Comb Filter                                    | 5V      | 80P QFP            | 202  |

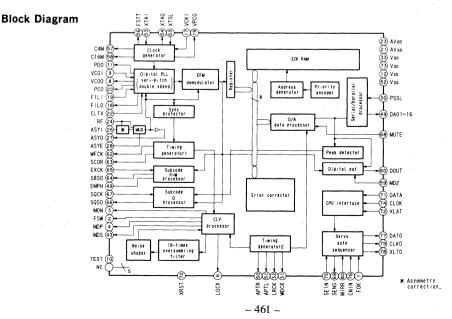

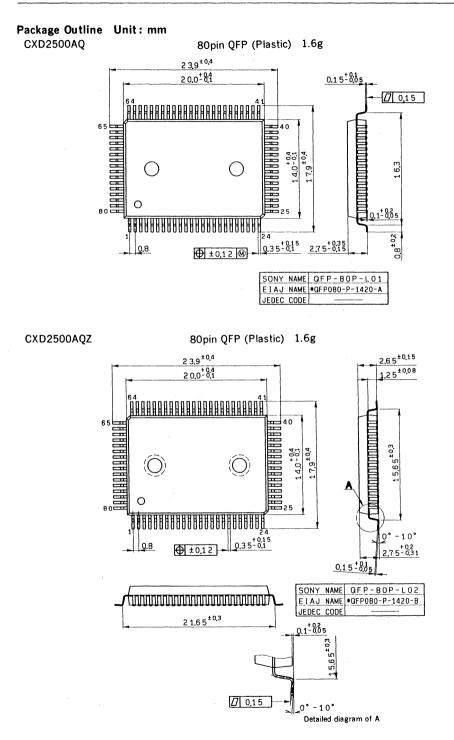

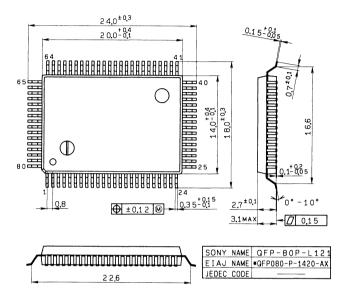

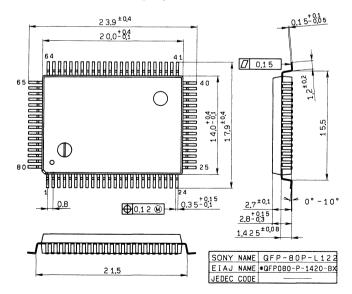

| CXD2500AQ/AQZ            | CD-ROM                  | CD Digital Signal Processor                    | 5V      | 80P QFP            | 460  |

| CXD2552Q                 | Audio Processing        | Pulse D/A Converter                            | 5V      | 44P QFP            | 364  |

| CXD2555Q                 | Audio Processing        | Audio Delta Sigma Type<br>A/D+D/A+D/F          | 5V      | 48P QFP            | 372  |

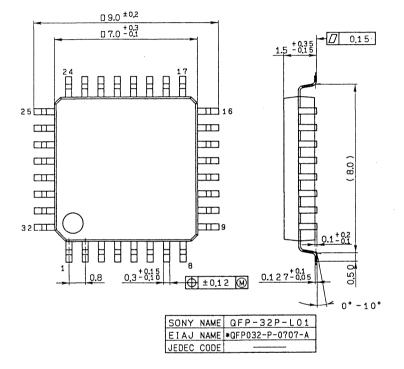

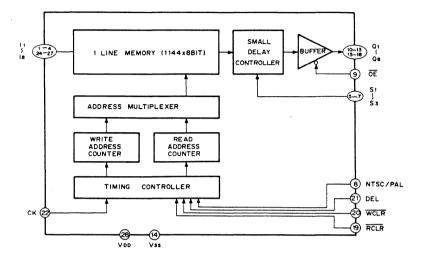

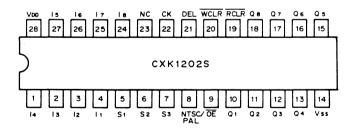

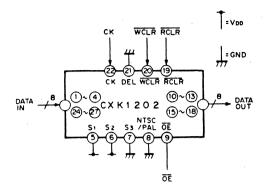

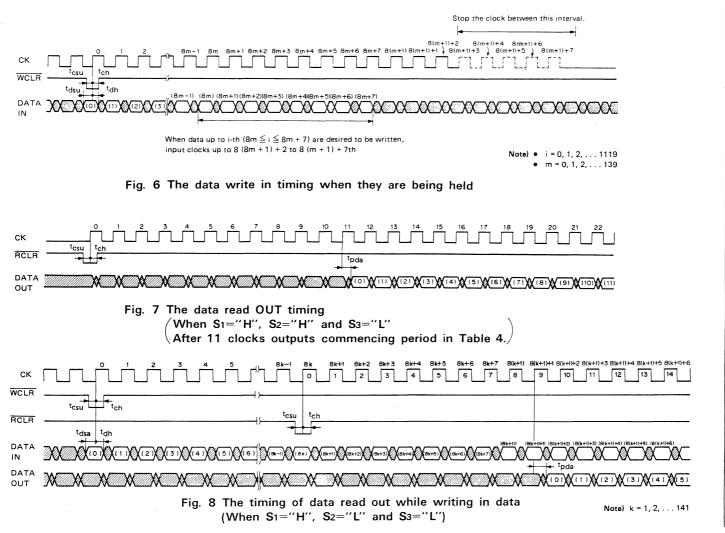

| CXK1202Q                 | Digital Processing      | Digital Delay Line Memory                      | 5V      | 32P QFP            | 213  |

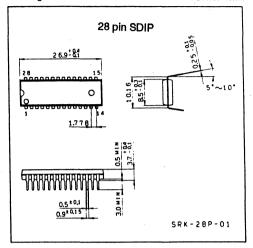

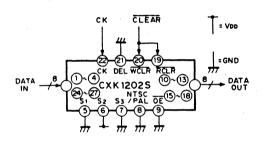

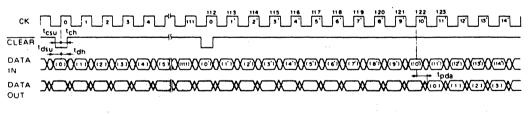

| CXK1202S                 | Digital Processing      | Digital Delay Line Memory                      | 5V      | 28P SDIP           | 222  |

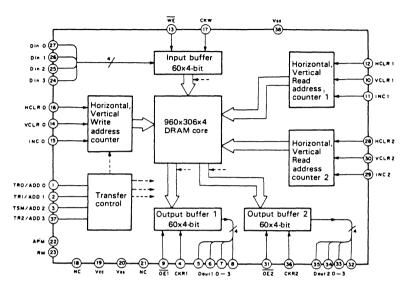

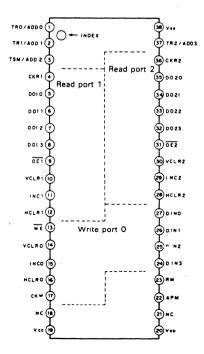

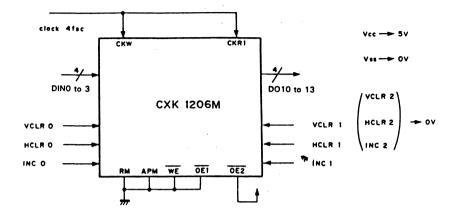

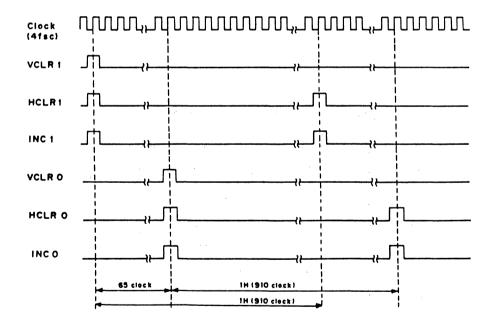

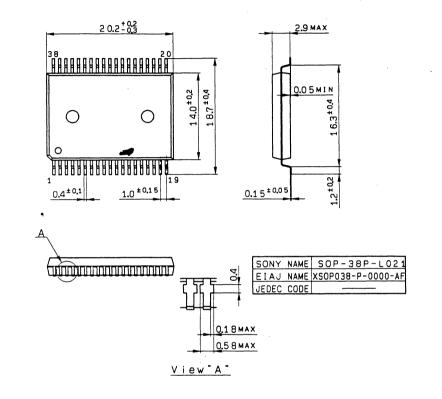

| CXK1206M                 | Digital Processing      | 1Mbit, 3 port Video Memory                     | 5V      | 38P SOP            | 232  |

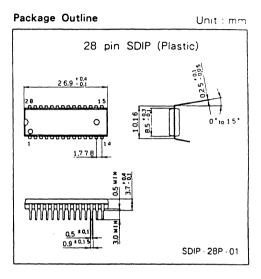

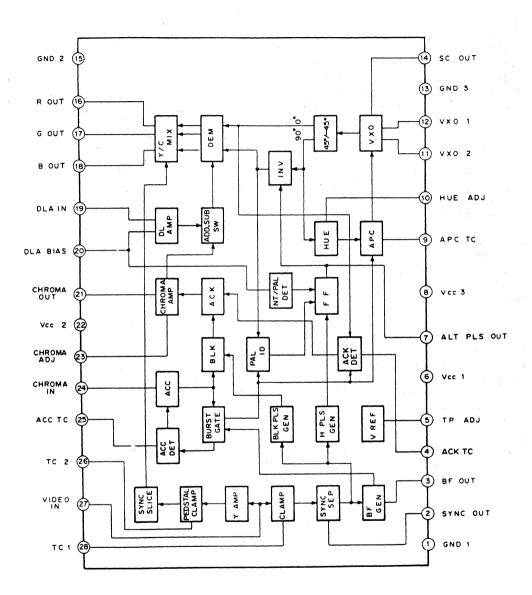

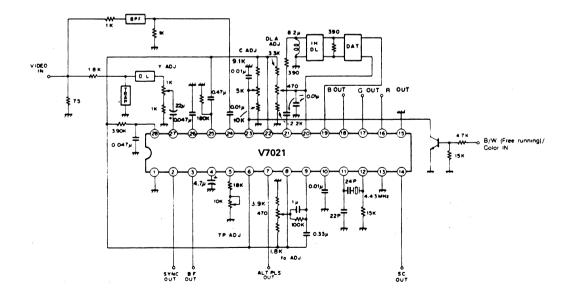

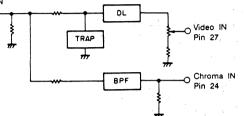

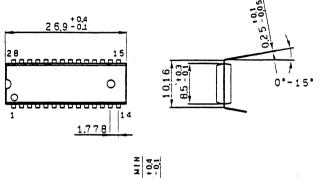

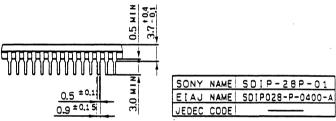

| V7021                    | Color Decoding (Analog) | NTSC/PAL, Video in, RGB output                 | 5V      | 28P SDIP           | 99   |

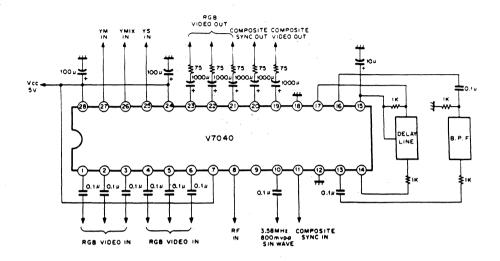

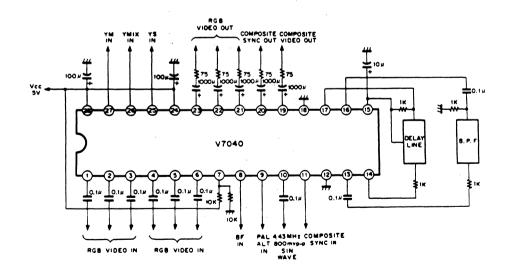

| V7040                    | Color Encoding (Analog) | RGB input, NTSC/PAL Video out,<br>Superimpose  | 5V      | 28P SDIP           | 142  |

# **Functional Index**

### **Video Processing**

### Color Decoding (Analog)

| Part Number                                                                                                                                                                                                                                      | Function                                                                                                                                                                                                                                                                                                                                                                                                                     | Voltage                                                                                       | Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| CXA1213AS                                                                                                                                                                                                                                        | Chrominance Processor, RGB out                                                                                                                                                                                                                                                                                                                                                                                               | 9V                                                                                            | 48P SDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 25                                                                            |

| CXA1214P                                                                                                                                                                                                                                         | SECAM, Video in, UV output                                                                                                                                                                                                                                                                                                                                                                                                   | 9V                                                                                            | 24P DIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 51                                                                            |

| CXA1218S/1228S                                                                                                                                                                                                                                   | NTSC/PAL, Video in, YUV output                                                                                                                                                                                                                                                                                                                                                                                               | 5V                                                                                            | 28P SDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 65                                                                            |

| CXA1385Q                                                                                                                                                                                                                                         | NTSC, Video in, RGB output with BPF & DL                                                                                                                                                                                                                                                                                                                                                                                     | 5V                                                                                            | 32P QFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 80                                                                            |

| V7021                                                                                                                                                                                                                                            | NTSC/PAL, Video in, RGB output                                                                                                                                                                                                                                                                                                                                                                                               | 5V                                                                                            | 28P SDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 99                                                                            |

| Color Encodin                                                                                                                                                                                                                                    | g (Analog)                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                               |

| CXA1145P/M                                                                                                                                                                                                                                       | RGB input, NTSC/PAL Video out                                                                                                                                                                                                                                                                                                                                                                                                | 5V                                                                                            | 24P DIP/SOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 116                                                                           |

| CXA1219/1229P/M                                                                                                                                                                                                                                  | YUV input, NTSC/PAL Video out,                                                                                                                                                                                                                                                                                                                                                                                               | 5V                                                                                            | 24P DIP/SOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 131                                                                           |

| V7040                                                                                                                                                                                                                                            | RGB input, NTSC/PAL Video out, Superimpose                                                                                                                                                                                                                                                                                                                                                                                   | 5V                                                                                            | 28P SDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 142                                                                           |

| Synchronizati                                                                                                                                                                                                                                    | on/Timing                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                               |

| CXA1365S                                                                                                                                                                                                                                         | Sync Separator for CRT                                                                                                                                                                                                                                                                                                                                                                                                       | 9V                                                                                            | 28P SDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 156                                                                           |

| CXD1030M                                                                                                                                                                                                                                         | NTSC/PAL Sync Generator                                                                                                                                                                                                                                                                                                                                                                                                      | 5V                                                                                            | 28P SOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 167                                                                           |

| CXD1225M                                                                                                                                                                                                                                         | Frequency Synthesizer                                                                                                                                                                                                                                                                                                                                                                                                        | 5V                                                                                            | 14P SOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 176                                                                           |

|                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                              | 5V                                                                                            | 48P OFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 187                                                                           |

| CXD1229Q                                                                                                                                                                                                                                         | NTSC Sync Processor                                                                                                                                                                                                                                                                                                                                                                                                          | ) V                                                                                           | 40P QFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 107                                                                           |

|                                                                                                                                                                                                                                                  | jital Conversion (For more information refer                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                               |

| Analog to Dig                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                               |

| Analog to Dig<br>CXA1496AQ                                                                                                                                                                                                                       | jital Conversion (For more information refer                                                                                                                                                                                                                                                                                                                                                                                 | to the Sony C                                                                                 | onverter Data E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | look)                                                                         |

| Analog to Dig<br>CXA1496AQ<br>CXA1693Q                                                                                                                                                                                                           | <b>Jital Conversion (For more information refor</b><br>10-bit 20MSPS A/D Converter                                                                                                                                                                                                                                                                                                                                           | to the Sony C<br>±5V                                                                          | <b>Converter Data E</b><br>48P QFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>look)</b><br>195                                                           |

| Analog to Dig<br>CXA1496AQ<br>CXA1693Q<br>CXA1172AM/AP                                                                                                                                                                                           | Jital Conversion (For more information refer<br>10-bit 20MSPS A/D Converter<br>High Speed Sample and Hold A/D Converter                                                                                                                                                                                                                                                                                                      | to the Sony C<br>±5V<br>±5V                                                                   | 48P QFP<br>32P QFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>look)</b><br>195<br>196                                                    |

|                                                                                                                                                                                                                                                  | Jital Conversion (For more information refer<br>10-bit 20MSPS A/D Converter<br>High Speed Sample and Hold A/D Converter<br>6bit 20MSPS Video A/D Converter                                                                                                                                                                                                                                                                   | to the Sony (<br><u>+</u> 5V<br><u>+</u> 5V<br>5V                                             | A Solution Content of | <b>look)</b><br>195<br>196<br>197                                             |

| <b>Analog to Dig</b><br>CXA1496AQ<br>CXA1693Q<br>CXA1172AM/AP<br>CXD1176Q<br>CXD1179Q                                                                                                                                                            | Jital Conversion (For more information refer<br>10-bit 20MSPS A/D Converter<br>High Speed Sample and Hold A/D Converter<br>6bit 20MSPS Video A/D Converter<br>8bit 20MSPS Video A/D Converter                                                                                                                                                                                                                                | to the Sony (<br><u>+</u> 5V<br><u>+</u> 5V<br>5V<br>5V<br>5V<br>5V                           | 48P QFP<br>32P QFP<br>16 SOP/DIP<br>32P QFP<br>32P QFP<br>32P QFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 195<br>196<br>197<br>198<br>199                                               |

| <b>Analog to Dig</b><br>CXA1496AQ<br>CXA1693Q<br>CXA1172AM/AP<br>CXD1176Q<br>CXD1179Q                                                                                                                                                            | <b>jital Conversion</b> (For more information refer<br>10-bit 20MSPS A/D Converter<br>High Speed Sample and Hold A/D Converter<br>6bit 20MSPS Video A/D Converter<br>8bit 20MSPS Video A/D Converter<br>8bit 35MSPS Video A/D Converter                                                                                                                                                                                      | to the Sony (<br><u>+</u> 5V<br><u>+</u> 5V<br>5V<br>5V<br>5V<br>5V                           | 48P QFP<br>32P QFP<br>16 SOP/DIP<br>32P QFP<br>32P QFP<br>32P QFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 195<br>196<br>197<br>198<br>199                                               |

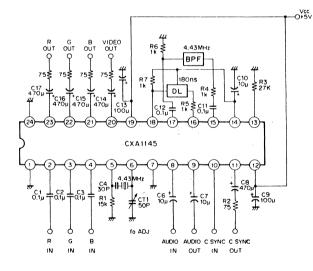

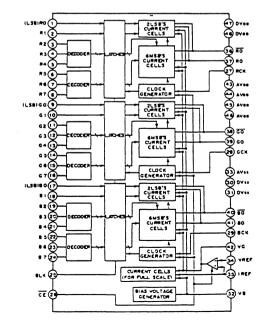

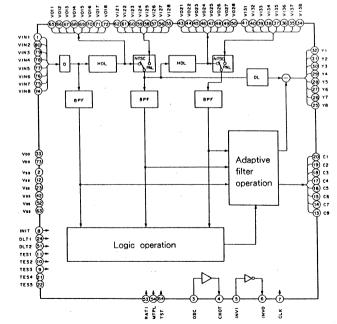

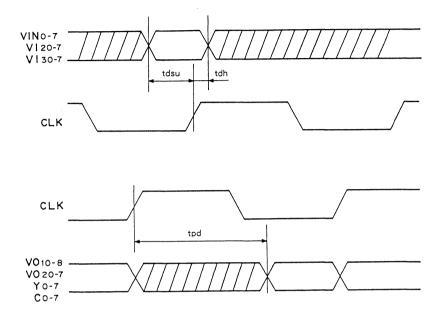

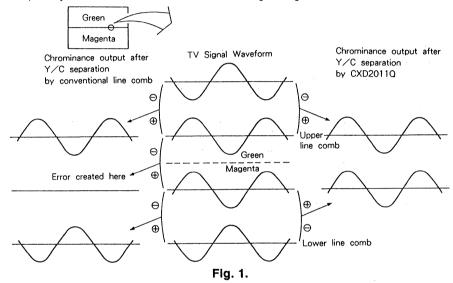

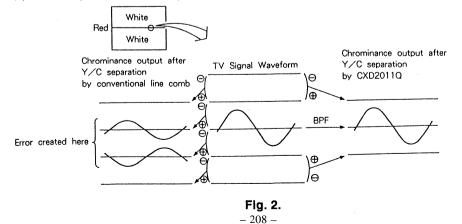

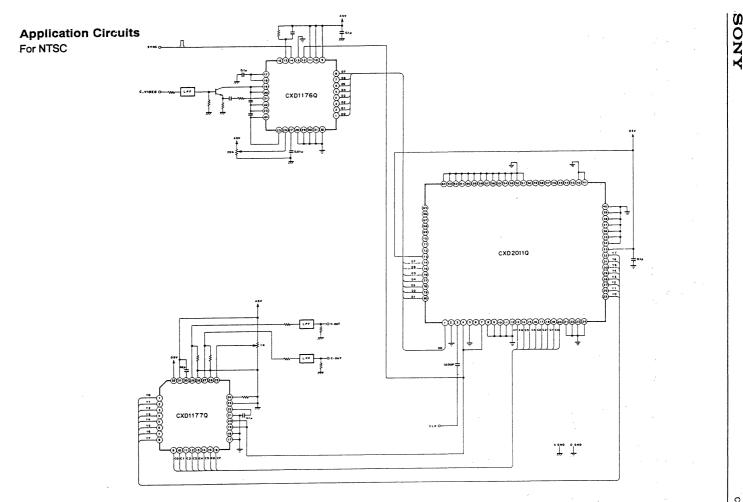

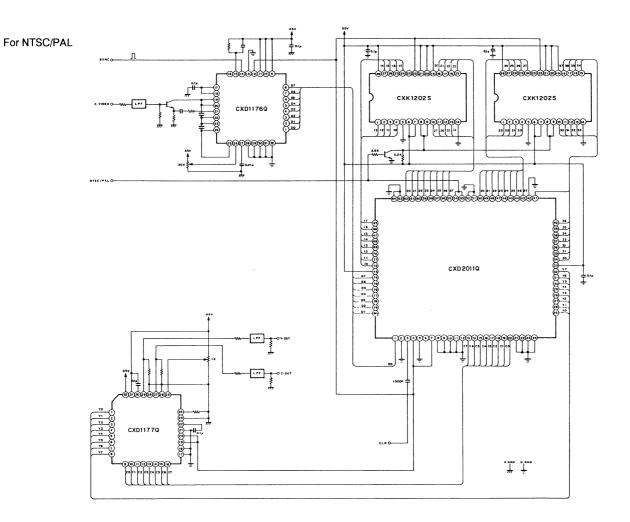

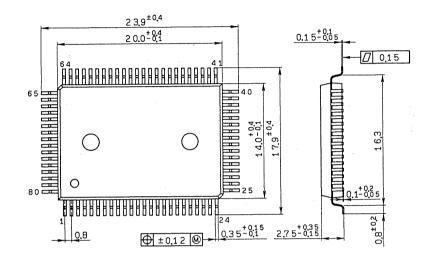

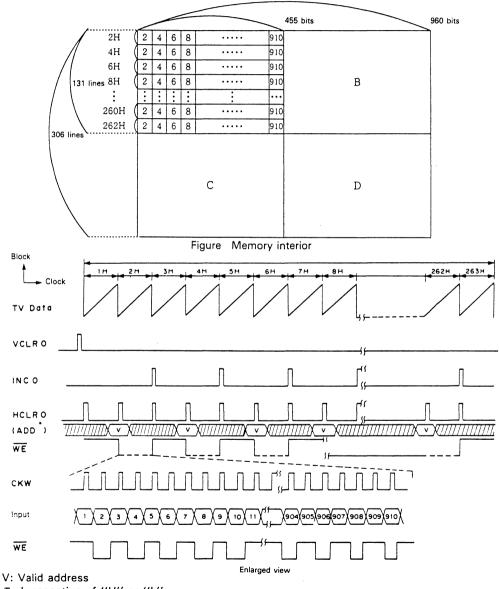

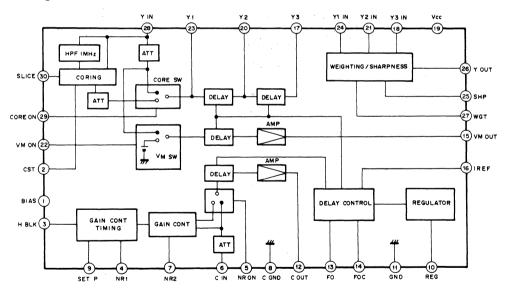

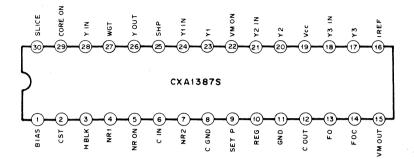

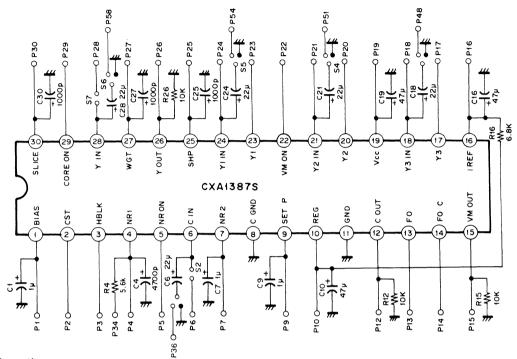

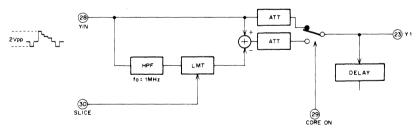

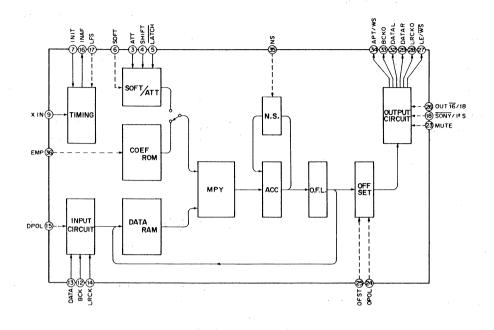

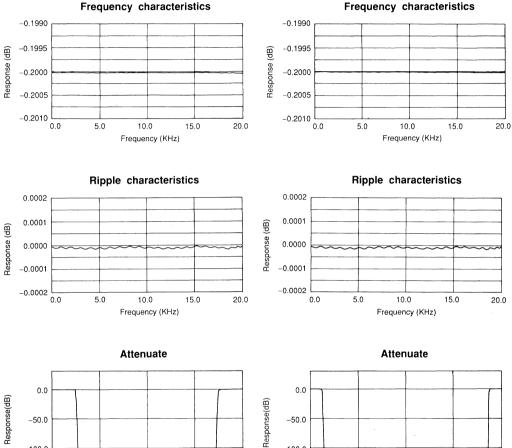

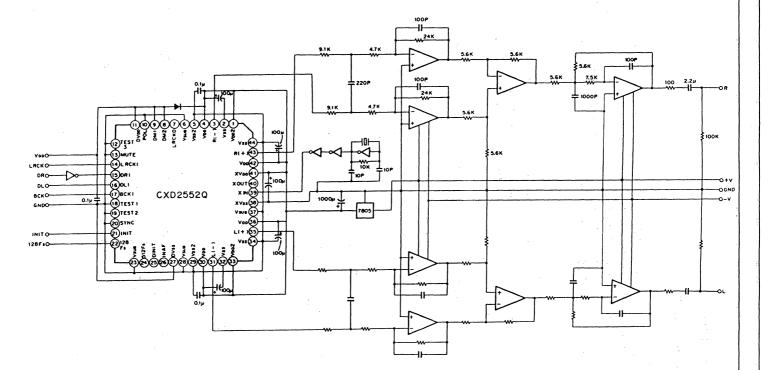

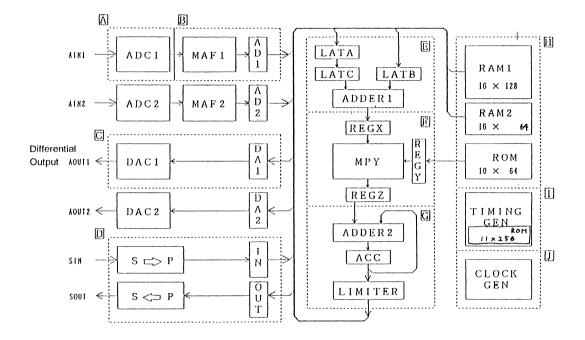

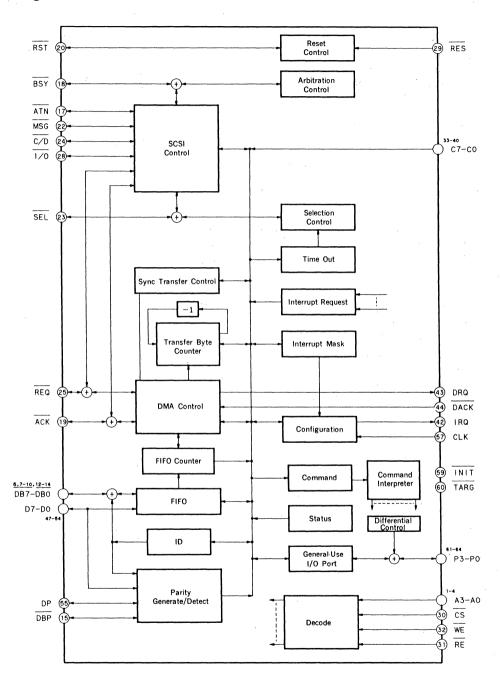

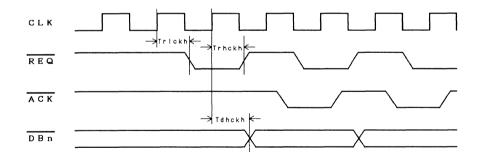

| Analog to Dig<br>CXA1496AQ<br>CXA1693Q<br>CXA1172AM/AP<br>CXD1176Q<br>CXD1176Q<br>CXD1179Q<br>Digital to Anc                                                                                                                                     | Jital Conversion (For more information refer<br>10-bit 20MSPS A/D Converter<br>High Speed Sample and Hold A/D Converter<br>6bit 20MSPS Video A/D Converter<br>8bit 20MSPS Video A/D Converter<br>8bit 35MSPS Video A/D Converter<br><b>alog Conversion (For more information refer</b>                                                                                                                                       | to the Sony (<br>±5V<br>±5V<br>5V<br>5V<br>5V<br>to the Sony (                                | 48P QFP<br>32P QFP<br>16 SOP/DIP<br>32P QFP<br>32P QFP<br>32P QFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | iook)<br>195<br>196<br>197<br>198<br>199<br>iook)                             |