# SONY

# Semiconductor IC

# Data Book 1991 Radio Communication System ICs

SOZK.

# SONY<sub>®</sub>

# Semiconductor Integrated Circuit Data Book 1991

| List of Model Names/<br>Index by Usage | 1 |

|----------------------------------------|---|

| Description                            | 2 |

| FM IF Amplifier                        | 3 |

| MODEM ICs                              | 4 |

| PLL ICs                                | 5 |

| GaAs MES FET                           | 6 |

# Semiconductor Integrated Circuit Data Book 1991

#### PREFACE

This is the 1991 version of the Sony semiconductor IC data book. This book covers all the semiconductor products manufactured and marketed by Sony.

In preparation of this data book, as much characteristic and application data as possible have been collected and added with a view of making this book a convenient reference for users of Sony products. If, however, you are dissatisfied with this book in any way, please write; we welcome suggestions and comments.

Sony reserves the right to change products and specifications without prior notice. Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same. Unauthorized reproduction of the contents, even partial, is prohibited.

## Sony Semiconductor Data Books

The following data books are available for the respective products applications.

- 1. TVs

- 2. Videos

- 3. CCD Cameras & Peripherals

- 4. Compact Discplayers

- 5. Analog Audio

- 6. Floppy Disk/Hard Disk Drive ICs

- 7. Radio Communication System ICs

- 8. A/D, D/A Converters

- 9. SPECL Standard Logic

- 10. Microcomputers

- 11. Microprocessors

- 12. Memories

- 13. Discrete Semiconductors

In addition, a List of Semiconductor Products covering all manufacutured device on the market, is issued twice a year.

Data books offer information pertaining to the listed products.

### Contents

|    |      |                                            | age |

|----|------|--------------------------------------------|-----|

| 1. | List | t of Model Names ·····                     | 6   |

| 2. | Ind  | ex by Usage ·····                          | 7   |

| 3. | IC   | Nomenclature                               | 10  |

| 4. | Pre  | cautions for IC Application                | 12  |

|    | 1)   | Absolute maximum ratings                   | 12  |

|    | 2)   | Protection against electrostatic breakdown | 13  |

|    | 3)   | Mounting method ·····                      |     |

| 5. | Qua  | ality Assurance and Reliability            | 19  |

| 6. | Dat  | ta Sheets                                  | 25  |

|    | 1)   | FM IF Amplifier ·····                      | 25  |

|    | 2)   | MODEM ICs                                  | 111 |

|    | 3)   | PLL ICs                                    | 175 |

|    | 4)   | GaAs MES FET ······                        | 221 |

| Туре                         | Page | Туре         | Page | Туре       | Page |

|------------------------------|------|--------------|------|------------|------|

| CX-7925B/B-1<br>CXD1225M/M-1 | 177  | CXA1356M/N   | 211  | CXD1231Q-Z | 147  |

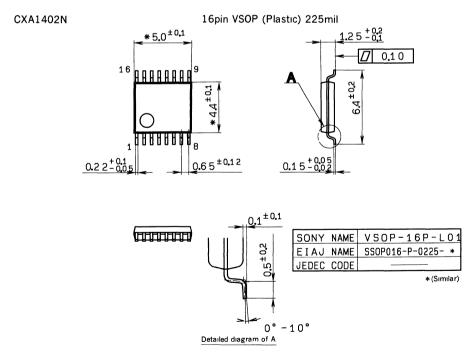

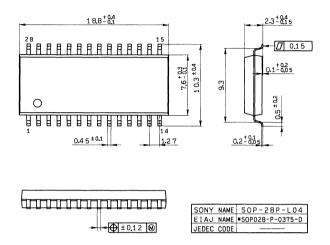

| CX-7961A/A-1                 | 188  | CXA1402M/N   | 35   | CXD1233M   | 166  |

| CXA1002M/N                   | 27   | CXA1474M/N   | 103  | CXD1237Q/R | 129  |

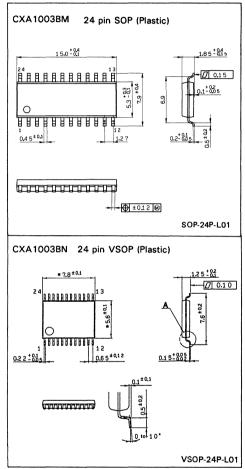

| CXA1003BM/BN                 | 38   | CXA1484M/N   | 107  | CXD1270Q/R | 155  |

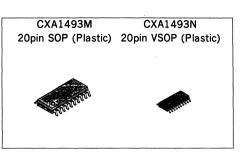

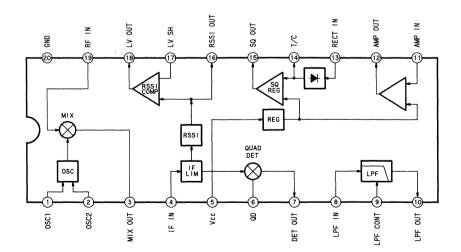

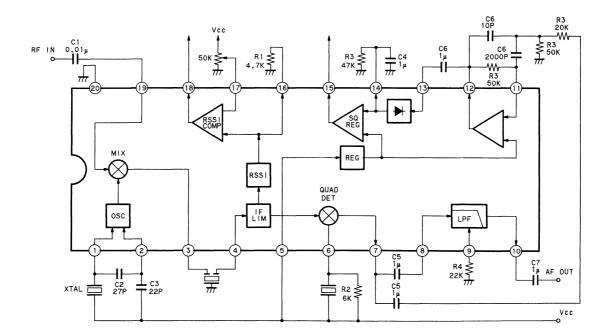

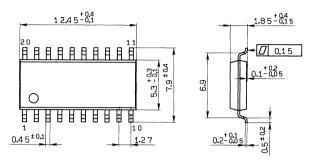

| CXA1183M                     | 71   | CXA1493M/N   | 84   | 3SK165     | 223  |

| CXA1184M/N                   | 88   | CXA1541M     | 219  | 3SK166     | 227  |

| CXA1293M/N                   | 51   | CXD1118M/M-1 | 199  | SGM2004M   | 231  |

| CXA1343M/N                   | 58   | CXD1230M     | 113  | SGM2006M/P | 235  |

# 1. List of Model Names

# 2. Index by Usage

#### 1) FM IF Amplifier

| Туре         | Function                                                                                                                               | Page |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------|------|

| CXA1002M/N   | FM IF amplifier for cellular radio for 2nd IF I <sub>CC</sub> = 2.5mA<br>CXA1002N : VSOP package                                       | 27   |

| CXA1402M/N   | FM IF amplifier for cellular radio for 2nd IF(NEW) $I_{CC} = 1.5mA CXA1002M/N$ pin compatible(NEW)                                     | 35   |

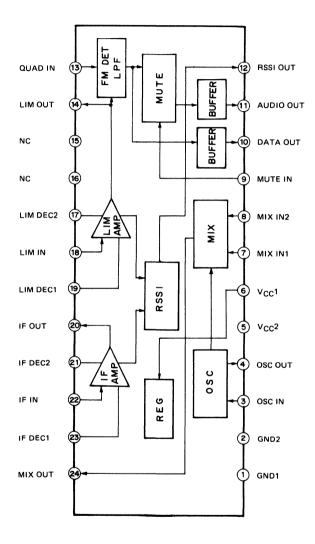

| CXA1003BM/BN | FM IF amplifier for cellular radio for 2nd MIX $\rm I_{CC}\!=\!5.7mA$ CXA1003BN : VSOP package                                         | 38   |

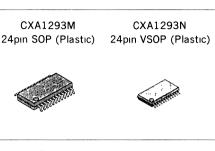

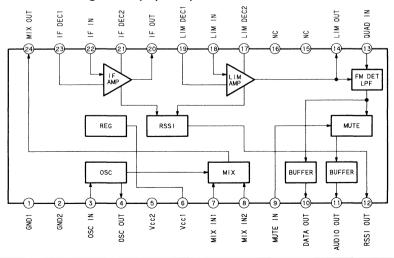

| CXA1293M/N   | FM IF amplifier for cellular pin replaceable with CXA1003BM/BN $I_{CC}$ = 3.0mA CXA1293N : VSOP (NEW) package                          | 51   |

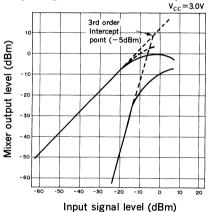

| CXA1343M/N   | FM IF amplifier for cellular built in gain control amplifier and RSSI output buffer                                                    | 58   |

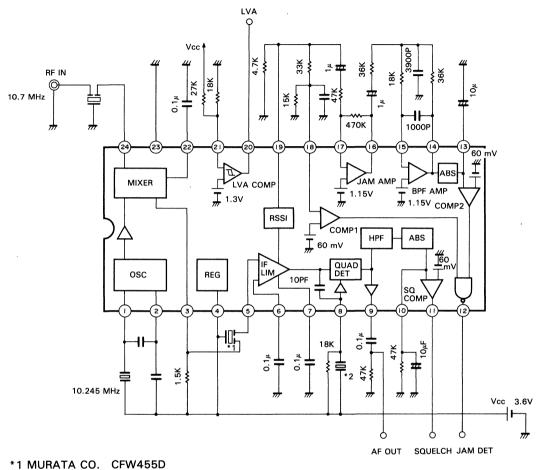

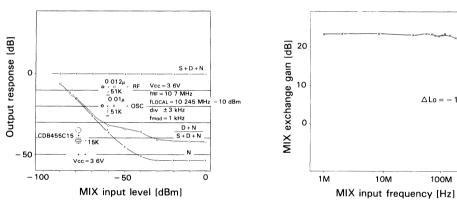

| CXA1183M     | FM IF amplifier for cordless phone built in JAM detect circuit                                                                         | 71   |

| CXA1493M/N   | FM IF amplifier for cordless phone built in detect output LPF and highly efficient RSSI function $\stackrel{i_{\pi}}{\longrightarrow}$ | 84   |

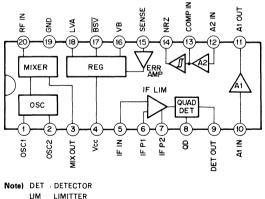

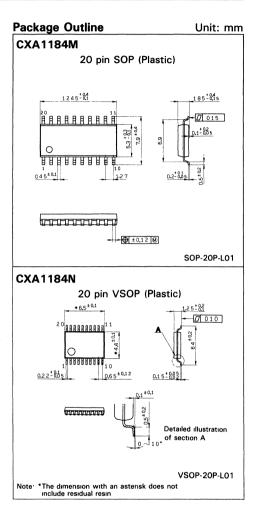

| CXA1184M/N   | FM IF amplifier for double conversion pocket pager                                                                                     | 88   |

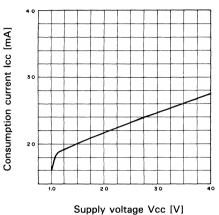

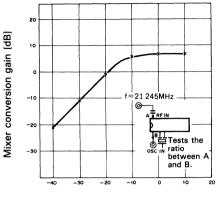

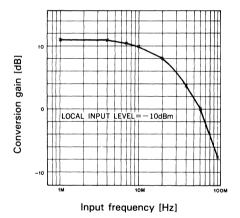

| CXA1474M/N   | FM IF amplifier for single conversion pocket pager (NEW) $I_{CC} = 500 \mu A \ 16P \ VSOP \ package$                                   | 103  |

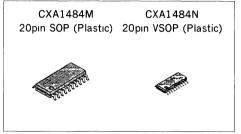

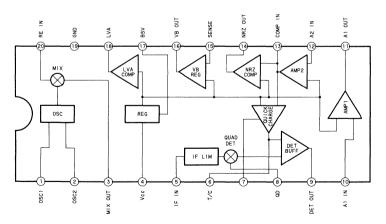

| CXA1484M/N   | FM IF amplifier for double conversion pocket pager $20P$ VSOP package $I_{CC}=1.4mA$ (NEW)                                             | 107  |

☆: Under development (New): New device

#### 2) MODEM ICs

| Туре       | Function                                             |       | Page |

|------------|------------------------------------------------------|-------|------|

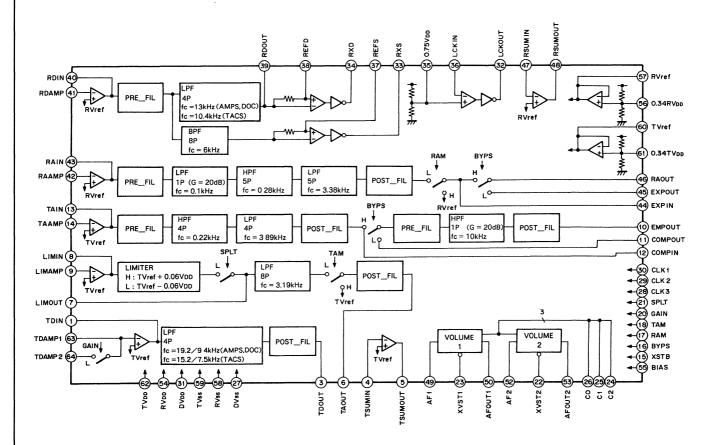

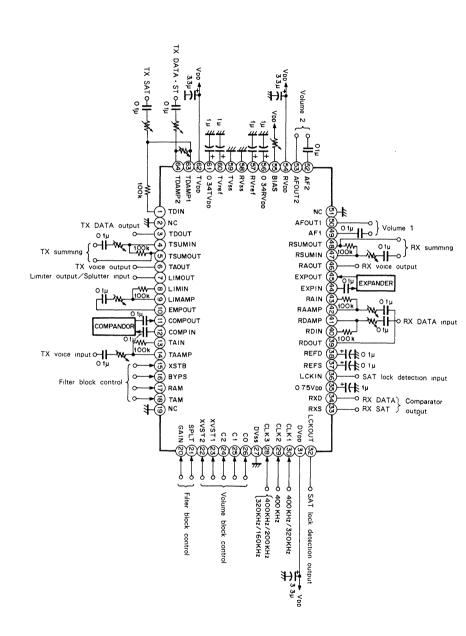

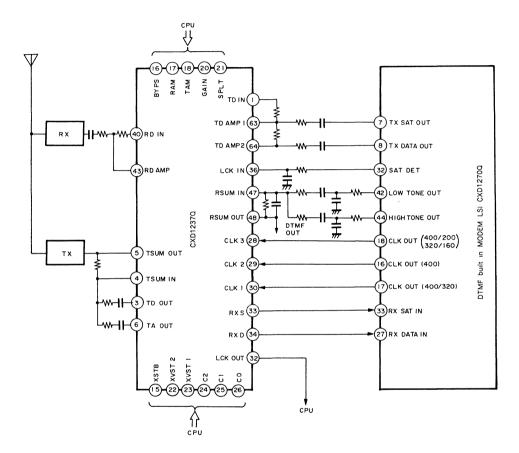

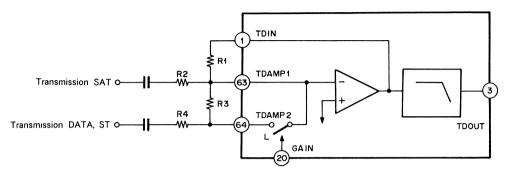

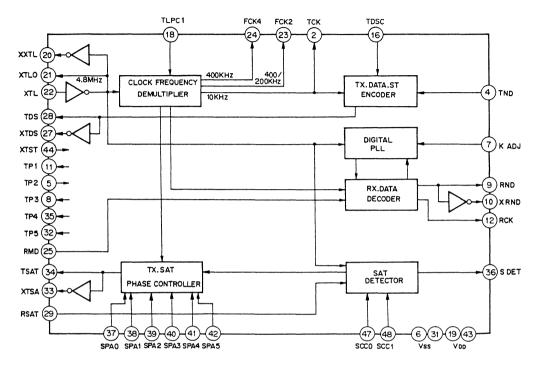

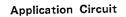

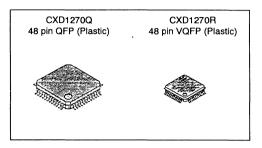

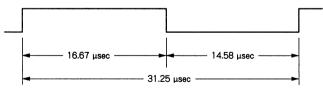

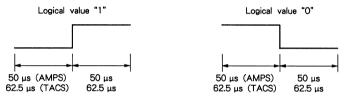

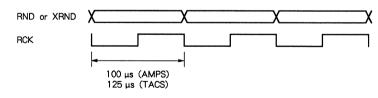

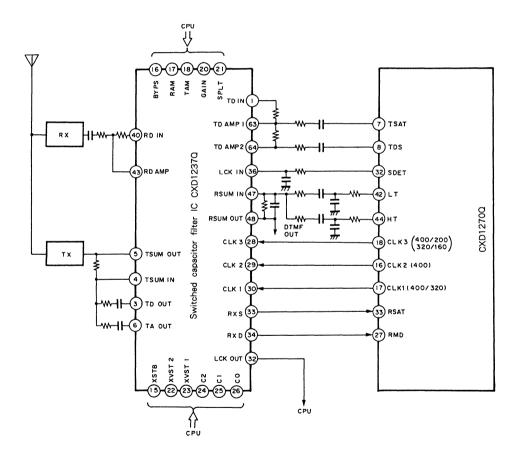

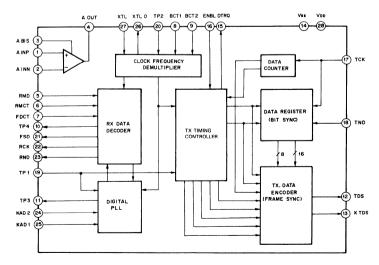

| CXD1230M   | DATA SCF IC for AMPS/TACS cellular radio             |       | 113  |

| CXD1237Q/R | 1 chip SCF for AMPS/TACS/DOC cellular radio          | (NEW) | 129  |

| CXD1231Q-Z | MODEM LSI for AMPS/TACS cellular radio               |       | 147  |

| CXD1270Q/R | MODEM LSI for AMPS/TACS cellular radio built in DTMF | (NEW) | 155  |

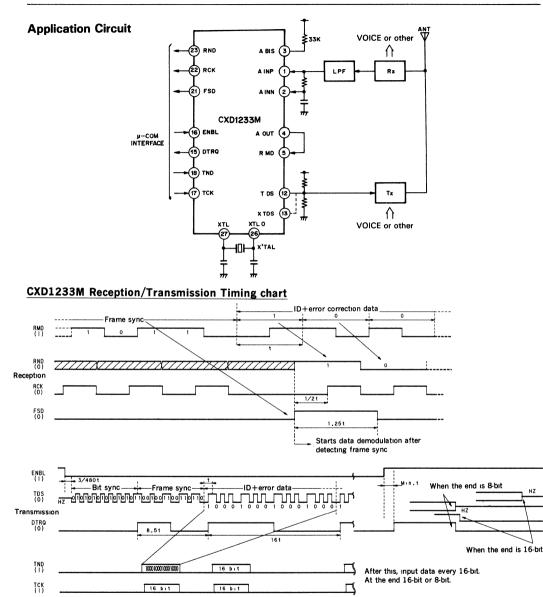

| CXD1233M   | MODEM LSI for cordless phone                         |       | 166  |

(New): New device

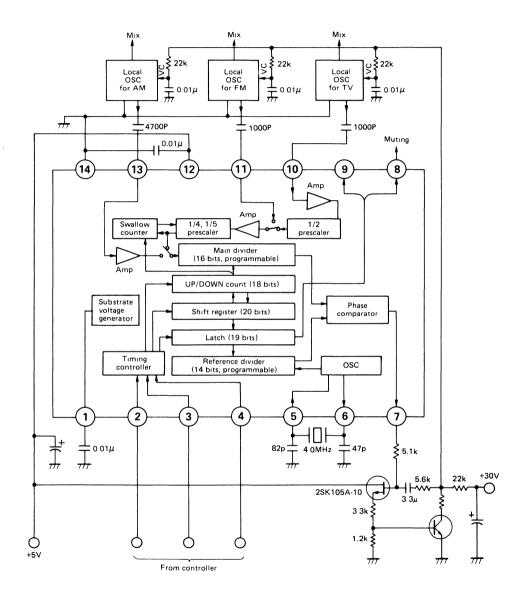

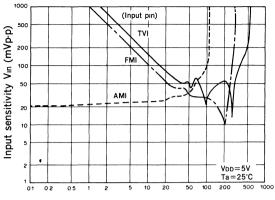

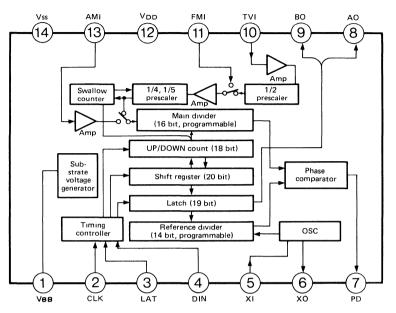

#### 3) PLL ICs

| Туре                         | Function                                                                                                                 |       | Page |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------|------|

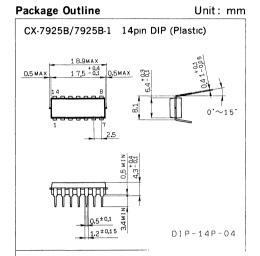

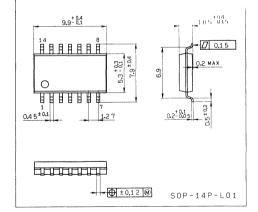

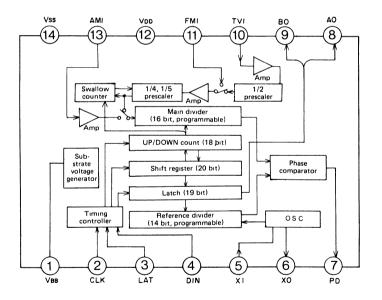

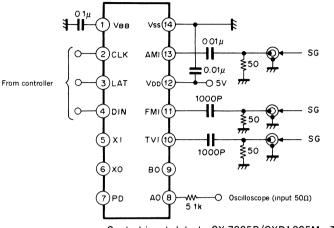

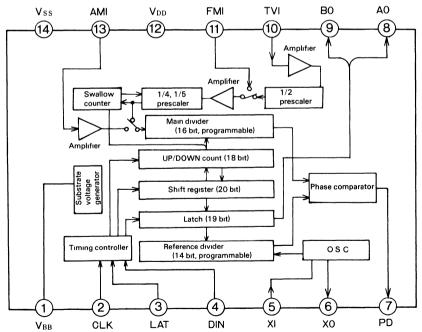

| CX-7925B/B-1<br>CXD1225M/M-1 | 1 chip PLL IC for low power cordless phone in Japan $f_{MAX} = 382MHz$<br>CXD1225M/M-1 is CX-7925B's SOP package version |       | 177  |

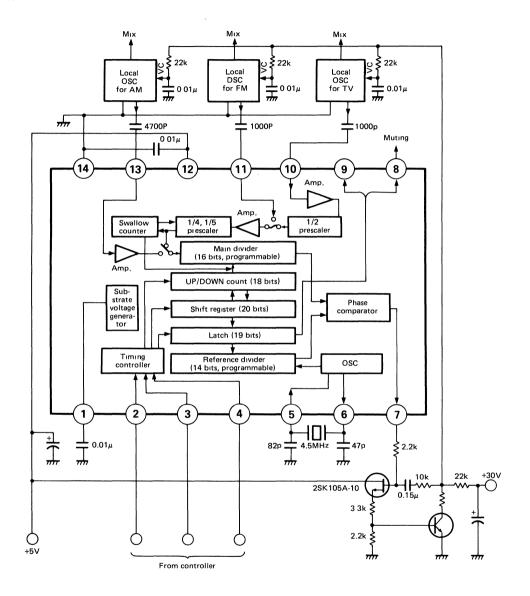

| CX-7961A/A-1                 | 1 chip PLL IC for low power cordless phone in Japan $f_{MAX} = 255 MHz$                                                  |       | 188  |

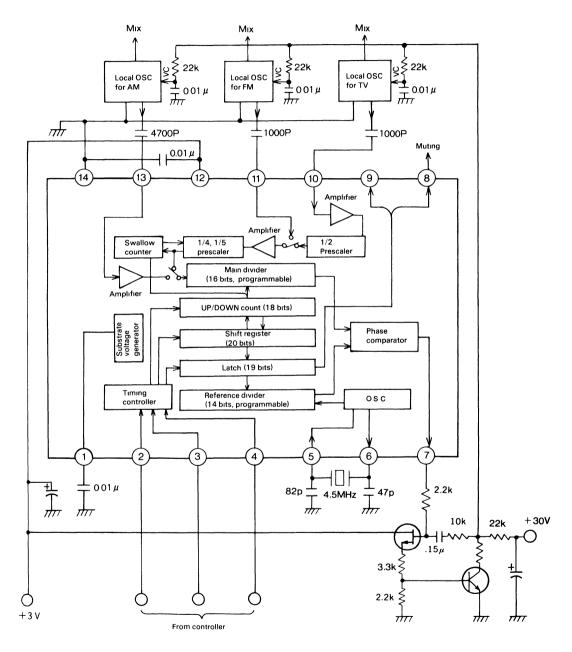

| CXD1118M/M-1                 | CX-7961A's SOP package version                                                                                           |       | 199  |

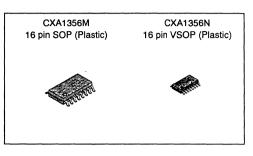

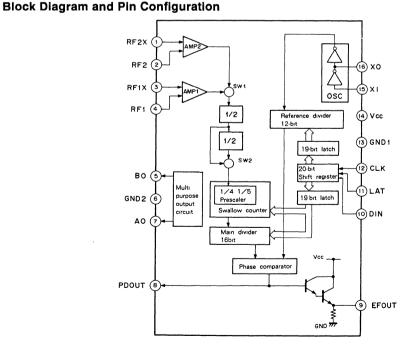

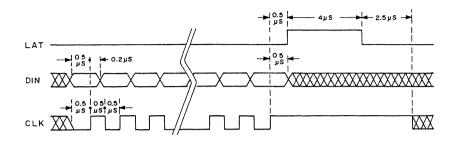

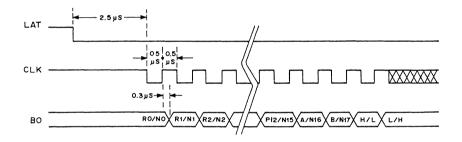

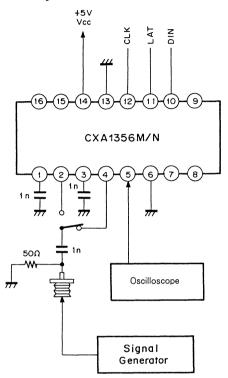

| CXA1356M/N                   | 1.5GHz synthesizer PLL for cellular equipment<br>16P VSOP package                                                        | (NEW) | 211  |

| CXA1541M                     | $1.2GHz$ dual mudulus prescaler for cellular equipment $I_{CC} = 3.5mA$ MB501 pin compatible                             | ☆     | 219  |

☆: Under development (New): New device

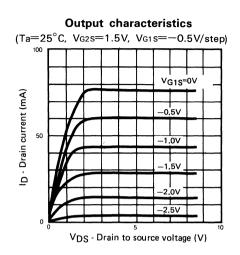

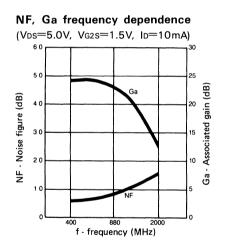

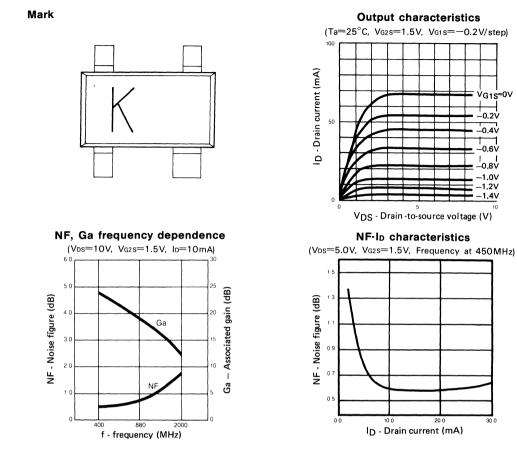

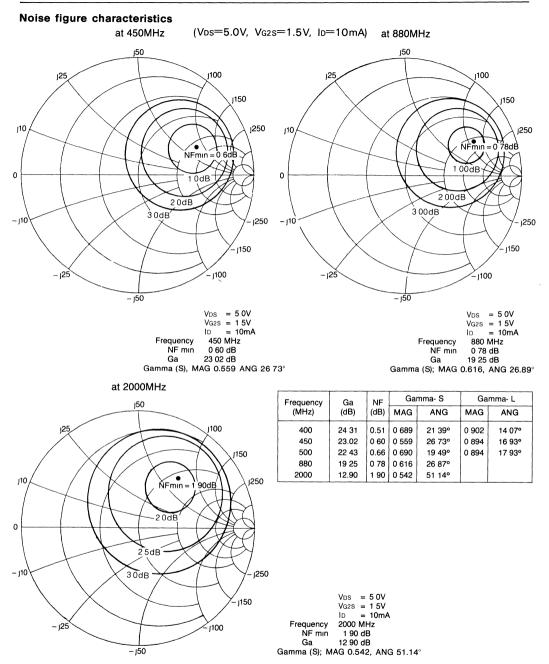

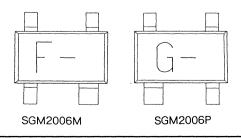

#### 4) GaAs MES FET

| Туре       | Function                                                | Page |

|------------|---------------------------------------------------------|------|

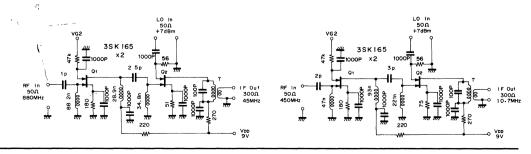

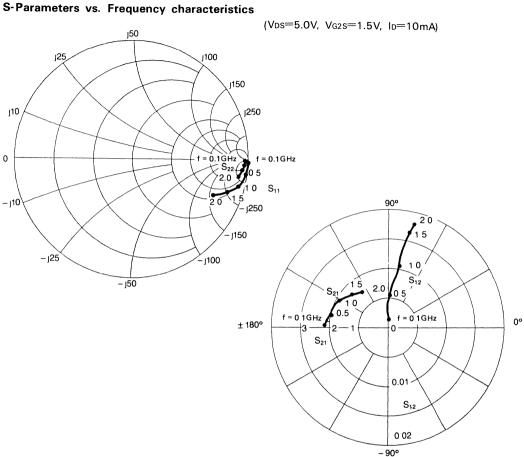

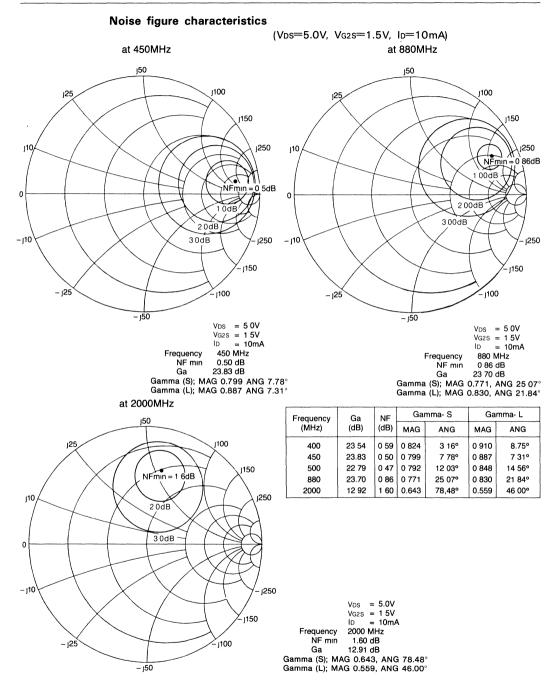

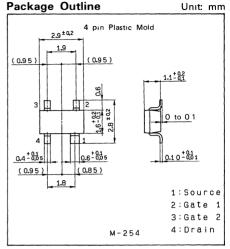

| 3SK165     | RF amplifier, mixer, oscillator, GaAs dual gate MES FET | 223  |

| 3SK166     | RF amplifier, mixer, oscillator, GaAs dual gate MES FET | 227  |

| SGM2004M   | RF amplifier, mixer, oscillator, GaAs dual gate MES FET | 231  |

| SGM2006M/P | RF amplifier, mixer, oscillator, GaAs dual gate MES FET | 235  |

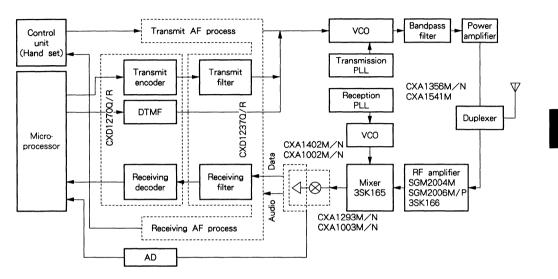

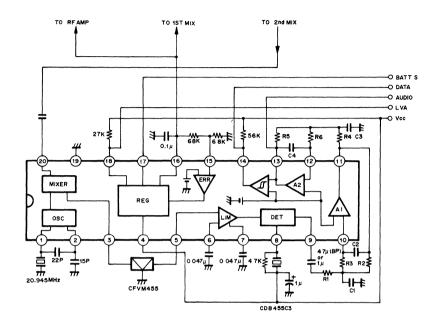

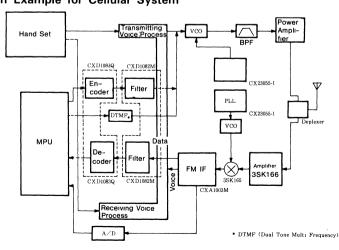

#### Cellular System Block Diagram

Note) DTMF (Dual Tone Multi Frequency)

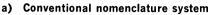

## 3. IC Nomenclature

#### 1) Nomenclature of IC product name

Currently, both the conventional and new nomenclature systems are mixed in naming IC products.

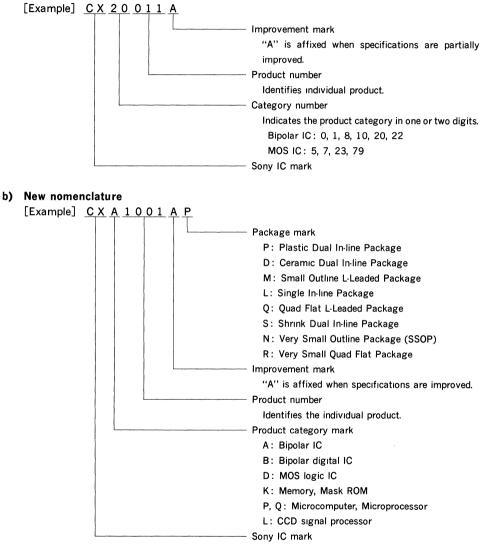

#### c) Nomenclature of field effect transistors

| No.1     | No.2     | No.3     | No.4     | No.5     |

|----------|----------|----------|----------|----------|

| (Figure) | (Letter) | (Letter) | (Figure) | (Letter) |

The No.1 figure denotes the type of semiconductor device.

The device's number of effective electrical connections minus one is used for this number (n-1).

The No.2 letter shows the symbol "S" representing semiconductor device's registered with the Electronic Industries Association of Japan (EIAJ).

The No.3 letter shows the polarity and application of the semiconductor device. For example, "K" indicates an N-Channel FET.

The No.4 figure represents a sequential number registered with the Electronic Industries Association of Japan for each of the preceding types (No.1 figure, No.2 and No.3 letters).

The No.5 letter changes in A, B, C, .... alphabet order every are modified for improvement.

#### d) Nomenclature of GaAs discrete devices

### 4. Precautions for IC Application

#### 1) Absolute maximum ratings

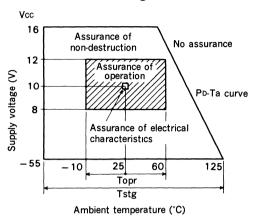

The maximum ratings for semiconductor devices are normally specified by "absolute maximum ratings". The values shown in the maximum ratings table must never be exceeded even for a moment.

If the maximum rating is ever exceeded, device deterioration or damage will occur immediately. Then, even if the affected device can operate, the life will be considerably shortened.

#### IC maximum ratings

The following maximum ratings are used for ICs.

#### (1) Maximum power supply voltage Vcc (VDD)

The maximum voltage that can be applied between the power supply pin and ground pin.

This power supply voltage rating is directly related to the dielectric voltage of transistors in the internal circuit. The transistors may be destroyed if this voltage is exceeded.

#### (2) Allowable power dissipation PD

The maximum power consumption allowed in IC.

Usage beyond the Allowable power dissipation will cause ultimate destruction through the IC's heat generation.

#### (3) Operating ambient temperature Topr

The temperature range within which IC can operate satisfactorily.

Even if this temperature range is exceeded and some deterioration in operating characteristics is noted, the IC is not always damaged.

For some ICs, the electrical characteristics at  $Ta=25^{\circ}C$  are not guaranteed even in this temperature range.

#### (4) Storage temperature Tstg

The temperature range for storing the IC which is not operating.

This temperature is restricted by the package material, and the intrinsic properties of the semiconductor.

#### (5) Other values

The input voltage Vin, output voltage Vout, input current lin, output current lout and other values may be specified in some IC's.

# A general example on the relation with Absolute Maxium Ratings.

#### Main points on Circuit design.

In the circuit design the absolute maximum ratings must not be exceeded, and it must be designed only after considering the worst situations among the following :

- Fluctuation in source voltage

- Scattering in the electrical characteristics of electrical parts (transistors, resistors, capacitors, etc.)

- Power dissipation in circuit adjustment

- Ambient temperature

- Fluctuation in input signal

- Abnormal pulses

If this allowable power dissipation is exceeded, electrical and thermal damage may result.

This value varies with amount of IC integration in package types.

#### 2) Protection against electrostatic breakdown

There have been problems concerning electrostatic destruction of electronic devices since the 2nd World War. Those are closely related to the advancement made in the field of semiconductor devices; this is, with the development of semiconductor technology, new problems in electrostatic destruction have arisen. This situation, perhaps, can be understood by recalling the case of MOS FET.

Today, electrostatic destruction is again drawing people's attention as we are entering the era of LSI and VLSI. Here are our suggestions for preventing such destruction in the device fabrication process.

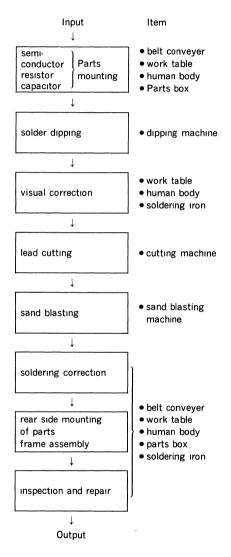

# Factors causing electrostatic generation in manufacture process

A number of dielectric materials are used in manufacture process. Friction of these materials with the substrate can generate static electricity which may destroy the semiconductor device.

Factors that can cause electrostatic destruction in the manufacture process are shown below:

# Causes of electrostatic destruction of semiconductor parts in manufacture process

# Handling precautions for the prevention of electrostatic destruction

Explained below are procedures that must be taken in fabrication to prevent the electrostatic destruction of semiconductor devices.

The following basic rules must be obeyed. ①Equalize potentials of terminals when transporting or storing.

- (2)Equalize the potentials of the electric device, work bench, and operator's body that may come in contact with the semi-conductor device.

- ③Prepare an environment that does not generate static electricity.

One method is keeping relative humidity in the work room to about 50%.

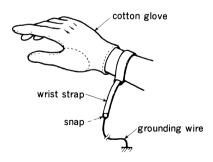

#### Operator

#### (1) Clothes

Do not use nylon, rubber and other materials which easily generate static electricity. For clothes, use cotton, or antistatic-treated materials. Wear gloves during operation.

#### (2) Grounding of operator's body

The operator should connect the specified wrist strap to his arm. If the wrist strap is not available, then the operator should touch the grounding point with his hand, before handling and semiconductor device.

#### example of grounding band

When using a copper wire for grounding, connect a  $1\,M\Omega$  resistance in series near the hand for safety.

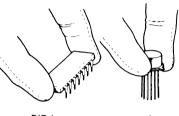

#### (3) Handling of semiconductor device

Do not touch the lead. Touch the body of the semiconductor device when holding. Limit the number of handling times to a minimum. Do not take the device out of the magazine or package box unless it is absolutely necessary.

#### holding of semiconductor device

can type

#### Equipment and tools

#### (1) Grounding of equipment and tools

Ground the equipments and tools that are to be used. Check insulation beforehand to prevent leakage.

[Check point]

- measuring instrument

- conveyer

- electric deburr brush

- carrier

- solder dipping tank

- lead cutter

- shelves and racks

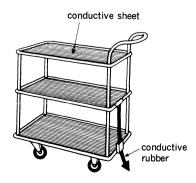

#### grounding of carrier

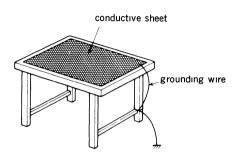

#### (2) Grounding of work table

Ground the work table as illustrated. Do not put anything which can easily generate static electricity, such as foam styrol, on the work table.

#### grounding of work table

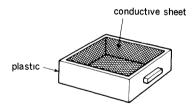

#### (3) Semiconductor device case

Use a conductive case, or an antistatic plastic case (lined with conductive sheet).

#### (4) Insertion of semiconductor device

Insert the semiconductor device during the mounting process or on the belt conveyer. The insertion should be done on a conductive sheet.

#### (5) Other points of caution

Take note of the kind of brush material used for removing lead chips. Use metal or antistatic-treated plastic brushes.

# Transporting, storing and packaging methods

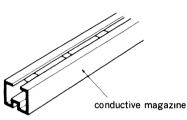

#### (1) Magazine

Use conductive, or antistatic-treated plastic IC magazines.

Plastic magazines used for shipping ICs are antistatic-treated, and they can be used for storing ICs.

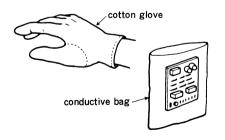

#### (2) Bag

Use a conductive bag to store ICs. If the use of vinyl bag is unavoidable, be sure to wrap the IC with aluminum foil.

conductive bag

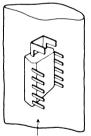

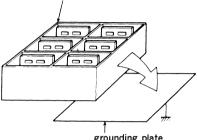

#### (3) Handling of delivery box

The delivery box used for carrying substrates must be made of conductive plastic. Do not use a vinyl chloride or acrylic delivery box, otherwise static electricity will be generated.

#### handling of delivery box

grounding plate

#### (4) Treatment after vehicle transport

After truck transport, place the magazine, package box or delivery box on the grounded rack, work table for discharging.

#### (5) Handling of mounted substrates

Wear cotton gloves when handling. As far as possible, avoid touching soldered faces. When handling mounted substrates individually, be sure to use a conductive bag. Do not use a polyethylene bag.

#### handling of mounted substrate

#### Soldering operation (1) Soldering iron

Use a soldering iron with a grounded metal part or a soldering iron with an insulation resistance greater than  $10M\Omega$  (DC 500V) after five minutes from energizing.

#### (2) Operation

After inserting the semiconductor device into the substrate, solder it as quickly as possible. Do not carry the substrate with the inserted semiconductor device by car.

#### (3) Correction

When correcting parts (semiconductor device and CR parts) after solder-dipping, be sure to wear cotton gloves. Also, connect the grounding band to the arm, or touch the grounding point before operation.

#### (4) Manual soldering

Solder with wrist strap connected to the hand, or by touching the grounding point from time to during operation.

#### (5) Removing semiconductor device

Do not use the Solder-Pult when removing the semiconductor device. Use a Solder-wick or equivalent.

solder remover

#### (6) Soldering work table

Use a grounded work table for soldering. Do not solder on foam styrol, vinyl, or melamine resin.

# Mounting method Soldering and solderability Solderability by JIS

JIS specifies solderability of an IC terminal (lead) in "JIS-C7022 Test Procedure A-2". An abstract of this standard follows:

- Rosin flux must be used, and the terminal must be dipped in it for 5-10 seconds.

- H63A or equivalent solder must be used, and the terminal must be dipped in the solder which been heated to 230°C±5°C for 5±1 seconds.

- Using a microscope, measure the area (%) deposited with solder. JIS specifies that more than 95% of the total area should be coated with solder.

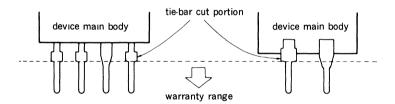

#### (2) Area for soldering warranty

Soldering is warranted for a specific portion of the terminal. The warranted portion is shown in the following figure.

The tie-bar cut portion also serves as a dam to prevent the sealing resin flowing out during device fabrication; it is cut off at the end of the process. Since the terminal is exposed at the cut-off end, the area for soldering is restricted. The portion near the resin is often covered with burrs when sealing with resin; it is not in the soldering warranty area.

#### warranty area for soldering

# Resistance to soldering heat (1) Specification of JIS

JIS specifies the method for testing the resistance to soldering heat. This method is used for guaranteeing the IC resistance against thermal stresses by soldering. An abstract of this standard is as follows:

• Dip the device terminal only once for  $10\pm1$  seconds in a solder bath of  $260^{\circ}C\pm5^{\circ}C$ , or for  $3\pm^{0.5}_{0.5}$  seconds in a solder bath of  $350^{\circ}C\pm10^{\circ}C$ , for a distance of up to 1 to 1.5 mm from the main body.

For the solder flow system temperature should be  $260^{\circ}C\pm5^{\circ}C$ . To solder by soldering iron temperature should be  $350^{\circ}C\pm10^{\circ}C$ .

- Leave the device for more than two hours after dipping, then measure the device characteristics.

- Normally, the warranty is limited to 10 seconds at 260°C±5°C. The distance between the device main body and solder bath is 1.6 mm.

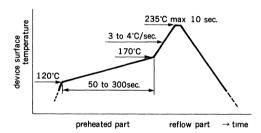

# (2) Resistance to soldering heat when mounting infrared reflow.

When surface mount Devices (SOP, QFP etc) are dipped directly into a solder pot.

The device moisture resistance may deteriorate and thermal stress generate cracks in the pallet.

Carefully observe the mounting conditions. Recommended temperature profile when mounting infrared reflows is shown in the figure below.

# 5. Quality Assurance and Reliability

#### The Concept to Quality Assurance

There are 2 fundamental principles guiding Sony Semiconductors.

- 1. Customer satisfaction

- 2. Top level performance

What comes first is the ability to respond convincingly to given requirements in terms of Quality, Delivery, Cost and Servicing. This involves all operations involved in the process. The second requisite is the quest for superior accomplishment. Here, talent is demanded to fulfill customer expectations, where quality is concerned, and pursue related activities.

To this effect an elaborate system of quality assurance is firmly established. From the early stages of research and development well into production, sales and servicing, orderly control is applied for the maintenance of high standards and further improvement. Systematization and automation are pushed ahead to provide a stable output of high quality production.

In this respect, the force in charge of implementing the program is nonetheless subject to constant polishing. Gifted people well aware of the problems inherent to their tasks are at the core of the excellence reflected on their yield.

With the aim of providing the most economical, the most useful and at the same time the most gratifying products where quality is the criterion, Sony keeps fueling a relentless urge for achievement.

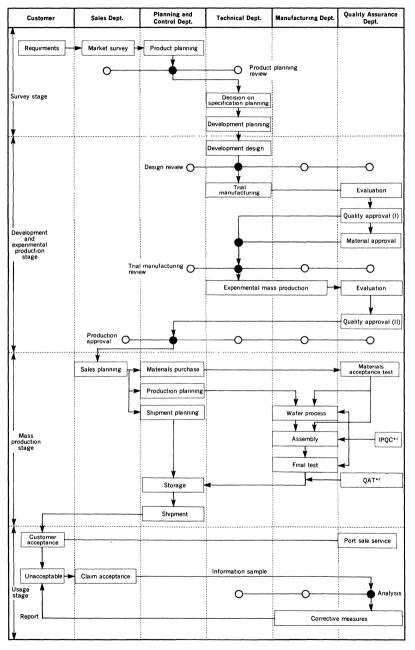

#### Quality assurance system of semiconductor products

\*1 IPQC In Process Quality Control \*2 QAT Quality Assurance Test

# Quality assurance criteria and reliability test criteria

#### 1) Quality assurance in shipping

Establishing quality in the design and in fabrication is essential to keep the quality and reliability levels of the semiconductor devices at a high level. This is done by the "Zero-defect" (ZD) movement. Further sampling checks, in units of shipping lot, is done on products that have been "totallyinspected" at the final fabrication stage, thus ensuring no detective items. This sampling inspection is done in accordance with MIL-STD-105D.

#### 2) Reliability

The reliability test is done, periodically, to confirm reliability level.

|                         | Item                                                    | Testing time                                                                       | LTPD |

|-------------------------|---------------------------------------------------------|------------------------------------------------------------------------------------|------|

| Electrical Characterist | tics Test                                               | In order to know the initial qu<br>level, some types are selected<br>tested again. | 2    |

| Life Test               | high temperature operation<br>high temperature and high | up to 1000 h                                                                       | 10%  |

|                         | humidity with bias                                      | up to 1000 h                                                                       | 10%  |

|                         | pressure cooker                                         | up to 200 h                                                                        | 10%  |

| Environmental Test      | soldering heat resistance                               | 10s                                                                                | 15%  |

|                         | heat cycle                                              | 100 cycles                                                                         | 15%  |

| Mechanical Test         | solderability                                           | Japan Industrial                                                                   | 15%  |

|                         | length strength                                         | Standard (JIS)                                                                     | 15%  |

| Other Tests             | If necessary, tests are selected acc                    | ording to                                                                          |      |

|                         | JIS C7021 C7022 and EIAJ SD12                           | 1 IC121.                                                                           |      |

#### Periodic Reliability Test

\*These tests are selected by sampling standard.

LTPD: Lot Tolerance Percent Defective

These tests and inspection data are useful not only to improve design and wafer processes, but also serve to forecast reliability at the consumer level.

#### **Reliability Test Standards**

| Types of test                                   | Condition                                                                                                                                                        | Supply<br>voltages                               | Testing time                    | LTPD |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------------------------------|------|

| High temperature<br>operation                   | Ta=125℃, 150℃                                                                                                                                                    | Typical                                          | 1000h                           | 5%   |

| High temperature<br>with bias                   | Ta=125°C, 150°C                                                                                                                                                  | Typical                                          | 1000h                           | 5%   |

| High temperature<br>storage                     | Ta=150°C                                                                                                                                                         |                                                  | 1000h                           | 5%   |

| Low temperature<br>storage                      | Ta=-65°C                                                                                                                                                         |                                                  | 1000h                           | 5%   |

| High temperature and<br>high humidity storage   | Ta=85°C 85%RH                                                                                                                                                    |                                                  | 1000h                           | 5%   |

| High temperature and<br>high humidity with bias | Ta=85℃ 85%RH                                                                                                                                                     | Typical                                          | 1000h                           | 5%   |

| Pressure cooker                                 | Ta=121°C 100%RH<br>30 pounds per square inc                                                                                                                      | Ta=121°C 100%RH<br>30 pounds per square inch     |                                 |      |

| Temperature cycle                               | Ta=-65°C to+150°C                                                                                                                                                | Ta=-65°C to+150°C                                |                                 |      |

| Heat shock                                      | Ta=-65°C to+150°C                                                                                                                                                | Ta=-65°C to+150°C                                |                                 | 10%  |

| Soldering heat resistance                       | T solder=260°C                                                                                                                                                   | T solder=260°C                                   |                                 | 10%  |

| Solderability                                   | T solder=230°C (rosin ty                                                                                                                                         | vpe flux)                                        | 5s                              | 10%  |

| Mechanical shock                                | X, Y, Z 1500G<br>Half part of sinusoidal w                                                                                                                       | vave of 0.5ms                                    | 3times for<br>each direction    | 10%  |

| Vibration                                       | X, Y, G 20G<br>10Hz to 2000Hz to 10Hz<br>Sinusoidal wave vibration                                                                                               | • •                                              | 16minutes for<br>each direction | 10%  |

| Constant acceleration                           | X, Y, Z 20,000G<br>Centrifugal acceleration                                                                                                                      |                                                  | 1minute<br>for each direction   | 10%  |

| Free fall                                       | Free fall from the heigh plate                                                                                                                                   | Free fall from the height of 75cm to maple plate |                                 |      |

| Lead strength<br>(bend)<br>(pull)               | based on JIS                                                                                                                                                     |                                                  |                                 | 10%  |

| Electrostatic strength                          | Device must be designed again, when electrostatic strength below standard supplying surge voltage to each pin under the condition of C=200pF and Rs= $0\Omega$ . |                                                  |                                 |      |

LTPD: Lot Tolerance Percent Defective

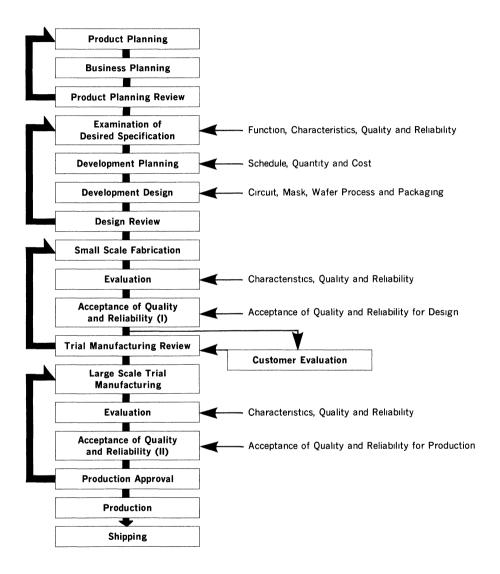

#### Flow Chart from Development to Manufacturing

Sony attains high quality and high reliability of semiconductor products by designing devices with quality and reliability from the initial steps of development and evaluating them sufficiently in each step of the development.

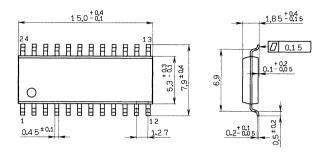

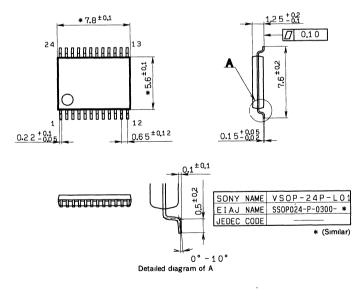

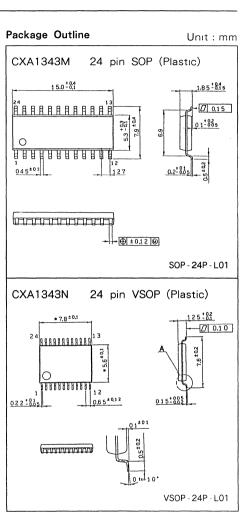

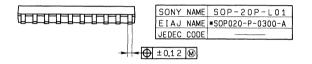

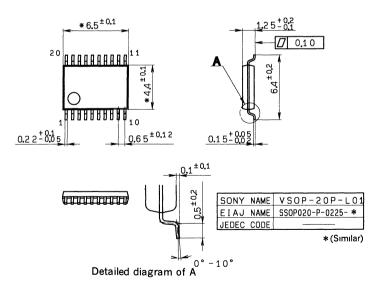

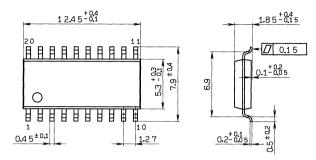

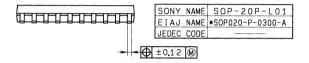

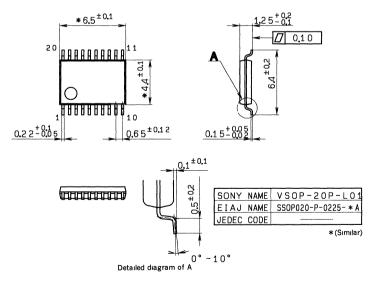

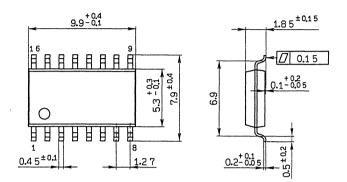

### Package Name

|                 | π                                       | Pacl          | kage name                                | D1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            | Fea                                      | atures                  |                            |

|-----------------|-----------------------------------------|---------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------------------------|-------------------------|----------------------------|

|                 | Туре                                    | Symbol        | Description                              | Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Maternal * | Lead pitch                               | Lead shape              | Lead pull<br>out direction |

|                 |                                         | DIP           | DUAL<br>IN-LINE<br>PACKAGE               | N CHANNAN AND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P<br>C     | 2.54mm<br>(100MIL)                       | Through<br>Hole<br>Lead | 2-direction                |

|                 |                                         | SIP           | SINGLE<br>IN-LINE<br>PACKAGE             | TUTTI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Р          | 2.54mm<br>(100MIL)                       | Through<br>Hole<br>Lead | 1-direction                |

|                 | Standard                                | ZIP           | ZIG-ZAG<br>IN-LINE<br>PACKAGE            | THE REPORT OF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Р          | 2.54mm<br>(100MIL)<br>Zıg-Zag<br>in-line | Through<br>Hole<br>Lead | 1-direction                |

| Inserted        |                                         | PGA           | PIN<br>GRID<br>ARRAY                     | PPERSONAL PROPERTY OF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | с          | 2.54mm<br>(100MIL)                       | Through<br>Hole<br>Lead | Package<br>under<br>side   |

|                 |                                         | PIGGY<br>BACK | PIGGY<br>BACK                            | Gostadori Manufertulari                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | с          | 2 54mm<br>(100MIL)                       | Through<br>Hole<br>Lead | 2-direction                |

|                 | Shrink                                  | SDIP          | SHRINK<br>DUAL<br>IN-LINE<br>PACKAGE     | D. T. WHITHHIMM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Р          | 1 778mm<br>(70MIL)                       | Through<br>Hole<br>Lead | 2-direction                |

|                 |                                         | SZIP          | SHRINK<br>ZIG-ZAG<br>IN-LINE<br>PACKAGE  | TANADAN Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Р          | 1.778mm<br>(70MIL)<br>Zig-Zag<br>in-line | Through<br>Hole<br>Lead | 1-direction                |

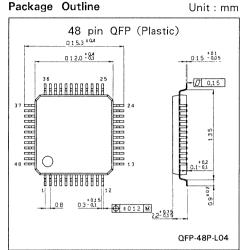

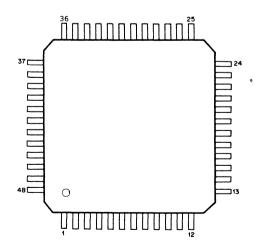

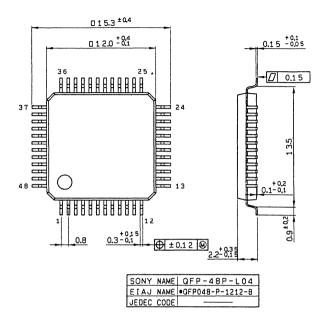

|                 | Standard flat<br>package                | QFP           | QUAD<br>FLAT<br>L-LEADED<br>PACKAGE      | Solo and a second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | P<br>C     | 1.0mm<br>0.8mm<br>0.65mm                 | Gull-<br>Wing           | 4-direction                |

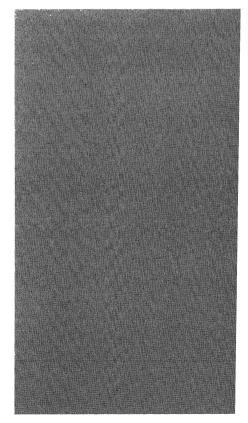

|                 |                                         | SOP           | SMALL<br>OUTLINE<br>L-LEADED<br>PACKAGE  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Р          | 1 27mm<br>(50MIL)                        | Gull-<br>Wing           | 2-direction                |

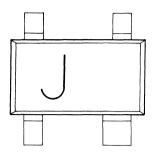

| ed              | Standard<br>2-direction<br>chip carrier | SOJ           | SMALL<br>OUTLINE<br>J-LEADED<br>PACKAGE  | HARAARA MAAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Р          | 1.27mm<br>(50MIL)                        | J-Lead                  | 2-direction                |

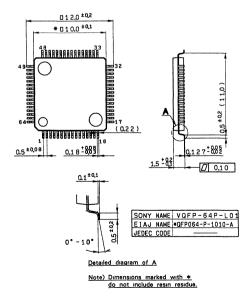

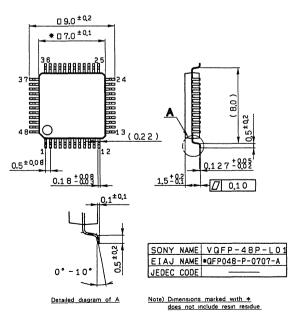

| Surface mounted |                                         | VQFP          | VERY<br>SMALL<br>QUAD<br>FLAT<br>PACKAGE |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Р          | 0.5mm                                    | Gull-<br>Wing           | 4-direction                |

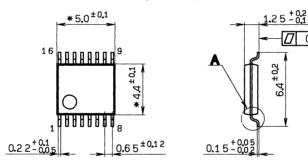

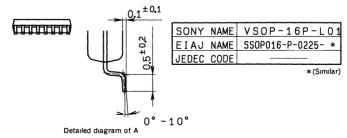

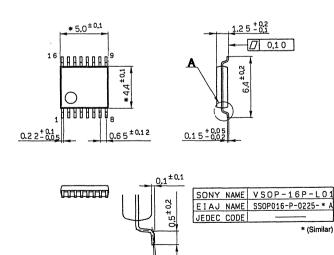

| Su              | Shrınk flat<br>package                  | VSOP          | VERY<br>SMALL<br>OUTLINE<br>PACKAGE      | Constanting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Р          | 0.65mm                                   | Gull-<br>Wing           | 2-direction                |

|                 |                                         | TSOP          | THIN<br>SMALL<br>OUTLINE<br>PACKAGE      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Р          | 0.5mm<br>(0.55mm)                        | Gull-<br>Wing           | 2-direction                |

|                 | Standard chip                           | QFJ           | QUAD<br>FLAT<br>J-LEADED<br>PACKAGE      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Р          | 1 27mm<br>(50MIL)                        | J-Lead                  | 4-direction                |

|                 | carrier                                 | QFN           | QUAD<br>FLAT<br>NON-LEADED<br>PACKAGE    | and a state of the | с          | 1 27mm<br>(50MIL)                        | Leadless                | Package<br>under<br>side   |

\* P······Plastic, C······Ceramic

# FM IF Amplifier

#### 1) FM IF Amplifier

| Туре         | Function                                                                                                                  | Page |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------|------|--|--|

| CXA1002M/N   | FM IF amplifier for cellular radio for 2nd IF I <sub>CC</sub> = 2.5mA<br>CXA1002N : VSOP package                          | 27   |  |  |

| CXA1402M/N   | FM IF amplifier for cellular radio for 2nd IF(NEW) $I_{CC} = 1.5mA CXA1002M/N$ pin compatible(NEW)                        | 35   |  |  |

| CXA1003BM/BN | FM IF amplifier for cellular radio for 2nd MIX $I_{cc}$ =5.7mA CXA1003BN : VSOP package                                   | 38   |  |  |

| CXA1293M/N   | FM IF amplifier for cellular pin replaceable with<br>CXA1003BM/BN I <sub>CC</sub> =3.0mA CXA1293N : VSOP (NEW)<br>package | 51   |  |  |

| CXA1343M/N   | FM IF amplifier for cellular built in gain control amplifier and RSSI output buffer                                       |      |  |  |

| CXA1183M     | FM IF amplifier for cordless phone built in JAM detect circuit                                                            | 71   |  |  |

| CXA1493M/N   | FM IF amplifier for cordless phone built in detect output LPF and highly efficient RSSI function                          | 84   |  |  |

| CXA1184M/N   | FM IF amplifier for double conversion pocket pager                                                                        | 88   |  |  |

| CXA1474M/N   | FM IF amplifier for single conversion pocket pager (NEW) $I_{cc} = 500 \mu A \ 16P \ VSOP \ package$                      | 103  |  |  |

| CXA1484M/N   | $      FM \ IF \ amplifier \ for \ double \ conversion \ pocket \ pager \ (NEW)                                    $      | 107  |  |  |

☆: Under development (New): New device

# SONY.

#### Low Power FM IF Amplifier

#### Description

CXA1002M/N is an FM IF amplifier most suitable for cellular and FM radios.

#### Features

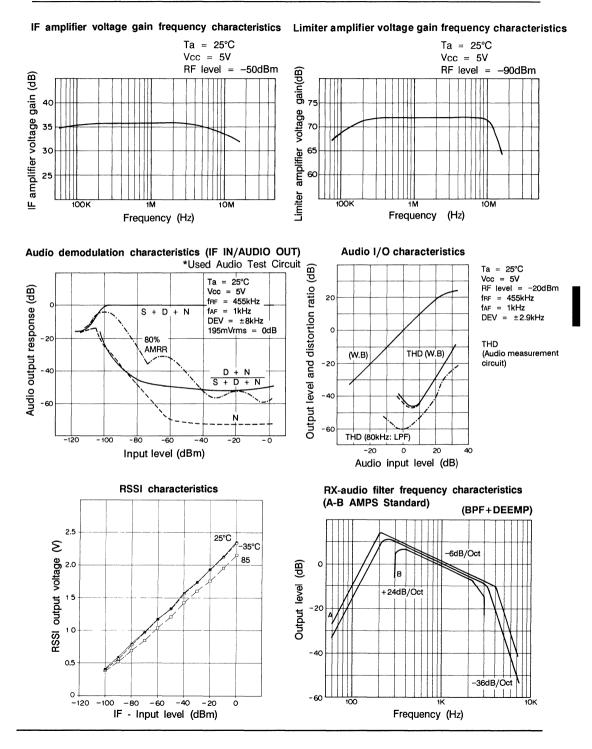

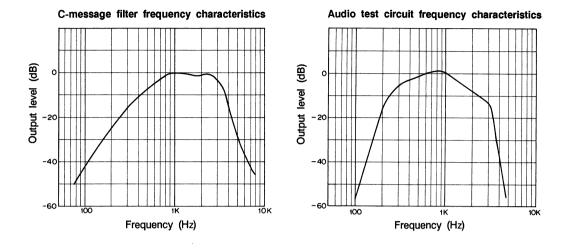

- Includes all the functions needed for cellular radios such as FM detecting circuit, RSSI, IF amplifier and others.

- Wide operating voltage range 4.5 to 9.5 V and low current consumption. (During Vcc=5 V, lcc=2.5 mA Typ.)

- Built-in audio output buffer circuit reduces external parts to a minimum.

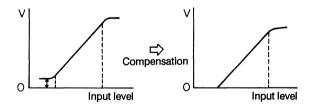

- Wide range RSSI and excellent temperature characteristics.

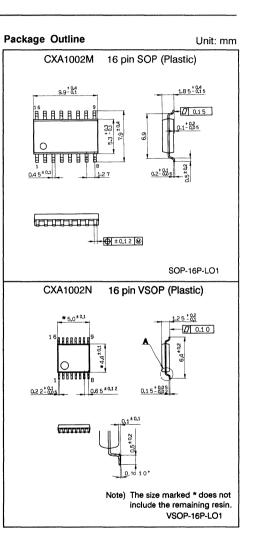

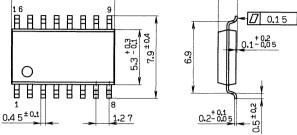

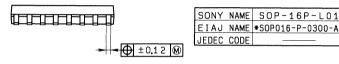

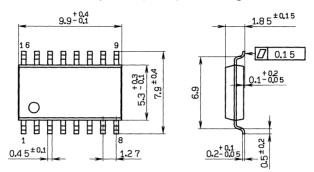

- Compact 16 pin SOP and 16 pin VSOP package.

#### Functions

- IF amplifier and limiter

- RSSI (Received Signal Strength Indicator)

- FM detecting circuit

#### Structure

Bipolar silicon monolithic IC

#### Absolute Maximum Ratings (Ta=25°C)

- Supply voltage Vcc 17 V

- Operating temperature

Tstg –35 to +85 °C

- Storage temperature Topr –55 to +150 °C

- Allowable power dissipation Pp 500 mW

#### **Recommended Operating Condition**

Supply voltage

Vcc 4.5 to 9.5 V

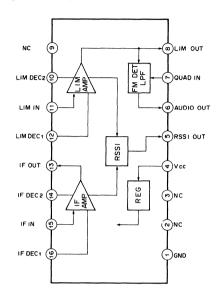

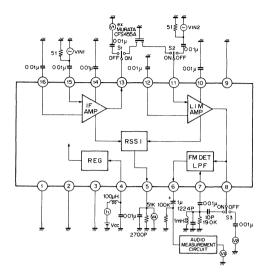

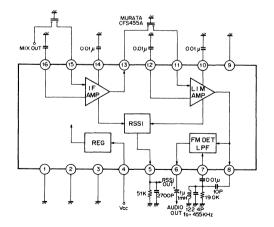

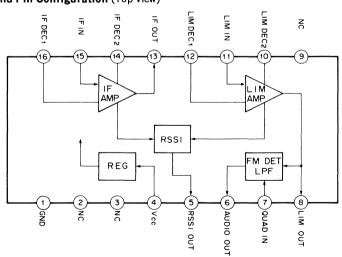

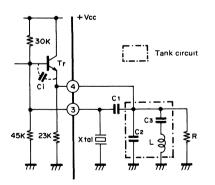

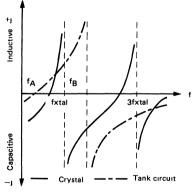

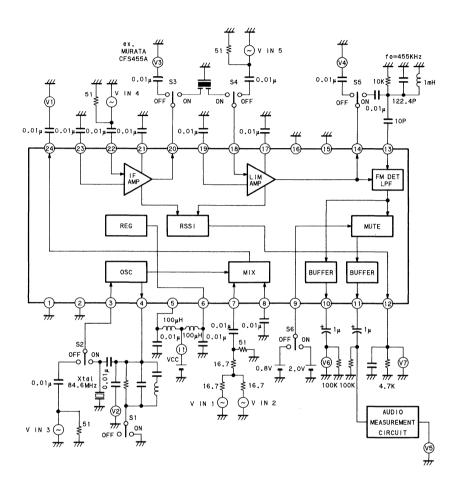

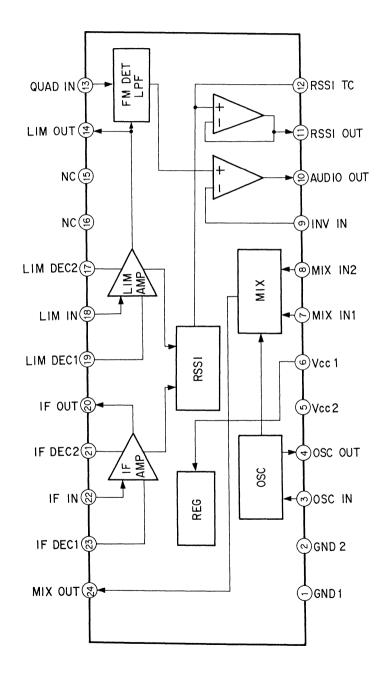

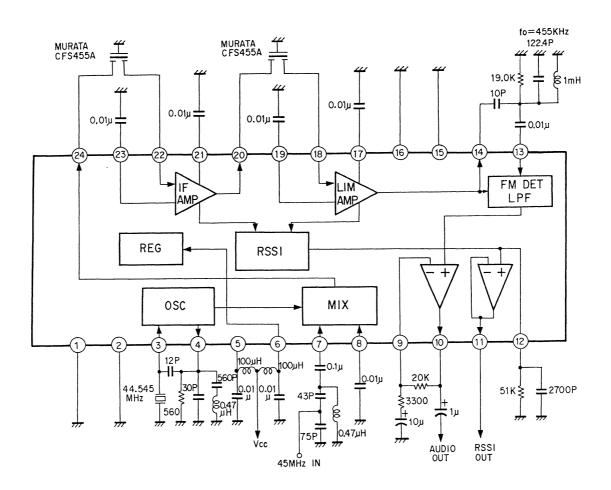

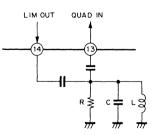

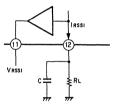

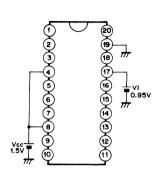

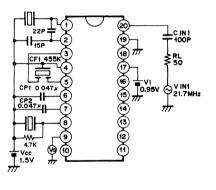

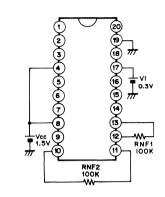

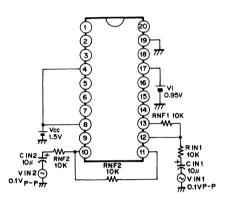

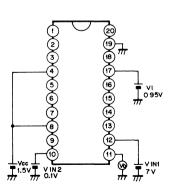

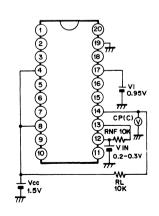

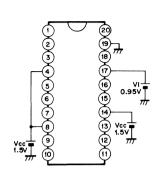

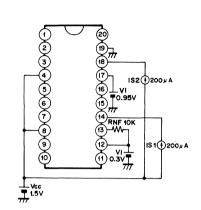

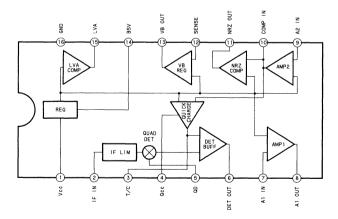

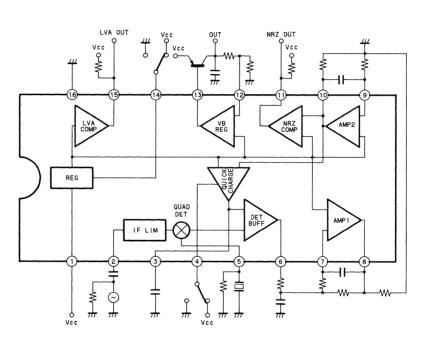

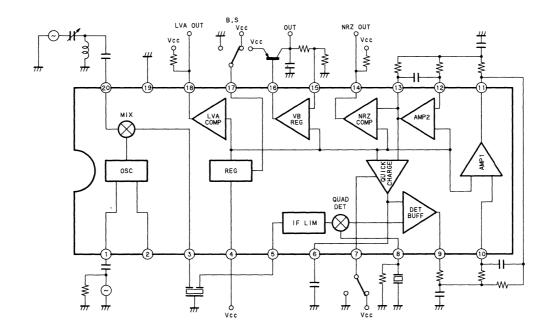

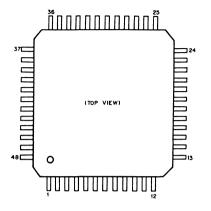

#### Block Diagram and Pin Configuration (Top View)

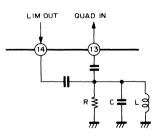

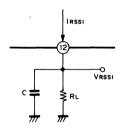

#### Pin Description and Equivalent circuit

| No. | Symbol       | Voltage<br>(Typ) | Equivalent Circuit                                                                                                                                                                          | Description                                                                              |  |  |  |

|-----|--------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|--|--|

| 1   | GND          | 0 V              |                                                                                                                                                                                             | Ground pin                                                                               |  |  |  |

| 4   | Vcc          | 5.0 V            |                                                                                                                                                                                             | Supply pin                                                                               |  |  |  |

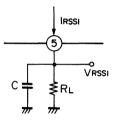

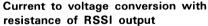

| 5   | RSSI OUT     |                  | y y y y y y y y y y y y y y y y y y y                                                                                                                                                       | The current output corresponds<br>to the input signal level to IF and<br>LIM amplifiers. |  |  |  |

| 6   | AUDIO<br>OUT | 2.5 V            | 930<br>930<br>930<br>930<br>930<br>7<br>7<br>7<br>7<br>7<br>7<br>7                                                                                                                          | FM detected signal is output.                                                            |  |  |  |

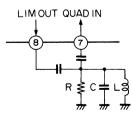

| 7   | QUAD IN      | 3.3 V            | Усс<br><u>3.3</u> ∨<br><del>8</del> 00к<br><del>8</del> 00к<br><del>1</del><br><del>1</del><br><del>1</del><br><del>1</del><br><del>1</del><br><del>1</del><br><del>1</del><br><del>1</del> | Input pin of quadrature detecting circuit.                                               |  |  |  |

#### SONY<sub>®</sub>