# SONY

# Semiconductor IC

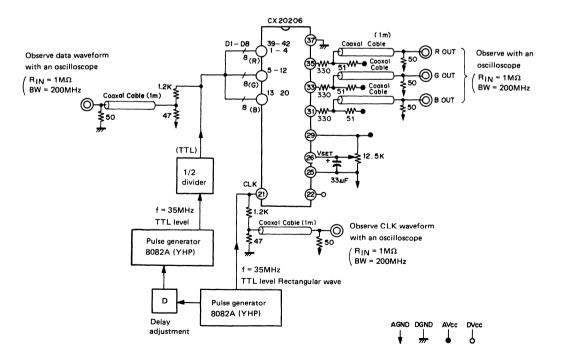

# Data Book 1987 A/D,D/A Converters & D.S.P.

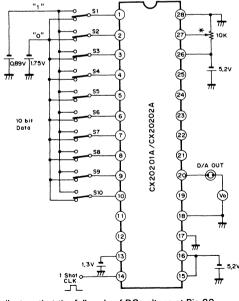

1987

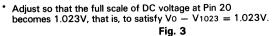

NON Y

## SONY.

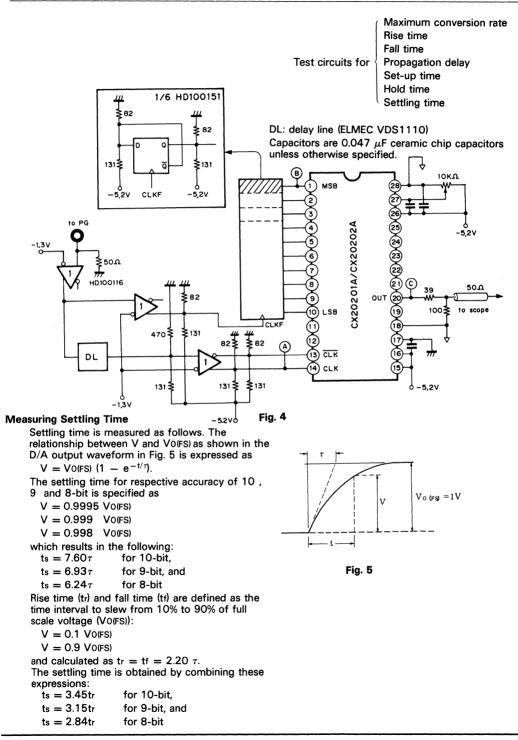

# Semiconductor Integrated Circuit Data Book 1987

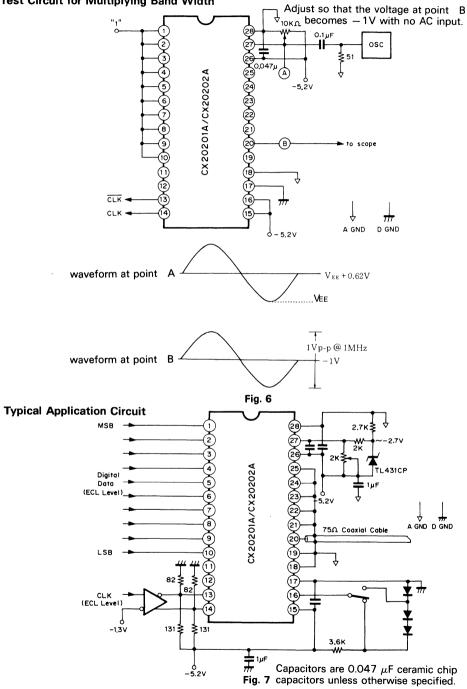

| List of Model Names/<br>Index by Usage | 1 |

|----------------------------------------|---|

| Description                            | 2 |

| A/D, D/A Converters<br>Audio           | 3 |

| A/D, D/A Converters<br>Video           | 4 |

| Digital Signal<br>Processors           | 5 |

| Evaluation Printed<br>Circuit Boards   | 6 |

| Application Notes                      | 7 |

|                                        |   |

## Semiconductor Integrated Circuit Data Book 1987

#### PREFACE

This is the 1987 version of the Sony semiconductor IC databook. This book covers all the semiconductor products manufactured and marketed by Sony.

In preparation of this databook, as much characteristic and application data as possible have been collected and added with a view of making this book a convenient reference for users of Sony products. If, however, you are dissatisfied with this book in any way, please write; we welcome suggestions and comments. The Sony semiconductor IC databook has been edited to include only accurate and reliable data. However, because of technical improvements and other modifications the contents are subject to change without notice.

The circuit examples used in this book are for illustration of typical applications only; we are not responsible for any problems that may occur in the circuitry and patents of any third party if these examples are put in practice.

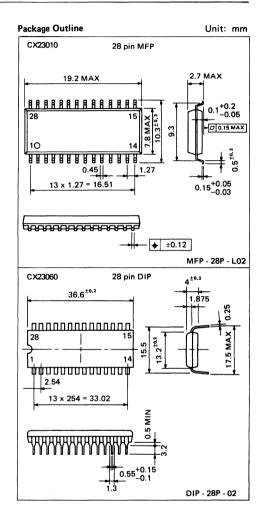

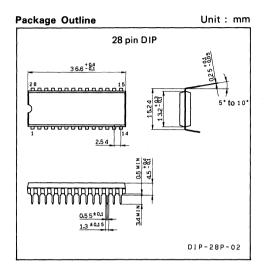

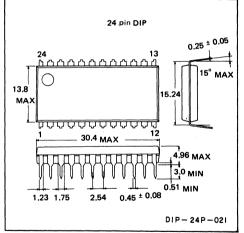

#### **Package abbreviations**

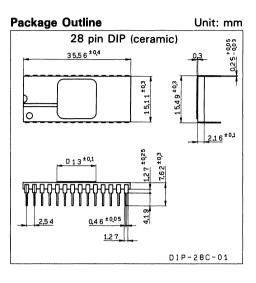

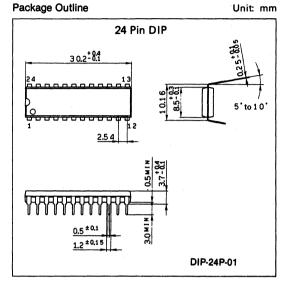

- DIP : Dual Inline Package

- MFP : Mini Flat Package (= Flat DIP)

- QIP : Quad Inline Package (=Flat QUIP)

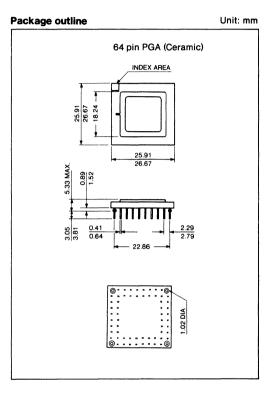

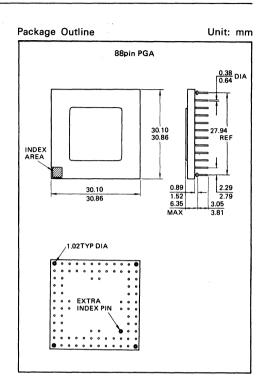

- PGA: Pin Grid Array

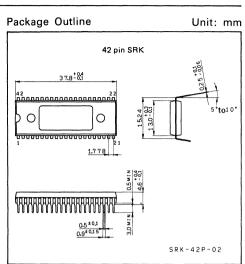

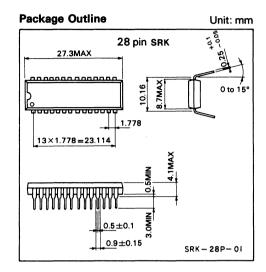

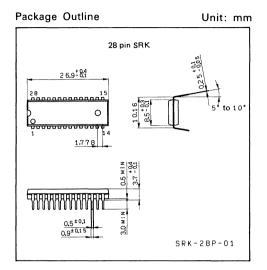

- SRK : Shrink Dual Inline Package

- SIP : Single Inline Package

## Contents

|    |                                                | Pag |   |

|----|------------------------------------------------|-----|---|

| 1. | List of Model Names(                           | 6   | ) |

| 2. | Index by Usage(                                | 7   | ) |

| 3. | IC Nomenclature(                               | 9   | ) |

| 4. | Precautions for IC Application(                | 10  | ) |

|    | A) Absolute maximum ratings                    |     |   |

|    | B) Protection against electrostatic break down |     |   |

|    | C) Mounting method                             |     |   |

| 5. | Quality Assurance and Reliability(             | 16  | ) |

| 6. | Data Sheet ·······(                            | 21  | ) |

|    | 1) A/D, D/A Converters(                        | 21  | ) |

|    | 2) A/D, D/A Converters(1                       | 03  | ) |

|    | 3) Digital Signal Processors                   | 217 | ) |

|    | 4) Evaluation Printed Circuit Boards           |     | - |

|    | 5) Application Notes                           |     |   |

|    |                                                |     |   |

## 1. List of Model Names

| Туре                                               | Page | Туре                                 | Page | Туре                                 | Page |

|----------------------------------------------------|------|--------------------------------------|------|--------------------------------------|------|

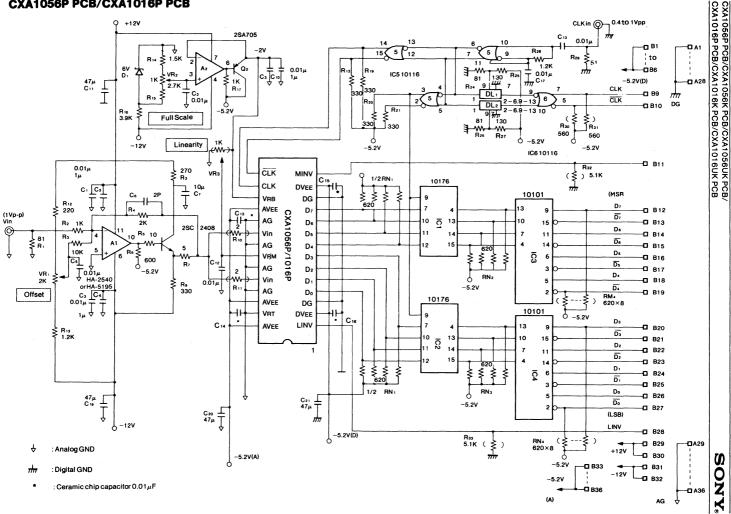

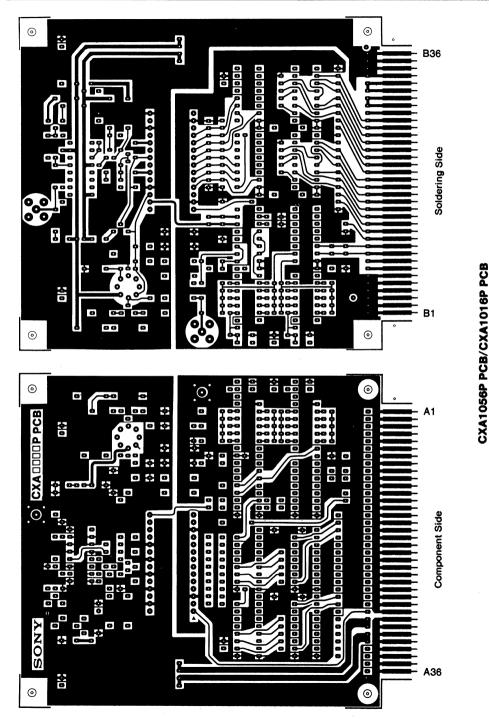

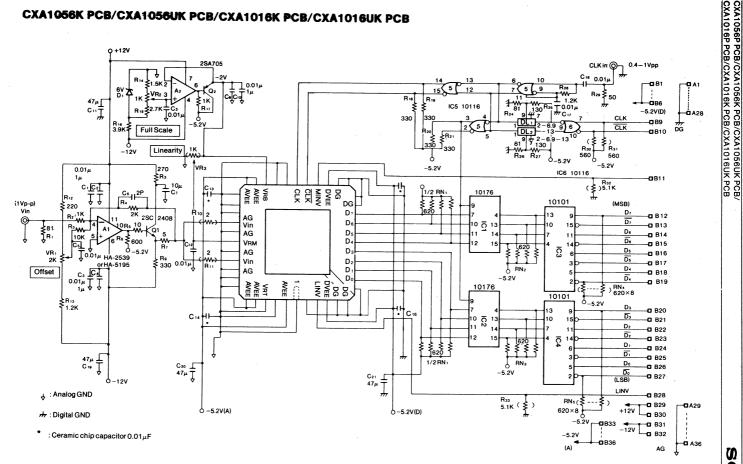

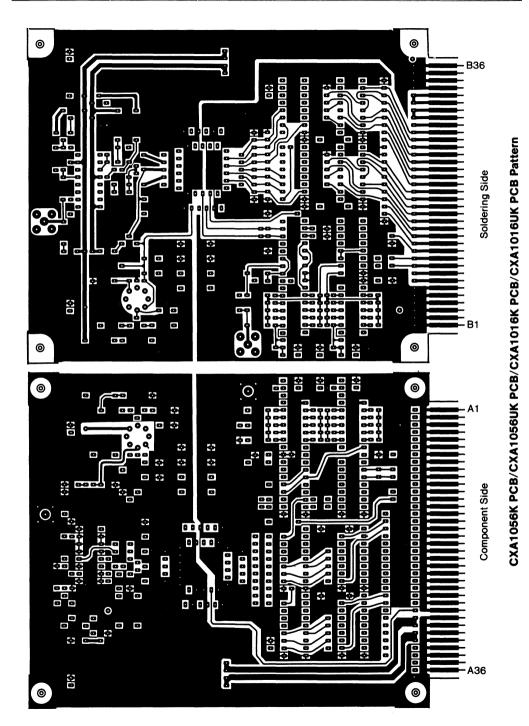

| CX-7997                                            | 219  | CX20133                              | 56   | CXA1016P/K/UK<br>CXA1056P/K/UK } PCB | 343  |

| CX20017                                            | 23   | CX20152                              | 69   | CXA1096P                             | 196  |

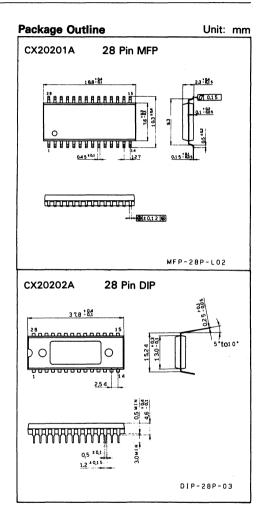

| СХ20017 РСВ                                        | 307  | CX20201A-1/-2/-3<br>CX20202A-1/-2/-3 | 132  | CXA1106P                             | 203  |

| CX20018                                            | 37   | CX20206                              | 144  | CXD1018G                             | 266  |

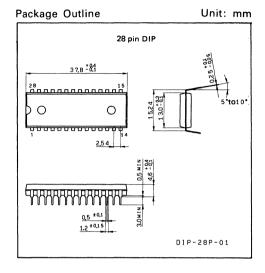

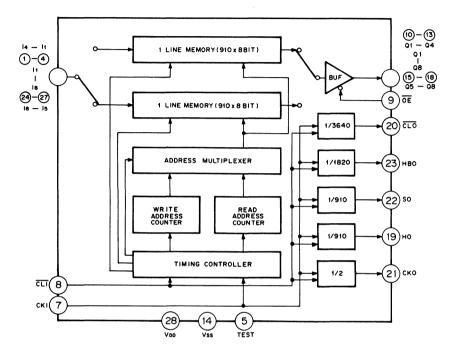

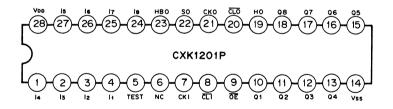

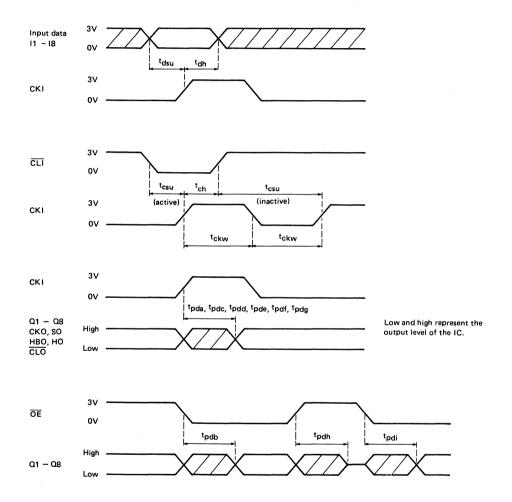

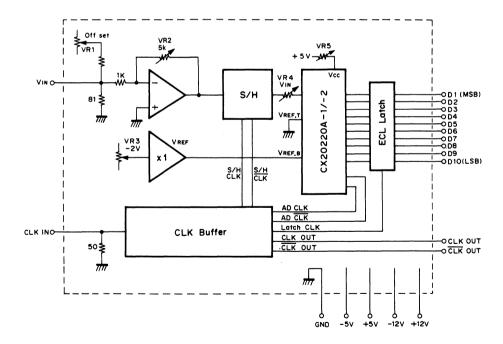

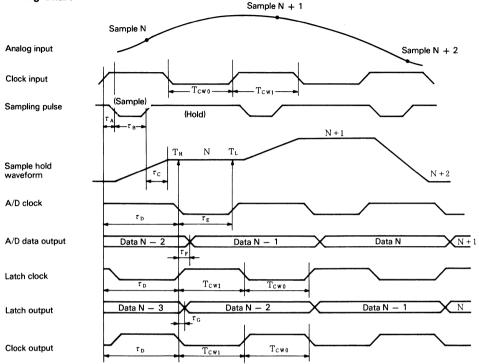

| СХ20018 РСВ                                        | 311  | CX20220A-1/-2                        | 160  | СХК1201Р                             | 283  |

| CX20051A                                           | 105  | CX23010<br>CX23060                   | 87   | CXK1202S                             | 295  |

| CX20052A                                           | 116  | СХ23060 РСВ                          | 336  | FCX20220A-1/-2                       | 352  |

| CX20052A<br>PCB·3A/3B                              | 322  | CX23024<br>CX23067                   | 230  | BX-1300                              | 208  |

| CX20052A<br>Application Note                       | 363  | CX23034                              | 238  |                                      |      |

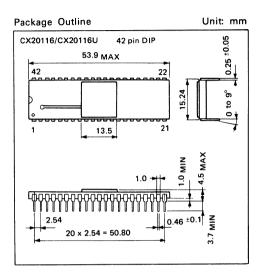

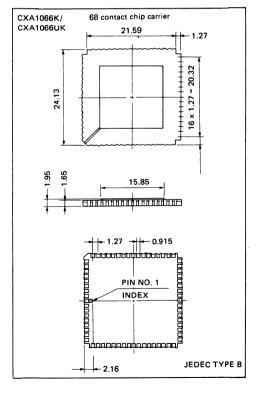

| CX20116/U<br>CXA1066K/UK                           | 125  | CX23038                              | 249  |                                      |      |

| CX20116/U<br>CXA1066K/UK } PCB                     | 328  | CX23043                              | 257  |                                      |      |

| CX20116/U<br>CXA1066K/UK<br>CXA1056P/K/UK          | 370  | CXA1008P<br>CXA1009P                 | 174  |                                      |      |

| CXA1056P/K/UK<br>CXA1016P/K/UK<br>Application Note | 370  | CXA1016P/K/UK<br>CXA1056P/K/UK       | 186  |                                      |      |

## 2. Index by Usage

| Туре               | Function                                   | Page |

|--------------------|--------------------------------------------|------|

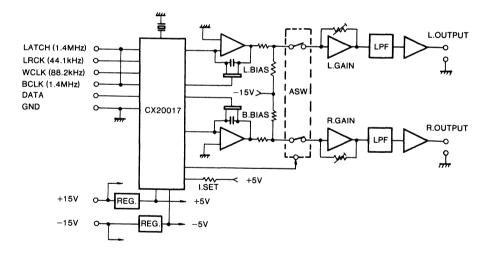

| CX20017            | Dual 16bit 44kHz Multiplexed D/A Converter | 23   |

| CX20018            | Dual 16bit 44kHz Multiplexed A/D Converter | 37   |

| CX20133            | 16bit D/A Converter                        | 56   |

| CX20152            | Dual 16bit 88kHz Multiplexed D/A           | 69   |

| CX23010<br>CX23060 | Dual 10bit 50kHz Multiplexed A/D + D/A     | 87   |

#### 1) A/D, D/A Converters - Audio -

#### 2) A/D, D/A Converters - Video -

| Туре                                 | Function                                 | Page |

|--------------------------------------|------------------------------------------|------|

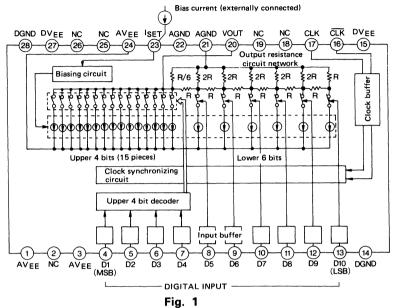

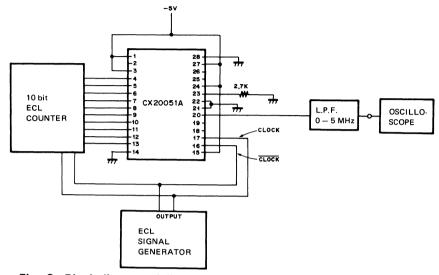

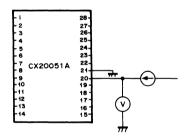

| CX20051A                             | 10bit 30MHz D/A Converter                | 105  |

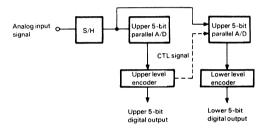

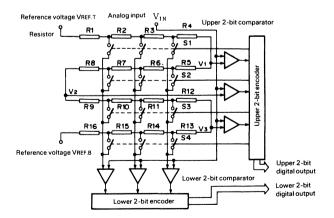

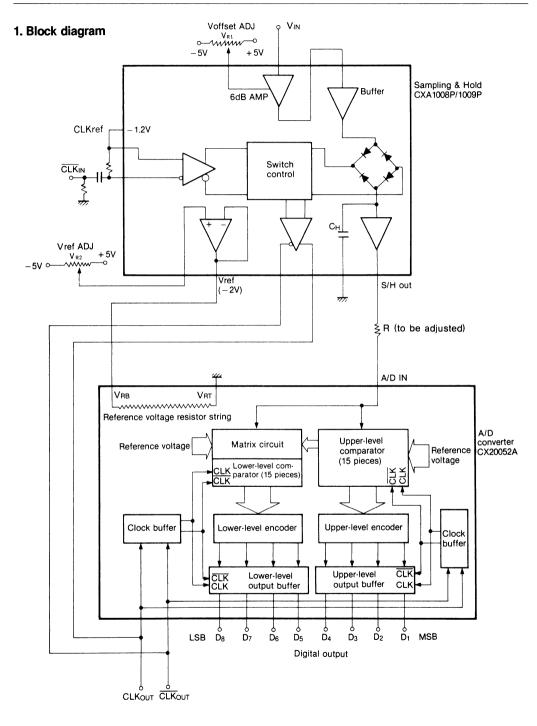

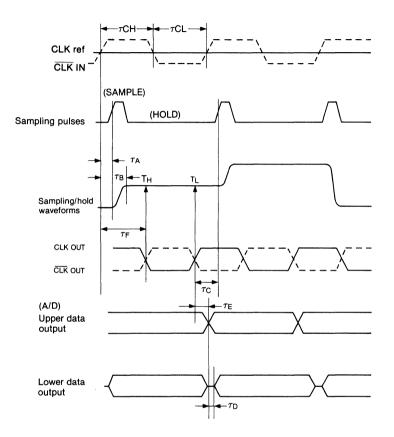

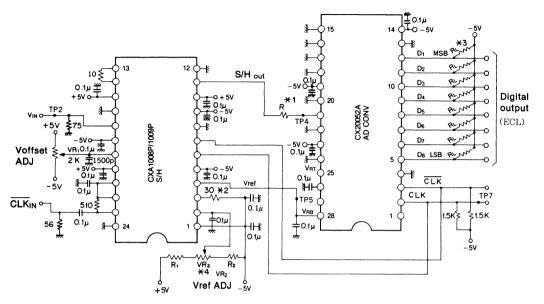

| CX20052A                             | 8bit 20MHz Sub-ranging A/D Conveter      | 116  |

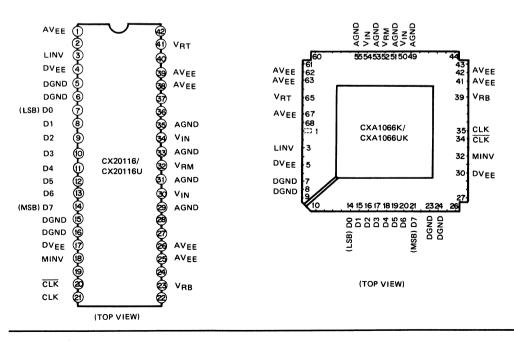

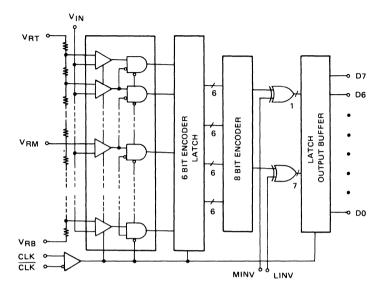

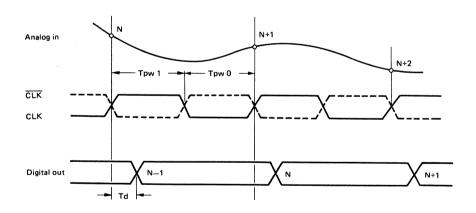

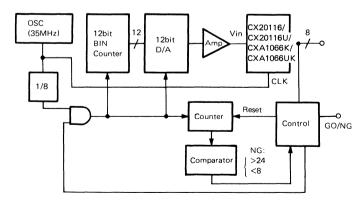

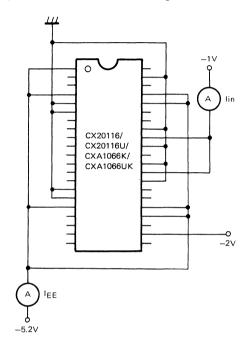

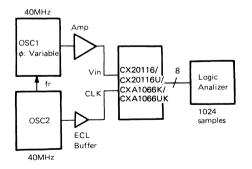

| CX20116/U<br>CXA1066K/UK             | 8bit 100MHz Flash A/D Converter          | 125  |

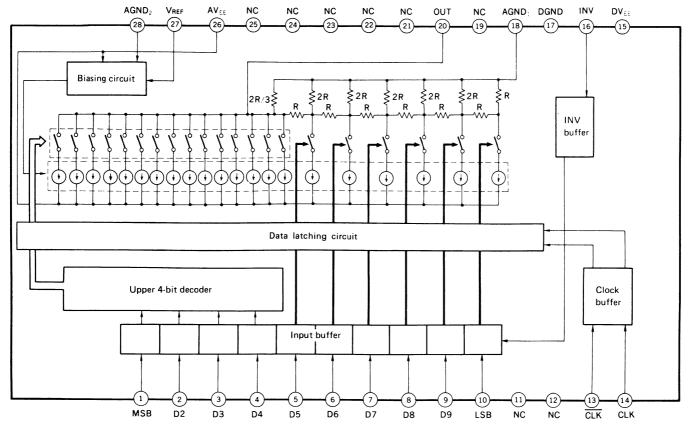

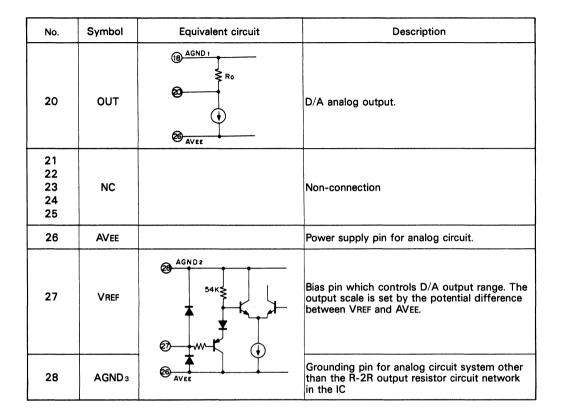

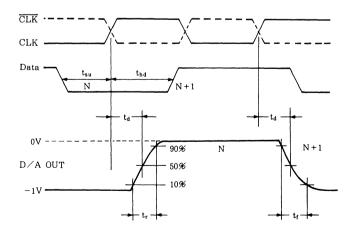

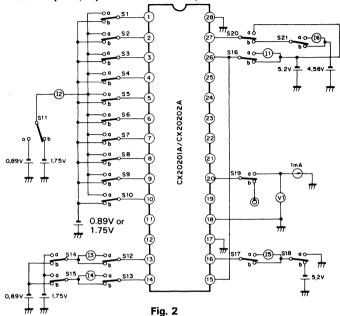

| CX20201A-1/-2/-3<br>CX20202A-1/-2/-3 | 10/ 9/ 8bit 160MHz D/A Converter         | 132  |

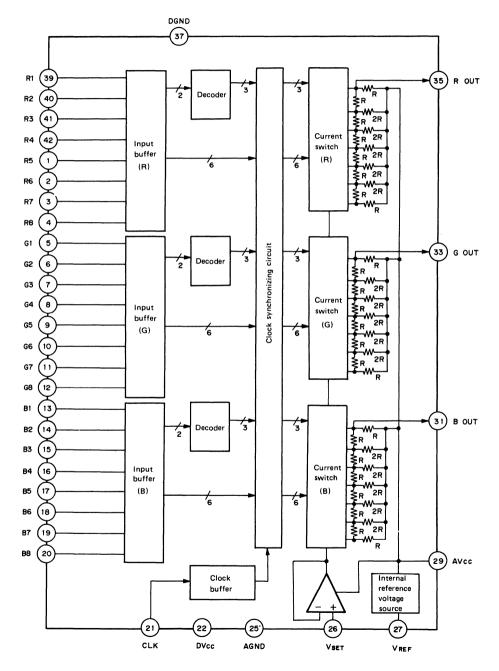

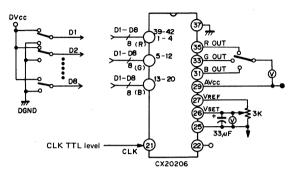

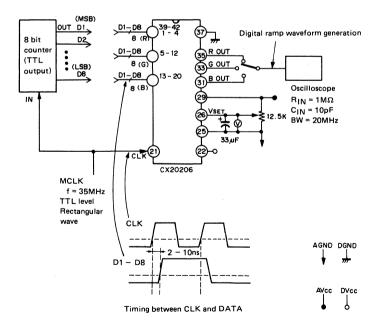

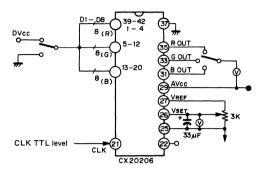

| CX20206                              | 8bit 35MHz RGB 3-channel D/A Converter   | 144  |

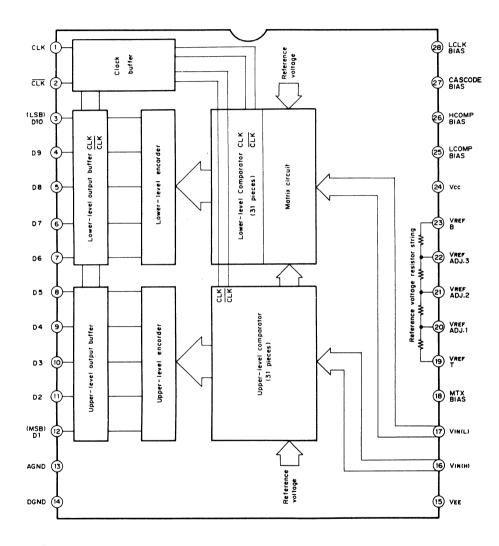

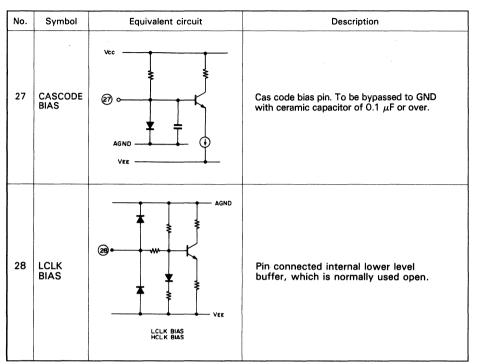

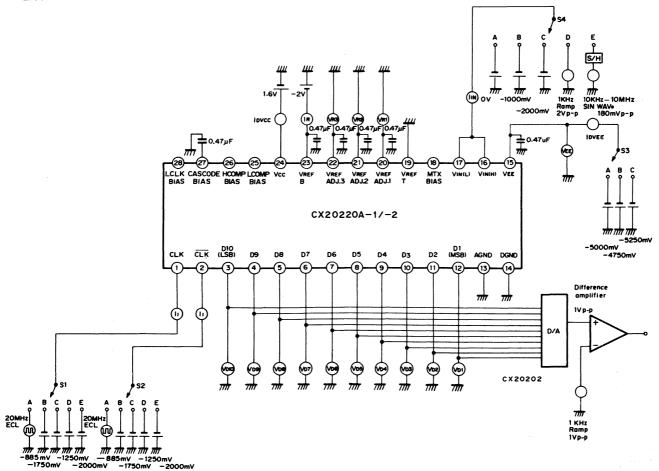

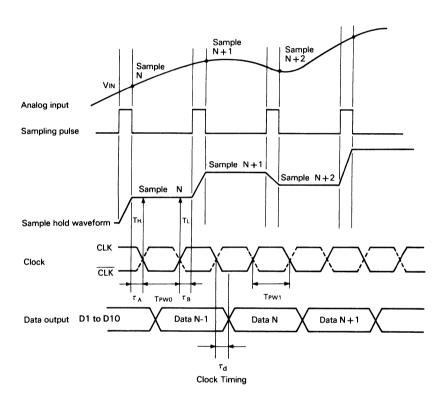

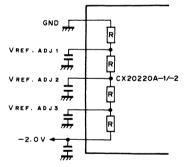

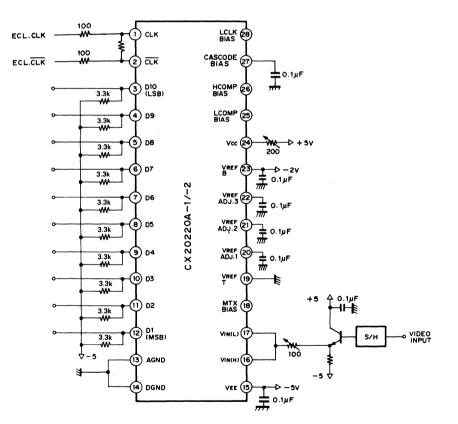

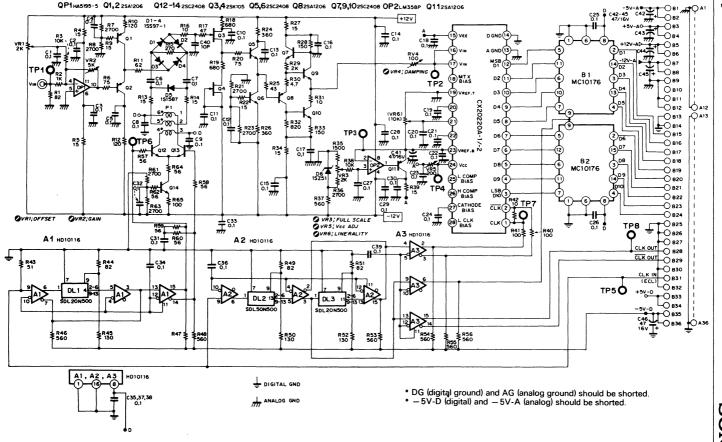

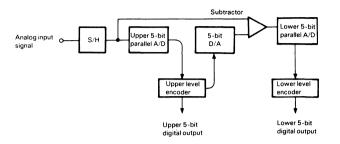

| CX20220A-1/-2                        | 10/ 9bit 20MHz Sub-ranging A/D Converter | 160  |

| CXA1008P/1009P                       | High-speed Sample and Hold Amplifier     | 174  |

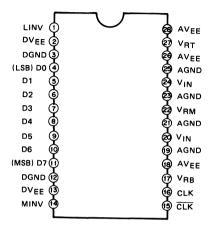

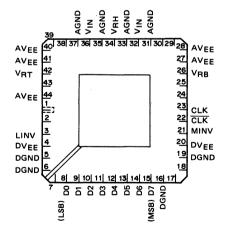

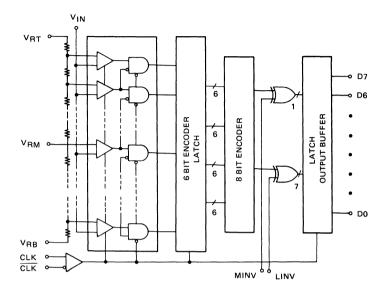

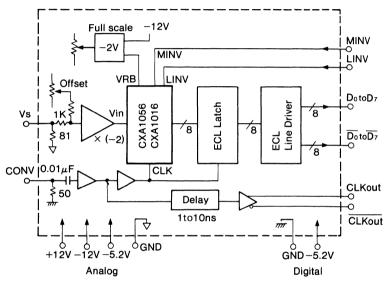

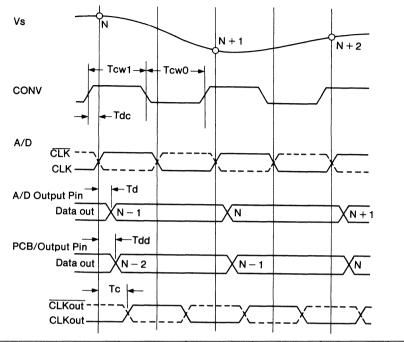

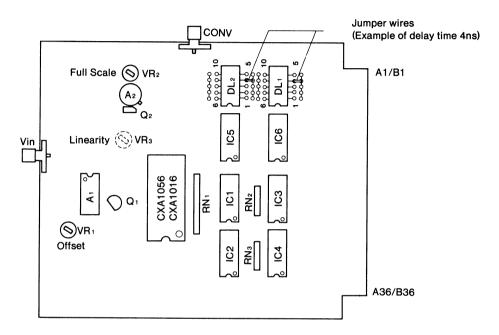

| CXA1016P/K/UK<br>CXA1056P/K/UK       | 8bit 30/50MHz Flash A/D Converter        | 186  |

| CXA1096P                             | 8bit 20MHz Flash A/D Converter (P)       | 196  |

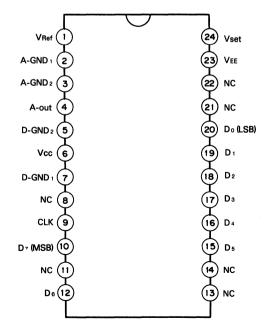

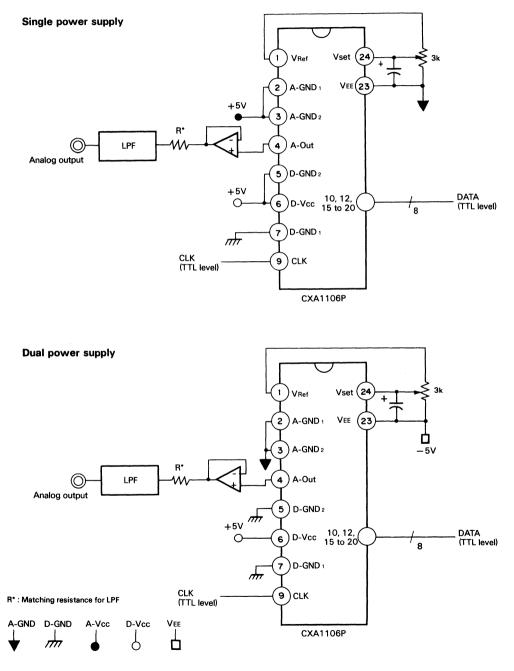

| CXA1106P                             | 8bit 35MHz High-speed D/A Converter (P)  | 203  |

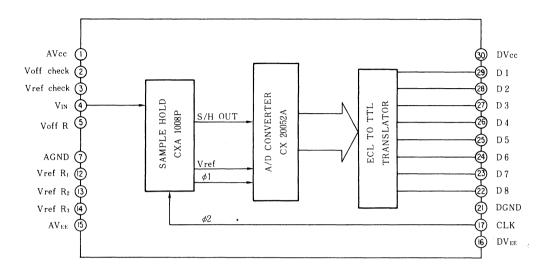

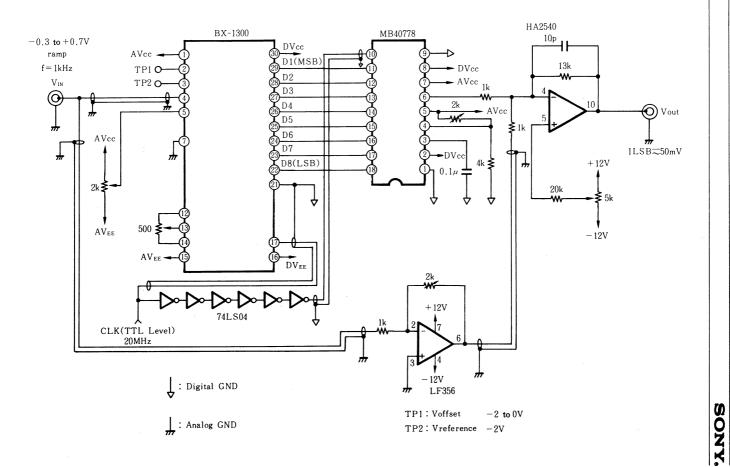

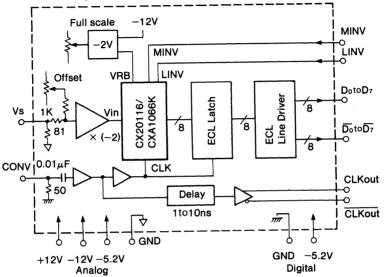

| BX-1300                              | 8bit 20MHz A/D Converter Module          | 208  |

(P): Preliminary

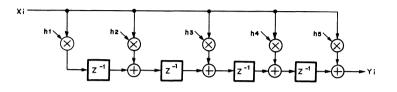

#### 3) Digital Signal Processors

| Туре               | Function                            | Page |

|--------------------|-------------------------------------|------|

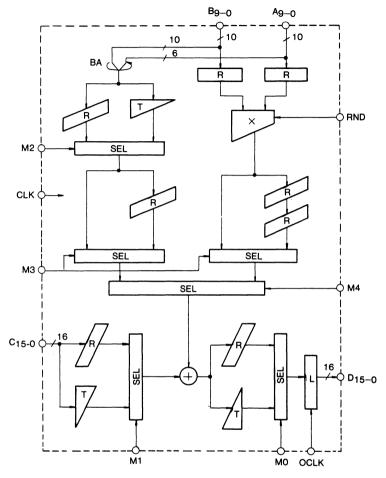

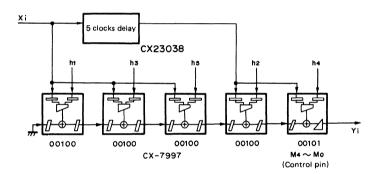

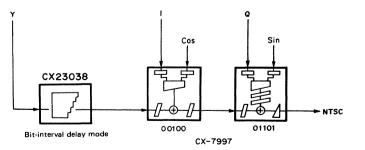

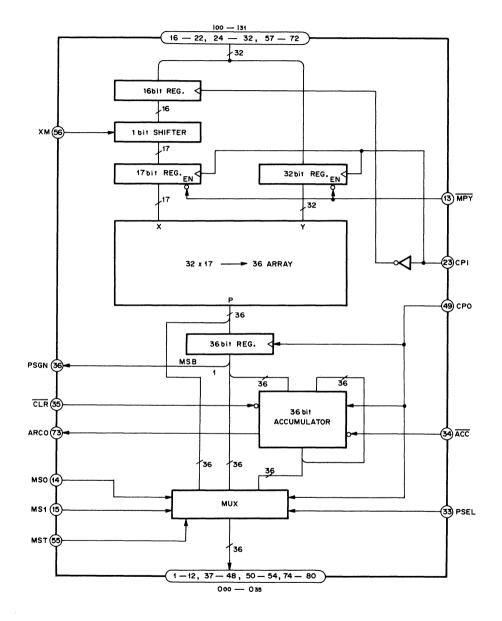

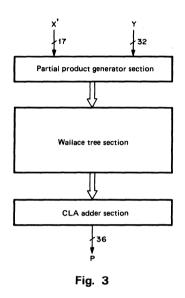

| CX-7997            | 10×10bit 15MHz Multiplier/Adder     | 219  |

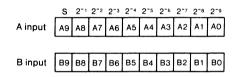

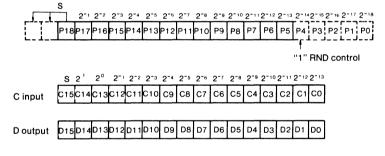

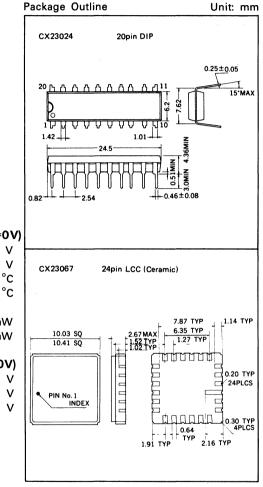

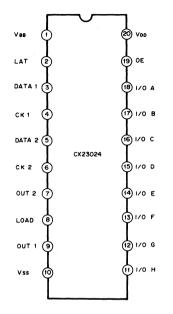

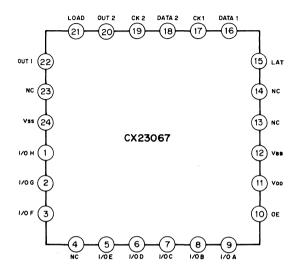

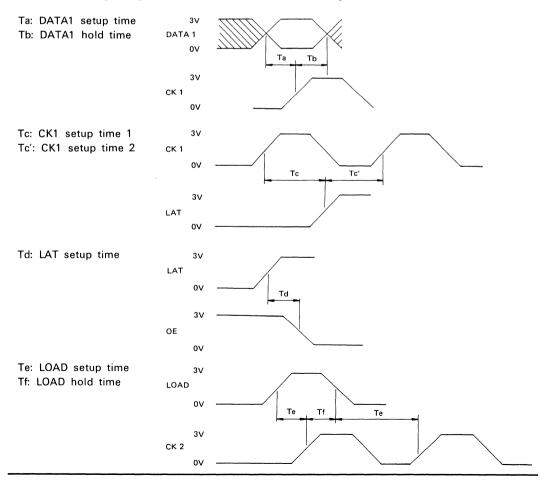

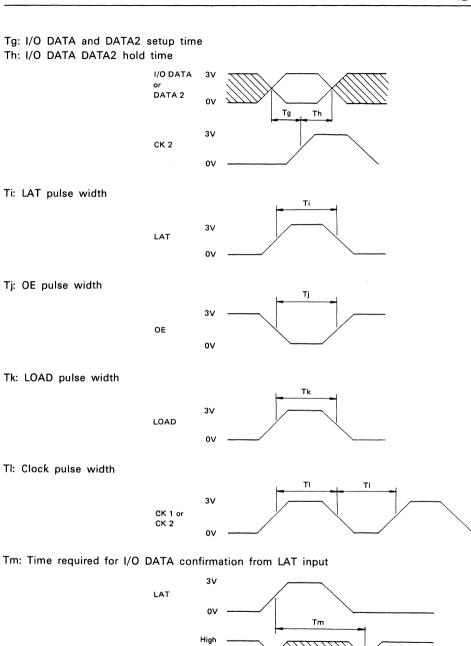

| CX23024<br>CX23067 | 8bit S-P-S Converter                | 230  |

| CX23034            | Digital Filter for CD               | 238  |

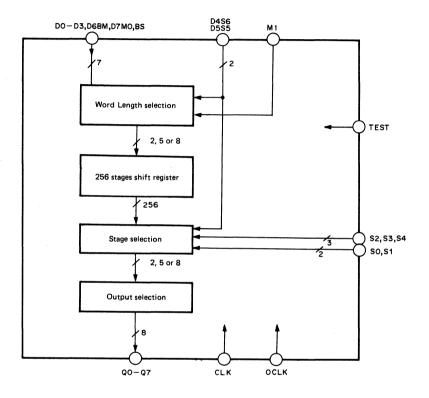

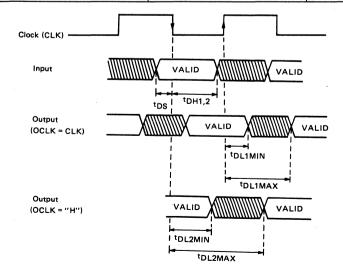

| CX23038            | Programmable Shift Register         | 249  |

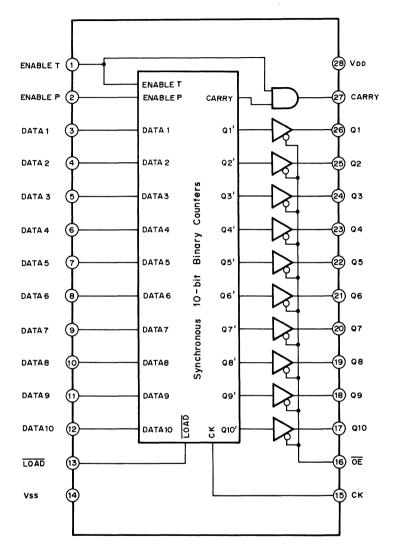

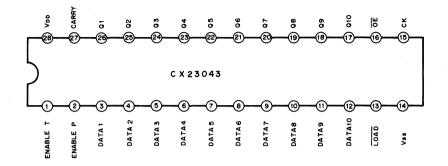

| CX23043            | 10bit Synchronous Binary Counter    | 257  |

| CXD1018G           | Degital Signal Processing Multipler | 266  |

| CXK1201P           | Double Scan Converter (P)           | 283  |

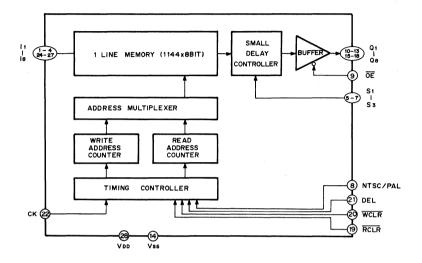

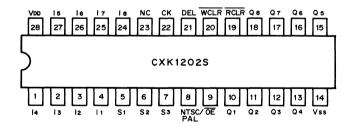

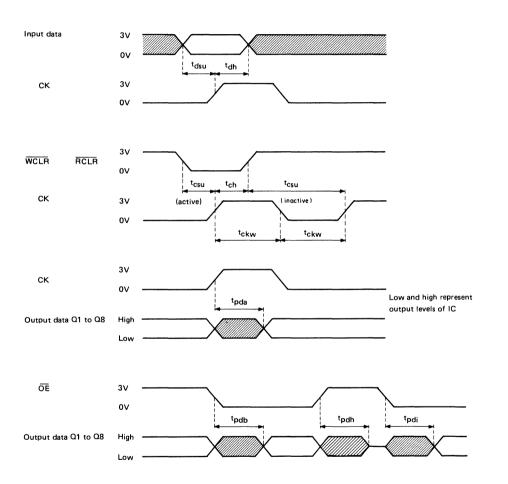

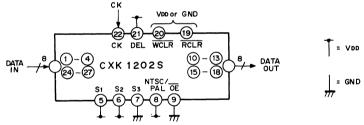

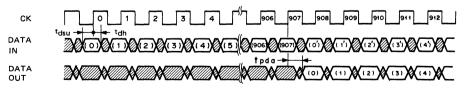

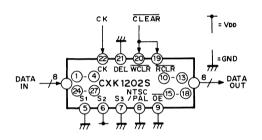

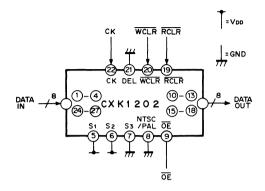

| CXK1202S           | Digital Delay Line                  | 295  |

(P): Preliminary

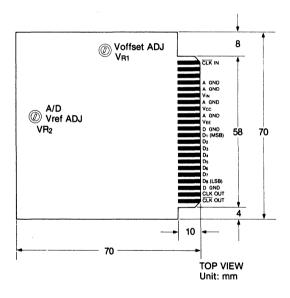

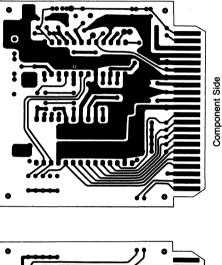

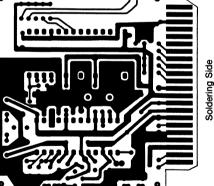

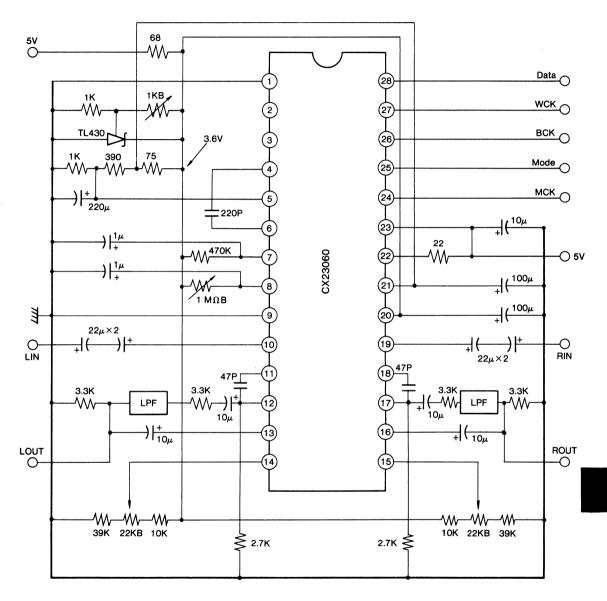

#### 4) Evaluation Printed Circuit Boards

| Туре                               | Function                                                       | Page |

|------------------------------------|----------------------------------------------------------------|------|

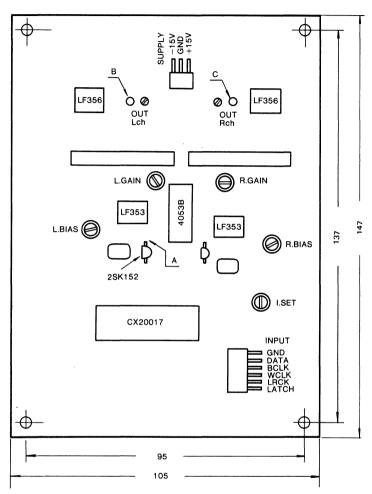

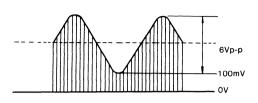

| СХ20017 РСВ                        | CX20017 Evaluation Board                                       | 307  |

| СХ20018 РСВ                        | CX20018 Evaluation Board                                       | 311  |

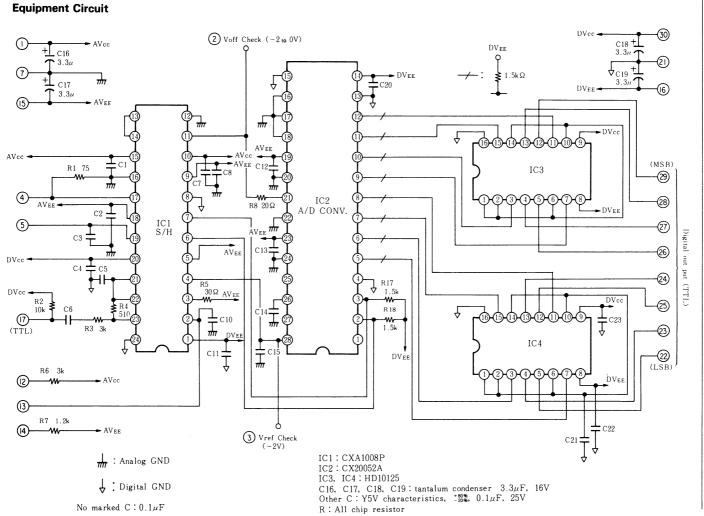

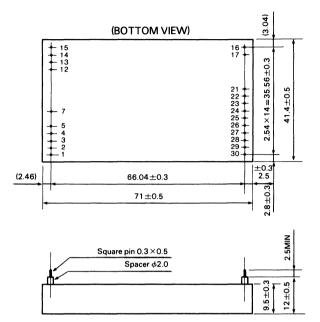

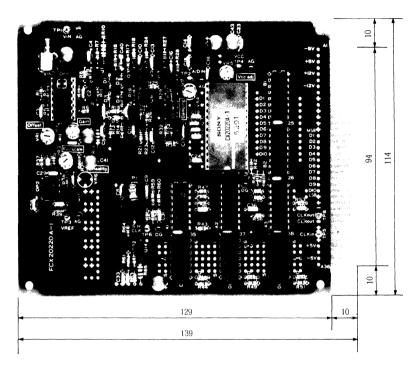

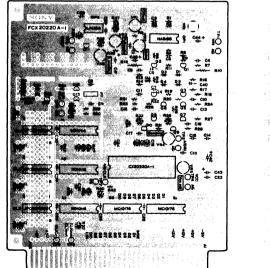

| СХ20052А РСВ-ЗА/ЗВ                 | 8bit 20/15MHz A/D Converter Evaluation Board                   | 322  |

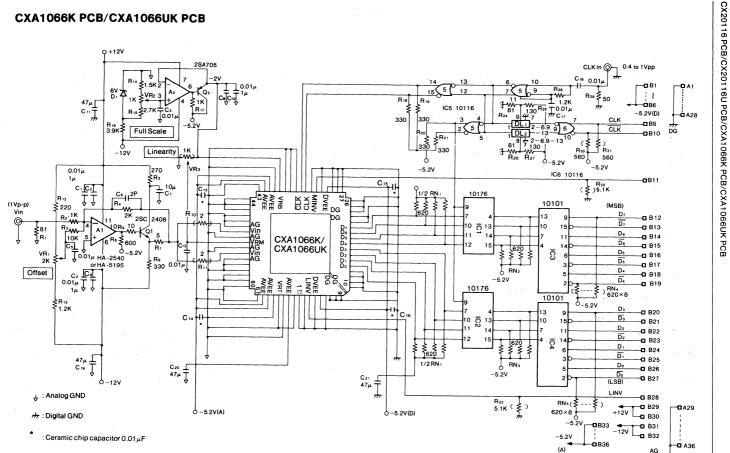

| CX20116/U<br>CXA1066K/UK PCB       | 8bit 100MHz A/D Evaluation Board                               | 328  |

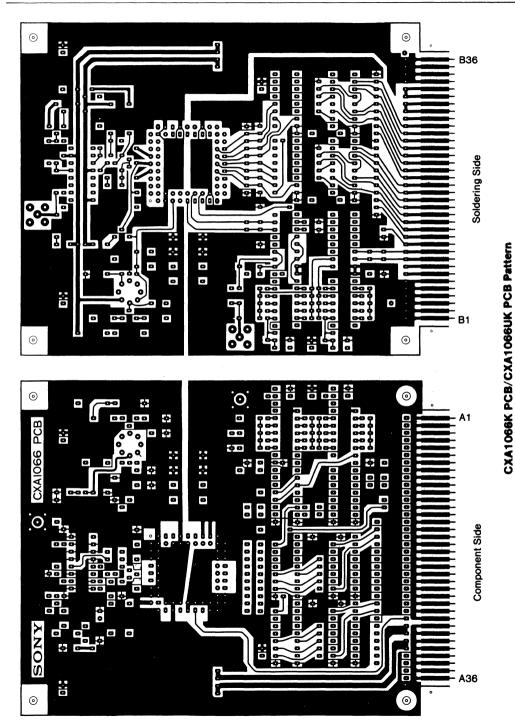

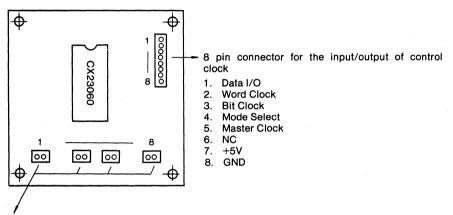

| СХ23060 РСВ                        | CX23060 Evaluation Board                                       | 336  |

| CXA1016P/K/UK<br>CXA1056P/K/UK PCB | 8bit 50MHz/30MHz A/D Evaluation Board                          | 343  |

| FCX20220A-1/-2                     | 10bit/9bit 20MHz Sub-ranging A/D Converter<br>Evaluation Board | 352  |

#### 5) Application Notes

| Туре                                                       | Function                             | Page |

|------------------------------------------------------------|--------------------------------------|------|

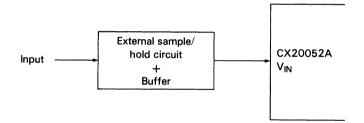

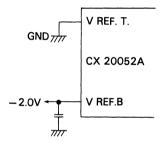

| CX20052A                                                   | 8bit 20MHz Sub-ranging A/D Converter | 363  |

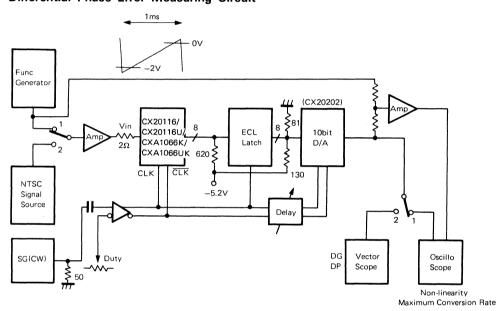

| CX20116/U<br>CXA1066K/UK<br>CXA1056P/K/UK<br>CXA1016P/K/UK | 8bit High-speed A/D Converter        | 370  |

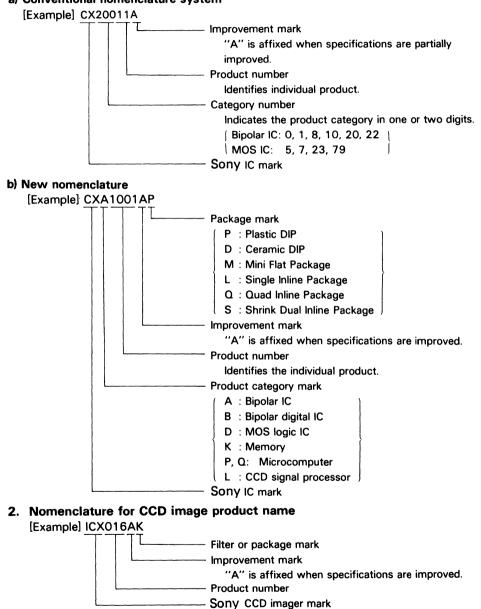

### 3. IC Nomenclature

#### 1. Nomenclature of IC product name

Currently, both the conventional and new nomenclature systems are mixed in naming IC products.

#### a) Conventional nomenclature system

-9-

### 4. Precautions for IC Application

#### A) Absolute maximum ratings

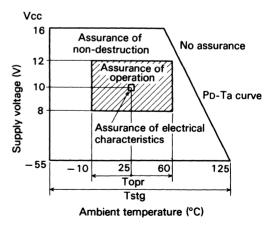

The maximum ratings for semiconductor devices are normally specified by "absolute maximum ratings". The values shown in the maximum ratings table must never be exceeded even in a moment.

If the maximum rating is ever exceeded, device deterioration or damage will occur immediately. Then, even if the affected device can operate, the life will be considerably short.

Maximum rating must never be reached for two items at the same time.

#### **IC maximum ratings**

The following maximum ratings are used for ICs.

(1) Maximum power supply voltage Vcc (VDD)

The maximum voltage that can be applied between the power supply terminal and ground terminal.

This power supply voltage rating is directly related to the dielectric voltage of transistors in the internal circuit; the transistors may be destroyed if this voltage is exceeded.

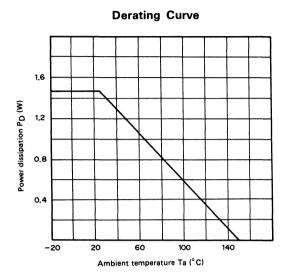

#### (2) Allowable power dissipation PD

The maximum power consumption allowed in IC

In the circuit design the absolute maximum ratings must not be exceeded, and it must be designed only after considering the worst situations among the following:

- Fluctuation in source voltage

- Scattering in the electrical characteristics of electrical parts (transistors, resistors, capacitors, etc.)

- Power dissipation in circuit adjustment

- Ambient temperature

- Fluctuation in input signal

- Abnormal pulses

If this allowable power dissipation is exceeded, electrical and thermal damage may result.

This value varies with the amount of IC integration in package types.

(3) Operating ambient temperature Topr The temperature range within which IC

can operate satisfactorily. Even if this temperature range is exceeded and some deterioration in operating characteristics is noted, the IC is not always damaged.

For some ICs, the electrical characteristics at Ta = 25 °C are not guaranteed even in this temperature range.

#### (4) Storage temperature Tstg

The temperature range for storing the IC which is not operating.

This temperature is restricted by the package material, and the intrinsic properties of the semiconductor.

#### (5) Other values

The input voltage Vin, output voltage Vout, input current lin, output current lout and other values may be specified in some IC's.

The relationship among these maximum ratings for IC is shown below.

#### B) Protection against electrostatic breakdown

There have been problems of electrostatic destruction of electronic devices since the 2nd World War. Their history is closely related to the advancement in the semiconductor devices; that is, with the development of semiconductor technology, new problems in electrostatic destruction have arisen. This situation, perhaps, can be understood by recalling the case of MOS FET.

Today, the problem of electrostatic destruction is again drawing people's attention as we are entering the era of LSI and VLSI. Here are our suggestions for preventing electrostatic destruction in the device fabrication process.

## Factors causing electrostatic generation in manufacture process

A number of dielectric materials are used in manufacture process. Friction of these materials with the substrate can generate static electricity which may destroy the semiconductor device.

Factors that can cause electrostatic destruction in the manufacture process are shown below:

# Causes of electrostatic destruction of semiconductor parts in manufacture process

## Handling precautions for preventing electrostatic destruction

Explained below are procedures that must be taken in fabrication for preventing the electrostatic destruction of semiconductor devices.

The following basic rules must be obeyed.

- (1) Equalize potentials of terminals when transporting or storing.

- (2) Equalize the potentials of the electric device, work bench, and operator's body that may come in contact with the semiconductor device.

- (3) Prepare an environment that does not generate static electricity.

One method is keeping relative humidity in the work room about 50%.

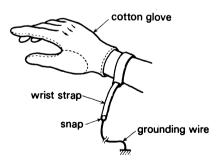

#### Operator

#### 1) Clothes

Do not use nylon, rubber and other materials which easily generate static electricity. For clothes, use cotton, or antistatic-treated materials. Wear gloves during operation.

#### 2) Grounding of operator's body

The operator should connect the specified wrist strap to his arm. If wrist strap cannot be used, then the operator should touch the grounding point with his hand, before handling any semiconductor device.

example of grounding band

When using a copper wire for grounding, connect a 1M resistance in series near the hand for safety.

#### 3) Handling of semiconductor device

Do not touch the lead. Touch the body of semiconductor device when holding. Limit the number of handling times to a minimum. Do not take the device out of the magazine or package box unless it is absolutely necessary.

#### holding of semiconductor device

can type

#### **Equipment and tools**

**DIP type**

#### 1) Grounding of equipment and tools

Ground the equipments and tools that are to be used. Check insulation beforehand to prevent leakage.

[Check point]

- measuring instrument

- conveyer

- electric deburr brush

- carrier

- solder dipping tank

- lead cutter

- shelves and racks

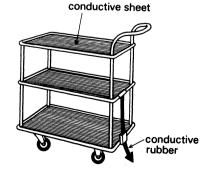

#### grounding of carrier

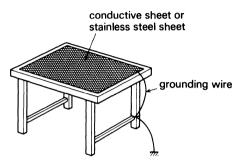

#### 2) Grounding of work table

Ground the work table as illustrated. Do not put anything which can easily generate static electricity, such as foam styrol, on the work table.

#### grounding of work table

#### 6) Other points of caution

Take note of the kind of the brush material used for removing lead chips. Use metal or antistatic-treated plastic brushes.

## Transporting, storing and packaging methods

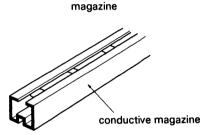

#### 1) Magazine

Use the metal, or antistatic-treated plastic IC magazines.

The plastic magazines used for shipping ICs are antistatic-treated, and they can be used for storing ICs.

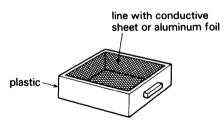

#### 3) Semiconductor device case

Use the metal case, or the antistatic plastic case (lined with conductive sheet or aluminum foil).

## plastic case for semiconductor devices

#### 4) Insertion of semiconductor device

Insert the semiconductor device in mounting process or on the belt conveyer. The insertion should be done on a conductive sheet, or a wood or metal carrier.

#### 5) Operation in energized state

When the substrate is checked while energizing the substrate where the delicate semiconductor device is mounted, be sure to place the substrate on corrugated cardboard, wood, or on a metal carrier.

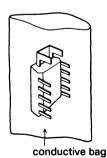

#### 2) Bag

Use a conductive bag for keeping ICs. If use of a vinyl bag is unavoidable, be sure to wrap the IC with aluminum foil.

bag

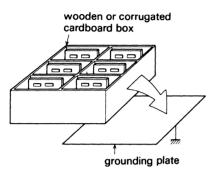

#### 3) Handling of delivery box

The delivery box used for carrying substrates must be made of wood or corrugated cardboard. Do not use a vinyl chloride or acrylic delivery box, otherwise static electricity will be generated.

#### handling of delivery box

#### 4) Treatment after vehicle transport

After truck transport, place the magazine, package box or delivery box on the grounded rack, work table, or concrete floor for discharging. Do not pull the delivery box for more than 1 meter except on a concrete or a wooden floor.

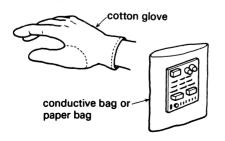

#### 5) Handling of mounted substrates

Wear cotton gloves when handling. As far as possible, avoid touching soldered faces. When handling mounted substrates individually, be sure to use a conductive or paper bag. Do not use a polyethylene bag.

#### handling of mounted substrate

#### Soldering operation

#### 1) Soldering iron

Use a soldering iron with a grounded metal part or a soldering iron whose insulation resistance after five minutes from energizing is greater than 10 M $\Omega$  (DC 500V).

#### 2) Operation

After inserting the semiconductor device into the substrate, solder it as quickly as possible. Do not carry the substrate with the inserted semiconductor device by car.

#### 3) Correction

When correcting parts (semiconductor device and CR parts) after solder-dipping, be sure to wear cotton gloves. Also, connect the grounding band to the arm, or touch the grounding point before operation.

#### 4) Manual soldering

Solder with wrist strap connected to the hand, or by touching the grounding point from time to time during operation.

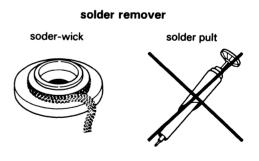

#### 5) Removing semiconductor device

Do not use the Solder-Pult when removing the semiconductor device. Use a Soder-wick or equivalent.

#### 6) Soldering work table

Use a grounded work table, corrugated cardboard, or wooden work table for soldering. Do not solder on foam styrol, vinyl, or decorative board.

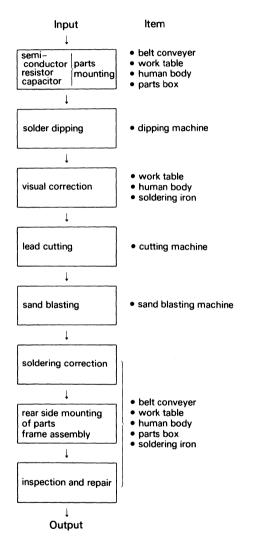

#### **C)** Mounting method

#### Soldering and solderability

#### (1) Solderability guaranteed by JIS

JIS specifies solderability of an IC terminal (lead) in "JIS-C7022 Test Procedure A-2". An abstract of this standard follows:

- Rosin flux must be used, and the terminal must be dipped in it for 5-10 seconds.

- H63A or equivalent solder must be used, and the terminal must be dipped in the solder which has been heated to 230°C±5°C for 5±1 seconds.

- Using a microscope, measure the area (%) deposited with solder. JIS specifies that more than 95% of the

total area should be coated with solder.

#### (2) Area for soldering warranty

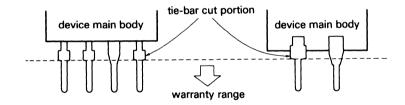

Soldering is warranted for a specific portion of the terminal. The warranted portion is shown in the following figure.

The tie-bar cut portion also serves as a dam to prevent the sealing resin flowing out during device fabrication; it is cut off at the end of the process. Since the terminal is exposed at the cut-off end, the area for soldering is restricted. The portion near the resin is often covered with burrs when sealing with resin; it is not in the soldering warranty area.

#### warranty area for soldering

#### **Resistance to soldering heat**

#### (1) Specification of JIS

JIS specifies the method for testing the resistance to soldering heat. This method is used for guaranteeing the IC resistance against thermal stresses by soldering. An abstract of this standard is as follows:

• Dip the device terminal only once for  $10\pm1$  seconds in a solder bath of  $260^{\circ}C\pm5^{\circ}C$ , or for  $3^{+0.5}_{-0}$  seconds in a solder bath of  $350^{\circ}C\pm10^{\circ}C$ , for a distance of up to 1 to 1.5 mm from the main body.

The temperature of  $260^{\circ}C \pm 5^{\circ}C$  assumes the soldering with solder flow system, and the temperature  $350^{\circ}C \pm 10^{\circ}C$  assumes soldering by soldering iron.

- Leave the device for more than two hours after dipping, then measure the device characteristics.

- Normally, the warranty is limited for 10 seconds at  $260^{\circ}C \pm 5^{\circ}C$ . The distance between the device main body and solder bath is assumed as 1.6 mm.

- 15 -

### 5. Quality Assurance and Reliability

#### Sony's Policy of Quality Assurance

The Sony semiconductor embodies two fundamental ideas: "highest quality" and "lowest cost". There are the two key points for realizing these ideas.

One is the "quality" of men fabricating the semiconductor devices. The reliability of these people is reflected in the Sony products. Accordingly, Sony is making a continuous effort to raise the "quality" of people capable of manufacturing and fabricating Sony semiconductor devices. The other point is a source management system combined with the concept of thorough quality design. With this system, higher quality products can be steadily manufactured through automation of device design, process design, and the fabrication process.

Sony is making constant efforts to supply the most economical and most useful products of very high quality for users.

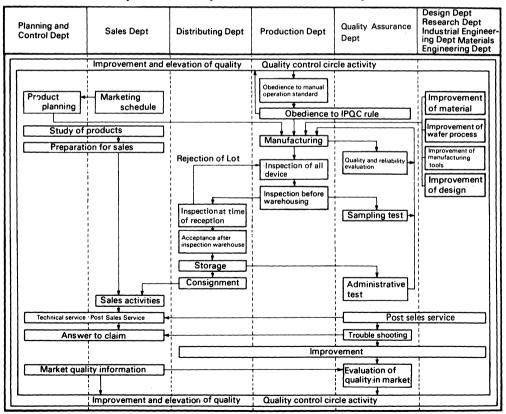

#### Quality assurance system of semiconductor products

## Quality assurance criteria and reliability test criteria

#### 1) Quality assurance in shipping

Establishing quality in the design and in fabrication is essential to keep the quality and reliability levels of the semiconductor devices at a high level. This is done by the "Zero-defect" (ZD) movement. Further sampling checks, in units of shipping lot, is done on products that have been "total-inspected" at the final fabrication stage, thus ensuring no detective items. This sampling inspection is done in accordance with MIL-STD-105D.

#### 2) Reliability

The reliability test is done, periodically, to confirm reliability level.

|             | ltem                                              | Test Hour                                                                     | LTPD (%)   |  |

|-------------|---------------------------------------------------|-------------------------------------------------------------------------------|------------|--|

|             | Electrical characteristic test                    | In order to know the quality level, some types are selected and tested again. |            |  |

| LIFE TEST   | High temperature operation                        | Up to 1000 hr                                                                 | 10%        |  |

|             | High temperature storage                          | Up to 1000 hr                                                                 | 10%        |  |

|             | Low temperature storage                           | Up to 1000 hr                                                                 | 10%        |  |

|             | High temperature and high humidity storage        | Up to 1000 hr                                                                 | 10%        |  |

|             | High humidity bias test                           | Up to 1000 hr                                                                 | 10%        |  |

|             | High temperature and high humidity with<br>bias   | Up to 500 hr                                                                  | 10%        |  |

|             | Pressure cooker                                   | Up to 200 hr                                                                  | 10%        |  |

| ENVIRONMENT | Soldering heat resistance heat cycle              | 10 s                                                                          | 15%        |  |

| TEST        | Heat cycle                                        | 10 cycle                                                                      | 15%        |  |

| MECHANICAL  | Solderability                                     | Japan Industrial                                                              | 15%        |  |

| TEST        | Lead strength                                     | Standard (JIS)                                                                | 15%        |  |

| OTHER TESTS | if necessary test, are selected accordingly to JI | S C7021, C7022, EIAJ SD1                                                      | 21, IC121. |  |

#### **Periodical reliability test**

\* These tests are selected by sampling standard.

These tests and Inspection data are useful not only to estimate quality in the market place but also as data to improve design and wafer processes.

#### Reliability test standard for acceptance of products

| Type of Test                                    | Condition                                                                 | Supply voltage                                              | Testing time                  | LTPD (%)     |

|-------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------|--------------|

| High temperature operation                      | Ta=125°C, 150°C                                                           | ТҮР                                                         | 1000 hr                       | 5%           |

| High temperature with bias                      | Ta = 125°C, 150°C                                                         | ТҮР                                                         | 1000 hr                       | 5%           |

| High temperature storage                        | Ta = 150°C                                                                |                                                             | 1000 hr                       | 5%           |

| Low temperature storage                         | Ta = - 65°C                                                               |                                                             | 1000 hr                       | 5%           |

| High temperature and<br>humidity storage        | Ta = 85°C, 85%RH                                                          |                                                             | 1000 hr                       | 5%           |

| High temperature and<br>High humidity with bias | Ta = 85°C, 85%RH                                                          | TYP<br>(I hr on/3 hr off)                                   | 500hr                         | 5%           |

| Pressure cooker                                 | Ta = 121°C, 100%RH,<br>per square inch                                    | Ta = 121°C, 100%RH, 30 pounds<br>per square inch            |                               | 5%           |

| Temperature cycle                               | $Ta = -65^{\circ}C \text{ to } +150^{\circ}C$                             |                                                             | 100 C                         | 10%          |

| Heat shock                                      | $Ta = 0^{\circ}C to + 100^{\circ}C$                                       |                                                             | 5 C                           | 10%          |

| Soldering heat resistance                       | Tsolder = 260°C                                                           |                                                             | 10 S                          | 105          |

| Solderability                                   | Tsolder =230°C (Ros                                                       | sin type flux)                                              | 5 S                           | 10%          |

| Mechanical shock                                | X, Y, Z 1500G<br>0.5 ms half sine wave                                    |                                                             | 3 times for<br>each direction | 10%          |

| Vibration                                       | X, Y, Z 20G 10 to 20<br>sine wave vibration                               | X, Y, Z 20G 10 to 2000 to 10 Hz (4 min) sine wave vibration |                               | 10%          |

| Constant acceleration                           | X, Y, Z 20,000 G centrifugal acceleratio                                  | X, Y, Z 20,000 G<br>centrifugal acceleration                |                               | 10%          |

| Fall by gravity                                 | Falling from the height of 75cm to maple plate by gravity                 |                                                             | 3 times                       | 10%          |

| Lead strength (Bend)<br>(Pull)                  | Based on JIS                                                              |                                                             |                               | 10%          |

| Electrostatics strength                         | Device must be design<br>supplying surge voltage<br>To each pin under the | je                                                          | -                             | below standa |

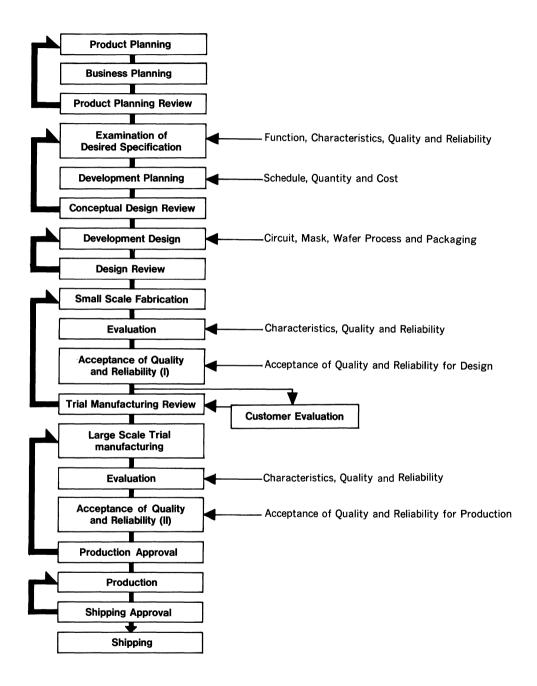

#### From development to production

# A/D,D/A Converters Audio

#### 1) A/D, D/A Converters – Audio –

| Туре               | Function                                   | Page |

|--------------------|--------------------------------------------|------|

| CX20017            | Dual 16bit 44kHz Multiplexed D/A Converter | 23   |

| CX20018            | Dual 16bit 44kHz Multiplexed A/D Converter | 37   |

| CX20133            | 16bit D/A Converter                        | 56   |

| CX20152            | Dual 16bit 88kHz Multiplexed D/A           | 69   |

| CX23010<br>CX23060 | Dual 10bit 50kHz Multiplexed A/D + D/A     | 87   |

- 22 -

### SONY

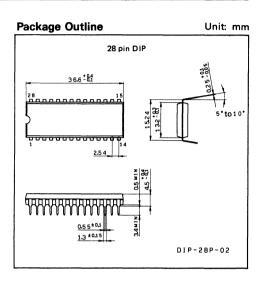

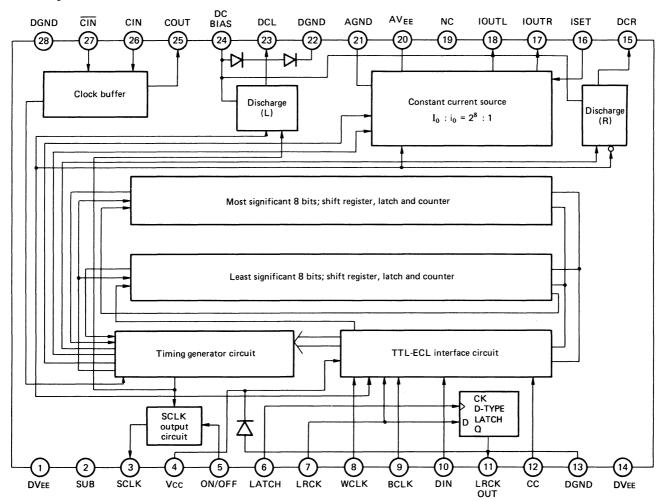

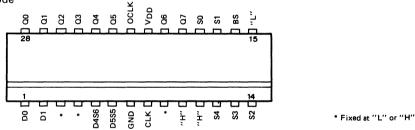

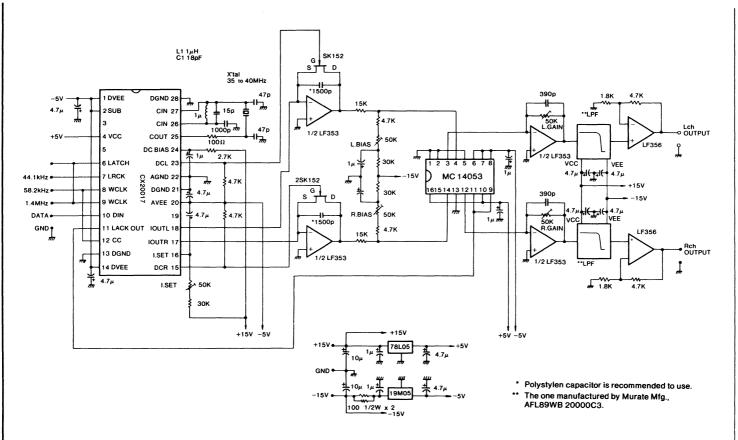

### Dual 16 bit 44 kHz Multiplexed D/A Converter

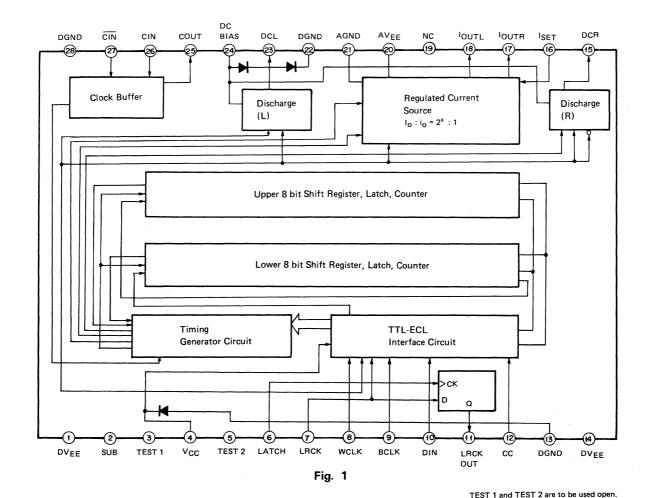

#### Description

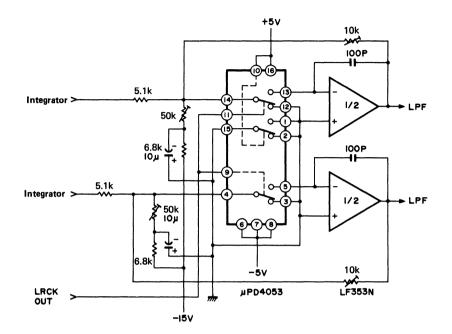

The CX20017 is a 16 bit D/A converter IC for PCM audio using an integration system. Analog signals can be regenerated from 16 bit digital signals by adding an integrator, an analog switch, and a low-pass filter outside the IC.

#### Features

- 16 bit D/A converter.

- · Clock buffer.

- TTL-ECL interface circuit.

- Discharge drive circuit.

- Analog switch drive circuit.

#### Functions

- Two channels for integral current output and discharge signal output.

- Level shift circuit for direct interface with TTLs and MOS LSIs.

- · Analog switch drive circuits, etc.

#### Structure

Silicon Monolithic IC

#### Absolute Maximum Ratings (Ta=25°C)

| <ul> <li>Supply voltage</li> </ul>              | Vcc to Ve | E 12        | _ V |

|-------------------------------------------------|-----------|-------------|-----|

| <ul> <li>Operating temperature</li> </ul>       | Topr      | -10 to +75  | °C  |

| Storage temperature                             | Tstg      | -50 to +150 | °C  |

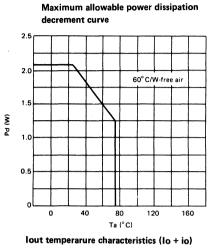

| <ul> <li>Allowable power dissipation</li> </ul> | Po        | 2.1         | w   |

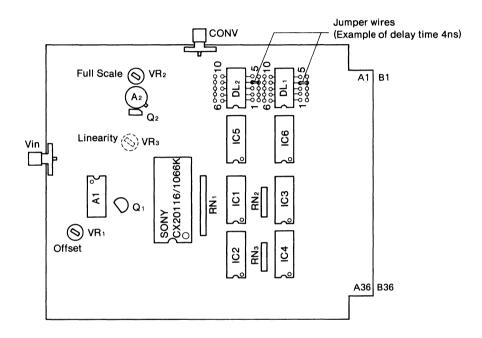

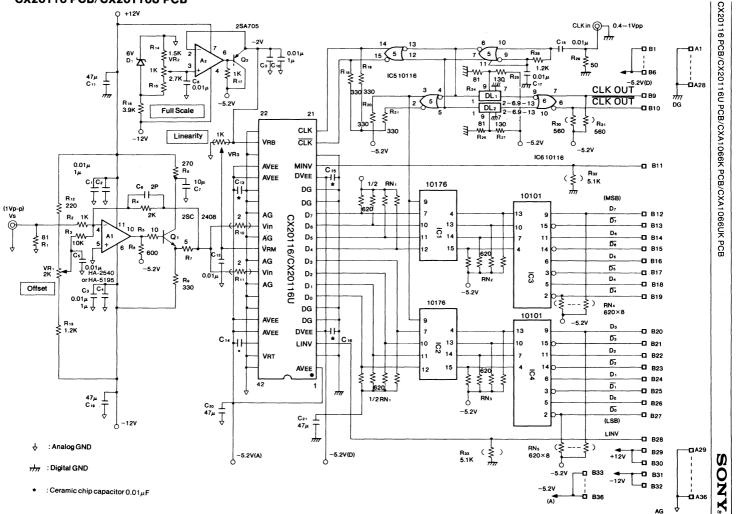

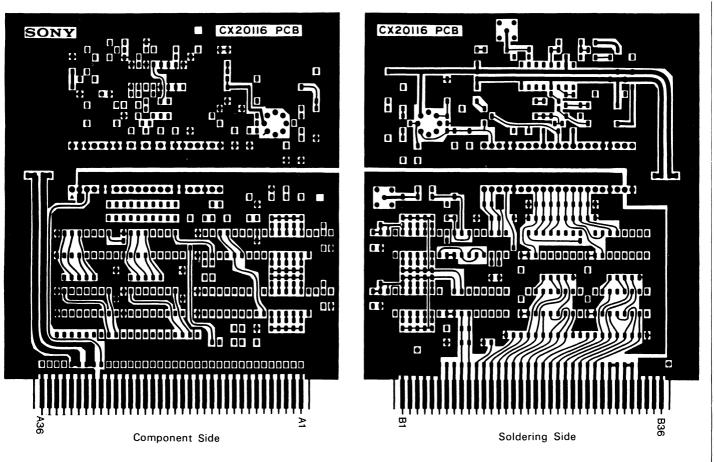

#### **Recommended Operating Conditions**

| <ul> <li>Supply voltage</li> </ul> | Vcc | 5 :  | ± 0.25 | v |

|------------------------------------|-----|------|--------|---|

|                                    | Vee | -5 = | ± 0.25 | v |

200

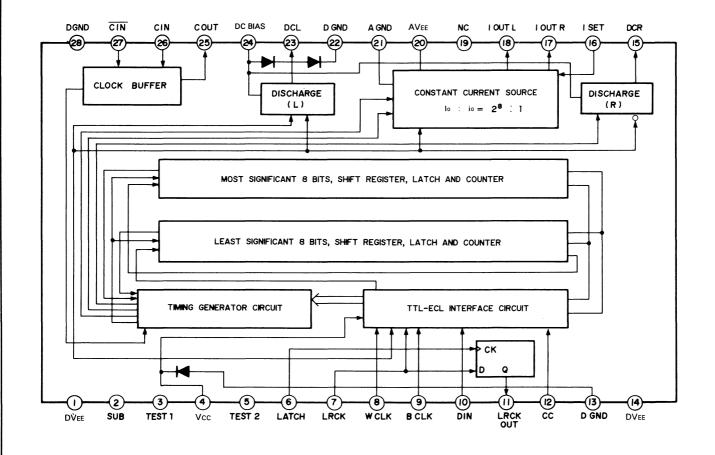

**Block Diagram**

SONY

CX 20017

#### SONY.

#### CX20017

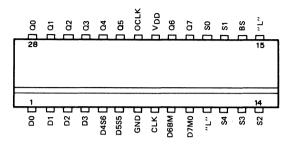

#### **Pin Description**

| No. | Symbol   | Description                                             |

|-----|----------|---------------------------------------------------------|

| 1   | DVEE     | Digital system power supply pin Apply -5V               |

| 2   | SUB      | Board of IC. It is used always being connected to pin 1 |

| 3   | TEST 1   | Test pin. It is used normally in the open state.        |

| 4   | Vcc      | Digital system power supply pin Apply +5V               |

| 5   | TEST 2   | Test pin. It is used normally in the open state.        |

| 6   | LATCH    | Clock pin of D type latch                               |

| 7   | LRCK     | LRCK input pin                                          |

| 8   | WCLK     | WCLK input pin                                          |

| 9   | BCLK     | BCLK input pin                                          |

| 10  | DIN      | DIN (Data input pin)                                    |

| 11  | LRCK OUT | LRCK output pin                                         |

| 12  | сс       | CC input pin                                            |

| 13  | DGND     | Digital system GND pin                                  |

| 14  | DVEE     | Digital system power supply pin Apply -5V               |

| 15  | DCR      | Right channel discharge drive signal output pin         |

| 16  | ISET     | Integral current setting pin                            |

| 17  | IOUTR    | Right channel current output pin                        |

| 18  | Ιουτι    | Left channel current output pin                         |

| 19  | NC       | No connection                                           |

| 20  | AVEE     | Analog system power supply pin                          |

| 21  | AGND     | Analog system GND pin                                   |

| 22  | DGND     | Digital system GND pin                                  |

| 23  | DCL      | Left channel discharge drive signal output pin          |

| 24  | DCBIAS   | Discharge circuit bias pin                              |

| 25  | COUT     | Clock oscillator output pin                             |

| 26  | CIN      | Clock oscillator positive input pin                     |

| 27  | CIN      | Clock oscillator negative input pin                     |

| 28  | DGND     | Digital system GND pin                                  |

#### **Electrical Characteristics**

CX20017

(Ta =  $25^{\circ}$ C, Vee = -5.0V, Vcc = 5.0V)

| ltem                               | Symbol | Pin and test condition                                                                     | Min. | Тур. | Max. | Unit | Note |

|------------------------------------|--------|--------------------------------------------------------------------------------------------|------|------|------|------|------|

| Circuit Current                    | İEE    | 1, 2, 14, 20                                                                               | -112 | -85  |      | mA   | 1    |

| Circuit Current                    | lcc    | 4                                                                                          |      | 9.5  | 12.5 | mA   | 1    |

| Input Threshold<br>Voltage 1       | VTH1   | 6, 7, 8, 9, 10, 12                                                                         |      | -2.9 |      | v    | 2    |

| Input Threshold<br>Voltage 2       | Vth2   | 6, 7, 8, 9, 10, 12                                                                         |      | 2.1  |      | V    | 3    |

| High Level Input<br>Voltage 1      | Vін1   | 6, 7, 8, 9, 10, 12                                                                         | -2.2 |      |      | v    | 2    |

| High Level Input<br>Voltage 2      | Vih2   | 6, 7, 8, 9, 10, 12                                                                         | 2.8  |      |      | v    | 3    |

| Low Level Input<br>Voltage 1       | VIL1   | 6, 7, 8, 9, 10, 12                                                                         |      |      | -4.2 | v    | 2    |

| Low Level Input<br>Voltage 2       | VIL2   | 6, 7, 8, 9, 10, 12                                                                         |      |      | 0.8  | v    | 3    |

| High Level Input<br>Current 1      | Іінт   | 6, 7, 8, 9, 10, 12 VIH = -0.5V                                                             |      |      | 500  | μA   | 2    |

| High Level Input<br>Current 2      | Іін2   | 6, 7, 8, 9, 10, 12 Viн = 4.5V                                                              |      |      | 500  | μA   | 3    |

| Low Level Input<br>Current 1       | liL1   | 6, 7, 8, 9, 10, 12 VIL = −0.5V                                                             |      |      | -15  | μA   | 2    |

| Low Level Input<br>Current 2       | lıl2   | 6, 7, 8, 9, 10, 12 VIL = 0V                                                                |      |      | 500  | μA   | 3    |

| High Level Output<br>Voltage       | Vlrckh | 11 Іон = $-100 \mu$ A after making<br>Pin7 to be 4.5V. Supply a<br>OV-5V-OV clock to pin 6 | 2.7  |      |      | v    |      |

| Low Level Output<br>Voltage        | Vlrckl | 11 $I_{OL} = 100\mu A$ after setting<br>Pin 7 OV. Supply a OV-5V-OV<br>to pin 6.           | 1    |      | -2.7 | v    |      |

| Clock Input Bias<br>Voltage        | Vcin   | 26, 27                                                                                     |      | -1.3 |      | v    |      |

| Clock High Level<br>Output Voltage | Vccr   | 25                                                                                         |      | -0.8 |      | v    |      |

| Clock Low Level<br>Output Voltage  | Vcol   | 25                                                                                         |      | -1.6 |      | v    |      |

| Current Output Pin<br>Leak         | Ioleak | 17, 18 Pins17 and 18 voltage<br>OV. When current output is<br>off.                         | 1    |      | 1.5  | μΑ   |      |

| Item                                              | Symbol   | Pin and test condition                                                       | Min.  | Тур.  | Max.  | Unit | Note |

|---------------------------------------------------|----------|------------------------------------------------------------------------------|-------|-------|-------|------|------|

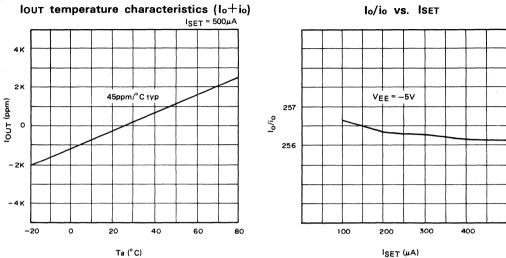

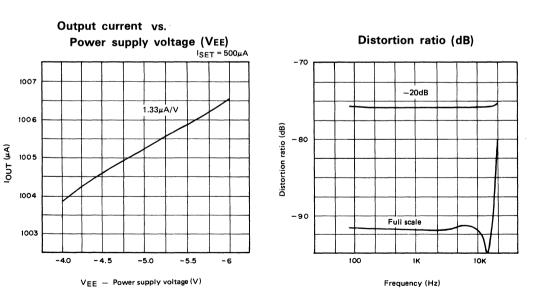

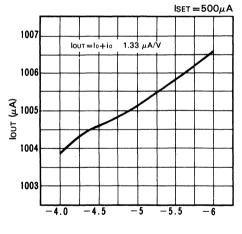

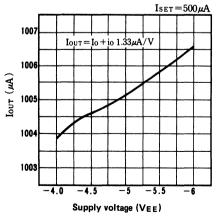

| Ιουτ Output Current                               | Ιουτ     | 17, 18 Pins17 and 18 voltage OV. Pin 16 ISET = 500 $\mu$ A, (Iout = Io + io) |       | 2.008 |       | mA   |      |

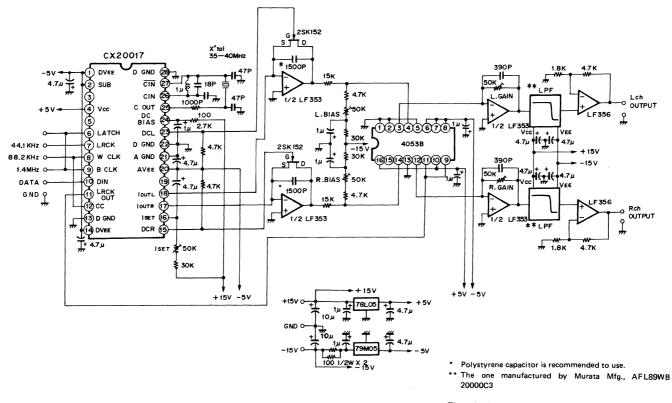

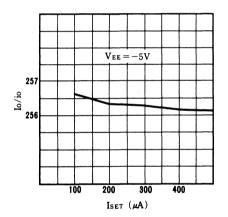

| Current Ratio *2                                  | lo/io    | 17, 18 Pin16 ISET = 250 $\mu$ A                                              | 255.0 | 256.0 | 257.5 | _    | 4    |

| Discharge Circuit<br>Current Consumption          | Ірс      | 24 Set Pin24 OV                                                              | 1.35  | 1.9   | 2.5   | mA   |      |

| Discharge Circuit<br>High Level Output<br>Voltage | Vdcн     | 15, 23 Pin24 voltage = 1.4V.<br>Load current = $-100 \mu A$                  | 0.27  | 0.45  | 0.77  | v    |      |

| Discharge Circuit<br>Low Level Output<br>Voltage  | VDCL     | 15, 23 Pin24 voltage = 1.4V.<br>Load current = $-100 \mu\text{A}$            |       | 4.2   | -3.5  | v    |      |

| Maximum Iset<br>Current                           | Iset max | 16 Range in which current ratio<br>of Io∪TL (R) meets 255 ≤ I₀/i₀<br>< 257   |       |       | 520   | μΑ   |      |

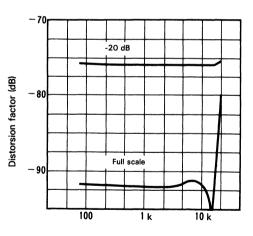

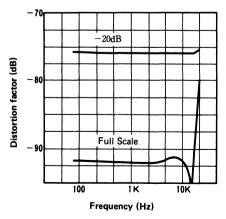

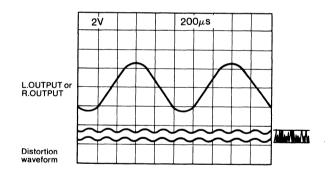

| Distortion Factor                                 | THD      | During O dB (full scale)<br>playback for both right and left                 |       | 0.003 | 0.005 | %    | 5    |

|                                                   |          | During —20 dB playback for both right and left                               |       | 0.02  | 0.025 | %    | 5    |

| Operating Clock<br>Frequency                      | fсlк     | Self-excitation/separate<br>excitation                                       |       |       | 40    | MHz  |      |

- Note) 1. Pins13, 17, 18, 21, 22, 24 and 28 are for grounding, pin16 is connected through 5.1  $k\Omega$  to ground. Other pins are open.

- 2. When Pin 4 (Vcc) is opened.

- 3. When Pin 4 (Vcc) is made to be 5.0V.

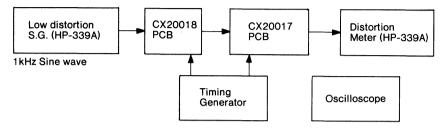

- 4. Measurement circuit See Fig. 2 Conversion frequency 44.1 kHz. Input data 16 bit data generated by ROM SG., Full scale data (0 dB) and data of a level -20 dB below it are used. Distortion meter HP339A (all filters are turned on) or its equivalent that has an 80 kHz LPF, 30 kHz LPF and 400 Hz HPF.

- \*1 Recommended operating voltage

- \*2 In the current ratio measurement circuit (Fig. 3):

$-3.9~(mV) < 1~(k\Omega) imes$  Io ( $\mu$ A) - 256 ( $k\Omega$ ) imes io ( $\mu$ A) < 5.9 (mV)

#### **Description of CX20017 Conversion Process**

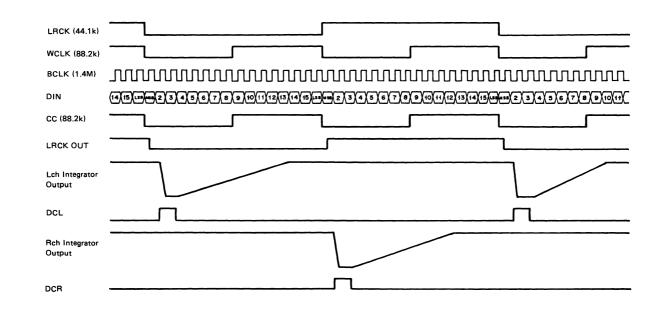

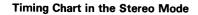

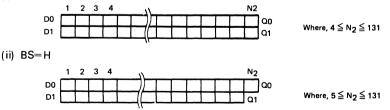

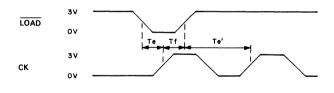

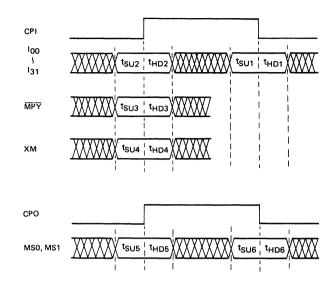

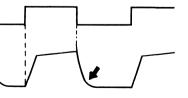

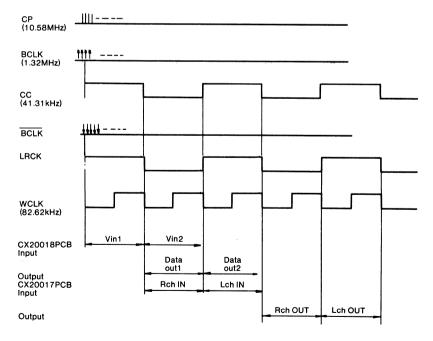

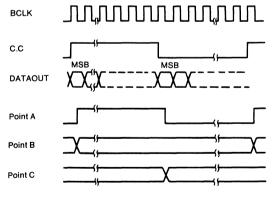

(1) Data Call In (BCLK, DIN, WCLK, LRCK.) See Fig. 5.

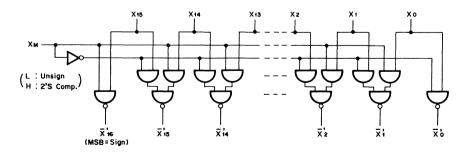

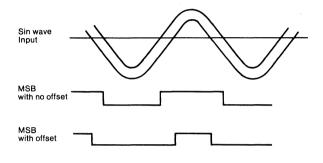

Data is 16 bit serial signals and is of a 2's complement type (2's complement). Data is synchronized with a rising edge of the bit clock (BCLK) from MSB and is sent to the IC sequentially. (Data variations occur with the fall of BCLK.)

Changing the word clock (WCLK) from a high to a low level during the 17th fall of the BCLK, 16 bit data is transferred from the shift register to the latch. Data from the other channel is sent in to the system at the 17th BCLK when CX20017 is used in the stereo mode.

When allocating data in the stereo mode, Rch data is called in while the level of LRCK is low, calling in Lch data while the level of LRCK is high. lout and DCL operate only when the level of LRCK is low, and lout and DCR, operate only when the level of LRCK is high.

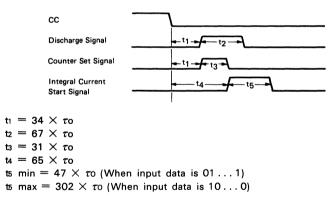

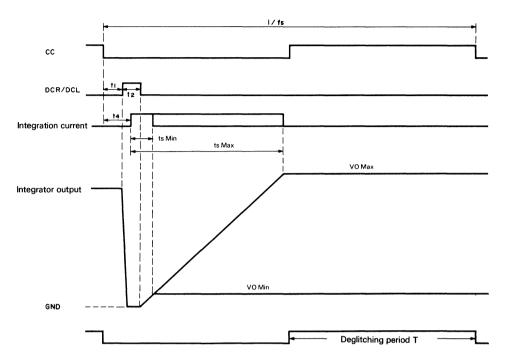

(2) Conversion Process (CC, LRCK, CIN, IOUTL, IOUTR, DCL, and DCR)

All the timing circuits inside are reset, by inputting more than three clocks from the clock input (CIN) after setting the level of the conversion command (CC) to high.

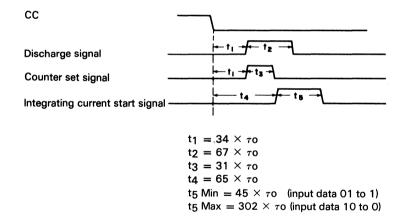

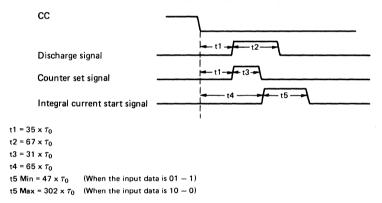

After resetting, the level of CC is set to low, and a clock is supplied into CIN, to start the functioning of the internal timing circuit. It produces three signals: a discharge, a counter set, and an integral current start signals. Depending on periods of clocks and the number of clocks the timings of these three signals are determined as follows:

The counter set signal sets data entered in the latch to the counter, and is not output outside. The discharge signal is output from DCL and DCR and is controlled by LRCK. The signal is output from DCL when the level of LRCK is low, and from DCR when the level is high.

The upper current I<sub>0</sub> and lower current i<sub>0</sub> flow on the instruction of the integral current start signal. The counter starts counting the value preset simultaneously with the turning off the discharge signal. The counter counts eleven offsets and then sends a signal to stop the integral current. The value of t5 is changed by the input data value preset in the counter and is changed over the range 0 to 255. For this reason, a maximum (t4 + t5 max) is needed for the conversion time, i.e., the time period between the level of CC becoming low and the completion of integration.

As is the case with the discharge signal, the integral current outputs lout when the level of LRCK is low, outputting lout when the level is high.

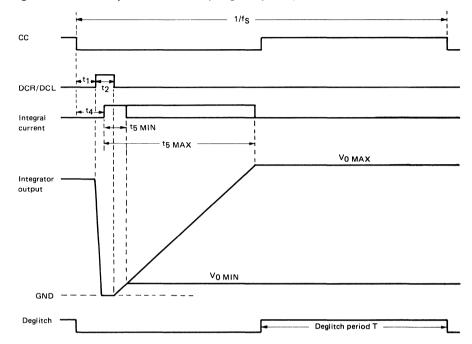

#### Regarding the relationship between sampling frequency fs and clock.

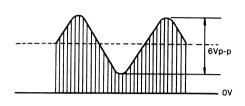

By denoting the clock frequency  $f_{CLK}$  cycle as  $\tau_0$ , the maximum value VOMAX and minimum value VOMIN of the integral voltage output can be given as the following equations.

$$V_{OMAX} = \frac{I_0}{C} * \tau_0 * 267 + \frac{I_0}{C} * \tau_0 * 266 \quad (t_4 + t_5 \text{ max})$$

$$V_{OMIN} = \frac{I_0}{C} * \tau_0 * 12 + \frac{I_0}{C} * \tau_0 * 11 \quad (t_4 + t_5 \text{ min})$$

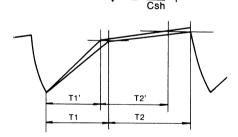

This integral voltage is held to the capacitor C of the integrator when the current switch is turned off. This voltage is utilized as the D/A conversion output in the deglitch period T. This T is determined by the settling time of the deglitch circuit.

If setting of the conversion time and deglitch period are equal, the relationship between the conversion synchronization  $f_s$  and the clock frequency  $f_{CLK}$  can be given as follows:

$$fs = \frac{f_{CLK}}{2 \times (t_4 + t_{5MAX})} = \frac{f_{CLK}}{734}$$

CX20017

Assuming that  $f_s$ =44.1 kHz, fcLK becomes 32.4 MHz.

However, when it is used in practice, it is sufficient to consider that  $f_5 = f_{CLK} / \{(t_4+t_5 \text{ MAX}+1.0 \mu s)+T\}$ , since approximately 0.5 to 1.0  $\mu s$  will become necessary to the settling of the integrator after the current of t5 is being switched off.

Where,  $i_0$  is the integrated current which is corresponding to 1LSB, and  $l_0$  is that of corresponding to  $2^8 LSB.$

- CX20017

- (3) Setting Integral Current (ISET, IOUTL, IOUTR)

The integral current is determined by the value of a regulated current flowing from  $I_{\text{SET}}$  pin. Its relationship can be expressed as follows:

$IOUTL (R) = I_0 + i_0$

$$= (4 + \frac{1}{64})$$

iset

Assuming that  $D_0$ ; MSB,  $D_{15}$ ; LSB, the integrator output voltage  $V_0$  can be given as the following equations.

$$V_{0} = \frac{I_{0}}{C} (\overline{D}_{0} * 2^{7} + \overline{D}_{1} * 2^{6} + \ldots + \overline{D}_{7} * 2^{0} + 12) \tau_{0}$$

$$+ \frac{I_{0}}{C} (\overline{D}_{0} * 2^{7} + \overline{D}_{9} * 2^{6} + \ldots + \overline{D}_{15} * 2^{0} + 11) \tau_{0}$$

Assuming that IsET=500  $\mu$ A,  $\tau_0$ =1/35(MHz)=28.6(ns), and C=2000 pF, the output voltage of the integrator becomes maximum when the input data is "10 to 0", and that value VOMAX becomes as follows:

$$I_{0}=4*I_{SET}$$

As  $i_{0}=\frac{1}{64}*I_{SET}$

$$V_{OMAX}=\frac{2.0\times10^{-3}}{2000\times10^{-12}}*267*28.6\times10^{9}$$

$$+\frac{500*10^{-6}/64}{2000\times10^{-12}}*266*28.6\times10^{9}$$

=7.67(V)

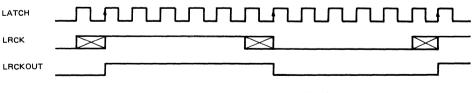

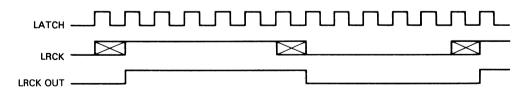

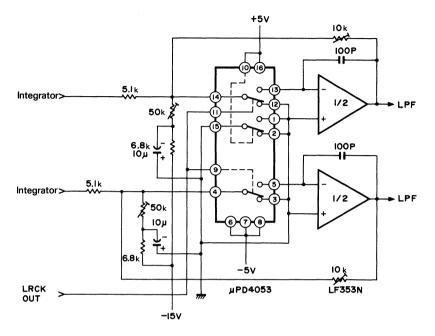

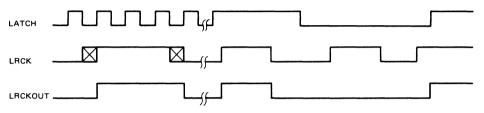

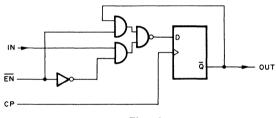

(4) Function of LRCK OUT (LATCH, LRCK, LRCK OUT)

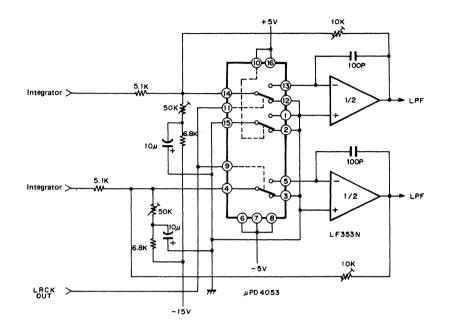

The LRCK OUT output drives the analog switch IC (MC 14053B or its equivalent) to cut the output converted by CX20017 and the integrator as a PAM wave.

Jitter in a PAM wave causes conversion errors, and a D-type flip flop is contained to absorb this jitter. The LATCH input is used as a clock to drive the flip flop. The D-type flip flop changes the output condition in synchronization with the rise of the clock.

This LRCK OUT functions only when +5V is applied to Vcc. The output voltage level is -3 to +3V and can efficiently drive the CMOS analog switch.

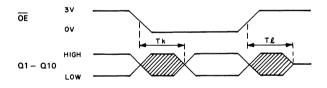

LATCH, LRCK, and LRCKOUT Timing

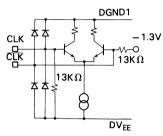

- (5) Clock Input/Output Pin (COUT, CIN CIN) The clock buffer has a configuration similar to that of an ECL logic circuit, and its input pin is biased by an internal bias circuit. (≈−1.3V) output amplitude level is 0.8V.

- (6) Bias Pin (DVEE, SUB, DGND, Vcc, AVEE, AGND, and DC BIAS)

SUB is the IC substrate and can be used by making its potential common to DVEE. The standard values of DVEE and AVEE are -5.0V.

The CX20017 can be operated regardless of whether the digital input pin is in the ranges 0 to -5V, or 0 to +5V. When operating with an input voltage between 0 and +5V, raise the level of the Vcc pin to +5V. As mentioned before, LRCKOUT is output in this case.

Open the Vcc pin when using an input voltage between 0 and -5V. The DC BIAS is the bias circuit for the output circuit of the discharge signal. A current of approximately 2.5 mA is required for the standard value. Supply a current higher than (2.5 mA +  $\alpha$ ) from a +5V and higher power source. The potential of this pin is biased to 2Vf.

The value of  $\alpha$  is determined as follows. In order to maintain this pin voltage of 2Vf ( $\approx$ 1.4V), approximately 0.5 mA is required. In addition, the maximum current flowing to load resistance RL which is connected to DCR (pin 15) and DCL (pin 23) can be obtained by the following:

$\frac{1}{RL} \times (V_{DCH} + |DV_{EE}|) \times 2$

when RL=4.7 kΩ, VDCH=0.4V and DVEE=-5V,  $\alpha$ =0.5+1.32=1.82 (mA) and the total becomes 4.32 mA. As the recommended value, it is 5 mA at RL=4.7 kΩ.

- 31 -

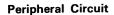

Fig. 2

The evaluation boards applying the above circuit are prepared.

CX20017

1

SONY

Fig. 3

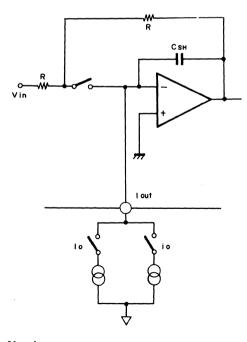

#### A circuit example by which deglitcher is carried out with sample/hold type

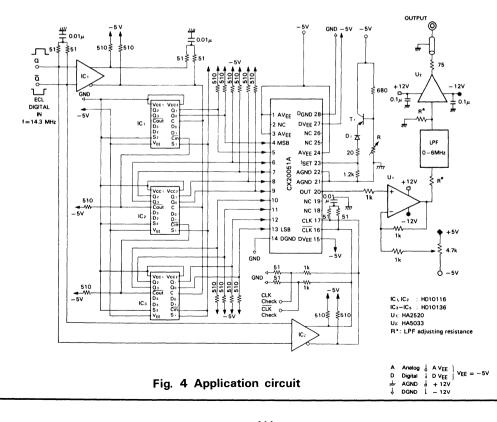

Fig. 4

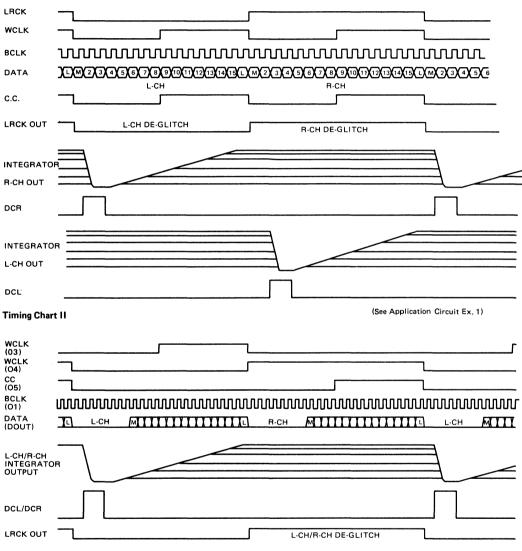

Timing Chart During Stereo Mode

Fig. 5

SONY

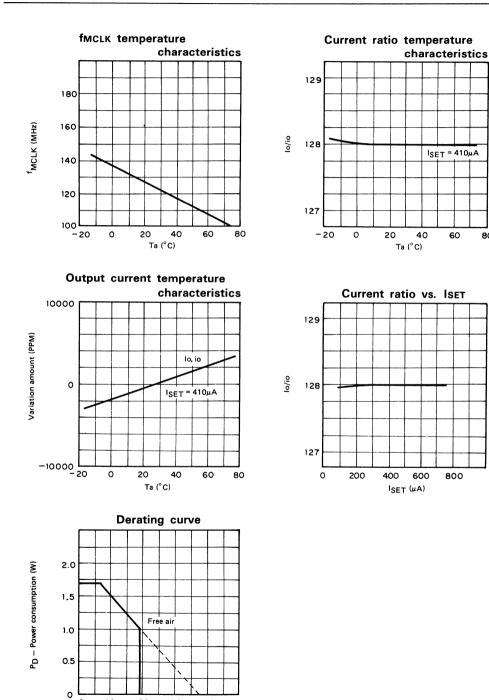

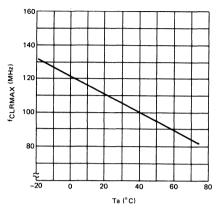

Ta (°C)

- 36 -

CX20017

## SONY

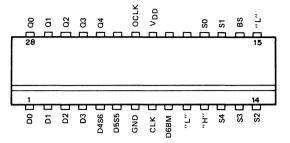

# CX20018

## Dual 16 bit 44 kHz Multiplexed A/D Converter

#### Description

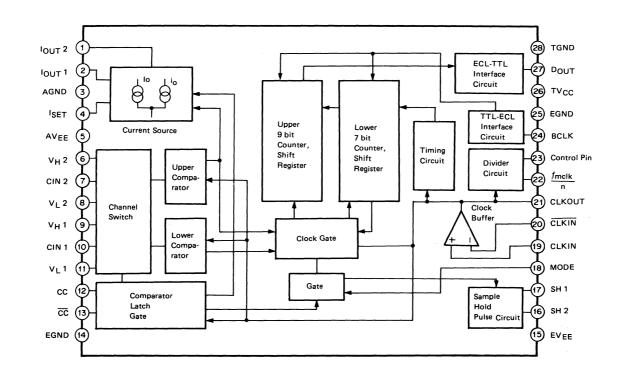

The CX20018 is a monolithic bipolar IC designed for PCM (Pulse Code Modulation) audio. This IC consists of 16 bit counters, shift registers, clock buffer, clocked synchronous comparator, stabilized current source and TTL compatible interface circuits, etc.

#### Features

- · Line monotonicity

- · Low noise

- TTL compatible input/output

- Stereo or monaural modes can be selected by external control

#### Structure

Bipolar silicon monolithic IC

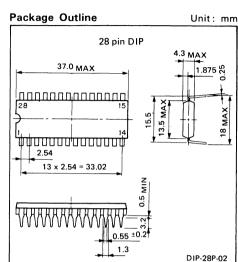

#### **Absolute Maximum Ratings**

| <ul> <li>Supply voltage</li> </ul>              | Vcc to Vee | 12            | V  |

|-------------------------------------------------|------------|---------------|----|

| <ul> <li>Operating temperature</li> </ul>       | Topr       | -20 to $+75$  | °C |

| <ul> <li>Strange temperature</li> </ul>         | Tstg       | -50 to $+150$ | °C |

| <ul> <li>Allowable power dissipation</li> </ul> | PD         | 1.7           | W  |

#### **Recommended Operating Conditions**

| <ul> <li>Supply voltage</li> </ul> | Vcc | 4.75 to 5.25   | V |

|------------------------------------|-----|----------------|---|

|                                    | Vee | -5.25 to -4.75 | V |

\*Note: Refer to page 311 (CX20018PCB) as the application note.

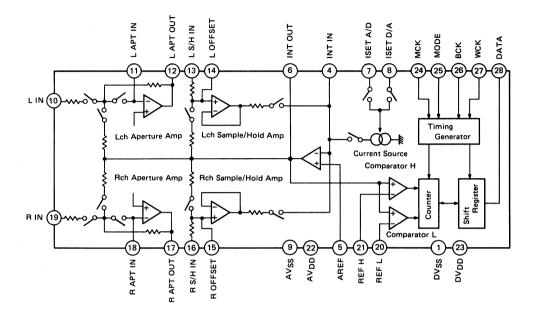

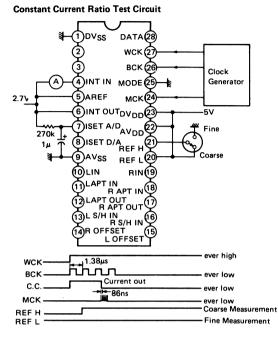

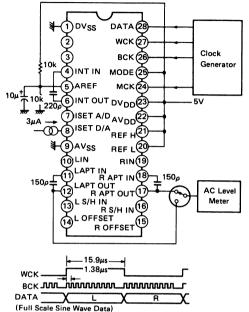

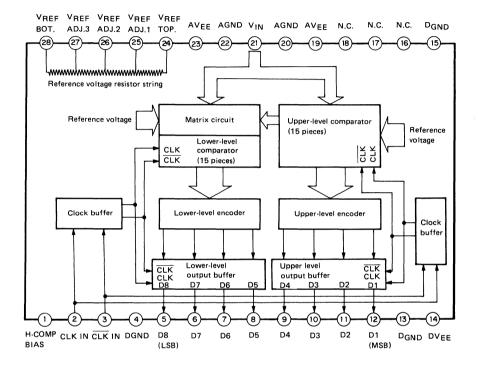

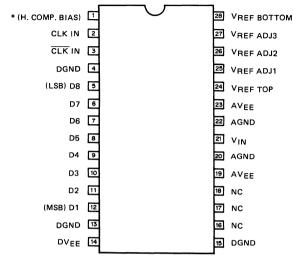

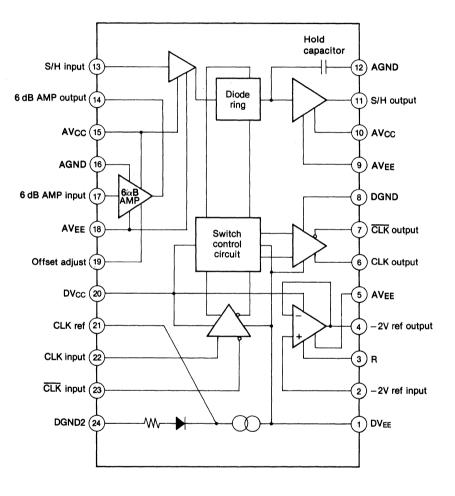

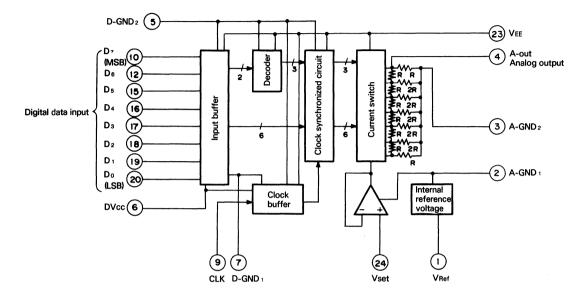

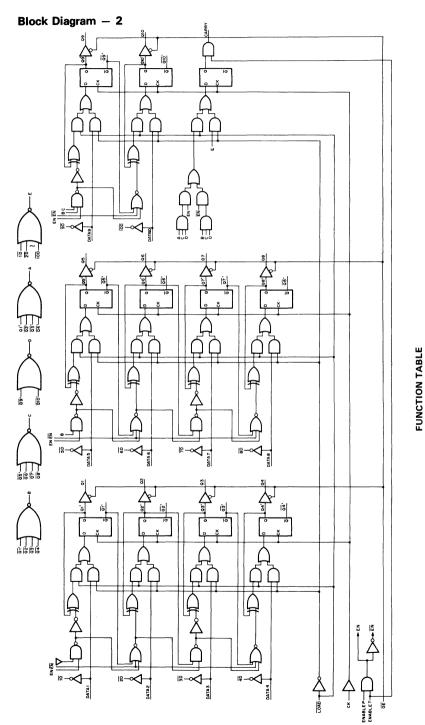

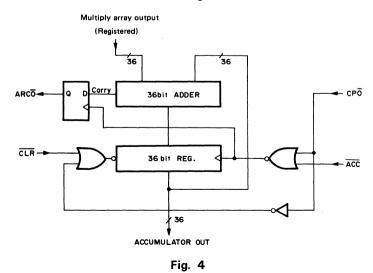

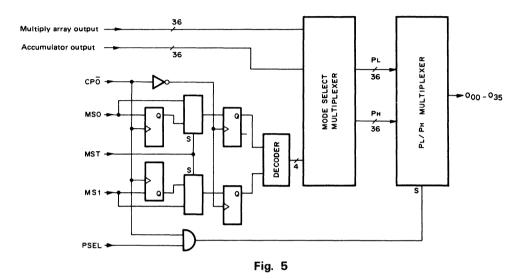

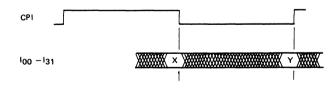

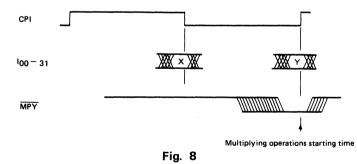

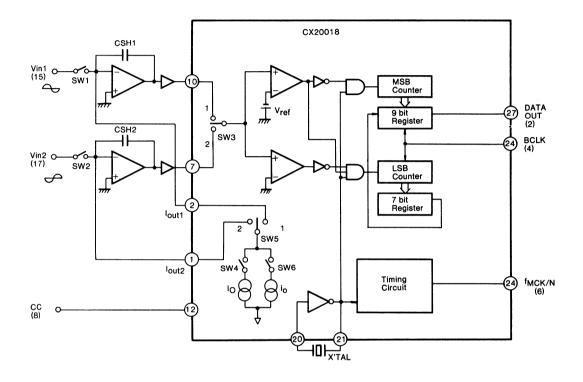

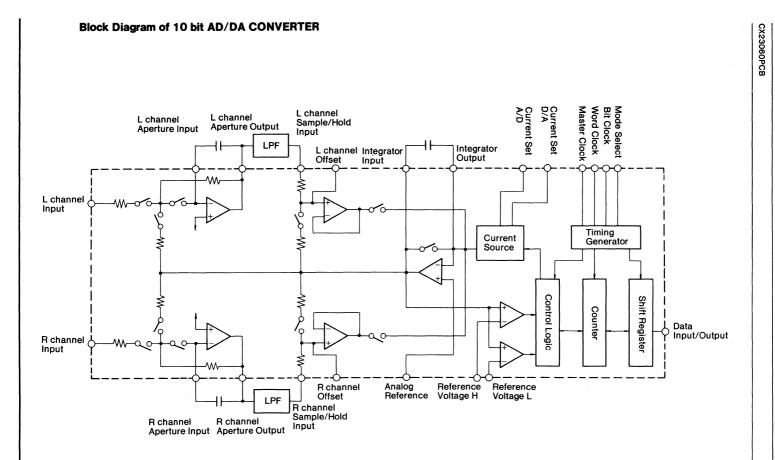

**Block Diagram**

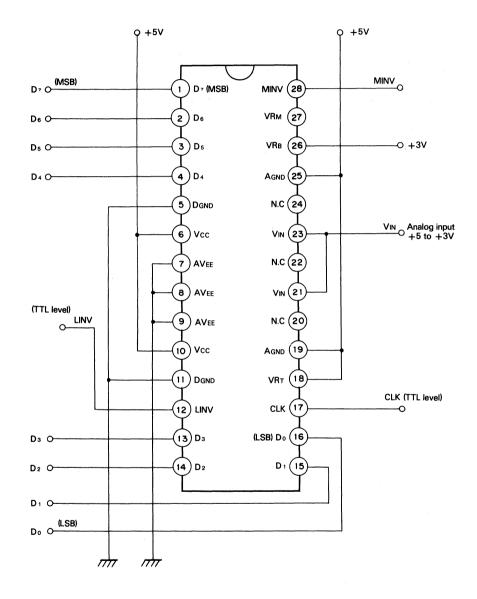

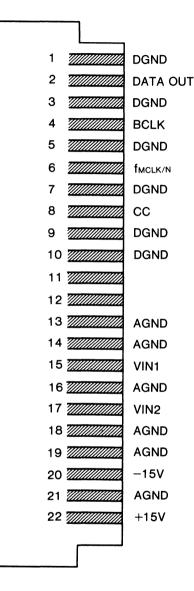

#### CX20018

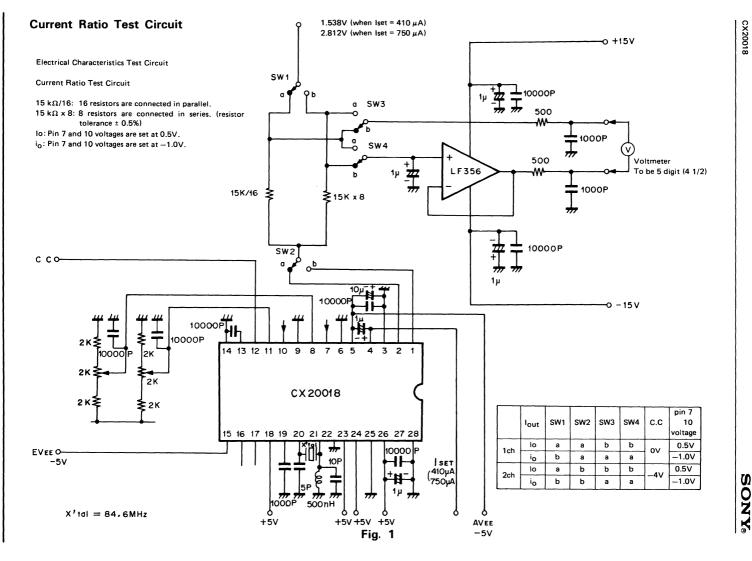

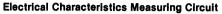

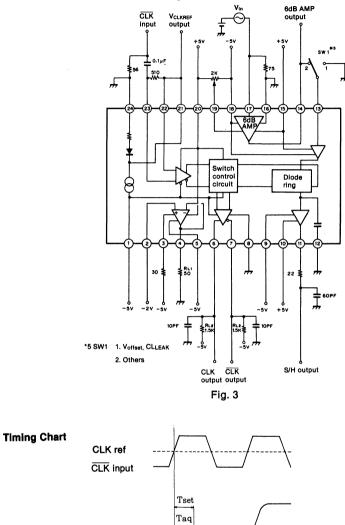

### **Electrical Characteristics**

| Electrical Charact                                | eristics         |                                                           |       | (Ta=25 | °C, Vee= | =—5V, | Vcc=5V |

|---------------------------------------------------|------------------|-----------------------------------------------------------|-------|--------|----------|-------|--------|

| Item                                              | Symbol           | Pin No. and Test Conditions                               | Min.  | Тур.   | Max.     | Unit  | Note   |

| Supply Voltage<br>Range <sup>*1</sup>             | Vee              |                                                           | -4.75 | -5.00  | -5.25    | V     | 1      |

| Supply Voltage<br>Range <sup>*1</sup>             | Vcc              |                                                           | 4.75  | 5.00   | 5.25     | V     | 1      |

| Circuit Current                                   | IEE              |                                                           | 70.0  | 102.0  | 130.0    | mA    | 1      |

| Circuit Current                                   | Icc              |                                                           | 4.0   | 10.0   | 15.0     | mA    | 1      |

| Current Output<br>Pin Leak                        | IOLEAK           | 1, 2 (Pins 1, 2 Voltage=0V<br>when current output is off) |       |        | 1.0      | μΑ    | 2      |

| lout Output Current                               | lout             | 1, 2 (Pins 1, 2 Voltage=0V.<br>Iset=410 μA)               |       | 1.64   |          | mA    | 2      |

| Current Ratio *2                                  | lo/io            | 1, 2 (Iset=410 μA)                                        | 127.0 | 128.0  | 129.0    |       | 2      |

| Maximum Iset<br>Current                           | Iset Max.        | 4<br>127.0≦ <u>lo</u> ≦129.0                              |       |        | 750      | μΑ    | 2      |

| Sample Hold Pulse<br>High Level Output<br>Voltage | Vsн1н<br>Vsн2н   | 16, 17                                                    | -0.05 | 0      | 0.1      | V     |        |

| Sample Hold Pulse<br>Low Level Output<br>Voltage  | VSH1L<br>VSH2L   | 16, 17                                                    | -4.40 | -4.25  | -3.50    | V     |        |

| Clock Input Bias<br>Voltage                       | Vclkin<br>Vclkin | 19, 20                                                    | -1.90 | -1.72  | -1.50    | v     |        |

| Clock Output Low<br>Level Output Current          | ICLKOUTL         | 21                                                        |       | 3.0    | 4.0      | mA    |        |

| CC, CC Input Bias<br>Voltage                      | Vccin<br>Vccin   | 12, 13                                                    | -2.20 | -1.92  | -1.60    | V     |        |

| Data Output High<br>Level Output Voltage          | VDOUTH           | 27 Іон=0.1 mA                                             | 3.2   |        |          | V     |        |

| Data Output Low<br>Level Output Voltage           | VDOUTL           | 27 IoL=−0.4 mA                                            |       |        | 0.4      | V     |        |

| Bit Clock High Level<br>Input Voltage             | VBCLKH           | 24                                                        | 2.0   |        |          | V     |        |

| Bit Clock Low Level<br>Input Voltage              | VBCLKL           | 24                                                        |       |        | 0.5      | V     |        |

| Bit Clock High Level<br>Input Current             | Івсікн           | 24                                                        |       | 4      |          | μΑ    |        |

| Bit Clock Low Level<br>Input Current              | IBCLKL           | 24                                                        | 0.2   | 1      |          | μΑ    |        |

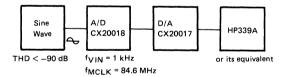

| Distortion *3 Factor                              | THD .            | During 0 dB (full scale) playback for both channel        |       | 0.005  | 0.006    | %     | 3      |

|                                                   |                  | During —20 dB playback for both channel                   |       |        | 0.05     | %     | 3      |

| Item                                 | Symbol    | Pin No. and Test Conditions            | Min. | Тур. | Max. | Unit |

|--------------------------------------|-----------|----------------------------------------|------|------|------|------|

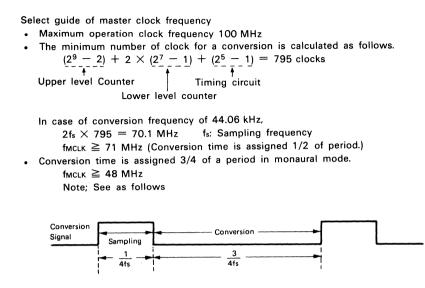

| Maximum Operating<br>Clock Frequency | fMCLK     | Self-excitation or separate excitation |      |      | 100  | MHz  |

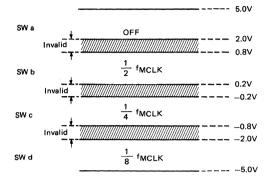

|                                      | Vст∟ (∞)  | 23                                     | 2.0  |      | 5.0  | V    |

| Dividing Ratio                       | Vctl (2)  | 23                                     | 0.2  |      | 0.8  | v    |

| Control Voltage                      | Vc⊺∟ (4)  | 23                                     | -0.8 |      | -0.2 | v    |

|                                      | Vc⊤∟ (8)  | 23                                     | -5.0 |      | -2.0 | V    |

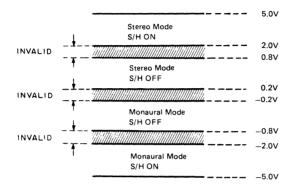

|                                      | VMODE (1) | 18 Stereo, S/H ON                      | 2.0  |      | 5.0  | V    |

| Mode Control<br>Voltage              | VMODE (2) | 18 Stereo, S/H OFF                     | 0.2  |      | 0.8  | v    |

|                                      | Vmode (3) | 18 Monaural, S/H OFF                   | -0.8 |      | -0.2 | V    |

|                                      | Vmode (4) | 18 Monaural, S/H ON                    | -5.0 |      | -2.0 | V    |

Note) 1 Pins 1, 2, 3, 6, 7, 8, 9, 10, 11, 14, 21, 25 and 28 are for grounding, pins 18, 22, 23, are connected V<sub>cc</sub>. Pin 4 draws 410 μA of current by external current source.

2 Reference to the current ratio test circuit.

3 Conversion Frequency 44.1 kHz

Distortion Meter HP339A (all Filters are turned on) or its equivalent that has an 80 kHz, LPF, 30 kHz LPF and 400 Hz HPF.

\*1 Recommended operating voltage

\*2 In the current ratio test circuit (See Fig. 1)

$|15 \times 8 (k\Omega) \times i_0 (\mu A) - \frac{15}{16} (k\Omega) \times I_0 (\mu A)| < 12.0 \text{ mV}$

\*3 Measurement Method (See Note 3)

- 41 -

#### **Description of CX20018 Conversion Process**

#### **Conversion process**

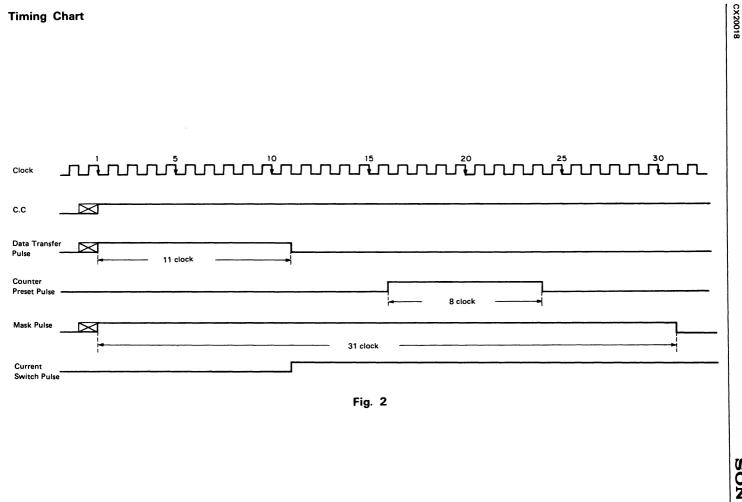

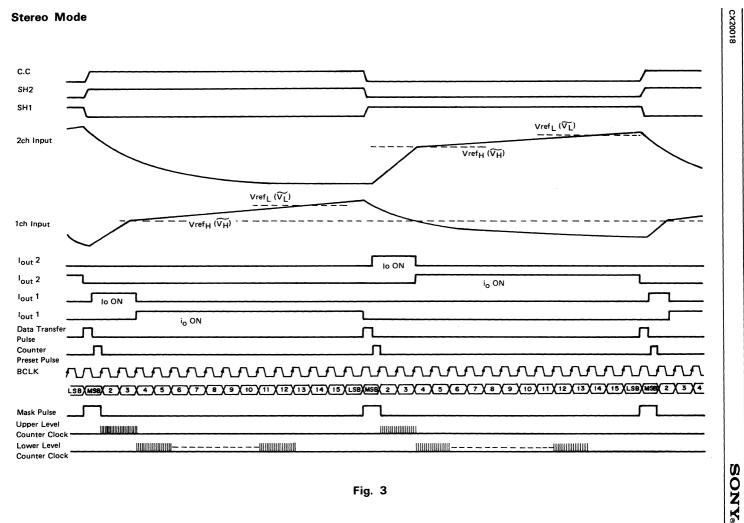

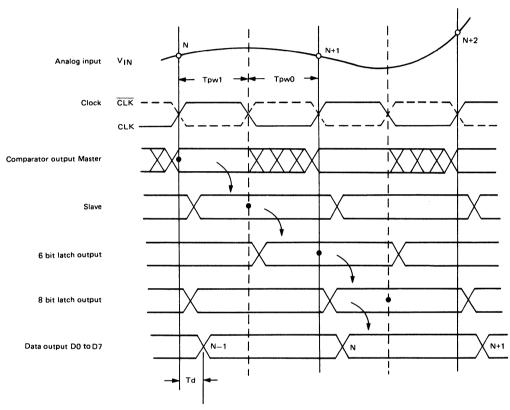

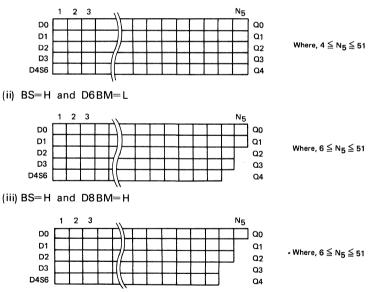

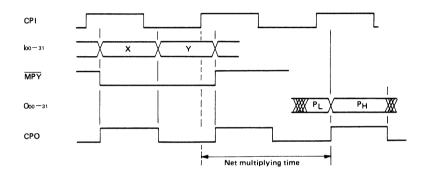

The timing circuit controls a conversion cycle and send "Data Transfer Pulse" to the 16 bit shift register for transmitting the last converted data. It is reset by both the edge of CC (Conversion Command), and the master clock pulse is fed to the timing circuit.

"Data Transfer Pulse" and "Mask Pulse" become "H" level as soon as the timing circuit starts to count clocks. "Data Transfer Pulse" becomes "L" when the timing circuit counts 11 clocks, and then the last data is transferred. Simultaneously, "Current Switch Pulse" becomes "H", and integral current starts to flow. "Counter Preset Pulse" becomes "H" when the timing circuit counts 16 clocks. And then, upper and lower level counters are reset. Counter Preset Pulse holds "H" level during the period of 8 clocks.

When the timing circuit counts 31 clocks, Mask Pulse becomes "L" and A/D conversion starts.

The coarse current "Io" discharges the sampled charge of integrator until the output voltage of integrator crosses the reference voltage (VrefH). During this period the upper level counter counts the number of clock. After crossing the VrefH the fine current discharges the remaining charge of integrator. The lower level counter counts the number of clock until the output voltage of integrator crosses the lower level references voltage (VrefL). (See Figs. 2, 3, 4)

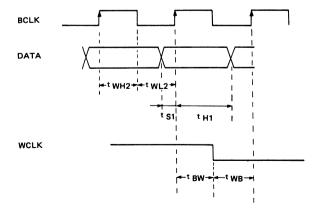

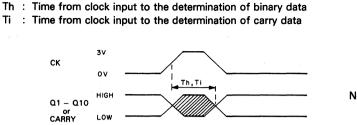

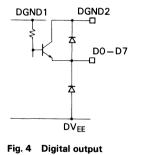

#### Data output

Data are 16 bit serial signals and 2's complement. The serial data are synchronous with a rising edge of Bit clock (BCLK), and only MSB data is synchronized with a edge of "Data Transfer Pulse". (See Fig. 3)

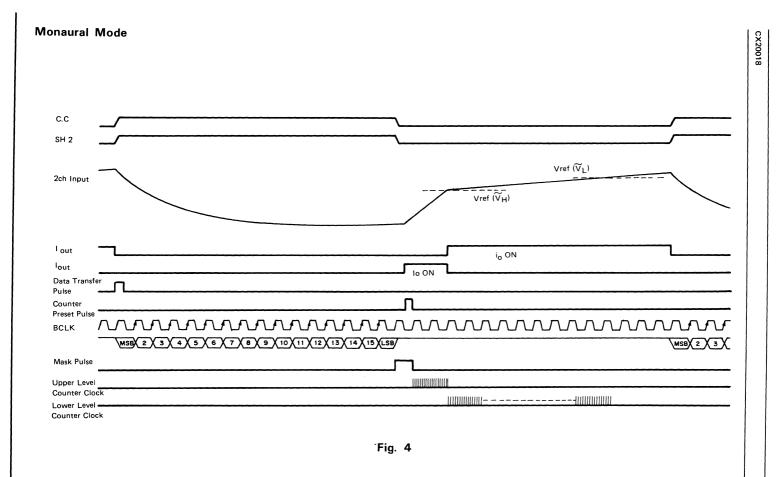

#### Monaural operation mode

In monaural mode the external integrator is tracking the input signal during CC is "H" state. At the moment when CC goes "L" state, the CX20018 starts conversion. The data is transferred to the output from MSB sequentially.

After 16 bit data are transferred, "Data Out" comes to the "H" level and keeps "H" level until next conversion. (See Fig. 4)

- 43 -

SONY

44 T

SONY

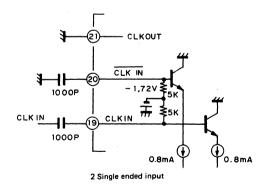

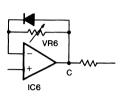

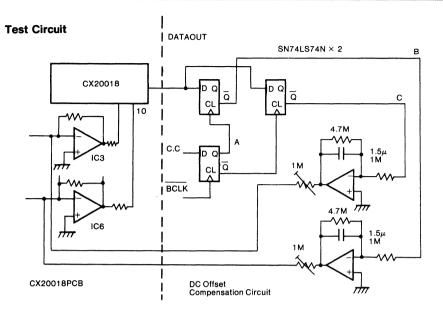

#### Interface Circuit, Divider Circuit, Sample Hold Circuit

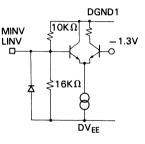

(1) Integral current output

Recommended value;  $I_{set} = 410 \ \mu A$   $\begin{pmatrix} I_0 = 4 \ I_{set} = 1.64 \ mA \\ I_0 = \frac{1}{32} \ I_{set} = 12.8 \ \mu A \end{pmatrix}$  $I_{set} = 750 \ \mu A$

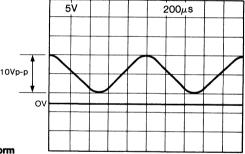

at C = 1000 pF fmcLk = 84.6 MHz full scale 10V

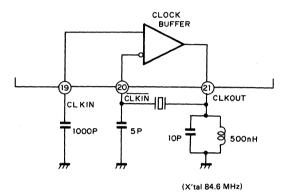

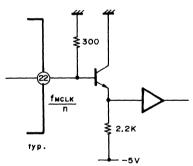

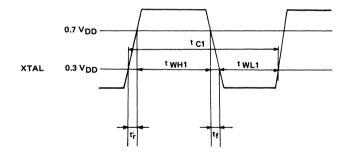

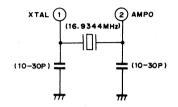

(2) Clock Buffer

(a) Internal clock (Excited circuit with crystal)

1 Balanced input

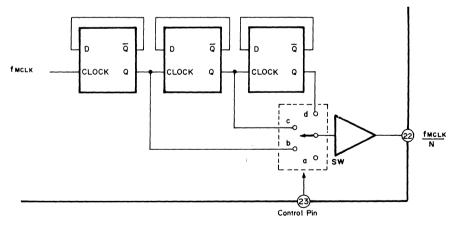

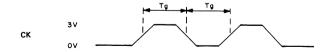

(3) fMCLK/N Output

The output of fMCLK/N is prepared for synchronous operation with digital circuit. Divided Value "N" is determined by external control, and N is 2, 4, 8 or  $\infty$ .

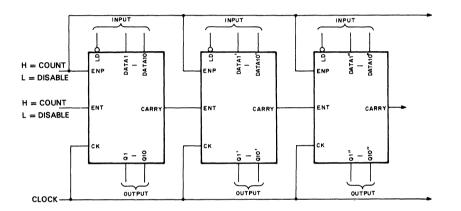

**Basic Divider Block**

| N | V <sub>CTL</sub> Range         |

|---|--------------------------------|

| 8 | $5.0V \ge V_{CTL} \ge 2.0V$    |

| 2 | $0.8V \ge V_{CTL} \ge 0.2V$    |

| 4 | –0.2V≧V <sub>CTL</sub> ≧ –0.8V |

| 8 | –2.0V≧V <sub>CTL</sub> ≧–5.0V  |

Threshould value of Control Pin

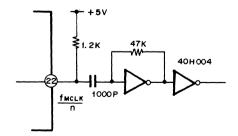

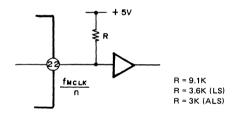

#### (4) Recommended Interface Circuit

(a) ECL 10k (N=2)

(c) High Speed CMOS (N=8)

(b) TTLs (N=4 or 8)

#### CX20018

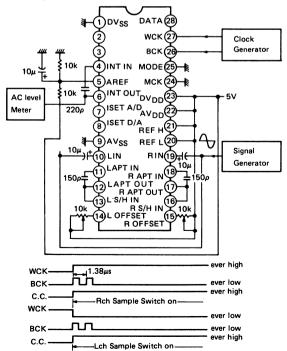

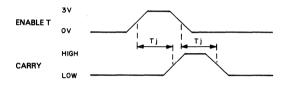

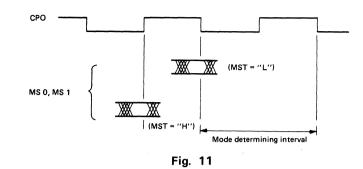

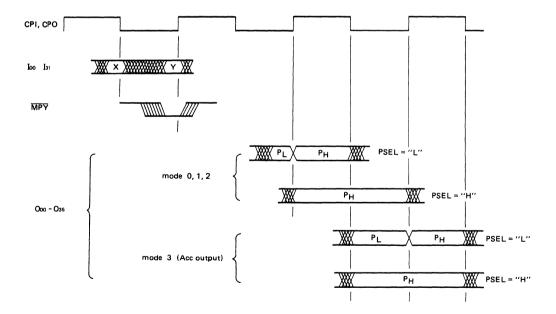

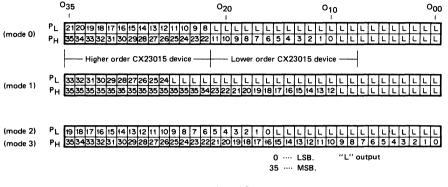

#### (5) Stereo mode, Monaural mode

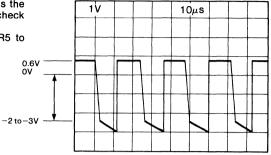

Stereo or Monaural modes can be selected by mode pin. And "ON" or "OFF" state of Sample Hold Pulse is selected similary.

This is illustrated in the following way.

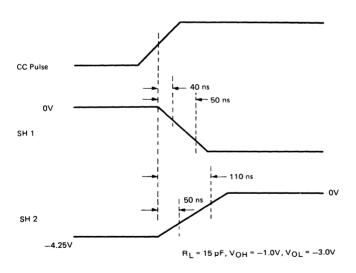

S/H Pulse

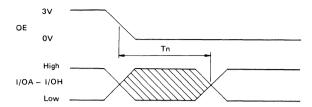

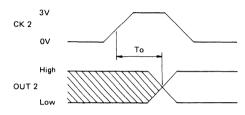

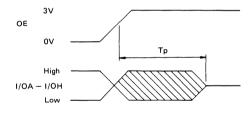

Propagation Delay Times from CC input to SH1, SH2 output

SONY

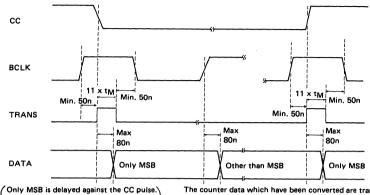

#### (6) Data Out

Only MSB is delayed against the CC pulse. Others are delayed against the bit clock. t<sub>M</sub>; One cycle of master clock The counter data which have been converted are transmitted to the shift register with the TRANS pulse. However, due to the circuit structure of the shift register, it cannot be transmitted unless the BCLK and TRANS are simultaneously at high.

Propagation Delay Time from CC or BCLK Data Out

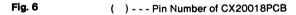

- (7) Relationship of Vin max, CSH, Iset, Io and io

- (1) Vin is defined as the input voltage of integrator.

- (2) Io, io are defined as the coarse and fine integral current respectively.

- (3) In case of a full scale input voltage.

Vin max =

$$\frac{I_0}{CSH} \frac{\tau_0}{(2^9 - 1)} + \frac{i_0}{CSH} \frac{\tau_0}{(2^7 - 1)}$$

Using I<sub>0</sub> = 4I<sub>set</sub>, i<sub>0</sub> =  $\frac{1}{32}$  I<sub>set</sub>

Vin max =  $\frac{1}{32} \cdot \frac{I_{set} \tau_0}{CSH} (2^{16} - 1)$

Assuming, Vin max = 10 Vp-p,  $\tau_0 = \frac{1}{f} = \frac{1}{84.6 \text{ MHz}}$

CSH = 1500 PF

$\therefore$ I<sub>set</sub> = 620  $\mu$ A

$\therefore$ ILSB =  $\frac{i_0 \tau_0}{CSH} = 152 \text{ uV}$

Note) In case of non-inverting operation, Vin Max. is limited to 5 Vp-p.

CX20018

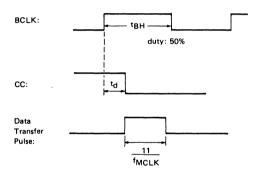

(8) The maximum frequency of BCLK. The maximum frequency of BCLK is derived as follows:

$$f_{BCLK} = \frac{1}{2t_{BH}}$$

$t_{BH} \geqq td + \frac{11}{f_{MCLK}} + 50^{ns}$   $O^{ns} \leqq td \leqq 100^{ns}$

Therefore,

$\label{eq:bclk} \begin{array}{l} f_{BCLK} \leqq 1.7 \; \text{MHz} \; \text{on condition that the duty of BCLK is 50\%.} \\ f_{BCLK} \leqq 1.7 \; \times \frac{X}{50} \; \text{MHz} \; \text{on condition that the duty is X\%.} \end{array}$

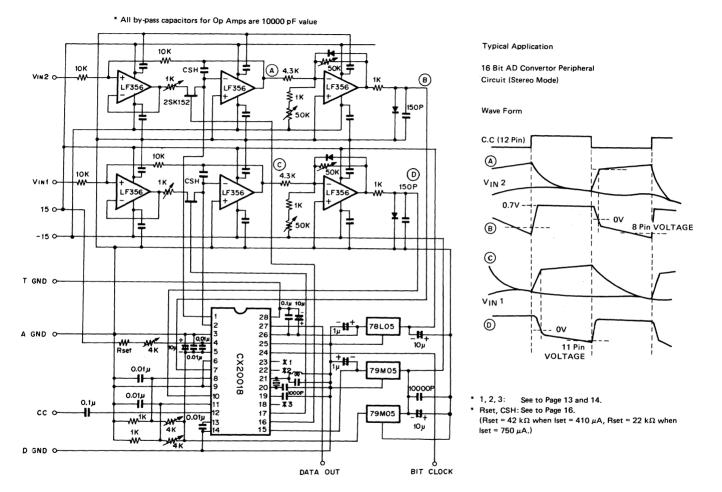

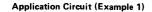

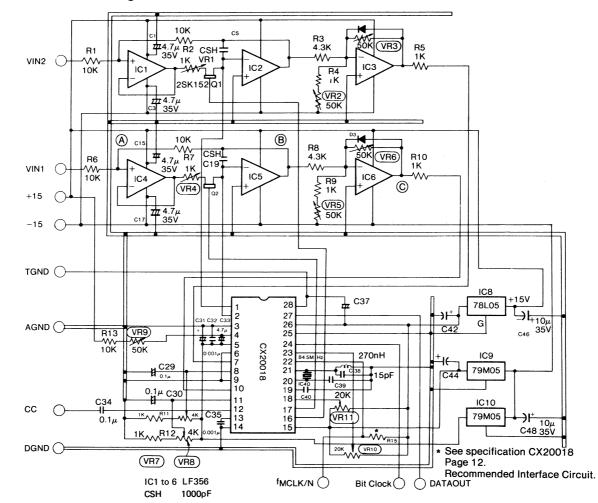

Fig. 5 16 bit A/D Converter Peripheral Circuit (Stereo Mode)

- 52 -

SONY

CX20018

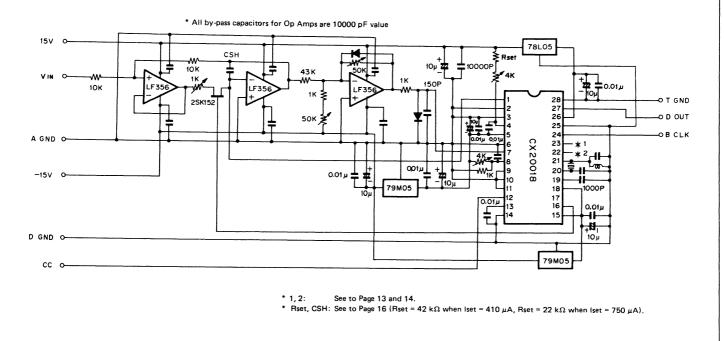

Typical Application - Monaural Mode

16 Bit AD Convertor Peripheral Circuit (Monaural Mode)

Fig. 6 16 bit A/D Converter Peripheral Circuit (Monaural Mode)

CX:20018

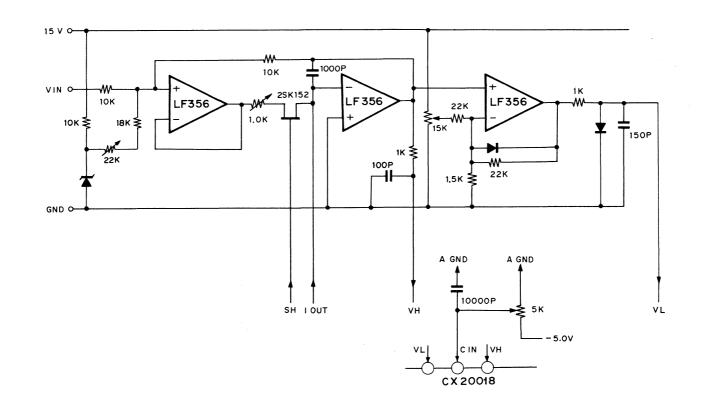

Fig. 7 Application Circuit (Non-inverting Circuit)

SONY®

- 54 -

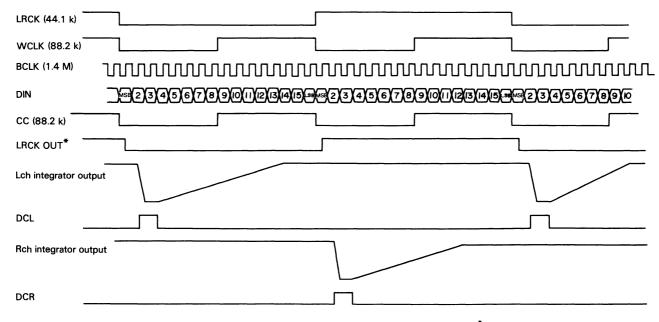

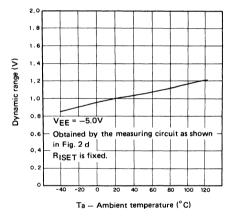

Ambient temperature (°C)

# SONY

# CX20133

## 16 bit D/A Converter

#### Description

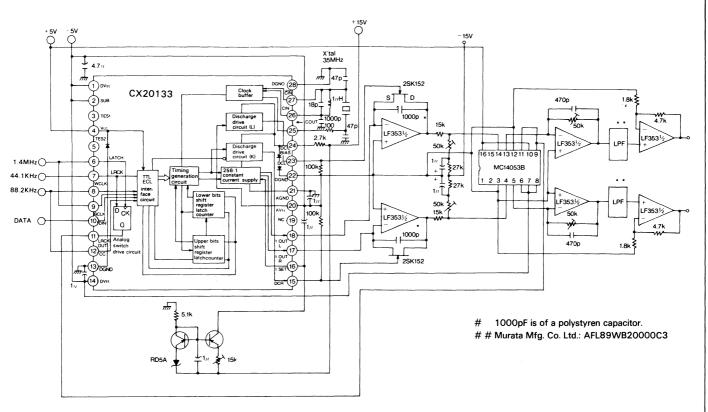

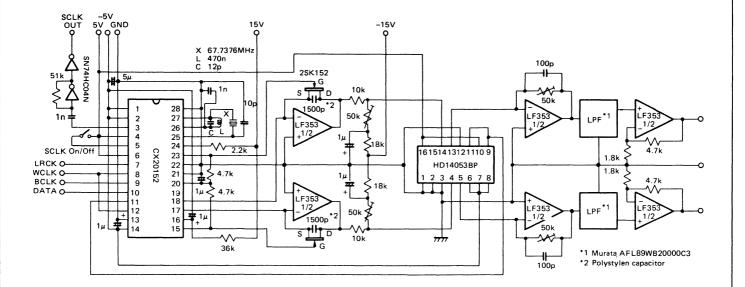

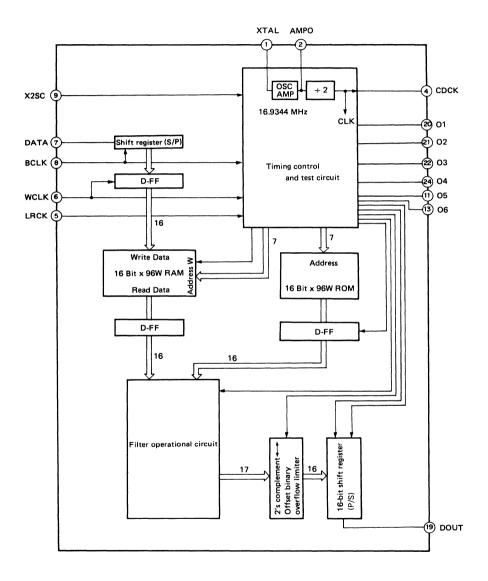

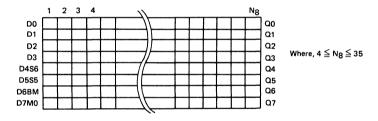

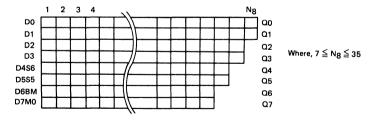

The CX20133 is a 16 bit D/A converter IC for PCM audio using the integrating formula. Analog signal is reproduced from the 16 bit digital signal by combining an integrator, analog switch and low-pass filter to the IC exterior. Following circuits are also built-in so that it can be operated in sync with the CX23035, LSI for CD (compact disc) system.

- Integrating current output

- Two channels of discharge signal output

- Level shifting for interface direct with TTL/MOS LSIs.

- Analog switch drive.

#### Features

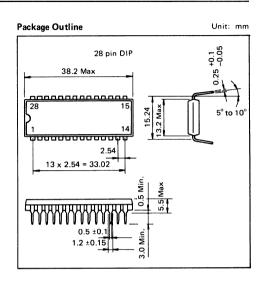

- Miniature flat package requires only small mounting area.

- Conversion frequency of 44.1 kHz.

- Serial data input.

- Low distortion factor typically at 0.003%.

#### Structure

Bipolar Silicon Monolithic IC

#### Absolute Maximum Ratings (Ta = $25^{\circ}$ C)

| <ul> <li>Supply voltage</li> </ul>        | VCC to VEE | 12          | V  |

|-------------------------------------------|------------|-------------|----|

| <ul> <li>Operating temperature</li> </ul> | Topr       | - 10 to +75 | °C |

| <ul> <li>Storage temperature</li> </ul>   | Tstg       | -50 to +125 | °C |

| Allowable power dissipation               | PD         | 1.1         | W  |

#### **Recommended Operating Conditions**

| <ul> <li>Supply voltage</li> </ul> | Vcc | 5 ± 0.25      | v |

|------------------------------------|-----|---------------|---|

|                                    | VEE | $-5 \pm 0.25$ | v |

CX20133

Fig. 1

- 57 -

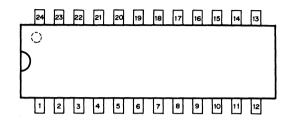

### **Pin Description**

| No. | Symbol   | Description                                                    |

|-----|----------|----------------------------------------------------------------|

| 1   | DVEE     | Power supply pin for the digital circuit. Applied with $-5$ V. |

| 2   | SUB      | IC substrate. Always connected to 1 pin.                       |

| 3   | TEST 1   | Test pin, normally open.                                       |

| 4   | Vcc      | Power supply pin for the digital circuit. Applied with +5 V.   |

| 5   | TEST 2   | Test pin, normally open.                                       |

| 6   | LATCH    | Clock pin of D-type clutch.                                    |

| 7   | LRCK     | LRCK input pin.                                                |

| 8   | WCLK     | WCLK input pin.                                                |

| 9   | BCLK     | BCLK input pin.                                                |

| 10  | DIN      | DIN (data input pin).                                          |

| 11  | LRCK OUT | LRCK output pin.                                               |

| 12  | сс       | CC input pin.                                                  |

| 13  | DGND     | Ground pin for the digital circuit.                            |

| 14  | DVEE     | Power supply pin for the digital circuit. Applied with $-5$ V. |

| 15  | DCR      | Output pin of R-channel discharge driving signal.              |

| 16  | ISET     | Pin for setting integration current.                           |

| 17  | IOUTR    | Output pin for R-channel current.                              |

| 18  | IOUTL    | Output pin for L-channel current.                              |

| 19  | NC       | No connection.                                                 |

| 20  | AVEE     | Power supply pin for the analog circuit.                       |

| 21  | AGND     | Ground pin for the analog circuit.                             |

| 22  | DGND     | Ground pin for the digital circuit.                            |

| 23  | DCL      | Output pin for L-channel discharge driving signal.             |

| 24  | DCBIAS   | Bias pin for the discharge circuit.                            |

| 25  | СОИТ     | Output pin for the clock oscillator.                           |

| 26  | CIN      | Positive input pin for the clock oscillator.                   |

| 27  | CIN      | Negative input pin for the clock oscillator.                   |

| 28  | DGND     | Ground pin for the digital circuit.                            |

SONY.

#### **Electrical Characteristics**

$(Ta = 25^{\circ}C, VEE = -5.0V, Vcc = 1.0V)$

|                                                   | T           |                                                                                                                                                           |       |       |             |      |      |

|---------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------------|------|------|

| ltem                                              | Symbol      | Condition                                                                                                                                                 | Min.  | Тур.  | Max.        | Unit | Note |

| Circuit current                                   | IEE         | 1, 2, 14, 20                                                                                                                                              | - 112 | - 85  |             | mA   | 1    |

| Circuit current                                   | lcc         | 4                                                                                                                                                         |       | 9.5   | 12.5        | mA   | 1    |

| Input threshold<br>voltage                        | Vтн         | 6, 7, 8, 9, 10, 12                                                                                                                                        |       | 2.1   |             | v    |      |

| High-level<br>input voltage                       | Viн         | 6, 7, 8, 9, 10, 12                                                                                                                                        | 2.8   |       |             | v    |      |

| Low-level<br>input voltage                        | VIL         | 6, 7, 8, 9, 10, 12                                                                                                                                        |       |       | 0. <b>8</b> | v    |      |

| High-level<br>input current                       | Ін          | 6, 7, 8, 9, 10, 12 VIH =4.5V                                                                                                                              |       |       | 500         | μA   |      |

| Low-level<br>input current                        | հւ          | 6, 7, 8, 9, 10, 12 VIL = 0V                                                                                                                               |       |       | 500         | μΑ   |      |

| High-level<br>output voltage                      | VLRCKH      | 11 Pin 7 = $4.5V$ IOH = $-100\mu$ A<br>Pin 6:1 clock input:0V - 5V - 0V                                                                                   | 2.7   |       |             | v    |      |

| Low-level<br>output voltage                       | VLRCKL      | $11 \begin{array}{l} \text{Pin 7} = 0\text{V}  \text{IoL} = 100\mu\text{A} \\ \text{Pin 6:1 clock input: } 0\text{V} - 5\text{V} - 0\text{V} \end{array}$ |       |       | -2.7        | v    |      |

| Clock input<br>bias voltage                       | Vcin        | 26, 27                                                                                                                                                    |       | - 1.3 |             | v    |      |

| Clock high-level<br>output voltage                | VCCR        | 25                                                                                                                                                        |       | - 0.8 |             | v    |      |

| Clock low-level<br>output voltage                 | VCOL        | 25                                                                                                                                                        |       | - 1.6 |             | v    |      |

| Current output<br>pin leak                        | lo<br>LEAK  | 17, 18 Pins 17, 18: voltage = 0V<br>when current output is off.                                                                                           |       |       | 1.5         | μA   |      |

| lo∪⊤ output<br>current                            | Ιουτ        | Pins 17, 18: voltage         OV           17, 18         Pin 16 ISET         500μA           (IoUT         Io         - io)                               |       | 2.008 |             | mA   |      |

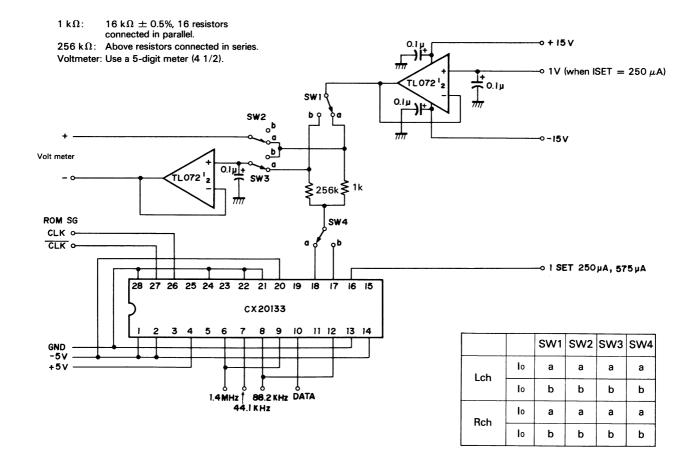

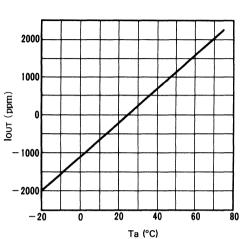

| Current ratio * 1                                 | la/io       | 17, 18 Pin 16 ISET = 250µA                                                                                                                                | 255.0 | 256.0 | 257.5       | -    | 2    |

| Discharge<br>circuit current<br>dissipation       | lDC         | 24 Set Pin 24 to 0V.                                                                                                                                      | 1.35  | 1.9   | 2.5         | mA   |      |

| Discharge circuit<br>high-level output<br>voltage | Vdch        | 15, 23 Pin 24 voltage = $1.4V$<br>Load current = $-100\mu A$                                                                                              | 0.27  | 0.45  | 0.77        | v    |      |

| Discharge circuit<br>low-level output<br>voltage  | VDCL        | 15, 23 Pin 24 voltage = $1.4V$<br>Load current = $-100\mu A$                                                                                              |       | -4.2  | -3.5        | v    |      |

| Maximum ISET<br>current                           | ISET<br>MAX | 16 In the range when the IOUTL(R)<br>current ratio satisfies 255<10/io<257                                                                                |       |       | 575         | μA   |      |

| Distortion factor                                 | тнр         | Both right and left, OdB (full scale)<br>reproduction 680Hz                                                                                               |       | 0.003 | 0.005       | %    | 3    |

| Distortion ractor                                 |             | Both right and left, – 20dB<br>reproduction 680Hz                                                                                                         |       | 0.02  | 0.025       | %    | 3    |

| Operating clock<br>frequency                      | fclk        | Self-activating/Activated                                                                                                                                 |       |       | 36          | MHz  |      |

Note 1) Ground Pins 13, 17, 18, 21, 22, 24 and 28. Connect Pin 16 via a resistor of 5.1 k Ω and keep other pins open.

2) I<sub>0</sub> and i<sub>0</sub> must satisfy the relation below in the Current Ratio Test Circuit (Fig. 3): -3.9 (mV) < 1 (k $\Omega$ ) × I<sub>0</sub> ( $\mu$ A) - 256 (k $\Omega$ ) × i<sub>0</sub> ( $\mu$ A) < 5.9 (mV)

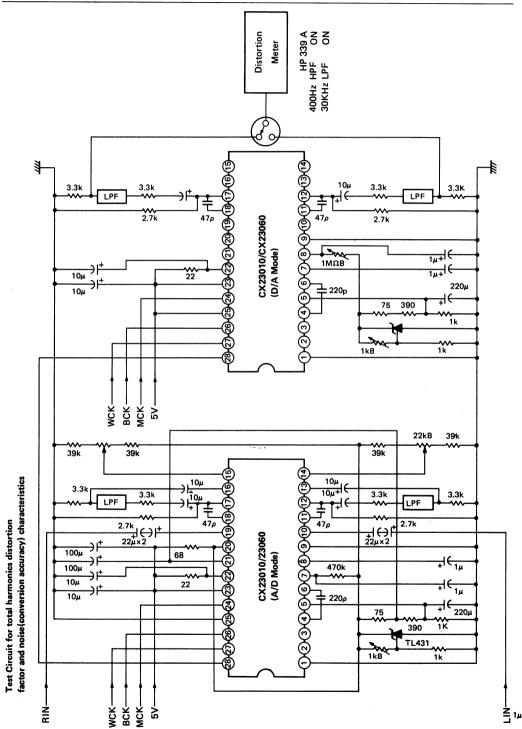

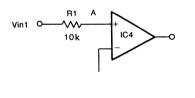

3) See the Test Circuit (Fig. 2).

Conversion frequency: 44.1 kHz

Input data: Use the 16 bit full-scale data (0 dB) generated by the data generator.

Distortion meter: Use the HP339A (with all filters on) or the like provided with 80 kHz LPF, 30 kHz LPF and 400 Hz HPF.

\*1 In the Current Ratio Test Circuit (Fig. 3),  $20(m)(1 < 1/(m)) \times lo(mA) = 256/(m)(1 + 1/(m))$

$-3.9 (\textrm{mV}) < 1 (\textrm{k}\,\Omega) \times \textrm{lo}(\mu\textrm{A}) - 256 (\textrm{k}\,\Omega) \times \textrm{io}(\mu\textrm{A}) < 5.9 (\textrm{mV})$

#### **Description of the Conversion Operation**

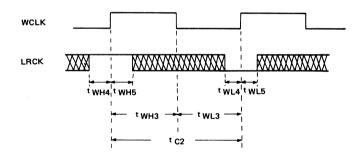

(1) Data call (BCLK, DIN, WCLK, LRCK). Refer to Fig. 6.

The data comes in 16 bit serial signal with 2's compliment. The data is sent sequencially into the IC beginning from MSB in sync with the rise of the bit clock (BCLK). (The data change represents the BCLK fall).

When the word clock (WCLK) is changed from the high-level to low-level at the 17th fall of BCLK, the 16 bit data is transferred from the shift register to the latch by the fall signal.

When the CX20133 is used in the stereo mode, data from other channels are sent in from the 17th BCLK.

In the stereo mode, Rch data is called when LRCK at the low level and Lch data is called in when the LRCK is at the high level. IOUTL and DCL operate only when LRCK is at the low level and IOUTR and DCR operate only when LRCK is at the high level.

#### (2) Conversion operation (CC, LRCK, CIN, IOUTL, IOUTR, DCL, DCR)

When more than 3 clocks are input from the clock input (CIN) with conversion command at the high level, all inner timing circuits are reset.

After resetting, the inner timing circuit starts operation when a clock is input from CIN with CC at the low level. The three signal generated this way are the discharge signal, counter set signal and integrating signal. Time of these three signals is determined depending on the clock cycle and their number of quantity:

The counter set signal is to set the data input to the latch to the counter and it is not output externally.

The discharge signal is output from DCL and DCR and it is controlled by LRCK. It is output from DCL when LRCK is at the low level and from the DCR when LRCK is at the high level.

By the integrating current start signal, the upper current lo and lower current io start flowing. The counter starts counting from the preset value simultaneously when the discharge signal is off, measures the 11 offsets after completion of counting and outputs a signal to stop the integrating current.

The t5 value is varied between 0 and 255 by the preset input data in the counter.

Therefore, the conversion time from the start of low CC level to the completion of integrating requires t4 + t5 sec max.

The integrating current, like the discharge signal, is controlled by LRCK; IOUTL is output when LRCK is at the low level and IOUTR is output when LRCK is at the high level.

#### The Relation between Sampling Frequency fs and Clock

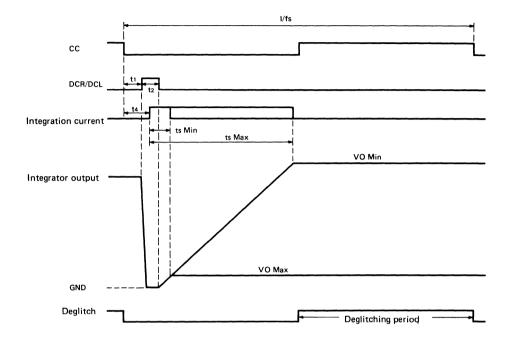

The maximum and minimum values of the integration voltage output, V $_0$  Max and V $_0$  Min, are expressed as follows:

$V_{0} Max = \frac{I_{0}}{C} * \tau_{0} * 267 + \frac{i_{0}}{C} * \tau_{0} * 266 \qquad (t_{4} + t_{5} Max)$  $V_{0} Min = \frac{I_{0}}{C} * \tau_{0} * 12 + \frac{i_{0}}{C} * \tau_{0} * 11 \qquad (t_{4} + t_{5} Min)$

where fCLK is a clock frequency and  $\tau$  is a period.

The integration voltage is held by the capacitor C in the integrator when the current is switched off. This voltage is used as D/A conversion output during the deglitching period T which is given according to the settling time of the deglitching circuit.

The relation between the conversion frequency fs and the clock frequency fCLK is given as below assuming that the conversion time and deglitching period are equivalent:

$$fs = \frac{fCLK}{2 \times (t_4 + t_5 Max)} = \frac{fCLK}{734}$$

where  $f_s = 44.1$  kHz results in 32.4 MHz of fCLK.

It is, however, recommendable to specify  $f_s$  as the follow for the practical use because a settling time of 0.5 to 1.0  $\mu$ s is required for the integrator after the current for ts disappears:

$$fs = \frac{fCLK}{(t_4 + t_5 Max + 1.0 (\mu s)) + T}$$

CX20133

#### SONY.

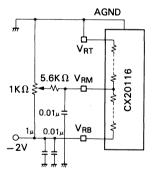

#### (3) Integration current setting (ISET, IOUTL, LOUTR)

Integration current is determined by a constant current value input through the ISET pin, which is given as below:

IOUTL (R) =

$$I_0 + i_0$$

=  $(4 + \frac{1}{64})$  ISET

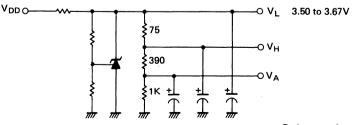

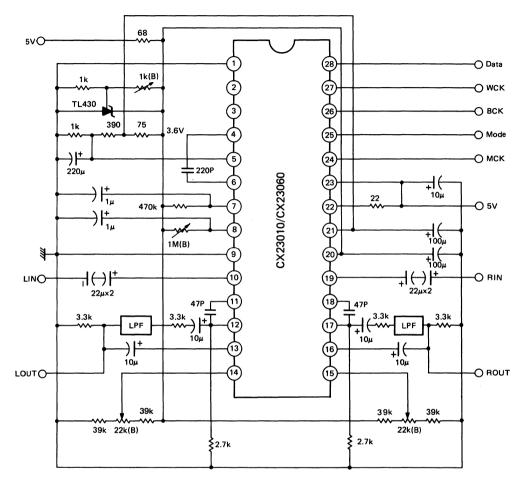

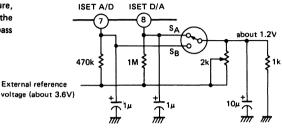

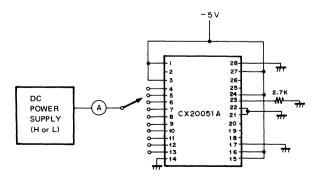

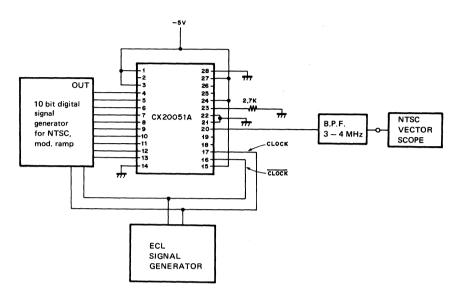

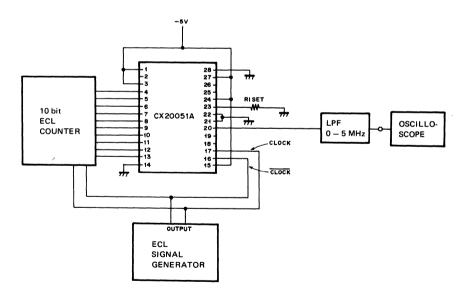

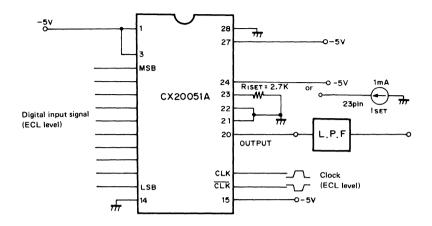

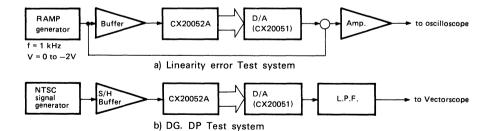

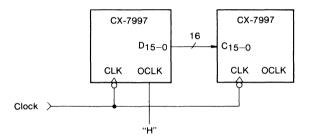

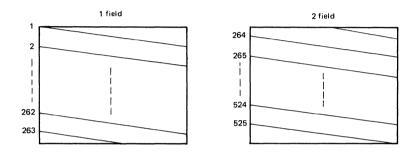

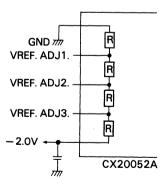

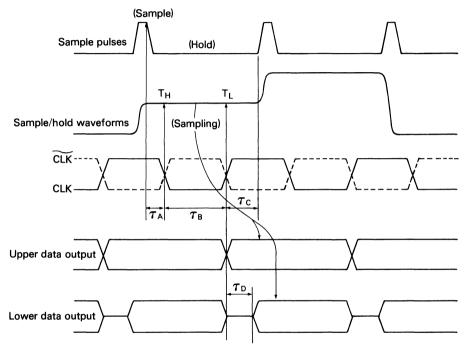

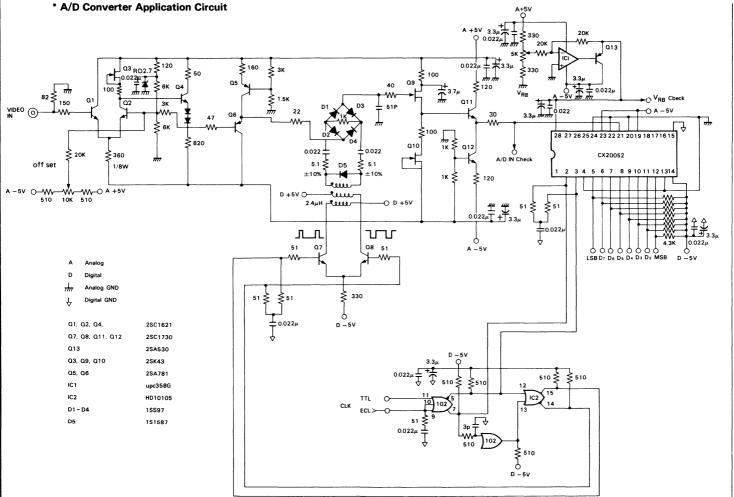

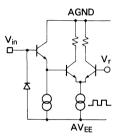

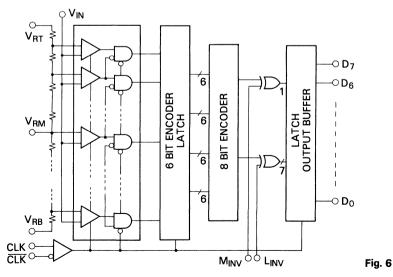

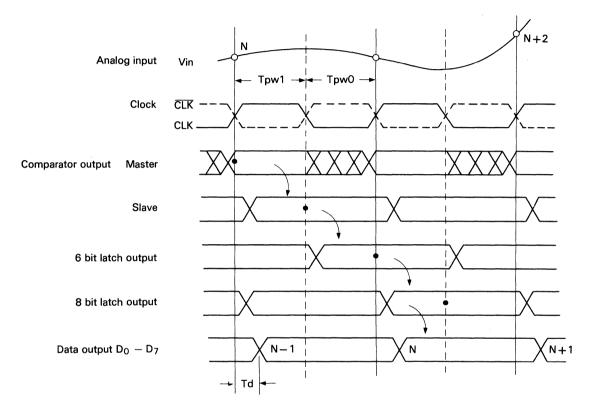

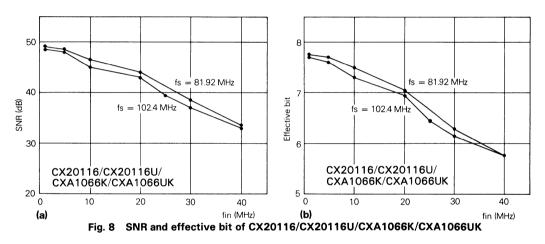

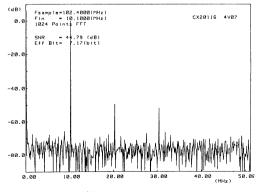

where io and lo are integration currents corresponded to the ILSB and 28 LSB, respectively.