# CMOS Integrated Circuit Data Book

AUGUST 1990

#### Sierra at a Glance

Sierra Semiconductor Corporation designs and manufactures CMOS mixed-signal integrated circuits, which combine analog and digital functions on a single chip or chip set. The company's proprietary Triple Technology® process optimizes the combination of analog and digital capabilities and also permits the efficient addition of reprogrammable nonvolatile memory.

Sierra's standard product lines serve three markets: Data Communications, Telecommunications, and Graphics. Sierra's cell-based semicustom ASICs serve the same markets plus the computer and computer peripheral markets with special emphasis on disk drives.

Sierra's products are sold primarily to original equipment manufacturers (OEMs) serving the computer, computer peripheral, instrumentation, telecommunications and business machine markets. The Company's products are sold through manufacturers' representatives and distributors in North America, Japan and Southeast Asia. In Europe, the Company's sales are through Sierra Semiconductor, B.V. headquartered in the Netherlands. Sierra Semiconductor, B.V. also employs manufacturers' representatives.

Sierra operates a 6-inch, 6000 wafer/month fabrication and test facility in Singapore. This facility utilizes Sierra's advanced CMOS process and is employed to produce Sierra's leading-edge products. Independent foundries are used for mature, high volume products. The Singapore operation is a joint venture between Sierra and Singapore Technologies Industrial Corporation.

® Triple Technology is a registered trademark of Sierra Semiconductor Corporation.

#### Terms of Sale

Devices sold by Sierra Semiconductor Corp. are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. Sierra Semiconductor Corp. makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. Sierra Semiconductor Corp. makes no warranty of merchantability or fitness for any purpose. Sierra Semiconductor Corp. reserves the right to discontinue production and change specifications and prices at any time and without notice.

This product is intended for use in normal commercial applications. Applications requiring an extended temperature range, unusual environmental requirements, or high reliability applications, such as military and aerospace, are specifically not recommended without additional processing by Sierra Semiconductor Corp.

Sierra Semiconductor assumes no responsibility for the use of any circuitry other than circuitry embodied in a Sierra Semiconductor Corp. product. No other circuits, patents, licenses are implied.

## **Life Support Policy**

Sierra Semiconductor Corporation's products are not authorized for use as critical components in life support devices or systems.

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

# **Table of Contents**

|        |              |        |        | la               | dex.  |   |

|--------|--------------|--------|--------|------------------|-------|---|

| Data   | Comm         | aunic  | ation  | Pedi             | icts: | 1 |

| Tale   | Comi         | terite | ation  | Piedu            | cts   | 2 |

|        |              | Graj   | diics  | Pod              | icts: | 3 |

|        | Sent<br>Sint | -USIV  | in Ca  | <b>Paisill</b> i | iles  | 4 |

| Packag | jing/0       | rderi  | ng Inf | omial            | lon   | 5 |

Sales Office/Distributors

#### Introduction

The functional index beginning on the following page is arranged to facilitate the quick location of products of interest. Within the three product groupings (Data Communications, Telecommunications, and Graphics), the individual data sheets are in alphanumeric sequence. The numerical index on page xii is provided to quickly locate products where the product number is known.

Sierra Semiconductor uses 9-digit and 11-digit alphanumeric codes to uniquely identify the Company's products. The Company's product line consists of both individual components and kits, or chip sets. The components used in kits are often used in more than one kit. Hence, separate data sheets are provided for each component. The two charts below explain the significance of each digit in the code.

#### COMPONENTS C PACKAGE TYPE (See Section 5 for dimensions) G = Glass Seal N = Molded DIP V = Plastic LCC T = Plastic Transfer Molded PGA = Plastic PGA = Plastic QFP = Ceramic M = Small Outline TEMPERATURE RANGE $C = 0^{\circ}$ to $70^{\circ}$ C $E = -40^{\circ} \text{ to } 85^{\circ}\text{C}$ PRODUCT IDENTIFICATION CODE 5 Numeric Digits; Unique for Each Product COMPONENT **SIERRA** Modem Package Type Controller Package Type KITS EEPROM Package Type (If applicable) PACKAGE TYPE (See Section 5 for dimensions) G = Glass Seal N = Molded DIP V = Plastic LCC T = Plastic Transfer Molded PGA U = Plastic PGA Q = Plastic QFP I = Ceramic M = Small Outline TEMPERATURE RANGE $C = 0^{\circ}$ to $70^{\circ}C$ $E = -40^{\circ}$ to $85^{\circ}$ C EEPROM OPTION X = None1 = SC22201LAST 2 DIGITS OF MODEM CONTROLLER LAST 2 DIGITS OF MODEM KIT SIERRA

| TYPE OF<br>PRODUCT  | PRODUCT<br>NUMBER | DESCRIPTION OR<br>KEY FEATURES                                 | PAGE<br>NO. |

|---------------------|-------------------|----------------------------------------------------------------|-------------|

| 300 bps Modems      | SC11002CN/CM      | Bell 103 Compatible ±5 Volts                                   | 15          |

|                     | SC11003CN/CM      | Same as SC11002, 5 Volt Only                                   | 15          |

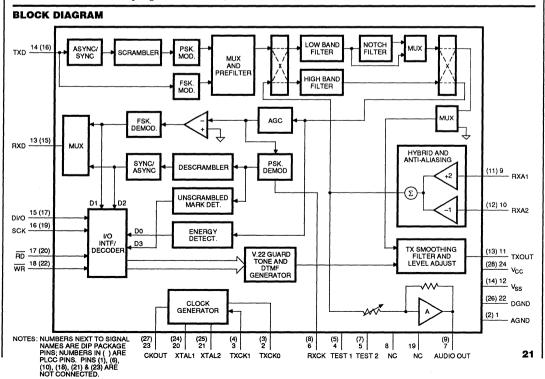

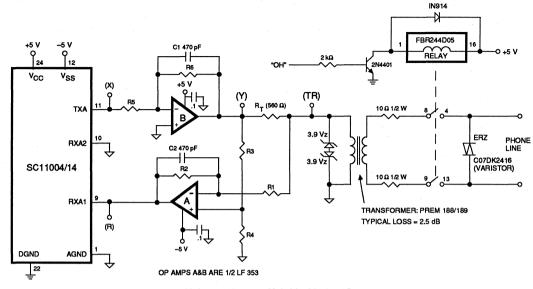

| 1200 bps Modems     | SC11004CN/CV      | Bell 212A, Bell 103 Compatible, V.22 ±5 Volts                  | 21          |

|                     | SC11014CN/CV      | Same as SC11004 with V.21                                      | 21          |

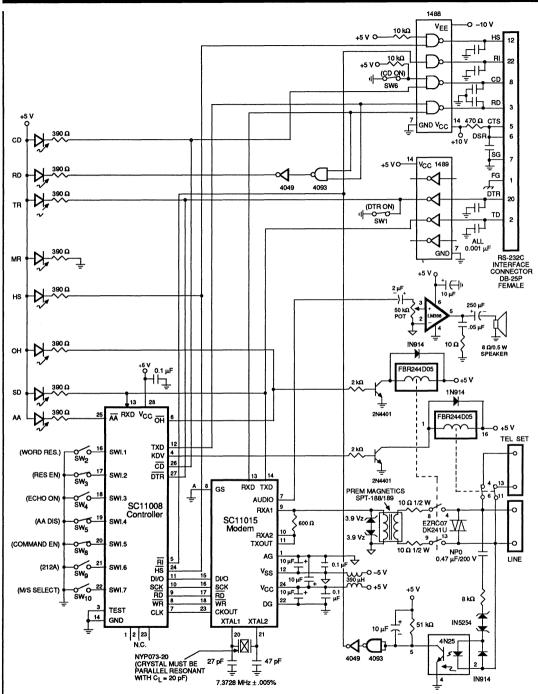

|                     | SC11015CN/CV      | Same as SC11014 with Programmable Gain Stage                   | 115         |

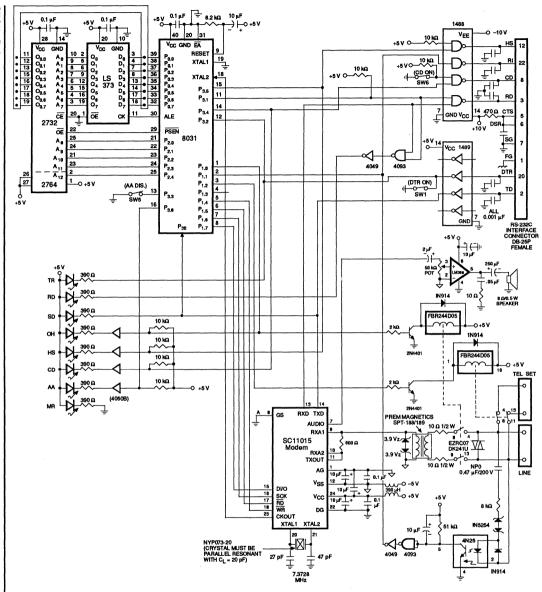

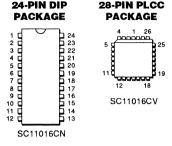

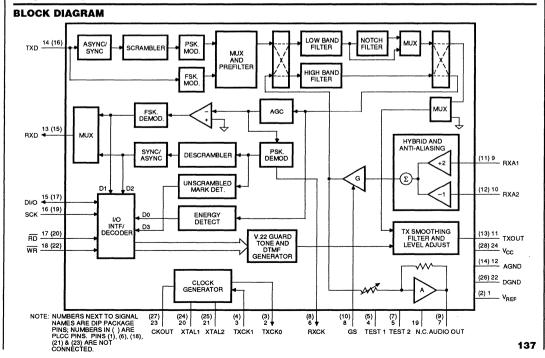

|                     | SC11016CN/CV      | Same as SC11015, 5 Volt Only                                   | 137         |

| 1200 bps Modem Kits | SK0407XC          |                                                                | 21          |

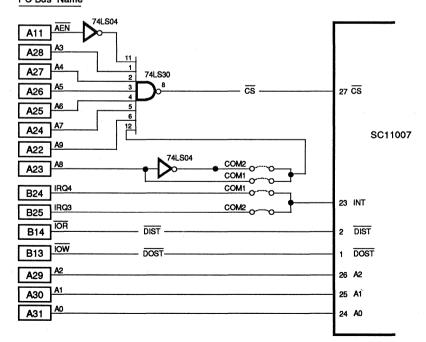

|                     |                   | SC11007 Parallel Controller                                    | 73          |

|                     | SK0417XC          | SC11004 Modem                                                  | 21          |

|                     |                   | SC11017 Turbo Parallel Controller                              | 157         |

|                     | SK0408XC          | SC11004 Modem                                                  | 21          |

|                     |                   | SC11008 Serial Controller                                      | 85          |

|                     | SK1407XC          | SC11014 Modem                                                  | 21          |

|                     |                   | SC11007 Parallel Controller                                    | 73          |

|                     | SK1417XC          | SC11014 Modem                                                  | 21          |

|                     |                   | SC11017 Turbo Parallel Controller                              | 157         |

|                     | SK1408XC          | SC11014 Modem                                                  | 21          |

|                     |                   | SC11008 Serial Controller                                      | 85          |

|                     | SK1507XC          | SC11015 Modem                                                  | 115         |

|                     |                   | SC11007 Parallel Controller                                    | 73          |

|                     | SK1508XC          | SC11015 Modem                                                  | 115         |

|                     | DICIDOOXC         | SC11008 Serial Controller                                      | 85          |

|                     | SK1517XC          |                                                                | 115         |

|                     | SKISI/XC          | SC11013 Modeln<br>SC11017 Turbo Parallel Controller            | 157         |

| 1200 bps Modem Kits | SK1627XC          | SC11016 Modem                                                  | 137         |

| • 5 Volt Only       | 011102//10        | SC11027 Parallel Controller                                    | 253         |

| -                   | SK1628XC          | SC11016 Modem                                                  | 137         |

|                     | DICTOZOAC         | SC11028 Serial Controller                                      | 265         |

|                     | SK1637XC          | SC11016 Modem                                                  | 137         |

|                     | biclos/xc         | SC11037 Turbo Parallel Controller                              | 281         |

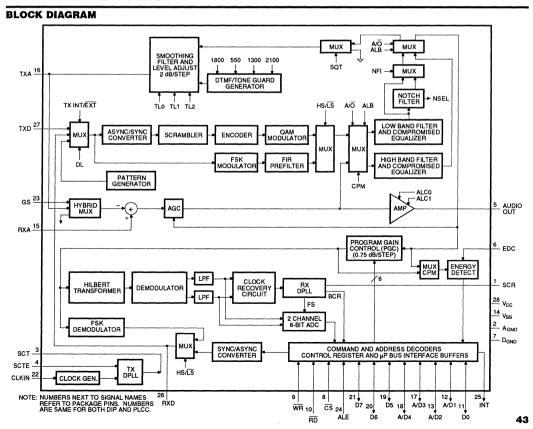

| 2400 bps Modems     | SC11006CN/CV      | Modem for V.22 bis, V.22, V.21; Bell 212A & 103                | 43          |

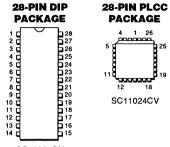

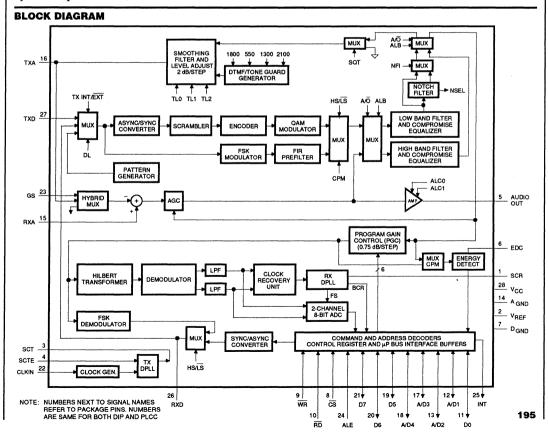

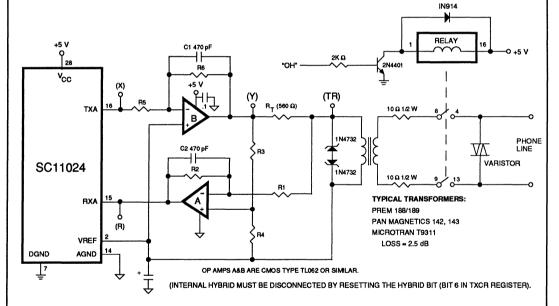

|                     | SC11024CN/CV      | 5 Volt Only Version of SC11006                                 | 195         |

|                     | SC11026CN/CV      | Modem for V.23, V.22 bis, V.22, V.21; Bell 212A & 103          | 225         |

|                     | SC11046CN/CV      | Sendfax <sup>™</sup> Modem adds V.27 ter fax to SC11006        | 293         |

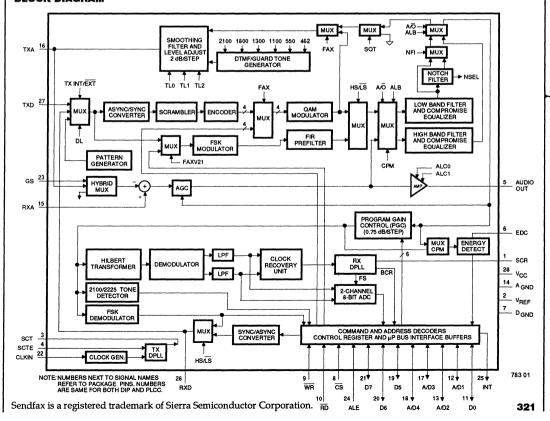

|                     | SC11054CN/CV      | Sendfax <sup>™</sup> Modern adds V.27ter & V.29 fax to SC11024 | 321         |

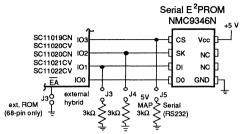

| 2400 bps Modem Kits | SK0611XC          | SC11006 Modem                                                  | 43          |

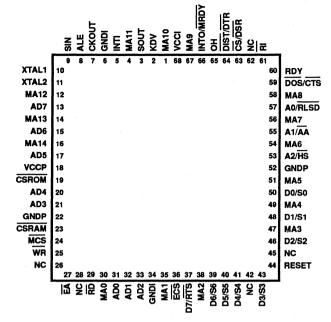

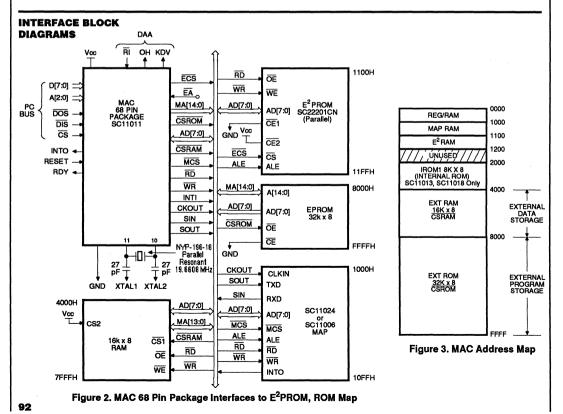

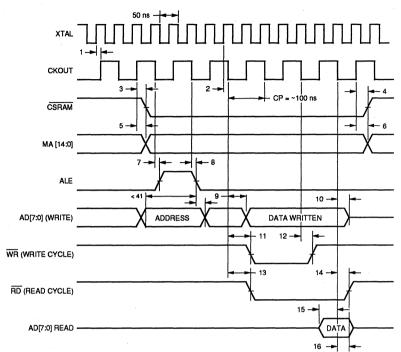

|                     |                   | SC11011 ROMless Controller                                     | 91          |

|                     | SK06111C          | SC11006 Modem                                                  | 43          |

|                     | DAUDITIC          | SC11000 Modelit SC11011 ROMless Controller                     | 91          |

|                     |                   | SC22201 EE Non-Volatile Memory                                 | 459         |

|                     |                   | SCZZZOT EE INOH- VOIGINE MEMORY                                | <b>4</b> 07 |

| TYPE OF<br>PRODUCT  | PRODUCT<br>NUMBER | DESCRIPTION OR<br>KEY FEATURES                    | PAG<br>NO |

|---------------------|-------------------|---------------------------------------------------|-----------|

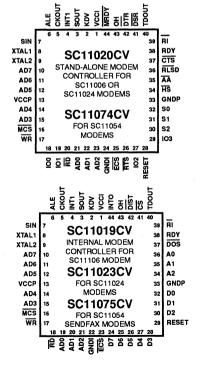

| 2400 bps Modem Kits | SK0619XC          | SC11006 Modem                                     | 43        |

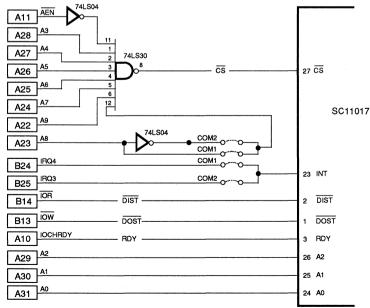

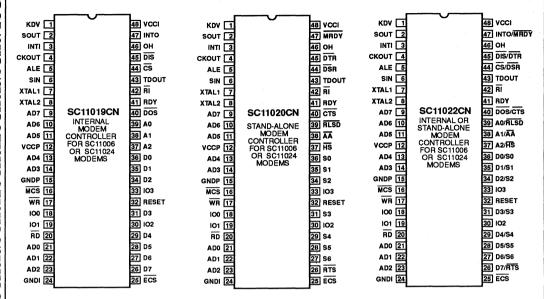

| CONT.)              |                   | SC11019 Turbo Parallel Controller                 | 169       |

|                     | SK06191C          | SC11006 Modem                                     | 43        |

|                     |                   | SC11019 Turbo Parallel Controller                 | 169       |

|                     |                   | SC22201 EE Non-Volatile Memory                    | 459       |

|                     | SK0620XC          | SC11006 Modem                                     | 43        |

|                     |                   | SC11020 Serial Controller                         | 169       |

|                     | SK06201C          | SC11006 Modem                                     | 43        |

|                     |                   | SC11020 Serial Controller                         | 169       |

|                     |                   | SC22201 EE Non-Volatile Memory                    | 459       |

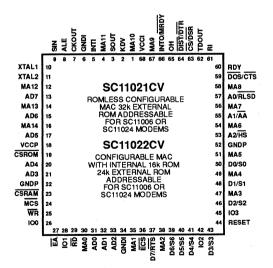

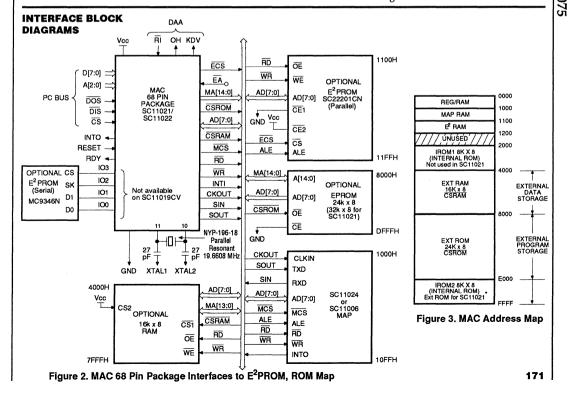

|                     | SK0621XC          | SC11006 Modem                                     | 43        |

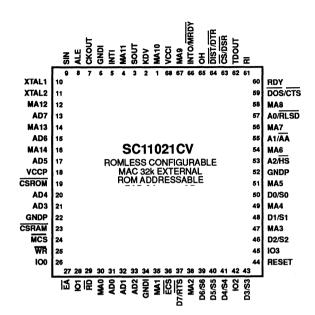

|                     |                   | SC11021 ROMless Controller                        | 169       |

|                     | SK06211C          | SC11006 Modem                                     | 43        |

|                     |                   | SC11021 ROMless Controller                        | 169       |

|                     |                   | SC22201 EE Non-Volatile Memory                    | 459       |

|                     | SK0622XC          | SC11006 Modem                                     | 4         |

|                     |                   | SC11022 Configurable Controller                   | 16        |

|                     | SK06221C          | SC11006 Modem                                     | 43        |

|                     |                   | SC11022 Configurable Controller                   | 16        |

|                     |                   | SC22201 EE Non-Volatile Memory                    | 45        |

|                     | SK0661XC          | SC11006 Modem                                     | 4         |

|                     |                   | SC11061 Fast MAC Configurable Controller (ROMless | ) 35      |

|                     | SK06611C          | SC11006 Modem                                     | 4         |

|                     |                   | SC11061 Fast MAC Configurable Controller (ROMless | 35        |

|                     |                   | SC22201 EE Non-Volatile Memory                    | 459       |

|                     | SK0691XC          | SC11006 Modem                                     | 4         |

|                     |                   | SC11091 UMAC Configurable Controller (ROMless)    | 375       |

|                     | SK06911C          | SC11006 Modem                                     | 43        |

|                     |                   | SC11091 UMAC Configurable Controller (ROMless)    | 37        |

|                     |                   | SC22201 EE Non-Volatile Memory                    | 45        |

| 2400 bps Modem Kits | SK2411XC          | SC11024 Modem                                     | 19        |

| 5 Volt Only         |                   | SC11011 ROMless Controller                        | 9         |

|                     | SK24111C          | SC11024 Modem                                     | 19        |

|                     |                   | SC11011 ROMless Controller                        | 9         |

|                     |                   | SC22201 EE Non-Volatile Memory                    | 45        |

|                     | SK2419XC          | SC11024 Modem                                     | 19        |

|                     |                   | SC11019 Turbo Parallel Controller                 | 169       |

|                     | SK24191C          | SC11024 Modem                                     | 19        |

|                     | -                 | SC11019 Turbo Parallel Controller                 | 16        |

|                     |                   | SC22201 EE Non-Volatile Memory                    | 45        |

|                     | SK2420XC          |                                                   | 19        |

|                     |                   | SC11020 Serial Controller                         | 16        |

|                     | SK24201C          | SC11024 Modem                                     | 19        |

|                     |                   | SC11020 Serial Controller                         | 16        |

|                     |                   | SC22201 EE Non-Volatile Memory                    | 45        |

| TYPE OF<br>PRODUCT                | PRODUCT<br>NUMBER | DESCRIPTION OR<br>KEY FEATURES                     | PAGE<br>NO. |

|-----------------------------------|-------------------|----------------------------------------------------|-------------|

| 2400 bps Modem Kits               | SK2421XC          | SC11024 Modem                                      | 195         |

| • 5 Volt Only                     |                   | SC11021 ROMless Controller                         | 169         |

| (CONT.)                           | SK24211C          | SC11024 Modem                                      | 195         |

|                                   |                   | SC11021 ROMless Controller                         | 169         |

|                                   |                   | SC22201 EE Non-Volatile Memory                     | 459         |

|                                   | SK2422XC          | SC11024 Modem                                      | 195         |

|                                   |                   | SC11022 Configurable Controller                    | 169         |

|                                   | SK24221C          | SC11024 Modem                                      | 195         |

|                                   |                   | SC11022 Configurable Controller                    | 169         |

|                                   |                   | SC22201 EE Non-Volatile Memory                     | 459         |

|                                   | SK2423XC          | SC11024 Modem                                      | 195         |

|                                   |                   | SC11023 Parallel Controller                        | 169         |

|                                   | SK24231C          | SC11024 Modem                                      | 195         |

|                                   |                   | SC11023 Parallel Controller                        | 169         |

|                                   |                   | SC22201 EE Non-Volatile Memory                     | 459         |

|                                   | SK2461XC          | SC11024 Modem                                      | 195         |

|                                   |                   | SC11061 Fast MAC Configurable Controller (ROMless) | 351         |

|                                   | SK24611C          | SC11024 Modem                                      | 195         |

|                                   |                   | SC11061 Fast MAC Configurable Controller (ROMless) | 351         |

|                                   |                   | SC22201 EE Non-Volatile Memory                     | 459         |

|                                   | SK2491XC          | SC11024 Modem                                      | 195         |

|                                   |                   | SC11091 UMAC Configurable Controller (ROMless)     | 375         |

|                                   | SK24911C          | SC11024 Modem                                      | 195         |

|                                   |                   | SC11091 UMAC Configurable Controller (ROMless)     | 375         |

|                                   |                   | SC22201 EE Non-Volatile Memory                     | 459         |

| 2400 bps Modem Kits               | SK2611XC          | SC11026 Modem                                      | 225         |

| <ul> <li>Quatro Modems</li> </ul> |                   | SC11011 ROMless Controller                         | 91          |

|                                   | SK26111C          | SC11026 Modem                                      | 225         |

|                                   |                   | SC11011 ROMless Controller                         | 91          |

|                                   |                   | SC22201 EE Non-Volatile Memory                     | 459         |

|                                   | SK2621XC          | SC11026 Modem                                      | 225         |

|                                   |                   | SC11021 ROMless Controller                         | 169         |

|                                   | SK26211C          | SC11026 Modem                                      | 225         |

|                                   |                   | SC11021 ROMless Controller                         | 169         |

|                                   |                   | SC22201 EE Non-Volatile Memory                     | 459         |

|                                   | SK2622XC          | •                                                  | 225         |

|                                   |                   | SC11022 Configurable Controller                    | 169         |

|                                   | SK26221C          | SC11026 Modem                                      | 225         |

|                                   |                   | SC11022 Configurable Controller                    | 169         |

|                                   |                   | SC22201 EE Non-Volatile Memory                     | 459         |

| TYPE OF PRODUCT                       | PRODUCT<br>NUMBER | DESCRIPTION OR KEY FEATURES                        | PAC |

|---------------------------------------|-------------------|----------------------------------------------------|-----|

| 2400 bps Modem Kits                   | SK2661XC          | SC11026 Modem                                      | 225 |

| <ul> <li>Quatro Modems</li> </ul>     |                   | SC11061 Fast MAC Configurable Controller (ROMless) | 351 |

| (CONT.)                               | SK26611C          | SC11026 Modem                                      | 225 |

|                                       |                   | SC11061 Fast MAC Configurable Controller (ROMless) | 351 |

|                                       |                   | SC22201 EE Non-Volatile Memory                     | 459 |

|                                       | SK2691XC          | SC11026 Modem                                      | 225 |

|                                       |                   | SC11091 UMAC Configurable Controller (ROMless)     | 375 |

|                                       | SK26911C          | SC11026 Modem                                      | 225 |

|                                       |                   | SC11091 UMAC Configurable Controller (ROMless)     | 375 |

|                                       |                   | SC22201 EE Non-Volatile Memory                     | 459 |

| 2400 bps Modem Kits                   | SK4611XC          | SC11046 Sendfax Modem                              | 293 |

| <ul> <li>4800 bps Sendfax®</li> </ul> |                   | SC11011 ROMless Controller                         | 91  |

|                                       | SK46111C          | SC11046 Sendfax Modem                              | 293 |

|                                       |                   | SC11011 ROMless Controller                         | 91  |

|                                       |                   | SC22201 EE Non-Volatile Memory                     | 459 |

|                                       | SK4621XC          | SC11046 Sendfax Modem                              | 293 |

|                                       |                   | SC11021 ROMless Controller                         | 169 |

|                                       | SK46211C          | SC11046 Sendfax Modem                              | 293 |

|                                       |                   | SC11021 ROMless Controller                         | 169 |

|                                       |                   | SC22201 EE Non-Volatile Memory                     | 459 |

|                                       | SK4622XC          | SC11046 Sendfax Modem                              | 293 |

|                                       |                   | SC11022 Configurable Controller                    | 169 |

|                                       | SK46221C          | SC11046 Sendfax Modem                              | 293 |

|                                       |                   | SC11022 Configurable Controller                    | 169 |

|                                       |                   | SC22201 EE Non-Volatile Memory                     | 459 |

|                                       | SK4661XC          | SC11046 Sendfax Modem                              | 293 |

|                                       |                   | SC11061 Fast MAC Configurable Controller (ROMless) | 351 |

|                                       | SK46611C          | SC11046 Sendfax Modem                              | 293 |

|                                       |                   | SC11061 Fast MAC Configurable Controller (ROMless) | 351 |

|                                       |                   | SC22201 EE Non-Volatile Memory                     | 459 |

| ı                                     | SK4691XC          | SC11046 Sendfax Modem                              | 293 |

|                                       |                   | SC11091 UMAC Configurable Controller (ROMless)     | 375 |

|                                       | SK46911C          | SC11046 Sendfax Modem                              | 293 |

|                                       |                   | SC11091 UMAC Configurable Controller (ROMless)     | 375 |

|                                       |                   | SC22201 EE Non-Volatile Memory                     | 459 |

| 2400 bps Modem Kits                   | SK5411XC          | SC11054 Sendfax Modem                              | 321 |

| • 5 Volt Only                         |                   | SC11011 ROMless Controller                         | 91  |

| • 9600 bps Sendfax®                   | SK54111C          | SC11054 Sendfax Modem                              | 321 |

|                                       |                   | SC11011 ROMless Controller                         | 91  |

|                                       |                   | SC22201 EE Non-Volatile Memory                     | 459 |

<sup>®</sup> Sendfax is a registered trademark of Sierra Semiconductor Corporation.

| TYPE OF PRODUCT         | PRODUCT       |                                                                | PAGE |

|-------------------------|---------------|----------------------------------------------------------------|------|

| PRODUCT                 | NUMBER        | KEY FEATURES                                                   | NO.  |

| 2400 bps Modem Kits     | SK5421XC      | SC11054 Sendfax Modem                                          | 321  |

| • 5 Volt Only           |               | SC11021 ROMless Controller                                     | 169  |

| • 9600 bps Sendfax®     | SK54211C      | SC11054 Sendfax Modem                                          | 321  |

| (CONT.)                 |               | SC11021 ROMless Controller                                     | 169  |

|                         |               | SC22201 EE Non-Volatile Memory                                 | 459  |

|                         | SK5461XC      | SC11054 Sendfax Modem                                          | 321  |

|                         |               | SC11061 Fast MAC Configurable Controller (ROMless)             | 351  |

|                         | SK54611C      | SC11054 Sendfax Modem                                          | 321  |

|                         |               | SC11061 Fast MAC Configurable Controller (ROMless)             | 351  |

|                         |               | SC22201 EE Non-Volatile Memory                                 | 459  |

|                         | SK5474XC      | SC11054 Sendfax Modem                                          | 321  |

|                         |               | SC11074 Configurable Controller                                | 169  |

|                         | SK5475XC      | SC11054 Sendfax Modem                                          | 321  |

|                         |               | SC11075 Configurable Controller                                | 169  |

|                         | SK5491XC      | SC11054 Sendfax Modem                                          | 321  |

|                         |               | SC11091 Configurable Controller                                | 375  |

|                         | SK54911C      | SC11054 Sendfax Modem                                          | 321  |

|                         |               | SC11091 UMAC Configurable Controller (ROMless)                 | 375  |

|                         |               | SC22201 EE Non-Volatile Memory                                 | 459  |

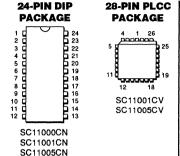

| Modem Filters           | SC11000CN/CV  | Band Split Filter                                              | 3    |

|                         | SC11001CN/CV  | Band Split Filter with Call Progress                           | 3    |

|                         |               | Monitoring and Analog Loopback                                 |      |

|                         | SC11005CN/CV  | Band Split Filter with Analog Loopback                         | 3    |

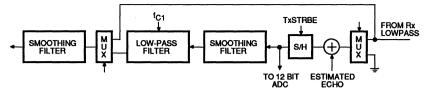

| Modem Analog            | SC11033CN/CV  | High Speed Modem AFE                                           | 271  |

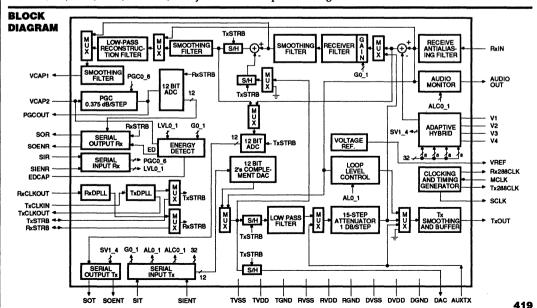

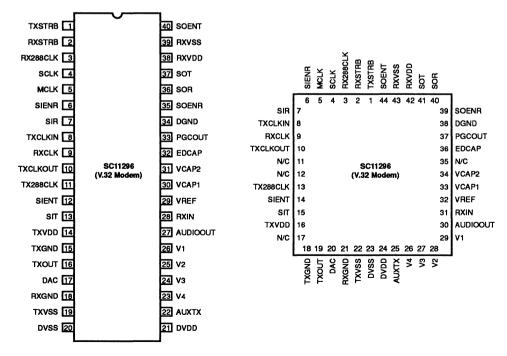

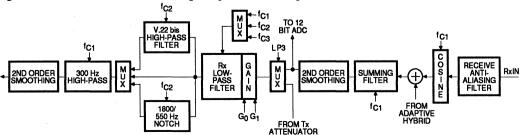

| Front End Circuits      | SC11296CN/CV  | FAX High Speed Modem                                           | 419  |

|                         | DC11230CIV/CV | 177/ 11gh opeca woden                                          | 417  |

| EEPROM Memory<br>Arrays | SC22201CN/CM  | 128 x 8-Bit Multiplexed Data & Address Modem<br>Support Memory | 459  |

# **FUNCTIONAL INDEX—Telecommunication Products**

| TYPE OF<br>PRODUCT       | PRODUCT<br>NUMBER       | DESCRIPTION OR<br>KEY FEATURES                         | PAG<br>NO. |  |

|--------------------------|-------------------------|--------------------------------------------------------|------------|--|

| DTMF Products            | SC11202CN               | DTMF Receiver                                          |            |  |

|                          | SC11203CN               | DTMF Receiver with Early Detect                        | 467        |  |

|                          | SC11204CN               | DTMF Receiver                                          | 467        |  |

|                          | SC11270CN               | DTMF Receiver                                          | 473        |  |

|                          | SC11271CN               | DTMF Receiver – European                               | 473        |  |

|                          | SC11280CN               | DTMF Transceiver                                       | 483        |  |

|                          | SC11289CN               | DTMF Transceiver                                       | 495        |  |

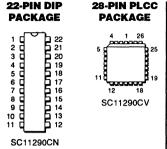

|                          | SC11290CN               | DTMF Transceiver                                       | 501        |  |

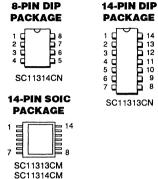

| Line Conditioning        | SC11310CN/CV            | Programmable Gain/Loss Control                         | 512        |  |

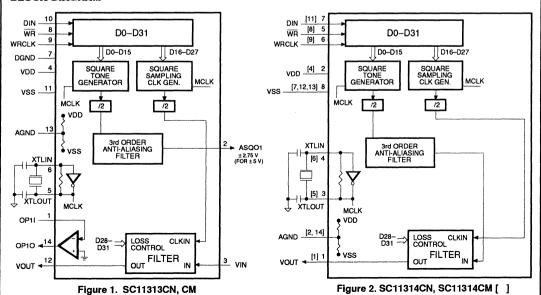

| Products                 | SC11313CN               | Programmable Sinewave/Squarewave Generator             | 52:        |  |

|                          | SC11314CN               | Programmable Sinewave/Squarewave Generator             | 52         |  |

|                          | SC11319CN               | Telephone Line Equalizer w/Programmable                | 52         |  |

|                          |                         | Gain/Loss Circuit                                      |            |  |

|                          | SC11330CN               | 2713 Hz Loopback Detector                              | 57         |  |

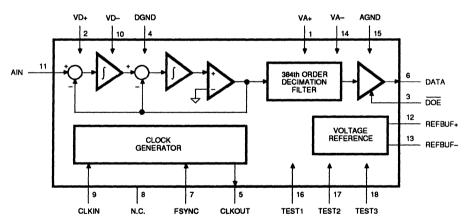

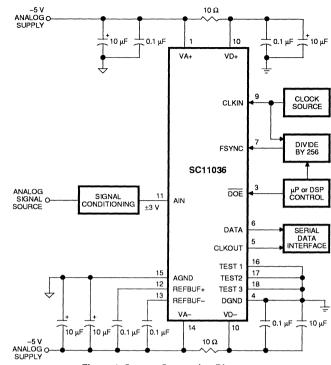

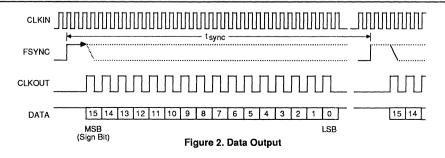

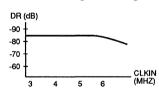

| Switching and            | SC11036CN               | Delta Sigma A/D Converter                              | 61         |  |

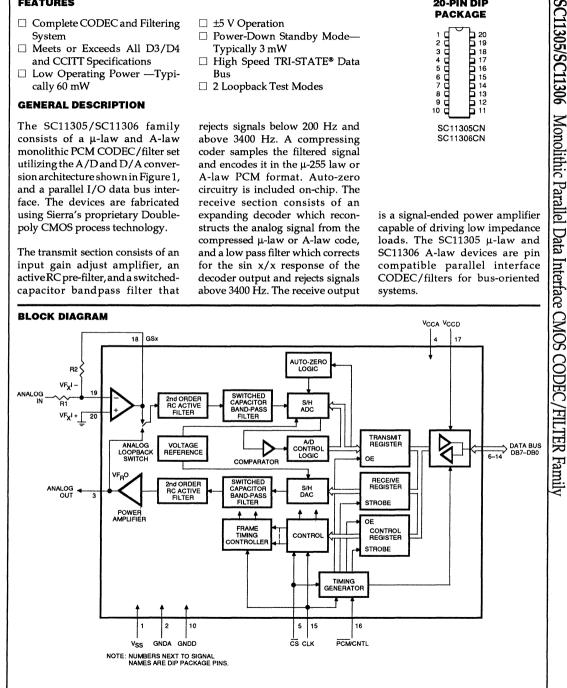

| Transmission<br>Products | SC11305CN               | Parallel μ-Law COMBO CODEC/FILTER                      | 50         |  |

| riouucts                 | SC11306CN               | Parallel A-Law COMBO CODEC/FILTER                      | 50         |  |

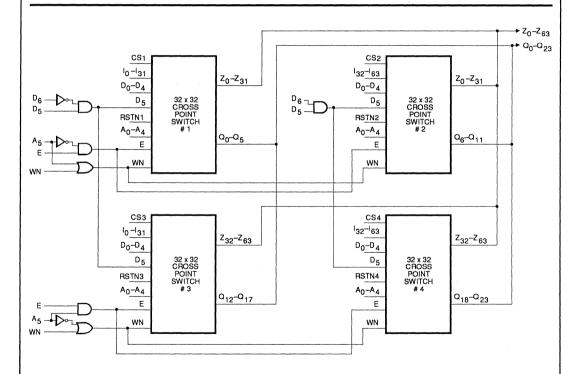

|                          | SC11320<br>SC11360CN/CV | 32 x 32 Digital Cross Point Switch<br>ADPCM Transcoder | 54<br>58   |  |

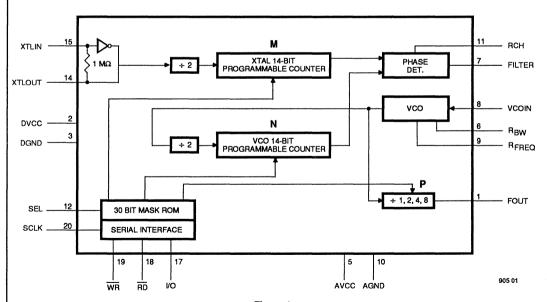

| PLL and Frequency        | SC11346                 | Phase Lock Loop                                        | 57         |  |

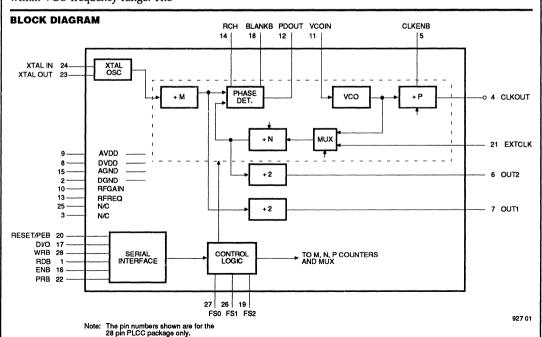

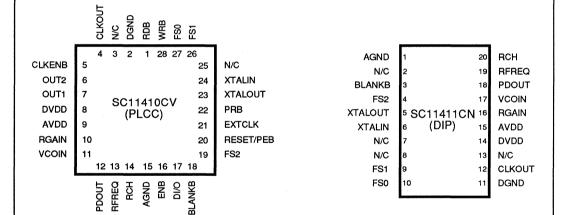

| Synthesizers             | SC11410                 | Frequency Synthesizer                                  | 66         |  |

|                          | SC11411                 | Frequency Synthesizer                                  | 66         |  |

|                          | SC11327                 | Programmable Frequency Synthesizer                     | 55         |  |

|                          | SC11328                 | Programmable Frequency Synthesizer                     | 56         |  |

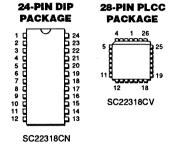

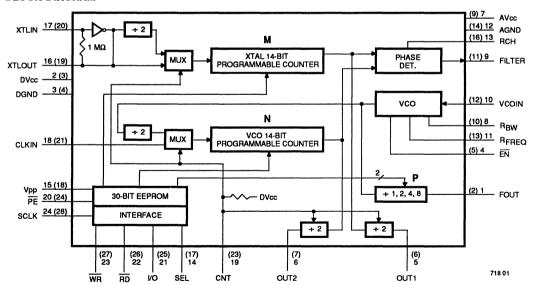

|                          | SC22318                 | Programmable Frequency Synthesizer                     | 59         |  |

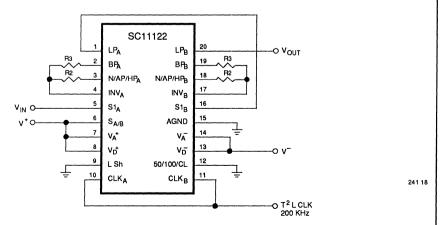

| Filters                  | SC11122CN               | MF10 30 kHz Universal Monolithic SCF                   | 62         |  |

|                          | SC11322CN               | Mask Programmable Universal Filter                     | 54         |  |

|                          | SC11324CN               | Mask Programmable Universal Filter                     | 54         |  |

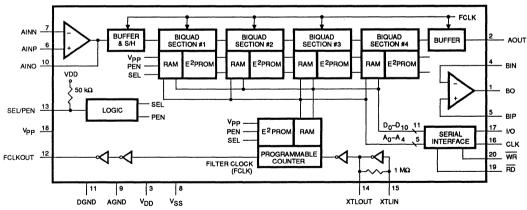

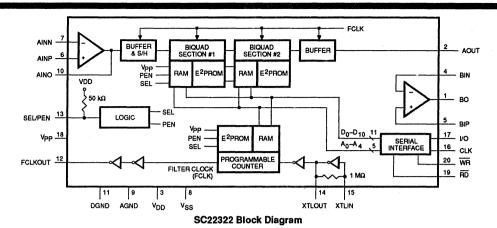

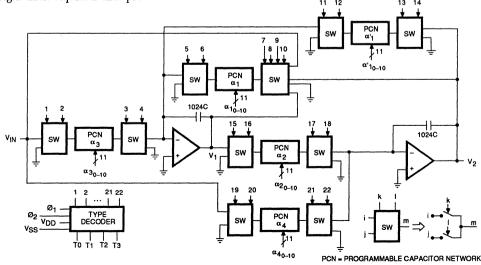

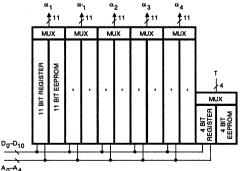

|                          | SC22322CN               | E <sup>2</sup> Programmable Dual Biquad SCF            | 60         |  |

|                          | SC22324CN               | E <sup>2</sup> Programmable Quad Biquad SCF            | 60         |  |

# **FUNCTIONAL INDEX—Graphics Products**

| TYPE OF<br>PRODUCT | PRODUCT<br>NUMBER | DESCRIPTION OR<br>KEY FEATURES     | PAGE<br>NO. |

|--------------------|-------------------|------------------------------------|-------------|

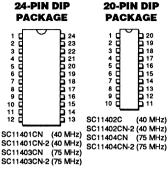

| Video DAC          | SC11401CN         | 8-Bit, 40 MHz Video DAC            | 659         |

|                    | SC11402CN         | 8-Bit, 40 MHz Video DAC            | 659         |

|                    | SC11403CN         | 8-Bit, 75 MHz Video DAC            | 659         |

|                    | SC11404CN         | 8-Bit, 75 MHz Video DAC            | 659         |

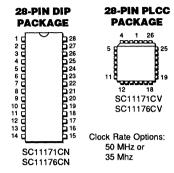

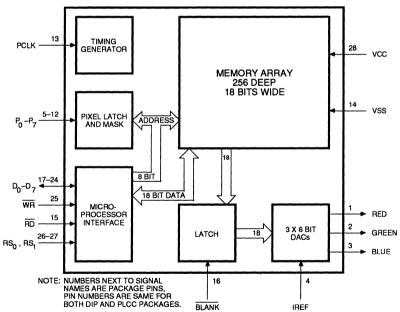

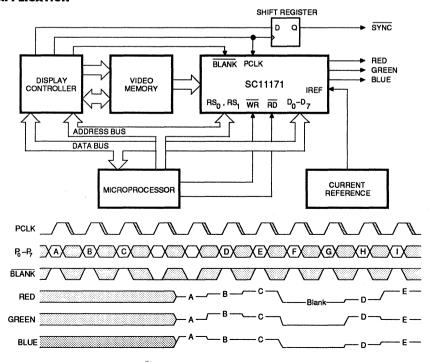

|                    | SC11171CN/CV      | Triple 6-Bit, 35 MHz Color Palette | 643         |

|                    | SC11176CN/CV      | Triple 6-Bit, 50 MHz Color Palette | 643         |

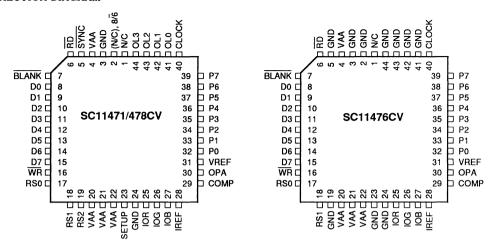

|                    | SC11471CV         | Triple 6-Bit, 35 MHz Color Palette | 675         |

|                    | SC11471CV         | Triple 6-Bit, 50 MHz Color Palette | 675         |

|                    | SC11471CV         | Triple 6-Bit, 66 MHz Color Palette | 675         |

|                    | SC11471CV         | Triple 6-Bit, 80 MHz Color Palette | 675         |

|                    | SC11476CV/CN      | Triple 6-Bit, 35 MHz Color Palette | 675         |

|                    | SC11476CV/CN      | Triple 6-Bit, 50 MHz Color Palette | 675         |

|                    | SC11476CV/CN      | Triple 6-Bit, 66 MHz Color Palette | 675         |

|                    | SC11478CV         | Triple 8-Bit, 35 MHz Color Palette | 675         |

|                    | SC11478CV         | Triple 8-Bit, 50 MHz Color Palette | 675         |

|                    | SC11478CV         | Triple 8-Bit, 66 MHz Color Palette | 675         |

|                    | SC11478CV         | Triple 8-Bit, 80 MHz Color Palette | 675         |

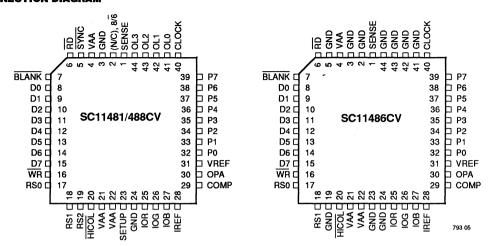

|                    | SC11481CV         | Triple 6-Bit, 35 MHz Color Palette | 691         |

|                    | SC11481CV         | Triple 6-Bit, 50 MHz Color Palette | 691         |

|                    | SC11481CV         | Triple 6-Bit, 66 MHz Color Palette | 691         |

|                    | SC11481CV         | Triple 6-Bit, 80 MHz Color Palette | 691         |

|                    | SC11486CV/CN      | Triple 6-Bit, 35 MHz Color Palette | 691         |

|                    | SC11486CV/CN      | Triple 6-Bit, 50 MHz Color Palette | 691         |

|                    | SC11486CV/CN      | Triple 6-Bit, 66 MHz Color Palette | 691         |

|                    | SC11488CV         | Triple 8-Bit, 35 MHz Color Palette | 691         |

|                    | SC11488CV         | Triple 8-Bit, 50 MHz Color Palette | 691         |

|                    | SC11488CV         | Triple 8-Bit, 66 MHz Color Palette | 691         |

|                    | SC11488CV         | Triple 8-Bit, 80 MHz Color Palette | 691         |

| PLL and Frequency  | SC11346           | Phase Lock Loop                    | 579         |

| Synthesizers       | SC11410           | Frequency Synthesizer              | 665         |

|                    | SC11411           | Frequency Synthesizer              | 665         |

|                    | SC11327           | Programmable Frequency Synthesizer | 557         |

|                    | SC11328           | Programmable Frequency Synthesizer | 565         |

|                    | SC22318           | Programmable Frequency Synthesizer | 597         |

## **NUMERICAL INDEX**

| Product<br>Type |     |   | Product<br>Type | Page<br>No. |

|-----------------|-----|---|-----------------|-------------|

| SC11000         | 3   |   | SC11204         | 467         |

| SC11001         | 3   |   | SC11270         | 473         |

| SC11002         | 15  |   | SC11271         | 473         |

| SC11003         | 15  |   | SC11280         | 481         |

| SC11004         | 21  |   | SC11289         | 495         |

| SC11005         | . 3 |   | SC11290         | 501         |

| SC11006         | 43  |   | SC11296         | 419         |

| SC11007         | 73  |   | SC11305         | 507         |

| SC11008         | 85  |   | SC11306         | 507         |

| SC11011         | 91  |   | SC11310         | 517         |

| SC11014         | 21  |   | SC11313         | 523         |

| SC11015         | 115 |   | SC11314         | 523         |

| SC11016         | 137 |   | SC11319         | 529         |

| SC11017         | 157 |   | SC11320         | 541         |

| SC11019         | 169 |   | SC11322         | 549         |

| SC11020         | 169 |   | SC11324         | 549         |

| SC11021         | 169 |   | SC11327         | 557         |

| SC11022         | 169 |   | SC11328         | 565         |

| SC11023         | 169 |   | SC11330         | 573         |

| SC11024         | 195 |   | SC11346         | 579         |

| SC11026         | 225 |   | SC11360         | 587         |

| SC11027         | 253 |   | SC11401         | 659         |

| SC11028         | 265 |   | SC11402         | 659         |

| SC11033         | 271 |   | SC11403         | 659         |

| SC11036         | 617 |   | SC11404         | 659         |

| SC11037         | 281 |   | SC11410         | 665         |

| SC11046         | 293 |   | SC11411         | 665         |

| SC11054         | 321 |   | SC11471         | 675         |

| SC11061         | 351 |   | SC11476         | 675         |

| SC11074         | 169 |   | SC11478         | 675         |

| SC11075         | 169 |   | SC11481         | 691         |

| SC11091         | 375 |   | SC11486         | 691         |

| SC11122         | 629 | - | SC11488         | 691         |

| SC11171         | 643 |   | SC22201         | 459         |

| SC11176         | 643 |   | SC22318         | 597         |

| SC11202         | 467 |   | SC22322         | 607         |

| SC11203         | 467 |   | SC22324         | 607         |

# 1

# Data Communication Products

# THIS PAGE INTENTIONALLY LEFT BLANK

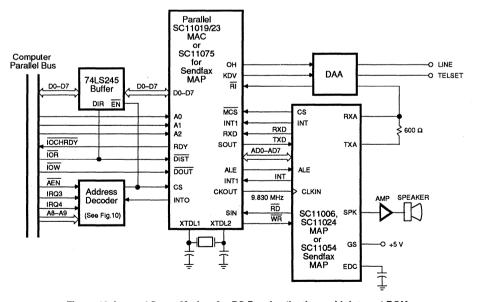

#### **FEATURES**

- ☐ Transmit and Receive filters with half-channel compromise equalizers

- ☐ Call Progress Mode Answer/ Originate mode switching

#### **GENERAL DESCRIPTION**

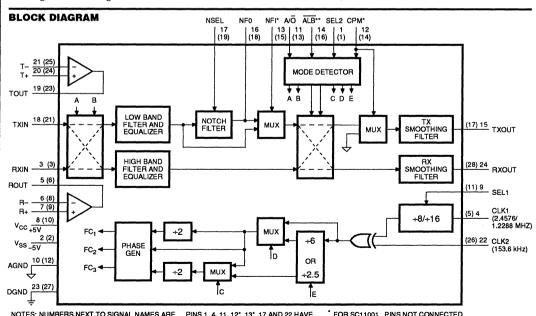

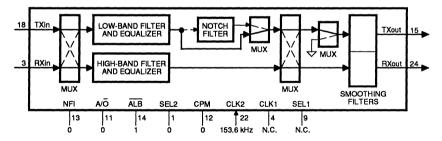

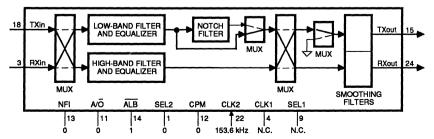

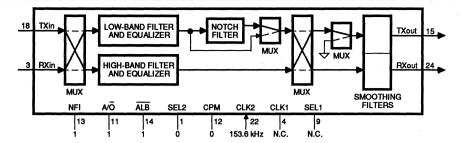

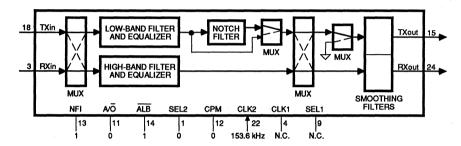

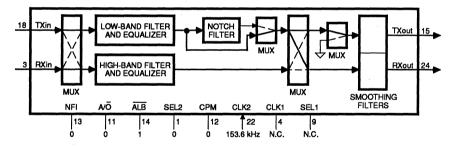

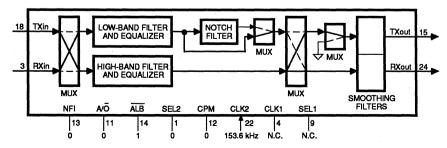

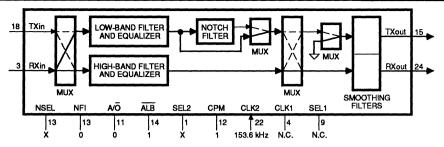

The SC11000, SC11001 and SC11005 modem filters are monolithic CMOS switched-capacitor filter circuits designed for use in full duplex 1200 and 2400 Bit Per Second modems. They meet the requirements of the Bell 212A, CCITT V.22 and V.22bis specifications and include high-band (2400 Hz) and low-band (1200 Hz) filters, half-channel compromise amplitude and group delay equalizers and smoothing filters for both bands. For CCITT V.22 and V.22bis applications, a notch filter is included that can be programmed for either 550 Hz or 1800 Hz. Also included in the filters are two uncommitted operational amplifiers that can be used for antialiasing filters or for gain control.

- ☐ Bell 212A, CCITT V.22 and V.22bis compatible with V.22 notch filters

- ☐ Analog Loopback capability

The SC11000 is pin and function compatible to the AMI S35212 and the Reticon R5632. Like the S35212, the high-band filter in the SC11000 can be scaled down by a factor of 6 so that it can be used to monitor call progress tones in an intelligent modem.

The SC11005 is pin and function compatible to the AMI S35212A. It contains all of the features of the SC11000, and like the S35212A, it contains an analog loopback mode—ALB (pin 14)—for testing the signal path.

The SC11001 is an enhanced version of the SC11005. In addition to all of the features of the SC11005, it

contains two additional control pins, CPM (pin 12) and NFI (pin 13) that allow more accurate call progress monitoring and easier V.22 implementation without the need for external multiplexers or logic. Besides being able to scale the highband filter by a factor of six, the lowband filter can be scaled by a factor of 2.5 for better centering over the call progress frequency range of 300 to 660 Hz. It also allows the unscaled high-band filter to be used for monitoring the modem answer tone, simplifying the design of full auto-dial/auto-answer modems.

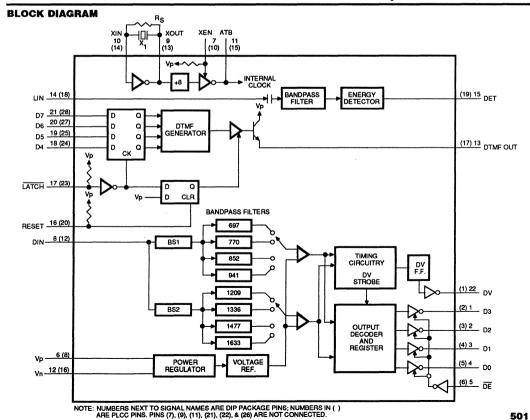

NOTES: NUMBERS NEXT TO SIGNAL NAMES ARE DIP PACKAGE PINS; NUMBERS IN () ARE PLCC PINS. PLCC PINS (4), (7), (20), & (22) ARE NOT CONNECTED.

PINS 1, 4, 11. 12", 13", 17 AND 22 HAVE INTERNAL PULL-DOWN REGISTERS TO GROUND. PIN 14 HAS AN INTERNAL PULL-UP TO VCC .

- FOR SC11001. PINS NOT CONNECTED ON SC11000 AND SC11005.

- FOR SC11001 AND SC11005. PINS NOT CONNECTED ON SC11000.

#### PIN DESCRIPTIONS

| PIN DESC   | RIPTIONS        | <b>.</b>                                                                                                                                                   |

|------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN<br>NO. | PIN<br>NAME     | DESCRIPTION                                                                                                                                                |

| 1 (1)      | SEL2            | Call progress mode selection; SEL2 low for normal operation, SEL2 High scales down the high-<br>band, filter by 6 for call progress monitoring             |

| 2 (2)      | V <sub>ss</sub> | Negative supply                                                                                                                                            |

| 3 (3)      | RXin            | Receive signal input                                                                                                                                       |

| 4 (5)      | CLK1            | Clock input 1; 2.4576 MHz with SEL1 high, or 1.2288 MHz with SEL1 low                                                                                      |

| 5 (6)      | Rout            | Output of the R amplifier                                                                                                                                  |

| 6 (8)      | R-              | Inverting input to the R amplifier                                                                                                                         |

| 7 (9)      | R+              | Noninverting input to the R amplifier                                                                                                                      |

| 8 (10)     | V <sub>cc</sub> | Positive supply                                                                                                                                            |

| 9 (11)     | SEL1            | Selects clock frequency into pin 4; low for 1.2288 MHz, high for 2.4576 MHz                                                                                |

| 10 (12)    | AGND            | Analog ground                                                                                                                                              |

| 11 (13)    | A/Ō             | Answer/originate mode selection; high for answer, low for originate                                                                                        |

| 12 (14)    | СРМ             | Enhanced call progress mode selection; CPM low for normal operation; CPM high scales down the low-band filter by 2.5 for enhanced call progress monitoring |

| 13 (15)    | NFI             | Notch filter insert; low for notch filter bypass, high for inserting                                                                                       |

| 14 (16)    | ALB             | Analog loopback; high for normal operation, low to loopback TXin to RXout                                                                                  |

| 15 (17)    | TXout           | Transmit signal output                                                                                                                                     |

| 16 (18)    | NFO             | Notch filter output                                                                                                                                        |

| 17 (19)    | NSEL            | Notch filter selection; low for 550 Hz, high for 1800 Hz                                                                                                   |

| 18 (21)    | TXin            | Transmit signal input                                                                                                                                      |

| 19 (23)    | Tout            | Output of the T amplifier                                                                                                                                  |

| 20 (24)    | T+              | Noninverting input to the T amplifier                                                                                                                      |

| 21 (25)    | T-              | Inverting input to the T amplifier                                                                                                                         |

| 22 (26)    | CLK2            | Clock input 2; 153.6 kHz                                                                                                                                   |

| 23 (27)    | DGND            | Digital ground                                                                                                                                             |

| 24 (28)    | RXout           | Receive signal output                                                                                                                                      |

Note: Pin numbers in ( ) refer to 28-lead PLCC pinout.

#### **FUNCTIONAL DESCRIPTION**

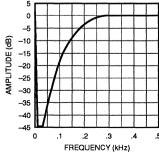

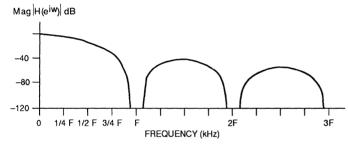

#### **Low-Band Filter**

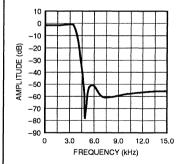

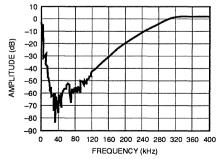

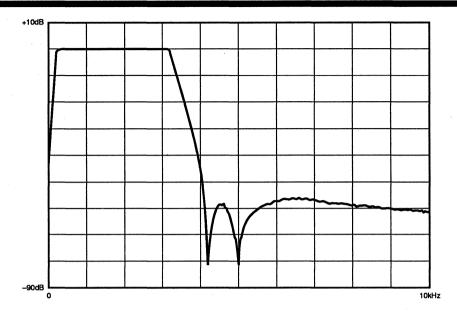

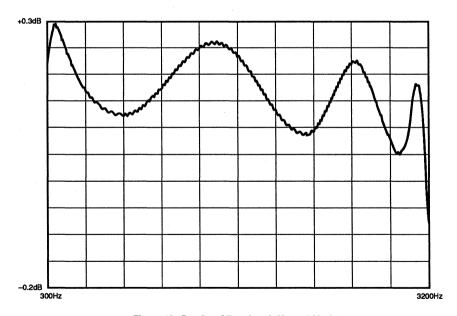

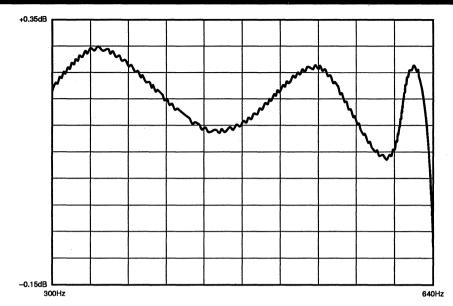

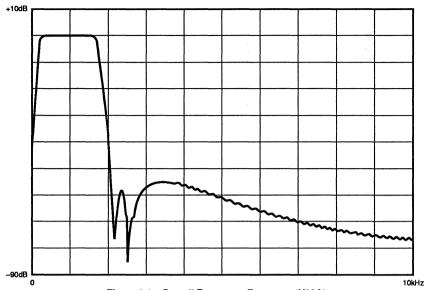

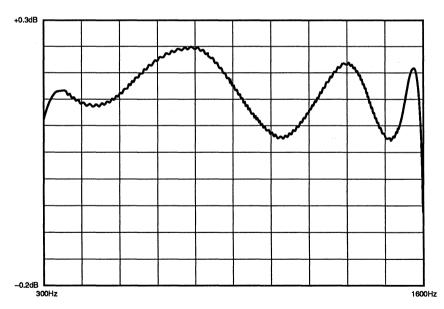

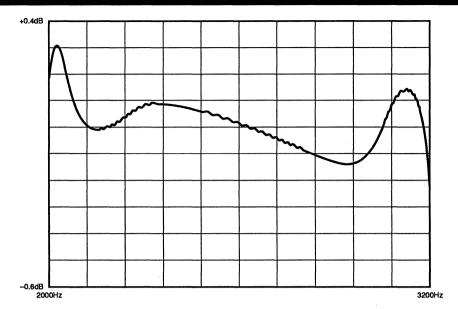

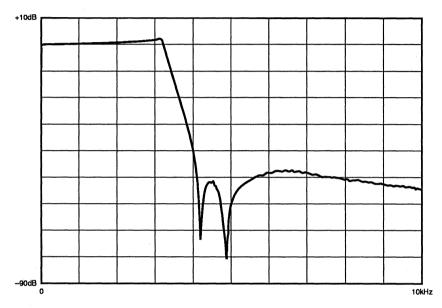

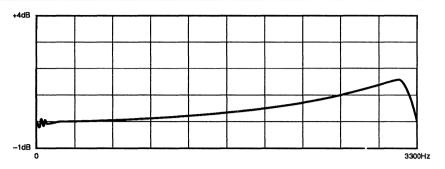

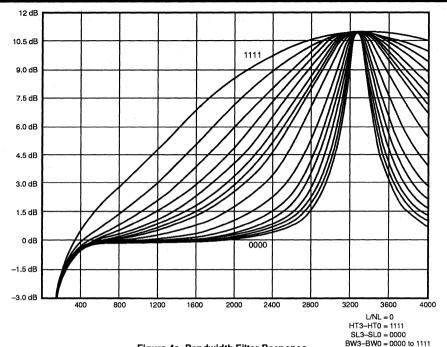

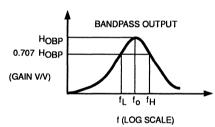

The low-band filter is a 10th order switched-capacitor band-pass filter with a center frequency of 1200 Hz. See Figure 3 for the amplitude response of this filter. In the originate mode this filter is used in the transmit direction: in the answer mode it is used in the receive direction. When analog loopback is used in the originate mode, this filter, together with the low-band delay equalizer, will be in the test loop. In the Call Progress Monitoring mode with SEL2 (pin 1) high and CPM (pin 12) low, the center frequency of this filter is shifted down by a factor of 6 to 200 Hz. If pin 12 (CPM) is high, then the filter response will be scaled down by 2.5, moving the center frequency to 480 Hz.

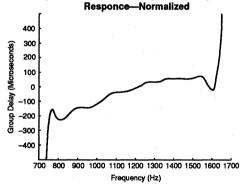

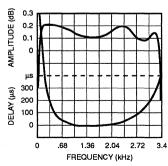

#### Low-Band Delay Equalizer

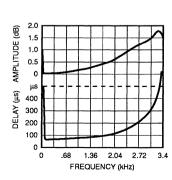

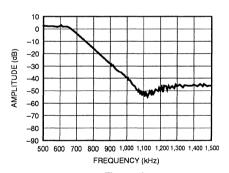

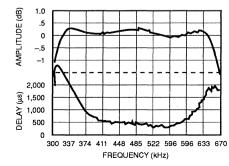

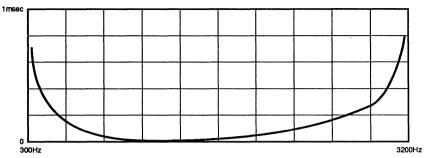

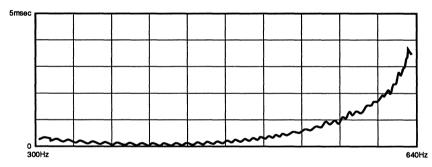

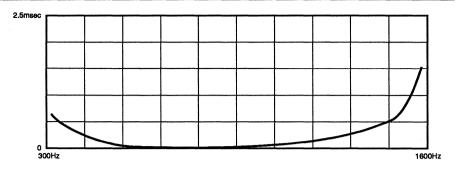

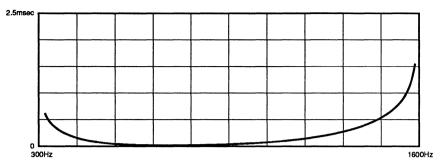

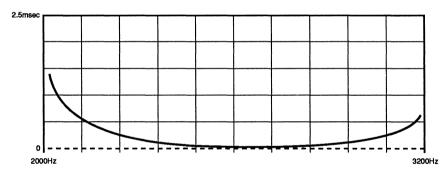

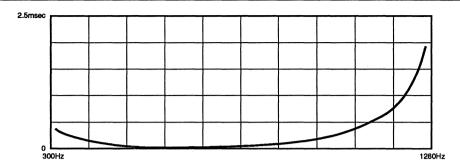

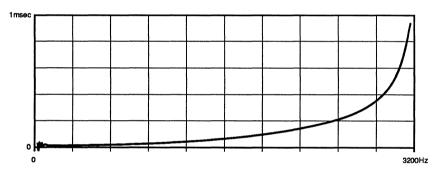

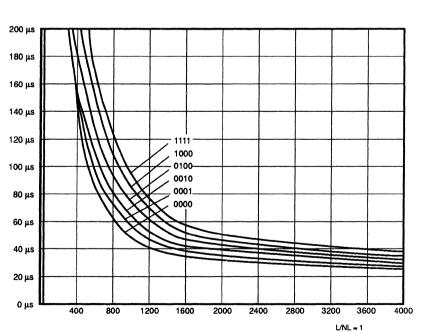

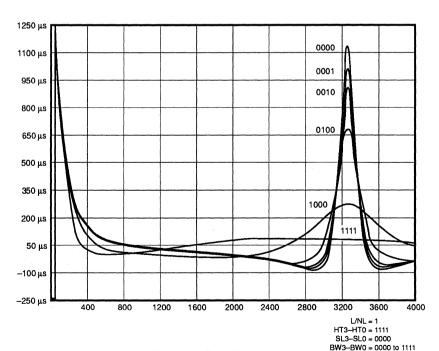

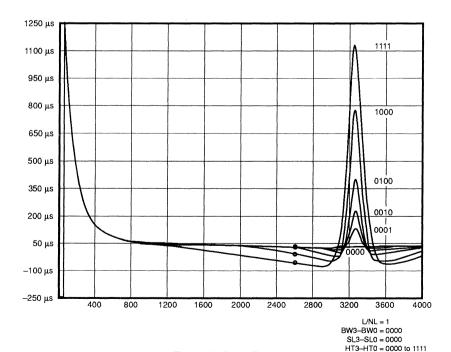

The low-band delay equalizer is a 10th order switched-capacitor allpass filter that compensates for the group delay variation of the low-band filter and half of the compromise line characteristics, producing a flat delay response within the pass-band. See Figure 4 for the group delay response of the low-band filter cascaded with the low-band delay equalizer.

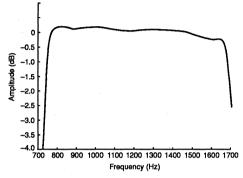

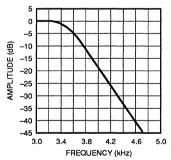

#### **High-Band Filter**

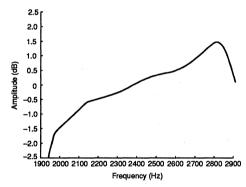

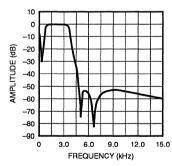

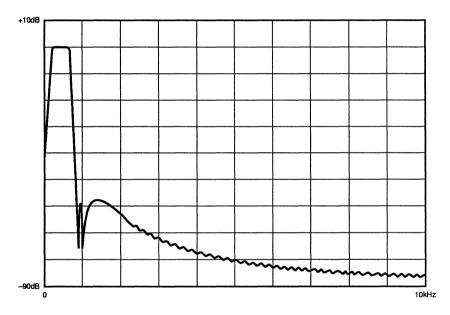

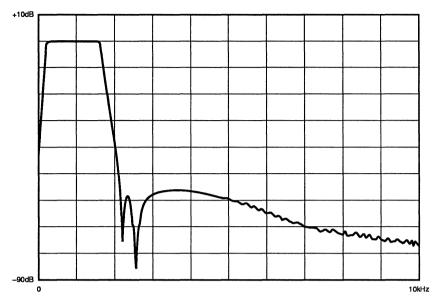

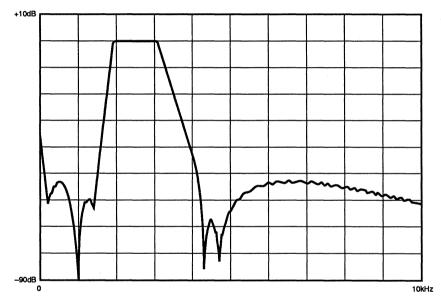

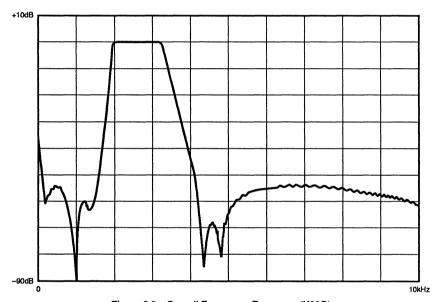

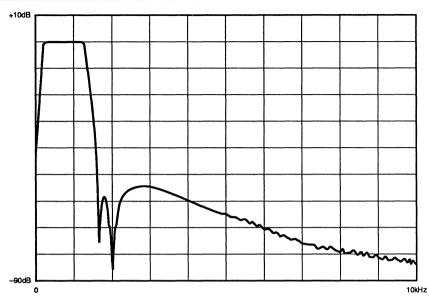

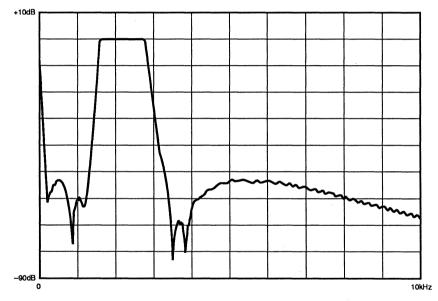

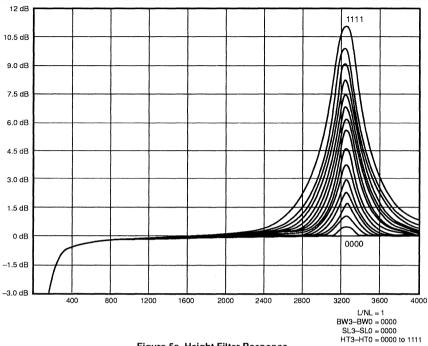

The high-band filter is a 10th order switched-capacitor band-pass filter with a center frequency of 2400 Hz. See Figure 5 for the amplitude response of this filter. In the answer mode, this filter is used in the transmit direction; in the originate mode, it is used in the receive direction. When analog loopback is used in the answer mode, this filter, together with the high-band delay equalizer, will be in the test loop. In the Call Progress Monitoring mode, with SEL2 (pin 1) high and CPM (pin 12) low, the center frequency will be shifted down by a factor of 6 to 400 Hz. If pin 1 is low or pin 12 is high, this filter operates in the normal data mode.

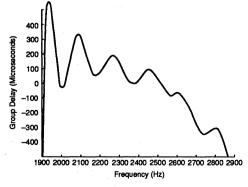

#### **High-Band Delay Equalizer**

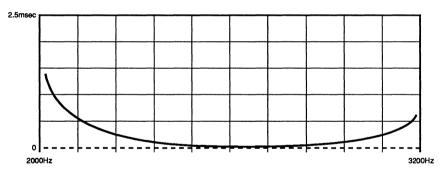

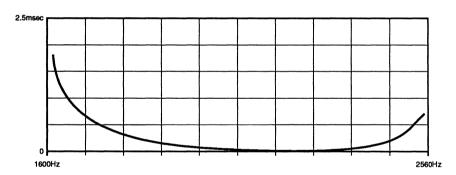

The high-band delay equalizer is a 10th order switched-capacitor allpass filter that compensates for the group delay variation of the high-band filter and half of the compromise line characteristics, producing a flat delay response within the pass-band. See Figure 6 for the group delay response of the high-band filter cascaded with the high-band delay equalizer.

#### **Transmit Smoothing Filter**

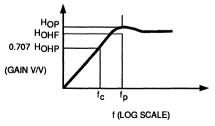

The transmit smoothing filter is a first order low-pass switched-capacitor filter.

#### **Receive Smoothing Filter**

The Receive Smoothing Filter consists of a 2nd order low-pass switched-capacitor filter cascaded with a 2nd order, active RC, low-pass filter.

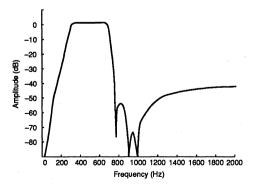

#### V.22 Notch Filter

The V.22 Notch Filter is a 2nd order switched-capacitor notch filter. The center frequency of the filter is at 550 Hz when NSEL (pin 17) is low and is shifted to 1800 Hz when NSEL is high. This filter is bypassed in the low-band if NFI (pin 13) is low. Its output, however, will always be available at pin 16 (NFO).

# Uncommitted Operational Amplifiers

Two operational amplifiers—called the R amplifier and the T amplifier—are included as part of the SC11001 and SC11005. They are not used by the filter circuit and can be used, for example, as anti-aliasing filters or gain stages in a complete 212A modem circuit.

#### **Analog Loop-Back**

When ALB (pin 14) is low, the signal transmitted by the modem, TXin, is looped back to the modem through the RXout pin. If the low (high)-band filter/equalizer is to be

tested, the  $A/\overline{O}$  pin should be low (high). The receive smoothing filter is in this loop regardless of the  $A/\overline{O}$  level. An internal pull up resistor keeps this pin high when it is not connected externally.

#### Answer/Originate Mode Selection

When  $A/\overline{O}$  (pin 11) is low, the modem operates in the originate mode, transmitting in the low-band and receiving in the high-band. If  $A/\overline{O}$  is high, the modem operates in the answer mode, transmitting in the high-band and receiving in the low-band. An internal pull down resistor keeps this pin low when it is not connected externally.

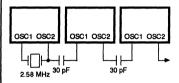

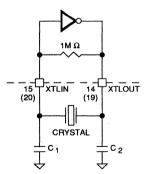

#### **Clock Selection**

SEL1 (pin 9) is used to select the correct internal divider, depending on the frequency of the external clock. SEL1 is set high for use with a 2.4576 MHz clock input on CLK1 (pin 4), and set low for a 1.2288 MHz input on CLK1 (pin 4). If a 153.6 kHz clock is used on CLK2 (pin 22), CLK1 (pin 4) and SEL1 (pin 9) should be left open.

#### Normal/Call Progress Mode

When SEL2 (pin 1) and CPM (pin 12) are low, the filter operates in the normal data mode—the modem mode. When either pin is high, the filter operates in the Call Progress Monitoring mode. When SEL2 is high and CPM is low, the center frequencies of both the low-band and the high-band filters are shifted down to one sixth of the frequencies used in the normal data mode. SEL2 is internally pulled down to keep it at a low level when it is not connected externally.

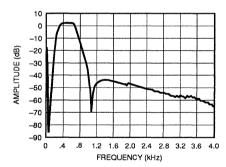

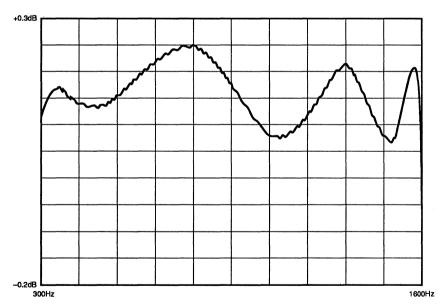

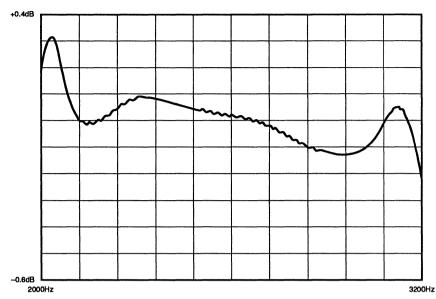

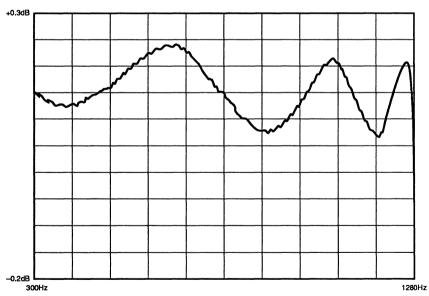

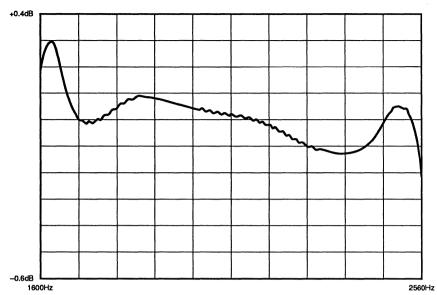

When CPM is high, the low-band filter is scaled down by a factor of 2.5 (Figure 7) and RXout is either the output of the scaled low-band filter, or the unscaled high-band filter, depending on the logic levels at  $\overline{ALB}$  (pin 14) and  $\overline{AO}$  (pin 11) as shown in Table 1.

# Transmit Squelch in Call Progress Mode

When CPM is high—Call Progress Mode—the input of the transmit smoothing filter is disconnected and shorted to ground, squelching the transmitter. In the handshake sequence of a 212A modem, this feature can be used to eliminate any

transmit signal output. An internal pull down resistor keeps the CPM pin low when it is not connected externally.

SEL2 (pin 1), CPM (pin 12),  $\overline{ALB}$  (pin 14), and A/ $\overline{O}$  (pin 11) control the modes of operation of the filter as shown in Table 1. For each combination of these pins, the table

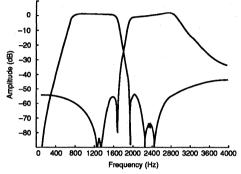

shows to which filter each input or output is connected. "L" refers to the low-band filter with the response shown in Figure 2. "H" is used to denote the high-band filter as characterized in Figure 2. When L or H are divided by a factor (6 or 2.5), this is indicated as L/6, H/6, etc., meaning the frequency response is scaled down by 6.

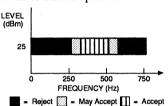

Figure 2. Low-Ban and High-Band Amplitude

Responce—Normalized

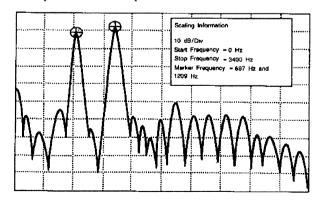

Figure 4. Low-Band Group Delay

Figure 6. High-Band Group Delay (Hz)

Figure 3. Low-Band Response—Normalized

Figure 5. High-Band Response—Normalized

Figure 7. Low-Band Divided by 2.5 Amplitude Response—Normalized

| Mode | СРМ | SEL2 | ALB | A/O | TXin | TXout | RXin        | RXout |

|------|-----|------|-----|-----|------|-------|-------------|-------|

| 0    | 0   | 0    | 1   | 0   | L    | L     | Н           | Н     |

| 1    | 0   | 0    | 1   | 1   | Н    | Н     | L           | L     |

| 2    | 0   | 0    | 0   | 0   | L    | L     | Н           | L     |

| 3    | 0   | 0    | 0   | 1   | Н    | Н     | L           | Н     |

| 4    | 0   | 1    | 1   | 0   | L/6  | L/6   | H/6         | H/6   |

| 5    | 0   | 1    | 1   | 1   | H/6  | H/6   | L/6         | L/6   |

| 6    | 0   | 1    | 0   | 0   | L/6  | L/6   | H/6         | L/6   |

| 7    | 0   | 1    | 0   | 1   | H/6  | H/6   | L/6         | H/6   |

| 8    | 1   | Х    | 1   | 0   |      | SQT   | (L/2.5 + H) | Н     |

| 9    | 1   | Х    | 1   | 1   | Н    | SQT   | L/2.5       | L/2.5 |

| 10   | 1   | Х    | 0   | 0   | _    | SQT   | (L/2.5 + H) | L/2.5 |

| 11   | 1   | Х    | 0   | 1   | Н    | SQT   | L/2.5       | Н     |

Note: SQT means the transmitter output is squelched.

"L" refers to center frequency of 1200 Hz.

"H" refers to center frequency of 2400 Hz.

- means no filter connection

+ means connection to both filters

X means "don't care"

By switching between modes 8 and 10, the filter can be used to detect reception of the call progress tones in the L/2.5 band as well as the answer tone in the H band.

Table 1. Operating Modes

| 7 V                                              |

|--------------------------------------------------|

| –7 V                                             |

| V <sub>CC</sub> +0.6 V<br>V <sub>SS</sub> -0.6 V |

| V <sub>CC</sub> +0.6 V<br>V <sub>SS</sub> -0.6 V |

| -65 to +150°C                                    |

| 500 mW                                           |

| 300°C                                            |

| 0 to +70°C                                       |

|                                                  |

Note 1. "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed.

Except for "Operating Temperature Range", the device should not be operated at these limits. The table of "Electrical Characteristics" provides actual operating limits.

2. Power dissipation temperature derating—plastic "N" package: -12 mW/°C from 65°C to 85°C.

## DC ELECTRICAL CHARACTERISTICS

# $T_A$ = 0°C to 70°C, $V_{cc}$ = +5 V ±10%, $V_{ss}$ = -5 V ±10%

| PARAM.            | DESCRIPTION                                                                      | CONDITIONS                                                                                        | MIN  | TYP  | MAX  | UNITS |

|-------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>cc</sub>   | Positive Supply Voltage                                                          |                                                                                                   | 4.5  | 5.0  | 5.5  | v     |

| V <sub>ss</sub>   | Negative Supply Voltage                                                          |                                                                                                   | -4.5 | -5.0 | -5.5 | v     |

| I <sub>cc</sub>   | Quiescent Current                                                                | No Load                                                                                           |      | 7.5  | 15   | mA    |

| I <sub>ss</sub>   | Quiescent Current                                                                | No Load                                                                                           |      | 7.5  | 15   | mA    |

| V <sub>IH</sub>   | High Level Input Voltage; Digital Signal<br>Pins 1, 4, 9, 11, 12, 13, 14, 17, 22 |                                                                                                   | 2.0  |      |      | V     |

| V <sub>IL</sub>   | Low Level Input Voltage; Digital Signal<br>Pins 1, 4, 9, 11, 12, 13, 14, 17, 22  |                                                                                                   |      |      | 0.8  | v     |

| V <sub>OMAX</sub> | Output Signals, Pins 5, 15, 16, 19, 24                                           | $V_{CC}$ = +5 V, $V_{SS}$ = -5 V<br>$R_L$ = 10 kΩ (Pins 5, 19)<br>$R_L$ = 20 kΩ (Pins 15, 16, 24) | ±3   |      |      | V     |

#### PERFORMANCE CHARACTERISTICS

## $T_A = 25$ °C, $V_{cc} = +5$ V, $V_{ss} = -5$ V

| PARAMETER                                                                                          | CONDITIONS                                                                             | MIN            | TYP        | MAX                                             | UNITS                            |

|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------|------------|-------------------------------------------------|----------------------------------|

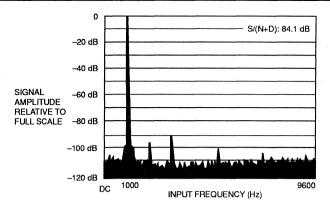

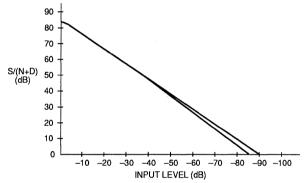

| Output Noise RXout, TXout                                                                          |                                                                                        |                | 30         | 33                                              | dBrnCo                           |

| Crosstalk                                                                                          |                                                                                        | 55             | 60         |                                                 | dB                               |

| Total Harmonic Distortion                                                                          |                                                                                        |                | 0.3        |                                                 | %                                |

| Dynamic Range                                                                                      |                                                                                        |                | 70         |                                                 | dB                               |

| Adjacent Channel Rejection Low band High band Passband Gain at Center Frequency (1200 Hz, 2400 Hz) |                                                                                        | 55<br>55<br>-1 | 65<br>75   | +1                                              | dB<br>dB                         |

| Relative Gain—Low Band<br>Reference = 1200 Hz                                                      | @ 400 Hz<br>@ 800 Hz<br>@ 1600 Hz<br>@ 1800 Hz<br>@ 2000 Hz<br>@ 2400 Hz<br>@ 2800 Hz  | -1<br>-1.5     |            | -35<br>+1<br>+1<br>-18<br>-48<br>-55<br>-50     | dB<br>dB<br>dB<br>dB<br>dB<br>dB |

| Relative Gain—High Band<br>Reference = 2400 Hz                                                     | @ 800 Hz<br>@ 1200 Hz<br>@ 1600 Hz<br>@ 2000 Hz<br>@ 2800 Hz<br>@ 3200 Hz<br>@ 3500 Hz | -2.5<br>0      |            | -50<br>-53<br>-50<br>+0.5<br>+2.5<br>-10<br>-20 | dB<br>dB<br>dB<br>dB<br>dB<br>dB |

| Relative Gain—Low Band<br>NFI = High                                                               | @ 550 Hz, NSEL = Low<br>@ 1800 Hz, NSEL = High                                         |                | -40<br>-40 |                                                 | dB<br>dB                         |

#### **APPLICATIONS**

#### **Modes of Operation**

The SC11000, SC11001 and SC11005 filters can be operated in three basic modes—a normal data mode, a test mode and a call progress monitor mode.

#### Normal Data Mode

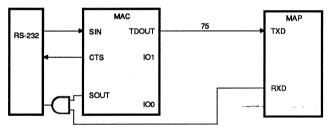

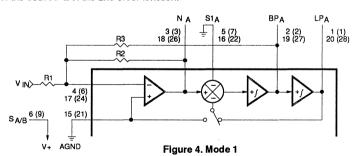

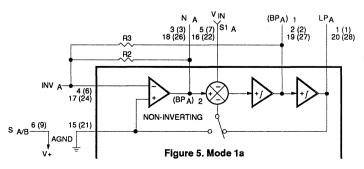

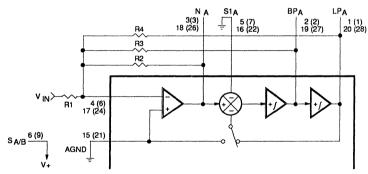

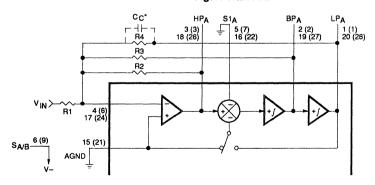

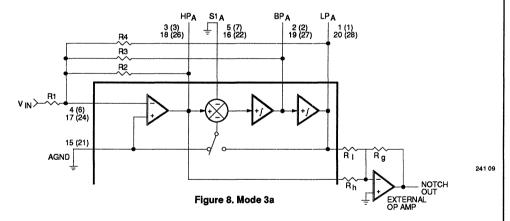

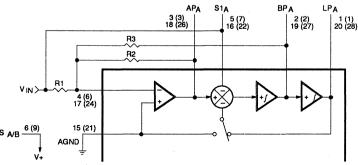

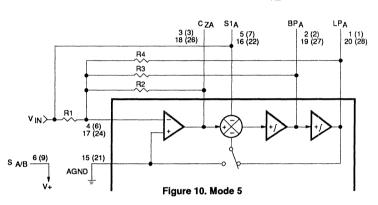

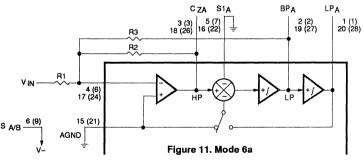

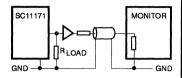

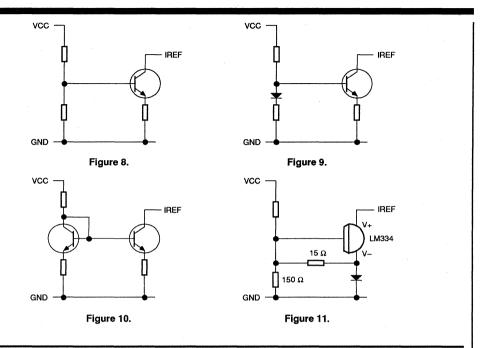

Figures 8 through 11 illustrate the signal flow diagrams for the filter in the normal data mode for either a 212A or a V.22 modem. In the originate mode, the transmit signal goes through the low-band filter and the receive signal goes through the high-band filter. In the answer mode, the transmit signal goes through the high-band filter and the receive signal goes through the low-band filter.

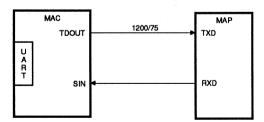

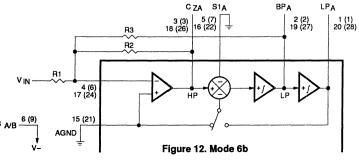

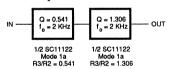

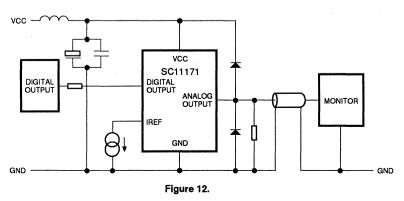

#### Test Mode

The filter can be tested by entering the analog loopback mode as illustrated in Figures 12 and 13. In this mode, the transmit signal is looped back to the RXout pin after going through either the low-band filter or the high-band filter, depending on originate or answer mode selec-

tion. The analog loopback mode facilitates testing of the modem locally, without having to make a data call.

#### **Call Progress Monitor Mode**

The filter operates in one of two different call progress monitor modes, depending on whether the SEL2 or CPM pin is taken high. If SEL2 is taken high, the center frequency of both the low-band and high-band filters is shifted down by a factor of 6 and the bandwidth of the filters is also reduced by a factor of 6. Thus the high-band filter is shifted down to 400 Hz ±80 Hz while the low-band filter is shifted down to 200 Hz ±80 Hz. By selecting the originate mode, the receive signal will go through the modified high-band filter which now has a pass-band of approximately 300 Hz to 480 Hz. This allows precision dial tone of 350/440 Hz as well as audible ringing tone of 440/480 Hz to pass. However, only a portion of the busy or reorder tone of 480/620 Hz will pass through. An external energy detector circuit, combined with a method of cadence and timing determination, distinguishes between different conditions on the line during establishing a call.

The SC11001 features an additional mode for monitoring the call progress tones. This mode is initiated by taking the CPM pin high. Two deficiencies, inherent in the first mode described above, are overcome in this enhanced mode. First, the passband is more accurately centered over the call progress tone frequencies because the low-band filter is scaled down by a factor of 2.5. The low-band filter thus has a passband of 290 Hz to 670 Hz which allows the busy tone to pass through completely. Secondly, since the high-band filter is not scaled, answer tone can be easily monitored. The receive signal is connected to both the high-band filter and the scaled low-band filter. By toggling the ALB pin between high and low levels, either the answer tone or the call progress tone can be monitored on the RXout pin.

Figures 14 and 15 show the signal flow diagrams in the call progress monitor mode. A method for determining conditions on the line during establishing a call is described in the following section.

Figure 8. 212A Originate Mode

Figure 9. 212A Answer Mode

Figure 10. V.22 Answer Mode

Figure 11. V.22 Originate Mode

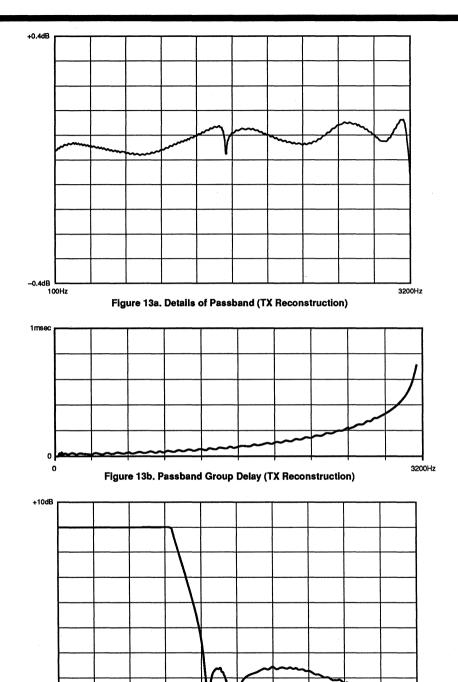

Figure 12. 212A Analog Loopback Mode Using Low-Band Filter (Originate Mode)

Figure 13. 212A Analog Loopback Mode Using High-Band Filter (Answer Mode)

Figure 14. Call Progress Monitor Mode: Monitoring Answer Tone/Voice

Figure 15. Call Progress Monitor Mode: Monitoring Call Progress Tones

#### **Circuit Description**

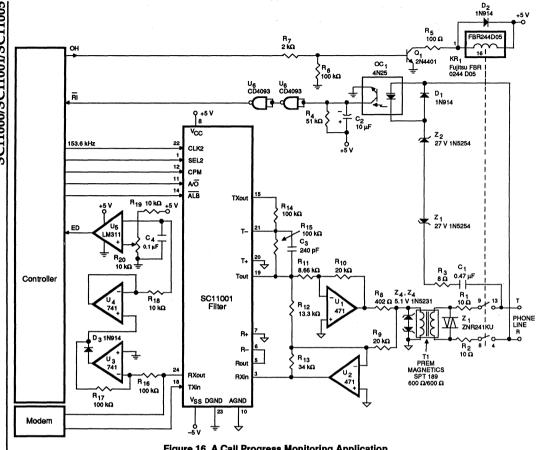

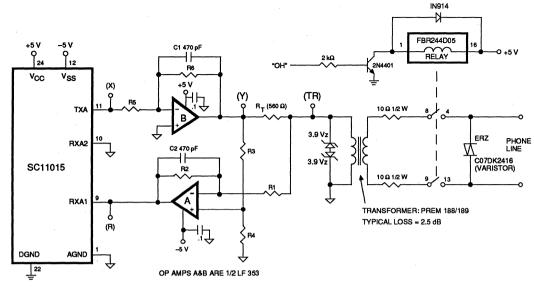

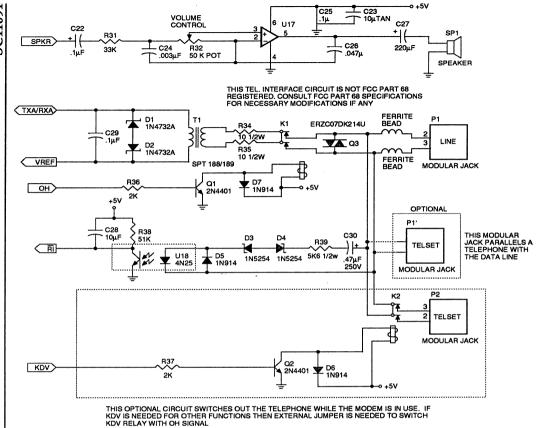

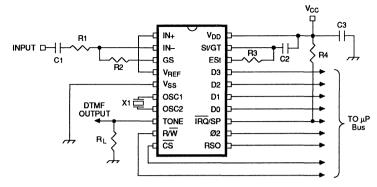

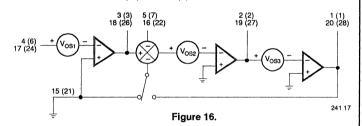

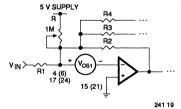

In the circuit of Figure 16, op amps U<sub>1</sub> and U<sub>2</sub> and resistors R<sub>8</sub> thru R<sub>13</sub> form a 2 to 4 wire converter that seperates the line signal into the transmit and receive components. The receive signal is connected to the RXin input of the SC11001 filter. In the call originate mode, it goes through the high-band filter and comes out on the RXout pin. For call progress monitoring the low-band filter operates in the scaled mode, thus filtering the receive signal over the range of 290 Hz to 670 Hz. Op amps U<sub>2</sub> and U<sub>4</sub>, comparator U<sub>5</sub> and associated discrete components form the energy detector. U<sub>3</sub> operates as a full wave rectifier. U, is a buffer that drives a low pass filter formed by  $R_{18}$  and  $C_4$ . The filtered signal is compared to a level set by  $R_{19}$  and  $R_{20}$ . The output of  $U_5$  goes high if the signal level exceeds the level set by  $R_{19}$  and  $R_{20}$ . This output corresponds to the cadence information in the call progress tone signals and can be sampled by the controller according to the detection algorithm.

The rest of the circuitry in Figure 16 performs the functions of the DAA. Transformer  $T_1$  provides isolation and sinks the line current in the off hook state.  $R_1$ ,  $R_2$ ,  $V_1$ ,  $Z_3$  and  $Z_4$  provide surge protection. Relay  $KR_1$  and transistor  $Q_1$  control on hook/off hook condition.  $C_1$ ,  $R_2$ ,  $Z_1$ ,  $Z_2$ ,  $Z_1$ , and  $OC_1$ 's internal diode limit and rectify the high voltage AC ringing signal.  $OC_1$  provides isolation.  $R_4$  and  $C_2$  filter the rectified ring signal and Schmidt Trigger IC.  $U_6$  converts it into a logic level for the controller.

#### A Call Progress Monitoring Application

Figure 16 shows a schematic for using the SC11001 filter in a call progress monitoring application.

Specifically, this arrangement is well suited for implementing an intelligent 212A or V.22 modem. The modem can be designed to be either stand-alone with RS-232 interface to DTE or integrated in a computer with a parallel bus interface. It is assumed that a controller is available that can control the various operating modes of the filter, monitor the output of the energy detector and ring indicator, and control the switch-hook relay in the Data Access Arrangement (DAA). This application illustrates how the modem filter can be used with minimum of external circuitry to implement a fully automatic call establishment procedure.

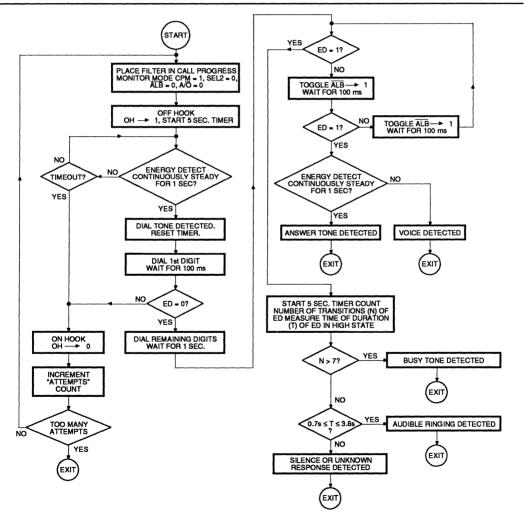

Table 2 summarizes various call progress tone frequencies and their cadences. A call progress monitoring algorithm based on timing and cadence characteristics is described in the flow chart of Figure 17.

Figure 16. A Call Progress Monitoring Application

| Call Progress Tone | Frequency (Hz)                                         | Cadence                          |

|--------------------|--------------------------------------------------------|----------------------------------|

| Dial tone          | 350 + 440*<br>400, 425<br>600 x 120 IPS**              | Continuous steady tone           |

| Audible ring       | 440 + 480*<br>400, 450<br>420 x 40 IPS<br>400 x 25 IPS | 2 s on/4 s off<br>1 s on/3 s off |

| Busy (station)     | 480 + 620*<br>400, 425, 450<br>600 x 120 IPS           | 0.5 s on/0.5 s off               |

| Busy (circuit)     | Same as above                                          | 0.25 s on/0.25 s off             |

| Off hook alert     | Multifrequency                                         | 1 s on/1 s off                   |

<sup>\*</sup>Precision tone specified by AT&T

**Table 2. Call Progress Tone Characteristics**

<sup>\*\*</sup>IPS means interruptions per second

#### **Detection Algorithm**

Figure 17 shows the flowchart of a detection algorithm that utilizes the features provided in the SC11001 filter and that uses the cadence information contained in the call progress tones to determine the status of the line. The main criterion in this algorithm was the high degree of reliability it provides, rather than the speed in which it executes. For instance, dial tone is detected only when the output of the energy

detector is continuously high for at least one second. If dial tone is not detected within 5 seconds of going off hook, the call is aborted. Many dialers do not wait for the initial dial tone and begin dialing as soon as going off hook. This is termed blind dialing and is avoided by this algorithm.

Once dial-tone is detected, the first digit is dialed using the tone mode. Provision is made to check the absence of the dial-tone after the digit

is dialed. If dial-tone remains on the line, the controller can either hang up the line or try to dial using rotary pulse dialing. If dial-tone is absent, the rest of the digits can be pulse dialed.

The algorithm waits for 1 second after dialing is done to monitor the energy detector. This insures that any clicks on the line will not cause a false detection. The ALB pin of the filter is then toggled at a 100 ms rate and the energy detector output is

Figure 17. Call Progress Monitoring Algorithm

sampled to see if there is energy in the call progress band or in the voice band. If energy is detected in the call progress band, a 5 second timer is started and the number of transitions of the ED output are counted (N). The cumulative duration in which the ED output is in the high state is also measured (T).

The algorithm makes a determination of various conditions based on N and T. The line is determined to be busy if N exceeds 7. If N is less than 7 and T is in the range of 0.7 seconds to 3.8 seconds, the signal is determined to be audible ringing. The controller can then count the ring cycles or start a timer. It can choose to hang up if the timer overflows or if the number of ring cycles exceeds a preset value. Any other value of N or T is classified as unknown response and it is left to the controller to take the next action.

If energy is detected in the high band, ED output is monitored to see if it is continuously high for at least one second. If so, this is interpreted as the distant modem answertone, indicating that the connection is made. If not, it indicates either silence or voice. In either case the controller can terminate the call and take the next step. Minor variations of this algorithm or fine tuning of the decision values can provide the designer with the flexibility he needs to deal with different situations. It should be emphasized that the algorithm does not stand alone and must be integrated in the application software for satisfactory performance.

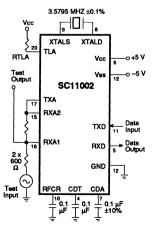

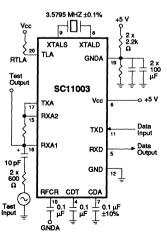

#### **FEATURES**

- ☐ Full duplex answer and originate operation

- ☐ All filters and Hybrid circuits on

The SC11002 and SC 11003 are full

duplex, 0 to 300 Bit Per Second

single chip modems compatible

with Bell 103 specifications. They are intended for data communica-

tions over the general switched

telephone network and can also be

used on other voice-band channels.

The SC11002 requires +5 volts and

-5 volts; the SC11003 requires a

single +5 volt supply. These 3-

micron, CMOS, switched capacitor

filter circuits are pin compatible

☐ Analog loopback capacity

**GENERAL DESCRIPTION**

# $\Box$ Output drives 600 $\Omega$ at 0 dbm (–9 dbm for SC11003)

☐ Lower power CMOS design with power down mode

# with the National Semiconductor 74HC942 (SC11002) and the 74HC943 (11003) and are a functional replacement for Texas

Instruments' TMS99532.

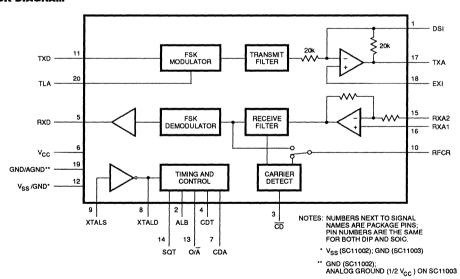

Included on chip are high-band and low-band filters, an FSK modulator and demodulator and a line driver and hybrid for directly driving a  $600~\Omega$  phone line.

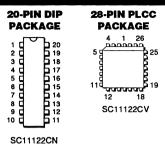

Applications include integrated and stand-alone low speed

#

SC11003CN

20-PIN DIP

modems for terminals, personal computers and small business computers and as built-in modems used for remote diagnostics in electronic test systems, computer installations, industrial control systems and business machines. Since they are CMOS, they are ideal as built-in modems for portable or lap-top computers.

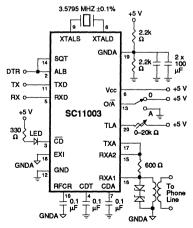

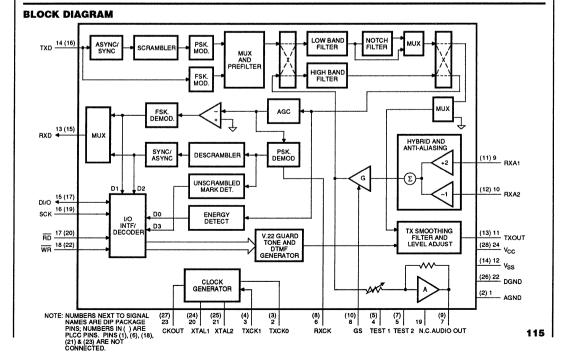

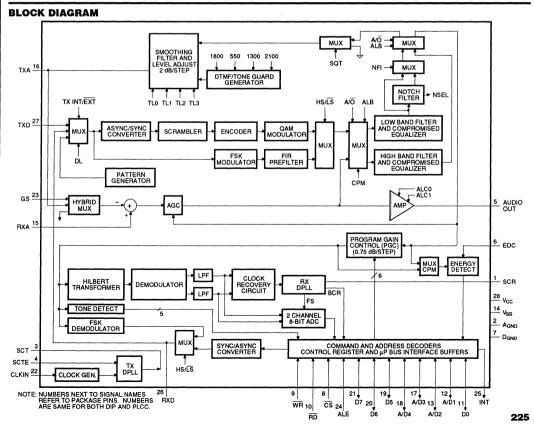

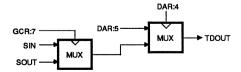

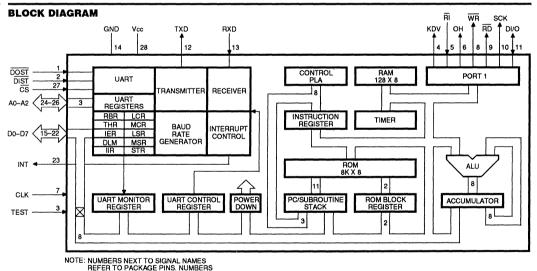

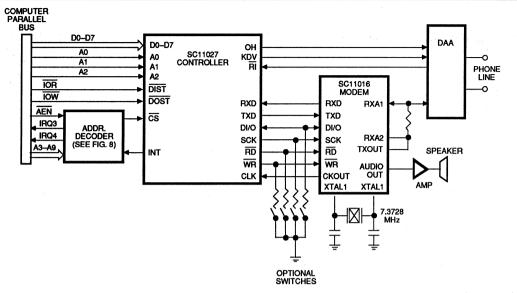

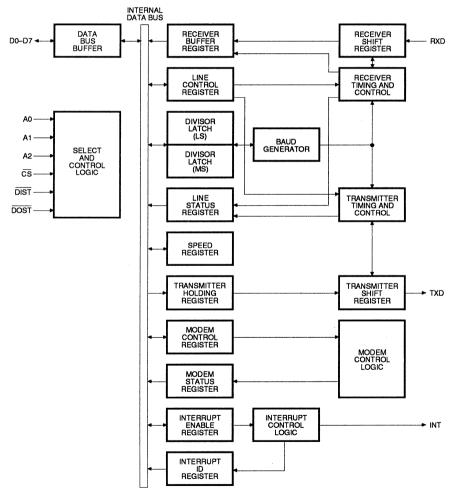

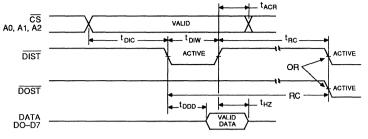

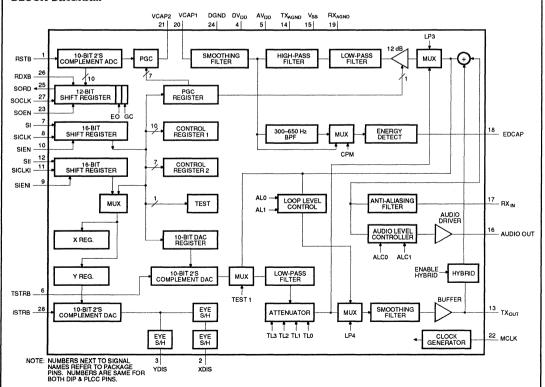

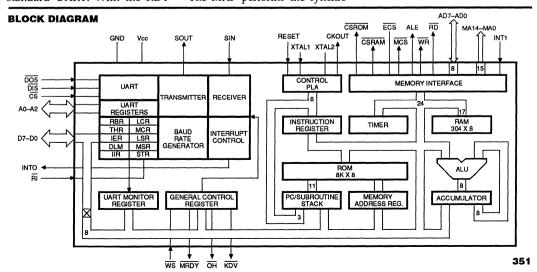

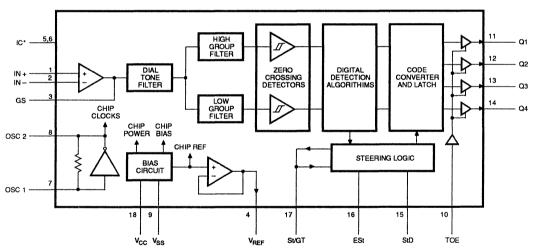

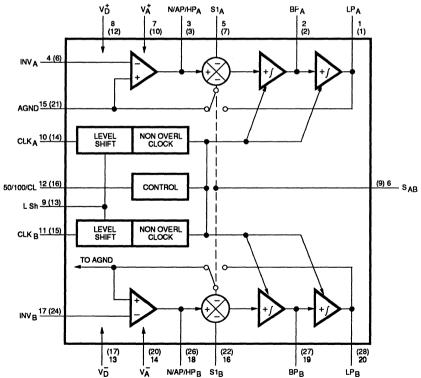

#### **BLOCK DIAGRAM**

#### PIN DESCRIPTION

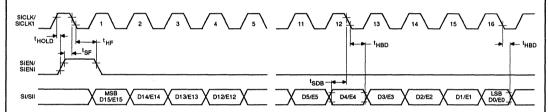

| PIN<br>NO. | PIN NAME             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1          | DSI                  | Driver summing Input; used to transmit externally generated tones such as DTMF dialing signals. When not used, this pin should be left open. See functional description for details on how to use this input.                                                                                                                                                                                                            |  |  |  |

| 2          | ALB                  | alog loopback; low for normal operation, high for looping back the modulator output to the modulator input. If ALB and SQT are simultaneously held high, the chip powers down.                                                                                                                                                                                                                                           |  |  |  |

| 3          | CD                   | Carrier detect output; goes low when carrier is detected.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 4          | CDT                  | Carrier detect timing input; a capacitor on this pin sets the time interval that the carrier must be present before CD goes low. For testing purposes, if this pin is connected to Pin 12, then RFCR will be connected to the output of the receive filter.                                                                                                                                                              |  |  |  |

| 5          | RXD                  | Received data—the data output.                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |