) Maria

ER'S MANUA

# **SB-1 USER'S MANUAL**

**COPYRIGHT SIBYTE, 2000**

#### Trademarks

SiByte is a registered trademark of SiByte, Inc.

All other trademarks referenced herein are the property of their respective owners.

#### Copyright

Copyright © 2000 SiByte, Inc. All Rights Reserved.

SiByte, Inc. reserves the right to amend or discontinue this product without notice. Circuit and timing diagrams used to describe SiByte product operations and applications are included as a means of illustrating a typical product application. Complete information for design purposes is not necessarily given. This information has been carefully checked and is believed to be entirely reliable. SiByte, however, will not assume any responsibility for inaccuracies. Life Support Applications: SiByte products are not designed for use in life support applications devices, or systems where malfunctions of the Sibyte product can reasonably be expected to result in personal injury. SiBytes customers using or selling SiByte products for use in such applications do so at their own risk and agree to fully indemnify SiByte for any damages resulting in such improper use or sale.

v

.

# Table of Contents

| CHAPTER 1 | Introduction 21                                                   |

|-----------|-------------------------------------------------------------------|

|           | Introduction 21                                                   |

|           | Document Organization 21                                          |

|           | Additional Documentation 23                                       |

|           | What is Missing or Incomplete in this Version of the Document? 23 |

|           |                                                                   |

| CHAPTER 2 | SB-1 Overview 25                                                  |

|           | Introduction 25                                                   |

|           | High Level Features 25                                            |

|           | SB-1 Units 28                                                     |

|           | The PC Unit 28                                                    |

|           | The Branch Unit 28                                                |

|           | Two Level GShare, Branch Direction Predictor 28                   |

|           | Return Stack (RS) 28                                              |

|           | Jump Register Cache (JRC) 28                                      |

|           | The Issue Unit (IBox) 28                                          |

|           | The Execute Unit (E0, E1) 29                                      |

|           | The Load/Store Unit (LS0, LS1) 29                                 |

|           | The Floating Point Unit (F0, F1) 29                               |

|           | <i>The MDMX Unit (A0, A1)</i> <b>29</b>                           |

|           | The Memory Unit (MBox) 29                                         |

|           | The Bus Interface Unit (BIU) 30                                   |

|           | Level One Instruction and Data Caches 30                          |

|           | SB-1 Specifics 30                                                 |

| CHAPTER 3 | The CPU Instructions 31                                           |

|           | Introduction 31                                                   |

Introduction 31 List of Instructions 31 CPU Load, Store and Memory Control Instructions 31

CPU Arithmetic Instructions 32 CPU Logical Instructions 33 CPU Move Instructions 34 CPU Shift Instruction 34 CPU Branch and Jump Instructions 35 CPU Trap Instructions 35 **Obsolete Branch Instructions** 36 Embedded Application Instructions 37 Block and Pipeline Diagrams 37 The EXE0 Unit 38 The EXE1 Unit 40 The LSO Unit 42 The LSI Unit 44 Instruction Latency and Throughput by Category of Instructions 46 Available Bypasses 46 Instruction Types Issued to each Pipe 47 Issue Rules and Restrictions 47 Differences between 32 and 64-bit Modes of Operation 48

**CHAPTER 4**

#### The FPU (CP1) and MIPS-3D ASE Instructions 49

Introduction 49 High Level Description of FP Block 49 Block and Pipeline Diagrams 50 Instruction Latency and Throughput by Category of Instructions 51 MIPS-3D ASE Instructions 54 Available Bypasses 55 Differences between the Pipes 55 Issue Rules and Restrictions 56 Implementation Details on Special Instructions 56 MADD, MSUB, NMADD, NMSUB 56 DIV Operation 57 SQRT Operation 58 RECIP1 and RSQRT1 Operations 58 RECIP2 58 RSQRT2 58 Supplemental FP Instruction in SB-1 58 FIR Register Implementation in SB-1 67

Exception Processing 67 RESET 68 FP Instruction Issue Policy with Exception Off Mode 68 FP Instruction Issue Policy with Exception On Mode 68 Denormals 68 Exception Flags 69

**CHAPTER 5**

#### The MDMX ASE Instructions 71

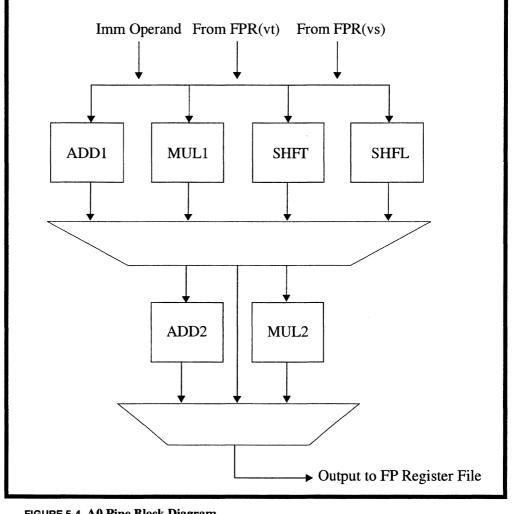

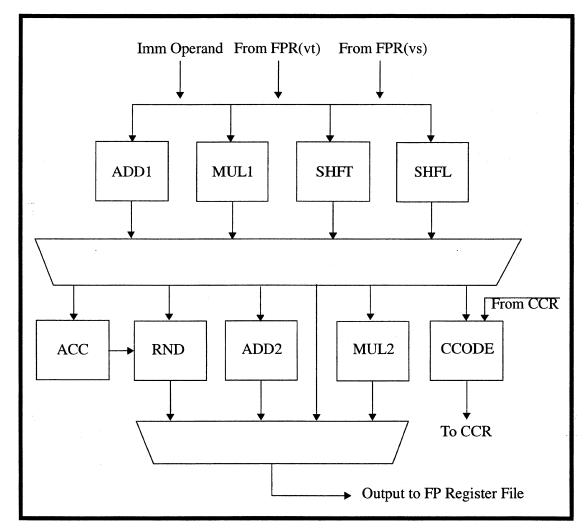

Introduction 71 List of Supplemental Instructions 71 MDMX ASE Instruction Categories in SB-1 78 MDMX Unit Block Diagram 79 Pipeline Flow by Category of Instructions 81 *TYPE I Pipe* 81 *TYPE II Pipe* 81 *TYPE III Pipe* 81 Instruction Latency and Throughput by Category of Instructions 82 Available Bypasses 82 Differences between the Pipes 82 Issue Rules and Restrictions 83

**CHAPTER 6**

# Memory Hierarchy and the Primary Instruction and Data Caches 85

Introduction **85** Supported Cache and Memory Hierarchy **85**  *Level One (Primary) Caches 87* Instruction Cache (I-Cache) 87 Accessing the Instruction Cache 88 Address Fields Decoding 89 Parity/ECC Support 89 Notes on the Virtual Nature of the Instruction Cache 89 Data Cache (D-Cache) 90 Accessing the Data Cache 91 Address Fields Decoding 92

Parity/ECC Support 92 Rules for Uncached Data Accesses 92 Operation of the Write Buffer 93 Merging Rules 93 Prefetch Support for Primary Data Cache (User Level Prefetching and Streaming) 94 **Regular Data Prefetching 95** Streaming Prefetch Support in SB-1 95 The PREF and PREFX Instructions in SB-1 96 CACHE Instructions 100 CACHE Variants 100 Index Invalidate (I) 102 Index Load Tag (1) 102 Index Store Tag (1) 102 Hit Invalidate (I) 102 Index Load Data (I) 103 Index Store Data (I) 103 Index Invalidate (D) 103 Index Load Tag (D) 104 Index Store Tag (D) 104 Hit Invalidate (D) 104 Hit Writeback Invalidate (D) 104 Hit Writeback (D) 105 Index Load Data (D) 105 Index Store Data (D) 105 Cache Operation Effects on Duplicate Tags 106 CACHE Instruction Issue Rules 106 Register Definitions 106 Tag Registers (MIPS Compliant) 107 Data Registers (SiByte Debug Defined) 109 Cache Coherency Attributes 111

#### **CHAPTER 7**

#### Virtual Memory Address Space and the TLB Format 113

Introduction 113 Supported Memory Address Space in SB-1 114 The TLB 118 *TLB Entry Format* 119

SB-1 Users Manual

viii

#### **CHAPTER 8**

### The CP0 Architecture 121

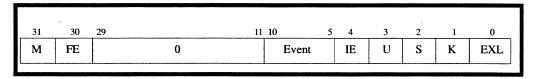

Introduction 121 Overview of CP0 Registers 121 Processor Status and Control (Status, CP0 Register 12, sel0) 124 Processor Identification and Revision (PRId, CPO Register 15, sel0) 125 Configuration Register (Config, CP0 Register 16, sel0) 126 Load Linked Address (LLAddr, CP0 Register 17, sel0) 127 Watchpoint Address (WatchLo, CP0 Register 18, sel0-n) 127 Watchpoint Control (WatchHi, CP0 Register 19, sel0-n) 127 EJTAG Debug Register (Debug, CPO Register 23, sel0) 127 Program Counter at Last EJTAG Debug Exception (DEPC, CP0 Register 24, sel0) 128 Performance Counter Interface (PerfCnt, CP0 Register 25, sel0) 128 Parity/ECC Error Control and Status (ErrCtl, CP0 Register 26, sel0) 128 Cache Error Control and Status (CacheErr, CPO Register 27, sel0-3) 128 Low-order Portion of Cache Data Interface (DataLo, CP0 Register 28, sel1) 128 High-order Portion of Cache Data Interface (DataHi, CP0 Register 29, sell) 128 EJTAG Debug Exception Save Register (DESAVE, CP0 Register 31, sel0) 128 Privileged Resource Hazards 129

Privileged Resources and Instructions 129 Privileged Resource Hazards 130 CP0 Register Side-Effects 131 Fetch Hazards 131 Execution Hazards 132

CHAPTER 9

#### The Debug Architecture 137

Introduction 137 Debug Features 137 *Watch Registers* 137 EJTAG 139 Extended Debug Mode 141 Debug Signal Pins 143

**CHAPTER 10**

# Error Handling 145

Introduction 145 Instruction Cache 147 Implementation Notes: 147 Data Cache 148 Implementation Notes 149 TLB 150 Implementation Notes 150 BIU 151 General 151 Implementation Notes: 152 Error Reporting Registers 152

#### **CHAPTER 11**

# The Performance Monitor Architecture 157

#### Introduction 157

Architecture State and Features 158

Event Counter and Control Registers (Register = 25, Select = 0x00, 0x01, 0x02, 0x03, 0x04, 0x05, 0x06, 0x07) 159 Counter Overflow Interrupt 160 Event Control and Address Registers (Select = 0x10, 0x11, 0x12) 161 Performance Events 167 Pending Issues 169

#### **CHAPTER 12**

#### Multiprocessing Support 171

Introduction 171 Support for Atomic Operations 171 Processor Synchronization 173 *Test and Set 173 Counter Based Synchronization 173* Coherency 173 *Memory Model 173* Cache Organization and Coherency in SB-1 174 *Instruction Stream Modifications 174 Caching Attributes 174* Processor Bringup 175

#### CHAPTER 13

# SB-1 Implementation Specific Details 177

Introduction177Clarifications on Implementation-Dependent Non-Privileged Instructions177Clarifications on Implementation-Dependent Privileged Instructions178

SB-1 Users Manual

xii

50

# List of Figures

**Introduction 21**

SB-1 Overview 25

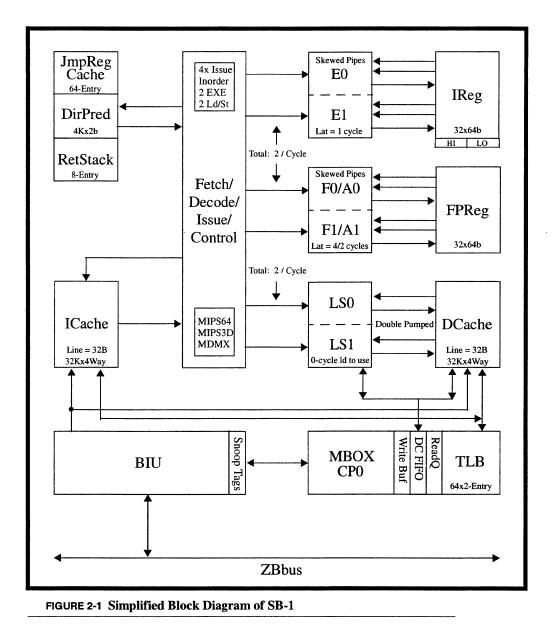

FIGURE 2-1 Simplified Block Diagram of SB-1 27

#### **The CPU Instructions 31**

FIGURE 3-1EXE and LS Pipes in SB-137FIGURE 3-2EXE0 Block Diagram38FIGURE 3-3EXE1 Block Diagram40FIGURE 3-4LS0 Unit Block Diagram42FIGURE 3-5LS1 Block Diagram44

#### The FPU (CP1) and MIPS-3D ASE Instructions 49

| FIGURE 4-1 Block Diagram of the Floating | g Point Unit |

|------------------------------------------|--------------|

| FIGURE 4-2 DIV Format 59                 |              |

| FIGURE 4-3 RECIP Format 61               |              |

| FIGURE 4-4 RSQRT Format 63               |              |

| FIGURE 4-5 SQRT Format 65                |              |

| FIGURE 4-6 FIR Register Format in SB-1   | 67           |

#### **The MDMX ASE Instructions 71**

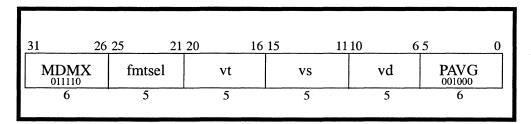

| FIGURE 5-1 | PAVG.OB Format 72     |    |

|------------|-----------------------|----|

| FIGURE 5-2 | PAVG.OB Format 74     |    |

| FIGURE 5-3 | PAVG.OB Format 76     |    |

| FIGURE 5-4 | A0 Pipe Block Diagram | 79 |

| FIGURE 5-5 | A1 Pipe Block Diagram | 80 |

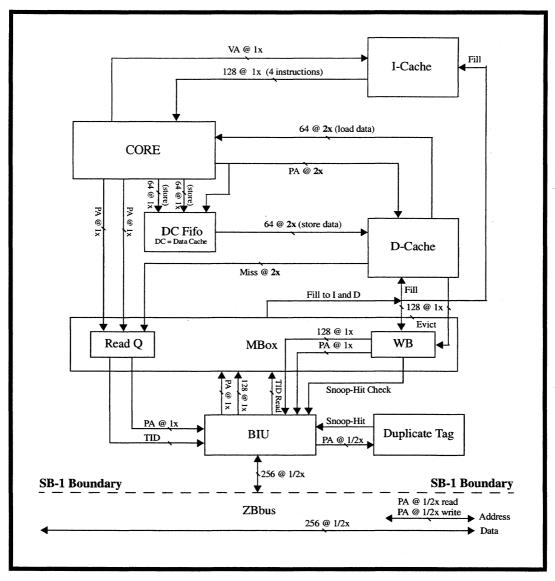

#### Memory Hierarchy and the Primary Instruction and Data Caches 85

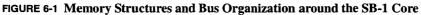

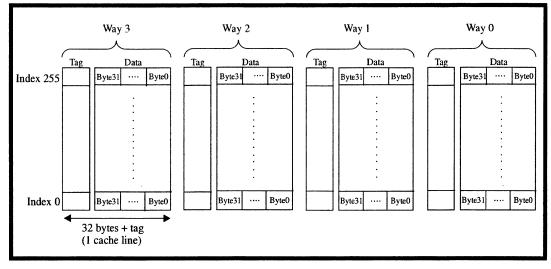

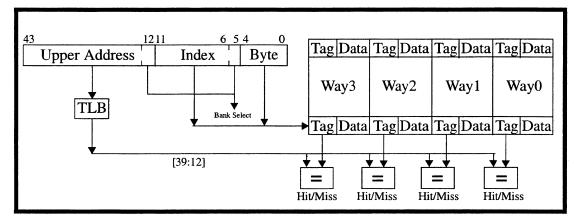

FIGURE 6-1 Memory Structures and Bus Organization around the SB-1 Core 86

| FIGURE 6-2 | Primary Instruction Cache Indexing in SB-1 | 88 |

|------------|--------------------------------------------|----|

| FIGURE 6-3 | Instruction Cache Organization in SB-1 89  |    |

| FIGURE 6-4 | Primary Data Cache Indexing in SB-1 91     |    |

| FIGURE 6-5 | Data Cache Organization in SB-1 92         |    |

| FIGURE 6-6 | Format for PREF Instruction 96             |    |

| FIGURE 6-7 | Format for PREFX Instruction 96            |    |

#### Virtual Memory Address Space and the TLB Format 113

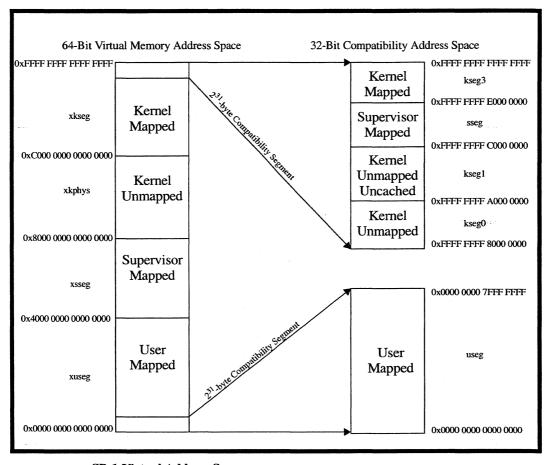

| FIGURE 7-1 | SB-1 Virtual Address Space | 116 |

|------------|----------------------------|-----|

| FIGURE 7-2 | TLB Entry Format in SB-1   | 119 |

#### The CP0 Architecture 121

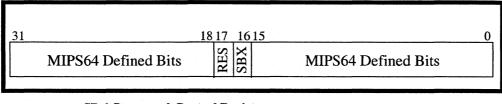

| FIGURE 8-1 | SB-1 Status and Control Register 124  |

|------------|---------------------------------------|

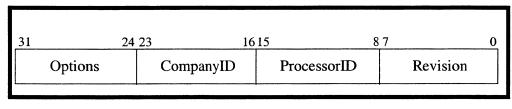

| FIGURE 8-2 | PRId Register Format 125              |

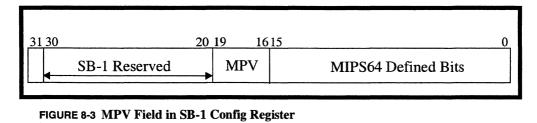

| FIGURE 8-3 | MPV Field in SB-1 Config Register 126 |

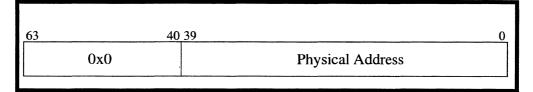

| FIGURE 8-4 | LLAddr Register Format in SB-1 127    |

#### **The Debug Architecture 137**

# **Error Handling 145**

#### **The Performance Monitor Architecture 157**

FIGURE 11-1Performance Counter Control Register159FIGURE 11-2Performance Counter Register160FIGURE 11-3Cache Event Control Register163FIGURE 11-4Event Instruction Address Register164FIGURE 11-5Event Data Address Register165

**Multiprocessing Support 171**

**SB-1** Implementation Specific Details 177

# List of Tables

| Introduction 21      |                   |                                                                                |

|----------------------|-------------------|--------------------------------------------------------------------------------|

|                      | TABLE 1-1         | Supplemental Documents to SB-1 Users Manual 23                                 |

|                      |                   |                                                                                |

| SB-1 Overview 25     |                   |                                                                                |

|                      | TABLE 2-1         | SB-1 High Level Specification 25                                               |

|                      | 21                |                                                                                |

| The CPU Instructions |                   |                                                                                |

|                      | TABLE 3-1         | CPU Load, Store, and Memory Control Instructions 31                            |

|                      | TABLE 3-2         | CPU Arithmetic Instructions 32                                                 |

|                      | TABLE 3-3         | CPU Logical Instructions 33                                                    |

|                      | TABLE 3-4         | CPU Move Instructions 34                                                       |

|                      | TABLE 3-5         | CPU Shift Instructions 34                                                      |

|                      | TABLE 3-6         | CPU Branch and Jump Instructions 35                                            |

|                      | TABLE 3-7         | CPU Trap Instructions 35                                                       |

|                      | TABLE 3-8         | Obsolete Branch Instructions 36                                                |

|                      | TABLE 3-9         | Embedded Application Instructions 37                                           |

|                      | TABLE 3-10        | Instructions Supported by the EXE0 Unit 39                                     |

|                      | TABLE 3-11        | EXE0 Pipe Stages in SB-1 39                                                    |

|                      | <b>TABLE 3-12</b> | Instructions Supported by the EXE1 Unit 41                                     |

|                      | TABLE 3-13        | EXE1 Pipe Stages in SB-1 (All Except Divide) 41                                |

|                      | <b>TABLE 3-14</b> | EXE1 Pipe Stages in SB-1 for Divide Instructions 42                            |

|                      | <b>TABLE 3-15</b> | Instructions Supported by the LSO Unit 43                                      |

|                      | TABLE 3-16        | LSO Pipe Stages in SB-1 43                                                     |

|                      | <b>TABLE 3-17</b> | Instructions Supported by the LS1 Unit 45                                      |

|                      | TABLE 3-18        | LS1 Pipe Stages in SB-1 45                                                     |

|                      | TABLE 3-19        | Instruction Throughput and Latency for EXE and LS Units by Inst<br>Category 46 |

|                      | TABLE 3-20        | List of Available Bypasses in SB-1 Core for EX0, EX1, LS0, and LS1 Units 46    |

|                      | TABLE 3-21        | Instruction Types Issued to each Pipe 47                                       |

SB-1 Users Manual

XV

TABLE 3-22Instruction Issue Rules and Restrictions for CPU instructions47

# The FPU (CP1) and MIPS-3D ASE Instructions 49

| TABLE 4-1         | FP Block Description 49                                         |

|-------------------|-----------------------------------------------------------------|

| TABLE 4-2         | FP0 and FP1 Pipe Operation 51                                   |

| TABLE 4-3         | FPU Load/Store Instructions Supported in CPU Unit (Chapter      |

|                   | 3) 51                                                           |

| TABLE 4-4         | FPU Arithmetic Instructions 51                                  |

| TABLE 4-5         | FPU Move Instructions 52                                        |

| TABLE 4-6         | FPU Convert Instructions 53                                     |

| TABLE 4-7         | FPU Branch Instructions 53                                      |

| TABLE 4-8         | Obsolete FPU Branch Instructions 54                             |

| TABLE 4-9         | MIPS-3D Instructions in the SB-1 Core 54                        |

| TABLE 4-10        | List of Available Bypasses in SB-1 Core for EX0, EX1, LS0, and  |

|                   | LS1 Units 55                                                    |

| TABLE 4-11        | Instruction Types Issued to each Pipe 55                        |

| <b>TABLE 4-12</b> | Issue Rules and Restrictions for Floating Point Instructions 56 |

| <b>TABLE 4-13</b> | FIR Register Field Descriptions 67                              |

| TABLE 4-14        | SB-1 Exception Behavior 69                                      |

#### **The MDMX ASE Instructions 71**

| TABLE 5-1 | SiByte Supported Additional MDMX Instructions 71                            |

|-----------|-----------------------------------------------------------------------------|

| TABLE 5-2 | MDMX Instruction Categories in SB-1 78                                      |

| TABLE 5-3 | MDMX TYPE-I Pipe Operation 81                                               |

| TABLE 5-4 | MDMX TYPE-II Pipe Operation 81                                              |

| TABLE 5-5 | MDMX TYPE-III Pipe Operation 81                                             |

| TABLE 5-6 | MDMX Instruction Latency and Throughput 82                                  |

| TABLE 5-7 | List of Available Bypasses in SB-1 Core for EX0, EX1, LS0, and LS1 Units 82 |

| TABLE 5-8 | Instruction Types Issued to each Pipe 82                                    |

| TABLE 5-9 | Issue Rules and Restrictions for MDMX Instructions 83                       |

# Memory Hierarchy and the Primary Instruction and Data Caches 85

| TABLE 6-1 | SB-1 Primary Instruction Cache Characteristics | 87 |

|-----------|------------------------------------------------|----|

| TABLE 6-2 | SB-1 Primary Data Cache Characteristics 90     |    |

| TABLE 6-3 | Cache Prefetch Support for Primary Data Cache  | 94 |

SB-1 Users Manual

xvi

| TABLE 6-4         | Regular Data Prefetch Support Provided by SB-1 95              |

|-------------------|----------------------------------------------------------------|

| TABLE 6-5         | Streaming Prefetch Support in SB-1 95                          |

| TABLE 6-6         | PREF Hint Field Encodings 97                                   |

| TABLE 6-7         | Instruction Cache 100                                          |

| TABLE 6-8         | Data Cache 101                                                 |

| TABLE 6-9         | TagLo Register: Register 28, Select 0 (Instruction Cache) 107  |

| TABLE 6-10        | TagHi Register:Register 29, Select 0 (Instruction Cache)107    |

| TABLE 6-11        | TagLo Register: Register 28, Select 2 (Data Cache) 107         |

| <b>TABLE 6-12</b> | TagHi Register: Register 29, Select 2 (Data Cache) 108         |

| TABLE 6-13        | State/Coherent/Check Field Encodings 108                       |

| TABLE 6-14        | DataLo Register: Register 28, Select 1 (Instruction Cache) 109 |

| TABLE 6-15        | DataHi Register: Register 29, Select 1 (Instruction Cache) 109 |

| TABLE 6-16        | DataLo Register: Register 28, Select 3 (Data Cache) 109        |

| TABLE 6-17        | DataHi Register: Register 29, Select 3 (Data Cache) 110        |

| TABLE 6-18        | SB-1 Cache Coherency Attributes 111                            |

|                   |                                                                |

# Virtual Memory Address Space and the TLB Format 113

| TABLE 7-1 | Virtual Memory Address Space   | 114   |

|-----------|--------------------------------|-------|

| TABLE 7-2 | SB-1 Cache Coherency Attribute | s 117 |

| TABLE 7-3 | TLB Organization in SB-1 118   |       |

# The CP0 Architecture 121

| TABLE 8-1 | List of CP0 Registers in SB-1 121                                        |

|-----------|--------------------------------------------------------------------------|

| TABLE 8-2 | PRId Register Fields in SB-1 125                                         |

| TABLE 8-3 | LLAddr Register Field Descriptions 127                                   |

| TABLE 8-4 | Resources Required by MIPS64 Privileged Instructions 129                 |

| TABLE 8-5 | Processor Activities Requiring Privileged Resources 130                  |

| TABLE 8-6 | Operation Grouping of Privileged and Miscellaneous CPU<br>Operations 130 |

| TABLE 8-7 | Implemented Interlocks for Each Pair of Operation Groups 131             |

| TABLE 8-8 | CP0 Registers that Affect Instruction Fetch 132                          |

| TABLE 8-9 | Required/Generated CP0 States by SB-1 Instructions and Activities 132    |

# The Debug Architecture 137

| TABLE 9-1 | WatchLo/Hi Register Specifics 138                      |     |

|-----------|--------------------------------------------------------|-----|

| TABLE 9-2 | Debug Register: CP0 Register 23, Sel = $0$ , EDM = $0$ | 139 |

| TABLE 9-3 | EDebug Register(CP0 Register 23, Sel = 3) 141          |     |

| TABLE 9-4 | Debug, $Sel = 0$ , $EDM = 1$ 141                       |     |

| TABLE 9-5 | Debug Reset Behavior 142                               |     |

| TABLE 9-6 | Debug Signal Pins 143                                  |     |

# **Error Handling 145**

| TABLE 10-1        | SB-1 Error Types 146                                    |

|-------------------|---------------------------------------------------------|

| <b>TABLE 10-2</b> | Instruction Cache Tag Field Protection 147              |

| TABLE 10-3        | Instruction Access Error Types 148                      |

| TABLE 10-4        | Data Cache Tag Protection 148                           |

| TABLE 10-5        | Load Errors 149                                         |

| TABLE 10-6        | Store Errors 149                                        |

| <b>TABLE 10-7</b> | Cacheline Errors due to Evicts 150                      |

| <b>TABLE 10-8</b> | Error-Exception Types and Interventions 150             |

| <b>TABLE 10-9</b> | Duplicate Tag State/Address Parity Cache Errors 151     |

| TABLE 10-10       | CP0 Err Ctl Register Fields 152                         |

| TABLE 10-11       | CacheErr-I Format 153                                   |

| TABLE 10-12       | Validity of Idx and Way Fields in ICache Errors 153     |

| TABLE 10-13       | CacheErr- D Format 154                                  |

| TABLE 10-14       | Validity of Idx, Way and PA Fields in DCache Errors 155 |

| TABLE 10-15       | Error Reporting Registers 156                           |

# The Performance Monitor Architecture 157

| TABLE 11-1        | Performance Counter Register Mapping 158                   |

|-------------------|------------------------------------------------------------|

| TABLE 11-2        | Performance Counter Control Register Field Description 159 |

| TABLE 11-3        | Performance Counter Register Field Description 160         |

| TABLE 11-4        | Cache Event Control Register Field Description 163         |

| TABLE 11-5        | Event Instruction Address Register Field Description 164   |

| TABLE 11-6        | Event Data Address Register Field Description 165          |

| TABLE 11-7        | Instruction Count 167                                      |

| <b>TABLE 11-8</b> | Microarchitectural Events 168                              |

# Multiprocessing Support 171

**SB-1 Implementation Specific Details 177**

# CHAPTER 1 Introduction

#### 1.1 Introduction

This document supplements MIPS64 Specification by MIPS Technologies Incorporated (MTI). The user should refer to the MIPS64 document for any specifics regarding the MIPS64 instruction set architecture. The aforementioned document provides a history of the MIPS64 architecture together with details on the CPU, FPU and coprocessor architectures, and the MIPS64 Privileged Resource Architecture.

This specification describes the actual implementation of SB-1 processor. The purpose of this document is to clarify any and all implementation-specific features listed in the MIPS64 Specification document.

The intended audience for this document is hardware designers and software engineers comprising compiler designers, operating system kernel writers, and application writers wishing to optimize software performance on the SB-1 processor.

# 1.2 Document Organization

This document is organized as follows:

Chapter 2 provides a general block diagram for the overall CPU and covers the functionality of the basic blocks.

**Document Organization**

Chapter 3 presents a general description of the ALU block together with an overview of the integer and load/ store instructions and their latencies.

Chapter 4 delves into floating point architecture specifics and covers FP instructions, latencies, and restrictions for CP1 category of instructions. This chapter also covers MIPS-3D Application Specific Extension (ASE) category of instructions.

Chapter 5 deals with MIPS MDMX ASE and related issues.

Chapter 6 provides a basic description of SB-1 supported memory hierarchy, Caches, TLBs, Cache Operations, and Cache Coherency Attributes.

Chapter 7 covers the MIPS64 Address Space as implemented by SB-1 core.

Chapter 8 specifies a complete listing of the CP0 registers supported in SB-1 core.

Chapter 9 details the debug architecture for SB-1. SiByte-specific enhancements to the standard MIPS64 Debug architecture are described here.

Chapter 10 describes the Error handling capabilities of SB-1.

Chapter 11 addresses the performance monitoring architecture supported by SB-1. A complete listing of these features and their usage through CP0 architecture space registers is described in this chapter.

Chapter 12 provides a high level overview of the multiprocessing features supported by SB-1. Example code segments featuring the MP capabilities of the processor are provided here.

Chapter 13 provides a list of all implementation-specific features in the MIPS64 Specification and provides the SB-1 resolutions of these features.

SB-1 Users Manual

1-22

# 1.3 Additional Documentation

The following documents are required as supplement to this specification.

| TABLE 1-1 | Supplemental | Documents to SB-2 | l Users Manual |

|-----------|--------------|-------------------|----------------|

|           |              |                   |                |

| Document                                       | Description                                                                                                                                | Source                         |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| MIPS64 Specification, Revision 1.0             | Consolidated MIPS I, II, III, IV, and V ISA<br>Specifications with a new Privileged Resource<br>Architecture based on MIPS R4000 Processor | MIPS Technologies Incorporated |

| MIPS-3D ASE Specification, Revision 1.0        | Describes 3D enhancements to the basic<br>MIPS64 Architecture                                                                              | MIPS Technologies Incorporated |

| MDMX Version 2.0 Specification, Revision 0.3.2 | Describes MIPS Multimedia Extensions to the basis MIPS64 Architecture                                                                      | MIPS Technologies Incorporated |

| MIPS RISC Architecture Volume I                | Describes MIPS basic instructions in detail                                                                                                | MIPS Technologies Incorporated |

| MIPS RISC Architecture Volume II               | Describes MIPS basic instructions in detail                                                                                                | MIPS Technologies Incorporated |

| MIPS Extended JTAG (EJTAG), Version 2.5        | Describes MIPS EJTAG Specification                                                                                                         | MIPS Technologies Incorporated |

# 1.4 What is Missing or Incomplete in this Version of the Document?

The following Chapters need additional work. A future revision of this document will provide further details.

- Chapter 4: *The FPU (CP1) and MIPS-3D ASE Instructions*. The exception specific implementation details for the FPU unit need to be additionally elaborated upon.

- Chapter 5: *The MDMX ASE Instructions*. The implementation details of this unit are not finalized and are subject to change from their current description in Chapter 5.

- Chapter 11: *The Performance Monitor Architecture*. The implementation details of this unit are not finalized and are subject to change from their current description in Chapter 11.

# CHAPTER 2 SB-1 Overview

# 2.1 Introduction

This chapter elaborates on high level features supported by SB-1 core. Further detail on specific SB-1 functionality is provided in subsequent chapters.

12

# 2.2 High Level Features

Table 2-1 shows the high level features supported by SB-1.

|           | ARA. A         |                  |

|-----------|----------------|------------------|

| TABLE 2-1 | SB-1 High Leve | el Specification |

| FEATURE                            | SPECIFICATION                                         |

|------------------------------------|-------------------------------------------------------|

| Instruction Set Architecture (ISA) | MIPS64 with SIMD Floating Point Functionality         |

| ji <sup>n</sup>                    | MIPS-3D ASE                                           |

|                                    | MDMX ASE                                              |

| Frequency                          | 600-1000 MHz                                          |

| Issue Type                         | Quad Inorder                                          |

| Pipe Architecture                  | Dual Enhanced-Skew Execute                            |

|                                    | Dual Memory                                           |

|                                    | Support for 0-cycle load-to-use instruction sequences |

#### TABLE 2-1 SB-1 High Level Specification

| FEATURE                           | SPECIFICATION                                                   |

|-----------------------------------|-----------------------------------------------------------------|

| Caches                            | Split I and D (Harvard Architecture)                            |

| Instruction                       | 32K, 4-way, 32-Byte Lines, LRU Replacement Policy               |

| Data                              | 32K, 4-way, Non-blocking, 32-Byte Lines, LRU Replacement Policy |

| Branch Predictors                 | 3x Structures                                                   |

| Direction Predictor               | 2-Level GShare, 4K-entry x 2-bit                                |

| Jump Register Cache               | 64-entry                                                        |

| Return Stack                      | 8-entry                                                         |

| Peak OPS at 1000 MHz <sup>a</sup> |                                                                 |

| Integer                           | 4 per cycle, 4 BOPS                                             |

| Floating Point                    | 8 per cycle, 8 GFLOPS                                           |

| Power Consumption at 1000 MHz     | < 4 Watts                                                       |

| Dhrystone 2.1 MIPS at 1000 MHz    | > 2000                                                          |

a. MADD instruction is counted as 2 distinct operations: one multiply and one add

Figure 2-1 shows a simplified block diagram for SB-1 core. Subsequent sections provide additional detail with regard to the internals of SB-1.

SB-1 Users Manual

2-27

#### SB-1 Units

#### 2.3 SB-1 Units

Internally, the SB-1 core comprises the PC Unit, the Issue Unit, the Execute Unit, the Load/Store Unit, the Floating Point Unit, the MDMX Unit, the Memory Unit, the Bus Interface Unit, and the Level One Instruction and Data Caches. The following sections briefly describe the functionality of each unit.

#### 2.3.1 The PC Unit

The PC Unit performs the sequencing of the instruction fetch together with completing instructions and detecting exceptions. These functions are implemented via two subunits: the Fetch Unit and the Graduation Unit. The responsibility of the Fetch Unit is to predict the program flow and qualify fetched instructions. The Graduation Unit ensures that the instructions modify architected state in program order in light of branch mispredicts and instruction exceptions.

#### 2.3.1.1 The Branch Unit

As shown in Figure 2-1, SB-1 supports three unique structures to aid program control flow in three distinct areas.

#### 2.3.1.1.1 Two Level GShare, Branch Direction Predictor

This structure, with 4K x 2bit entries works in conjunction with a 9-bit Branch History Register (BHR). The contents of BHR are Exclusive-ORed with 11 PC bits to provide an index into the direction predictor table which uses the 2-bit counter scheme to predict branch outcome (taken vs. not-taken). There can be up to 2 predictions per cycle.

#### 2.3.1.1.2 Return Stack (RS)

The eight entry processor-based Return Stack provides a mechanism to predict return addresses for subroutine calls. SB-1 supports an 8-entry Return Stack.

#### 2.3.1.1.3 Jump Register Cache (JRC)

The Jump Register Cache is used to accelerate the execution of indirect branches through registers. SB-1 supports a 64-entry JRC. It provides a prediction mechanism for the target of indirect jumps through registers.

#### **2.3.2** The Issue Unit (IBox)

The Issue Unit is responsible for issuing instructions to various functional units, and for tracking their progress until they can be handed off to the graduation part of the PC Unit. This unit examines and keeps track of all structural hazards as well as data dependencies in order to issue up to 4 instructions per cycle.

SB-1 Units

SB-1 supports decoupled front and back ends; the machine can continue processing instructions on instruction cache misses. An instruction queue (IQ) buffers instructions as they are fetched from memory.

#### 2.3.3 The Execute Unit (E0, E1)

The Execute Unit is responsible for execution of ALU, Shift, and Branch instructions in the MIPS64 ISA. This unit supports thirty-two 64-bit Integer registers and 64-bit HI/LO registers for multiplies. The execute unit supports dual 8-stage, fully pipelined, 1-cycle execution latency pipes with enhanced skewing to allow zero-cycle load-to-use sequences. Multiply and divide instructions take additional cycles to complete.

#### 2.3.4 The Load/Store Unit (LS0, LS1)

The Load/Store Unit executes memory load and store operations supported by the MIPS64 ISA. The load/store unit supports dual 8-stage load/store pipelines with the ability to execute simple ALU instructions in one pipe. This reduces ALU to address generation penalty for load/store address computations.

#### 2.3.5 The Floating Point Unit (F0, F1)

The Floating Point Unit executes MIPS64 floating point and MIPS-3D ASE categories of instructions. It is IEEE-754 compatible and has support for Single, Double, and Paired-Single data formats.

There are thirty-two 64-bit Floating Point Registers in the FP Unit. The unit supports dual 11-stage, fully pipelined, 4-cycle execution latency pipes with enhanced skewing to allow zero-cycle load-to-use sequences.

#### 2.3.6 The MDMX Unit (A0, A1)

The MDMX unit implements MIPS MDMX instructions using the same registers as the Floating Point Unit. It supports thirty-two 64-bit Floating Point Registers. The unit supports dual 9-stage, fully pipelined, 2-cycle execution latency pipes with enhanced skewing to allow zero-cycle load-to-use sequences.

The MDMX unit has extended accumulator support, with 24 and 48-bit modes for 8 and 16-bit SIMD computations, respectively.

#### 2.3.7 The Memory Unit (MBox)

The Memory Unit implements the memory management functionality, as outlined in the MIPS64 Privileged Resource Architecture. In particular, it supports Coprocessor 0 (CP0) functionality of TLB, CACHE, and SYNC category of instructions.

SB-1 Specifics

#### **2.3.8** The Bus Interface Unit (BIU)

This unit provides the interface between the core and the external bus.

#### **2.3.9 Level One Instruction and Data Caches**

SB-1 supports a 32KB, 4-way set associative, virtually-indexed and virtually-tagged instruction cache and a 32KB, 4-way set associative, physically-indexed and physically-tagged data cache. This provides the processor with a sizable portion of fast, on-chip memory.

SB-1 has a non-blocking data cache with support for up to 8 outstanding cachelines.

# 2.4 SB-1 Specifics

The remaining chapters in this document provide further details on the specifics of the major units in SB-1 core.

# CHAPTER 3 The CPU Instructions

#### 3.1 Introduction

This chapter provides a general overview of MIPS64 CPU instructions, as supported in SB-1 implementation. The information provided here should be regarded as a supplement to MIPS64 Specification document.

# 3.2 List of Instructions

Table 3-1 through Table 3-9 provide the list of CPU category instructions supported in SB-1.

3.2.1 CPU Load, Store and Memory Control Instructions

| Mnemonic Instruction |                        |

|----------------------|------------------------|

| LB                   | Load Byte              |

| LBU                  | Load Byte Unsigned     |

| LH                   | Load Halfword          |

| LHU                  | Load Halfword Unsigned |

#### TABLE 3-1 CPU Load, Store, and Memory Control Instructions

| Mnemonic | Instruction                   |  |

|----------|-------------------------------|--|

| LW       | Load Word                     |  |

| LWL      | Load Word Left                |  |

| LWR      | Load Word Right               |  |

| SB       | Store Byte                    |  |

| SH       | Store Halfword                |  |

| sw       | Store Word                    |  |

| SWL      | Store Word Left               |  |

| SWR      | Store Word Right              |  |

| LL       | Load Linked Word              |  |

| SC       | Store Conditional Word        |  |

| SYNC     | Synchronize Memory Operations |  |

| LD       | Load Doubleword               |  |

| LDL      | Load Doubleword Left          |  |

| LDR      | Load Doubleword Right         |  |

| LLD      | Load Linked Doubleword        |  |

| LWU      | Load Word Unsigned            |  |

| SCD      | Store Conditional Doubleword  |  |

| SD       | Store Doubleword              |  |

| SDL      | Store Doubleword Left         |  |

| SDR      | Store Doubleword Right        |  |

| PREF     | Prefetch Memory Data          |  |

| PREFX    | Prefetch Memory Data Indexed  |  |

TABLE 3-1 CPU Load, Store, and Memory Control Instructions

Mnemonic Instruction

#### 3.2.2 CPU Arithmetic Instructions

| TADEL 5-2 CI O ATTUMICUC INSULUCIONS | TABLE | 3-2 | CPU | Arithmetic | Instructions |

|--------------------------------------|-------|-----|-----|------------|--------------|

|--------------------------------------|-------|-----|-----|------------|--------------|

| Mnemonic | Instruction                 |

|----------|-----------------------------|

| ADD      | Add Word                    |

| ADDI     | Add Immediate Word          |

| ADDIU    | Add Immediate Unsigned Word |

| ADDU     | Add Unsigned Word           |

#### TABLE 3-2 CPU Arithmetic Instructions

| Mnemonic | Instruction                         |

|----------|-------------------------------------|

| DIV      | Divide Word                         |

| DIVU     | Divide Unsigned Word                |

| MULT     | Multiply Word                       |

| MULTU    | Multiply Unsigned Word              |

| SLT      | Set on Less Than                    |

| SLTI     | Set on Less Than Immediate          |

| SLTIU    | Set on Less Than Immediate Unsigned |

| SLTU     | Set on Less Than Unsigned           |

| SUB      | Subtract Word                       |

| SUBU     | Subtract Unsigned Word              |

| DADD     | Add Doubleword                      |

| DADDI    | Add Immediate Doubleword            |

| DADDIU   | Add Immediate Unsigned Doubleword   |

| DADDU    | Add Unsigned Doubleword             |

| DDIV     | Divide Doubleword                   |

| DDIVU    | Divide Unsigned Doubleword          |

| DMULT    | Multiply Doubleword                 |

| DMULTU   | Multiply Unsigned Doubleword        |

| DSUB     | Subtract Doubleword                 |

| DSUBU    | Subtract Unsigned Doubleword        |

# 3.2.3 CPU Logical Instructions

| TABLE 3-3 | CPU | Logical | Instructions |

|-----------|-----|---------|--------------|

|-----------|-----|---------|--------------|

|          | 0                     |

|----------|-----------------------|

| Mnemonic | Instruction           |

| AND      | Logical AND           |

| ANDI     | Logical AND Immediate |

| LUI      | Load Upper Immediate  |

| NOR      | Logical NOR           |

| OR       | Logical OR            |

| ORI      | Logical OR Immediate  |

#### TABLE 3-3 CPU Logical Instructions

| Mnemonic | Instruction           |

|----------|-----------------------|

| XOR      | Logical XOR           |

| XORI     | Logical XOR Immediate |

# 3.2.4 CPU Move Instructions

| Mnemonic | Instruction                              |

|----------|------------------------------------------|

| MFHI     | Move from HI                             |

| MFLO     | Move from LO                             |

| MTHI     | Move to HI                               |

| MTLO     | Move to LO                               |

| MOVF     | Move Conditional on Floating Point False |

| MOVN     | Move Conditional on Not Zero             |

| MOVT     | Move Conditional on Floating Point True  |

| MOVZ     | Move Conditional on Zero                 |

#### TABLE 3-4 CPU Move Instructions

#### 3.2.5 CPU Shift Instruction

#### TABLE 3-5 CPU Shift Instructions

| Mnemonic | Instructions                            |

|----------|-----------------------------------------|

| SLL      | Shift Word Left Logical                 |

| SLLV     | Shift Word Left Logical Variable        |

| SRA      | Shift Word Right Arithmetic             |

| SRAV     | Shift Word Right Arithmetic Variable    |

| SRL      | Shift Word Right Logical                |

| SRLV     | Shift Word Right Logical Variable       |

| DSLL     | Shift Doubleword Left Logical           |

| DSLL32   | Shift Doubleword Left Logical +32       |

| DSLLV    | Shift Doubleword Right Logical Variable |

| DSRA     | Shift Doubleword Right Arithmetic       |

3-34

#### TABLE 3-5 CPU Shift Instructions

| Mnemonic | Instructions                               |

|----------|--------------------------------------------|

| DSRA32   | Shift Doubleword Right Arithmetic +32      |

| DSRAV    | Shift Doubleword Right Arithmetic Variable |

| DSRL     | Shift Doubleword Right Logical             |

| DSRL32   | Shift Doubleword Right Logical +32         |

| DSRLV    | Shift Doubleword Right Logical Variable    |

## 3.2.6 CPU Branch and Jump Instructions

# TABLE 3-6 CPU Branch and Jump Instructions

| Mnemonic | Instructions                                  |

|----------|-----------------------------------------------|

| BEQ      | Branch on Equal                               |

| BGEZ     | Branch on Greater Than or Equal Zero          |

| BGEZAL   | Branch on Greater Than or Equal Zero and Link |

| BGTZ     | Branch on Greater Than Zero                   |

| BLEZ     | Branch on Less Than or Equal Zero             |

| BLTZ     | Branch on Less Than Zero                      |

| BLTZAL   | Branch on Less Than Zero and Link             |

| BNE      | Branch on Not Equal                           |

| J        | Jump                                          |

| JAL      | Jump and Link                                 |

| JALR     | Jump and Link Register                        |

| JR       | Jump Register                                 |

# **3.2.7 CPU Trap Instructions**

| TABLE 3-7 | CPU | Trap | Instrue | ctions |

|-----------|-----|------|---------|--------|

|-----------|-----|------|---------|--------|

| Mnemonic | Instruction   |

|----------|---------------|

| BREAK    | Breakpoint    |

| SYSCALL  | System Call   |

| TEQ      | Trap if Equal |

| Mnemonic | Instruction                                      |

|----------|--------------------------------------------------|

| TEQI     | Trap if Equal Immediate                          |

| TGE      | Trap if Greater Than or Equal                    |

| TGEI     | Trap if Greater Than or Equal Immediate          |

| TGEIU    | Trap if Greater Than or Equal Immediate Unsigned |

| TGEU     | Trap if Greater Than or Equal Unsigned           |

| TLT      | Trap if Less Than                                |

| TLTI     | Trap if Less Than Immediate                      |

| TLTIU    | Trap if Less Than Immediate Unsigned             |

| TLTU     | Trap if Less Than Unsigned                       |

| TNE      | Trap if Not Equal                                |

| TNEI     | Trap if Not Equal Immediate                      |

#### TABLE 3-7 CPU Trap Instructions

#### 3.2.8 Obsolete Branch Instructions

Software is strongly encouraged to avoid use of the Branch Likely instructions, as they will be removed from a future revision of the MIPS64 Architecture.

#### **TABLE 3-8** Obsolete Branch Instructions

| Mnemonic | Instruction                                          |

|----------|------------------------------------------------------|

| BEQL     | Branch on Equal Likely                               |

| BGEZALL  | Branch on Greater Than or Equal Zero and Link Likely |

| BGEZL    | Branch on Greater Than or Equal Zero Likely          |

| BGTZL    | Branch on Greater Than Zero Likely                   |

| BLEZL    | Branch on Less Than or Equal Zero Likely             |

| BLTZALL  | Branch on Less Than Zero and Link Likely             |

| BLTZL    | Branch on Less Than Zero Likely                      |

| BNEL     | Branch on Not Equal Likely                           |

SB-1 Users Manual

3-36

#### **3.2.9 Embedded Application Instructions**

| Mnemonic | Instruction                         |

|----------|-------------------------------------|

| CLO      | Count Leading Ones in Word          |

| CLZ      | Count Leading Zeros in Word         |

| DCLO     | Count Leading Ones in Doubleword    |

| DCLZ     | Count Leading Zeros in Doubleword   |

| MADD     | Multiply and Add Word               |

| MADDU    | Multiply and Add Unsigned Word      |

| MSUB     | Multiply and Subtract Word          |

| MSUBU    | Multiply and Subtract Unsigned Word |

| MUL      | Multiply Word to Register           |

| SSNOP    | Superscalar Inhibit NOP             |

#### **TABLE 3-9 Embedded Application Instructions**

# 3.3 Block and Pipeline Diagrams

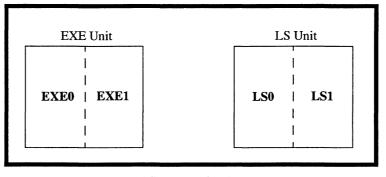

The CPU block of SB-1 consists of a an Execute unit (EXE) and a Load/Store Unit (LS). Figure 3-1 shows the pipes in each unit.

FIGURE 3-1 EXE and LS Pipes in SB-1

#### 3.3.1 The EXE0 Unit

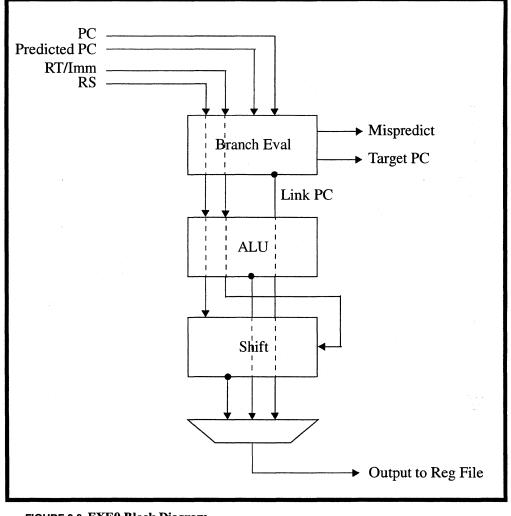

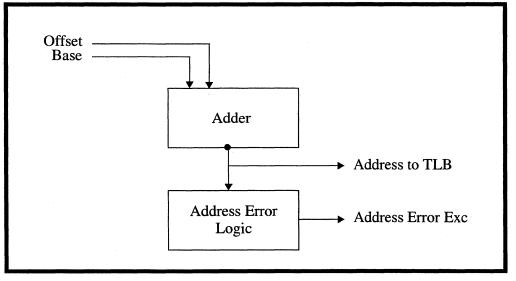

Figure 3-2 shows a block diagram of instruction execution flow in the EXE0 pipe.

FIGURE 3-2 EXE0 Block Diagram

SB-1 Users Manual

3-38

The List of instructions supported by EXE0 Unit is shown in Table 3-10.

TABLE 3-10 Instructions Supported by the EXE0 Unit

| List of Instructions supported by EXE0 Unit |

|---------------------------------------------|

| ADDs, SUBs, Logical Ops                     |

| Shifts                                      |

| LUI                                         |

| Branches/Jumps                              |

| CP1 Branches                                |

| Sets                                        |

| Traps                                       |

| CLZ/CLO                                     |

| Conditional Moves                           |

| MOVT, MOVF                                  |

| MOVZ, MOVN                                  |

The pipeline diagram for EXE0 unit is shown in Table 3-11.

| <b>TABLE 3-11</b> | EXE0 | Pipe | Stages | in | SB-1 |

|-------------------|------|------|--------|----|------|

|-------------------|------|------|--------|----|------|

| Stage             | F     | D      | I     | 1     | 2     | 3 <sup>a</sup>         | 4                                                                                         | 5                           |

|-------------------|-------|--------|-------|-------|-------|------------------------|-------------------------------------------------------------------------------------------|-----------------------------|

| ALU and Shift     | Fetch | Decode | Issue | Skew1 | Skew2 | Read RF                | Execute                                                                                   | Write RF                    |

| Branch Ops        | Fetch | Decode | Issue | Skew1 | Skew2 | Read RF                | Check Prediction signal redirect if<br>mispredicted; Compute target and link<br>addresses | Write Link<br>Address to RF |

| CP1 Branch<br>Ops | Fetch | Decode | Issue | Skew1 | Skew2 | Read RF<br>Read FP CCs | Check Prediction signal redirect if<br>mispredicted; Compute target and link<br>addresses | Write Link<br>Address to RF |

| MOVF, MOVT        | Fetch | Decode | Issue | Skew1 | Skew2 | Read FP CCs            | Evaluate Condition                                                                        | Write RF                    |

| MOVZ,<br>MOVN     | Fetch | Decode | Issue | Skew1 | Skew2 | Read RF                | Compare rt to zero, Signal result to FP Unit                                              |                             |

a. FP Condition Codes are not bypassed

The skewed slots in pipe stages 1 and 2 allow the coissuing of load/store and dependent EXE instructions in the same cycle.

#### 3.3.2 The EXE1 Unit

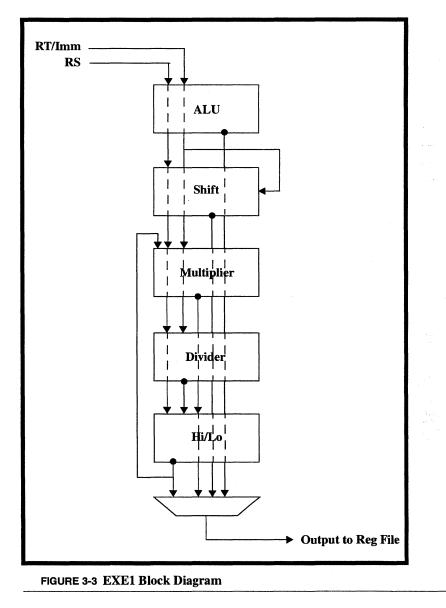

The block diagram for EXE1 Unit is shown in Figure 3-3.

SB-1 Users Manual

3-40

The List of instructions supported by EXE0 Unit is shown in Table 3-12.

TABLE 3-12 Instructions Supported by the EXE1 Unit

| List of Instructions supported by EXE1 Unit |

|---------------------------------------------|

| ADDs, SUBs, Logical Ops                     |

| Shifts                                      |

| LUI                                         |

| Conditional Moves                           |

| Multiplies                                  |

| Divides                                     |

| MT/MF HI/LO                                 |

| MOVT, MOVF                                  |

| MOVZ, MOVN                                  |

The pipeline diagram for EXE1 unit is shown in Table 3-13.

#### TABLE 3-13 EXE1 Pipe Stages in SB-1 (All Except Divide)

| Stage                        | F     | D      | I     | 1     | 2     | 3 <sup>a</sup> | 4                              | 5        | 6                       | 7                     | 8        |

|------------------------------|-------|--------|-------|-------|-------|----------------|--------------------------------|----------|-------------------------|-----------------------|----------|

| Simple ALU Ops<br>and Shifts | Fetch | Decode | Issue | Skew1 | Skew2 | Read RF        | Execute                        | Write RF |                         |                       |          |

| MULT                         | Fetch | Decode | Issue | Skew1 | Skew2 | Read RF        | Execute1                       | Execute2 | Execute3                | Write HI/LO           |          |

| DMULT                        | Fetch | Decode | Issue | Skewl | Skew2 | Read RF        | Execute1                       | Execute2 | Execute3                | Execute4;<br>Write LO | Write HI |

| MUL                          | Fetch | Decode | Issue | Skew1 | Skew2 | Read RF        | Execute1                       | Execute2 | Execute3                | Write RF              |          |

| MADD/MSUB                    | Fetch | Decode | Issue | Skew1 | Skew2 | Read RF        | Execute1                       | Execute2 | Read HI/LO;<br>Execute3 | Write HI/LO           |          |

| MTHI/MTLO                    | Fetch | Decode | Issue | Skew1 | Skew2 | Read RF        |                                |          |                         | Write HI/LO           |          |

| MFHI/MFLO                    | Fetch | Decode | Issue | Skew1 | Skew2 |                | Read HI/LO                     | Write RF |                         |                       |          |

| MOVF, MOVT                   | Fetch | Decode | Issue | Skew1 | Skew2 | Read FP CCs    | Evaluate<br>Condition          | Write RF |                         |                       |          |

| MOVZ, MOVN                   | Fetch | Decode | Issue | Skew1 | Skew2 | Read RF        | Compare rt<br>to zero,         |          |                         |                       |          |

|                              |       |        |       |       |       |                | Signal<br>result to FP<br>Unit |          |                         |                       |          |

a. FP Condition Codes are not bypassed

(D)

As in EXE0, the skewed slots in pipe stages 1 and 2 allow the coissuing of load/store and dependent EXE instructions in the same cycle.

Table 3-14 shows the pipeline stages for integer divide operations supported in EXE1 unit.

| Stage      | F     | D      | I     | 1     | 2     | 3       | 4                            | <br>36/68                           | <br>40/72       |

|------------|-------|--------|-------|-------|-------|---------|------------------------------|-------------------------------------|-----------------|

| DIV/DIVU   | Fetch | Decode | Issue | Skew1 | Skew2 | Read RF | Assert div_busy;<br>Execute1 | <br>Execute33;<br>Deassert div_busy | <br>Write HI/LO |

| DDIV/DDIVU | Fetch | Decode | Issue | Skew1 | Skew2 | Read RF | Assert div_busy;<br>Execute1 | <br>Execute65;<br>Deassert div_busy | <br>Write HI/LO |

TABLE 3-14 EXE1 Pipe Stages in SB-1 for Divide Instructions

### 3.3.3 The LS0 Unit

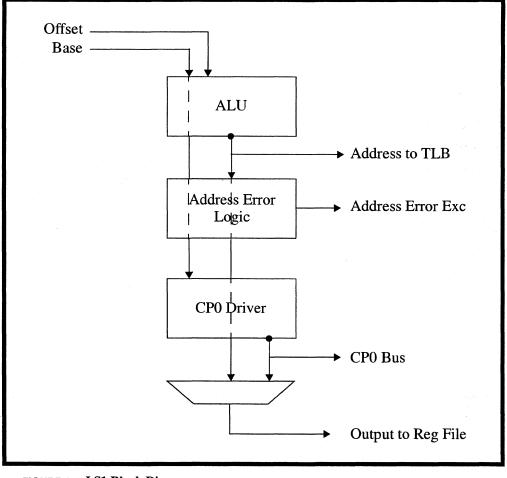

The block diagram for LS0 Unit is shown in Figure 3-4.

FIGURE 3-4 LS0 Unit Block Diagram

SB-1 Users Manual

3-42

The List of instructions supported by LS0 Unit is shown in Table 3-15.

#### TABLE 3-15 Instructions Supported by the LS0 Unit

| List of Instructions supported by LS0 Unit  |  |

|---------------------------------------------|--|

| Integer and Floating Point Loads and Stores |  |

The pipeline diagram for LSO unit is shown in Table 3-16. The diagram applies to both integer and floating point loads and stores.

#### TABLE 3-16 LS0 Pipe Stages in SB-1

| Stage  | F     | D      | I       | 1                              | 2                                                      | 3 | 4        | 5                          | <br>9                                                                                                    |

|--------|-------|--------|---------|--------------------------------|--------------------------------------------------------|---|----------|----------------------------|----------------------------------------------------------------------------------------------------------|

| Loads  | Fetch | Decode | Read RF |                                | Cache Tag Lookup,<br>Cache Data Read<br>and Way Select | - | Write RF |                            | _                                                                                                        |

| Stores | Fetch | Decode | Read RF | Compute Address;<br>Access TLB | PA Pushed into<br>DCFIFO                               | - | -        | Data Pushed<br>into DCFIFO | Cache accessed after<br>graduation of store<br>instruction and<br>availability of free slot<br>in DCache |

#### 3.3.4 The LS1 Unit

The block diagram for LS1 Unit is shown in Figure 3-5.

FIGURE 3-5 LS1 Block Diagram

SB-1 Users Manual

3-44

The list of instructions supported by LS1 Unit is shown in Table 3-17.

TABLE 3-17 Instructions Supported by the LS1 Unit

| List of Instructions supported by LS1 Unit |  |  |  |  |  |  |  |  |  |

|--------------------------------------------|--|--|--|--|--|--|--|--|--|

| ADDs, SUBs, Logi <b>cal</b> Ops            |  |  |  |  |  |  |  |  |  |

| LUI                                        |  |  |  |  |  |  |  |  |  |

| Loads and Stores                           |  |  |  |  |  |  |  |  |  |

| Indexed Loads/Stores                       |  |  |  |  |  |  |  |  |  |

| TLB OPs                                    |  |  |  |  |  |  |  |  |  |

| MT/MF CP0                                  |  |  |  |  |  |  |  |  |  |

| Cache Ops                                  |  |  |  |  |  |  |  |  |  |

The pipeline diagram for LS1 unit is shown in Figure 3-18.

| Stage     | F     | D      | I       | 1                  | 2                                             | 3                                    | 4        | 5                                | 6                | 7        | <br>9                                                                                                                       |

|-----------|-------|--------|---------|--------------------|-----------------------------------------------|--------------------------------------|----------|----------------------------------|------------------|----------|-----------------------------------------------------------------------------------------------------------------------------|

| Loads     | Fetch | Decode | Read RF | Compute<br>Address | Access<br>TLB,<br>Cache Tag<br>Lookup         | Cache Data<br>Read and<br>Way Select | Write RF |                                  |                  |          |                                                                                                                             |

| Stores    | Fetch | Decode | Read RF | Compute<br>Address | Access<br>TLB;<br>PA Pushed<br>into<br>DCFIFO |                                      |          | Data<br>Pushed<br>into<br>DCFIFO |                  |          | <br>Cache<br>accessed<br>after<br>graduation<br>of store<br>instruction<br>and<br>availability<br>of free slot<br>in DCache |

| ALU Ops   | Fetch | Decode | Read RF | Execute            | Pipe                                          | Pipe                                 | Write RF |                                  |                  |          |                                                                                                                             |

| MF C0     | Fetch | Decode |         | Drive<br>Control   | Drive CP0<br>Bus                              | Pipe                                 | Write RF |                                  |                  |          |                                                                                                                             |

| MT C0     | Fetch | Decode | Read RF | Pipe               | Pipe                                          | Pipe                                 | Pipe     | Drive<br>Control                 | Drive<br>CP0 Bus | Write RF |                                                                                                                             |

| Cache Ops | Fetch | Decode | Read RF | Compute<br>Address |                                               |                                      |          |                                  |                  |          |                                                                                                                             |

TABLE 3-18 LS1 Pipe Stages in SB-1

## 3.4 Instruction Latency and Throughput by Category of Instructions

Table 3-19 shows the latency and throughput by category for all instructions supported in the EXE and LS Units.

| Instruction Category | Latency          | Throughput (1 Instruction/x cycles<br>per supported pipe) | Co-issue w/ Dependent Op? |

|----------------------|------------------|-----------------------------------------------------------|---------------------------|

| ALU ops to EXE Pipes | 1                | 1                                                         | No                        |

| ALU ops to LS1 Pipe  | 1                | 1                                                         | Yes to EXE Pipes Only     |

| Shifts               | 1                | 1                                                         | No                        |

| Branches             | 1                | 1                                                         | NA                        |

| 32-bit Multiplies    | 3                | 1                                                         | No                        |

| 64-bit Multiplies    | 3 to LO, 4 to HI | 2                                                         | No                        |

| MTLO/MTHI            | -                | 1                                                         | No                        |

| MFLO/MFHI            | -                | 1                                                         | No                        |

| 32-bit Divides       | 36               | 35                                                        | No                        |

| 64-bit Divides       | 68               | 67                                                        | No                        |

| Load                 | -                | 1                                                         | Yes to EXE Pipes Only     |

| Stores               | -                | 1                                                         | No                        |

| MFC0                 | -                | 1                                                         | Yes to EXE Pipes Only     |

| MTC0                 | -                | 1                                                         | No                        |

TABLE 3-19 Instruction Throughput and Latency for EXE and LS Units by Inst Category

## 3.5 Available Bypasses

Table 3-20 shows the available bypasses among EX0, EX1, LS0 and LS1 units.

| From/To             | EX0 | EX1 | LS0 | LS1 |

|---------------------|-----|-----|-----|-----|

| EX0                 | Yes | Yes |     |     |

| EX1                 | Yes | Yes |     |     |

| EX1 (MUL Inst Only) | Yes | Yes |     |     |

| LS0 Load            | Yes | Yes | Yes | Yes |

| LS1 Data            | Yes | Yes | Yes | Yes |

| LS1 Load            | Yes | Yes | Yes | Yes |

## 3.6 Instruction Types Issued to each Pipe

Table 3-21 summarizes the types of instructions that can be issued to each one of EX0, EX1, LS0, and LS1 pipes.

| Instruction Type        | EX0 Pipe | EX1 Pipe | LS0 Pipe | LS1 Pipe |

|-------------------------|----------|----------|----------|----------|

| ADDs, SUBs, Logical Ops | Yes      | Yes      |          | Yes      |

| Shifts                  | Yes      | Yes      |          |          |

| LUI                     | Yes      | Yes      |          | Yes      |

| Branches/Jumps          | Yes      |          |          |          |

| Sets                    | Yes      |          |          |          |

| Traps                   | Yes      |          |          |          |

| CLZ/CLO                 | Yes      |          |          |          |

| Integer MOVZ, MOVN      | Yes      | Yes      |          |          |

| FP MOVZ, MOVN           | Yes      | Yes      |          |          |

| MOVF, MOVT              | Yes      | Yes      |          |          |

| Multiplies              |          | Yes      |          |          |

| Divides                 |          | Yes      |          |          |

| MT/MF HI/LO             |          | Yes      |          |          |

| Loads/Stores            |          |          | Yes      | Yes      |

| Indexed Loads/Stores    |          |          |          | Yes      |

| Cache OPs               |          |          |          | Yes      |

| TLB OPs                 |          |          |          | Yes      |

| MT/MF CP0               |          |          |          | Yes      |

TABLE 3-21 Instruction Types Issued to each Pipe

## 3.7 Issue Rules and Restrictions

Table 3-22 identifies issue rules and restrictions for EXE and LS pipes. These restrictions are enforced by hardware interlocks.

| TABLE 3-22 Instruction Issue Rules and Restrictions for CPU instruction | <b>TABLE 3-22</b> | Instruction | <b>Issue Rules a</b> | nd Restrictions for | CPU instructions |

|-------------------------------------------------------------------------|-------------------|-------------|----------------------|---------------------|------------------|

|-------------------------------------------------------------------------|-------------------|-------------|----------------------|---------------------|------------------|

| Instruction A | Instruction B                  | Restrictions                                  |

|---------------|--------------------------------|-----------------------------------------------|

| MUL           | Any dependent op to EX0 or EX1 | Dependent op can issue 3 cycles after MUL     |

| MUL           | Any dependent op to LS0 or LS1 | Dependent op can issue 8 cycles after the MUL |

| F                            |                         |                                                                                   |

|------------------------------|-------------------------|-----------------------------------------------------------------------------------|

| Instruction A                | Instruction B           | Restrictions                                                                      |

| MULT, MADD, MSUB             | MFLO, MFHI              | MF* instruction can issue two cycles after the multiply                           |

| DMULT                        | MFLO                    | MFLO can issue two cycles after DMULT                                             |

| DMULT                        | MFHI                    | MFHI can issue three cycles after DMULT                                           |

| DMULT                        | Any Multiply            | No multiply instructions may be issued in the cycle immediately following a DMULT |

| DIV, DDIV                    | DIV, DDIV               | Another divide cannot be issued while there is a divide in the pipe               |

| DIV, DDIV                    | MFLO, MFHI              | HI/LO reads cannot be issued while there is a divide in the pipe                  |

| DIV, DDIV                    | Any multiply except MUL | Multiplies that write HI/LO cannot be issued while there is a divide in the pipe  |

| Shift or ALU op to EXE pipes | Any dependent LS op     | Dependent op can issue 4 cycles after the shift                                   |

| ALU op to LS1 pipe           | Dependent LS op         | Dependent op can issue the next cycle after the ALU op; cannot co-<br>issue       |

| Load, Store, MFC0            | Dependent LS op         | Dependent op can issue 4 cycles after the LD/ST                                   |

TABLE 3-22 Instruction Issue Rules and Restrictions for CPU instructions

## 3.8 Differences between 32 and 64-bit Modes of Operation

EXE Ops: In 32-bit mode, 64-bit instructions cause reserved instruction exceptions

LS/ST Ops: Address errors are generated based on the mode as specified in the MIPS64 Specification.

# CHAPTER 4 The FPU (CP1) and MIPS-3D ASE Instructions

## 4.1 Introduction

This chapter provides a general overview of MIPS64 CP1 and MIPS-3D ASE (Application Specific Extension) instructions, as supported in SB-1. The information provided here should be regarded as a supplement to MIPS64 Specification and MIPS-3D ASE documents.

## 4.2 High Level Description of FP Block

Table 4-1 provides high level characteristics of the FP Units in SB-1.

## TABLE 4-1 FP Block Description

| Feature                      | Description                                                             |

|------------------------------|-------------------------------------------------------------------------|

| Number of FP Pipes           | 2: FP0 Pipe and FP1 Pipe                                                |

| Symmetrical Pipes?           | No (See detailed pipe descriptions)                                     |

| Number of Stages per FP Pipe | 11                                                                      |

| FP Latency                   | 4 for a majority of the instructions (See detailed pipe descriptions)   |

| Fully Pipelined?             | Yes for a majority of the instructions (See detailed pipe descriptions) |

#### TABLE 4-1 FP Block Description

| Feature                                            | Description                                                     |

|----------------------------------------------------|-----------------------------------------------------------------|

| Maximum Number of FP Operations per Cycle per Pipe | 4 Single Precision FP Operations                                |

|                                                    | (2 Multiply Adds on Paired Single Operands per One Instruction) |

| Maximum Number of FP Operations per Cycle in SB-1  | 8 Single Precision FP Operations                                |

## 4.3 Block and Pipeline Diagrams

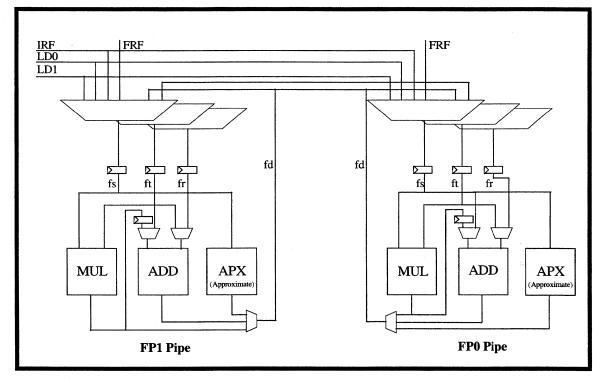

Figure 4-1 shows a high level block diagram of the Floating Point Unit in SB-1.

SB-1 Users Manual

4-50

Table 4-2 shows Floating Point pipe diagram for FP0 and FP1 pipes.

TABLE 4-2 FP0 and FP1 Pipe Operation

| Stage  | F     | D      | I     | 1  | 2  | 3       | 4        | 5        | 6        | 7        | 8        |

|--------|-------|--------|-------|----|----|---------|----------|----------|----------|----------|----------|

| FP Ops | Fetch | Decode | Issue | S1 | S2 | Read RF | Execute1 | Execute2 | Execute3 | Execute4 | Write RF |

## 4.4 Instruction Latency and Throughput by Category of Instructions

The following tables present the list of supported instructions in SB-1 Floating Point Unit and their associated latencies.

| Instruction | Description        |

|-------------|--------------------|

| LWC1        | Refer to Chapter 3 |

| SWC1        | Refer to Chapter 3 |

| LDC1        | Refer to Chapter 3 |

| SDC1        | Refer to Chapter 3 |

| LDXC1       | Refer to Chapter 3 |

| LWXC1       | Refer to Chapter 3 |

| SDXC1       | Refer to Chapter 3 |

| SWXC1       | Refer to Chapter 3 |

| LUXC1       | Refer to Chapter 3 |

| SUXC1       | Refer to Chapter 3 |

#### TABLE 4-3 FPU Load/Store Instructions Supported in CPU Unit (Chapter 3)

All instructions in Table 4-3 can be issued to LS1 pipe. The first four instructions can be additionally issued to LS0 pipe.

TABLE 4-4 FPU Arithmetic Instructions

| Instruction | Supported Data Formats        | Latency  | Throughput (1 Instruction/x cycles per supported pipe)               |

|-------------|-------------------------------|----------|----------------------------------------------------------------------|

| ABS         | Single, Double, Paired Single | 4/4/4    | 1                                                                    |

| ADD         | Single, Double, Paired Single | 4/4/4    | 1                                                                    |

| C.cond      | Single, Double, Paired Single | 4/4/4    | 1                                                                    |

| DIV         | Single, Double, Paired Single | 24/32/24 | 4 Insts/24 cycles (S), 4 Insts/32 cycles (D), 4 Insts/24 cycles (PS) |

| MUL         | Single, Double, Paired Single | 4/4/4    | 1                                                                    |

#### TABLE 4-4 FPU Arithmetic Instructions

| Instruction | Supported Data Formats        | Latency  | Throughput (1 Instruction/x cycles per supported pipe)               |

|-------------|-------------------------------|----------|----------------------------------------------------------------------|

| NEG         | Single, Double, Paired Single | 4/4/4    | 1                                                                    |

| SUB         | Single, Double, Paired Single | 4/4/4    | 1                                                                    |

| SQRT        | Single, Double, Paired Single | 28/40/28 | 4 Insts/28 cycles (S), 4 Insts/40 cycles (D), 4 Insts/28 cycles (PS) |

| MADD        | Single, Double, Paired Single | 8/8/8    | 1                                                                    |

| MSUB        | Single, Double, Paired Single | 8/8/8    | 1                                                                    |

| NMADD       | Single, Double, Paired Single | 8/8/8    | 1                                                                    |

| NMSUB       | Single, Double, Paired Single | 8/8/8    | 1                                                                    |

| RECIP       | Single, Double, Paired Single | 12/20/12 | 4 Insts/12 cycles (S), 4 Insts/20 cycles (D), 4 Insts/12 cycles (PS) |

| RSQRT       | Single, Double, Paired Single | 16/28/16 | 4 Insts/16 cycles (S), 4 Insts/28 cycles (D), 4 Insts/16 cycles (PS) |

#### TABLE 4-5 FPU Move Instructions

| Instruction | Supported Data Formats        | Latency | Throughput (1 Instruction/x cycles per supported pipe) |

|-------------|-------------------------------|---------|--------------------------------------------------------|

| CFC1        | -                             | 1       | 1                                                      |

| CTC1        | -                             | 4       | 1                                                      |

| MFC1        | -                             | 1       | 1                                                      |

| MTC1        | -                             | 4       | 1                                                      |

| DMFC1       | -                             | 1       | 1                                                      |

| DMTC1       | -                             | 4       | 1                                                      |

| MOV         | Single, Double, Paired Single | 4       | 1                                                      |

| MOVF        | Single, Double, Paired Single | 4       | 1                                                      |

| MOVN        | Single, Double                | 4       | 1                                                      |