# EEPROM MEMORY PRODUCTS

DATABOOK

2<sup>nd</sup> EDITION

57

EEPROM MEMORY PRODUCTS

RYSTON Electronics

# EEPROM MEMORY PRODUCTS

DATABOOK

2<sup>nd</sup> EDITION

**APRIL 1999**

599

#### USE IN LIFE SUPPORT DEVICES OR SYSTEMS MUST BE EXPRESSLY AUTHORIZED

STMicroelectronics PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF STMicroelectronics. As used herein:

- Life support devices or systems are those which (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided with the product, can be reasonably expected to result in significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can reasonably be expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

| TABLE OF CONTENTS                       |        |

|-----------------------------------------|--------|

|                                         |        |

| Overview of the ST EEPROM product range | Page 5 |

| Serial EEPROM, I <sup>2</sup> C Bus     | 11     |

| Serial EEPROM, SPI Bus                  | 113    |

| Serial EEPROM, Microwire Bus            | 247    |

| Parallel EEPROM                         | 289    |

| FLASH <sup>+</sup>                      | 403    |

| Application Specific Memory             | 501    |

| Application Notes                       | 637    |

|                                         |        |

EEPROM (Electrically Erasable Programmable Memory) is non volatile, and can be erased and programmed a byte at a time. This is as opposed to: RAM (Random Access Memory) that is volatile, and loses its data when the power is removed; and Flash memory that, though non volatile, can only be erased on a device-wise or sector-wise basis.

The uses to which EEPROM is put, therefore, are those for which its particular mix of properties are better suited than are those of RAM or Flash memory. Examples might include the storing of set-up parameters for a piece of equipment, or data tables and persistent variables, which might need to be changed regularly, but must retained from one power-down to the next power-up sequence. (These issues are discussed in *AN997*, on page 701).

Since the previous edition of this data book, there has been a significant increase in the code size of application programs, with an associated increase in the number of non-volatile parameters that need to be retained. To cater for this trend, EEPROM devices are being introduced to market at ever increasing memory capacities. For this edition of the data book, devices of up to 1 Mbit capacity are available.

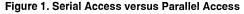

Two distinct families of EEPROM have established themselves:

- Serial Access EEPROM

- Parallel Access EEPROM

The parallel access EEPROM devices generally need one pin per address and data bit. The integrated circuit package tends to have a fairly large footprint, with at least 28 external pins.

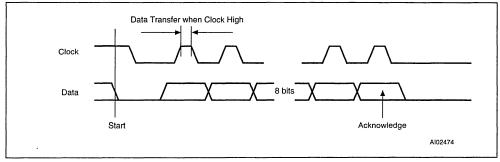

The serial access EEPROM devices can all be placed in an 8-pin package, irrespective of their memory capacity. This is because there is always only one line (perhaps two) to carry all of the address and data bits, multiplexed one after the other.

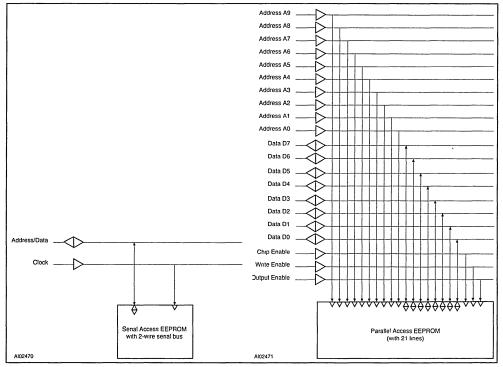

This multiplexing involves adhering to a standard protocol. There are three of these that are currently widely adopted (as described in *AN1001*, on page 647):

- Serial I<sup>2</sup>C Bus EEPROM

- Serial SPI Bus EEPROM

- Serial Microwire Bus EEPROM

These, then, constitute the first three sections of data sheets in this book, with parallel access EEPROM making the fourth.

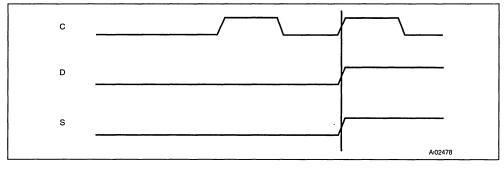

A new technology from STMicroelectronics, FLASH+, allows a single chip to contain an area of Flash memory and an area of EEPROM, thereby offering footprint and electrical power advantages to many applications. These devices are included in the fifth section of this book (and are described in the application notes from page 637 to 762).

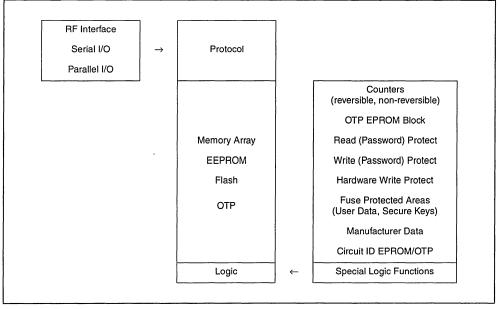

The sixth section presents a number of Application Specific Memory devices. These are devices whose cost, architecture, or other properties, have been optimized to meet specific market needs (as described in *AN1120*, on page 743).

The seventh section contains a number of application notes that have been written to describe various aspects of using EEPROM technology.

STMicroelectronics is permanently committed to extensive investment in process research, process development, and product design. As a result, it is constantly adding new products to these families, and adding new families to its portfolio. Please contact to your nearest ST Sales Office, or see the latest information in our pages on the world wide web: *www.st.com*.

-----

#### Table 1. Product Overview

|          | Serial I <sup>2</sup> C        | Serial SPI                   | Serial<br>Microwire | Parallel                                 | FLASH+           | ASM                                                                                 |

|----------|--------------------------------|------------------------------|---------------------|------------------------------------------|------------------|-------------------------------------------------------------------------------------|

| 256 bit  |                                |                              | M93C06              |                                          |                  |                                                                                     |

| 512 bit  |                                |                              |                     |                                          |                  |                                                                                     |

| 1 Kbit   | M24C01                         | M95010<br>ST95010            | M93C46<br>M93S46    |                                          |                  | M24LC21B<br>M24LW21<br>M24FC21<br>M24FW21<br>M2201                                  |

| 2 Kbit   | M24C02                         | M95020<br>ST95020<br>ST95022 | M93C56<br>M93S56    |                                          |                  | M34C02                                                                              |

| 4 Kbit   | M24C04                         | M95040<br>ST95040            | M93C66<br>M93S66    |                                          |                  | ST24C04<br>ST25C04<br>ST24W04<br>ST25W04                                            |

| 8 Kbit   | M24C08                         | M95080<br>ST95P08            | M93C76              |                                          |                  | M35080<br>ST24C08<br>ST25C08<br>ST24W08<br>ST25W08                                  |

| 16 Kbit  | M24C16                         | M95160                       | M93C86              | M28C16A<br>M28C17A<br>M28C16B<br>M28C17B |                  | M24164<br>ST24C16<br>ST25C16<br>ST24W16<br>ST25W16<br>ST25W16<br>ST24E16<br>ST25E16 |

| 32 Kbit  | M24C32                         | M95320                       |                     |                                          | ·                |                                                                                     |

| 64 Kbit  | M24C64                         | M95640                       |                     | M28C64<br>M28C64C<br>M28C64X             | M39208           |                                                                                     |

| 128 Kbit | M24128-B<br>M24128             | M95128                       |                     |                                          |                  |                                                                                     |

| 256 Kbit | M24256-B<br>M24256-A<br>M24256 | M95256                       |                     | M28256                                   | M39432<br>M39832 |                                                                                     |

| 512 Kbit | M24512                         | M95512                       |                     |                                          |                  |                                                                                     |

| 1 Mbit   |                                |                              |                     | M28010                                   |                  |                                                                                     |

| SERIAL EEPRON<br>M24C01,<br>M24C02,                                  | M, I <sup>2</sup> C BUS                                                           | 11   |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------|------|

| M24C04,<br>M24C08,<br>M24C16                                         | 16/8/4/2/1 Kbit Serial I <sup>2</sup> C Bus EEPROM                                | . 13 |

| M24C32,<br>M24C64<br>M24256-A                                        | 64/32 Kbit Serial I <sup>2</sup> C Bus EEPROM                                     |      |

| M24128-B,                                                            |                                                                                   |      |

| M24256-B<br>M24128,                                                  | 256/128 Kbit Serial I <sup>2</sup> C Bus EEPROM with Three Chip Enable Lines      |      |

| M24256<br>M24512                                                     | 256/128 Kbit Serial I <sup>2</sup> C Bus EEPROM without Chip Enable Lines         |      |

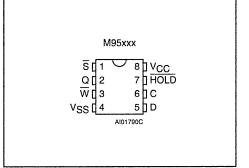

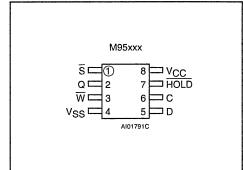

| SERIAL EEPRO                                                         | M, SPI BUS                                                                        | 113  |

| M95010,<br>M95020,                                                   |                                                                                   |      |

| M95040                                                               | 4/2/1 Kbit Serial SPI EEPROM with High Speed Clock<br>and Positive Clock Strobe   | 115  |

| M95080,<br>M95160,<br>M95320.                                        |                                                                                   |      |

| M95640                                                               | 64/32/16/8 Kbit Serial SPI EEPROM with High Speed Clock and Positive Clock Strobe | 135  |

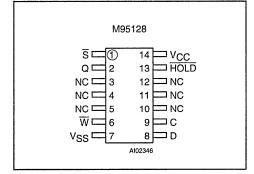

| M95128,<br>M95256                                                    | 256/128 Kbit Serial SPI EEPROM with High Speed Clock and Positive Clock Strobe    | 155  |

| M95512                                                               | 512 Kbit Serial SPI EEPROM with High Speed Clock and Positive Clock Strobe        | 177  |

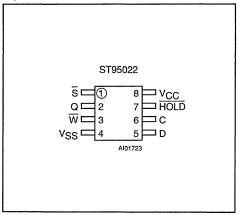

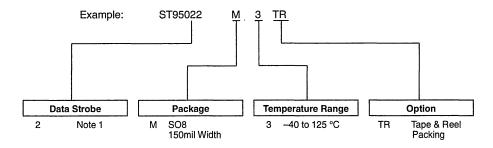

| ST95022<br>ST95010,                                                  | 2 Kbit Serial SPI EEPROM with High Speed Clock                                    | 197  |

| ST95020,<br>ST95040                                                  | 4/2/1 Kbit Serial SPI EEPROM with Positive Clock Strobe                           |      |

| ST95P08                                                              | 8 Kbit Serial SPI EEPROM with Single Address Byte and Positive Clock Strobe .     |      |

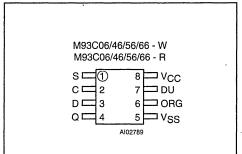

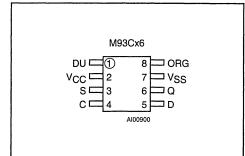

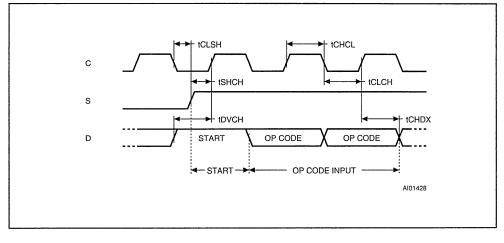

| SERIAL EEPROF<br>M93C06,<br>M93C46,<br>M93C56,<br>M93C66,<br>M93C76, | M, MICROWIRE BUS                                                                  | 247  |

| M93C86<br>M93S46,<br>M93S56,                                         | 16K/8K/4K/2K/1K/256 bit (x8/x16) Serial Microwire Bus EEPROM                      |      |

| M93S66                                                               | 4/2/1 Kbit (x16) Serial Microwire Bus EEPROM with Block Write Protection          | 20/  |

4/2/1 Kbit (x16) Serial Microwire Bus EEPROM with Block Write Protection .... 267

**A77**

| PARALLEL EEP           | ROM                                                                                 | 289 |

|------------------------|-------------------------------------------------------------------------------------|-----|

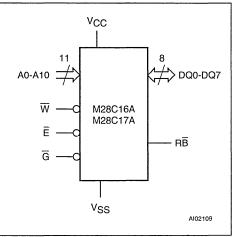

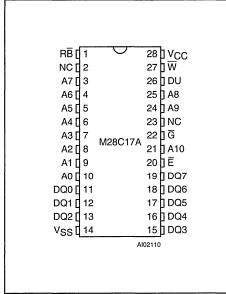

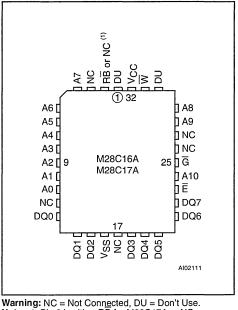

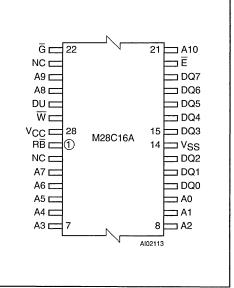

| M28C16A,<br>M28C17A    | 16 Kbit (2K x 8) Parallel EEPROM                                                    | 291 |

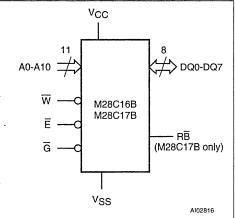

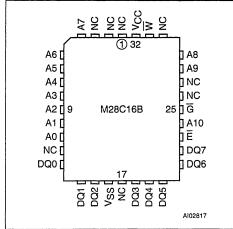

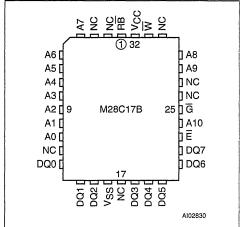

| M28C16B.               |                                                                                     | 201 |

| M28C17B                | 16 Kbit (2K x 8) Parallel EEPROM with Software Data Protection                      | 311 |

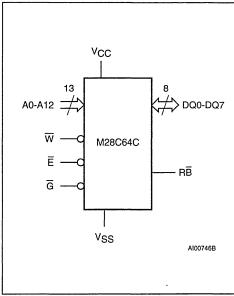

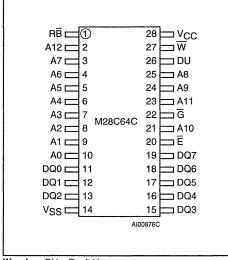

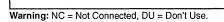

| M28C64C,               |                                                                                     | ~~~ |

| M28C64X                | 64 Kbit (8K x 8) Parallel EEPROM                                                    |     |

| M28C64                 | 64 Kbit (8K x 8) Parallel EEPROM with Software Data Protection                      |     |

| M28256                 | 256 Kbit (32K x 8) Parallel EEPROM with Software Data Protection                    |     |

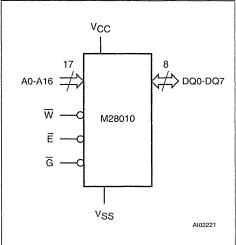

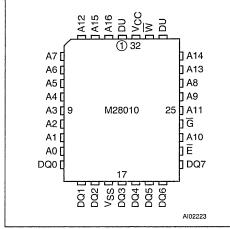

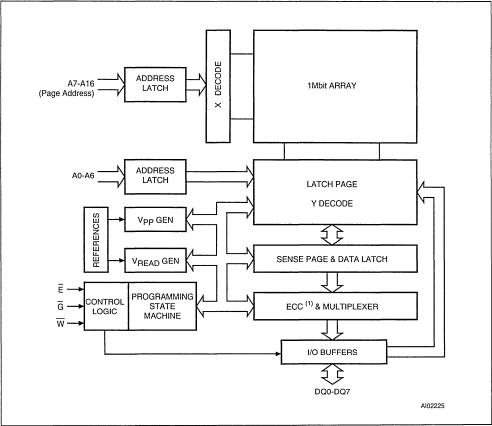

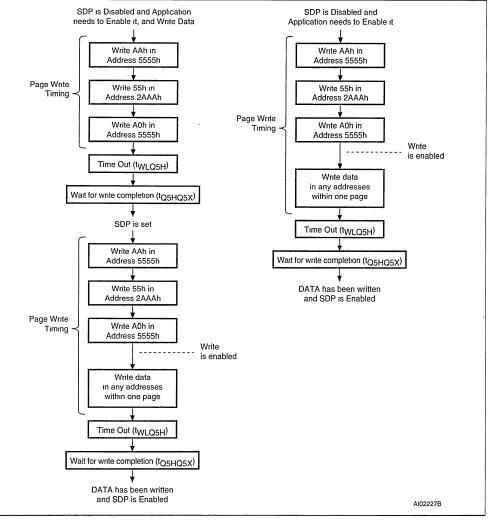

| M28010                 | 1 Mbit (128K x 8) Parallel EEPROM with Software Data Protection                     | 381 |

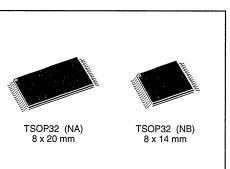

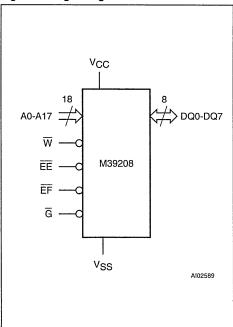

| FLASH+                 |                                                                                     | 403 |

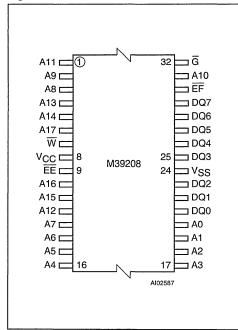

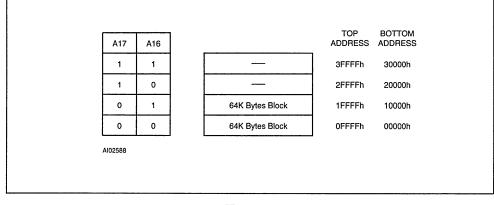

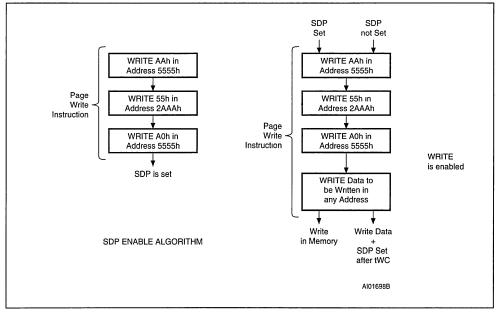

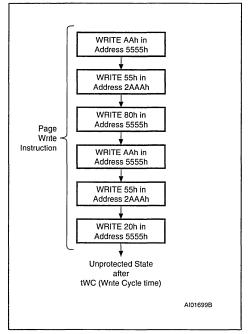

| M39208                 | Single Chip 2 Mbit Flash Memory and 64 Kbit Parallel EEPROM                         | 405 |

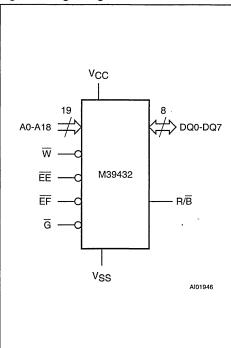

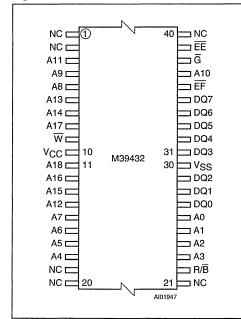

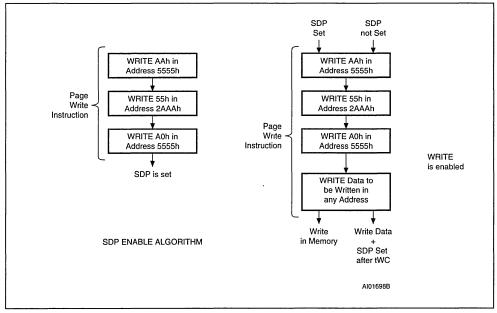

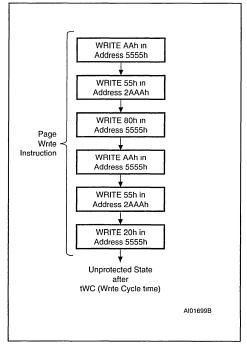

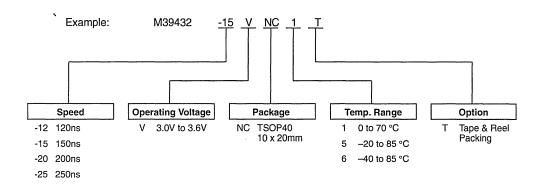

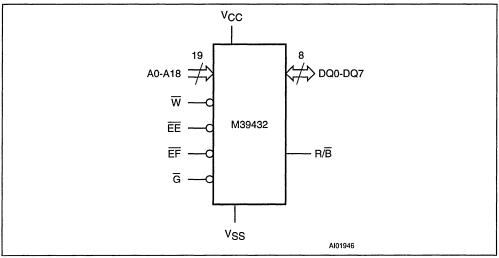

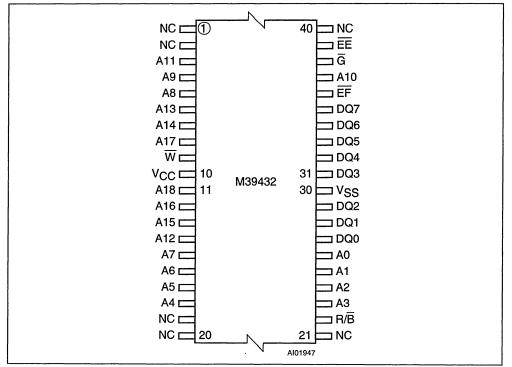

| M39432                 | Single Chip 4 Mbit Flash Memory and 256 Kbit Parallel EEPROM                        | 435 |

| M39832                 | Single Chip 8 Mbit (1M x 8 or 512K x 16) Flash Memory                               |     |

|                        | and 256 Kbit Parallel EEPROM                                                        | 465 |

|                        |                                                                                     | 504 |

|                        | SPECIFIC MEMORIES (ASM)                                                             | 501 |

| M24164                 | 16 Kbit Serial I <sup>2</sup> C Bus EEPROM                                          |     |

| M34C02                 | 2 Kbit Serial EEPROM for DIMM Serial Presence Detect                                |     |

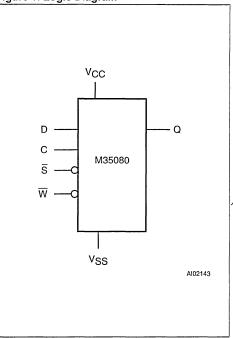

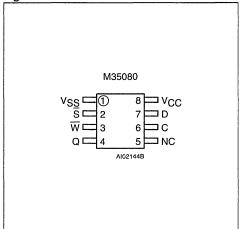

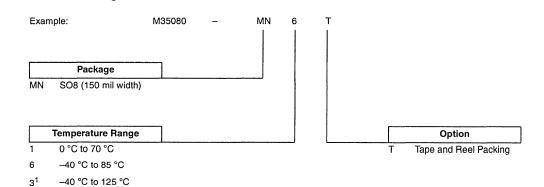

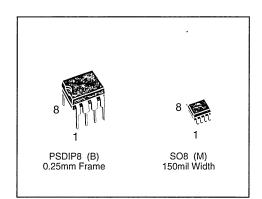

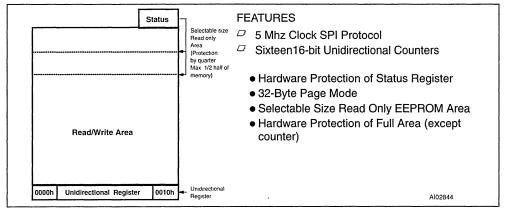

| M35080                 | 8 Kbit Serial SPI Bus EEPROM with Unidirectional Counters                           | 537 |

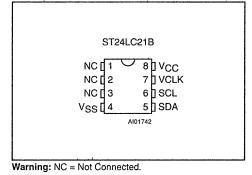

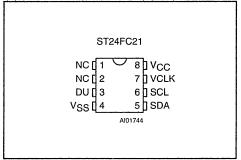

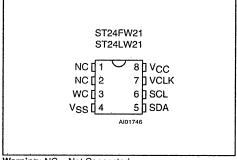

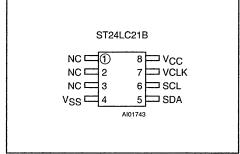

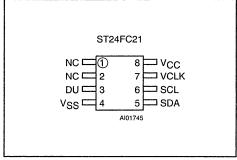

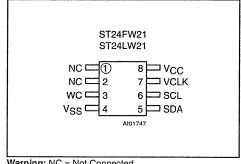

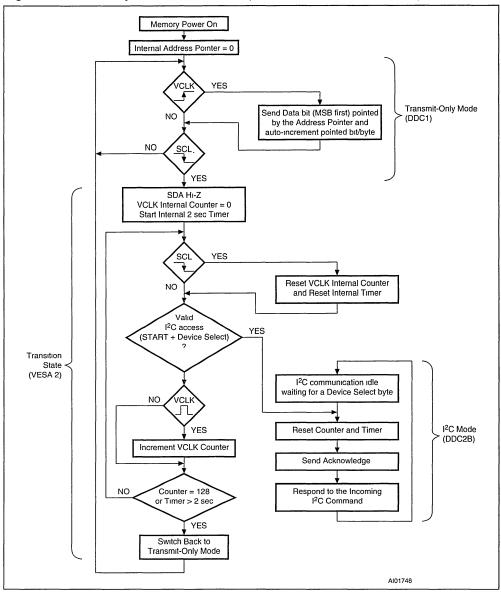

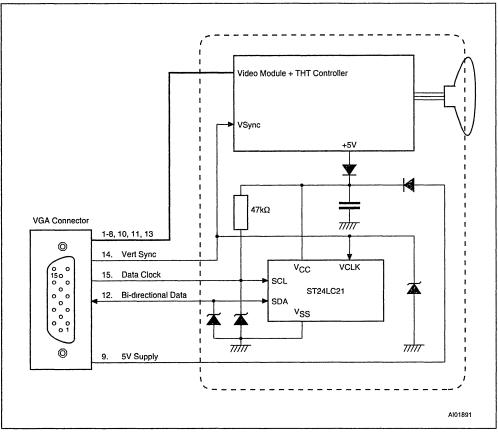

| ST24LC21B,             |                                                                                     |     |

| ST24LW21,<br>ST24FC21, |                                                                                     |     |

| ST24FW21               | 1 Kbit (x8) Dual Mode Serial EEPROM for VESA Plug & Play                            | 539 |

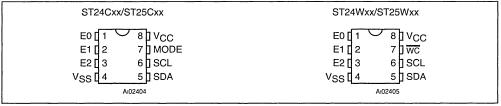

| ST24C04,               |                                                                                     |     |

| ST25C04,               |                                                                                     |     |

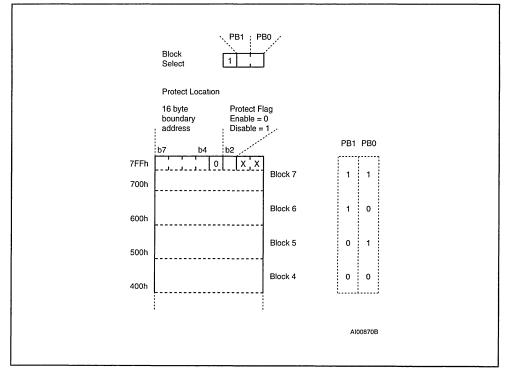

| ST24W04,               | 4 Kbit Serial I <sup>2</sup> C Bus EEPROM with User-Defined Block Write Protection  | 550 |

| ST25W04                | 4 KDIL Serial PC Bus EEFROM WILL User-Denned Block While Protection                 | 009 |

| ST24C08,<br>ST25C08,   |                                                                                     |     |

| ST24W08,               |                                                                                     |     |

| ST25W08                | 8 Kbit Serial I <sup>2</sup> C Bus EEPROM with User-Defined Block Write Protection  | 575 |

| ST24C16,               |                                                                                     |     |

| ST25C16,<br>ST24W16,   |                                                                                     |     |

| ST25W16                | 16 Kbit Serial I <sup>2</sup> C Bus EEPROM with User-Defined Block Write Protection | 591 |

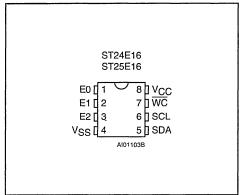

| ST24E16,               |                                                                                     |     |

| ST25E16                | 16 Kbit Serial I <sup>2</sup> C Bus EEPROM with Extended Addressing                 | 607 |

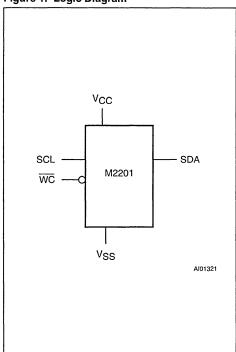

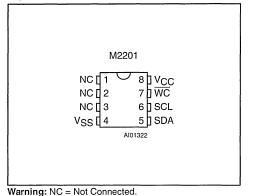

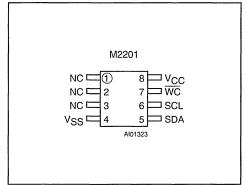

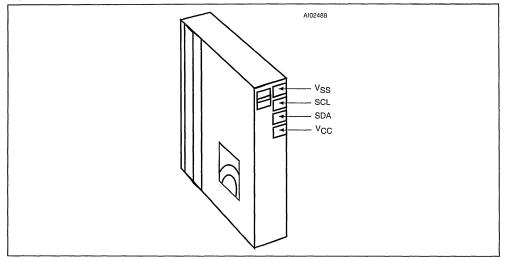

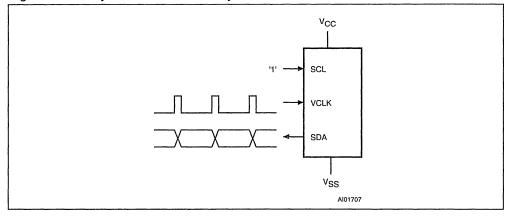

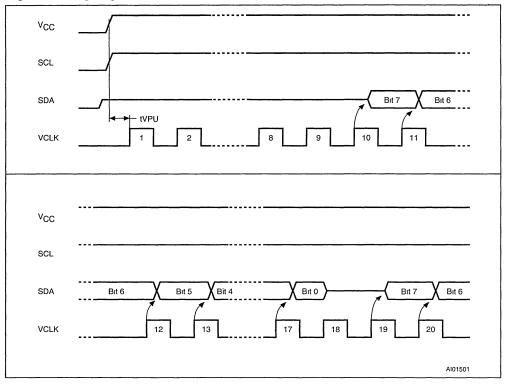

| M2201                  | 2-Wires 1 Kbit (x8) Serial EEPROM                                                   | 623 |

\_

57

| ٢                |                                                                                              |     |

|------------------|----------------------------------------------------------------------------------------------|-----|

| APPLICATION N    | OTES                                                                                         | 637 |

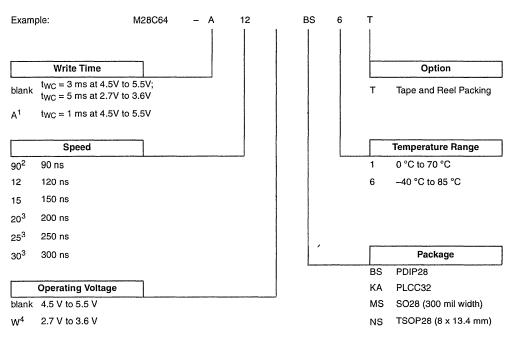

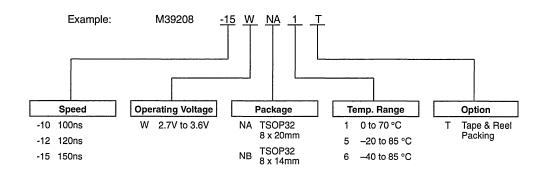

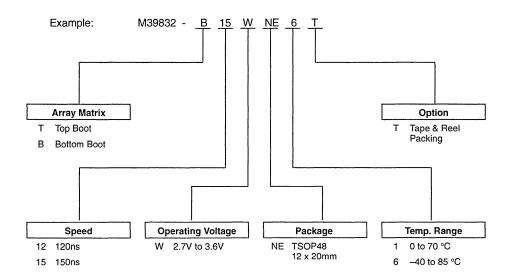

| AN626            | EEPROM Product Numbering                                                                     |     |

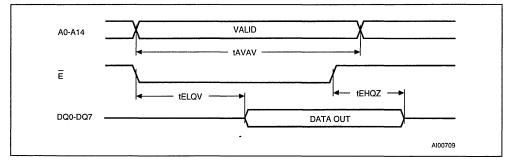

| AN397            | Timing Specifications for Memory Products                                                    | 643 |

| AN1001           | Choice of Serial EEPROMs Requires Understanding of Bus Differences                           | 647 |

| Serial EEPROM,   | I <sup>2</sup> C Bus                                                                         |     |

| AN995            | Changing from the ST24xxx and ST25xxx to the M24xxx in Your Application                      | 655 |

| AN1005           | Extending the I <sup>2</sup> C Bus – XI <sup>2</sup> C                                       | 659 |

| AN1006           | The Write Control Feature on I <sup>2</sup> C EEPROM                                         | 663 |

| Serial EEPROM,   | SPI Bus                                                                                      |     |

| AN1116           | Changing from the ST95P08 to the M95080 in Your Application                                  |     |

|                  | Using a Simple Software Recognition Method                                                   | 665 |

| Serial EEPROM,   | Microwire Bus                                                                                |     |

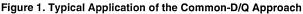

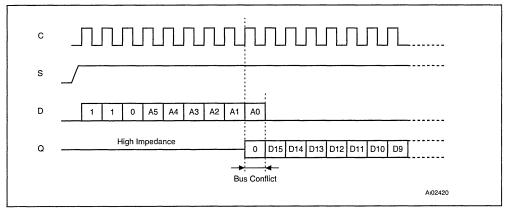

| AN394            | Microwire EEPROM Common I/O Operation                                                        | 669 |

| AN1119 ·         | Correct Power-On and Power-Off for the M93Cxx and M93Sxx                                     | 679 |

| FLASH+           |                                                                                              |     |

| AN1118           | FLASH+: The End of the Emulation Compromise                                                  | 685 |

| AN996            | Emulating the Unification of Flash and EEPROM: A Glossary                                    | 687 |

| AN931            | On-Chip Hardware EEPROM Emulation versus Flash Memory Software Solutions                     | 693 |

| AN997            | M39432: a FLASH+ Multiple Memory Device                                                      | 701 |

| AN998            | FLASH+ Multiple Memory Technology                                                            | 709 |

| AN999            | Software Drivers for the M39432 FLASH+ Multiple Memory                                       | 713 |

| Application Spec | cific Memories                                                                               |     |

| AN1120           | EEPROM-Based Application Specific Memories                                                   | 743 |

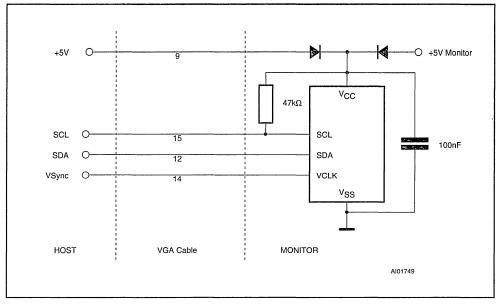

| AN627            | Serial EEPROM Compatible With Plug-and-Play VESA Display Data Channel (Versions 1.0 and 2.0) | 749 |

For more information on all ST products, please consult our pages on the world wide web: www.st.com

\_\_\_\_\_

### NOTES

## SERIAL EEPROM, I<sup>2</sup>C BUS

### NOTES

### M24C16, M24C08 M24C04, M24C02, M24C01

### 16/8/4/2/1 Kbit Serial I<sup>2</sup>C Bus EEPROM

- Two Wire I<sup>2</sup>C Serial Interface Supports 400 kHz Protocol

- Single Supply Voltage:

- 4.5V to 5.5V for M24Cxx

- 2.5V to 5.5V for M24Cxx-W

- 1.8V to 3.6V for M24Cxx-R

- Hardware Write Control

- BYTE and PAGE WRITE (up to 16 Bytes)

- RANDOM and SEQUENTIAL READ Modes

- Self-Timed Programming Cycle

- Automatic Address Incrementing

- Enhanced ESD/Latch-Up Behaviour

- 1 Million Erase/Write Cycles (minimum)

- 40 Year Data Retention (minimum)

#### DESCRIPTION

These electrically erasable programmable memory (EEPROM) devices are fabricated with STMicroelectronics' High Endurance, Single Polysilicon, CMOS technology. This guarantees an endurance typically well above one million Erase/Write cycles, with a data retention of 40 years. The memories are organised as 2048/ 1024 x 8 bit (M24C16, M24C08) and 512/256/128 x 8 bit (M24C04, M24C02, M24C01), and operate with a power supply down to 2.5 V (for the -W ver-

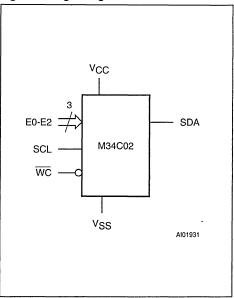

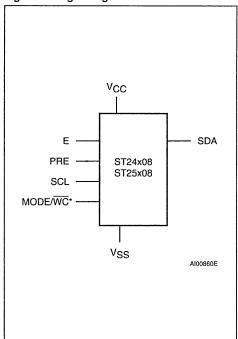

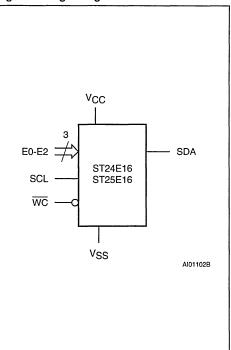

#### **Table 1. Signal Names**

| E0, E1, E2      | Chip Enable Inputs                   |

|-----------------|--------------------------------------|

| SDA             | Serial Data/Address Input/<br>Output |

| SCL             | Serial Clock                         |

| WC              | Write Control                        |

| Vcc             | Supply Voltage                       |

| V <sub>SS</sub> | Ground                               |

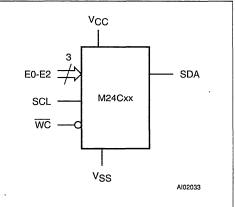

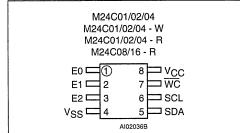

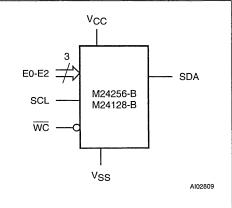

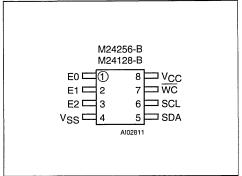

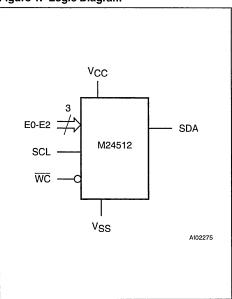

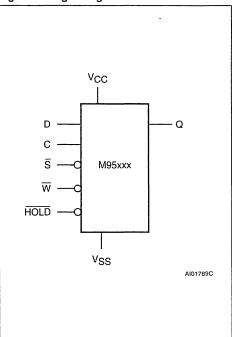

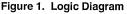

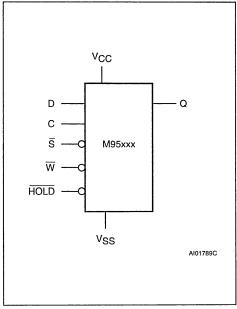

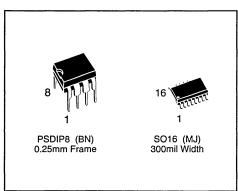

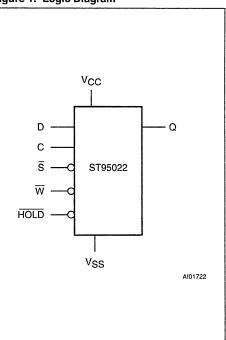

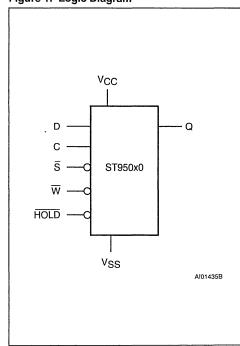

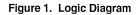

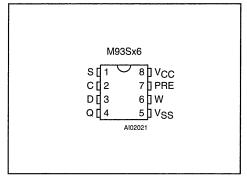

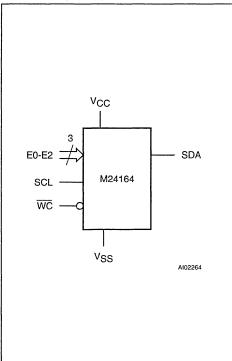

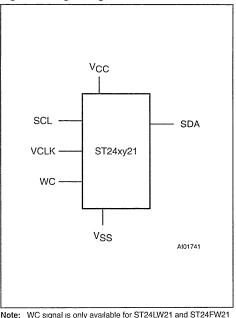

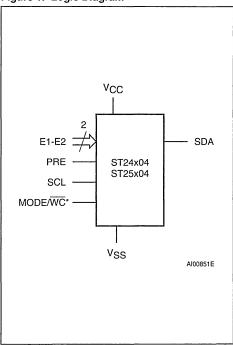

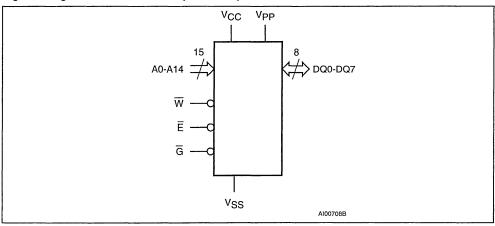

#### Figure 1. Logic Diagram

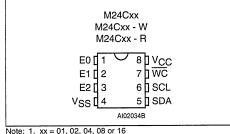

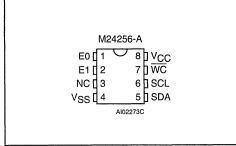

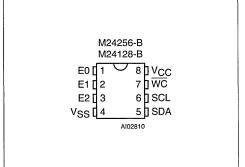

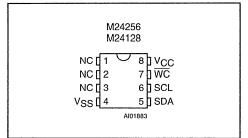

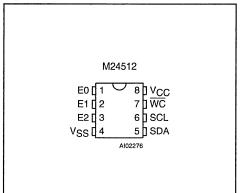

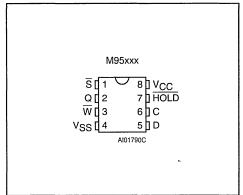

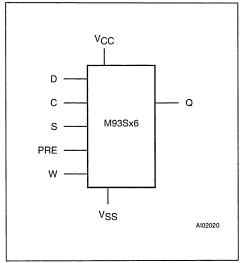

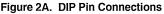

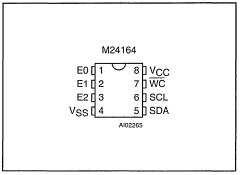

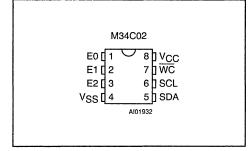

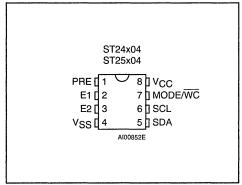

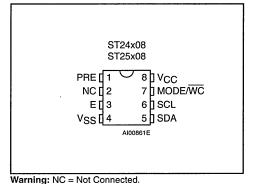

#### Figure 2A. DIP Connections

- - 2. Pin 1 is Not Connected for 4 Kbit devices

- 3. Pins 1 and 2 are Not Connected for 8 Kbit devices

- 4. Pins 1, 2 and 3 are Not Connected for 16 Kbit devices

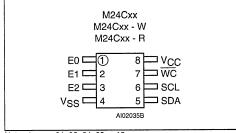

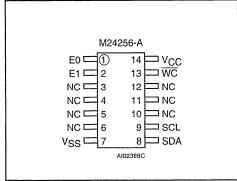

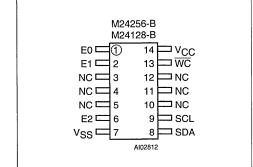

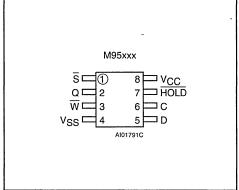

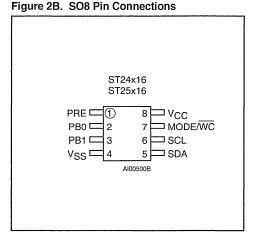

#### Figure 2B. SO Connections

- Note: 1, xx = 01, 02, 04, 08 or 16

- 2. Pin 1 is Not Connected for 4 Kbit devices

- 3. Pins 1 and 2 are Not Connected for 8 Kbit devices

- 4. Pins 1, 2 and 3 are Not Connected for 16 Kbit devices

#### Table 2. Absolute Maximum Ratings <sup>1</sup>

| Symbol            | Parameter                                |                                                 | Value                | Unit |

|-------------------|------------------------------------------|-------------------------------------------------|----------------------|------|

| T <sub>A</sub>    | Ambient Operating Temperature            |                                                 | -40 to 125           | °C   |

| T <sub>STG</sub>  | Storage Temperature                      |                                                 | -65 to 150           | °C   |

| T <sub>LEAD</sub> | Lead Temperature during Soldering        | PSDIP8: 10 sec<br>SO8: 40 sec<br>TSSOP8: t.b.c. | 260<br>215<br>t.b.c. | °C   |

| VIO               | Input or Output range                    |                                                 | -0.6 to 6.5          | v    |

| V <sub>cc</sub>   | Supply Voltage                           | -0.3 to 6.5                                     | v                    |      |

|                   | Electrostatic Discharge Voltage (Human I | 4000                                            | V                    |      |

| V <sub>ESD</sub>  | Electrostatic Discharge Voltage (Machine | model) <sup>3</sup>                             | 500                  | V    |

Note: 1 Except for the rating "Operating Temperature Range", stresses above those listed in the Table "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the ST SURE Program and other relevant quality documents

2. MIL-STD-883C, 3015.7 (100 pF, 1500 Ω)

3 EIAJ IC-121 (Condition C) (200 pF, 0 Ω)

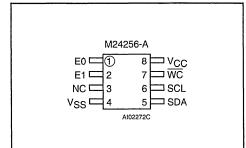

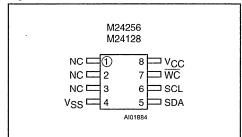

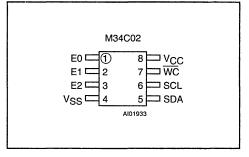

#### Figure 2C. Standard-TSSOP Connections

Note: 1. Pin 1 is Not Connected for 4 Kbit devices

- 2. Pins 1 and 2 are Not Connected for 8 Kbit devices

- 3. Pins 1, 2 and 3 are Not Connected for 16 Kbit devices

#### Figure 2D. Turned-TSSOP Connections

2. Pin 5 is Not Connected for 16 Kbit devices

sion of each device), and down to 1.8 V (for the -R version of each device).

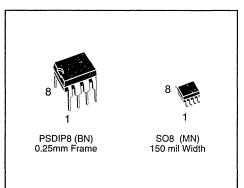

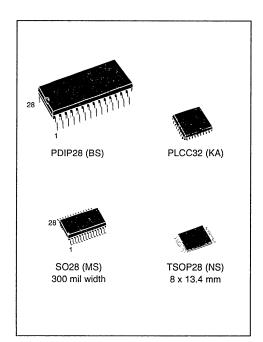

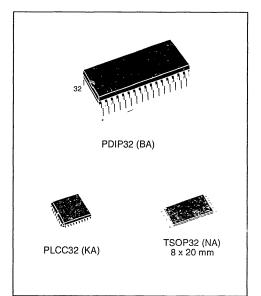

The M24C16, M24C08, M24C04, M24C02, M24C01 are available in Plastic Dual-in-Line, Plastic Small Outline and Thin Shrink Small Outline packages.

These memory devices are compatible with the  $I^2C$  extended memory standard. This is a two wire serial interface that uses a bi-directional data bus and serial clock. The memory carries a built-in 4-bit unique Device Type Identifier code (1010) in accordance with the  $I^2C$  bus definition.

The memory behaves as a slave device in the  $l^2C$  protocol, with all memory operations synchronized by the serial clock. Read and Write operations are initiated by a START condition, generated by the bus master. The START condition is followed by a Device Select Code and RW bit (as described in Table 3), terminated by an acknowledge bit.

When writing data to the memory, the memory inserts an acknowledge bit during the 9<sup>th</sup> bit time, following the bus master's 8-bit transmission. When data is read by the bus master, the bus master acknowledges the receipt of the data byte in the same way. Data transfers are terminated by a STOP condition after an Ack for WRITE, and after a NoAck for READ.

#### Power On Reset: V<sub>CC</sub> Lock-Out Write Protect

In order to prevent data corruption and inadvertent write operations during power up, a Power On Reset (POR) circuit is included. The internal reset is held active until the V<sub>CC</sub> voltage has reached the POR threshold value, and all operations are disabled – the device will not respond to any command. In the same way, when V<sub>CC</sub> drops from the operating voltage, below the POR threshold value,

**⟨**▼/

all operations are disabled and the device will not respond to any command. A stable and valid  $V_{CC}$  must be applied before applying any logic signal.

#### SIGNAL DESCRIPTION

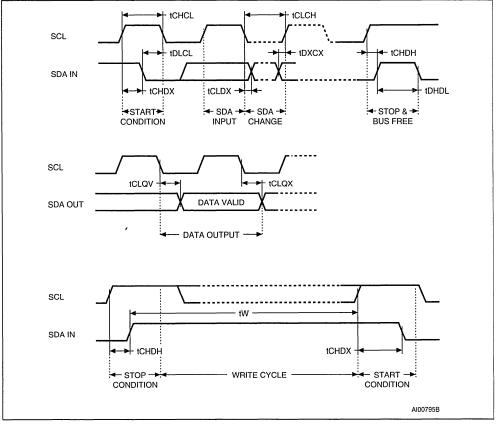

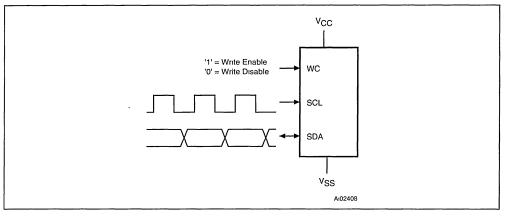

#### Serial Clock (SCL)

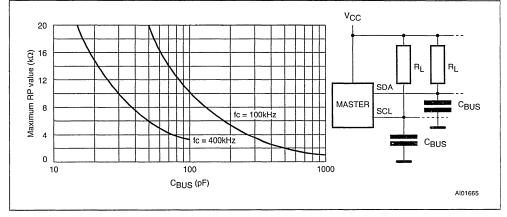

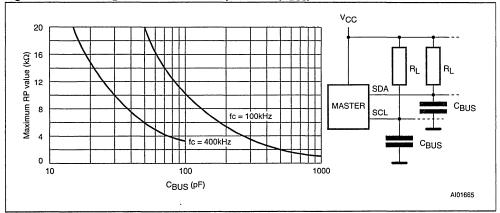

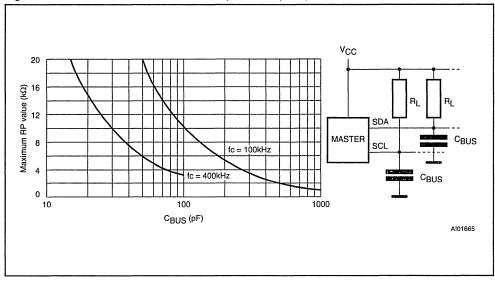

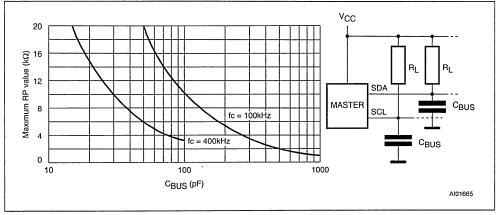

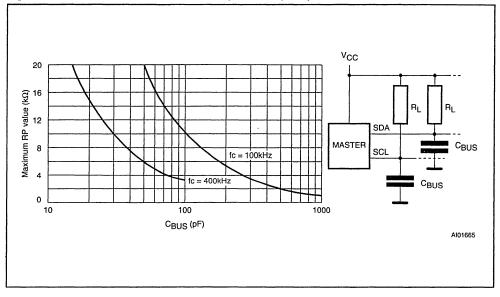

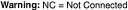

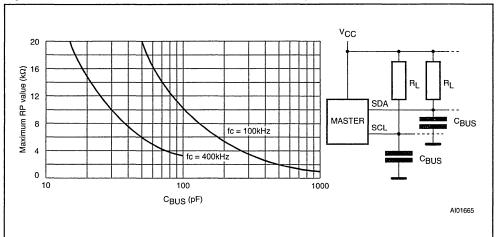

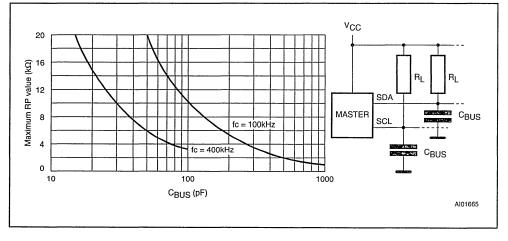

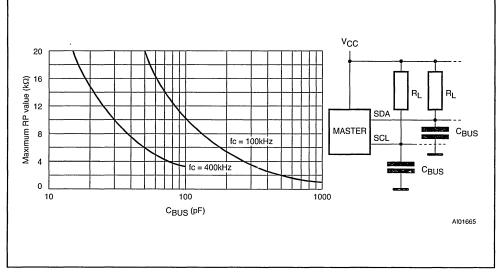

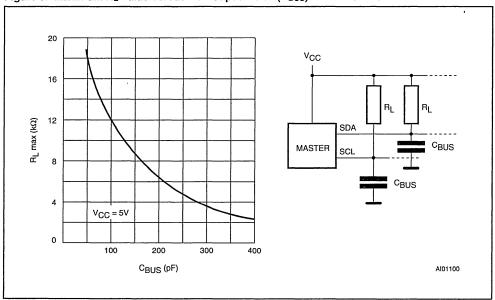

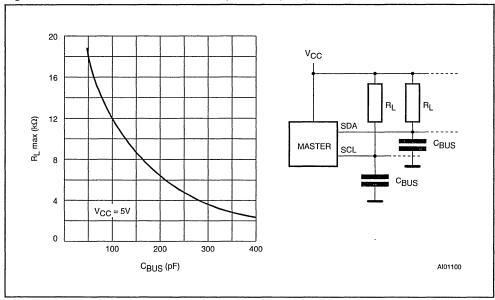

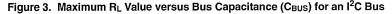

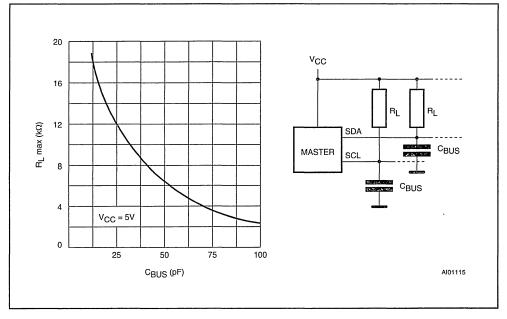

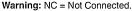

The SCL input pin is used to strobe all data in and out of the memory. In applications where this line is used by slaves to synchronize the bus to a slower clock, the master must have an open drain output, and a pull-up resistor must be connected from the SCL line to  $V_{CC}$ . (Figure 3 indicates how the value of the pull-up resistor can be calculated). In most applications, though, this method of synchronization is not employed, and so the pull-up resistor is not necessary, provided that the master has a push-pull (rather than open drain) output.

#### Serial Data (SDA)

The SDA pin is bi-directional, and is used to transfer data in or out of the memory. It is an open drain output that may be wire-OR'ed with other open drain or open collector signals on the bus. A pull up resistor must be connected from the SDA bus to V<sub>CC</sub>. (Figure 3 indicates how the value of the pull-up resistor can be calculated).

#### Chip Enable (E2, E1, E0)

These chip enable inputs are used to set the value that is to be looked for on the three least significant bits (b3, b2, b1) of the 7-bit device select code (but see the description of memory addressing, on page 5, for more details). These inputs may be driven dynamically or tied to  $V_{CC}$  or  $V_{SS}$  to establish the device select code (but note that the  $V_{IL}$  and  $V_{IH}$  levels for the inputs are CMOS compatible, not TTL compatible).

Figure 3. Maximum R<sub>L</sub> Value versus Bus Capacitance (C<sub>BUS</sub>) for an I<sup>2</sup>C Bus

#### Write Control (WC)

The hardware Write Control pin ( $\overline{WC}$ ) is useful for protecting the entire contents of the memory from inadvertent erase/write. The Write Control signal is used to enable ( $\overline{WC}=V_{IL}$ ) or disable ( $\overline{WC}=V_{IH}$ ) write instructions to the entire memory area. When unconnected, the  $\overline{WC}$  input is internally read as  $V_{IL}$ , and write operations are allowed.

When  $\overline{\text{WC}}$ =1, Device Select and Address bytes are acknowledged, Data bytes are not acknowledged.

Please see the Application Note *AN404* for a more detailed description of the Write Control feature.

#### **DEVICE OPERATION**

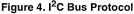

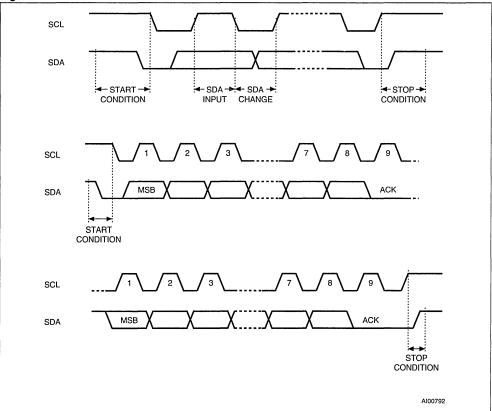

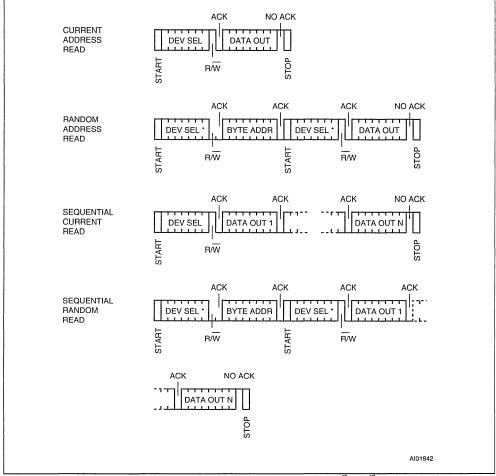

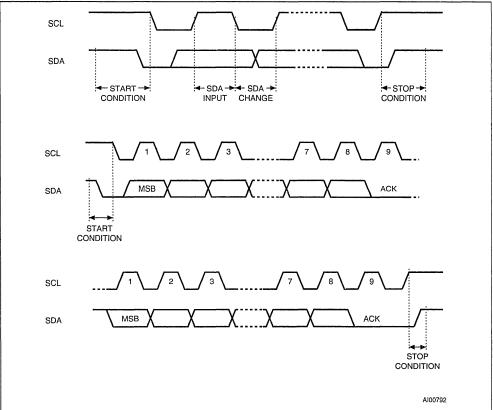

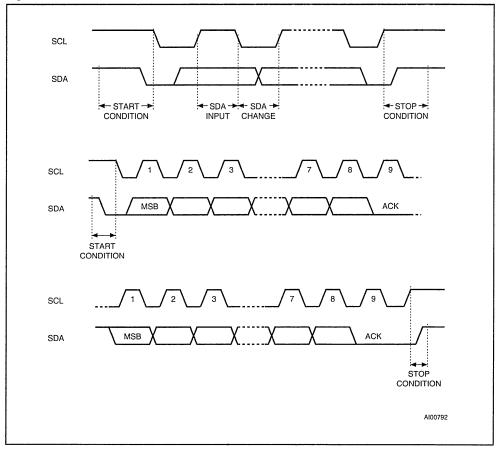

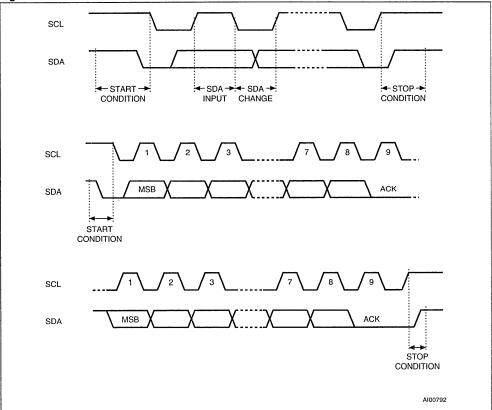

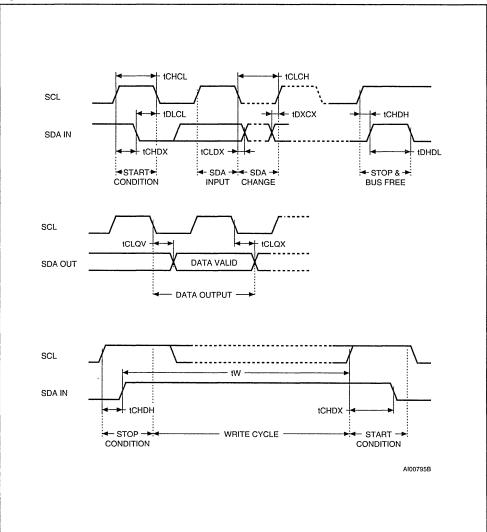

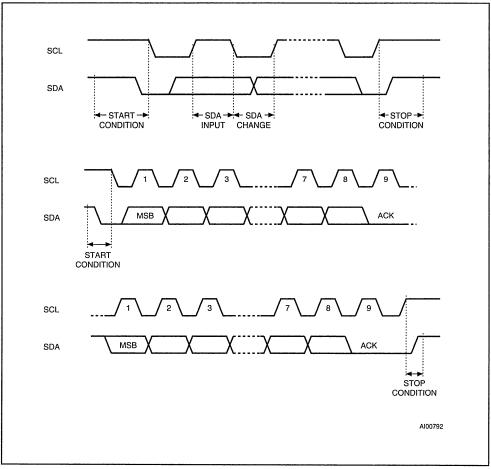

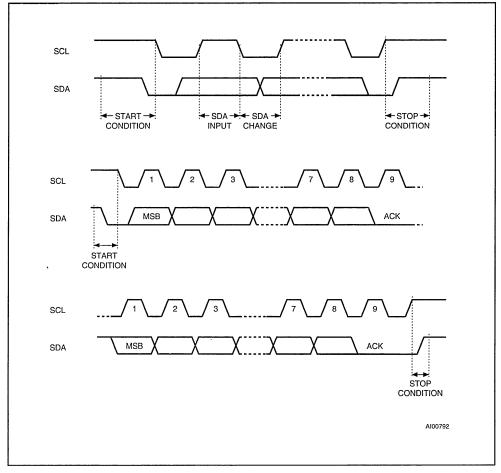

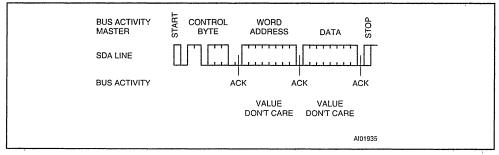

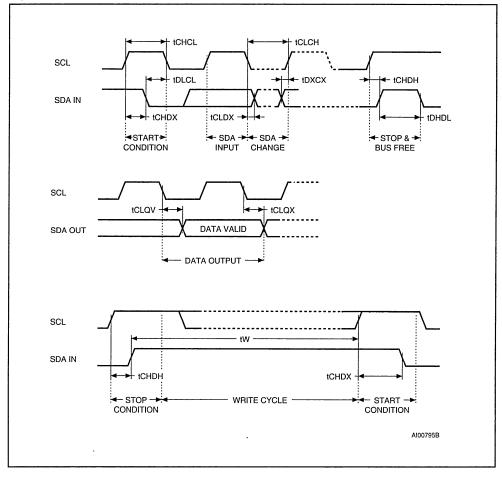

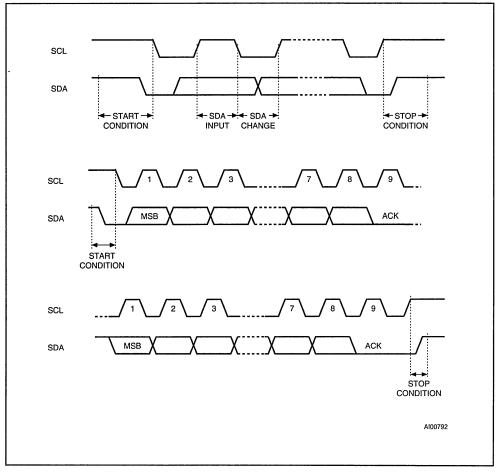

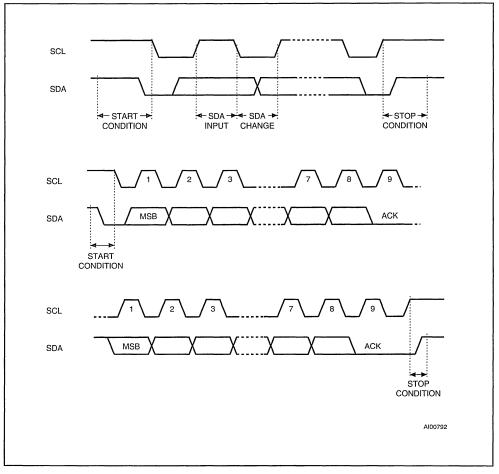

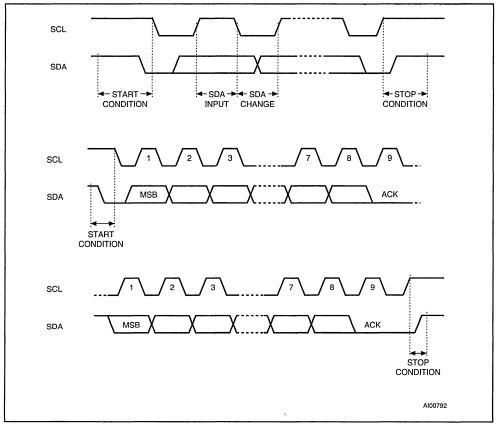

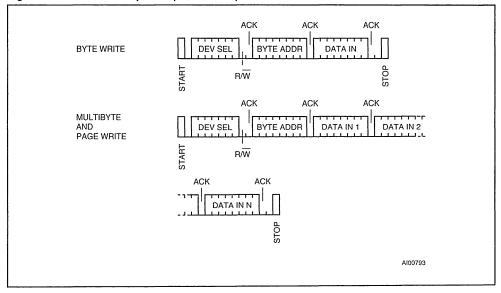

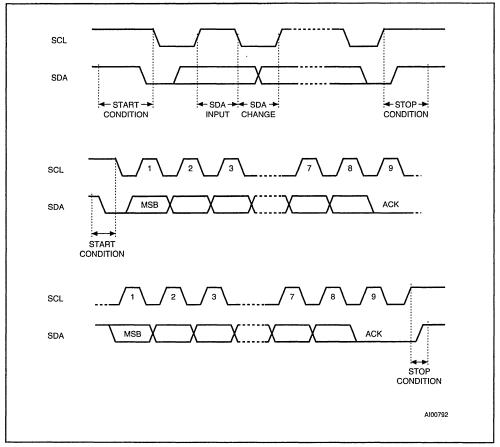

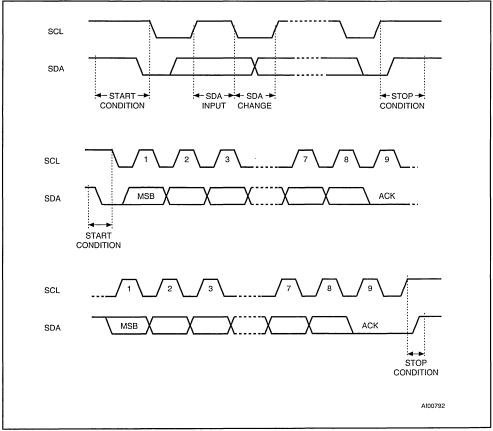

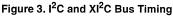

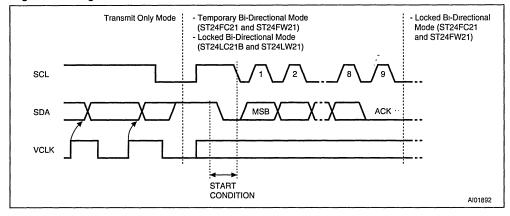

The memory device supports the  $I^2C$  protocol. This is summarized in Figure 4, and is compared with other serial bus protocols in Application Note *AN1001*. Any device that sends data on to the bus is defined to be a transmitter, and any device that reads the data to be a receiver. The device that controls the data transfer is known as the master, and the other as the slave. A data transfer can only be initiated by the master, which will also provide the serial clock for synchronization. The memory device is always a slave device in all communication.

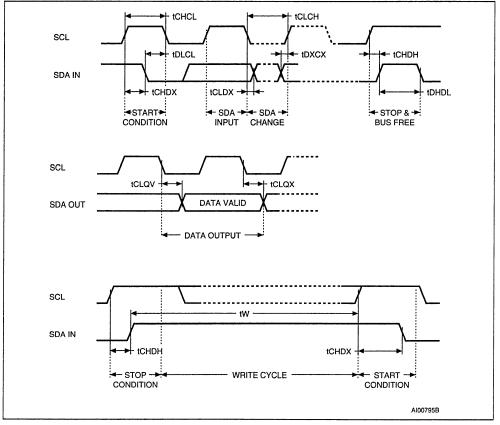

#### Start Condition

START is identified by a high to low transition of the SDA line while the clock, SCL, is stable in the high state. A START condition must precede any data transfer command. The memory device continuously monitors (except during a programming cycle) the SDA and SCL lines for a START condition, and will not respond unless one is given.

#### Stop Condition

STOP is identified by a low to high transition of the SDA line while the clock SCL is stable in the high state. A STOP condition terminates communica-

|                    |    | Device Ty | pe Identifie | ·  | Chip Enable |    |    | RW |

|--------------------|----|-----------|--------------|----|-------------|----|----|----|

|                    | b7 | b6        | b5           | b4 | b3          | b2 | b1 | b0 |

| M24C01 Select Code | 1  | 0         | 1            | 0  | E2          | E1 | E0 | RW |

| M24C02 Select Code | 1  | 0         | 1            | 0  | E2          | E1 | E0 | RW |

| M24C04 Select Code | 1  | 0         | 1            | 0  | E2          | E1 | A8 | R₩ |

| M24C08 Select Code | 1  | 0         | 1            | 0  | E2          | A9 | A8 | R₩ |

| M24C16 Select Code | 1  | 0         | 1            | 0  | A10         | A9 | A8 | RW |

#### Table 3. Device Select Code <sup>1</sup>

Note: 1. The most significant bit, b7, is sent first

2. E0, E1 and E2 are compared against the respective external pins on the memory device.

3. A10, A9 and A8 represent high significant bits of the address

tion between the memory device and the bus master. A STOP condition at the end of a Read command, after (and only after) a NoAck, forces the memory device into its standby state. A STOP condition at the end of a Write command triggers the internal EEPROM write cycle.

#### Acknowledge Bit (ACK)

An acknowledge signal is used to indicate a successful byte transfer. The bus transmitter, whether it be master or slave, releases the SDA bus after sending eight bits of data. During the 9<sup>th</sup> clock pulse period, the receiver pulls the SDA bus low to acknowledge the receipt of the eight data bits.

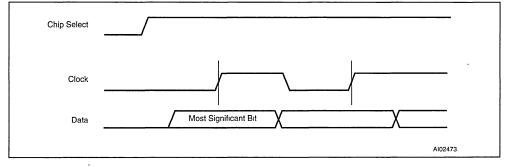

#### Data Input

During data input, the memory device samples the SDA bus signal on the rising edge of the clock, SCL. For correct device operation, the SDA signal must be stable during the clock low-to-high transition, and the data must change *only* when the SCL line is low.

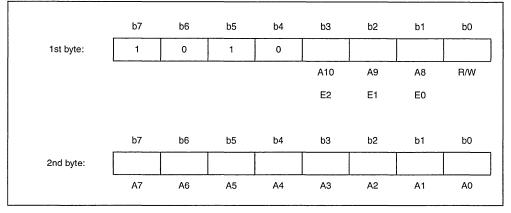

#### Memory Addressing

To start communication between the bus master and the slave memory, the master must initiate a START condition. Following this, the master sends the 8-bit byte, shown in Table 3, on the SDA bus line (most significant bit first). This consists of the 7-bit Device Select Code, and the 1-bit Read/Write Designator (RW). The Device Select Code is further subdivided into: a 4-bit Device Type Identifier, and a 3-bit Chip Enable "Address" (E2, E1, E0).

To address the memory array, the 4-bit Device Type Identifier is 1010b.

If all three chip enable inputs are connected, up to eight memory devices can be connected on a single  $1^2$ C bus. Each one is given a unique 3-bit code on its Chip Enable inputs. When the Device Select Code is received on the SDA bus, the memory only responds if the Chip Select Code is the same as the pattern applied to its Chip Enable pins.

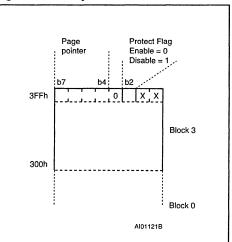

Those devices with larger memory capacities (the M24C16, M24C08) need more address bits. E0 is not available for use on devices that need to use address line A8; E1 is not available for devices that need to use address line A9, and E2 is not available for devices that need to use address line A10 (see Figure 2A to Figure 2D for details). Using the E0, E1 and E2 inputs pins, up to eight M24C02 (or M24C01), four M24C04, two M24C08 or one M24C16 device can be connected to one  $l^2C$  bus. In each case, and in the hybrid cases, this gives a total memory capacity of 16 Kbits, 2 KBytes (except where M24C01 devices are used).

| Mode                  | RW bit | WC <sup>1</sup> | Bytes | Initial Sequence                                     |  |  |

|-----------------------|--------|-----------------|-------|------------------------------------------------------|--|--|

| Current Address Read  | '1'    | x               | 1     | START, Device Select, $R\overline{W} = '1'$          |  |  |

| Develop Address Devel | '0'    | х               |       | START, Device Select, $R\overline{W}$ = '0', Address |  |  |

| Random Address Read   | '1'    | х               |       | reSTART, Device Select, RW = '1'                     |  |  |

| Sequential Read       | '1'    | Х               | ≥1    | Similar to Current or Random Address Read            |  |  |

| Byte Write            | '0'    | VIL             | 1     | START, Device Select, $R\overline{W}$ = '0'          |  |  |

| Page Write            | '0'    | VIL             | ≤ 16  | START, Device Select, $R\overline{W} = '0'$          |  |  |

#### Table 4. Operating Modes

Note: 1.  $X = V_{IH} \text{ or } V_{IL}$ .

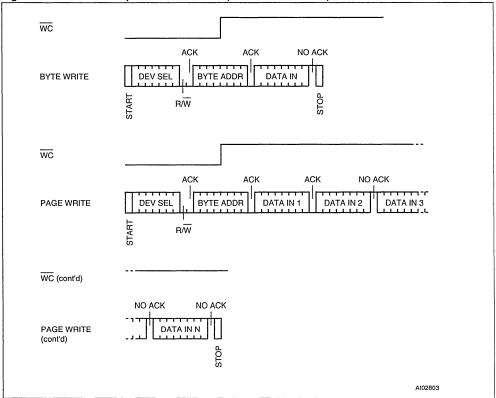

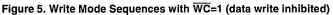

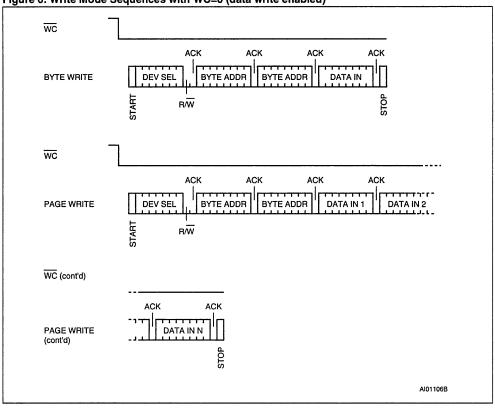

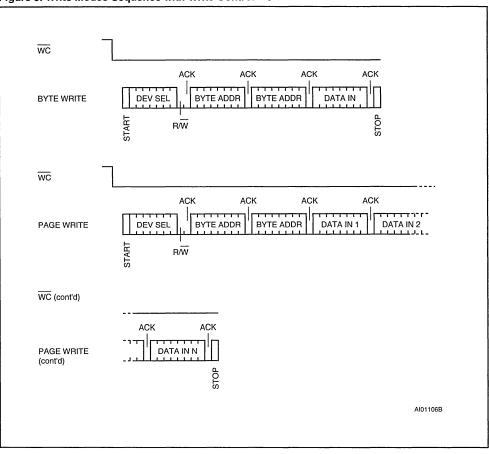

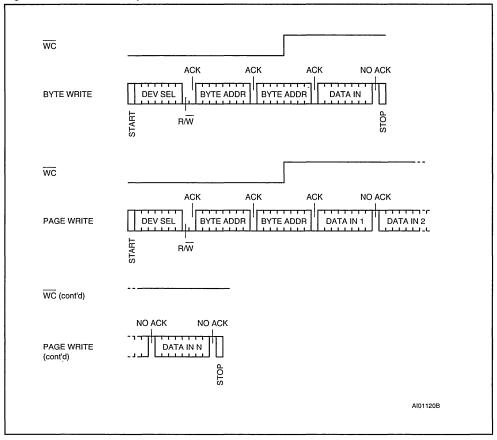

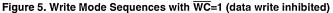

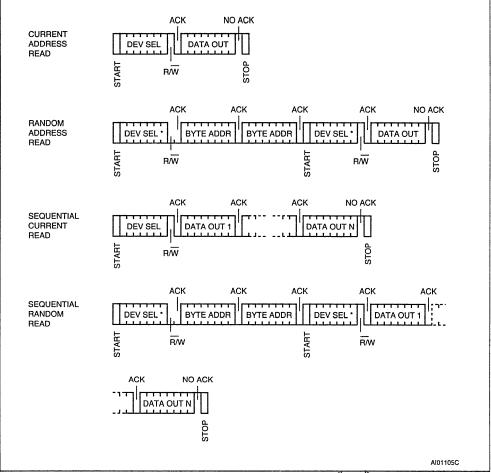

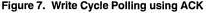

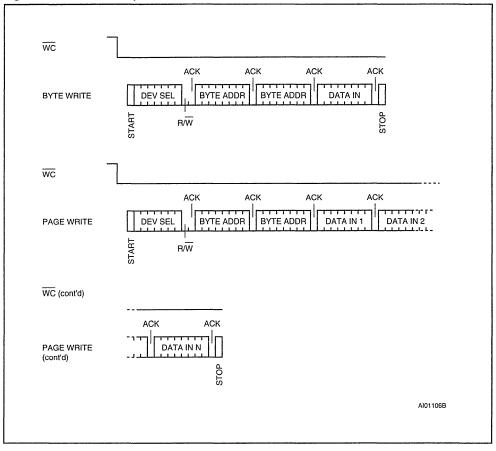

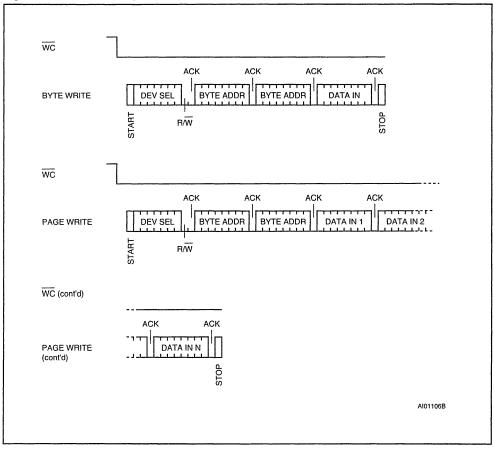

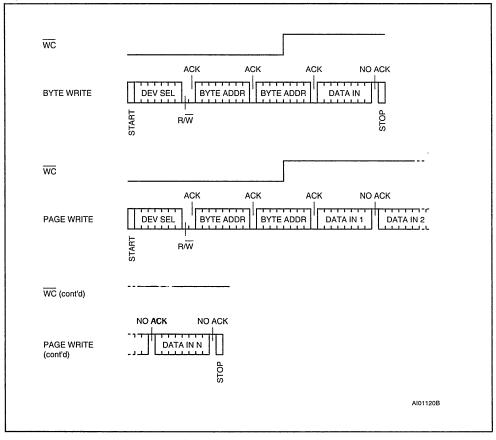

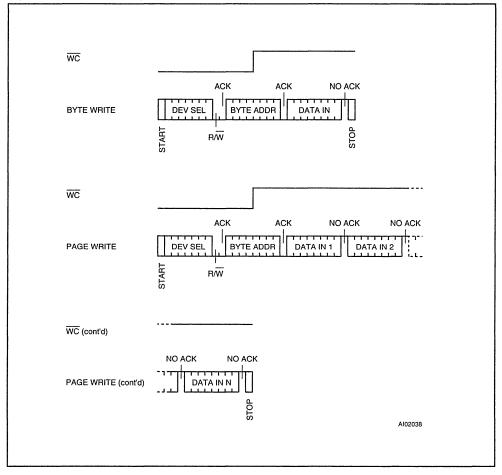

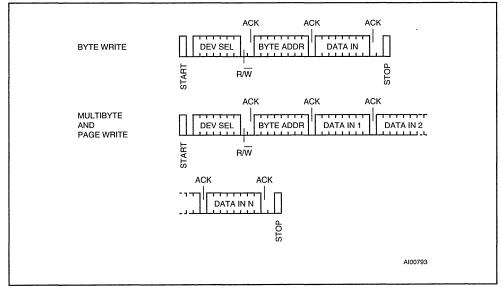

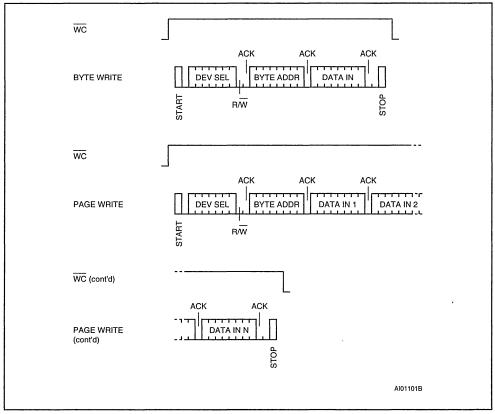

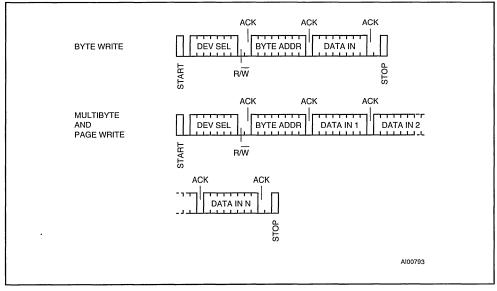

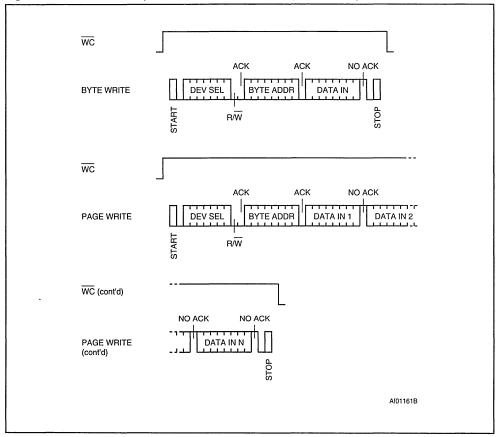

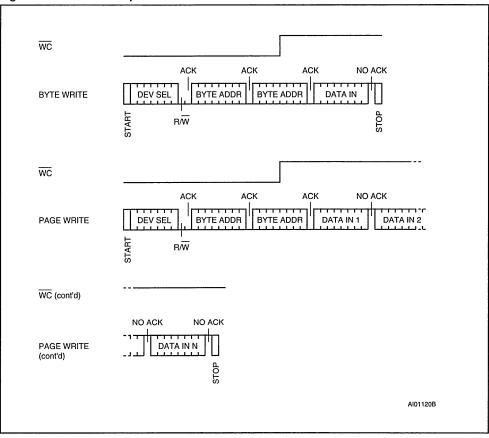

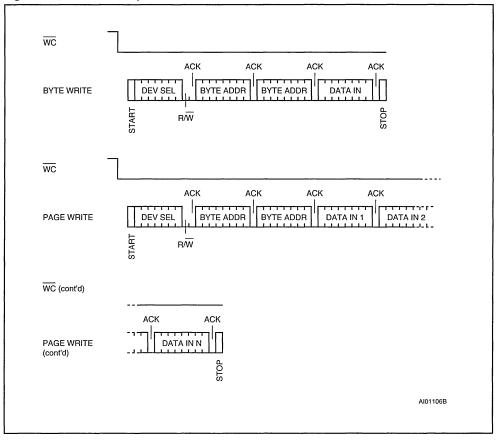

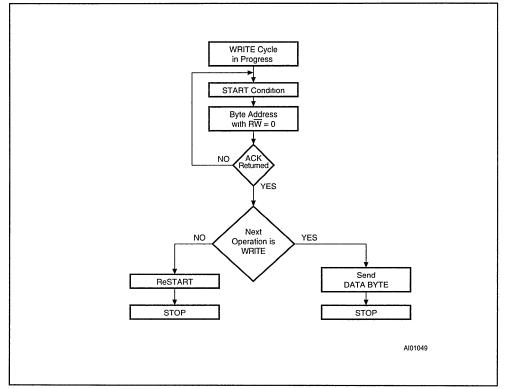

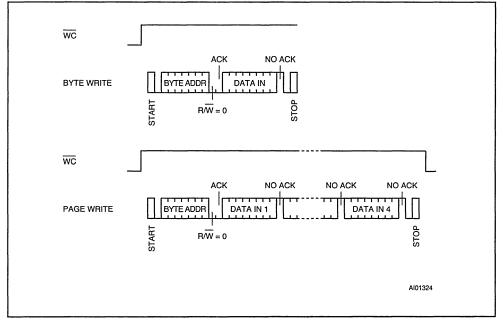

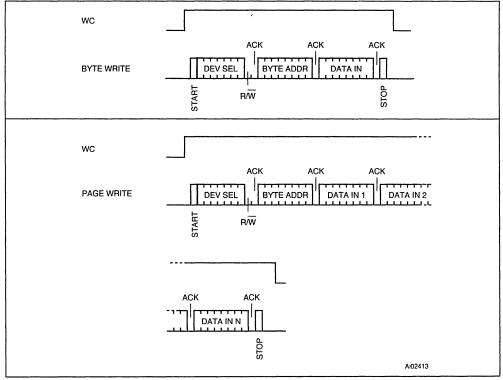

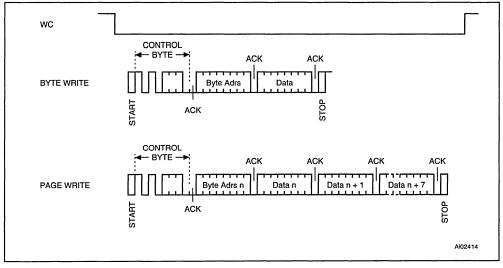

#### Figure 5. Write Mode Sequences with WC=1 (data write inhibited)

The 8<sup>th</sup> bit is the RW bit. This is set to '1' for read and '0' for write operations. If a match occurs on the Device Select Code, the corresponding memory gives an acknowledgment on the SDA bus during the 9<sup>th</sup> bit time. If the memory does not match the Device Select Code, it deselects itself from the bus, and goes into stand-by mode.

There are two modes both for read and write. These are summarized in Table 4 and described later. A communication between the master and the slave is ended with a STOP condition.

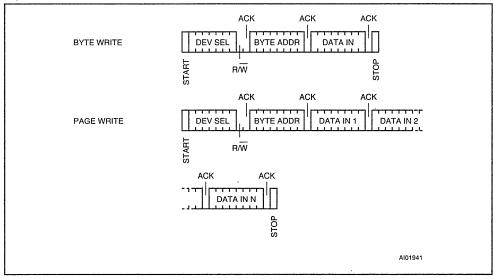

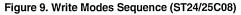

#### Write Operations

Following a START condition the master sends a Device Select Code with the  $R\overline{W}$  bit set to '0', as shown in Table 4. The memory acknowledges this, and waits for an address byte. The memory responds to the address byte with an acknowledge bit, and then waits for the data byte.

Writing to the memory may be inhibited if the  $\overline{\text{WC}}$ input pin is taken high. Any write command with  $\overline{\text{WC}}$ =1 (during a period of time from the START condition until the end of the address byte) will not modify the memory contents, and the accompanying data bytes will *not* be acknowledged (as shown in Figure 5).

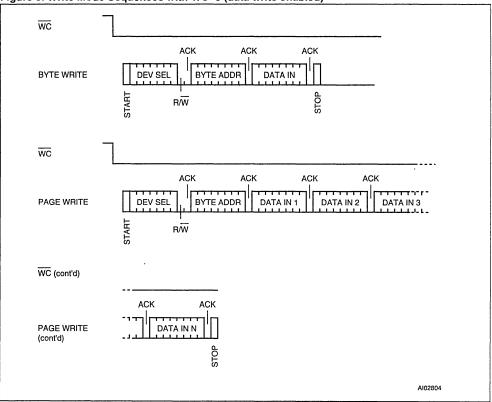

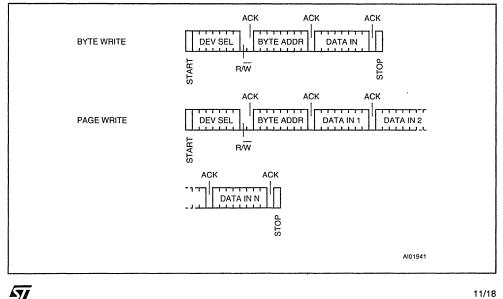

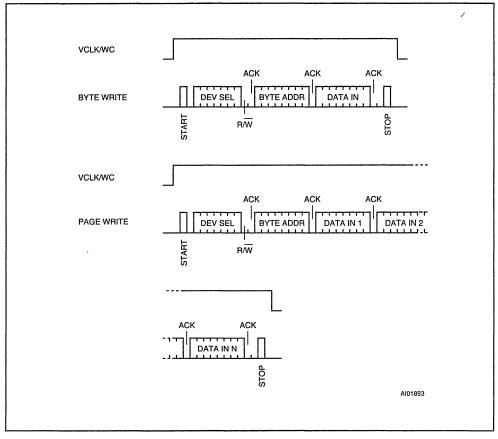

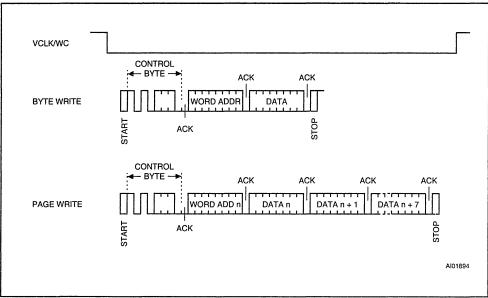

#### Byte Write

In the Byte Write mode, after the Device Select Code and the address bytes, the master sends one data byte. If the addressed location is write protected by the WC pin, the memory replies with a NoAck, and the location is not modified. If, instead, the WC pin has been held at 0, as shown in

Figure 6. Write Mode Sequences with WC=0 (data write enabled)

Figure 6, the memory replies with an Ack. The master terminates the transfer by generating a STOP condition.

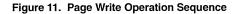

#### Page Write

The Page Write mode allows up to 16 bytes to be written in a single write cycle, provided that they are all located in the same 'row' in the memory: that is the most significant memory address bits are the same. If more bytes are sent than will fit up to the end of the row, a condition known as 'rollover' occurs. Data starts to become overwritten (in a way not formally specified in this data sheet).

The master sends from one up to 16 bytes of data, each of which is acknowledged by the memory if the  $\overline{WC}$  pin is low. If the  $\overline{WC}$  pin is high, the contents of the addressed memory location are not modified, and each data byte is followed by a NoAck. After each byte is transferred, the internal byte address counter (the 4 least significant bits only) is incremented. The transfer is terminated by the master generating a STOP condition. When the master generates a STOP condition immediately after the Ack bit (in the "10<sup>th</sup> bit" time slot), either at the end of a byte write or a page write, the internal memory write cycle is triggered. A STOP condition at any other time does not trigger the internal write cycle.

During the internal write cycle, the SDA input is disabled internally, and the device does not respond to any requests.

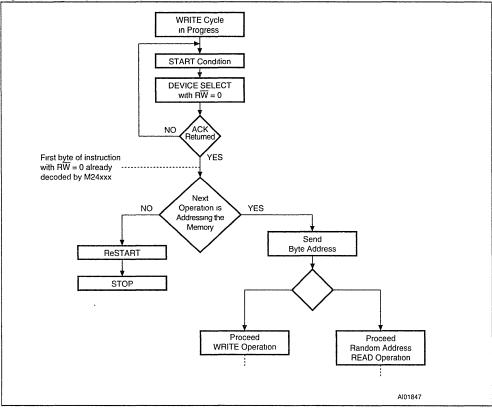

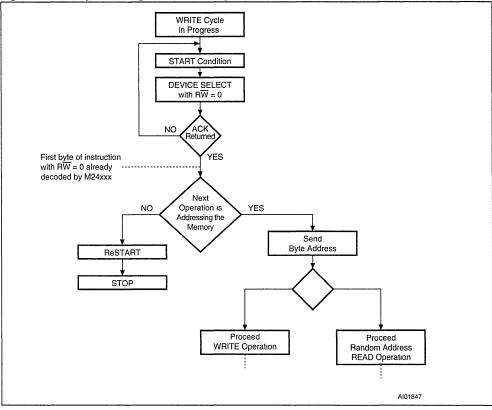

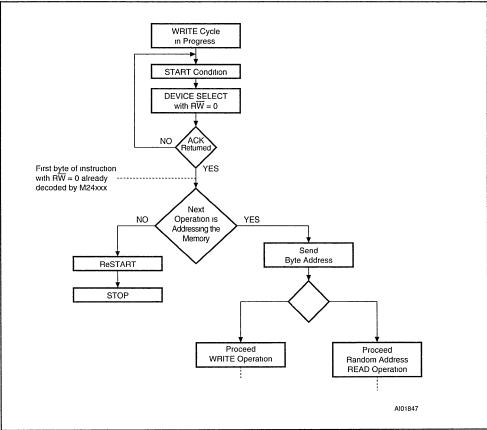

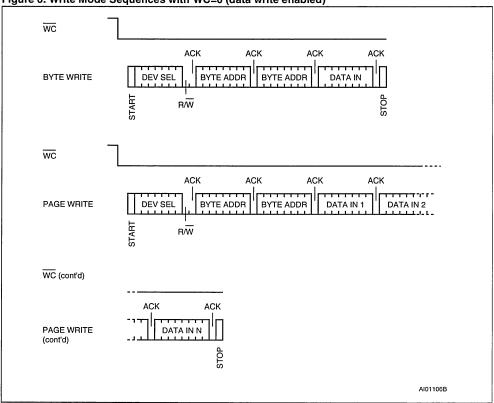

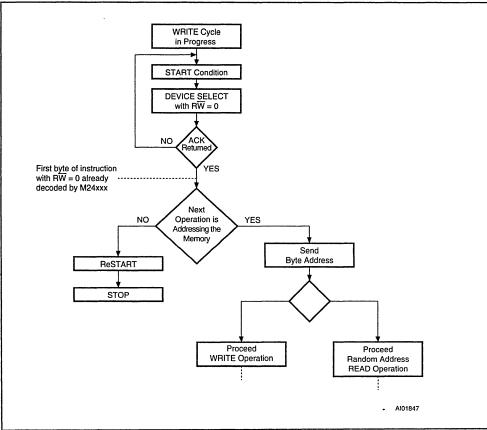

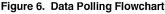

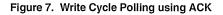

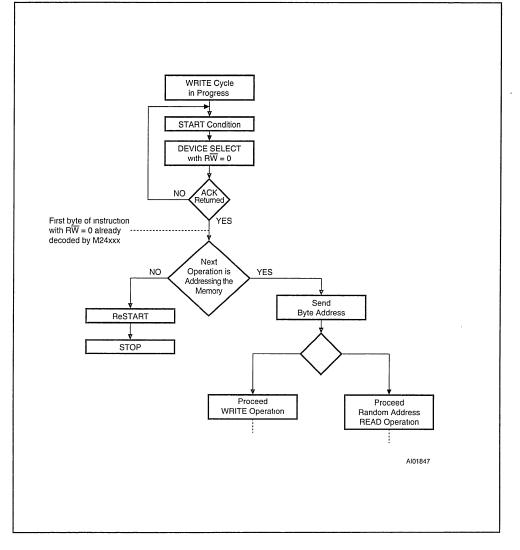

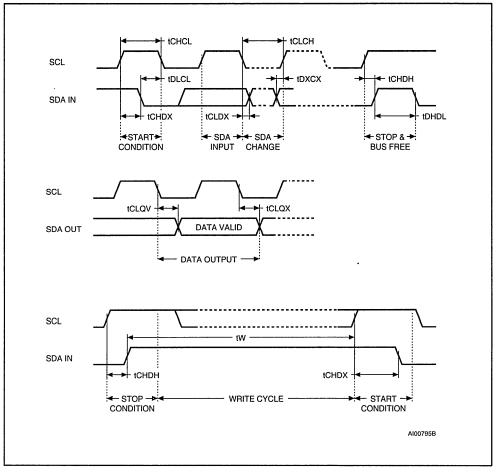

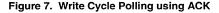

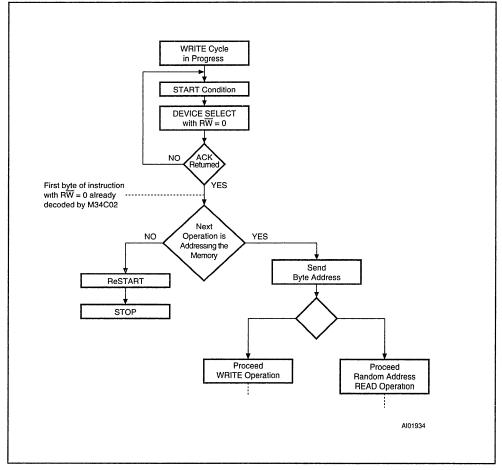

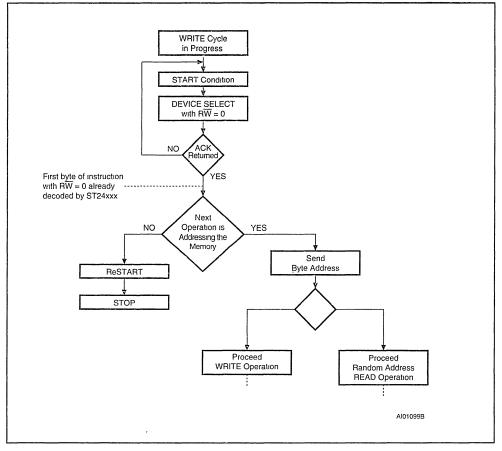

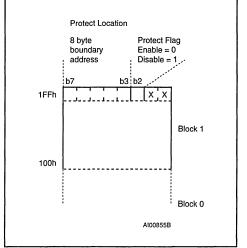

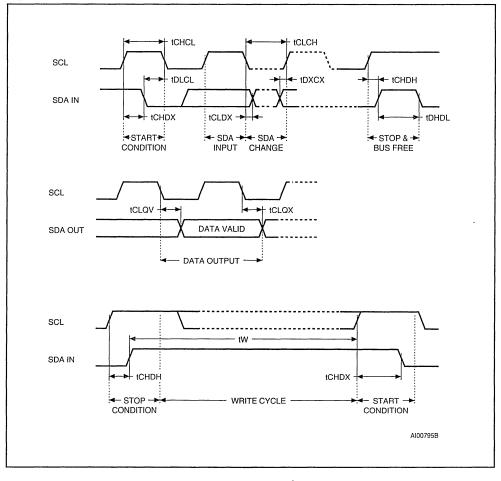

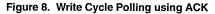

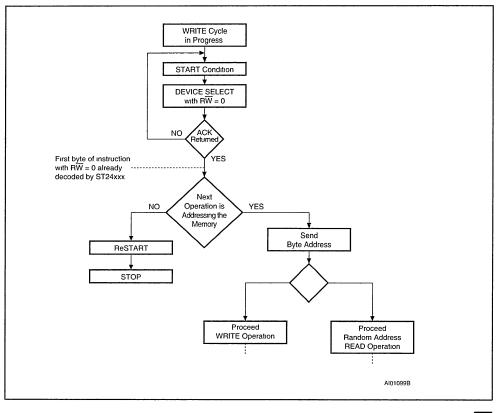

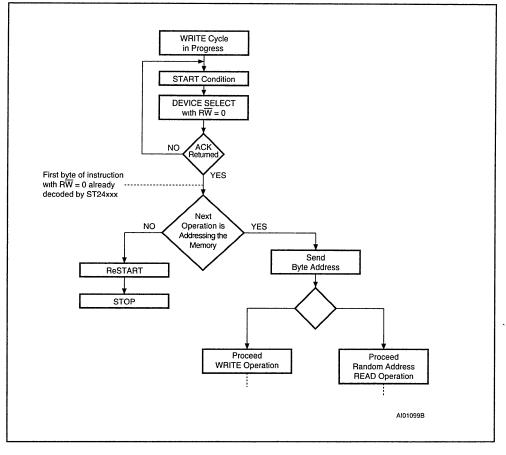

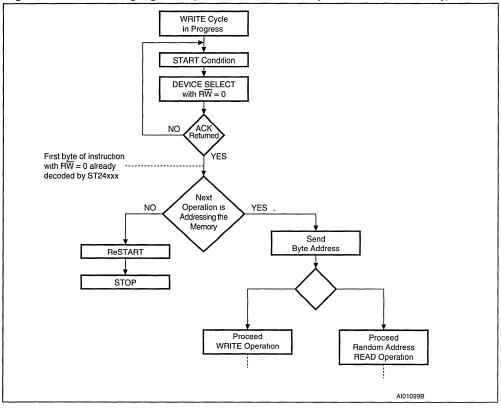

#### Figure 7. Write Cycle Polling Flowchart using ACK

#### Minimizing System Delays by Polling On ACK

During the internal write cycle, the memory disconnects itself from the bus, and copies the data from its internal latches to the memory cells. The maximum write time ( $t_W$ ) is shown in Table 6, but the typical time is shorter. To make use of this, an Ack polling sequence can be used by the master.

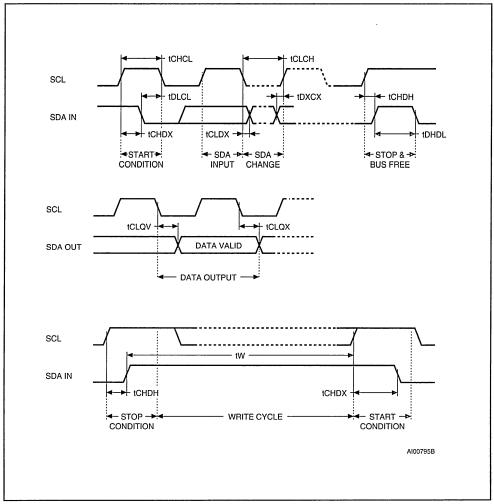

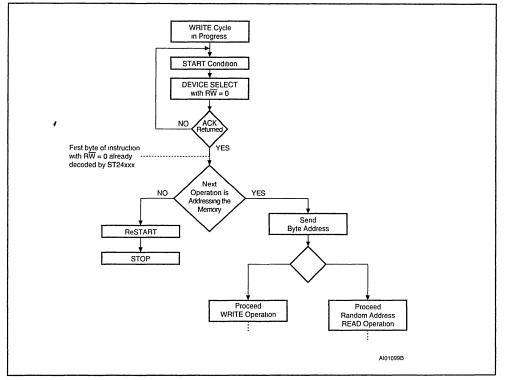

The sequence, as shown in Figure 7, is:

- Initial condition: a Write is in progress.

- Step 1: the master issues a START condition followed by a Device Select Code (the first byte of the new instruction).

- Step 2: if the memory is busy with the internal write cycle, no Ack will be returned and the master goes back to Step 1. If the memory has terminated the internal write cycle, it responds with an Ack, indicating that the memory is ready to receive the second part of the next instruction (the first byte of this instruction having been sent during Step 1).

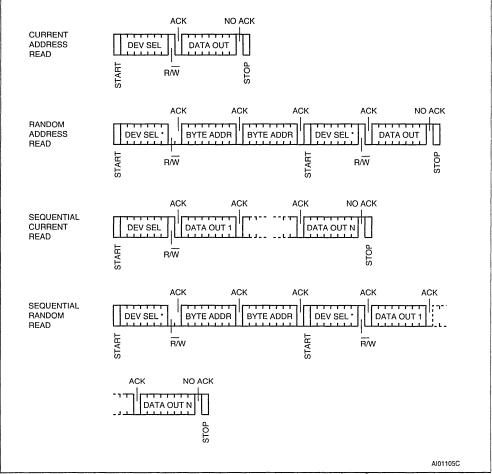

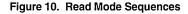

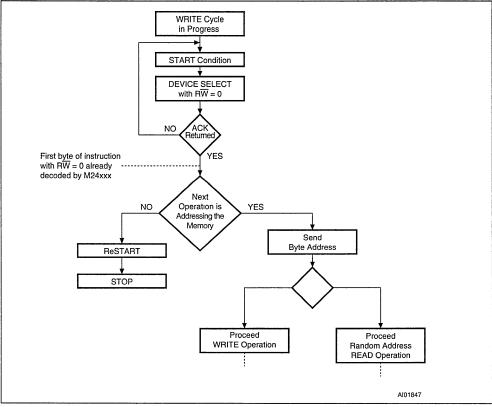

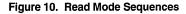

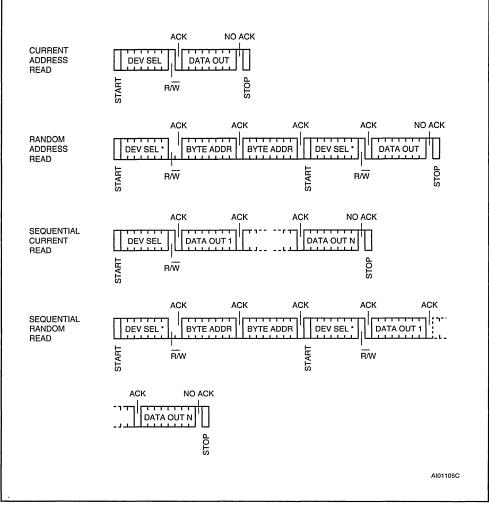

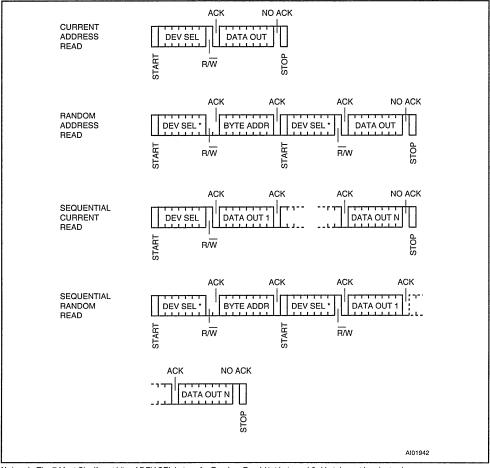

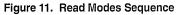

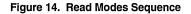

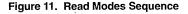

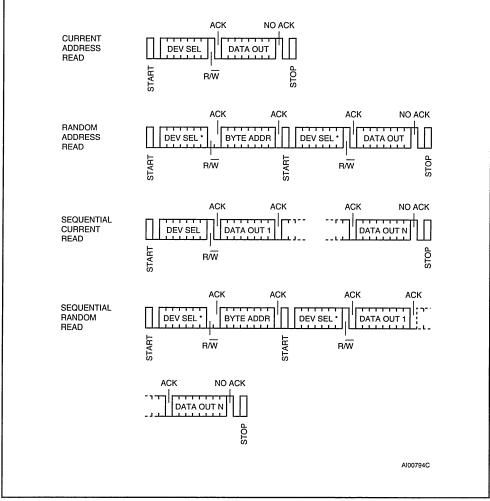

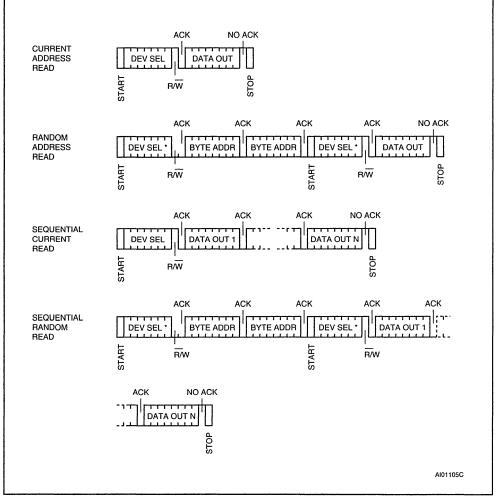

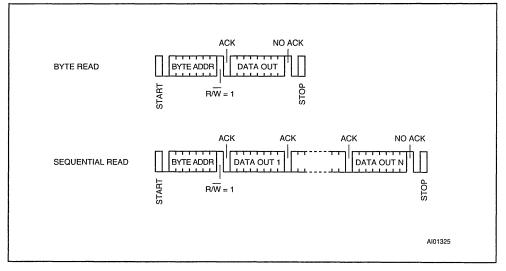

#### **Read Operations**

Read operations are performed independently of the state of the  $\overline{WC}$  pin.

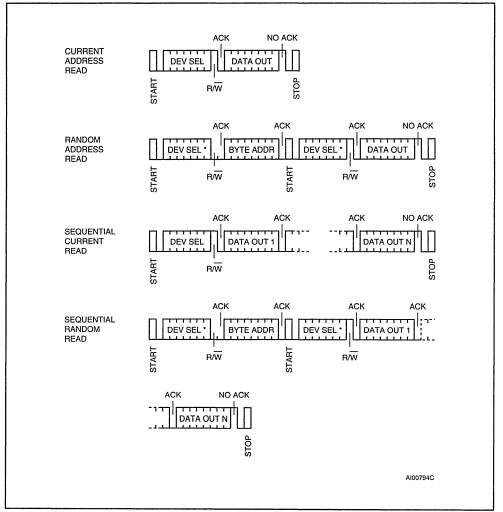

#### **Random Address Read**

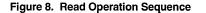

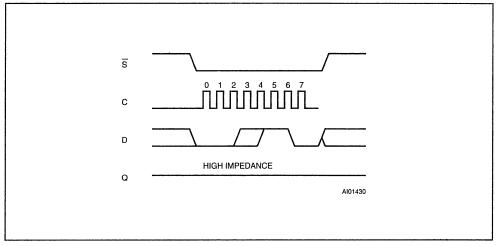

A dummy write is performed to load the address into the address counter, as shown in Figure 8. Then, *without* sending a STOP condition, the master sends another START condition, and repeats the Device Select Code, with the RW bit set to '1'. The memory acknowledges this, and outputs the contents of the addressed byte. The master must *not* acknowledge the byte output, and terminates the transfer with a STOP condition.

#### **Current Address Read**

The device has an internal address counter which is incremented each time a byte is read. For the Current Address Read mode, following a START condition, the master sends a Device Select Code with the RW bit set to '1'. The memory acknowledges this, and outputs the byte addressed by the

#### Figure 8. Read Mode Sequences

Note: 1 The seven most significant bits of the Device Select Code of a Random Read (in the 1<sup>st</sup> and 3<sup>rd</sup> bytes) must be identical.

internal address counter. The counter is then incremented. The master terminates the transfer with a STOP condition, as shown in Figure 8, *without* acknowledging the byte output.

#### Sequential Read

57/

This mode can be initiated with either a Current Address Read or a Random Address Read. The master *does* acknowledge the data byte output in this case, and the memory continues to output the next byte in sequence. To terminate the stream of bytes, the master must *not* acknowledge the last byte output, and *must* generate a STOP condition. The output data comes from consecutive addresses, with the internal address counter automatically incremented after each byte output. After the last memory address, the address counter 'rolls-over' and the memory continues to output data from the start of the memory block.

#### Acknowledge in Read Mode

In all read modes, the memory waits, after each byte read, for an acknowledgment during the 9<sup>th</sup> bit time. If the master does not pull the SDA line low during this time, the memory terminates the data transfer and switches to its standby state.

#### **Table 5. DC Characteristics**

$(T_A = 0 \text{ to } 70 \text{ °C}, \text{ or } -40 \text{ to } 85 \text{ °C}; V_{CC} = 4.5 \text{ to } 5.5 \text{ V or } 2.5 \text{ to } 5.5 \text{ V})$  $(T_A = 0 \text{ to } 70 \text{ °C}, \text{ or } -40 \text{ to } 85 \text{ °C}; V_{CC} = 1.8 \text{ to } 3.6 \text{ V})$

| Symbol           | Parameter                               |                                                                         | Test Condition                                                   | Min.               | Max.                | Unit |

|------------------|-----------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------|--------------------|---------------------|------|

| ILI              | Input Leakage Cu<br>(SCL, SDA)          | Input Leakage Current 0 V $\leq$ V <sub>IN</sub> $\leq$ V <sub>CC</sub> |                                                                  |                    | ± 2                 | μA   |

| ILO              | Output Leakage C                        | Current                                                                 | $0 \text{ V} \leq V_{OUT} \leq V_{CC} \text{, SDA in Hi-Z}$      |                    | ± 2                 | μA   |

|                  |                                         |                                                                         | $V_{CC}$ =5V, f <sub>c</sub> =400kHz (rise/fall time < 30ns)     |                    | 2                   | mA   |

| Icc              | Supply Current                          | -W series:                                                              | $V_{CC}$ =2.5V, f <sub>c</sub> =400kHz (rise/fall time < 30ns)   |                    | 1                   | mA   |

|                  |                                         | -R series:                                                              | $V_{CC}$ =1.8V, f <sub>c</sub> =400kHz (rise/fall time < 30ns)   |                    | 0.8 <sup>1</sup>    | mA   |

| I <sub>CC1</sub> | Supply Current<br>(Stand-by)            |                                                                         | $V_{\rm IN}$ = $V_{\rm SS}$ or $V_{\rm CC}$ , $V_{\rm CC}$ = 5 V |                    | 1                   | μA   |

| I <sub>CC2</sub> | Supply Current<br>(Stand-by)            | -W series:                                                              | $V_{IN} = V_{SS}$ or $V_{CC}$ , $V_{CC} = 2.5$ V                 |                    | 0.5                 | μA   |

| I <sub>CC3</sub> | Supply Current<br>(Stand-by)            | -R series:                                                              | $V_{IN} = V_{SS}$ or $V_{CC}$ , $V_{CC} = 1.8$ V                 |                    | 0.1 <sup>1</sup>    | μA   |

| VIL              | Input Low Voltage<br>(E0, E1, E2, SCL,  |                                                                         |                                                                  | - 0.3              | 0.3 V <sub>CC</sub> | v    |

| VIH              | Input High Voltage<br>(E0, E1, E2, SCL, |                                                                         |                                                                  | 0.7V <sub>CC</sub> | V <sub>cc</sub> +1  | v    |

| VIL              | Input Low Voltage                       | (WC)                                                                    |                                                                  | - 0.3              | 0.5                 | V    |

| VIH              | Input High Voltage                      | e (WC)                                                                  |                                                                  | 0.7V <sub>CC</sub> | V <sub>CC</sub> +1  | V    |

|                  |                                         |                                                                         | $I_{OL} = 3 \text{ mA}, \text{ V}_{CC} = 5 \text{ V}$            |                    | 0.4                 | V    |

| Vol              | Output Low<br>Voltage                   | -W series:                                                              | $I_{OL} = 2.1 \text{ mA}, V_{CC} = 2.5 \text{ V}$                |                    | 0.4                 | v    |

|                  |                                         | -R series:                                                              | I <sub>OL</sub> = 1 mA, V <sub>CC</sub> = 1.8 V                  |                    | 0.4 <sup>1</sup>    | v    |

Note: 1. This is preliminary data.

|                                  |                     |                                                                              | M24 | C16, M24                                                                     | C08, M24 | C04, M24                                                                           | IC02, M24 | 4C01 |     |

|----------------------------------|---------------------|------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------|-----------|------|-----|

| Symbol Alt.                      | Parameter           | V <sub>CC</sub> =4.5 to 5.5 V<br>T <sub>A</sub> =0 to 70°C or<br>-40 to 85°C |     | V <sub>CC</sub> =2.5 to 5.5 V<br>T <sub>A</sub> =0 to 70°C or<br>-40 to 85°C |          | $V_{CC}$ =1.8 to 3.6 V<br>T <sub>A</sub> =0 to 70°C or<br>-40 to 85°C <sup>4</sup> |           | Unit |     |

|                                  |                     |                                                                              | Min | Max                                                                          | Min      | Max                                                                                | Min       | Max  | 1   |

| t <sub>CH1CH2</sub>              | t <sub>R</sub>      | Clock Rise Time                                                              |     | 300                                                                          |          | 300                                                                                |           | 300  | ns  |

| t <sub>CL1CL2</sub>              | t⊨                  | Clock Fall Time                                                              |     | 300                                                                          |          | 300                                                                                |           | 300  | ns  |

| t <sub>DH1DH2</sub> <sup>2</sup> | t <sub>R</sub>      | SDA Rise Time                                                                | 20  | 300                                                                          | 20       | 300                                                                                | 20        | 300  | ns  |

| t <sub>DL1DL2</sub> <sup>2</sup> | t⊨                  | SDA Fall Time                                                                | 20  | 300                                                                          | 20       | 300                                                                                | 20        | 300  | ns  |

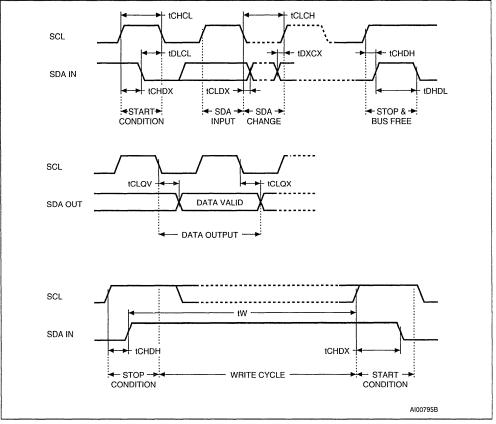

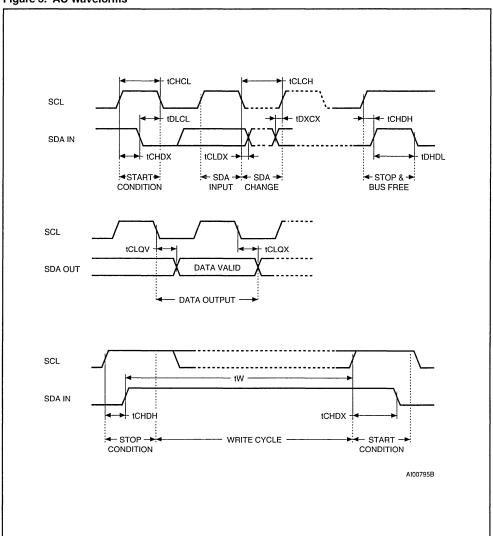

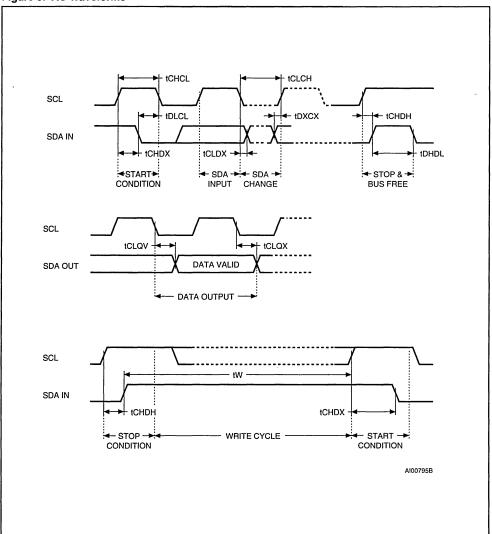

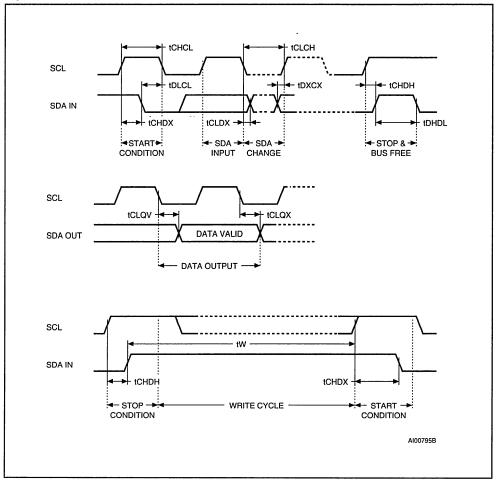

| t <sub>CHDX</sub> <sup>1</sup>   | tsu sta             | Clock High to Input Transition                                               | 600 |                                                                              | 600      |                                                                                    | 600       |      | ns  |

| tCHCL                            | t <sub>HIGH</sub>   | Clock Pulse Width High                                                       | 600 |                                                                              | 600      |                                                                                    | 600       |      | ns  |

| t <sub>DLCL</sub>                | t <sub>HD STA</sub> | Input Low to Clock Low (START)                                               | 600 |                                                                              | 600      |                                                                                    | 600       |      | ns  |

| t <sub>CLDX</sub>                | t <sub>HD DAT</sub> | Clock Low to Input Transition                                                | 0   |                                                                              | 0        |                                                                                    | 0         |      | μs  |

| t <sub>CLCH</sub>                | t <sub>LOW</sub>    | Clock Pulse Width Low                                                        | 1.3 |                                                                              | 1.3      |                                                                                    | 1.3       |      | μs  |

| t <sub>DXCX</sub>                | t <sub>su dat</sub> | Input Transition to Clock<br>Transition                                      | 100 |                                                                              | 100      |                                                                                    | 100       |      | ns  |

| t <sub>CHDH</sub>                | t <sub>SU STO</sub> | Clock High to Input High (STOP)                                              | 600 |                                                                              | 600      |                                                                                    | 600       |      | ns  |

| t <sub>DHDL</sub>                | t <sub>BUF</sub>    | Input High to Input Low (Bus<br>Free)                                        | 1.3 |                                                                              | 1.3      |                                                                                    | 1.3       |      | μs  |

| t <sub>CLQV</sub> 3              | t <sub>AA</sub>     | Clock Low to Data Out Valid                                                  | 200 | 900                                                                          | 200      | 900                                                                                | 200       | 900  | ns  |

| tcLax                            | t <sub>DH</sub>     | Data Out Hold Time After Clock<br>Low                                        | 200 |                                                                              | 200      |                                                                                    | 200       |      | ns  |

| f <sub>C</sub>                   | f <sub>SCL</sub>    | Clock Frequency                                                              |     | 400                                                                          |          | 400                                                                                |           | 400  | kHz |

| tw                               | t <sub>WR</sub>     | Write Time                                                                   |     | 5                                                                            |          | 10                                                                                 |           | 10   | ms  |

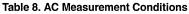

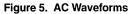

#### Table 6. AC Characteristics

Note: 1 For a reSTART condition, or following a write cycle

2. Sampled only, not 100% tested

3. To avoid spurious START and STOP conditions, a minimum delay is placed between SCL=1 and the falling or rising edge of SDA

4 This is preliminary data

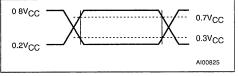

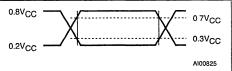

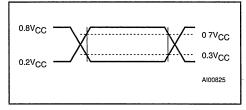

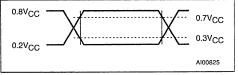

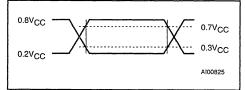

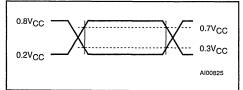

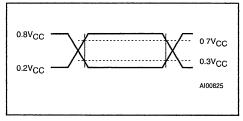

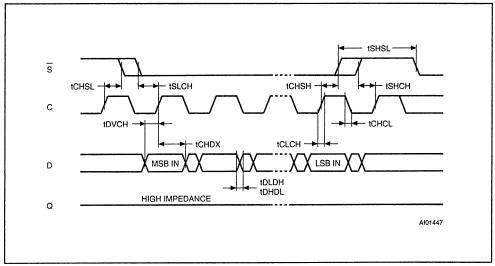

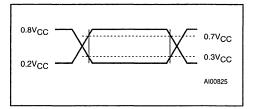

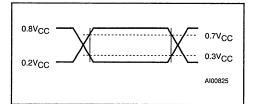

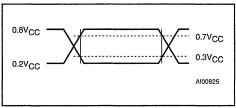

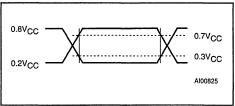

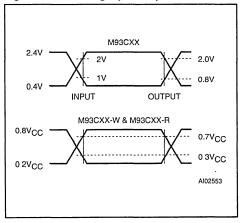

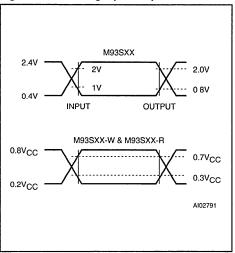

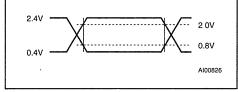

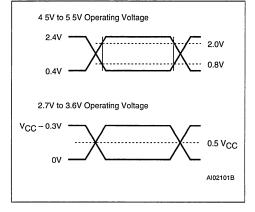

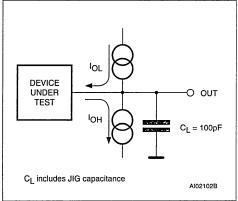

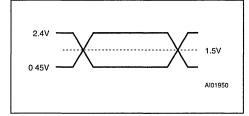

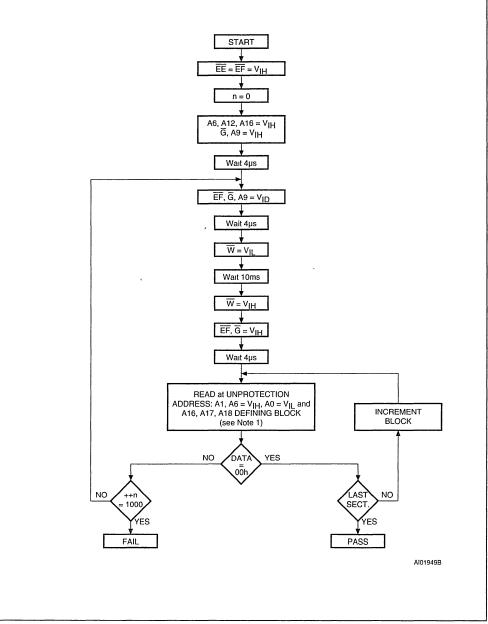

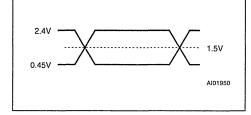

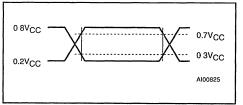

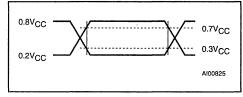

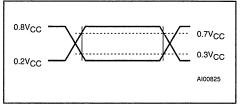

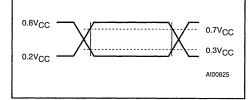

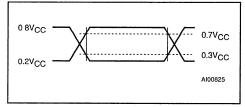

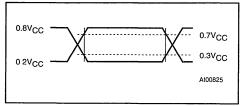

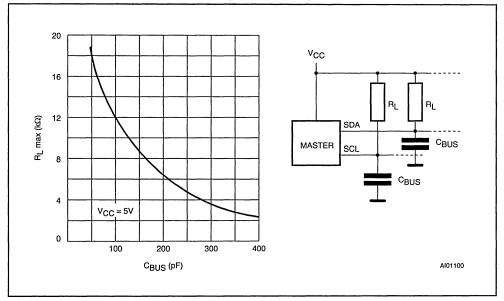

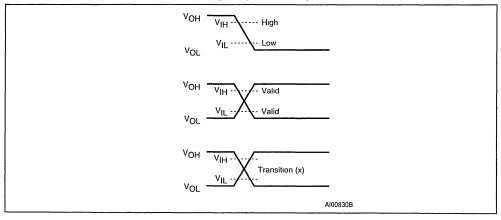

#### **Table 7. AC Measurement Conditions**

57

| Input Rise and Fall Times                     | ≤ 50 ns                                  |

|-----------------------------------------------|------------------------------------------|

| Input Pulse Voltages                          | 0.2V <sub>CC</sub> to 0.8V <sub>CC</sub> |

| Input and Output Timing<br>Reference Voltages | 0.3V <sub>CC</sub> to 0.7V <sub>CC</sub> |

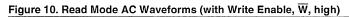

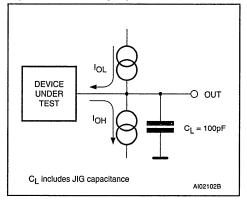

#### Figure 9. AC Testing Input Output Waveforms

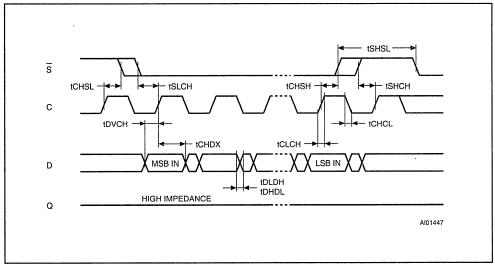

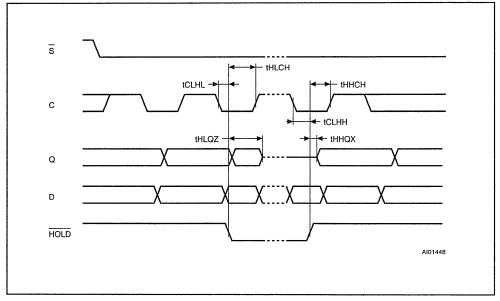

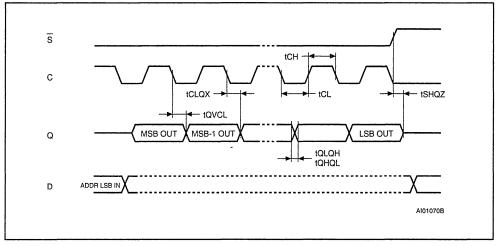

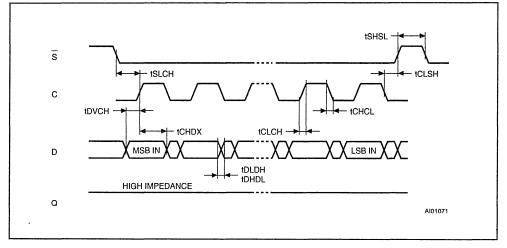

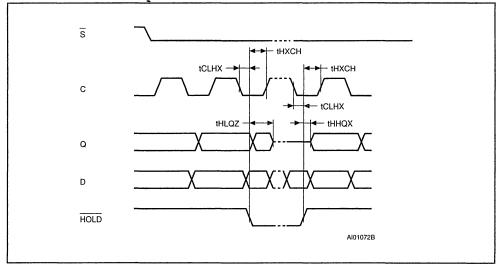

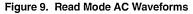

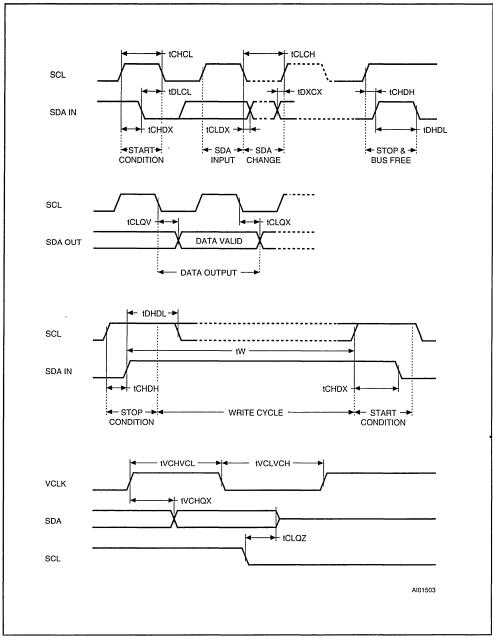

#### Figure 10. AC Waveforms

#### Table 8. Input Parameters<sup>1</sup> (T<sub>A</sub> = 25 °C, f = 400 kHz)

| Symbol           | Parameter                                            | Test Condition                       | Min. | Max. | Unit |

|------------------|------------------------------------------------------|--------------------------------------|------|------|------|

| CIN              | Input Capacitance (SDA)                              |                                      |      | 8    | pF   |

| CIN              | Input Capacitance (other pins)                       |                                      |      | 6    | pF   |

| Z <sub>WCL</sub> | WC Input Impedance                                   | $V_{IN} < 0.3 V_{CC}$                | 5    | 20   | kΩ   |

| Z <sub>WCH</sub> | WC Input Impedance                                   | V <sub>IN</sub> > 0.7V <sub>CC</sub> | 500  |      | kΩ   |

| t <sub>NS</sub>  | Low Pass Filter Input Time<br>Constant (SCL and SDA) |                                      | 200  | 500  | ns   |

Note: 1. Sampled only, not 100% tested.

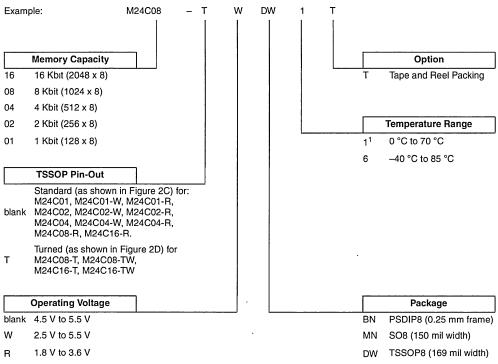

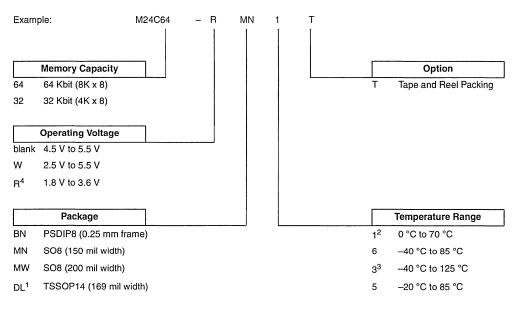

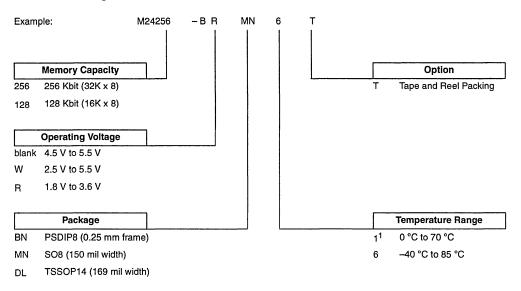

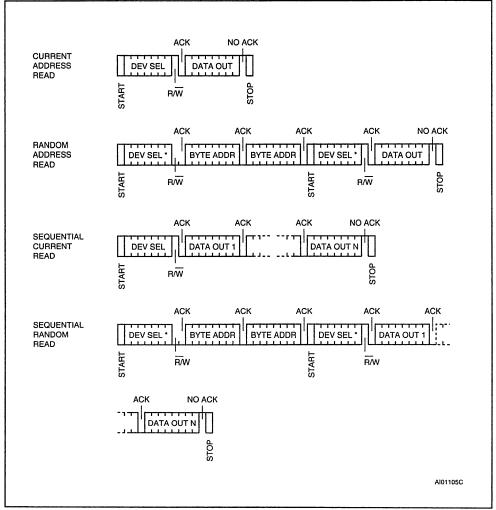

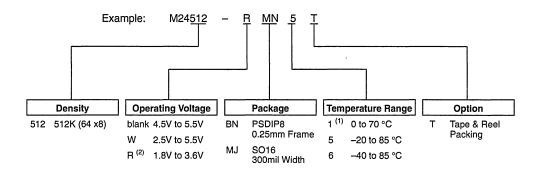

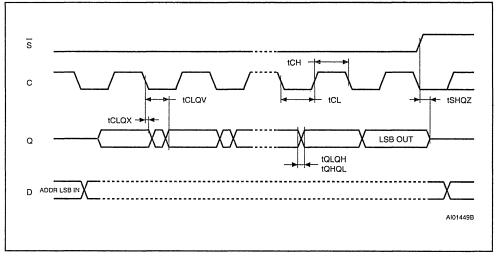

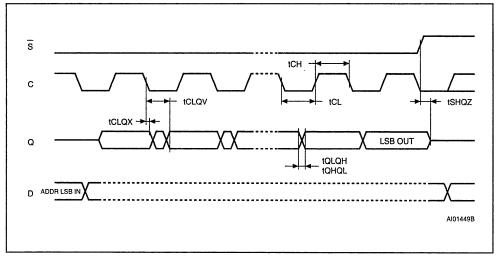

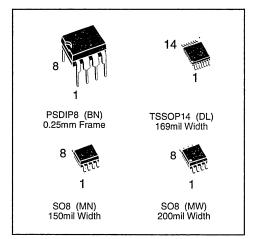

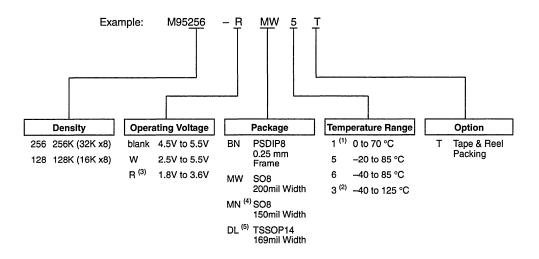

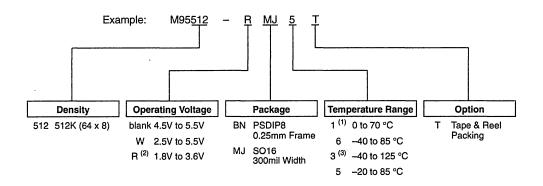

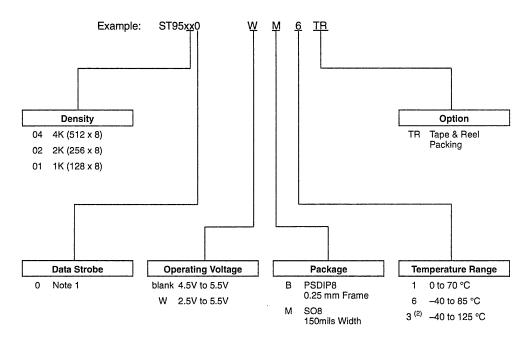

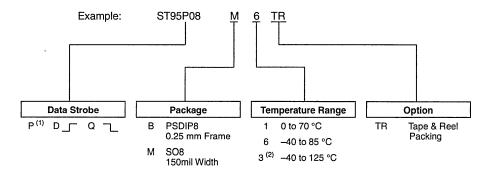

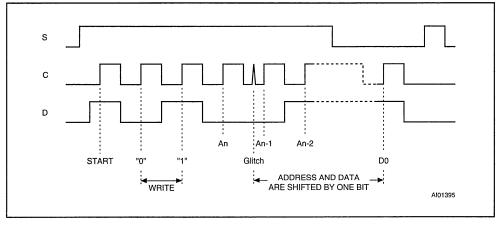

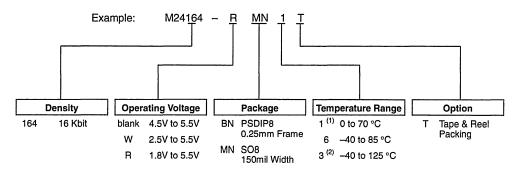

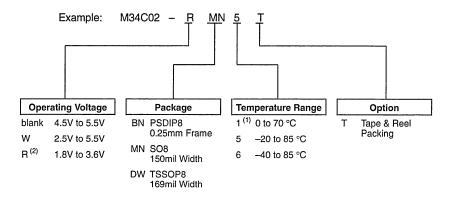

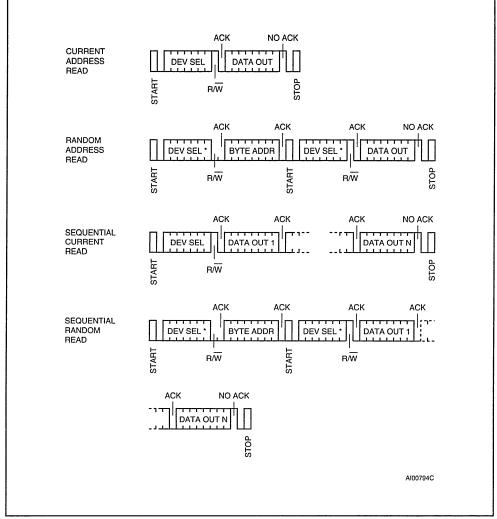

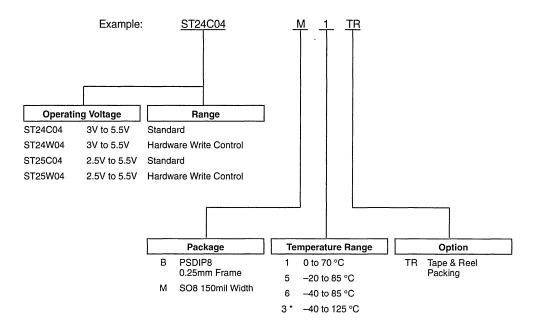

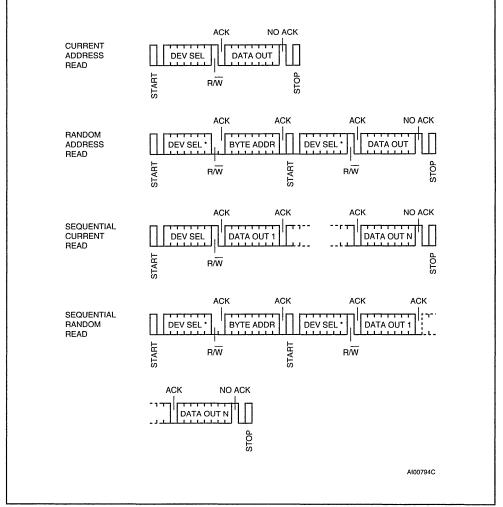

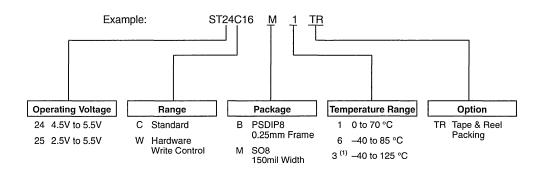

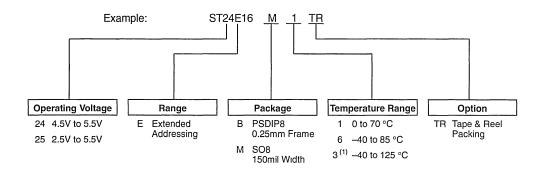

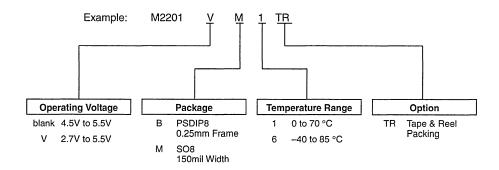

#### **Table 9. Ordering Information Scheme**

Note: 1. Temperature range 1 available only on request.

#### **ORDERING INFORMATION**

Devices are shipped from the factory with the memory content set at all '1's (FFh).

The notation used for the device number is as shown in Table 9. For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact the ST Sales Office nearest to you.

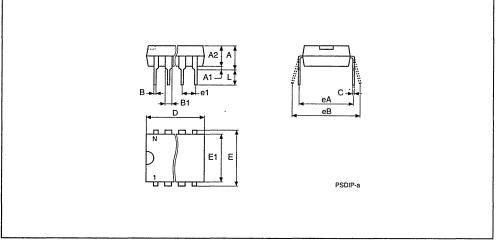

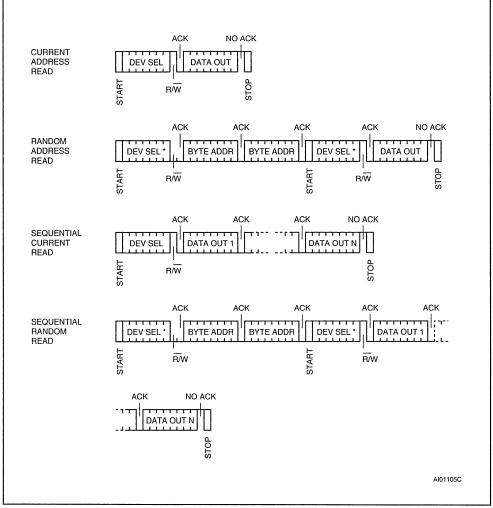

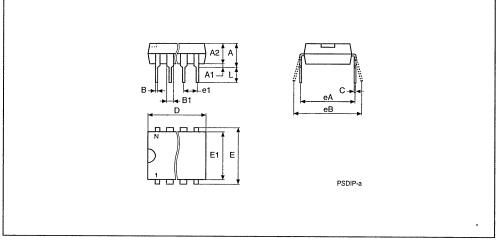

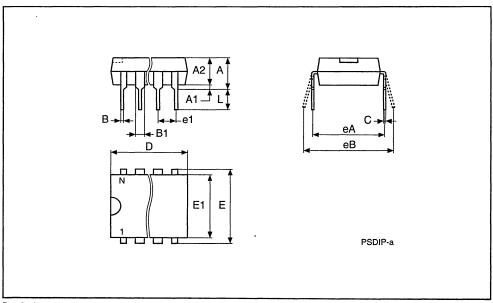

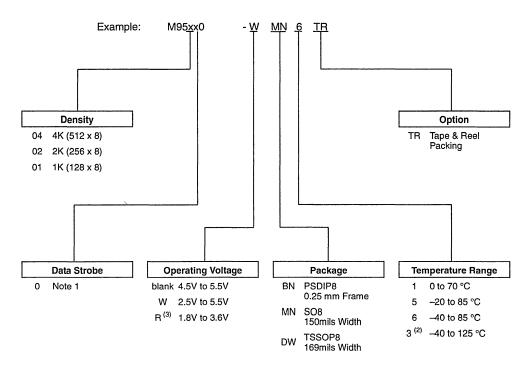

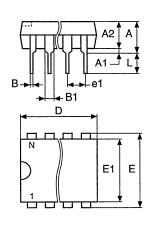

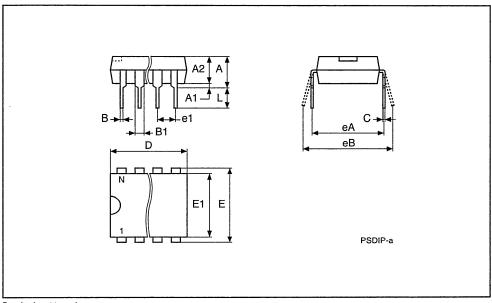

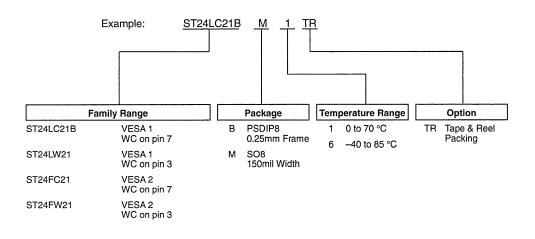

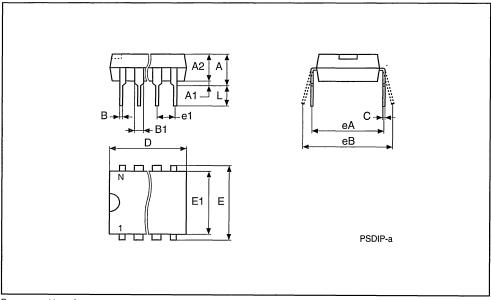

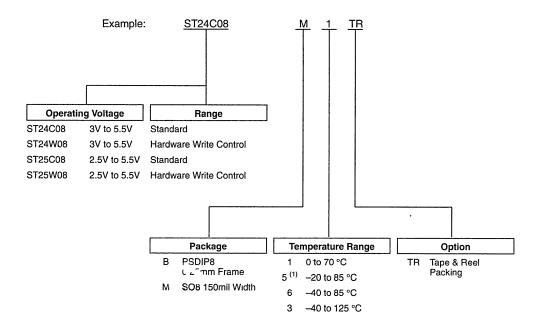

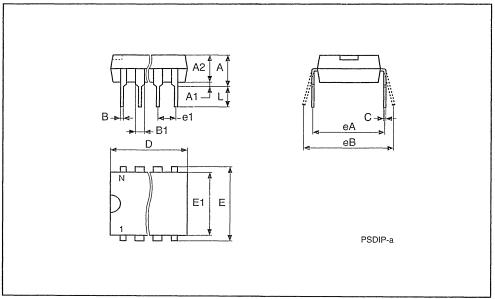

| Cumh  |      | mm   |                                       | inches |       |       |  |  |

|-------|------|------|---------------------------------------|--------|-------|-------|--|--|

| Symb. | Тур. | Min. | Max.                                  | Тур.   | Min.  | Max.  |  |  |

| A     |      | 3.90 | 5.90                                  |        | 0.154 | 0.232 |  |  |

| A1    |      | 0.49 | -                                     |        | 0.019 | _     |  |  |

| A2    |      | 3.30 | 5.30                                  |        | 0.130 | 0.209 |  |  |

| В     |      | 0.36 | 0.56                                  |        | 0.014 | 0.022 |  |  |

| B1    |      | 1.15 | 1.65                                  |        | 0.045 | 0.065 |  |  |

| С     |      | 0.20 | 0.36                                  |        | 0.008 | 0.014 |  |  |

| D     |      | 9.20 | 9.90                                  |        | 0.362 | 0.390 |  |  |

| E     | 7.62 | -    | -                                     | 0.300  | -     | -     |  |  |

| E1    |      | 6.00 | 6.70                                  |        | 0.236 | 0.264 |  |  |

| e1    | 2.54 | -    | -                                     | 0.100  | -     | -     |  |  |

| eA    |      | 7.80 | -                                     |        | 0.307 | -     |  |  |

| eB    |      |      | 10.00                                 |        |       | 0.394 |  |  |

| L     |      | 3.00 | 3.80                                  |        | 0.118 | 0.150 |  |  |

| N     |      | 8'   | · · · · · · · · · · · · · · · · · · · |        | 8     | •     |  |  |

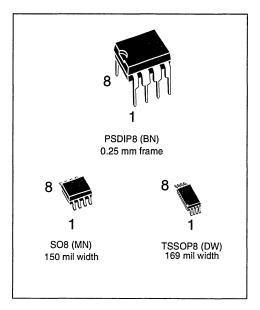

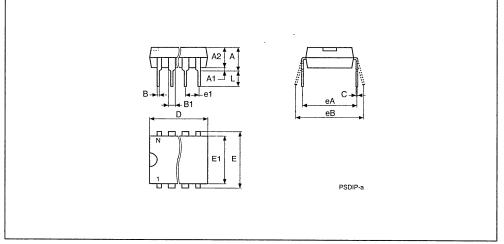

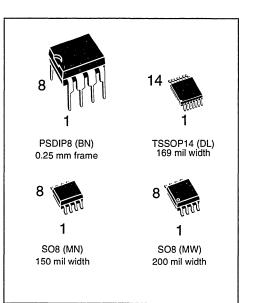

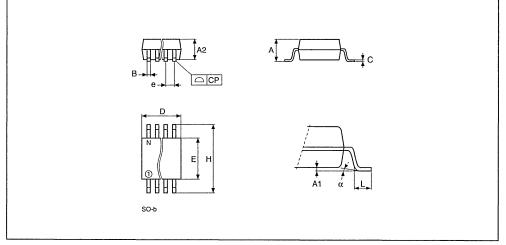

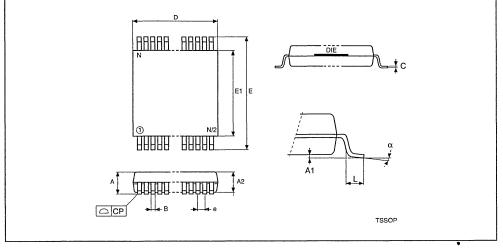

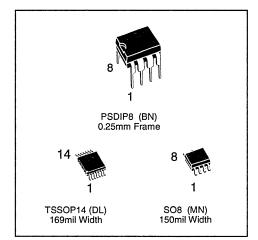

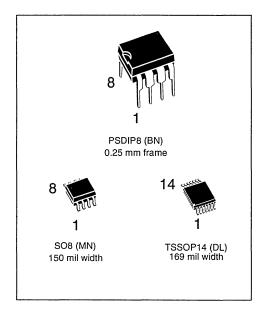

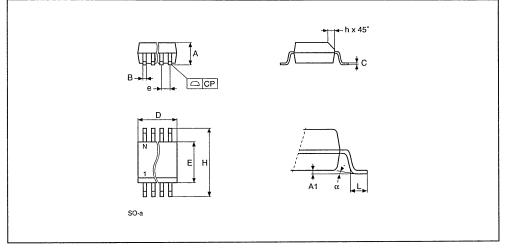

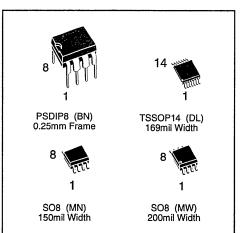

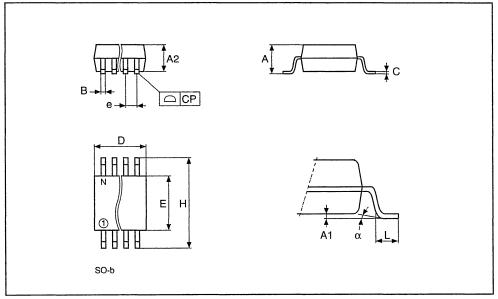

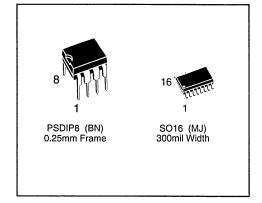

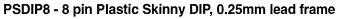

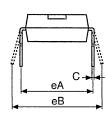

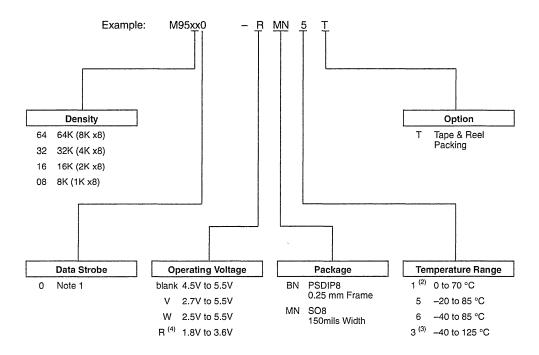

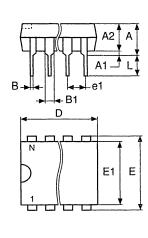

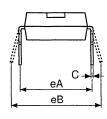

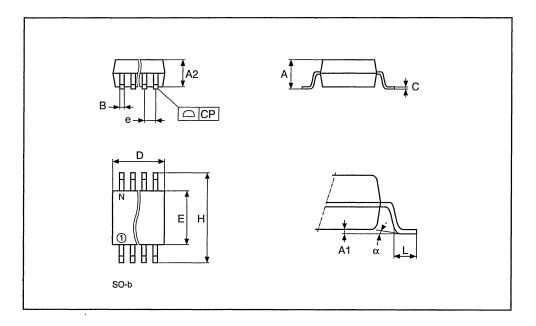

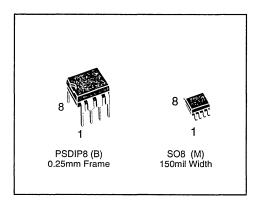

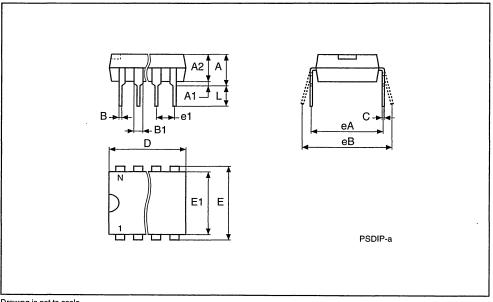

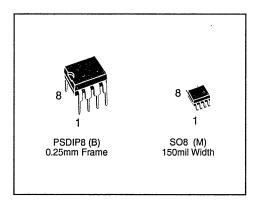

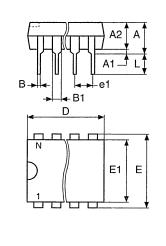

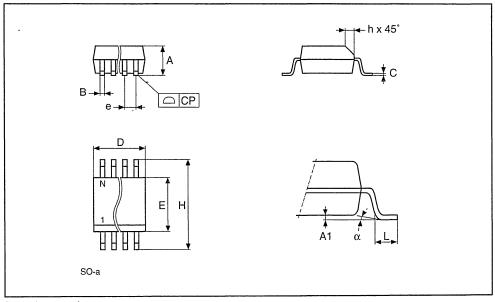

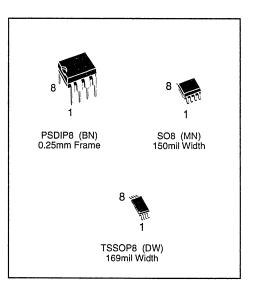

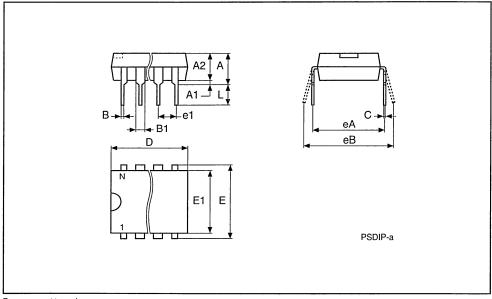

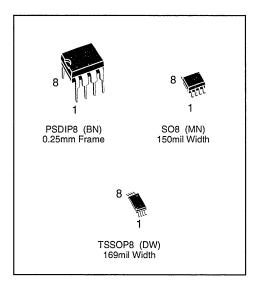

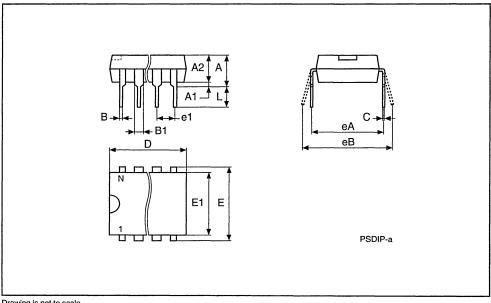

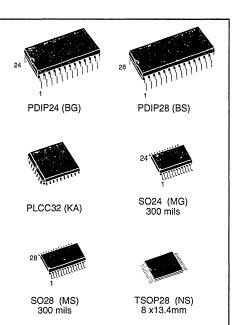

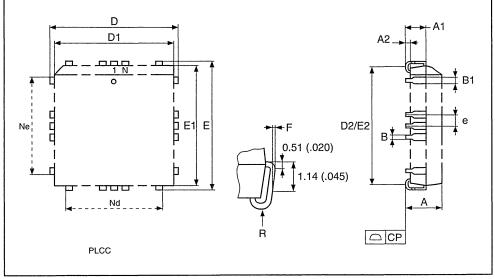

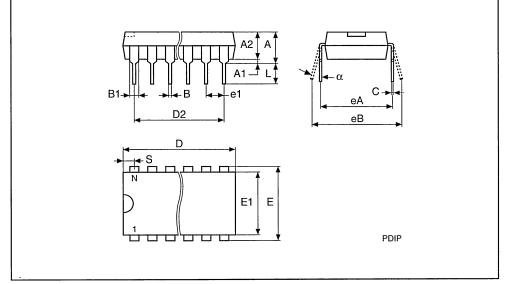

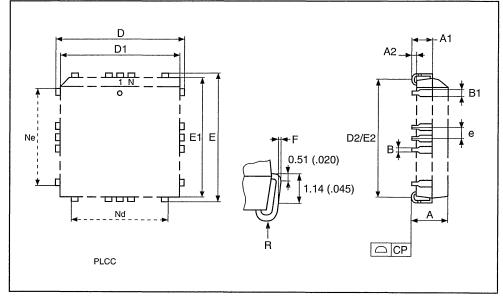

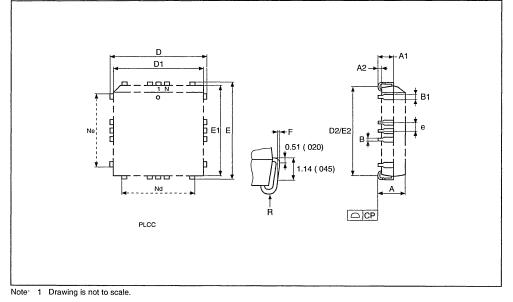

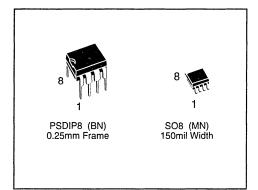

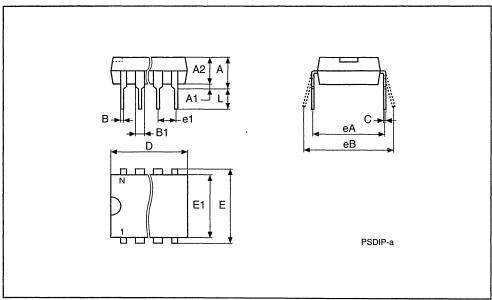

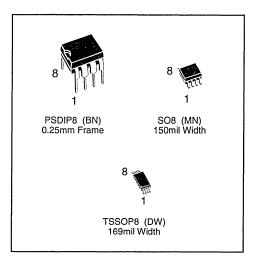

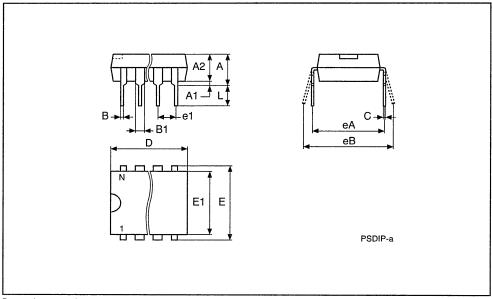

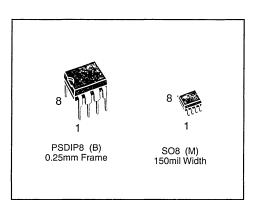

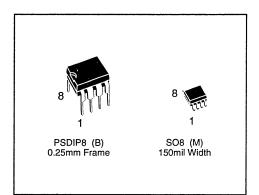

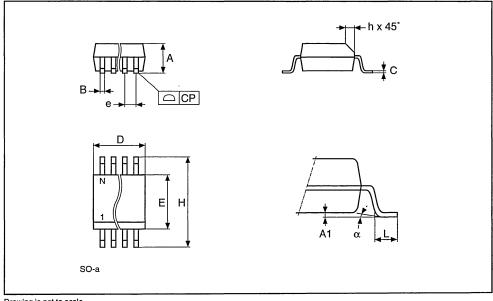

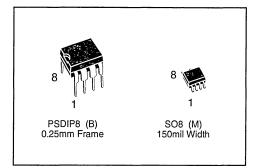

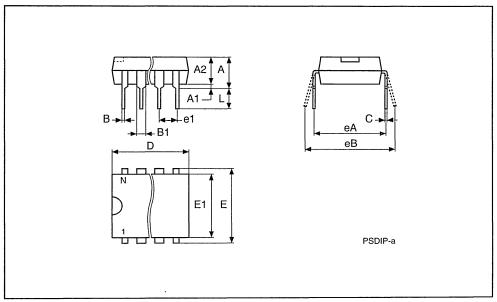

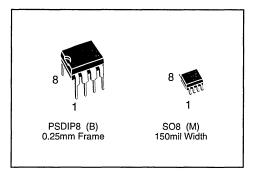

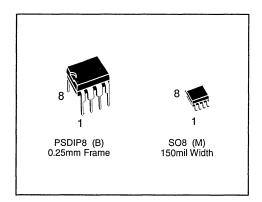

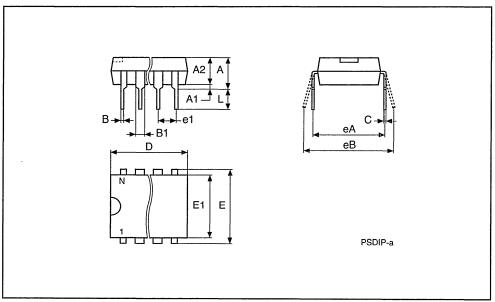

#### Table 10. PSDIP8 - 8 pin Plastic Skinny DIP, 0.25mm lead frame

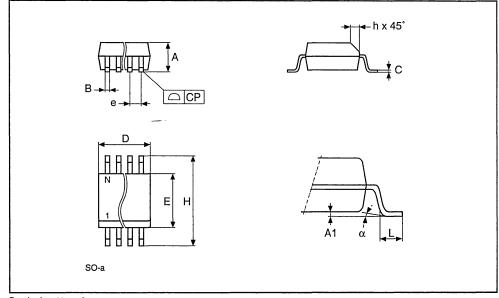

#### Figure 11. PSDIP8 (BN)

Note: 1. Drawing is not to scale

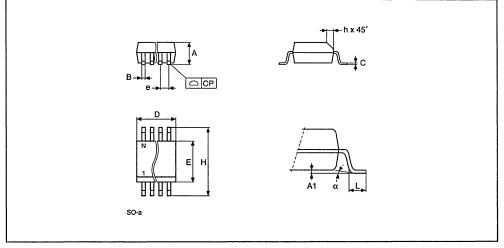

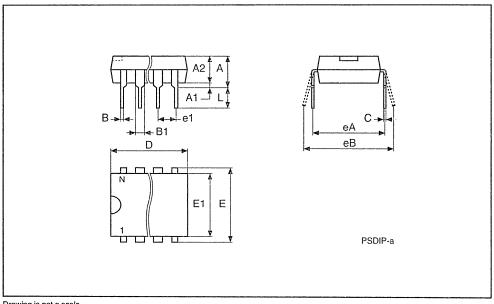

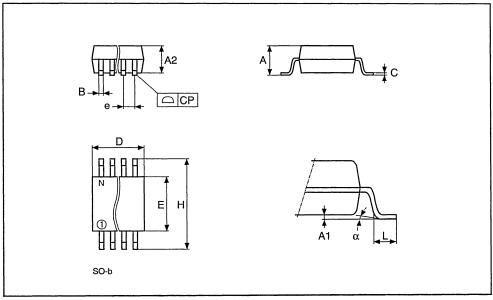

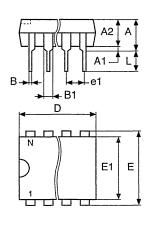

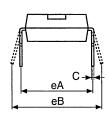

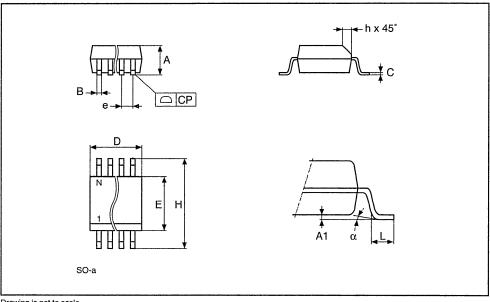

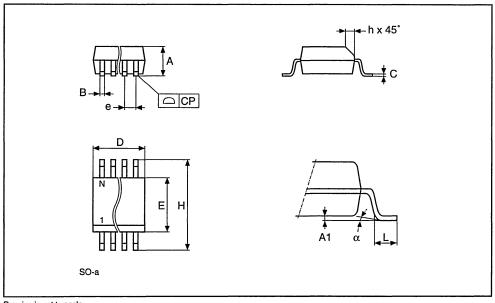

| 0h    |      | mm   |      | inches |       |       |  |  |

|-------|------|------|------|--------|-------|-------|--|--|

| Symb. | Тур. | Min. | Max. | Тур.   | Min.  | Max.  |  |  |

| A     |      | 1.35 | 1.75 |        | 0.053 | 0.069 |  |  |

| A1    |      | 0.10 | 0.25 |        | 0.004 | 0.010 |  |  |

| В     |      | 0.33 | 0.51 |        | 0.013 | 0.020 |  |  |

| С     |      | 0.19 | 0.25 |        | 0.007 | 0.010 |  |  |

| D     |      | 4.80 | 5.00 |        | 0.189 | 0.197 |  |  |

| E     |      | 3.80 | 4.00 |        | 0.150 | 0.157 |  |  |

| е     | 1.27 | -    | -    | 0.050  | -     | -     |  |  |

| Н     |      | 5.80 | 6.20 |        | 0.228 | 0.244 |  |  |

| h     |      | 0.25 | 0.50 |        | 0.010 | 0.020 |  |  |

| L     |      | 0.40 | 0.90 |        | 0.016 | 0.035 |  |  |

| α     |      | 0°   | 8°   |        | 0°    | 8°    |  |  |

| N     |      | 8    | ·    |        | 8     |       |  |  |

| CP    |      |      | 0.10 |        |       | 0.004 |  |  |

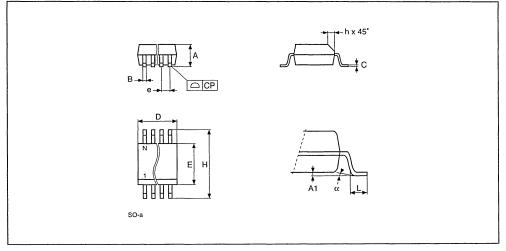

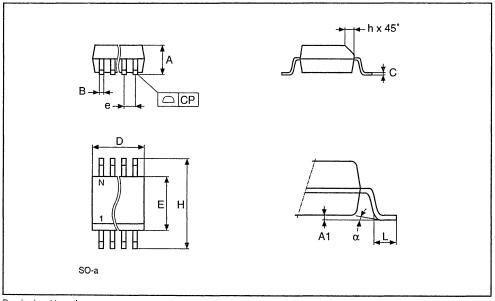

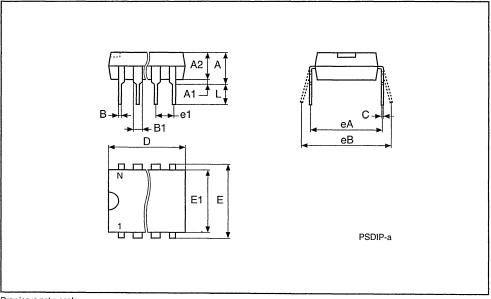

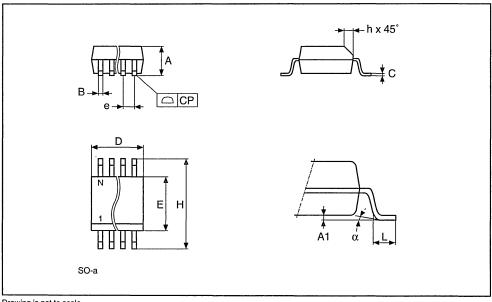

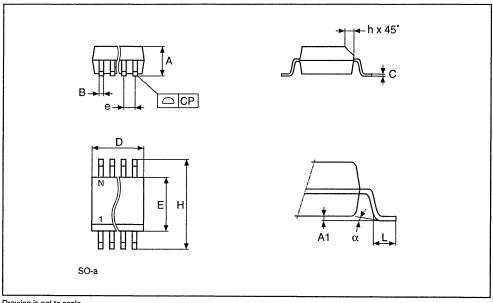

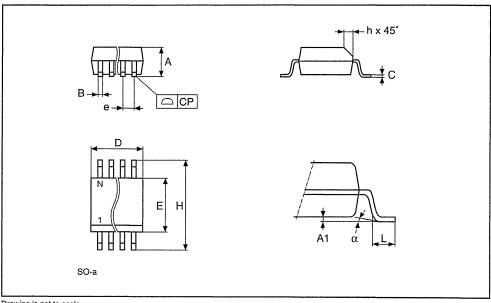

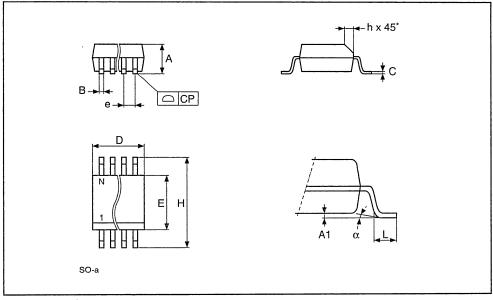

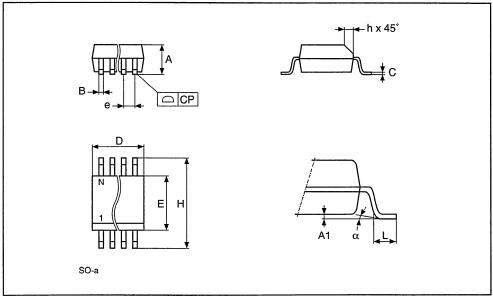

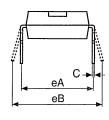

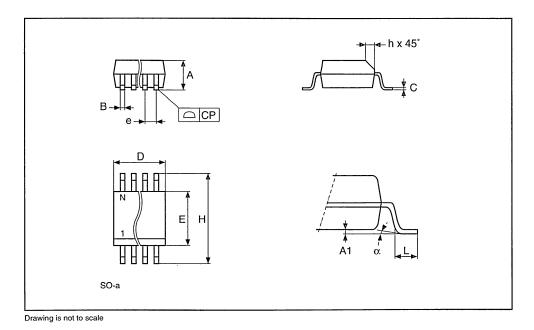

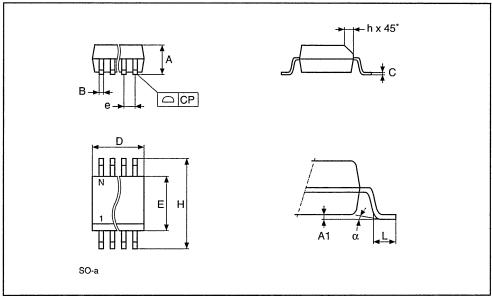

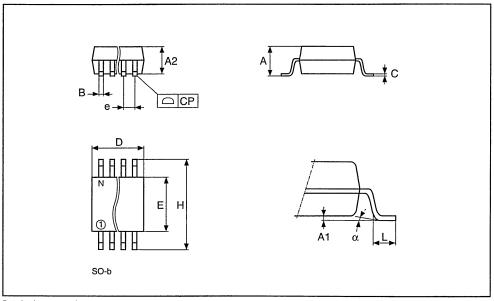

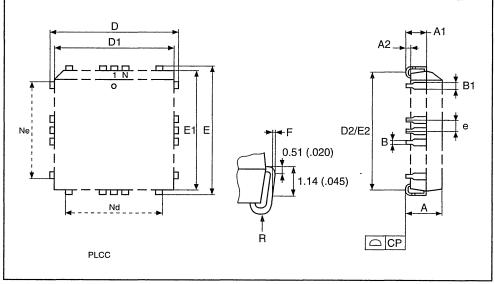

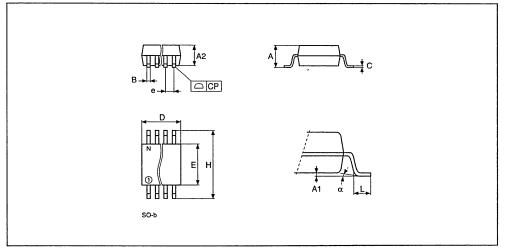

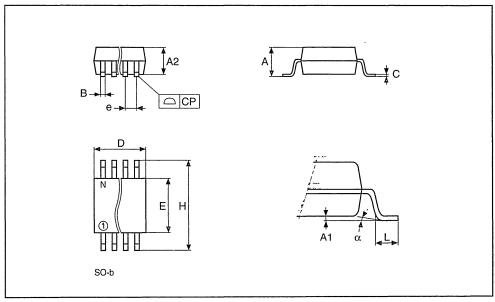

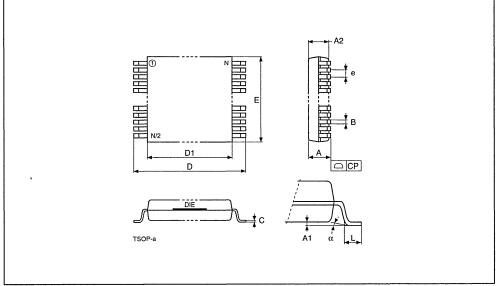

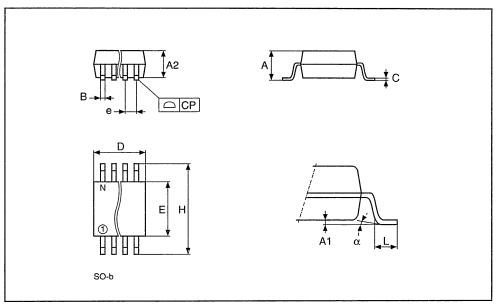

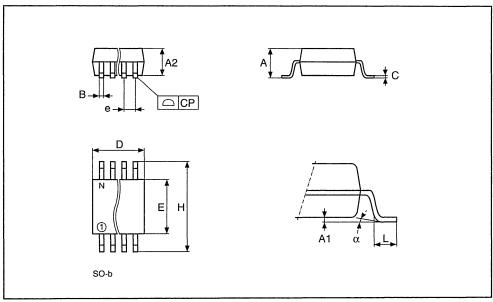

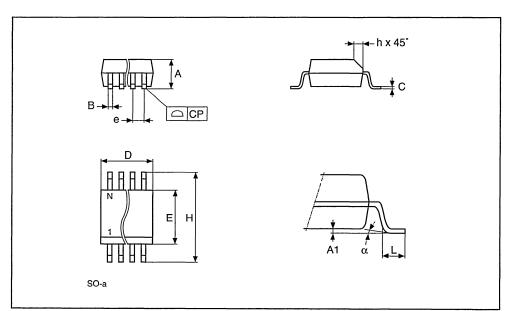

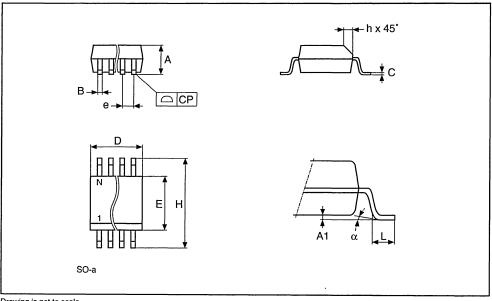

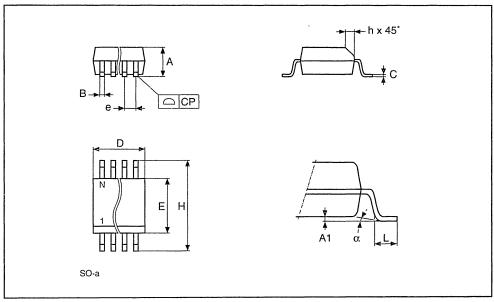

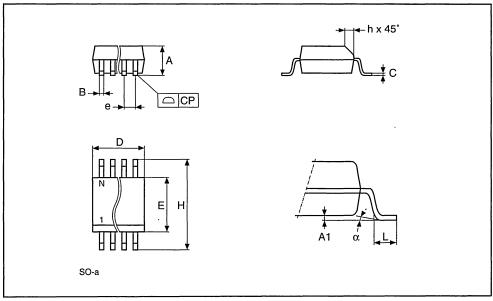

Table 11. SO8 - 8 lead Plastic Small Outline, 150 mils body width

Figure 12. SO8 narrow (MN)

Note. 1. Drawing is not to scale.

T

.

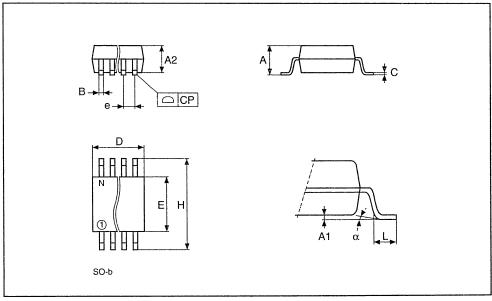

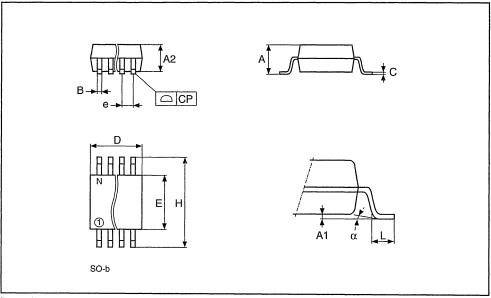

| 0     | mm   |      |                                          | inches |       |       |  |  |

|-------|------|------|------------------------------------------|--------|-------|-------|--|--|

| Symb. | Тур. | Min. | Max.                                     | Тур.   | Min.  | Max.  |  |  |

| A     |      |      | 1.10                                     |        |       | 0.043 |  |  |

| A1    |      | 0.05 | 0.15                                     |        | 0.002 | 0.006 |  |  |

| A2    |      | 0.85 | 0.95                                     |        | 0.033 | 0.037 |  |  |

| В     |      | 0.19 | 0.30                                     |        | 0.007 | 0.012 |  |  |

| С     |      | 0.09 | 0.20                                     |        | 0.004 | 0.008 |  |  |

| D     |      | 2.90 | 3.10                                     |        | 0.114 | 0.122 |  |  |

| E     |      | 6.25 | 6.50                                     |        | 0.246 | 0.256 |  |  |

| E1    |      | 4.30 | 4.50                                     |        | 0.169 | 0.177 |  |  |

| е     | 0.65 | -    | -                                        | 0.026  | -     | -     |  |  |

| L     |      | 0.50 | 0.70                                     |        | 0.020 | 0.028 |  |  |

| α     |      | 0°   | 8°                                       |        | 0°    | 8°    |  |  |

| N     |      | 8    | ын түүн түүн түүн түүн түүн түүн түүн тү |        | 8     | •     |  |  |

| CP    |      |      | 0.08                                     |        |       | 0.003 |  |  |

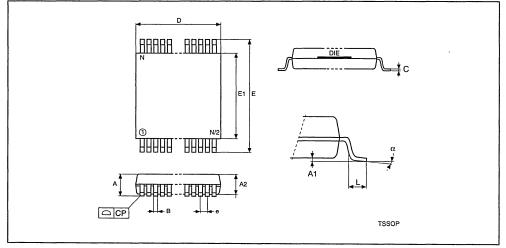

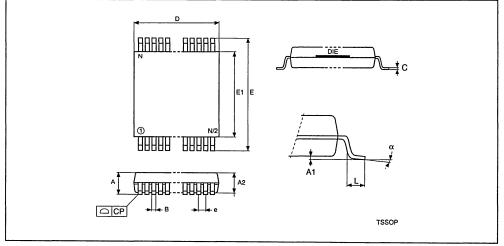

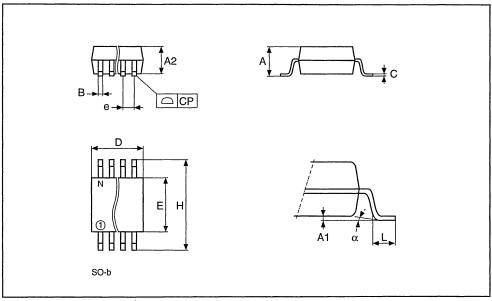

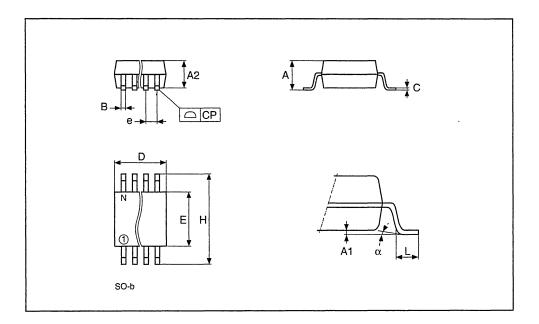

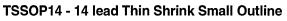

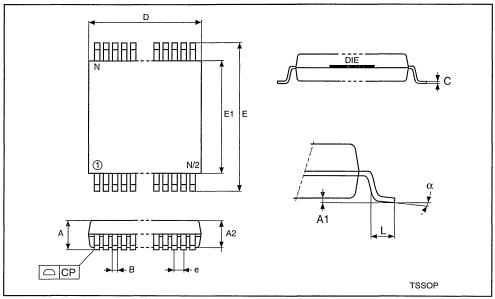

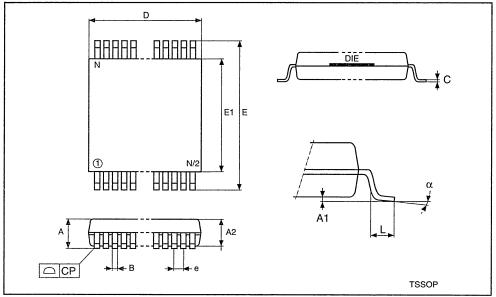

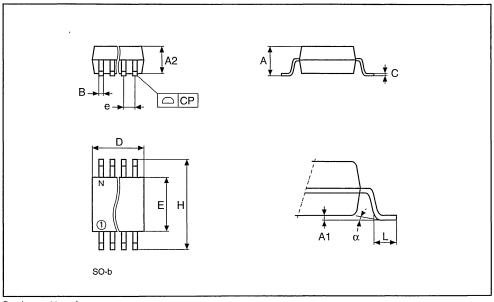

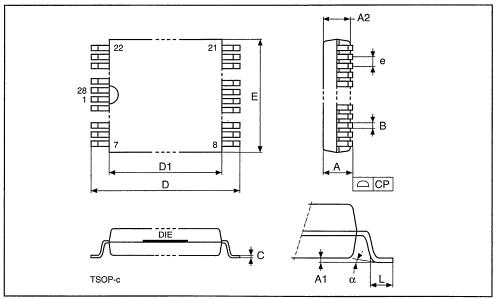

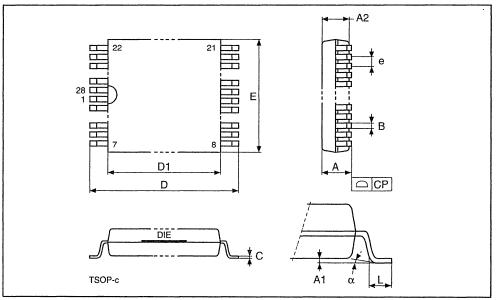

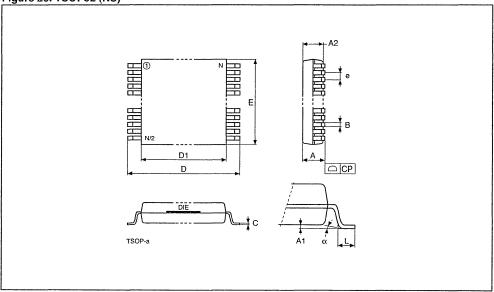

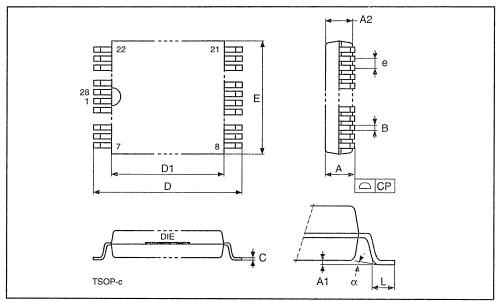

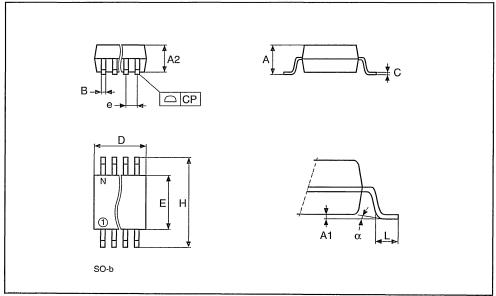

#### Table 12. TSSOP8 - 8 lead Thin Shrink Small Outline

Figure 13. TSSOP8 (DW)

Note: 1. Drawing is not to scale.

AT/

### M24C64 M24C32

### 64/32 Kbit Serial I<sup>2</sup>C Bus EEPROM

- Compatible with I<sup>2</sup>C Extended Addressing

- Two Wire I<sup>2</sup>C Serial Interface Supports 400 kHz Protocol

- Single Supply Voltage:

- 4.5V to 5.5V for M24Cxx

- 2.5V to 5.5V for M24Cxx-W

- 1.8V to 3.6V for M24Cxx-R

- Hardware Write Control

- BYTE and PAGE WRITE (up to 32 Bytes)

- RANDOM and SEQUENTIAL READ Modes

- Self-Timed Programming Cycle

- Automatic Address Incrementing

- Enhanced ESD/Latch-Up Behaviour

- 1 Million Erase/Write Cycles (minimum)

- 40 Year Data Retention (minimum)

#### DESCRIPTION

These electrically erasable programmable memory (EEPROM) devices are fabricated with STMicroelectronics' High Endurance, Single Polysilicon, CMOS technology. This guarantees an endurance typically well above one million Erase/Write cycles, with a data retention of 40 years. The memories are organised as 8192x8 bits (M24C64) and 4096x8 bits (M24C32), and operate down to 2.5 V (for the -W version of each de-

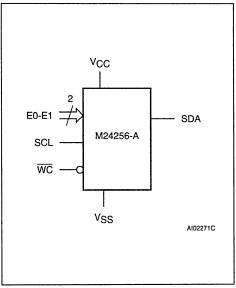

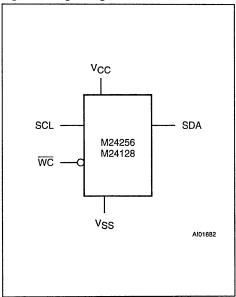

#### Table 1. Signal Names

| E0, E1, E2      | Chip Enable Inputs                   |

|-----------------|--------------------------------------|

| SDA             | Serial Data/Address Input/<br>Output |

| SCL             | Serial Clock                         |

| WC              | Write Control                        |

| Vcc             | Supply Voltage                       |

| V <sub>SS</sub> | Ground                               |

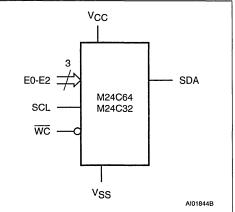

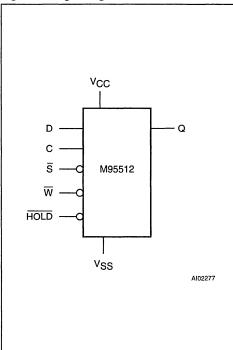

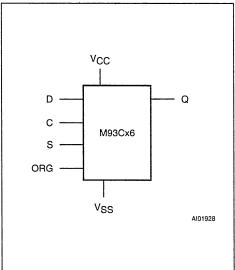

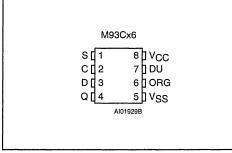

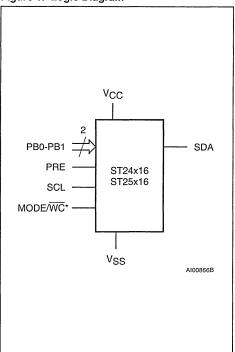

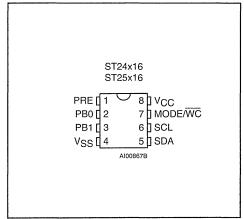

#### Figure 1. Logic Diagram

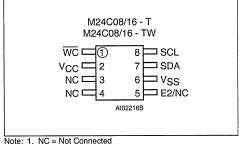

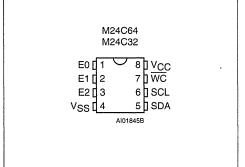

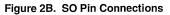

#### Figure 2A. DIP Connections

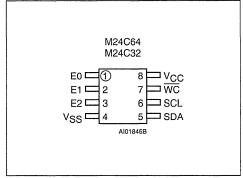

#### Figure 2B. SO Connections

#### Table 2. Absolute Maximum Ratings <sup>1</sup>

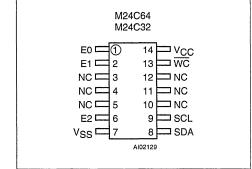

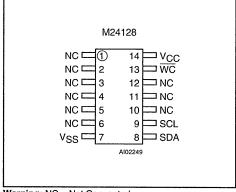

### Figure 2C. TSSOP Connections

Note: 1 NC = Not Connected

vice), and down to 1.8 V (for the -R version of each device).

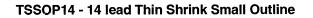

The M24C64 and M24C32 are available in Plastic Dual-in-Line, Plastic Small Outline and Thin Shrink Small Outline packages.

These memory devices are compatible with the  $I^2C$  extended memory standard. This is a two wire serial interface that uses a bi-directional data bus and serial clock. The memory carries a built-in 4-bit unique Device Type Identifier code (1010) in accordance with the  $I^2C$  bus definition.

The memory behaves as a slave device in the  $l^2C$  protocol, with all memory operations synchronized by the serial clock. Read and Write operations are initiated by a START condition, generated by the bus master. The START condition is followed by a

| Symbol            | Parameter                                |                                                  | Value                | Unit |

|-------------------|------------------------------------------|--------------------------------------------------|----------------------|------|

| T <sub>A</sub>    | Ambient Operating Temperature            | -40 to 125                                       | °C                   |      |

| T <sub>STG</sub>  | Storage Temperature                      |                                                  | -65 to 150           | °C   |

| T <sub>LEAD</sub> | Lead Temperature during Soldering        | PSDIP8: 10 sec<br>SO8: 40 sec<br>TSSOP14: t.b.c. | 260<br>215<br>t.b.c. | °C   |

| VIO               | Input or Output range                    |                                                  | -0.6 to 6.5          | V    |

| V <sub>cc</sub>   | Supply Voltage                           |                                                  | -0.3 to 6.5          | V    |

| V <sub>ESD</sub>  | Electrostatic Discharge Voltage (Human E | Body model) <sup>2</sup>                         | 4000                 | v    |

| V ESD             | Electrostatic Discharge Voltage (Machine | 500                                              | V                    |      |

Note: 1. Except for the rating "Operating Temperature Range", stresses above those listed in the Table "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and operation of the device at these or any other condutions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended penods may affect device reliability. Refer also to the ST SURE Program and other relevant quality documents

2. MIL-STD-883C, 3015.7 (100 pF, 1500 Ω)

3. EIAJ IC-121 (Condition C) (200 pF, 0 Ω)

Device Select Code and  $R\overline{W}$  bit (as described in Table 3), terminated by an acknowledge bit.

When writing data to the memory, the memory inserts an acknowledge bit during the 9<sup>th</sup> bit time, following the bus master's 8-bit transmission. When data is read by the bus master, the bus master acknowledges the receipt of the data byte in the same way. Data transfers are terminated by a STOP condition after an Ack for WRITE, and after a NoAck for READ.

#### Power On Reset: V<sub>CC</sub> Lock-Out Write Protect

In order to prevent data corruption and inadvertent write operations during power up, a Power On Reset (POR) circuit is included. The internal reset is held active until the  $V_{CC}$  voltage has reached the POR threshold value, and all operations are disabled – the device will not respond to any command. In the same way, when  $V_{CC}$  drops from the operating voltage, below the POR threshold value, all operations are disabled and the device will not respond to any command. A stable and valid  $V_{CC}$  must be applied before applying any logic signal.

#### SIGNAL DESCRIPTION

#### Serial Clock (SCL)

67/

The SCL input pin is used to strobe all data in and out of the memory. In applications where this line is used by slaves to synchronize the bus to a slower clock, the master must have an open drain output, and a pull-up resistor must be connected from the SCL line to V<sub>CC</sub>. (Figure 3 indicates how the value of the pull-up resistor can be calculated). In most applications, though, this method of synchronization is not employed, and so the pull-up resistor is not necessary, provided that the master has a push-pull (rather than open drain) output.

#### Serial Data (SDA)

The SDA pin is bi-directional, and is used to transfer data in or out of the memory. It is an open drain output that may be wire-OR'ed with other open drain or open collector signals on the bus. A pull up resistor must be connected from the SDA bus to V<sub>CC</sub>. (Figure 3 indicates how the value of the pull-up resistor can be calculated).

#### Chip Enable (E2, E1, E0)

These chip enable inputs are used to set the value that is to be looked for on the three least significant bits (b3, b2, b1) of the 7-bit device select code. These inputs may be driven dynamically or tied to  $V_{CC}$  or  $V_{SS}$  to establish the device select code (but note that the  $V_{IL}$  and  $V_{IH}$  levels for the inputs are CMOS compatible, not TTL compatible).

#### Write Control (WC)

The hardware Write Control pin ( $\overline{WC}$ ) is useful for protecting the entire contents of the memory from inadvertent erase/write. The Write Control signal is used to enable ( $\overline{WC}$ =V<sub>IL</sub>) or disable ( $\overline{WC}$ =V<sub>IH</sub>) write instructions to the entire memory area. When unconnected, the  $\overline{WC}$  input is internally read as V<sub>IL</sub>, and write operations are allowed.

When  $\overline{\text{WC}}$ =1, Device Select and Address bytes are acknowledged, Data bytes are not acknowledged.

Please see the Application Note *AN404* for a more detailed description of the Write Control feature.

#### **DEVICE OPERATION**

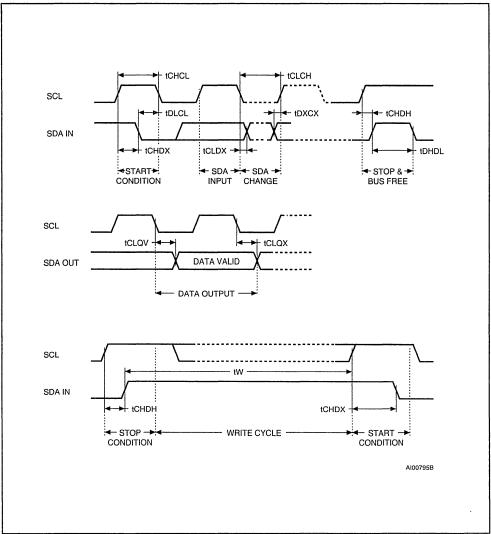

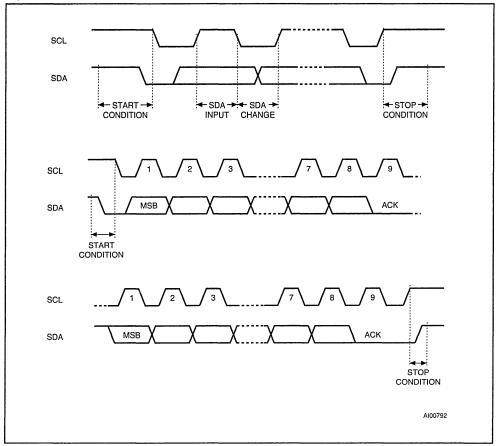

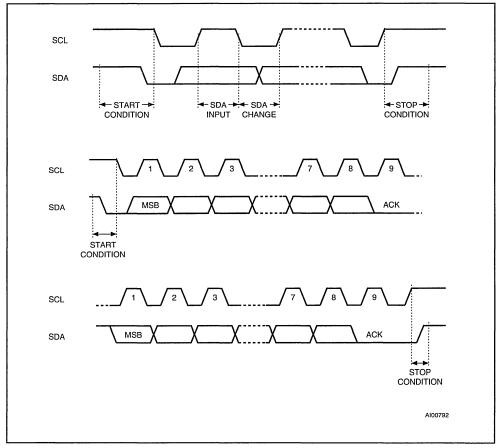

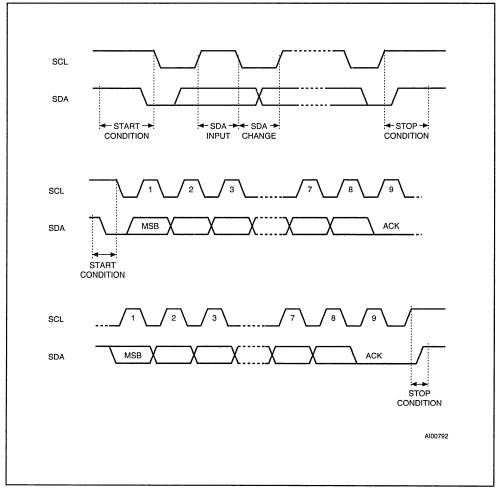

The memory device supports the  $l^2C$  protocol. This is summarized in Figure 4, and is compared with other serial bus protocols in Application Note *AN1001*. Any device that sends data on to the bus is defined to be a transmitter, and any device that

#### Figure 3. Maximum R<sub>L</sub> Value versus Bus Capacitance (C<sub>BUS</sub>) for an I<sup>2</sup>C Bus

#### Figure 4. I<sup>2</sup>C Bus Protocol

reads the data to be a receiver. The device that controls the data transfer is known as the master, and the other as the slave. A data transfer can only be initiated by the master, which will also provide the serial clock for synchronization. The memory device is always a slave device in all communication.

#### Start Condition

START is identified by a high to low transition of the SDA line while the clock, SCL, is stable in the high state. A START condition must precede any data transfer command. The memory device continuously monitors (except during a programming cycle) the SDA and SCL lines for a START condition, and will not respond unless one is given.

#### **Stop Condition**

STOP is identified by a low to high transition of the SDA line while the clock SCL is stable in the high state. A STOP condition terminates communica-

tion between the memory device and the bus master. A STOP condition at the end of a Read command, after (and only after) a NoAck, forces the memory device into its standby state. A STOP condition at the end of a Write command triggers the internal EEPROM write cycle.

#### Acknowledge Bit (ACK)

An acknowledge signal is used to indicate a successful byte transfer. The bus transmitter, whether it be master or slave, releases the SDA bus after sending eight bits of data. During the 9<sup>th</sup> clock pulse period, the receiver pulls the SDA bus low to acknowledge the receipt of the eight data bits.

#### Data Input

During data input, the memory device samples the SDA bus signal on the rising edge of the clock, SCL. For correct device operation, the SDA signal must be stable during the clock low-to-high transition, and the data must change *only* when the SCL line is low.

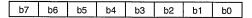

#### Table 3. Device Select Code <sup>1</sup>

|                    | Device Type Identifier |    |    | Chip Enable |    |    | RW |    |

|--------------------|------------------------|----|----|-------------|----|----|----|----|

|                    | b7                     | b6 | b5 | b4          | b3 | b2 | b1 | b0 |

| Device Select Code | 1                      | 0  | 1  | 0           | E2 | E1 | E0 | RW |

Note: 1. The most significant bit, b7, is sent first.

#### Memory Addressing

To start communication between the bus master and the slave memory, the master must initiate a START condition. Following this, the master sends the 8-bit byte, shown in Table 3, on the SDA bus line (most significant bit first). This consists of the 7-bit Device Select Code, and the 1-bit Read/Write Designator (RW). The Device Select Code is further subdivided into: a 4-bit Device Type Identifier, and a 3-bit Chip Enable "Address" (E2, E1, E0).

To address the memory array, the 4-bit Device Type Identifier is 1010b.

If all three chip enable inputs are connected, up to eight memory devices can be connected on a single  $l^2C$  bus. Each one is given a unique 3-bit code on its Chip Enable inputs. When the Device Select Code is received on the SDA bus, the memory only responds if the Chip Select Code is the same as the pattern applied to its Chip Enable pins.

The 8<sup>th</sup> bit is the  $R\overline{W}$  bit. This is set to '1' for read and '0' for write operations. If a match occurs on the Device Select Code, the corresponding memory gives an acknowledgment on the SDA bus during the 9<sup>th</sup> bit time. If the memory does not match the Device Select Code, it deselects itself from the bus, and goes into stand-by mode.

There are two modes both for read and write. These are summarized in Table 6 and described later. A communication between the master and the slave is ended with a STOP condition.

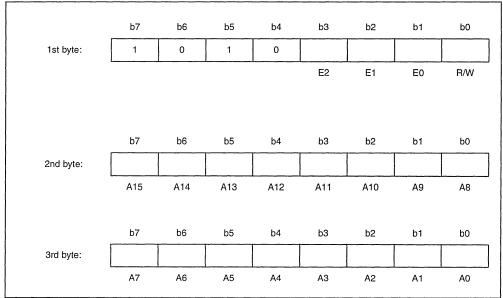

Each data byte in the memory has a 16-bit (two byte wide) address. The Most Significant Byte (Table 4) is sent first, followed by the Least significant

#### Table 4. Most Significant Byte

| b15                                                    | b14 | b13 | b12 | b11 | b10 | b9 | b8 |  |

|--------------------------------------------------------|-----|-----|-----|-----|-----|----|----|--|

| Note: 1 b15 to b12 are Dep't Care on the M24C64 series |     |     |     |     |     |    |    |  |

bite: 1 b15 to b13 are Don't Care on the M24C64 series. b15 to b12 are Don't Care on the M24C32 series.

#### Table 5. Least Significant Byte

|   | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|---|----|----|----|----|----|----|----|----|

| 1 |    |    |    |    |    |    |    |    |

Byte (Table 5). Bits b15 to b0 form the address of the byte in memory. Bits b15 to b13 are treated as a Don't Care bit on the M24C64 memory. Bits b15 to b12 are treated as Don't Care bits on the M24C32 memory.

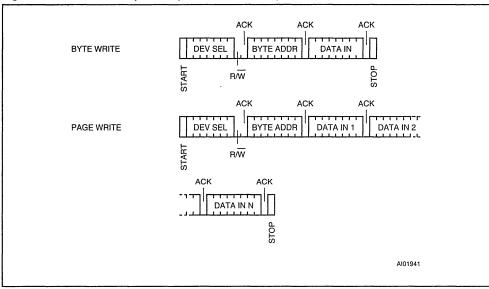

#### Write Operations

Following a START condition the master sends a Device Select Code with the RW bit set to '0', as shown in Table 6. The memory acknowledges this, and waits for two address bytes. The memory responds to each address byte with an acknowledge bit, and then waits for the data byte.

Writing to the memory may be inhibited if the  $\overline{WC}$  input pin is taken high. Any write command with  $\overline{WC}$ =1 (during a period of time from the START condition until the end of the two address bytes) will not modify the memory contents, and the accompanying data bytes will *not* be acknowledged (as shown in Figure 5).

#### Byte Write

In the Byte Write mode, after the Device Select Code and the address bytes, the master sends

| Mode                 | R₩ bit | WC <sup>1</sup> | Bytes | Initial Sequence                                     |

|----------------------|--------|-----------------|-------|------------------------------------------------------|

| Current Address Read | - '1'  | Х               | 1     | START, Device Select, RW = '1'                       |

|                      | '0'    | Х               |       | START, Device Select, $R\overline{W}$ = '0', Address |

| Random Address Read  | '1'    | х               |       | reSTART, Device Select, $R\overline{W}$ = '1'        |

| Sequential Read      | '1'    | х               | ≥ 1   | Similar to Current or Random Address Read            |

| Byte Write           | '0'    | VIL             | 1     | START, Device Select, $R\overline{W}$ = '0'          |

| Page Write           | '0'    | VIL             | ≤ 32  | START, Device Select, $R\overline{W} = '0'$          |

#### **Table 6. Operating Modes**

Note. 1.  $X = V_{IH} \text{ or } V_{IL}$ .

one data byte. If the addressed location is write protected by the  $\overline{WC}$  pin, the memory replies with a NoAck, and the location is not modified. If, instead, the  $\overline{WC}$  pin has been held at 0, as shown in Figure 6, the memory replies with an Ack. The master terminates the transfer by generating a STOP condition.

#### Page Write

The Page Write mode allows up to 32 bytes to be written in a single write cycle, provided that they are all located in the same 'row' in the memory: that is the most significant memory address bits (b12-b5 for the M24C64 and b11-b5 for the M24C32) are the same. If more bytes are sent than will fit up to the end of the row, a condition known as 'roll-over' occurs. Data starts to become overwritten (in a way not formally specified in this data sheet).

The master sends from one up to 32 bytes of data, each of which is acknowledged by the memory if the  $\overline{WC}$  pin is low. If the  $\overline{WC}$  pin is high, the contents of the addressed memory location are not modified, and each data byte is followed by a NoAck. After each byte is transferred, the internal byte address counter (the 5 least significant bits only) is incremented. The transfer is terminated by the master generating a STOP condition.

When the master generates a STOP condition immediately after the Ack bit (in the " $10^{lh}$  bit" time slot), either at the end of a byte write or a page write, the internal memory write cycle is triggered. A STOP condition at any other time does not trigger the internal write cycle.

During the internal write cycle, the SDA input is disabled internally, and the device does not respond to any requests.

Figure 6. Write Mode Sequences with WC=0 (data write enabled)

51

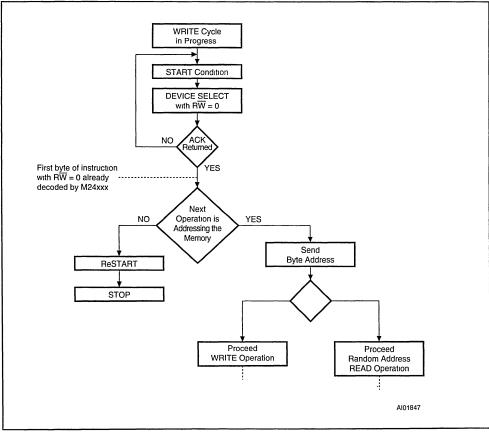

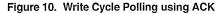

## Figure 7. Write Cycle Polling Flowchart using ACK

### Minimizing System Delays by Polling On ACK

During the internal write cycle, the memory disconnects itself from the bus, and copies the data from its internal latches to the memory cells. The maximum write time ( $t_W$ ) is shown in Table 9, but the typical time is shorter. To make use of this, an Ack polling sequence can be used by the master.

The sequence, as shown in Figure 7, is:

- Initial condition: a Write is in progress.

- Step 1: the master issues a START condition followed by a Device Select Code (the first byte of the new instruction).

- Step 2: if the memory is busy with the internal write cycle, no Ack will be returned and the master goes back to Step 1. If the memory has terminated the internal write cycle, it responds with an Ack, indicating that the memory is ready to receive the second part of the next instruction (the first byte of this instruction having been sent during Step 1).

### Read Operations

Read operations are performed independently of the state of the  $\overline{\text{WC}}$  pin.

### Random Address Read

A dummy write is performed to load the address into the address counter, as shown in Figure 8. Then, *without* sending a STOP condition, the master sends another START condition, and repeats the Device Select Code, with the RW bit set to '1'. The memory acknowledges this, and outputs the contents of the addressed byte. The master must *not* acknowledge the byte output, and terminates the transfer with a STOP condition.

### **Current Address Read**

The device has an internal address counter which is incremented each time a byte is read. For the Current Address Read mode, following a START condition, the master sends a Device Select Code with the RW bit set to '1'. The memory acknowledges this, and outputs the byte addressed by the

### Figure 8. Read Mode Sequences

Note: 1. The seven most significant bits of the Device Select Code of a Random Read (in the 1<sup>st</sup> and 4<sup>th</sup> bytes) must be identical

internal address counter. The counter is then incremented. The master terminates the transfer with a STOP condition, as shown in Figure 8, *without* acknowledging the byte output.

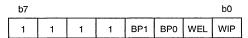

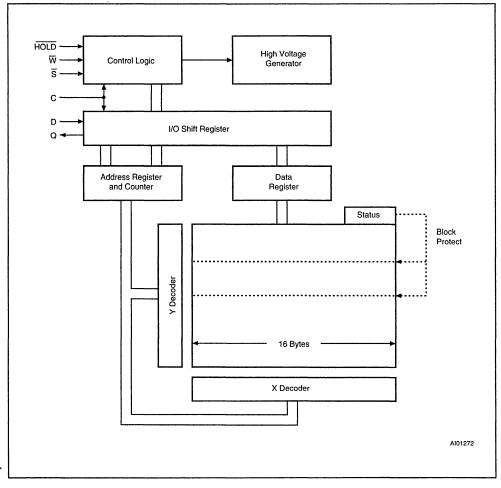

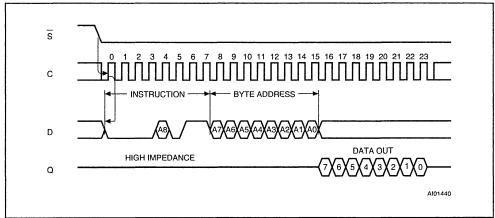

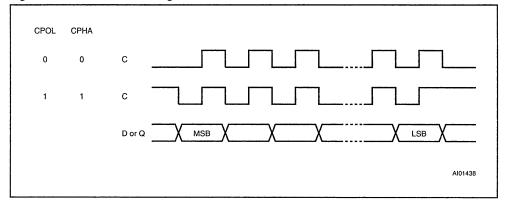

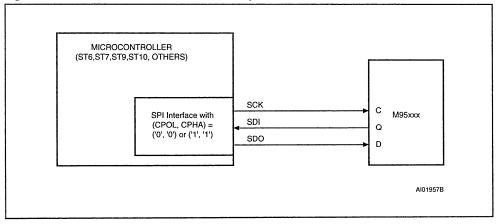

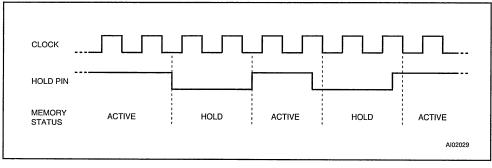

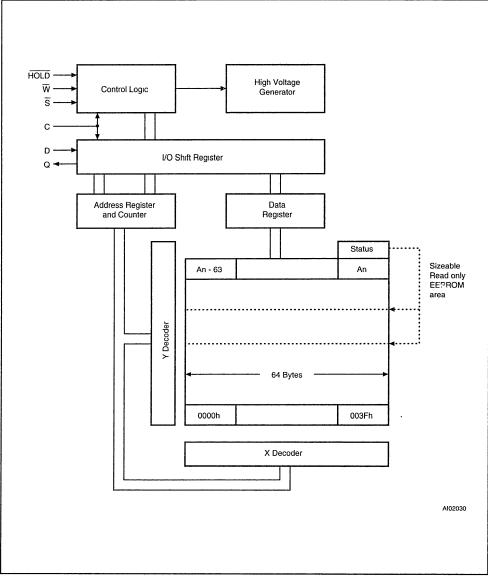

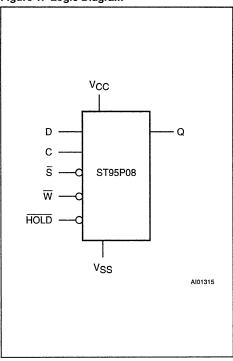

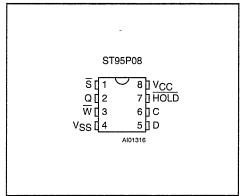

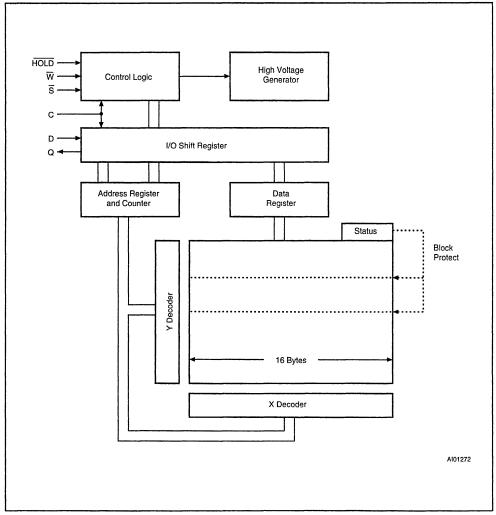

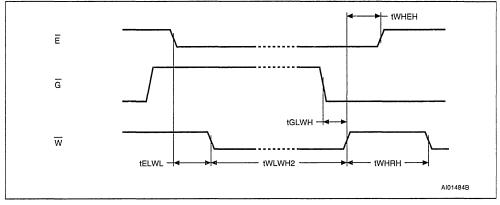

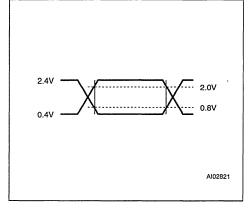

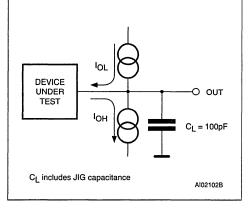

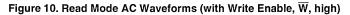

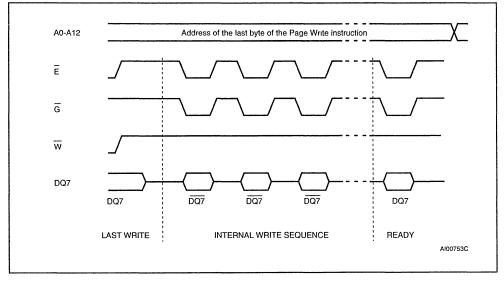

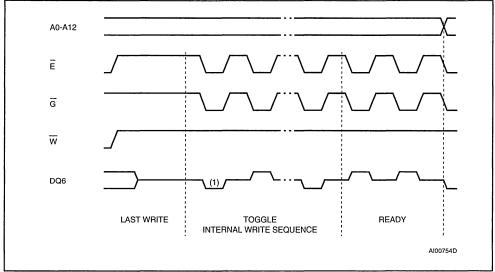

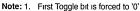

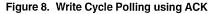

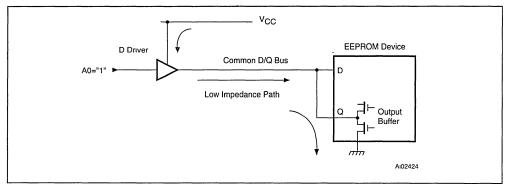

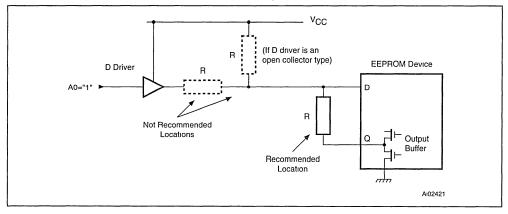

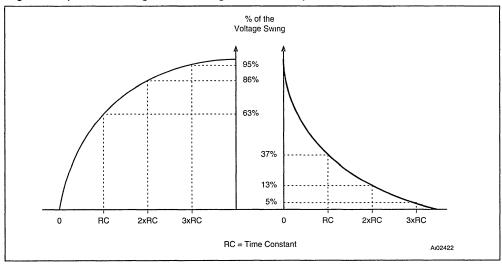

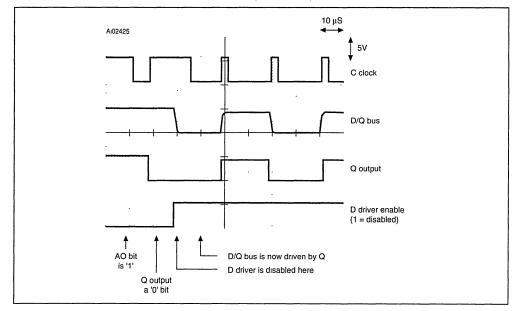

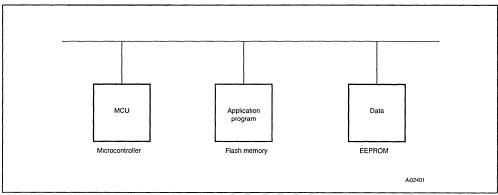

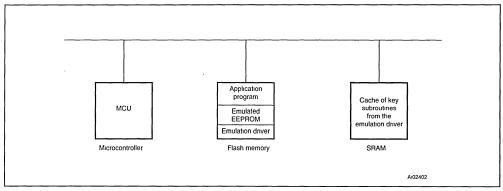

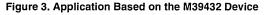

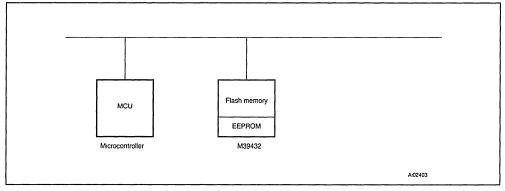

### Sequential Read