# MODEM INTEGRATED CIRCUITS

DATASHEETS & APPLICATION NOTES

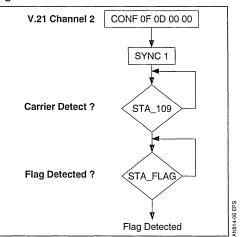

2<sup>nd</sup> EDITION

DATASHEETS & APPLICATION NOTES

MODEM

000520 RYSTON Electronics

# MODEM INTEGRATED CIRCUITS

## DATASHEETS AND APPLICATION NOTES

2<sup>nd</sup> EDITION

**AUGUST 1995**

, .

#### USE IN LIFE SUPPORT DEVICES OR SYSTEMS MUST BE EXPRESSLY AUTHORIZED

SGS-THOMSON PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF SGS-THOMSON Microelectronics. As used herein:

- Life support devices or systems are those which (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided with the product, can be reasonably expected to result in significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can reasonably be expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

| TABLE OF CONTENTS                                                                                                                     |        |

|---------------------------------------------------------------------------------------------------------------------------------------|--------|

| ·                                                                                                                                     |        |

|                                                                                                                                       | Page 5 |

| ALPHANUMERICAL INDEX<br>SELECTION GUIDE                                                                                               | 9      |

| PRODUCT FAMILIES         ANALOG FRONT-END         HIGH SPEED MODEM         FAX MODEM         LOW SPEED MODEM         POWER LINE MODEM |        |

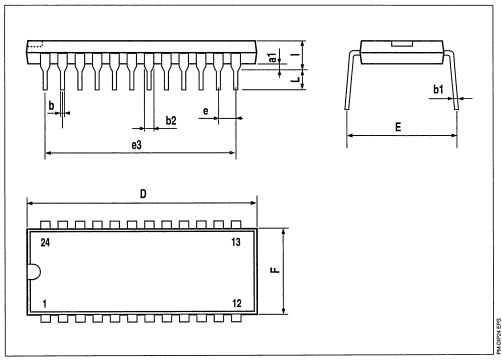

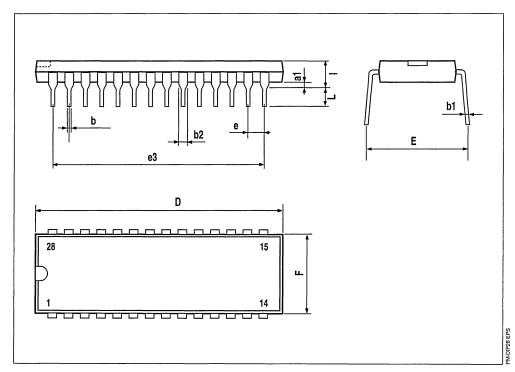

| PACKAGES                                                                                                                              | 685    |

.

•

## INTRODUCTION

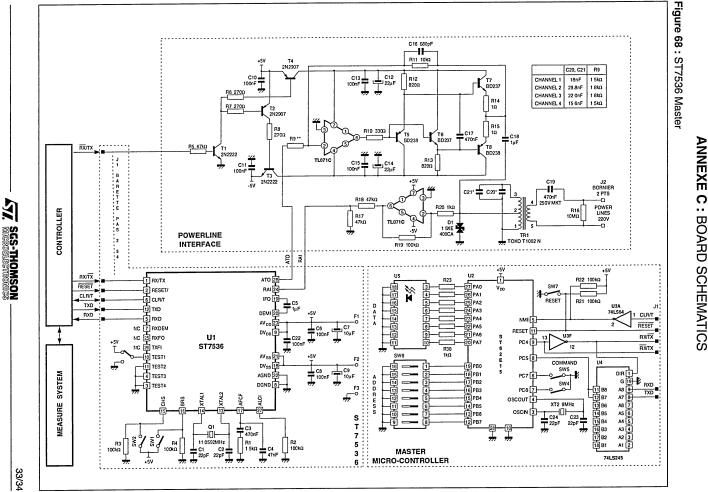

With Modem integrated circuits from SGS-THOMSON, data, be it fax or voice, can be transmitted via any telephone or power line, any time, at any speed, in any standard or protocol and in any size down to PCMICIA type II format.

The SGS-THOMSON Modem and Power Line Modem IC product range focuses on high performance and high quality devices. All are made with the most appropriate choice of technology, carefully selected from a broad portfolio that is unique to SGS-THOMSON.

With the information contained in the following pages, an optimum solution can be selected in a few seconds. The first table enables selection of a Telephone Line Modem, according to the transmission standard needed. The selection depends on the needs of the user : a complete solution; just a Data Pump; or a leading Modem Analog Front End for V.34 implementation.

Intentionally, the table has been simplified to enable quick selection of a device. It does not pretend to show all embedded functions. For a comprehensive function list, the first page of the datasheet should be consulted. For example, some Modem ICs also include voice functions; Analog Front-end devices include clock generation and can also be used as an Audio Front-end.

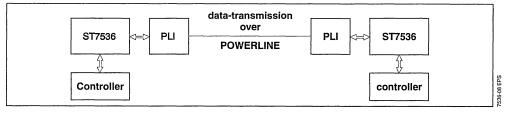

The second tables gives a quick summary of Power Line Modem products, arranged according to the required data transmission speed. Again, this table is intentionally simplified and does not pretend to show all the capabilities of the devices or the powerful development tools which allow the user quick turnaround time for a working solution.

Should an appropriate solution not be found in this databook, please contact the nearest SGS-THOMSON Microelectronics representative or salesperson. The solution required may already be in development stage, close to being introduced. And if quantity justifies it, a custom solution can be tailored to meet specific needs, using SGS-THOMSON's wide and proven telecom design experience.

Should other semiconductor components be needed for completion of designs - memories, micros, standard circuits, for instance ask for the SGS-THOMSON Shortform Catalog or CD "Data on Disc" which contain details of the Company's entire product range.

. .

## ALPHANUMERICAL INDEX \_\_\_\_\_

#### DATASHEETS

| Type<br>Number | Function                                  | Page<br>Number |  |

|----------------|-------------------------------------------|----------------|--|

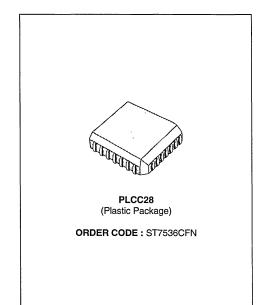

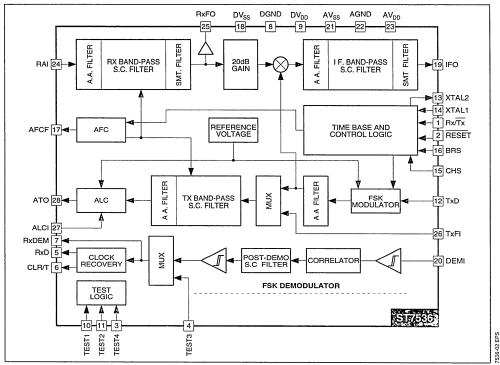

| ST7536         | Power Line Mode                           | 535            |  |

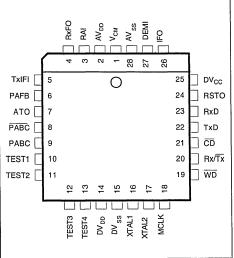

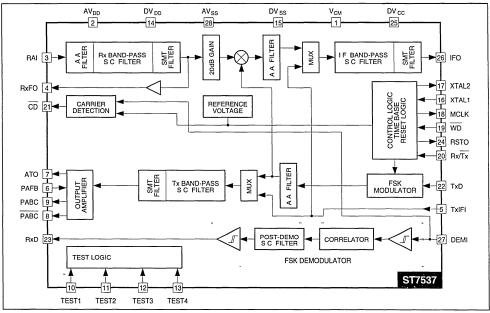

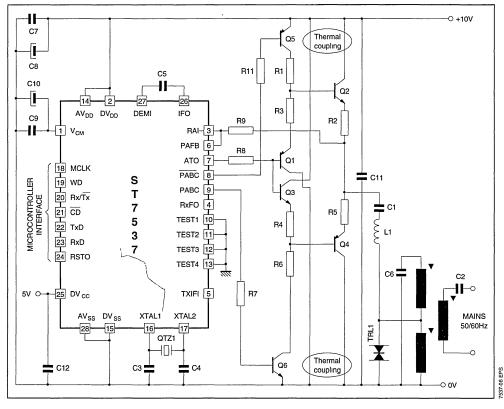

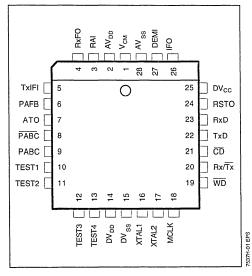

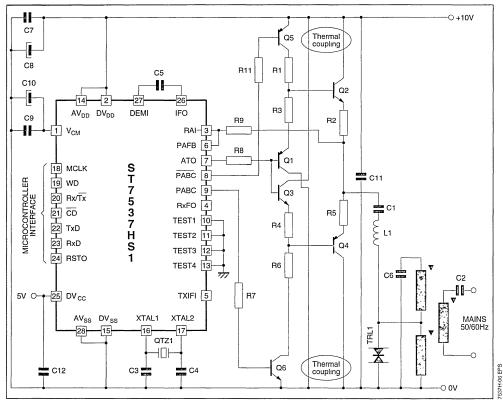

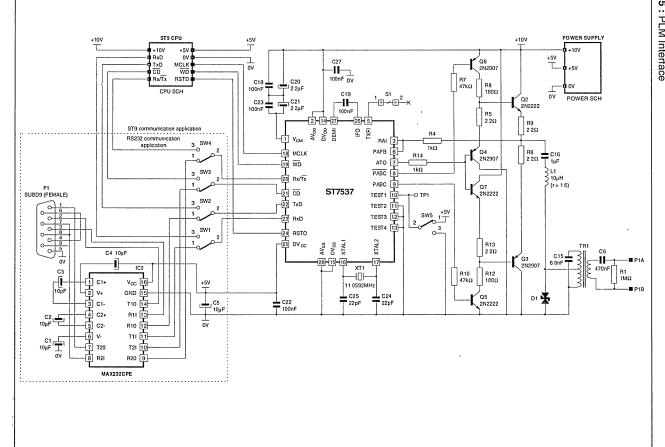

| ST7537         | Home Automation Modem                     | 543            |  |

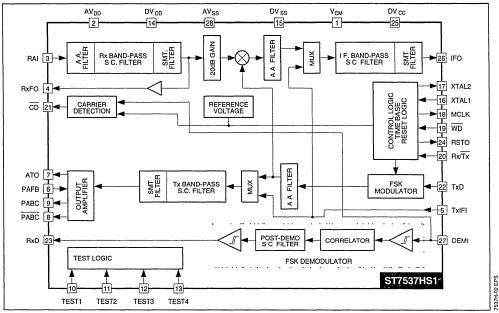

| ST7537HS1      | Home Automation Modem                     | 551            |  |

| ST7544         | Universal Modem Analog Front-End (UMAFE)  | 13             |  |

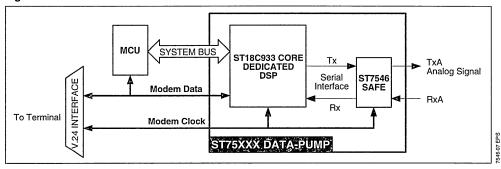

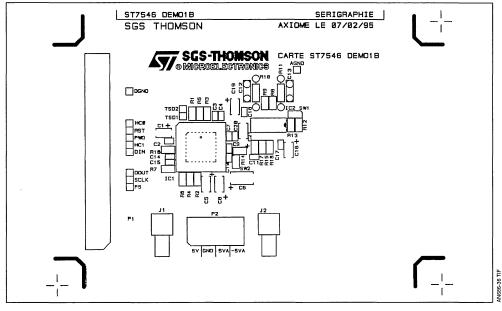

| ST7546         | Simplified V.34 Analog Front-End          |                |  |

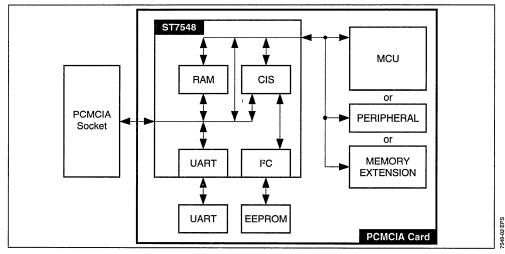

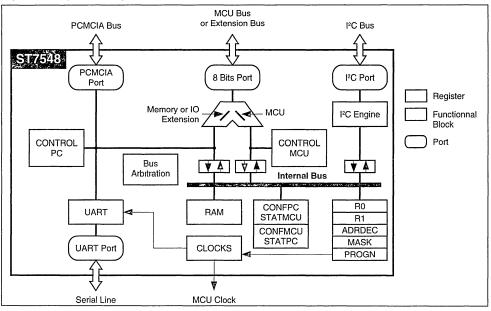

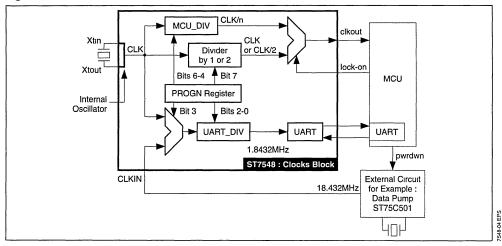

| ST7548         | PCMCIA and PC General Purpose Interface   |                |  |

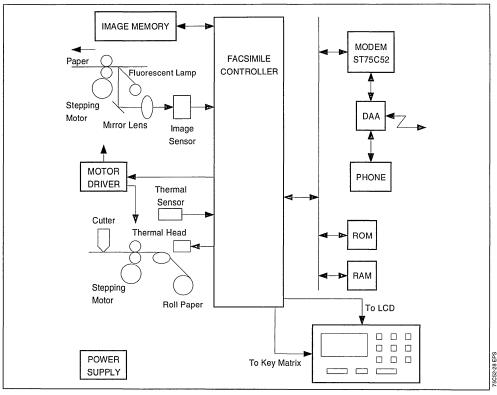

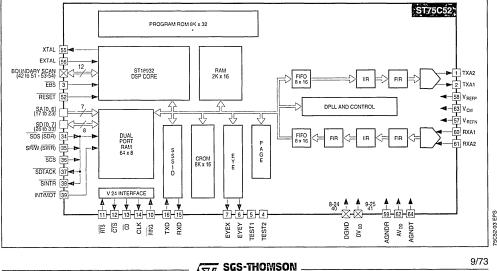

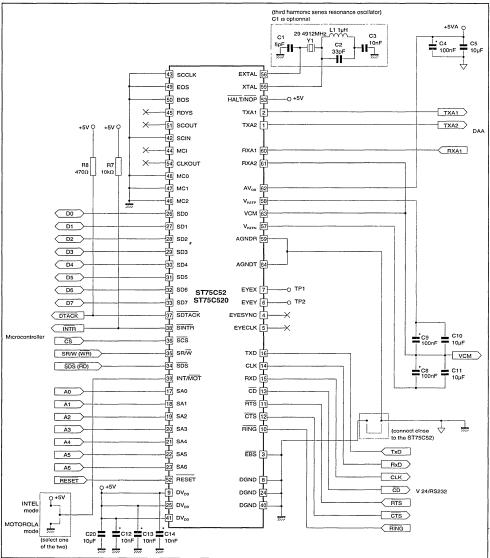

| ST75C52        | High Speed Fax Modem Data Pump            | 305            |  |

| ST75C502       | V.32bis / V.17 High Speed Modem Data Pump | 157            |  |

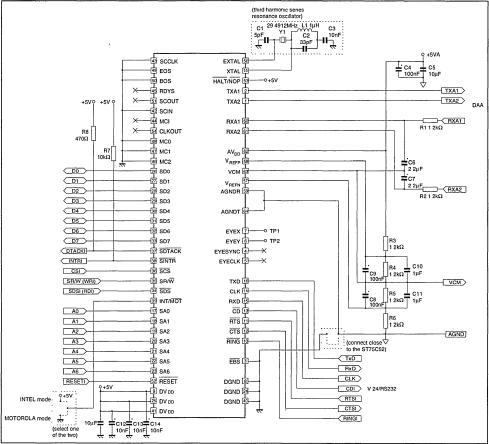

| ST75C520       | High Speed Fax Modem Data Pump            | 351            |  |

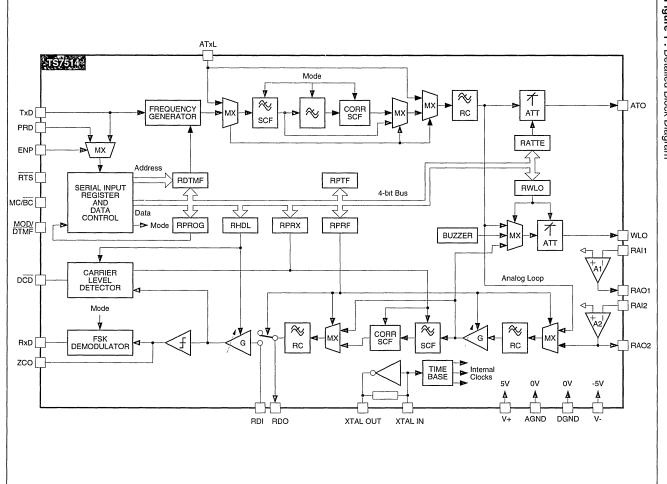

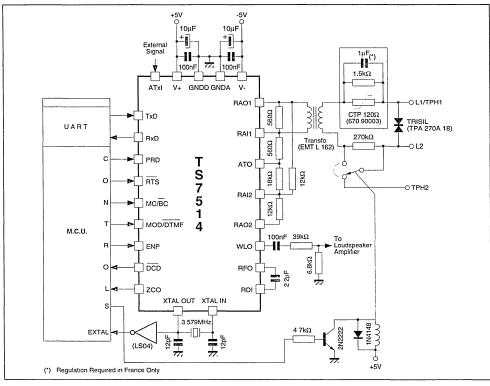

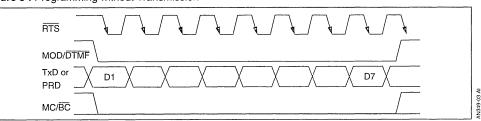

| TS7514         | Programmable V.23 Modem with DTMF         | 491            |  |

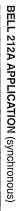

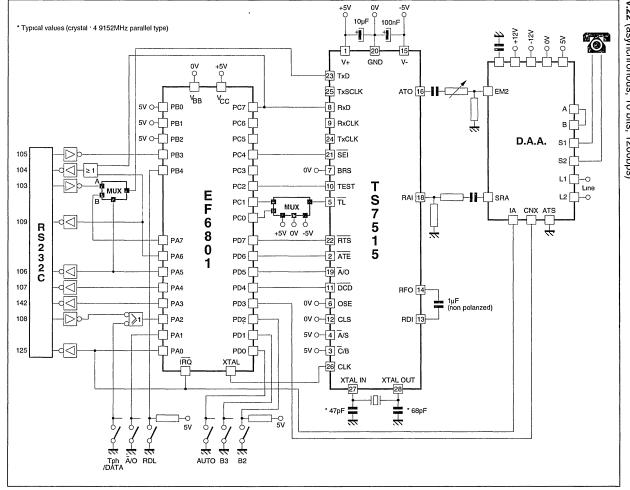

| TS7515         | Single Chip DPSK and FSK Modem            | 509            |  |

#### **APPLICATION NOTES**

| Number | Title                                                                                       | Page<br>Number |

|--------|---------------------------------------------------------------------------------------------|----------------|

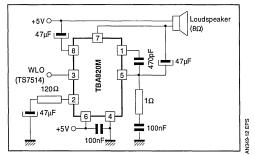

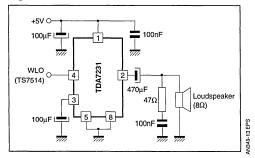

| AN349  | TS7514 - A Very Low Cost and Powerful Solution for V.23 Application                         | 523            |

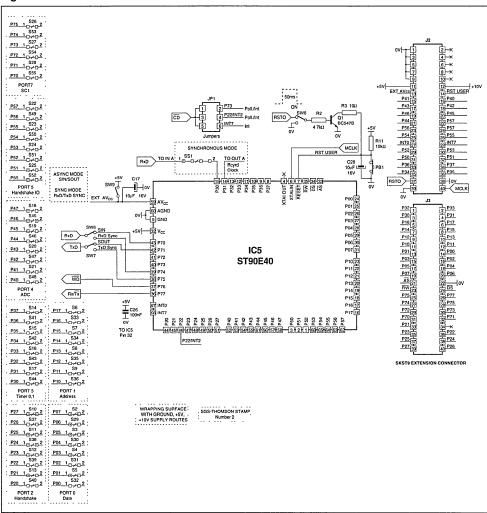

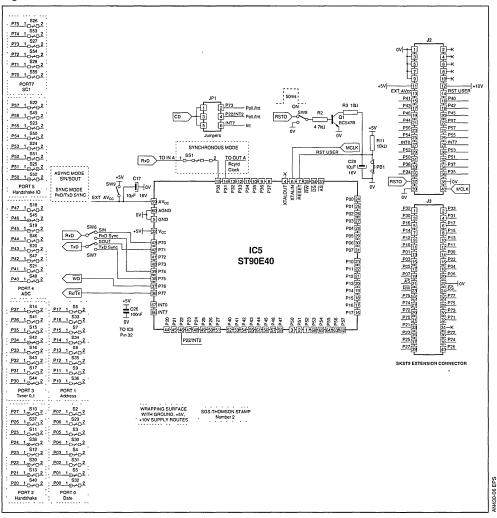

| AN430  | Synchronous Power Line Modem Communication with ST9 Multifunction Timer                     | 677            |

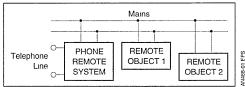

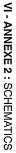

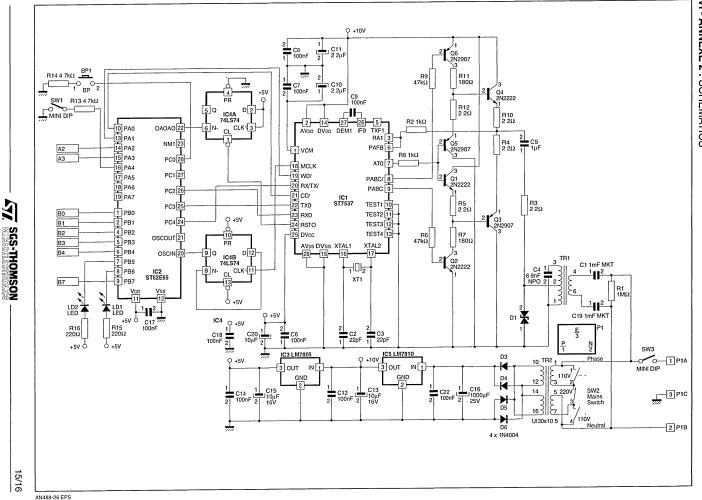

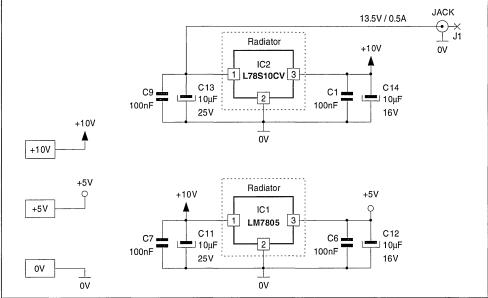

| AN488  | Phone Remote System                                                                         | 645            |

| AN534  | 4.5W Flyback Converter for Power Line Modem Applications                                    | 661            |

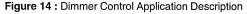

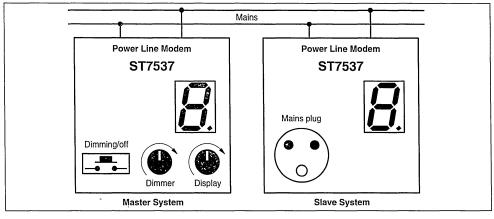

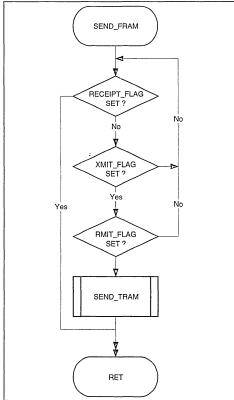

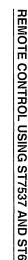

| AN535  | Power Line Modem Application Remote Control using ST7537 and ST6                            | 625            |

| AN537  | ST75C502 - Default Tone Detectors                                                           | 251            |

| AN538  | ST75C502 - Bulk Delay Management                                                            | 257            |

| AN539  | ST75C502 - RAM Mapping                                                                      | 261            |

| AN653  | ST7536                                                                                      | 559            |

| AN654  | ST7544 - Universal Analog Front-End                                                         | 75             |

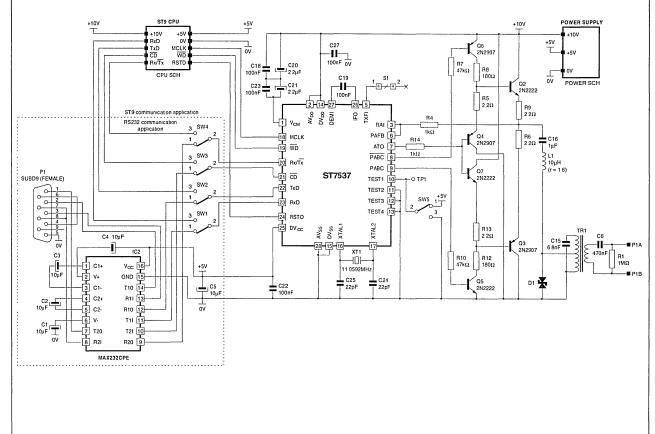

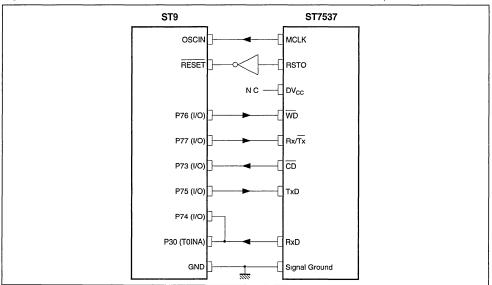

| AN655  | ST7537 - Power Line Modem Application                                                       | 593            |

| AN684  | How to Use the Dual Port RAM for Parallel Data Transfer with ST75C502                       | 271            |

| AN686  | ST7546 - Simplified ANALOG Front-End                                                        | 103            |

| AN814  | V.17 Fax Equipment replacing the R144EFX with the ST75C52/ST75C520                          | 469            |

| AN815  | A Stereo Audio Solution for Multimedia Applications using Two ST7546 A/D and D/A Converters | 117            |

| AN816  | Set-up, Handshake and Communication Monitoring in Modem and Fax Mode with the ST75C502      | 281            |

| AN817  | ST75C5XX - Low Power Mode                                                                   | 297            |

| AN822  | Computation of Tone Detector Coefficients using TD Software for ST75C502                    | 299            |

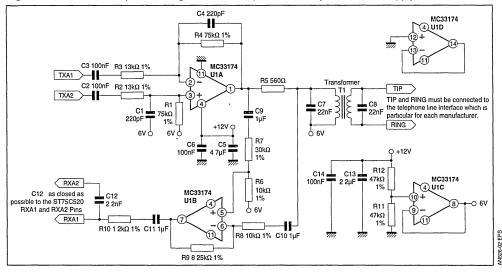

| AN823  | ST75C520 - Single Ended and Single Power Supply Hybrid Circuit                              | 483            |

## ALPHANUMERICAL INDEX \_\_\_\_\_

#### MISCELLANEOUS

| Type<br>Number | Title         | Page<br>Number |

|----------------|---------------|----------------|

| SATURN         | Product Info  | 211            |

| SATURN         | User's Manual | 213            |

| ST75C52/C520   | User's Manual | 395            |

| ST7537         | Starter Kit   | 671            |

#### MODEM

|             |                   | ITU-T      |             |              |              |                                |                                  |              |                      |                                |

|-------------|-------------------|------------|-------------|--------------|--------------|--------------------------------|----------------------------------|--------------|----------------------|--------------------------------|

|             | V.21              | V.23       | V.22        | V.22bis      | V.32         | V.32bis                        | V.34                             | V.27T        | V.29                 | V.17                           |

| BELL        | 103               |            | 212A        |              |              |                                |                                  |              |                      |                                |

| Modulation  | FSK / FDM         |            | DPSł        | K / FDM      |              | DPSK / E.C.                    |                                  | DPSK         |                      |                                |

| Bps         | 0-300             | 75<br>1200 | 600<br>1200 | 1200<br>2400 | 4800<br>9600 | 7200<br>9600<br>12000<br>14400 | 14400<br>19200<br>24000<br>28800 | 2400<br>4800 | 4800<br>7200<br>9600 | 7200<br>9600<br>12000<br>24000 |

| Mode        |                   |            | Full        | Duplex       |              |                                | Full Duplex<br>Half Duplex       | Н            | alf Dupl             | эх                             |

| Application |                   | Teletext   |             | Р            | С            |                                | PC / FAX                         |              | FAX                  |                                |

| r           |                   | TS7514     | ]           | -            |              |                                |                                  |              |                      |                                |

|             | TS7515            |            | TS7515      | ;            |              |                                |                                  |              |                      |                                |

| PUMPS       | ST75C502 / ST7544 |            |             |              |              |                                | ST75C502 / ST7544                |              |                      |                                |

|             | ST75C             | 52 / C520  | ]           |              |              |                                | [                                | ST7          | ′5C52 / C            | 520                            |

| MAFE        | ST7544 / ST7546   |            |             |              |              |                                |                                  |              |                      |                                |

| PCMCIA      | ST7548            |            |             |              |              |                                |                                  |              |                      |                                |

Note: For clarity purpose, the slection table is simplified. Data Pumps include many functions which do not appear on this table such as Tone/DTMF generation and detection or caller ID demodulation. Please look at the first page of datasheet to have a complete view of functionalities.

#### **POWER LINE MODEM**

|                   | ST7536          | ST7537           | ST7537HS1        |

|-------------------|-----------------|------------------|------------------|

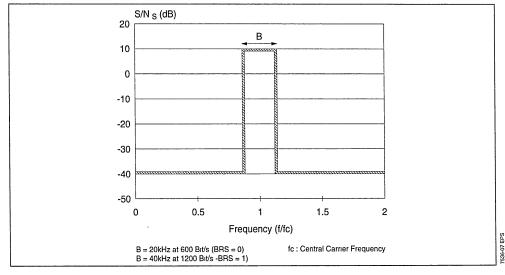

| Modulation        | FSK Synchronous | FSK Asynchronous | FSK Asynchronous |

| Bps               | 600/1200        | Up to 1200       | Up to 2400       |

| Mode              | Half Duplex     | Half Duplex      | Half Duplex      |

| Carrier Frequency | < 95kHz         | ≤ 132.5kHz       | ≤ 132.5kHz       |

## ANALOG FRONT-END

### UNIVERSAL MODEM ANALOG FRONT-END (UMAFE)

- FULL ECHO CANCELLING CAPABILITY

- FULLY COMPATIBLE WITH THE ST7543 (7543 mode)

SGS-THOMSON MICROFLECTRONICS

- 16-BIT OVERSAMPLING A/D AND D/A CONVERTERS

- Programmable down-sampling frequency from 7200 to 16000Hz

- Sampling frequency can be 3, 4, 6, 8, 12, 16 x symbol rate

- Programmable Over sampling frequency (128 or 160 x sampling frequency)

- The ST7544 can work with external oversampling clocks

- Programmable symbol rate (600, 1200, 1600, 2400, 2560, 2743, 2800, 2954, 3000, 3200, 3429 and 3491)

- Bit rates of 300bps, 600bps, 1200 and all multiples of 2400bps up to 28800bps can be generated

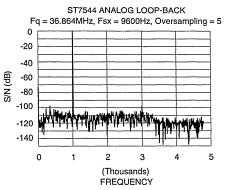

- Dynamic range : 92dB with a sampling frequency 9600Hz, oversampling ratio 160

- Total harmonic distortion : -89dB

- ON CHIP REFERENCE VOLTAGE

- THREE PROGRAMMABLE DIGITAL FILTERS SEC-TIONS :

- Tx interpolation filter

- Rx decimation filter (up to 14th order each)

- Rx reconstruction filter (coefficients loaded into RAM)

- ANCILLARY CONVERTERS FOR EYE-DIAGRAM MONITORING

- CLOCK SYSTEM BASED ON DIGITAL PHASE LOCKED LOOPS

- Separate Tx DPLL and Rx DPLL

- Terminal clock input for Tx synchronization on all multiples of 2400Hz (VFast synchronization mode) or on sub-multiple of baud rate (7543 synchronization mode)

- Bit, Baud, sampling and highest synchronous clock outputs

- Maximum master clock frequency is 38MHz

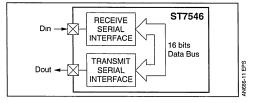

- SINGLE OR DUAL SYNCHRONOUS SERIAL INTER-FACE TO DSP

- SINGLE POWER SUPPLY VOLTAGE : +5V

- ■LOW POWER CONSUMPTION :

- 260mW operating power at the nominal crystal frequency of 36.864MHz

- 160mW operating power at the crytal frequency of  $18.432 \mbox{MHz}$

- Less than 5mW in the Low-Power Reset Mode

- 1.2µm CMOS PROCESS

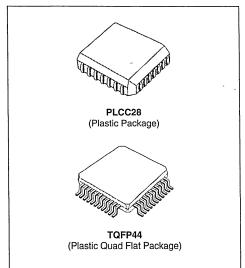

- PLCC44 OR TQFP44 (1.4mm body thickness)

#### DESCRIPTION

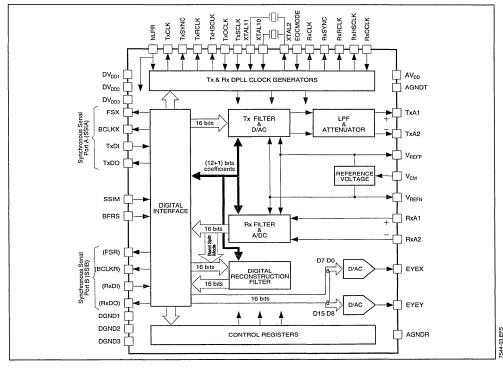

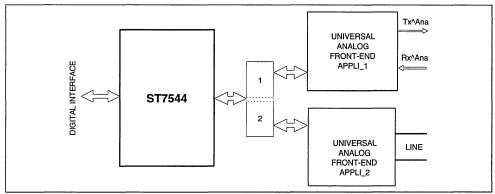

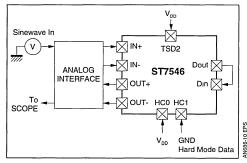

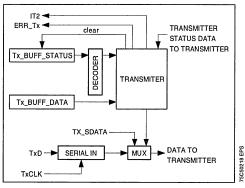

The ST7544 is a single chip Analog Front-End (AFE) designed to implement high speed voice-grade Modems up to 28800 bps with echo cancelling capability.

Associated with one or several Digital Signal Processors (DSP), such as the ST189XX family, it provides a powerful solution for the implementation of multi-mode Modems meeting CCITT (V.21, V.22, V.22 bis, V.23, V.26, V.27, V.29, V.32,V.32 bis and V.33) and BELL (103, 202, 212A...) recommendations. It is fully compatible with the ST7543 in 7543 mode and is also well suited emerging applications involving bit rates up to 28800 bps (in the VFast synchronization mode).

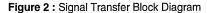

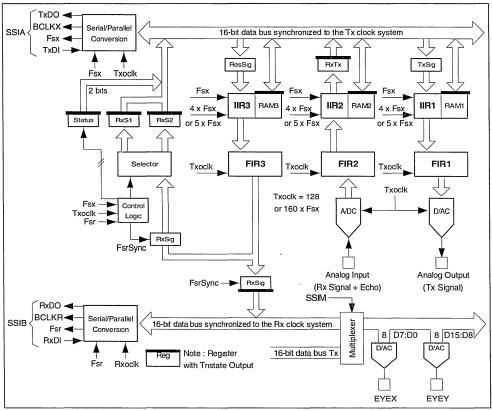

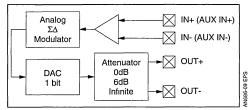

The transmit section includes a 16-bit over-sampling D/A converter with a programmable interpolating filter. The receive section includes a 16-bit oversampling A/D converter with two programmable filters (one for decimation and the other for reconstruction). Oversampling ratio is selectable to either 128 or 160. Two additional 8-bit D/A converters allow eyediagram monitoring on a scope for modem performance adjustment.

Two independant clock generator systems are provided, one synchronized on the Tx rate and the other on the Rx rate.

In External Clock Mode, external oversampling clocks can be provided to the chip.

Two independant synchronous serial interfaces (SSI) allow several versatile ways of communicating with standard DSPs.

To save power, e.g. in lap-top modem applications, the lowpower reset mode can be used to reduce the power consumption to less than 5mW.

#### TABLE OF CONTENTS

#### Document page

| I                                                                                         | PIN DESCRIPTION                                                                                                          | 5                                |

|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 1.1                                                                                       | PIN CONNECTIONS (Top View)                                                                                               | 5                                |

| 1.2                                                                                       | PIN LIST                                                                                                                 | 6                                |

| 1.3                                                                                       | PIN FUNCTION                                                                                                             | 7                                |

| II                                                                                        | BLOCK DIAGRAM                                                                                                            | 9                                |

| III                                                                                       | FUNCTIONAL DESCRIPTION                                                                                                   | 10                               |

| III.1                                                                                     | SIGNAL TRANSFER BLOCK DIAGRAM                                                                                            | 10                               |

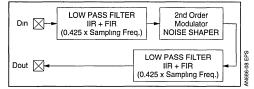

| III.2                                                                                     | TRANSMIT D/A SECTION                                                                                                     | 11                               |

| .2.1<br>   .2.1.1<br>   .2.1.2<br>   .2.2                                                 | Interpolation Filters<br>Programmable Interpolation Filter (IIR1)<br>FIR Filter (FIR1)<br>D/A Converter.                 | 11<br>11<br>11<br>11             |

| 111.3.                                                                                    | Receive A/D Section                                                                                                      | 11                               |

| .3.1<br>   .3.2<br>   .3.2.1<br>   .3.2.2<br>   .3.3                                      | A/D Converter<br>Decimation Filters<br>FIR Filter (FIR2)<br>Programmable Decimation Filter (IIR2)<br>Eye-diagram Display | 11<br>11<br>11<br>12<br>12       |

| 111.4                                                                                     | RECEIVE RECONSTRUCTION SECTION                                                                                           | 12                               |

| III.4.1<br>III.4.2                                                                        | Programmable Interpolation Filter (IIR3)                                                                                 | 12<br>12                         |

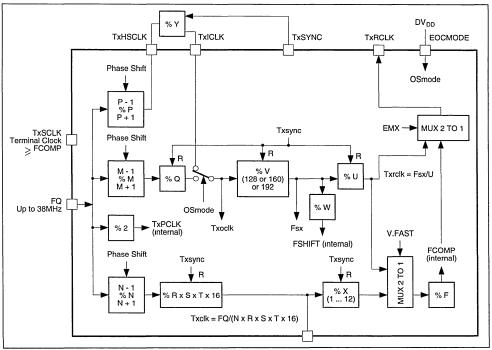

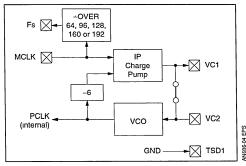

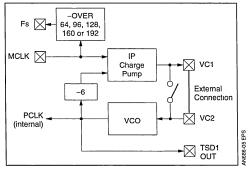

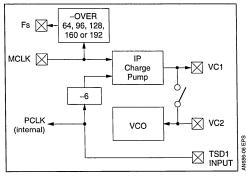

| III.5                                                                                     | CLOCK GENERATION.                                                                                                        | 13                               |

| .5.1<br>   .5.2<br>   .5.2.1<br>   .5.2.2<br>   .5.3<br>   .5.4<br>   .5.4.1<br>   .5.4.2 | Transmit DPLL                                                                                                            | 14<br>14<br>14<br>15<br>15<br>15 |

| III.6                                                                                     | SERIAL INPUT/OUTPUT SYNCHRONOUS INTERFACES                                                                               | 15                               |

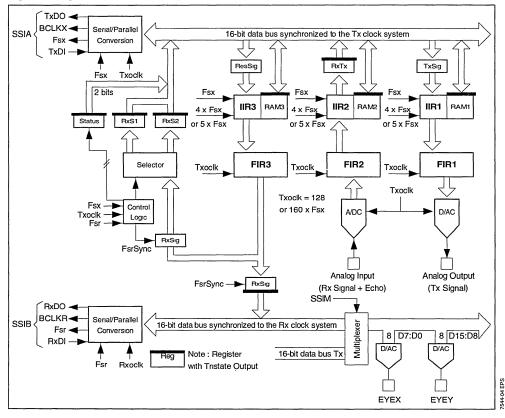

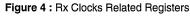

| III.6.1<br>III.6.2                                                                        | Tx Clock Related Registers<br>Rx Clock Related Registers                                                                 | 16<br>16                         |

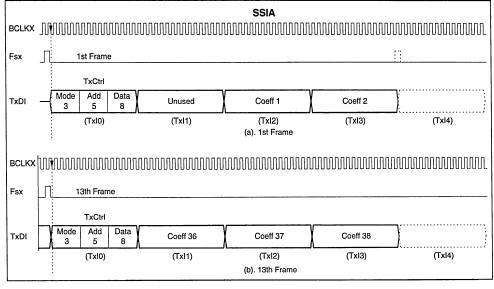

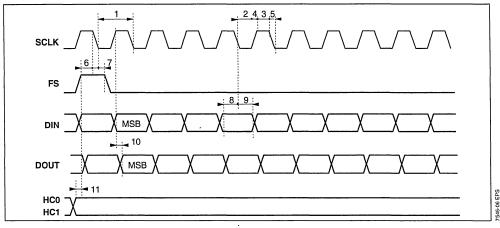

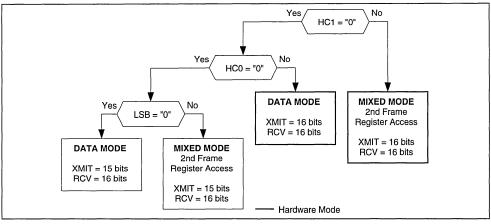

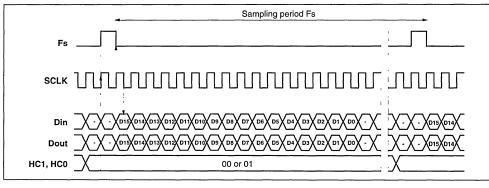

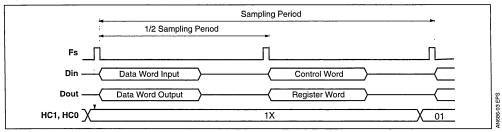

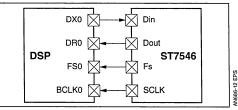

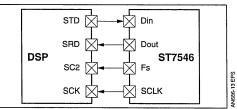

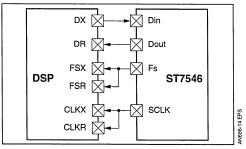

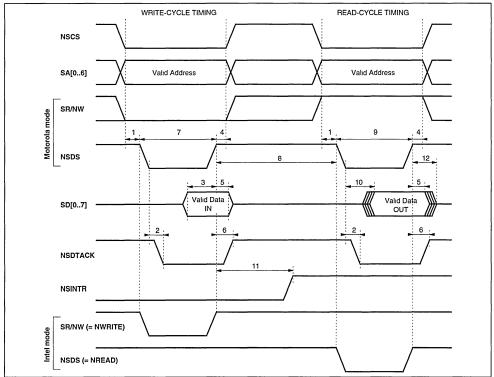

| IV                                                                                        | SERIAL INTERFACE OPERATION                                                                                               | 17                               |

| IV.1<br>IV.2<br>IV.3<br>IV.4                                                              | DUAL SERIAL INTERFACE MODE (SSIA, SSIB)                                                                                  | 17<br>18<br>19<br>20             |

| IV.4<br>IV.5<br>IV.6                                                                      | COEFFICIENT READING<br>CRYSTAL SELECTION (XTAL10, XTAL11)<br>FRAME FREQUENCY PROGRAMMING                                 | 20<br>20<br>20                   |

| IV.7                                                                                      | INITIALIZATION and LOW-POWER RESET MODE                                                                                  | 20                               |

#### TABLE OF CONTENTS (continued)

#### **Document page**

| CIRCUIT PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE FIELD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ADDRESS FIELD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RAM Address Field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 22<br>22<br>23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CONTROL REGISTER DATA FIELD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Transmit Control Register Programming<br>Receive Control Register Programming<br>Control Bit Function Summary<br>TxCTRL Word<br>RxCTRL Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23<br>23<br>24<br>24<br>24<br>24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PROGRAMMABLE FUNCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TRANSMIT SECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Transmit Bit Rate Clock Frequency Programming with FQ=36.864MHz         Transmit Bit Rate Clock Frequency Programming with FQ=25.8048MHz         Transmit Bit Rate Clock Frequency Programming with FQ=18.432MHz         Transmit Bit Clock Frequency Programming With FQ=36.864MHz         Transmit Sampling Clock Frequency Programming with FQ=36.864MHz         Transmit Sampling Clock Frequency Programming with FQ=25.8048MHz         Transmit Sampling Clock Frequency Programming with FQ=18.432MHz         Transmit Sampling Clock Frequency Programming. Divisor Rank         Transmit Baud Rate Frequency Programming. Divisor Rank         Highest Synchronous Transmit Frequency Programming. Divisor Rank         Band Split Mode         Transmit Synchronization Signal Programming         Clock Mode Programming & R2 Divisor         Transmit Attenuator Programming         Phase Comparator Frequency and Decimation or Interpolation Ratio         Phase Shift Frequency         Transmit Test Programming | 26<br>27<br>27<br>28<br>28<br>29<br>29<br>29<br>29<br>30<br>30<br>30<br>30<br>31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RECEIVE SECTION.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Receive Bit Rate Clock Frequency Programming with FQ=36.864MHz.<br>Receive Bit Rate Clock Frequency Programming with FQ=25.8048MHz.<br>Receive Bit Rate Clock Frequency Programming. Divisor Rank.<br>Receive Sampling Clock Frequency Programming with FQ=36.864MHz.<br>Receive Sampling Clock Frequency Programming with FQ=25.8048MHz.<br>Receive Sampling Clock Frequency Programming with FQ=25.8048MHz.<br>Receive Sampling Clock Frequency Programming with FQ=18.432MHz.<br>Receive Sampling Clock Frequency Programming. Divisor Rank.<br>Receive Sampling Clock Frequency Programming. Divisor Rank.<br>Receive Baud Rate Frequency Programming. Divisor Rank.<br>Highest Synchronous Transmit Bit Frequency Programming. Divisor Rank.<br>Receive Fine Phase Shift Programming.<br>Receive Coarse Phase Shift Programming.<br>Interpolation Ratio.<br>Receive Test Programming & R2 Divisor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 33<br>34<br>34<br>35<br>35<br>36<br>36<br>36<br>36<br>37<br>37<br>38<br>38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MODE FIELD         ADDRESS FIELD         RAM Address Field         Transmit Control Register Address Field         Receive Control Register Address Field         CONTROL REGISTER DATA FIELD         Transmit Control Register Programming         Receive Control Register Programming         Receive Control Register Programming         Control Bit Function Summary         TXCTRL Word         RXCTRL Word         RXCTRL Word         PROGRAMMABLE FUNCTIONS         Transmit Bit Rate Clock Frequency Programming with FQ=36.864MHz         Transmit Bit Rate Clock Frequency Programming with FQ=618.432MHz         Transmit Sampling Clock Frequency Programming with FQ=36.864MHz         Transmit Baud Rate Frequency Programming Divisor Rank.         Transmit Baud Rate Frequency Programming Divisor Rank         Transmit Baud Rate Frequency Programming. Divisor Rank         Band Split Mode |

TABLE OF CONTENTS (continued)

#### **Document page**

|                                          | -                                                                                                                             | -                    |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------|

| VII                                      | ELECTRICAL SPECIFICATIONS                                                                                                     | 39                   |

| VII.1                                    | ABSOLUTE MAXIMUM RATINGS (referenced to GND)                                                                                  | 39                   |

| VII.2                                    | DC CHARACTERISTICS                                                                                                            | 39                   |

| VII.2.1<br>VII.2.2<br>VII.2.3<br>VII.2.4 | Power Supply And Common Mode Voltage<br>Digital Interface<br>Crystal Oscillator Interface (XTAL10,XTAL11)<br>Analog Interface | 39<br>39<br>39<br>40 |

| VII.3                                    | AC ELECTRICAL SPECIFICATIONS.                                                                                                 | 41                   |

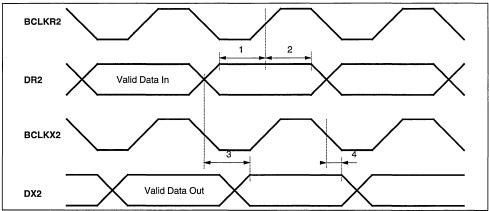

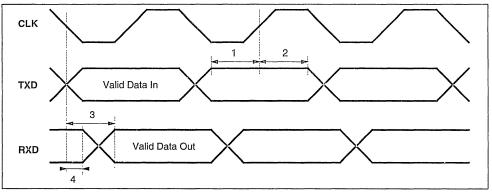

| VII.3.1                                  | Serial Channel Timing                                                                                                         | 41                   |

| VIII                                     | TRANSMIT CHARACTERISTICS                                                                                                      | 42                   |

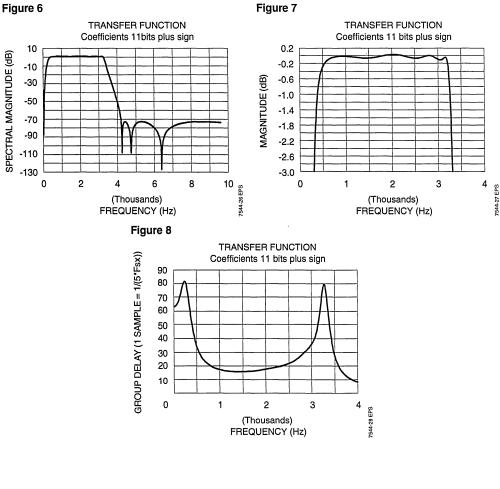

| VIII.1<br>VIII.2<br>VIII.3               | TEST CONDITIONS<br>PERFORMANCE OF THE TX CHAIN<br>SMOOTHING FILTER TRANSFER CHARACTERISTICS                                   | 42<br>42<br>42       |

| IX                                       |                                                                                                                               | 43                   |

| IX.1<br>IX.2                             | TEST CONDITIONS PERFORMANCE OF THE RX CHAIN                                                                                   | 43<br>43             |

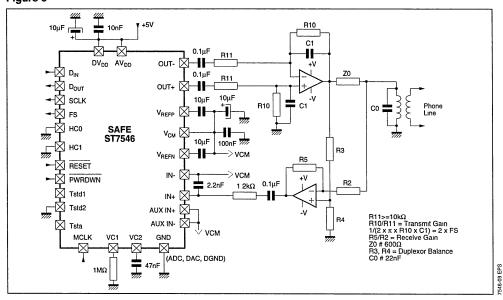

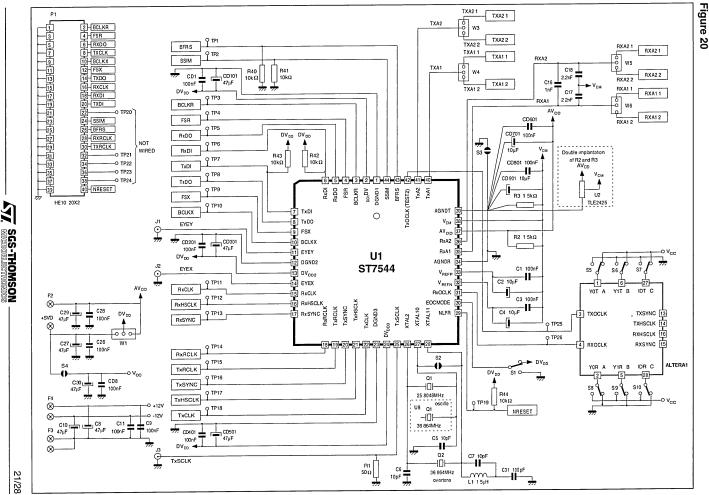

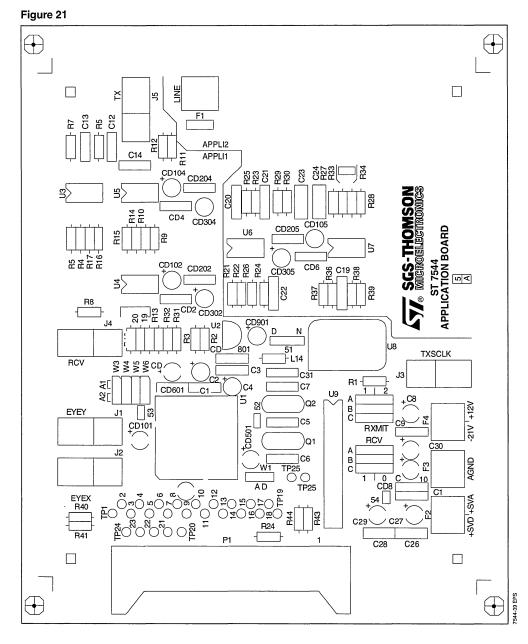

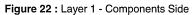

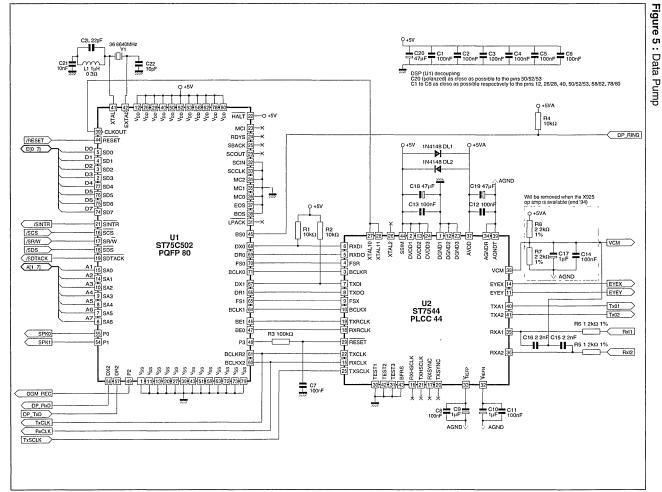

| х                                        | TYPICAL APPLICATIONS.                                                                                                         | 44                   |

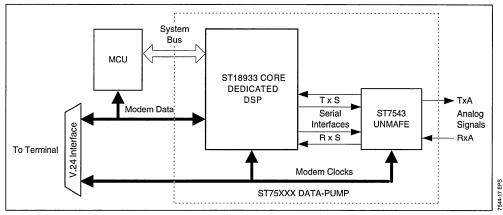

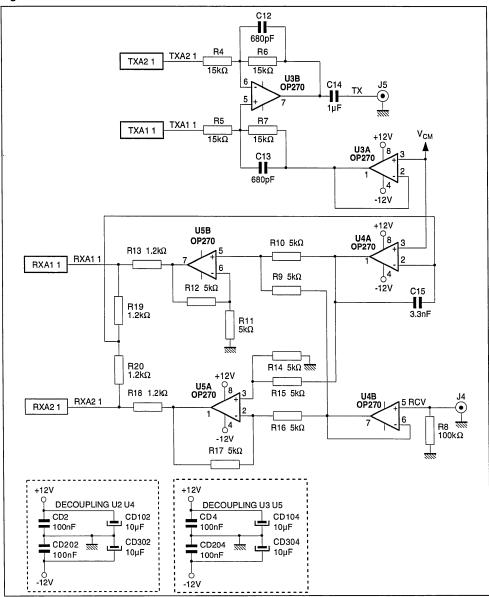

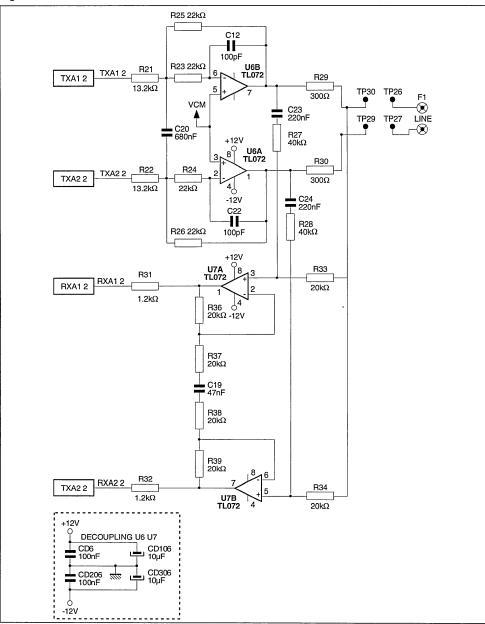

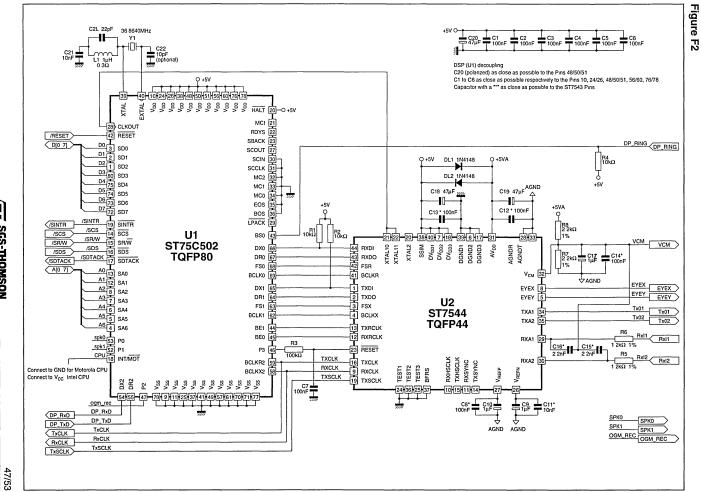

| X.1                                      | MULTI-STANDARD MODEM WITH ECHO CANCELLING                                                                                     | 44                   |

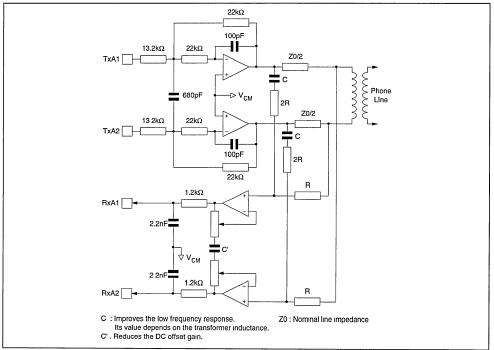

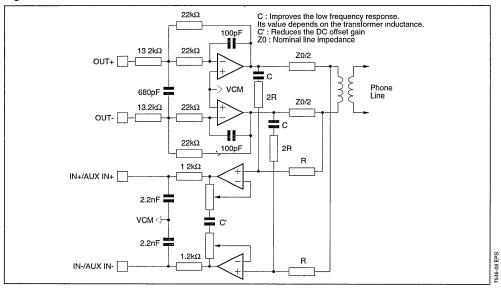

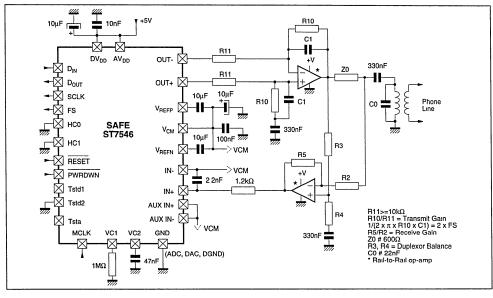

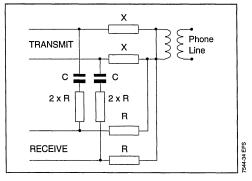

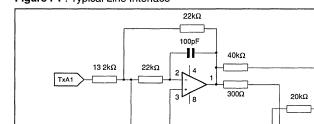

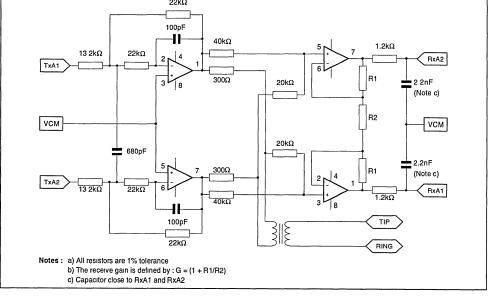

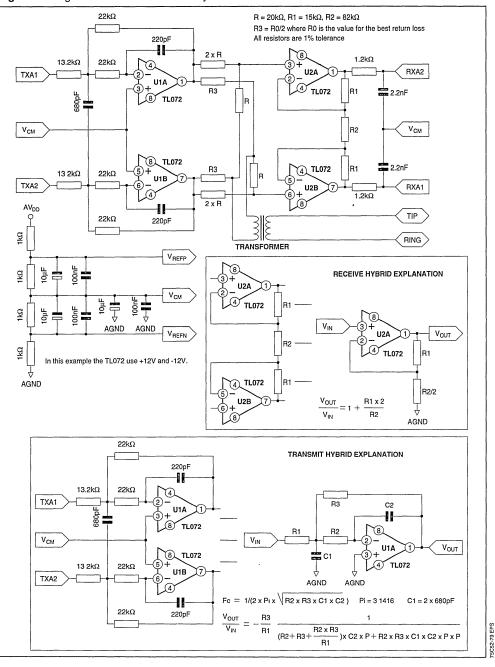

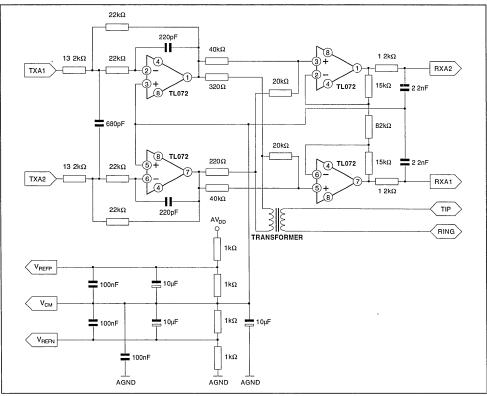

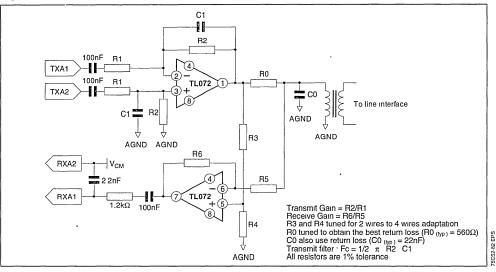

| X.2                                      | LINE INTERFACE                                                                                                                | 44                   |

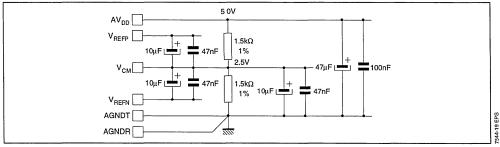

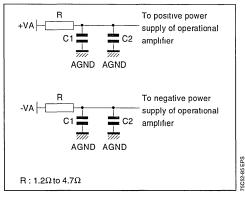

| X.3                                      | COMMON MODE VOLTAGE GENERATION AND DECOUPLING                                                                                 | 45                   |

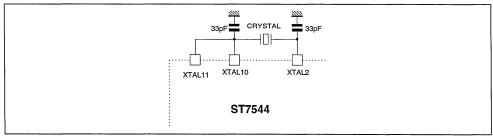

| X.4                                      | CRYSTAL OSCILLATOR                                                                                                            | 45                   |

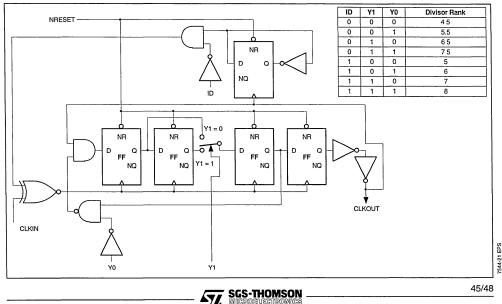

| X.5                                      | EXEMPLE OF PROGRAMMABLE HALF-INTEGER DIVIDER                                                                                  | 45                   |

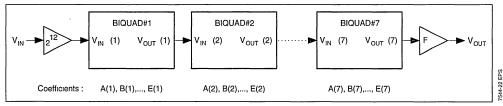

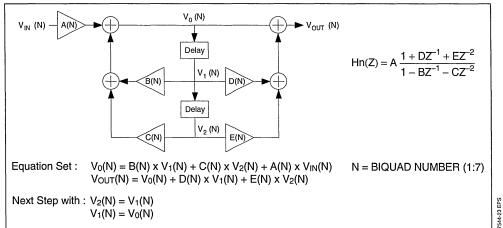

| XI                                       | ANNEXE A                                                                                                                      | 46                   |

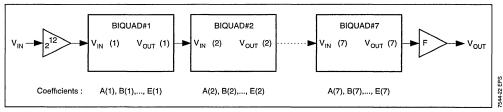

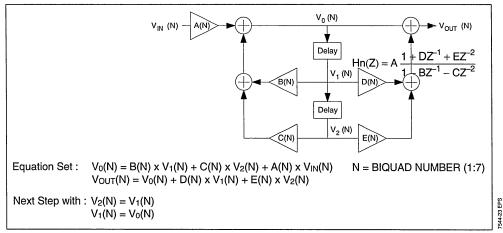

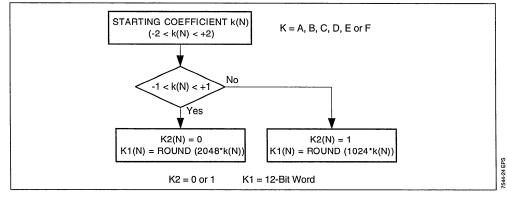

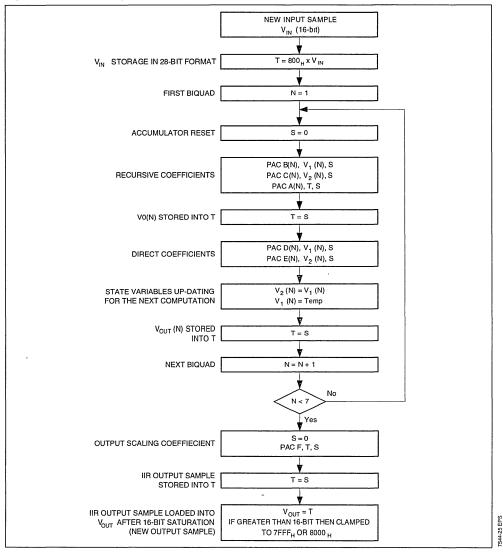

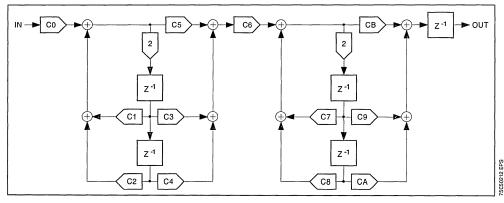

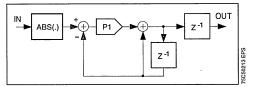

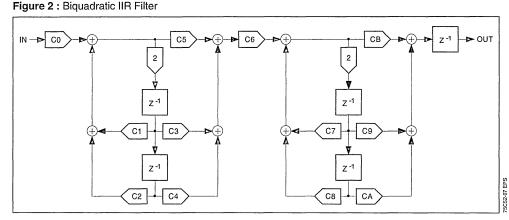

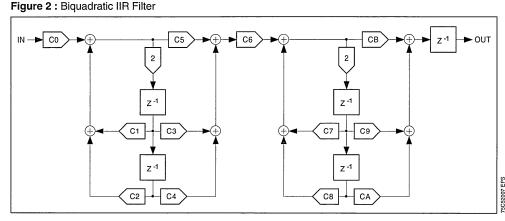

| XI.1                                     | IIR FILTER OPERATION                                                                                                          | 46                   |

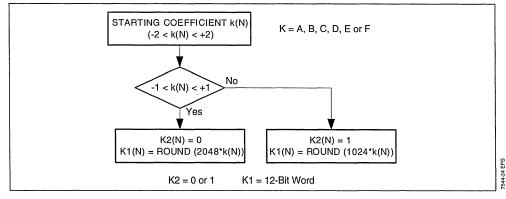

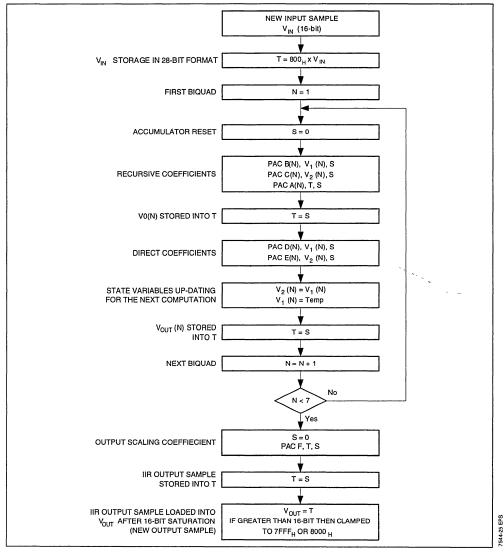

| XI.1.1                                   |                                                                                                                               | 46                   |

| XI.1.2                                   | DETAILED OPERATION                                                                                                            | 46                   |

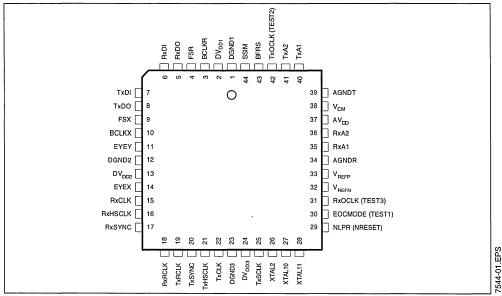

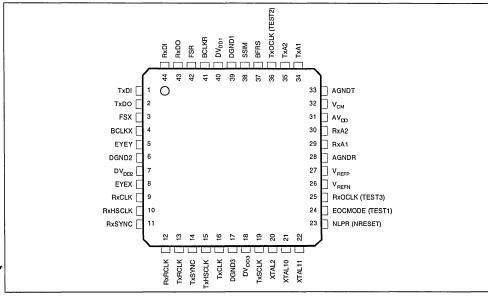

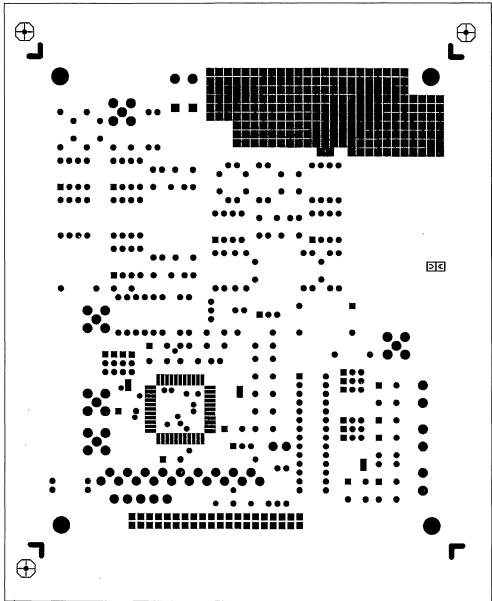

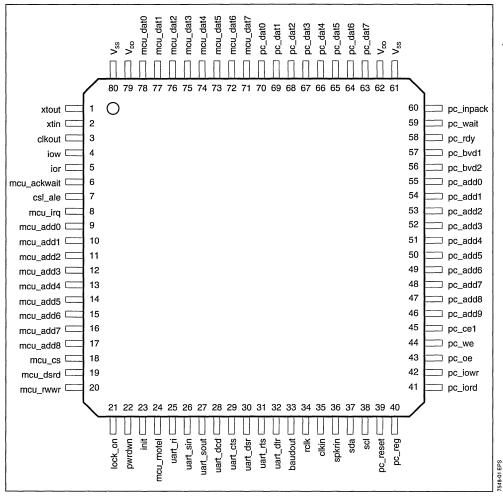

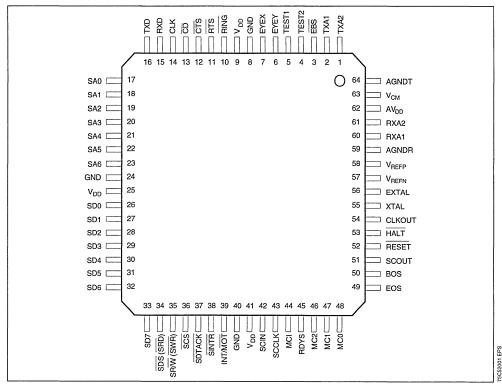

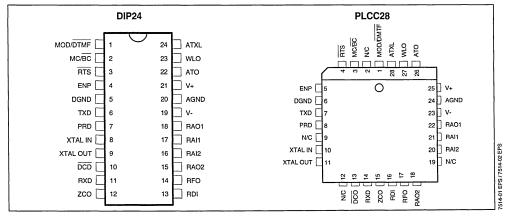

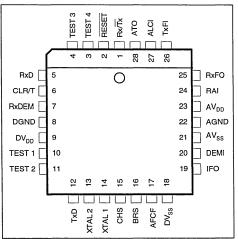

#### I - PIN DESCRIPTION

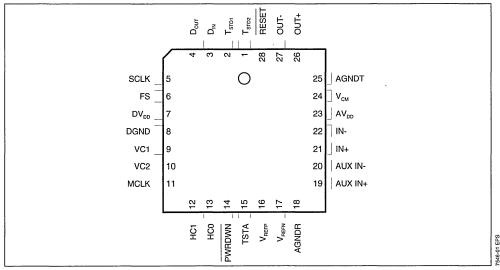

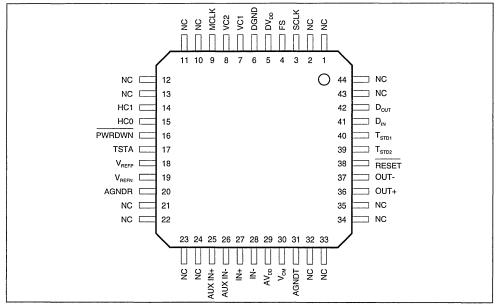

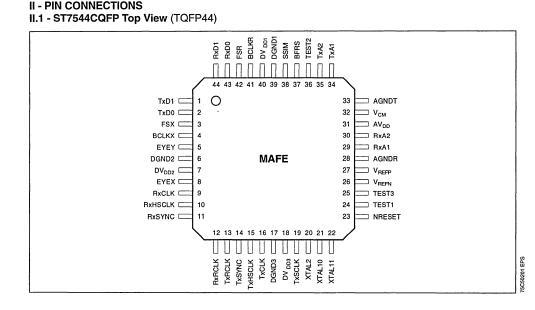

#### I.1 - PIN CONNECTIONS (Top View)

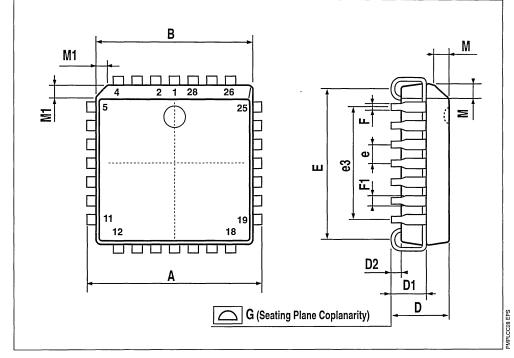

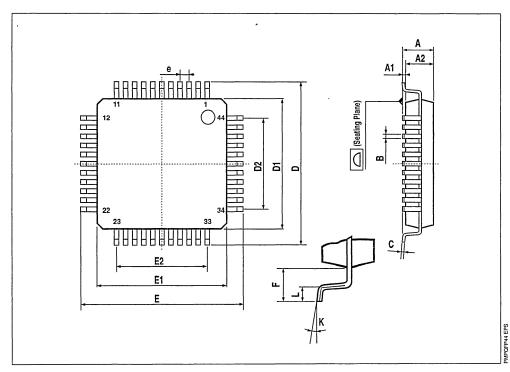

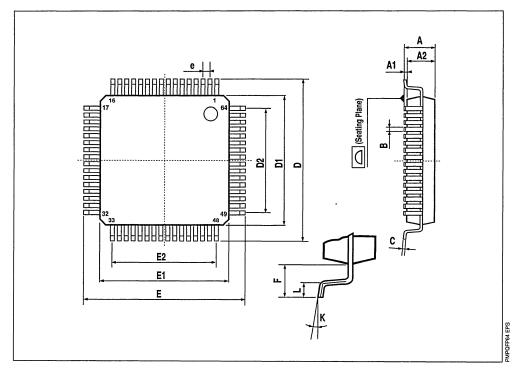

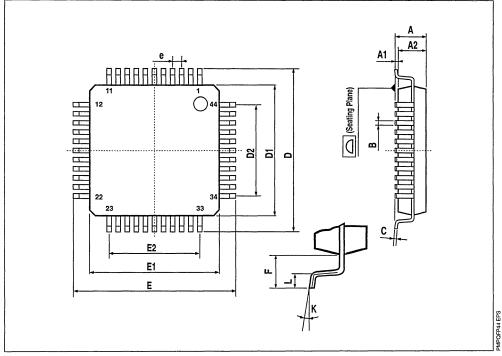

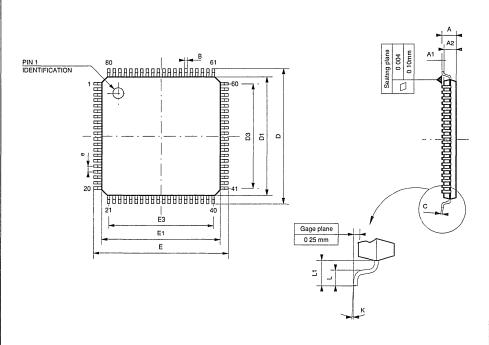

#### PLCC44

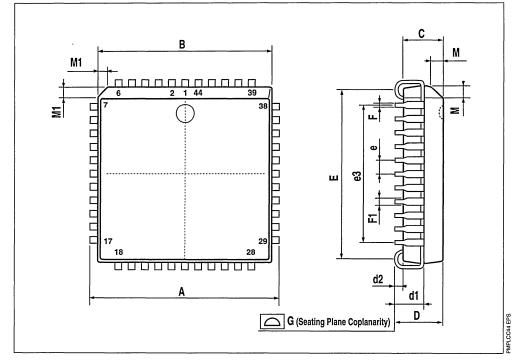

#### TQFP44

SGS-THOMSON

Note : The pin names in the parenthesis are the corresponding for the ST7543.

5/48

7544-01.EPS

#### I.2 - PIN LIST

| PQFP | PLCC | NAME               | DESCRIPTION                                                                                                     |

|------|------|--------------------|-----------------------------------------------------------------------------------------------------------------|

| 39   | 1    | DGND1              | Digital Ground (0V)                                                                                             |

| 40   | 2    | DV <sub>DD1</sub>  | Positive Digital Power Supply. (+5V±5%)                                                                         |

| 41   | 3    | BCLKR              | Receive bit Clock Output                                                                                        |

| 42   | 4    | FSR                | Receive Frame Synchronization Output                                                                            |

| 43   | 5    | RxDO               | Receive Serial Data Output                                                                                      |

| 44   | 6    | RxDI               | Receive Serial Data Input                                                                                       |

| 1    | 7    | TxDI               | Transmit Serial Data Input                                                                                      |

| 2    | 8    | TxDO               | Transmit Serial Data Output                                                                                     |

| 3    | 9    | FSX                | Transmit Frame Synchronization Output                                                                           |

| 4    | 10   | BCLKX              | Transmit Bit Clock Output                                                                                       |

| 5    | 11   | EYEY               | 8 bit YD/AC Output for Eye Pattern display                                                                      |

| 6    | 12   | DGND2              | Digital Ground (0V)                                                                                             |

| 7    | 13   | DV <sub>DD2</sub>  | Positive Digital Power Supply. (+5V±5%)                                                                         |

| 8    | 14   | EYEX               | 8bit XD/AC Output for Eye Pattern display                                                                       |

| 9    | 15   | RxCLK              | Receive Bit Rate Clock Output                                                                                   |

| 10   | 16   | RxHSCLK            | Receive Highest Clock Output                                                                                    |

| 11   | 17   | RxSYNC             | Receive Synchronization Pulse Output                                                                            |

| 12   | 18   | RxRCLK             | Receive Baud Rate Clock Output                                                                                  |

| 13   | 19   | TxRCLK             | Transmit Baud Rate Clock Output                                                                                 |

| 14   | 20   | TxSYNC             | Transmit Synchronous Pulse Output                                                                               |

| 15   | 21   | TxHSCLK            | Transmit Highest Clock Output                                                                                   |

| 16   | 22   | TxCLK              | Transmit Bit Rate Clock Output                                                                                  |

| 17   | 23   | DGND3              | Digital Ground (0V)                                                                                             |

| 18   | 24   | DV <sub>DD3</sub>  | Positive Digital Power Supply. (+5V±5%)                                                                         |

| 19   | 25   | TxSCLK             | Transmit Synchronization Clock Input                                                                            |

| 20   | 26   | XTAL2              | Crystal Output                                                                                                  |

| 21   | 27   | XTAL10             | External Clock/Crystal Input 1                                                                                  |

| 22   | 28   | XTAL11             | External Clock/Crystal Input 2                                                                                  |

| 23   | 29   | NLPR               | Low Power Reset Input                                                                                           |

| 24   | 30   | EOCMODE<br>(TEST1) | External Oversampling Clock Mode Input. Must be tied to DGND in either the ST7544 normal mode or the 7543 mode. |

| 25   | 31   | RxOCLK<br>(TEST3)  | Receive Oversampling Clock Input. Output high-impedance in normal mode.                                         |

| 26   | 32   | VREFN              | 16 bit D/AC and A/DC Negative Reference Voltage                                                                 |

| 27   | 33   | VREFP              | 16 bit D/AC and A/DC Positive Reference Voltage                                                                 |

| 28   | 34   | AGNDR              | Analog Ground (0V)                                                                                              |

| 29   | 35   | RxA1               | Receive Positive Analog Input                                                                                   |

| 30   | 36   | RxA2               | Receive Negative Analog Input                                                                                   |

| 31   | 37   | AV <sub>DD</sub>   | Positive Analog Power Supply (+5V±5%)                                                                           |

| 32   | 38   | V <sub>CM</sub>    | Common Mode Voltage Input (2.5V ±10%)                                                                           |

| 33   | 39   | AGNDT              | Analog ground (0V)                                                                                              |

| 34   | 40   | TxA1               | Smoothing filter positive Output                                                                                |

| 35   | 41   | TxA2               | Smoothing filter negative Output                                                                                |

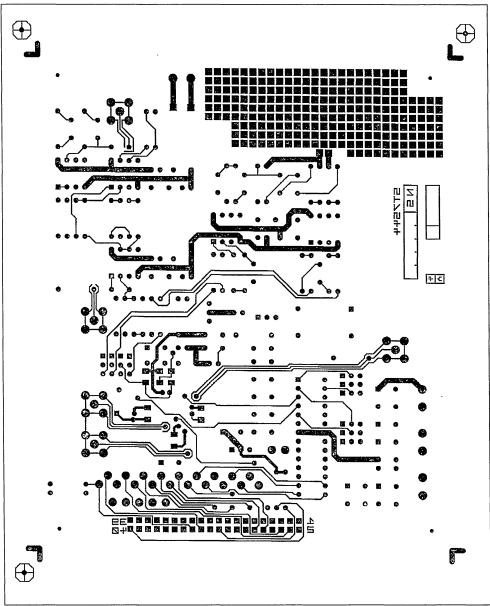

| 36   | 42   | TxOCLK<br>(TEST2)  | Transmit Oversampling Clock Input. Output high-impedance in normal mode.                                        |

| 37   | 43   | BFRS               | Bit Frame Rate Select Input                                                                                     |

| 38   | 44   | SSIM               | Serial Synchronous Interface Mode Input                                                                         |

Note : The pin names in brackets are the corresponding names for the ST7543.

#### **I.3 - PIN FUNCTION**

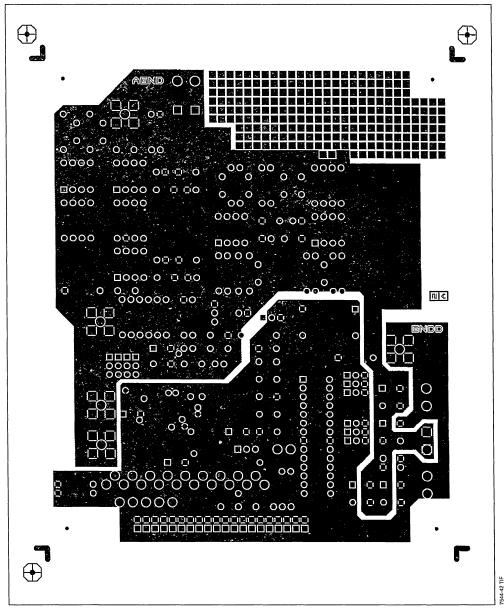

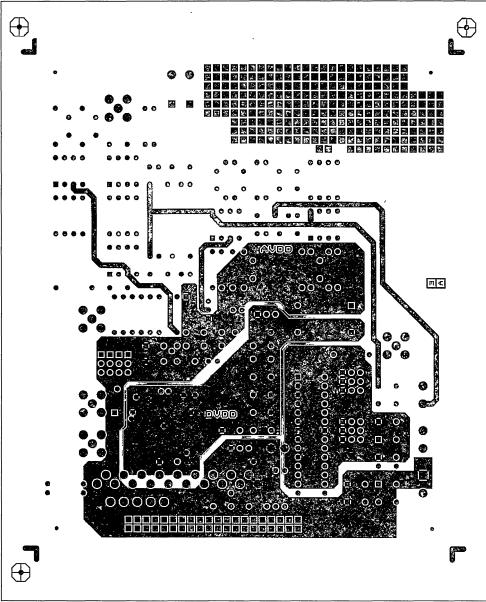

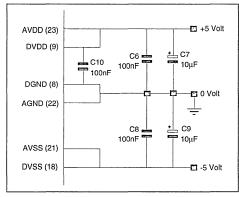

I.3.1 - Power Supply (9 Pins)

#### Analog VDD Supply (AVDD)

This pin is the positive analog power supply ( $+5V\pm5\%$ ) for the Transmit and the Receive sections. It is not internally connected to digital V<sub>DD</sub> supply (DV<sub>DD1-3</sub>).

#### Digital VDD Supply (DVDD1, DVDD2, DVDD3)

These pins are the positive digital power supply (+5V±5%) for Transmit and Receive digital internal circuitry.

#### Analog Ground (AGNDT, AGNDR)

These pins are the analog ground return of the analog Transmit (Receive) section.

**Digital Ground** (DGND1,DGND2,DGND3) These pins are the ground connections for Transmit and Receive internal digital circuitry.

- Note 1: To obtain published performance, the analog  $V_{DD}$  and Digital  $V_{DD}$  should be decoupled with respect to AGND and DGND, respectively. The decoupling is intended to isolate digital noise from the analog section; decoupling capacitors should be as close as possible to the respective analog and digital supply pins.

- Note 2: All the ground pins must be tied together. In the following section, the ground and supply pins are refered to as GND and V<sub>DD</sub>, respectively.

#### I.3.2 - Clock and Control Signals (16 Pins)

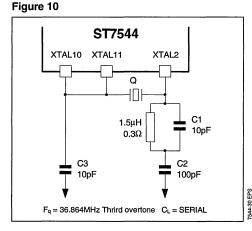

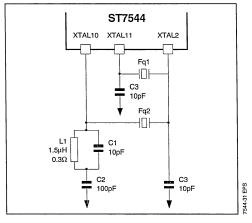

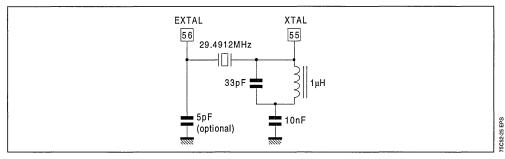

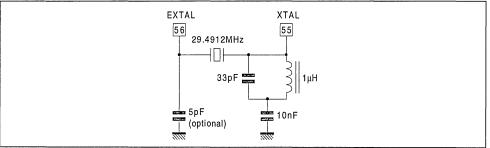

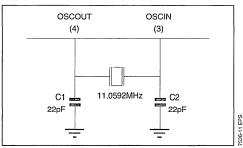

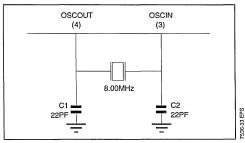

External Clock/Crystal Inputs (XTAL10,XTAL11) XTAL10 and XTAL11 inputs must be tied to external crystal(s) or external clock(s). These inputs are selected from the TxCtrl register. The maximum clock rate is 38MHz. XTAL10 is the default External Clock/Crystal input. It is mandatory to shortcircuit XTAL10 and XTAL11 when a single external crystal or clock generator is used. The nominal master clock frequency is 36.864MHz (this frequency and the frequency 25.8048MHz are well suited for the V.Fast application) but the onchip amplifier is designed for a parrallel crystal oscillator with a frequency equal to 18.432MHz. The other master clocks frequencies (18.432MHz, 25.8048MHz and 29.4912MHz) are well suited for the well known CCITT recommendations (V.21 through V.32bis).

#### Crystal Outputs (XTAL2)

This output is to be tied to one or two external crystals (see Figure 1). If an external clock is used, XTAL2 should be left open circuit.

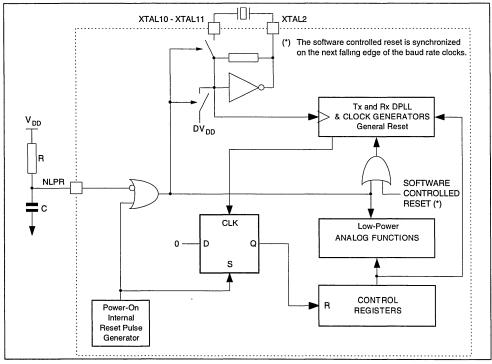

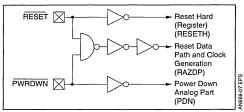

#### Low power and Reset Input (NLPR)

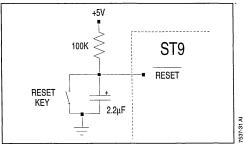

This pin, when low, synchronizes the ST7544 clock system and puts it in low power mode. NLPR pin must be tied to V<sub>DD</sub> during normal operation. Access to the chip is disabled during power-on reset

until the clock oscillator starts. The reset time duration can be increased by connecting the NLPR input to an external RC network (see Figure 9). The Low-Power Reset Mode is actived when this pin is tied to GND (Operation of all clocks and the analog section is stopped).

#### Transmit Synchronization Clock Input (TxSCLK)

This pin can be connected to an external terminal clock to phase-lock to the internal transmit clocks. It can be disabled under software control to allow the Tx DPLL to free run or phase lock to on the Rx clock system.

#### Transmit Bit Rate Clock Output (TxCLK)

This pin outputs the synchronous transmit bit clock selected for the MODEM.

#### Transmit Baud Rate Clock Output (TxRCLK)

This pin, when the bit D4 within receive register RxCR3 is set to 0, outputs the synchronous transmit baud rate clock (initial state). When bit D4 is set to 1 this pin outputs the frequency comparison signal FCOMP (used by the TxDPLL in both 7543 mode and V.Fast synchronization).

## Transmit Synchronization Pulse Output (TxSYNC)

This pin outputs the synchronization transmit reset pulse when a soft reset is applied to the ST7544. Combined with TxHSCLK clock it can be used to externally provide any synchronous transmit clock.

Transmit Highest Clock Output (TxHSCLK) This pin outputs the highest synchronous transmit clock to provide any external or multiplexing clock.

**Transmit Oversampling Clock input** (TxOCLK) This input can be connected to an external clock to provide the chip with the over-sampling clock, depending on the External Over sampling Mode input (EOCMODE). In normal mode this pin should be static (tied to GND or V<sub>DD</sub>).

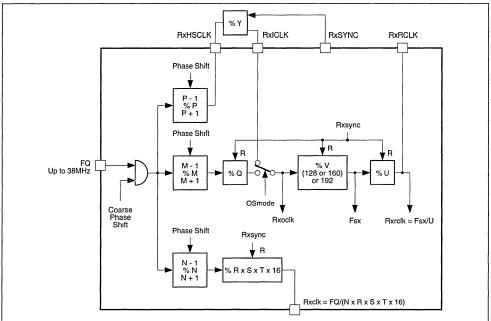

Receive Bit Rate Clock Output (RxCLK)

This pin outputs the synchronous receive bit clock selected for the MODEM.

**Receive Baud Rate Clock Output** (RxRCLK) This pin outputs the synchronous Receive baud rate clock.

Receive Synchronization Pulse Output (RxSYNC) This pin outputs the synchronization receive reset pulse when a soft reset is applied to the ST7544. Combined with RxHSCLK clock it can be used to externally provide any synchronous receive clock.

#### **Receive Highest Clock Output** (RxHSCLK) This pin outputs the highest synchronous receive clock to give any external or multiplexing clock.

#### Receive Oversampling Clock input (RxOCLK)

This input can be connected to an external clock to provide the chip with the oversampling clock, depending on the External Over sampling Mode input (EOCMODE). In normal mode this pin should be static (tied to GND or V<sub>DD</sub>).

## External Oversampling Clock Mode (EOCMODE)

This pin is used for selecting one of the two possible oversampling modes. When EOCMODE is tied to GND, all the clock are provide internally (mode compatible with the ST7543). When EOCMODE is tied to V<sub>DD</sub>, the oversampling clocks must be input on TxOCLK and RxOCLK pins. The TxHSCLK (RxHCLK) and TxSync (RxSync) signals along with external fractional divider can be used to provide the oversampling clocks to the ST7544.

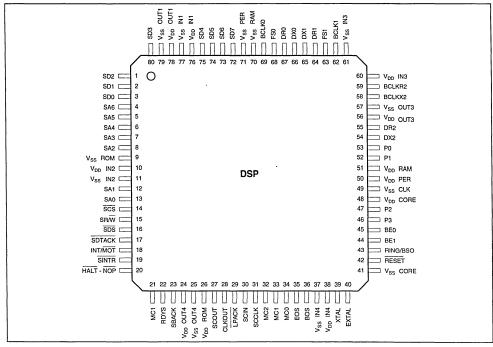

#### I.3.3 - Synchronous Serial Interfaces (SSIA,SSIB) (10 pins)

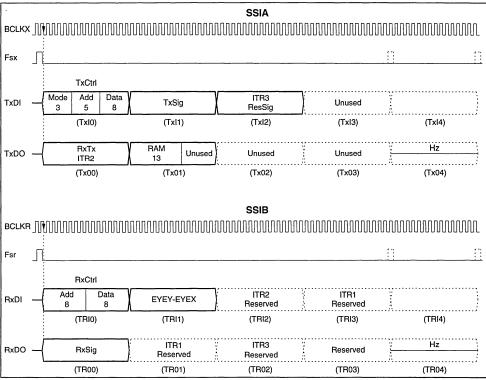

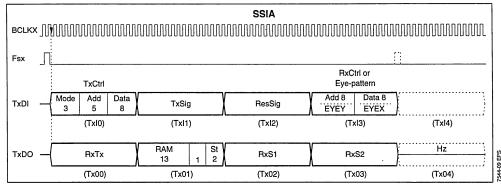

#### Serial Synchronous Interface Mode input (SSIM)

This input activates one or both serial interfaces. When SSIM is tied to  $V_{DD}$ , both A and B ports are functional : port A (SSIA) is dedicated to the Transmit channel and port B (SSIB) is dedicated to the Receive channel.

When SSIM is tied to GND only port A (SSIA) is selected. In this case SSIA carries both Tx and Rx Signals and EYE pattern.

#### Bit Frame Rate Select input (BFRS)

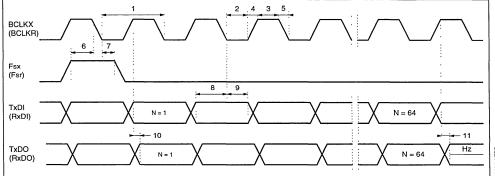

This input selects one of the two possible bit frequencies for the BCLKX and BCLKR clocks. When BFRS is tied to  $V_{DD}$  the BCLKX (BCLKR) frequencies are 128 (160 (1)) times the FSX (FSR) frequencies. When BFRS is tied to GND, BCLKX (BCLKR) frequencies are 64 (80 (1)) times the FSX (FSR) frequencies.

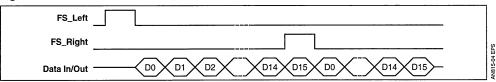

#### Frame Synchronization Transmit output (FSX)

This output clock is the Transmit Frame synchronization pulse signal of the SSIA port which has nominal frequency equal to the transmit sampling frequency. This pulse indicates the beginning of the 16-bit serial words on the serial data input/output port A.

#### Bit Clock Transmit output (BCLKX)

This output pin provides the serial bit clock for the SSI port A. The BCLKX frequency equals 128 (160 (1)) or 64 (80 (1)) times the Transmit sampling frequency, depending on the Bit Frame Select Input (BFRS).

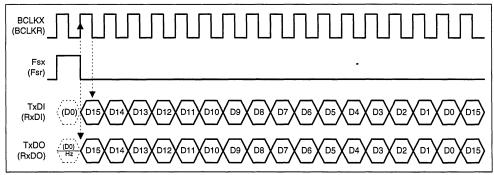

#### Serial Data Transmit input (TxDI)

This input receives word-oriented serial data. Data is loaded from TxDI into the Transmit Shift Register

(TSRIN) on the falling edge of BCLKX and transfered to the Transmit Buffer Register (TBRIN) when a complete 16 bit word has been received. Data is assumed to be received MSB first.

#### Serial Data Transmit output (TxDO)

This output sends word-oriented serial data. The 16 bit Data Word loaded in the Transmit Buffer Register (TBROUT) is transfered to the Transmit Shift Register (TSROUT) and clocked out of TSROUT on the rising edge of BCLKX. Serial words are transmitted MSB first.

#### Receive Frame Synchronization output (FSR)

This output clock is the Receive Frame synchronization pulse signal of SSI port B which has frequency equal to the receive sampling frequency. This pulse is used to indicate the beginning of serial words on the serial data input/output port B.

#### Receive Bit Clock output (BCLKR)

This output pin provides the serial bit clock for the SSI port B. The BCLKR frequency is 128 (160 (1)) times or 64 (80 (1)) times, selected by BFRS ) the receive sampling frequency.

#### Receive Serial Data input (RxDI)

This input receives word-oriented serial data. Data is clocked from RxDI into the Receive Shift Register (RSRIN) on the falling edge of BCLKR and transfered to the Receive Buffer Register (RBRIN) when a complete 16-bit word has been received. Data is assumed to be received MSB first.

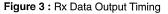

#### Receive Serial Data output (RxDO)

This output sends word-oriented serial data. The 16-bit Data Word loaded in the Receive Buffer Register (RBROUT) is transfered to the Receive Shift Register (RSROUT) and clocked out of RSROUT on the rising edge of BCLKR. Serial words are transmitted MSB first.

Note 1: The oversampling ratio is selectable using the V divider (Table 40)

#### I.3.4 - Analog Interface (9 pins)

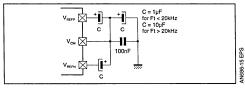

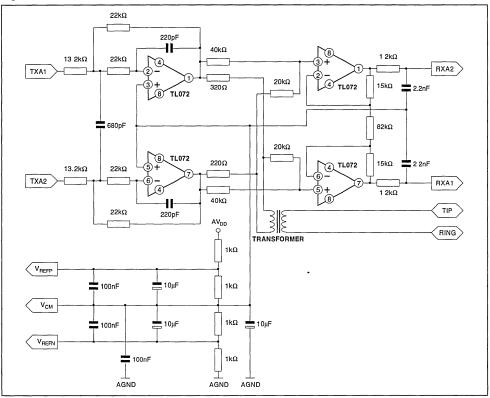

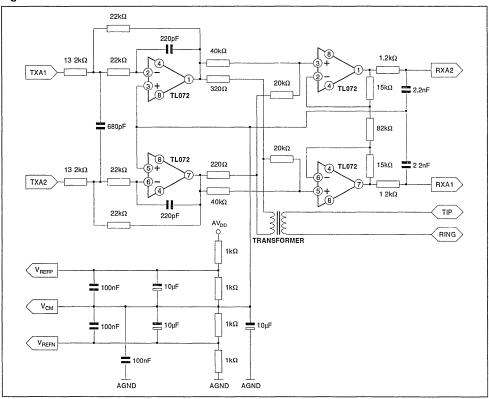

## D/AC and A/DC Positive Reference Voltage output (VREFP)

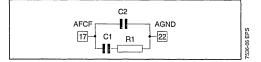

This pin provides the Positive Reference Voltage used by the 16-bit converters. The reference voltage,  $V_{REF}$ , is the voltage difference between the  $V_{REFP}$  and  $V_{REFN}$  outputs, and its nominal value is 2.5V.  $V_{REFP}$  should be externally decoupled with respect to  $V_{CM}$  (see Figure 17).

## D/AC and A/DC Negative Reference Voltage $(V_{\mathsf{REFN}})$

This pin provides the Negative Reference Voltage used by the 16 bit converters, and should be externally decoupled with respect to  $V_{CM}$ .

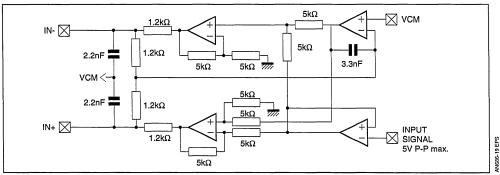

#### Common Mode Voltage input (V<sub>CM</sub>)

This input pin is the common mode Voltage (AV<sub>DD</sub>-AGND)/2 that should be externally provided. This input must be decoupled with respect to GND.

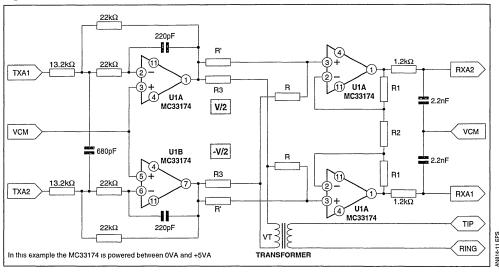

#### Smoothing filter positive Output (TxA1)

This pin is the positive output of the fully differential analog smoothing filter.

#### Smoothing filter negative Output (TxA2)

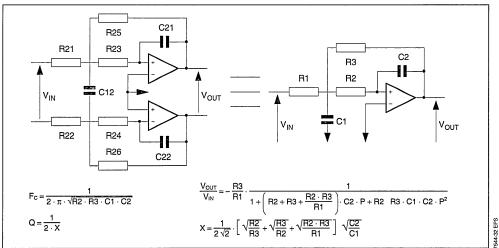

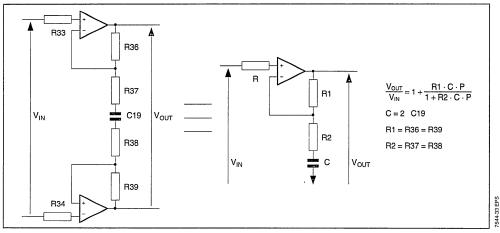

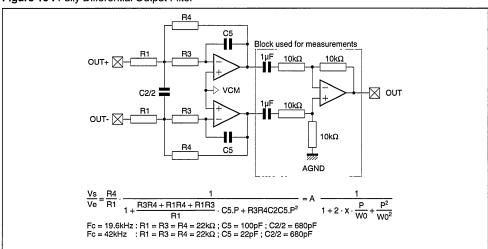

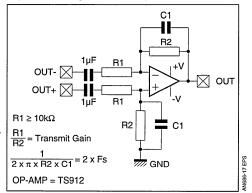

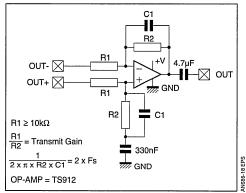

This pin is the negative output of the fully differential analog smoothing filter. Outputs TxA1 and TxA2 provide analog signals with maximum peak to peak amplitude 2 x V<sub>REF</sub>, and must be followed by an external continuous time two pole smoothing filter (see Figure 16) (1). The external filter follows the internal single pole switch capacitor filter (see section V.2.2). The cutoff frequency of the external filter must be greater than two times the transmit sampling frequency (Fsx), so that the combined frequency response of both the internal and external filters is flat in the pass band.

#### Receive Positive Analog Input (RxA1)

This pin is the differential positive A/DC Input.

#### Receive Negative Analog Input (RxA2)

This pin is the differential negative A/DC Input. These analog inputs (RxA1,RxA2) are presented to the SigmaDelta modulator, the analog input peak to peak signal range must be less than 2 x V<sub>REF</sub>, and must be preceded by an external continuoustime single pole anti-aliasing filter (see Figure 16). The cut-off frequency of the filter must be lower than one half the transmit over-sampling frequency (TxOSCK). These filters should be set as close as possible to the RxA1 (RxA2) pins.

#### D/AC output for Eye Pattern (EYEX, EYEY)

These pins are the outputs of two 8-bit digital to analog converters used to monitor, on a CRT, the X and Y quadrature signals of the eye pattern of the demodulated signal.

Note 1 : The smoothing filter order depends of the acceptable transmit signal spectrum on the line

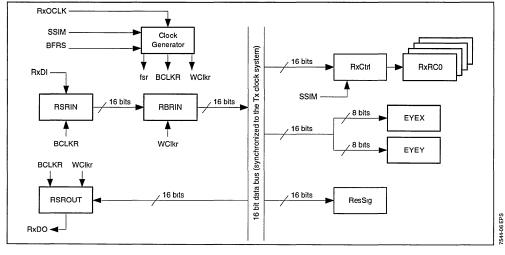

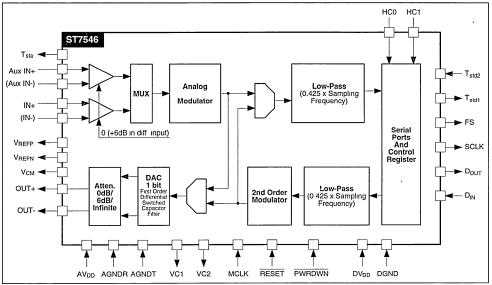

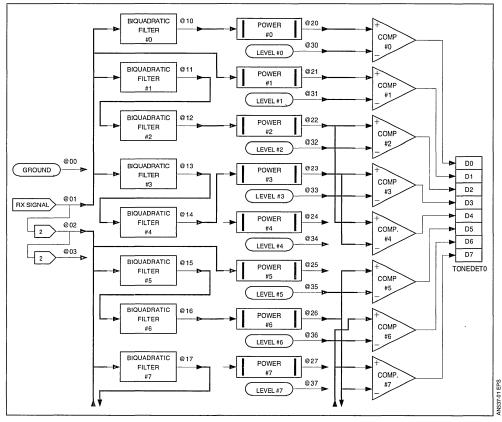

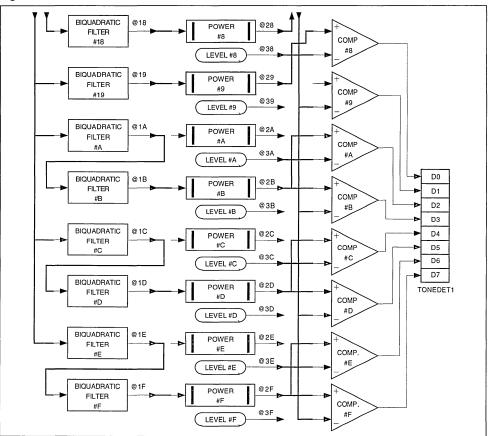

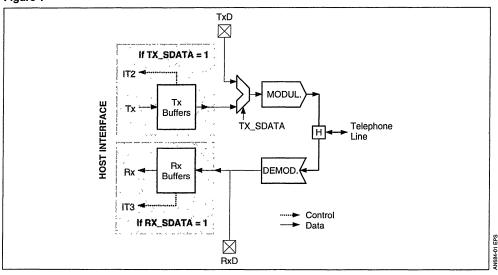

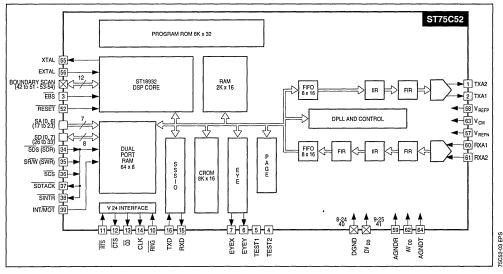

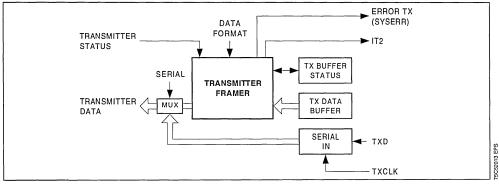

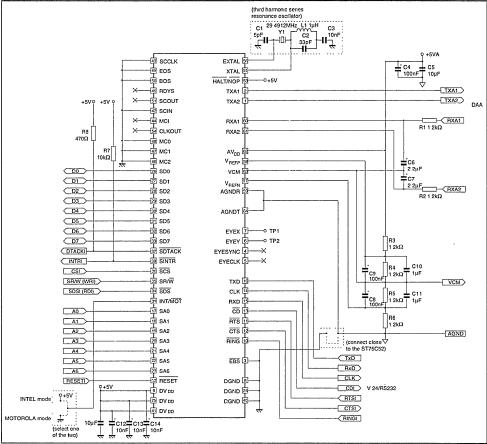

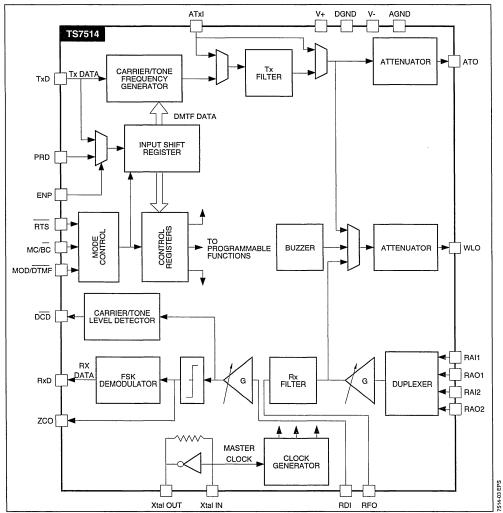

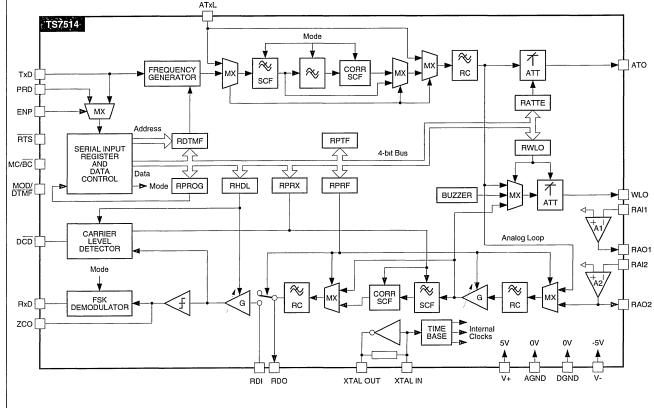

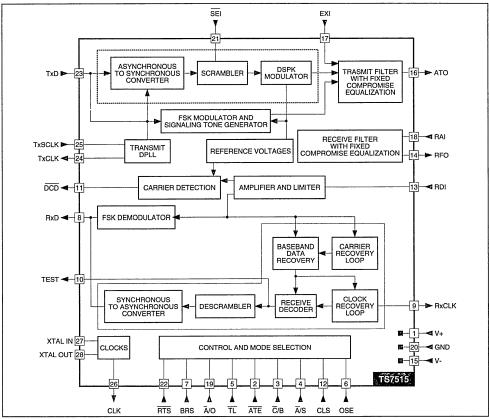

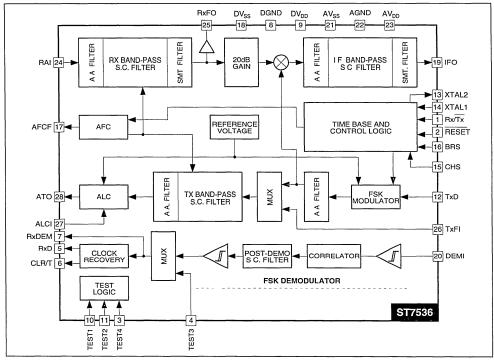

#### **II - BLOCK DIAGRAM**

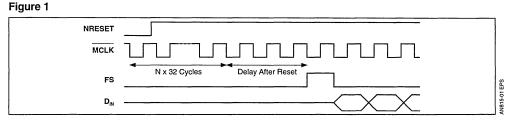

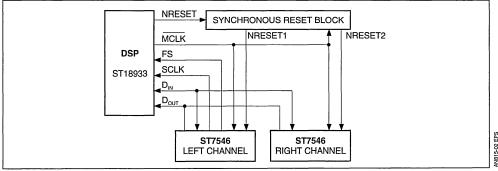

Figure 1 : General Block Diagram

#### **III - FUNCTIONAL DESCRIPTION**

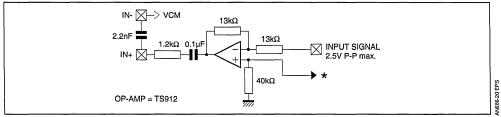

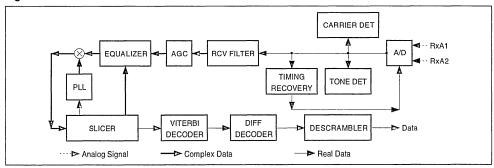

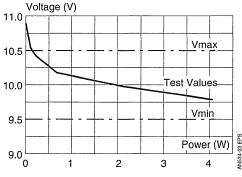

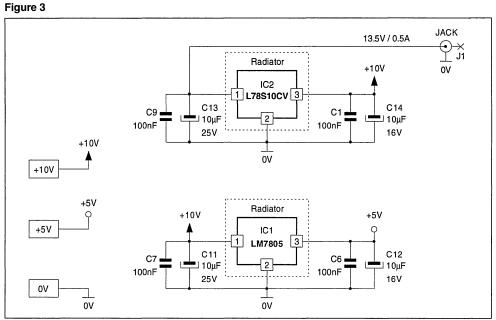

#### III.1 - SIGNAL TRANSFER BLOCK DIAGRAM