# EEPROM MEMORY PRODUCTS

DATABOOK

1<sup>st</sup> EDITION

**RYSTON Electronics**

000488

**EEPROM MEMORY**

PRODUC

## EEPROM MEMORY PRODUCTS

DATABOOK

1<sup>st</sup> EDITION

**JUNE 1995**

#### USE IN LIFE SUPPORT DEVICES OR SYSTEMS MUST BE EXPRESSLY AUTHORIZED

SGS-THOMSON PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF SGS-THOMSON Microelectronics. As used herein:

- Life support devices or systems are those which (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided with the product, can be reasonably expected to result in significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can reasonably be expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

| TABLE OF CONTENTS            |        |

|------------------------------|--------|

| INTRODUCTION                 | Page 5 |

| GENERAL INDEX                | 7      |

| I <sup>2</sup> C BUS EEPROM  | 9      |

| XI <sup>2</sup> C BUS EEPROM | 93     |

| MICROWIRE BUS EEPROM         | 159    |

| SPI BUS EEPROM               | 259    |

| PARALLEL EEPROM              | 417    |

| DEDICATED EEPROM             | 547    |

SGS-THOMSON Microelectronics is a broad range semiconductor company. The product range includes memory products which satisfy the needs of a wide range of applications. They include:

- Non-Volatile Memories: OTP Memories, UV EPROMs, FLASH Memories, Serial and Parallel EEPROMs and NVRAMs (battery backed SRAMs)

- Synchronous and Asynchronous Fast SRAMs

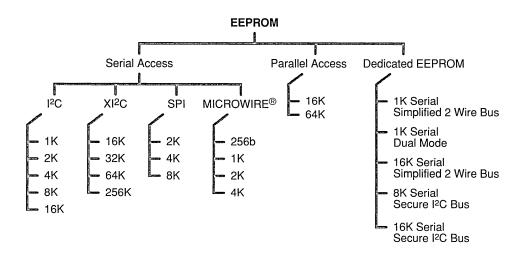

This databook provides comprehensive technical information on the Serial and Parallel Access EEPROM products.

#### EEPROMs (Electrically Eraseable Programable Memories).

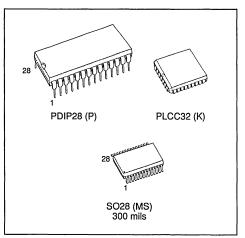

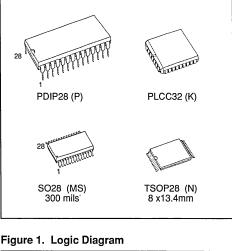

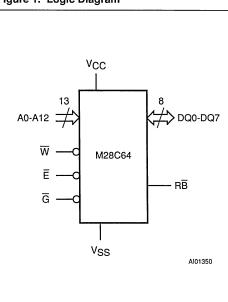

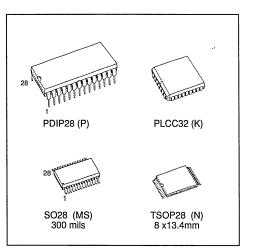

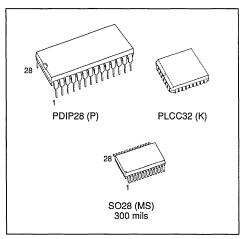

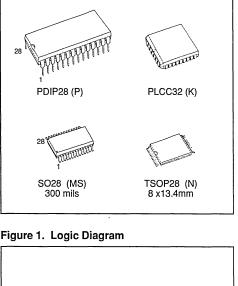

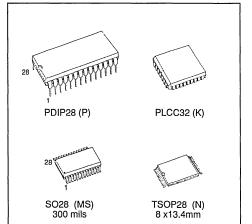

The EEPROM may be erased and programmed byte-by-byte, giving it an added flexibility compared to FLASH Memory which must be erased in bulk or sector conditions. Two distinct families of EEPROM are Serial or Parallel Access types. The Serial Access EEPROMs feature low pin counts (typically they are packaged in 8 pin packages) and a lower range of densities from 256 bit up to 64K bit. The Parallel Access EEPROMs, needing external access to both parallel Address and Data lines, are packaged in multi-pin packages, typically 28 or 32 pin for 64K density, and focus only on the higher memory densities from 16K bit upwards.

EEPROMs are widely used for storing equipment set-up parameters or data tables. The special CMOS process and cell designs used by SGS-THOMSON allows us to offer products with a very high endurance against wear-out that occurs after many erase/write cycles in this type of memory. Typically our EEPROMs are able to withstand 5 to 10 million cycles together with over 10 years data retention.

SGS-THOMSON has an extensive program of both process research and development and product design which results in many new product updates and introductions every year. Please contact your nearest Sales Office to learn about new products that have been introduced since this databook was published.

| SERIAL ACC | CESS I <sup>2</sup> C BUS EEPROM                                                                               | 9  |

|------------|----------------------------------------------------------------------------------------------------------------|----|

| ST24C01    |                                                                                                                | 11 |

| ST24W01    |                                                                                                                | 11 |

| ST25C01    | SERIAL ACCESS I <sup>2</sup> C BUS 1K (128 x 8) EEPROM                                                         | 11 |

| ST25W01    |                                                                                                                | 11 |

| ST24C02    |                                                                                                                | 27 |

| ST24W02    |                                                                                                                | 27 |

| ST25C02    |                                                                                                                | 27 |

| ST25W02    |                                                                                                                | 27 |

| ST24C04    |                                                                                                                | 43 |

| ST24W04    |                                                                                                                | 43 |

| ST25C04    |                                                                                                                | 43 |

| ST25W04    |                                                                                                                | 43 |

| ST24C08    |                                                                                                                | 59 |

| ST24W08    |                                                                                                                | 59 |

| ST25C08    |                                                                                                                | 59 |

| ST25W08    |                                                                                                                | 59 |

| ST24C16    |                                                                                                                | 75 |

| ST24W16    |                                                                                                                | 75 |

| ST25C16    |                                                                                                                | 75 |

| ST25W16    | SERIAL ACCESS I <sup>2</sup> C BUS 16K (2K x 8) EEPROM                                                         | 75 |

| SERIAL ACC |                                                                                                                | 93 |

| ST24E16    | SERIAL ACCESS EXTENDED ADDRESSING COMPATIBLE<br>WITH I <sup>2</sup> C BUS 16K (2K x 8) EEPROM                  | 95 |

| ST25E16    | SERIAL ACCESS EXTENDED ADDRESSING COMPATIBLE<br>WITH I <sup>2</sup> C BUS 16K (2K x 8) EEPROM                  | 95 |

| ST24E32    | SERIAL ACCESS EXTENDED ADDRESSING COMPATIBLE                                                                   | 11 |

| ST25E32    | SERIAL ACCESS EXTENDED ADDRESSING COMPATIBLE           WITH I <sup>2</sup> C BUS 32K (4K x 8) EEPROM         1 | 11 |

| ST24E64    | SERIAL ACCESS EXTENDED ADDRESSING COMPATIBLE                                                                   | 27 |

| ST25E64    | WITH I <sup>c</sup> C BUS 64K (8K x 8) EEPROM                                                                  | 27 |

| ST24E256   | SERIAL ACCESS EXTENDED ADDRESSING COMPATIBLE<br>WITH I <sup>2</sup> C BUS 256K (32K x 8) EEPROM                | 43 |

| ST25E256   | SERIAL ACCESS EXTENDED ADDRESSING COMPATIBLE<br>WITH I <sup>2</sup> C BUS 256K (32K x 8) EEPROM                | 43 |

| SERIAL ACC | CESS MICROWIRE BUS EEPROM                                                                                      | 59 |

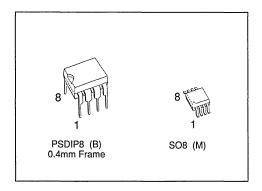

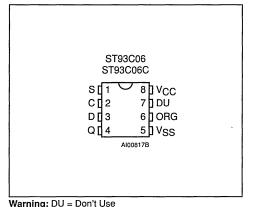

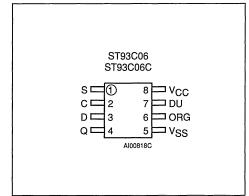

| ST93C06    |                                                                                                                | 61 |

| ST93C06C   |                                                                                                                | 61 |

| ST93C46A   |                                                                                                                | 75 |

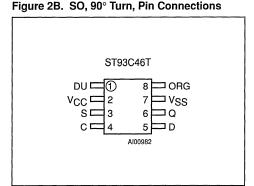

| ST93C46T   |                                                                                                                | 75 |

| ST93C46C   |                                                                                                                | 75 |

| ST93C56    |                                                                                                                | 87 |

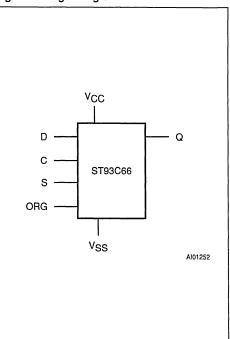

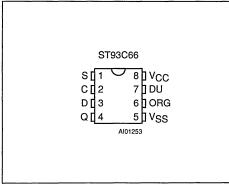

| ST93C66    |                                                                                                                | 99 |

## GENERAL INDEX

#### SERIAL ACCESS MICROWIRE BUS EEPROM (cont'd)

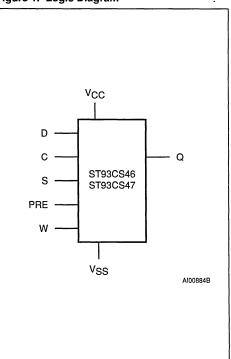

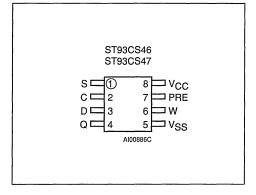

| ST93CS46  | SERIAL ACCESS MICROWIRE BUS 1K (64 x 16) EEPROM               | 211 |

|-----------|---------------------------------------------------------------|-----|

| ST93CS47  | SERIAL ACCESS MICROWIRE BUS 1K (64 x 16) EEPROM               | 211 |

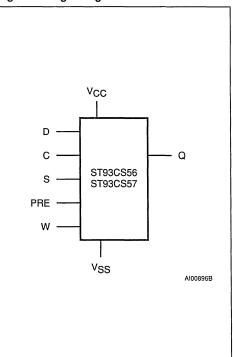

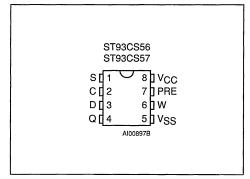

| ST93CS56  | SERIAL ACCESS MICROWIRE BUS 2K (128 x 16) EEPROM              | 227 |

| ST93CS57  | SERIAL ACCESS MICROWIRE BUS 2K (128 x 16) EEPROM              | 227 |

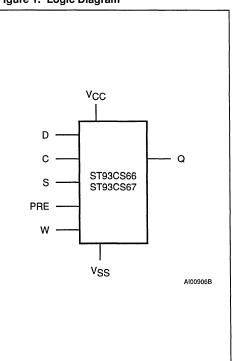

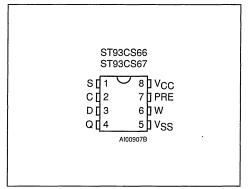

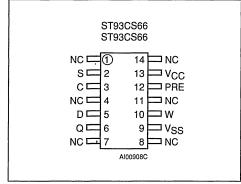

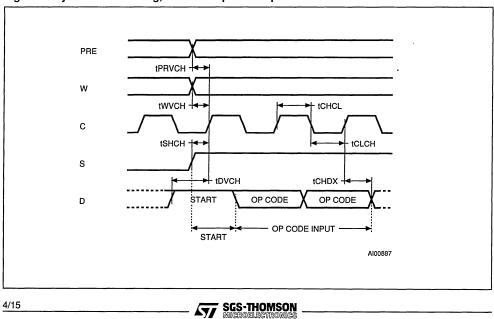

| ST93CS66  | SERIAL ACCESS MICROWIRE BUS 4K (256 x 16) EEPROM              | 243 |

| ST93CS67  | SERIAL ACCESS MICROWIRE BUS 4K (256 x 16) EEPROM              | 243 |

| SERIAL AC | CESS SPI BUS EEPROM                                           | 259 |

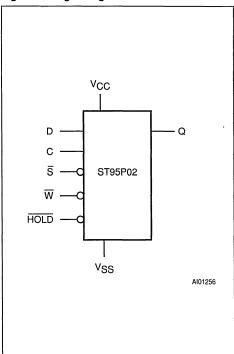

| ST95P02   | SERIAL ACCESS SPI BUS 2K (256 x 8) EEPROM                     | 261 |

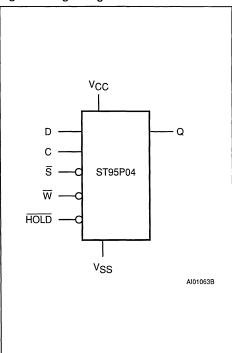

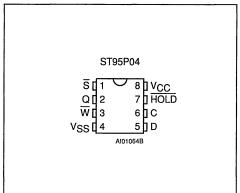

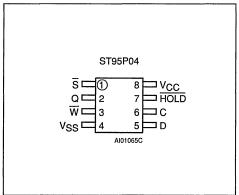

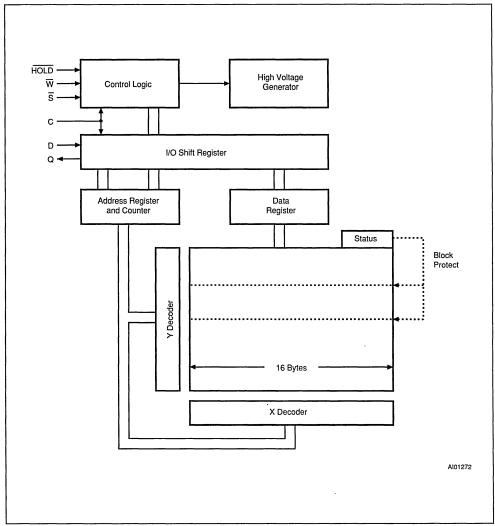

| ST95P04   | SERIAL ACCESS SPI BUS 4K (512 x 8) EEPROM                     | 277 |

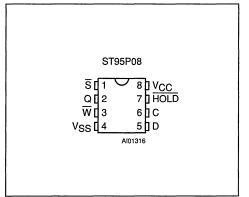

| ST95P08   | SERIAL ACCESS SPI BUS 8K (1K x 8) EEPROM                      | 293 |

| ST95020   | SERIAL ACCESS SPI BUS 2K (256 x 8) EEPROM                     | 309 |

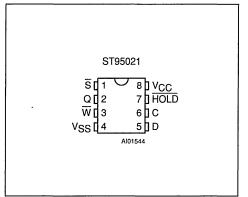

| ST95021   | SERIAL ACCESS SPI BUS 2K (256 × 8) EEPROM                     | 327 |

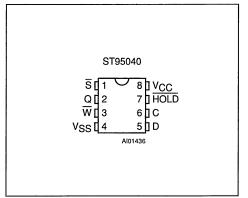

| ST95040   | SERIAL ACCESS SPI BUS 4K (512 x 8) EEPROM                     | 345 |

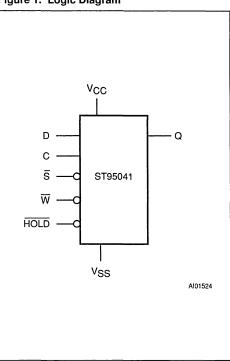

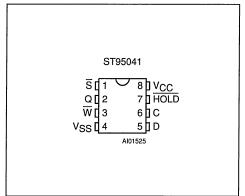

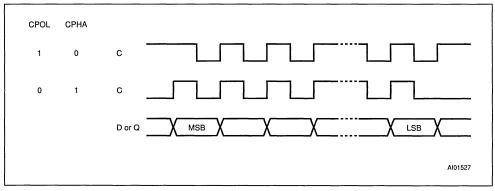

| ST95041   | SERIAL ACCESS SPI BUS 4K (512 x 8) EEPROM                     | 363 |

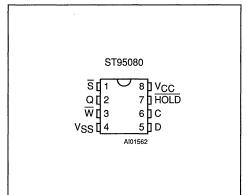

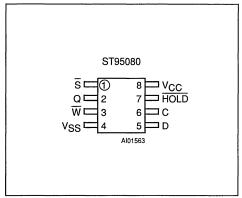

| ST95080   | SERIAL ACCESS SPI BUS 8K (1K x 8) EEPROM                      | 381 |

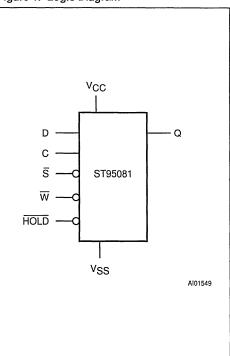

| ST95081   | SERIAL ACCESS SPI BUS 8K (1K x 8) EEPROM                      | 399 |

| PARALLEL  | EEPROM                                                        | 417 |

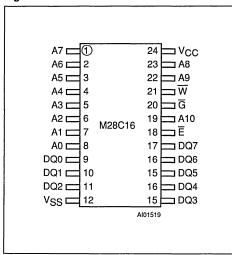

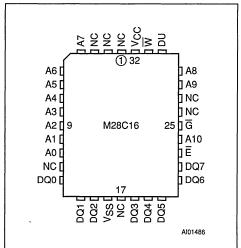

| M28C16    | PARALLEL ACCESS 16K (2K x 8) EEPROM                           | 419 |

| M28C17    | PARALLEL ACCESS 16K (2K x 8) EEPROM                           | 435 |

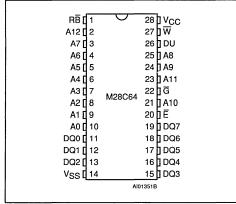

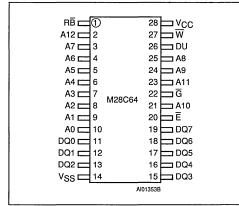

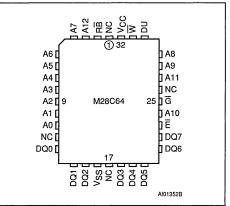

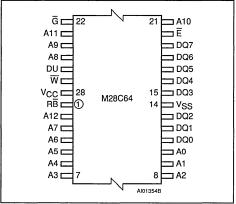

| M28C64    | PARALLEL ACCESS 64K (8K x 8) EEPROM                           | 451 |

| M28C64C   | PARALLEL ACCESS 64K (8K x 8) EEPROM                           | 469 |

| M28C64X   | PARALLEL ACCESS 64K (8K x 8) EEPROM                           | 469 |

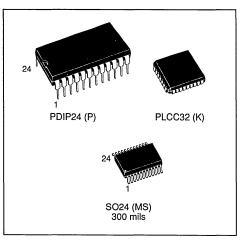

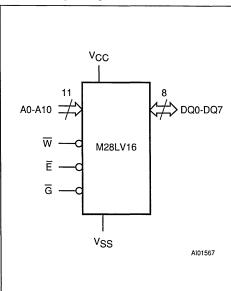

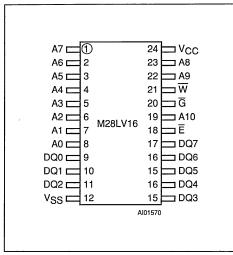

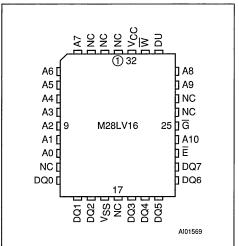

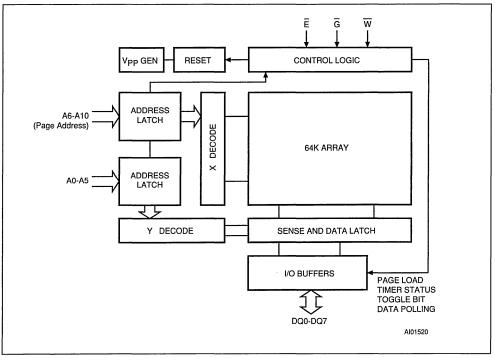

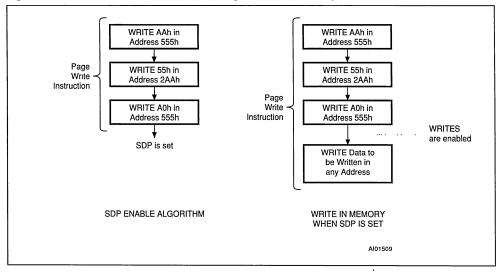

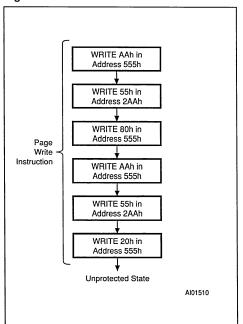

| M28LV16   | LOW VOLTAGE PARALLEL ACCESS 16K (2K x 8) EEPROM               | 483 |

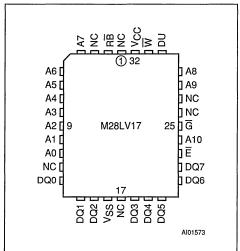

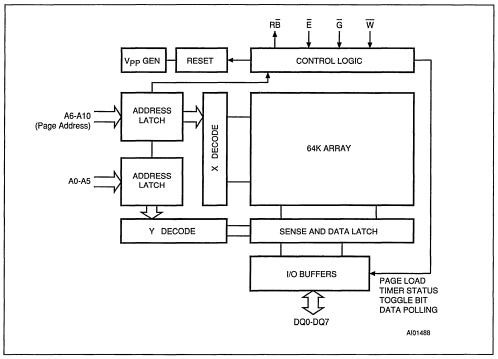

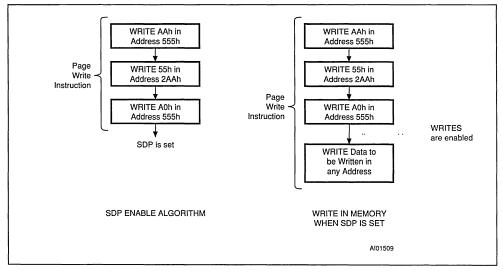

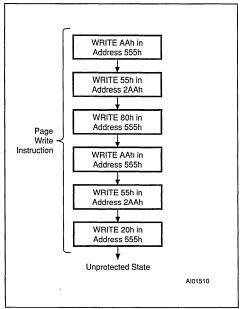

| M28LV17   | LOW VOLTAGE PARALLEL ACCESS 16K (2K x 8) EEPROM               | 499 |

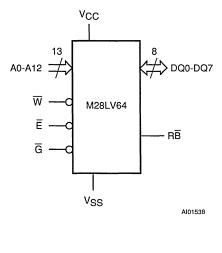

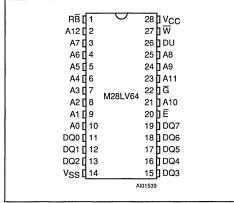

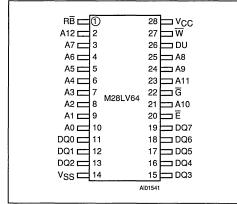

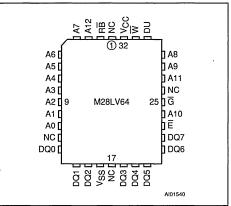

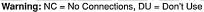

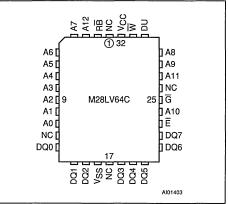

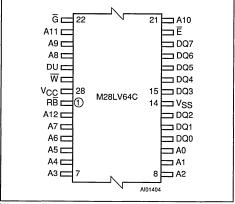

| M28LV64   | LOW VOLTAGE PARALLEL ACCESS 64K (8K x 8) EEPROM               | 515 |

| M28LV64C  | LOW VOLTAGE PARALLEL ACCESS 64K (8K x 8) EEPROM               | 533 |

| M28LV64X  | LOW VOLTAGE PARALLEL ACCESS 64K (8K x 8) EEPROM               | 533 |

| DEDICATED | EEPROM                                                        | 547 |

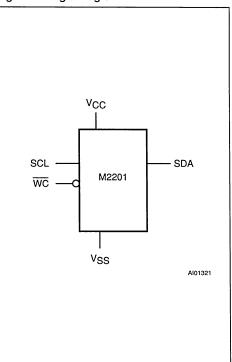

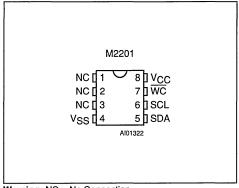

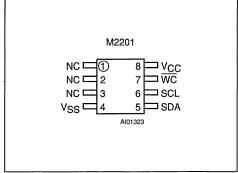

| M2201     | SERIAL ACCESS 1K (128 x 8) EEPROM                             | 549 |

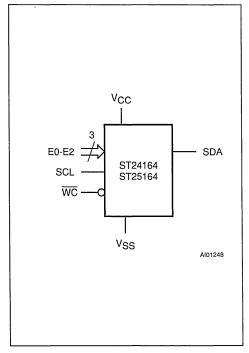

| ST24164   | SERIAL ACCESS 16K (2K x 8) EEPROM                             | 561 |

| ST25164   |                                                               | 561 |

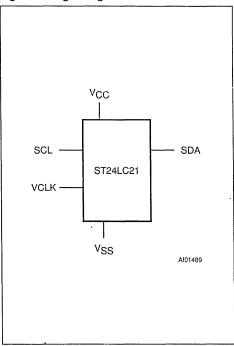

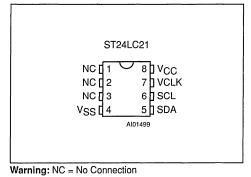

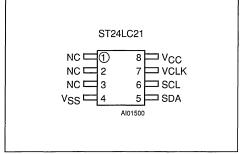

| ST24LC21  | DUAL MODE SERIAL ACCESS 1K (128 x 8) EEPROM                   | 577 |

| ST24S08   | SECURE SERIAL ACCESS I <sup>2</sup> C BUS 8K (1K x 8) EEPROM  | 593 |

| ST25S08   | SECURE SERIAL ACCESS I <sup>2</sup> C BUS 8K (1K x 8) EEPROM  | 593 |

| ST24S16   | SECURE SERIAL ACCESS I <sup>2</sup> C BUS 16K (2K x 8) EEPROM | 593 |

| ST25S16   | SECURE SERIAL ACCESS I <sup>2</sup> C BUS 16K (2K x 8) EEPROM | 593 |

## SERIAL ACCESS I<sup>2</sup>C BUS EEPROM

.

## SERIAL ACCESS 1K (128 x 8) EEPROM

- 1 MILLION ERASE/WRITE CYCLES with 10 YEARS DATA RETENTION

- SINGLE SUPPLY VOLTAGE:

- 3V to 5.5V for ST24 versions

- 2.5V to 5.5V for ST25 versions

- HARDWARE WRITE CONTROL VERSIONS: ST24W01 and ST25W01

- TWO WIRE SERIAL INTERFACE, FULLY I<sup>2</sup>C BUS COMPATIBLE

- BYTE and MULTIBYTE WRITE (up to 4 BYTES)

- PAGE WRITE (up to 8 BYTES)

- BYTE, RANDOM and SEQUENTIAL READ MODES

- SELF TIMED PROGRAMMING CYCLE

- AUTOMATIC ADDRESS INCREMENTING

- ENHANCED ESD/LATCH UP PERFORMANCES

#### DESCRIPTION

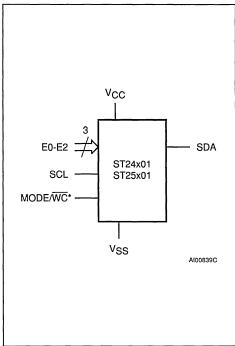

This specification covers a range of 1K bits  $I^2C$  bus EEPROM products, the ST24/25C01, and the ST24/25W01. In the text, products are referred to as ST24/25x01, where "x" is: "C" for Standard version and "W" for hardware Write Control version.

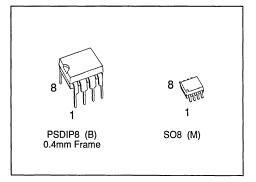

#### Table 1. Signal Names

| E0-E2           | Chip Enable Inputs                       |

|-----------------|------------------------------------------|

| SDA             | Serial Data Address Input/Output         |

| SCL             | Serial Clock                             |

| MODE            | Multibyte/Page Write Mode<br>(C version) |

| WC              | Write Control (W version)                |

| Vcc             | Supply Voltage                           |

| V <sub>SS</sub> | Ground                                   |

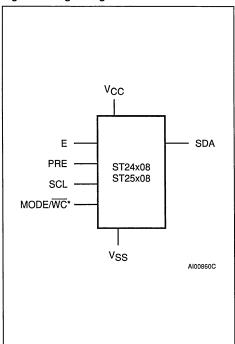

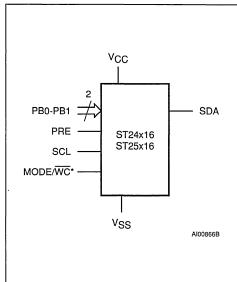

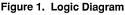

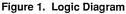

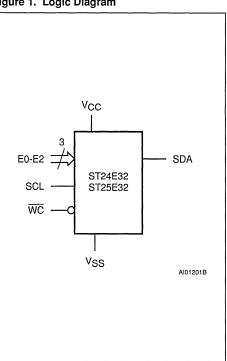

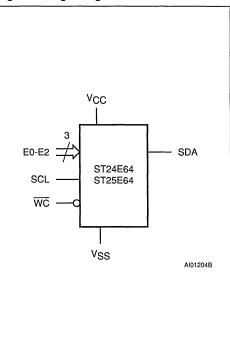

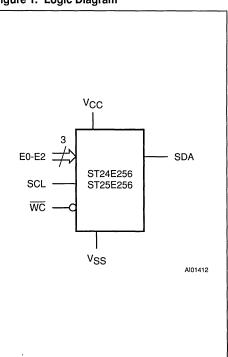

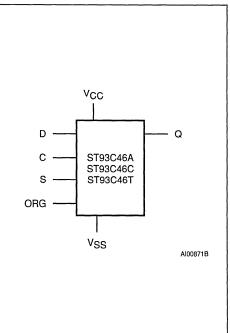

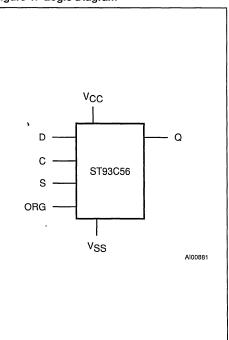

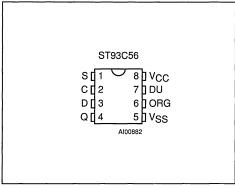

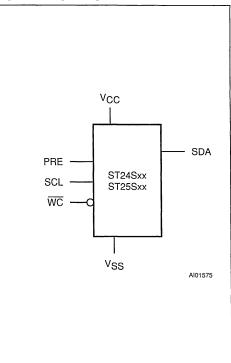

Figure 1. Logic Diagram

Note: WC signal is only available for ST24/25W01 products.

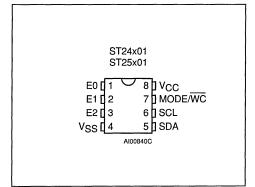

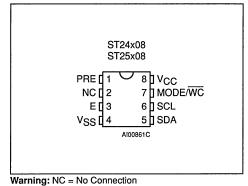

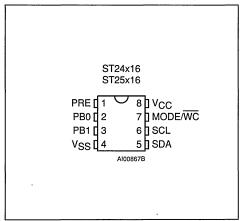

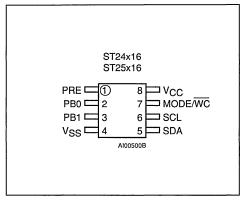

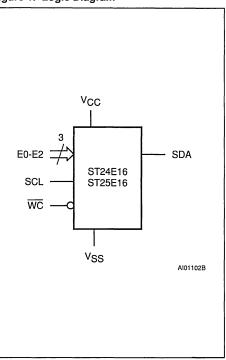

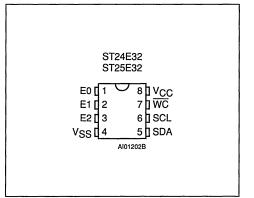

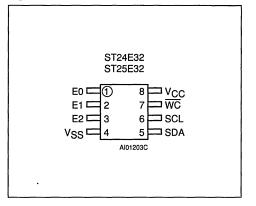

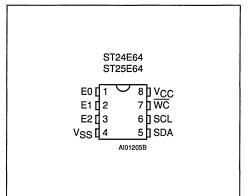

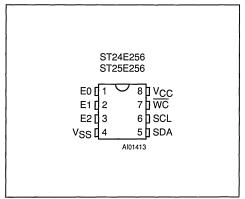

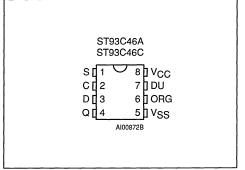

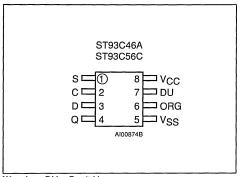

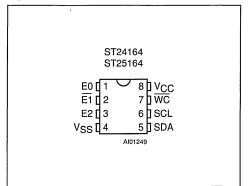

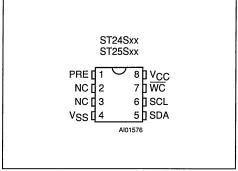

#### Figure 2A. DIP Pin Connections

#### Table 2. Absolute Maximum Ratings (1)

| Symbol            | F                                                      | Parameter                         |                    | Value               | Unit |

|-------------------|--------------------------------------------------------|-----------------------------------|--------------------|---------------------|------|

| TA                | Ambient Operating Temperature                          |                                   | grade 1<br>grade 6 | 0 to 70<br>40 to 85 | °C   |

| TSTG              | Storage Temperature                                    |                                   |                    | 65 to 150           | °C   |

| T <sub>LEAD</sub> | Lead Temperature, Soldering                            | (SO8 package)<br>(PSDIP8 package) | 40 sec<br>10 sec   | 215<br>260          | °C   |

| V <sub>IO</sub>   | Input or Output Voltages                               |                                   |                    | -0.3 to 6.5         | v    |

| Vcc               | Supply Voltage                                         |                                   |                    | -0.3 to 6.5         | V    |

| V <sub>ESD</sub>  | Electrostatic Discharge Voltage (Human Body model) (2) |                                   |                    | 4000                | v    |

| ▼ ESD             | Electrostatic Discharge Voltage (                      | Machine model) <sup>(3)</sup>     |                    | 500                 | v    |

Notes: 1. Except for the rating "Operating Temperature Range", stresses above those listed in the Table "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the SGS-THOMSON SURE Program and other relevant quality documents. 2. MIL-STD-883C, 3015.7 (100pF, 1500 Ω).

3. EIAJ IC-121 (Condition C) (200pF, 0 Ω).

#### **DESCRIPTION** (cont'd)

The ST24/25x01 are 1K bit electrically erasable programmable memories (EEPROM), organized as 128 x 8 bits. They are manufactured in SGS-THOMSON's Hi-Endurance Advanced CMOS technology which guarantees an endurance of one million erase/write cycles with a data retention of 10 years. The memories operate with a power supply value as low as 2.5V.

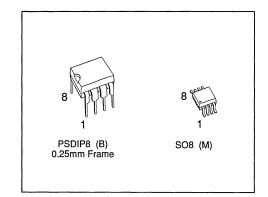

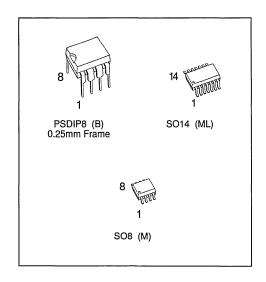

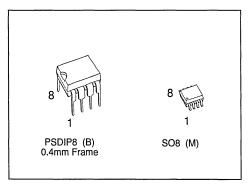

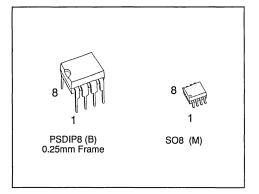

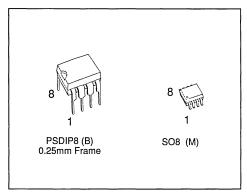

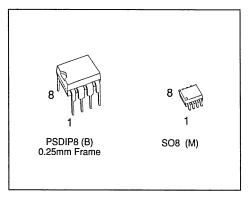

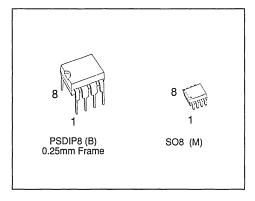

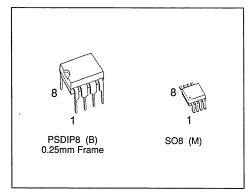

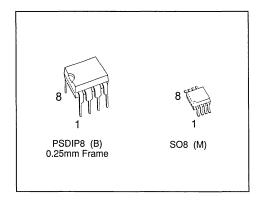

Both Plastic Dual-in-Line and Plastic Small Outline packages are available.

The memories are compatible with the I<sup>2</sup>C standard, two wire serial interface which uses a bi-direc-

tional data bus and serial clock. The memories carry a built-in 4 bit, unique device identification code (1010) corresponding to the I<sup>2</sup>C bus definition. This is used together with 3 chip enable inputs (E2, E1, E0) so that up to 8 x 1K devices may be attached to the I<sup>2</sup>C bus and selected individually. The memories behave as a slave device in the I<sup>2</sup>C protocol with all memory operations synchronized by the serial clock. Read and write operations are initiated by a START condition generated by the bus master. The START condition is followed by a stream of 7 bits (identification code 1010), plus one read/write bit and terminated by an acknowledge bit.

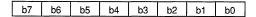

#### Table 3. Device Select Code

|               | Device Code |    |    |    |    | Chip Enable | )  | RW |

|---------------|-------------|----|----|----|----|-------------|----|----|

| Bit           | b7          | b6 | b5 | b4 | b3 | b2          | b1 | b0 |

| Device Select | 1           | 0  | 1  | 0  | E2 | E1          | E0 | R₩ |

Note: The MSB b7 is sent first.

#### Table 4. Operating Modes (1)

| Mode                      | RW bit | MODE | Bytes                                                 | Initial Sequence                              |

|---------------------------|--------|------|-------------------------------------------------------|-----------------------------------------------|

| Current Address Read      | '1'    | x    | 1                                                     | START, Device Select, $R\overline{W} = '1'$   |

| Bandom Address Bead '0' X |        | 1    | START, Device Select, $R\overline{W}$ = '0', Address, |                                               |

| Handom Address Head       | '1'    |      |                                                       | reSTART, Device Select, $R\overline{W} = '1'$ |

| Sequential Read           | '1'    | x    | 1 to 128                                              | Similar to Current or Random Mode             |

| Byte Write                | '0'    | X    | 1                                                     | START, Device Select, $R\overline{W}$ = '0'   |

| Multibyte Write (2)       | '0'    | VIH  | 4                                                     | START, Device Select, $R\overline{W} = '0'$   |

| Page Write                | ,0,    | VIL  | 8                                                     | START, Device Select, $R\overline{W}$ = '0'   |

Notes: 1. X = VIH or VIL

2. Multibyte Write not available in ST24/25W01 versions.

When writing data to the memory it responds to the 8 bits received by asserting an acknowledge bit during the 9th bit time. When data is read by the bus master, it acknowledges the receipt of the data bytes in the same way. Data transfers are terminated with a STOP condition.

Power On Reset: V<sub>CC</sub> lock out write protect. In order to prevent data corruption and inadvertent write operations during power up, a Power On Reset (POR) circuit is implemented. Until the V<sub>CC</sub> voltage has reached the POR threshold value, the internal reset is active, all operations are disabled and the device will not respond to any command. In the same way, when V<sub>CC</sub> drops down from the operating voltage to below the POR threshold value, all operations are disabled and the device will not respond to any command. A stable V<sub>CC</sub> must be applied before applying any logic signal.

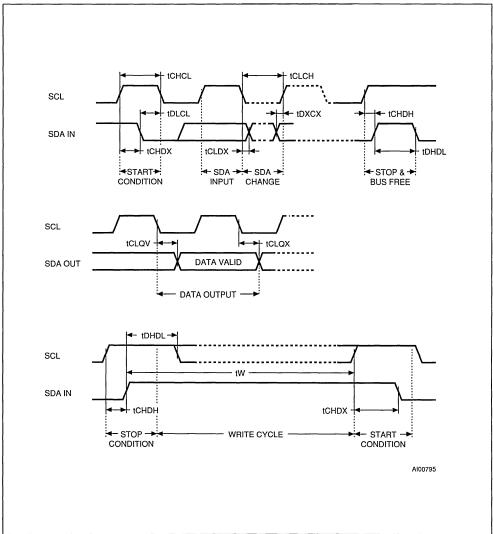

#### SIGNAL DESCRIPTIONS

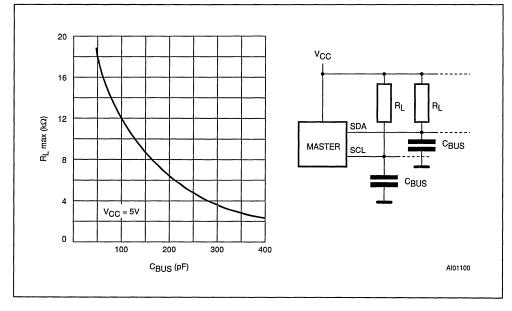

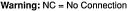

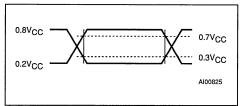

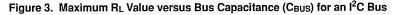

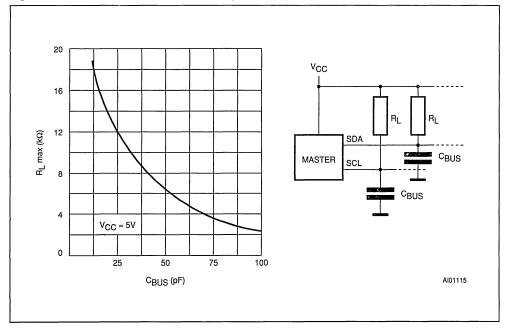

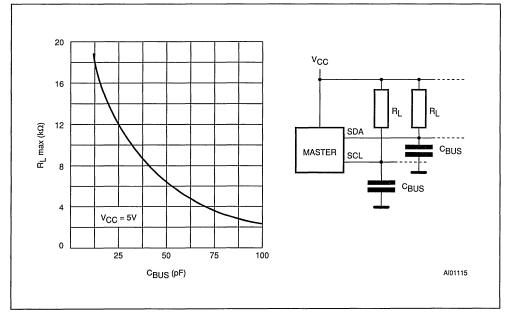

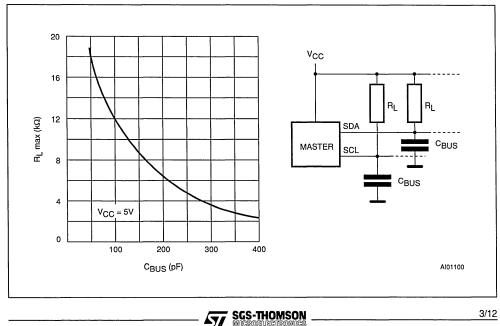

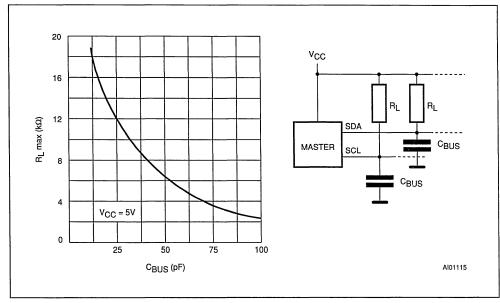

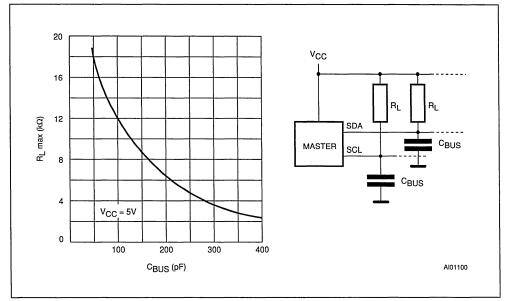

Serial Clock (SCL). The SCL input pin is used to synchronize all data in and out of the memory. A resistor can be connected from the SCL line to  $V_{CC}$  to act as a pull up (see Figure 3).

Serial Data (SDA). The SDA pin is bi-directional and is used to transfer data in or out of the memory. It is an open drain output that may be wire-OR'ed with other open drain or open collector signals on the bus. A resistor must be connected from the SDA bus line to V<sub>CC</sub> to act as pull up (see Figure 3).

**Chip Enable (E0 - E2).** These chip enable inputs are used to set the 3 least significant bits (b3, b2, b1) of the 7 bit device select code. These inputs may be driven dynamically or tied to V<sub>CC</sub> or V<sub>SS</sub> to establish the device select code.

**Mode (MODE).** The MODE input is available on pin 7 (see also WC feature) and may be driven dynamically. It must be at  $V_{IL}$  or  $V_{IH}$  for the Byte Write mode,  $V_{IH}$  for Multibyte Write mode or  $V_{IL}$  for Page Write mode. When unconnected, the MODE input is internally read as  $V_{IH}$  (Multibyte Write mode).

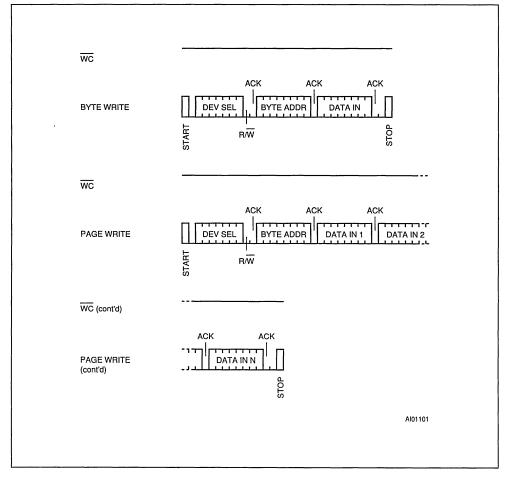

Write Control ( $\overline{WC}$ ). An hardware Write Control feature ( $\overline{WC}$ ) is offered only for ST24W01 and ST25W01 versions on pin 7. This feature is usefull to protect the contents of the memory from any erroneous erase/write cycle. The Write Control signal is used to enable ( $\overline{WC} = V_{IL}$ ) or disable ( $\overline{WC} = V_{IL}$ ) the internal write protection. When unconnected, the  $\overline{WC}$  input is internally read as  $V_{IL}$ .

#### SIGNAL DESCRIPTION (cont'd)

The devices with this Write Control feature no longer support the Multibyte Write mode of operation, however all other write modes are fully supported.

Refer to the AN404 Application Note for more detailed information about Write Control feature.

#### **DEVICE OPERATION**

#### I<sup>2</sup>C Bus Background

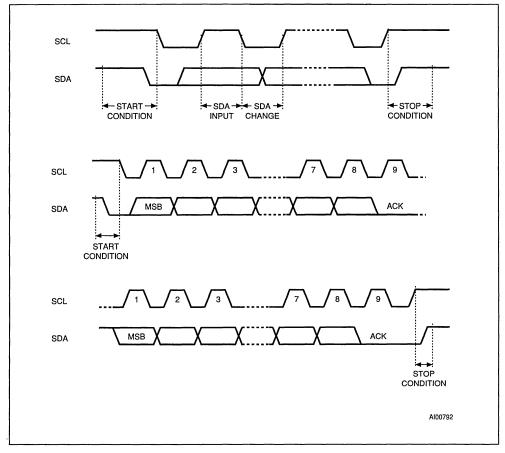

The ST24/25x01 support the I<sup>2</sup>C protocol. This protocol defines any device that sends data onto the bus as a transmitter and any device that reads the data as a receiver. The device that controls the data transfer is known as the master and the other as the slave. The master will always initiate a data transfer and will provide the serial clock for synchronisation. The ST24/25x01 are always slave devices in all communications.

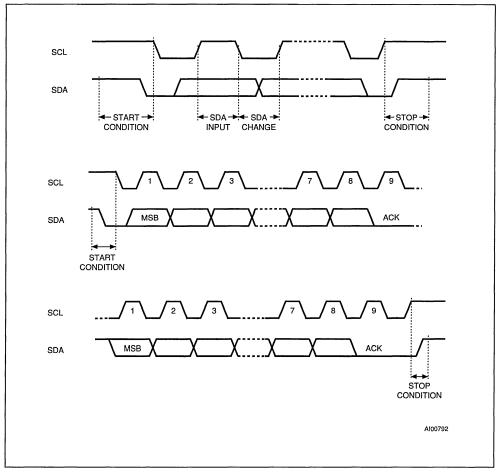

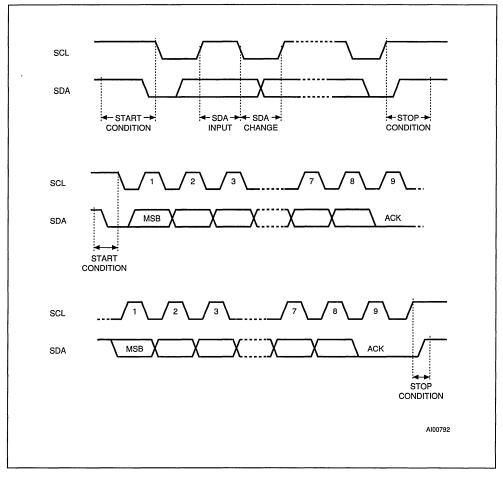

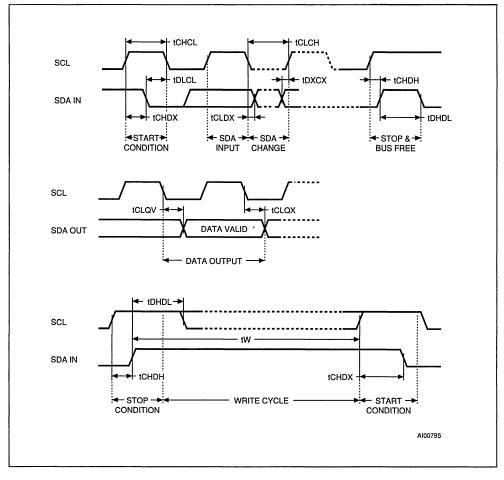

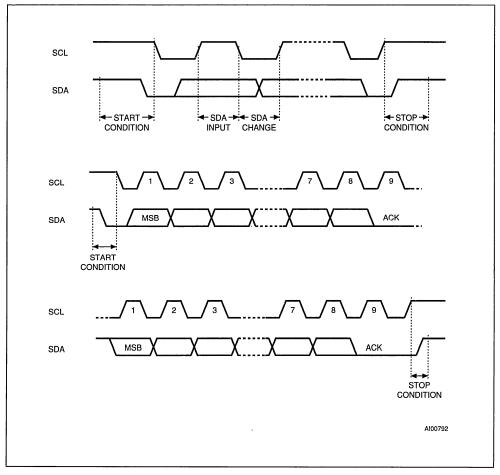

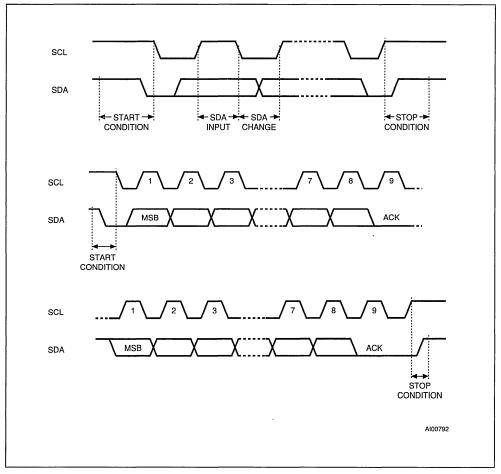

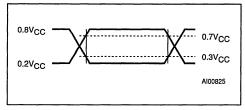

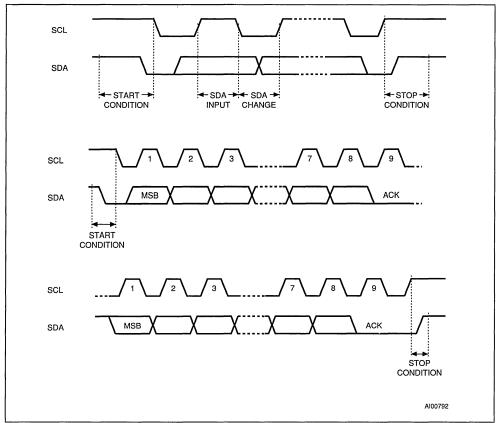

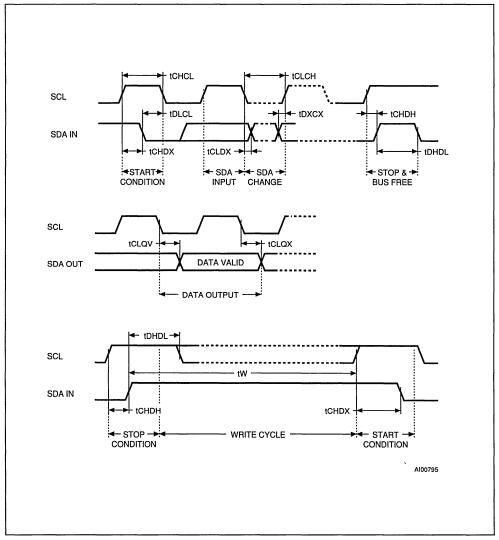

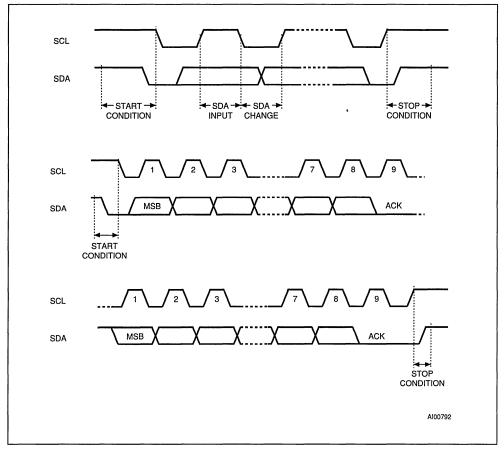

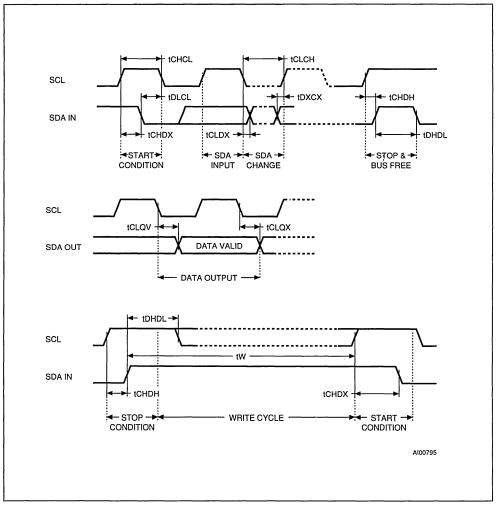

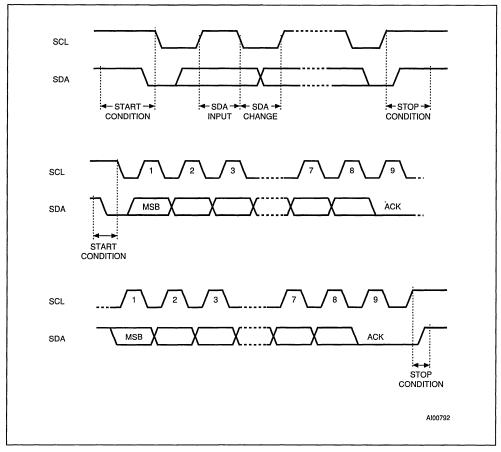

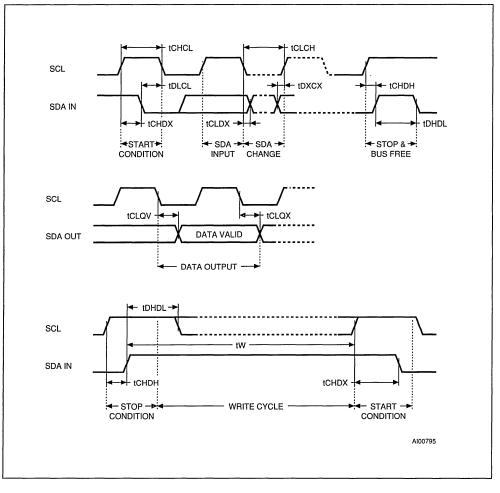

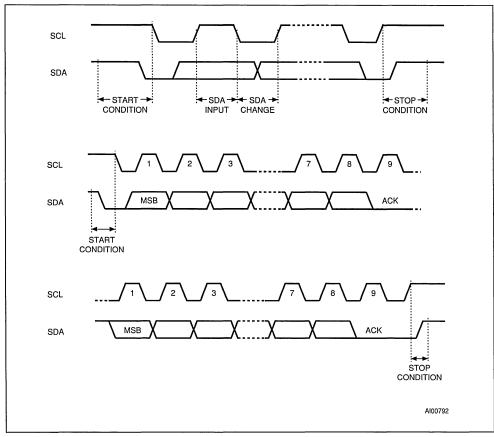

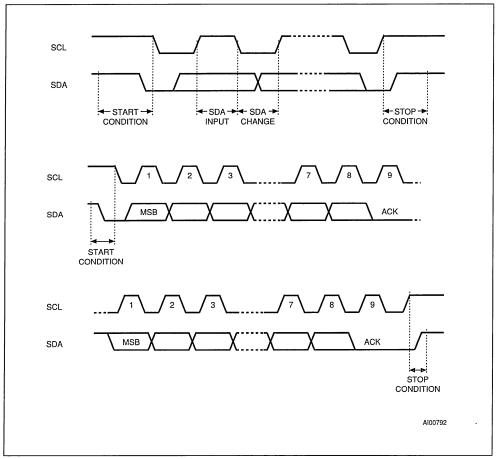

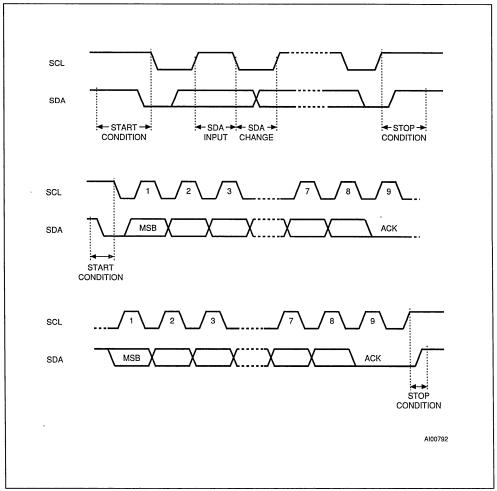

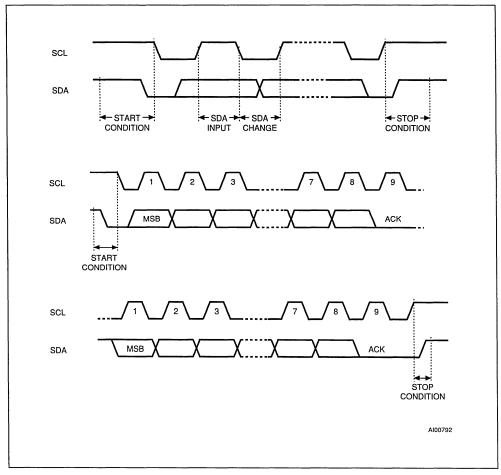

Start Condition. START is identified by a high to low transition of the SDA line while the clock SCL is stable in the high state. A START condition must precede any command for data transfer. Except during a programming cycle, the ST24/25x01 continuously monitor the SDA and SCL signals for a START condition and will not respond unless one is given. Stop Condition. STOP is identified by a low to high transition of the SDA line while the clock SCL is stable in the high state. A STOP condition terminates communication between the ST24/25x01 and the bus master. A STOP condition at the end of a Read command forces the standby state. A STOP condition at the end of a Write command triggers the internal EEPROM write cycle.

Acknowledge Bit (ACK). An acknowledge signal is used to indicate a successfull data transfer. The bus transmitter, either master or slave, will release the SDA bus after sending 8 bits of data. During the 9th clock pulse period the receiver pulls the SDA bus low to acknowledge the receipt of the 8 bits of data.

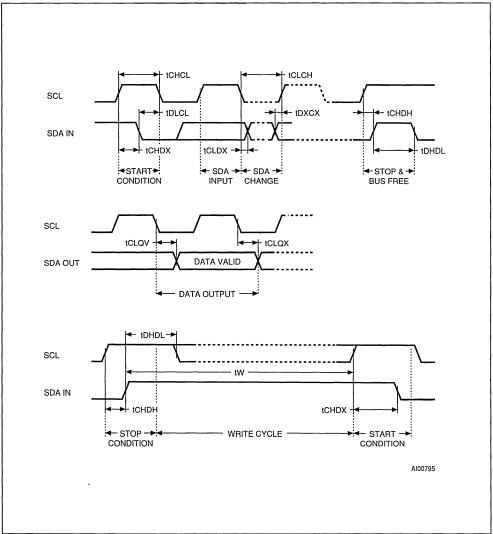

**Data Input.** During data input the ST24/25x01 sample the SDA bus signal on the rising edge of the clock SCL. Note that for correct device operation the SDA signal must be stable during the clock low to high transition and the data must change ONLY when the SCL line is low.

Memory Addressing. To start communication between the bus master and the slave ST24/25x01, the master must initiate a START condition. Following this, the master sends onto the SDA bus line 8 bits (MSB first) corresponding to the device select code (7 bits) and a READ or WRITE bit.

SGS-THOMSON

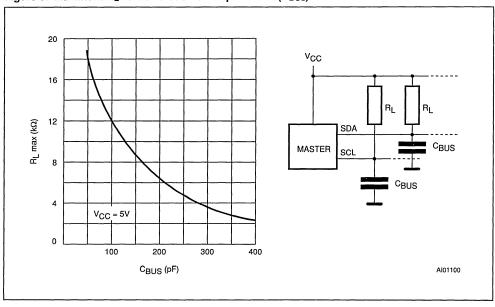

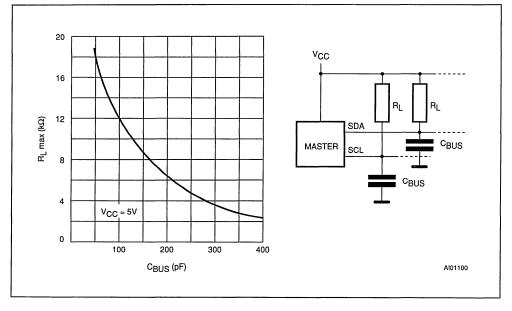

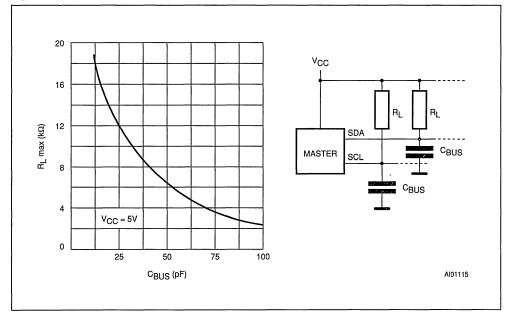

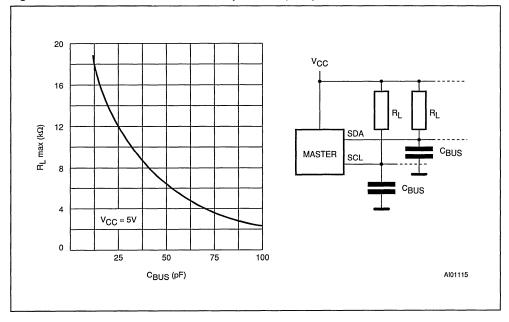

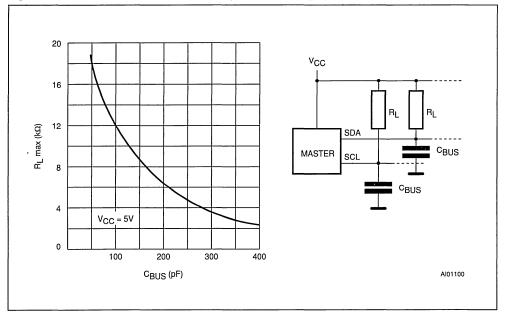

#### Figure 3. Maximum R<sub>L</sub> Value versus Bus Capacitance (C<sub>BUS</sub>) for an I<sup>2</sup>C Bus

| Symbol          | Parameter                                         | Test Condition          | Min | Max | Unit |

|-----------------|---------------------------------------------------|-------------------------|-----|-----|------|

| Cin             | Input Capacitance (SDA)                           |                         |     | 8   | pF   |

| CIN             | Input Capacitance (other pins)                    |                         |     | 6   | pF   |

| ZwcL            | WC Input Impedance (ST24/25W01)                   | $V_{IN} \le 0.3 V_{CC}$ | 5   | 20  | kΩ   |

| Zwch            | WC Input Impedance (ST24/25W01)                   | $V_{IN} \ge 0.7 V_{CC}$ | 500 |     | kΩ   |

| t <sub>LP</sub> | Low-pass filter input time constant (SDA and SCL) |                         |     | 100 | ns   |

Table 5. Input Parameters <sup>(1)</sup> ( $T_A = 25 \text{ °C}$ , f = 100 kHz )

Note: 1. Sampled only, not 100% tested.

#### Table 6. DC Characteristics

$(T_A = 0 \text{ to } 70 \text{ °C or } -40 \text{ to } 85 \text{ °C}; V_{CC} = 3V \text{ to } 5.5V \text{ or } 2.5V \text{ to } 5.5V)$

| Symbol           | Parameter                               | Test Condition                                                                                                            | Min                   | Max                 | Unit |

|------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------|------|

| ILI              | Input Leakage Current                   | $0V \leq V_{IN} \leq V_{CC}$                                                                                              |                       | ±2                  | μA   |

| ILO              | Output Leakage Current                  | $0V \le V_{OUT} \le V_{CC}$<br>SDA in Hi-Z                                                                                |                       | ±2                  | μA   |

| Icc              | Supply Current (ST24 series)            | V <sub>CC</sub> = 5V, f <sub>C</sub> = 100kHz<br>(Rise/Fall time < 10ns)                                                  |                       | 2                   | mA   |

|                  | Supply Current (ST25 series)            | $V_{CC} = 2.5V$ , f <sub>C</sub> = 100kHz                                                                                 |                       | 1                   | mA   |

|                  | Supply Current (Standby)                | $V_{IN} = V_{SS} \text{ or } V_{CC},$<br>$V_{CC} = 5V$                                                                    |                       | 100                 | μA   |

|                  | (ST24 series)                           | $V_{IN} = V_{SS} \text{ or } V_{CC},$<br>$V_{CC} = 5V, f_C = 100 \text{kHz}$                                              |                       | 300                 | μA   |

| I <sub>CC2</sub> | Supply Current (Standby)                | $V_{IN} = V_{SS} \text{ or } V_{CC},$<br>$V_{CC} = 2.5V$                                                                  |                       | 5                   | μA   |

| 1002             | (ST25 series)                           | $\label{eq:VIN} \begin{array}{l} V_{IN} = V_{SS} \text{ or } V_{CC}, \\ V_{CC} = 2.5V,  f_C = 100 \text{kHz} \end{array}$ |                       | 50                  | μA   |

| VIL              | Input Low Voltage (SCL, SDA)            |                                                                                                                           | -0.3                  | 0.3 V <sub>CC</sub> | v    |

| ViH              | Input High Voltage (SCL, SDA)           |                                                                                                                           | 0.7 V <sub>CC</sub>   | V <sub>cc</sub> + 1 | v    |

| VIL              | Input Low Voltage<br>(E0-E2, MODE, WC)  |                                                                                                                           | -0.3                  | 0.5                 | v    |

| VIH              | Input High Voltage<br>(E0-E2, MODE, WC) |                                                                                                                           | V <sub>CC</sub> – 0.5 | V <sub>CC</sub> + 1 | v    |

| Vol              | Output Low Voltage (ST24 series)        | I <sub>OL</sub> = 3mA, V <sub>CC</sub> = 5V                                                                               |                       | 0.4                 | v    |

| V OL             | Output Low Voltage (ST25 series)        | I <sub>OL</sub> = 2.1mA, V <sub>CC</sub> = 2.5V                                                                           |                       | 0.4                 | v    |

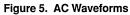

#### Table 7. AC Characteristics

| (T <sub>A</sub> = 0 to 70 °C or -40 to 85 °C; V <sub>CC</sub> = 3V to 5.5V or 2.5V | to 5.5V) |

|------------------------------------------------------------------------------------|----------|

|------------------------------------------------------------------------------------|----------|

| Symbol                           | Alt              | Parameter                                             | Min | Max | Unit |

|----------------------------------|------------------|-------------------------------------------------------|-----|-----|------|

| tCH1CH2                          | t <sub>R</sub>   | Clock Rise Time                                       |     | 1   | μs   |

| tCL1CL2                          | t⊧               | Clock Fall Time                                       |     | 300 | ns   |

| tDH1DH2                          | t <sub>R</sub>   | Input Rise Time                                       |     | 1   | μs   |

| tDL1DL1                          | t⊨               | Input Fall Time                                       |     | 300 | ns   |

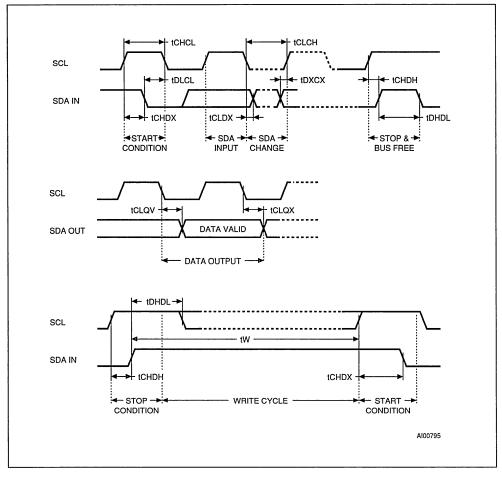

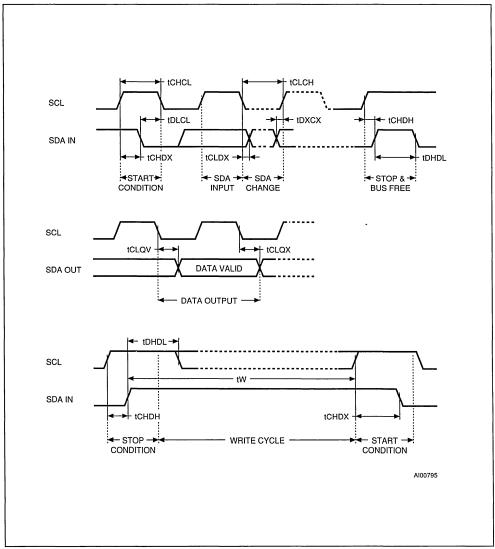

| t <sub>CHDX</sub> <sup>(1)</sup> | tsu sta          | Clock High to Input Transition                        | 4.7 |     | μs   |

| tCHCL                            | tнigн            | Clock Pulse Width High                                | 4 . |     | μs   |

| <b>t</b> DLCL                    | thd sta          | Input Low to Clock Low (START)                        | 4   |     | μs   |

| tCLDX                            | thd dat          | Clock Low to Input Transition                         | 0   |     | μs   |

| tclch                            | tLOW             | Clock Pulse Width Low                                 | 4.7 |     | μs   |

| toxcx                            | tsu dat          | Input Transition to Clock Transition                  | 250 |     | ns   |

| tснрн                            | tsu sto          | Clock High to Input High (STOP)                       | 4.7 |     | μs   |

| t <sub>DHDL</sub>                | t <sub>BUF</sub> | Input High to Input Low (Bus Free)                    | 4.7 |     | μs   |

| tCLQV                            | taa              | Clock Low to Data Out Valid                           | 0.3 | 3.5 | μs   |

| tcLQX                            | t <sub>DH</sub>  | Clock Low to Data Out Transition                      | 300 |     | ns   |

| fc                               | f <sub>SCL</sub> | Clock Frequency                                       |     | 100 | kHz  |

| t <sub>NS</sub>                  | Tı               | Noise Suppression Time Constant<br>(SCL & SDA Inputs) |     | 100 | ns   |

| tw <sup>(2)</sup>                | twR              | Write Time                                            |     | 10  | ms   |

Notes: 1. For a reSTART condition, or following a write cycle.

In the Multibyte Write mode only, if accessed bytes are on two consecutive 8 bytes rows (6 address MSB are not constant) the maximum programming time is doubled to 20ms.

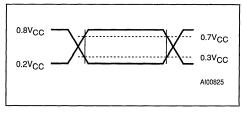

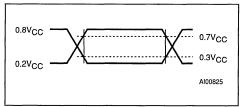

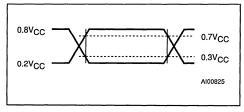

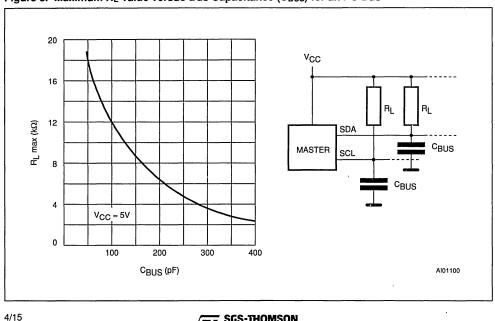

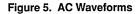

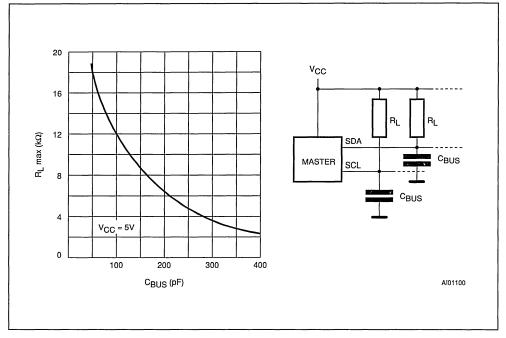

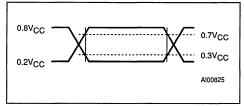

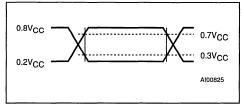

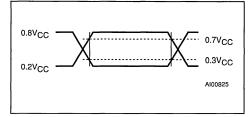

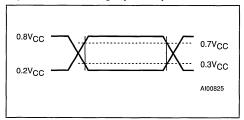

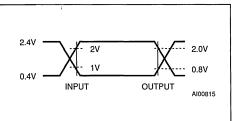

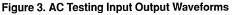

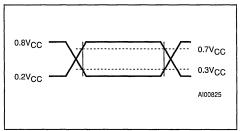

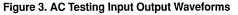

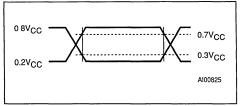

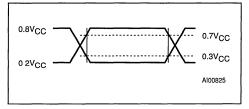

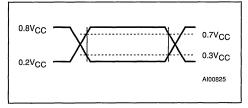

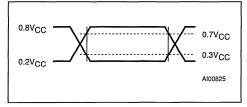

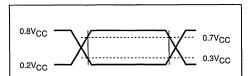

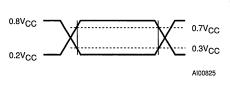

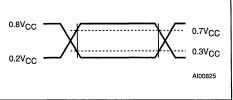

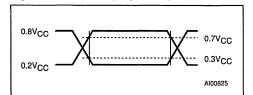

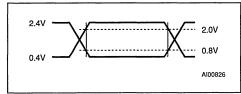

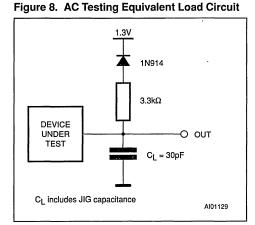

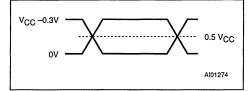

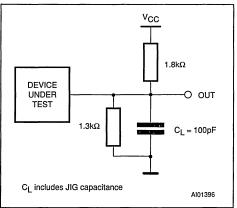

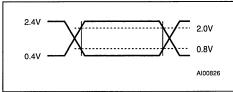

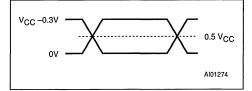

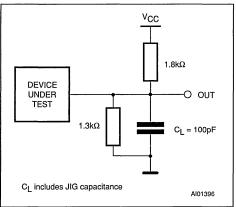

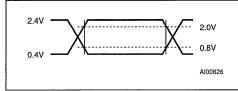

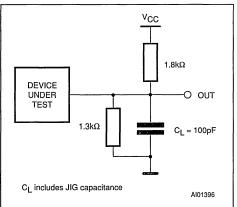

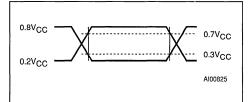

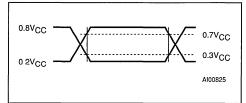

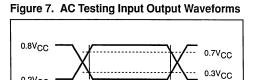

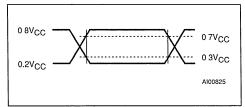

#### AC MEASUREMENT CONDITIONS

| Input Rise and Fall Times | ≤ 50ns           |

|---------------------------|------------------|

| Input Pulse Voltages      | 0.2Vcc to 0.8Vcc |

Input and Output Timing Ref. Voltages 0.3Vcc to 0.7Vcc

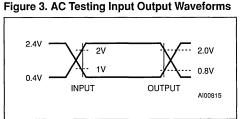

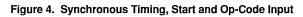

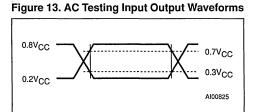

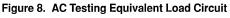

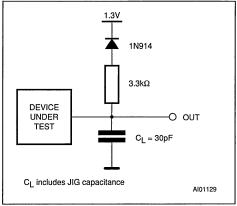

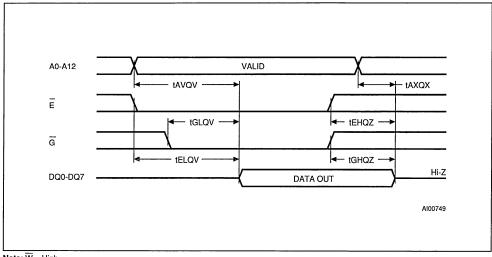

#### Figure 4. AC Testing Input Output Waveforms

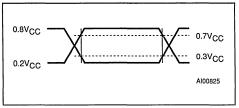

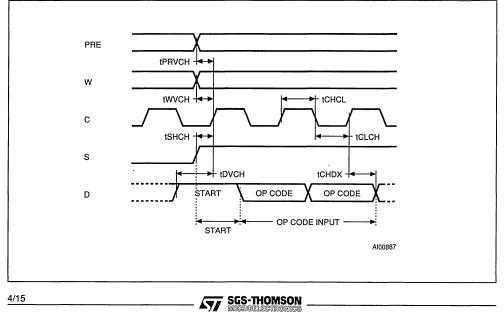

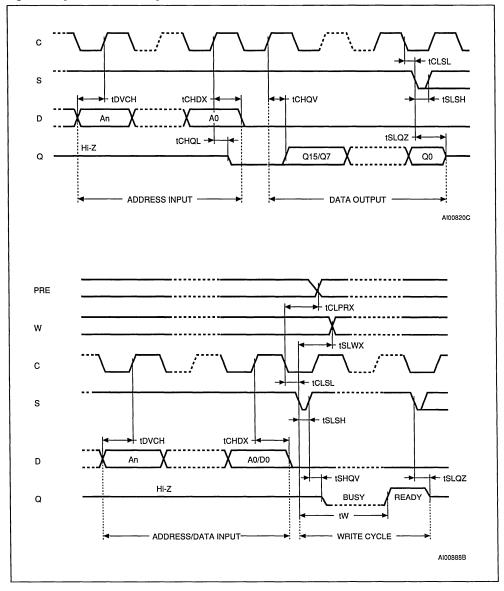

#### DEVICE OPERATION (cont'd)

The 4 most significant bits of the device select code are the device type identifier, corresponding to the  $l^2C$  bus definition. For these memories the 4 bits are fixed as 1010b. The following 3 bits identify the specific memory on the bus. They are matched to the chip enable signals E2, E1, E0. Thus up to 8 x 1K memories can be connected on the same bus giving a memory capacity total of 8K bits. After a START condition any memory on the bus will identify the device code and compare the following 3 bits to its chip enable inputs E2, E1, E0.

The 8th bit sent is the read or write bit  $(R\overline{W})$ , this bit is set to '1' for read and '0' for write operations. If a match is found, the corresponding memory will acknowledge the identification on the SDA bus during the 9th bit time.

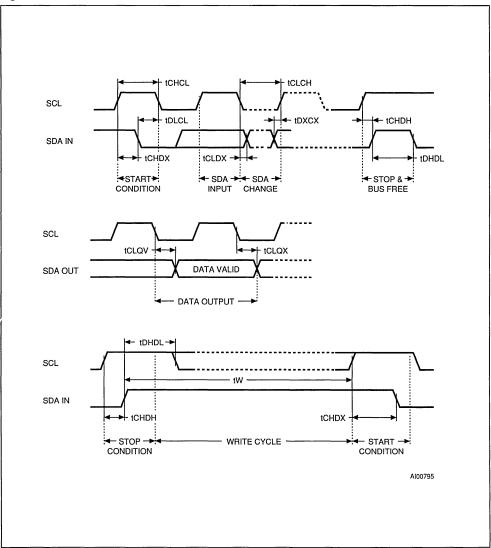

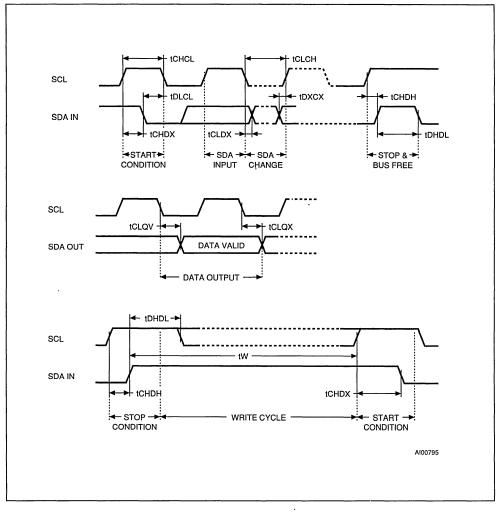

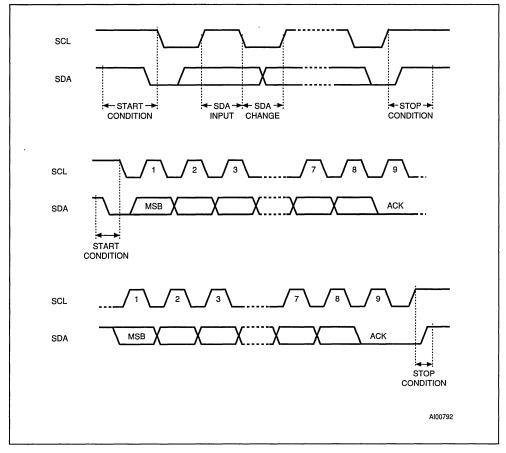

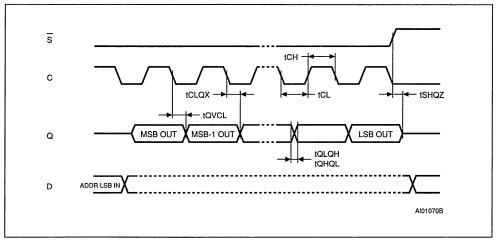

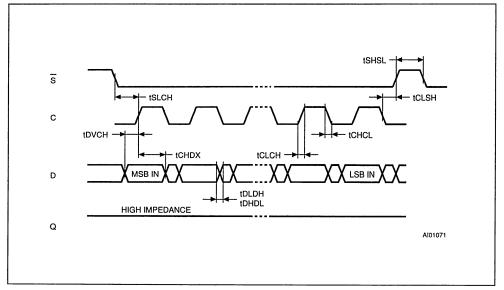

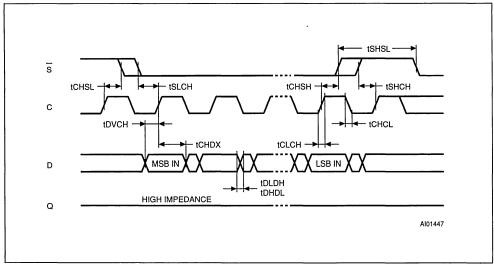

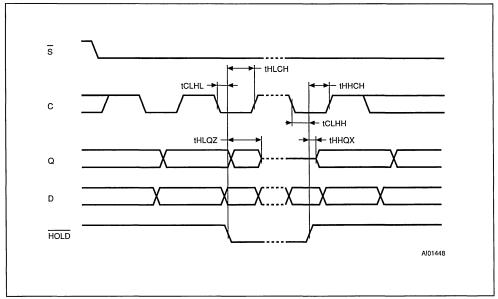

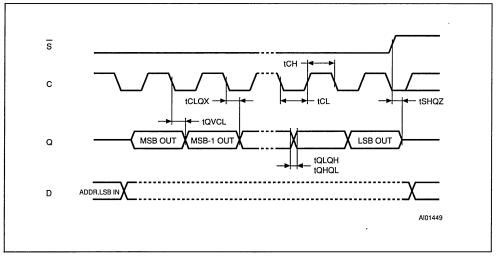

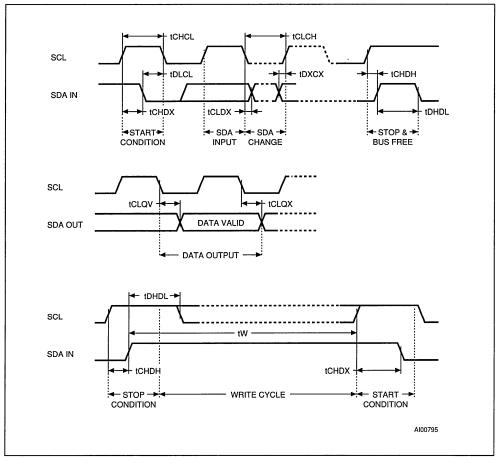

#### Figure 5. AC Waveforms

#### Figure 6. I<sup>2</sup>C Bus Protocol

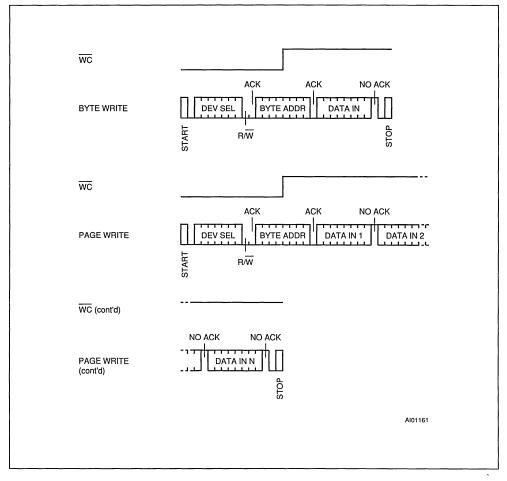

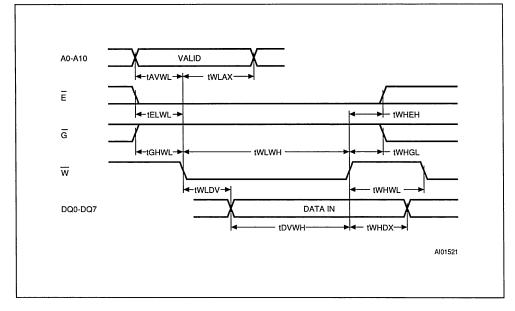

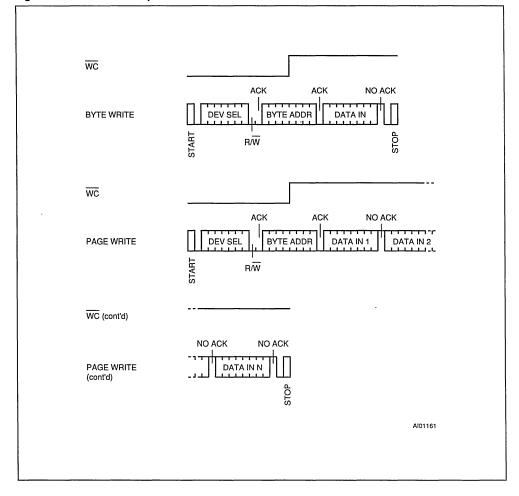

#### Write Operations

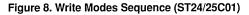

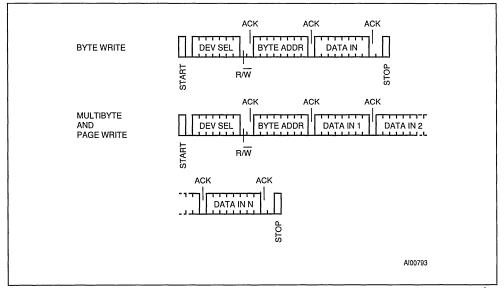

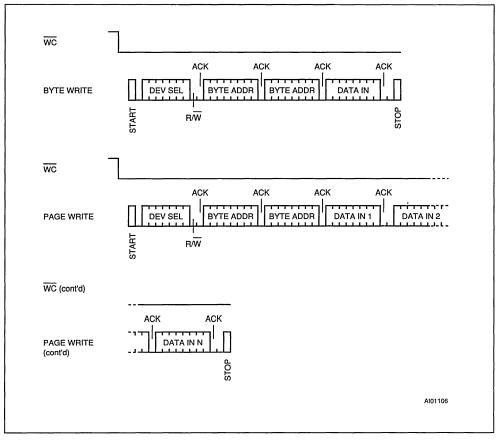

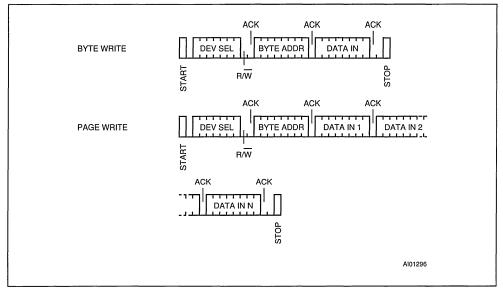

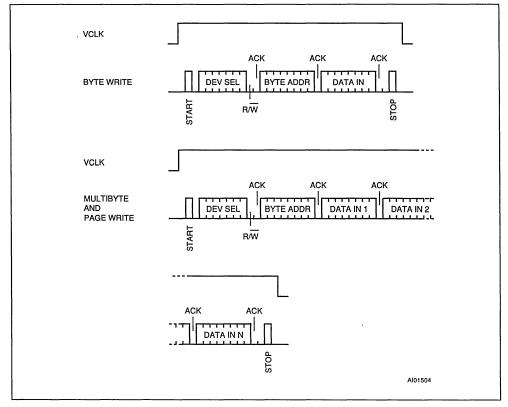

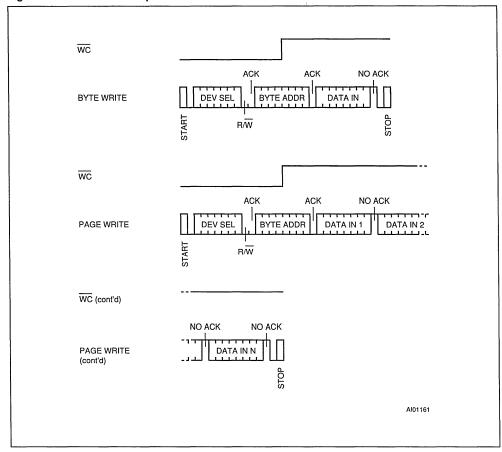

The Multibyte Write mode (only available on the ST24/25C01 versions) is selected when the MODE pin is at V<sub>IH</sub> and the Page Write mode when MODE pin is at V<sub>IL</sub>. The MODE pin may be driven dynamically with CMOS input levels.

Following a START condition the master sends a device select code with the  $R\overline{W}$  bit reset to '0'. The memory acknowledges this and waits for a byte address. The byte address of 7 bits (the Most Significant Bit is ignored) provides access to any of the 128 bytes of the memory. After receipt of the byte address the device again responds with an acknowledge.

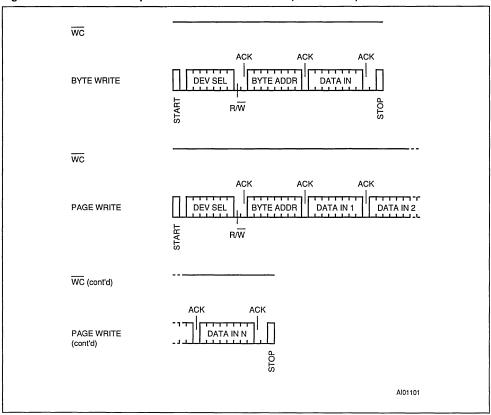

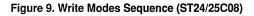

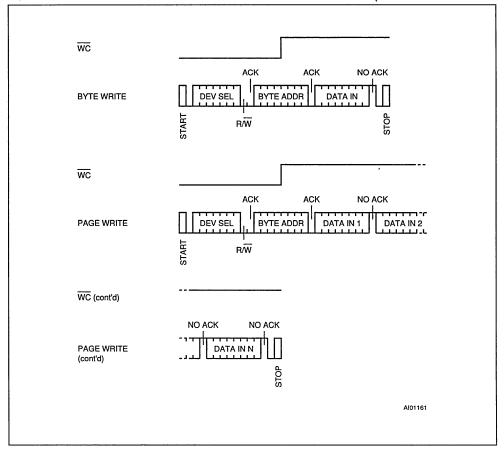

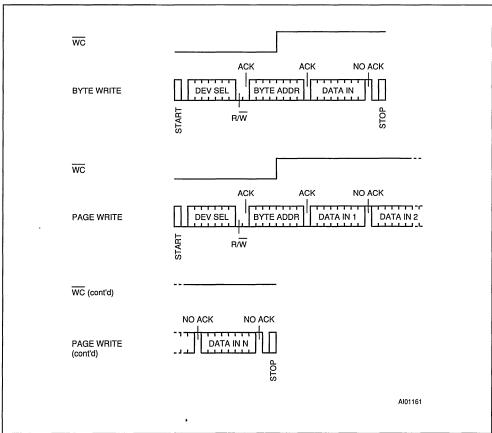

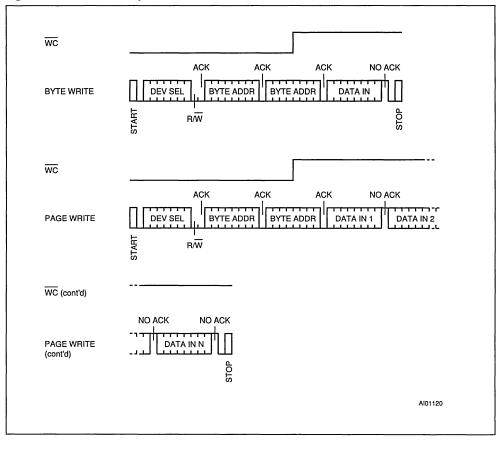

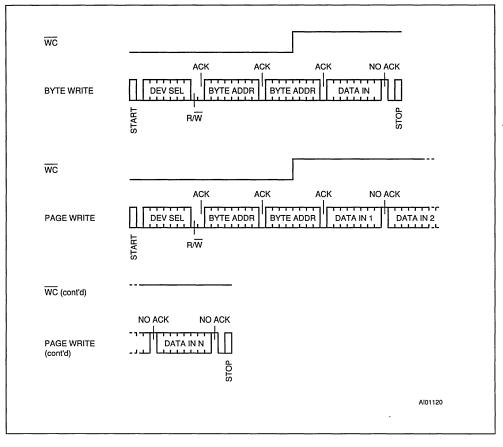

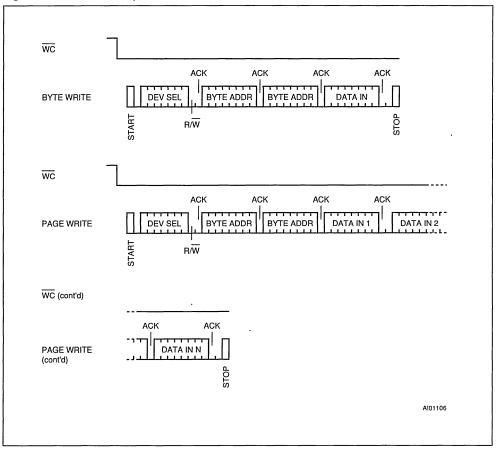

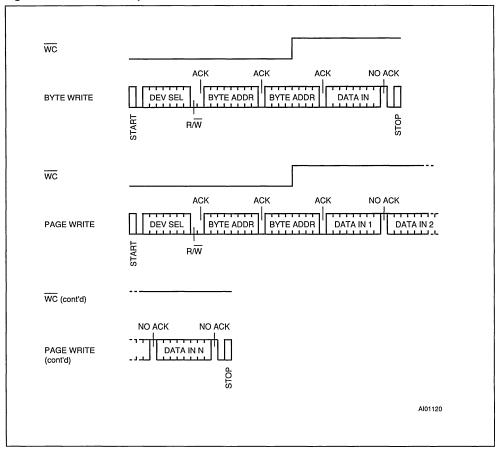

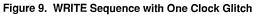

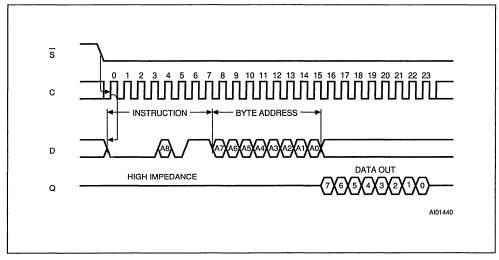

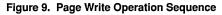

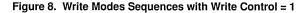

For the ST24/25W01 versions, any write command with  $\overline{WC} = 1$  (during a period of time from the START condition untill the end of the Byte Address) will not modify data and will NOT be acknowledged on data bytes, as in Figure 9.

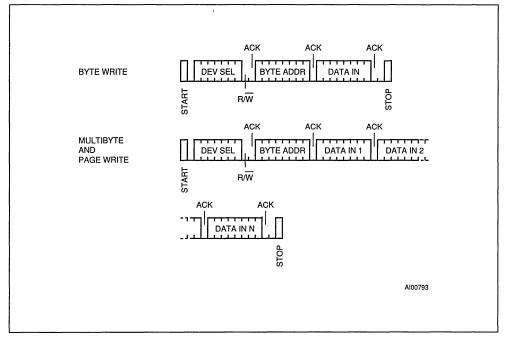

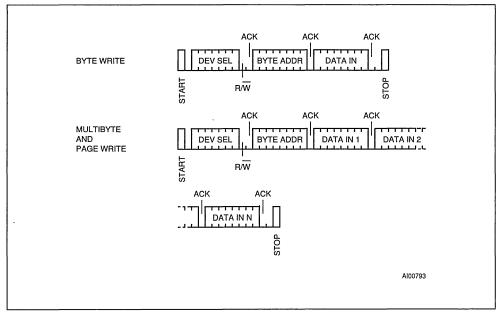

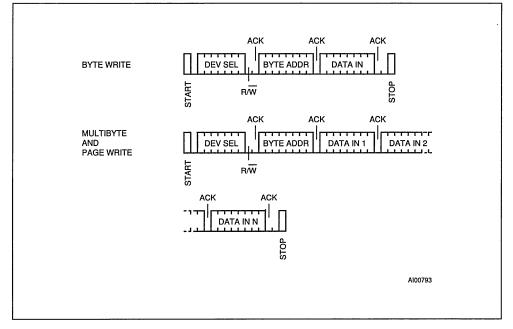

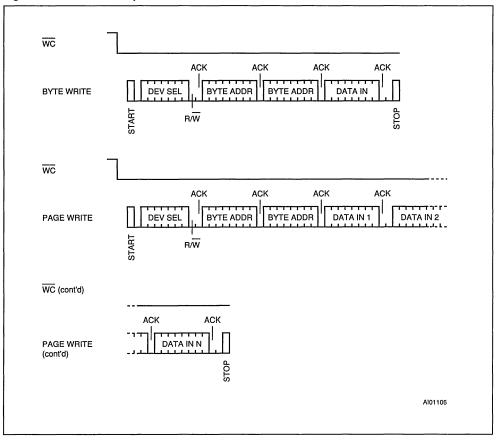

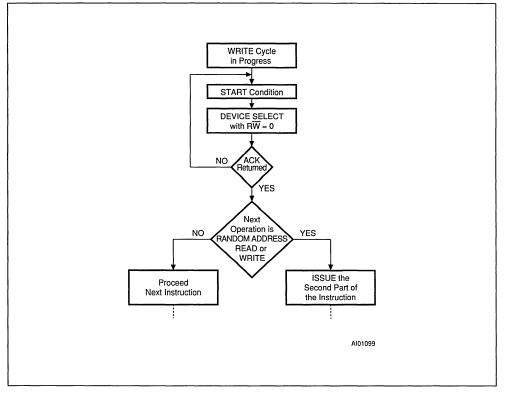

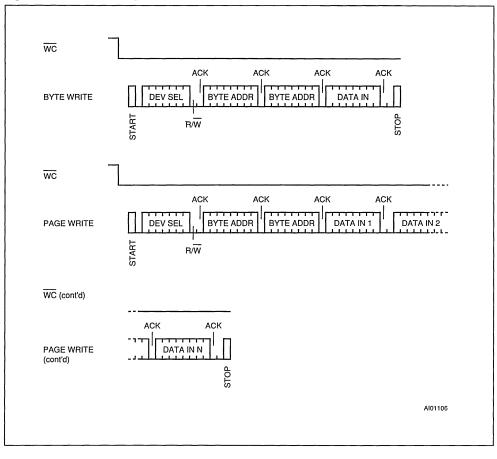

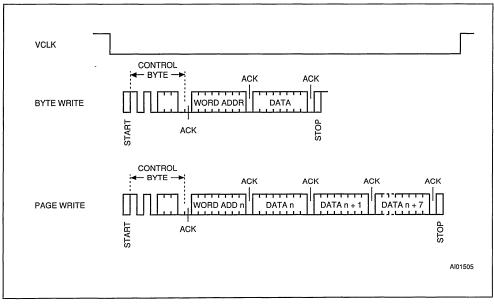

Byte Write. In the Byte Write mode the master sends one data byte, which is acknowledged by the memory. The master then terminates the transfer by generating a STOP condition. The Write mode is independant of the state of the MODE pin which could be left floating if only this mode was to be used. However it is not a recommended operating mode, as this pin has to be connected to either V<sub>IH</sub> or V<sub>IL</sub>, to minimize the stand-by current.

8/15

Multibyte Write. For the Multibyte Write mode, the MODE pin must be at VIH. The Multibyte Write mode can be started from any address in the memory. The master sends from one up to 4 bytes of data, which are each acknowledged by the memory. The transfer is terminated by the master generating a STOP condition. The duration of the write cycle is  $t_W = 10$  maximum except when bytes are accessed on 2 rows (that is have different values for the 5 most significant address bits A6-A2), the programming time is then doubled to a maximum of 20ms. Writing more than 4 bytes in the Multibyte Write mode may modify data bytes in an adjacent row (one row is 8 bytes long). However, the Multibyte Write can properly write up to 8 consecutive bytes only if the first address of these 8 bytes is the first address of the row, the 7 following bytes being written in the 7 following bytes of this same row.

Page Write. For the Page Write mode, the MODE pin must be at VIL. The Page Write mode allows up to 8 bytes to be written in a single write cycle. provided that they are all located in the same 'row' in the memory: that is the 5 most significant memory address bits (A7-A3) are the same. The master sends from one up to 8 bytes of data, which are each acknowledged by the memory. After each byte is transfered, the internal byte address counter (3 least significant bits only) is incremented. The transfer is terminated by the master generating a STOP condition. Care must be taken to avoid address counter 'roll-over' which could result in data being overwritten. Note that, for any write mode, the generation by the master of the STOP condition starts the internal memory program cycle. All inputs are disabled until the completion of this cycle and the memory will not respond to any request.

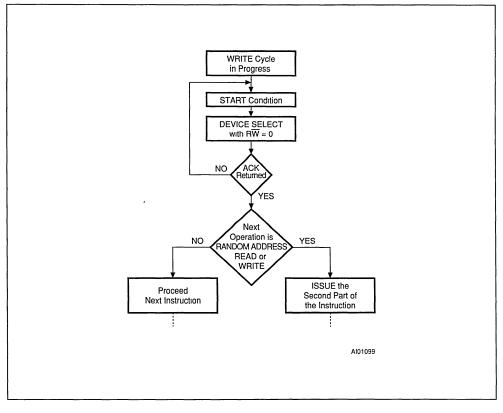

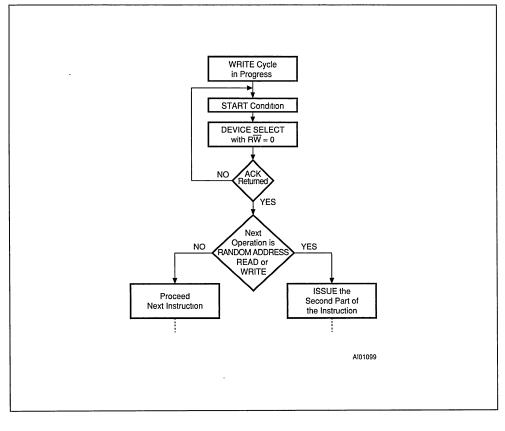

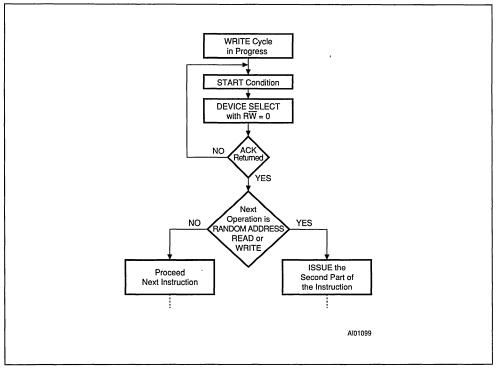

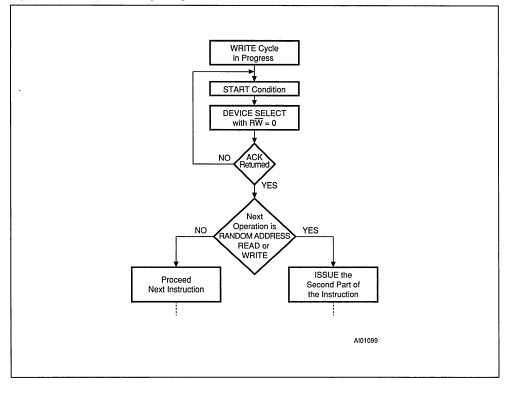

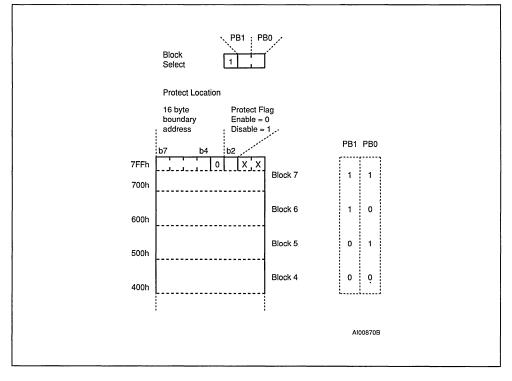

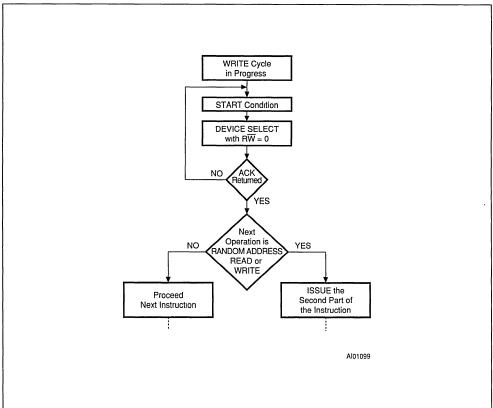

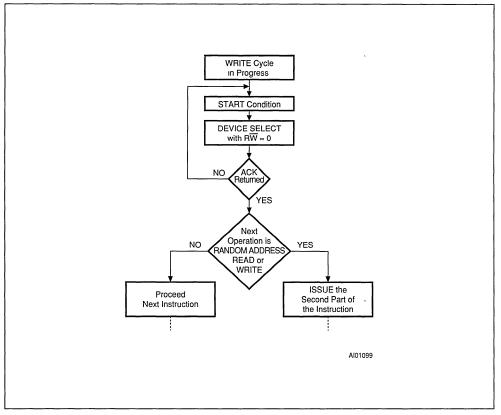

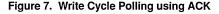

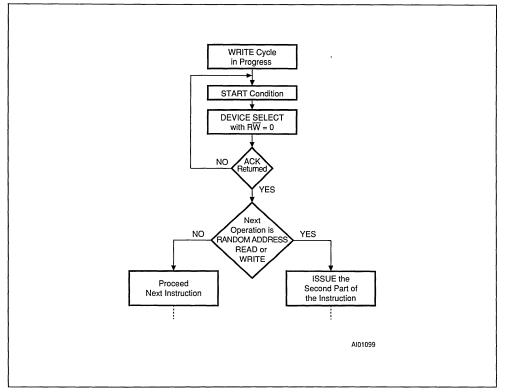

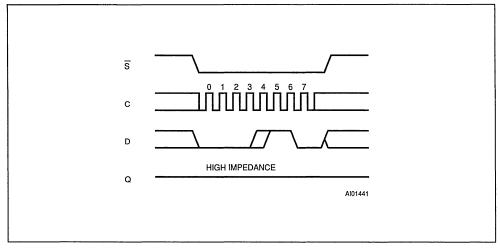

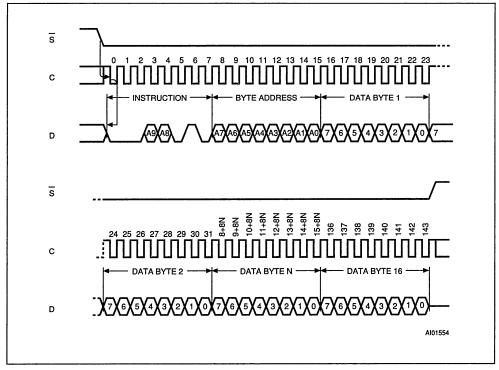

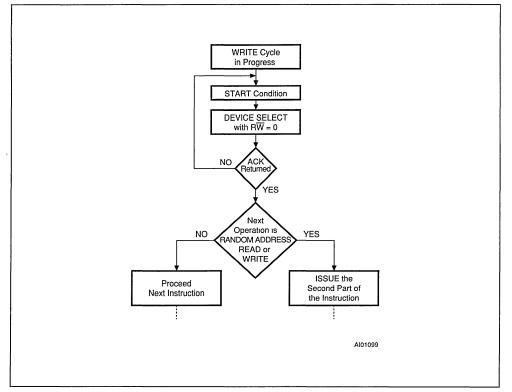

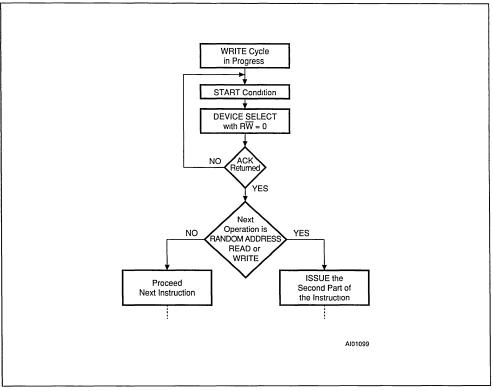

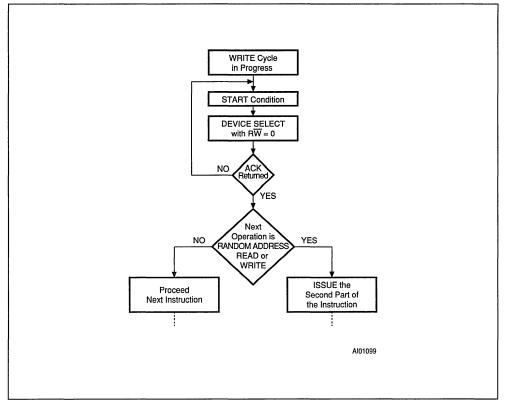

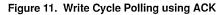

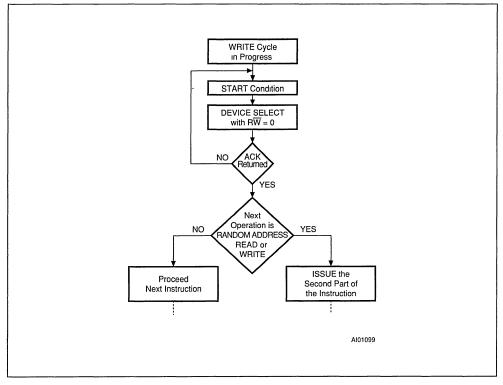

Figure 7. Write Cycle Polling using ACK

Minimizing System Delays by Polling On ACK. During the internal write cycle, the memory disconnects itself from the bus in order to copy the data from the internal latches to the memory cells. The maximum value of the write time (tW) is given in the AC Characteristics table, since the typical time is shorter, the time seen by the system may be reduced by an ACK polling sequence issued by the master. The sequence is as follows:

- Initial condition: a Write is in progress (see Figure 7).

- Step 1: the Master issues a START condition followed by a Device Select byte (1st byte of the new instruction).

- Step 2: if the memory is busy with the internal write cycle, no ACK will be returned and the master goes back to Step 1. If the memory has terminated the internal write cycle, it will respond with an ACK, indicating that the memory is ready to receive the second part of the next instruction (the first byte of this instruction was already sent during Step 1).

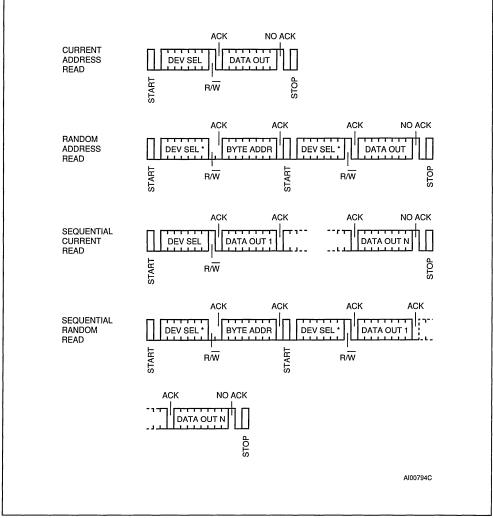

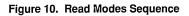

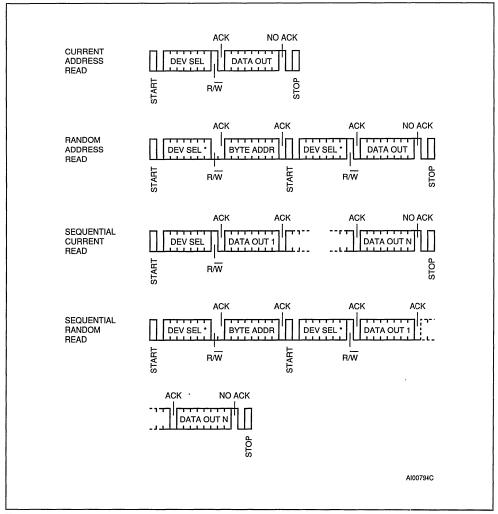

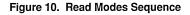

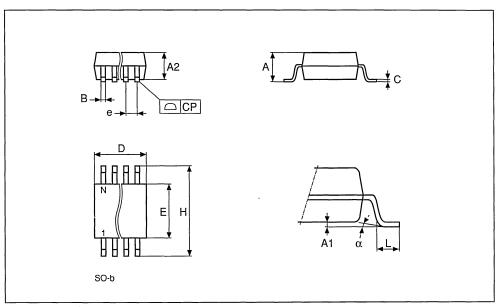

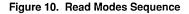

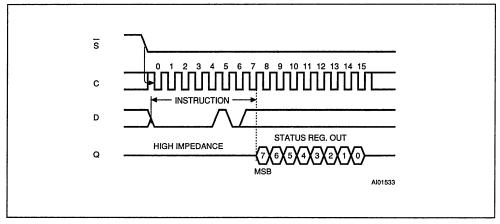

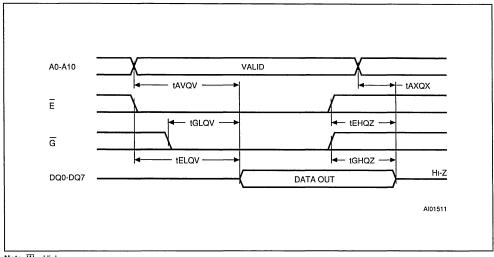

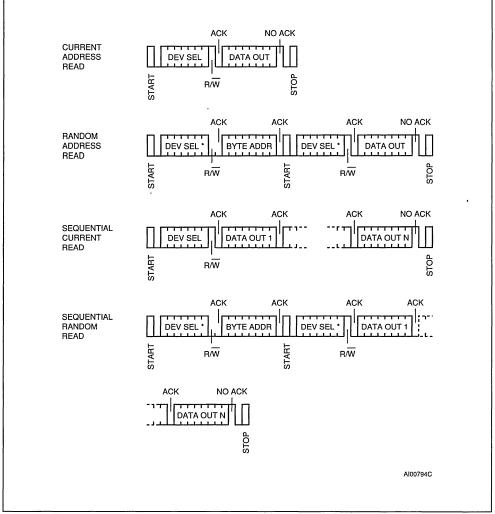

#### **Read Operations**

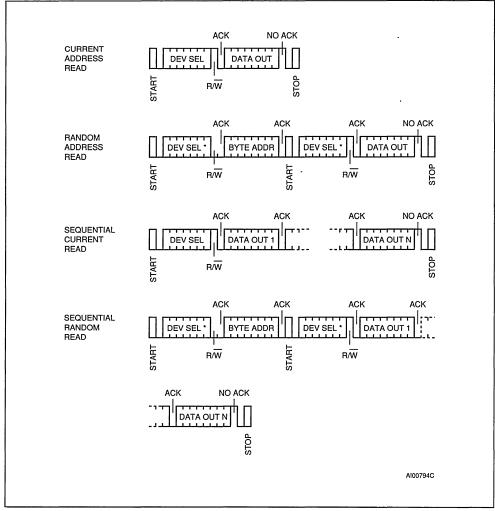

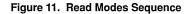

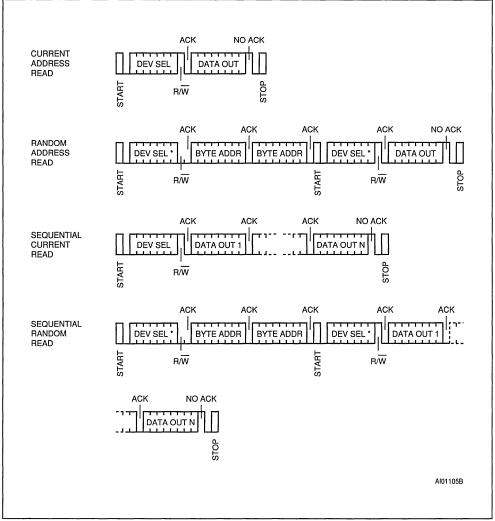

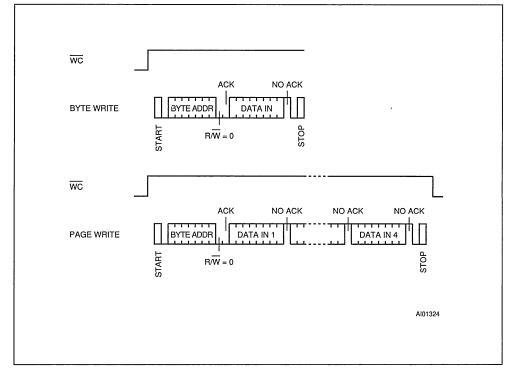

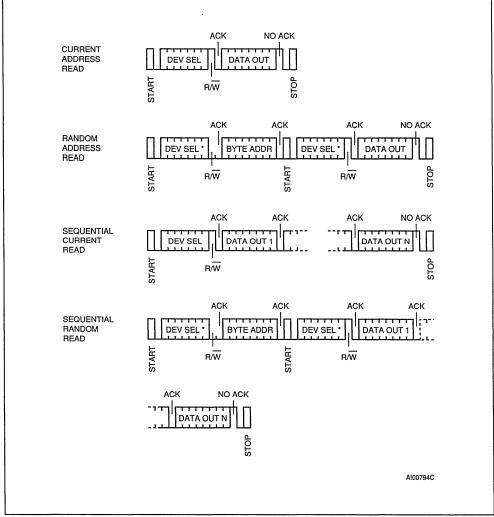

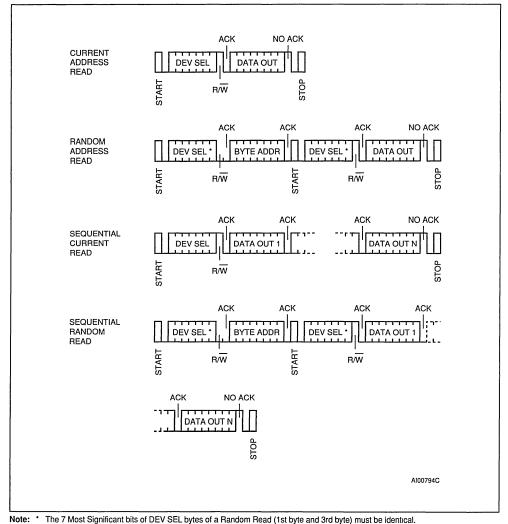

Read operations are independent of the state of the MODE pin. On delivery, the memory content is set at all "1's" (or FFh).

Current Address Read. The memory has an internal byte address counter. Each time a byte is read, this counter is incremented. For the Current Address Read mode, following a START condition, the master sends a memory address with the RW bit set to '1'. The memory acknowledges this and outputs the byte addressed by the internal byte address counter. This counter is then incremented. The master does NOT acknowledge the byte output, but terminates the transfer with a STOP condition.

Random Address Read. A dummy write is performed to load the address into the address counter, see Figure 10. This is followed by another START condition from the master and the byte address is repeated with the RW bit set to '1'. The memory acknowledges this and outputs the byte addressed. The master does NOT acknowledge the byte output, but terminates the transfer with a STOP condition.

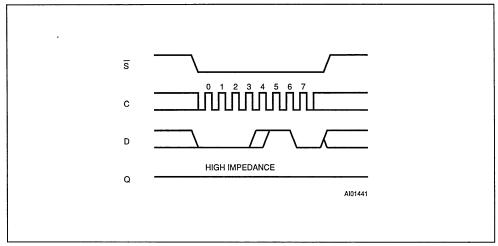

Figure 9. Write Modes Sequence with Write Control = 1 (ST24/25W01)

Sequential Read. This mode can be initiated with either a Current Address Read or a Random Address Read. However, in this case the master DOES acknowledge the data byte output and the memory continues to output the next byte in sequence. To terminate the stream of bytes, the master must NOT acknowledge the last byte output, but MUST generate a STOP condition. The output data is from consecutive byte addresses, with the internal byte address counter automatically incremented after each byte output. After a count of the last memory address, the address counter will 'roll- over' and the memory will continue to output data.

Acknowledge in Read Mode. In all read modes the ST24/25x01 wait for an acknowledge during the 9th bit time. If the master does not pull the SDA line low during this time, the St24/25x01 terminate the data transfer and switches to a standby state.

#### Figure 10. Read Modes Sequence

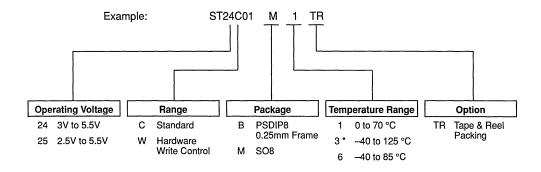

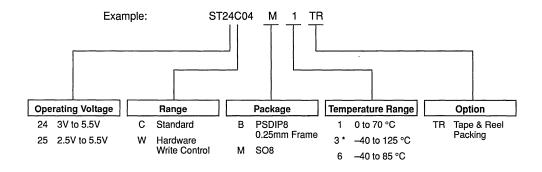

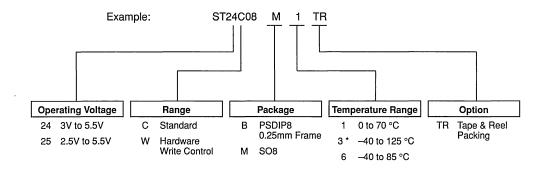

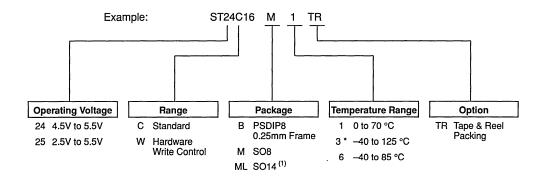

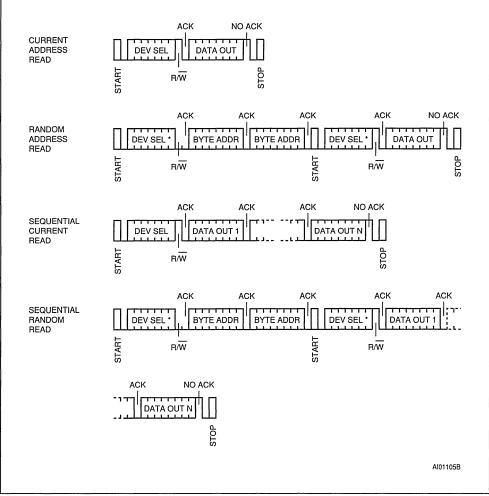

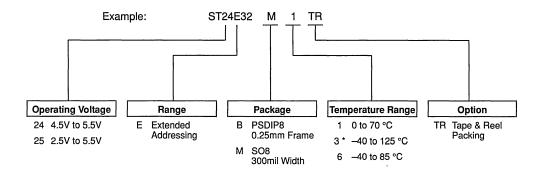

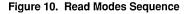

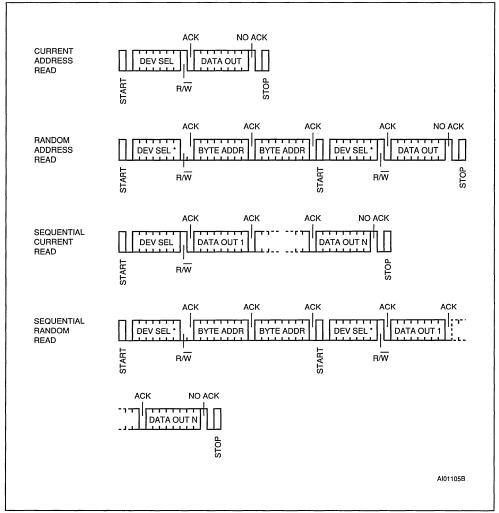

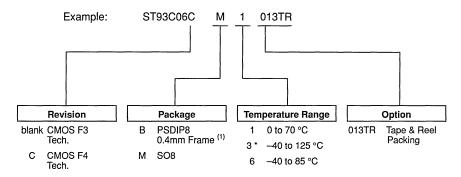

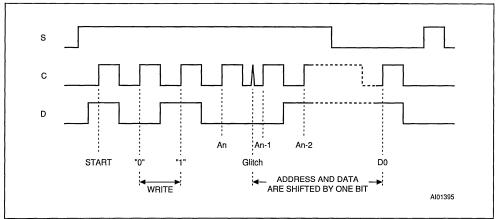

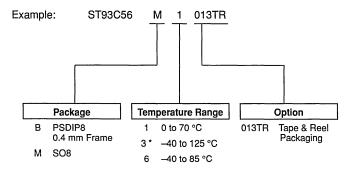

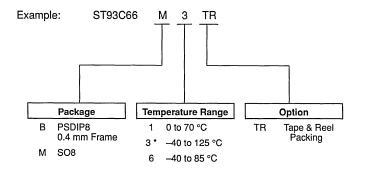

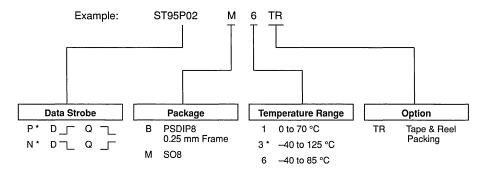

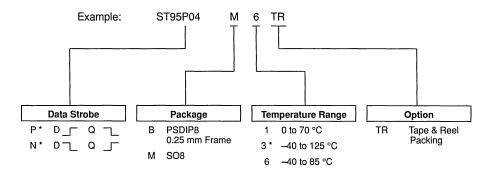

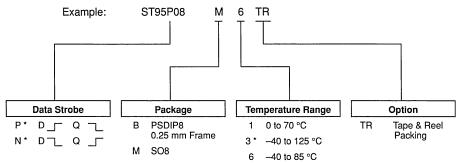

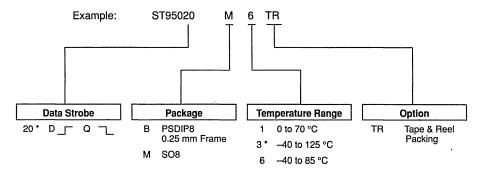

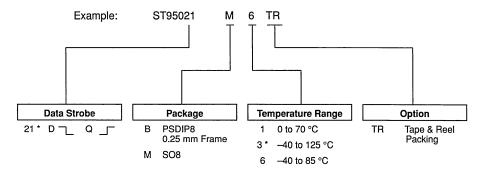

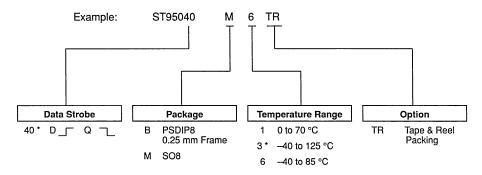

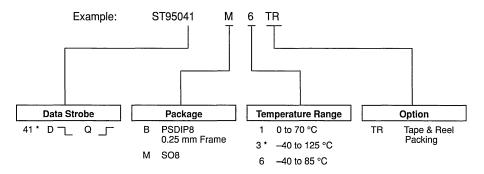

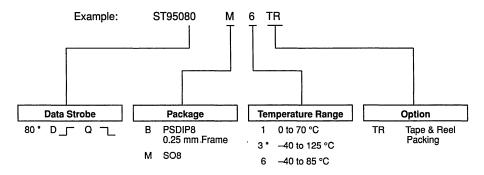

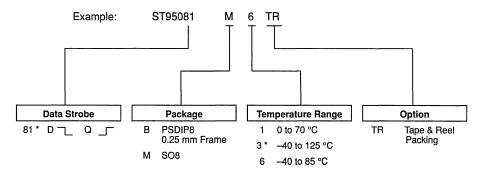

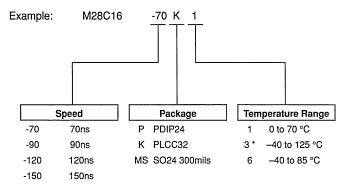

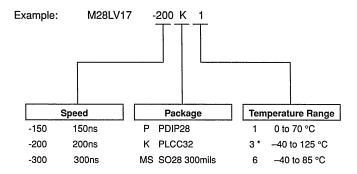

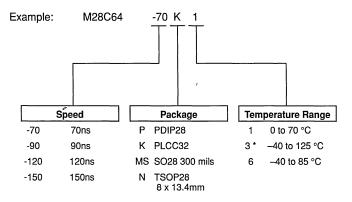

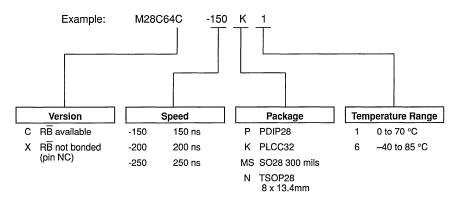

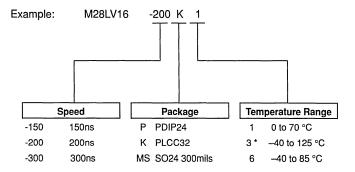

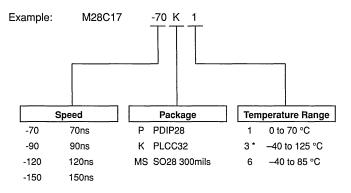

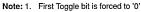

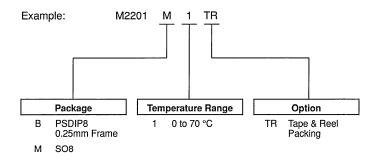

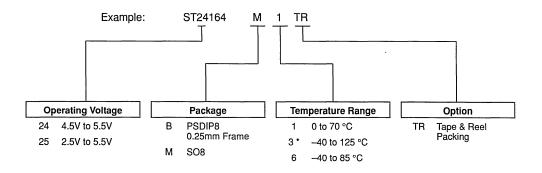

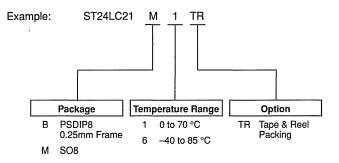

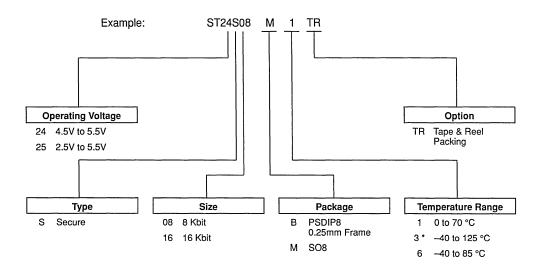

#### ORDERING INFORMATION SCHEME

Note: 3 \* Temperature range on special request only.

Parts are shipped with the memory content set at all "1's" (FFh).

For a list of available options (Operating Voltage, Range, Package, etc...) refer to the current Memory Shortform catalogue.

For further information on any aspect of this device, please contact SGS-THOMSON Sales Office nearest to you.

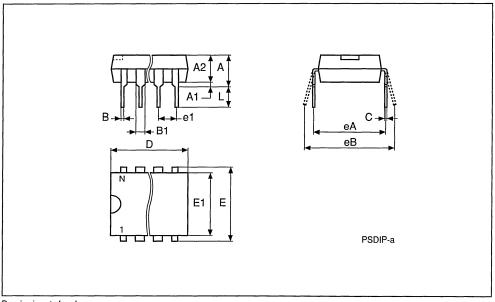

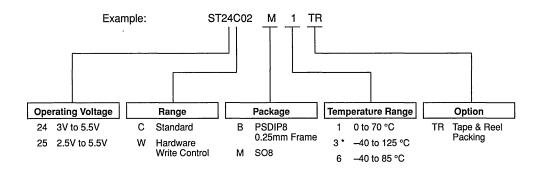

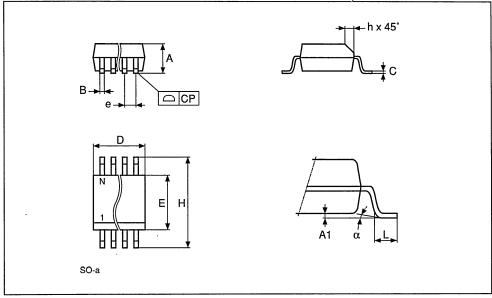

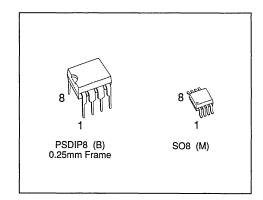

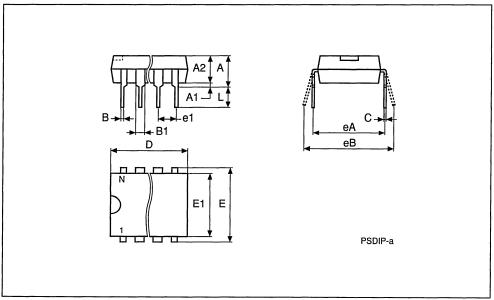

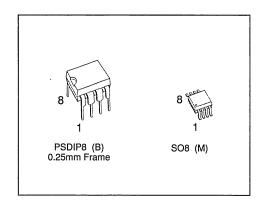

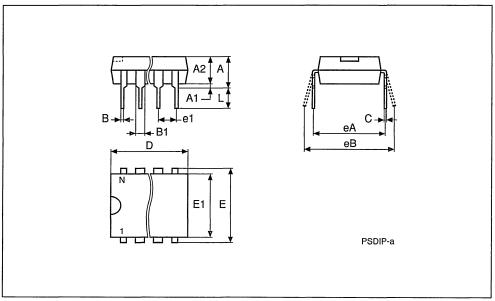

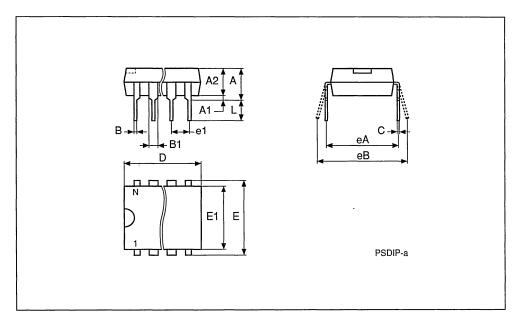

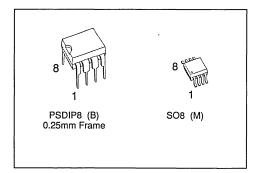

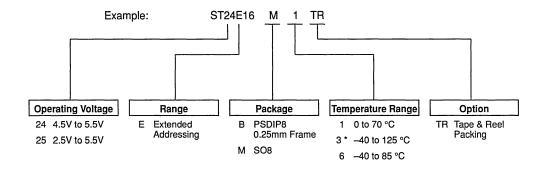

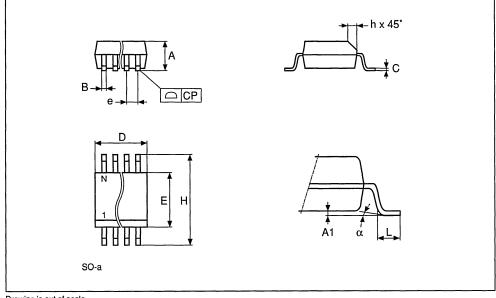

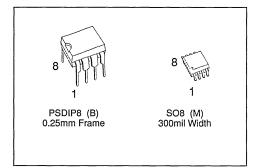

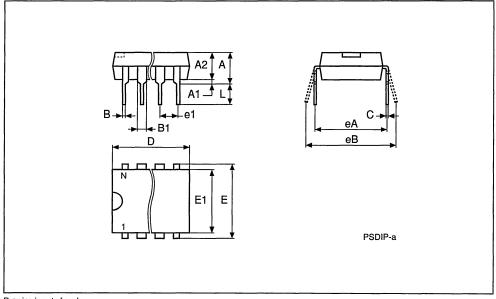

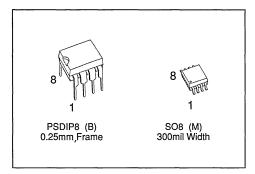

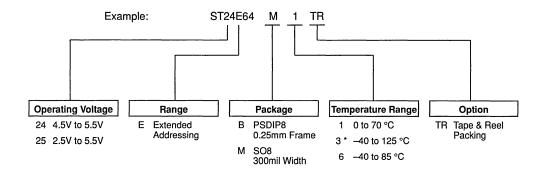

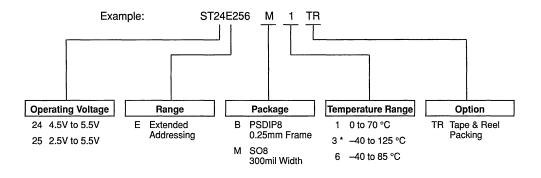

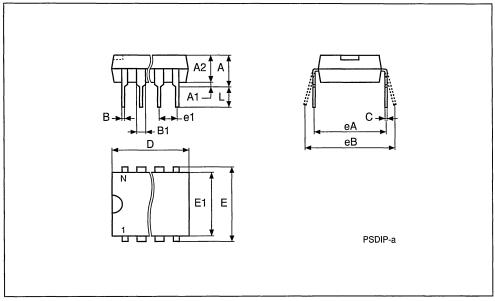

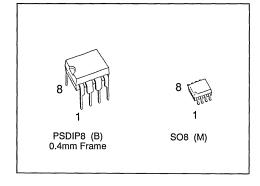

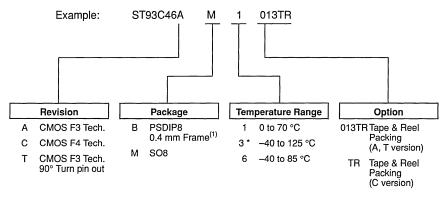

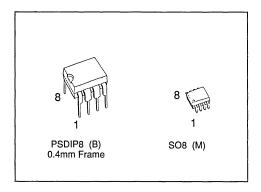

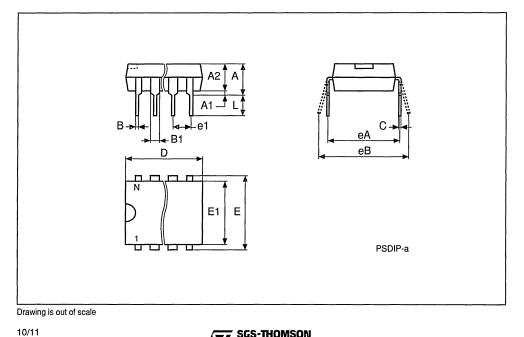

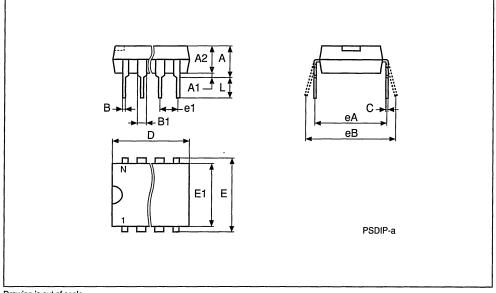

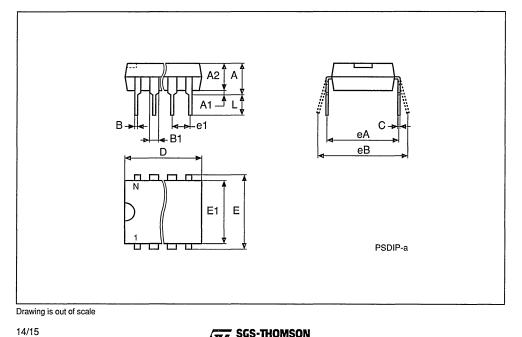

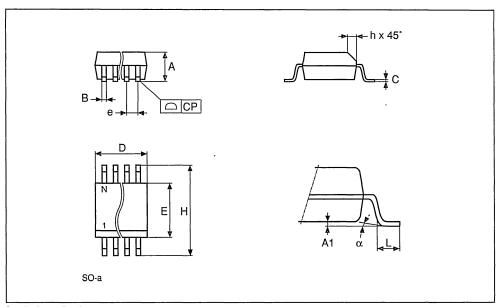

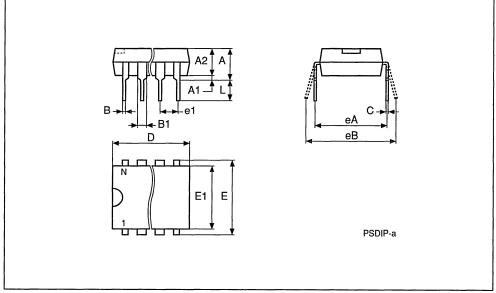

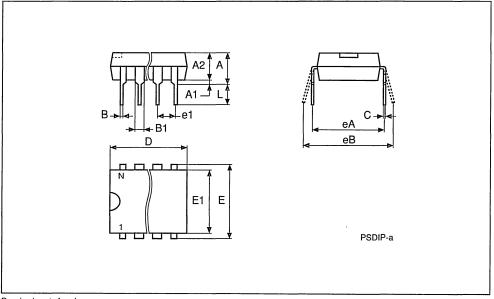

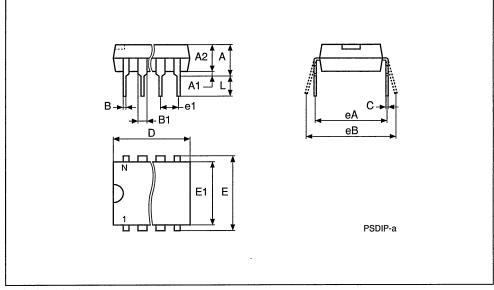

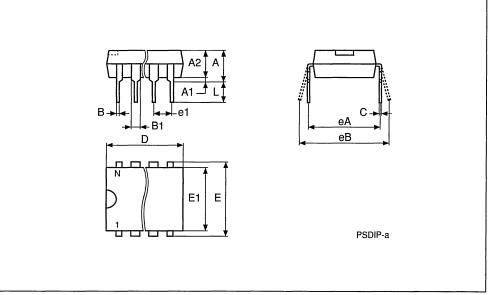

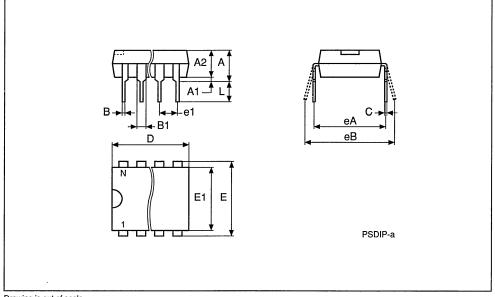

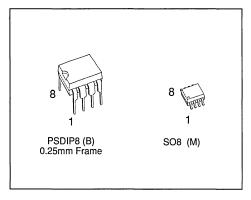

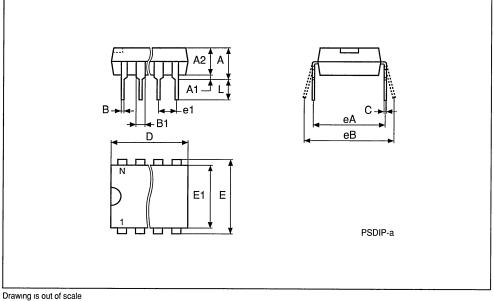

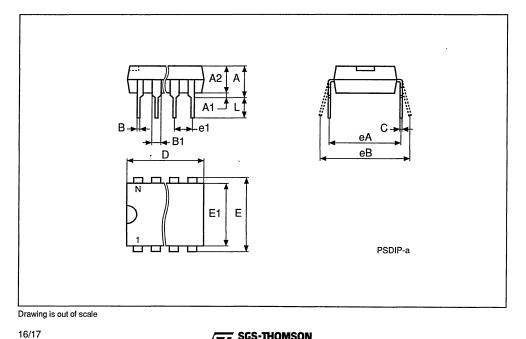

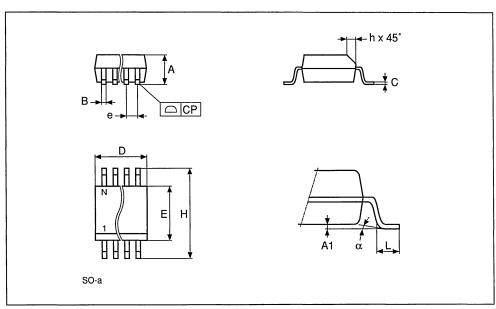

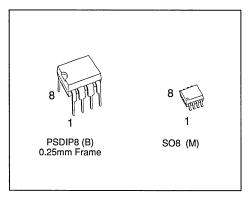

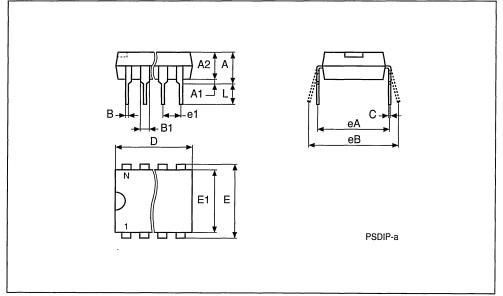

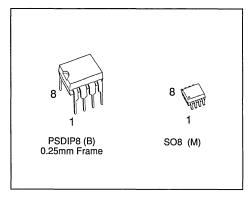

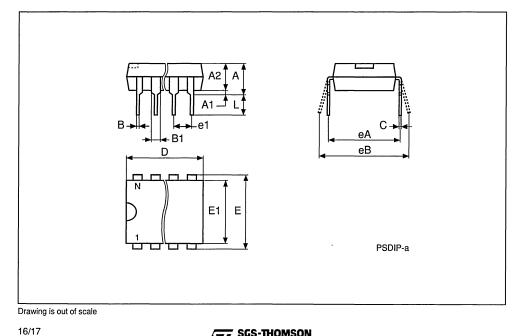

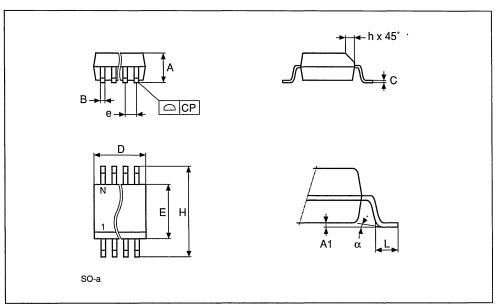

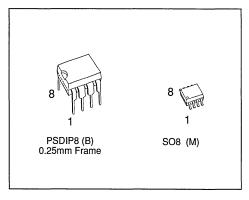

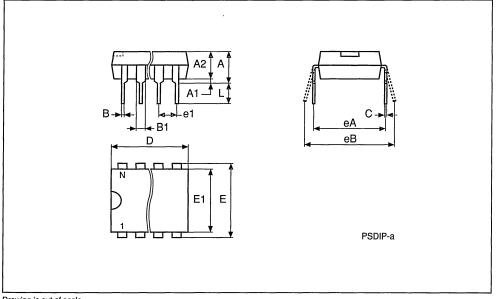

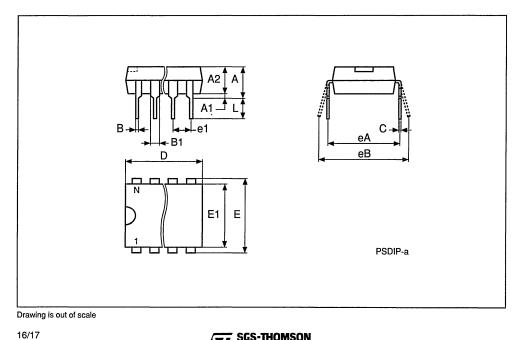

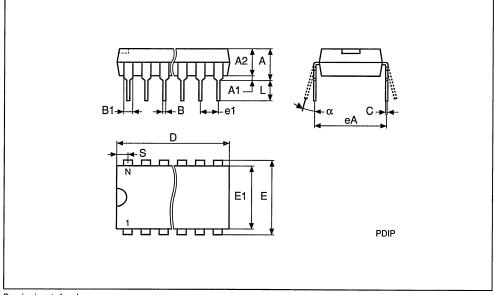

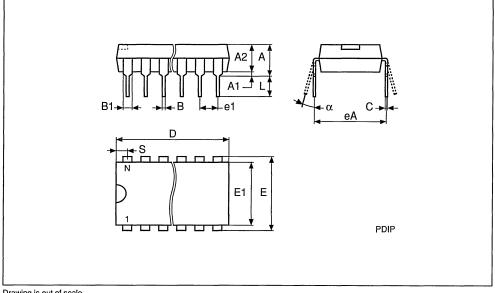

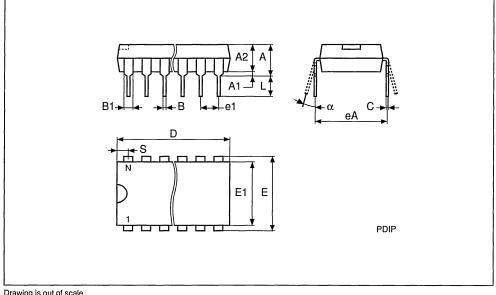

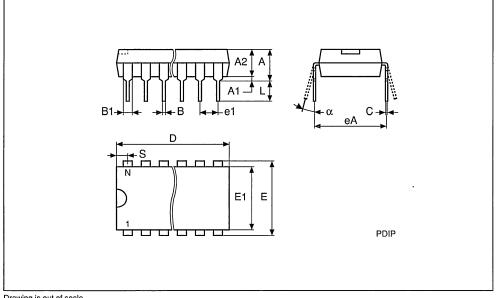

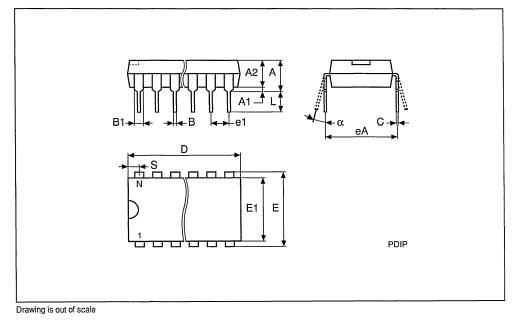

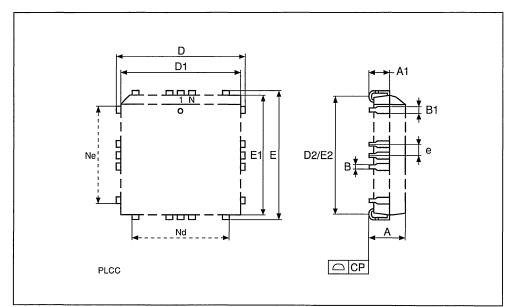

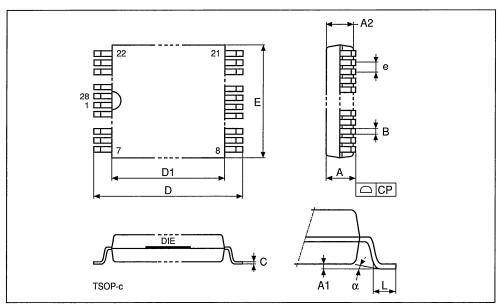

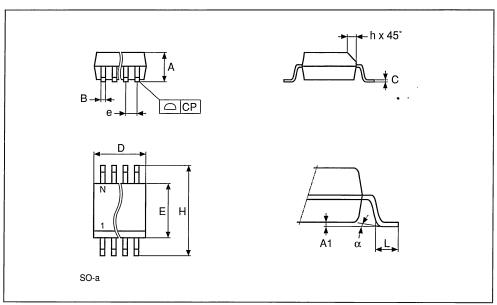

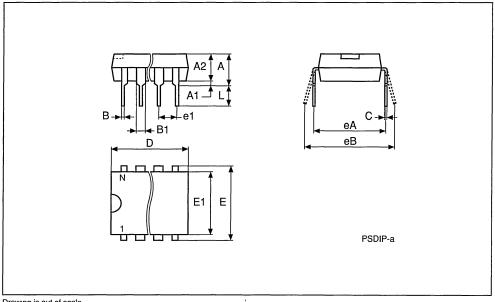

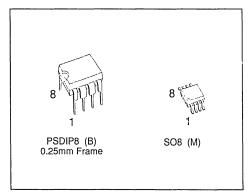

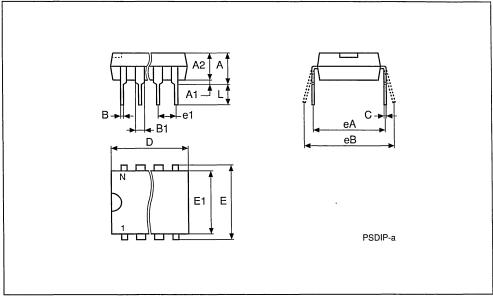

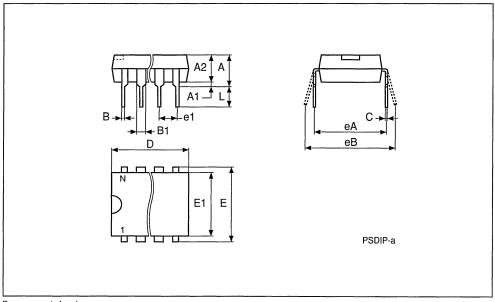

#### PSDIP8 - 8 pin Plastic Skinny DIP, 0.25mm lead frame

| Symb  |      | mm   |       |       | inches |       |

|-------|------|------|-------|-------|--------|-------|

| Synto | Тур  | Min  | Max   | Тур   | Min    | Max   |

| A     |      | 3.90 | 5.90  |       | 0.154  | 0.232 |

| A1    |      | 0.49 | -     |       | 0.019  | -     |

| A2    |      | 3.30 | 5.30  |       | 0.130  | 0.209 |

| В     |      | 0.36 | 0.56  |       | 0.014  | 0.022 |

| B1    |      | 1.15 | 1.65  |       | 0.045  | 0.065 |

| С     |      | 0.20 | 0.36  |       | 0.008  | 0.014 |

| D     |      | 9.20 | 9.90  |       | 0.362  | 0.390 |

| E     | 7.62 | _    | -     | 0.300 | _      | -     |

| E1    |      | 6.00 | 6.70  |       | 0.236  | 0.264 |

| e1    | 2.54 | _    | -     | 0.100 | -      | -     |

| eA    |      | 7.80 | _     |       | 0.307  | -     |

| eB    |      |      | 10.00 |       |        | 0.394 |

| L     |      | 3.00 | 3.80  |       | 0.118  | 0.150 |

| N     |      | 8    |       |       | 8      |       |

PSDIP8

Drawing is out of scale

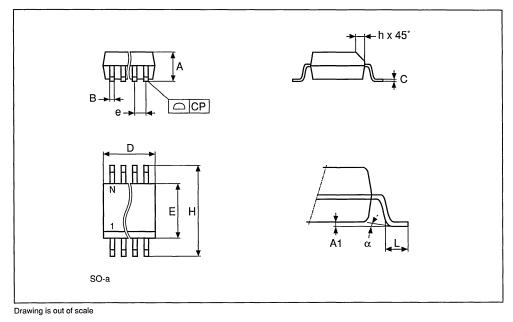

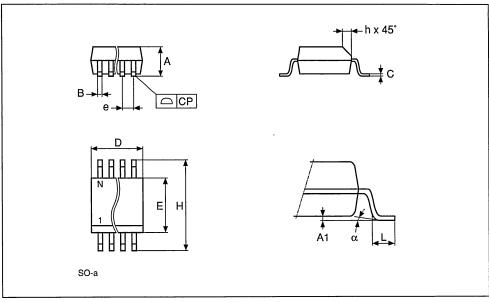

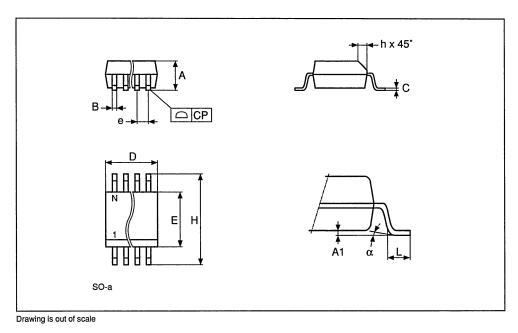

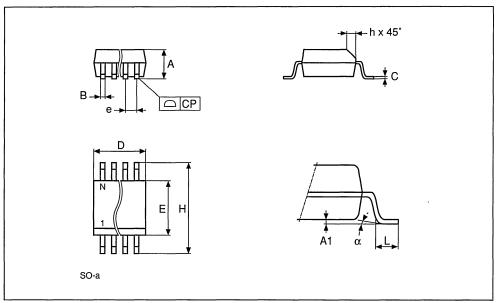

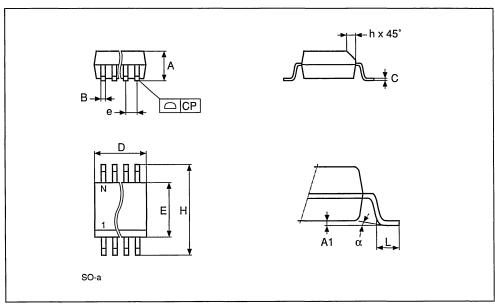

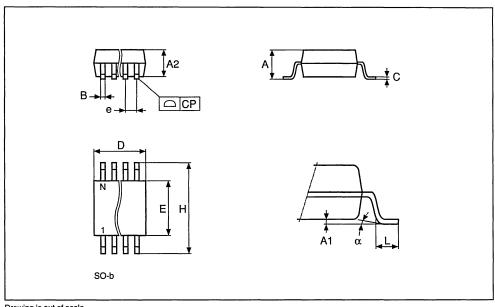

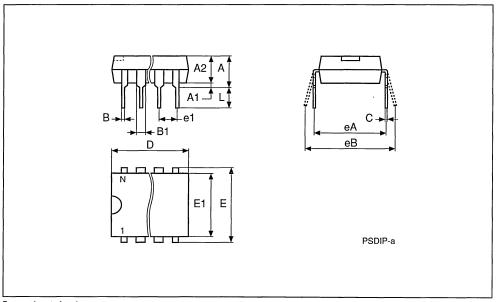

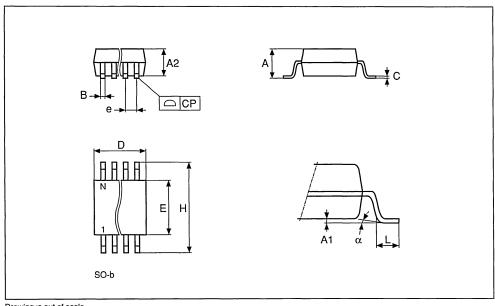

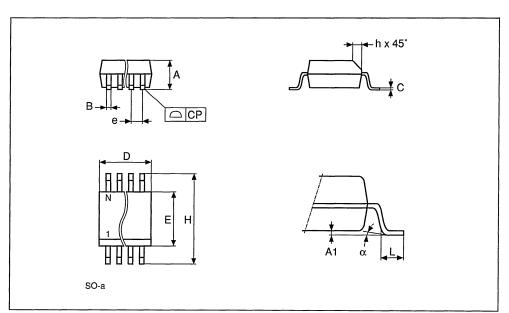

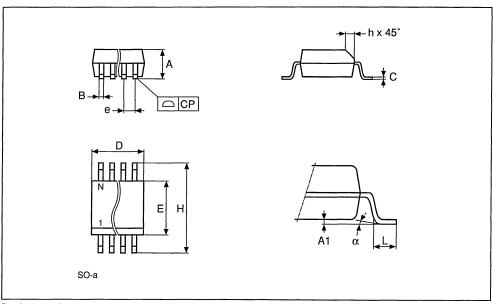

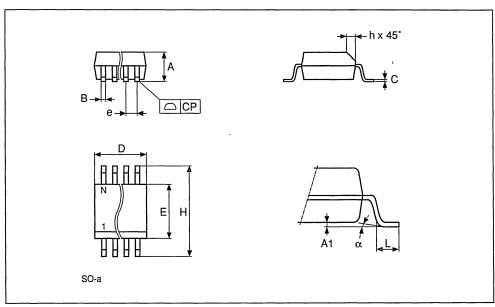

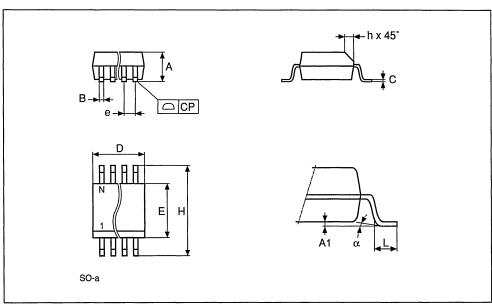

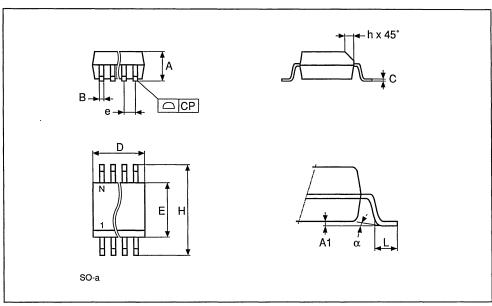

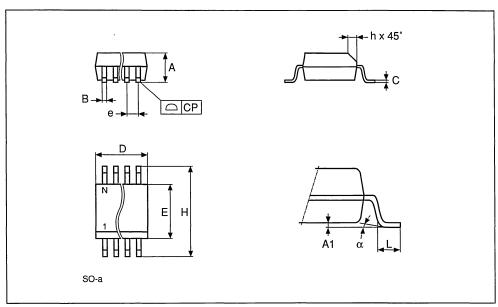

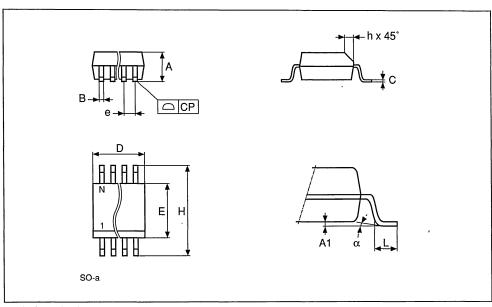

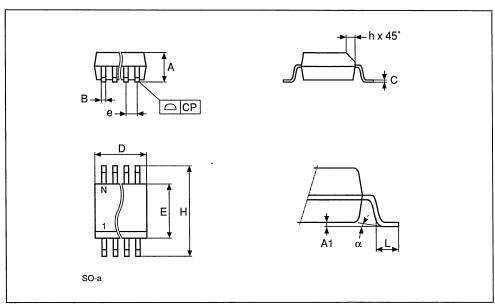

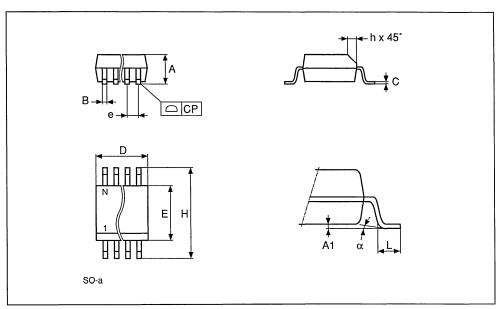

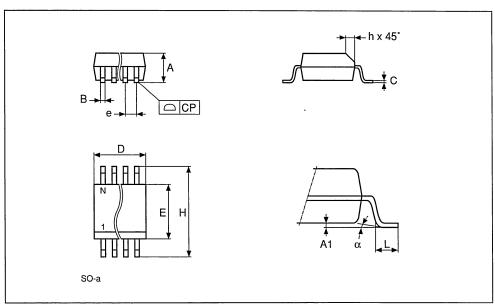

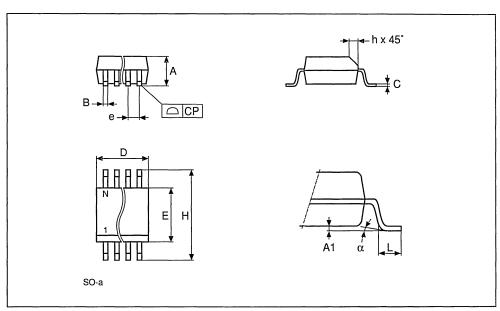

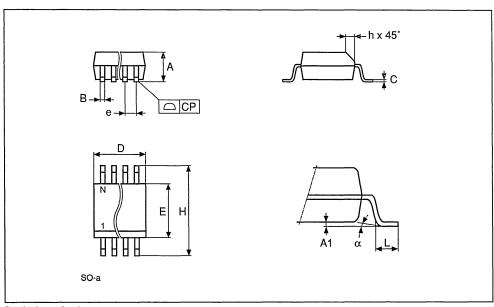

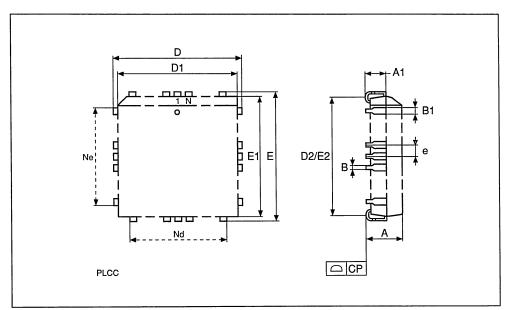

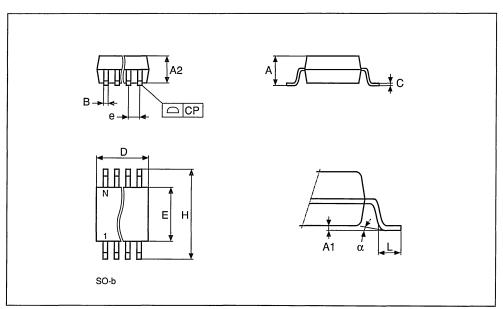

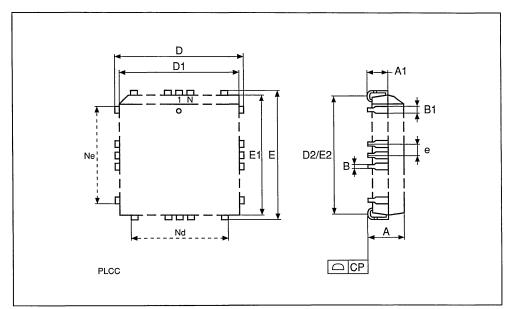

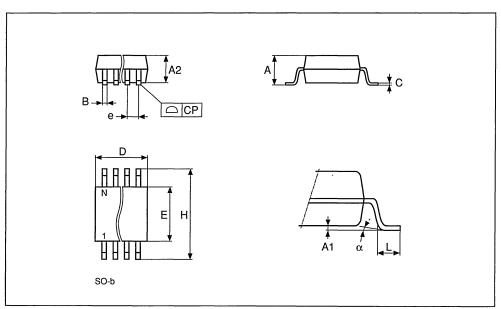

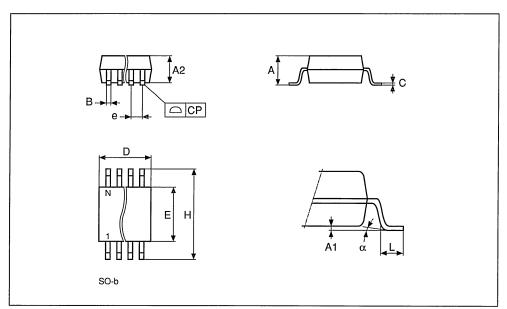

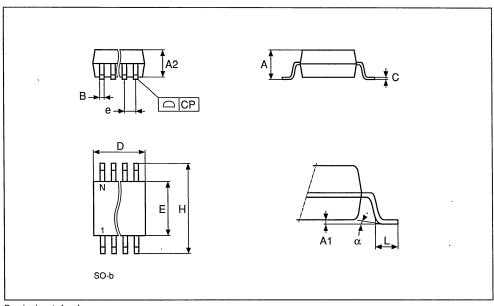

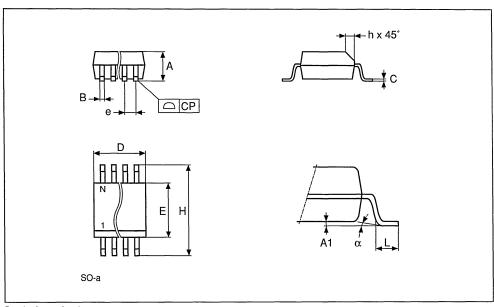

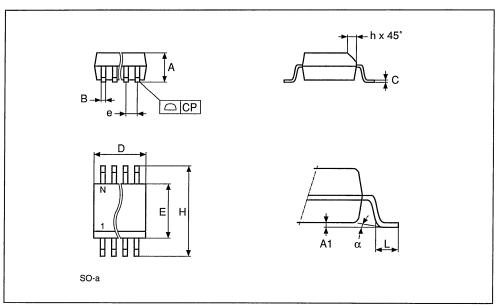

### SO8 - 8 lead Plastic Small Outline, 150 mils body width

| Symb |      | mm   |      | inches |       |       |  |

|------|------|------|------|--------|-------|-------|--|

| Symb | Тур  | Min  | Max  | Тур    | Min   | Max   |  |

| A    |      | 1.35 | 1.75 |        | 0.053 | 0.069 |  |

| A1   |      | 0.10 | 0.25 |        | 0.004 | 0.010 |  |

| В    |      | 0.33 | 0.51 |        | 0.013 | 0.020 |  |

| С    |      | 0.19 | 0.25 |        | 0.007 | 0.010 |  |

| D    |      | 4.80 | 5.00 |        | 0.189 | 0.197 |  |

| E    |      | 3.80 | 4.00 |        | 0.150 | 0.157 |  |

| е    | 1.27 | -    | -    | 0.050  | -     | -     |  |

| н    |      | 5.80 | 6.20 |        | 0.228 | 0.244 |  |

| h    |      | 0.25 | 0.50 |        | 0.010 | 0.020 |  |

| L    |      | 0.40 | 0.90 |        | 0.016 | 0.035 |  |

| α    |      | 0°   | 8°   |        | 0°    | 8°    |  |

| N    |      | 8    |      |        | 8     |       |  |

| СР   |      |      | 0.10 |        |       | 0.004 |  |

SO8

## ST24C02, ST25C02 ST24W02, ST25W02

## SERIAL ACCESS 2K (256 x 8) EEPROM

- 1 MILLION ERASE/WRITE CYCLES with 10 YEARS DATA RETENTION

- SINGLE SUPPLY VOLTAGE:

- 3V to 5.5V for ST24x02 versions

- 2.5V to 5.5V for ST25x02 versions

- HARDWARE WRITE CONTROL VERSIONS: ST24W02 and ST25W02

- TWO WIRE SERIAL INTERFACE, FULLY I<sup>2</sup>C BUS COMPATIBLE

- BYTE and MULTIBYTE WRITE (up to 4 BYTES)

- PAGE WRITE (up to 8 BYTES)

- BYTE, RANDOM and SEQUENTIAL READ MODES

- SELF TIMED PROGRAMMING CYCLE

- AUTOMATIC ADDRESS INCREMENTING

- ENHANCED ESD/LATCH-UP PERFORMANCES

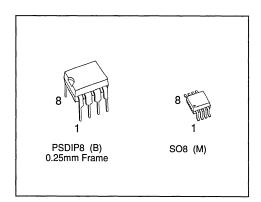

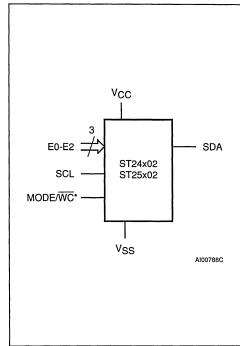

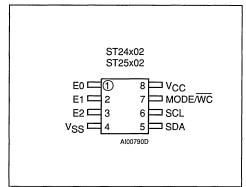

Figure 1. Logic Diagram

Note: WC signal is only available for ST24/25W02 products.

#### DESCRIPTION

This specification covers a range of 2K bits  $I^2C$  bus EEPROM products, the ST24/25C02 and ST24/25W02. In the text, products are referred to as ST24/25x02, where "x" is: "C" for Standard version and "W" for hardware Write Control version.

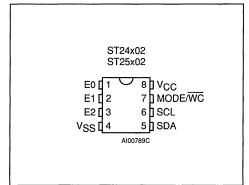

#### Table 1. Signal Names

| E0-E2           | Chip Enable Inputs                       |

|-----------------|------------------------------------------|

| SDA             | Serial Data Address Input/Output         |

| SCL             | Serial Clock                             |

| MODE            | Multibyte/Page Write Mode<br>(C version) |

| WC              | Write Control (W version)                |

| V <sub>cc</sub> | Supply Voltage                           |

| V <sub>SS</sub> | Ground                                   |

#### Figure 2A. DIP Pin Connections

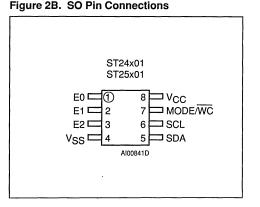

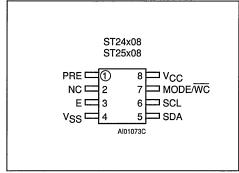

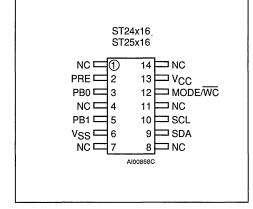

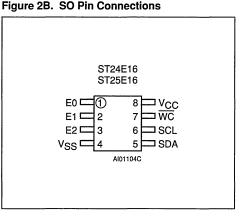

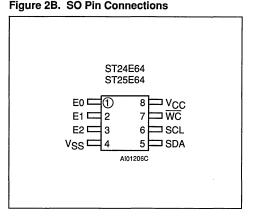

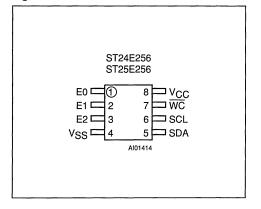

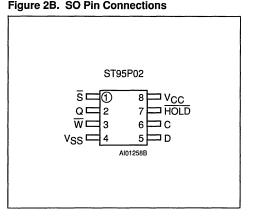

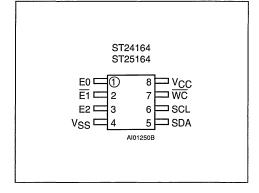

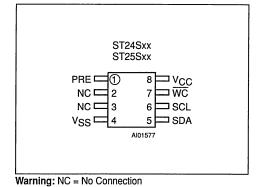

#### Figure 2B. SO Pin Connections

#### Table 2. Absolute Maximum Ratings (1)

| Symbol            | F                                                      | Parameter                         |                     | Value       | Unit |

|-------------------|--------------------------------------------------------|-----------------------------------|---------------------|-------------|------|

| TA                | Ambient Operating Temperature                          | grade 1<br>grade 6                | 0 to 70<br>40 to 85 | °C          |      |

| T <sub>STG</sub>  | Storage Temperature                                    |                                   |                     | -65 to 150  | °C   |

| T <sub>LEAD</sub> | Lead Temperature, Soldering                            | (SO8 package)<br>(PSDIP8 package) | 40 sec<br>10 sec    | 215<br>260  | °C   |

| Vio               | Input or Output Voltages                               |                                   |                     | 0.3 to 6.5  | v    |

| Vcc               | Supply Voltage                                         |                                   |                     | -0.3 to 6.5 | v    |

| V <sub>ESD</sub>  | Electrostatic Discharge Voltage (Human Body model) (2) |                                   |                     | 4000        | v    |

| • = 50            | Electrostatic Discharge Voltage (                      | Machine model) <sup>(3)</sup>     |                     | 500         | v    |

Notes: 1. Except for the rating "Operating Temperature Range", stresses above those listed in the Table "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the SGS-THOMSON SURE Program and other relevant quality documents. 2. MIL-STD-883C, 3015.7 (100pF, 1500  $\Omega$ ).

EIAJ IC-121 (Condition C) (200pF, 0 Ω).

#### **DESCRIPTION** (cont'd)

The ST24/25x02 are 2K bit electrically erasable programmable memories (EEPROM), organized as 256 x 8 bits. They are manufactured in SGS-THOMSON's Hi-Endurance Advanced CMOS technology which guarantees an endurance of one million erase/write cycles with a data retention of 10 years. The memories operate with a power supply value as low as 2.5V.

Both Plastic Dual-in-Line and Plastic Small Outline packages are available.

The memories are compatible with the I<sup>2</sup>C standard, two wire serial interface which uses a bi-direc-

tional data bus and serial clock. The memories carry a built-in 4 bit, unique device identification code (1010) corresponding to the I<sup>2</sup>C bus definition. This is used together with 3 chip enable inputs (E2, E1, E0) so that up to 8 x 2K devices may be attached to the I<sup>2</sup>C bus and selected individually. The memories behave as a slave device in the I<sup>2</sup>C protocol with all memory operations synchronized by the serial clock. Read and write operations are initiated by a START condition generated by the bus master. The START condition is followed by a stream of 7 bits (identification code 1010), plus one read/write bit and terminated by an acknowledge bit.

#### Table 3. Device Select Code

|               | Device Code |    |    |    | Chip Enable | •  | RW |    |

|---------------|-------------|----|----|----|-------------|----|----|----|

| Bit           | b7          | b6 | b5 | b4 | b3          | b2 | b1 | ь0 |

| Device Select | 1           | 0  | 1  | 0  | E2          | E1 | E0 | R₩ |

Note: The MSB b7 is sent first.

#### Table 4. Operating Modes (1)

| Mode                           | R₩ bit | MODE | Bytes    | Initial Sequence                                      |

|--------------------------------|--------|------|----------|-------------------------------------------------------|

| Current Address Read           | '1'    | x    | 1        | START, Device Select, $R\overline{W}$ = '1'           |

| Random Address Read            | '0'    | x    | 1        | START, Device Select, $R\overline{W}$ = '0', Address, |

| Nandolii Address nead          | '1'    |      |          | reSTART, Device Select, $\overline{RW}$ = '1'         |

| Sequential Read                | '1'    | x    | 1 to 256 | Similar to Current or Random Mode                     |

| Byte Write                     | '0'    | х    | 1        | START, Device Select, $R\overline{W}$ = '0'           |

| Multibyte Write <sup>(2)</sup> | '0'    | VIH  | 4        | START, Device Select, $R\overline{W}$ = '0'           |

| Page Write                     | '0'    | VIL  | 8        | START, Device Select, $R\overline{W} = '0'$           |

Notes: 1. X = VIH or VIL

2. Multibyte Write not available in ST24/25W02 versions.

When writing data to the memory it responds to the 8 bits received by asserting an acknowledge bit during the 9th bit time. When data is read by the bus master, it acknowledges the receipt of the data bytes in the same way. Data transfers are terminated with a STOP condition.

**Power On Reset:** V<sub>CC</sub> lock out write protect. In order to prevent data corruption and inadvertent write operations during power up, a Power On Reset (POR) circuit is implemented. Until the V<sub>CC</sub> voltage has reached the POR threshold value, the internal reset is active, all operations are disabled and the device will not respond to any command. In the same way, when V<sub>CC</sub> drops down from the operating voltage to below the POR threshold value, all operations are disabled and the device will not respond to any command. A stable V<sub>CC</sub> must be applied before applying any logic signal.

#### SIGNAL DESCRIPTIONS

Serial Clock (SCL). The SCL input pin is used to synchronize all data in and out of the memory. A resistor can be connected from the SCL line to V<sub>CC</sub> to act as a pull up (see Figure 3).

Serial Data (SDA). The SDA pin is bi-directional and is used to transfer data in or out of the memory. It is an open drain output that may be wire-OR'ed with other open drain or open collector signals on the bus. A resistor must be connected from the SDA bus line to V<sub>CC</sub> to act as pull up (see Figure 3).

**Chip Enable (E2 - E0).** These chip enable inputs are used to set the 3 least significant bits (b3, b2, b1) of the 7 bit device select code. These inputs may be driven dynamically or tied to  $V_{CC}$  or  $V_{SS}$  to establish the device select code.

**Mode (MODE).** The MODE input is available on pin 7 (see also  $\overline{WC}$  feature) and may be driven dynamically. It must be at  $V_{IL}$  or  $V_{IH}$  for the Byte Write mode,  $V_{IH}$  for Multibyte Write mode or  $V_{IL}$  for Page Write mode. When unconnected, the MODE input is internally read as a  $V_{IH}$  (Multibyte Write mode).

Write Control (WC). An hardware Write Control feature (WC) is offered only for ST24W02 and ST25W02 versions on pin 7. This feature is usefull to protect the contents of the memory from any erroneous erase/write cycle. The Write Control signal is used to enable (WC = V<sub>IH</sub>) or disable (WC = V<sub>IL</sub>) the internal write protection.

#### SIGNAL DESCRIPTIONS (cont'd)

The devices with this Write Control feature no longer support the Multibyte Write mode of operation, however all other write modes are fully supported.

Refer to the AN404 Application Note for more detailed information about Write Control feature.

#### **DEVICE OPERATION**

#### I<sup>2</sup>C Bus Background

The ST24/25x02 support the I<sup>2</sup>C protocol. This protocol defines any device that sends data onto the bus as a transmitter and any device that reads the data as a receiver. The device that controls the data transfer is known as the master and the other as the slave. The master will always initiate a data transfer and will provide the serial clock for synchronisation. The ST24/25x02 are always slave devices in all communications.

Start Condition. START is identified by a high to low transition of the SDA line while the clock SCL is stable in the high state. A START condition must precede any command for data transfer. Except during a programming cycle, the ST24/25x02 continuously monitor the SDA and SCL signals for a START condition and will not respond unless one is given.

**Stop Condition.** STOP is identified by a low to high transition of the SDA line while the clock SCL is stable in the high state. A STOP condition terminates communication between the ST24/25x02 and the bus master. A STOP condition at the end of a Read command forces the standby state. A STOP condition at the end of a Write command triggers the internal EEPROM write cycle.

Acknowledge Bit (ACK). An acknowledge signal is used to indicate a successfull data transfer. The bus transmitter, either master or slave, will release the SDA bus after sending 8 bits of data. During the 9th clock pulse period the receiver pulls the SDA bus low to acknowledge the receipt of the 8 bits of data.

**Data Input.** During data input the ST24/25x02 sample the SDA bus signal on the rising edge of the clock SCL. Note that for correct device operation the SDA signal must be stable during the clock low to high transition and the data must change ONLY when the SCL line is low.

Memory Addressing. To start communication between the bus master and the slave ST24/25x02, the master must initiate a START condition. Following this, the master sends onto the SDA bus line 8 bits (MSB first) corresponding to the device select code (7 bits) and a READ or WRITE bit.

Figure 3. Maximum R<sub>L</sub> Value versus Bus Capacitance (C<sub>BUS</sub>) for an I<sup>2</sup>C Bus

| Symbol          | Parameter                                         | Test Condition                     | Min | Max | Unit |

|-----------------|---------------------------------------------------|------------------------------------|-----|-----|------|

| CIN             | Input Capacitance (SDA)                           |                                    |     | 8   | pF   |

| C <sub>IN</sub> | Input Capacitance (other pins)                    |                                    |     | 6   | pF   |

| Zwcl            | WC Input Impedance (ST24/25W02)                   | $V_{\rm IN} \le 0.3 \; V_{\rm CC}$ | 5   | 20  | kΩ   |

| Zwch            | WC Input Impedance (ST24/25W02)                   | $V_{IN} \ge 0.7 V_{CC}$            | 500 |     | kΩ   |

| tLP             | Low-pass filter input time constant (SDA and SCL) |                                    |     | 100 | ns   |

Table 5. Input Parameters <sup>(1)</sup> ( $T_A = 25 \text{ °C}$ , f = 100 kHz )

Note: 1. Sampled only, not 100% tested.

#### Table 6. DC Characteristics

$(T_A = 0 \text{ to } 70 \text{ °C or } -40 \text{ to } 85 \text{ °C}; V_{CC} = 3V \text{ to } 5.5V \text{ or } 2.5V \text{ to } 5.5V)$

| Symbol | Parameter                                | Test Condition                                                                                                                                               | Min                   | Max                 | Unit |

|--------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------|------|

| ILI    | Input Leakage Current                    | $0V \leq V_{\text{IN}} \leq V_{\text{CC}}$                                                                                                                   |                       | ±2                  | μA   |

| ILO    | Output Leakage Current                   | $0V \le V_{OUT} \le V_{CC}$<br>SDA in Hi-Z                                                                                                                   |                       | ±2                  | μA   |

| Icc    | Supply Current (ST24 series)             | V <sub>CC</sub> = 5V, f <sub>C</sub> = 100kHz<br>(Rise/Fall time < 10ns)                                                                                     |                       | 2                   | mA   |

|        | Supply Current (ST25 series)             | $V_{CC}$ = 2.5V, $f_C$ = 100kHz                                                                                                                              |                       | 1                   | mA   |

|        | Supply Current (Standby)                 |                                                                                                                                                              |                       | 100                 | μA   |

|        | (ST24 series)                            | $\label{eq:Vin} \begin{split} V_{\text{IN}} &= V_{\text{SS}} \text{ or } V_{\text{CC}}, \\ V_{\text{CC}} &= 5 V,  f_{\text{C}} = 100 \text{kHz} \end{split}$ |                       | 300                 | μA   |

| Icc2   | Supply Current (Standby)                 | $\label{eq:VIN} \begin{array}{l} V_{IN} = V_{SS} \text{ or } V_{CC}, \\ V_{CC} = 2.5 V \end{array}$                                                          |                       | 5                   | μA   |

| 1002   | (ST25 series)                            | $\label{eq:VIN} \begin{array}{l} V_{IN} = V_{SS} \text{ or } V_{CC}, \\ V_{CC} = 2.5 \text{V}, \text{ f}_{C} = 100 \text{kHz} \end{array}$                   |                       | 50                  | μA   |

| VIL    | Input Low Voltage (SCL, SDA)             |                                                                                                                                                              | -0.3                  | 0.3 V <sub>CC</sub> | v    |

| VIH    | Input High Voltage (SCL, SDA)            |                                                                                                                                                              | 0.7 V <sub>CC</sub>   | Vcc + 1             | v    |

| VIL    | Input Low Voltage<br>(E0-E2, MODE, WC)   |                                                                                                                                                              | -0.3                  | 0.5                 | v    |

| ViH    | Input High Voltage_<br>(E0-E2, MODE, WC) |                                                                                                                                                              | V <sub>CC</sub> – 0.5 | V <sub>CC</sub> + 1 | v    |

| Vol    | Output Low Voltage (ST24 series)         | $I_{OL} = 3mA$ , $V_{CC} = 5V$                                                                                                                               |                       | 0.4                 | v    |

| VOL    | Output Low Voltage (ST25 series)         | I <sub>OL</sub> = 2.1mA, V <sub>CC</sub> = 2.5V                                                                                                              |                       | 0.4                 | v    |

#### Table 7. AC Characteristics

$(T_A = 0 \text{ to } 70 \text{ °C or } -40 \text{ to } 85 \text{ °C}; V_{CC} = 3V \text{ to } 5.5V \text{ or } 2.5V \text{ to } 5.5V)$

| Symbol                           | Alt                 | Parameter                                             | Min | Max | Unit |

|----------------------------------|---------------------|-------------------------------------------------------|-----|-----|------|

| tCH1CH2                          | t <sub>R</sub>      | Clock Rise Time                                       |     | 1   | μs   |

| tCL1CL2                          | tF                  | Clock Fall Time                                       |     | 300 | ns   |

| tDH1DH2                          | tR                  | Input Rise Time                                       |     | 1   | μs   |

| tDL1DL1                          | tF                  | Input Fall Time                                       |     | 300 | ns   |

| t <sub>CHDX</sub> <sup>(1)</sup> | t <sub>SU.STA</sub> | Clock High to Input Transition                        | 4.7 |     | μs   |

| tCHCL                            | tнigн               | Clock Pulse Width High                                | 4   |     | μs   |

| t <sub>DLCL</sub>                | thd sta             | Input Low to Clock Low (START)                        | 4   |     | μs   |

| tCLDX                            | thd dat             | Clock Low to Input Transition                         | 0   |     | μs   |

| tclch                            | tLOW                | Clock Pulse Width Low                                 | 4.7 |     | μs   |

| t <sub>DXCX</sub>                | tsu.dat             | Input Transition to Clock Transition                  | 250 |     | ns   |

| tснрн                            | tsu sto             | Clock High to Input High (STOP)                       | 4.7 |     | μs   |

| <b>t</b> DHDL                    | t <sub>BUF</sub>    | Input High to Input Low (Bus Free)                    | 4.7 |     | μs   |

| tcLQV                            | taa                 | Clock Low to Data Out Valid                           | 0.3 | 3.5 | μs   |

| tCLQX                            | tон                 | Clock Low to Data Out Transition                      | 300 |     | ns   |

| fc                               | fscl                | Clock Frequency                                       |     | 100 | kHz  |

| t <sub>NS</sub>                  | Tı                  | Noise Suppression Time Constant<br>(SCL & SDA Inputs) |     | 100 | ns   |

| tw <sup>(2)</sup>                | twR                 | Write Time                                            |     | 10  | ms   |

Notes: 1. For a reSTART condition, or following a write cycle.

In the Multibyte Write mode only, if accessed bytes are on two consecutive 8 bytes rows (6 address MSB are not constant) the

maximum programming time is doubled to 20ms.

#### AC MEASUREMENT CONDITIONS

| Input Rise and Fall Times | ≤ 50ns |

|---------------------------|--------|

|                           |        |

Input Pulse Voltages

0.2V<sub>CC</sub> to 0.8V<sub>CC</sub>

Input and Output Timing Ref. Voltages  $~0.3V_{CC}$  to  $0.7V_{CC}$

#### Figure 4. AC Testing Input Output Waveforms

#### **DEVICE OPERATION** (cont'd)

The 4 most significant bits of the device select code are the device type identifier, corresponding to the  $l^2C$  bus definition. For these memories the 4 bits are fixed as 1010b. The following 3 bits identify the specific memory on the bus. They are matched to the chip enable signals E2, E1, E0. Thus up to 8 x 2K memories can be connected on the same bus giving a memory capacity total of 16K bits. After a START condition any memory on the bus will identify the device code and compare the following 3 bits to its chip enable inputs E2, E1, E0.

The 8th bit sent is the read or write bit  $(R\overline{W})$ , this bit is set to '1' for read and '0' for write operations. If a match is found, the corresponding memory will acknowledge the identification on the SDA bus during the 9th bit time.

#### Figure 5. AC Waveforms

#### Figure 6. I<sup>2</sup>C Bus Protocol

#### Write Operations

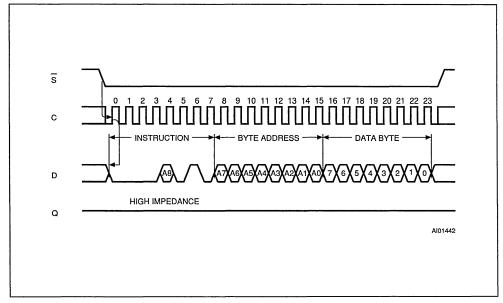

The Multibyte Write mode (only available on the ST24/25C02 versions) is selected when the MODE pin is at V<sub>IH</sub> and the Page Write mode when MODE pin is at V<sub>IL</sub>. The MODE pin may be driven dynamically with CMOS input levels.

Following a START condition the master sends a device select code with the RW bit reset to '0'. The memory acknowledges this and waits for a byte address. The byte address of 8 bits provides access to 256 bytes of the memory. After receipt of the byte address the device again responds with an acknowledge.

For the ST24/25W02 versions, any write command with  $\overline{WC} = 1$  will not modify the memory content.

Byte Write. In the Byte Write mode the master sends one data byte, which is acknowledged by the memory. The master then terminates the transfer by generating a STOP condition. The Write mode is independant of the state of the MODE pin which could be left floating if only this mode was to be used. However it is not a recommended operating mode, as this pin has to be connected to either V<sub>IH</sub> or V<sub>IL</sub>, to minimize the stand-by current.

Multibyte Write. For the Multibyte Write mode, the MODE pin must be at VIH. The Multibyte Write mode can be started from any address in the memory. The master sends from one up to 4 bytes of data, which are each acknowledged by the memory. The transfer is terminated by the master generating a STOP condition. The duration of the write cycle is tw = 10ms maximum except when bytes are accessed on 2 rows (that is have different values for the 6 most significant address bits A7-A2), the programming time is then doubled to a maximum of 20ms. Writing more than 4 bytes in the Multibyte Write mode may modify data bytes in an adjacent row (one row is 8 bytes long). However, the Multibyte Write can properly write up to 8 consecutive bytes only if the first address of these 8 bytes is the first address of the row, the 7 following bytes being written in the 7 following bytes of this same row.

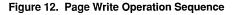

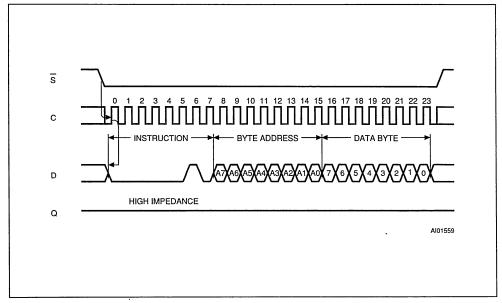

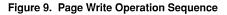

Page Write. For the Page Write mode, the MODE pin must be at VIL. The Page Write mode allows up to 8 bytes to be written in a single write cycle. provided that they are all located in the same 'row' in the memory: that is the 5 most significant memory address bits (A7-A3) are the same. The master sends from one up to 8 bytes of data, which are each acknowledged by the memory. After each byte is transfered, the internal byte address counter (3 least significant bits only) is incremented. The transfer is terminated by the master generating a STOP condition. Care must be taken to avoid address counter 'roll-over' which could result in data being overwritten. Note that, for any write mode, the generation by the master of the STOP condition starts the internal memory program cycle. All inputs are disabled until the completion of this cycle and the memory will not respond to any request.

Figure 7. Write Cycle Polling using ACK

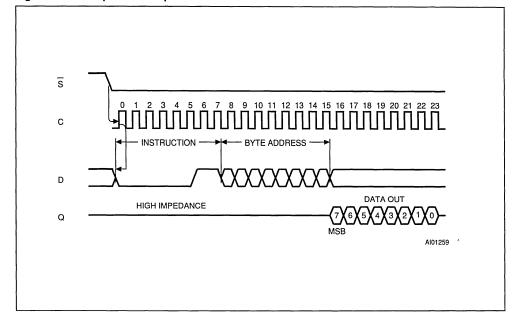

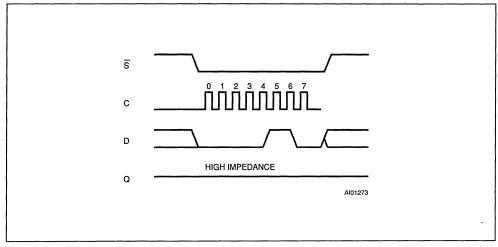

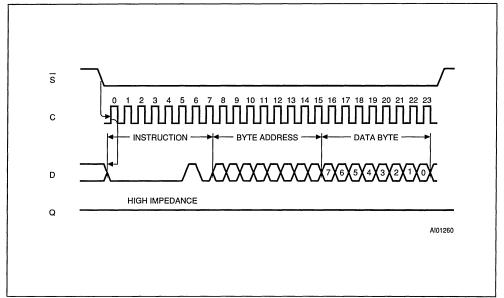

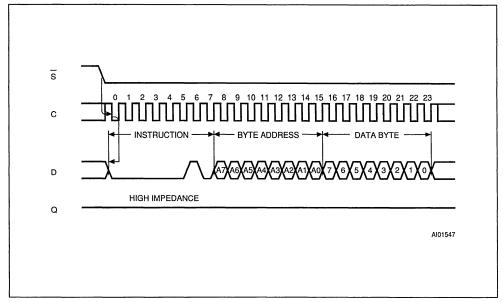

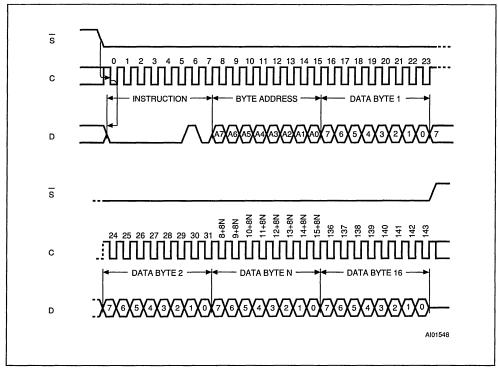

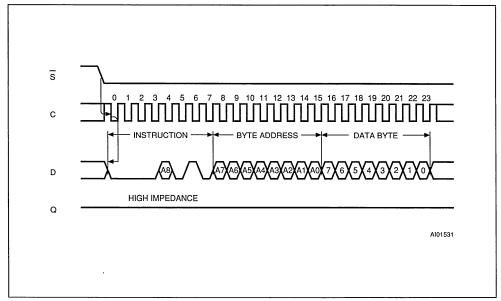

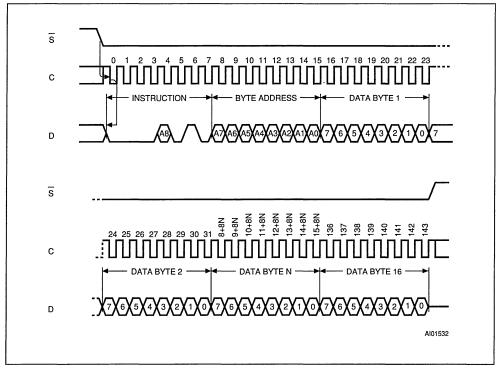

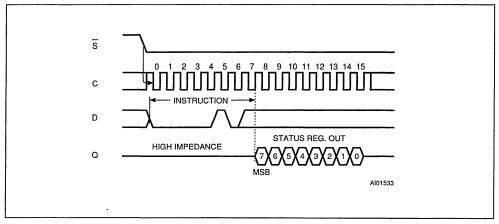

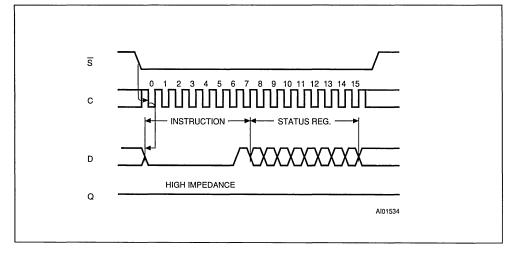

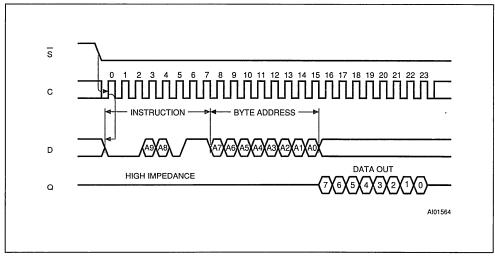

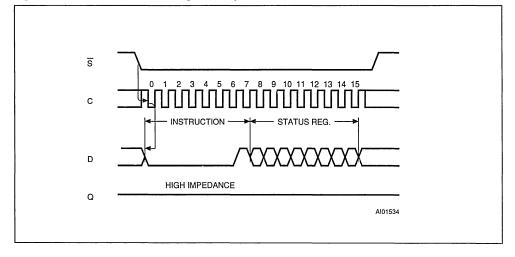

### Figure 8. Write Modes Sequence (ST24/25C02)

Minimizing System Delays by Polling On ACK. During the internal write cycle, the memory disconnects itself from the bus in order to copy the data from the internal latches to the memory cells. The maximum value of the write time (tw) is given in the AC Characteristics table, since the typical time is shorter, the time seen by the system may be reduced by an ACK polling sequence issued by the master. The sequence is as follows:

- Initial condition: a Write is in progress (see Figure 7).

- Step 1: the master issues a START condition followed by a device select byte (1st byte of the new instruction).

- Step 2: if the memory is busy with the internal write cycle, no ACK will be returned and the master goes back to Step 1. If the memory has terminated the internal write cycle, it will respond with an ACK, indicating that the memory is ready to receive the second part of the next instruction (the first byte of this instruction was already sent during Step 1).

### **Read Operations**

Read operations are independent of the state of the MODE pin. On delivery, the memory content is set at all "1's" (or FFh).

Current Address Read. The memory has an internal byte address counter. Each time a byte is read, this counter is incremented. For the Current Address Read mode, following a START condition, the master sends a memory address with the RW bit set to '1'. The memory acknowledges this and outputs the byte addressed by the internal byte address counter. This counter is then incremented. The master does NOT acknowledge the byte output, but terminates the transfer with a STOP condition.

Random Address Read. A dummy write is performed to load the address into the address counter, see Figure 10. This is followed by another START condition from the master and the byte address is repeated with the RW bit set to '1'. The memory acknowledges this and outputs the byte addressed. The master does NOT acknowledge the byte output, but terminates the transfer with a STOP condition.

Figure 9. Write Modes Sequence with Write Control = 1 (ST24/25W02)

Sequential Read. This mode can be initiated with either a Current Address Read or a Random Address Read. However, in this case the master DOES acknowledge the data byte output and the memory continues to output the next byte in sequence. To terminate the stream of bytes, the master must NOT acknowledge the last byte output, but MUST generate a STOP condition. The output data is from consecutive byte addresses, with the internal byte address counter automatically incremented after each byte output. After a count of the last memory address, the address counter will 'roll- over' and the memory will continue to output data.

Acknowledge in Read Mode. In all read modes the ST24/25x02 wait for an acknowledge during the 9th bit time. If the master does not pull the SDA line low during this time, the ST24/25x02 terminate the data transfer and switches to a standby state.

Note: \* The 7 Most Significant bits of DEV SEL bytes of a Random Read (1st byte and 3rd byte) must be identical.

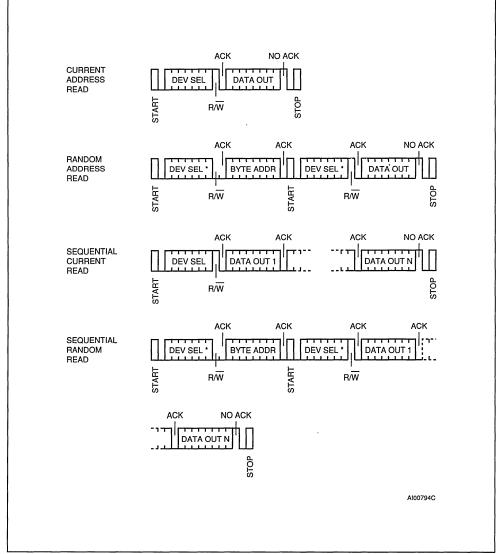

### **ORDERING INFORMATION SCHEME**

Note: 3 \* Temperature range on special request only.

Parts are shipped with the memory content set at all "1's" (FFh).

For a list of available options (Operating Voltage, Range, Package, etc...) refer to the current Memory Shortform catalogue.

For further information on any aspect of this device, please contact SGS-THOMSON Sales Office nearest to you.

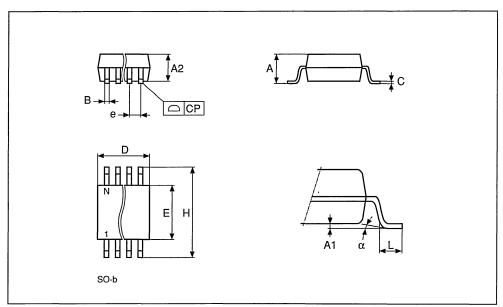

### PSDIP8 - 8 pin Plastic Skinny DIP, 0.25mm lead frame

| Symb  | mm   |      |       |       | inches |                                   |

|-------|------|------|-------|-------|--------|-----------------------------------|

| Cynto | Тур  | Min  | Max   | Тур   | Min    | Max                               |

| A     |      | 3.90 | 5.90  |       | 0.154  | 0.232                             |

| A1    |      | 0.49 | -     |       | 0.019  | -                                 |

| A2    |      | 3.30 | 5.30  |       | 0.130  | 0.209                             |

| В     |      | 0.36 | 0.56  |       | 0.014  | 0.022                             |

| B1    |      | 1.15 | 1.65  |       | 0.045  | 0.065                             |

| С     |      | 0.20 | 0.36  |       | 0.008  | 0.014                             |

| D     |      | 9.20 | 9.90  |       | 0.362  | 0.390                             |

| E     | 7.62 | -    | -     | 0.300 | -      | -                                 |

| E1    |      | 6.00 | 6.70  |       | 0.236  | 0.264                             |

| e1    | 2.54 | -    | _     | 0.100 | -      | -                                 |

| eA    |      | 7.80 | -     |       | 0.307  | -                                 |

| eB    |      |      | 10.00 |       |        | 0.394                             |

| L     |      | 3.00 | 3.80  |       | 0.118  | 0.150                             |

| N     |      | 8    |       |       | 8      | · · · · · · · · · · · · · · · · · |

PSDIP8

Drawing is out of scale

# SO8 - 8 lead Plastic Small Outline, 150 mils body width

| Symb  |      | mm   |      |       | inches |       |  |

|-------|------|------|------|-------|--------|-------|--|

| Synno | Тур  | Min  | Max  | Тур   | Min    | Мах   |  |

| А     |      | 1.35 | 1.75 |       | 0.053  | 0.069 |  |

| A1    |      | 0.10 | 0.25 |       | 0.004  | 0.010 |  |

| В     |      | 0.33 | 0.51 |       | 0.013  | 0.020 |  |

| С     |      | 0.19 | 0.25 |       | 0.007  | 0.010 |  |

| D     |      | 4.80 | 5.00 |       | 0.189  | 0.197 |  |

| E     |      | 3.80 | 4.00 |       | 0.150  | 0.157 |  |

| е     | 1.27 | -    | _    | 0.050 | -      | _     |  |

| н     |      | 5.80 | 6.20 |       | 0.228  | 0.244 |  |

| h     |      | 0.25 | 0.50 |       | 0.010  | 0.020 |  |

| L     |      | 0.40 | 0.90 |       | 0.016  | 0.035 |  |

| α     |      | 0°   | 8°   |       | 0°     | 8°    |  |

| N     | 8    |      |      |       | . 8    |       |  |

| CP    |      |      | 0.10 |       |        | 0.004 |  |

SO8

Drawing is out of scale

#### SGS-THOMSON MICROELECTRONICS

. .

# SERIAL ACCESS 4K (512 x 8) EEPROM

- 1 MILLION ERASE/WRITE CYCLES with 10 YEARS DATA RETENTION

- SINGLE SUPPLY VOLTAGE:

- 3V to 5.5V for ST24x04 versions

- 2.5V to 5.5V for ST25x04 versions

- HARDWARE WRITE CONTROL VERSIONS: ST24W04 and ST25W04

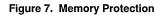

- PROGRAMMABLE WRITE PROTECTION

- TWO WIRE SERIAL INTERFACE, FULLY I<sup>2</sup>C BUS COMPATIBLE

- BYTE and MULTIBYTE WRITE (up to 4 BYTES)

- PAGE WRITE (up to 8 BYTES)

- BYTE, RANDOM and SEQUENTIAL READ MODES

- SELF TIMED PROGRAMMING CYCLE

- AUTOMATIC ADDRESS INCREMENTING

- ENHANCED ESD/LATCH UP PERFORMANCES

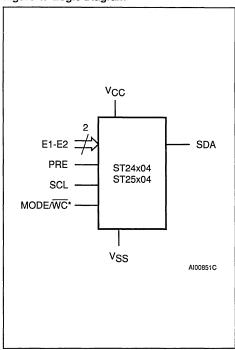

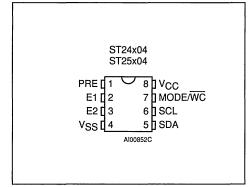

### DESCRIPTION

This specification covers a range of 4K bits I<sup>2</sup>C bus EEPROM products, the ST24/25C04 and the ST24/25W04. In the text, products are referred to as ST24/25x04, where "x" is: "C" for Standard version and "W" for hardware Write Control version.

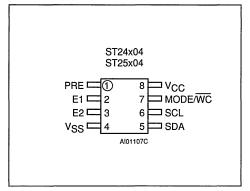

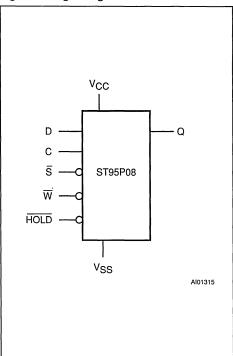

| Table | 1. | Signal | Names |

|-------|----|--------|-------|

|-------|----|--------|-------|

| PRE             | Write Protect Enable                     |

|-----------------|------------------------------------------|

| E1-E2           | Chip Enable Inputs                       |

| SDA             | Serial Data Address Input/Output         |

| SCL             | Serial Clock                             |

| MODE            | Multibyte/Page Write Mode<br>(C version) |

| WC              | Write Control (W version)                |

| Vcc             | Supply Voltage                           |

| V <sub>SS</sub> | Ground                                   |

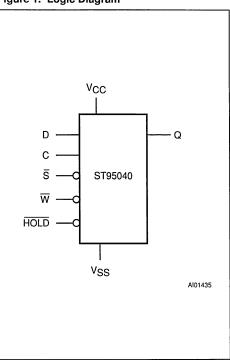

Figure 1. Logic Diagram

Note: WC signal is only available for ST24/25W04 products.

### Figure 2A. DIP Pin Connections

### Figure 2B. SO Pin Connections

### Table 2. Absolute Maximum Ratings (1)

| Symbol            | F                                                                 | arameter                          |                    | Value               | Unit |

|-------------------|-------------------------------------------------------------------|-----------------------------------|--------------------|---------------------|------|

| T <sub>A</sub>    | Ambient Operating Temperature                                     |                                   | grade 1<br>grade 6 | 0 to 70<br>40 to 85 | °C   |

| T <sub>STG</sub>  | Storage Temperature                                               |                                   |                    | -65 to 150          | °C   |

| T <sub>LEAD</sub> | Lead Temperature, Soldering                                       | (SO8 package)<br>(PSDIP8 package) | 40 sec<br>10 sec   | 215<br>260          | °C   |

| Vio               | Input or Output Voltages                                          |                                   |                    | -0.3 to 6.5         | V    |

| Vcc               | Supply Voltage                                                    |                                   |                    | -0.3 to 6.5         | V    |

| V <sub>ESD</sub>  | Electrostatic Discharge Voltage (Human Body model) <sup>(2)</sup> |                                   |                    | 4000                | V    |

| ▼ ESD             | Electrostatic Discharge Voltage (Machine model) (3)               |                                   |                    | 500                 | V    |

Notes: 1. Except for the rating "Operating Temperature Range", stresses above those listed in the Table "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the SGS-THOMSON SURE Program and other relevant quality documents. 2. MIL-STD-883C, 3015.7 (100pF, 1500 Ω).

EIAJ IC-121 (Condition C) (200pF, 0 Ω).

### DESCRIPTION (cont'd)

The ST24/25x04 are 4K bit electrically erasable programmable memories (EEPROM), organized as 2 blocks of 256 x 8 bits. They are manufactured in SGS-THOMSON's Hi-Endurance Advanced CMOS technology which guarantees an endurance of one million erase/write cycles with a data retention of 10 years. The memories operate with a power supply value as low as 2.5V.

Both Plastic Dual-in-Line and Plastic Small Outline packages are available.

The memories are compatible with the I<sup>2</sup>C standard, two wire serial interface which uses a bi-directional data bus and serial clock. The memories carry a built-in 4 bit, unique device identification code (1010) corresponding to the I<sup>2</sup>C bus definition. This is used together with 2 chip enable inputs (E2, E1) so that up to 4 x 4K devices may be attached to the I<sup>2</sup>C bus and selected individually. The memories behave as a slave device in the I<sup>2</sup>C protocol with all memory operations synchronized by the serial clock. Read and write operations are initiated by a START condition generated by the bus master. The START condition is followed by a stream of 7 bits (identification code 1010), plus one read/write bit and terminated by an acknowledge bit.

| Table 3. | Device | Select | Code |

|----------|--------|--------|------|

|----------|--------|--------|------|

|               | Device Code |    |    |    | Chip Enable |    | Block<br>Select | R₩ |

|---------------|-------------|----|----|----|-------------|----|-----------------|----|

| Bit           | b7          | b6 | b5 | b4 | b3          | b2 | b1              | b0 |