DEDI

FOR ]

DATABOOK

**1st EDITION**

DEI

3

ECTRONICS

# **DEDICATED MCU FAMILY** FOR TELEPHONE SET APPLICATIONS

DATABOOK

**1st EDITION**

# **JANUARY 1994**

#### USE IN LIFE SUPPORT DEVICES OR SYSTEMS MUST BE EXPRESSLY AUTHORIZED

SGS-THOMSON PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF SGS-THOMSON Microelectronics. As used herein:

- Life support devices or systems are those which (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided with the product, can be reasonably expected to result in significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can reasonably be expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

| TABLE OF CONTENTS |      |     |

|-------------------|------|-----|

|                   |      |     |

|                   |      |     |

|                   |      |     |

| INTRODUCTION      | Page | 5   |

| GENERAL INDEX     |      | 8   |

| 8 Bit MCUs        |      | 9   |

| 16/32 Bit DSP     |      | 223 |

# INTRODUCTION

SGS-THOMSON's extensive dedicated telephone set product range can meet virtually all needs of developers and producers of low, mid and high end telephone sets, answering machines and related applications.

Complementing our devices for line protection, interface and speech, tone and ring drivers, is SGS-THOMSON's dedicated microcontroller product line for telephone sets. Performing the central control functions and user features of modern feature phone telephone sets, the microcontroller range has been expanded to cover all model requirements: from basic telephones with Last Number Redial and 3 to 10 stored numbers - to Hands Free telephones and feature phones - to integrated telephone answering machine controllers.

Since each microcontroller device is applicable for more than one area of use, the entire product line is covered in the Telephone Set ICs Databook and Application Manuals.

SGS-THOMSON's microcontrollers have two roots. Firstly, the successful non-dedicated families for general applications, and secondly the Company's capabilities in non-volatile memory technologies. With experience gained from a long history of involvement in telephone set applications, SGS-THOMSON has developed two families of dedicated microcontrollers and a dedicated DSP device, each with integrated features making them attractive and cost-effective system solutions.

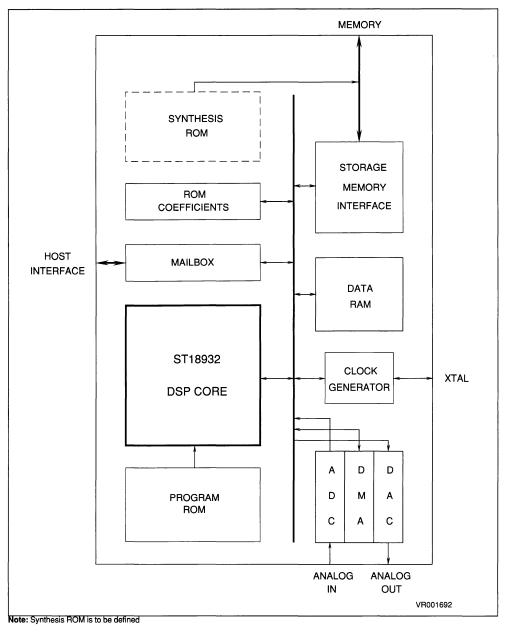

These integrated functions offer features such as: on-chip EEPROM for number storage and user preferences; I/O port wakeup functions for low power operation; on-chip digital to analog converters for analog controls; voice compression and synthesis, tone and DTMF detectors (DSP based); and optimized interfaces to SGS-THOMSON dedicated telephone set products. The microcontroller-based system complements and adds to the dedicated functions the flexibility that only a microcontroller-based system can offer.

#### ST62 8-bit MCUs with ADC and SPI

\_\_\_\_

| DEVICE | ROM<br>(Bytes) | RAM<br>(Bytes) | EEPROM<br>(Bytes) | I/O | TIMER/<br>WDOG | TEMP<br>RANGE | OP.<br>VOLTAGE | PACKAGE      | EMULATING<br>DEVICES |

|--------|----------------|----------------|-------------------|-----|----------------|---------------|----------------|--------------|----------------------|

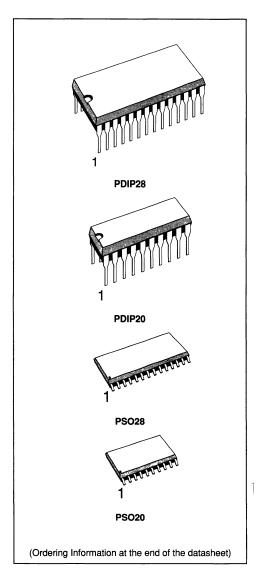

| ST6260 | 4K             | 128            | 128               | 13  | 2/1            | -40,+85°C     | 3 0V-6.0V      | PDIP20,PSO20 | 1                    |

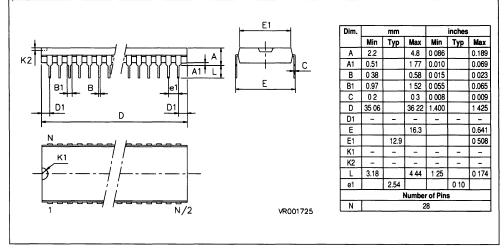

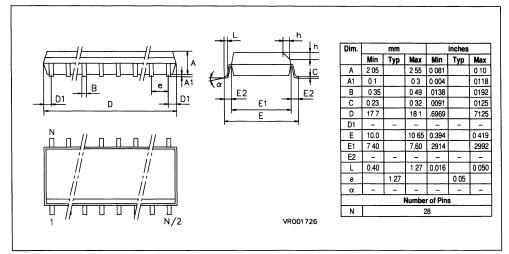

| ST6294 | 4K             | 128            | 128               | 21  | 2/1            | -40,+85℃      | 3.0V-6 0V      | PDIP28,PSO28 | ST62E94              |

# ST72 8-bit MCUs

| DEVICE | ROM<br>(Bytes) | RAM<br>(Bytes) | EEPROM<br>(Bytes) | I/O | TIMER/<br>WDOG | TEMP<br>RANGE | OP.<br>VOLTAGE | PACKAGE      | EMULATING<br>DEVICES |

|--------|----------------|----------------|-------------------|-----|----------------|---------------|----------------|--------------|----------------------|

| ST7291 | 16K            | 256            | - 1               | 19  | 1/-            | 0,+70°c       | 3 0V-5 5V      | PDIP28.PSO28 | -                    |

| ST7293 | 3.3K           | 128            | 128               | 22  | 1/1            | -25,+85°C     | 2 5V-5 5V      | PDIP28,PSO28 | ST72E94              |

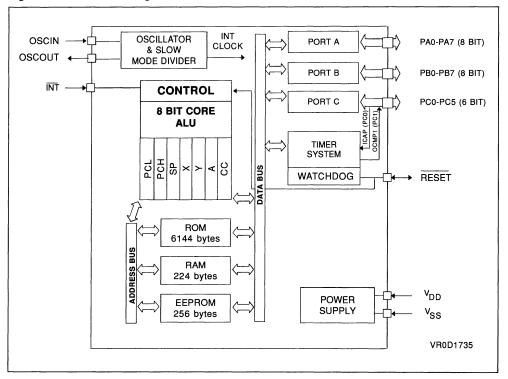

| ST7294 | 6K             | 224            | 256               | 22  | 1/1            | -25.+85℃      | 2.5V-5.5V      | PDIP28,PSO28 | ST72E94              |

# ST62 8-bit OTP/EPROM MCUs

| DEVICE  | EPROM   | OTP<br>ROM | RAM     | EEPROM  | I/O | TIMER/<br>WDOG | TEMP<br>RANGE | OP.<br>VOLTAGE | PACKAGE         | EMULATED<br>DEVICES |

|---------|---------|------------|---------|---------|-----|----------------|---------------|----------------|-----------------|---------------------|

|         | (Bytes) | (Bytes)    | (Bytes) | (Bytes) |     |                |               |                |                 |                     |

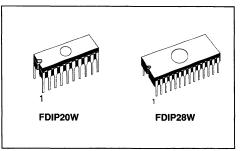

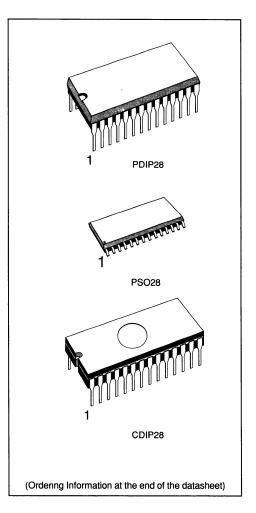

| ST62E94 | 4K      | -          | 128     | 128     | 21  | 2/1            | 0,+70°c       | 3 0V-6 0V      | CDIP28W         | ST6294              |

| ST62T94 | -       | 4K         | 128     | 128     | 21  | 2/1            | -25,+85℃      | 3 0V-6 0V      | PDIP28<br>PSO28 | ST6294              |

# ST72 8-bit OTP/EPROM MCUs

| DEVICE  | EPROM   | OTP<br>ROM | RAM     | EEPROM  | I/O | TIMER/<br>WDOG | TEMP<br>RANGE | OP.<br>VOLTAGE | PACKAGE         | EMULATED<br>DEVICES |

|---------|---------|------------|---------|---------|-----|----------------|---------------|----------------|-----------------|---------------------|

|         | (Bytes) | (Bytes)    | (Bytes) | (Bytes) |     |                |               |                |                 | ·                   |

| ST72E94 | 6К      | -          | 224     | 256     | 22  | 1/1            | 0,+70°c       | 3 0V-5 5V      | CDIP28W         | ST7294<br>ST7293    |

| ST72T94 | -       | 6K         | 224     | 256     | 22  | 1/1            | -25.+85℃      | 3.0V-5 5V      | PDIP28<br>PSO28 | ST7294<br>ST7293    |

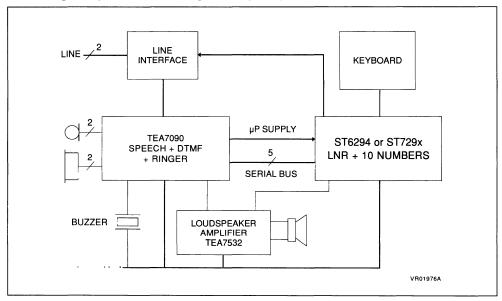

# Middle-range Telephone Set With Ringer, 10 Repertory Numbers and Loudspeaker

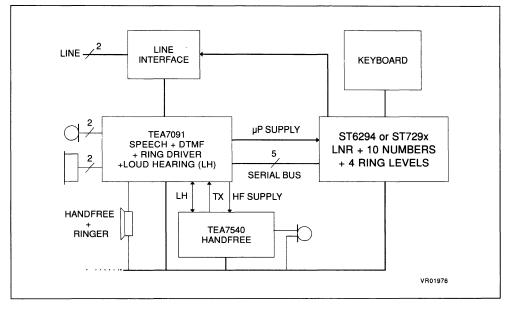

Middle-range Telephone Set With Ringer, 10 Repertory Numbers and Handfree.

# 8 Bit MCUs

| Type<br>Number | Function                                                             | Page<br>Number |

|----------------|----------------------------------------------------------------------|----------------|

| ST6260/65      | 8-Bit HCMOS MCU with A/D Converter, EEPROM & Auto-Reload             | 11             |

| ST62E60/T60    | 8-Bit EPROM HCMOS MCU with A/D Converter, EEPROM & Auto-Reload Timer | 75             |

| ST62E65/T65    | 8-Bit EPROM HCMOS MCU with A/D Converter, EEPROM & Auto-Reload Timer | 75             |

| ST6294         | 8-Bit HCMOS MCU with A/D Converter, EEPROM & Auto-Reload             | 87             |

| ST62E94/T94    | 8-Bit EPROM HCMOS MCUs with A/D Converter, EEPROM & Autoreload Timer | 101            |

| ST7291         | 8-Bit HCMOS MCUs with 16K ROM and wake-up Function                   | 113            |

| ST7293         | 8-Bit HCMOS MCUs with EEPROM                                         | 141            |

| ST7294         | 8-Bit HCMOS MCUs with EEPROM                                         | 169            |

| ST72E94/T94    | 8-Bit EPROM HCMOS MCUs with EEPROM                                   | 213            |

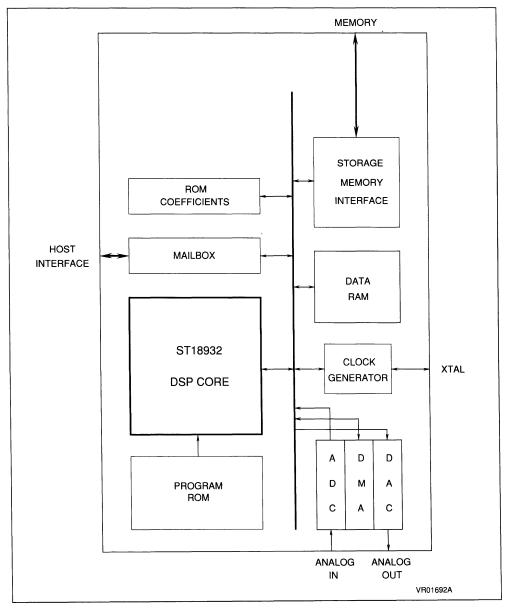

# 16/32 Bit DSP

| Type<br>Number | Function                                    |  |  |  |  |

|----------------|---------------------------------------------|--|--|--|--|

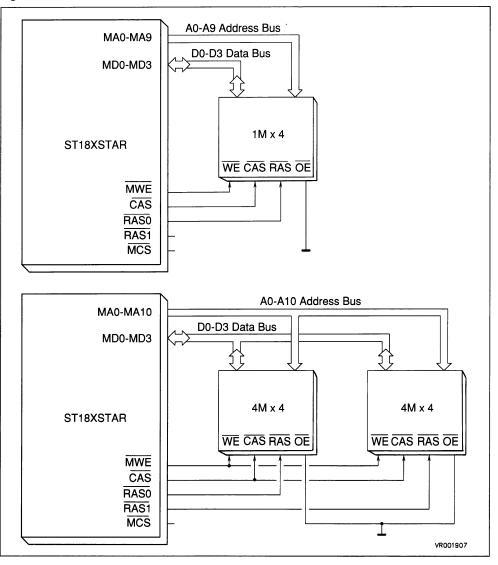

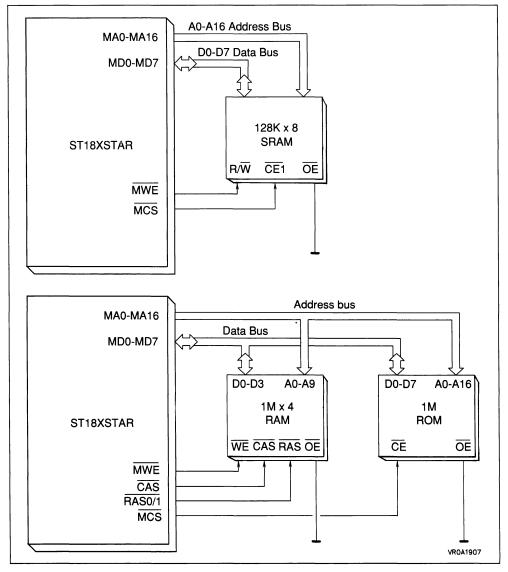

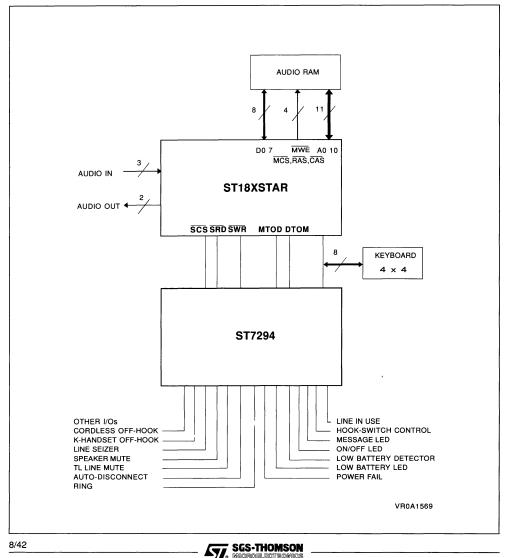

| ST18XSTAR      | Static Answering and Recording Chip         |  |  |  |  |

| ST18RXSTAR     | Romless Static Answering and Recording Chip |  |  |  |  |

# 8 Bit MCUs

# ST6260 ST6265

# 8-BIT HCMOS MCUs WITH A/D CONVERTER, EEPROM & AUTO-RELOAD TIMER

## PRELIMINARY DATA

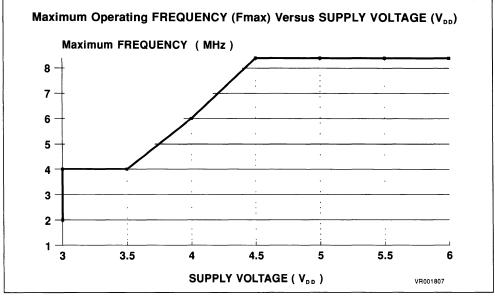

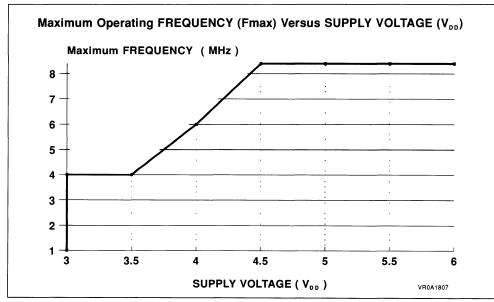

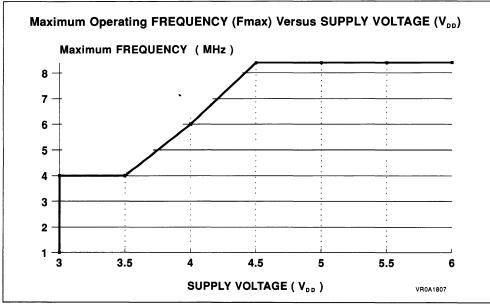

- 3.0 to 6.0V Supply Operating Range

- 8 MHz Maximum Clock Frequency

- -40 to +85°C Operating Temperature Range

SGS-THOMSON MICROELECTRONICS

- Run, Wait & Stop Modes

- 5 different interrupt vectors

- Look-up table capability in ROM

- User ROM: 3868 bytes

- Data ROM: User selectable size (in program ROM)

- Data RAM:

- 128 bytes 128 bytes

- EEPROM: 1

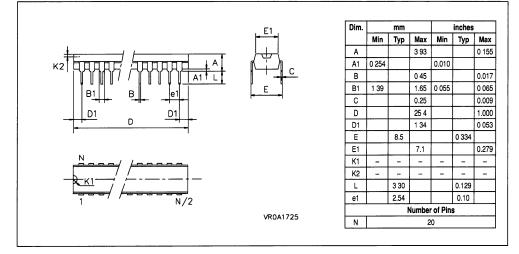

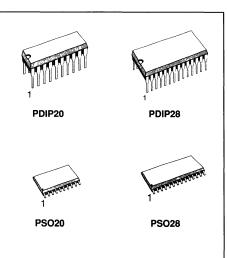

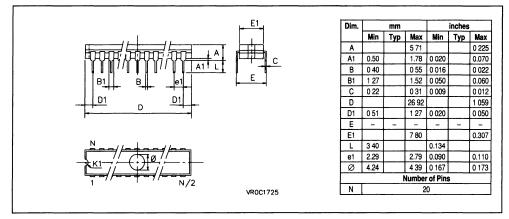

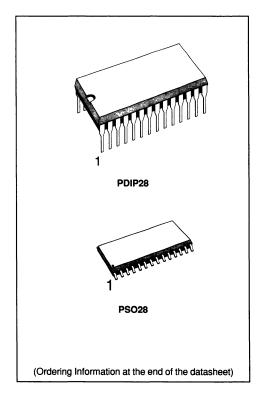

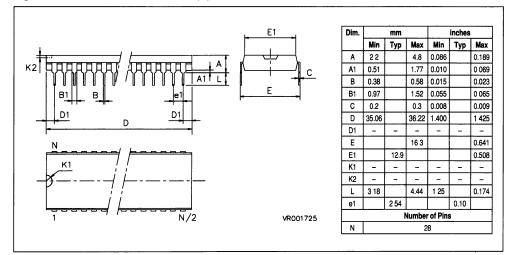

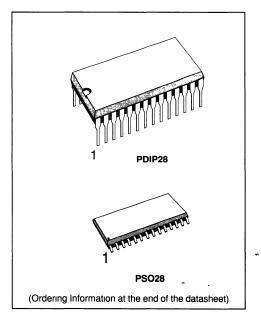

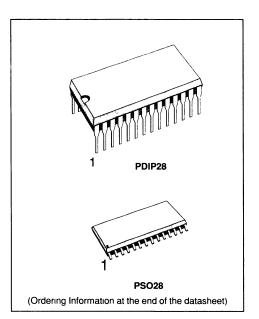

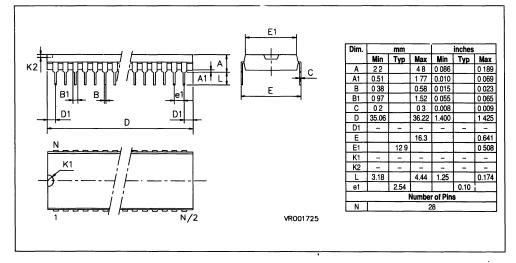

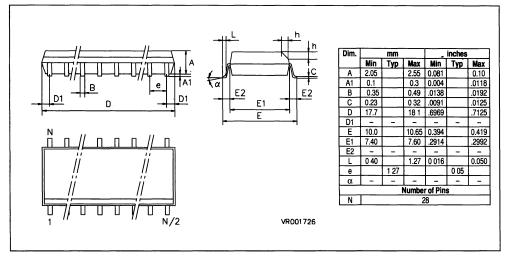

- PDIP20, PSO20 (ST6260) packages

- PDIP28, PSO28 (ST6265) packages

- 13/21 fully software programmable I/O as:

Input with pull-up resistor

- Input without pull-up resistor

- Input with interrupt generation

- Open-drain or push-pull outputs

- Analog Inputs

- 6/8 I/O lines can sink up to 20mA for direct LED or TRIAC driving

- 8 bit counter with a 7-bit programmable prescaler (Timer1)

- 8 bit auto-reload timer with 7-bit programmable prescaler (AR Timer)

- Digital Watchdog

- 8 bit A/D Converter with up to 7 (ST6260) and up to 13 (ST6265) analog inputs

- 8 bit Synchronous Peripheral Interface (SPI)

- On-chip clock oscillator (Quartz Crystal or Ceramic)

- Power-on Reset

- One external not maskable interrupt

- 9 powerful addressing modes

- The development tool of the ST626x microcontrollers consists of the ST626x-EMU emulation and development system connected via a standard RS232 serial line to an MS-DOS Personal Computer

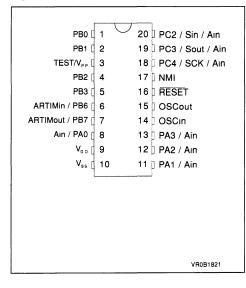

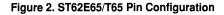

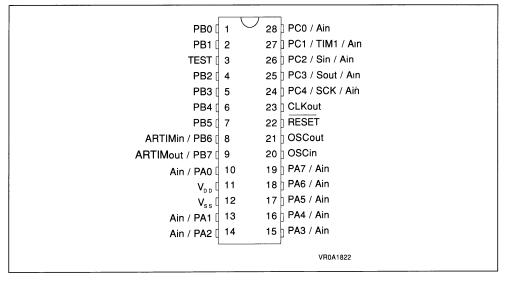

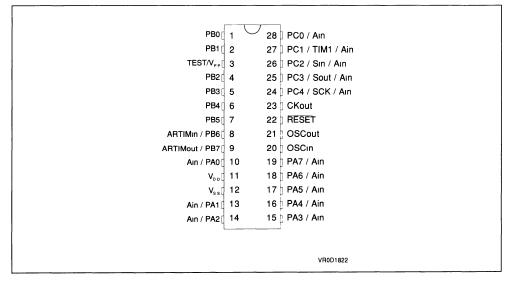

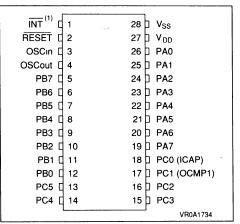

Figure 2. ST6265 Pin Configuration

| PBO                |    | 28 ] PC0 / Ain        |

|--------------------|----|-----------------------|

| PB1                | 2  | 27 🛛 PC1 / TIM1 / Ain |

| TEST               | 3  | 26 🛛 PC2 / Sin / Ain  |

| PB2[               | 4  | 25 🛛 PC3 / Sout / Ain |

| PB3 [              | 5  | 24 ] PC4 / SCK / Ain  |

| PB4[               | 6  | 23 🛛 NMI              |

| PB5[               | 7  | 22 RESET              |

| ARTIMin / PB6[     | 8  | 21 OSCout             |

| ARTIMout / PB7     | 9  | 20 ] OSCin            |

| Ain / PA0          | 10 | 19 ] PA7 / Ain        |

| V <sub>DD</sub>    | 11 | 18 ] PA6 / Ain        |

| V <sub>s s</sub> [ | 12 | 17 ] PA5 / Ain        |

| Ain / PA1 [        | 13 | 16   PA4 / Ain        |

| Ain / PA2[         | 14 | 15 🏽 PA3 / Ain        |

| l                  |    |                       |

|                    |    |                       |

|                    |    | VR001822              |

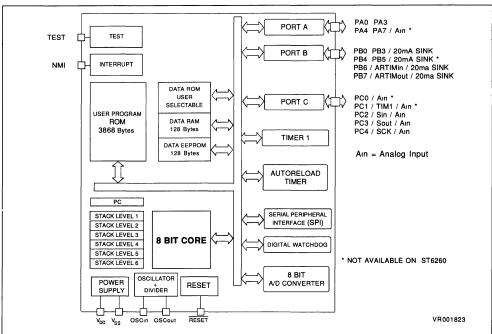

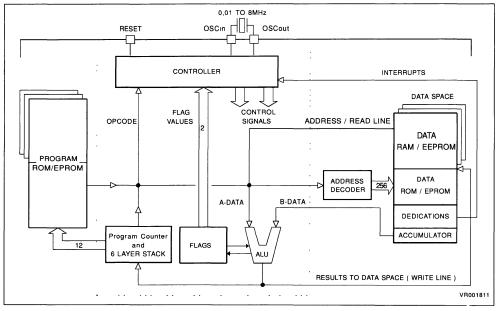

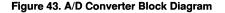

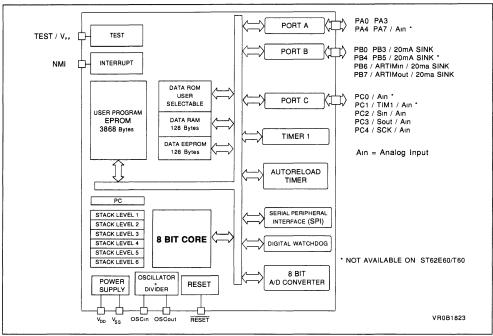

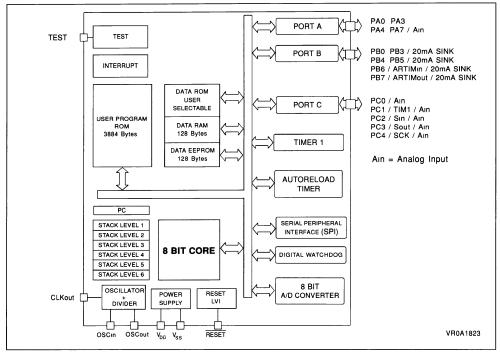

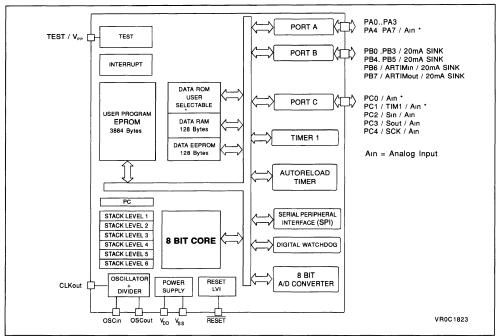

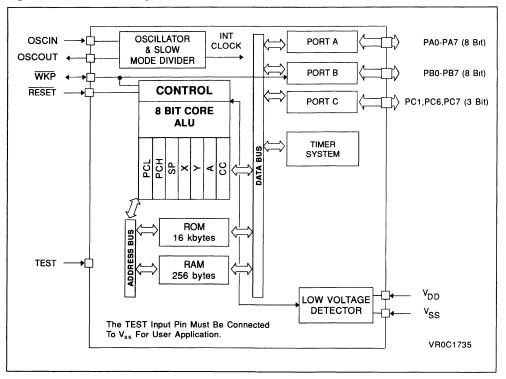

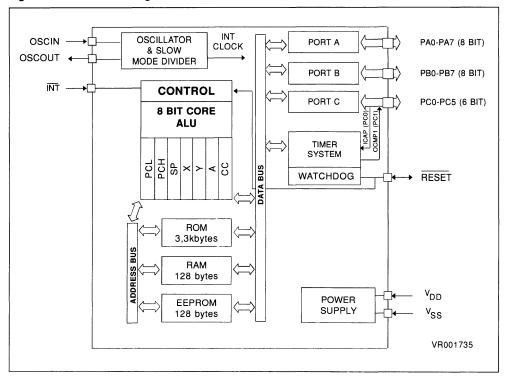

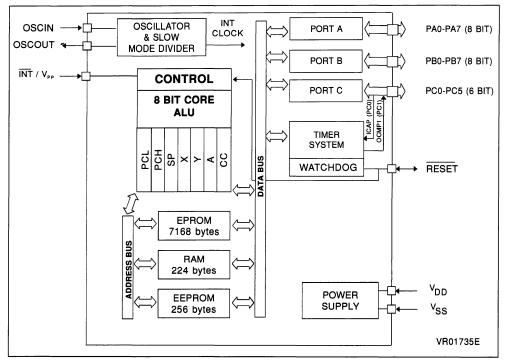

# Figure 3. ST6260,65 Block Diagram

# **GENERAL DESCRIPTION**

The ST6260 and ST6265 microcontrollers are members of the 8-bit HCMOS ST62xx family, a series of devices oriented to low-medium complexity applications. All ST62xx members are based on a building block approach: a common core is surrounded by a combination of on-chip peripherals (macrocells). The macrocells of the ST6260 and ST6265 are: the Timer peripheral that includes an 8-bit counter with a 7-bit software programmable prescaler (Timer1), the 8-bit Auto-reload Timer with 7 bit programmable prescaler (AR Timer), the 8-bit A/D Converter with up to 7 (ST6260) and up to 13 (ST6265) analog inputs (A/D inputs are alternate functions of I/O pins), the Digital Watchdog (DWD) and an 8-bit Serial synchronous Peripheral Interface (SPI). In addition, these devices offer 128 bytes of EEPROM for non volatile data storage.

ST6260 and ST6265 are well suited for automotive, appliance and industrial applications. The ST62E60 and ST62E65 EPROM versions are available for prototypes and low-volume production; also OTP versions are available.

#### **PIN DESCRIPTION**

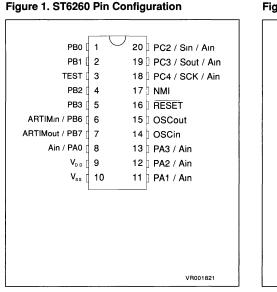

$\textbf{V_{DD}}$  and  $\textbf{V_{SS}}$ . Power is supplied to the MCU using these two pins.  $V_{DD}$  is power and  $V_{SS}$  is the ground connection.

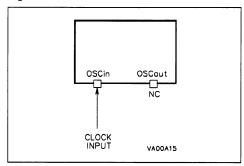

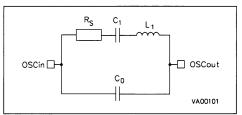

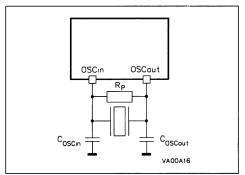

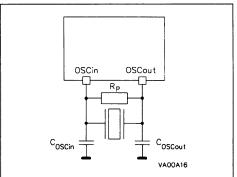

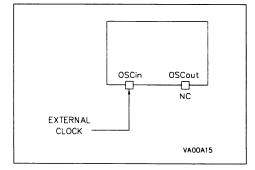

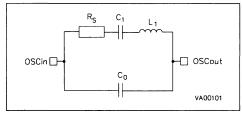

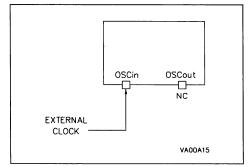

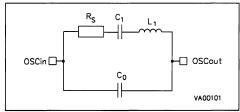

**OSCin and OSCout.** These pins are internally connected with the on-chip oscillator circuit. A quartz crystal, a ceramic resonator or an external clock signal can be connected between these two pins in order to allow the correct operation of the MCU with various stability/cost trade-offs. The frequency at OSCin and OSCout is internally divided by 1, 2 or 4 by a software controlled divider. The OSCin pin is the input pin, the OSCout pin is the output pin.

**RESET**. The active low **RESET** pin is used to restart the microcontroller to the beginning of its program.

**TEST.** The TEST must be held at VSS for normal operation (an internal pull-down resistor selects normal operating mode if TEST pin is not connected).

**NMI.** The NMI pin provides the capability for asynchronous interrupt applying an external not maskable interrupt to the MCU. The NMI is falling edge sensitive. It is provided with an on-chip pull-up resistor and Schmitt trigger characteristics.

**PC1/TIM1/Ain.** This pin can be used as a Port C I/O bit, as Timer 1 I/O pin or as analog input for the on-chip A/D converter. This pin is available only on the ST6265 (28 pin version). If programmed to be the Timer 1 pin, in input mode it is connected to the prescaler and acts as external timer clock or as control gate for the internal timer clock. In the output mode the timer pin outputs the data bit when a time out occurs.

To use this pin as Timer 1 output a dedicated bit in the TIMER 1 Status/Control Register must be set. To use this pin as input pin the I/O pin has to be programmed as input. The analog mode should be programmed to use the line as an analog input.

**PB6/ARTIMin, PB7/ARTIMout.** These pins are either Port B I/O bits or the Input and Output pins of the Auto-reload Timer. To be used as timer input function PB6 has to be programmed as input with or without pull-up. A dedicated bit in the AR TIMER Mode Control Register sets PB7 as timer output function.

**PA0-PA7.** These 8 lines are organized as one I/O port (A). PA4-PA7 are not available on ST6260 (20 pin version). Each line may be configured under software control as input with or without internal pull-up resistor, interrupt generating input with pull-up resistor, analog input, open-drain or push-pull output.

**PB0-PB3, PB4, PB5.** These 6 lines are organized as one I/O port (B). PB4, PB5 are available only on the ST6265 (28 pin version). Each line may be configured under software control as input with or without internal pull-up resistor, interrupt generating input with pull-up resistor, open-drain or pushpull output. In output mode these lines can also sink 20mA for direct LED and TRIAC driving. The reset configuration of PB0-PB3 can be selected by mask option (pull-up or high impedance).

**PC0-PC4.** These 5 lines are organized as one I/O port (C). PC0 and PC1 are not available on ST6260 (20 pin version). Each line may be configured under software control as input with or without internal pull-up resistor, interrupt generating input with pull-up resistor, analog input for the A/D converter, open-drain or push-pull output. PC2-PC4 can also be used as respectively Data in, Data out and Clock I/O pins for the on-chip SPI to carry the synchronous serial I/O signals.

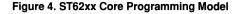

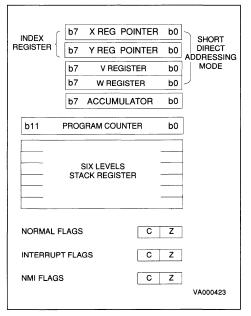

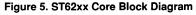

# ST62xx CORE

The core of the ST62xx Family is implemented independently from the I/O or memory configuration. Consequently, it can be treated as an independent central processor communicating with I/O and memory via internal addresses, data, and control busses. The in-core communication is arranged as shown in Figure 5; the controller being externally linked to both the reset and the oscillator, while the core is linked to the dedicated on-chip macrocells peripherals via the serial data bus and indirectly for interrupt purposes through the control registers.

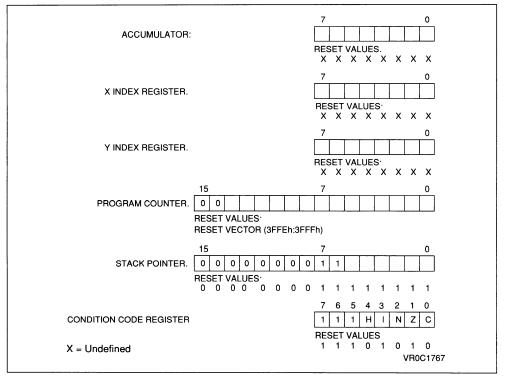

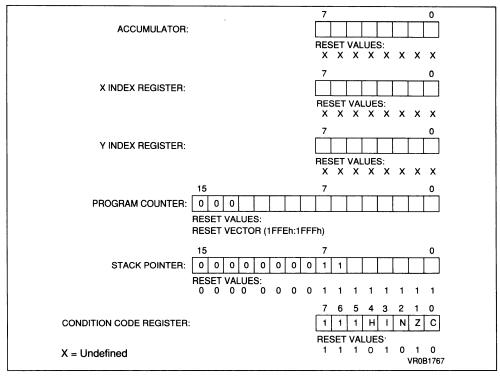

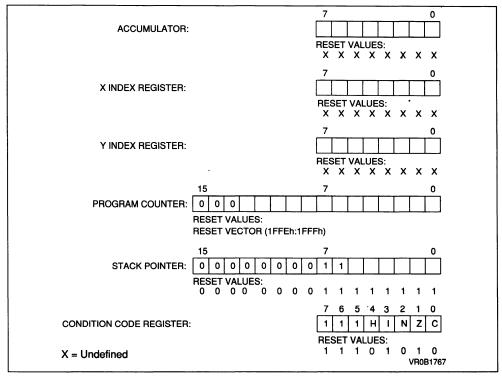

#### Registers

The ST62xx Family core has six registers and three pairs of flags available to the programmer. They are shown in Figure 4 and are explained in the following paragraphs.

Accumulator (A). The accumulator is an 8-bit general purpose register used in all arithmetic calculations, logical operations, and data manipulations. The accumulator is addressed in the data space as RAM location at address FFh. Accordingly the ST62xx instruction set can use the accumulator as any other register of the data space.

# ST62xx CORE (Continued)

Indirect Registers (X, Y). These two indirect registers are used as pointers to the memory locations in the data space. They are used in the register-indirect addressing mode. These registers can be addressed in the data space as RAM locations at addresses 80h (X) and 81h (Y). They can also be accessed with the direct, short direct, or bit direct addressing modes. Accordingly, the ST62xx instruction set can use the indirect registers as any other register of the data space.

Short Direct Registers (V, W). These two registers are used to save one byte in short direct addressing mode. These registers can be addressed in the data space as RAM locations at addresses 82h (V) and 83h (W). They can also be accessed with the direct and bit direct addressing modes. Accordingly, the ST62xx instruction set can use the short direct registers as any other register of the data space.

#### Program Counter (PC)

The program counter is a 12-bit register that contains the address of the next ROM location to be processed by the core. This ROM location may be an opcode, an operand, or an address of operand. The 12-bit length allows the direct addressing of 4096 bytes in the program space. Nevertheless, if the program space contains more than 4096 locations, the further program space can be addressed by using the Program Bank Switch register.

The PC value is incremented, after it is read the address of the current instruction. To execute relative jumps the PC and the offset are shifted through the ALU, where they will be added, and the result is shifted back into the PC. The program counter can be changed in the following ways:

- JP (Jump) instruction . . . PC= Jump address

- CALL instruction . . . . PC= Call address

- Relative Branch Instructions.PC= PC ± offset

- Interrupt . . . . . . . PC= Interrupt vector

- Reset . . . . . . . . . PC= Reset vector

- RET & RETI instructions . PC= Pop (stack)

- Normal instruction . . . . PC= PC + 1

#### Flags (C, Z)

The ST62xx core includes three pairs of flags that correspond to 3 different modes: normal mode, interrupt mode and Non-Maskable-Interrupt-mode. Each pair consists of a CARRY flag and a ZERO flag. One pair (CN, ZN) is used during normal operation, one pair is used during the interrupt mode (CI, ZI) and one is used during the not-maskable interrupt mode (CNMI, ZNMI).

The ST62xx core uses the pair of flags that correspond to the actual mode: as soon as an interrupt (resp. a Non-Maskable-Interrupt) is generated, the ST62xx core uses the interrupt flags (resp. the NMI flags) instead of the normal flags. When the RETI instruction is executed, the normal flags (resp. the interrupt flags) are restored if the MCU was in the normal mode (resp. in the interrupt mode) before the interrupt. It should be observed that each flag set can only be addressed in its own routine (Notmaskable interrupt, normal interrupt or main routine). The flags are not cleared during the context switching and so remain in the state they were at the exit of the last routine switching.

The Carry flag is set when a carry or a borrow occurs during arithmetic operations, otherwise it is cleared. The Carry flag is also set to the value of the bit tested in a bit test instruction, and participates in the rotate left instruction.

The Zero flag is set if the result of the last arithmetic or logical operation was equal to zero, otherwise it is cleared.

The switching between the three sets of flags is automatically performed when an NMI, an interrupt or a RETI instructions occurs. As the NMI mode is automatically selected after the reset of the MCU, the ST62xx core uses at first the NMI flags.

## ST62xx CORE (Continued)

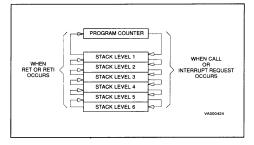

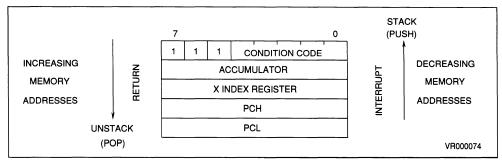

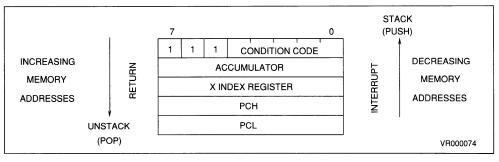

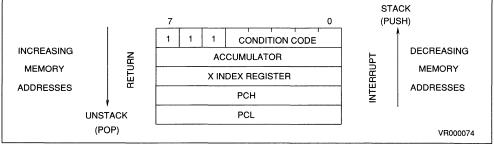

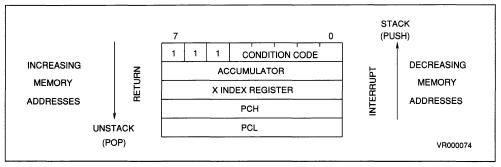

#### Stack

The ST62xx core includes true LIFO hardware stack that eliminates the need for a stack pointer. The stack consists of six separate 12-bit RAM locations that do not belong to the data space RAM area. When a subroutine call (or interrupt request) occurs, the contents of each level is shifted into the next level while the content of the PC is shifted into the first level (the value of the sixth level will be lost). When a subroutine or interrupt return occurs (RET or RETI instructions), the first level register is shifted back into the PC and the value of each level is popped back into the previous level. These two operating modes are described in Figure 6. Since the accumulator, as all other data space registers, is not stored in this stack the handling of these registers should be performed inside the subroutine. The stack pointer will remain in its deepest position if more than 6 calls or interrupts are executed, so that the last return address will be lost. It will also remain in its highest position if the stack is empty and a RET or RETI is executed. In this case the next instruction will be executed.

#### Figure 6. Stack Operation

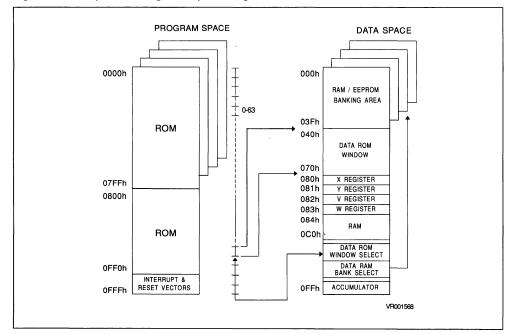

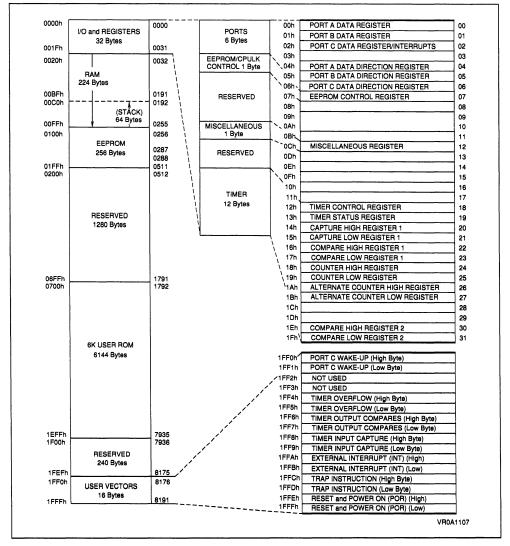

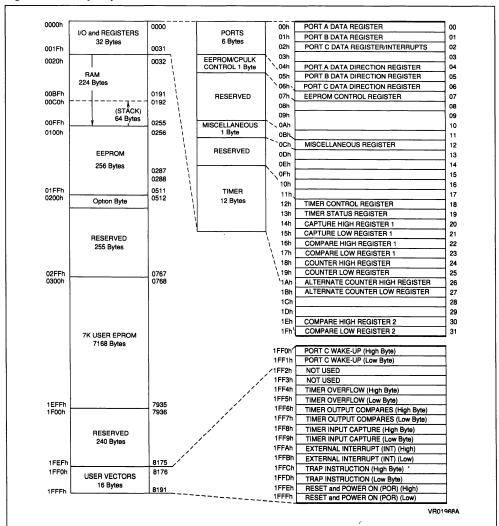

#### MEMORY SPACES

The MCU operates in three different memory spaces: program space, data space, and stack space. A description of these spaces is shown in the following figures.

#### Program Space

The program space is physically implemented in the ROM memory and includes all the instructions that are to be executed, as well as the data required for the immediate addressing mode instructions, the reserved test area and the user vectors. It is addressed by the 12-bit Program Counter register (PC register) and so the ST62xx core can directly address up to 4K bytes of Program Space.

| Device Address                                                          | Description                                                                  |  |  |

|-------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|

| 0000h-007Fh                                                             | Reserved                                                                     |  |  |

| 0080h-0F9Fh                                                             | User Program ROM<br>3856 Bytes                                               |  |  |

| OFA0h-OFEFh<br>OFF0h-OFF7h<br>OFF8h-OFFBh<br>OFFCh-OFFDh<br>OFFEh-OFFFh | Reserved<br>Interrupt Vectors<br>Reserved<br>NMI Vector<br>User Reset Vector |  |  |

#### Table 1. ST6260/65 Program ROM Memory Map

#### Figure 7. Memory Addressing Description Diagram

#### Data Space

The instruction set of the ST62xx core operates on a specific space, named Data Space, that contains all the data necessary for the processing of the program. The Data Space allows the addressing of RAM and EEPROM memory, ST62xx core/peripheral registers, and read-only data such as constants and look-up tables.

Data ROM. All the read-only data is physically implemented in the ROM memory in which the Program Space is also implemented. The ROM memory contains consequently the program to be executed, the constants and the look-up tables needed for the program.

The locations of Data Space in which the different constants and look-up tables are addressed by the ST62xx core can be considered as being a 64-byte window through which it is possible to access to the read-only data stored in the ROM memory.

Data RAM/EEPROM. The ST6260/65 offer 128 bytes of data RAM memory and 128 bytes of EEPROM. 64 bytes of RAM are directly addressed in data space in the range 080h-0BFh (static space). The additional RAM and EEPROM are addressed using the banks of 64 bytes located between addresses 00h and 3Fh.

#### Stack Space

The stack space consists of six 12 bit registers that are used for stacking subroutine and interrupt return addresses plus the current program counter register.

#### Figure 8. ST6260,65 Data Memory Space

| DATA and EEPROM                   | 000h            |

|-----------------------------------|-----------------|

|                                   | 03Fh            |

|                                   | 040h            |

| DATA ROM WINDOW AREA              | 04011           |

|                                   | 07Fh            |

| X REGISTER                        | _ 080h          |

| Y REGISTER                        | 081h            |

| V REGISTER                        | 082h            |

| W REGISTER                        | _ 083h          |

| DATA RAM                          | 084h            |

|                                   | 0BFh            |

| PORT A DATA REGISTER              | 0C0h            |

| PORT B DATA REGISTER              | _ 0C1h          |

| PORT C DATA REGISTER              | 0C2h            |

| RESERVED                          | _ 0C3h          |

| PORT A DIRECTION REGISTER         | 0C4h            |

| PORT B DIRECTION REGISTER         | 0C5h            |

| PORT C DIRECTION REGISTER         | 0C6h            |

| RESERVED                          | 0C7h            |

| INTERRUPT OPTION REGISTER         | 0C8h*           |

| DATA ROM WINDOW REGISTER          | 0C9h*           |

|                                   | 0CAh            |

| RESERVED                          | 0CBh            |

| PORT A OPTION REGISTER            | OCCh            |

| PORT B OPTION REGISTER            | OCDh            |

| PORT C OPTION REGISTER            | 0CEh            |

| RESERVED                          | 0CFh            |

| A/D DATA REGISTER                 | ODOh            |

| A/D CONTROL REGISTER              | 0D1h            |

| TIMER 1 PRESCALER REGISTER        | 0D2h            |

| TIMER 1 COUNTER REGISTER          | 0D3h            |

| TIMER 1 STATUS/CONTROL REGISTER   | 0D4h            |

| AR TIMER MODE CONTROL REGISTER    | 0D5h            |

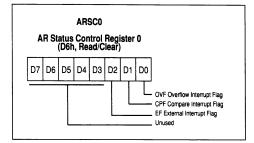

| AR TIMER STATUS/CONTROL REGISTER1 | 0D6h            |

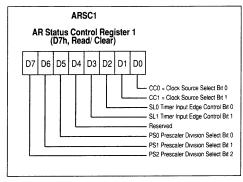

| AR TIMER STATUS/CONTROL REGISTER2 | 0D7h            |

| WATCHDOG REGISTER                 | 0D8h            |

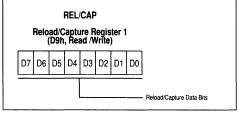

| AR TIMER RELOAD/CAPTURE REGISTER  | 0D9h            |

| AR TIMER COMPARE REGISTER         | 0DAh            |

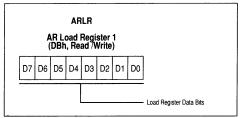

| AR TIMER LOAD REGISTER            | ODBh            |

| OSCILLATOR CONTROL REGISTER       | ODCh*           |

| MISCELLANEOUS                     | 0DDh            |

| RESERVED                          | 0DEh<br>0DFh    |

| SPI DATA REGISTER                 | OEOh            |

| SPI DIVIDER REGISTER              | 0E1h            |

| SPI MODE REGISTER                 | 0E2h            |

| RESERVED                          | 0E3h            |

| DATA RAM PAGE REGISTER            | 0E7h            |

| RESERVED                          | _ 0E8h*<br>0E9h |

| EEPROM CONTROL REGISTER           |                 |

|                                   | 0EAh            |

| RESERVED                          | 0EBh            |

| ACCUMULATOR                       | OFEh            |

|                                   | 0FFh            |

\* WRITE ONLY REGISTER

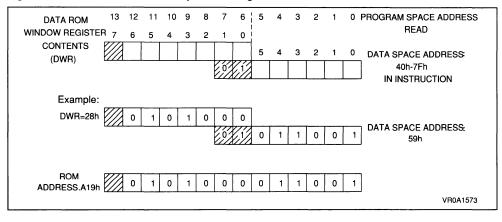

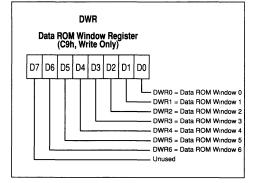

#### Data Window register (DWR)

The Data ROM window is located from address 040h to address 7Fh in the Data space. It allows the direct reading of 64 consecutive bytes located anywhere in the ROM memory between the addresses 0000h and 1FFFh. All the bytes of the ROM memory can be used to store either instructions or read-only data. Indeed, the window can be moved by step of 64 bytes along the ROM memory in writing the appropriate code in the Write-only Data Window register (DWR register, location C9h).

The DWR register can be addressed like a RAM location in the Data Space at the address C9h. nevertheless it is a write only register that cannot be accessed with single-bit operations. This register is used to move the 64-byte read-only data window (from the 40h address to 7Fh address of the Data Space) up and down the ROM memory of the MCU in steps of 64 bytes. The effective address of the byte to be read as a data in the ROM memory is obtained by the concatenation of the 6 least significant bits of the register address given in the instruction (as least significant bits) and the content of the DWR register (as most significant bits, see Figure 8). So when addressing location 40h of dataspace, and 0 is loaded in the DWR register, the phisycal addressed location in ROM is 00h. The DWR register is not cleared at reset, therefore it must be written to before the first access to the Data ROM window area.

#### Figure 9. Data ROM Window Memory Addressing

SGS-THOMSON

Figure 10. Data ROM Window Register

**D7.** This bit is not used.

**DWR6-DWR0.** These are the Data ROM Window bits that correspond to the upper bits of the data ROM space.

#### This register is undefined on reset. Neither read nor single bit instructions may be used to address this register.

Note: Care is required when handling the DWR register as it is write only. For this reason, it is not allowed to change the DWR contents while executing interrupt service routine, as the service routine cannot save and then restore its previous content. If it is impossible to avoid the writing of this register in the interrupt service routine, an image of this register must be saved in a RAM location, and each time the program writes to the DWR it must write also to the image register. The image register must be written first, so if an interrupt occurs between the two instructions the DWR is not affected.

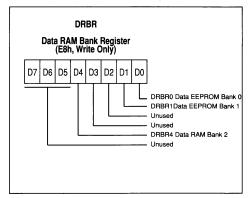

#### Data RAM/EEPROM Bank Register (DRBR)

The selection of the bank is made by programming the Data RAM Bank Switch register (DRBR register) located at address E8h of the Data Space according to Table 2. No more than one bank should be set at a time.

The DRBR register can be addressed like a RAM location in the Data Space at the address E8h; nevertheless it is a write only register that cannot be accessed with single-bit operations. This register is used to select the desired 64-byte RAM/EEPROM bank of the Data Space. The number of bank has to be loaded in the DRBR register and the instruction has to point to the selected location as if it was in bank 0 (from 00h address to 3Fh address).

This register is not cleared during the MCU initialization, therefore it must be written before the first access to the Data Space bank region. Refer to the Data Space description for additional information. The DRBR register is not modified when an interrupt or a subroutine occurs.

#### Table 2. Data RAM Bank Register Set-up

| DRBR Value | Selection     |

|------------|---------------|

| 00h        | None          |

| 01h        | EEPROM Page 0 |

| 02h        | EEPROM Page 1 |

| 10h        | RAM Page 2    |

| Other      | Reserved      |

#### Figure 11. Data RAM Bank Register

D7-D5. These bits are not used.

**DRBR4.** This bit, when set, selects RAM page 2.

D3-D2. These bits are not used.

DRBR1. This bit, when set, selects EEPROM page 1. DRBR0. This bit, when set, selects EEPROM page 0.

#### Notes:

Care is required when handling the DRBR register as it is write only. For this reason, it is not allowed to change the DRBR contents while executing interrupt service routine, as the service routine cannot save and then restore its previous content. If it is impossible to avoid the writing of this register in interrupt service routine, an image of this register must be saved in a RAM location, and each time the program writes to DRBR it must write also to the image register. The image register must be written first, so if an interrupt occurs between the two instructions the DRBR is not affected.

In DRBR Register, *only 1 bit must be set*. Otherwise two or more pages are enabled in parallel, producing errors.

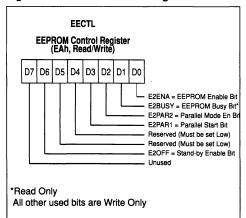

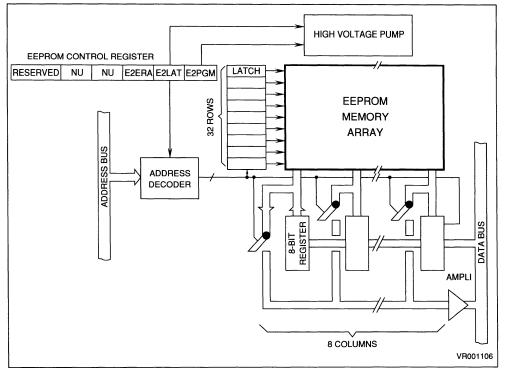

#### EEPROM Description

The data space of ST62xx family from 00h to 3Fh is paged as described in Table 3. The ST6260/65 has 128 bytes of EEPROM located in two pages of 64 bytes (page 0 and 1).

The EEPROM is physically organized in 32 byte modules (2 modules per page) and does not require dedicated instructions to be accessed in reading or writing. Once selected through the Data RAM Bank Register, the active EEPROM page is controlled by the EEPROM Control Register (EECTL) located at address EAh. E20FF bit of the EECTL register must be cleared to "0" prior to any write or read access to the EEPROM. If no bank is selected or if E2OFF is set, any access is meaningless.

Programming must be enabled by setting bit E2ENA of register EECTL.

Bit E2BUSY of EECTL register is set to 1 when the EEPROM is performing a programming cycle. Any access to the EEPROM when E2BUSY is set to 1 is meaningless.

Provided E2OFF and E2BUSY are cleared to 0, an EEPROM location is read like any other data location, also in term of access time.

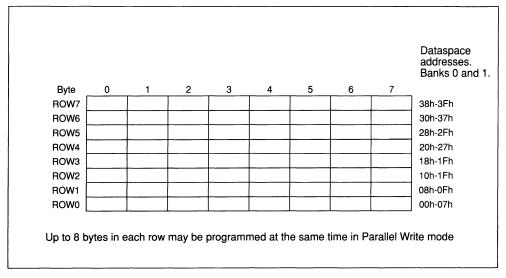

Writing the EEPROM can work in two modes: Byte Mode (BMODE) and Parallel Mode (PMODE). BMODE is the normal way to use the EEPROM and consists in accessing one byte at a time. PMODE consists in simultaneously programing 8 bytes of the same row.

#### Figure 12. EEPROM Control Register

#### D7. Not Used

**E2OFF.** WRITE ONLY. If this bit is set the EEPROM is disabled (any access will be meaningless) and the power consumption of the EEPROM is reduced to the lowest values.

D5, D4. Reserved, must be set to zero.

**E2PAR1.** WRITE ONLY. Once in Parallel Mode, as soon as the user software sets the E2PAR1 bit the parallel writing of the 8 adjacent registers will start. It is internally reset at the end of the programming procedure. Note that less than 8 bytes can be written; the undefined bytes are unaffected by the parallel programming.

**E2PAR2.** WRITE ONLY. This bit must be set by the user program in order to perform parallel programming (more than one byte at a time). If E2PAR2 is set and the parallel start bit (E2PAR1) is low, up to 8 adjacent bytes can be written at maximum speed, the contents being stored in volatile registers. These 8 adjacent bytes are considered as a row, whose address lines A7, A6, A5, A4, A3 are fixed while A2, A1 and A0 are the changing bits. E2PAR2 is automatically reset at the end of any parallel programming procedure. It can be reset by the user software before starting the programming procedure, leaving the EEPROM registers unchanged.

**E2BUSY.** *READ ONLY.* This bit is automatically set by the EEPROM control logic when the EEPROM is in programming mode. The user program should test it before any read or write EEPROM operation; any attempt to access the EEPROM while the busy bit is set will be aborted and the writing procedure in progress completed.

**E2ENA.** WRITE ONLY. This bit enables programming of the EEPROM cells. It must be set to one before any write into the EEPROM register. Any attempt to write to the EEPROM when E2ENA is low is meaningless and will not trigger a write cycle.

This register is cleared at reset.

#### Notes:

The data to write has to be written directly at the address that it will have inside the EEPROM space. There is no buffer memory between the data RAM and the EEPROM spaces.

When the EEPROM is busy (E2BUSY = "1") EECTL can not be accessed in write mode, it is only possible to read the status of E2BUSY. This implies that as long as the EEPROM is busy, it is not possible to change the status of the EEPROM Control Register. EECTL bits 4 and 5 are reserved and must never be set to "1".

Additional Notes on Parallel Mode. If the user wishes to perform parallel programming, the first action should be to set the E2PAR2 bit to one. From this time the EEPROM will be addressed in writing, the ROW address will be latched and it will be possible to change it only at the end of the programming procedure or by resetting E2PAR2 without programming the EEPROM. After the ROW address latching the ST62xx can "see" only one EEPROM row (the selected one) and any attempt to write or read other rows will produce errors. Do not read the EEPROM while E2PAR2 is set.

As soon as E2PAR2 bit is set, the 8 volatile ROW latches are cleared. From this moment the user can load data in the whole ROW or in a subset. Setting E2PAR1 will modify the EEPROM registers corre-

sponding to the ROW latches accessed after E2PAR2. For example, if the software sets E2PAR2 and accesses the EEPROM by writing to addresses 18h. 1Ah. 1Bh and then sets E2PAR1. these three registers will be modified at the same time; the remaining bytes will be unaffected. Note that E2PAR2 is internally reset at the end of the programming procedure. This implies that the user must set E2PAR2 bit between two parallel programming procedures. Note that if the user tries to set E2PAR1 while E2PAR2 is not set there will not be any programming procedure and the E2PAR1 bit will be unaffected. Consequently E2PAR1 bit cannot be set if E2ENA is low. E2PAR1 can be affected by the user to set it, only if E2ENA and E2PAR2 bits are also set to one.

# TEST MODE

For normal operation the TEST pin must be held low when reset is active. An on-chip  $100k\Omega$  pull-down resistor is internally connected to the TEST pin.

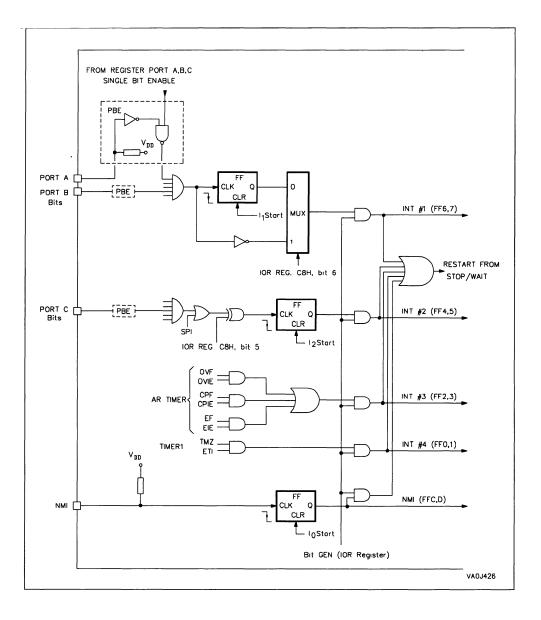

#### INTERRUPTS

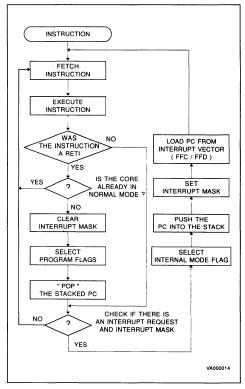

The ST62xx core can manage 4 different maskable interrupt sources, plus one non-maskable interrupt source (top priority level interrupt). Each source is associated with a particular interrupt vector that contains a Jump instruction to the related interrupt service routine. Each vector is located in the Program Space at a particular address (see Table 1).

When a source provides an interrupt request, and the request processing is also enabled by the ST62xx core, then the PC register is loaded with the address of the interrupt vector (i.e. of the Jump instruction).

Finally, the PC is loaded with the address of the Jump instruction and the interrupt routine is processed.

The ST6260 and ST6265 microcontrollers have eight different interrupt sources associated to five interrupt vectors as it is described in table below.

| Interrupt Source | Vector              | Vector Address |

|------------------|---------------------|----------------|

| NMI              | Interrupt vector #0 | (FFCh, FFDh)   |

| Port A & B       | Interrupt vector #1 | (FF6h, FF7h)   |

| Port C & SPI     | Interrupt vector #2 | (FF4h, FF5h)   |

| AR TIMER         | Interrupt vector #3 | (FF2h, FF3h)   |

| TIMER1 & ADC     | Interrupt vector #4 | (FF0h, FF1h)   |

#### Interrupt Vectors Description

The ST62xx core includes 5 different interrupt vectors in order to branch to 5 different interrupt routines in the static page of the Program Space.

- The interrupt vector associated with the nonmaskable interrupt source is named interrupt vector #0. It is located at addresses FFCh,FFDh in the Program Space. On ST6260 and ST6265 this vector is associated with the external falling edge sensitive interrupt pin (NMI).

- The interrupt vector located at addresses FF6h, FF7h is named interrupt vector #1. It is associated with Port A and Port B pins. It can be programmed by software either in the falling edge detection mode or in the low level sensitive detection mode according to the code loaded in the Interrupt Option Register (IOR).

- The interrupt vector located at addresses FF4h, FF5h is named interrupt vector #2. It is associate with Port C pins and the SPI peripheral can be programmed by software either in the falling edge detection mode or in the positive edge detection mode according to the code loaded in the Interrupt Option Register (IOR).

- The interrupt vector located at addresses FF2h, FF3h is named interrupt vector #3. It is associated with the AR TIMER peripheral.

- The interrrupt vector loaded at address FF0h, FF1h is named interrupt vector #4. It is associated with the TIMER 1 and the A/D converter peripherals.

All the on-chip peripherals have an interrupt request flag bit (TMZ for timer, EOC for A/D), this bit is set to one when the device wants to generate an interrupt request and a mask bit (ETI for timer, EAI for A/D) that must be set to one to allow the transfer of the flag bit to the core.

#### Interrupt Priority

The non-maskable interrupt request NMI has the highest priority and can interrupt any other interrupt routines at any time, nevertheless the four other interrupts can not interrupt each other. If more than one interrupt request are pending, they are processed by the ST62xx core according to their priority level: vector #1 has the higher priority while vector #4 the lower.

The priority of each interrupt source is fixed.

# **INTERRUPT** (Continued)

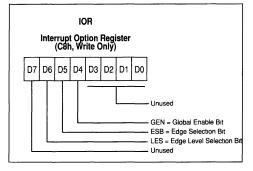

## Interrupt Option Register

The Interrupt Option Register (IOR register, location C8h) is used to enable/disable the individual interrupt sources and to select the operating mode of the external interrupt inputs. This register can be addressed in the Data Space as RAM location at the address C8h, nevertheless it is a write-only register that cannot be accessed with single-bit operations. The operating modes of the external interrupt inputs associated to interrupt vectors #1 and #2 are selected through bits 5 and 6 of the IOR register.

# Figure 13. Interrupt Option Register

D7. D3-D0 These bits are not used.

**LES.** Level/Edge Selection Bit. When this bit is set to one, the interrupt #1 (Port A, B lines) is low level sensitive, when cleared to zero the negative edge sensitive interrupt is selected.

**ESB.** Edge Selection Bit. When this bit is set to one, the interrupt #2 (Port C lines) is positive edge sensitive, when cleared to zero the negative edge sensitive interrupt is selected.

**GEN.** Global Enable Interrupt. When this bit is set to one, all the interrupts are enabled. When this bit is cleared to zero all the interrupts (excluding NMI) are disabled.

This register is cleared on reset.

# Table 5. Interrupt Option Register Description

| GEN    | SET      | Enable all interrupts                         |  |

|--------|----------|-----------------------------------------------|--|

|        | CLEARED  | Disable all interrupts                        |  |

| ESB    | SET      | Rising edge mode on<br>interrupt input #2     |  |

|        | CLEARED  | Falling edge mode on<br>interrupt input #2    |  |

| LES    | SET      | Level-sensitive mode on<br>interrupt input #1 |  |

|        | CLEARED  | Falling edge mode on<br>Interrupt input #1    |  |

| OTHERS | NOT USED |                                               |  |

# **External Interrupts Operating Modes**

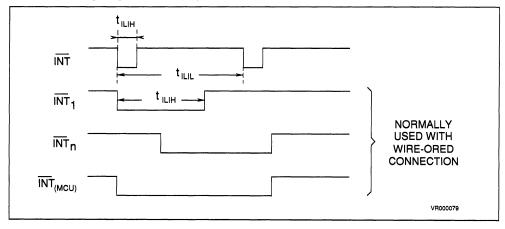

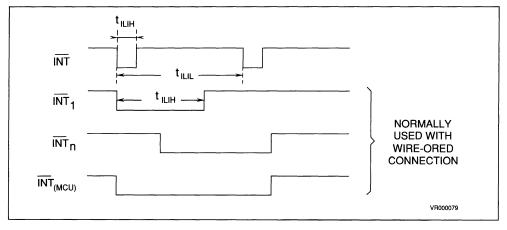

The NMI interrupt is associated to the NMI pin of the ST6260/65. The interrupt request is generated by a falling edge applied to the NMI pin. The NMI interrupt pin signal is latched and is automatically reset by the core at the beginning of the non-maskable interrupt service routine. An on-chip pull-up resistor and a Schmitt trigger are available at pin NMI.

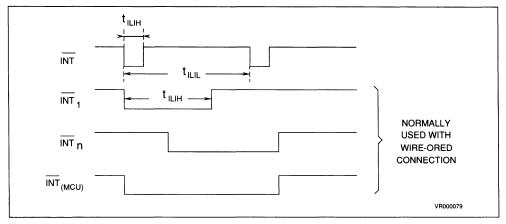

The two interrupt sources associated with the falling/rising edge mode of the external interrupt pins (Ports A and B vector #1, Ports C vector #2) are connected to two internal latches. Each latch is set when a falling/rising edge occurs and is cleared when the associated interrupt routine is started. So, the occurrence of an external interrupt request is stored: a second interrupt, that occurs during the processing of the first one, will be processed as soon as the first one has been finished (if there is not an higher priority interrupt request). If more than one interrupt occurs during the processing of the first one, these other interrupt requests will be lost.

The storage of the interrupt requests is not available in the level sensitive detection mode. To be taken into account, the low level must be present on the interrupt pin when the core samples the line after the execution of the instructions. At the end of each instruction the core tests the interrupt lines and if there is a pending interrupt request the next instruction is not executed and the related interrupt routine is executed.

#### Note:

When GEN bit is low, the NMI interrupt is active but cannot cause a wake up from STOP/WAIT modes.

# **INTERRUPT** (Continued)

Interrupt Procedure. The interrupt procedure is very similar to a call procedure, indeed the user can consider the interrupt as an asynchronous call procedure. As this is an asynchronous event, the user does not know about the context and the time at which it occurred. As a result the user should save all the data space registers which will be used inside the interrupt routines. There are separate sets of processor flags for normal, interrupt and non-maskable interrupt modes which are automatically switched and so these do not need to be saved.

The following list summarizes the interrupt procedure:

#### ST62xx actions

- Interrupt detection

- The flags C and Z of the main routine are exchanged with the flags C and Z of the interrupt routine (or the NMI flags)

- The value of the PC is stored in the first level of the stack

- The normal interrupt lines are inhibited (NMI still active)

- First internal latch is cleared

- The related interrupt vector is loaded in the PC.

#### User actions

- User selected registers are saved inside the interrupt service routine (normally on a software stack)

- The source of the interrupt is found by polling (if more than one source is associated to the same vector) the interrupt flag of the source.

- Interrupt servicing

- Return from interrupt (RETI)

#### ST62xx actions

Automatically the ST62xx core switches back to the normal flags (or the interrupt flags) and pops the previous PC value from the stack

The interrupt routine begins usually by the identification of the device that has generated the interrupt request (by polling). The user should save the registers which are used inside the interrupt routine (that holds relevant data) into a software stack. After the RETI instruction execution, the core carries out the previous actions and the main routine can continue.

# **INTERRUPT** (Continued)

# Table 6. Interrupt Requests and Mask Bits

| Peripheral    | Register | Register Address | Mask bit            | Masked Interrupt Source                                                         |

|---------------|----------|------------------|---------------------|---------------------------------------------------------------------------------|

| All           | IOR      | C8h              | GEN                 | All Interrupts, excluding NMI                                                   |

| I/O Ports     | IOR      | C8h              | GEN                 | All I/O Pins Interrupt Request                                                  |

| TIMER 1       | TSCR1    | D4h              | ETI                 | TMZ: TIMER 1 Overflow                                                           |

| A/D Converter | ADCR     | D1h              | EAI                 | EOC: End of Conversion                                                          |

| AR TIMER      | ARMC     | D5h              | OVIE<br>CPIE<br>EIE | OVF: AR TIMER Overflow<br>CPF: Successful compare<br>EF: Active edge on ARTIMin |

| SPI           | SPIMOD   | E2h              | SPIE                | SPIF: End of Transmission                                                       |

۰.

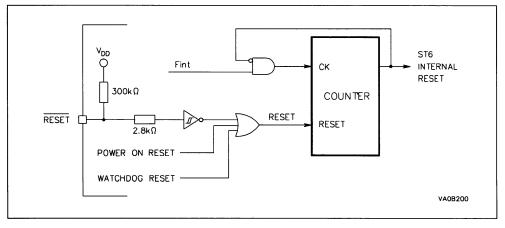

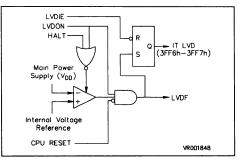

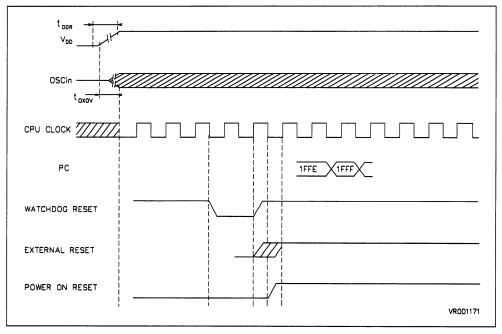

#### RESET

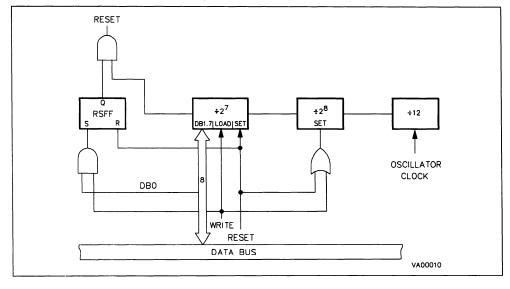

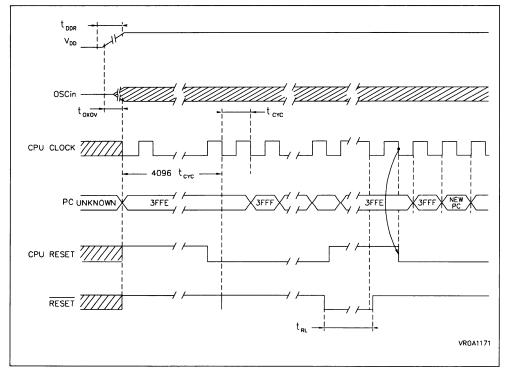

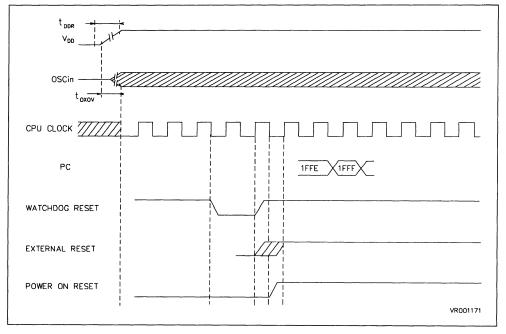

The ST6260/65 can be reset in three ways: by the external reset input ( $\overline{\text{RESET}}$ ) tied low, by power-on reset and by the digital Watchdog peripheral

#### **RESET Input**

The RESET pin can be connected to a device of the application board in order to restart the MCU during its operation. The activation of the RESET pin may occur in the RUN, WAIT or STOP mode. This input has to be used to reset the MCU internal state and provide a correct start-up procedure. The pin is active low and has a schmitt trigger input. The internal reset signal is generated by adding a delay to the external signal. Therefore even short pulses at the RESET are accepted, provided V<sub>DD</sub> has finished its rising phase and the oscillator is running correctly (normal RUN or WAIT modes). The MCU is kept in the Reset state as long as the RESET pin is held low.

If the RESET activation occurs in the RUN or WAIT mode, the processing of the program is stopped (in RUN mode only) and the Input/Outputs are placed in input with pull-up resistors. When the level on the RESET pin becomes high, the initialization seguence is executed just after the internal delay.

If a RESET pin activation occurs in the STOP mode, the oscillator starts and all the inputs/outputs are configured in input with pull-up resistors. When the level of the RESET pin becomes high, the initialization sequence is started just after the internal delay.

#### Power-on Reset

The function of the POR consists in waking up the MCU during the power-on sequence. At the beginning of this sequence, the MCU is configured in the Reset state: every Input/Output port is configured in input with pull-up resistor and no instruction is executed. When the power supply voltage becomes sufficient, the oscillator starts to operate, nevertheless an internal delay is generated to allow the oscillator to be completely stabilized before the execution of the first instruction. The initialization sequence is executed just after the internal delay.

The internal delay is generated by an on-chip counter. This releases the internal reset of the MCU 2048 oscillator cycles after the RESET pin becomes high.

#### Note:

To have a correct start-up, the user should take care that the internal reset is not released before the V<sub>DD</sub> level is sufficient to allow MCU operation at the chosen frequency (see Recommended Operating Conditions).

A proper reset signal for slow rising V<sub>DD</sub> can be generally provided by an external RC network connected at pin RESET.

## **RESET** (Continued)

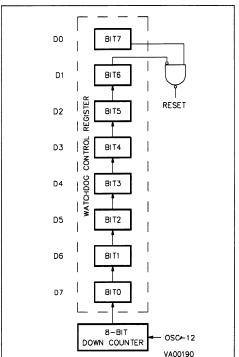

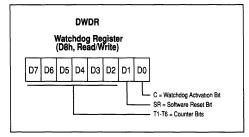

#### Watchdog Reset

The ST6260 and ST6265 provide an on-chip watchdog function in order to provide a graceful recovery from a software upset. If the watchdog register is not refreshed, preventing the end-of-count being reached, the internal reset is activated. This, in particular, resets the watchdog. The MCU restarts as with normal reset from RESET pin including the internal delay.

#### **Application Notes**

An external resistor between  $V_{DD}$  and reset pin is not required because an internal pull-up device is provided.

The POR device operates in a dynamic manner in the way that it brings about the initialization of the MCU when it detects a dynamic rising edge of the V<sub>DD</sub> voltage. The typical detected threshold is about 2 volts, but the actual value of the detected threshold depends on the way in which the V<sub>DD</sub> voltage rises up. The POR device *DOES NOT* allow the supervision of a static or slowly rising or falling edge of the V<sub>DD</sub> voltage.

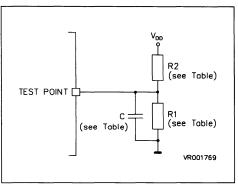

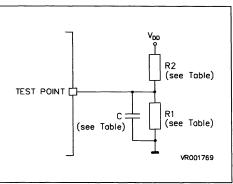

# Figure 16. Reset Circuit

## **RESET** (Continued)

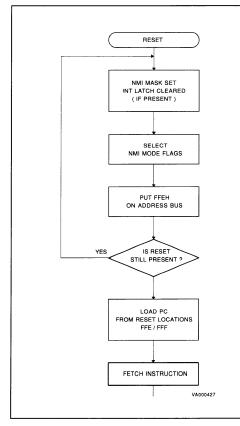

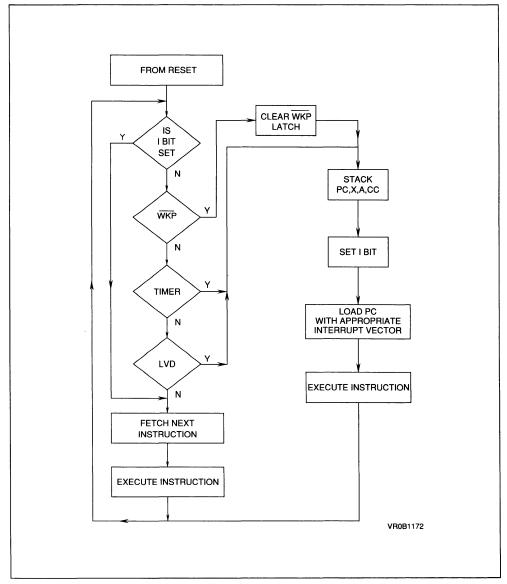

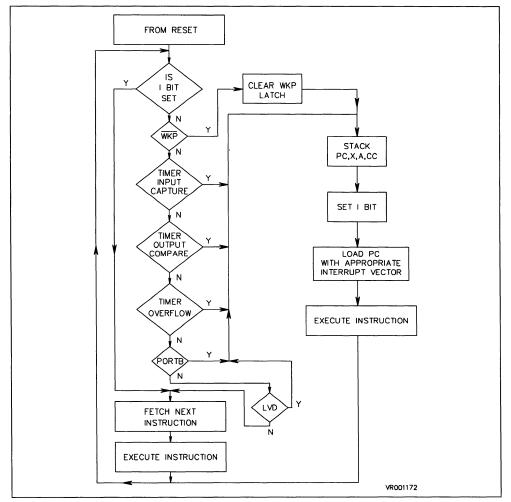

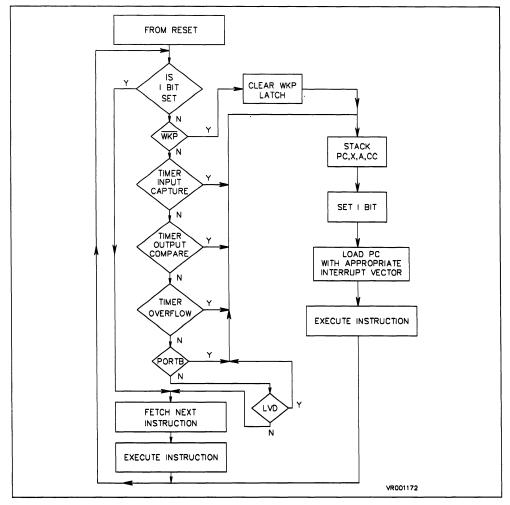

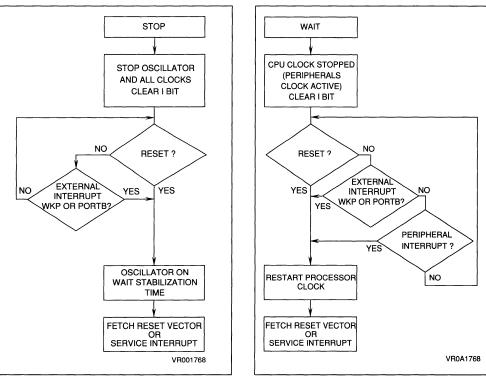

# Figure 17. Reset and Interrupt Processing Flow-Chart

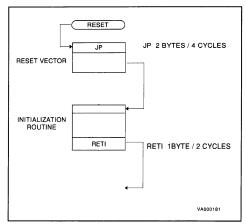

#### **MCU Initialization Sequence**

When a reset occurs the stack is reset to the program counter, the PC is loaded with the address of the reset vector (located in the program ROM at addresses FFEh & FFFh). A jump instruction to the beginning of the program has to be written into these locations. After a reset a NMI is automatically activated so that the core is in non-maskable interrupt mode to prevent false or ghost interrupts during the restart phase. Therefore the restart routine should be terminated by a RETI instruction to switch to normal mode and enable interrupts. If no pending interrupt is present at the end of the reset routine the ST62xx will continue with the instruction after the RETI; otherwise the pending interrupt will be serviced

#### Figure 18. Restart Initialization Program Flow-Chart

# **RESET** (Continued)

# Table 7. Reset Value

| Register                                                                                                                                                                                                                                                                                                                                                                                 | Address                                                                                                                      | Value                           | Comment                                                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Oscillator Control Register<br>Data RAM Page Register<br>EEPROM Control Register<br>Port Data Registers<br>Port Direction Register<br>Port Option Register<br>Interrupt Option Register<br>Data ROM Window Register<br>Timer 1 Status/Control<br>AR Timer Mode Control Register<br>AR Timer Status/Control 1 Register<br>AR Timer Status/Control 2 Register<br>AR Timer Compare Register | 0DCh<br>0E8h<br>0EAh<br>0C0h to 0C3h<br>0C4h to 0C6h<br>0CCh to 0CEh<br>0C8h<br>0C9h<br>0D4h<br>005h<br>006h<br>007h<br>0DAh | 00h                             | f <sub>INT</sub> = f <sub>OSC</sub> , user must set bit3 to 1<br>All Data Banks disabled<br>EEPROM disabled<br>I/O are Input with pull-up<br>I/O are Input with pull-up<br>Interrupt disabled<br>Timer 1 disabled<br>AR Timer stopped |

| Miscellaneous Register<br>SPI Registers                                                                                                                                                                                                                                                                                                                                                  | 0DDh<br>0E0h to 0E2h                                                                                                         |                                 | SPI output not connected to PC3<br>SPI disabled                                                                                                                                                                                       |

| X, Y, V, W, Register<br>Accumulator<br>Data RAM<br>EEPROM<br>A/D Result Register<br>AR Timer Load Register<br>AR Timer Reload/Capture Register                                                                                                                                                                                                                                           | 080h to 083h<br>0FFh<br>084h to 0BFh<br>00h to 03Fh<br>0D0h<br>0DBh<br>0D9h                                                  | Undefined                       |                                                                                                                                                                                                                                       |

| Timer 1 Counter Register<br>Timer 1 Prescaler Register<br>Watchdog Counter Register<br>A/D Control Register                                                                                                                                                                                                                                                                              | 0D3h<br>0D2h<br>0D8h<br>0D1h                                                                                                 | FFh<br>7Fh<br>FEh<br>FFh<br>40h | Max count loaded<br>Software Watchdog <sup>(1)</sup><br>Hardware Watchdog <sup>(1)</sup><br>A/D in Standby                                                                                                                            |

Note 1. Mask option selected

.

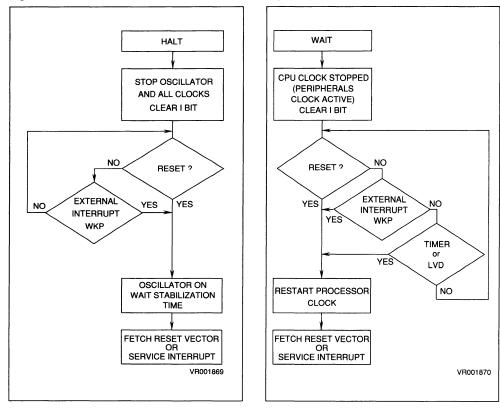

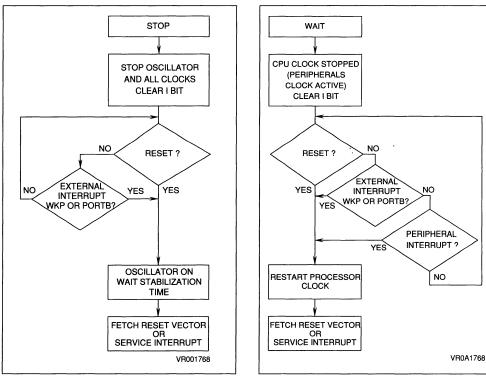

## WAIT & STOP MODES

The WAIT and STOP modes have been implemented in the ST62xx core in order to reduce the consumption of the product when the latter has no instruction to execute. These two modes are described in the following paragraphs

#### WAIT Mode

The MCU goes into the WAIT mode as soon as the WAIT instruction is executed. The microcontroller can also be considered as being in a "software frozen" state where the core stops processing the instructions of the routine, the contents of the RAM locations and peripheral registers are saved as long as the power supply voltage is higher than the RAM retention voltage, but where the peripherals are still working.

The WAIT mode can be used when the user wants to reduce the consumption of the MCU when it is idle, while not losing count of time or monitoring of external events. The oscillator is not stopped in order to provide a clock signal to the peripherals. The Timer 1 and auto-reload Timer counting may be enabled as well as both Timer interrupts before entering the WAIT mode; this allows the WAIT mode to be left when timer interrupt occurs. The above explanation related to the timers applies also

If the exit from the WAIT mode is performed with a general RESET (either from the activation of the external pin or by watchdog reset) the MCU enters a normal reset procedure as described in the RE-SET chapter. If an interrupt is generated during WAIT mode the MCU behavior depends on the state of the ST62xx core before the initialization of the WAIT sequence, but also of the kind of the interrupt request that is generated. This case is described in the following paragraphs. In any case, the ST62xx core does not generate any delay after the occurrence of the interrupt because the oscillator clock is still available.

#### STOP Mode

If the Watchdog is disabled the STOP mode is available. When in STOP mode the MCU is placed in the lowest power consumption mode. In this operating mode the microcontroller can be considered as being "frozen", no instruction is executed, the oscillator is stopped, the contents of the RAM locations and peripheral registers are saved as long as the power supply voltage is higher than the RAM retention voltage, and the ST62xx core waits for the occurrence of an external interrupt request or Reset activation to cutput from the STOP state.

If the exit from the STOP mode is performed with a general RESET (by the activation of the external pin) the MCU will enter a normal reset procedure as described in the RESET chapter. The case of an interrupt depends on the state of the ST62xx core before the initialization of the STOP sequence and also of the kind of the interrupt request that is generated.

This case will be described in the following paragraphs. In any case, the ST62xx core generates a delay after the occurrence of the interrupt request in order to wait the complete stabilization of the oscillator before the execution of the first instruction.

#### Exit from WAIT and STOP Modes

The following paragraphs describe the output procedure of the ST62xx core from WAIT and STOP modes when an interrupt occurs (not a RESET). It must be noted that the restart sequence depends on the original state of the MCU (normal, interrupt or non-maskable interrupt mode) before the start of the WAIT or STOP sequence, but also of the type of the interrupt request that is generated.

Normal Mode. If the ST62xx core was in the main routine when the WAIT or STOP instruction has been executed, the ST62xx core outputs from the stop or wait mode as soon as any interrupt occurs; the related interrupt routine is executed and at the end of the interrupt service routine the instruction that follows the STOP or the WAIT instruction is executed if no other interrupts are pending.

#### WAIT & STOP MODES (Continued)

Not Maskable Interrupt Mode. If the STOP or WAIT instruction has been executed during the execution of the non-maskable interrupt routine, the ST62xx core outputs from the stop or wait mode as soon as any interrupt occurs: the instruction that follows the STOP or the WAIT instruction is executed and the ST62xx core is still in the non-maskable interrupt mode even if another interrupt has been generated.

Normal Interrupt Mode. If the ST62xx core was in the interrupt mode before the initialization of the STOP or WAIT sequence, it outputs from the stop or wait mode as soon as any interrupt occurs. Nevertheless, two cases have to be considered:

- If the interrupt is a normal interrupt, the interrupt routine in which the wait or stop was entered will be completed with the execution of the instruction that follows the STOP or the WAIT and the ST6xx core is still in the interrupt mode. At the end of this routine pending interrupts will be serviced in accordance to their priority.

- If the interrupt is a non-maskable interrupt, the non-maskable routine is processed at first. Then the routine in which the wait or stop was entered will be completed with the execution of the instruction that follows the STOP or the WAIT and the ST6xx core remains in the normal interrupt mode.

#### Notes:

To reach the lowest power consumption during RUN or WAIT modes, the user software must take care of:

- selecting 4 as ratio of the Oscillator divider.

- configuring unused I/O as input without pull-up with well defined logic levels.

- placing the A/D converter in its power down mode by clearing the PDS bit in the A/D control register before entering the STOP instruction.

- putting the EEPROM on-chip memory in standby mode by setting the E2OFF bit in EEPROM Control Register to one.

When the hardware activated watchdog is selected or the software watchdog enabled, the STOP instruction is deactivated and any attempt to execute the STOP instruction will cause an execution of a WAIT instruction.

If all the interrupt sources are disabled (including NMI if GEN is low), the restart of the MCU can only be done by a Reset activation. The WAIT and STOP instructions are not executed if an enabled interrupt request is pending.

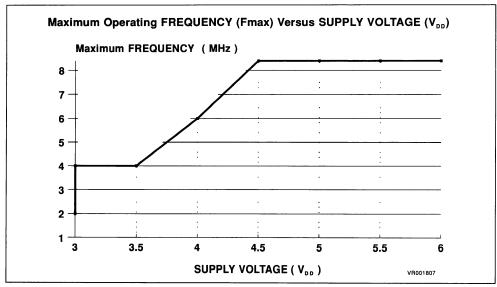

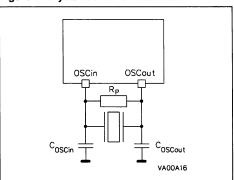

#### **ON-CHIP CLOCK OSCILLATOR**

The ST6260/65 on-chip oscillator has been designed to require a minimum of external components and to reduce the oscillator power consumption.

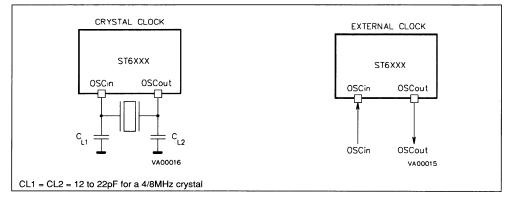

A quartz crystal, a ceramic resonator or an external signal (provided to the OSCin pin) may be used to generate a system clock with various stability/cost tradeoffs. The clock generator options connection methods are shown in Figure 21.

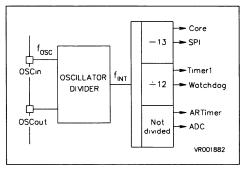

A programmable divider is provided in order to adjust the internal clock of the micro (core and peripherals) to the best power consumption/performance trade-off. The Division Ratio is selected through the Oscillator Control Register located at address 0DCh.

The internal frequency is directly used to clock the A/D Converter and the AR Timer. It is further divided by 12 to produce the Timer 1 and Watchdog clock and by 13 for the core and SPI clock.

With a 8MHz external frequency, the fastest machine cycle is therefore 1.625µs.

The machine cycle is the smallest unit needed to execute any operation (i.e.increment the program counter). An instruction may need two, four, or five machine cycles to be executed.

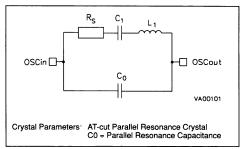

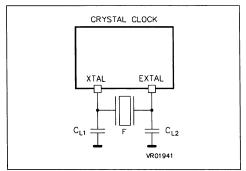

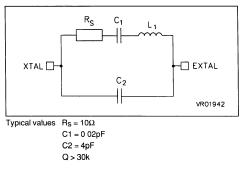

#### Figure 20. Crystal Parameters

#### Figure 19. Internal Clock Circuits

# **ON-CHIP CLOCK OSCILLATOR** (Continued)

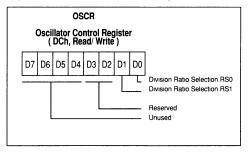

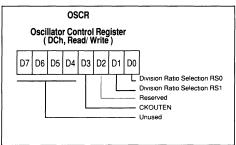

# **Oscillator Control Register**

# Figure 21. Oscillator Control Registers

D7-D4. These bits are not used.

**D3.** Reserved - Cleared at Reset. THIS BIT MUST BE SET TO 1 BY USER PROGRAM to achieve lowest power consumption.

D2. Reserved must be kept low.

**RS1-RS0.** These bits select the division ratio of the Oscillator Divider in order to generate the internal frequency. The following selections are available:

| RS1 | RS0 | Division Ratio |

|-----|-----|----------------|

| 0   | 0   | 1              |

| 0   | 1   | 2              |

| 1   | 0   | 4              |

| 1   | 1   | 4              |

# Figure 22. Oscillator Connection

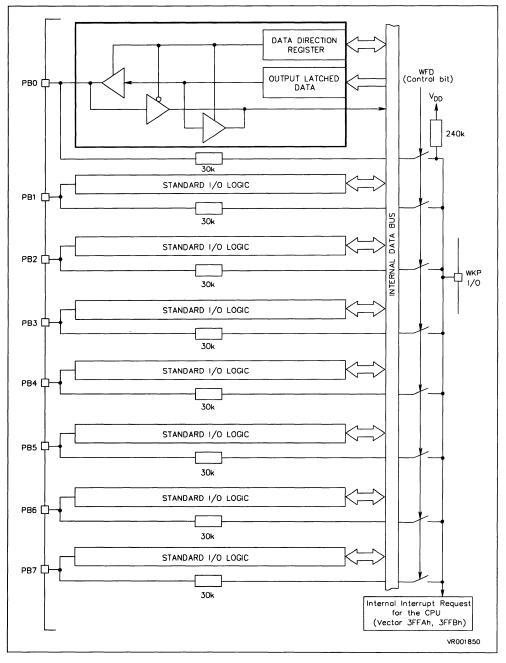

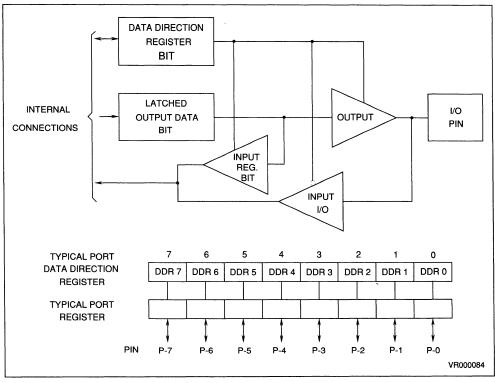

# **INPUT/OUTPUT PORTS**

The ST6260 and ST6265 microcontroller have respectively 13 and 21 Input/Output lines that can be individually programmed either in the input mode or the output mode with the following software selectable options:

- Input without pull-up and without interrupt

- Input with pull-up and with interrupt

- Input with pull-up without interrupt

- Analog inputs (PA0-PA7, PC0-PC3)

- Timer 1 I/O line (PC1, not available on ST6260)

- AR Timer I/O lines (PB6, PB7)

- SPI control signals (PC2-PC4)

- Push-pull output

- Standard Open drain output

- 20mA Open drain output PB lines.

The lines are organized in three Ports (Port A, B and C).

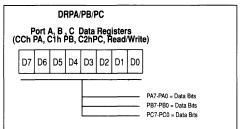

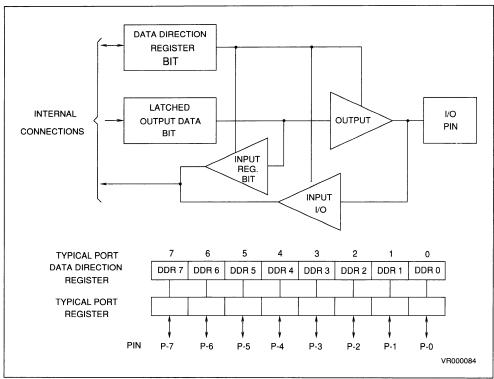

Each port occupies 3 registers in the data space. Each bit of these registers is associated with a particular line (for instance, the bits 0 of the Port A Data, Direction and Option registers are associated with the PA0 line of Port A). The three DATA registers (DRA, DRB, DRC), are used to read the voltage level values of the lines programmed in the input mode, or to write the logic value of the signal to be output on the lines configured in the output mode. The port data registers can be read to get the effective logic levels of the pins, but they can be also written by the user software, in conjunction with the related option registers, to select the different input mode options.

Single-bit operations on I/O registers are possible but care is necessary because reading in input mode is done from I/O pins while writing will directly affect the Port data register causing an undesired change of the input configuration.

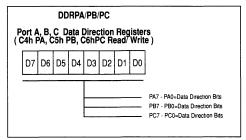

The three Data Direction registers (DDRA, DDRB and DDRC) allow the selection of the data direction of each pin (input or output).

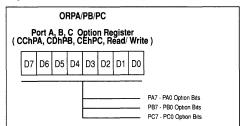

The three Option registers (ORPA, ORPB and ORPC) are used to select the different port options available both in input and in output mode.

All the I/O registers can be read or written as any other RAM location of the data space, so no extra RAM cell is needed for port data storing and manipulation. During the initialization of the MCU, all the I/O registers are cleared and the input mode with pull-up/no-interrupt is selected on all the pins, thus avoidng pin conflicts.

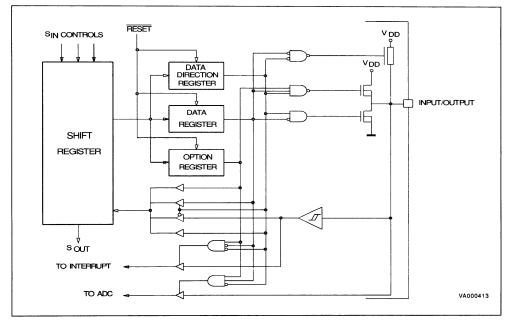

#### Figure 23. I/O Port Block Diagram

29/84

# INPUT/OUTPUT PORTS (Continued)

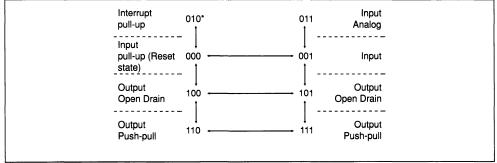

### I/O Pin Programming

Each pin can be individually programmed as input or output with different input and output configurations.

This is achieved by writing the relevant bit in the data (DR), data direction register (DDR) and option registers (OR). Table 7 shows all the port configurations that can be selected by user software.

### **Input Option Description**

**Pull-up, High Impedance Option.** All the input lines can be individually programmed with or without an internal pull-up according to the codes programmed in the OR and DR registers. If the pull-up option is not selected, the input pin is in the high-impedance state.

Interrupt Option. All the input lines can be individually connected by software to the interrupt lines of the ST62xx core according to the codes programmed in the OR and DR registers. The pins of Port A and B are "ORed" and are connected to the interrupt associated to the vector #1. Pins of ports C are "ORed" with the SPI interrupt line and connected to interrupt vector #2. The interrupt modes (falling edge sensitive, rising edge sensitive) can be selected by software for each port by programming the IOR register.

**Analog Input Option.** The seven PA5-PA7, PB0-PB3 pins can be configured to be analog inputs according to the codes programmed in the OR and DR registers. These analog inputs are connected to the on-chip 8-bit Analog to Digital Converter. *ONLY ONE* pin should be programmed as analog input at a time, otherwise the selected inputs will be shorted.

# Figure 24. I/O Port Data Registers

### Figure 25. I/O Port Data Direction Registers

## Figure 26. I/O Port Option Registers

Note: For complete coding explanation refer to Table 7

| DDR | OR | DR | Mode   | Option                                                |                                   |

|-----|----|----|--------|-------------------------------------------------------|-----------------------------------|

| 0   | 0  | 0  | Input  | With pull-up, no interrupt (Reset state)              |                                   |

| 0   | 0  | 1  | Input  | No pull-up, no interrupt                              |                                   |

| 0   | 1  | 0  | Input  | With pull-up, with interrupt                          |                                   |

| 0   | 4  |    | Input  | No pull-up, no interrupt (Port B pins)                |                                   |

| U   |    |    |        | Input                                                 | Analog input (Ports A and C pins) |

| 1   | 0  | X  | Output | Open-drain output (20mA sink current for Port B pins) |                                   |

| 1   | 1  | X  | Output | Push-pull output (20mA sink current for Port B pins)  |                                   |

# I/O Port Options Selection

Notes: X Means don't care.

30/84

# INPUT/OUTPUT PORTS (Continued)

# Timer 1 Alternate function Option.

When bit TOUT of register TSCR1 is low, pin PC1/Timer 1 is configured through the port registers as any standard pin of Port B. It is in addition connected to the Timer 1 input for Gated and Event counter modes. When bit TOUT of register TSCR1 is high, pin PC1/Timer 1 is forced as Timer 1 output. The port registers configuration is meaningless.

# AR Timer Alternate function Option

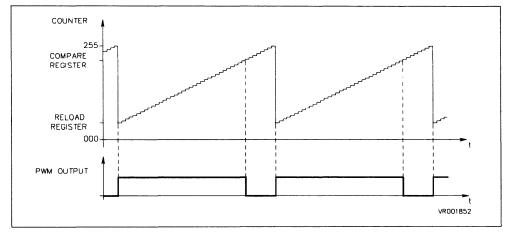

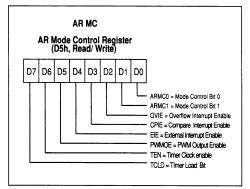

When bit PWMOE of register ARMC is low, pin ARTIMout/PB7 is configured as any standard pin of port B through the port registers. When PWMOE is high, ARTIMout/PB7 is the PWM output. The port registers configuration is meaningless.

ARTIMin/PB6 is connected to the AR Timer input. It is configured through the port registers as any standard pin of port B. To use ARTIMin/PB6 as AR Timer input, it must be configured as input through DDRB.

PC2/PC4 are used as standard I/O as long as SPCLK is kept low.

PC3/SOUT is configured as SPI push-pull output by setting bit 0 of the Miscellaneous register (address 0DDh), regardless of the state of Port C registers.

PC4/SCK is configured as push-pull output clock (master mode) by programming it as push-pull output through DDRC register and by setting bit SPCLK of the SPI Mode Register.

PC4/SCK is configured as input clock (slave mode) by programming it as input through DDRC register and by clearing bit SPCLK of the SPI Mode Register. With this configuration, PC4 can simultaneously be used as an input. Note. Switching the I/O ports from one state to another should be done in a way that no unwanted side effects can happen. The recommended safe transitions are shown below. All other transitions are risky and should be avoided during change of operation mode as it is most likely that there will be an unwanted side-effect such as interrupt generation or two pins shorted together by the analog input lines.

Single bit SET and RES instructions should be used very carefully with Port A and B data registers because these instructions make an implicit read and write back of the whole addressed register byte. In port input mode however data register address reads from input pins, not from data register latches and data register information in input mode is used to set characteristics of the input pin (interrupt, pull-up, analog input), therefore these characteristics may be unintentionally reprogrammed depending on the state of input pins. As general rule is better to use SET and RES instructions on data register only when the whole port is in output mode. If input or mixed configuration is needed it is recommended to keep a copy of the data register in RAM. On this copy it is possible to use single bit instructions, then the copy register could be written into the port data register.

| SET | bit, datacopy |

|-----|---------------|

| LD  | a, datacopy   |

| LD  | DRA, a        |

The WAIT and STOP instructions allow the ST62xx to be used in situations where low power consumption is needed. The lowest power consumption is achieved by configuring I/Os in input mode with well-defined logic levels.

The user has to take care not to switch outputs with heavy loads during the conversion of one of the analog inputs in order to avoid any disturbance in the measurement.

#### State Transition Diagram for Safe Transitions

# INPUT/OUTPUT PORTS (Continued)

# TIMERS

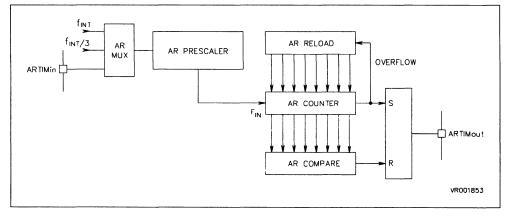

The ST6260/65 offer two on-chip Timer peripherals named Timer 1 and Auto-reload Timer. Timer 1 consists of an 8-bit counter with a 7-bit programmable prescaler, thus giving a maximum count of 2<sup>15</sup>, and control logic that allows configuring the peripheral in three operating modes. The Auto-reload Timer is an 8-bit Timer with Auto-reload, Input Capture and Output Compare capabilities. 4 modes are available for PWM, PLL, time measurement and period measurement.

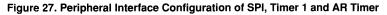

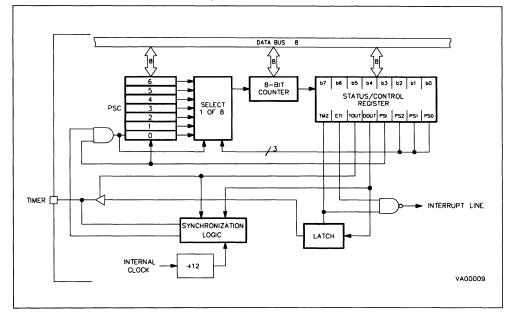

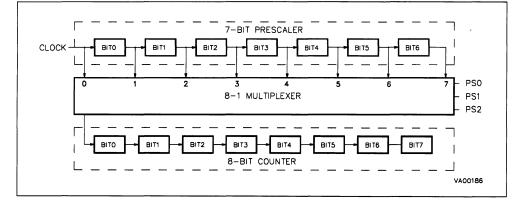

### Timer 1

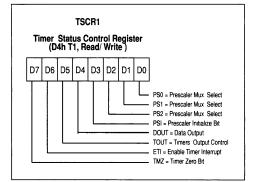

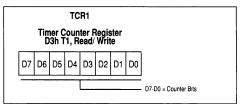

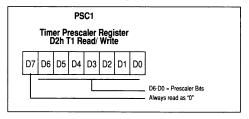

Figure 28 shows the Timer 1 block diagram. An external Timer pin is available for the user (ST6265 only). The content of the 8-bit counter can be read/written in the Timer/Counter register TCR which is addressed in the data space as a RAM location at addresses D3h. The state of the 7-bit prescaler is read in the PSC register at addresses D2h. The control logic device is managed in the TSCR1 register (addresses D4h) as described in the following paragraphs.

The 8-bit counter is decremented by the output (rising edge) coming from the 7-bit prescaler and can be loaded and read under program control.

When it decrements to zero then the TMZ (Timer Zero) bit in the TSCR1 is set to one. If the ETI (Enable Timer Interrupt) bit in the TSCR1 is also set to one an interrupt request, associated to interrupt vector #4, is generated. The interrupt service routine then should poll bit TMZ in TSCR1 to determine if the interrupt has been generated by Timer 1 or by the A/D Converter. The Timer 1 interrupt can be used to exit the MCU from the WAIT mode.

The Timer 1 Prescaler input can be the internal clock (after Oscillator Divider) divided by 12 or an external clock at the Timer I/O pin. The prescaler decrements on the rising edge. Depending on the division factor programmed by PS2, PS1 and PS0 bits in TSCR1, the clock input of the timer/counter register is multiplexed to different sources. On division factor 1, the clock input of the prescaler is also that of timer/counter; on factor 2, bit 0 of prescaler register is connected to the clock input of TCR1. This bit changes its state with the half frequency of prescaler clock input. On factor 4, bit 1 of PSC1 is connected to clock input of TCR1, and so on. The prescaler initialize bit PSI in the TSCR1 register must be set to one to allow the prescaler (and hence the counter) to start. If it is cleared to zero then

all of the prescaler bits are set to one and the counter is inhibited from counting. The prescaler can be given any value between 0 and 7Fh by writing to addresses D2h, if bit PSI in the TSCR1 register is set to one. The tap of the prescaler is selected using the PS2,PS1,PS0 bits in the control register. Figure 29 shows the Timer 1 working principle.

Timer 1 can be configured in 3 modes using the TOUT and DOUT bits of the TSCR1 register. These modes are Event counter, Gated or Output signal.

The internal Timer I/O can in addition be connected to either the PC1/TIM1 pin or the DRC1 bit depending on the configuration of bit DDRC1. Table 8 summarize the modes of Timer 1.

- Event counter: The Prescaler is decremented at each rising edge of the Timer I/O. The Timer I/O is either the PC1/TIM1 pin or the DRC1 bit of the DRC register depending on DDRC1.

- Gated: The Timer 1 is decremented by the Timer clock (f<sub>INT</sub> divided by 12) when the internal Timer I/O is held high. The Timer I/O is either pin PC1/TIM1 or the DRC1 bit of register DDRC1.

Output signal: The PC1/TIM1 pin is connected to the DOUT latch and is configured as output regardless of DOUT and DDRC1 bits. The low to high transition of bit TMZ (when counter reaches 00h) is used to latch the data previously stored in DOUT and pass it to the PC1/TIM1 through the Timer I/O. This operating mode allows signal generation.

### Timer 1 Interrupt

When the counter register decrements to zero and the software controlled ETI (Enable Timer Interrupt) bit is set to one then an interrupt request associated to interrupt vector #4 is generated. When the counter decrements to zero also the TMZ bit in the TSCR register is set to one.

Since only one interrupt vector is available for both Timer 1 and the A/D Converter, the interrupt service routine should determine from which source the interrupt came by polling the TMZ bit and the EOC bit of the A/D Converter Control Register.

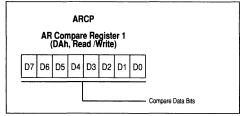

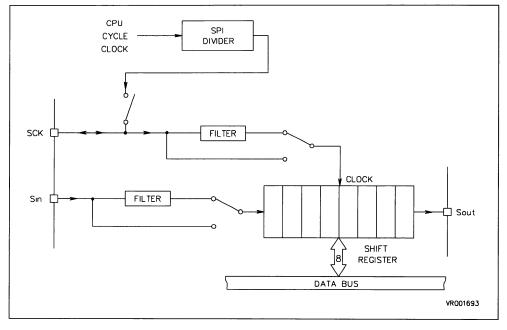

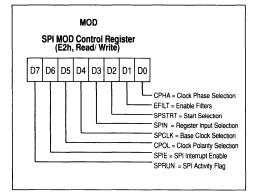

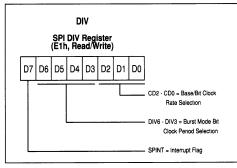

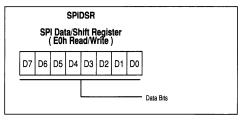

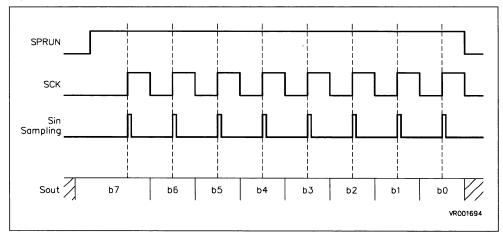

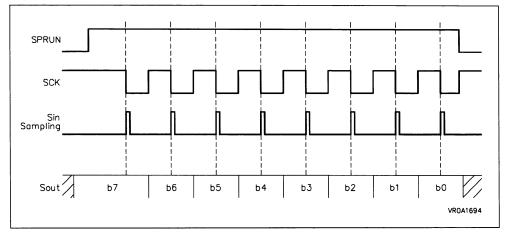

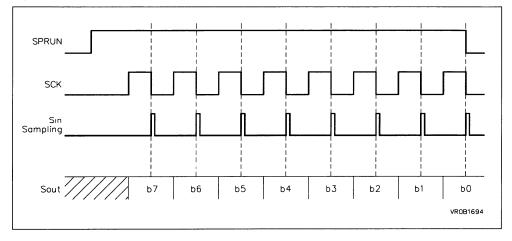

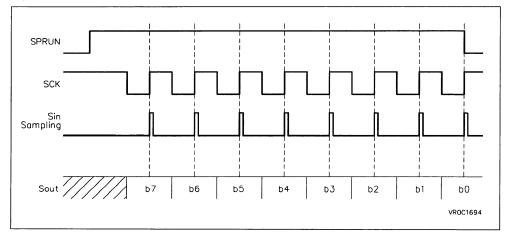

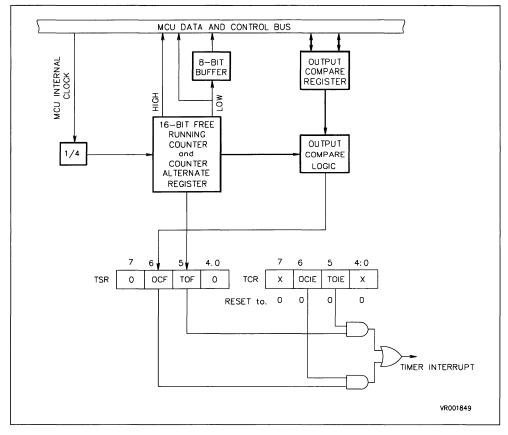

#### Notes: