# **TELEPHONE SET ICs**

## DATABOOK

2<sup>nd</sup> EDITION

DECEMBER 1993

#### USE IN LIFE SUPPORT DEVICES OR SYSTEMS MUST BE EXPRESSLY AUTHORIZED

SGS-THOMSON PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF SGS-THOMSON Microelectronics. As used herein:

- Life support devices or systems are those which (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided with the product, can be reasonably expected to result in significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can reasonably be expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

545

| TABLE OF CONTENTS                                                             |      |

|-------------------------------------------------------------------------------|------|

|                                                                               |      |

|                                                                               |      |

|                                                                               |      |

|                                                                               |      |

| INTRODUCTION                                                                  | Page |

| ALPHANUMERICAL INDEX                                                          |      |

| SELECTION GUIDE                                                               |      |

| DATASHEETS                                                                    |      |

| DEDICATED ICs                                                                 | 1    |

| DEDICATED MCUs                                                                | 46   |

|                                                                               | 48   |

|                                                                               |      |

| STANDARD LINEAR ICs       MEMORIES         MEMORIES       PROTECTION CIRCUITS | 52   |

## INTRODUCTION

## SGS-THOMSON IN TELEPHONE SET IC MARKET: THE WORLDWIDE SUPPLIER

SGS-THOMSON Microelectronics has been designing and producing dedicated integrated circuits for telephone sets for two decades.

Today the company offers the widest product range and probably manufactures more telephone ICs than any other company in the world -- about 60 million ICs per year, not including protection devices and memories.

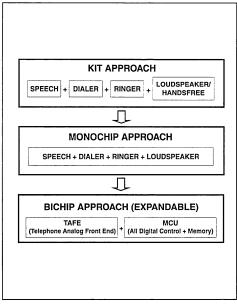

The SGS-THOMSON portfolio for analog telephone sets is moving from the traditional domain of single functions (speech, dialer, ringer, handsfree) to a more integrated approach with single chip phones, "spedials" (speech + repertory dialer) and various two-chip solutions (analog section IC + MCU).

While the individual functions still con-

EVOLUTION OF ANALOG TELEPHONE FUNCTION

stitute the core of the current production activity, the new concept of a two-chip solution is generating the real added value in the telephones of the nineties. The idea is to combine a single analog chip, able to handle all of the Telephone Analog Front End (TAFE) functions, with a microcontroller unit (MCU), taking care of all logic activities. The two ICs can be separately upgraded in order to provide flexibility for different markets and modular growth of the functions offered.

In parallel with the consolidation of the traditional offerings in the corded analog telephone domain, new products appear in the wider scenario of digital corded, ISDN and cordless (analog and digital) telephones.

ADVANCED TECHNOLOGY. Using an advanced CMOS Technology SGS-THOMSON has produced the L3916 SPEDIAL Family (Speech + Repertory Dialer).

# ALPHANUMERICAL INDEX ——

| Type<br>Number | Function                                                    | Page<br>Number |

|----------------|-------------------------------------------------------------|----------------|

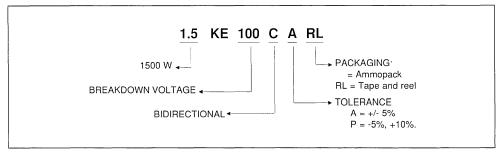

| 1.5KE Series   | Uni and Bidirectional Transils                              | 547            |

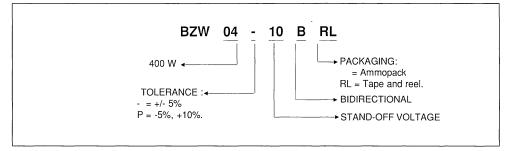

| BZW04 Series   | Uni and Bidirectional Transils                              | 555            |

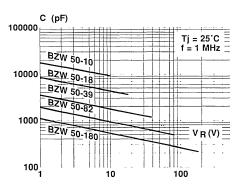

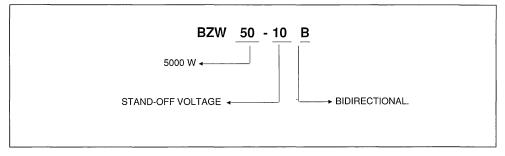

| BZW50 Series   | Uni and Bidirectional Transils                              | 563            |

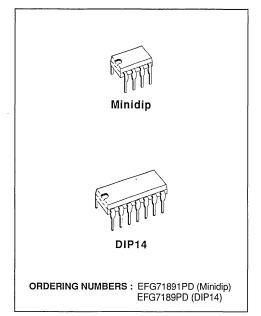

| EFG7189        | DTMF Generation for Binary Coded Hexadecimal Data           | 19             |

| EFG71891       | DTMF Generation for Binary Coded Hexadecimal Data           | 19             |

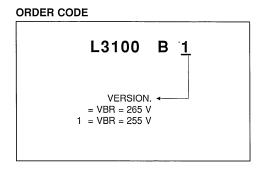

| L3100B/B1      | Unidirectional Programmable Suppressor                      | 569            |

| L3240          | Electronic Two-Tone Ringer                                  | 29             |

| L3280          | Low Voltage Telephone Speech Circuit                        | 33             |

| L3281          | Low Voltage Telephone Speech Circuit                        | 39             |

| L3845          | Trunk Interfaces                                            | 47             |

| L3913          | Monochip Telephone                                          | 51             |

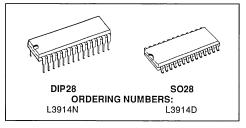

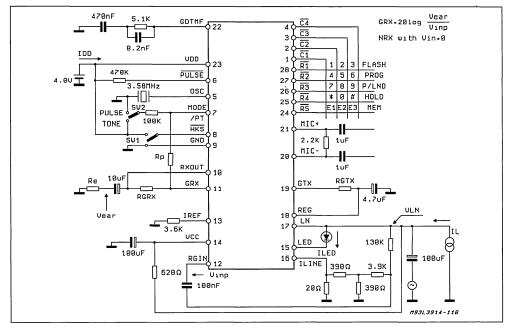

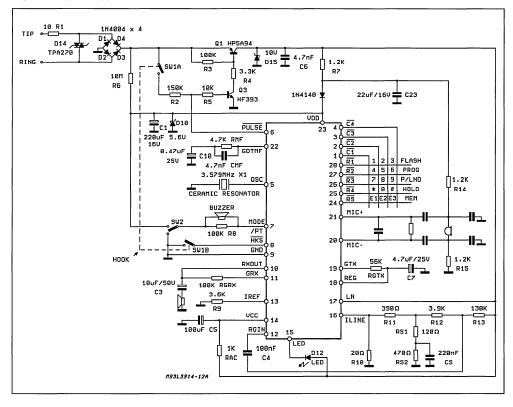

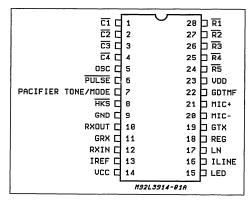

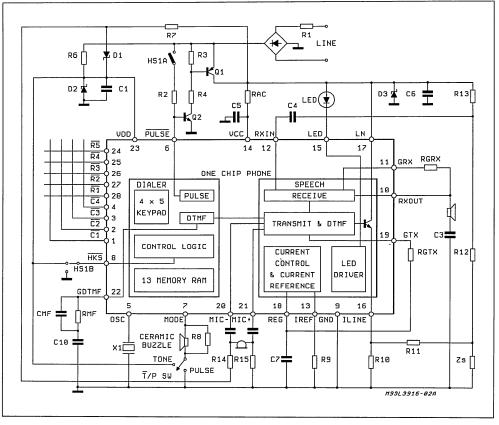

| L3914          | Low Range One Chip Phone (speech and dialer)                | 63             |

| L3916          | Low Range One Chip Phone (speech and dialer)                | 75             |

| LM883          | Low Noise Dual Operational Amplifier                        | 485            |

| LS204          | High Performance Dual Operational Amplifier                 | 487            |

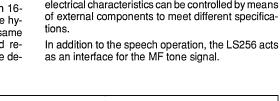

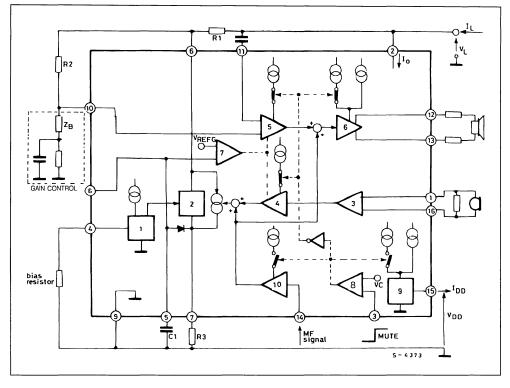

| LS256          | Speech Circuit with Multifrequency Tone Generator Interface | 87             |

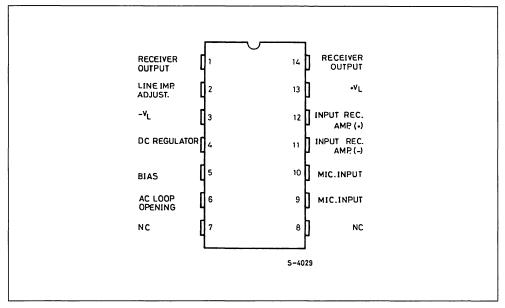

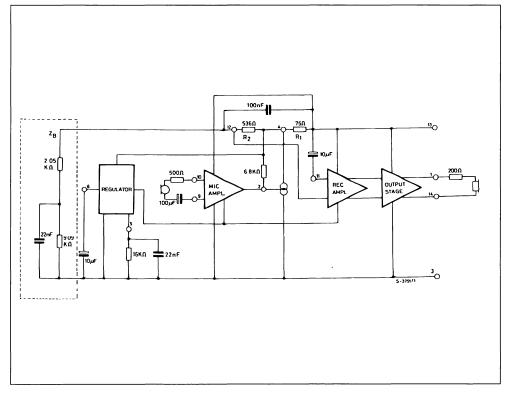

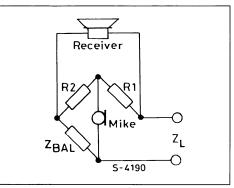

| LS285          | Telephone Speech Circuit                                    | 93             |

| LS404          | High Performance Quad Operational Amplifier                 | 489            |

| LS588          | Programmable Telephone Speech Circuit                       | 101            |

| LS656          | Speech Circuit with Multifrequency Tone Generator Interface | 111            |

| LS1240/1240A   | Electronic Two - Tone Ringer                                | 123            |

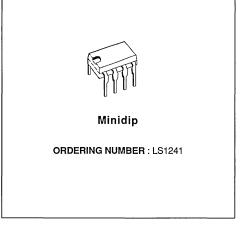

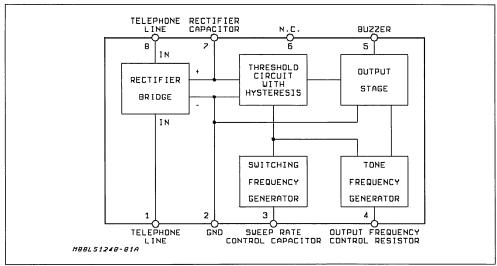

| LS1241         | Electronic Two - Tone Ringer                                | 127            |

| LS5018B        | Bidirectional Trisil                                        | 577            |

| L55060B        | Bidirectional Trisil                                        | 577            |

| LS5120B        | Bidirectionl Trisil                                         | 577            |

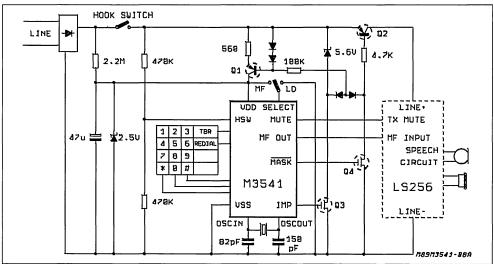

| M3541          | Single Number Pulse Tone Switchable Dialer                  | 131            |

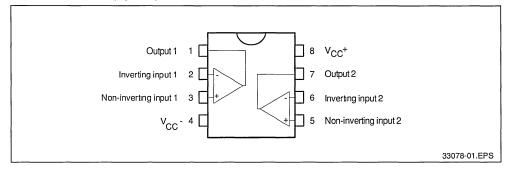

| MC33078        | Low Noise Dual Operational Amplifiers                       | 491            |

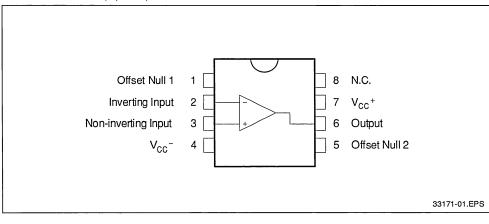

| MC33171        | Low Power Single Bipolar Operational Amplifiers             | 493            |

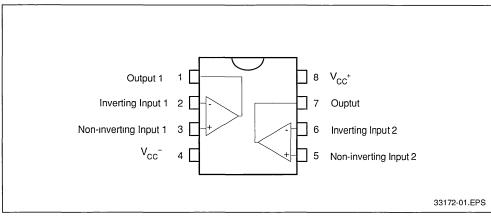

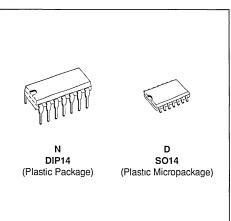

| MC33172        | Low Power Dual Bipolar Operational Amplifiers               | 495            |

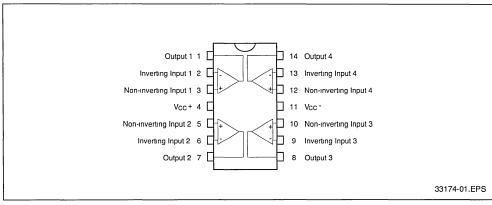

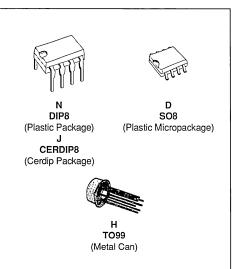

| MC33174        | Low Power Quad Bipolar Operational Amplifiers               | 497            |

| MC35171        | Low Power Single Bipolar Operational Amplifiers             | 493            |

| MC35172        | Low Power Dual Bipolar Operational Amplifiers               | 495            |

| MC35174        | Low Power Quad Bipolar Operational Amplifiers               | 497            |

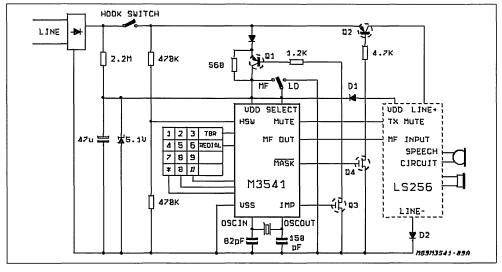

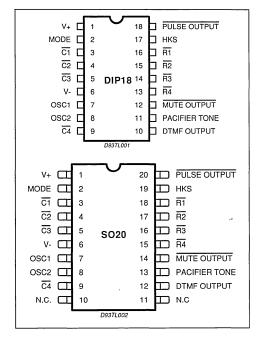

| MK53731        | Single Number Pulse Tone Switchable Dialer                  | 141            |

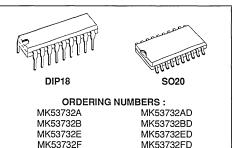

| MK53732        | Tone Pulse Dialer with Last Number Save Function            | 149            |

| MK53761        | Repertory Dialer                                            | 159            |

| MK53762        | Repertory Dialer                                            | 167            |

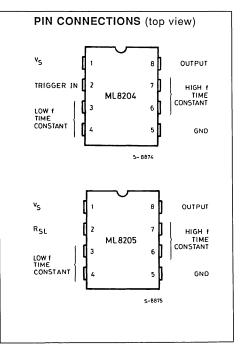

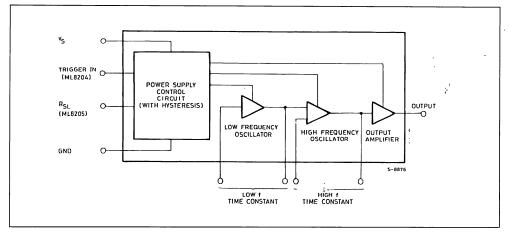

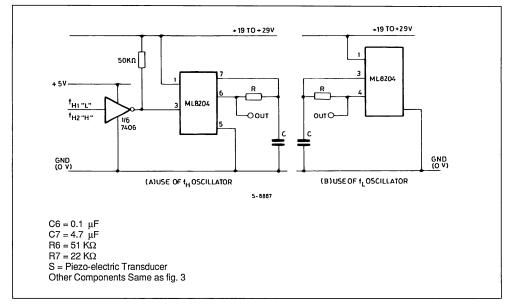

| ML8204/8205    | Tone Ringer                                                 | 175            |

| P6KE Series    | Uni and Bidirectional Transils                              | 583            |

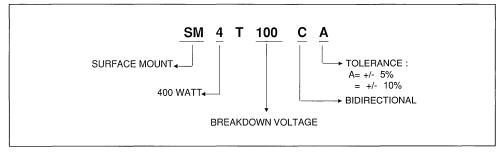

| SM4T Series    | Uni and Bidirectional Surface Mount Transils                | 591            |

## ALPHANUMERICAL INDEX

| Type<br>Number | Function                                                      | Page<br>Number |

|----------------|---------------------------------------------------------------|----------------|

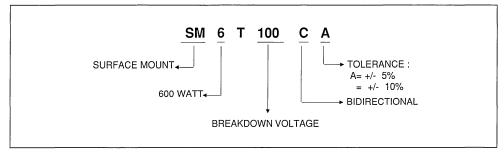

| SM6T Series    | Uni and Bidirectional Surface Mount Transils                  | 597            |

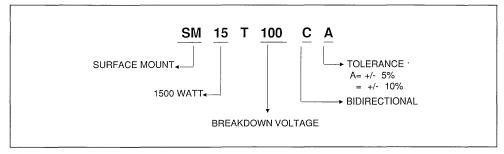

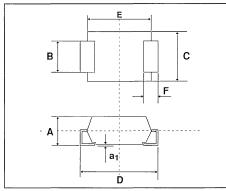

| SM15T Series   | Uni and Bidirectional surface Mount Transil                   | 603            |

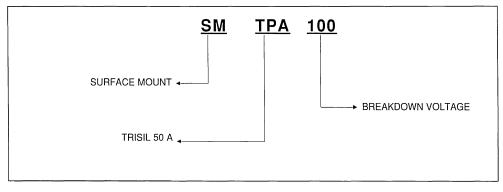

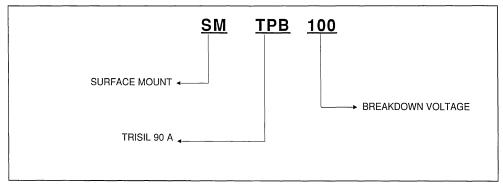

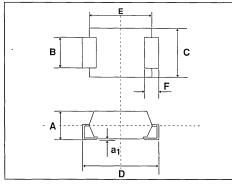

| SMTPA Series   | Surface Mount Trisil                                          | 609            |

| SMTPB Series   | Surface Mount Trisil                                          | 615            |

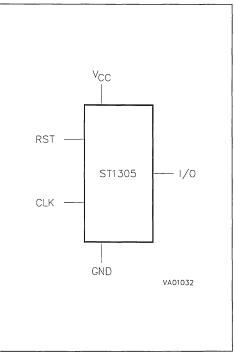

| ST1305         | Hi End CMOS 192 Bit EEPROM with Secure Logic Access Control   | 531            |

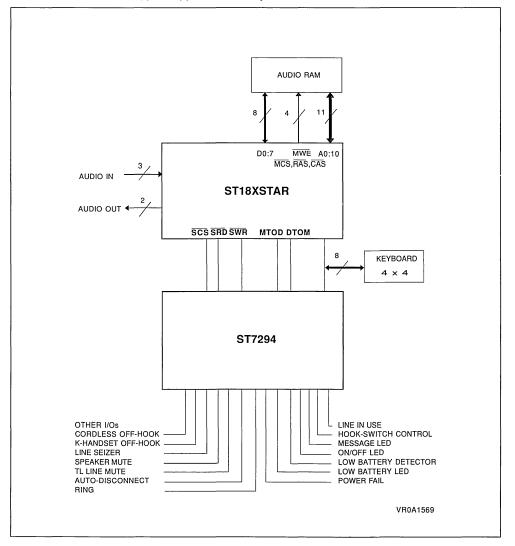

| ST18XSTAR      | Static Answering and Recording Chip                           | 481            |

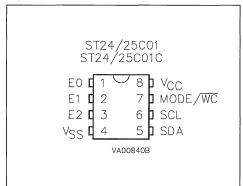

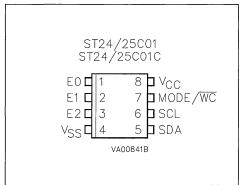

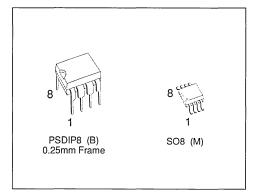

| ST24/25C01     | CMOS 1K (128 x 8) Serial EEPROMs                              | 533            |

| ST24/25C01C    | CMOS 1K (128 x 8) Serial EEPROMs                              | 533            |

| ST24/25W01C    | CMOS 1K (128 x 8) Serial EEPROMs                              | 533            |

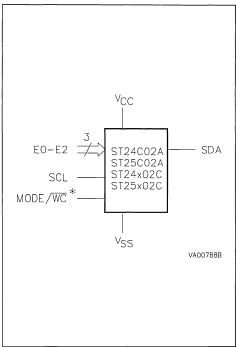

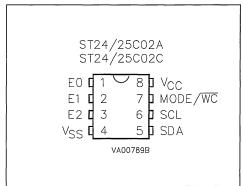

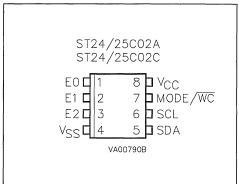

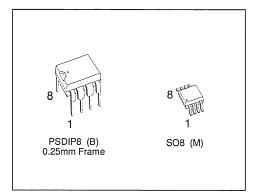

| ST24/25C02A    | CMOS 2K (256 x 8) Serial EEPROMs                              | 535            |

| ST24/25C02C    | CMOS 2K (256 x 8) Serial EEPROMs                              | 535            |

| ST24/25W02C    | CMOS 2K (256 x 8) Serial EEPROMs                              | 535            |

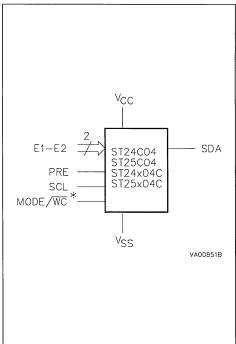

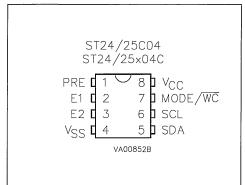

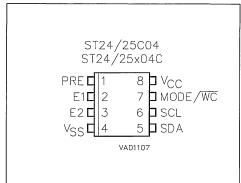

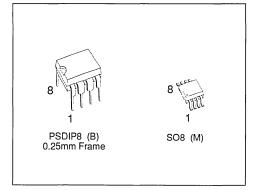

| ST24/25C04     | CMOS 4K (512 x 8) Serial EEPROMs                              | 537            |

| ST24/25C04C    | CMOS 4K (512 x 8) Serial EEPROMs                              | 537            |

| ST24/25W04C    | CMOS 4K (512 x 8) Serial EEPROMs                              | 537            |

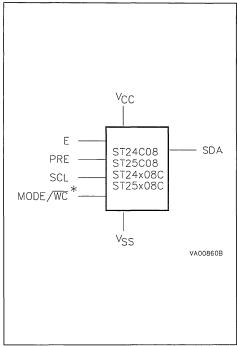

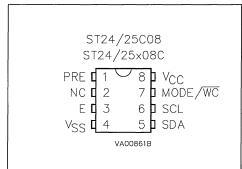

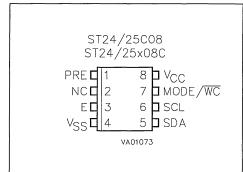

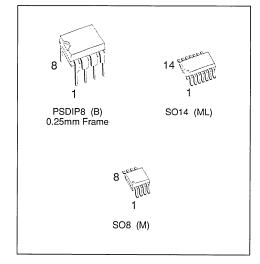

| ST24/25C08     | CMOS 8K (1024 x 8) Serial EEPROMs                             | 539            |

| ST24/25C08C    | CMOS 8K (1024 x 8) Serial EEPROMs                             | 539            |

| ST24/25W08C    | CMOS 8K (1024 x 8) Serial EEPROMs                             | 539            |

| ST24/25C16     | CMOS 16K (2048 x 8) Serial EEPROMs                            | 541            |

| ST24/25W16     | CMOS 16K (2048 x 8) Serial EEPROMs                            | 541            |

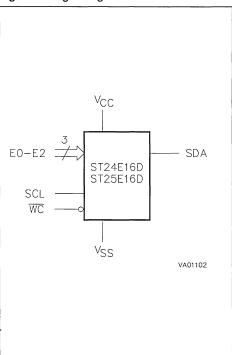

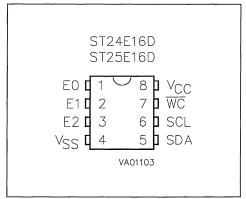

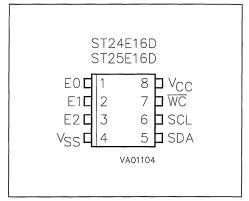

| ST24/25E16D    | CMOS 16K (2048 x 8) Serial EEPROMs, Ext. I2C Bus              | 543            |

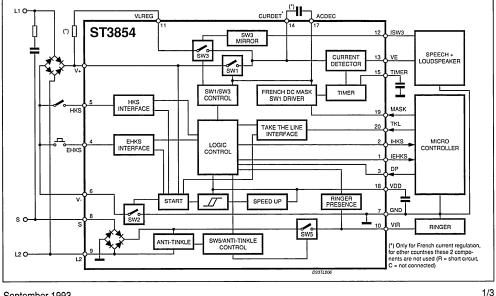

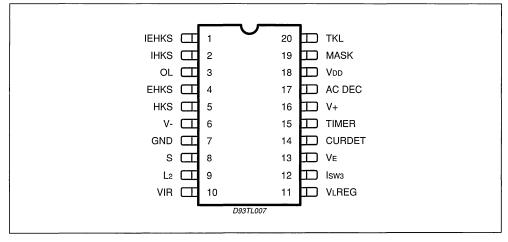

| ST3854         | Eletronic Hook Switch                                         | 189            |

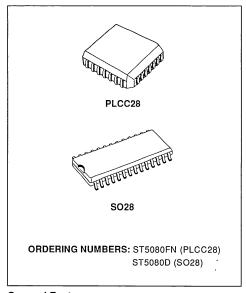

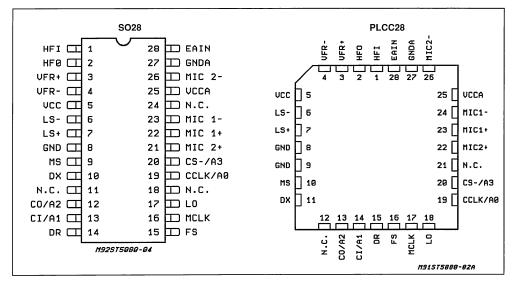

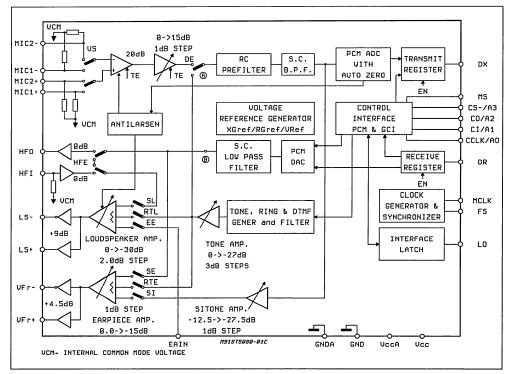

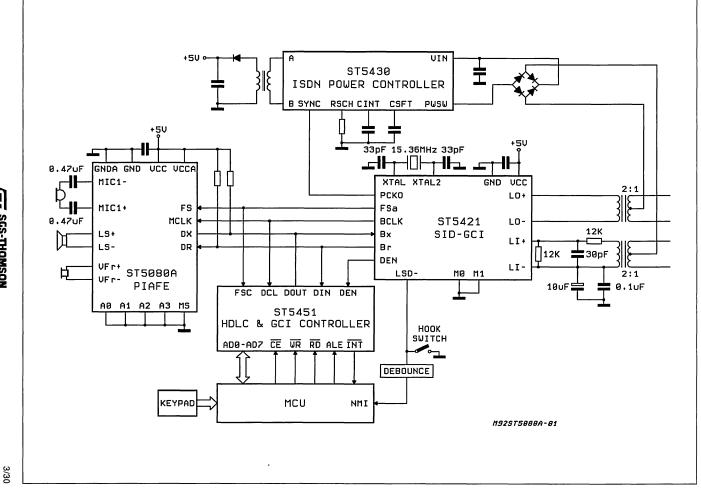

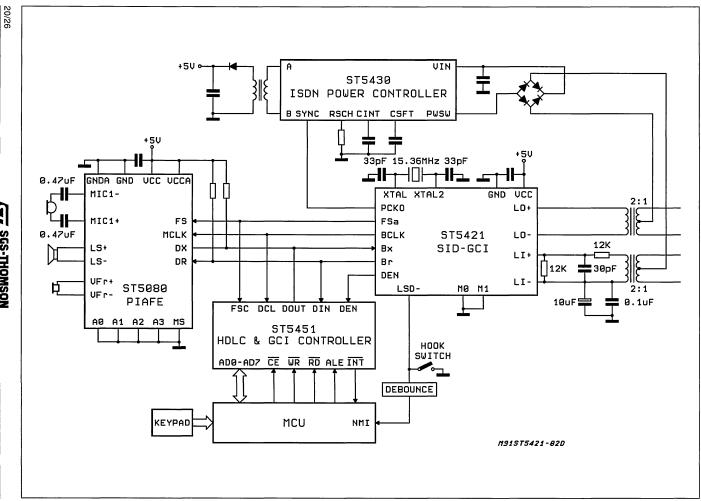

| ST5080A        | Programmable ISDN Audio Front End                             | 193            |

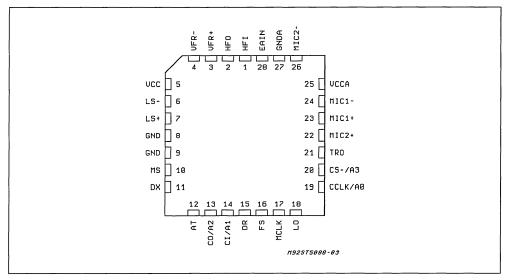

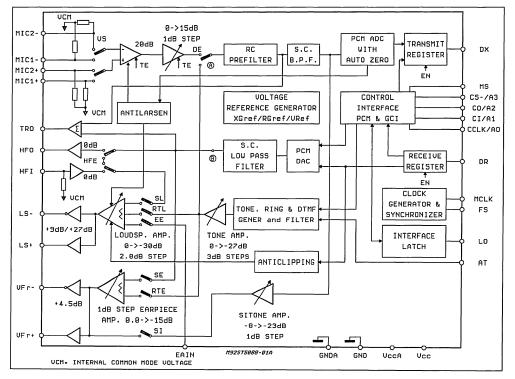

| ST5088         | Programmable ISDN Audio Front End                             | 223            |

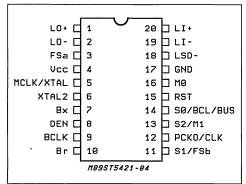

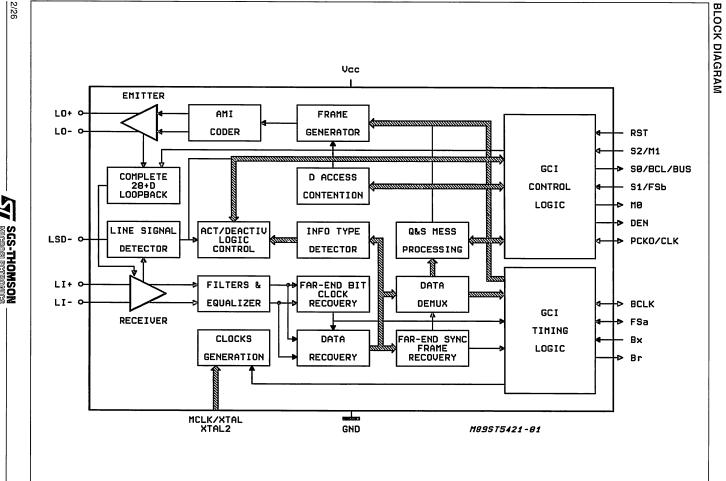

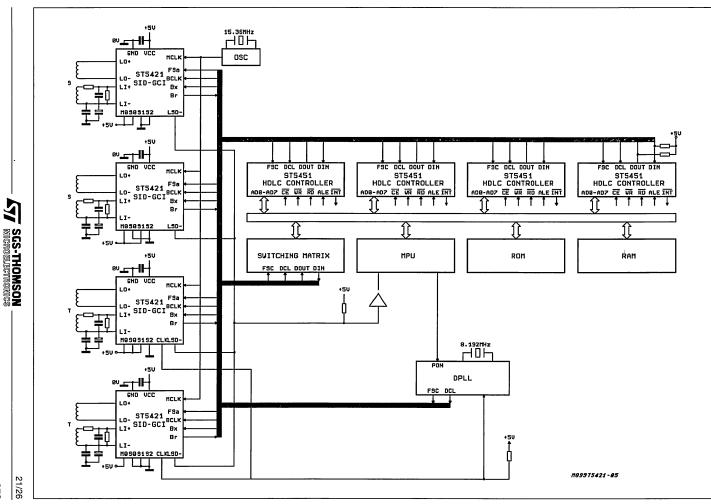

| ST5421         | SID-GCI: S/T Interface Device with GCI                        | 253            |

| ST5451         | ISDN HDLC and GCI Controller                                  | 2,79           |

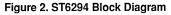

| ST6294         | 8-Bit HCMOS MCU with A/D Converter EEPROM & Auto-Reload Timer | 469            |

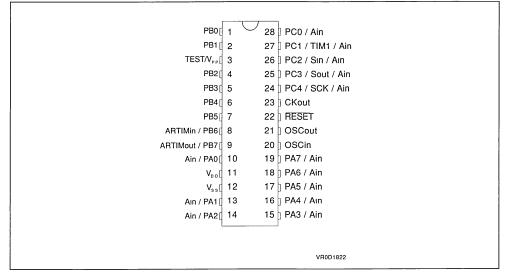

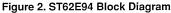

| ST62E94/T94    | 8-Bit EPROM HCMOS MCUs with A/D Converter, EEPROM &           |                |

|                | Auto-Reload Timer                                             | 471            |

| ST7162         | Universale Programmable Dual PLL                              | 311            |

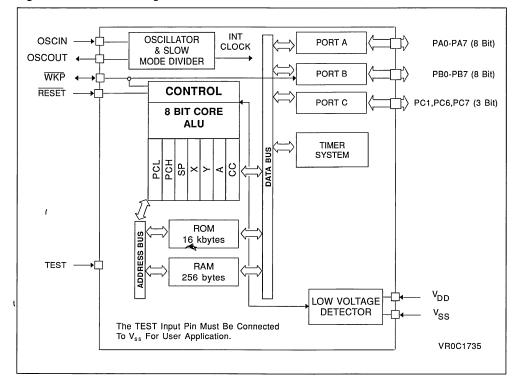

| ST7291         | 8-Bit HCMOS MCUs with 16K ROM and Wake-up Function            | 473            |

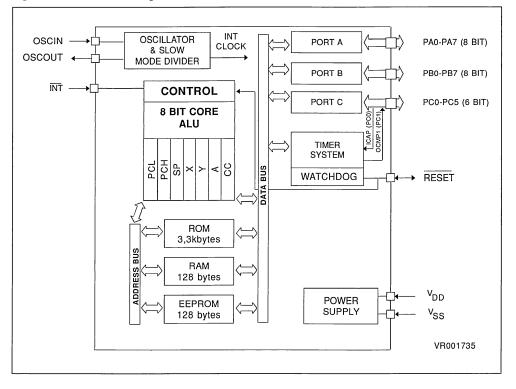

| ST7293         | 8-Bit HCMOS MCUs with EEPROM                                  | 475            |

| ST7294         | 8-Bit, HCMOS MCUs with EEPROM                                 | 477            |

| ST72E94/T94    | 8-Bit EPROM HCMOS MCUs with EEPROM                            | 479            |

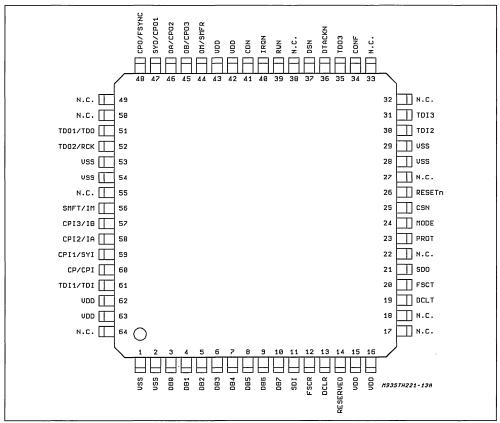

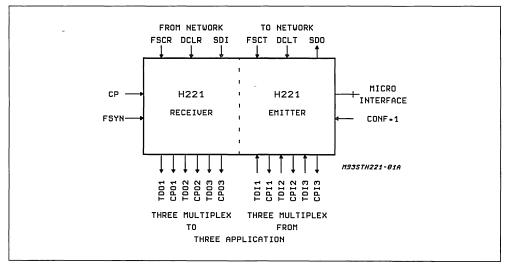

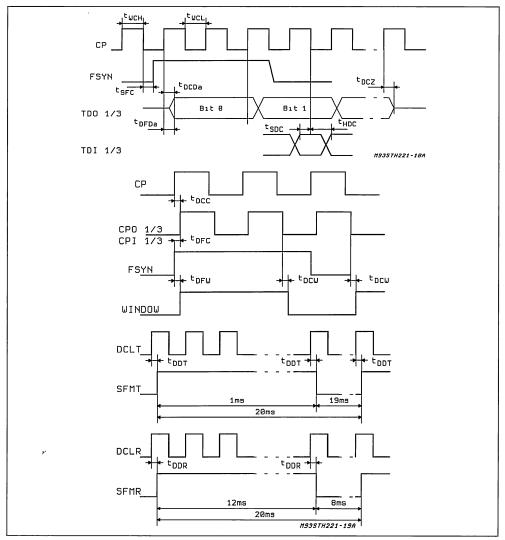

| STH221         | Muldex IC for Multimedia Teleservices                         | 325            |

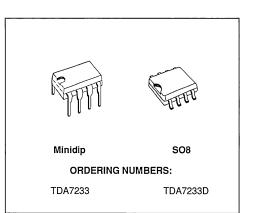

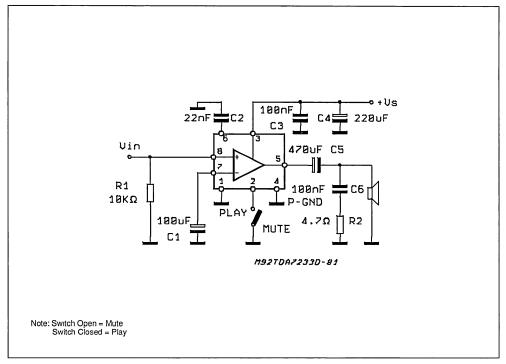

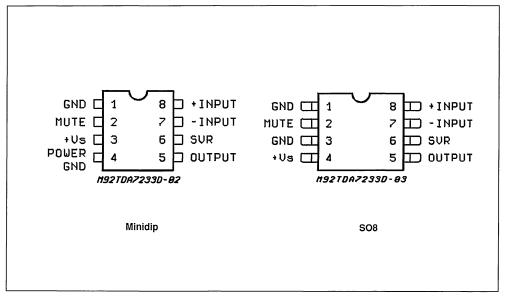

| TDA7233/D      | 1W Audio Amplifier with Mute                                  | 355            |

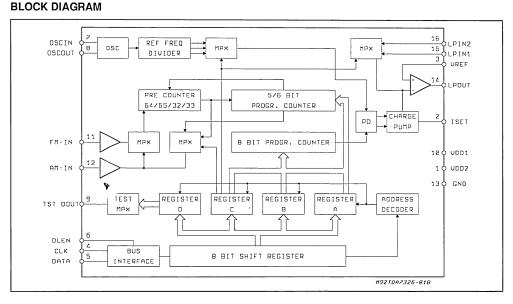

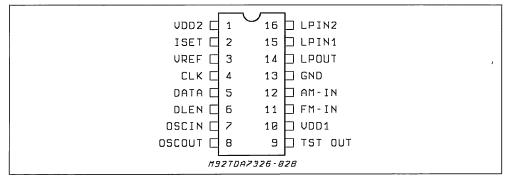

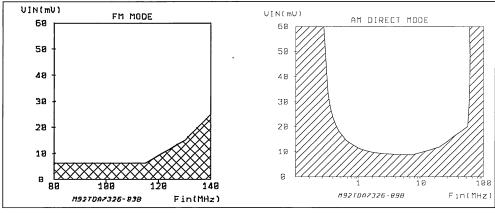

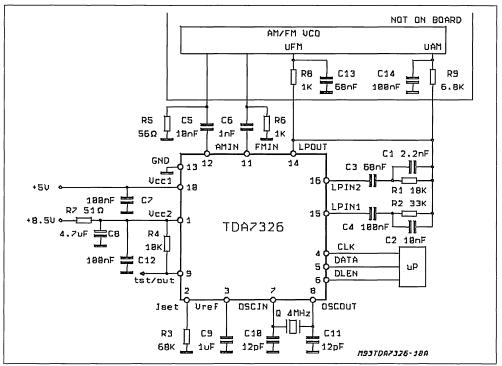

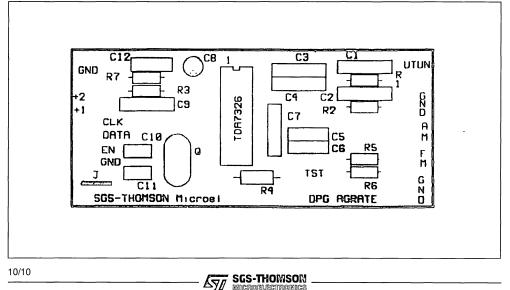

| TDA7326        | AM-FM Radio Frequency Synthesizer                             | 359            |

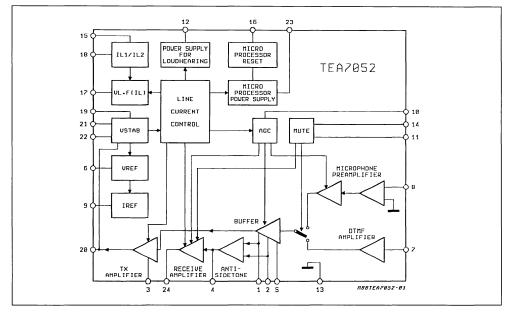

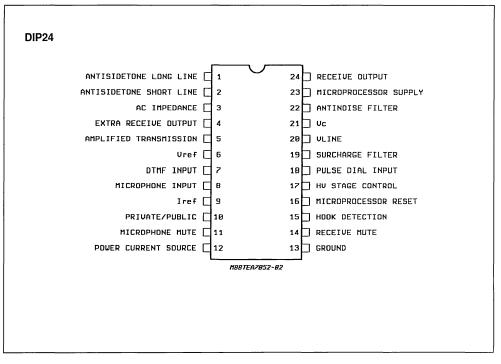

| TEA7052        | Speech Circuit with Power Management                          | 369            |

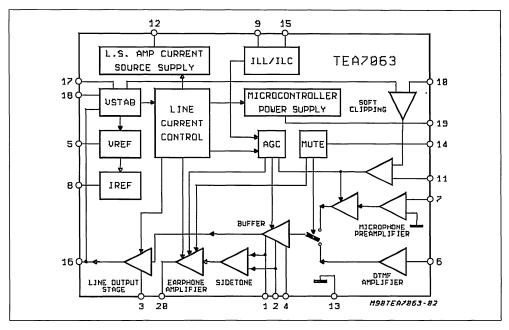

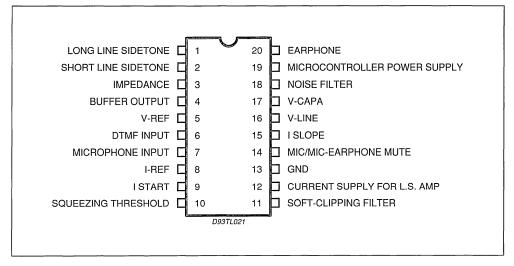

| TEA7063        | Speech Circuit with Multifrequency Tone Generator Interface   | 383            |

| TEA7088        | Low Range Phone Dedicated Analog Front End                    | 395            |

# ALPHANUMERICAL INDEX ——

| Type<br>Number | Function                                                   | Page<br>Number |

|----------------|------------------------------------------------------------|----------------|

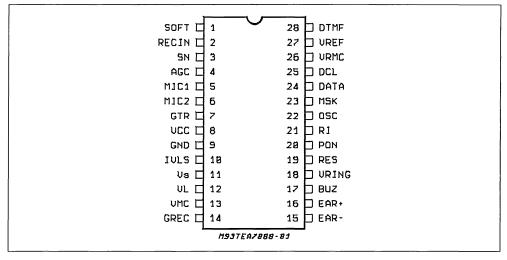

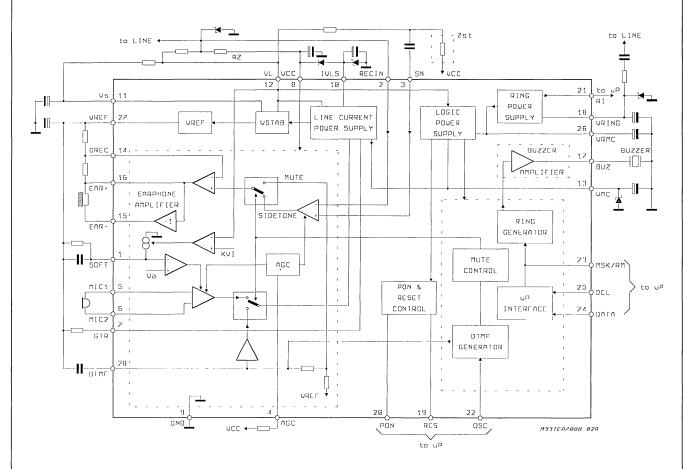

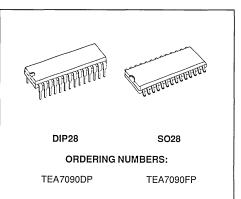

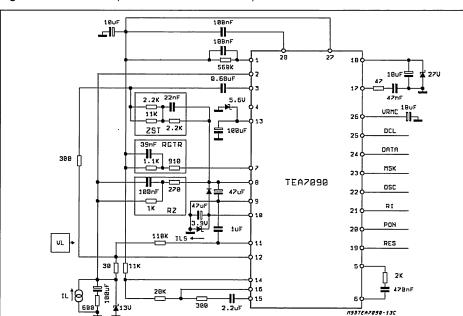

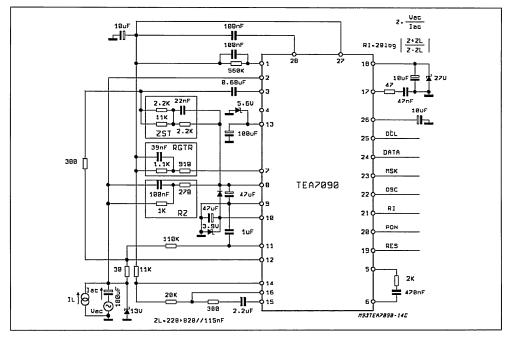

| TEA7090        | Low Range Phone Dedicated Analog Front End                 | 399            |

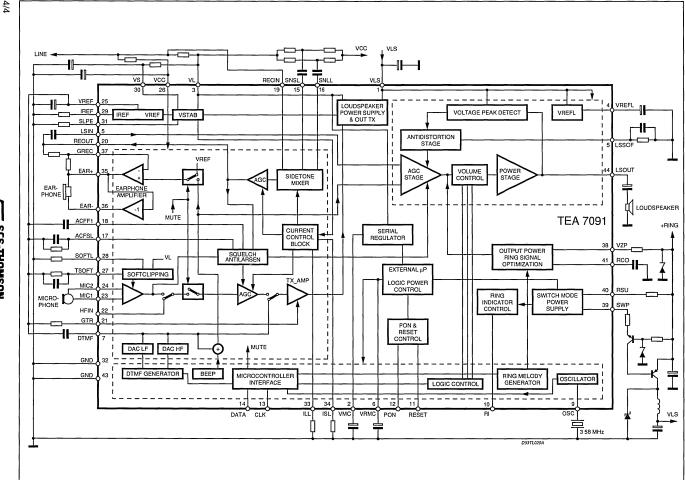

| TEA7091        | Telephone Analog Front End                                 | 415            |

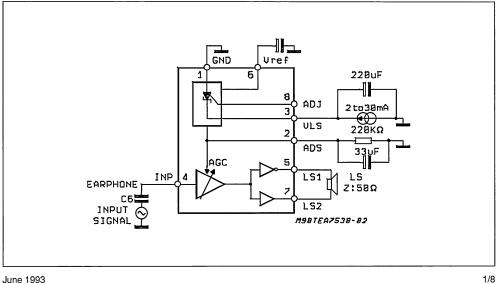

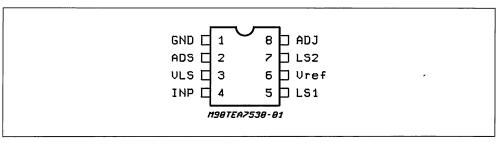

| TEA7530        | Monitor Amplifier                                          | 419            |

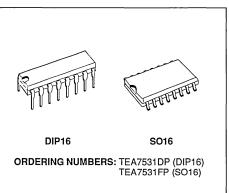

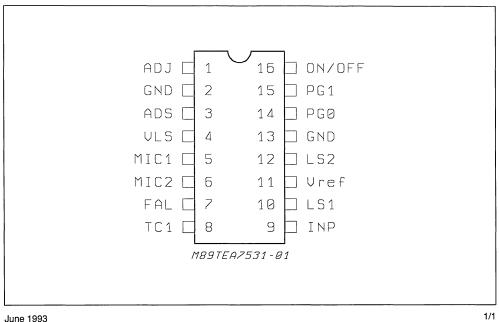

| TEA7531        | Monitor Amplifier                                          | 427            |

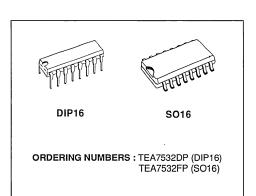

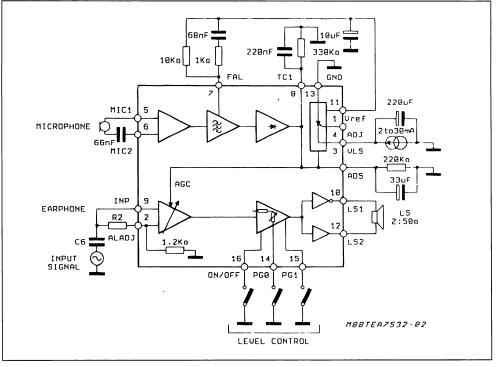

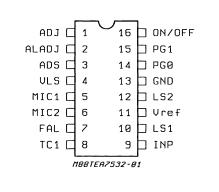

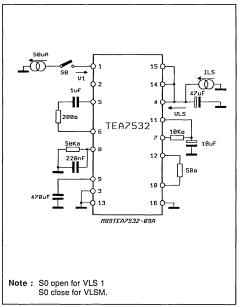

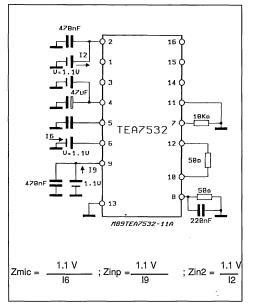

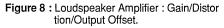

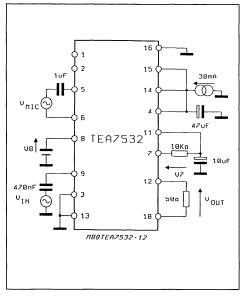

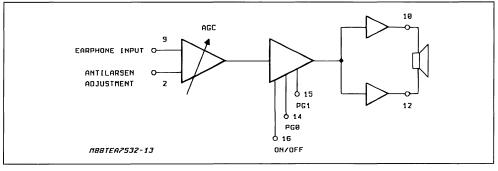

| TEA7532        | Monitor Amplifier                                          | 429            |

| TEA7533        | Monitor Amplifier                                          | 443            |

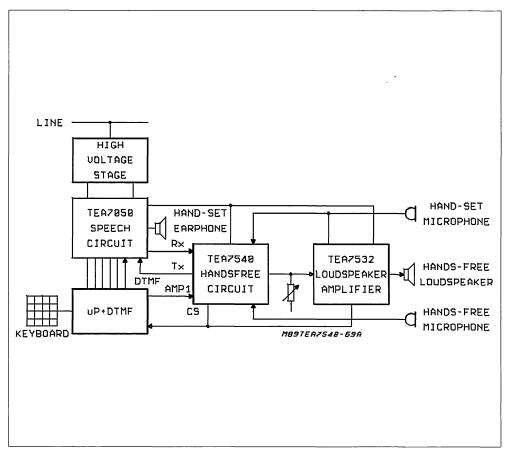

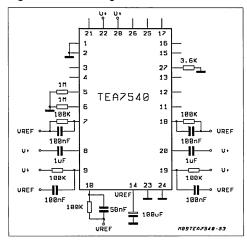

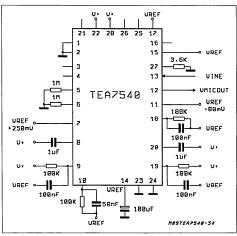

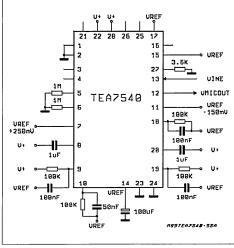

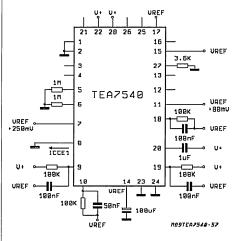

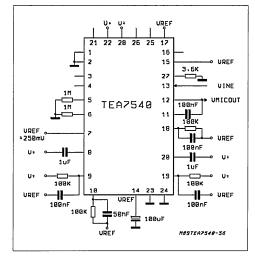

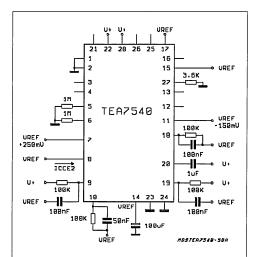

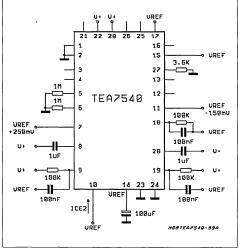

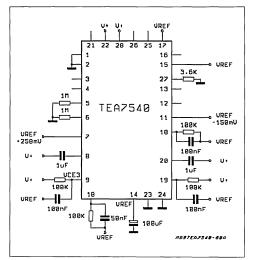

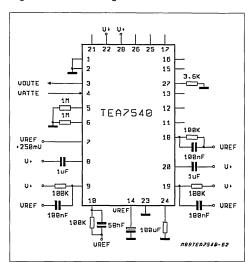

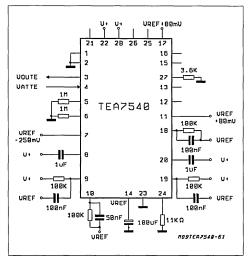

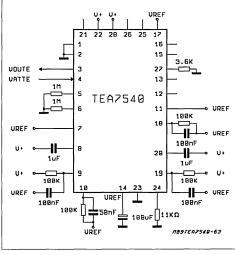

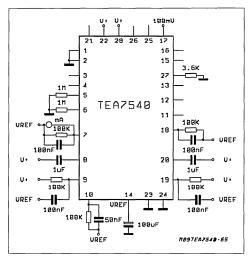

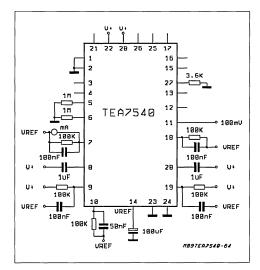

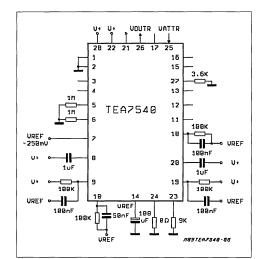

| TEA7540        | Hans Free Circuit for All Range Sets                       | 449            |

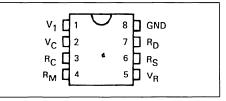

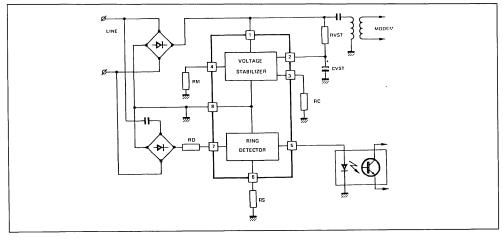

| TEA7868        | Line Interface                                             | 459            |

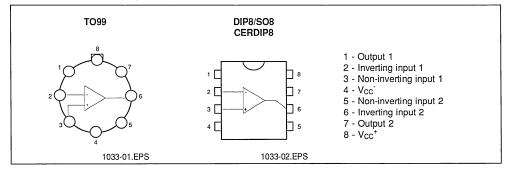

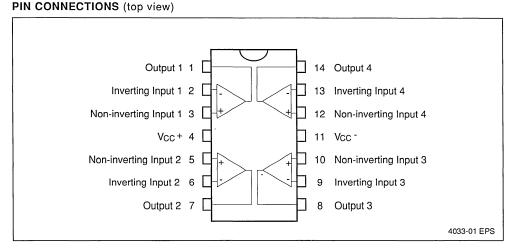

| TEB1033        | Dual Bipolar Operational Amplifiers                        | 499            |

| TEB4033        | Quad Bipolar Operational Amplifier                         | 501            |

| TEC1033        | Dual Bipolar Operational Amplifiers                        | 499            |

| TEC4033        | Quad Bipolar Operational Amplifiers                        | 501            |

| TEF1033        | Dual Bipolar Operational Amplifiers                        | 499            |

| TEF4033        | Quad Bipolar Operational Amplifiers                        | 501            |

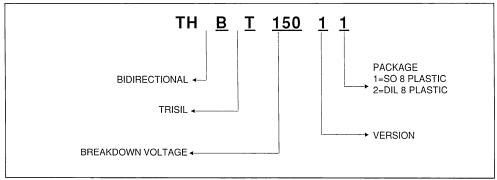

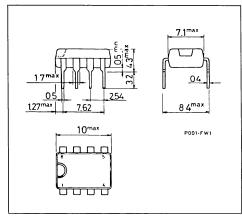

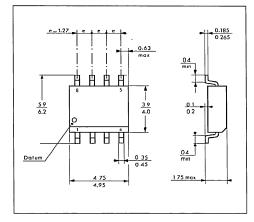

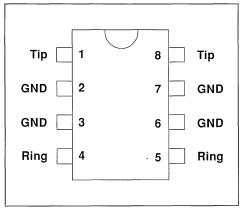

| THBT Series    | Triple Symmetrical Trisils                                 | 621            |

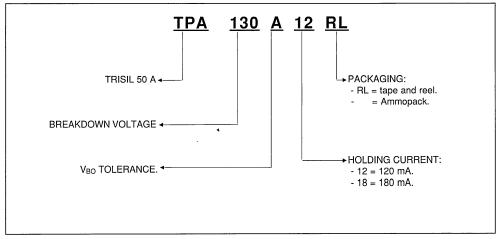

| TPA Series     | Symmetrical Trisils                                        | 629            |

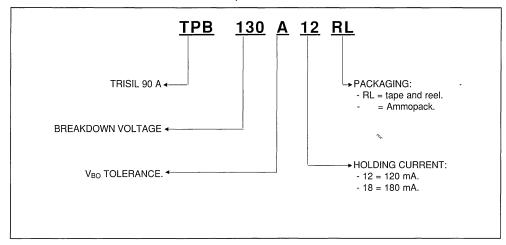

| TPB Series     | Symmetrical Trisils                                        | 635            |

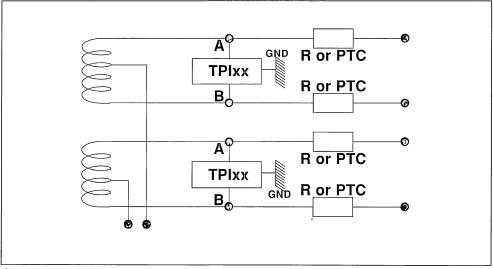

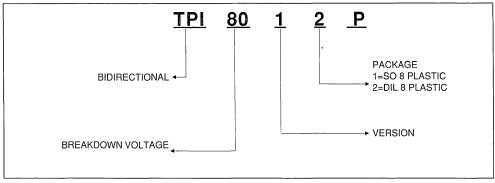

| TPI Series     | Trisil Tribalancer Protectors for ISDN                     | 641            |

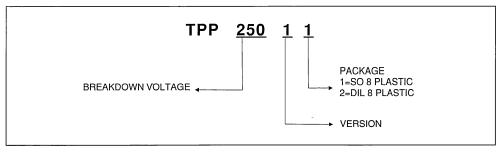

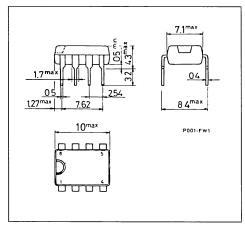

| TPP25011/12    | Programmable Supressor                                     | 649            |

| TSI Series     | Telephone Set Interface                                    | 657            |

| TS27L2C/I/M    | Very Low Power Dual CMOS Operational Amplifiers            | 503            |

| TS27L4C/I/M    | Very Low Power Quad CMOS Operational Amplifiers            | 505            |

| TS27M2C/I/M    | Low Power Dual CMOS Operational Amplifiers                 | 507            |

| TS27M4C/I/M    | Low Power Quad CMOS Operational Amplifiers                 | 509            |

| TS271C/I/M     | Programmable CMOS Single Operational Amplifiers            | 511            |

| TS272C/I/M     | High Speed Dual CMOS Operational Amplifiers                | 513            |

| TS274C/I/M     | High Speed Quad CMOS Operational Amplifiers                | 515            |

| TS339C/I/M     | Micropower Quad CMOS Voltage Comparators                   | 517            |

| TS393C/I/M     | Micropower Dual CMOS Voltage Comparators                   | 519            |

| TS902          | Input/Output RAIL-TO-RAIL Dual CMOS Operational Amplifiers | 521            |

| TS912          | Input/Output RAIL-TO-RAIL Dual CMOS Operational Amplifiers | 523            |

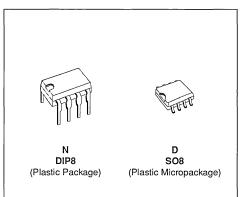

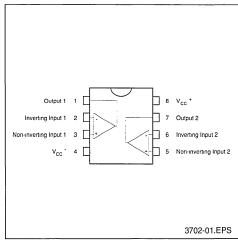

| TS3702C/I/M    | Micropower Dual CMOS Voltage Comparators                   | 525            |

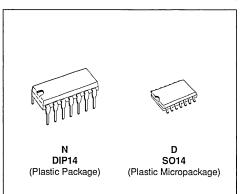

| TS3704C/I/M    | Micropower Quad CMOS Voltage Comparators                   | 527            |

# **SELECTION GUIDE**

#### SPEECH CIRCUITS

| Туре    | Function                                                    | Package     | Page |

|---------|-------------------------------------------------------------|-------------|------|

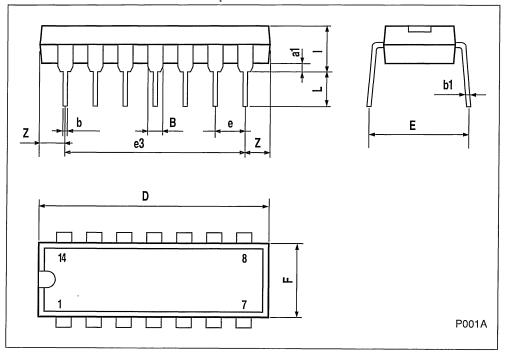

| L3280   | Low Voltage Telephone Speech Circuit                        | DIP14       | 33   |

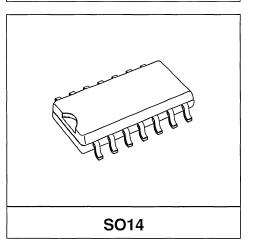

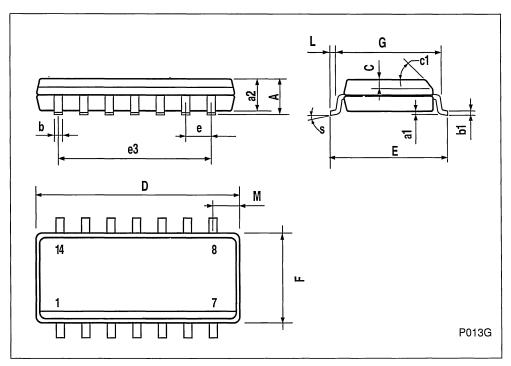

| L3281   | Low Voltage Telephone Speech Circuit                        | DIP14/SO14  | 39   |

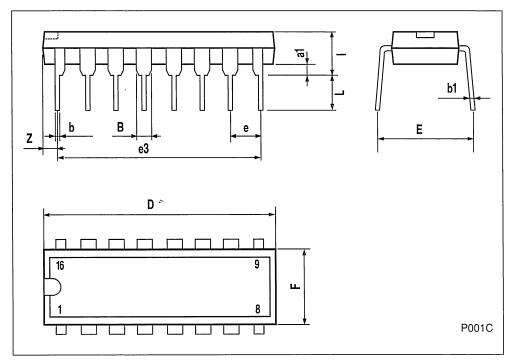

| LS256   | Speech Circuit with Multifrequency Tone Generator Interface | DIP16       | 87   |

| LS285   | Telephone Speech Circuit                                    | DIP16       | 93   |

| LS588   | Programmable Telephone Speech Circuits                      | DIP16       | 101  |

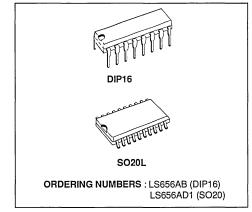

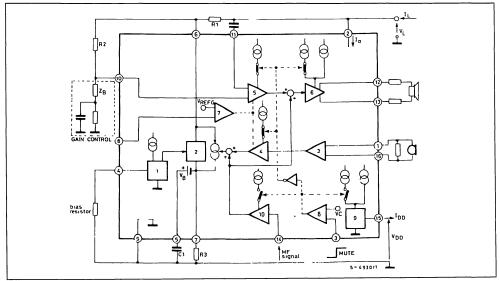

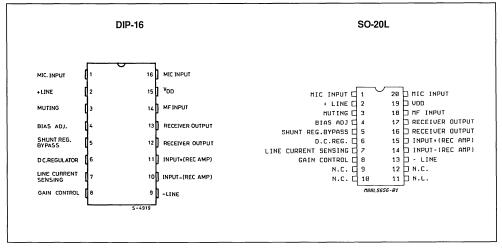

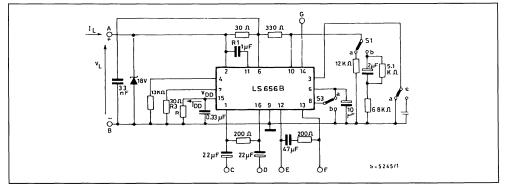

| LS656   | Speech Circuit with Multifrequency Tone Generator Interface | DIP16/SO20L | 111  |

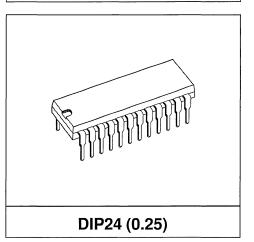

| TEA7052 | Speech Circuit with Power Management                        | DIP24       | 369  |

| TEA7063 | Speech Circuit with Multifrequency Tone Generator Interface | DIP20/SO20L | 383  |

#### TONE RINGERS/RINGING DETECTORS

| Туре    | Function                   | Package     | Page |

|---------|----------------------------|-------------|------|

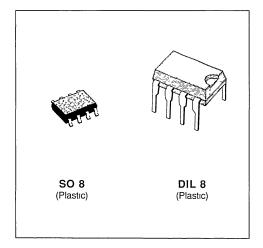

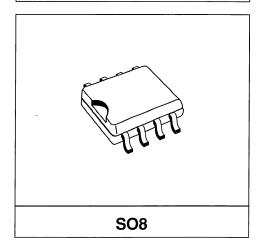

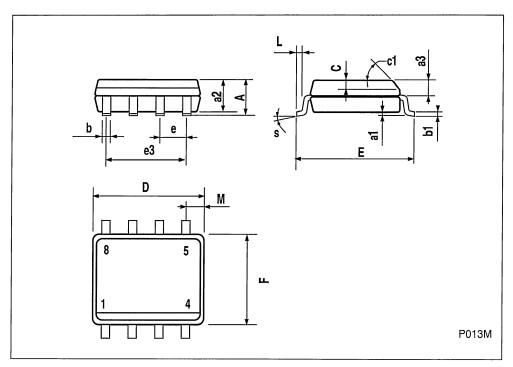

| L3240   | Electronic Two-Tone Ringer | Minidip/SO8 | 29   |

| LS1240  | Electronic Two-Tone Ringer | Minidip     | 123  |

| LS1240A | Electronic Two Tone Ringer | Minidip/SO8 | 123  |

| LS1241  | Electronic Two-Tone Ringer | Minidip     | 127  |

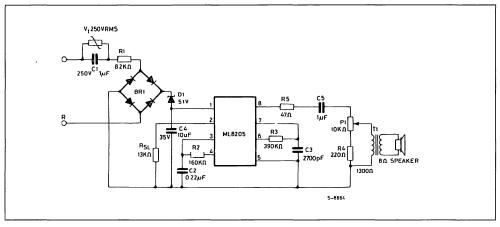

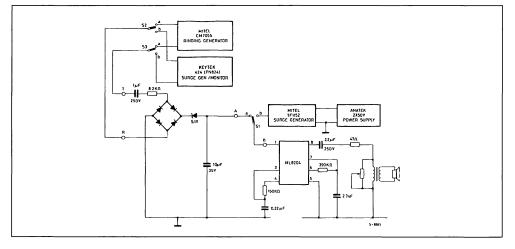

| ML8204  | Tone Ringer                | Minidip     | 175  |

| ML8205  | Tone Ringer                | Minidip     | 175  |

#### LOUDSPEAKING

| Туре        | Function          | Package     | Page |

|-------------|-------------------|-------------|------|

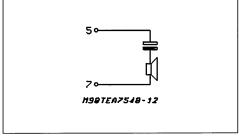

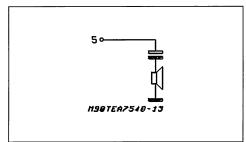

| TEA7530     | Monitor Amplifier | Minidip/SO8 | 419  |

| TEA7531 (*) | Monitor Amplifier | DIP16/SO16  | 427  |

| TEA7532     | Monitor Amplifier | DIP16/SO16  | 429  |

| TEA7533     | Monitor Amplifier | SO20        | 443  |

#### HANDS FREE

| Туре    | Function                              | Package    | Page |

|---------|---------------------------------------|------------|------|

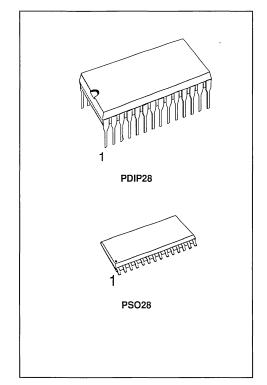

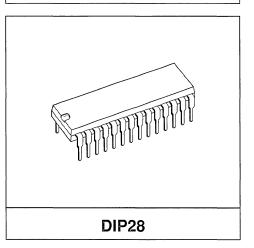

| TEA7540 | Hands Free Circuit for All Range Sets | DIP28/SO28 | 449  |

#### MONOCHIP / BICHIP

| Туре    | Function                                     | Package       | Page |

|---------|----------------------------------------------|---------------|------|

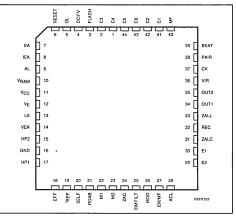

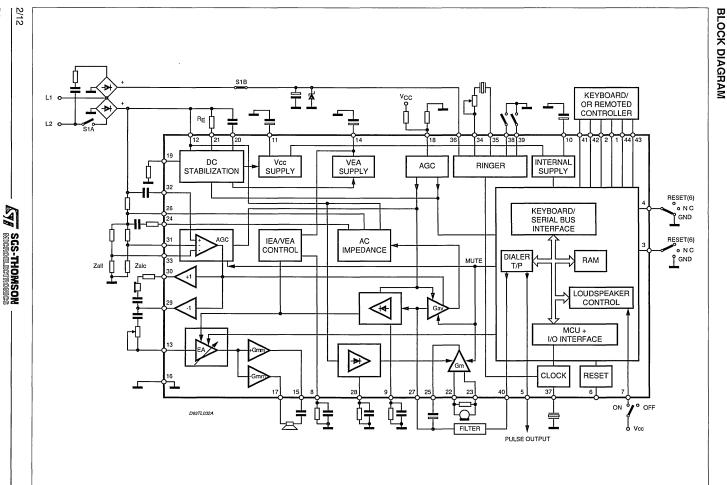

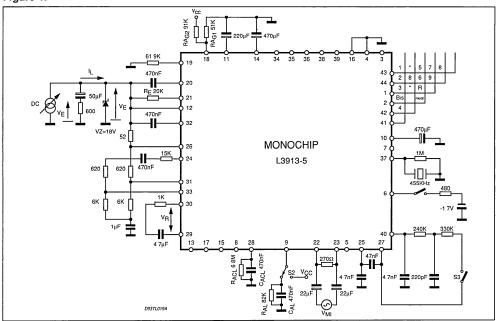

| L3913   | Monochip Telephone                           | PLCC44        | 51   |

| L3914   | Low Range One Chip Phone (Speech and Dialer) | DIP28/SO28    | 63   |

| L3916   | Low Range One Chip Phone (Speech and Dialer) | DIP28/SO28    | 75   |

| TEA7088 | Low Range Phone Dedicated Analog Front End   | DIP28/SO28    | 395  |

| TEA7090 | Low Range Phone Dedicated Analog Front End   | DIP28/SO28    | 399  |

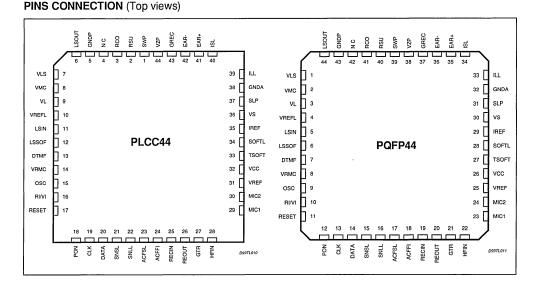

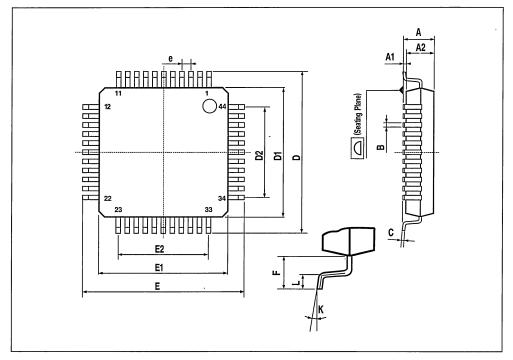

| TEA7091 | Telephone Analog Front End                   | PLCC44/PQFP44 | 415  |

(\*) Replaced by TEA7532 for New Designs

#### DIALERS

| Туре     | Function                                             | Package    | Page |

|----------|------------------------------------------------------|------------|------|

| EFG7189  | DTMF Generator for Binary Coded Hexadecimal Data     | DIP14      | 19   |

| EFG71891 | DTMF Generator for Binary Coded Hexadecimal Data     | Minidip    | 19   |

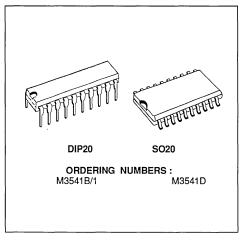

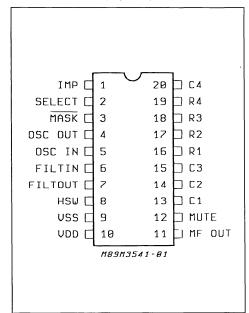

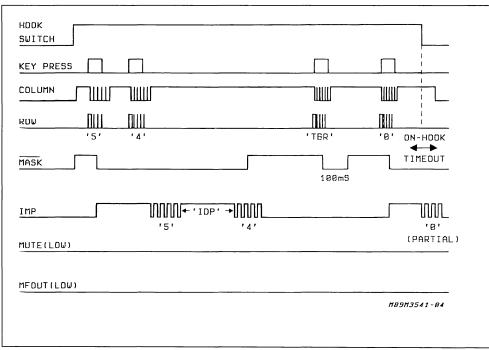

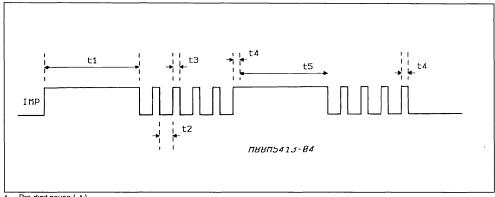

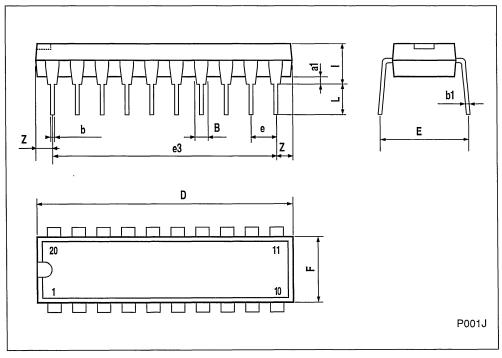

| M3541    | Single Number Pulse Tone Switchable Dialer           | DIP20/SO20 | 131  |

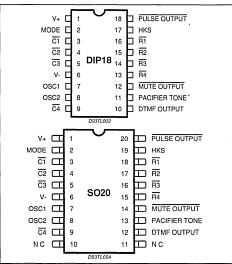

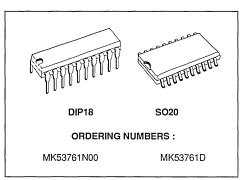

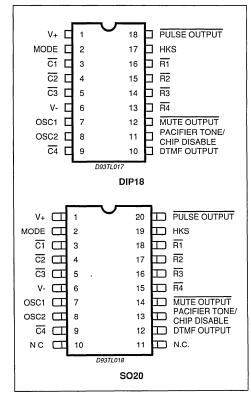

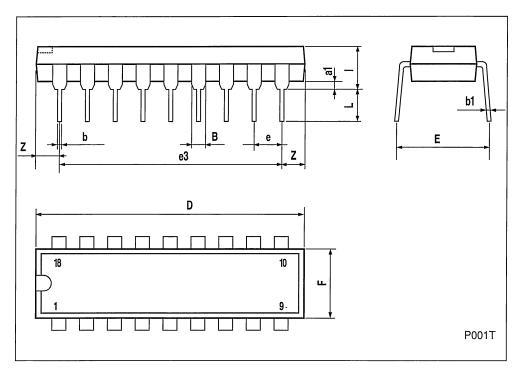

| MK53731  | Single Number Pulse Tone Switchable Dialer           | DIP18/SO20 | 141  |

| MK53732  | Tone Pulse Dialer with Last Number and Save Function | DIP18/SO20 | 149  |

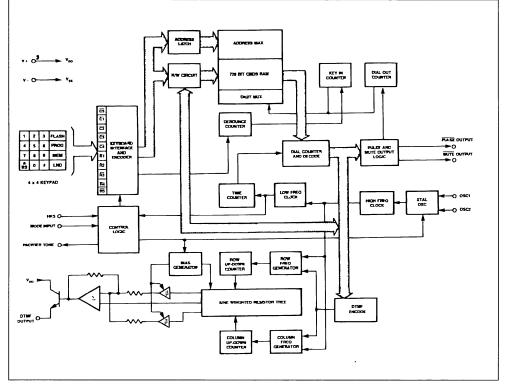

| MK53761  | Repertory Dialer                                     | DIP18/SO20 | 159  |

| MK53762  | Repertory Dialer                                     | DIP18/SO20 | 167  |

#### LINE INTERFACES

| Туре    | Function               | Package     | Page |

|---------|------------------------|-------------|------|

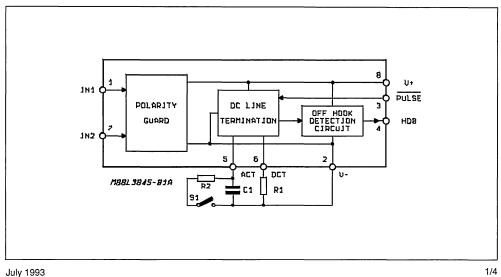

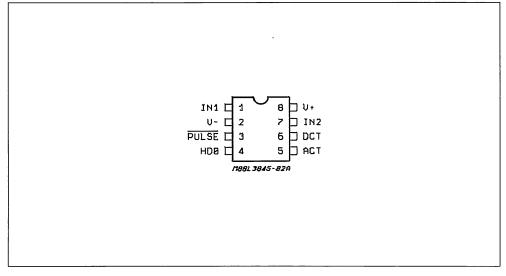

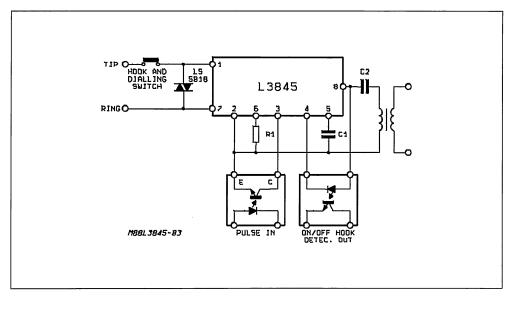

| L3845   | Trunk Interfaces       | Minidip/SO8 | 47   |

| ST3854  | Electronic Hook Switch | SO20        | 189  |

| TEA7868 | Line Interface         | Minidip     | 459  |

#### **ISDN/DIGITAL PHONE**

| Туре    | Function                               | Package     | Page |

|---------|----------------------------------------|-------------|------|

| ST5080A | Programmable ISDN Audio Fron End       | PLCC28/SO28 | 193  |

| ST5088  | Programmable ISDN Audio Front End      | PLCC28      | 223  |

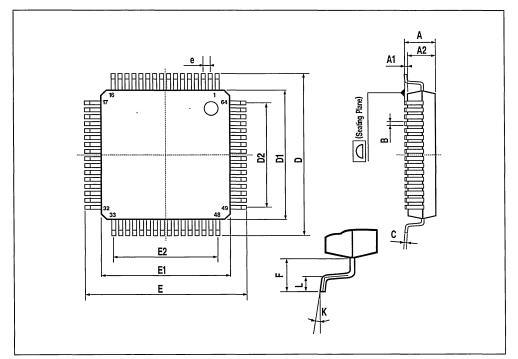

| STH221  | Muldex IC for Multimedia Teleservices  | PQFP64      | 325  |

| ST5421  | SID-GCI: S/T Interface Device with GCI | DIP20       | 253  |

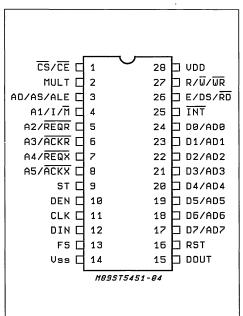

| ST5451  | ISDN HDLC and GCI Controller           | DIP28/SO28  | 279  |

#### CORDLESS

| Туре     | Function                          | Package     | Page |

|----------|-----------------------------------|-------------|------|

| ST7162   | Universal Programmable Dual PLL   | DIP16/SO16  | 311  |

| TDA7233  | 1W Audio Amplifier with Mute      | Minidip     | 355  |

| TDA7233D | 1W Audio Amplifier with Mute      | SO8         | 355  |

| TDA7326  | AM-FM Radio Frequency Synthesizer | DIP16/SO16L | 359  |

| Size | Part Number    | Organis. | V <sub>CC</sub> min<br>(V) | Feature         | Temp.<br>Range (°C) | Package |

|------|----------------|----------|----------------------------|-----------------|---------------------|---------|

| 1K   | ST24C01B1      | 128 x 8  | 4.5                        | Byte/Page Write | 0 to 70             | PSDIP8  |

|      | ST24W01B1      | 128 x 8  | 4.5                        | Write Control   | 0 to 70             | PSDIP8  |

|      | ST24C01CB1     | 128 x 8  | 3.0                        | Byte/Page Write | 0 to 70             | PSDIP8  |

|      | ST24W01CB1     | 128 x 8  | 3.0                        | Write Control   | 0 to 70             | PSDIP8  |

|      | ST25C01B1      | 128 x 8  | 2.5                        | Byte/Page Write | 0 to 70             | PSDIP8  |

|      | ST25C01CB1     | 128 x 8  | 2.5                        | Byte/Page Write | 0 to 70             | PSDIP8  |

|      | ST25W01CB1     | 128 x 8  | 2.5                        | Write Control   | 0 to 70             | PSDIP8  |

|      | ST24C01B6      | 128 x 8  | 4.5                        | Byte/Page Write | -40 to 85           | PSDIP8  |

|      | ST24W01B6      | 128 x 8  | 4.5                        | Write Control   | -40 to 85           | PSDIP8  |

|      | ST24C01CB6     | 128 x 8  | 3.0                        | Byte/Page Write | -40 to 85           | PSDIP8  |

|      | ST24W01CB6     | 128 x 8  | 3.0                        | Write Control   | -40 to 85           | PSDIP8  |

|      | ST25C01B6      | 128 x 8  | 2.5                        | Byte/Page Write | -40 to 85           | PSDIP8  |

|      | ST25C01CB6     | 128 x 8  | 2.5                        | Byte/Page Write | -40 to 85           | PSDIP8  |

|      | ST25W01CB6     | 128 x 8  | 2.5                        | Write Control   | -40 to 85           | PSDIP8  |

|      | ST24C01M1      | 128 x 8  | 4.5                        | Byte/Page Write | 0 to 70             | SO8     |

|      | ST24C01M1013TR | 128 x 8  | 4.5                        | Byte/Page Write | 0 to 70             | SO8TR   |

|      | ST24W01M1      | 128 x 8  | 4.5                        | Write Control   | 0 to 70             | SO8     |

|      | ST24W01M1013TR | 128 x 8  | 4.5                        | Write Control   | 0 to 70             | SO8TR   |

|      | ST24C01CM1     | 128 x 8  | 3.0                        | Byte/Page Write | 0 to 70             | SO8     |

|      | ST24C01CM1TR   | 128 x 8  | 3.0                        | Byte/Page Write | 0 to 70             | SO8TR   |

|      | ST24W01CM1     | 128 x 8  | 3.0                        | Write Control   | 0 to 70             | SO8     |

|      | ST24W01CM1TR   | 128 x 8  | 3.0                        | Write Control   | 0 to 70             | SO8TR   |

# EEPROM, I<sup>2</sup>C Serial Access Bus

| Size | Part Number    | Organis. | V <sub>CC</sub> min<br>(V) | Feature                             | Temp.<br>Range (°C) | Package |

|------|----------------|----------|----------------------------|-------------------------------------|---------------------|---------|

| 1K   | ST25C01CM1     | 128 x 8  | 2.5                        | Byte/Page Write                     | 0 to 70             | SO8     |

|      | ST25C01CM1TR   | 128 x 8  | 2.5                        | <ul> <li>Byte/Page Write</li> </ul> | 0 to 70             | SO8TR   |

|      | ST25C01M1      | 128 x 8  | 2.5                        | Byte/Page Write                     | 0 to 70             | SO8     |

|      | ST25C01M1013TR | 128 x 8  | 2.5                        | Byte/Page Write                     | 0 to 70             | SO8TR   |

|      | ST25W01CM1     | 128 x 8  | 2.5                        | Write Control                       | 0 to 70             | SO8     |

|      | ST25W01CM1TR   | 128 x 8  | 2.5                        | Write Control                       | 0 to 70             | SO8TR   |

|      | ST24C01M6      | 128 x 8  | 4.5                        | Byte/Page Write                     | -40 to 85           | SO8     |

|      | ST24C01M6013TR | 128 x 8  | 4.5                        | Byte/Page Write                     | -40 to 85           | SO8TR   |

|      | ST24W01M6      | 128 x 8  | 4.5                        | Write Control                       | -40 to 85           | SO8     |

|      | ST24W01M6013TR | 128 x 8  | 4.5                        | Write Control                       | -40 to 85           | SO8TR   |

|      | ST24C01CM6     | 128 x 8  | 3.0                        | Byte/Page Write                     | -40 to 85           | SO8     |

|      | ST24C01CM6TR   | 128 x 8  | 3.0                        | Byte/Page Write                     | -40 to 85           | SO8TR   |

|      | ST24W01CM6     | 128 x 8  | 3.0                        | Write Control                       | -40 to 85           | SO8     |

|      | ST24W01CM6TR   | 128 x 8  | 3.0                        | Write Control                       | -40 to 85           | SO8TR   |

|      | ST25C01CM6     | 128 x 8  | 2.5                        | Byte/Page Write                     | -40 to 85           | SO8     |

|      | ST25C01CM6TR   | 128 x 8  | 2.5                        | Byte/Page Write                     | -40 to 85           | SO8TR   |

|      | ST25C01M6      | 128 x 8  | 2.5                        | Byte/Page Write                     | -40 to 85           | SO8     |

|      | ST25C01M6013TR | 128 x 8  | 2.5                        | Byte/Page Write                     | -40 to 85           | SO8TR   |

|      | ST25W01CM6     | 128 x 8  | 2.5                        | Write Control                       | -40 to 85           | SO8     |

|      | ST25W01CM6TR   | 128 x 8  | 2.5                        | Write Control                       | -40 to 85           | SO8TR   |

|      | ST24C01M3      | 128 x 8  | 4.5                        | Byte/Page Write                     | -40 to 125          | SO8     |

| Size | Part Number     | Organis. | V <sub>CC</sub> min<br>(V) | Feature         | Temp.<br>Range (°C) | Package |

|------|-----------------|----------|----------------------------|-----------------|---------------------|---------|

| 2K   | ST24C02AB1      | 256 x 8  | 3.0                        | Byte/Page Write | 0 to 70             | PSDIP8  |

|      | ST24C02AB1/AAB  | 256 x 8  | 3.0                        | Content all 00  | 0 to 70             | PSDIP8  |

|      | ST24C02CB1      | 256 x 8  | 3.0                        | Byte/Page Write | 0 to 70             | PSDIP8  |

|      | ST24W02CB1      | 256 x 8  | 3.0                        | Write Control   | 0 to 70             | PSDIP8  |

|      | ST25C02AB1      | 256 x 8  | 2.5                        | Byte/Page Write | 0 to 70             | PSDIP8  |

|      | ST25C02CB1      | 256 x 8  | 2.5                        | Byte/Page Write | 0 to 70             | PSDIP8  |

|      | ST25W02CB1      | 256 x 8  | 2.5                        | Write Control   | 0 to 70             | PSDIP8  |

|      | ST24C02AB6      | 256 x 8  | 3.0                        | Byte/Page Write | -40 to 85           | PSDIP8  |

|      | ST24C02CB6      | 256 x 8  | 3.0                        | Byte/Page Write | -40 to 85           | PSDIP8  |

|      | ST24W02CB6      | 256 x 8  | 3.0                        | Write Control   | -40 to 85           | PSDIP8  |

|      | ST25C02AB6      | 256 x 8  | 2.5                        | Byte/Page Write | -40 to 85           | PSDIP8  |

|      | ST25C02CB6      | 256 x 8  | 2.5                        | Byte/Page Write | -40 to 85           | PSDIP8  |

|      | ST25W02CB6      | 256 x 8  | 2.5                        | Write Control   | -40 to 85           | PSDIP8  |

|      | ST24C02CB3      | 256 x 8  | 3.0                        | Byte/Page Write | -40 to 125          | PSDIP8  |

|      | ST25C02CB3      | 256 x 8  | 2.5                        | Byte/Page Write | -40 to 125          | PSDIP8  |

|      | ST24C02AB3      | 256 x 8  | 3.0                        | Byte/Page Write | -40 to 125          | PSDIP8  |

|      | ST24C02AM1      | 256 x 8  | 3.0                        | Byte/Page Write | 0 to 70             | SO8     |

|      | ST24C02AM1013TR | 256 x 8  | 3.0                        | Byte/Page Write | 0 to 70             | SO8TR   |

|      | ST24C02CM1      | 256 x 8  | 3.0                        | Byte/Page Write | 0 to 70             | SO8     |

|      | ST24C02CM1TR    | 256 x 8  | 3.0                        | Byte/Page Write | 0 to 70             | SO8TR   |

|      | ST24W02CM1      | 256 x 8  | 3.0                        | Write Control   | 0 to 70             | SO8     |

|      | ST24W02CM1TR    | 256 x 8  | 3.0                        | Write Control   | 0 to 70             | SO8TR   |

## EEPROM, I<sup>2</sup>C Serial Access Bus (cont'd)

| Size | Part Number     | Organis. | V <sub>CC</sub> min<br>(V) | Feature          | Temp.<br>Range (°C) | Package |

|------|-----------------|----------|----------------------------|------------------|---------------------|---------|

| 2K   | ST25C02AM1      | 256 x 8  | 2.5                        | Byte/Page Write  | 0 to 70             | SO8     |

|      | ST25C02AM1013TR | 256 x 8  | 2.5                        | Byte/Page Write  | 0 to 70             | SO8TR   |

|      | ST25C02CM1      | 256 x 8  | , 2.5                      | Byte/Page Write  | 0 to 70             | SO8     |

| )    | ST25C02CM1TR    | 256 x 8  | 2.5                        | Byte/Page Write  | 0 to 70             | SO8TR   |

|      | ST25W02CM1      | 256 x 8  | 2.5                        | Write Control    | 0 to 70             | SO8     |

|      | ST25W02CM1TR    | 256 x 8  | 2.5                        | Write Control    | 0 to 70             | SO8TR   |

|      | ST24C02AM6      | 256 x 8  | 3.0                        | Byte/Page Write  | -40 to 85           | SO8     |

|      | ST24C02AM6013TR | 256 x 8  | 3.0                        | Byte/Page Write  | -40 to 85           | SO8TR   |

|      | ST24C02CM6      | 256 x 8  | 3.0                        | Byte/Page Write  | -40 to 85           | SO8     |

|      | ST24C02CM6TR    | 256 x 8  | 3.0                        | Byte/Page Write  | -40 to 85           | SO8TR   |

|      | ST24W02CM6      | 256 x 8  | 3.0                        | Write Control    | -40 to 85           | SO8     |

|      | ST24W02CM6TR    | 256 x 8  | 3.0                        | Write Control    | -40 to 85           | SO8TR   |

|      | ST25C02AM6      | 256 x 8  | 2.5                        | Byte/Page Write  | -40 to 85           | SO8     |

|      | ST25C02AM6013TR | 256 x 8  | 2.5                        | Byte/Page Write  | -40 to 85           | SO8TR   |

|      | ST25C02CM6      | 256 x 8  | 2.5                        | Byte/Page Write  | -40 to 85           | SO8     |

|      | ST25C02CM6TR    | 256 x 8  | 2.5                        | Byte/Page Write  | -40 to 85           | SO8TR   |

|      | ST25W02CM6      | 256 x 8  | 2.5                        | Write Control    | -40 to 85           | SO8     |

|      | ST25W02CM6TR    | 256 x 8  | 2.5                        | Write Control    | -40 to 85           | SO8TR   |

|      | ST24C02AM3      | 256 x 8  | 3.0                        | Byte/Page Write  | -40 to 125          | SO8     |

| 4K   | ST24C04B1       | 512 x 8  | 4.5                        | Write Protection | 0 to 70             | PSDIP8  |

|      | ST24C04CB1      | 512 x 8  | 3.0                        | Write Protection | 0 to 70             | PSDIP8  |

|      | ST24W04CB1      | 512 x 8  | 3.0                        | Write Control    | 0 to 70             | PSDIP8  |

|      | ST25C04B1       | 512 x 8  | 2.5                        | Write Protection | 0 to 70             | PSDIP8  |

| Size | Part Number  | Organis. | V <sub>CC</sub> min<br>(V) | Feature          | Temp.<br>Range (°C) | Package |

|------|--------------|----------|----------------------------|------------------|---------------------|---------|

| 4K   | ST25C04CB1   | 512 x 8  | 2.5                        | Write Protection | 0 to 70             | PSDIP8  |

|      | ST25W04CB1   | 512 x 8  | 2.5                        | Write Control    | 0 to 70             | PSDIP8  |

|      | ST24C04B6    | 512 x 8  | 4.5                        | Write Protection | -40 to 85           | PSDIP8  |

|      | ST24C04CB6   | 512 x 8  | 3.0                        | Write Protection | -40 to 85           | PSDIP8  |

|      | ST24W04CB6   | 512 x 8  | 3.0                        | Write Control    | -40 to 85           | PSDIP8  |

|      | ST25C04B6    | 512 x 8  | 2.5                        | Write Protection | -40 to 85           | PSDIP8  |

|      | ST25C04CB6   | 512 x 8  | 2.5                        | Write Protection | -40 to 85           | PSDIP8  |

|      | ST25W04CB6   | 512 x 8  | 2.5                        | Write Control    | -40 to 85           | PSDIP8  |

|      | ST24C04CB3   | 512 x 8  | 3.0                        | Write Protection | -40 to 125          | PSDIP8  |

|      | ST24C04CM1   | 512 x 8  | 3.0                        | Write Protection | 0 to 70             | SO8     |

|      | ST24C04CM1TR | 512 x 8  | 3.0                        | Write Protection | 0 to 70             | SO8TR   |

|      | ST24W04CM1   | 512 x 8  | 3.0                        | Write Control    | 0 to 70             | SO8     |

|      | ST24W04CM1TR | 512 x 8  | 3.0                        | Write Control    | 0 to 70             | SO8TR   |

|      | ST25C04CM1   | 512 x 8  | 2.5                        | Write Protection | 0 to 70             | SO8     |

|      | ST25C04CM1TR | 512 x 8  | 2.5                        | Write Protection | 0 to 70             | SO8TR   |

|      | ST25W04CM1   | 512 x 8  | 2.5                        | Write Control    | 0 to 70             | SO8     |

|      | ST25W04CM1TR | 512 x 8  | 2.5                        | Write Control    | 0 to 70             | SO8TR   |

|      | ST24C04CM6   | 512 x 8  | 3.0                        | Write Protection | -40 to 85           | SO8     |

|      | ST24C04CM6TR | 512 x 8  | 3.0                        | Write Protection | -40 to 85           | SO8TR   |

|      | ST24W04CM6   | 512 x 8  | 3.0                        | Write Control    | -40 to 85           | SO8     |

|      | ST24W04CM6TR | 512 x 8  | 3.0                        | Write Control    | -40 to 85           | SO8TR   |

|      | ST25C04CM6   | 512 x 8  | 2.5                        | Write Protection | -40 to 85           | SO8     |

|      | ST25C04CM6TR | 512 x 8  | 2.5                        | Write Protection | -40 to 85           | SO8TR   |

## EEPROM, I<sup>2</sup>C Serial Access Bus (cont'd)

| Size | Part Number  | Organis. | V <sub>CC</sub> min<br>(V) | Feature                    | Temp.<br>Range (°C) | Package |

|------|--------------|----------|----------------------------|----------------------------|---------------------|---------|

| 4K   | ST25W04CM6   | 512 x 8  | 2.5                        | Write Control              | -40 to 85           | SO8     |

|      | ST25W04CM6TR | 512 x 8  | 2.5                        | Write Control              | -40 to 85           | SO8TR   |

| 8K   | ST24C08B1    | 1K x 8   | 4 5                        | Write Protection           | 0 to 70             | PSDIP8  |

|      | ST24C08CB1   | 1K x 8   | 3.0                        | Write Protection           | 0 to 70             | PSDIP8  |

|      | ST25C08CB1   | 1K x 8   | 2.5                        | Write Protection           | 0 to 70             | PSDIP8  |

|      | ST24C08B6    | 1K x 8   | 4.5                        | Write Protection           | -40 to 85           | PSDIP8  |

|      | ST24C08CB6   | 1K x 8   | 3.0                        | Write Protection           | -40 to 85           | PSDIP8  |

|      | ST25C08CB6   | 1K x 8   | 2.5                        | Write Protection           | -40 to 85           | PSDIP8  |

|      | ST24C08CM1   | 1K x 8   | 3.0                        | Write Protection           | 0 to 70             | SO8     |

|      | ST24C08CM1TR | • 1Kx 8  | 3.0                        | Write Protection           | 0 to 70             | SO8TR   |

|      | ST25C08CM1   | 1K x 8   | 2.5                        | Write Protection           | 0 to 70             | SO8     |

| 1    | ST25C08CM1TR | 1Kx 8    | 2.5                        | Write Protection           | 0 to 70             | SO8TR   |

|      | ST24C08CM6   | 1K x 8   | 3.0                        | Write Protection           | -40 to 85           | SO8     |

|      | ST24C08CM6TR | 1Kx 8    | 3.0                        | Write Protection           | -40 to 85           | SO8TR   |

|      | ST25C08CM6   | 1K x 8   | 2.5                        | Write Protection           | -40 to 85           | SO8     |

|      | ST25C08CM6TR | 1Kx 8    | 2.5                        | Write Protection           | -40 to 85           | SO8TR   |

| 16K  | ST24C16CB1   | 2K x 8   | 3.0                        | Write Protection           | 0 to 70             | PSDIP8  |

|      | ST24E16DB1   | 2K x 8   | 3.0                        | XI <sup>2</sup> C Bus & WC | 0 to 70             | PSDIP8  |

|      | ST25C16CB1   | 2K x 8   | 2.5                        | Write Protection           | 0 to 70             | PSDIP8  |

|      | ST25E16DB1   | 2K x 8   | 2.5                        | XI <sup>2</sup> C Bus & WC | 0 to 70             | PSDIP8  |

|      | ST24C16CB6   | 2K x 8   | 3.0                        | Write Protection           | -40 to 85           | PSDIP8  |

|      | ST24E16DB6   | 2K x 8   | 3.0                        | XI <sup>2</sup> C Bus & WC | -40 to 85           | PSDIP8  |

|      | ST25C16CB6   | 2K x 8   | 2.5                        | Write Protection           | -40 to 85           | PSDIP8  |

| Size | Part Number   | Organis. | V <sub>CC</sub> min<br>(V) | Feature                    | Temp.<br>Range (°C) | Package |

|------|---------------|----------|----------------------------|----------------------------|---------------------|---------|

| 16K  | ST25E16DB6    | 2K x 8   | 2.5                        | XI <sup>2</sup> C Bus & WC | -40 to 85           | PSDIP8  |

|      | ST24C16CB3    | 2K x 8   | 3.0                        | Write Protection           | -40 to 125          | PSDIP8  |

|      | ST24C16CM1    | 2K x 8   | 3.0                        | Write Protection           | 0 to 70             | SO8     |

|      | ST24C16CM1TR  | 2K x 8   | 3.0                        | Write Protection           | 0 to 70             | SO8TR   |

|      | ST24C16DM1    | 2K x 8   | 3.0                        | Write Protection           | 0 to 70             | SO8     |

|      | ST24C16DM1TR  | 2K x 8   | 3.0                        | Write Protection           | 0 to 70             | SO8TR   |

|      | ST24E16DM1    | 2K x 8   | 3.0                        | XI <sup>2</sup> C Bus & WC | 0 to 70             | SO8     |

|      | ST24E16DM1TR  | 2K x 8   | 3.0                        | XI <sup>2</sup> C Bus & WC | 0 to 70             | SO8TR   |

|      | ST25C16DM1    | 2K x 8   | 2.5                        | Write Protection           | 0 to 70             | SO8     |

|      | ST25C16DM1TR  | 2K x 8   | 2.5                        | Write Protection           | 0 to 70             | SO8TR   |

|      | ST25E16DM1    | 2K x 8   | 2.5                        | XI <sup>2</sup> C Bus & WC | 0 to 70             | SO8     |

|      | ST25E16DM1TR  | 2K x 8   | 2.5                        | XI <sup>2</sup> C Bus & WC | 0 to 70             | SO8TR   |

|      | ST24C16DM6    | 2K x 8   | 3.0                        | Write Protection           | -40 to 85           | SO8     |

|      | ST24C16DM6TR  | 2K x 8   | 3.0                        | Write Protection           | -40 to 85           | SO8TR   |

|      | ST24E16DM6    | 2K x 8   | 3.0                        | XI <sup>2</sup> C Bus & WC | -40 to 85           | SO8     |

|      | ST24E16DM6TR  | 2K x 8   | 3.0                        | XI <sup>2</sup> C Bus & WC | -40 to 85           | SO8TR   |

|      | ST25C16DM6    | 2K x 8   | 2.5                        | Write Protection           | -40 to 85           | SO8     |

|      | ST25C16DM6TR  | 2K x 8   | 2.5                        | Write Protection           | -40 to 85           | SO8TR   |

|      | ST25E16DM6    | 2K x 8   | 2.5                        | XI <sup>2</sup> C Bus & WC | -40 to 85           | SO8     |

|      | ST25E16DM6TR  | 2K x 8   | 2.5                        | XI <sup>2</sup> C Bus & WC | -40 to 85           | SO8TR   |

|      | ST24C16CML1   | 2K x 8   | 3.0                        | Write Protection           | 0 to 70             | SO14    |

|      | ST24C16CML1TR | 2K x 8   | 3.0                        | Write Protection           | 0 to 70             | SO14TR  |

|      | ST25C16CML1   | 2K x 8   | 2.5                        | Write Protection           | 0 to 70             | SO14    |

# EEPROM, I<sup>2</sup>C Serial Access Bus (cont'd)

| Size | Part Number   | Organis. | V <sub>CC</sub> min<br>(V) | Feature          | Temp.<br>Range (°C) | Package |

|------|---------------|----------|----------------------------|------------------|---------------------|---------|

| 16K  | ST25C16CML1TR | 2K x 8   | 2.5                        | Write Protection | 0 to 70             | SO14TR  |

|      | ST24C16CML6   | 2K x 8   | 3.0                        | Write Protection | -40 to 85           | SO14    |

|      | ST24C16CML6TR | 2K x 8   | 3.0                        | Write Protection | -40 to 85           | SO14TR  |

|      | ST25C16CML6   | 2K x 8   | 2.5                        | Write Protection | -40 to 85           | SO14    |

|      | ST25C16CML6TR | 2K x 8   | 2.5                        | Write Protection | -40 to 85           | SO14TR  |

### SELECTION GUIDE

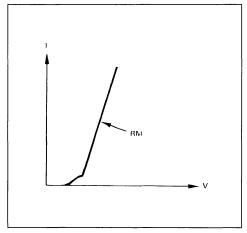

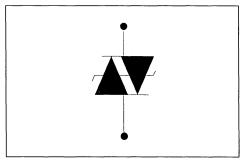

#### TRANSIL

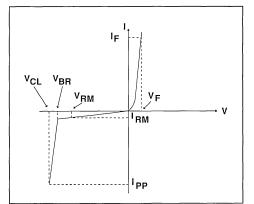

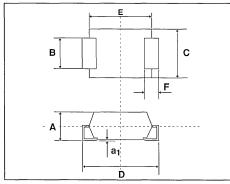

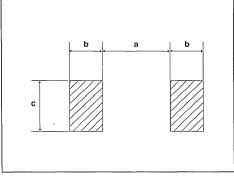

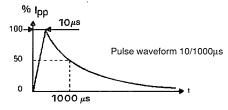

| D- (14/)           | V= (\/)             | Ту                           | /pe            | Casa   | Domo |

|--------------------|---------------------|------------------------------|----------------|--------|------|

| Р <sub>Р</sub> (W) | V <sub>RM</sub> (V) | Unidirectional Bidirectional |                | Case   | Page |

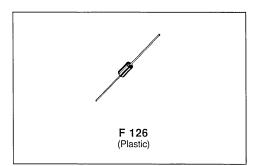

| 400/1 ms           | 5.8 to 376          | BZW04/BZW04P                 | BZW04B/BZW04PB | F126   | 555  |

| 400/1 ms           | 5.8 to 188          | SM4TxxA                      | SM4TxxCA       | SOD6   | 591  |

| 600/1 ms           | 5.8 to 376          | P6KE P,A                     | P6KE CP, CA    | CB-417 | 583  |

| 600/1 ms           | 5.8 to 188          | SM6TxxA                      | SM6TxxCA       | SOD6   | 597  |

| 1500/1 ms          | 5.8 to 376          | 1.5KE P, A                   | 1.5KECP, CA    | CB-429 | 547  |

| 1550/1 ms          | 5.8 to 188          | SM15TxxA                     | SM15TxxCA      | SOD15  | 603  |

| 5000/1 ms          | 10 to 180           | BZW50                        | BZW50B         | AG     | 563  |

#### TRISIL

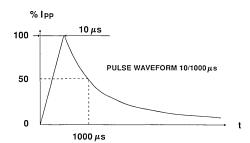

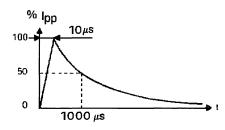

| IPP (A)     | V <sub>BR</sub> (V) | Types                 | Case  | Page |  |  |

|-------------|---------------------|-----------------------|-------|------|--|--|

| SINGLE FUNC | SINGLE FUNCTION     |                       |       |      |  |  |

| 50/10/1000  | 58 to 270           | TPA Series            | F126  | 629  |  |  |

|             | 58 to 270           | SMTPA Series          | SOD6  | 609  |  |  |

| 90/10/1000  | 58 to 270           | TPB Series            | CB429 | 635  |  |  |

|             | 58 to 270           | SMTPB Series          | SOD15 | 615  |  |  |

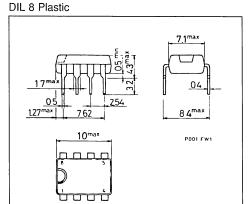

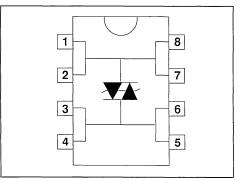

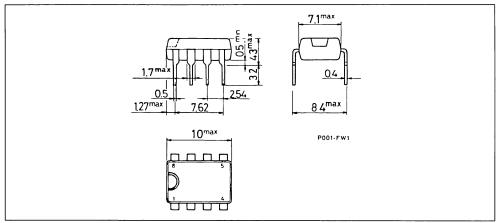

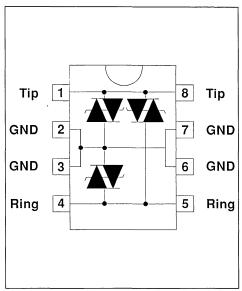

| 100/10/1000 | 18 to 120           | LS5018B, 5060B, 5120B | DIL8  | 577  |  |  |

| TRIPLE FUNC | ΓΙΟΝ                |                       |       |      |  |  |

| 30/10/1000  | 150 to 270          | THBTxxx11 Series      | SO8   | 621  |  |  |

|             | 150 to 270          | THBTxxx12 Series      | DIL8  | 621  |  |  |

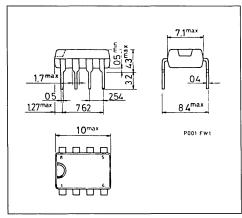

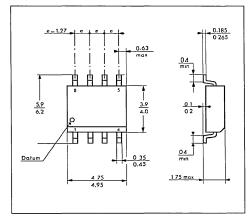

|             | 80 to 120           | TPIxx11 Series        | SO8   | 641  |  |  |

|             | 80 to 120           | TPIxx12 Series        | DIL8  | 641  |  |  |

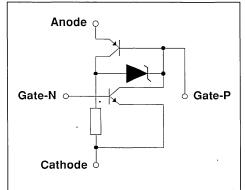

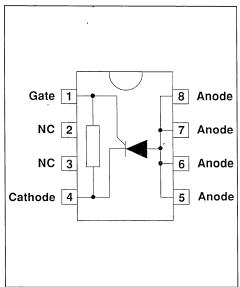

#### GATE TRIGGERED PROTECTIONS

| IPP (A)     | V <sub>BR</sub> (V) | Types      | Case | Page |

|-------------|---------------------|------------|------|------|

| 30/10/1000  | 250                 | TPP25011   | SO8  | 649  |

|             | 250                 | TPP25012   | DIL8 | 649  |

| 100/10/1000 | 250                 | L3100B, B1 | DIL8 | 569  |

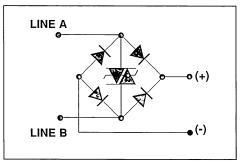

#### **TELEPHONE SET INTERFACE: DIODE BRIDGE + PROTECTION**

| IPP (A)    | V <sub>BR</sub> (V) | Types           | Case | Page |

|------------|---------------------|-----------------|------|------|

| 30/10/1000 | 150 to 270          | TSIxxxB5 Series | SO16 | 657  |

# **DEDICATED ICs**

## DTMF GENERATOR FOR BINARY CODED HEXADECIMAL DATA

■ GENERATES 16 STANDARD DTMF TONE PAIRS

SGS-THOMSON MICROELECTRONICS

- USES LOW COST 3.579 MHz CRYSTAL

- DIRECT MICROPROCESSOR INTERFACE

- ACCEPTS 4 BIT DATA IN SERIAL OR PARAL-LEL FORMAT

- DATA IS STORED DURING TRANSMISSION PERIOD

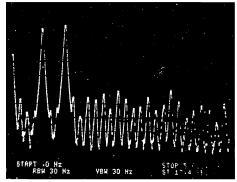

- LOW HARMONIC DISTORTION

- HIGH GROUP PRE EMPHASIS

- LOW POWER CONSUMPTION IN STANDBY MODE

- PULL-UP TO V<sup>+</sup> ON ALL LOGIC INPUTS

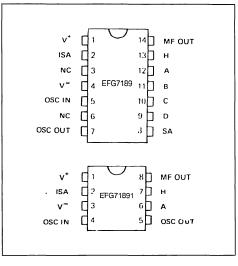

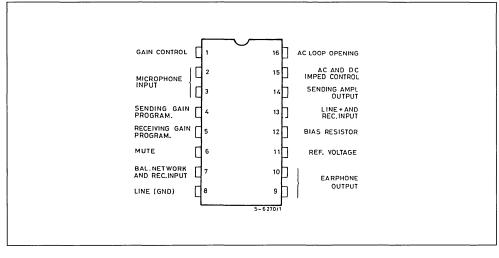

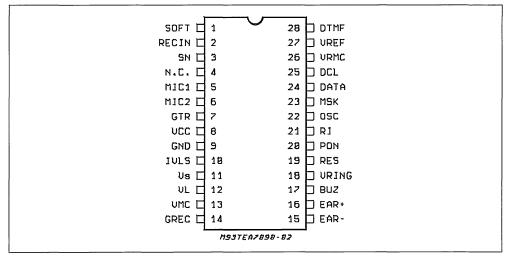

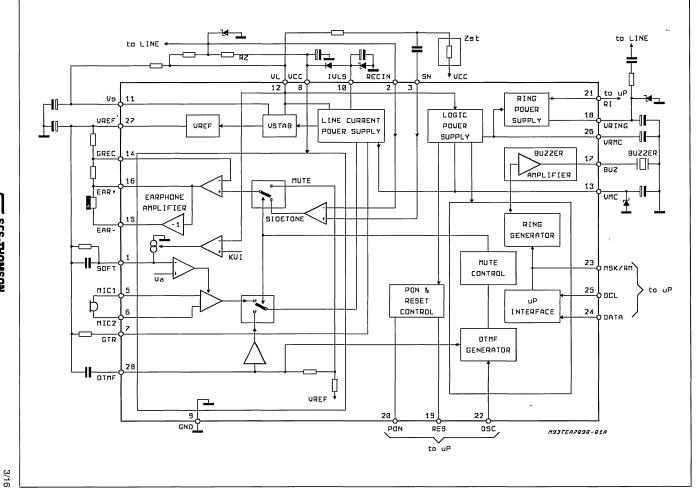

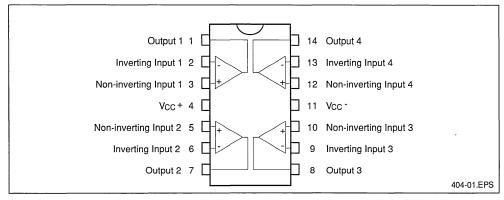

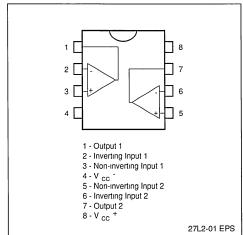

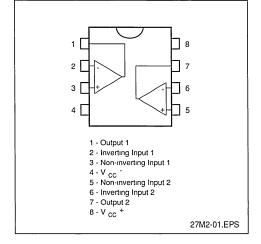

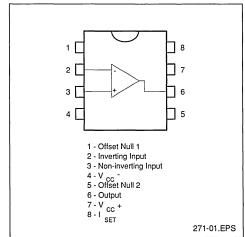

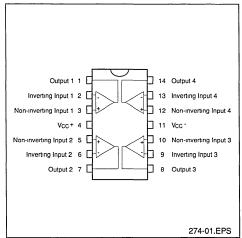

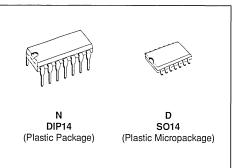

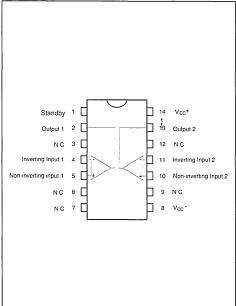

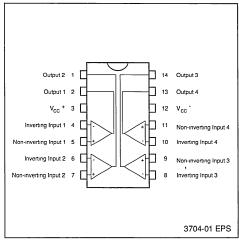

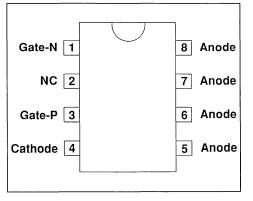

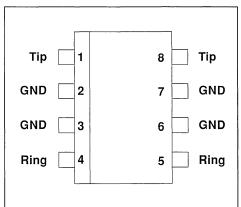

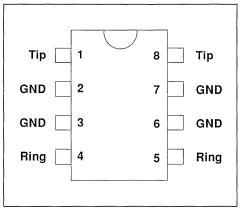

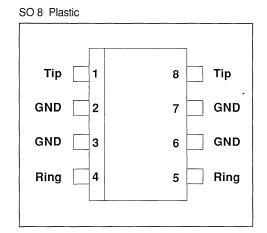

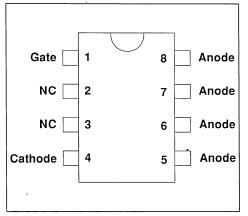

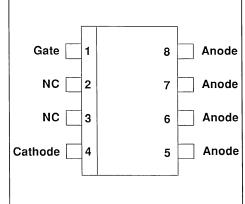

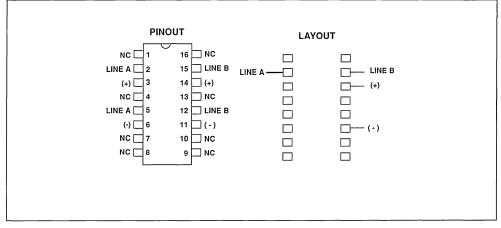

#### PIN CONNECTIONS (Top view)

This CMOS circuit is designed specifically to provide, with a minimum number of external components, a low cost DTMF dialer for microprocessor controlled telephone sets operating in accordance with existing standards. The 4 bits identifying the frequency pair to be generated may be supplied via either 5 connections between the EFG7189 and the microprocessor in parallel format or in serial format through 3 connections linking the EFG7189 to the microprocessor. This feature eliminates the necessity to simulate keyboard type inputs normally required by standard DTMF generators. Input data is stored on trailing edge of ISA signal. The tone pair selected by this code is generated while ISA remains low. With ISA high, the oscillator is inhibited and the device is in standby mode. SA pin is connected to V while device is outputting any tone pair.

1/10

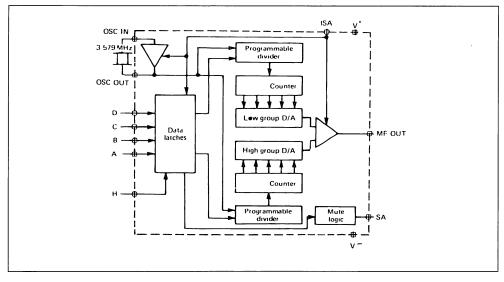

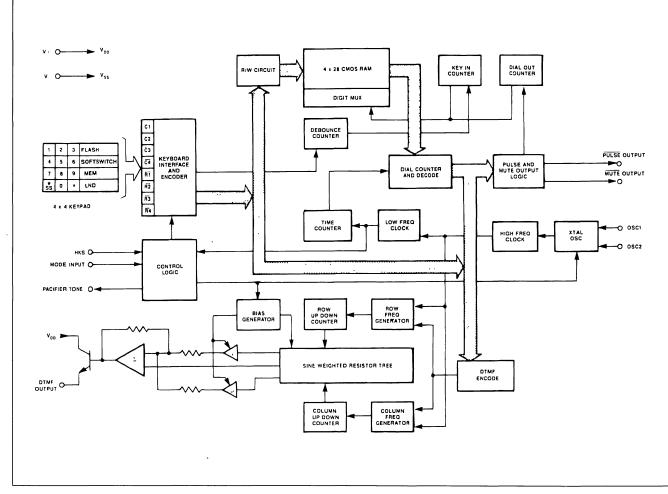

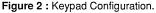

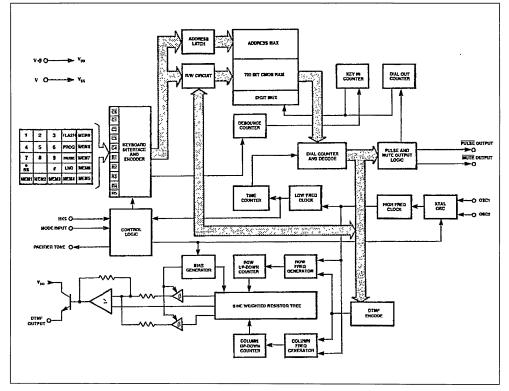

#### **BLOCK DIAGRAM**

#### PIN DESCRIPTION

| N°            | Name        | Function                                  | Description                                                                                                                                                                                                                                                                                                                    |

|---------------|-------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>4        | V +<br>V -  | Supply Voltage<br>Supply Voltage          | Positive Supply<br>0V                                                                                                                                                                                                                                                                                                          |

| 11<br>10<br>9 | B<br>C<br>D | Logic Input<br>Logic Input<br>Logic Input | Parallel input for hexadecimal code allowing<br>the selection of 2 frequencies constituting the<br>DTMF signal (see attached table).                                                                                                                                                                                           |

| 12            | A           | Logic Input                               | Serial or Parallel Input for Hexadecimal Code                                                                                                                                                                                                                                                                                  |

| 13            | Н           | Serial Input Clock                        | Clock Input for Hexadecimal Code Serial Input<br>Register on Pin A Furthermore, it allows for<br>the selection of the serial or parallel operating<br>mode of this code.<br>When ISA input goes low, the validated code<br>is :<br>• the parallel input code if input H is high.<br>• the serial input code if input H is low. |

| 2             | ISA         | Logic Input                               | This pin allows for the inhibition of the analog<br>output MF OUT :<br>• when ISA is high, output MF OUT is idle and<br>connected to V <sup>−</sup> .<br>• when ISA is low, the hexadecimal code is<br>validated and MF OUT<br>output is activated.                                                                            |

| 8             | SA          | Logic Output                              | This pin indicates the state of the analog<br>output :<br>• if ISA is low, SA is a low impedance output<br>at V <sup>-</sup> .<br>• if ISA is high, SA is a high impedance output.                                                                                                                                             |

| 14            | MF OUT      | Analog Output                             | This pin is the DTMF signal output.                                                                                                                                                                                                                                                                                            |

| 5             | OSC IN      | Oscillator Input                          | This pin corresponds to the input of the inverter of the oscillator.<br>The nominal frequency of the oscillator is 3.579 MHz.                                                                                                                                                                                                  |

#### ABSOLUTE MAXIMUM RATINGS

| Symbol           | Parameter                 | Value                         | Unit |  |

|------------------|---------------------------|-------------------------------|------|--|

| V <sup>+</sup>   | Supply Voltage            | Voltage - 0.3 to + 5.5        |      |  |

| Vin              | Digital Input Range       | - 0.3 to V <sup>+</sup> + 0.3 | V    |  |

| T <sub>stg</sub> | Storage Temperature Range | - 55 to + 125                 | °C   |  |

# ELECTRICAL OPERATING CHARACTERISTICS All voltages referenced to V

| Symbol         | Parameter                   | Min. | Тур.     | Max. | Unit |

|----------------|-----------------------------|------|----------|------|------|

| V <sup>+</sup> | Positive Supply Voltage     | 3    | -        | 5.25 | V    |

| Toper          | Operating Temperature Range | - 25 | -        | 70   | °C   |

| fc             | Crystal Frequency           | _    | 3.579545 | _    | MHz  |

#### DC ELECTRICAL CHARACTERISTICS

#### $T_{amb} = -25$ °C to 70 °C, V<sup>+</sup> = -3 to 5.25 V, f<sub>c</sub> = 3.579 MHz (all voltages are referenced to V<sup>-</sup>)

| Symbol | Parameter                                                                     | Min.               | Тур. | Max.   | Unit |

|--------|-------------------------------------------------------------------------------|--------------------|------|--------|------|

| IDD    | Operating Current in Transmission Mode ( $V^+ = 4 V$ , output not loaded)     | -                  | 0.6  | 1      | mA   |

| ISB    | Standby Current (ISA, H, A, B, C, D open circuit or connected to $V^{\rm +})$ | -                  | _    | 10     | μA   |

| VIL    | Input Low Voltage (ISA, H, A, B, C, D)                                        | 0                  | -    | 0.3 V* | V    |

| VIH    | Input High Voltage (ISA, H, A, B, C, D)                                       | 0.7 V <sup>+</sup> | _    | V*     | V    |

| RT     | Pull up Resistor on Logic Inputs ISA, H, A, B, C, D                           | 100                | -    | -      | kΩ   |

| IOLSA  | SA Output Current (V <sub>OLSA</sub> = 0.5 V)                                 | 500                | -    | -      | μA   |

| IFSA   | SA Leakage Current, Open Current (V <sub>OHSA</sub> = 5 V)                    | -                  | _    | 2      | μΑ   |

#### A.C. ELECTRICAL CHARACTERISTICS

#### $T_{amb}$ = – 25 °C to 70 °C, $~V^{*}$ – 3 V to 5.25 V, $~f_{c}$ = 3.579 MHz

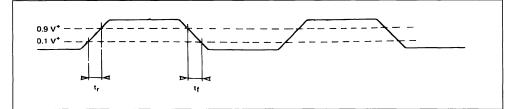

| Symbol                        | Parameter                                       | Min. | Тур. | Max. | Unit |

|-------------------------------|-------------------------------------------------|------|------|------|------|

| t <sub>r</sub> t <sub>f</sub> | Rise/Fall Time on Input Signals                 |      | -    | 50   | ns   |

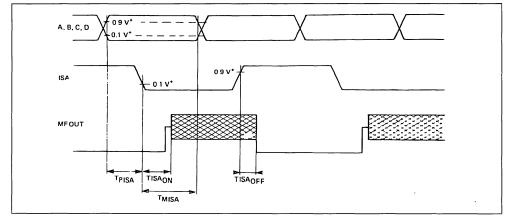

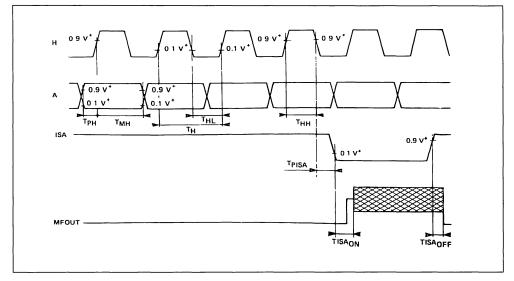

| TISAON                        | Transmission Delay                              | -    | -    | 5    | ms   |

| TISAOFF                       | Blocking Delay                                  | -    | -    | 5    | ms   |

| Τ <sub>Η</sub>                | Clock Period                                    | 10   | -    | -    | μs   |

| Тнн                           | High Level Clock Width                          | 5    | -    | -    | μs   |

| T <sub>HL</sub>               | Low Level Clock Width                           | 5    | -    | -    | μs   |

| T <sub>PH</sub>               | Set-up Time of A Related to Clock               | 1    | -    | -    | μs   |

| T <sub>MH</sub>               | Hold Time of A Related to Clock                 | 7    | -    | -    | μs   |

| T <sub>PISA</sub>             | Set-up Time of the Code or Clock Related to ISA | 1    | -    | -    | μs   |

| TMISA                         | Hold Time of Code Related to ISA                | 2    | -    | -    | μs   |

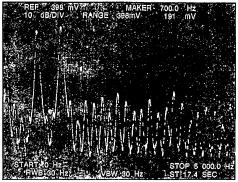

| TRANSMISSION CHARACTERISTICS Tamb = | – 25 °C to 70 °C, | $V^+$ 3 V to 5.25 V, $f_c = 3.579$ |

|-------------------------------------|-------------------|------------------------------------|

|-------------------------------------|-------------------|------------------------------------|

| Symbol  | Parameter                                                        | Min. | Тур. | Max. | Unit |

|---------|------------------------------------------------------------------|------|------|------|------|

| DFH DFB | High and Low Frequency Precision                                 | -    | -    | 1    | %    |

| AFB     | Low Frequency Transmission Level (V <sup>+</sup> = 4 V) - Note 1 | - 8  | - 7  | - 6  | dBm  |

| GBH     | High Band Pre-emphasis                                           | 2.3  | 2.7  | 3.5  | dB   |

| D       | Output Distortion                                                | -    | -    | - 20 | dB   |

Note: 1.0 dBm = 0.775 Vms

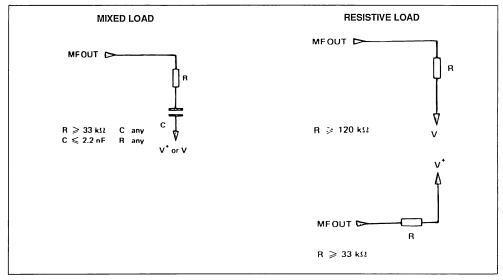

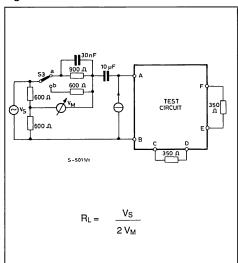

These specifications are related to the following loads.

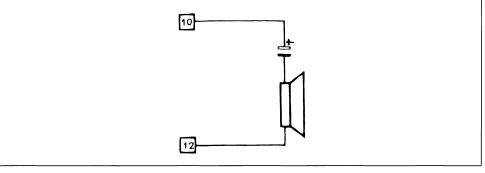

#### Figure 1.

#### FUNCTIONAL DESCRIPTION

With ISA input at logic level "1", the device is in low power mode. The oscillator is inhibited and analog output MF OUT is at ground level. DTMF input data is detected on trailing edge of ISA. This transition enables both the oscillator and the analog output then the data is stored and corresponding DTMF pair is generated during the low state interval of the ISA signal. Any modification to H, A, B, C and D signals during this period will not have any further effect on DTMF pair generated.

The device accepts input data in two different formats :

- Parallel format : this requires 4 connections (A, B, C, D) between the microprocessor and the circuit.

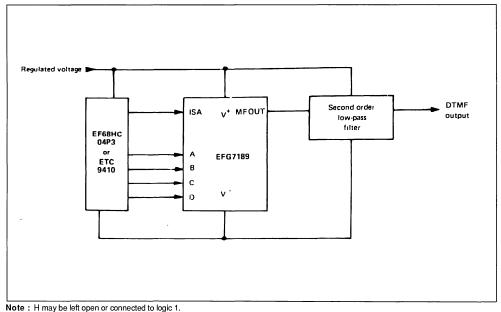

- Serial format : in this case data is supplied to the circuit by the microprocessor via 2 connections A and H (see typical application diagram).

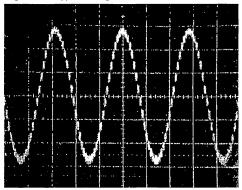

Pre-emphasis is applied to high group tone and both

tones of DTMF pair are supplied through analog output pin.

#### DATA ACQUISITION LOGIC

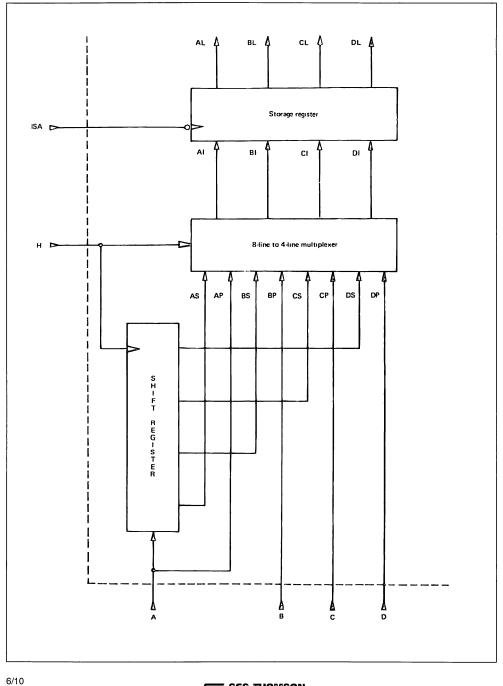

This section includes : A 4-bit shift register, an 8-line to 4-line multiplexer and a 4-bit storage register.

- The 4-bit shift register has its input connected to pin A and is enabled by the signal applied to pin H. Its outputs are AS, BS, CS and DS signals.

- The multiplexer is enabled by signal H and operates according to the following law : AI = H.AP + H.AS.

- The 4-bit storage register operates on trailing edge of ISA signal. AI, BI, CI, DI and AL, BL, CL, DL are its inputs and outputs respectively.

During the low state period of ISA input, AL, BL, CL and DL signals determine the DTMF pair to be generated.

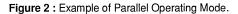

Note : If the circuit operates permanently in parallel mode, then the H input may be left floating (internally pulled-up to V<sup>+</sup>) or tied to logic 1. With ISA at logic 0, H,A,B,C, and D inputs cannot modify the generated DTMF pair.

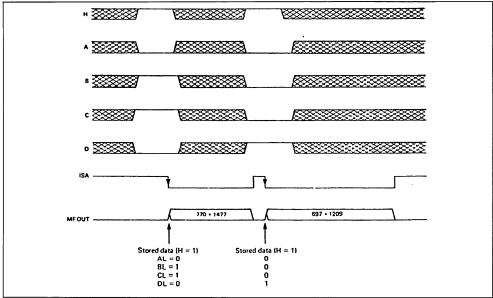

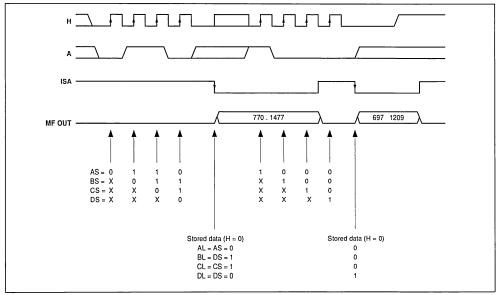

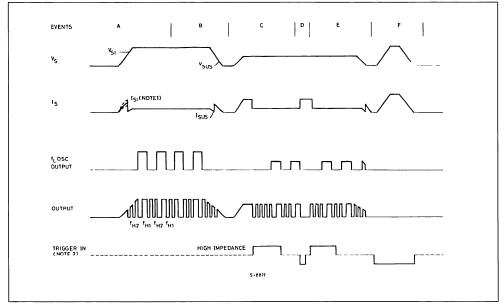

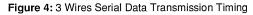

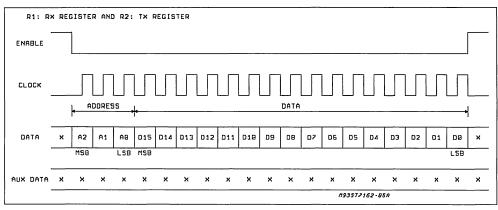

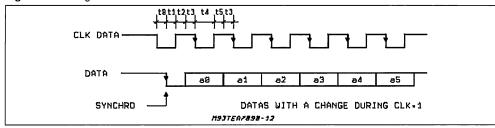

Figure 3 : Example of Serial-Operating Mode.

Notes: 1. With ISA at logic 0, H, A, B, C and D signals cannot modify the generated DTMF pair. As a result, in serial operating mode, it is possible to enter AS, BS, CS and DS data while another DTMF pair is being generated.

2. First data to be entered is DS.

5/10

#### Figure 4 : Data Acquisition Logic.

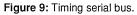

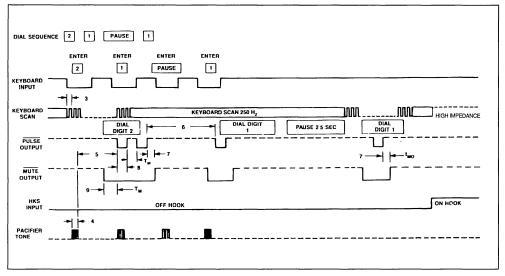

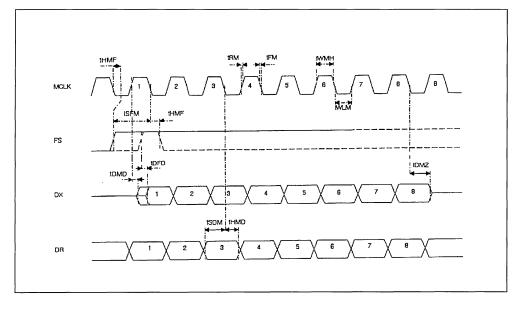

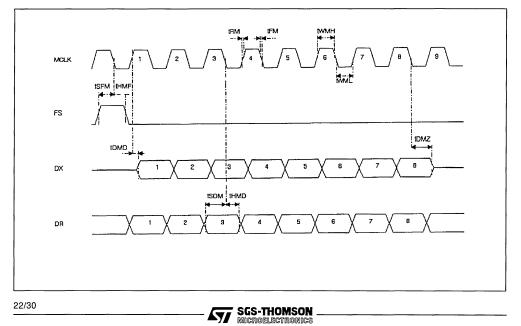

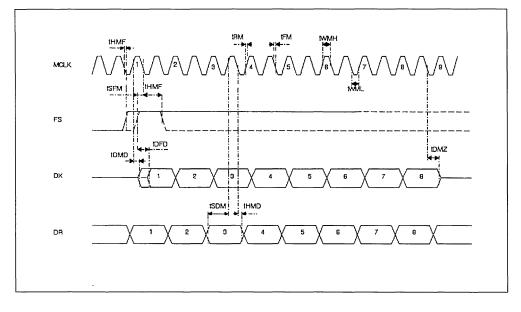

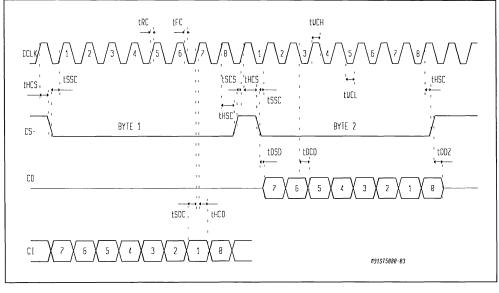

#### TIMING DIAGRAM

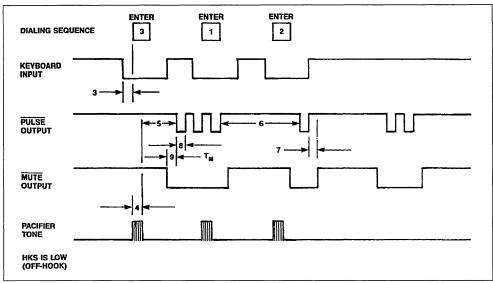

Figure 5 : Rise/Fall Time on Input Signals.

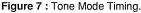

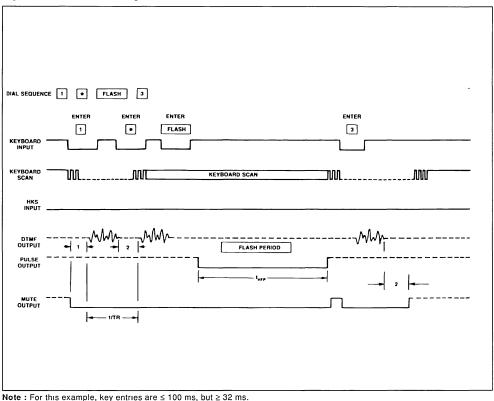

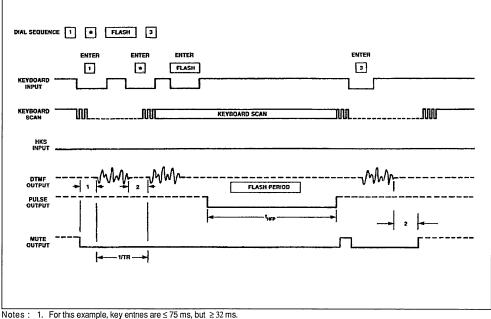

Figure 6 : Parallel Operating Mode (H = "1").

Figure 7 : Serial Operating Mode.

### EFG7189 - EFG71891

#### Table 1

|    | DTMF Specification<br>(Hz) | Frequencies Derived<br>from<br>a 3.579 MHz Quartz (Hz) | Division<br>Rank | % Deviation<br>from<br>Standard |

|----|----------------------------|--------------------------------------------------------|------------------|---------------------------------|

| f1 | 697                        | 701.3                                                  | 5104             | 0.62                            |

| f2 | 770                        | 771.4                                                  | 4640             | 0.19                            |

| f3 | 852                        | 857.2                                                  | 4176             | 0.61                            |

| f4 | 941                        | 935.1                                                  | 3828             | - 0.63                          |

| f5 | 1209                       | 1215.9                                                 | 2944             | 0.57                            |

| f6 | 1336                       | 1331.7                                                 | 2688             | - 0.32                          |

| f7 | 1477                       | 1471.9                                                 | 2432             | - 0.35                          |

| f8 | 1633                       | 1645                                                   | 2176             | 0.74                            |

#### Table 2

| Keyboard | H | lexadeci | mal Cod | е | ISA | Generated F | requencies |

|----------|---|----------|---------|---|-----|-------------|------------|

| Ćode     | Α | В        | С       | D | ISA | f(Hz)       | f(Hz)      |

| Х        | Х | X        | X       | X | 1   |             |            |

| 1        | 0 | 0        | 0       | 1 | Ļ   | 697         | 1209       |

| 2        | 0 | 0        | 1       | 0 | Ļ   | 697         | 1336       |

| 3        | 0 | 0        | 1       | 1 | Ļ   | 697         | 1477       |

| 4        | 0 | 1        | 0       | 0 | ↓   | 770         | 1209       |

| 5        | 0 | 1        | 0       | 1 | ↓   | 770         | 1336       |

| 6        | 0 | 1        | 1       | 0 | Ļ   | 770         | 1477       |

| 7        | 0 | 1        | 1       | 1 | Ļ   | 852         | 1209       |

| 8        | 1 | 0        | 0       | 0 | Ļ   | 852         | 1336       |

| 9        | 1 | 0        | 0       | 1 | Ļ   | 852         | 1477       |

| 0        | 1 | 0        | 1       | 0 | Ļ   | 941         | 1336       |

| •        | 1 | 0        | 1       | 1 | Ļ   | 941         | 1209       |

| ≠        | 1 | 1        | 0       | 0 | Ļ   | 941         | 1477       |

| А        | 1 | 1        | 0       | 1 | Ļ   | 697         | 1633       |

| В        | 1 | 1        | 1       | 0 | Ļ   | 770         | 1633       |

| С        | 1 | 1        | 1       | 1 | Ļ   | 852         | 1633       |

| D        | 0 | 0        | 0       | 0 | Ļ   | 941         | 1633       |

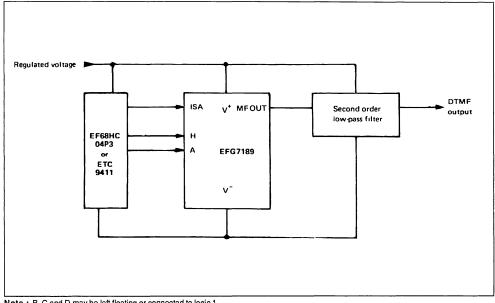

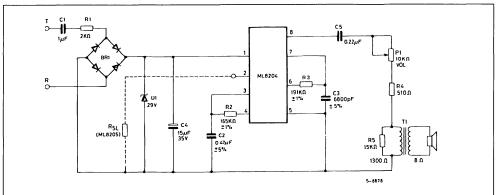

#### TYPICAL APPLICATION (european standards)

Figure 8 : Parallel Connection.

Note : B, C and D may be left floating or connected to logic 1.

9/10

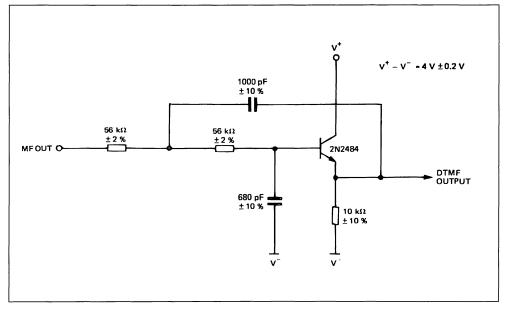

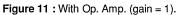

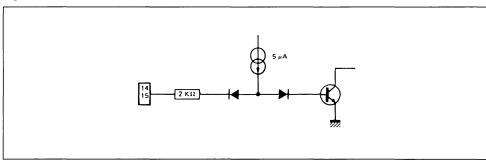

#### SECOND ORDER LOW-PASS FILTERS

Figure 10 : With Transistor (gain = 1).

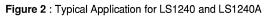

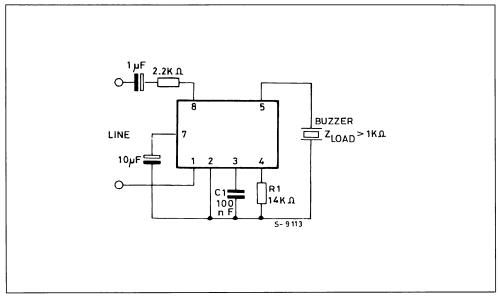

## ELETRONIC TWO-TONE RINGER

- LOW CURRENT CONSUMPTION, IN ORDER TO ALLOW THE PARALLEL OPERATION OF 4 DEVICES

- INTEGRATED RECTIFIER BRIDGE WITH ZENER DIODES TO PROTECT AGAINST OVERVOLTAGES

- LITTLE EXTERNAL CIRCUITRY

- TONE AND SWITCHING FREQUENCIES AD-JUSTABLE BY EXTERNAL COMPONENTS

- INTEGRATED VOLTAGE AND CURRENT HYSTERESIS

- COMPLEMENTARY OUTPUT CONFIGURA-TION

#### DESCRIPTION

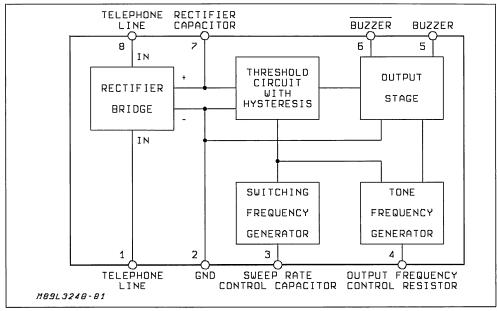

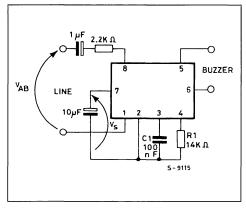

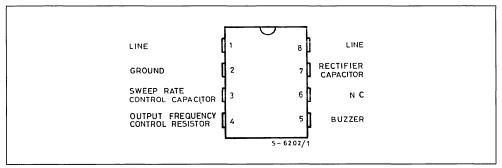

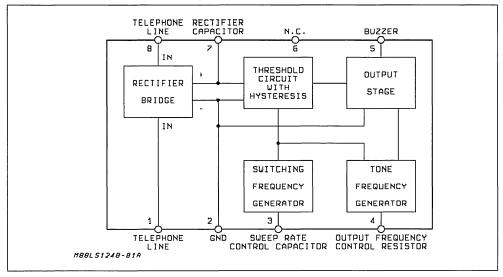

L3240 is a monolithic integrated circuit designed to replace the mechanical bell in telephone sets, in connection with an electro acoustical converter. The device can drive either directly a piezo ceramic converter (buzzer) or a small loudspeaker. In this case a transformer is needed. The two tone frequencies generated are switched by an internal oscillator in a fast sequence and made audible across output amplifiers in the transducer ; both tone frequencies and the switching frequency can be externally adjusted.

The supply voltage is obtained from the AC ring signal and the circuit is designed so that noise on the line or variations of the ringing signal cannot affect the correct operation of the devices.

The output bridge configuration allows to use a high impedance transducer with acoustical results much better than in a single ended configuration.

The two outputs can also be connected independently to different converters or actuators (acoustical, opto, logic).

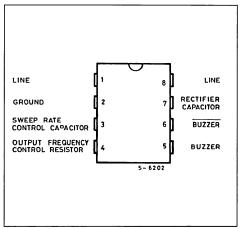

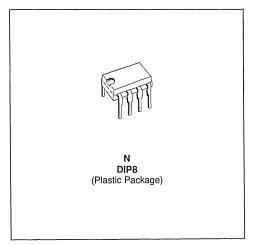

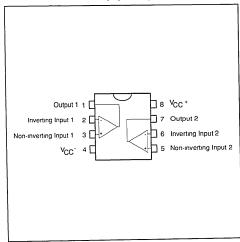

#### PIN CONNECTION (top view)

#### **BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                                | Value       | Unit |

|------------------|------------------------------------------|-------------|------|

| V <sub>AB</sub>  | Calling Voltage (f = 50 Hz) Continuous   | 120         | VRMS |

| V <sub>AB</sub>  | Calling Voltage (f = 50 Hz) 5s N/10s OFF | 200         | VRMS |

| DC               | Supply Current                           | 30          | mA   |

| T <sub>op</sub>  | Operating Temperature                    | - 20, + 70  | °C   |

| T <sub>stg</sub> | Storage and Junction Temperature         | - 65, + 150 | °C   |

#### THERMAL DATA

| [ | Symbol    | Parameter                               | Value | Unit |

|---|-----------|-----------------------------------------|-------|------|

|   | Rth J-amb | Thermal Resistance Junction-ambient Max | 100   | °C/W |

#### **ELECTRICAL CHARACTERISTICS**

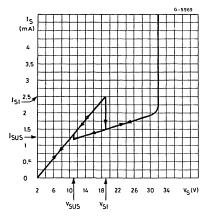

$(T_{amb} = 25^{\circ}C; V_s = applied between pins 7-2; otherwise specified)$

| Symbol | Parameter                                           | Test Conditions                   | Min. | Тур.               | Max. | Unit |

|--------|-----------------------------------------------------|-----------------------------------|------|--------------------|------|------|

| Vs     | Supply Voltage                                      |                                   |      |                    | 26   | V    |

| IB     | Current Consumption Without Load (Pins 8-1)         | V <sub>8-1</sub> = 16.5 to 29.5 V |      | 1.5                | 1.8  | mA   |

| VON    | Activation Voltage                                  |                                   | 12   |                    | 13.5 | V    |

| VOFF   | Sustaining Voltage                                  |                                   | 7.8  |                    | 9.3  | V    |

| RD     | Differential Resistance in OFF Condition (Pins 8-1) |                                   | 6.4  |                    |      | kΩ   |

| Vout   | Output Voltage Swing                                |                                   |      | V <sub>s</sub> – 5 |      | V    |

| lout   | Short Circuit Current (pins 5-6)                    | V <sub>s</sub> = 20 V             |      | 35                 |      | mA   |

| Vs     | Voltage Drop between Pins 8-1 and Pins 7-2          |                                   |      | 3                  |      | V    |

#### ELECTRICAL CHARACTERISTICS

$(T_{amb}$  = 25°C ;  $V_S$  = applied between pins 7-2 ;otherwise specified) AC OPERATION

| Symbol | Parameter                              | Test Conditions                                                                                           | Min.        | Тур. | Max.       | Unit |

|--------|----------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------|------|------------|------|

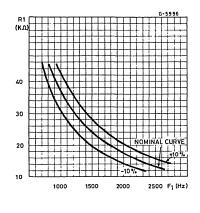

|        | Output Frequencies<br>Fout 1<br>Fout 2 | $ \begin{array}{l} V_{s} = 26 \ V, \ R_{1} = 14 \ K\Omega \\ V_{s} = 0 \ V \\ V_{s} = 6 \ V \end{array} $ | 2,29<br>1.6 |      | 2,8<br>2.1 | kHz  |

|        | Fout 1<br>Fout 2                       |                                                                                                           | 1.33        |      | 1.43       |      |

|        | Programming Resistor Range             |                                                                                                           | 8           |      | 56         | kΩ   |

|        | Sweep Frequency                        | R <sub>1</sub> = 14kΩ, C1 =100nF                                                                          | 5.25        | 7,5  | 9.75       | Hz   |

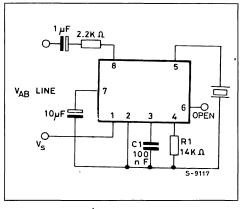

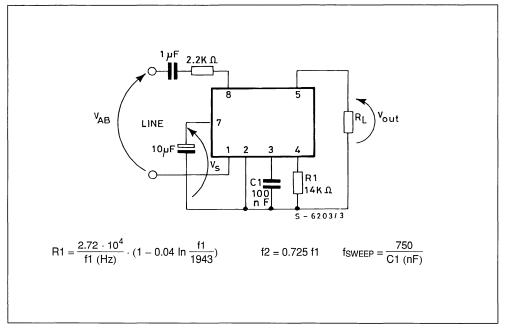

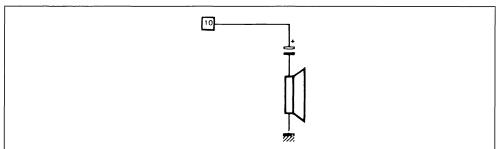

Figure 1 : Test Circuit.

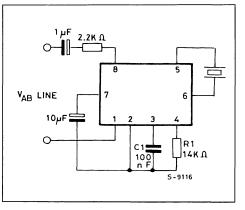

Figure 3 : Application Compatible with LS1240 (single ended output).

$R_1 \approx \frac{-3.56 \text{ x } 10^4}{F_1 \text{ (HZ)}} \text{ x } \left(1 - 0.12 \text{ x } \ln \frac{F_1}{2543}\right)$

#### Figure 2 : Typical Application with Balanced Output.

$f_2 = 0.725 f_1$   $f_{SWEEP} = -\frac{750}{C1 (nF)}$

.

SGS-THOMSON MICROELECTRONICS

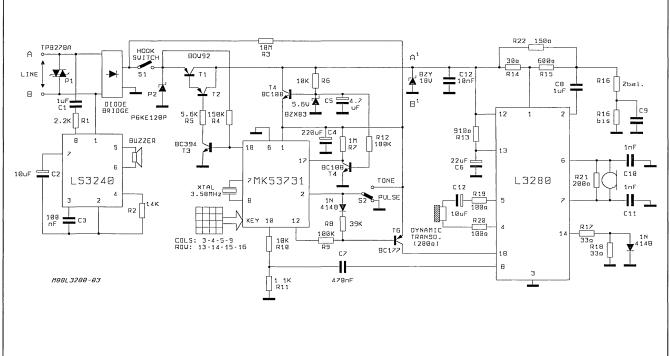

# L3280

## LOW VOLTAGE TELEPHONE SPEECH CIRCUIT

#### ADVANCE DATA

- OPERATION DOWN TO 1.3 V/5 mA

- DTMF & BEEP TONE INPUTS

- EXTERNAL MUTING FOR EARPHONE AND MICROPHONE

- MUTE TURNS ON BEEP TONE & DTMF IN-PUTS AND TURNS OFF EARPHONE & MI-CROPHONE

- SUITABLE FOR DYNAMIC OR PIEZO EAR-PHONES AND PIEZO, DYNAMIC OR ELEC-TRET MICROPHONES

#### DESCRIPTION

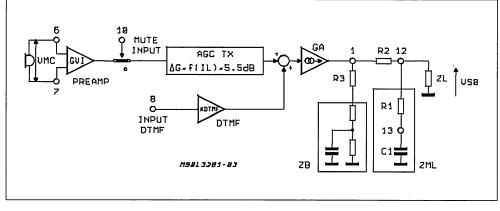

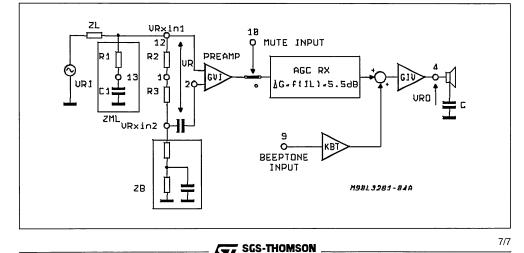

The L3280 is a brand new low voltage speech circuit designed to replace hybrid circuits in telephone sets. It is designed for sets that may be operated in parallel. It features both DTMF input and Beep tone input ; ALC on send and receive and muting input.

Various DC - characteristics can be programmed at pin 14 replacing testing resistor (43 $\Omega$ ) with proper network value.

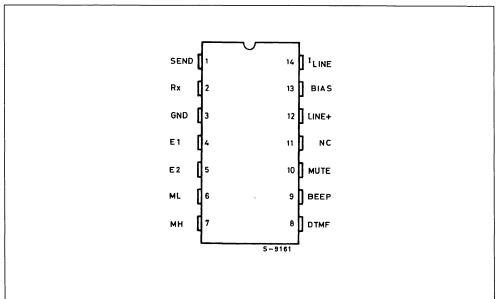

#### PIN CONNECTION (top view)

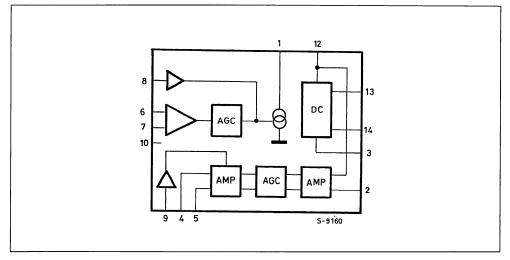

#### **BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol          | Parameter                             | Value       | Unit |  |

|-----------------|---------------------------------------|-------------|------|--|

| VL              | Line Voltage (3 ms pulse)             | 20          | V    |  |

| ۱L              | Line Current                          | 150         | mA   |  |

| Ptot            | Total Power Dissipation, Tamb = 70 °C | 1           | W    |  |

| T <sub>op</sub> | Operating Temperature                 | - 20 to 55  | °C   |  |

| Тј              | Junction Temperature                  | - 65 to 150 | °C   |  |

#### THERMAL DATA

| Symbol    | Parameter                           |     | Value | Unit |

|-----------|-------------------------------------|-----|-------|------|

| Rth J-amb | Thermal Resistance Junction-ambient | Max | 80    | °C/W |

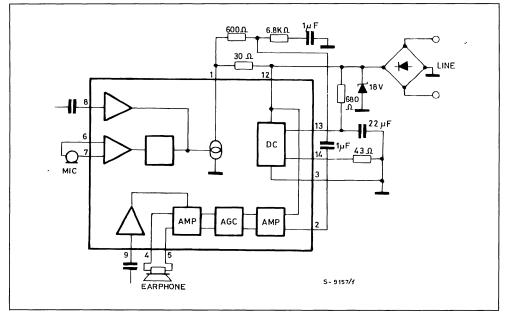

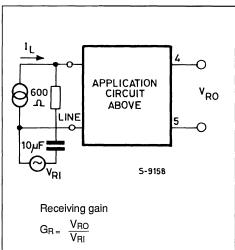

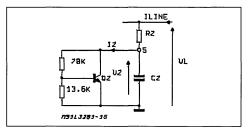

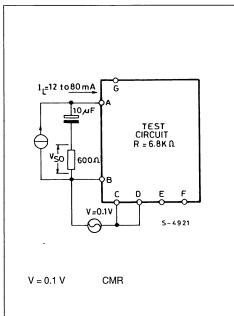

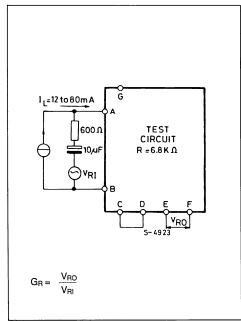

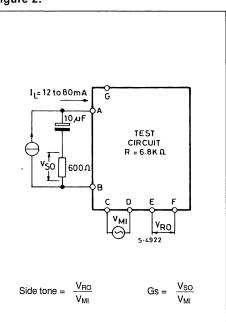

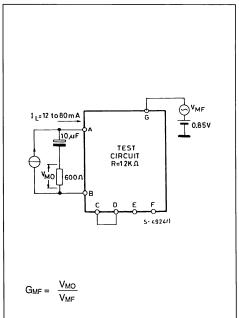

#### Figure 1 : Test Circuits.

Figure 3.

#### Figure 2.

6 -0 <sub>V<sub>MI</sub></sub> 7 10µF A PPLICATION CIRCUIT O 4 LINE ABOVE С V<sub>RO</sub> 5 6001 S-9159 V<sub>SO</sub> Sending gain and sidetone : <u>Vso</u>; V<sub>MI</sub>; VRO ST = Gs= Vм

### ELECTRICAL CHARACTERISTICS

$(T_{amb} = 25^{\circ}C; f = 1 \text{ kHz}; I_{L} = 20 \text{ mA} : \text{ mute low}; R1 (pin 14) = 43\Omega, unless otherwise specified)$

| Symbol            | Parameter                                          | Test Conditions                                 | Min. | Тур.  | Max. | Unit |

|-------------------|----------------------------------------------------|-------------------------------------------------|------|-------|------|------|

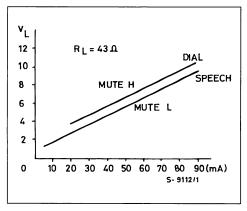

| VL                | Line Voltage                                       | I <sub>L</sub> = 20 mA                          |      | 3.05  | 3.35 | V    |

| VL                | V <sub>L</sub> Line Voltage I <sub>L</sub> = 50 mA |                                                 |      | 5.8   | 6.2  | v    |

| VL                | Line Voltage                                       | I <sub>L</sub> = 80 mA                          |      | 8.5   | 10   | v    |

| CMRR              | Common Mode Rej. Ratio                             |                                                 | 50   |       |      | dB   |

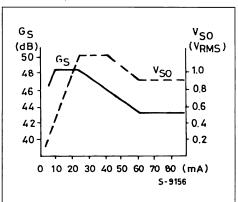

| Gs                | Sending Gain                                       | $V_{MI} = 2 \text{ mV}, I_L = 20 \text{ mA}$    | 47.8 | 49.3  | 50.8 | dB   |

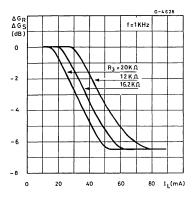

| D <sub>GS</sub>   | Delta Sending Gain                                 | $I_L = 70 \text{ mA}, V_{MI} = 2 \text{ mV}$    | - 7  | - 5.5 | - 4  | dB   |

| T <sub>HDS</sub>  | Sending Distortion                                 | V <sub>SO</sub> = 700 mV                        |      |       | 5    | %    |

| NTX               | Sending Noise                                      | I <sub>L</sub> = 50 mA, V <sub>MI</sub> = 0 V   |      | - 71  |      | dBr  |

| Z <sub>MI</sub>   | Mic. Input Impedance                               | V <sub>MI</sub> = 2 mV                          | 40   |       |      | KΩ   |

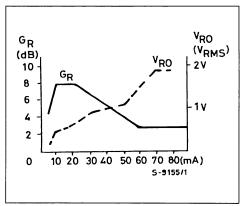

| GR                | Receiving Gain                                     | I <sub>L</sub> = 20 mA, V <sub>RI</sub> = 0.2 V | 7.7  | 9.2   | 10.7 | dB   |

| D <sub>GR</sub>   | Delta Receiving Gain                               | $I_L = 70 \text{ mA}, V_{RI} = 0.2 \text{ V}$   | - 7  | - 5.5 | - 4  | dB   |

| T <sub>HDR</sub>  | Receiving Distortion                               | V <sub>RO</sub> = 615 mV                        |      |       | 5    | %    |

| N <sub>RX</sub>   | Receiving Noise                                    | V <sub>RI</sub> = 0 V                           |      | 300   |      | μV   |

| Z <sub>RO</sub>   | Receiving Output Imped.                            | $R_1 = 200 \ \Omega, \ V_{RO} = 50 \ mV$        |      | 10    |      | Ω    |

|                   | Sidetone                                           | V <sub>MI</sub> = 2 mV                          |      | 40    |      | dB   |

| Z <sub>ML</sub>   | Line Match. Impedance                              | V <sub>RI</sub> = 0.2 V                         | 500  | 600   | 700  | Ω    |

| VL                | Line Voltage                                       | l <sub>L</sub> = 5.5 mA                         |      | 1.5   | 1.8  | V    |

| Vso               | Sending Output Voltage                             | $I_L = 5.5 \text{ mA}, T_{HD} = 5 \%$           | 100  |       |      | m۷   |

| I <sub>RO</sub>   | Rec. Output Current                                | $I_L = 5.5 \text{ mA}, T_{HD} = 5 \%$           | 0.7  |       |      | mA   |

|                   | OPERATION @ IL = 16 mA                             |                                                 |      |       |      |      |

| MULO              | Mute Input Low                                     | (speaking mode)                                 |      |       | 1    | V    |

| MUHI              | Mute Input High                                    | (dialling mode)                                 | 2    |       |      | v    |

| GMF               | DTMF Gain                                          | $V_{in} = 2 \text{ mV}$ ; Mute = 2 V            | 25   | 26.5  | 28   | dB   |

| RMF               | DTMF Input Impedance                               | Mute = 2 V                                      | 6    | 8.5   |      | KΩ   |

| THDMF             | DTMF Distorsion                                    | Mute = 2 V ; $V_{in}$ = 25 mV                   |      |       | 5    | %    |

| G <sub>beep</sub> | Beeptone Gain                                      | Mute = 2 V ; $V_{in}$ = 25 mV                   |      | 8.5   |      | dB   |

| Rbeep             | Beeptone Input Imped.                              | Mute = 2 V                                      | 12   |       |      | KΩ   |

| THD               | Beeptone Distorsion                                | Mute = 2 V ; V <sub>Bt</sub> = 100 mV           |      |       | 5    | %    |

| $DV_L$            | DELTA V <sub>LINE</sub>                            | Mute = 2 V ; I <sub>L</sub> = 20 mA             | 0.5  |       | 1.2  | V    |

| GBACK             | Back Tone Gain                                     |                                                 | -    | -     | -3.0 | dB   |

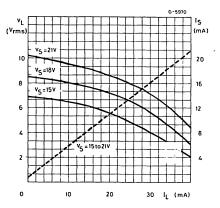

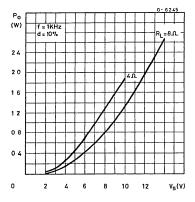

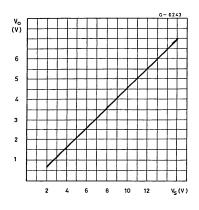

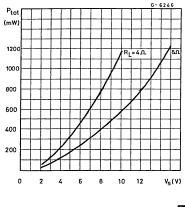

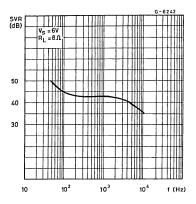

#### CHARACTERISTIC AT 1 KHZ

Figure 4 : Receive Characteristic and Max Output at 2 % THD.

Figure 6 : DC Characteristic Measured between Line and GND.

#### LOGIC OF MUTE SWITCHING

|        | DTMF                     | BEEP                         | MIC INPUT | RECEIVE INPUT |

|--------|--------------------------|------------------------------|-----------|---------------|

| MUTE H | ACTIVE TO LINE<br>OUTPUT | ACTIVE TO<br>EARPHONE OUTPUT | MUTED     | MUTED         |

| MUTE L | MUTED                    | MUTED                        | ACTIVE    | ACTIVE        |

Figure 5 : Sending ALC Characteristic and Max Output at 2 % THD.

Figure 7 : Application Circuit for Dynamic Transducer.

L3280

38

6/6

<u>15</u>

SGS-THOMSON

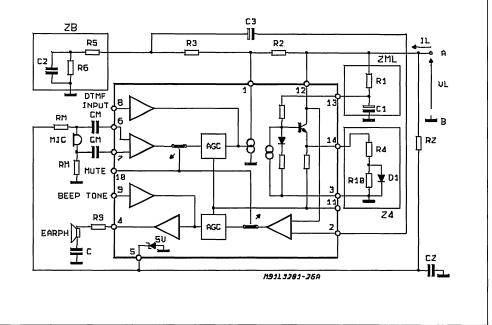

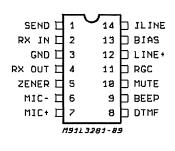

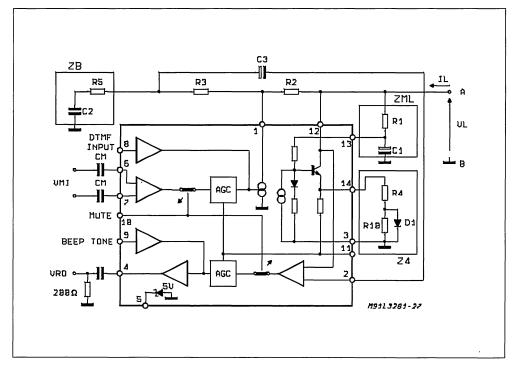

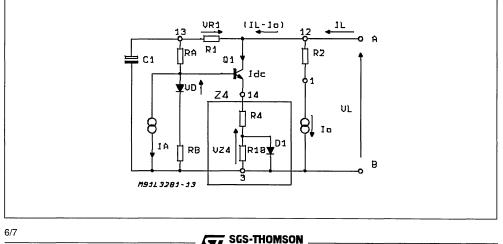

The L3281 is an electronic speech circuit developed to replace hybrid circuits in telephone sets that can be operated in parallel with other phones.

## DESCRIPTION

MICROPHONE

RECEIVING

**BLOCK DIAGRAM**

### EXTERNAL MUTING FOR EARPHONE AND SUITABLE FOR DYNAMIC EARPHONE AND DYNAMIC OR ELECTRET MICROPHONE AGC CONTROL ON BOTH SENDING AND SO14 DIP14

LOW VOLTAGE TELEPHONE SPEECH CIRCUITS

ORDERING NUMBERS:

L3281AB

L3281AD1

### PRELIMINARY DATA

L3281

OPERATION DOWN TO 1.6V / 6.5mA **DTMF & BEEP TONE INPUTS**

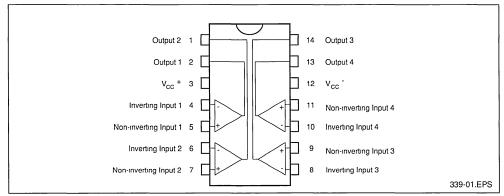

#### PIN CONNECTION (top view)

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                            | Va     | Value |      |  |

|------------------|--------------------------------------|--------|-------|------|--|

| Symbol           | Farameter                            | DIP-14 | SO-14 | Unit |  |

| VL               | Line Voltage (3 ms pulse)            | 1      | 5     | V    |  |

| ار               | Line Current                         | 15     | 50    | mA   |  |

| P <sub>tot</sub> | Total Power Dissipation, Tamb = 55°C | 1.0    | 0.6   | W    |  |

| Top              | Operating Temperature                | - 20   | to 55 | °C   |  |

| Tj               | Junction Temperature                 | – 65 t | o 150 | °C   |  |

#### THERMAL DATA

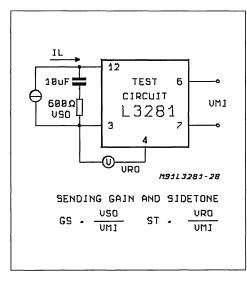

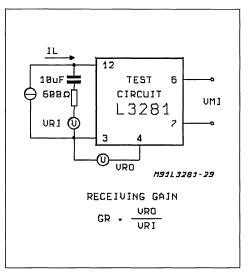

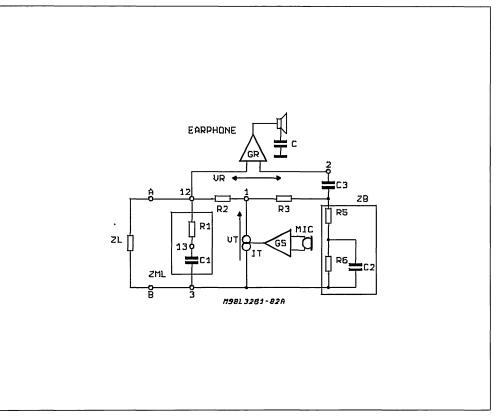

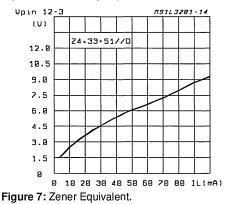

| Symbol                 | Parameter                               | Va     | Value |      |  |