# GAL PROGRAMMABLE LOGIC DEVICES

DATABOOK

1<sup>st</sup> EDITION

000486

**GAL** PROGRAMMABLELOGIC DEVICES

## GAL PROGRAMMABLE LOGIC DEVICES

DATABOOK

1<sup>st</sup> EDITION

MAY 1992

#### USE IN LIFE SUPPORT DEVICES OR SYSTEMS MUST BE EXPRESSLY AUTHORIZED.

SGS-THOMSON PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS OF LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF SGS-THOMSON Microelectronics.

- Life support devices or systems are those which (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided with the product, can be reasonably expected to result in significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can reasonably be expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

| TABLE OF CONTENTS        |     |

|--------------------------|-----|

| GENERAL INDEX            | 5   |

| INTRODUCTION             | 7   |

| GAL DATASHEETS           | 13  |

| ST-CUPL DOCUMENTATION    | 89  |

| LOGIC CONCEPT            | 95  |

| DEVELOPMENT TOOLS        | 111 |

| PROGRAMMING THE GAL6001S | 117 |

| PROGRAMMING EXAMPLES     | 141 |

| MEMORY CELL              | 201 |

| LATCH-UP IMMUNITY        | 207 |

| POWER CONSUMPTION        | 215 |

| QUALITY AND RELIABILITY  | 227 |

.

### GENERAL INDEX

#### Page

| INTRODUCTION                               |     |

|--------------------------------------------|-----|

| GAL IN PLD SCENARIO                        | 9   |

| DC PARAMETERS                              | 11  |

| AC PARAMETERS                              | 12  |

| DATASHEETS                                 |     |

| GAL6001S                                   | 15  |

| GAL16V8AS                                  | 29  |

| GAL20V8AS                                  | 43  |

| GAL16V8S                                   | 57  |

| GAL20V8S                                   | 73  |

| ST-CUPL DOCUMENTATION                      |     |

| ST-CUPL PACKAGE                            | 91  |

| LOGIC CONCEPT                              |     |

|                                            | 97  |

| PLD REPRESENTATION                         |     |

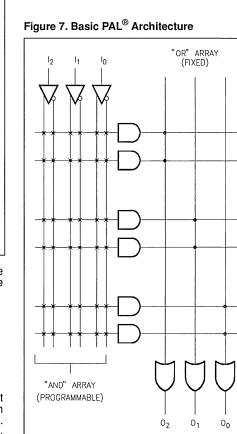

| PAL DEVICES                                | 100 |

| GAL DEVICES                                | 102 |

| GAL CONFIGURATION EXAMPLE                  | 104 |

| DEVELOPMENT TOOLS                          |     |

| SOFTWARE AND HARDWARE TOOLS                | 113 |

| PROGRAMMING THE GAL6001S                   | 117 |

|                                            |     |

| PROGRAMMING EXAMPLES                       | 141 |

| MEMORY CELL                                | 201 |

| GAL: THE MEMORY STRUCTURE IN THE AND ARRAY | 201 |

|                                            |     |

| LATCH-UP IMMUNITY                          | 207 |

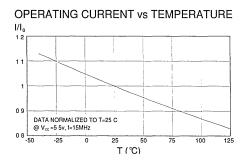

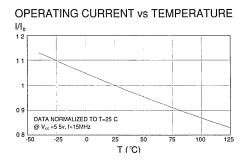

| POWER CONSUMPTION                          |     |

| EVALUATING THE POWER CONSUMPTION OF A GAL  | 217 |

| POWER DISSIPATION IN CMOS CIRCUITS         |     |

| THE DC COMPONENT                           |     |

| THE AC COMPONENT                           | 222 |

| CONSUMPTION VERSUS SUPPLY VOLTAGE          |     |

| CONSUMPTION VERSUS TEMPERATURE             |     |

|                                            |     |

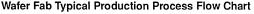

| QUALITY AND RELIABILITY                    | 227 |

N

#### GAL<sup>®</sup> IN PLD SCENARIO

SGS-THOMSON is today committed to serving the market with high volume families including Programmable Logic Devices (PLDs), which shows one of the fastest growth rates in the semiconductor market.

#### PLDs IN THE ASIC SCENARIO

PLDs represent today one of the largest families in the ASIC market.

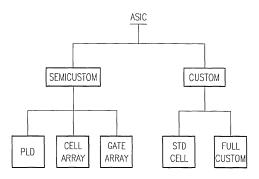

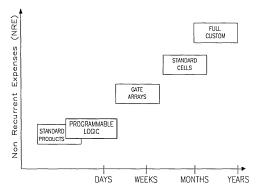

The devices in the ASIC category offer advantages over other alternatives, in that they perform a function defined by the user that is optimized for a specific application. The ASIC family can be segmented into sub-families of devices — according to the degree of physical specialization that the customer design imprints into the device — as shown in Figure 1.

#### Figure 1. The ASIC scenario

The standard cell approach uses pre-configured, pre-tested and pre-characterized logic blocks to construct a custom silicon chip for the designer. The chip is usually designed by hand, using a graphics terminal. The outcome is a fairly efficient logic design that may take weeks or months to complete, while incurring a hefty up-front engineering charge, or non-recurring expense (NRE).

In addition, the custom piece of silicon will take additional weeks, if not months, to manufacture. The development time and complexity of a standard cell design severely impacts the ability to incorporate changes or corrections to the design. In addition, the customer is typically obligated for some minimum production lot size to cover the manufacturer's expenses. Since most logic designs are subject to revision during the debug phase, the time and dollar penalties of the standard cell approach make this a relatively high risk one. The gate array approach has gained extensive market recognition as a more optimum "bridge" between the standard cell (full custom) and programmable alternatives. The gate array is a premanufactured silicon matrix that awaits only a custom interconnected pattern to establish functionality. The designer can choose from NAND gates, flip-flops, and various types of buffers to construct the logic.

The flexibility of a gate array is less than that of a standard cell device, since the user must interconnect existing structures. However, since the device usually has many pins (68 or more) it offers greater logic functionality than a typical PLD. This increased functionality, however, comes at the penalty of lower speed performance.

Since the gate array relies on only one or two custom mask layers, the wafer fabrication can be done much more quickly than with a standard cell. The turn time from design completion to final chip for a gate array is, at best, 4 to 8 weeks. Although not as costly up front as a standard cell, there is still an up front development cost, a minimum lot size, and a long and costly cycle for logic changes. These features make this, too, a risky approach.

#### Advantages of PLDs

SGS-THOMSON

งกรบระการกับไดะ

57

The previous alternatives are ideal choices for high volume applications where, once debugged, the design is not subject to change. The average customer, however, uses hundreds to thousands of devices of a given logic pattern, each year. He cannot afford the NRE of a gate array or standard cell, since the volume is not high enough to dilute this expense. Figure 2 shows the cost and development time relationships of the various design alternatives.

The PLD offers a solution to these woes. The simple, but powerful and affordable development tools, associated with the low unit cost, flexibility, high performance, and proven reliability of these devices result in a cost-efficient, higher-performance, lower-risk, and more timely design cycle.

Programmable logic is ideal for simplifying the design process, because the designer can implement the exact logic function whenever and wherever required. Programmable logic offers more efficient utilization, as well as reduced chip count, by simplifying the lay-out process at both conceptual and implementation stage.

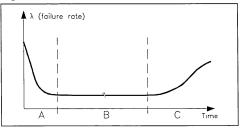

As a consequence PLDs contributes to increase substantially system reliability. It has been statistically demonstrated that systems with higher levels of integration such as those designed with programmable logic, have much higher reliability than equivalent systems designed with many low density standard components.

#### GAL®

SGS-THOMSON has decided to enter the PLD market by producing the GAL<sup>®</sup> (Generic Array Logic) family of devices. GAL<sup>®</sup> are ideal devices among PLDs for several reasons:

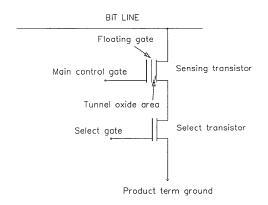

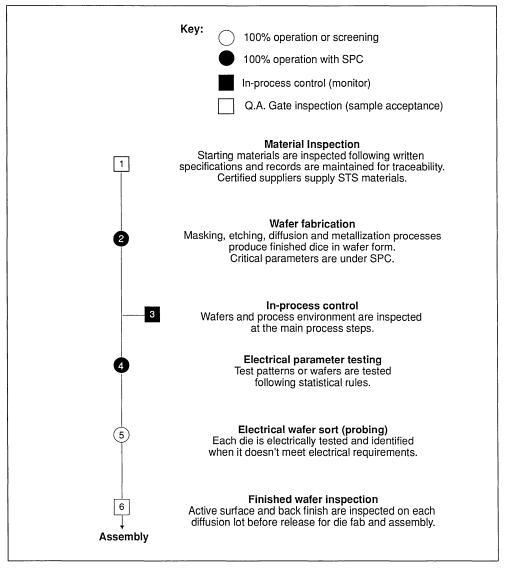

- GAL<sup>®</sup> devices are fabricated using very high speed Electrically Erasable CMOS technology which offers the highest degree of testability and quality of any process technology. In fact AC, DC and functionality can be 100% tested and that guarantees 100% programming and functional yield to the customer with no further board rework. With PLDs in bipolar technologies, complete testing is not possible and manufacturers must rely on complex schemes using test rows and columns to simulate and correlate device performances, since the fuse array cannot be tested prior to programming. Due to the incomplete test of these bipolar PLDs, rejects may be found when the user programs them, with no recovery possibility

- since mis-programmed parts must be discarded. Instant erasability, instead, makes  $\text{GAL}^{\oplus}_{}$  ideal for unforecasted design changes.

- GAL<sup>®</sup> switching speed is as fast as any other bipolar programmable logic devices except

ECL, but they have the low power consumption of CMOS.

GAL<sup>®</sup> devices utilize the Output Logic Macrocell (OLMC) which allows the user to configure outputs as needed and to replace several other programmable logic devices and low complexity gate arrays.

The main advantage of GAL<sup>®</sup> devices comes from their intrinsic "genericity" that allows the user to define the architecture and functionality of each output and also has advantages at the shop floor level: users can put in inventory one generic GAL<sup>®</sup> type instead of many different PAL<sup>®</sup> device types; this will not only save money, but also minimize the paper work, reduce manufacturing flow because the handling process is simplified, reduce the risk or running out of inventory. For example, the GAL16V8AS can replace 21 different bipolar PAL<sup>®</sup>.

#### GAL<sup>®</sup> Development Tools

GAL<sup>®</sup> devices have been developed to support the philosophy that users should not be required to purchase special development tools. GAL<sup>®</sup> are in fact supported by existing programmable logic development tools and device programmers.

Software packages such as ABEL<sup>®</sup> from DATA I/O and CUPL<sup>™</sup> from Logical Devices, offer generic development support for all programmable logic devices.

They allow an almost instantaneous compilation of a description of the logic circuit that the  $GAL^{\textcircled{B}}$  is expected to implement.

Their output is a file (the JEDEC file) that can be fed into the hardware programming tool (the device programmer), which in turn performs the task of writing the corresponding pattern into the GAL<sup>®</sup> memory.

SGS-THOMSON, together with Logical Devices, supplies a dedicated GAL<sup>®</sup> high level software development tool, named ST-CUPL<sup>™</sup>.

GAL<sup>®</sup> are supported by several device programmers that ensure the highest quality.

An updated list of device programmers, qualified by SGS-THOMSON for its GAL<sup>®</sup>, may be obtained from the nearest SGS-THOMSON sales office.

#### DC PARAMETERS

| Symbol | Parameter                                 | Description                                                                                                                                                                                                          |

|--------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcc    | Supply Voltage                            | The range of power supply voltage over which the device is guarantied to operate within specified limits.                                                                                                            |

| VIH    | Input HIGH Voltage                        | The range of input voltages that represents a logic HIGH in the system.                                                                                                                                              |

| VIL    | Input LOW Voltage                         | The range of input voltages that represents a logic LOW in the system.                                                                                                                                               |

| Vон    | Output HIGH Voltage (min.)                | The minimum voltage at an output terminal for the<br>specified output current IOH and the minimum value of<br>V <sub>CC</sub> .                                                                                      |

| Vol    | Output LOW Voltage (max.)                 | The maximum voltage at an output terminal sinking the maximum specified LOW current IOL.                                                                                                                             |

| lcc    | Supply Current                            | The current flowing into the VCC supply terminal of a<br>circuit with the specified inputs conditions and the<br>outputs open. When not specified, input conditions are<br>chosen to guarantee worst case operation. |

| Ін     | Input Leakage Current (High)              | The current flowing into an input when a specified HIGH level voltage is applied to that input.                                                                                                                      |

| ΪL     | Input Leakage Current (Low)               | The current flowing out of an input when a specified LOW voltage is applied to the input.                                                                                                                            |

| Юн     | Output High Current                       | The current flowing out of an output which is in the HIGH state.                                                                                                                                                     |

| IOL    | Output Low Current                        | The current flowing into an output which is in the LOW state.                                                                                                                                                        |

| los    | Output Short Circuit Current              | The current flowing out of an output which is in the HIGH state when that output is connected to a reference of 0.5 V.                                                                                               |

| Івн    | Bidirectional pin Leakage<br>Current HIGH | The current flowing into a disabled 3-state output with a specified HIGH output voltage applied.                                                                                                                     |

| IBL    | Bidirectional pin Leakage<br>Current LOW  | The current flowing out of a disabled 3-state output with a specified LOW output voltage applied.                                                                                                                    |

#### AC PARAMETERS

| Symbol         | Parameter                                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| fcik,<br>fcikf | Clock Frequency without and with<br>Feedback                                 | The maximum input frequency at a clock input for predictable<br>performance. Above this frequency the device may cease to<br>function.                                                                                                                                                                                                                                                                                                                        |

| tpd,<br>tco    | Combinational Propagation Delay and<br>Clock to Output Delay                 | The time between the specified reference points on the input<br>and output waveforms with the output changing from the<br>defined LOW level to the defined HIGH level or vice versa.                                                                                                                                                                                                                                                                          |

| tdıs,<br>tdısr | Product Term Output Disable to Output and Output Register Disable to Output  | The delay time between the specified reference points on the input and output voltage waveforms with the 3-state output changing from the HIGH (or LOW) level to a high impedance "off" state.                                                                                                                                                                                                                                                                |

| ten,<br>tenr   | Product Term Output Enable to Output<br>and Output Register Enable to Output | The delay time between the specified reference points on the<br>input and output voltage waveforms with the 3-state output<br>changing from a high impedance "off" state to the HIGH (or<br>LOW) level.                                                                                                                                                                                                                                                       |

| th             | Input or Feedback Hold Time<br>(after Clock Rise)                            | The interval immediately following the active transition of the timing pulse (usually the clock pulse) or following the transition of the control input to its latching level, during which interval the data to be recognized must be maintained at the input to ensure its continued recognition. A negative set-up time indicates that the correct logic level may be released prior to the active transition of the timing pulse and still be recognized. |

| tsu            | Input or Feedback Set-up Time<br>(before Clock Rise)                         | The interval immediately preceding the active transition of the timing pulse (usually the clock pulse) or preceding the transition of the control input to its latching level, during which interval the data to be recognized must be maintained at the input to ensure its recognition. A negative set-up time indicates that the correct logic level may be initiated sometimes after the active transition of the timing pulse and still be recognized.   |

| twh,<br>twi    | Minimum Clock Width,<br>High and Low                                         | The time between the specified reference points on the leading and trailing edges of a pulse.                                                                                                                                                                                                                                                                                                                                                                 |

## **GAL DATASHEETS**

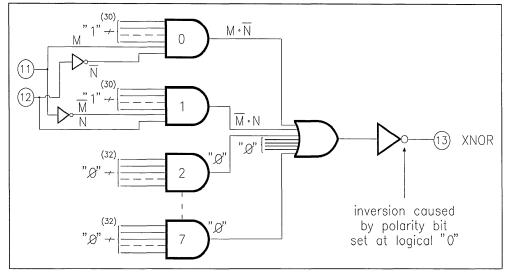

### GAL6001S

### E<sup>2</sup>PROM CMOS PROGRAMMABLE LOGIC DEVICE

- ELECTRICALLY ERASABLE CELL TECHNOLOGY

- Instantly reconfigurable logic

- Instantly reprogrammable cells

- Guaranteed 100% yields

- HIGH PERFORMANCE E<sup>2</sup>CMOS TECHNOLOGY

- Low power: 90mA typical

- High speed: 12ns max. clock to output delay, 25ns max. setup time, 30ns max. propagation delay

- TTL COMPATIBLE INPUTS AND OUTPUTS

- UNPRECEDENTED FUNCTIONAL DENSITY

- 10 Output Logic Macrocells

- 8 Buried Logic Macrocells

- 20 Input and I/O Logic Macrocells

- HIGH-LEVEL DESIGN FLEXIBILITY

- $-78 \times 64 \times 36$  FPLA Architecture

- Separate buried register and input clock pins

- Functionally supersets existing 24 pin PAL<sup>®</sup> and IFL<sup>™</sup> devices

- Asynchronous or Synchronous clocking

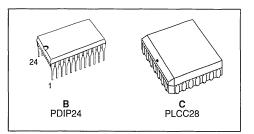

- SPACE SAVING 24 PINS, 300 MILS DIP USE SAVING 24 PINS, 300 MILS DIP

- HIGH SPEED PROGRAMMING ALGORITHM A SOLUTION AND ALGORITHM

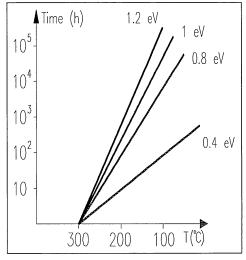

- 20 YEAR DATA RETENTION

#### DESCRIPTION

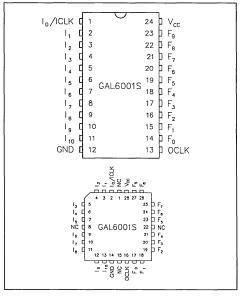

Using a high performance E<sup>2</sup>CMOS technology, SGS-THOMSON has produced a next-generation programmable logic device, the GAL6001S. Using FPLA architecture known for its superior flexibility in state machine design, the GAL6001S offers the highest degree of functional integration and flexibility currently available in a 24 pin, 300 mils package.

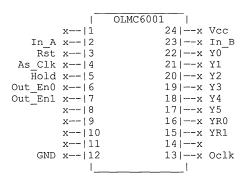

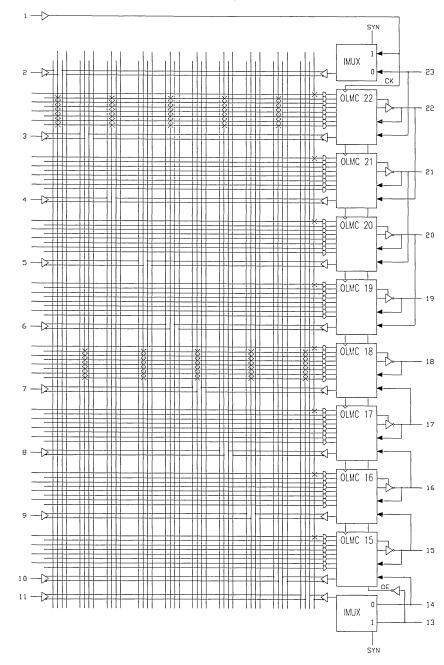

The GAL6001S has 10 programmable Output Logic Macrocells (OLMCs) and 8 programmable Buried Logic Macrocells (BLMCs). In addition, there are 10 Input Logic Macrocells (ILMCs) and 10 I/O Logic Macrocells (IOLMC). Two Clock inputs are provided for independent control of the Input and Output Macrocells.

Advanced features that simplify programming and reduce test time, coupled with E<sup>2</sup>PROM CMOS reprogrammable cells, enable complete AC, DC, programmability, and functionality test of each GAL6001S during manufacture. This allows SGS-THOMSON to guarantee 100% field programmability and functionality to datasheet specifications.

#### **Pin Connections**

#### Pin Names

| lo-l10 | Input        |

|--------|--------------|

| Fo-F9  | I/O          |

| ICLK   | Input Clock  |

| OCLK   | Output Clock |

| Vcc    | Power        |

| GND    | Ground       |

GAL® is a registered trademark of Lattice Semiconductor Corp.; PAL® is a registered trademark of Monolithic Memories Inc.

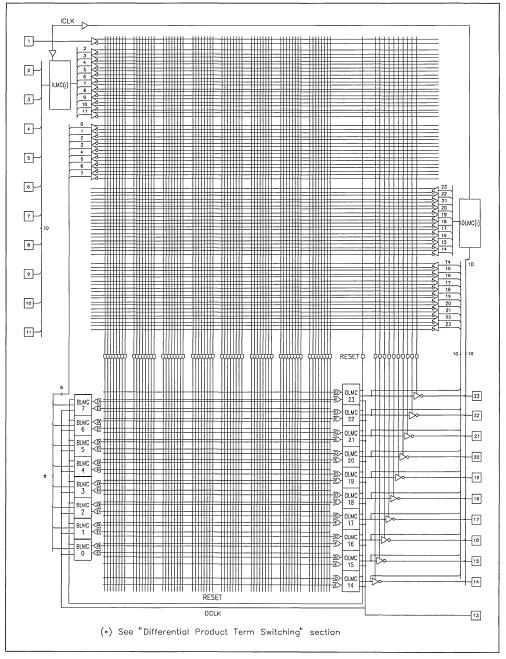

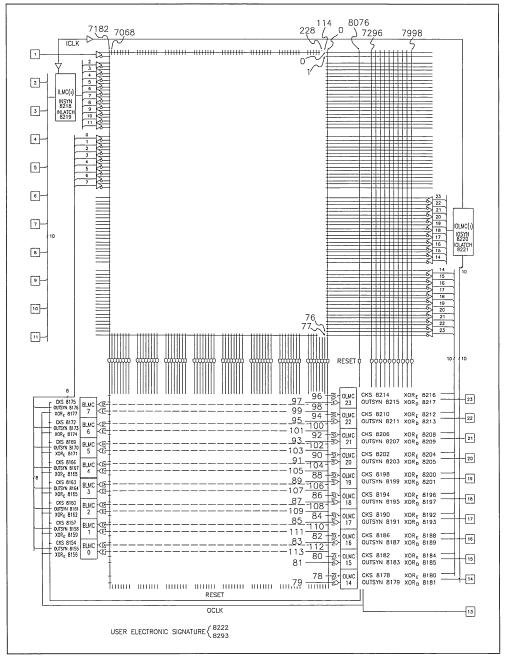

#### GAL6001S Logic Diagram

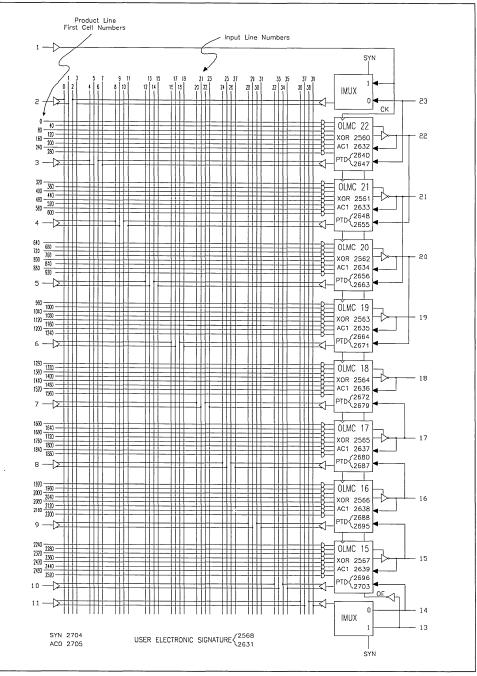

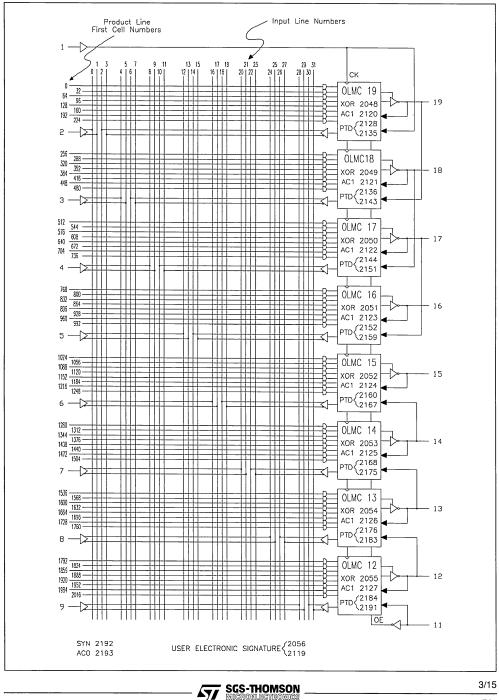

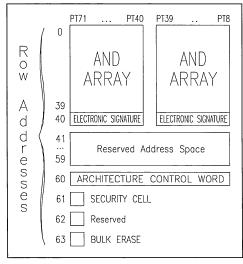

#### GAL6001S Jedec Map

Programming is accomplished using standard hardware and software tools. SGS-THOMSON guarantees a minimum of 100 erase write cycles, and data retention to exceed 20 years. An Electronic Signa-

ture word has been provided for user-defined data. In addition, a security cell is available to protect proprietary designs.

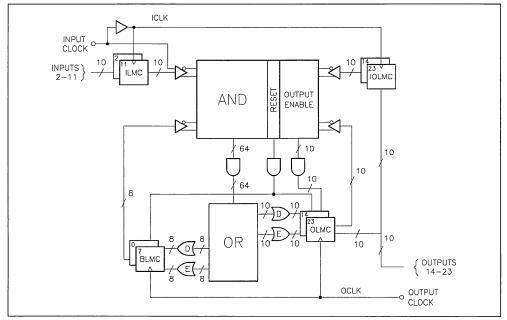

#### GAL6001S Functional Block Diagram

#### Macrocells Names

| ILMC  | Input Logic Macrocell  |  |

|-------|------------------------|--|

| IOLMC | I/O Logic Macrocell    |  |

| BLMC  | Buried Logic Macrocell |  |

| OLMC  | Output Logic Macrocell |  |

#### **Absolute Maximum Ratings**

| Symbol | Parameter                                        | Value                     | Unit |

|--------|--------------------------------------------------|---------------------------|------|

| Vcc    | Supply Voltage                                   | -0.5 to +7                | V    |

| VI     | Input Voltage Applied                            | -2.5 to VCC+1             | V    |

| VB     | Off-State Output (Bidirectional) Voltage Applied | -2.5 to V <sub>CC+1</sub> | v    |

| Tstg   | Storage Temperature                              | -65 to +125               | °C   |

| Tj     | Junction Temperature (Operating)                 | -40 to +125               | °C   |

| TL     | Lead Temperature (Soldering)                     | 260 (for 10s max.)        | °C   |

Stresses above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress only ratings and functional operation of the device at these or at any other conditions above those indicated in the operational sections of this specification is not implied.

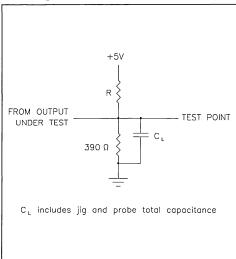

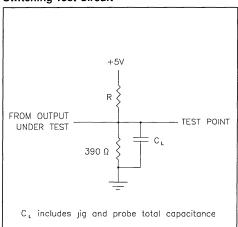

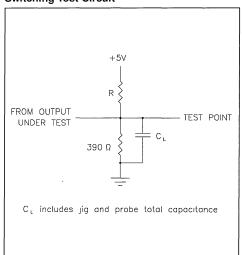

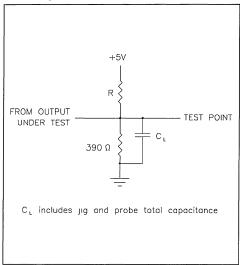

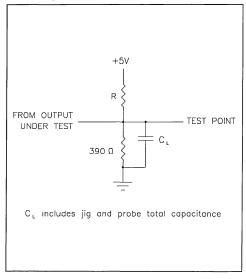

#### **Switching Test Conditions**

| Input Pulse Levels                | GND to 3.0V |

|-----------------------------------|-------------|

| Input Rise and Fall Times         | 3ns 10%-90% |

| Input Timing Reference<br>Levels  | 1.5V        |

| Output Timing Reference<br>Levels | 1.5V        |

| Output Load                       | See figure  |

3-state levels are measured 0.5V from steady-state active level.

#### **Test Conditions**

| # | <b>R</b> [Ω]                      | C <sub>L</sub> [pF] |

|---|-----------------------------------|---------------------|

| 1 | 300                               | 50                  |

| 2 | Active High: ∞<br>Active Low: 300 | 50                  |

| 3 | Active High: ∞<br>Active Low: 300 | 5                   |

#### Switching Test Circuit

#### Capacitance (TA=25°C, f=1.0MHz, V<sub>CC</sub>=5V)

| Symbol | Parameter                     | Test Conditions    | Maximum <sup>*</sup> | Units |

|--------|-------------------------------|--------------------|----------------------|-------|

| CI     | Input Capacitance             | VI=2V              | 8                    | pF    |

| CB     | Bidirectional Pin Capacitance | V <sub>B</sub> =2V | 10                   | pF    |

\* Guarantied but not 100% tested

#### **DC Operating Conditions**

| Symbol | Parameter                 |          | Commercial<br>Temperature Range |                       | Industrial<br>Temperature Range |    |

|--------|---------------------------|----------|---------------------------------|-----------------------|---------------------------------|----|

|        |                           | Min.     | Max.                            | Min.                  | Max.                            |    |

| Vcc    | Supply Voltage            | 4.75     | 5.25                            | 4.5                   | 5.5                             | V  |

| TA     | Ambient Temperature       | 0        | 70                              | -40                   | 85                              | °C |

| VIL    | Input Low Voltage         | Vss*-0.5 | 0.8                             | Vss <sup>∻</sup> -0.5 | 0.8                             | v  |

| ViH    | Input High Voltage        | 2.0      | V <sub>CC</sub> +1              | 2.0                   | Vcc+1                           | V  |

| IOL    | Low Level Output Current  | -        | 16                              | -                     | 16                              | mA |

| Юн     | High Level Output Current | -3.2     | -                               | -3.2                  | -                               | mA |

$\overline{\ }\ v_{ss}$  is the voltage applied to the GND pin

#### **Electrical Characteristics Over Operating Conditions**

| Symbol                            | Parameter                         | Test Conditions                             | Commercial<br>Temperature Range |      | Industrial<br>Temperature Range |      | Units |

|-----------------------------------|-----------------------------------|---------------------------------------------|---------------------------------|------|---------------------------------|------|-------|

|                                   |                                   |                                             | Min.                            | Max. | Min.                            | Max. |       |

| Iih, Iil                          | Input Leakage Current             | GND≤VI≤V CC <sub>Max</sub>                  | -                               | ±10  | -                               | ±10  | μA    |

| I <sub>BH</sub> , I <sub>BL</sub> | Bidirectional Pin Leakage Current | GND≤VI≤V <sub>CC Max</sub>                  | -                               | ±10  | _                               | ±10  | μA    |

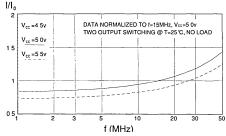

| Icc                               | Operating Power Supply Current    | f=15MHz<br>VIL=0.5V<br>VIH=3.0V             | 1                               | 150  | -                               | 180  | mA    |

| los*                              | Output Short Circuit Current      | V <sub>CC</sub> =5.0V, V <sub>B</sub> =0.5V | -130                            | -30  | -130                            | -30  | mA    |

| Vol                               | Output Low Voltage                | _                                           | _                               | 0.5  | -                               | 0.5  | V     |

| Vон                               | Output High Voltage               | -                                           | 2.4                             | -    | 2.4                             | -    | V     |

<sup>•</sup> One output at a time for a maximum duration of one second.

#### Switching Characteristics Over Operating Conditions

| Symbol            | Devenueter                                                       | From                            | То                              | 6001S-30 | 6001S-35 |       | Test   |

|-------------------|------------------------------------------------------------------|---------------------------------|---------------------------------|----------|----------|-------|--------|

| Symbol            | Parameter                                                        |                                 | 10                              | Max.**   | Max.+    | Units | Cond.+ |

| tpda              | Combinational<br>Propagation Delay<br>(ILMC Async.)              | Input                           | Output                          | 30       | 35       | ns    | 1      |

| tpdf              | Combinational<br>Propagation Delay<br>(With Feedback)            | Output,<br>Registered<br>Output | Output                          | 30       | 35       | ns    | 1      |

| tpdl              | Combinational<br>Propagation Delay<br>(ILMC Latch)               | Input                           | Output                          | 35       | 40       | ns    | 1      |

| t <sub>coir</sub> | Input Clock to<br>Output Delay<br>(ILMC Reg., OLMC<br>Comb.)     | ICLK                            | Output                          | 35       | 40       | ns    | 1      |

| t <sub>coil</sub> | Input Clock to<br>Output Delay<br>(ILMC Latch, OLMC<br>Comb.)    | ICLK                            | Output                          | 35       | 40       | ns    | 1      |

| t <sub>coo</sub>  | Output Clock to<br>Registered Output<br>Delay (OLMC D/E Reg.)    | OCLK                            | Registered<br>Output            | 12       | 13.5     | ns    | 1      |

| tcos              | Sum Term Clock<br>to Registered<br>Output Delay<br>(OLMC D Reg.) | STCLK                           | Registered<br>Output            | 35       | 40       | ns    | 1      |

| ten               | Product Term<br>Output Enable to<br>Output Delay                 | Input, I/O                      | Output,<br>Registered<br>Output | 25       | 30       | ns    | 2      |

| tdis              | Product Term Output<br>Disable to<br>Output Delay                | Input, I/O                      | Output,<br>Registered<br>Output | 25       | 30       | ns    | 3      |

| tres              | Register Reset Delay                                             | Input, I/O                      | Registered<br>Output            | 35       | 35       | ns    | 1      |

\* Refer to Switching Test Conditions".

\* Commercial Temperature range only

\* Industrial Temperature range only

6/13

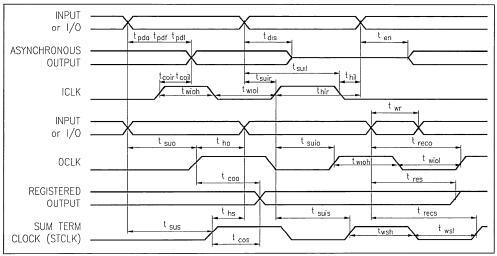

#### **AC Operating Conditions**

| Symbol            | Parameter                                                     | 6001S-30 |      | 6001 | S-35 <sup>+</sup> | Units |

|-------------------|---------------------------------------------------------------|----------|------|------|-------------------|-------|

| Symbol            | ratameter                                                     | Min.     | Max. | Min. | Max.              | Units |

| tsuil             | Input Setup Time Before ICLK Fall (ILMC Latch)                | -        | 2.5  | -    | 3.5               | ns    |

| t <sub>suir</sub> | Input Setup Time Before ICLK Rise (ILMC Reg.)                 | -        | 2.5  | -    | 3.5               | ns    |

| t <sub>suo</sub>  | Input or Feedback Setup Time Before OCLK Rise (OLMC D/E Reg.) | -        | 25   | -    | 30                | ns    |

| tsus              | Input or Feedback Setup Time Before STCLK Rise (OLMC D Reg.)  | -        | 7.5  | -    | 10                | ns    |

| tsuio             | ICLK Rise Setup Time Before OCLK Rise (OLMC D/E Reg.)         | -        | 30   | -    | 35                | ns    |

| t <sub>suis</sub> | ICLK Rise Setup Time Before STCLK Rise (OLMC D Reg.)          | -        | 15   |      | 17                | ns    |

| thil              | Hold Time After ICLK Fall (ILMC Latch)                        | -        | 5    | -    | 5                 | ns    |

| thir              | Hold Time After ICLK Rise (ILMC Reg.)                         | -        | 5    | -    | 5                 | ns    |

| tho               | Hold Time After OCLK Rise (OLMC D/E Reg.)                     | -        | 5    | -    | 5                 | ns    |

| t <sub>hs</sub>   | Hold Time After STCLK Rise (OLMC D Reg.)                      | -        | 10   | -    | 12.5              | ns    |

| twich             | ICLK or OCLK Pulse Duration High                              | -        | 10   | -    | 10                | ns    |

| twiol             | ICLK or OCLK Pulse Duration Low                               | -        | 10   | -    | 10                | ns    |

| twsh              | STCLK Pulse Duration High                                     | -        | 15   | -    | 15                | ns    |

| t <sub>wsl</sub>  | STCLK Pulse Duration Low                                      | -        | 15   | -    | 15                | ns    |

| twr               | Reset Pulse Duration                                          | -        | 15   | -    | 15                | ns    |

| treco             | Reset to OCLK Recovery Time                                   | -        | 20   | -    | 20                | ns    |

| t <sub>recs</sub> | Reset to STCLK Recovery Time                                  | -        | 10   | -    | 10                | ns    |

| f <sub>clk</sub>  | OCLK or STCLK Maximum Frequency                               | 27       | -    | 22.9 | -                 | MHz   |

\* Commercial Temperature range only

\* Industrial Temperature range only

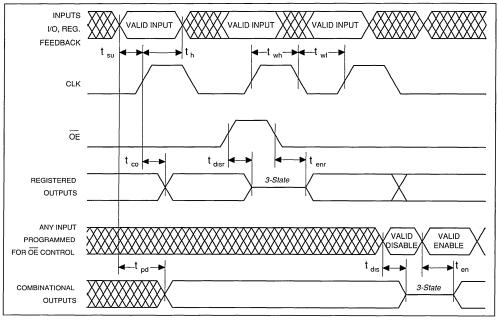

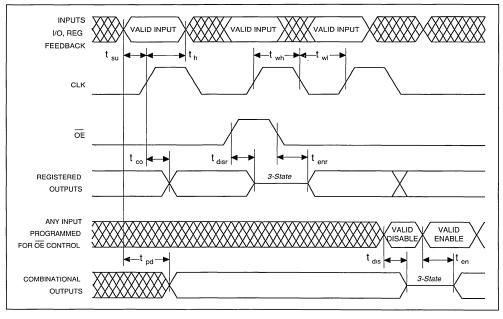

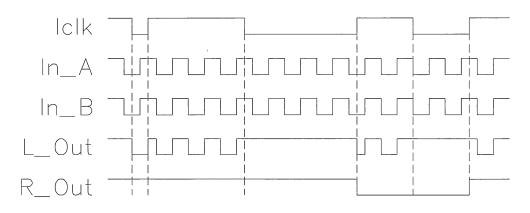

#### Switching Waveforms

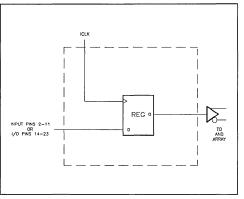

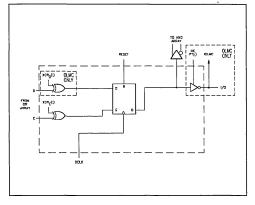

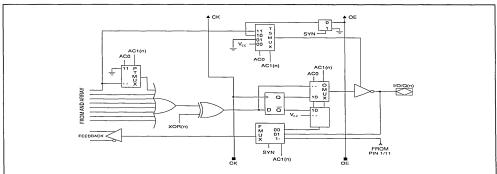

### INPUT LOGIC MACROCELL (ILMC) AND I/O LOGIC MACROCELL (IOLMC)

The GAL6001S features two configurable input sections.

The ILMC section corresponds to the dedicated input pins (2-11) and the IOLMC section to the I/O pins (14-23). Each input section is configurable as a block for asynchronous, latched, or registered inputs. Pin 1 (ICLK) is used as an enable input for latched macrocells (transparent when high) and as a clock for registered macrocells (positive edge triggered).

Configurable input blocks can be used to advantage by system designers. Registered inputs are popular for synchronization and data merging. Transparent

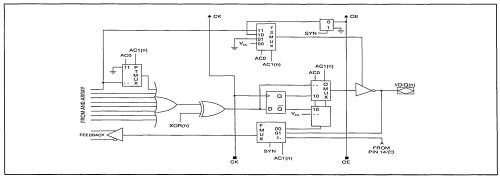

#### ILMC/IOLMC Generic Block Diagram

Registered Input (LATCH=1, SYN=0)

latches are useful when the input data is invalid outside a known time window. Direct inputs are used in systems where the input data is well ordered in time. With the GAL6001S, external registers and latches are not necessary.

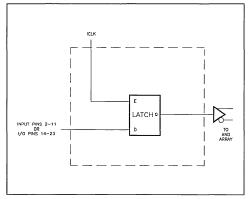

The various configurations of the Input and I/O Macrocells are controlled by programming four architecture control bits (LATCH and SYN both for Input and I/O Macrocells) within the 68 bits Architecture Control Word. The SYN bits determine whether the macrocells will have register/latch capability or will be strictly asynchronous. The LATCH bits select between latched and registered inputs.

The three valid macrocell configurations are shown in the macrocell equivalent diagrams shown below.

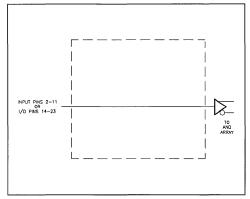

#### Asynchronous Input (LATCH=1, SYN=1)

#### Latched Input (LATCH=0, SYN=0)

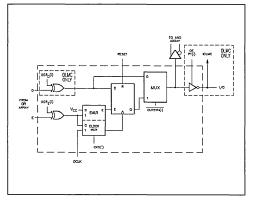

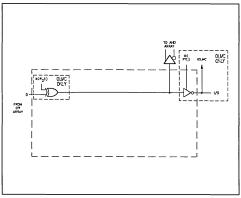

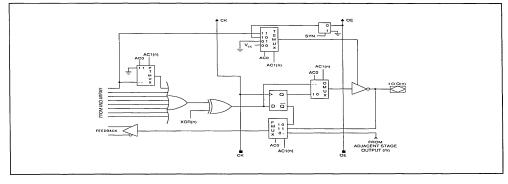

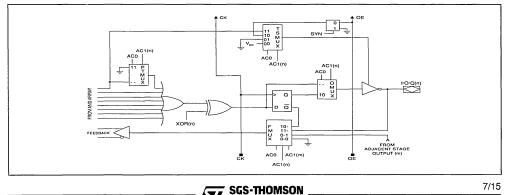

#### OUTPUT LOGIC MACROCELL (OLMC) AND BU-RIED LOGIC MACROCELL (BLMC)

The outputs of the OR array feed two groups of macrocells. One group of eight macrocells is buried; its output feed back directly into the AND array rather than to device pins. These cells are called the Buried Logic Macrocells (BLMC): they are useful for building state machines. The second group of macrocells consists of 10 cells whose outputs, in addition to feeding back into the AND array, are available at the device pins. Cells in this group are known as Output Logic Macrocells (OLMC).

Like the ILMCs and IOLMCs discussed above, Output and Buried Logic Macrocells are configured by programming specific bits in the Architecture Control Word (CKS(i), OUTSYN(i), XOR<sub>D</sub>(i), XOR<sub>E</sub>(i)),

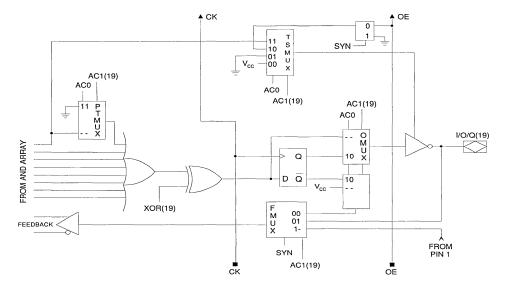

#### OLMC/BLMC Generic Block Diagram

#### D/E Type Registered (CKS(i)=1, OUTSYN(i)=0)

but unlike the Input Macrocells which must be configured in blocks, these macrocells are configurable on a macrocell-by-macrocell basis. Throughout this data sheet, i=[14..23] for OLMCs and i=[0...7] for BLMCs.

Buried and Output Logic Macrocells may be set to one of three valid configurations: combinational, D type registered with sum term (asynchronous) clock or D/E type registered.

Output macrocells always have I/O capability, with directional control provided by the 10 output enable (OE) product terms. Additionally, the polarity of each OLMC output is selectable through the  $XOR_D(i)$  architecture bits. Polarity selection is available for BLMCs, since both the true and complemented forms of their outputs are available in the AND array.

#### Combinational (CKS(i)=0, OUTSYN(i)=1)

Polarity of all "E" sum terms is selectable through the  $XOR_E(i)$  architecture control bits.

When CKS(i) = 1 and OUTSYN(i) = 0, macrocell "i" is set as "D/E type registered". In this configuration, the register is clocked from the common OCLK and the register clock enable input is controlled by the associated "E" sum term. This configuration is useful for building counters and state-machines with state hold functions.

When the macrocell is configured as a "D type registered with a sum term asynchronous clock" (CKS(i) = 0 and OUTSYN(i) = 0), the register is always enabled and its "E" sum term is routed directly to the clock input. This permits asynchronous programmable clocking, selected on a register-by-register basis.

When CKS(i) = 0 and OUTSYN(i) = 1, macrocell "i" is set as "combinational". Configuring a BLMC in this manner turns it into a complement array. Complement arrays are used to construct multi-level logic. Registers in both the Output and Buried Logic Macrocells feature a common RESET product term. This active high product term allows the registers to be asynchronously reset. Registers are reset to a logic zero. If connected to an output pin, a logic one will occur because of the inverting output buffer.

There are two possible feedback paths from each OLMC: one directly from the OLMC (this feedback is before the output buffer and always present), and one from OLMC after the output buffer through the IOLMC. The second path is usable as a feedback only when the associated bidirectional pin is being used as an output. With this dual feedback arrangement, the OLMC can be permanently buried (the associate OLMC pin is an input), or dynamically buried with the use of the output enable product term. The D/E registers used in this device offer the designer the ultimate in flexibility and utility. The D/E registers with the same efficiency as a dedicated RS, JK, or T register.

The three valid macrocell configurations are shown in the macrocell equivalent diagrams shown in the previous page.

#### ARRAY DESCRIPTION

The GAL6001S  $E^2$  reprogrammable array is subdivided into two smaller arrays; the first is an AND and the second is an OR array. These arrays are described in detail below.

#### AND ARRAY

The AND array is organized as 78 input terms by 75 product term outputs. The 10 ILMC, 10 I/O Logic Macrocells, 8 BLMC feedbacks, 10 OLMC feedbacks, and ICLK comprise the 39 inputs to this array (each available in true and complemented forms). Product terms 0-63 serve as inputs to the OR array. Product term 64 is the RESET PT; it generates the RESET signal described in the earlier discussion of Output and Buried Logic Macrocells. Product terms

65-74 are the output enable product terms; they control the output buffers, thus enabling device pins 14-23 to be bidirectional or 3-state.

#### OR ARRAY

The OR array is organized as 64 inputs by 36 sum term outputs. 64 product terms from the AND array serve as the inputs to the OR array. Of the 36 sum term outputs, 18 are data ("D") terms and 18 are enable/clock ("E") terms. These terms feed into the 10 OLMCs and 8 BLMCs, one "D" term and one "E" term to each.

The programmable OR array offers unparalleled versatility in product term usage. This programmability allows from 1 to 64 product terms to be connected to a single sum term. A programmable OR array is more flexible than a fixed, shared, or variable product term architecture.

#### ARCHITECTURE CONTROL WORD

The various configurations of the GAL6001S are enabled by programming cells within the Architecture Control Word. This 68 bits word contains all of the chip configuration data. This data includes:  $XOR_D(i)$ ,  $XOR_E(i)$ , CKS(i), OUTSYN(i), and LATCH and SYN bits both for ILMCs and IOLMCs. The function of each of these bits has been previously explained.

#### USER ELECTRONIC SIGNATURE WORD

An User Electronic Signature word (UES) is provided with GAL6001S device. The User Electronic Signature word is a 72 bits user definable storage area, which can be used to save inventory control data, pattern revision numbers, manufacture date, etc. Signature data is always available to the user, regardless of the state of the security cell.

*Note:* UES is included in checksum calculations. Changing the UES will alter the checksum.

#### SECURITY CELL

A security cell is provided with GAL6001S device as a deterrent to unauthorized copying of the array patterns. Once programmed, this cell prevents further read access to the AND and OR arrays. This cell can be erased only during a bulk erase cycle, so the original configuration can never be examined once this cell is programmed. User Electronic Signature data is always available to the user, regardless of the state of this control cell.

#### BULK ERASE

Before writing a new pattern into a previously programmed part, the old pattern must first be erased. This erasure is done automatically by the programming hardware as part of the programming cycle and takes only 50 milliseconds.

#### REGISTERED PRELOAD

When testing state machine designs, all possible states and state transitions must be verified, not just those required during normal operations. This verification is necessary because in system operation

certain events may occur that cause the logic to assume an illegal state: power-up, brown out, line voltage glitches, etc. To test a design for proper management of these conditions, a method must be provided to break the feedback paths and force any desired state (e.g. an illegal state) into the registers. Then the machine can be sequenced and the outputs tested for correct next state generation. All registers in the GAL6001S can be preloaded, including the ILMC, IOLMC, OLMC, and BLMC registers. The programming hardware takes care or all preload timing and voltage requirements.

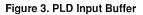

#### INPUT BUFFERS

GAL devices are designed with TTL level compatible input buffers. These buffers, with their characteristically high impedance, load driving logic much less than traditional bipolar devices.

This allows for a greater fan out from the driving logic.

$G\tilde{A}L6001S$  does not include active pull-ups within its input structures. As a result, SGS-THOMSON recommends that all unused inputs and 3-state I/O pins be connected to another active input, V<sub>CC</sub>, or GND. This precaution improves the noise immunity and reduces the I<sub>CC</sub> consumption.

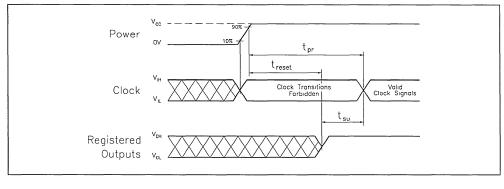

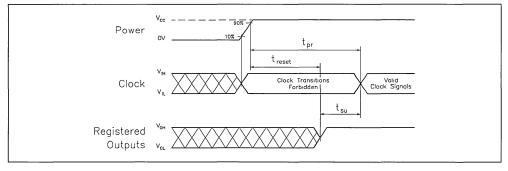

#### POWER-UP RESET

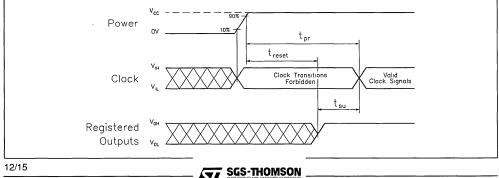

Circuitry within the GAL6001S provides a reset signal to all registers during power-up. All internal registers will have their Q outputs set low after a specified time ( $t_{reset}=10\mu s$ ). As a result, the state on the registered output pins (if they are enabled) will always be high after power-up, regardless of the programmed polarity of the output pins. This feature can greatly simplify state machine design by providing a known state upon power-up.

The timing diagram for power-up is shown below. Because of the asynchronous nature of system power-up, the V<sub>CC</sub> rise must be monotonic to guarantee a valid power-up reset of the GAL6001S. The registers will reset within a maximum of t<sub>reset</sub> time. As in normal system operation, avoid clocking the

Power-Up Reset Timing Diagram

device until all input and feedback path setup times have elapsed (i.e. avoid clocking before the  $t_{pr}$ =treset+tsu time interval).

### DIFFERENTIAL PRODUCT TERM SWITCHING (DPTS)

The number of "Differential Product Term Switching" (DPTS) for a given design is calculated by taking the absolute value of:

- the total number of product terms that are switching from a logical level high to a logical level low

- minus the total number of those switching from a logical level low to a logical level high

within a 5ns time window.

DPTS = | PTLH - PTHL |

The correct behaviour of the device is guaranteed for applications where the number of DPTS is not greater than 15. This limit is believed to be largely conservative. For the device to exhibit an incorrect behaviour, other conditions of supply voltage, clock timing, temperature, etc., should be simultaneously present. As each of these conditions may, to some extent, lay partly within the operating range limits, it is simpler to refer to a DPTS boundary that ensures ample margin in all conditions for a correct operation.

There is no limit on the number of product terms that can be used at the same time.

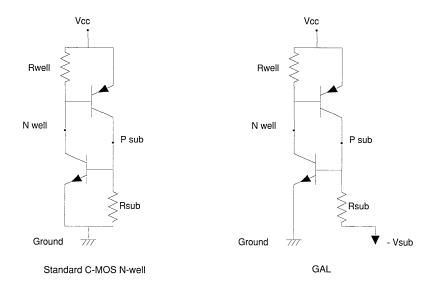

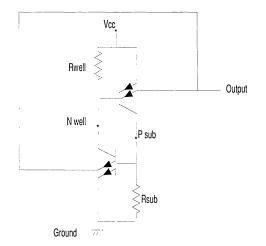

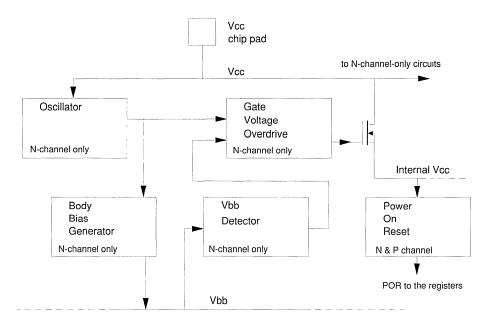

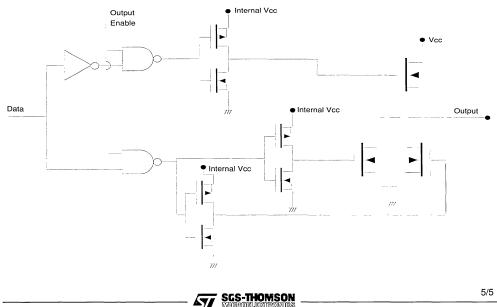

#### LATCH-UP PROTECTION

GAL6001S devices are designed with an on-board charge pump to negatively bias the substrate. The negative bias is of sufficient magnitude to prevent external disturbances from causing the circuitry to latch. Additionally, outputs are designed with nchannel pull-ups instead of the traditional p-channel pull-ups to eliminate any possibility of SCR induced latching.

SGS-THOMSON

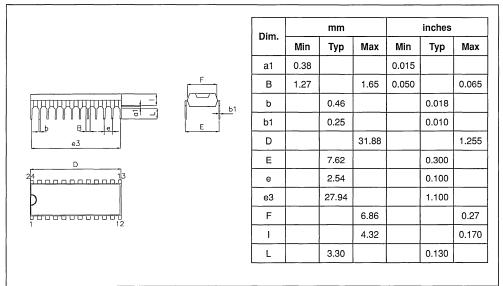

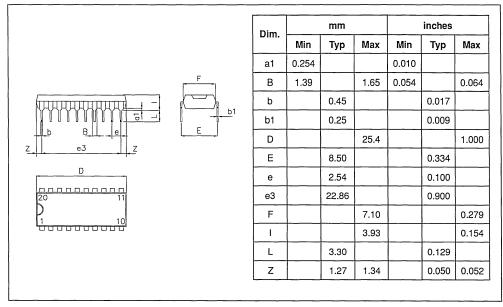

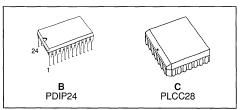

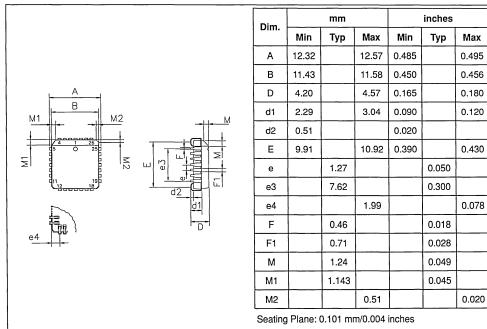

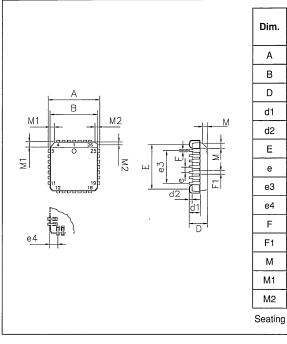

#### PDIP 24 Pins

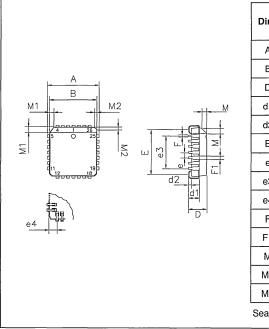

#### PLCC 28 Pins

|      |       | mm    |       | inches |       |       |  |

|------|-------|-------|-------|--------|-------|-------|--|

| Dim. | Min   | Тур   | Max   | Min    | Тур   | Max   |  |

| А    | 12.32 |       | 12.57 | 0.485  |       | 0.495 |  |

| В    | 11.43 |       | 11.58 | 0.450  |       | 0.456 |  |

| D    | 4.20  |       | 4.57  | 0.165  |       | 0.180 |  |

| d1   | 2.29  |       | 3.04  | 0.090  |       | 0.120 |  |

| d2   | 0.51  |       |       | 0.020  |       |       |  |

| E    | 9.91  |       | 10.92 | 0.390  |       | 0.430 |  |

| е    |       | 1.27  |       |        | 0.050 |       |  |

| e3   |       | 7.62  |       |        | 0.300 |       |  |

| e4   |       |       | 1.99  |        |       | 0.078 |  |

| F    |       | 0.46  |       |        | 0.018 |       |  |

| F1   |       | 0.71  |       |        | 0.028 |       |  |

| М    |       | 1.24  |       |        | 0.049 |       |  |

| M1   |       | 1.143 |       |        | 0.045 |       |  |

| M2   |       |       | 0.51  |        |       | 0.020 |  |

Seating Plane: 0.101 mm/0.004 inches

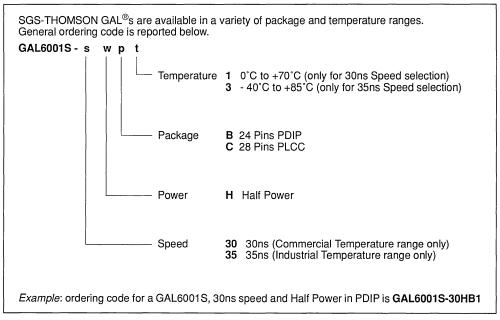

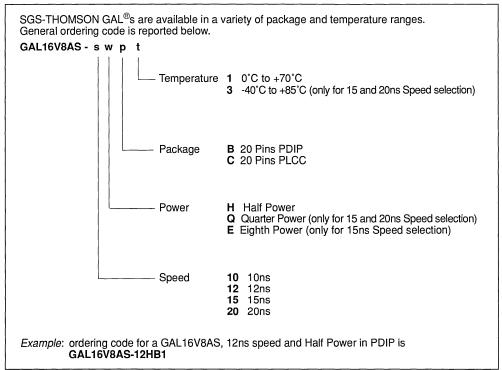

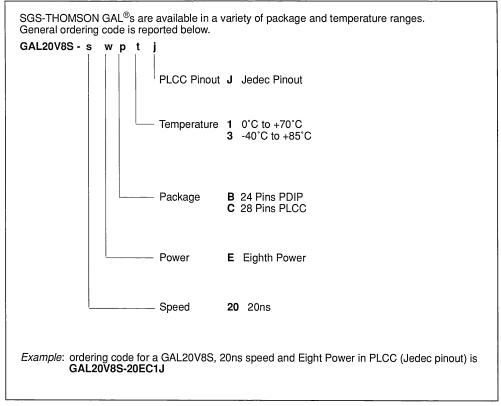

#### **Ordering Informations\***

\* Please contact local Product Marketing for latest update on package / temperature range availability.

,

### GAL16V8AS

### E<sup>2</sup>PROM CMOS PROGRAMMABLE LOGIC DEVICE

- HIGH PERFORMANCE SGS-THOMSON SINGLE-POLY E<sup>2</sup>PROM CMOS TECHNOLOGY

- 10ns maximum propagation delay

- (GAL16V8AS-10xxx)

- F<sub>max</sub> = 62.5MHz

- 7ns max. from clock input to data output

- TTL compatible 24mA outputs

- SGS-THOMSON proprietary Single-Poly F3-G<sup>™</sup> technology

- GLITCH FREE DEVICE

- Enhanced design minimises ground bounce

- VERY LOW POWER 00 m A two (115 m A m a)

- 90mA typ. (115mA max.) I<sub>CC</sub> Half power selection, 45mA typ. (55 mA max.) I<sub>CC</sub> Quarter power selection, 27mA typ. (30 mA max.) I<sub>CC</sub> Eighth power selection

- ELEČTRICAL ERASABLE CELL TECHNOLOGY

- Reconfigurable logic/reprogrammable cells

100% tested: guaranteed 100% final programming yield

- High speed electrical program & erase

- EIGHT OUTPUT MACROCELLS

- Maximum flexibility for complex logic design

- Programmable output polarity

- Also emulates 21 types of 20 pin PAL<sup>®</sup> devices with full function/fuse map/parametric compatibility

- PRELOAD AND POWER-ON RESET OF ALL REGISTERS

- 100% functional testability

- ELECTRONIC SIGNATURÉ FOR USER'S IDENTIFICATION

#### DESCRIPTION

The GAL16V8AS, at 10ns maximum propagation delay time, combines a high performance CMOS process with Electrical Erasable Single-Poly F3-G<sup>™</sup> technology — SGS-THOMSON proprietary — to provide one of the highest speed-power performance products available in PLD market.

CMOS circuit allows GAL16V8AS to consume just 27mA typ. I<sub>CC</sub> (Eighth power selection, 15ns) which represents a 75% saving in power when compared to its bipolar counterparts. Its E<sup>2</sup>PROM CMOS technology offers high speed (50ms) erase time providing the ability to reprogram or reconfigure the device quickly and efficiently.

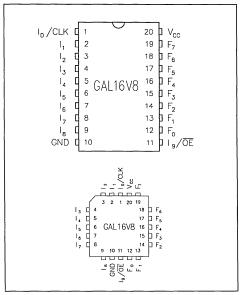

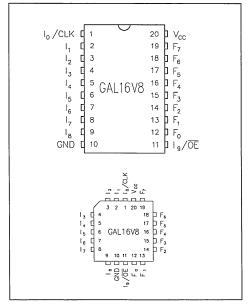

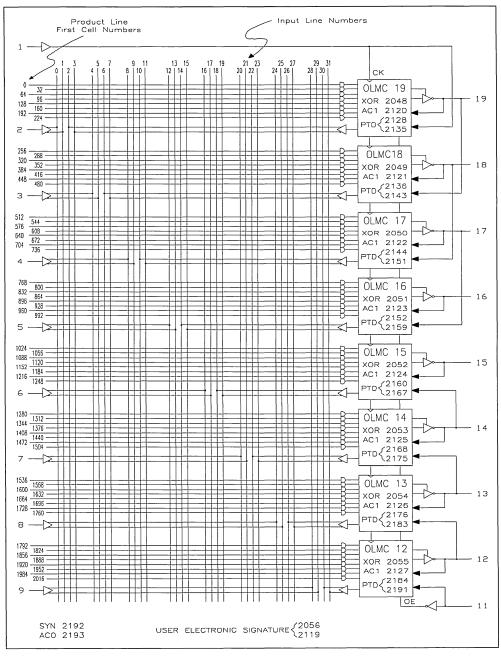

#### Pin Connections

#### Pin Names

| l0l9  | Input         |  |  |  |  |

|-------|---------------|--|--|--|--|

| CLK   | Clock Input   |  |  |  |  |

| Fo-F7 | I/O           |  |  |  |  |

| ŌĒ    | Output Enable |  |  |  |  |

| Vcc   | Power         |  |  |  |  |

| GND   | Ground        |  |  |  |  |

GAL<sup>©</sup> is a registered trademark of Lattice Semiconductor Corp ; PAL<sup>©</sup> is a registered trademark of Monolithic Memories Inc.

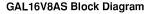

GAL16V8AS features 8 programmable Output Logic Macro Cells (OLMCs) allowing each output to be configured by the user. Additionally, the GAL16V8AS is capable of emulating, in a functional/fuse map/parametric compatible mode, 21 types of 20 pin PAL<sup>®</sup> devices. Unique test circuits and reprogrammable cells allow complete AC, DC and functional testing during manufacture.

Therefore, SGS-THOMSON guarantees 100% field programmability and functionality of GAL<sup>®</sup> devices. SGS-THOMSON also guarantees 100 erase/write cycles and data retention exceeding 20 years.

#### GAL16V8AS PAL<sup>®</sup> Architecture Emulation

| 16L8 | 16R8  | 16RP6 | 16L2 | 14L4 | 12L6 | 10L8 |

|------|-------|-------|------|------|------|------|

| 16H8 | 16RP8 | 16R4  | 16H2 | 14H4 | 12H6 | 10H8 |

| 16P8 | 16R6  | 16RP4 | 16P2 | 14P4 | 12P6 | 10P8 |

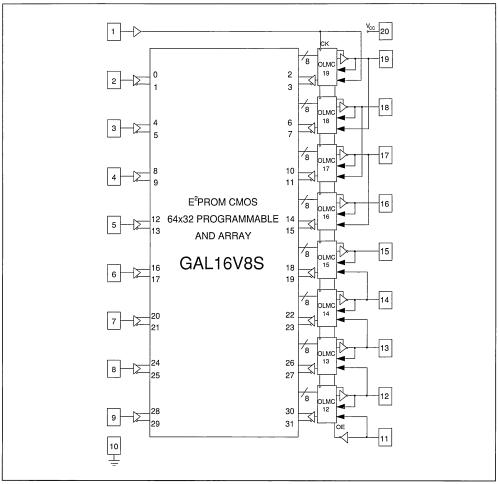

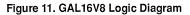

#### GAL16V8AS Logic Diagram

#### **Absolute Maximum Ratings**

| Symbol | Parameter                                        | Value                     | Unit |

|--------|--------------------------------------------------|---------------------------|------|

| Vcc    | Supply Voltage                                   | -0.5 to +7                | V    |

| Vi     | Input Voltage Applied                            | -2.5 to V <sub>CC+1</sub> | V    |

| VB     | Off-State Output (Bidirectional) Voltage Applied | -2.5 to V <sub>CC+1</sub> | V    |

| TSTG   | Storage Temperature                              | -65 to +125               | °C   |

| TJ     | Junction Temperature (Operating)                 | -40 to +125               | °C   |

| TL     | Lead Temperature (Soldering)                     | 260 (for 10s max.)        | °C   |

Stresses above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress only ratings and functional operation of the device at these or at any other conditions above those indicated in the operational sections of this specification is not implied.

#### **ESD** Immunity

Test Method: Human Body Model (HBM) ESD Tolerance  $\geq$  2000V (See MIL-STD 883c).

Test Method: Charge Device Model (CDM) ESD Tolerance ≥ 500V Test Instrument: KeyTek ZapMaster

CDM is an additional test only for GAL<sup>®</sup>s not yet adopted as a company standard test.

#### Switching Test Conditions

| Input Pulse Levels                | GND to 3.0V |  |  |

|-----------------------------------|-------------|--|--|

| Input Rise and Fall Times         | 3ns 10%-90% |  |  |

| Input Timing Reference<br>Levels  | 1.5V        |  |  |

| Output Timing Reference<br>Levels | 1.5V        |  |  |

| Output Load                       | See figure  |  |  |

3-state levels are measured 0.5V from steady-state active level.

#### **Test Conditions**

| # | <b>R</b> [Ω]                      | C <sub>L</sub> [pF] |

|---|-----------------------------------|---------------------|

| 1 | 200                               | 50                  |

| 2 | Active High: ∞<br>Active Low: 200 | 50                  |

| 3 | Active High: ∞<br>Active Low: 200 | 5                   |

Switching Test Circuit

#### Capacitance (TA=25°C, f=1.0MHz, Vcc=5V)

| Symbol | Parameter                     | Test Conditions    | Maximum <sup>*</sup> | Units |

|--------|-------------------------------|--------------------|----------------------|-------|

| Cı     | Input Capacitance             | VI=2V              | 8                    | pF    |

| CB     | Bidirectional Pin Capacitance | V <sub>B=2</sub> V | 10                   | pF    |

\* Guarantied but not 100% tested

#### **DC Operating Conditions**

| Symbol | Parameter                 | Commercial<br>Temperature Range |                   | Indus<br>Temperati    | Units              |    |

|--------|---------------------------|---------------------------------|-------------------|-----------------------|--------------------|----|

|        |                           | Min.                            | Max.              | Min.                  | Max.               |    |

| Vcc    | Supply Voltage            | 4.75                            | 5.25              | 4.5                   | 5.5                | V  |

| TA     | Ambient Temperature       | 0                               | 70                | -40                   | 85                 | °C |

| VIL    | Input Low Voltage         | Vss <sup>÷</sup> -0.5           | 0.8               | Vss <sup>∻</sup> -0.5 | 0.8                | V  |

| VIH    | Input High Voltage        | 2.0                             | V <sub>CC+1</sub> | 2.0                   | V <sub>CC</sub> +1 | V  |

| IOL    | Low Level Output Current  | -                               | 24                | _                     | 24                 | mA |

| ЮН     | High Level Output Current | -3.2                            | _                 | -3.2                  | _                  | mA |

+ Vss is the voltage applied to the GND pin

#### Electrical Characteristics Over Operating Conditions (Commercial Temperature Range)

| Symbol                            | Parameter                         | Test Conditions                                                        |                                        | Min. | Max. | Units |

|-----------------------------------|-----------------------------------|------------------------------------------------------------------------|----------------------------------------|------|------|-------|

| lı∺, lı∟                          | Input Leakage Current             | GND≤VI≤V CC <sub>Max</sub>                                             |                                        | -    | ±10  | μA    |

| I <sub>BH</sub> , I <sub>BL</sub> | Bidirectional Pin Leakage Current | GND≤Vi≤                                                                | GND≤VI≤V CC <sub>Max</sub>             |      | ±10  | μA    |

|                                   | Operating Power Supply Current    |                                                                        | Half Power                             | -    | 115  |       |

| lcc                               |                                   | f=15MHz (Q, E)<br>f=25MHz (H)<br>VCC = V CC <sub>Max</sub><br>VIL=0.5V | Quarter Power<br>(only 15<br>and 20ns) | -    | 55   | mA    |

|                                   |                                   | V <sub>IH</sub> =3.0V                                                  | Eighth Power<br>(only 15ns)            | _    | 30   |       |

| los <sup>®</sup>                  | Output Short Circuit Current      | V <sub>CC</sub> =5.0V, V <sub>B</sub> =0.5V                            |                                        | -150 | -30  | mA    |

| Vol                               | Output Low Voltage                | -                                                                      |                                        | -    | 0.5  | V     |

| VOH                               | Output High Voltage               | _                                                                      |                                        | 2.4  | -    | v     |

#### Electrical Characteristics Over Operating Conditions (Industrial Temperature Range)

| Symbol           | Parameter                         | Test Co                                                                                         | Min.                                   | Max. | Units |    |

|------------------|-----------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------|------|-------|----|

| IIH, IIL         | Input Leakage Current             | GND≤VI≤V CC <sub>Max</sub>                                                                      |                                        | -    | ±10   | μA |

| IBH, IBL         | Bidirectional Pin Leakage Current | GND≤VI≤V <sub>CC Max</sub>                                                                      |                                        | _    | ±10   | μA |

|                  | Operating Power Supply Current    |                                                                                                 | Half Power                             | -    | 130   |    |

| lcc              |                                   | f=15MHz (Q, E)<br>f=25MHz (H)<br>V <sub>CC</sub> = V <sub>CC Max</sub><br>V <sub>II</sub> =0.5V | Quarter Power<br>(only 15<br>and 20ns) | -    | 65    | mA |

|                  |                                   | VIH=3.0V                                                                                        | Eighth Power<br>(only 15ns)            | -    | 40    |    |

| los <sup>‡</sup> | Output Short Circuit Current      | V <sub>CC</sub> =5.0V, V <sub>B</sub> =0.5V                                                     |                                        | -150 | -30   | mA |

| VOL              | Output Low Voltage                | -                                                                                               |                                        | -    | 0.5   | V  |

| Vон              | Output High Voltage               | -                                                                                               |                                        | 2.4  | -     | V  |

<sup>•</sup> One output at a time for a maximum duration of one second

| Symbol           | Parameter                                | From  | То                   | 16V8AS<br>10 | 16V8AS<br>12 | 16V8AS<br>15 | 16V8AS<br>20 | Units | Test<br>Cond.* |

|------------------|------------------------------------------|-------|----------------------|--------------|--------------|--------------|--------------|-------|----------------|

|                  |                                          |       |                      | Max.*        | Max.*        | Max.         | Max.         |       |                |

| tpd              | Combinational<br>Propagation Delay       | Input | Output               | 10           | 12           | 15           | 20           | ns    | 1              |

| tco              | Clock to Output Delay                    | Clock | Registered<br>Output | 7            | 10           | 10           | 15           | ns    | 1              |

| ten              | Product Term Output<br>Enable to Output  | Input | Output               | 10           | 12           | 15           | 20           | ns    | 2              |

| tenr             | Output Register<br>Enable to Output      | ŌĒ    | Registered<br>Output | 10           | 12           | 15           | 18           | ns    | 2              |

| t <sub>dis</sub> | Product Term Output<br>Disable to Output | Input | Output               | 10           | 12           | 15           | 20           | ns    | 3              |

| tdisr            | Output Register<br>Disable to Output     | ŌĒ    | Registered<br>Output | 10           | 12           | 15           | 18           | ns    | 3              |

#### AC Operating Conditions

| Symbol            | Parameter                                           | 16V8AS<br>10 <sup>**</sup> |      | 16V8AS<br>12 <sup>-4</sup> |      | 16V8AS<br>15 |      | 16V8AS<br>20 |      | Units | Test<br>Cond.* |

|-------------------|-----------------------------------------------------|----------------------------|------|----------------------------|------|--------------|------|--------------|------|-------|----------------|

|                   |                                                     | Min.                       | Max. | Min.                       | Max. | Min.         | Max. | Min.         | Max. |       | Cond.          |

| t <sub>su</sub>   | Input or Feedback Setup<br>Time (Before Clock Rise) | -                          | 10   | -                          | 12   | -            | 12   | -            | 15   | ns    | -              |

| th                | Input or Feedback Hold<br>Time (After Clock Rise)   | -                          | 0    | -                          | 0    | _            | 0    |              | 0    | ns    | -              |

| twh               | Minimum Clock Width High                            | -                          | 8    | -                          | 8    | -            | 10   | -            | 12   | ns    | -              |

| twl               | Minimum Clock Width Low                             | -                          | 8    | -                          | 8    | -            | 10   | -            | 12   | ns    | -              |

| fclk <sup>♦</sup> | Clock Frequency<br>Without Feedback                 | 62.5                       | -    | 62.5                       | -    | 50           | -    | 41.7         | -    | MHz   | 1              |

| fclkf             | Clock Frequency<br>With Feedback                    | 58.8                       | -    | 48.5                       | _    | 41.6         | -    | 33.3         | -    | MHz   | 1              |

$^{\scriptscriptstyle \lambda}$  Commercial Temperature range only.

<sup>1</sup> Refer to "Switching Test Conditions"

$$\label{eq:fclk} \ensuremath{^{\diamond}} f_{clk} \, = \, \frac{1}{t_{wh} + t_{wl}} \quad \ensuremath{^{\diamond}} f_{clkl} \, = \, \frac{1}{t_{su} + t_{co}}$$

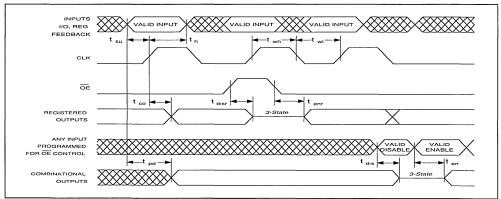

#### Switching Waveforms

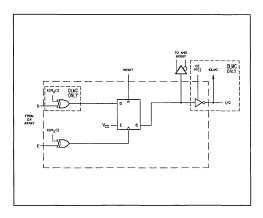

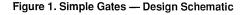

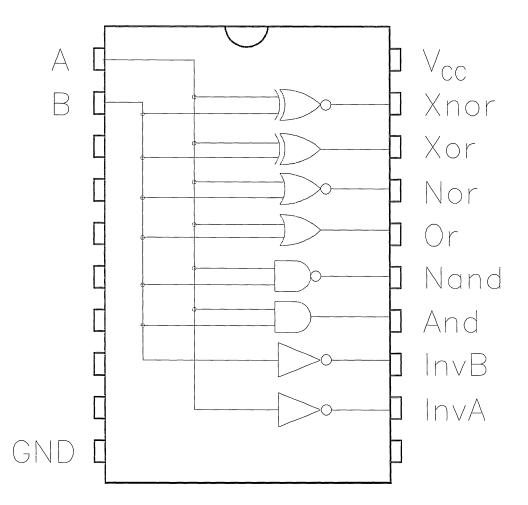

#### FUNCTIONAL DESCRIPTION

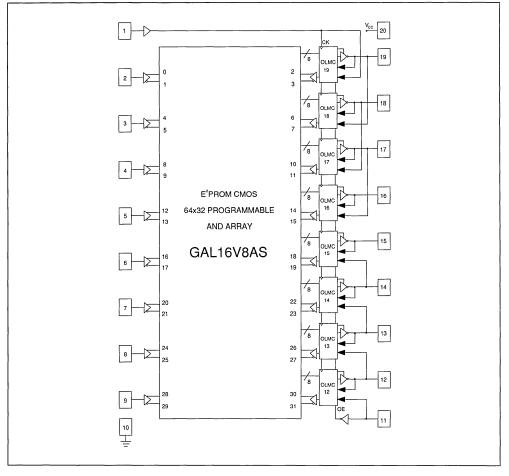

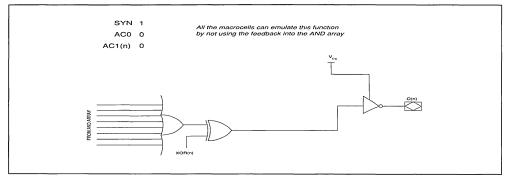

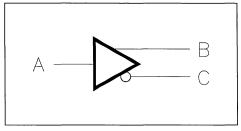

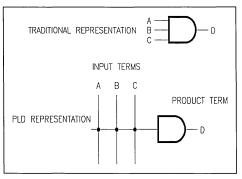

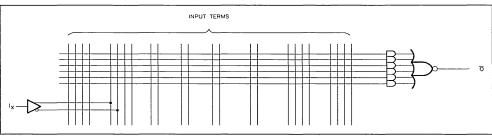

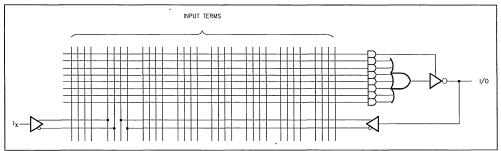

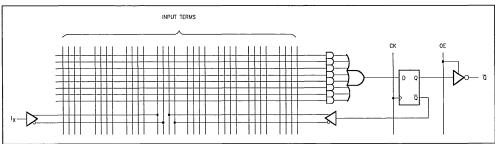

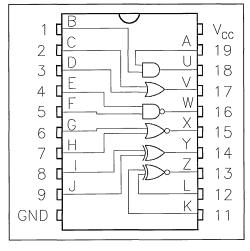

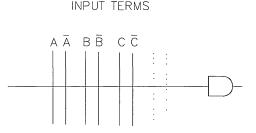

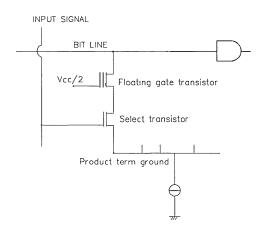

GAL16V8AS has a programmable AND array whose output terms feed a fixed (non programmable) OR array, as bipolar PAL<sup>®</sup>. The  $2 \times 8$  input lines enter the AND array as true or complemented form. 64 product terms are available allowing standard Sum of Products Logic implementation. Each product term is obtained by appropriate connections between the input lines and the product term line. The connections can be made by programming the E<sup>2</sup>PROM memory cell at each intersection of the AND matrix (2048 memory cells). The 64 product terms are divided into eight groups of 8 terms each. One product term for each group can be used to provide Output Enable control for combinational output, the others are connected with an OR gate into the corresponding OLMC (Output Logic Macrocell). The output buffer is in 3-state when the corresponding output enable signal is low.

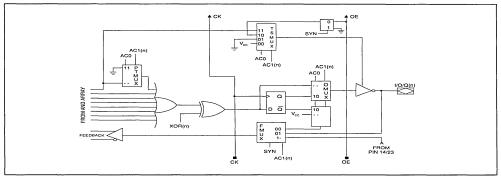

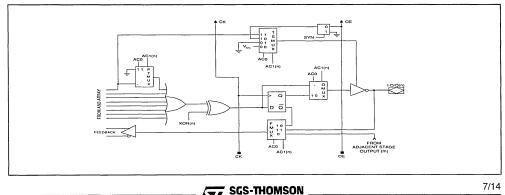

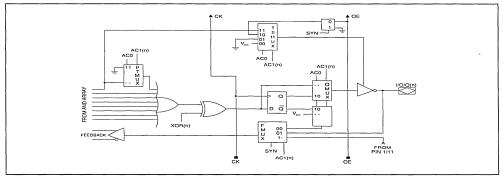

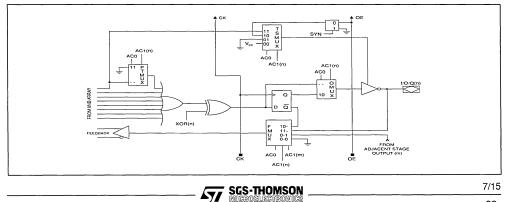

#### OUTPUT LOGIC MACROCELL (OLMC)

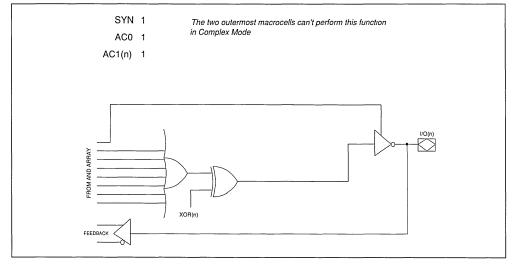

The following discussion pertains to configuring the output logic macrocells. It should be noted that

#### GAL16V8AS Output Logic Macrocell Pin 12 and 19

actual implementation is accomplished by development software/hardware and is completely transparent to the user.

The outputs of the AND array are fed into an OLMC, where each output can be individually set to active high or active low, with either combinational (asynchronous) or registered (synchronous) configurations. A common output enable is connected to all registered outputs; product terms can be used to provide individual output enable control for combinational outputs. All outputs have always programmable polarity.

The output logic macrocell provides the designer with maximum output flexibility in matching signal requirements, thus providing more functions than existing 20 pin  $\mathsf{PAL}^{\textcircled{B}}$  devices.

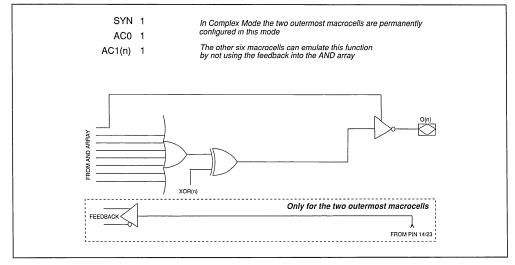

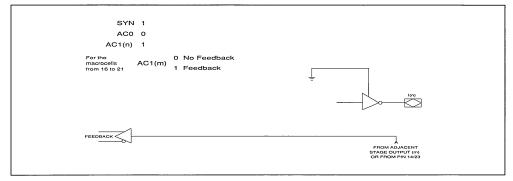

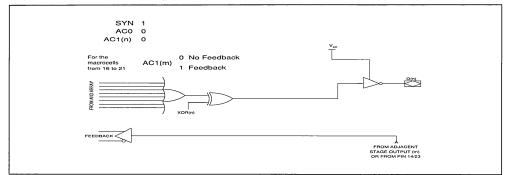

Three different configuration modes of the OLMCs are possible: registered, complex and simple. The output of an OLMC in registered mode can be either registered or combinational. Different modes cannot be mixed: i.e. all OLMCs of a device have to be configured in simple, complex or registered mode.

#### GAL16V8AS Output Logic Macrocell Pin 13 to 18

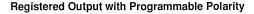

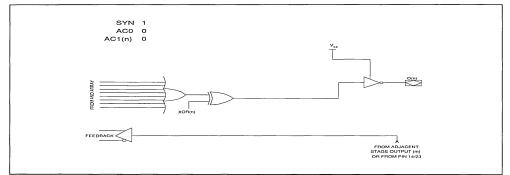

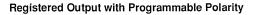

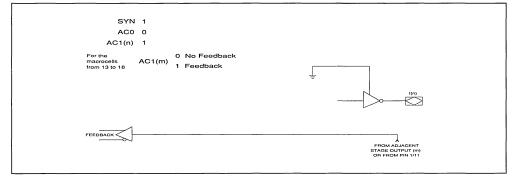

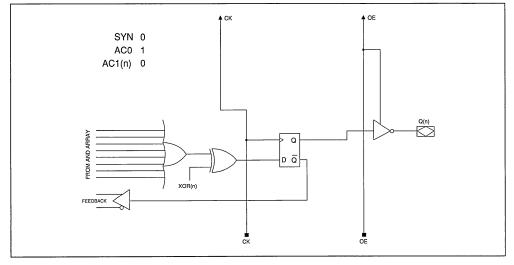

## REGISTERED MODE

In registered mode macrocells are configured as registered outputs or combinational inputs/outputs. Any macrocell can be configured as registered output or combinational input/output. Up to 8 registered outputs or up to 8 inputs/outputs are possible in this mode.

All registered macrocells share common clock and output enable control. Registered outputs have 8 data product terms per output, while combinational inputs/outputs have only 7 data product terms per output: in the latter case the eighth product term serves as individual output enable control for each macrocell.

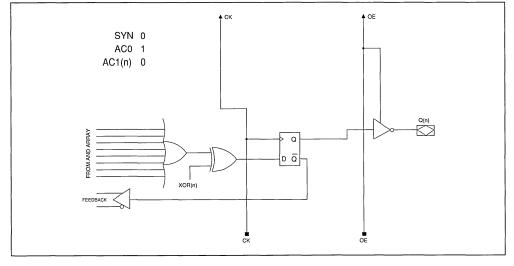

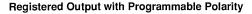

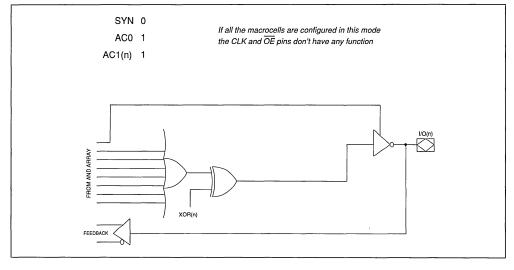

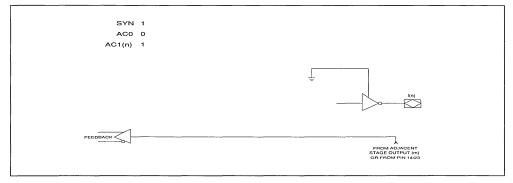

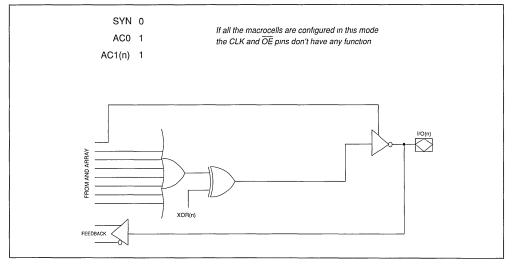

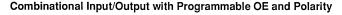

## Combinational Input/Output with Programmable OE and Polarity

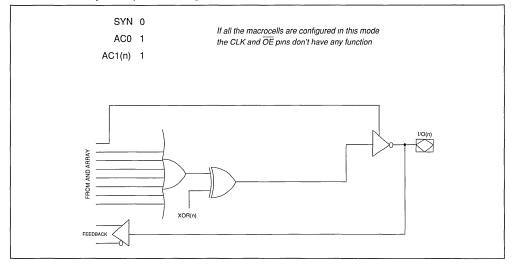

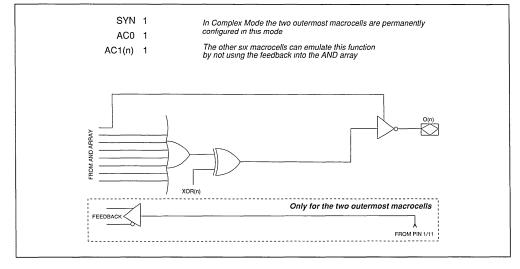

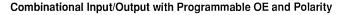

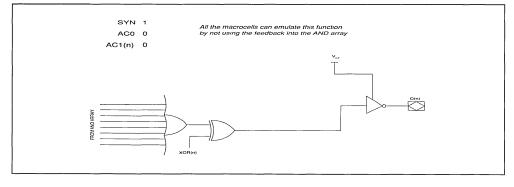

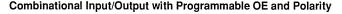

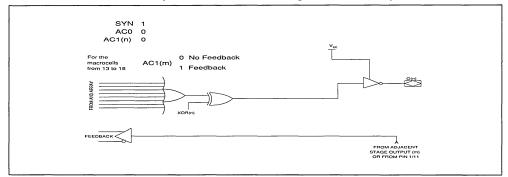

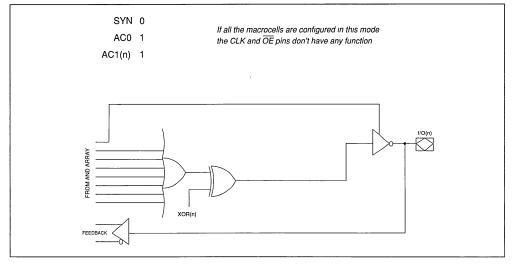

#### COMPLEX MODE

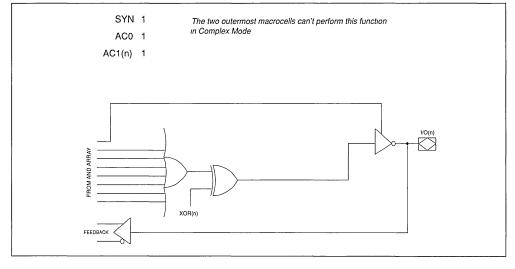

In complex mode macrocells are configured as combinational inputs/outputs or outputs only. The two outermost macrocells (12 and 19) do not have input capability: so only 6 inputs/outputs are possible in this mode. Applications requiring 8 inputs/outputs must be implemented in registered mode. All macrocells have 7 data product terms per output; the eighth product term is used as individual output enable control for each macrocell. The clock and output enable pins (pins 1 and 11 respectively) are always available as inputs.

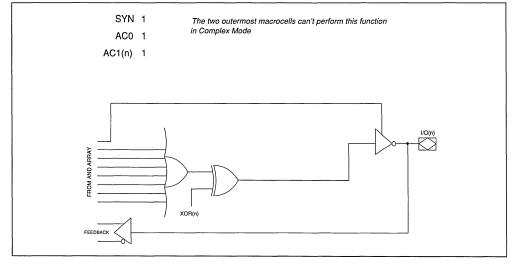

#### Combinational Output with Programmable OE and Polarity

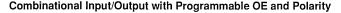

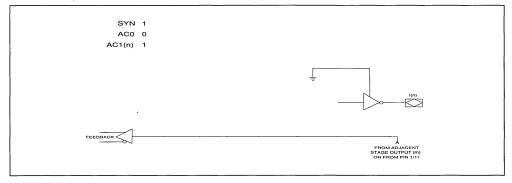

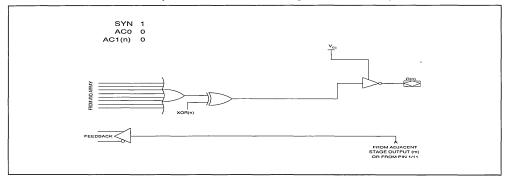

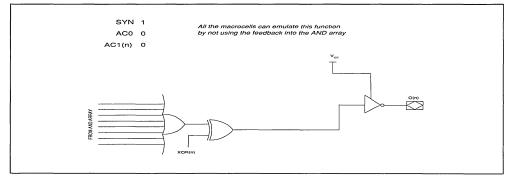

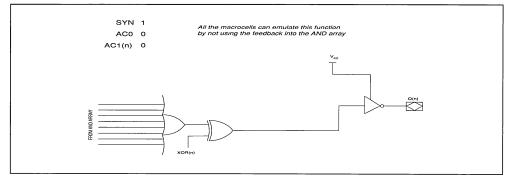

## SIMPLE MODE

In simple mode macrocells are configured as dedicated inputs or as dedicated, always active, combinational outputs. All macrocells have 8 data product terms per output. The clock and output enable pins (pins 1 and 11 respectively) are always available as inputs.

#### **Dedicated Input Mode**

#### Dedicated Combinational Output with Feedback and Programmable Polarity

#### Dedicated Combinational Output with Programmable Polarity

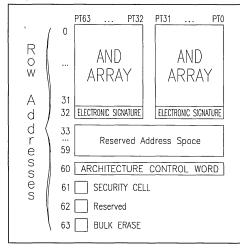

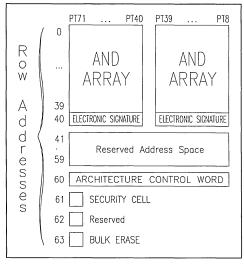

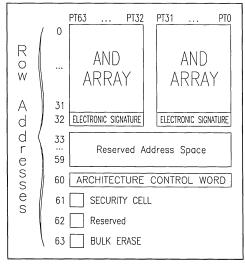

## ROW ADDRESS MAP DESCRIPTION

There are a total of 36 unique row addresses available to the user when programming the GAL16V8AS device. Row addresses 0-31 each contain 64 bits of input term data. This is the AND array where the custom logic pattern is programmed. Row 32 is the Electronic Signature Word. It has 64 bits available for any user defined purpose. Row 33-59 are reserved by the manufacturer and are not available to users.

Row 60 contains the architecture and output polarity information. The 82 bits within this word are programmed to configure the device for a specific application. Row 61 contains a one bit security cell that when programmed prevents further pattern verification of the array. Row 63 is the row that is addressed to perform a bulk erase of the device, resetting it back to a virgin state. Each of these functions is described in the following sections.

#### GAL16V8AS Row Addresses Map Block Diagram

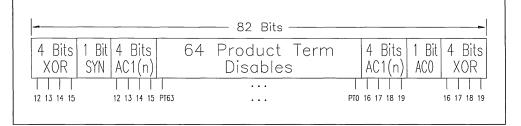

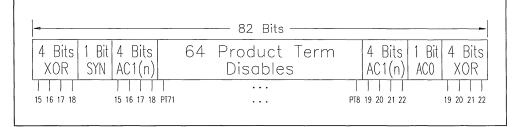

# GAL16V8AS Architecture Control Word Diagram

## ELECTRONIC SIGNATURE WORD DESCRIPTION

An electronic signature word is provided with every GAL16V8AS device. It resides at row address 32 and contains 64 bits of reprogrammable memory that can contain user-defined data. Some uses include user ID codes, revision numbers, or inventory control. This signature data is always available to the user independent of the state of the security cell.

# ARCHITECTURE CONTROL WORD

All the various output configurations of the GAL16V8AS devices are controlled by programming cells within the 82 bit Architecture Control Word that resides at row 60. The location of specific bits within the Architecture Control Word is shown in the control word diagram in figure below. The function of the SYN, ACO and AC1(n) bits have been explained in the OUTPUT LOGIC MACROCELL description. The eight polarity bits determine each output's polarity individually. The numbers below the XOR(n) and AC1(n) bits in the architecture control word diagram shows the output device pin number that the polarity bits control.

## SECURITY CELL

Row address 61 contains the Security Cell (one bit). The Security Cell is provided on all GAL16V8AS devices as a deterrent to unauthorized copying of the array configuration patterns. Once programmed, the circuitry enabling array access is disabled, preventing further verification of the array (rows 0-31). The cell can be erased only in conjunction with the array during a bulk erase cycle, so the original configuration can never be examined once this cell is programmed. Signature data is always available to the user.

#### **BULK ERASE MODE**

By addressing row 63 during a programming cycle, a clear function performs a bulk erase of the array and the Architecture Control Word. In addition, the Electronic Signature Word and the Security Cell are erased. This mode resets a previously configured device back to its virgin state.

## **OUTPUT REGISTER PRELOAD**

When testing state machine designs, all possible

states and state transitions must be verified in the design, not just those required in the normal machine operations. This is because in system operation, certain events occur that may throw the logic into an illegal state (power-up, line voltage glitches, brown-outs, etc.). To test a design for proper management of these conditions, a method must be provided to break the feedback paths, and force any desired (e.g. illegal) state into a register. Then the machine can be sequenced and the outputs tested for the correct next state condition. The GAL16V8AS device includes circuitry that allows each registered output to be synchronously set either high or low. Thus, any present state condition can be forced for test sequencing. If necessary, approved GAL programmers capable of executing test vectors can perform output register preload automatically.

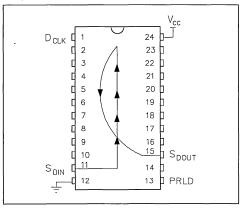

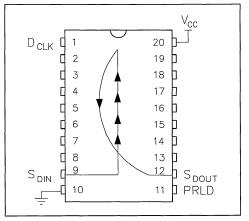

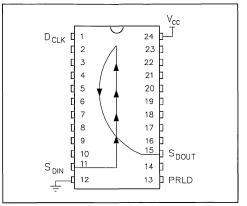

The figure on the right shows the pin functions necessary to preload the register. This test mode is entered by raising PRLD to VIES (register preload input voltage, typically 15V), which enables the serial data in (SDIN) buffer and the serial data out (SDOUT) buffer. Data is then serially shifted into the registers on each rising edge of the clock, DCLK. Only the macrocells with registered output configurations are loaded. If only 3 outputs have registers, then only 3 bits need be shifted in. The registers are loaded from the bottom up as shown in the figure on the right.

## LATCH-UP PROTECTION

GAL® devices are designed with an on board charge pump to negatively bias the substrate. The negative bias is of sufficient magnitude to prevent input undershoots from causing the circuitry to latch. Additionally, outputs are designed with nchannel pullups instead of the traditional p-channel pullups to eliminate any possibility of SCR induced latching.

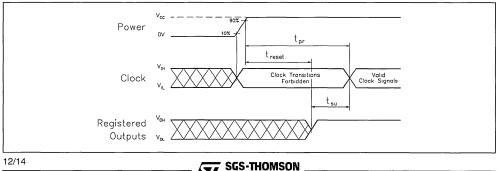

#### POWER-UP RESET

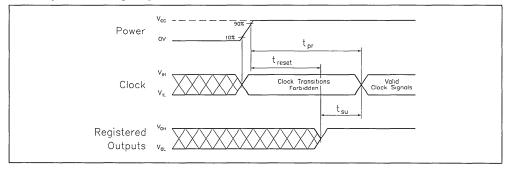

Circuitry within the GAL16V8AS provides a reset signal to all registers during power-up. All internal registers will have their Q outputs set low after a

#### **Output Register Preload Pinout**

specified time (treset=10µs). As a result, the state on the registered output pins (if they are enabled through OE) will always be high on power-up, regardless of the programmed polarity of the output pins. This features can greatly simplify state machine design by providing a known state on powerup.

The timing diagram for power-up is shown below. Because of the asynchronous nature of system power-up, the V<sub>CC</sub> rise must be monotonic to guarantee a valid power-up reset of the GAL16V8AS. The registers will reset within a maximum of treset time: before this time any clock transition from low to high is forbidden to avoid undesired commutations. As in normal system operation, avoid clocking the device until all input and feedback path setup times have been met (i.e. avoid clocking before the tpr=treset+tsu time interval).

#### DEVICES PROGRAMMING

SGS-THOMSON strongly recommends the use of qualified programming hardware. Programming on unapproved equipment will invalidate all guarantees.

47/

## Power-Up Reset Timing Diagram

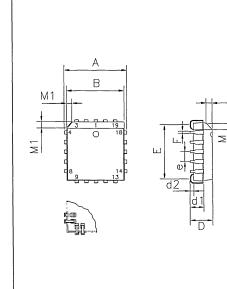

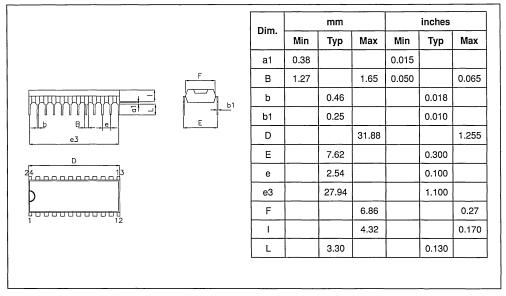

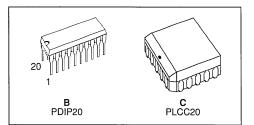

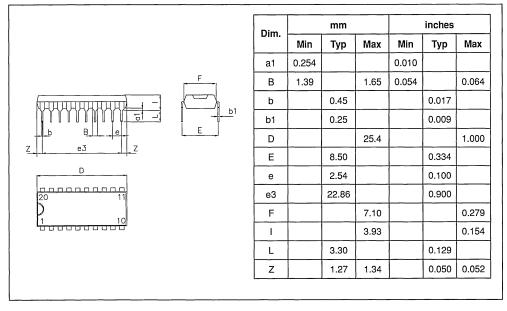

## PACKAGE MECHANICAL DATA

## PDIP 20 Pins

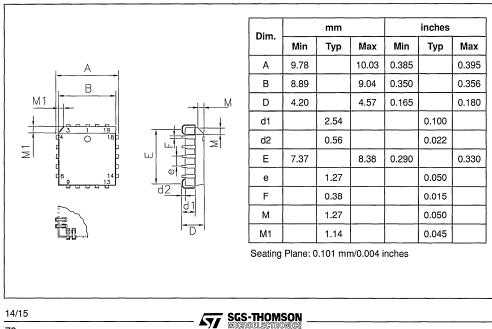

## PLCC 20 Pins

| Dim.  |      | mm   |       | inches |       |       |  |  |

|-------|------|------|-------|--------|-------|-------|--|--|

| Dini. | Min  | Тур  | Max   | Min    | Тур   | Мах   |  |  |

| А     | 9.78 |      | 10.03 | 0.385  |       | 0.395 |  |  |

| В     | 8.89 |      | 9.04  | 0.350  |       | 0.356 |  |  |

| D     | 4.20 |      | 4.57  | 0.165  |       | 0.180 |  |  |

| d1    |      | 2.54 |       |        | 0.100 |       |  |  |

| d2    |      | 0.56 |       |        | 0.022 |       |  |  |

| E     | 7.37 |      | 8.38  | 0.290  |       | 0.330 |  |  |

| е     |      | 1.27 |       |        | 0.050 |       |  |  |

| F     |      | 0.38 |       |        | 0.015 |       |  |  |

| М     |      | 1.27 |       |        | 0.050 |       |  |  |

| M1    |      | 1.14 |       |        | 0.045 |       |  |  |

Seating Plane: 0.101 mm/0.004 inches

Μ

## **Ordering Informations\***

\* Please contact local Product Marketing for latest update on package / temperature range availability.

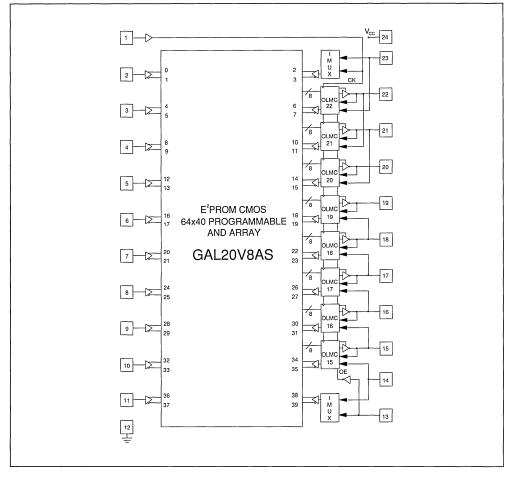

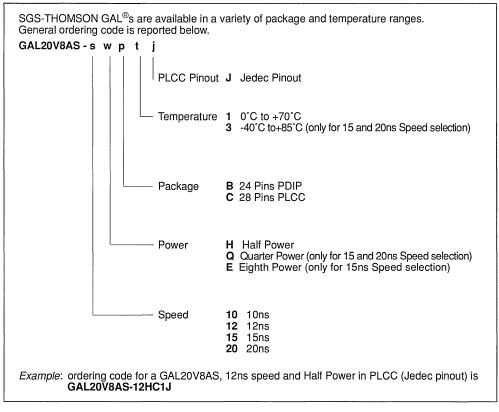

# GAL20V8AS

# E<sup>2</sup>PROM CMOS PROGRAMMABLE LOGIC DEVICE

- HIGH PERFORMANCE SGS-THOMSON SINGLE-POLY E<sup>2</sup>PROM CMOS TECHNOLOGY

- 10ns maximum propagation delay (GAL20V8AS-10xxx)

- $-F_{max} = 62.5MHz$

- 7ns max. from clock input to data output

- TTL compatible 24mA outputs

- SGS-THOMSON proprietary Single-Poly F3-G<sup>™</sup> technology

- GLITCH FREE DEVICE

Enhanced design mini

- Enhanced design minimises ground bounce

- VERY LOW POWER

- 90mA typ. (115mA max.) I<sub>CC</sub> Half power selection, 45mA typ. (55mA max.) I<sub>CC</sub> Quarter power selection, 27mA typ. (30mA max.) I<sub>CC</sub> Eighth power selection

- ELECTRICAL ÉRASABLE CELL TECHNOLOGY

- Reconfigurable logic/reprogrammable cells

100% tested: guaranteed 100% final programming yield

- High speed electrical program & erase

- EIGHT OUTPUT MACROCELLS

- Maximum flexibility for complex logic design

- Programmable output polarity

- Also emulates 21 types of 24 pin PAL<sup>®</sup> devices with full function/fuse map/parametric compatibility

- PRELOAD AND POWER-ON RESET OF ALL REGISTERS

- 100% functional testability

- ELECTRONIC SIGNATURÉ FOR USER'S IDENTIFICATION

# DESCRIPTION

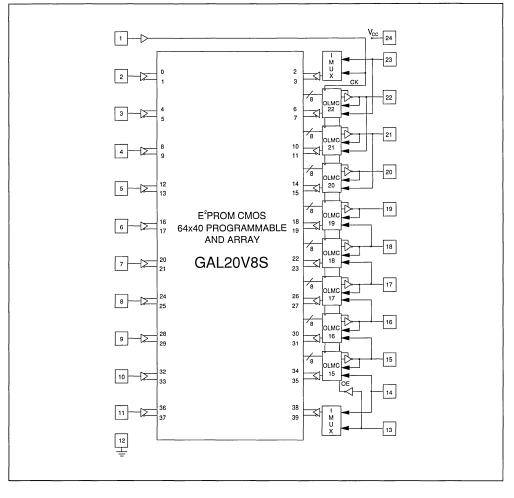

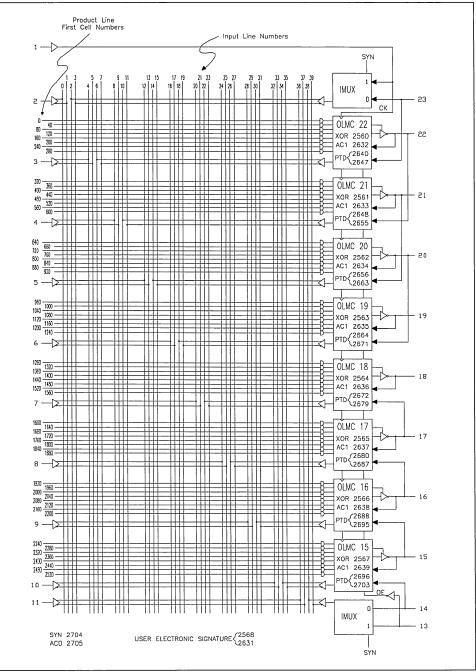

The GAL20V8AS, at 10ns maximum propagation delay time, combines a high performance CMOS process with Electrical Erasable Single-Poly F3-G<sup>™</sup> technology — SGS-THOMSON proprietary — to provide one of the highest speed-power performance products available in PLD market.

CMOS circuit allows GAL20V8AS to consume just 27mA (typ.)  $I_{CC}$  (Eighth power selection, 15ns) which represents a 75% saving in power when compared to its bipolar counterparts. Its  $E^2$ PROM CMOS technology offers high speed (50ms) erase time providing the ability to reprogram or reconfigure the device quickly and efficiently.

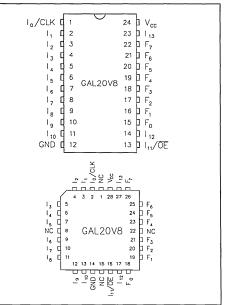

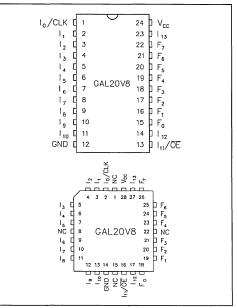

# Pin Connections

#### Pin Names

| l0-l13 | Input         |

|--------|---------------|

| CLK    | Clock Input   |

| F0-F7  | I/O           |

| ŌĒ     | Output Enable |

| Vcc    | Power         |

| GND    | Ground        |

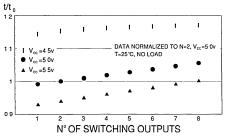

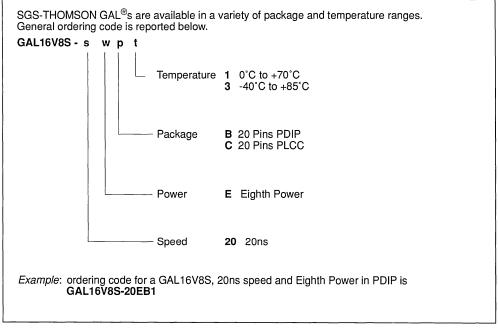

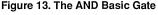

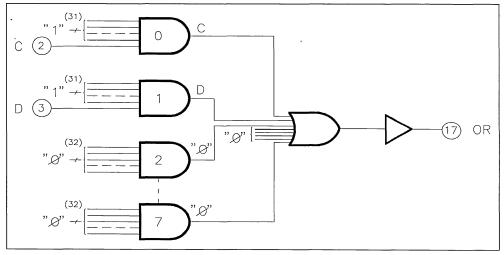

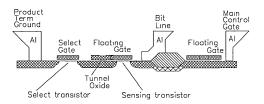

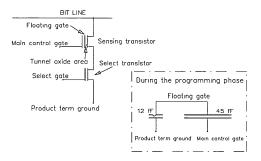

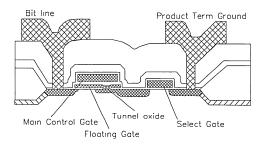

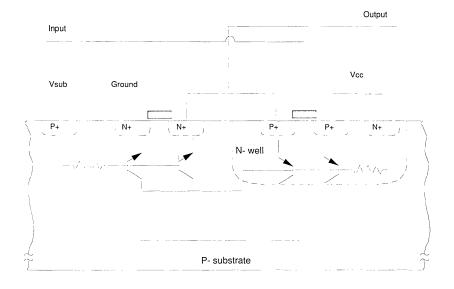

GAL<sup>®</sup> is a registered trademark of Lattice Semiconductor Corp.; PAL<sup>®</sup> is a registered trademark of Monolithic Memories Inc