# ST9 FAMILY 8/16 **BIT MCU**

**DATABOOK**

1<sup>st</sup> EDITION

# ST9 FAMILY 8/16 BIT MCU

**DATABOOK**

1st EDITION

JULY 1991

# USE IN LIFE SUPPORT DEVICES OR SYSTEMS MUST BE EXPRESSLY AUTHORIZED SGS-THOMSON PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF SGS-THOMSON Microelectronics. As used herein: 1. Life support devices or systems are those which (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided

with the product, can be reasonably expected to result in

significant injury to the user.

# **TABLE OF CONTENTS**

| INTRODUCTION      | Page 4 |

|-------------------|--------|

| GENERAL INDEX     | 7      |

| SELECTION GUIDE   | 9      |

| DATASHEETS        | 13     |

| DEVELOPMENT TOOLS | 575    |

#### INTRODUCTION

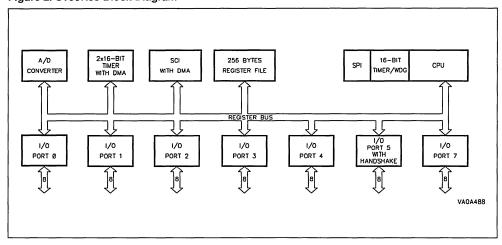

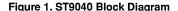

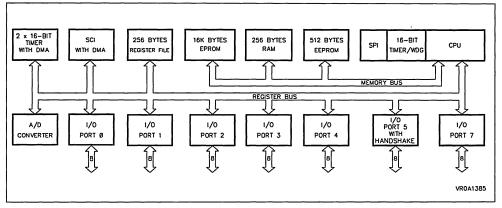

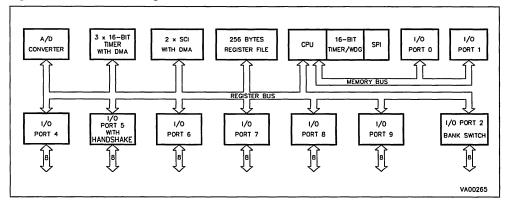

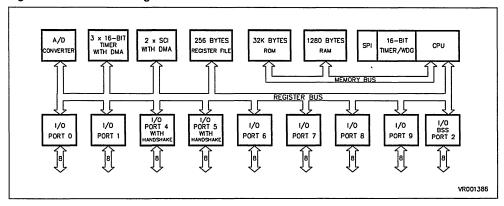

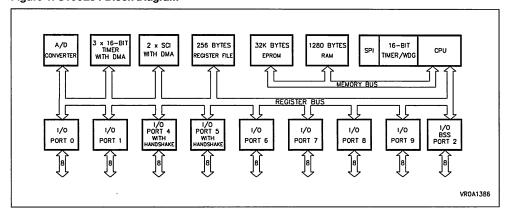

Driven by the new advanced technologies developed internally by SGS-THOMSON Microelectronics, the ST9 family of microcontrollers offers advanced peripheral functions, an 8/16 bit core and ROM/EPROM/EEPROM plus RAM capabilities. This family of products is based on a common core of features, with variations in the peripheral organisation to suit the different requirements of the middle to high end embedded applications.

The ST9 family of microcontrollers offers a powerful CISC based Core, capable of 16 bit operations, built in Timer Watchdog functions for secure operation, Serial Peripheral Interfaces adaptable to low-cost external I<sup>2</sup>C-bus, S-bus and IM-bus devices plus an external memory interface with full, expandable vectored interrupt and DMA facilities. The instruction set encompasses 14 addressing modes linked with 187 instruction types with special instructions added for improved efficiency of the high level language development tools.

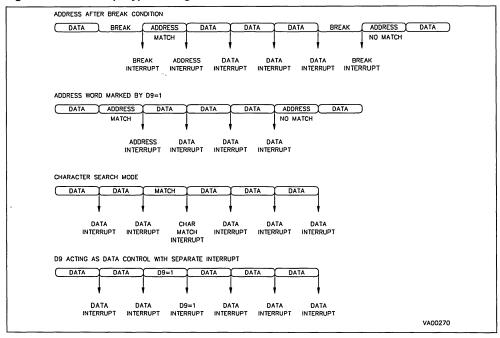

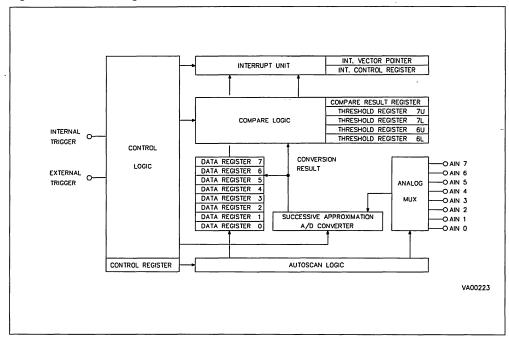

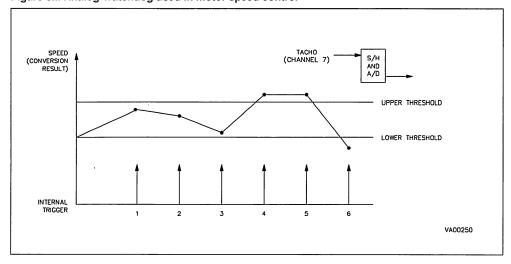

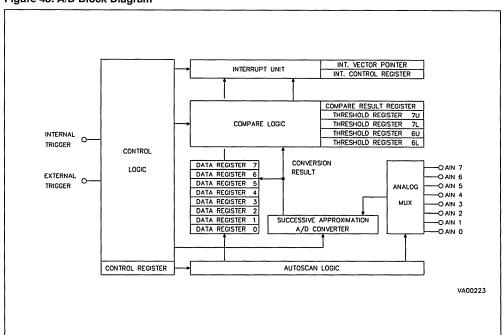

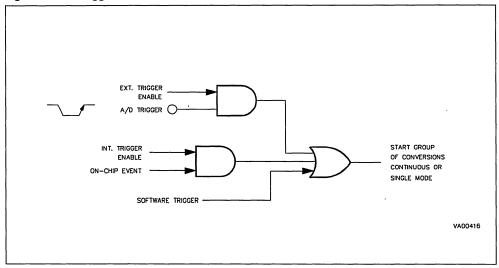

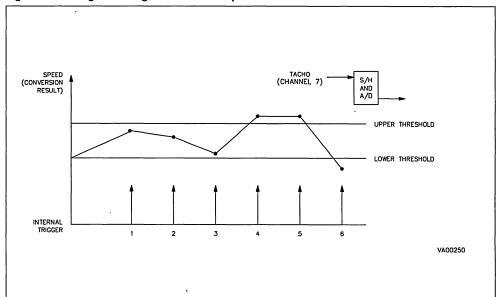

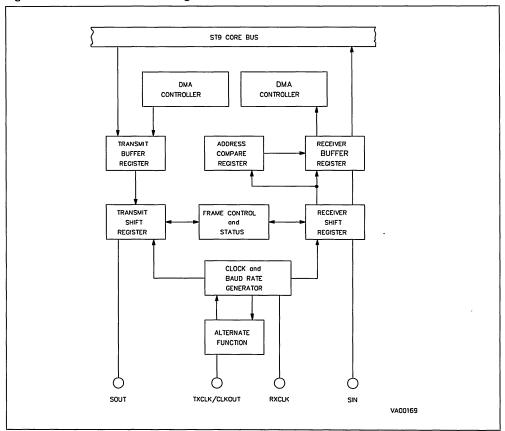

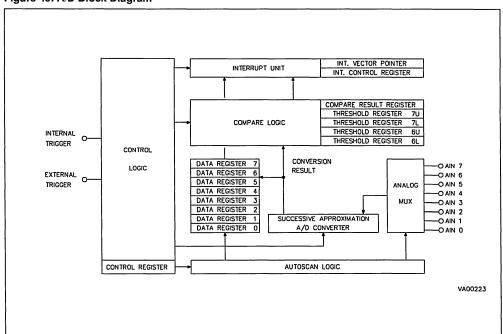

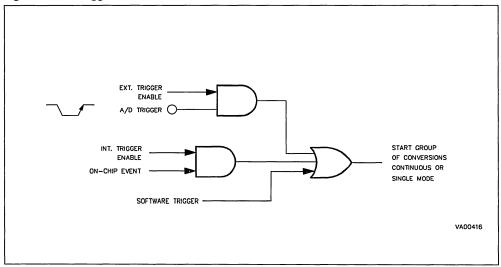

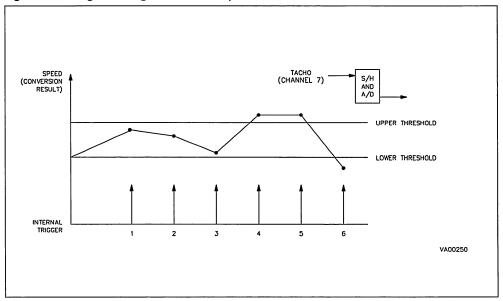

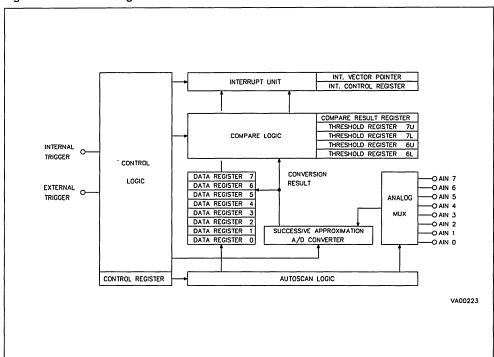

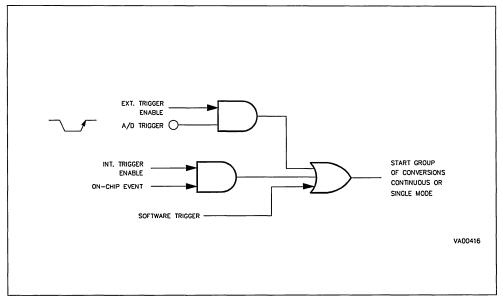

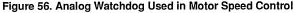

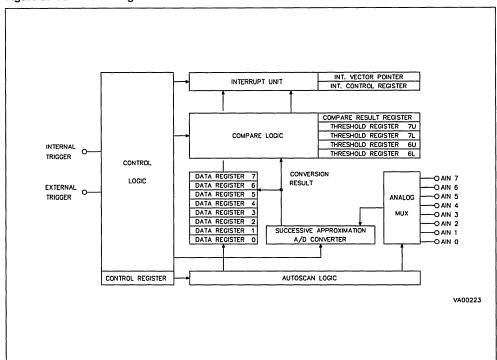

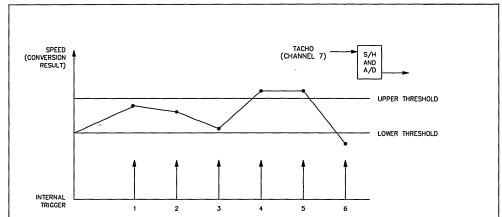

The peripherals linked to this Core include Multifunction Timers, with operating modes to cover almost all timing requirements, including the optior of DMA to the timing constants and the triggering of other on-chip peripherals such as the Analog-to-Digital Converter. This converter, offering 8 bit resolution, includes an automatic threshold sensing watchdog on two of its 8 multiplexed input channels. Serial communication is handled (in addition to the SPI) by the Serial Communication is Interface, a fast asynchronous and byte synchronous interface with capability. This, together with the automatic DMA operation and the Address/9th bit of the character word, simplifies network operation.

Core and megacell Library

#### INTRODUCTION

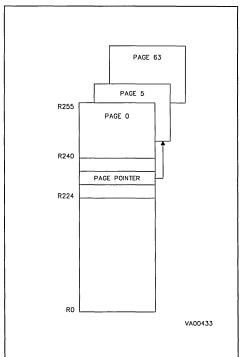

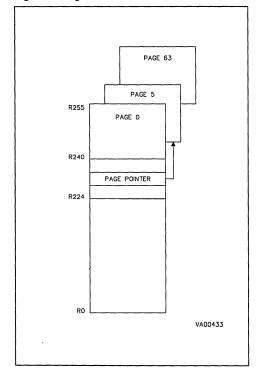

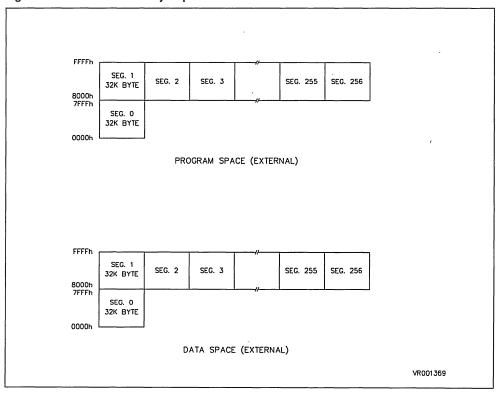

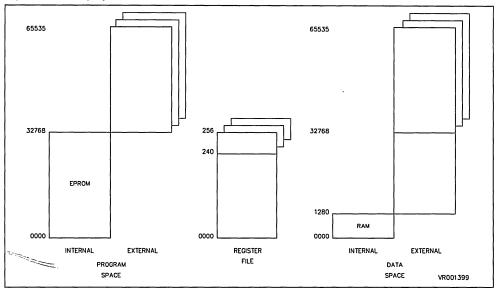

Memory options range from ROMLESS devices for flexibility, EPROM based prototyping vehicles, OTP for pre-production runs and ROM for volume production in the 64K program space, while the separate 64K data space (expandable to 8M bytes for both program and data spaces with the Bankswitch logic) includes RAM and high-reliability EEPROM. The RAM exists in addition to the versatile Register File - 224 General Purpose Registers all with Arithmetic (8 and 16 bit) capability, Stack, and Index pointer mechanisms, and functions as fast access RAM memory. 16 Registers hold the system functions, the two independent stack pointers and I/O port data registers for immediate access, while the top 16 bytes of the Register File is paged, with pages containing the standard peripheral data and control registers.

New peripheral functions are in development to expand the ST9 family, leading to devices suitable for applications ranging from TV and VCR to Automotive Multiplex Wiring Systems and High Security banking applications.

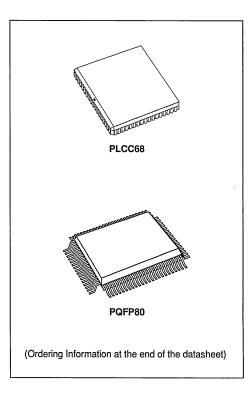

The selection guide which follows in the next section shows the current ST9 family members, with all the packaging options.

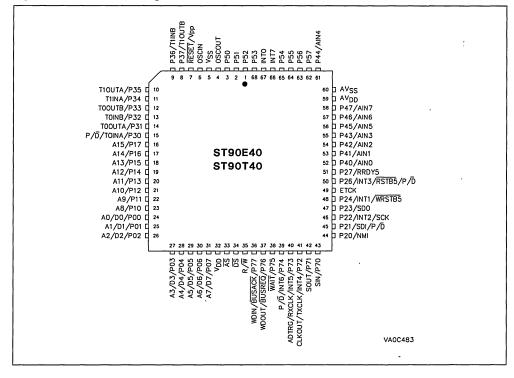

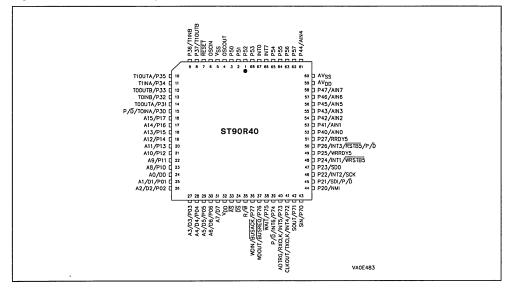

ST90E40

# **DATASHEETS**

| · |  |  | , |  |

|---|--|--|---|--|

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

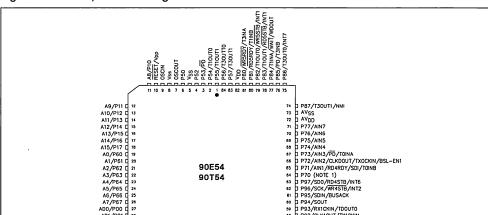

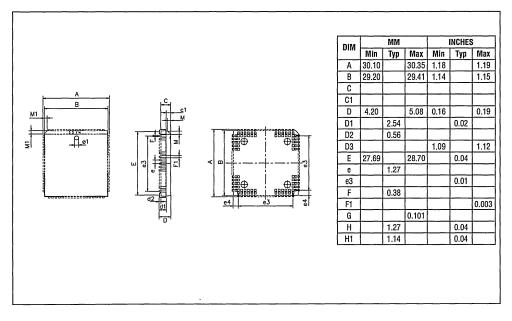

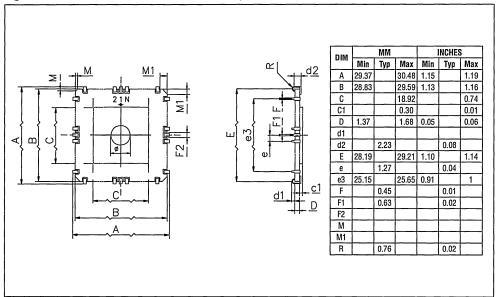

## ST9026,ST9027,ST9028

#### 16K ROM HCMOS MCUs WITH RAM

- Single chip microcontroller with 16K bytes of ROM, 256 bytes of RAM and 256 bytes of register file with 224 general purpose registers available as RAM, accumulators or index pointers.

- 8/16 bit CORE with full feature DMA controller, a powerful interrupt handler and a Standard Serial Peripheral Interface (SPI) handling S-bus, I<sup>2</sup>Cbus, IM-bus and Standard Serial Peripheral Interfaces.

- Up to 8 external interrupts edge-selectable plus 1 non-maskable interrupt.

- 16 bit programmable Timer with 8 bit Prescaler, able to be used as a Watchdog Timer for system integrity.

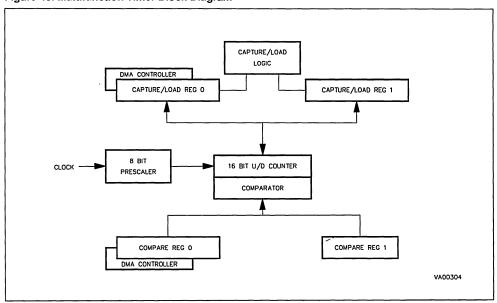

- A 16 bit Multifunction Timer module, with an 8 bit prescaler and 12 operating modes, allowing simple use for complex waveform generation and measurement, PWM functions and many other system timing operations.

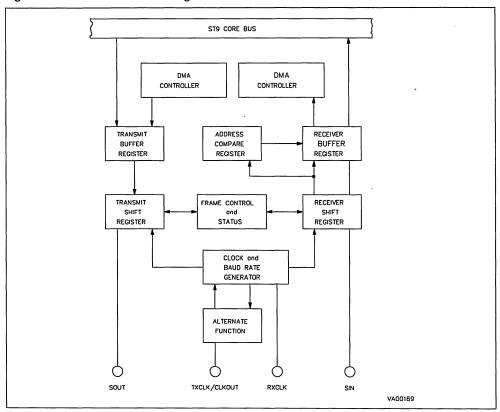

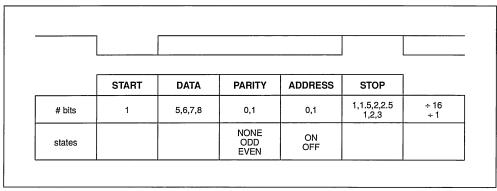

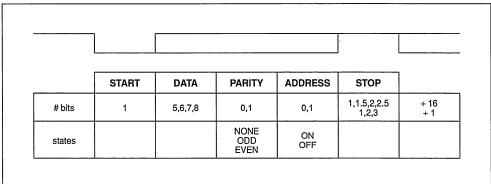

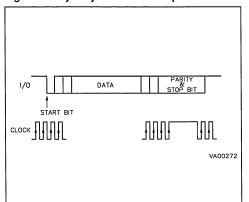

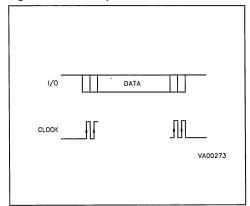

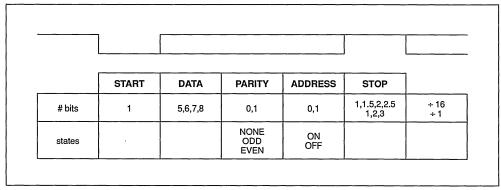

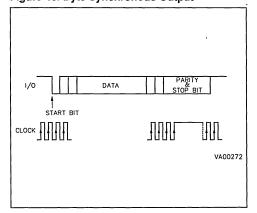

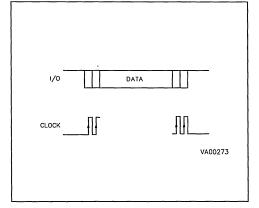

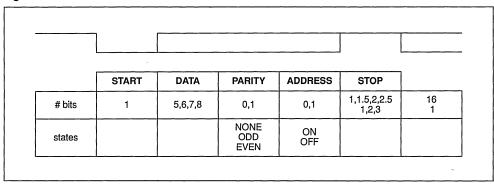

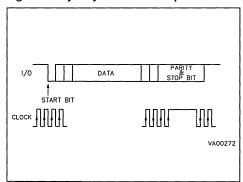

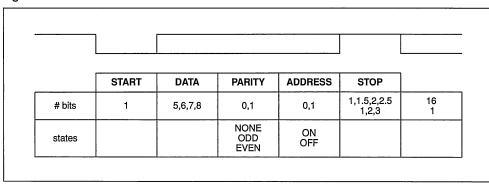

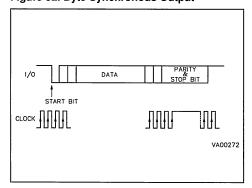

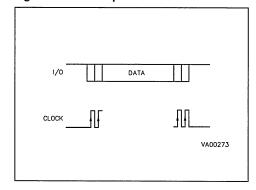

- Full function Serial Communications Interface with 110 to 375000 baud rate generator, asynchronous and byte synchronous capability (fully programmable format) and address/wake-up bit option.

- On-chip DMA channels associated to the Multifunction Timer and the Serial Communications Interface.

- Up to five 8 bit I/O ports with programmable input thresholds and output characteristics. Alternative functions allow the full use of all pins.

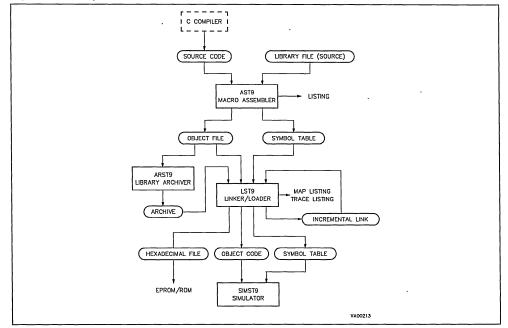

- Powerful software development tools, including assembler, linker, C-compiler, archiver, software and hardware emulators.

- Windowed and One Time Programmable EPROM parts available for prototyping and preproduction development phases.

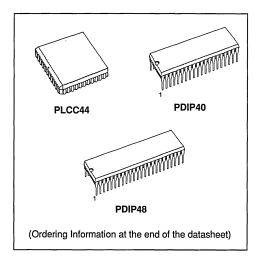

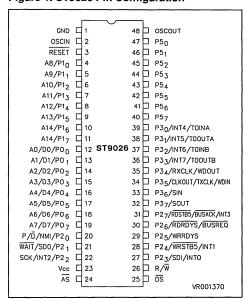

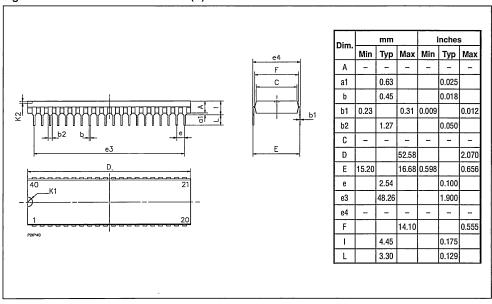

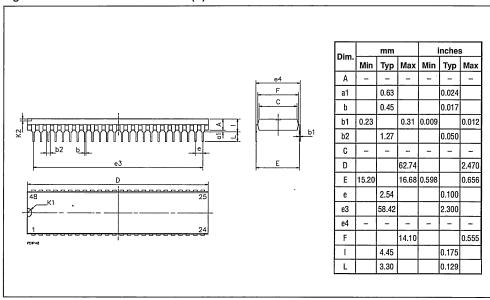

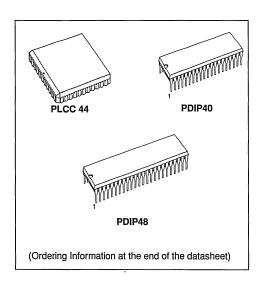

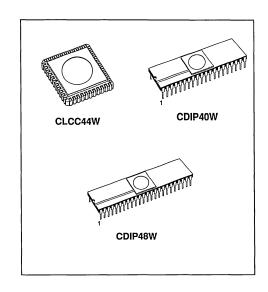

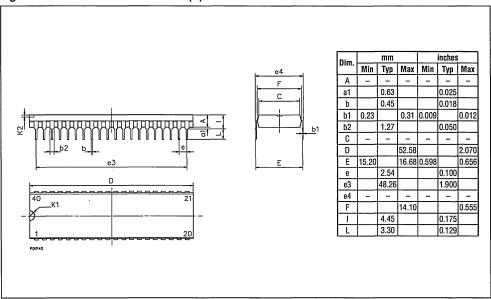

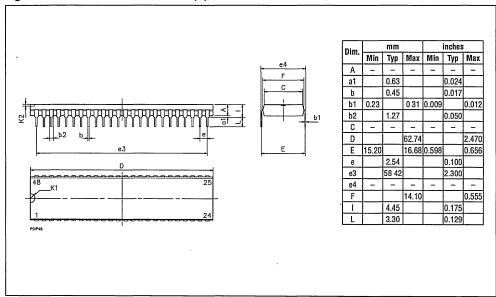

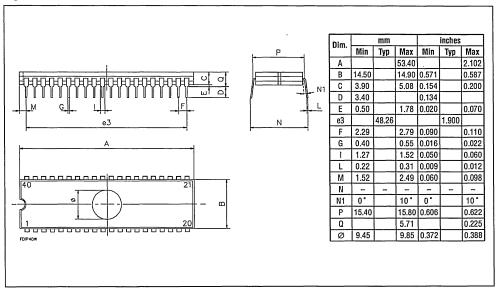

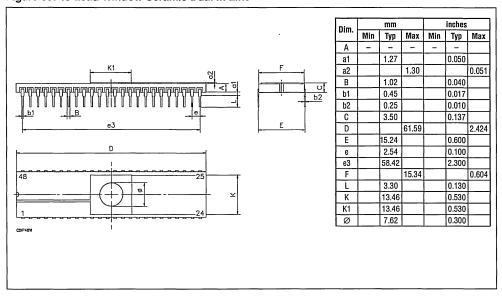

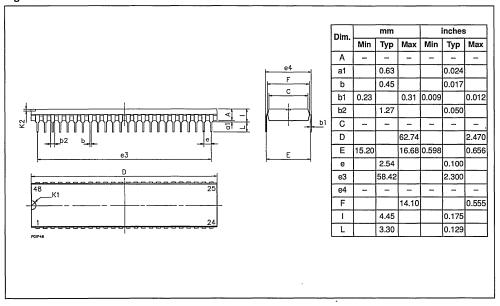

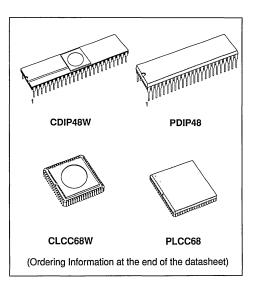

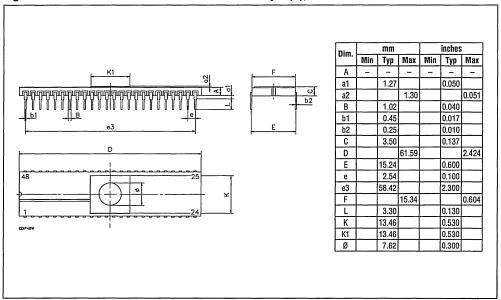

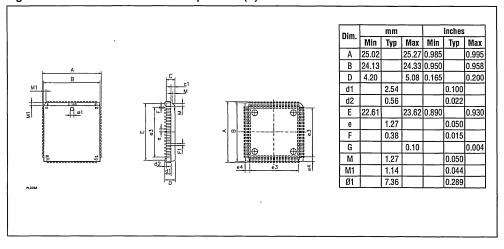

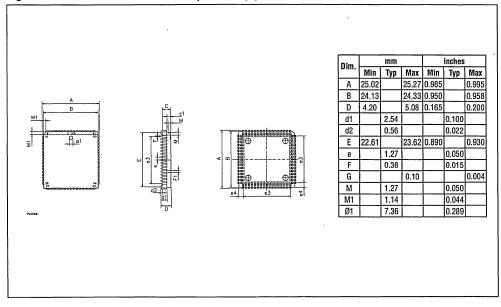

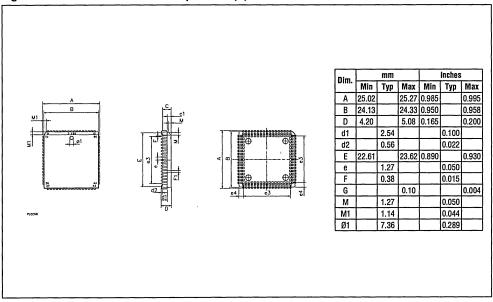

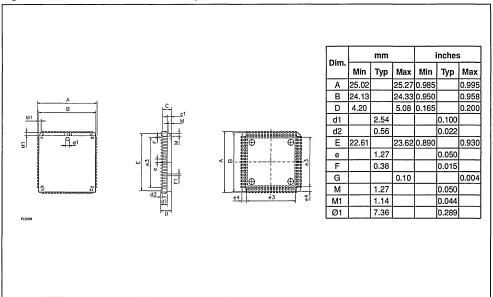

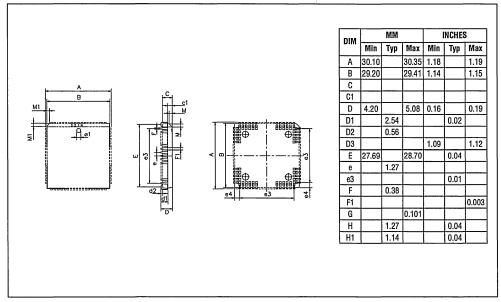

- 48-pin Dual in Line Plastic package for ST9026.

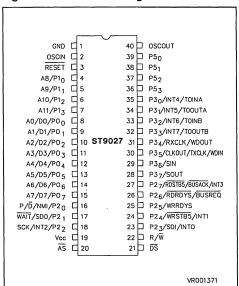

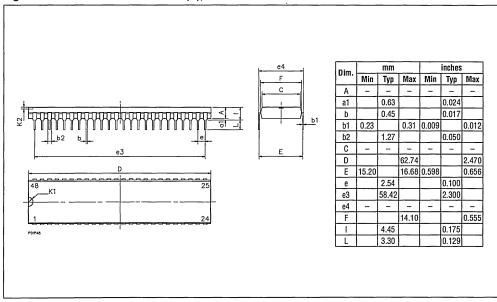

- 40-pin Dual in Line Plastic package for ST9027.

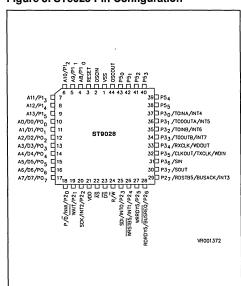

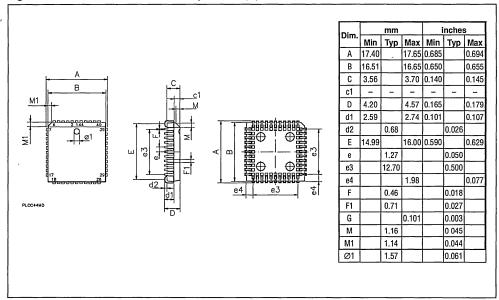

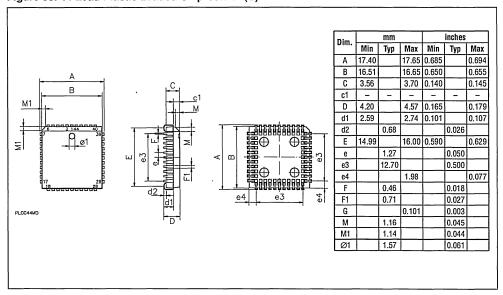

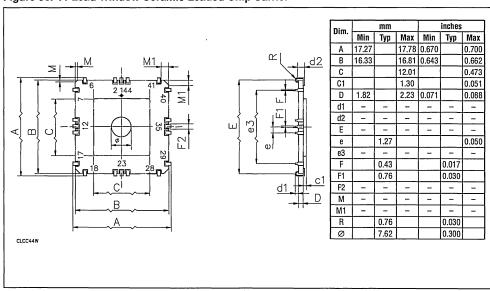

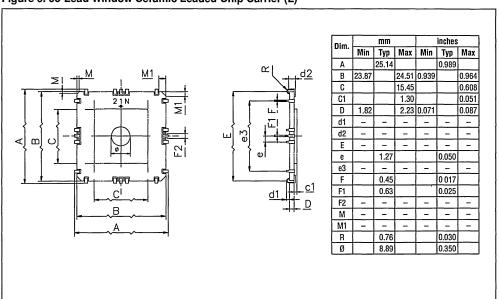

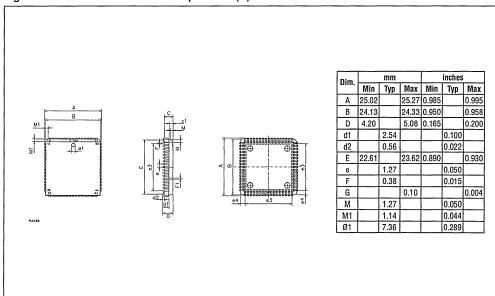

- 44-lead Plastic Leaded Chip Carrier package for ST9028.

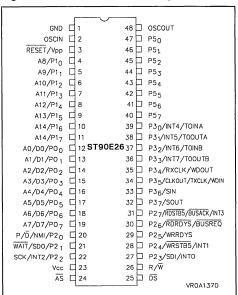

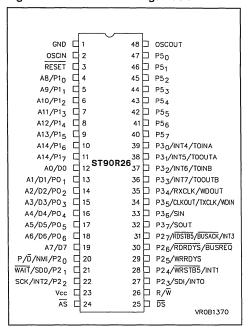

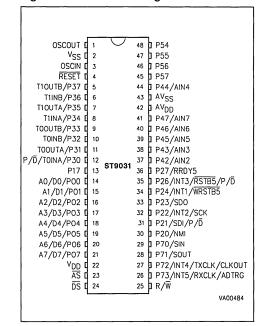

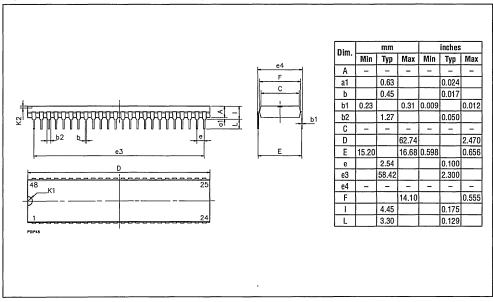

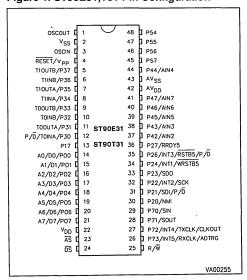

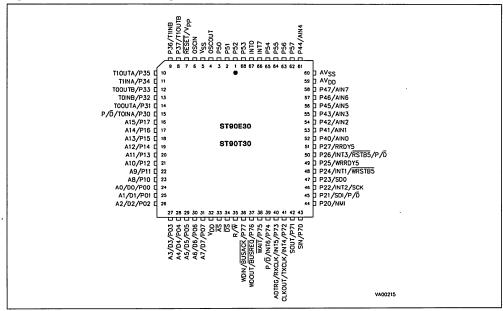

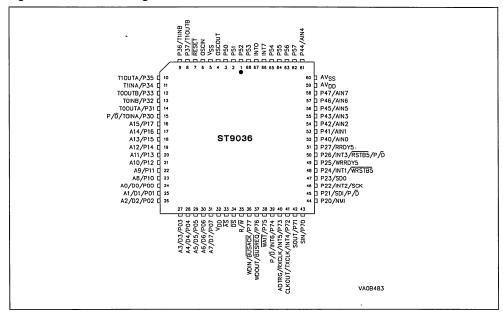

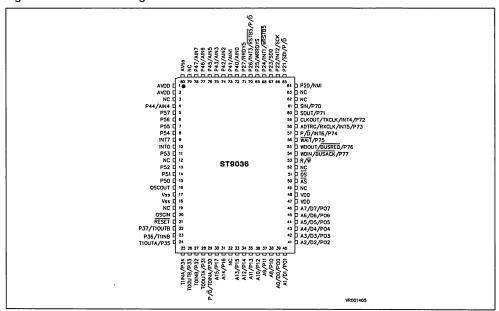

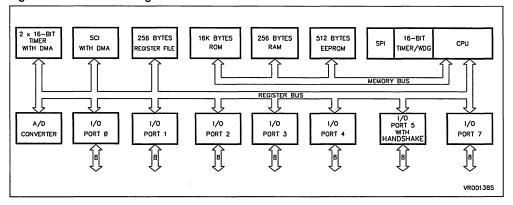

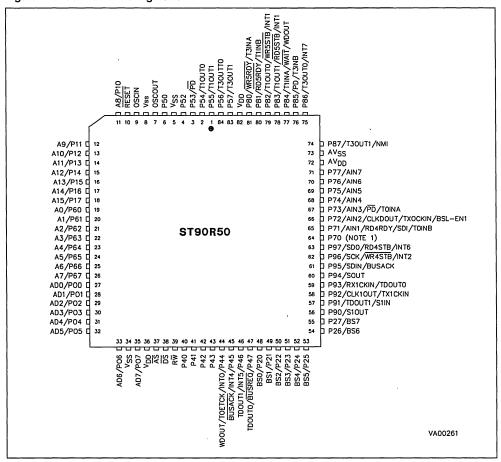

Figure 1. ST9026 Pin Configuration

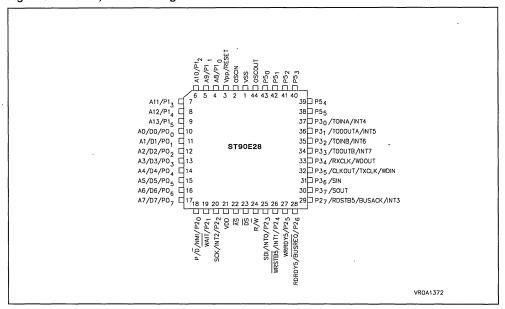

Figure 2. ST9027 Pin Configuration

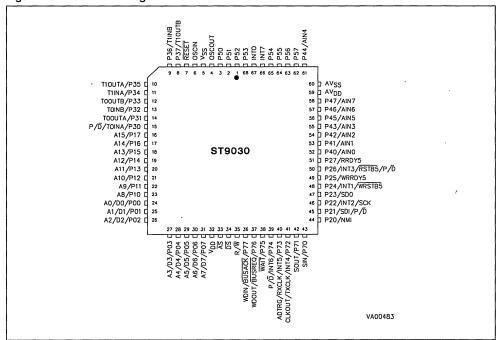

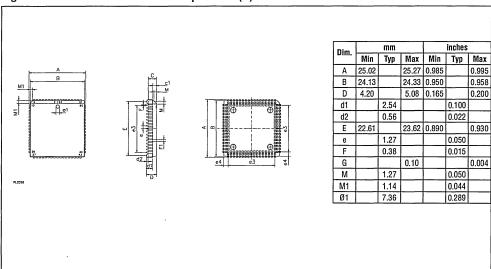

Figure 3. ST9028 Pin Configuration

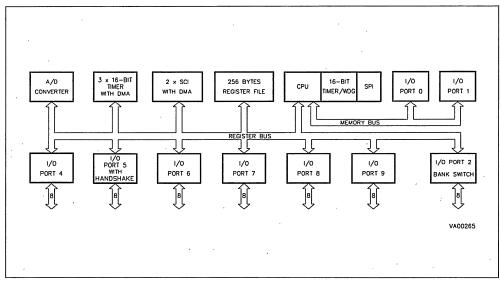

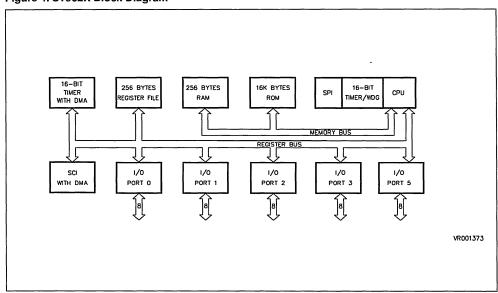

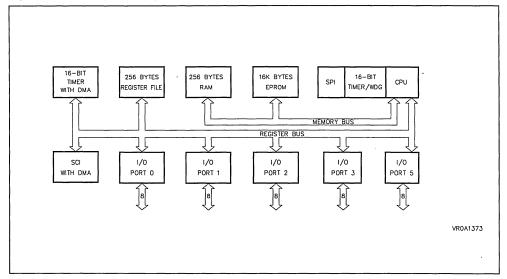

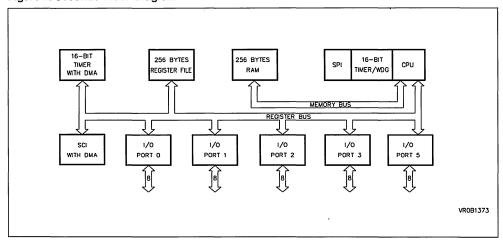

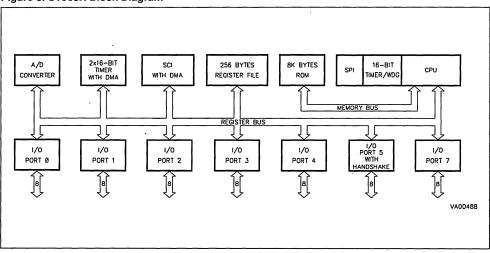

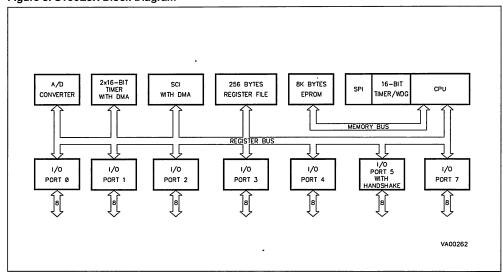

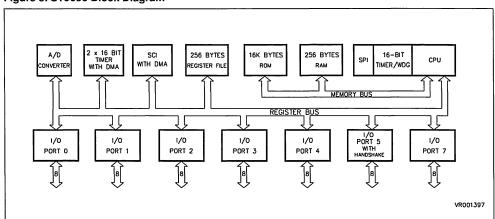

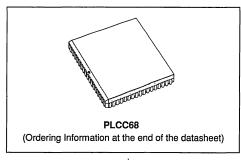

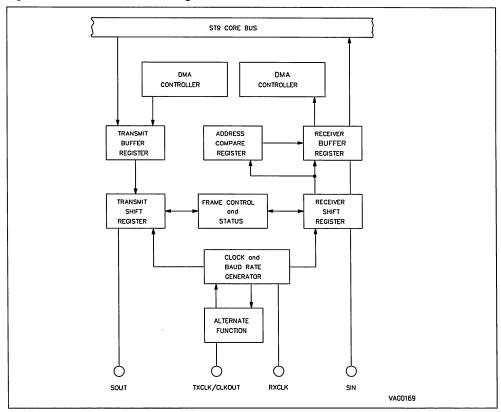

Figure 4. ST902X Block Diagram

Note: Refer to Table 1 for ST902X I/O PORT SUMMARY.

2/64

#### GENERAL DESCRIPTION

The ST9026, ST9027 and ST9028 (following mentioned as ST902X) are ROM members of the ST9 family of microcontrollers, completely developed and produced by SGS-THOMSON Microelectronics using a proprietary n-well HCMOS process.

The ROM parts are fully compatible with their EPROM versions, which may be used for the prototyping and pre-production phases of development, and can be configured as: standalone microcontrollers with 16K bytes of on-chip ROM, microcontrollers able to manage up to 112K bytes of external memory, or as parallel processing elements in a system with other processors and peripheral controllers.

A key point of the ST902X architecture is its modular approach which allows software commonality with all other members of the ST9 family.

The nucleus of the modular design of the ST902X is the advanced Core which includes the Central Processing Unit (CPU), the Register File, a 16 bit Timer/Watchdog with 8 bit Prescaler, a Serial Peripheral Interface supporting S-bus, I<sup>2</sup>C-bus and IM-bus Interface, plus two 8 bit I/O ports. The Core has independent memory and register buses allowing a high degree of pipelining to add to the efficiency of the code execution speed of the extensive instruction set.

The powerful I/O capabilities demanded by micro-controller applications are fulfilled by the ST902X with up to 40 I/O lines dedicated to digital Input/Output. These lines are grouped into up to five 8 bit I/O Ports and can be configured on a bit basis under software control to provide timing, status signals, an address/data bus for interfacing external memory, timer inputs and outputs, external interrupts and serial or parallel I/O with or without handshake.

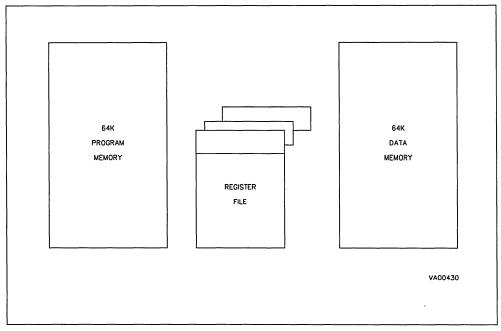

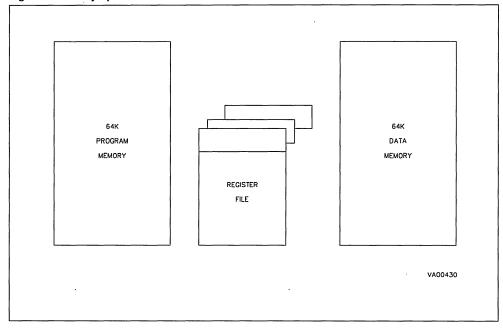

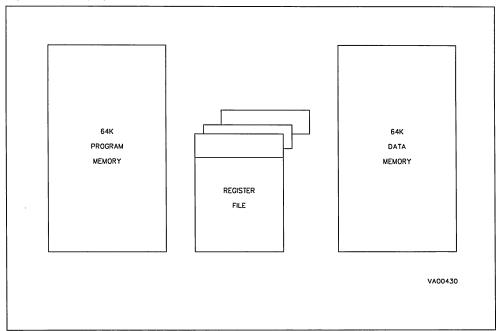

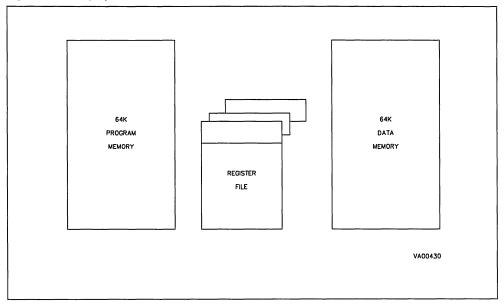

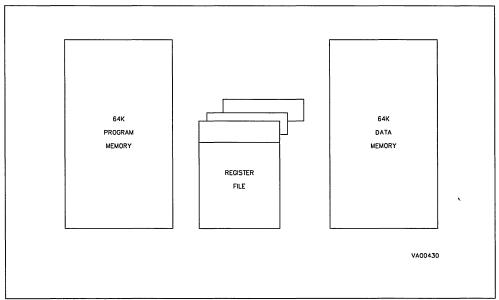

Three basic memory spaces are available to support this wide range of configurations: Program Memory (internal and external), Data Memory (external) and the Register File, which includes the control and status registers of the on-chip peripherals.

The 16 bit MultiFunction Timer, with an 8 bit Prescaler and 12 operating modes allows simple use for complex waveform generation and measurement, PWM functions and many other system timing functions by the usage of the two associated DMA channels for each timer.

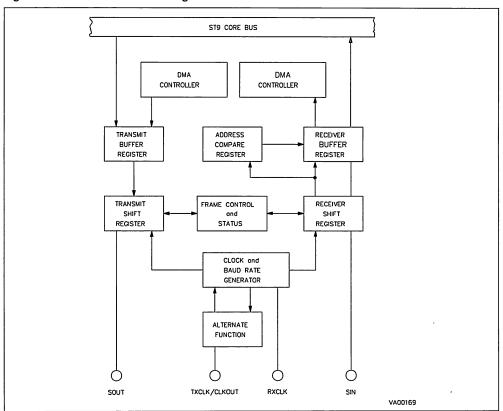

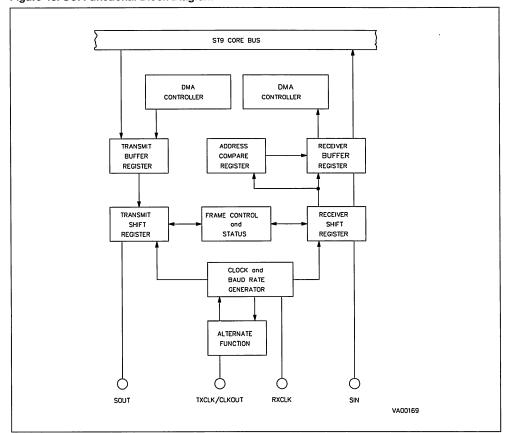

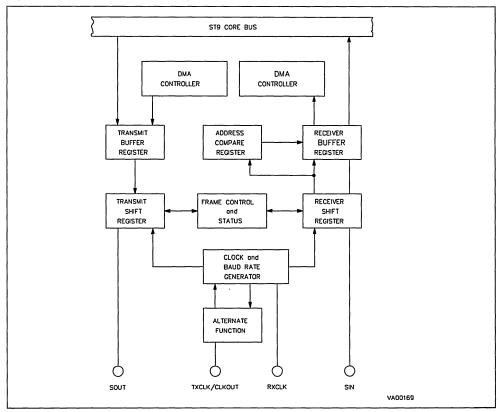

Completing the device is a full duplex Serial Communications Interface with an integral 110 to 375000 baud rate generator, asynchronous and byte synchronous capability (fully programmable format) and associated address/wake-up option, plus two DMA channels.

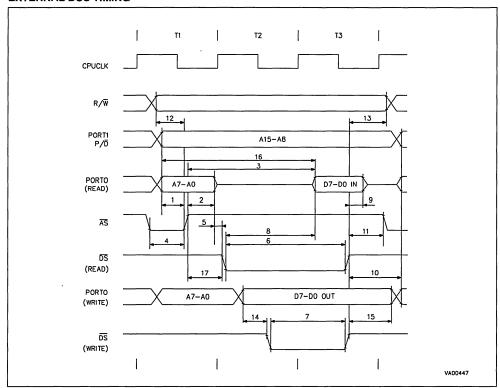

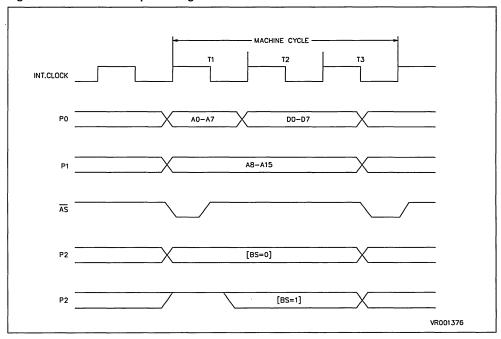

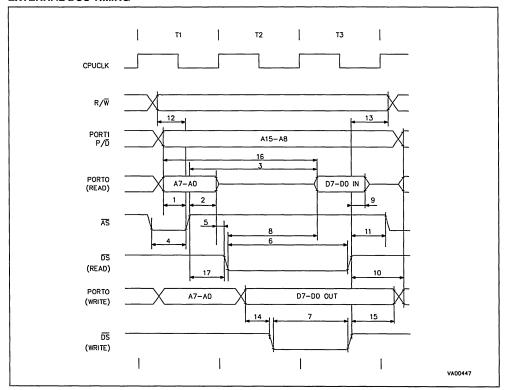

#### PIN DESCRIPTION

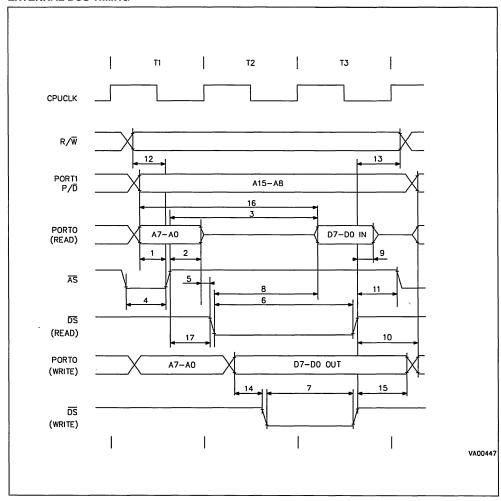

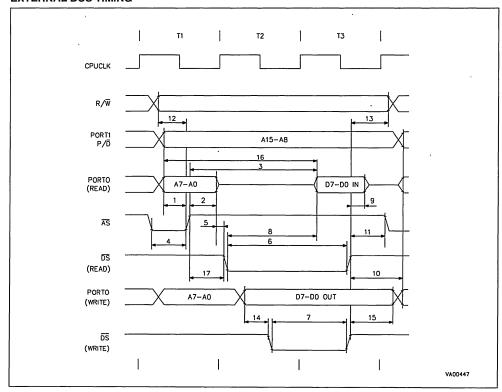

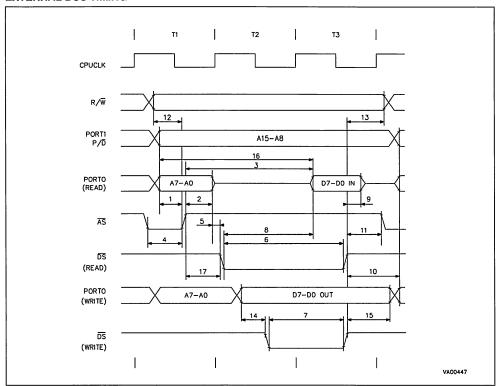

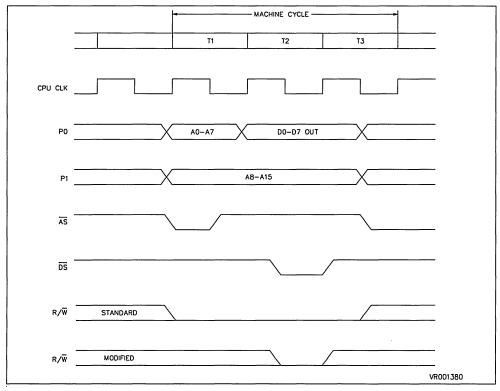

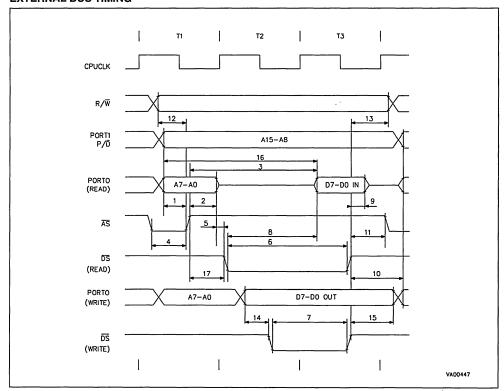

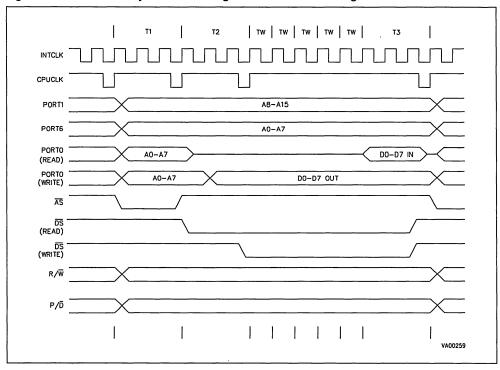

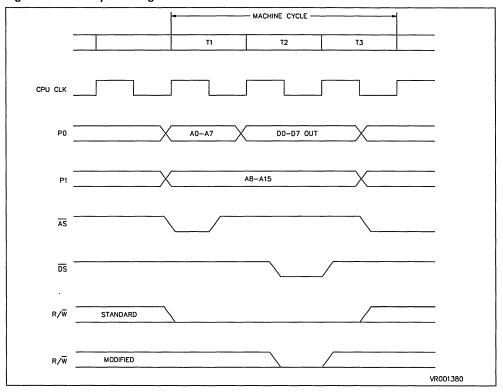

AS. Address Strobe (output, active low, 3-state). Address Strobe is pulsed low once at the beginning of each memory cycle. The rising edge of AS indicates that address, Read/Write (R/W), and Data Memory signals are valid for program or data memory transfers. Under program control, AS can be placed in a high-impedance state along with Port 0 and Port 1, Data Strobe (DS) and R/W.

DS. Data Strobe (output, active low, 3-state). Data Strobe provides the timing for data movement to or from Port 0 for each memory transfer. During a write cycle, data out is valid at the leading edge of DS. During a read cycle, Data In must be valid prior to the trailing edge of DS. When the ST902X accesses on-chip memory, DS is held high during the whole memory cycle. It can be placed in a high impedance state along with Port 0, Port 1, AS and RW.

R/W. Read/Write (output, 3-state). Read/Write determines the direction of data transfer for external memory transactions. R/W is low when writing to external program or data memory, and high for all other transactions. It can be placed in a high impedance state along with Port 0, Port 1, AS and DS.

RESET. Reset (input, active low). The ST9 is initialised by the Reset signal. With the deactivation of RESET, program execution begins from the Program memory location pointed to by the vector contained in program memory locations 00h and 01h.

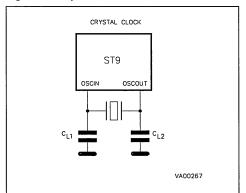

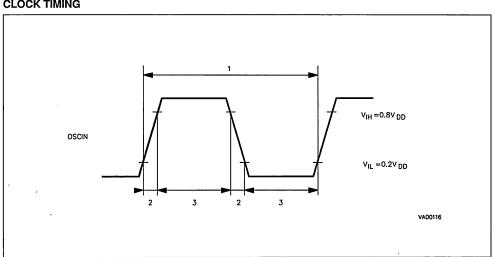

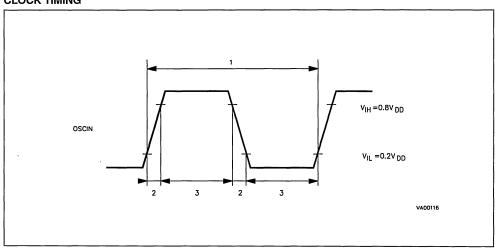

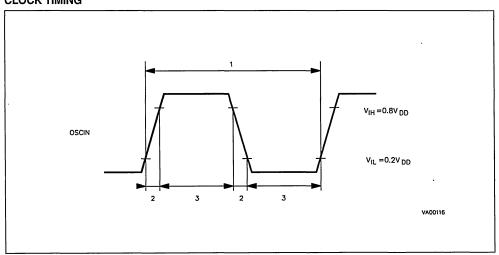

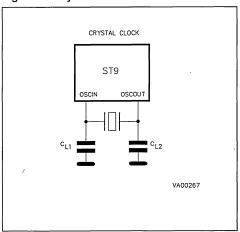

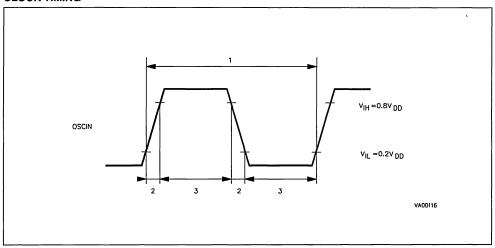

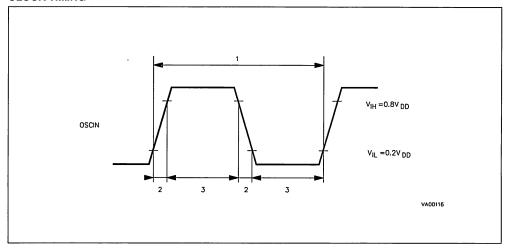

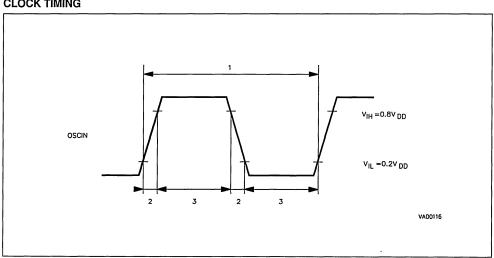

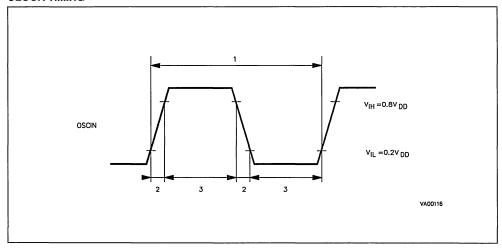

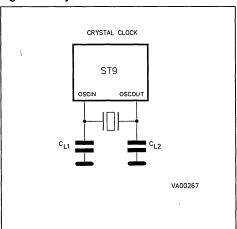

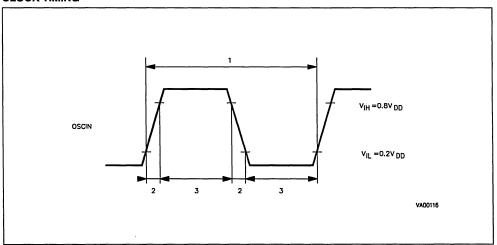

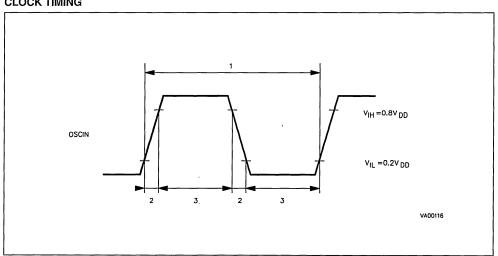

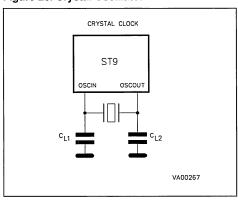

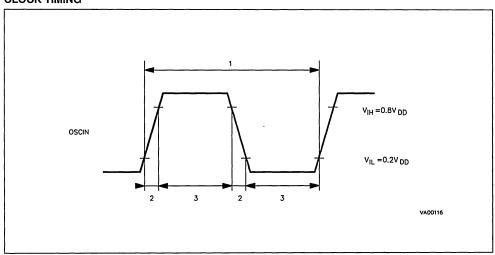

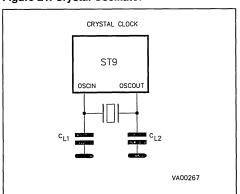

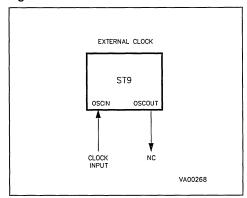

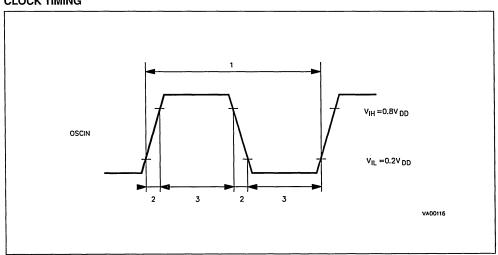

OSCIN, OSCOUT. Oscillator (input and output). These pins connect a parallel-resonant crystal (24MHz maximum), or an external source to the on-chip clock oscillator and buffer. OSCIN is the input of the oscillator inverter and internal clock generator; OSCOUT is the output of the oscillator inverter.

V<sub>DD</sub>. Main Power Supply Voltage (+5V ±10%)

Vss. Digital Circuit Ground.

P0.0-P0.7, P1.0-P1.7, P2.0-P2.7 P3.0-P3.7, P5.0-P5.7. I/O Port Lines (Input/Output, TTL or CMOS compatible). 8 lines grouped into I/O ports of 8 bits, bit programmable under program control as general purpose I/O or as Alternate functions (see next section).

I/O Port Alternate Functions. Each pin of the I/O ports of the ST902X may assume software programmable Alternative Functions as shown in the Pin Configuration Drawings. Due to Bonding options for the packages, some functions may not be present, Table 1 shows the Functions allocated to each I/O Port pins and a summary of packages for which they are available.

#### PIN DESCRIPTION (Continued)

Table 1. ST902X I/O Port Alternate Function Summary

| I/O PORT | Name    | Function | Alternate Function        | P    | in Assignme | nt   |

|----------|---------|----------|---------------------------|------|-------------|------|

| Port.bit | Ivaille | Function | Alternate Function        | 9026 | 9027        | 9028 |

| P0.0     | A0/D0   | 1/0      | Address/Data bit 0 mux    | 12   | 8           | 10   |

| P0.1     | A1/D1   | 1/0      | Address/Data bit 1 mux    | 13   | 9           | 11   |

| P0.2     | A2/D2   | 1/0      | Address/Data bit 2 mux    | 14   | 10          | 12   |

| P0.3     | A3/D3   | 1/0      | Address/Data bit 3 mux    | 15   | 11          | 13   |

| P0.4     | A4/D4   | 1/0      | Address/Data bit 4 mux    | 16   | 12          | 14   |

| P0.5     | A5/D5   | 1/0      | Address/Data bit 5 mux    | 17   | 13          | 15   |

| P0.6     | A6/D6   | 1/0      | Address/Data bit 6 mux    | 18   | 14          | 16   |

| P0.7     | A7/D7   | 1/0      | Address/Data bit 7 mux    | 19   | 15          | 17   |

| P1.0     | A8      | 0        | Address bit 8             | 4    | 4           | 4    |

| P1.1     | A9      | 0        | Address bit 9             | 5    | 5           | 5    |

| P1.2     | A10     | 0        | Address bit 10            | 6    | 6           | 6    |

| P1.3     | A11     | 0        | Address bit 11            | 7    | 7           | 7    |

| P1.4     | A12     | 0        | Address bit 12            | 8    |             | 8    |

| P1.5     | A13     | 0        | Address bit 13            | 9    |             | 9    |

| P1.6     | A14     | 0        | Address bit 14            | 10   |             |      |

| P1.7     | A15     | 0        | Address bit 15            | 11   |             |      |

| P2.0     | NMI     | 1        | Non-Maskable Interrupt    | 20   | 16          | 18   |

| P2.0     | P/D     | 0        | Program/Data Space Select | 20   | 16          | 18   |

| P2.0     | ROMless | 1        | ROMless Select*           | 20   | 16          | 18   |

| P2.1     | SDI     | t        | SPI Serial Data Out       | 21   | 17          | 19   |

| P2.1     | WAIT    | t        | External Wait Input       | 21   | 17          | 19   |

| P2.2     | INT2    | t        | External Interrupt 2      | 22   | 18          | 20   |

| P2.2     | SCK     | 0        | SPI Serial Clock          | 22   | 18          | 20   |

| P2.3     | INT0    | ı        | External Interrupt 0      | 27   | 23          | 25   |

| P2.3     | SDO     | 0        | SPI Serial Data In        | 27   | 23          | 25   |

| P2.4     | INT1    | 1        | External Interrupt 1      | 28   | 24          | 26   |

| P2.4     | WRSTB5  | 0        | Handshake Write Strobe P5 | 28   | 24          | 26   |

| P2.5     | WRRDY5  | ı        | Handshake Write Ready P5  | 29   | 25          | 27   |

| P2.6     | RDRDY5  | 0        | Handshake Read Ready P5   | 30   | 26          | 28   |

| P2.6     | BUSREQ  | ı        | External Bus Request      | 30   | 26          | 28   |

#### PIN DESCRIPTION (Continued)

Table 1. ST902X I/O Port Alternate Function Summary (Continued)

| I/O PORT | ORT Name | Function | Alternate Function         | Р    | in Assignme | nt   |

|----------|----------|----------|----------------------------|------|-------------|------|

| Port.bit | Name     | Function | Alternate Function         | 9026 | 9027        | 9028 |

| P2.7     | INT3     | ı        | External Interrupt 1       | 31   | 27          | 29   |

| P2.7     | RDSTB5   | ı        | Handshake Read Strobe P5   | 31   | 27          | 29   |

| P2.7     | BUSACK   | 0        | External Bus Acknowledge   | 31   | 27          | 29   |

| P3.0     | INT4     | Ī        | External Interrupt 4       | 39   | 35          | 37   |

| P3.0     | TOINA    | ı        | MF Timer 0 Input A         | 39   | 35          | 37   |

| P3.1     | INT5     | 1        | External Interrupt 5       | 38   | 34          | 36   |

| P3.1     | TOOUTA   | 0        | MF Timer 0 Output A        | 38   | 34          | 36   |

| P3.2     | INT6     | ı        | External Interrupt 6       | 37   | 33          | 35   |

| P3.2     | TOINB    | ī        | MF Timer 0 Input B         | 37   | 33          | 35   |

| P3.3     | INT7     | ī        | External Interrupt 7       | 36   | 32          | 34   |

| P3.3     | TOOUTB   | 0        | MF Timer 0 Output B        | 36   | 32          | 34   |

| P3.4     | RXCLK    | ī        | SCI Receive Clock Input    | 35   | 31          | 33   |

| P3.4     | WDOUT    | 0        | T/WD Output                | 35   | 31          | 33   |

| P3.5     | CLKOUT   | 0        | SCI Byte Sync Clock Output | 34   | 30          | 32   |

| P3.5     | TXCLK    | ī        | SCI Transmit Clock Input   | 34   | 30          | 32   |

| P3.5     | WDIN     | Ī        | T/WD Input                 | 34   | 30          | 32   |

| P3.6     | SIN      | ı        | SCI Serial Input           | 33   | 29          | 31   |

| P3.7     | SOUT     | 0        | SCI Serial Output          | 32   | 28          | 32   |

| P3.7     | ROMless  | 1        | ROMless Select*            | 32   | 28          | 32   |

| P5.0     |          | 1/0      | I/O Handshake Port 5       | 47   | 39          | 43   |

| P5.1     |          | 1/0      | I/O Handshake Port 5       | 46   | 38          | 42   |

| P5.2     |          | 1/0      | I/O Handshake Port 5       | 45   | 37          | 41   |

| P5.3     |          | , 1/0    | I/O Handshake Port 5       | 44   | 36          | 40   |

| P5.4     |          | 1/0      | I/O Handshake Port 5       | 43   |             | 39   |

| P5.5     |          | 1/0      | I/O Handshake Port 5       | 42   |             | 38   |

| P5.6     |          | 1/0      | I/O Handshake Port 5       | 41   |             |      |

| P5.7     |          | 1/0      | I/O Handshake Port 5       | 40   |             |      |

\* Note: Mask Option

#### ST902X CORE

The Core or Central Processing Unit (CPU) of the ST902X includes the 8 bit Arithmetic Logic Unit and the 16 bit Program Counter, System and User Stack Pointers. The microcoded Instruction Set is highly optimised for both byte (8 bit) and word (16 bit) data, BCD and Boolean data types, with 14 addressing modes. Two 8 bit I/O ports are connected to the Core module for external memory interfacing, while a 16 bit Timer/Watchdog gives system security and timing functions, and a Serial Peripheral Interface allows for synchronous communication. Three independent buses are controlled by the Core, a 16 bit Memory bus, an 8 bit Register addressing bus and a 6 bit Interrupt/DMA bus connected to the interrupt and DMA controllers in the on-chip peripherals and the Core. This multiple bus architecture allows a high degree of pipelining and parallel operation within the ST902X, giving it its efficiency in both numerical calculations and communication with the on-chip peripherals.

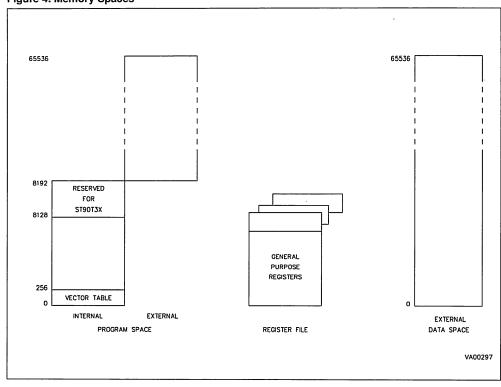

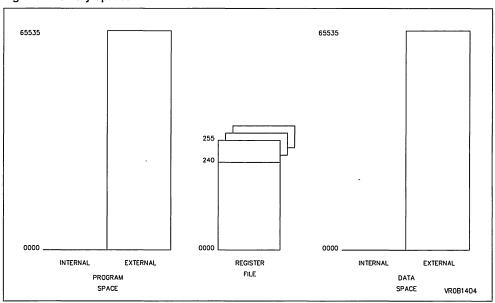

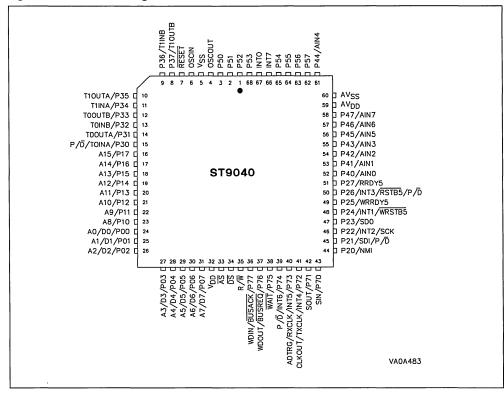

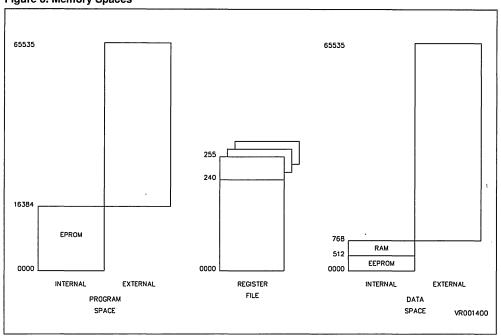

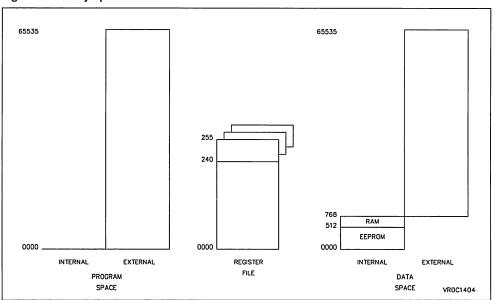

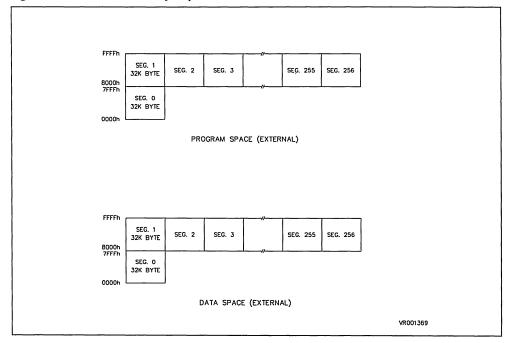

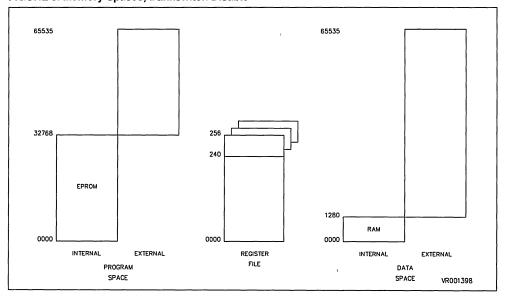

#### MEMORY

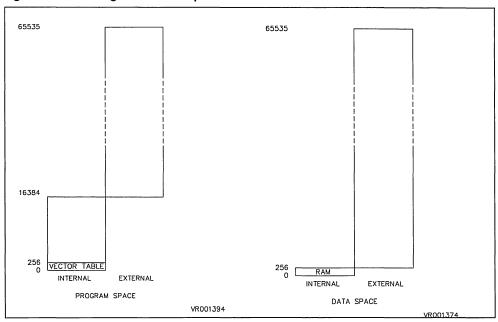

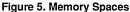

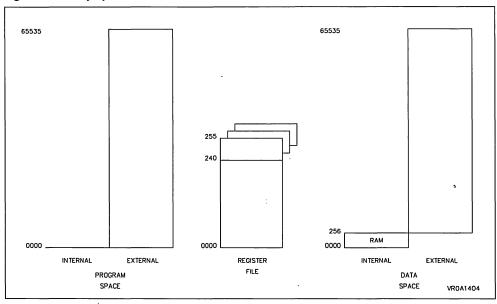

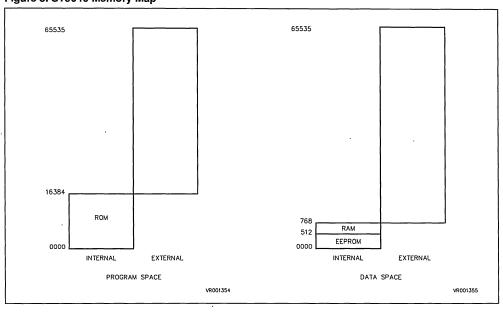

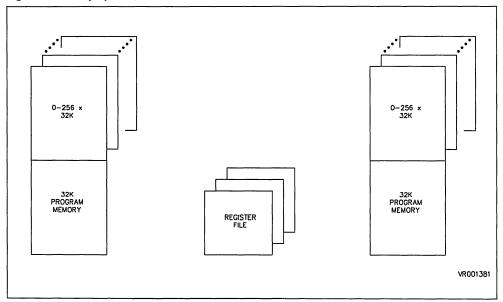

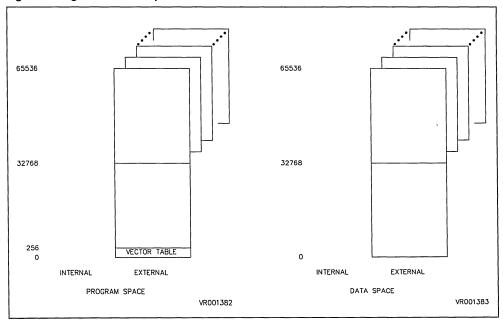

The memory of the ST902X is functionally divided into two areas, the Register File and Memory. The Memory is divided into two spaces, each having a maximum of 65,536 bytes. The two memory spaces are separated by function, one space for Program code, the other for Data. The ST902X 16K bytes of on-chip ROM memory is selected at memory addresses 0 through 3FFh (hexadecimal) in the PROGRAM space and the 256 bytes of on-chip RAM memory is selected at memory addresses 0 through 0FFh in the DATA space.

Off-chip memory, addressed using the multiplexed address and data buses (Ports 0 and 1) may be divided into the Program and Data spaces by the external decoding of the Program/Data select pin (P/ $\overline{D}$ ) available as an Alternate function, allowing a full 128K byte memory. The memory spaces are selected by the execution of the SDM and SPM instructions (Set Data Memory and Set Program Memory, respectively). There is no need to use either of these instructions again until the memory

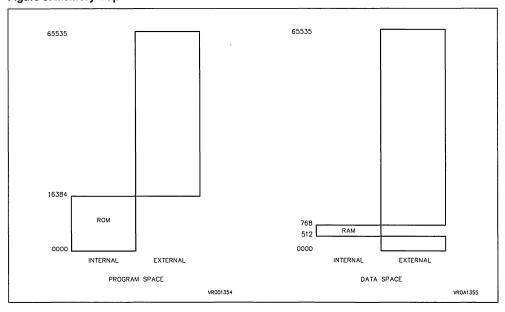

Figure 5. Memory Spaces

#### **MEMORY** (Continued)

area required is to be changed. This requirement is not necessary in two cases: first, when operating with external stacks (the Data memory is automatically selected) and, secondly, when using the memory indirect to memory indirect post-increment addressing mode (the memory types are specified in the instructions: LDPP, LDPD, LDDP, LDDD).

Either the Data Memory or the Program Memory can be addressed using any of the memory addressing modes.

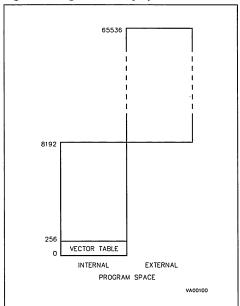

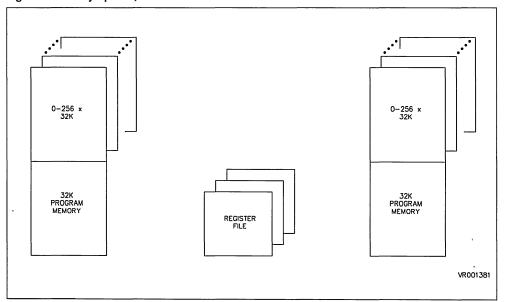

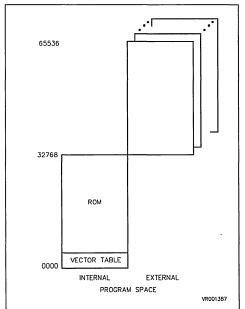

#### **Program Space**

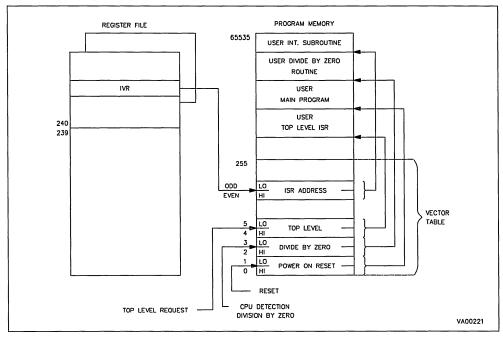

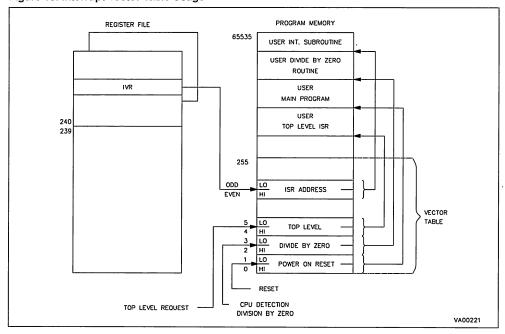

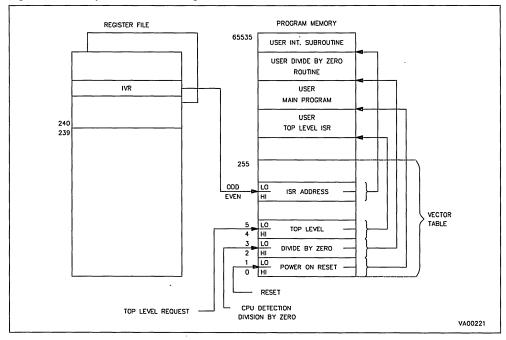

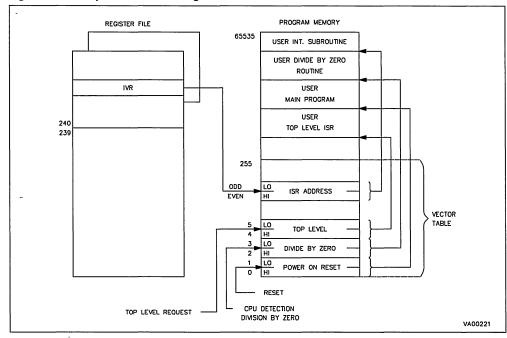

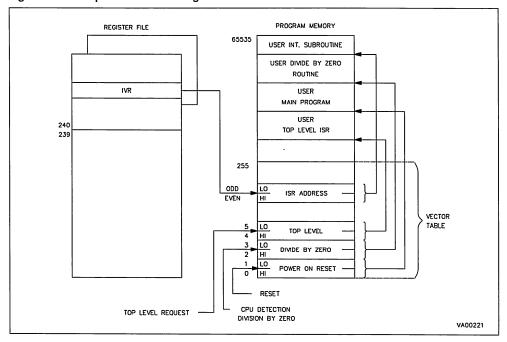

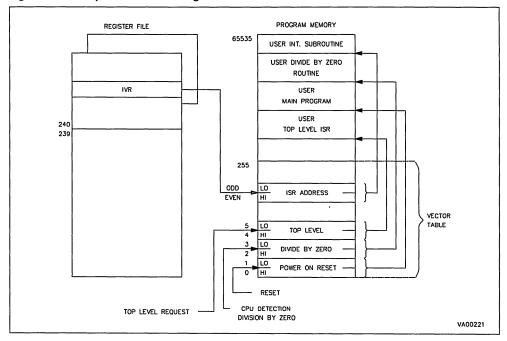

The Program memory space of the ST902X, from the 16K bytes of on-chip ROM memory to the full 64K bytes with off-chip memory expansion, is fully available to the user. At addresses greater than the first 16K bytes of program space, the ST902X executes external memory cycles for instruction fetches. The first 256 memory locations from address 0 to 0FFh (hexadecimal) hold the Reset Vector, the Top-Level (Pseudo Non-Maskable) interrupt, the Divide by Zero Trap vector and, optionally, the interrupt vector table for use with the

on-chip peripherals and the external interrupt sources. Each vector is contained in two consecutive byte locations, the high order address held in the lower (even) byte, the low order address held in the upper (odd) byte, forming the address which is loaded into the Program Counter when selected by the interrupt vector provided by the interrupt source. This should point to the relevant Interrupt Service routine provided by the user for immediate response to the interrupt.

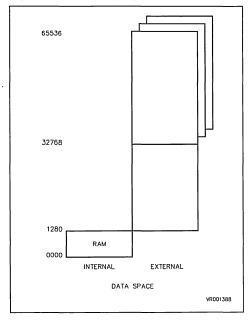

#### **Data Space**

The ST902X addresses the 256 bytes of on-chip RAM memory in the Data Space from addresses 0 to 255 (0FFh). It may also address up to 65,280 locations of External Data through the External Memory Interface when decoded with the P/\(\bar{D}\) pin. The on-chip general purpose Registers may be used as additional RAM memory for minimum chip count systems.

The Data Space is selected by the execution of the SDM instruction. All subsequent memory references will access the Data Space. Data may also be stored in external RAM or ROM memory within the Program Space.

Figure 6. ST902X Program and Data Spaces

#### **MEMORY** (Continued)

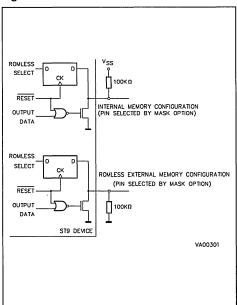

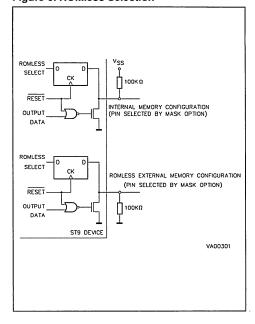

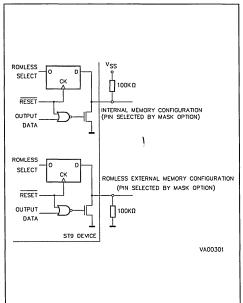

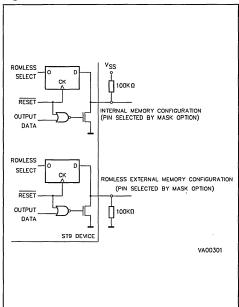

#### **ROMless Option**

In the event of a program revision being required after the development of a ROM-based ST902X, a mask option is available which enables the reconfiguration of the memory spaces to give a fully ROMless device. This means that the on-chip program ROM is disabled and ALL program memory is seen as external, allowing the use of replacement program code in external ROM memory. The on-chip memory in Data space is not affected.

To give the ROMless function (when enabled by the MASK option), the pin selected by mask for ROMless as an Alternate Function should be held to ground (Vss) with a high resistance (eg 100k ohm) during the RESET cycle. The pin status is latched on the rising edge of the RESET input. After this time, the pin is free for normal operation.

If the ROMless option is enabled, and the on-chip program is to be used, the pin enabled for the ROMless function must to held to a high potential during the RESET cycle (eg with a 100k ohm resistor to VDD).

Figure 7. ROMless Selection

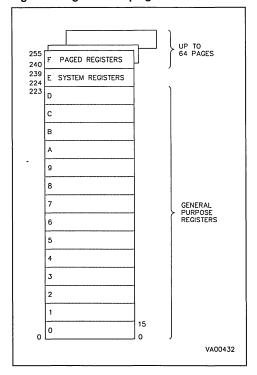

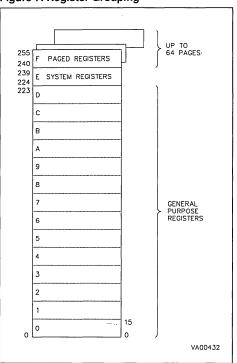

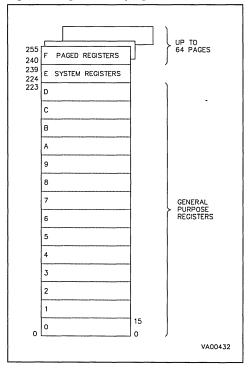

#### REGISTERS

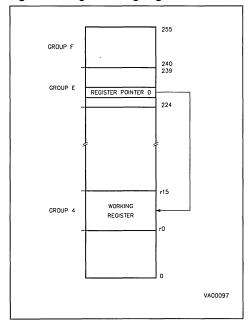

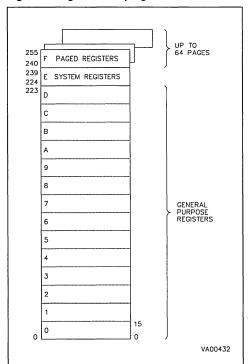

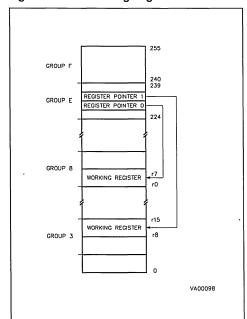

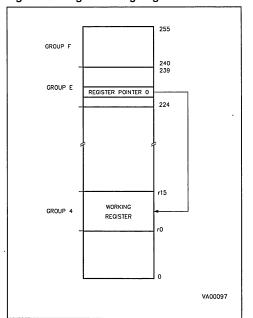

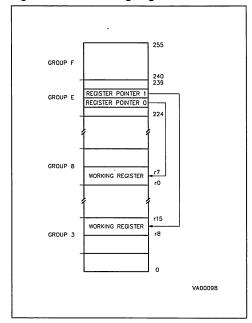

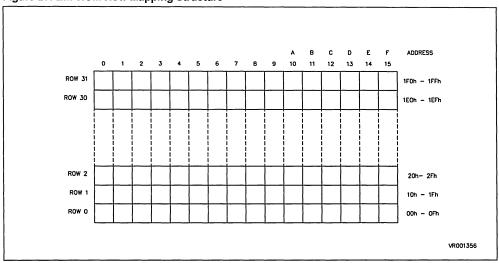

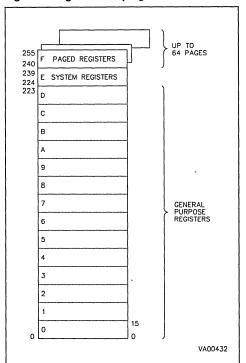

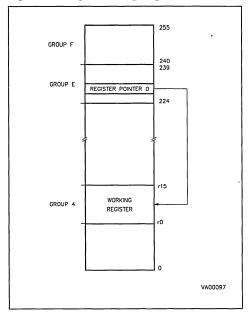

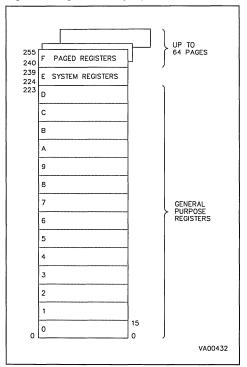

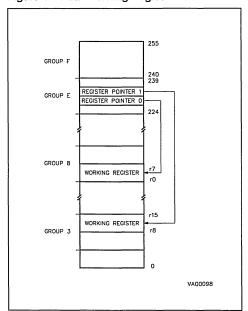

The ST902X register file consists of 240 registers (224 general purpose) plus pages of 16 registers supporting the configuration and control registers for the on-chip peripherals. The 224 general purpose registers all have 8 and 16 bit arithmetic capability and may be used as accumulators, on-chip RAM, internal Stack areas (for system and/or user stacks), or, with the appropriate addressing modes, as index, offset or stack pointers.

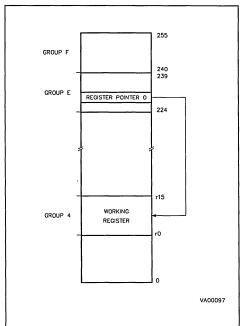

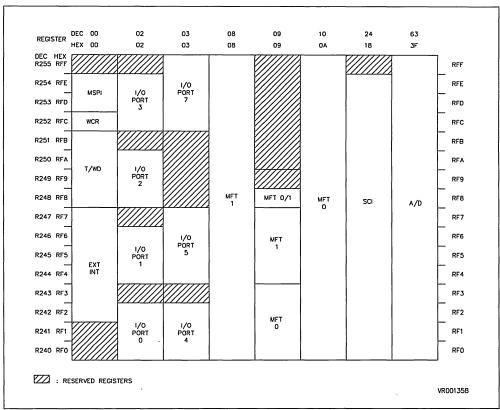

The register file is arranged into 16 groups of 16 registers, where the general purpose registers occupy the first 14 groups. The 15th group, E, contains the system registers and Group F contains the pages of the on-chip peripheral control registers.

Figure 8. Register Grouping

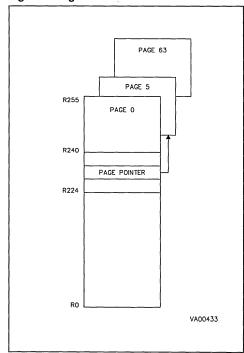

#### **REGISTERS** (Continued)

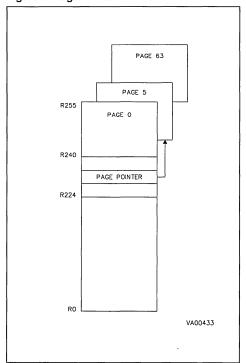

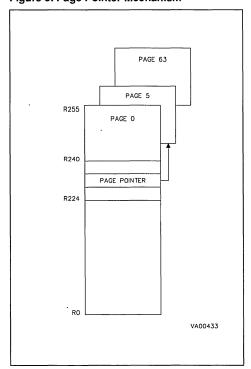

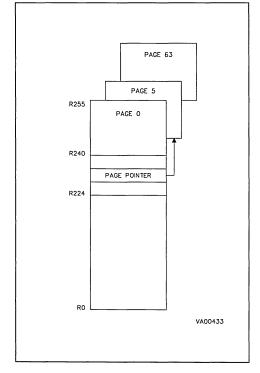

Group F is paged in this manner due to the modularity of the ST9 family of microcontrollers. Each member of the family retains all general purpose and system registers, only the paged register groups changing owing to the different on-chip peripheral organizations of each device. The user can therefore generate code libraries which use the general purpose registers knowing that they will not be lost on future ST9 devices. To address a paged register, the Page Pointer (PPR, R234) within the system register group must be loaded with the

relevant page number using the SPP instruction. Subsequently any access to registers in the top group (R240-R255) will refer to the selected page. This remains set until the next change to the Page Pointer register (by the SPP instruction).

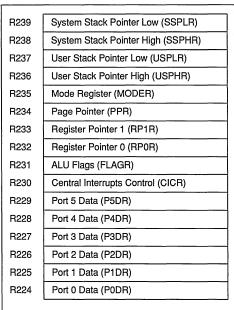

The System group (Group E, registers RE0 to REF) includes the system and user stack pointers, the Mode register, the ALU FLAG register and the Page pointer register. In addition the data registers for the first 5 I/O ports are present, the configuration registers for the ports being in the paged area. This allows the immediate access to these I/O ports at all times.

Figure 9. Page Pointer Mechanism

Figure 10. Group E Register Map

| R239 | System Stack Pointer Low (SSPLR)  |  |  |  |

|------|-----------------------------------|--|--|--|

| R238 | System Stack Pointer High (SSPHR) |  |  |  |

| R237 | User Stack Pointer Low (USPLR)    |  |  |  |

| R236 | User Stack Pointer High (USPHR)   |  |  |  |

| R235 | Mode Register (MODER)             |  |  |  |

| R234 | Page Pointer (PPR)                |  |  |  |

| R233 | Register Pointer 1 (RP1R)         |  |  |  |

| R232 | Register Pointer 0 (RP0R)         |  |  |  |

| R231 | ALU Flags (FLAGR)                 |  |  |  |

| R230 | Central Interrupts Control (CICR) |  |  |  |

| R229 | Port 5 Data (P5DR)                |  |  |  |

| R228 | Port 4 Data (P4DR)                |  |  |  |

| R227 | Port 3 Data (P3DR)                |  |  |  |

| R226 | Port 2 Data (P2DR)                |  |  |  |

| R225 | Port 1 Data (P1DR)                |  |  |  |

| R224 | Port 0 Data (P0DR)                |  |  |  |

|      |                                   |  |  |  |

|      |                                   |  |  |  |

#### **REGISTERS** (Continued)

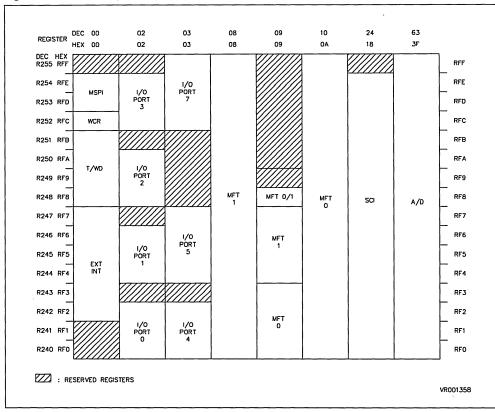

Figure 11. ST9026 Group F Peripheral Organisation

| DEC  | DEC | 00<br>00 | 02<br>02 | 03<br>03                                 | 09<br>09 | 10<br>0A | 24<br>18 |     |

|------|-----|----------|----------|------------------------------------------|----------|----------|----------|-----|

| R255 | RFF | RESERVED |          |                                          |          |          | RESERVED | RFF |

| R254 | RFE | MSPI     | PORT 3   |                                          |          |          |          | RFE |

| R253 | RFD |          |          | RESERVED                                 |          |          |          | RFC |

| R252 | RFC | WCR      |          | HESERVED                                 |          |          |          | RFD |

| R251 | RFB |          |          |                                          | RESERVED |          |          | RFE |

| R250 | RFA | T/WD     | PORT 2   |                                          |          | MFT 0    |          | RFA |

| R249 | RF9 |          |          |                                          |          | IVII-1 U | SCI      | RF  |

| R248 | RF8 |          |          | 10 1 10 10 10 10 10 10 10 10 10 10 10 10 |          |          |          | RF8 |

| R247 | RF7 |          |          |                                          |          |          |          | RF7 |

| R246 | RF6 |          | PORT1    | PORT 5                                   |          |          |          | RF6 |

| R245 | RF5 | EXT INT  |          |                                          | · ,      |          |          | RF5 |

| R244 | RF4 |          |          |                                          |          |          |          | RF4 |

| R243 | RF3 |          |          |                                          |          |          |          | RF3 |

| R242 | RF2 |          | PORT 0   | RESERVED                                 | MFT0     |          |          | RF2 |

| R241 | RF1 | RESERVED |          |                                          |          |          |          | RF1 |

| R240 | RF0 |          |          |                                          |          |          |          | RFC |

#### **REGISTERS** (Continued)

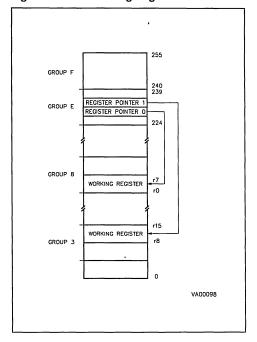

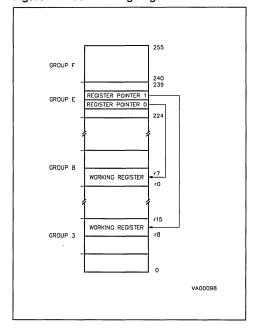

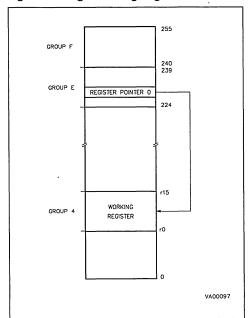

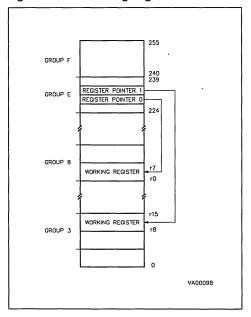

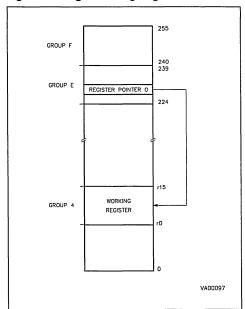

The Register Pointers, present in the system register group, select groups of registers as "Working Registers", which have faster addressing modes than direct Register addressing and allows smaller code size. The Register Pointers may either be used singly, creating a register group of 16 working registers, or as two independent groups of 8 working registers which may be placed at any 8 register boundary within the register file. The single and twin working register modes are automatically set by hardware when the respective SRP and either SRPO or SRP1 instructions are executed. If working registers are used as accumulators and RAM locations for particular tasks, fast context switching on interrupts may be achieved by setting the register pointer to another group for the Interrupt Service Routine, ISR, (e.g. saving the Register pointer on the stack), using the new group in the ISR and subsequently restoring the original group before the Return from Interrupt instruction. Working registers also allow the use of the ABAR - Any Bit-Any Register Boolean operations (including directly on the I/O port data registers).

In the ST9 syntax, directly addressed Registers are indicated with a capital R e.g. R0, R224, RBF, with Register Pairs (16 bit accumulators or memory pointers) as RR0, RR24. When using Working Registers, groups of 16 registers (SRP instruction) are denoted as r0 to r15 (rr0 to rr14), while the dual working register group are addressed as r0 to r7 (rr0 to rr6), for the first group of 8 registers (SRP0), with r8 to r15 (rr8 to rr15) for the second set (SRP1).

Working register addressing requires a 4 bit field within the instruction. When packed into a byte, the upper nibble is set to Dh (1101b), this being the escape code to indicate the use of the working registers. As a result, group D CANNOT be selected with direct register addressing, it is recommended that this group be used as internal stacking area when using register file based system or user stack pointers.

Figure 12. Single Working Register Bank

Figure 13. Dual Working Register Bank

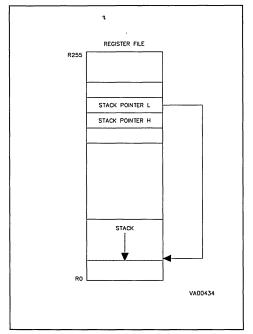

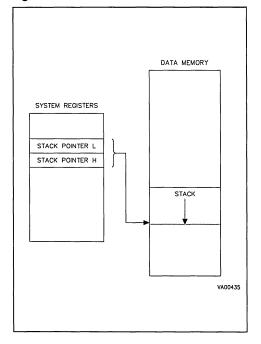

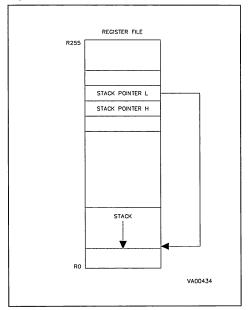

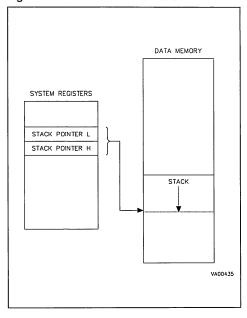

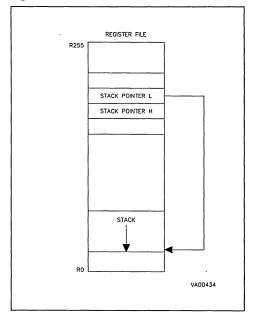

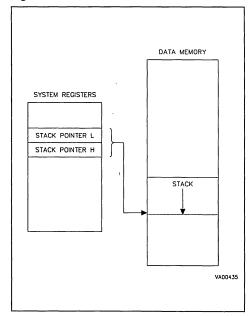

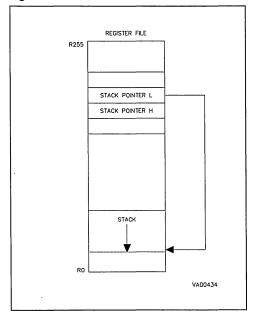

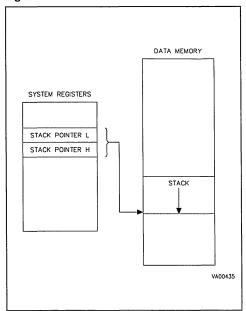

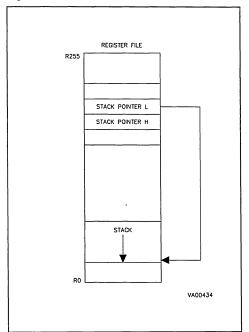

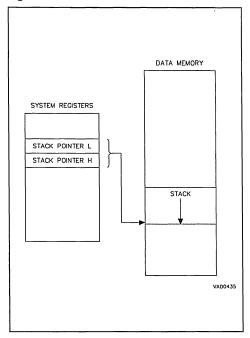

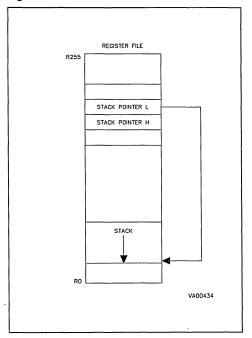

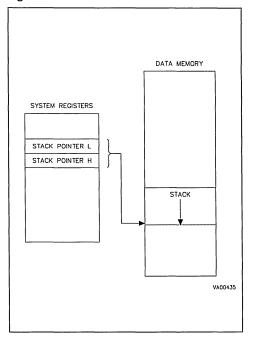

#### STACK POINTERS

There are two separate, double register stack pointers available (System and User), both of which can operate in register or Data memory address spaces. These operate in a Pre-Decrement mode when data is PUSHed onto the Stack and in a Post-Increment mode when data is POPed from the stack.

The SYSTEM Stack Pointer (SSPR, R238:R239) is used for the storage of temporarily suspended system and/or control registers (ie the the Program Counter and FLAG register) while interrupts are being serviced, and is used for the storage of the Program Counter following the CALLing of a subroutine.

The USER Stack Pointer (USPR, R236:R237) is completely free from all interference from automatic operations and so provides for a totally user controlled stack area.

Both Stack pointers may operate with both byte (PUSH,POP) and word (PUSHW,POPW) data, and are

differentiated by appending a "U" to the instruction mnemonic for the User Stack (PUSHU/PUSHUW, POPU/POPUW).

When the Stack Pointers are using RAM Memory as the stack areas, a full word register is used as the pointer, while when operating with the stack area within the Register File (Groups 0 to 14 only, but not the within the system and paged groups) only an 8 bit register is required for addressing and consequently only the low byte of the word registers are used (R239 for the System Stack and R237 for the User Stack). In this latter case the upper byte of the stack pointer registers (R238 and R236) must be considered as reserved. The Stack Pointers may be selected to point to RAM or Register file by the setting of the SSP (MODER.7) and USP (MODER.6) of the ST902X configuration register (MODER, Ŕ235) where a "1" denotes Register file operation (Default at Reset) and "0" causes external Data space operation.

Figure 14. Internal Stack Pointers

Figure 15. External Stack Pointers

#### INTERRUPTS

The ST902X offers a powerful solution to the response requirements of real-time systems with its advanced interrupt structure. Interrupt trigger sources can be prioritized within 8 levels to match the priorities assigned to the application. In addition a top-level or non-maskable interrupt is available.

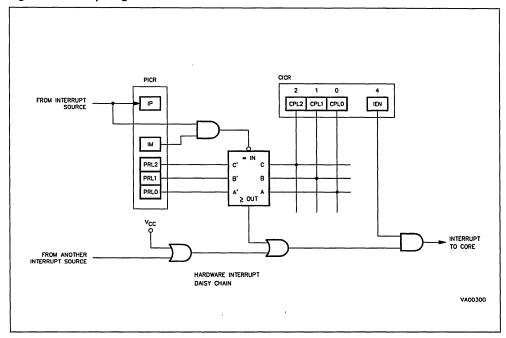

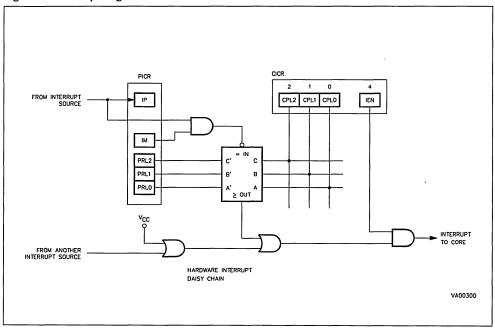

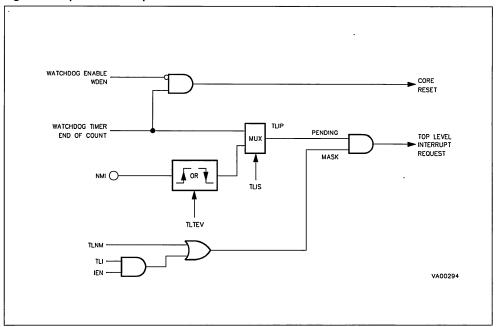

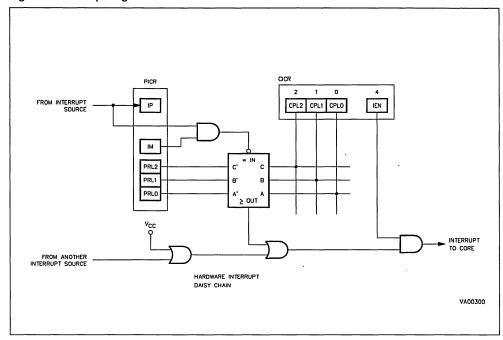

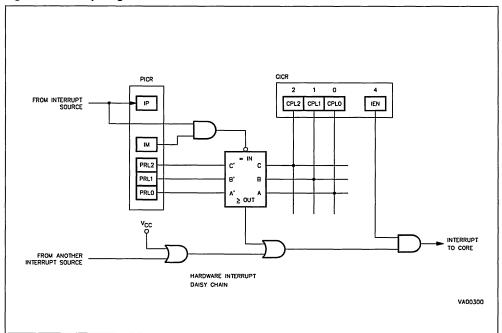

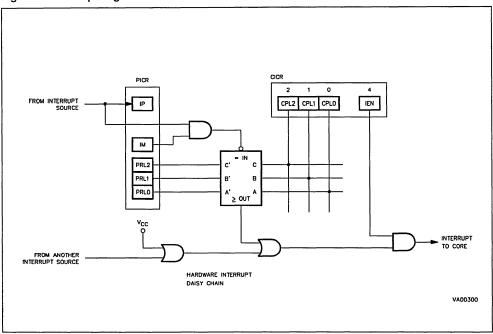

The ST902X interrupts follow the logical flow of Figure 16.

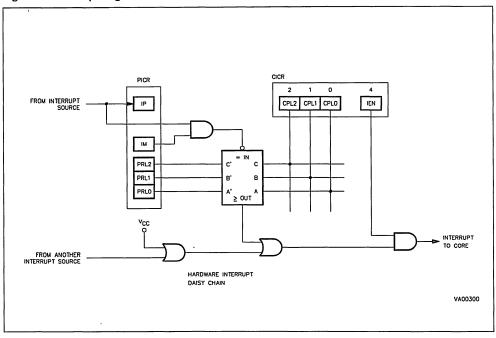

Interrupt events (selectable with each function) cause the setting of the Interrupt Pending (IP) bit within the status register of the peripheral. This bit may also be set by software in order to generate a software interrupt, and should normally be reset by software within the interrupt service routine. If the interrupt is not Masked with the corresponding Interrupt Mask bit, the interrupt is passed to the central interrupt control logic where the priority level assigned by the user to the interrupt source is compared with the priority level of the core (user programmed dynamically in the 3 bits of the Central Priority register (CPL, CICR.0-2, Level 7 is the lowest priority and level 0 the highest). If the incoming priority level is higher than the CPL, and Global

Interrupts are enabled (by the EI instruction, interrupts are disabled by the execution of the DI instruction), the interrupt is acknowledged. If interrupts are globally disabled, the priority level of the source is lower than or equal to the CPL or the Interrupt is masked, then the IP bit remains set and the interrupt is held pending until the EI instruction is executed, the CPL is set to a lower level AND the interrupt is un-masked. Alternatively the IP bit of a masked interrupt source may be used in a polled interrupt environment, with the IP bit being reset by software within the service routine.

The interrupt acknowledge cycle causes the Program Counter and FLAGS register to be pushed onto the System Stack (PC low byte first, PC high byte, then FLAGS Register) and all maskable interrupts to be disabled by resetting the IEN bit (CICR.4). The peripheral Interrupt Vector, IVR, a user programmable feature of the peripheral interrupt control registers, is used as an offset into the vector table, pointing to the high byte (even address) of the 16 bit address which should contain the starting address of the interrupt service routine. Addresses 0 through 255 of the program space comprise the interrupt vector table. Where multiple

Figure 16. Interrupt Logic

#### **INTERRUPTS** (Continued)

Figure 17. Interrupt Vector Table Usage

interrupt sources may occur within a peripheral, the peripheral interrupt vector source may be encoded by hardware set bits within the IVR register. This means that the vector address defined in the peripheral IVR is the base address for a block of vectors servicing that peripheral. The address pointed to by the vector is loaded into the Program Counter and execution restarts from this point.

The interrupt service routine should clear the interrupt pending flag of the interrupt source and take the appropriate action. The last instruction of the interrupt service routine should be the IRET instruction, the action of this is to restore the Program Counter and Flags register to their value prior to the interrupt acknowledgment, and to re-enable interrupts. Within the interrupt service routine, use may be made of the working register pointer mechanism to reduce the context switching time.

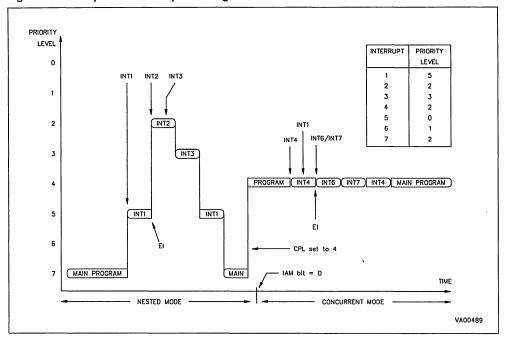

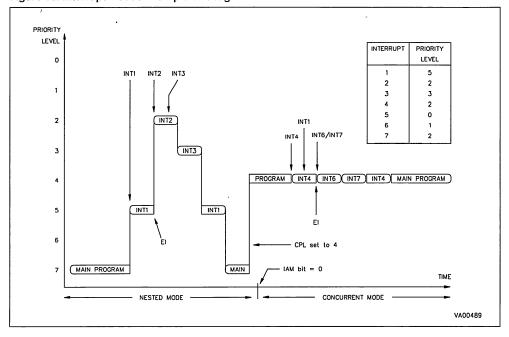

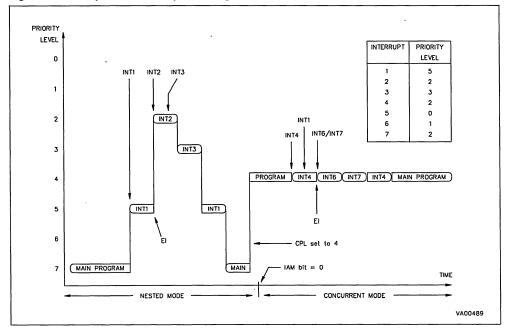

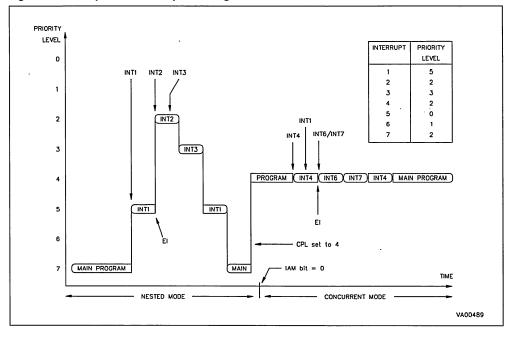

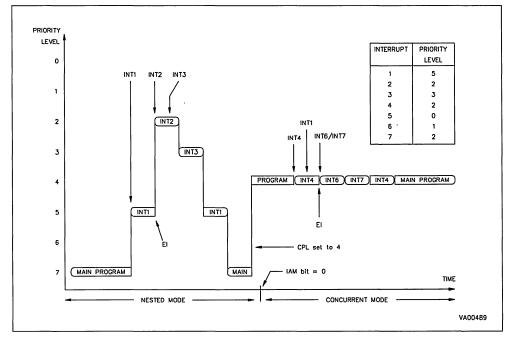

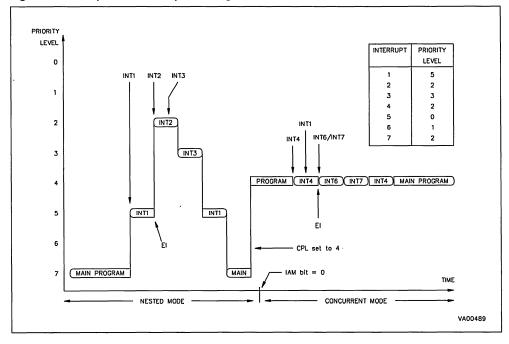

Two interrupt arbitration modes are available for use with the 8 level priority scheme, Nested and Concurrent modes. These are selected by the status of the IAM bit (CICR.3).

Concurrent mode, selected when IAM = "0" (the reset condition) is the standard interrupt arbitration mode, where the arbitration phase of every instruction acknowledges interrupts according to their priority level (if higher than the CPL) and follows the sequence shown. All pending interrupts existing or having eventually occurred during interrupt service routine execution, remain pending until the Enable Interrupt instruction (EI) (even if it is executed during the interrupt service routine). EI within the interrupt service routine is not recommended for use with the Concurrent arbitration mode as this can trigger a Last In, First Out condition where high priority interrupts are masked by lower priority interrupts which are all higher than the CPL value.

Nested mode, selected when IAM = "1", uses the same arbitration phase as concurrent mode, the difference being that the CPL is modified during the interrupt processing cycle to that of the acknowledged interrupt level. The CPL value is pushed by hardware into the Nested Interrupt Control register (NICR, R247 page 0) by setting the NICR bit corresponding to the CPL value. The interrupt service

#### INTERRUPTS (Continued)

Figure 18. Interrupt Modes Example of Usage

routine is entered in the normal manner. The revised CPL level is used for arbitration of further interrupts, each higher level being saved on the NICR stack, and being restored automatically by hardware with the IRET instruction. This allows the execution of the EI instruction within the interrupt service routine to operate the correct nesting of interrupts. The two modes are shown graphically in Figure 18, where the Y axis shows the CPL value. It should be noted that in the example INT1 will not be acknowledged until the CPL level is programmed to a lower level.

Interrupts coming from on-chip sources at the same instant, and at the same priority level, are resolved during the arbitration phase according to a hardware daisy-chain. This follows the priorities of the table shown in Table 2.

Table 2. ST902X Interrupt Hardware Daisy Chain

| INTA     | High Priority   |

|----------|-----------------|

| INTB     |                 |

| INTC     |                 |

| INTD     |                 |

| MFTIMER0 |                 |

| SCI      | Lowest Priority |

#### **INTERRUPTS** (Continued)

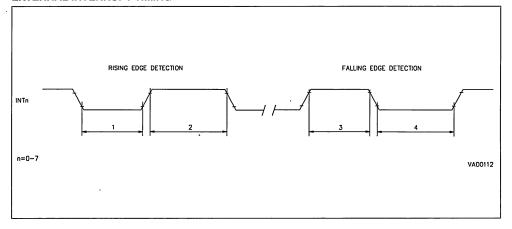

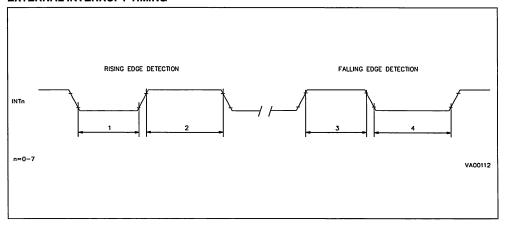

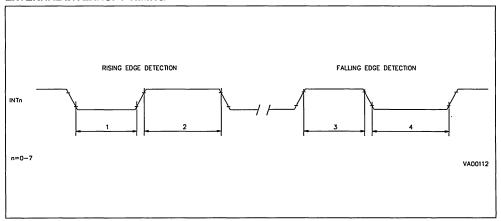

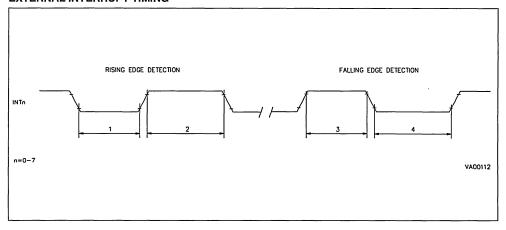

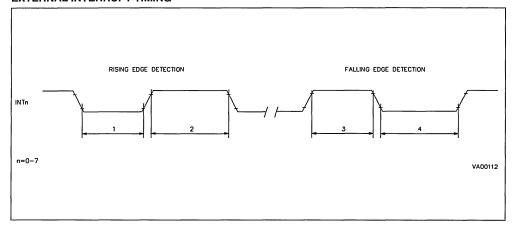

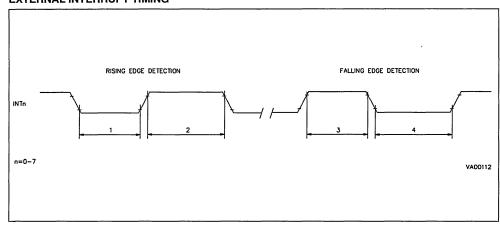

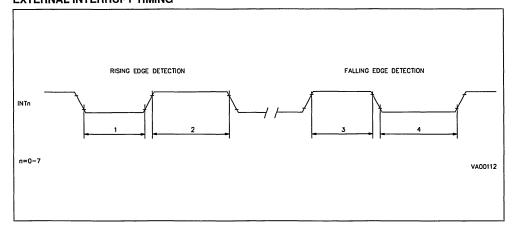

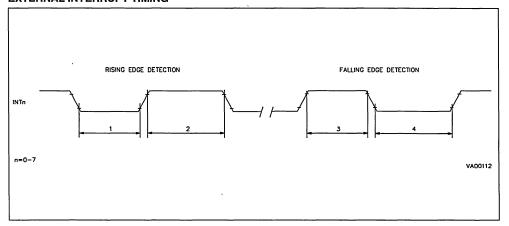

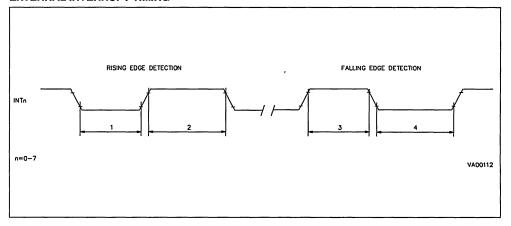

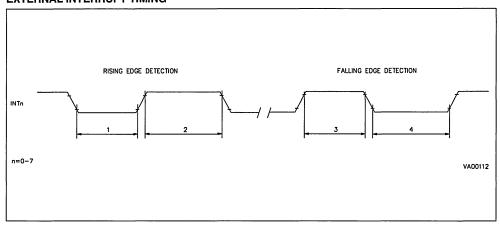

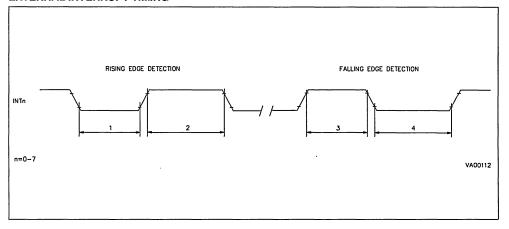

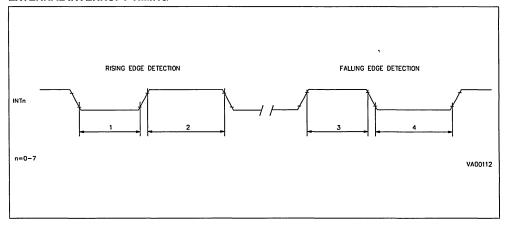

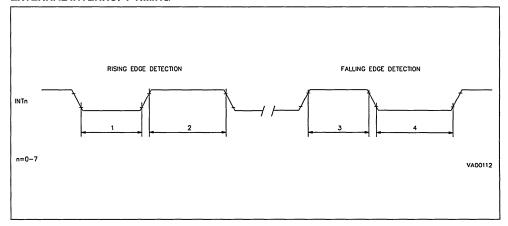

**External Interrupts.** Up to 7 external interrupts are available on the ST902X as alternate function inputs of I/O pins. These may be selected to be triggered on rising or falling edges and can be independently masked. The eight external interrupt sources are grouped into four pairs or channels which can be assigned to independent interrupt priority levels. Within each channel the even interrupt number takes the even priority level and the odd channel the odd priority level (even+1).

Table 3. External Interrupt Channel Grouping

| External Interrupt | Channel |

|--------------------|---------|

| INT7               | INTD1   |

| INT6               | INTD0   |

| INT5               | INTC1   |

| INT4               | INTC0   |

| INT3               | INTB1   |

| INT2               | INTB0   |

| INT1               | INTA1   |

| INT0               | INTA0   |

Several of the External Interrupt channels have their inputs selectable between the external interrupt source and on-chip peripheral sources.

Table 4. ST902X External Interrupt Souce Selection

| INT0                           |       |

|--------------------------------|-------|

| Timer/Watchdog<br>End of Count | INTA0 |

| INT2                           | INTB0 |

| SPI Interrupt                  | 55    |

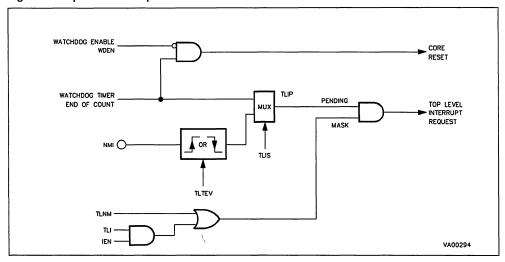

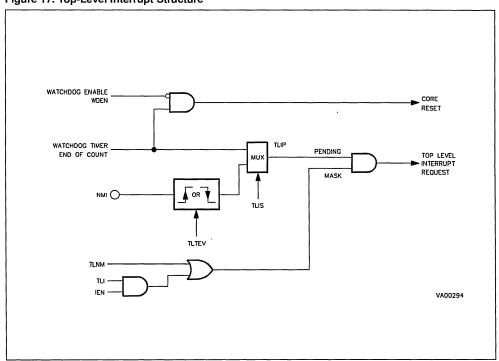

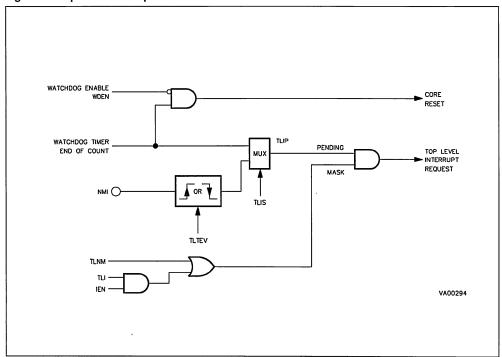

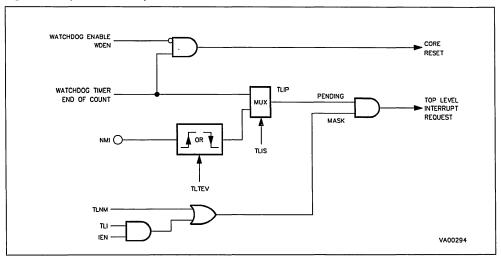

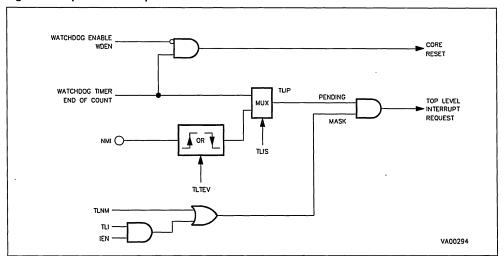

Top Level Interrupt. The Top Level Interrupt channel can be assigned either to the external NMI pin or to the Timer/Watchdog output. When selected as the external NMI pin, the active edge may be programmed to be rising or falling. The TLI event will cause the setting of the TLIP bit (CICR.6) and according to the mask situation, a Top Level Interrupt request may be generated. Two masking conditions are available, a Maskable Mask and a Not-Maskable Mask.

The Maskable Top Level Interrupt may be enabled or disabled by software and follows the state of the Global Interrupt Enable bit IEN (CICR.4), while the Not-Maskable Mask bit (TLI, CICR.5) is a set-only mask. Once set, the Top Level Interrupt is active independently of IEN and cannot be disabled until the next Reset cycle.

Figure 19. Top-Level Interrupt Structure

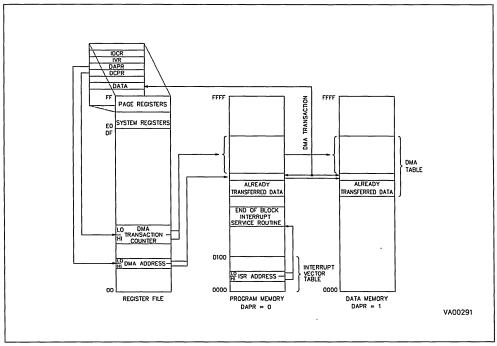

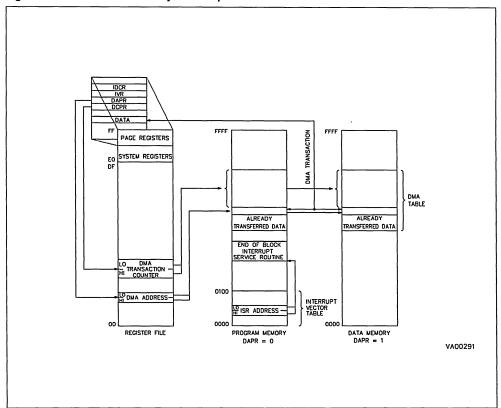

#### DMA

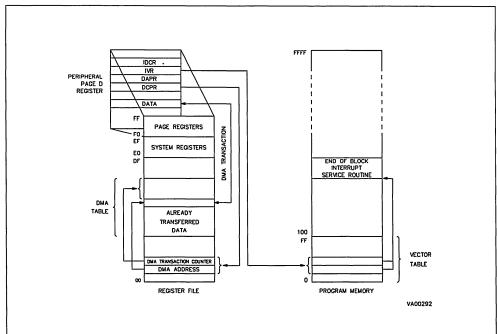

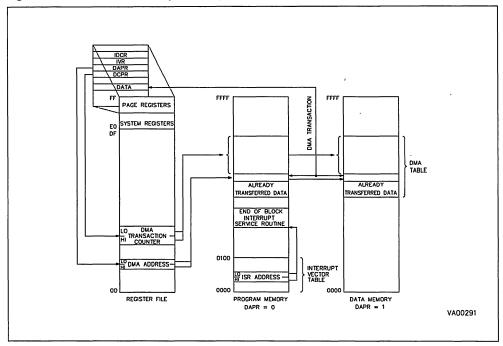

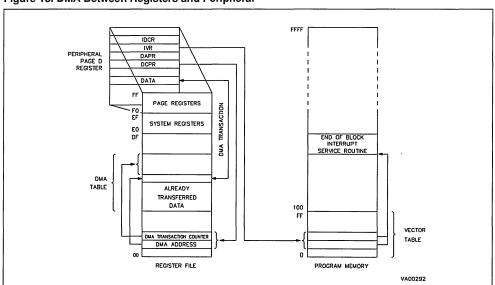

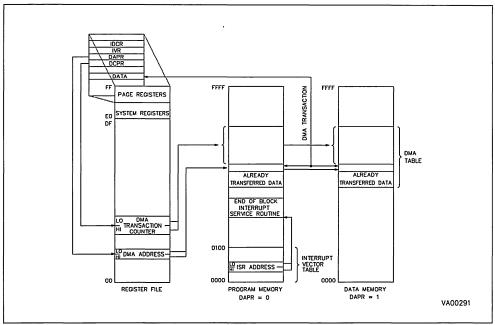

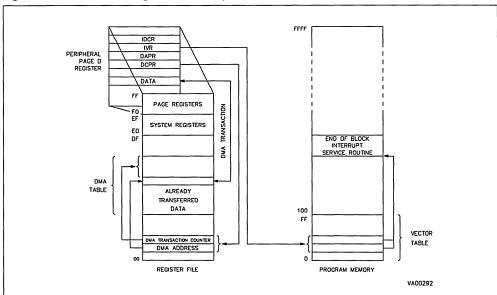

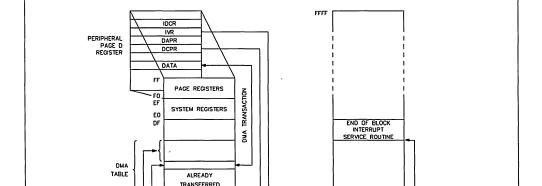

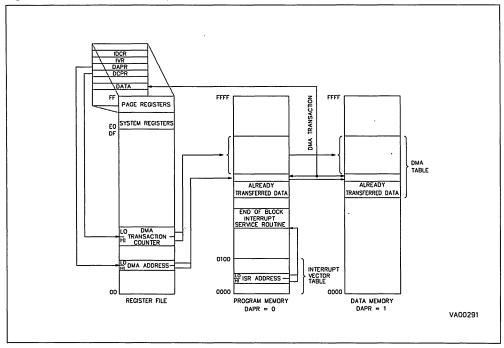

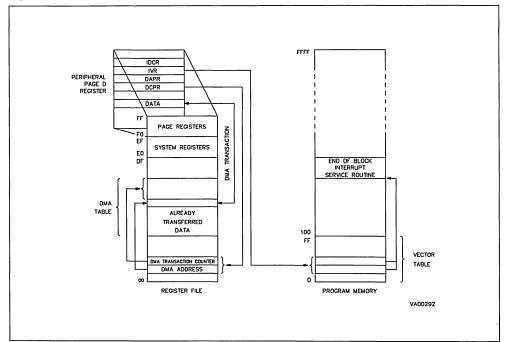

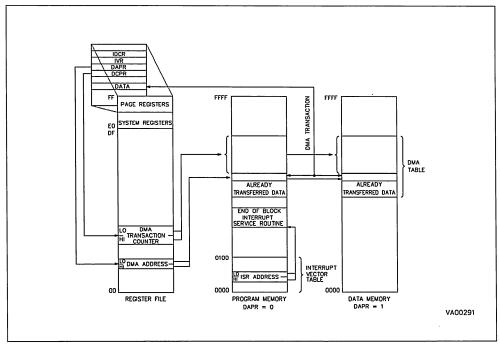

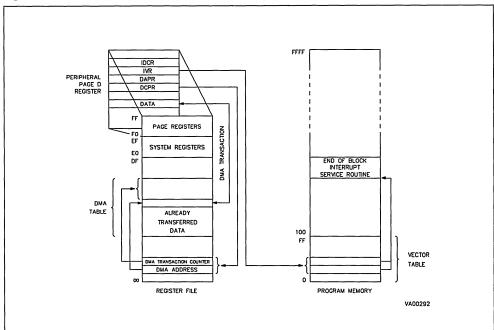

The ST902X has on-chip DMA channels to provide high-speed data transaction between peripherals and Memory or Register File. Multi-channel DMA is fully supported because each peripheral can have its own DMA channel(s). Each DMA channel transfers data to/from contiguous locations of the Register File, Program Memory or Data Memory. The maximum number of transactions that each DMA channel can perform is 222 if the Register File is selected and 65536 if Program or Data Memory are selected.

DMA transfer to (or from) the Register File takes 8 INTCLK cycles, DMA transfer to (or from) Memory takes 16 INTCLK cycles. If the ST902X is in the idle mode (following the execution of the WFI instruction), DMA requests are acknowledged according to their priority and control is returned to the idle mode pending an interrupt, this operation increases the number of INTCLK cycles by 2 for both Register File and Memory DMA transactions.

Each DMA channel has its own control registers located in the page(s) related to the peripheral.

There are two pointer registers, DAPR which points to a register or register pair containing the current DMA address to/from which data will be transferred, and DCPR, which points to a register or register pair which contain the transaction counter for the DMA operations. Each DMA transfer consists of three operations:

- A load from/to the peripheral data register to/from a location of Register File (or Memory) addressed through the DMA Address Register (or Register Pair)

- A post-increment of the DMA Address Register (or Register Pair)

- A post-decrement of the DMA transaction counter, which contains the number of transactions that have still to be performed.

When the transaction counter reaches 0 (all data has been transferred) an End of Block Interrupt event is generated to allow the processing of the DMA data block, or, by reloading the Address and counter registers and retriggering, a repeated DMA cycle.

Figure 20. DMA Between Registers and Peripheral

#### **DMA** (Continued)

A SWAP mode, allowing continuous DMA operation, is available for the Multifunction Timer and is described in the section relating to the Multifunction Timer.

The ST902X has DMA channels associated with the Serial Communications Interface Input and Output Serial data channels, the 16 bit Load/Capture Register 0, CAPTOR, of the Multifunction Timer allowing the timing of external signals to be captured into a table for off-line analysis or for the automatic output of PWM signals of variable width and timing, and the 16 bit Comparison Register 0, COMPOR, of the Multifunction Timer which can be programmed to cause output or input of parallel data through the handshake port 5 under DMA.

Figure 21. DMA Between Memory and Peripheral

#### **CLOCK GENERATION, WAIT, HALT AND RESET**

#### Clock Generation

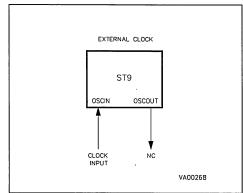

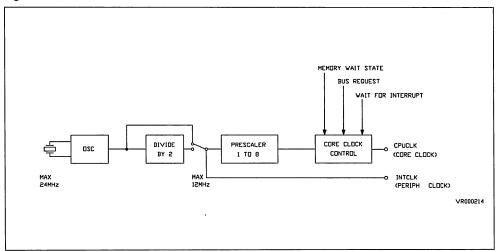

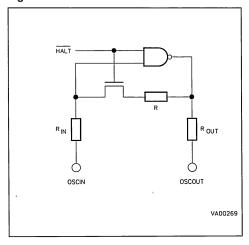

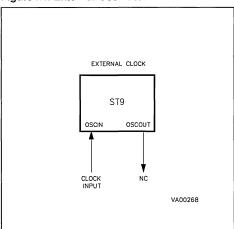

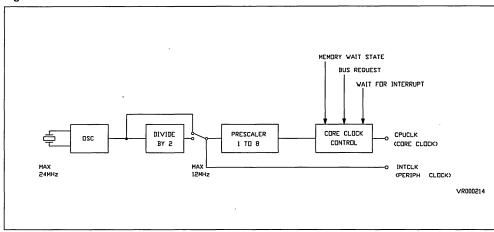

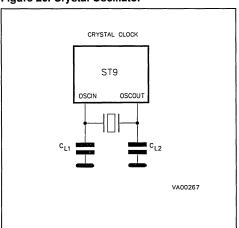

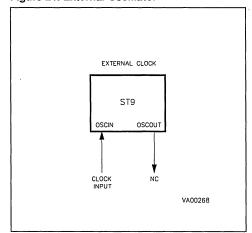

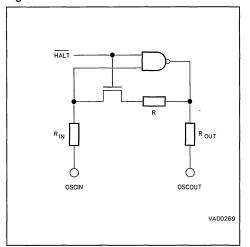

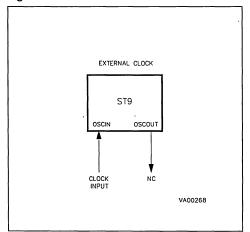

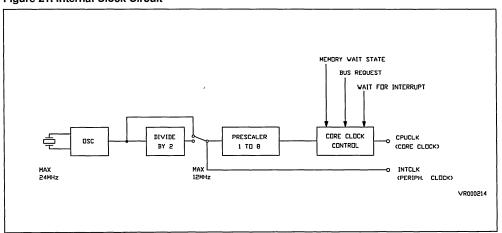

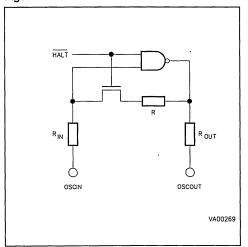

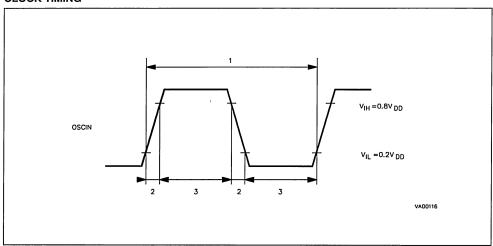

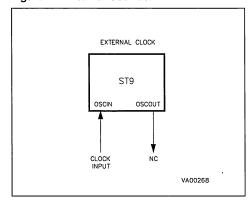

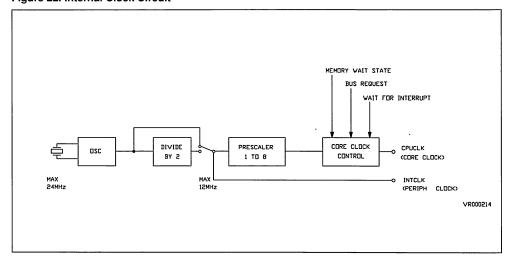

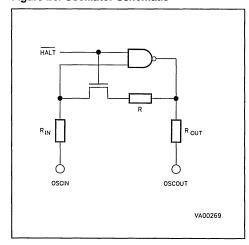

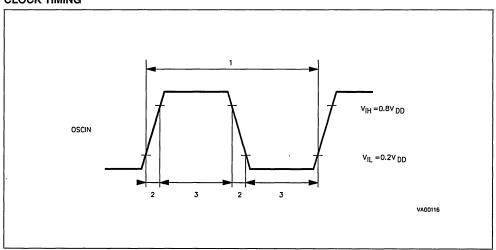

The ST902X Clock Generator module generates the internal clock for the ST9 core and the on-chip peripherals, it may be driven by an external quartz crystal circuit, connected to the OSCIN and OSCOUT pins, or by an external pulse generator connected to OSCIN (Figure 22, Figure 23).

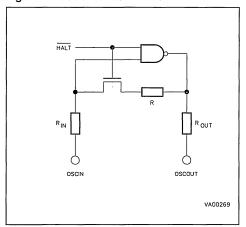

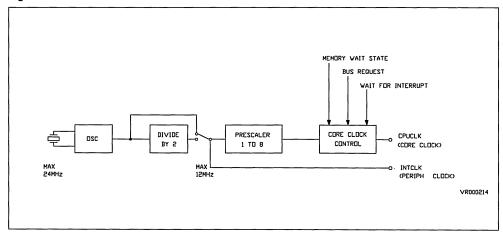

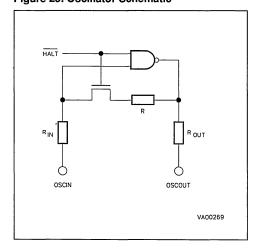

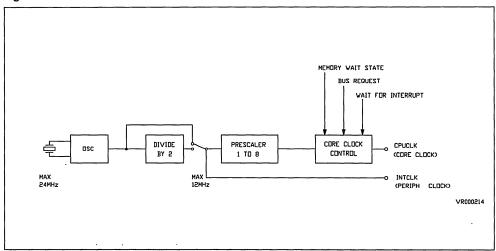

The conceptual schematic of the ST9 internal clock circuit is shown in Figure 24.

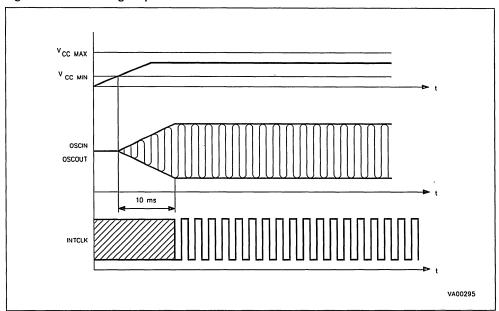

Figure 22. Crystal Oscillator

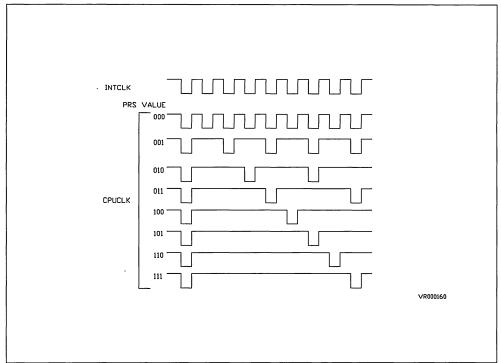

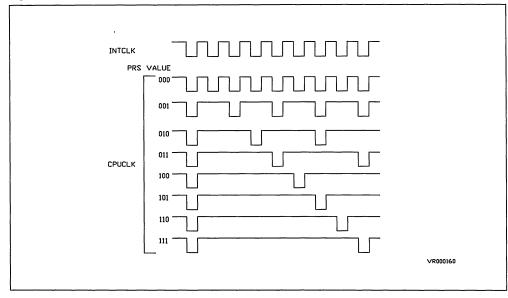

The maximum external frequency of the ST9 is 24 MHz, while the maximum internal operating frequency is 12 MHz, thus a programmable divide by two circuit is present, this allows the use of high frequency crystals for economy, or low frequency crystals for reduction in radiated noise. This divider is active upon exit from the reset condition, the user may bypass the divide by two circuit by setting the DIV2 bit (MODER.5). The resulting clock from this section is named INTCLK, the internal clock which drives the timebases of the on-chip clock for the ST902X peripherals (eg the Multifunction Timer, Timer/Watchdog, Serial Communications Interface) and also the input of the CPU prescaler

Figure 23. External Oscillator

Figure 24. Internal Clock Circuit

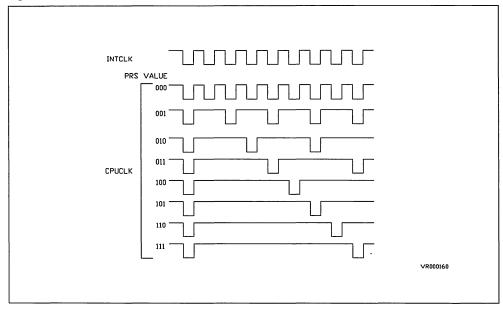

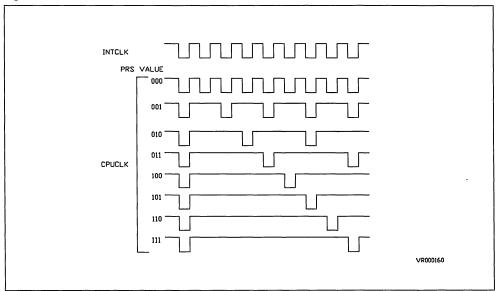

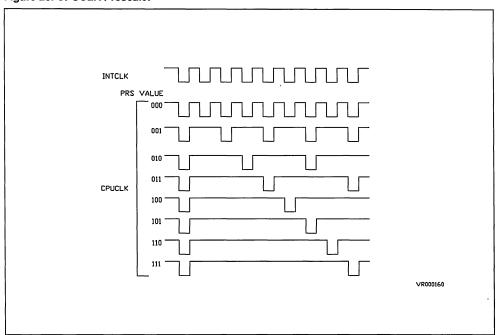

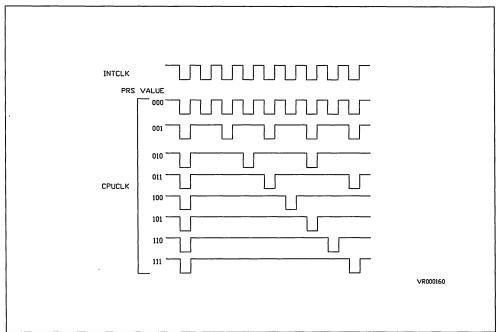

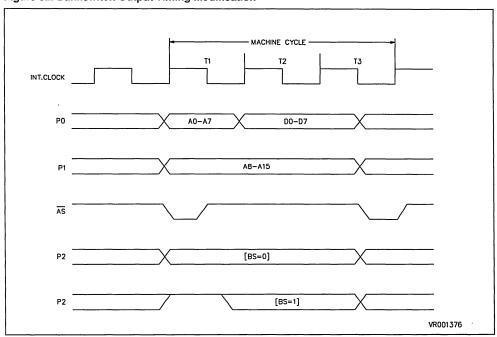

section. The CPU of the ST9 includes the instruction execution logic and may run at different rates according to the setting of the PRS2,PRS1 and PRS0 bits (MODER.4-2) (Figure 25). The resulting clock is named CPUCLK and it should be noted that this does not maintain a 50% duty cycle, but stretches the high level of the clock until completion. The CPUCLK prescaler allows the user to slow down the program execution time (eg for lower power consumption), while time-critical sections of the program may tune the CPUCLK execution speed to high speed and then restore it to its original speed.

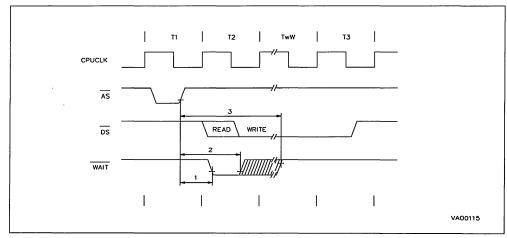

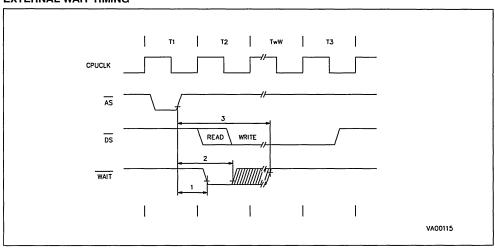

#### **Wait States**

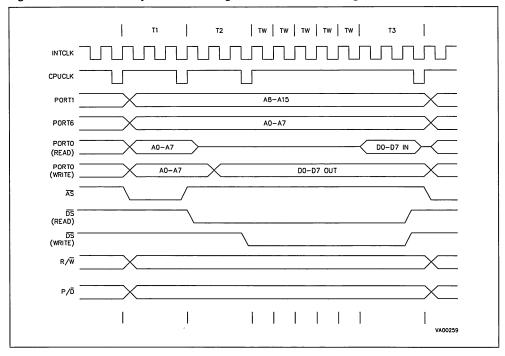

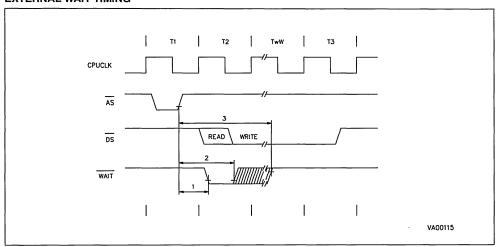

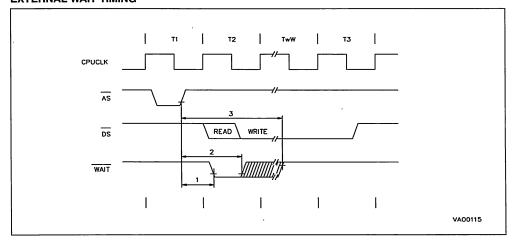

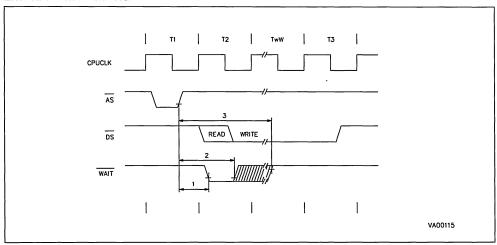

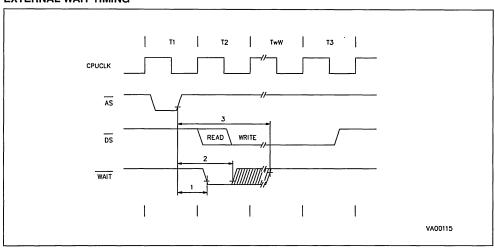

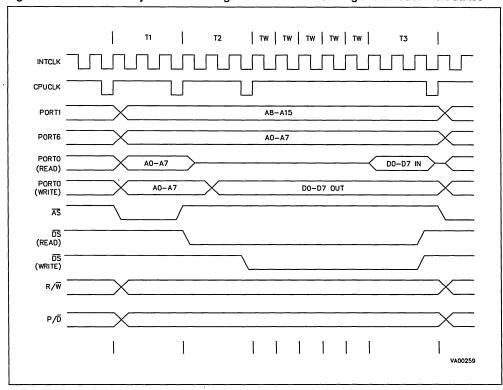

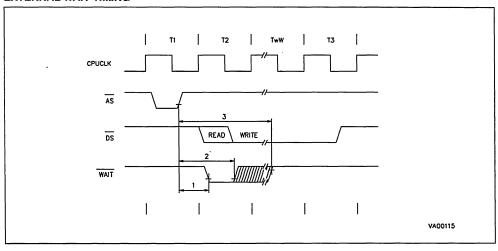

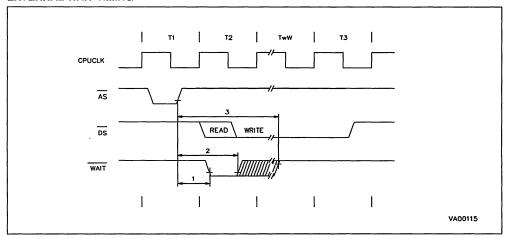

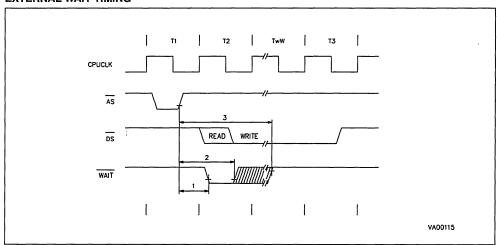

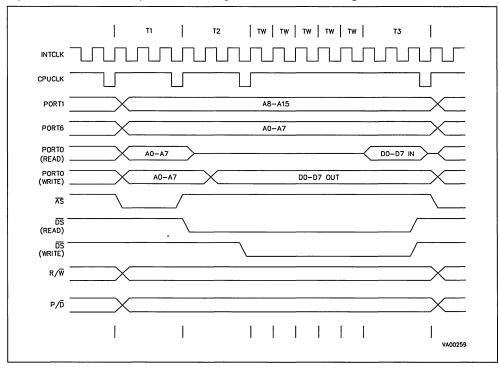

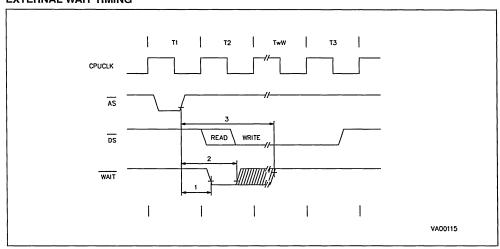

The output from the prescaler can also be affected by wait states. Wait states from two sources allow the user to tailor timing for slow external memories or peripherals.

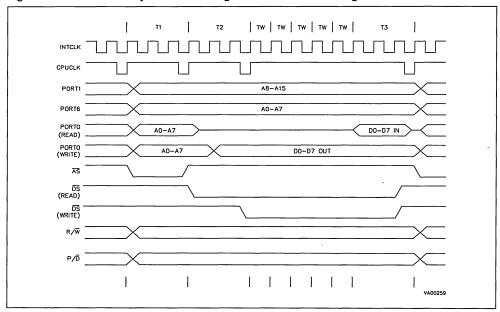

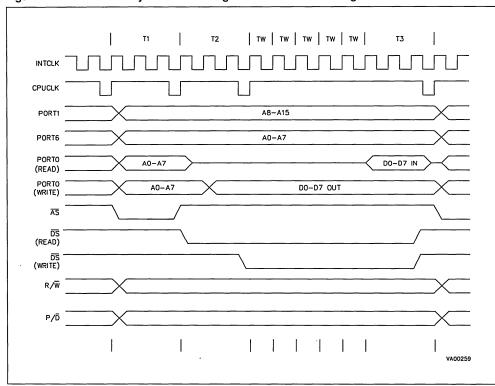

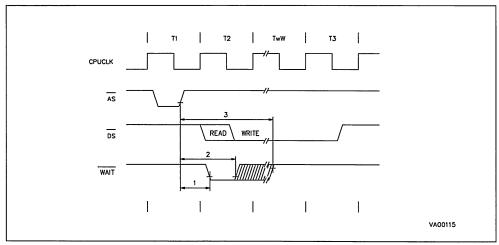

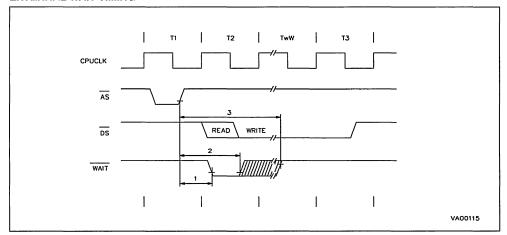

The internal Wait State generator will insert from 0 to 7 wait states, independently programmable for both Program and Data Spaces, via the Wait Control Register WCR (R252, page 0). The second source of wait states is the external Wait input pin when enabled as the Alternate Function. Figure 26 shows the External Memory Interface timing as it relates to CPUCLK prescaling of 2 and 5 added wait states. The added wait states are derived from the INTCLK clock cycle, not CPUCLK. Internal memory is always accessed with no Wait states.

Figure 25. CPUCLK Prescaler

Figure 26. External Memory Interface Timing with CPUCLK Prescaling and 5 Added Wait States

#### Halt and Wait for Interrupt (WFI) States

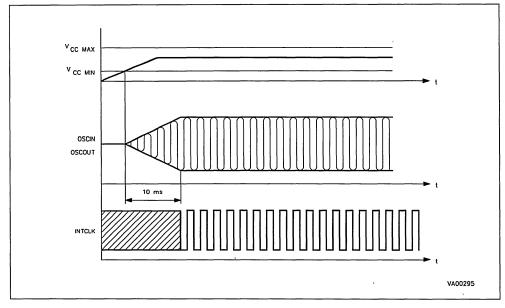

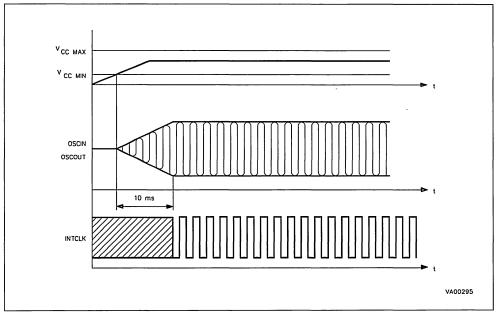

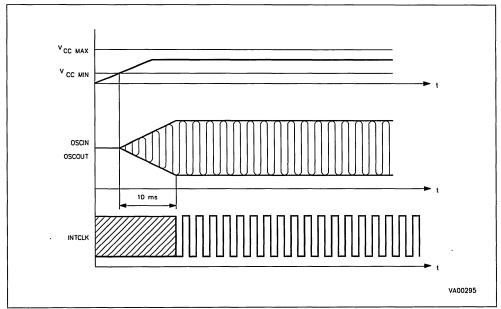

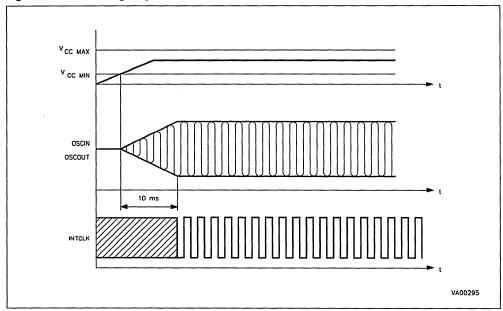

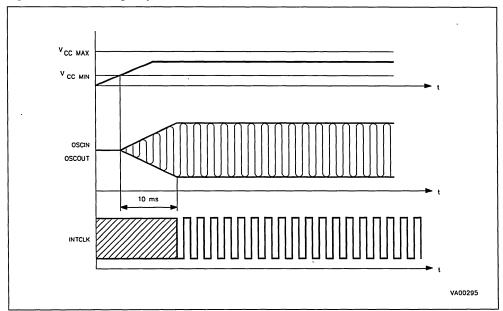

The schematic of the on-chip oscillator circuit is shown in figure 27. The HALT condition, caused by the execution of the HALT instruction, disables the oscillator, forcing OSCOUT high. This places the ST902X into the lowest power mode. The exit of the HALT condition and the restarting of the oscillator requires a RESET pulse with a minimum duration of 10ms (figure 28). It must be noted that if the TIMER/WATCHDOG has the WATCHDOG mode enabled, a HALT instruction will not disable the oscillator; this is to avoid stopping the Watchdog if, by an error, a HALT instruction is executed. If this occurs, the ST902X runs in an endless loop terminated only by the Watchdog reset (or hardware reset).

The WFI (Wait for Interrupt) instruction suspends program execution until an interrupt request is acknowledged. During this period, DMA transactions are allowed if their priority is higher than or equal to the CPL level; the ST902X returns to WFI

Figure 27. Oscillator Schematic

mode after completion of the DMA transfer. The CPUCLK is halted during Wait For Interrupt while INTCLK continues to run, thus the power consumption of the processor is lowered by the CORE power consumption value.

The External Memory Interface lines status during HALT and WFI modes is shown in Table 5.

Table 5. External Memory Interface Line Status During WFI and Halt

| P0 (AD0-AD7) | High Impedance                   |

|--------------|----------------------------------|

| P1 (A8-A15)  | Forced to Address of Next Opcode |

| ĀS           | Forced High                      |

| DS           | Forced High                      |

| R/W          | Forced High                      |

#### Reset

The processor Reset overrides all other conditions and forces the ST902X to the reset state. During Reset, the internal registers are set to their Reset values, as shown in Table 6 for the system and Page 0 Registers. The I/O Ports pins are set to the Bidirectional Weak Pull-up mode. The user must then initialize the ST902X registers to give the required functions.

The Reset condition can be generated from the external RESET pin or by the on-chip TIMER/WATCHDOG operating in Watchdog mode. To guarantee the complete reset of the ST902X, the RESET input pin must be held low for at minimum of 53 crystal periods in addition to the crystal start-up period. The Watchdog RESET will occur if the Watchdog mode is enabled (WDEN, WCR.6, is reset) and if the programmed period has elapsed without the code 0AAh,55h written to the appropriate register. The input pin RESET is not driven low by the on-chip reset generated by the TIMER/WATCHDOG.

Figure 28. Reset Timing Requirements from Halt State

Table 6. System and Page 0 Reset Values

| Register<br>Number | System Register<br>Reset Value | Page 0 Register<br>Reset Value |

|--------------------|--------------------------------|--------------------------------|

| F                  | (SSPLR) = undefined            | Reserved                       |

| E                  | (SSPHR) = undefined            | (SPICR) = 00h                  |

| D                  | (USPLR) = undefined            | (SPIDR) = undefined            |

| С                  | (USPHR) = undefined            | (WCR) = 7Fh                    |

| В                  | (MODER) = E0h                  | (WDTCR) = 12h                  |

| А                  | (Page Ptr) = undefined         | (WDTPR) = undefined            |

| 9                  | (Reg Ptr 1) = undefined        | (WDTLR) = undefined            |

| 8                  | (Reg Ptr 0) = undefined        | (WDTHR) = undefined            |

| 7                  | (FLAGR) = undefined            | (NICR) = 00h                   |

| 6                  | (CICR) = 87h                   | (EIVR) = x2h                   |

| 5                  | (PORT5) = FFh                  | (EIPLR) = FFh                  |

| 4                  | Reserved                       | (EIMR) = 00h                   |

| 3                  | (PORT3) = FFh                  | (EIPR) = 00h                   |

| 2                  | (PORT2) = FFh                  | (EITR) = 00h                   |

| 1                  | (PORT1) = FFh                  | Reserved                       |

| 0                  | (PORT 0) = FFh                 | Reserved                       |

During the RESET state,  $\overline{\rm DS}$  is held low and  $\overline{\rm AS}$  is toggled with the frequency of the crystal (OSCIN) divided by 32. This condition may be recognized by external peripherals as a Reset condition. It may also be used to enable the synchronization of multiple ST902X running from the same clock in a

multi-processing or high security majority voting system.

Once the Reset pin reaches a logical high, the ST902X fetches the starting address from locations 0 and 1 of the program space and begins program execution from this address after 67 crystal cycles.

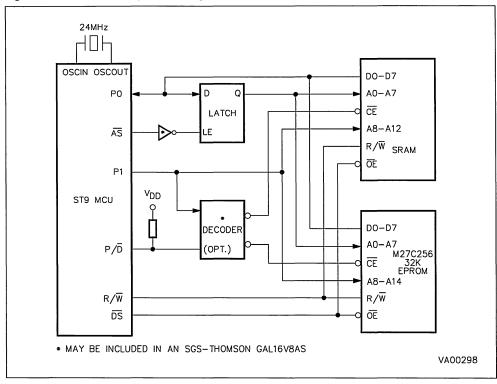

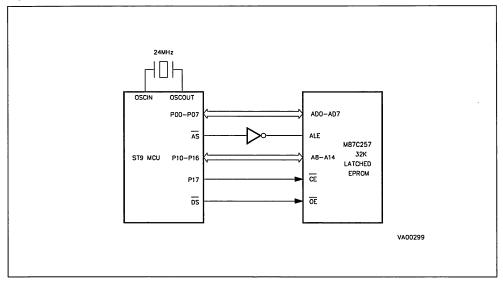

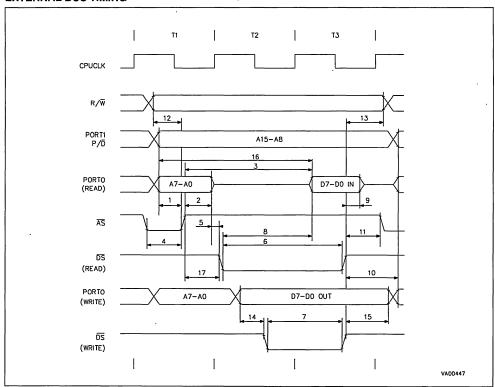

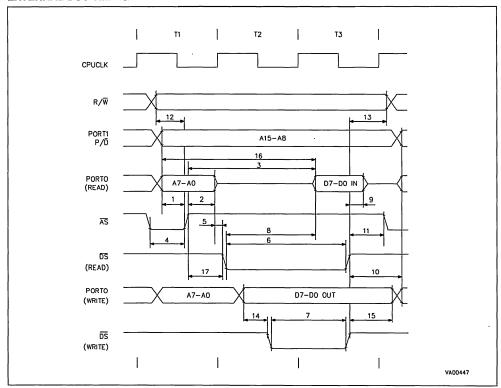

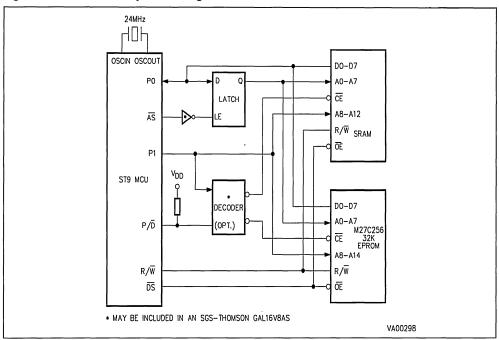

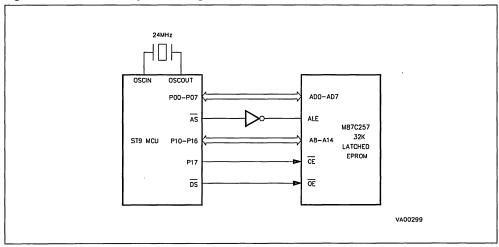

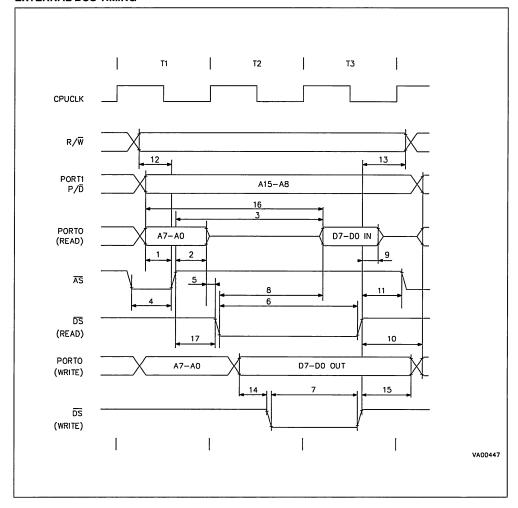

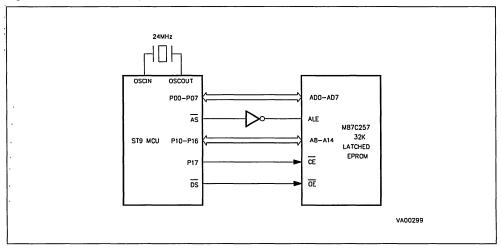

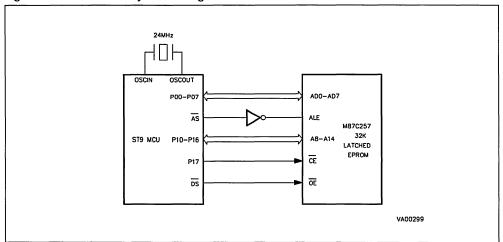

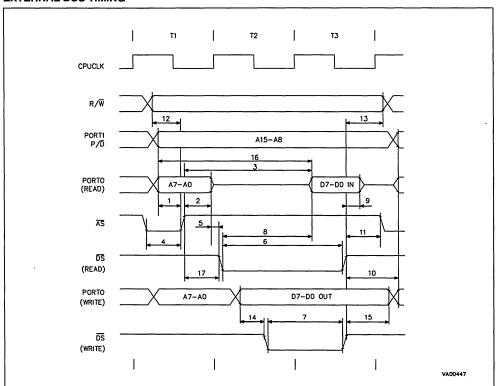

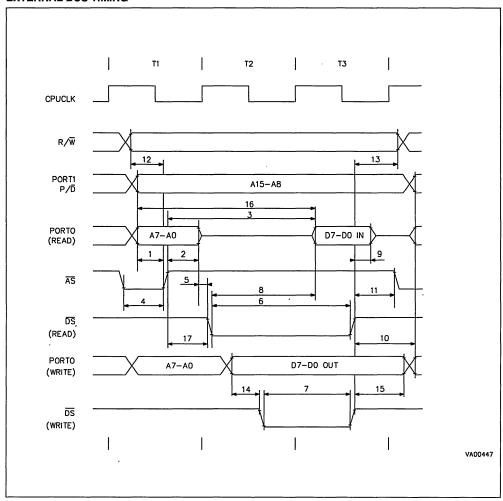

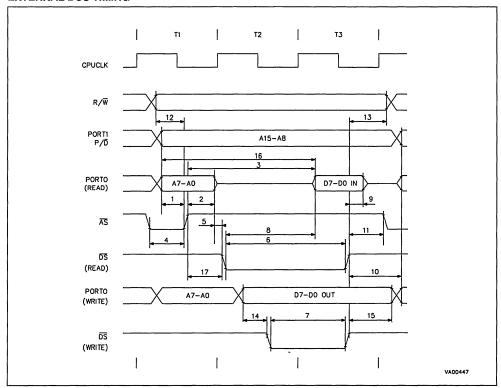

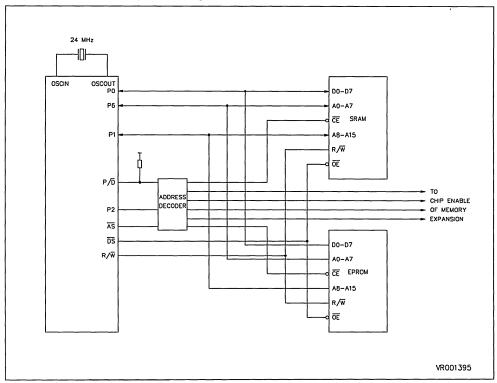

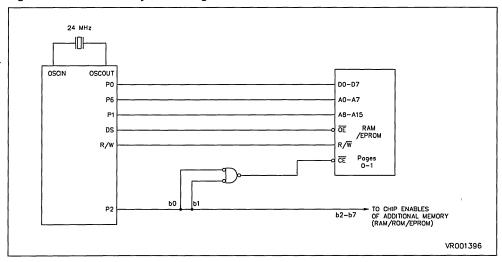

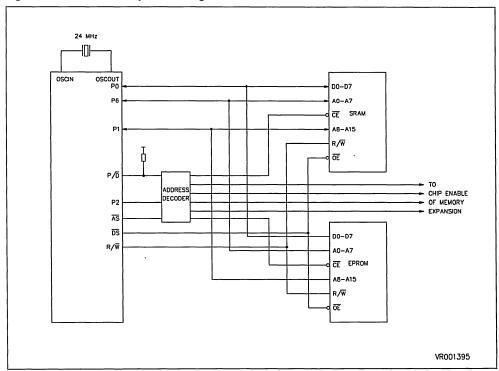

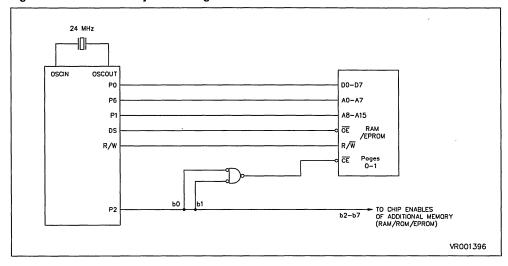

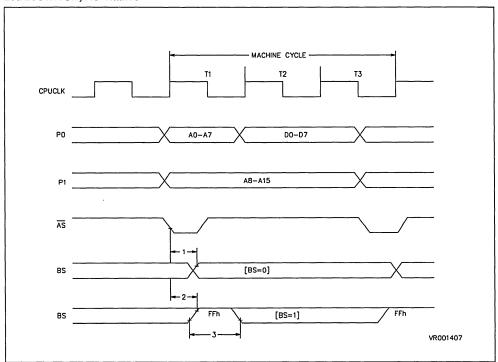

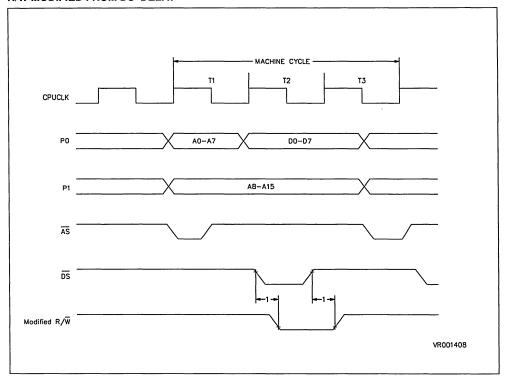

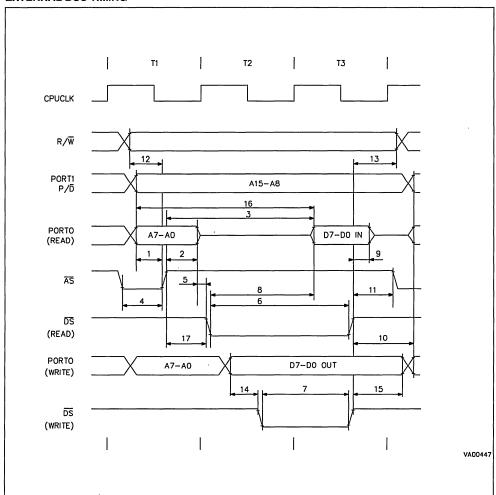

#### INTERFACING TO EXTERNAL MEMORY

External Memory and/or peripherals may be connected to the ST902X through its External memory interface. This provides the multiplexed Address bits A0 to A7 and Data bits D0 to D7 as Alternative Functions of Port 0, and the higher order address bits A8 to A15 as Alternative Functions of Port 1, giving the full 64K bytes addressing capability. The Program/Data (P/ $\overline{D}$ ) output, when selected as an Alternate function, allows external decoding to provide for the two independent pages of 64K bytes for Program and Data.

Data transfer timing is generated by the Address strobe  $\overline{AS}$  and the data strobe  $\overline{DS}$ . Address strobe low indicates that the data present on AD0 to AD7

is the low order address and is guaranteed valid on the rising edge of  $\overline{AS}$  allowing for latching of the address bits by an external latch. Data transfer direction is indicated by the status of the Read/Write (R/W) pin; for write cycles (R/W low), data out is valid at the falling edge of  $\overline{DS}$ ; for read cycles (R/W high), data in must be valid prior to the rising edge of  $\overline{DS}$ . The Data Strobe low period may be extended to accomodate slow external devices by the adding of internally generated wait cycles (0 to 7 cycles for program and/or data memory maps) or by an external input on the WAIT input pin also available as an Alternative Function of an I/O bit. Suggested interface circuits are shown in Figure 20 and Figure 30.

Figure 29. External Memory Addressing Circuit

#### **INTERFACING TO EXTERNAL MEMORY** (Continued)

Figure 30. External Memory Addressing Circuit

#### **BUS CONTROL**

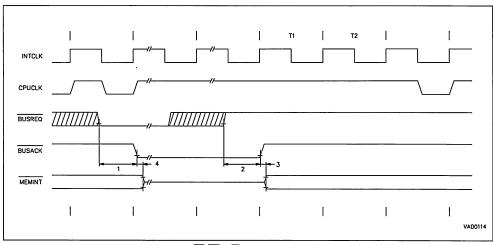

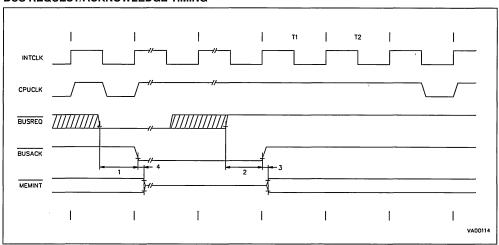

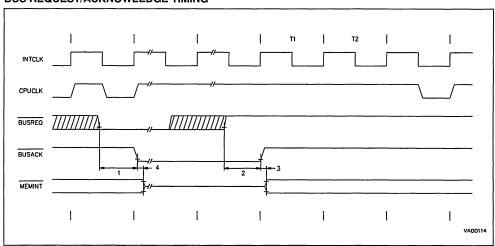

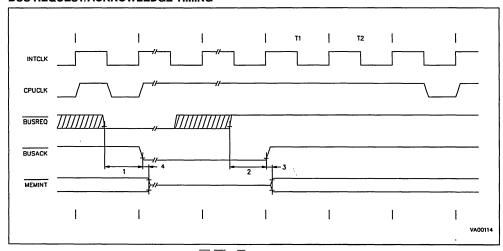

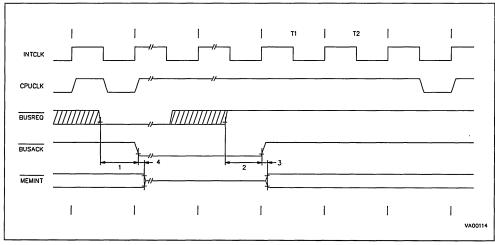

Multi-processing or external program testing may be accomplished by disabling the I/O ports used for external memory addressing and the associated timing signals.

#### High Impedance Mode

The user may place the External Memory Interface (I/O ports 0 and 1, Address Strobe, Data Strobe and Read/Write) into the high impedance state by setting the HIMP bit (MODER.0). External test equipment may then drive the memory lines for automatic test, external memory validation or programming. The ST9 will continue to execute internal programs, providing no external memory is addressed, allowing the execution of security routines without showing externally the addresses used.

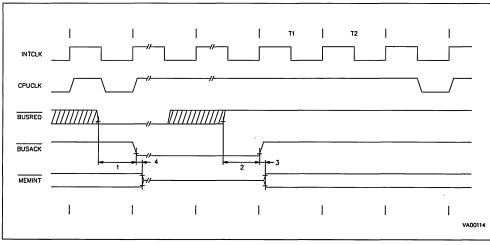

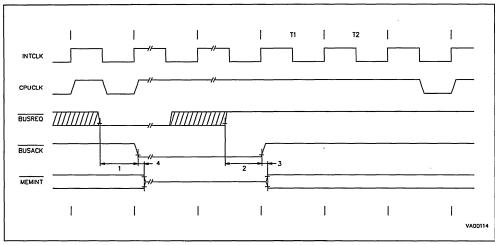

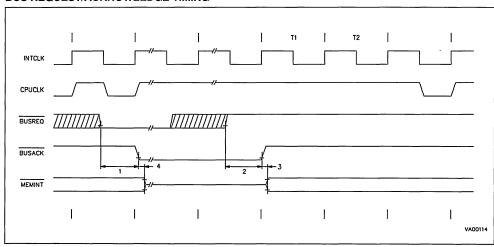

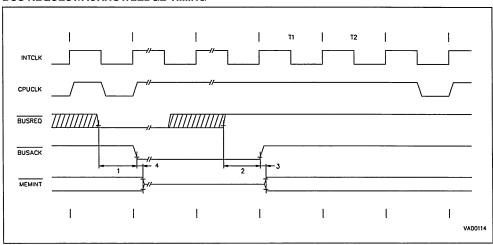

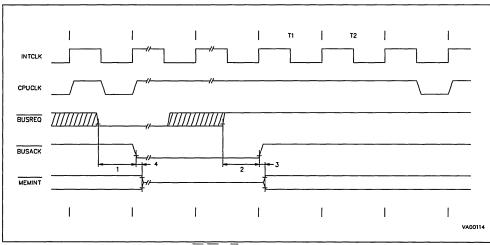

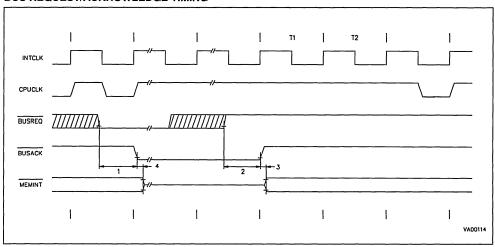

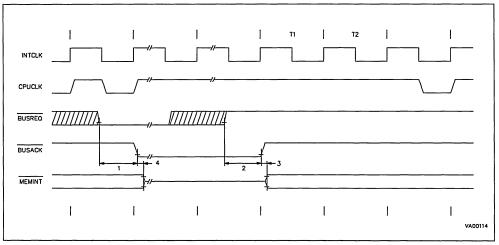

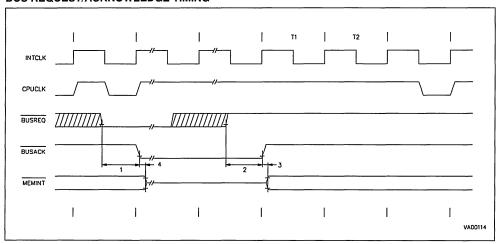

#### Bus Request/Acknowledge

The External Memory Interface address ports and timing signals may be forced to their high impedance state by utilizing the BUSREQ, Bus Request, and BUSACK, Bus Acknowledge, signals available as Alternate Functions of two I/O pins (please refer to the pin configuration drawings for availability of these lines for the package chosen). The signals, BUSREQ and BUSACK, must be enabled by setting the BRQEN bit (MODER.1). Once enabled, a low level detected on the BUSREQ pin at the start of an internal machine cycle will cause the stretching of the CPUCLK, and BUSACK to go low indicating that the External Memory Interface is disabled. The BUSREQ pin is then continuously monitored, and when sampled high, the External Memory Interface pins are driven by the ST9 within two INTCLK cycles.

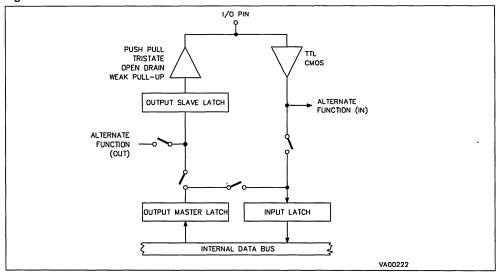

#### I/O PORTS

#### Summary of Function

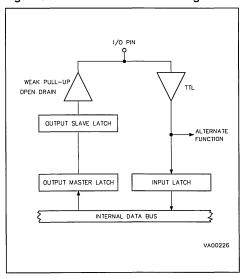

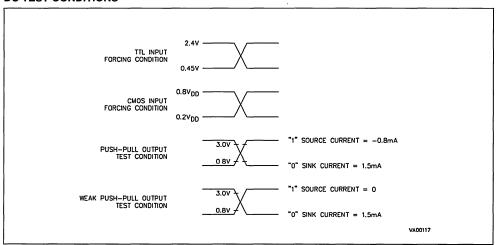

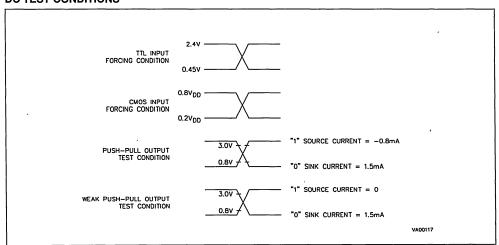

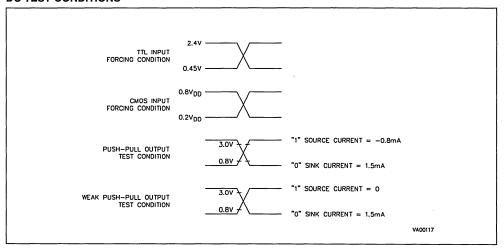

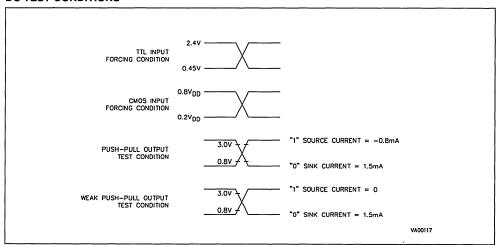

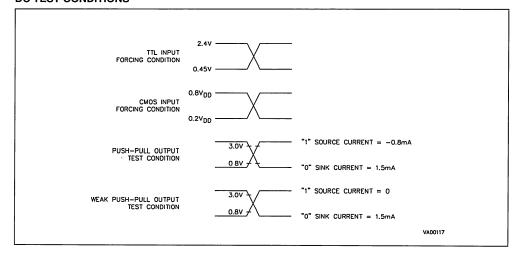

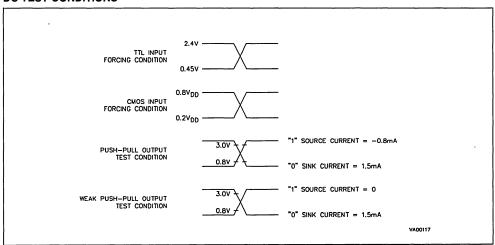

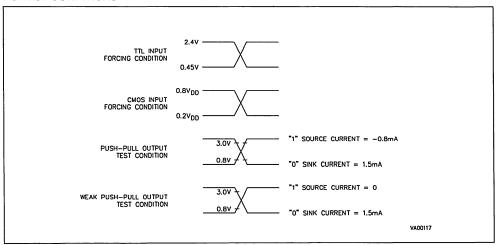

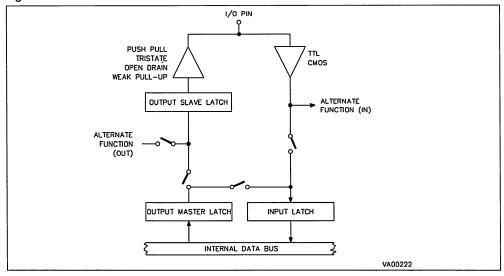

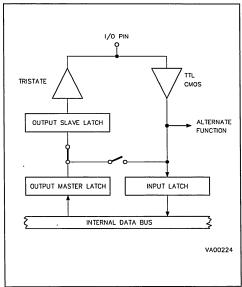

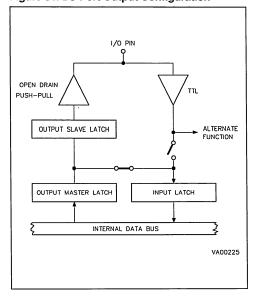

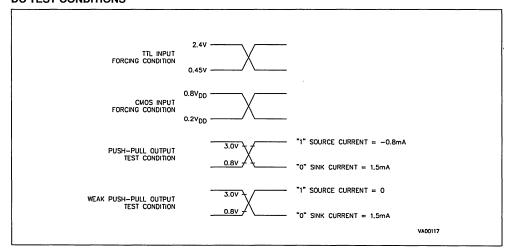

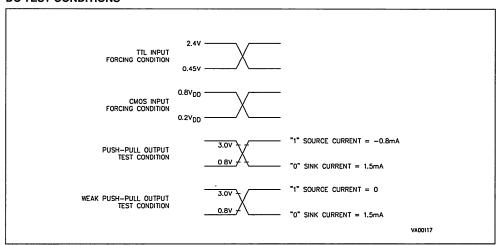

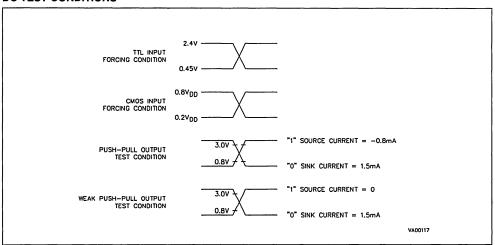

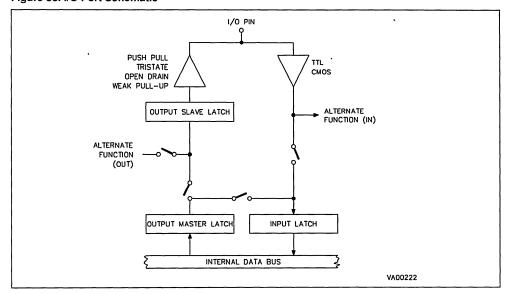

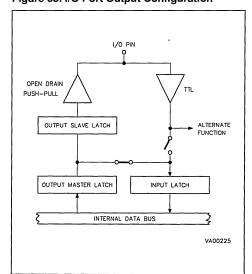

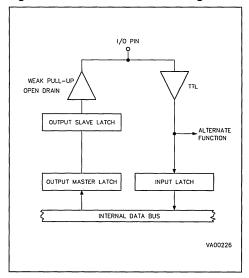

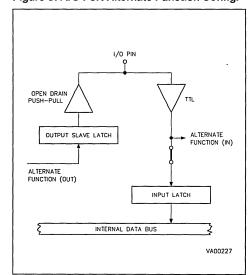

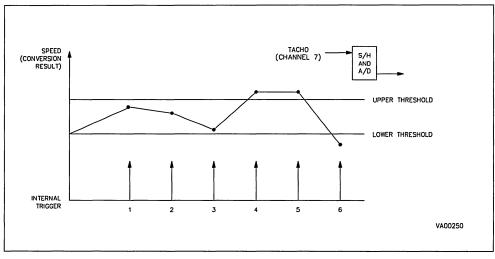

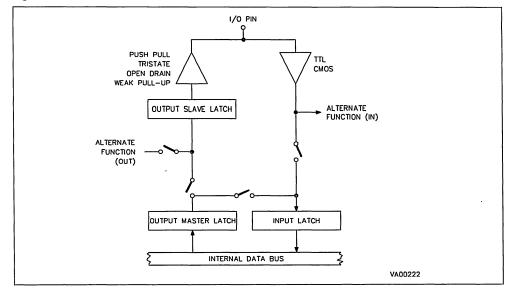

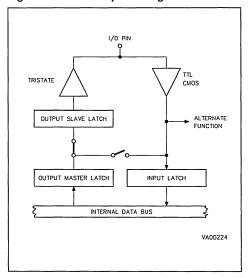

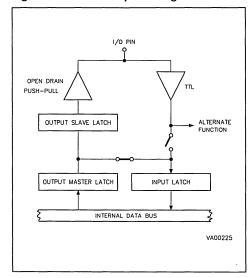

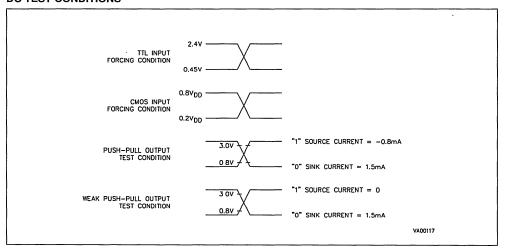

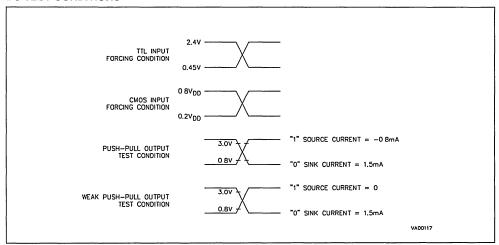

For each package type of the ST902X, only eight pins have a Reserved function: VDD, VSS, RESET,  $\overline{AS}$ ,  $\overline{DS}$ , R/ $\overline{W}$ , OSCIN, OSCOUT. All other pins are available as Input/Output (I/O) for the user, grouped into Ports of 8 bits. These may be programmed to be Input, Output, Bidirectional or Alternate Function (Peripheral or Memory Interface), on a bit by bit basis, at any time. When programmed as an Input the pin may be set to TTL or CMOS input threshold levels, while, when programmed as Output, Push-Pull or Open Drain configuration may be selected. The Bidirectional mode sets the pin with a weak pull-up resistor to V<sub>DD</sub> or to Open Drain, allowing bidirectional communication with external logic. The Alternate Function setting is predetermined for each pin as shown in the Pin Configuration Table.

The circuitry of the I/O port allows for several ST902X peripheral functions to address, as Alternate Functions, the same pin, for both input and output, the user selects which peripheral function is to be active by enabling its individual Input or Output function. This multi-function I/O capability of the ST902X allows for easy adaptation to external circuits. The options available for each bit are summarized in Table 8

Table 7. I/O Setting Options

| Input               | TTL Thresholds  |

|---------------------|-----------------|

| Imput               | CMOS Thresholds |

| Output              | Open Drain      |

| Culput              | Push Pull       |

| Bidirectional       | Open Drain      |

| Bidirectional       | Weak Pull-up    |

| Alternate Function  | Open Drain      |

| / itemate i unotion | Push Pull       |

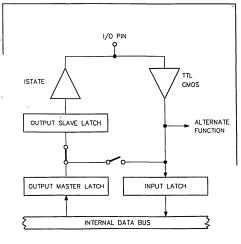

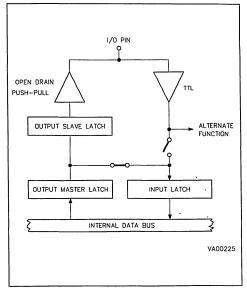

#### I/O Port Configuration

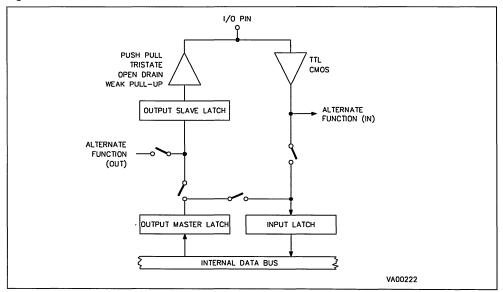

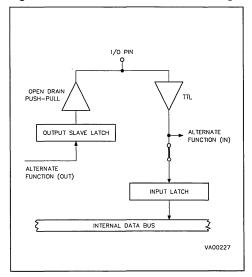

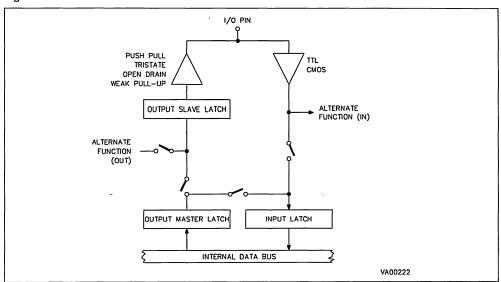

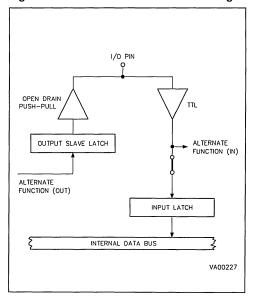

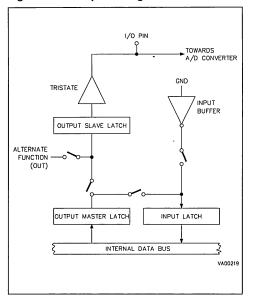

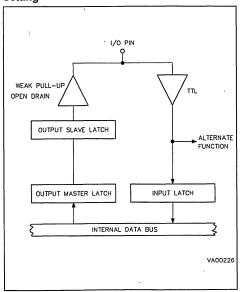

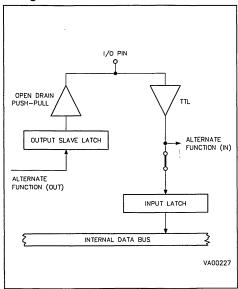

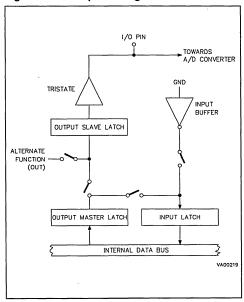

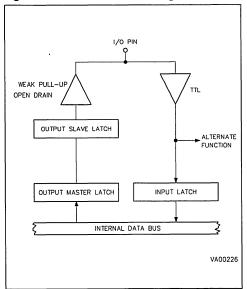

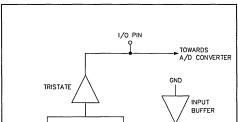

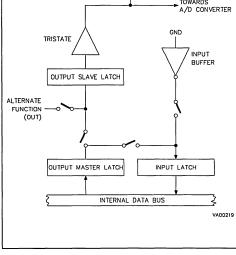

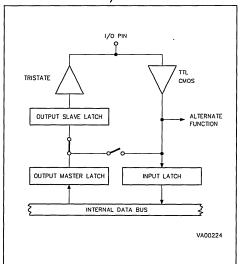

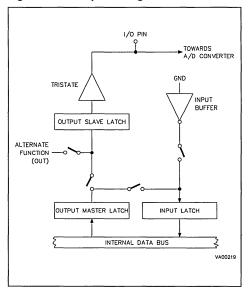

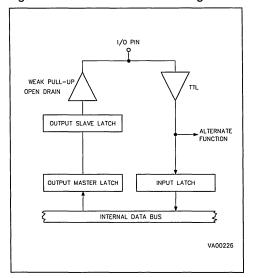

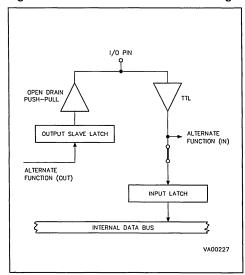

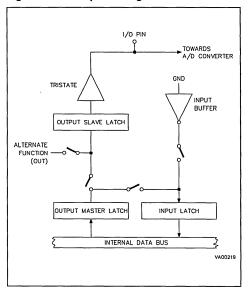

The configuration of each general I/O bit of the ST902X is set by the corresponding bits in three I/O Port control registers. These affect the status of the input and output buffers of the pin, and enable the Alternate function Outputs. Alternate Function inputs are always connected, and are used by enabling the function from within the configuration registers of the relevant peripheral function. The configuration of an I/O bit is shown in Figure 31. Outputs follow a Master/Slave buffer, data is transferred from the ST9 internal data bus at the beginning of the machine cycle, and, if enabled as

Figure 31. I/O Port Schematic

#### I/O PORTS (Continued)

output, is passed to the output latch at the end of the cycle. This synchronization allows for the Bidirectional use of the pin without potential conflicts.

Configuration Registers. Three registers are used to allow the setting of each pin, generically PxC2R, PxC1R, PxC0R, where x relates to the 8 bit I/O port in which the bit is present. The setting of the corresponding bit in each register to achieve the desired functionality of the I/O pin is shown in

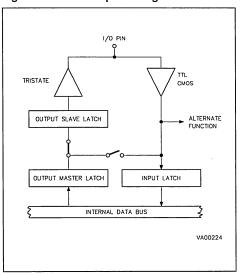

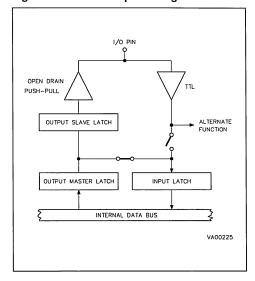

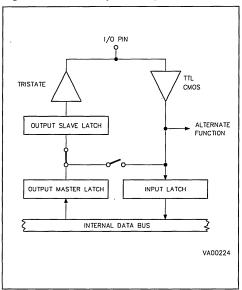

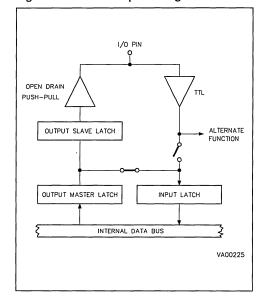

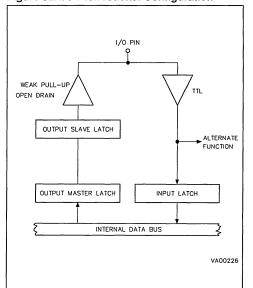

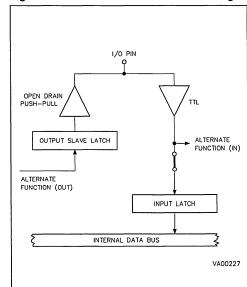

The effect of the configuration settings of Table 8 on the I/O ports structure is shown in Figures 32 to

**Table 8. Port Configuration Status Bits**

| PxC2n             | 0   | 1   | 0   | 1   | 0    | 1   | 0   | 1   |

|-------------------|-----|-----|-----|-----|------|-----|-----|-----|

| PxC1n             | 0   | 0   | 1   | 1   | 0    | 0   | 1   | 1   |

| PxC0n             | 0   | 0   | 0   | 0   | 1    | 1   | 1   | 1   |

| Pxn Configuration | BID | BID | OUT | OUT | IN   | IN  | AF  | AF  |

| Pxn Output        | WP  | OD  | PP  | OD  | н    | ні  | PP  | OD  |

| Pxn Input         | TTL | TTL | TTL | TTL | CMOS | TTL | TTL | TTL |

#### Legend:

= Port х = Bit

BID = Bidirectional

= Input

OUT = Output

AF = Alternate Function

WP = Weak Pull-up

OD = Open Drain

PP = Push Pull

= High Impedance

Figure 32. I/O Port Input Configuration

Figure 33. I/O Port Output Configuration

# I/O PORTS (Continued)

Figure 34. I/O Port Bidirectional Configuration

I/O Register Map

The Data Registers which correspond to the pin status (after configuration) of I/O port 0 to 5, are

Figure 35. I/O Port Alternate Function Config.

found in Group E of the Register File, for immediate access at all times, while the configuration registers and the Data Registers for Additional Ports are found within I/O pages (Group F) 2 and 3.

Figure 36. I/O Register Maps

|         |     |          |      |     |          | ·        |

|---------|-----|----------|------|-----|----------|----------|

| GROUP E |     | GROUP F  |      | PA  | GE       |          |

| DEC     | HEX |          | DEC  | HEX | 02       | 03       |

|         |     |          | R255 | RFF | RESERVED | RESERVED |

|         |     |          | R254 | RFE | P3C2     | RESERVED |

|         |     | ,        | R253 | RFD | P3C1     | RESERVED |

|         |     |          | R252 | RFC | P3C0     | RESERVED |

|         |     |          | R251 | RFB | RESERVED | RESERVED |

|         |     |          | R250 | RFA | P2C2     | RESERVED |

|         |     |          | R249 | RF9 | P2C1     | RESERVED |

|         |     |          | R248 | RF8 | P2C0     | RESERVED |

|         | •   |          | R247 | RF7 | RESERVED | HDC5     |

|         |     |          | R246 | RF6 | P1C2     | P5C2     |

| R229    | RE5 | P5D      | R245 | RF5 | P1C1     | P5C1     |

| R228    | RE4 | RESERVED | R244 | RF4 | P1C0     | P5C0     |

| R227    | RE3 | P3D      | R243 | RF3 | RESERVED | RESERVED |

| R226    | RE2 | P2D      | R242 | RF2 | P0C2     | RESERVED |

| R225    | RE1 | P1D      | R241 | RF1 | P0C1     | RESERVED |

| R224    | RE0 | P0D      | R240 | RF0 | P0C0     | RESERVED |

|         |     |          |      |     |          |          |

## I/O PORTS (Continued)

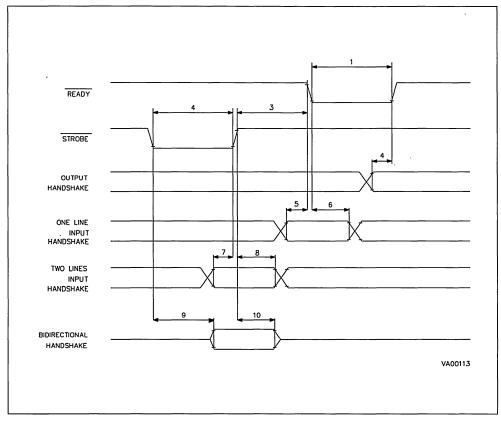

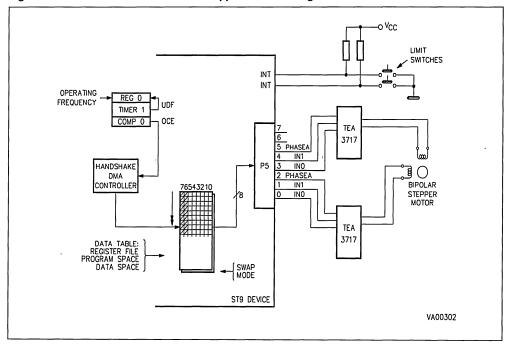

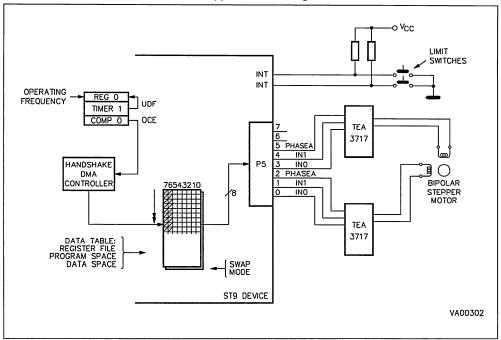

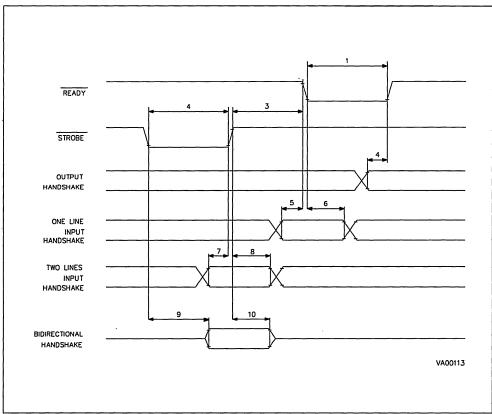

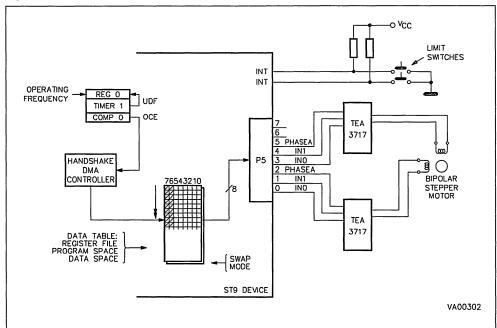

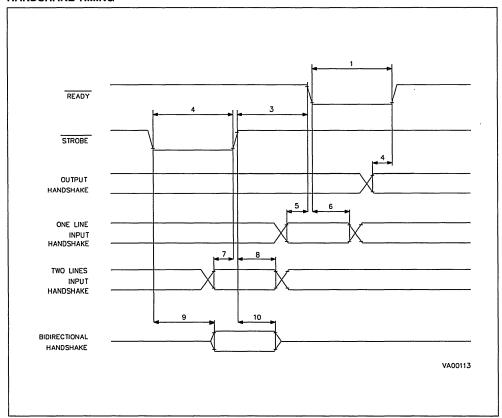

# Handshake and DMA

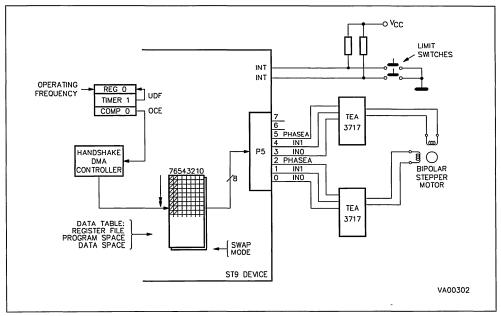

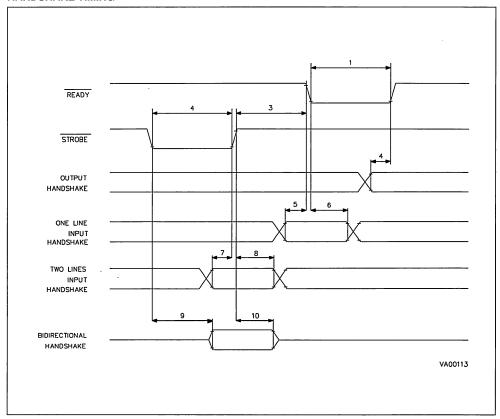

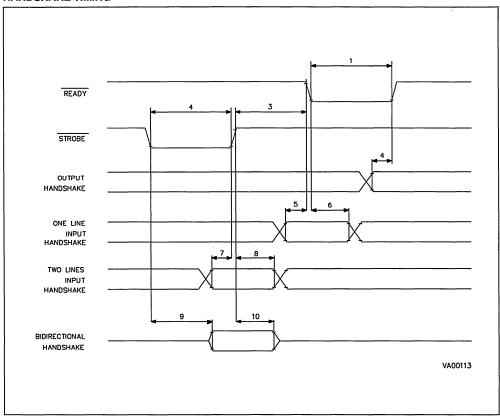

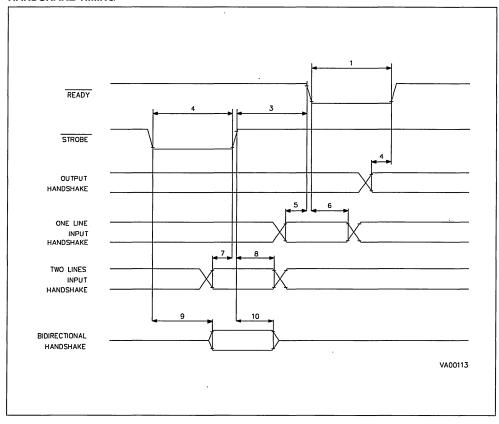

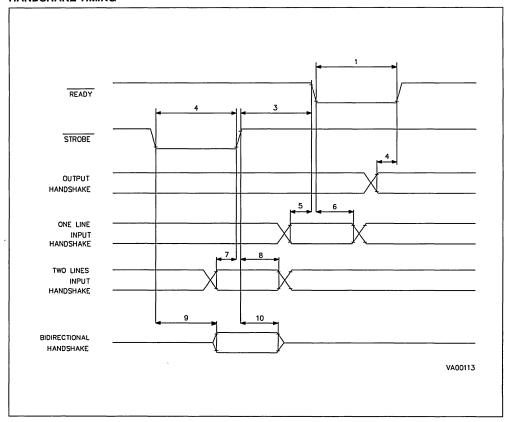

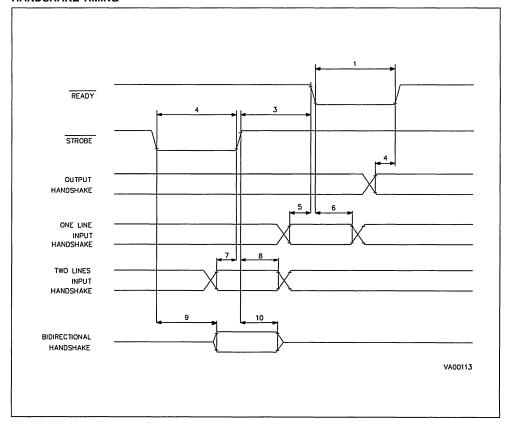

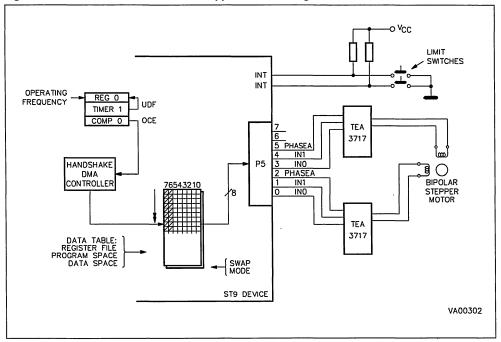

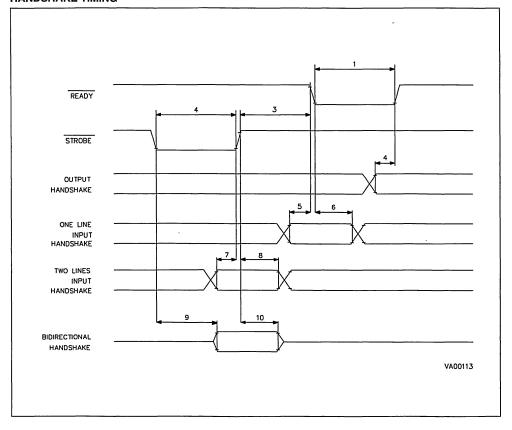

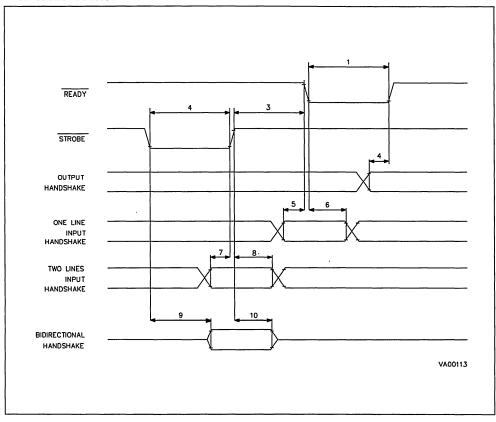

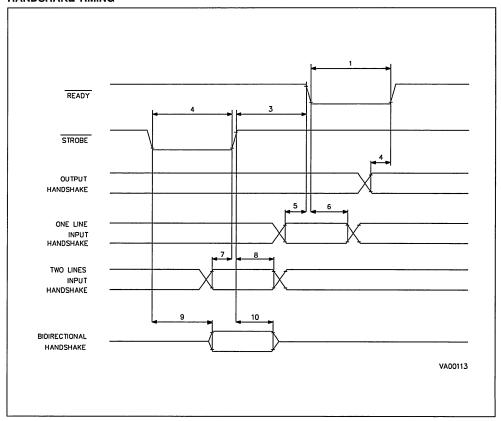

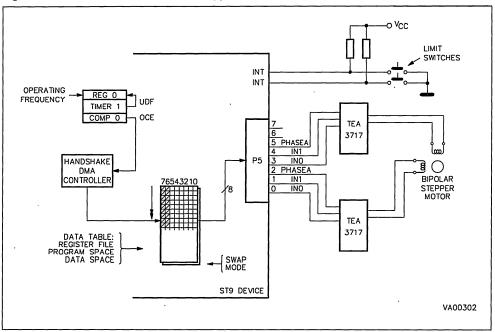

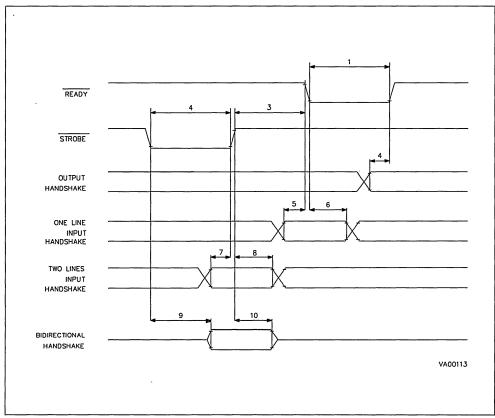

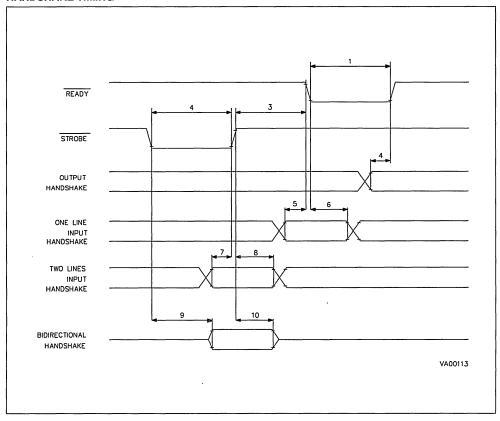

I/O Port 5 of the ST902X (please refer to the pin configuration table for the availability of all 8 bits of Port 5, as this is dependent on the package type) is able to support a parallel interface port with handshake capability. This allows one, two or four wire interconnecting handshake signals and facilitates very fast parallel transfer of data for input and output, or for the interconnection of peripheral devices requiring strobe signals for synchronization. Table 9 shows the available options for input and output status and strobe signals available as Alternate Functions of I/O port bits (see Pin Configuration). The Handshake configuration is set within the Handshake Control Register (HDCnR) for the relevant I/O port ni.

Data transfer through the parallel I/O port with handshake can also be triggered through a DMA channel. Timing is generated by the ST902X TIMER ON-CHIP EVENT strobe signal (see the TIMER section for information on generating these signals), which causes the programmed transfer of data to or from the memory source which can be Register File, Program space memory or Data

space memory. An example of application of this technique is shown in figure 37, a complex stepper motor timing sequence automatically being transferred from a table in the Register File (or memory spaces) to the stepper motor drivers. After initialization, this operation is transparent until the task (complex microstepping) is completed.

Table 9. Handshake Control Signal Options

| Mode          | Handshake<br>Lines | Names                            |  |

|---------------|--------------------|----------------------------------|--|

| Input         | 1                  | WRRDY                            |  |

| to<br>Port    | 2                  | WRSTB<br>WRRDY                   |  |

| Output        | 1                  | RDRDY                            |  |

| from<br>Port  | 2                  | RDSTB<br>RDRDY                   |  |

| Bidirectional | 4                  | WRSTB<br>WRRDY<br>RDSTB<br>RDRDY |  |

Figure 37. Handshake + DMA Used for Stepper Motor Driving

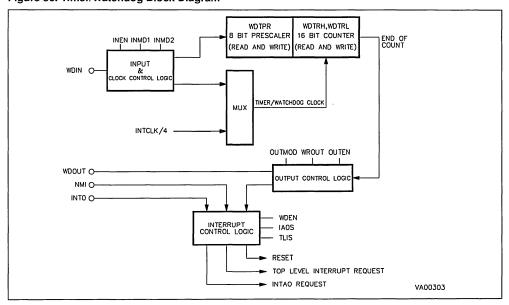

### TIMER/WATCHDOG

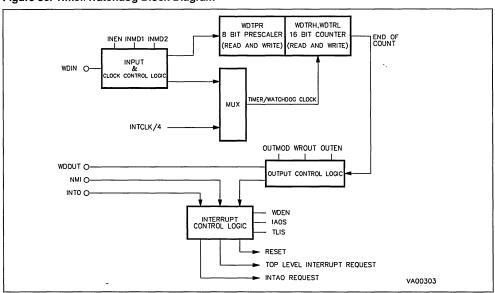

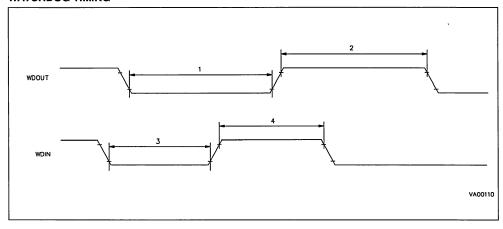

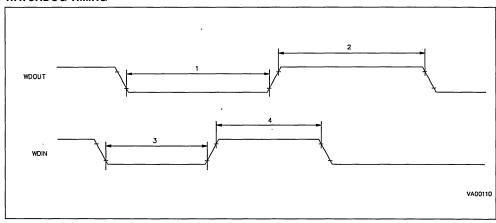

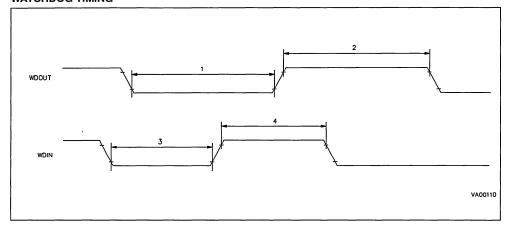

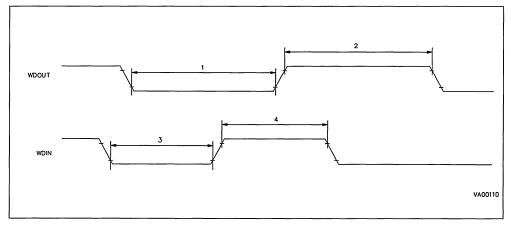

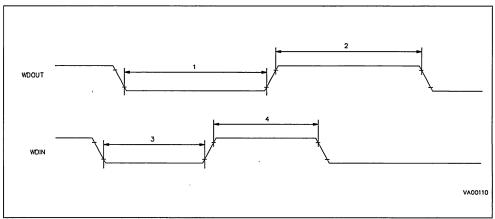

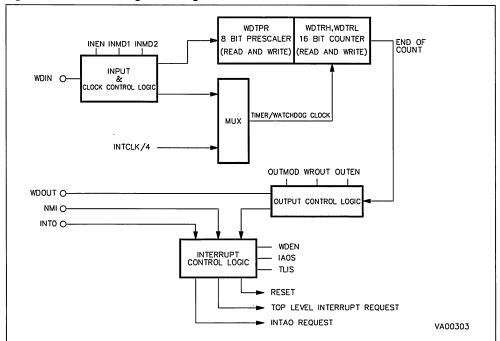

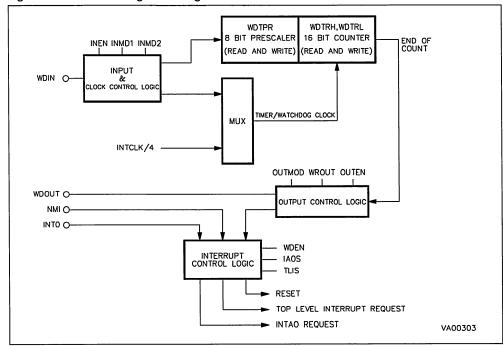

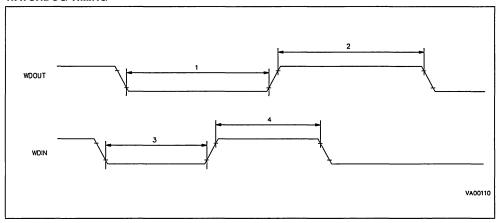

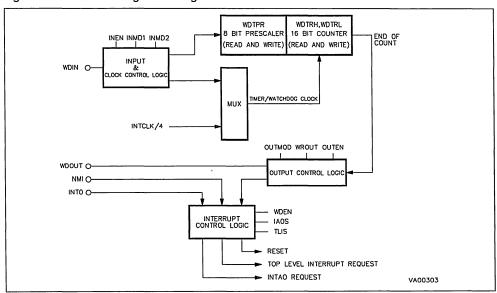

A 16 bit down-counter, complete with 8 bit prescaler, is integrated into the ST902X core. This is able to operate both as a general purpose timer with associated input and output pins for timing functions, and also as a Watchdog Timer offering a security against possible processor malfunctions due to external events.

### **Timer Modes**

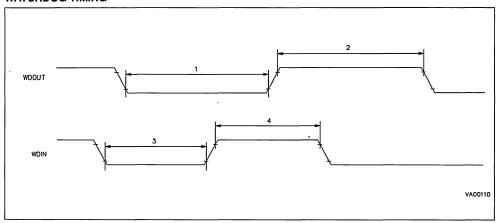

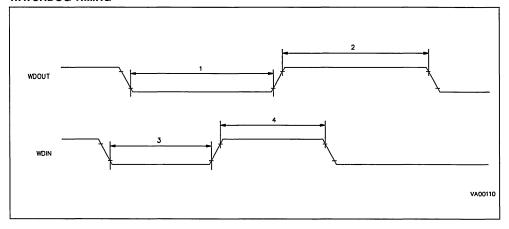

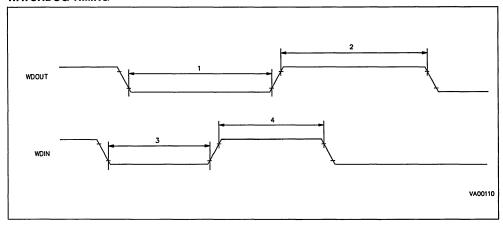

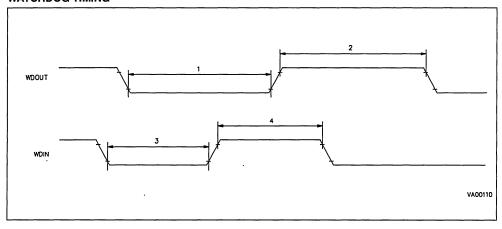

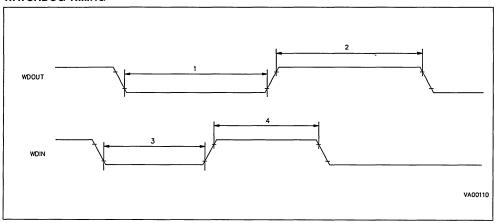

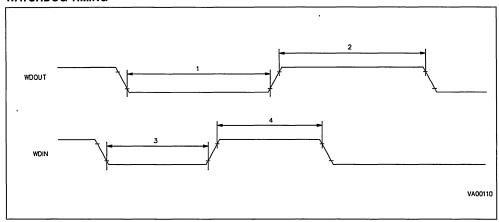

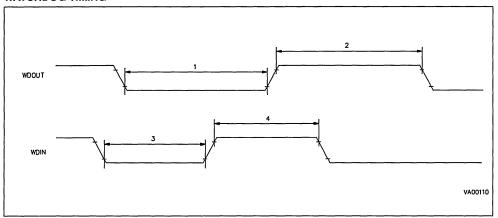

When operating as a Timer, with a timing resolution from 333ns to 5.59s (INTCLK = 12MHz), an input pin (WDIN) and output pin (WDOUT) may be selected as the Alternate Functions of two I/O pins. When WDIN is enabled by the user by setting INEN high (WDTCR.3) and the Alternate Function is set, 4 operating modes are available: The WDIN input may be programmed to act as an event counter input, with high to low transitions causing the counter to decrement (the time duration between the falling edges of the input clock must be at least 333ns, allowing a maximum input frequency of 3MHz). It may also be used for pulse width measurement by being selected as a counter clock gate signal (prescaler to the counter being driven by INTCLK/4), counting being enabled when WDIN is at a high level. Trigger and Re-trigger modes cause a reload of the timer user preset values (providing STSP, WDTCR.7 is active) for a high to low transition on WDIN at any time (Re-trigger mode) or when the counter is at the end of count (Trigger mode). The counter decrements at a rate driven by INTCLK/4.

The WDOUT pin, when set as the Alternate Function, is enabled by OUTEN high (WDTCR.0), and may either toggle the state of the I/O bit (frequency generation, OUTMD = "0", WDTCR.2) or pass the state of the WROUT bit to the output allowing PWM generation (OUTMD = "1") at the end of count (timer value = 0) condition.

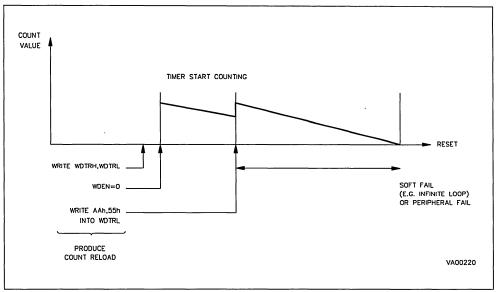

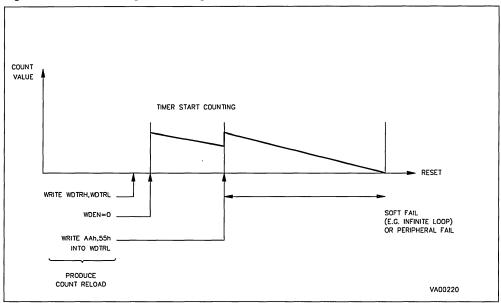

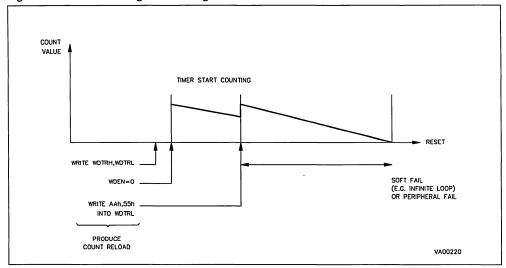

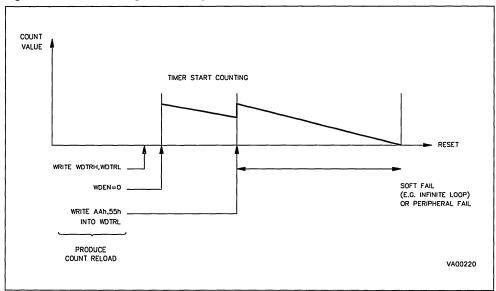

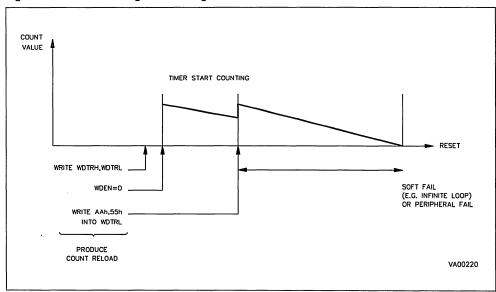

# Watchdog Mode

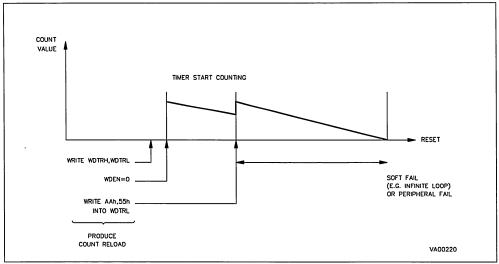

The timer functions may be disabled, and the Timer configured for a Watchdog operation by re-setting WDEN (WCR.6) to zero. Once the Watchdog has been selected it CANNOT be set back into the standard timer mode until the next Hardware Reset cycle. The user should set the watchdog timer prescaler and timer reload value before enabling the Watchdog mode. The Watchdog Timer must then be retriggered, causing the reloading of the timer value, by the operation of writing of the byte sequence 0AAh, 055h to the WDTLR register. If this is not done before the Watchdog counts to zero, the Watchdog Timeout condition occurs. This causes a Hardware Reset of the ST902X. The Watchdog reset signal is not output on the external RESET pin.

# TIMER/WATCHDOG (Continued)

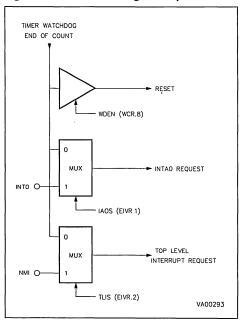

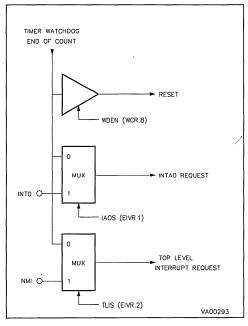

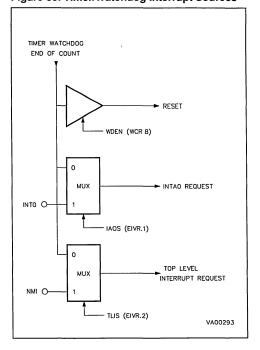

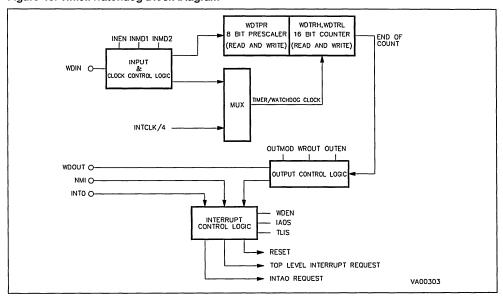

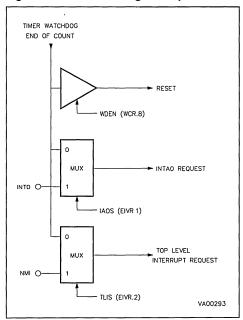

# Timer/Watchdog Interrupts

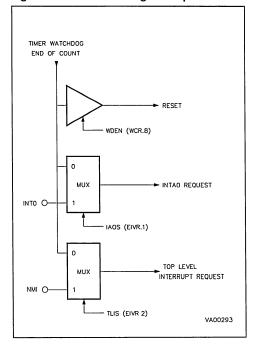

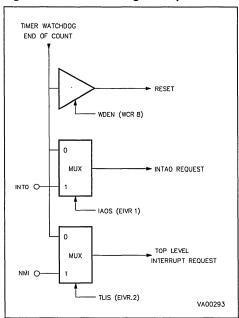

The Timer/Watchdog may provide several levels of interrupts selectable by the user. The Timer mode offers two interrupt sources, triggered on the timer value reaching 0, either a prioritized level (by taking the Interrupt priority channel from the External Interrupt INTAO) or by a top level, non-maskable interrupt (taking the external NMI input channel). The interrupt channels are multiplexed from the alternative source according to the status of the IAOS (EIVR.1) and TLIS (EIVR.2) bits as shown in Figure 40. Please refer to the ST9 Technical Manual for further details on changing the interrupt sources of the Timer/Watchdog. When the Watchdog mode is set (WDEN = "0"), the timer value equal to 0 event generates a Hardware reset of the ST902X. The Timer/Watchdog control registers are located within Page 0 of the Paged I/O register group.

Figure 40. Timer/Watchdog Interrupt Sources

Figure 39. Timer/Watchdog in Watchdog Mode

### MULTIFUNCTION TIMERS

The ST902X includes a 16 bit Multifunction Timers (MFT) in addition to the TIMER/WATCHDOG.

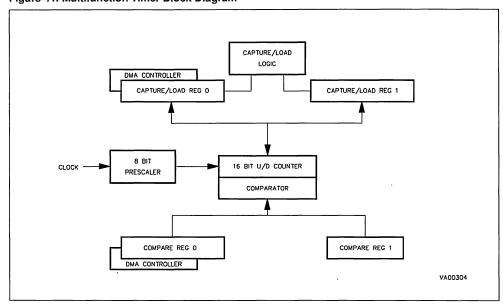

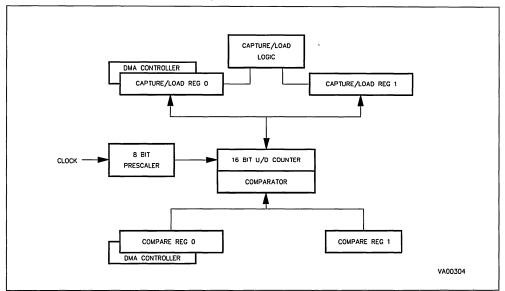

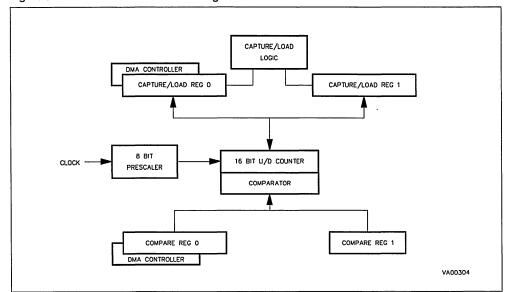

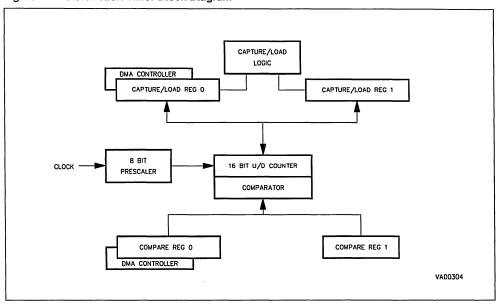

The Multifunction Timer is a 16 bit Up/Down counter, driven by the output of an 8 bit prescaler which may be driven by INTCLK/3 (giving a minimum timing resolution of 250ns at INTCLK = 12 MHz) or by an external source. This timer is supported by two 16 bit Comparison Registers for generating timed functions and two 16 bit Capture/Load Registers for timing and variable time-base functions. These features coupled with 2 input pins (TxINA and TxINB) and 2 output pins (TxOUTA and TxOUTB, where x = 0 or 1), available as Alternate Functions, give the timer 12 operating modes for virtually all required timing functions.

# MFT Operating Modes

The operating modes are selected by the programming of the Timer Control Register (TCR Timer x) and the Timer Mode Register (TMR) as follows:

**ONE-SHOT MODE.** The counter stops at the End Of Count Condition (up or down count).

**CONTINUOUS MODE.** At End Of Count the timer is reloaded from a Load Register.

**TRIGGER MODE.** A Trigger causes reload from a load register only if the Timer is at End of Count.

**RETRIGGER MODE.** A Trigger causes reload from a load register at any time.

**GATE MODE.** Counting is performed only when the external gate input (TxINA or TxINB) is active (logical 0).

**CAPTURE MODE.** A Trigger causes the timer value to be latched into the selected Capture register

**UP/DOWN MODE.** A Trigger causes a count up or down, or a change in counting direction.

**FREE-RUNNING MODE.** Up or Down counting is performed to the full range with no action at End of Count. This is used in Bicapture and Capture Modes.

**MONITOR MODE.** One Capture register follows the contents of the timer.

**AUTOCLEAR MODE.** The timer is reset to 0000h or FFFFh (up or down count respectively) on a trigger. This gives delta time measurement or free running with a modulo of less than 2<sup>16</sup>.

**BILOAD MODE.** The counter is reloaded on an End Of Count condition alternately from the two Load Registers. (PWM output).

Figure 41. Multifunction Timer Block Diagram

# MULTIFUNCTION TIMER (Continued)

**BICAPTURE MODE.** A Trigger causes the current timer value to be transferred alternately to the two Capture registers. (Pulse width measurement).

The trigger events may be either caused by software, or an action on the two input pins which may be programmed to respond to rising, falling or both edges of the input. The input modes are selected in the Input Control Register (ICR) as shown in Table 10. This includes the Autodiscriminator mode, which causes the timer to count up or down depending on the phase between the two input edges, such as the signals generated by optical encoders.

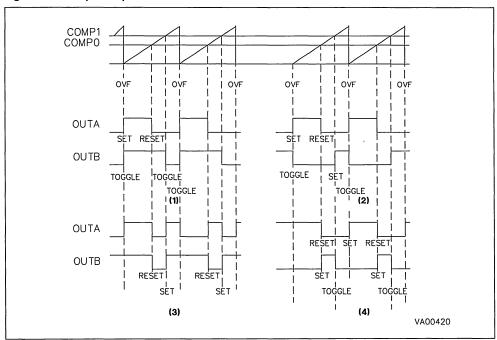

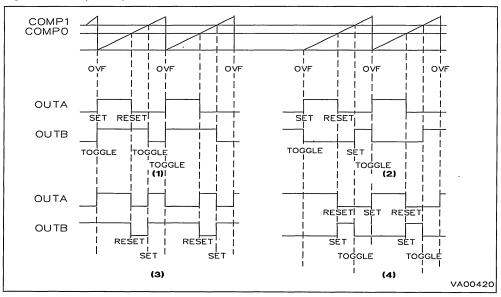

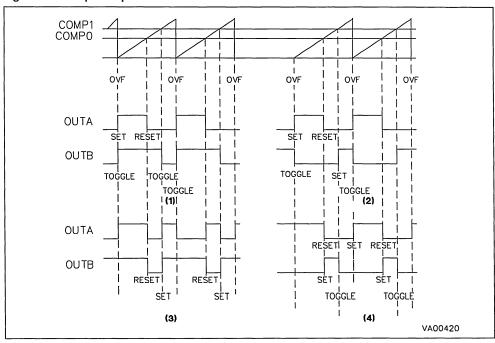

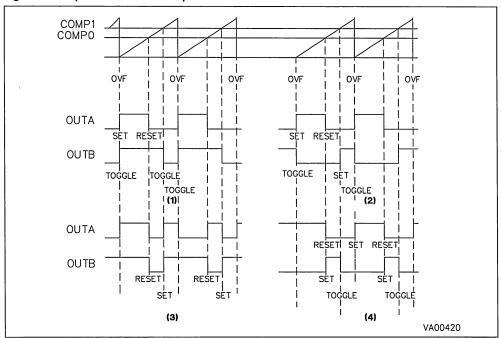

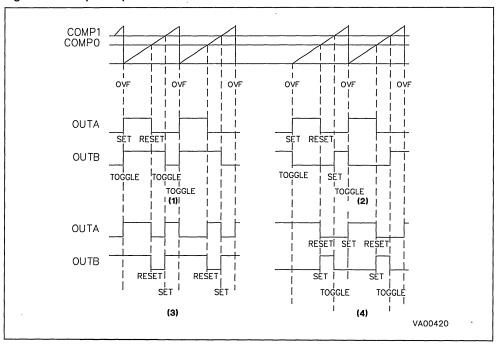

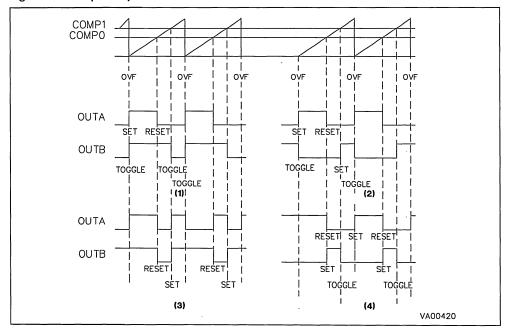

The two output pins (available as Alternate Functions) may be programmed through the Output Control Registers OACR and OBCR to be modified (Set, Reset, Toggle or No Operation) on each of Overflow/Underflow (OVF/UNF), Compare on CMP0 valid (CM0), or Compare on CMP1 (COMP1) valid events. This allows repetitive signals such as PWM drive to be output with minimum CPU overhead. Fig 42 shows some typical waveforms available from these signals.

Table 10. Input Pin Function Settings

| Input Control<br>Register<br>IN3-IN0 bits | TOINA Input<br>Function | TOINB Input<br>Function |  |  |  |  |

|-------------------------------------------|-------------------------|-------------------------|--|--|--|--|

| 0000                                      | 1/0                     | 1/0                     |  |  |  |  |

| 0001                                      | 1/0                     | Trigger                 |  |  |  |  |

| 0010                                      | Gate                    | 1/0                     |  |  |  |  |

| 0011                                      | Gate                    | Trigger                 |  |  |  |  |

| 0100                                      | 1/0                     | Ext.clock               |  |  |  |  |

| 0101                                      | Trigger                 | I/O                     |  |  |  |  |

| 0110                                      | Gate                    | Ext.clock               |  |  |  |  |

| 0111                                      | Trigger                 | Trigger                 |  |  |  |  |

| 1000                                      | Clock Up                | Clock Down              |  |  |  |  |

| 1001                                      | Up/Down                 | Ext.clock               |  |  |  |  |

| 1010                                      | Trigger Up              | Trigger Down            |  |  |  |  |

| 1011                                      | Up/Down                 | 1/0                     |  |  |  |  |

| 1100                                      | Autodiscr.              | Autodiscr.              |  |  |  |  |

| 1101                                      | Trigger                 | Ext.clock               |  |  |  |  |

| 1110                                      | Ext.clock               | Trigger                 |  |  |  |  |

| 1111                                      | Trigger                 | Gate                    |  |  |  |  |

Figure 42. Example Output Waveforms

# **MULTIFUNCTION TIMER** (Continued)

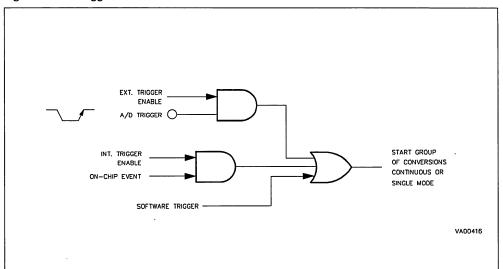

The Overflow/Underflow event and the Compare 0 event may also be programmed to give On-chip Event timing signals to trigger other peripheral operations on the ST902X. These are as shown in Table 11.

Table 11. ST902X On-Chip Event Settings

| MFT0 | Handshake Trigger Port 5 |

|------|--------------------------|

|------|--------------------------|

The TxOUTA and TxINA lines for the timer may be connected internally, by setting of the SCx bits of the I/O Connection Register (IOCR).

The Multifunction Timer is enabled for counting by the Counter Enable bit (CEN, TCR.7). When CEN is low, both prescaler and timer are halted. CEN is logically ANDed with the Global Counter Enable bit (GCEN, CICR.7).

## MFT Interrupts

The Multifunction Timer can generate interrupt requests from 5 different interrupt sources which are grouped into 3 independent groups. The Interrupt Vector has the source of the interrupt group encoded by hardware into the least significant 3 bits of the vector. This allows the programming of the base address to an 8 byte block within the interrupt vector area of the Program Space. The groups and respective addresses are shown in Table 12.

Table 12. MFT Interrupt Vectors

| Interrupt Source   | Vector Address |  |  |

|--------------------|----------------|--|--|

| COMP0<br>COMP1     | xxxx x110      |  |  |

| CAPT0<br>CAPT1     | xxxx x100      |  |  |

| Overflow/Underflow | xxxx x000      |  |  |

Each source may be independently masked, in addition all Timer interrupts may be disabled by the Global Timer Interrupt enable (GTIEN, IDMR.7) control bit. If a Timer interrupt on Compare 0 or Capture 0 does not have its corresponding pending

bit reset before the next interrupt, then an overrun condition occurs. This condition is flagged in two dedicated overrun bits in the Timer FLAGS register.

### MFT DMA Channels

Two independent DMA channels are present within the MFT, associated to the Compare 0 and Capture 0 sources. This allows 16 bit DMA transactions from Register File/Memory to COMPO registers, and from CAPTO registers to Register File/Memory. The DMA channels allow the capture of external event timings in memory allowing off-line analysis, and creating of variable pulse width signal trains, as required by the drive of Triacs in certain modes.

The two interrupt mask sources are independently masked by two DMA mask bits, mapped in the IDMR register. The End of Block (EOB) procedures are as described in the INTERRUPT/DMA section.

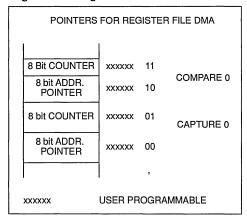

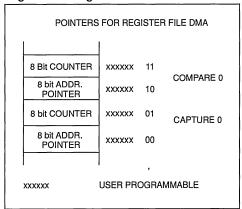

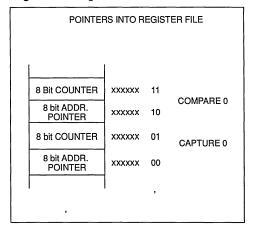

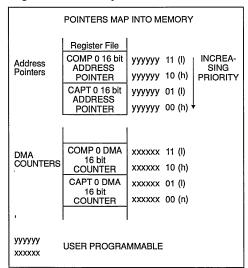

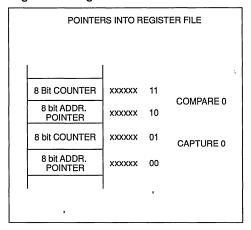

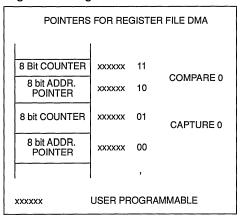

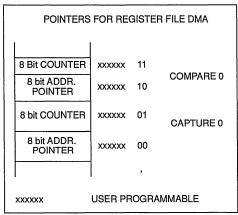

The DMA counter and address pointer registers share the most significant user-programmable 6 bits for both DMA channels (COMP 0 and CAPT 0), thus the mapping of the counter and address registers use automatic offsets from the base address. The actual mapping changes dependent on whether the Register File or Memory is addressed for the transfer. The offsets are shown in Table 13.

Table 13-1. MFT DMA Address and Counter Registers for Memory DMA Transfers

| POINTERS MAP INTO MEMORY |                                                                           |                                                                    |  |  |  |  |  |

|--------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------|--|--|--|--|--|

| Address<br>Pointers      | Register File COMP 0 16 bit ADDRESS POINTER CAPT 0 16 bit ADDRESS POINTER | yyyyyyy 11 (I) INCREA-<br>SING<br>Yyyyyyy 01 (I)<br>yyyyyyy 00 (h) |  |  |  |  |  |

| DMA<br>COUNTERS          | COMP 0 DMA<br>16 bit<br>COUNTER<br>CAPT 0 DMA<br>16 bit<br>COUNTER        | xxxxxx 11 (l)<br>xxxxxx 10 (h)<br>xxxxxx 01 (l)<br>xxxxxx 00 (n)   |  |  |  |  |  |

| yyyyyy USER PROGRAMMABLE |                                                                           |                                                                    |  |  |  |  |  |

# **MULTIFUNCTION TIMER** (Continued)

Table 13-2. MFT DMA Address and Counter Registers for Register File DMA Transfers

After the transfer of the complete block of data to/from the MFT, the count registers reach the zero value and an end of block interrupt occurs so that the ST9 may process the new data. In many cases, the time taken to reload the data tables and to re-trigger the DMA action causes speed limitations, especially in those applications requiring a continu-

ous high speed data flow, because of the time consumed by the restore routine. An additional DMA function, the SWAP mode, overcomes this limitation. This is enabled by the setting of the SWEN (IDCR.3) bit. This causes hardware generated signals to replace the user address bit 2 of both the address and counter pointers. The address and counter registers are thus duplicated at an offset of 4 registers. At the End Of Block condition, the EOB interrupt is generated to signal the end of DMA, and the state of pointer address bit 2 toggles state automatically and the new address and count values are used. Thus the ST9 can safely process the previous block of data while the new block is being transferred. This will continue until the SWAP mode is disabled.

A software protection scheme is implemented to prevent non-updated pointer registers from being used if a second EOB interrupt arrives during the servicing of the first. This mechanism locks the state of the DMA mask bit to prevent further transfers from taking place. The user should check for this condition in the EOB routine to ensure that all the DMA transfers are properly serviced.

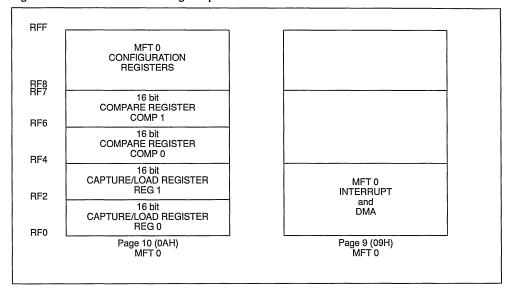

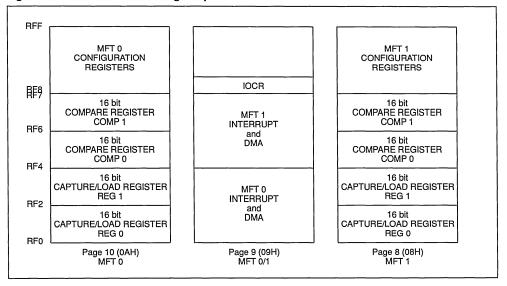

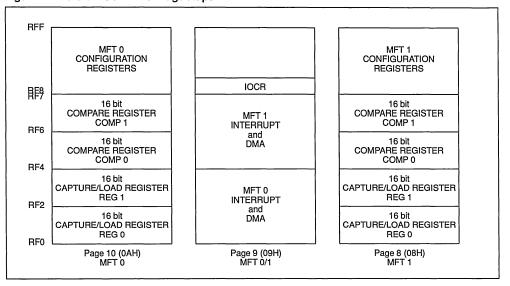

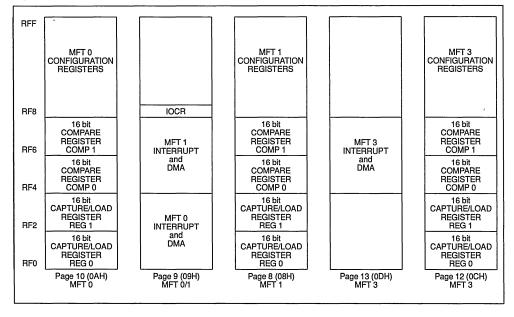

The control Registers of each MFT occupies 20 registers within the I/O paged area. These are mapped as follows:

In addition the MFT is able to trigger byte DMA transfers in both directions through an I/O port with Handshake (see I/O Handshake and DMA).

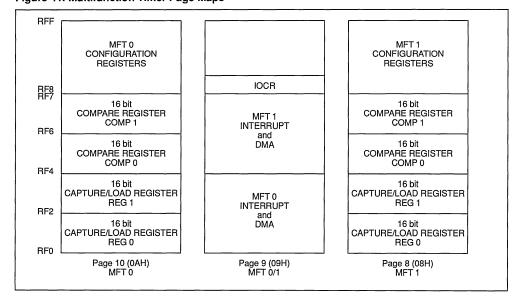

Figure 43. Multifunction Timer Page Maps

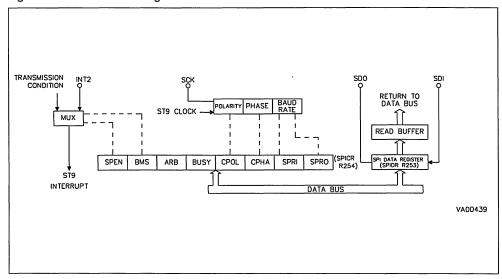

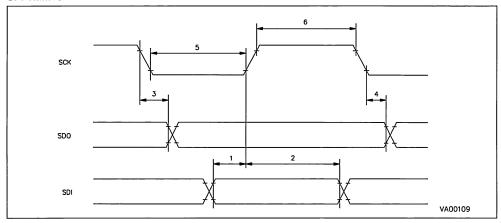

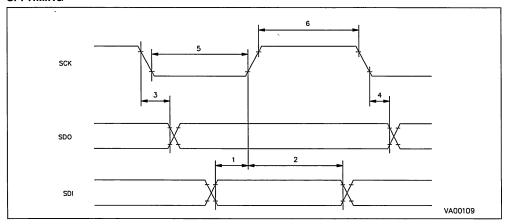

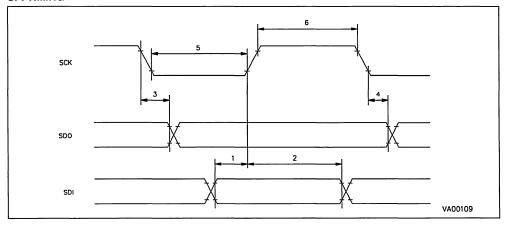

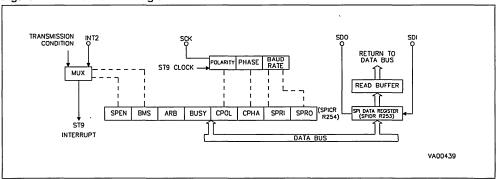

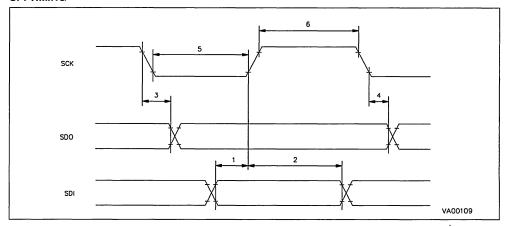

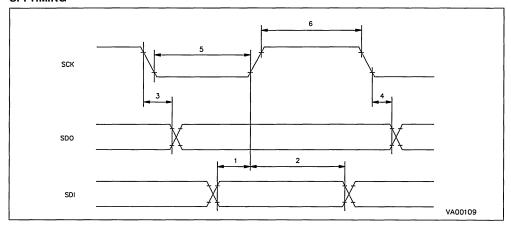

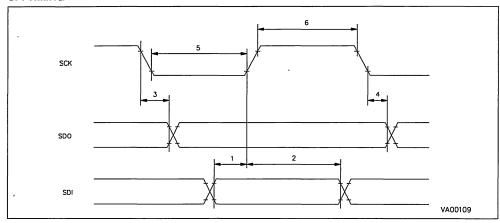

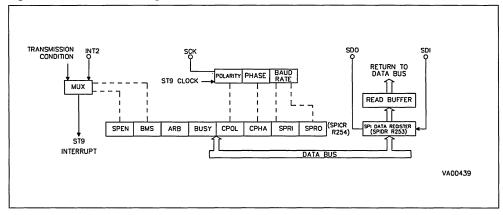

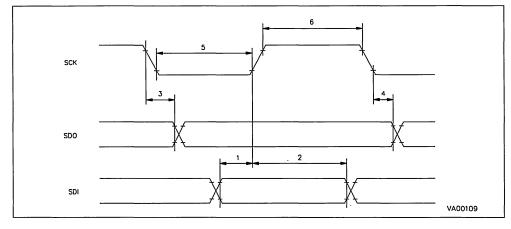

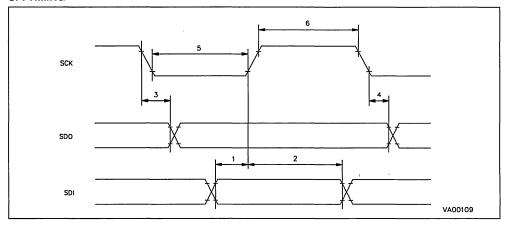

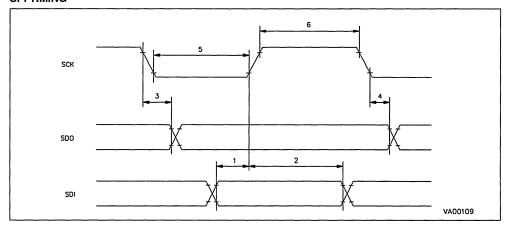

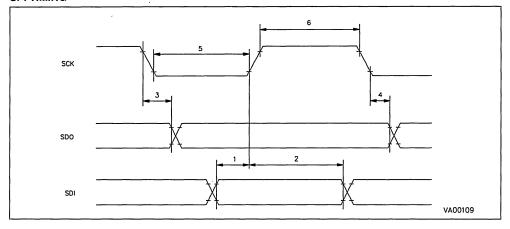

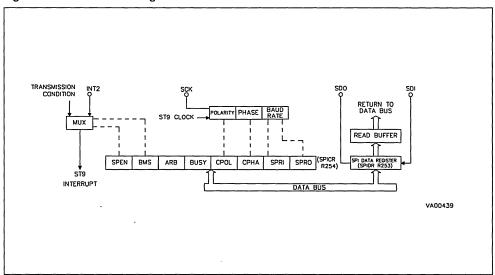

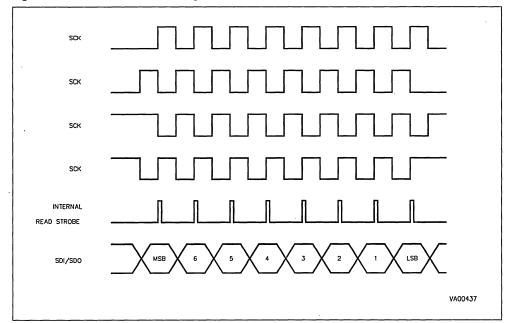

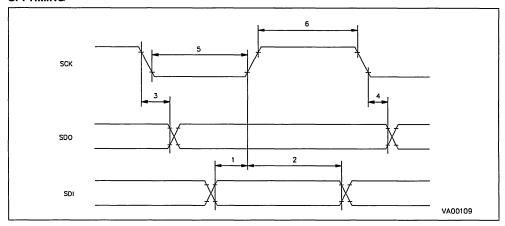

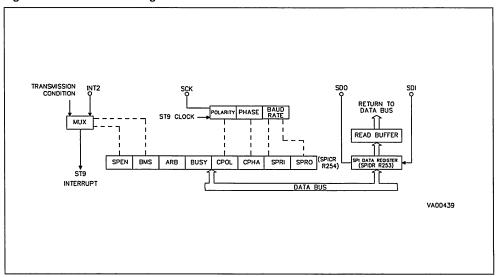

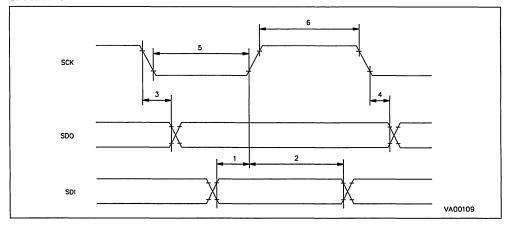

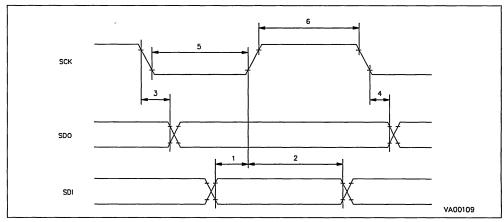

# SERIAL PERIPHERAL INTERFACE (SPI)

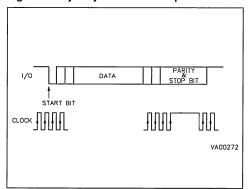

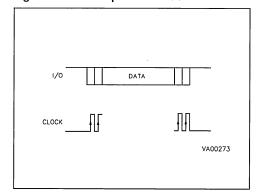

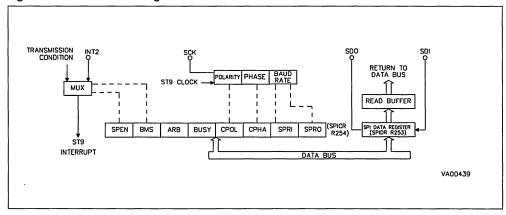

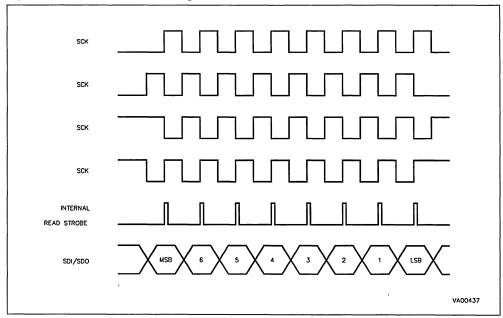

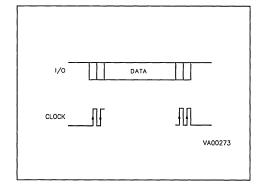

The Serial Peripheral Interface (SPI) is integrated into the Core module of the ST902X and provides a general purpose shift register based peripheral allowing synchronous serial I/O, with special modes allowing compatibility with I<sup>2</sup>C-bus and IMbus Communication standards in addition to the standard serial bus protocol. The SPI uses 3 lines comprising Serial Data Out (SDO), Serial Data In

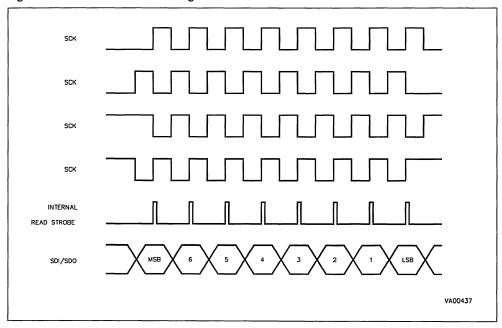

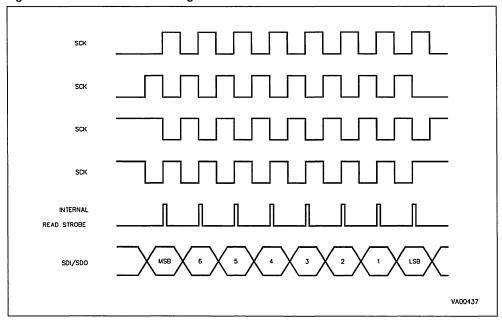

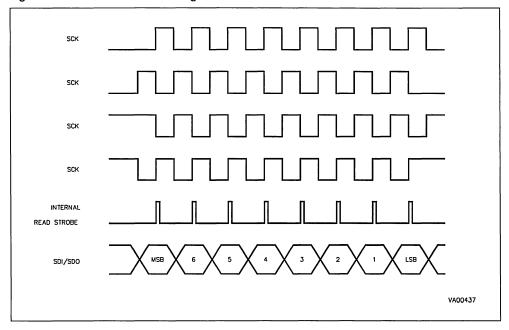

full duplex transmission with both data-out and data-in synchronized with the same clock signal. Thus the byte transmitted is replaced by the byte received, eliminating the need to separate "Tx Empty" and "Rx full" status bits. After the 8 clock cycles have been concluded, the received data in SPIDR is parallel transferred to the read buffer and data becomes available for the ST902X during the next read cycle of SPIDR. The BUSY bit (SPICR.4)

Figure 44. SPI Functional Diagram

(SDI) and the Synchronous Serial Clock (SCK) which are available as Alternate Functions of I/O pins. Additional I/O pins may act as device selects or IM-bus address ident signals. The functional diagram of the SPI is shown in Figure 44.

The SPI, when enabled (SPEN, SPICR.7, high), receives input data from the ST9 internal data bus into the SPIDR, and originates the SCK to shift the data serially through SDO (Most Significant bit first) to the slave device which responds by sending data to the master device via the SDI pin. This implies

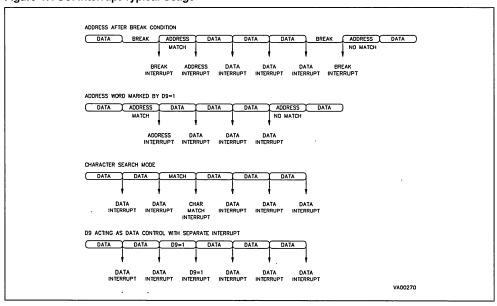

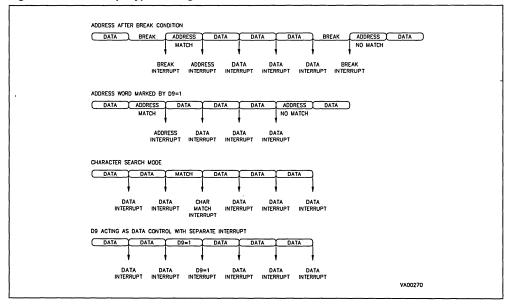

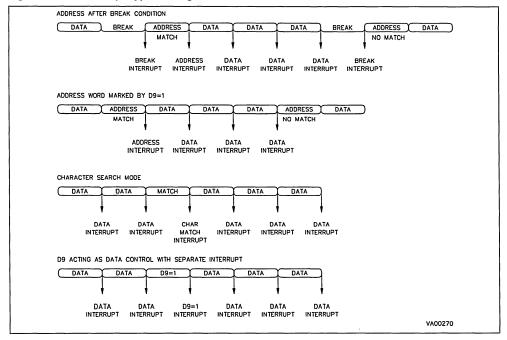

is set when transmission is in progress, this allows the user to monitor the status of the SPI by polling of this bit.