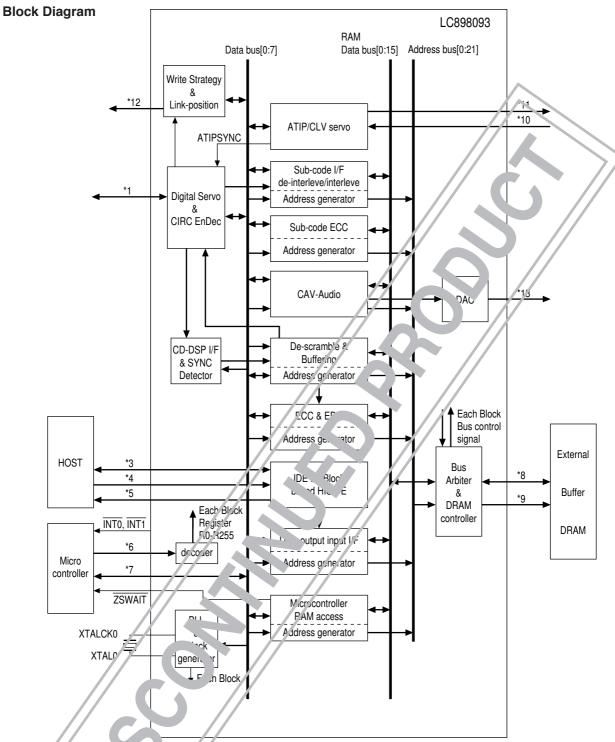

# 40× Playback/12× Write CD-R/RW Encoder/Decoder IC with Built-in ATAPI Interface

# **Preliminary**

# BURN-Proof

# **Functions**

- CD-ROM decoder/encoder functions

- CD decoder/encoder functions

- Pit and wobble CLV servo

- · CAV audio functions

- ATAPI interface (include the register block)

- Subcode encoder/decoder functions

- · ATIP demodulator/ATIP decoder

- Write strategy function (CD-R/RW)

## **Features**

- ECC and EDC correction/addition (decoding/encoding) for CD-ROM data.

- ECC error correction/addition (decoding/encoding) for subcode data

- Servo control implemented in a digital servo system (decoding/encoding)

- CLV servo control using ATIP data (encoding)

- ATIP decoding function and CRC check function (decoding/encoding)

- CIRC code generation and addition and EFM modulation (encoding)

- CAV audio functions

- Provides high-precision CD-R/KW write \_\_rate<sub>s\_</sub> signal output

- Built-in ATAPI interface (vita Ultra DMA, 23 support)

- Supports 40× decoding and 12× enco. o. Clock frequency: 33.8685 MHz

- Transfer rates: Up to 16.6 ... (v. en 32x JORDY used), up to 33 M5/s who Ultra DMA used. These values apply when 16-bit in S DRAW is used.

"BURN-Proof" stand for Proof agains. Fuffer Under RuN error, not 10' proof again ou ling.

"BURN-Proof" is a rademart of SANYC Electric Co., Ltd.

- From 1 to 64 Mbits of buffer P M can be used. (16-bit data bus EDO DRAM)

- The user can freely set up 1 e CD main channel, C2 flag, and subcode areas in buffer `AM.

- Batch transfer function (F. stion for transferring the CD main channel, C2 fr. sub ode, and other data in a single operation)

- Multi-transfer a petion (Function for automatically transferring trip block to the host in a single operation)

- CAV auci fu. 4: s

- Support U DMA modes 0, 1, and 2.

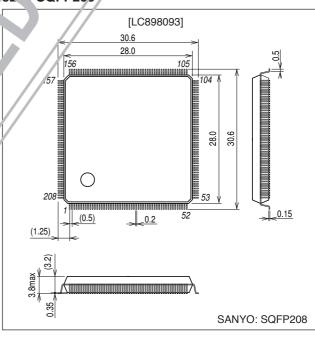

# Pa ka je Dimensions

unit: m.

#### J\_ '9-SQFP203

- To ano all SANYO products described or contained herein do not have specifications that can handle apply a one that require extremely high levels of reliability, such as life-support systems, aircraft's control systems or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO essumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained berein

# **Specifications**

# Absolute Maximum Ratings at $V_{SS} = 0 V$

| Parameter                        | Symbol                             | Conditions | Ratings                         | Unit |

|----------------------------------|------------------------------------|------------|---------------------------------|------|

| Supply voltage                   | V <sub>DD</sub> 5 max              | Ta≤25°C    | -0.3 to +6.0                    | V    |

| Supply voltage                   | V <sub>DD</sub> 3 max              | Ta≤25°C    | -0.3 to +4.6                    | V    |

| I/O voltages                     | V <sub>I</sub> 5, V <sub>O</sub> 5 | Ta ≤ 25°C  | -0.3 เว V <sub>DD</sub> 5 + 0.3 | V    |

| 1/O voltages                     | V <sub>I</sub> 3, V <sub>O</sub> 3 | Ta ≤ 25°C  | −0.3 ເວ V <sub>DD</sub> 3 + 0.3 | V    |

| Allowable power dissipation      | Pd max                             | Ta ≤ 70°C  | 750                             | mW   |

| Operating temperature            | Topr                               |            | -30 to +70                      | °C   |

| Storage temperature              | Tstg                               |            | 55 to +125                      | °C   |

| Soldering conditions (pins only) |                                    | 10 seconds | 250                             | °C   |

# Allowable Operating Ranges at $Ta = -30 \text{ to } +70^{\circ}\text{C}, V_{SS} = 0 \text{ V}$

| Parameter                            | Symbol            | Conditions |     | Rating s | max               | Unit |

|--------------------------------------|-------------------|------------|-----|----------|-------------------|------|

| [I/O cells, 5.0 V power supply]      |                   |            |     |          |                   | I    |

| Supply voltage                       | V <sub>DD</sub> 5 |            | 4.5 | 5.0      | 5.5               | V    |

| Input voltage range                  | V <sub>IN</sub>   |            | 0   |          | V <sub>DD</sub> 5 | V    |

| [Internal cells, 3.3 V power supply] |                   | // 🗡       |     |          |                   |      |

| Supply voltage                       | V <sub>DD</sub> 3 |            | 3,0 | 3.3      | 3.6               | V    |

| Input voltage range                  | V <sub>IN</sub>   |            | 0   |          | V <sub>DD</sub> 3 | V    |

# Electrical Characteristics at Ta = -30 to +70°C, $V_{S5}$ = 0 V, $V_{DD}$ 4.5 to 5.5 V

| Parameter                 | Cumbal           | Contions                                                                 |                       | Ratings |                     | Unit    |

|---------------------------|------------------|--------------------------------------------------------------------------|-----------------------|---------|---------------------|---------|

| Farameter                 | Symbol           | COLUMN                                                                   | min                   | typ     | max                 | Offic   |

| High-level input voltage  | V <sub>IH</sub>  | TTL level inputs: (1)                                                    | 2.2                   |         |                     | V       |

| Low-level input voltage   | V <sub>IL</sub>  | TTE level inputs. (1)                                                    |                       |         | 0.8                 | V       |

| High-level input voltage  | V <sub>IH</sub>  | TTL level inputs with . "*-in pull-up resistors: (4)                     | 2.2                   |         |                     | V       |

| Low-level input voltage   | V <sub>IL</sub>  | TTE level inputs with the first pair-up resistors. (4)                   |                       |         | 0.8                 | V       |

| High-level input voltage  | V <sub>IH</sub>  | T'L level Sci '4 trigs inputs: (5), (7)                                  | 2.4                   |         |                     | V       |

| Low-level input voltage   | V <sub>IL</sub>  | The level Sch. Kings Imputs. (9), (1)                                    |                       |         | 0.8                 | V       |

| High-level input voltage  | VIH              | TTL Icrel S mitt trigger inputs                                          | 2.4                   |         |                     | V       |

| Low-level input voltage   | Уц               | Built-in, "-up. istors: (9), (14)                                        |                       |         | 0.8                 | V       |

| High-level input voltage  | Уін              | Mc 'evel inputs with built-in pull-up resistors: (10)                    | $0.7~V_{DD}$          |         |                     | V       |

| Low-level input voltage   | V <sub>IL</sub>  | We wer imputs with built-in pull-up resistors. (10)                      |                       |         | 0.3 V <sub>DD</sub> | V       |

| Analog input voltage      | V <sub>ANI</sub> |                                                                          | 1/4 V <sub>DD</sub>   |         | 3/4 V <sub>DD</sub> | V       |

| High-level output voltage | V <sub>OH</sub>  | I <sub>OH</sub> – 3 mA: (3), (5)                                         | V <sub>DD</sub> – 2.1 |         |                     | V       |

| Low-level output voltage  | U.               | - 8 mA: (5), (8)                                                         |                       |         | 0.4                 | V       |

| High-level output voltage | V <sub>OH</sub>  | $_{OH} = -2 \text{ mA} \cdot (2), (4), (6)$                              | V <sub>DD</sub> – 2.1 |         |                     | V       |

| Low-level output voltage  |                  | $I_{OL} = 2 / n A.$ (2), (4), (6)                                        |                       |         | 0.4                 | V       |

| Low-level output vol/age  | YnL              | I <sub>OL</sub> = 2 r <sub>1</sub> A: (5)                                |                       |         | 0.4                 | V       |

| High-level output vo'lage | Н                | I <sub>C/1</sub> = -8 mA: (7), (12), (14), (15)                          | V <sub>DD</sub> – 2.1 |         |                     | V       |

| Low-level output oltage   | √ <sub>OL</sub>  | ı <sub>O'</sub> = 24 mA: (7), (12), (14), (15)                           |                       |         | 0.4                 | V       |

| Input leakarje rurrent    | ΙιL              | $V_{I} = V_{SS}, V_{DD}$ : (0), (1), (7), (9)                            | -10                   |         | +10                 | $\mu$ A |

| Output leal age current   | loz              | In the high-impedance output state: (2), (7), (8), (12), (13) (14), (15) | -10                   |         | +10                 | μΑ      |

| Pull-up resistan          | Pup              | (10)                                                                     | 50                    | 100     | 200                 | kΩ      |

| Pull-up resistance        | R <sub>UP</sub>  | (4), (5)                                                                 | 40                    | 80      | 160                 | kΩ      |

| Pull-up resistance        | R <sub>UP</sub>  | (9), (13), (14)                                                          | 7                     | 10      | 13                  | kΩ      |

| Pull-up resistance        | R <sub>UP</sub>  | (15)                                                                     | 7                     | 10      | 13                  | kΩ      |

The applicable pin groups are listed on the following page.

# **Applicable Pins**

# [INPUT]

- $(0) \cdot \cdot \cdot \cdot \overline{CS}, \overline{RD}, \overline{WR}, WRITE, SUA0 to SUA7, \overline{RESET}, WOBBLE, \overline{CS1FX}, \overline{CS3FX}, \overline{DIOR}, \overline{DIOW}, \overline{HRST}$

- $(9) \cdot \cdots \cdot \overline{\mathrm{DMACK}}$

- (1) · · · · · TEST0 to TEST4

- $(10) \cdot \cdot \cdot \cdot FG$

- (11) · · · · · AD0, AD1, RREC, FE, TE, VREF, AD2, TES

# [OUTPUT]

- $(2) \cdot \cdot \cdot \cdot \cdot PDS1$  to PDS3, DSLB

- (3)····· RA0 to RA9, CAS0 and CAS1, RAS0 to RAS2, LWE, UWE, OF, SSP2/1, k PC, APC, H/1T0, LDH, ATEST3/1, WDAT, NWDAT, EFMG, SHOCK, LOCK, EFMO, ATIPSYN ACKONG, LCK2

- $(6) \cdot \cdot \cdot \cdot \cdot LDON$

- $(12) \cdot \cdot \cdot \cdot \cdot INTRQ, \overline{IOCS16}$

- (13) · · · · · IORDY

- $(15) \cdot \cdot \cdot \cdot DMARQ$

# [INOUT]

- $(4) \cdot \cdot \cdot \cdot \cdot D0$  to D7, IO0 to IO15

- $(5) \cdots \overline{INT0}$  and  $\overline{INT1}$ ,  $\overline{SWAIT}$

- $(7) \cdot \cdots \cdot DD0$  to DD15

- (8) · · · · · · BIDATA, BICLK

- $(14) \cdot \cdot \cdot \cdot DASP, \overline{PDIAG}$

Note: The XTAL0 pin is not specified in the DC chara term is.

The pull-up and pull-down resistors on pins  $(9 (1^7), (14), and (15))$  are disabled after a reset.

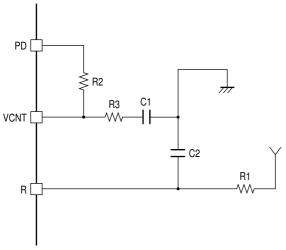

# **External Circuit for the PLL Circuit**

# 1. Internal Reference Clock Oscillator Block

| Symbol | Value (typ) | Unit |

|--------|-------------|------|

| R1     | 5.6 k       | Ω    |

| R2     | 10 k        | Ω    |

| R3     | 200         |      |

| C1     | 0.1 μ       |      |

| C2     | 0.1 μ       | E    |

A13192

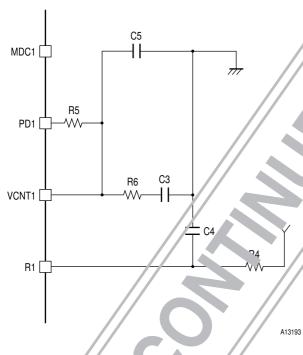

# 2. Write Strategy Block

| vmbol      | Valus (typ) | Unit |  |  |  |  |  |

|------------|-------------|------|--|--|--|--|--|

| 4          | 5.6 k       | Ω    |  |  |  |  |  |

| R5         | 15 k        | Ω    |  |  |  |  |  |

| R6         | 220         | Ω    |  |  |  |  |  |

| C3         | 0.1 μ       | F    |  |  |  |  |  |

| C4/        | 0.1 μ       | F    |  |  |  |  |  |

| <b>C</b> 5 | 0.1 μ       | F    |  |  |  |  |  |

The analog  $V_{DD}$  and  $V_{3P}$  functions 52/53, 90, and 91) must be completely isolated from the logic system power supply and must not be influence by fluctuations in the logic system power supply.

- \*1 DSLE (pin9 to sUP YNC (pin145), SHOCK (pin147) to PCK2 (pin155)

- \*3 DDJ to  $DD^{1}5$ , NSP,  $\overline{PDI}/\overline{C}$

- \*4 CSIFX CS3F. DA0 to D/2, DIOR, DIOW, DMACK

- \*5 DMARQ, "N" AQ, TO C516, IORDY

- \*6  $\overline{RD}$ ,  $\overline{WP}$ ,  $\overline{SU}$  to  $\overline{SU}$   $\overline{A7}$ ,  $\overline{CS}$

- \*7 D0 to D7

- \*8 IO0 to IO15

- \*9 RA0 to RA9,  $\overline{RAS0}$ ,  $\overline{RAS1}$ ,  $\overline{RAS2}$ ,  $\overline{CAS0}$ ,  $\overline{CAS1}$ ,  $\overline{OE}$ ,  $\overline{UWE}$ ,  $\overline{LWE}$

- \*10 WOBBLE

- \*11 ATIPSYNC, BIDATA, BICLK

- \*12 WRITE, SSP2/1, RAPC, WAPC, H11T0, LDH, ATEST3, ATEST1, WDAT, NWDAT, EFMG

- \*13 LOUT, ROUT

- \*\*1 HISIDE (WD25C32) is made by WESTERN DIGITAL.

A13194

# **Pin Functions**

|   |        |   | Pin type          |    |               |

|---|--------|---|-------------------|----|---------------|

| I | Input  | В | Bidirectional pin | NC | Not connected |

| 0 | Output | Р | Power supply      | Α  | Analog pin    |

| Pin No. | Pin name        | Туре | Pin function                                 |

|---------|-----------------|------|----------------------------------------------|

| 1       | V <sub>SS</sub> | Р    | Digital system ground (V <sub>SS</sub> )     |

| 2       | RA4             | 0    |                                              |

| 3       | RA5             | 0    |                                              |

| 4       | RA6             | 0    | OD DOM and de Control of DDAM address from   |

| 5       | RA7             | 0    | CD-ROM encoder/decoder DRAM address lines    |

| 6       | RA8             | 0    |                                              |

| 7       | RA9             | 0    |                                              |

| 8       | $V_{DD}$        | Р    | Digital system power supply (5 V)            |

| 9       | V <sub>SS</sub> | Р    | Digital system ground (V <sub>SS</sub> )     |

| 10      | IO0             | В    |                                              |

| 11      | IO1             | В    |                                              |

| 12      | IO2             | В    | CD-ROM encoder/decoder buffer RAM data lines |

| 13      | IO3             | В    | These pins have built-in pull-up resistors.  |

| 14      | IO4             | В    |                                              |

| 15      | IO5             | В    |                                              |

| 16      | $V_{DD}$        | Р    | Digital system power supply (3.3 V)          |

| 17      | V <sub>SS</sub> | Р    | Digital system ground (V <sub>SS</sub> )     |

| 18      | 106             | В    |                                              |

| 19      | IO7             | В    | CD-ROM encoder/decoder buffer RAM data lines |

| 20      | IO8             | В    | These pins have built-in prolif-up resistro. |

| 21      | 109             | В    | Those pins have built in pin ip resist i.    |

| 22      | IO10            | В    |                                              |

| 23      | V <sub>SS</sub> | Р    | Digital system ground (V <sub>SS</sub> )     |

| 24      | $V_{DD}$        | Р    | Digital system power supply (5.              |

| 25      | IO11            | В    |                                              |

| 26      | IO12            | В    | CD-ROM ancoder/denode. Iffer I IM data lines |

| 27      | IO13            | В    | These runs have built-in , "-up resistors.   |

| 28      | IO14            | В    |                                              |

| 29      | IO15            | В    |                                              |

| 30      | ATIPSYNC        | 0    | /\tau's SYNC steck signal                    |

| 31      | BIDATA          | В    |                                              |

| 32      | BICLK           | В    | ATIP d rodulator jnals                       |

| 33      | WOBBLE          | 1    |                                              |

| 34      | $V_{DD}$        | //   | Digita. rstem power sur/pl/ (5 V)            |

| 35      | V <sub>SS</sub> | Р    | Julyi. Visic i ground (V <sub>SS</sub> )     |

| 36      | ACRCNG          | 0    | ATIP C result output signal                  |

| 37      | WRITE           |      | ategy signal control input                   |

| 38      | SSP2            | _?_  | rvo sampling julse output                    |

| 39      | 581/1           | -    | rvo sampling pulse output                    |

| 40      | FIAPC           | -    | Laser crintrol sampling pulse output         |

| 41      | WAPC            | 0    | Laser control sampling pulse output          |

| 42      | H11T0           |      | Running OPC sampling pulse                   |

# Continued from preceding page.

| Pin No. | Pin name        | Туре | Pin function                                                  |

|---------|-----------------|------|---------------------------------------------------------------|

| 43      | LDH             | 0    | Recording laser diode control signal output                   |

| 44      | V <sub>DD</sub> | Р    | Analog system power supply (3.3 V)                            |

| 45      | V <sub>SS</sub> | Р    | Analog system ground (V <sub>SS</sub> )                       |

| 46      | ATEST3          | 0    | RW output                                                     |

| 47      | ATEST1          | 0    | Internal monitor test output                                  |

| 48      | WDAT            | 0    | Recording laser diode control signal output                   |

| 49      | NWDAT           | 0    | Recording laser diode control signal output (WDAT inverted)   |

| 50      | $V_{DD}$        | Р    | Analog system power supply (3.3 V)                            |

| 51      | V <sub>SS</sub> | Р    | Analog system ground (V <sub>SS</sub> )                       |

| 52      | V <sub>DD</sub> | Р    | Digital system power supply (5 V)                             |

| 53      | V <sub>SS</sub> | Р    | Digital system ground (V <sub>SS</sub> )                      |

| 54      | R1              | ı    |                                                               |

| 55      | VCNT1           | 1    |                                                               |

| 56      | MDC1            | 0    | Write strategy analog signals                                 |

| 57      | PD1             | 0    |                                                               |

| 58      | SWAIT           | 0    | Wait signal to the microcontroller                            |

| 59      | ĪNT0            | 0    | Interrupt request signal outputs to the microcontroller       |

| 60      | ĪNT1            | 0    | These are open-drain outputs with built-in pull-up resistors. |

| 61      | D0              | В    |                                                               |

| 62      | D1              | В    |                                                               |

| 63      | D2              | В    |                                                               |

| 64      | D3              | В    | Microcontroller data signal lines                             |

| 65      | D4              | В    | These pins have built-in pull-up resistors.                   |

| 66      | D5              | В    |                                                               |

| 67      | D6              | В    |                                                               |

| 68      | $V_{DD}$        | Р    | Digital system power supply (5 )                              |

| 69      | V <sub>SS</sub> | Р    | Digital system groun (V <sub>SS</sub> )                       |

| 70      | D7              | В    | Microcontroller da'a signal ii.                               |

| 71      | SUA0            | I    |                                                               |

| 72      | SUA1            | I    |                                                               |

| 73      | SUA2            | I    |                                                               |

| 74      | SUA3            | I    |                                                               |

| 75      | SUA4            | I    | Conn and region section address                               |

| 76      | SUA5            | I    |                                                               |

| 77      | SUA6            | 1 /  |                                                               |

| 78      | SUA7            | 1//  |                                                               |

| 79      | CS              | / /  | Chip recognized input from the microcontroller                |

| 80      | RD              | l l  | reau anal input iro n the microcontroller                     |

| 81      | WR              | I    | Data w. 3 signal inrut from the microcontroller               |

| 82      | TEST0           |      | at ni This pin must be tied to V <sub>SS</sub> .              |

| 83      | VCMT            |      | VCO control vultage                                           |

| 84      | /R/             |      | O bias rosinor connection                                     |

| 85      | ρD              |      | Charge rum p output                                           |

| 86      | V <sub>DD</sub> | P    | Analog system power supply (3.3 V)                            |

| 87      | V <sub>SS</sub> |      | Anglory system ground (V <sub>SS</sub> )                      |

| 88      | TF              | I    | Test pin. This pin must be tied to V <sub>SS</sub> .          |

| 59      | , SET           | I    | Fleset input                                                  |

| 90      | XTALC.          | 1//  | Crystal oscillator circuit input (33.8688 MHz)                |

# Continued from preceding page.

| Pin No. | Pin name                           | Туре                                             | Pin function                                       |

|---------|------------------------------------|--------------------------------------------------|----------------------------------------------------|

| 91      | XTAL0                              | 0                                                | Crystal oscillator circuit output                  |

| 92      | ROUT                               | 0                                                | D/A converter output                               |

| 93      | V <sub>SS</sub>                    | Р                                                | Analog system ground (V <sub>SS</sub> )            |

| 94      | V <sub>DD</sub>                    | Р                                                | Analog system power supply (5 V)                   |

| 95      | LOUT                               | 0                                                | D/A converter output                               |

| 96      | DSLB                               | 0                                                | SLC PWM output                                     |

| 97      | SLCIST1                            | 1                                                |                                                    |

| 98      | SLCIST2                            | ı                                                | EFM slice level setting input                      |

| 99      | V <sub>SS</sub>                    | Р                                                | Analog system ground (V <sub>SS</sub> )            |

| 100     | V <sub>DD</sub>                    | Р                                                | Analog system power supply (3.3 V)                 |

| 101     | SLC00                              | 0                                                |                                                    |

| 102     | SLCO1                              | 0                                                | EFM slice level output                             |

| 103     | SLCO2                              | 0                                                |                                                    |

| 104     | V <sub>DD</sub>                    | Р                                                | Digital system power supply (5 V)                  |

| 105     | V <sub>SS</sub>                    | P                                                | Digital system ground (V <sub>SS</sub> )           |

| 106     | SLCO3                              | 0                                                | EFM slice level output                             |

| 107     | EFMIN                              | 1                                                |                                                    |

| 108     | EFMIN2                             | 1                                                | EFM input                                          |

| 109     | JITIN                              | i                                                | Jitter discrimination input                        |

| 110     | JITC                               | 0                                                | Jitter output                                      |

| 111     | RPO                                | 0                                                |                                                    |

| 112     | OPP                                | ī                                                | P/N balance adjustment                             |

| 113     | PCKISTF                            | i                                                | Frequency comparator charge rump                   |

| 114     | PCKISTP                            | i                                                | Phase comparator charge pump                       |

| 115     | V <sub>SS</sub>                    | Р                                                | Analog system ground (V <sub>S</sub> S)            |

| 116     | V <sub>SS</sub><br>V <sub>DD</sub> | Р                                                | Analog system power supply (3 V)                   |

| 117     | PDO                                | 0                                                | Charge pump filte                                  |

| 118     | PDS1                               | 0                                                | Charge paint max                                   |

| 119     | PDS2                               | 0                                                | Charge pump selection                              |

| 120     | V <sub>DD</sub>                    | P                                                | Digital system power hopey 3.3                     |

| 121     | V <sub>SS</sub>                    | '<br>Р                                           | Digital system ground (V <sub>S</sub>              |

| 122     | PDS3                               | 0                                                | Charge pump seleu n                                |

| 123     | FR                                 | ı                                                | VCC frequer y suring                               |

| 123     | TEST2                              | 1 /                                              | Test pin. The pin musual tied to $V_{SS}$ .        |

| 125     | TEST2                              |                                                  | Test pin. This pin. Test be tied to VSS.           |

| 126     | TEST3                              | <del>                                     </del> | Test pin. 1. pin must be ti d (o V <sub>SS</sub> . |

| 127     | AD0                                | 1                                                | AD "I                                              |

| 128     | RREC                               | //_                                              | al signal discrimination input                     |

| 129     | FE                                 | <del>/                                    </del> | FE inpu                                            |

| 130     | TE /                               | 1-                                               | Since                                              |

| 131     | VREF                               |                                                  | VREF input                                         |

| 132     | ADI                                |                                                  | A input                                            |

| 133     | Yss                                | P                                                | Analog system ground (V <sub>SS</sub> )            |

| 134     | DAO                                | 0                                                | DA output                                          |

| 135     | DA1                                |                                                  | DA ov'put                                          |

| 136     |                                    | 0                                                | DA Sutput                                          |

| 137     | 70                                 | 0                                                | Tracking output                                    |

| 101     |                                    |                                                  | Tracking output                                    |

# Continued from preceding page.

| Pin No. | Pin name        | Туре         | Pin function                             |

|---------|-----------------|--------------|------------------------------------------|

| 138     | V <sub>DD</sub> | P            | Analog system power supply (5 V)         |

| 139     | V <sub>SS</sub> | Р            | Analog system ground (V <sub>SS</sub> )  |

| 140     | FDO             | 0            | Focus output                             |

| 141     | SLDO            | 0            | Sled output                              |

| 142     | SPDO            | 0            | Spindle output                           |

| 143     | V <sub>SS</sub> | Р            | Digital system ground (V <sub>SS</sub> ) |

| 144     | V <sub>DD</sub> | Р            | Digital system power supply (3.3 V)      |

| 145     | SUBSYNC         | 0            | Subcode SYNC signal                      |

| 146     | EFMG            | 0            | Write gate signal                        |

| 147     | SHOCK           | 0            | Shock detection signal                   |

| 148     | LOCK            | 0            | PLL lock state output                    |

| 149     | DEF             | ı            | Defect detection signal input            |

| 150     | HFL             | ı            | Mirror detection signal input            |

| 151     | TES             | ı            | Tracking zero cross signal input         |

| 152     | EFMO            | 0            | Post-binarization EFM signal output      |

| 153     | LDON            | 0            | Laser control                            |

| 154     | FG              | ı            | FG input                                 |

| 155     | PCK2            | 0            | PCK output                               |

| 156     | V <sub>DD</sub> | P            | Digital system power supply (5 V)        |

| 157     | V <sub>SS</sub> | P            | Digital system ground (V <sub>SS</sub> ) |

| 158     | HRST            | ı            | 25mm 5, 11mm 3, 12mm (133)               |

| 159     | DASP            | В            |                                          |

| 160     | CS3FX           | 1            |                                          |

| 161     | CS1FX           | i            |                                          |

| 162     | DA2             | 1            |                                          |

| 163     | DA0             | ı            |                                          |

| 164     | PDIAG           | В            |                                          |

| 165     | DAI             | 1            | IDE interface signal's                   |

| 166     | IOCS16          | 0            |                                          |

| 167     | INTRQ           | 0            |                                          |

| 168     | DMACK           | ı            |                                          |

| 169     | IORDY           | 0            |                                          |

| 170     | DIOR            | ı            |                                          |

| 171     | DIOW            | ı            |                                          |

| 172     | V <sub>DD</sub> | P            | Digital cystem pur supply (5 V)          |

| 173     | V <sub>SS</sub> | E E          | Digital sys. ground (V <sub>SS</sub> )   |

| 174     | DMARQ           | 9            | 5-7.7.5                                  |

| 175     | DD15            | В            |                                          |

| 176     | DD0             | В            |                                          |

| 177     | DD14            | В            | = int lace signals                       |

| 178     | DDI             | 3            |                                          |

| 179     | DD13            |              |                                          |

| 180     | DD2             | R            |                                          |

| 181     |                 | Р            | Digital system ground (V <sub>SS</sub> ) |

| 182     | DD12            |              | 3 / J / J / J / J / J / J / J / J / J /  |

| 183     | F U             | В            | J'DF interface signals                   |

| 134     | 711             | В            | 7                                        |

|         |                 | <del>/</del> | 1/                                       |

Continued from preceding page.

| Pin No. | Pin name        | Туре | Pin function                               |

|---------|-----------------|------|--------------------------------------------|

| 185     | DD4             | В    |                                            |

| 186     | DD10            | В    |                                            |

| 187     | DD5             | В    | IDE interface signals                      |

| 188     | DD9             | В    |                                            |

| 189     | DD6             | В    |                                            |

| 190     | $V_{DD}$        | Р    | Digital system power supply (3.3 V)        |

| 191     | V <sub>SS</sub> | Р    | Digital system ground (V <sub>SS</sub> )   |

| 192     | DD8             | В    | IDE interface signals                      |

| 193     | DD7             | В    | IDE IIIterrace signals                     |

| 194     | RAS0            | 0    |                                            |

| 195     | RAS1            | 0    | DRAM RAS signal outputs                    |

| 196     | RAS2            | 0    |                                            |

| 197     | LWE             | 0    | DRAM lower write enable                    |

| 198     | $V_{DD}$        | Р    | Digital system power supply (5 V)          |

| 199     | $V_{SS}$        | Р    | Digital system ground (V <sub>SS</sub> )   |

| 200     | UWE             | 0    | DRAM upper write enable                    |

| 201     | CAS0            | 0    | DRAM CAS signal output                     |

| 202     | CAS1            | 0    | Di Awi OAO signal output                   |

| 203     | ŌĒ              | 0    | DRAM output enable                         |

| 204     | RA0             | 0    |                                            |

| 205     | RA1             | 0    | CD-ROM encoder/decoder DRAM address lights |

| 206     | RA2             | 0    | OD HOW CHOOLONG DITTWICHOLOSS II           |

| 207     | RA3             | 0    |                                            |

| 208     | $V_{DD}$        | Р    | Digital system power supr y (5 V)          |

#### **Pin Functions**

<ATAPI Pins>

**CS1FX** (input)

Chip select signal that selects the command block regions. er.

**CS3FX** (input)

Chip select signal that selects the control look is ister.

DA0 to DA2 (input)

Address for accessing the ATAPI interface gisters.

**DASP** (input/output)

Drive 1 is output and drive 0 is inp

Signal used to indicate to driv ve 1 exists.

DD0 to DD15 (input output)

16-bit data bus. This inter ce su, vorts both 8-bit and 16-bit transfers.

**DIOR** (input)

Read strobe from the lost.

DIOW (input)

Write strope fro the 1 ost.

DMACK (input)

Acknowledge signal from the host used during DMA transfers. Corresponds to the DMARQ request signal from the drive.

DMARQ (inp.

Drive request signal used during DMA transfers.

HINTRQ (output)

Drive interrupt request signal to the host.

**IOCS16** (output)

Signal asserted by the drive when the drive supports 16-bit transfers.

This signal is not asserted during DMA transfers.

#### **IORDY** (output)

Indicates that the drive is ready to respond. Used during data transfers.

This signal will be low when the drive is not ready.

# **PDIAG** (input/output)

Signal asserted by drive 1 to indicate to drive 0 that diagnostics have completed.

#### **HRST** (input)

Reset signal from the host. The IDE interface is reset by a low-level input to this pin.

#### <Microcontroller Interface Pins>

#### **CS** (input)

Chip select signal from the microcontroller. The microcontroller interface is active whe this pin is low.

#### RD, WR (input)

Connect the microcontroller read and write lines to these inputs.

#### **SWAIT** (input)

Wait signal output to the microcontroller. When accessing buffer RAM, the reconcoller must wait if this pin is low

#### **SUA0 to SUA7** (input)

Internal register address lines

#### **D0 to D7** (input/output)

Microcontroller data bus. These pins have built-in pull-up resistors

#### INTO, INT1 (output)

Interrupt request signals output to the microcontroller INT1 can e sec to output the ATAPI interrupt by setting INT1EN (Conf-R11 bit 7)

These are open drain outputs with built-in 80 k $\Omega$  (at room temperature, 5 V) pull-up resistors.

## <Buffer RAM Pins>

#### I/O0 to I/O15 (input/output)

Buffer RAM data bus. These pins have built-in pal-up residents.

# RA0 to RA9 (output)

Buffer RAM address lines.

#### RASO, RAS1, RAS2 (output)

Buffer DRAM RAS outputs. Normally, R. 10 is used. However, if two 16-Mbit DRAMs are used, connect the RASO and RAS1 lines to the RAS pins on the D. 10-Mbit DRAMs are used, connect the RAS0, RAS1, RAS2, and LWE lines to the RAS pins on . DRAMs.

#### CASO, CAS1 (output)

Buffer DRAM CAS outputs. Norman. CASO is used. However, if two 16-Mbit DRAMs are used, connect the CASO output to the CAS pins on the Dr. 'Ms. If 2-CAS type DRAMs are used, connect CASO to UCAS and CASI to LCAS.

#### **OE** (output)

Buffer RAM read out at.

#### UWE, LWE (output)

Buffer RAM writ output. Connect these to the corresponding pins. If 2-CAS type DRAMs are used, UWE must be connected. (Lea of ve open.)

# 1. Analog Inter acc Pinc

# RIPEC (input,

Optical discrim nation input.

#### **FE** (input)

Focus error signal input.

#### **TE** (input)

Tracking error signal input.

#### **VREF** (input)

Input for the servo system reference voltage.

#### AD0, AD1 (input)

A/D converter auxiliary inputs.

#### DA0, DA1, DA2 (input)

D/A converter auxiliary inputs.

#### TES (input)

TES comparator input.

#### **TDO** (output)

Tracking control signal output.

#### FDO (output)

Focus control signal output.

#### **SLDO** (output)

Sled control signal output.

#### SPDO (output)

Spindle control signal output.

#### 2. EFM Input Block Pins

# **EFMIN** (input)

EFM signal input.

The high-frequency components of the RF signal acquired from the P m<sub>P</sub> are cut with a capacitor, and this pin inputs that signal biased by the value of the SLCO0 to SLCO3 atproximately seed through a low-pass filter.

#### **EFMIN2** (input)

Used to change the time constant of the low-pass filter.

### SLCIST1, SLCIST2 (input)

Slice level controller charge pump bias resistor cornection

#### SLCO0, SLCO1, SLCO2, SLCO3 (output)

Slice level controller charge pump outputs.

These levels bias the RF signal input to the LFMIN in after being passed through a low-pass filter.

#### **DSLB** (output)

Slice level control PWM output.

#### **EFMO** (output)

Post-binarization EFM signal output. (For montaing)

# 3. EFM Clock Generation Block Pins

#### **FR** (input)

EFM reproduction PLI. VCO bias . sistor connection.

#### PDO, PDS1, PDS2, PDS3 (ou. ...

EFM reproduction PLL lag '1 th. connection.

#### **PCKISTF** (input)

EFM reproduction PLI frequency comparator charge pump bias resistor connection.

#### PCKISTP (input)

EFM reproduction PL. phase comparator charge pump bias resistor connection.

#### RPO (output)

P/N balance a vius...nent

# **OPP** (input)

I/N balar e adjutment.

# PCK2 (output,

EFM reproduction bit clock output.

## 4. Jitter Discrimination Fins

#### JITIN (input)

Jitter discrimination input.

#### JITC (output)

Jitter output.

#### 5. Spindle Speed Detection Pins

#### FG (input)

Input for the speed monitor signal from the spindle driver.

#### 6. Audio Interface Pins

## LOUT, ROUT (output)

Left and right channel audio signal outputs.

#### 7. RF Amplifier Interface Pins

#### **LDON** (output)

RF amplifier interface.

#### 8. Write Strategy Pins

# WRITE, SSP2/1, RAPC, WAPC, H11T0, LDH, ATEST3, 1, WDAT, NWD/

Write strategy signal connections.

#### 9. ATIP Decoder Related Pins

#### **ATIPSYNC** (output)

ATIP synchronization detection signal. (For monitoring)

#### **BIDATA, BICLK** (I/O)

Input mode: Input for the biphase data and biphase clock wher in evernal ATIP demodulator is used.

Output mode: Output of the biphase data and biphase clock when a internal ATIP demodulator is used. (For monitoring)

#### **WOBBLE** (input)

Wobble signal input when the internal ATIP demodu' tor 1. 19 1.

#### **ACRCNG** (output)

Outputs the result of the ATIP decoder CPC che (It monitoring)

#### <Other Pins>

#### **RESET** (input)

The LC898093 reset input. A low level input resets the I C898093.

This pin must be held low for at least 1 \mus \ en power is first applied.

### TEST4 to TEST0 (input)

Test inputs. These pins must be corrected to ground.

## XTALCKO (input), XT/AJ.O (out

Drive these pins at 35.8688 MHz. This signal is used, without modification, as main clock for the CD-ROM encoder and decoder blocks, incluing the DRAM interface.

Consult the manufacturer of the c cillator element concerning the design of the oscillator circuit.

# R, VCNT, PDO/R1, V SNT1 PD1, MCC1 (I/O)

Clock reproduction Procinc it pins

### SUBSYNC (output

Subcode SYNC couput gnal from the CIRC encoder during encoding. (For monitoring)

#### EFMG (output)

Oveputs 2 agh-1 ver signal (5 V) during write operations.

#### Sr!OCK (out, +)

Outputs a high revel (5 V) when a mechanical shock is detected during decodeing.

#### LOCK (output)

Outputs a high level (5 V) when the PLL circuit is locked.

#### **DEF** (input)

Inputs the defect detection signal.

#### **HFL** (input)

Inputs the mirror detection signal.

- Specifications of any and all SANY products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance character lics, and functions of the described products as mounted in the customer's products or equipment. To varie and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., ' to suprily high-quality high-reliability products. However, any and all semiconductor products. 'I with some probability. It is possible that these probabilistic failures could give rise to accide to the vertex so that could endanger human lives, that could give rise to smoke or fire, or that could cause damate to other property. When designing equipment, adopt safety measures so that these kinds of a lider or events cannot occur. Such measures include but are not limited to protective circuits and ever prevenuen circuits for safe design, redundant design, and structural design.

- In the event of any or all S/NYO products (including technical data, services) described or contained herein a controllor under any of applicable local export control laws and regulations, such products must not be or the inhout obtaining the export license from the authorities concerned in accordance with the aboveraw.

- No to his publication may be reproduced or transmitted in any form or by any means, electronic or echal ral, including photocopying and recording, or any information storage or retrieval system, or there se, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all irro mation described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the CANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of August, 2000. Specifications and information herein are subject to change without notice.