# Chapter 1

# Introduction to KS9245 ATAPI Automated CD-ROM Controller

### 1.0 Introduction

The KS9245 is a high performance single-chip CD-ROM decoder with an ATAPI interface. The KS9245 integrates a Buffer Manager which supports a high performance 16-bit DRAM interface, CD-ROM decoder, ECC engine, microcontroller interface, and ATAPI host interface logic. The chip decodes CD-ROM media according to the Sony-Philips® CD-ROM, CD-DA™, CD-ROM/XA, CD-I and CD Enhanced formats, and is designed for operation in a cost effective CD-ROM drive system with industry standard DRAMs, DSPs, and microcontrollers. The KS9245 has sufficient data rates to support up to 50X speed CD-ROM drives which can be daisy-chained to a hard drive through the IDE/ATA interface. Thus, the KS9245 will continue to promote the CD-ROM drive as a new standard device in multimedia PCs.

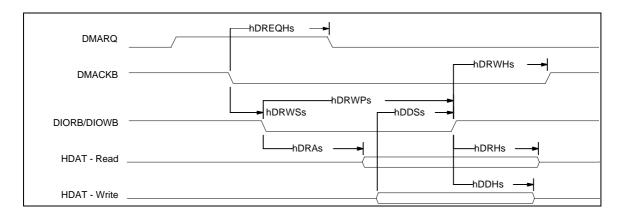

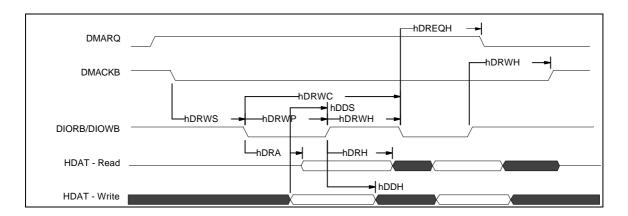

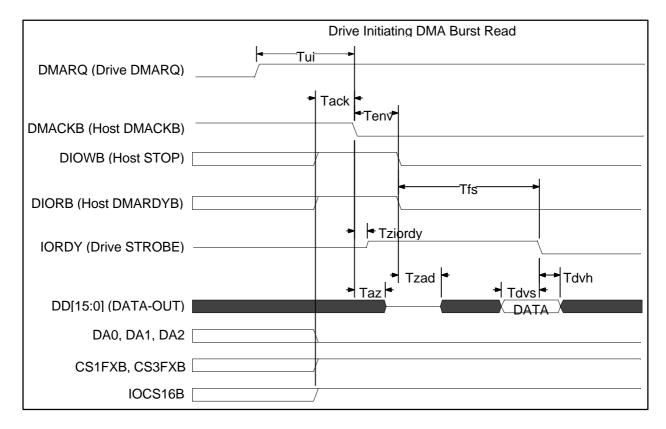

The Host Interface logic supports ATAPI protocols and handles ATAPI packet commands all from hardware to maximize system performance and reduce firmware overhead. The ATAPI Command and Control Block registers are included in the KS9245's register set, allowing both the host and local microcontroller access. The KS9245 supports PIO modes 3 and 4, DMA modes 1 and 2, and UltraDMA modes 1 and 2, allowing for super fast host transfers. In addition, the KS9245 also supports command overlapping to prevent the slower CD-ROM drive from becoming a bottleneck at the system level when daisy-chained to a faster EIDE/ATA device.

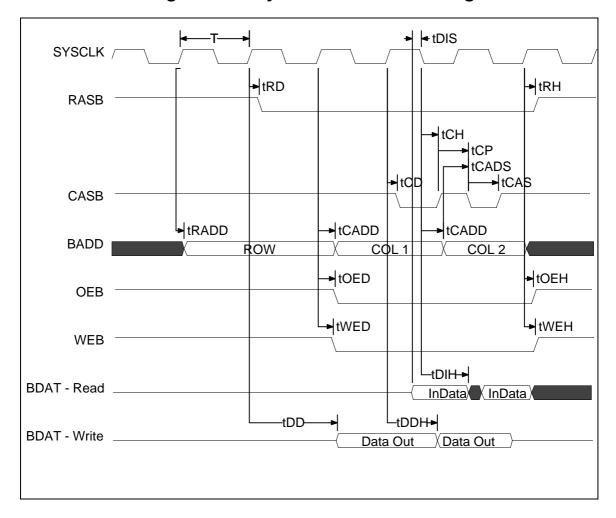

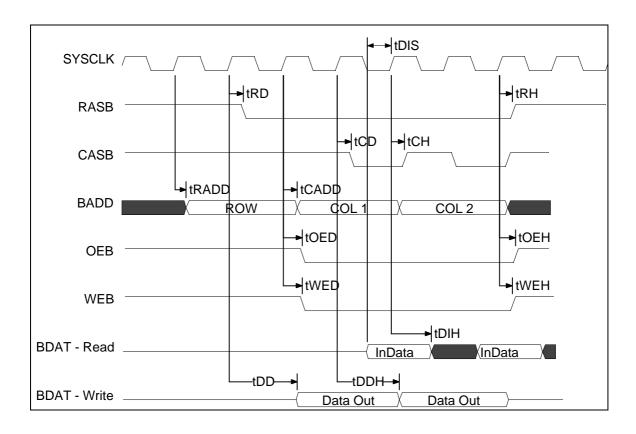

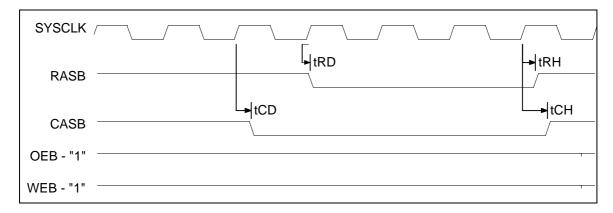

The Buffer Manager controls data flow between the host and a CD DSP. The buffer manager supports Fast Page Mode and EDO DRAMs for high performance application. The buffer manager is programmable and provides all the necessary address and control signals for up to 512K bytes of DRAM. Additionally, the Buffer Manager provides up to 42 MB/sec memory bandwidth with Fast Page DRAM and up to 80 MB/sec with EDO DRAM for host transfers such as PIO mode-3/4 and high speed CD-ROM data access.

The KS9245 uniquely integrates and automates the ATAPI sequences, CD Cache Manager, DRQ Packet handler and Scatter/Gather features. This allows Multiple Block Transfers of up to 1024K bytes in single burst and auto data transfers up to 128M bytes. The entire data transfer for ATAPI Read, and Read CD commands are completely processed by the KS9245 without firmware intervention. As a result, low CPU utilization is achieved in high speed CD-ROM applications.

The CD-DA copy and audio data buffering is supported for audio application. The raw P-W subcode buffering and Q-subcode de-intervealing with CRC check are automated in the KS9245. The audio playback in CAV mode is fully supported by KS9245. With superior CD-DA concatenated techniques and Audio Hardware Buffer Manager, the KS9245 guarantees that the audio data can be played without losing audio frames during CAV playback.

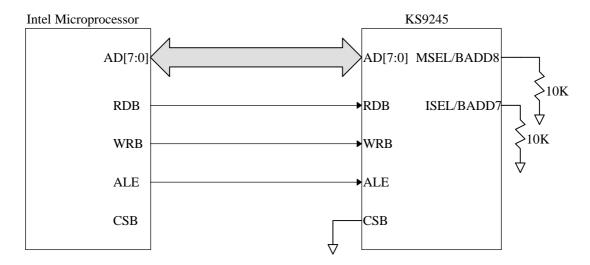

The microcontroller Interface supports high speed, low cost Intel® and Motorola® microcontrollers, such as the 8051 or 68HC11. It supports multiplexed address and data buses. Thus, external glue logic previously required may be removed and system cost minimized. For further flexibility, four general purpose I/O pins are provided by the KS9245, which may be used for various control purposes, such as tray and volume control, etc.

### 1.0.1 Features Summary

### General

- Fully compatible with ATAPI Specification SFF-8020i.

- ATAPI command and control registers contained in the KS9245 register set.

- Automatic power-down on interfaces when idle.

- Supports up to 50X CD-ROM drive.

- 0.5 micron, low-power CMOS technology.

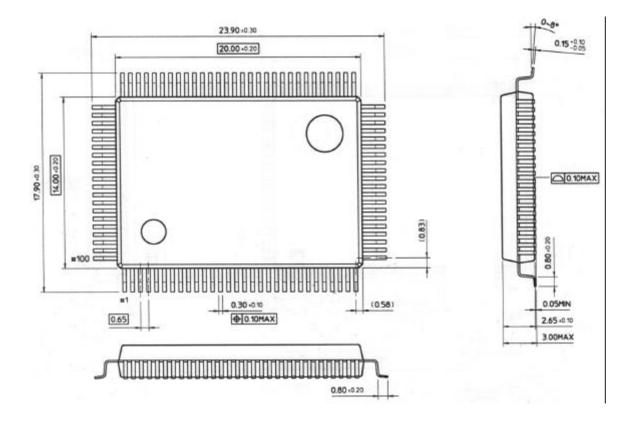

- 100-pin PQFP package.

- low power consumption 0.6W typical.

- System Clock running at 33.868 / 50.8 MHz.

### Buffer Manager

- Advanced CD Cache Manger for low CPU utilization rate and auto data transfer.

- Advanced priority arbitration scheme to maximize buffer bandwidth for all requests.

- Multiple Block Transfer Up to 1M bytes.

- Auto data transfer for Read, Read CD command Up to 128M bytes.

- External 16-bit wide DRAM supports up to 512K-bytes with EDO option.

- Supports both physical or block addressing modes for microcontroller DRAM access.

- Scatter/Gather host transfer for Read CD command.

- Up to 42 MB/sec buffer bandwidth with Fast Page DRAM.

- Up to 80 MB/sec buffer bandwidth with EDO DRAM.

- Up to 64 K bytes direct host transfer for TOC data.

### ATAPI Host Interface

- Support Industry Standard UltraDMA Mode 0, 1 and Mode 2.

- True real-time hardware/firmware ATAPI compatibility.

- Hardware implementation of ATAPI packet command receiving.

- Automated ATA shadow command process.

- Automated ATAPI Signature response.

- Automated protocol control on block transfers for ATAPI read commands.

- Automated command completion control for all ATAPI commands.

- Automated DRQ Packet handler to obtain the best CPU utilization.

- Hardware Service/Release process for overlap command.

- Supports PIO modes 3 and 4 bus transfer rate.

- Supports DMA modes 0. 1 and 2 transfer rate.

- Provision for daisy-chaining two ATA/IDE or ATAPI-embedded drives.

- Supports automatic DASP handshake based on master or slave mode.

### CD-ROM DSP interface

- Supports Sony-Philips® CD-ROM, CD-DA<sup>TM</sup>, CD-I and CD Enhanced formats.

- Supports various compact DSP controllers such as Philips, Toshiba, Sanyo, Matsushita.

- Supports erasure correction up to 2 errors per Codeword.

- Supports P,Q correction up to 1 error per Codeword.

- Repeated error correction support.

- On-The-Fly<sup>™</sup> EDC correction up to 50X data rate.

- C2PO error flags, Raw subcode, and CD-DA buffering support.

- Supports automatic sync pattern search and protection for DRAM data.

- Sector header validity check done by hardware during data transfer.

- Supports real-time de-interleaved Q-subcode buffering and CRC error checking.

- Supports serial DSP programming interface.

- CD-to-DSP data transfer rates up to 50X drive speed.

- Audio Playback in CAV Mode support.

### Microcontroller Interface

- Supports high speed Intel® and Motorola® microcontrollers, such as 8051 & 68HC11.

- Supports multiplexed address and data buses.

- Supports separate host/buffer and disk interrupt signals.

- Four General Purpose I/O pins are provided.

- Interrupt or polled-microcontroller interface.

- Automatic power-down when idle; automatic power-up when command is received.

- Direct register access to facilitate low CPU utilization.

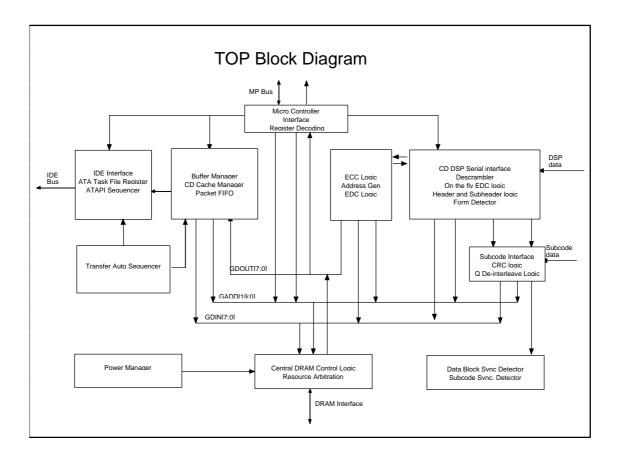

# 1.0.2 Description of Block Diagram

There are six key functional blocks integrated in the KS9245:

- 1) CD-ROM DSP Interface

- 2) Buffer Manager

- 3) Host Interface

- 4) Microcontroller Interface

- 5) ECC Data Corrector

- 6) EDC-CRC Checker.

The CD-ROM DSP Interface logic performs sync-mark detection and insertion for CD-ROM sector synchronization. After descrambling and assembling data from the CD-DSP, the KS9245 sends the data through the On-The-Fly-EDC Data Checker before storing the data into buffer DRAM.

The On-The-Fly-EDC $^{\text{TM}}$  logic then verifies the CD-DSP incoming data stream. If an error is encountered, the On-The-Fly-EDC $^{\text{TM}}$  logic invokes the ECC logic to correct the error. If no error is encountered, the ECC logic remains idle.

The ECC Correction Code circuit performs CIRC Error Correction on each data block. The EDC-CRC Checker then performs a cyclic redundancy check on the corrected data. All ECC correction, including erasure pointer correction, are done in real-time without microcontroller. This reduces firmware overhead and complexity, and minimizes microcontroller performance requirements.

# 1.0.3 KS9245 Functional Block Diagram

The Buffer Manager controls the data flow between the IDE and DSP interfaces. These interfaces store and retrieve data to / from the external DRAM buffer memory using interleaved access cycles.

The Host Interface supports ATAPI protocol, and provides the control for the corrected data to be transferred from the DRAM to the host CPU. Diagnostic data can be transferred from the host CPU to the DRAM to allow testing of the ECC, EDC, and Host Interface logic.

The Microcontroller Interface logic allows the KS9245 to be controlled by the microcontroller through an 8-bit bus. The chip also provides registers and control functions for transferring data between the microcontroller and DRAM through Microcontroller Interface.

Version: TM 2.4

# 1.1. Functional and Features Description

### 1.1.1 Microprocessor Interface Functional Descriptions

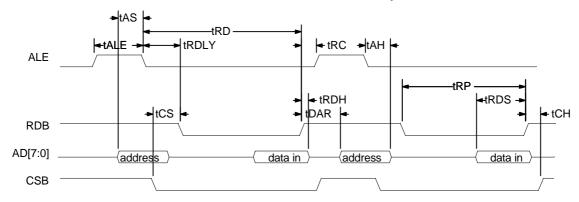

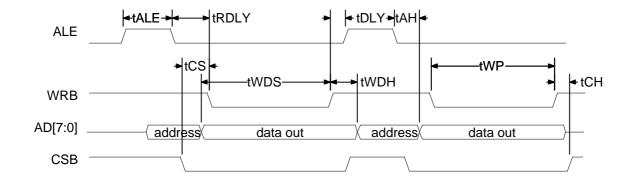

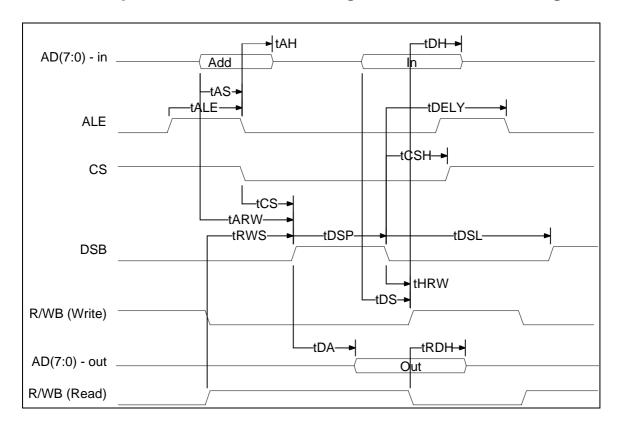

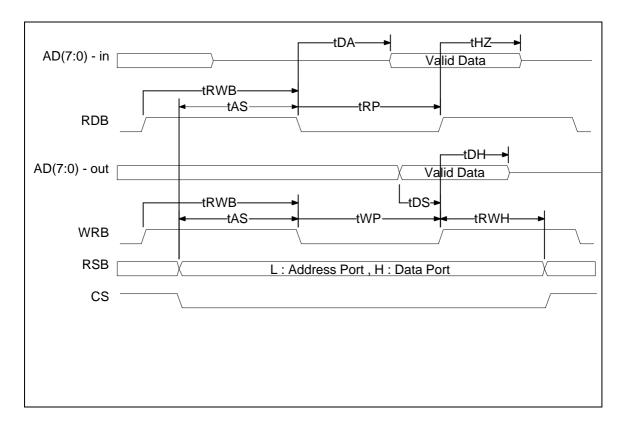

### Intel and Motorola microprocessor interface support

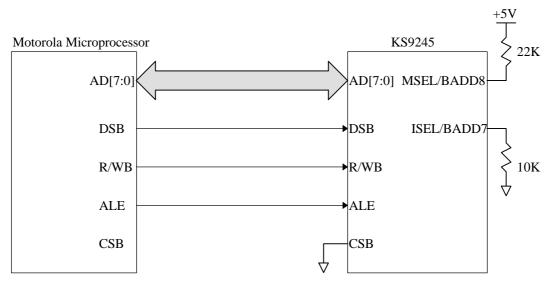

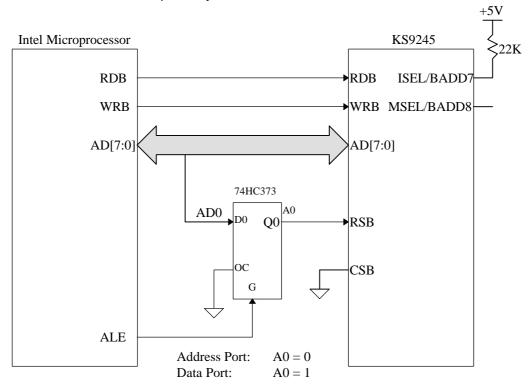

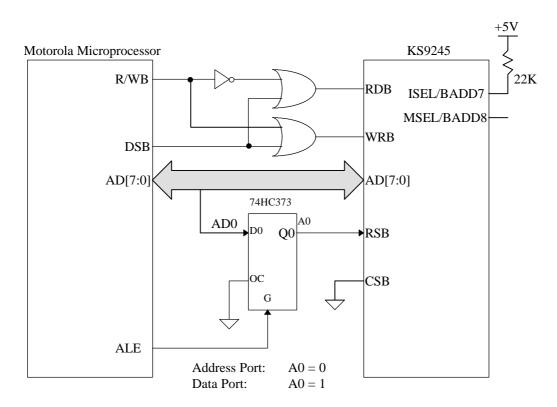

The KS9245 supports both Intel and Motorola type microprocessor interfaces with multiplexed addressing mode. In this mode, the microprocessor address and data lines are shared in AD0-7 pins. Addresses are latched on the trailing edge of the ALE signal. The RDB/WRB pins are used as read and write strobes respectively. Supporting both Intel and Motorola type microprocessors directly enhances the flexibility of the KS9245.

### Combined host/buffer and disk interrupt circuit

The KS9245 supports host/buffer interrupts via the HINTB pin and decoder/disk interrupts via the DINTB pin. Using separate interrupt signals, the interrupt priorities are easily realized. This increases the real-time firmware processing capabilities for high speed CD-ROM applications.

Also, all interrupts can be combined onto the HINTB pin by clearing the *IntMode* bit in the *Interface Configuration Control Register* (0Bh, bit 7). When power-on or reset occurs, the combined interrupt on the HINTB pin is the default configuration.

The host/buffer interrupt includes host command received, reset, or data transfer completed interrupts. The decoder interrupt includes CD decoder or subcode interrupts. The interrupt status is reported in the Host Interrupt Status Register (10h) and the Decoder Interrupt Status Register (11h).

Both HINTB and DINTB are active low, level triggered signals. With the organized interrupt control in the *Host Interrupt Clear/Mask Register* (10h) and *Disk Interrupt Clear/Mask Register* (11h), the firmware is ensured of obtaining interrupts without accidentally clearing or disabling of the interrupts. As a result, reliability of real-time process is achieved.

Polling mode for interrupt processing is also supported in the KS9245 by clearing the mask bits in *Host Interrupt Mask Register* (10h) and *Disk Interrupt Mask Register* (11h).

### Direct register access from microprocessor

The KS9245 supports direct register accesses. Normally, no external glue logic is required to use this feature. Using direct register access, firmware overhead is minimized and system performance enhanced.

### General purpose IO pins support

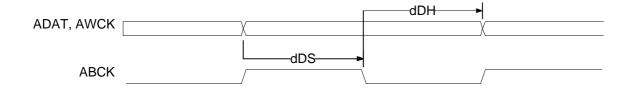

Four General purpose I/O pins are supported in the KS9245. They are the GPIO0-3 pins. Also, these pins are shared with Audio Output pins AWCK/ABCK/ADAT. When the APCE bit in the *Global Configuration Register* (2F, Bit 3) is set, these pins are configured as general purpose Input or Output functions. These pins can be configured as Input or Output by programming the *Port Control Register* (44h, Bit 7, Bit 6, Bit 5, Bit4). These pins may be used for Eject, CD tray, and volume, etc. controls without external glue logic.

### Power Management/Auto wake-up support

The Sleep Mode power management is supported by KS9245. In this mode, the Decoder, Buffer Manager, and host interface circuits are in power savings mode. During Sleep Mode, the buffer DRAM contents are sustained by the KS9245's internal refresh logic and the ATA Task File Registers are available to the host. The Sleep Mode is enabled by setting SSleep bit in Global Control Register (2Fh,

\_\_\_\_\_\_

Bit7). Sleep Mode will automatically wake up and switch into the normal operation mode if the host has written a command to the *ATAPI Command Register* (07h) or ATA Reset occurs. The auto wake up is performed transparently and automatically. The Sleep Mode can only be applied when there is no host transfers and the decoder is in Stop Mode. Thus, the KS9245's power management features provides good solutions for power restricted environments.

# 1.1.2 ATAPI Host Interface Functional Descriptions

The ATAPI interface logic is completely automated. The KS9245 can receive the ATAPI Packet Command and store the 12-byte command packet in a Packet FIFO. During data transfer stage, the ATAPI transfer protocols are processed by KS9245 without firmware intervention. When the total number of host requested blocks are transferred, the ATAPI command completion is posted if automatic command completion is enabled.

### Automated DASP handle to increase Master/Slave Compatibility

The KS9245 will assert the DASPB pin of the ATA interface signals in the slave mode when Power-on Reset, Hardware Reset, or ATA SRST command is received. By asserting the DASPB pin, it allows the master drive to identify the existence of the KS9245 as a slave drive. In some cases, the DASPB signal is sampled by master drive as soon as the above event occurs. If the DASPB signal does not assert fast enough, some master drives cannot recognize the existence of the slave drive. This feature is provided to insure the most compatibility in the Master/Slave handshaking sequence. The master or slave drive is configured by the MSTB pin. The KS9245 will sample this pin when the above events occur. If the KS9245 is configured as a master drive, the PDIAGB and DASPB signals will be negated and left the slave drive to control these signals. Additionally, the PDIAGB and DASPB pins can be asserted or negated by setting SetDASPB, SetPDIAGB, CIrDASPB, CIrPDIAGB bits in Host Interface Control Register (0Ah, bit 6,5,2,1). The microprocessor can read DASPB and PDIAGB signals of the ATA interface.

### Automated ATAPI Signature process

The ATAPI Signature is the required information for host to identify an ATAPI device. The ATAPI Signature is reported in the *ATAPI Byte Count Registers* (04h, 05h) as 14h/EBh. The KS9245 will initialize the ATA Task File Registers and setup the ATAPI Signature automatically. Moreover, the KS9245 supports the ATAPI Signature for ATA Read and ATA Identify commands. The ATAPI Signature is reported and command abort sequence will be posted by the KS9245 if the shadow feature is enabled.

### Automated Packet Command Receiving

The KS9245 will process the ATAPI Packet Command (A0h) and receive 12-byte command packet after host has written the command packet into the ATAPI Data Register. The 12-byte command packet is stored in a Packet FIFO. The firmware is able to retrieve 12-byte command packet by consecutively reading the *Packet FIFO Register* (00h). The 12-byte Packet FIFO is protected from over-run if more than twelve bytes have written. Also, the data pointer of the Packet FIFO is reset whenever a new ATAPI command is received. The Packet Command Interrupt mode assertion of the INTRQ line with the assertion of command packet DRQ is supported. This is enabled by setting the *PcmdInt* bit in the *Interface Configuration Control Register* (0Bh, bit 1).

### Automated DRQ Packet Handle

The KS9245 is able to calculate the transfer byte count and load it into the *ATAPI Byte Count Registers* (04h, 05h) when host transfer occurs. Moreover, the KS9245 will break the block-oriented transfers in the Buffer Manager into byte-oriented transfers in the ATAPI interface without firmware intervention. Before a DRQ packet transfer starts, the ATAPI Byte Count Registers are calculated and the ATAPI data transfer protocol are processed by the KS9245.

### Automated BSY bit handle

The BSY bit of ATAPI Task File Register is controlled by KS9245. It ensures that the protocol is in compliance with the ATA Specification. Using this feature, the firmware is assured to be compatible with the Win 95/OS2/Win NT Operating Systems.

Also, the BSY bit can be set or cleared by firmware as manual mode by setting SetBSY or ClrBSY bits in Host Interface Control Register (0Ah, bit 7, 3), respectively.

### • Automated DRQ bit handle

The *DRQ* bit in ATAPI Status Register is automated by the KS9245. The *DRQ* bit in the ATAPI Status Register is set automatically where appropriate.

### Automated DSC bit handle

The *DSC* bit in the ATAPI Status Register is fully automated. This is used to post overlap seek command completion. This sequence starts by setting the *SDSC* bit in the *Host Sequence Command Register* (0Eh, bit 0).

### Automated command completion handle

The command with either Successful or Error Completion sequence is supported by the KS9245. The sequence starts by setting the SCpl or SCplChk bits in the Host Sequence Command Register (0Eh, bit 2, 1) for ATAPI error or successful conditions, respectively. Also, the automated command completion is extended into data transfers. With the completion of an entire host transfer, the ATAPI completion status is posted to the host if the ACplE bit in the Transfer Sequence Command Register is set (0Fh, bit 6).

### ATAPI Overlap Command - Service/Release support

Overlap command operations are supported by the KS9245. The ATAPI Release and Service protocols are implemented by the KS9245. The Release sequence starts by setting the *Srelease* bit in the *Host Sequence Command Register* (0Eh, Bit 4). The Service sequence starts by setting the *Sservice* bit in the *Host Sequence Command Register* (0Eh, Bit 5). Both interrupts on Release or Service can be disabled by setting the *DisSerInt* or *DisRelInt* bits in the *Host Interface Diagnostic Control 2 Register* (51h, bit 7, 6).

### Automated ATA Shadow command support

The shadow command is used when the drive is in the master mode and there is no slave drive connected. The KS9245 will abort the command without firmware intervention when the host has issued the command to a non-existent slave drive. The sequence is enabled by clearing the *DisShaR* bit in the *Interface Configuration Control Register* (0Bh, bit 2) when the *CDRV* bit is cleared (0Bh, bit 4) and the *SShadow* (0Bh, bit 3) bit is set in the *Interface Configuration Control Register*.

# 1.1.3 Buffer Interface/Manager Functional Descriptions

The CD Cache Manager is supported by hardware in the KS9245. With the automated and integrated architecture, the data transfers for entire Read and Read CD command are achieved. The Buffer Manager state machine will monitor the buffer block count. The maximum number of blocks that can be automatically transferred is 64K blocks, or about 128M bytes. With the powerful DRQ packet handling of the KS9245, the host transfers are realized with very high performance. As a result, low CPU utilization for high speed CD-ROM is achieved and code size minimized. The KS9245 supports up to 512K bytes of 16-bit Fast Page mode and EDO (Extended Data Output) DRAMs. The CD data block are organized in either 2.5K bytes or 3K bytes per block. The CD data and subcode can be chosen to be buffered in both configurations. In the latter case, the buffering for C2PO error flags and Block Error flags are included.

All data blocks are linearly arranged without separating as auxiliary or data block. With the straight addressing mechanism, firmware overhead and programming mistakes are minimized.

### • Multiple Block Transfer support

Multiple Block Transfer is supported by the KS9245. The transfer block is specified in the *Current Host Transfer Block Length Registers* (18h, 19h). For Multiple Block Transfers, up to 256 blocks, or 512K bytes, can be burst to the host without firmware intervention. In the ATAPI specification, the maximum host transfer in a single DRQ packet is 64K bytes. The KS9245 will send the maximum number of bytes in a DRQ packet transfer.

### Automated transfer for entire Read command

The KS9245, with its advanced hardware CD Cache Manager, supports host transfers for entire Read or Read CD commands of up to 64K blocks, or 128M bytes, without firmware intervention. When the *ACachE* bit in the *Transfer Sequence Command Register* (0Fh, bit 7) is set, the CD Cache Manger is enabled. At the completion of the total transfers specified in the *Total Host Transfer Block Length Registers* (16h, 17h), the ATAPI completion status will be posted to the host if the *ACplE* bit in the *Transfer Sequence Command Register* (0Fh, bit 6) is set. Also, the *TxfrDone* bit in the *Host Interrupt Status Register* (10h, bit 7) will be set and a microprocessor interrupt will be generated if the *TxfrDoneE* bit in the *Host Interrupt Mask Register* (12h, bit 7) is set.

### • Scatter/Gather Support

The KS9245 provides two sets of segment registers which specify the start offset address and the transfer byte lengths within a data block. When the transfer is completed in the first segment, the hardware will automatically chain the second segment and continue the host transfers. The advantage to using Scatter/Gather feature is to avoid breaking transfer into two or more sub-transfers if data is scattered within a block. Two segment registers are specified in the *Transfer Offset Length Low/High 1/2* (1Eh, 1Fh, 22h, 23h) and *Host Block Offset Address Low/High 1/2 Registers* (1Ch, 1Dh, 20h, 21h). In a Read CD command, the host requested data may not be in a contiguous location. For example, the 2048-byte data block and 294-byte C2PO error flags are requested in the same transfer. The firmware can utilize this Scatter/Gather feature to chain these transfers together.

### CD Cache Manager

A hardware CD Cache Manager is supported in KS9245. When the *ACachE* bit in the *Transfer Sequence Command Register* (0Fh, bit 7) is set, the CD Cache Manager initiates the host transfer as soon as data is available in the cache. That is, the *Valid Cache Block Count Registers* (14h, 15h) are not equal to zero, until the *Total Host Transfer Block Length Registers* (16h, 17h) is decreased to zero. The host transfer process is continuously monitored by hardware until all data are transferred.

### • Block Address support

All data blocks can be addressed by a sequential block number which starts from zero at the top of the buffer DRAM and ends at the last or bottom of the block address specified in the *Buffer Bottom Block Address Register* (2Ch). Before starting host transfers, the *Host Transfer Block Address Low/High Registers* (1Ah, 1Bh) must be loaded with the starting block address. Before starting the decoder transfers, the *Disk Transfer Block Address Register* (38h) must be loaded with the starting block address. Both host and disk address pointers are automatically increased by one when a block of data is transferred to host or from the disk. When these registers reach the values of *Buffer Bottom Block Address Register* plus one, they are wrapped around to the top of the buffer DRAM.

### • Microprocessor Physical and Block access DRAM support

Both the physical and block addressing modes for accessing DRAM by the microprocessor are supported. The *PAMb* bit in the *Buffer Access Control Register* (29h, bit 2) is used to specify the addressing mode. Using Physical Address Mode (PAM), the DRAM physical address must be loaded into

the MP Access Physical Address LSB/MID/MSB registers (24h, 25h, 26h). This mode is used for accessing the firmware variables such as TOC data in the System Area. Using Block Address Mode (BAM), the block and offset addresses must be loaded into the MP Block Address Register (26h) and MP Block Offset Low/High Address Registers (24h, 25h). This mode is used to access data within the CD by the KS9245. This allows the firmware to easily check the contents of the data block, such as Sync Pattern, without converting the block address into a DRAM physical address. The DRAM read or write operation will be initiated when the SDramRd and SDramWrt bits are set in the Buffer Access Control Register (29h, bit 0, 1), respectively. The data for read operations will be available in the MP Access Data Port Register (28h) after the DramBsy bit of the Buffer Access Control Register is cleared (29h, bit 7). The data for write operation must be loaded into the MP Access Data Port Register is cleared (29h, bit 7).

### • Segmented Buffer support

The buffer DRAM is partitioned into two segments: The Data and System areas. The Data area, is used for storing the CD data block as cache area while the System area is for storing CD system information such as TOC data, Identify device information, Inquiry data, and firmware variables. The System area starts below the last byte of the bottom of the block address which is specified in the *Buffer Bottom Block Address Registers* (2Ch, 2Dh). Therefore, the size of the System Area can be adjustable by setting the *Buffer Bottom Block Address Registers* (2Ch, 2Dh).

### Up to 64K bytes direct transfer from DRAM

Host transfers from the System Area is not limited to block boundaries. Up to 64K bytes can be directly transferred from the buffer DRAM to the host. This allows the TOC (Table of Contents) data to be transferred without the limitation of the 2.5K-byte or 3K-byte block boundary. This avoids having to break a transfer into multiple sub-transfers. As a result, the firmware can support the TOC efficiently and code size is reduced. By setting the *Transfer Offset Length Low/High 1/2 Registers* (1Eh, 1Fh, 22h, 23h) with the desired transfer length, the transfer will not complete until the total number of bytes specified in these registers are transferred.

# 1.1.4 CD Decoder Interface/Manager Functional Descriptions

The KS9245 supports various DSP devices such as Toshiba, Sony, Sanyo, and Matsushita by setting the DSP Device Type Selection Register (3Eh). Also, various subcode interface such as Philips V4, EIAJI and EIAJ2 can be programmed by setting Subcode Device Type Selection Register (42h).

The main DSP data, C2PO error flags, and subcode buffering are supported by setting the *DSP Channel Sel* bit in the *Buffer Configuration Control 1 Register* (2Ah, bit 6, 4, 5). Moreover, the KS9245 uses the C2PO error flags to perform the Erasure Correction up to 2-byte error per Codeword by setting the *EraCorr* bit in the *ECC Control 1 Register* (3Bh, bit 0). The Q-subcode with de-interleaving and CRC check are done by hardware.

Sync pattern protection logic is implemented in the KS9245 to prevent lost sync in the DSP incoming streams. The sync patterns in buffer DRAM are further protected to facilitate the Read Raw operations. This assures that the application is able to retrieve the correct sync pattern when Sync Insertion occurs.

The decoder logic operates in various modes according to the setting of the *Decoder Control Register* (3Ah). The Monitor Mode is used to search the target block and synchronize the Sync Mark in the main data channel before data buffering operation occurs. In this mode, no buffering or ECC operation is active. The decoder interrupt occurs at the relative location of Header or Subheader of the incoming DSP data streams.

The Audio Buffering Mode is used for CD-DA copy operations. In this mode, the descrambler, ECC, and EDC logic are not active and a decoder interrupt is generated to the microprocessor for every 2352-byte. The buffering operation for data stream is active. The CD-DA data can be accurately synchronized with the subcode data stream if the *AsynWrt* bit in the *ECC Control 2 Register* (3Ch, bit 3) is set.

In the ECC mode, the descrambler, EDC, and ECC are all active with various correction configurations. This mode is normally used for buffering CD data such as Yellow Book, CD-ROM XA, or CD-I data. The correction modes are configured by setting the *ECC Control 1 Register* (3Bh). The decoder interrupts occur at either the completion of *On-The-Fly-EDC*<sup>TM</sup> check when there is no EDC error, or at the end of ECC operations in this mode. The *Decoder Header Min/Sec/Frame/Mode Registers* (30h, 31h, 32h, 33h), *Decoder Subheader 0-3 Registers* (34h, 35h, 36h, 37h), and the *ECC Status Register* (3Dh) contains the information for the block just processed.

The Buffering Only Mode is used for processing Yellow Book Mode 0 and 2 data. In this mode, only the descrambler is active. Neither ECC nor EDC logic will be applied in this mode. The settings of the ECC Control 1 Register (3Bh) is ignored by hardware. The decoder interrupt occurs at the end of buffering a block to the buffer DRAM.

If no correction is applied, there is a full sector time for firmware to process the decoder interrupt in most cases. For the KS9245, the maximum time allowed for firmware to process the interrupt is a half sector time. In the Firmware Sector Process Time of the Hardware Application Note section, detailed information is provided for various disk speeds.

# • On-the-fly-EDC<sup>™</sup> correction

The KS9245 supports On-The-Fly-EDC<sup>TM</sup> correction. Both Yellow Book Mode 1 and XA Mode 2, Form 1 of incoming DSP data streams are automatically checked by the EDC circuit. If there is no EDC error, the decoder interrupt is immediately generated without further delay and no redundant ECC is applied. As a result, the Buffer Manager can transfer the data to host without ECC latency and lower CPU utilization is achieved. If there is an EDC error, the consecutive ECC correction will be applied. On-The-Fly-EDC<sup>TM</sup> check can also resolve the buffer DRAM requirements. Therefore, the KS9245 can support the high speed CD application up to 50X with standard DRAMs.

### Advanced Erasure Correction up to 2-byte error per Codeword

The KS9245 supports high performance erasure correction up to 2-byte error per Codeword. The Erasure Correction is enabled by setting the *EraCorr* bit in the *ECC Control 1 Register* (3Bh, bit 0). The erasure correction logic uses the C2PO error flags as correction indication. Therefore, C2PO error flags must be provided in this mode. The standard P and Q Parity Correction are supported for 1-byte error per Codeword. The P and Q Parity are enabled by setting the *EccPen* or *EccQen* bits in the *ECC Control 1 Register* (3Bh, bit 2, 1).

### CD-DA COPY support

The KS9245 also supports CD-DA buffering operations. By setting the *AudiWrt* bit in the *Decoder Control Register* (3Bh, bit 4), the decoder is placed into Audio Buffering Mode. The decoder circuit starts to synchronize with the first left channel. If the *ASynWrt* bit in the *ECC Control 2 Register* (3Ch, bit 3) is set, the CD-DA data stream will be synchronized with the subcode Sync Mark. As a result, the data of CD-DA operations are smoothly connected for different accesses. In Audio Buffering Mode, the internal counter is active and an interrupt is generated to the host for every 2352-bytes.

### Audio Playback in CAV mode support

In CAV (Constant Angular Velocity) applications, the KS9245 allows audio data to be buffered and played at regular CAV speeds without changing the speed to CLV (Constant Linear Velocity) or single speed modes. Along with the CD-DA subcode synchronization techniques in KS9245, Audio frame data

\_\_\_\_\_

is guaranteed to be smoothly concatenated without losing audio frames during CAV playback. In the KS9245, up to 50X CAV operation in outer tracks is supported.

The buffered audio data is output to the external audio DAC at 44.1Khz (Word Clock) in either EIAJ or I2S audio formats regardless of the disk speed. Also, the audio data underrun condition is masked by muting both output channels to guard against undesired audio noise. As results, in CAV applications, the audio playback can be achieved by CD-ROM controller in a low cost design.

In order to simplify firmware efforts and efficiently control the audio playback sequences, the Audio Hardware Buffer Manager implemented will automatically keep track of the available audio block(s) in buffer DRAM. When this buffer is full, firmware is able to stop the DSP buffering operation. If the buffer is empty or underrun, the audio mute operation is automatically performed by hardware to avoid any noise from being outputted.

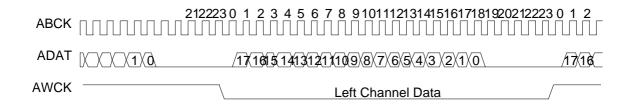

The audio output pins can be selected and configured via the AWCK, ABCK, ADAT and EBUO pins. The clock source is derived directly from the system clock thus eliminating the need for another crystal for the audio clock.

### • Repeated Correction support

Repeated correction is supported by the KS9245 for intensively non real-time correction environments. By setting the appropriate *Disk Transfer Block Address Registers* (38h, 39h) and writing a one in the *RepCorr* bit in the *ECC Control 2 Register* (3Ch, bit 2), the correction is started. An interrupt will be generated with the *DecInt* bit set in the *Decoder Interrupt Status Register* (11h, bit 0) if the *DecIntE* bit in *Decoder Interrupt Mask Register* (13h, bit 0) is set.

### • Sync Mark Insertion support

The Sync Mark insertion is supported by the KS9245. When the decoder is in the ECC, Buffering Only Mode, or Monitor Mode, the Sync Insertion logic is active. This allows the DSP Interface logic to recover from lost synchronization errors. If the decoder is in the Monitor Mode, the Sync Insertion logic will always re-synchronize with the most recent Sync Mark to insure that synchronization is never lost.

### Q-Subcode deinterleave with CRC check support

The 12-byte de-interleaved Q subcode is supported by the KS9245. The de-interleaved Q subcode data with four zeros data are written into buffer DRAM without firmware intervention. Also, the CRC check for Q subcode is done by hardware and this CRC result is reported in the *Subcode Status Register* (41h, bit 7, 6) when a subcode interrupt occurs.

### Real-time ECC and Sector Synchronized method support

ECC operation starts as soon as the previous block has finished buffering operation with EDC error. The ECC operation is synchronized with the sector sync pattern. As a result, the data block address for ECC operation is always one block behind the DSP buffering operation. Because of the sector synchronized architecture of ECC corrections, blocks are processed in real-time. In other "buffered data correction" or "delayed pipeline ECC correction" methods, the buffer DRAM will quickly fill when some erroneous blocks occur. As a result, a consequent seek may be required. Therefore, the real-time ECC correction of the KS9245 offers a superior correction scheme to other methods.

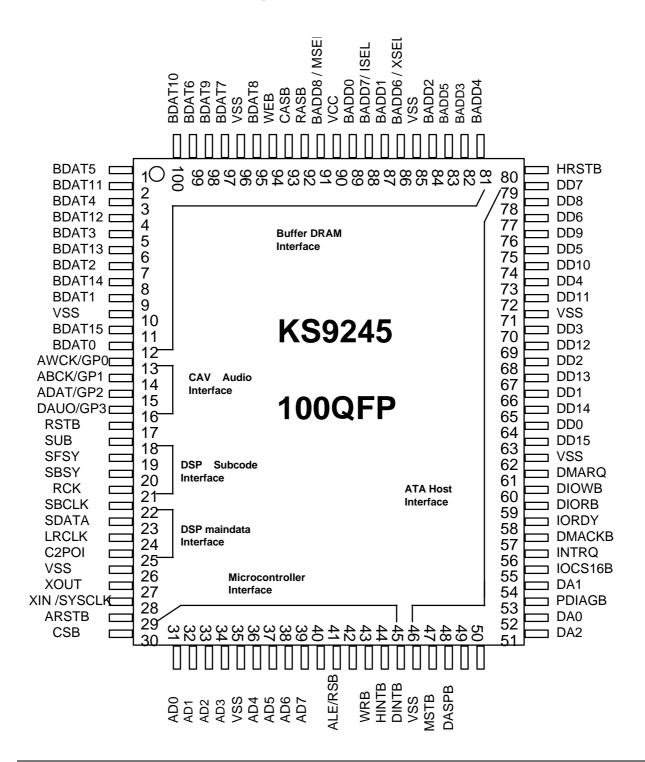

# 1.2 KS9245 QFP Pin Diagram

Note: BADD0 (Pin 89) should be pulled high by a 22K Ohm Resistor for KS9246 compatibility.

# 1.3 Pin Assignment

The pin assignments are listed in sequential order of pin number with short description in the following table.

|                                                   | S          | ymbol and Convention                          |  |  |  |  |  |

|---------------------------------------------------|------------|-----------------------------------------------|--|--|--|--|--|

| D                                                 | Open-Drain | pin used as an open-drain signal              |  |  |  |  |  |

| 0                                                 | Output     | pin used as an output signal                  |  |  |  |  |  |

| I                                                 | Input      | pin used as an input signal                   |  |  |  |  |  |

| Т                                                 | Tristate   | pin used as a tristate signal                 |  |  |  |  |  |

| t To pin is an output signal to outside component |            |                                               |  |  |  |  |  |

| f                                                 | From       | pin is an input signal from outside component |  |  |  |  |  |

| х                                                 | don't care | pin may either be used or not used            |  |  |  |  |  |

| MP                                                |            | Microprocessor or Microcontroller             |  |  |  |  |  |

| DSP                                               |            | CD DSP main data channel interface            |  |  |  |  |  |

| DSPSUB                                            |            | CD DSP Subcode interface                      |  |  |  |  |  |

| DRAM                                              |            | Dynamic Random Access Memory                  |  |  |  |  |  |

| Host                                              |            | IDE Host                                      |  |  |  |  |  |

| Master                                            |            | IDE Master Drive, drive 0                     |  |  |  |  |  |

| Slave                                             |            | IDE Slave Drive, drive 1                      |  |  |  |  |  |

| DAC                                               |            | External Audio DAC                            |  |  |  |  |  |

|        |     | Phy         | sical Pin Assignment   |            |

|--------|-----|-------------|------------------------|------------|

| Signal | Pin | Description | Source/<br>Destination |            |

| BDAT5  | 1   | I/O         | DRAM data bus 5        | t, f, DRAM |

| BDAT11 | 2   | I/O         | DRAM data bus 11       | t, f, DRAM |

| BDAT4  | 3   | I/O         | DRAM data bus 4        | t, f, DRAM |

| BDAT12 | 4   | I/O         | DRAM data bus 12       | t, f, DRAM |

| BDAT3  | 5   | I/O         | DRAM data bus 3        | t, f, DRAM |

| BDAT13 | 6   | I/O         | DRAM data bus 13       | t, f, DRAM |

| BDAT2  | 7   | I/O         | DRAM data bus 2        | t, f, DRAM |

| BDAT14 | 8   | I/O         | DRAM data bus 14       | t, f, DRAM |

| BDAT1  | 9   | I/O         | DRAM data bus 1        | t, f, DRAM |

### KS9245 ATAPI Automated CD-ROM Controller Preliminary Technical Manual

|            |     | Ph  | ysical Pin Assignment                                                 |                        |  |  |

|------------|-----|-----|-----------------------------------------------------------------------|------------------------|--|--|

| Signal     | Pin | 1/0 | Description                                                           | Source/<br>Destination |  |  |

| VSS        | 10  | 1   | Ground                                                                | -                      |  |  |

| BDAT15     | 11  | I/O | DRAM data bus 15                                                      | t, f, DRAM             |  |  |

| BDAT0      | 12  | I/O | DRAM data bus 0                                                       | t, f, DRAM             |  |  |

| AWCK/GP0   | 13  | I/O | Audio word clock output or General Purpose I/O Line 0                 | t,DAC                  |  |  |

| ABCK/GP1   | 14  | I/O | Audio bit clock output or<br>General Purpose I/O Line 1               | t,DAC                  |  |  |

| ADCK/GP2   | 15  | I/O | Audio data output or<br>General Purpose I/O Line 2                    | t,DAC                  |  |  |

| DAUO/GP3   | 16  | I/O | Digital Audio output or<br>General Purpose I/O Line 3                 | t,DAC                  |  |  |

| RSTB       | 17  | ı   | Chip power on reset                                                   | -                      |  |  |

| SUB        | 18  | ı   | Subcode serial data in                                                | f, DSPSUB              |  |  |

| SFSY       | 19  | I   | Subcode frame sync                                                    | f, DSPSUB              |  |  |

| SBSY/CFLG  | 20  | I   | EIAJ Subcode block sync / CFLAG f, D                                  |                        |  |  |

| RCK        | 21  | I/O | Subcode bit clock                                                     | t, DSPSUB              |  |  |

| SBCLK      | 22  | ı   | DSP Bit Clock                                                         | f, DSP                 |  |  |

| SDATA      | 23  | I   | DSP Channel Data                                                      | f, DSP                 |  |  |

| LRCLK      | 24  | I   | DSP Left Channel Clock                                                | f, DSP                 |  |  |

| C2POI      | 25  | I   | C2PO Error Flags                                                      | f, DSP                 |  |  |

| VSS        | 26  | I   | Ground                                                                | -                      |  |  |

| XOUT       | 27  | 0   | oscillator output                                                     | t,Oscillator           |  |  |

| XIN/SYSCLK | 28  | I   | oscillator input/system clock input<br>Normally, 33.868 MHz / 50.8MHz | f,Oscillator           |  |  |

| ARSTB      | 29  | 0   | ATAPI 08 Cmd reset                                                    | t, MP                  |  |  |

| CSB        | 30  | I   | Chip select                                                           | f, MP                  |  |  |

| AD0        | 31  | I/O | microprocessor data/address bus 0                                     | t, f, MP               |  |  |

| AD1        | 32  | I/O | microprocessor data/address bus 1                                     | t, f, MP               |  |  |

| AD2        | 33  | I/O | microprocessor data/address bus 2                                     | t, f, MP               |  |  |

| AD3        | 34  | I/O | microprocessor data/address bus 3                                     | t, f, MP               |  |  |

| VSS        | 35  | ı   | Ground                                                                | -                      |  |  |

| AD4        | 36  | I/O | microprocessor data/address bus 4                                     | t, f, MP               |  |  |

| AD5        | 37  | I/O | microprocessor data/address bus 5                                     | t, f, MP               |  |  |

| AD6        | 38  | I/O | microprocessor data/address bus 6                                     | t, f, MP               |  |  |

| AD7        | 39  | I/O | microprocessor data/address bus 7                                     | t, f, MP               |  |  |

| VCC        | 40  | ı   | Power                                                                 | -                      |  |  |

|             |     | Phy | /sical Pin Assignment                                                                      |                        |  |

|-------------|-----|-----|--------------------------------------------------------------------------------------------|------------------------|--|

| Signal      | Pin | 1/0 | Description                                                                                | Source/<br>Destination |  |

| ALE<br>RSB  | 41  | Ι   | microprocessor Address Latch Enable<br>Address Register select in indirect<br>access mode. | f, MP                  |  |

| RDB<br>DSB  | 42  | _   | microprocessor read strobe (Intel) data strobe signal (Motorola)                           | f, MP                  |  |

| WRB<br>R/WB | 43  | Ι   | microprocessor write strobe (Intel) read/write strobe (Motorola)                           | f, MP                  |  |

| HINTB       | 44  | OD  | microprocessor Host interrupt                                                              | t, MP                  |  |

| DINTB       | 45  | OD  | microprocessor Disk interrupt                                                              | t, MP                  |  |

| VSS         | 46  | ı   | Ground                                                                                     | -                      |  |

| MSTB        | 47  | I   | Master/Slave Configuration                                                                 | Drive SEL              |  |

| DASPB       | 48  | I/O | IDE drive active-slave present                                                             | Mast/Slave             |  |

| CS3FXB      | 49  | I   | IDE host chip select 1                                                                     | f, Host                |  |

| CS1FXB      | 50  | I   | IDE host chip select 0                                                                     | f, Host                |  |

| DA2         | 51  | I   | IDE host address 2                                                                         | f, Host                |  |

| DA0         | 52  | I   | IDE host address 0                                                                         | f, Host                |  |

| PDIAGB      | 53  | I/O | IDE Passed Diagnostics                                                                     | Mast/Slave             |  |

| DA1         | 54  | I   | IDE host address 1                                                                         | f, Host                |  |

| IOCS16B     | 55  | OD  | IDE 16-bit data transfer                                                                   | t, Host                |  |

| INTRQ       | 56  | OT  | IDE host interrupt request                                                                 | t, Host                |  |

| DMACKB      | 57  | I   | IDE host DAM acknowledge                                                                   | f, Host                |  |

| IORDY       | 58  | OT  | IDE I/O channel ready                                                                      | t, Host                |  |

| DIORB       | 59  | I   | IDE I/O read strobe                                                                        | f, Host                |  |

| DIOWB       | 60  | I   | IDE I/O write strobe                                                                       | f, Host                |  |

| DMARQ       | 61  | OT  | IDE drive DMA request                                                                      | t, Host                |  |

| VSS         | 62  | I   | Ground                                                                                     | -                      |  |

| DD15        | 63  | I/O | IDE host data bus 15                                                                       | t, f, Host             |  |

| DD0         | 64  | I/O | IDE host data bus 0                                                                        | t, f, Host             |  |

| DD14        | 65  | I/O | IDE host data bus 14                                                                       | t, f, Host             |  |

| DD1         | 66  | I/O | IDE host data bus 1                                                                        | t, f, Host             |  |

| DD13        | 67  | I/O | IDE host data bus 13                                                                       | t, f, Host             |  |

| DD2         | 68  | I/O | IDE host data bus 2                                                                        | t, f, Host             |  |

| DD12        | 69  | I/O | IDE host data bus 12 t, f, I                                                               |                        |  |

| DD3         | 70  | I/O | IDE host data bus 3                                                                        | t, f, Host             |  |

### KS9245 ATAPI Automated CD-ROM Controller Preliminary Technical Manual

|                |     | Phy | ysical Pin Assignment                                                                               |                        |

|----------------|-----|-----|-----------------------------------------------------------------------------------------------------|------------------------|

| Signal         | Pin | 1/0 | Description                                                                                         | Source/<br>Destination |

| VSS            | 71  | I   | Ground                                                                                              | -                      |

| DD11           | 72  | I/O | IDE host data bus 11                                                                                | t, f, Host             |

| DD4            | 73  | I/O | IDE host data bus 4                                                                                 | t, f, Host             |

| DD10           | 73  | I/O | IDE host data bus 10                                                                                | t, f, Host             |

| DD5            | 75  | I/O | IDE host data bus 5                                                                                 | t, f, Host             |

| DD9            | 76  | I/O | IDE host data bus 9                                                                                 | t, f, Host             |

| DD6            | 77  | I/O | IDE host data bus 6                                                                                 | t, f, Host             |

| DD8            | 78  | I/O | IDE host data bus 8                                                                                 | t, f, Host             |

| DD7            | 79  | I/O | IDE host data bus 7                                                                                 | t, f, Host             |

| HRSTB          | 80  | I   | ATA Host reset                                                                                      | -                      |

| BADD4          | 81  | 0   | DRAM Address line 4                                                                                 | t, DRAM                |

| BADD3          | 82  | 0   | DRAM Address line 3                                                                                 | t, DRAM                |

| BADD5          | 83  | I/O | DRAM address line 5  Must also be pulled up by 22K  Ohm Resistor                                    | t, DRAM                |

| BADD2          | 84  | 0   | DRAM address line 2                                                                                 | f, DRAM                |

| VSS            | 85  | ı   | Ground                                                                                              | -                      |

| BADD6/XSEL     | 86  | I/O | DRAM address line 6<br>22K Pull-up for 50.8MHz Sysclk<br>10K Pull-down for 33.86MHz Sysclk          | t, DRAM                |

| BADD1          | 87  | 0   | DRAM address line 1                                                                                 | t, DRAM                |

| BADD7/ISEL     | 88  | I/O | DRAM Address line 7 Pull-up for MP Register Indirect Select Pull-down for MP Register Direct Select | t, DRAM                |

| BADD0          | 89  | 0   | DRAM address line 0<br>Should be pulled up by 22K Resistor                                          | t, DRAM                |

| VCC            | 90  | ı   | Power                                                                                               | -                      |

| BADD8/MSE<br>L | 91  | I/O | DRAM address line 8 Pull-up for Motorola MP Select Pull-down for Intel MP Select                    | t, DRAM                |

| RASB           | 92  | 0   | DRAM RASB line                                                                                      | t, DRAM                |

| CASB           | 93  | 0   | DRAM, CASB line                                                                                     | t, DRAM                |

| WEB            | 94  | 0   | DRAM write enable                                                                                   | t, DRAM                |

| BDAT8          | 95  | I/O | DRAM data bus 8                                                                                     | t, f, DRAM             |

| VSS            | 96  | ı   | Ground                                                                                              | -                      |

| BDAT7          | 97  | I/O | DRAM data bus 7                                                                                     | t, f, DRAM             |

| BDAT9          | 98  | I/O | DRAM data bus 9                                                                                     | t, f, DRAM             |

| BDAT6          | 99  | I/O | DRAM data bus 6                                                                                     | t, f, DRAM             |

| BDAT10         | 100 | I/O | DRAM data bus 10                                                                                    | t, f, DRAM             |

# 1.4 Pin Description

# 1.4.1 Pin Description in ATA Host Interface

CS1FXB (Drive chip select 0)

**Pin 50**

This is the chip select signal decoded from the host address bus used to select the Command Block Registers.

**CS3FXB** (Drive chip select 1)

**Pin 49**

This is the chip select signal decoded from the host address bus used to select the Control Block Registers.

**DA0,1,2** (Drive address bus)

Pin 52,54,51

This is the chip select signal decoded from the host address bus used to select the Control Block Registers.

**DASPB** (Drive active slave present)

Pin 48

This is a time-multiplexed signal which indicates that a drive is active or drive 1 is present. This signal is an open collector output with a 10K ohm pull-up resistor.

**DD0-DD15** (Drive data bus)

Pin 64,66,,68,70,73,75,77,79, 78,76,74,72,69,67,65,63

Version: TM 2.4

These signals are used for 16-bit bidirection data bus between the host and the KS9245. The DD0-7 are used for accessing 8-bit ATA Task File Registers.

In ATAPI data transfer mode, it is always 16-bit wide.

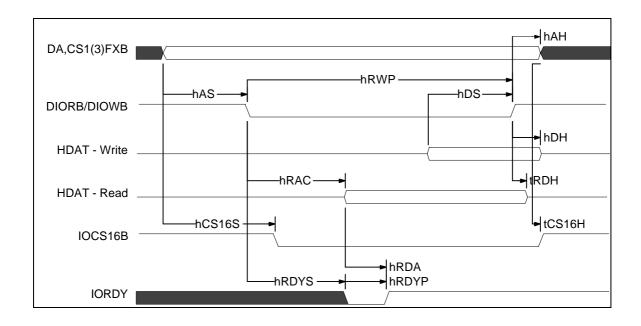

**DIORB** (Drive I/O Read)

Pin 59

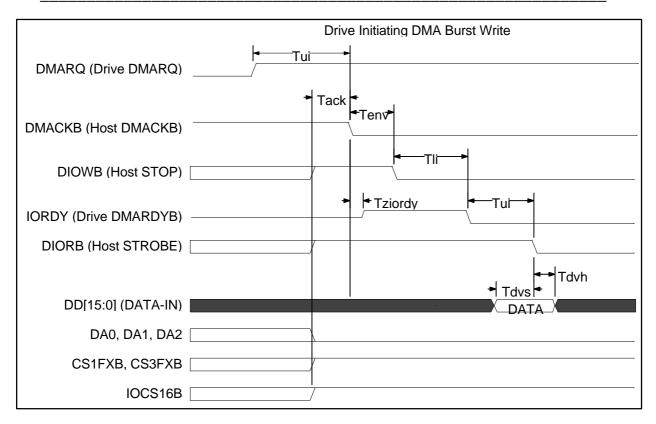

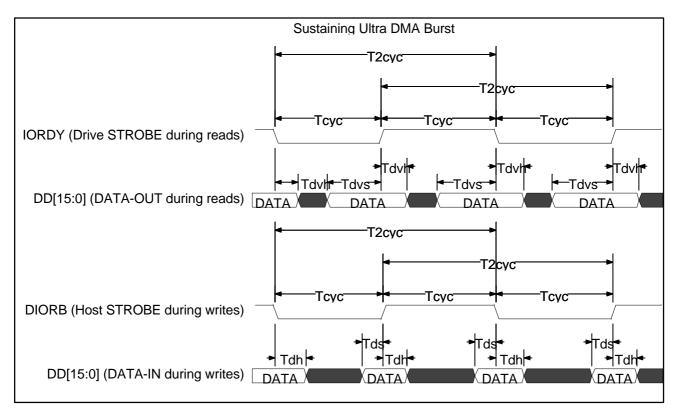

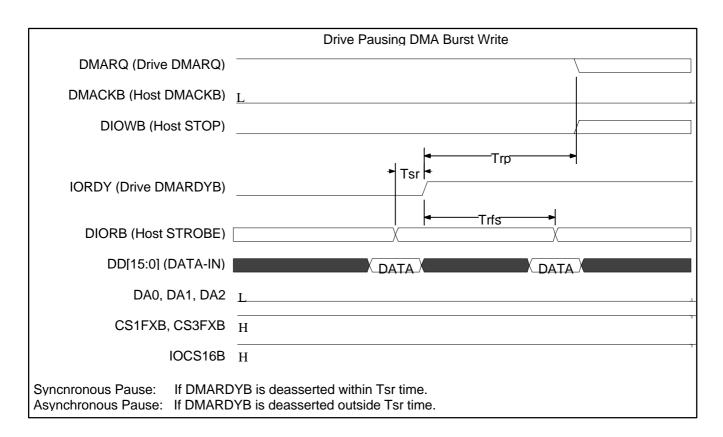

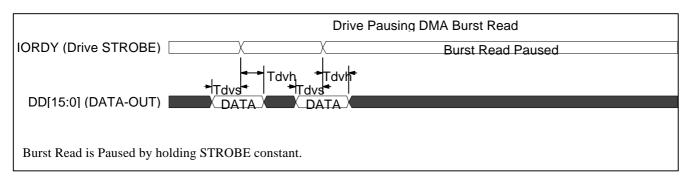

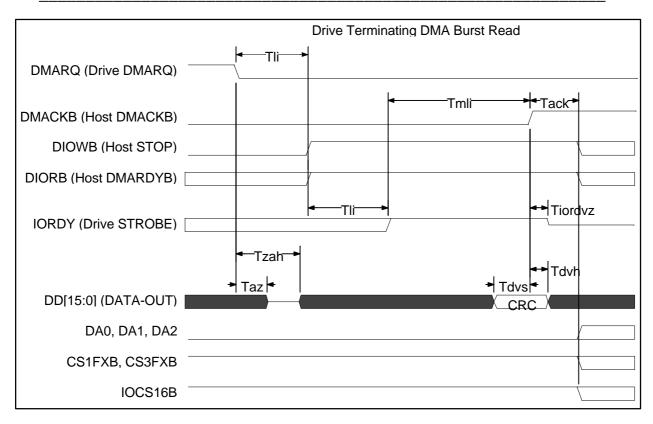

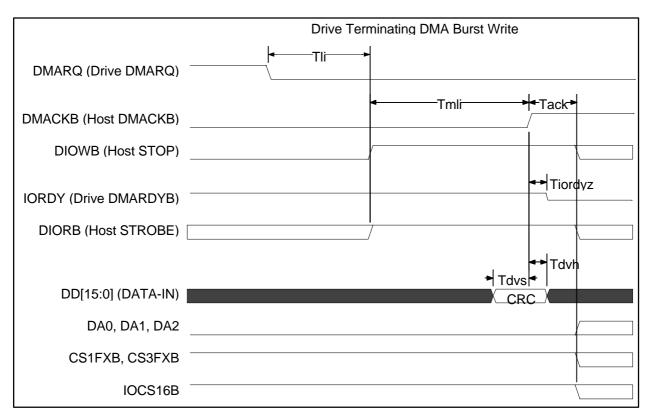

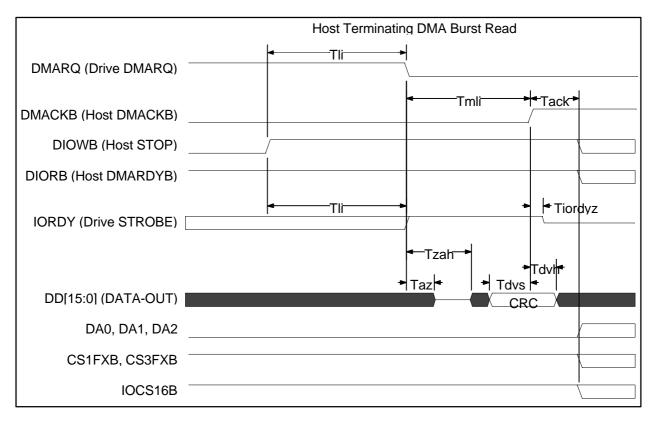

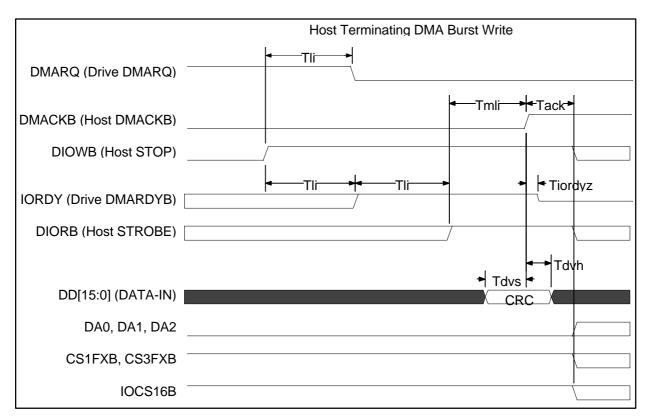

This is the Read strobe signal. The rising edge of DIORB enables data from a register or the data port of the KS9245 onto the host data bus, DD0-DD7 or DD0-DD15. The rising edge of DIORB latches data at the host. In Ultra DMA mode, this signal is used by the Host as the DMARDYB signal during host reads, and as the data STROBE signal during Host writes.

**DIOWB** (Drive I/O Write)

Pin 60

This is the Write strobe signal. The rising edge of DIOWB clocks data from the host data bus, DD0-DD7 or DD0-DD15, into the data port of the KS9245. In Ultra DMA mode, this signal is used by the HOST as the STOP signal.

**DMACKB** (DMA Acknowledge)

Pin 57

This signal is used by the host in response to DMARQ to either acknowledge that data has been accepted, or that data is available.

**DMARQ** (DMA Request)

Pin 61

This signal is used for DMA data transfer between host and KS9245. It is asserted by the KS9245 when it is ready to transfer data to or from the host. The direction of transfer is controlled by DIORB and DIOWB. This signal is used in a handshake manner with DMACKB signal.

When a DMA operation is enabled, IOCS16B, CS1FXB and CS3FXB are not asserted and data transfer are 16-bits wide.

IORDY (Host IO Ready)

**Pin 58**

This signal is deasserted in order to extend the host access when KS9245 is not ready to response to the request. In Ultra DMA mode, this signal is used by the KS9245 as the drive's DMARDYB signal during Host writes, and as the drive's data STROBE signal during Host reads.

### **INTRQ** (Drive interrupt)

#### Pin 56

This signal is used to interrupt the host. INTRQ pin is asserted only when the KS9245 has a pending interrupt while the drive is selected, and the host has cleared nIEN in the ATA Device Control Register. If nIEN=1 or the drive is not selected, this output is in a high impedance state, regardless of the presence or absence of a pending interrupt.

### IOCS16B (Device 16-bit I/O)

### **Pin 55**

Except for DMA transfers, IOC16B indicates to the host that the 16-bit data port has been addressed. This is an open collector output.

In ATAPI PIO data transfer mode, the IOCS16B shall always be asserted.

### **PDIAGB** (Drive passed diagnostics)

### Pin 53

This signal is asserted by drive 1 (slave drive) to indicate to drive 0 (master drive) that it has completed diagnostics. A 10K ohm pull-up resistor is used on this signal by each drive on the same cable.

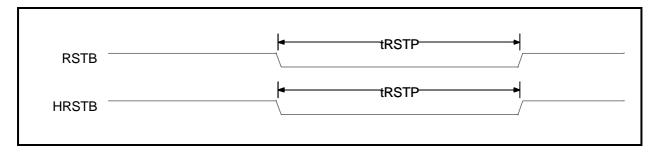

### **HRSTB** (ATA Host Reset)

### Pin 80

This signal from the host system is asserted for at least 25 usec after voltage levels during power-on and negated thereafter unless some event requires that the drive be reset following power on. When this input signal is asserted, the ATA Task File Registers will be initialized and the BSY bit in ATA Status Register will be set. The *Hrst* bit in *Host Interrupt Status Register* will be set (10h, bit 3), if *HrstE* bit in *Host Interrupt Mask Register* (12h, bit 3) is set.

# 1.4.2 Pin Description in Buffer DRAM Interface

BDAT 0-15 (Buffer DRAM data bus)

Pin 12,9,7,5,3,1,99,97,95,98,100,2,4,6,

8,11

These signals are used for buffer DRAM data bus with 16-bit parallel data path to/from the buffer memory.

### **BADD 0-8** (Buffer DRAM address bus)

Pin 89,87,84,82,81,83,86,88,91

These signals are used for buffer DRAM address bus. Up to 512K bytes DRAM are supported by KS9245.

### IMPORTANT: BADD5 pin 83 must also be pulled high by a 22K Ohm resistor.

**CASB** (Column address strobe)

Pin 93

This signal is used as column address strobe for buffer DRAM.

**RASB** (Row address strobe)

Pin 92

This signal is used as row address strobe for buffer DRAM.

**WEB** (DRAM write enable)

Pin 94

This signal is used as the memory write enable for buffer DRAM.

# 1.4.3 Pin Description in Microprocessor Interface

AD0-7 (Microprocessor address and data bus) Pin 31,32,33,34,36,37,38,39

These signals are bi-directional multiplexed microprocessor address and data lines.

ALE(Address latch enable)

Pin 41

**RSB**(Register Select)

The falling edge of this signal is used as address latch for register access in Intel Mode.

This signal is used as Address Register Select in indirect register access mode. In this mode, RSB pin is asserted as logic low state for Address Register and RSB pin is negated as logic high state for Data Register.

**RDB** (microprocessor read strobe)

Pin 42

**DSB** (data strobe)

This signal is used as the read strobe signal in Intel multiplexed register addressing mode. When the Motorola microprocessor is selected, this signal is acted as data strobe signal.

WRB (microprocessor write strobe)

Pin 43

R/WB (R/W Strobe)

This signal is used as the write strobe signal in Intel multiplexed register addressing mode. When the Motorola microprocessor is selected, this signal is acted as read/write strobe signal.

**HINTB** (Microprocessor host/buffer interrupt)

Pin 44

This signal is asserted as logic low state when interrupt status is available to microprocessor. This interrupt indicates there is at least one host or buffer event which needs to be serviced by microprocessor.

**DINTB** (Microprocessor disk interrupt)

Pin 45

This signal is asserted as logic low state when interrupt status is available to microprocessor. This interrupt indicates there is at least one decoder or disk event which needs to be serviced by microprocessor. The disk interrupt can be combined with host interrupt in HINTB signal by clearing *IntMode* bit in *Interface Configuration Control Register* (0Bh, bit 7). The combined mode is the default mode at power-on.

**CSB** (Chip Select)

Pin 30

This signal must be asserted as logic low state for accessing registers of KS9245.

**MSEL** (Microprocessor select)

Pin 91

This pin is used to select the Motorola microprocessor when it connects with pull-up resistor 22K. Otherwise, with pull-down resistor 10K, the Intel microprocessor is selected. This pin is sampled only when ISEL pin is negated at the power on stage.

**ISEL** (microprocessor indirect register access select)

Pin 88

This pin is used to select the indirect register access mode when it connects with pull-up resistor 22K. Otherwise, with pull-down resistor 10K, the direct register access mode is selected. This pin is sampled only at the power on stage.

In the indirect register access mode, the ALE/RSB pin is used to select register input. When RSB is asserted, the Address Register is selected. When RSB is negated, the internal register addressed by Address Register is accessed by microprocessor.

# 1.4.4 Pin Description in DSP Interface

**SUB** (Subcode Serial data in)

**Pin 18**

This pin is used to input the subcode channel data.

**SFSY** (Subcode Frame Sync)

**Pin 19**

This pin is used to indicate the subcode Frame Sync Mark. The subcode data is available at the falling edge of this signal. In Philips V4 Subcode mode, this pin should be grounded.

SBSY/ CFLG (Subcode Block Sync/CLAG)

Pin 20

This pin is used to indicate the subcode Block Sync Mark. In Philips V4 Subcode mode, this pin should connect to CFLAG.

RCK (Subcode Clock)

**Pin 21**

This pin is used to input, output and clock the subcode data from DSP. In Philips V4 Subcode mode, this pin should not be connected.

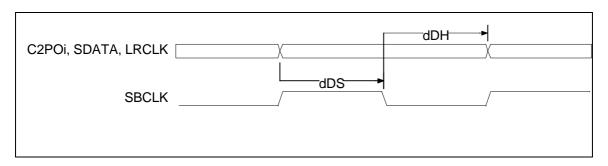

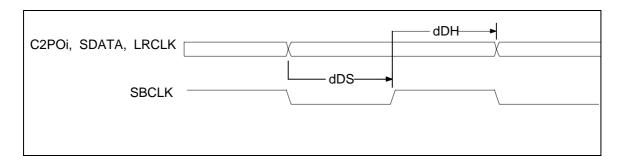

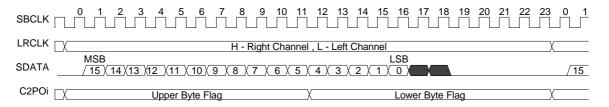

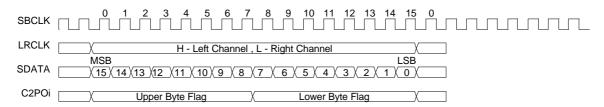

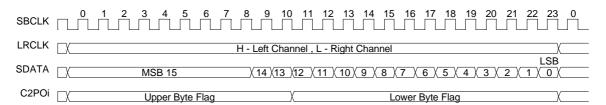

LRCLK (DSP Left Channel Clock)

Pin 24

This pin is used to indicate the left/right channel data.

**SDATA** (DSP main channel data)

**Pin 23**

This pin is used to input the DSP main channel data.

**SBCLK** (DSP bit clock)

Pin 22

This pin is used to input the data clock of DSP main channel.

C2POI (C2 Pointer Input)

Pin 25

This pin is used to indicate the error flags of DSP main channel data.

# 1.4.5 Pin Description in Power/Ground/Rest Pins

VSS (Ground)

Pin 10,26,35, 46,62,71,85,96

**VDD** (Power Supply with 5 volt source)

Pin 40,90

# 1.4.6 Pin Description in System Configuration

**MSTB** (Master/Slave Configuration)

Pin 47

This signal is used to inform the KS9245 that the drive is configured as master or slave. When this signal is asserted as logic low state, it indicates the drive is configured as master. When this signal is negated as logic high state, it indicates the drive is configured as slave.

The DASPB signal will be asserted when the MSTB pin is negated (slave mode) during Power-on/Hardware Reset/ATA SRST.

The PDIAGB signal will be negated when the MSTB pin is asserted (master mode) during Power-on/Hardware Reset/ATA SRST and ATA Diagnostic command.

### SAMSUNG Version: TM 2.4

### KS9245 ATAPI Automated CD-ROM Controller Preliminary Technical Manual

\_\_\_\_\_

### **RSTB** (Chip Reset)

### **Pin 17**

A logic low input will reset the KS9245. All host interface outputs are set to the high-impedance state. The registers of KS9245 will be initialized as their default values.

### ARSTB (ATAPI 08 Cmd Reset)

#### Pin 29

A logic low pulse with 40 usec will be asserted when host issues the ATAPI Reset Command (08h) to the KS9245. This signal could use as the pulse to reset the micro-controller. The output of 60 usec clock pulse is assumed that the System Clock of 33.8688 MHz is used.

### XIN/SYSCLK (Crystal or System clock input)

### Pin 28

This signal is the crystal or CMOS-level clock input as system clock. The KS9245 contains an internal resister between XIN/XOUT. There is no external resister required to connect these pins. The standard crystal or CMOS-level clock is either 33.8688 MHz or 50.8MHz.

### XOUT (Oscillator output)

**Pin 27**

This signals is the oscillator output.

### XSEL (System Clock Select)

### Pin 86

The KS9245 supports two frequencies. This pin can use an external jumper select to configure for either 33.86MHz or 50.8MHz. This pin should be pulled-up by a 22K Ohm resistor for 50.8 MHz operation, and strapped-down by a 10K Ohm resistor for 33.86MHz operation.

### **GPI 0-3** (general purpose Input/Output Lines)

### Pin 13,14, 15, 16

These signals are used as general purpose input pins. The Input or Output can be configured by setting or clearing the *GPC3*, *GPC2*, *GPC1*, *GPC0* bits in *Port Control Register* (44h, bit 7,6,5, 4) and *APCE* bit in Global *Control Register* (2Fh, bit3) is cleared.

# 1.4.7 Pin Description in Audio DAC Interface

### **DAUO** ( Digital Audio Output)

### **Pin 16**

This pin is used to output the digital audio as IEC-958 format. This bit is enabled when *APCE* bit in Global *Control Register* (2Fh, bit 3) is set.

### **ADAT** (Audio Data output)

### **Pin 15**

This pin is used to as a audio data output pin when the audio playback in CAV mode is selected to be used. This bit is enabled when *APCE* bit in Global *Control Register* (2Fh, bit 3) is set.

### ABCK (Audio bit clock output)

### Pin 14

This pin is used to as a audio bit clock output pin. This bit is enabled when *APCE* bit in Global *Control Register* (2Fh, bit 3) is set.

### **AWCK** (Audio word clock output)

### **Pin 13**

This pin is used to as a audio word clock output pin. This bit is enabled when *APCE* bit in Global *Control Register* (2Fh, bit 3) is set.

Version: TM 2.4

# 1.4.8 Register Map for KS9245

| Page #  | Addres<br>s | Name          | BIT 7         | BIT 6                                        | BIT 5         | BIT 4        | BIT 3       | BIT 2        | BIT 1         | BIT 0        |  |  |  |  |

|---------|-------------|---------------|---------------|----------------------------------------------|---------------|--------------|-------------|--------------|---------------|--------------|--|--|--|--|

| Host Ir | nterface    | Register      | s (Chapte     | er 2)                                        |               |              |             | •            |               |              |  |  |  |  |

|         | 00h R       | PFIFO         |               |                                              |               | Packet F     | IFO Regis   | ter          |               |              |  |  |  |  |

|         | 01h R       | AFEAT         |               |                                              | Reserv        | /ed          |             |              | Overlap       | DMA          |  |  |  |  |

|         | 01h W       | AERR          |               | Sense Key MCR ABRT EOM ILI                   |               |              |             |              |               |              |  |  |  |  |

|         | 02h R       | ASECC         |               |                                              | Α             | TA Sector    | Count Re    | gister       |               |              |  |  |  |  |

|         | 02h W       | AINTR         |               |                                              | Reserved      |              |             | Releas<br>e  | Ю             | CoD          |  |  |  |  |

|         | 03h<br>R/W  | ASAM          |               |                                              | ATAPI SAN     | /I Tag Regi  | ster/ ATA   | Sector Nun   | nber          |              |  |  |  |  |

|         | 04h<br>R/W  | ABCL          |               | ATAP                                         | Byte Count    | Low Regis    | ster/ ATA ( | Cylinder Lo  | w Register    |              |  |  |  |  |

|         | 05h<br>R/W  | ABCH          |               | ATAPI                                        | Byte Count    | High Regi    | ster/ ATA   | Cylinder Hi  | gh Register   |              |  |  |  |  |

|         | 06h<br>R/W  | ADSEL         | Rsvd          | LBA                                          | Rsvd          | DRV          |             |              | eserved       |              |  |  |  |  |

|         | 07h R       | ACMD          |               | ATAPI Command Register/ ATA Command Register |               |              |             |              |               |              |  |  |  |  |

|         | 08h R       | ADCV          |               | Reserved Rs                                  |               |              |             |              | nIEN          | Rsvd         |  |  |  |  |

|         | 09h R       | AISTAT        | BSY           | DRDY                                         | Rsvd          | DSC          | DRQ         | Corr         | Rsvd          | CHECK        |  |  |  |  |

|         | 09h W       | HSC           | Rsvd          | DRDY                                         | Rsvd          | DSC          | DRQ         | Corr         | Rsvd          | CHECK        |  |  |  |  |

|         | 0Ah R       | HISV          |               | Rese                                         | erved         |              | MSTB        | DASPB        | PDIAGB        | 0            |  |  |  |  |

|         | 0Ah W       | HIC           | SetBSY        | SetDAS<br>PB                                 | SetPDIA<br>GB | SetHIN<br>T  | CIrBS<br>Y  | CIrDASP<br>B | CirPDIAG<br>B | CIrHINT      |  |  |  |  |

|         | 0Bh<br>R/W  | ICC           | IntMod<br>e   | d ATA Transfer Mode CDRV                     |               |              |             | DisShad<br>R | PcmdInt       | DisIORDY     |  |  |  |  |

|         | 0Ch         |               |               |                                              |               | Re           | served      |              |               |              |  |  |  |  |

|         | 0Dh         |               |               |                                              |               | Re           | served      |              |               |              |  |  |  |  |

| Hardw   | are Seq     | uence Co      | mmand l       | Registers                                    | (Chapter      | 3)           |             |              |               |              |  |  |  |  |

|         | 0Eh W       | HSC           | Rsvd          | SAAbort                                      | Sservice<br>e | Srelea<br>se | STFIni<br>t | SCpl         | SCplChk       | SDSC         |  |  |  |  |

|         | 0Fh W       | TSC           | ACache<br>E   | ACplE                                        | Rsvd          | SSxfr        | SAbor<br>t  | SPaus<br>e   | WRDir         | SDxfr        |  |  |  |  |

|         | 0Fh R       | TSS           | ACache<br>E   | ACplE                                        |               | Reserve      | d           | SPaus<br>e   | WRDir         | HxfrBsy      |  |  |  |  |

| Microp  | processo    | or Interru    | pt Regist     | ers (Cha                                     | pter 4)       |              |             |              |               |              |  |  |  |  |

|         | 10h<br>R/W  | HISR/HI<br>CR | TxfrDon<br>e  | Rsvd                                         | Asrst         | Srst         | Hrst        | ScmdR<br>v   | C AcmdRc V    | PcmdRcv      |  |  |  |  |

|         | 11h<br>R/W  | DISR/DI<br>CR |               |                                              | Reserved      |              |             | DACIn        | SubInt        | DecInt       |  |  |  |  |

|         | 12h<br>R/W  | HIM           | TxfrDon<br>eE | CxfrDone<br>E                                | e AsrstE      | SrstE        | HrstE       | ScmdRe<br>vE | C AcmdRc vE   | PcmdRcv<br>E |  |  |  |  |

|         | 13h<br>R/W  | DIM           |               |                                              | Reserved      |              |             | DACInt       |               | DecIntE      |  |  |  |  |

| Buffer  | /CD Cac     | he mange      | er Regist     | ers (Cha <sub>l</sub>                        | pter 5)       |              |             |              |               |              |  |  |  |  |

|         | 14h<br>R/W  | VCBCL         |               |                                              | Valid Ca      | che Block    | Count Reg   | gister B7:B  | 0             |              |  |  |  |  |

| _       | 15h         |               |               | -                                            | -             | Re           | served      |              | -             |              |  |  |  |  |

|         | 16h         | TTBLL         |               |                                              | Total Host T  | ransfer Blo  | ock Length  | n Register E | 37:B0         |              |  |  |  |  |

|   | R/W        |       |                                                   |

|---|------------|-------|---------------------------------------------------|

|   | 17h        |       | Reserved                                          |

|   | 18h<br>R/W | CHTBL | Current Host Transfer Block Length Register B7:B0 |

|   | 19h        |       | Reserved                                          |

|   | 1Ah<br>R/W | HTBLA | Host Transfer Block Address Low Register B7:B0    |

| _ | 1Bh<br>R/W |       | Reserved                                          |

# Version: TM 2.4 TAPI Automated CD-ROM Controller

### KS9245 ATAPI Automated CD-ROM Controller Preliminary Technical Manual

| Page   | Addres<br>s | Name            | BIT 7                         | BIT 6                              | BIT 5                  | BIT         | 4 BIT       | 3 BIT      | 2 B         | BIT 1   | BIT 0   |  |

|--------|-------------|-----------------|-------------------------------|------------------------------------|------------------------|-------------|-------------|------------|-------------|---------|---------|--|

|        | 1Ch<br>R/W  | HBOAL1          |                               | Hos                                | t Block Offs           | set Addre   | ss Low 1    | Register E | 7:B0        |         |         |  |

|        | 1Dh<br>R/W  | НВОАН1          |                               | Rese                               | rved                   |             | B1          | 11 B1      | 10          | B9      | В8      |  |

|        | 1Eh<br>R/W  | TOLL1           |                               | Tr                                 | ansfer Offs            | et Length   | Low 1 R     | egister B7 | :B0         |         |         |  |

|        | 1Fh<br>R/W  | TOLH1           |                               | Rese                               | rved                   |             | B1          | 1 B1       | 0           | B9      | В8      |  |

|        | 20h<br>R/W  | HBOAL2          |                               | Hos                                | t Block Off            | set Addre   | ss Low 2    | Register E | 37:B0       |         |         |  |

|        | 21h<br>R/W  | HBOAH2          |                               | Rese                               | rved                   |             | B1          | 1 B1       | 0           | B9      | B8      |  |

|        | 22h<br>R/W  | TOLL2           |                               |                                    | ansfer Offs            | et Length   | Low 2 Ro    | egister B7 | :B0         |         |         |  |

|        | 23h<br>R/W  | TOLH2           |                               | Rese                               |                        |             | B1          |            |             | B9      | B8      |  |

|        | 24h<br>R/W  | MPALSB<br>MBOAL |                               |                                    | MP Access P Block Off  |             |             |            |             |         |         |  |

|        | 25h         | MPAMID          |                               |                                    | MP Access              | Physical    | Address     | MID B15:B  | 8           |         |         |  |

|        | R/W<br>26h  | MBOAH<br>MPAMS  |                               |                                    | Block Offs IP Access I |             |             |            |             |         |         |  |

|        | R/W         | B<br>MBA        |                               |                                    |                        |             | ss Registe  |            | 10          |         |         |  |

|        | 27h         |                 |                               |                                    |                        | Rese        | erved       |            |             |         |         |  |

|        | 28h<br>R/W  | MPDP            |                               | MP Access Data Port Register B7:B0 |                        |             |             |            |             |         |         |  |

|        | 29h R       | BAC             | DramBs<br>y                   |                                    | Reserv                 | ed          |             | PAMb       | Rsvd        | i       | Rsvd    |  |

|        | 29h W       | BAC             | IncAudC<br>nt                 | IncBlkCnt                          |                        | Reserved    |             | PAMb       | SDram\<br>t | Wr      | SDramRd |  |

|        | 2Ah<br>R/W  | BCC1            | C2ErrOR                       | Dsec                               | Ssel                   | Csel        | BlkCon<br>f |            | Dran        | nsz     |         |  |

|        | 2Bh<br>R/W  |                 |                               |                                    |                        |             | erved       |            |             |         |         |  |

|        | 2Ch<br>R/W  | BBBA            |                               | Ві                                 | uffer Bottor           | n Block A   | ddress R    | egister B7 | :B0         |         |         |  |

|        | 2Dh<br>R/W  |                 |                               |                                    |                        | Rese        | erved       |            |             |         |         |  |