1120-7061 June 1997

1997 SRAM

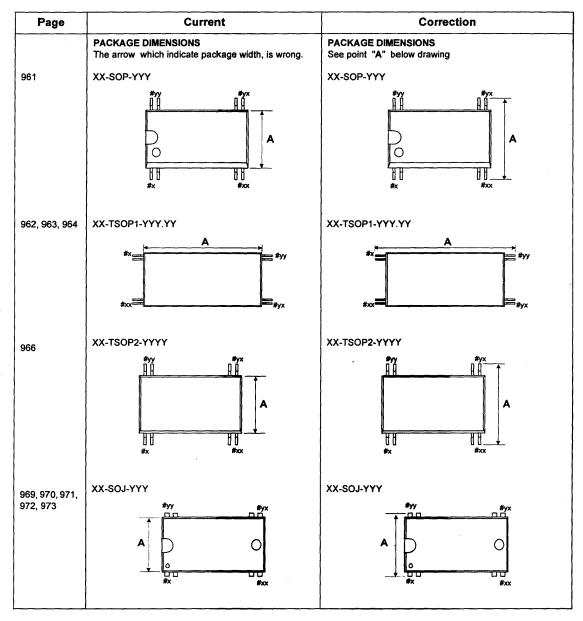

| Page                                         | Current                                                                                                      | Correction                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 5                                            | TABLE OF CONTENTS  22. KM68FV1000 ~ , 128x8, Commercial~, 195  23. KM68FS1000Z ~ , 128x8, 48-CSP~, 206       | TABLE OF CONTENTS  22. KM68FV1000 ~ , 128Kx8, Commercial~, 195  23. KM68FS1000Z ~ , 128Kx8, 48-CSP~, 206                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

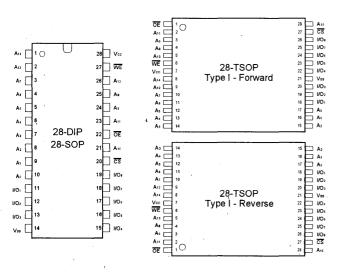

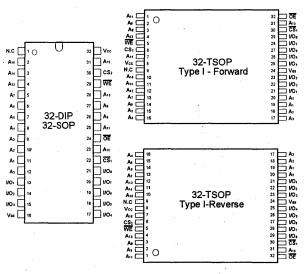

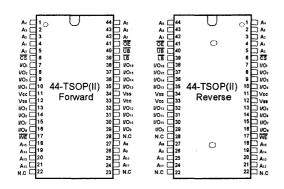

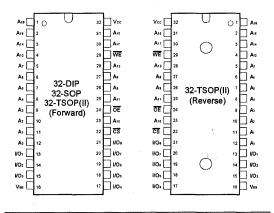

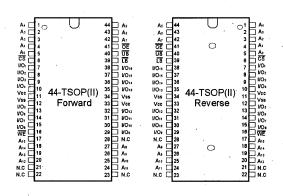

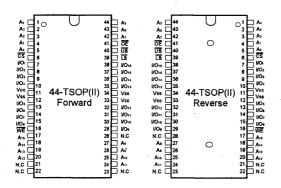

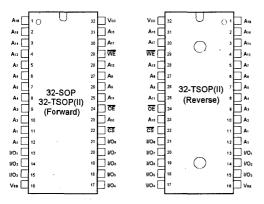

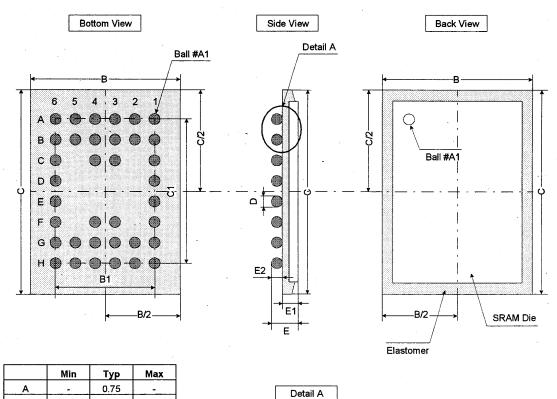

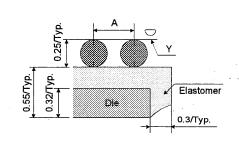

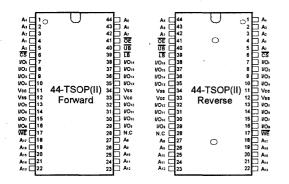

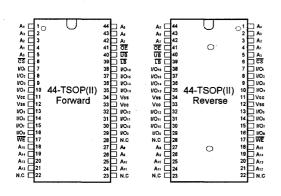

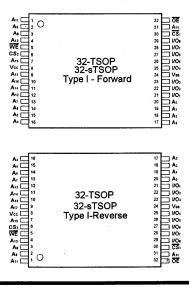

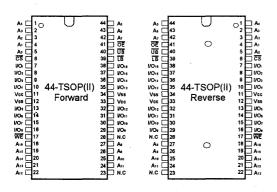

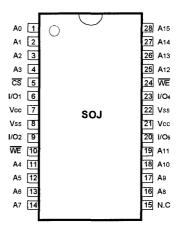

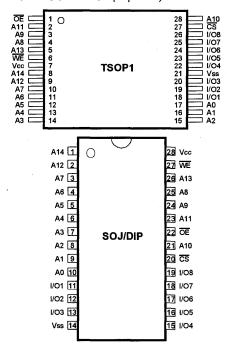

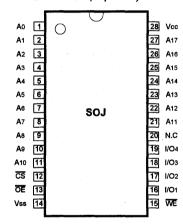

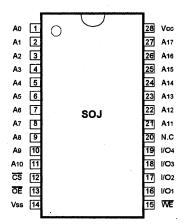

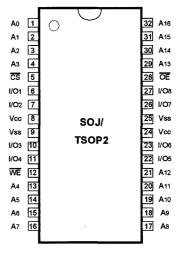

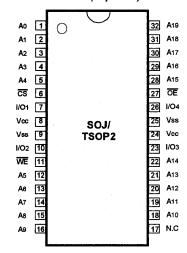

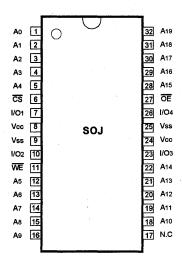

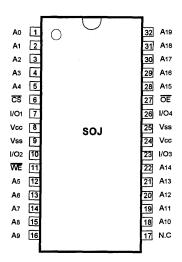

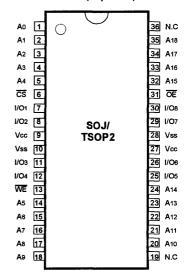

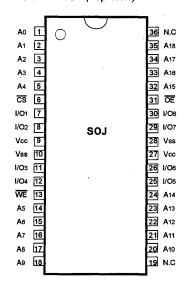

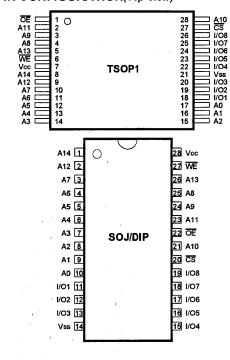

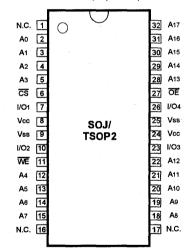

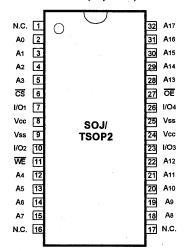

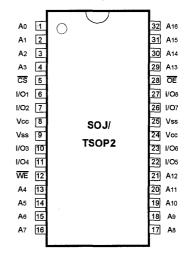

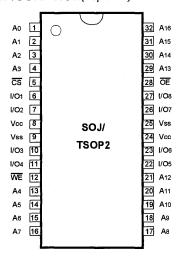

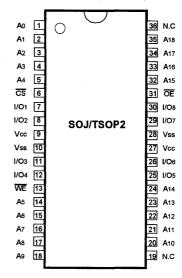

| 98                                           | PIN DESCRIPTION Pin name of 44-TSOP(II) Forward and Reverse : 1.A4, 2.A3, ~ , 44.A5                          | PIN DESCRIPTION Changed Pin name of 44-TSOP(II)Forward and Reverse: 1.A4, 2.A3, 3.A2, 4.A1, 5.A0, 6.CS, 7.I/O1, 8.I/O2, 9.I/O3, 10.I/O4, 11.Vcc, 12.Vss, 13.I/O5, 14.I/O6, 15.I/O7, 16.I/O8, 17.WE, 18.A17, 19.A16, 20.A15, 21.A14, 22.A13, 23.A12, 24.A11, 25.A10, 26.A9, 27.A8, 8.N.C, 29.I/O19, 30.I/O10, 31.I/O11, 32.I/O12, 33.Vcc, 34.Vss, 35.I/O13, 36.I/O14, 37.I/O15, 38.I/O16, 39.LB, 40.UB, 41.OE, 42.A7, 43.A6, 44.A5 |  |  |  |  |

| 130                                          | DC AND OPERATING CHARACTERISTICS Standby Current, ISB, Test conditions: CS1=VIH, CS2=VIH                     | DC AND OPERATING CHARACTERISTICS Standby Current, IsB, Test conditions: CS1=ViH, CS2=ViL                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

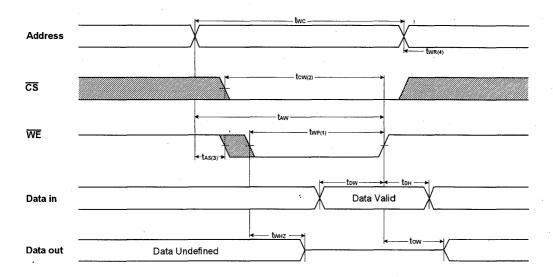

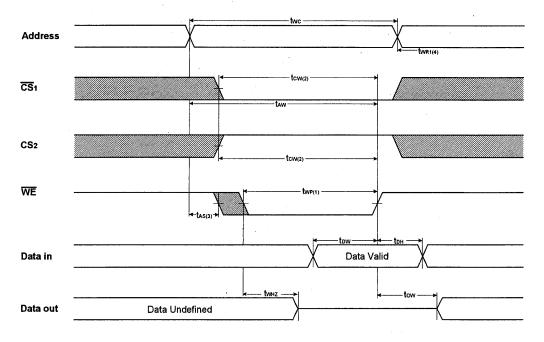

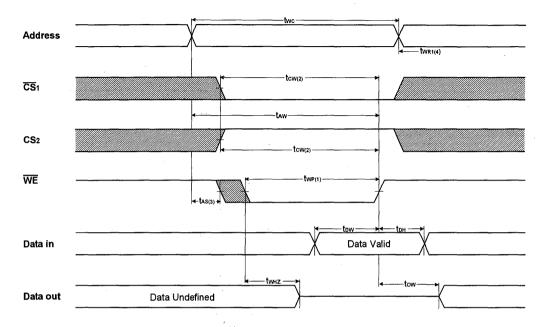

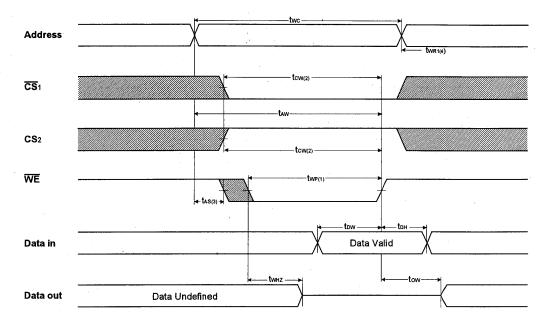

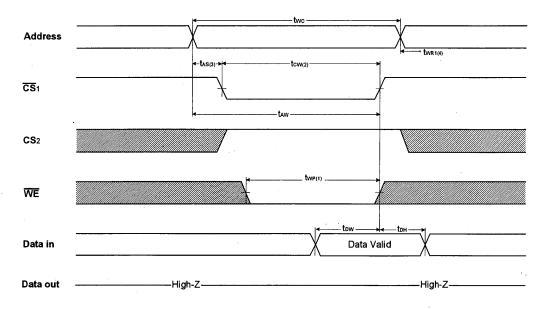

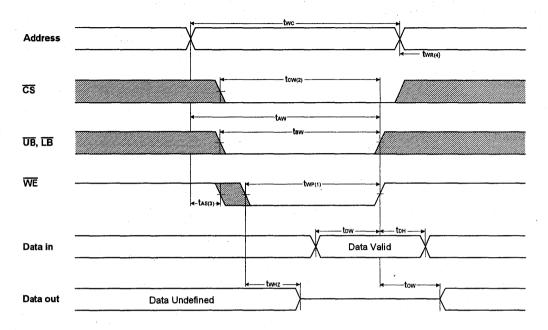

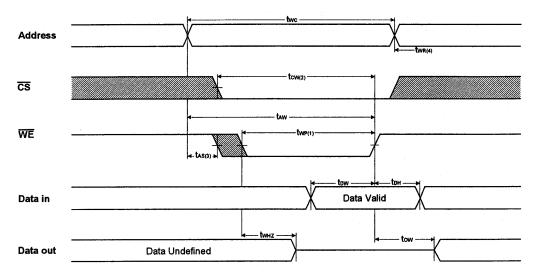

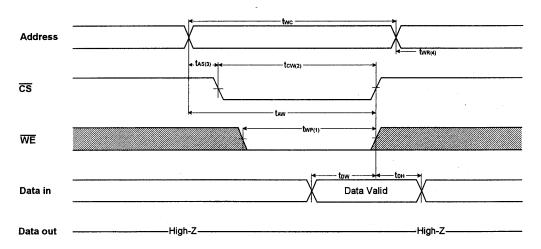

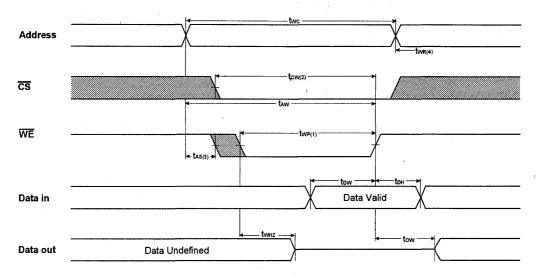

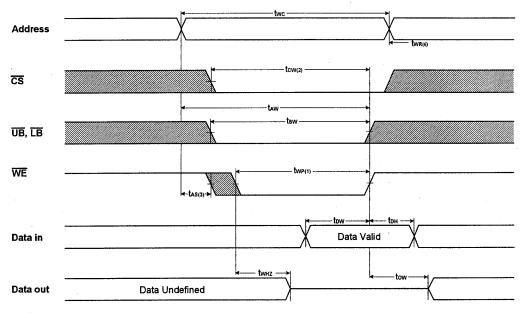

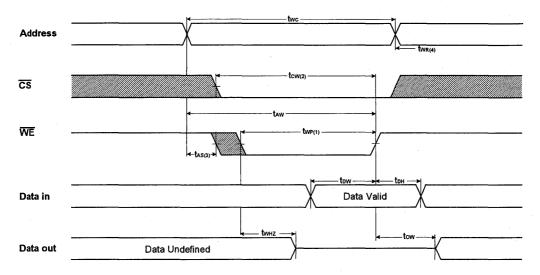

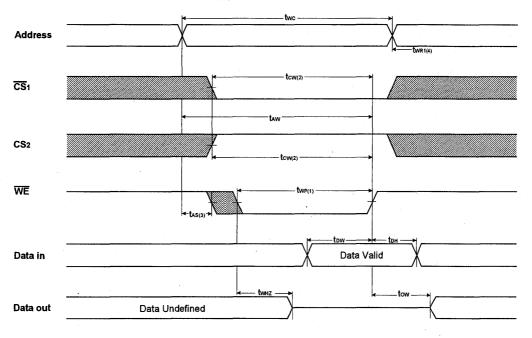

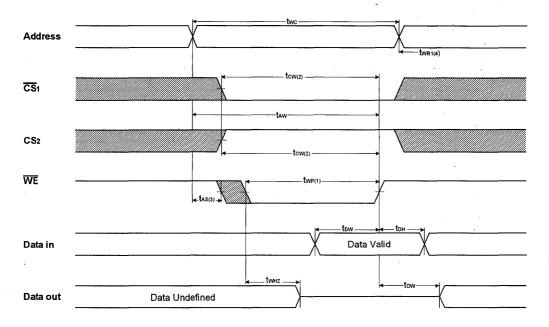

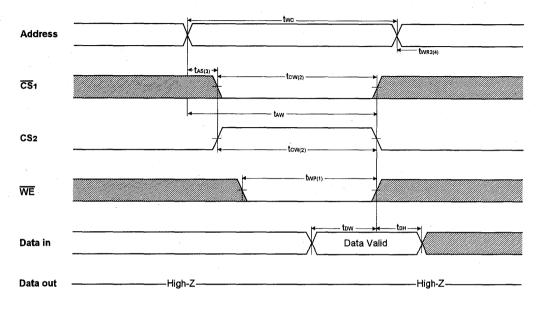

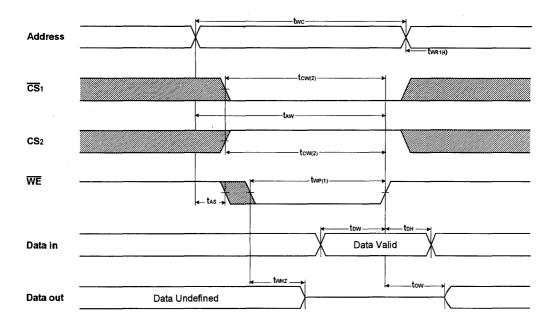

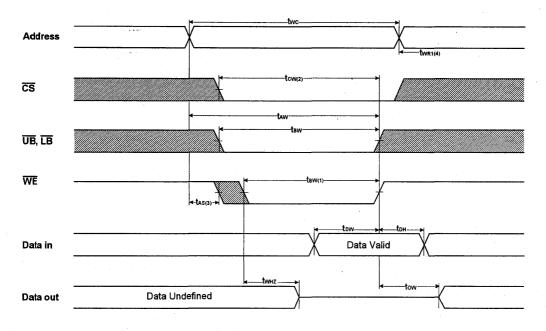

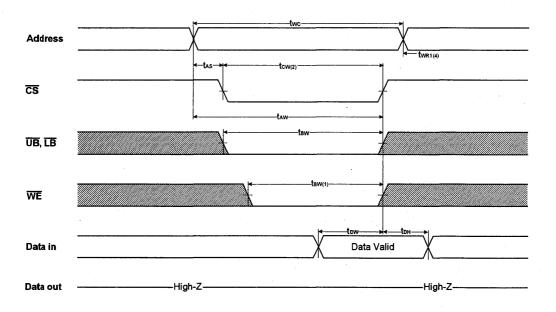

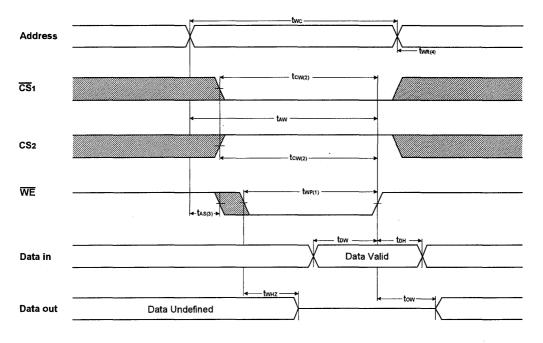

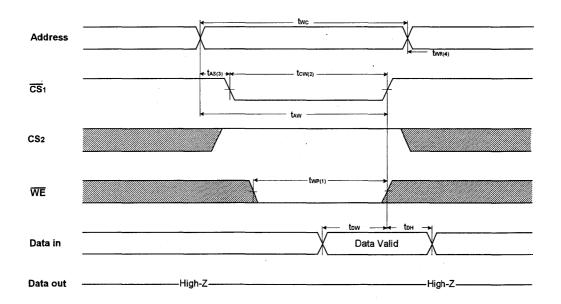

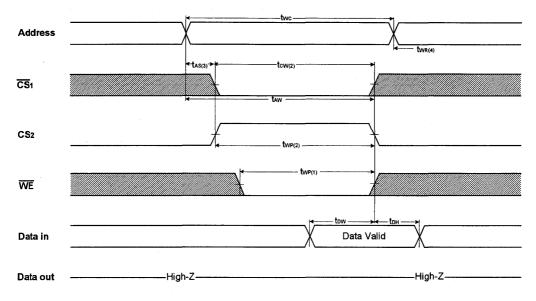

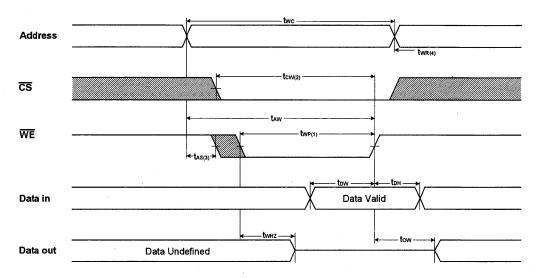

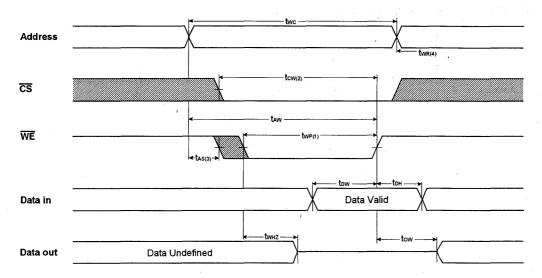

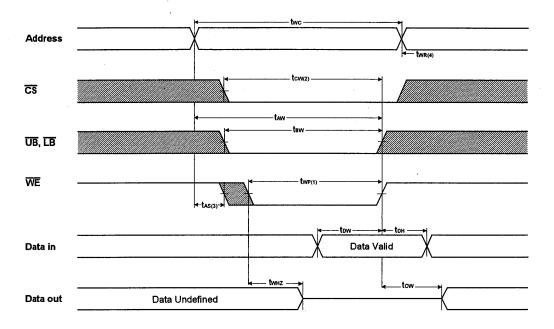

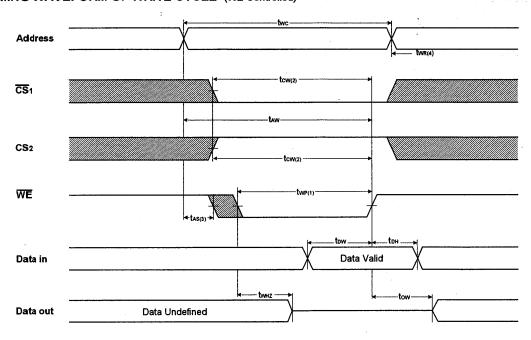

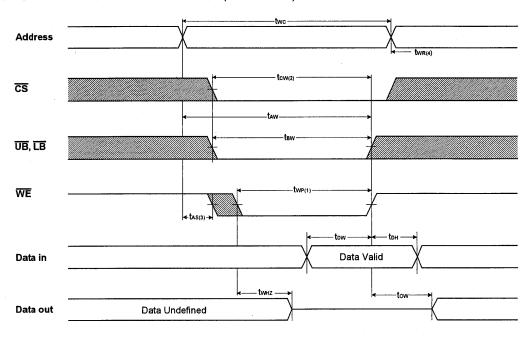

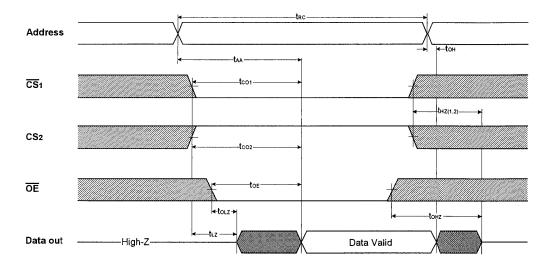

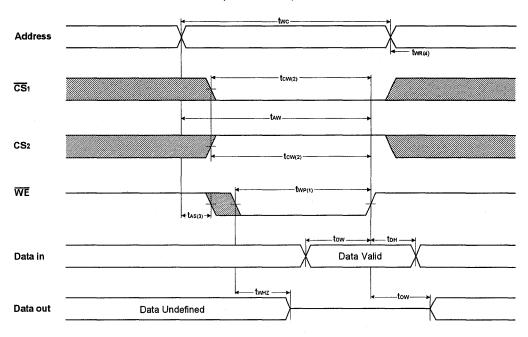

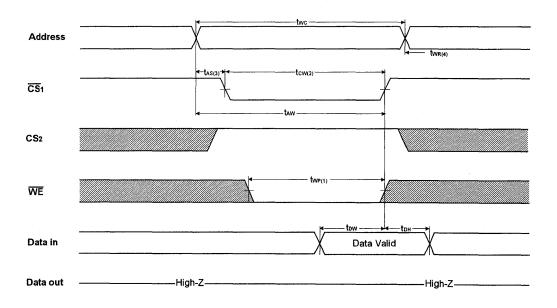

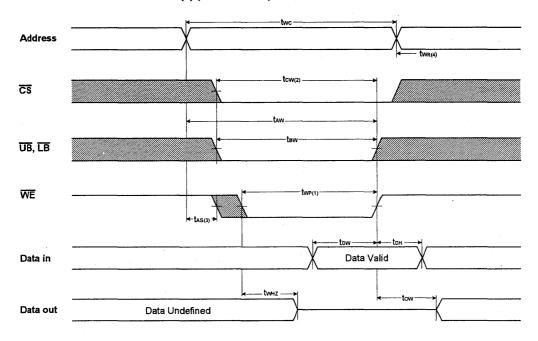

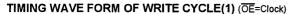

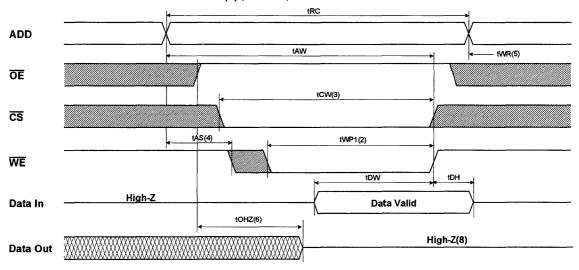

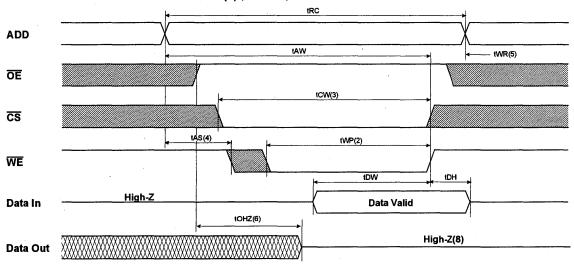

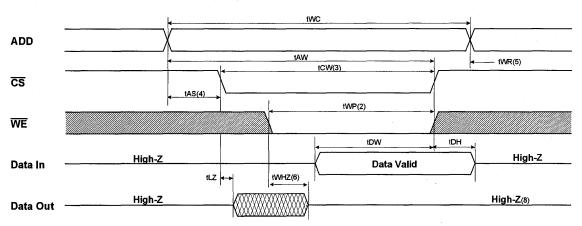

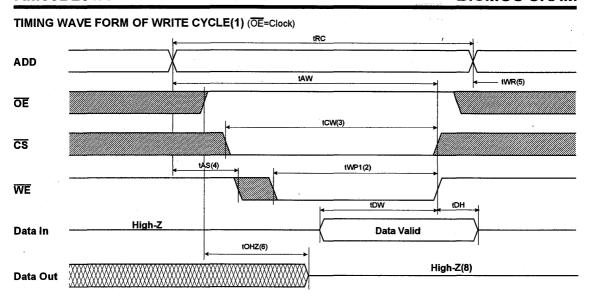

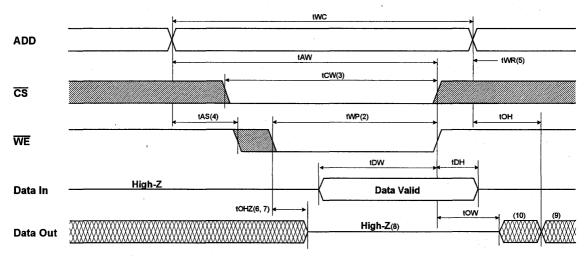

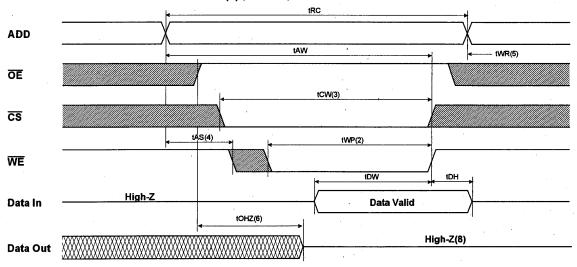

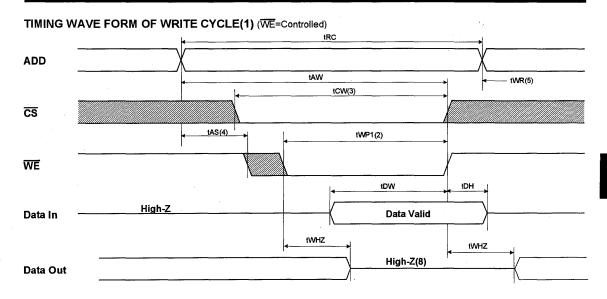

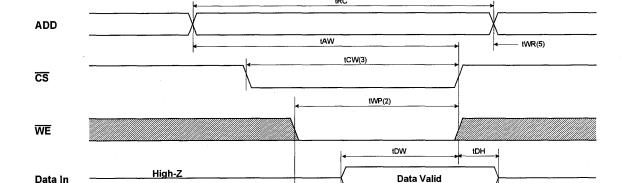

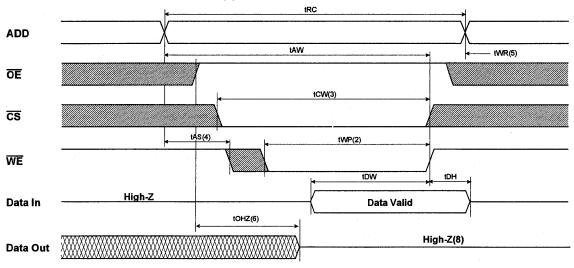

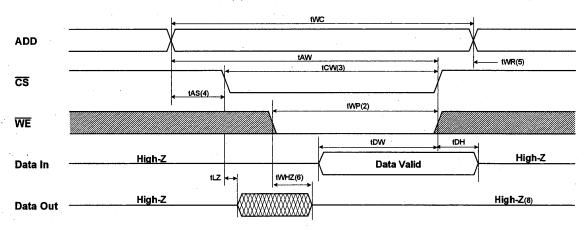

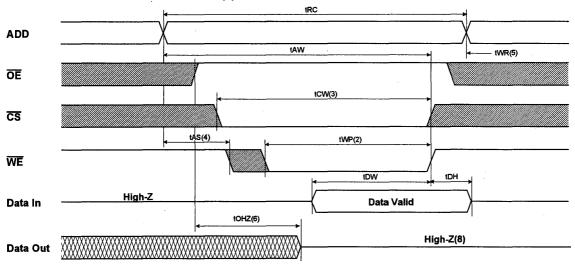

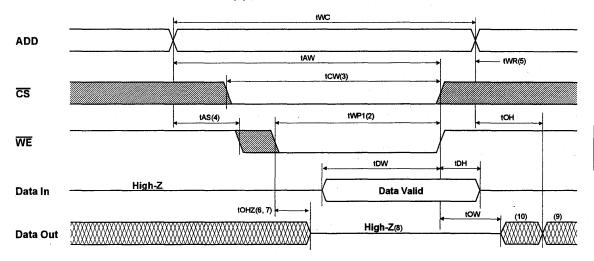

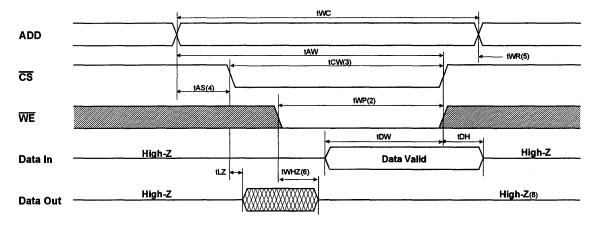

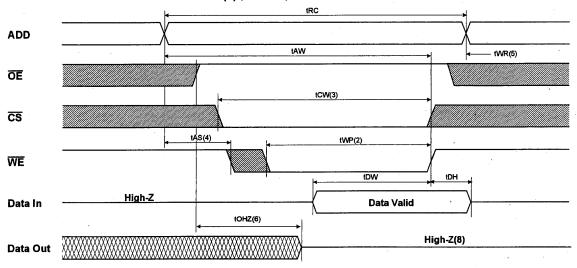

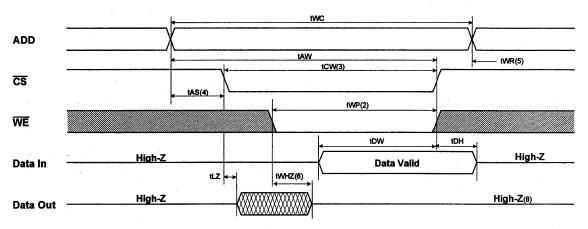

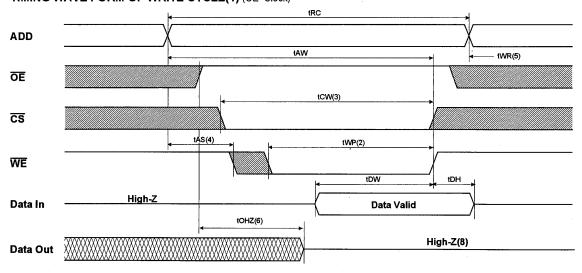

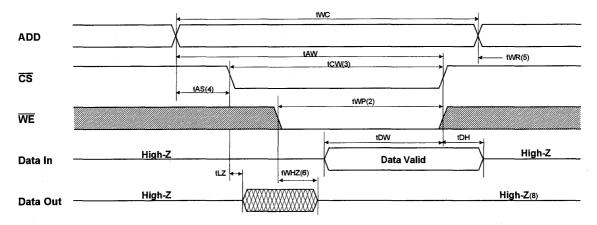

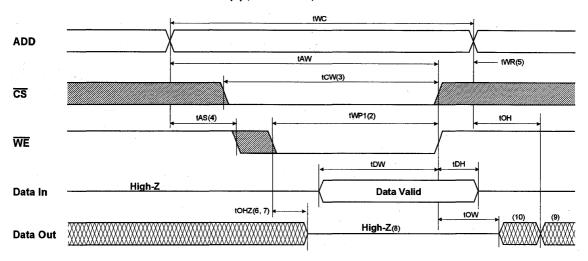

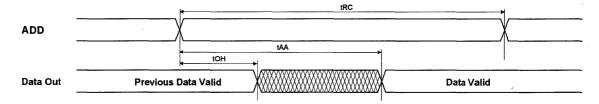

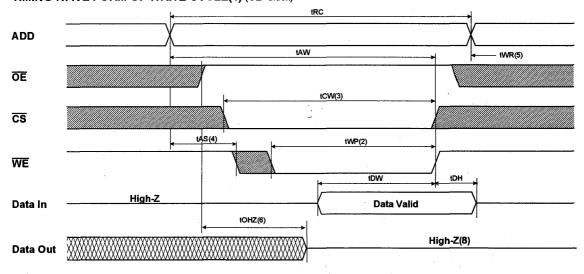

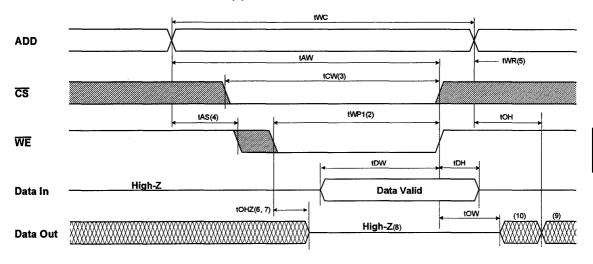

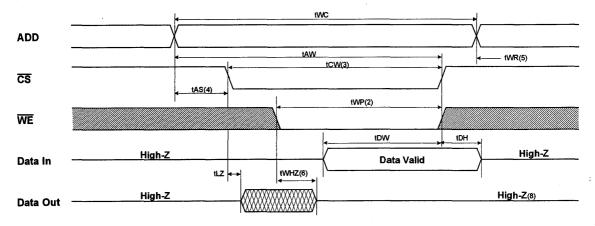

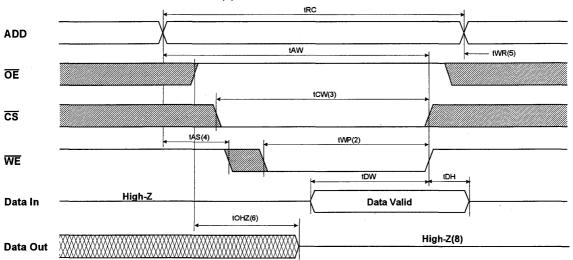

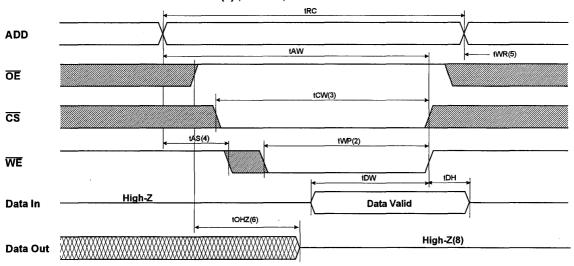

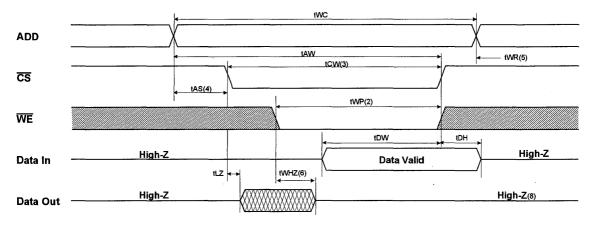

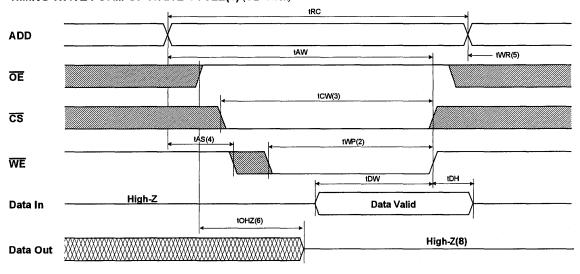

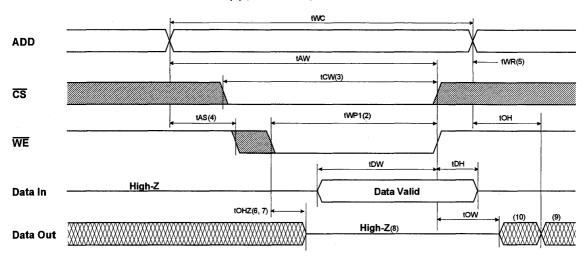

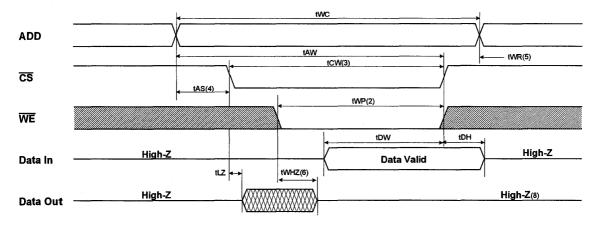

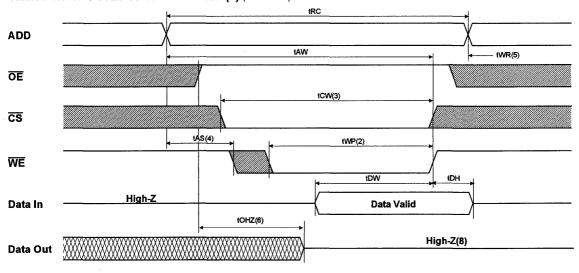

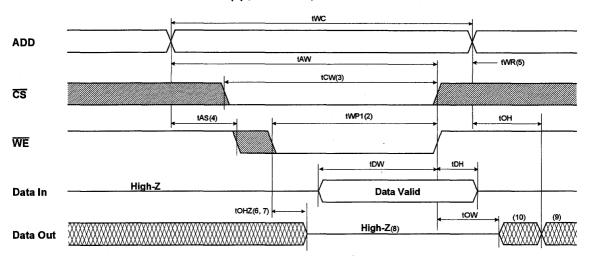

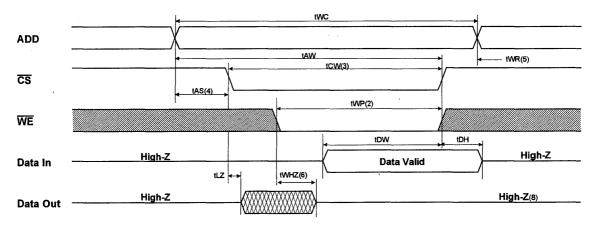

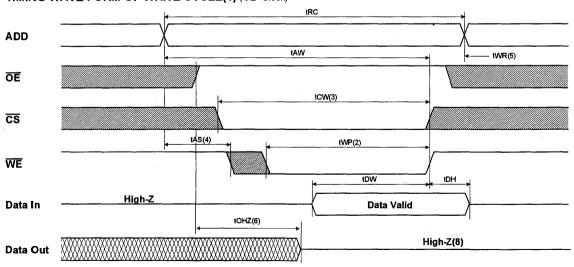

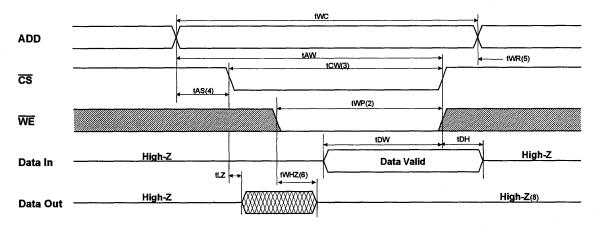

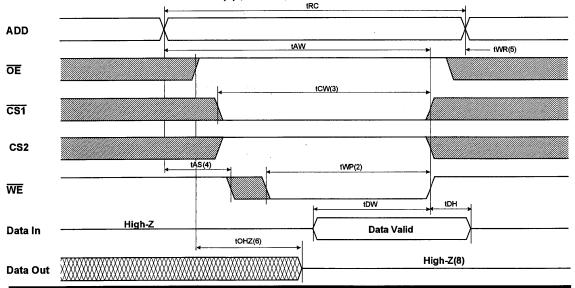

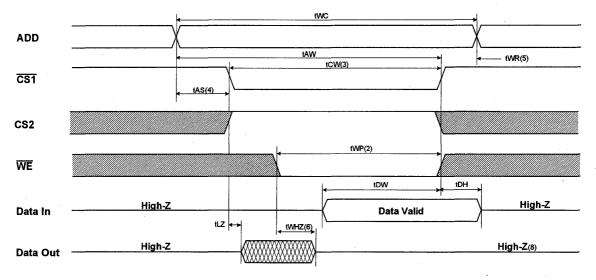

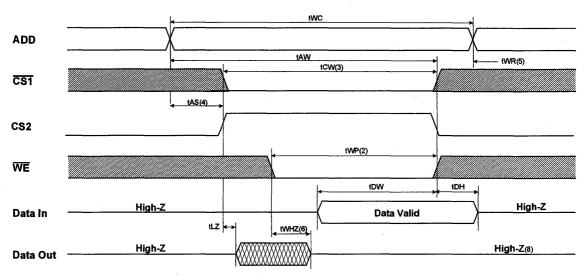

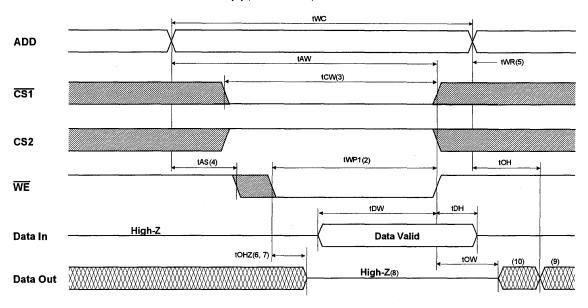

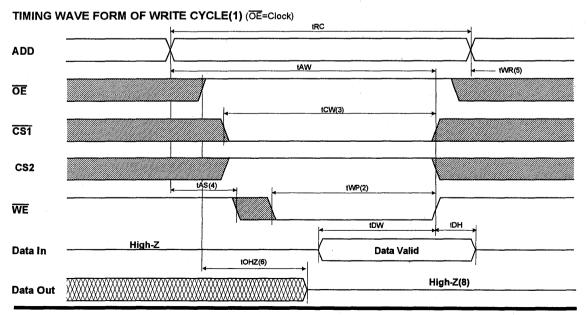

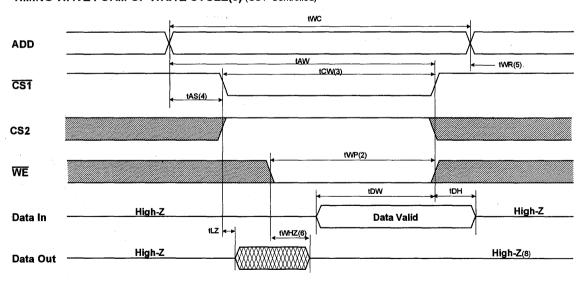

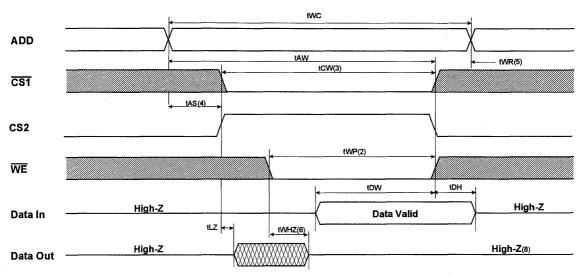

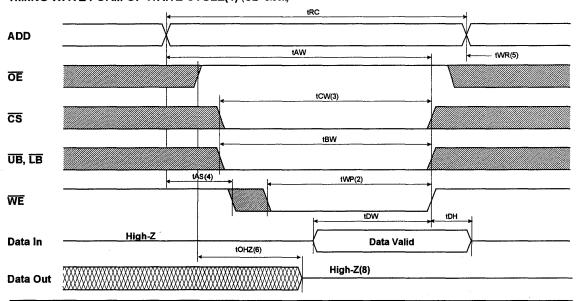

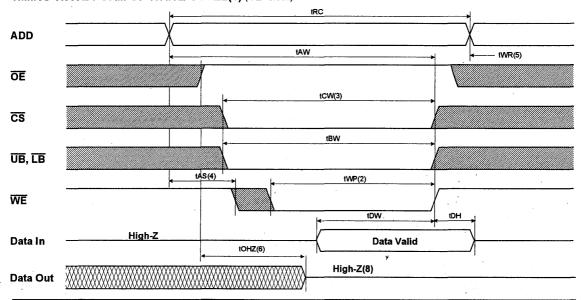

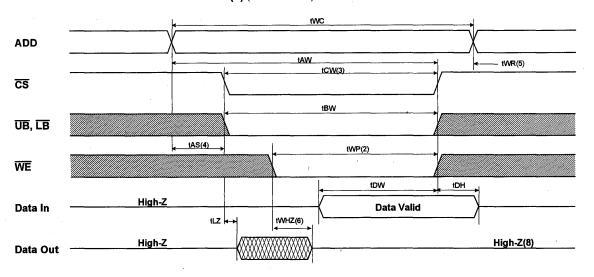

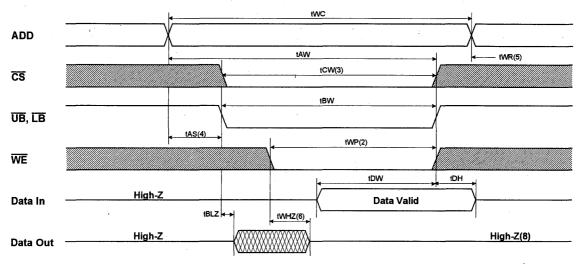

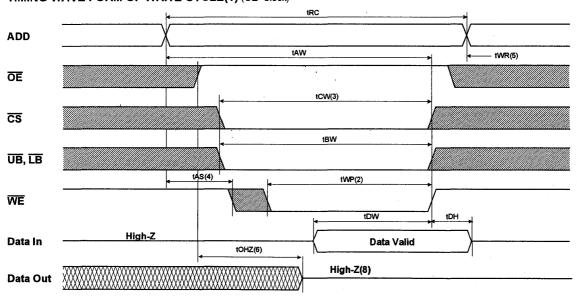

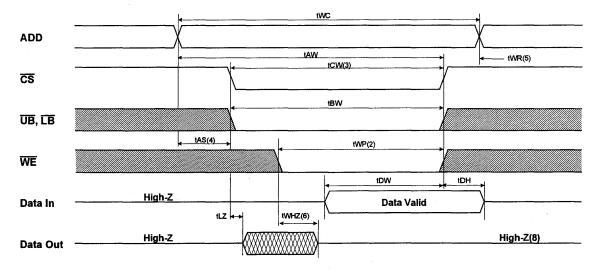

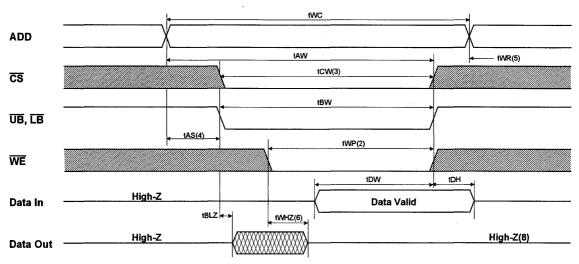

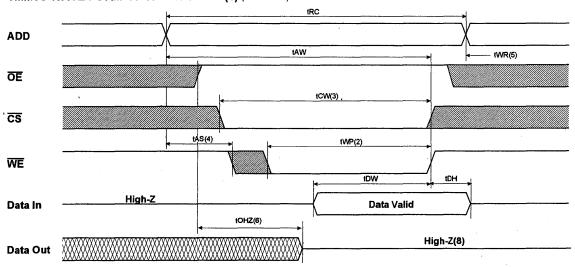

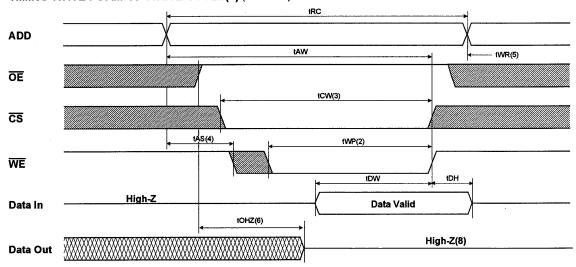

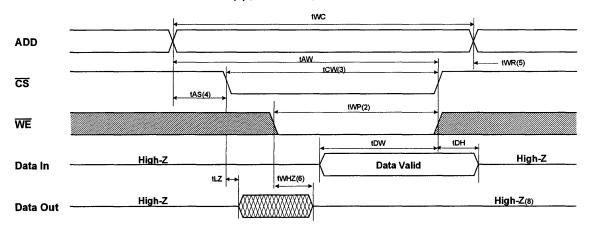

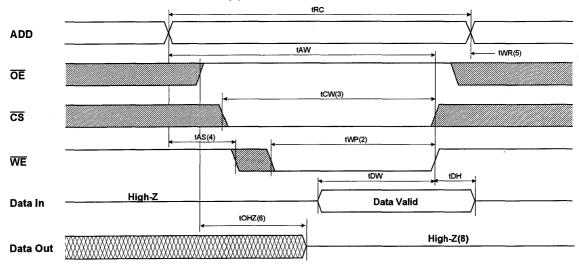

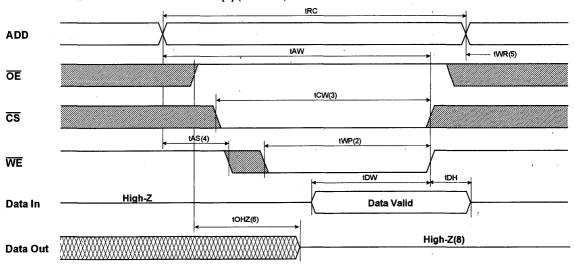

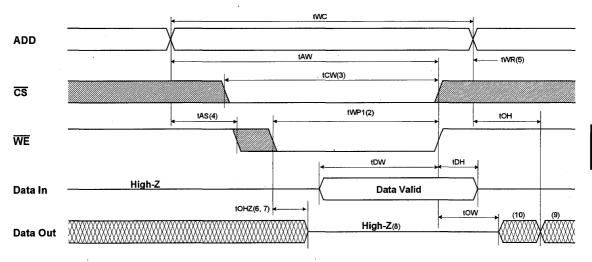

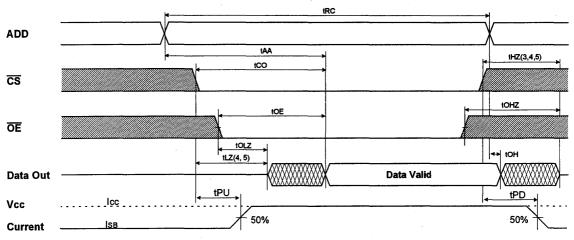

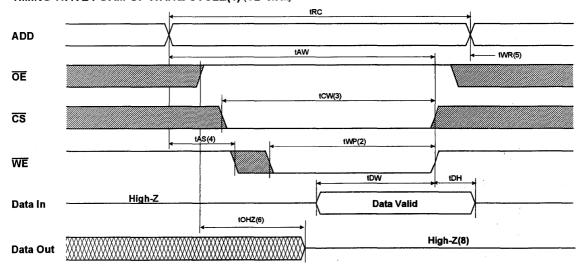

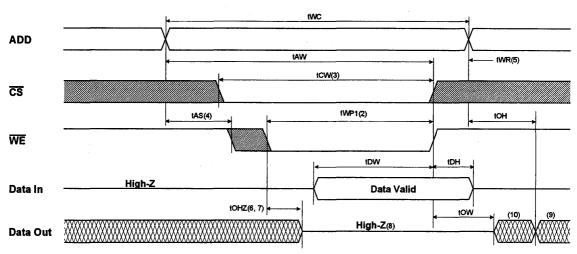

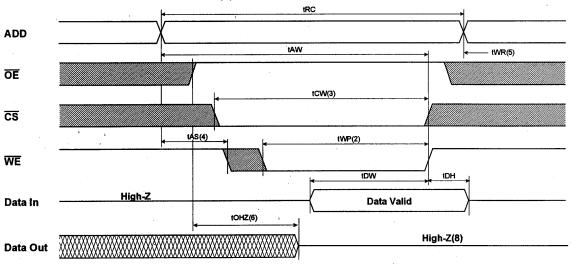

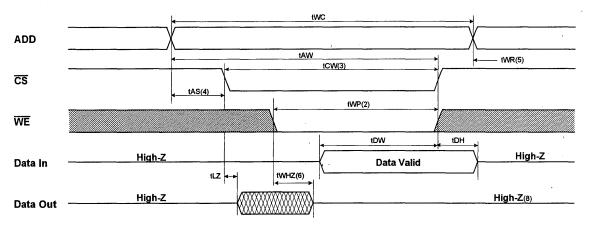

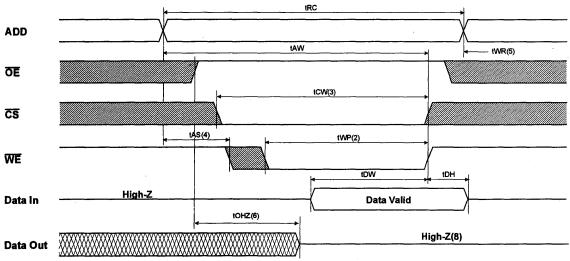

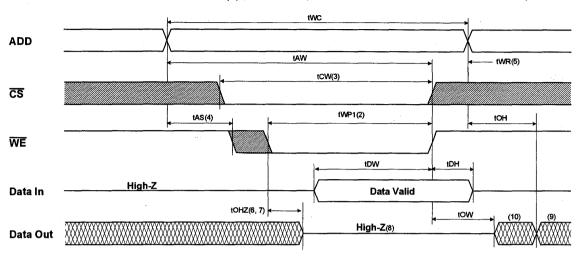

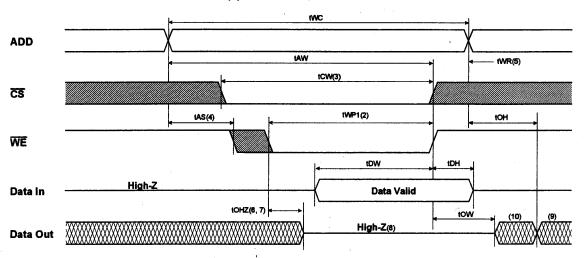

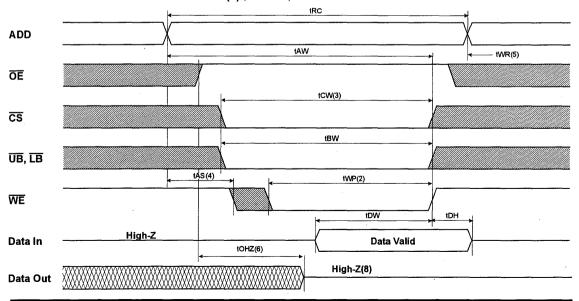

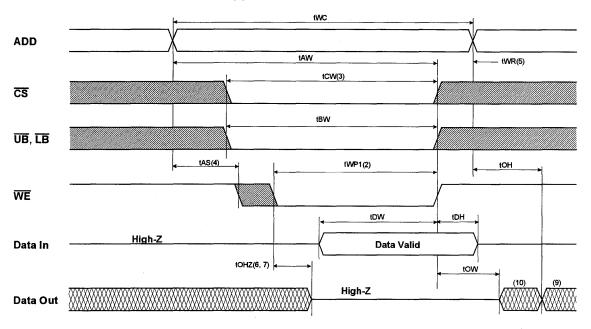

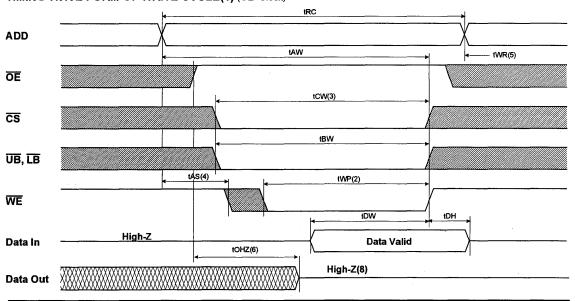

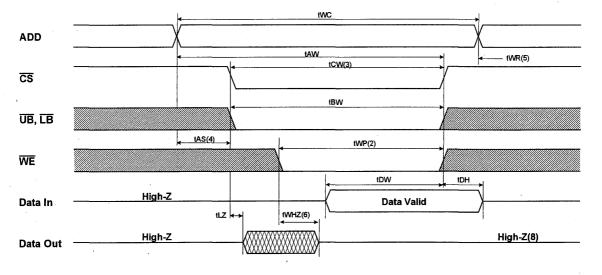

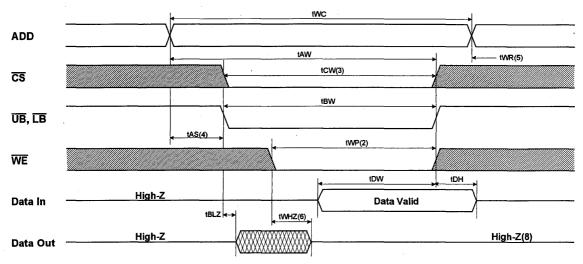

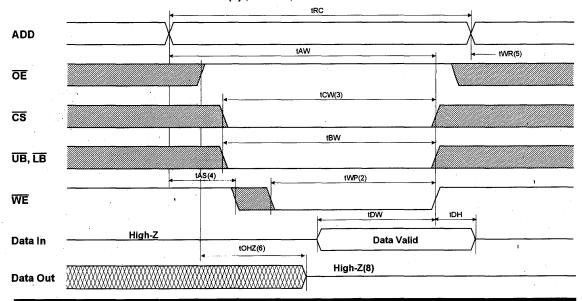

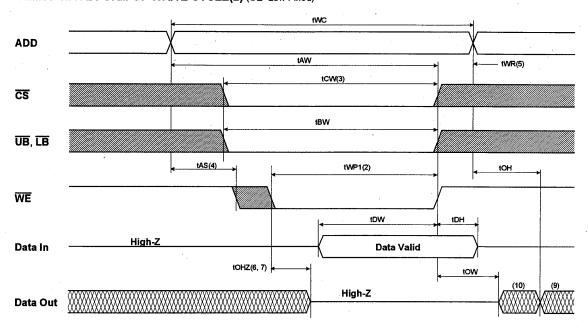

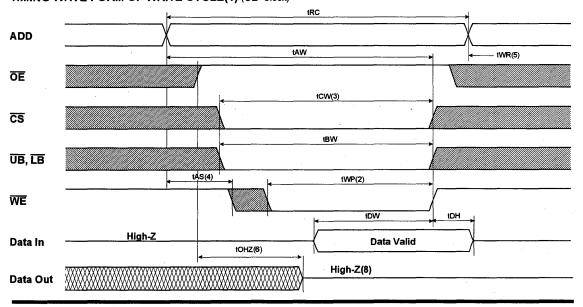

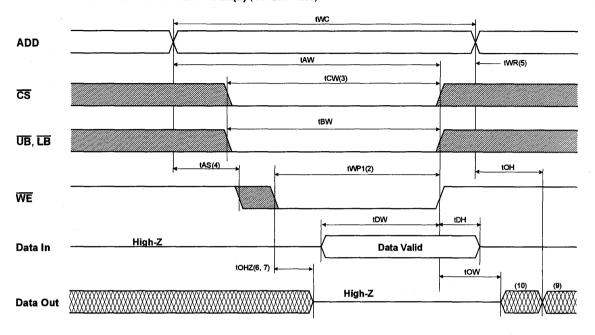

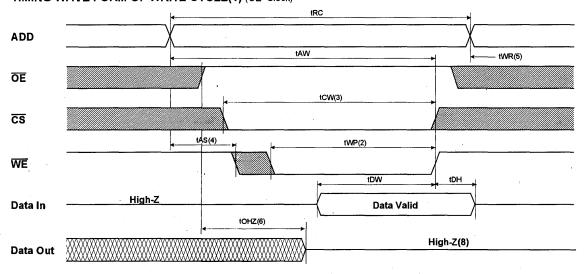

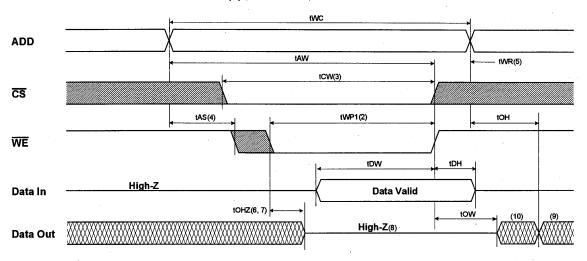

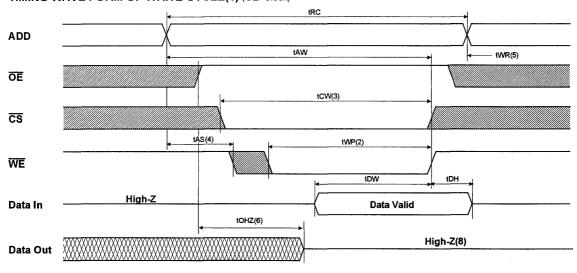

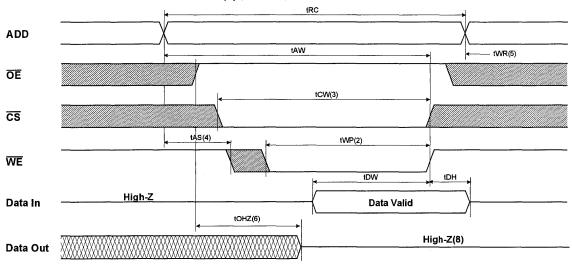

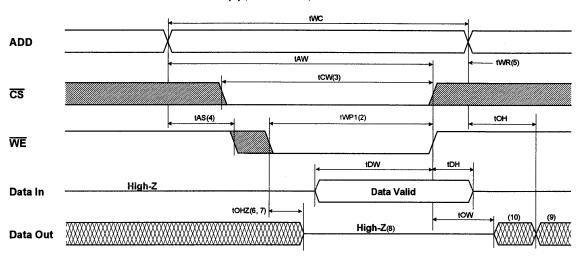

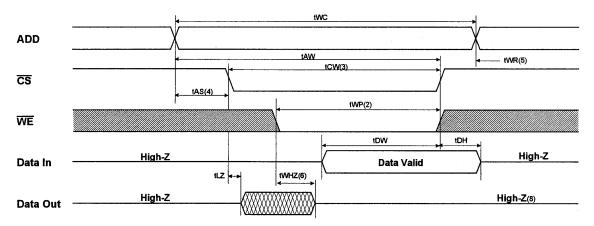

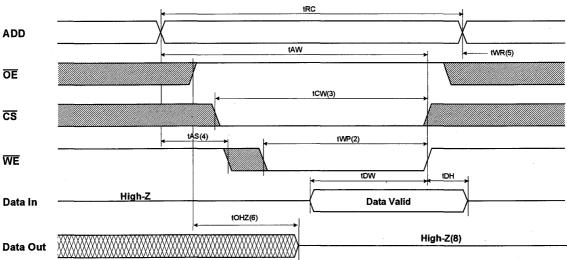

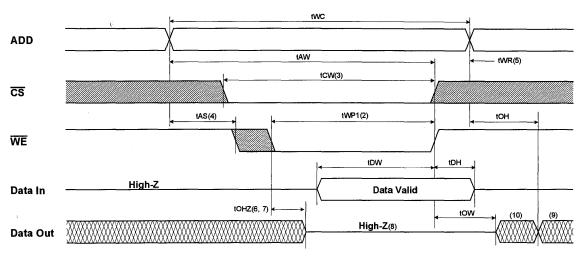

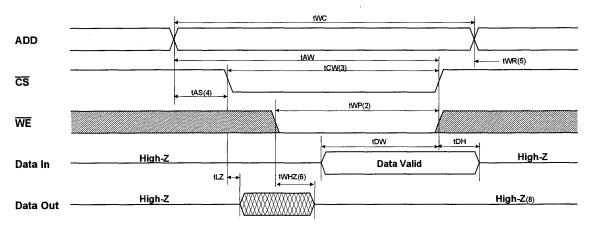

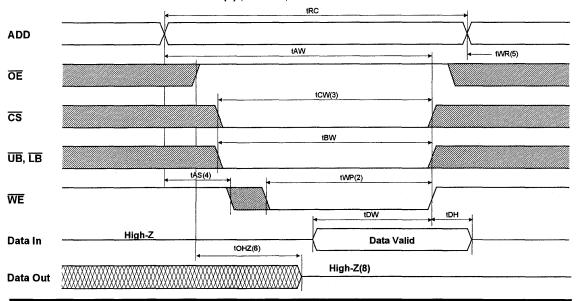

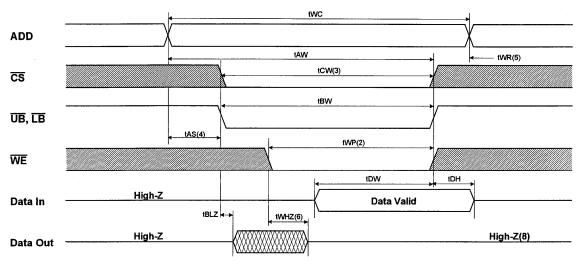

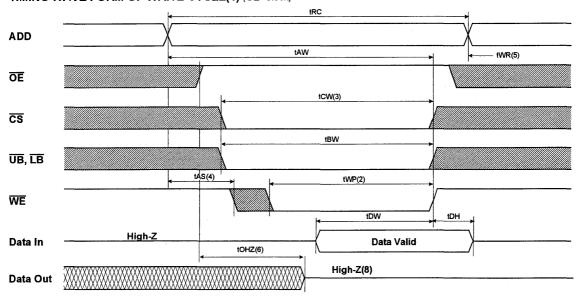

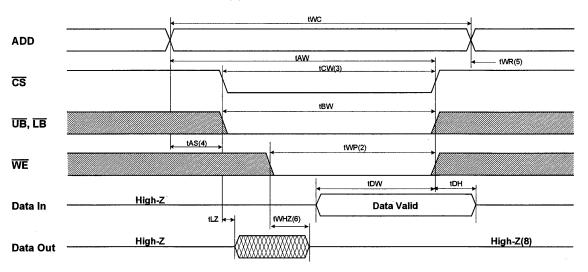

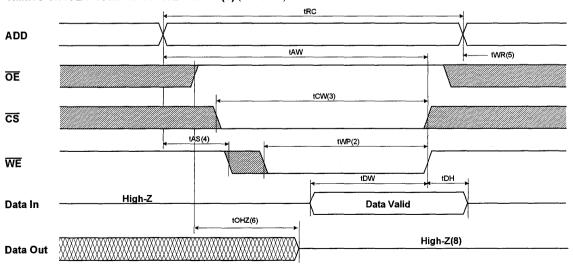

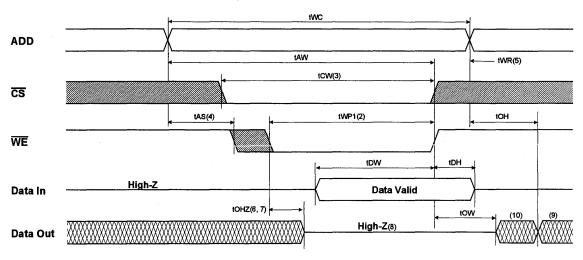

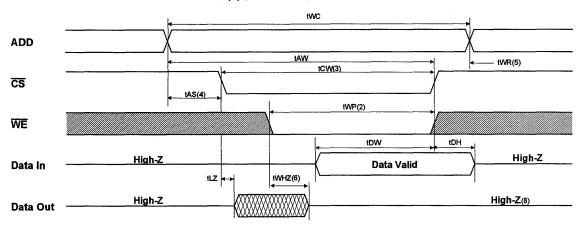

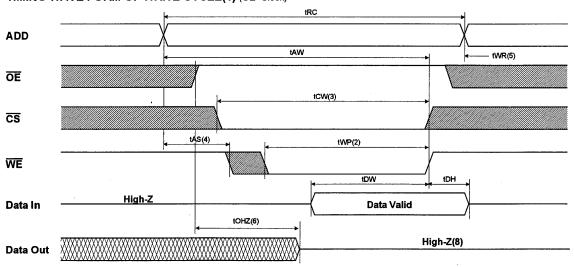

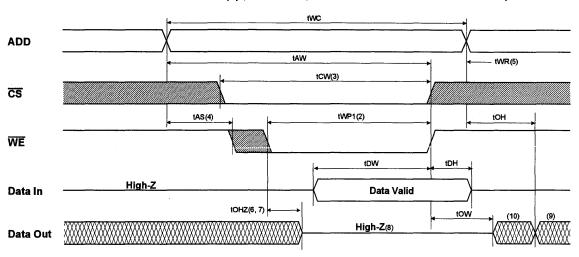

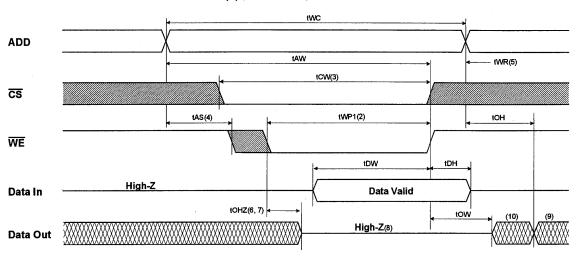

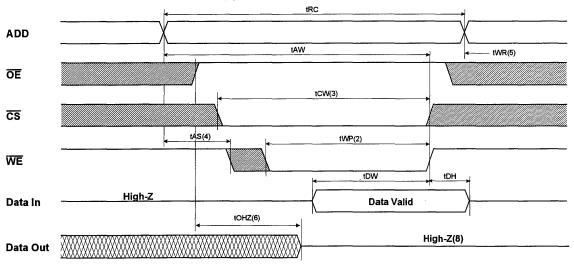

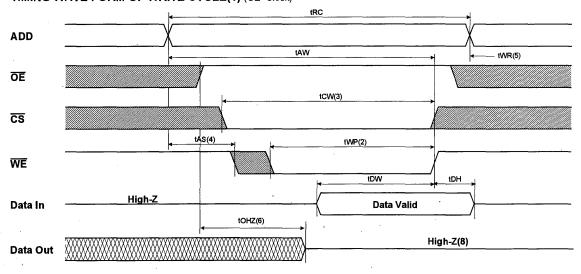

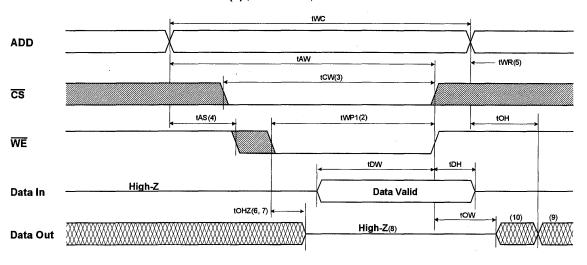

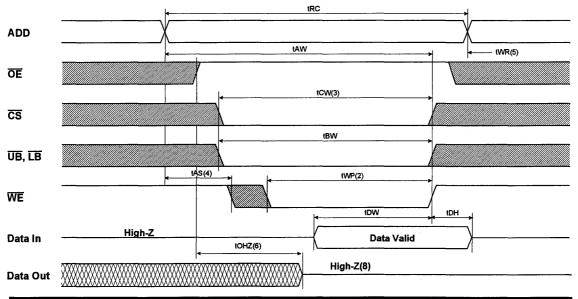

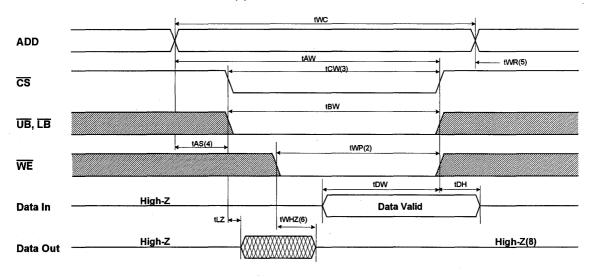

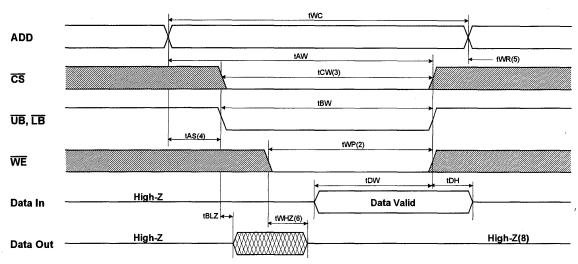

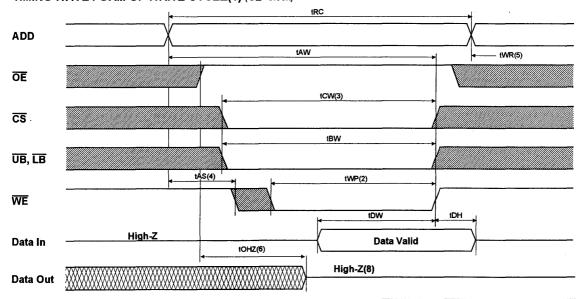

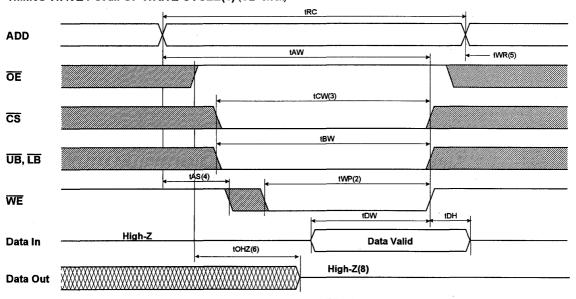

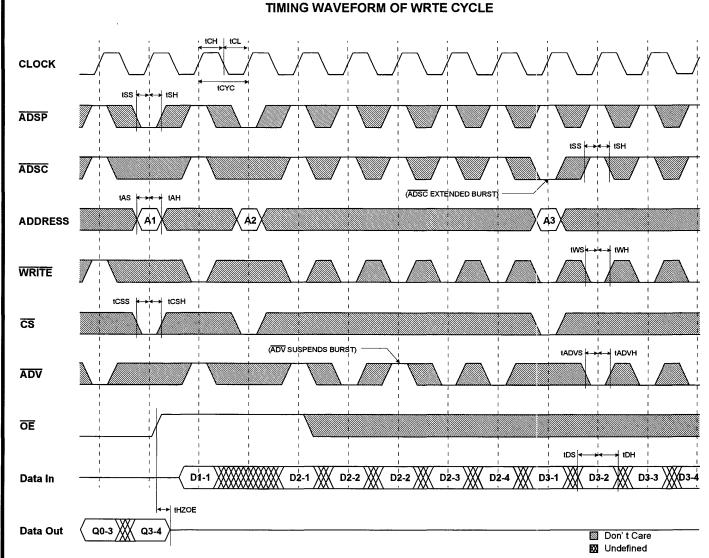

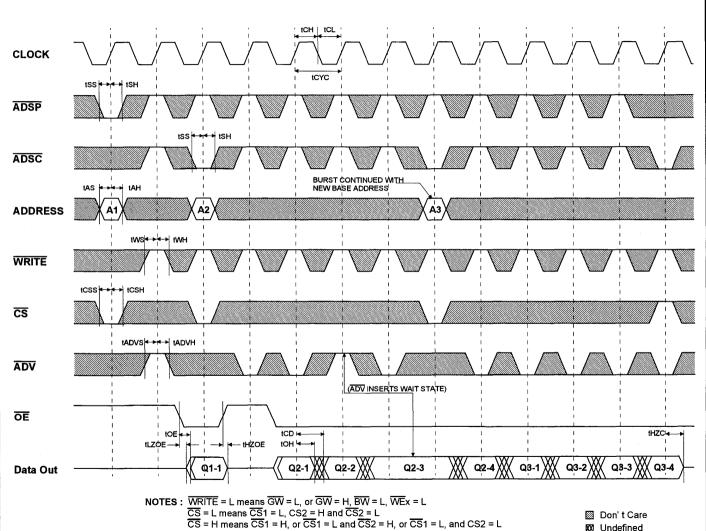

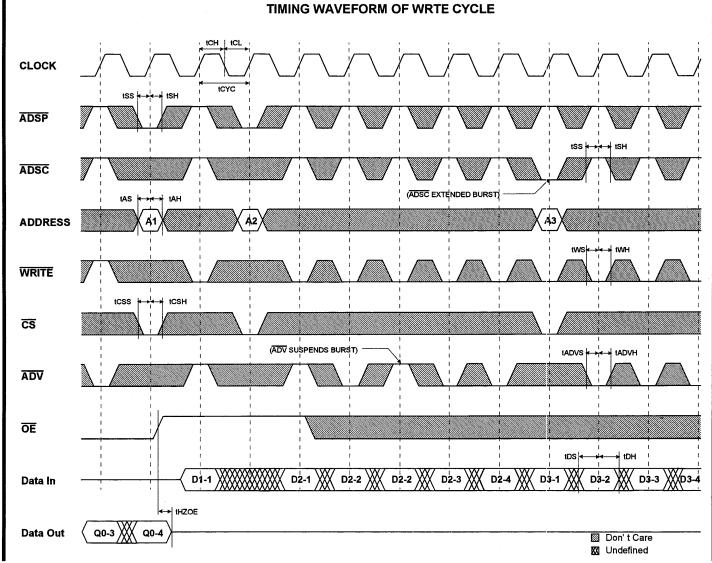

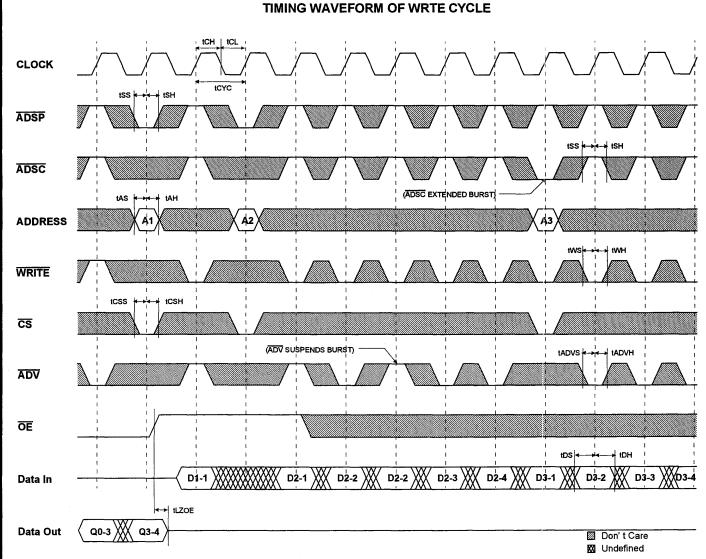

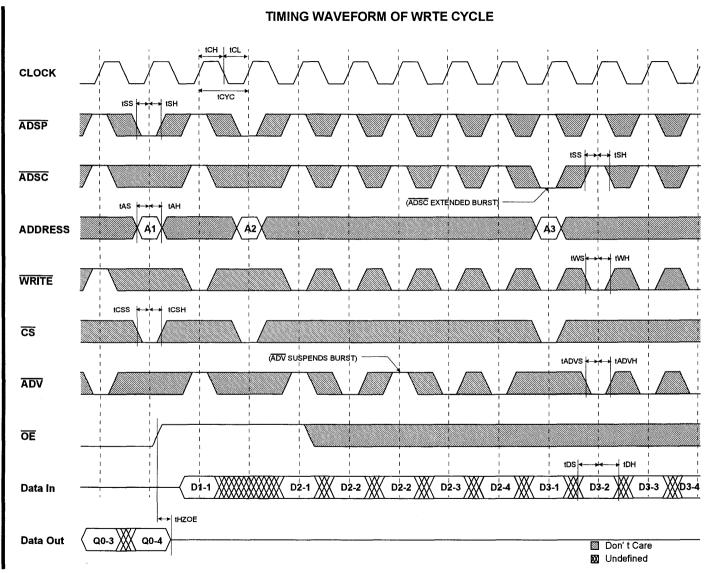

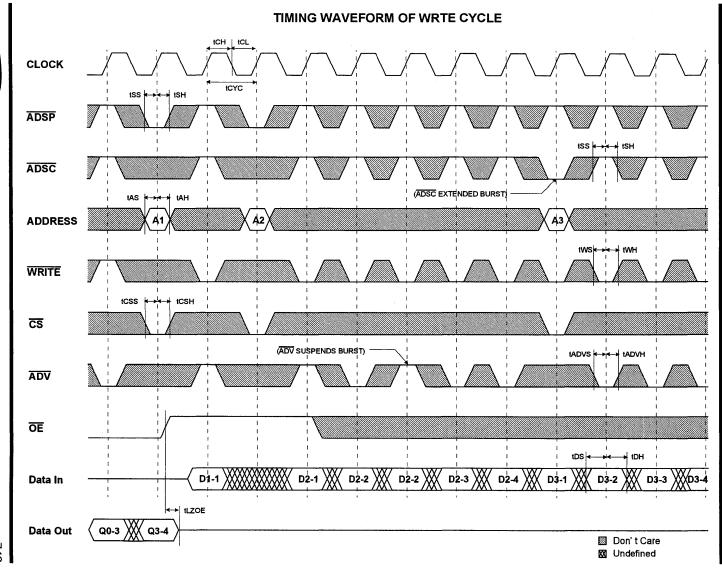

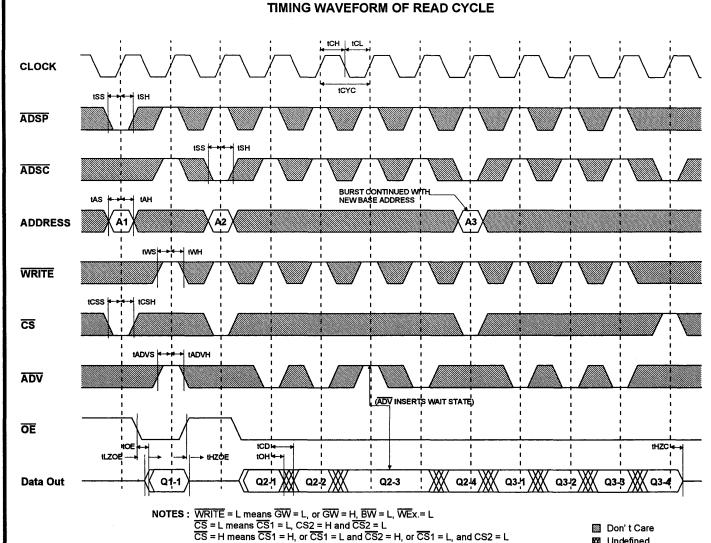

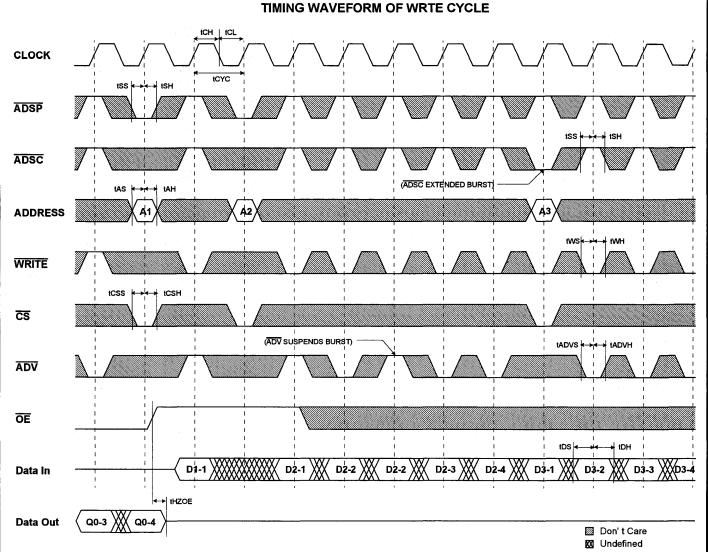

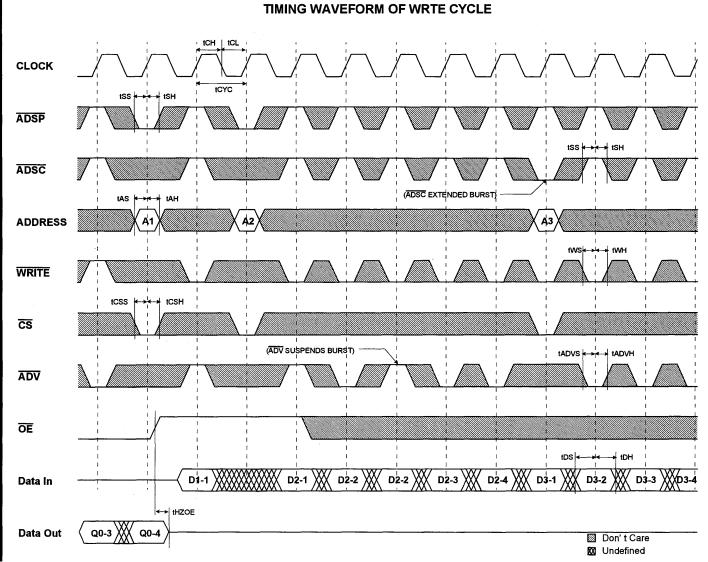

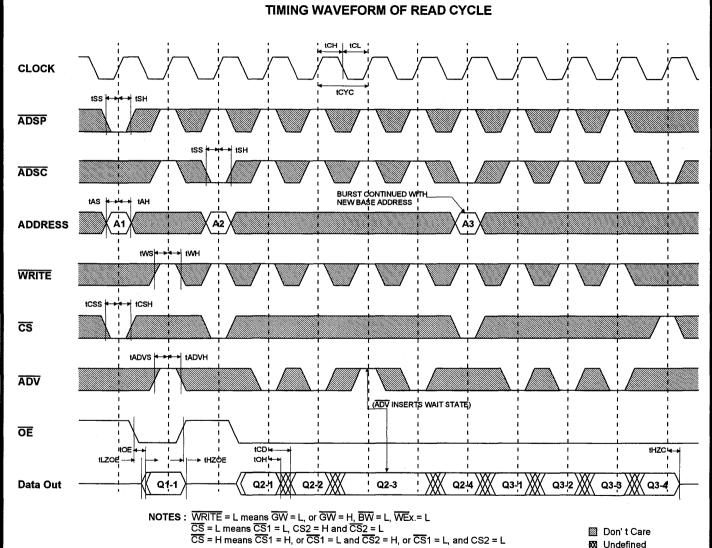

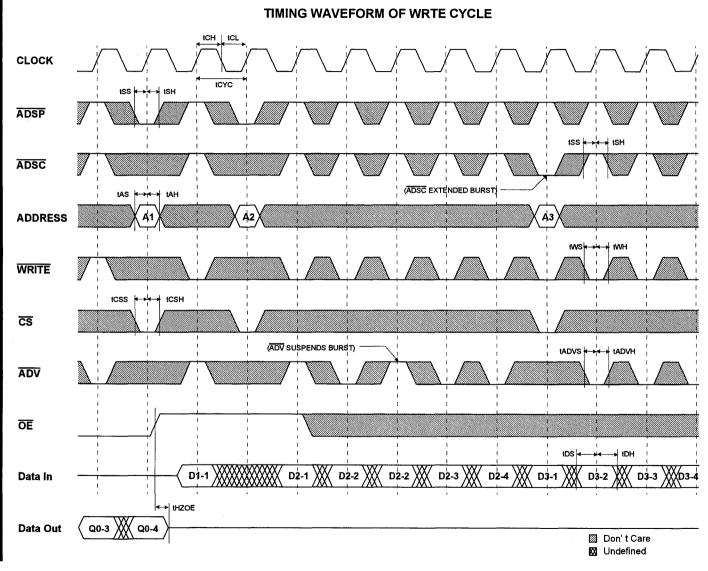

| 255, 268                                     | TIMING WAVE FORM OF WRITE CYCLE(1) (OE=Controlled) tWP1(2)                                                   | TIMING WAVE FORM OF WRITE CYCLE(1) (OE=Controlled) tWP(2)                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

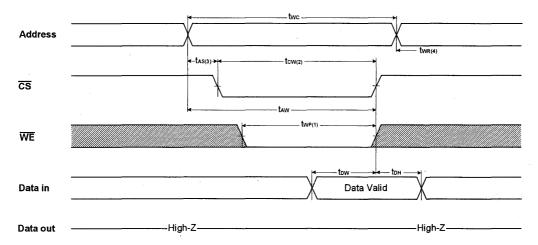

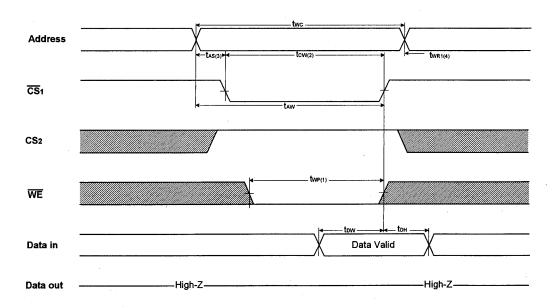

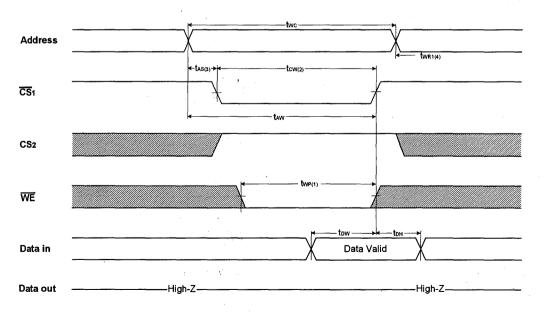

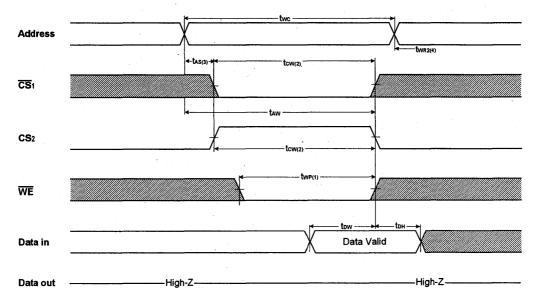

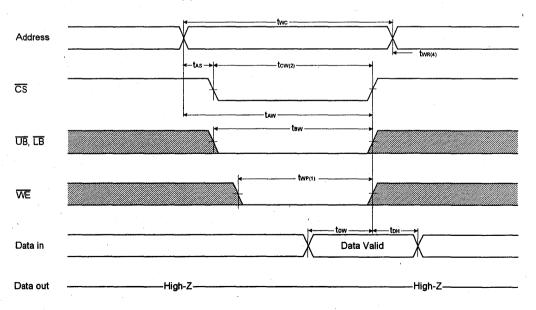

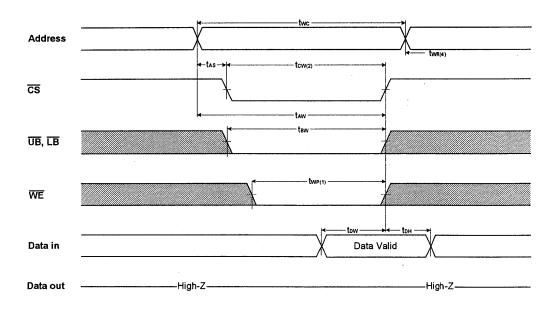

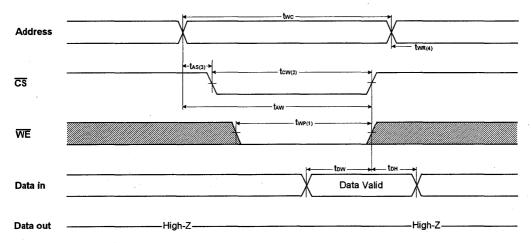

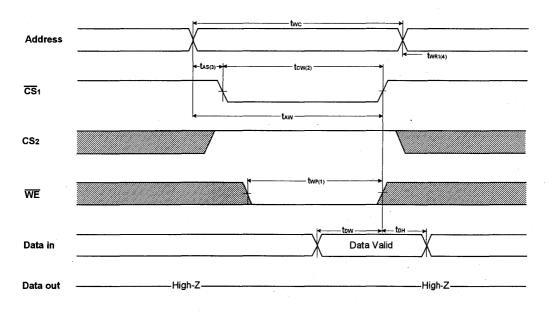

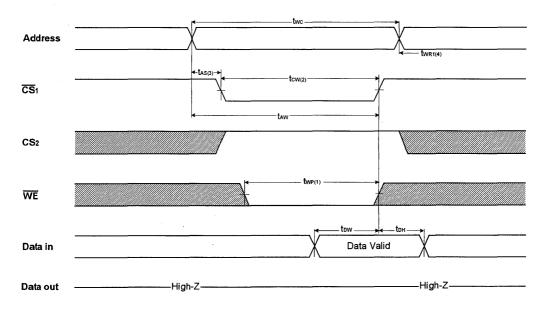

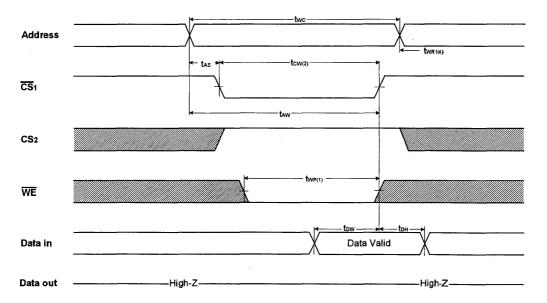

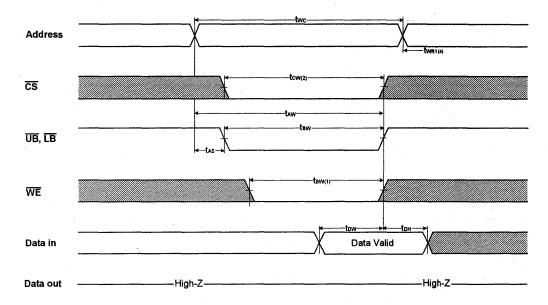

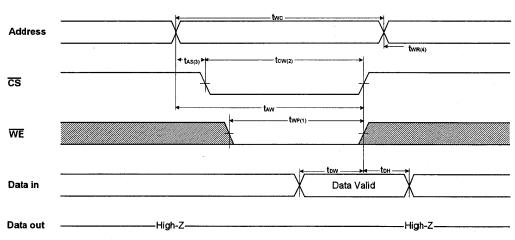

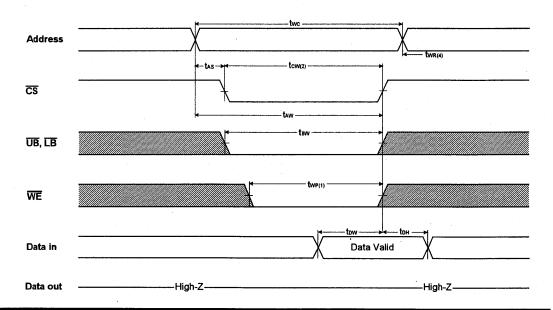

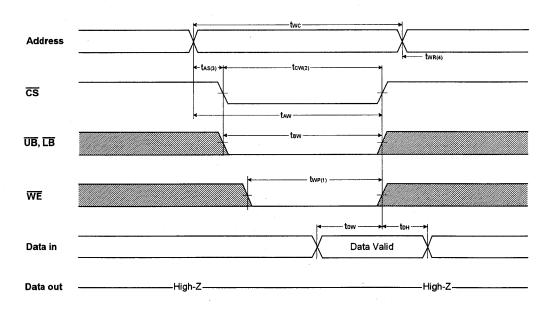

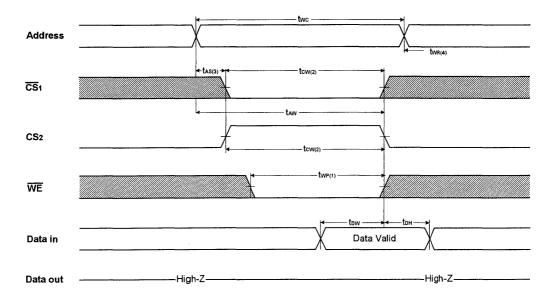

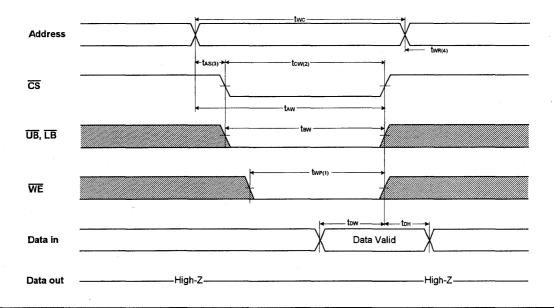

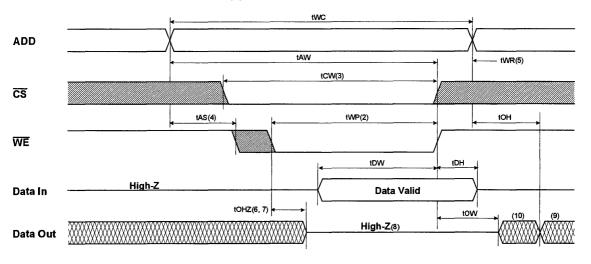

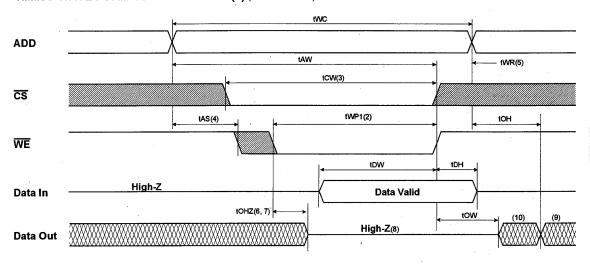

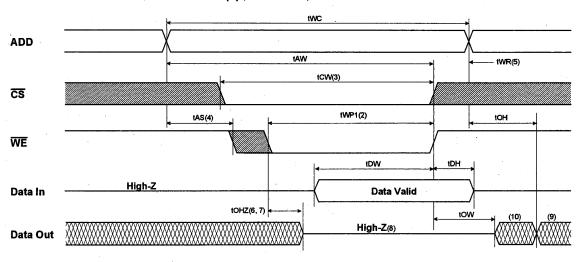

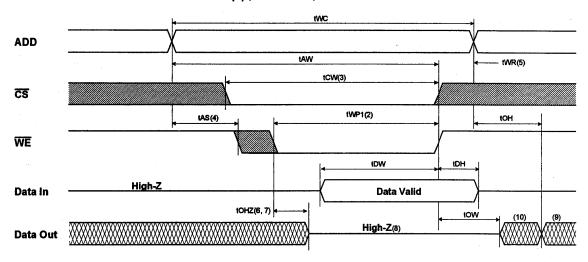

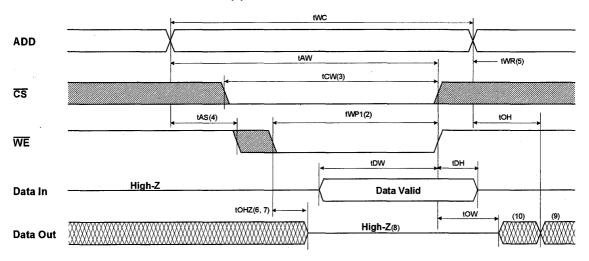

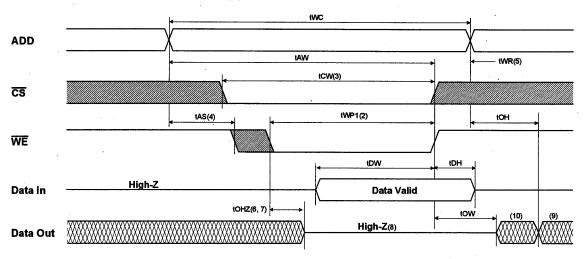

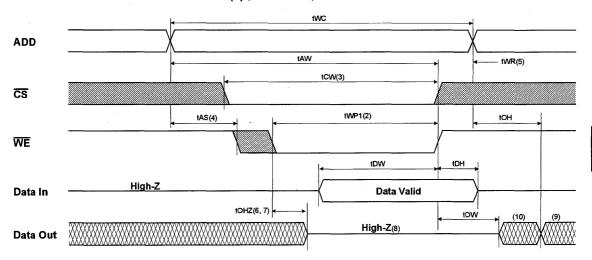

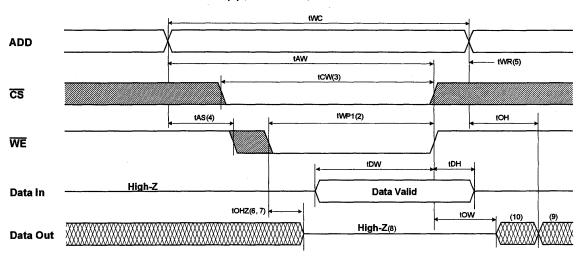

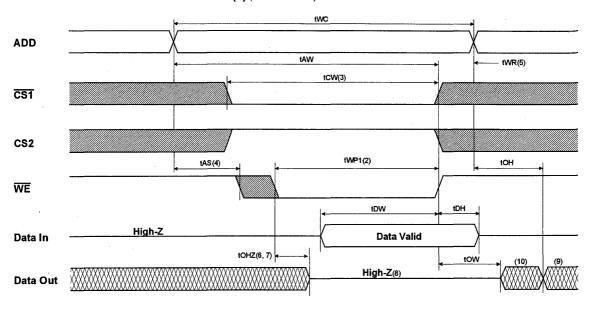

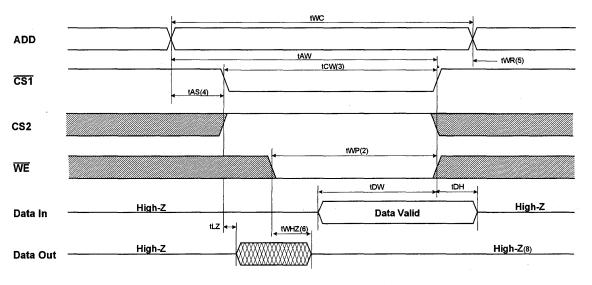

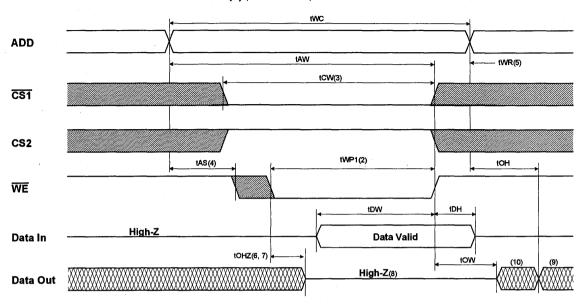

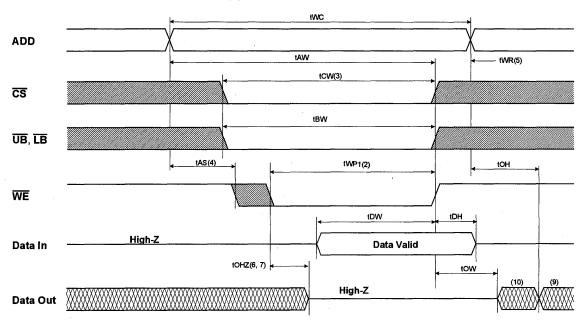

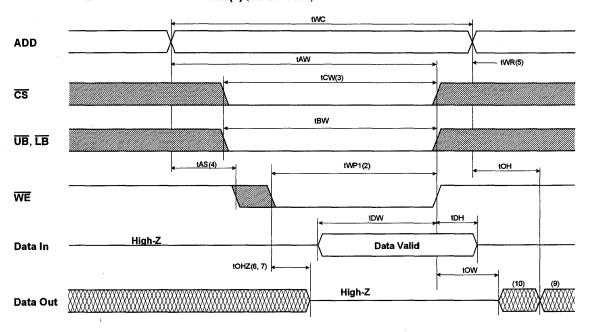

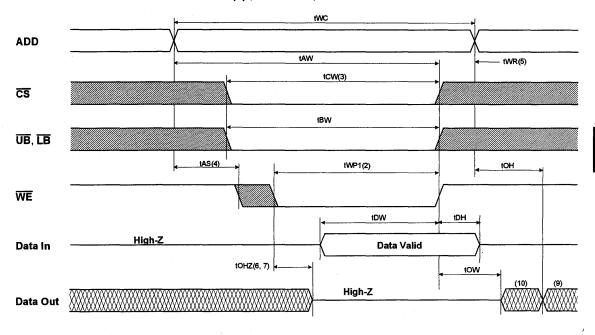

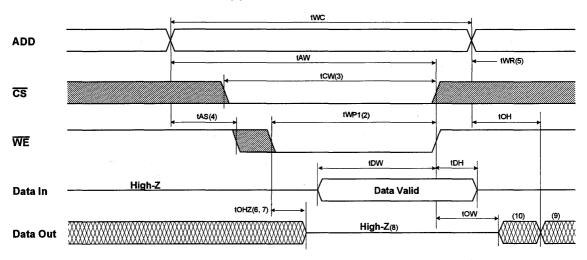

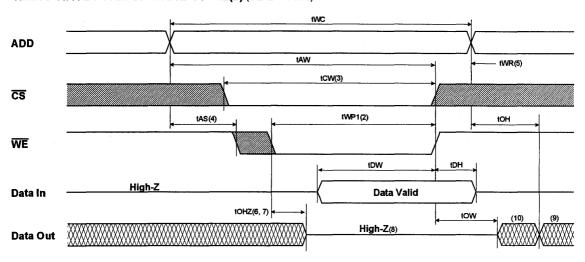

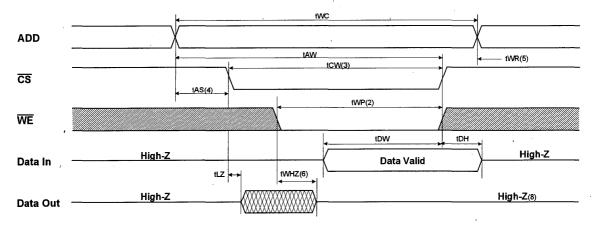

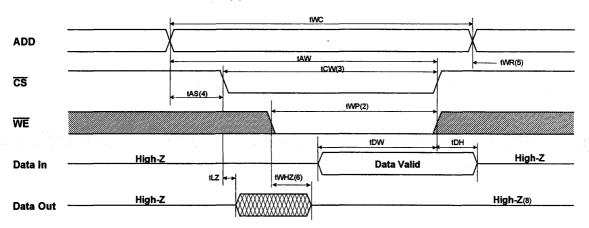

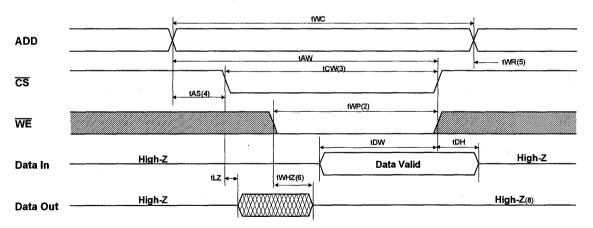

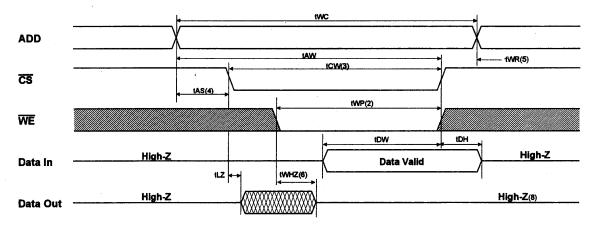

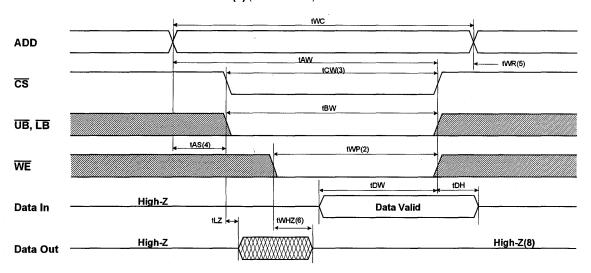

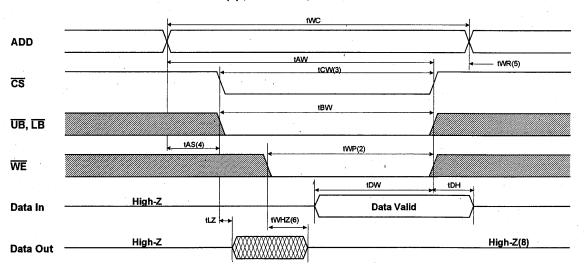

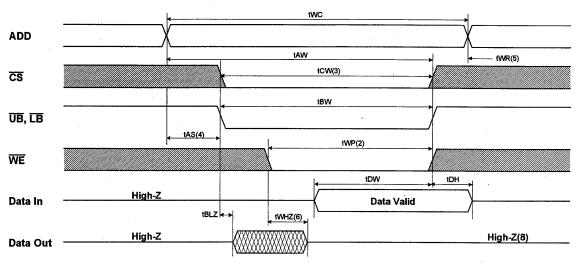

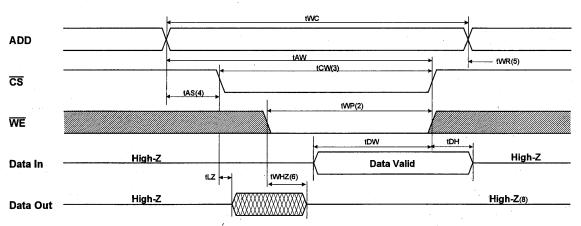

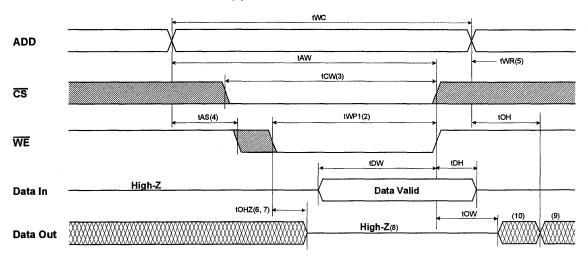

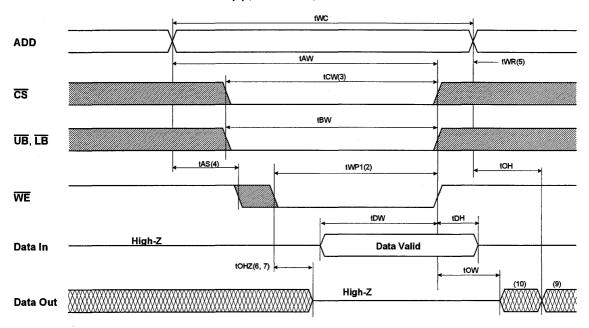

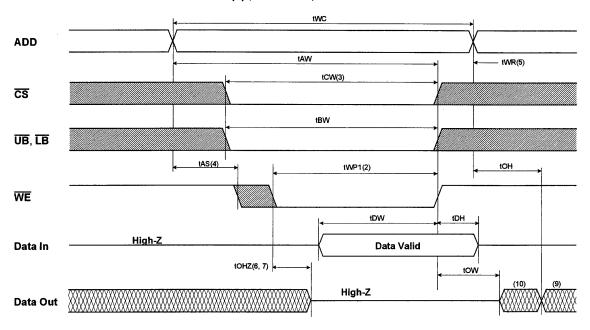

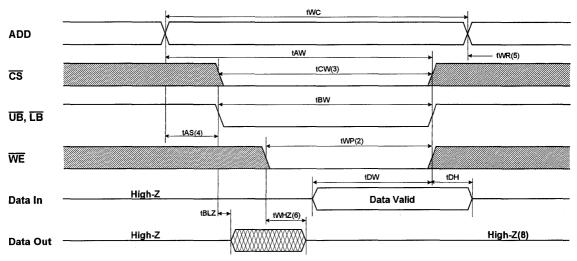

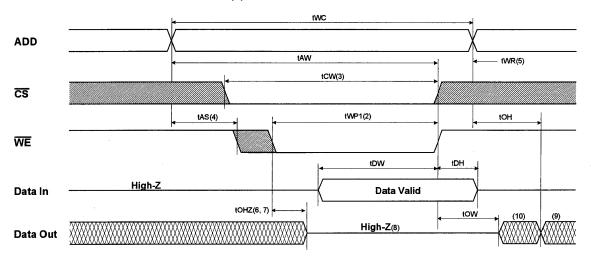

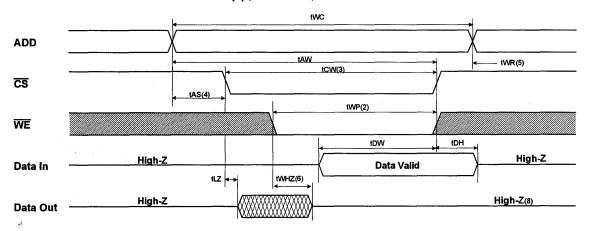

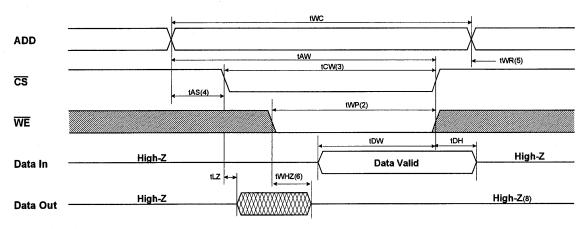

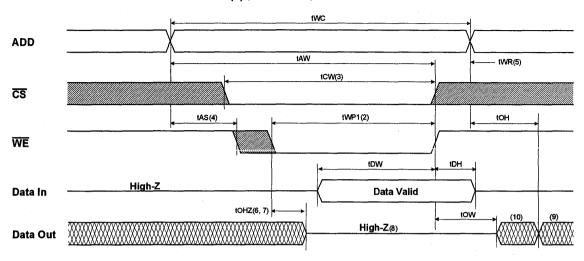

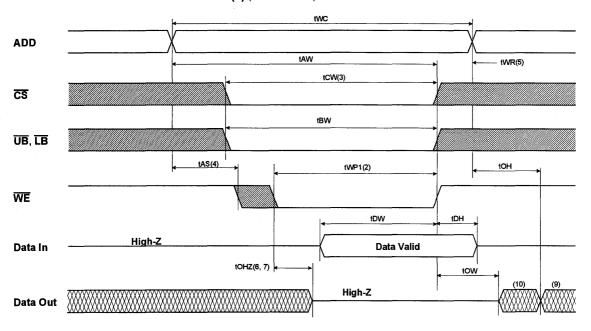

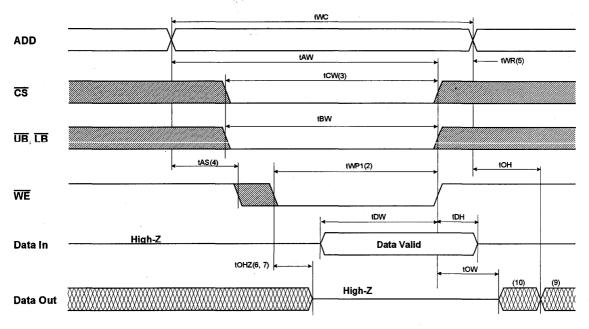

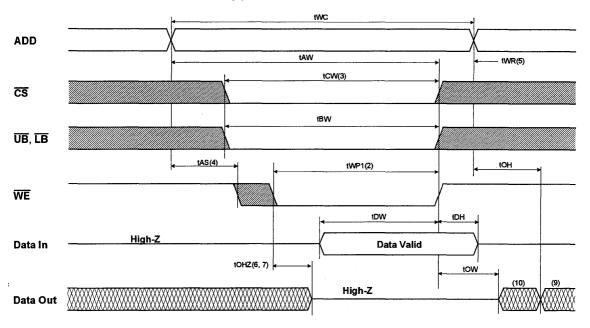

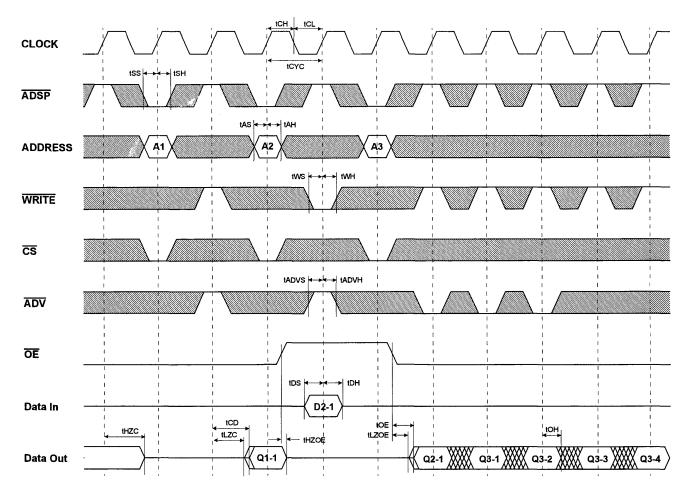

| 255, 268                                     | TIMING WAVE FORM OF WRITE CYCLE(2) (OE=Low Fixed) tWP(2)                                                     | TIMING WAVE FORM OF WRITE CYCLE(2) (OE=Low Fixed) tWP1(2)                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

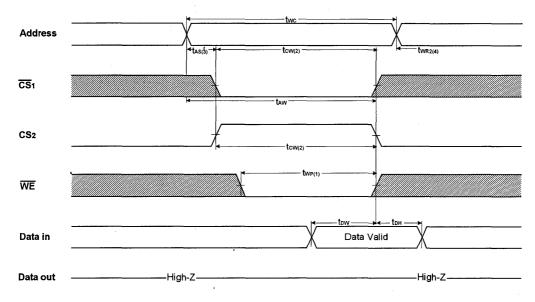

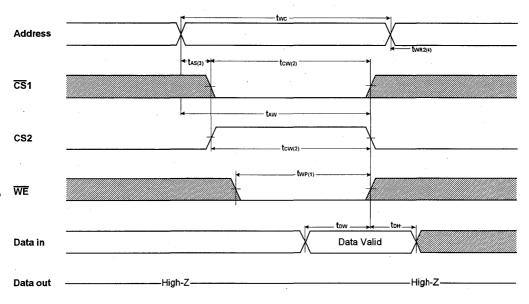

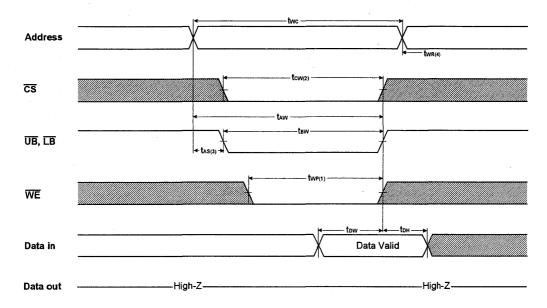

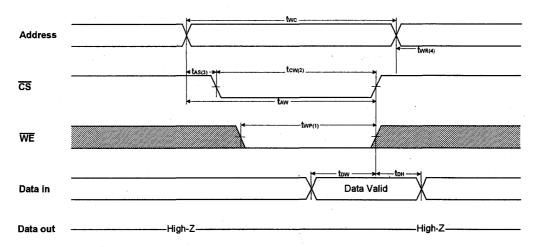

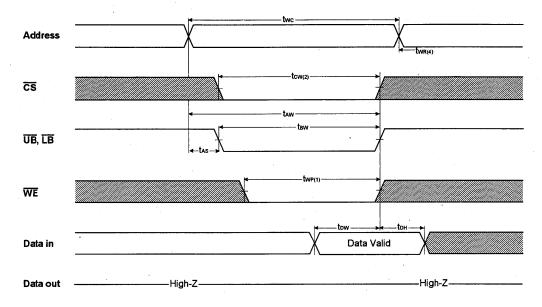

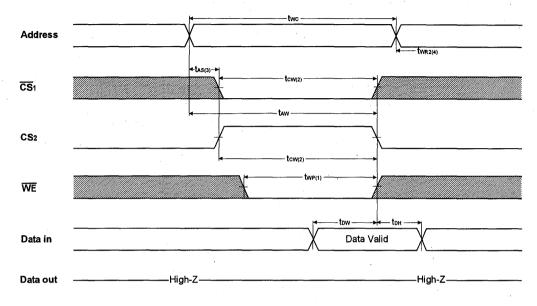

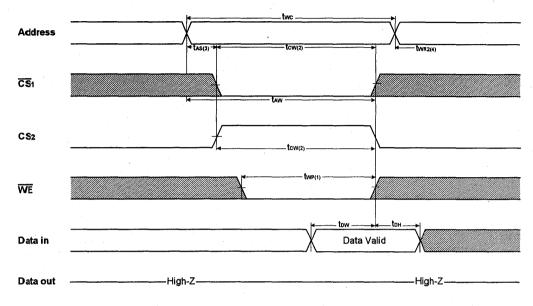

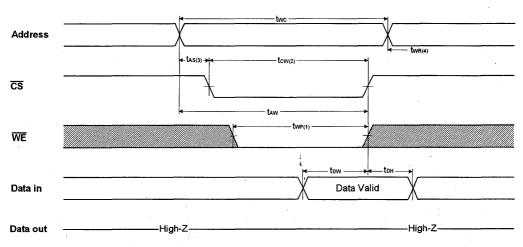

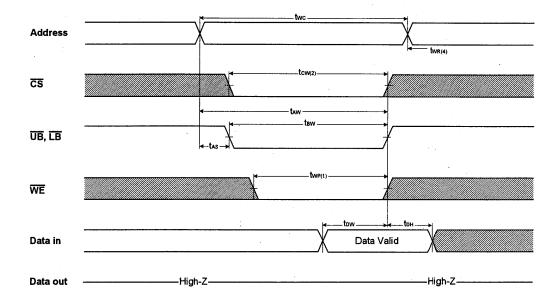

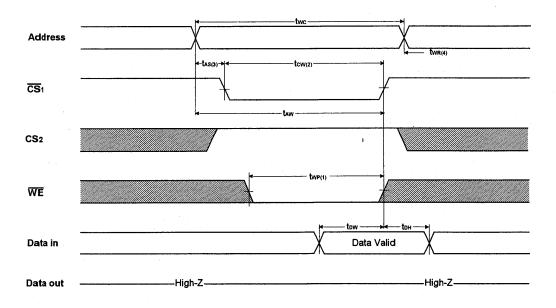

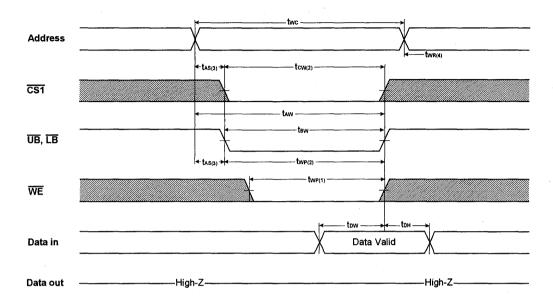

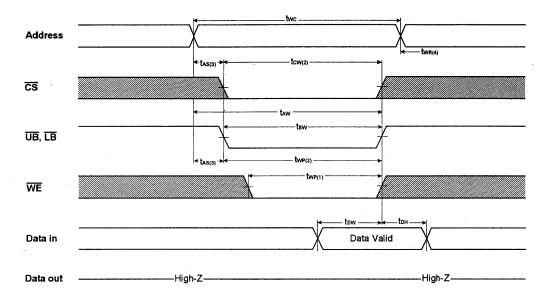

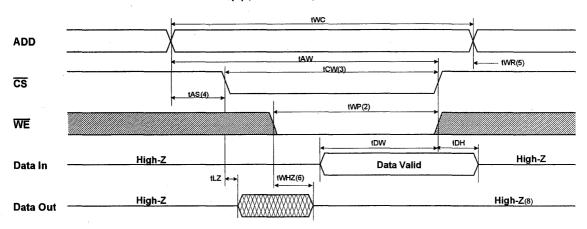

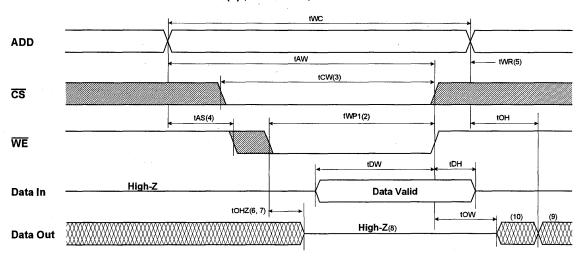

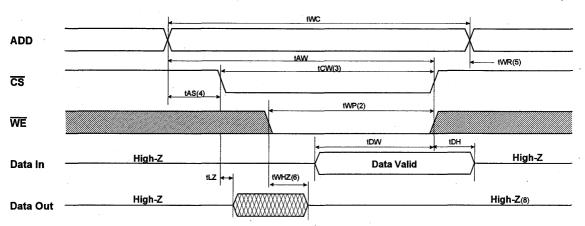

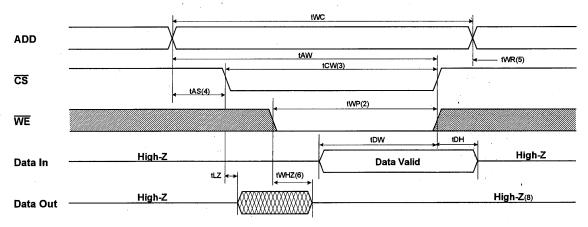

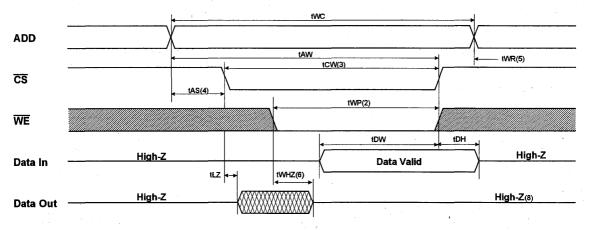

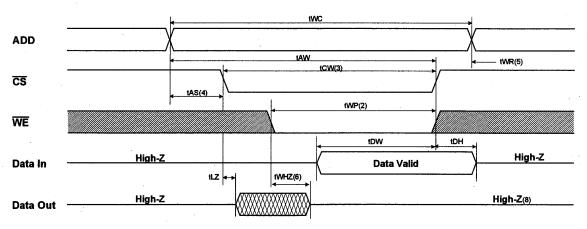

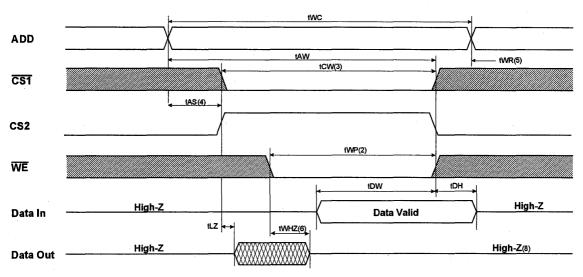

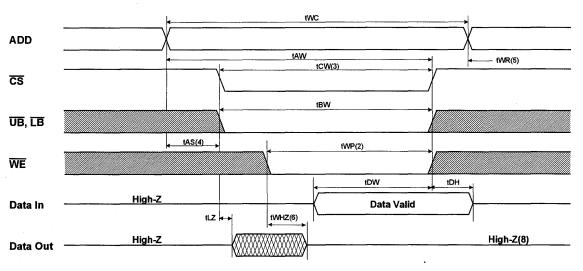

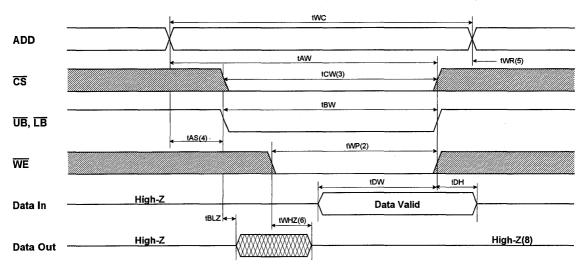

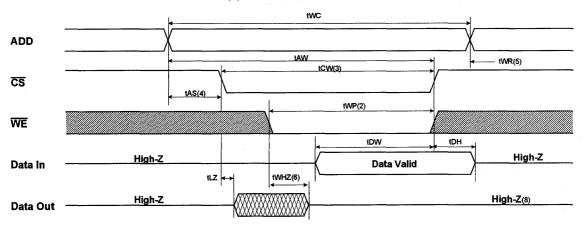

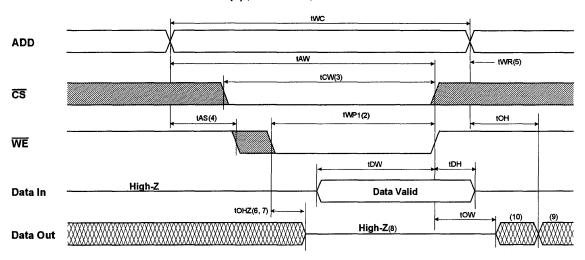

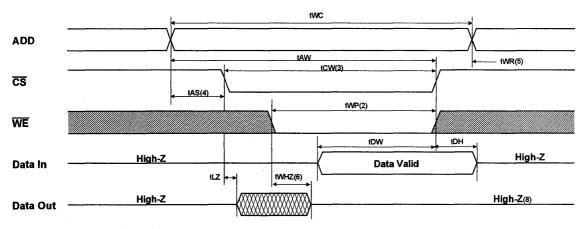

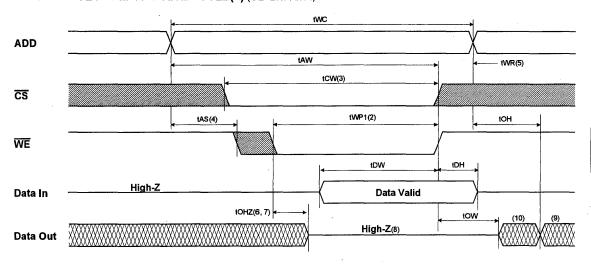

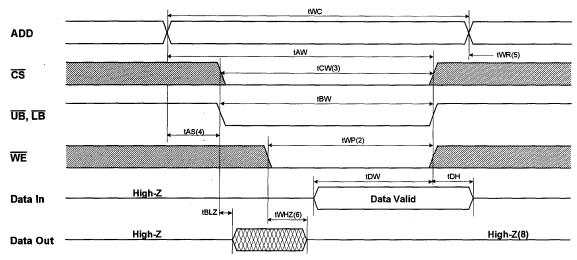

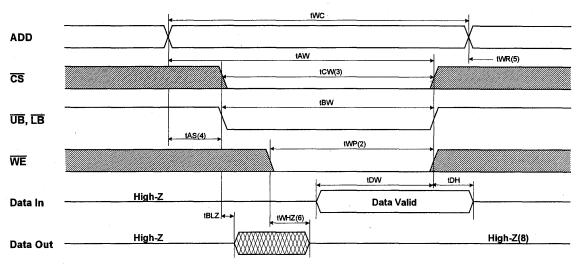

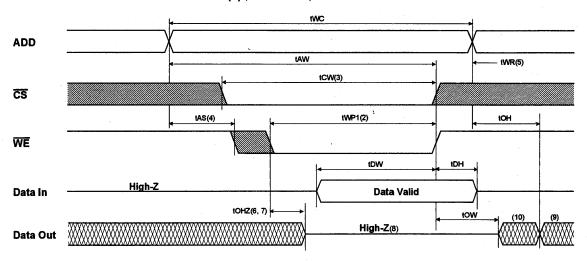

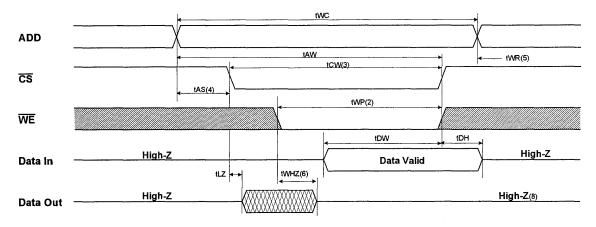

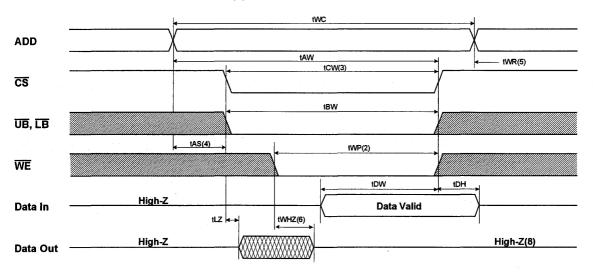

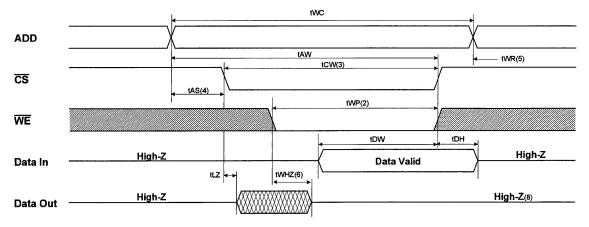

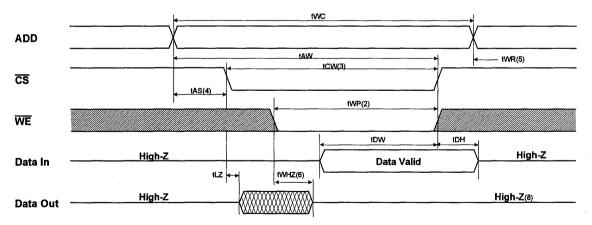

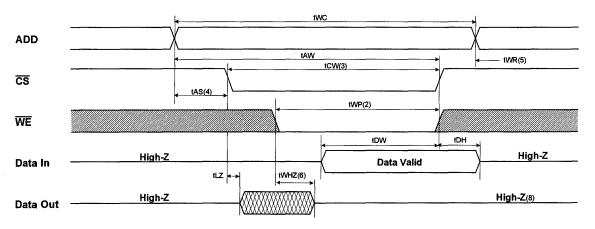

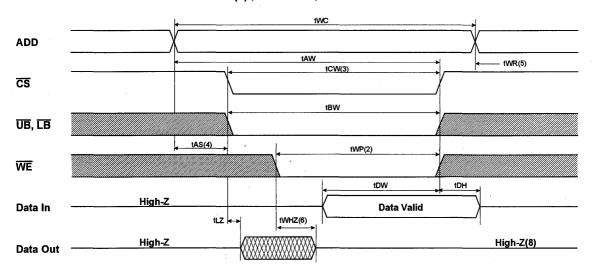

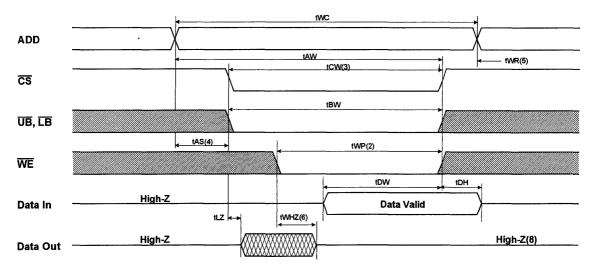

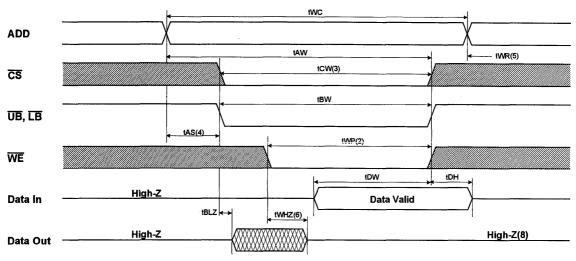

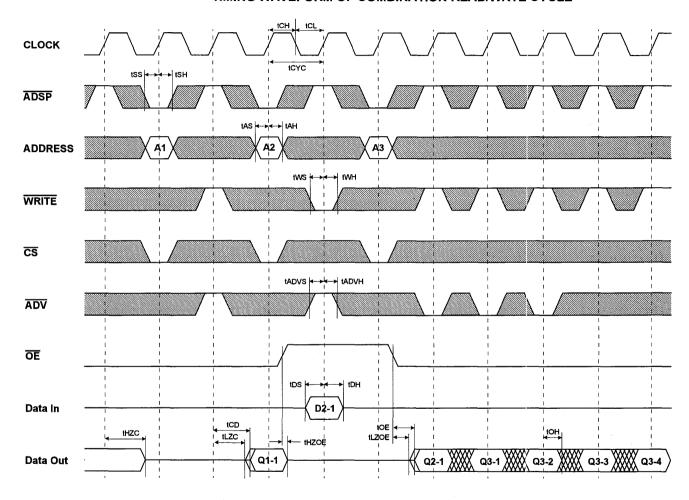

| 283                                          | TIMING WAVE FORM OF WRITE CYCLE(1) (CS=Controlled) tWP1(2)                                                   | TIMING WAVE FORM OF WRITE CYCLE(1) (CS=Controlled) tWP(2)                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

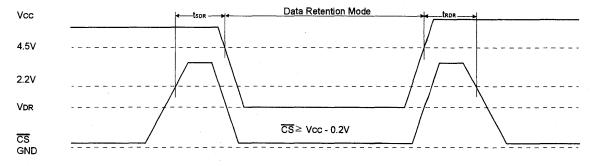

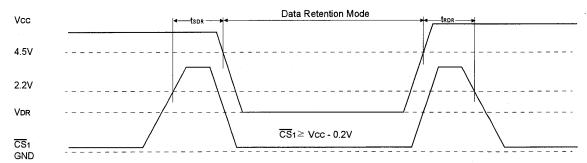

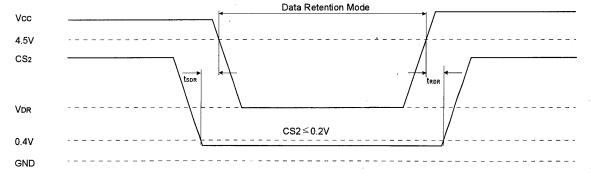

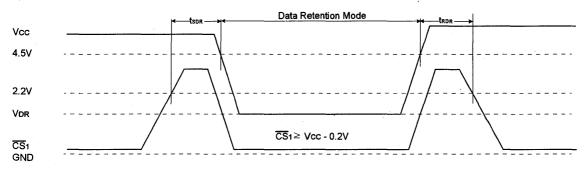

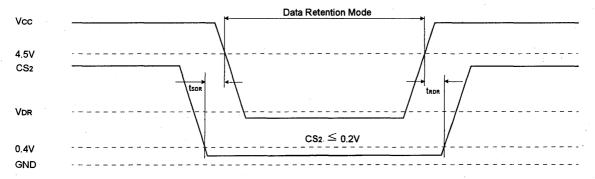

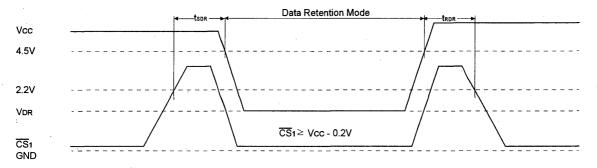

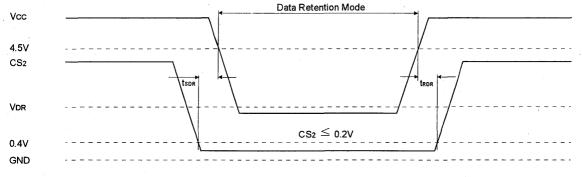

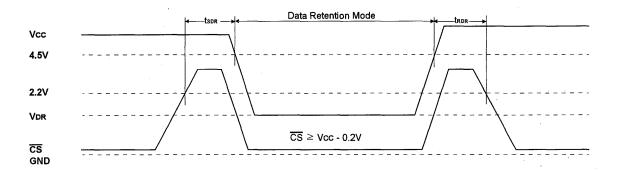

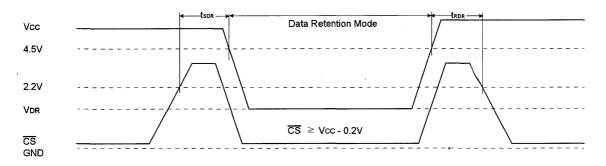

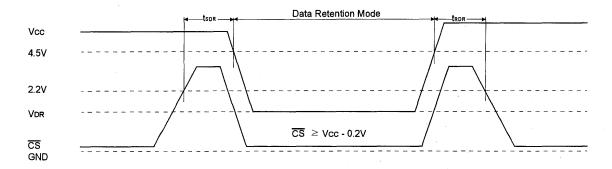

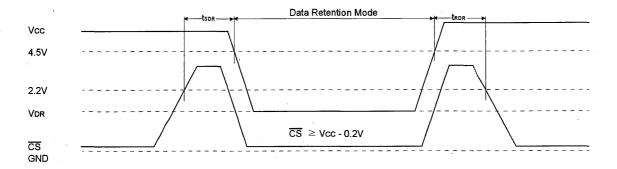

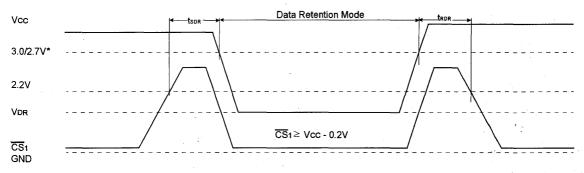

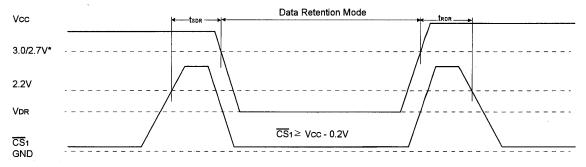

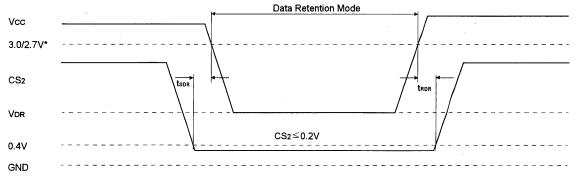

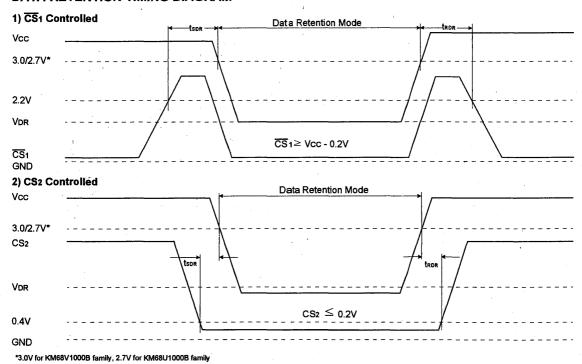

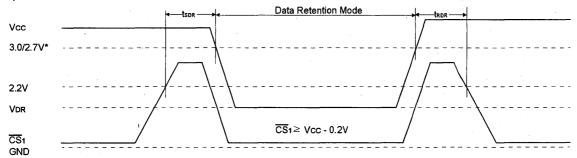

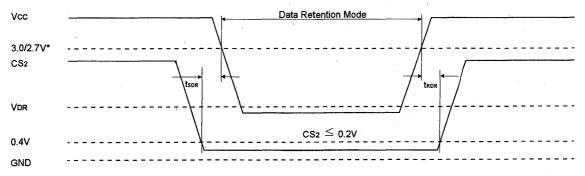

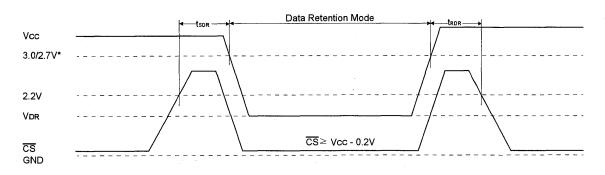

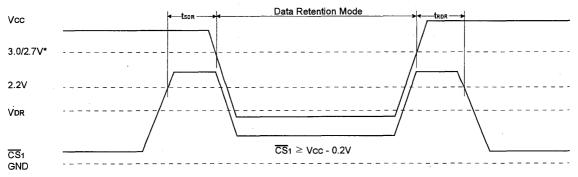

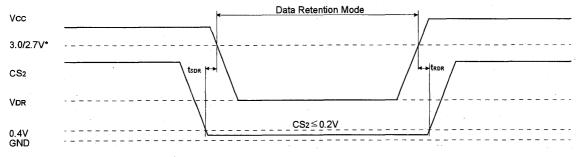

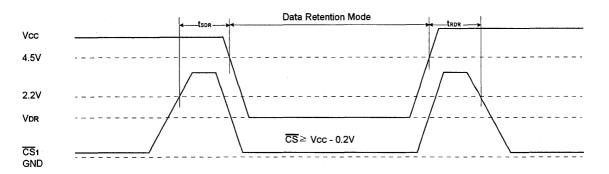

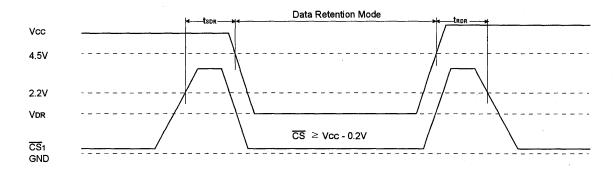

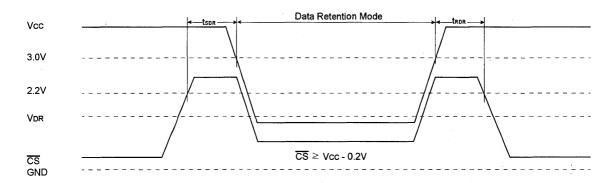

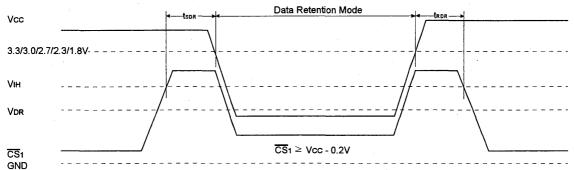

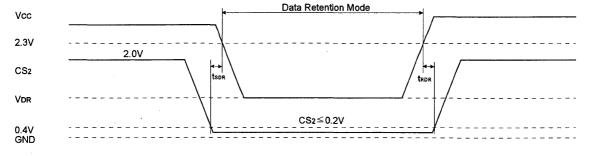

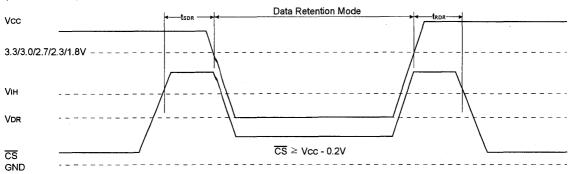

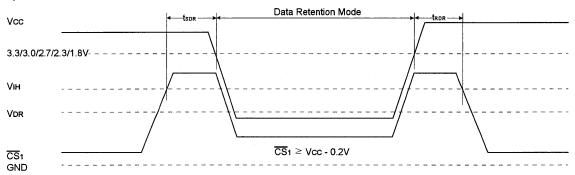

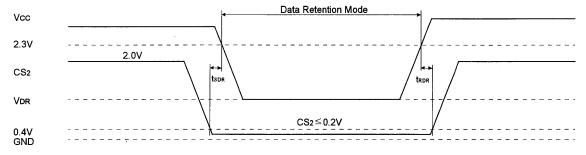

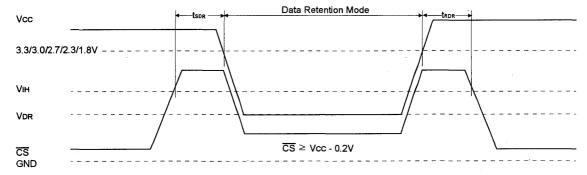

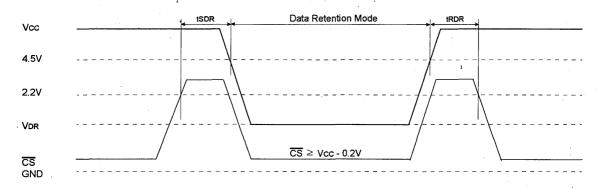

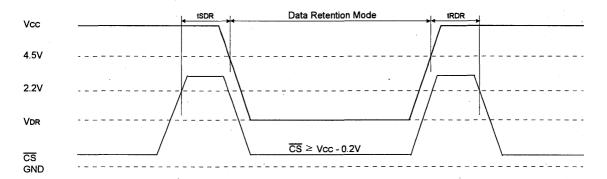

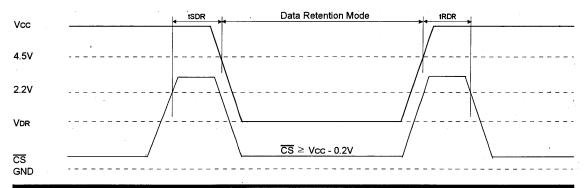

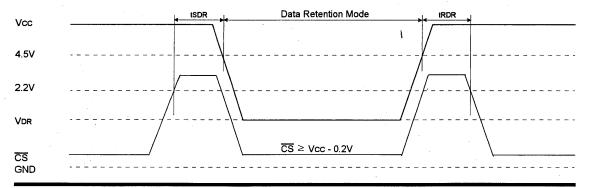

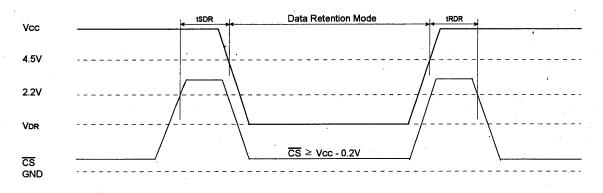

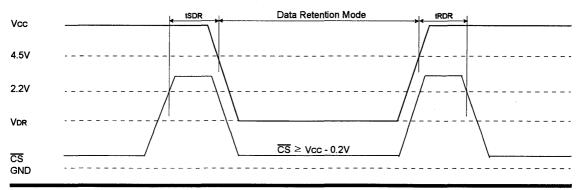

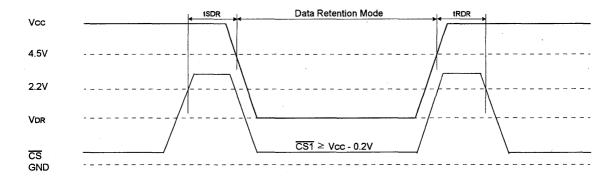

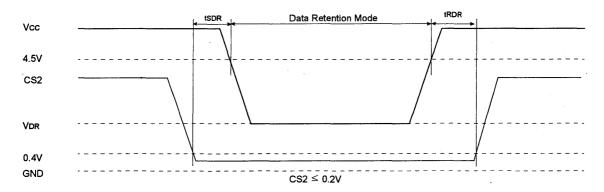

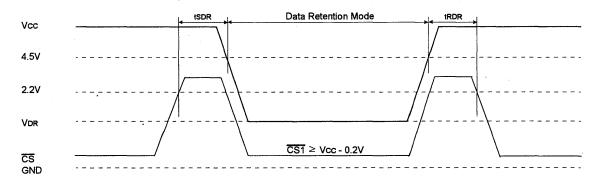

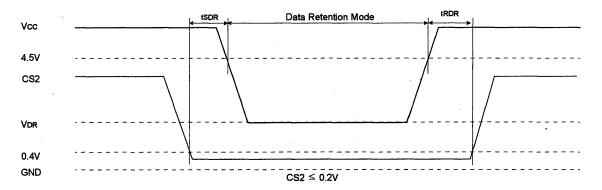

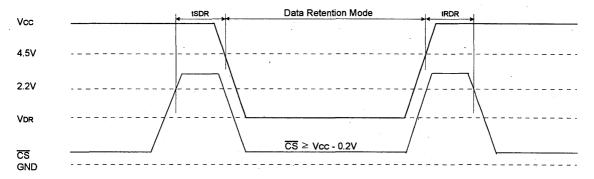

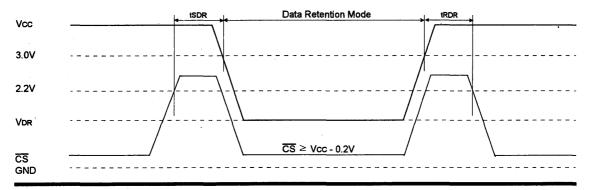

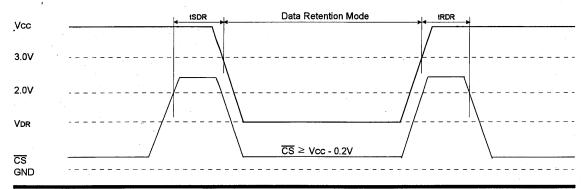

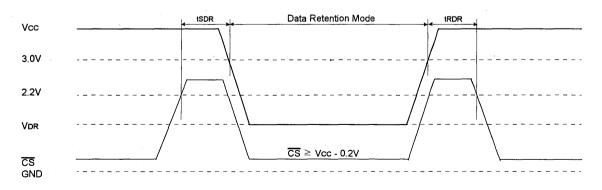

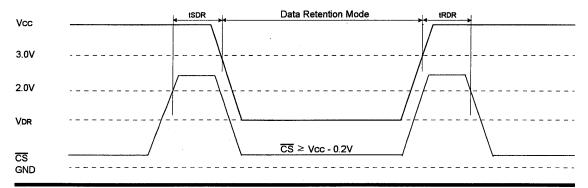

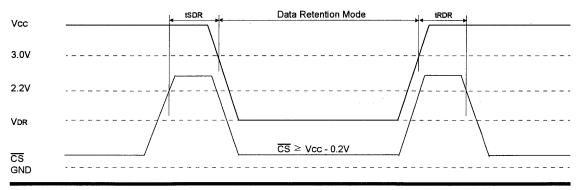

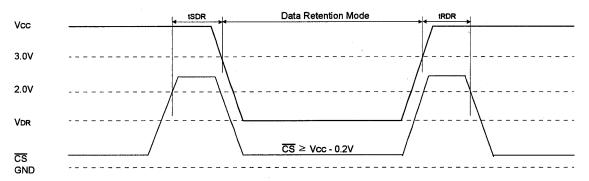

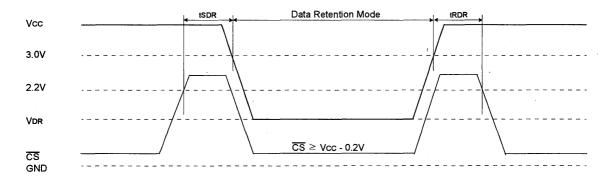

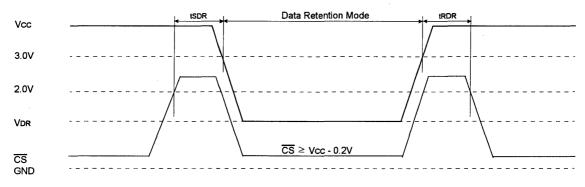

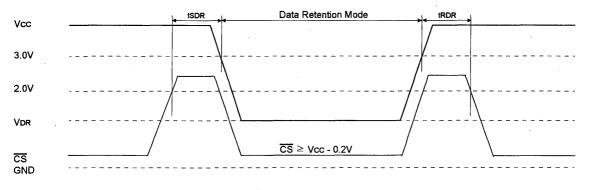

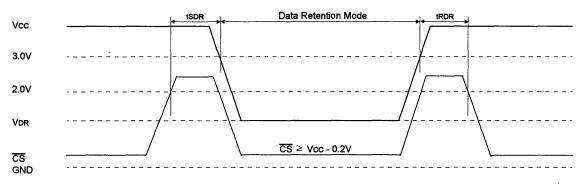

| 276, 284, 333,<br>384, 501, 518,<br>532, 548 | DATA RETENTION CHARACTERISTICS*<br>VCC =2.0V, CS •• VCC - 0.2V, ~                                            | DATA RETENTION CHARACTERISTICS*<br>VCC = 3.0V, CS •• VCC - 0.2V, ~                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 363                                          | DC AND OPERATING CHARACTERISTICS Standby Current, Test conditions: Isв: Min. Cycle, CS=VIH                   | DC AND OPERATING CHARACTERISTICS Standby Current, Test conditions: ISB: Min. Cycle, CS1=VIH or CS2=VIL                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                              | ISB1: f=0MHz, CS •• Vcc-0.2V, VIN •• Vcc-0.2V or VIN •• 0.2V                                                 | ISB1 : f=0MHz, CS1 •• Vcc-0.2V or CS2 •• 0.2V,<br>Vin •• Vcc-0.2V or Vin •• 0.2V                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 308, 357, 402                                | " NOTE: Above test conditions are ~ " below TEST CONDITIONS                                                  | Remove "NOTE: Above test conditions are ~" below TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 411, 439, 467                                | Blank below TEST CONDITIONS                                                                                  | Add "NOTE: Above test conditions are also applied at industrial temperature range" below TEST CONDITIONS                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 411, 439, 467                                | Blank below READ CYCLE                                                                                       | Add " NOTE: Above parameters are also guaranteed at industrial temperature range" below READ CYCLE                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 412, 440, 468                                | Blank below WRITE CYCLE                                                                                      | Add "NOTE: Above parameters are also guaranteed at industrial temperature range" below WRITE CYCLE                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 932, 941, 950                                | DC ELECTRICAL CHARACTERISTICS Standby Current, ISB1, Test conditions: f=Max, 100% Duty, Device deselected, ~ | DC ELECTRICAL CHARACTERISTICS Standby Current, Iss1, Test conditions: f=0 MHz, Device deselected, ~                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

If you want to get a revised specification, you can see and download the specification form web site, www.sec.samsung.com/sram, by pdf file.

| Page           | Current                                                                                                            | Correction           |

|----------------|--------------------------------------------------------------------------------------------------------------------|----------------------|

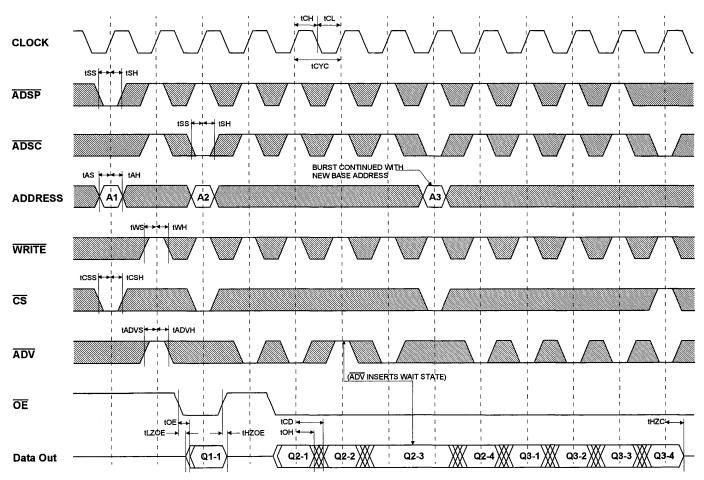

| 903, 912, 921, | A-1. SYNCHRONOUS PIPELINE BURST TRUTH<br>TABLE(Data field), 256KB Module<br>KMM764V41AG2,KMM764V41AG7, KMM764V45AG | Refer to below table |

#### A-1. SYNCHRONOUS PIPELINE BURST TRUTH TABLE(Data field)

| CCS | ECS | ADSP | CADS | CADV | WRITE | K  | Address Accessed | Operation                  |

|-----|-----|------|------|------|-------|----|------------------|----------------------------|

| Н   | X*  | Х    | L    | X    | Х     | •• | · N/A            | Not Selected               |

| L   | Н   | L    | X    | X    | X     | •• | N/A              | Not Selected               |

| L   | Н   | X    | L    | X    | Х     | •• | N/A              | Not Selected               |

| L   | L   | L    | Х    | X    | Х     | •• | External Address | Begin Burst Read Cycle     |

| L   | L   | Н    | L    | X    | L     | •• | External Address | Begin Burst Write Cycle    |

| L   | L   | Н    | L    | Х    | Н     | •• | External Address | Begin Burst Read Cycle     |

| Х   | X   | Н    | Н    | L    | Н     | •• | Next Address     | Continue Burst Read Cycle  |

| Н   | Х   | Х    | Н    | L    | Н     | •• | Next Address     | Continue Burst Read Cycle  |

| Х   | Х   | Н    | Н    | L    | L     | •• | Next Address     | Continue Burst Write Cycle |

| Н   | Х   | Х    | Н    | L    | L     | •• | Next Address     | Continue Burst Write Cycle |

| Х   | Х   | Н    | Н    | Н    | Н     | •• | Current Address  | Suspend Burst Read Cycle   |

| Н   | Х   | Х    | Н    | Н    | Н     | •• | Current Address  | Suspend Burst Read Cycle   |

| х   | х   | Н    | Н    | Н    | L     | •• | Current Address  | Suspend Burst Write Cycle  |

| Н   | Х   | Х    | Н    | Н    | L     | •• | Current Address  | Suspend Burst Write Cycle  |

| Page          | Current                                                                                                                     | Correction           |

|---------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------|

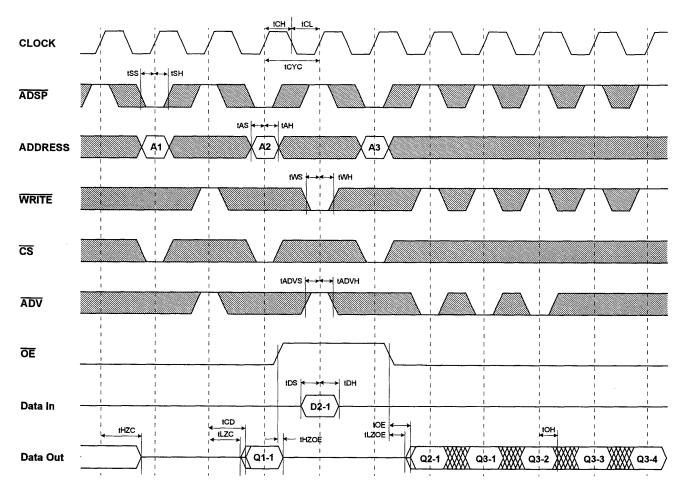

| 930, 939, 948 | A-1. SYNCHRONOUS PIPELINE BURST TRUTH<br>TABLE(Data field), 512KB Single Bank Module<br>KMM764V72G2,KMM764V72G7, KMM764V75G | Refer to below table |

#### A-1. SYNCHRONOUS PIPELINE BURST TRUTH TABLE(Data field)

| CCS | ADSP | CADS | CADV | WRITE | K      | Address Accessed | Operation                  |

|-----|------|------|------|-------|--------|------------------|----------------------------|

| Н   | X    | L    | х    | Х     | ••     | N/A              | Not Selected               |

| Н   | L    | Х    | Х    | X     | •• N/A |                  | Not Selected               |

| L   | L    | Х    | X    | X     | ••     | External Address | Begin Burst Read Cycle     |

| L   | Н    | L    | Х    | L     | ••     | External Address | Begin Burst Write Cycle    |

| L   | Н    | L    | х    | Н     | ••     | External Address | Begin Burst Read Cycle     |

| Х   | Н    | Н    | L    | н     | ••     | Next Address     | Continue Burst Read Cycle  |

| Н   | X    | Н    | L    | Н     | ••     | Next Address     | Continue Burst Read Cycle  |

| х   | Н    | Н    | L    | L     | ••     | Next Address     | Continue Burst Write Cycle |

| Н   | X    | Н    | L    | L     | ••     | Next Address     | Continue Burst Write Cycle |

| X   | Н    | Н    | Н    | Н     | ••     | Current Address  | Suspend Burst Read Cycle   |

| Н   | X    | Н    | Н    | Н     | ••     | Current Address  | Suspend Burst Read Cycle   |

| X   | Н    | Н    | Н    | L     | ••     | Current Address  | Suspend Burst Write Cycle  |

| Н   | Х    | Н    | Н    | L     | ••     | Current Address  | Suspend Burst Write Cycle  |

If you want to get a revised specification, you can see and download the specification form web site, www.sec.samsung.com/sram, by pdf file.

If you want to get a revised specification, you can see and download the specification form web site, www.sec.samsung.com/sram, by pdf file.

#### **PRINTED IN KOREA**

Circuit diagrams utilizing SAMSUNG products are included as a means of illustrating typical semiconductor applications; consequently, complete information sufficient for construction purposes is not necessarily given. The information has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described herein any license under the patent rights of SAMSUNG or others. SAMSUNG reserves the right to change device specifications.

Certificate No FM 24651

# TABLE OF CONTENTS

# I. FUNCTION GUIDE

| 1.      | Product Tree                                              |                  |                                                                   | 13            |

|---------|-----------------------------------------------------------|------------------|-------------------------------------------------------------------|---------------|

| 2.      | i reador adide                                            |                  |                                                                   | 22            |

| 3.      | Ordering Information ———————————————————————————————————— |                  |                                                                   | <b>— 29</b>   |

| II.SRAI | M DATA SHEET                                              |                  |                                                                   |               |

| Low P   | ower SRAM(5.0V Operation)                                 |                  |                                                                   |               |

| 1.      | KM62256C Family                                           | 32Kx8            | Commercial, Extended, Industrial Products                         | <b>— 37</b>   |

| 2.      | KM62256D Family                                           | 32Kx8            | Commercial, Industrial Products                                   | <b>—</b> 45   |

| 3.      | KM68512A Family                                           | 64Kx8            | Commercial, Industrial Products                                   |               |

| 4.      | KM681000B Family                                          | 128Kx8           | Commercial, Extended, Industrial Products —                       | 55            |

| 5.      | KM681000C Family                                          | 128Kx8           | Commercial, Industrial Products                                   |               |

| 6.      | KM6161000B Family                                         | 64Kx16           | Commercial, Industrial Products                                   |               |

| 7.      | KM684000A Family                                          | 512Kx8           | Commercial, Industrial Products —                                 | 82            |

| 8.      | KM684000B Family                                          | 512Kx8           | Commercial, Industrial Products                                   | 90            |

| 9.      | KM6164000B Family                                         | 256Kx16          | Commercial, Industrial Products                                   | 98            |

| Low Po  | ower and Low Voltage SRAM(3.0V, 3.3V (                    | Operation)       |                                                                   |               |

| 10.     | KM62V256C, KM62U256C Family                               | 32Kx8            | Commercial, Extended, Industrial Products                         | 109           |

| 11.     | KM62V256D, KM62U256D Family                               | 32Kx8            | Commercial, Extended, Industrial Products                         | — 117         |

| 12.     | KM68V512A, KM68U512A Family                               | 64Kx8            | Commercial, Extended, Industrial Products                         |               |

| 13.     | KM68V1000B, KM68U1000B Family                             | 128Kx8           | Commercial, Extended, Industrial Products —                       | 127           |

| 14.     | KM68V1000C, KM68U1000C Family                             | 128Kx8           | Commercial, Extended, Industrial Products                         | 136           |

| 15.     | KM616V1000B,KM616V1000B Family                            | 64Kx16           | Commercial, Extended, Industrial Products —                       |               |

| 16.     | KM68V2000, KM68U2000 Family                               | 256Kx8           | Commercial, Industrial Products                                   | 154           |

| 17.     | KM68V4000A, KM68U4000A Family                             | 512Kx8           | Commercial, Industrial Products                                   | <u> </u>      |

| 18.     | KM68V4000B, KM68U4000B Family                             | 512Kx8           | Commercial, Industrial Products ————                              | 171           |

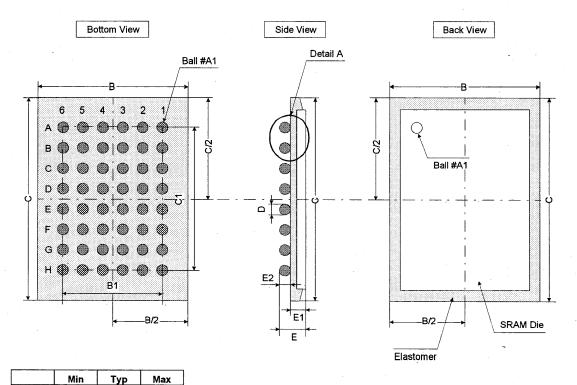

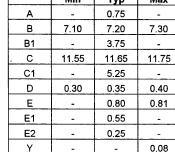

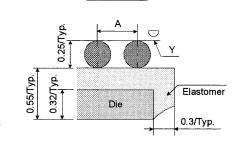

| 19.     | KM68V4000BZ, KM68U4000BZ Family                           | 512Kx8           | 48-CSP, Commercial, Industrial Products ——                        |               |

| 20.     | KM616V4000B, KM616U4000B Family                           | 256Kx16          | Commercial, Industrial Products                                   | 181           |

| 21.     | KM616V4000BZ, KM616U4000BZ Family                         | 256Kx16          | 48-CSP, Commercial, Industrial Products ——                        | 190           |

| Super   | Low Power and Low Voltage SRAM(Full (                     | CMOS)            |                                                                   |               |

| 22.     | KM68FV1000, KM68FS1000,                                   | 128x8            | Commercial, Industrial Products                                   | 195           |

|         | KM68FR1000 Family                                         |                  |                                                                   |               |

| 23.     | KM68FS1000Z, KM68FR1000Z Family                           | 128x8            | 48-CSP, Commercial, Industrial Products                           | 206           |

| 24.     | KM616FV1000, KM616FS1000,<br>KM616FR1000 Family           | 64Kx16           | Commercial, Industrial Products                                   | 208           |

| 25.     | KM616FS1000Z, KM616FR1000Z Family                         | 64Kx16           | 48-CSP, Commercial, Industrial Products                           | 218           |

| 26.     | KM68FV2000, KM68FS2000,<br>KM68FR2000 Family              | 256Kx8           | Commercial, Industrial Products —————                             | 220           |

| 27.     | KM68FS2000Z, KM68FR2000Z Family                           | 256Kx8           | 48-CSP, Commercial, Industrial Products                           | 230           |

| 28.     | KM616FV2000, KM616FS2000,<br>KM616FR2000 Family           | 128Kx16          | Commercial, Industrial Products                                   | 232           |

| 29.     | KM616FS2000Z, KM616FR2000Z Family                         | 128Kx16          | 48-CSP, Commercial, Industrial Products                           | 242           |

| Applica | ation Specification Memory for Mobile                     | Communica        | tion                                                              |               |

| 30.     | KM88FS87, KM88FR87 Family                                 | 256Kx8<br>128Kx8 | Commercial, Industrial Products,<br>256K x8 MaskROM + 128Kx8 SRAM | — <b>24</b> 7 |

| 256K F      | ligh Speed SRAM(5.0V Operation)   |                     |                                                     |                 |

|-------------|-----------------------------------|---------------------|-----------------------------------------------------|-----------------|

| 31.         | KM64B261A-6/7/8                   | 64Kx4               | With OE, BiCMOS Center PWR                          | <b>— 251</b>    |

| 32.         | KM64258C-12/15/20                 | 64Kx4               | With OE, CMOS Corner PWR                            | 257             |

| 33.         | KM68B261A-6/7/8                   | 32Kx8               | BiCMOS Center PWR                                   | <b>— 264</b>    |

| 34.         | KM68257C/CL-12/15/20              | 32Kx8               | CMOS Corner PWR, Data Retention —                   | <b>– 270</b>    |

| 1M Hig      | ph Speed SRAM(5.0V Operation)     |                     |                                                     |                 |

| 35.         | KM611001/L-20/25/35               | 1Mx1                | CMOS Corner PWR, Data Retention -                   | 279             |

| 37.         | KM641003B/BL, BI/BLI-8/10/12      | 256Kx4              | With OE, CMOS Center PWR, Data Retention -          | <b>— 285</b>    |

| 38.         | KM64B1003-8/10/12                 | 256Kx4              | With OE, BiCMOS Center PWR                          | 292             |

| 39.         | KM641003A, Al-12/15/17/20         | 256Kx4              | With OE, CMOS Center PWR                            | - 299           |

| 40.         | KM641003-15/17/20                 | 256Kx4              | With OE, CMOS Center PWR                            | <b>— 306</b>    |

| 41.         | KM641001B/BL, BI/BLI-15/17/20     | <sup>1</sup> 256Kx4 | With OE, CMOS Corner PWR, Data Retention -          | <b>— 313</b>    |

| 42.         | KM641001A-15/17/20                | 256Kx4              | With OE, CMOS Corner PWR                            | <b>— 320</b>    |

| 43.         | KM641001/L-20/25/35               | 256Kx4              | With OE, CMOS Corner PWR, Data Retention            | <b>— 327</b>    |

| 44.         | KM681002B/BL, BI/BLI-8/10/12      | 128Kx8              | CMOS Center PWR, Data Retention, SOJ-300 -          | <b>— 334</b>    |

| 45.         | KM68B1002-8/10/12                 | 128Kx8              | BiCMOS Center PWR                                   | <b> 341</b>     |

| 46.         | KM681002A, Al-12/15/17            | 128Kx8              | CMOS Center PWR, SOJ-300 —————                      | <b>348</b>      |

| 47.         | KM681002-15/17/20                 | 128Kx8              | CMOS Center PWR                                     | <b>— 355</b>    |

| 48.         | KM681001B/BL, BI/BLI-15/17/20     | 128Kx8              | CMOS Corner PWR, Data Retention, SOJ-300 -          | <b>— 362</b>    |

| 49.         | KM681001A-15/17/20                | 128Kx8              | CMOS Corner PWR, SOJ-300 —                          | 370             |

| 50.         | KM681001/L-20/25/35               | 128Kx8              | CMOS Corner PWR, Data Retention                     | 377             |

| 51.         | KM6161002B/BL, BI/BLI-8/10/12     | 64Kx16              | CMOS Center PWR, Data Retention                     | <b>—</b> 385    |

| 52.         | KM6161002A, Al-12/15/17/20        | 64Kx16              | CMOS Center PWR —                                   | <b>- 393</b>    |

| 53.         | KM6161002-15/17/20                | 64Kx16              | CMOS Center PWR                                     | <b>— 400</b>    |

| 4M Hig      | h Speed SRAM(5.0V Operation)      |                     |                                                     |                 |

| 54.         | KM644002B, BI-10/12/15            | 1Mx4                | With OE, CMOS Center PWR, TSOP2                     | <b></b> 409     |

| 55.         | KM64B4002-12/15                   | 1Mx4                | With OE, BiCMOS Center PWR                          | <del></del> 416 |

| <b>56</b> . | KM644002A-15/17/20                | 1Mx4                | With OE, CMOS Center PWR                            | <b>423</b>      |

| <b>57</b> . | KM644002, E, I -17/20/25          | 1Mx4                | With OE, CMOS Center PWR                            | <b> 430</b>     |

| 58.         | KM684002B, BI-10/12/15            | 512Kx8              | CMOS Center PWR, TSOP2                              | <b> 437</b>     |

| 59.         | KM68B4002-12/15                   | 512Kx8              | BiCMOS Center PWR -                                 |                 |

| 60.         | KM684002A-15/17/20                | 512Kx8              | CMOS Center PWR                                     | <b> 451</b>     |

| 61.         | KM684002, E, I - 17/20/25         | 512Kx8              | CMOS Center PWR ——————————————————————————————————— | <b></b> 458     |

| <b>62</b> . | KM6164002B, BI-10/12/15           | 256Kx16             | CMOS Center PWR, TSOP2                              | <b> 465</b>     |

| 63.         | KM616B4002-12/15                  | 256Kx16             | BiCMOS Center PWR                                   | 472             |

| 64.         | KM6164002A-15/17/20               | 256Kx16             | CMOS Center PWR                                     | <b></b> 479     |

| 65.         | KM6164002, E, I - 20/25/35        | 256Kx16             | CMOS Center PWR                                     | <b>- 486</b>    |

| 256K H      | ligh Speed SRAM(3.3V Operation)   |                     |                                                     |                 |

| 66.         | KM68V257C-15/17/20                | 32Kx8               | CMOS Corner PWR, Data Retention —————               | <b>− 495</b>    |

| 1M Hig      | h Speed SRAM(3.3V Operation)      |                     |                                                     |                 |

| 67.         | KM64V1003B/BL, BI/BLI-8/10/12     | 256Kx4              | With OE, CMOS Center PWR, Data Retention -          | <b> 505</b>     |

| 68.         | KM64V1003A/AL, Al/ALI-12/15/17/20 | 256Kx4              | With OE, CMOS Center PWR, Data Retention -          | - 512           |

| 69.         | KM68V1002B/BL, BI/BLI-8/10/12     | 128Kx8              | CMOS Center PWR, Data Retention, SOJ-300            | 519             |

| 70.         | KM68V1002A/AL, Al/ALI-12/15/17/20 | 128Kx8              | CMOS Center PWR, Data Retention, SOJ-300            | <b>- 526</b>    |

| 71.         | KM616V1002B/BL, BI/BLI-8/10/12    | 64Kx16              | CMOS Center PWR, Data Retention ————                | 533             |

| 72          | KM616V1002A/AL AL/ALL-12/15/17/20 | 64Kv16              | CMOS Center DWD Data Retention                      | E44             |

| 73     | n Speed SRAM(3.3V Operation)<br>KM64V4002B/BL, BI/BLI-10/12/15 | 1Mx4    | With OE, CMOS, Data Retention, TSOP2               | 551              |

|--------|----------------------------------------------------------------|---------|----------------------------------------------------|------------------|

|        | KM64BV4002-12/15                                               | 1Mx4    | With OE, BiCMOS Center PWR                         |                  |

| 75.    | KM64V4002A-15/17/20                                            | 1Mx4    | With OE, CMOS Center PWR                           | - 565            |

| 75.    | KM68V4002B/BL, BI/BLI-10/12/15                                 | 512Kx8  | CMOS Center PWR, Data Retention, TSOP2 ——          |                  |

| 77.    | KM68BV4002-12/15                                               | 512Kx8  | BiCMOS Center PWR                                  |                  |

| 78.    | KM68V4002A-15/17/20                                            | 512Kx8  | CMOS Center PWR                                    |                  |

| 79.    | KM616V4002B/BL, BI/BLI-10/12/15                                | 256Kx16 | CMOS Center PWR, Data Retention, TSOP2             |                  |

| 80.    | KM616BV4002-12/15                                              | 256Kx16 | BiCMOS Center PWR                                  |                  |

| 81.    | KM616V4002A-15/17/20                                           | 256Kx16 | CMOS Center PWR                                    |                  |

| 1M Mid | Range Synchronous SRAM                                         |         |                                                    |                  |

| 82.    | KM718B86-8/9/10/12                                             | 64Kx18  | Sync. Bust SRAM with Interleave Bust Order (5V) -  | <del></del> 617  |

| 83.    | KM718B90-8/9/10/12                                             | 64Kx18  | Sync. Bust SRAM with Linear Bust Order (5V)        | <b>– 633</b>     |

| 84.    | KM718BV87-9/10/12                                              | 64Kx18  | Sync. Bust SRAM with 3.3V I/O Interface            | <b>- 644</b>     |

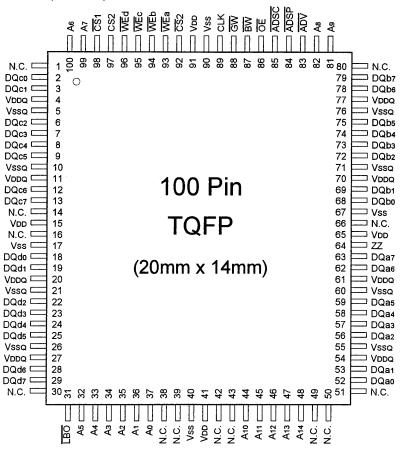

| 85.    | KM732V589/L-13/15/17                                           | 32Kx32  | Sync. Piped & Bust SRAM with 3.3V Interface ———    | <b></b> 655      |

| 86.    | KM732V589A/L-13/15                                             | 32Kx32  | Sync. Piped & Bust SRAM with 3.3V Interface        | <b>– 668</b>     |

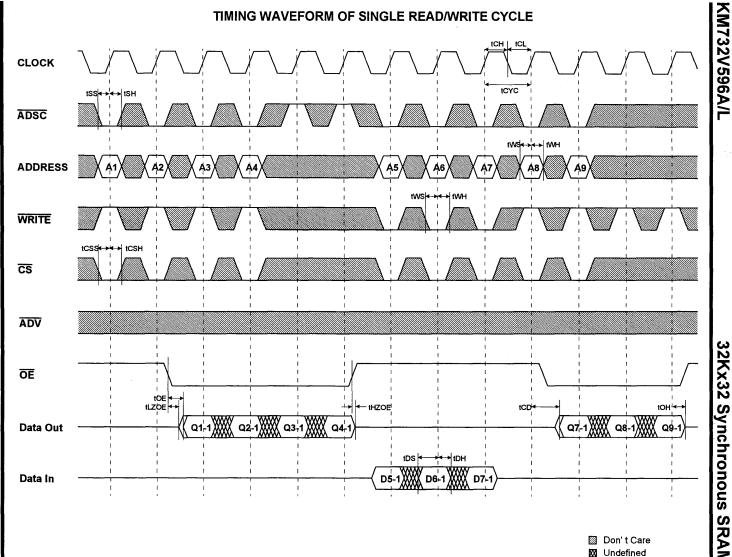

| 87.    | KM732V596A/L-13/15                                             | 32Kx32  | Sync. Piped & Bust SRAM with 2.5/3.3V Interface —  | 681              |

| 88.    | KM732V595A/L-6/7/8/10                                          | 32Kx32  | Sync. Piped & Bust SRAM with 2.5V Interface ——     | <b>– 695</b>     |

| 89.    | KM732V599A/L-7/8/10                                            | 32Kx32  | Sync. Piped & Bust SRAM with 3.3V I/O Interface —  | <b> 708</b>      |

| 90.    | KM736V595A/L-6/7/8/10                                          | 32Kx36  | Sync. Piped & Bust SRAM with 2.5V I/O Interface —  | <b>– 721</b>     |

| 91.    | KM736V599A/L-7/8/10                                            | 32Kx36  | Sync. Piped & Bust SRAM with 3.3V I/O Interface —  | <b>- 734</b>     |

| 92.    | KM718V687-8/9/10                                               | 64Kx18  | Sync. Bust SRAM with 3.3V I/O Interface            | <b>– 747</b>     |

| 93.    | KM736V587-8/9/10                                               | 32Kx36  | Sync. Bust SRAM with 3.3V I/O Interface ————       | 755              |

| M Mid  | Range Synchronous SRAM                                         |         |                                                    |                  |

| 94.    | KM732V688-13/15                                                | 64Kx32  | Sync. Piped & Bust SRAM with 3.3V Interface ——     | <del>- 771</del> |

| 95.    | KM732V696-13/15                                                | 64Kx32  | Sync. Piped & Bust SRAM with 2.5V/3.3V Interface - | <b> 785</b>      |

| 96.    | KM718V789-7/8/10                                               | 128Kx18 | Sync. Piped & Bust SRAM with 3.3V Interface ———    | <b>- 799</b>     |

| 97.    | KM736V689-7/8/10                                               | 64Kx36  | Sync. Piped & Bust SRAM with 3.3V Interface        | <del>-</del> 812 |

| 98.    | KM718V787-8/9/10                                               | 128Kx18 | Sync. Bust SRAM with 3.3V I/O Interface            | - <b>825</b> .   |

| 99.    | KM736V687-8/9/10                                               | 64Kx36  | Sync. Bust SRAM with 3.3V I/O Interface            | <b>- 838</b>     |

| M High | Performance Synchronous SRAM                                   |         |                                                    |                  |

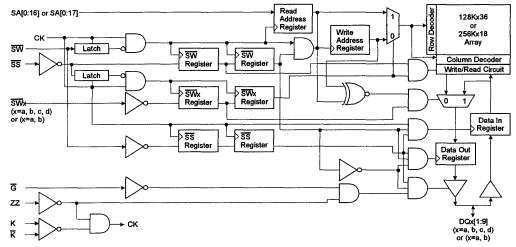

| 100.   | KM736FV4011                                                    | 128Kx36 | Sync. Pipelined                                    | <b>– 853</b>     |

|        | KM718FV4011                                                    | 256Kx18 | Sync. Pipelined                                    |                  |

| 101.   | KM736FV4021                                                    | 128Kx36 | Sync. Pipelined                                    | - 865            |

|        | KM718FV4021                                                    | 256Kx18 | Sync. Pipelined                                    |                  |

| 102.   | KM736FV4002                                                    | 128Kx36 | Register to Latch                                  | <del>-</del> 876 |

|        | KM718FV4002                                                    | 256Kx18 | Register to Latch                                  |                  |

| 103.   | KM736FV4022                                                    | 128Kx36 | Register to Latch                                  | - 887            |

|        | KM718FV4022                                                    | 256Kx18 | Register to Latch                                  |                  |

| Synchr   | onous SRAM Module   |                |                                                                |       |

|----------|---------------------|----------------|----------------------------------------------------------------|-------|

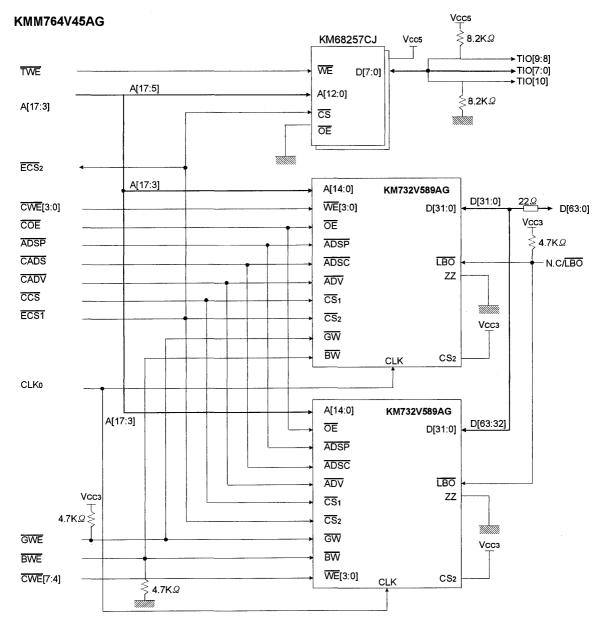

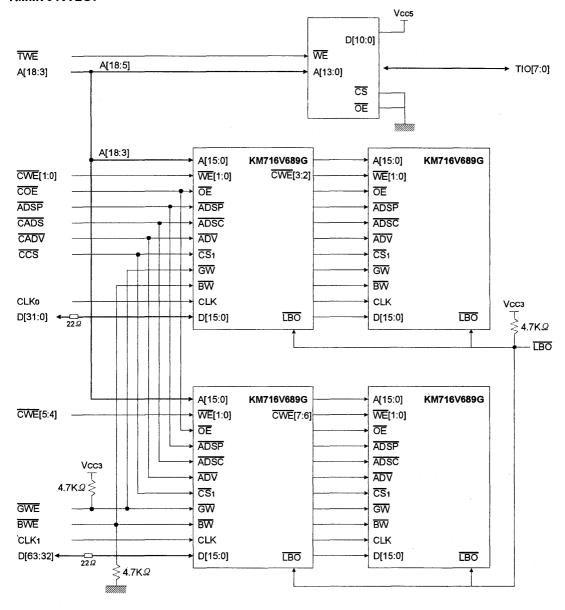

| 104.     | KMM764V41AG2        | 64Kx64         | 256K SPB SRAM Module, 8bit tag                                 | - 901 |

| 105.     | KMM764V41AG7        | 64Kx64         | 256K SPB SRAM Module, 8bit tag with resister                   | - 910 |

| 106.     | KMM764V45AG         | 64Kx64         | 256K SPB SRAM Module, 11bit tag with resister                  | - 919 |

| 107.     | KMM764V72G2         | 64Kx64         | 512K SPB SRAM Module, 8bit tag, Single bank                    | - 928 |

| 108.     | KMM764V72G7         | 64Kx64         | 512K SPB SRAM Module, 8bit tag with resister, ——Single bank    | - 937 |

| 109.     | KMM764V75G          | 64Kx64         | 512K SPB SRAM Module,11bit tag with resister,——<br>Single bank | - 946 |

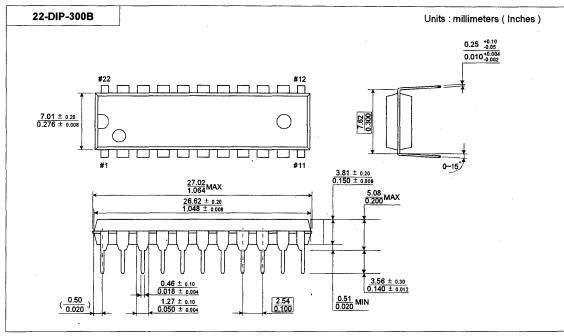

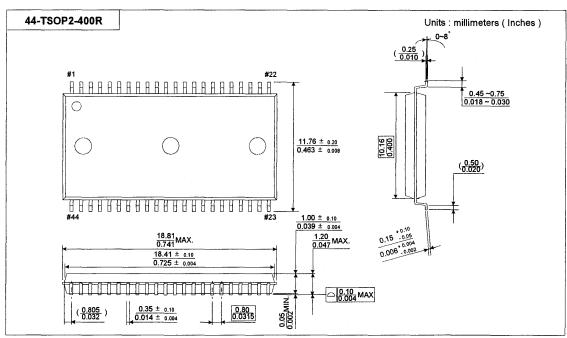

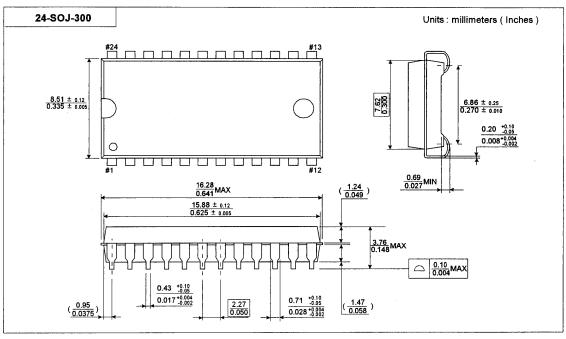

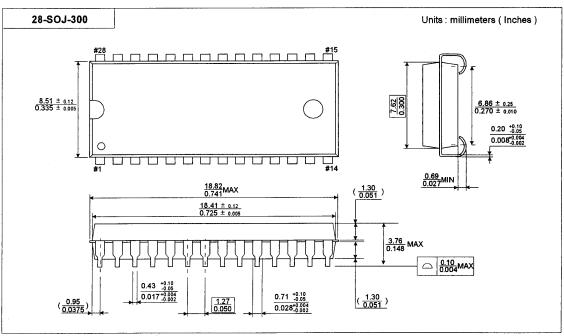

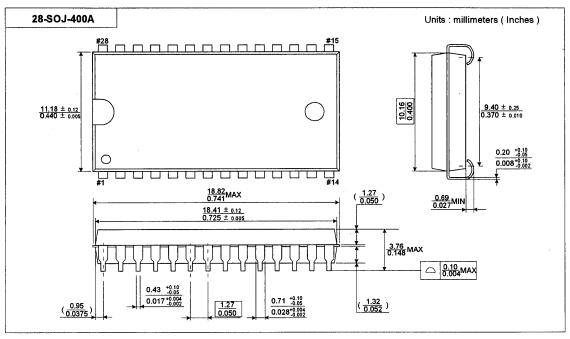

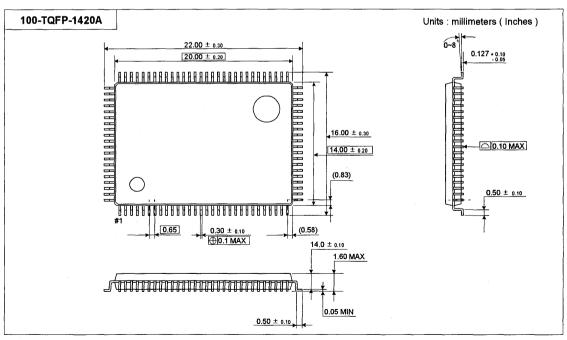

| III. PAC | CKAGE DIMENSIONS —  |                |                                                                | - 957 |

| IV. SAI  | ES OFFICES and MANL | IFACTURES REPE | RESENTATIVES                                                   | ~ 977 |

|                      | · A SEC 发现的影响。 第二十五章 |

|----------------------|----------------------|

| <b>Function Guid</b> |                      |

|                      |                      |

|                      |                      |

| Data Chasta          |                      |

| Data Sheets          |                      |

|                      | THE RESIDENCE        |

|                      |                      |

| Package Dime         | ensions              |

| . donago zam         |                      |

|                      |                      |

| Sales Offices        | and Manufacturer's   |

| Representativ        |                      |

| nepresentativ        | 700                  |

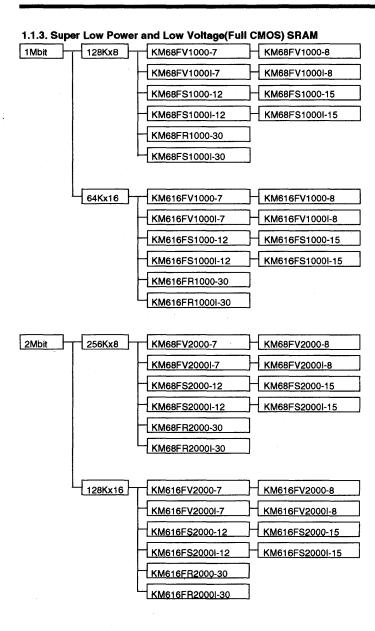

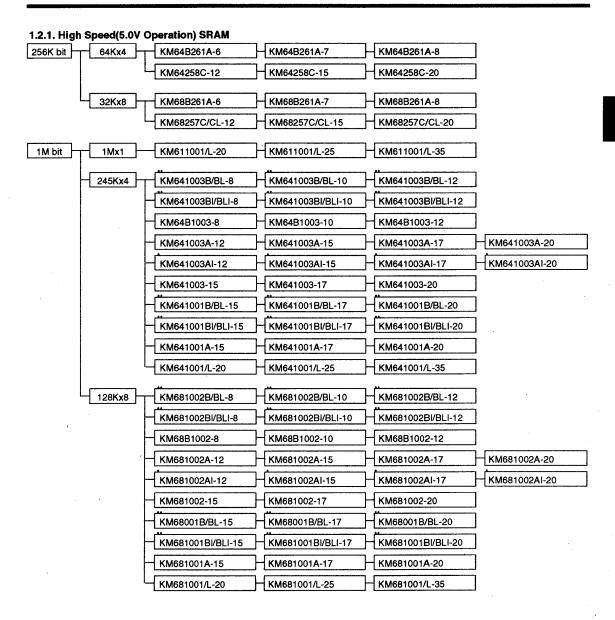

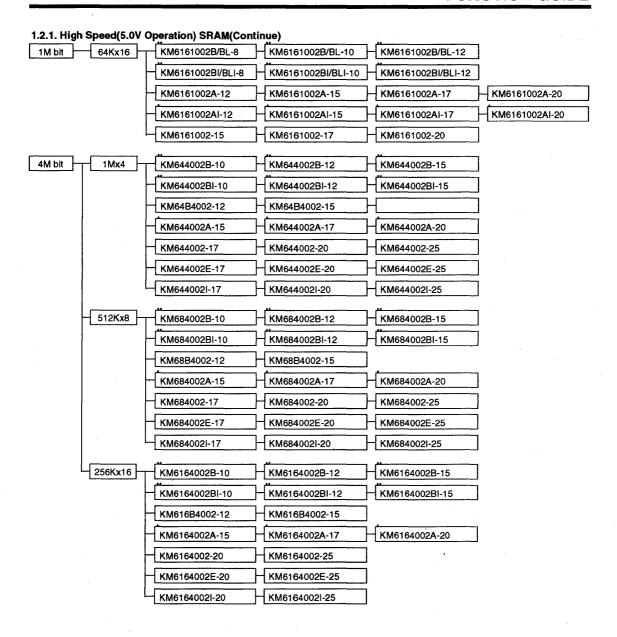

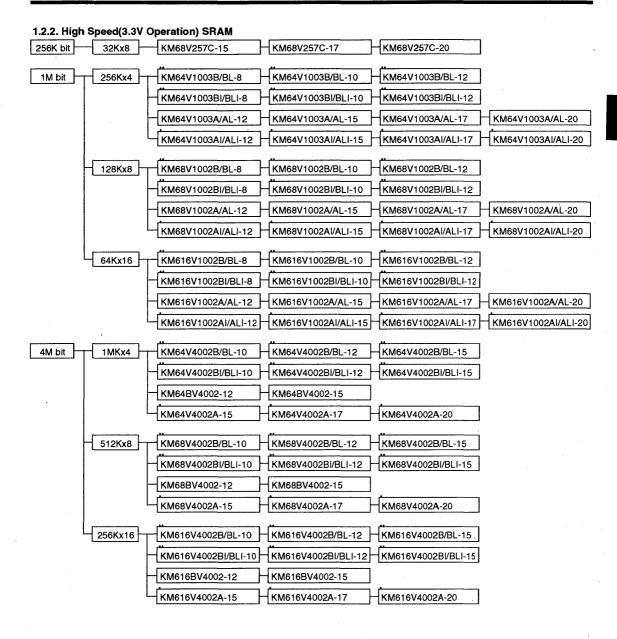

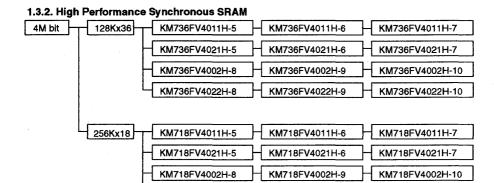

#### 1. SRAM PRODUCT TREE

1.1.1. Low Power(5.0V Operation) SRAM 256K bit KM62256CL-7/7L 32Kx8 KM62256CL-4/4L KM62256CL-5/5L KM62256CLI/-7/7L KM62256CLI/-10/10L KM62256DL-5/5L KM62256DL-7/7L KM62256DLI/-7/7L KM62256DLI/-10/10L 64Kx8 512K bit KM68512AL-4/4L KM68512AL-5/5L KM68512AL--7/7L KM68512ALI-7/7L KM68512ALI-10/10L 128Kx8 KM681000BL-5/5L KM681000BL-7/7L 1Mbit KM681000BLE-7/7L KM681000BLE-10/10L KM681000BLI-7/7L KM681000BLI-10/10L KM681000CL-4/4L KM681000CL-5/5L KM681000CL-7/7L KM681000CLI-5/5L KM681000CLI-7/7L KM681000CLI-10/10L 64Kx16 KM6161000BL-5/5L KM6161000BL-7/7L KM6161000BLI-7/7 KM6161000BLI-10/10L 4Mbit 512Kx8 KM684000AL-5/5L KM684000AL-7/7L KM684000ALI-7/7L KM684000ALI-10/10L KM684000BL-5/5L KM684000BL-7/7L KM684000BLI-7/7L KM684000BLI-10/10L 256Kx16 KM6164000BL-5/5L KM6164000BL-7/7L KM6164000BLI-7/7I KM6164000BLI-10/10L

<sup>\*\* :</sup> Preliminary

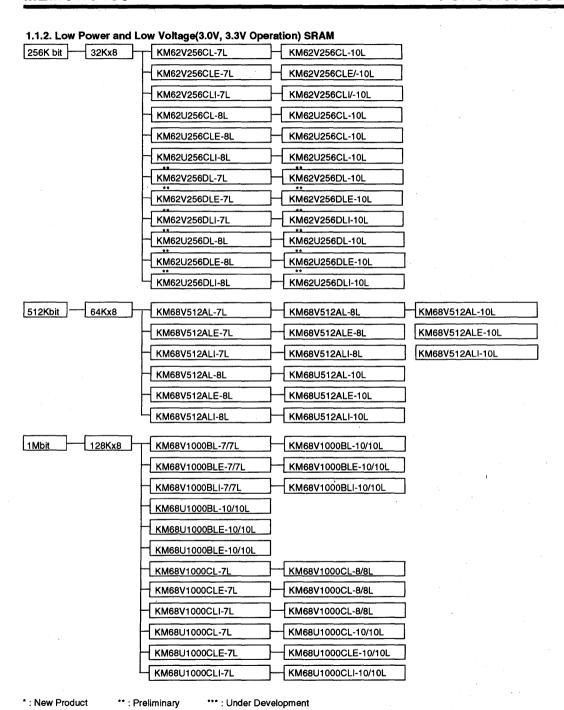

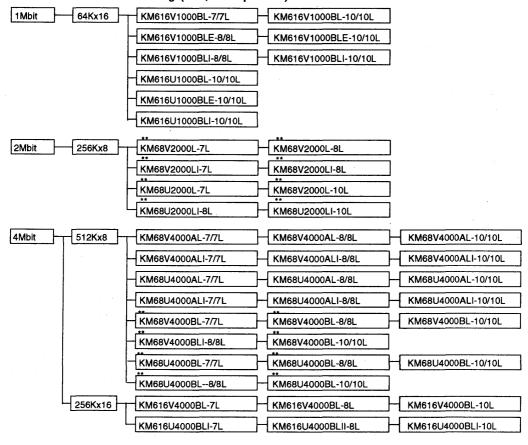

#### 1.1.2. Low Power and Low Voltage(3.0V, 3.3V Operation) SRAM

\*: New Product

\*\* : Preliminary

\*\*\* : Under Development

\*: New Product

\*\* : Preliminary

\*\*\* : Under Development

<sup>\*\*\* :</sup> Under Development

<sup>\*:</sup> New Product

<sup>\*\* :</sup> Preliminary

<sup>\*:</sup> New Product

<sup>\*\* :</sup> Preliminary

<sup>\*\*\* :</sup> Under Development

<sup>\*:</sup> New Product

<sup>\*\* :</sup> Preliminary

<sup>\*\*\* :</sup> Under Development

1.3.1. Synchronous SRAM 1M bit 32Kx32 KM732V589G/T-13 KM732V589G/T-15 KM732V589G/T-17 KM732V589LG/T-17 KM732V589LG/T-13 KM732V589LG/T-15 KM732V589AG/T-13 KM732V589AG/T-15 KM732V589ALG/T-15 KM732V589ALG/T-13 KM732V595AT-6 KM732V595AT-7 KM732V595AT-8 KM732V595AT-10 KM732V595ALT-6 KM732V595ALT-7 KM732V595ALT-8 KM732V595ALT-10 KM732V596AT-13 KM732V596AT-15 KM732V596ALT-13 KM732V596ALT-15 KM732V599AT-7 KM732V599AT-8 KM732V599AT-10 KM732V599ALT-7 KM732V599ALT-8 KM732V599ALT-10 32Kx36 KM736V595AT-10 KM736V595AT-6 KM736V595AT-7 KM736V595AT-8 KM736V595ALT-6 KM736V595ALT-7 KM736V595ALT-8 KM736V595ALT-10 KM736V599AT-7 KM736V599AT-8 KM736V599AT-10 KM736V599ALT-7 KM736V599ALT-8 KM736V599ALT-10 KM736V587T-8 KM736V587T-9 KM736V587T-10 64Kx18 KM718BV87J-9 KM718BV87J-10 KM718BV87J-12 KM718V687T-8 KM718V687T-9 KM718687T-10 KM718B90J-11 KM718B90J-8 KM718B90J-9 KM718B90J-10 KM718B86J-8 KM718B86J-9 KM718B86J-10 KM718B86J-12 2M bit 64Kx32 KM732V688G/T-13 KM732V688G/T-15 KM732V688LG/T-13 KM732V688LG/T-15 KM732V696T-13 KM732V696T-15 KM732V696LT-13 KM732V696LT-15 64Kx36 KM736V689T-11 KM736V689T-7 KM736V689T-8 KM736V689T-10 KM736V689LT-7 KM736V689LT-8 KM736V689LT-10 KM736V689LT-11 KM736V687T-10 KM736V687T-8 KM736V687T-9 KM718V789T-11 128Kx18 KM718V789T-7 KM718V789T-8 KM718V789T-10 KM718V789LT-7 KM718V789LT-8 KM718V789LT-10 KM718V789LT-11 KM718V787T-8 KM718V787T-9 KM718V787T-10

\*\* : Preliminary

\*\*\* : Under Development

\*: New Product

KM718FV4022H-9

KM718FV4022H-10

KM718FV4022H-8

## 2. SRAM FUNCTION GUIDE

#### 2.1.1. Low Power(5.0V Operation) SRAM

| Den.       | Org.     | Product No <sup>Note1</sup>    | Op.Temp | Speed     | Icc2/Isв1<br>(mA/μA) | Package                    |

|------------|----------|--------------------------------|---------|-----------|----------------------|----------------------------|

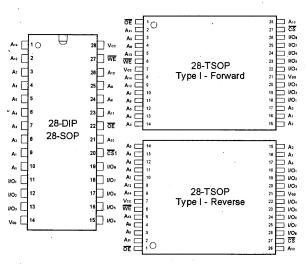

| 256K       | 32K x 8  | KM62256CL<br>KM62256CL-L       | 0~70℃   | 45/55/70  | 70/100<br>70/20      | 28-TSOP(I)<br>Rew/Forward  |

|            |          | KM62256CLE<br>KM62256CLE-L     | -25~85℃ | 70/100    | 70/100<br>70/50      | 28-DIP                     |

|            |          | KM62256CLI<br>KM62256CLI-L     | -40~85℃ | 70/100    | 70/100<br>70/50      | 28-SOP                     |

|            |          | KM62256DL**<br>KM62256DL-L**   | 0~70℃   | 55/70     | 70/50<br>70/10       | 28-TSOP(I)<br>Rew/Forward  |

|            |          | KM62256DLI**<br>KM62256DLI-L** | -40~85℃ | 70/100    | 70/50<br>70/15       | 28-DIP                     |

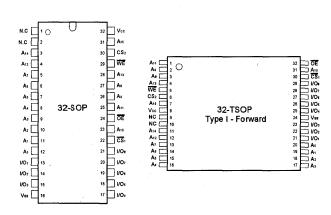

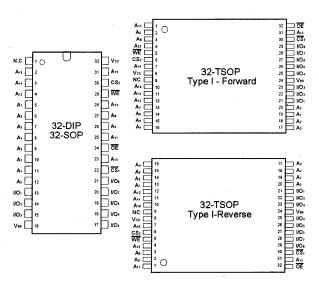

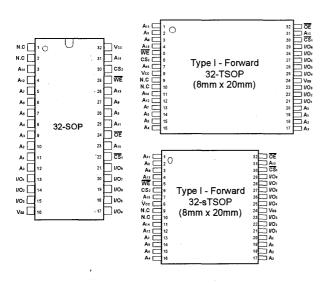

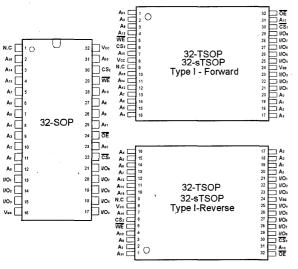

| 512K       | 64K x 8  | KM68512AL<br>KM68512AL-L       | 0~70℃   | 45/55/70  | 70/100<br>70/20      | 32-TSOP(I)<br>Forward      |

|            |          | KM68512ALI<br>KM68512ALI-L     | -40~85℃ | 70/100    | 70/100<br>70/50      | 32-SOP                     |

| 1 <b>M</b> | 128K x 8 | KM681000BL<br>KM681000BL-L     | 0~70℃   | 55/70     | 70/100<br>70/20      |                            |

|            |          | KM681000BLE<br>KM681000BLE-L   | -25~85℃ | 70/100    | 70/100<br>70/50      | 32-TSOP(I)<br>Rev/Forward  |

|            |          | KM681000BLI<br>KM681000BLI-L   | -40~85℃ | 70/100    | 70/100<br>70/50      | 32-DIP                     |

|            |          | KM681000CL<br>KM681000CL-L     | 0~70℃   | 45/55/70  | 90/50<br>90/10       | 32-SOP                     |

|            |          | KM681000CLI<br>KM681000CLI-L   | -40~85℃ | 55/70/100 | 90/50<br>90/15       |                            |

|            | 64K x 16 | KM6161000BL<br>KM6161000BL-L   | 0~70℃   | 55/70     | 120/100<br>120/20    | 44-TSOP(i)                 |

|            |          | KM6161000BLI<br>KM6161000BLI-L | -40~85℃ | 70/100    | 120/100<br>120/50    | Rev/Forward                |

| 4M         | 512K x 8 | KM684000AL<br>KM684000AL-L     | 0~70℃   | 55/70     | 90/100<br>90/20      |                            |

|            |          | KM684000ALI<br>KM684000ALI-L   | -40~85℃ | 70/100    | 90/100<br>90/50      | 32-TSOP(II)<br>Rev/Forward |

|            |          | KM684000BL<br>KM684000BL-L     | 0~70℃   | 55/70     | 90/100<br>90/20      | 32-SOP<br>32-DIP           |

|            |          | KM684000BLI<br>KM684000BL-LI   | -40~85℃ | 70/100    | 90/100<br>90/50      | 32 3                       |

|            | 256Kx16  | KM6164000BL-L                  | 0~70℃   | 55/70     | 130/20               | AATCOD(!!)                 |

|            |          | KM6164000BLI-L                 | -40~85℃ | 70/100    | 130/50               | 44TSOP(II)                 |

Note1. Refer to the ordering information for more detail description of each product.

<sup>\*\*\* :</sup> Under development

<sup>\* :</sup> New Product

<sup>\*\* :</sup> Preliminary

# 2.1.2. Low Power and Low Voltage(3.0V, 3.3V Operation) SRAM

| Den.       | Org. & Vcc                 | Product No note1                                                                                       | Op.Temp                        | Speed                                                    | Icc2/IsB1<br>(mA/#A)                                 | Package                             |

|------------|----------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------------------------|------------------------------------------------------|-------------------------------------|

| 256K       | 32K x 8<br>(Vcc=3.0~3.6V)  | KM62V256CL-L<br>KM62V256CLE-L<br>KM62V256CLI-L                                                         | 0~70℃<br>-25~85℃<br>-40~85℃    | 70/100<br>70/100<br>70/100                               | 35/10<br>35/20<br>35/20                              |                                     |

|            | 32K x 8<br>(Vcc=2.7~3.3V)  | KM62U256CL-L<br>KM62U256CLE-L<br>KM62U256CIL-L                                                         | 0~70℃<br>-25~85℃<br>-40~85℃    | 85/100<br>85/100<br>85/100                               | 35/10<br>35/15<br>35/15                              | 28-TSOP(I)<br>Reverse<br>28-TSOP(I) |

|            | 32K x 8<br>(Vcc=3.0~3.6V)  | KM62V256DL-L**<br>KM62V256DLE-L**<br>KM62V256DIL-L**                                                   | 0~70℃<br>-25~85℃<br>-40~85℃    | 70/100<br>70/100<br>70/100                               | 35/10<br>35/20<br>35/20                              | Forward<br>28-SOP                   |

|            | 32K x 8<br>(Vcc=2.7~3.3V)  | KM62U256DL-L**<br>KM62U256DLE-L**<br>KM62U256DIL-L**                                                   | 0~70℃<br>-25~85℃<br>-40~85℃    | 85/100<br>85/100<br>85/100                               | 35/10<br>35/15<br>35/15                              |                                     |

| 512K       | 64K x 8<br>(Vcc=3.0~3.6V)  | KM68V512AL-L<br>KM68V512ALE-L<br>KM68V512ALI-L                                                         | 0~70℃<br>-25~85℃<br>-40~85℃    | 70/85/100<br>70/85/100<br>70/85/100                      | 40/10<br>40/20<br>40/20                              | 32-TSOP(I)<br>Forward               |

|            | 64K x 8<br>(Vcc=2.7~3.3V)  | KM68U512AL-L<br>KM68U512ALE-L<br>KM68U512ALI-L                                                         | 0~70℃<br>-25~85℃<br>-40~85℃    | 85/100<br>85/100<br>85/100                               | 45/10<br>45/15<br>45/15                              | 32-SOP                              |

| 1 <b>M</b> | 128K x 8<br>(Vcc=3.0~3.6V) | KM68V1000BL<br>KM68V1000BL-L<br>KM68V1000BLE<br>KM68V1000BLE-L<br>KM68V1000BLI<br>KM68V1000BLI-L       | 0~70℃<br>-25~85℃<br>-40~85℃    | 70/100<br>70/100<br>70/100<br>70/100<br>70/100<br>70/100 | 40/50<br>40/15<br>40/100<br>40/20<br>40/100<br>40/20 | 32-TSOP(I)<br>Rev/Forward<br>32-SOP |

|            |                            | KM68V1000CL-L<br>KM68V1000CLE-L<br>KM68V1000CLI-L                                                      | 0~70℃<br>-25~85℃<br>-40~85℃    | 70/85<br>70/85<br>70/85                                  | 40/10<br>40/20<br>40/20                              | 32-TSOP(I)<br>Rev/Forward<br>32-SOP |

|            | 128K x 8<br>(Vcc=2.7~3.3V) | KM68U1000BL<br>KM68U1000BL-L<br>KM68U1000BLE<br>KM68U1000BLE-L<br>KM68U1000BLI-L                       | 0~70℃<br>-25~85℃<br>-40~85℃    | 100<br>100<br>100<br>100<br>100<br>100                   | 40/50<br>40/15<br>40/50<br>40/15<br>40/50<br>40/15   | 32-TSOP(I)<br>Rev/Forward<br>32-SOP |

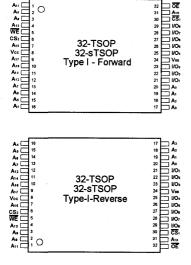

|            | 128K x 8<br>(Vcc=2.7~3.3V) | KM68U1000CL-L<br>KM68U1000CLE-L<br>KM68U1000CLI-L                                                      | 0~70˚C<br>-25~85˚C<br>-40~85˚C | 70/100<br>70/100<br>70/100                               | 40/10<br>40/20<br>40/20                              | 32-TSOP(I)<br>32-sTSOP<br>32-SOP    |

|            | 64K x 16<br>(Vcc=3.0~3.6V) | KM616V1000BL<br>KM616V1000BL-L<br>KM616V1000BLE<br>KM616V1000BLE-L<br>KM616V1000BLI<br>KM616V1000BLI-L | 0~70℃<br>-25~85℃<br>-40~85℃    | 70/100<br>70/100<br>85/100<br>85/100<br>85/100<br>85/100 | 65/50<br>65/15<br>65/100<br>65/20<br>65/100<br>65/20 | 44-TSOP(II)<br>Reverse              |

|            | 64K x 16<br>(Vcc=2.7~3.3V) | KM616U1000BL<br>KM616U1000BL-L<br>KM616U1000BLE<br>KM616U1000BLE-L<br>KM616U1000BLI<br>KM616U1000BLI-L | 0~70℃<br>-25~85℃<br>-40~85℃    | 100<br>100<br>100<br>100<br>100<br>100                   | 65/50<br>65/15<br>65/100<br>65/20<br>65/100<br>65/20 | 44-TSOP(II)<br>Forward              |

| 2M         | 256K x 8<br>(Vcc=2.7~3.6V) | KM68V2000L-L**<br>KM68V2000LI-L**                                                                      | 0~70˚C<br>-40~85˚C             | 70/85<br>85/100                                          | 40/15<br>40/30                                       | 32-TSOP(I)<br>32-sTSOP(I)           |

|            |                            | KM68U2000L-L**<br>KM68U2000LI-L**                                                                      | 0~70℃<br>-40~85℃               | 70/100<br>85/100                                         | 40/15<br>40/30                                       | 32-TSOP(I)<br>32-sTSOP(I)           |

#### 2.1.2. Low Power and Low Voltage(3.0V, 3.3V Operation) SRAM(Continue)

| Den. | Org. & Vcc                  | Product No note1                   | Op.Temp          | Speed                  | Icc2/Isв1<br>(mA/µA) | Package                    |

|------|-----------------------------|------------------------------------|------------------|------------------------|----------------------|----------------------------|

| 4M   | 512K x 8<br>(Vcc=3.0~3.6V)  | KM68V4000AL<br>KM68V4000AL-L       | 0~70℃            | 70/85/100<br>70/85/100 | 50/50<br>50/15       | 32-TSOP(II)<br>Rev/Forward |

|      |                             | KM68V4000ALI<br>KM68V4000ALI-L     | -40~85℃          | 70/85/100<br>70/85/100 | 50/50<br>50/20       | 32-SOP                     |

|      | 512K x 8<br>(Vcc=2.7~3.3V)  | KM68U4000AL<br>KM68U4000AL-L       | 0~70℃            | 70/85/100<br>70/85/100 | 50/30<br>50/10       | 32-SOP                     |

|      | , , , , ,                   | KM68U4000ALI<br>KM68U4000ALI-L     | -40~85℃          | 70/85/100<br>70/85/100 | 50/30<br>50/15       | 32-TSOP(II)                |

|      | 512K x 8<br>(Vcc=3.0~3.6V)  | KM68V4000BL**<br>KM68V4000BL-L**   | 0~70℃            | 70/85/100<br>70/85/100 | 50/50<br>50/15       | 32-SOP                     |

|      |                             | KM68V4000BLI**<br>KM68V4000BLI-L** | -40~85℃          | 85/100<br>85/100       | 50/50<br>50/20       | 32-TSOP(II)                |

|      | 512K x 8<br>(Vcc=2.7~3.3V)  | KM68U4000BL**<br>KM68U4000BL-L**   | 0~70℃            | 70/85/100<br>70/85/100 | 50/30<br>50/15       | 32-SOP                     |

|      |                             | KM68U4000BLI**<br>KM68U4000BLI-L** | -40~85℃          | 85/100<br>85/100       | 50/30<br>50/20       | 32-TSOP(II)                |

|      | 256K x 16<br>(Vcc=3.0~3.6V) | KM616V4000BL-L<br>KM616V4000BLI-L  | 0~70℃<br>-40~85℃ | 70/85/100<br>70/85/100 | 70/15<br>70/20       | 44-TSOP(II)                |

Note1. Refer to the ordering information for more detail description of each product.

<sup>\* :</sup> New Product

<sup>\*\* :</sup> Preliminary

<sup>\*\*\* :</sup> Under development

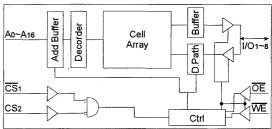

# 2.1.3. Super Low Power and Low Voltage(Full CMOS) SRAM

| Den. | Org.     | Product No <sup>Note1</sup> | Op.Temp  | Speed            | lcc2/lsa1<br>(mÅ/#Å) | Package                        |

|------|----------|-----------------------------|----------|------------------|----------------------|--------------------------------|

| 1M   | 128K x 8 | KM68FV1000                  | 0~70℃    | 70/85            | 55/5                 |                                |

|      |          | KM68FV1000I                 | -40~85℃  | 70/85            | 55/5                 | 32-TSOP(I)                     |

|      |          | KM68FS1000                  | 0~70℃    | 120/150<br>70/85 | 30/5<br>50/5         | Forward/Reverse<br>32-sTSOP(I) |

|      |          | KM68FS1000I                 | -40~85℃  | 120/150<br>70/85 | 30/5<br>50/5         | Forward/Reverse                |

|      |          | KM68FR1000                  | 0~70℃    | 300              | 15/5                 | 7                              |

|      |          | KM68FR1000I                 | -40~85℃  | 300              | 15/5                 | 7                              |

|      | 64Kx16   | KM616FV1000                 | 0~70℃    | 70/85            | 80/5                 |                                |

|      |          | KM616FV1000I                | -40~85℃  | 70/85            | 80/5                 | 1                              |

|      |          | KM616FS1000                 | 0~70℃    | 120/150<br>70/85 | 50/5<br>80/5         | 44-TSOP(II) Forward/Reverse    |

|      |          | KM616FS1000I                | -40~85℃  | 120/150<br>70/85 | 50/5<br>80/5         | Totward/Neverse                |

|      |          | KM616FR1000                 | 0~70℃    | 300              | 20/5                 |                                |

|      |          | KM616FR1000I                | -40~85℃  | 300              | 20/5                 |                                |

| 2M   | 256K x 8 | KM68FV2000                  | 0~70℃    | 70/85            | 60/10                |                                |

|      |          | KM68FV2000I                 | -40~85℃  | 70/85            | 60/10                | 32-TSOP(I)                     |

|      |          | KM68FS2000                  | 0~70℃    | 120/150<br>70/85 | 30/10<br>55/10       | Forward/Reverse<br>32-sTSOP(I) |

|      |          | KM68FS2000I                 | -40~85℃  | 120/150<br>70/85 | 30/10<br>55/10       | Forward/Reverse<br>32-SOP      |

|      |          | KM68FR2000                  | 0~70℃    | 300              | 15/10                |                                |

|      |          | KM68FR2000I                 | -40~85 C | 300              | 15/10                |                                |

|      | 128Kx16  | KM616FV2000                 | 0~70℃    | 70/85            | 80/10                |                                |

|      |          | KM616FV2000I                | -40~85℃  | 70/85            | 80/10                |                                |

|      |          | KM616FS2000                 | 0~70℃    | 120/150<br>70/85 | 50/10<br>80/10       | 44-TSOP(II)<br>Forward/Reverse |

|      |          | KM616FS2000I                | -40~85℃  | 120/150<br>70/85 | 50/10<br>80/10       | 1 Olwalu/nevelse               |

|      |          | KM616FR2000                 | 0~70℃    | 300              | 20/10                |                                |

|      |          | KM616FR2000I                | -40~85℃  | 300              | 20/10                | ]                              |

Note1. Refer to the ordering information for more detail description of each product.

<sup>\* :</sup> New Product

<sup>\*\* :</sup> Preliminary

<sup>\*\*\* :</sup> Under development

# 2.2.1. High Speed SRAM(5V Operation)

|                                                                                                                                                       | Org.      | Product No <sup>Note1</sup>                                                                     | Speed(ns)                                                | Tech.                                        | Power Di                                                         | issipation            |                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------|------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------|

| Den.                                                                                                                                                  |           |                                                                                                 |                                                          |                                              | Active<br>Max(mA)                                                | Standby<br>Max(mA)    | Package                                                                       |

| 256K                                                                                                                                                  | 64K x 4   | KM64B261A<br>KM64258C                                                                           | 6/7/8<br>12/15/20                                        | BICMOS<br>CMOS                               | 160<br>160                                                       | 20<br>2               | 28SOJ<br>28DIP/SOJ                                                            |

| 250K                                                                                                                                                  | 32K x 8   | KM68B261A<br>KM68257C/CL                                                                        | 6/7/8<br>12/15/20                                        | BICMOS<br>CMOS                               | 170<br>165                                                       | 20<br>2/0.1           | 32SOJ<br>28DIP/SOJ/TSOP1F                                                     |

| 1 <b>M</b>                                                                                                                                            | 1M x 1    | KM611001/L                                                                                      | 20/25/35                                                 | смоѕ                                         | 130                                                              | 2/0.5                 | 28DIP/SOJ                                                                     |

| 256K x 4 KM641003B/BL/BI/BLI** 8/10/12 CM: KM64B1003 B/10/12 BICM: KM641003A 12/15/17/20 CM: KM641003 15/17/20 CM: KM641001B/BL/BI/BLI** 15/17/20 CM: |           | CMOS<br>BICMOS<br>CMOS<br>CMOS<br>CMOS<br>CMOS                                                  | 150<br>165<br>150<br>170<br>120<br>125<br>150            | 10/1<br>10<br>8<br>10<br>5/0.5<br>8<br>2/0.5 | 32SOJ/TSOP2F<br>32SOJ<br>32SOJ/TSOP2F<br>32SOJ<br>28SOJ<br>28SOJ |                       |                                                                               |

|                                                                                                                                                       | 128K x 8  | KM641001/L<br>KM681002B/BL/BI/BLI**<br>KM681002<br>KM681002A<br>KM681002                        | 8/10/12<br>8/10/12<br>8/10/12<br>12/15/17/20<br>15/17/20 | CMOS<br>BICMOS<br>CMOS<br>CMOS               | 160<br>170<br>170<br>170                                         | 10/1<br>10<br>8<br>10 | 28DIP/SOJ<br>32SOJ(300/400)/TSOP2F<br>32SOJ<br>32SOJ(300/400)/TSOP2F<br>32SOJ |

|                                                                                                                                                       |           | KM681001B/BL/BI/BLI**<br>KM681001A<br>KM681001/L                                                | 15/17/20<br>15/17/20<br>20/25/35                         | CMOS<br>CMOS<br>CMOS                         | 130<br>125<br>170                                                | 5/0.5<br>8<br>2/0.5   | 32SOJ(300/400)<br>32SOJ(300/400)<br>32DIP/SOJ                                 |

|                                                                                                                                                       | 64K x 16  | KM6161002B/BL/BI/BLI**<br>KM6161002A<br>KM6161002                                               | 8/10/12<br>12/15/17/20<br>15/17/20                       | CMOS<br>CMOS<br>CMOS                         | 200<br>190<br>230                                                | 10/1<br>8<br>10       | 44SOJ/TSOP2F<br>44SOJ/TSOP2F<br>44SOJ                                         |

| 4M                                                                                                                                                    | 1 M x 4   | KM644002B/BI**<br>KM64B4002<br>KM644002A*<br>KM644002                                           | 10/12/15<br>12/15<br>15/17/20<br>17/20/25                | CMOS<br>BICMOS<br>CMOS<br>CMOS               | 190<br>185<br>150<br>170                                         | 10<br>30<br>10<br>10  | 32SOJ/TSOP2F<br>32SOJ<br>32SOJ<br>32SOJ                                       |

|                                                                                                                                                       | 512K x 8  | KM684002B/B **<br>KM68B4002<br>KM684002A*<br>KM684002                                           | 10/12/15<br>12/15<br>15/17/20<br>17/20/25                | CMOS<br>BICMOS<br>CMOS<br>CMOS               | 200<br>195<br>170<br>180                                         | 10<br>30<br>10<br>10  | 36SOJ/TSOP2F<br>36SOJ<br>36SOJ<br>36SOJ                                       |

|                                                                                                                                                       | 256K x 16 | 6K x 16 KM6164002B/BI** 10/12/1<br>KM616B4002 12/15<br>KM6164002A* 15/17/2<br>KM6164002 20/25/3 |                                                          | CMOS<br>BICMOS<br>CMOS<br>CMOS               | 250<br>270<br>210<br>240                                         | 10<br>30<br>10<br>10  | 44SOJ/TSOP2F<br>44SOJ<br>44SOJ<br>44SOJ                                       |

<sup>\*:</sup> New product \*\*: Preliminary

<sup>\*\*\* :</sup> Under development

# 2.2.2. High Speed SRAM(3.3V Operation)

| Den. | Org.      | Product No <sup>Note1</sup>                            | Speed(ns)                     | Tech.                  | Power Dissipation              |                    |                                                |  |

|------|-----------|--------------------------------------------------------|-------------------------------|------------------------|--------------------------------|--------------------|------------------------------------------------|--|

|      |           |                                                        |                               |                        | Active<br>Max(m <sup>A</sup> ) | Standby<br>Max(mA) | Package                                        |  |

| 256K | 32K x 8   | KM68V257C                                              | 15/17/20                      | смоѕ                   | 90                             | 0.1                | 28DIP/SOJ/TSOP1F                               |  |

| 1M   | 256K x 4  | KM64V1003B/BL/BI/BLI**<br>KM64V1003A/AL/AI/ALI         | 8/10/12<br>12/15/17/20        | CMOS<br>CMOS           | 150<br>130                     | 5/0.5<br>5/0.5     | 32SOJ/TSOP2F<br>32SOJ/TSOP2F                   |  |

|      | 128K x 8  | KM68V1002B/BL/BI/BLI**<br>KM68V1002A/AL/AI/ALI         | 8/10/12<br>12/15/17/20        | CMOS<br>CMOS           | 160<br>140                     | 5/0.5<br>5/0.5     | 32SOJ(300/400)/TSOP2F<br>32SOJ(300/400)/TSOP2F |  |

|      | 64K x 16  | KM616V1002B/BL/BI/BLI**<br>KM616V1002A/AL/AI/ALI       | 8/10/12<br>12/15/17/20        | CMOS<br>CMOS           | 200<br>170                     | 5/0.5<br>5/0.5     | 44SOJ/TSOP2F<br>44SOJ/TSOP2F                   |  |

| 4M   | 1M x 4    | KM64V4002B/BL/BI/BLI**<br>KM64BV4002<br>KM64V4002A*    | 10/12/15<br>12/15<br>15/17/20 | CMOS<br>BICMOS<br>CMOS | 160<br>160<br>140              | 10/1<br>30<br>10   | 32SOJ/TSOP2F<br>32SOJ<br>32SOJ                 |  |

|      | 512K x 8  | KM68V4002B/BL/BI/BLI**<br>KM68BV4002<br>KM68V4002A*    | 10/12/15<br>12/15<br>15/17/20 | CMOS<br>BICMOS<br>CMOS | 170<br>170<br>160              | 10/1<br>30<br>10   | 36SOJ/TSOP2F<br>36SOJ<br>36SOJ                 |  |

|      | 256K x 16 | KM616V4002B/BL/BI/BLI**<br>KM616BV4002<br>KM616V4002A* | 10/12/15<br>12/15<br>15/17/20 | CMOS<br>BICMOS<br>CMOS | 240<br>240<br>200              | 10/1<br>30<br>10   | 44SOJ/TSOP2F<br>44SOJ<br>44SOJ                 |  |

<sup>\* :</sup> New product \*\* : Preliminary

<sup>\*\*\*:</sup> Under development

## 2.3.1. Specialty SRAM

| Den. | Org. & Vcc       | Product No*                                                       | Mode                            | Op.Temp                              | 1/0                                       | tCYC                                                    | tCD                                          | Package                                  |

|------|------------------|-------------------------------------------------------------------|---------------------------------|--------------------------------------|-------------------------------------------|---------------------------------------------------------|----------------------------------------------|------------------------------------------|

| 1M   | 32Kx32, 3.3V     | KM732V589<br>KM732V589A<br>KM732V595A<br>KM732V596A<br>KM732V599A | SPB<br>SPB<br>SPB<br>SPB<br>SPB | CMOS<br>CMOS<br>CMOS<br>CMOS<br>CMOS | 3.3V<br>3.3V<br>2.5V<br>2.5V/3.3V<br>3.3V | 13/15<br>13/15<br>6.6/7.5/8.6/10<br>13/15<br>7.5/8.6/10 | 7/8<br>7/8<br>4.4/5/5/5.5<br>7/8<br>4.5/5/5  | (T)QFP<br>(T)QFP<br>TQFP<br>TQFP<br>TQFP |

|      | 32Kx36, 3.3V     | KM736V595A<br>KM736V599A<br>KM736V587                             | SPB<br>SPB<br>SB                | CMOS<br>CMOS<br>CMOS                 | 2.5V<br>3.3V<br>3.3V                      | 6.6/7.5/8.6/10<br>7.5/8.6/10<br>12/15/17                | 4.4/5/5/5.5<br>4.5/5/5<br>8.5/9/10           | TQFP<br>TQFP<br>TQFP                     |

|      | 64Kx18, 3.3V     | KM718BV87<br>KM718V687                                            | SB<br>SB                        | BICMOS<br>CMOS                       | 3.3V<br>3.3V                              | 12/15/17<br>12/15/17                                    | 8.5/9/10<br>8.5/9/10                         | 52PLCC<br>TQFP                           |

|      | 64Kx18, 5V       | KM718B90<br>KM718B86                                              | SB<br>SB                        | BICMOS<br>BICMOS                     | 5.0V<br>5.0V                              | 11/15/17/20<br>12/15/17/20                              | 8/9/10/12<br>8/9/10/12                       | 52PLCC<br>52PLCC                         |

| 2M   | 64Kx32, 3.3V     | KM732V688<br>KM732V696                                            | SPB<br>SPB                      | CMOS<br>CMOS                         | 3.3V<br>2.5V/3.3V                         | 13/15<br>13/15                                          | 7/8<br>7/8                                   | (T)QFP<br>TQFP                           |

|      | 64Kx36, 3.3V     | KM736V689<br>KM736V687                                            | SPB<br>SB                       | CMOS<br>CMOS                         | 3.3V<br>3.3V                              | 7.5/8.6/10<br>12/15/17                                  | 4.5/5/5<br>8.5/9/10                          | TQFP<br>TQFP                             |

|      | 128Kx18,<br>3.3V | KM718V789<br>KM718V787                                            | SPB<br>SB                       | CMOS<br>CMOS                         | 3.3V<br>3.3V                              | 7.5/8.6/10<br>12/15/17                                  | 4.5/5/5<br>8.5/9/10                          | TQFP<br>TQFP                             |

| 4M   | 128Kx36,<br>3.3V | KM736FV4011<br>KM736FV4021<br>KM736FV4002<br>KM736FV4022          | SP<br>SP<br>RL<br>RL            | CMOS<br>CMOS<br>CMOS<br>CMOS         | 1.5V<br>3.3V<br>2.5V<br>3.3V              | 5/6/7<br>5/6/7<br>8/9/10<br>8/9/10                      | 2.5/3.0/3.5<br>2.5/3.0/3.5<br>7/8/9<br>7/8/9 | 119BGA<br>119BGA<br>119BGA<br>119BGA     |

|      | 256Kx18,<br>3.3V | KM718FV4011<br>KM718FV4021<br>KM718FV4002<br>KM718FV4022          | SP<br>SP<br>RL<br>RL            | CMOS<br>CMOS<br>CMOS<br>CMOS         | 1.5V<br>3.3V<br>2.5V<br>3.3V              | 5/6/7<br>5/6/7<br>8/9/10<br>8/9/10                      | 2.5/3.0/3.5<br>2.5/3.0/3.5<br>7/8/9<br>7/8/9 | 119BGA<br>119BGA<br>119BGA<br>119BGA     |

\*: New product

\*\* : Preliminary

\*\*\* : Under development

- SPB : Synchronous pipelined burst - SB : Synchronous burst - RL : Register to Latch

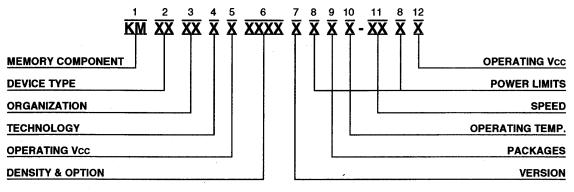

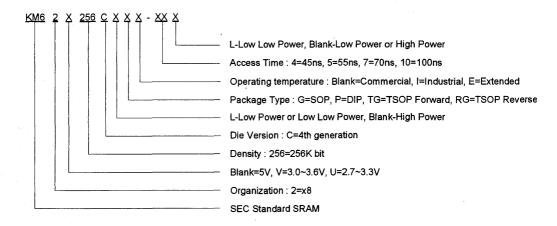

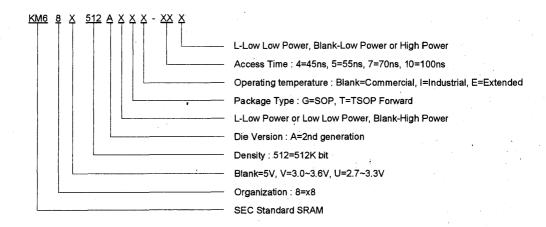

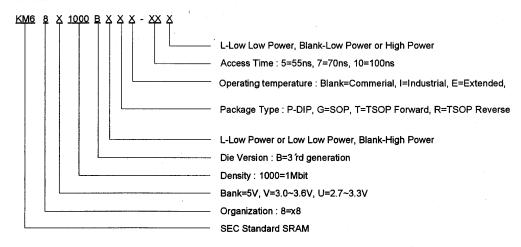

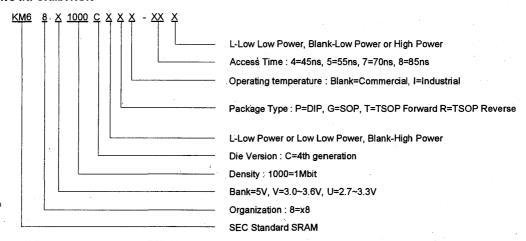

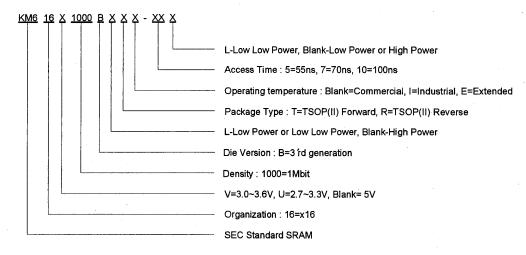

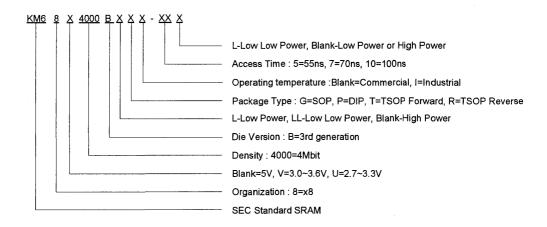

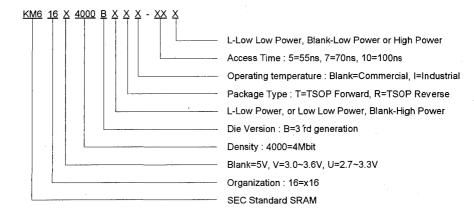

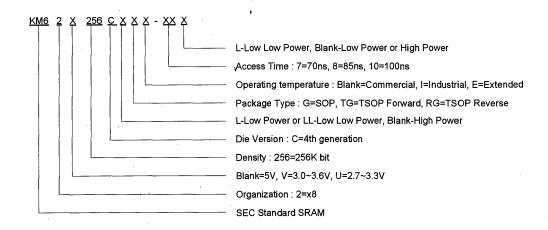

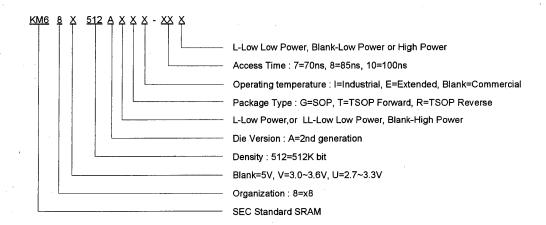

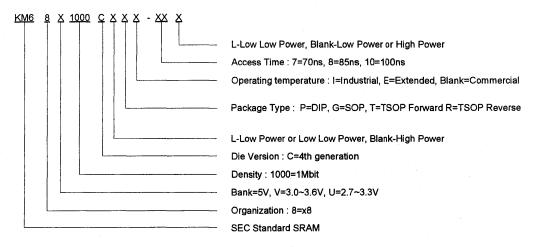

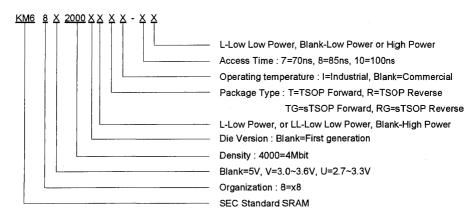

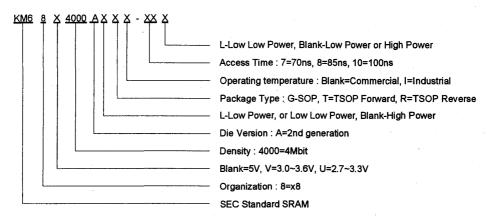

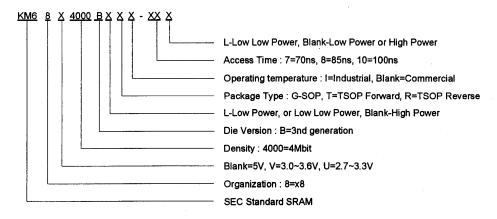

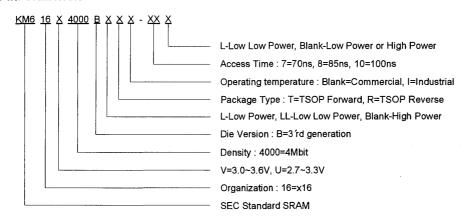

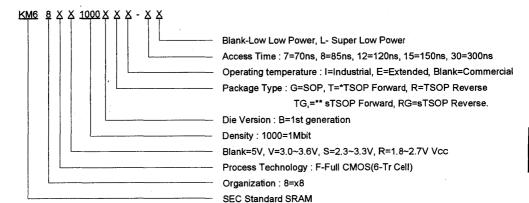

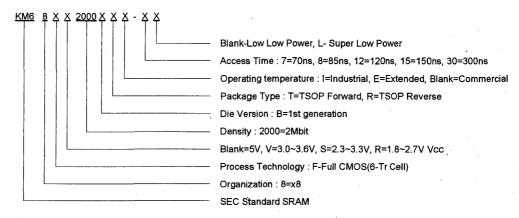

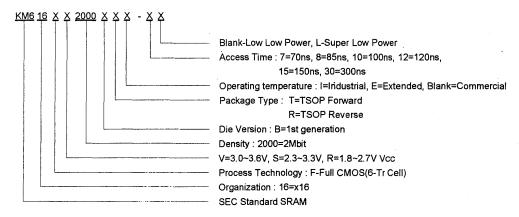

#### 3. ORDERING INFORMATION

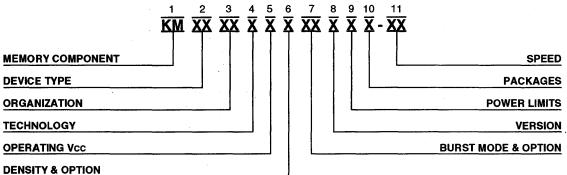

#### 3.1.1. Asynchronous SRAM

| 1. MEMORY COMPONENT                           |                                         | 8. POWER LIMITS                         |                  |

|-----------------------------------------------|-----------------------------------------|-----------------------------------------|------------------|

| A DEMOS TABLE                                 |                                         | . BLANK                                 | High Power(Fast) |

| 2. DEVICE TYPE                                |                                         | In Full CMOS Low F                      | Power SRAM(Slow) |

| . 6                                           | Asynch, SRAM                            | • • • • • • • • • • • • • • • • • • • • | Low Power        |

| .7                                            | Synch. SRAM                             | . L-L                                   | Low Low Power    |

| 3. ORGANIZATION                               |                                         | 9. PACKAGES                             |                  |

| .1                                            | x1 bit                                  | . P                                     | DIP              |

| . 4                                           | x4 bit                                  | C                                       | SOI              |

| . 2 or 8                                      | x8 bit                                  | . J                                     | SOJ or PLCC      |

| . 9                                           | x9 bit                                  | . T                                     | TSOP(Standard)   |

| . 16                                          | x16 bit                                 | . R                                     | TSOP(Standard)   |

| . 32                                          | x32 bit                                 |                                         | , ,              |

| 4. TECHNOLOGY                                 |                                         | 10. OPERATING TEMP.                     |                  |

|                                               |                                         | . BLANK                                 | Commercial       |

| . BLANK                                       | CMOS                                    | · E                                     | Extended         |

| . BLANK                                       | BICMOS                                  |                                         | Industrial       |

|                                               | Full CMOS                               | • •                                     |                  |

| 5. OPERATING Vcc                              |                                         | 11. SPEED                               |                  |

| . BLANK                                       | 5.0V                                    | SLOW SRAM                               |                  |

| _ V                                           | 3.3V                                    |                                         | 4Ema             |

| . Ů · · · · · · · · · · · · · · · · · ·       | 3.0V                                    | . 4                                     | 45f18<br>55no    |

| . S                                           | 2.5V                                    | . 7 · · · · · · · · · · · · · · · · · · | 70no             |

| . T                                           | 2.0V                                    | . 8                                     | 7011S            |

|                                               |                                         | . 10                                    | 10000            |

| 6. DENSITY & OPTION                           |                                         | 12                                      | 100115<br>120nc  |

|                                               | 64:64K Slow                             | . 12                                    | 15000            |

| . 64                                          | 256:256K Slow                           | . 15                                    | 130118           |

| . 257                                         | 257:257K Fast                           | FAST SRAM                               |                  |

| . 258                                         | 258:256K Fast(with OE)                  |                                         | _                |

| . 512                                         | 512:512K Slow                           | . 6                                     | 6ns              |

| . 1000                                        | 1000:1M Slow                            | . 7                                     | 7ns              |

| . 1001                                        | 1001:1M Fast                            | . 8                                     | 8ns              |

| . 1002                                        | 1002:1M Fast(Revolutionary)             | . 10                                    | 10ns             |

|                                               |                                         | . 12                                    | 12ns             |

| - 2000.                                       | 2000: 2M Slow                           | . 15                                    | 15ns             |

| . 4000                                        | 4000:4M Slow                            | . 17                                    | 17ns             |

| - 2000 · · · · · · · · · · · · · · · · ·      | 4002:4M Fast(Revolutionary)             | . 20                                    | 20ns             |

| 7. VERSION                                    | • • • • • • • • • • • • • • • • • • • • | . 25                                    | 25ns             |

|                                               | First Con                               | . 30                                    | 30ns             |

| • BLANK • • • • • • • • • • • • • • • • • • • | First Gen.                              |                                         |                  |

| • A                                           | Second Gen.                             |                                         |                  |

Third Gen.

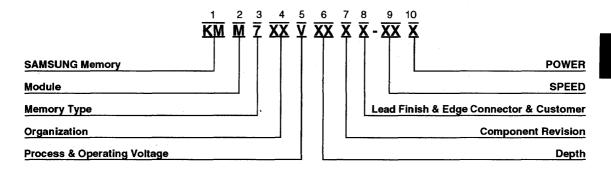

#### 3.2.1. Synchronous Burst SRAM

| DENSITY & OPTION                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |