1130 - 4051

# **MOS Memory**

1994

Video RAM

ALL AMERICAN 230 Devcon Dr. San Jose, CA 95112 408 441-1300 800-222-6001

#### **PRINTED IN KOREA**

Circuit diagrams utilizing SAMSUNG products are included as a means of illustrating typical semiconductor applications; consequently, complete information sufficient for construction purposes is not necessarily given. The information has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described herein any license under the patent rights of SAMSUNG or others. SAMSUNG reserves the right to change device specifications.

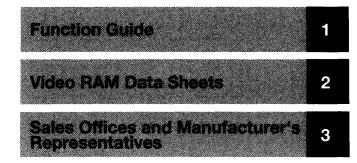

## **TABLE OF CONTENTS**

| I. FUNCTION GUIDE | 11 |

|-------------------|----|

|-------------------|----|

II. VIDEO RAM DATA SHEETS

| 1.  | KM428C64 · · · · · · · · · M/F, 64Kx8 · · · · · · · · · · 17                  |

|-----|-------------------------------------------------------------------------------|

| 2.  | KM424C257 ······E/F, 256Kx4 ······44                                          |

| 3.  | KM428C128 · · · · · · · · · E/F, 128Kx8 · · · · · · · · · · · · · · · · · · · |

| 4.  | KM428C/V256 ·······E/F, 256Kx8 ······114                                      |

| 5.  | KM428C/V257 ······F/F(EDO), 256Kx8 ······155                                  |

| 6.  | KM428C/V258 ·······F/F(EDO, 2WE), 256x8 ······199                             |

| 7.  | KM4216C/V255 · · · · · · · · · F/F(2WE), 256Kx16 · · · · · · · · · · · · 244  |

| 8.  | KM4216C/V256 · · · · · · · · · F/F(EDO, 2WE), 256Kx16 · · · · · · · 284       |

| 9.  | KM4216C/V257 ······F/F(2CAS), 256Kx16 ·······326                              |

| 10. | KM4216C/V258 ······F/F(EDO, 2CAS), 256Kx16 ······367                          |

##

Ę.

# FUNCTION GUIDE 1

## **MEMORY ICs**

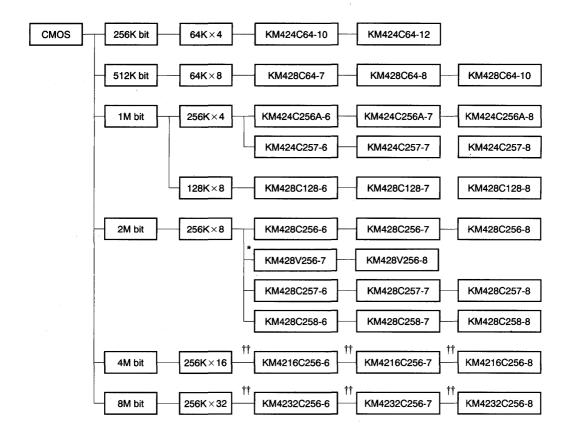

#### Video RAM

†† Under Development

#### Video RAM

| Capacity | Part Number  | Orgnization | Speed(ns) | Technology | Features  | Package            | Remark |

|----------|--------------|-------------|-----------|------------|-----------|--------------------|--------|

| 256K     | KM424C64     | 64K×4       | 100/120   | CMOS       | M/F       | 24Pin DIP/ZIP      | NOW    |

| 512K     | KM428C64     | 64K×8       | 70/80/100 | CMOS       | M/F       | 40PIN SOJ          | NOW    |

| 1M       | KM424C256A   | 256K×4      | 60/70/80  | CMOS       | M/F       | 28Pin ZIP/SOJ      | NOW    |

|          | KM424C257    | 256K×4      | 60/70/80  | CMOS       | E/F       | 28Pin ZIP/SOJ      | NOW    |

|          | KM428C128    | 128K×8      | 60/70/80  | CMOS       | E/F       | 40Pin SOJ/TSOP- I  | NOW    |

| 2M       | KM428C256    | 256K×8      | 60/70/80  | CMOS       | E/F       | 40Pin SOJ/TSOP- I  | NOW    |

|          | KM428V256    | 256K×8      | 70/80     | CMOS       | E/F(3.3V) | 40Pin SOJ/TSOP- I  | NOW    |

|          | KM428C257    | 256K×8      | 60/70/80  | CMOS       | Ê/F       | 40Pin SOJ/TSOP- I  | NOW    |

|          | KM428C258    | 256K×8      | 60/70/80  | CMOS       | F/F       | 40Pin SOJ/TSOP- I  | NOW    |

| 4M       | † KM4216C256 | 256K×16     | 60/70/80  | CMOS       | F/F       | 64Pin SSOP/TSOP- I | 2Q '94 |

| *: | New | Product | t : Under Develop | ment |

|----|-----|---------|-------------------|------|

|    |     |         |                   |      |

#### Video RAM

| Density | Feature  | Organization | Samsung    | Micron        | Toshiba   | NEC       | Hitachi    | Ti         |

|---------|----------|--------------|------------|---------------|-----------|-----------|------------|------------|

| 256K    | Minimum  | 64K×4        | KM424C64   | MT42C4064     |           | μPD41264  | HM53461(2) | TMS4461    |

|         |          |              |            |               |           | μPD42264  |            |            |

| 512K    | Minimum  | 64K×8        | KM428C64   |               |           |           |            |            |

|         | Minimum  | 256K×4       | KM424C256  |               | TC524256  | μPD42273  | HM534251   | TMS44C250  |

|         |          |              | KM424C256A |               | TC524256A |           | HM534251A  | SMJ44C250  |

|         |          |              |            |               | TC524256B |           | HM534252   |            |

|         |          |              |            |               | TC524257  |           |            |            |

|         |          | 128K×8       |            |               | TC528126A |           | HM538121   | TMS48C121  |

| 1M      |          |              |            |               | TC528126B |           | HM538121A  |            |

|         | Extended | 256K×4       | KM424C257  | MT42C4256     | TC524258A | μPD42274  |            | TMS44C251  |

|         |          |              |            | MT42C4255     | TC524258B |           | HM534253A  | SMJ44C251  |

|         |          |              |            |               | TC524259B |           |            | SMJ44C251A |

|         |          | 128K×8       | KM428C128  | MT42C8128     | TC528128A | μPD42275  |            |            |

|         |          |              |            | MT42C8128     | TC528128B |           | HM538123A  |            |

|         |          |              |            |               | TC528129B |           |            |            |

|         | Extended | 256K×8       | KM428C256  | MT42C8255     |           |           |            |            |

| 2M      |          |              |            |               |           |           |            |            |

|         | Full     | 256K×8       | KM428C257  | MT42C8256     | TC528267  | μPD482234 | HM538253   |            |

|         |          |              | KM428C258  | MT42C8254     |           | μPD482235 |            |            |

| 4M      | Full     | 256K×32      | KM4216C256 | MT42C256K16A1 |           |           |            |            |

1

## **MEMORY ICs**

## **FUNCTION GUIDE**

VRAM

## 64K X 8 Bit CMOS Video RAM FEATURES

- Dual port Architecture 64K x 8 bits RAM port 256 x 8 bits SAM port

- · Performance range :

| Speed<br>Parameter        | -7    | -8    | -10   |

|---------------------------|-------|-------|-------|

| RAM access time (tRAC)    | 70ns  | 80ns  | 100ns |

| RAM access time (tcac)    | 20ns  | 20ns  | 25ns  |

| RAM cycle time (tRc)      | 130ns | 150ns | 180ns |

| RAM page mode cycle (tpc) | 45ns  | 50ns  | 60ns  |

| SAM access time (tsca)    | 20ns  | 20ns  | 25ns  |

| SAM cycle time (tscc)     | 25ns  | 25ns  | 30ns  |

| RAM active current        | 85mA  | 80mA  | 70mA  |

| SAM active current        | 45mA  | 40mA  | 40mA  |

- · Fast Page Mode

- · RAM Read, Write, Read-Modify-Write

- · Serial Read and Serial Write

- · Read Transfer and Write Transfer

- Real time read transfer capability

- · Write per bit masking on RAM write cycles

- CAS-before-RAS, RAS-only and Hidden Refresh Common Data I/O Using three state RAM Output

- control

- All Inputs and Outputs TTL Compatible

- · Refresh: 256 Cycle/4ms

- $\cdot$  Single +5V $\pm$  10% Supply Voltage

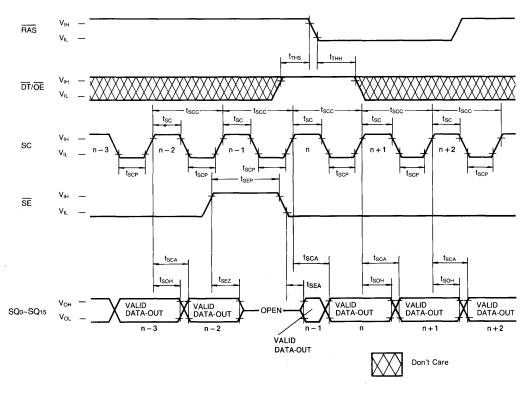

- Plastic 40-Pin 400 mil SOJ

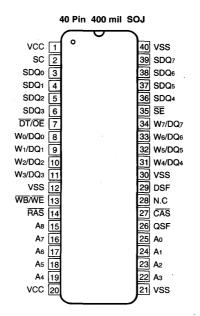

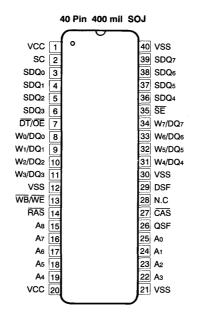

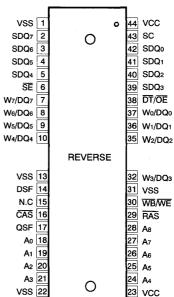

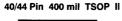

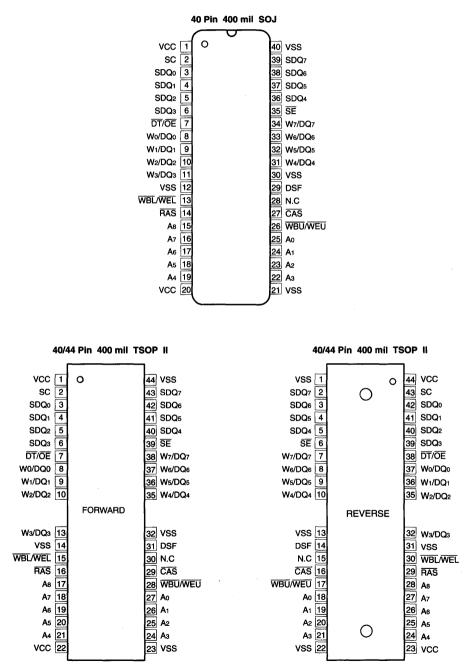

#### PIN CONFIGURATION (TOP VIEWS) 40 Pin 400 mil SOJ

| SC 1      |     | 1  | VSS1             |

|-----------|-----|----|------------------|

|           | l C |    |                  |

| SDQ0 2    |     |    | SDQ7             |

| SDQ1 3    |     |    | SDQ6             |

| SDQ2 4    |     |    | SDQ5             |

| SDQ3 5    |     | 36 | SDQ4             |

| DT/OE 6   |     | 35 | SE               |

| Wo/DQ0 7  |     | 34 | W7/DQ7           |

| W1/DQ1 8  |     | 33 | W6/DQ6           |

| W2/DQ2 9  |     | 32 | W5/DQ5           |

| W3/DQ3 10 |     | 31 | W4/DQ4           |

| VCC1 11   |     | 30 | VSS <sub>2</sub> |

| WB/WE 12  |     | 29 | N.C.             |

| N.C. 13   |     | 28 | N.C.             |

| RAS 14    |     | 27 | CAS              |

| N.C. 15   |     | 26 | N.C.             |

| N.C. 16   |     | 25 | Ao               |

| A6 17     |     | 24 | Aı               |

| A5 18     |     | 23 | A2               |

| A4 19     |     | 22 | Аз               |

| VCC2 20   |     | 21 | A7               |

|           |     |    |                  |

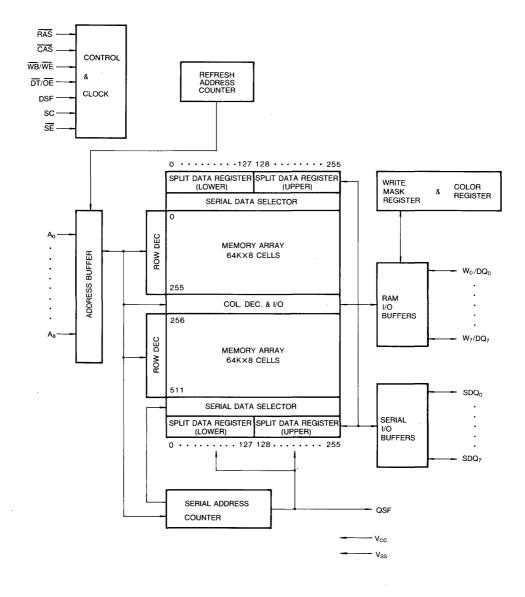

#### **GENERAL DESCRIPTION**

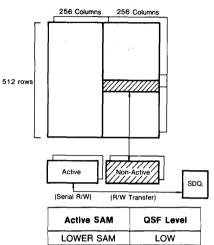

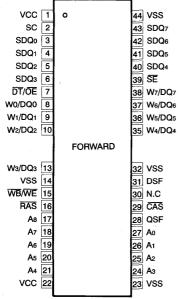

The Samsung KM428C64 is a CMOS 64K x 8 bit Dual Port DRAM. It consists of a 64K x 8 dynamic random access memory (RAM) port and 256 x 8 static serial access memory (SAM) port. The RAM and SAM ports operate asynchronously except during data transfer between the ports.

The RAM array consists of 256 bit rows of 2048 bits. It operates like a conventional 64K x 8 CMOS DRAM. The RAM port has a write per bit mask capability.

The SAM port consists of four 256 bit high speed shift registers that are connected to the RAM array through a 2048 bit data transfer gate. The SAM port has serial read and write capabilities.

Data may be internally transferred bi-directionally between the RAM and SAM ports using read or write transfers.

Refresh is accomplished by familiar DRAM refresh modes. The KM428C64 supports RAS-only, Hidden, and CAS -before-RAS refresh for the RAM port. The SAM port does not require refresh.

All inputs and I/O's are TTL level compatible. All address lines and data inputs are latched on chip to simplify system design. The outputs are unlatched to allow greater system flexibility.

## **PIN DESCRIPTION**

| Symbol  | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAS     | IN     | Row Address Strobe. $\overline{\text{RAS}}$ is used to clock in the 9 row bits for another input signal. The RAM port is placed in standby mode when the $\overline{\text{RAS}}$ control is held "High"                                                                                                                                                                                                                   |

| CAS     | IN     | Column Address Strobe. $\overline{\text{CAS}}$ is used to clock in the 9 column address bits as a strobe for the DSF inputs                                                                                                                                                                                                                                                                                               |

| ADDRESS | IN     | Address inputs for the DRAM operation, these inputs are multiplexed and clocked by RAS and CAS to select one 16-bit word out of the 262,144 available. 9 row address bits are latched on the falling edge of the row address strobe(RAS) and the following nine column address bits are latched on the falling edge of the column address strobe(CAS).                                                                    |

| WB/WE   | IN     | The $\overline{\text{WB/WE}}$ input is a multifunction pin. when $\overline{\text{WB/WE}}$ is "High" at the falling edge of $\overline{\text{RAS}}$ , during RAM port operation, it is used to write data into the memory array in the same manner as a standard DRAM. When $\overline{\text{WB/WE}}$ is "Low" at the falling edge of $\overline{\text{RAS}}$ , during RAM port operation, the W-P-B function is enabled. |

| DT/OE   | IN     | The DT/OE input is also a multifunction pin. Enables an internal Transfer operation at the falling edge of RAS when Transfer enable.                                                                                                                                                                                                                                                                                      |

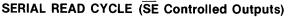

| SE      | IN     | In a serial read cycle, $\overline{SE}$ is used as an output control. When $\overline{SE}$ is "High", Serial access is disabled, however, the serial address pointer location is still incremented when SC is clocked even when $\overline{SE}$ is "High"                                                                                                                                                                 |

| Wi/DQi  | IN/OUT | Data I/O for DRAM access. These pins act as inputs for Mask and register load cycles, DQ Mask and Column Mask for BW.                                                                                                                                                                                                                                                                                                     |

| SC      | IN     | Clock input to the serial address counter and data latch for the SAM register                                                                                                                                                                                                                                                                                                                                             |

| SDQi    | IN/OUT | Serial input and serial output share common I/O pins. Serial input or output mode is determined by the most recent read, write or pseudo write transfer cycle.                                                                                                                                                                                                                                                            |

| Vcc     | SUPPLY | Power supply                                                                                                                                                                                                                                                                                                                                                                                                              |

| Vss     | SUPPLY | Ground                                                                                                                                                                                                                                                                                                                                                                                                                    |

| NC      |        | No Connection                                                                                                                                                                                                                                                                                                                                                                                                             |

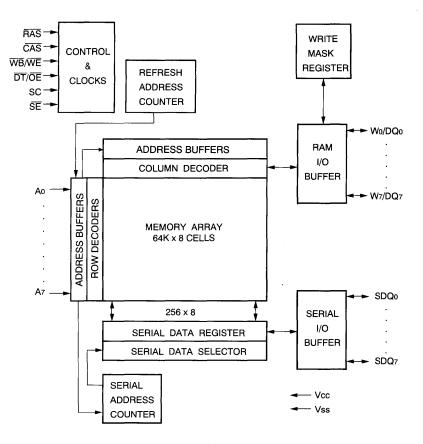

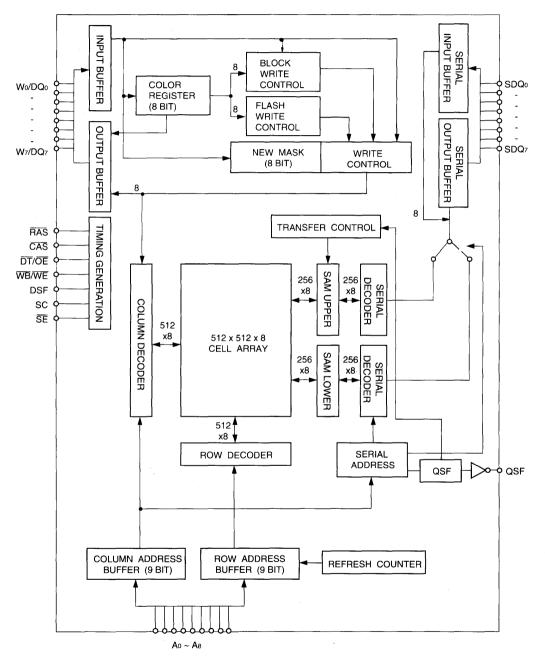

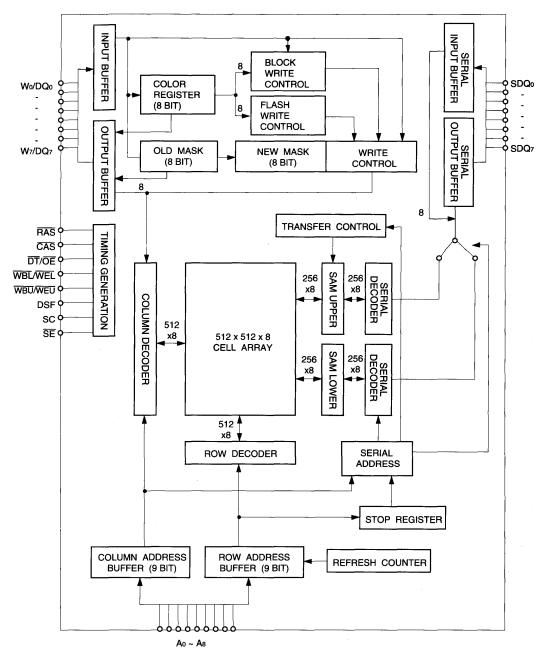

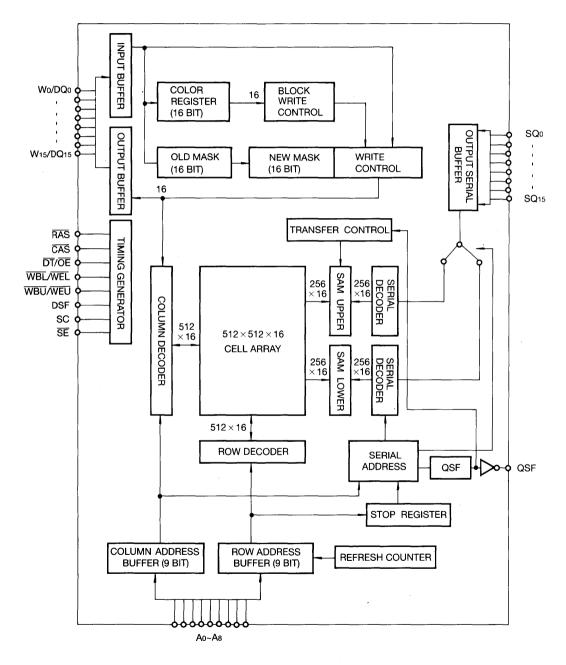

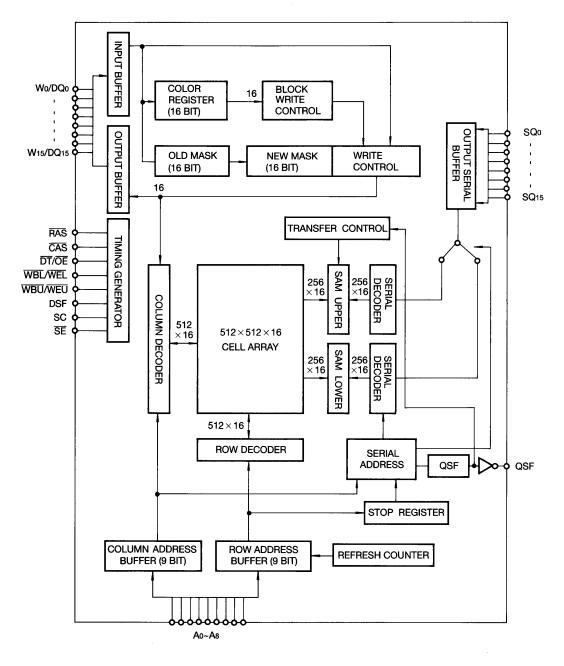

## FUNCTIONAL BLOCK DIAGRAM

2

## FUNCTION TRUTH TABLE

| Mnemonic | Inemonic RAS |       |    | Address*1 |                   | DQi Input <sup>*2</sup> |     | Write  |      |                             |

|----------|--------------|-------|----|-----------|-------------------|-------------------------|-----|--------|------|-----------------------------|

| Code     | CAS          | DT/OE | WE | SE        | RAS               | CAS                     | RAS | CAS/WE | Mask | Function                    |

| CBR      | 0            | X     | х  | Х         | Х                 | Х                       | х   | -      | ·    | CBR Refresh                 |

| ROR      | 1            | 1     | х  | Х         | Row               | -                       | х   |        | _    | RAS-Only Refresh            |

| RW       | 1            | 1     | 1  | Х         | Row               | Col.                    | х   | Data   | No   | Normal DRAM R/W(No Mask)    |

| RW/NM    | 1            | 1     | 0  | Х         | Row               | Col.                    | WMi | Data   | Use  | Masked DRAM Write(New Mask) |

| RT       | 1            | 0     | 1  | Х         | Row               | Тар                     | х   | Х      | _    | Read Transfer               |

| PWT      | 1            | 0     | 0  | 1         | Row <sup>∗3</sup> | Тар                     | x   | X      | -    | Pesudo Write Transfer       |

X: Don't Care, -: Not Applicable, Tap: SAM Start(column)Address Note

\*1 : These column show what must be present on the  $A_0 \sim A_7$  inputs at the falling edge of RAS and CAS.

\*2 : These column show what must be present on the DQ0~DQ7 outputs at the falling edge of RAS, CAS or WB/WE, whichever is later.

\*3 : The Row that is addressed will be refreshed.

#### **ABSOLUTE MAXIMUM RATINGS\***

| Item                               | Symbol   | Rating       | Unit |

|------------------------------------|----------|--------------|------|

| Voltage on Any Pin Relative to Vss | VIN,VOUT | -1 to + 7.0  | V    |

| Voltage on Supply Relative to Vss  | Vcc      | -1 to + 7.0  | V    |

| Storage Temperature                | Tstg     | -55 to + 150 | r    |

| Power Dissipation                  | Po       | 1            | w    |

| Short Circuit Output Current       | los      | 50           | mA   |

\* Permanent device damage may occur if "ABSOLUTE MAXIMUM RATINGS" are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **RECOMMENDED OPERATING CONDITIONS** (Voltage reference to Vss, TA=0 to 70° C)

| ltem               | Symbol | Min   | Тур | Max    | Unit |

|--------------------|--------|-------|-----|--------|------|

| Supply Voltage     | Vcc    | 4.5   | 5.0 | 5.5    | V    |

| Ground             | Vss    | 0     | 0   | 0      | v    |

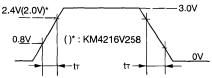

| Input High Voltage | Viн    | 2.4   | -   | Vcc+1V | V    |

| Input Low Voltage  | VIL    | - 1.0 | -   | 0.8    | v    |

#### DC AND OPERATING CHARACTERISTICS

(Recommended operating conditions unless otherwise noted)

|          | Baramatar (DA)                  |                                    | SAM port | Symbol | к   | M428C64 |      | 11 |

|----------|---------------------------------|------------------------------------|----------|--------|-----|---------|------|----|

|          | Parameter (RAI                  | SAM port                           | Symbol   | -7     | -8  | -10     | Unit |    |

|          | g Current*                      | Standby                            | Icc1     | 85     | 80  | 70      | mA   |    |

| (RAS an  | d CAS Cycling @ tR              | C=min)                             | Active   | Icc1A  | 130 | 120     | 110  | mA |

| Standby  | RAS, CAS, DT/OE,                | SE = VIH, SC= VIL                  | Standby  | ICC2   | 5   | 5       | 5    | mA |

| Current  |                                 | $\overline{SE}$ = VIL, SC= Cycling | Active   | Icc2A  | 45  | 40      | 40   | mA |

|          | RAS Only Refresh Current*       |                                    |          | Іссз   | 85  | 80      | 70   | mA |

| (CAS=VII | H, RAS Cycling @ tRC            | C=min)                             | Active   | ІссзА  | 130 | 120     | 110  | mA |

|          | ge Mode Current*                |                                    | Standby  | ICC4   | 65  | 60      | 50   | mA |

| (RAS=Vit | , CAS Cycling @ tPC             | =min)                              | Active   | Icc4A  | 110 | 100     | 90   | mA |

| CAS-Bef  | ore-RAS Refresh Curr            | rent*                              | Standby  | ICC5   | 85  | 80      | 70   | mA |

| (RAS an  | d CAS Cycling @ tR              | C=min)                             | Active   | Icc5A  | 130 | 120     | 110  | mA |

| Data Tra | insfer Current*                 |                                    | Standby  | Icce   | 115 | 110     | 100  | mA |

| (RAS an  | (RAS and CAS Cycling @ tRC=min) |                                    |          | Icc6A  | 160 | 150 _   | 140  | mA |

\*NOTE: Real values are dependent on output loading and cycle rates. Specified values are obtained with the output open. Icc is specified as average current.

In Icc1, Icc3, Icc6, address transition should be changed only while RAS=VIL

In Icc4 address transition should be changed only once while  $\overline{CAS} = V_{H}$ .

## INPUT/OUTPUT CURRENT (Recommended operating conditions unless otherwise noted.)

| ltem                                                                                                       | Symbol | Min | Max | Unit |

|------------------------------------------------------------------------------------------------------------|--------|-----|-----|------|

| Input Leakage Current (Any Input $0 \le V_{IN} \le V_{CC} + 0.5V$ , all other pins not under test=0 volts) | liL.   | -10 | 10  | μA   |

| Output Leakage Current (Data out is disabled, $0V\!\leq\!Vout\!\leq\!Vcc$ )                                | loL    | -10 | 10  | μA   |

| Output High Voltage Level<br>(RAM Іон=-2mA, SAM Іон=-2mA)                                                  | Vон    | 2.4 | -   | v    |

| Output Low Voltage Level<br>(RAM IoL=2mA, SAM IoL=2mA)                                                     | Vol    | -   | 0.4 | V    |

#### CAPACITANCE (Vcc=5V, f=1MHz, Ta=25°C)

| Item                                                  | Symbol | Min | Max | Unit |  |

|-------------------------------------------------------|--------|-----|-----|------|--|

| Input Capacitance (A <sub>0</sub> ~A <sub>7</sub> )   | CIN1   | 2   | 6   | pF   |  |

| Input Capacitance (RAS, CAS, WB/WE,<br>DT/OE, SE, SC) | Cin2   | 2   | 7   | pF   |  |

| Input/Output Capacitance (Wo/DQo~W7/DQ7)              | CDQ    | 2   | 7   | · pF |  |

| Input/Output Capacitance (SDQo~SDQ7)                  | Csda   | 2   | 7   | pF   |  |

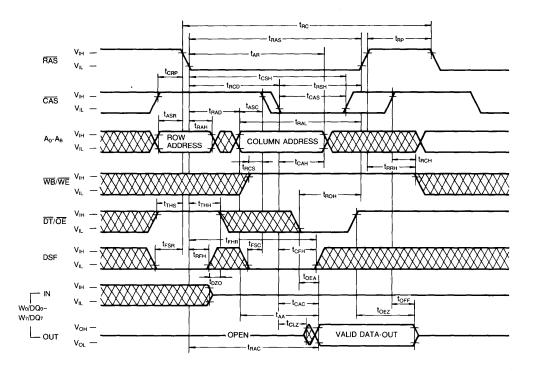

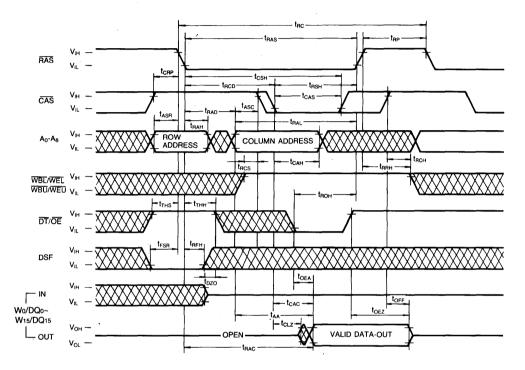

## AC CHARACTERISTICS (0 ℃≤TA≤70 ℃, Vcc=5.0V±10%, See notes 1,2)

|                                  |        | 7            | 0ns  | 80  | Ons  | 100 | Ons  |      | Natas |

|----------------------------------|--------|--------------|------|-----|------|-----|------|------|-------|

| Parameter                        | Symbol | Min          | Max  | Min | Max  | Min | Max  | Unit | Notes |

| Random read or write cycle time  | tRC    | 130          |      | 150 |      | 180 |      | ns   |       |

| Read-modify-write cycle time     | tRWC   | 175          |      | 200 |      | 240 |      | ns   |       |

| Fast page mode cycle time        | tPC    | 45           |      | 50  |      | 60  |      | ns   |       |

| Fast page mode read-modify-write | tPRWC  | 85           |      | 90  |      | 115 |      | ns   |       |

| Access time from RAS             | TRAC   |              | 70   |     | 80   |     | 100  | ns   | 3     |

| Access time from CAS             | tCAC   | _            | 20   |     | 20   |     | 25   | ns   | 3     |

| Access time from column address  | taa    | - Annotation | 35   |     | 40   |     | 50   | ns   | 3,11  |

| Access time from CAS precharge   | tCPA   |              | 40   |     | 45   |     | 55   | ns   | 3     |

| CAS to output in Low-Z           | tc∟z   | 3            |      | 3   |      | 3   |      | ns   | 3     |

| Output buffer turn-off delay     | torr   | 0            | 15   | 3   | 15   | 3   | 15   | ns   | 7     |

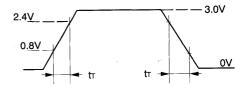

| Transition time (rise and fall)  | tτ     | 3            | 50   | 3   | 50   | 3   | 50   | ns   | 2     |

| RAS precharge time               | tRP    | 50           |      | 60  |      | 70  |      | ns   |       |

| RAS pulse width                  | tRAS   | 70           | 10K  | 80  | 10K  | 100 | 10K  | ns   |       |

| RAS pulse width (fast page mode) | TRASP  | 70           | 100K | 80  | 100K | 100 | 100K | ns   |       |

| RAS hold time                    | trsh   | 20           |      | 20  |      | 25  |      | ns   |       |

| CAS hold time                    | tcsн   | 70           |      | 80  |      | 100 |      | ns   |       |

| CAS pulse width                  | tCAS   | 20           | 10K  | 20  | 10K  | 25  | 10K  | ns   |       |

## AC CHARACTERISTICS (Continued)

•

|                                                   |        | 7   | Ons | 8   | Ons | 100ns |     |       |       |

|---------------------------------------------------|--------|-----|-----|-----|-----|-------|-----|-------|-------|

| Parameter                                         | Symbol | Min | Max | Min | Max | Min   | Max | Units | Notes |

| RAS to CAS delay time                             | tRCD   | 20  | 50  | 25  | 60  | 25    | 75  | ns    | 5,6   |

| RAS to column address delay time                  | tRAD   | 15  | 35  | 20  | 40  | 20    | 50  | ns    | 11    |

| CAS to RAS precharge time                         | tCRP   | 5   |     | 5   |     | 5     |     | ns    |       |

| CAS precharge time (CBR Counter Test)             | tCPT   | 10  |     | 10  |     | 15    |     | ns    |       |

| CAS precharge time (fast page mode)               | tCP    | 10  |     | 10  |     | 15    |     | ns    |       |

| Row address set-up time                           | tasr   | 0   |     | 0   |     | 0     |     | ns    |       |

| Row address hold time                             | trah   | 10  |     | 15  |     | 15    |     | ns    |       |

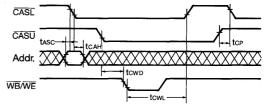

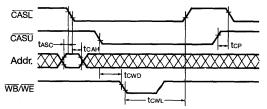

| Column address set-up time                        | tASC   | 0   |     | 0   |     | 0     |     | ns    |       |

| Column address hold time                          | tCAH   | 15  |     | 15  |     | 25    |     | ns    |       |

| Column address hold time referenced to RAS        | tar    | 55  |     | 60  |     | 75    |     | ns    |       |

| Column address to RAS lead time                   | tRAL   | 35  |     | 40  |     | 50    |     | ns    |       |

| Read command set-up time                          | tRCS   | 0   |     | 0   | ~   | 0     |     | ns    |       |

| Read command hold referenced to CAS               | trch   | 0   |     | 0   |     | 0     |     | ns    | 9     |

| Read command hold referenced to RAS               | tRRH   | 0   |     | 0   |     | 0     |     | ns    | 9     |

| Write command hold time                           | twcн   | 15  |     | 15  |     | 20    |     | ns    |       |

| Write command referenced to RAS                   | twcr   | 55  |     | 60  |     | 75    |     | ns    |       |

| Write command pulse width                         | twp    | 15  |     | 15  |     | 20    |     | ns    |       |

| Write command to RAS lead time                    | tRWL   | 15  |     | 20  |     | 25    |     | ns    |       |

| Write command to CAS lead time                    | tcwL   | 15  |     | 20  |     | 25    |     | ns    |       |

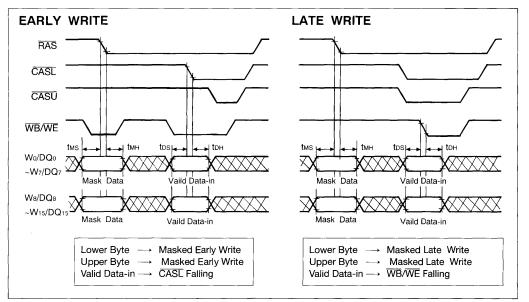

| Data set-up time                                  | tDS    | 0   |     | 0   |     | 0     |     | ns    | 10    |

| Data hold time                                    | tDH    | 15  |     | 15  |     | 20    |     | ns    | 10    |

| Data hold referenced to RAS                       | tDHR   | 55  |     | 60  |     | 75    |     | ns    |       |

| Write command set-up time                         | twcs   | 0   |     | 0   |     | 0     | ,   | ns    | 8     |

| CAS to WE delay                                   | tcwD   | 45  |     | 45  |     | 50    |     | ns    | 8     |

| CAS precharge to WE delay(Fast Page mode)         | tCPWD  | 65  |     | 70  |     | 85    |     | ns    |       |

| RAS to WE delay                                   | trwD   | 95  |     | 105 |     | 130   |     | ns    | 8     |

| Column address to WE delay time                   | tawd   | 60  |     | 65  |     | 80    |     | ns    | 8     |

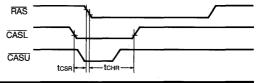

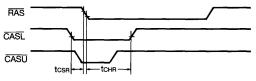

| CAS set-up time (C-B-R refresh)                   | tCSR   | 10  |     | 10  |     | 10    |     | ns    |       |

| CAS hold time(C-B-R refresh)                      | tCHR   | 10  |     | 10  |     | 20    |     | ns    |       |

| RAS precharge to CAS hold time                    | tRPC   | 10  |     | 10  |     | 10    |     | ns    |       |

| Access time from output enable                    | toea   |     | 20  |     | 20  |       | 25  | ns    |       |

| Output enable to data input delay                 | toed   | 15  |     | 15  |     | 20    |     | ns    |       |

| Output buffer turn-off delay from $\overline{OE}$ | toez   | 0   | 15  | 3   | 15  | 3     | 20  | ns    | 7     |

| Output enable command hold time                   | toeh   | 15  |     | 15  |     | 20    |     | ns    |       |

| Data to CAS delay                                 | tDZC   | 0   |     | 0   |     | 0     |     | ns    |       |

| Data to output enable delay                       | tdzo   | 0   |     | 0   |     | 0     |     | ns    |       |

| Refresh period(256 cycle)                         | tref   |     | 4   |     | 4   |       | 4   | ms    |       |

## AC CHARACTERISTICS (Continued)

| Devent store                                                         | Combel       | 7   | Ons  | 8   | 0ns  | 10  | )0ns | منعد  | Notes |

|----------------------------------------------------------------------|--------------|-----|------|-----|------|-----|------|-------|-------|

| Parameter                                                            | Symbol       | Min | Max  | Min | Мах  | Min | Max  | Units |       |

| WB set-up time                                                       | twsR         | 0   |      | 0   |      | 0   |      | ns    |       |

| WB hold time                                                         | trwn         | 10  |      | 10  |      | 15  |      | ns    |       |

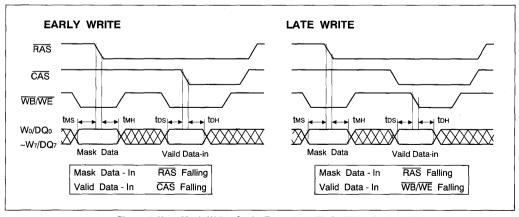

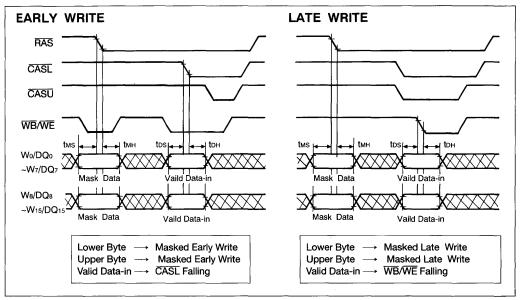

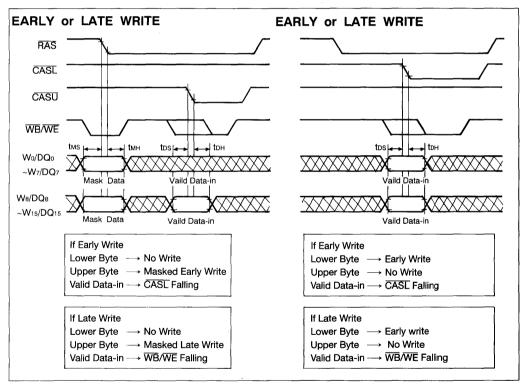

| Write per bit mask data set-up time                                  | tms          | 0   |      | 0   |      | 0   |      | ns    |       |

| Write per bit mask data hold time                                    | tмн          | 10  |      | 15  |      | 15  |      | ns    |       |

| DT high set-up time                                                  | tTHS         | 0   |      | 0   |      | 0   |      | ns    |       |

| DT high hold time                                                    | tтнн         | 10  |      | 15  |      | 15  |      | ns    |       |

| DT low set-up time                                                   | tTLS         | 0   |      | 0   |      | 0   |      | ns    |       |

| DT low hold time                                                     | ttlh         | 10  |      | 15  |      | 15  |      | ns    |       |

| DT low hold ref. to RAS(real time read transfer)                     | tRTH         | 60  |      | 65  |      | 80  |      | ns    |       |

| DT low hold ref. to CAS(real time read transfer)                     | tстн         | 20  | ayı, | 25  |      | 30  |      | ns    |       |

| DT low hold ref. to col.addr.(real time read transfer)               | tATH         | 25  |      | 30  |      | 35  |      | ns    |       |

| SE set-up time referenced to RAS                                     | tesr         | 0   |      | 0   |      | 0   |      | ns    |       |

| SE hold time referenced to RAS                                       | <b>t</b> REH | 10  |      | 15  |      | 15  |      | ns    |       |

| DT to RAS precharge time                                             | tTRP         | 50  |      | 60  |      | 70  |      | ns    |       |

| DT precharge time                                                    | tTP          | 20  |      | 25  |      | 30  |      | ns    |       |

| RAS to first SC delay(read transfer)                                 | tRSD         | 70  |      | 80  |      | 100 |      | ns    |       |

| CAS to first SC delay(read transfer)                                 | tCSD         | 30  |      | 35  |      | 50  |      | ns    |       |

| Col. Addr.to first SC delay(read transfer)                           | tASD         | 40  |      | 40  |      | 55  |      | ns    |       |

| Last SC to DT lead time                                              | tTSL         | 5   |      | 5   |      | 5   |      | ns    |       |

| DT to first SC delay time(read transfer)                             | ttsd         | 10  |      | 15  |      | 15  |      | ns    |       |

| Last SC to RAS set-up time(serial input)                             | tSRS         | 30  | ~    | 30  |      | 30  |      | ns    |       |

| RAS to first SC delay time(serial input)                             | tSRD         | 20  |      | 25  |      | 25  |      | ns    |       |

| RAS to serial input delay time                                       | tSDD         | 40  |      | 50  |      | 50  |      | ns    |       |

| Serial output buffer turn-off delay from RAS (pseudo write transfer) | tsdz         | 10  | 30   | 10  | / 35 | 10  | 50   | ns    | 7     |

| Serial Input to first SC delay time                                  | tszs         | 0   |      | 0   |      | 0   |      | ns    |       |

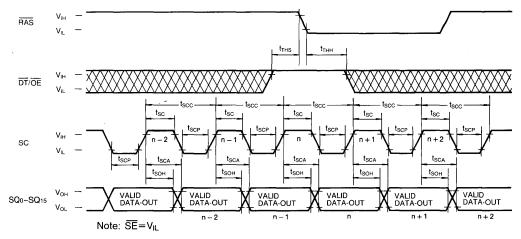

| SC cycle time                                                        | tscc         | 25  |      | 25  |      | 30  |      | ns    |       |

| SC pulse width(SC high time)                                         | tsc          | 7   |      | 7   |      | 10  |      | ns    |       |

| SC precharge(SC low time)                                            | tSCP         | 7   |      | 7   |      | 10  |      | ns    |       |

| Access time from SC                                                  | tSCA         |     | 20   |     | 20   |     | 25   | ns    | 4     |

| Serial output hold time from SC                                      | tsoн         | 5   |      | 5   |      | 5   |      | ns    |       |

| Serial input set-up time                                             | tsps         | 0   |      | 0   |      | 0   |      | ns    |       |

| Serial input hold time                                               | tSDH         | 15  |      | 15  |      | 20  |      | ns    |       |

| Access time from SE                                                  | tsea         |     | 20   |     | 20   |     | 25   | ns    | 4     |

| SE pulse width                                                       | tSE          | 20  |      | 25  |      | 25  |      | ns    |       |

| SE precharge time                                                    | tSEP         | 20  |      | 25  |      | 25  |      | ns    |       |

| Serial output turn-off from SE                                       | tsez         | 3   | 15   | 3   | 15   | 3   | 15   | ns    | 7     |

| Serial input to SE delay time                                        | tsze         | 0   |      | 0   |      | 0   |      | ns    |       |

#### AC CHARACTERISTICS (Continued)

| Devenue deve                     | Symbol | 70ns |     | 80ns |     | 100ns |     | Units |       |

|----------------------------------|--------|------|-----|------|-----|-------|-----|-------|-------|

| Parameter                        | Symbol | Min  | Max | Min  | Max | Min   | Max | Units | Notes |

| Serial write enable set-up time  | tsws   | 5    |     | 5    |     | 5     |     | ns    |       |

| Serial write enable hold time    | tswн   | 15   |     | 15   |     | 20    |     | ns    |       |

| Serial write disable set-up time | tswis  | 5    |     | 5    |     | 5     |     | ns    |       |

| Serial write disable hold time   | tswih  | 15   |     | 15   |     | 20    |     | ns    |       |

#### NOTES

- An initial pause of 200/s is required after power-up followed by any 8 RAS, 8SC cycles before proper device operation is achieved. If the internal refresh counter is used a minimum of 8 CAS-before-RAS initialization cycles are required instead of 8 RAS cycles.

- VIH(min) and VIL(max) are reference levels for measuring timing of input signals. Transition times are measured between VIH(min) and VIL(max), and are assumed to be 5ns for all inputs.

- 3. RAM port outputs are measured with a load equivalent to 1 TTL load and 50pF. DOUT comparator level: VOH/VOL=2.0/0.8V

- SAM port outputs are measured with a load equijalent to 1TTL load and 30pF Dout comparator level: Voн/VoL=2.0/0.8V

- 5. Operation within the tRCD(max) limit insures that tRAC(max) can be met. The tRCD(max) is specified as a reference point only: If tRCD is greater than the specified tRCD(max) limit, then access time is controlled exclusively by tCAC.

- 6. Assumes that tRCD ≥ tRCD(max).

- The parameters, toFF(max), toEz(max), tsDz(max) and tsEz(max), define the time at which the output achieves the open circuit condition and are not reverenced to VOH or VOL.

- 8. The twcs, tRwb, tcwb and tAwb are non restrictive operating parameters. They are included in the data sheet as electrical characteristics only. If twcs ≥ twcs(min) the cycle is an early write cycle and the data out pin will remain high impedance for the duration of the cycle. If tcwb ≥ tcwb(min)and tRwb ≥ tRwb(min)and tAwb ≥ tAwb(min), then the cycle is a read-write cycle and the data out will contain the data read from the selected address. If neither of the above conditions are satisfied, the condition of the data out is indeterminate.

- 9. Either tRCH or tRRH must be satisfied for a read cycle.

- These parameters are referenced to the CAS leading edge in early write cycles and to the WE leading edge in read-write cycle.

- 11. Operation within the tRAD(max) limit insured that tRCD(max) can be met. The tRAD(max) is specified as a reference point only. If the tRAD is greater than the specified tRAD(max) limit, then access time is controlled by tAA.

- During power-up RAS, DT/OE must be held High or track with Vcc. After power-up, initial status of chip is described below.

| PIN         | STATUS     |

|-------------|------------|

| Tap Pointer | Invalid    |

| Wi/DQi      | Hi-Z       |

| SAM Port    | Input Mode |

| SDQi        | Hi-Z       |

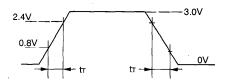

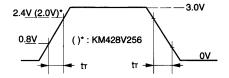

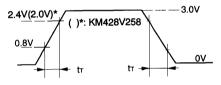

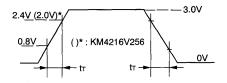

13. Input pulse levels are from 0.0V to 3.0Volts. All timing measurements are reverenced from VIL (max) and VIH(min) with transition time=3.0ns

14. twcr, tDHR are reverenced to tRAD(max).

#### **DEVICE OPERATION**

The KM428C64 contains 524,288 memory locations.

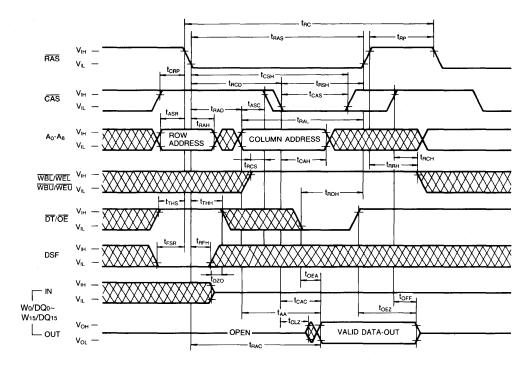

Sixteen address bits are required to address a particular 8bit word in the memory array. Since the KM428C64 has only 8 address input pins, time multiplexed addressing is used to input 8 row and 8 column addresses. The multiplexing is controlled by the timing relationship between the row address strobe (RAS), the column address strobe (CAS) and the valid row and column address inputs.

Operation of the KM428C64 begins by strobing in a valid row address with RAS while CAS remains high.

Then the address on the 8 address input pins is changed from a row address to a column address and is strobed in by  $\overline{CAS}$ . This is the beginning of any KM428C64 cycle in which a memory location is accessed. The specific type of cycle is determined by the state of the write enable pin and various timing relationship. The cycle is terminated when both  $\overline{RAS}$  and  $\overline{CAS}$  have returned to the high state. Another cycle can be initiated after  $\overline{RAS}$  remains high long enough to satisfy the  $\overline{RAS}$  precharge time (tnp) requirement.

#### RAS and CAS Timing

The minimum  $\overline{\text{RAS}}$  and  $\overline{\text{CAS}}$  pulse widths are specified by tras (min) and tcas (min) respectively. These minimum pulse widths must be satisfied for proper device operation and data integrity. Once a cycle is initiated by bringing  $\overline{\text{RAS}}$  low, it must not be aborted prior to satisfying the minimum  $\overline{\text{RAS}}$  and  $\overline{\text{CAS}}$  pulse widths.

In addition, a new cycle must not begin until the minimum RAS precharge time, tRP, has been satisfied. Once a cycle begins, internal clocks and other circuits within the KM428C64 begin a complex sequence of events.

If the sequence is broken by violating minimum timing requirement, loss of data integrity can occur.

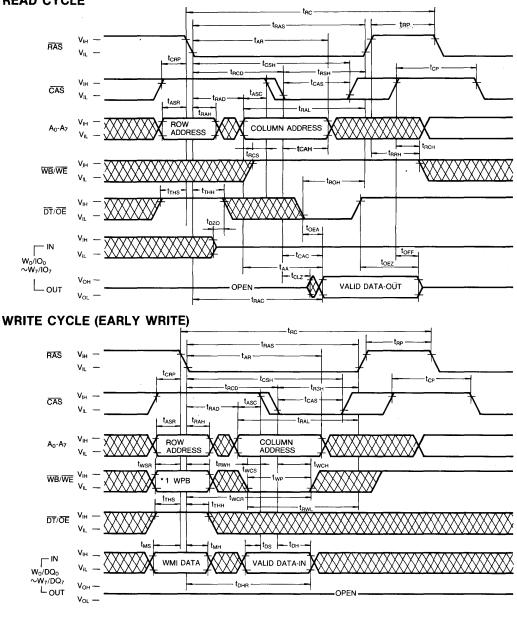

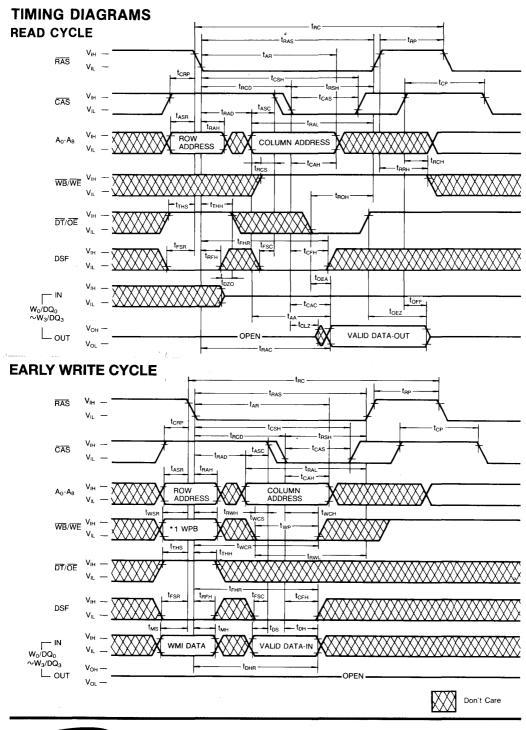

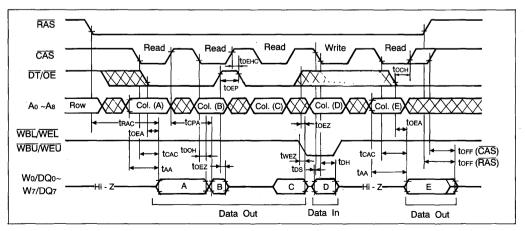

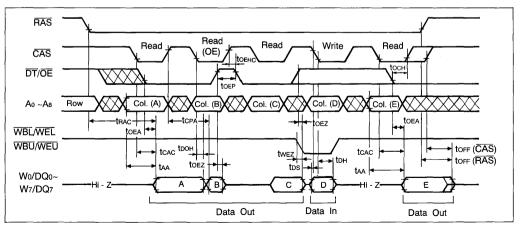

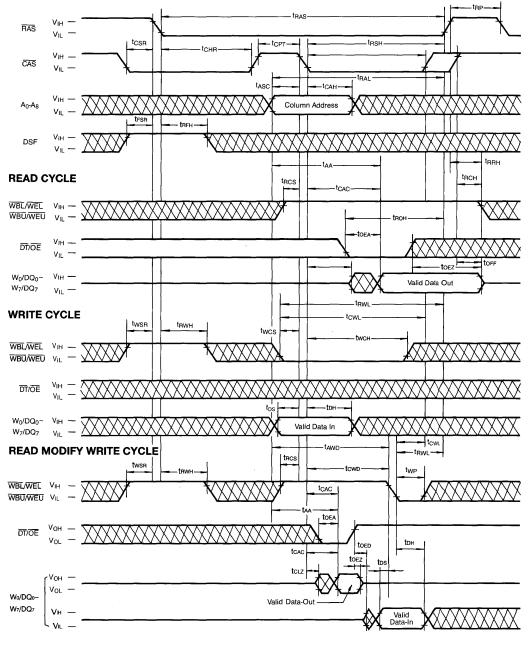

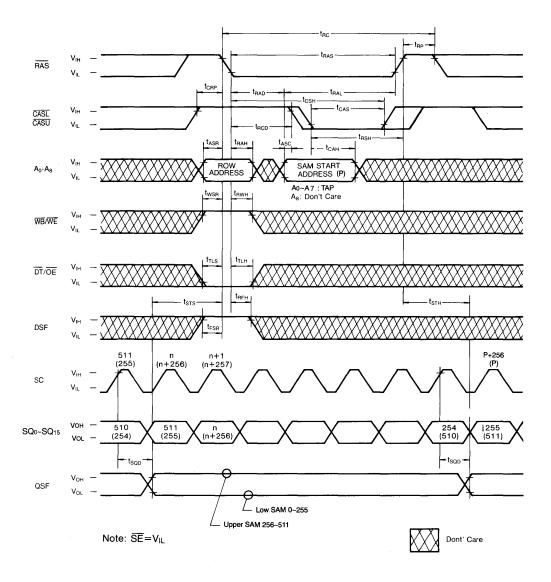

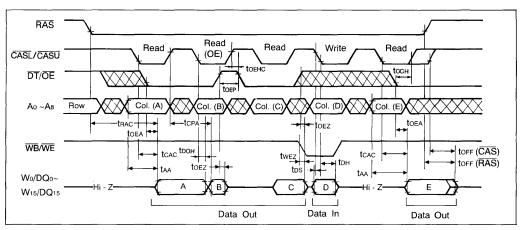

#### Read

A read cycle is achieved by maintaining  $\overline{WB}/\overline{WE}$  high during a  $\overline{RAS}$  /  $\overline{CAS}$  cycle. The access time is normally specified with respect to the falling edge of  $\overline{RAS}$ . But the access time also depends on the falling edge of  $\overline{CAS}$  and on the valid column address transition.

If CAS goes low before tRCD (max) and if the column

address is valid before trad (max) then the access time to valid data is specified by trac (min). However, if  $\overline{CAS}$  goes low after trad (max) or the column address becomes valid after trad (max), access is specified by tcac or trad.

The KM428C64 has common data I/O pins. The  $\overline{\text{DT}/\text{OE}}$  has been provided so the output buffer can be precisely controlled. For data to appear at the outputs,  $\overline{\text{DT}/\text{OE}}$  must be low for the period of time defined by toEA.

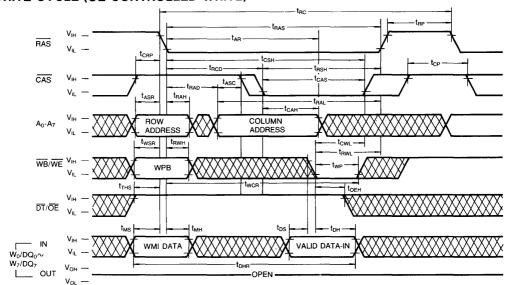

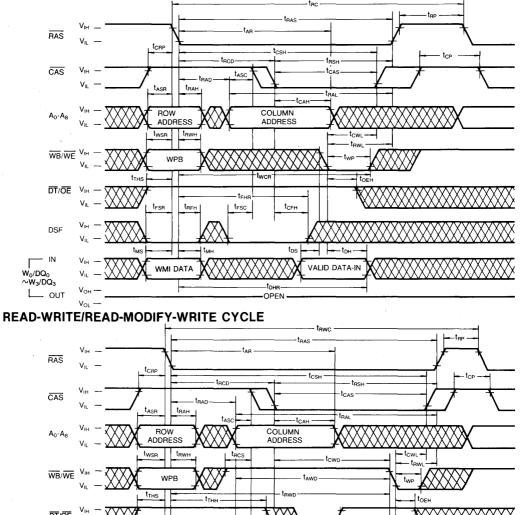

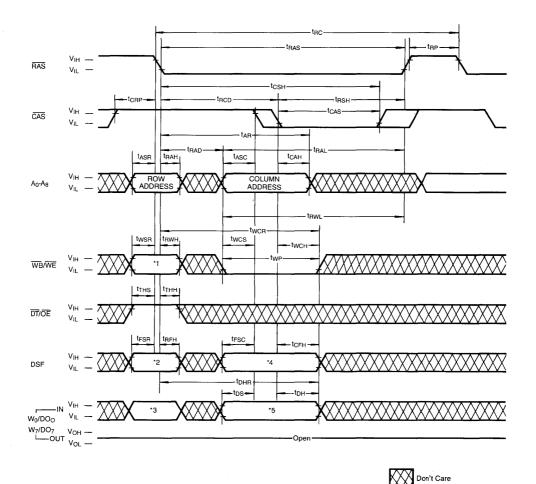

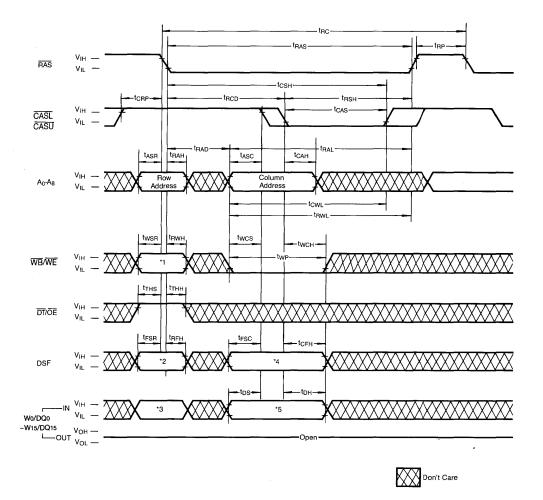

#### Write

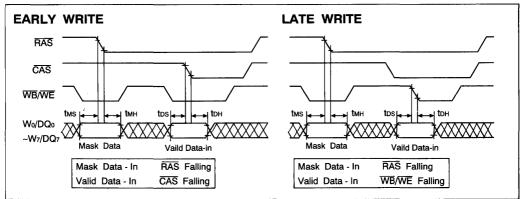

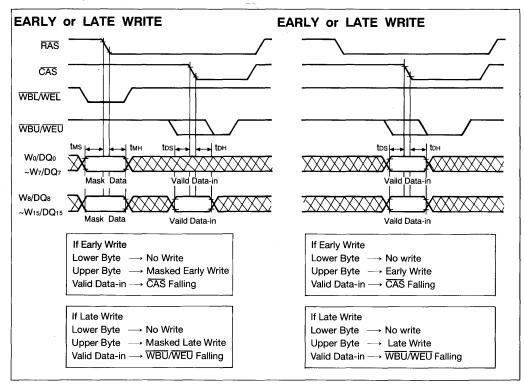

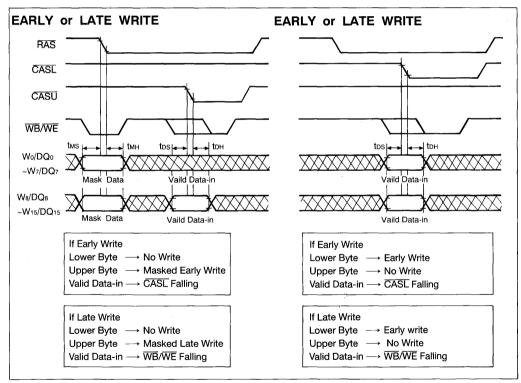

The KM428C64 can perform early write and read-modify -write cycles. The difference between these cycles is in the state of data-out and is determined by the timing relationship between  $\overline{WB}/\overline{WE}$ ,  $\overline{DT}/\overline{OE}$  and  $\overline{CAS}$ . In any type of write cycle. Data-in must be valid at or before the falling edge of  $\overline{WB}/\overline{WE}$ , whichever is later.

#### **Fast Page Mode**

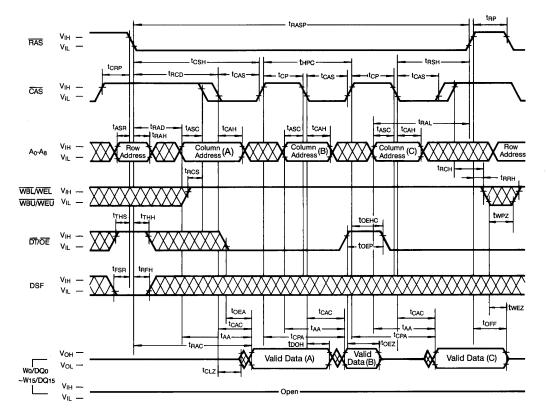

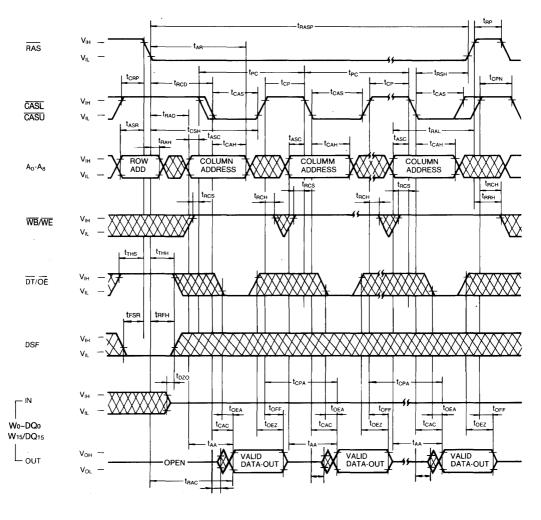

Fast page mode provides high speed read,write or readmodify-write access to all memory cells within a selected row. These cycles may be mixed in any order. A fast page mode cycle begins with a normal cycle. Then, while **FAS** is kept low to maintain the row address, **CAS** is cycled to strobe in additional column addresses. This eliminates the time required to set up and strobe sequential row addresses for the same page.

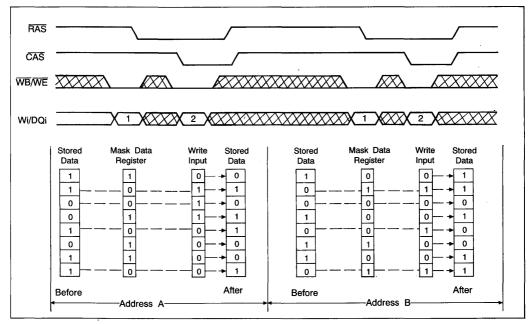

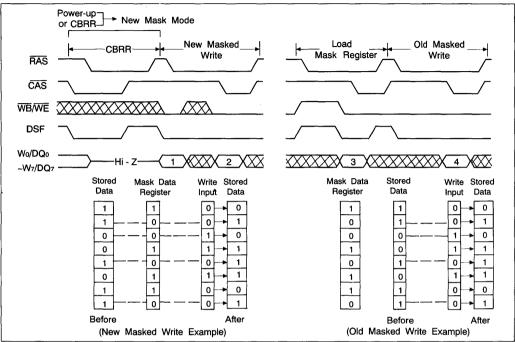

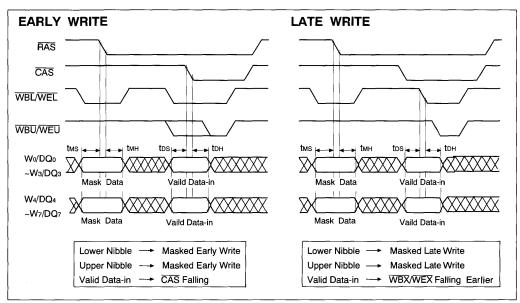

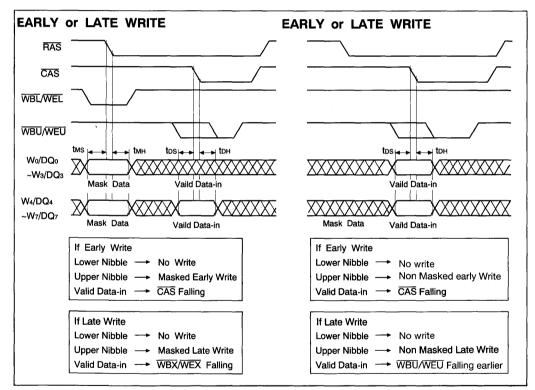

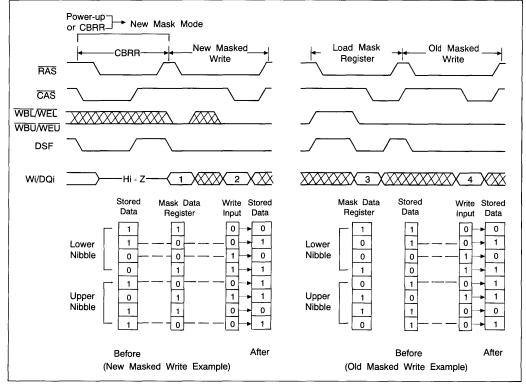

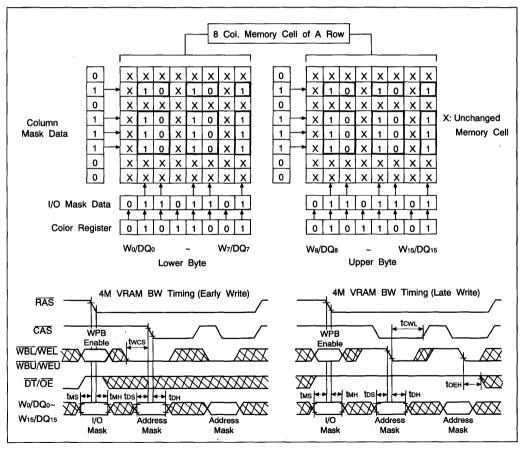

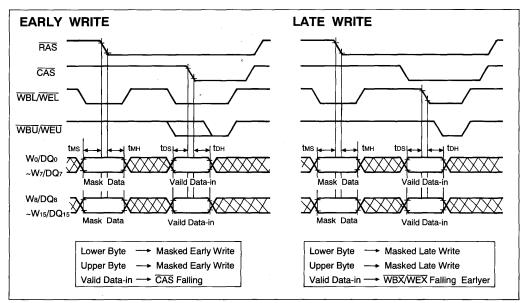

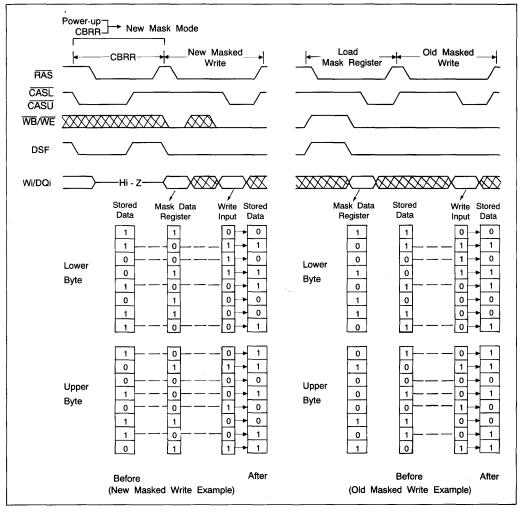

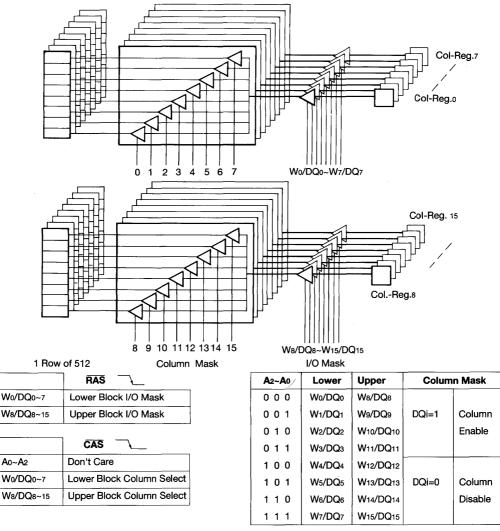

#### Writer-Per-Bit

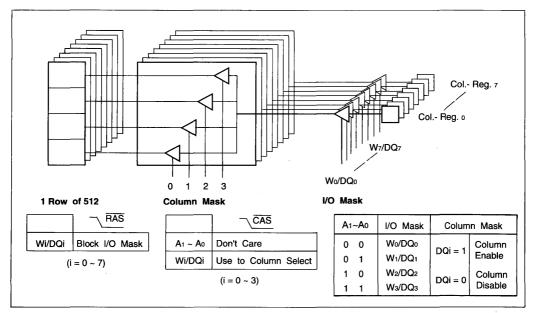

The write-per-bit function selectively controls the internal write-enable circuits of the RAM port. When  $\overline{WB}/\overline{WE}$  is held "low" at the falling edge of  $\overline{RAS}$ , during a random access operation, the write-mask is enabled. At the same time, the mask data on the Wi/DQi pins is latched onto the write-mask register (WM1). When a "0" is sensed on any of the Wi/DQi pins, their corresponding write circuits are disabled and new data will not be written.

When a "1" is sensed on any of the Wi/DQi pins, their corresponding write circuits will remain enabled so that new data is written. The write mask data is valid for only one cycle the truth table of the write-per-bit function are shown in table 1.

| RAS | CAS | DT/OE | WB/WE | Wi/DQi | FUNCTION     |

|-----|-----|-------|-------|--------|--------------|

|     | н   | н     | Н     | *      | WRITE ENABLE |

|     |     |       |       | 1      | WRITE ENABLE |

| ▲   | н   | н     | L     | 0      | WRITE MASK   |

#### DEVICE OPERATION (Continued) Data Output

The KM428C64 has a three-state output buffer which are controlled by  $\overline{CAS}$  and  $\overline{DT}/\overline{OE}$ . When either  $\overline{CAS}$  or  $\overline{DT}/\overline{OE}$  is high (VIH) the output is in the high impedance (Hi-Z) state. In any cycle in which valid data appears at the output goes into the low impedance state in a time specified by tcL2 after the falling edge of  $\overline{CAS}$ . Invalid data may be present at the output during the time after tcL2 and before the valid data appears at the output. The timing parameter tcAc, tRAC and tAA specify when the valid data will be present at the output. The valid data will  $\overline{CAS}$  returns high. This is true even if a new  $\overline{RAS}$  cycle occurs (as in hidden refresh). Each of the KM428C64 operating cycles is listed below after the corresponding output state produced by the cycle.

Valid Output Data: Read, Read-Modify-Write, Hidden refresh, Fast page mode Read, Fast Page Mode Read-Modify-Write.

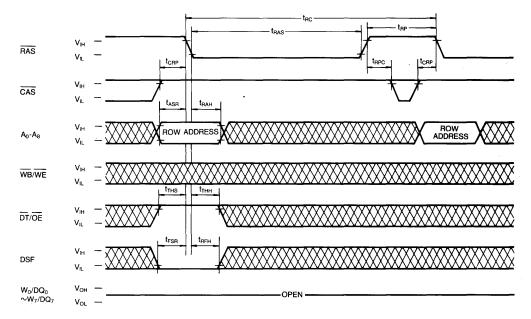

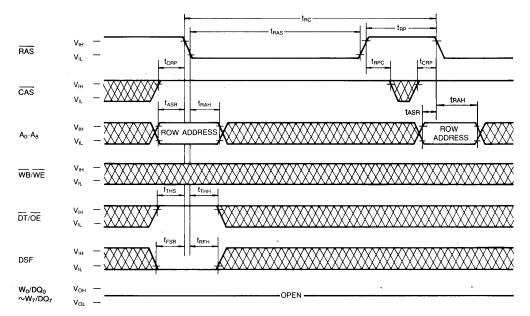

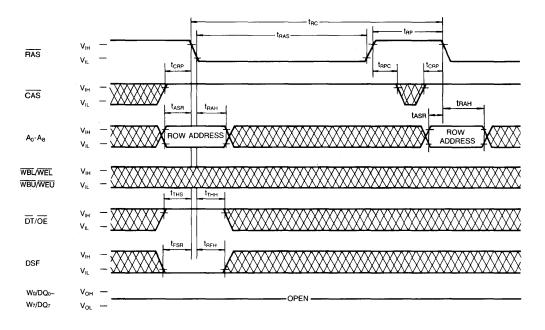

#### Refresh

The data in the KM428C64 is stored on a tiny capacitor within each memory cell. Due to leakage the data may leak off after a period of time. To maintain data integrity it is necessary to refresh each of the 256 rows every 4 ms. Any operation cycle performed in the RAM port refreshes the 2048 bits selected by the row addresses or an on-chip refresh address counter.

Either a burst refresh or distributed refresh may be used. There are several ways to accomplish this.

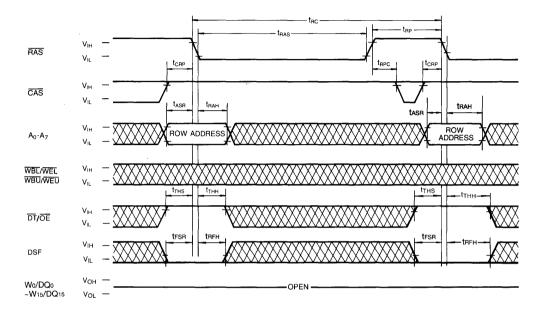

**RAS-Only Refresh:** This is the most common method for performing refresh. It is performed by strobing in a row address with RAS while  $\overline{CAS}$  remains high. This cycle must be repeated for each of the 256 row address,  $(A_0 \sim A_7)$ .

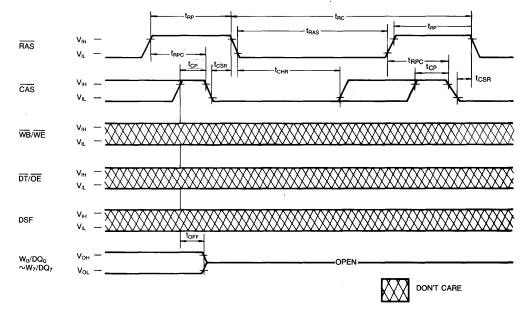

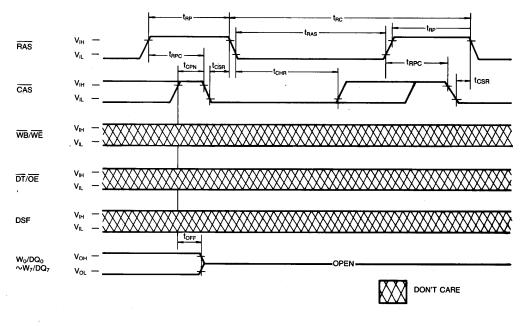

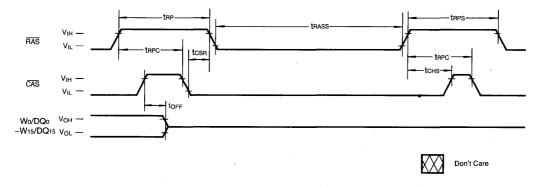

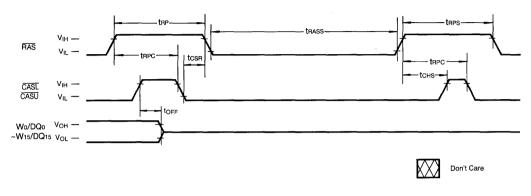

$\overline{\text{CAS-before-RAS}}$  Refresh: The KM428C64 has  $\overline{\text{CAS-before-RAS}}$  on-chip refresh capability that eliminates the need for external refresh addresses. If  $\overline{\text{CAS}}$  is held low for the specified set up time (tcsR) before  $\overline{\text{RAS}}$  goes low the on-chip refresh circuitry is enabled. An internal refresh operation automatically occurs. The refresh address is supplied by the on-chip refresh address counter which is then internally incremented in preparation for the next  $\overline{\text{CAS-before-RAS}}$  refresh cycle.

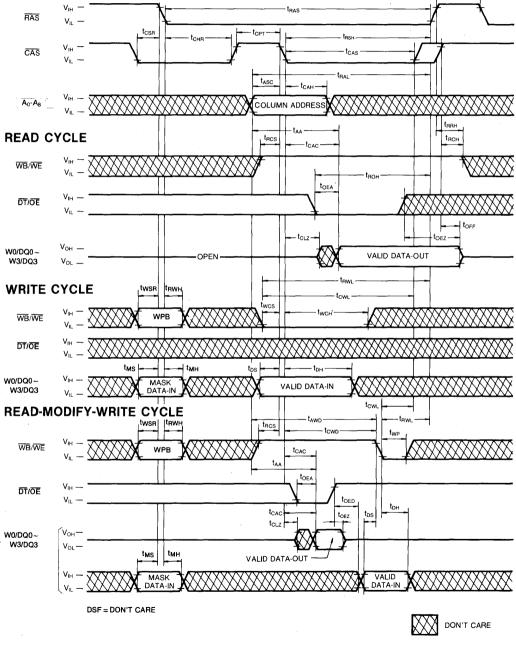

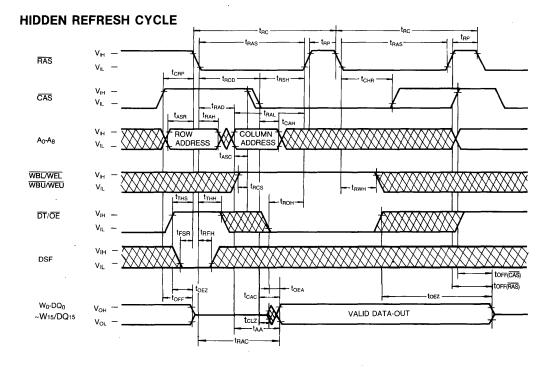

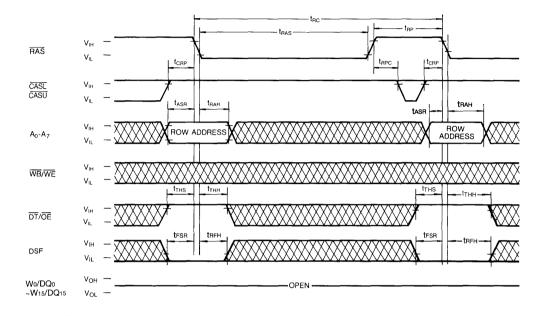

**Hidden Refresh:**A hidden refresh cycle may be performed while maintaining the latest valid data at the output by extending the CAS active time and cycling RAS.

The KM428C64 hidden refresh cycle is actually a CASbefore-RAS refresh cycle within an extended read cycle. The refresh row address is the preferred method.

#### **Transfer Operation**

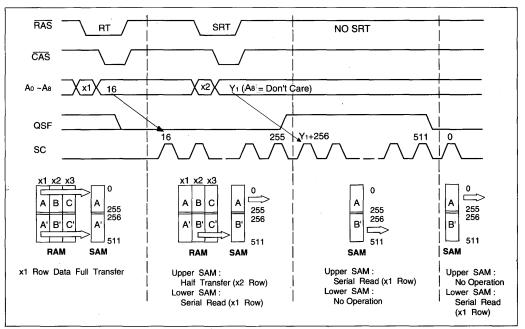

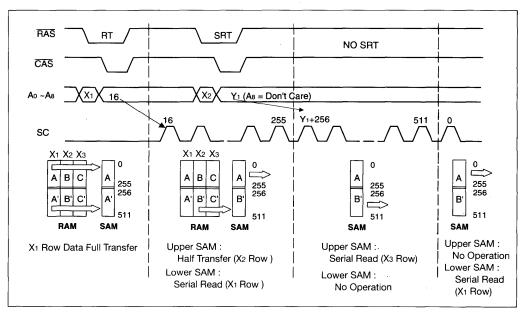

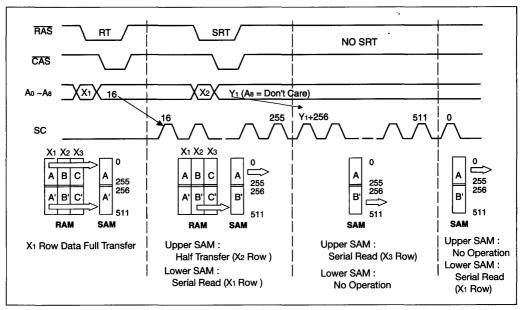

- 1. Normal Write/Read Transfer. (SAM → RAM / RAM → SAM)

- Pseudo Write Transfer (Switches serial port from serial Read to serial Write. No actual data transfer takes place between the RAM and the SAM).

- Real Time Read Transfer (On the fly Read Transfer Operation).

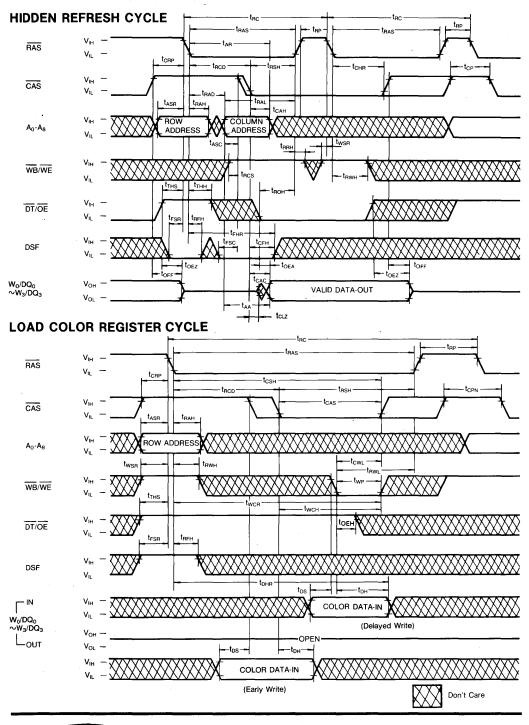

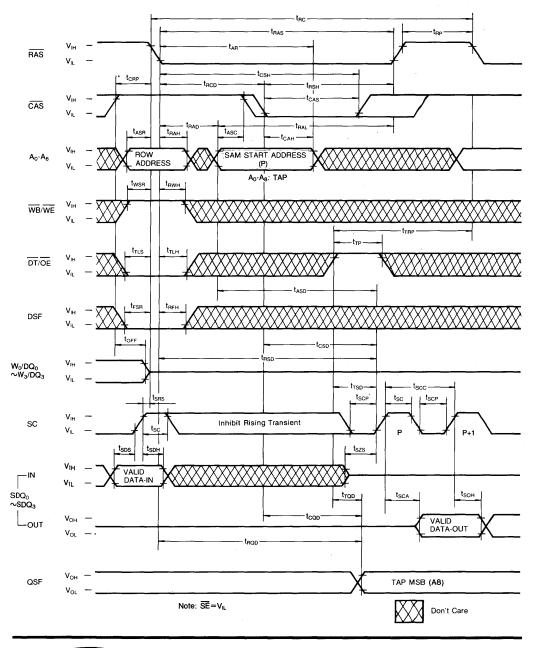

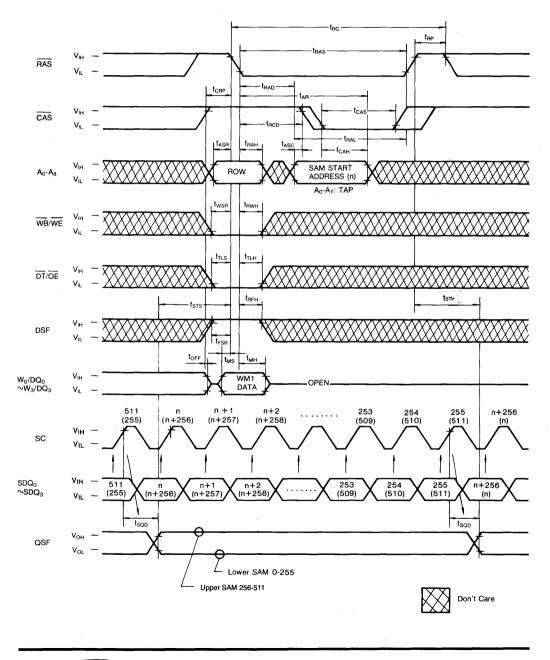

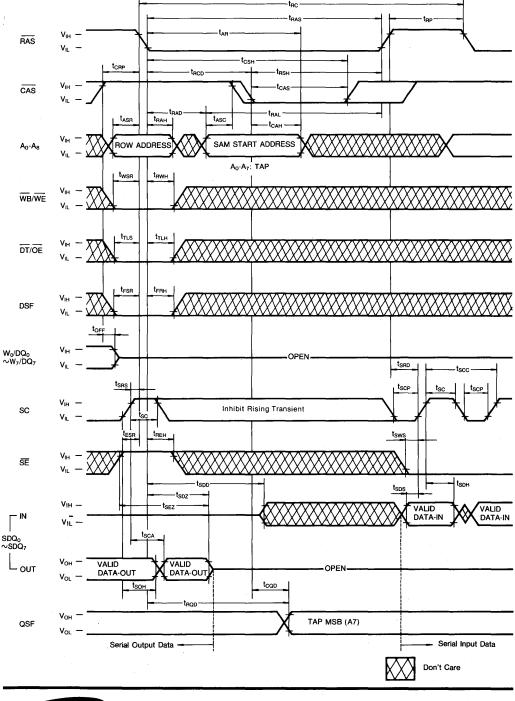

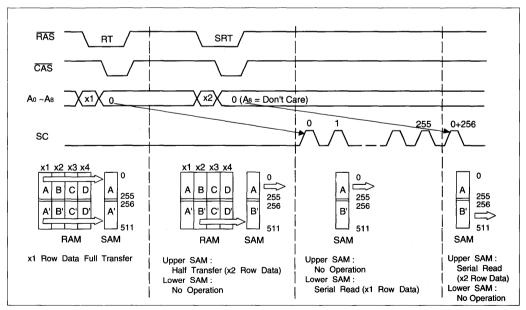

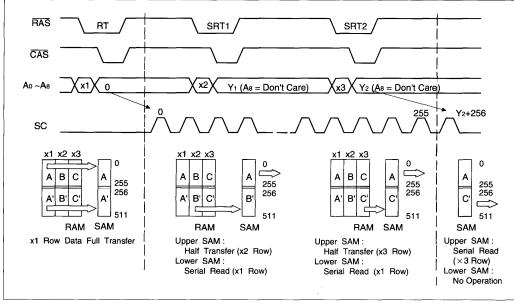

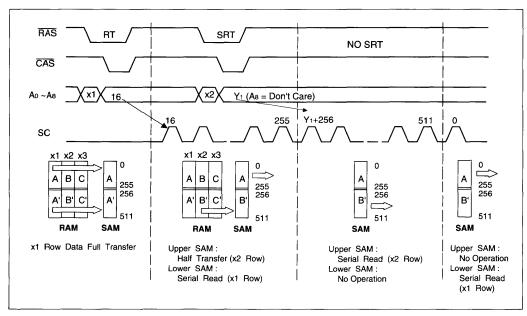

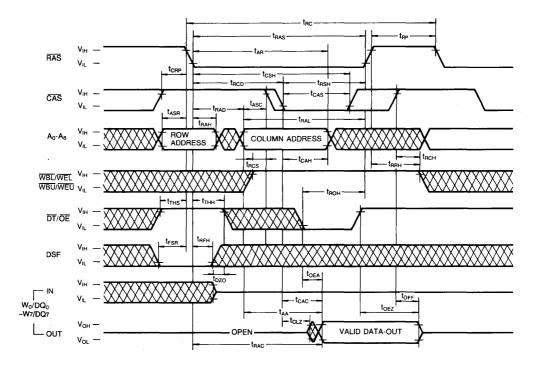

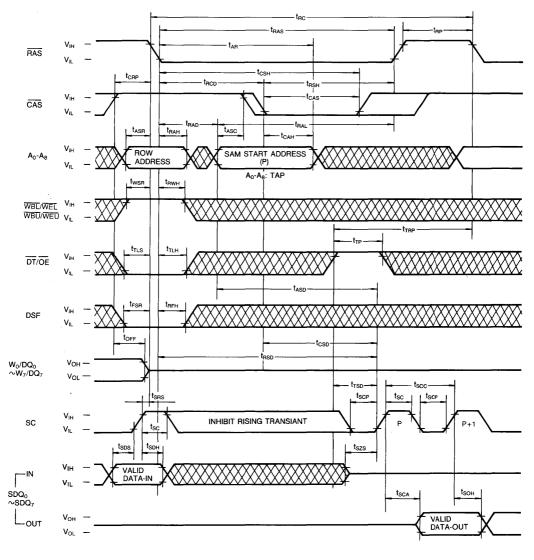

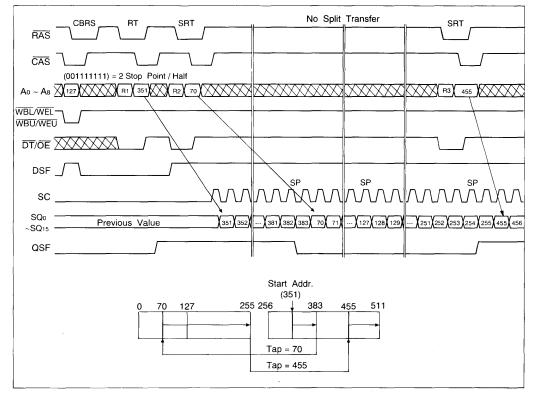

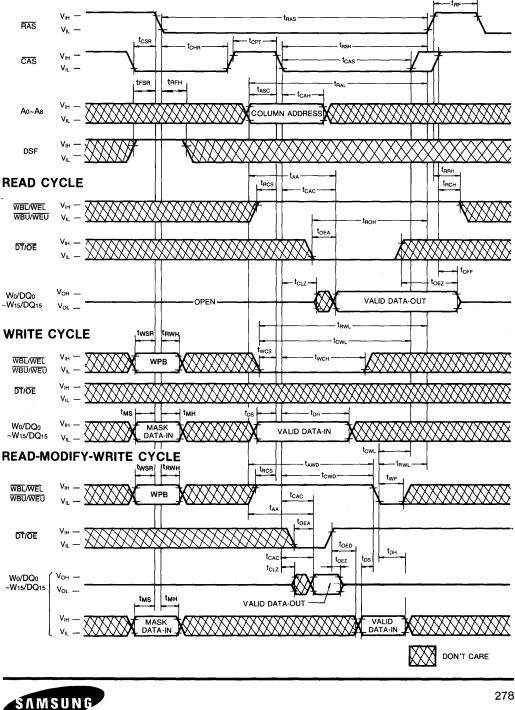

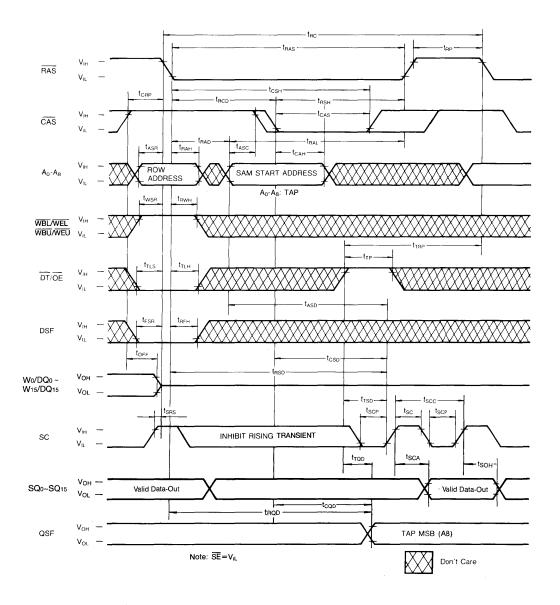

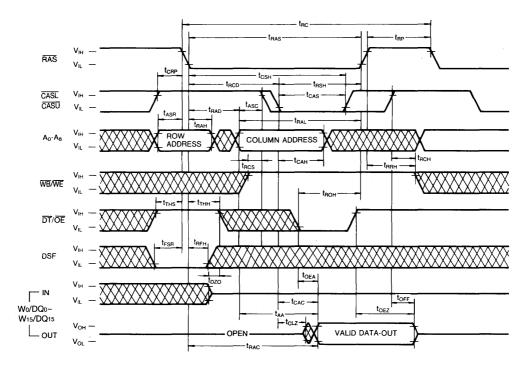

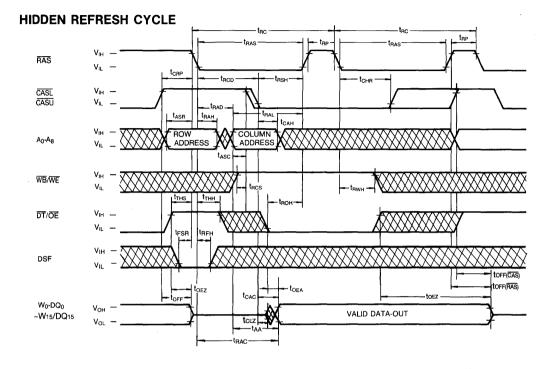

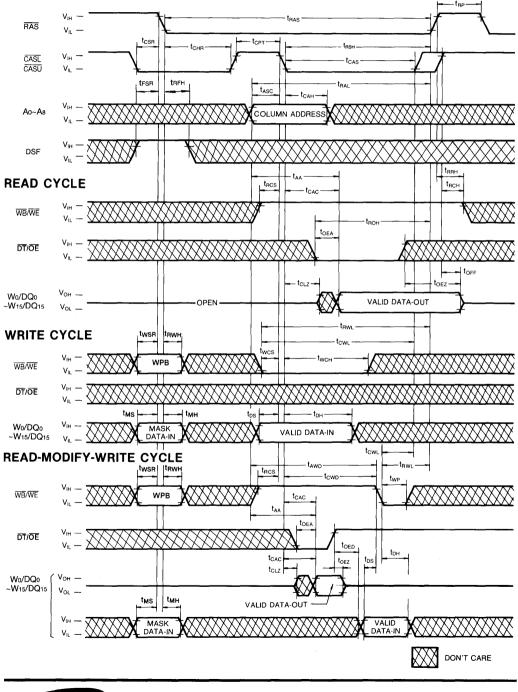

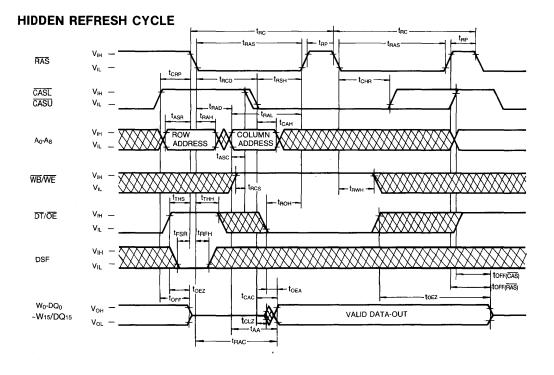

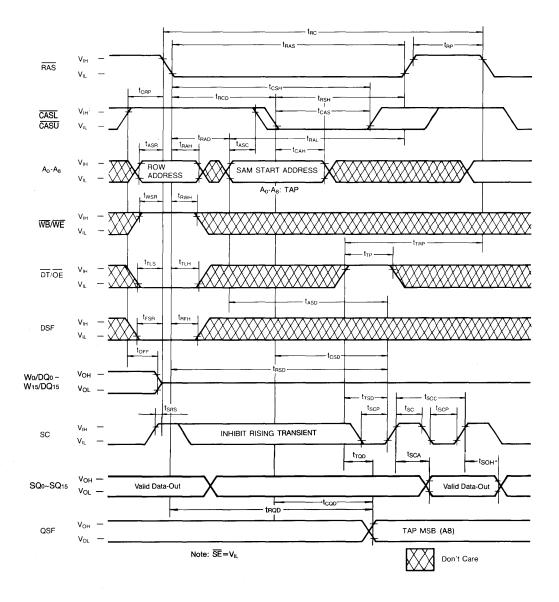

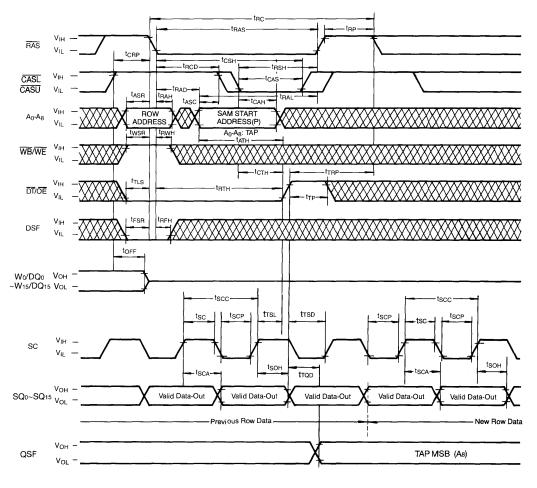

#### **Read-Transfer Cycle**

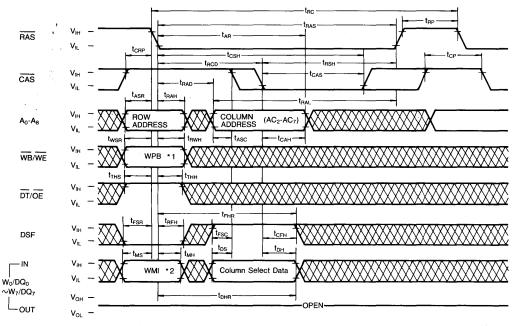

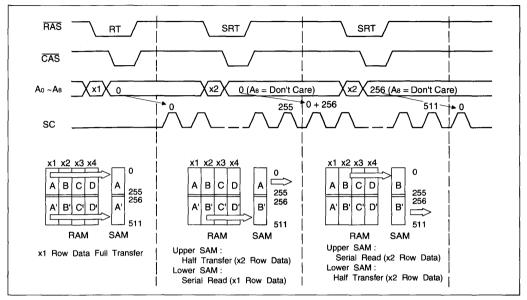

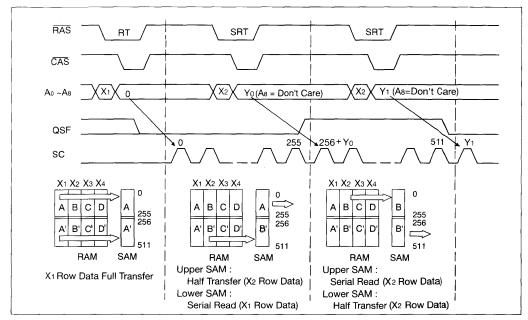

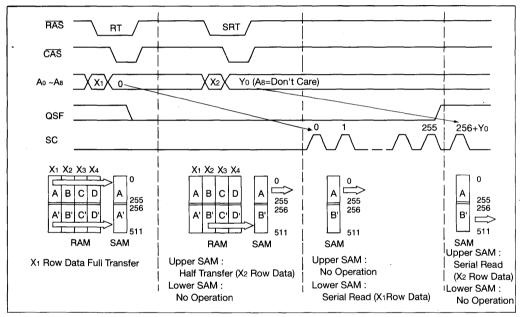

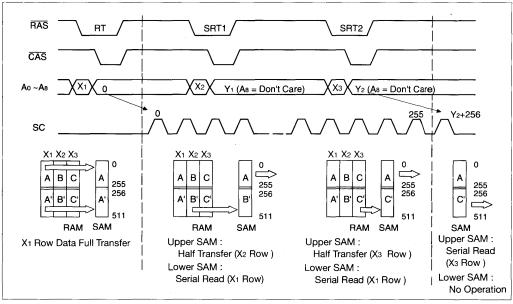

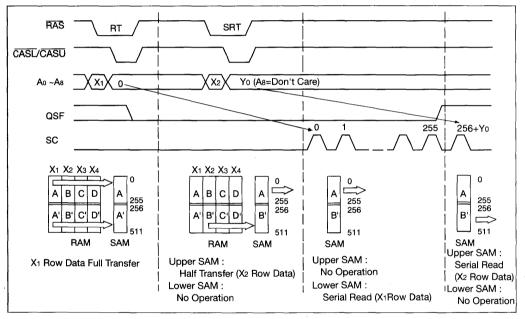

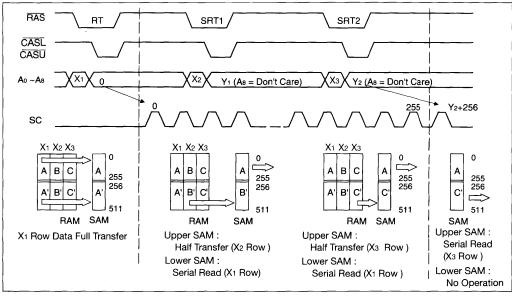

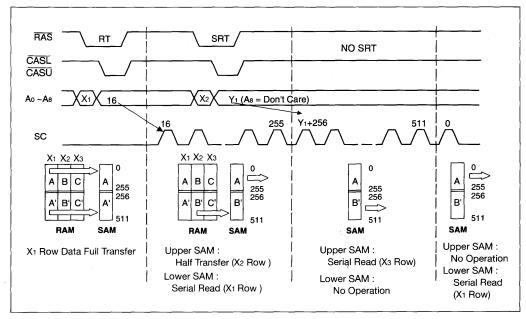

A read-transfer consists of loading a selected row of data from the RAM array into the SAM register.

A read-transfer is accomplished by holding  $\overline{CAS}$  high,  $\overline{DT}/\overline{OE}$  low and  $\overline{WB}/\overline{WE}$  high at the falling edge of  $\overline{RAS}$ . The row address selected at the falling edge of  $\overline{RAS}$  determines the RAM row to be transferred into the SAM.

The actual data transfer completed at the rising edge of  $\overline{\text{DT}/\text{OE}}$ . When the transfer is completed, the SDQ lines are set into the output mode.

In a read/real-time read-transfer cycle, the transfer of a new row of data is completed at the rising edge of  $\overline{\text{DT}}/\overline{\text{OE}}$  and becomes valid on the SDQ lines after the specified access time tsca from the rising edge of the subsequent serial clock (SC) cycle. The start address of the serial pointer of the SAM is determined by the column address selected at the falling edge of  $\overline{\text{CAS}}$

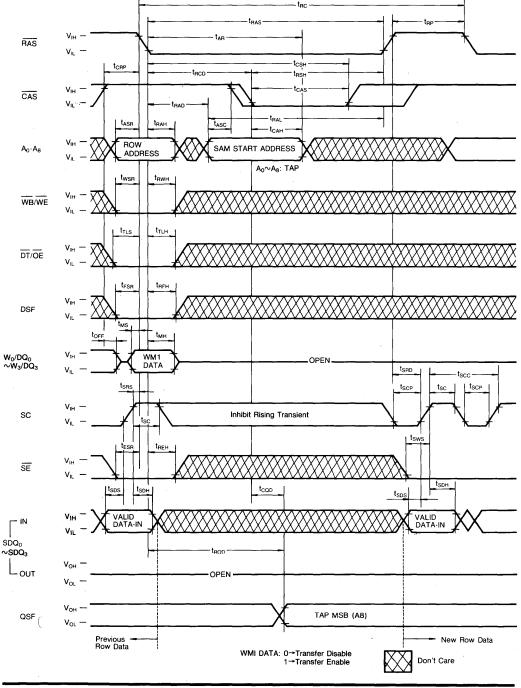

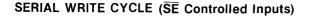

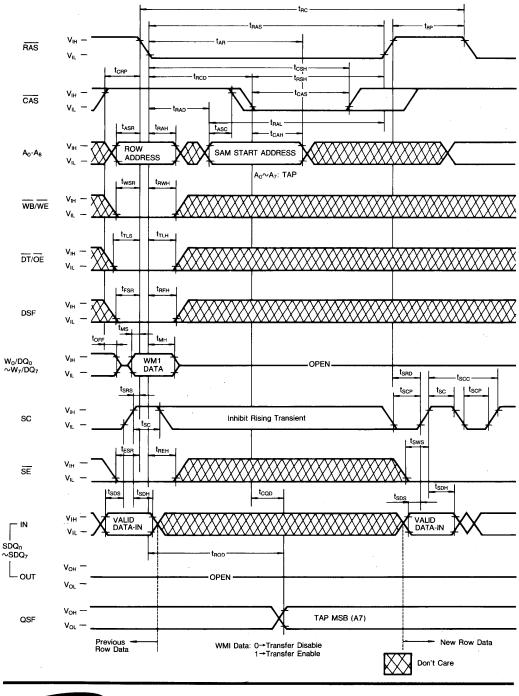

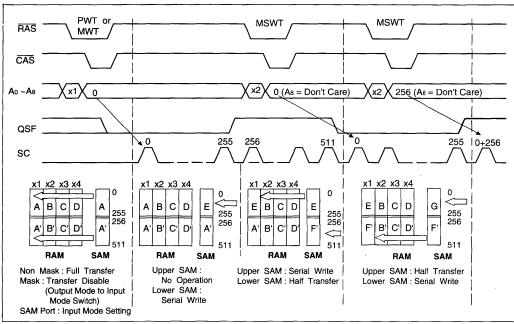

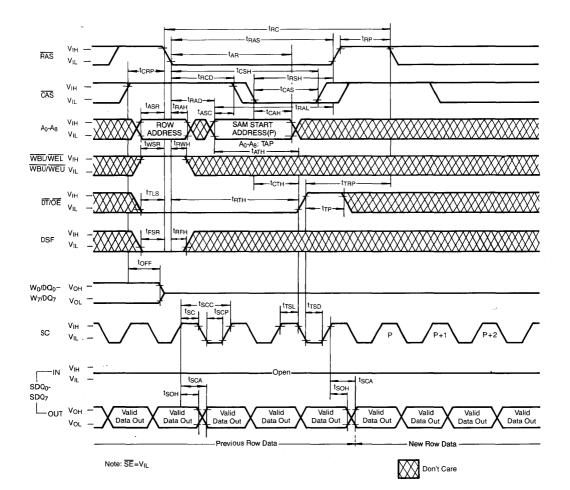

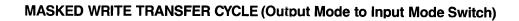

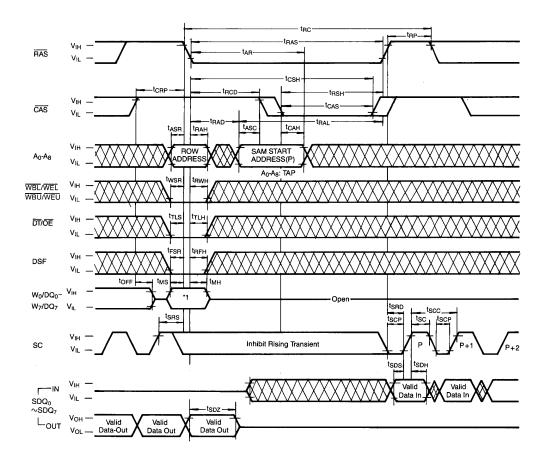

#### Write Transfer Cycle

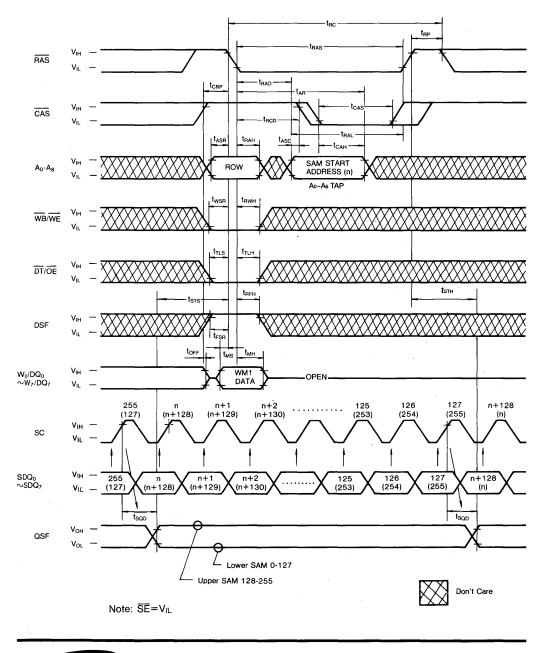

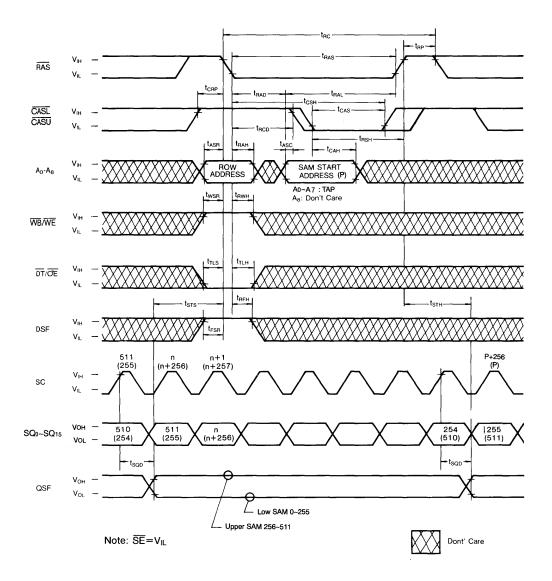

A write transfer cycle consist of loading the content of the SAM data register into a selected row of RAM array. A write transfer is accomplished by CAS high, DT/OE low, WB/WE low and SE low at the falling edge of RAS. The row address selected at the falling edge of RAS determines the RAM row address into which the data will be transferred. The column address selected at the falling edge of CAS determines the start address of the serial pointer of the SAM. After the write transfer is completed, the SDQ lines are in the input mode so that serial data synchronized with SC can be loaded. When consecutive write transfer operations are performed, there as a delay in availability between the last bit of the previous row and the first bit of the new row. Consequently the SC clock must be held at a constant ViL or ViH after the SC precharge time tscp has seen satisfied. A rising edge of the SC clock must not occur until after a specified delay tSRD from the falling edge of RAS.

#### **DEVICE OPERATION** (Continued)

#### Table 2. Truth table for Transfer operation

| RAS              | CAS | DT/OE | WB/WE | ŜĒ | FUNCTION                    | TRANSFER DIRECTION |

|------------------|-----|-------|-------|----|-----------------------------|--------------------|

| _                | н   | L     | н     | *  | Read transfer cycle         | RAM -> SAM         |

| $\sum_{i=1}^{n}$ | Л   | L     | L     | L  | Write transfer cycle        | SAM> RAM           |

|                  | н   | L     | L     | н  | Pseudo write transfer cycle |                    |

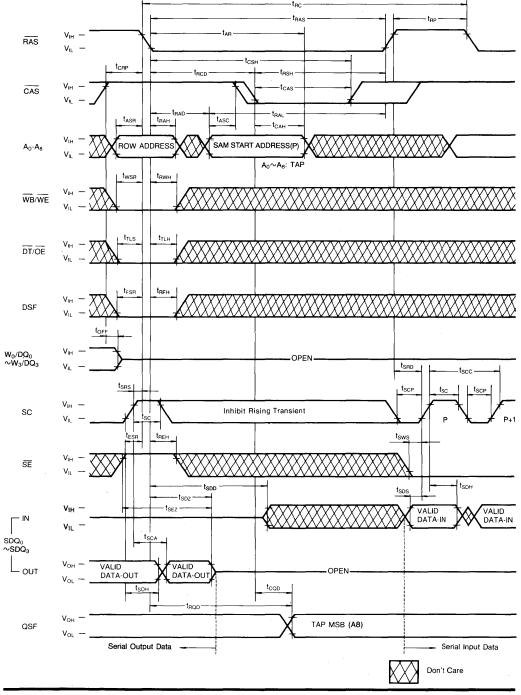

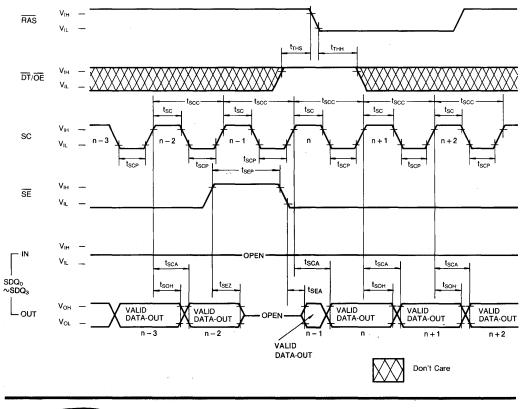

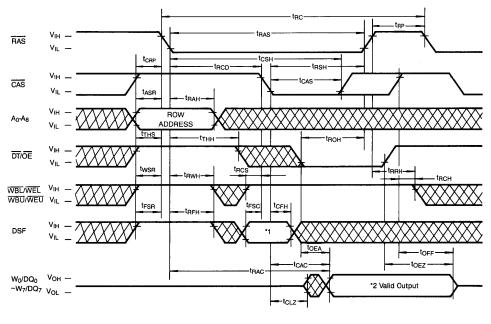

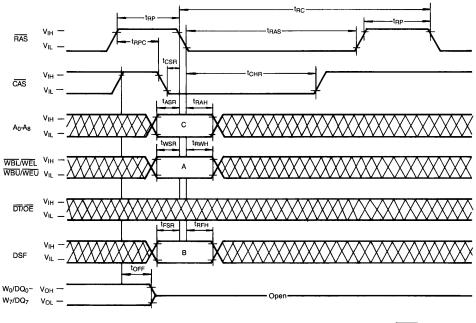

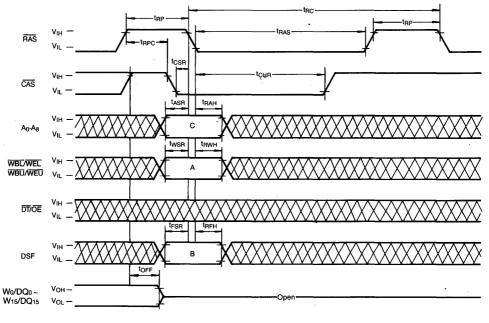

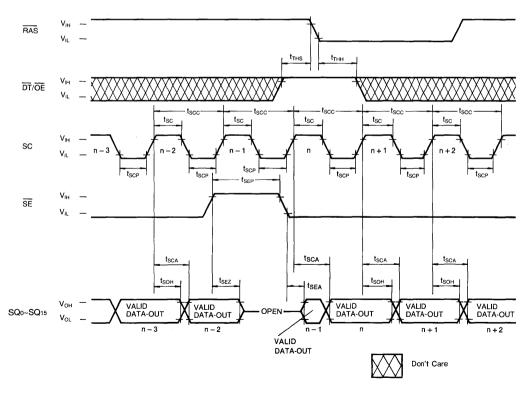

#### **Pseudo Write Transfer Cycle**

The pseudo write transfer cycle switches SDQ lines from serial read mode to serial write mode. It doesn't perform data transfer. A pseudo write transfer is accomplished by holding CAS high,  $\overline{DT}/\overline{OE}$  low,  $\overline{WB}/\overline{WE}$  low and SE high at the falling edge of RAS. The pseudo write transfer cycle must be performed after a read transfer cycle if the subsequent operation is a write transfer cycle. There is a timing delay associated with the switching of the SDQ lines from serial output mode to serial input mode. During this period, the SC clock must be held at a constant V<sub>IL</sub> or V<sub>IH</sub> after the tsc precharge time has been satisfied. A rising edge of the SC clock must not occur until after the specified delay tsRD from the falling edge of RAS.

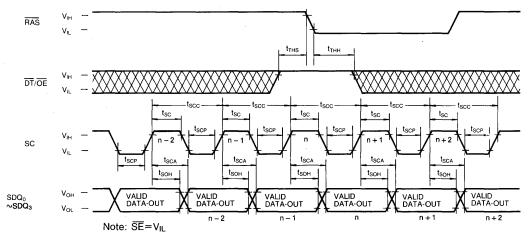

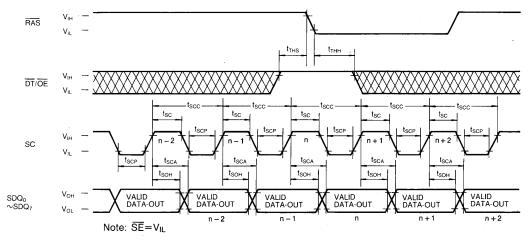

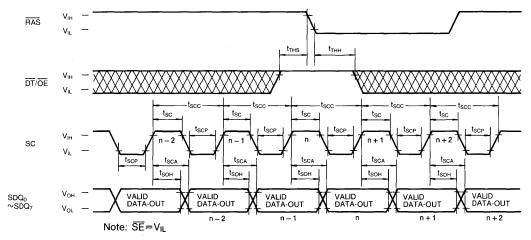

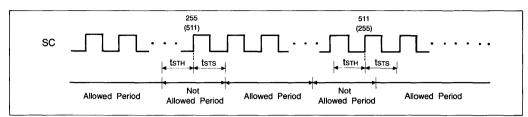

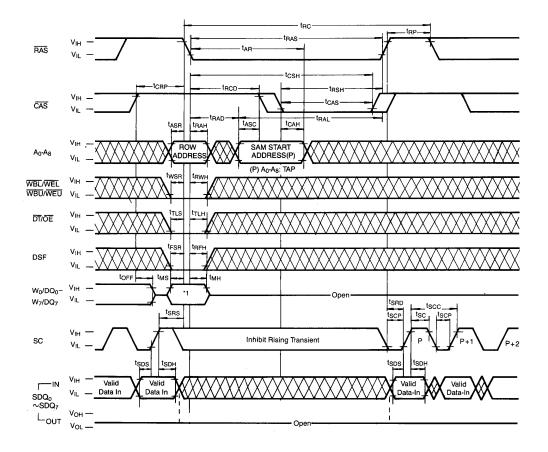

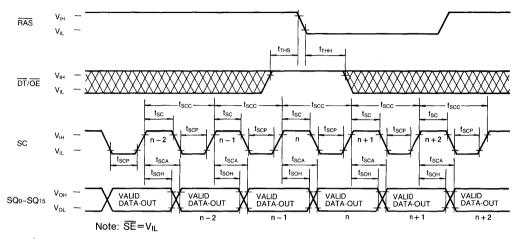

#### Serial Clock (SC)

All operation of the SAM port are synchronized with the serial clock SC. Data is shifted in or out of the SAM registers at the rising edge of SC. In a serial read, the output data becomes valid on the SDQ pins after the maximum specified serial access time tsca from the rising edge of SC. The serial clock SC also increments the 8 bit serial pointer which is used to select the SAM address. The pointer address is incremented in a wrap around mode to select sequential locations after the starting location which is determined by the column address in the read transfer cycle.

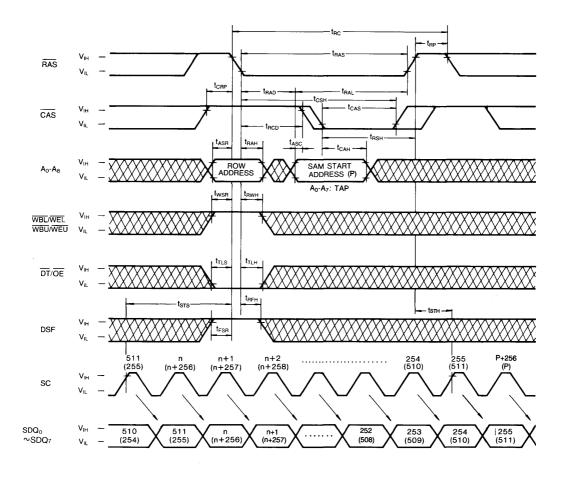

#### Serial Input / Output (SDQ0 ~ SDQ7)

Serial input and serial output share common I/O pins. Serial input or output mode is determined by the most recent transfer cycle. When a read transfer cycle is performed, the SAM port is in the output mode. When a pseudo write transfer is performed, the SAM port operation is switched from output mode to input mode. During subsequent write transfer cycle, the SAM port remains is the input mode.

#### Power - up

An initial pause of 200  $\mu$ sec is required, after power-up followed by 8 initialization cycles before proper device operation is assured.

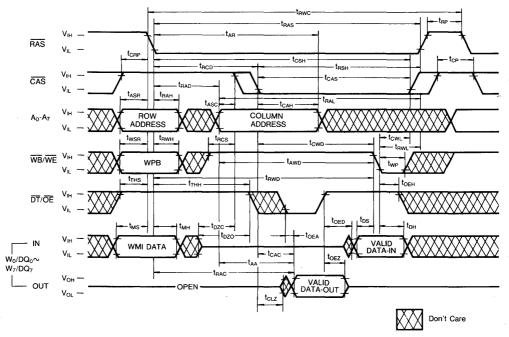

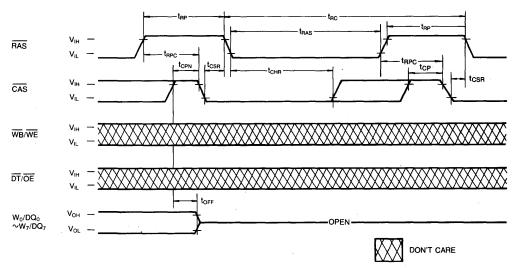

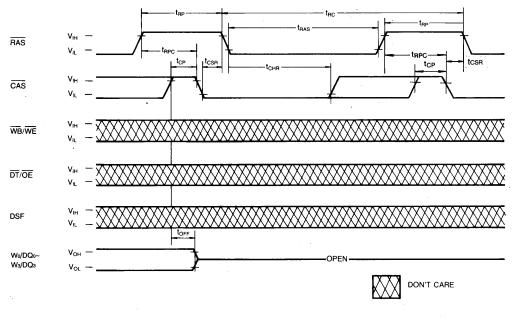

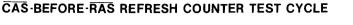

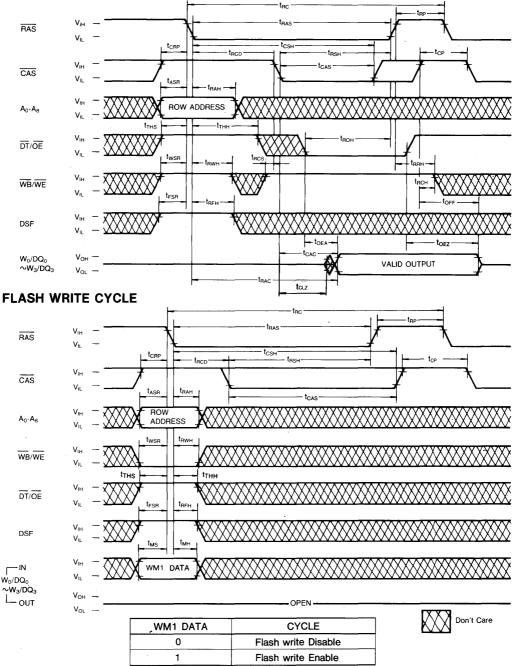

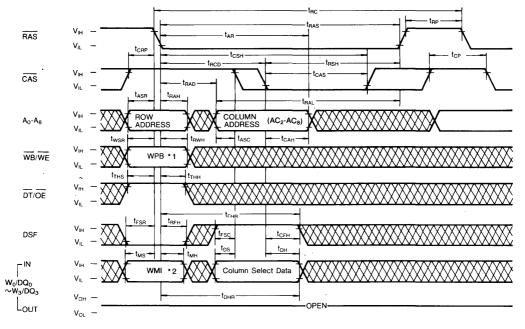

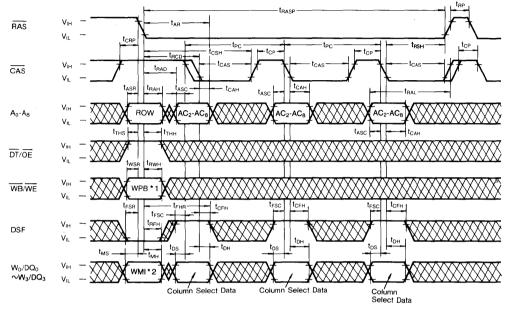

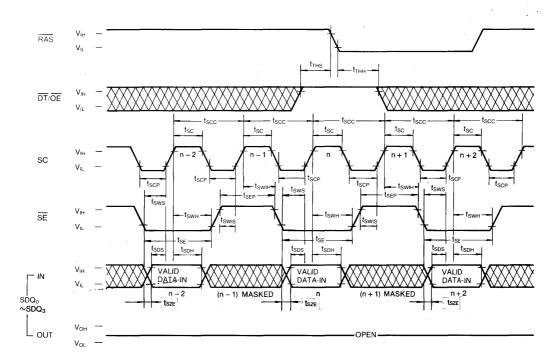

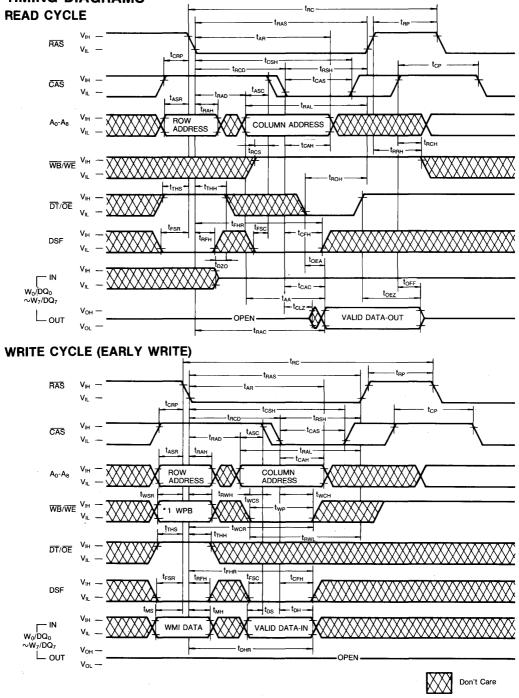

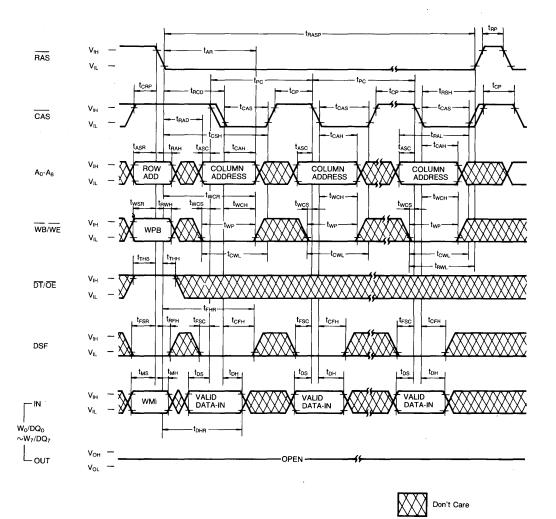

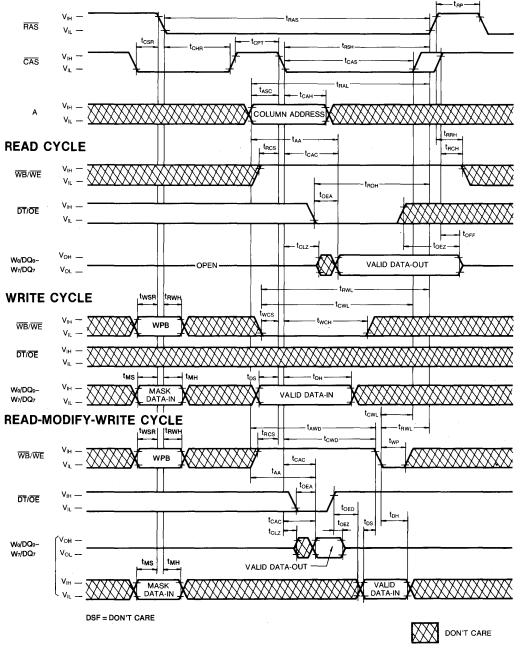

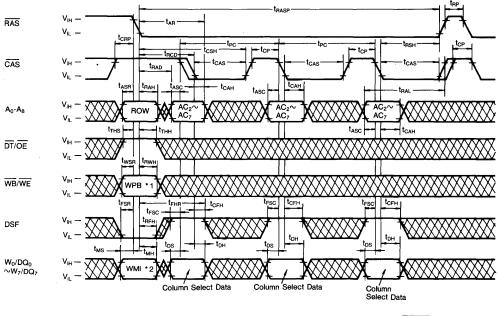

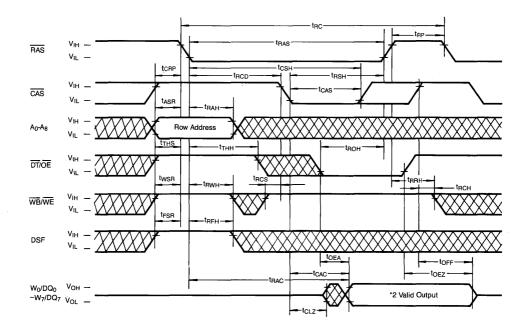

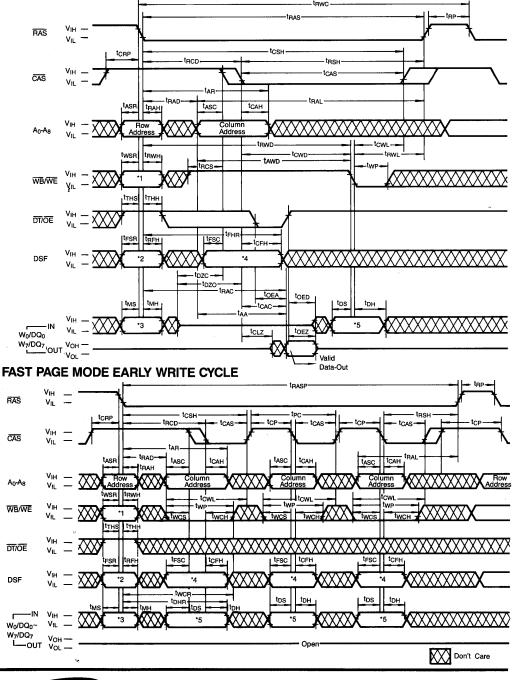

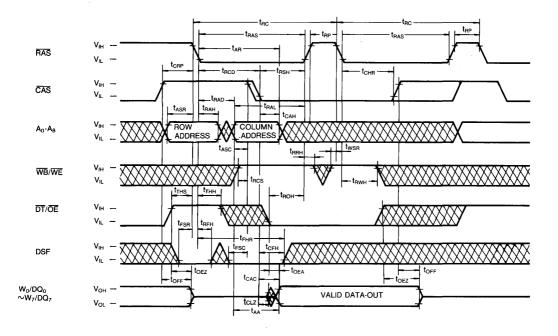

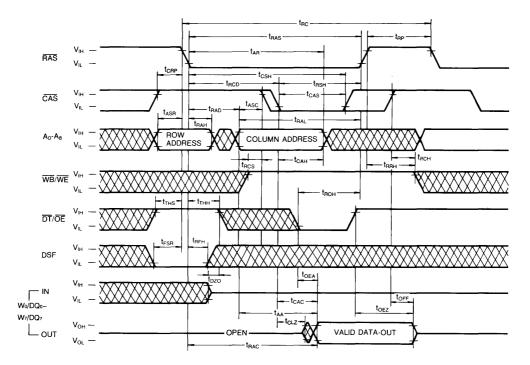

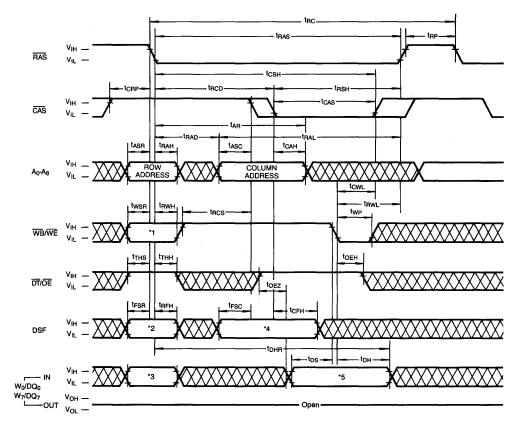

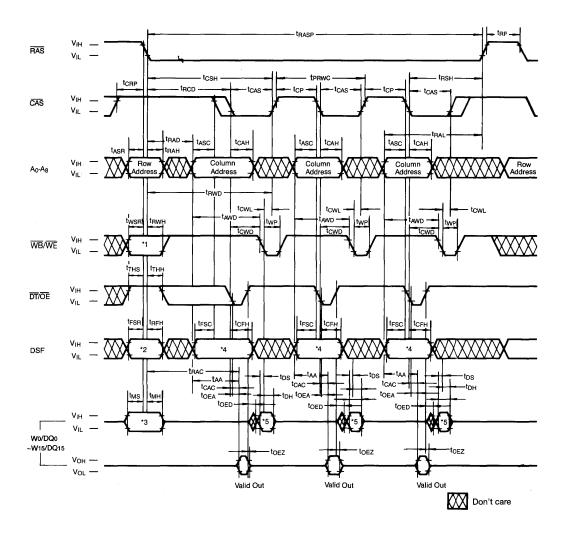

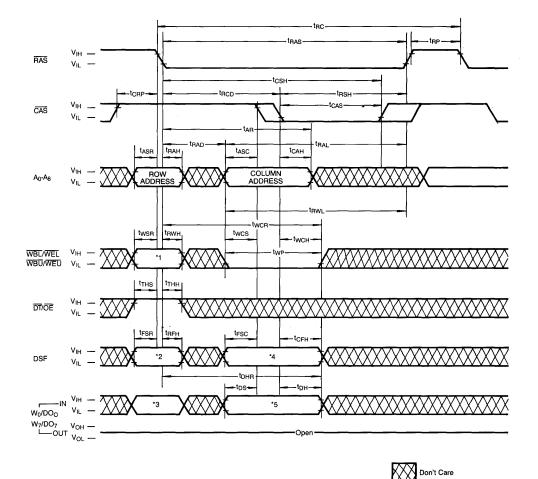

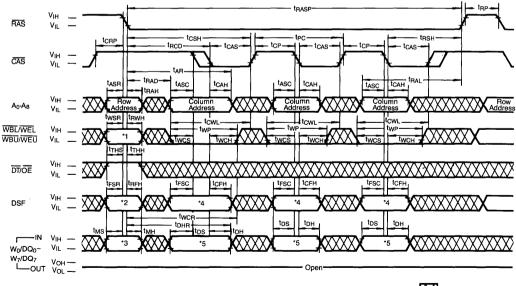

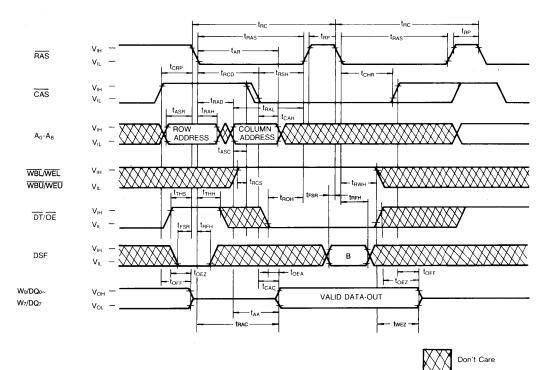

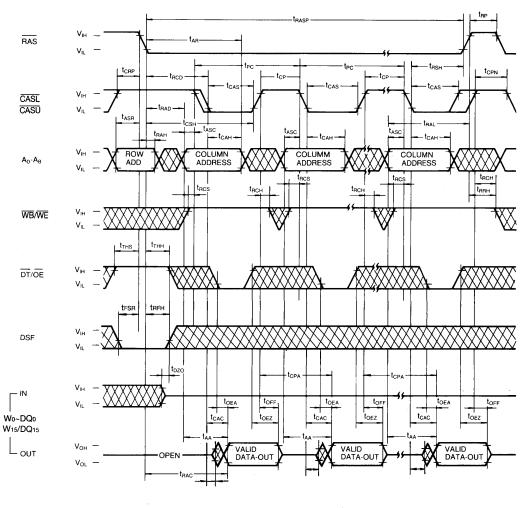

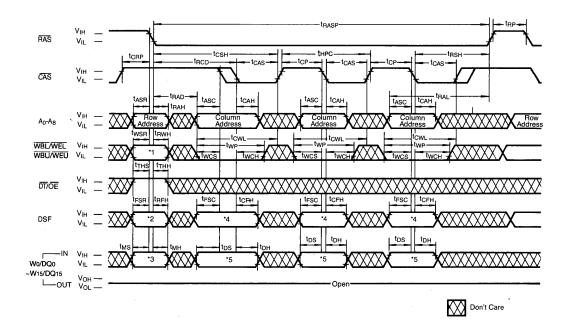

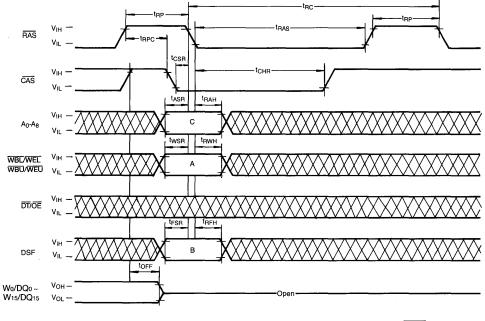

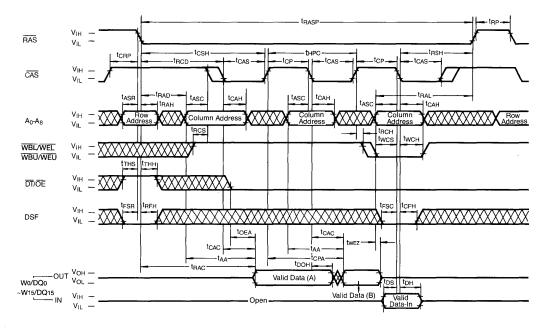

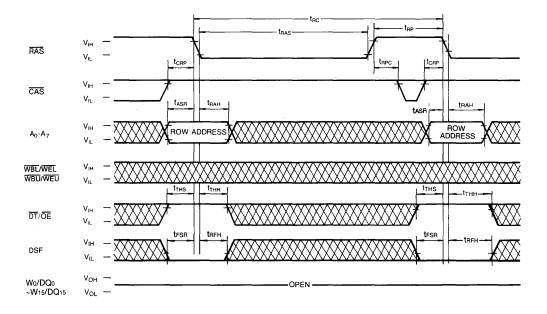

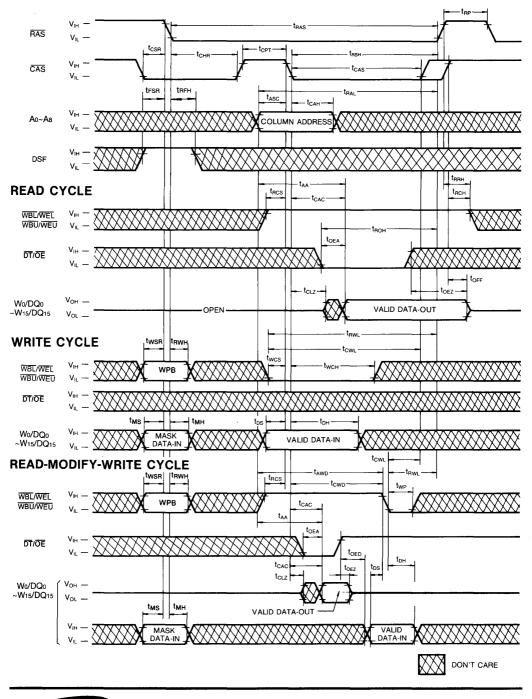

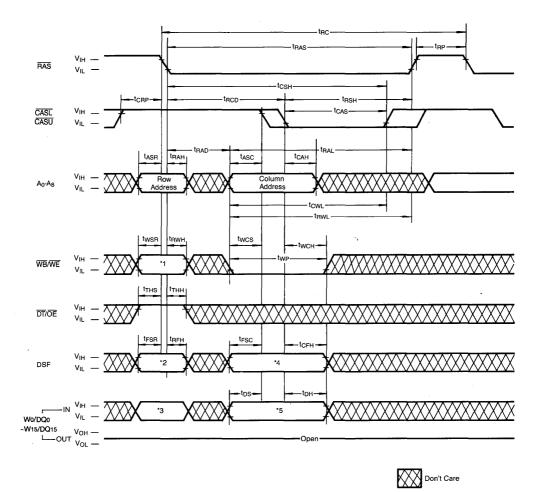

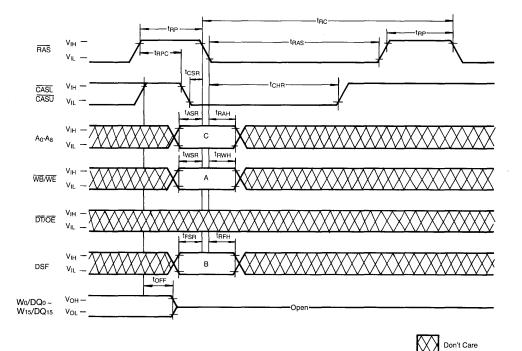

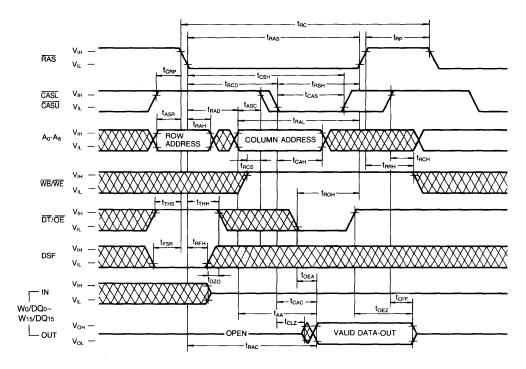

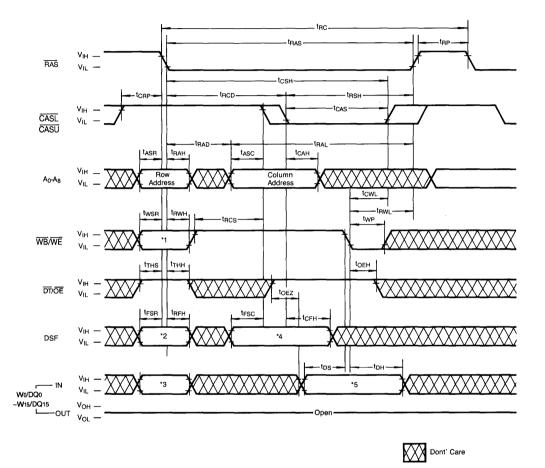

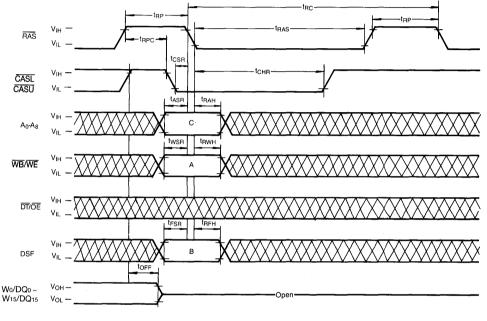

**TIMING DIAGRAMS**

Don't Care

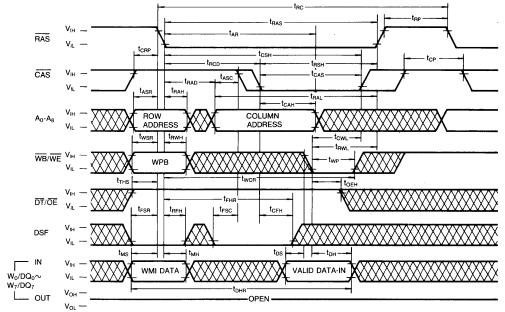

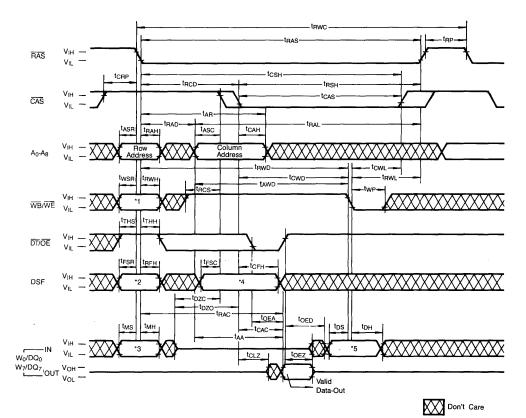

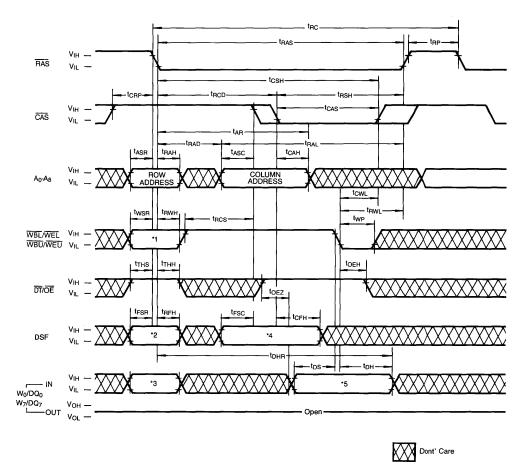

### TIMING DIAGRAMS (Continued) WRITE CYCLE (OE CONTROLLED WRITE)

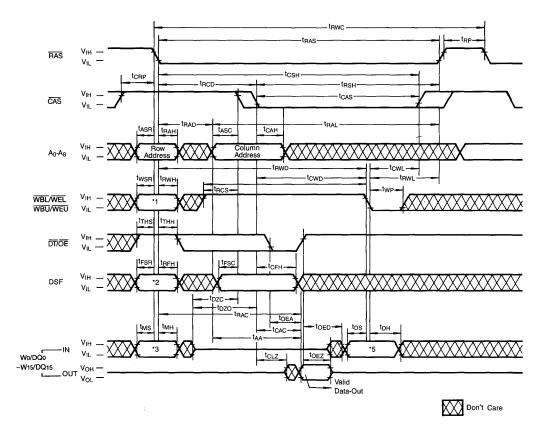

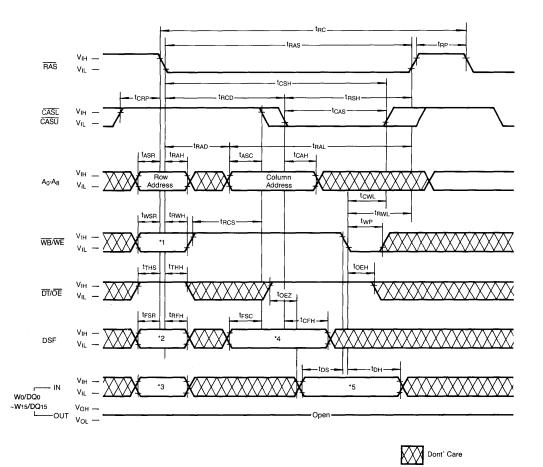

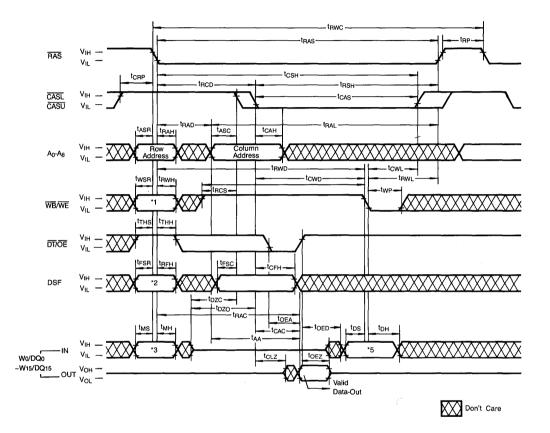

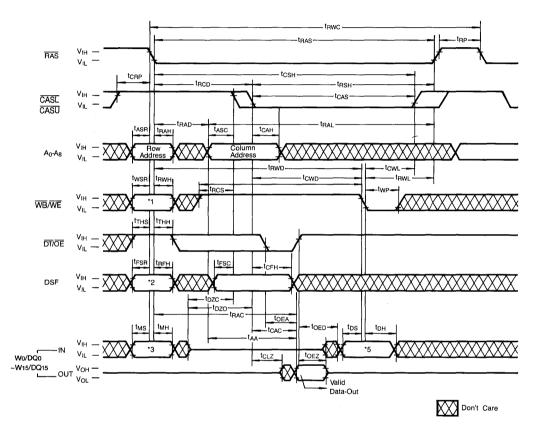

#### **READ-WRITE/READ-MODIFY-WRITE CYCLE**

SЛМSUNG

~~~~~

30

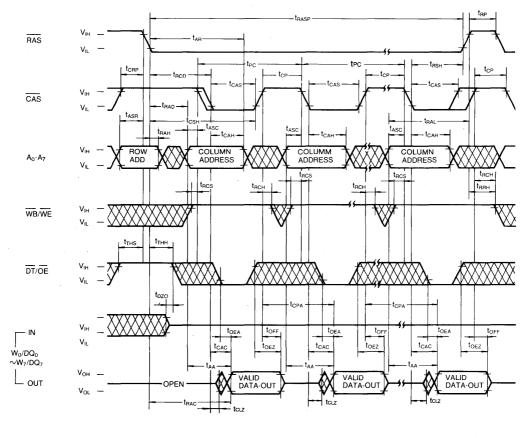

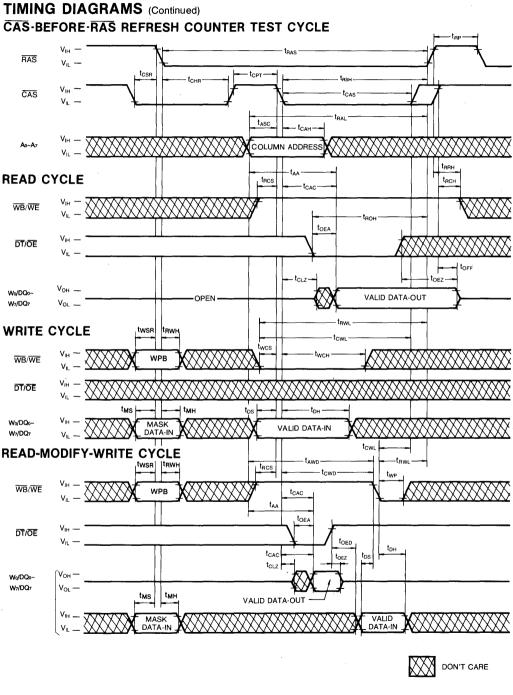

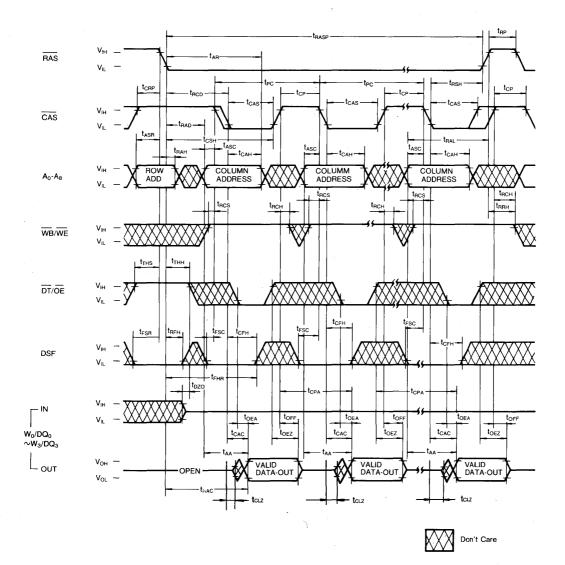

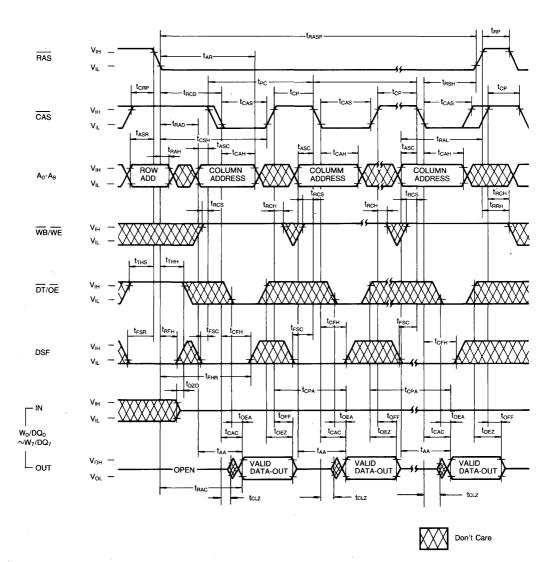

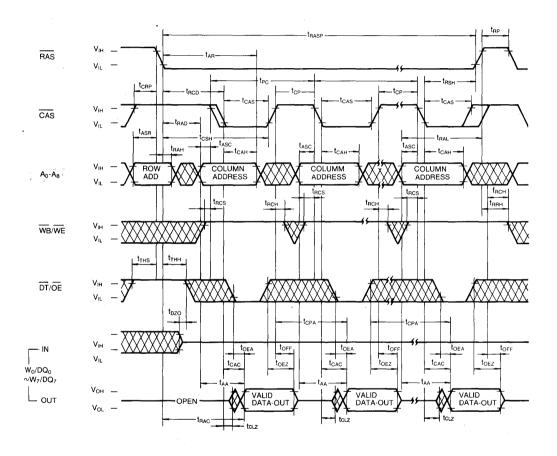

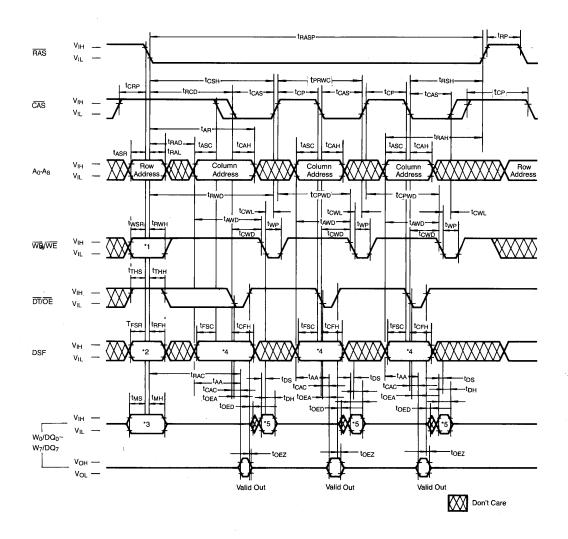

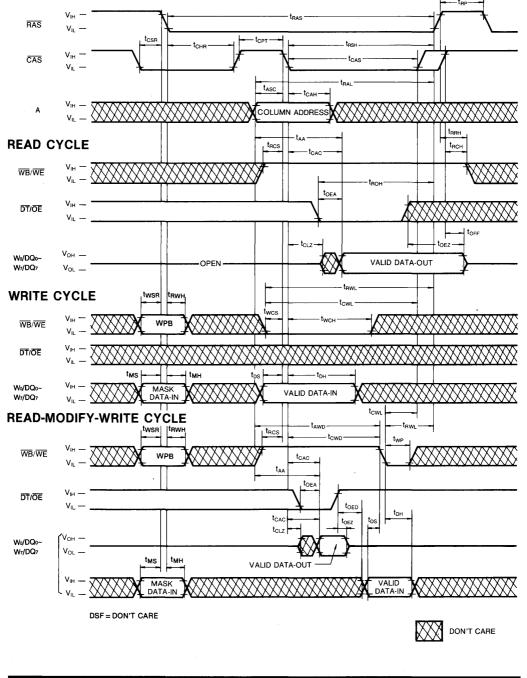

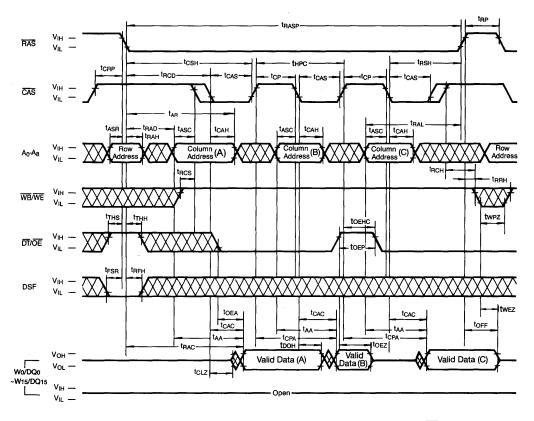

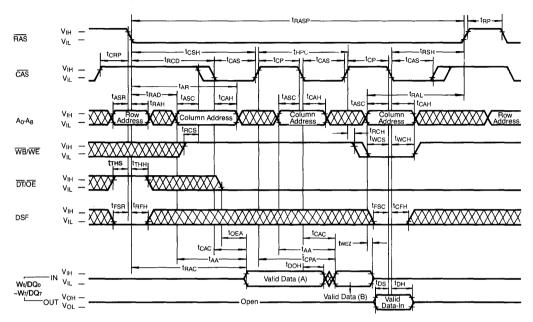

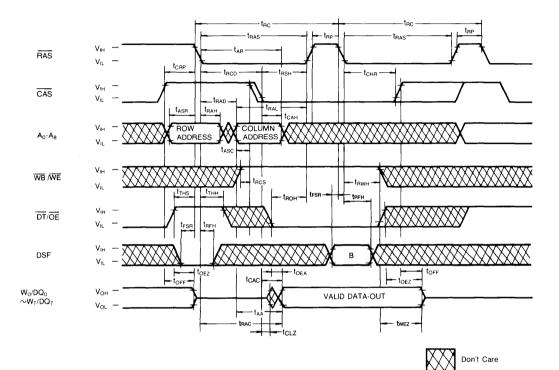

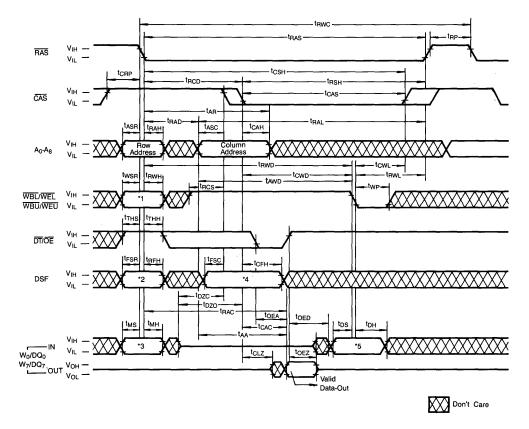

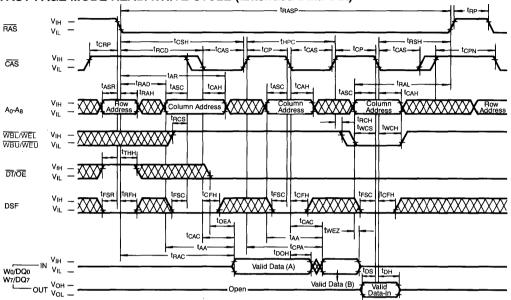

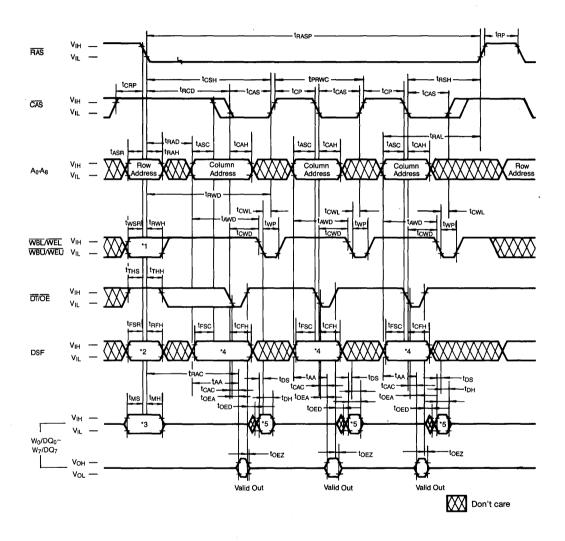

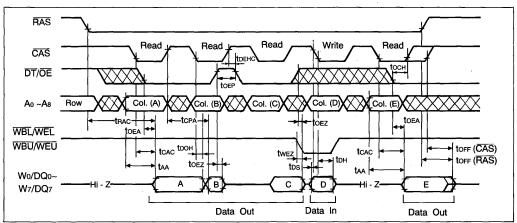

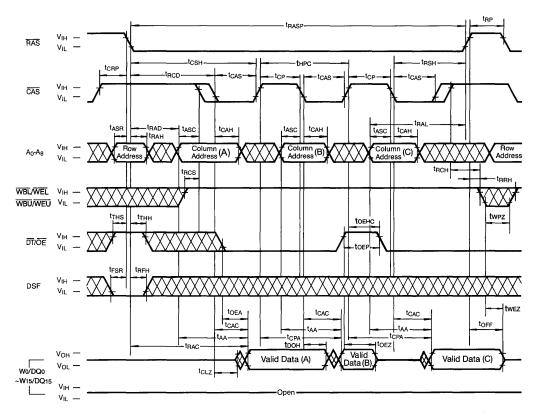

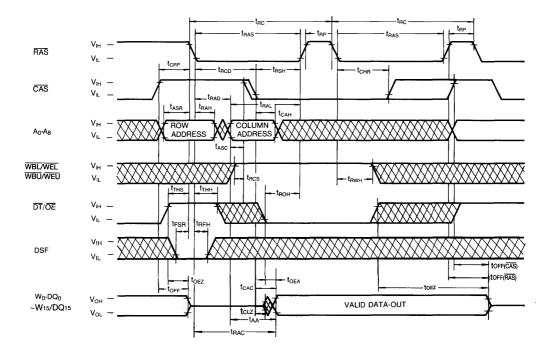

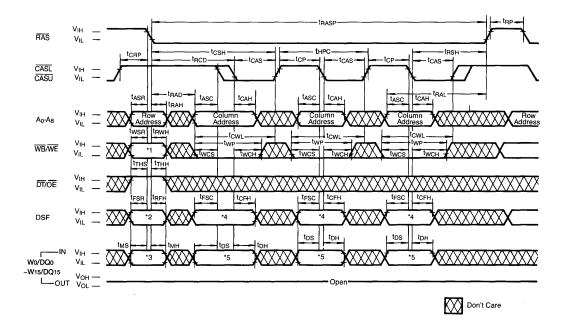

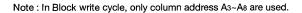

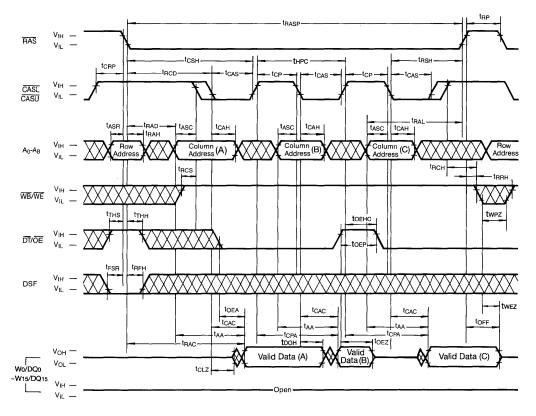

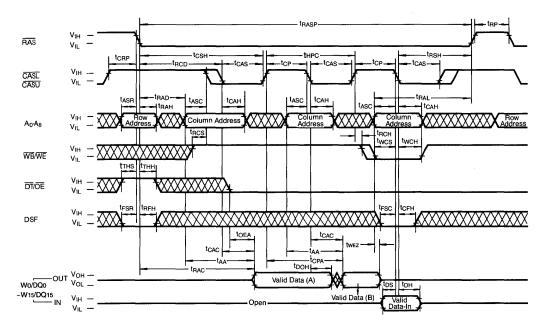

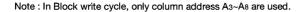

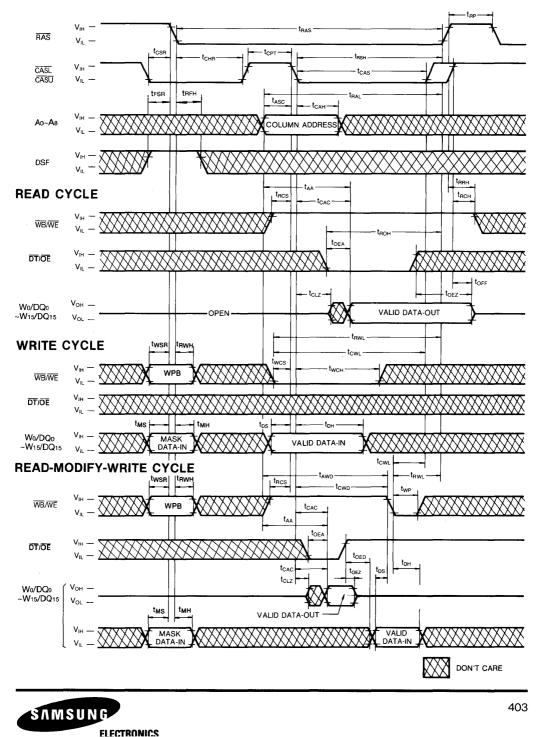

## TIMING DIAGRAMS (Continued) PAGE MODE READ CYCLE

## KM428C64

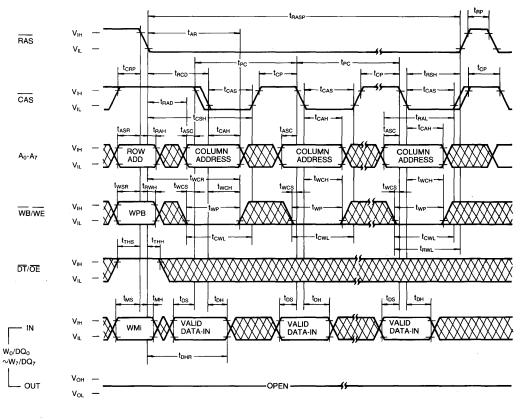

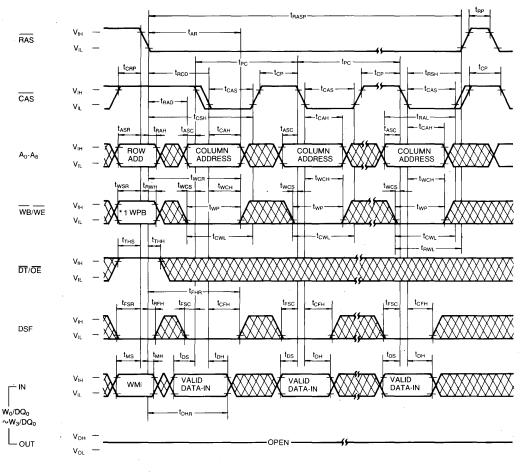

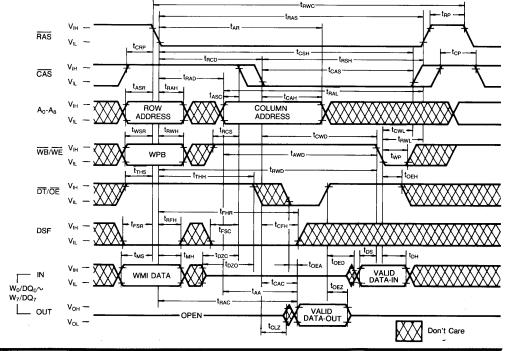

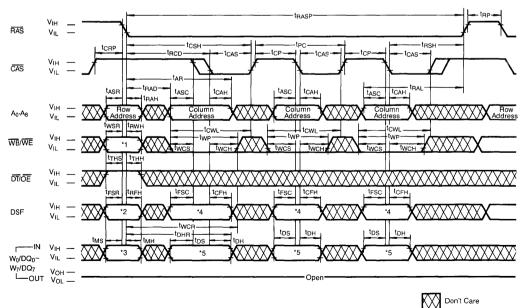

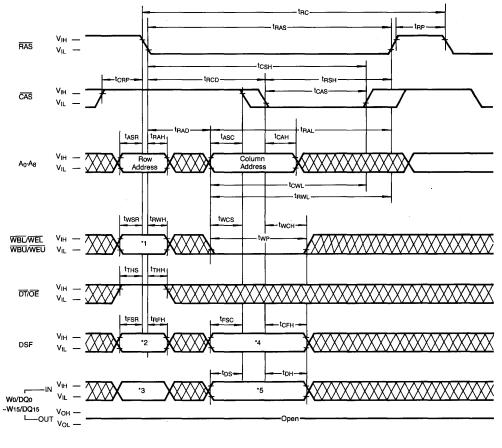

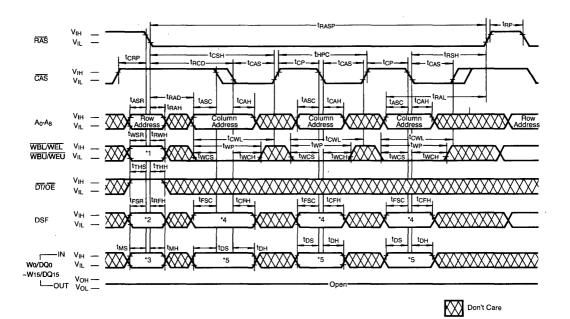

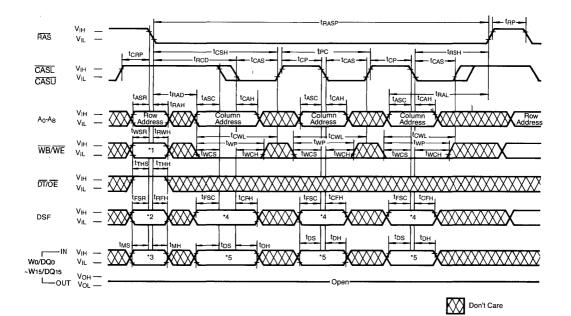

## TIMING DIAGRAMS (Continued) PAGE MODE WRITE CYCLE (EARLY WRITE)

Don't Care

.

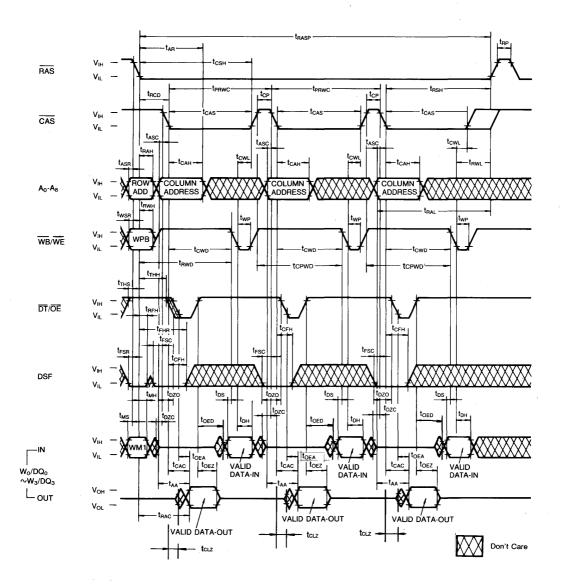

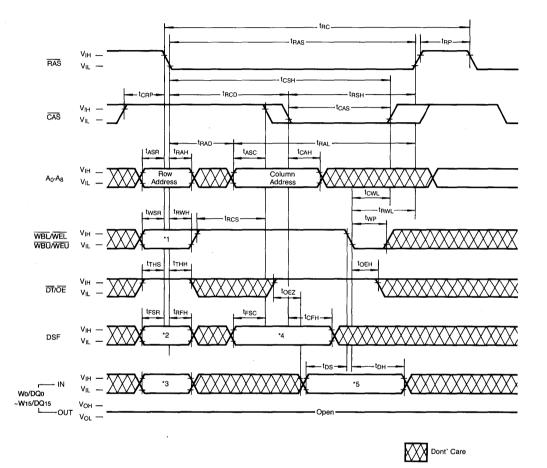

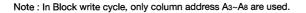

## TIMING DIAGRAMS (Continued) PAGE MODE READ-MODIFY-WRITY CYCLE

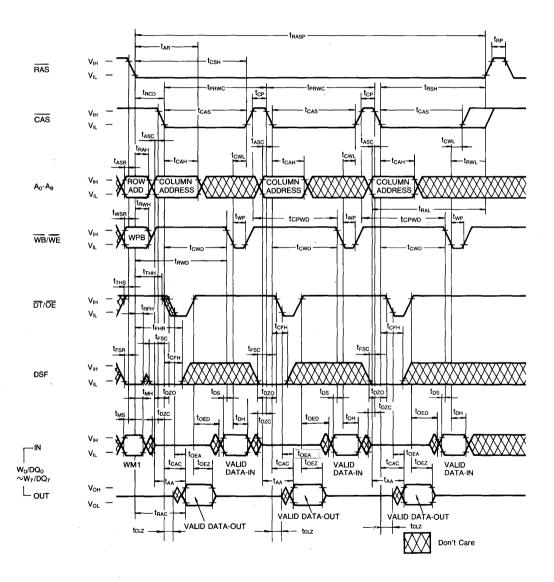

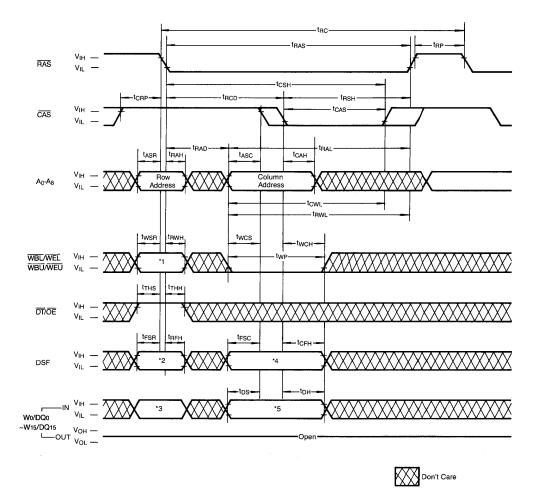

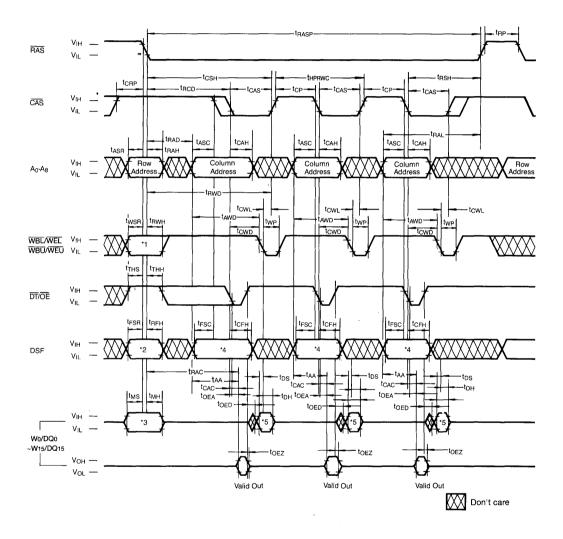

## TIMING DIAGRAMS (Continued)

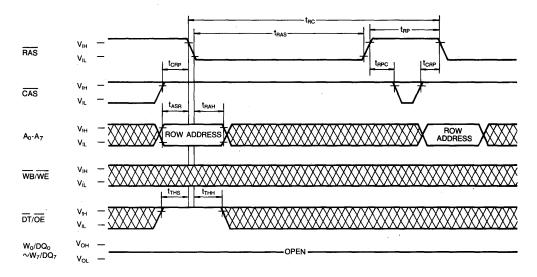

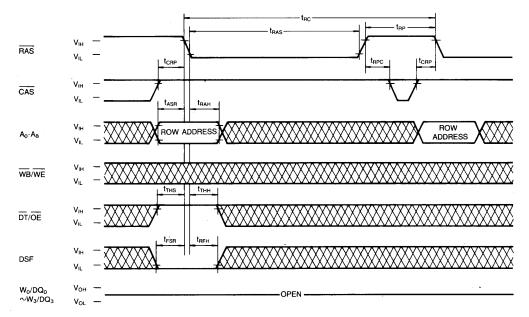

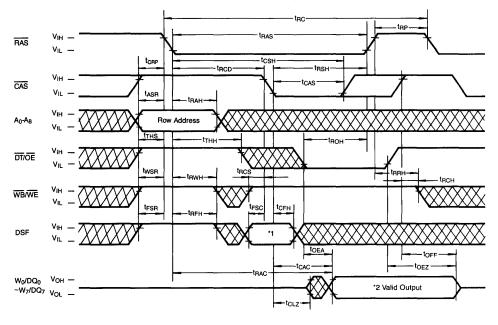

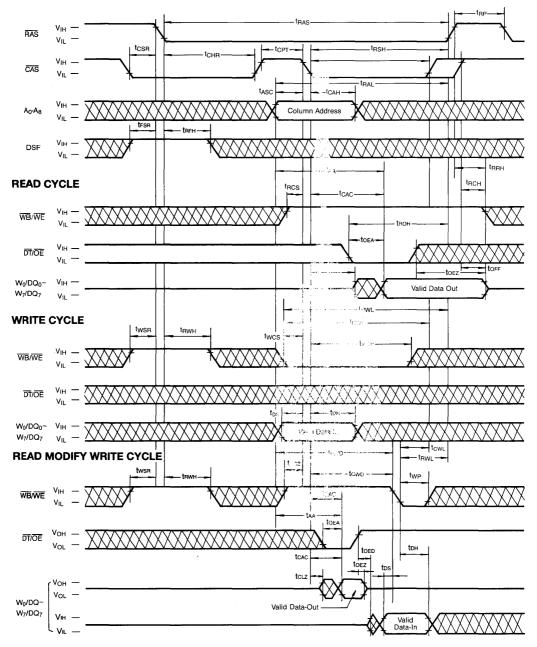

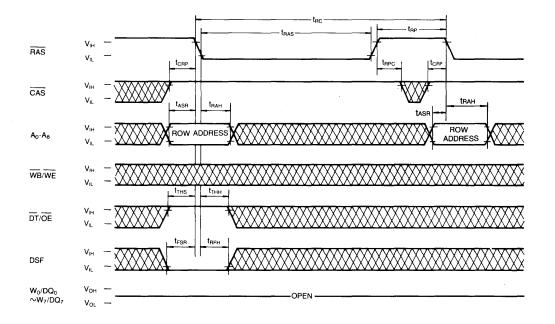

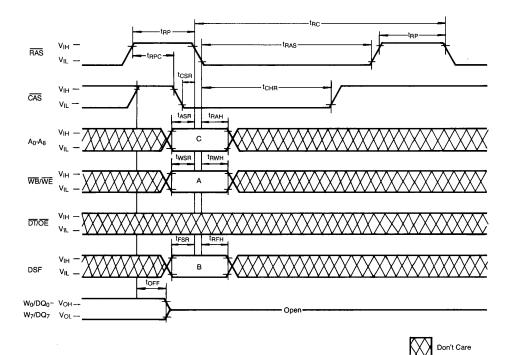

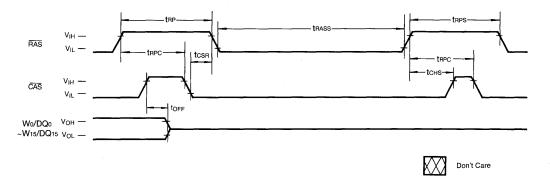

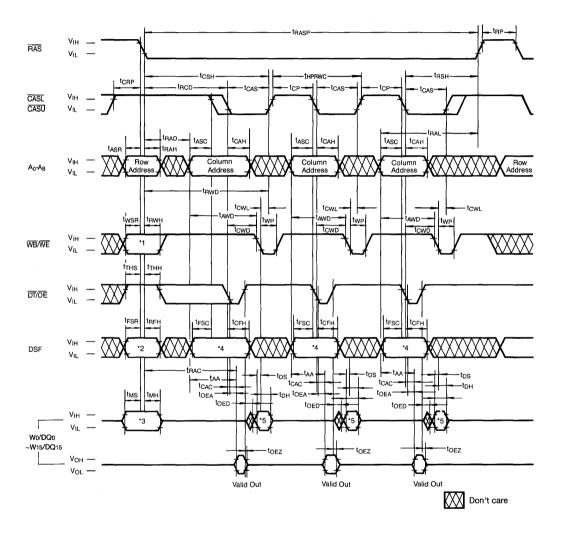

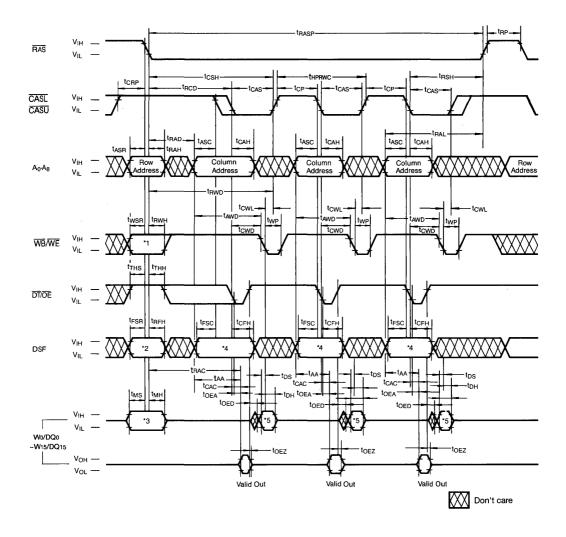

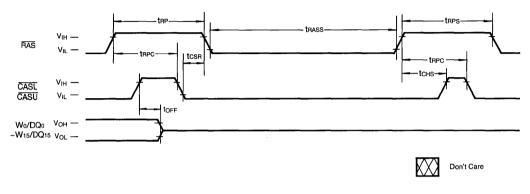

#### **CAS BEFORE RAS REFRESH**

2

## TIMING DIAGRAMS (Continued)

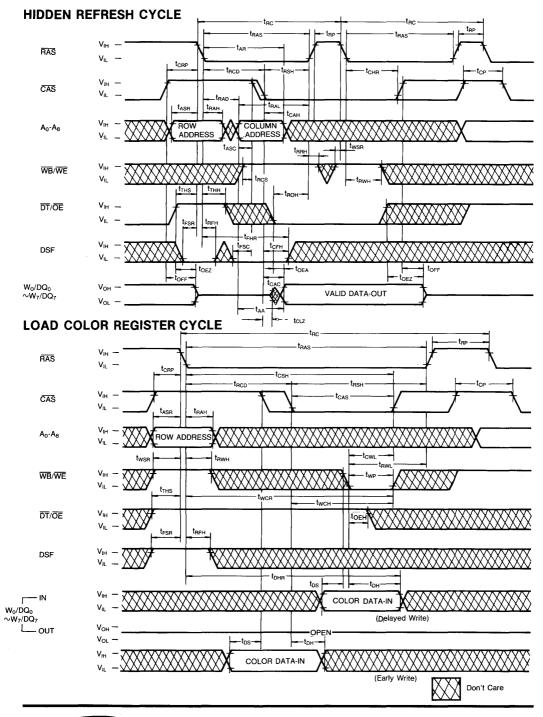

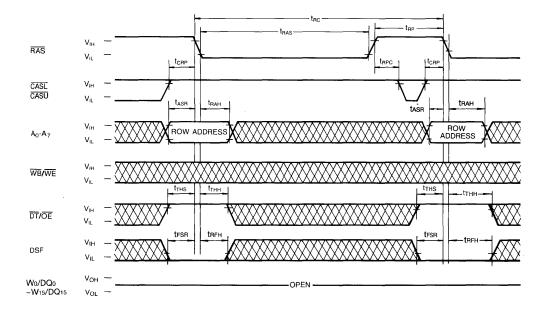

#### **HIDDEN REFRESH CYCLE**

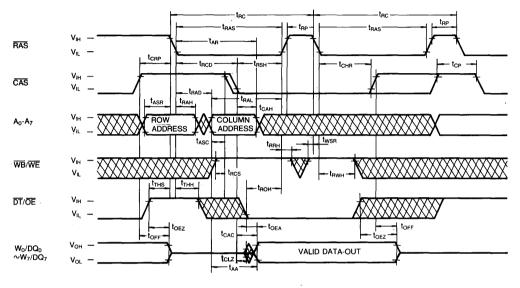

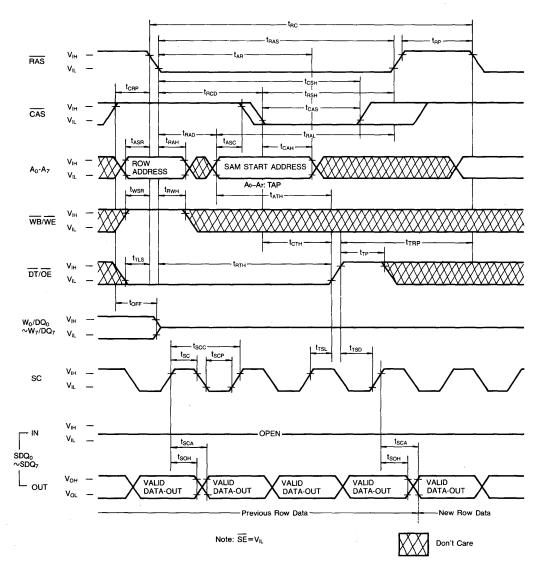

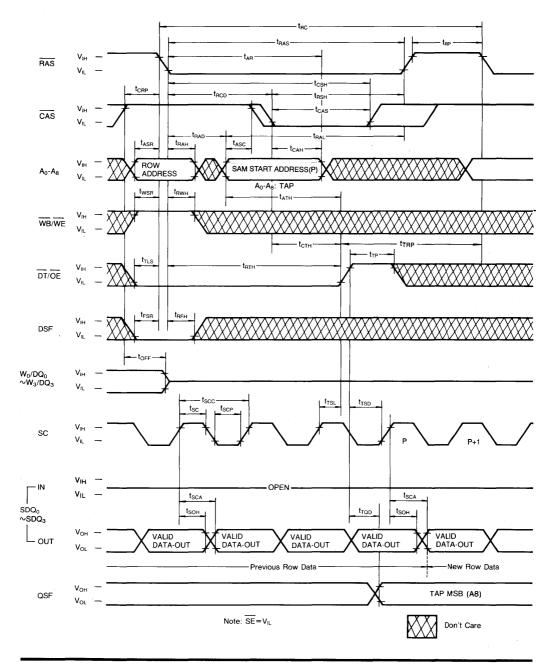

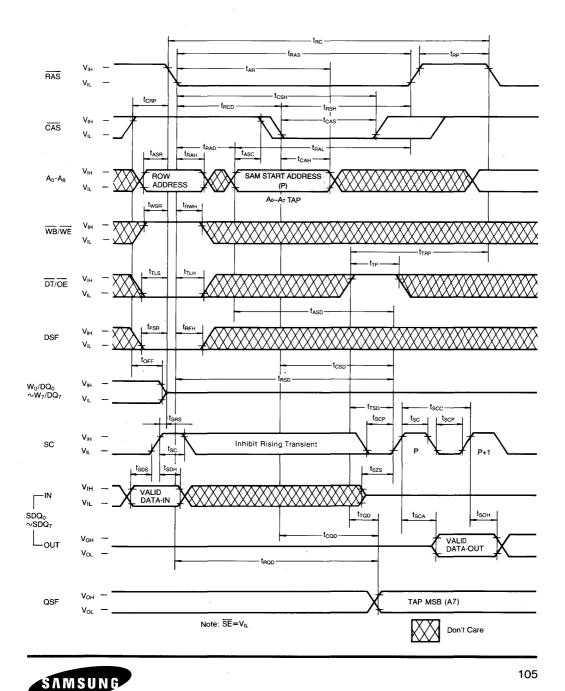

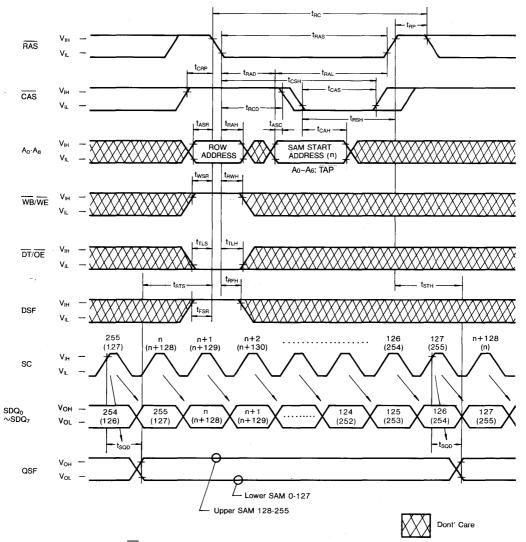

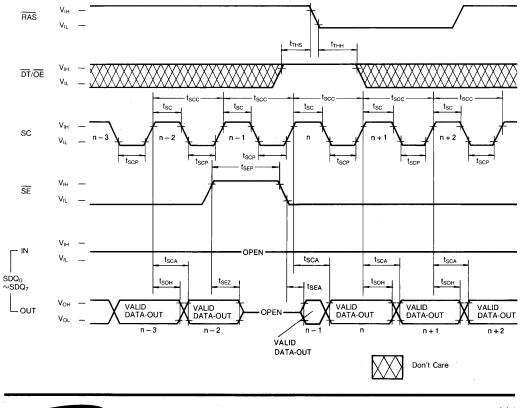

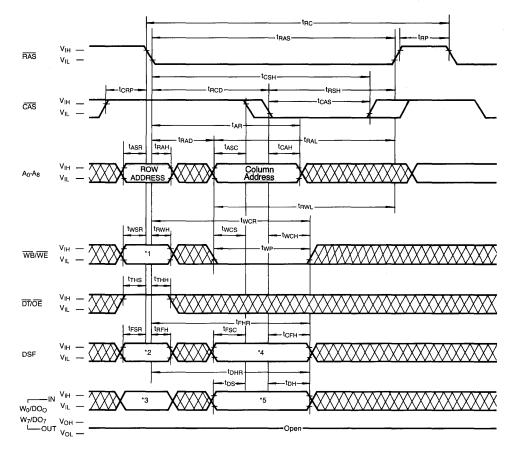

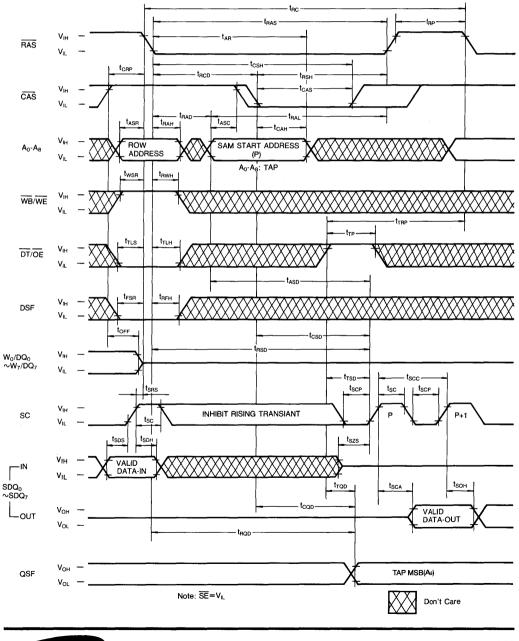

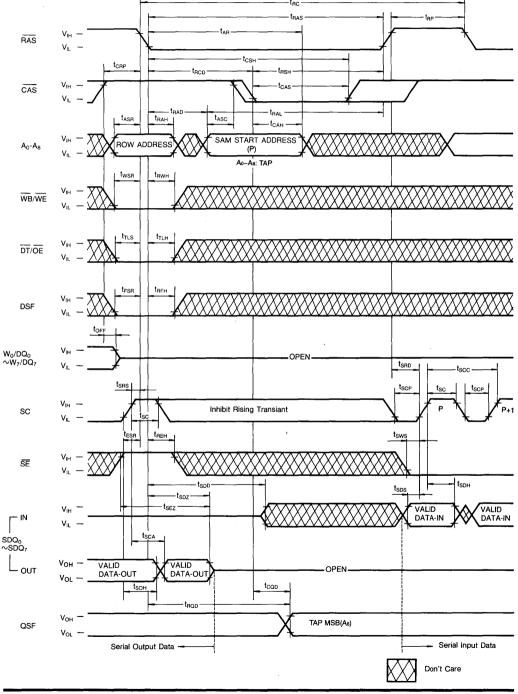

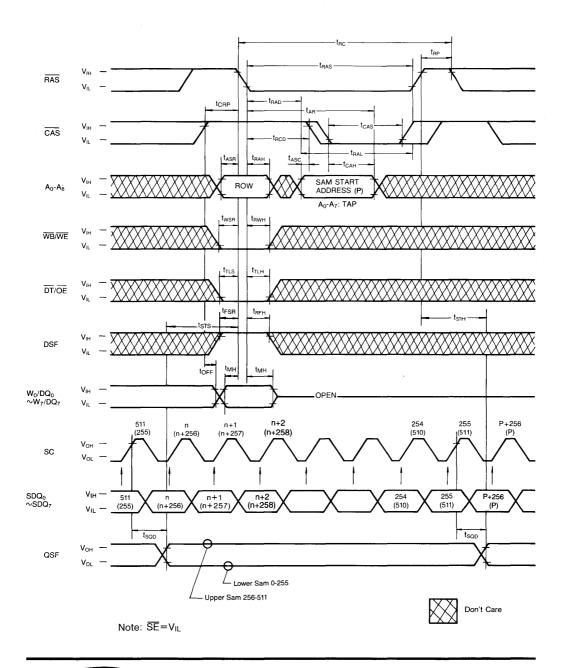

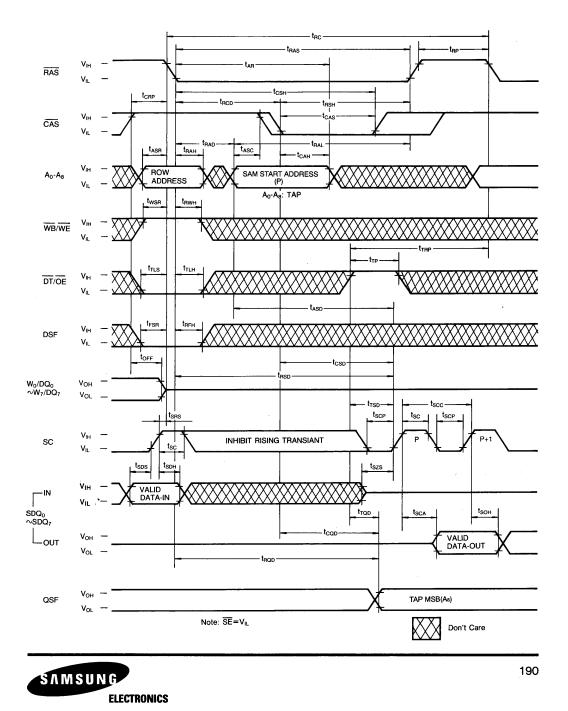

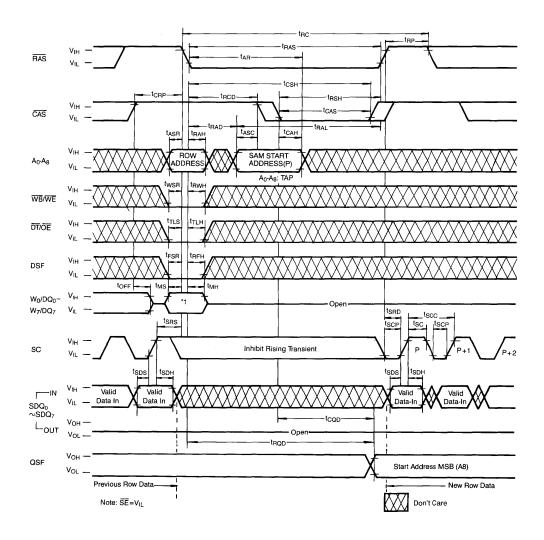

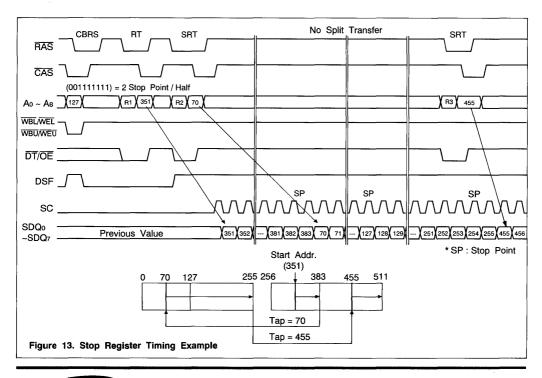

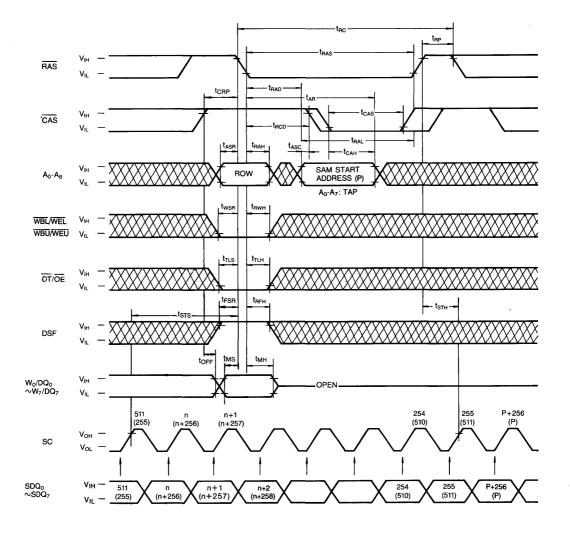

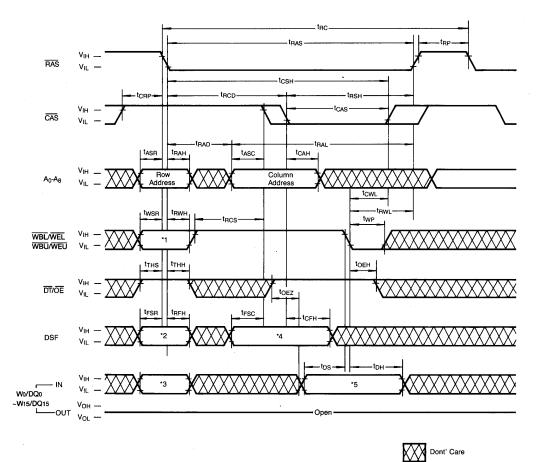

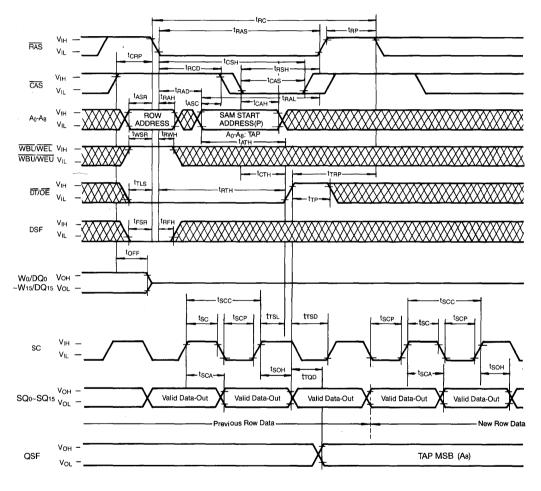

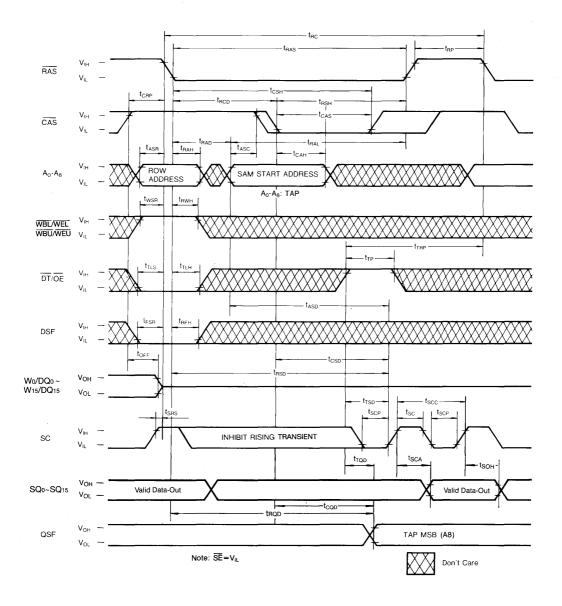

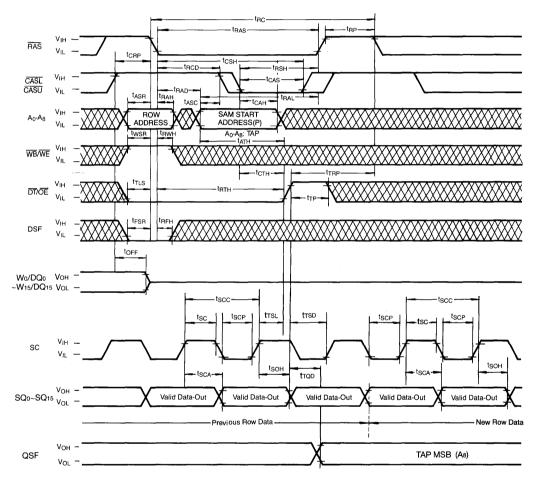

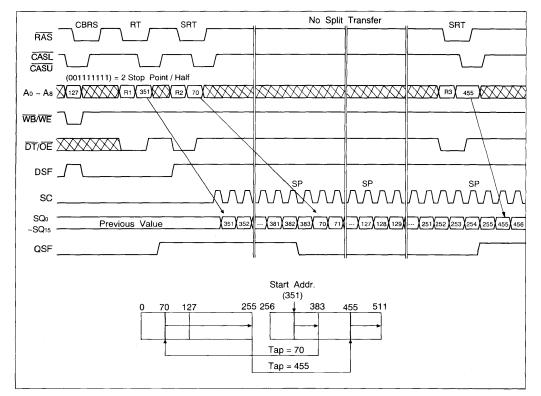

TIMING DIAGRAMS (Continued) READ TRANSFER CYCLE

•

Don't Care

2

## KM428C64

SAMSUNG

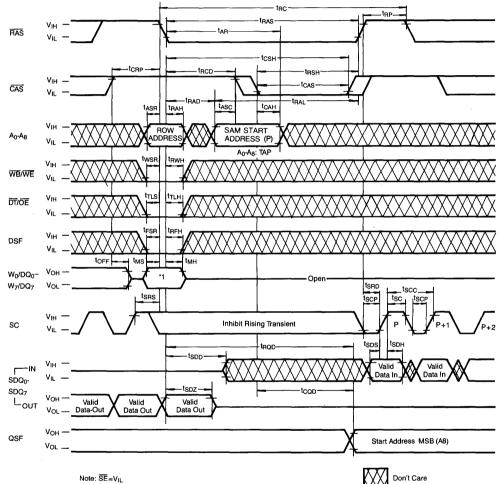

## TIMING DIAGRAMS (Continued)

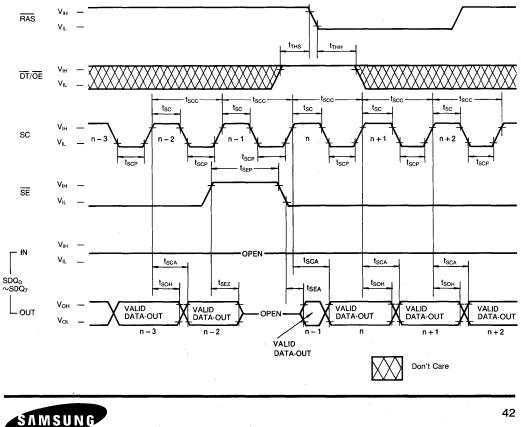

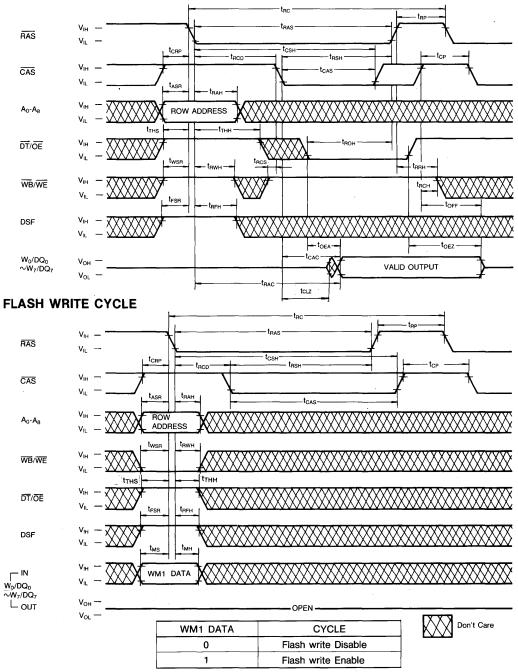

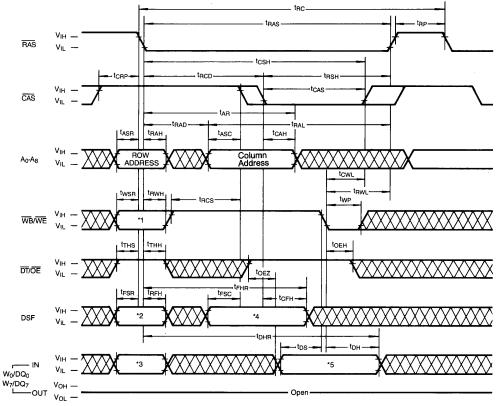

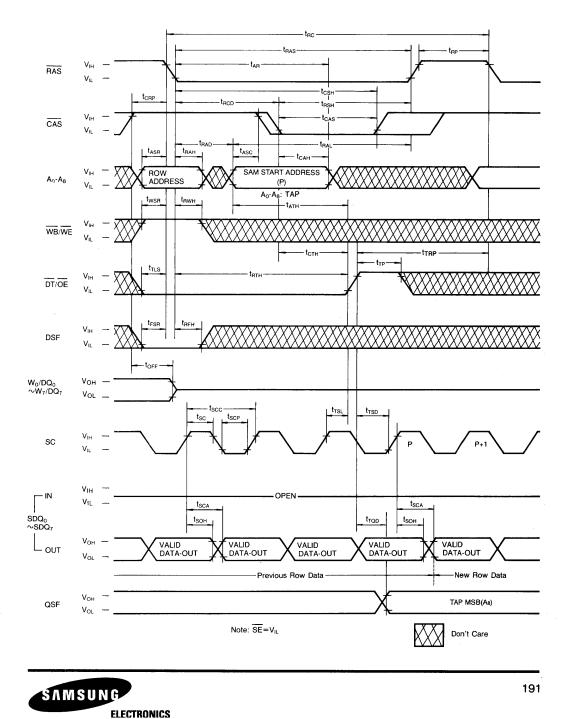

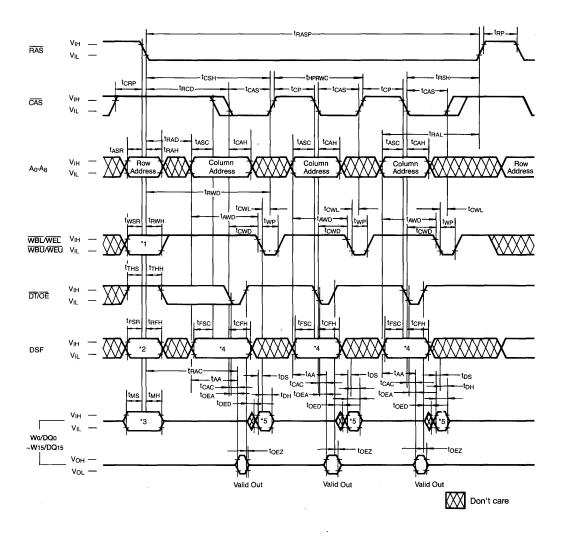

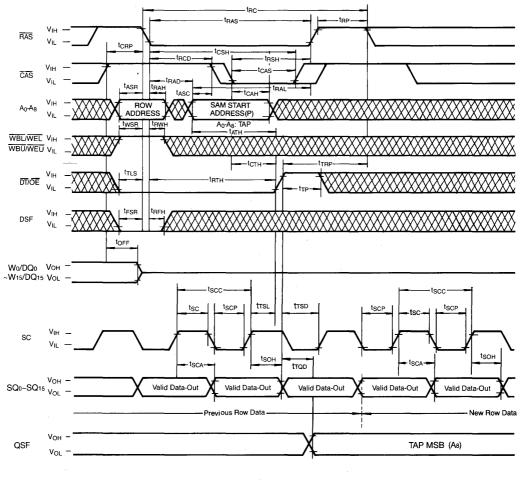

#### **REAL TIME READ TRANSFER CYCLE**

SAMSUNG

-----

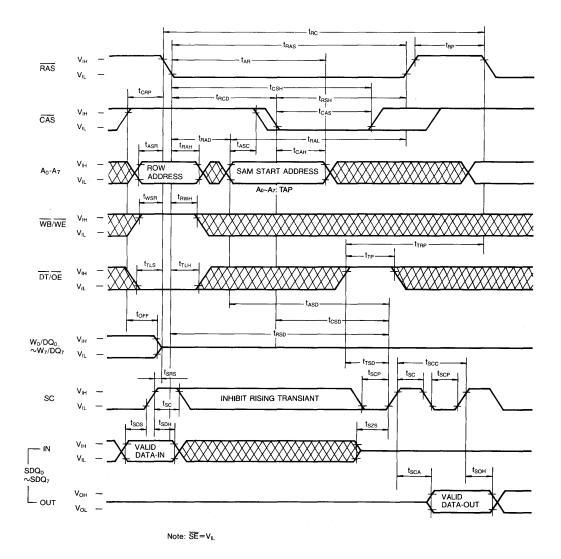

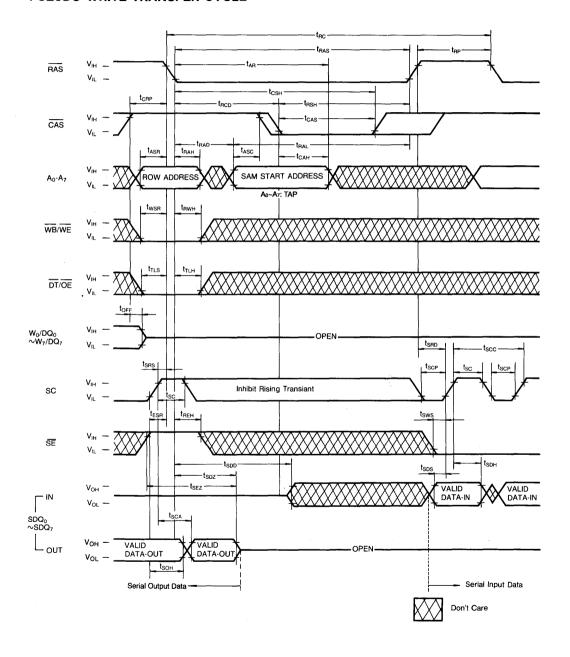

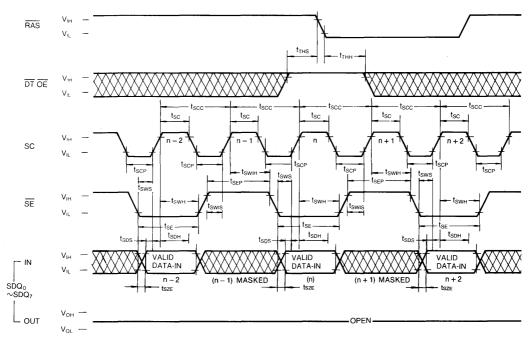

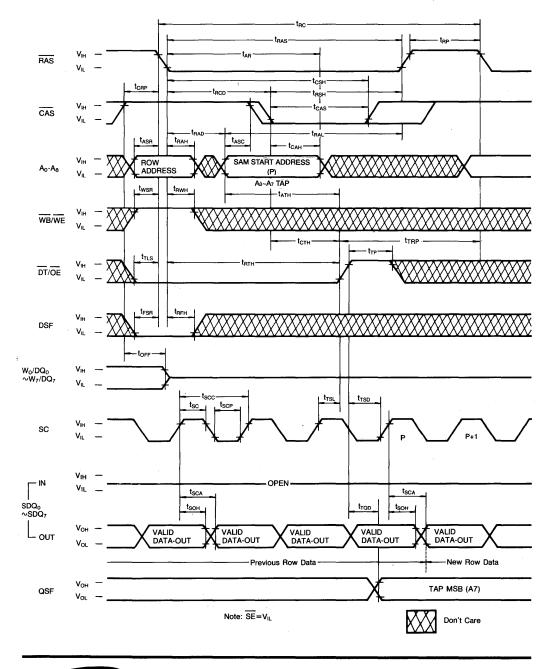

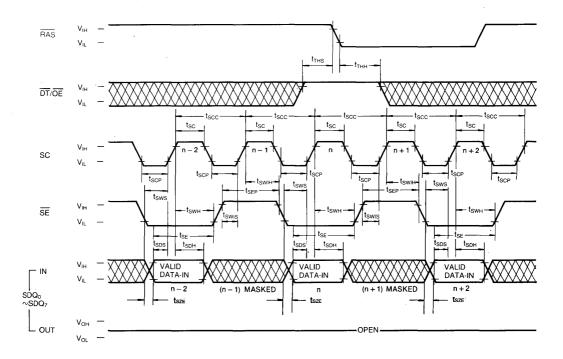

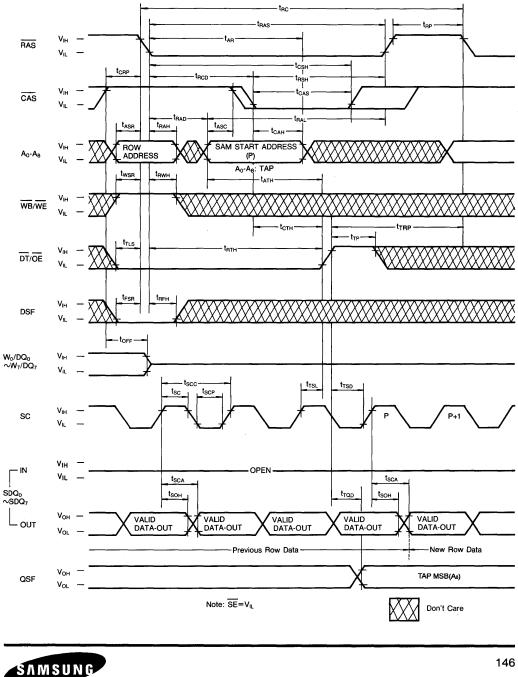

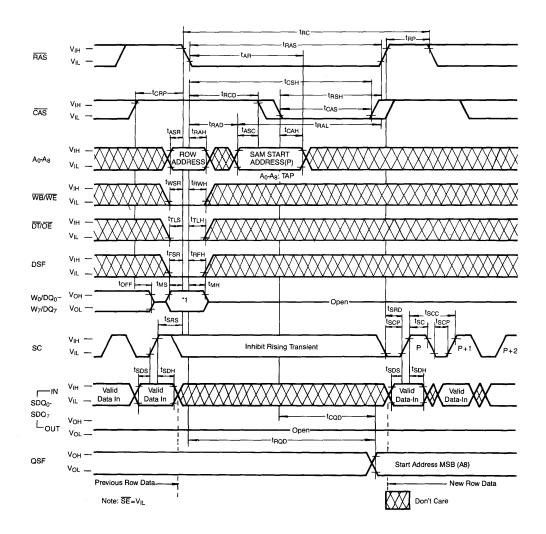

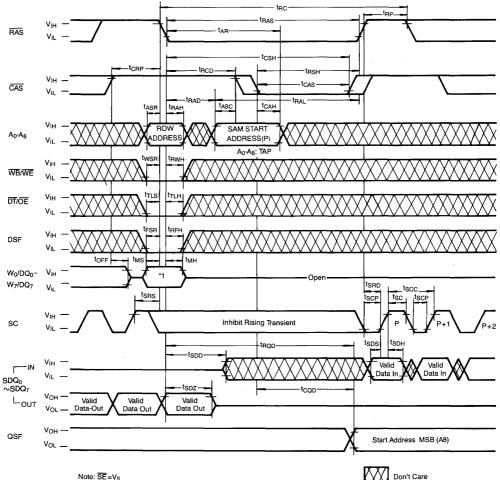

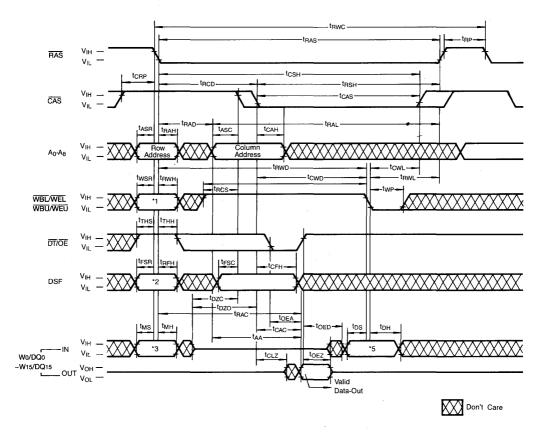

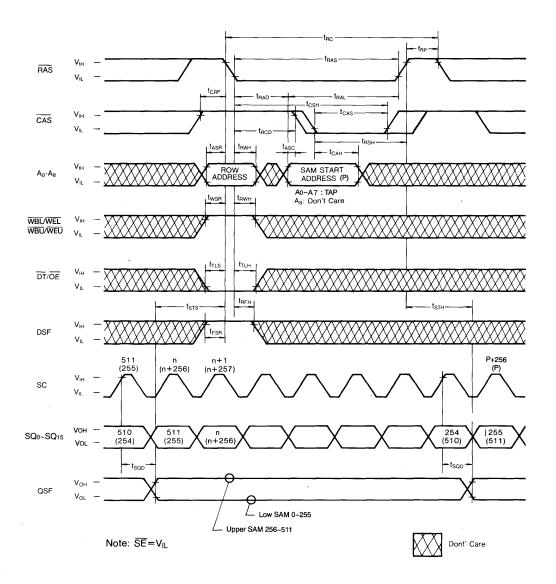

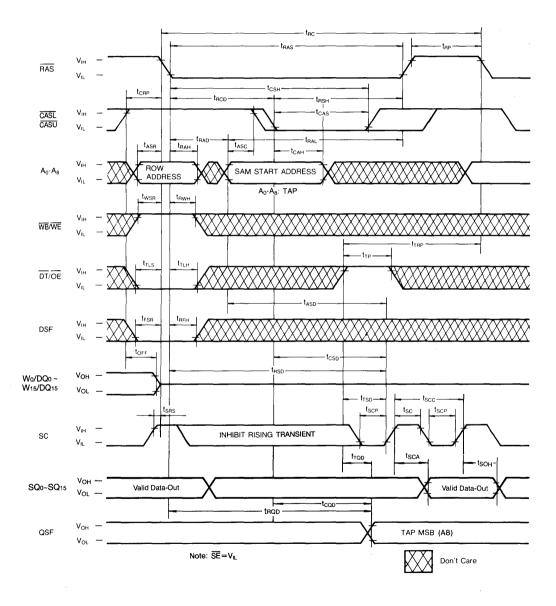

## TIMING DIAGRAMS (Continued) PSEUDO WRITE TRANSFER CYCLE

#### KM428C64

#### TIMING DIAGRAMS (Continued)

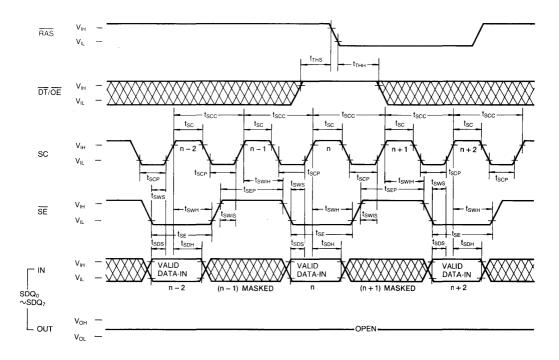

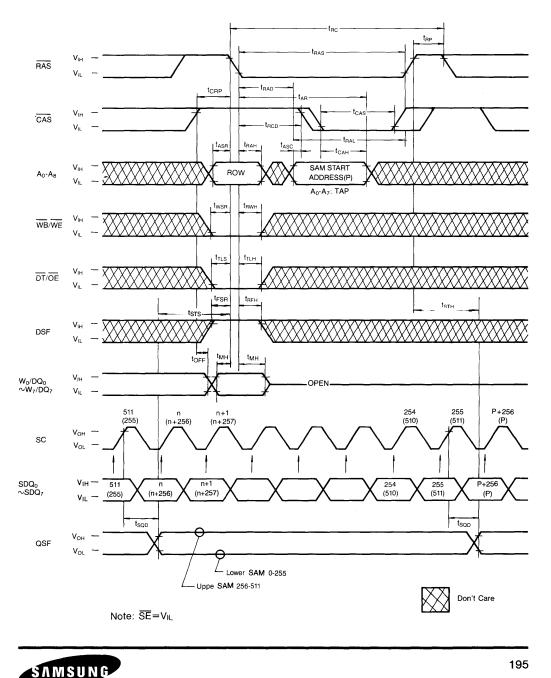

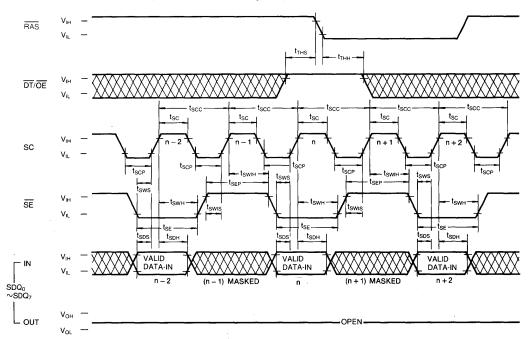

#### WRITE TRANSFER CYCLE

SAMSUNG

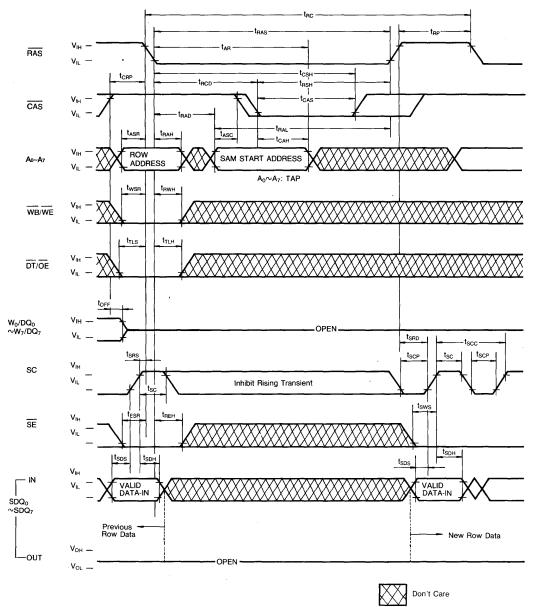

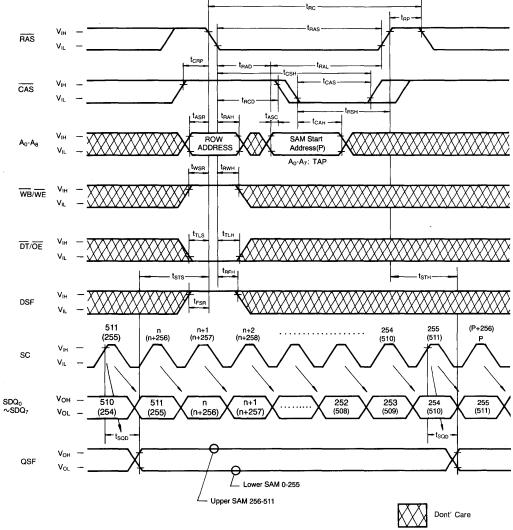

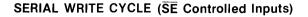

# TIMING DIAGRAMS (Continued)

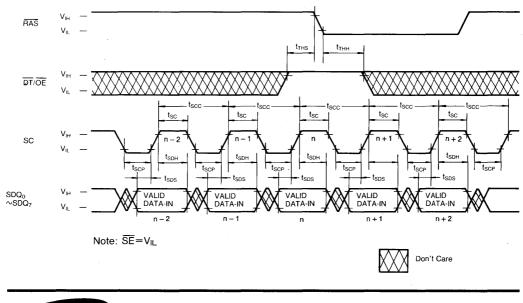

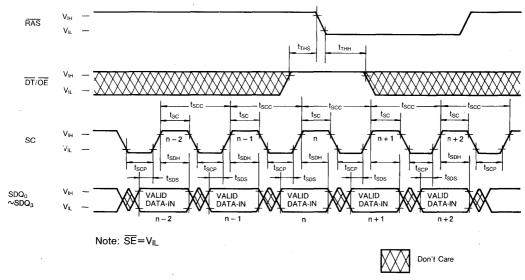

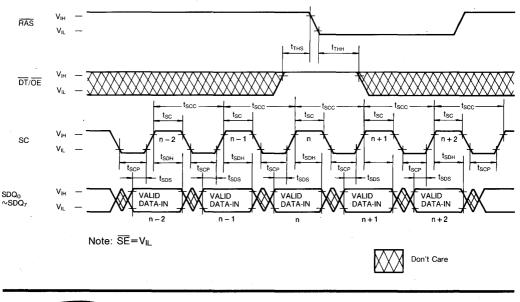

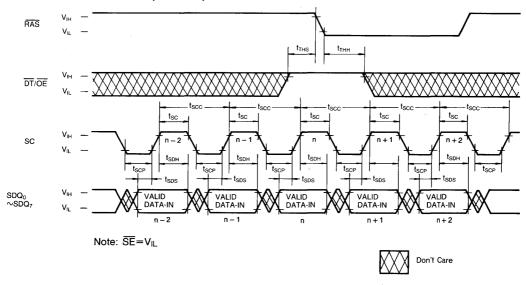

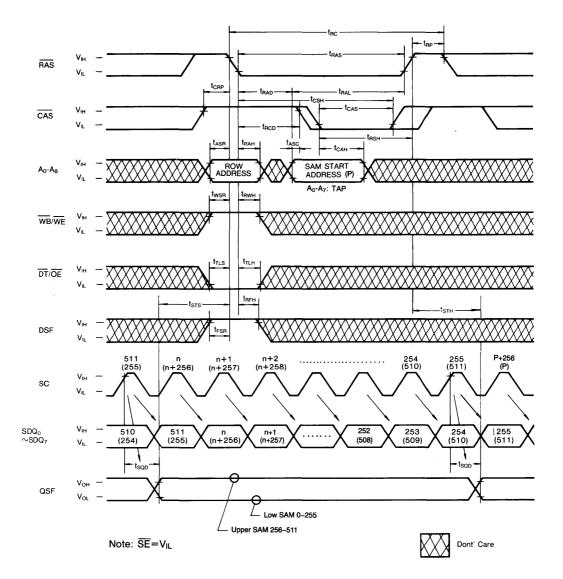

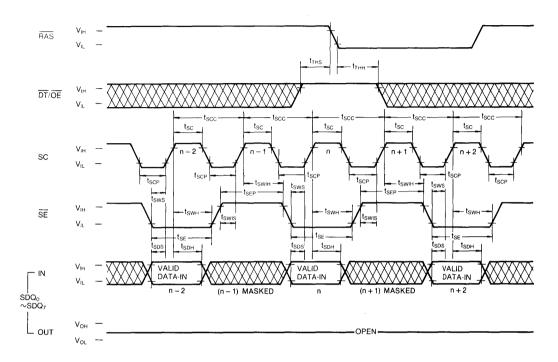

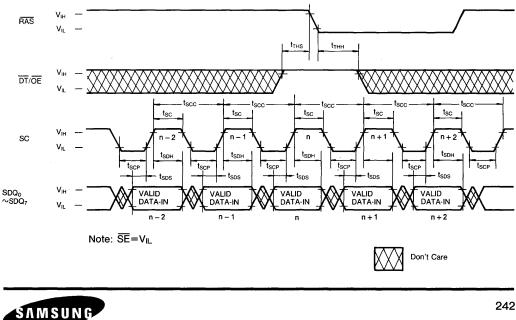

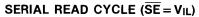

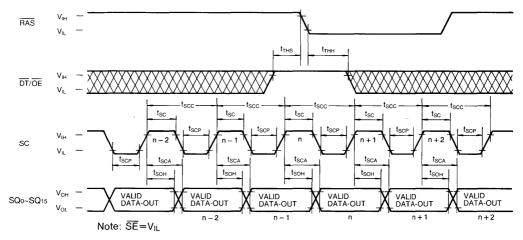

SERIAL WRITE CYCLE ( $\overline{SE} = V_{IL}$ )

SAMSUNG

FI FOTRONICS

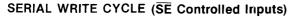

# KM428C64

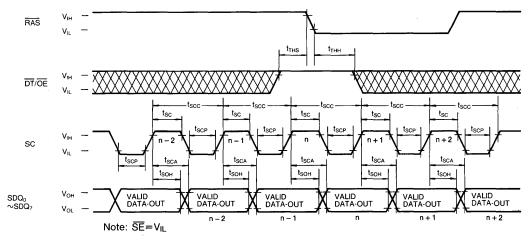

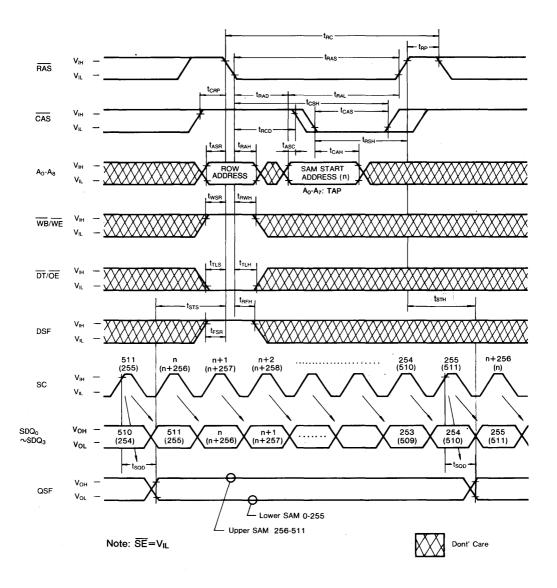

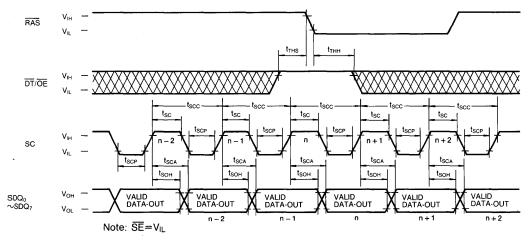

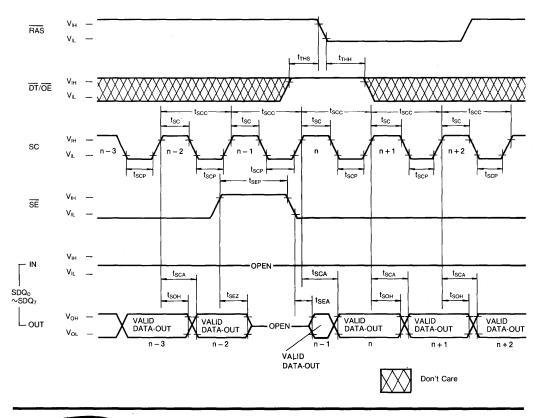

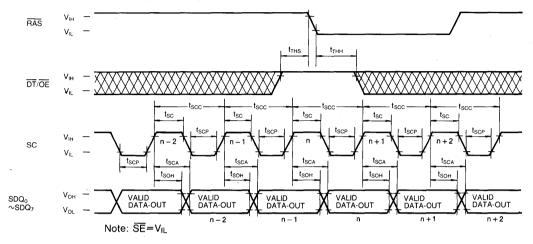

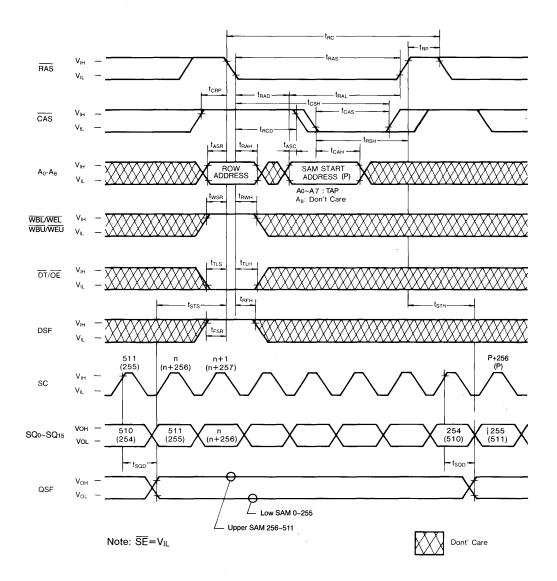

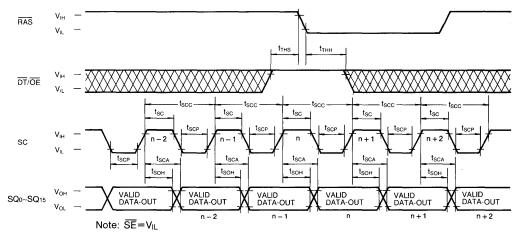

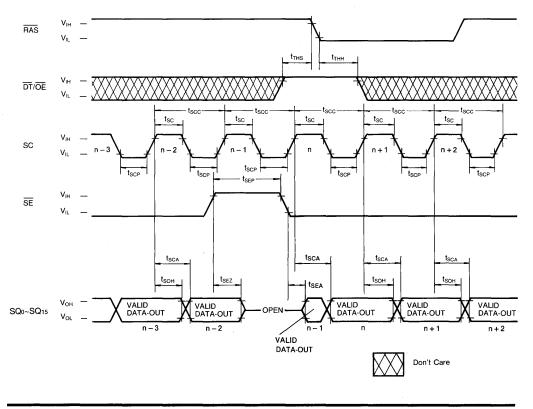

### SERIAL READ CYCLE ( $\overline{SE} = V_{IL}$ )

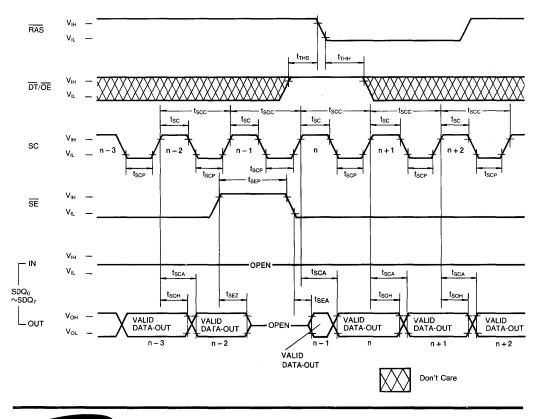

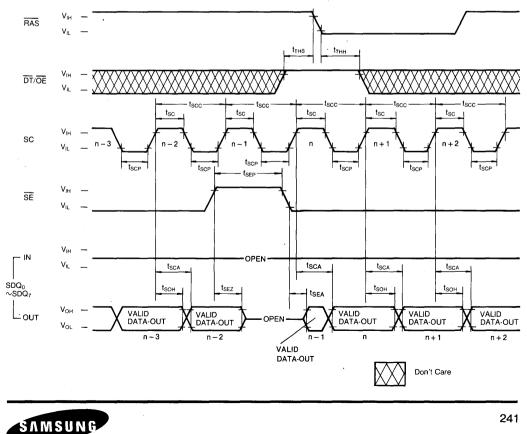

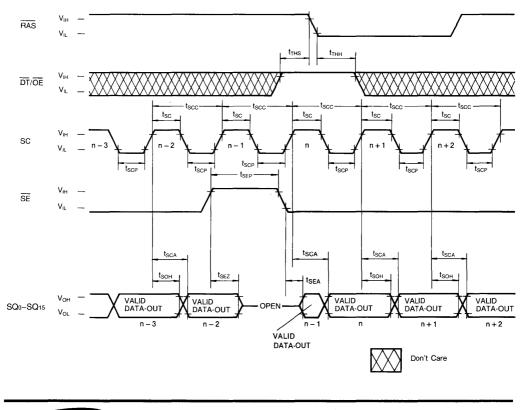

## SERIAL READ CYCLE (SE Controlled Outputs)

EI EFTRANICO

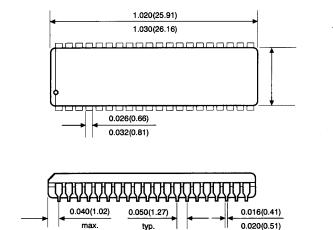

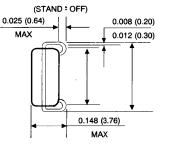

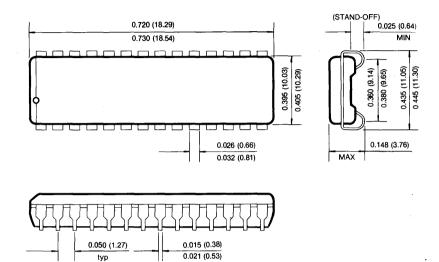

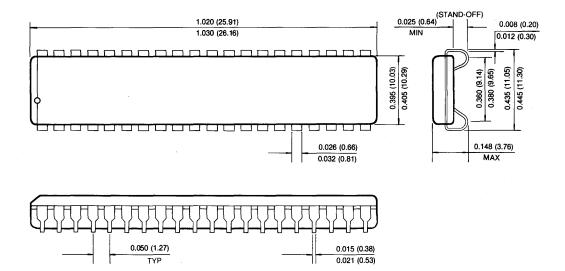

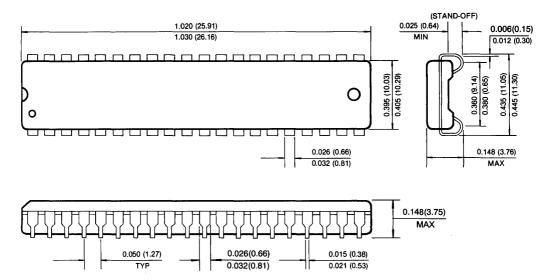

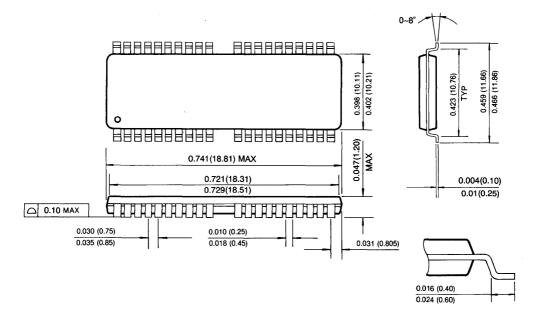

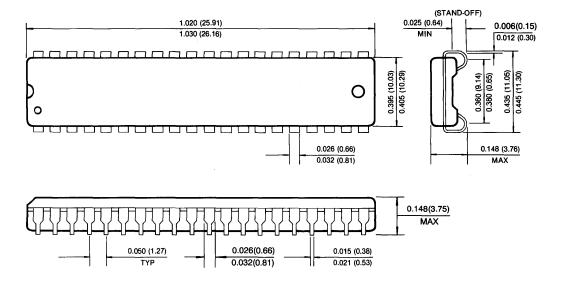

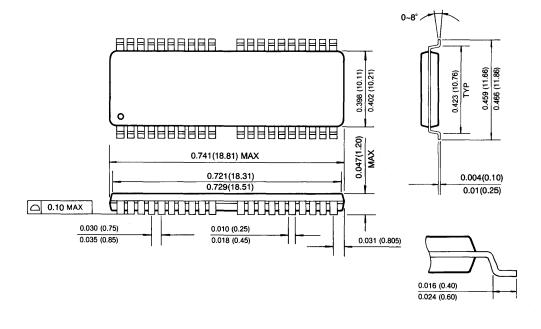

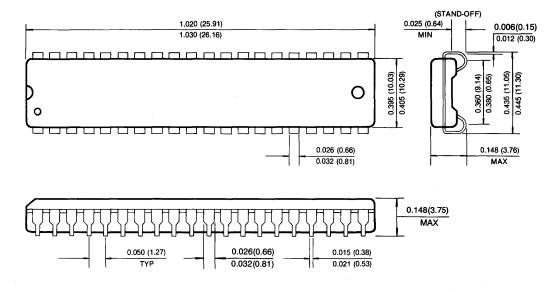

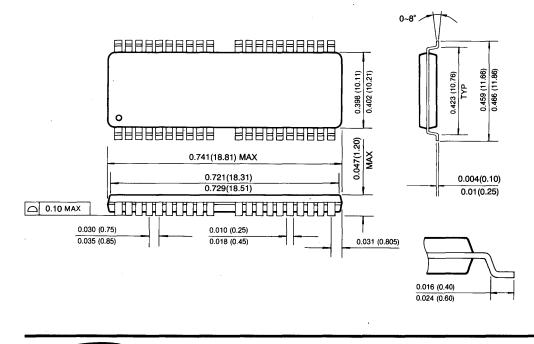

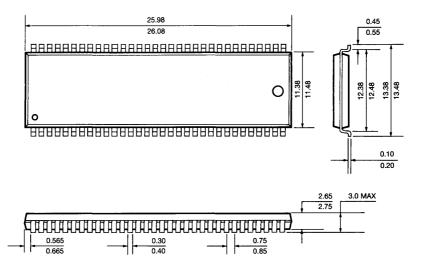

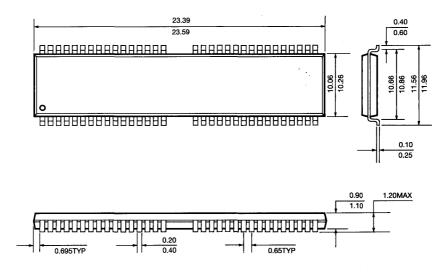

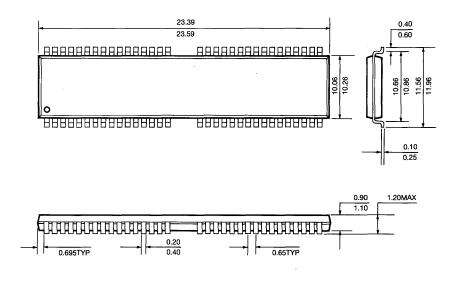

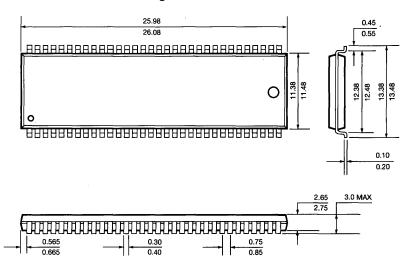

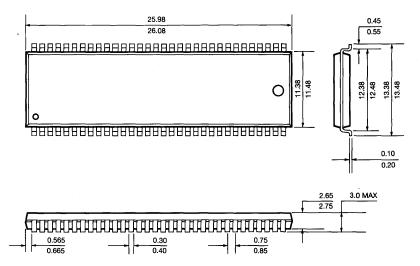

### PACKAGES DIMENSION

40 LEAD PLASTIC SMALL OUT LINE J FORM PACKAGE

Unit : Inches (millimeters)

# 256K×4 Bit CMOS Video RAM

### **FEATURES**

- Dual port Architecture 256K × 4 bits RAM port 512 × 4 bits SAM port

- Performance

| Speed Parameter           | -6    | -7    | -8    |

|---------------------------|-------|-------|-------|

| RAM access time (tRAC)    | 60ns  | 70ns  | 80ns  |

| RAM access time (tcac)    | 20ns  | 20ns  | 20ns  |

| RAM cycle time (tRc)      | 110ns | 130ns | 150ns |

| RAM page mode cycle (tPc) | 40ns  | 45ns  | 50ns  |

| SAM access time (tsca)    | 18ns  | 20ns  | 20ns  |

| SAM cycle time (tscc)     | 20ns  | 25ns  | 25ns  |

| RAM active current        | 90mA  | 85mA  | 80mA  |

| SAM active current        | 50mA  | 45mA  | 40mA  |

- Fast Page Mode

- RAM Read, Write, Read-Modify-Write

- Serial Read and Serial Write

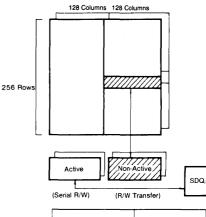

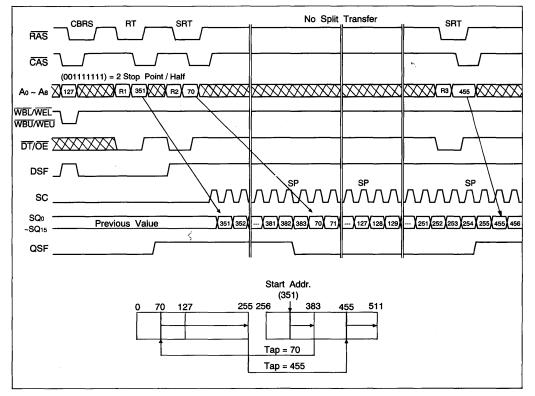

- Read, Real Time Read and Split Read Transfer (RAM→SAM)

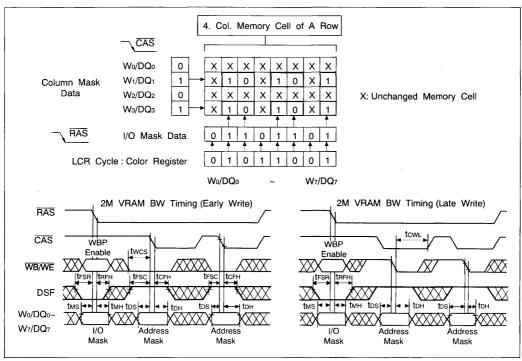

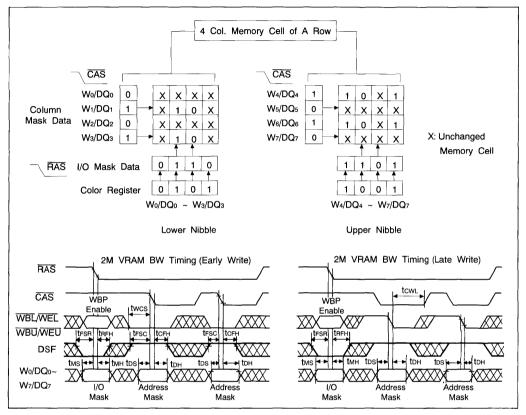

- Write, Split Write Transfer with Masking operation (New Mask)

- Block Write, Flash Write and Write per bit with Masking operation (New Mask)

- CAS-before-RAS, RAS-only and Hidden Refresh

- Common Data I/O Using three state RAM Output Control

- All Inputs and outputs TTL compatible

- Refresh: 512 Cycle/8ms

Single +5V±10% Supply Voltage

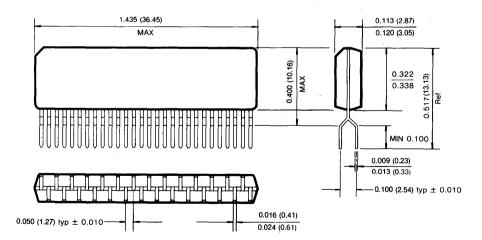

- Plastic 28-PIN 400 mil SOJ and ZIP

### **GENERAL DESCRIPTION**

The Samsung KM424C257 is a CMOS 256K×4 bit Dual Port DRAM. It consists of a 256K×4 dynamic random access memory (RAM) port and 512×4 static serial access memory (SAM) port. The RAM and SAM ports operate asynchronously except during data transfer between the ports.

The RAM array consists of 512 bit rows of 2048 bits. It operates like a conventional  $256K \times 4$  CMOS DRAM. The RAM port has a write per bit mask capability.

The SAM port consists of four 512 bit high speed shift registers that are connected to the RAM array through a 2048 bit data transfer gate. The SAM port has serial read and write capabilities.

Data may be internally transferred bi-directionally between the RAM and SAM ports using read or write transfers.

Refresh is accomplished by familiar DRAM refresh modes. The KM424C257 supports RAS-only, Hidden, and CAS-before-RAS refresh for the RAM port. The SAM port does not require refresh.

All inputs and I/O's are TTL level compatible. All address lines and Data Inputs are latched on chip to simplify system design. The outputs are unlatched to allow greater system flexibility.

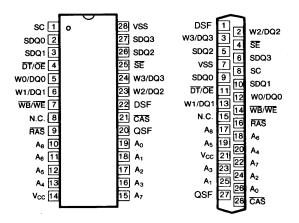

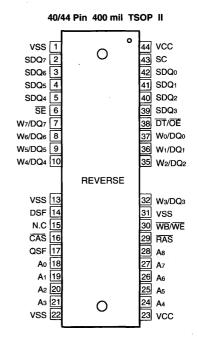

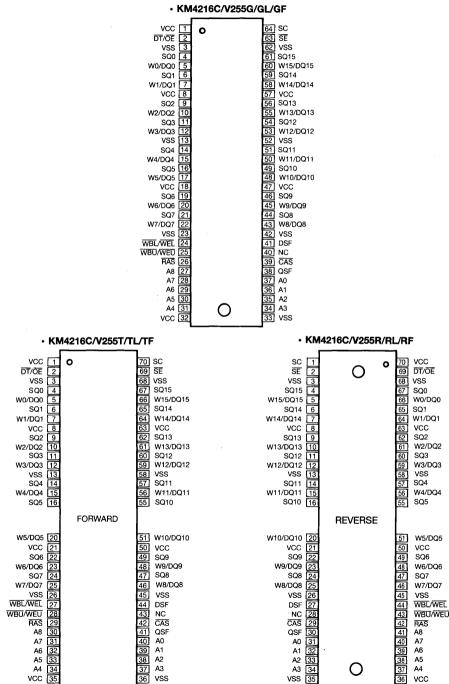

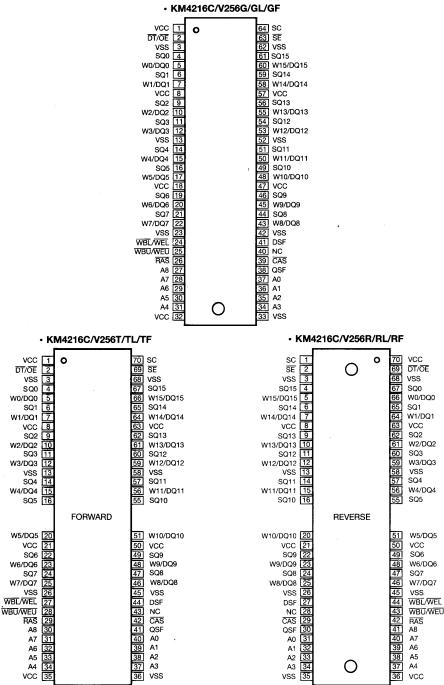

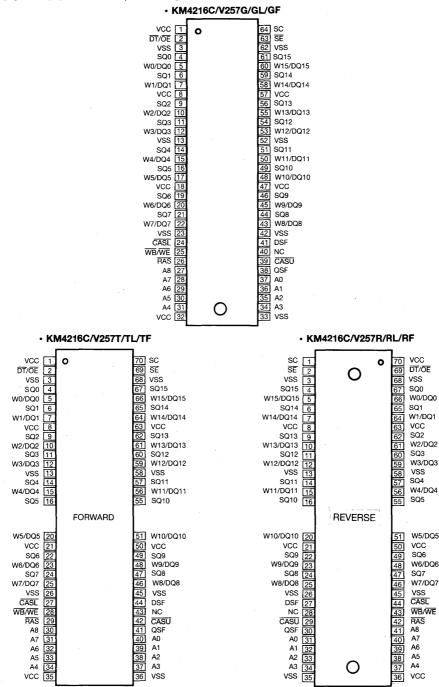

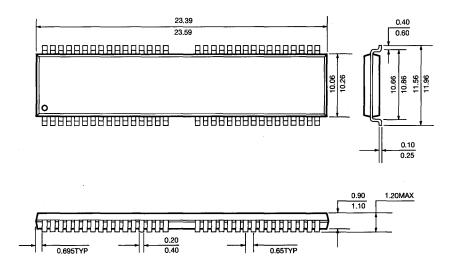

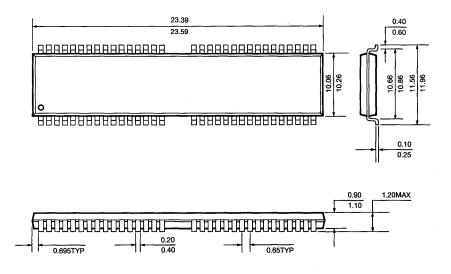

### **PIN CONFIGURATION (Top Views)**

28 Pin 400 mil SOJ

28 Pin 400 mil ZIP

# **PIN DESCRIPTION**

| Symbol  | Туре   | Description                                                                                                                                                                                                                                                                                                                                            |

|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAS     | IN     | Row Address Strobe. $\overline{\text{RAS}}$ is used to clock in the 9 row bits for another input signal. The RAM port is placed in standby mode when the $\overline{\text{RAS}}$ control is held "High"                                                                                                                                                |

| CAS     | IN     | Column Address Strobe. $\overline{\text{CAS}}$ is used to clock in the 9 column address bits as a strobe for the DSF inputs                                                                                                                                                                                                                            |

| ADDRESS | IN     | Address inputs for the DRAM operation, these inputs are multiplexed and clocked by RAS and CAS to select one 16-bit word out of the 262,144 available. 9 row address bits are latched on the falling edge of the row address strobe(RAS) and the following nine column address bits are latched on the falling edge of the column address strobe(CAS). |

| WB/WE   | IN     | The WB/WE input is a multifunction pin. when WB/WE is "High" at the falling edge of RAS, during RAM port operation, it is used to write data into the memory array in the same manner as a standard DRAM. When WB/WE is "Low" at the falling edge of RAS, during RAM port operation, the W-P-B function is enabled.                                    |

| DT/OE   | IN     | The DT/OE input is also a multifunction pin. Enables an internal Transfer operation at the falling edge of RAS when Transfer enable.                                                                                                                                                                                                                   |

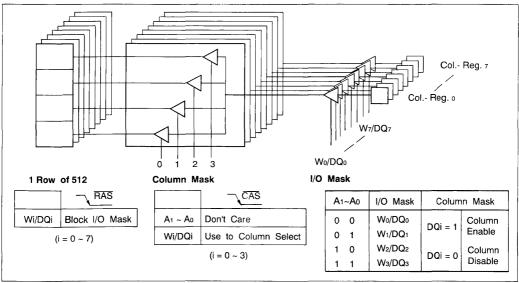

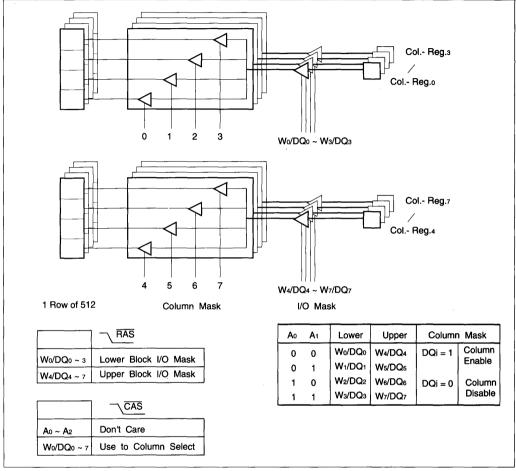

| DSF     | IN     | DSF is used to indicate which special functions(BW, FW, Split Transfer, etc)are used for a particular access cycle.                                                                                                                                                                                                                                    |

| Wi/DQi  | IN/OUT | Data I/O for DRAM access. These pins act as inputs for Mask and register load cycles, DQ Mask and Column Mask for BW.                                                                                                                                                                                                                                  |

| SC      | IN     | Clock input to the serial address counter and data latch for the SAM register                                                                                                                                                                                                                                                                          |

| SDQi    | IN/OUT | Serial input and serial output share common I/O pins. Serial input or output mode is determined by the most recent read, write or pseudo write transfer cycle.                                                                                                                                                                                         |

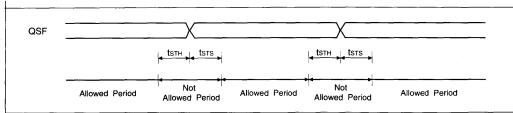

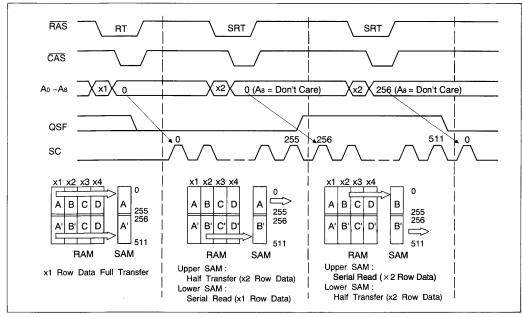

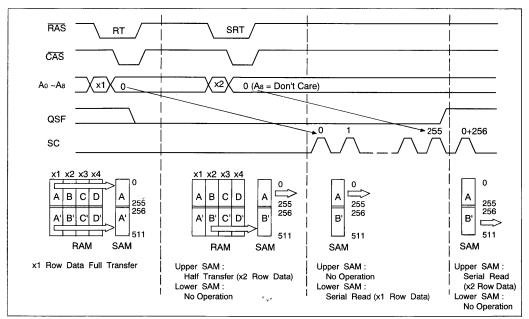

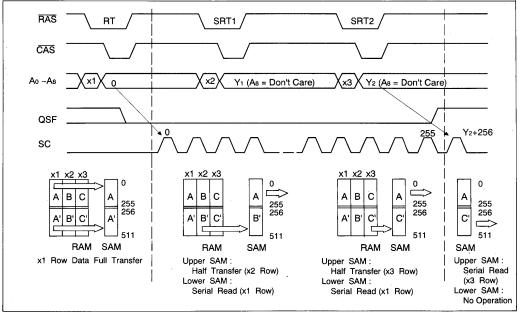

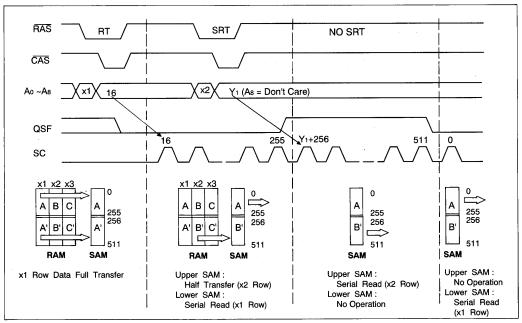

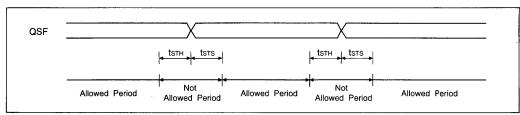

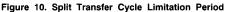

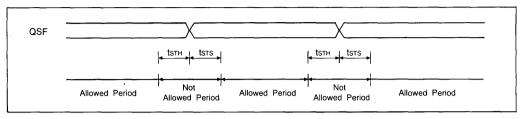

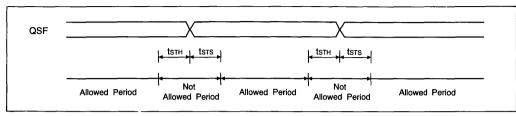

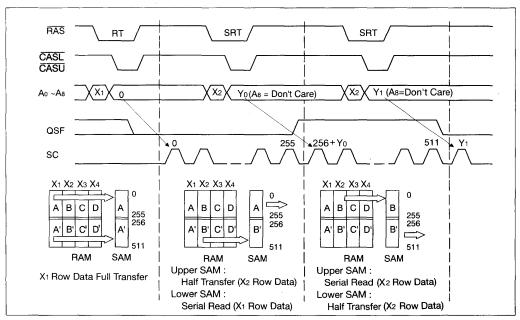

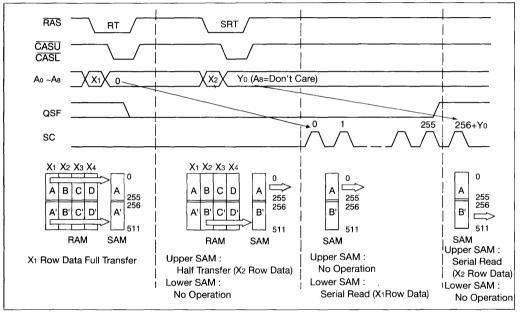

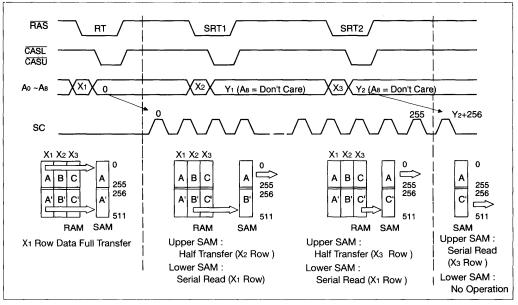

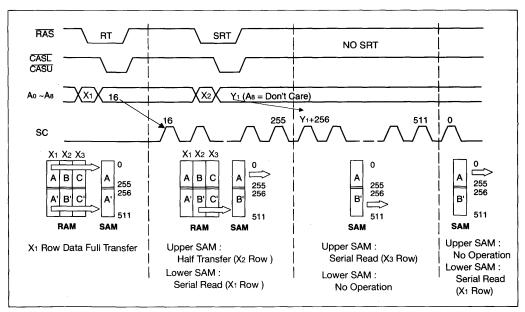

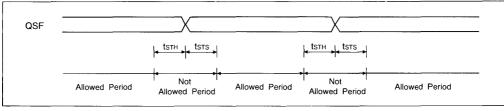

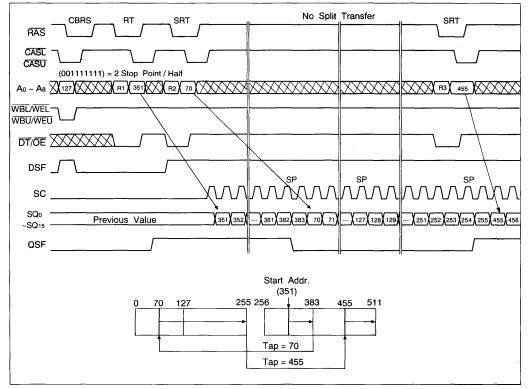

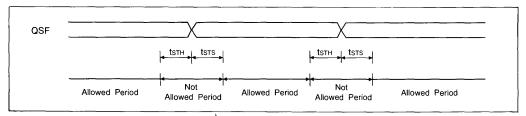

| QSF     | OUT    | QSF indicates which half of the SAM is being accessed. Low if address is 0-255,<br>High if address is 256-511.                                                                                                                                                                                                                                         |

| SE      | IN     | In a serial read cycle. $\overline{SE}$ is used as an output control. When $\overline{SE}$ is "High", serial access is disabled, however, the serial address pointer is still incremented while SC is clocked.                                                                                                                                         |

| Vcc     | SUPPLY | Power supply                                                                                                                                                                                                                                                                                                                                           |

| Vss     | SUPPLY | Ground                                                                                                                                                                                                                                                                                                                                                 |

|         |        |                                                                                                                                                                                                                                                                                                                                                        |

2

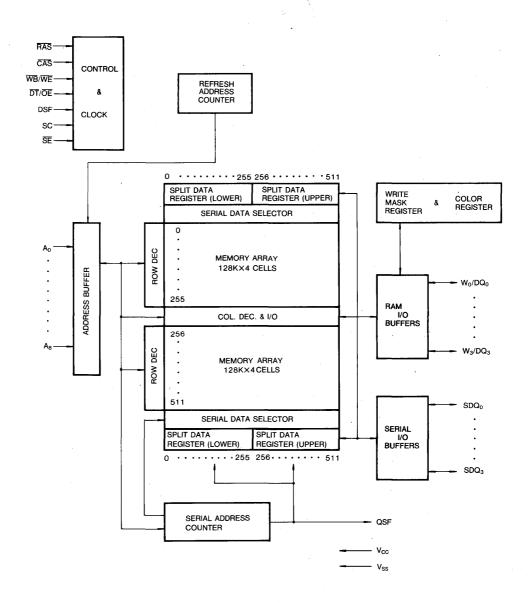

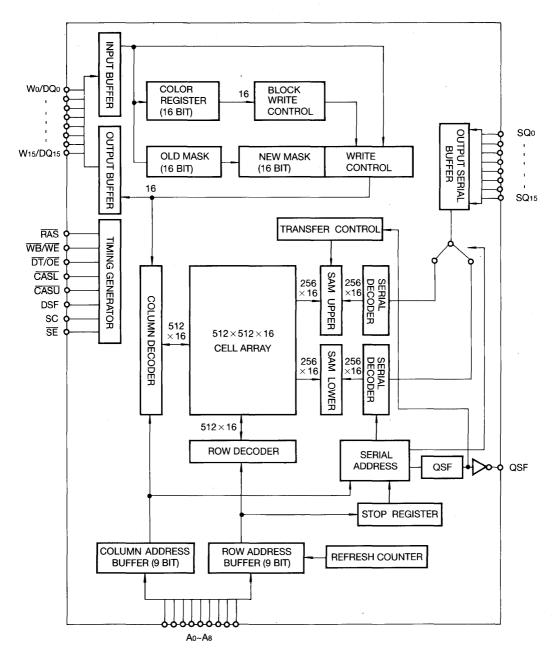

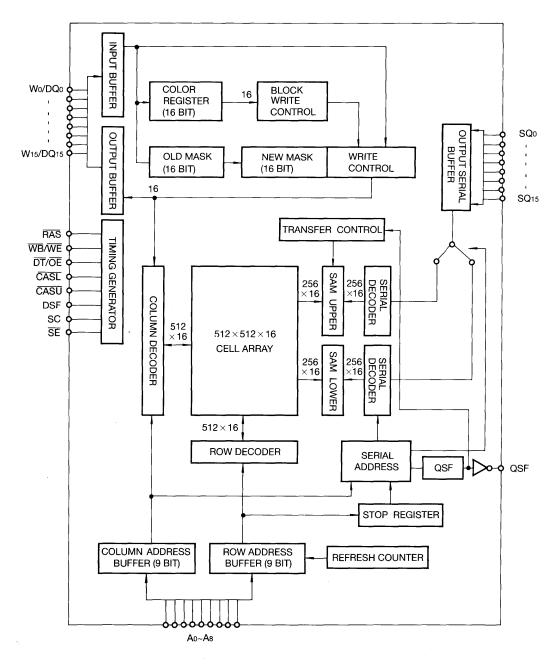

## FUNCTIONAL BLOCK DIAGRAM

SAMSUNG ELECTRONICS

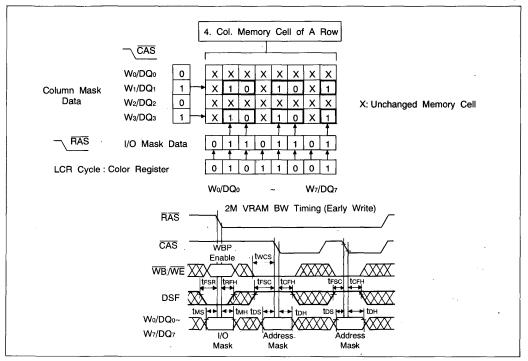

### **FUNCTION TRUTH TABLE**

| Mnemonic |     |       | RAS      |     |    | CAS | Addı   | ress*1  | DQi    | Input*2 | Write | Color    |                        |                       |

|----------|-----|-------|----------|-----|----|-----|--------|---------|--------|---------|-------|----------|------------------------|-----------------------|

| Code     | CAS | DT/OE | WE       | DSF | SE | DSF | RAS    | CAS     | RAS    | CAS/WE  | Mask  | Register | Function               |                       |

| CBR      | 0   | Х     | х        | х   | х  | _   | х      | х       | Х      | -       | -     | -        | CBR Refresh            |                       |

| ROR      | 1   | 1     | х        | 0   | х  | -   | Row    | х       | X      | -       |       | -        | RAS-only Refresh       |                       |

| BW       | 1   | 1     | 1        | 0   | x  |     | Row    | Col.    | x      | Data    |       |          | Normal DRAM Read/      |                       |

|          |     |       |          |     | ^  | 0   | now    | 00.     | ^      | Data    | _     | _        | Write(No. Mask)        |                       |

| BW/NM    | 1   | 1     | 0        | 0   | x  |     | Row    | Col.    | WMi    | Data    |       |          | Masked DRAM Write      |                       |

|          | I   |       | U        | U   | ^  | 0   | now    | 00.     | VVIVI  |         | Use   | _        | (New Mask)             |                       |

| MFLW     | 1   | 1     | 0        | 1   | x  |     | Row    | x       | WMi >  | x       | Use   | Use      | Masked Flash Write     |                       |

|          | 1   | 1     | 0        | I   | ^  | X   | now    | ^       | VVIVII | ^       | Use   | Use      | (New Mask)             |                       |

| BW       | 1   | 1     | 1        | 0   | х  |     | Row    | Col.    | x      | Col.    | _     | _        | Use                    | Block Write (No Mask) |

|          |     |       | <u>'</u> | 0   | ^  | 1   | HOW    | (A2~A8) | ^      | Mask    |       | Use      | DIOCK WITTE (NO WIASK) |                       |

| BW/NW    | 1   | 1     | 0        | 0   | х  | 1   | Row    | Col.    | WMi    | Col.    | Use   | Use      | Masked Block Write     |                       |

| DW/INW   |     | 1     | U        | Ŭ   | ^  | 1   | now    | (A2~A8) | VVIVII | Mask    | Use   | Use      | (New Mask)             |                       |

| LCR      | 1   | 1     | 1        | 1   | х  | 1   | Row    | •x      | x      | Coor    |       | Load     | Load Color Register    |                       |

| LOIT     | 1   |       | '        | •   |    | 1   | now    | •^      | ^      | Mask    |       | LUau     |                        |                       |

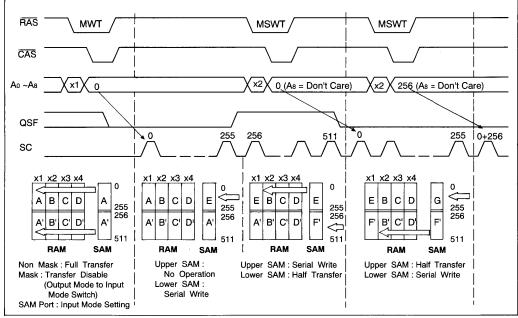

| RT       | 1   | 0     | 1        | 0   | х  | х   | Row    | Тар     | х      | Х       | _     |          | Read Transfer          |                       |

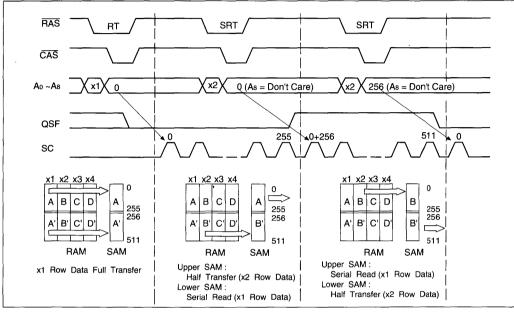

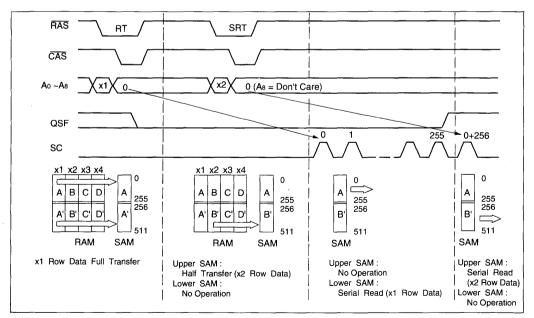

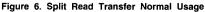

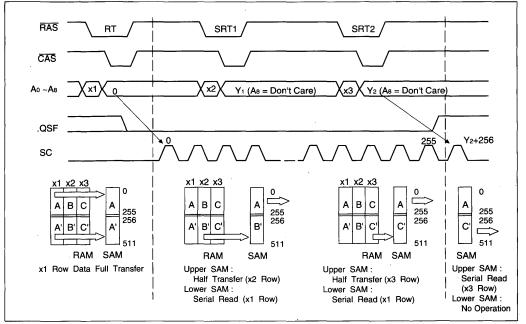

| SRT      | 1   | 0     | 1        | 1 ` | х  | х   | Row    | Тар     | х      | х       | _     | —        | Split Read Transfer    |                       |

| PWT      | 1   | 0     | 0        | 0   | 1  | х   | Row    | Тар     | х      | Х       | _     | -        | Pseudo Write Transfer  |                       |

| мут      | 1   | 0     | 0        | 0   | 0  | x   | Row *3 | Тар     | ŴMi    | x       |       |          | Masked Write           |                       |

|          | '   |       |          | Ů   |    | ×   | now    | ιαp     | 441411 | ^       | _     |          | Transfer(New Mask)     |                       |

| MSWT     | 1   | 0     | 0        | 1   | х  | v   | Row    | Тар     | WMi    | x       |       |          | Masked Split Write     |                       |

|          | I   | U     | 0        | '   | ^  | Х   | HOW    | ιαp     | 441411 | ^       |       | _        | Transfer(New Mask)     |                       |

X: Don't Care, -: Not Applicable

Note

\*1 : These column show what must be present on the Ao~As outputs at the falling edge of RAS and CAS.

\*2 : These column show what must be present on the DQ0~DQ3 outputs at the falling edge of RAS, CAS or WB/WE, whichever is later.

\*3 : The Row that is addressed will be refreshed.

# **ABSOLUTE MAXIMUM RATINGS\***

| Item                                                          | Symbol           | Rating      | Unit |

|---------------------------------------------------------------|------------------|-------------|------|

| Voltage on Any Pin Relative to V <sub>SS</sub>                | VIN, VOUT        | -1 to +7.0  | V    |

| Voltage on V <sub>CC</sub> Supply Relative to V <sub>SS</sub> | Vcc              | -1 to +7.0  | ٧    |

| Storage Temperature                                           | T <sub>stg</sub> | -55 to +150 | °C   |

| Power Dissipation                                             | PD               | 1           | W    |

| Short Circuit Output Current                                  | los              | 50          | mA   |

\* Permanent device damage may occur if "ABSOLUTE MAXIMUM RATINGS" are exceeded. Functional Operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### RECOMMENDED OPERATING CONDITIONS (Voltage reference to V<sub>SS</sub>, T<sub>A</sub>=0 to 70°C)

| ltem               | Symbol          | Min  | Тур | Max    | Unit |

|--------------------|-----------------|------|-----|--------|------|

| Supply Voltage     | V <sub>CC</sub> | 4.5  | 5.0 | 5.5    | V    |

| Ground             | V <sub>SS</sub> | 0    | 0   | 0      | V    |

| Input High Voltage | VIH             | 2.4  | _   | Vcc+1V | V    |

| Input Low Voltage  | VIL             | -1.5 |     | 0.8    | ·V   |

# INPUT/OUTPUT CURRENT (Recommended operating conditions unless otherwise noted.)

| Item                                                                                                       | Symbol          | Min | Мах | Unit |

|------------------------------------------------------------------------------------------------------------|-----------------|-----|-----|------|

| Input Leakage Current (Any Input $0 \le V_{IN} \le V_{CC} + 0.5V$ , all other pins not under test=0 volts) | l <sub>IL</sub> | -10 | 10  | μA   |

| Output Leakage Current (Data out is disabled,<br>0V≤Vout≤Vcc)                                              | lol             | -10 | 10  | μA   |

| Output High Voltage Level<br>(RAM I <sub>OH</sub> =-5mA, SAM I <sub>OH</sub> =-2mA)                        | V <sub>OH</sub> | 2.4 |     | V    |

| Output Low Voltage Level<br>(RAM I <sub>OL</sub> =4.2mA, SAM I <sub>OL</sub> =2mA)                         | V <sub>OL</sub> | _   | 0.4 | V    |

# CAPACITANCE (VCC=5V, f=1MHz, TA=25°C)

| Item                                                                                         | Symbol           | Min | Max | Unit |

|----------------------------------------------------------------------------------------------|------------------|-----|-----|------|

| Input Capacitance (A <sub>0</sub> -A <sub>8</sub> )                                          | C <sub>IN1</sub> | 2   | 6   | pF   |

| Input Capacitance (RAS, CAS, WB/WE,<br>DT/OE, SE, SC, DSF)                                   | C <sub>IN2</sub> | 2   | 7   | pF   |

| Input/Output Capacitance (W <sub>0</sub> /DQ <sub>0</sub> -W <sub>3</sub> /DQ <sub>3</sub> ) | C <sub>DQ</sub>  | 2   | 7   | pF   |

| Input/Output Capacitance (SDQ0-SDQ3)                                                         | C <sub>SDQ</sub> | 2   | 7   | pF   |

| Output Capacitance (QSF)                                                                     | C <sub>QSF</sub> | 2   | 7   | pF   |

## DC AND OPERATING CHARACTERISTICS

(Recommended operating conditions unless otherwise noted)

|                                                              |          |        | 1   | KM424C25 | 7    |      |

|--------------------------------------------------------------|----------|--------|-----|----------|------|------|

| Parameter(RAM Port)                                          | SAM Port | Symbol | -6  | -7       | -8   | Unit |

| Operating Current*1                                          | Standby  | ICC1   | 90  | 85       | 80   | mA   |

| (RAS and CAS Cycling @trc=min.)                              | Active   | Icc1A  | 140 | 130      | 120  | mA   |

| Standby Current*1                                            | Standby  | ICC2   | 5   | 5        | 5    | mA   |

| (RAS=CAS=DT/OE=WB/WE=VIH,DSF=VIL)                            | Active   | ICC2A  | 50  | 45       | 40   | mA   |

| RAS Only Refresh Current*1                                   | Standby  | Іссз   | 90  | 85       | 80   | mA   |

| (CAS=Vin, RAS Cycling @trc=min.)                             | Active   | ІссзА  | 140 | 130      | 120  | mA   |

| Fast Page Mode Current*₁<br>(RAS=Vi∟, CAS Cycling @tբc=min.) | Standby  | ICC4   | 70  | 65       | 60   | mA   |

|                                                              | Active   | Icc4A  | 120 | 110      | 100  | mA   |

| CAS-Before-BAS Refresh Current*1                             | Standby  | ICC5   | 90  | 85       | 80   | mA   |

| (RAS and CAS Cycling @trc=min.)                              | Active   | ICC5A  | 140 | 130      | 120  | mA   |

| Data Transfer Current*1                                      | Standby  | ICC6   | 120 | 115      | 110  | mA   |

| (RAS and CAS Cycling @trc=min.)                              | Active   | ICC6A  | 170 | 160      | 150  | mA   |

| Flash Write Cycle                                            | Standby  | ICC7   | 90  | 85       | . 80 | mA   |

| (RAS and CAS Cycling @tRc=min.)                              | Active   | ICC7A  | 140 | 130      | 120  | mA   |

| Block Write Cycle                                            | Standby  | Іссв   | 100 | 95       | 90   | mA   |

| (RAS and CAS Cycling @tRc=min.)                              | Active   | Icc8A  | 150 | 140      | 130  | mA   |

| Color Register Load or Read Cycle                            | Standby  | lcca   | 90  | 85       | 80   | mA   |

| (RAS and CAS Cycling @trc=min.)                              | Active   | ІссяА  | 140 | 130      | 120  | mA   |

NOTE\*1: Real values are dependent on output loading and cycle rates. Specified values are obtained with the output open, lcc is Specified as average current.

In Icc1, Icc3, Icc6, Icc7, Icc8, Icc9 address transition should be changed only while RAS=VIL

In Icc4, address transition should be changed only once while CAS=VIH.

# AC CHARACTERISTICS (0°C $\leq$ Ta $\leq$ 70°C, Vcc=5.0V $\pm$ 10%, see notes 1,2)

| _                                     |              |     | -6   |      | -7   |     | -8   |      | Í     |

|---------------------------------------|--------------|-----|------|------|------|-----|------|------|-------|

| Parameter                             | Symbol       | Min | Max  | Min  | Max  | Min | Max  | Unit | Notes |

| Random read or write cycle time       | tRC          | 110 |      | 130  |      | 150 |      | ns   |       |

| Read-modify-write cycle time          | tRWC         | 155 |      | 175  |      | 20  |      | ns   |       |

| Fast page mode cycle time             | tPC          | 40  |      | 45   |      | 50  |      | ns   |       |

| Fast page mode read-modify-write      | <b>tPRWC</b> | 80  |      | . 85 |      | 90  |      | ns   |       |

| Access time from RAS                  | tRAC         |     | 60   |      | 70   |     | 80   | ns   | 3,4   |

| Access time from CAS                  | tCAC         |     | 20   |      | 20   |     | 20   | ns   | 4     |

| Access time from column address       | taa          |     | 30   |      | 35   |     | 40   | ns   | 3,11  |

| Access time from CAS precharge        | tCPA         |     | 35   |      | 40   |     | 45   | ns   | 3     |

| CAS to output in Low-Z                | tcLz         | 3   |      | 3    |      | 3   |      | ns   | 3     |

| Output buffer turn-off delay          | tOFF         | 0   | 15   | 0    | 15   | 0   | 15   | ns   | 7     |

| Transition time(rise and fall)        | tτ           | 3   | 50   | 3    | 50   | 3   | 50   | ns   | 2     |

| RAS precharge time                    | tRP          | 40  |      | 50   |      | 60  |      | ns   |       |

| RAS pulse width                       | tRAS         | 60  | 10K  | 70   | 10K  | 80  | 10K  | ns   |       |

| RAS pulse width(fast page mode)       | tRASP        | 60  | 100K | 70   | 100K | 80  | 100K | ns   |       |

| RAS hold time                         | tRSH         | 20  |      | 20   |      | 20  |      | ns   |       |

| CAS hold time                         | tCSH         | 60  |      | 70   |      | 80  |      | ns   |       |

| CAS pulse width                       | tCAS         | 20  | 10K  | 20   | 10K  | 20  | 10K  | ns   |       |

| RAS to CAS delay time                 | tRCD         | 20  | 40   | 20   | 50   | 25  | 60   | ns   | 5,6   |

| RAS to column address delay time      | tRAD         | 15  | 30   | 15   | 35   | 20  | 40   | ns   | 11    |

| CAS to RAS precharge time             | tCRP         | 5   |      | 5    |      | 5   |      | ns   |       |

| CAS precharge time (CBR Counter Test) | tCPT         | 10  |      | 10   |      | 10  |      | ns   |       |

| CAS precharge time(fast page mode)    | tCP          | 10  |      | 10   |      | 10  |      | ns   |       |

| Row address set-up time               | tASR         | 0   |      | 0    |      | 0   |      | ns   |       |

| Row address hold time                 | tRAH         | 10  |      | 10   |      | 15  |      | ns   |       |

| Column address set-up time            | tasc         | 0   |      | 0    |      | 0   |      | ns   |       |

| Column address hold time              | tCAH .       | 15  |      | 15   |      | 15  |      | ns   |       |

| Column address hold referenced to RAS | tar          | 50  |      | 55   |      | 60  |      | ns   |       |

| Column address to RAS lead time       | tRAL         | 30  |      | 35   |      | 40  |      | ns   |       |

| Read command set-up time              | tRCS         | 0   |      | 0    |      | 0   |      | ns   |       |

| Read command hold referenced to CAS   | tRCH         | 0   |      | 0    |      | 0   |      | ns   | 9     |

| Read command hold referenced to RAS   | tRRH         | 0   |      | 0    |      | 0   |      | ns   | 9     |

| Write command hold time               | twch         | 15  |      | 15   |      | 15  |      | ns   |       |

| Write command hold referenced to RAS  | twcn         | 45  |      | 55   |      | 60  |      | ns   |       |

| Write command pulse width             | twp          | 10  |      | 15   |      | 15  |      | ns   |       |

| Write command to RAS lead time        | tRWL         | 15  |      | 15   |      | 20  |      | ns   |       |

| Write command to CAS lead time        | tCWL         | 15  |      | 15   |      | 20  |      | ns   |       |

# AC CHARACTERISTICS (0°C ≤ TA ≤ 70°C, Vcc=3.3V±0.3V, See notes 1,2)

|                                                        |              |     | -6  |     | -7  | 1   | -8  | مغاملا |       |

|--------------------------------------------------------|--------------|-----|-----|-----|-----|-----|-----|--------|-------|

| Parameter                                              | Symbol       | Min | Max | Min | Max | Min | Max | Units  | Notes |

| Data set-up time                                       | tDS          | 0   |     | 0   |     | 0   |     | ns     | 10    |

| Data hold time                                         | tDH          | 15  |     | 15  |     | 15  |     | ns     | 10    |

| Data hold referenced to RAS                            | <b>t</b> DHR | 45  |     | 55  |     | 60  |     | ns     |       |