# 4M DRAM The

# SAMSUNG

#### **PRINTED IN KOREA**

¢

Circuit diagrams utilizing SAMSUNG products are included as a means of illustrating typical semiconductor applications; consequently, complete information sufficient for construction purposes is not necessarily given. The information has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described herein any license under the patent rights of SAMSUNG or others. SAMSUNG reserve the right to change device specifications.

# TABLE OF CONTENTS

#### I. FUNCTION GUIDE

| 1. | Introduction          | 11 |

|----|-----------------------|----|

| 2. | Product Guide ······  | 14 |

| З. | Cross Reference Guide | 16 |

| 4. | Ordering Information  | 17 |

#### II. 4M DRAM DATA SHEETS

#### 4M X 1

| 1.  | KM41C4000 ······21   |

|-----|----------------------|

| 2.  | KM41C1000L           |

| З.  | KM41C4001            |

| 4.  | KM41C4002            |

| 5.  | KM41C4000A           |

| 6.  | KM41C4000AL          |

| 7.  | KM41C4000ASL         |

| 8.  | KM41C4001A           |

| 9.  | KM41C4002A           |

| 1M  |                      |

| 10. | КМ44С1000 ······ 155 |

| 11. | KM44C1000L155        |

| 12. | KM44C1002 ······ 171 |

| 13. | KM44C1000A           |

| 14. | KM44C1000AL          |

| 15. | KM44C1000ASL         |

| 16. | KM44C1002A242        |

| 17. | KM44C1010A           |

| 18. | KM44C1012A           |

| 256 | K X 16               |

|     | KM416C256            |

| 256 | K X 18               |

|     | KM418C256 ······ 284 |

| 512 | KX8                  |

|     | KM48C512             |

|     | K X 9                |

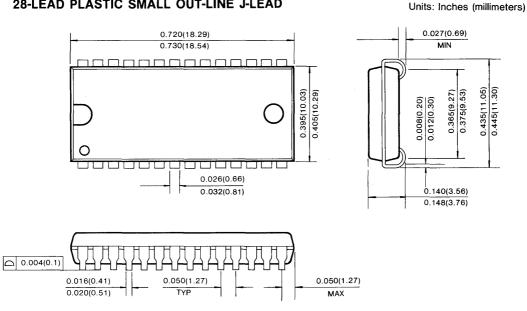

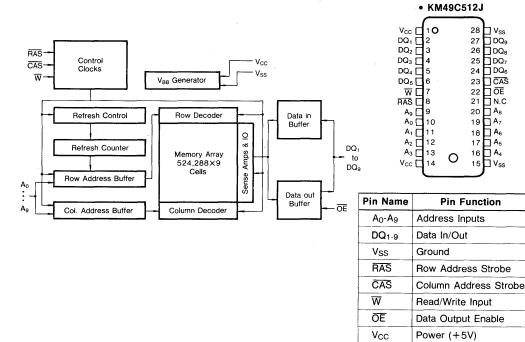

| 22. | KM49C512 ······320   |

|     |                      |

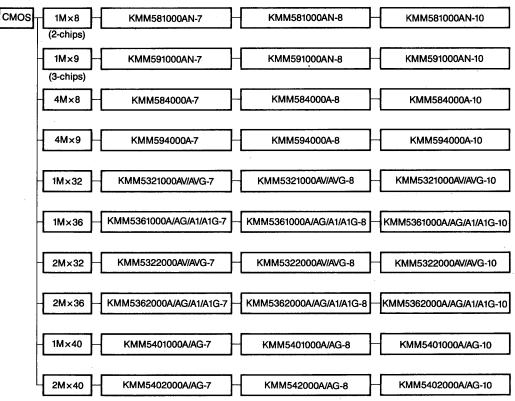

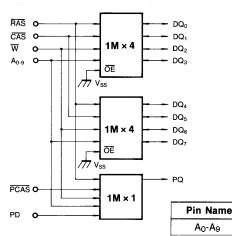

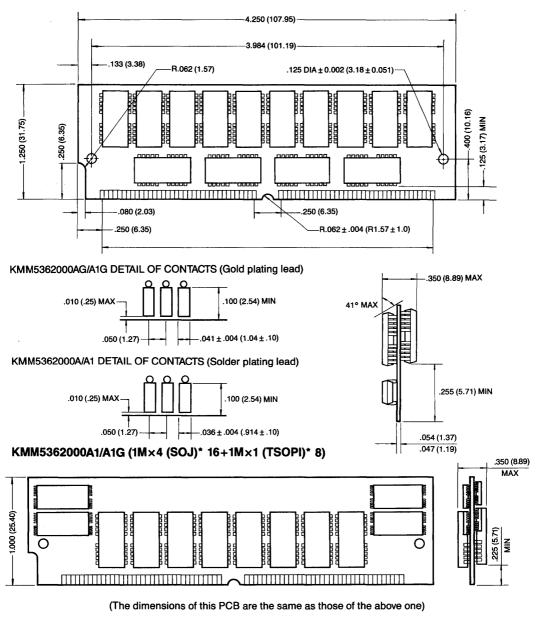

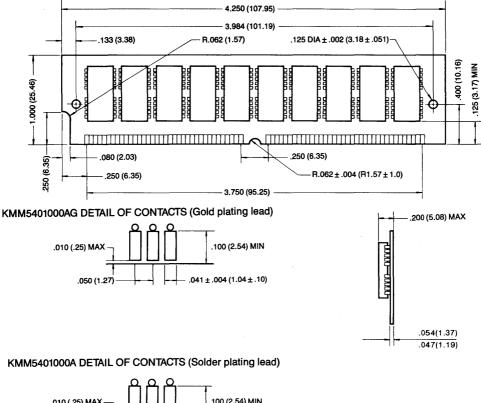

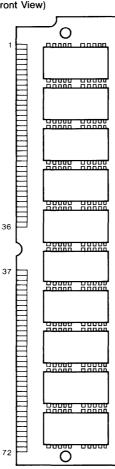

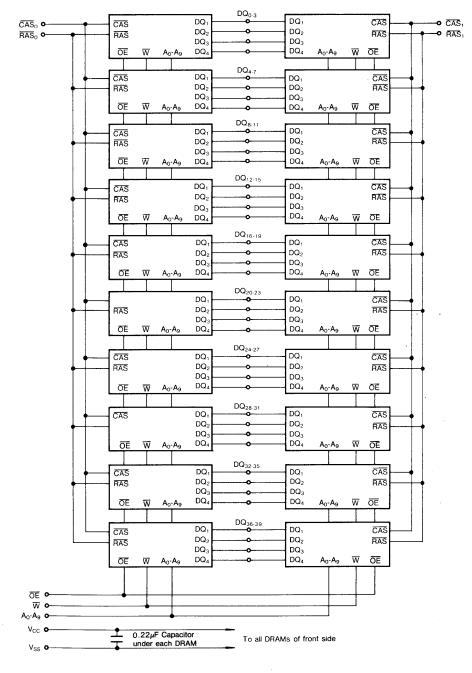

# III. 4M DRAM MODULES DATA SHEETS

|     | 1. KMM581000AN         2. KMM591000AN         3. KMM584000A         4. KMM594000A         5. KMM5321000AV/AVG         6. KMM5361000A/AG/A1/A1G         7. KMM5322000AV/AVG         8. KMM5362000A/AG/A1/A1G         9. KMM5401000A/AG         10. KMM5402000A/AG |  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IV. | SALES OFFICES AND MANUFACTURER'S                                                                                                                                                                                                                                 |  |

| REPRESENTATIVES | 447 |

|-----------------|-----|

|-----------------|-----|

| Function Guide                                   | 1 |

|--------------------------------------------------|---|

| 4M DRAM Data Sheets                              | 2 |

| 4M DRAM MODULES Data Sheets                      | 3 |

| Sales Offices and Manufacturer's Representatives | 4 |

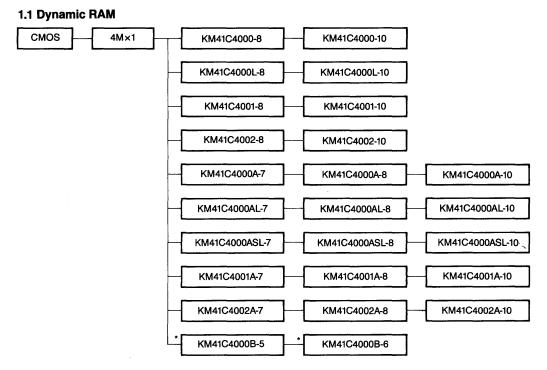

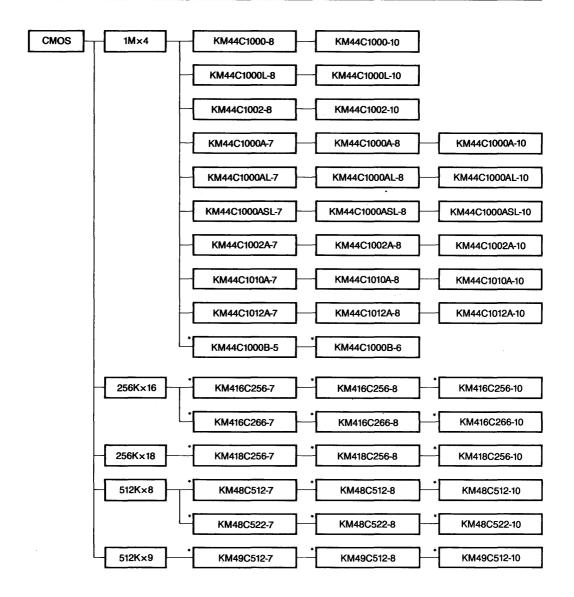

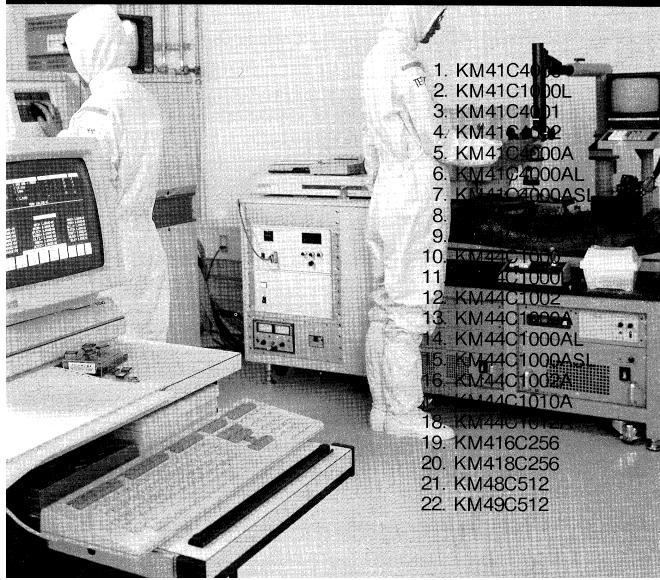

#### 1. Introduction

1

\* New Product

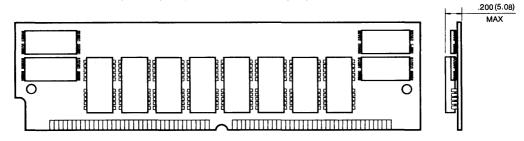

#### 1.2 Dynamic RAM Module

# 2. Product Guide

#### 2.1 Dynamic RAM

| Generation | Part Number       | Organization | Speed (ns)             | Technology   | Feature                   | Package                   | Remark            |

|------------|-------------------|--------------|------------------------|--------------|---------------------------|---------------------------|-------------------|

| 1st Gen.   | KM41C4000J        | 4M × 1       | 80/100                 | CMOS         | Fast Page                 | 20 Pin SOJ                | Now               |

|            | KM41C4000Z        | 4M × 1       | 80/100                 | CMOS         | Fast Page                 | 20 Pin ZIP                | Now               |

|            | KM41C4000LJ       | 4M×1         | 80/100                 | CMÓS         | Fast Page                 | 20 Pin SOJ                | Now               |

|            | KM41C4000LZ       | 4M × 1       | 80/100                 | CMOS         | Fast Page                 | 20 Pin ZIP                | Now               |

|            | KM41C4001J        | 4M × 1       | 80/100                 | CMOS         | Nibble                    | 20 Pin SOJ                | Now               |

|            | KM41C4001Z        | 4M × 1       | 80/100                 | CMOS         | Nibble                    | 20 Pin ZIP                | Now               |

|            | KM41C4002J        | 4M × 1       | 80/100                 | CMOS         | Static Column             | 20 Pin SOJ                | Now               |

|            | KM41C4002Z        | 4M × 1       |                        | CMOS         |                           |                           |                   |

|            |                   | 411/1 X 1    | 80/100                 | CMUS         | Static Column             | 20 Pin ZIP                | Now               |

|            | KM44C1000J        | 1M × 4       | 80/100                 | CMOS         | Fast Page                 | 20 Pin SOJ                | Now               |

|            | KM44C1000Z        | 1M × 4       | 80/100                 | CMOS         | Fast Page                 | 20 Pin ZIP                | Now               |

|            | KM44C1000LJ       | 1M×4         | 80/100                 | CMOS         | Fast Page                 | 20 Pin SOJ                | Now               |

|            | KM44C1000LZ       | 1M×4         | 80/100                 | CMOS         | Fast Page                 | 20 Pin ZIP                | Now               |

|            | KM44C1002J        | 1M×4         | 80/100                 | CMOS         | Static Column             | 20 Pin SOJ                | Now               |

|            | KM44C1002Z        | 1M×4         | 80/100                 | CMOS         | Static Column             | 20 Pin ZIP                | Now               |

| 2nd Gen.   | KM41C4000AJ       | 4M × 1       | 70/80/100              | CMOS         | Fast Page                 | 20 Pin SOJ                | Now               |

|            | KM41C4000AP       | 4M × 1       | 70/80/100              | CMOS         | Fast Page                 | 18 Pin DIP                | Now               |

|            | KM41C4000AZ       | 4M × 1       | 70/80/100              | CMOS         | Fast Page                 | 20 Pin ZIP                | Now               |

|            | KM41C4000AT       | 4M × 1       | 70/80/100              | CMOS         | Fast Page                 | 20 Pin TSOP               | Now               |

|            | KM41C4000ALJ/ASLJ | 4M × 1       | 70/80/100              | CMOS         | Fast Page                 | 20 Pin SOJ                | Now               |

|            | KM41C4000ALP/ASLP | 4M × 1       | 70/80/100              | CMOS         | Fast Page                 | 18 Pin DIP                | Now               |

|            | KM41C4000ALZ/ASLZ |              |                        |              |                           |                           |                   |

|            | KM41C4000ALZ/ASLZ | 4M×1<br>4M×1 | 70/80/100<br>70/80/100 | CMOS<br>CMOS | Fast Page<br>Fast Page    | 20 Pin ZIP<br>20 Pin TSOP | Now<br>Now        |

|            |                   |              |                        |              |                           |                           |                   |

|            | KM41C4001AJ       | 4M × 1       | 70/80/100              | CMOS         | Nibble                    | 20 Pin SOJ                | Now               |

|            | KM41C4001AP       | 4M × 1       | 70/80/100              | CMOS         | Nibble                    | 18 Pin DIP                | Now               |

|            | KM41C4001AZ       | 4M × 1       | 70/80/100              | CMOS         | Nibble                    | 20 Pin ZIP                | Now               |

|            | KM41C4002AJ       | 4M × 1       | 70/80/100              | CMOS         | Static Column             | 20 Pin SOJ                | Now               |

|            | KM41C4002AP       | 4M × 1       | 70/80/100              | CMOS         | Static Column             | 18 Pin DIP                | Now               |

|            | KM41C4002AZ       | 4M × 1       | 70/80/100              | CMOS         | Static Column             | 20 Pin ZIP                | Now               |

|            | KM44C1000AJ       | 1M×4         | 70/80/100              | CMOS         | Fast Page                 | 20 Pin SOJ                | Now               |

|            | KM44C1000AP       | 1M×4         | 70/80/100              | CMOS         | Fast Page                 | 20 Pin DIP                | Now               |

|            | KM44C1000AZ       | 1M×4         | 70/80/100              | CMOS         | Fast Page                 | 20 Pin ZIP                | Now               |

|            | KM44C1000AT       | 1M×4         | 70/80/100              | CMOS         | Fast Page                 | 20 Pin TSOP               | Now               |

|            | KM441000ALJ/ASLJ  | 1M×4         | 70/80/100              | CMOS         | Fast Page                 | 20 Pin SOJ                | Now               |

|            | KM441000ALP/ASLP  | 1M×4         | 70/80/100              | CMOS         | Fast Page                 | 20 Pin DIP                | Now               |

|            | KM44C1000ALZ/ASLZ | 1M×4         | 70/80/100              | CMOS         | Fast Page                 | 20 Pin ZIP                | Now               |

|            | KM44C1000ALT/ASLT | 1M×4         |                        |              |                           |                           |                   |

|            |                   |              | 70/80/100              | CMOS         | Fast Page                 | 20 Pin TSOP               | Now               |

|            | KM44C1002AJ       | 1M×4         | 70/80/100              | CMOS         | Static Column             | 20 Pin SOJ                | Now               |

|            | KM44C1002AP       | 1M×4         | 70/80/100              | CMOS         | Static Column             | 20 Pin DIP                | Now               |

|            | KM44C1002AZ       | 1M×4         | 70/80/100              | CMOS         | Static Column             | 20 Pin ZIP                | Now               |

|            | KM44C1010AJ       | 1M×4         | 70/80/100              | CMOS         | Fast Page<br>with WPB     | 20 Pin SOJ                | Now               |

|            | KM44C1010AP       | 1M×4         | 70/80/100              | CMOS         | Fast Page<br>with WPB     | 20 Pin DIP                | Now               |

|            | KM44C1010AZ       | 1M×4         | 70/80/100              | CMOS         | Fast Page<br>with WPB     | 20 Pin ZIP                | Now               |

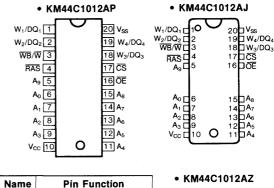

|            | KM44C1012AJ       | 1M×4         | 70/80/100              | CMOS         | Static Column<br>with WPB | 20 Pin SOJ                | Now               |

|            | KM44C1012AP       | 1M×4         | 70/80/100              | CMOS         | Static Column<br>with WPB | 20 Pin DIP                | Now               |

|            | KM44C1012AZ       | 1M×4         | 70/80/100              | CMOS         | Static Column with WPB    | 20 Pin ZIP                | Now               |

| 3rd Gen.   | *KM41C4000B       | 4M × 1       | 50/60                  | CMOS         | Fast Page                 | 20 Pin SOJ                | 2Q, '92           |

| S.G.Gom    | *KM44C1000B       | 1M×4         | 50/60                  | CMOS         | Fast Page                 | 20 Pin SOJ<br>20 Pin SOJ  | 2Q, 92<br>2Q, '92 |

|            | *KM416C256J       | 256K×16      | 70/80/100              | CMOS         | Fast Page                 | 40 Pin SOJ                | 2Q, '92           |

|            |                   | 256K × 16    | 70/80/100              | CMOS         |                           |                           | , 02              |

| Dynamic | RAM | (Continued) |

|---------|-----|-------------|

|---------|-----|-------------|

| Generation | Part Number | Organization | Speed (ns) | Technology | Feature               | Package    | Remark  |

|------------|-------------|--------------|------------|------------|-----------------------|------------|---------|

|            | *KM416C266J | 256K×16      | 70/80/100  | CMOS       | Fast Page<br>with WPB | 40 Pin SOJ | 2Q, '92 |

|            | *KM416C266Z | 256K × 16    | 70/80/100  | CMOS       | Fast Page<br>with WPB | 40 Pin ZIP | 2Q, '92 |

|            | *KM418C256J | 256K × 18    | 70/80/100  | CMOS       | Fast Page             | 40 Pin SOJ | 2Q, '92 |

|            | *KM418C256Z | 256K × 18    | 70/80/100  | CMOS       | Fast Page             | 40 Pin ZIP | 2Q, '92 |

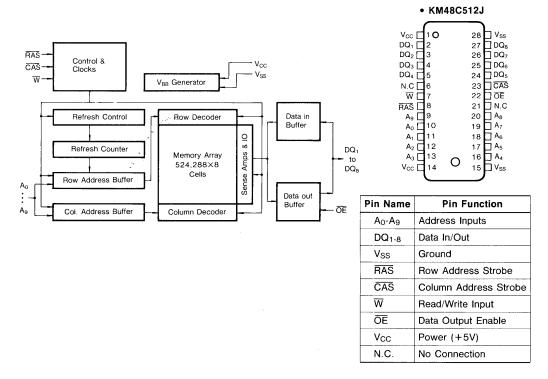

|            | *KM48C512J  | 512K × 8     | 70/80/100  | CMOS       | Fast Page             | 28 Pin SOJ | 2Q, '92 |

|            | *KM48C512Z  | 512K x 8     | 70/80/100  | CMOS       | Fast Page             | 28 Pin ZIP | 2Q, '92 |

|            | *KM48C522J  | 512K × 8     | 70/80/100  | CMOS       | Fast Page<br>with WPB | 28 Pin SOJ | 2Q, '92 |

|            | *KM48C522Z  | 512K×8       | 70/80/100  | CMOS       | Fast Page<br>with WPB | 28 Pin SOJ | 2Q, '92 |

|            | *KM49C512J  | 512K×9       | 70/80/100  | CMOS       | Fast Page             | 28 Pin SOJ | 2Q, '92 |

|            | *KM49C512Z  | 512K×9       | 70/80/100  | CMOS       | Fast Page             | 28 Pin ZIP | 2Q, '92 |

#### 2.2 Dynamic RAM Module

\*S: Single Side \*D: Double Side

| Part Number           | Organization | Speed<br>(ns) | Technology | Feature        | Package                                | PCB<br>Height [ln]        |

|-----------------------|--------------|---------------|------------|----------------|----------------------------------------|---------------------------|

| KMM581000AN           | 1M×8         | 70/80/100     | CMOS       | Fast Page Mode | *S, 30 Pin SIMM                        | 0.65                      |

| KMM591000AN           | 1M×9         | 70/80/100     | CMOS       | Fast Page Mode | *S, 30 Pin SIMM                        | 0.65                      |

| KMM584000A            | 4M × 8       | 70/80/100     | CMOS       | Fast Page Mode | *S, 30 Pin SIMM                        | 0.805                     |

| KMM594000A            | 4M × 9       | 70/80/100     | CMOS       | Fast Page Mode | *S, 30 Pin SIMM                        | 0.805                     |

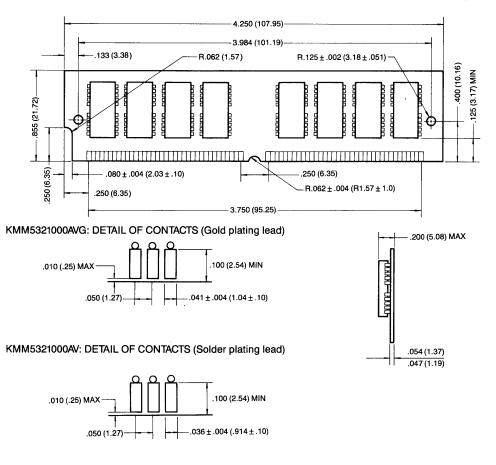

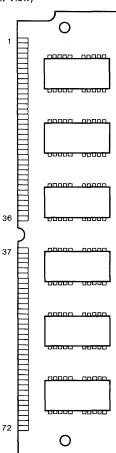

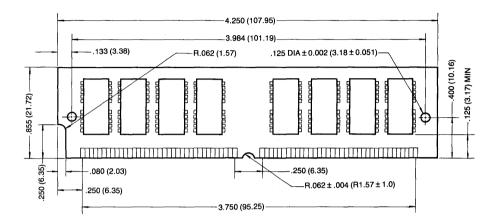

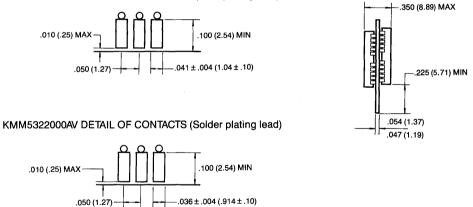

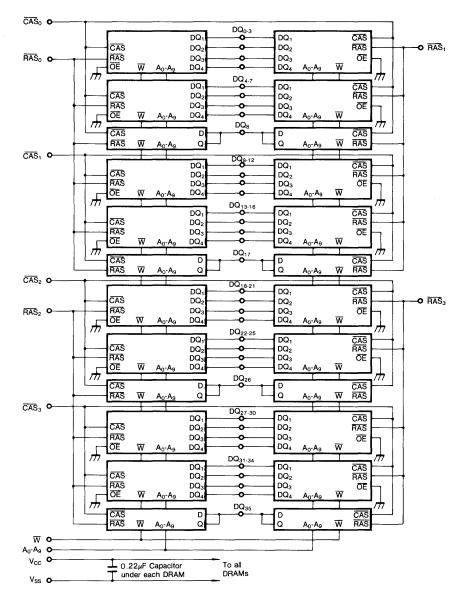

| KMM5321000AV/AVG      | 1M × 32      | 70/80/100     | CMOS       | Fast Page Mode | *S, 72 Pin SIMM                        | 0.855                     |

| KMM5361000A/AG/A1/A1G | 1M × 36      | 70/80/100     | CMOS       | Fast Page Mode | A/AG: *D, 72 Pin<br>A1/A1G: *S, 72 Pin | A/AG: 1.25<br>A1/A1G: 1.0 |

| KMM5322000AV/AVG      | 2M × 32      | 70/80/100     | CMOS       | Fast Page Mode | *D, 72 Pin SIMM                        | 0.855                     |

| KMM5362000A/AG/A1/A1G | 2M × 36      | 70/80/100     | CMOS       | Fast Page Mode | *D, 72 Pin SIMM                        | A/AG: 1.25<br>A1/A1G: 1.0 |

| KMM5401000A/AG        | 1M × 40      | 70/80/100     | CMOS       | Fast Page Mode | *S, 72 Pin SIMM                        | 1.0                       |

| KMM5402000A/AG        | 2M × 40      | 70/80/100     | CMOS       | Fast Page Mode | *D, 72 Pin SIMM                        | 1.0                       |

#### 3. Cross Reference

#### 3.1 Dynamic RAM

| Org. | Mode      | Samsung   | Toshiba  | Hitachi  | Fujitsu  | NEC       | Oki       |

|------|-----------|-----------|----------|----------|----------|-----------|-----------|

| X1   | F. Page   | KM41C4000 | TC514100 | HM514100 | MB814100 | MPD424100 | MSM514100 |

|      | Nibble    | KM41C4001 | TC514101 | HM514101 | MB814101 | MPD424101 | MSM514101 |

|      | S. Column | KM41C4002 | TC514102 | HM514102 | MB814102 | MPD424102 | MSM514102 |

| X4   | F. Page   | KM44C1000 | TC514400 | HM514400 | MB814400 | MPD424400 | MSM514400 |

|      | S. Column | KM44C1002 | TC514402 | HM514402 | MB814402 | MPD424402 | MSM514402 |

#### 3.2 Dynamic RAM Module

| Density | Organization | Samsung     | Toshiba    | Hitachi  | NEC          |

|---------|--------------|-------------|------------|----------|--------------|

| 8M bit  | 1M × 8 (2C)  | KMM581000AN |            | HB56G18  |              |

| 9M bit  | 1M×9 (3C)    | KMM591000AN | -          | HB56G19  |              |

| 32M bit | 4M × 8       | KMM584000   | THM84000   | HB56A48  | MC-424100A8  |

| 36M bit | 4M × 9       | KMM594000   | THM94000   | HB56A49  | MC-424100A9  |

| 32M bit | 1M × 32      | KMM5321000  | THM321000  | HB56D132 |              |

| 36M bit | 1M×36        | KMM5361000  | THM5361020 | HB56D136 | MC-421000A36 |

| 64M bit | 2M × 32      | KMM5322000  | THM322020  | HB56D232 |              |

| 72M bit | 2M × 36      | KMM5362000  | THM362020  | HB56D236 | MC-422000A36 |

| 40M bit | 1M × 40      | KMM5401000  | THM401020  | HB56A140 |              |

| 80M bit | 2M × 40      | KMM5402000  | THM402020  |          |              |

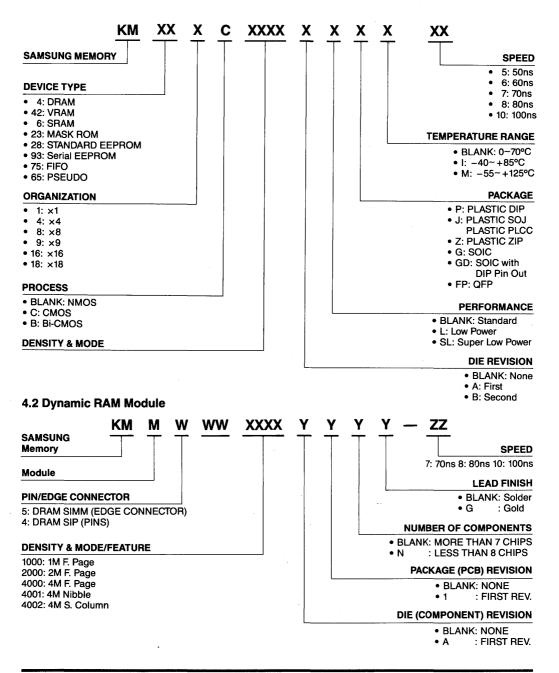

#### 4. Ordering Information

#### 4.1 Dynamic RAM

17

2

# 4M DRAM DATA SHEETS 2

. 1

# 4M×1 Bit CMOS Dynamic RAM with Fast Page Mode

#### **FEATURES**

• Performance range:

|                | tRAC  | tCAC | tRC   |

|----------------|-------|------|-------|

| KM41C4000/L- 8 | 80ns  | 20ns | 150ns |

| KM41C4000/L-10 | 100ns | 25ns | 180ns |

- Fast Page Mode operation

- CAS-before-RAS refresh capability

- RAS-only and Hidden Refresh capability

- · 8-bit fast parallel test mode capability

- TTL compatible inputs and output

- Common I/O capability using Early Write

- Single + 5V ± 10% power supply

- Refresh Cycles: -1024 cycles/16ms

- -1024 cycles/128ms (L-Version)

- Power dissipation — Standby: 5.5mW

1.7mW (L-Version) —Active : 550mW (80ns) 468mW (100ns)

- JEDEC standard pinout

- Available in Plastic SOJ/ZIP

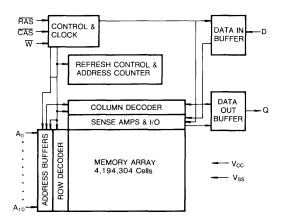

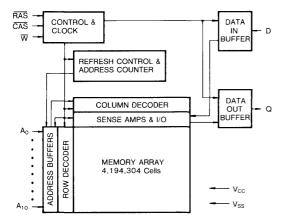

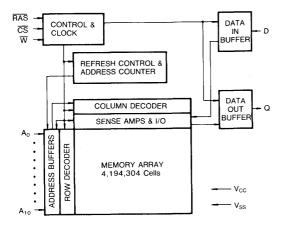

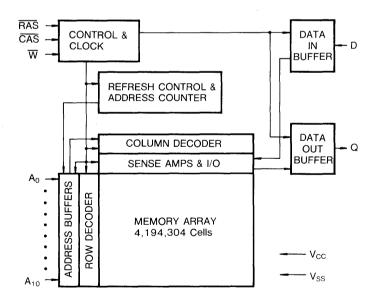

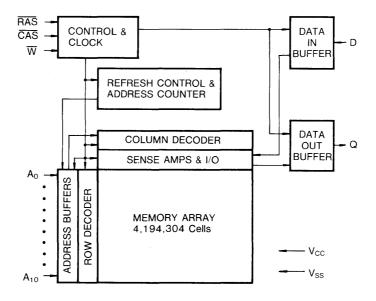

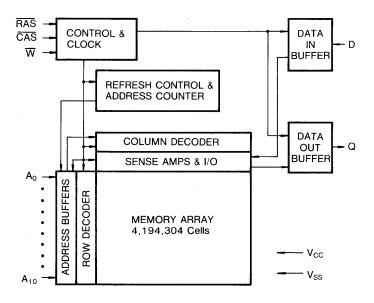

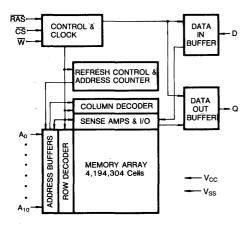

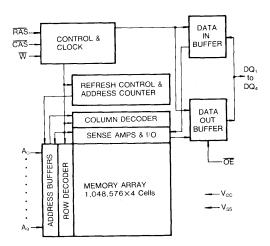

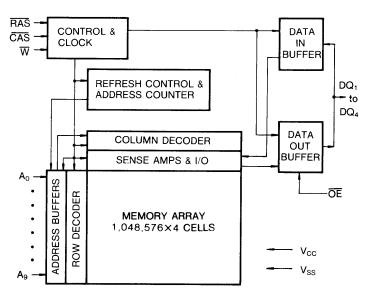

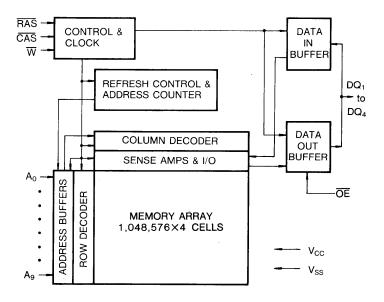

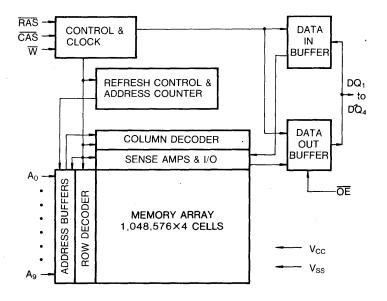

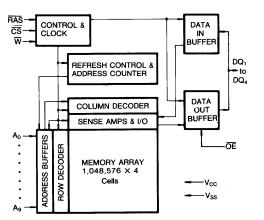

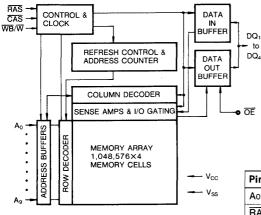

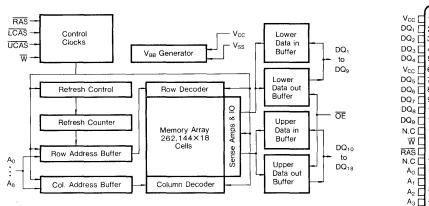

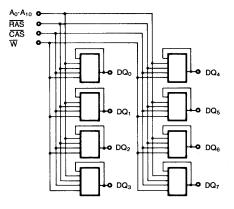

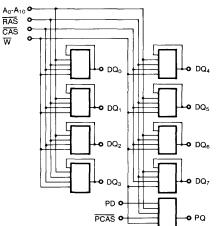

# FUNCTIONAL BLOCK DIAGRAM

#### **GENERAL DESCRIPTION**

The Samsung KM41C4000/L is a high speed CMOS 4,194,304 bit  $\times$  1 dynamic Random Access Memory. Its design is optimized for high performance applications such as mainframes and mini computers, graphics and high performance microprocessor systems.

The KM41C4000/L features Fast Page Mode operation which allows high speed random access of memory cells within the same row.

CAS-before-RAS refresh capability provides on-chip auto refresh as an alternative to RAS-only Refresh. All inputs and output are fully TTL compatible.

The KM41C4000/L is fabricated using Samsung's advanced CMOS process.

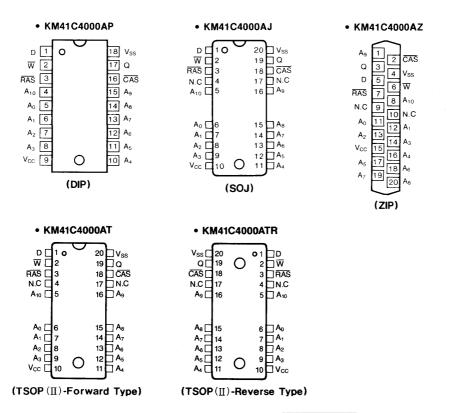

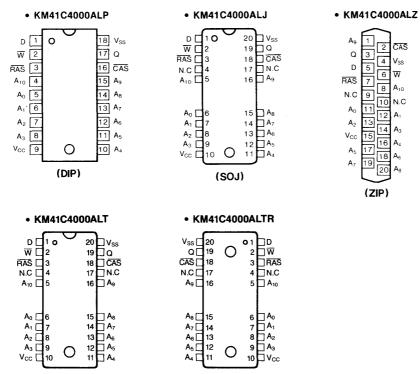

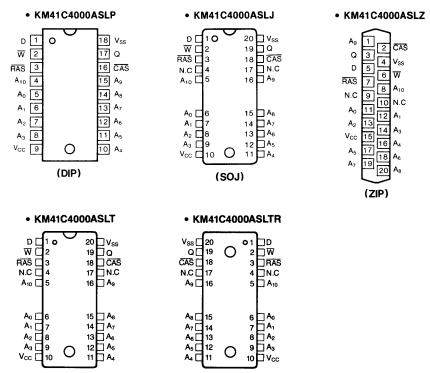

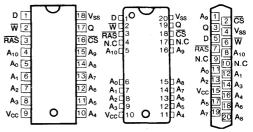

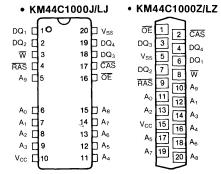

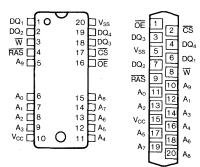

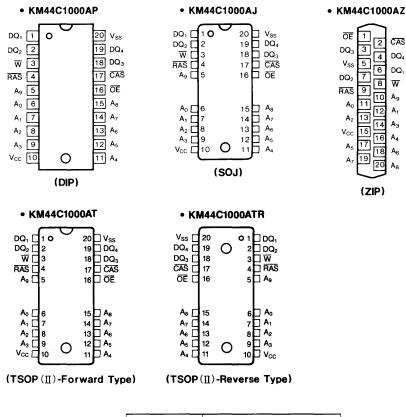

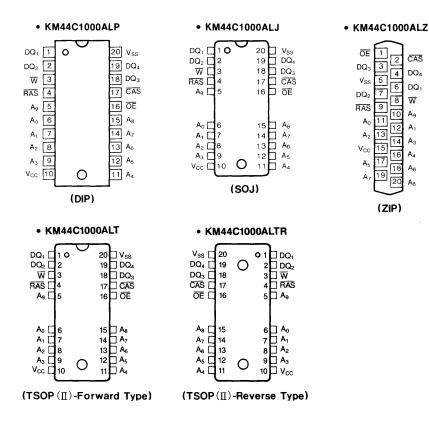

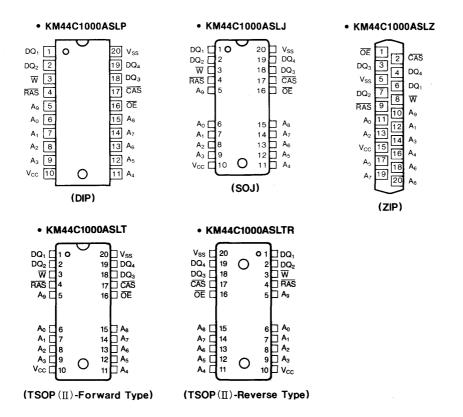

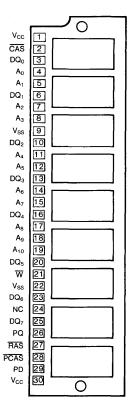

#### PIN CONFIGURATION (Top Views)

#### • KM41C4000Z/LZ KM41C4000J/LJ 10 20 Vss D Ag 1 2 CAS ₩ 🛛 2 19 🗖 Q 3 Q 4 $V_{SS}$ 18 🗖 CAS RAS 3 D 5 6 $\overline{W}$ N.C. 🗖 17 🗖 N.C. 4 RAS 7 A<sub>10</sub> 8 A10 05 16 🗋 A<sub>9</sub> N.C. 9 10 N.C. Ao 11 12 A<sub>1</sub> A<sub>0</sub> [] 6 15 🗋 A<sub>8</sub> $A_2$ 13 14 A<sub>3</sub> 7 14 A7 Vcc 15 16 A4 A<sub>2</sub> 13 🗖 A<sub>6</sub> $A_5$ 17 18 Ae A<sub>3</sub> **9** 12 A5 A; 19 20 11 A₄ $A_8$ Vcc 🗖 10

| Pin Name        | Pin Function          |  |

|-----------------|-----------------------|--|

| A0-A10          | Address Inputs        |  |

| D               | Data In               |  |

| Q               | Data Out              |  |

| W               | Read/Write Input      |  |

| RAS             | Row Address Strobe    |  |

| CAS             | Column Address Strobe |  |

| Vcc             | Power (+5V)           |  |

| V <sub>SS</sub> | Ground                |  |

| N.C.            | No connection         |  |

# **ABSOLUTE MAXIMUM RATINGS\***

| Item                                                          | Symbol           | Rating      | Unit |

|---------------------------------------------------------------|------------------|-------------|------|

| Voltage on Any Pin Relative to V <sub>SS</sub>                | VIN, VOUT        | -1 to +7.0  | V    |

| Voltage on V <sub>CC</sub> Supply Relative to V <sub>SS</sub> | Vcc              | -1 to +7.0  | V    |

| Storage Temperature                                           | T <sub>stg</sub> | -55 to +150 | °C   |

| Power Dissipation                                             | PD               | 600         | mW   |

| Short Circuit Output Current                                  | los              | 50          | mA   |

\* Permanent device damage may occur if "ABSOLUTE MAXIMUM RATINGS" are exceeded. Functional Operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS (Voltage reference to V<sub>SS</sub>, T<sub>A</sub>=0 to 70°C)

| Item               | Symbol          | Min  | Тур | Max                | Unit |

|--------------------|-----------------|------|-----|--------------------|------|

| Supply Voltage     | Vcc             | 4.5  | 5.0 | 5.5                | V    |

| Ground             | V <sub>SS</sub> | 0    | 0   | 0                  | V    |

| Input High Voltage | ViH             | 2.4  |     | V <sub>CC</sub> +1 | V    |

| Input Low Voltage  | VIL             | -1.0 |     | 0.8                | V    |

# DC AND OPERATING CHARACTERISTICS (0°C<TA<70°C, V<sub>CC</sub>=5.0V±10%)

(Recommended operating conditions unless otherwise noted)

| Parameter                                                                                                                                                                                                                                                                                                                                    |                                   | Symbol | Min | Max       | Unit     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------|-----|-----------|----------|

| Operating Current*<br>(RAS, CAS, Address Cycling @ t <sub>RC</sub> =min)                                                                                                                                                                                                                                                                     | KM41C4000/L- 8<br>KM41C4000/L-10  | Icc1   | _   | 100<br>85 | mA<br>mA |

| Standby Current<br>(RAS=CAS=V <sub>IH</sub> )                                                                                                                                                                                                                                                                                                |                                   | lcc2   | _   | 2         | mA       |

| RAS-Only Refresh Current*<br>(CAS=V <sub>IH</sub> , RAS Cycling @ t <sub>RC</sub> =min)                                                                                                                                                                                                                                                      | KM41C4000/L- 8<br>KM41C4000/L-10  | Іссз   | _   | 100<br>85 | mA<br>mA |

| Fast Page Mode Current*<br>(RAS=VIL, CAS Cycling @ t <sub>PC</sub> =min.)                                                                                                                                                                                                                                                                    | KM41C4000/L- 8<br>KM41C4000/L-10  | Icc4   |     | 60<br>50  | mA<br>mA |

| Standby Current<br>(RAS=CAS=V <sub>CC</sub> -0.2V)                                                                                                                                                                                                                                                                                           | KM41C4000-8/10<br>KM41C4000L-8/10 | lcc5   |     | 1<br>300  | mA<br>μA |

| CAS-Before-RAS Refresh Current*<br>(RAS and CAS Cycling @ t <sub>RC</sub> =min.)                                                                                                                                                                                                                                                             | KM41C4000/L- 8<br>KM41C4000/L-10  | Icce   | _   | 100<br>85 | mA<br>mA |

| Battery Back Up Current<br>Average Power Supply Current, Battery Back Up Mode<br>Input High Voltage ( $V_{IH}$ )=V <sub>CC</sub> -0.2V<br>Input Low Voltage ( $V_{IL}$ )=0.2V<br>CAS=CAS Before RAS Cycling or 0.2V<br>D <sub>IN</sub> =Don't Care<br>T <sub>RC</sub> =125 $\mu$ s, T <sub>RAS</sub> =t <sub>RAS</sub> min. $\sim$ 1 $\mu$ s | KM41C4000L- 8<br>KM41C4000L-10    | Icc7   | —   | 400       | μΑ       |

| Stand Current<br>(RAS=V <sub>IH</sub> , CAS=V <sub>IL</sub> Dout Enable)                                                                                                                                                                                                                                                                     |                                   | Іссв   | -   | 5         | mA       |

# DC AND OPERATING CHARACTERISTICS (Continued)

| Parameter                                                                                              | Symbol          | Min | Max | Unit |

|--------------------------------------------------------------------------------------------------------|-----------------|-----|-----|------|

| Input Leakage Current<br>(Any input 0≼V <sub>IN</sub> ≼6.5V,<br>all other pins not under test=0 volts) | lıL             | -10 | 10  | μΑ   |

| Output Leakage Current<br>(Data out is disabled, 0≤V <sub>OUT</sub> ≤5.5V)                             | l <sub>OL</sub> | -10 | 10  | μΑ   |

| Output High Voltage Level $(I_{OH} = -5mA)$                                                            | V <sub>OH</sub> | 2.4 |     | v    |

| Output Low Voltage Level<br>(I <sub>OL</sub> =4.2mA)                                                   | Vol             | _   | 0.4 | v    |

\*NOTE: I<sub>CC1</sub>, I<sub>CC3</sub>, I<sub>CC4</sub> and I<sub>CC6</sub> are dependent on output loading and cycle rates. Specified values are obtained with the output open. I<sub>CC</sub> is specified as average current. I<sub>CC1</sub>, I<sub>CC3</sub>, I<sub>CC6</sub> Address can be changed maximum two times while RAS=V<sub>IL</sub>. I<sub>CC4</sub>, Address can be changed maximum once while CAS=V<sub>IH</sub>.

#### CAPACITANCE (T<sub>A</sub>=25°C)

| Item                                                    | Symbol           | Min | Мах | Unit |

|---------------------------------------------------------|------------------|-----|-----|------|

| Input Capacitance (A <sub>O</sub> -A <sub>10</sub> , D) | C <sub>IN1</sub> |     | 5   | pF   |

| Input Capacitance (RAS, CAS, W)                         | C <sub>IN2</sub> | _   | 7   | pF   |

| Output Capacitance (Q)                                  | Cout             |     | 7   | pF   |

#### AC CHARACTERISTICS (0°C≤Ta≤70°C, V<sub>CC</sub>=5.0V±10%, See notes 1,2)

| Parameter                                   | Symbol            | KM4 | C4000/L-8 | 8 KM41C4000/L-10 |         | Unit | Notes |

|---------------------------------------------|-------------------|-----|-----------|------------------|---------|------|-------|

| Falameter                                   | e je.             | Min | Max       | Min              | Max     | onn  | NUCES |

| Random read or write cycle time             | t <sub>RC</sub>   | 150 |           | 180              |         | ns   |       |

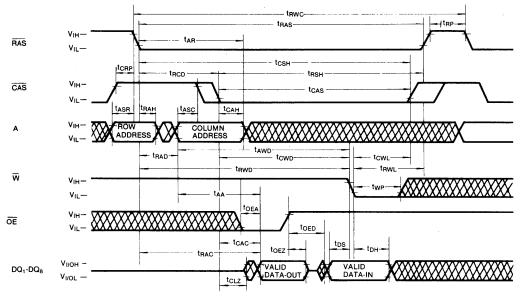

| Read-modify-write cycle time                | t <sub>RWC</sub>  | 175 |           | 210              |         | ns   |       |

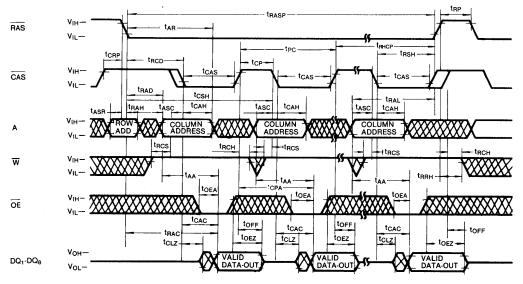

| Fast Page mode cycle time                   | tPC               | 55  |           | 60               |         | ns   |       |

| Fast Page mode read-modify-write cycle time | t <sub>PRWC</sub> | 80  |           | 90               |         | ns   |       |

| Access time from RAS                        | t <sub>RAC</sub>  |     | 80        |                  | 100     | ns   | 3,4   |

| Access time from CAS                        | tCAC              |     | 20        |                  | 25      | ns   | 3,4   |

| Access time from column address             | t <sub>AA</sub>   |     | 40        |                  | 50      | ns   | 3,10  |

| Access time from CAS precharge              | t <sub>CPA</sub>  |     | 50        |                  | 55      | ns   |       |

| CAS to output in Low-Z                      | t <sub>CLZ</sub>  | 5   |           | 5                |         | ns   | З     |

| Output buffer turn-off delay                | tOFF              | 0   | 15        | 0                | 20      | ns   | 6     |

| Transition time (rise and fall)             | t⊤                | 3   | 50        | 3                | 50      | ns   | 2     |

| RAS precharge time                          | t <sub>RP</sub>   | 60  |           | 70               |         | ns   |       |

| RAS pulse width                             | t <sub>RAS</sub>  | 80  | 10,000    | 100              | 10,000  | ns   |       |

| RAS pulse width (Fast page mode)            | tRASP             | 80  | 200,000   | 100              | 200,000 | ns   |       |

| RAS hold time                               | t <sub>RSH</sub>  | 20  |           | 25               |         | ns   |       |

| CAS hold time                               | tcsн              | 80  |           | 100              |         | ns   |       |

| CAS pulse width                             | tCAS              | 20  | 10,000    | 25               | 10,000  | ns   |       |

| RAS to CAS delay time                       | t <sub>RCD</sub>  | 20  | 60        | 25               | 75      | ns   | 4,5   |

| RAS to column address delay time            | t <sub>RAD</sub>  | 15  | 40        | 20               | 50      | ns   | 10    |

| CAS to RAS precharge time                   | t <sub>CRP</sub>  | 5   |           | 10               |         | ns   |       |

23

## AC CHARACTERISTICS (Continued)

| Parameter                                        | Symbol           | KM41 | C4000/L-8 | KM41 | C4000/L-10 | Unit | Notes |

|--------------------------------------------------|------------------|------|-----------|------|------------|------|-------|

| Farameter                                        | Symbol           | Min  | Max       | Min  | Max        | Unit |       |

| CAS precharge time                               | t <sub>CP</sub>  | 10   |           | 10   |            | ns   |       |

| Row address set-up time                          | tASR             | 0    |           | 0    |            | ns   |       |

| Row address hold time                            | t <sub>RAH</sub> | 10   |           | 15   |            | ns   |       |

| Column address set-up time                       | tASC             | 0    |           | 0    |            | ns   |       |

| Column address hold time                         | t <sub>CAH</sub> | 15   |           | 20   |            | ns   |       |

| Column address hold referenced to RAS            | t <sub>AR</sub>  | 60   |           | 75   |            | ns   | 12    |

| Column Address to RAS lead time                  | tRAL             | 40   |           | 50   |            | ns   |       |

| Read command set-up time                         | tRCS             | 0    |           | 0    |            | ns   |       |

| Read command hold referenced to CAS              | tRCH             | 0    |           | 0    |            | ns   | 8     |

| Read command hold referenced to RAS              | t <sub>RRH</sub> | 0    |           | 0    |            | ns   | 8     |

| Write command hold time                          | twcH             | 15   |           | 20   |            | ns   |       |

| Write command hold referenced to RAS             | twcr             | 60   |           | 75   |            | ns   | 12    |

| Write command pulse width                        | twp              | 15   |           | 20   |            | ns   |       |

| Write command to RAS lead time                   | t <sub>RWL</sub> | 20   |           | 25   |            | ns   |       |

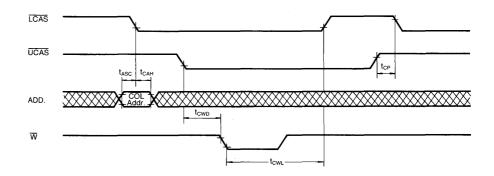

| Write command to CAS lead time                   | tcwL             | 20   |           | 25   | -          | ns   |       |

| Data-in set-up time                              | t <sub>DS</sub>  | 0    |           | 0    |            | ns   | 9     |

| Data-in hold time                                | t <sub>DH</sub>  | 15   |           | 20   |            | ns   | 9     |

| Data-in hold referenced to RAS                   | tDHR             | 60   |           | 75   |            | ns   | 12    |

| Refresh period (1024 cycles)                     | tREF             |      | 16        |      | 16         | ms   |       |

| Refresh period (only for L-version, 1024 cycles) | t <sub>REF</sub> |      | 128       |      | 128        | ms   | i     |

| Write command set-up time                        | twcs             | 0    |           | 0    |            | ns   | 7     |

| $\overline{CAS}$ to $\overline{W}$ delay time    | tcwD             | 20   |           | 25   |            | ns   | 7     |

| $\overline{RAS}$ to $\overline{W}$ delay time    | t <sub>RWD</sub> | 80   |           | 100  |            | ns   | 7     |

| Column address to W delay time                   | t <sub>AWD</sub> | 40   |           | 50   |            | ns   | 7     |

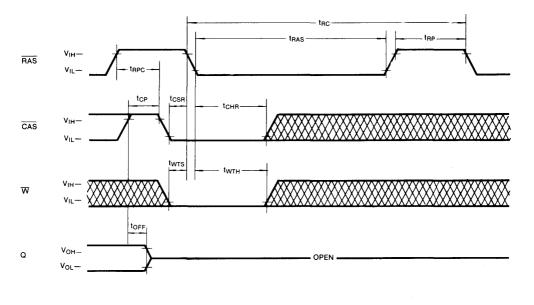

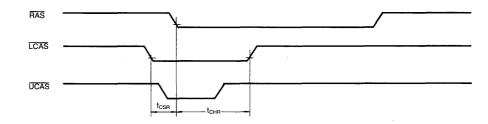

| CAS setup time (CAS before RAS refresh)          | t <sub>CSR</sub> | 10   |           | 10   |            | ns   |       |

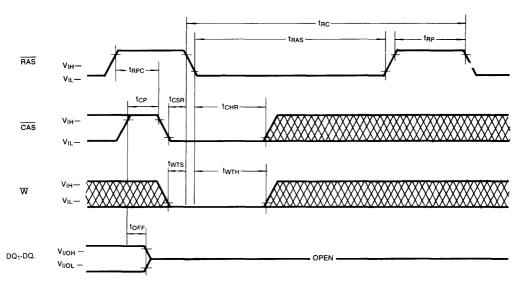

| CAS hold time (CAS before RAS refresh)           | t <sub>CHR</sub> | 30   |           | 30   |            | ns   |       |

| RAS to CAS precharge time                        | t <sub>RPC</sub> | 0    |           | 0    |            | ns   |       |

| CAS precharge time (CAS before RAS counter test) | t <sub>CPT</sub> | 40   |           | 50   |            | ns   |       |

| Write command set-up time (Test mode in)         | twrs             | 10   |           | 10   |            | ns   |       |

| Write command hold time (Test mode in)           | twrн             | 10   |           | 10   |            | ns   |       |

| W to RAS precharge time (CAS before RAS cycle)   | t <sub>WRP</sub> | 10   |           | 10   |            | ns   |       |

| W to RAS hold time (CAS before RAS cycle)        | twRH             | 10   |           | 10   |            | ns   |       |

| RAS hold time from CAS precharge                 | <b>t</b> RHCP    | 50   |           | 55   |            | ns   |       |

(Note. 11)

#### **TEST MODE CYCLE**

| Parameter                             | Symbol           | KM41 | C4000/L-8 | C4000/L-8 KM41C4000/L-10 |         | Unit | Notes |

|---------------------------------------|------------------|------|-----------|--------------------------|---------|------|-------|

| Falameter                             | Symbol           | Min  | Max       | Min                      | Max     | Unit | NULES |

| Random Read or Write Cycle Time       | t <sub>RC</sub>  | 155  |           | 185                      |         | ns   |       |

| Read-Write Cycle Time                 | tRWC             | 180  | _         | 215                      | —       | ns   |       |

| Fast Page Mode Cycle Time             | tPC              | 60   | _         | 65                       |         | ns   |       |

| Fast Page Mode Read-Write Cycle Time  | tPRWC            | 85   |           | 95                       | _       | ns   |       |

| Access Time from RAS                  | tRAC             | _    | 85        | -                        | 105     | ns   | 3,4   |

| Access Time from CAS                  | tCAC             | -    | 25        |                          | 30      | ns   | 3,4   |

| Access Time from Column Address       | t <sub>AA</sub>  | -    | 45        | _                        | 55      | ns   | 3,10  |

| Access Time from CAS Precharge        | t <sub>CPA</sub> | _    | 55        | -                        | 60      | ns   |       |

| RAS Pulse Width                       | tras             | 85   | 10,000    | 105                      | 10,000  | ns   |       |

| RAS Pulse Width (Fast Page Mode)      | trasp            | 85   | 200,000   | 105                      | 200,000 | ns   |       |

| RAS Hold Time                         | t <sub>RSH</sub> | 25   | _         | 30                       | _       | ns   |       |

| CAS Hold Time                         | t <sub>CSH</sub> | 85   | _         | 105                      | -       | ns   |       |

| CAS Pulse Width                       | tCAS             | 25   | 10,000    | 30                       | 10,000  | ns   |       |

| Column Address to RAS Lead Time       | t <sub>RAL</sub> | 45   | _         | 55                       | _       | ns   |       |

| CAS to W Delay Time                   | t <sub>CWD</sub> | 25   | _         | 30                       | —       | ns   | 7     |

| RAS to W Delay Time                   | tRWD             | 85   | _         | 105                      |         | ns   | 7     |

| Column Address to $\overline{W}$ Time | tAWD             | 45   |           | 55                       | _       | ns   | 7     |

#### NOTES

- An initial pause of 200µs is required after powerup followed by any 8 CBR or ROR cycles before proper device operation is achieved.

- 2.  $V_{IH(min)}$  and  $V_{IL(max)}$  are reference levels for measuring timing of input signals. Transition times are measured between  $V_{IH(min)}$  and  $V_{IL(max)}$  and are assumed to be 5ns for all inputs.

- 3. Measured with a load equivalent to 2 TTL loads and 100pF

- 4. Operation within the  $t_{RCD(max)}$  limit insures that  $t_{RAC(max)}$  can be met.  $t_{RCD(max)}$  is specified as a reference point only. If  $t_{RCD}$  is greater than the specified  $t_{RCD(max)}$  limit, then access time is controlled exclusively by  $t_{CAC}$ .

- 5. Assumes that t<sub>RCD</sub>≥t<sub>RCD(max)</sub>.

- This parameter defines the time at which the output achieves the open circuit condition and is not refernced to V<sub>OH</sub> or V<sub>OL</sub>.

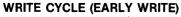

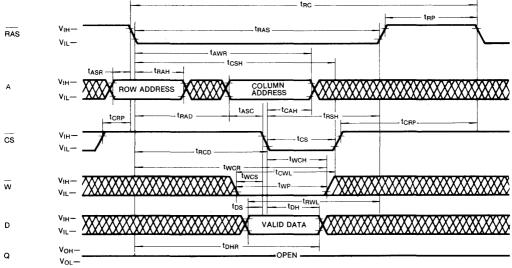

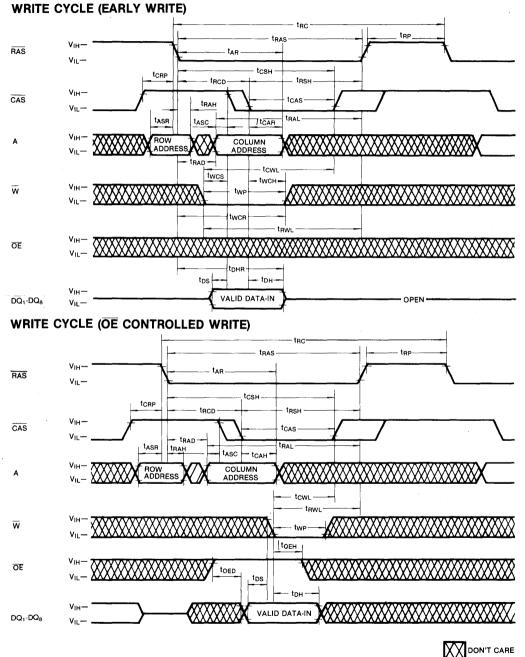

- twcs, t<sub>RWD</sub>, t<sub>CWD</sub> and t<sub>AWD</sub> are non restrictive operating parameters. They are included in the data

sheet as electrical characteristics only. If twcs>twcs(min) the cycle is an early write cycle and the data out pin will remain high impedance for the duration of the cycle. If  $t_{CWD}>t_{CWD}(min)$  and  $t_{RWD}>t_{RWD}(min)$  and  $t_{AWD}>t_{AWD}(min)$ , then the cycle is a read-write cycle and the data out will contain the data read from the selected address. If neither of the above conditions are satisfied, the condition of the data out is indeterminate.

- 8. Either  $t_{\text{RCH}}$  or  $t_{\text{RRH}}$  must be satisfied for a read cycle.

- 9. These parameters are referenced to the  $\overline{CAS}$  leading edge in early write cycles and to the  $\overline{W}$  leading edge in read-write cycles.

- 10. Operation within the  $t_{RAD}(max)$  limit insures that  $t_{RAC}(max)$  can be met.  $t_{RAD}(max)$  is specified as a reference point only. If  $t_{RAD}$  is greater than the specified  $t_{RAD}(max)$  limit, then access time is controlled by  $t_{AA}$ .

- 11. These specifications are applied in the test mode.

- 12. tAR, twcR, tDHR are refrerenced to tRAD(max).

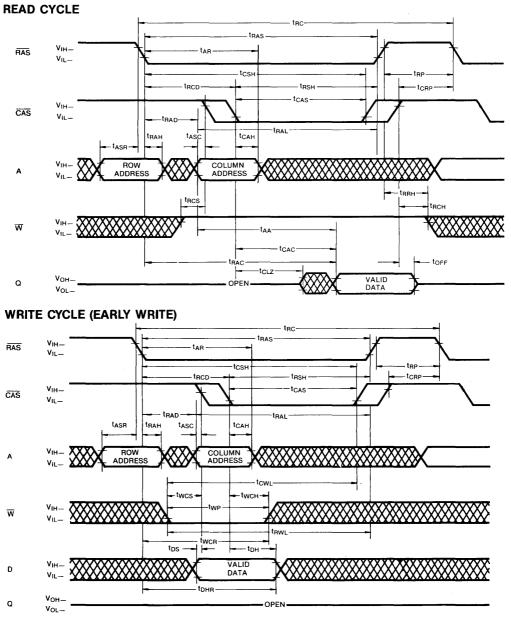

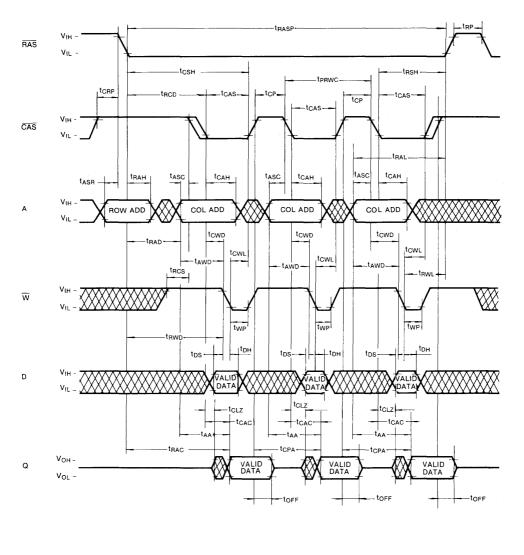

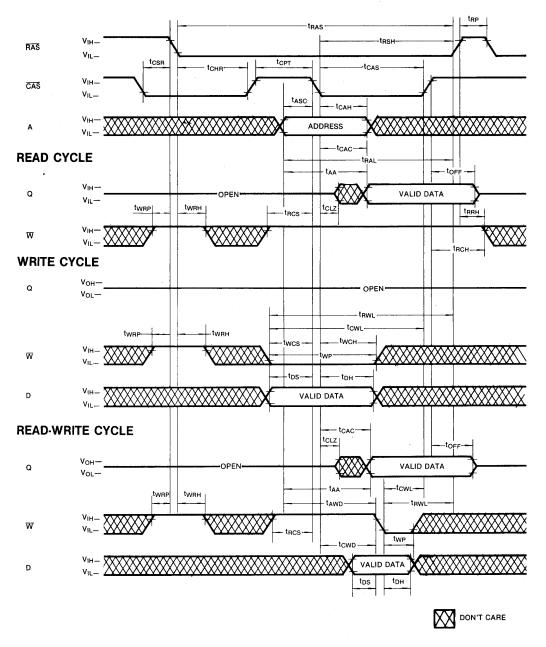

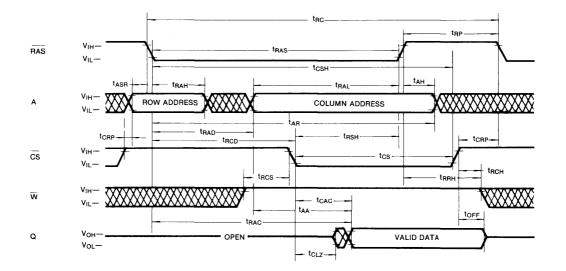

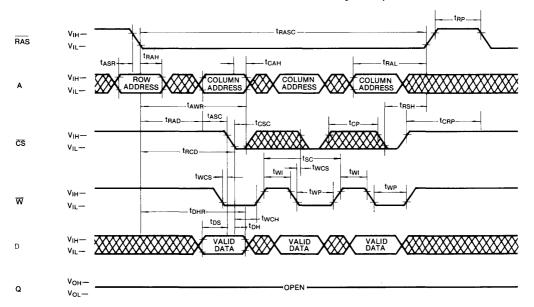

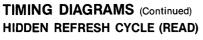

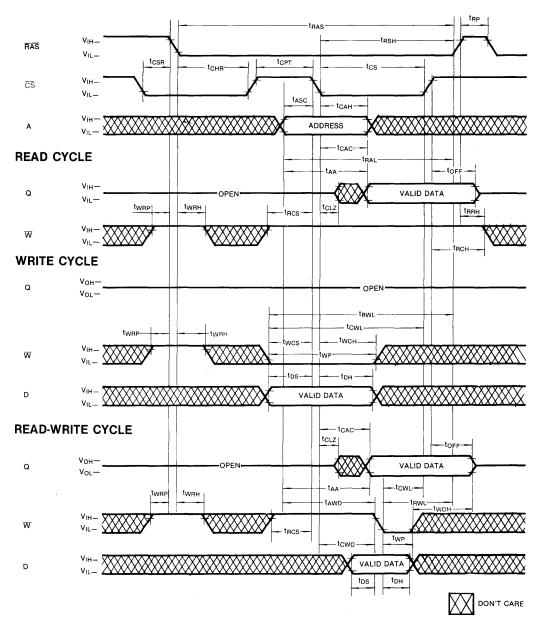

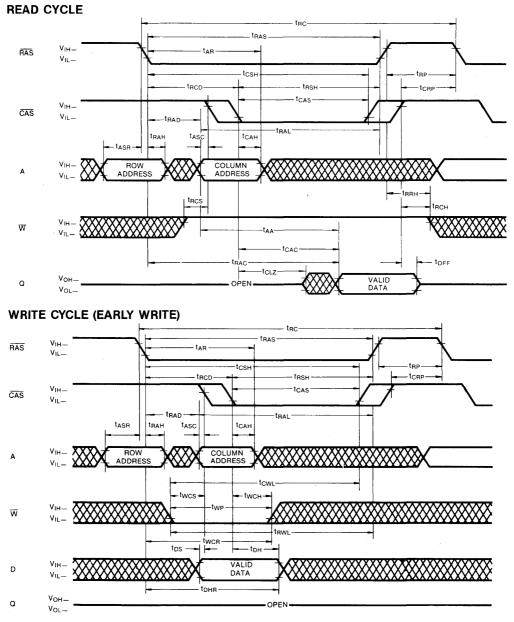

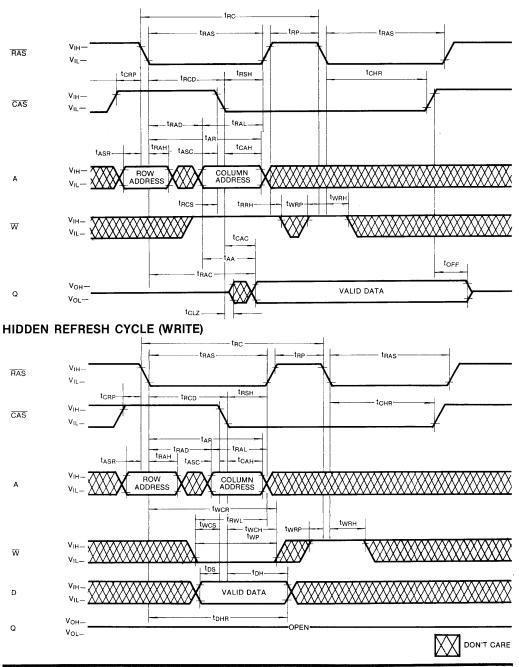

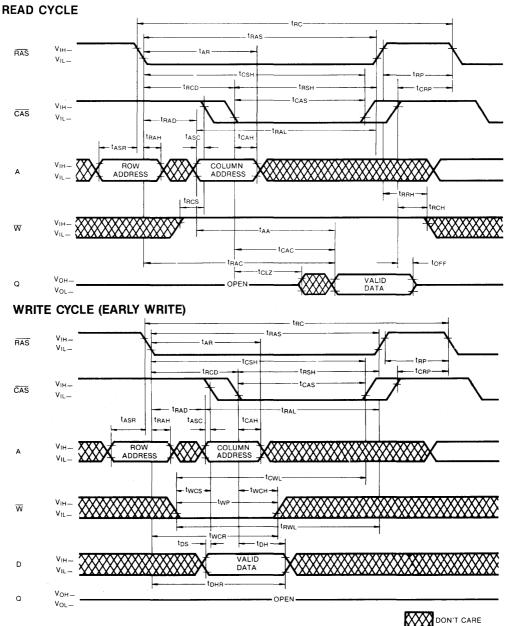

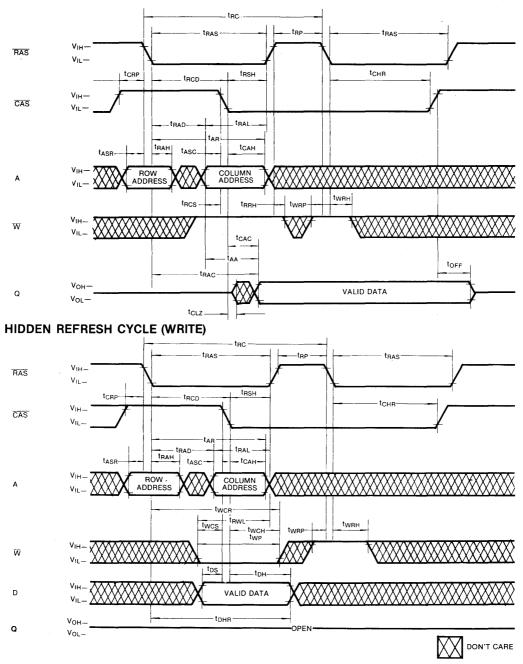

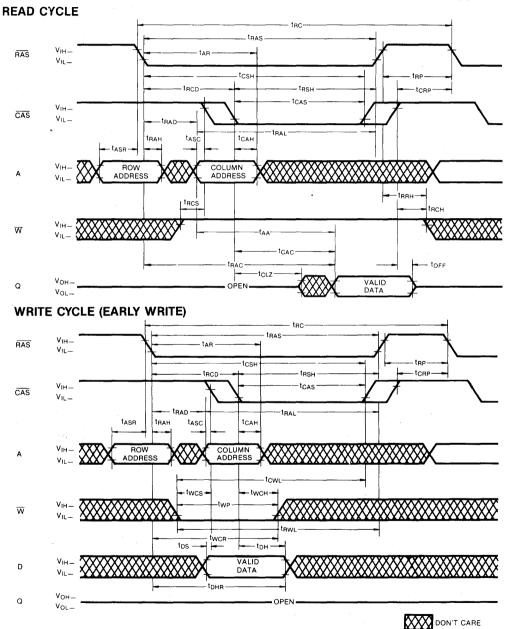

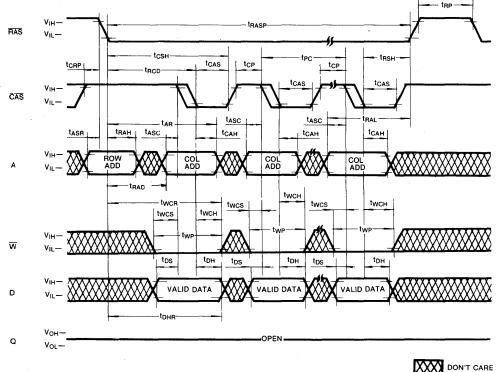

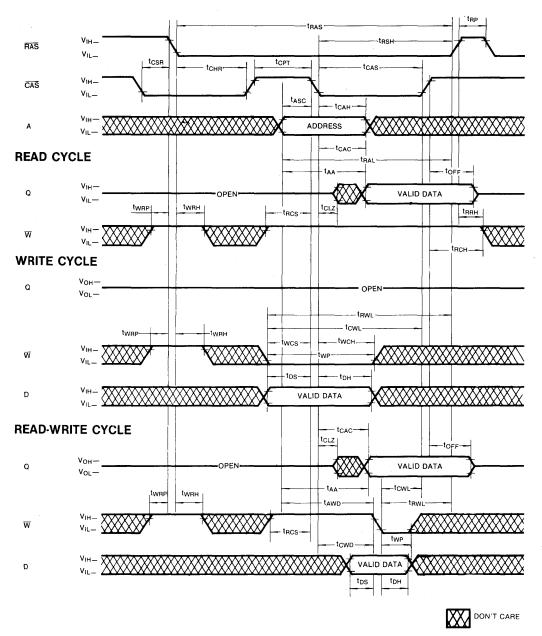

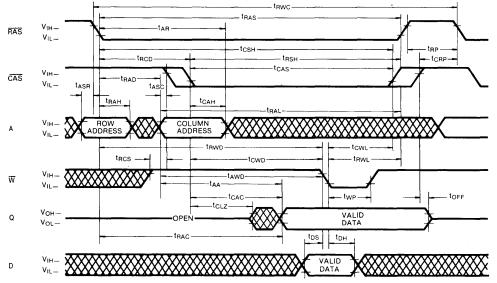

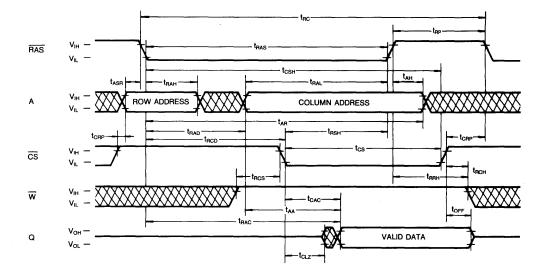

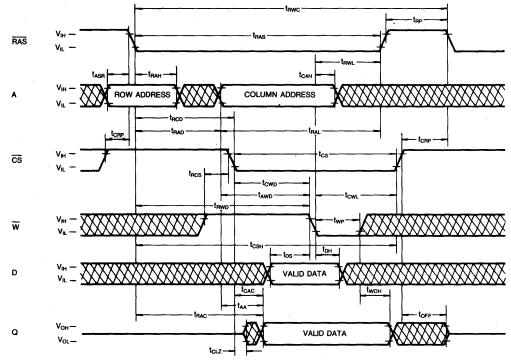

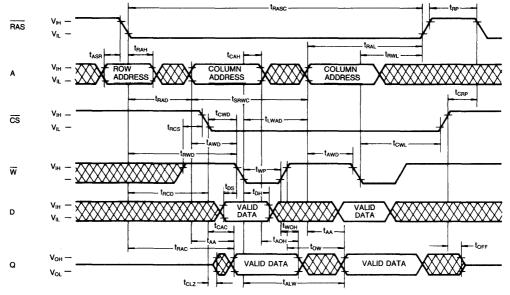

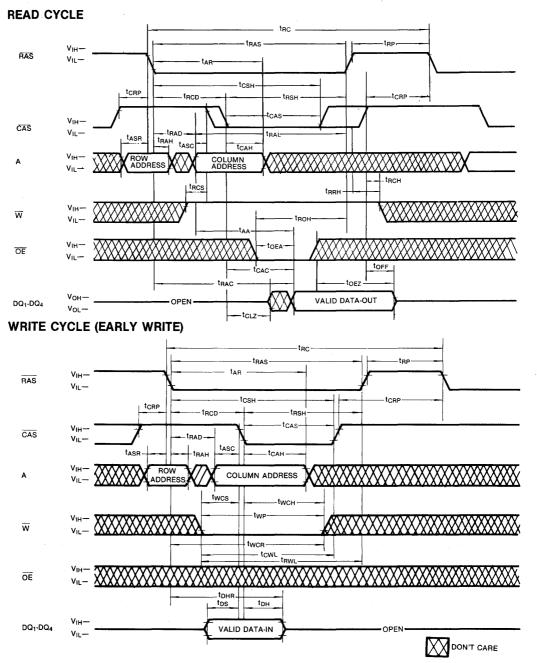

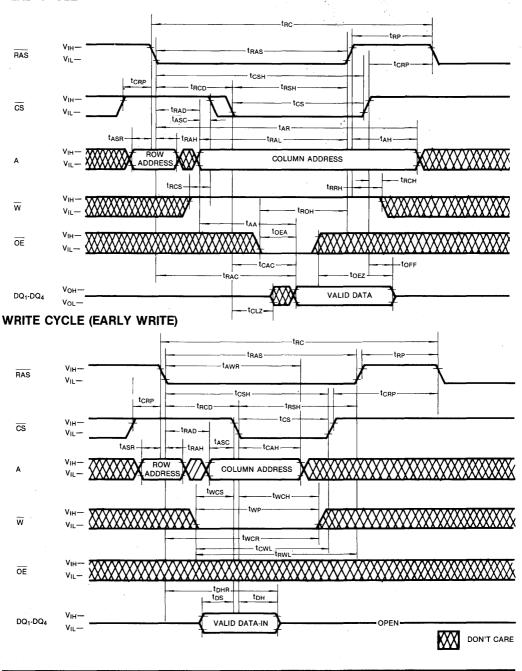

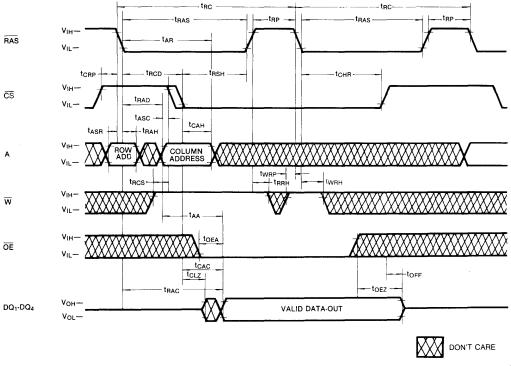

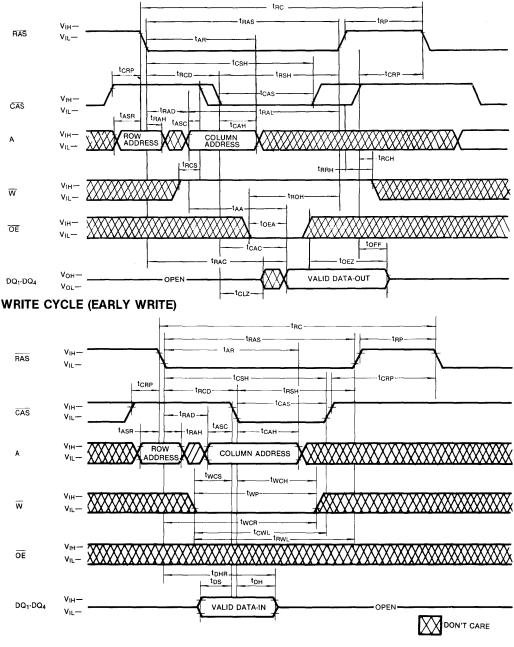

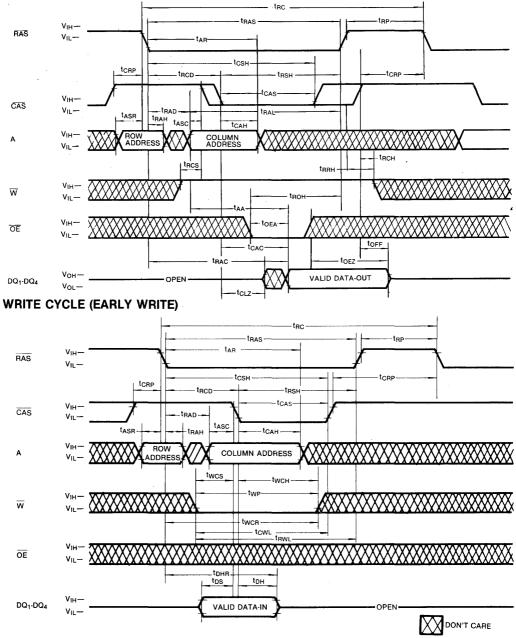

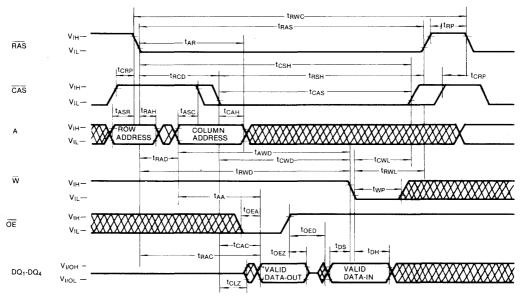

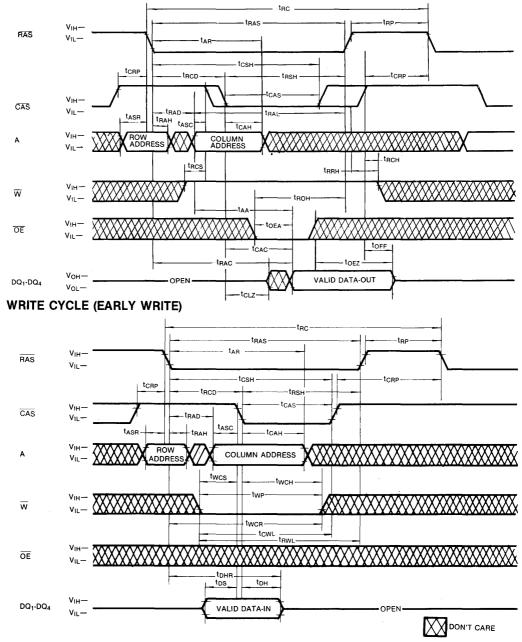

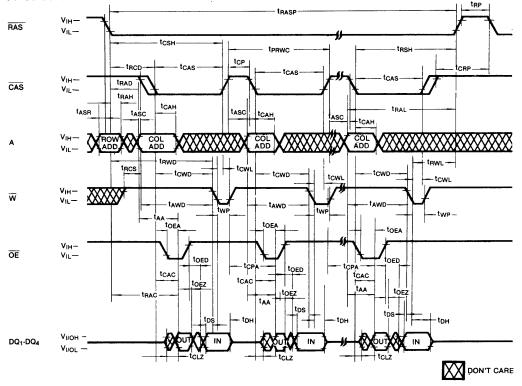

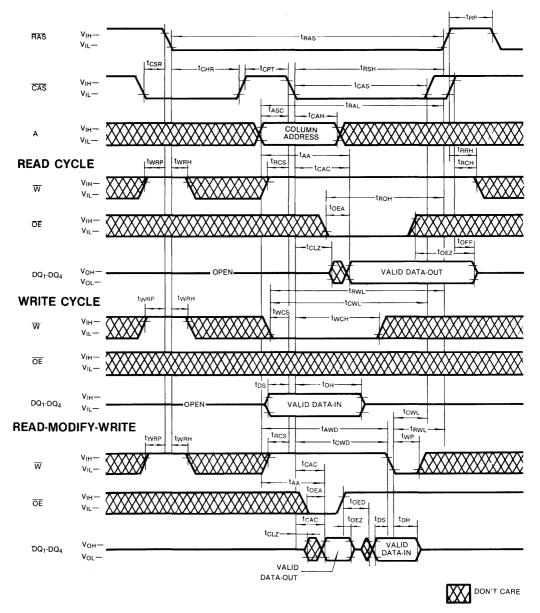

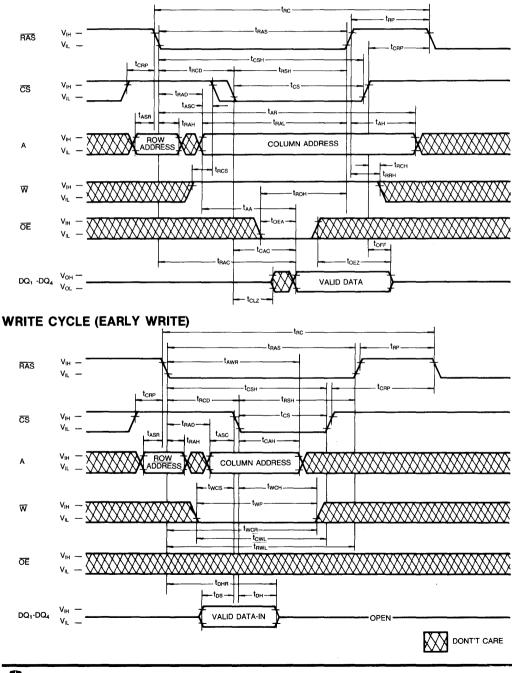

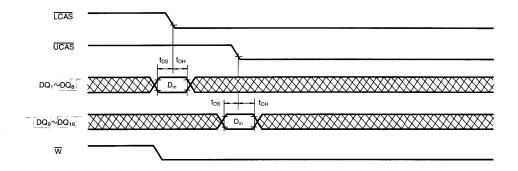

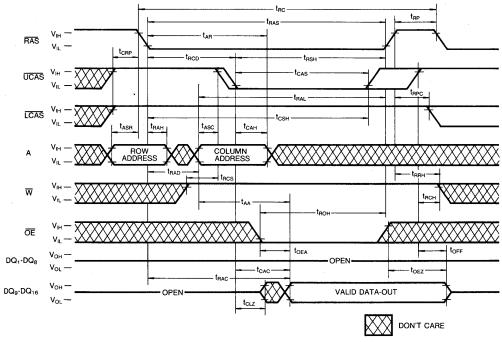

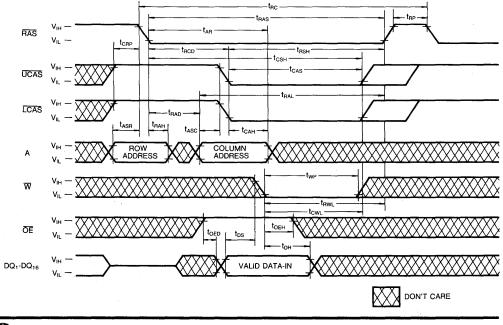

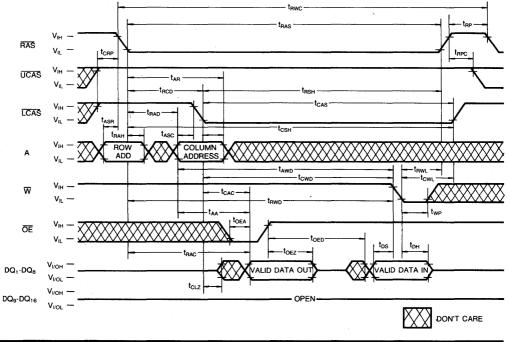

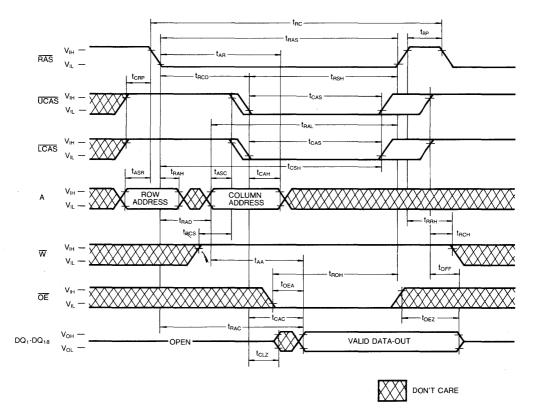

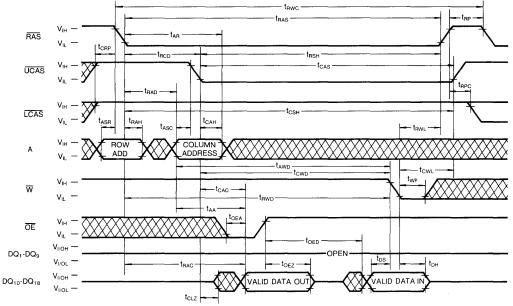

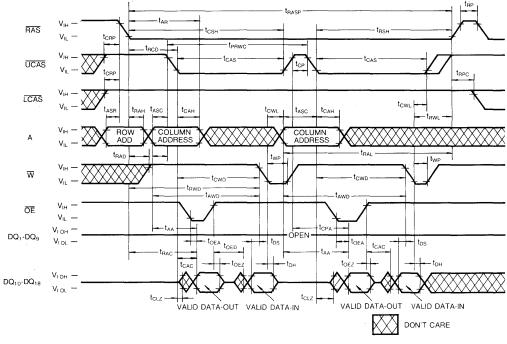

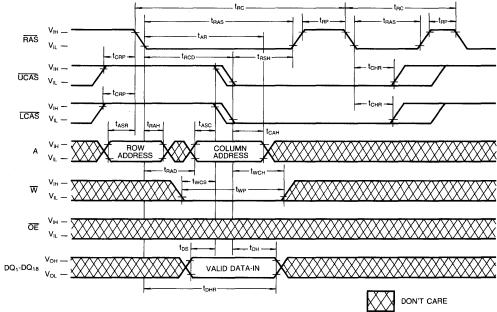

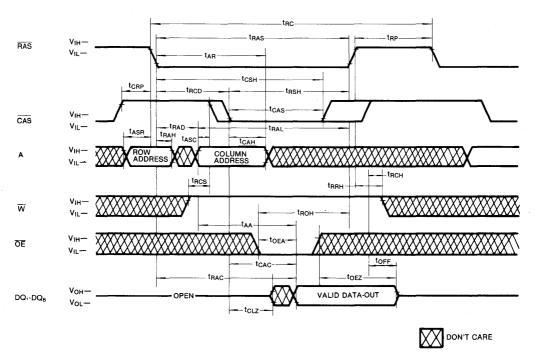

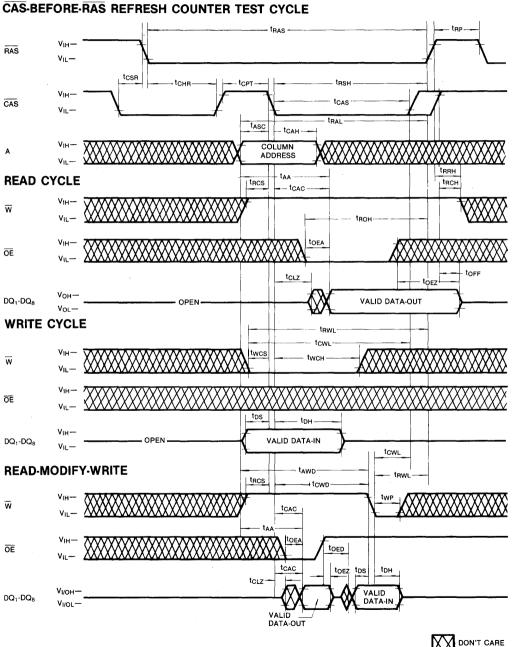

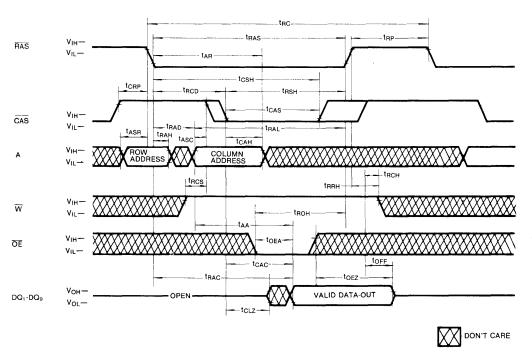

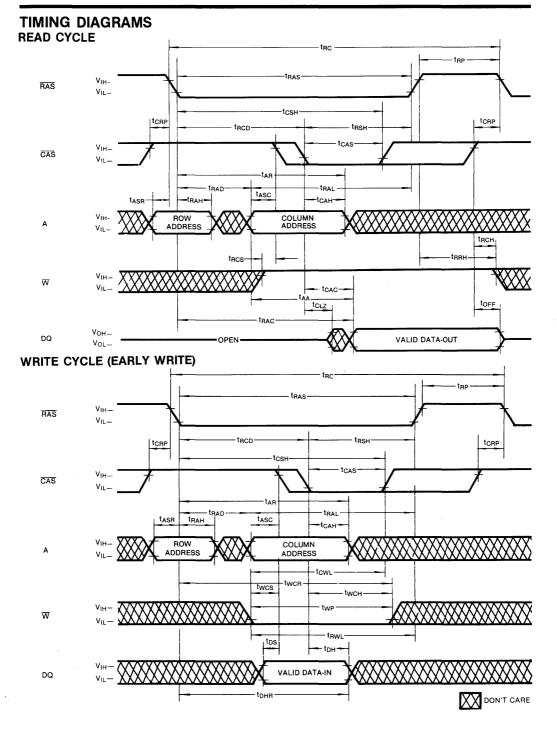

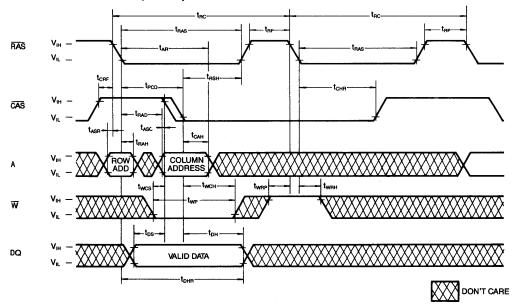

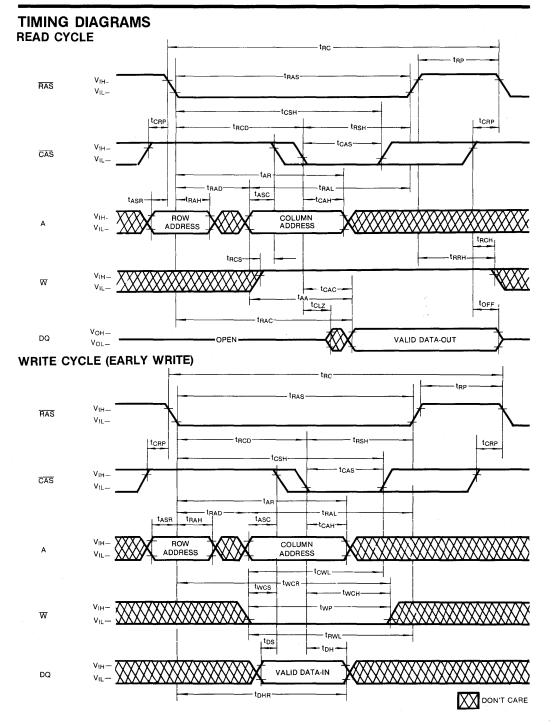

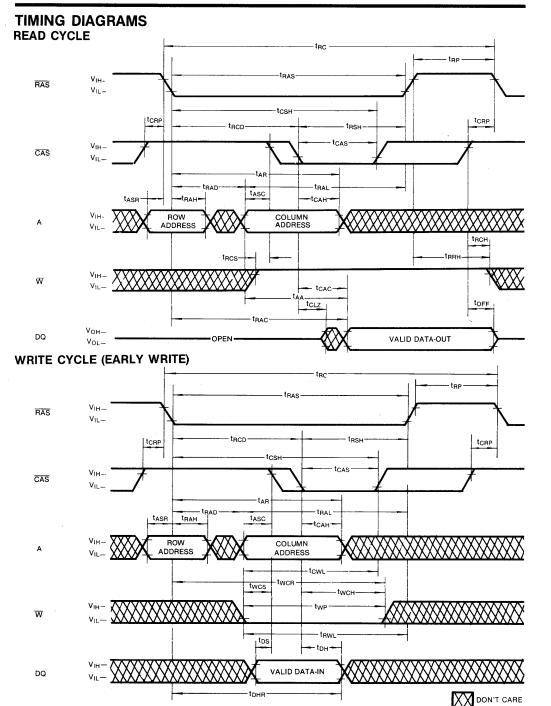

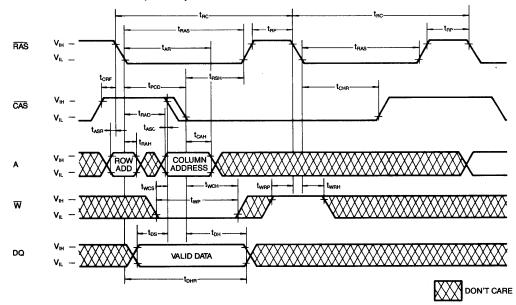

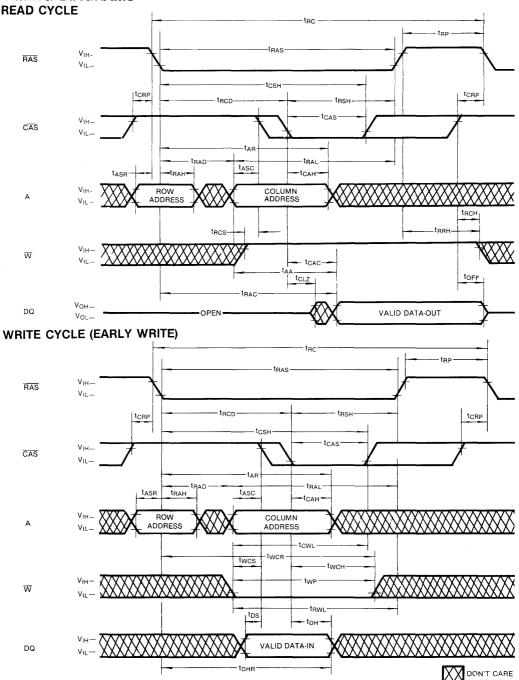

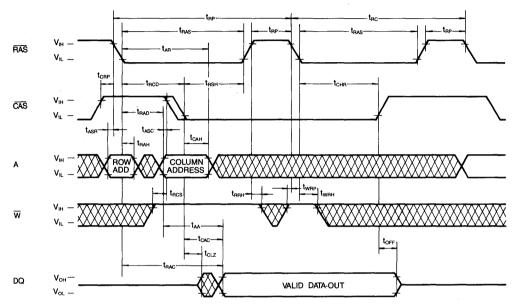

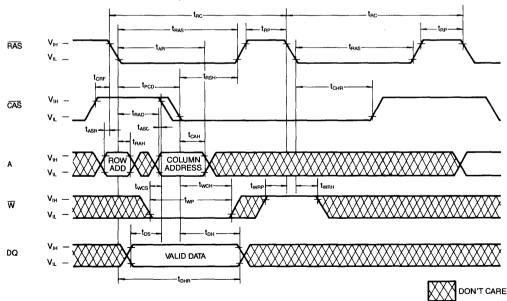

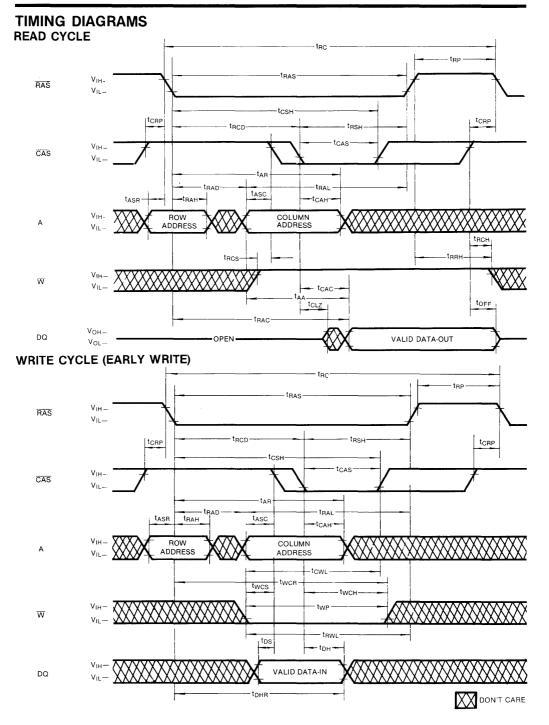

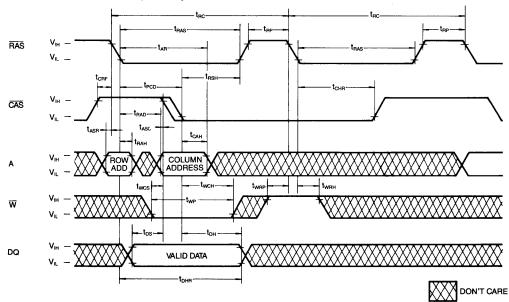

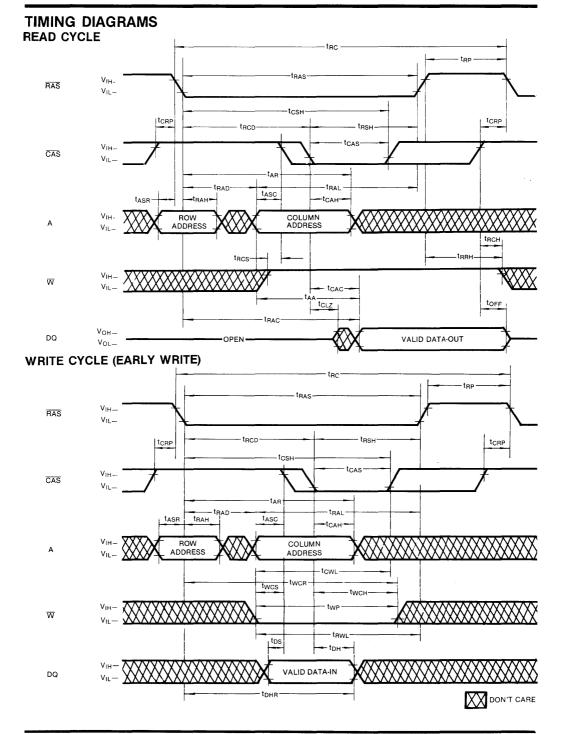

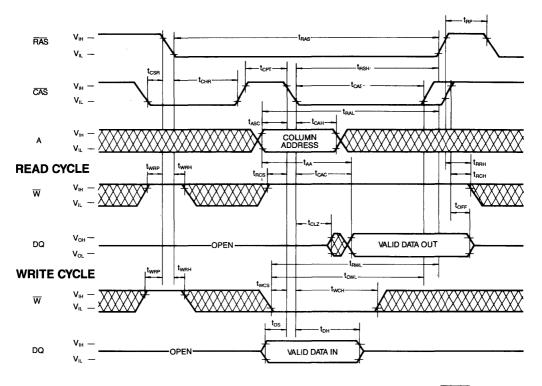

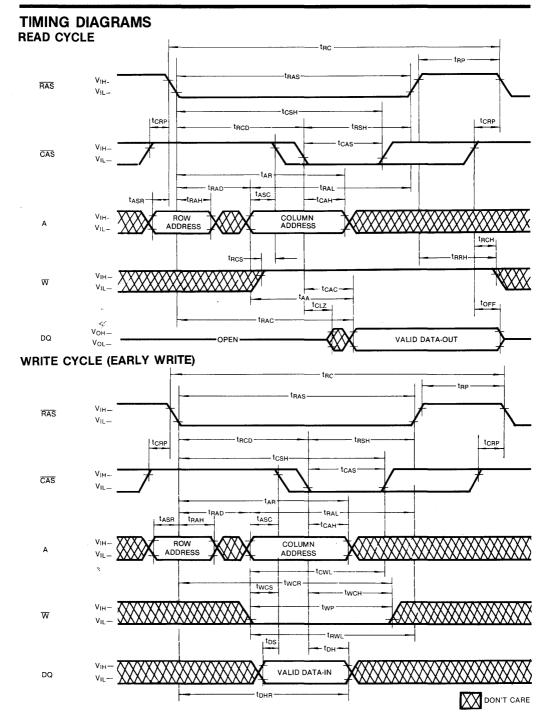

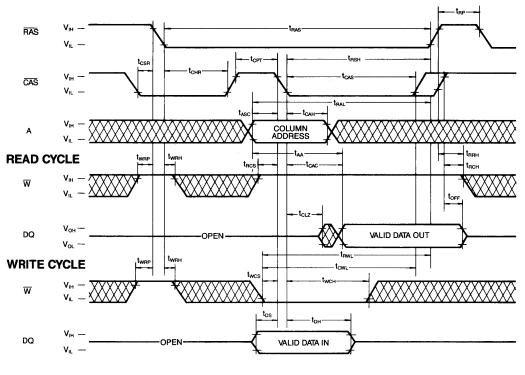

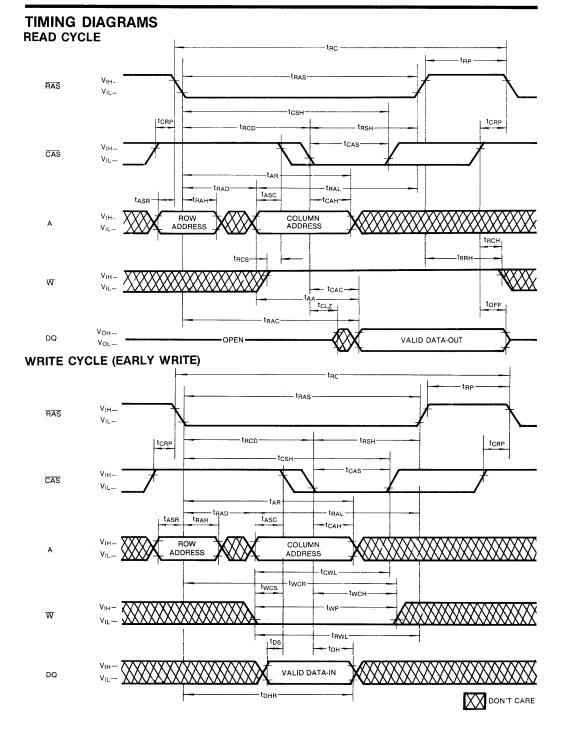

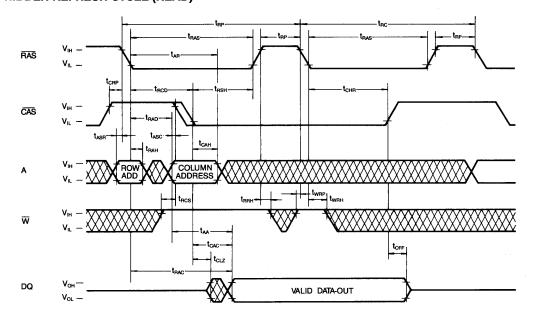

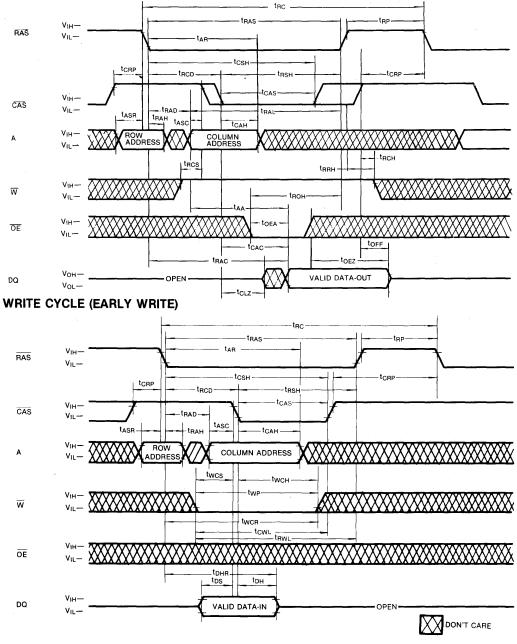

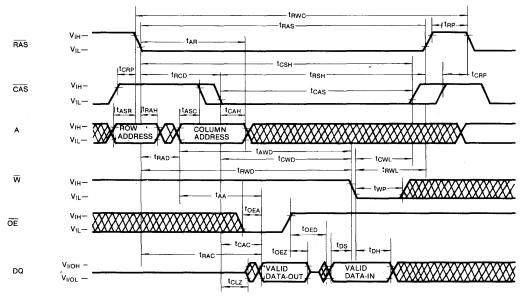

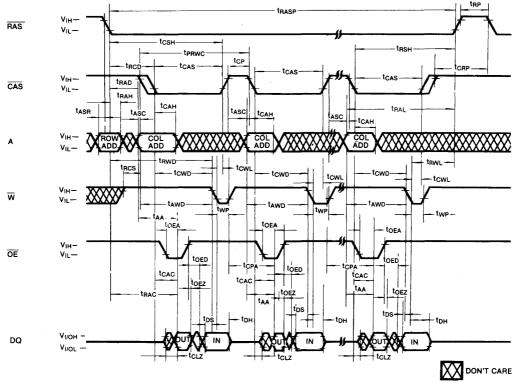

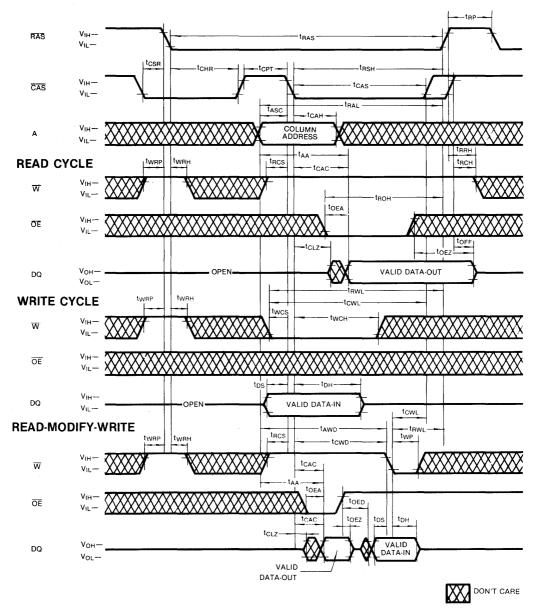

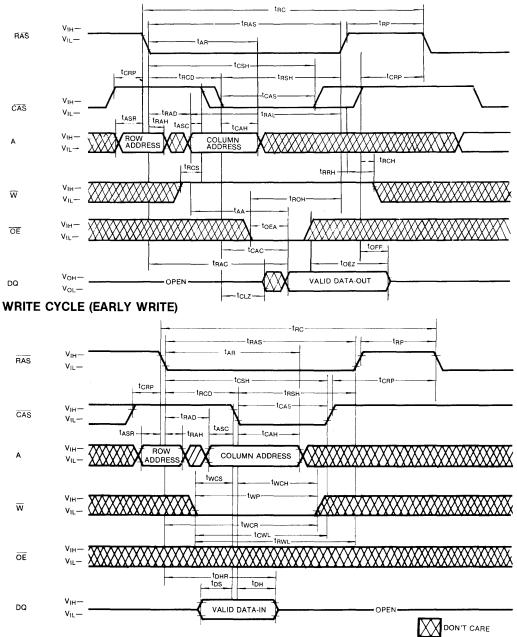

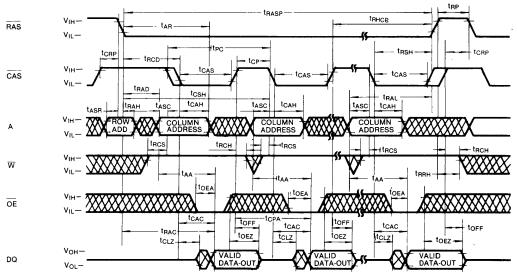

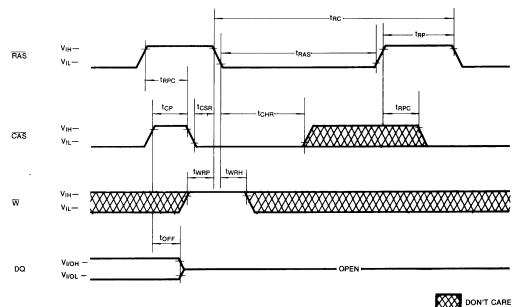

# TIMING DIAGRAMS

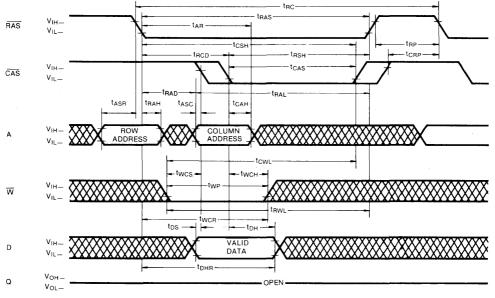

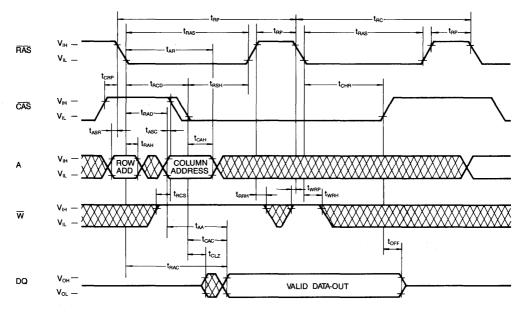

#### tawc TRAS VIHtAR RAS VIL--tcs+tee -tRCD - trsh -tcaptCAS VIH-CAS RAD VILtASR tas **t**RAH **tCAH** TRAL $\infty \infty$ COLUMN ADDRESS $\infty$ ADDRESS $\infty$ $\bigotimes$ $\infty$ Α - trwDtown tecs -tcwD tewn -tawdw taa VILtCAC twp torr tcLz Vон---VALID DATA Q ορεν Vol-TRAC tos tон VALID D VIL-

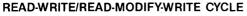

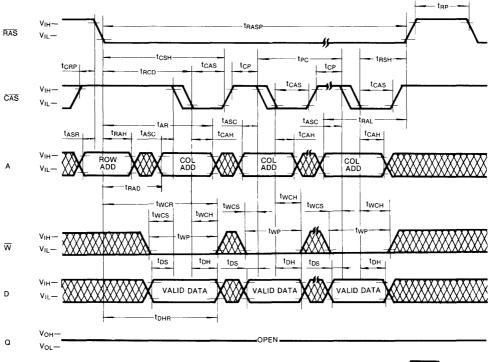

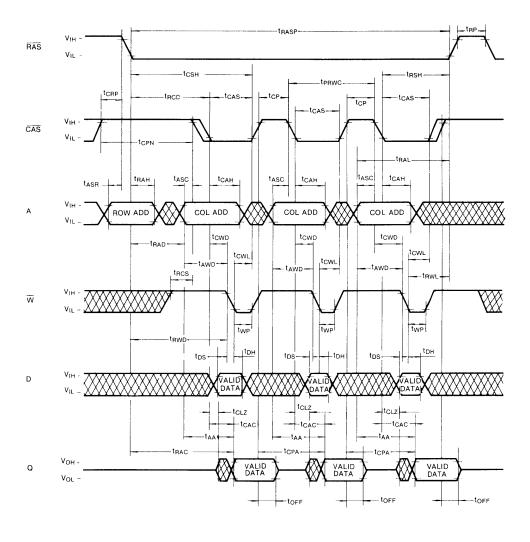

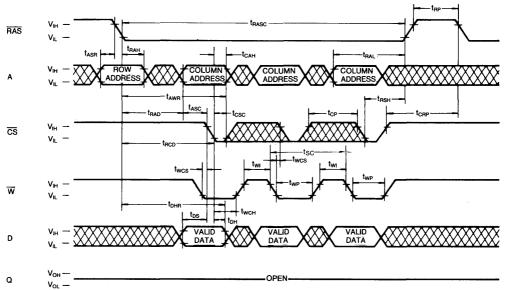

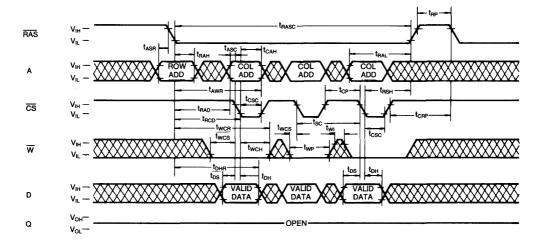

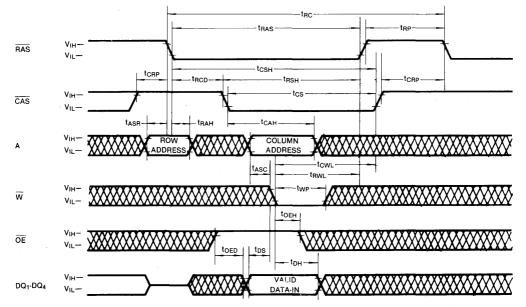

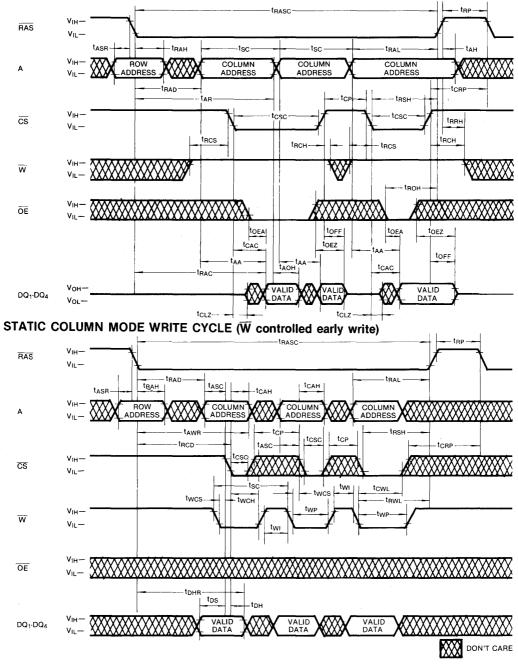

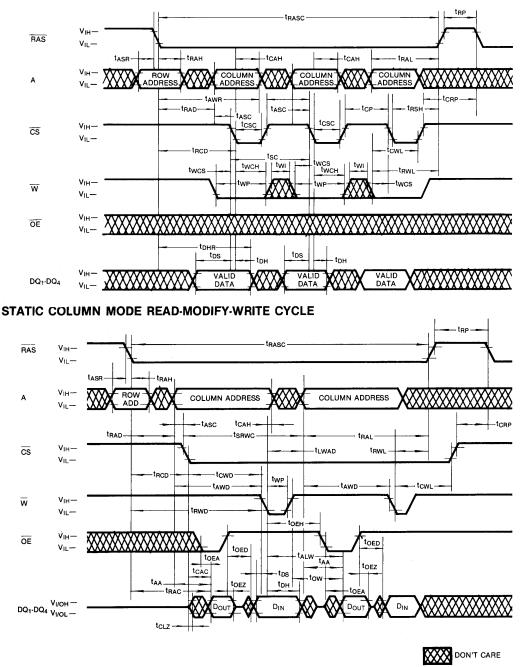

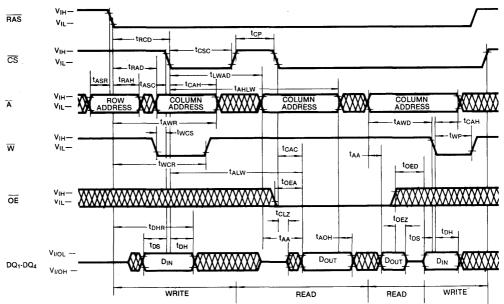

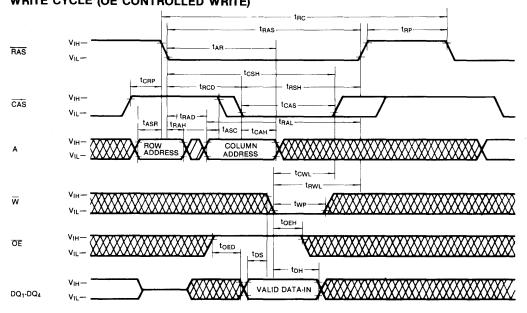

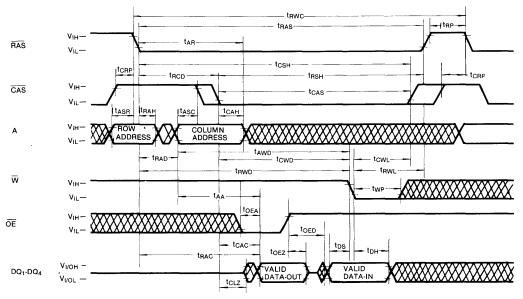

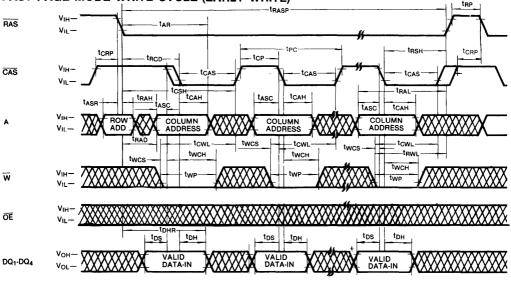

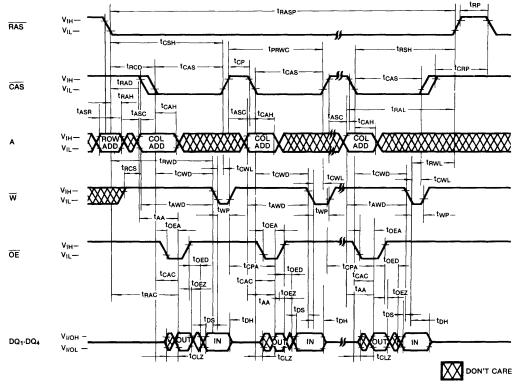

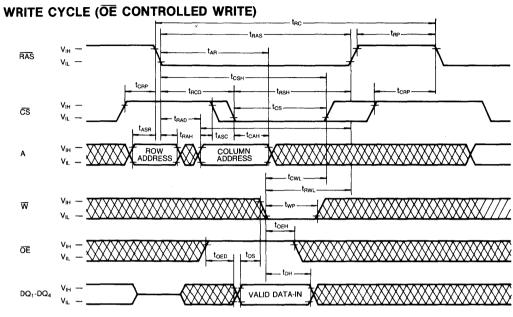

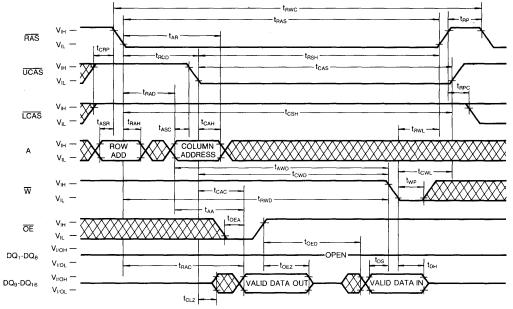

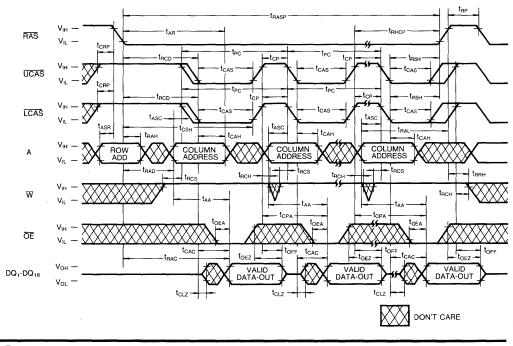

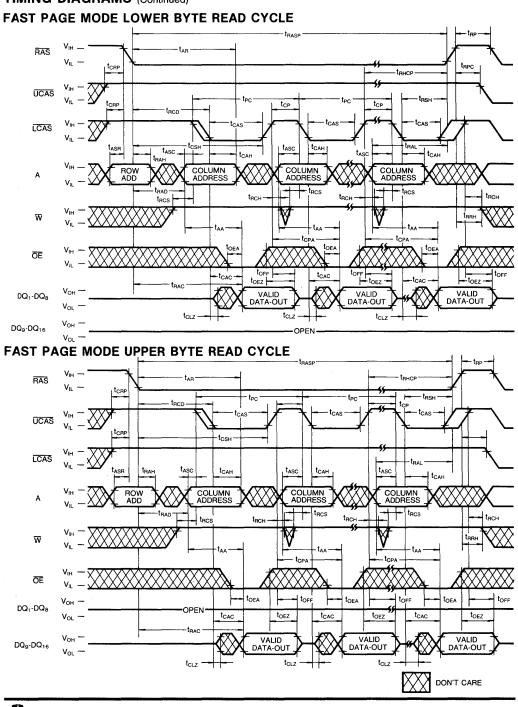

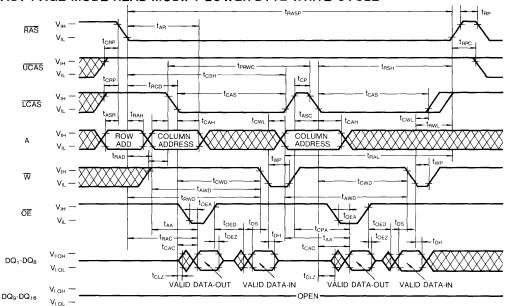

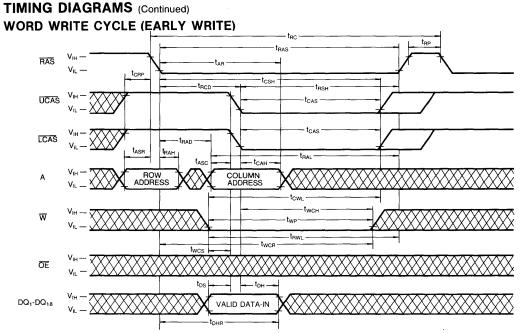

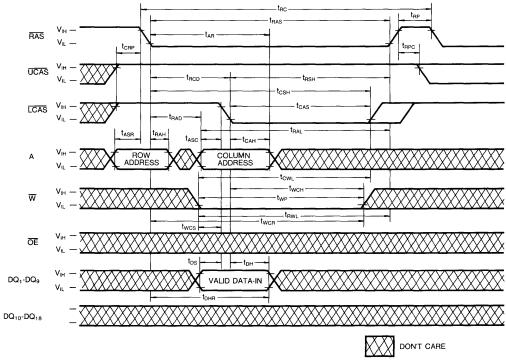

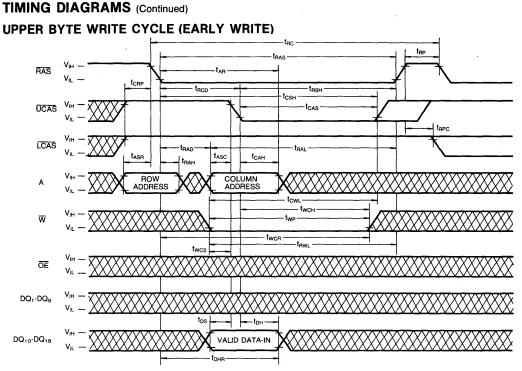

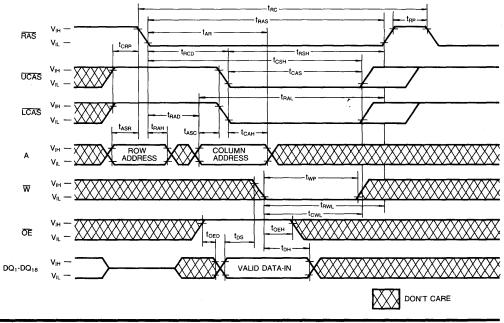

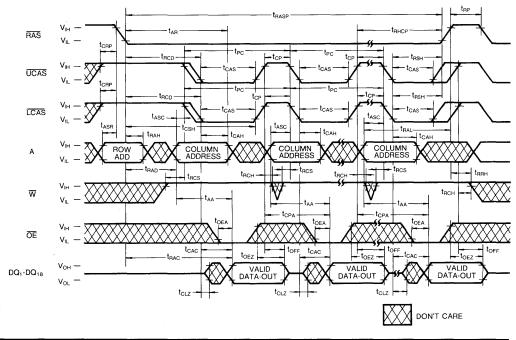

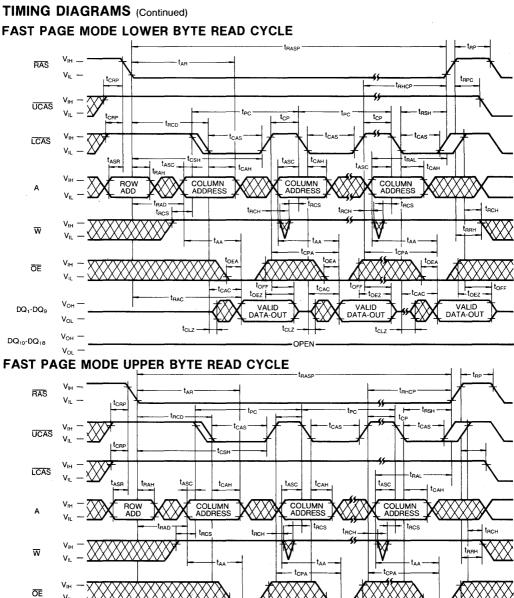

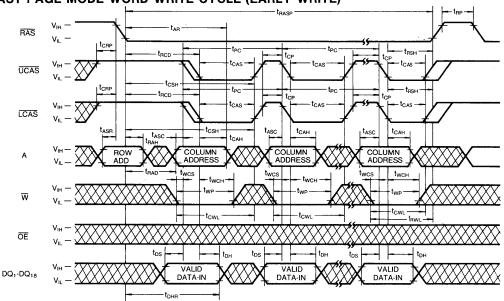

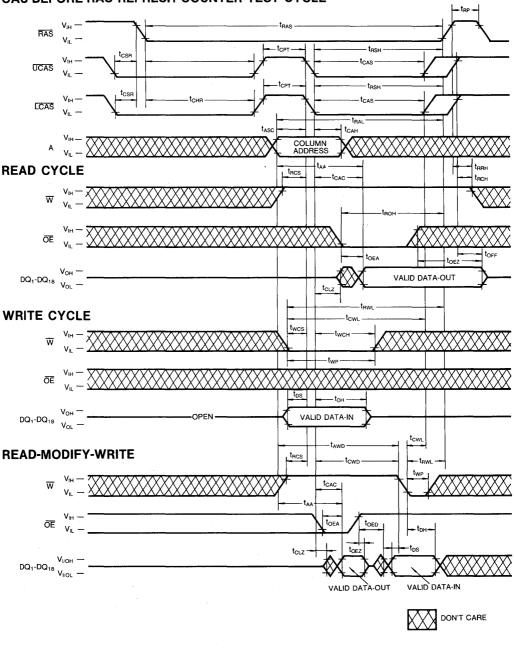

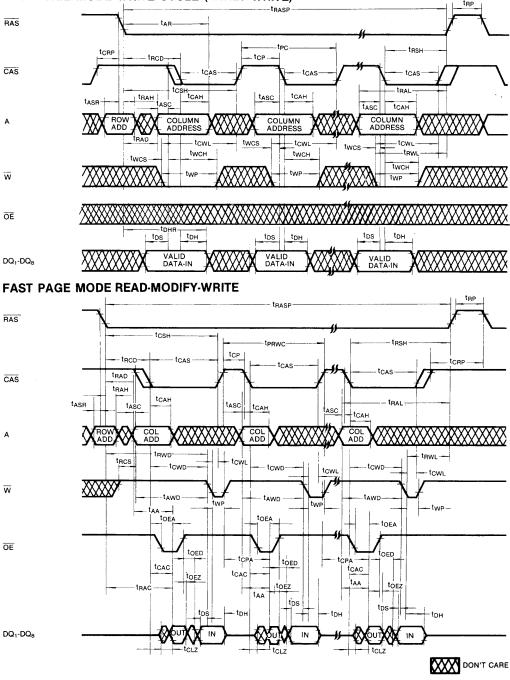

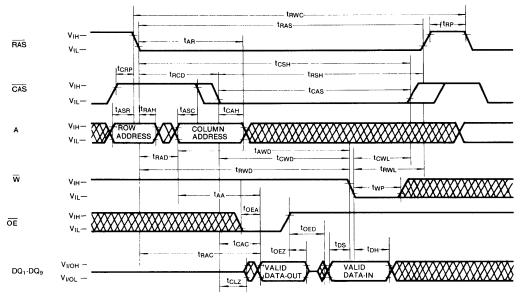

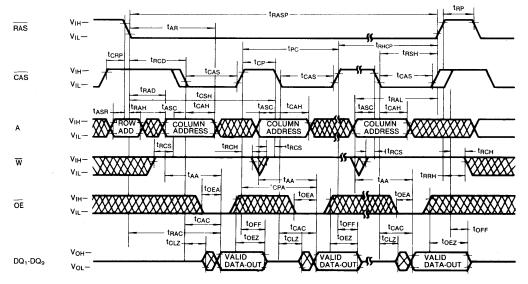

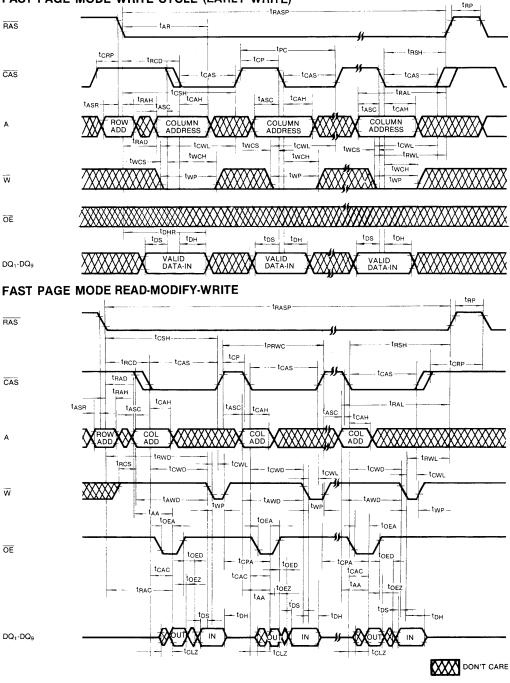

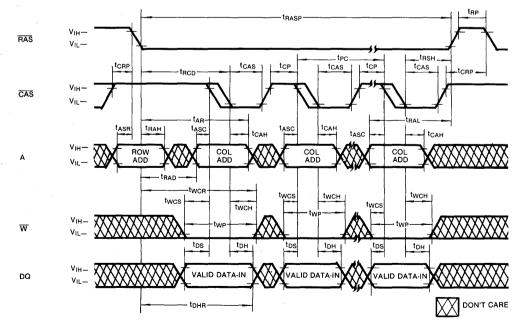

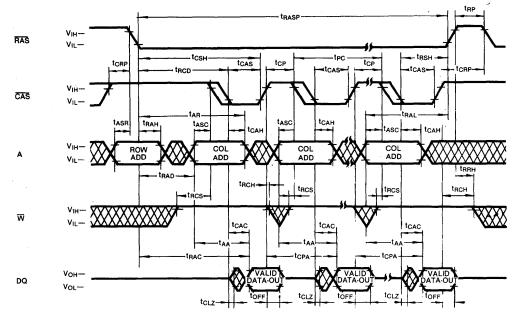

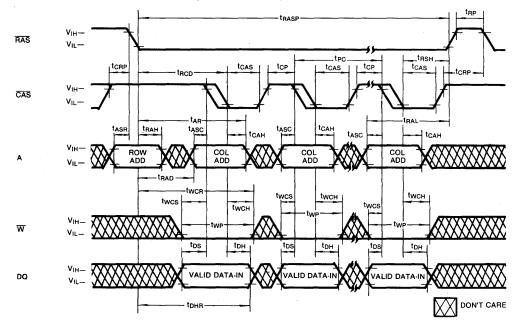

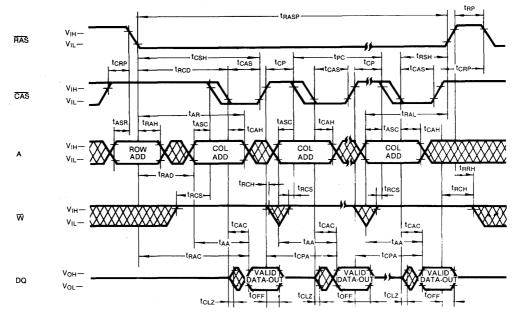

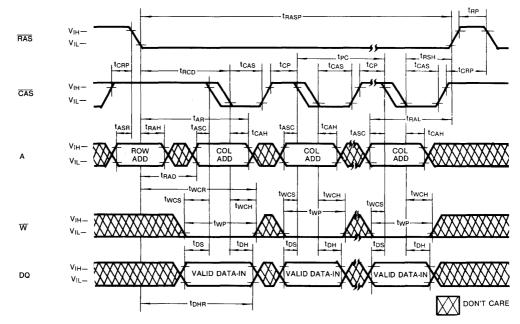

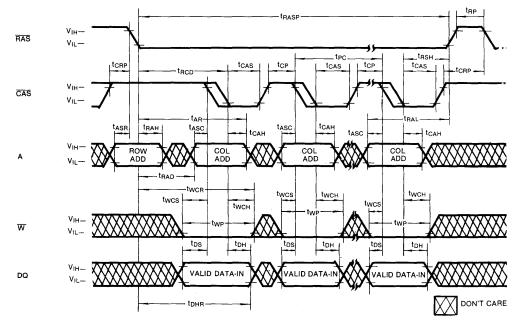

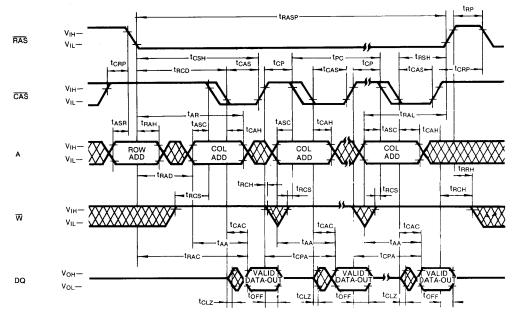

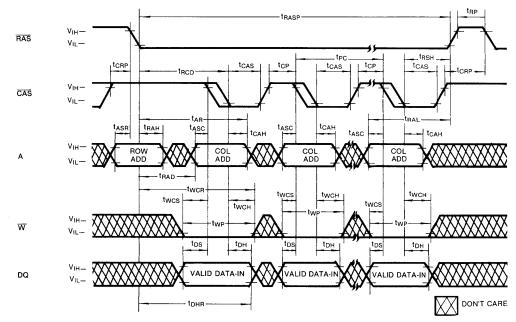

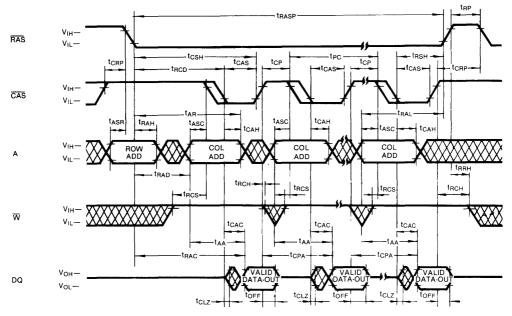

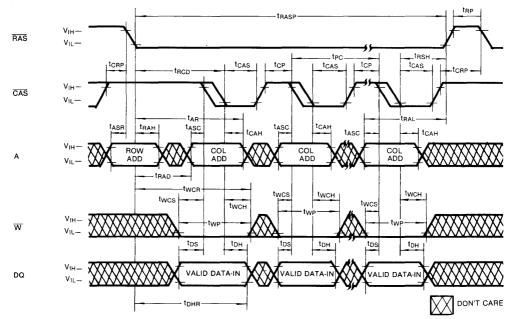

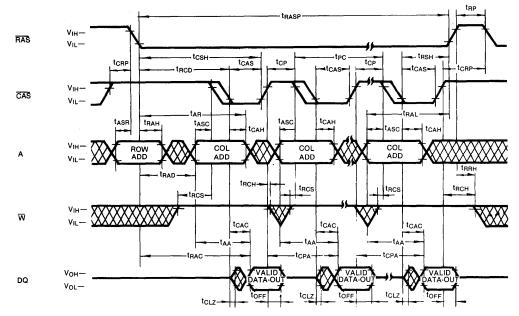

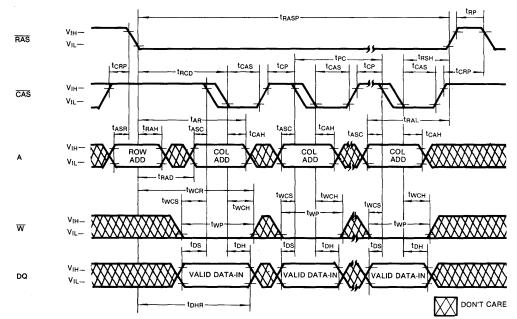

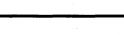

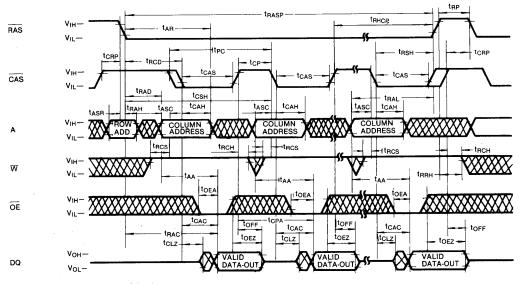

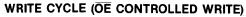

### TIMING DIAGRAMS (Continued)

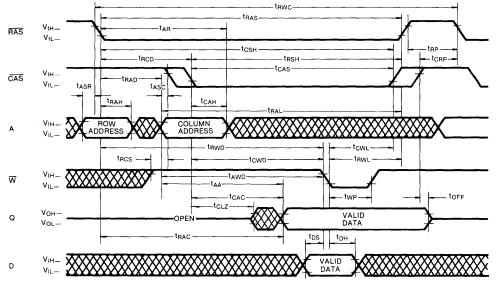

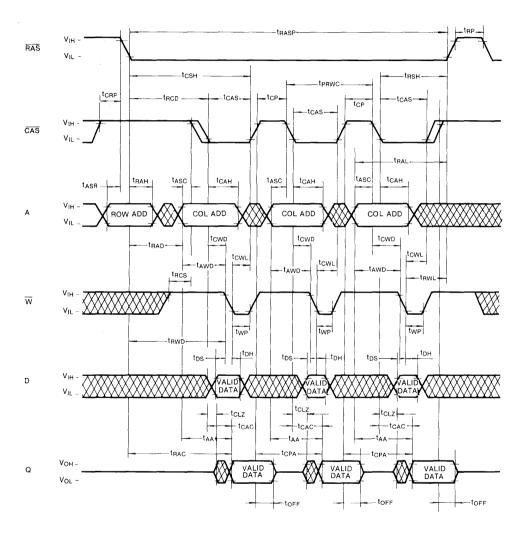

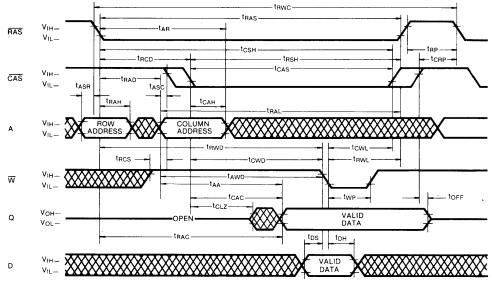

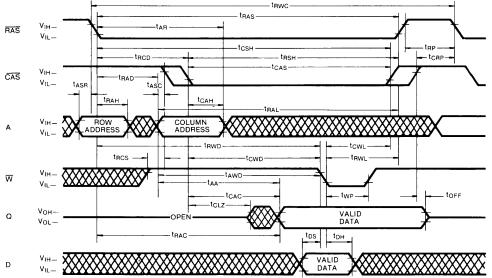

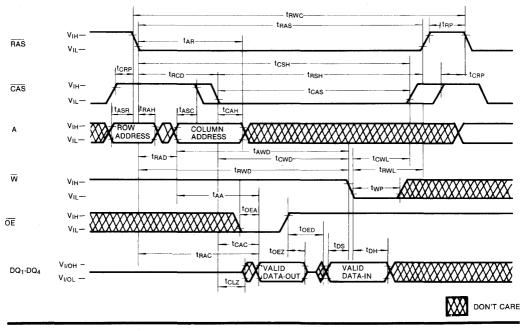

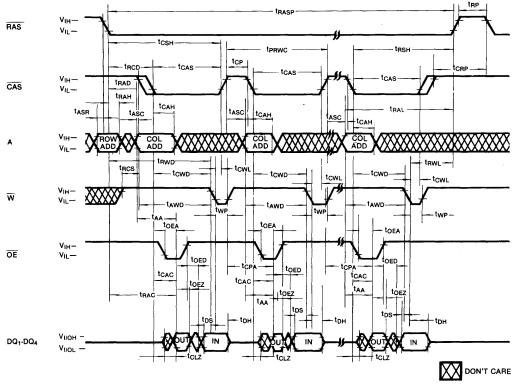

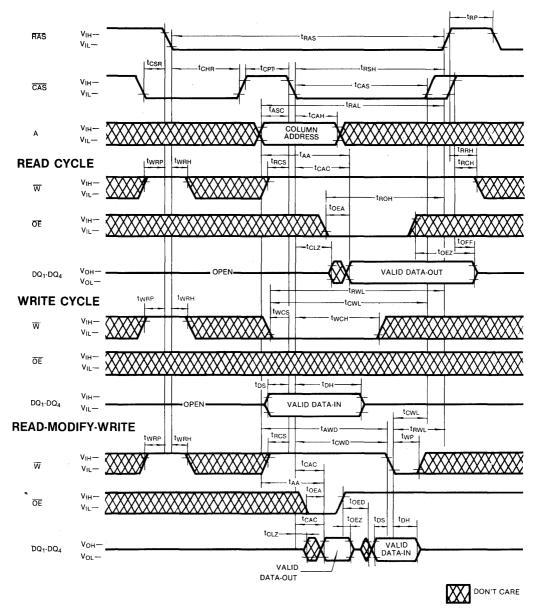

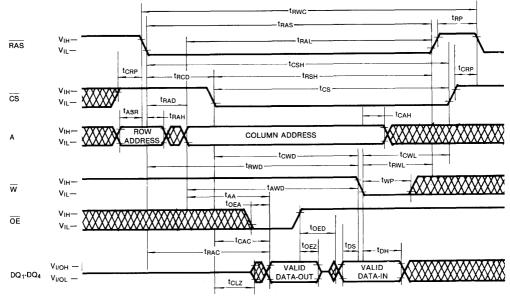

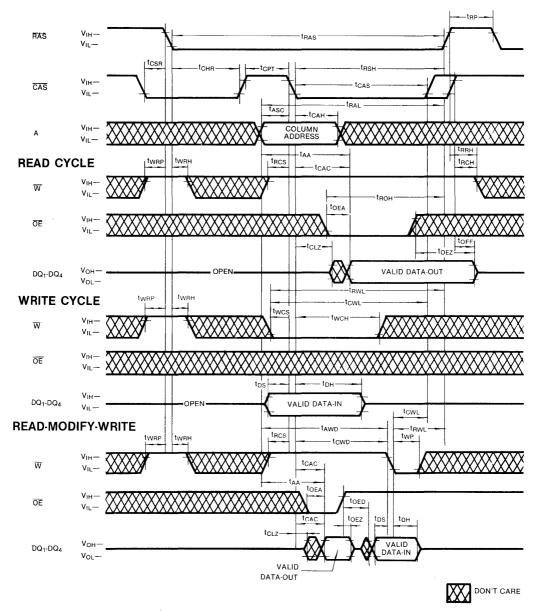

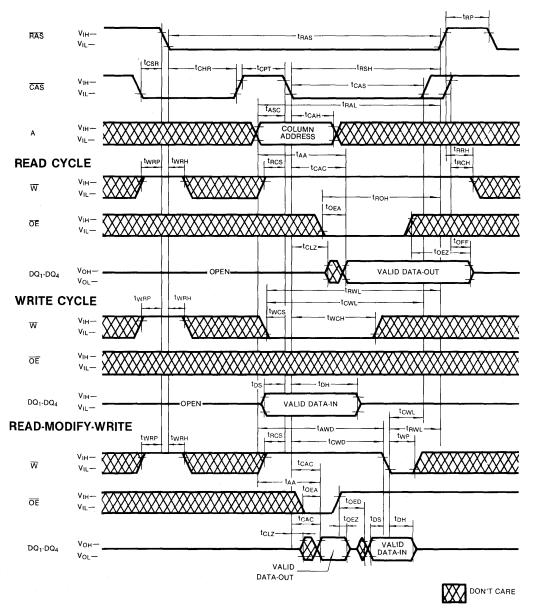

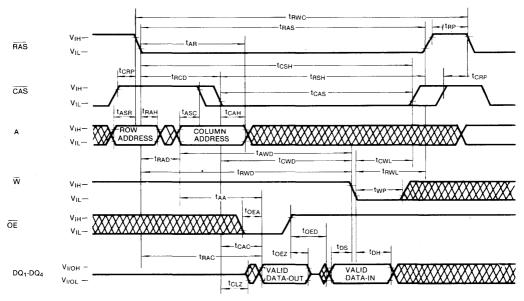

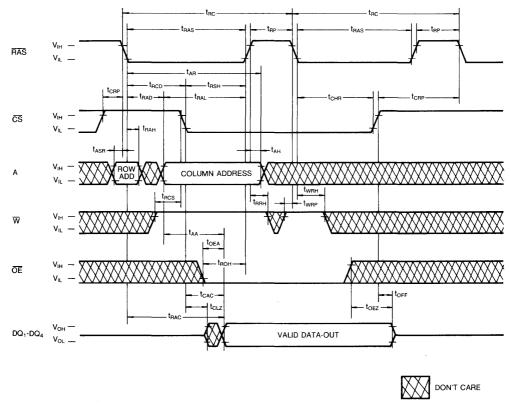

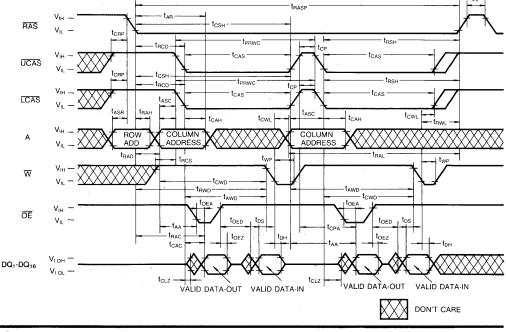

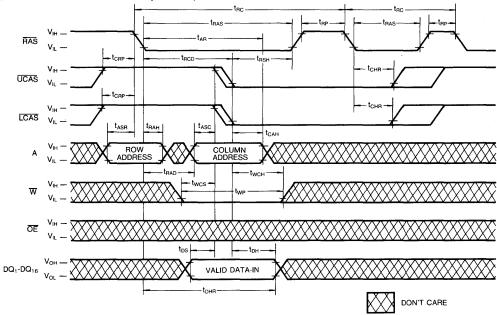

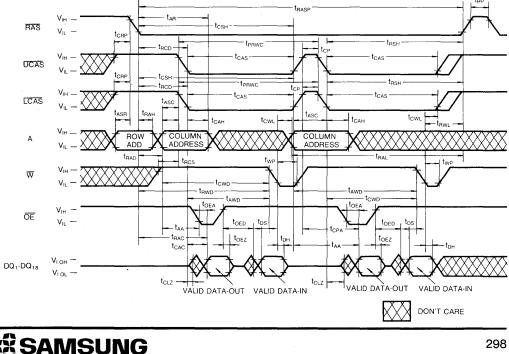

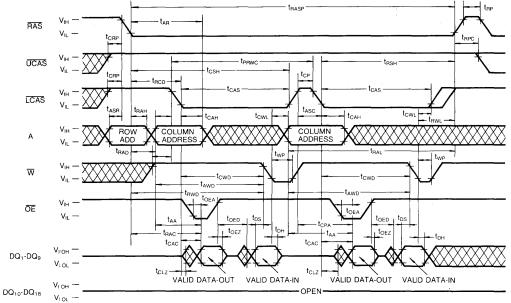

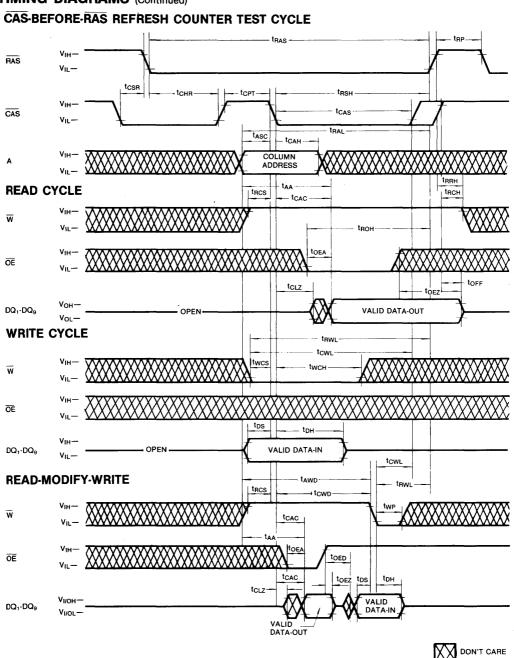

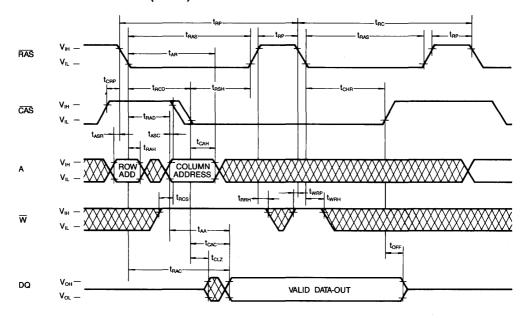

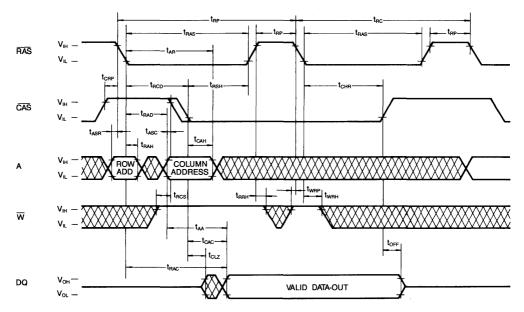

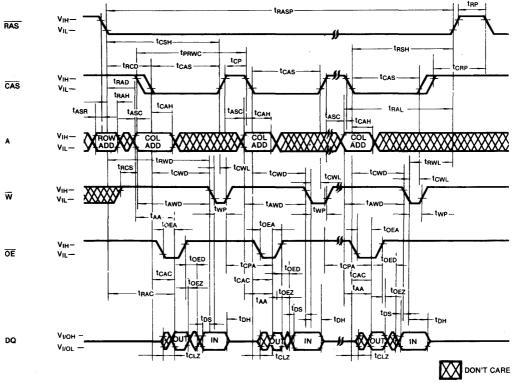

#### READ-WRITE/READ-MODIFY-WRITE CYCLE

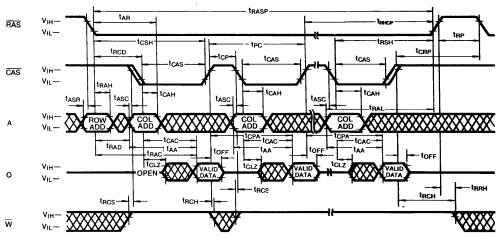

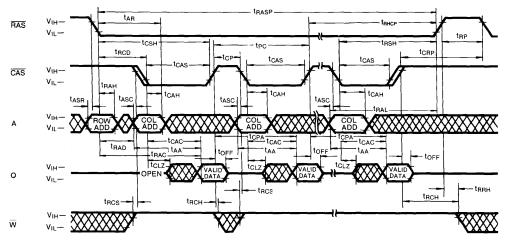

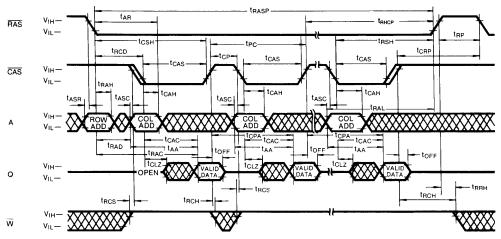

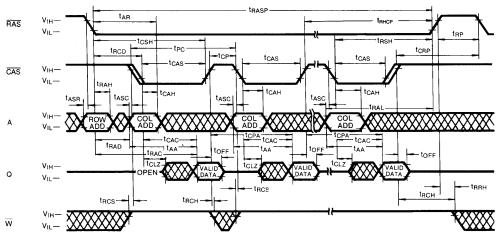

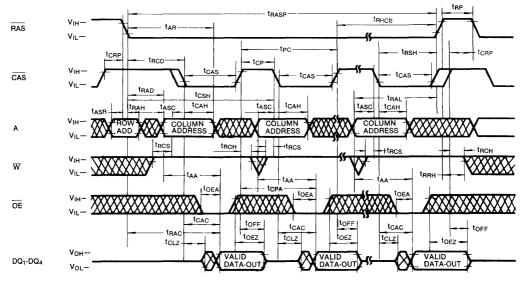

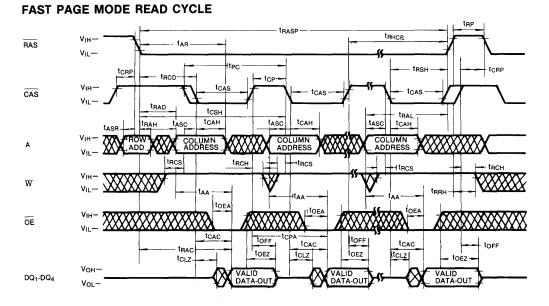

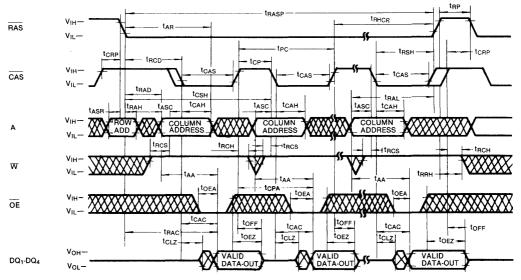

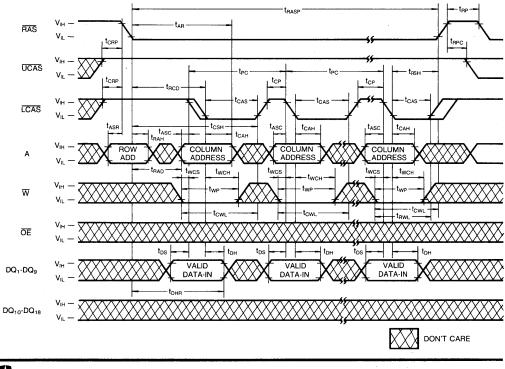

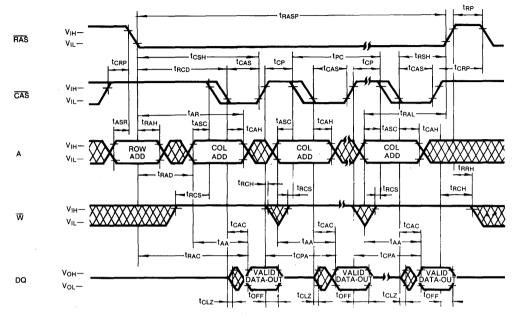

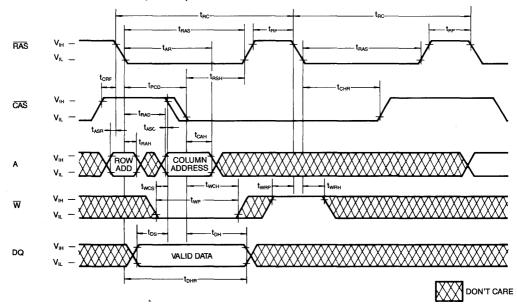

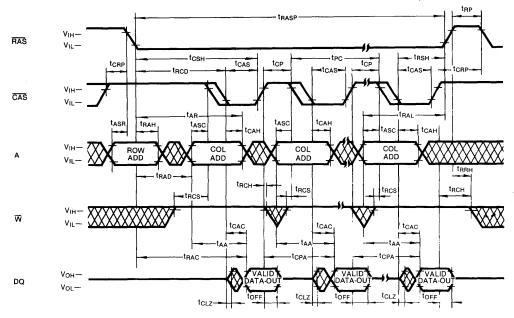

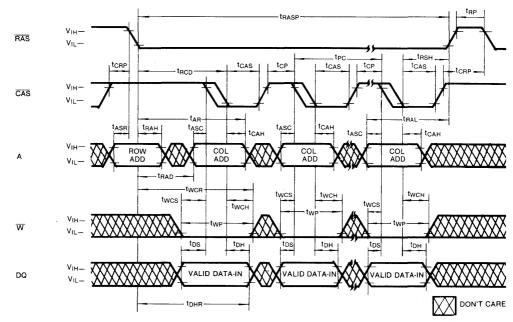

#### FAST PAGE MODE READ CYCLE

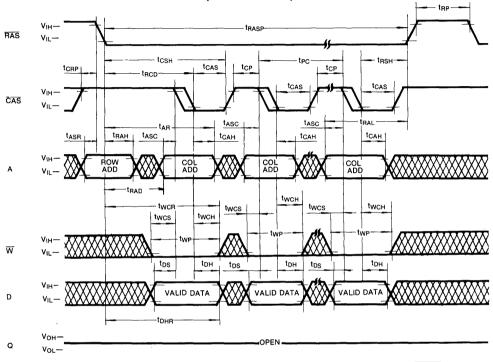

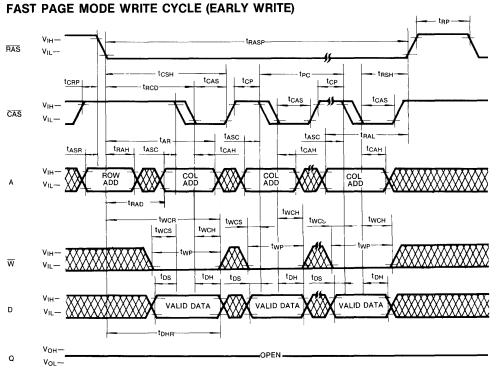

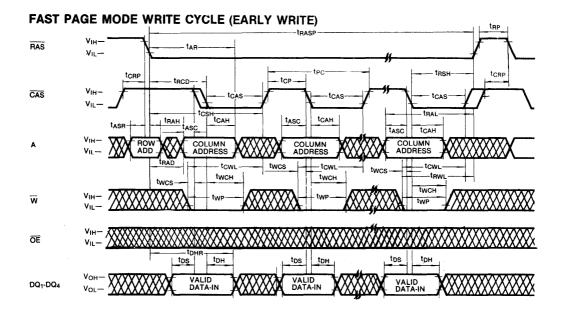

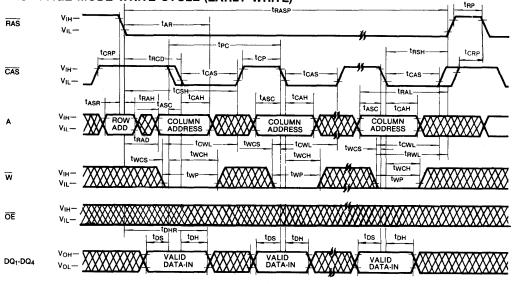

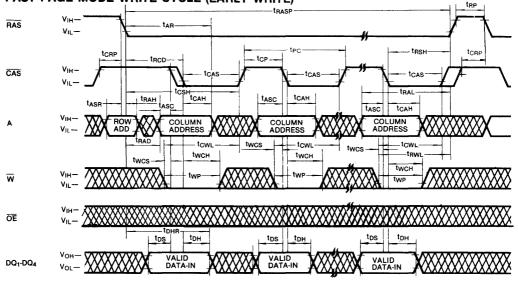

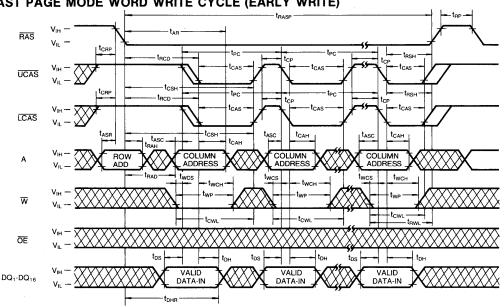

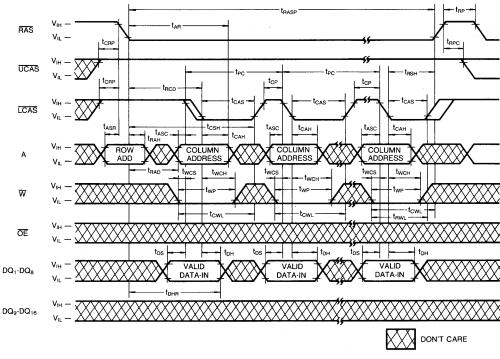

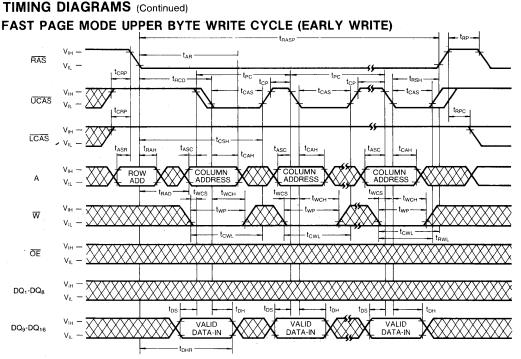

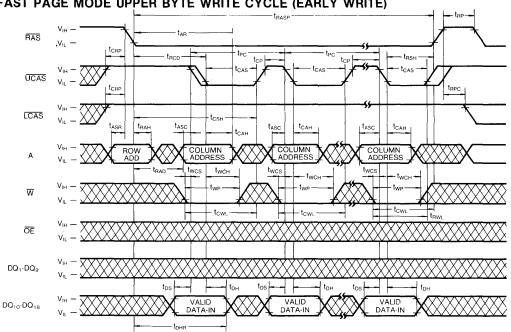

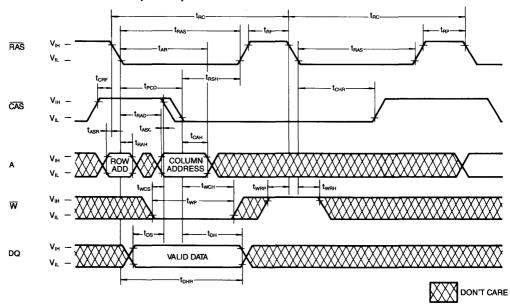

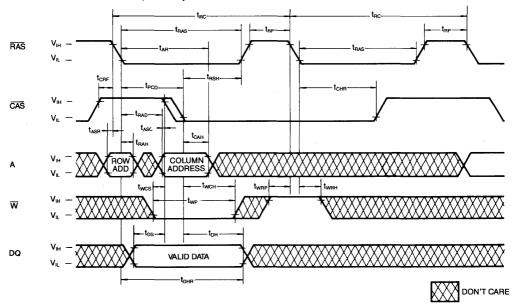

#### FAST PAGE MODE WRITE CYCLE (EARLY WRITE)

DON'T CARE

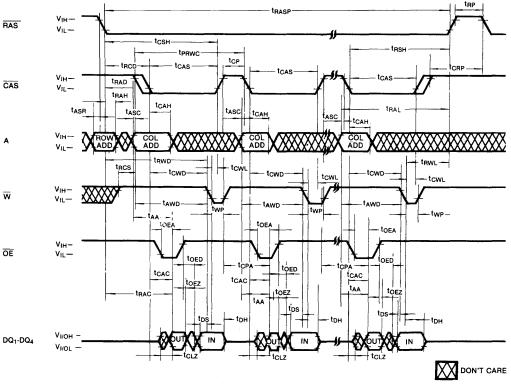

#### FAST PAGE MODE READ-WRITE CYCLE

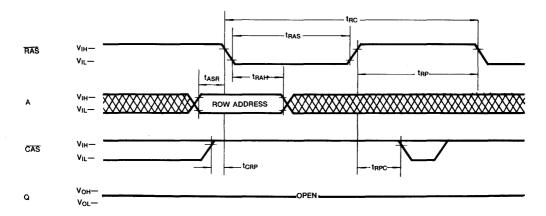

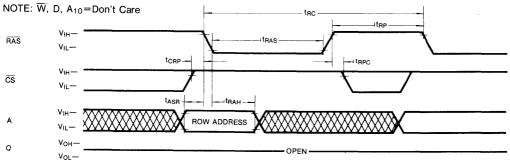

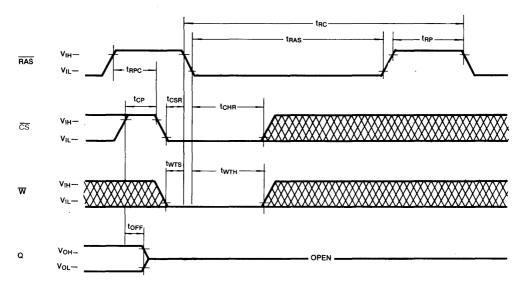

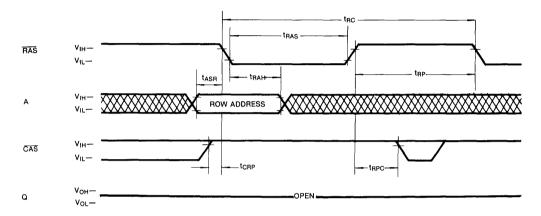

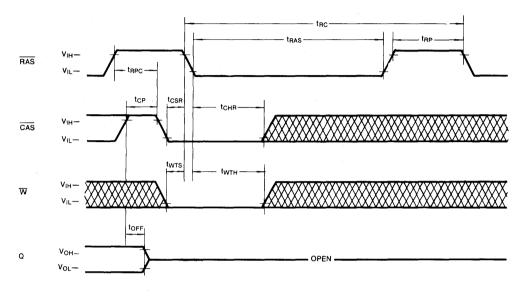

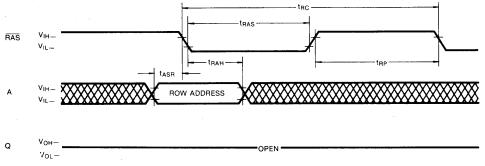

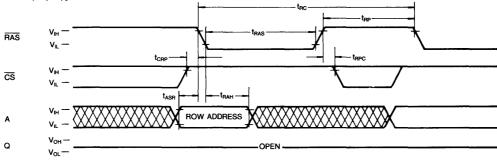

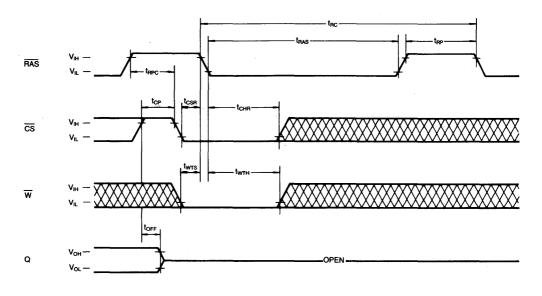

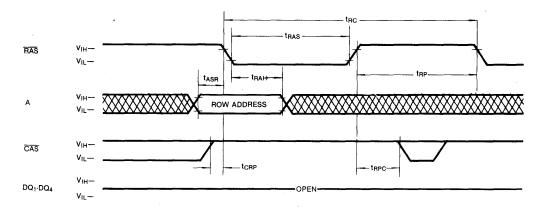

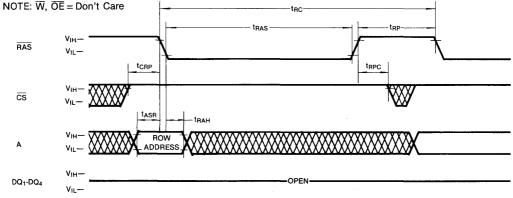

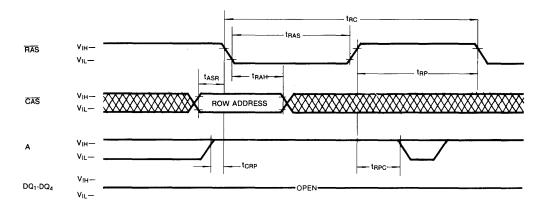

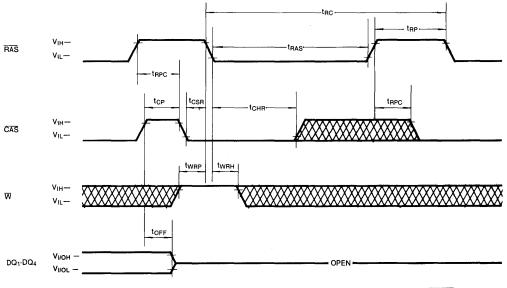

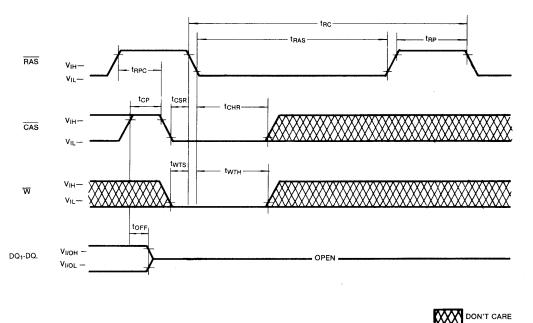

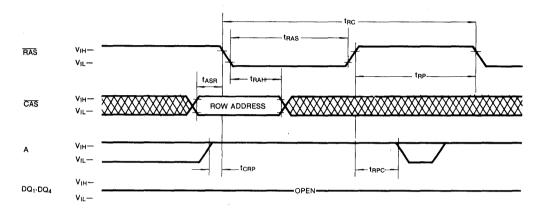

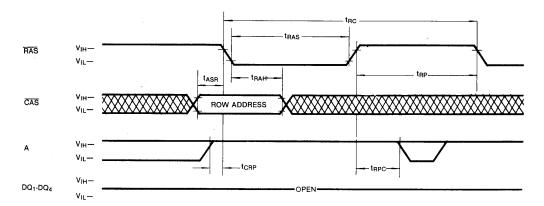

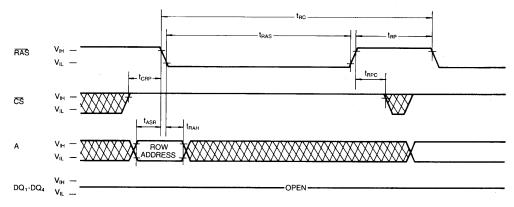

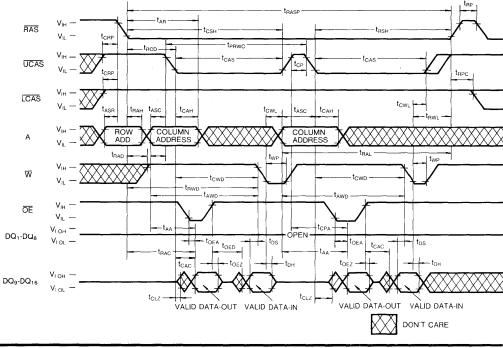

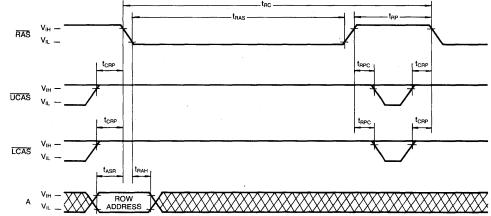

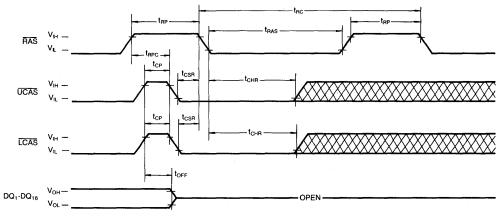

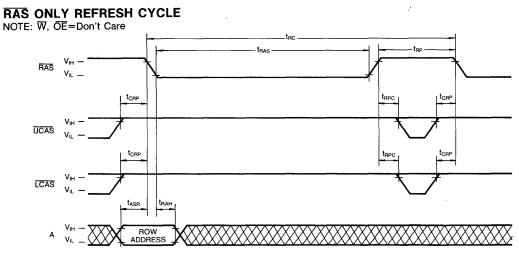

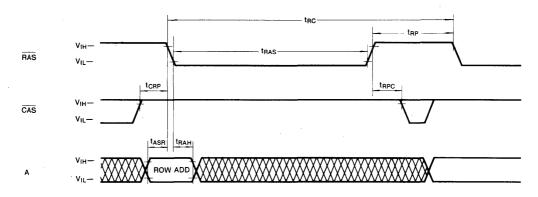

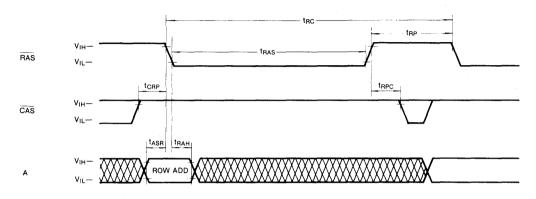

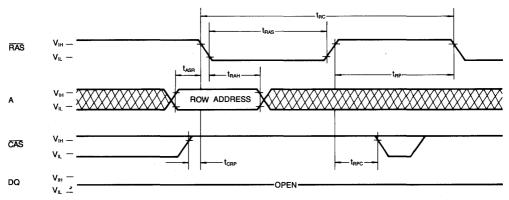

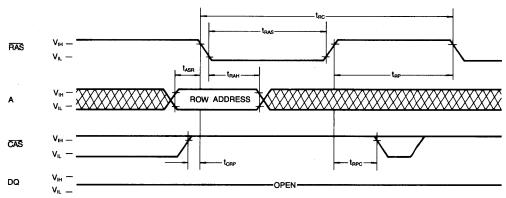

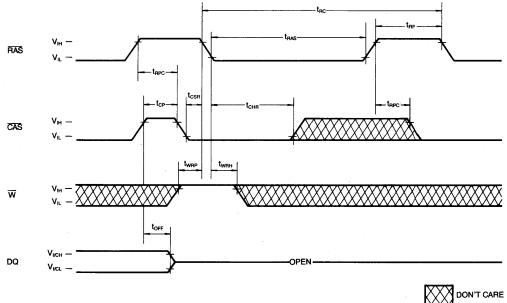

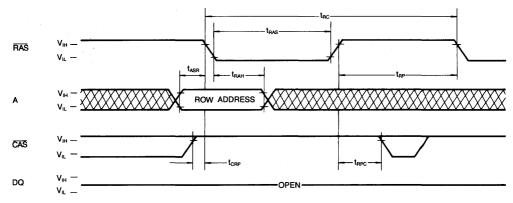

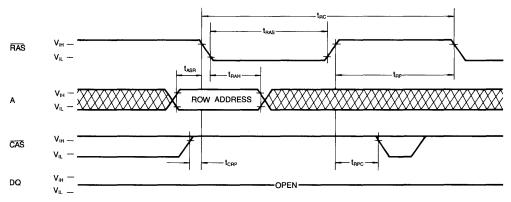

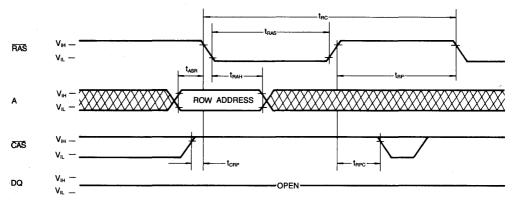

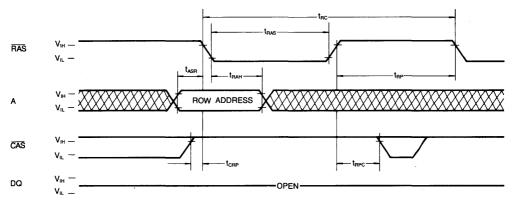

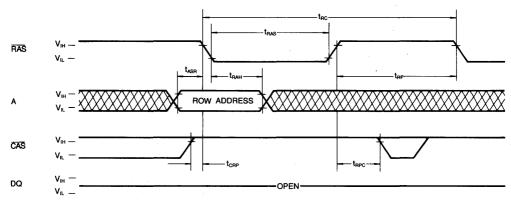

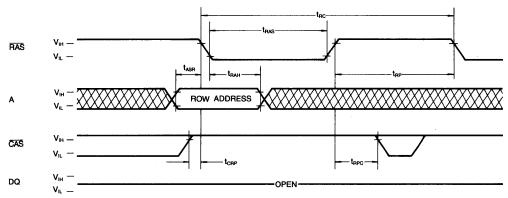

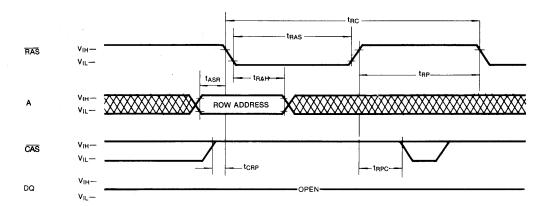

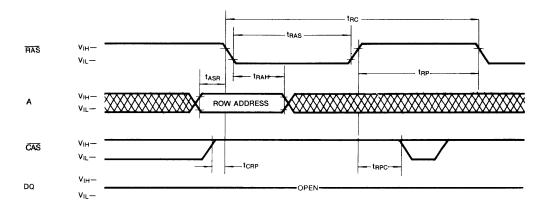

#### **RAS-ONLY REFRESH CYCLE**

Note:  $\overline{W}$ , D, A<sub>10</sub> = Don't Care

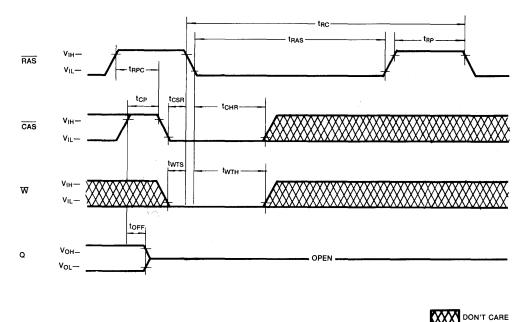

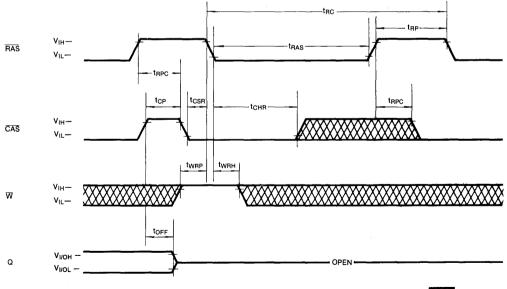

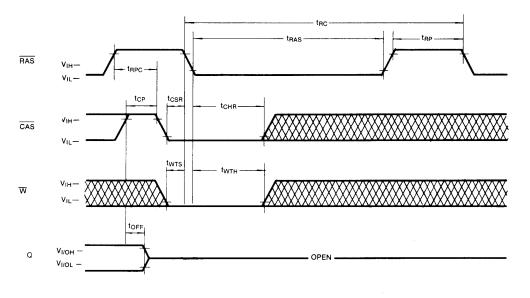

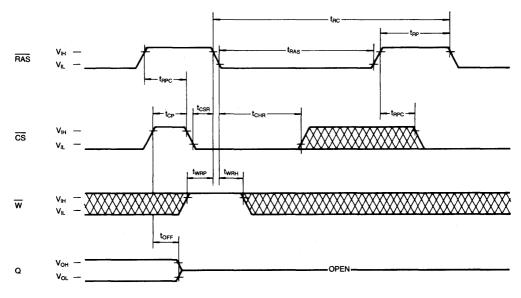

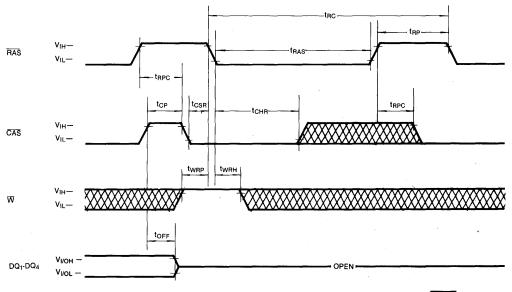

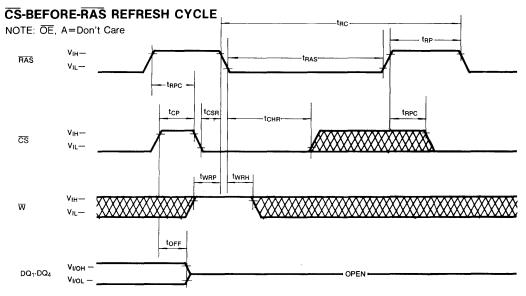

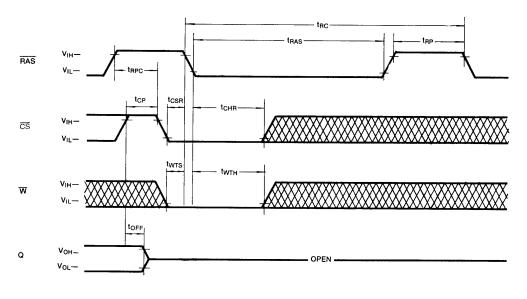

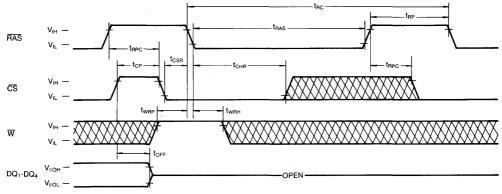

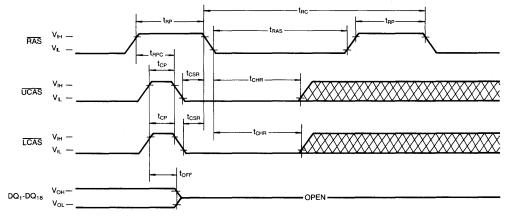

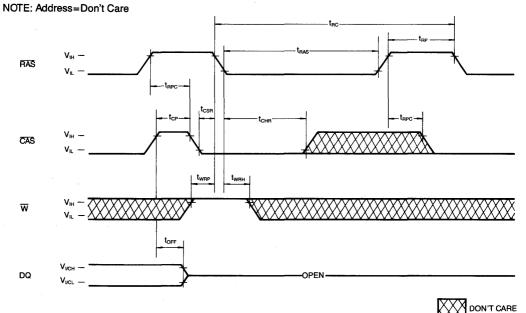

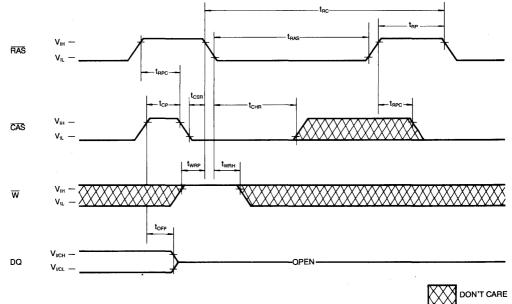

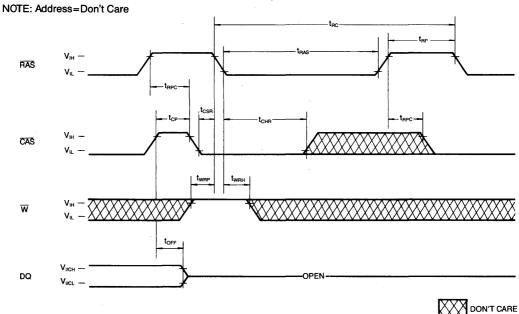

#### CAS-BEFORE-RAS REFRESH CYCLE

NOTE: Address = Don't Care

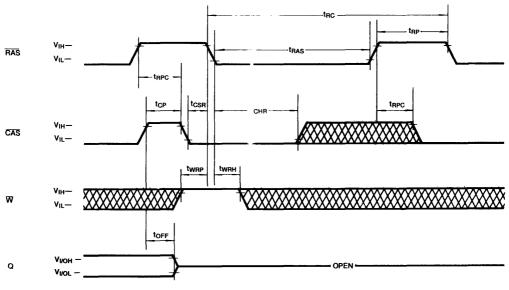

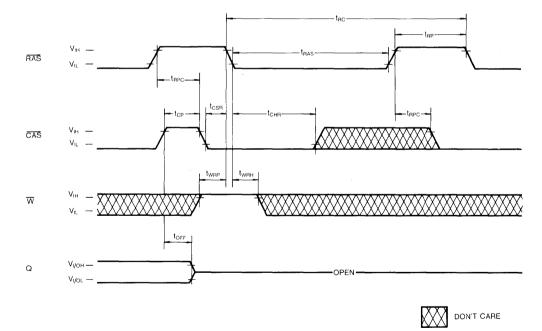

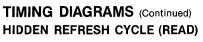

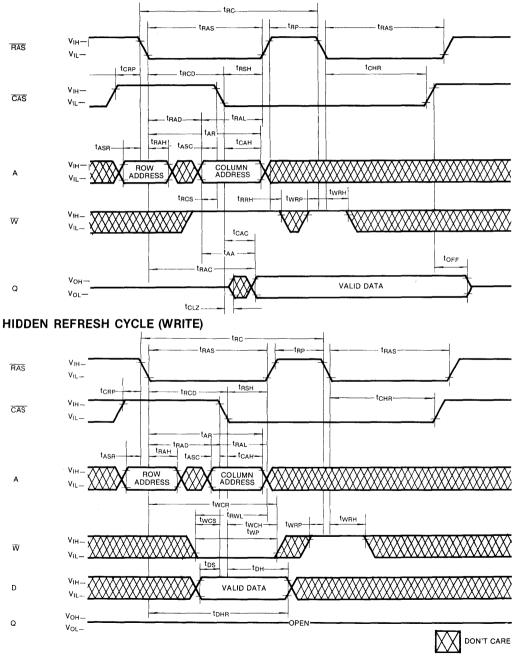

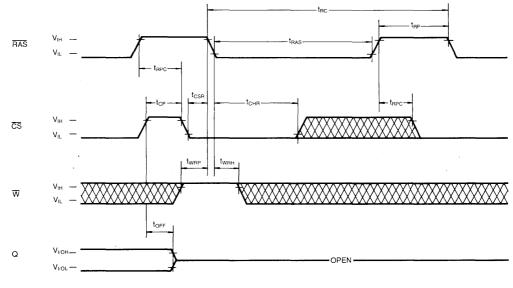

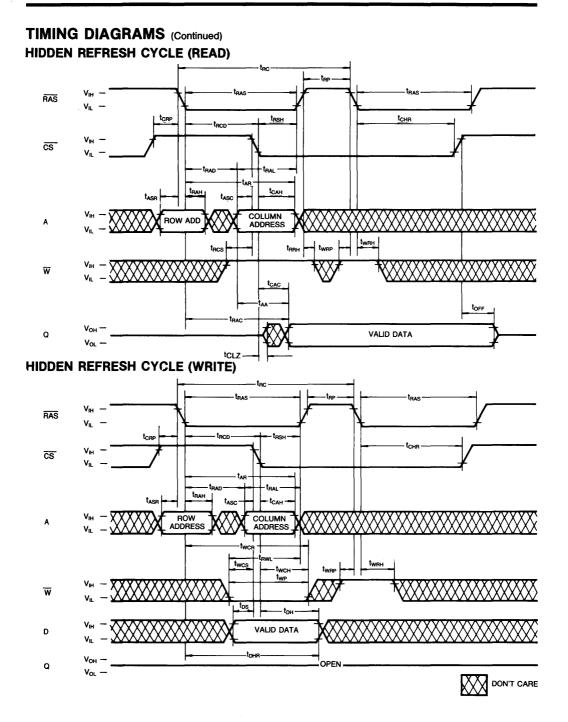

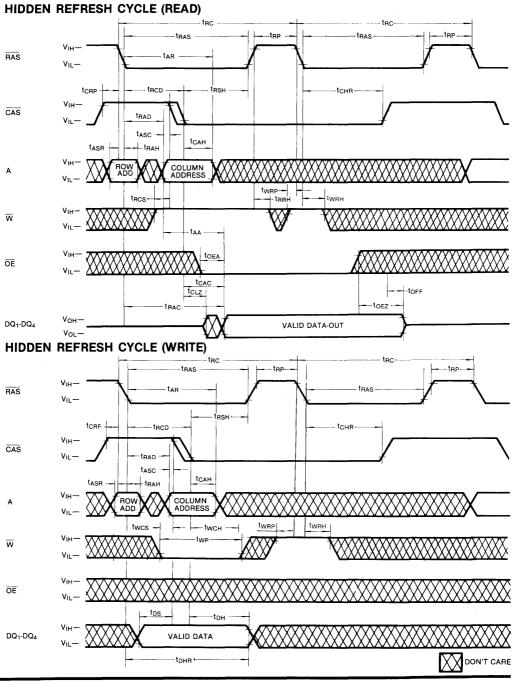

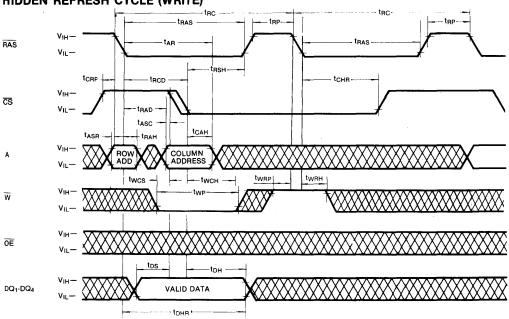

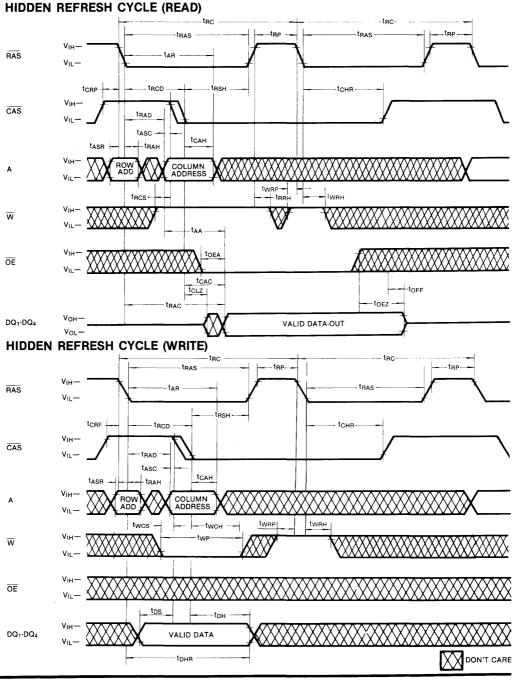

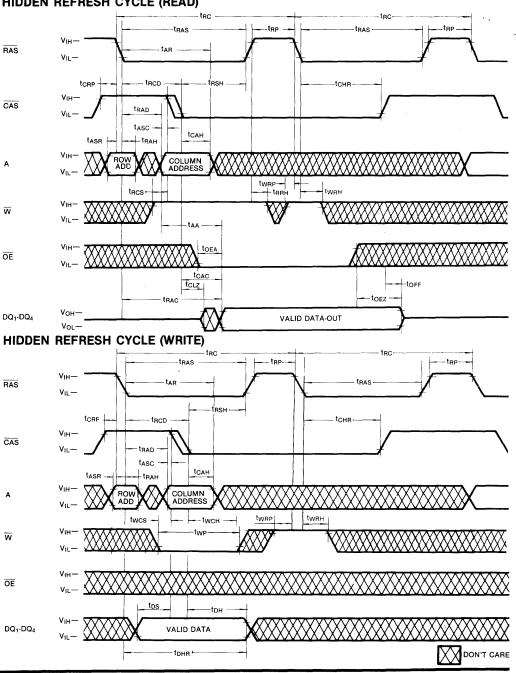

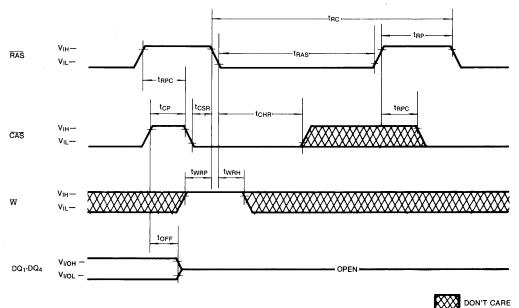

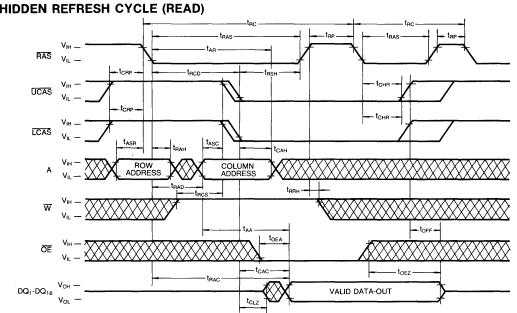

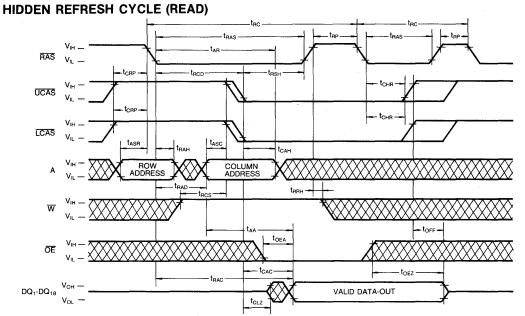

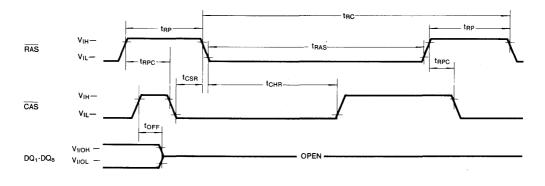

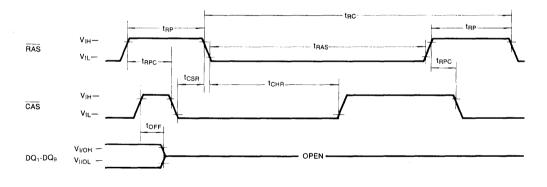

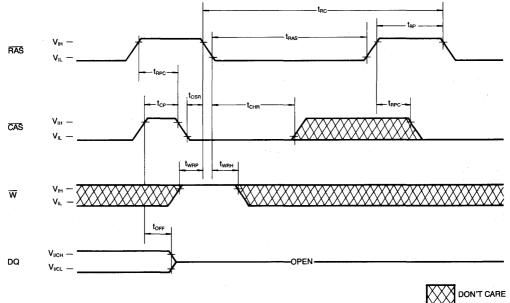

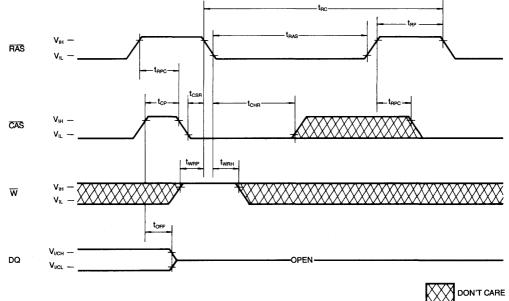

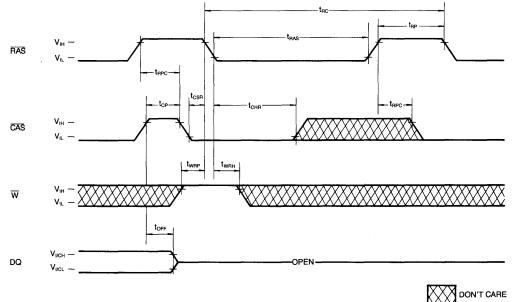

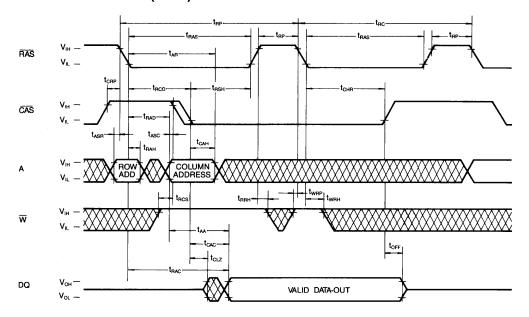

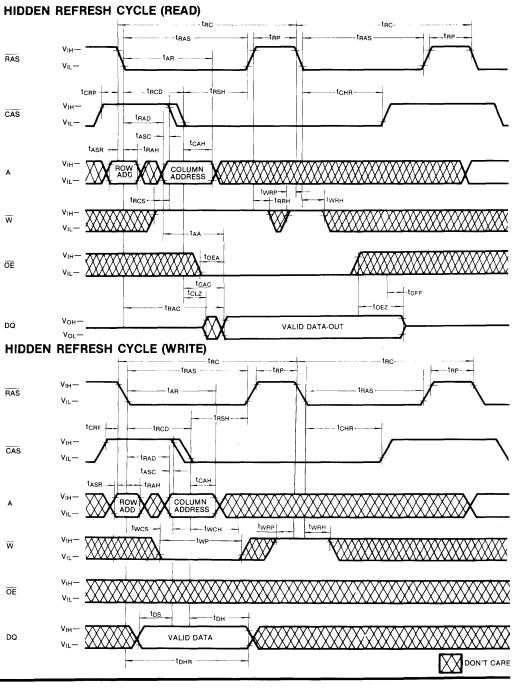

#### TIMING DIAGRAMS (Continued) HIDDEN REFRESH CYCLE (READ)

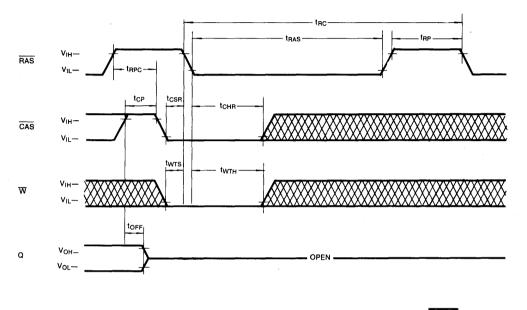

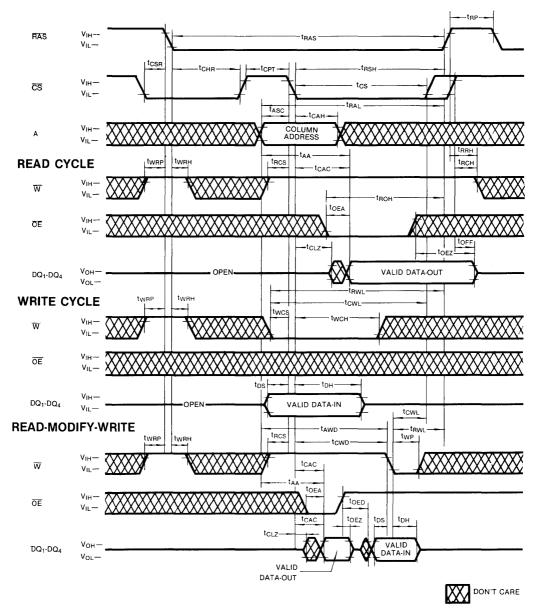

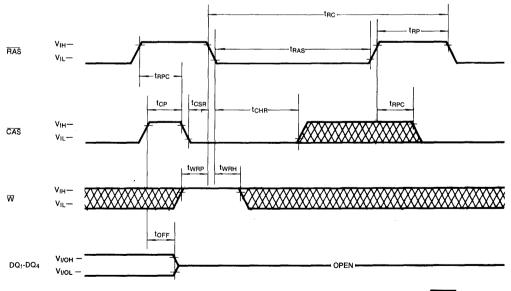

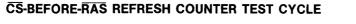

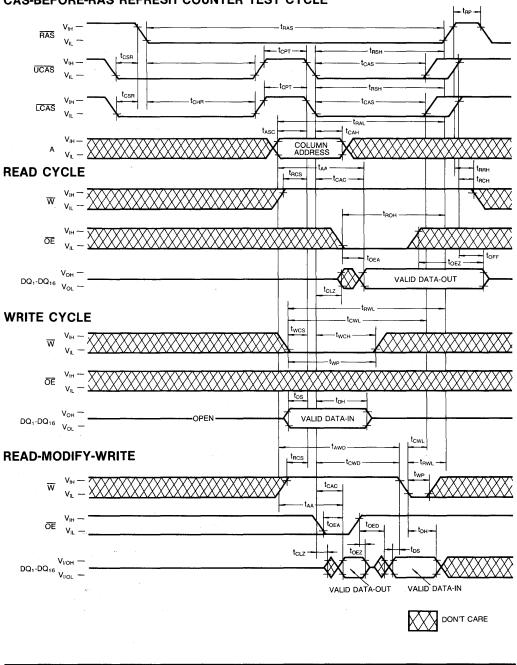

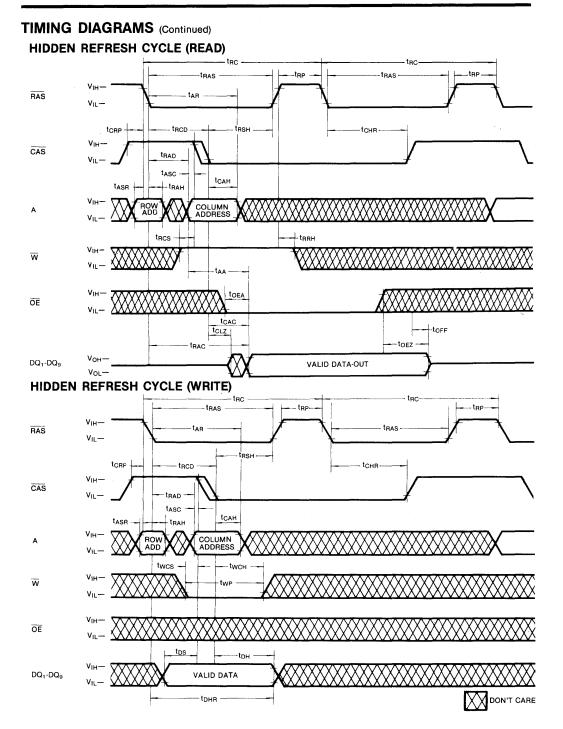

#### CAS-BEFORE-RAS REFRESH COUNTER TEST CYCLE

#### TEST MODE IN CYCLE

NOTE: D. Address=Don't Care

#### **TEST MODE DESCRIPTION**

The KM41C4000L is the RAM organized 4,194,304 words by 1 bit, it is internally organized 524,288 words by 8 bits. In "Test Mode", data are written into 8 sectors in parallel and retrieved the same way. A<sub>10R</sub>. A<sub>10C</sub> and A<sub>OC</sub> are not used. If, upon reading, all bits are equal (all "1"s or "0"s), the data output pin indicates a "1".

dicate a "0" In "Test Mode", the 4M DRAM can be tested as if it were a 512K DRAM W, CAS Before RAS Cycle (Test Mode in Cycle) puts the device into "Test Mode". And "CAS Before RAS Refresh Cycle" or "RAS only Refresh Cycle" puts it back into "Normal Mode". The "Test Mode" function reduces test time (1/8 in cases of N test pattern).

## **DEVICE OPERATION**

#### **Device Operation**

The KM41C4000/L contains 4,194,304 memory locations Twenty two address bits are required to address a particular memory location. Since the KM41C4000/L has only 11 address input pins, time multiplexed addressing is used to input 11 row and 11 column address. The multiplexing is controlled by the timing relationship between the row address strobe ( $\overline{RAS}$ ), the column address strobe ( $\overline{CAS}$ ) and the valid row and column address inputs.

Operating of the KM41C4000/L begins by strobing in a valid row address with  $\overline{\text{RAS}}$  while  $\overline{\text{CAS}}$  remains high. Then the address on the 11 address input pins is changed from a row address to a column address and is strobed in by  $\overline{\text{CAS}}$ . This is the beginning of any KM41C4000/L cycle in which a memory location is accessed. The specific type of cycle is determined by the state of the write enable pin and various timing relationships. The cycle is terminated when both  $\overline{\text{RAS}}$  and  $\overline{\text{CAS}}$  have returned to the high state. Another cycle can be initiated after  $\overline{\text{RAS}}$  remains high long enough to satisfy the  $\overline{\text{RAS}}$  precharge time (t\_{RP}) requirement.

#### RAS and CAS Timing

The minimum RAS and CAS pulse widths are specified by  $t_{RAS}(min)$  and  $t_{CAS}(min)$  respectively. These minimum pulse widths must be satisfied for proper device operation and data integrity. Once a cycle is initiated by bringing RAS low, it must not be aborted prior to satisfying the minimum RAS and CAS pulse widths. In addition, a new cycle must not begin until the minimum RAS precharge time,  $t_{RP}$ , has been satisfied. Once a cycle begins, internal clocks and other circuits within the KM41C4000/L begin a complex sequence of events. If the sequence is broken by violating minimum timing requirements, loss of data integrity can occur.

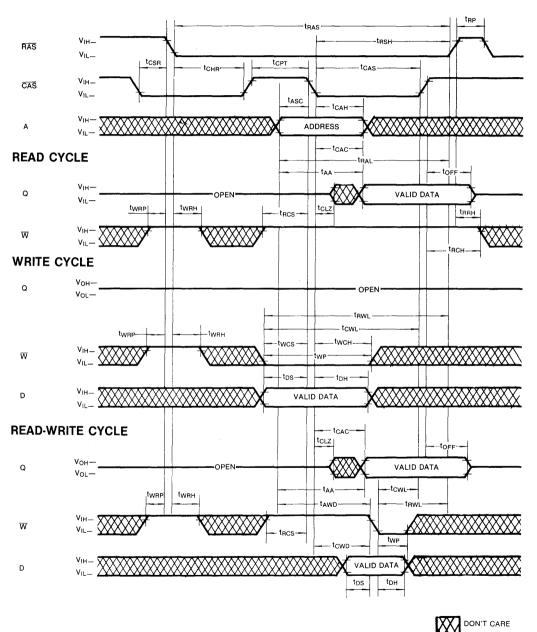

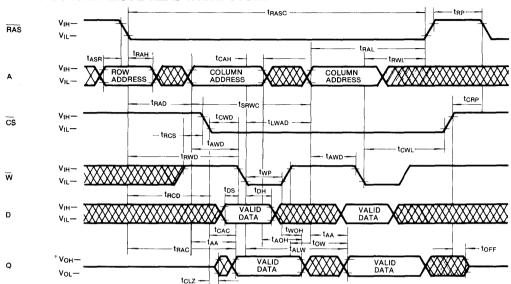

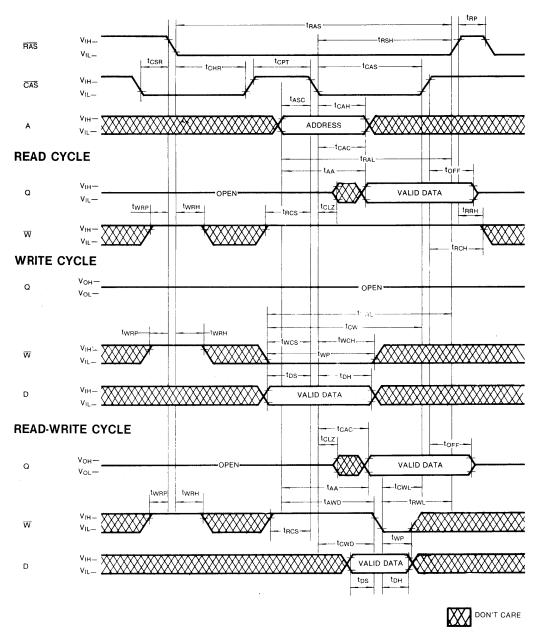

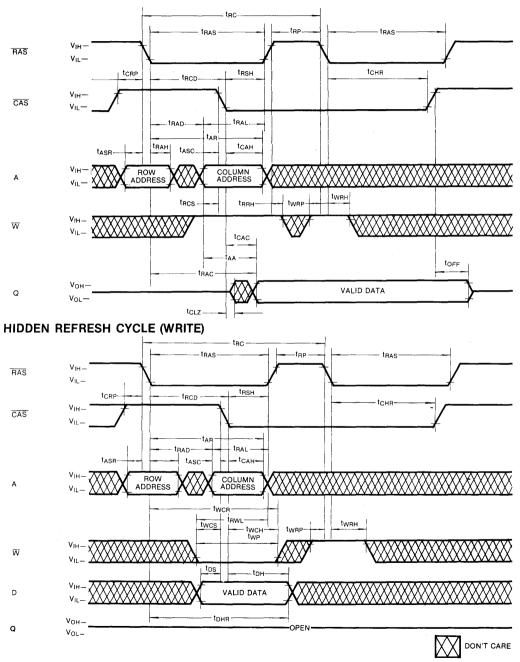

#### Read

A read cycle is achieved by maintaining the write enable input( $\overline{W}$ ) high during a  $\overline{RAS}/\overline{CAS}$  cycle. If  $\overline{CAS}$  goes low before  $t_{RCD}(max)$ , the access time to valid data is specified by  $t_{RAC}$ . If  $\overline{CAS}$  goes low after  $t_{RCD}(max)$ , the access time is measured from  $\overline{CAS}$  and is specified by  $t_{CAC}$ . In order to achieve the minimum access time,  $t_{RAC}(min)$ , it is necessary to bring  $\overline{CAS}$  low before  $t_{RCD}(max)$ .

#### Write

The KM41C4000/L can perform early write late write and read-modify-write cycles. The difference between these cycles is in the state of data-out and is determined by the timing relationship between  $\overline{W}$  and  $\overline{CAS}$ . In any type of write cycle, Date-in must be valid at or before the falling edge of  $\overline{W}$  or  $\overline{CAS}$ , whichever is later.

*Early Write:* An early write cycle is performed by bringing  $\overline{W}$  low before  $\overline{CAS}$ . The data at the data input pin(D) is written into the addressed memory cell. Throughout the early write cycle the output remains in the Hi-Z state. This cycle is good for common I/O applications because the data-in and data-out pins may be tied together without bus contention.

Read-Modify-Write: In this cycle, valid data from the addressed cell appears at the output before and during the time that data is being written into the same cell location. This cycle is achieved by bringing  $\overline{W}$  low after  $\overline{CAS}$  and meeting the data sheet read-modify-write cycle timing requirements. This cycle requires using a separate I/O to avoid bus contention.

*Late Write:* If  $\overline{W}$  is brought low after  $\overline{CAS}$ , a late write cycle will occur. The late write cycle is very similar to the read-modify-write cycle except that the timing parameters,  $t_{RWD}$ ,  $t_{CWD}$  and  $t_{AWD}$ , are not necessarily met. The state of date-out is indeterminate since the output can be either Hi-Z or contain data depending on the timing conditions. This cycle requires a separate I/O to avoid bus contention.

#### Data Output

The KM41C4000/L has a three-state output buffer which is controlled by  $\overline{CAS}$ . Whenever  $\overline{CAS}$  is high (V<sub>IH</sub>) the output is in the high impedance (Hi-Z) state. In any cycle in which valid data appears at the output the output goes into the low impedance state in a time specified by t<sub>CLZ</sub> after the falling edge of  $\overline{CAS}$ . Invalid data may be present at the output during the time after t<sub>CLZ</sub> and before the valid data appears at the output. The timing parameters t<sub>CAC</sub>, t<sub>RAC</sub> and t<sub>AA</sub> specify when the valid data will be present at the output. The valid data remains at the output until  $\overline{CAS}$  returns high. This is true even if a new RAS cycle occurs (as in hidden refresh). Each of the KM41C4000/L operating cycles is listed below after the cycle.

Valid Output Data: Read, Read-Modify-Write, Hidden Refresh, Fast Page Mode Read, Fast Page Mode Read-Modify-Write.

*Hi-Z Output State:* Early Write, RAS-only Refresh, Fast Page Mode Write, CAS-before-RAS Refresh, CAS-only cycle.

Indeterminate Output State: Delayed Write

#### Refresh

The data in the KM41C4000/L is stored on a tiny capacitor within each memory cell. Due to leakage the data may leak off after a period of time. To maintain data integrity it is necessary to refresh each of the rows every

# **DEVICE OPERATION** (Continued)

$16/128 \ (\mbox{L-version})\mbox{ms}.$  There are several ways to accomplish this.

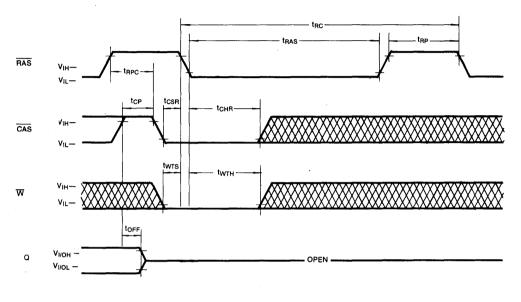

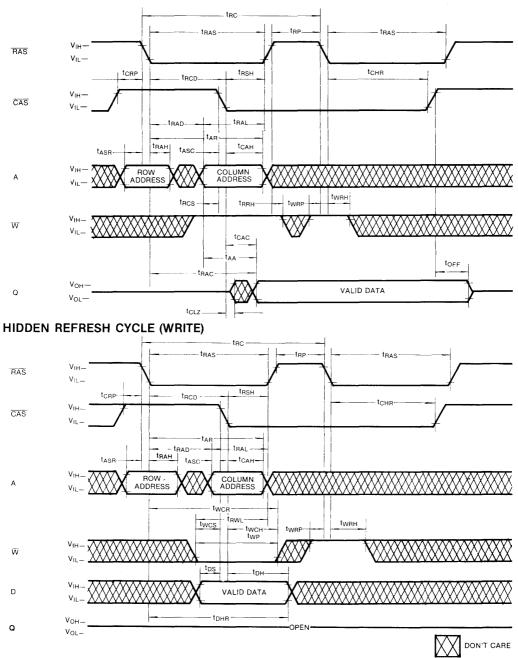

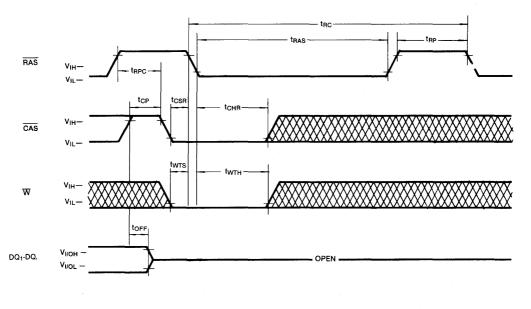

$\overline{RAS}$ -Only Refresh: This is the most common method for performing refresh. It is performed by strobing in a row address with  $\overline{RAS}$  while  $\overline{CAS}$  remains high. This cycle must be repeated for each row.

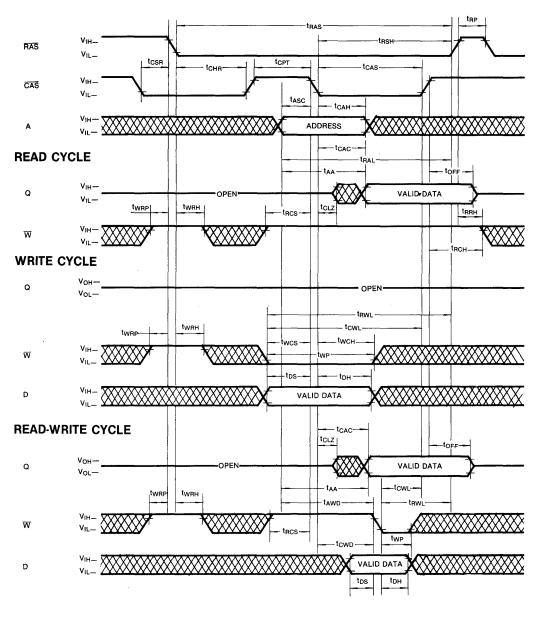

$\overline{CAS}$ -before- $\overline{RAS}$  Refresh: The KM41C4000/L has  $\overline{CAS}$ before- $\overline{RAS}$  on-chip refreshing capability that eliminates the need for external refresh addresses. If  $\overline{CAS}$  is held low for the specified set up time ( $t_{CSR}$ ) before  $\overline{RAS}$  goes low, the on-chip refresh circuity is enabled. An internal refresh operation automatically occurs. The refresh address is supplied by the on-chip refresh address counter which is then internally incremented in preparation for the next  $\overline{CAS}$ -before- $\overline{RAS}$  refresh cycle.

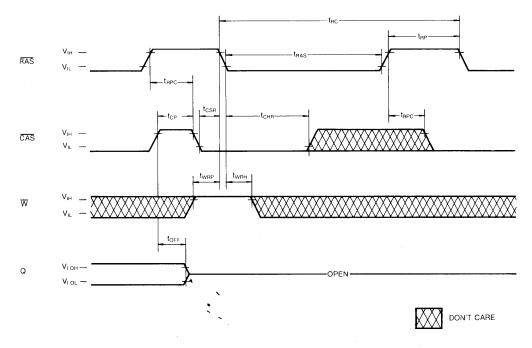

Hidden Refresh: A hidden refresh cycle may be performed while maintaining the latest valid data at the output by extending the  $\overline{CAS}$  active time and cycling  $\overline{RAS}$ . The KM41C4000/L hidden refresh cycle is actually a  $\overline{CAS}$  before  $\overline{RAS}$  refresh cycle within an extended read cycle. The refresh row address is provided by the on-chip refresh address counter.

Other Refresh Methods: It is also possible to refresh the KM41C4000/L by using read, write or read-modify-write cycles. Whenever a row is accessed, all the cells in that row are automatically refreshed. These are certain applications in which it might be advantageous to perform refresh in this manner but in general RAS-only or CAS-before.RAS refresh is the preferred method.

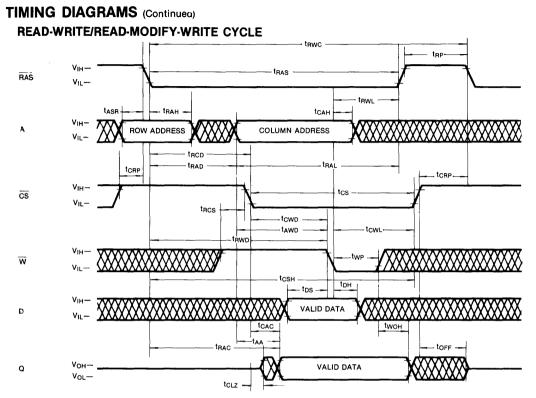

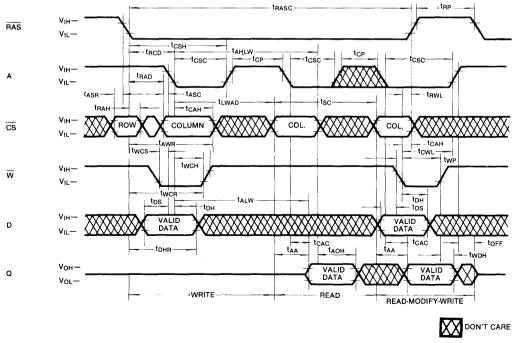

#### Fast Page Mode

The KM41C4000/L has Fast Page mode capability. Fast Page mode memory cycles provide faster access and lower power dissipation than normal memory cycles. In Fast Page mode, it is possible to perform read, write or read-modify-write cycles. As long as the applicable timing requirements are observed, it is possible to mix these cycles in any order. A Fast Page mode cycle begins with a normal cycle. Then, while RAS is kept low to maintain the row address, CAS is cycled to strobe in additional column addresses. This eliminates the time required to set up and strobe sequential row address for the same page. Up to 2048 memory cells can be accessed with the same row address.

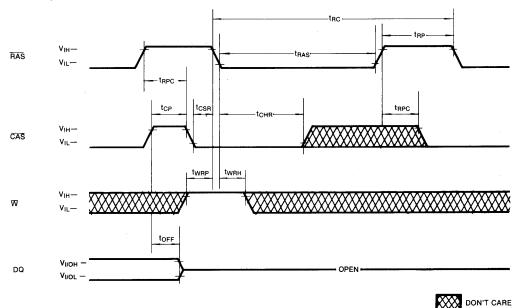

#### CAS-Before-RAS Refresh Counter Test Cycle

A special timing sequence using the CAS-before-RAS

counter test cycle provides a convenient method of verifying the functionality of the CAS-before-RAS refresh activated circuitry.

After the CAS-before-RAS refresh operation, if CAS goes high and then low again while RAS is held low, the read and write operations are enabled.

This is shown in the CAS-before-RAS counter test cycle timing diagram. A memory cell can be addressed with 11 row address bits and 11 column address bits defined as follows:

Row Address—Bits  $A_0$  through  $A_9$  are supplied by the on-chip refresh counter. This  $A_{10}$  bit is set high internally.

Column Address—Bits  $A_0$  through  $A_{10}$  are strobedin by the falling edge of  $\overrightarrow{CAS}$  as in a normal memory cycle.

#### Suggested CAS-Before-RAS Counter Test Procedure

The CAS-before-RAS refresh counter test cycle timing is used in each of the following steps:

- Initialize the internal refresh counter by performing 8 CAS-before-RAS cycles.

- Write a test pattern of "lows" into the memory cells at a single column address and 1024 row addresses. (The row addresses are supplied by the on-chip refresh counter.)

- Using read-modify-write cycles, read the "lows" written during step 2 and write "highs" into the same memory locations. Perform this step 1024 times so that highs are written into the 1024 memory cells.

- 4. Read the "highs" written during step 3.

- 5. Complement the test pattern and repeat steps 2, 3 and 4.

#### Power-up

If  $\overline{RAS}$ =V<sub>SS</sub> during power-up, the KM41C4000/L could begin an active cycle. This condition results in higher than necessary current demands from the power supply during power-up. It is recommended that  $\overline{RAS}$  and  $\overline{CAS}$  track with V<sub>CC</sub> during power-up or be held at a valid VIH in order to minimize the power-up current.

An initial pause of  $200\mu s$  is required after power-up followed by any 8 CBR or ROR cycles before proper device operation is achieved.

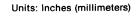

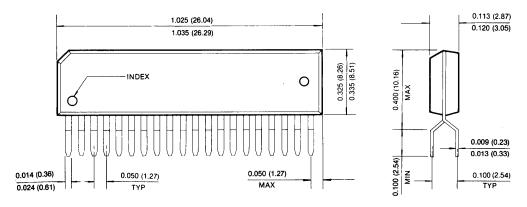

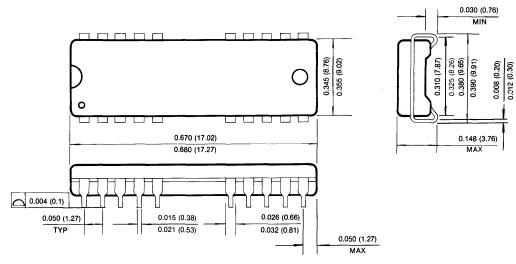

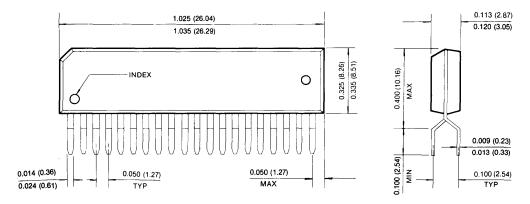

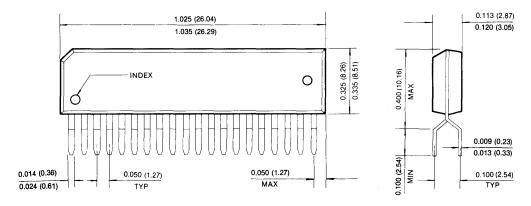

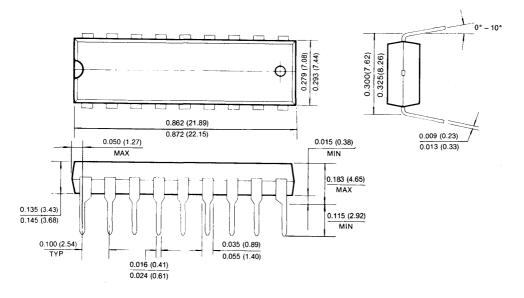

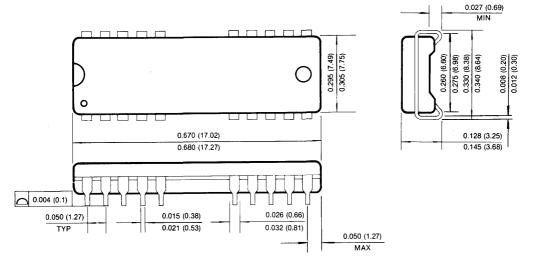

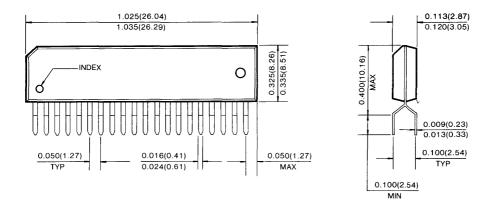

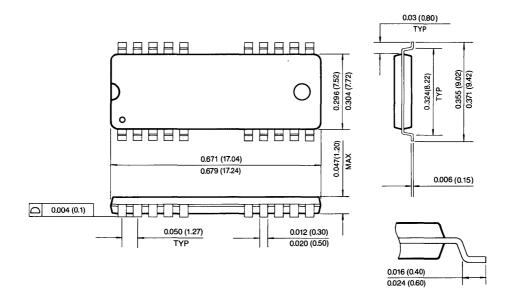

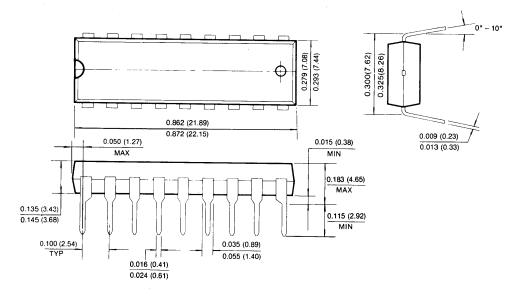

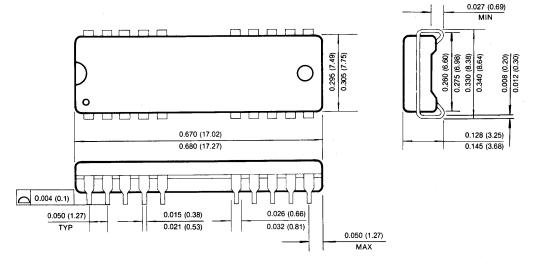

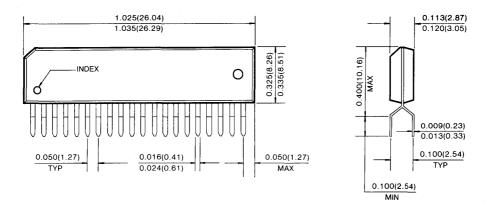

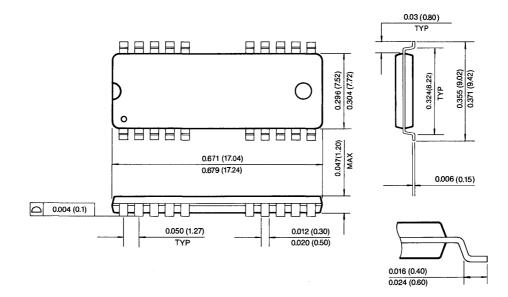

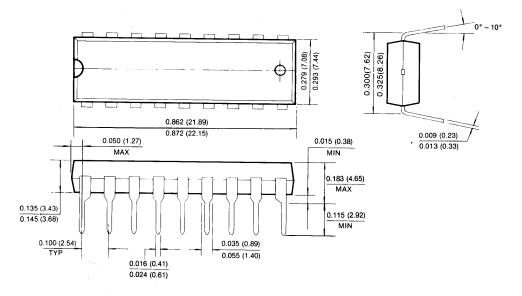

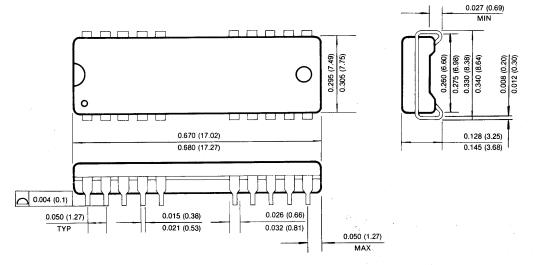

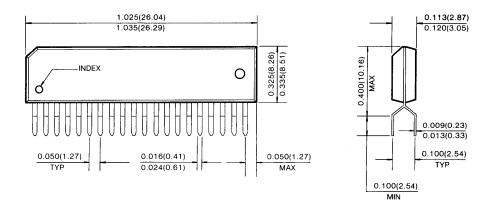

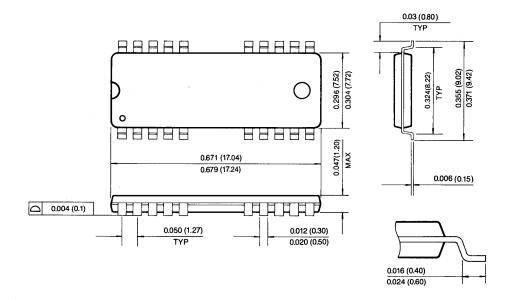

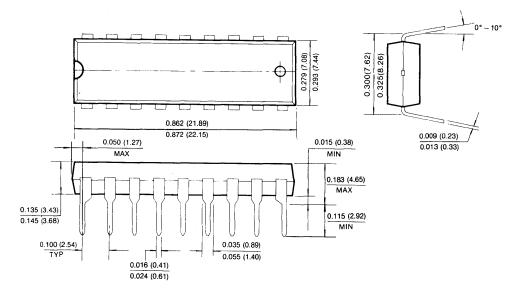

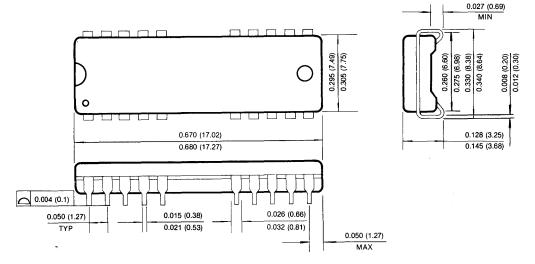

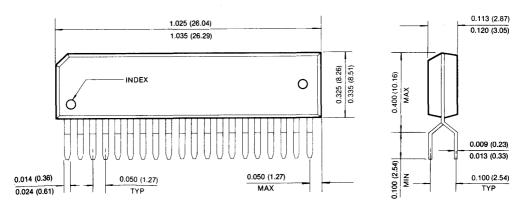

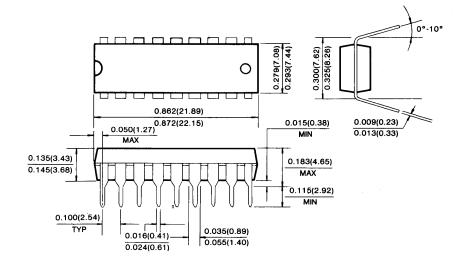

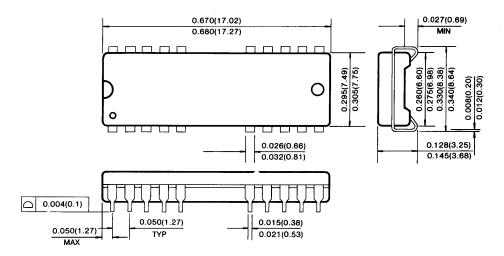

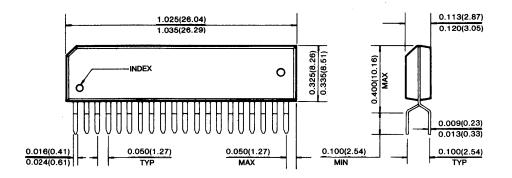

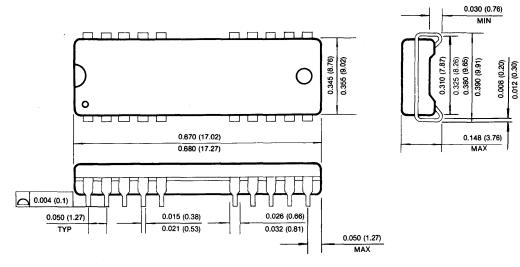

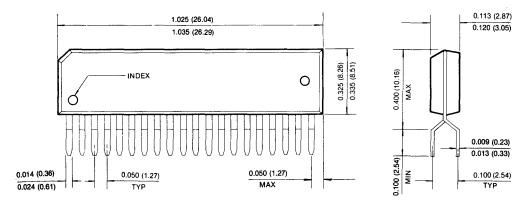

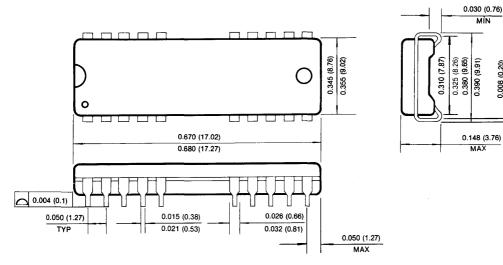

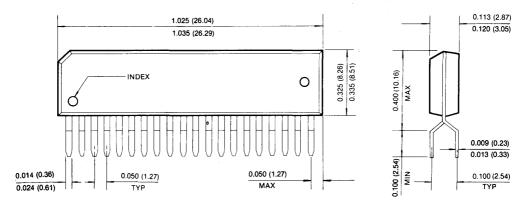

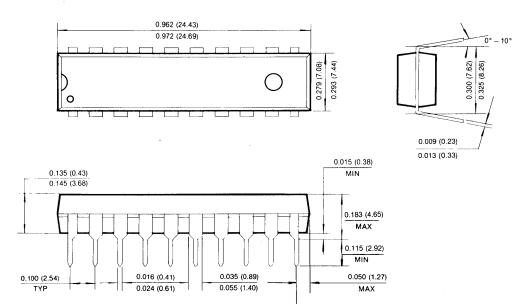

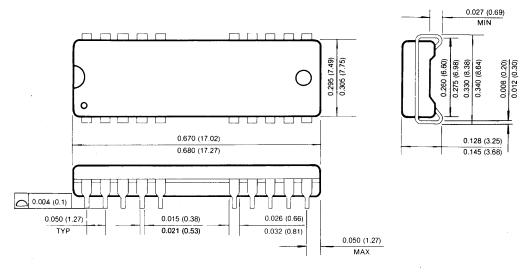

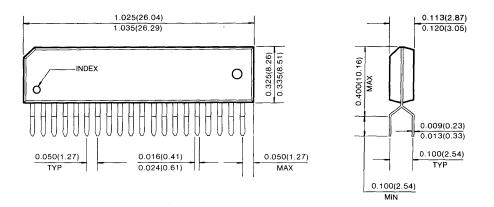

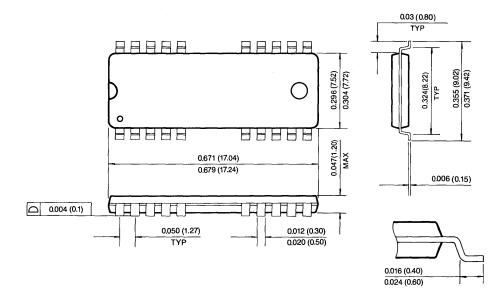

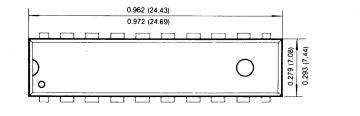

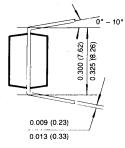

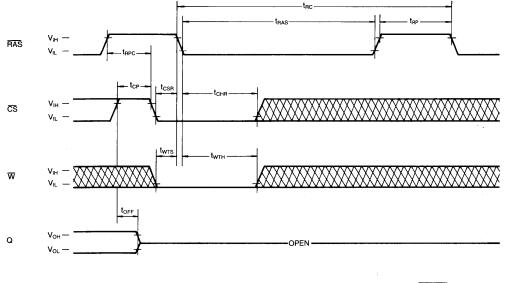

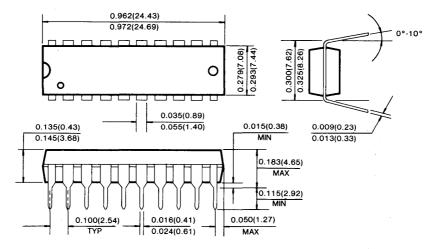

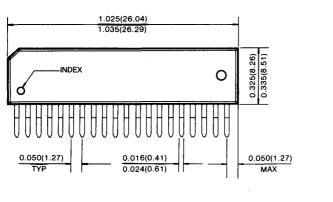

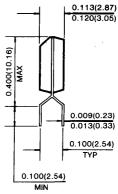

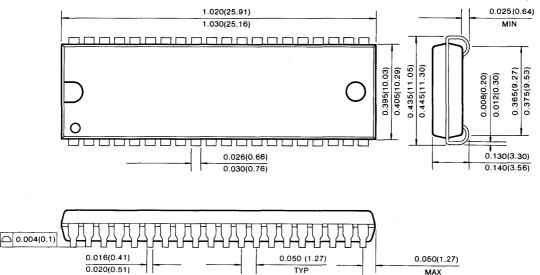

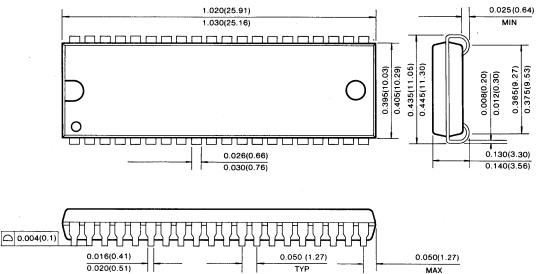

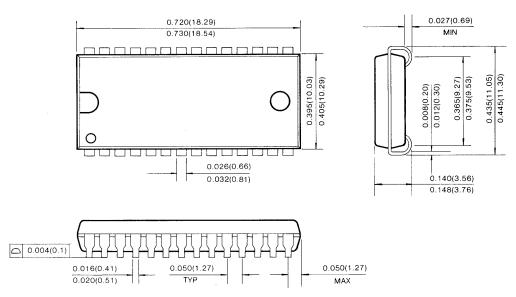

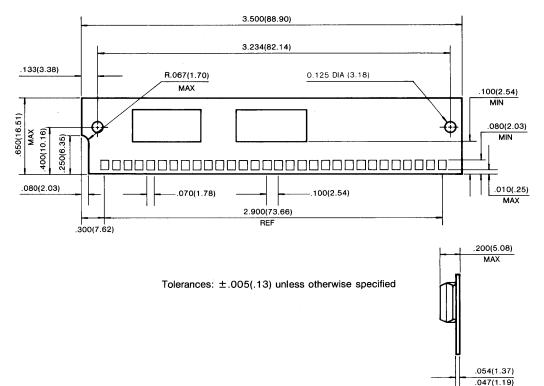

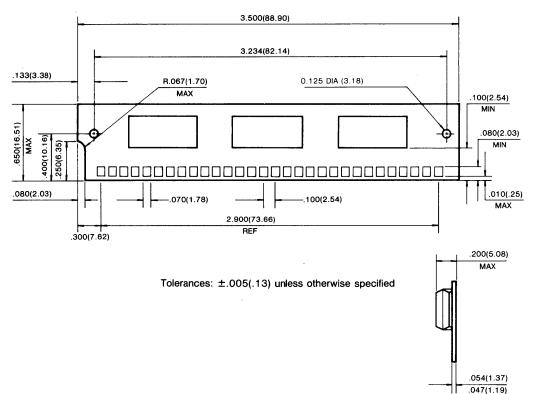

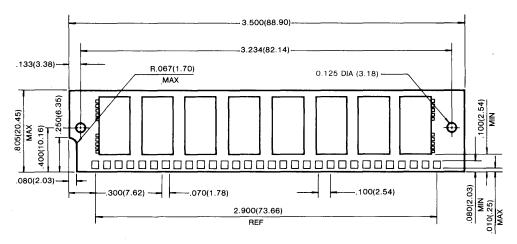

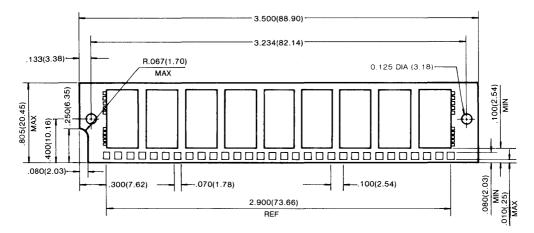

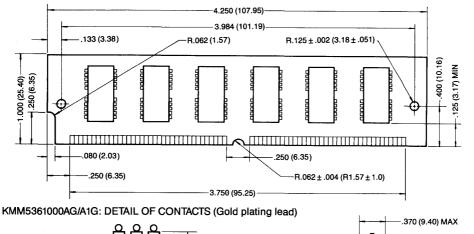

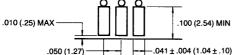

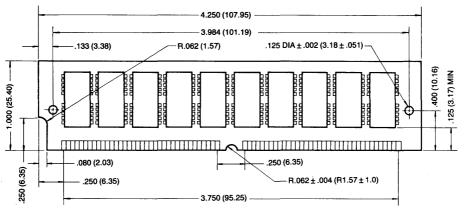

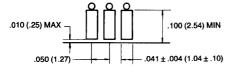

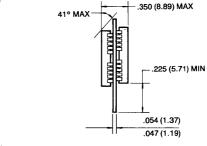

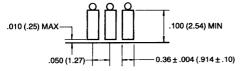

# PACKAGE DIMENSIONS

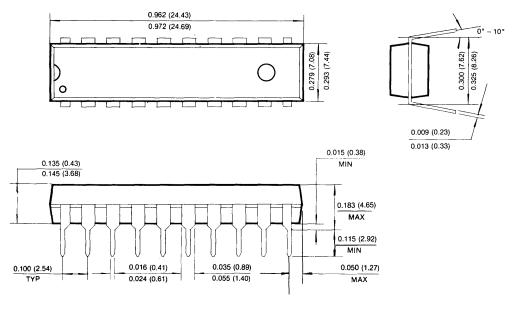

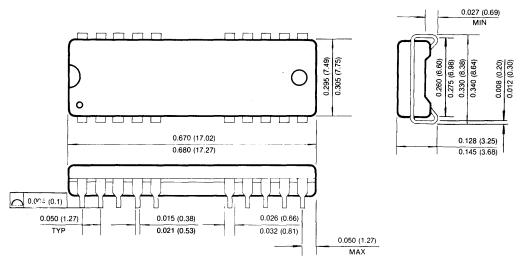

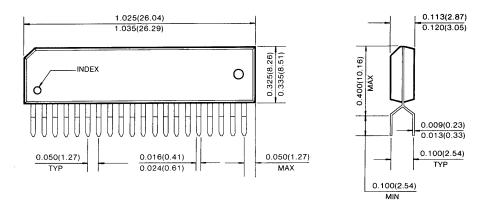

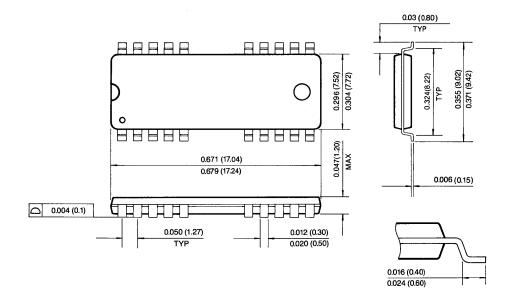

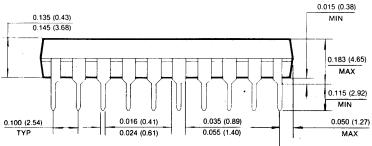

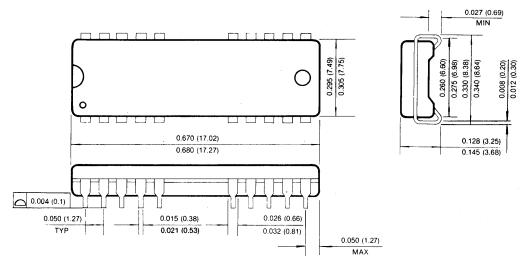

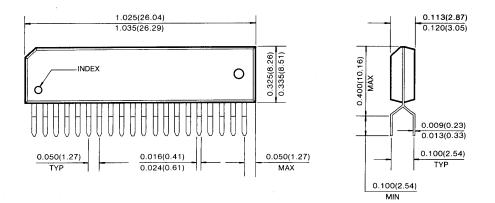

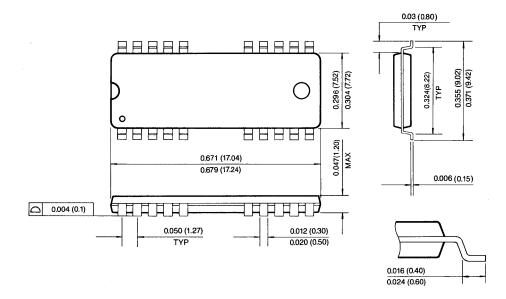

#### 20-LEAD PLASTIC SMALL OUT-LINE J-LEAD

#### 20-LEAD PLASTIC ZIGZAG-IN-LINE PACKAGE

# 4M×1 Bit CMOS Dynamic RAM with Nibble Mode

#### **FEATURES**

• Performance range:

|              | tRAC  | tCAC | t <sub>RC</sub> |

|--------------|-------|------|-----------------|

| KM41C4001- 8 | 80ns  | 20ns | 150ns           |

| KM41C4001-10 | 100ns | 25ns | 180ns           |

- Nibble Mode operation

- CAS-before-RAS refresh capability

- · RAS-only and Hidden Refresh capability

- · 8-bit fast parallel test mode capability

- · TTL compatible inputs and output

- · Common I/O using Early Write

- Single +5V±10% power supply

- 1024 cycles/16ms refresh

- JEDEC standard pinout

- Available in Plastic SOJ, ZIP

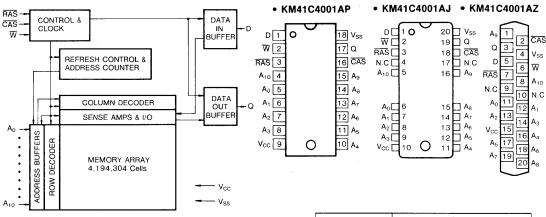

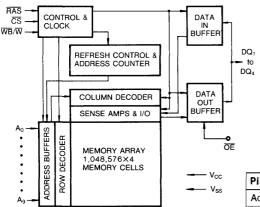

# FUNCTIONAL BLOCK DIAGRAM

#### **GENERAL DESCRIPTION**

The Samsung KM41C4001 is a high speed CMOS 4,194,304 bit  $\times$  1 Dynamic Random Access Memory. Its design is optimized for high performance applications such as mainframes and mini computers, graphics and high performance microprocessor systems.

The KM41C4001 features Nibble Mode operation which allows high speed serial access of up to 4 bits of data.

CAS-before-RAS refresh capability provides on-chip auto refresh as an alternative to RAS-only refresh. All inputs and output are fully TTL compatible.

The KM41C4001 is fabricated using Samsung's advanced CMOS process.

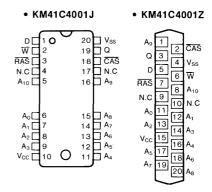

#### PIN CONFIGURATION (Top Views)

| Pin Name        | Pin Function          |  |  |

|-----------------|-----------------------|--|--|

| A0-A10          | Address Inputs        |  |  |

| D               | Data In               |  |  |

| Q               | Data Out              |  |  |

| W               | Read/Write Input      |  |  |

| RAS             | Row Address Strobe    |  |  |

| CAS             | Column Address Strobe |  |  |

| Vcc             | Power (+5V)           |  |  |

| V <sub>SS</sub> | Ground                |  |  |

| N.C.            | No connection         |  |  |

#### **ABSOLUTE MAXIMUM RATINGS\***

| Item                                                          | n Symbol Rating  |             | Unit |

|---------------------------------------------------------------|------------------|-------------|------|

| Voltage on Any Pin Relative to V <sub>SS</sub>                | VIN, VOUT        | -1 to +7.0  | V    |

| Voltage on V <sub>CC</sub> Supply Relative to V <sub>SS</sub> | Vcc              | -1 to +7.0  | V    |

| Storage Temperature                                           | T <sub>stg</sub> | -55 to +150 | °C   |

| Power Dissipation                                             | PD               | 600         | mW   |

| Short Circuit Output Current                                  | los              | 50          | mA   |

\* Permanent device damage may occur if "ABSOLUTE MAXIMUM RATINGS" are exceeded. Functional Operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS (Voltage reference to V<sub>SS</sub>, T<sub>A</sub>=0 to 70°C)

| Item               | Symbol          | Min  | Тур | Max                | Unit |

|--------------------|-----------------|------|-----|--------------------|------|

| Supply Voltage     | Vcc             | 4.5  | 5.0 | 5.5                | V    |

| Ground             | V <sub>SS</sub> | 0    | 0   | 0                  | V    |

| Input High Voltage | ViH             | 2.4  |     | V <sub>CC</sub> +1 | V    |

| Input Low Voltage  | VIL             | -1.0 |     | 0.8                | V    |

#### DC AND OPERATING CHARACTERISTICS (0°C<Ta<70°C, V<sub>CC</sub>=5.0V±10%)

(Recommended operating conditions unless otherwise noted)

| Parameter                                                                                                |                              |      | Min | Max       | Unit     |

|----------------------------------------------------------------------------------------------------------|------------------------------|------|-----|-----------|----------|

| Operating Current*<br>(RAS, CAS, Address Cycling @ t <sub>RC</sub> =min)                                 | KM41C4001- 8<br>KM41C4001-10 | Icc1 |     | 100<br>85 | mA<br>mA |

| Standby Current<br>(RAS=CAS=V <sub>IH</sub> )                                                            |                              | Icc2 | _   | 2         | mA       |

| RAS-Only Refresh Current*<br>(RAS Cycling, CAS=V <sub>IH</sub> , @ t <sub>RC</sub> =min)                 | KM41C4001- 8<br>KM41C4001-10 | Іссз | _   | 100<br>85 | mA<br>mA |

| Nibble Mode Current*<br>(RAS=V <sub>IL</sub> , CAS, Address cycling: @ t <sub>NC</sub> =min.)            | KM41C4001- 8<br>KM41C4001-10 | ICC4 | _   | 60<br>50  | mA<br>mA |

| Standby Current<br>(RAS=CAS=V <sub>CC</sub> -0.2V)                                                       |                              | Icc5 |     | 1         | mA       |

| CAS-Before-RAS Refresh Current*<br>(RAS and CAS cycling @ t <sub>RC</sub> =min.)                         | KM41C4001- 8<br>KM41C4001-10 | Icc6 | _   | 100<br>85 | mA<br>mA |

| Standby Current<br>(RAS=V <sub>IH</sub> , CAS=V <sub>IL</sub> Dout=Enable)                               |                              |      | _   | 5         | mA       |

| Input Leakage Current<br>(Any input $0 \le V_{IN} \le 6.5V$ ,<br>all other pins not under test=0 volts.) |                              | lı_  | -10 | 10        | μΑ       |

| Output Leakage Current<br>(Data out is disabled, 0V≼V <sub>OUT</sub> ≼5.5V)                              |                              |      | -10 | 10        | μΑ       |

| Output High Voltage Level (I <sub>OH</sub> =-5mA)                                                        |                              |      | 2.4 | _         | V        |

| Output Low Voltage Level (I <sub>OL</sub> =4.2mA)                                                        |                              |      | -   | 0.4       | V        |

\*NOTE: Icc1, Icc3, Icc4 and Icc6 are dependent on output loading and cycle rates. Icc is specified as an average current. Specified value are obtained with the output open. Icc1, Icc3, Icc6 Address can be changed maximum two times while  $\overline{RAS} = V_{IL}$ . Icc4, Address can be changed maximum once while  $\overline{CAS} = V_{IH}$ .

# **CAPACITANCE** (T<sub>A</sub>=25°C)

| Item                                                    | Symbol           | Min | Max | Unit |

|---------------------------------------------------------|------------------|-----|-----|------|

| Input Capacitance (A <sub>0</sub> -A <sub>10</sub> , D) | C <sub>IN1</sub> |     | 5   | pF   |

| Input Capacitance (RAS, CAS, W)                         | C <sub>IN2</sub> |     | 7   | pF   |

| Output Capacitance (Q)                                  | Cout             | _   | 7   | pF . |

# AC CHARACTERISTICS (0°C<Ta<70°C, V<sub>CC</sub>=5.0V±10%, See notes 1,2)

| Standard Operation                    | Symbol            | KM41C4001-8 |        | KM41C4001-10 |        | Unit |       |

|---------------------------------------|-------------------|-------------|--------|--------------|--------|------|-------|

|                                       | Symbol            | Min         | Max    | Min          | Max    | Unit | Notes |

| Random read or write cycle time       | t <sub>RC</sub>   | 150         |        | 180          |        | ns   |       |

| Read-modify-write cycle time          | t <sub>RWC</sub>  | 175         |        | 210          |        | ns   |       |

| Nibble Mode Cycle Time                | t <sub>NC</sub>   | 40          |        | 45           |        | ns   |       |

| Nibble Mode Read-Write Cycle Time     | t <sub>NRWC</sub> | 65          |        | 70           |        | ns   |       |

| Access time from RAS                  | tRAC              |             | 80     |              | 100    | ns   | 3,4   |

| Access time from CAS                  | tCAC              |             | 20     |              | 25     | ns   | 3,4   |

| Nibble Mode Access Time               | t <sub>NCAC</sub> |             | 20     |              | 25     | ns   |       |

| Access time from column address       | t <sub>AA</sub>   |             | 40     |              | 50     | ns   | 3,10  |

| CAS to output in Low-Z                | tcLZ              | 5           |        | 5            |        | ns   | 3     |

| Output buffer turn-off delay          | toff              | 0           | 15     | 0            | 20     | ns   | 6     |

| Transition time (rise and fall)       | tT                | 3           | 50     | 3            | 50     | ns   | 2     |

| RAS precharge time                    | t <sub>RP</sub>   | 60          |        | 70           |        | ns   |       |

| RAS pulse width                       | t <sub>RAS</sub>  | 80          | 10,000 | 100          | 10,000 | ns   |       |

| RAS hold time                         | t <sub>RSH</sub>  | 20          |        | 25           |        | ns   |       |

| CAS hold time                         | tcsн              | 80          |        | 100          |        | ns   |       |

| CAS pulse width                       | tCAS              | 20          | 10,000 | 25           | 10,000 | ns   |       |

| RAS to CAS delay time                 | t <sub>RCD</sub>  | 20          | 60     | 25           | 75     | ns   | 4,5   |

| RAS to column address delay time      | t <sub>RAD</sub>  | 15          | 40     | 20           | 50     | ns   | 10    |

| CAS to RAS precharge time             | tCRP              | 5           |        | 10           |        | ns   |       |

| Row address set-up time               | t <sub>ASR</sub>  | 0           |        | 0            |        | ns   |       |

| Row address hold time                 | tRAH              | 10          |        | 15           |        | ns   |       |

| Column address set-up time            | t <sub>ASC</sub>  | 0           |        | 0            |        | ns   |       |

| Column address hold time              | tсан              | 20          |        | 20           |        | ns   |       |

| Column address hold referenced to RAS | t <sub>AR</sub>   | 60          |        | 75           |        | ns   | 12    |

| Column Address to RAS lead time       | tRAL              | 40          |        | 50           |        | ns   |       |

| Read command set-up time              | t <sub>RCS</sub>  | 0           |        | 0            |        | ns   |       |

| Read command hold referenced to CAS   | t <sub>RCH</sub>  | 0           |        | 0            |        | ns   | 8     |

| Read command hold referenced to RAS   | t <sub>RRH</sub>  | 0           |        | 0            |        | ns   | 8     |

| Write command hold time               | twcн              | 15          |        | 20           |        | ns   | 1     |

| Write command hold referenced to RAS  | twcr              | 60          |        | 75           |        | ns   | 12    |

| Write command pulse width             | twp               | 15          |        | 20           |        | ns   |       |

# AC CHARACTERISTICS (Continued)

| Standard Operation                                                                        | Symbol            | KM41C4001-8 |     | KM41C4001-10 |             | Unit | Notes |

|-------------------------------------------------------------------------------------------|-------------------|-------------|-----|--------------|-------------|------|-------|

|                                                                                           |                   | Min         | Max | Min          | Max         | onit | NOLES |

| Write command to RAS lead time                                                            | t <sub>RWL</sub>  | 20          |     | 25           |             | ns   |       |

| Write command to CAS lead time                                                            | tcw∟              | 20          |     | 25           |             | ns   |       |

| Data-in set-up time                                                                       | t <sub>DS</sub>   | 0           |     | 0            |             | ns   | 9     |

| Data-in hold time                                                                         | t <sub>DH</sub>   | 15          |     | 20           |             | ns   | 9     |

| Data-in hold referenced to RAS                                                            | t <sub>DHR</sub>  | 60          |     | 75           |             | ns   | 12    |

| Refresh period (1024 cycles)                                                              | t <sub>REF</sub>  |             | 16  |              | 16          | ms   |       |

| Write command set-up time                                                                 | twcs              | 0           |     | 0            |             | ns   | . 7   |

| CAS to write enable delay                                                                 | tcwp              | 20          |     | 25           |             | ns   | 7     |

| RAS to write enable delay                                                                 | tRWD              | 80          |     | 100          | 0. M. MIROL | ns   | 7     |

| Column address to $\overline{W}$ delay time                                               | tAWD              | 40          |     | 50           |             | ns   | 7     |

| CAS setup time (C-B-R refresh)                                                            | tCSR              | 10          |     | 10           |             | ns   |       |

| CAS hold time (C-B-R refresh)                                                             | tCHR              | 30          |     | 30           |             | ns   |       |

| RAS percharge to CAS hold time                                                            | tRPC              | 0           |     | 0            |             | ns   |       |

| CAS precharge (C-B-R counter test)                                                        | t <sub>CPT</sub>  | 40          |     | 50           |             | ns   |       |

| Nibble mode CAS pulse width                                                               | t <sub>NCAS</sub> | 20          |     | 25           |             | ns   |       |

| Nibble mode CAS precharge time                                                            | t <sub>NCP</sub>  | 10          |     | 10           |             | ns   |       |

| Nibble mode RAS hold time                                                                 | t <sub>NRSH</sub> | 20          |     | 25           |             | ns   |       |

| Nibble mode CAS to W delay time                                                           | t <sub>NCWD</sub> | 20          |     | 25           |             | ns   |       |

| Nibble mode $\overline{W}$ to $\overline{RAS}$ lead time                                  | t <sub>NRWL</sub> | 20          |     | 25           |             | ns   |       |

| Nibble mode W to CAS lead time                                                            | tNCWL             | 20          |     | 25           |             | ns   |       |

| Write command set-up time (Test mode In)                                                  | twrs              | 10          |     | 10           |             | ns   |       |

| Write command hold time (Test mode In)                                                    | twrн              | 10          |     | 10           |             | ns   |       |

| W to RAS precharge time (C-B-R refresh)                                                   | twRP              | 10          |     | 10           |             | ns   |       |

| $\overline{W}$ to $\overline{RAS}$ hold time ( $\overline{C}$ -B- $\overline{R}$ refresh) | twRH              | 10          |     | 10           |             | ns   |       |

## TEST MODE CYCLE

| Parameter                                   | Symbol          | KM41C4001-8 |        | KM41C4001-10 |        | Unit | Notes |

|---------------------------------------------|-----------------|-------------|--------|--------------|--------|------|-------|

|                                             |                 | Min         | Max    | Min          | Max    |      | Notes |

| Random read or write cycle time             | tRC             | 155         |        | 185          |        | ns   |       |

| Read-modify-write cycle time                | tRWC            | 180         |        | 215          |        | ns   |       |

| Access time from RAS                        | tRAC            |             | 85     |              | 105    | ns   | 3,4   |

| Access time from CAS                        | tCAC            |             | 25     |              | 30     | ns   | 3,4   |

| Access time from column address             | t <sub>AA</sub> |             | 45     |              | 55     | ns   | 3,10  |

| RAS pulse width                             | tRAS            | 85          | 10,000 | 105          | 10,000 | ns   |       |

| CAS pulse width                             | tCAS            | 25          | 10,000 | 30           | 10,000 | ns   |       |

| RAS hold time                               | trsh            | 25          |        | 30           |        | ns   |       |

| CAS hold time                               | tсsн            | 85          |        | 105          |        | ns   |       |

| Column address to RAS lead time             | tRAL            | 45          |        | 55           |        | ns   |       |

| CAS to W delay time                         | tcwp            | 25          |        | 30           |        | ns   | 7     |

| RAS to W delay time                         | tRWD            | 85          |        | 105          |        | ns   | 7     |

| Column address to $\overline{W}$ delay time | tawd            | 45          |        | 55           |        | ns   | 7     |

#### NOTES

- 1. An initial pause of  $200\mu s$  is required after powerup followed by any 8 CAS-before-RAS or RAS only refresh before proper device operation is achieved.

- 2.  $V_{IH(min)}$  and  $V_{IL(max)}$  are reference levels for measuring timing of input signals. Transition times are measured between  $V_{IH(min)}$  and  $V_{IL(max)}$ , and are assumed to be 5ns for all inputs.

- 3. Measured with a load equivalent to 2 TTL loads and 100pF  $\,$

- 4. Operation within the  $t_{RCD(max)}$  limit insures that  $t_{RAC(max)}$  can be met.  $t_{RCD(max)}$  is specified as a reference point only. If  $t_{RCD}$  is greater than the specified  $t_{RCD(max)}$  limit, then access time is controlled exclusively by  $t_{CAC}$ .

- 5. Assumes that t<sub>RCD</sub>≥t<sub>RCD(max)</sub>.

- This parameter defines the time at which the output achieves the open circuit condition and is not refernced to V<sub>OH</sub> or V<sub>OL</sub>.

- 7. t<sub>WCS</sub>, t<sub>RWD</sub>, t<sub>CWD</sub> and t<sub>AWD</sub> are non restrictive operating parameters. They are included in the data

sheet as electrical characteristics only. If  $t_{WCS} \ge t_{WCS}(min)$  the cycle is an early write cycle and the data out pin will remain high impedance for the duration of the cycle. If  $t_{CWD} \ge t_{CWD(min)}$  and  $t_{RWD} \ge t_{RWD(min)}$  and  $t_{AWD} \ge t_{AWD(min)}$ , then the cycle is a read-write cycle and the data out will contain the data read from the selected address. If neither of the above conditions are satisfied, the condition of the data out is indeterminate.

- 8. Either  $t_{\text{RCH}}$  or  $t_{\text{RRH}}$  must be satisfied for a read cycle.

- These parameters are referenced to the CAS leading edge in early write cycles and to the W leading edge in read-write cycles.

- 10. Operation within the  $t_{RAD(max)}$  limit insures that  $t_{RAC(max)}$  can be met.  $t_{RAD(max)}$  is specified as a reference point only. If  $t_{RAD}$  is greater than the specified  $t_{RAD(max)}$  limit, then access time is controlled by  $t_{AA}$ .

- 11. These specifications are applied in the test mode.

- 12. tAR, twcR, tDHR are refrerenced to tRAD(max).

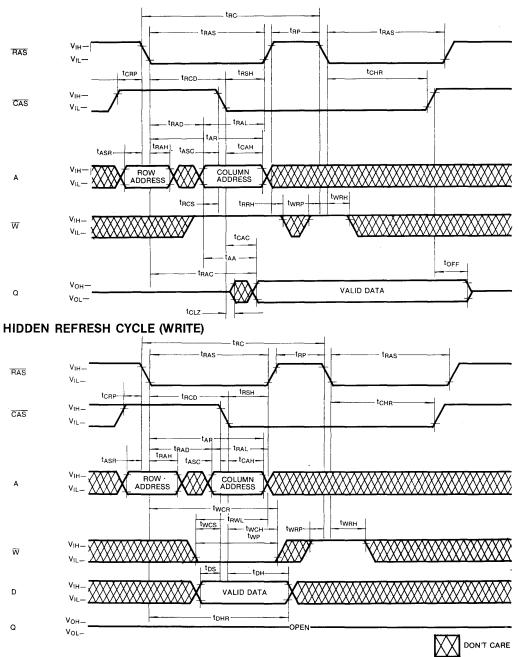

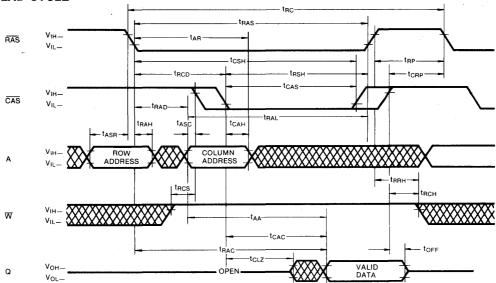

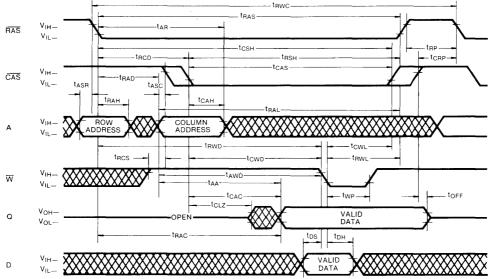

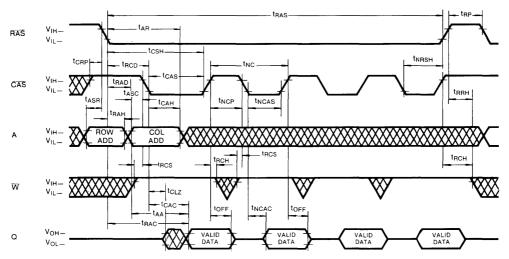

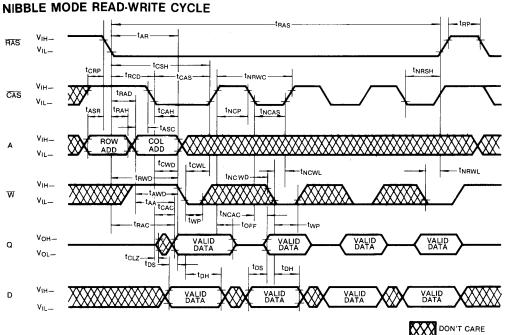

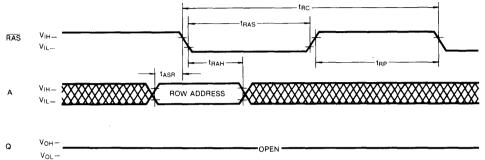

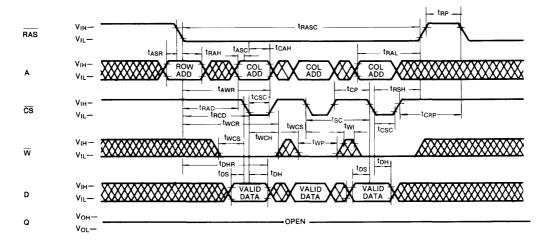

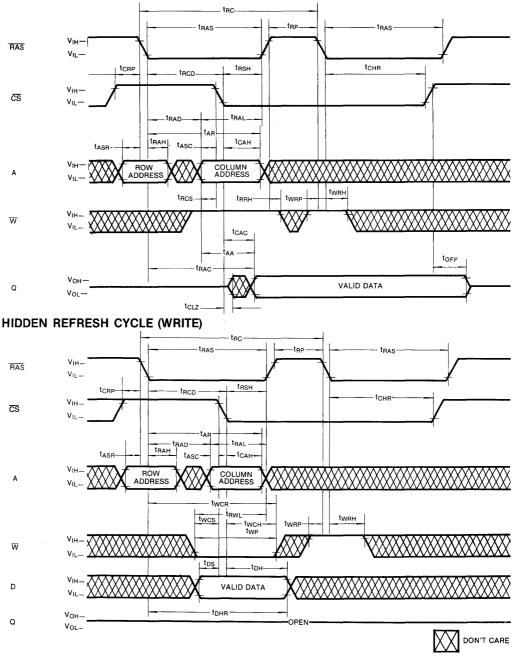

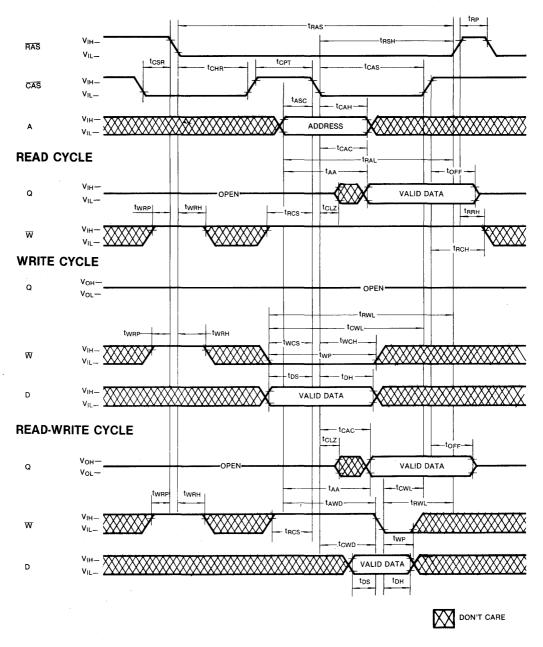

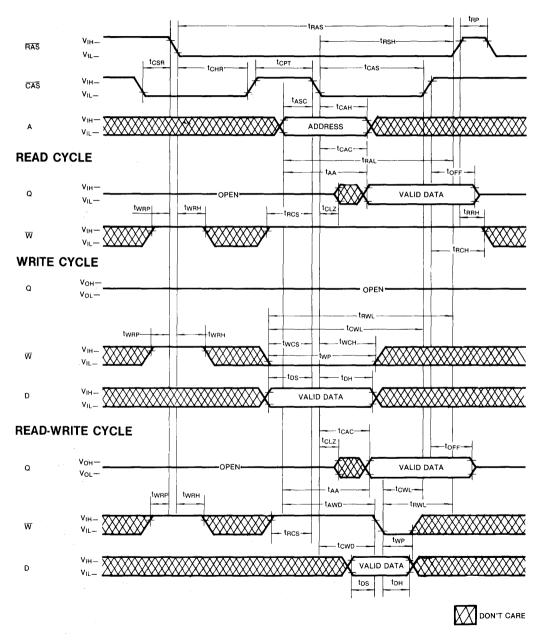

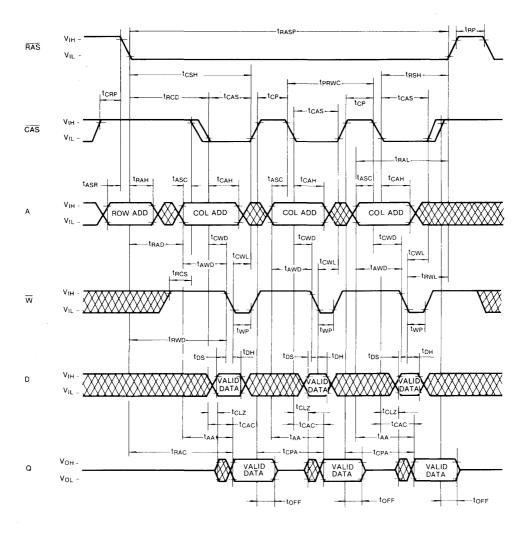

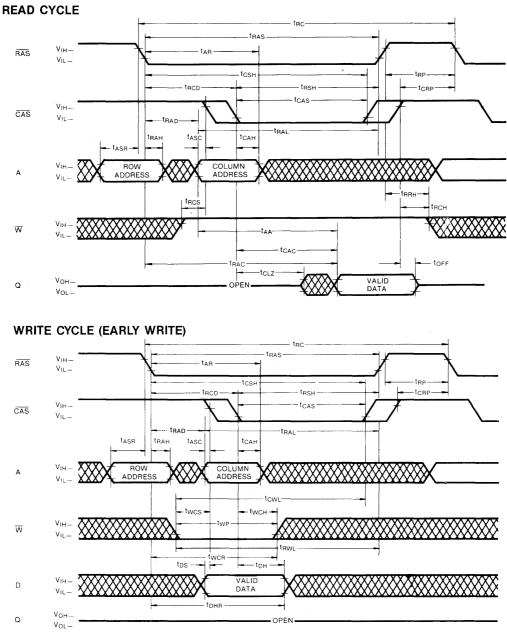

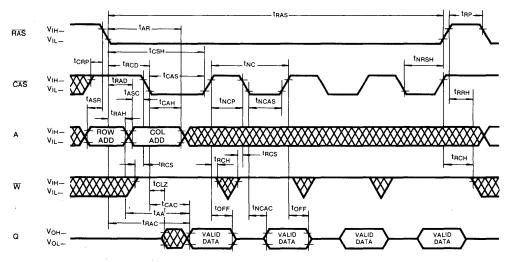

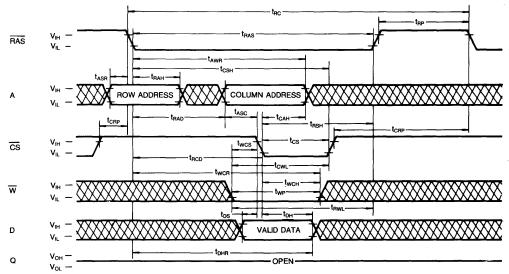

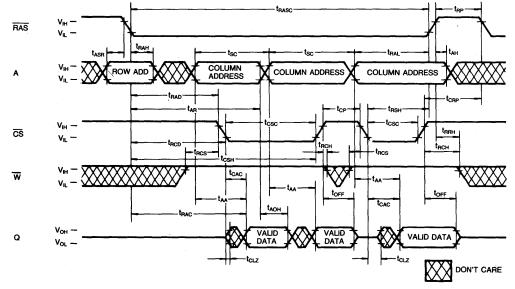

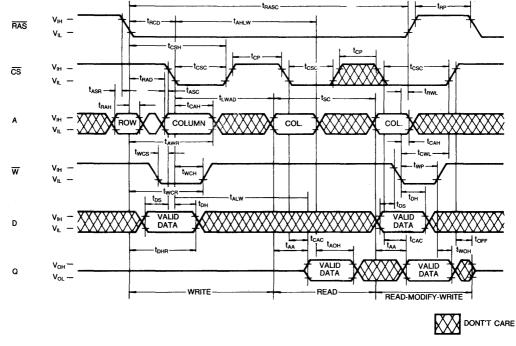

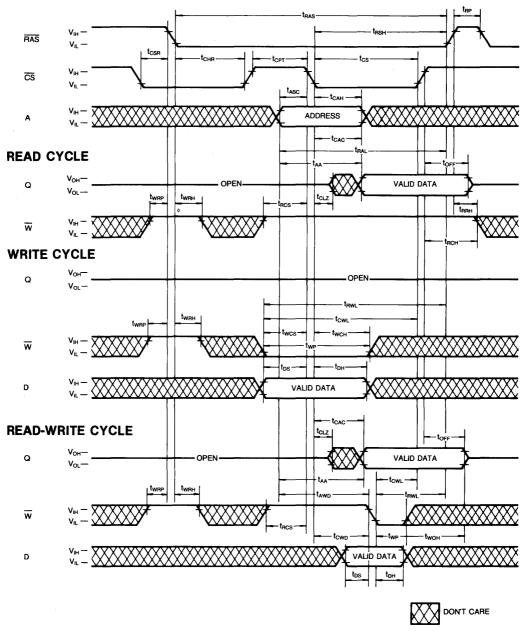

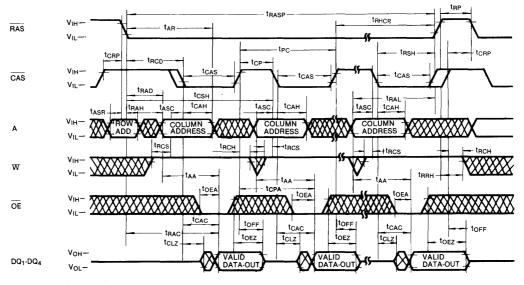

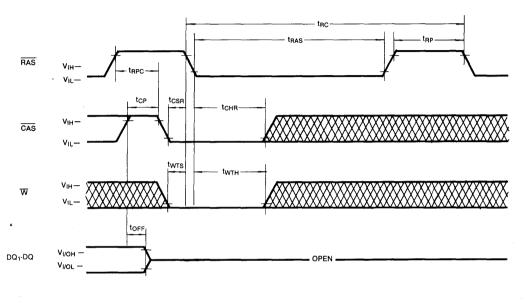

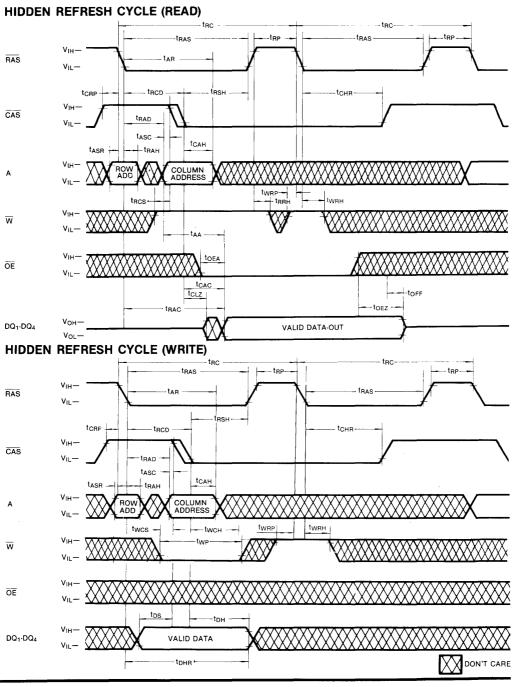

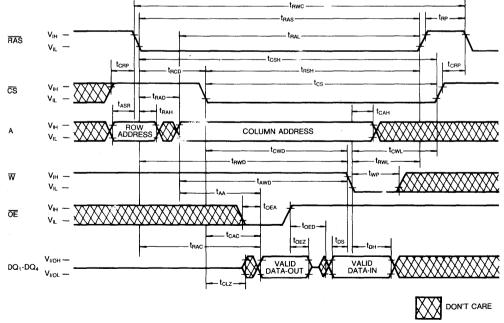

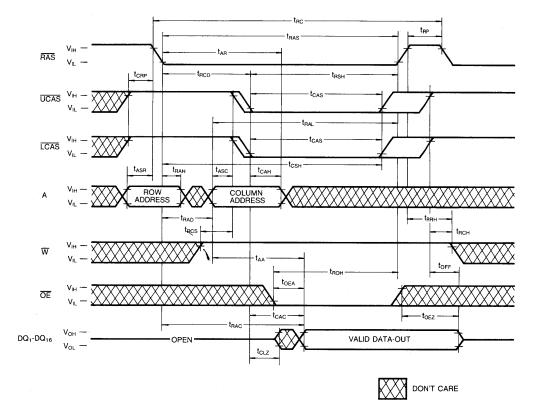

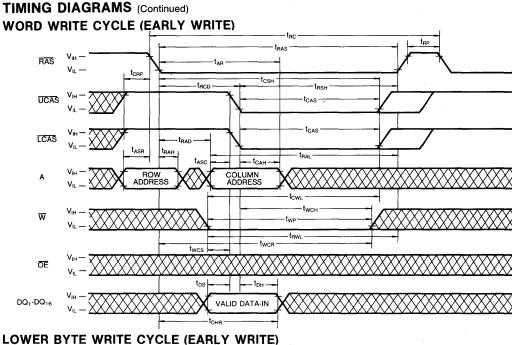

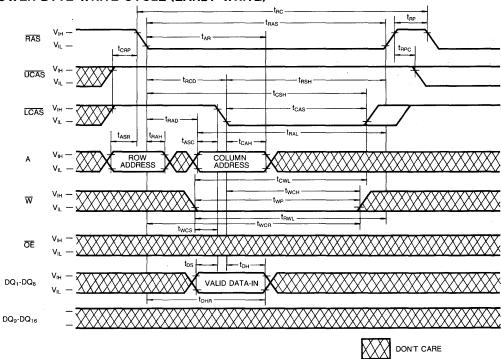

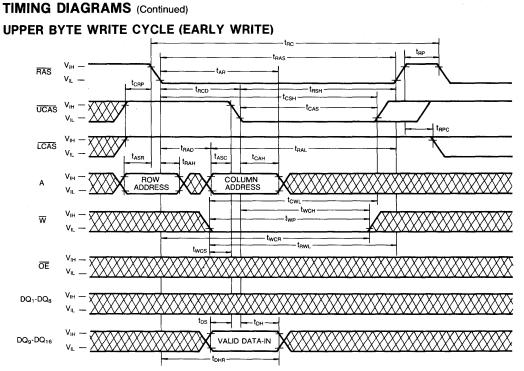

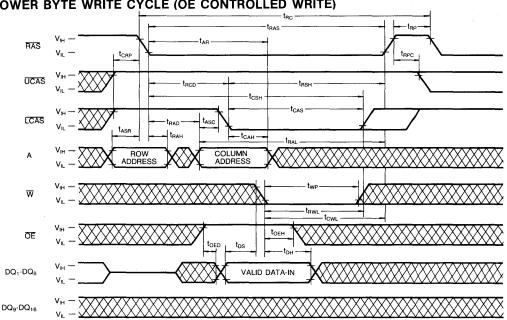

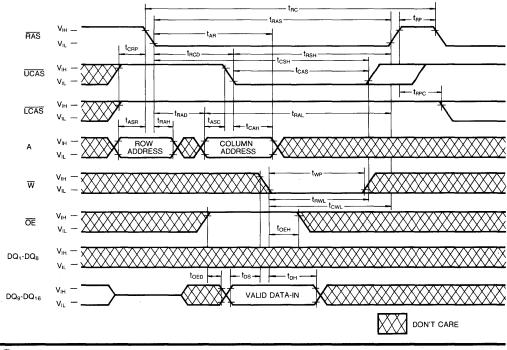

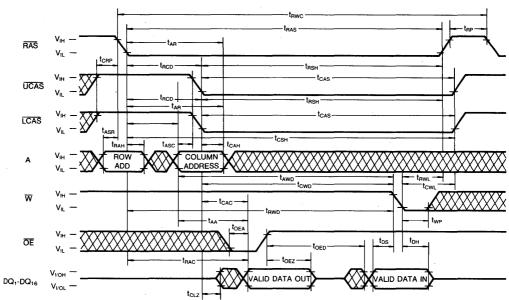

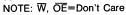

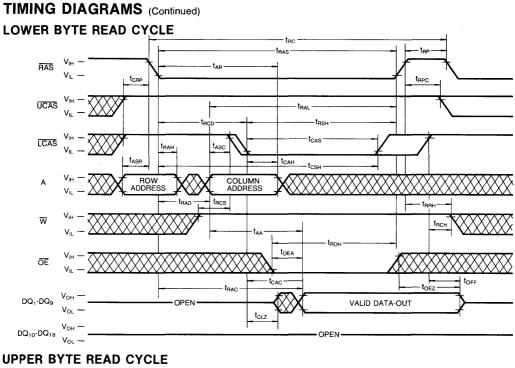

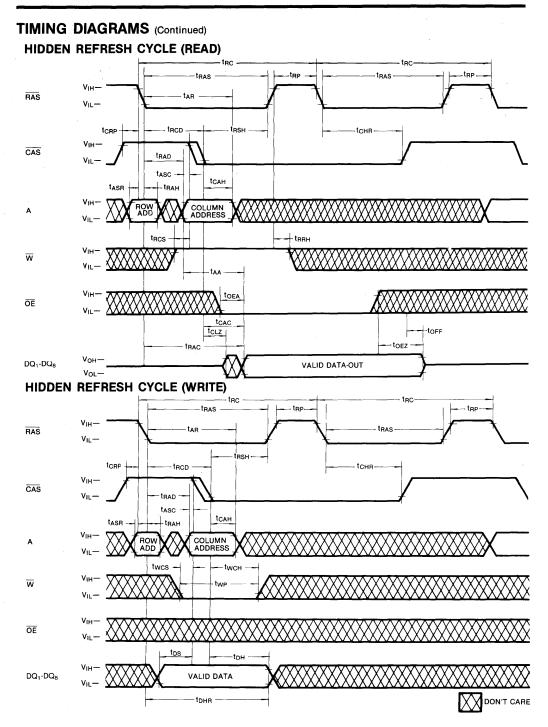

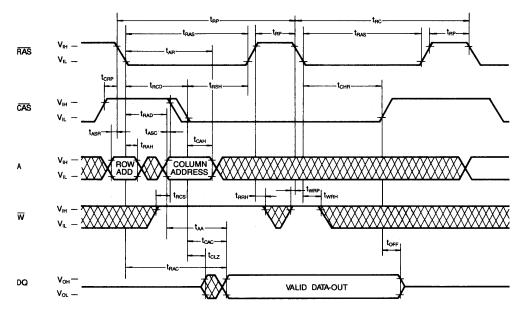

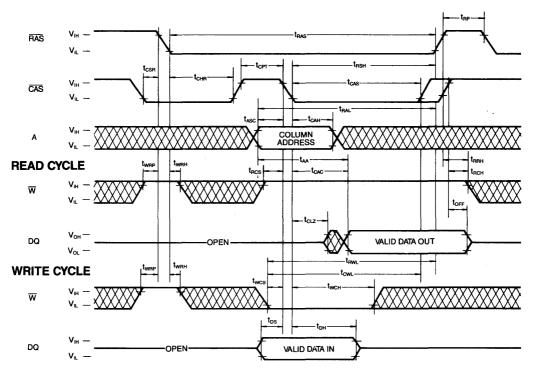

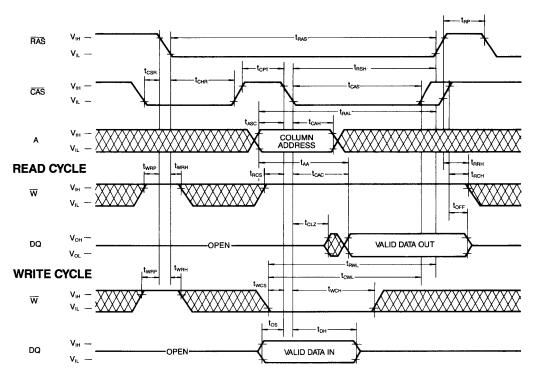

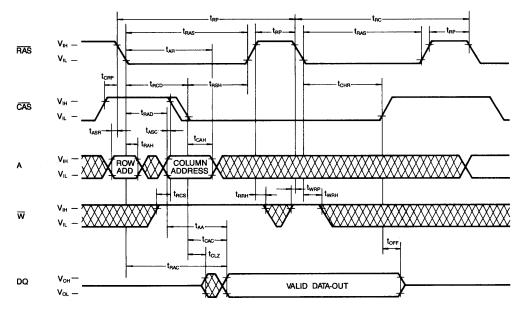

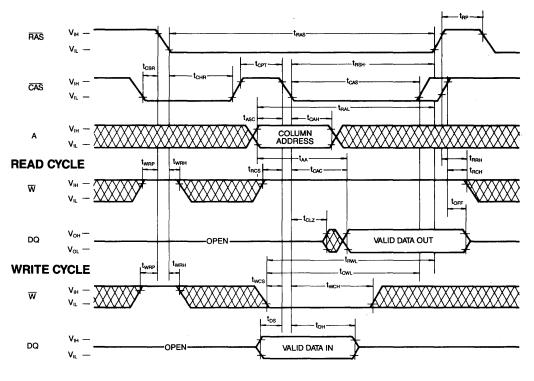

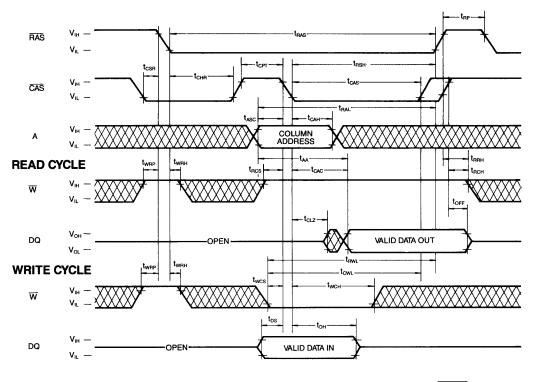

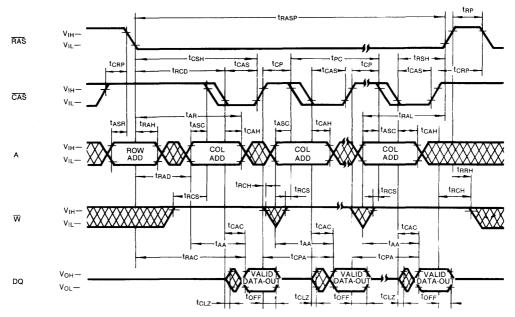

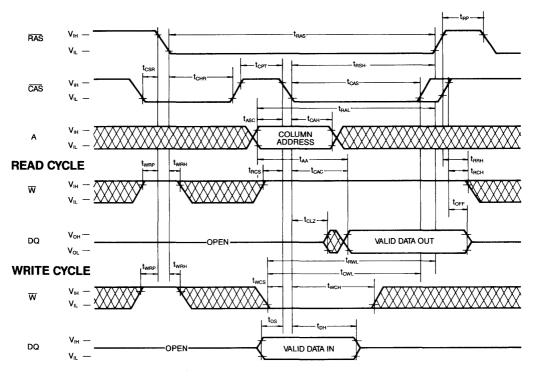

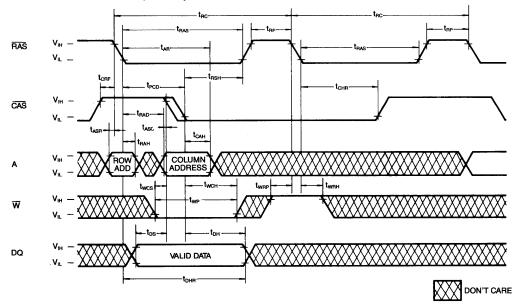

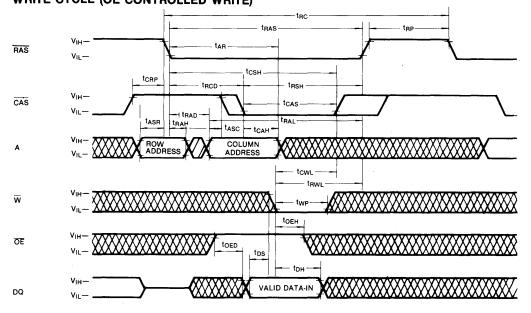

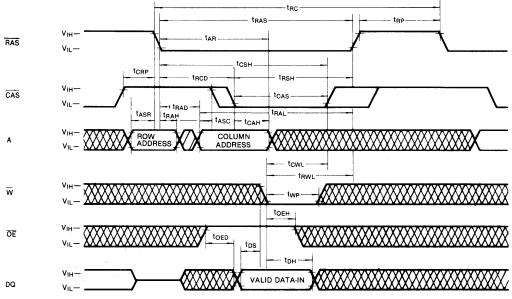

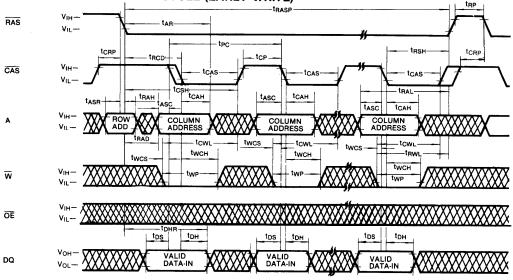

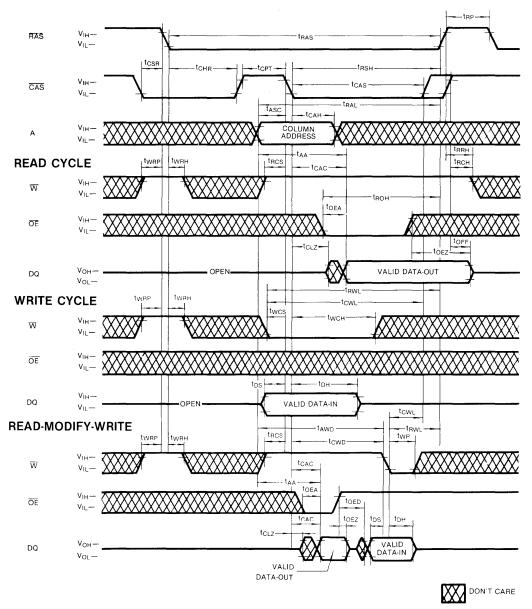

# TIMING DIAGRAMS

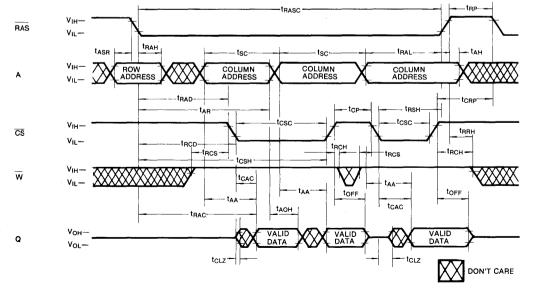

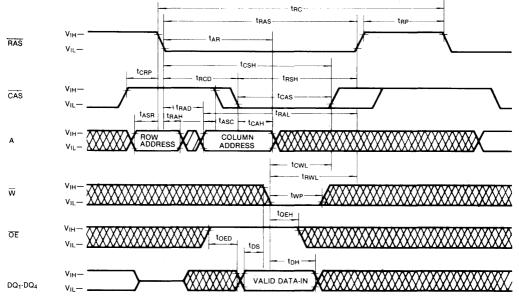

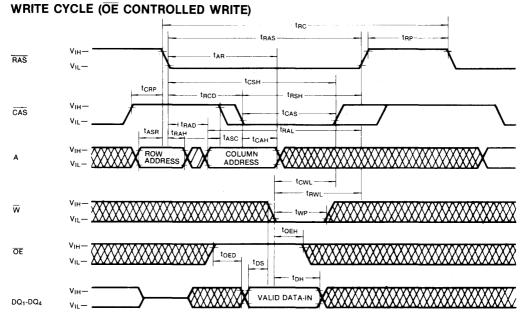

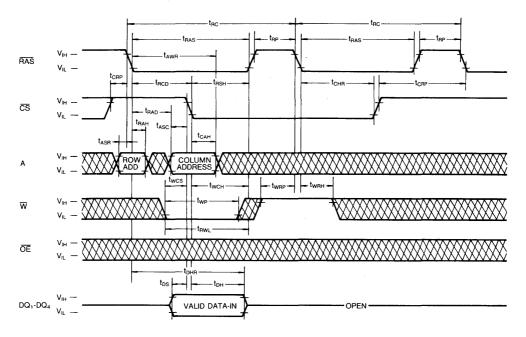

### WRITE CYCLE (EARLY WRITE)

### NIBBLE MODE READ CYCLE

\_\_\_\_

43

#### tras -t<sub>RP</sub> tAR VIH-RAS VILtcsHtCRP **t**NRSH tRCD**t**NC tCAS VIH-CAS tRAD VILtasr trah **t**CAH **t**NCP **t**NCAS -tasc ROW COL Α $\times\!\!\times\!\!\times$ ADD ADD twcн twch - t<sub>NRWL</sub> twics -tNCWL twcs twp XXXXX Ŵ $\sim$ $\langle XX \rangle$ ton I twp tos tbs tон VALID DATA VALID VIH-XXXX VALID VALID D XXXXXXXXX 883 VIL--tdhr . V<sub>OH</sub> – Q OPEN Vol-

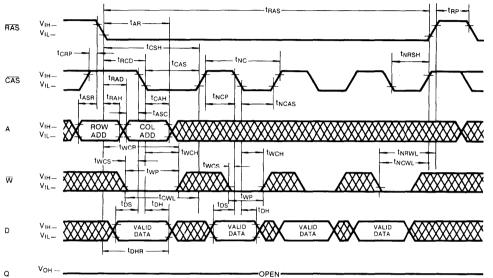

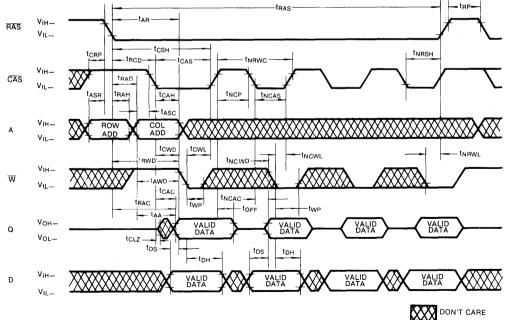

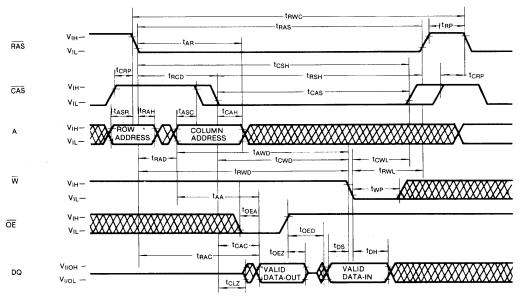

### TIMING DIAGRAMS (Continued) NIBBLE MODE WRITE CYCLE (EARLY WRITE)

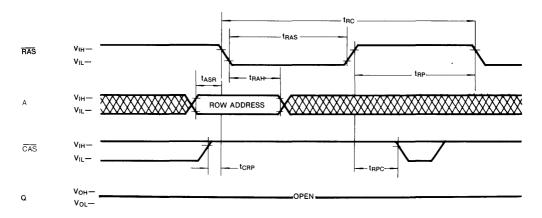

#### RAS-ONLY REFRESH CYCLE

Note: CAS=VIH, W,D, A10=Don't Care

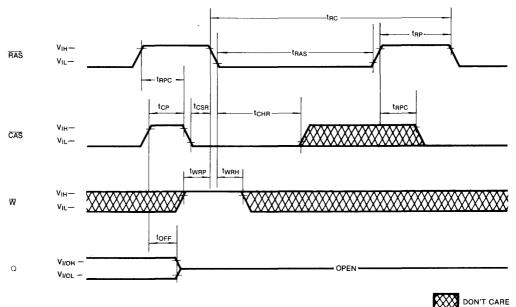

### CAS-BEFORE-RAS REFRESH CYCLE

NOTE: Address=Don't Care

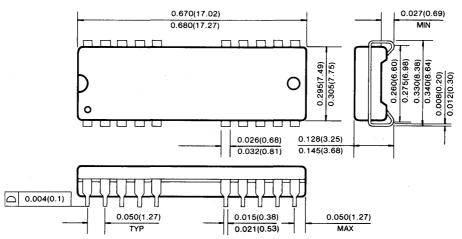

### CAS-BEFORE-RAS REFRESH COUNTER TEST CYCLE

### TEST MODE IN CYCLE

NOTE: D, Address = Don't Care

DON'T CARE

### TEST MODE DESCRIPTION

The KM41C4001 is the RAM organized 4,194,304 words by 1 bit, it is internally organized 524,288 words by 8 bits. In "Test Mode", data are written into 8 sectors in parallel and retrieved the same way.  $A_{10R}$ .  $A_{10C}$  and  $A_{OC}$  are not used. If, upon reading, all bits are equal (all "1"s or "0"s), the data output pin indicates a "1".

dicate a "0" In "Test Mode", the 4M DRAM can be tested as if it were a 512K DRAM.  $\overline{W}$ ,  $\overline{CAS}$  Beofre RAS Cycle (Test Mode in Cycle) puts the device into "Test Mode". And "CAS Before RAS Refresh Cycle" or "RAS only Refresh Cycle" puts it back into "Normal Mode". The "Test Mode" function reduces test time (1/8 in cases of N test pattern).

### **DEVICE OPERATION**

#### **Device Operation**

The KM41C4001 contains 4,194,304 memory locations. Twenty-two address bits are required to address a particular memory location. Since the KM41C4001 has only 11 address input pins, time multiplexed addressing is used to input 11 row and 11 column address. The multiplexing is controlled by the timing relationship between the row address strobe ( $\overline{RAS}$ ), the column address strobe ( $\overline{CAS}$ ) and the valid row and column address inputs.

Operating of the KM41C4001 begins by strobing in a valid row address with  $\overline{\text{RAS}}$  while  $\overline{\text{CAS}}$  remains high. Then the address on the 11 address input pins is changed from a row address to a column address and is strobed in by  $\overline{\text{CAS}}$ . This is the beginning of any KM41C4001 cycle in which a memory location is accessed. The specific type of cycle is determined by the state of the write enable pin and various timing relationships. The cycle is terminated when both  $\overline{\text{RAS}}$  and  $\overline{\text{CAS}}$  have returned to the high state. Another cycle can be initiated after  $\overline{\text{RAS}}$  remains high long enough to satisfy the  $\overline{\text{RAS}}$  precharge time (t\_{\text{RP}}) requirement.

#### **RAS and CAS Timing**

The minimum  $\overline{RAS}$  and  $\overline{CAS}$  pulse widths are specified by  $t_{RAS(min)}$  and  $t_{CAS(min)}$  respectively. These minimum pulse widths must be satisfied for proper device operation and data integrity. Once a cycle is initiated by bringing  $\overline{RAS}$  low, it must not be aborted prior to satisfying the minimum  $\overline{RAS}$  and  $\overline{CAS}$  pulse widths. In addition, a new cycle must not begin until the minimum  $\overline{RAS}$  precharge time,  $t_{RP}$ , has been satisfied. Once a cycle begins, internal clocks and other circuits within the KM41C4001 begin a complex sequence of events. If the sequence is broken by violating minimum timing requirements, loss of data integrity can occur.

#### Read

A read cycle is achieved by maintaining the write enable input( $\overline{W}$ ) high during a RAS/CAS cycle. If CAS goes low before  $t_{RCD}(max)$ , the access time to valid data is specified by  $t_{RAC}$ . If CAS goes low after  $t_{RCD}(max)$ , the access time is measured from CAS and is specified by  $t_{CAC}$ . In order to achieve the minimum access time,  $t_{RAC}(max)$ , it is necessary to bring CAS low before  $t_{RCD}(max)$ .

#### Write

The KM41C4001 can perform early write, late write and read-modify-write cycles. The difference between these cycles is in the state of data-out and is determined by the timing relationship between  $\overline{W}$  and  $\overline{CAS}$ . In any type of write cycle, Date-in must be valid at or before the falling edge of  $\overline{W}$  or  $\overline{CAS}$ , whichever is later.