# SAMSUNG

# **Data Book**

# MPR (Microprocessor Peripheral)

1990

# **PRINTED IN KOREA**

Circuit diagrams utilizing SAMSUNG products are included as a means of illustrating typical semiconductor applications; consequently, complete information sufficient for construction purposes is not necessarily given. The information has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described herein any license under the patent rights of SAMSUNG or others. SAMSUNG reserve the right to change device specifications.

# SAMSUNG DATA BOOK LIST

I. Semiconductor Product Guide

# II. Transistor Data Book

Vol. 1: Small Signal TR

Vol. 2: Bipolar Power TR

Vol. 3: TR Pellet

# III. Linear IC Data Book

Vol. 1: Audio/CDP/Toy

Vol. 2: Video

Vol. 3: Telecom

Vol. 4: Industrial

Vol. 5: Data Converter IC

IV. CMOS Consumer IC Data Book

V. High Speed CMOS Logic Data Book

- VI. MOS Memory Data Book

- VII. SFET Data Book

- VIII. MPR Data Book

IX. CPL Data Book

X. Dot Matrix Data Book

# MICROPROCESSOR PERIPHERAL

# Data Book

# CONTENTS

# Chapter 1: Product Guide

| Overview                        | 13 |

|---------------------------------|----|

| Samsung's Total System Solution | 14 |

| Alpha Numeric Index             | 15 |

| Cross Reference Guide           | 16 |

# Chapter 2: Quality/Reliability ..... 17

# Chapter 3: Data Sheets

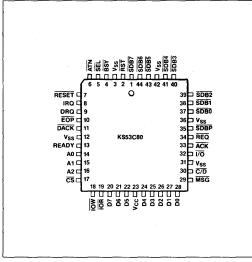

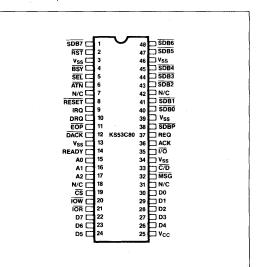

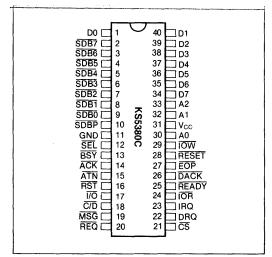

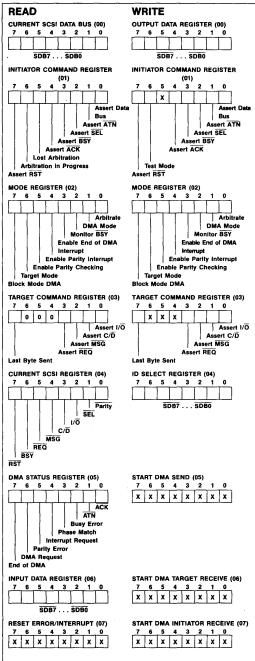

| KS53C80/KS5380C | 49             |

|-----------------|----------------|

| KS68C45S        | 76             |

| KS82C37A 9      | 97             |

| KS82C450/50A 11 | 19             |

| KS82C52 14      | 44             |

| KS82C54 16      | 60             |

| KS82C55A 17     | 75             |

| KS82C59A 19     | <del>)</del> 3 |

| KS82C84A 21     | 19             |

| KS82C88A 22     | 28             |

| KS82C288 23     | 37             |

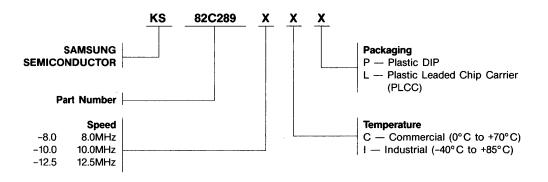

| KS82C289 25     | 57             |

| KS82C411        | 77             |

| KS82C452/462 28 | 35             |

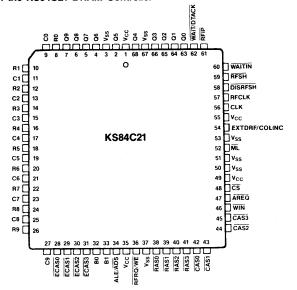

| KS84C21/C22 29  | <del>)</del> 6 |

| KS84C31/C32     | 27             |

|                 |                |

| Chapter 4: Sa | ales Offices | • | 38 | 33 |

|---------------|--------------|---|----|----|

|               |              |   |    |    |

Overview Alpha Numeric Index Selection Guide Cross Reference

# OVERVIEW

Samsung microprocessor peripherals provide a complete solution to increasing complex and performance-oriented applications environment. Standard functions in high performance CMOS technology reduce designers time-to-market by shortening design, testing and debug activities.

At Samsungs world class manufacturing facilities in Korea and San Jose, product reliability and failure rates are carefully monitored. This emphasis on manufacturing products of the highest quality and reliability translates into higher system reliability, reduced down time and reduced repair costs.

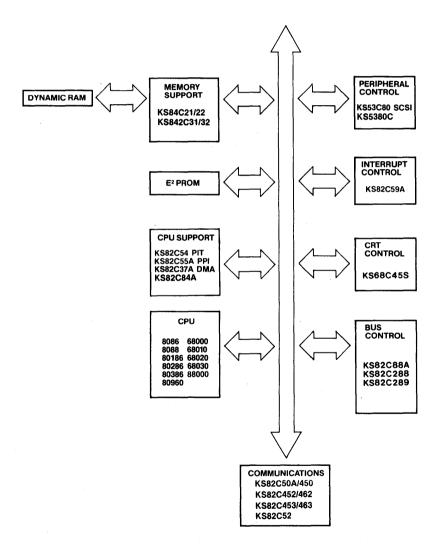

Our advanced CMOS technology, CSPIIA, provides performance levels to match today's high speed microprocessors. CSPIIA features dual-layer metal, single-layer poly, and features sizes down to  $2\mu$  drawn. This 11 mask process results in cost-effective manufacturing to produce high performance CMOS building blocks at competitive prices. Figure 1 summarizes microprocessor support from Samsung peripheral products.

13

# SAMSUNG'S TOTAL SYSTEM SOLUTION

**PRODUCT GUIDE**

# ALPHA NUMERIC INDEX

| Device          | Function                                              | Page |

|-----------------|-------------------------------------------------------|------|

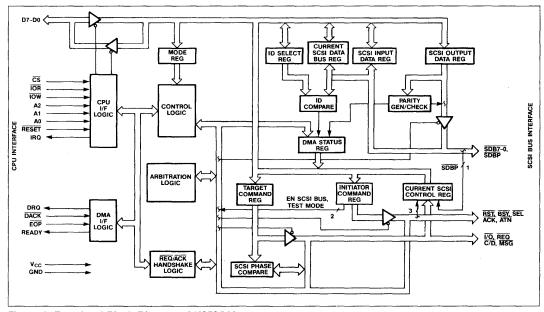

| KS53C80/KS5380C | SCSI Bus Controller                                   | 49   |

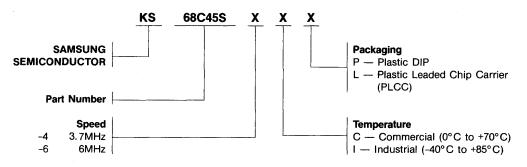

| KS68C45S        | CRT Controller                                        | 76   |

| KS82C37A        | DMA Controller                                        | 97   |

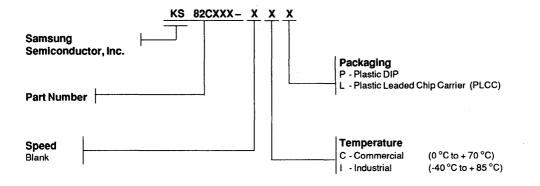

| KS82C450/50A    | Asynchronous Communications Element                   | 119  |

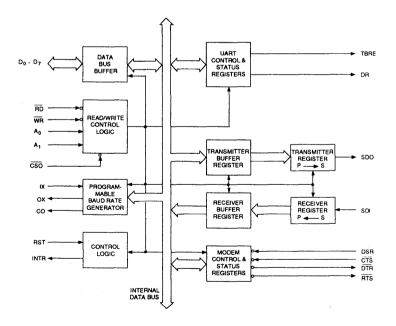

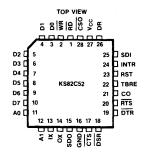

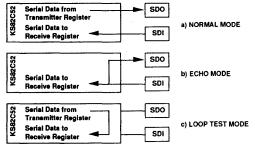

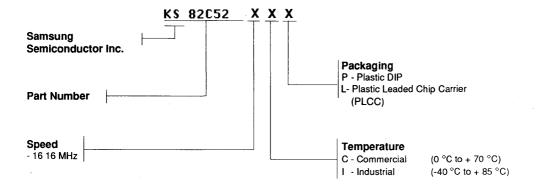

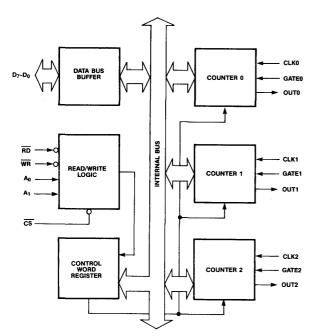

| KS82C52         | Serial Controller Interface                           | 144  |

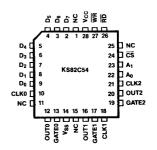

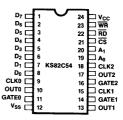

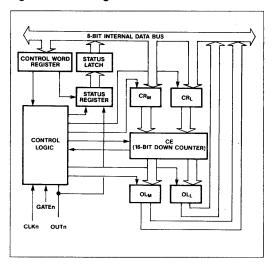

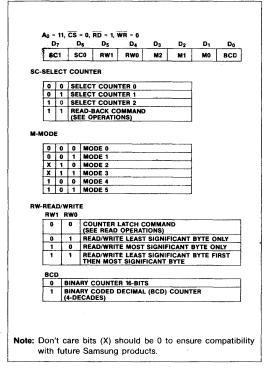

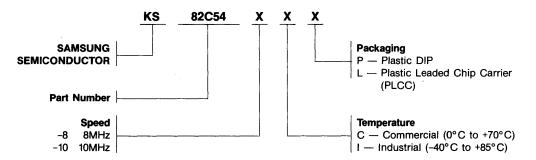

| KS82C54         | Interval Timer                                        | 160  |

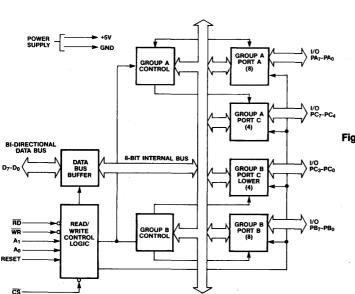

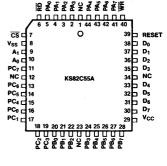

| KS82C55A        | Programmable Peripheral Interface                     | 175  |

| KS82C59A        | Interrupt Controller                                  | 193  |

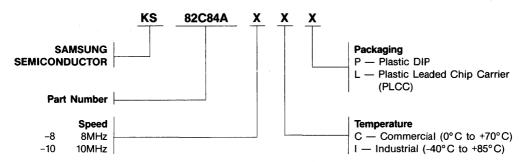

| KS82C84A        | Clock Generator                                       | 219  |

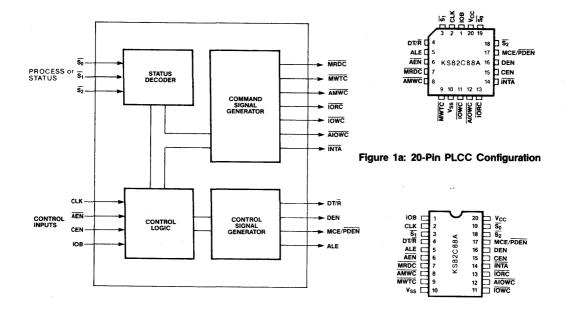

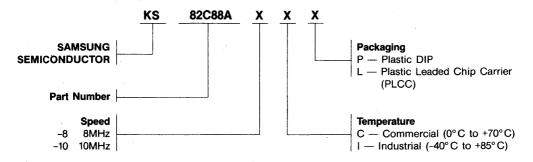

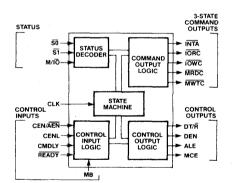

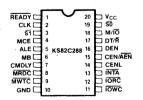

| KS82C88A        | Bus Controller                                        | 228  |

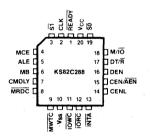

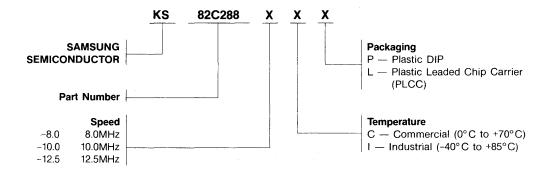

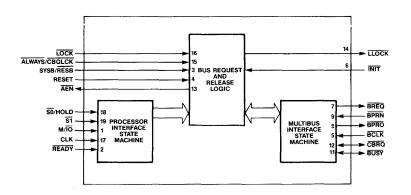

| KS82C288        | 80286 Bus Controller                                  | 237  |

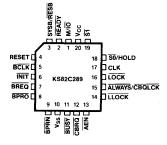

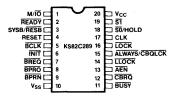

| KS82C289        | 80286 Bus Arbiter                                     | 257  |

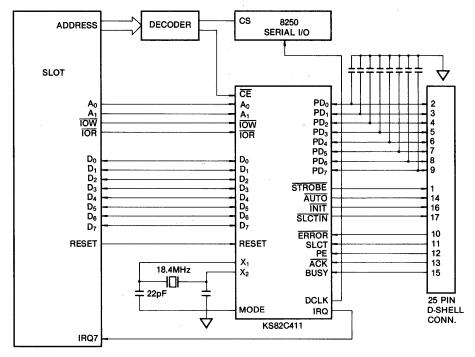

| KS82C411        | Parallel I/O Interface                                | 277  |

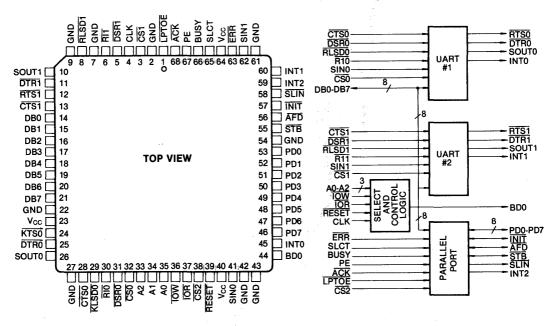

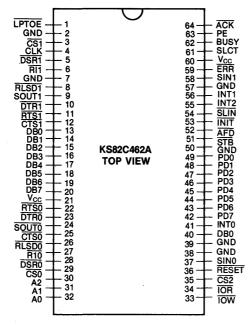

| KS82C452/462    | Parallel and Dual Asynchronous Communications Element | 285  |

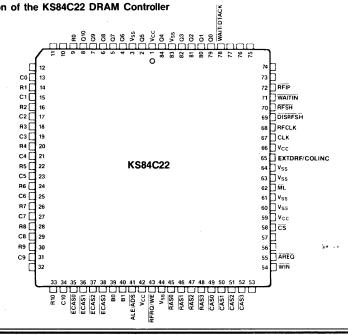

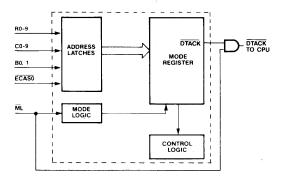

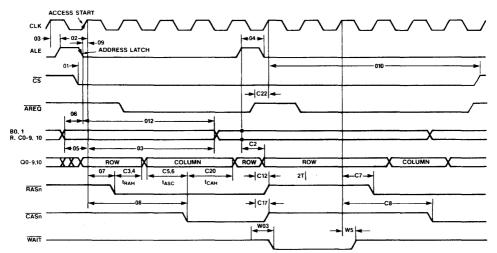

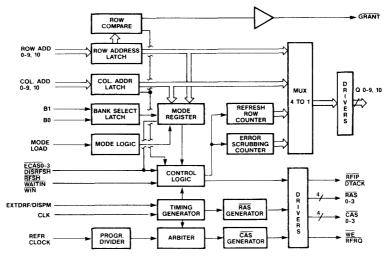

| KS84C21/22      | 1M/4M DRAM Controller (Mask Programmable)             | 296  |

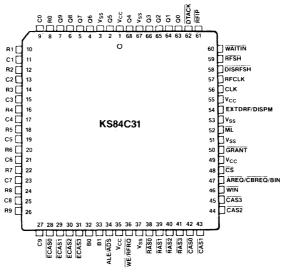

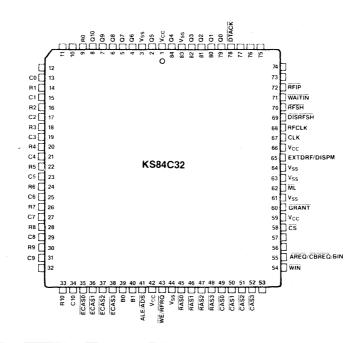

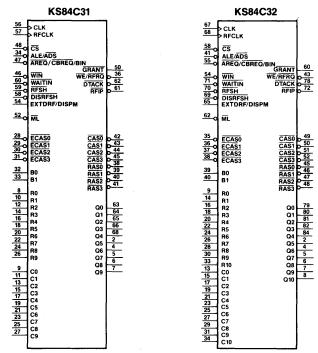

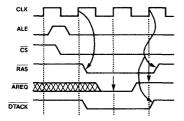

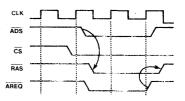

| KS84C31/32      | Enhanced Dynamic RAM Controllers                      | 327  |

15

# **CROSS REFERENCE GUIDE**

| AMD       | SAMSUNG     |

|-----------|-------------|

| AM5380    | KS53C80     |

| D8237A    | KS82C37A-5  |

| D8237A-4  | KS82C37A-5  |

| D8237A-5  | KS82C37A-5  |

| D82C54-8  | KS82C54-8   |

| D82C54-10 | KS82C54-10  |

| D8255A-2  | KS82C55A-5  |

| D8255A-3  | KS82C55A-5  |

| D8259A-5  | KS82C59A-8  |

| D8259A-8  | KS82C59A-8  |

| D8284A-8  | KS82C84A-8  |

| D8284A-10 | KS82C84A-10 |

| D8288-5   | KS82C8A-5   |

| HARRIS   | SAMSUNG    |

|----------|------------|

| 82C37A-5 | KS82C37A-5 |

| 82C37A-8 | KS82C37A-8 |

| 82C52    | KS82C52    |

| 82C54-8  | KS82C54-8  |

| 82C55A-5 | KS82C55A-5 |

| 82C55A-8 | KS82C55A-8 |

| 82C59A-5 | KS82C59A-8 |

| 82C59A-8 | KS82C59A-8 |

| 82C84A-8 | KS82C84A-8 |

| 82C88-5  | KS82C88A-5 |

| 82C88-8  | KS82C88A-8 |

| INTEL    | SAMSUNG     |

|----------|-------------|

| 82C37A   | KS82C37A-5  |

| 82C37A-4 | KS82C37A-5  |

| 82C37A-5 | KS82C37A-5  |

| 8255A    | KS82C55A-5  |

| 8255A-5  | KS82C55A-5  |

| 82C54A   | KS82C54-8   |

| 82C55A-8 | KS82C55A-8  |

| 82C55A-8 | KS82C55A-8  |

| 82C59A   | KS82C59A-8  |

| 82C59A-2 | KS82C59A-8  |

| 82C59A-8 | KS82C59A-8  |

| 82C84    | KS82C84A-5  |

| 82C84A   | KS82C84A-8  |

| 82C84A-1 | KS82C84A-10 |

| 82C88    | KS82C88A-8  |

| 8288     | KS82C88A-8  |

| LOGIC<br>DEVICES | SAMSUNG |

|------------------|---------|

| L5380            | KS5380C |

| L53C80           | KS53C80 |

| MITSUBISHI           | SAMSUNG                  |

|----------------------|--------------------------|

| 82C37A-4<br>82C37A-5 | KS82C37A-5<br>KS82C37A-5 |

| 82C54-6              | KS82C54-8                |

| 82C54-8              | KS82C54-8                |

| 82C55A-5<br>82C55A-8 | KS82C55A-5<br>KS82C55A-8 |

| 82C59A-5             | KS82C59A-8               |

| 82C59A-8             | KS82C59A-8               |

| NCR  | SAMSUNG |

|------|---------|

| 5380 | KS53C80 |

| NEC      | SAMSUNG    |

|----------|------------|

| 82C37A-5 | KS82C37A-5 |

| 82C54-8  | KS82C54-8  |

| 82C55A-8 | KS82C55A-8 |

| 82C59A-8 | KS82C59A-8 |

| 82C84A-8 | KS82C84A-8 |

| 82C88-8  | KS82C88A-8 |

| ΟΚΙ       | SAMSUNG    |

|-----------|------------|

| M82C37A-5 | KS82C37A-5 |

| M82C54-8  | KS82C54-8  |

| M82C54-10 | KS82C54-10 |

| M82C55A-8 | KS82C55A-8 |

| M82C59A-5 | KS82C59A-8 |

| M82C59A-8 | KS82C59A-8 |

| M82C84A-5 | KS82C84A-5 |

| M82C84A-8 | KS82C84A-8 |

| M82C88-5  | KS82C88A-5 |

| M82C88-8  | KS82C88A-8 |

| UMC                                 | SAMSUNG                               |

|-------------------------------------|---------------------------------------|

| UM8237A-3<br>UM8237A-4<br>UM8237A-5 | KS8237A-5<br>KS82C37A-5<br>KS82C37A-5 |

| UM8250A<br>UM8250B                  | KS82C50A<br>KS82C50A                  |

| UM8254-2                            | KS82C54-8                             |

| UM8255A                             | KS82C55A-5                            |

| UM8259A-5                           | KS82C59A-8                            |

| UM82C84AE-8<br>UM82C84AE-10         | KS82C84A-8<br>KS82C84A-10             |

| UM82C88-5                           | KS82C88A-5                            |

# **1. INTRODUCTION**

SEC has been providing a wide variety of semiconductor products to the world since 1974. Since this time, extensive in-sights have been gained to create methods which most effectively result in reliable products. The worldwide customers of SEC have encouraged and helped develop the existing manufacturing and quality philosophy that is a way of life for SEC management and it's employees. This philosophy dictates the need for a zero defect environment through out SEC's processes leading ultimately to total customer satisfaction. By developing and using methods of Statistical Process Control and Statistical Quality Control, SEC has made great strides in improving product quality a reliability. The direct result of these improvements has been reduced product DPM (Defects Per Million) to levels below customer requirements. SEC's repeated ability to exceed requirements for customer's "Dock to Stock" programs and our commitment to all our customers needs, has made SEC the company to watch as we move ahead into the 1990's and beyond.

SEC's MPR products are among the most reliable in the industry. SEC has always made a commitment to achieve the highest possible quality, reliability, and customer satisfaction with its products. Extensive qualification, monitor and outgoing programs are used to scrutinize product quality and reliability. Stringent controls are applied to every wafer fabrication and assembly lot to achieve reproducibility, and therefore maintain product reliability.

In this chapter, the quality and reliability programs established at SEC will be discussed. In addition, a description of reliability theory, reliability tests and various support efforts provides a broad framework from which to comprehend SEC quality and reliability.

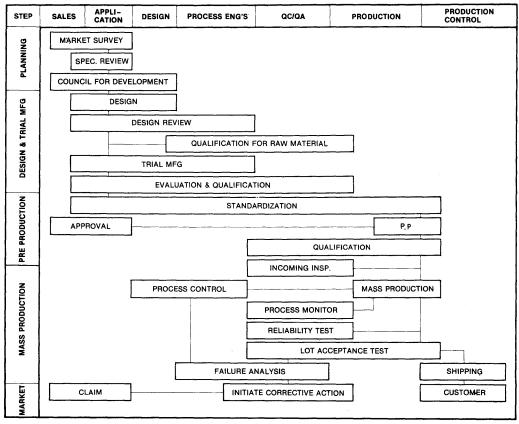

To better understand the Quality Department's role in product development and manufacturing, a detailed diagram is listed below. As can be noted, Quality Engineering is involved in all phases, save that of initial product planning.

**Quality Assurance During Development**

# 2. QUALITY & RELIABILITY PROGRAM

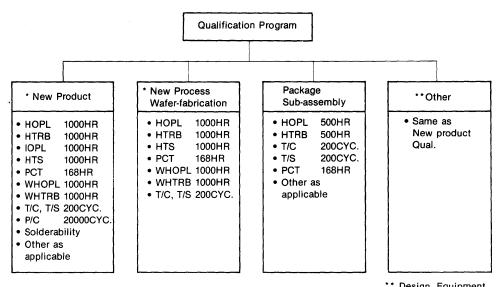

## 2.1 QUALIFICATION

Procedures to qualify devices are listed below. There are both general and product-specific requirements. Procedures are detailed for new products, die-only qualifications, and package-only qualifications. The latter two are for products and/or packages already qualified, but where there is room for further product optimization.

\*Testing time for each test items depends on the grade (group) of devices. (see the device group list 2.1 2)) \* Design, Equipment, Material(s), etc....

# 1) PROCESS DEVELOPMENT QUALIFICATION

Purpose: To investigate the change of a process parameter and then apply it to a production process by reliability testing of a process which has been newly developed.

#### New Process, Wafer Fabrication Qualification

| No | Test Item                                      | Test Condition                                                             | Package |          |  |

|----|------------------------------------------------|----------------------------------------------------------------------------|---------|----------|--|

| NO | iest item                                      | Test Condition                                                             | L-IC    | Discrete |  |

| 1  | High Temperature<br>Operating Life (HOPL)      | $T_{a} = T_{opr}(max)$ $V_{CC} = V_{CC}(max)$ STATIC, DYNAMIC<br>1000HRS   | YES     | _        |  |

| 2  | High Temperature<br>Reverse Bias (HTRB)        | $T_a = T_j(max)$<br>$V_{CB} = 0.8 \times V_{CBO}$<br>1000HRS               | _       | YES      |  |

| 3  | High Temperature<br>Storage (HTS)              | T <sub>a</sub> = T <sub>j</sub> (max)<br>1000HRS                           | YES     | YES      |  |

| 4  | Pressure Cooker<br>Test (PCT)                  | T <sub>a</sub> = 121°C ± 2°C<br>RH = 100% 15 PSIG<br>168HRS                | YES     | YES      |  |

| 5  | Wet High Temperature<br>Operating Life (WHOPL) | $T_a = 85^{\circ}C, RH = 85\%$<br>$V_{CC} = V_{CC}(min)$<br>1000HRS        | YES     | _        |  |

| 6  | Wet High Temperature<br>Reverse Bias (WHTRB)   | $T_a = 85^{\circ}C, RH = 85\%$<br>$V_{CB} = 0.8 \times V_{CBO}$<br>1000HRS | _       | YES      |  |

| 7  | Thermal Shock (T/S)                            | – 65°C≓150°C (Liquid)<br>5min, <10sec, 5min<br>200 cycles                  | YES     | YES      |  |

| 8  | Temperature Cycle (T/C)                        | – 65°C≓150°C (Air)<br>10min, 10min<br>200 Cycles                           | YES     | YES      |  |

When the results of a reliability test are good, the process characteristics good and the yield level is satisfied, the process can be applied to production. If there are any problems found in a process after it has been applied to production, the problem will be investigated in detail and the process will be revised. Once the process has been revised and approved it will again be applied to production.

# 2) PRODUCT DEVELOPMENT QUALIFICATION

Purpose: To develop a stable and uniform product that satisfies the customer's requirements for quality by using the exact reliability test specification called out for the new product.

Products are grouped according to the importance of their application.

| Group 1                                                                                                                                 | Group 2                                                                                                                                                                     | Group 3                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1. A/D, D/A Converter<br>2. IC for LCD<br>3. IC for PC<br>4. ASIC Master<br>5. Codec<br>6. MPR<br>7. IC for Exchange<br>8. New Products | <ol> <li>Transistor</li> <li>Regulator/OP AMP</li> <li>IC for Telephone</li> <li>Comparator/Timer</li> <li>MICOM</li> <li>Audio/Video IC</li> <li>General Mos IC</li> </ol> | <ol> <li>ASIC Opinion Product</li> <li>Toy/Melody IC</li> <li>MICOM family</li> <li>Products Except Group 1,<br/>Group 2 Products</li> </ol> |

# **QUALITY and RELIABILITY**

#### **New Product Qualification Test Items**

| No. | Test Item                                            | Item Test Condition                                                                          |      | Part     | Reference             | Note                        |

|-----|------------------------------------------------------|----------------------------------------------------------------------------------------------|------|----------|-----------------------|-----------------------------|

| NO. |                                                      | Test Condition                                                                               | L-IC | Discrete | Method                | Note                        |

| 1   | High Temperature<br>Reverse Bias (HTRB)              | $Ta = T_j(max)$<br>$V_{CB} = 0.8 \times V_{CBO}$<br>1000HRS                                  | _    | YES      | <br> <br>             |                             |

| 2   | High Temperature<br>Operating Life<br>(HOPL)         | $Ta = T_{opr}(max)$ $V_{CC} = V_{CC}(max)$ Static, Dynamic<br>1000HRS                        | YES  | _        | MIL-STD-883<br>1005   |                             |

| 3   | High Temperature<br>Storage (HTS)                    | Ta = T <sub>stg</sub> (max)<br>1000HRS                                                       | YES  | YES      |                       |                             |

| 4   | Operating Life (OPL)                                 | $Ta = 25^{\circ}C$ $P_{c} = P_{c}(max)$ 1000HRS                                              | _    | YES      | MIL-STD-750<br>1026.3 | For Small-<br>Signal Device |

| 5   | Intermittent<br>OPL (IOPL)                           | $Ta = 25^{\circ}C$ $P_{c} = P_{c}(max)$ $2min/2min On/Off$ $1000HRS$                         |      | YES      | MIL-STD-750<br>1036.3 |                             |

| 6   | Power Cycle<br>(P/C)                                 | ∆T <sub>j</sub> = 125°C<br>120Sec/120Sec On/Off<br>10000CYC.                                 | YES  | YES      |                       | For<br>PWR TR,<br>PWR IC    |

| 7   | Pressure Cooker<br>Test (PCT)                        | Ta = 121°C ± 2°C<br>RH = 100% 15PSIG<br>168HRS                                               | YES  | YES      |                       |                             |

| 8   | Wet High<br>Temperature<br>Reverse Bias<br>(WHTRB)   | $Ta = 85^{\circ}C, RH = 85\%$<br>$V_{CB} = 0.8 \times V_{CBO}$<br>1000HRS                    | _    | YES      |                       |                             |

| 9   | Wet High<br>Temperature<br>Operating Life<br>(WHOPL) | $Ta = 85^{\circ}C, RH = 85\%$<br>V <sub>CC</sub> = V <sub>CC</sub> (min) Pdmin<br>1000HRS    | YES  |          |                       |                             |

| 10  | Thermal Shock<br>(T/S)<br>(Liquid)                   | – 65°C⇔150°C<br>5min, <10Sec, 5min<br>200 Cycles                                             | YES  | YES      | MIL-STD-883<br>1011   |                             |

| 11  | Temperature Cycle<br>(T/C)<br>(Air)                  | – 65°C↔150°C<br>10min, 10min<br>200 Cycles                                                   | YES  | YES      | MIL-STD-883<br>1011   |                             |

| 12  | Solder Heat<br>Resistance<br>(S/H)                   | $Ta = 260^{\circ}C \pm 5^{\circ}C$ $t = 10 \pm 2Sec$                                         | YES  | YES      | MIL-STD-750<br>2031.1 |                             |

| 13  | Solderability                                        | $Ta = 245^{\circ}C \pm 5^{\circ}C$<br>t = 5 ± 0.5sec<br>Reject is > 10%<br>uncovered surface | YES  | YES      | MIL-STD-883<br>2003   |                             |

| 14  | Salt Atmosphere                                      | Ta = 35°C, 5% NaCl<br>24HRS                                                                  | YES  | YES      | MIL-STD-883<br>1009A  |                             |

2

| No. | Test                         | Test lise                                                    |      | Part     | Reference           |                 |

|-----|------------------------------|--------------------------------------------------------------|------|----------|---------------------|-----------------|

|     | Test Item                    | Test Condition                                               | L-IC | Discrete | Method              | Note            |

| 15  | Mechanical<br>Shock          | 1500G, 0.5ms<br>3 Times Each direction<br>of X, Y and Z Axis | YES  | YES      | MIL-STD-750<br>2016 | For<br>Hermetic |

| 16  | Vibration                    | 20G, 3 Axis<br>f=20 to 2000 cps<br>for 4 min, 4 cycles       | YES  | YES      | MIL-STD-883<br>2007 | For<br>Hermetic |

| 17  | Constant<br>Acceleration     | 2000G<br>X,Y,Z Axis<br>1min for each Axis                    | YES  | YES      | MIL-STD-883<br>2001 | For<br>Hermetic |

| 18  | ESD<br>(Human Body<br>Model) | R = 1.5kΩ<br>C = 100pF<br>5 Discharge<br>V≥ ± 1000V          | YES  | YES      | MIL-STD-883<br>3015 |                 |

| 19  | Latch-up Test                |                                                              | YES  | -        |                     | For<br>CMOS     |

| 20  | Fine Leak<br>Gross Leak      | Helium<br>Fluoro Carbon                                      | YES  | YES      | MIL-STD-883<br>1014 | For<br>Hermetic |

### New Products Qualification Test Item (Continued)

Note) • SOT-23, TO-92S PKG: PCT-48HR

# 3) PACKAGE DEVELOPMENT QUALIFICATION

Purpose: Whenever a new package type is developed, it must meet the specifications for devices that have been qualified and have maintained certain specified quality levels before the new package type may be applied to production.

| Flow   | Contents                     | Remarks                                                                                                                                       |  |  |  |

|--------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0      | Beginning of PKG development | Select representative device for product group<br>(proceed at least 2 lots)                                                                   |  |  |  |

| ¢      | Ass'y Qual                   | Push Test     Die Thick     Dimension     Bond Pull     Carter     Solderability                                                              |  |  |  |

| $\phi$ | Reliability Qual             | • HTRB (TR)         • PCT         • Vibration           • HOPL (IC)         • LTS         • M/S           • T/C         • S/H         • Const |  |  |  |

| 6      | Approvement of Qual          | <ul> <li>New PKG Development will be approved<br/>when Rel qual is good for 500HR.</li> </ul>                                                 |  |  |  |

#### Package Sub-Assembly Qualification Test Items

| N-  | Test Item                                 | Test Oredities                                                     | Pa      | ckage    | N                                        |

|-----|-------------------------------------------|--------------------------------------------------------------------|---------|----------|------------------------------------------|

| No. |                                           | Test Condition                                                     | Plastic | Hermetic | Notes                                    |

| 1   | High Temperature<br>Reverse Bias (HTRB)   | $Ta = T_j(max)$ $V_{CB} = 0.8 \times V_{CBO}$ $500 HRS$            | YES     | YES      | For<br>Discrete                          |

| 2   | High Temperature<br>Operating Life (HOPL) | $Ta = T_{opr}(max)$ $V_{CC} = V_{CC}(max)$ Static, Dynamic, 500HRS | YES     | YES      | For IC                                   |

| 3   | Temperature Cycle<br>(T/C)                | - 65°C≓25°C≓150°C<br>10min, 5min, 10min<br>200 CYCLES              | YES     | YES      |                                          |

| 4   | Pressure Cooker Test<br>(PCT)             | Ta = 121°C ± 2°C<br>RH = 100%, 15PSIG<br>168HRS                    | YES     | _        |                                          |

| 5   | Thermal Shock (T/S)                       | - 65°C≓150°C (Liquid)<br>5min, < 10sec, 5min<br>200 CYCLES         | YES     | YES      |                                          |

| 6   | Solder Heat Resistance<br>(S/H)           | 260°C±5°C<br>10±1 sec<br>Once without Flux                         | YES     | YES      |                                          |

| 7   | Vibration (Variable-<br>Frequency)        | 100~2000~100Hz<br>20G, 5min, 5Times, X, Y, Z                       |         | YES      | For Discrete,<br>others as<br>applicable |

| 8   | Mechanical Shock (M/S)                    | 1500G, 0.5ms<br>3 Times, X, Y, Z                                   | -       | YES      | same as above                            |

| 9   | Constant Acceleration                     | 20000G<br>X, Y, Z Axis<br>1 min for each Axis                      | _       | YES      | same as above                            |

### 4) CHANGE QUALIFICATIONS:

Purpose: To apply changes to production processes and designs by evaluating the quality levels for those processes and designs of devices in production.

| Classification |           | Change                                                                                    |  |

|----------------|-----------|-------------------------------------------------------------------------------------------|--|

| De             | esign     | Change of more than 1EA MASK for the product in production.                               |  |

| D              | Ass'y     | D/A     Coating     W/B     Mold                                                          |  |

| Process        | Diffusion | <ul> <li>Diffusion/Photo/Etch, etc.</li> <li>Metalization</li> <li>Passivation</li> </ul> |  |

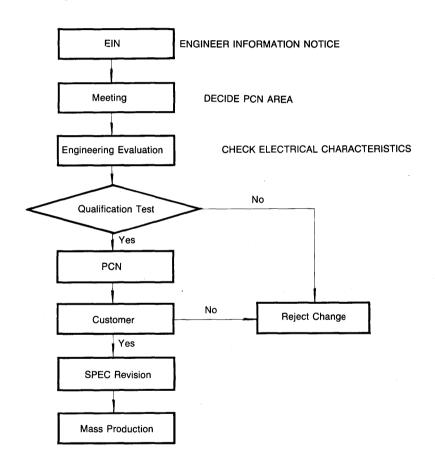

Procedure: Issuance of EIN for the change  $\rightarrow$  Review of initial characteristics  $\rightarrow$  Reliability test  $\rightarrow$  Issuance of ECN (register of specification) $\rightarrow$  Application for production. Evaluation level: LTPD 10% (1/2)

## 2.2 MONITOR PROGRAM

## 1) ON GOING PROCESS CONTROL

All parameters of each process are controlled by SPC (Statistical Process Control). All resultant SPC data is gathered by computers and recorded automatically. Trends of each parameter are plotted on control charts by the computer and corrective actions are immediately taken whenever a parameter goes "out-of-control" beyond the control limits. Whenever a parameter goes "out-of-control" in a process, engineers involved with that particular process have meetings to decide the disposition of those lots that were effected by the out-of-control process and corrective actions are im-

plemented. In the case of critical defects, all lots are scrapped by MRB (Material Review Board).

As the key item of ongoing process control, Cp or Cpk value is controlled by computer for each process. The UCL and LCL for each process is then determined by the computer generated Cp or Cpk value. Cp or Cpk values are continually upgraded to insure the stabilization of process and a QIP (quality improvement plan) is made out to drive defects down to zero.

Process capabilities of each process are totaled and analyzed and those results of analysis are reflected on the QIP. The stabilization and maximization of process capabilities are driven by SPC.

### 2) PRODUCT RELIABILITY MONITOR

The reliability monitor program begins where the qualification program ends, at the start-up of limited production. Everything that is subject to qualification is considered subject to the monitor program. Generally, the product to be used for reliability monitors is gathered from each fab lot each month, where the product selected is representative of:

- 1) each fab process technology

- 2) each generic product type

- 3) each package technology

- 4) each subassembly plant

The product is shipped directly to the appropriate Q & R group, which puts the product through a series of electrical, mechanical, thermal, and environmental tests that usually are identical to those used initially for qualifying the product. Most tests are of short duration, but some may extend out to thousands of hours. Each month the test results are evaluated and problems, should they exist, identified.

Each monitor failure is analyzed. If a problem is detected where the failure rate is greater than that considered acceptable, or a reliability problem is suspected, a Material Review Board (MRB) is called. This meeting is attended by appropriate Q & R personnel, scheduling personnel, engineering, and any other affected group.

This group reviews the data, decides on disposition of the affected material, decides on appropriate corrective action, and basically controls the problem or issue until it is satisfactorily resolved.

### 3) FINAL QUALITY ASSURANCE PROGRAM

After the completion of the entire manufacturing process a sample of each lot is pulled and the data sheet verification test is repeated. This final verification objective is to ensure that test system to test system variations are not compromising the quality, and that inadvertent system or handling problems have not occurred.

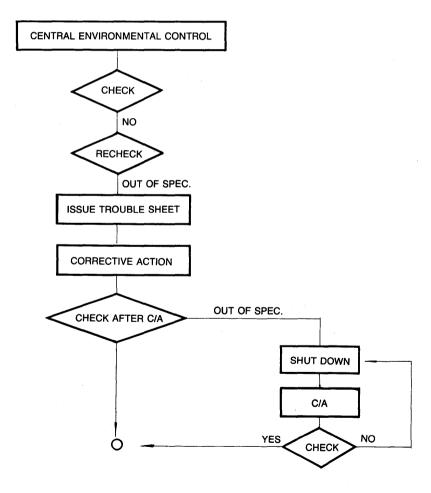

#### 4) ENVIRONMENT MONITOR

#### • instruments

Block Diagram

- F.M.S #1 (HIAC/ROYCO System 1 Set)

F.M.S #2 (P.M.S System 1 Set)

Control Particle Monitoring System (2 Set)

On line monitoring system (Central control room)

- Portable Particle Counter, Sensors

- (CENTRAL CONTROL ROOM) PATROL INSPECTION FMS #1 FMS #2 R/HUMIDITY DIFF./PRESSURE D.I RESISTIVITY GAS PRESSURE AIR PARTICLE 0.3um ≦30 45±5% ≥0.01 mmH2O <u>≥</u>16 MΩ ≧50 PSI TEMPERATURE D.I PARTICLE GAS DEW POINT BACTERIC INSP HEPA AIRVELOCITY ≦ – 70°C ≤10 COL'Y 23±0.5°C ≧0.3 m/s ≤2ea/ml HEPA P/C INSP ≤ 10ea (0.3um) PRODUCT AREA (CLEAN ROOM CLASS 1~100)

#### • Environment Monitor

| Item                                                                      | Frequency            |

|---------------------------------------------------------------------------|----------------------|

| 1. Particle (Air, D-I Water)                                              | 5 min                |

| 2. Temperature, Relative Humidity                                         | 5 min                |

| 3. D.I Resistivity                                                        | 5 min                |

| 4. Differential Pressure                                                  | 5 min                |

| 5. HEPA Air Velocity                                                      | 5 min                |

| 6. Gas (H <sub>2</sub> , O <sub>2</sub> , N <sub>2</sub> , Air) Dew Point | 5 min                |

| 7. Gas Pressure                                                           | 5 min                |

| 8. HEPA Filter Particle                                                   | All HEPAs/1 room/Day |

| 9. D-I Bacteria Main Lot                                                  | Weekly               |

| 10. D-I Bacteria Using Lot                                                | Monthly              |

#### **Corrective Action Requirement**

#### 2.3 QUALITY CONFORMANCE PROGRAM

#### 1) DESCRIPTION

SEC has established a comprehensive reliability program to monitor and ensure the ongoing reliability of the MPR family. This program involves not only reliability data collection and analysis on existing parts, but also rigorous in-line quality controls for all products.

Listed below are details of tests performed to ensure that manufactured product continues to meet SEC's stringent quality standards. In line quality controls are reviewed extensively in later sections.

The tests run by the quality department are accelerated tests, serving to model "real world" applications through boosted temperature, voltage, and/or humidities. Accelerated conditions are used to derive device knowledge through means quicker than that of typical application situations. These accelerated conditions are then used to assess differing failure rate mechanisms that correlate directly with ambient conditions. Following are summaries of various stresses (and their conditions) run by SEC on Linear IC products.

# 2) HIGH TEMPERATURE OPERATING LIFE TEST (HOPL)

$(T_j = 125^{\circ}C, V_{CC} = V_{CC} max, static)$

High temperature operating life test is performed to measure actual field reliability. Life tests of 1000HR to 2000HR durations are used to accelerate failure mechanisms by operating the device at an elevated ambient temperature (125°C). Data obtained from this test are used to predict product infant mortality, early life, and random failure rates. Data are translated to standard operating temperatures via failure analysis to determine the activation energy of each of the observed failures, using the Arrhenius relationship as previously discussed.

### 3) WET HIGH TEMPERATURE OPERATING LIFE TEST (WHOPL)

$(Ta = 85^{\circ}C, R.H. = 85\%, V_{CC} = V_{CC} \text{ opt, static})$

Wet high temperature operating life test is performed to evaluate the moisture resistance characteristics of plastic encapsulated components. Long time testing is performed under static bias conditions at 85°C/85 percent relative humidity with nominal voltages. To maximize metal corrosion, the biasing configuration utilizes low power levels.

#### 4) INTERMITTENT OPERATING LIFE (IOPL)

(Pmax, 25°C, 2min on/2 min off)

This test is normally applied to scrutinize die bond thermal fatigue. A stressed device undergoes an "ON" cycle, where there is thermal heating due to power dissipation, and an "OFF" cycle, where there is thermal cooling due to lack of inputted power. Die attach (between die and package) and bond attach (between wire and die) are the critical areas of concern.

# 5) HIGH TEMPERATURE STORAGE TEST (HTS)

(Ta = 125°C, UNBIASED)

High temperature storage is a test in which devices are subjected to elevated temperatures with no applied bias. The test is used to detect mechanical instabilities such as bond integrity, and process wearout mechanisms.

#### 6) PRESSURE COOKER TEST (PCT)

(121°C, 15PSIG, 100% R.H., UNBIASED)

The pressure cooker test checks for resistance to moisture penetration. A highly pressurized vessel is used to force water (thereby promoting corrosion) into packaged devices located within the vessel.

#### 7) TEMPERATURE CYCLING (T/C)

$(-65^{\circ}C \text{ to } + 150^{\circ}C, \text{ AIR, UNBIASED})$

This stess uses a chamber with alternating temperatures of  $-65^{\circ}$ C and  $+150^{\circ}$ C (air ambient) to thermally cycle devices within it. No bias is applied. The cycling checks for mechanical integrity of the packaged device, in particular bond wires and die attach, along with metal/polysilicon microcracks.

#### 8) THERMAL SHOCK (T/S)

(-65°C to +150°C, LIQUID, UNBIASED)

This stress uses a chamber with alternating temperatures of -65°C to +150°C (liquid ambient) to thermally cycle devices within it. No bias is applied. The cycling is very rapid, and primarily checks for die/package compatibility.

29

#### 9) RESISTANCE TO SOLDER HEAT

(UNBIASED, 260°C, 10 sec)

Solder Heat Resistance is performed to establish that devices can withstand the thermal effects of solder dip, soldering iron, or solder wave operations.

#### **10) MECHANICAL SHOCK**

(UNBIASED, 1500g, Pulse = 0.5msec)

This test determines the suitability of a device to be used in equipment where mechanical "shocks" may occur. Such shocks result from sudden or abrupt changes produced by rough (non-standard) handling, transportation, or field operations.

#### **11) VARIABLE FREQUENCY VIBRATION**

(UNBIASED, Range = 100 to 2000Hz)

Variable Frequency Vibration is done to model the effects of differential vibration in the specified range. Die attach and bonding integrity are particularly stressed, testing the mechanical soundness of device packaging.

#### **12) CONSTANT ACCELERATION**

(UNBIASED, 10kg to 20kg)

This is an accelerated test designed to indicate types or modes of structural and mechanical weaknesses not necessarily detectable in Mechanical Shock and Variable Frequency Vibration stressing.

#### **13) RELATIVE STRESS COMPARISONS**

Many stresses are run at SEC on many different devices. Through both theoretical and actual results, it was clearly determined which stresses were most effective. Also established were the stresses which weren't fully effective.

Comparisons have been made on the basis of defects able to be determined, efficiency in detection, and cost. For the reader's benefit, SEC provides the results of its conclusions on the following pages.

# 3. CUSTOMER SUPPORT SYSTEM

## 3.1 INTRODUCTION

Manufacturing companies have developed customer support systems for the purpose of uniting communications. Through these communications pass the information and knowledge required to satisfy the customers needs in areas such as quality and reliability, customer claims, customer training, field service technical issues, pricing or availability and above all, trust. Open lines of communication establishes thorough trust between the customer and vendor and are essential for such programs as dock-to-stock in order to achieve the ultimate in customer/vendor relations. SEC, in its commitment to customer satisfaction, has installed within its organization a support system that is designed to produce the open lines of communication between all facets of relations for both the customer and SEC.

# 3.2 POLICY

5

SEC has developed within its organization, a customer support system. SEC's policy requires that this system be manned with the proper personnel that are thoroughly trained in the areas that each represent and are dedicated to opening and maintaining lines of communication with the customer. Technical data used by SEC to support the customer must be up to date and always available for use by the customer (privileged or confidential information maybe excluded). Customer training is provided to the customer by only the most knowledgeable SEC personnel. SEC will provide customer field service in the form of periodic goodwill visits to customer sites or specialized problem solving services as required. Process change notification procedures as well as safety standards are also strictly adhered to.

## 3.3 CUSTOMER SUPPORT SYSTEM

### 1) QUALITY ASSURANCE SERVICE

SEC has felt the need to reorganize its current Quality Assurance Sections in order to better service our customers. From this new organizational change, a new QA section was born. This new QA section, known as QA Section 3, was developed specifically for the customer. The customer service team in QA3, was organized to respond prombtly to customers quality requirements. The purpose of this team is to form a more responsive communication channel between plant R & D, the sales department and the customer. Customers will achieve satisfaction with our company's products by use of the newly organized customer service system. This service system is openly available to customers for comments concerning problems oropinions about SEC's devices. An 800 number is published on the inside of the hand-books cover.

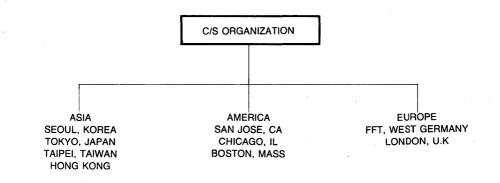

### 2) CUSTOMER SERVICE TEAM

The following organizational chart illustrates the world-wide base that the customer service team of SEC has established. Maintaining continuity between all of SEC's worldwide customer service teams is accomplished through the use of a newly installed computer network which allows constant communication between all teams.

# 3) CUSTOMER CLAIM SUPPORT SYSTEM

Information from the field concerning quality is an essential factor for the improvement of product quality. Equally important, is the investigation of field failures. Timely feedback of the results from the analysis is required to better service customers properly. This data also serves as a direct guide to the improvement of reliability and quality for both SEC and our customers.

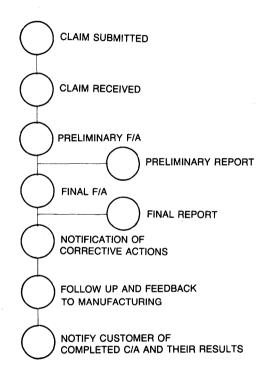

The flowchart below demonstrates the process in which SEC currently follows for customer claims.

### 4) CUSTOMER TRAINING SYSTEM

SEC has recently established a training team for the purpose of teaching SEC's customers the methods currently used by SEC to insure the product quality and reliability at the customers site. SEC offers this training in the form of group seminars or presentations and when requested or deemed necessary, individualized training is offered. In some cases, the training will take place at the customers site at the customers convenience while in other cases, SEC will extend on invitation to the customer to visit our manufacturing site.

### 5) CUSTOMER FIELD SERVICE

SEC has developed field service teams that are devoted to making customer contact when there aren't any problems. In other words, SEC is interested in making periodic goodwill visits. The visiting team would be comprised of those managers and engineers that are involved with the product types that the customer currently uses. The main goal of this team is to establish customer trust through communication.

### 3.4 PROCESS CHANGE NOTIFICATION SYSTEM (PCN)

Changes in a process are sometimes required to produce a higher quality product at a lower price. These changes can include new or different types of material, new or modified designs and new or different processes. SEC has developed a PCN procedure that is followed whenever a major or critical change is to be considered for any process. The idea behind the PCN is to allow change to a process by submitting the planned change for qualification by SEC engineering and then presenting the PCN to the customer for final approval. By following this procedure, the customer is assured that no major or critical change will occur to the process without the customers consent.

### 3.5 SAFETY STANDARDS

Most customers express the desire to use only products which have been manufactured with materials that meet the safety specifications of the Underwriters Laboratories. SEC has chosen to adhere to the specifications called out in the UL standard 94 by purchasing and using only those plastic materials that conform to this standard. UL 94 tests for a number of different flammability conditions that effect the plastic material used in semiconductor devices including horizontal burning, vertical burning and flame spread.

# 4. FAILURE ANALYSIS

## **4.1 PROCEDURE**

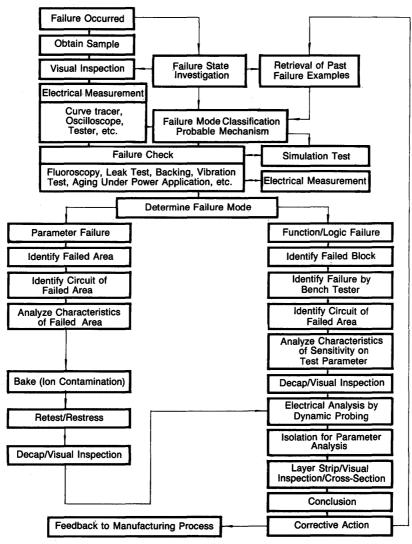

A general failure analysis procedure is shown below. The method demonstrated in the flow chart applies to all rejects. However, each analysis is specific unto itself, so that a completely exhaustive analytical flow is impossible for the limits of this manual. Specific instances and examples of interest are provided later in the chapter. Also included in this section is a typical day-by-day accounting of a failure analysis in progress. A two-week turnaround is the objective, with greater than 90% of analysis lasting equal to or less than this duration. A sample analysis plan and report are attached at the conclusion of this section.

Failure Analysis Procedure Flow Chart

Applicable Comments for the above flow chart are made below.

#### 1) DETERMINATION OF FAILURE MODE

The basic failure mode shall be determined with data from computer and bench testing. As a defect can represent various electrical failure modes, it is critical to determine the most basic failure mode. (For example, a  $V_{OL}/V_{OH}$  parameter failure may be also analyzed as a functional failure. However, it is very important to determine  $V_{OL}/V_{OH}$  as the basic failure mode.)

# 2) IDENTIFICATION AND ANALYSIS OF FAILED CIRCUIT AREA

Correlation shall be derived with general (macroscopic) failure phenomenon through circuit interpretation of the failed area.

### 3) SENSITIVITY OF TEST

Parametric value of failed sample shall be determined through adjusting DC and AC parameters, temperature range, etc.

#### 4) ION CONTAMINATION

For a sample assumed to have an inversion phenomenon caused by ionic contamination, characteristics shall be identified by conducting a Ta = 150 °C, 24 hour cure and repeating test/restress. Contamination of a specific layer shall be determined by stripping each layer.

#### 5) DECAPSULATION

There are 5 decap methods with respective merits and demerits. The appropriate method must be utilized on the basis of the characteristics and potential cause for each failure.

#### 6) ISOLATION AND DYNAMIC PROBING

It is essential to isolate the probable failing part of the circuit for its electrical failure mode. Without isolation, exact detection of a failed part can not be accurately accomplished as an electrical failure mode has an influence on other parts of the circuit.

# 7) LAYER STRIPPING

Each layer strip should meet specification requirements with respect to time. It should never be the case that chemical attack is mistaken for causing the failure of a part.

# 8) GENERATION OF ACTIVATION ENERGY

Accelerated life testing requires generation of actual activation energies based upon establishing a definitive failure mode. This generation has a great effect in determining the acceleration factor of Arrehenius' model.

### 9) CORRECTIVE ACTION

Failure analysis is fully completed only by establishing a future plan and corrective action, which are taken to resolve a problem and prevent its recurrence.

## 4.2 Failure Modes and Mechanisms

1) Failure mechanisms for devices vary widely. They are caused by both front-end (wafer) and back-end (assembly) processing. To classify problems and their instigations, the table listed below is provided.

| Item                   | Type of Failure                             | Failure Mode                                        | Cause                                               |  |

|------------------------|---------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|--|

|                        | Wire Disconnection                          | Open                                                | Incomplete                                          |  |

|                        | Wire Short                                  | Short                                               | Manufacture or                                      |  |

|                        | Purple Plague                               | Open, High Resistance                               | Misuse                                              |  |

| Wire                   | Bond Detaching                              | Open, High Resistance                               |                                                     |  |

| Bonding                | Misplaced Bonding,<br>Loose Contact         | Open, High Resistance<br>Short                      |                                                     |  |

|                        | Improper Bond Shape<br>Erroneous Bonding    | Open, High Resistance<br>Open, High Resistance      | Incomplete<br>Manufacture                           |  |

| Junction               | Destruction by Surge                        | Low Breakdown Voltage,                              | Incomplete                                          |  |

| Region                 | Hot Spot                                    | Short, Open                                         | Manufacture or<br>Misuse                            |  |

| Case                   | Lead Disconnection                          | Open, High Resistance                               | Same as above                                       |  |

|                        | Lead Short                                  | Short, High Leakage                                 |                                                     |  |

|                        | Incomplete Seal                             |                                                     |                                                     |  |

| Seal                   | Enclosed High<br>Humidity Gas               | Breakdown Voltage<br>Deterioration, High<br>Leakage | Same as above                                       |  |

|                        | Contamination of Surface                    |                                                     |                                                     |  |

|                        | Dust and Dirt                               | Short, Low Breakdown Voltage<br>Large Leakage       |                                                     |  |

|                        | High Current Density                        | Open, Short                                         | Misuso                                              |  |

|                        | Electromigration                            | Open, High Resistance Misuse                        |                                                     |  |

| Metallization          | Scratch                                     | Open, Short                                         | Incon1-4-                                           |  |

|                        | Insufficient Thickness<br>Excessive Etching | Open, High Resistance                               | <ul> <li>Incomplete</li> <li>Manufacture</li> </ul> |  |

|                        | Contamination, Dust and Dirt                | Onen High Resistance                                | Incomplete                                          |  |

|                        | Poor Wiring and Element<br>Connection       | Open, High Resistance                               | Manufacture or<br>Misuse                            |  |

| Chip                   | Chip Crack                                  | Open, Short                                         | Same as above                                       |  |

| Mounting               | Chip Detaching                              | Open, Short, High<br>Thermal Resistance             |                                                     |  |

| Ovidiand               | Pinhole, Crack                              | Low Breakdown Voltage, Short                        | Incomplete                                          |  |

| Oxidized<br>Film       | Insufficiently Oxidized<br>Film Thickness   | Low Breakdown Voltage                               | Incomplete<br>Manufacture                           |  |

| Surface                | Channel Formation                           | Low Breakdown Voltage                               | Como on observa                                     |  |

| Treatment              | Contamination                               | High Leakage                                        | Same as above                                       |  |

| ······                 | Insufficient Photoresist                    | Low Breakdown Voltage                               |                                                     |  |

|                        |                                             | Short, Open, High Leakage                           | Same as above                                       |  |

| Material and Diffusion | Improper Impurity Density                   | Same as above                                       | Same as above                                       |  |

2) Standard product reliability tests can naturally generate failures. Here, in this section, a table is given which lists tests and their associated rejects. Each test has a specific purpose, and if there exists a particular product weakness, a given test will expose it. In this manner, by knowing a test and it's function, a clear determination can be made as to the relevance of a failure for that particular test.

| Reliability  | / Tests | and  | Associated | Failure  | Modes |

|--------------|---------|------|------------|----------|-------|

| I CONCEPTING | 10303   | 4114 | Auguoratou | i unai c | mouco |