Data Book

# **Linear IC** VOL. 3, 1990

•Telephone •Exchange •Interface •Driver

#### Copyright 1990 by Samsung

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photo copying, recording, or otherwise, without the prior written permission of Samsung.

The information contained herein is subject to change without notice. Samsung assumes no responsibility for the use of any circuitry other than circuitry embodied in a Samsung product.

No other circuit patent licenses are implied.

## SAMSUNG DATA BOOK LIST

I. Semiconductor Product Guide

## II. Transistor Data Book

Vol. 1: Small Signal TR Vol. 2: Bipolar Power TR Vol. 3: TR Pellet

## III. Linear IC Data Book

Vol. 1: Audio/CDP/Toy

Vol. 2: Video

Vol. 3: Telecom

Vol. 4: Industrial

Vol. 5: Data Converters

IV. CMOS Consumer IC Data Book

V. High Speed CMOS Logic Data Book

VI. MOS Memory Data Book

VII. SFET Data Book

VIII. MPR Data Book

IX. CPL Data Book

X. Dot Matrix Data Book

## TABLE OF CONTENTS

| ١.    | QUALITY AND RELIABILITY                                                                                                                           | 9      |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| ١١.   | PRODUCT GUIDE                                                                                                                                     |        |

|       | 1. Function Guide       4         2. Cross Reference Guide       4         3. Application Guide       50         4. Ordering Information       50 | 7<br>0 |

| 111.  | TELEPHONE ICs                                                                                                                                     | 7      |

| IV.   | EXCHANGE ICs                                                                                                                                      | 1      |

| V.    | INTERFACE ICs                                                                                                                                     | 5      |

| VI.   | DRIVER & OTHERS                                                                                                                                   | 7      |

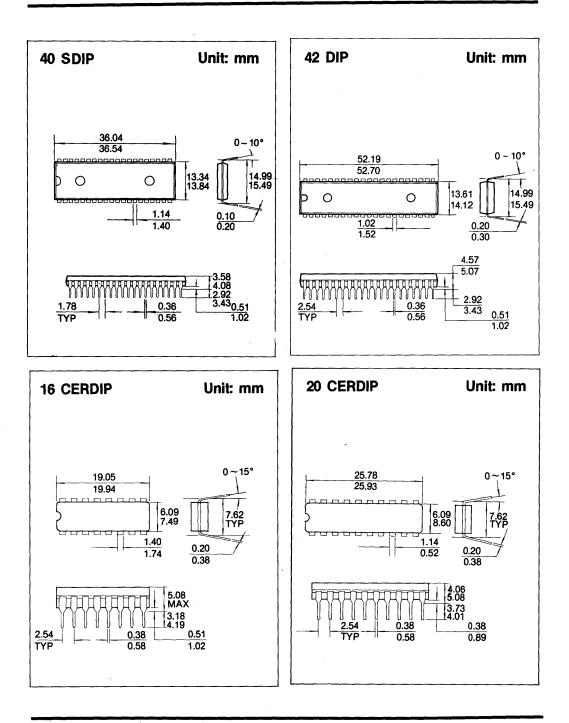

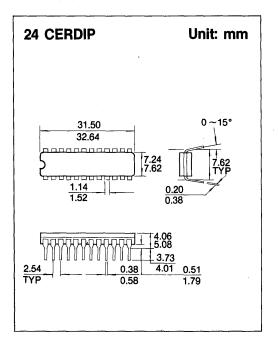

| VII.  | PACKAGE DIMENSIONS                                                                                                                                | 7      |

| VIII. | SALES OFFICES and MANUFACTURER'S<br>REPRESENTATIVES                                                                                               | 5      |

## PRODUCT INDEX

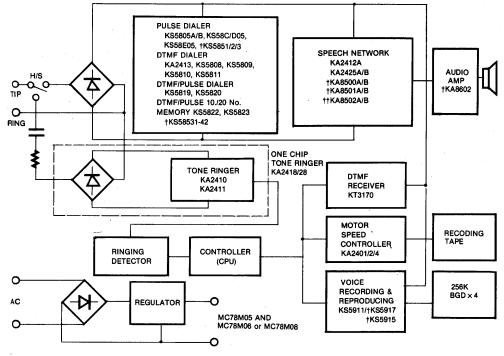

## **TELECOMMUNICATION APPLICATION**

| Device                                                                                                                            | Function                                             | Package                      | Page       |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------|------------|

| KA2410                                                                                                                            | Tone Ringer                                          | 8 DIP                        | 59         |

| KA2411                                                                                                                            | Tone Ringer                                          | 8 DIP                        | 59         |

| KA2412A                                                                                                                           | Telephone Speech Circuits                            | 14 DIP                       | 65         |

| KA2413                                                                                                                            | Dual Tone Multi Frequency Generator                  | 16 DIP                       | 73         |

| <a2418 28<="" td=""><td>Tone Ringer with Bridge Diode</td><td>8 DIP</td><td>78</td></a2418>                                       | Tone Ringer with Bridge Diode                        | 8 DIP                        | 78         |

| <a2425a b<="" td=""><td>Telephone Speech Network with Dialer Interface</td><td>18 DIP</td><td>81</td></a2425a>                    | Telephone Speech Network with Dialer Interface       | 18 DIP                       | 81         |

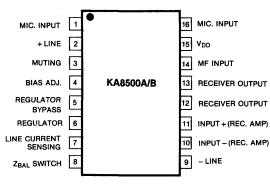

| KA8500A/B                                                                                                                         | Speech Network with Dialer Interface                 | 16 DIP                       | 88         |

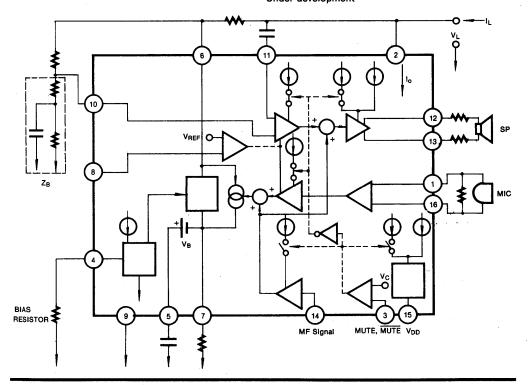

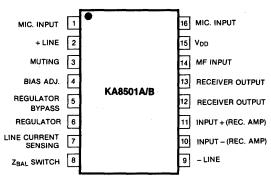

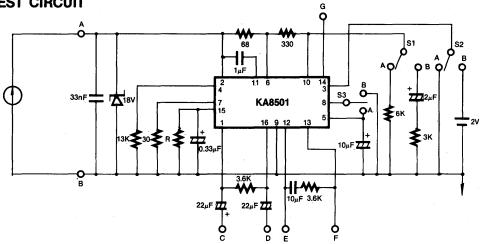

| (A8501A/B                                                                                                                         | Speech Network with Dialer Interface                 | 16 DIP                       | 92         |

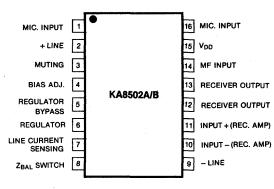

| (A8502A/B                                                                                                                         | Speech Network with Dialer Interface                 | 16 DIP                       | 96         |

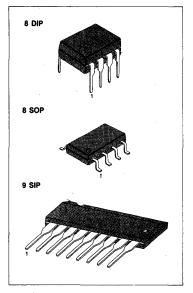

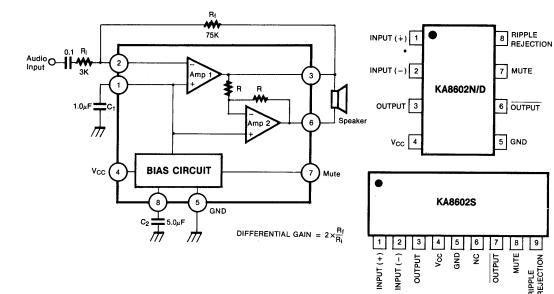

| CA8602                                                                                                                            | Low Voltage Audio Amplifier                          | 8 DIP/8 SOP/9 SIP            | 100        |

| (S5805A/B                                                                                                                         | Telephone Pulse Dialer with Redial (17 Digit)        | 18 DIP                       | 108        |

| (S58C/D05                                                                                                                         | Telephone Pulse Dialer with Redial (32 Digit)        | 18 DIP                       | 114        |

| (S58E05                                                                                                                           | Telephone Pulse Dialer with Redial (32 Digit)        | 16 DIP                       | 119        |

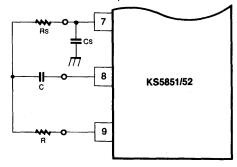

| <\$5851/52                                                                                                                        | Telephone Pulse Dialer with Redial (32 Digit)        | 18 DIP                       | 124        |

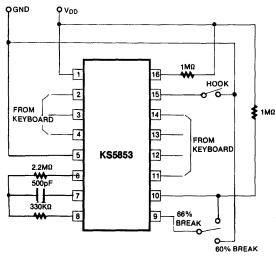

| <s5853< td=""><td>Telephone Pulse Dialer with Redial (32 Digit)</td><td>16 DIP</td><td>129</td></s5853<>                          | Telephone Pulse Dialer with Redial (32 Digit)        | 16 DIP                       | 129        |

| <s5808< td=""><td>DTMF Dialer</td><td>16 DIP</td><td>134</td></s5808<>                                                            | DTMF Dialer                                          | 16 DIP                       | 134        |

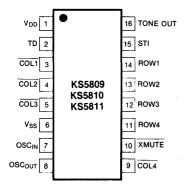

| <s5809< td=""><td>DTMF Dialer</td><td>16 DIP</td><td>140</td></s5809<>                                                            | DTMF Dialer                                          | 16 DIP                       | 140        |

| (S5810/11                                                                                                                         | DTMF Dialer with Redial (16 Digit)                   | 16 DIP                       | 140        |

| (S58A/B/C/D19                                                                                                                     | Tone/Pulse Dialer with Redial                        | 22 DIP/22 SDIP               | 144        |

| (S58A/B/C/D20                                                                                                                     | Tone/Pulse Dialer with Redial                        | 18 DIP                       | 154        |

| (\$5822                                                                                                                           | 10 Memory Tone/Pulse Repertory Dialer                | 22 DIP/22 SDIP               | 162        |

| (S58A/B/C/D23                                                                                                                     |                                                      | 18 DIP                       | 170        |

|                                                                                                                                   | 10 Memory Tone/Pulse Repertory Dialer                |                              |            |

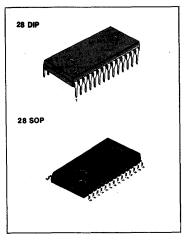

| (\$58531~42                                                                                                                       | 20 Memory Tone/Pulse Repertory Dialer                | 28 DIP/28 SOP                | 178        |

| <\$8800/01<br>_M567C                                                                                                              | Cordlessphone PLL IC<br>Tone Decoder                 | 18 DIP/18 SOP<br>8 DIP/8 SOP | 188<br>197 |

| _M567L                                                                                                                            | Micropower Tone Decoder                              | 8 DIP/8 SOP                  | 205        |

|                                                                                                                                   |                                                      |                              |            |

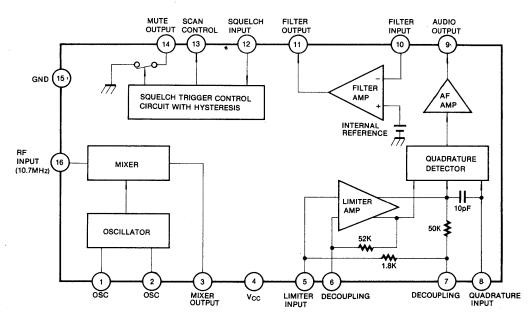

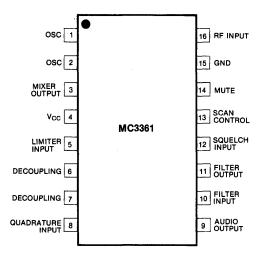

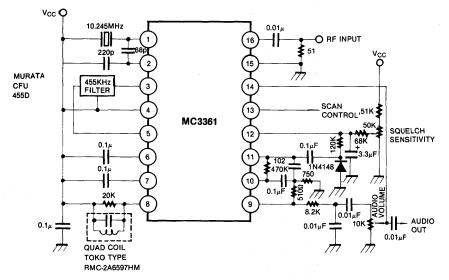

| MC3361                                                                                                                            | Low Power Narrow Band FM IF                          | 16 DIP/16 SOP                | 209        |

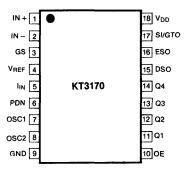

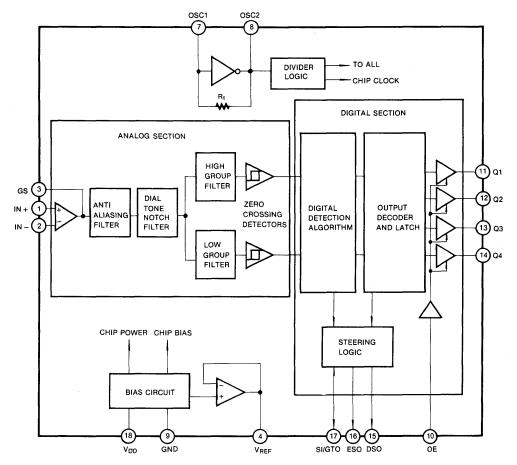

| <t3170< td=""><td>DTMF Receive</td><td>18 DIP</td><td>220</td></t3170<>                                                           | DTMF Receive                                         | 18 DIP                       | 220        |

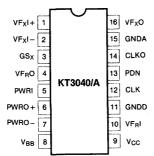

| <t3040 a<="" td=""><td>PCM Monolithic Filter</td><td>16 CERDIP</td><td>233</td></t3040>                                           | PCM Monolithic Filter                                | 16 CERDIP                    | 233        |

| CT5116                                                                                                                            | μ-Law Companding CODEC                               | 16 CERDIP                    | 245        |

| KT8520                                                                                                                            | μ-Law Companding CODEC                               | 24 CERDIP                    | 258        |

| <t8521< td=""><td>A-Law Companding CODEC</td><td>22 CERDIP</td><td>258</td></t8521<>                                              | A-Law Companding CODEC                               | 22 CERDIP                    | 258        |

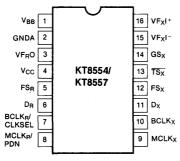

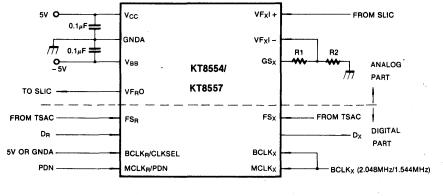

| KT8554                                                                                                                            | μ-Law COMBO CODEC                                    | 16 CERDIP/16 DIP             | 267        |

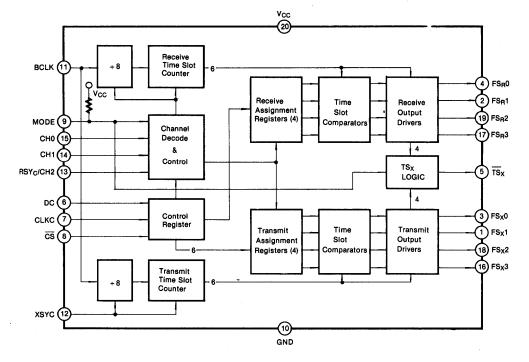

| KT8555                                                                                                                            | Time Slot Assignment Circuit                         | 20 CERDIP                    | 278        |

| <b>CT8557</b>                                                                                                                     | A-Law COMBO CODEC                                    | 16 CERDIP/16 DIP             | 267        |

| <b>KT8564</b>                                                                                                                     | μ-Law COMBO CODEC                                    | 20 CERDIP/20 DIP             | 286        |

| (T8567                                                                                                                            | A-Law COMBO CODEC                                    | 20 CERDIP/20 DIP             | 286        |

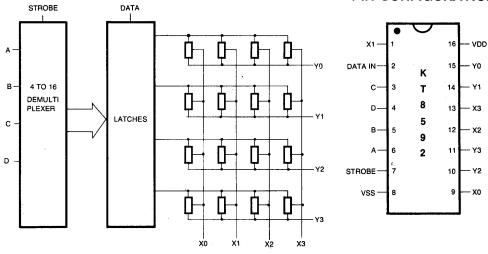

| (T8592                                                                                                                            | 4×4 Crosspoint Switch with Control Memory            | 16 DIP                       | 296        |

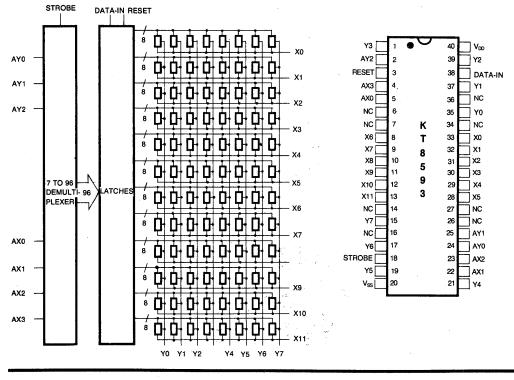

| KT8593                                                                                                                            | 12×8 Crosspoint Switch with Control Memory           | 40 DIP                       | 304        |

| (A2654                                                                                                                            | Line Transceiver                                     | 8 DIP                        | 317        |

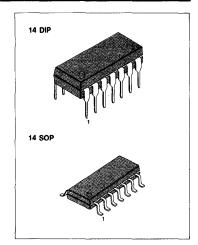

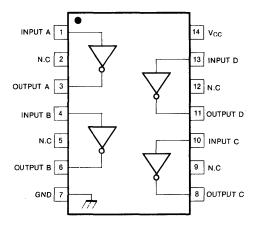

| KS5788                                                                                                                            | Quad CMOS Line Driver                                | 14 DIP/14 SOP                | 321        |

| (S5789A                                                                                                                           | Quad CMOS Line Receiver                              | 14 DIP/14 SOP                | 324        |

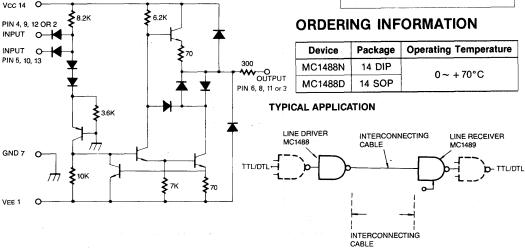

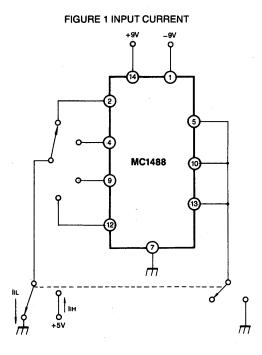

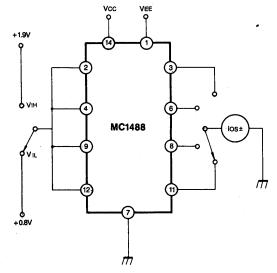

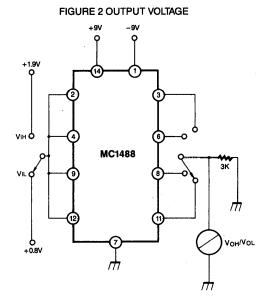

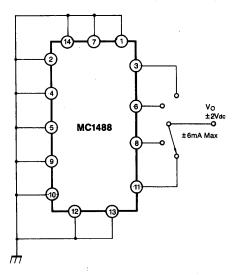

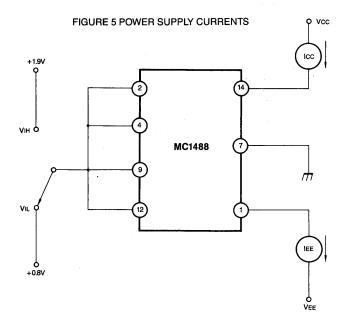

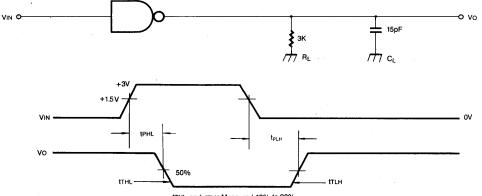

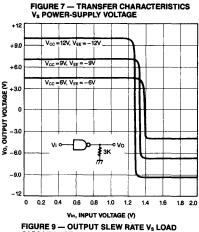

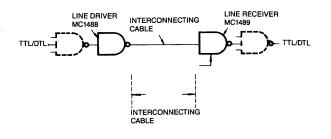

| MC1488                                                                                                                            | Quad Lind Driver                                     | 14 DIP/14 SOP                | 327        |

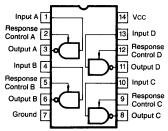

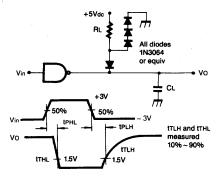

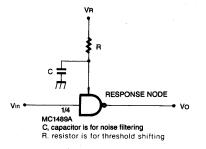

| VIC1489/A                                                                                                                         | Quad Line Receiver                                   | 14 DIP/14 SOP                | 332        |

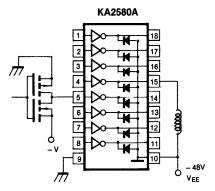

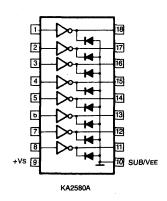

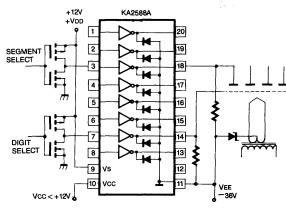

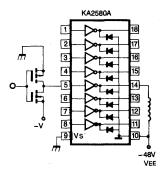

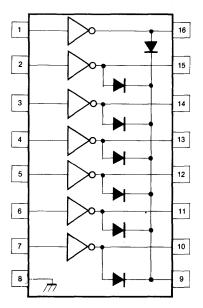

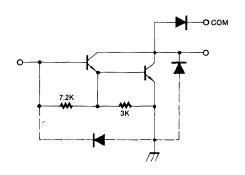

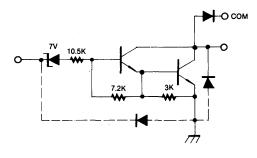

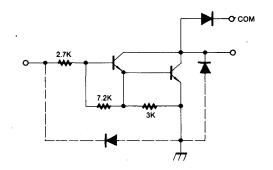

| (A2580A                                                                                                                           | 8-Channel Source Drivers                             | 18 DIP                       | 339        |

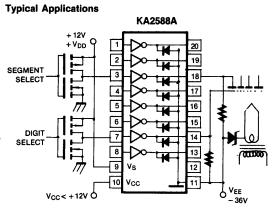

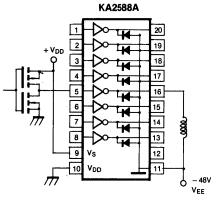

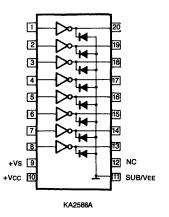

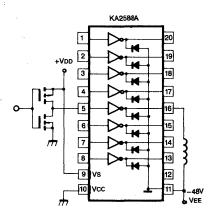

| <a>2588A</a>                                                                                                                      | 8-Channel Source Drivers                             | 20 DIP                       | 339        |

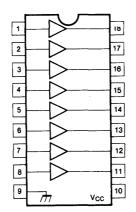

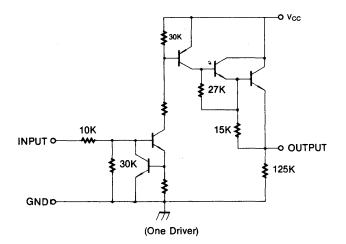

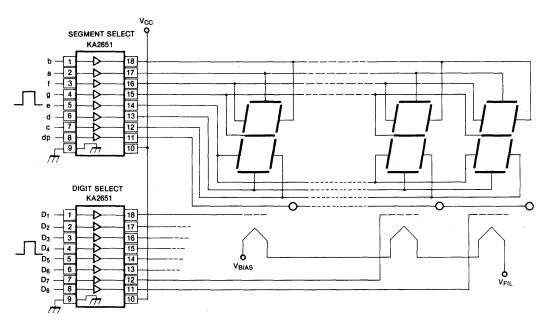

| <a2651< td=""><td>Fluorescent Display Drivers</td><td>18 DIP</td><td>344</td></a2651<>                                            | Fluorescent Display Drivers                          | 18 DIP                       | 344        |

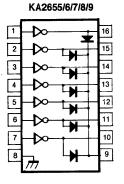

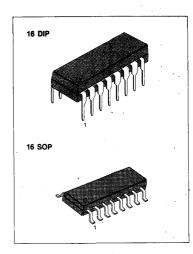

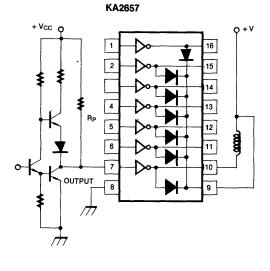

| <a2655 6="" 7="" 8="" 9<="" td=""><td>High Voltage, High Current Darlingtor Arrays</td><td>16 DIP/16 SOP</td><td>347</td></a2655> | High Voltage, High Current Darlingtor Arrays         | 16 DIP/16 SOP                | 347        |

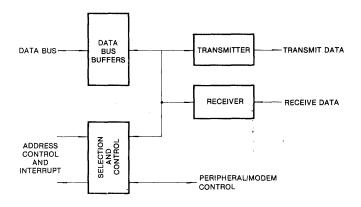

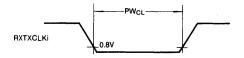

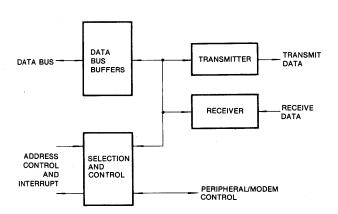

| <b>&lt;</b> \$5812                                                                                                                | Quad Universial Asychronous Receiver and Transmitter | 40 DIP                       | 352        |

| <b>&lt;</b> \$5824                                                                                                                | Universial Asychronous Receiver and Transmitter      | 24 DIP                       | 362        |

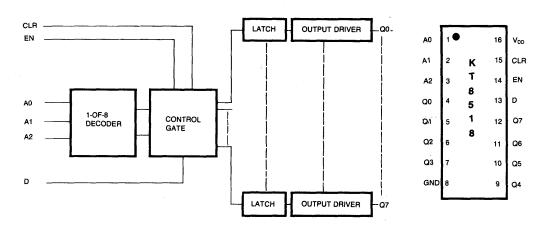

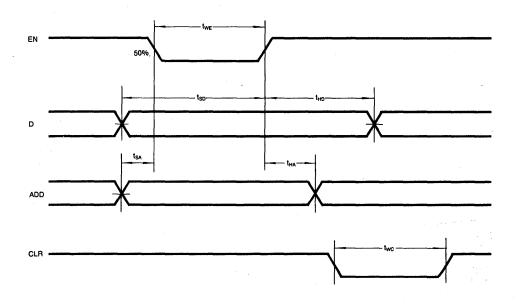

| <b><t8518< b=""></t8518<></b>                                                                                                     | 8-Bit Latch & Driver                                 | 16 DIP                       | 373        |

ē.

## 一动行为 经通知折旧 了

a second a second second

a da anticipada de la composición de la Esta de la composición de la composición

## **1. INTRODUCTION**

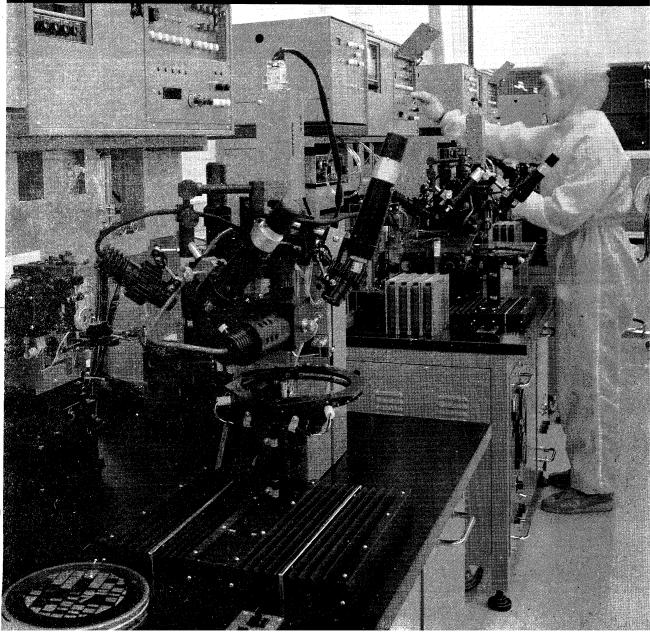

SEC has been providing a wide variety of semiconductor products to the world since 1974. Since this time, extensive in-sights have been gained to create methods which most effectively result in reliable products. The worldwide customers of SEC have encouraged and helped develop the existing manufacturing and quality philosophy that is a way of life for SEC management and it's employees. This philosophy dictates the need for a zero defect environment through out SEC's processes leading ultimately to total customer satisfaction. By developing and using methods of Statistical Process Control and Statistical Quality Control, SEC has made great strides in improving product quality a reliability. The direct result of these improvements has been reduced product DPM (Defects Per Million) to levels below customer requirements. SEC's repeated ability to exceed requirements for customer's "Dock to Stock" programs and our commitment to all our customers needs, has made SEC the company to watch as we move ahead into the 1990's and beyond.

SEC's linear IC products are among the most reliable in the industry. SEC has always made a commitment to achieve the highest possible quality, reliability, and customer satisfaction with its products. Extensive qualification, monitor and outgoing programs are used to scrutinize product quality and reliability. Stringent controls are applied to every wafer fabrication and assembly lot to achieve reproducibility, and therefore maintain product reliability.

In this chapter, the quality and reliability programs established at SEC will be discussed. In addition, a description of reliability theory, reliability tests and various support efforts provides a broad framework from which to comprehend SEC quality and reliability.

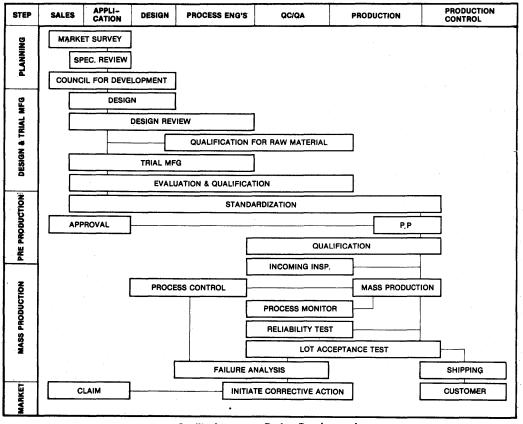

To better understand the Quality Department's role in product development and manufacturing, a detailed diagram is listed below. As can be noted, Quality Engineering is involved in all phases, save that of initial product planning.

Quality Assurance During Development

## QUALITY and RELIABILITY

#### 2. QUALITY & RELIABILITY PROGRAM

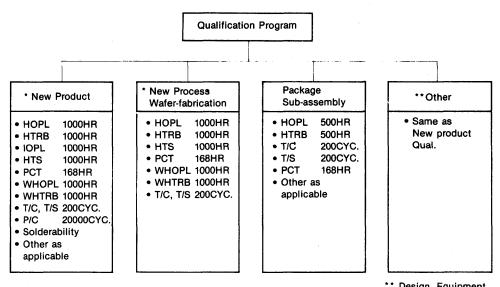

#### 2.1 QUALIFICATION

Procedures to qualify devices are listed below. There are both general and product-specific requirements. Procedures are detailed for new products, die-only qualifications, and package-only qualifications. The latter two are for products and/or packages already qualified, but where there is room for further product optimization.

\*Testing time for each test items depends on the grade (group) of devices. (see the device group list 2.1 2))  Design, Equipment, Material(s), etc....

#### 1) PROCESS DEVELOPMENT QUALIFICATION

Purpose: To investigate the change of a process parameter and then apply it to a production process by reliability testing of a process which has been newly developed.

#### New Process, Wafer Fabrication Qualification

| No | Test Item                                      | Test Condition                                                             | Package |          |  |

|----|------------------------------------------------|----------------------------------------------------------------------------|---------|----------|--|

| NO | iest nem                                       | Test Condition                                                             | L-IC    | Discrete |  |

| 1  | High Temperature<br>Operating Life (HOPL)      | $T_{a} = T_{opr}(max)$ $V_{CC} = V_{CC}(max)$ STATIC, DYNAMIC<br>1000HRS   | YES     | _        |  |

| 2  | High Temperature<br>Reverse Bias (HTRB)        | $T_{a} = T_{j}(max)$<br>$V_{CB} = 0.8 \times V_{CBO}$<br>1000HRS           | _       | YES      |  |

| 3  | High Temperature<br>Storage (HTS)              | T <sub>a</sub> = T <sub>i</sub> (max)<br>1000HRS                           | YES     | YES      |  |

| 4  | Pressure Cooker<br>Test (PCT)                  | T <sub>a</sub> = 121°C ± 2°C<br>RH = 100% 15 PSIG<br>168HRS                | YES     | YES      |  |

| 5  | Wet High Temperature<br>Operating Life (WHOPL) | $T_a = 85^{\circ}C, RH = 85\%$<br>$V_{CC} = V_{CC}(min)$<br>1000HRS        | YES     |          |  |

| 6  | Wet High Temperature<br>Reverse Bias (WHTRB)   | $T_a = 85^{\circ}C, RH = 85\%$<br>$V_{CB} = 0.8 \times V_{CBO}$<br>1000HRS | _       | YES      |  |

| 7  | Thermal Shock (T/S)                            | – 65°C≓150°C (Liquid)<br>5min, <10sec, 5min<br>200 cycles                  | YES     | YES      |  |

| 8  | Temperature Cycle (T/C)                        | – 65°C≓150°C (Air)<br>10min, 10min<br>200 Cycles                           | YES     | YES      |  |

When the results of a reliability test are good, the process characteristics good and the yield level is satisfied, the process can be applied to production. If there are any problems found in a process after it has been applied to production, the problem will be investigated in detail and the process will be revised. Once the process has been revised and approved it will again be applied to production.

#### 2) PRODUCT DEVELOPMENT QUALIFICATION

Purpose: To develop a stable and uniform product that satisfies the customer's requirements for quality by using the exact reliability test specification called out for the new product.

Products are grouped according to the importance of their application.

| Group 1                                                                                                                                 | Group 2                                                                                                                                  | Group 3                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1. A/D, D/A Converter<br>2. IC for LCD<br>3. IC for PC<br>4. ASIC Master<br>5. Codec<br>6. MPR<br>7. IC for Exchange<br>8. New Products | 1. Transistor<br>2. Regulator/OP AMP<br>3. IC for Telephone<br>4. Comparator/Timer<br>5. MICOM<br>6. Audio/Video IC<br>7. General Mos IC | <ol> <li>ASIC Opinion Product</li> <li>Toy/Melody IC</li> <li>MICOM family</li> <li>Products Except Group 1,<br/>Group 2 Products</li> </ol> |

#### **New Product Qualification Test Items**

| No. | Test item                                            | Test Condition                                                                               |               | Part | Reference             | Note                        |

|-----|------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------|------|-----------------------|-----------------------------|

| NO. | iest item                                            | rest condition                                                                               | L-IC Discrete |      | Method                | NOTE                        |

| 1   | High Temperature<br>Reverse Bias (HTRB)              | $Ta = T_i(max)$ $V_{CB} = 0.8 \times V_{CBO}$ 1000HRS                                        |               | YES  |                       |                             |

| 2   | High Temperature<br>Operating Life<br>(HOPL)         | $Ta = T_{opr}(max)$ $V_{CC} = V_{CC}(max)$ Static, Dynamic<br>1000HRS                        | YES           | _    | MIL-STD-883<br>1005   |                             |

| 3   | High Temperature<br>Storage (HTS)                    | Ta = T <sub>stg</sub> (max)<br>1000HRS                                                       | YES           | YES  |                       |                             |

| 4   | Operating Life (OPL)                                 | Ta = 25°C<br>P <sub>c</sub> = P <sub>c</sub> (max)<br>1000HRS                                |               | YES  | MIL-STD-750<br>1026.3 | For Small-<br>Signal Device |

| 5   | Intermittent<br>OPL (IOPL)                           | $Ta = 25^{\circ}C$ $P_{c} = P_{c}(max)$ $2min/2min On/Off$ $1000HRS$                         |               | YES  | MIL-STD-750<br>1036.3 |                             |

| 6   | Power Cycle<br>(P/C)                                 | ∆T <sub>j</sub> = 125°C<br>120Sec/120Sec On/Off<br>10000CYC.                                 | YES           | YES  |                       | For<br>PWR TR,<br>PWR IC    |

| 7   | Pressure Cooker<br>Test (PCT)                        | Ta = 121°C ± 2°C<br>RH = 100% 15PSIG<br>168HRS                                               | YES           | YES  |                       |                             |

| 8   | Wet High<br>Temperature<br>Reverse Bias<br>(WHTRB)   | Ta = 85°C, RH = 85%<br>V <sub>CB</sub> = 0.8 × V <sub>CBO</sub><br>1000HRS                   | <u> </u>      | YES  |                       |                             |

| 9   | Wet High<br>Temperature<br>Operating Life<br>(WHOPL) | Ta = 85°C, RH = 85%<br>V <sub>cc</sub> = V <sub>cc</sub> (min) Pdmin<br>1000HRS              | YES           |      |                       |                             |

| 10  | Thermal Shock<br>(T/S)<br>(Liquid)                   | - 65°C↔150°C<br>5min, <10Sec, 5min<br>200 Cycles                                             | YES           | YES  | MIL-STD-883           |                             |

| 11  | Temperature Cycle<br>(T/C)<br>(Air)                  | – 65°C↔150°C<br>10min, 10min<br>200 Cycles                                                   | YES           | YES  | MIL-STD-883<br>1011   |                             |

| 12  | Solder Heat<br>Resistance<br>(S/H)                   | Ta = 260°C ± 5°C<br>t = 10 ± 2Sec                                                            | YES           | YES  | MIL-STD-750<br>2031.1 |                             |

| 13  | Solderability                                        | $Ta = 245^{\circ}C \pm 5^{\circ}C$<br>t = 5 ± 0.5sec<br>Reject is > 10%<br>uncovered surface | YES           | YES  | MIL-STD-883<br>2003   |                             |

| 14  | Salt Atmosphere                                      | Ta = 35°C, 5% NaCl<br>24HRS                                                                  | YES           | YES  | MIL-STD-883<br>1009A  |                             |

Ľ

| No. | Test item                    | Test Condition                                               |      | Part     | Reference           | Note            |

|-----|------------------------------|--------------------------------------------------------------|------|----------|---------------------|-----------------|

| NO. | lest tiem                    | Test Condition                                               | L-IC | Discrete | Method              | Note            |

| 15  | Mechanical<br>Shock          | 1500G, 0.5ms<br>3 Times Each direction<br>of X, Y and Z Axis | YES  | YES      | MIL-STD-750<br>2016 | For<br>Hermetic |

| 16  | Vibration                    | 20G, 3 Axis<br>f = 20 to 2000 cps<br>for 4 min, 4 cycles     | YES  | YES      | MIL-STD-883<br>2007 | For<br>Hermetic |

| 17  | Constant<br>Acceleration     | 2000G<br>X,Y,Z Axis<br>1min for each Axis                    | YES  | YES      | MIL-STD-883<br>2001 | For<br>Hermetic |

| 18  | ESD<br>(Human Body<br>Model) | R = 1.5kΩ<br>C = 100pF<br>5 Discharge<br>V≥ ± 1000V          | YES  | YES      | MIL-STD-883<br>3015 |                 |

| 19  | Latch-up Test                | •                                                            | YES  | _        | _                   | For<br>CMOS     |

| 20  | Fine Leak<br>Gross Leak      | Helium _<br>Fluoro Carbon                                    | YES  | YES      | MIL-STD-883<br>1014 | For<br>Hermetic |

New Products Qualification Test Item (Continued)

Note) • SOT-23, TO-92S PKG: PCT-48HR

## 3) PACKAGE DEVELOPMENT QUALIFICATION

Purpose: Whenever a new package type is developed, it must meet the specifications for devices that have been qualified and have maintained certain specified quality levels before the new package type may be applied to production.

| Flow             | Contents                     | Remarks                                                                                         |                         |                                                       |  |  |

|------------------|------------------------------|-------------------------------------------------------------------------------------------------|-------------------------|-------------------------------------------------------|--|--|

| 0                | Beginning of PKG development | Select representative device for product group (proceed at least 2 lots)                        |                         |                                                       |  |  |

| $\left  \right $ | Ass'y Quai                   | Push Test     Die Thick     Dimension     Bond Pull     X-Ray     Lead Torque     Solderability |                         |                                                       |  |  |

| \$               | Reliability Qual             | • HTRB (TR)<br>• HOPL (IC)<br>• T/C                                                             | • PCT<br>• LTS<br>• S/H | <ul><li>Vibration</li><li>M/S</li><li>Const</li></ul> |  |  |

| 6                | Approvement of Qual          | <ul> <li>New PKG Development will be approved<br/>when Rel qual is good for 500HR.</li> </ul>   |                         |                                                       |  |  |

#### Package Sub-Assembly Qualification Test Items

| No. | Test Item                                 | Test Condition                                                     | Pa         | ckage         | N - 4                                    |  |

|-----|-------------------------------------------|--------------------------------------------------------------------|------------|---------------|------------------------------------------|--|

| NO. | lest item                                 | Test Condition                                                     | Plastic    | Hermetic      | Notes                                    |  |

| 1   | High Temperature<br>Reverse Bias (HTRB)   | $Ta = T_i(max)$ $V_{CB} = 0.8 \times V_{CBO}$ $500 HRS$            | YES        | YES           | For<br>Discrete                          |  |

| 2   | High Temperature<br>Operating Life (HOPL) | $Ta = T_{opr}(max)$ $V_{CC} = V_{CC}(max)$ Static, Dynamic, 500HRS | YES        | YES           | For IC                                   |  |

| 3   | Temperature Cycle<br>(T/C)                | - 65°C≓25°C≓150°C<br>10min, 5min, 10min<br>200 CYCLES              | YES        | YES           |                                          |  |

| 4   | Pressure Cooker Test<br>(PCT)             | Ta = 121°C ± 2°C<br>RH = 100%, 15PSIG<br>168HRS                    | YES        |               | -                                        |  |

| 5   | Thermal Shock (T/S)                       | – 65°C≓150°C (Liquid)<br>5min, < 10sec, 5min<br>200 CYCLES         | YES        | YES           |                                          |  |

| 6   | Solder Heat Resistance<br>(S/H)           | 260°C±5°C<br>10±1 sec<br>Once without Flux                         | YES        | YES           | -                                        |  |

| 7   | Vibration (Variable-<br>Frequency)        | 100~2000~100Hz<br>20G, 5min, 5Times, X, Y, Z                       | , <u> </u> | YES           | For Discrete,<br>others as<br>applicable |  |

| 8   | Mechanical Shock (M/S)                    | 1500G, 0.5ms<br>3 Times, X, Y, Z – YES                             |            | same as above |                                          |  |

| 9   | Constant Acceleration                     | 20000G<br>X, Y, Z Axis<br>1 min for each Axis                      | —          | YES           | same as above                            |  |

#### 4) CHANGE QUALIFICATIONS:

Purpose: To apply changes to production processes and designs by evaluating the quality levels for those processes and designs of devices in production.

| Class    | ification |                                                                            |         | Change | ara na | . A K ANA A | -<br>Maria (s. |

|----------|-----------|----------------------------------------------------------------------------|---------|--------|--------|-------------|----------------|

| De       | esign     | Change of more than 1EA MASK for the product in production.                |         |        |        |             |                |

| <b>.</b> | Ass'y     | • D/A<br>• W/B<br>• Mold                                                   | Coating |        |        | •           |                |

| Process  | Diffusion | <ul> <li>Diffusion/P</li> <li>Metalization</li> <li>Passivation</li> </ul> |         |        |        |             | e ya e         |

Procedure: Issuance of EIN for the change  $\rightarrow$  Review of initial characteristics  $\rightarrow$  Reliability test  $\rightarrow$  Issuance of ECN (register of specification) $\rightarrow$  Application for production. Evaluation level: LTPD 10% (1/2)

#### 2.2 MONITOR PROGRAM

#### 1) ON GOING PROCESS CONTROL

All parameters of each process are controlled by SPC (Statistical Process Control). All resultant SPC data is gathered by computers and recorded automatically. Trends of each parameter are plotted on control charts by the computer and corrective actions are immediately taken whenever a parameter goes "out-of-control" beyond the control limits.

Whenever a parameter goes "out-of-control" in a process, engineers involved with that particular process have meetings to decide the disposition of those lots that were effected by the out-of-control process and corrective actions are implemented. In the case of critical defects, all lots are scrapped by MRB (Material Review Board).

As the key item of ongoing process control, Cp or Cpk value is controlled by computer for each process. The UCL and LCL for each process is then determined by the computer generated Cp or Cpk value. Cp or Cpk values are continually upgraded to insure the stabilization of process and a QIP (quality improvement plan) is made out to drive defects down to zero.

Process capabilities of each process are totaled and analyzed and those results of analysis are reflected on the QIP. The stabilization and maximization of process capabilities are driven by SPC.

#### 2) PRODUCT RELIABILITY MONITOR

The reliability monitor program begins where the qualification program ends, at the start-up of limited production. Everything that is subject to qualification is considered subject to the monitor program. Generally, the product to be used for reliability monitors is gathered from each fab lot each month, where the product selected is representative of:

- 1) each fab process technology

- 2) each generic product type

- 3) each package technology

- 4) each subassembly plant

The product is shipped directly to the appropriate Q & R group, which puts the product through a series of electrical, mechanical, thermal, and environmental tests that usually are identical to those used initially for qualifying the product. Most tests are of short duration, but some may extend out to thousands of hours. Each month the test results are evaluated and problems, should they exist, identified.

Each monitor failure is analyzed. If a problem is detected where the failure rate is greater than that considered acceptable, or a reliability problem is suspected, a Material Review Board (MRB) is called. This meeting is attended by appropriate Q & R personnel, scheduling personnel, engineering, and any other affected group.

This group reviews the data, decides on disposition of the affected material, decides on appropriate corrective action, and basically controls the problem or issue until it is satisfactorily resolved.

#### 3) FINAL QUALITY ASSURANCE PROGRAM

After the completion of the entire manufacturing process a sample of each lot is pulled and the data sheet verification test is repeated. This final verification objective is to ensure that test system to test system variations are not compromising the quality, and that inadvertent system or handling problems have not occurred.

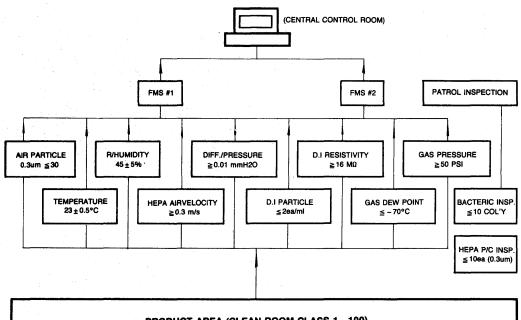

#### 4) ENVIRONMENT MONITOR

- Instruments

- F.M.S #2 (P.M.S System 1 Set) - Control Particle Monitoring System (2 Set)

On line monitoring system (Central control room)

- Portable Particle Counter, Sensors

- Block Diagram

#### PRODUCT AREA (CLEAN ROOM CLASS 1~100)

## **QUALITY and RELIABILITY**

#### • Environment Monitor

| Item                                                                      | Frequency            |

|---------------------------------------------------------------------------|----------------------|

| 1. Particle (Air, D-I Water)                                              | 5 min                |

| 2. Temperature, Relative Humidity                                         | 5 min                |

| 3. D.I Resistivity                                                        | 5 min                |

| 4. Differential Pressure                                                  | 5 min                |

| 5. HEPA Air Velocity                                                      | 5 min                |

| 6. Gas (H <sub>2</sub> , O <sub>2</sub> , N <sub>2</sub> , Air) Dew Point | 5 min                |

| 7. Gas Pressure                                                           | 5 min                |

| 8. HEPA Filter Particle                                                   | All HEPAs/1 room/Day |

| 9. D-I Bacteria Main Lot                                                  | Weekly               |

| 10. D-I Bacteria Using Lot                                                | Monthly              |

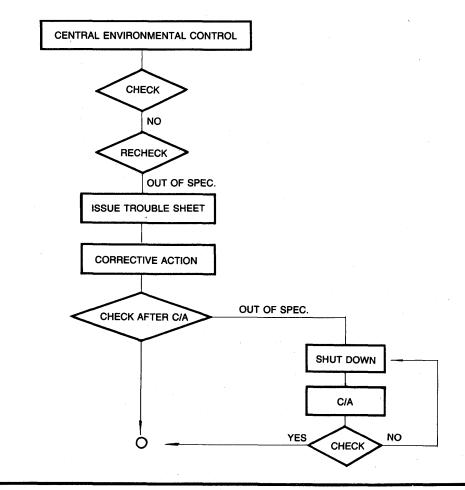

#### **Corrective Action Requirement**

#### 2.3 QUALITY CONFORMANCE PROGRAM

#### 1) DESCRIPTION

SEC has established a comprehensive reliability program to monitor and ensure the ongoing reliability of the Linear IC family. This program involves not only reliability data collection and analysis on existing parts, but also rigorous in-line quality controls for all products.

Listed below are details of tests performed to ensure that manufactured product continues to meet SEC's stringent quality standards. In line quality controls are reviewed extensively in later sections.

The tests run by the quality department are accelerated tests, serving to model "real world" applications through boosted temperature, voltage, and/or humidities. Accelerated conditions are used to derive device knowledge through means quicker than that of typical application situations. These accelerated conditions are then used to assess differing failure rate mechanisms that correlate directly with ambient conditions. Following are summaries of various stresses (and their conditions) run by SEC on Linear IC products.

#### 2) HIGH TEMPERATURE OPERATING LIFE TEST (HOPL)

$(T_j = 125^{\circ}C, V_{CC} = V_{CC} max, static)$

High temperature operating life test is performed to measure actual field reliability. Life tests of 1000HR to 2000HR durations are used to accelerate failure mechanisms by operating the device at an elevated ambient temperature (125°C). Data obtained from this test are used to predict product infant mortality, early life, and random failure rates. Data are translated to standard operating temperatures via failure analysis to determine the activation energy of each of the observed failures, using the Arrhenius relationship as previously discussed.

#### 3) WET HIGH TEMPERATURE OPERATING LIFE TEST (WHOPL)

$(Ta = 85^{\circ}C, R.H. = 85\%, V_{CC} = V_{CC} opt, static)$

Wet high temperature operating life test is performed to evaluate the moisture resistance characteristics of plastic encapsulated components. Long time testing is performed under static bias conditions at 85°C/85 percent relative humidity with nominal voltages. To maximize metal corrosion, the biasing configuration utilizes low power levels.

#### 4) INTERMITTENT OPERATING LIFE (IOPL)

(Pmax, 25°C, 2min on/2 min off)

This test is normally applied to scrutinize die bond thermal fatigue. A stressed device undergoes an "ON" cycle, where there is thermal heating due to power dissipation, and an "OFF" cycle, where there is thermal cooling due to lack of inputted power. Die attach (between die and package) and bond attach (between wire and die) are the critical areas of concern.

#### 5) HIGH TEMPERATURE STORAGE TEST (HTS)

(Ta = 125°C, UNBIASED)

High temperature storage is a test in which devices are subjected to elevated temperatures with no applied bias. The test is used to detect mechanical instabilities such as bond integrity, and process wearout mechanisms.

#### 6) PRESSURE COOKER TEST (PCT)

(121°C, 15PSIG, 100% R.H., UNBIASED)

The pressure cooker test checks for resistance to moisture penetration. A highly pressurized vessel is used to force water (thereby promoting corrosion) into packaged devices located within the vessel.

#### 7) TEMPERATURE CYCLING (T/C)

(-65°C to +150°C, AIR, UNBIASED)

This stess uses a chamber with alternating temperatures of  $-65^{\circ}$ C and  $+150^{\circ}$ C (air ambient) to thermally cycle devices within it. No bias is applied. The cycling checks for mechanical integrity of the packaged device, in particular bond wires and die attach, along with metal/polysilicon microcracks.

#### 8) THERMAL SHOCK (T/S)

(-65°C to +150°C, LIQUID, UNBIASED)

This stress uses a chamber with alternating temperatures of -65°C to +150°C (liquid ambient) to thermally cycle devices within it. No bias is applied. The cycling is very rapid, and primarily checks for die/package compatibility.

## **QUALITY and RELIABILITY**

#### 9) RESISTANCE TO SOLDER HEAT

#### (UNBIASED, 260°C, 10 sec)

Solder Heat Resistance is performed to establish that devices can withstand the thermal effects of solder dip, soldering iron, or solder wave operations.

#### **10) MECHANICAL SHOCK**

(UNBIASED, 1500g, Pulse = 0.5msec)

This test determines the suitability of a device to be used in equipment where mechanical "shocks" may occur. Such shocks result from sudden or abrupt changes produced by rough (non-standard) handling, transportation, or field operations.

#### 11) VARIABLE FREQUENCY VIBRATION

(UNBIASED, Range = 100 to 2000Hz)

Variable Frequency Vibration is done to model the effects of differential vibration in the specified range. Die attach and bonding integrity are particularly stressed, testing the mechanical soundness of device packaging.

#### **12) CONSTANT ACCELERATION**

(UNBIASED, 10kg to 20kg)

This is an accelerated test designed to indicate types or modes of structural and mechanical weaknesses not necessarily detectable in Mechanical Shock and Variable Frequency Vibration stressing.

#### **13) RELATIVE STRESS COMPARISONS**

Many stresses are run at SEC on many different devices. Through both theoretical and actual results, it was clearly determined which stresses were most effective. Also established were the stresses which weren't fully effective.

Comparisons have been made on the basis of defects able to be determined, efficiency in detection, and cost. For the reader's benefit, SEC provides the results of its conclusions on the following pages.

#### 3. CUSTOMER SUPPORT SYSTEM

#### 3.1 INTRODUCTION

Manufacturing companies have developed customer support systems for the purpose of uniting communications. Through these communications pass the information and knowledge required to satisfy the customers needs in areas such as quality and reliability, customer claims, customer training, field service technical issues, pricing or availability and above all, trust. Open lines of communication establishes thorough trust between the customer and vendor and are essential for such programs as dock-to-stock in order to achieve the ultimate in customer/vendor relations. SEC, in its commitment to customer satisfaction, has installed within its organization a support system that is designed to produce the open lines of communication between all facets of relations for both the customer and SEC.

#### 3.2 POLICY

SEC has developed within its organization, a customer support system. SEC's policy requires that this system be manned with the proper personnel that are thoroughly trained in the areas that each represent and are dedicated to opening and maintaining lines of communication with the customer. Technical data used by SEC to support the customer must be up to date and always available for use by the customer (privileged or confidential information maybe excluded). Customer training is provided to the customer by only the most knowledgeable SEC personnel. SEC will provide customer field service in the form of periodic goodwill visits to customer sites or specialized problem solving services as required. Process change notification procedures as well as safety standards are also strictly adhered to.

#### 3.3 CUSTOMER SUPPORT SYSTEM

#### 1) QUALITY ASSURANCE SERVICE

SEC has felt the need to reorganize its current Quality Assurance Sections in order to better service our customers. From this new organizational change, a new QA section was born. This new QA section, known as QA Section 3, was developed specifically for the customer. The customer service team in QA3, was organized to respond prombtly to customers quality requirements. The purpose of this team is to form a more responsive communication channel between plant R & D, the sales department and the customer. Customers will achieve satisfaction with our company's products by use of the newly organized customer service system. This service system is openly available to customers for comments concerning problems oropinions about SEC's devices. An 800 number is published on the inside of the hand-books cover.

#### 2) CUSTOMER SERVICE TEAM

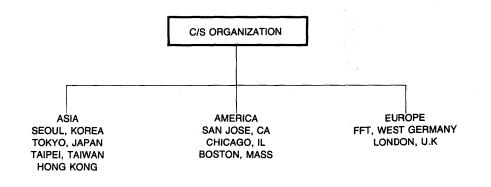

The following organizational chart illustrates the world-wide base that the customer service team of SEC has established. Maintaining continuity between all of SEC's worldwide customer service teams is accomplished through the use of a newly installed computer network which allows constant communication between all teams.

#### 3) CUSTOMER CLAIM SUPPORT SYSTEM

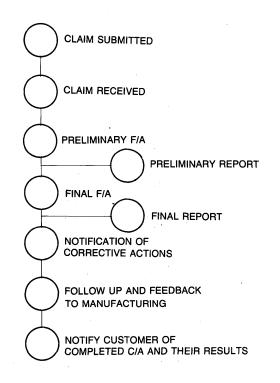

Information from the field concerning quality is an essential factor for the improvement of product quality. Equally important, is the investigation of field failures. Timely feedback of the results from the analysis is required to better service customers properly. This data also serves as a direct guide to the improvement of reliability and quality for both SEC and our customers.

The flowchart below demonstrates the process in which SEC currently follows for customer claims.

#### 4) CUSTOMER TRAINING SYSTEM

SEC has recently established a training team for the purpose of teaching SEC's customers the methods currently used by SEC to insure the product quality and reliability at the customers site. SEC offers this training in the form of group seminars or presentations and when requested or deemed necessary, individualized training is offered. In some cases, the training will take place at the customers site at the customers convenience while in other cases, SEC will extend on invitation to the customer to visit our manufacturing site.

#### 5) CUSTOMER FIELD SERVICE

SEC has developed field service teams that are devoted to making customer contact when there aren't any problems. In other words, SEC is interested in making periodic goodwill visits. The visiting team would be comprised of those managers and engineers that are involved with the product types that the customer currently uses. The main goal of this team is to establish customer trust through communication.

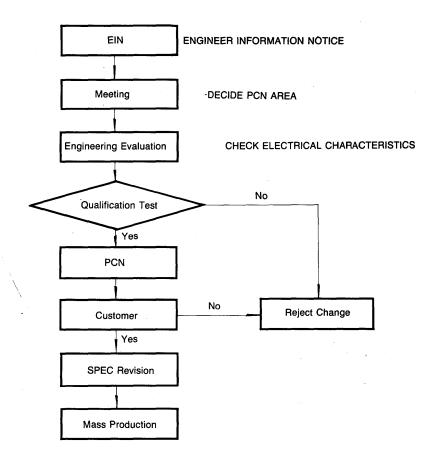

#### 3.4 PROCESS CHANGE NOTIFICATION SYSTEM (PCN)

Changes in a process are sometimes required to produce a higher quality product at a lower price. These changes can include new or different types of material, new or modified designs and new or different processes. SEC has developed a PCN procedure that is followed whenever a major or critical change is to be considered for any process. The idea behind the PCN is to allow change to a process by submitting the planned change for qualification by SEC engineering and then presenting the PCN to the customer for final approval. By following this procedure, the customer is assured that no major or critical change will occur to the process without the customers consent.

#### 3.5 SAFETY STANDARDS

Most customers express the desire to use only products which have been manufactured with materials that meet the safety specifications of the Underwriters Laboratories. SEC has chosen to adhere to the specifications called out in the UL standard 94 by purchasing and using only those plastic materials that conform to this standard. UL 94 tests for a number of different flammability conditions that effect the plastic material used in semiconductor devices including horizontal burning, vertical burning and flame spread.

STRACTURE MENDES

## 4. FAILURE ANALYSIS

#### 4.1 PROCEDURE

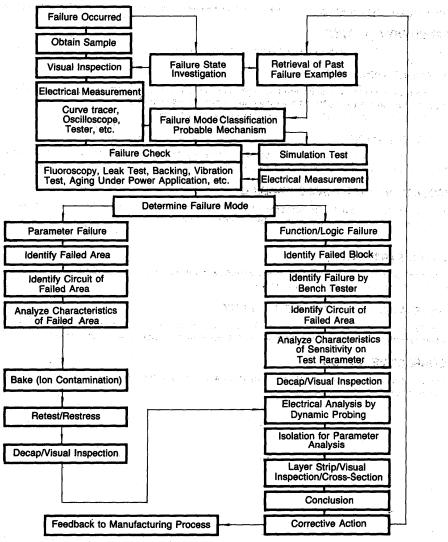

A general failure analysis procedure is shown below. The method demonstrated in the flow chart applies to all rejects. However, each analysis is specific unto itself, so that a completely exhaustive analytical flow is impossible for the limits of this manual. Specific instances and examples of interest are provided later in the chapter. Also included in this section is a typical day-by-day accounting of a failure analysis in progress. A two-week turnaround is the objective, with greater than 90% of analysis lasting equal to or less than this duration. A sample analysis plan and report are attached at the conclusion of this section.

1.1 M & A & S

Failure Analysis Procedure Flow Chart

Applicable Comments for the above flow chart are made below.

#### 1) DETERMINATION OF FAILURE MODE

The basic failure mode shall be determined with data from computer and bench testing. As a defect can represent various electrical failure modes, it is critical to determine the most basic failure mode. (For example, a  $V_{OL}/V_{OH}$  parameter failure may be also analyzed as a functional failure. However, it is very important to determine  $V_{OL}/V_{OH}$  as the basic failure mode.)

#### 2) IDENTIFICATION AND ANALYSIS OF FAILED CIRCUIT AREA

Correlation shall be derived with general (macroscopic) failure phenomenon through circuit interpretation of the failed area.

#### 3) SENSITIVITY OF TEST

Parametric value of failed sample shall be determined through adjusting DC and AC parameters, temperature range, etc.

#### 4) ION CONTAMINATION

For a sample assumed to have an inversion phenomenon caused by ionic contamination, characteristics shall be identified by conducting a Ta = 150°C, 24 hour cure and repeating test/restress. Contamination of a specific layer shall be determined by stripping each layer.

#### 5) DECAPSULATION

There are 5 decap methods with respective merits and demerits. The appropriate method must be utilized on the basis of the characteristics and potential cause for each failure.

#### 6) ISOLATION AND DYNAMIC PROBING

It is essential to isolate the probable failing part of the circuit for its electrical failure mode. Without isolation, exact detection of a failed part can not be accurately accomplished as an electrical failure mode has an influence on other parts of the circuit.

#### 7) LAYER STRIPPING

Each layer strip should meet specification requirements with respect to time. It should never be the case that chemical attack is mistaken for causing the failure of a part.

#### 8) GENERATION OF ACTIVATION ENERGY

Accelerated life testing requires generation of actual activation energies based upon establishing a definitive failure mode. This generation has a great effect in determining the acceleration factor of Arrehenius' model.

#### 9) CORRECTIVE ACTION

Failure analysis is fully completed only by establishing a future plan and corrective action, which are taken to resolve a problem and prevent its recurrence.

#### 4.2 Failure Modes and Mechanisms

1) Failure mechanisms for devices vary widely. They are caused by both front-end (wafer) and back-end (assembly) processing. To classify problems and their instigations, the table listed below is provided.

| item                                  | Type of Failure                             | Failure Mode                                        | Cause                               |  |

|---------------------------------------|---------------------------------------------|-----------------------------------------------------|-------------------------------------|--|

|                                       | Wire Disconnection                          | Open                                                | Incomplete                          |  |

|                                       | Wire Short                                  | Short                                               | Manufacture or                      |  |

|                                       | Purple Plague                               | Open, High Resistance                               | Misuse                              |  |

| Wire                                  | Bond Detaching                              | Open, High Resistance                               |                                     |  |

| Bonding                               | Misplaced Bonding,<br>Loose Contact         | Open, High Resistance<br>Short                      | Incomplete                          |  |

|                                       | Improper Bond Shape<br>Erroneous Bonding    | Open, High Resistance<br>Open, High Resistance      | Incomplete<br>Manufacture           |  |

| Junction                              | Destruction by Surge                        | Low Breakdown Voltage,                              | Incomplete                          |  |

| Region                                | Hot Spot                                    | Short, Open                                         | Manufacture or<br>Misuse            |  |

| •                                     | Lead Disconnection                          | Open, High Resistance                               | 0                                   |  |

| Case                                  | Lead Short                                  | Short, High Leakage                                 | Same as above                       |  |

| · · · · · · · · · · · · · · · · · · · | Incomplete Seal                             |                                                     |                                     |  |

| Seal                                  | Enclosed High<br>Humidity Gas               | Breakdown Voltage<br>Deterioration, High<br>Leakage | Same as above                       |  |

|                                       | Contamination of Surface                    | Leanaye                                             |                                     |  |

|                                       | Dust and Dirt                               | Short, Low Breakdown Voltage<br>Large Leakage       |                                     |  |

|                                       | High Current Density                        | Open, Short                                         | Misuse<br>Incomplete<br>Manufacture |  |

|                                       | Electromigration                            | Open, High Resistance                               |                                     |  |

| Metallization                         | Scratch                                     | Open, Short                                         |                                     |  |

|                                       | Insufficient Thickness<br>Excessive Etching | Open, High Resistance                               |                                     |  |

|                                       | Contamination, Dust<br>and Dirt             | One lifet Decidence                                 | Incomplete                          |  |

|                                       | Poor Wiring and Element<br>Connection       | Open, High Resistance                               | Manufacture or<br>Misuse            |  |

| Ohia                                  | Chip Crack                                  | Open, Short                                         |                                     |  |

| Chip<br>Mounting                      | Chip Detaching                              | Open, Short, High<br>Thermal Resistance             | Same as above                       |  |

| 0                                     | Pinhole, Crack                              | Low Breakdown Voltage, Short                        | 1                                   |  |

| Oxidized<br>Film                      | Insufficiently Oxidized<br>Film Thickness   | Low Breakdown Voltage                               | Incomplete<br>Manufacture           |  |

| Surface                               | Channel Formation                           | Low Breakdown Voltage                               | Somo as about                       |  |

| Treatment                             | Contamination                               | High Leakage                                        | Same as above                       |  |

| Mask                                  | Insufficient Photoresist                    | Low Breakdown Voltage                               | Same on shour                       |  |

| mask                                  | Mask Misalignment                           | Short, Open, High Leakage                           | Same as above                       |  |

| Material and<br>Diffusion             | Improper Impurity Density                   | Same as above                                       | Same as above                       |  |

#### Items and Causes of Failure Modes

2) Standard product reliability tests can naturally generate failures. Here, in this section, a table is given which lists tests and their associated rejects. Each test has a specific purpose, and if there exists a particular product weakness, a given test will expose it. In this manner, by knowing a test and it's function, a clear determination can be made as to the relevance of a failure for that particular test.

|                          | Failure Cause                                                                  | Diffusion                                                   | Oxide                                                           | Metalization                           | Wire Bonding                                                                    | Package<br>Environment                          | Package<br>Seal    | Lead<br>Fatigue | Solderability | Mark              | Die bonding                                                |

|--------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------|--------------------|-----------------|---------------|-------------------|------------------------------------------------------------|

| Item                     | Test Condition                                                                 | Contamination     Crystal Defect     Photoresist     Reject | •Contamination<br>•Pin Hole<br>•Crack<br>•Thickness<br>Unstable | •Conpos.<br>•Scratch<br>•Void<br>•Open | Interface     Corrosion     Misbonding     Wire Open     Chemical     Interface | Conductive ions     Inadequate     Environments | •Sealing<br>Reject | •Conpos.        | •Marking      | •Themal<br>Reject | Resistance<br>Reject<br>•Crack<br>•Chip Position<br>Reject |

| T/C                      | - 65°C→150°C<br>200 Cycles                                                     |                                                             | 0                                                               | 0                                      | 0                                                                               |                                                 | 0                  |                 |               |                   | 0                                                          |

| T/S                      | - 65°C → 125°C<br>200 Cycles                                                   |                                                             | 0                                                               | 0                                      | 0                                                                               |                                                 | 0                  |                 |               |                   | 0                                                          |

| Moisture<br>Resistance   | 90-98%R.H./65°C3HRS<br>80-98%R.H./25°C8HRS<br>90-98%R.H./65°C3HRS<br>10 Cycles |                                                             | 0                                                               | 0                                      | 0                                                                               | 0                                               | 0                  |                 |               |                   |                                                            |

| Vibration<br>Fatigue     | 20G-3 Axis<br>Orientation<br>f = 20 to 2000 cpe<br>for 4 min. 4 cycles         |                                                             |                                                                 |                                        | 0                                                                               | 0                                               |                    |                 |               |                   | 0                                                          |

| Constant<br>Acceleration | Pulse Duration:<br>0.1-1m sec<br>Shock pulse: 0.5-3Kg                          |                                                             |                                                                 |                                        | 0                                                                               |                                                 |                    |                 |               |                   | 0                                                          |

| Mechanical<br>Shock      | 1500g, 0.5ns<br>Each Direction of X, Y<br>and Z Axis                           |                                                             |                                                                 |                                        | 0                                                                               |                                                 |                    |                 |               |                   | 0                                                          |

| Lead<br>Integrity        | W = 227g<br>90°C 3 times                                                       |                                                             |                                                                 |                                        |                                                                                 |                                                 | 0                  |                 |               |                   |                                                            |

| Marking                  | Isoprophylalcohol                                                              |                                                             |                                                                 |                                        |                                                                                 |                                                 |                    |                 |               | 0                 |                                                            |

| Solderability            | Ta = 230° 5 Sec.<br>Once With Flux                                             |                                                             |                                                                 |                                        |                                                                                 |                                                 |                    |                 | 0             |                   |                                                            |

| Salt Spray               | Ta=35°C, 5% NaCl                                                               |                                                             |                                                                 |                                        | 0                                                                               |                                                 |                    |                 | 0             |                   |                                                            |

| OPL                      | Individual Spec                                                                | 0                                                           | 0                                                               | 0                                      | 0                                                                               | 0                                               |                    |                 |               |                   | 0                                                          |

| IOPL                     | Individual Spec                                                                | 0                                                           | 0                                                               | 0                                      | 0                                                                               | 0                                               |                    |                 |               |                   | 0                                                          |

| HTRB                     | Individual Spec                                                                | 0                                                           | 0                                                               | 0                                      | 0                                                                               | 0                                               |                    |                 |               |                   | 0                                                          |

| HTS                      | Individual Spec                                                                |                                                             | 0                                                               |                                        | 0                                                                               | 0                                               |                    | · · ·           | 0             |                   |                                                            |

| WHTS                     | 80°C, 90% RH<br>85°C, 85% RH                                                   |                                                             | 0                                                               | 0                                      |                                                                                 |                                                 | 0                  | 0               | 0             |                   |                                                            |

| WHTRB                    | 85°C, 85% RH<br>Bias                                                           | 0                                                           | 0                                                               | 0                                      | 0                                                                               | 0                                               | 0                  | 0               | 0             |                   | 0                                                          |

#### **Reliability Tests and Associated Failure Modes**

3) An anomalous manufacturing step can manifest itself in many ways with respect to product reliability. The chart below depicts process steps, the types of rejects they can generate, and the way to defect such failures. Of course, there are numerous QC and Production checks along all stages of the manufacturing process. However, a semiconductor product typically involves so many operations it's nearly impossible to detect all potential reliability hazards. Thus, there are final electrical and visual tests, reliability tests, and statistical analyses which are run prior to product releasal. The chart below speaks to the electrical, visual, and reliability tests.

#### Failure Mechanisms of Integrated Circuits

| Process Step<br>Affecting<br>Reliability | Failure Mechanism                                                         | Failure Mode                                                            | Failure Detection Method                                                                                                      |

|------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

|                                          | Dislocation and Stacking<br>Fault                                         | Degradation of Function<br>Characteristics                              | Electrical Test<br>Operation Life                                                                                             |

|                                          | Non-Uniform Resistivity                                                   | Unpredictable Characteristic<br>Values                                  | Electrical Test                                                                                                               |

| Wafer<br>Fabrication                     | Surface Abnormalities                                                     | Improper Electrical<br>Characteristics,<br>Short and Open               | Electrical Test<br>Operation Test                                                                                             |

|                                          | Cracks, Chips,<br>Scratches (Usually<br>Caused During Handling)           | Open and Short                                                          | Electrical Test<br>Visual Inspection<br>(Before Seal)<br>Temperature Cycling                                                  |

|                                          | Contamination                                                             | Degradation of Junction<br>Characteristics                              | Visual Inspection (Before<br>Seal), Temperature<br>Cycling, High Temperature<br>Storage, Reverse Bias                         |

| Passivation                              | Cracks and Pin Holes                                                      | Shorts, Low Breakdown<br>Voltage                                        | Temperature Cycling<br>High Temperature Storage<br>High-Voltage Test,<br>Operation Life<br>Visual Inspection<br>(Before Seal) |

|                                          | Non-Uniformity of Film<br>Thickness                                       | Low Breakdown Voltage<br>Increase of Leakage Current<br>in Oxide Film   | Same as Above                                                                                                                 |

|                                          | Scratch, Crack, Scar of<br>Photo Mask                                     | Open, Short                                                             | Visual Inspection (Before<br>Seal),<br>Electrical Test                                                                        |

| Mask                                     | Misalignment                                                              | Open, Short                                                             | Same as Above                                                                                                                 |

|                                          | Abnormality of Photo-<br>Resist Pattern (Line-<br>Width, Space, Pin Hole) | Degradation of Characteristics<br>Due to Parameter Drift<br>Open, Short | Same as Above                                                                                                                 |

| Etching                                  | Improper Elimination of<br>Oxide Film                                     | Open, Short, Intermittent<br>Failure                                    | Visual Inspection (Before<br>Seal)<br>Electrical Test<br>Operation Life                                                       |

|                                          | Under-Cut                                                                 | Short or Open in<br>Metallization                                       | Visual Inspection<br>(Before Seal)<br>Electrical Test                                                                         |

| Process Step<br>Affecting<br>Reliability                                                                        | Failure Meçhanism                                                             | Failure Mode                                                  | Failure Detection Method                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Etching                                                                                                         | Spotting (Smear)<br>Inhomogeneous Etching                                     | Latent Short                                                  | Visual Inspection<br>(Before Seal)<br>Temperature Cycle,<br>High Temperature Storage                                        |

|                                                                                                                 | · · · · · · · · · · · · · · · · · · ·                                         |                                                               | Operation Life                                                                                                              |

| Result of the second | Contamination<br>(Photo Resist, Residue<br>of Chemical Substance)             | Low Breakdown Voltage<br>Increase of Leak Current             | Same as Above<br>Reverse Bias                                                                                               |

| Diffusion                                                                                                       | Improper Control of<br>Doping Profile                                         | Performance Degradation<br>Caused by Instability<br>and Fault | High Temperature Storage<br>Temperature Cycling<br>Operation Life<br>Electrical Test                                        |

| · · · · · · ·                                                                                                   | Scratched and Smeared<br>Metallization<br>(Caused During Handling)            | Open and Short                                                | Visual Inspection<br>(Before Seal)<br>Temperature Cycling<br>Operation Life                                                 |

| 1)<br>2944 - 11<br>1968 - 1999<br>1968 - 1999                                                                   | Thin Metallization Due<br>to Insufficient<br>Deposition or Oxide<br>Film Step | Open or High Impedance<br>Internal Connection                 | Electrical Test<br>Operation Life<br>Temperature Cycle                                                                      |

| Metallization                                                                                                   | Oxid Film Contamination<br>Material Incompatibility                           | Open Metallization Caused<br>by Poor Adhesion                 | High Temperature Storage<br>Temperature Cycling<br>Operation Life Test                                                      |

|                                                                                                                 | Corrosion (Residue of<br>Chemical Substance)                                  | Open Metallization                                            | Visual Inspection<br>(Before Seal),<br>High Temperature Storage<br>Temperature Cycle,<br>Operation Life                     |