### Copyright 1989 by Samsung

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photo copying, recording, or otherwise, without the prior written permission of Samsung. The information contained herein is subject to change without notice. Samsung assumes no responsibility for the use of any circuitry other than circuitry embodied in a Samsung product.

No other circuit patent licenses are implied.

# SAMSUNG DATA BOOK LIST

I. Semiconductor Product Guide

II. Transistor Data Book

Vol. 1: Small Signal TR Vol. 2: Bipolar Power TR Vol. 3: TR Pellet

III. Linear IC Data Book

Vol. 1: Audio/Video Vol. 2: Telecom/Industrial Vol. 3: Data Converter IC

IV. CMOS Consumer IC Data Book

V. High Speed CMOS Logic Data Book

VI. MOS Memory Data Book

VII. SFET Data Book

VIII. MPR Data Book

IX. CPL Data Book

X. Dot Matrix Data Book

# TABLE OF CONTENTS

| Ι. | PRODUCT | GUIDE | <br>9 |

|----|---------|-------|-------|

|    |         |       |       |

## II. WHAT IS DATA CONVERTER ...... 13

# III. A/D CONVERTER

| 1. K | SV3100A   | 27 |

|------|-----------|----|

| 2. K | SV3110    | 37 |

| 3. K | SV3208    | 48 |

| 4. K | AD0206    | 56 |

| 5. K | AD0808/09 | 61 |

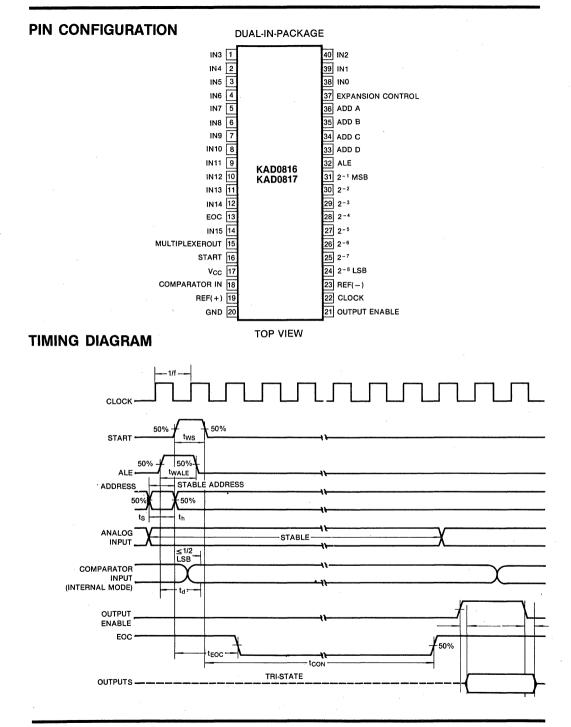

| 6. K | AD0816/17 | 72 |

| 7. K | AD0820    | 82 |

|      | 57126     |    |

|      | ·         |    |

# IV. D/A CONVERTER

| 1. KDA3310       | 105 |

|------------------|-----|

| 2. KDA0406       | 115 |

| 3. KDA0800/08    | 121 |

| 4. KS25C02/03/04 | 127 |

## V. APPLICATION NOTE

|       | 1. A/D, D/A CONVERTER<br>2. KSV3110, KSV3208<br>3. KSV3110 DEMO BOARD<br>4. DIGITAL FILTER | 151<br>161 |

|-------|--------------------------------------------------------------------------------------------|------------|

| VI.   | DATA CONVERSION GLOSSARY                                                                   | 181        |

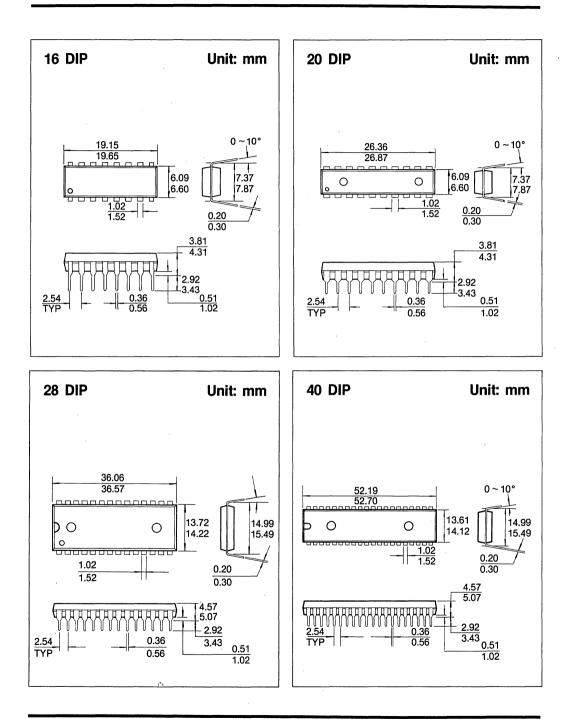

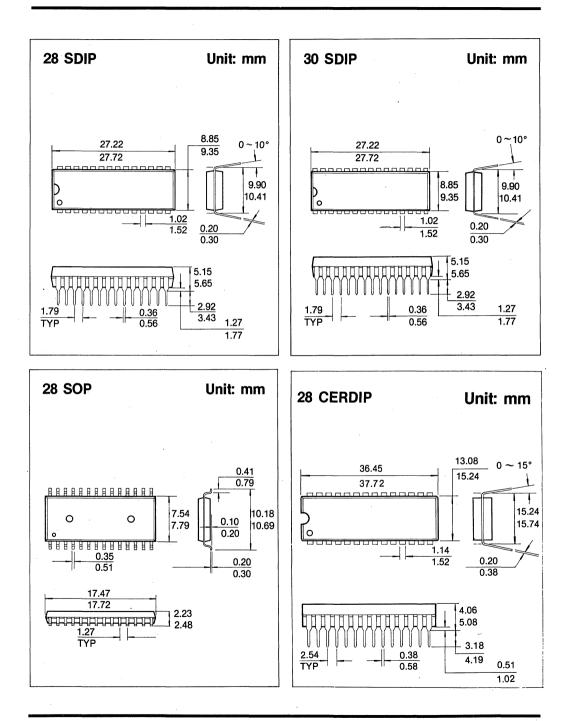

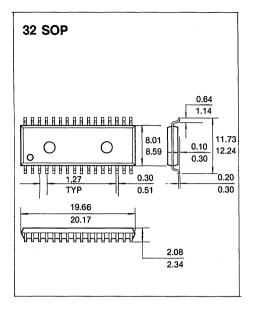

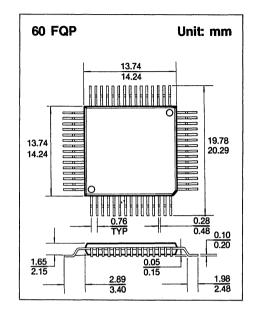

| VII.  | PACKAGE DIMENSIONS                                                                         | 195        |

| VIII. | SALES OFFICES                                                                              | 201        |

# **PRODUCT INDEX**

| Device      | Function                                      | Package        | Page |

|-------------|-----------------------------------------------|----------------|------|

| KSV3100A    | 8 Bit A/D Converter + 10 Bit D/A Converter    | 40 DIP         | 27   |

| *KSV3110    | 8 Bit A/D Converter + 10 Bit D/A Converter    | 40 DIP         | 37   |

| *KSV3208    | 8 Bit A/D Converter (20 MSPS)                 | 28 DIP         | 48   |

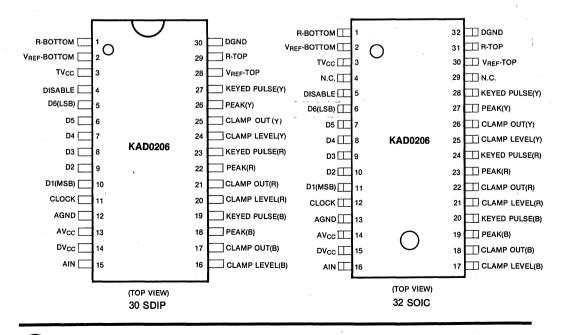

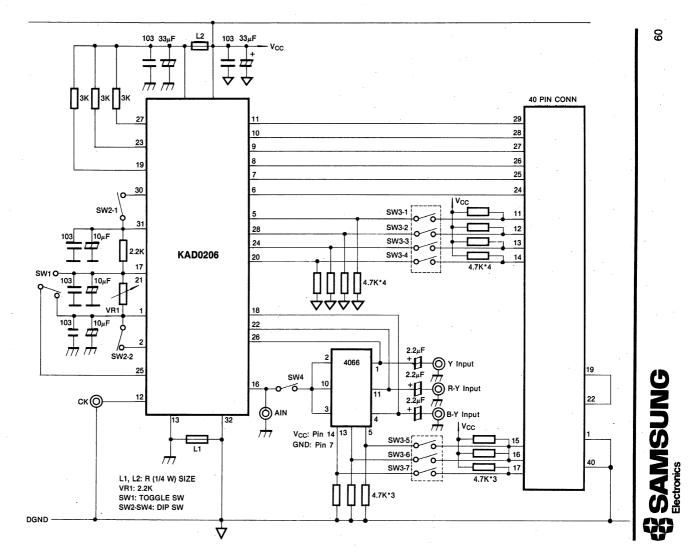

| **KAD0206   | 6 Bit A/D Converter (20 MSPS)                 | 32SOIC/30 SDIP | 56   |

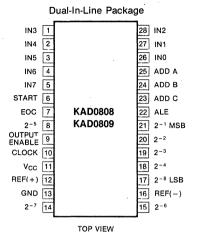

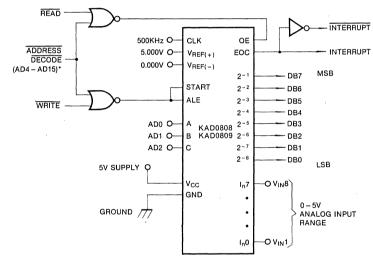

| KAD0808/09  | 8 Bit up-Compatible A/D Converter (8 CH)      | 28 DIP         | 61   |

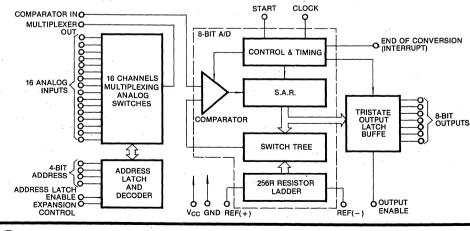

| *KAD0816/17 | 8 Bit up-Compatible A/D Converter (16 CH)     | 40 DIP         | 72   |

| KAD0820     | 8 Bit up-Compatible A/D Converter             | 20 DIP         | 82   |

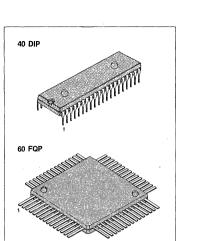

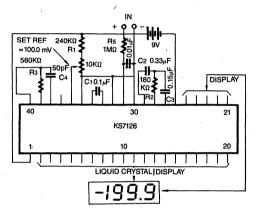

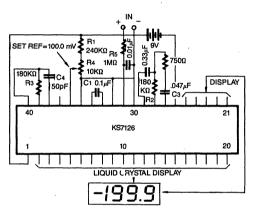

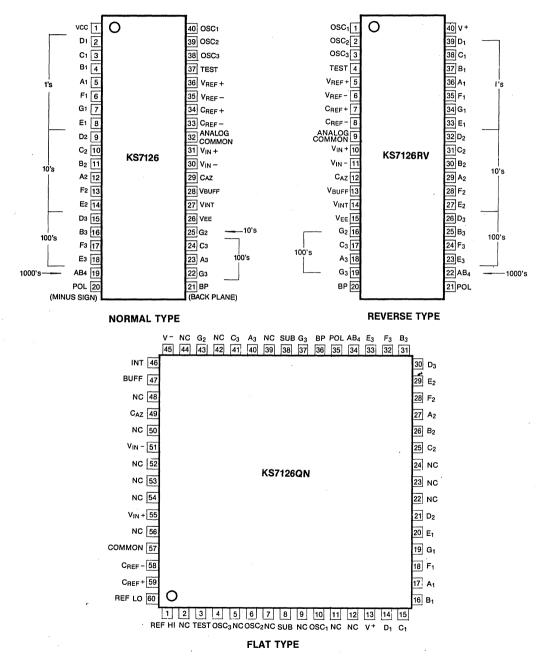

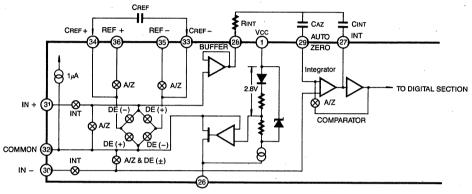

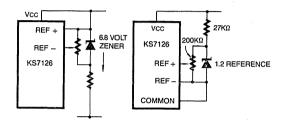

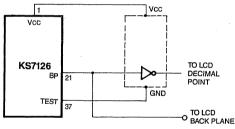

| KS7126      | 3 1/2 Digit A/D Converter                     | 40 DIP/60 FQP  | 90   |

| *KDA3310    | 10 Bit D/A Converter (25 MSPS)                | 28 CERDIP      | 105  |

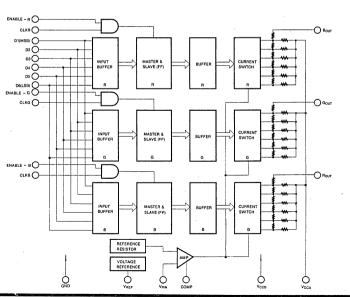

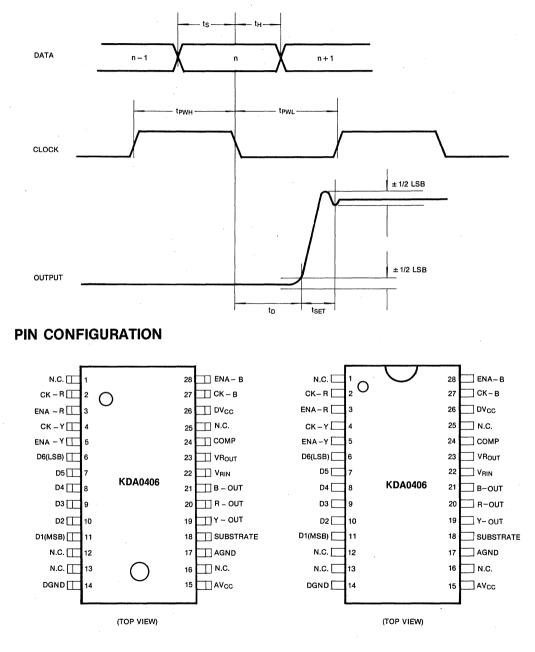

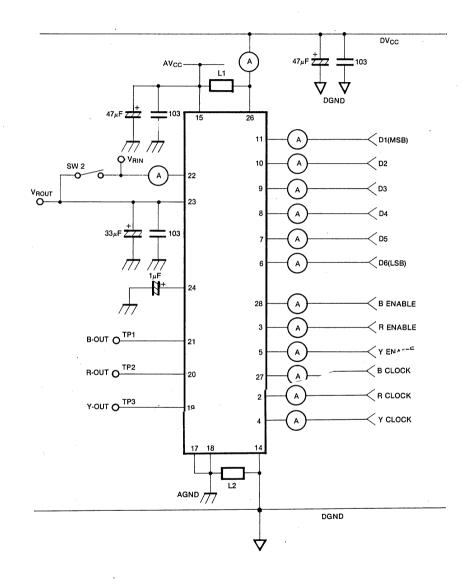

| *KDA0406    | Tripple 6 Bit D/A Converter (20 MSPS)         | 28SOIC/28 SDIP | 115  |

| KDA0800/08  | 8 Bit D/A Converter                           | 16 DIP         | 121  |

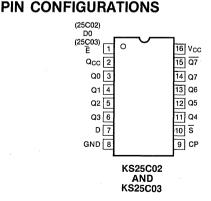

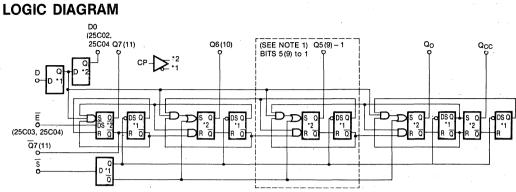

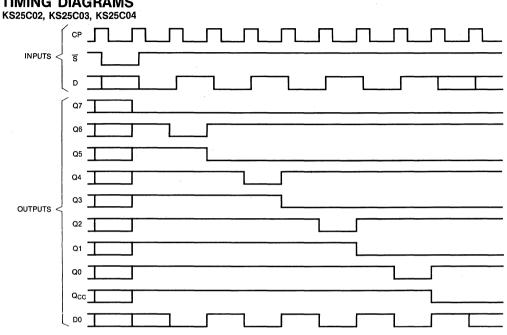

| KS25C02     | 8 Bit CMOS Successive Approximation Register  | 16 DIP         | 127  |

| KS25C03     | 8 Bit CMOS Successive Approximation Register  | 16 DIP         | 127  |

| KS25C04     | 12 Bit CMOS Successive Approximation Register | 16 DIP         | 127  |

\*: New Product

\*\*: Under Development

| পিকটোজন উচ্চাটাই      | 1 |

|-----------------------|---|

| Terror and a hardware | 2 |

| AND COMMENCE          | 3 |

| D/A Convenier         | 4 |

| শ্বহাদিল্যাকান্যগাৰে  | 5 |

| ୌତ୍ୟଙ୍ଗନ୍ତ            | 6 |

| Persiver Dimensions   | 7 |

| Sales Offices         | 8 |

.

# **1. FUNCTION GUIDE**

| Function  | Device           | Package            | Feature                                | Application      |  |

|-----------|------------------|--------------------|----------------------------------------|------------------|--|

| A/D + D/A | KSV3100A         | 40 DIP             | High speed 8 bit A/D + 10 bit D/A      | Image processing |  |

| Converter | *KSV3110         | 40 DIP             | Enhanced version of KSV3100A           | video graphics   |  |

| A/D       | *KSV3200         | 26 DIP             | High speed 8 bit A/D converter         |                  |  |

| Converter | **KAD0206        | 30 SDIP<br>32 SOIC | High speed 6 bit A/D converter         |                  |  |

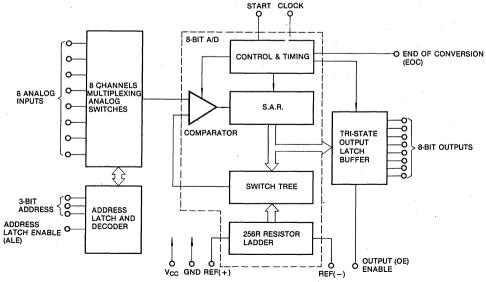

|           | KAD0808/9        | 28 DIP             | 8 bit up-interface A/D with 8 channel  | General purpose  |  |

|           | *KAD0817 40 DIP  |                    | 8 bit up-interface A/D with 16 channel |                  |  |

|           | KAD0820          | 20 DIP             | 8 bit up-interface A/D converter       |                  |  |

| DMM A/D   | KS7126           | 40 DIP/60 FQP      | 3 1/2 digit A/D converter              | DMM              |  |

|           | **KAD7000 48 QFP |                    | 2000-3000 CNT converter                | ] .              |  |

|           | **KAD7001        | 80 QFP             | 3200 CNT converter                     |                  |  |

| D/A       | *KDA3310         | 28 CERDIP          | High speed 10 bit D/A                  | Image processing |  |

| Converter | *KDA0406         | 28 SOIC<br>28 SDIP | High speed tripple 6 bit D/A converter | video graphics   |  |

|           | KDA0800/08       | 16 DIP             | 8 bit D/A converter                    | General purpose  |  |

| S.A.R.    | KS25002/03       | 16 DIP             | 6 bit CMOS S.A.R.                      | SAR of A/D       |  |

|           | KS25C04          | 24 SDIP            | 12 bit CMOS S.A.R.                     | converter        |  |

\* New Product

\*\* Under Development

# 2. CROSS REFERENCE GUIDE

| Application         | SAMSUNG              | N.S.       | ті        | Intersil | Other              | Remark            |

|---------------------|----------------------|------------|-----------|----------|--------------------|-------------------|

| A/D + D/A Converter | KSV3100A             |            |           |          | UVC3101<br>UVC3100 |                   |

|                     | *KSV3110             |            |           |          | UVC3130            | Not<br>Pin to Pin |

| High Speed A/D      | *KSV3208<br>(8 bit)  |            |           |          | CXA1096            | Not<br>Pin to Pin |

|                     | **KAD0206<br>(6 bit) |            |           |          | MB40576            | Not<br>Pin to Pin |

| 8 bit A/D Converter | KAD0808/9            | ADC0808/9  | ADC0808/9 |          |                    |                   |

|                     | *KAD0817             | ADC0817    | ADC0817   |          |                    |                   |

|                     | KAD0820              | ADC0820    |           |          |                    |                   |

| 3-1/2 Digit A/D     | KS7126               |            |           | ICL 7126 | TSC 7126           |                   |

| High Speed D/A      | *KDA3310<br>(10 bit) |            |           |          | TDC1016            | Not<br>Pin to Pin |

|                     | *KDA0406<br>(6 bit)  |            |           | -        |                    |                   |

| 8 bit D/A           | KDA0800/08           | DAC0800/08 |           | AD1408   | MC1408             |                   |

| S.A.R.              | KS25C02/03           | DM25C02/03 |           |          |                    |                   |

|                     | KS25C04              | DM2504     |           |          |                    |                   |

\* New Product

\*\* Under Development

### Introduction to A/D, D/A Converter

### 1. Preface

Digital and analog signal processing correspond to two fundamental, yet distinctly different, modes of information handling. In the analog case, the signals are handled in a nonquantized, continuously variable manner; in digital processing, they are quantized in binary bits, that is, in 1's and 0's. In many cases, it is necessary to interface these two fundamental means of signal processing and to convert the data from digital to analog or vice versa. This is accomplished by the use of digital to analog (D/A) and analog-to-digital (A/D) converter circuits.

In their natural state, all variables (such as current, voltage, pressure, distance, time) appear in analog form. However, for signal transmission and computation purposes, they are often handled in a digital manner. Therefore, the A/D and D/A converter can be considered to be a class of coding and decodig devices, respectively. The input to a D/A converter is a digital word of a prescribed number of bits, and the output is an analog voltage level uniquely corresponding to the input word. Conversely, the analog input applied to the A/D converter results in a digital word of a prescribed number of bits.

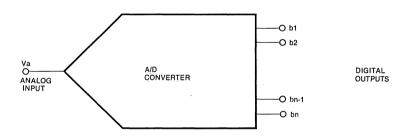

### 2. A/D Converter

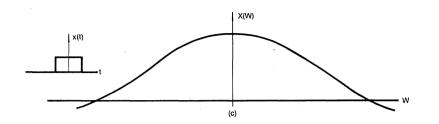

Analog-to-digital converters, also called ADC's or encoders, employ a variety of different circuit techniques to implement the conversion function. The function of an A/D converter is to convert any analog quantity such as a voltage, or a current into a digital word. Figure 1 shows the very simplistic block diagram of an A/D converter circuit.

Fig. 1 Symbolic Block Diagram of A/D Converter

The A/D converter encodes an analog input into a digital output of predetermined bit length. The analog input voltage Va of figure 1 is approximated as a binary fraction of a full-scale output voltage Vfs. Thus, the output of the converter corresponds to an n-bit digital word D given as

$$\frac{Va}{Vfs} = \frac{b1}{2^1} + \frac{b2}{2^2} + \dots + \frac{bn}{2^n}$$

where b1, b2, ..., bn are the binary bit coefficients having a value of either a 1 or a 0.

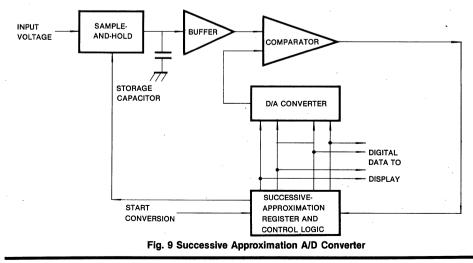

### 1) Successive-Approximation A/D Converters

Of the various A/D conversion techniques available, the choice depends on the resolution and speed required. By far, the most popular A/D conversion technique in general use for moderate to high speed applicatioons is the successive-approximation type A/D. This method falls into a class of techniques known as feedback type A/D converters. In the successive-approximation converter, the DAC is controlled in an optimum manner to complete a conversion in just n-step, where n is the resolution of the converter in bits.

The operation of this converter is analogous to weighing an unknown on a laboratory balance scale using standard weights in a binary sequence such as 1, 1/2, 1/4, 1/8, ....., 1/2<sup>n-1</sup>. The correct procedure is to begin with the largest standard weight and proceed in order down to the smallest one.

The largest weight is placed on the balance pan first; if it does not tip, the weight is left on and the next largest weight is added. The same procedure is used for the next largest weight and so on down to the smallest. After the n'th standard weight has been tried and a decision made, the weighing is finished. The total of the standard weights remaining on the balance is the closest possible approximation to the unknown.

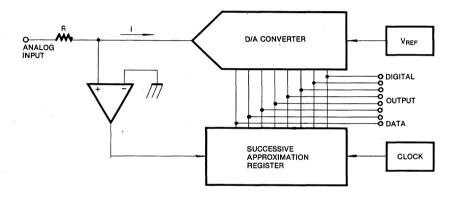

Fig. 2 Functional Block Diagram of Successive-Approximation A/D Converter.

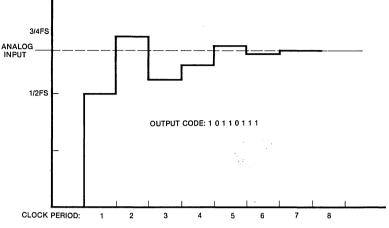

In the successive-approximation A/D converter illustrated in Figure 2, a successive-approximation register (SAR) controls the D/A converter by implementing the weighting logic just described. The SAR first turns on the MSB of the DAC and the comparator tests this output against the analog input. A decision is made by the comparator to leave the bit on or turn it off after which bit 2 is turned on and a second comparision made. After n-comparisions the digital output of the SAR indicates all those bits which remain on and produces the desired digital code. The clock circuit controls the timing of the SAR. Fig. 3 shows the D/A converter output during a typical conversion.

The conversion efficiency of this technique means that high resolution conversions can be made in very short times. For example, it is possible to perform a 10 bit conversion in 1  $\mu$ sec. or less and a 12 bit conversion in 2  $\mu$ sec. or less. Of course the speed of the internal circuitry, in particular the D/A and comparator, are critical for high speed performance.

## What is Data Converter?

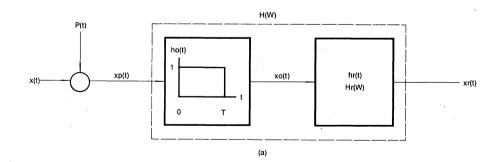

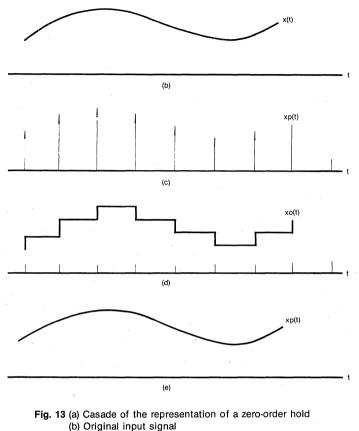

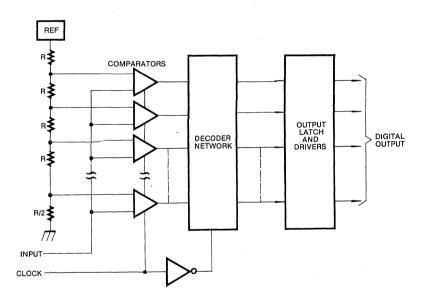

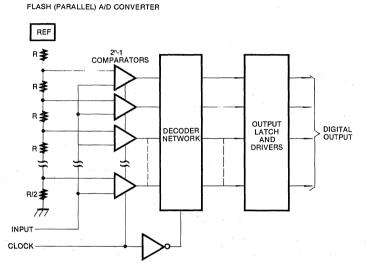

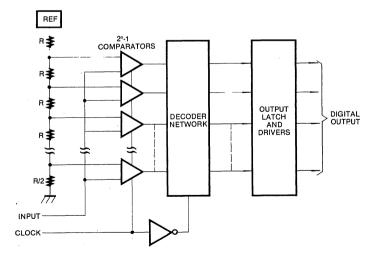

### 2) The Flash (Parallel) A/D Converter

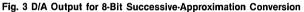

For ultra-fast conversions required in video signal processing, image processing and radar applications where up to 8 bits or the more high bits resolution is required, a different technique is employed; it is known as the flash (also parallel) method and is illustrated in figure 4.

Fig. 4 Functional Block Diagram of Flash A/D Converter

This circuit employs  $2^n - 1$  analog comparators to directly implement the quantizer transfer function of an A/D converter.

The comparator trip-points are spaced a LSB apart by the series resistor chain and voltage reference. For a given analog input voltage all comparators biased below the voltage turn on and all those biased above it remain off. Since all comparators change state simultaneously, the quantization process is a one-step operation.

A second step is required, however, since the logic output of the comparators is not in binary form.

Therefore an ultra-fast decoder circuit is employed to make the logic conversion to binary. The flash technique reaches the ultimate in high speed because only two sequential operations are required to make the conversion.

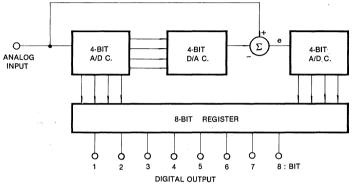

### 3) Subranging (Half-flash) A/D Converter

The limitation of the flash method, however, is in the large number of comparators required for even moderate resolutions. A 4-bit converter, for example, requires only 15 comparators, but an 8-bit converter needs 255. For this reason it is common practice to implement an 8-bit A/D with two 4-bit stage as shown in figure 5.

Fig. 5 Functional Block Diagram of Subranging A/D Converter

The result of the first 4-bit conversion is converted back to analog by means of an ultra-fast 4-bit D/A and then subtracted from the analog input. The resulting residue is then converted by the second 4-bit converter, and the two sets of data are accumulated in the 8-bit output register.

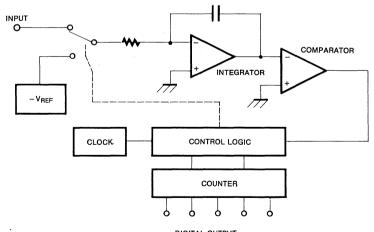

### 4) Integrating A/D Converter (Dual-slope A/D converter)

Integrating A/D converters perform the A/D conversion in an indirect manner. The analog input is first converted to a timing pulse whose duration is proportional to the analog voltage Va. The duration of the timing pulse is then measured in a digital format by counting the number of cycles of a stable reference frequency (the clock signal) between the beginning and the end of the timing pulse. Because of this basic principle of operation, such converters are often called indirect or pulse-width-modulating converters.

The dual-slope-type A/D converter is one of the most popular types of integrating A/D converters. Figure 6 shows the functional block diagram of a dual-slope converter.

DIGITAL OUTPUT Fig. 6 Functional Block Diagram of Dual-Slope A/D Converter.

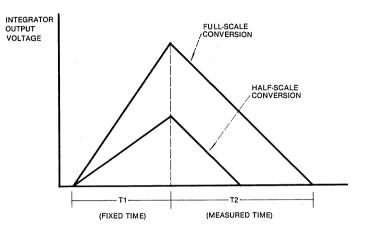

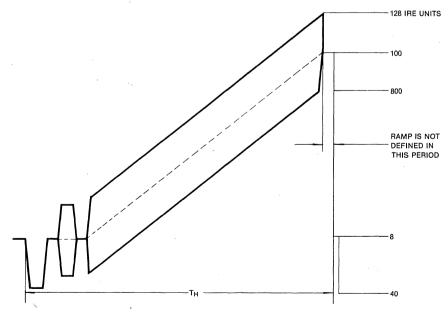

Conversion begins when the unknown input voltage is switched to the integrator input; at the same time the counter begins to count clock pulses and counts up to overflow. At this point the control circuit switches the integrator to the negative reference voltage which is integrated until the output is back to zero. Clock pulses are counted during this time until the comparator detects the zero crossing and turns them off. Figure 7 shows the integrator output waveform for dual-slope A/D converter.

Fig. 7 Integrator Output Waveform for Dual-Slop A/D Converter

The counter output is then the converted digital word. Where T1 is a fixed time and T2 is a time proportional to the input voltage. The times are related as follows:

$$T2 = T1 \frac{V^{|N|}}{V_{REF}}$$

....

The digital output word therefore represents the ratio of the input voltage to the reference. Dual-slope convertion has several important features. First, convertion accuracy is independent of the stability of the clock and integrating capacitor so long as they are constant during the conversion period. Accuracy depends only on the reference accuracy and the integrator circuit linearity. Second, the noise rejection of the converter can be infinite if T1 is set to equal the period of the noise. To reject 60Hz power noise therefore requires that T1 be 16.667 msec.

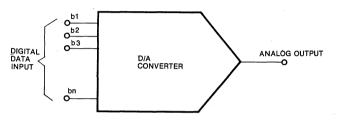

### 3. D/A Converter

The digital-to analog conversion circuits, which are also called D/A converters, or DACs, can be considered as decoding devices that accept digitally coded signals and provide analog outputs in the form of circuits or voltages. In this manner, they provide an interface between the digital signals of the computer systems and continuous signals of the analog world. They are employed in a variety of applications from CRT display systems and voice synthesizers to automatic test systems, digital controlled attenuators, and process control actuators. In addition, they are key components inside most A/D converters.

Figure 8 shows the functional block diagram of a basic D/A converter system. The input to the D/A converter is a digital word, made up a stream of binary bits comprised of 1's and 0's. The output analog quantity A, which can be a voltage or current, is related to the input as

$$A = KV_{REF} \left( \frac{b1}{2^1} + \frac{b2}{2^2} + \dots + \frac{bn}{2^n} \right)$$

where K is a scale factor,  $V_{REF}$  is a reference voltage, n is the total number of bits, and b1, b2, ... bn are the bit coefficient, which are quantized to be a 1 or a 0.

Fig. 8 Functional Block Diagram of a Basic D/A Converter

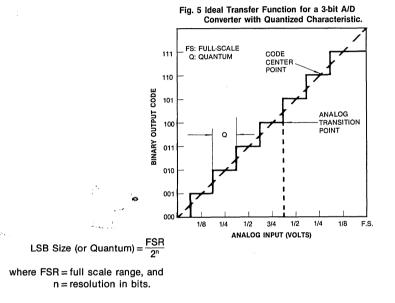

As a function of the input binary word which determines the bit coefficients, the output exhibits 2<sup>n</sup> discrete voltage levels ranging from zero to a maximum value of

$$(Vo)max = V_{REF} \frac{2^n - 1}{2^n}$$

with a minimum step change riangle Vo given as

$$\triangle Vo = \frac{V_{REF}}{2^n}$$

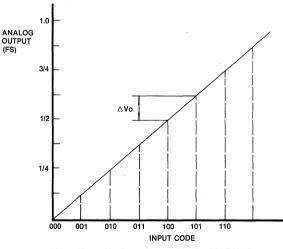

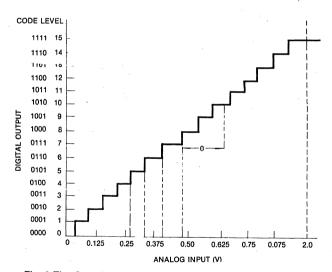

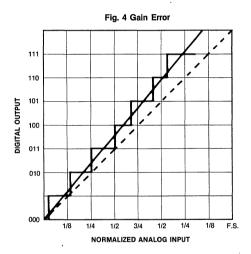

The transfer function of an ideal 3-bit D/A converter is shown in figure 9.

Fig. 9 Transfer Function of Ideal 3-bit D/A Converter

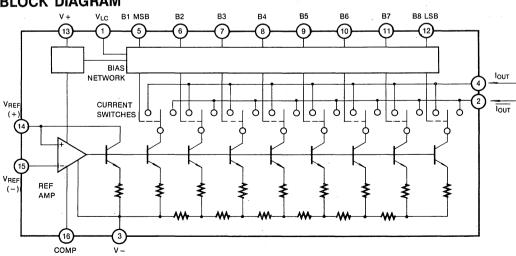

### 1) Current Scaling D/A Converter

#### A. Weighted Current Source D/A Converter

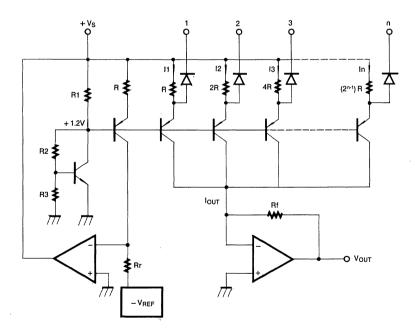

The most popular D/A converter design in use today is the weighted current sources circuit illustrated in figure 10. An array of switched transistor current sources is used with binary weighted currents.

$I_1 = 2 I_2 = 4 I_3 = \dots = (2_n - 1) I_n$

The binary weighting is achieved by using emitter resistors with binary related values of R, 2R, 4R, ... 2<sup>n-1</sup>R. The resulting collector currents are then added together at the current summing line.

The current sources are switched on or off from standard TTL input by means of the control diodes connected to each emitter. When the TTL input is high the current source is on; when the input is low it is off, with the current flowing through the control diode. Fast switching speed is achieved because there is direct control of the transistor current, and the current source never go into saturation.

To interface with standard TTL levels, the current sources are biased to a base voltage of +1.2V. The emitter currents are regulated to constant values by means of the control amplifier and a precision voltage reference circuit together with a bipolar transistor.

The summed output currents from all current source that are on go to an operational amplifier summing junction; the amplifier converts this output current into an output voltage. In some D/A converters the output current is used to directly drive a resistor load for maximum speed, but the positive output voltage in this case is limited to about +1 volt.

Fig. 10 Weighted Current Source D/A Converter

#### B. R-2R Ladder D/A Converter

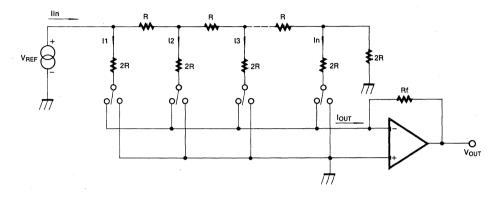

A second popular technique for D/A convertion is the R-2R ladder method. As shown in figure 11, the network consists of series resistor of value R and shunt resistors of value 2R. The bottom of each shunt resistor has a singlepole duble-throw electronic switch which connects the resistor to either ground or the output current summing line.

Fig. 11 R-2R Ladder D/A Converter

The operation of the R-2R ladder network is based on the binary division of current as it flows down the ladder. Examination of the ladder configuration reveals that at point a looking to the right, one measures a resistance of 2R; therefore the reference input to the ladder has a resistance of R. At the reference input the current splits into two equal parts since it sees equal resistances in either direction. Likewise, the current flowing down the ladder to the right continues to divide into two equal parts at each resistor junction.

The result is binary weighted currents flowing down each shunt resistor in the ladder. The digitally controlled switches direct the currents to either the summing line or ground. Assuming all bits are on as shown in the diagram, the output current is

$$I_{OUT} = \frac{V_{REF}}{R} (1/2 + 1/4 + 1/8 \dots + 1/2^n)$$

which is a binary series. The sum of all currents is then

$$I_{OUT} = \frac{V_{REF}}{B} (1 - 2^{-n})$$

where the 2 term physically represents the portion of the input current flowing through the 2R terminating resistor to ground at the far right.

As in the previous circuit, the output current summing line goes to an operational amplifier which converts current to voltage.

### $V_{OUT} = - Rf I_{OUT}$

The advantage of the R-2R ladder technique is that only two values of resistors are required, with the resultant ease of matching or trimming and excellent temperature tracking. In addition, for high speed applications relatively low resistor values can be used. Excellent results can be obtained for high resolution D/A converters by using laser-trimmed thin film resistor networks.

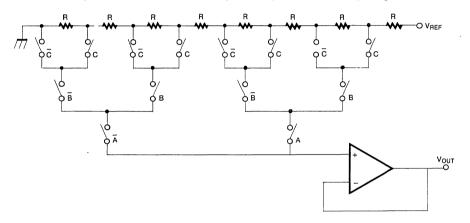

### 2) Voltage-Scaling D/A Converter

Voltage-scaling D/A converters produce an analog output voltage by selectively "tapping" a voltage-divider resistor string connected between the reference voltage and ground. For n-bit converter circuit, the resistor string is made up of 2 identical segments connected in series, and it is used as a potentiometer where the voltage levels between the resistor segments are sampled by means of binary switches. For this reason, these types of converters are also called potentiometric D/A converters. Figure 12 shows the conceptual diagram of a 3-bit D/A converter operating on the voltage-scaling principle. The resistor string is comprised of eight identical resistor, connected between V<sub>REF</sub> and ground. The voltage drop across each resistor section is equal to 1 LSB of output voltage change, or V<sub>REF</sub>/2<sup>n</sup>. The output is sampled by means of a decoding switch matrix, and is sensed by a high-impedance buffer amplifier or voltage follower.

With reference to figure 12, the operation of the switch matrix which decodes the input logic signal into an analog voltage can be described as follows. The analog switches marked A, B, and C are driven by the input logic lines corresponding to the input bits b1, b2 and b3, where b1 corresponds to the MSB and b3 corresponds to the LSB. The switches designated A, B and C are driven by the complements of the input logic levels.

Fig. 12 3-Bit D/A Converter Example Using Voltage-Scaling Principle

The voltage-scaling D/A converter finds its widest application as a building block in MOS A/D conversion systems, where it is used as the D/A converter subsection of a successive-approximation-type A/D converter.

# NOTES

### **HIGH-SPEED A/D-D/A CONVERTER**

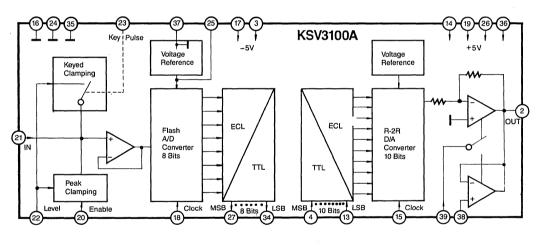

Samsung KSV3100A, VLSI circuit in CI (Collector Implanted) technology, consists of a high-speed flash-type 8-bit A/D converter and a high-speed low-glitch 10-bit D/A converter designed as an R-2R network with switched current sources. Also, the various auxiliary circuits, as reference voltage sources, pre-amplifier, input clamping circuit and feed-in output amplifier are integrated on the single chip.

KSV3100A has been developed for use in all applications which call for a high-speed A/D-D/A converter.

For instance, this VLSI circuit can be used to advantage to decode television signals in Pay-TV converters or for MAC converters used in direct satellite broadcast.

Other promising applications can be seen in industrial electronics, e.g. in conjunction with signal processing.

Although KSV3100A was initially designed as high-speed codecs for the video range, it can be used with equal benefits for lower frequencies, even down to zero.

3

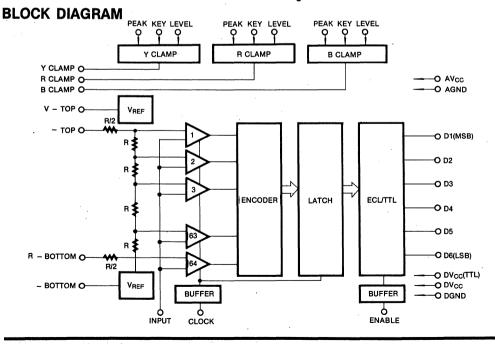

## **BLOCK DIAGRAM**

Fig. 1

The auxiliary circuits contained on-chip provide versatile potential applications needing a minimum of external components. For example, an impedance converter is connected upstream of the A/D converter to provide a high-impedance signal input, in spite of the high input capacitance of the A/D converter. The reference voltage for the A/D converter is generated on-chip, but both the ground of the circuit and the reference voltage are fed to pins, so that an external filter capacitor may be connected.

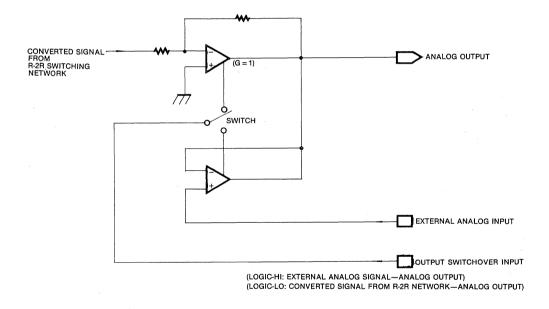

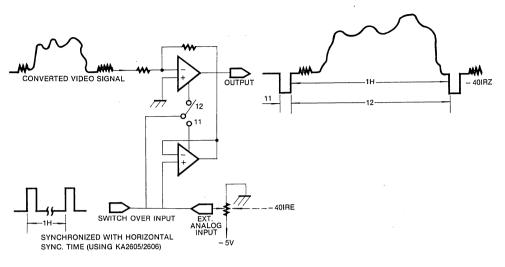

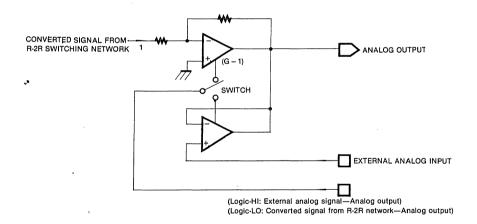

Further, the input is equipped with switches which optionally provide operation with keyed clamping or peak clamping or without clamping. Also the D/A converter's reference voltage is generated on-chip, and a gated amplifier is arranged at the output of the D/A converter so that an external analog signal can be fed-in instead of the signal delivered by the D/A converter.

Separate clock inputs are provided for the A/D converter and the D/A converter thus enabling the application of time compression procedures.

All inputs and outputs are TTL compatible.

## **PIN DESCRIPTION**

| Pin No. | Description                              | Pin No. | Description                       |

|---------|------------------------------------------|---------|-----------------------------------|

| 1       | No Connection                            | 21      | Analog Input A/D Converter        |

| 2       | Analog Output D/A Converter              | 22      | Clamping Level Input              |

| 3       | -5V Supply D/A Converter-Analog          | 23      | Clamping Pulse Input              |

| 4       | Digital Input Bit 9 (MSB)                | 24      | Analog Ground A/D Converter       |

| 5       | Digital Input Bit 8                      | 25      | Reference Voltage A/D Converter   |

| 6       | Digital Input Bit 7                      | 26      | +5V Supply A/D Converter-Digital  |

| 7       | Digital Input Bit 6                      | 27      | Digital Output Bit 7 (MSB)        |

| 8       | Digital Input Bit 5                      | 28      | Digital Output Bit 6              |

| 9       | Digital Input Bit 4                      | 29      | Digital Output Bit 5              |

| 10      | Digital Input Bit 3                      | 30      | Digital Output Bit 4              |

| 11      | Digital Input Bit 2                      | 31      | Digital Output Bit 3              |

| 12      | Digital Input Bit 1                      | 32      | Digital Output Bit 2              |

| 13      | Digital Input Bit 0 (LSB)                | 33      | Digital Output Bit 1              |

| 14      | + 5V Supply D/A Converter-Analog-Digital | 34      | Digital Output Bit 0 (LSB)        |

| 15      | Clock Input D/A Converter                | 35      | Digital Ground A/D Converter      |

| 16      | GND D/A Conv. & Clock A/D Converter      | 36      | +5V Supply A/D Converter-Analog   |

| 17      | -5V Supply A/D Converter-Analog          | 37      | GND of Ref. Voltage A/D Converter |

| . 18    | Clock Input A/D Converter                | 38      | External Analog Input             |

| 19      | +5V Supply A/D Converter                 | 39      | Output Signal Switchover Input    |

| 20      | Peak Clamping Enable Input               | 40      | No Connection                     |

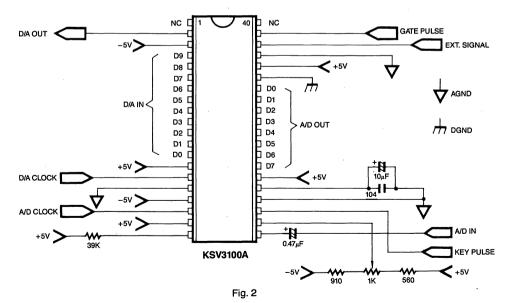

# **TEST CIRCUIT**

# **ABSOLUTE MAXIMUM RATINGS**

| Characteristics                     | Symbol           | Value                        | Unit |

|-------------------------------------|------------------|------------------------------|------|

| Positive Supply Voltage             | Vcc              | 6                            | v    |

| Negative Supply Voltage             | VEE              | -6                           | v    |

| Input Voltages (Digital)            | V <sub>1</sub>   | $-0.5 \sim V_{\rm cc} + 0.5$ | v    |

| Input Voltages (Analog)             | V <sub>I</sub>   | $-0.5 \sim V_{\rm cc} + 0.5$ | v    |

| Output Current Pin 2                | I.               | ± 10                         | mA   |

| Ambient Operating Temperature Range | Ta               | 0 ~ + 70                     | •C   |

| Storage Temperature Range           | T <sub>stg</sub> | -40 ~ +125                   | °C   |

# **RECOMMENDED OPERATING CONDITIONS**

| Characteristics                       | Symbol           | Min    | Тур           | Max                | Unit       |

|---------------------------------------|------------------|--------|---------------|--------------------|------------|

| Positive Supply Voltage               | V <sub>cc</sub>  | 4.75   | 5             | 5.25               | v          |

| Negative Supply Voltage               | VEE              | - 4.75 | -5            | - 5.25             | v          |

| A/D Converter                         |                  |        |               |                    |            |

| Analog Input Voltage                  | V1               | 0      | _             | 2                  | v          |

| Input Frequency, Analog Input         | f <sub>1</sub>   | . —    | i —           | f <sub>cl</sub> /2 | _          |

| Clock Amplitude                       | V <sub>18H</sub> | 2.0    | _             | V <sub>cc</sub>    | v          |

|                                       | V <sub>18L</sub> | 0      | _             | 0.8                | V I        |

| Conversion Rate                       | f <sub>18</sub>  | 0      | -             | 20                 | MSPS*      |

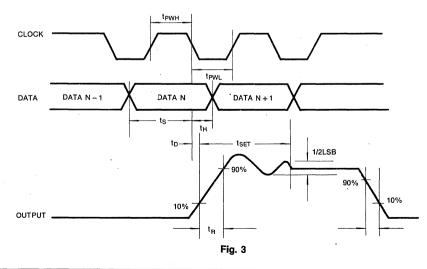

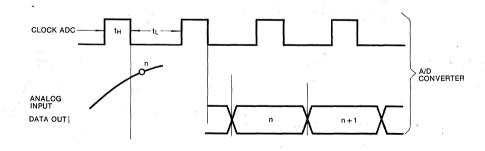

| Clock High Time (See Fig. 3)          | t <sub>H</sub>   | 15     | -             | —                  | ns         |

| Clock Low Time (See Fig. 3)           | t_               | 35     | _             | -                  | ns         |

| A/D Output Voltage                    | V <sub>он</sub>  | 2.4    | —             | Vcc                | V          |

|                                       | VoL              | · 0    | —             | 0.4                | v          |

| Clamping Level                        | V <sub>22</sub>  | -1     | -             | +2                 | V          |

| Clamping Pulse                        | V <sub>23H</sub> | 2.0    | —             | Vcc                | V          |

|                                       | V <sub>23L</sub> | 0      | _             | 0.8                | V          |

| Activation of Peak Clamping           | }                | 1      | stor of 20 to |                    |            |

| Activation of Feak Olamping           |                  | fron   | n Pin 20 to   | + 5V               |            |

| D/A Converter                         |                  |        |               |                    |            |

| Clock Amplitude                       | V <sub>15H</sub> | 2.0    | - 1           | V <sub>cc</sub>    | v          |

|                                       | V <sub>15L</sub> | 0      | _             | 0.8                | v          |

| Conversion Rate                       | f <sub>15</sub>  | 0      |               | 20                 | MSPS*      |

| Digital Input Voltage                 | VIH              | 2.0    | _             | Vcc                | V          |

|                                       | V <sub>IL</sub>  | 0      | —             | 0.8                | <b>V</b> . |

| Analog Input Voltage at Pin 38        | V <sub>38</sub>  | -1     | - 1           | +3                 | v          |

| Output Signal Switch Over Input       | ļ                |        |               | l                  |            |

| for the D/A Converter Out             | V <sub>39</sub>  | 0      | —             | 0.8                | v          |

| for the Ext. Signal (from Pin 38) Out | V <sub>39</sub>  | 2      |               | V <sub>cc</sub>    | v          |

\* MSPS (Mega Sample Per Second)

# KSV3100A

# LINEAR INTEGRATED CIRCUIT

# **ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 5V$ , $V_{EE} = -5V$ , $f_{15} = 20MHz$ , $f_{18} = 20MHz$ , $Ta = 25^{\circ}C$ )

| Characteristic                                                                        | Symbol                             | Min                        | Тур           | Мах                                   | Unit     |

|---------------------------------------------------------------------------------------|------------------------------------|----------------------------|---------------|---------------------------------------|----------|

| Current Consumption                                                                   | I <sub>CC</sub><br>I <sub>EE</sub> | -                          | 90<br>- 80    | 120<br>- 110                          | mA<br>mA |

| Power Dissipation                                                                     | Ртот                               |                            | -             | 1.2                                   | w        |

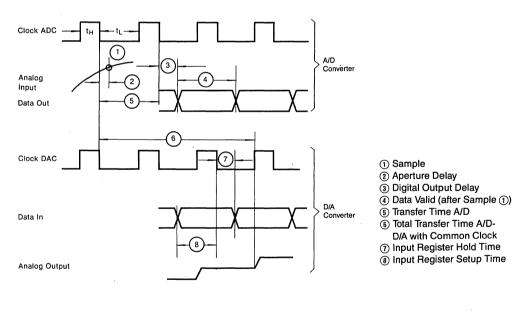

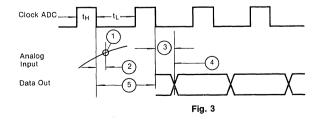

| Total Transfer Time A/D-D/A                                                           | t <sub>TOT</sub>                   |                            | See Fig. 3    | · · · · · · · · · · · · · · · · · · · | -        |

| A/D Converter                                                                         |                                    |                            |               |                                       |          |

| Input Current Pin 21                                                                  | lı lı                              |                            | 2             | -                                     | μΑ       |

| Input Capacitance Pin 21                                                              | Cı                                 | -                          | 10            | · _                                   | pF       |

| Input Impedance Pin 21                                                                |                                    |                            | ,             |                                       |          |

| at f=1KHz                                                                             | Zı                                 | -                          | 20            | -                                     | MΩ       |

| at f=10MHz                                                                            | Zı                                 |                            | 100           |                                       | ΚΩ       |

| 3dB Bandwidth of the Input Amp.                                                       | _                                  | -                          | 50            |                                       | MHz      |

| Keyed Clamping Active Level                                                           | V <sub>23</sub>                    | 2.0                        | _             | Vcc                                   | v        |

| On Resistance of the Clamping Switch<br>Between Pin 21 and 22                         | R <sub>on</sub>                    | -                          | 300           | -                                     | Ohm      |

| Input Current of the Clamping Level<br>Input Pin 22 ( $V_{20} = 3V$ , $V_{22} = 2V$ ) | I <sub>22</sub>                    |                            | 150           |                                       | μA       |

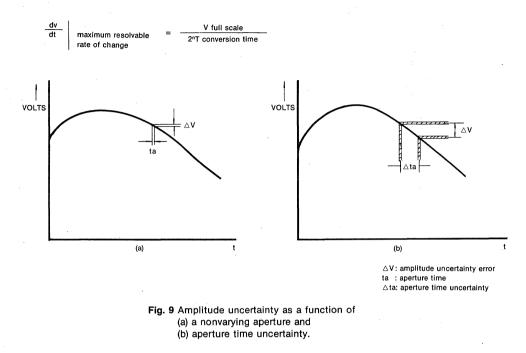

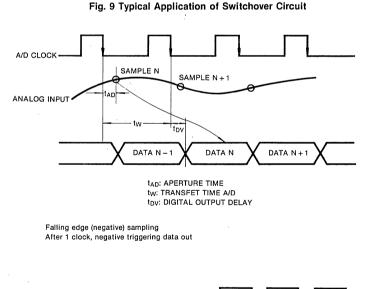

| Aperture Delay ( 2 in Fig. 3)                                                         | t <sub>AD</sub>                    | -                          | -             | 10                                    | ns       |

| Digital Output Delay ( 3 in Fig. 3)                                                   | t <sub>DV</sub>                    | -                          | 25            | -                                     | ns       |

| Transfer Time ( 6 in Fig. 3)                                                          | tw                                 | C                          | Dne clock pe  | riod                                  | _        |

| Differential Non-Linearity                                                            | -                                  | See "Ordering Information" |               | -                                     |          |

| Absolute Non-Linearity                                                                | _                                  | _                          | 1             |                                       | %        |

| Number of Bits                                                                        | -                                  |                            | 8             |                                       | _        |

| Code of the Digital Output Signal                                                     | _                                  |                            | Binary        |                                       | _        |

| Output CODE at the Input with $V_{21} = 0V$<br>with $V_{21} = V_{ref}$                |                                    | 00000000                   |               | _                                     |          |

| Internal Reference Voltage                                                            | V <sub>25</sub>                    | 1.8                        | 2.0           | 2.2                                   | v        |

| D/A Converter                                                                         |                                    |                            |               |                                       |          |

| Output Impedance Pin 2                                                                | Zo                                 | _                          | 15            | —                                     | Ω        |

| Input Current Pin 38 (V <sub>38</sub> =2V)                                            | l <sub>iD</sub>                    | -                          | 0.6           |                                       | mA       |

| Internal Reference Voltage                                                            | V <sub>ref</sub>                   | 1.8                        | 2.0           | 2.2                                   | v        |

| Input Resister Hold Time ( ① in Fig. 3)                                               | t <sub>ін</sub>                    | 6.0                        | -             | -                                     | ns       |

| Input Resister Setup Time ( () in Fig. 3)                                             | t <sub>iH</sub>                    | 20                         |               |                                       | ns       |

| Differential Non-Linearity                                                            | -                                  | See "(                     | Ordering Info | rmation"                              | _        |

| Absolute Non-Linearity                                                                | _                                  | -                          | 1             |                                       | %        |

| Number of Bits                                                                        | -                                  | -                          | 10            | _                                     | _        |

| Code of the Digital Input Signal                                                      | _                                  |                            | Binary        |                                       | _        |

| Output Signal at the Input<br>with 0 0 0 0 0 0 0 0 0 0<br>with 1 1 1 1 1 1 1 1 1 1    | V <sub>2</sub><br>V <sub>2</sub>   | -                          | 0 2           | •                                     | v<br>v   |

| Settling Time                                                                         | t <sub>s</sub>                     | <u> </u>                   | 50            |                                       | ns       |

## **ORDERING INFORMATION**

KSV3100A has four kind of version according to the accuracy bit (so called 'Precision') of D/A Converter, and their marking specifications are as follow;

| Device        | Package | Temperature Range | D/A Converter |                    | A/D Converter      |

|---------------|---------|-------------------|---------------|--------------------|--------------------|

|               |         |                   | Accurary Bit  | Diff. Nonlinearity | Diff. Nonlinearity |

| KSV3100ACN-10 | 40 DIP  | 0 ~ + 70°C        | 10 bit        | ± 1/2 LSB          | ± 1/2 LSB          |

| KSV3100ACN-9  |         |                   | 9 bit         | ±1 LSB             |                    |

| KSV3100ACN-8  |         |                   | 8 bit         | ±2 LSB             |                    |

| KSV3100ACN-7  |         |                   | 7 but         | ±4 LSB             |                    |

\* The accuracy of A/D Converter can be guaranteed as '8 bit' (differential nonlinearity =  $\pm 1/2$  LSB) regardless of the D/A Converter's accuracy.

## TIMING DIAGRAM

Fig. 3

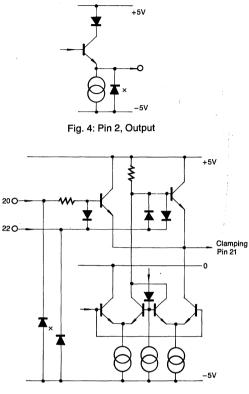

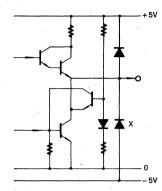

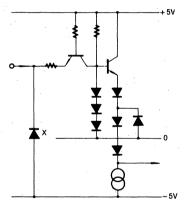

## INNER CONFIGURATION OF THE CONNECTION PINS

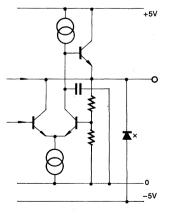

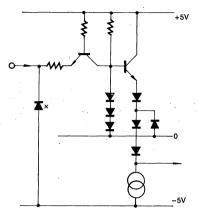

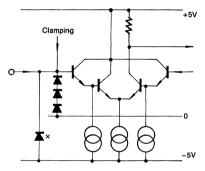

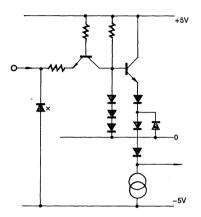

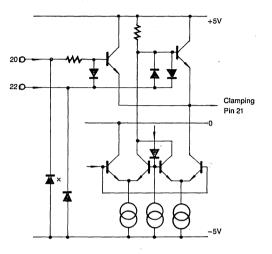

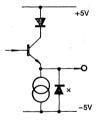

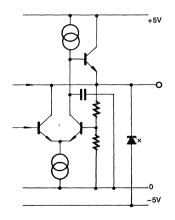

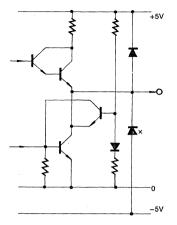

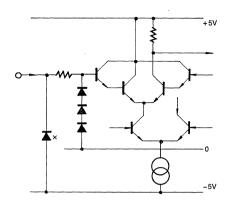

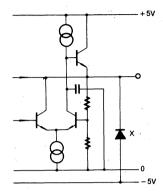

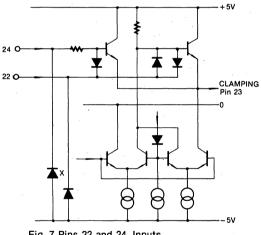

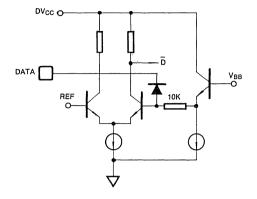

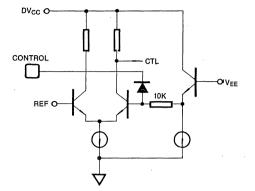

The following figures schematically show the circuitry at the various pins.

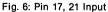

Fig. 6: Pins 20 and 22, Inputs

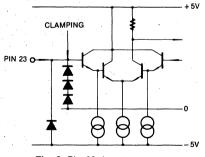

Fig. 8: Pin 25, Reference Voltage Pin

Fig. 5: Pins 4 to 13, 15, 18, 23 and 39, Inputs

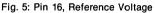

Fig. 7: Pin 21, Input

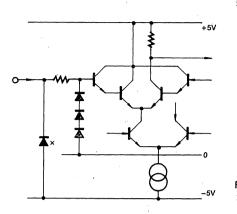

Fig. 10: Pin 38, Input x=protection diode

# DESCRIPTION OF THE CONNECTIONS AND THE SIGNALS

| Pin No.     | Description                                                                                                                                                                                                    |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin 1       | No Connection                                                                                                                                                                                                  |  |  |  |

| Pin 2       | Analog Output D/A Converter<br>This pin whose diagram is shown in Fig. 4, is the output for the processed analog signal<br>either originating from the D/A converter or from the external analog input pin 38. |  |  |  |

| Pin 3       | –5 Volt Supply D/A Converter, Analog<br>This pin gets the negative supply for the analog part of the D/A converter.                                                                                            |  |  |  |

| Pin 4 to 13 | Digital Inputs Bit 9 to Bit 0<br>This diagram of these pins is shown in Fig. 5. They are the inputs of the D/A converter and<br>not-used inputs should be connected to the ground.                             |  |  |  |

| Pin 14      | +5 Volt Supply D/A Converter, Digital<br>This pin gets the positive supply for the digital part of the D/A converter.                                                                                          |  |  |  |

| Pin 15      | Clock Input D/A Converter<br>This pin whose diagram is shown in Fig. 5 must be supplied with the clock signal for the<br>D/A converter.                                                                        |  |  |  |

| Pin 16      | Ground D/A Converter and Clock A/D Converter<br>This pin serves as ground pin for the D/A converter and for the clock of the A/D converter.                                                                    |  |  |  |

| Pin 17      | –5 Volt Supply A/D Converter, Analog<br>This pin is the negative supply pin for the analog part of the A/D converter.                                                                                          |  |  |  |

| Pin 18      | Clock Input A/D Converter<br>The diagram of this pin is shown in Fig. 5. Pin 18 is supplied with the clock of the A/D<br>converter.                                                                            |  |  |  |

| Pin 19      | +5 Volt Supply A/D Converter<br>Via this pin the A/D converter gets its positive supply.                                                                                                                       |  |  |  |

| Pin 20      | Peak Clamping Enable Input<br>Via pin 20 whose diagram is shown in Fig. 6, the peak clamping facility can be enabled.                                                                                          |  |  |  |

3

# DESCRIPTION OF THE CONNECTIONS AND THE SIGNALS (Continued)

| Pin No.      | Description                                                                                                                                                                                                                                   |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin 21       | Analog Input A/D Converter<br>Fig. 7 is the diagram of this input. To pin 21 is applied the analog signal to be converted<br>into digital.                                                                                                    |  |  |  |

| Pin 22       | Clamping Level Input<br>Via this pin whose diagram is shown in Fig. 6, the input of the A/D converter is supplied<br>with the desired clamping level.                                                                                         |  |  |  |

| Pin 23       | Clamping Pulse Input<br>Fig. 5 is the diagram of this input. Pin 23 must be supplied with the key pulse if keyed<br>clamping is required.                                                                                                     |  |  |  |

| Pin 24       | Analog Ground A/D Converter<br>This pin serves as ground pin for the analog part of the A/D converter.                                                                                                                                        |  |  |  |

| Pin 25       | Reference Voltage A/D Converter<br>This pin whose diagram is shown in Fig. 8, is intended for connecting a decoupling<br>capacitor to the A/D converter's reference voltage, the other end of this capacitor to pin 37.                       |  |  |  |

| Pin 26       | +5 Volt Supply A/D Converter, Digital<br>This pin is the positive supply pin for the digital part of the A/D converter.                                                                                                                       |  |  |  |

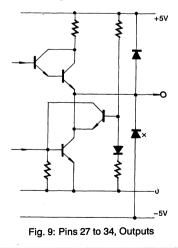

| Pin 27 to 34 | Digital Outputs Bit 7 to Bit 0<br>Fig. 9 shows the diagram of these outputs which supply the digitized analog signal in<br>parallel 8-bit code.                                                                                               |  |  |  |

| Pin 35       | Digital Ground A/D Converter<br>This pin is the ground connection for the digital part of the A/D converter.                                                                                                                                  |  |  |  |

| Pin 36       | +5 Volt Supply A/D Converter, Analog<br>This pin is the positive supply pin for the analog part of the A/D converter.                                                                                                                         |  |  |  |

| Pin 37       | Ground of Reference Voltage A/D Converter<br>To this pin must be connected the ground end of the decoupling which is at pin 25.                                                                                                               |  |  |  |

| Pin 38       | External Analog Input<br>The diagram of this input is shown in Fig. 10. Pin 38 serves for feeding an external analog<br>signal into the output amplifier of the KSV3100A instead of the D/A-converted signal<br>originating from pin 4 to 13. |  |  |  |

| Pin 39       | Output Signal Switchover Input<br>This pin whose diagram is shown in Fig. 5, is intended for enabling the external analog<br>signal fed to pin 38.                                                                                            |  |  |  |

| Pin 40       | No Connection                                                                                                                                                                                                                                 |  |  |  |

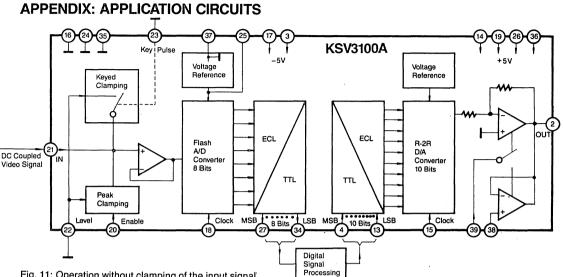

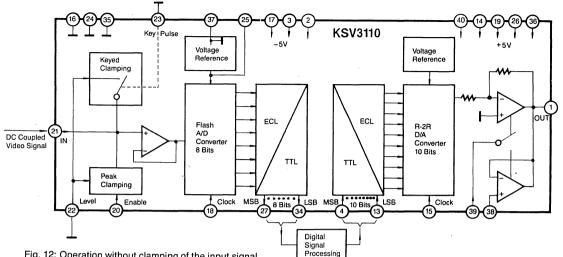

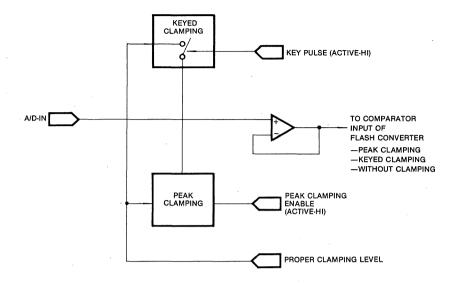

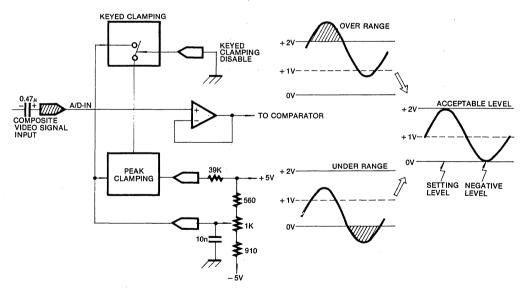

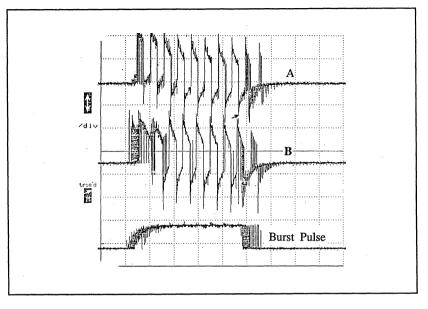

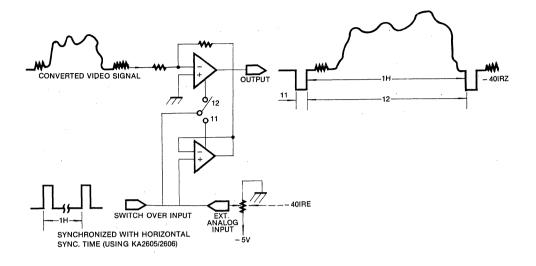

Fig. 11: Operation without clamping of the input signal

Pin 20 (peak clamping enable input) should be opened, while pin 23 (clamping pulse input) remains at 0V. The input signal is applied to the analog input, pin 21, without coupling capacitor such that it lies between 0 and + 2V.

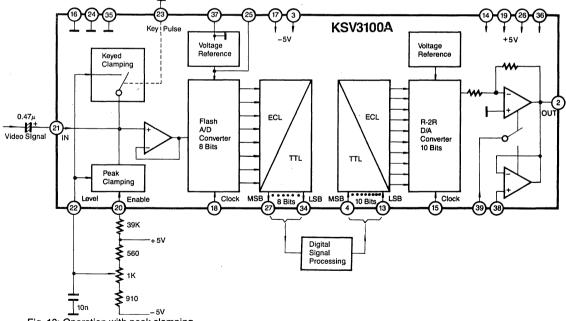

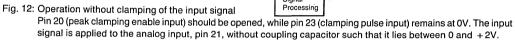

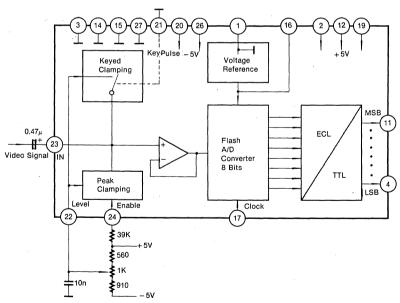

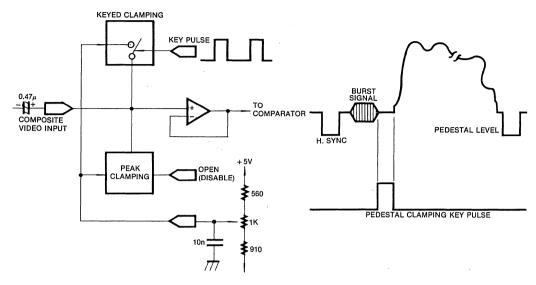

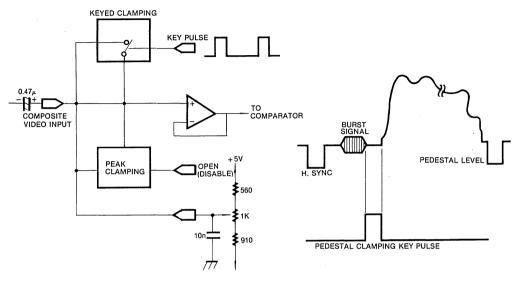

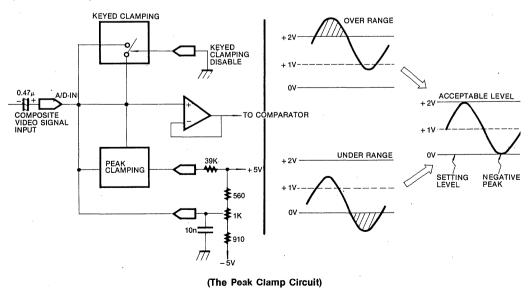

Fig. 12: Operation with peak clamping

The input signal is clamped automatically to the negative peak value. Pin 20 is connected to +5V via a 39KΩ resistor, and pin 22 (clamping level input) is connected, as desired, to zero or a voltage between - 1 and + 2V. The input signal is fed to pin 21 by way of a coupling capacitor, and no key pulse (clamping pulse) is needed.

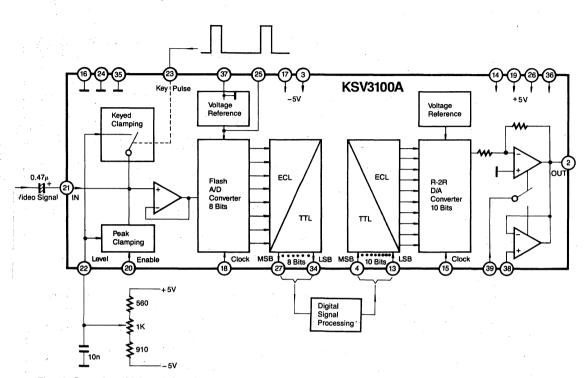

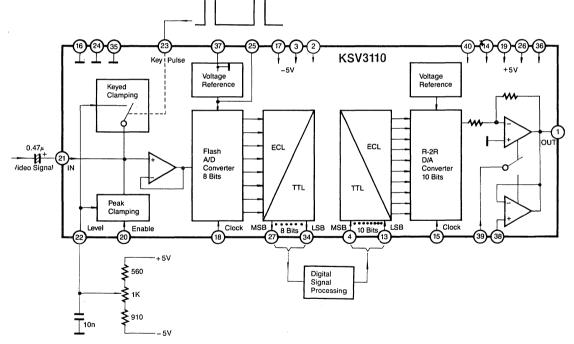

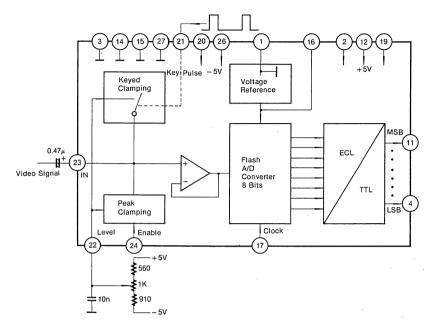

Fig. 13: Operation with keyed clamping

The input signal is applied to pin 21 through a coupling capacitor. Pin 20 must not be connected. While the input signal is at the desired clamping level, an high-level is applied at the clamping pulse input, pin 23. By this means the clamping switch in the KSV3100A connects the input with the clamping level at pin 22 and recharges the coupling capacitor accordingly. The clamping level can be set to zero or, by means of an external voltage devider, to any desired value between -1 and +2V.

# KSV3110

## PRELIMINARY LINEAR INTEGRATED CIRCUIT

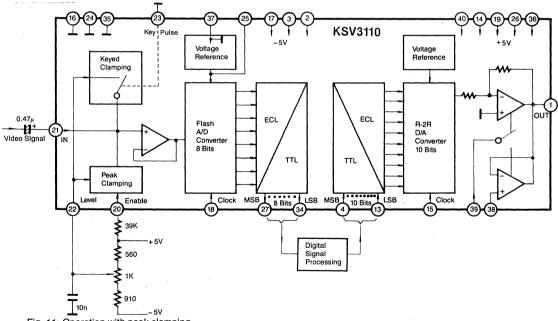

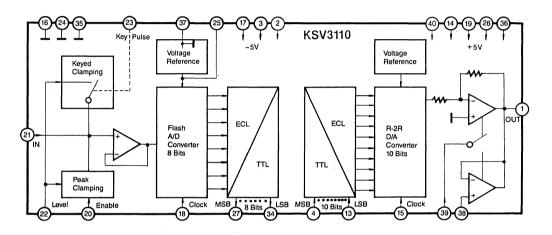

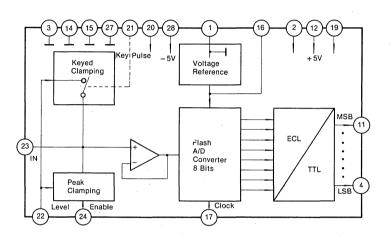

### HIGH-SPEED A/D-D/A CONVERTER (20MHz 8 bits A/D + 10 bits D/A)

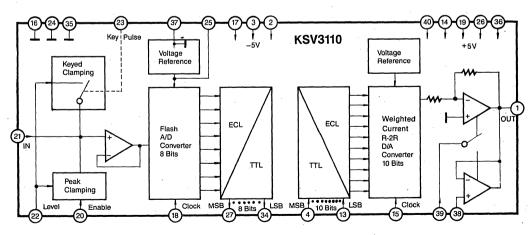

KSV3110 consist of high speed low glitch 10 bit DAC and high speed flash 8 bit ADC with the various auxiliary circuits (reference voltage source, pre buffer amp, input clamp circuit and feed in output amp).

KSV3110 is suitable for video application, capable of converting an analog signal with full power frequency components upto 6MHz into 8 bit digital signal.

All digital input and output are TTL compatible.

### **FEATURES**

- 8 bit A/D + 10 bit D/A resolution

- TTL digital interface

- · Internal input buffer amp

- · Internal clamp circuit (Peak, Keyed)

- 20MSPS conversion rate

- Internal reference voltage (2V)

- Internal feed-in Amp

- · Few external components for application

- Easy and simple video application

### **APPLICATION**

- Medical image processing

- · Data acquisition system

- · Radar data conversion

- · Video data conversion

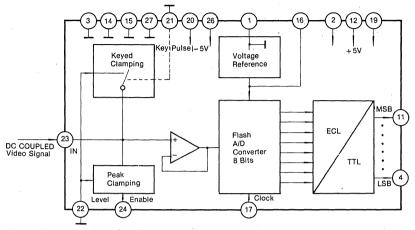

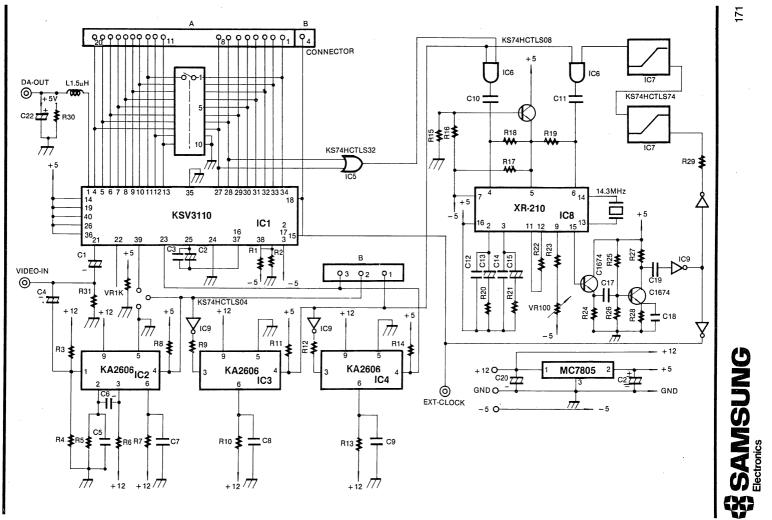

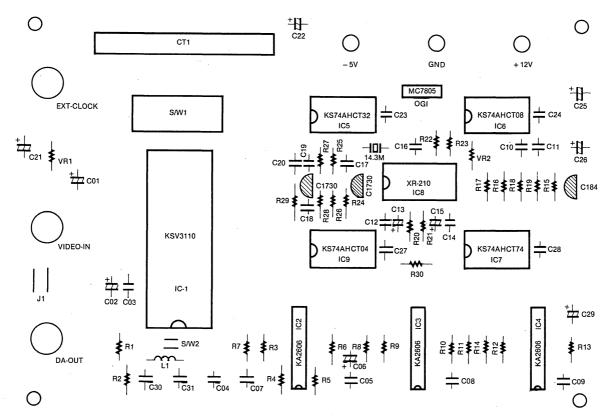

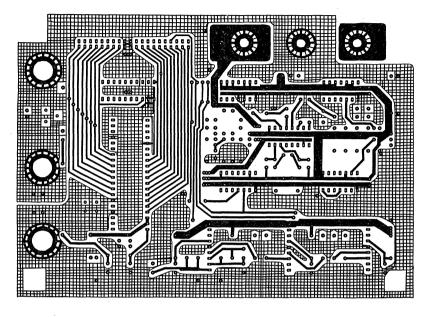

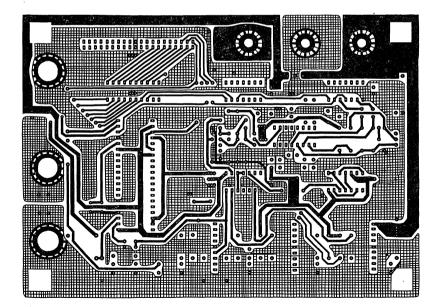

### **BLOCK DIAGRAM**

Fig. 1

37

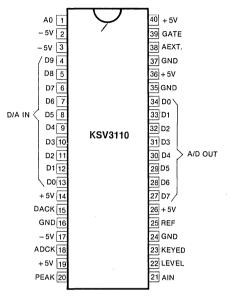

### KSV3110

#### **PIN DESCRIPTION**

| Pin No. | Description                              | Pin No. | Description                       |

|---------|------------------------------------------|---------|-----------------------------------|

| 1       | Analog Output D/A Converter              | 21      | Analog Input A/D Converter        |

| 2       | – 5V Supply D/A-Analog                   | 22      | Clamping Level Input              |

| 3       | - 5V Supply D/A Converter-Digital        | 23      | Clamping Pulse Input              |

| 4       | Digital Input Bit 9 (MSB)                | 24      | Analog Ground A/D Converter       |

| 5       | Digital Input Bit 8                      | 25      | Reference Voltage A/D Converter   |

| 6       | Digital Input Bit 7                      | 26      | +5V Supply A/D Converter-Digital  |

| 7       | Digital Input Bit 6                      | 27      | Digital Output Bit 7 (MSB)        |

| 8       | Digital Input Bit 5                      | 28      | Digital Output Bit 6              |

| 9       | Digital Input Bit 4                      | 29      | Digital Output Bit 5              |

| 10      | Digital Input Bit 3                      | 30      | Digital Output Bit 4              |

| 11      | Digital Input Bit 2                      | 31      | Digital Output Bit 3              |

| 12      | Digital Input Bit 1                      | 32      | Digital Output Bit 2              |

| 13      | Digital Input Bit 0 (LSB)                | 33      | Digital Output Bit 1              |

| 14      | + 5V Supply D/A Converter-Analog-Digital | 34      | Digital Output Bit 0 (LSB)        |

| 15      | Clock Input D/A Converter-Analog         | 35      | Digital Ground A/D Converter      |

| 16      | GND D/A Conv. & Clock A/D Converter      | 36      | +5V Supply A/D Converter-Analog   |

| 17      | -5V Supply A/D Converter-Analog          | 37      | GND of Ref. Voltage A/D Converter |

| 18      | Clock Input A/D Converter-Analog         | 38      | External Analog Input             |

| 19      | +5V Supply A/D Converter                 | 39      | Output Signal Switchover Input    |

| 20      | Peak Clamping Enable Input               | 40      | + 5V Supply D/A-Analog            |

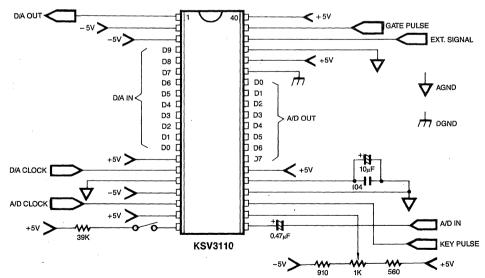

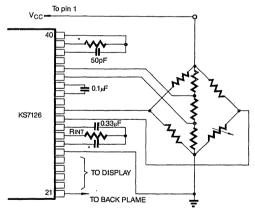

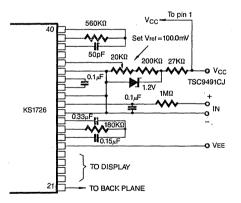

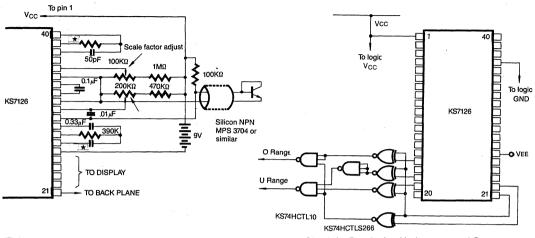

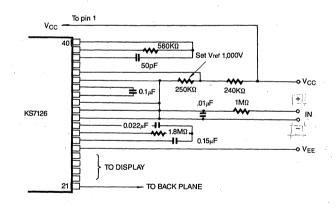

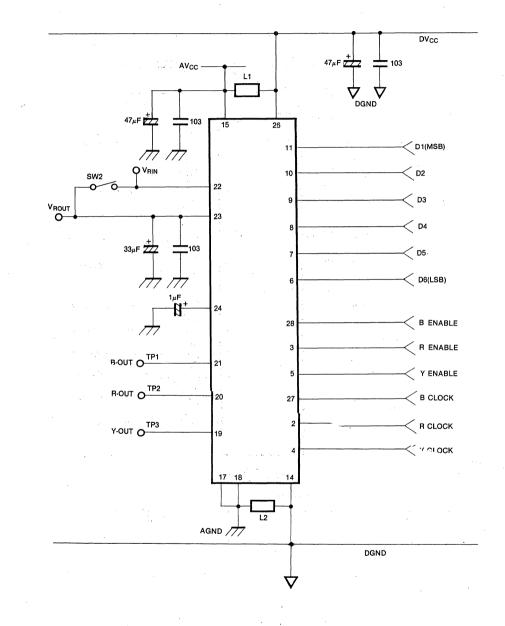

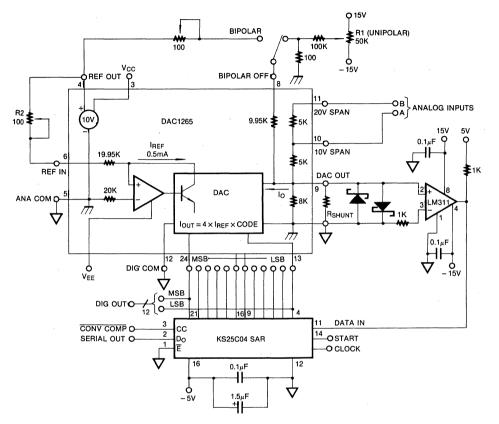

### **EVALUATION CIRCUIT**

Fig. 2

### **ABSOLUTE MAXIMUM RATINGS**

| Characteristics                | Symbol             | Value          | Unit   |

|--------------------------------|--------------------|----------------|--------|

| Positive Supply Voltage        | V <sub>cc</sub>    | -0.5 to +6     | V      |

| Negative Supply Voltage        | VEE                | +0.5 to -6     | V      |

| Input Voltages (digital)       |                    | -0.5 to +5.5   | V      |

| Input Voltages (analog)        | V <sub>AI</sub>    | -0.5 to +5.5   | V      |

| Digital Output Applied Voltage | Vpo                | - 0.5 to + 5.5 | V 1    |

| Digital Output Forced Current  | I <sub>DO</sub>    | -2.0 to +6.0   | mA     |

| Digital Output Short Time      | t <sub>SHORT</sub> | 1 .            | sec    |

| Analog Output Applied Voltage  | V <sub>AO</sub>    | -0.5 to +5.5   | V      |

| Analog Output Forced Current   | I <sub>AO</sub>    | - 10 to + 0.5  | mA     |

| Ambient Operating Temperature  | TA                 | – 25 to + 85   | degree |

| Storage Temperature Range      | T <sub>stg</sub>   | – 40 to + 125  | degree |

NOTE: 1. Absolute maximum ratings are limiting values applied individually while all other parameters are within specified operating conditions.

2. Functional operation under any of these conditions is NOT implied.

- 3. Applied voltage must be current limited to specified range.

- 4. Current is specified as positive when flowing into the device.

#### **OPERATING CONDITIONS**

| Characteristics                                                                                                                                                                                                                                                                                                         | Symbol                                                                                                                                                                        | Min                                    | Тур | Мах                                              | Unit                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----|--------------------------------------------------|--------------------------------------------------------|

| Positive Supply Voltage                                                                                                                                                                                                                                                                                                 | V <sub>cc</sub>                                                                                                                                                               | 4.75                                   | 5.0 | 5.25                                             | V                                                      |

| Negative Supply Voltage                                                                                                                                                                                                                                                                                                 | V <sub>EE</sub>                                                                                                                                                               | - 4.75                                 |     | - 5.25                                           | V                                                      |

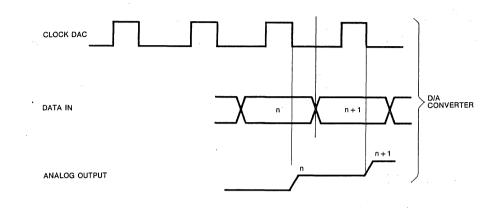

| A/D Converter<br>Clock High Time (1)<br>Clock Low Time (1)<br>Clamping Pulse High Time<br>Clamping Pulse Low Time<br>Digital Input High Voltage (1)<br>Digital Input Low Voltage (1)<br>Digital Output High Current<br>Digital Output Low Current<br>Peak Clamping Resistance<br>Analog Input Voltage<br>Clamping Level | t <sub>okh1</sub><br>t <sub>ckl1</sub><br>t <sub>clph</sub><br>t <sub>clpl</sub><br>V <sub>dl1</sub><br>looh<br>lool<br>R <sub>20</sub><br>V <sub>AI</sub><br>V <sub>22</sub> | 15<br>25<br>1<br>2.0<br>20<br>0<br>- 1 | 39  | 0.8<br>400<br>2.4<br>60<br>V <sub>ref</sub><br>2 | ns<br>μs<br>μs<br>V<br>V<br>μA<br>mA<br>Kohm<br>V<br>V |

| D/A Converter<br>Clock High Time (2)<br>Clock Low Time (2)                                                                                                                                                                                                                                                              | t <sub>скн2</sub><br>t <sub>скL2</sub>                                                                                                                                        | 20<br>20                               |     |                                                  | ns<br>ns                                               |

(Continue)

#### **OPERATING CONDITIONS** (Continued)

| Characteristics                | Symbol            | Min | Тур | Max | Unit   |

|--------------------------------|-------------------|-----|-----|-----|--------|

| Switch Over Pulse High Time    | t <sub>39H</sub>  | 1   |     |     | μS     |

| Switch Over Pulse Low Time     | t <sub>39L</sub>  | 1   |     |     | μS     |

| Digital Input High Voltage (2) | V <sub>DIH2</sub> | 2.0 |     |     | v      |

| Digital Input Low Voltage (2)  | V <sub>DIL2</sub> |     |     | 0.8 | · V    |

| Digital Input Set-up Time      | t <sub>SET</sub>  | 15  |     |     | ns     |

| Digital Input Hold Time        | t <sub>HOLD</sub> | 12  |     |     | ns     |

| External Analog Input Voltage  | V <sub>38</sub>   | -1  |     | 3   | v      |

| Ambient Temperature            | TA                | 0   |     | 70  | degree |

#### ELECTRICAL CHARACTERISTICS (within specified operation condition)

| Characteristics                                          | Symbol                                | Condition                                                          | Min   | Тур        | Max   | Unit    |

|----------------------------------------------------------|---------------------------------------|--------------------------------------------------------------------|-------|------------|-------|---------|

| Positive Supply Current                                  | Icc                                   | V <sub>cc</sub> = Max                                              |       | 105        | 140   | mA      |

| Negative Supply Current                                  | IEE                                   | V <sub>EE</sub> = Max                                              |       | - 95       | - 130 | mA      |

| A/D Converter                                            |                                       |                                                                    |       |            |       |         |

| Analog Input Bias Current                                | IAIN                                  | $V_{AI} = 2.0V, V_{EE} = Max$                                      |       |            | 5     | μA      |

| Analog Input Capacitance                                 |                                       |                                                                    |       | 5          |       | pF      |

| Analog Input Resistance                                  | RAIN                                  | $F_{AIN} = 100 KHz$                                                |       | 100        |       | Kohm    |

| Total String Resistance                                  | RSTRING                               | R(pin 25 – pin 37)                                                 | 350   | 450        | 550   | ohm     |

| Reference Voltage                                        | VREF                                  | V <sub>pin 25</sub>                                                | 1.8   |            | 2.2   | V       |

| Clock High Current                                       | I <sub>CKH1</sub>                     | $V_{CK} = 2.4V, V_{CC} = Max$                                      |       |            | 50    | μA      |

| Clock Low Current                                        | I <sub>CKL1</sub>                     | $V_{CK} = 0.4V, V_{CC} = Max$                                      |       |            | - 800 | μA      |

| Clamping Pulse High Current                              | ICLPH                                 | $V_{CLP} = 2.4V, V_{CC} = Max$                                     |       | 8          | 50    | μA      |

| Digital Outputse Low Current                             | ICLPL                                 | $V_{CLP} = 0.4V, V_{CC} = Max$                                     |       |            | - 500 | μA      |

| Digital Output Low Voltage<br>Digital Output Low Voltage | V <sub>DOH</sub>                      | $I_{DOH} = 0.4 \text{mA} V_{CC} = \text{Min}$                      | 2.4   |            |       | V       |

| Digital Output Low Voltage (2)                           | V <sub>DOL1</sub>                     | $I_{DOL} = 1.6 \text{mA} V_{CC} = \text{Min}$                      |       |            | 0.5   | V       |

| Maximum Conversion Rate                                  |                                       | $I_{DOL} = 2.4 \text{mA} V_{CC} = \text{Min}$                      |       |            | 0.7   | , V     |

| Aperture Delay Time                                      | F <sub>AS</sub>                       | $V_{\rm CC}$ , $V_{\rm EE} = Min$                                  | 20    |            |       | MSPS    |

| Digital Output Delay                                     | t <sub>AP</sub><br>t <sub>D</sub>     | $V_{CC}, V_{EE} = Min$                                             | - 10  |            | 0     | ns      |

| Clamp Level Sink Current                                 | 122 Izz                               | V <sub>CC</sub> , V <sub>EE</sub> = Min                            |       | 15         | 20    | ns      |

| Peak Clamp Level Difference                              | <sup>1</sup> 22<br>△V <sub>PEAK</sub> | Peak: off, Keyed: off                                              | 0     | 100        | 150   | μA      |

| Keyed Clamp Level Difference                             |                                       | V <sub>22</sub> V <sub>21</sub><br>V <sub>22</sub> V <sub>21</sub> | - 250 | - 100      | 0     | mV      |

| Peak Clamp Charge Resistance                             |                                       | $\triangle V_{21} / \triangle I_{22}, V_{21} < V_{22}$             | - 60  | 150        | -     | mV      |

| Keyed Clamp Charge Resistance                            |                                       |                                                                    |       | 150<br>150 |       | ohm     |

| Keyed Clamp Discharge Current                            |                                       | $V_{21} > V_{22}$                                                  |       | 100        |       | ohm     |

| Static Diff. Non Linearity                               | SDNL1                                 | $V_{21} > V_{22}$<br>$F_{IN} = 1 \text{KHz CK} = 1 \text{MHz}$     |       | 0.2        |       | μΑ<br>% |

|                                                          | CDITE                                 |                                                                    |       | 0.2        |       | 70      |

### ELECTRICAL CHARACTERISTICS (Continued)

| Characteristics                | Symbol            | Condition                            | Min   | Тур   | Max   | Unit   |

|--------------------------------|-------------------|--------------------------------------|-------|-------|-------|--------|

| Dynamic Diff. Non Linearity    | DDNL              | $A_{IN} = 1.02 MHz CK = 10 MHz$      |       | 0.3   |       | %      |

| · · ·                          |                   | $A_{IN} = 6.0018MHz$                 |       |       |       |        |

|                                |                   | CK = 25MHz (37.5% DUTY)              |       |       | 0.6   | %      |

| Dynamic Integral Non Linearity | DINL              | $A_{IN} = 1.02 MHz CK = 10 MHz$      |       | 0.8   |       | %      |

| Full Power Input Band Width    | BW                |                                      | 6     |       |       | MHz    |

| Full Code Offset Error         | EFULL             | (Full Code Input) – V <sub>REF</sub> | ·· 0  | + 100 | + 200 | mV     |

| Zero Code Offset Error         | EZERO             | (Zero Code Input) – V <sub>REF</sub> | - 100 | + 40  | + 100 | mV     |

| Signal to Noise Ratio          | SNR               | $A_{IN} = 1.02 MHz CK = 10 MHz$      |       | 42    |       | dB     |

| (RMS Signal/RMS Noise)         |                   | $A_{IN} = 1.02 MHz CK = 20 MHz$      |       | 35    |       | dB     |

|                                |                   | $A_{\rm IN} = 3.601 \rm MHz$         |       |       |       |        |

|                                |                   | CK = 25MHz (37.5% DUTY)              | 30    | 34    |       | dB     |

| Differential Gain Error        | DG                | $A_{IN} = 3.579545 MHz$              |       |       |       |        |

|                                |                   | CK = 14.318MHz                       | -1    |       | 3     | %      |

| Differential Phase Error       | DP                | $A_{IN} = 3.579545 MHz$              |       |       |       |        |

|                                |                   | CK = 14.318MHz                       | -2    |       | 2     | degree |

| D/A Converter                  | l                 |                                      |       |       |       |        |

| Digital Input High Current     | I <sub>DIH2</sub> | $V_{CC} = Max, V_{DIH2} = 2.4V$      |       |       | 50    | μA     |

| Digital Input Low Current      | I <sub>DIH2</sub> | $V_{CC} = Max, V_{DIL2} = 0.4V$      |       |       | - 500 | μA     |

| External Input Bias Current    | I <sub>38</sub>   | $V_{cc} = Max, V_{38} = 3V$          |       |       | 10    | μA     |

| External Input Capacitance     | C <sub>38</sub>   |                                      |       | 5     |       | pF     |

| External Input Equ. Resistance | R <sub>38</sub>   | F <sub>38</sub> = 10KHz              |       | 1     |       | Mohm   |

| External Amp. Offset Error     | EOFFSET           | $V_{38} = -1V$                       | - 100 |       | 100   | mV     |

| External Amp. Gain Error       | EGAIN             | {(V1/V38) – 1}*100                   | -5    |       | 5     | %      |

| Max. Data Conversion Rate      | FDC               |                                      | 20    |       |       | MSPS   |

| Analog Output Delay            | . t <sub>D</sub>  |                                      |       |       | 25    | ns     |

| Settling Time                  | t <sub>SET</sub>  | settle to 0.2%                       |       |       | 40    | ns     |

| Rising Time                    | t <sub>R</sub>    | 10% to 90%                           |       |       | 50    | ns     |

| Falling Time                   | t <sub>F</sub>    | 90% to 10%                           | ·     |       | 35    | ns     |

| Glitch Amplitude               | GA                |                                      |       |       | 80    | mV     |

| Glitch Duration                | G⊳                |                                      |       |       | 7     | ns     |

| Glitch Energy                  | GE                |                                      |       |       | 250   | pV-sec |

| Static Diff. Non Linearity     | SDNL2             | KSV3110-10                           |       |       | 0.05  | %      |

|                                |                   | KSV3110-9                            |       |       | 0.1   | %      |

|                                |                   | KSV3110-8                            |       |       | 0.2   | %      |

| Static Integral Non Linearity  | SINL              |                                      |       |       | 1     | %      |

| Full Scale Output Voltage      |                   | $V_{CC} = typ, V_{EE} = typ$         | 1.8   |       | 2.2   | v      |

| Zero Scale Output Voltage      | VZERO             | $V_{CC} = typ, V_{EE} = typ$         | - 60  |       | + 60  | mV     |

#### MARKING SPECIFICATIONS (Ordering Information)

KSV3110 has three kind of version according to the accuracy bit (so called 'precision') of D/A Converter, and their marking specifications are as follow:

| Marking Care  | D/A (        | Converter          | A/D Converter      | Deskars | T D         |  |

|---------------|--------------|--------------------|--------------------|---------|-------------|--|

| Marking Spec. | Accuracy Bit | Diff. Nonlinearity | Diff. Nonlinearity | Package | Temp. Range |  |

| KSV3110-10    | 10 BIT       | 0.05%              |                    |         |             |  |

| KSV3110-9     | 9 BIT        | 0.1%               | 0.2%               | .40 DIP | 0 ~ + 70°C  |  |

| KSV3110-8     | 8 BIT        | 0.2%               |                    |         |             |  |

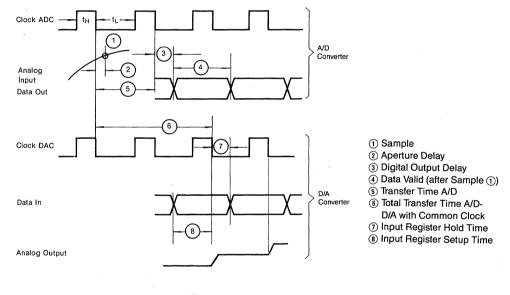

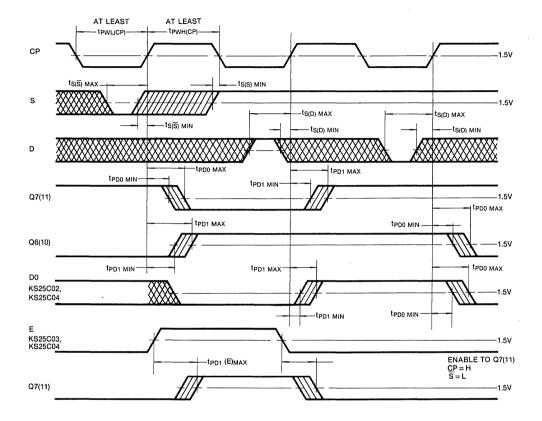

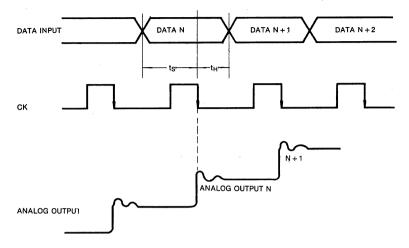

#### **TIMING DIAGRAM**

Fig. 3

#### PACKAGE LAYOUT

Fig. 4

#### DESCRIPTION OF THE CONNECTION AND THE SIGNALS

| Pin No.     | Description                                                                                                                                                                                                       |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin 1       | Analog Output D/A Converter<br>This pin whose diagram is shown in Fig. 7, is the output for the processed analog<br>signal either originating from the D/A converter or from the external analog input<br>pin 38. |

| Pin 2       | - 5 Volt Supply D/A Converter, Analog<br>This pin gets the negative supply for the analog part of the D/A converter                                                                                               |

| Pin 3       | -5 Volt Supply D/A Converter, Digital<br>This pin gets the negative supply for the digital part of the D/A converter.                                                                                             |

| Pin 4 to 13 | Digital Inputs Bit 9 to Bit 0<br>This diagram of these pins is shown in Fig. 5. They are the inputs of the D/A<br>converter and not-used inputs should be connected to the ground.                                |

| Pin 14      | + 5 Volt Supply D/A Converter, Digital<br>This pin gets the positive supply for the digital part of the D/A converter.                                                                                            |

| Pin 15      | Clock Input D/A Converter<br>This pin whose diagram is shown in Fig. 5 must be supplied with the clock signal<br>for the D/A converter.                                                                           |

| Pin 16      | Ground D/A Converter and Clock A/D Converter<br>This pin serves as ground pin for the D/A converter and for the clock of the A/D<br>converter.                                                                    |

-----

#### DESCRIPTION OF THE CONNECTION AND THE SIGNALS (Continued)

| Pin No.      | Description                                                                                                                                                                                                                                  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin 17       | - 5 Volt Supply A/D Converter, Analog<br>This pin is the negative supply pin for the analog part of the A/D Converter.                                                                                                                       |

| Pin 18       | Clock Input A/D Converter<br>The diagram of this pin is shown in Fig. 5 Pin 18 is supplied with the clock of the<br>A/D converter.                                                                                                           |

| Pin 19       | + 5 Volt Supply A/D Converter<br>Via this pin the A/D converter gets its positive supply.                                                                                                                                                    |

| Pin 20       | Peak Clamping Enable Input<br>Via pin 20 whose diagram is shown in Fig. 6, the peak clamping facility can be<br>enabled.                                                                                                                     |

| Pin 21       | Analog Input A/D Converter<br>Fig. 7 is the diagram of this input. To pin 21 is applied the analog signal to be<br>converted into digital.                                                                                                   |

| Pin 22       | Clamping Level Input<br>Via this pin whose diagram is shown in Fig. 6, the input of the A/D converter is<br>supplied with the desired clamping level.                                                                                        |

| Pin 23       | Clamping Pulse Input<br>Pin 23 must be supplied with the key pulse if keyed clamping is required.                                                                                                                                            |

| Pin 24       | Analog Ground A/D Converter<br>This pin serves as ground pin for the analog part of the A/D converter.                                                                                                                                       |

| Pin 25       | Reference Voltage A/D Converter<br>This pin whose diagram is shown in Fig. 8, is intended for connecting a<br>decoupling capacitor to the A/D converter's reference voltage, the other end of this<br>capacitor to pin 37.                   |

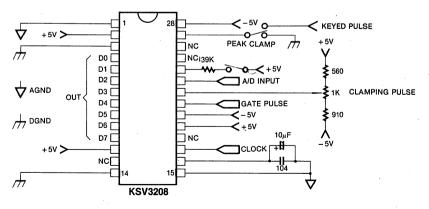

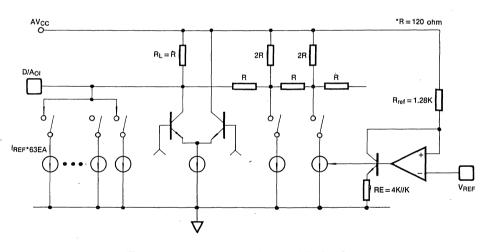

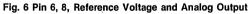

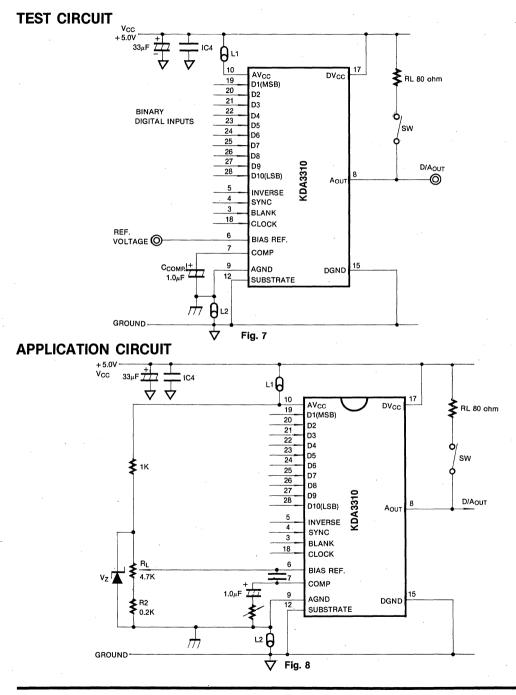

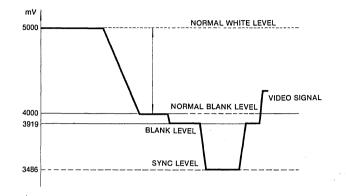

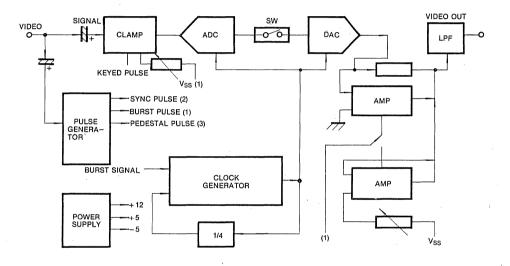

| Pin 26       | + 5 Volt Supply A/D Converter, Digital<br>This pin is the positive supply pin for the digital part of the A/D converter.                                                                                                                     |