# Linear IC Data Book (VOL. 2)

- Telecom

- Industrial

- Data Converter

### Copyright 1987 by Samsung Semiconductor

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photo copying, recording, or otherwise, without the prior written permission of Samsung Semiconductor.

The information contained herein is subject to change without notice. Samsung assumes no responsibility for the use of any circuitry other than circuitry embodied in a Samsung product.

No other circuit patent licenses are implied.

# SAMSUNG SEMICONDUCTOR DATA BOOK LIST

I. Semiconductor Product Guide

II. Transistor Data Book

III. Linear IC Data Book

IV. MOS Product Data Book

V. High Performance CMOS Logic Data Book

VI. MOS Memory Data Book

VII. SFET Data Book

# LINEAR IC DATA BOOK

# **VOLUME 1.**

AUDIO ICs VIDEO ICs

# **VOLUME 2.**

TELECOM ICs VOLTAGE REGURATORS VOLTAGE REFERENCES OPERATIONAL AMPLIFIERS COMPARATORS TIMERS DATA CONVERTER ICS MISCELLANEOUS ICS

# TABLE OF CONTENTS (VOLUME 2)

| ١.    | QUALITY AND RELIABILITY                                                                                                                               | . 19                     |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 11.   | PRODUCT GUIDE<br>1. Function Guide<br>2. Cross Reference Guide<br>3. Ordering Information                                                             | 51<br>60                 |

| III.  | TELECOMMUNICATION ICs                                                                                                                                 | 67                       |

| IV.   | INDUSTRIAL ICs         1. Voltage Regulators         2. Voltage References         3. Operational Amplifiers         4. Comparators         5. Timers | 277<br>393<br>407<br>468 |

| V.    | DATA CONVERTER ICs                                                                                                                                    | 519                      |

| VI.   | MISCELLANEOUS ICs                                                                                                                                     | 593                      |

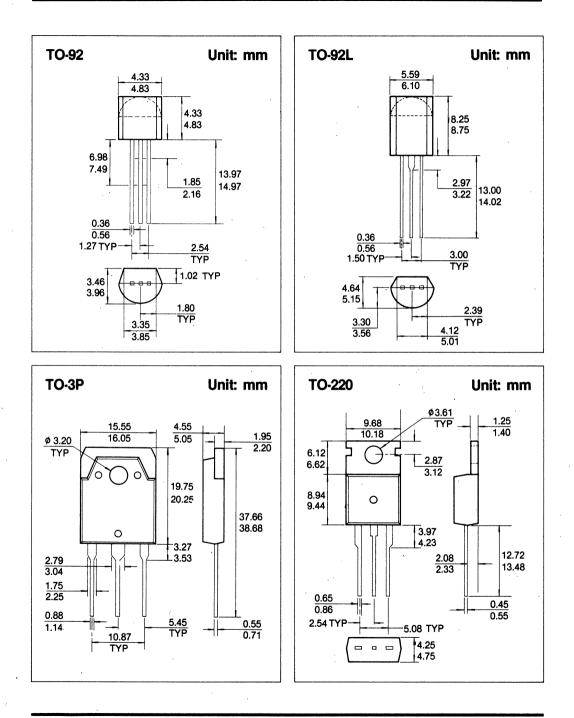

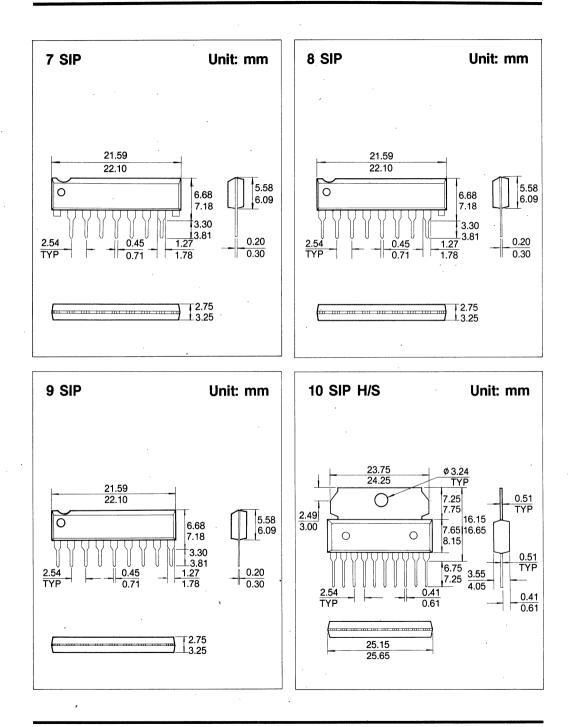

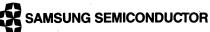

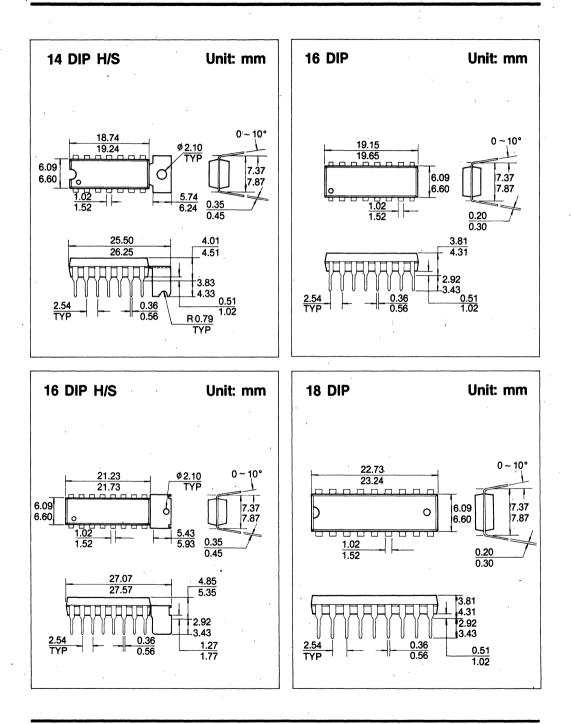

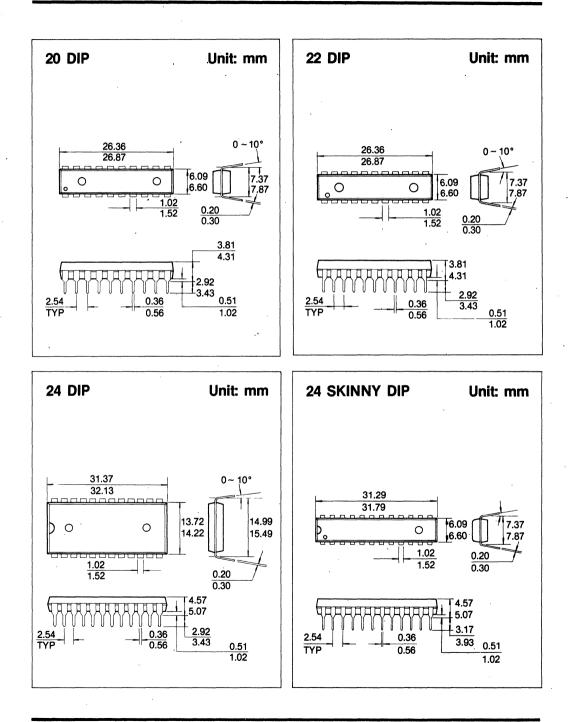

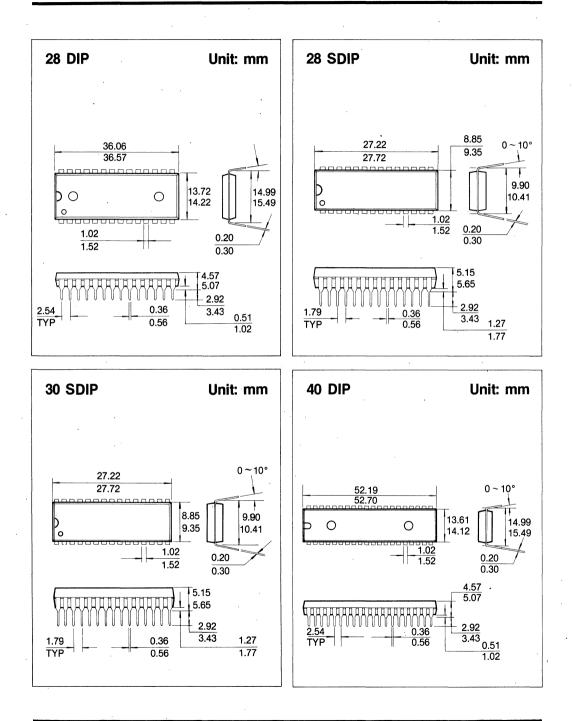

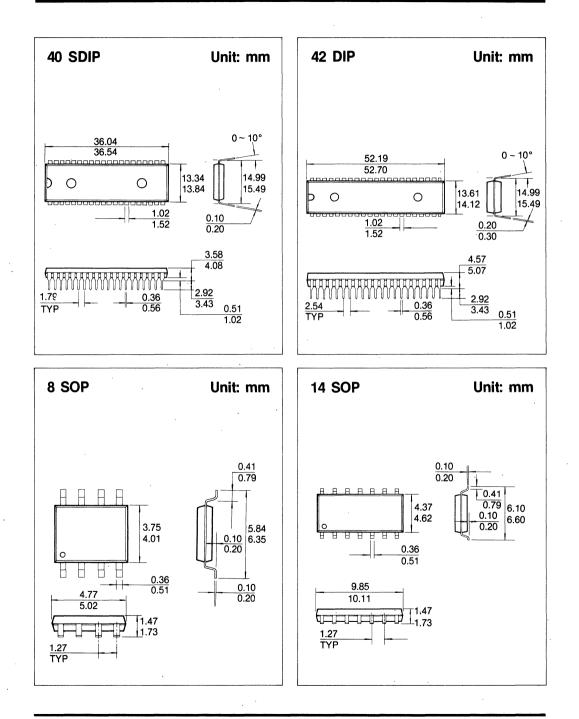

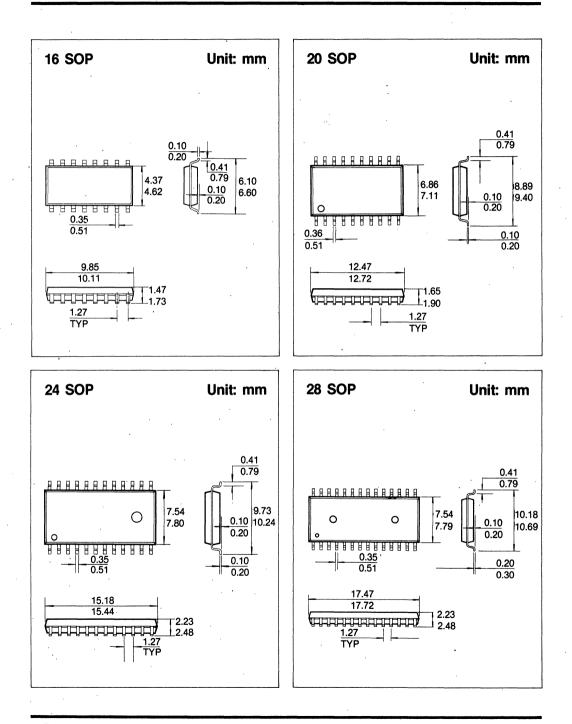

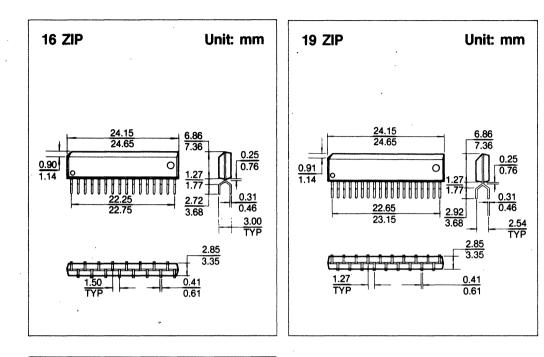

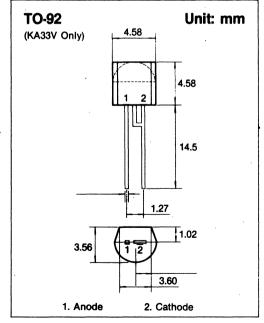

| VII.  | PACKAGE DIMENSIONS                                                                                                                                    | 617                      |

| VIII. | SALES OFFICES and MANUFACTURER'S<br>REPRESENTATIVES                                                                                                   | 629                      |

# (VOLUME 1)

### I. QUALITY AND RELIABILITY

### II. PRODUCT GUIDE

1. Function Guide

- 2. Cross Reference Guide

- 3. Ordering Information

### III. AUDIO ICs

IV. VIDEO ICs

## V. MISCELLANEOUS ICs

**VI. PACKAGE DIMENSIONS**

# VII. SALES OFFICES and MANUFACTURER'S REPRESENTATIVES

# **ALPHANUMERIC INDEX**

| Device                                                                              | Function                                                                                 | Package             | Page         |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------|--------------|

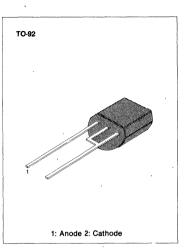

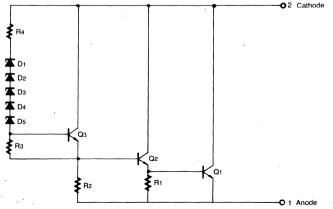

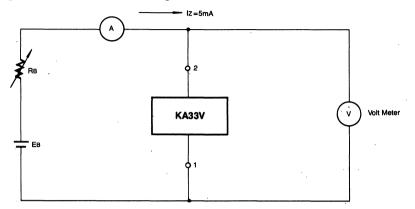

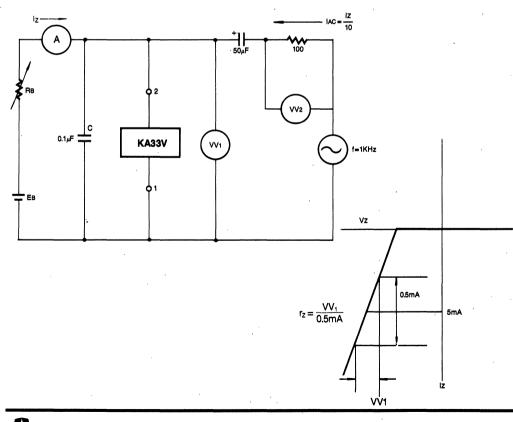

| KA33V                                                                               | Silicon Monolithic Bipolar Integrated Circuit Voltage<br>Stabilizer for Electronic Tuner | TO-92               | 595          |

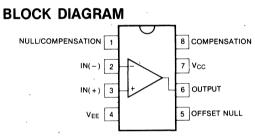

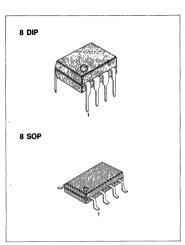

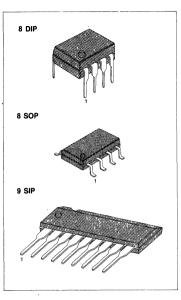

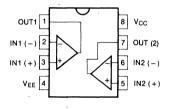

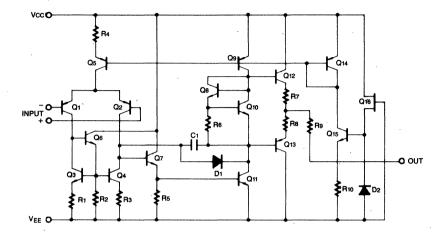

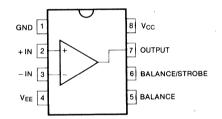

| KA201A                                                                              | Single Operational Amplifier                                                             | 8 DIP/8 SOP         | 407          |

| KA301A                                                                              | Single Operational Amplifier                                                             | 8 DIP/8 SOP         | 407          |

| KA319                                                                               | Dual High Speed Voltage Comparator                                                       | 14 DIP/14 SOP       | 468          |

| KA336-5.0                                                                           | Voltage Reference Diode                                                                  | TO-92               | 393          |

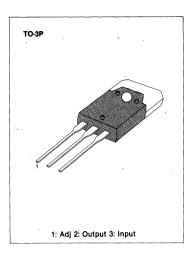

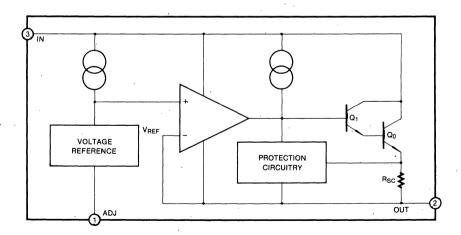

| KA350                                                                               | 3 AMP Adjustable Positive Voltage Regulator                                              | TO-3P               | 277          |

| KA361                                                                               | High Speed Voltage Comparator                                                            | 14 DIP/14 SOP       | 472          |

| KA385-1.2                                                                           | Micropower Voltage Reference Diode                                                       | TO-92               | 397          |

| KA431                                                                               | Programmable Precision Reference                                                         | TO-92/8 DIP/8 SOP   | 401          |

| KA710C                                                                              | High Speed Voltage Comparator                                                            | 14 DIP/14 SOP       | 474          |

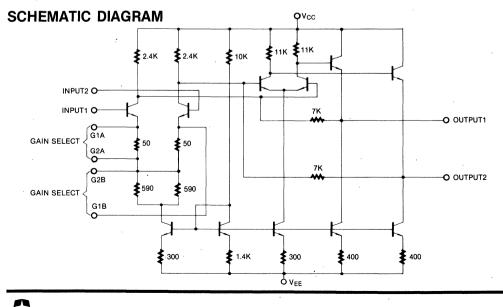

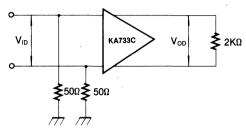

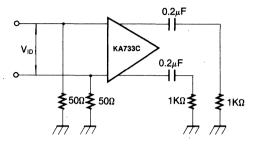

| KA733C                                                                              | Differential Video Amplifier                                                             | 14 DIP/14 SOP       | 412          |

| KA1222                                                                              | Dual Low Noise Equalizer AMP                                                             | 8 SIP               | Vol.         |

| KA2101                                                                              | TV Sound IF AMP                                                                          | 14 DIP              | Vol.         |

| KA2102A                                                                             | TV Sound System                                                                          | 14 DIP H/S          | Vol.         |

| KA2102A                                                                             | Sound Mute System for TV                                                                 | 8 SIP               | Vol.         |

| KA2103L                                                                             | Auto Power off and Sound Mute System for TV                                              | 9 SIP               | Vol.         |

| KA2105                                                                              | Limiter AMP and Detector for a TV SIF                                                    | 9 SIP               | Vol.         |

| KA2105                                                                              | Dual Sound Multiplex for a TV SIF                                                        | 16 DIP              | Vol.         |

| KA2100                                                                              | DC Volume, Tone Control Circuit                                                          | 12 SIP              | Vol.         |

| KA2107<br>KA2130A                                                                   | TV Vertical Deflection System                                                            | 10 SIP H/S          | Vol.         |

| KA2130A                                                                             | TV Vertical Deflection System                                                            | 10 SIP H/S          | Vol.         |

| KA2131                                                                              | 1 Chip Deflection System                                                                 | 16 DIP H/S          | Vol.<br>Vol. |

| KA2133                                                                              | Color TV Deflection Signal Processing IC                                                 | 18 DIP              | Vol.         |

|                                                                                     |                                                                                          | 12 SIP              | Vol.         |

| KA2135                                                                              | Horizontal Signal Processing IC                                                          | 12 SIP<br>12 ZDIP/F |              |

| KA2136                                                                              | Low Noise TV Vertical Deflection System<br>TV Horizontal Processor                       | 12 201P/F           | Vol.<br>Vol. |

| KA2137                                                                              |                                                                                          |                     |              |

| KA2153                                                                              | Video-Chroma Deflection System for a Color TV                                            | 42 DIP<br>42 DIP    | Vol.         |

| KA2154                                                                              | Video-Chroma Deflection System for a Color TV                                            | 8 SIP               | Vol.         |

| KA2181                                                                              | Remote Control Pre-AMP                                                                   |                     | Vol.         |

| KA2182                                                                              | Remote Control Pre-AMP                                                                   | 8 SIP               | Vol.         |

| KA2183                                                                              | Remote Control Pre-AMP                                                                   | 8 SIP               | Vol.         |

| KA2201B                                                                             | 0.5W Audio Power AMP                                                                     | 8 DIP               | Vol.         |

| KA2201/N                                                                            | 1.2W Audio Power AMP                                                                     | 8 DIP               | Vol.         |

| KA2206                                                                              | 2.3W Dual Audio Power AMP                                                                | 12 DIP/F            | Vol.         |

| KA22062                                                                             | 4.5W Dual Power AMP                                                                      | 12 SIP H/S          | Vol.         |

| KA2209                                                                              | Dual Low Voltage Power AMP                                                               | 8 DIP               | Vol.         |

| KA2210                                                                              | 5.5W Dual Power AMP                                                                      | 12 SIP H/S          | Vol.         |

| <a2211< td=""><td>5.8W Dual Power AMP</td><td>12 SIP H/S</td><td>Vol.</td></a2211<> | 5.8W Dual Power AMP                                                                      | 12 SIP H/S          | Vol.         |

| KA2212                                                                              | 0.5W Audio Power AMP                                                                     | 9 SIP               | Vol.         |

| KA2213                                                                              | One Chip Tape Recorder System                                                            | 14 DIP H/S          | Vol.         |

| KA22131                                                                             | Dual Pre-Power AMP for Auto Reverse                                                      | 24 SOP              | Vol.         |

| KA22135                                                                             | Dual Pre-Power AMP and DC Motor Speed Controller                                         | 22 SDIP             | Vol.         |

| <a2214< td=""><td>1W Dual Power AMP</td><td>14 DIP H/S</td><td>Vol.</td></a2214<>   | 1W Dual Power AMP                                                                        | 14 DIP H/S          | Vol.         |

| KA2220                                                                              | Equalizer AMP with ALC                                                                   | 9 SIP               | Vol.         |

| KA2221                                                                              | Dual Low Noise Equalizer AMP                                                             | 8 SIP               | Vol.         |

| KA22211                                                                             | Dual Low Noise Equalizer AMP                                                             | 8 SIP               | Vol.         |

| KA2223                                                                              | 5 Band Graphic Equalizer AMP                                                             | 16 DIP              | Vol.         |

| KA22233                                                                             | 3 Band Dual Graphic Equalizer AMP                                                        | 22 DIP              | Vol.         |

| KA22235                                                                             | 5 Band Graphic Equalizer AMP                                                             | 18 ZIP              | Vol.         |

| KA2224                                                                              | Dual Equalizer AMP with ALC                                                              | 14 DIP              | Vol.         |

# ALPHANUMERIC INDEX (Continued)

| Device    | Function                                           | Package       | Page   |

|-----------|----------------------------------------------------|---------------|--------|

| KA22241   | Dual Equalizer AMP with ALC                        | 9 SIP         | Vol. 1 |

| KA2225/D  | Dual Pre-AMP for 3V Using                          | 16 DIP/16 SOP | Vol. 1 |

| KA22261   | Dual Equalizer AMP with REC AMP                    | 16 DIP        | Vol. 1 |

| KA2230    | 9-Program Music Selector                           | 22 DIP        | Vol. 1 |

| KA22421/D | AM 1 Chip Radio                                    | 16 DIP/16 SOP | Vol. 1 |

| KA22424   | AM/FM 1 Chip Radio                                 | 16 DIP        | Vol. 1 |

| KA2243    | AM/FM IF System                                    | 16 DIP        | Vol. 1 |

| KA2244    | FM IF System for Car Radio                         | 9 SIP         | Vol. 1 |

| KA22441   | FM IF System for Car Stereo                        | 16 ZIP        | Vol. 1 |

| KA2245    | FM IF System for Car Radio                         | 7 SIP         | Vol. 1 |

| KA22461   | Electronic Tuning AM Radio Receiver for Car Stereo | 19 ZIP        | Vol. 1 |

| KA2247    | FM IF/AM Tuner System                              | 16 DIP        | Vol. 1 |

| KA22471   | FM IF/AM Tuner System                              | 16 DIP '      | Vol. 1 |

| KA2248A/D | 3V FM IF/AM Tuner System                           | 16 DIP/16 SOP | Vol. 1 |

| KA2249/D  | FM Front End for Portable Radio                    | 7 SIP/8 SOP   | Vol. 1 |

| KA2261    | FM Stereo Multiplex Decoder                        | 16 DIP        | Vol. 1 |

| KA2262    | FM Stereo Multiplex Decoder for Car Stereo         | 16 ZIP        | Vol. 1 |

| KA2263    |                                                    | 9 SIP         | Vol.   |

| KA2264/D  | FM Stereo Multiplex Decoder                        | 9 SIP/16 SOP  | Vol.   |

| KA2265    | VCO Non-Adjusting FM Stereo Multiplex Decoder      | 16 DIP        | Vol. 1 |

| KA22682   | 1 Chip TV MPX Demodulator                          | 28 DIP        | Vol. 1 |

| KA2268N   | 1 Chip TV Sound MPX                                | 28 DIP        | Vol.   |

| KA2281    | 5 DOT Dual LED Level Meter Driver                  | 16 DIP        | Vol.   |

| KA2283    | 5 DOT Dual LED Level Meter Driver                  | 16 DIP        | Vol. 1 |

| KA2284    | 5 DOT LED Level Meter Driver                       | 9 SIP         | Vol. 1 |

| KA2285    | 5 DOT LED Level Meter Driver                       | 9 SIP         | Vol. 1 |

| KA2286    | 5 DOT LED Linear Level Meter Driver                | 9 SIP         | Vol. 1 |

| KA2287    | 5 DOT LED Linear Level Meter Driver                | 9 SIP         | Vol. 1 |

| KA2288    | 7 DOT LED Level Meter Driver                       | 16 DIP        | Vol. 1 |

| KA2303    | Toy Radio Control Actuator                         | 9 SIP         | Vol. 1 |

| KA2304    | Toy Radio Control Actuator                         | 9 SIP         | Vol. 1 |

| KA2401    | DC Motor Speed Controller                          | 8 DIP         | Vol.   |

| KA2402    | Low Voltage DC Motor Speed Controller              | 8 DIP         | Vol. 1 |

| KA2404    | DC Motor Speed Controller                          | TO-92L        | Vol.   |

| KA2407    | DC Motor Speed Controller                          | TO-126        | Vol.   |

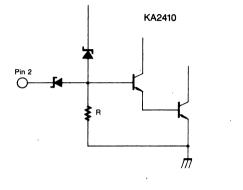

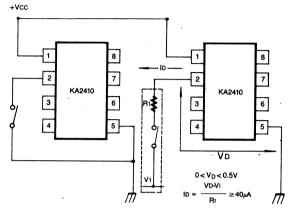

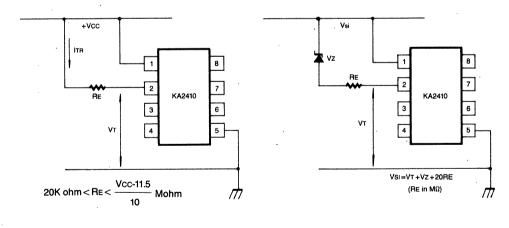

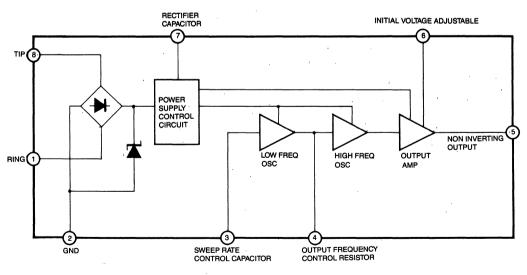

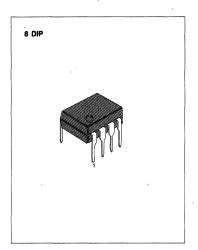

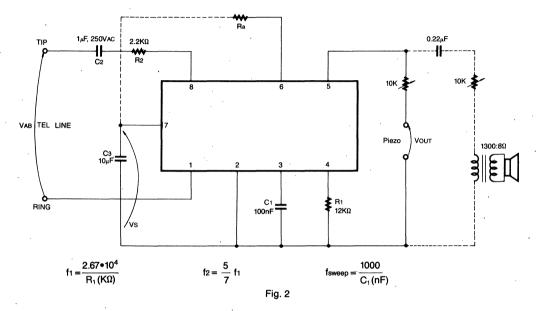

| KA2410    | Tone Ringer                                        | 8 DIP         | 69     |

| KA2411    | Tone Ringer                                        | 8 DIP         | 69     |

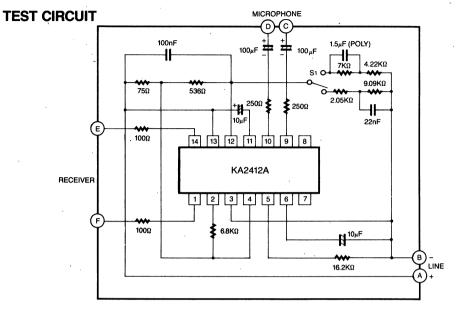

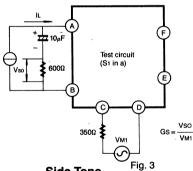

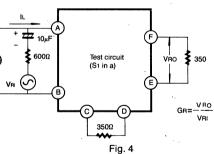

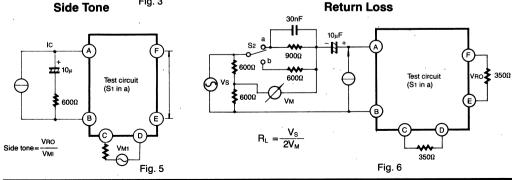

| KA2412A   | Telephone Speech Circuits                          | 14 DIP        | 75     |

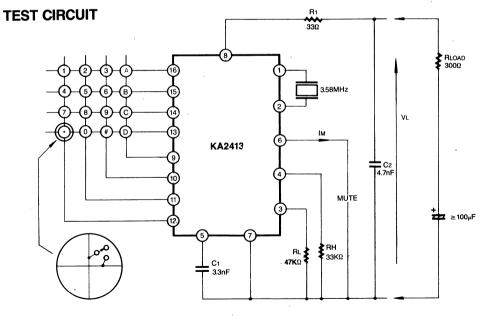

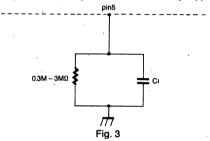

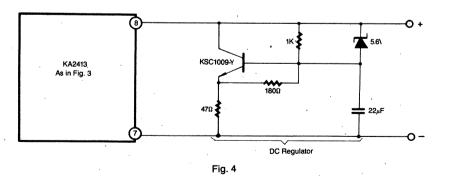

| KA2413    | Dual Tone Multi Frequency Generator                | 16 DIP        | 83     |

| KA2418    | Tone Ringer with Bridge Diode                      | 8 DIP         | 108    |

| KA2419    | Tone Ringer with Bridge Diode                      | 8 DIP         | 108    |

| KA2425A/B | Telephone Speech Network with Dialer Interface     | 18 DIP        | 122    |

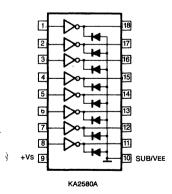

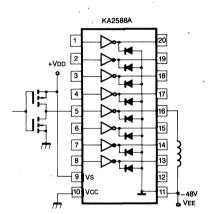

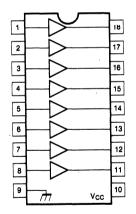

| KA2580A   | 8-Channel Source Drivers                           | 18 DIP        | 599    |

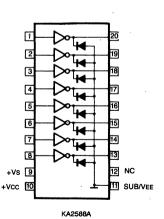

| KA2588A   | 8-Channel Source Drivers                           | 20 DIP        | 599    |

| KA2605    | SYNC Separator                                     | 9 SIP         | Vol.   |

| KA2606    | SYNC Separator                                     | 9 SIP         | Vol. 1 |

| KA2615    | LED and Lamp Driver                                | 9 SIP         | Vol. 1 |

| KA2616    | LED and Lamp Driver                                | 9 SIP         | Vol.   |

.

# ALPHANUMERIC INDEX (Continued)

| Device                                                                                                                        | Function                                                                 | Package        | Page   |

|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------|--------|

| KA2617                                                                                                                        | LED and Lamp Driver                                                      | 9 SIP          | Vol.   |

| KA2618                                                                                                                        | LED and Lamp Driver                                                      | 9 SIP          | Vol. 1 |

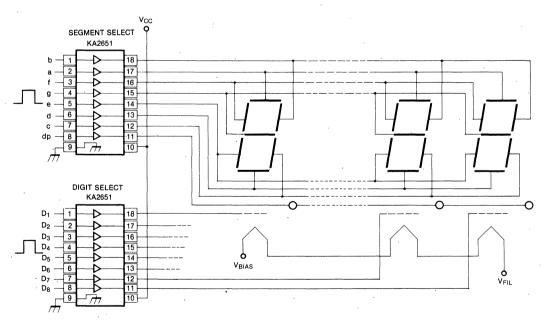

| KA2651                                                                                                                        | Fluorescent Display Drivers                                              | 18 DIP         | 604    |

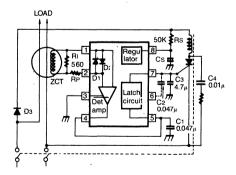

| KA2803                                                                                                                        | Low Power Consumption Earth Leakage Detector                             | 8 DIP          | 607    |

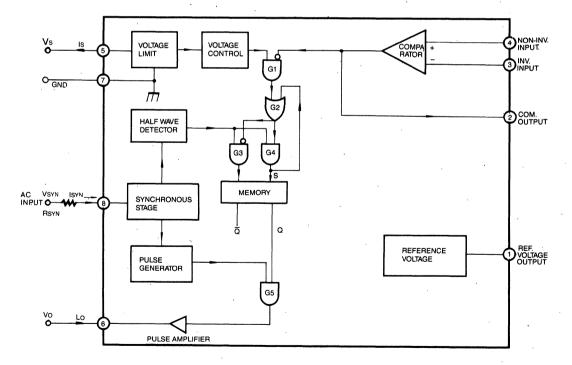

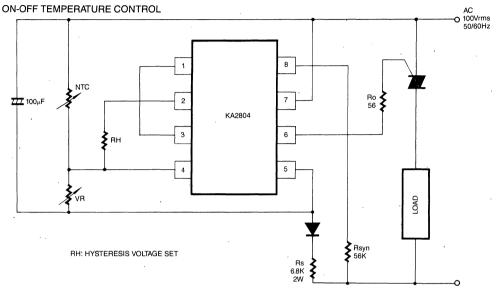

| KA2804                                                                                                                        | Zero Voltage Switch                                                      | 8 DIP          | 610    |

| KA2911                                                                                                                        | Video IF System for Color TV                                             | 16 DIP         | Vol.   |

| KA2912                                                                                                                        | Video IF Processor for B/W TV                                            | 14 DIP H/S     | Vol.   |

| KA2913A                                                                                                                       | Video and Sound IF AMP for Monochrome TV Receivers                       | 16 DIP         | Vol.   |

| KA2914A                                                                                                                       | Video IF + SIF System                                                    | 24 DIP         | Vol.   |

| KA2915                                                                                                                        | TV VIF & SIF & Deflection System                                         | 28 DIP         | Vol.   |

| KA2916                                                                                                                        | Video IF System for Color TV                                             | 16 DIP         | Vol.   |

| KA2917                                                                                                                        | Video and Sound IF AMP for Monochrome TV Receivers                       | 16 DIP         | Vol.   |

| KA2918                                                                                                                        | Video IF + SIF System                                                    | 24 DIP         | Vol.   |

| KA2919                                                                                                                        | VIF + SIF System for Color TV                                            | 30 SSD         | Vol.   |

| <a2944< td=""><td>Write &amp; Read AMP</td><td>28 DIP</td><td>Vol.</td></a2944<>                                              | Write & Read AMP                                                         | 28 DIP         | Vol.   |

| <a2945< td=""><td>Video AMP</td><td>28 DIP</td><td>Vol.</td></a2945<>                                                         | Video AMP                                                                | 28 DIP         | Vol.   |

| (A2983                                                                                                                        | Switchless Recording/Play Back AMP                                       | 18 DIP         | Vol.   |

| (A2988                                                                                                                        | Chroma Signal Processor                                                  | 28 DIP         | Vol.   |

| (A6101                                                                                                                        | Analog Interface Circuit for Teletex System                              | 18 DIP         | Vol.   |

| (A6102                                                                                                                        | Analog Interface Circuit for Teletex System                              | 18 DIP         | Vol.   |

| (A3524                                                                                                                        | Regulator Pulse Width Modulator                                          | 16 DIP         | 285    |

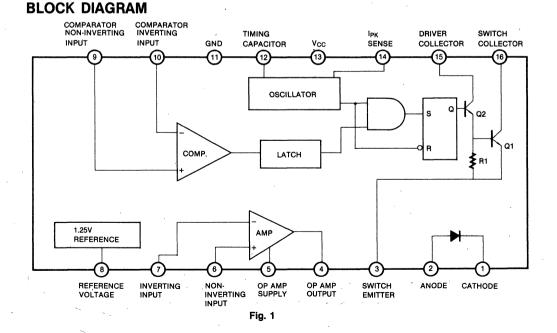

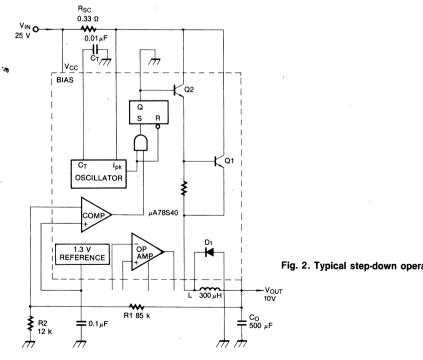

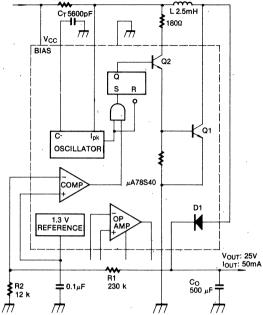

| (A78S40                                                                                                                       | Switching Regulator                                                      | 16 DIP         | 306    |

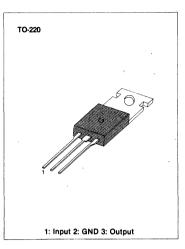

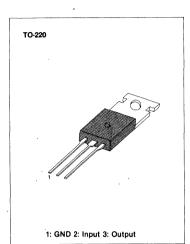

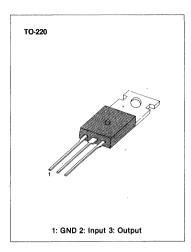

| (A78TXX                                                                                                                       | 3A Positive Voltage Regulator                                            | TO-220         | 312    |

| <a8301< td=""><td>Driver for VTR</td><td>10 SIP H/S</td><td>Vol.</td></a8301<>                                                | Driver for VTR                                                           | 10 SIP H/S     | Vol.   |

| (A8302                                                                                                                        | Servo Control AMP                                                        | 12 SIP         | Vol.   |

| <a8401< td=""><td>VTR Audio Switchless Recording/Play Back AMP</td><td>24 ZIP</td><td>Vol.</td></a8401<>                      | VTR Audio Switchless Recording/Play Back AMP                             | 24 ZIP         | Vol.   |

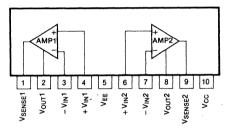

| <a9256< td=""><td>Dual Power Operational Amplifier</td><td>10 SIP H/S</td><td>419</td></a9256<>                               | Dual Power Operational Amplifier                                         | 10 SIP H/S     | 419    |

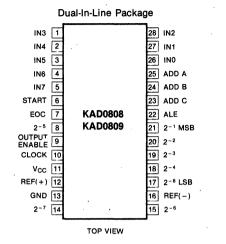

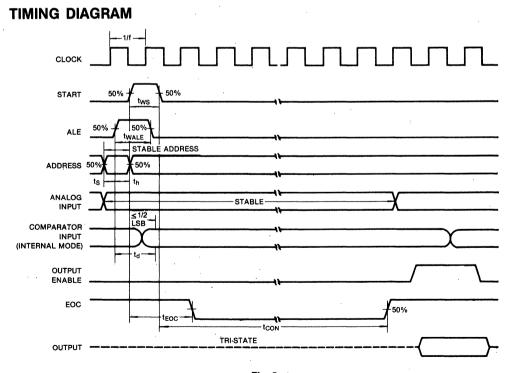

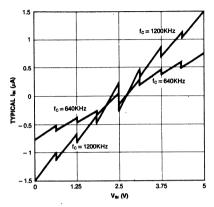

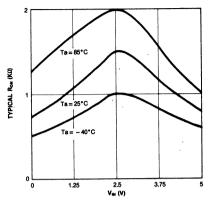

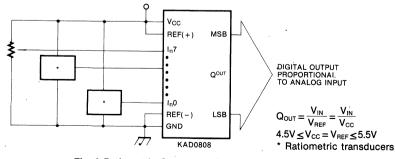

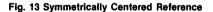

| KAD0808                                                                                                                       | 8 Bit μp-Compatible A/D Converter with 8-Channel<br>Multiplexer          | 28 DIP         | 549    |

| <ad0809< td=""><td>8 Bit μp-Compatible A/D Converter with 8-Channel<br/>Multiplexer</td><td>28 DIP</td><td>549</td></ad0809<> | 8 Bit μp-Compatible A/D Converter with 8-Channel<br>Multiplexer          | 28 DIP         | 549    |

| KAD0820A/B                                                                                                                    | 8 Bit High Speed μp Compatible A/D Converter with<br>Track/Hold Function | 20 DIP         | 560    |

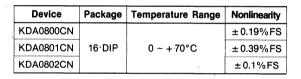

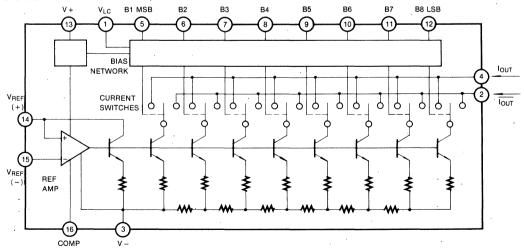

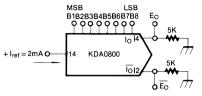

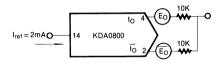

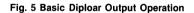

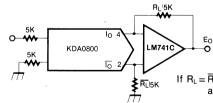

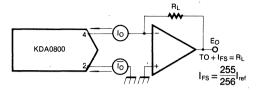

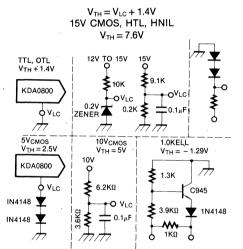

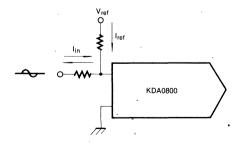

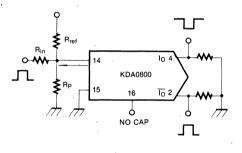

| KDA0800                                                                                                                       | 8 Bit D/A Converter                                                      | 16 DIP         | 580    |

| (DA0801                                                                                                                       | 8 Bit D/A Converter                                                      | 16 DIP         | 580    |

| (DA0802                                                                                                                       | 8 Bit D/A Converter                                                      | 16 DIP         | 580    |

| (F351                                                                                                                         | Single Operating Amplifier                                               | 8 DIP/8 SOP    | 421    |

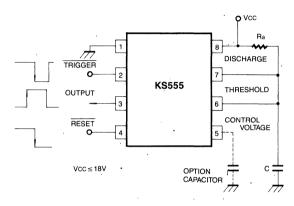

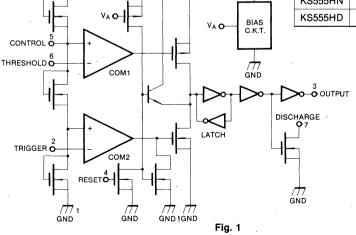

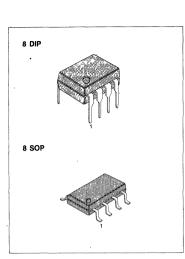

| (8555                                                                                                                         | CMOS Timer                                                               | 8 DIP/8 SOP    | 496    |

| (S555H                                                                                                                        | CMOS Timer                                                               | 8 DIP/8 SOP    | 501    |

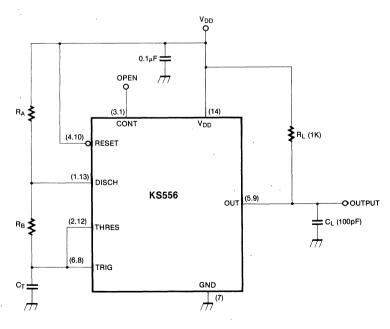

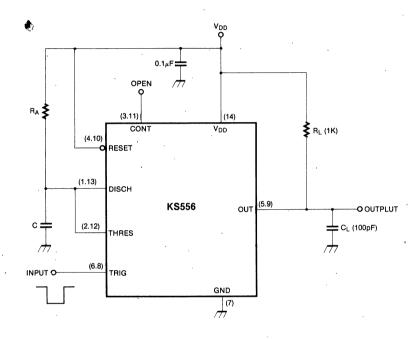

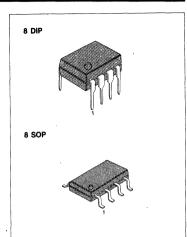

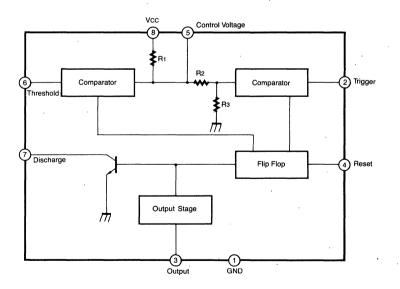

| (S556                                                                                                                         | CMOS Timer                                                               | 14 DIP/14 SOP  | 505    |

| (S5803A/B                                                                                                                     | Remote Control Transmitter                                               | 16 DIP/20 SOP  | Vol.   |

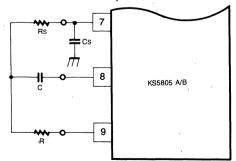

| (S5805A/B                                                                                                                     | Telephone Pulse Dialer with Redial                                       | 18 DIP         | 130    |

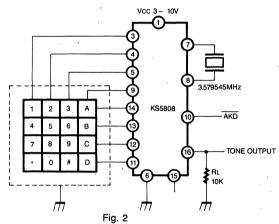

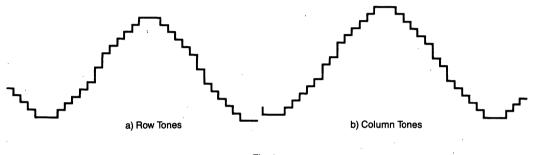

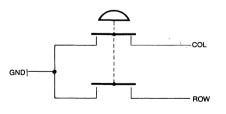

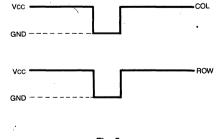

| <s5808< td=""><td>Dual Tone Multi Frequency Dialer</td><td>16 DIP</td><td>146</td></s5808<>                                   | Dual Tone Multi Frequency Dialer                                         | 16 DIP         | 146    |

| <b>(</b> \$5812                                                                                                               | Quad Universial Asychronous Receiver and Transmitter                     | 40 DIP         | 152    |

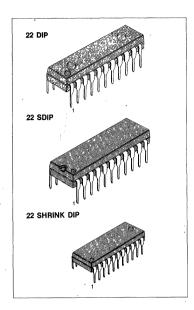

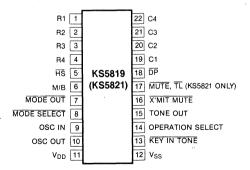

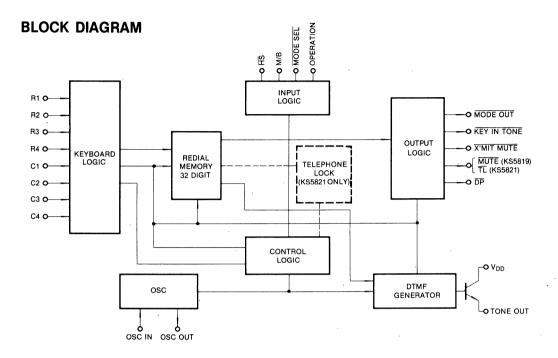

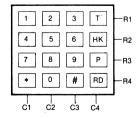

| <b>(</b> \$5819                                                                                                               | Tone/Pulse Dialer with Redial                                            | 22 DIP/SDIP    | 162    |

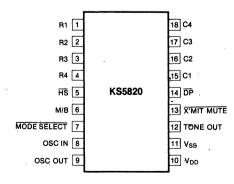

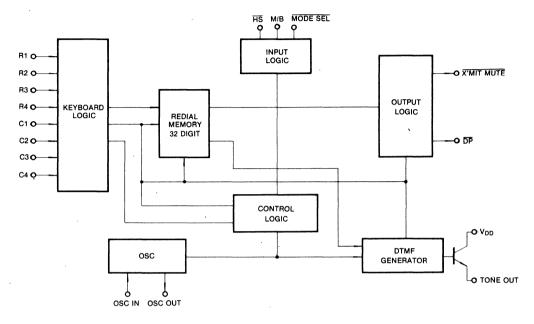

| <s5820< td=""><td>Tone/Pulse Dialer with Redial</td><td>18 DIP</td><td>172</td></s5820<>                                      | Tone/Pulse Dialer with Redial                                            | 18 DIP         | 172    |

| KS5821                                                                                                                        | Tone/Pulse Dialer with Redial                                            | 22 DIP/SDIP    | 162    |

| KS5824                                                                                                                        | Universial Asychronous Receiver and Transmitter                          | 24 DIP         | 180    |

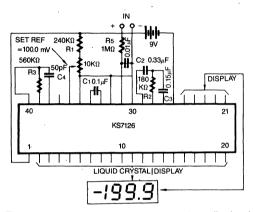

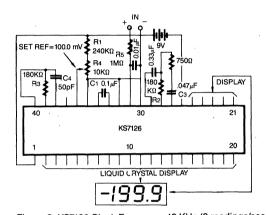

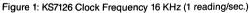

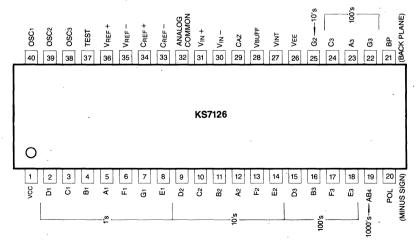

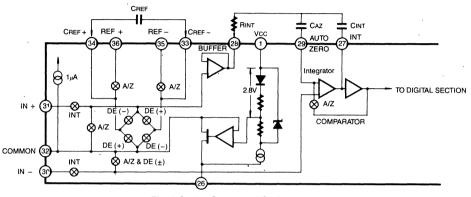

| KS7126                                                                                                                        | 3 1/2 Digit A/D Converter                                                | 40 DIP         | 568    |

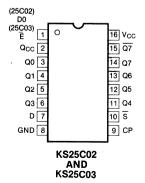

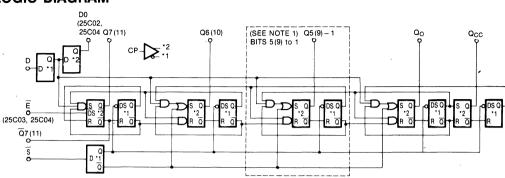

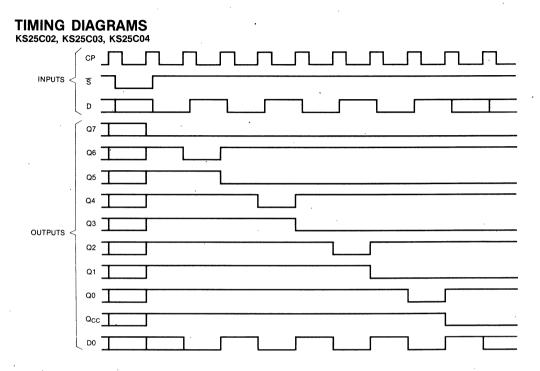

| KS25C02                                                                                                                       | 8 Bit CMOS Successive Approximation Register                             | 16 DIP/24 SDIP | 586    |

# ALPHANUMERIC INDEX (Continued)

| Device         | Function                                      | Package           | Page |

|----------------|-----------------------------------------------|-------------------|------|

| KS25C03        | 8 Bit CMOS Successive Approximation Register  | 16 DIP/24SDIP     | 586  |

| KS25C04        | 12 Bit CMOS Successive Approximation Register | 24 DIP/24SDIP     | 586  |

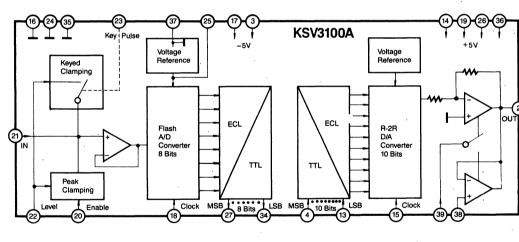

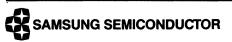

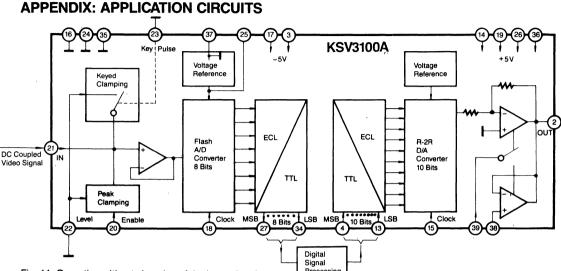

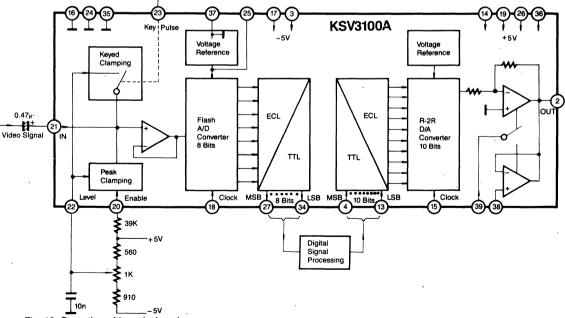

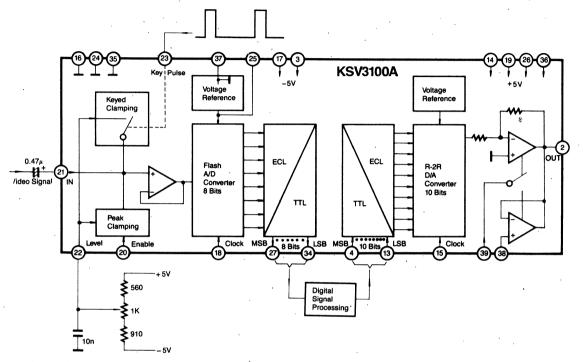

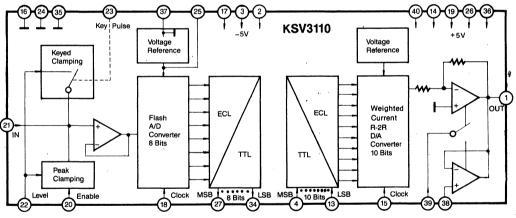

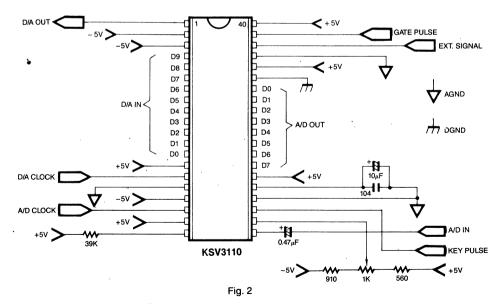

| KSV3100A       | High-Speed A/D-DA Converter                   | 40 DIP            | 521  |

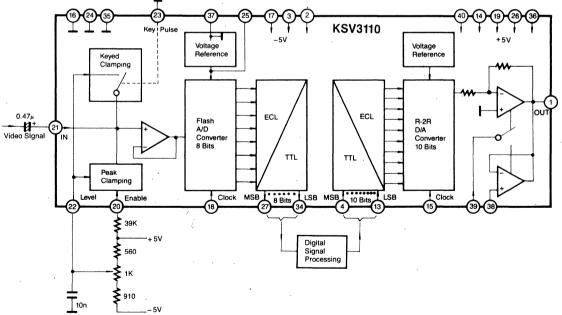

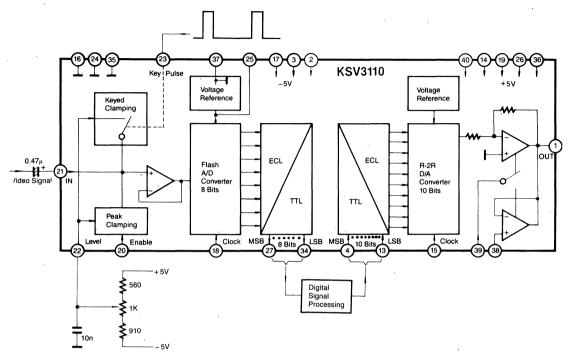

| KSV3110        | High-Speed A/D-DA Converter                   | 40 DIP            | 531  |

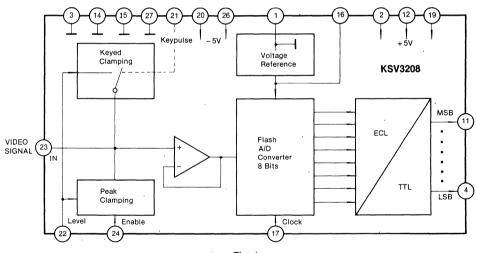

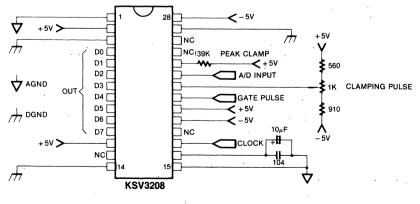

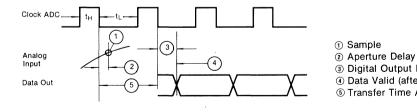

| KSV3208        | High-Speed A/D Converter                      | 28 DIP            | 541  |

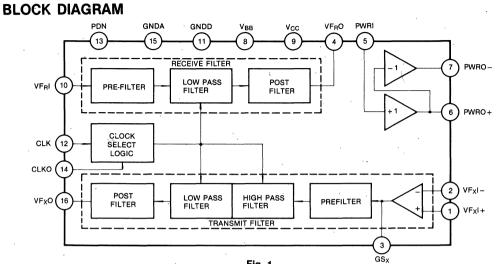

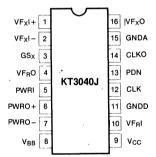

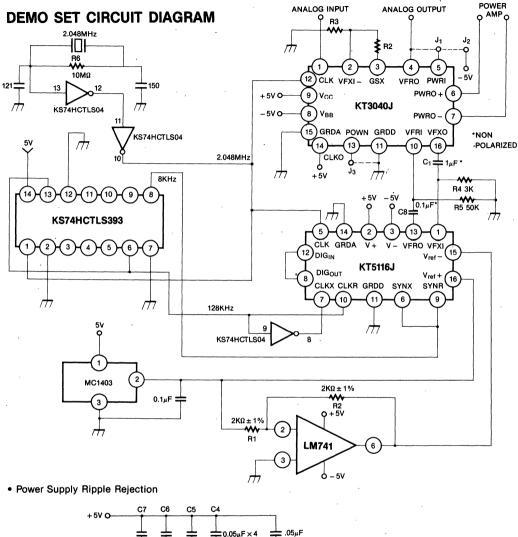

| KT3040J        | PCM Monolithic Filter                         | 16 CERDIP         | 191  |

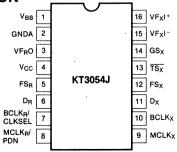

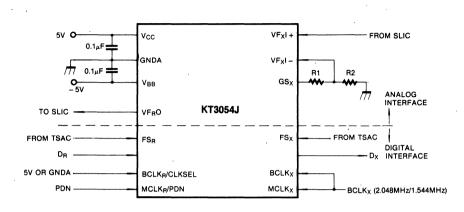

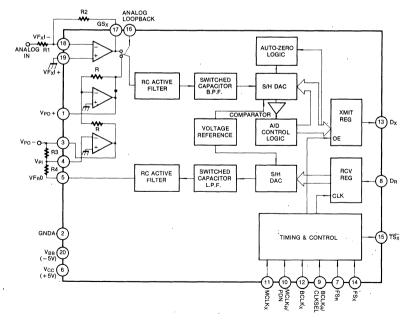

| KT3054J        | COMBO CODEC                                   | 16 CERDIP         | 200  |

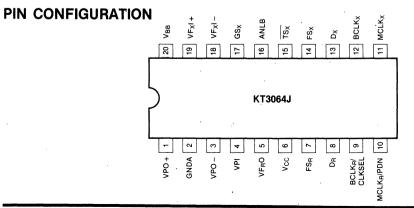

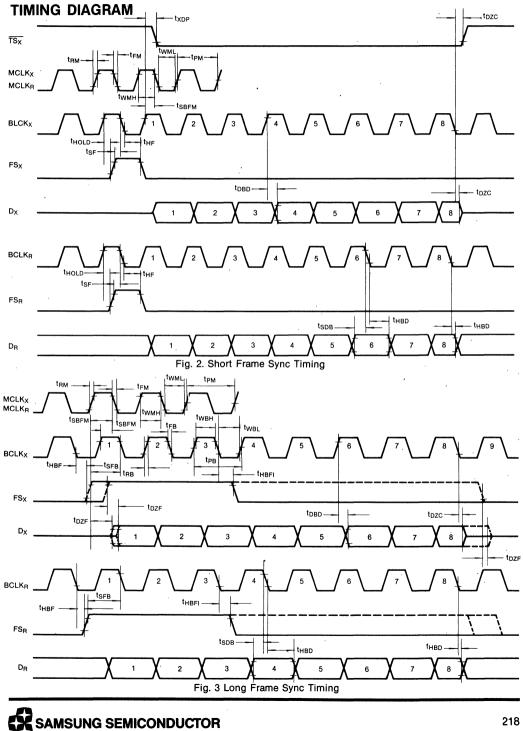

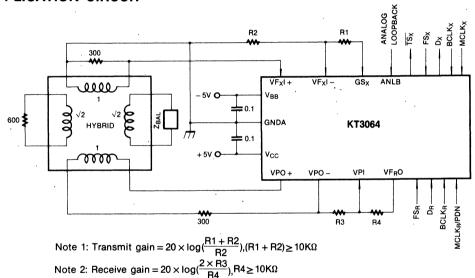

| KT3064J        | COMBO CODEC                                   | 20 CERDIP         | 214  |

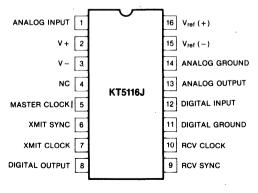

| KT5116J        | μ-Law Companding CODEC                        | 16 CERDIP         | 226  |

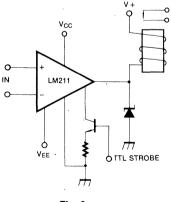

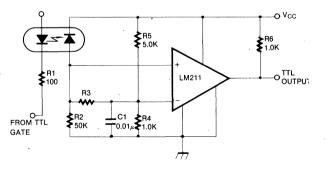

| LM211          | Voltage Comparator                            | 8 DIP/8 SOP       | 476  |

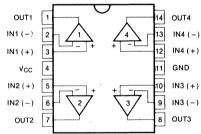

| LM224/A        | Quad Operational Amplifier                    | 14 DIP/14 SOP     | 423  |

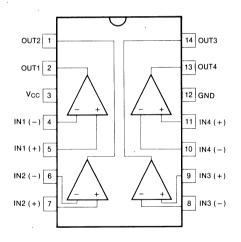

| LM239/A        | Quad Differential Comparator                  | 14 DIP/14 SOP     | 481  |

| LM248          | Quad Operational Amplifier                    | 14 DIP/14 SOP     | 432  |

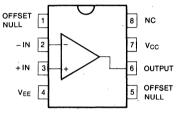

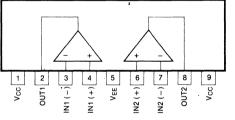

| LM258/A        | Dual Operational Amplifier                    | 8 DIP/8 SOP/9 SIP | 438  |

| _M293/A        | Dual Differential Comparator                  | 8 DIP/8 SOP       | 489  |

| LM311          | Voltage Comparator                            | 8 DIP/8 SOP       | 476  |

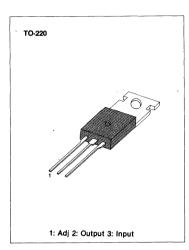

| LM317          | 3-Terminal Positive Adjustable Regulator      | TO-220            | 291  |

| _M323          | 3-Terminal Positive Voltage Regulator         | TO-3P             | 296  |

| _M324/A        | Quad Operational Amplifier                    | 14 DIP/14 SOP     | 423  |

| _M339/A        | Quad Differential Comparator                  | 14 DIP/14 SOP     | 481  |

| _M348 ·        |                                               | 14 DIP/14 SOP     | 432  |

|                | Quad Operational Amplifier                    |                   | 432  |

| _M358/A/S      | Dual Operational Amplifier                    | 8 DIP/8 SOP/9 SIP | 613  |

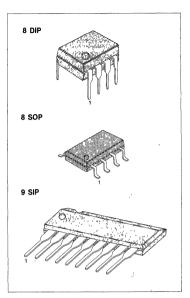

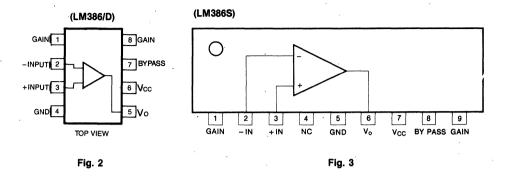

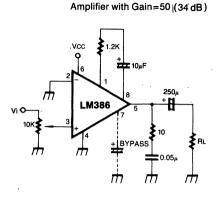

| _M386/S/D      | Low Voltage Audio Power AMP                   | 9 SIP/8 DIP/8 SOP |      |

| LM393/A/S      | Dual Differential Comparator                  | 8 DIP/8 SOP       | 489  |

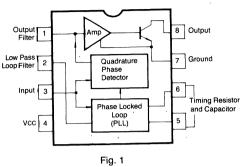

| LM567C         | Tone Decoder                                  | 8 DIP/8 SOP       | 239  |

| _M567L         | Micropower Tone Decoder                       | 8 DIP/8 SOP       | 247  |

| _M723          | Precision Voltage Regulator                   | 14 DIP/14 SOP     | 300  |

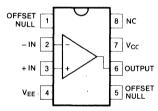

| LM741C/E/I     | Single Operational Amplifier                  | 8 DIP/8 SOP       | 446  |

| _M2901         | Quad Differential Comparator                  | 14 DIP/14 SOP     | 481  |

| _M2902         | Quad Operational Amplifier                    | 14 DIP/14 SOP     | 423  |

| _M2903         | Dual Differential Comparator                  | 8 DIP/8 SOP       | 489  |

| _M2904         | Dual Operational Amplifier                    | 8 DIP/8 SOP/9 SIP | 438  |

| _M3302         | Quad Differential Comparator                  | 14 DIP/14 SOP     | 481  |

| MC1458/C/S/I   | Dual Operational Amplifier                    | 8 DIP/8 SOP/9 SIP | 452  |

| VIC1488        | Quad Line Driver                              | 14 DIP/14 SOP     | 257  |

| /IC1489/A      | Quad Line Receiver                            | 14 DIP/14 SOP     | 264  |

| AC3303         | Quad Operational Amplifier                    | 14 DIP/14 SOP     | 456  |

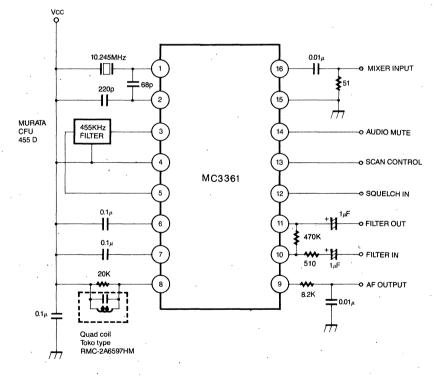

| MC3361         | Low Power Narrow Band FM IF                   | 16 DIP/16 SOP     | 270  |

| MC3403         | Quad Operational Amplifier                    | 14 DIP/14 SOP     | 456  |

| AC4558/C/A/S/I | Dual Operational Amplifier                    | 8 DIP/8 SOP/9 SIP | 463  |

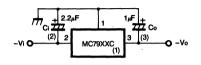

| MC78XX         | 3-Terminal 1A Positive Voltage Regulator      | TO-220            | 323  |

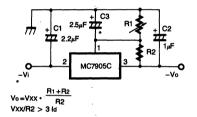

| MC78LXX        | 3-Terminal Positive Voltage Regulator         | TO-92             | 353  |

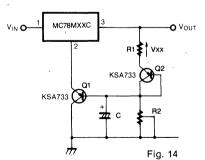

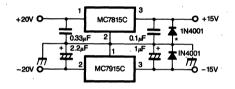

| MC78MXX        | 3-Terminal 0.5A Positive Voltage Regulator    | TO-220            | 364  |

| MC79XX         | 3-Terminal Negative Voltage Regulator         | TO-220            | 377  |

| MC79MXX        | 3-Terminal 0.5A Negative Voltage Regulator    | TO-220            | 387  |

| NE555          | Timer                                         | 8 DIP/8 SOP       | 509  |

| NE556          | Dual Timer                                    | 14 DIP/14 SOP     | 513  |

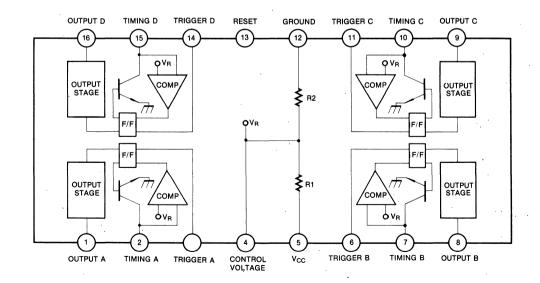

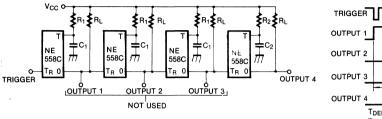

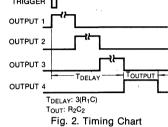

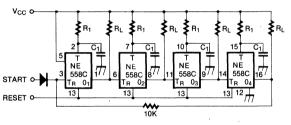

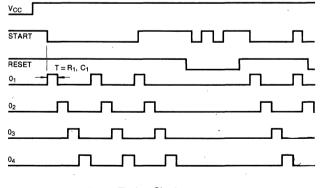

| NE558          | Quad Timer                                    | 16 DIP/16 SOP     | 516  |

| INEU00         | Quau milei                                    | 10 DIF/10 30F     | 510  |

# **PRODUCT INDEX**

1. Audio Application

| Device              | Function                                           | Package           | Page   |

|---------------------|----------------------------------------------------|-------------------|--------|

| KA1222              | Dual Low Noise Equalizer AMP                       | 8 SIP             | Vol. 1 |

| KA2201B             | 0.5W Audio Power AMP                               | 8 DIP             | Vol. 1 |

| KA2201/N            | 1.2W Audio Power AMP                               | 8 DIP             | Vol. 1 |

| KA2206              | 2.3W Dual Audio Power AMP                          | 12 DIP/F          | Vol. 1 |

| KA22062             | 4.5W Dual Power AMP                                | 12 SIP H/S        | Vol. 1 |

| KA2209              | Dual Low Voltage Power AMP                         | 8 DIP             | Vol. 1 |

| KA2210              | 5.5W Dual Power AMP                                | 12 SIP H/S        | Vol. 1 |

| KA2211              | 5.8W Dual Power AMP                                | 12 SIP H/S        | Vol. 1 |

| KA2212              | 0.5W Audio Power AMP                               | 9 SIP             | Vol. 1 |

| KA2213              | One Chip Tape Recorder System                      | 14 DIP H/S        | Vol. 1 |

| KA22131             | Dual Pre-Power AMP for Auto Reverse                | 24 SOP            | Vol. 1 |

| KA22135             | Dual Pre-Power AMP and DC Motor Speed Controller   | 22 SDIP           | Vol. 1 |

| KA2214              | 1W Dual Power AMP                                  | 14 DIP H/S        | Vol. 1 |

| KA2220              | Equalizer AMP with ALC                             | 9 SIP             | Vol. 1 |

| KA2221              | Dual Low Noise Equalizer AMP                       | 8 SIP             | Vol. 1 |

| KA22211             | Dual Low Noise Equalizer AMP                       | 8 SIP             | Vol. 1 |

| KA2223              | 5 Band Graphic Equalizer AMP                       | 16 DIP            | Vol. 1 |

| KA22233             | 3 Band Dual Graphic Equalizer AMP                  | 22 DIP            | Vol. 1 |

| KA22235             | 5 Band Graphic Equalizer AMP                       | 18 ZIP            | Vol. 1 |

| KA22235             | Dual Equalizer AMP with ALC                        | 14 DIP            | Vol. 1 |

| KA2224<br>KA22241   | Dual Equalizer AMP with ALC                        | 9 SIP             | Vol. 1 |

| KA22241<br>KA2225/D |                                                    | 16 DIP/16 SOP     | Vol. 1 |

|                     | Dual Pre-AMP for 3V Using                          | 16 DIP            | Vol. 1 |

| KA22261             | Dual Equalizer AMP with REC AMP                    |                   | Vol. 1 |

| KA2230              | 9-Program Music Selector                           | 22 DIP            | Vol. 1 |

| KA22421/D           | AM 1 Chip Radio                                    | 16 DIP/16 SOP     |        |

| KA22424             | AM/FM 1 Chip Radio                                 | 16 DIP            | Vol. 1 |

| KA2243              | AM/FM IF System                                    | 16 DIP            | Vol. 1 |

| KA2244              | FM IF System for Car Radio                         | 9 SIP             | Vol. 1 |

| KA22441             | FM IF System for Car Stereo                        | 16 ZIP            | Vol. 1 |

| KA2245              | FM IF System for Car Radio                         | .7 SIP            | Vol. 1 |

| KA22461             | Electronic Tuning AM Radio Receiver for Car Stereo | 19 ZIP            | Vol. 1 |

| KA2247              | FM IF/AM Tuner System                              | 16 DIP            | Vol. 1 |

| KA22471             | FM IF/AM Tuner System                              | 16 DIP            | Vol. 1 |

| KA2248A/D           | 3V FM IF/AM Tuner System                           | 16 DIP/16 SOP     | Vol. 1 |

| KA2249/D            | FM Front End for Portable Radio                    | 7 SIP/8 SOP       | Vol. 1 |

| KA2261              | FM Stereo Multiplex Decoder                        | 16 DIP            | Vol. 1 |

| KA2262              | FM Stereo Multiplex Decoder for Car Stereo         | 16 ZIP            | Vol. 1 |

| KA2263              | FM Stereo Multiplex Decoder                        | 9 SIP             | Vol. 1 |

| KA2264/D            | FM Stereo Multiplex Decoder                        | 9 SIP/16 SOP      | Vol. 1 |

| KA2265              | VCO Non-Adjusting FM Stereo Multiplex Decoder      | 16 DIP            | Vol. 1 |

| KA2281              | 5 DOT Dual LED Level Meter Driver                  | 16 DIP            | Vol. 1 |

| KA2283              | 5 DOT Dual LED Level Meter Driver                  | 16 DIP            | Vol. 1 |

| KA2284              | 5 DOT LED Level Meter Driver                       | 9 SIP             | Vol. 1 |

| KA2285              | 5 DOT LED Level Meter Driver                       | 9 SIP             | Vol. 1 |

| KA2286              | 5 DOT LED Linear Level Meter Driver                | 9 SIP             | Vol. 1 |

| KA2287              | 5 DOT LED Linear Level Meter Driver                | 9 SIP             | Vol. 1 |

| KA2288              | 7 DOT LED Level Meter Driver                       | 16 DIP            | Vol. 1 |

| LM386/S/D           | Low Voltage Audio Power AMP                        | 9 SIP/8 DIP/8 SOP | 613    |

| KA2303              | Toy Radio Control Actuator                         | 9 SIP             | Vol. 1 |

| KA2304              | Toy Radio Control Actuator                         | 9 SIP             | Vol. 1 |

| KA2401              | DC Motor Speed Controller                          | 8 DIP             | Vol. 1 |

# PRODUCT INDEX (Continued)

### 1. Audio Application (Continued)

| Device | Function                              | Package | Page   |

|--------|---------------------------------------|---------|--------|

| KA2402 | Low Voltage DC Motor Speed Controller | 8 DIP   | Vol. 1 |

| KA2404 | DC Motor Speed Controller             | TO-92L  | Vol. 1 |

| KA2407 | DC Motor Speed Controller             | TO-126  | Vol. 1 |

## 2. Video Application

| Device                                                                                                 | Function                                           | Package       | Page   |

|--------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------|--------|

| KA2101                                                                                                 | TV Sound IF AMP                                    | 14 DIP        | Vol. 1 |

| KA2102A                                                                                                | TV Sound System                                    | 14 DIP H/S    | Vol. 1 |

| KA2103L                                                                                                | Sound Mute System for TV                           | 8 SIP         | Vol. 1 |

| KA2104                                                                                                 | Auto Power off and Sound Mute System for TV        | 9 SIP         | Vol. 1 |

| KA2105                                                                                                 | Limiter AMP and Detector for a TV SIF              | 9 SIP         | Vol. 1 |

| KA2106                                                                                                 | Dual Sound Multiplex for a TV SIF                  | 16 DIP        | Vol. 1 |

| KA2107                                                                                                 | DC Volume, Tone Control Circuit                    | 12 SIP        | Vol. 1 |

| KA2130A                                                                                                | TV Vertical Deflection System                      | 10 SIP H/S    | Vol. 1 |

| KA2131                                                                                                 | TV Vertical Output Circuit                         | 10 SIP H/S    | Vol.   |

| KA2133                                                                                                 | 1 Chip Deflection System                           | 16 DIP H/S    | Vol.   |

| <a2134< td=""><td>Color TV Deflection Signal Processing IC</td><td>18 DIP</td><td>Vol.</td></a2134<>   | Color TV Deflection Signal Processing IC           | 18 DIP        | Vol.   |

| <a2135< td=""><td>Horizontal Signal Processing IC</td><td>12 SIP</td><td>Vol.</td></a2135<>            | Horizontal Signal Processing IC                    | 12 SIP        | Vol.   |

| <a2136< td=""><td>Low Noise TV Vertical Deflection System</td><td>12 ZDIP/F</td><td>Vol.</td></a2136<> | Low Noise TV Vertical Deflection System            | 12 ZDIP/F     | Vol.   |

| KA2137                                                                                                 | TV Horizontal Processor                            | 16 DIP        | Vol.   |

| KA2153                                                                                                 | Video-Chroma Deflection System for a Color TV      | 42 DIP        | Vol.   |

| (A2154                                                                                                 | Video-Chroma Deflection System for a Color TV      | 42 DIP        | Vol.   |

| (A2181                                                                                                 | Remote Control Pre-AMP                             | 8 SIP         | Vol.   |

| (A2182                                                                                                 | Remote Control Pre-AMP                             | 8 SIP         | Vol.   |

| (A2183                                                                                                 | Remote Control Pre-AMP                             | 8 SIP         | Vol.   |

| (A22682                                                                                                | 1 Chip TV MPX Demodulator                          | 28 DIP        | Vol.   |

| (A2268N                                                                                                | 1 Chip TV Sound MPX                                | 28 DIP        | Vol.   |

| <a2605< td=""><td>SYNC Separator</td><td>9 SIP</td><td>Vol.</td></a2605<>                              | SYNC Separator                                     | 9 SIP         | Vol.   |

| <a2606< td=""><td>SYNC Separator</td><td>9 SIP</td><td>Vol.</td></a2606<>                              | SYNC Separator                                     | 9 SIP         | Vol.   |

| (A2615                                                                                                 | LED and Lamp Driver                                | 9 SIP         | Vol.   |

| <a2616< td=""><td>LED and Lamp Driver</td><td>9 SIP</td><td>Vol.</td></a2616<>                         | LED and Lamp Driver                                | 9 SIP         | Vol.   |

| KA2617                                                                                                 | LED and Lamp Driver                                | 9 SIP         | Vol.   |

| <b>KA2618</b>                                                                                          | LED and Lamp Driver                                | 9 SIP         | Vol.   |

| (A2911                                                                                                 | Video IF System for Color TV                       | 16 DIP        | Vol.   |

| (A2912                                                                                                 | Video IF Processor for B/W TV                      | 14 DIP H/S    | Vol.   |

| KA2913A                                                                                                | Video and Sound IF AMP for Monochrome TV Receivers | 16 DIP        | Vol.   |

| (A2914A                                                                                                | Video IF + SIF System                              | 24 DIP        | Vol.   |

| (A2915                                                                                                 | TV VIF & SIF & Deflection System                   | 28 DIP        | Vol.   |

| <a2916< td=""><td>Video IF System for Color TV</td><td>16 DIP</td><td>Vol.</td></a2916<>               | Video IF System for Color TV                       | 16 DIP        | Vol.   |

| (A2917                                                                                                 | Video and Sound IF AMP for Monochrome TV Receivers | 16 DIP        | Vol.   |

| (A2918                                                                                                 | Video IF + SIF System                              | 24 DIP        | Vol.   |

| (A2919                                                                                                 | VIF + SIF System for Color TV                      | 30 SSD        | Vol.   |

| (A2944                                                                                                 | Write & Read AMP                                   | 28 DIP        | Vol.   |

| (A2945                                                                                                 | Video AMP                                          | 28 DIP        | Vol.   |

| (A2983                                                                                                 | Switchless Recording/Play Back AMP                 | 18 DIP        | Vol.   |

| <a2988< td=""><td>Chroma Signal Processor</td><td>28 DIP</td><td>Vol.</td></a2988<>                    | Chroma Signal Processor                            | 28 DIP        | Vol.   |

| KA6101                                                                                                 | Analog Interface Circuit for Teletex System        | 18 DIP        | Vol.   |

| KA6102                                                                                                 | Analog Interface Circuit for Teletex System        | 18 DIP        | Vol.   |

| KA8301                                                                                                 | Driver for VTR                                     | 10 SIP H/S    | Vol.   |

| KA8302                                                                                                 | Servo Control AMP                                  | 12 SIP        | Vol.   |

| KA8401                                                                                                 | VTR Audio Switchless Recording/Play Back AMP       | 24 ZIP        | Vol.   |

| KS5803A/B                                                                                              | Remote Control Transmitter                         | 16 DIP/20 SOP | Vol.   |

## PRODUCT INDEX (Continued)

# 3. Telecommunication Application

| Device    | Function                                             | Package       | Page |

|-----------|------------------------------------------------------|---------------|------|

| KA2410    | Tone Ringer                                          | 8 DIP         | 69   |

| KA2411    | Tone Ringer                                          | 8 DIP         | 69   |

| KA2412A   | Telephone Speech Circuits                            | 14 DIP        | 75   |

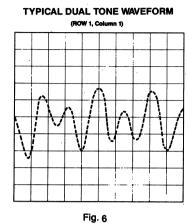

| KA2413    | Dual Tone Multi Frequency Generator                  | 16 DIP        | 83   |

| KA2418    | Tone Ringer with Bridge Diode                        | 8 DIP         | 108  |

| KA2419    | Tone Ringer with Bridge Diode                        | 8 DIP         | 108  |

| KA2425A/B | Telephone Speech Network with Dialer Interface       | 18 DIP        | 112  |

| KS5805A/B | Telephone Pulse Dialer with Redial                   | 18 DIP        | 130  |

| KS5808    | Dual Tone Multi Frequency Dialer                     | 16 DIP        | 146  |

| KS5812    | Quad Universial Asychronous Receiver and Transmitter | 40 DIP        | 152  |

| KS5819    | Tone/Pulse Dialer with Redial                        | 22 DIP/SDIP   | 162  |

| KS5820    | Tone/Pulse Dialer with Redial                        | 18 DIP        | 172  |

| KS5821    | Tone/Pulse Dialer with Redial                        | 22 DIP/SDIP   | 162  |

| KS5824    | Universial Asychronous Receiver and Transmitter      | 24 DIP        | 180  |

| KT3040J   | PCM Monolithic Filter                                | 16 CERDIP     | 191  |

| KT3054J   | COMBO CODEC                                          | 16 CERDIP     | 200  |

| KT3064J   | COMBO CODEC                                          | 20 CERDIP     | 214  |

| KT5116J   | μ-Law Companding CODEC                               | 16 CERDIP     | 226  |

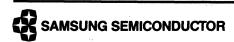

| LM567C    | Tone Decoder                                         | 8 DIP/8 SOP   | 239  |

| LM567L    | Micropower Tone Decoder                              | 8 DIP/8 SOP   | 247  |

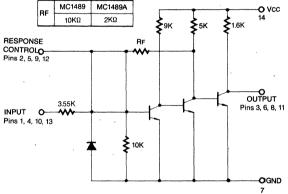

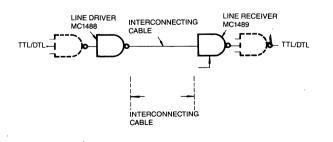

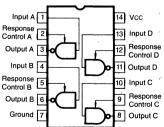

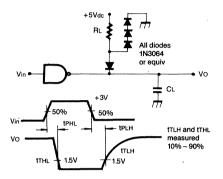

| MC1488    | Quad Line Driver                                     | 14 DIP/14 SOP | 257  |

| MC1489/A  | Quad Line Receiver                                   | 14 DIP/14 SOP | 264  |

| MC3361    | Low Power Narrow Band FM IF                          | 16 DIP/16 SOP | 270  |

| KA2580A   | 8-Channel Source Drivers                             | 18 DIP        | 599  |

| KA2588A   | 8-Channel Source Drivers                             | 20 DIP        | 599  |

| KA2651    | Fluorescent Display Drivers                          | 18 DIP        | 604  |

### 4. Industrial Application

| Device    | Function                                    | Package           | Page |

|-----------|---------------------------------------------|-------------------|------|

| KA201A    | Single Operational Amplifier                | 8 DIP/8 SOP       | 407  |

| KA301A    | Single Operational Amplifier                | 8 DIP/8 SOP       | 407  |

| KA319     | Dual High Speed Voltage Comparator          | 14 DIP/14 SOP     | 463  |

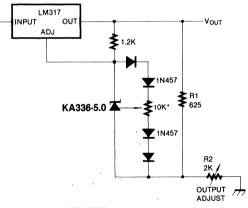

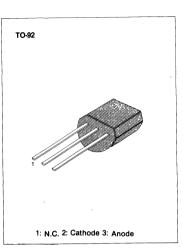

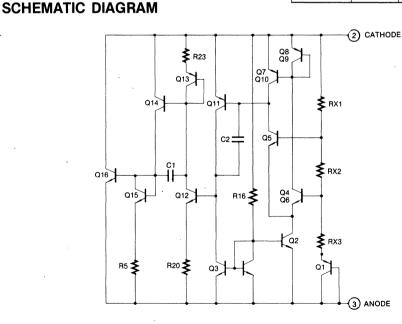

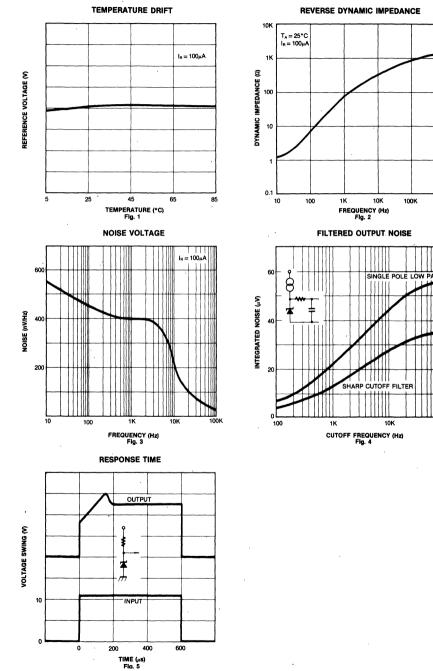

| KA336-5.0 | Voltage Reference Diode                     | TO-92             | 393  |

| KA350     | 3 AMP Adjustable Positive Voltage Regulator | TO-3P             | 277  |

| KA361     | High Speed Voltage Comparator               | 14 DIP/14 SOP     | 472  |

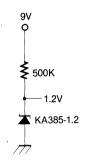

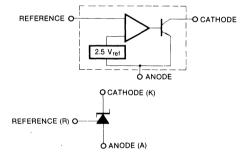

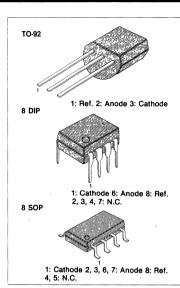

| KA385-1.2 | Micropower Voltage Reference Diode          | TO-92             | 397  |

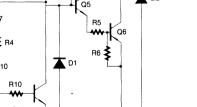

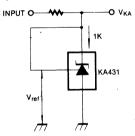

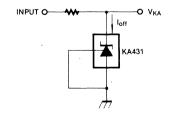

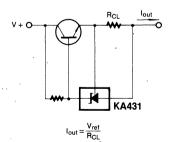

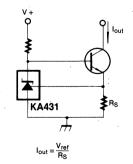

| KA431     | Programmable Precision Reference            | TO-92/8 DIP/8 SOP | 401  |

| KA710C    | High Speed Voltage Comparator               | 14 DIP/14 SOP     | 474  |

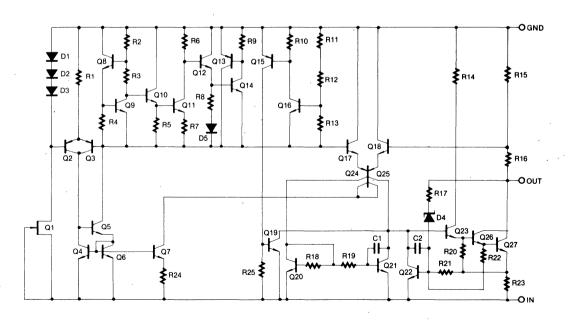

| KA733C    | Differential Video Amplifier                | 14 DIP/14 SOP     | 412  |

| KA3524    | Regulator Pulse Width Modulator             | 16 DIP            | 285  |

| KA9256    | Dual Power Operational Amplifier            | 10 SIP H/S        | 419  |

| KF351     | Single Operating Amplifier                  | 8 DIP/8 SOP       | 421  |

| KS555     | CMOS Timer                                  | 8 DIP/8 SOP       | 496  |

| KS555H    | CMOS Timer                                  | 8 DIP/8 SOP       | 501  |

| KS556     | CMOS Timer                                  | 14 DIP/14 SOP     | 505  |

| LM211     | Voltage Comparator                          | 8 DIP/8 SOP       | 476  |

# **PRODUCT INDEX** (Continued)

## Industrial Application (Continued)

| Device         | Function                                                                                 | Package           | Page  |

|----------------|------------------------------------------------------------------------------------------|-------------------|-------|

| LM224/A        | Quad Operational Amplifier                                                               | 14 DIP/14 SOP     | 423   |

| LM239/A        | Quad Differential Comparator                                                             | 14 DIP/14 SOP     | 481   |

| LM248          | Quad Operational Amplifier                                                               | 14 DIP/14 SOP     | 432   |

| LM258/A        | Dual Operational Amplifier                                                               | 8 DIP/8 SOP/9 SIP | 438   |

| LM293/A        | Dual Differential Comparator                                                             | · 8 DIP/8 SOP     | 489   |

| LM311          | Voltage Comparator                                                                       | 8 DIP/8 SOP       | 476   |

| LM317          | 3-Terminal Positive Adjustable Regulator                                                 | TO-220            | 291   |

| LM323          | 3-Terminal Positive Voltage Regulator                                                    | TO-3P             | 296   |

| LM324/A        | Quad Operational Amplifier                                                               | 14 DIP/14 SOP     | 423   |

| LM339/A        | Quad Differential Comparator                                                             | 14 DIP/14 SOP     | 481   |

| LM348          | Quad Operational Amplifier                                                               | 14 DIP/14 SOP     | 432   |

| LM358/A/S      | Dual Operational Amplifier                                                               | 8 DIP/8 SOP/9 SIP | 438   |

| LM393/A/S      | Dual Differential Comparator                                                             | 8 DIP/8 SOP       | 489   |

| LM723          | Precision Voltage Regulator                                                              | 14 DIP/14 SOP     | 300   |

| LM741C/E/I     | Single Operational Amplifier                                                             | 8 DIP/8 SOP       | 446   |

| LM2901         | Quad Differential Comparator                                                             | 14 DIP/14 SOP     | 481   |

| LM2902         | Quad Operational Amplifier                                                               | 14 DIP/14 SOP     | 423   |

| LM2903         | Dual Differential Comparator                                                             | 8 DIP/8 SOP       | 489   |

| LM2904         | Dual Operational Amplifier                                                               | 8 DIP/8 SOP/9 SIR | 438   |

| LM3302         | Quad Differential Comparator                                                             | 14 DIP/14 SOP     | 481   |

| MC1458/C/S/I   | Dual Operational Amplifier                                                               | 8 DIP/8 SOP/9 SIP | 452   |

| MC3303         | Quad Operational Amplifier                                                               | 14 DIP/14 SOP     | 456   |

| MC3403         | Quad Operational Amplifier                                                               | 14 DIP/14 SOP     | · 456 |

| MC4558/C/A/S/I | Dual Operational Amplifier                                                               | 8 DIP/8 SOP/9 SIP | 463   |

| MC78XX         | 3-Terminal 1A Positive Voltage Regulator                                                 | TO-220            | 323   |

| MC78LXX        | 3-Terminal Positive Voltage Regulator                                                    | TO-92             | 353   |

| MC78MXX        | 3-Terminal 0.5A Positive Voltage Regulator                                               | TO-220            | 364   |

| MC79XX         | 3-Terminal Negative Voltage Regulator                                                    | TO-220            | 377   |

| MC79MXX        | 3-Terminal 0.5A Negative Voltage Regulator                                               | TO-220            | 387   |

| KA78S40        | Switching Regulator                                                                      | 16 DIP            | 306   |

| KA78TXX        | 3A Positive Voltage Regulator                                                            | TO-220            | 312   |

| NE555          | Timer                                                                                    | 8 DIP/8 SOP       | 509   |

| NE556          | Dual Timer                                                                               | 14 DIP/14 SOP     | 513   |

| NE558          | Quad Timer                                                                               | 16 DIP/16 SOP     | 516   |

| KA2803         | Low Power Consumption Earth Leakage Detector                                             | 8 DIP             | 607   |

| KA2804         | Zero Voltage Switch                                                                      | 8 DIP             | 610   |

| KA33V          | Silicon Monolithic Bipolar Integrated Circuit Voltage<br>Stabilizer for Electronic Tuner | TO-92             | 295   |

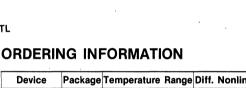

### 5. Data Converter Application

| Device     | Function                                                                 | Package | Page |

|------------|--------------------------------------------------------------------------|---------|------|

| KSV3100A   | High-Speed A/D-DA Converter                                              | 40 DIP  | 521  |

| KSV3110    | High-Speed A/D-DA Converter                                              | 40 DIP  | 531  |

| KSV3208    | High-Speed A/D Converter                                                 | 28 DIP  | 541  |

| KAD0808    | 8 Bit μp-Compatible A/D Converter with 8-Channel<br>Multiplexer          | 28 DIP  | 549  |

| KAD0809    | 8 Bit μp-Compatible A/D Converter with 8-Channel<br>Multiplexer          | 28 DIP  | 549  |

| KAD0820A/B | 8 Bit High Speed μp Compatible A/D Converter with<br>Track/Hold Function | 20 DIP  | 560  |

| KDA0800    | 8 Bit D/A Converter                                                      | 16 DIP  | 580  |

| KDA0801    | 8 Bit D/A Converter                                                      | 16 DIP  | 580  |

| KDA0802    | 8 Bit D/A Converter                                                      | 16 DIP  | 580  |

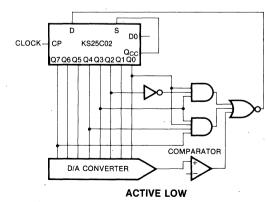

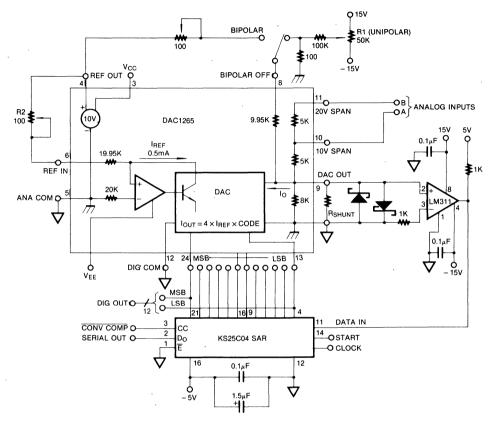

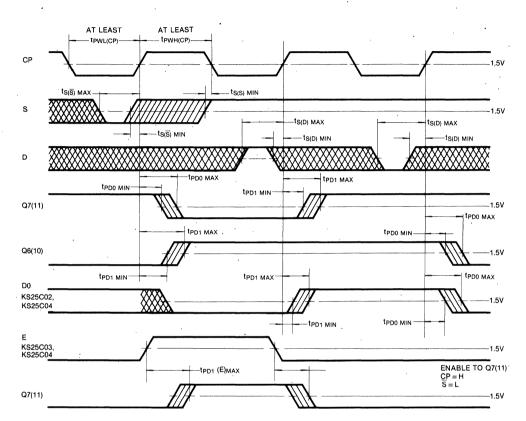

| KS25C02    | 8 Bit CMOS Successive Approximation Register                             | 16 DIP  | 586  |

| KS25C03    | 8 Bit CMOS Successive Approximation Register                             | 16 DIP  | 586  |

| KS25C04    | 12 Bit CMOS Successive Approximation Register                            | 24SDIP  | 586  |

| KS7126     | 3 1/2 Digit A/D Converter                                                | 40 DIP  | 568  |

| • | Quality & Reliability                               | 1 |

|---|-----------------------------------------------------|---|

|   | Product Guide                                       | 2 |

|   | Telecom ICs                                         | 3 |

|   | Industrial ICs                                      | 4 |

|   | Data Converter ICs                                  | 5 |

|   | Miscellaneous ICs                                   | 6 |

|   | Package Dimensions                                  | 7 |

|   | Sales Offices and Manufacturer's<br>Representatives | 8 |

. .

• •

.

### INTRODUCTION

Samsung's linear IC products are among the most reliable in the industry. Samsung has always made a commitment to achieve the highest possible quality, reliability, and customer satisfaction with its products.

Extensive qualification, monitor and outgoing programs are used to scrutinize product quality and reliability. Stringent controls are applied to every wafer fabrication and assembly lot to achieve reproducibility, and therefore maintain product reliability.

In this chapter, the quality and reliability programs established at Samsung will be discussed. In addition, a description of reliability theory, reliability tests and various support efforts provides a broad framework from which to comprehend Samsung quality and reliability.

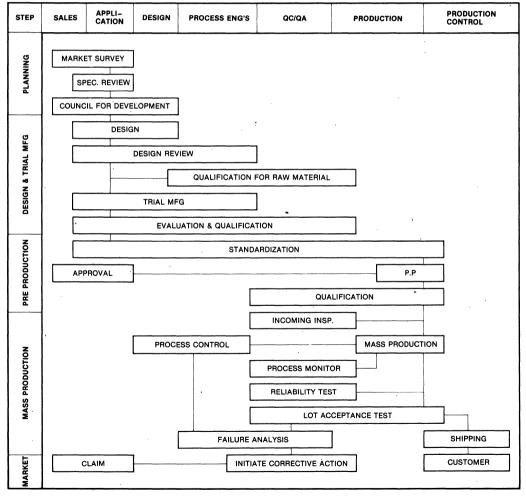

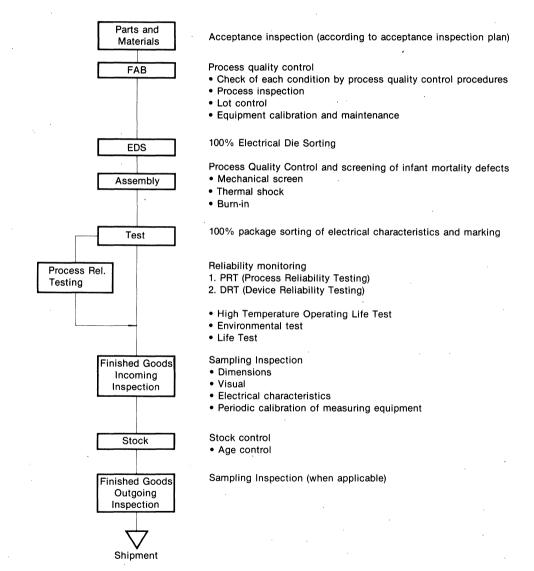

To better understand the Quality Department's role in product develoment and manufacturing, a detailed diagram is listed below. As can be noted, Quality Engineering is involved in all phases, save that of initial product planning.

Figure 1. Quality Assurance During Development

### QUALITY AND RELIABILITY PROGRAM

Since Samsung manufactures many different products using a variety of fab and assembly technologies, close attention must be paid to a variety of (potential) reliability hazards. The Samsung quality and reliability department has established a variety of procedures and programs to assess, understand, control, and eliminate reliability problems.

The major categories of reliability program management are:

- a. Qualification program

- b. Monitor program

- c. Outgoing quality program

### QUALIFICATION PROGRAM

Samsung qualification procedures are used mainly to confirm the major characteristics and reliability attributes of new technologies or products for introduction to Samsung manufacturing. The program is also utilited to evaluate changes to existing technologies or raw materials. The purpose of this program is to simulate all relevant user conditions, via accelerated and standard methods, prior to product shipment. The stresses used for qualification are detailed in following sections.

### **MONITOR PROGRAM**

Twice per year, devices duplicate their qualification tests to obtain long-term reliability data for Linear ICs. In this way historical data is collected and analyzed over all part types and thus assures the customer of ongoing device quality.

These results are summarized in reliability reports issued periodically by Samsung Semiconductor.

### **OUTGOING QUALITY PROGRAM**

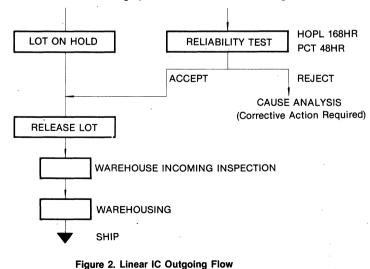

All wafer lots are required to pass a "QC-reliability-gate" prior to product shipment. The purpose is to track "Lotby-lot" quality and reliability to catch any potential product anomaly at the factory site.

The customer can then expect only quality material to be delivered from Samsung. Any lot that fails the procedure listed below is scrutinized heavily, to make sure that corrective action takes place immediately.

By paying such close attention to every lot, product costs are kept at a minimum. Samsung's customer return rate is extremely low, which is where our tough outgoing policy is most powerful. Such a tight clamp to protect our customers is how we can assure that all Samsung's products are released with the highest confidence level possible.

### **RELIABILITY TESTS**

Samsung has established a comprehensive reliability program to monitor and ensure the ongoing reliability of the linear IC family. This program involves not only reliability data collection and analysis on existing parts, but also rigorous in-line quality controls for all products.

Listed below are details of tests performed to ensure that manufactured product continues to meet Samsung's stringent quality standards. In line quality controls are reviewed extensively in later sections.

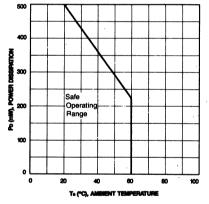

The tests run by the quality department are accelerated tests, serving to model "real world" applications through boosted temperature, voltage, and/or humidities. Accelerated conditions are used to derive device knowledge through means quicker than that of typical application situations. These accelerated conditions are then used to assess differing failure rate mechanisms that correlate directly with ambient conditions. Following are summaries of various stresses (and their conditions) run by Samsung on linear IC products.

### HIGH TEMPERATURE OPERATING LIFE TEST (HOPL)

$(T_i = 125^{\circ}C, V_{CC} = V_{CC} max, static)$

High temperature operating life test is performed to measure actual field reliability. Life tests of 1000HR to 2000HR durations are used to accelerate failure mechanisms by operating the device at an elevated ambient temperature (125°C). Data obtained from this test are used to predict product infant mortality, early life, and random failure rates. Data are translated to standard operating temperatures via failure analysis to determine the activation energy of each of the observed failures, using the Arrhenius relationship as previously discussed.

### WET HIGH TEMPERATURE OPERATING LIFE TEST (WHOPL)

$(Ta = 85^{\circ}C, R.H. = 81\%, V_{CC} = V_{CC} opt, static)$

Wet high temperature operating life test is performed to evaluate the moisture resistance characteristics of plastic encapsulated components. Long time testing is performed under static bias conditions at 85°C/81 percent relative humidity with nominal voltages. To maximize metal corrosion, the biasing configuration utilizes low power levels.

### INTERMITTENT OPERATING LIFE (IOPL)

(Pmax, 25°C, 2min on/2 min off)

This test is normally applied to scrutinize die bond thermal fatigue. A stressed device undergoes an "ON" cycle, where there is thermal heating due to power dissipation, and an "OFF" cycle, where there is thermal cooling due to lack of inputted power. Die attach (between die and package) and bond attach (between wire and die) are the critical areas of concern.

### HIGH TEMPERATURE STORAGE TEST (HTS)

#### (Ta = 125°C, UNBIASED)

High temperature storage is a test in which devices are subjected to elevated temperatures with no applied bias. The test is used to detect mechanical instabilities such as bond integrity, and process wearout mechanisms.

### PRESSURE COOKER TEST (PCT)

(121°C, 15PSIG, 100% R.H., UNBIASED)

The pressure cooker test checks for resistance to moisture penetration. A highly pressurized vessel is used to force water (thereby promoting corrosion) into packaged devices located within the vessel.

### **TEMPERATURE CYCLING (T/C)**

(-65°C to +150°C, AIR, UNBIASED)

This stess uses a chamber with alternating temperatures of  $-65^{\circ}$ C and  $+150^{\circ}$ C (air ambient) to thermally cycle devices within it. No bias is applied. The cycling checks for mechanical integrity of the packaged device, in particular bond wires and die attach, along with metal/polysilicon microcracks.

### THERMAL SHOCK (T/S)

(-65°C to +150°C, LIQUID, UNBIASED)

This stress uses a chamber with alternting temperatures of  $-65^{\circ}$ C to  $+150^{\circ}$ C (liquid ambient) to thermally cycle devices within it. No bias is applied. The cycling is very rapid, and primarily checks for die/package compatibility.

### RELIABILITY TEST RESULTS

This section is divided into two parts-actual and predicted test results. Actual test results are those derived via accelerated stressing done by the QC department. Predicted results are calculated by taking actual test results and derating them using statistical and mathematical models to determine device performance in "real-time" user conditions.

### ACTUAL TEST RESULTS

(KA2102A)

| Stress | Conditions                                              | Number of<br>Devices | Number of Device<br>Hours/Cycles | Number of<br>Failures | % Failures per<br>1000HRS (Cycles)<br>(60% UCL) |

|--------|---------------------------------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------------------|

| HOPL   | Tj = 125 °C<br>$V_{cc} = V_{cc} max$                    | 100                  | 100,000                          | 0                     | 0.91%/1K HR                                     |

| WHOPL  | 85° C/81% R.H.<br>V <sub>cc</sub> = V <sub>cc</sub> opt | 100                  | 100,000                          | 0                     | 0.91%/1K HR                                     |

| IOPL   | $Ta = 25^{\circ}C$ $V_{CC} = V_{CC} max$                | 100                  | 100,000                          | 0 .                   | 0.91%/1K HR                                     |

| HTS    | Ta = 125°C<br>Unbiased                                  | <sup>.</sup> 100     | 100,000                          | 0                     | 0.91%/1K HR                                     |

| PCT    | 121°C<br>15 PSIG                                        | 100                  | 16,800                           | 0                     | 5.4 %/1K HR                                     |

| T/C    | – 65°C to 150°C<br>Air to Air                           | 100                  | 10,000                           | 0                     | 9.1 %/1K CL                                     |

| T/S    | – 65°C to 150°C<br>Liquid to Liquid                     | 100                  | 10,000                           | 0                     | 9.1 %/1K CL                                     |

### PREDICTED TEST RESULTS

The Arrhenius equation, which is reviewed in another section of this chapter, can be applied to derive typical "usercondition" device failure rates.

### STESS: HOPL

100,000 Device Hours at 125°C Average Activation Energy: 1.0 eV. De Rating to User Conditions Yields:

70°C Operation

| Equivalent<br>Device Hours | % Failures Per<br>1000 Hours<br>(60% UCL) | *FITs | **MTBF<br>(Years) |

|----------------------------|-------------------------------------------|-------|-------------------|

| 10.7 × 10 <sup>6</sup>     | 0.0084                                    | 84    | 1359              |

\* FIT : Failure in time or failure unit. Represents the number of failures expected for 10<sup>9</sup> (one billion) device hours.

\*\* MTBF: Mean time between failures.

## 55°C Operation

| Equivalent<br>Device Hours | % Failures Per<br>1000 Hours<br>(600% UCL) | *FITs | **MTBF<br>(Years) |

|----------------------------|--------------------------------------------|-------|-------------------|

| 50.4 × 10 <sup>6</sup>     | 0.0018                                     | 18    | 6342              |

### **RELIABILITY AND PREDICTION THEORY**

### RELIABILITY

Reliability can be loosely characterized as long term product quality.

There are two types of reliability tests: those performed during design and development, and those carried out in production. The first type is usually performed on a limited sample, but for long periods or under very accelerated conditions to investigate wearout mechanisms and determine tolerances and limits in the design process. The second type of tests is performed periodically during production to check, maintain, and improve the assured quality and reliability levels. All reliability tests performed by Samsung are under conditions more severe than those encountered in the field, and although accelerated, are chosen to simulate stresses that devices will be subjected to in actual operation. Care is taken to ensure that the failure modes and mechanisms are unchanged.

### FUNDAMENTALS

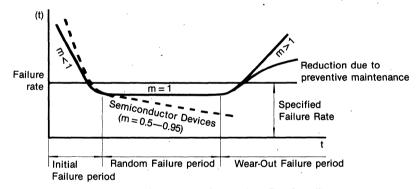

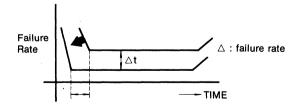

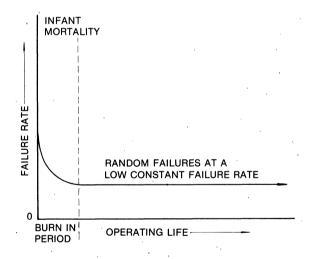

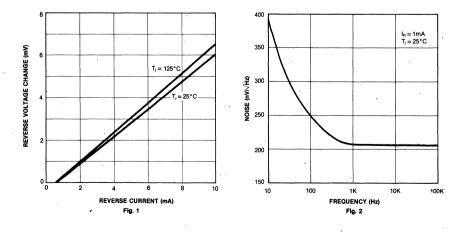

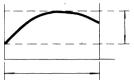

A semiconductor device is very dependent on its conditions of use (*e.g.*, junction temperature, ambient temperature, voltage, current, *etc.*). Therefore, to predict failure rates, accelerated reliability testing is generally used. In accelerated testing, special stress conditions are considered as parametrically related to actual failure modes. Actual operating life time is predicted using this method. Through accelerated stresses, component failure rates are ascertained in terms of how many devices (in percent) are expected to fail for every 1000 hours of operation. A typical failure rate versus time of activity graph is shown below (the so-called "bath tub curve")

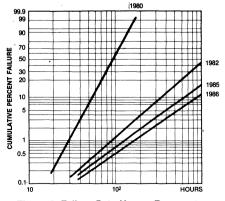

During their initial time period, products are affected by "infant mortality," intrinsic to all semiconductor technologies. End users are very sensitive to this parameter, which causes early assembly/operation failures in their own system. Periodically, Samsung reviews and publishes life time results. The goal is a steady shift of the limits as shown below.

### ACCELERATED HUMIDITY TESTS

To evaluate the reliability of products assembled in plastic packages, Samsung performs accelerated humidity stressing, such as the Pressure Cooker Test (PCT) and Wet High Temperature Operating Life Test (WHOPL).

Figure 5 shows some results obtained with these tests, which illustrate the improvements in recent years. These improvements result mainly from the introduction of purer molding resins, new process methods, and improved cleanliness.

Figure 5. Improvement in Humidity Reliability

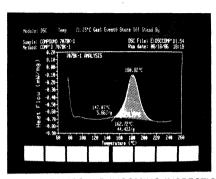

### ACCELERATED TEMPERATURE TESTS

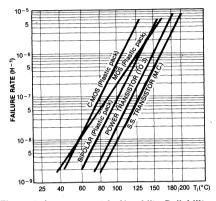

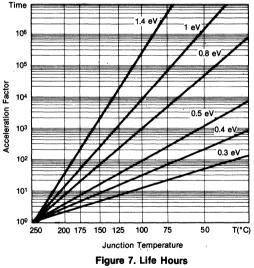

Accelerated temperature tests are carried out at temperatures ranging from 75°C to 200°C for up to 2000 hours. These tests allow Samsung to evaluate reliability rapidly and economically, as failure rates are strongly dependent on temperature.

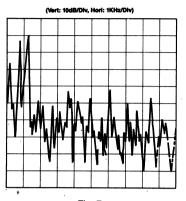

The validity of these tests is demonstrated by the good correlation between data collected in the field and laboratory results obtained using the Arrhenius model. Figure 6 shows the relationship between failure rates and temperatures obtained with this model.

Figure 6. Failure Rate Versus Temperature

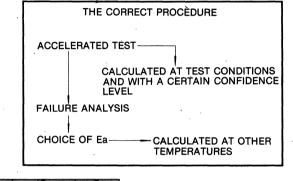

### FUNDAMENTAL THEORY FOR ACCELERATED TESTING

Accelerated life testing is powerful because of its strong relation to failure physics. The Arrhenius model, which is generally used for failure modelling, is explained below.

#### 1. Arrhenius model

This model can be applied to accelerated Operating Life Tests and uses absolute (Kelvin) temperatures.

- $L = A + Ea/K \cdot Tj$

- L : Lifetime

- A : Constant

- Ea : Activation Energy

- K : Boltzman's constant

- Tj : Absolute Junction temperature

If Lifetimes L1 and L2 correspond to Temperatures T1 and T2:

L1 = L2 exp