# 86CM65 Aurora64V+ Dual Display Accelerator

February 1996

S3 Incorporated P.O. Box 58058 Santa Clara, CA 95052-8058

#### NOTATIONAL CONVENTIONS

The following notational conventions are used in this data book:

Signal names are shown in all uppercase letters. For example, XD.

A bar over a signal name indicates an active low signal. For example,  $\overline{\text{OE}}.$

n-m indicates a bit field from bit n to bit m. For example, 7-0 specifies bits 7 through 0, inclusive.

n:m indicates a signal (pin) range from n to m. For example D[7:0] specifies data lines 7 through 0, inclusive

Use of a trailing letter H indicates a hexadecimal number. For example, 7AH is a hexadecimal number.

Use of a trailing letter b indicates a binary number. For example, 010b is a binary number.

When numerical modifiers such as K or M are used, they refer to binary rather than decimal form. Thus, for example, 1 KByte would be equivalent to 1024, not 1,000 bytes.

#### NOTICES

© Copyright 1995, 1996 S3 Incorporated. All rights reserved. If you have received this document from S3 Incorporated in electric form, you are permitted to make the following copies for business use related to products of S3 Incorporated: one copy onto your computer for the purpose of on-line viewing, and one printed copy. With respect to all documents, whether received in hard copy or electronic form, other use, copying or storage, in whole or in part, by any means electronic, mechanical, photocopying or otherwise, is permitted without the prior written consent of S3 Incorporated, P.O. Box 58058., Santa Clara CA 95052-8058. S3 and True Acceleration are registered trademarks of S3 Incorporated. The S3 Corporate Logo, S3 on Board, S3 on Board design, S3d design, Vision968, Trio, Trio64V+, Trio64UV+, VIRGE/VK, S3d, Scenic, Scenic/MK1, Scenic/MK2, Scenic Highway, Sonic, Sonic/AD, Aurora64V+, DuoView, Cooperative Accelerator Architecture, Streams Processor, MIC, Galileo, Native-MPEG, No Compromise Integration, No Compromise Acceleration and Innovations in Acceleration are trademarks of S3 Incorporated. Other trademarks referenced in this document are owned by their respective companies. The material in this document is for information only and is subject to change without notice. S3 Incorporated reserves the right to make changes in the product design without reservation and without notice to its users.

Additional information may be obtained from:

S3 Incorporated, Literature Department P.O. Box 58058, Santa Clara, CA 95052-8058.

Telephone: 408-980-5400, Fax: 408-980-5444

## **Table of Contents**

| List o | f Figures vi                    |  |

|--------|---------------------------------|--|

| List c | f Tables vii                    |  |

| Secti  | on 1: Introduction 1-1          |  |

| Secti  | on 2: Mechanical Data 2-1       |  |

| 2.1    | THERMAL SPECIFICATIONS 2-1      |  |

| 2.2    | MECHANICAL DIMENSIONS 2-1       |  |

| Secti  | on 3: Pins                      |  |

| 3.1    | PINOUT DIAGRAMS 3-1             |  |

|        | PIN DESCRIPTIONS                |  |

| 3.3    | PIN LISTS 3-8                   |  |

| Secti  | on 4: Electrical Data 4-1       |  |

| 4.1    | MAXIMUM RATINGS 4-1             |  |

| 4.2    | DC SPECIFICATIONS 4-1           |  |

| 4.3    | AC SPECIFICATIONS 4-3           |  |

| 4.3    | .1 RAMDAC AC Specifications 4-3 |  |

| 4.3    | .2 Clock Timing 4-4             |  |

| 4.3    | .3 Input/Output Timing 4-5      |  |

| Secti  | on 5: Reset and Power           |  |

| Cont   | ol                              |  |

|        | CONFIGURATION STRAPPING 5-1     |  |

| 5.2    | BOUNDARY SCAN 5-1               |  |

| 5.3    | FLAT PANEL POWER SEQUENCING 5-4 |  |

|        | POWER MANAGEMENT 5-4            |  |

|        | .1 Normal Mode 5-4              |  |

| 5.4    | 2 Standby Mode 5-4              |  |

| 5.4    | 3 Suspend Mode 5-6              |  |

| 5.5    | MIXED 3.3 VOLT AND 5 VOLT       |  |

|        | OPERATION 5-6                   |  |

|     | OPERATION               |  |  |  |  | 5-6 |

|-----|-------------------------|--|--|--|--|-----|

| 5.6 | <b>GREEN PC SUPPORT</b> |  |  |  |  | 5-7 |

| 6.1        | on 6: PCI Bus Interface       6-1         PCI CONFIGURATION       6-1         PCI CONTROLS       6-1 |

|------------|------------------------------------------------------------------------------------------------------|

|            | on 7: Display Memory 7-1                                                                             |

| 7.1        | DISPLAY MEMORY<br>CONFIGURATIONS                                                                     |

| 7.2        | DISPLAY MEMORY REFRESH 7-2                                                                           |

| 7.3        | DISPLAY MEMORY FUNCTIONAL                                                                            |

| 7.4        | TIMING                                                                                               |

| 7.4        | CONTROL 7-10                                                                                         |

| Section    | on 8: Clock Synthesis and                                                                            |

| Conti      |                                                                                                      |

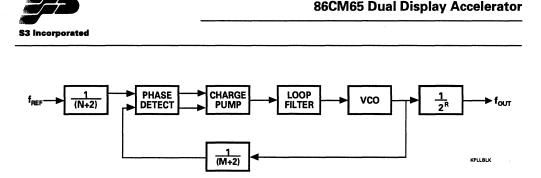

| 8.1        | CLOCK SYNTHESIS 8-1                                                                                  |

| 8.2        |                                                                                                      |

| 8.3        | CLOCK SELECTION AND CONTROL 8-3                                                                      |

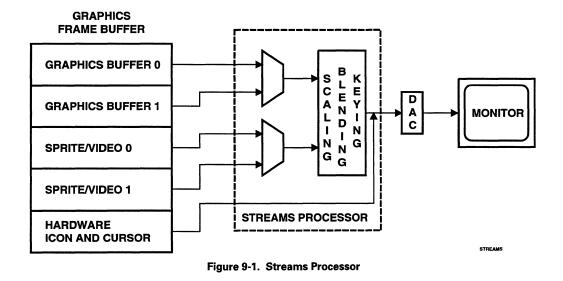

| Section    | on 9: Streams Processor 9-1                                                                          |

| 9.1        | INPUT STREAMS 9-1                                                                                    |

| 9.1        |                                                                                                      |

|            | .2 Secondary Stream Input 9-2                                                                        |

| 9.1        | .3 Hardware lcon and Cursor                                                                          |

|            | Generation 9-2                                                                                       |

| 9.1        | .4 Frame Buffer Organization/                                                                        |

| 0.0        | Double Buffering 9-2<br>INPUT PROCESSING 9-4                                                         |

| 9.2<br>9.2 |                                                                                                      |

| 9.2        |                                                                                                      |

| 9.3        |                                                                                                      |

| 9.3        | -                                                                                                    |

|            | .2 Blending                                                                                          |

| 9.3        | .3 Color/Chroma Keying 9-8                                                                           |

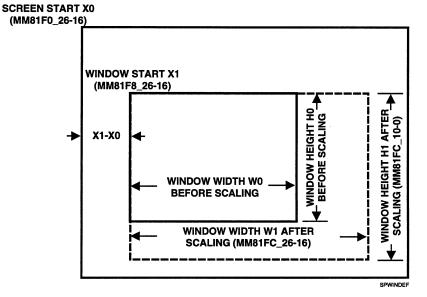

| 9.3        | .4 Window Location 9-8                                                                               |

| 9.4        | STREAMS FIFO CONTROL 9-8                                                                             |

iii

| Section 10: CRT/TV Interface 10                                                                   | -1  |

|---------------------------------------------------------------------------------------------------|-----|

| 10.1 CRT OUTPUT                                                                                   | )-1 |

| 10.1.1 Operating Modes                                                                            | )-1 |

| 10.1.2 Color Modes                                                                                | )-2 |

| 10.1.2.1 8 Bits/Pixel - Mode 0 10                                                                 | )-2 |

| 10.1.2.2 Output-doubled 8 Bits/Pixel -                                                            |     |

| Mode 8                                                                                            | )-2 |

| 10.1.2.3 15/16-Bits/Pixel - Modes 9                                                               |     |

| and 10                                                                                            | -3  |

| 10.1.2.4 Packed 24 Bits/Pixel- Mode 1210                                                          | 1-3 |

| 10.1.2.5 24 Bits/Pixel - Mode 13 10                                                               | -3  |

| 10.2 RAMDAC REGISTER ACCESS 10                                                                    | -3  |

| 10.3         RAMDAC SNOOPING         10           10.4         SENSE GENERATION         10        | -3  |

| 10.4 SENSE GENERATION 10                                                                          | -3  |

| 10.5 TV OUTPUT                                                                                    | -3  |

|                                                                                                   |     |

| Section 11: Flat Panel Interface . 11                                                             | -1  |

| 11.1 STN PANEL SUPPORT 11                                                                         | -1  |

| 11.1.1 STN Panel Selection 11                                                                     | -1  |

| 11.1.2 STN Panel Timing 11                                                                        | -1  |

| 11.1.3 STN Panel Control 11                                                                       | -1  |

| 11.1.4 STN Frame Rate Control 11                                                                  |     |

| 11.1.5 STN Panel Dithering 11                                                                     | -3  |

| 11.1.6 Dual-Scan STN Frame Buffer . 11                                                            | -6  |

| 11.2 TFT PANEL SUPPORT 11                                                                         | -9  |

| 11.2.1 TFT Panel Selection 11                                                                     | -9  |

| 11.2.2 TFT Panel Timing 11                                                                        | -9  |

| 11.2.3 TFT Panel Control 11                                                                       | -9  |

| 11.2.4 TFT Panel Dithering 11-                                                                    | 11  |

| 11.3 FLAT PANEL DISPLAY                                                                           |     |

| ENHANCEMENTS 11-                                                                                  |     |

| 11.3.1 Automatic Centering 11-                                                                    |     |

| 11.3.2 Horizontal Compensation 11-                                                                |     |

| 11.3.3 Vertical Compensation 11-                                                                  |     |

| 11.3.4 Pulse Width Modulation 11-                                                                 |     |

| 11.3.5 Blinking 11-                                                                               |     |

| 11.4 DuoView DISPLAY 11-                                                                          |     |

| 11.4.1 DuoView Display Setup 11-                                                                  |     |

| 11.4.2 DuoView Programming 11-                                                                    | 14  |

| 11.4.3 DuoView Programming                                                                        |     |

| Example 11-                                                                                       | 14  |

|                                                                                                   |     |

| Section 12: Local Peripheral Bus 12                                                               | -1  |

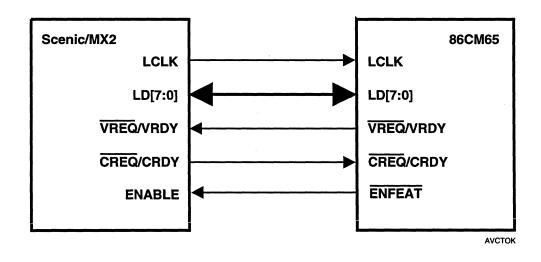

| 12.1 Scenic/MX2 INTERFACE 12                                                                      | -1  |

| 12.1.1 Scenic/MX2 Register/Memory                                                                 |     |

| Access                                                                                            | -2  |

| 12.1.2 Scenic/MX2 Compressed Data                                                                 |     |

| Transfer       12         12.1.3       Scenic/MX2         Video       Capture         12       12 | -4  |

| 12.1.3 Scenic/MX2 Video Capture 12                                                                | -5  |

| 12.2 DIGITIZER INTERFACE                                                                          | :-/ |

| 12.2.1 ITC Interface for SAA/110 12                                                               | :-/ |

| 12.2 | 2.2 SAA7110 Video Input | • | • | • | • | 12-7 |

|------|-------------------------|---|---|---|---|------|

| 12.3 | HOST PASS-THROUGH       |   |   |   |   | 12-8 |

| 12.4 | ZV PORT INTERFACE       | • | • | • | • | 12-9 |

## Section 13: Miscellaneous

| Funct | ions                       | 13-1 |

|-------|----------------------------|------|

| 13.1  | VIDEO BIOS ROM INTERFACE   | 13-1 |

| 13.2  | GENERAL INPUT PORT         | 13-1 |

| 13.3  | GENERAL OUTPUT PORT        | 13-2 |

| 13.4  | SERIAL COMMUNICATIONS PORT | 13-2 |

| 13.5  | INTERRUPT GENERATION       | 13-2 |

## **Section 14: Basic Software**

| Functions                           | 14-1 |

|-------------------------------------|------|

| 14.1 CHIP WAKEUP                    | 14-1 |

| 14.2 REGISTER ACCESS                |      |

| 14.2.1 Unlocking the S3 Registers . | 14-1 |

| 14.2.2 Locking the S3 Registers     | 14-3 |

| 14.3 TESTING FOR THE PRESENCE OF    |      |

| AN 86CM65 CHIP                      | 14-3 |

| 14.4 GRAPHICS MODE SETUP            | 14-3 |

## Section 15: VGA Compatibility

| Support                     | 15-1 |

|-----------------------------|------|

| 15.1 VGA COMPATIBILITY      | 15-1 |

| 15.2 VESA SUPER VGA SUPPORT | 15-2 |

## **Section 16: Enhanced Mode**

| Programming 10                       | 2.1         |

|--------------------------------------|-------------|

| • •                                  | <b>)- I</b> |

| 16.1 LINEAR ADDRESSING FOR DIRECT    |             |

| VIDEO MEMORY CPU ACCESSES 1          | 6-1         |

| 16.2 VIDEO MEMORY ACCESS             |             |

| THROUGH THE GRAPHICS ENGINE 1        | 6-2         |

| 16.3 MEMORY MAPPING OF               |             |

| REGISTERS 1                          | 6-4         |

|                                      | 6-4         |

|                                      | 6-6         |

|                                      | 6-7         |

|                                      |             |

|                                      | 6-7         |

| ·····                                | 6-8         |

| 16.4.3 Programming Examples 1        | 6-8         |

| 16.4.3.1 Solid Line 1                | 6-9         |

| 16.4.3.2 Textured Line 16            | -10         |

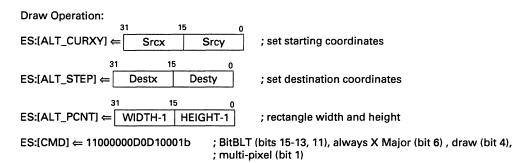

| 16.4.3.3 Rectangle Fill Solid 16     | -12         |

| 16.4.3.4 Image Transfer—Through      |             |

| the Plane                            | -13         |

| 16.4.3.5 Image Transfer—Across       |             |

|                                      | 10          |

| the Plane                            |             |

| 16.4.3.6 BitBLT—Through the Plane 16 | -17         |

|                                      |             |

| 16.4.3.7 BitBLT—Across the Plane .  | 16-18 |

|-------------------------------------|-------|

| 16.4.3.8 PatBLT—Pattern Fill        |       |

| Through the Plane                   | 16-20 |

| 16.4.3.9 PatBLT—Pattern Fill Across |       |

| the Plane                           | 16-21 |

| 16.4.3.10 Short Stroke Vectors      | 16-22 |

| 16.4.3.11 Programmable Hardware     |       |

| Cursor                              | 16-23 |

| 16.4.3.12 Programmable Hardware     |       |

|                                     | 16-25 |

| 16.5 RECOMMENDED READING            | 16-26 |

|                                     |       |

| Section 17: Standard VGA            |       |

| Register Descriptions               | 17-1  |

| negis |                              | /-1  |

|-------|------------------------------|------|

| 17.1  | GENERAL REGISTERS            | 17-1 |

| 17.2  | SEQUENCER REGISTERS          | 17-5 |

| 17.3  | CRT CONTROLLER REGISTERS . 1 | 7-10 |

| 17.4  | GRAPHICS CONTROLLER          |      |

|       | REGISTERS 1                  | 7-25 |

| 17.5  | ATTRIBUTE CONTROLLER         |      |

|       | REGISTERS 1                  | 7-32 |

| 17.6  | RAMDAC REGISTERS 1           | 7-38 |

|       |                              |      |

## Section 18: Extended Sequencer

|                               | Register Descriptions 18-1                    |  |  |

|-------------------------------|-----------------------------------------------|--|--|

| 18.1                          | MISCELLANEOUS EXTENDED                        |  |  |

|                               | SEQUENCER REGISTERS 18-1                      |  |  |

| 18.2                          | FLAT PANEL REGISTERS 18-24                    |  |  |

|                               | on 19: Extended CRTC<br>ter Descriptions 19-1 |  |  |

| •                             | ·                                             |  |  |

|                               | on 20: Enhanced Commands                      |  |  |

| Regis                         | ter Descriptions 20-1                         |  |  |

| Section 21: Streams Processor |                                               |  |  |

| Register | Descriptions |  |  | 21-1 |

|----------|--------------|--|--|------|

| •        | •            |  |  |      |

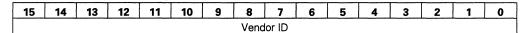

|      | on 23: PCI Register<br>riptions       |

|------|---------------------------------------|

| Арре | ndix A: Register Reference A-1        |

| A.1  | VGA REGISTERS                         |

| A.2  |                                       |

|      | REGISTERS                             |

| A.3  | EXTENDED CRTC REGISTERS A-21          |

| A.4  | ENHANCED COMMANDS                     |

|      | REGISTERS                             |

| A.5  | STREAMS PROCESSOR                     |

|      | REGISTERS                             |

| A.6  | LOCAL PERIPHERAL BUS                  |

|      | REGISTERS                             |

| A.7  | PCI CONFIGURATION SPACE               |

|      | REGISTERS A-41                        |

| •••  | ndix B: Panel Programming<br>ples B-1 |

| Anne | ndex C: Panel Attachment              |

| Abbender  |   |   |   |   |   |   |   |   |   |   |   |   |     |

|-----------|---|---|---|---|---|---|---|---|---|---|---|---|-----|

| Examples: | • | • | • | • | • | • | • | • | • | • | • | • | C-1 |

|           |   |   |   |   |   |   |   |   |   |   |   |   |     |

|           |   |   |   |   |   |   |   |   |   |   |   |   |     |

##

## List of Figures

| #            | Title Page                                                                 |

|--------------|----------------------------------------------------------------------------|

| 1-1          | System Block Diagram 1-2                                                   |

| 2-1          | 256-pin BGA Mechanical                                                     |

| 2.4          | Dimensions 2-2<br>Aurora64V+ Pin Locations                                 |

| 3-1          |                                                                            |

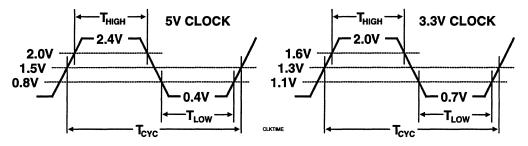

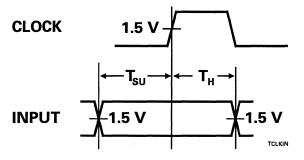

| 4-1          | (Top View) 3-2<br>Clock Waveform Timing 4-4                                |

| 4-1          | Input Timing 4-5                                                           |

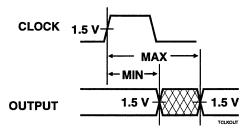

| 4-3          | Output Timing                                                              |

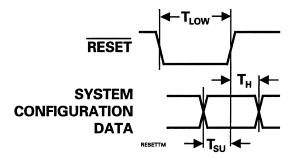

| 4-4          | Reset Timing 4-9                                                           |

| 5-1          | Flat Panel Power Sequencing 5-4                                            |

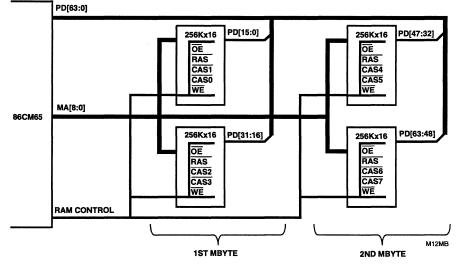

| 7-1          | 256Kx16 DRAM Configurations . 7-1                                          |

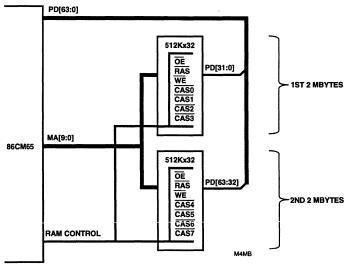

| 7-2          | 512Kx32 DRAM Configurations . 7-2                                          |

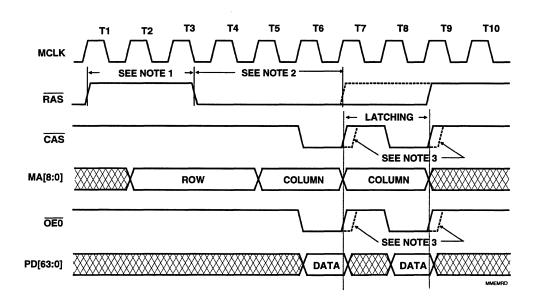

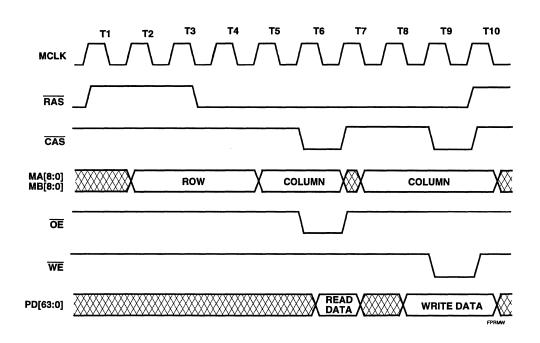

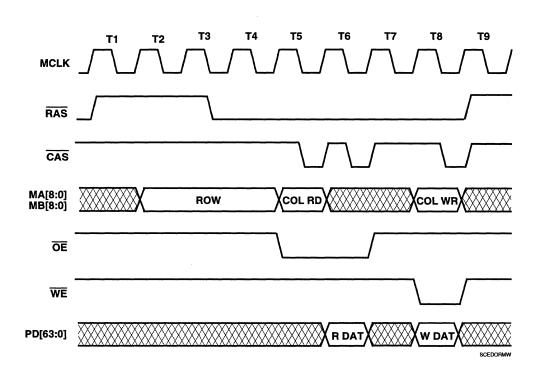

| 7-3          | Fast Page Mode Read Cycle 7-3                                              |

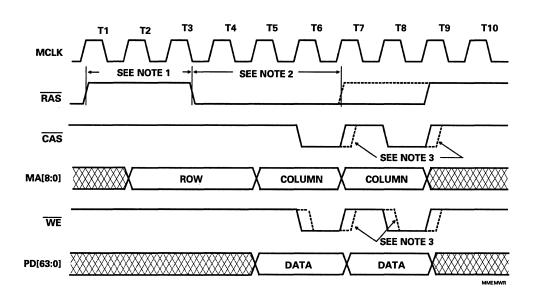

| 7-4          | Fast Page Mode Write Cycle 7-4                                             |

| 7-5          | Fast Page Write Following a                                                |

|              | Read Cycle 7-5                                                             |

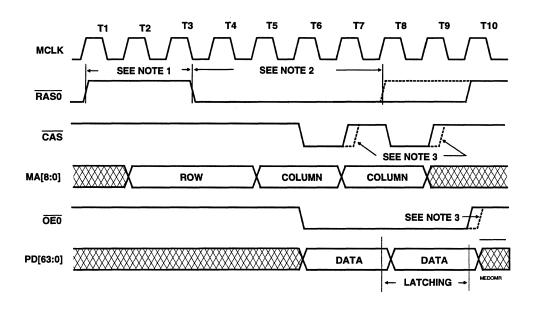

| 7-6          | 2-cycle EDO Mode Read Cycle 7-6                                            |

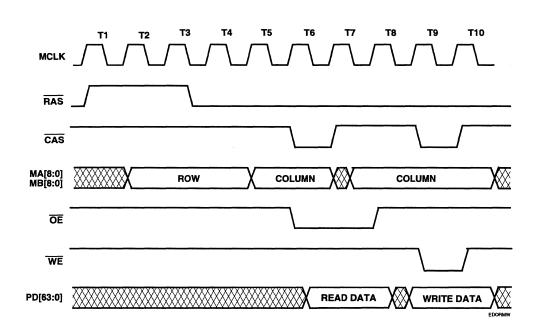

| 7-7          | 2-cycle EDO Write Following a                                              |

|              | Read Cycle 7-7                                                             |

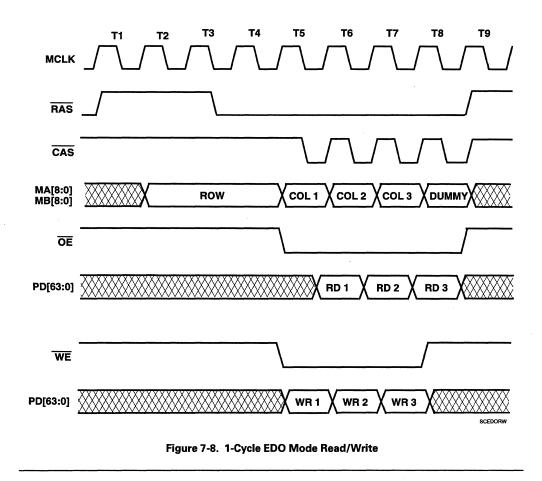

| 7-8          | 1-Cycle EDO Mode Read/Write . 7-8                                          |

| 7-9          | 1-cycle EDO Write Following a                                              |

|              | Read Cycle                                                                 |

| 8-1          | PLL Block Diagram 8-2                                                      |

| 8-2          | Clock Selection 8-3                                                        |

| 9-1          | Streams Processor 9-1                                                      |

| 9-2          | Screen Definition Parameters 9-5                                           |

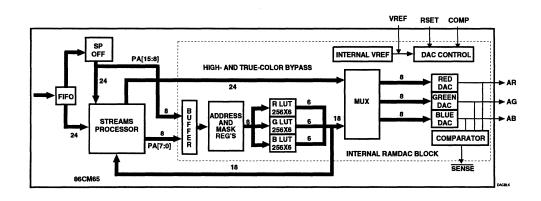

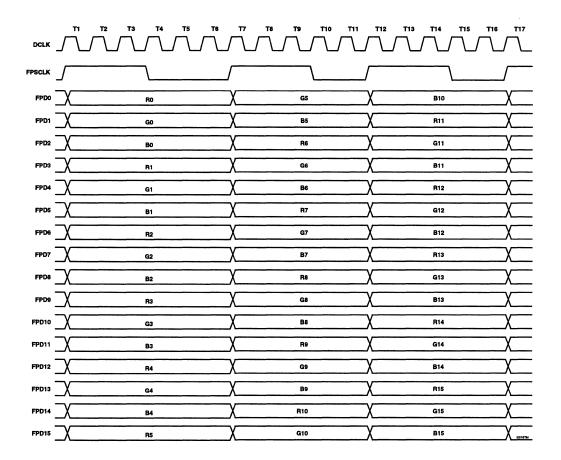

| 10-1<br>11-1 | Internal RAMDAC Block Diagram 10-1<br>8-bit Color DD-STN Panel Timing 11-3 |

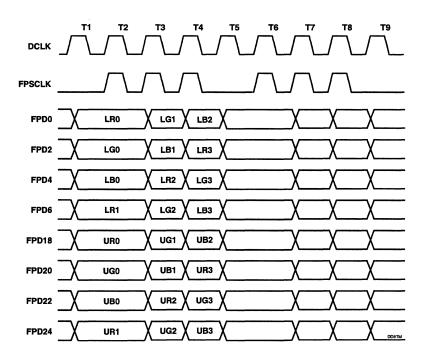

| 11-1         | 16-bit Color DD-STN Panel Timing 11-3                                      |

| 11-2         |                                                                            |

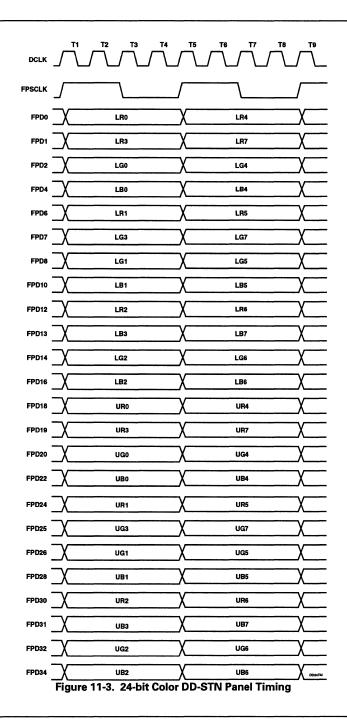

| 11-3         | Timing                                                                     |

| 11-5         | Timing                                                                     |

| 11-4         | 8-bit Color SS-STN Panel Timing 11-6                                       |

| 11-5         | 16-bit Color SS-STN Panel                                                  |

|              | Timing                                                                     |

| 11-6         | 24-bit Color SS-STN Panel                                                  |

|              | Timing                                                                     |

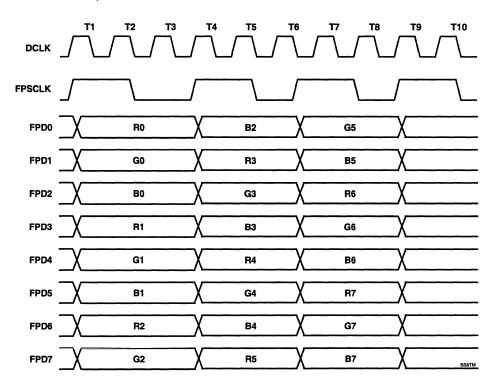

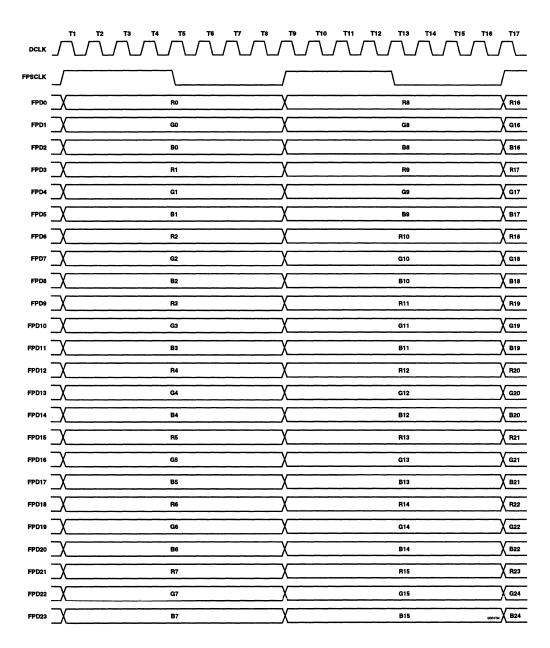

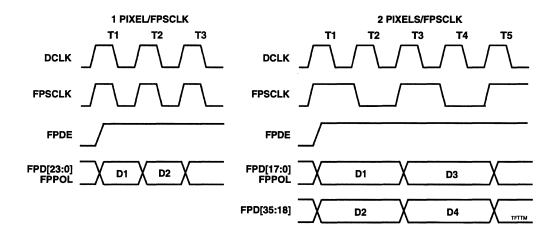

| 11-7         | TFT Panel Timing 11-9                                                      |

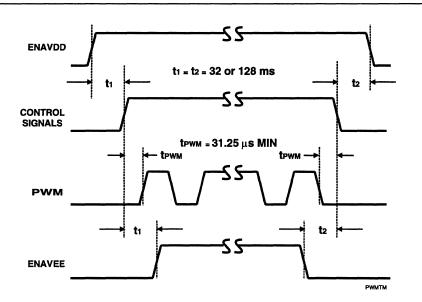

| 11-8         | PWM Timing 11-12                                                           |

|              | -                                                                          |

| #     | Title P                               | age  |

|-------|---------------------------------------|------|

| 11-9  | Internal Data Paths 1                 | 1-13 |

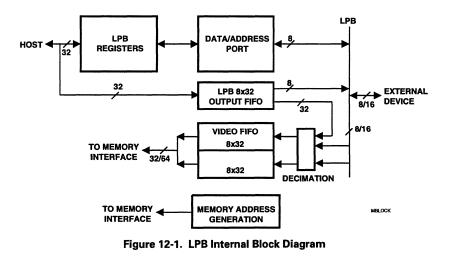

| 12-1  | LPB Internal Block Diagram            | 12-1 |

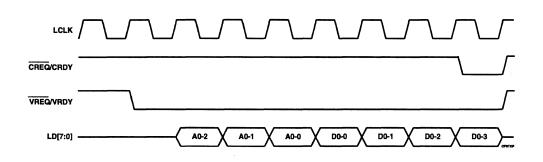

| 12-2  | -                                     | 12-2 |

| 12-3  | Scenic/MX2 Write (Scenic/MX2          |      |

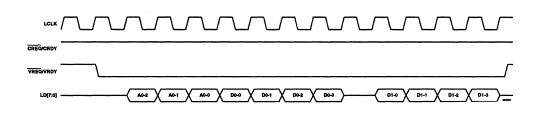

|       | Ready)                                | 12-3 |

| 12-4  | Scenic/MX2 Write (Scenic/MX2          |      |

|       |                                       | 12-3 |

| 12-5  | Scenic/MX2 Read (Scenic/MX2           |      |

|       |                                       | 12-3 |

| 12-6  | Scenic/MX2 Read (Scenic/MX2           |      |

|       | Not Ready)                            | 12-3 |

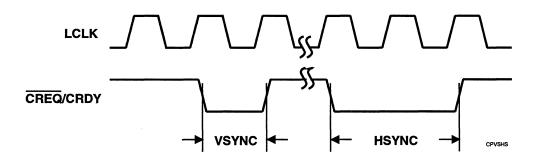

| 12-7  | Scenic/MX2 Compressed Transfer        |      |

|       | (Ready)                               | 12-4 |

| 12-8  | Scenic/MX2 Stopping a                 |      |

|       |                                       | 12-5 |

| 12-9  | Scenic/MX2 VSYNC and                  |      |

|       | HSYNC Protocols                       | 12-5 |

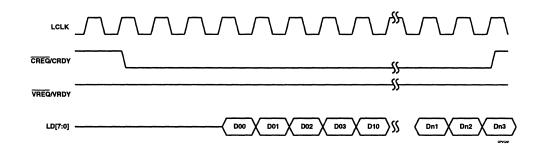

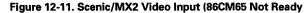

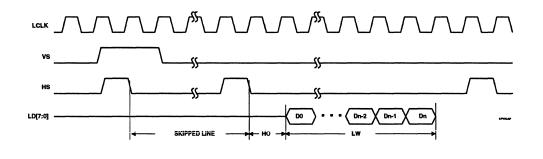

| 12-10 | Scenic/MX2 Video Input (86CM65        |      |

|       | Ready)                                | 12-6 |

| 12-11 | Scenic/MX2 Video Input (86CM65        |      |

|       | Not Ready                             | 12-6 |

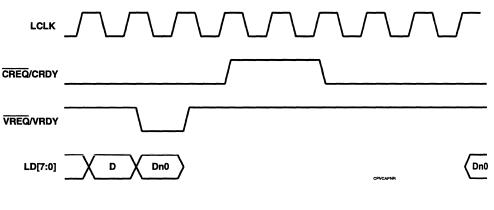

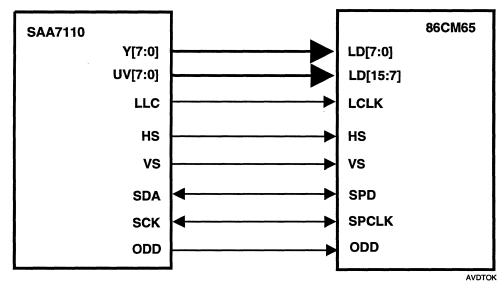

| 12-12 | 86CM65 to SAA7110 Digitizer           |      |

|       |                                       | 12-7 |

| 12-13 | the set of the the set of part of the | 12-8 |

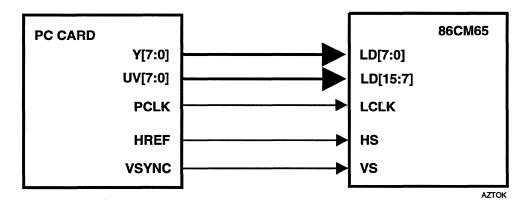

| 12-14 | ZV Port Interface                     | 12-9 |

| 13-1  | General I/O Port Timing               | 13-1 |

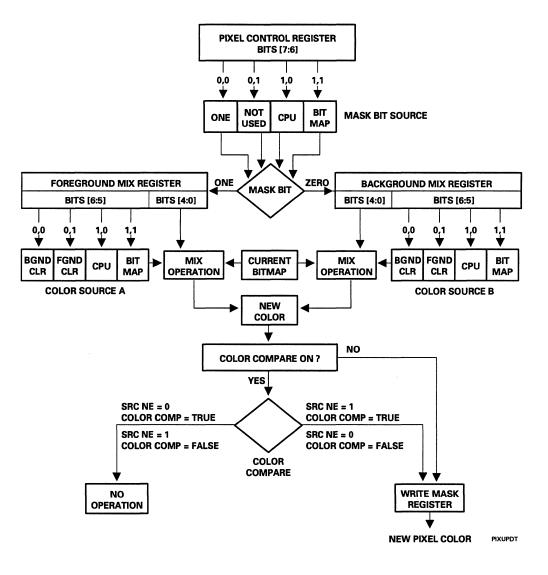

| 16-1  | Pixel Update Flowchart                | 16-3 |

vi

## List of Tables

#### # Title Page 3-1 Pin Descriptions 3-3 Alphabetical Pin Listing . . . . 3-8 3-2 3-3 Numerical Pin Listing . . . . . . . 3-10 Absolute Maximum Ratings . . . 4-1 4-1 RAMDAC/Clock Synthesizer DC 4-2 Specifications . . . . . . . . . . . . 4-1 4-3 RAMDAC Characteristics . . . . . 4-1 4-4 Digital DC Specifications . . . . 4-2 4-5 RAMDAC AC Specifications . . . 4-3 4-6 RAMDAC Output Specifications . 4-3 4-7 Clock Waveform Timing . . . . 4-4 4-8 SCLK-Referenced Input Timing . 4-5 4-9 CLK32-Referenced Input Timing . 4-5 4-10 MCLK-Referenced Input Timing . 4-6 4-11 LCLK-Referenced Input Timing . 4-6 4-12 SCLK-Referenced Output Timing 4-7 4-13 CLK32-Referenced Output Timing 4-7 MCLK-Referenced Output Timing 4-14 4-8 4-15 LCLK-Referenced Output Timing 4-8 FPSCLK-Referenced Output 4-16 4-8 4-17 Reset Timing . . . . . . . . . . 4-9 5-1 Definition of Strapping Bits at the Rising Edge of the Reset Signal . 5-2 7-1 Memory Size/PD Bus Width Specification . . . . . . . . . . . 7-2 PLL R Parameter Decoding . . . 8-1 8-1 Register Fields Used For Specifying 9=1 Frame Buffer Organization and Double Buffering . . . . . . . . 9-3 9=2 Register Fields Used For Scaling Up the Secondary Stream . . . 9-6 86CM65 Color Modes . . . . . . 10-2 10-1

| 10-2 | TV Output Options 10-4                |

|------|---------------------------------------|

| 11-1 | STN Flat Panel Data Outputs 11-2      |

| 11-2 | TFT Flat Panel Data Outputs 11-10     |

| 15-1 | Standard VGA Registers Modified       |

|      | or Extended in the 86CM65 15-1        |

| 16-1 | Enhanced Registers Memory             |

|      | Mapping                               |

| 16-2 | New MMIO Addresses 16-6               |

| A-1  | VGA Registers A-2                     |

| A-2  | Extended Sequencer Registers A-10     |

| A-3  | Extended CRTC Registers A-21          |

| A-4  | Enhanced Commands Registers A-30      |

| A-5  | Streams Processor Registers A-34      |

| A-6  | Local Peripheral Bus Registers . A-38 |

| A-7  | PCI Configuration Space               |

|      | Registers A-41                        |

|      |                                       |

## **Section 1: Introduction**

#### **High-Performance Graphics Accelerator Core**

- Integrated 64-bit graphics accelerator /RAMDAC/clock-synthesizer core enables desktop-level performance

- Supports VGA, SVGA, and XGA flat panel displays

- Provides 1280x1024x8-bit, 75 Hz refresh, non-interlaced CRT mode

- 3.3V/5V operation

#### **Direct Interface to Broad Range of LCDs**

- Support for VGA, SVGA and XGA dualscan/single-scan color panels with 8-bit, 16-bit, and 24-bit interfaces

- Support for VGA, SVGA and XGA TFT color panels with 9-bit, 12-bit and 18-bit (1 pixel/clock and 2 pixels/clock) interfaces

- Advanced frame rate control and dithering algorithms provide up to 16.7 million colors

- Panel data polarity switching for EMI reduction

- Auto-expansion and centering for VGA text and graphics modes on SVGA and XGA panels

## Industry-Leading Simultaneous Display Capability

- CRT and flat panel refresh rates are independently programmable to allow optimum image quality via DuoView architecture

- Simultaneous TV/flat panel display

#### **Multimedia Acceleration**

- Integrated S3 Streams Processor enables 30 frames-per-second, full-screen, 24-bit playback of full motion video

- Mixed-format (simultaneous YUV and RGB) data in video memory

- Blending of graphics and video streams of different color depths

- High-quality hardware scaling using filtered interpolation

- Color key/chroma key control of graphic/video overlay placement

#### **Comprehensive Power Management**

- Self-refresh and slow-refresh DRAM support

- Standby and low power suspend modes

- Hardware and software suspend support

- DPMS

- S3 Dynamic Power Management

#### 64x64x2 Pixel Hardware Pop-up Icon

- Available in all modes

- 8 separate bitmaps can be stored

## Integrated Programmable Frequency Synthesizers

- Dual, independent frequency synthesizers for DAC and memory control

- DCLK up to 110 MHz @ 3.3V, 135 MHz @ 5V

- MCLK up to 50 MHz @ 3.3V

## S3 Scenic Highway Video Bus For Low-Cost Multimedia Solutions

- ZV Port compliant

- Glueless 8- or 16-bit interface to video digitizers

- Glueless, bi-directional interface to S3

Scenic/MX2 MPEG decoder

#### **Integrated TV Encoder**

- Direct output to NTSC/PAL monitors

- Composite or SVideo format

#### **Flexible Memory Support**

- Fast page or EDO DRAMs

- 1-MByte with 2 256Kx16 DRAMs

- 2-MBytes with 4 256Kx16 DRAMs

- 2-MBytes with 1 512Kx32 DRAM

- 4-MBytes with 2 512Kx32 DRAMs

#### 24-bit True-Color RAMDAC

Glueless PCI Local Bus Interface

PowerPC<sup>™</sup> Support: Bi-endian Byte Ordering

#### Monitor Plug and Play Support: VESA® DDC

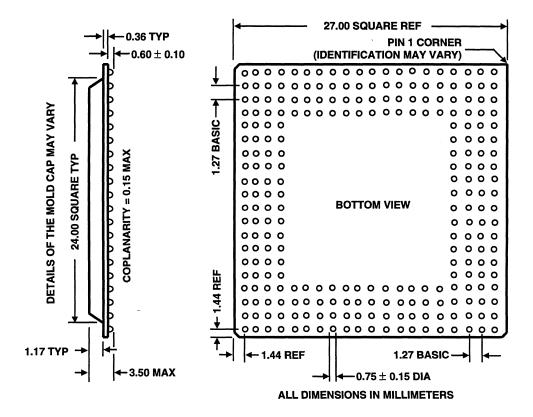

#### 256-pin PBGA Package

- 27.0 mm x 27.0 mm footprint

- 1.27 mm ball pitch

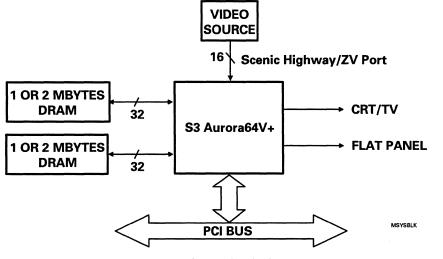

The S3<sup>®</sup> 86CM65 Aurora64V+™ dual display accelerator is the first in a series of highly-integrated flat-panel controller products to be offered by S3 with the goal of providing better-thandesktop features and performance to the notebook computer market. It combines a 64-bit memory interface and graphics engine with a 24-bit high-performance 135 MHz RAMDAC, a flat panel interface capable of controlling the latest STN and TFT panels, S3's Scenic Highway™ multimedia interface and Streams Processor™ video acceleration technology, and direct NTSC/PAL output. These elements, designed around S3's DuoView<sup>™</sup> architecture, provide the performance, flexibility, and display quality necessary for premium multimedia notebook computer systems. Comprehensive, flexible hooks are provided to simplify graphics subsystem power management.

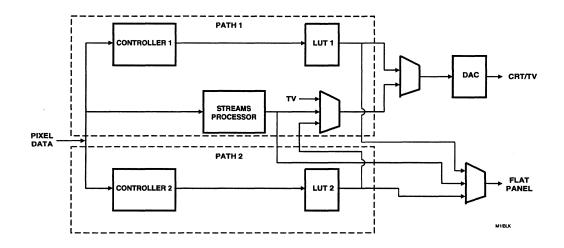

Figure 1-1. System Block Diagram

**1-2 INTRODUCTION**

## **Section 2: Mechanical Data**

## 2.1 THERMAL SPECIFICATIONS

| Parameter                          | Min | Тур | Max | Unit |

|------------------------------------|-----|-----|-----|------|

| Thermal Resistance OJC             |     | 5   |     | °C/W |

| Thermal Resistance OJA (Still Air) |     | 27  |     | °C/W |

| Junction Temperature               |     |     | 125 | °C   |

| Case Temperature                   |     |     | 105 | °C   |

## 2.2 MECHANICAL DIMENSIONS

The 86CM65 comes in a 256-pin BGA package. The mechanical dimensions are given in Figure 2-1.

MECHANICAL DATA 2-1

#### Figure 2-1. 256-pin BGA Mechanical Dimensions

2-2 MECHANICAL DATA

## **Section 3: Pins**

## 3.1 PINOUT DIAGRAMS

The 86CM65 comes in a 256-pin BGA package. The pin locations for this package are shown in Figure 3-1. Refer to the pin lists later in this section for pin names associated with each pin.

PINS 3-1

|    |    |    |    |    |        |            |    |            |     |      |     |     |     |     |     | ,   |     |     |     |

|----|----|----|----|----|--------|------------|----|------------|-----|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| A1 | A2 | A3 | A4 | A5 | A6     | A7         | A8 | A9         | A10 | A11  | A12 | A13 | A14 | A15 | A16 | A17 | A18 | A19 | A20 |

| B1 | B2 | B3 | B4 | B5 | B6     | B7         | B8 | B9         | B10 | B11  | B12 | B13 | B14 | B15 | B16 | B17 | B18 | B19 | B20 |

| C1 | C2 | СЗ | C4 | C5 | C6     | C7         | C8 | С9         | C10 | C11  | C12 | C13 | C14 | C15 | C16 | C17 | C18 | C19 | C20 |

| D1 | D2 | D3 | D4 | D5 | D6     | D7         | D8 | D9         | D10 | D11  | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 |

| E1 | E2 | E3 | E4 |    |        |            |    |            |     |      |     |     |     |     | E17 | E18 | E19 | E20 |     |

| F1 | F2 | F3 | F4 |    |        |            |    |            |     |      |     |     |     |     | F17 | F18 | F19 | F20 |     |

| G1 | G2 | G3 | G4 |    |        |            |    |            |     |      |     |     |     |     |     | G17 | G18 | G19 | G20 |

| H1 | H2 | нз | H4 |    |        |            |    |            |     |      |     |     |     | H17 | H18 | H19 | H20 |     |     |

| J1 | J2 | J3 | J4 |    | 86CM65 |            |    |            |     |      |     |     |     | J17 | J18 | J19 | J20 |     |     |

| K1 | K2 | КЗ | К4 |    |        |            |    |            |     |      |     |     |     | K17 | K18 | K19 | K20 |     |     |

| L1 | L2 | L3 | L4 |    |        |            |    | Т          | op  | Viev | N   |     |     |     |     | L17 | L18 | L19 | L20 |

| M1 | M2 | МЗ | M4 |    |        |            |    |            |     |      |     |     |     |     |     | M17 | M18 | M19 | M20 |

| N1 | N2 | N3 | N4 |    |        |            |    |            |     |      |     |     |     |     |     | N17 | N18 | N19 | N20 |

| P1 | P2 | P3 | P4 |    |        |            |    |            |     |      |     |     |     |     |     | P17 | P18 | P19 | P20 |

| R1 | R2 | R3 | R4 |    |        |            |    |            |     |      |     |     |     |     |     | R17 | R18 | R19 | R20 |

| T1 | T2 | тз | T4 |    |        |            |    |            |     |      |     |     |     |     |     | T17 | T18 | T19 | T20 |

| U1 | U2 | U3 | U4 | U5 | U6     | U7         | U8 | U9         | U10 | U11  | U12 | U13 | U14 | U15 | U16 | U17 | U18 | U19 | U20 |

| V1 | V2 | V3 | V4 | V5 | V6     | <b>V</b> 7 | V8 | V9         | V10 | V11  | V12 | V13 | V14 | V15 | V16 | V17 | V18 | V19 | V20 |

| W1 | W2 | WЗ | W4 | W5 | W6     | W7         | W8 | W9         | W10 | W11  | W12 | W13 | W14 | W15 | W16 | W17 | W18 | W19 | W20 |

| Y1 | Y2 | Y3 | Y4 | Y5 | ¥6     | <b>Y</b> 7 | Y8 | <b>Y</b> 9 | Y10 | Y11  | Y12 | Y13 | Y14 | Y15 | Y16 | Y17 | Y18 | Y19 | Y20 |

Figure 3-1. Aurora64V+ Pin Locations (Top View)

### 3.2 PIN DESCRIPTIONS

The following table provides a brief description of each pin on 86CM65. The following abbreviations are used for pin types.

l - Input signal

O - Output signal

B - Bidirectional signal

Some pins have multiple names. This either reflects the different functions performed by those pins depending on the bus configuration selected by power-on-strapping or multiplexed pins whose functions are selected via a register bit setting. The pin definitions and functions are given for each possible case.

| Table 3 | -1. Pin | n Descriptions |  |

|---------|---------|----------------|--|

|---------|---------|----------------|--|

| Symbol         | Туре     | Description                                                                                                                                                                     |

|----------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI BUS INTERF | ACE      | +                                                                                                                                                                               |

| Address        | and Data |                                                                                                                                                                                 |

| AD[31:0]       | В        | Multiplexed Address/Data Bus. A bus transaction (cycle) consists of an<br>address phase followed by one or more data phases.                                                    |

| C/BE[3:0]      | I        | Bus Command/Data Byte Enables. These signals carry the bus command<br>during the address phase and the byte enables during the data phase.                                      |

| Bus Con        | trol     |                                                                                                                                                                                 |

| SCLK           | 1        | PCI System Clock.                                                                                                                                                               |

| ĪNTĀ           | 0        | Interrupt Request.                                                                                                                                                              |

| IRDY           | I        | Initiator Ready. A bus data phase is completed when both IRDY and TRDY are asserted on the same cycle.                                                                          |

| TRDY           | 0        | Target Ready. A bus data phase is completed when both IRDY and TRDY are asserted on the same cycle.                                                                             |

| DEVSEL         | 0        | Device Select. 86CM65 drives this signal active when it decodes its<br>address as the target of the current access.                                                             |

| IDSEL          | l        | Initialization Device Select. This input is the chip select for PCI configuration register reads/writes.                                                                        |

| RESET          | I        | System Reset. Asserting this signal forces the registers and state<br>machines to a known state.                                                                                |

| FRAME          | l        | Cycle Frame. This signal is asserted by the bus master to indicate the<br>beginning of a bus transaction. It is deasserted during the final data phase<br>of a bus transaction. |

| PAR            | 0        | Parity. 86CM65 asserts this signal to verify even parity during reads.                                                                                                          |

| STOP           | 0        | Stop. 86CM65 asserts this signal to indicate a target disconnect.                                                                                                               |

| Symbol       | Туре        | Description                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLOCK CONT   | ROL         |                                                                                                                                                                                                                                                                                                                                                                                                                 |

| XIN          | I           | Reference Frequency Input. If an external 14.318 MHz crystal is used, it is connected between XOUT and this pin. A stable external frequency source can also be input via this pin. If this is done, the input must be the same voltage as AVDD. If PD11 is strapped low at power-on, this becomes the DCLK (dot clock) input, bypassing the internal oscillator. This is normally only used for test purposes. |

| XOUT         | 0           | Crystal Output. This pin drives the crystal via an internal oscillator.                                                                                                                                                                                                                                                                                                                                         |

| DISPLAY MEN  | MORY INTER  | RFACE                                                                                                                                                                                                                                                                                                                                                                                                           |

| Addre        | ss and Data |                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MA[9:0]      | 0           | Memory Address Bus. The video memory row and column addresses are multiplexed on these lines. MA9 is output on pin M17 when the memory type is 512Kx32.                                                                                                                                                                                                                                                         |

| PD[63:0]     | В           | Display Memory Pixel Data Bus Lines 63:0. PD[28:0] are also used as the<br>system configuration strapping bits, providing system configuration and<br>setup information upon power-on reset. See Section 5 for a description of<br>this function.                                                                                                                                                               |

| Memo         | ory Control |                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RAS0         | 0           | Row Address Strobe.                                                                                                                                                                                                                                                                                                                                                                                             |

| CAS[7:0]     | 0           | Column Address Strobe Lines 7:0.                                                                                                                                                                                                                                                                                                                                                                                |

| WE           | 0           | Write Enable.                                                                                                                                                                                                                                                                                                                                                                                                   |

| ŌĒ           | 0           | Output Enable.                                                                                                                                                                                                                                                                                                                                                                                                  |

| CRT VIDEO IN | ITERFACE    |                                                                                                                                                                                                                                                                                                                                                                                                                 |

| COMP         |             | Compensation. This pin is tied to VDD through a 0.1 $\mu$ F capacitor.                                                                                                                                                                                                                                                                                                                                          |

| VREF         |             | Voltage Reference. This pin is tied to VSS through a 0.1 $\mu$ F capacitor.                                                                                                                                                                                                                                                                                                                                     |

| RSET         |             | Reference Resistor. This pin is tied to VSS through an external resistor to<br>control the full-scale current value.                                                                                                                                                                                                                                                                                            |

| AR           | 0           | Analog Red. Analog red output to the CRT monitor. In TV output mode (CR3D_0 = 1), the output is determined by the setting of CR3D_3-1.                                                                                                                                                                                                                                                                          |

| AB           | 0           | Analog Blue. Analog blue output to the CRT monitor.                                                                                                                                                                                                                                                                                                                                                             |

| AG           | . 0         | Analog Green. Analog green output to the CRT monitor. In TV output mode (CR3D_0 = 1), the output is determined by the setting of CR3D_3-1.                                                                                                                                                                                                                                                                      |

| HSYNC        | В           | Horizontal Sync.                                                                                                                                                                                                                                                                                                                                                                                                |

| VSYNC        | В           | Vertical Sync.                                                                                                                                                                                                                                                                                                                                                                                                  |

| Symbol        | Туре    | Description                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FLAT PANEL IN | TERFACE |                                                                                                                                                                                                                                                                                                                                                                                                              |

| FPD[35:0]     | 0       | Flat Panel Data. The meanings of these outputs vary depending on the<br>type of panel. See Section 11 for tables listing all output combinations.                                                                                                                                                                                                                                                            |

| FPDE/<br>MOD  | 0       | Flat Panel Display Enable/AC Modulation Signal. When a TFT panel is<br>being driven, this is the display enable signal. When an STN panel is<br>being driven, this is by default the display enable signal, which is not<br>normally used but may be required for external panel control. If SR34_7 =<br>1, this is the AC modulation signal for those panels that require it.                               |

| FPSCLK        | 0       | Flat Panel Shift Clock. This is the shift (dot) clock for LCD panels.                                                                                                                                                                                                                                                                                                                                        |

| FPHSYNC/LP    | 0       | Flat Panel HSYNC. This is the HSYNC signal for TFT panels and the LP<br>(line pulse or new line start) signal for STN panels.                                                                                                                                                                                                                                                                                |

| FPVSYNC/FLM   | 0       | Flat Panel VSYNC. This is the VSYNC signal for TFT panels and the FLM (first line marker or new frame start) signal for STN panels.                                                                                                                                                                                                                                                                          |

| FPPOL         | 0       | Flat Panel Polarity. If SR1A_5 = 1, this signal tells the panel that the polarity of the data is reversed, thereby minimizing the number of data lines switching in each cycle. This is used in a few highly advanced panels. If SR1A_5= 0, this is the ROMEN output.                                                                                                                                        |

| PWM           | 0       | Pulse Width Modulation. This signal is output on pin M17 when the memory type is not $512Kx32$ (CR68_6 = 1) and SR52_0 = 1.                                                                                                                                                                                                                                                                                  |

| FLAT PANEL PO | WER COI | NTROL                                                                                                                                                                                                                                                                                                                                                                                                        |

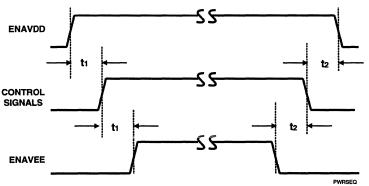

| ENAVDD        | 0       | Enable VDD. This signal is driven high to external logic to initiate a flat<br>panel power up sequence. It is driven low a programmable time (SR41_2)<br>after the panel control signals and ENAVEE are driven low when 86CM65<br>is placed in Standby or Suspend Mode or if the flat panel is shut off via<br>SR31_4.                                                                                       |

| ENAVEE        | 0       | Enable VEE. This signal is driven high a programmable time (SR41_3) after ENAVDD is driven high during a flat panel power up sequence. This signals external logic to turn on the bias voltage to the flat panel. It is driven low when 86CM65 is placed in Standby or Suspend Mode or if the flat panel is shut off via SR40_4. This signals external logic to turn off the bias voltage to the flat panel. |

| STANDBY       |         | Standby. If SR44_4 = 0, driving the STANDBY pin high initiates Standby mode and driving it low initiates exiting of Standby. If SR44_4 = 1, the system is always trying to go into Standby mode and 4 SCLK high pulses on the STANDBY pin either prevent this or take the system out of Standby, resetting the timer in either case.                                                                         |

| SUSPEND       | I       | Suspend. This pin is active when SR42_0 = 1. A low to high transition initiates a Suspend mode sequence and a high to low sequence initiates exiting from Suspend mode.                                                                                                                                                                                                                                      |

| CLK32         | 1       | 32 kHz Clock. An external TTL 32 kHz source is connected to this pin. It is<br>used for panel power sequencing and video memory refresh when in<br>Suspend mode.                                                                                                                                                                                                                                             |

| Symbol      | Туре                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|-------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MISCELLANEC | MISCELLANEOUS FUNCTIONS |                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| ROMEN       | 0                       | ROM Enable. This signal provides the chip output enable input for BIOS ROM reads. It is multiplexed with the FPPOL signal and is selected when $SR1A_5 = 0$ .                                                                                                                                                                                                                                                                  |  |  |  |  |

| RA[15:0}    | 0                       | ROM Address Bus. These signals are multiplexed on PD lines. If a video<br>BIOS is used, it must be immediately shadowed after boot up.                                                                                                                                                                                                                                                                                         |  |  |  |  |

| RD[7:0]     | I                       | ROM Data Bus. These signals are multiplexed on PD lines. If a video BIOS is used, it must be immediately shadowed after boot up.                                                                                                                                                                                                                                                                                               |  |  |  |  |

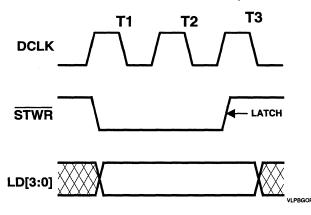

| STWR        | 0                       | Strobe Write. If SR1A_4 is set to 1, pin C3 acts as STWR. This signal is asserted whenever a write is made to CR5C. It is used to enable a General Output Port latch. MCLK is output instead of this signal if SR15_2 = 1. MCLK output is used only for test purposes.                                                                                                                                                         |  |  |  |  |

| GOP0        | 0                       | General Output Port. When SR1A_4 is cleared to 0, pin C3 acts as GOP0.<br>The content of CR5C_0 is reflected on this pin when this bit is<br>programmed.                                                                                                                                                                                                                                                                       |  |  |  |  |

| SPCLK       | 1/0                     | Serial Port Clock. This is the clock for serial data transfer, either for I <sup>2</sup> C or DDC2 monitor data communications. As an output, it is programmed via MMFF20_0. As an input, its status is read via MMFF20_2. In either case the serial port must be enabled by setting MMFF20_4 to 1. PD[26:25] can be strapped to allow I/O (E2H or E8H) port access to the Serial Port register while 86CM65 is disabled.      |  |  |  |  |

| SPDAT       | 1/0                     | Serial Port Data. This is the data signal for serial data transfer, either for I <sup>2</sup> C or DDC2 monitor data communications. As an output, it is programmed via MMFF20_1. As an input, its status is read via MMFF20_3. In either case the serial port must be enabled by setting MMFF20_4 to 1. PD[26:25] can be strapped to allow I/O (E2H or E8H) port access to the Serial Port register while 86CM65 is disabled. |  |  |  |  |

| Symbol         | Туре    | Description                                                                                                                                                                                 |  |  |  |  |

|----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ZV PORT        | ZV PORT |                                                                                                                                                                                             |  |  |  |  |

| LD[15:0]       | I       | Data. YUV input from PC Card                                                                                                                                                                |  |  |  |  |

| LCLK           | I       | Clock. PCLK input from PC Card                                                                                                                                                              |  |  |  |  |

| HS             | I       | HSYNC. HREF input from PC Card                                                                                                                                                              |  |  |  |  |

| VS             |         | VSYNC. VSYNC input from PC Card                                                                                                                                                             |  |  |  |  |

| SCENIC HIGHW   | VAY     |                                                                                                                                                                                             |  |  |  |  |

| Scenic/MX2 M   | ode     |                                                                                                                                                                                             |  |  |  |  |

| LD[7:0]        | I/O     | LPB Data. These lines carry compressed data to the Scenic/MX2 and video data from the Scenic/MX2.                                                                                           |  |  |  |  |

| LCLK           | I       | LPB Clock. This clock controls transactions between 86CM65 and the all<br>Scenic Highway peripherals.                                                                                       |  |  |  |  |

| VREQ/VRDY      | 0       | Video Request/Ready. This signal is part of the the data transfer protocol<br>between 86CM65 and the Scenic/MX2.                                                                            |  |  |  |  |

| CREQ/CRDY      | I       | Scenic/MX2 Request/Ready. This signal is part of the the data transfer<br>protocol between 86CM65 and the Scenic/MX2.                                                                       |  |  |  |  |

| LPBEN          | 0       | LPB Device Enable. This signal is connected to the Scenic/MX2 chip<br>enable input. The output level is controlled via SRD_0. This bit must be<br>programmed to 1 to enable the Scenic/MX2. |  |  |  |  |

| Video 8 and 16 | Modes   |                                                                                                                                                                                             |  |  |  |  |

| LD[15:0]       |         | LPB Data Bus [15:0]. Video data input. LD[7:0] are used for 8-bit interfaces.                                                                                                               |  |  |  |  |

| HS             | 1       | HSYNC. HSYNC input signaling the transition from one line to the next.                                                                                                                      |  |  |  |  |

| VS             | 1       | VSYNC. VSYNC input signaling the transition from one frame to the next.                                                                                                                     |  |  |  |  |

| ODD            |         | Odd/Even Field. High = odd field input from digitizer. Low = even field input. This input is active on pin M17 when the memory type is not 512Kx32 and SR52_0 = 0.                          |  |  |  |  |

| POWER          | AND GRO | DUND                                                                                                                                                                                        |  |  |  |  |

| VDDCORE        | 1       | Analog power supply to the core logic                                                                                                                                                       |  |  |  |  |

| VDDCRT         |         | Digital power supply to the CRT block pads                                                                                                                                                  |  |  |  |  |

| VDDFPI         |         | Digital power supply to the flat panel block pads                                                                                                                                           |  |  |  |  |

| VDDLPB         |         | Digital power supply to the LPB block pads                                                                                                                                                  |  |  |  |  |

| VDDMEM         |         | Digital power supply to the memory subsystem pads                                                                                                                                           |  |  |  |  |

| VDDSYS         |         | Digital power supply to the system bus interface pads                                                                                                                                       |  |  |  |  |

| AVDD           | I       | Analog power supply (RAMDAC). This must be the same voltage as VDDCORE.                                                                                                                     |  |  |  |  |

| CLKAVDD[1:2]   | ł       | Analog power supply (1 = MCLK synthesizer, 2 = DCLK synthesizer). This must be the same voltage as VDDCORE                                                                                  |  |  |  |  |

| VSSPAD         |         | Digital ground (dirty)                                                                                                                                                                      |  |  |  |  |

| VSSCORE        |         | Digital ground (core)                                                                                                                                                                       |  |  |  |  |

| VSSSUB         |         | Digital ground (substrate)                                                                                                                                                                  |  |  |  |  |

| AVSS           | Ι       | Analog ground                                                                                                                                                                               |  |  |  |  |

## 3.3 PIN LISTS

Table 3-2 lists all 86CM65 pins alphabetically. Table 3-3 lists all pins in numerical order.

### Table 3-2. Alphabetical Pin Listing

| Name         | PIN(S)                                                                   |

|--------------|--------------------------------------------------------------------------|

| AB           | G2                                                                       |

| AD[31:16]    | V1, W1, V2, W2, Y1, Y2, U3, W3, U4, W4, V4, Y4, W5, V5, Y5, V6,          |

| AD[15:0]     | W8, U9, W9,V9, Y9, W10, V10, Y10, V11, Y11, W12, V12, Y12, W13, V13, Y13 |

| AG           | G1                                                                       |

| AR           | F2                                                                       |

| AVDD         | D1, F3, F4,                                                              |

| AVSS         | C1, D3, E3, F1, G3,                                                      |

| CAS[7:0]     | Y14, W14, K18, J18, V14, U14, J19, H20                                   |

| C/BE[3:0]    | V3, Y6, Y8, W11                                                          |

| CLK32        | T1                                                                       |

| CLKAVDD[1:2] | C2, E4                                                                   |

| COMP         | E2                                                                       |

| CREQ/CRDY    | L1                                                                       |

| DEVSEL       | W7                                                                       |

| EMCLK        | N1                                                                       |

| EDCLK        | A1                                                                       |

| ENAVDD       | A2                                                                       |

| ENAVEE       | B2                                                                       |

| FLM          | A3                                                                       |

| FPD[35:27]   | A14, B14, C14, D14, A13, B13, C13, A12, B12,                             |

| FPD[26:18]   | C12, D12, A11, B11, C11, A10, B10, C10, A9,                              |

| FPD[17:9]    | B9, C9, A8, B8, C8, D8, A7, B7, C7,                                      |

| FPD[8:0]     | A6, B6, C6, D6, A5, B5, C5, A4, B4                                       |

| FPSCLK       | B3                                                                       |

| FPDE         | B15                                                                      |

| FPHSYNC      | C4                                                                       |

| FPPOL        | C15                                                                      |

| FPVSYNC      | A3                                                                       |

| FRAME        | W6                                                                       |

| GOP0         | C3                                                                       |

| HS           | K1                                                                       |

| HSYNC        | H1                                                                       |

| IDSEL        | Y3                                                                       |

| ĪNTĀ         | U2                                                                       |

| ĪRDY         | V7                                                                       |

| LCLK         | M1                                                                       |

| LD[15:0]     | R2, R1, P4, P3, P2, P1, N3, N2, L3, L2, K3, K2, J3, J2, J1, H3           |

| LP           | C4                                                                       |

## Table 3-2. Alphabetical Pin Listing (Continued)

| Name      | PIN(S)                                                                          |

|-----------|---------------------------------------------------------------------------------|

| LPBEN     | N1                                                                              |

| MA[9:0]   | M17, L18, L19, M19, N18, N19, N20, M18, M20, L20                                |

| MOD       | B15                                                                             |

| ODD       | M17                                                                             |

| ŌĒ        | K19                                                                             |

| PAR       | V8                                                                              |

| PD[63:48] | V16, W16, T17, U17, V17, W17, Y17, V15, W15, Y18, W18, V18, U18, T18, R18, P18, |

| PD[47:32] | C16, A17, B17, C17, D17, E17, G18, H18, H19, F18, E18, D18, C18, B18, A18, B16, |

| PD[31:16] | P19, R19, T19, U19, V19, W19, Y19, Y15, Y16, Y20, W20, V20, U20, T20, R20, P20, |

| PD[15:0]  | A16, A19, B19, C19, D19, E19, F19, G19, G20, F20, E20, D20, C20, B20, A20, A15  |

| PWM       | M17                                                                             |

| RA[15:0]  | A16, A19, B19, C19, D19, E19, F19, G19, G20, F20, E20, D20, C20, B20, A20, A15  |

| RASO      | K20                                                                             |

| RD[7:0]   | Y16, Y20, W20, V20, U20, T20, R20, P20                                          |

| RESET     | R3                                                                              |

| ROMEN     | C15                                                                             |

| RSET      | E1                                                                              |

| SCLK      | U1                                                                              |

| SPCLK     | M2                                                                              |

| SPDAT     | M3                                                                              |

| STANDBY   | T2                                                                              |

| STOP      | U8                                                                              |

| STWR      | C3                                                                              |

| SUSPEND   | T3                                                                              |

| TRDY      | Y7                                                                              |

| VDDFPI    | D5, D10, D13                                                                    |

| VDDCORE   | D16, K17, L4, U10                                                               |

| VDDCRT    | G4                                                                              |

| VDDLPB    | J4                                                                              |

| VDDMEM    | G17, N17, U15                                                                   |

| VDDSYS    | T4, U7, U12                                                                     |

| VREQ/VRDY | K1                                                                              |

| VREF      | D2                                                                              |

| VS        | L1                                                                              |

| VSSCORE   | D9, D11, J17, K4, L17, M4, U11                                                  |

| VSSPAD    | D4, D7, D15, F17, H4, H17, N4, P17, R4, U5, U6, U13, U16                        |

| VSSSUB    | R17                                                                             |

| VSYNC     | H2                                                                              |

| WE        | J20                                                                             |

| XIN       | A1                                                                              |

| XOUT      | B1                                                                              |

| Number | Name        | Number | Name        |

|--------|-------------|--------|-------------|

| A1     | XIN/EDCLK   | C1     | AVSS        |

| A2     | ENAVDD      | C2     | CLKAVDD1    |

| A3     | FPVSYNC/FLM | C3     | STWR/GOP0   |

| A4     | FPD1        | C4     | FPHSYNC/LP  |

| A5     | FPD4        | C5     | FPD2        |

| A6     | FPD8        | C6     | FPD6        |

| A7     | FPD11       | C7     | FPD9        |

| A8     | FPD15       | C8     | FPD13       |

| A9     | FPD18       | C9     | FPD16       |

| A10    | FPD21       | C10    | FPD19       |

| A11    | FPD24       | C11    | FPD22       |

| A12    | FPD28       | C12    | FPD26       |

| A13    | FPD31       | C13    | FPD29       |

| A14    | FPD35       | C14    | FPD33       |