# Scenic/MX2

# MPEG-1 Audio/Video Decoder

# Preliminary

June 1995

S3 Incorporated 2770 San Tomas Expressway Santa Clara, CA 95051-0968

#### NOTATIONAL CONVENTIONS

The following notational conventions are used in this data book:

Signal names are shown in all uppercase letters. For example, XD.

A bar over a signal name indicates an active low signal. For example,  $\overline{OE}$ .

n-m indicates a bit field from bit n to bit m. For example, 7-0 specifies bits 7 through 0, inclusive.

n:m indicates a signal (pin) range from n to m. For example D[7:0] specifies data lines 7 through 0, inclusive

Use of a trailing letter H indicates a hexadecimal number. For example, 7AH is a hexadecimal number.

Use of a trailing letter b indicates a binary number. For example, 010b is a binary number.

When K or M are used, they refer to binary rather than decimal form. Thus, for example, 1 KByte would be equivalent to 1024, not 1,000 bytes.

When k is used, it refers to the decimal form. For example, 1 kbit means 1000 bits.

#### NOTICES

© Copyright 1995 S3 Incorporated. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, or otherwise, without the prior written consent of S3 Incorporated, 2770 San Tomas Expwy, Santa Clara CA 95051-0968. The S3 Corporate Logo, S3 on Board, S3 on Board design, Vision868, Vision968, Trio, Trio, Trio, Trio, Trio, Trio, Trio, Kative-MPEG, No Compromise Integration, No Compromise Acceleration and Innovations in Acceleration are trademarks of S3 Incorporated and S3 and True Acceleration are registered trademarks of S3 Incorporated. Other trademarks referenced in this document are owned by their respective companies. The material in this document is for information only and is subject to change without notice. S3 Incorporated reserves the right to make changes in the product design without reservation and without

Additional information may be obtained from:

S3 Incorporated, Literature Department, 2770 San Tomas Expressway, Santa Clara, CA 95051-0968.

Telephone: 408-980-5400, Fax: 408-980-5444

# **Table of Contents**

| List of Figures v                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| List of Tables vi                                                                                                                                                                                                                                                                                                                                                                                            |

| Section 1: Introduction       1-1         1.1       GENERAL CAPABILITIES       1-1         1.2       PRODUCT FEATURES       1-2         1.2.1       General Features       1-2         1.2.2       Video Features       1-2         1.2.3       Audio Features       1-2         1.2.4       System Interface       1-2         1.2.5       Packaging       1-2         1.3       SOFTWARE SUPPORT       1-2 |

| Section 2: Mechanical Data 2-1<br>2.1 THERMAL SPECIFICATIONS 2-1<br>2.2 MECHANICAL DIMENSIONS 2-1                                                                                                                                                                                                                                                                                                            |

| Section 3: Pins                                                                                                                                                                                                                                                                                                                                                                                              |

| Section 4: Electrical Data                                                                                                                                                                                                                                                                                                                                                                                   |

| Section 5: Reset and Initialization         5-1           5.1         CONFIGURATION STRAPPING         5-1           5.2         RESET BEHAVIOR         5-4           5.2.1         Hardware Reset         5-4           5.2.2         Soft Reset         5-4                                                                                                                                                 |

| v              | Secti   | on 6: Hardware Interfaces 6-1                |

|----------------|---------|----------------------------------------------|

|                | 6.1     | Scenic Highway INTERFACE 6-1                 |

| vi             | 6.1     | .1 Scenic/MX2 Register/Memory                |

| VI             |         | Access 6-1                                   |

|                | 6.1     | .2 Scenic/MX2 Burst Writes 6-3               |

| -1             | 6.1     | .3 Scenic/MX2 Video Output 6-4               |

| -1             | 6.2     | LOCAL MEMORY INTERFACE 6-6                   |

| -2             | 6.2     | .1 Memory Configurations 6-6                 |

| -2<br>-2<br>-2 | 6.2     | .2 Memory Functional Timing 6-6              |

| -2             | 6.3     | SERIAL AUDIO INTERFACE 6-8                   |

| -2             | 6.4     | DIGITIZED VIDEO PORT (DVP)                   |

| -2             |         | INTERFACE 6-9                                |

| -2             | 6.4     | INTERFACE 6-9<br>.1 Digitizers Supported 6-9 |

| -2             | 6.4     | .2 DVP Input 6-9                             |

|                |         | .3 DVP Output 6-9                            |

| -1             | 6.5     | INTERRUPT GENERATION 6-9                     |

| -1             |         | .1 PCI Interrupts 6-10                       |

| - I<br>1       | 6.5     | .2 ISA Interrupts 6-10                       |

|                |         |                                              |

| -1             | Section | on 7: Functional Description . 7-1           |

| 1              | 7.1     | OVERVIEW                                     |

|                | 7.2     | OVERVIEW                                     |

|                |         | PARTITIONING                                 |

| -0             | 7.3     | VIDEO DECOMPRESSION ENGINE                   |

|                |         | (VDE)                                        |

| -1             | 7.4     |                                              |

| -1             |         | (ADE)                                        |

| -1             | 7.5     | (ADE)                                        |

| -1             | 7.6     | Scenic Highway UNIT 7-3                      |

|                | 7.7     | SERIAL AUDIO PORT (SP) 7-3                   |

| -1             | 7.8     | DIGITIZED VIDEO PORT (DVP) 7-3               |

| 1              | 7.9     | TIMER                                        |

| -1<br>-4       |         |                                              |

| -4             | Secti   | on 8: Software Driver 8-1                    |

| -4             | 8.1     | FUNCTIONS SUPPORTED BY                       |

|                | 0.1     | DRIVER SOFTWARE 8-1                          |

|                | 8.2     | DRIVER MEMORY ACCESS 8-1                     |

\_

### Section 9: Control Register

| Desc | riptions                       |  |

|------|--------------------------------|--|

| 9.1  | REGISTER MAPPING AND           |  |

|      | ADDRESSING                     |  |

| 9.2  | Scenic Highway REGISTERS 9-3   |  |

| 9.3  | MEMORY INTERFACE UNIT (MIU)    |  |

|      | REGISTERS                      |  |

| 9.4  | SERIAL PORT (SP) REGISTERS 9-9 |  |

| 9.5  | DIGITIZED VIDEO PORT (DVP)     |  |

CONTROL REGISTERS . . . . . . . 9-12

v

.

# List of Figures

| #    | Title F                          | <b>`</b> age |

|------|----------------------------------|--------------|

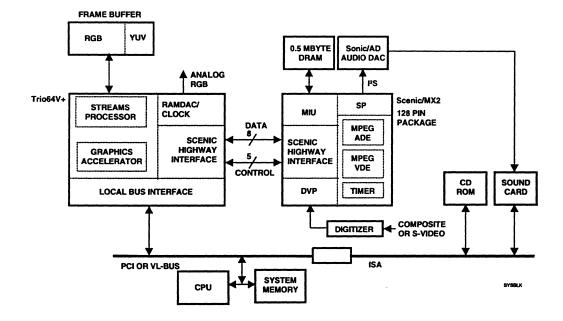

| 1-1  | System Architecture              | 1-3          |

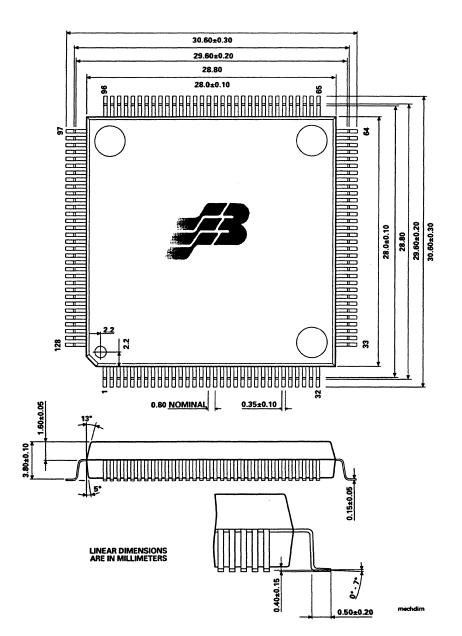

| 2-1  | 128-pin PQFP Mechanical          |              |

|      | Dimensions                       | 2-2          |

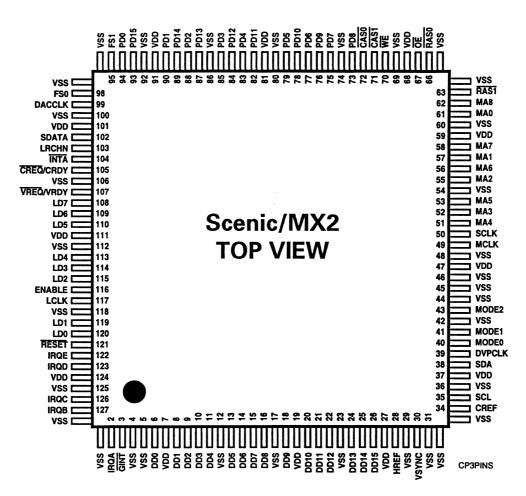

| 3-1  | Pinout                           | 3-2          |

| 6-1  | Scenic Highway Interface         | 6-1          |

| 6-2  | Register/Memory Write            |              |

|      | (Scenic/MX2 Ready)               | 6-2          |

| 6-3  | Register/Memory Write            |              |

|      | (Not Ready)                      | 6-2          |

| 6-4  | Register/Memory Read             |              |

|      | (Scenic/MX2 Ready)               | 6-3          |

| 6-5  | Register/Memory Read             |              |

|      | (Not Ready)                      | 6-3          |

| 6-6  | Burst Write (Scenic/MX2 Ready) . | 6-4          |

| 6-7  | VSYNC and HSYNC Protocols        | 6-4          |

| 6-8  | Video Output (Trio64V+ Ready) .  | 6-5          |

| 6-9  | Video Output (Trio64V+           |              |

|      | Not Ready)                       | 6-5          |

| 6-10 | 256Kx16 DRAM Configuration       | 6-6          |

| 6-11 | Fast Page Mode Read Cycle        | 6-7          |

| 6-12 | Fast Page Mode Write Cycle       | 6-7          |

| 6-13 | Audio DAC Interface              | 6-8          |

| 6-14 | First Audio Bits Latched on      |              |

|      | Rising Edge                      | 6-8          |

| 6-15 | First Audio Bits Latched on      |              |

|      | Falling Edge                     | <b>6-</b> 8  |

| 6-16 | Philips SAA7110 Digitizer        |              |

|      | Interface                        | 6-9          |

| 7-1  | System Data Flow                 | 7-1          |

| 7-2  | Control Hierarchy                | 7-2          |

| 7-3  | Internal Block Diagram           | 7-2          |

# **List of Tables**

| #   | Title Page                                |

|-----|-------------------------------------------|

| 3-1 | Scenic/MX2 Pin Descriptions 3-3           |

| 3-2 | Alphabetical Pin Listing 3-6              |

| 3-3 | Numerical Pin Listing 3-7                 |

| 4-1 | Absolute Maximum Ratings 4-1              |

| 4-2 | DC Specifications 4-1                     |

| 5-1 | Definition of PD[15:0} at the Rising      |

|     | Edge of the Reset Signal 5-1              |

| 5-2 | Setting <u>RAS</u> Precharge Length . 5-3 |

| 5-3 | Setting RAS Pulse Width 5-3               |

| 5-4 | Definition of MODE[2:0} at the            |

|     | Rising Edge of the Reset Signal . 5-4     |

| 9-1 | Module Register Base Addresses 9-2        |

## **Section 1: Introduction**

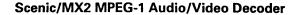

The Scenic/MX2<sup>TM</sup> MPEG-1 audio/video decoder (hereinafter referred to as the Scenic/MX2) is optimized for the PC platform. It can be used in conjunction with any S3<sup>®</sup> graphics accelerator that provides color space conversion and the S3 Scenic Highway<sup>TM</sup> interface (such as the Trio64V+<sup>TM</sup>). The other video features supported by these graphics accelerators, including video scaling, can be used to enhance the display of the MPEG-1 video decompressed by the Scenic/MX2.

#### **1.1 GENERAL CAPABILITIES**

Scenic/MX2 integrates into a single device the following functions:

- MPEG-1 30 frames/second video decoding

- MPEG-1 CD-quality audio decoding

- A timer to facilitate synchronization of decoded audio and video

- A serial output port for direct connection of a low cost stereo audio D/A converter

- A Scenic Highway interface to enable the host (via the S3 graphics/video accelerator) to access Scenic/MX2 registers and private memory and to burst write compressed audio and video data to the Scenic/MX2. The Scenic/MX2 uses the Scenic Highway to transmit decompressed video to the S3 graphics/video accelerator's frame buffer for, display in synchronization with the decompressed audio

Scenic/MX2 works in tandem with the host CPU and graphics accelerator to decode and display MPEG-1 video and audio:

- The host CPU is responsible for demultiplexing the MPEG-1 system stream into separate compressed video and audio data streams and for preprocessing the compressed audio data.

- The Scenic/MX2 is responsible for decompressing the MPEG-1 video stream into a sequence of YUV video images and for decompressing the preprocessed audio stream into 16-bit stereo audio samples for playback.

Scenic/MX2's on-chip timer enables the software driver to control the synchronization of audio and video during playback.

- The graphics accelerator is responsible for receiving the sequence of decompressed video images over the Scenic Highway, converting the YUV images into RGB format for display on a computer monitor, and for any additional video processing (video scaling and overlay, video effects, etc.).

#### **1.2 PRODUCT FEATURES**

Scenic/MX2's main features are listed below by functional area:

#### 1.2.1 General Features

- MPEG-1 video and audio decompression (30 frames per second)

- Simultaneous video decompression and audio decompression

- Complete audio and video synchronization support

#### 1.2.2 Video Features

- Decompression of "Constrained Parameter" MPEG-1 bit streams

- MPEG-1 video slow playback, fast search, fast forward, freeze frame, audio mute, single step, and random access

- MPEG-1 video error detection and resynchronization

- 4:2:2 video data format output

#### 1.2.3 Audio Features

- Decompression of any MPEG-1 level 1 or 2 compressed audio bit stream

- 32, 44.1 and 48 KHz sampling rates

- 32 to 448 kbit/sec compressed bit rates

- Single-channel, dual-channel, stereo, and joint-stereo stream decompression

- Decompressed audio is transmitted to an external stereo audio D/A converter through a serial audio port

- Audio mute and de-emphasis supported

#### 1.2.4 System Interface

Scenic/MX2 has four main functional interfaces:

- 8-bit Scenic Highway interface to an S3 graphics/video accelerator

- 16-bit page mode DRAM interface

- Serial audio interface to an audio DAC

- Digitized Video Port (DVP) Interface for NTSC/PAL input

#### 1.2.5 Packaging

Scenic/MX2 is available in a 128-pin plastic quad flat pack (PQFP) package.

#### 1.3 SOFTWARE SUPPORT

S3 will provide software drivers which allow Scenic/MX2, in conjunction with the appropriate graphics accelerator, to decode MPEG-1 compressed video and/or games conforming to the following standards and APIs:

- CD-I movies ("Green Book")

- Video CD movies ("White Book")

- Microsoft Windows<sup>®</sup> 3.1 and Windows<sup>®</sup> 95 MCI MPEG API

- Open MPEG (OM/1) DOS API

Figure 1-1. System Architecture

PRELIMINARY

**INTRODUCTION 1-3**

.

Scenic/MX2 MPEG-1 Audio/Video Decoder

# Section 2: Mechanical Data

#### 2.1 THERMAL SPECIFICATIONS

| Parameter                          | Тур  | Unit |

|------------------------------------|------|------|

| Thermal Resistance OJC             | TBD  | °C/W |

| Thermal Resistance OJA (Still Air) | 24.0 | °C/W |

| Power Dissipation                  | 2.25 | W    |

#### 2.2 MECHANICAL DIMENSIONS

The Scenic/MX2 comes in a 128-pin PQFP package. The mechanical dimensions are given in Figure 2-1.

PRELIMINARY

**MECHANICAL DATA 2-1**

2-2 MECHANICAL DATA

# **Section 3: Pins**

#### 3.1 PINOUT DIAGRAMS

The Scenic/MX2 comes in a 128-pin PQFP package. The pinout is shown in Figure 3-1. An active low pin is indicated by an overbar.

Figure 3-1. Pinout

### 3.2 PIN DESCRIPTIONS

The following table provides a brief description of each Scenic/MX2 pin. The following definitions are used in these descriptions:

- l Input signal O Output signal

B - Bidirectional signal

#### Table 3-1. Scenic/MX2 Pin Descriptions

| Symbol            | Туре    | Pin Number(s)                  | Description                                                                                                                                                                                            |  |  |

|-------------------|---------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PCI BUS INTERFACE |         |                                |                                                                                                                                                                                                        |  |  |

| ĪNTĀ              | 0       | 104                            | PCI Interrupt Output. This signal is asserted whenever<br>an internal interrupt is generated and bit 11 of R0000<br>is set to 1 or when the GINT input is asserted and bit<br>12 of R0000 is set to 1. |  |  |

| GINT              | I       | 3                              | PCI Interrupt Input. When this signal is asserted, INTA<br>is asserted if bit 12 of R0000 is set to 1. This allows<br>Scenic/MX2 to source one PCI interrupt output for a<br>board with two chips.     |  |  |

| ISA BUS INTERF    | ACE     |                                |                                                                                                                                                                                                        |  |  |

| RESET             | I       | 121                            | System Reset. Asserting this signal forces the<br>Scenic/MX2 registers and state machines to a known<br>state.                                                                                         |  |  |

| IRQ[E:A]          | 0       | 122, 123, 126,<br>127, 2       | ISA Interrupts. Bits 15-13 of R0000 determine which<br>of these signals is asserted upon generation of an<br>internal interrupt.                                                                       |  |  |

| Scenic Highway    | INTERFA | CE                             |                                                                                                                                                                                                        |  |  |

| LD[7:0]           | В       | 108-110, 113-<br>115, 119, 120 | Scenic Highway Bus Data. These signals also carry<br>address data for single register/memory reads and<br>writes.                                                                                      |  |  |

| LCLK              | 0       | 117                            | LPB Clock. LCLK controls transactions on the LPB.                                                                                                                                                      |  |  |

| CREQ/CRDY         | 0       | 105                            | Scenic/MX2 Request/Ready. When sending data:<br>low = requesting to send<br>high = not requesting to send<br>When receiving data:<br>low = not ready to receive<br>high = ready to receive             |  |  |

| VREQ/VRDY         | t       | 107                            | S3 Video Processor Request/Ready. When sending<br>data:<br>low = requesting to send<br>high = not requesting to send<br>When receiving data:<br>low = not ready to receive<br>high = ready to receive  |  |  |

| ENABLE            | 1       | 116                            | Scenic/MX2 Enable. Asserting this input enables<br>Scenic/MX2 operation on the Scenic Highway. When<br>this signal is low, Scenic/MX2 tri-states its LD[7:0] pins.                                     |  |  |

### Table 3-1. Scenic/MX2 Pin Descriptions (Continued)

| DIGITIZED VID              | EO PORT (  | DVP) INTERFACE                                                          |                                                                                                                                                                                                                                                                                                            |  |

|----------------------------|------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DD[15:8]                   | 1          | 26-24, 22-20,<br>18, 16                                                 | Digitized Video Data [15:8]. In 16-bit data mode ( $R0500_17 = 0$ ), these are Cb[7:0] and Cr[7:0], with the data expected in that order. These pins are not used in 8-bit data mode.                                                                                                                      |  |

| DD[7:0]                    | 1          | 15-13, 11-8, 6                                                          | Digitized Video Data [7:0]. In 16-bit data mode<br>(R0500_17 = 0), these are the luminance inputs Y[7:0].<br>In 8-bit data mode, these are multiplexed luminance<br>and difference inputs. If R0500_18 is 0, the input<br>sequence is Cb-Y0-Cr-Y1. If R0500_18 is 1, the input<br>sequence is Y0-Cb-Y1-Cr. |  |

| HREF                       | 1          | 28                                                                      | Horizontal Reference. HSYNC input from the digitizer.                                                                                                                                                                                                                                                      |  |

| VSYNC                      | 1          | 30                                                                      | VSYNC. Vertical sync input from the digitizer.                                                                                                                                                                                                                                                             |  |

| CREF                       | I          | 34                                                                      | Clock Reference. In 16-bit data mode ( $R0500_17 = 0$ ), this input can be used to qualify the clock. See the definition for bit 1 of R0500. This pin is pulled up internally.                                                                                                                             |  |

| DVPCLK                     |            | 39                                                                      | DVP Clock. 27 MHz input.                                                                                                                                                                                                                                                                                   |  |

| PRIVATE MEN                | IORY INTEI | RFACE                                                                   |                                                                                                                                                                                                                                                                                                            |  |

| Addres                     | s and Data | 1                                                                       |                                                                                                                                                                                                                                                                                                            |  |

| PD[15:0]                   | В          | 93, 89, 87, 84,<br>82, 78, 76, 73,<br>75, 77, 79, 83,<br>85, 88, 90, 94 |                                                                                                                                                                                                                                                                                                            |  |

| MA[8:0]                    | 0          | 62, 58, 56, 53,<br>51, 52, 55, 57,<br>61                                |                                                                                                                                                                                                                                                                                                            |  |

| Memo                       | ry Control |                                                                         |                                                                                                                                                                                                                                                                                                            |  |

| MCLK                       | I          | 49                                                                      | Memory Clock. External clock source input; controls<br>data transfer rate between Scenic/MX2 and private<br>memory.                                                                                                                                                                                        |  |

| RAS[1:0]                   | 0          | 63, 66                                                                  | Row Address Strobe.                                                                                                                                                                                                                                                                                        |  |

| CAS[1:0]                   | 0          | 71-72                                                                   | Column Address Strobes.                                                                                                                                                                                                                                                                                    |  |

| WE                         | 0          | 70                                                                      | Write Enable.                                                                                                                                                                                                                                                                                              |  |

| ŌĒ                         | 0          | 67                                                                      | Output Enable.                                                                                                                                                                                                                                                                                             |  |

| I <sup>2</sup> C INTERFACE | :          |                                                                         |                                                                                                                                                                                                                                                                                                            |  |

| SCL                        | В          | 35                                                                      | I <sup>2</sup> C clock.                                                                                                                                                                                                                                                                                    |  |

| SDA                        | В          | 38                                                                      | I <sup>2</sup> C data.                                                                                                                                                                                                                                                                                     |  |

| SERIAL INTER               | FACE       |                                                                         |                                                                                                                                                                                                                                                                                                            |  |

| SCLK                       | 0          | 50                                                                      | Serial Data Clock. Clock input to the audio DAC. Its<br>relationship with LRCHN and DACCLK is specified in<br>R0300_11-9.                                                                                                                                                                                  |  |

| SDATA                      | 0          | 102                                                                     | Serial Data. Data input to the audio DAC.                                                                                                                                                                                                                                                                  |  |

|             | T     | Γ                                                                                                                                                         |                                                                                                                                                                                                               |  |

|-------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LRCHN       | 0     | 103                                                                                                                                                       | Left/Right Channel Select. Channel indicator for the audio DAC. This is the same as the sampling                                                                                                              |  |

| FS[1:0]     | 0     | 95. 98                                                                                                                                                    | frequency.<br>Frequency Select. These outputs are reflections of the                                                                                                                                          |  |

|             |       | 55,55                                                                                                                                                     | values programmed in R0300_3-2. They specify a sampling frequency of 32, 44.1 or 48 KHz. These outputs are decoded externally to allow correct programming of the desired DACCLK frequency.                   |  |

| DACCLK      | 1     | 99                                                                                                                                                        | DAC Clock. This input is generated by an external<br>clock source and is used by Scenic/MX2 to generate<br>the audio DAC control signals. Its relationship with<br>LRCHN and SCLK is specified in R0300_11-9. |  |

| MODE SELECT |       |                                                                                                                                                           |                                                                                                                                                                                                               |  |

| MODEO       | 1     | 40                                                                                                                                                        | The strapping state of this pin on reset is latched in R0500_16. A value of 0 indicates the DVP is active. A value of 1 indicates the DVP is inactive (no digitizer).                                         |  |

| MODE1       | I     | 41                                                                                                                                                        | The strapping state of this pin on reset is latched in R0500_17. See Table 5-4 for a description of the options.                                                                                              |  |

| MODE2       | 1     | 43                                                                                                                                                        | The strapping state of this pin on reset is latched in R0500_18. See Table 5-4 for a description of the options.                                                                                              |  |

| POWER AND G | ROUND |                                                                                                                                                           |                                                                                                                                                                                                               |  |

| VDD         |       | 7, 19, 27, 37,<br>47, 59, 68, 81,<br>91, 101, 111,<br>124                                                                                                 | Power supply                                                                                                                                                                                                  |  |

| VSS         | 1     | 1, 4, 5, 12, 17,<br>23, 29, 31, 32,<br>33, 36, 42, 44-<br>46, 48, 54, 60,<br>64, 65, 69, 74,<br>80, 86, 92, 96,<br>97, 100, 106,<br>112, 118, 125,<br>128 | Ground                                                                                                                                                                                                        |  |

#### Table 3-1. Scenic/MX2 Pin Descriptions (Continued)

### 3.3 PIN LISTS

Table 3-2 lists all Scenic/MX2 pins alphabetically. Table 3-3 lists all Scenic/MX2 pins in numerical order.

#### Table 3-2. Alphabetical Pin Listing

| Name             | Pins                                                                                                                             |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CAS[1:0]         | 71-72                                                                                                                            |  |  |  |

| CREF             | 34                                                                                                                               |  |  |  |

| CREQ/CRDY        | 105                                                                                                                              |  |  |  |

| DACCLK           | 99                                                                                                                               |  |  |  |

| DD[15:0]         | 26-24, 22-20, 18, 16, 15-13, 11-8, 6                                                                                             |  |  |  |

| DVPCLK           | 39                                                                                                                               |  |  |  |

| ENABLE           | 116                                                                                                                              |  |  |  |

| FS[1:0]          | 95, 98                                                                                                                           |  |  |  |

| GINT             | 3                                                                                                                                |  |  |  |

| HREF             | 28                                                                                                                               |  |  |  |

| INTA             | 104                                                                                                                              |  |  |  |

| IRQ[E:A]         | 122, 123, 126, 127, 2                                                                                                            |  |  |  |

| LCLK             | 117                                                                                                                              |  |  |  |

| LD[7:0]          | 108-110, 113-115, 119, 120                                                                                                       |  |  |  |

| LRCHN            | 103                                                                                                                              |  |  |  |

| MA[8:0]          | 62, 58, 56, 53, 51, 52, 55, 57, 61                                                                                               |  |  |  |

| MCLK             | 49                                                                                                                               |  |  |  |

| MODE[2:0]        | 43, 41, 40                                                                                                                       |  |  |  |

| ŌĒ               | 67                                                                                                                               |  |  |  |

| PD[15:0]         | 93, 89, 87, 84, 82, 78, 76, 73, 75, 77, 79, 83, 85, 88, 90, 94                                                                   |  |  |  |

| RAS[1:0]         | 63, 66                                                                                                                           |  |  |  |

| RESET            | 121                                                                                                                              |  |  |  |

| SCL              | 35                                                                                                                               |  |  |  |

| SCLK             | 50                                                                                                                               |  |  |  |

| SDA              | 38                                                                                                                               |  |  |  |

| SDATA            | 102                                                                                                                              |  |  |  |

| VDD              | 7, 19, 27, 37, 47, 59, 68, 81, 91, 101, 111, 124                                                                                 |  |  |  |

| <b>VREQ/VRDY</b> | 107                                                                                                                              |  |  |  |

| VSS              | 1, 4, 5, 12, 17, 23, 29, 31, 32, 33, 36, 42, 44-46, 48, 54, 60, 64, 65, 69, 74, 80, 86, 92, 96, 97, 100, 106, 112, 118, 125, 128 |  |  |  |

| VSYNC            | 30                                                                                                                               |  |  |  |

| WE               | 70                                                                                                                               |  |  |  |

| Pin # | Nama        | Pin # | Namo  |

|-------|-------------|-------|-------|

| 1     | Name<br>VSS | 41    | MODE1 |

| 2     | IRQA        | 41    | VSS   |

| 3     | GINT        | 43    | MODE2 |

| 4     | VSS         | 43    | VSS   |

| 5     | VSS         | 45    | VSS   |

| 6     | DD0         | 46    | VSS   |

| 7     | VDD         | 40    | VDD   |

| 8     | DD1         | 48    | VSS   |

| 9     | DD2         | 49    | MCLK  |

| 10    | DD3         | 50    | SCLK  |

| 11    | DD4         | 51    | MA4   |

| 12    | VSS         | 52    | MA3   |

| 13    | V33<br>DD5  | 53    | MA5   |

| 13    | DD5         | 54    | VSS   |

| 15    | DD0         | 55    | MA2   |

| 16    | DD8         |       | MA6   |

| 17    | VSS         | 57    | MA1   |

| 18    | DD9         | 58    | MA7   |

| 19    | VDD         | 59    | VDD   |

| 20    | DD10        | 60    | VSS   |

| 20    | DD10        | 61    | MAO   |

| 22    | DD12        | 62    | MA8   |

| 23    | VSS         | 63    | RAS1  |

| 24    | DD13        | 64    | VSS   |

| 25    | DD14        | 65    | VSS   |

| 26    | DD15        | 66    | RASO  |

| 27    | VDD         | 67    | OE    |

| 28    | HREF        | 68    | VDD   |

| 29    | VSS         | 69    | VSS   |

| 30    | VSYNC       | 70    | WE    |

| 31    | VSS         | 71    | CAS1  |

| 32    | VSS         | 72    | CASO  |

| 33    | VSS         | 73    | PD8   |

| 34    | CREF        | 74    | VSS   |

| 35    | SCL         | 75    | PD7   |

| 36    | VSS         | 76    | PD9   |

| 37    | VDD         | 77    | PD6   |

| 38    | SDA         | 78    | PD10  |

| 39    | DVPCLK      | 79    | PD5   |

| 40    | MODE0       | 80    | VSS   |

| L     |             |       |       |

#### Table 3-3. Numerical Pin Listing

| Pin # | Name      |  |

|-------|-----------|--|

| 81    | VDD       |  |

| 82    | PD11      |  |

| 83    | PD4       |  |

| 84    | PD12      |  |

| 85    | PD3       |  |

| 86    | VSS       |  |

| 87    | PD13      |  |

| 88    | PD2       |  |

| 89    | PD14      |  |

| 90    | PD1       |  |

| 91    | VDD       |  |

| 92    | VSS       |  |

| 93    | PD15      |  |

| 94    | PD0       |  |

| 95    | FS1       |  |

| 96    | VSS       |  |

| 97    | VSS       |  |

| 98    | FS0       |  |

| 99    | DACCLK    |  |

| 100   | VSS       |  |

| 101   | VDD       |  |

| 102   | SDATA     |  |

| 103   | LRCHN     |  |

| 104   | ĪNTĀ      |  |

| 105   | CREQ/CRDY |  |

| 106   | VSS       |  |

| 107   | VREQ/VRDY |  |

| 108   | LD7       |  |

| 109   | LD6       |  |

| 110   | LD5       |  |

| 111   | VDD       |  |

| 112   | VSS       |  |

| 113   | LD4       |  |

| 114   | LD3       |  |

| 115   | LD2       |  |

| 116   | ENABLE    |  |

| 117   | LCLK      |  |

| 118   | VSS       |  |

| 119   | LD1       |  |

#### Table 3-3. Numerical Pin Listing (Continued)

| Pin # | Name  |  |

|-------|-------|--|

| 120   | LD0   |  |

| 121   | RESET |  |

| 122   | IRQE  |  |

| 123   | IRQD  |  |

| 124   | VDD   |  |

| 125   | VSS   |  |

| 126   | IRQC  |  |

| 127   | IRQB  |  |

| 128   | VSS   |  |

# **Section 4: Electrical Data**

### 4.1 MAXIMUM RATINGS

#### Table 4-1. Absolute Maximum Ratings

| Ambient temperature                 | 0° C to 70° C                  |

|-------------------------------------|--------------------------------|

| Storage temperature                 | -40° C to 125° C               |

| DC Supply Voltage                   | -0.5V to 7.0V                  |

| I/O Pin Voltage with respect to Vss | -0.5V to V <sub>DD</sub> +0.5V |

#### 4.2 DC SPECIFICATIONS

#### Table 4-2. DC Specifications (VDD = 5V $\pm$ 5%, operating temperature 0° C to 70° C)

| Symbol | Parameter                | Min | Max                   | Unit |

|--------|--------------------------|-----|-----------------------|------|

| VIL    | Input Low Voltage        |     | 0.8                   | V    |

| Viн    | Input High Voltage       | 2.0 |                       | V    |

| Vol    | Output Low Voltage       |     | V <sub>SS</sub> + 0.4 | V    |

| Vон    | Output High Voltage      | 2.4 |                       | v    |

| loz    | Output Tri-state Current |     | 1                     | μA   |

| CIN    | Input Capacitance        |     | TBD                   | pF   |

| COUT   | Output Capacitance       |     | TBD                   | pF   |

| lcc    | Power Supply Current     |     | TBD                   | mA   |

#### 4.3 AC SPECIFICATIONS

TBD

,

## Section 5: Reset and Initialization

The RESET signal resets Scenic/MX2's internal state machines and places all registers in their power-on default states. It also initiates several configuration actions, as described in this section.

#### **5.1 CONFIGURATION STRAPPING**

Certain Scenic/MX2 configuration information, as detailed in this section, is set by hardware strapping. The PD[15:0] pins can be individually pulled high or low through a 47 K $\Omega$  resistor. These pull-ups and pull-downs do not affect normal operation of the pins as part of the private memory data bus, but force the pins to a defined state during reset. The Scenic/MX2 samples this state at the rising edge of the reset signal and loads the data into register bits as noted in Table 5-1 and Section 10.

| Register<br>Number | Bit(s)               | PD Pins | Value | Function                                |

|--------------------|----------------------|---------|-------|-----------------------------------------|

|                    |                      | 15      |       | Reserved for future use                 |

|                    | SCLK Inv             | erted   |       |                                         |

| R0300              | 22                   | 14      | 0     | Data latched on rising edge of SCLK     |

|                    |                      |         | 1     | Data latched on falling edge of SCLK    |

|                    | Audio DAC Absent     |         |       |                                         |

| R0300              | 21                   | 13      | 0     | Audio DAC present                       |

|                    |                      |         | 1     | Audio DAC absent                        |

|                    | Audio Data Bit Order |         |       |                                         |

| R0300              | 20                   | 12      | 0     | Audio data bit 0 first                  |

|                    |                      |         | 1     | Audio data bit 15 first                 |

|                    | Lag Time             |         |       |                                         |

| R0300              | 19                   | 11      | 0     | First 16 bits latched on an LRCHN phase |

|                    |                      |         | 1     | Last 16 bits latched on an LRCHN phase  |

#### Table 5-1. Definition of PD[15:0] at the Rising Edge of the Reset Signal

| Register<br>Number | Bit(s)                    | PD Pins      | Value                           | Function                                                                                                                                                                   |  |

|--------------------|---------------------------|--------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                    | SCLK and LRCHN Definition |              |                                 |                                                                                                                                                                            |  |

| R0300              | 14 - 12                   | [10:8]       | 000                             | 256 DAC clocks per LRCHN, 2 DAC<br>clocks per SCLK                                                                                                                         |  |

|                    |                           |              | 001                             | 256 DAC clocks per LRCHN, 4 DAC<br>clocks per SCLK                                                                                                                         |  |

|                    |                           |              | 010                             | 384 DAC clocks per LRCHN, 2 DAC<br>clocks per SCLK                                                                                                                         |  |

|                    |                           |              | 011                             | 384 DAC clocks per LRCHN, 4 DAC<br>clocks per SCLK                                                                                                                         |  |

|                    |                           |              | 100                             | 384DAC clocks per LRCHN, 6 DAC clock<br>per SCLK                                                                                                                           |  |

|                    |                           |              | 101                             | 384 DAC clocks per LRCHN, 8 DAC<br>clocks per SCLK                                                                                                                         |  |

|                    |                           |              | 110                             | 512 DAC clocks per LRCHN, 4 DAC<br>clocks per SCLK                                                                                                                         |  |

|                    |                           |              | 111                             | 512 DAC clocks per LRCHN, 8 DAC<br>clocks per SCLK                                                                                                                         |  |

|                    | LRCHN C                   | hannel Inter | pretation                       |                                                                                                                                                                            |  |

| R0300              | 11                        | 7            | 0                               | LRCHN active high left channel                                                                                                                                             |  |

|                    |                           |              | 1                               | LRCHN active high right channel                                                                                                                                            |  |

|                    | RAS Len                   | gth Select   |                                 |                                                                                                                                                                            |  |

| R0230              | 6                         | 6            | See<br>Tables<br>5-2 and<br>5-3 | This bit together with bits 5-4 sets RAS<br>Precharge value - see Table 5-2 for<br>details. Also, this bit together with bits 3-<br>2 set RAS Pulse width - see Table 5-3. |  |

|                    | RAS Precharge             |              |                                 |                                                                                                                                                                            |  |

| R0230              | 5-4                       | [5:4]        | See<br>Table<br>5-2             | These bits together with bit 6 set the RAS Precharge Length                                                                                                                |  |

|                    | RAS Pulse Width           |              |                                 |                                                                                                                                                                            |  |

| R0230              | 3 - 2                     | [3:2]        | See<br>Table<br>5-3             | These bits together with bit 6 set the RAS Pulse Width                                                                                                                     |  |

|                    | CAS/OE                    | WE Stretch   |                                 |                                                                                                                                                                            |  |

| R0230              | 1-0                       | [1:0]        | 00                              | 6.5 ns (nominal)                                                                                                                                                           |  |

|                    |                           |              | 01                              | 5.0 ns (nominal)                                                                                                                                                           |  |

|                    |                           |              | 10                              | 3.5 ns (nominal)                                                                                                                                                           |  |

|                    |                           |              | 11                              | 0 ns - no stretch                                                                                                                                                          |  |

### Table 5-1. Definition of PD[15:0] at the Rising Edge of the Reset Signal (Continued)

5-2 RESET AND INITIALIZATION

### Table 5-2. Setting RAS Precharge Length

| R0230 bits 5-4<br>(default is the value<br>strapped on PD[5:4]) | R0230 bit 6 value:<br>RAS Length Select | Resulting RAS Precharge length used |

|-----------------------------------------------------------------|-----------------------------------------|-------------------------------------|

| 00                                                              | 0                                       | 4 MCLKs                             |

| 00                                                              | 1                                       | 4.5 MCLKs                           |

| 01                                                              | 0                                       | 3 MCLKs                             |

| 01                                                              | 1                                       | 3.5 MCLKs                           |

| 10                                                              | 0                                       | 2 MCLKs                             |

| 10                                                              | 1                                       | 2.5 MCLKs                           |

| 11                                                              | 0                                       | reserved                            |

| 11                                                              | 1                                       | reserved                            |

### Table 5-3. Setting RAS Pulse Width

| R0230 bits 3-2 value<br>(default is the value<br>strapped on PD[3:2]) | R0230 bit 6 value:<br>RAS Length Select | Resulting RAS Pulse Width used |

|-----------------------------------------------------------------------|-----------------------------------------|--------------------------------|

| 00                                                                    | 0                                       | 7 MCLKs                        |

| 00                                                                    | 1                                       | 6.5 MCLKs                      |

| 01                                                                    | 0                                       | 6 MCLKs                        |

| 01                                                                    | 1                                       | 5.5 MCLKs                      |

| 10                                                                    | 0                                       | 5 MCLKs                        |

| 10                                                                    | 1                                       | 4.5 MCLKs                      |

| 11                                                                    | 0                                       | 4 MCLKs                        |

| 11                                                                    | 1                                       | 3.5 MCLKs                      |

The MODE[2:0] strapping is shown in Table 5-4.

| Register<br>Number | Bit(s)  | MODE<br>Pin         | Value | Function                                                                                                                           |  |  |

|--------------------|---------|---------------------|-------|------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                    | DVP Mod | DVP Mode Definition |       |                                                                                                                                    |  |  |

| R0500              | 16      | 0                   | 0     | DVP active (LCLK = DVPCLK)                                                                                                         |  |  |

|                    |         |                     | 1     | DVP inactive (no digitizer)                                                                                                        |  |  |

|                    | 17      | 1                   | 0     | If bit 16 = 0, 16-bit data mode<br>If bit 16 = 1 and bit 18 = 1, LCLK = 1/2<br>MCLK                                                |  |  |

|                    |         |                     | 1     | If bit 16 = 0, 8-bit data mode<br>If bit 16 = 1 and bit 18 = 1, LCLK = 2/3<br>MCLK                                                 |  |  |

|                    | 18      | 2                   | 0     | If bit 16 = 0 and bit 17 = 1, data input<br>sequence is Cb-Y0-Cr-Y1<br>If bit 16 = 1, LCLK = DVPCLK                                |  |  |

|                    |         |                     | 1     | If bit 16 = 0 and bit 17 = 1, data input<br>sequence is Y0-Cb-Y1-Cr<br>If bit 16 = 1, LCLK determined by<br>MODE1 (bit 17) setting |  |  |

#### Table 5-4. Definition of MODE[2:0] at the Rising Edge of the Reset Signal

#### 5.2 RESET BEHAVIOR

#### 5.2.1 Hardware Reset

Hardware reset occurs when the RESET signal is asserted. Upon a hardware reset, these actions occur:

- All Scenic/MX2 internal operations are halted and the chip modules having powerdown or idle states enter those states

- All internal control and configuration registers assume their default values as specified in Section 9

- The memory control pins RAS, CAS, WE, and OE go high and the strappings on the PD and MODE pins are read

- The SP module stops driving the audio DAC

#### 5.2.2 Soft Reset

Soft reset occurs when software sets bit 16 of the R0034 register to 1. A soft reset has the same consequences as a hard reset.

5-4 RESET AND INITIALIZATION

## Section 6: Hardware Interfaces

Scenic/MX2 has four main interfaces:

- S3 Scenic Highway

- Local memory

- Audio DAC

- Video digitizer

This section describes the interfaces, their functional characteristics, and related information.

#### 6.1 Scenic Highway INTERFACE

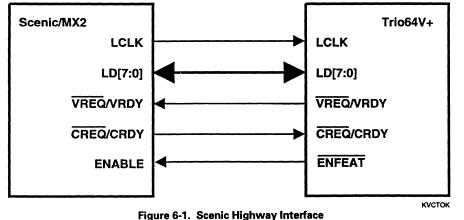

The hardware interface for the Scenic Highway is shown in Figure 6-1 for the S3 Trio64V+integrated graphics/video accelerator. The following protocols and functional timings will also reference this chip. The interface, protocols and timings will be the same for any S3 chip containing the Scenic Highway function as part of its Local Peripheral Bus (LPB) capability. This interface is

fully bi-directional. Scenic/MX2 registers and private memory can be accessed, compressed audio and video data received and decompressed video data sent to the S3 graphics/video accelerator.

If a digitizer is present, the 27 MHz clock from that device (DVPCLK) will be used to clock the LPB. If no digitizer is present, the MODE2 pin can be strapped high. On reset, this value is latched in R0500\_18 and causes the Scenic Highway to be clocked at 1/2 or 2/3 the MCLK rate, depending on the strapping of the MODE1 pin. If the MODE2 pin is strapped low, Scenic/MX2 expects an external LCLK source attached to the DVPCLK pin.

#### 6.1.1 Scenic/MX2 Register/Memory Access

To read/write a Scenic/MX2 register or private memory location (other than to transfer com-

PRELIMINARY

#### HARDWARE INTERFACES 6-1

pressed data), the LPB Direct Read/Write Address register in the Trio64V+ (offset FF14) is written. The new register/memory data is then read from or written to the LPB Direct Read/Write Data register (offset FF18).

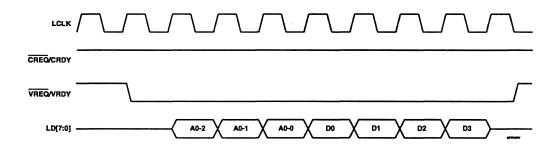

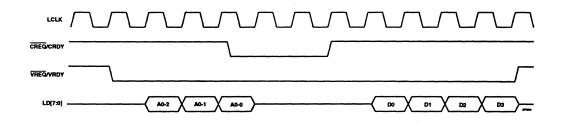

For a write access, the data register write triggers the sequence shown in Figure 6-2 if the Scenic/MX2 is ready to receive the data (CREQ/CRDY remains high). One cycle after the Trio64V+ asserts its VREQ/VRDY signal, it sends the address in three byte writes. The first byte is composed of bits 23-16 of the address register. The three upper bits are 000b to define this as a write. Bit 4 is 1 for a register access and 0 for a memory access. Bits 3-0 are bits 19-16 of the address. The second byte is bits 15-8 of the address register and the third byte is bits 7-0. The different interpretations of bits 19-0 for memory and register accesses are explained in Section 9-1. The data immediately follows the address information in four byte writes. Data is written in the opposite byte order to that for the address, i.e., least significant byte (bits 7-0) first and most significant byte (bits 31-24) last. The Trio64V+ then deasserts VREQ/VRDY. The Host repeats the above sequence for another write if required.

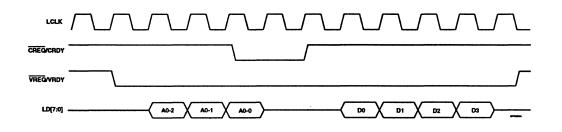

If the Scenic/MX2 is not ready to receive data, it drives its CREQ/CRDY signal low during the A0-0 byte (LSB) of the address phase. The Trio64V+ then delays sending the data until the Scenic/MX2 raises CREQ/CRDY. This is depicted in Figure 6-3.

Figure 6-2. Register/Memory Write (Scenic/MX2 Ready)

6-2 HARDWARE INTERFACES

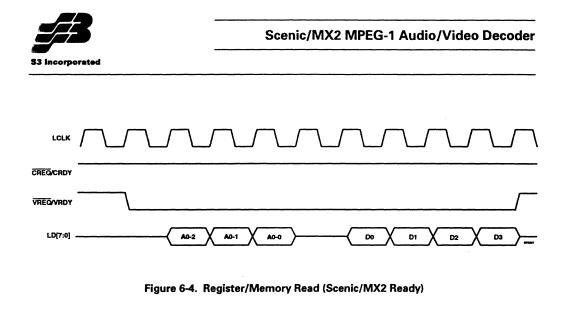

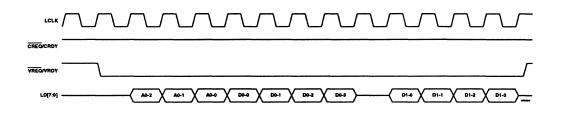

Figure 6-4 shows a Scenic/MX2 register/memory read when the Scenic/MX2 is ready to provide data. This is indicated by the Scenic/MX2 holding the CREO/CRDY high throughout the cycle. The three upper bits of the first address byte are 001 to define a read.

If the Scenic/MX2 is not ready to provide data, it drives its CREQ/CRDY signal low during the address phase. The Trio64V+ then waits until the Scenic/MX2 raises CREQ/CRDY and provides register data. This is depicted in Figure 6-5.

If CREQ/CRDY and VREQ/VRDY are both driven low on the same cycle (request contention), CREQ/CRDY (the Scenic/MX2) wins.

#### 6.1.2 Scenic/MX2 Burst Writes

The Trio64V+ has an output FIFO for handling the transfer of compressed video data from the Host to the Scenic/MX2. The Host must first check the number of empty slots (FF04\_3-0), then send no more than this many doublewords (32 bits) of compressed data to the FIFO. A sixteen doubleword address range (FF40H - FF5CH) is provided for this FIFO. Writes to any of these addresses are directed to the FIFO.

FF00\_17-16 are programmed to specify the number of doublewords of data to burst to the Scenic/MX2. R0020\_7-6 in the Scenic/MX2 must also be programmed with a value equal to or larger than the value programmed in the Trio64V+. If

Figure 6-6. Burst Write (Scenic/MX2 Ready)

FF00\_17-16 are programmed to 11b (8 doublewords), then R0020\_0 should be programmed to 0 to override R0020\_7-6 and allow the 8 doubleword burst.

A write to the output FIFO then initiates a compressed data burst write to the Scenic/MX2. This is depicted in Figure 6-6 for a burst count of 2 (FF00\_17-16 = 01b) for the case where the Scenic/MX2 is ready to receive the data. The address and first doubleword are transferred exactly as for a register write. Following doublewords in the burst are each separated by one dead cycle. The address has no meaning except for the upper three bits, which are forced to 110b by hardware to specify a compressed data transfer.

A compressed data transfer when the Scenic/MX2 is not ready to receive data is almost the same as a register write for the same circumstances (see Figure 6-3). The only difference is that after the Scenic/MX2 returns its CRDY signal, additional doubleword packets may be burst to the Scenic/MX2 as shown in Figure 6-6.

#### 6.1.3 Scenic/MX2 Video Output

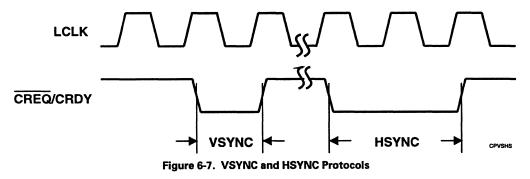

The Trio64V+ signals its readiness to accept data by driving VREQ/VRDY high. This is done automatically when the Trio64V+ does not need to drive this signal low such as to initiate a register access or to indicate an LPB video FIFO full state. The Scenic/MX2 responds by sending a VSYNC (CREQ/CRDY low for one cycle) possibly followed by an HSYNC (CREQ/CRDY low for two cycles). This is shown in Figure 6-7. As indicated in the figure, the time between VSYNC and HSYNC is variable. HSYNC can occur before or after a line, as selected by R0020\_10.

After the VSYNC/HSYNC sequence, the Scenic/MX2 can pull CREO/CRDY low at any time and begin sending data three clocks later. This is

6-4 HARDWARE INTERFACES

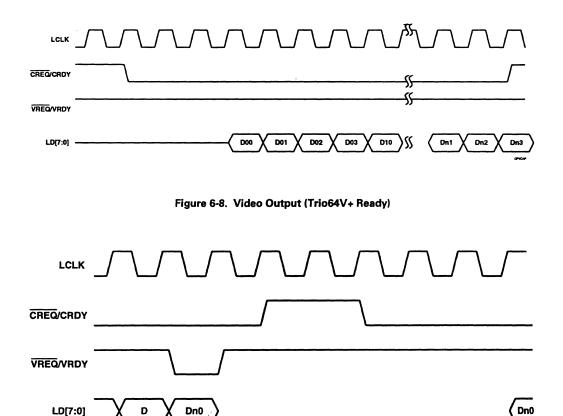

shown in Figure 6-8. The Trio64V+ assumes data has begun any time CREQ/CRDY is held low for more than two cycles. When the Scenic/MX2 is sending the last byte, it drives CREQ/CRDY high. The Scenic/MX2 always sends data in 4-byte packets.

Figure 6-8 shows what happens when the Trio64V+ is ready to receive all the data. If the Trio64V+ cannot accept more data, such as when its LPB video FIFO is full, it drives its VREQ/VRDY signal low during the first byte phase of a 4-byte packet. All bytes starting with this one are rejected by the Trio64V+ and must be resent by the Scenic/MX2 after the Trio64V drives its VREQ/VRDY signal high again. This is depicted in Figure 6-9, where the Dn0 byte, which is the first byte of the nth 4-byte packet, is rejected. When the Trio64V+ can accept more data, it drives VREQ/VRDY high. The Scenic/MX2 drives CREQ/CRDY high (two cycles later) and then drives it low when it is ready to resend the data. The resend of Dn0 and subsequent bytes starts two cycles later.

Figure 6-9. Video Output (Trio64V+ Not Ready)

PRELIMINARY

HARDWARE INTERFACES 6-5

#### 6.2 LOCAL MEMORY INTERFACE

Scenic/MX2 can use either 512 KBytes or 1 MByte of fast page mode 256Kx16 DRAMs. The memory interface operates at the system clock frequency of 40 MHz, allowing use of inexpensive DRAMs. Scenic/MX2 contains all necessary interface and refresh circuitry for these DRAMs.

#### 6.2.1 Memory Configurations

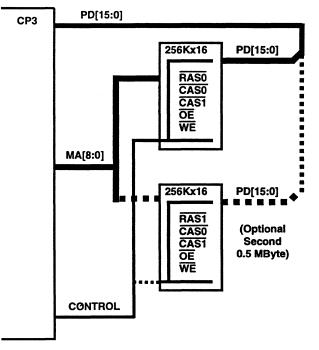

Figure 6-10 shows a 0.5 MByte configuration using a 256Kx16 DRAM. RAS0 selects the first 512K; when an additional 0.5 MByte is used, RAS1 selects the second 512K.

In general, 512 KBytes is sufficient for decoding most MPEG-1 data streams. 1 MByte is required for decoding streams such as Green Book encoded PAL video.

#### 6.2.2 Memory Functional Timing

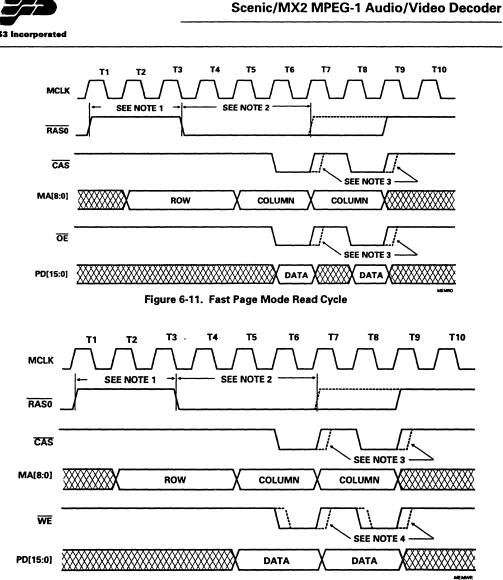

Figure 6-11 shows the functional timing for a fast page mode read cycle, and Figure 6-12 shows fast page mode write cycle timing. These diagrams also show how certain parameters for various control signals can be adjusted to meet the access time requirements of a variety of DRAMs.

#### Figure 6-10. 256Kx16 DRAM Configuration

6-6 HARDWARE INTERFACES

Figure 6-12. Fast Page Mode Write Cycle

#### Notes

- 1. The minimum  $\overline{\text{RAS}}$  Precharge time can be adjusted using register R0230 bits 5-4.

- 2. The minimum  $\overline{RAS}$  Pulse Width can be set using register R0230 bits 3-2.

- 3. The  $\overline{\text{CAS}}$  and  $\overline{\text{OE}}$  low times can be adjusted using register R0230 bits 1-0

- 4.The WE pulse can be delayed using R0230 bit 7.

#### 6.3 SERIAL AUDIO INTERFACE

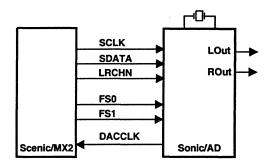

Scenic/MX2's programmable serial audio interface is designed to interface to a variety of audio DACs with few or no additional parts. When the S3 Sonic/AD™ audio DAC is used, as shown in Figure 6-13, no glue logic is required. A design using the Sonic/AD requires only a clock crystal plus a small number of analog discretes to implement the low-pass filters required on the analog outputs.

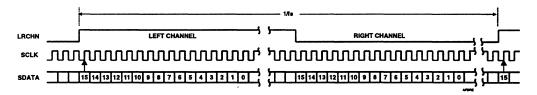

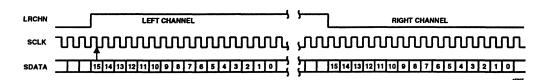

Functional timing for the audio DAC interface is shown in Figures 6-14 and 6-15.

Figure 6-13. Audio DAC Interface

Figure 6-14. First Audio Bits Latched on Rising Edge

Figure 6-15. First Audio Bits Latched on Falling Edge

#### 6.4 DIGITIZED VIDEO PORT (DVP) INTERFACE

The DVP allows direct, glueless connection of a number of 8- and 16-bit video digitizers. The video data is captured and transferred directly to the S3 graphics/video accelerator via the Scenic Highway. The Scenic/MX2 cannot decode audio or video data or drive its Serial Port while the DVP is in use.

#### 6.4.1 Digitizers Supported

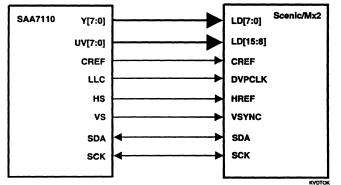

A glueless interface is provided for the ITT 3220 and Philips SAA7111 in both 8- and 16-bit modes. The Philips SAA7110 is also supported gluelessly in 16-bit mode. This interface is depicted in Figure 6-16. The interface is reasonably generic and should allow interfacing of other devices. For 8-bit mode, all data is transmitted on LD[7:0] and LD[15:8] are unused.

#### 6.4.2 DVP Input

The basic DVP mode is set by power-on strapping of the MODE[2:0] pins at power-on reset. This information is latched in R0500\_18-16. See Table 5-4 for a complete description of all the strapping options.

DVP operation is enabled by setting R0500\_0 to 1. R0500\_2-4 allow specification of the polarity of the CREF, HREF and VSYNC inputs respectively.

R0500\_1 allows use of an internal or external CREF for 16-bit modes.

The functional timing for the digitizer interface will vary according to the type of digitizer used. Scenic/MX2 conforms to the timing requirements of all of its supported digitizers and correct functional timing diagrams can be found in the appropriate digitizer data book.

#### 6.4.3 DVP Output

R0050\_5 is programmed to select the sequence for transmitting the video data over the Scenic Highway. R0050\_6 defines the timing of generation of a New Frame (VSYNC) sequence on the Scenic Highway. HSYNC sequence generation timing is specified by R0500\_7. (These sequences are described in Figure 6-7.)

The functional timing of the transfer of data from Scenic/MX2 to the S3 graphics/video accelerator over the Scenic Highway is the same as for the transfer of decoded MPEG data. This is described in Section 6.1.3. One difference is that if the S3 accelerator is not ready to receive DVP data, video data will be lost as the Scenic/MX2 does not store the digitized video input. This condition does not occur for supported video digitizers.

#### 6.5 INTERRUPT GENERATION

The Scenic/MX2 has both PCI and ISA (VL-Bus systems) interrupt handling capabilities.

#### Figure 6-16. Philips SAA7110 Digitizer Interface

#### 6.5.1 PCI Interrupts

The PCI specification requires that only one interrupt be sourced from a single card. Scenic/MX2 provides an interrupt input (GINT) and output (INTA) for PCI card designs. If R0000\_11 is set to 1, generation of a Scenic/MX2 internal interrupt causes assertion of the INTA signal. If R0000\_12 is set to 1, assertion by another device of the GINT input causes the Scenic/MX2 to assert INTA. This allows the Scenic/MX2 to be the single interrupt source for two devices.

\$

#### 6.5.2 ISA Interrupts

Five ISA interrupt outputs (IRQ[A:E]) are provided for VL-Bus system designs. R0000\_15-13 are programmed to select which of these interrupts (if any) is to be asserted upon generation of an internal Scenic/MX2 interrupt. Only one of the five can be asserted at a time.

6-10 HARDWARE INTERFACES

# **Section 7: Functional Description**

#### 7.1 OVERVIEW

This section provides a high level description of Scenic/MX2 operation and system data flow.

MPEG is described by the ISO/IEC document IS11172. An MPEG-encoded system stream contains a video stream and one or more audio streams, and optionally may also have private data streams. In a Scenic/MX2 application, the Host acts as a front end preprocessor, separating the video and audio streams, which it then routes to Scenic/MX2. The Host processor provides high level data flow control and sets control parameters for Scenic/MX2.

The primary functions of the Scenic/MX2 are:

- Decoding MPEG1 video and audio streams sent to it via the S3 graphics/video accelerator and the Scenic Highway by a Host processor

- Returning a stream of decompressed video data via the Scenic Highway to the S3 graphics/video processor

- Providing decompressed audio data output to an audio DAC

- Capturing digitized video and transferring this via the Scenic Highway to the S3 graphics/video accelerator

These processes are shown in the context of system data flow in Figure 7-1.

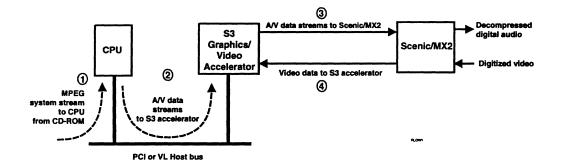

The overall hierarchy of system-level control is shown in Figure 7-2. The application accesses Scenic/MX2 through the application interface level, using Windows- or DOS-compatible calls. These are interpreted by Scenic/MX2 driver software, which commands and controls Scenic/MX2.

Figure 7-2. Control Hierarchy

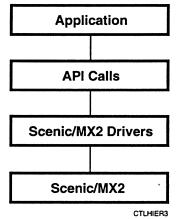

#### 7.2 Scenic/MX2 FUNCTIONAL PARTITIONING

Figure 7-3 shows the main functional modules within Scenic/MX2 together with the related external components. The functions of these modules are described in the following sections.

#### 7.3 VIDEO DECOMPRESSION ENGINE (VDE)

The Video Decompression Engine:

- Accepts input streams of MPEG compressed video data

- Outputs decompressed video data

#### 7.4 AUDIO DECOMPRESSION ENGINE (ADE)

The Audio Decoding Engine:

- Accepts input streams of MPEG compressed audio data

- Outputs decompressed audio data

Figure 7-3. Internal Block Diagram

7-2 FUNCTIONAL DESCRIPTION

#### 7.5 MEMORY INTERFACE UNIT (MIU)

The Memory Interface Unit:

- Controls buffers in private memory (local DRAM)

- Manages DMA access to/from private memory

- Provides DRAM refresh control

- Performs arbitration of memory access by all Scenic/MX2 functional modules

Scenic/MX2 uses external dedicated DRAM for data buffers. It needs only 0.5 MByte DRAM for data storage when decoding most MPEG-1 bit streams, but has provision for using 1 MByte (2 DRAMs). The memory size supported is 256Kx16.

#### 7.6 Scenic Highway UNIT

Handles all transactions with the S3 graphics/video accelerator across the Scenic Highway

For a complete description of Scenic Highway functions, see Section 6.1.

#### 7.7 SERIAL AUDIO PORT (SP)

- Provides digital stereo audio interface to an external audio DAC

- Accepts DACCLK timing from the audio

DAC

- Compatible with the I<sup>2</sup>S standard.

#### 7.8 DIGITIZED VIDEO PORT (DVP)

• Provides an 8- or 16-bit interface with a video digitizer

For a complete description of DVP functions, see Section 6.4.

#### 7.9 TIMER

The on-chip timer enable the software driver to control the synchronization of audio and video during playback.