# Vision868

# S3 Incorporated

# Vision868

# Multimedia

# Accelerator

April 1995

S3 Incorporated 2770 San Tomas Expressway Santa Clara, CA 95051-0968

#### NOTATIONAL CONVENTIONS

The following notational conventions are used in this data book:

Signal names are shown in all uppercase letters. For example, XD.

A bar over a signal name indicates an active low signal. For example, OE.

n-m indicates a bit field from bit n to bit m. For example, 7-0 specifies bits 7 through 0, inclusive.

n:m indicates a signal (pin) range from n to m. For example D[7:0] specifies data lines 7 through 0, inclusive

Use of a trailing letter H indicates a hexadecimal number. For example, 7AH is a hexadecimal number.

Use of a trailing letter b indicates a binary number. For example, 010b is a binary number.

When numerical modifiers such as K or M are used, they refer to binary rather than decimal form. Thus, for example, 1 KByte would be equivalent to 1024, not 1,000 bytes.

#### NOTICES

© Copyright 1995 S3 Incorporated. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, or otherwise, without the prior written consent of S3 Incorporated, 2770 San Tomas Expwy., Santa Clara CA 95051-0968. The S3 Corporate Logo, S3 on Board, S3 on Board design, Vision864, Vision868, Vision864, Vision868, Vision868, Trio, Trio32, Trio64, MIC, Galileo, SDAC, Native-MPEG, No Compromise Integration, No Compromise Acceleration and Innovations in Acceleration are trademarks of S3 Incorporated and S3 and True Acceleration are registered trademarks of S3 Incorporated. Other trademarks referenced in this document are owned by their respective companies. The material in this document is for information only and is subject to change without notice. S3 Incorporated reserves the right to make changes in the product design without reservation and without notice to its users.

Additional information may be obtained from:

S3 Incorporated, Literature Department, 2770 San Tomas Expressway, Santa Clara, CA 95051-0968.

Telephone: 408-980-5400, Fax: 408-980-5444

S3 Vision868 Multimedia Accelerator

# **Table of Contents**

| List of    | f Figures v                                                |

|------------|------------------------------------------------------------|

| List of    | f Tables vi                                                |

| Sectio     | on 1: Introduction 1-1                                     |

| 1.1        | OVERVIEW OF THIS DATA                                      |

|            | BOOKLET         1-1           PRODUCT OVERVIEW         1-1 |

| 1.2        |                                                            |

| 1.3        | ENHANCED DRAM SUPPORT 1-1                                  |

| 1.4<br>1.5 | PACKED PIXEL ACCELERATION 1-1<br>ENHANCED MEMORY-MAPPED    |

| 1.5        | I/O IMPLEMENTATION 1-1                                     |

| 1.6        | NEW DRAWING COMMANDS 1-2                                   |

| 1.0        | IMPROVED COPROCESSOR                                       |

| 1.7        |                                                            |

| 1.8        | SUPPORT 1-2<br>PCI SUPPORT ENHANCEMENTS . 1-2              |

| 1.9        |                                                            |

| 1.10       |                                                            |

|            |                                                            |

| Sectio     | on 2: Register Changes 2-1                                 |

| 2.1        | Vision868 REGISTER CHANGES 2-1                             |

| 2.2        | NEW Vision868 SR REGISTERS 2-5                             |

| 2.3        | NEW Vision868 CR REGISTERS 2-6                             |

| 2.4        | NEW Vision868 ENHANCED                                     |

|            | COMMANDS REGISTERS 2-7                                     |

| 2.5        | NEW Vision868 PCI CONFIGURATION                            |

|            | SPACE REGISTERS                                            |

| 2.6        | NEW Vision868 VIDEO ENGINE                                 |

|            | REGISTERS                                                  |

| 2.7        | Vision864 REGISTERS REMOVED                                |

|            | FROM THE Vision868 2-20                                    |

|            |                                                            |

|            | on 3: Functional Changes 3-1                               |

|            | CHIP IDENTIFICATION 3-1                                    |

| 3.2        | SHARED FRAME BUFFER MEMORY                                 |

|            | BANDWIDTH ALLOCATION 3-1                                   |

|            | PCI ENHANCEMENTS 3-1                                       |

|            | .1 Interrupt Support 3-1                                   |

| 3.3.       | .2 RAMDAC Snooping 3-2                                     |

| 3.3     | 3.3 Disconnect Related to FIFO    |    |

|---------|-----------------------------------|----|

|         | Status 3-                         | -2 |

| 3.3     | 8.4 Plug and Play Support 3-      | -2 |

| 3.4     | PACKED 24-BITS/PIXEL SUPPORT . 3- | -2 |

| 3.5     | RAMDAC ACCESS CYCLES 3-           | -2 |

| 3.6     | 50 MHz VL-BUS SUPPORT 3-          | -2 |

| 3.7     | WRITE PER BIT SUPPORT 3           | -6 |

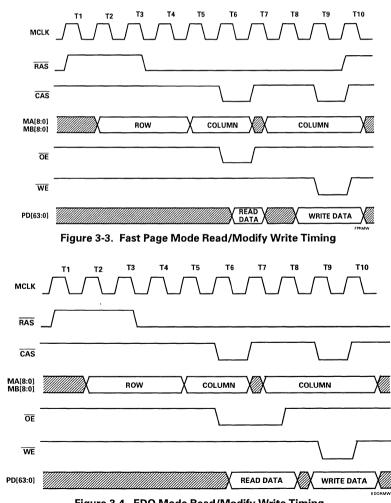

| 3.8     | READ/MODIFY/WRITE TIMING 3-       | -6 |

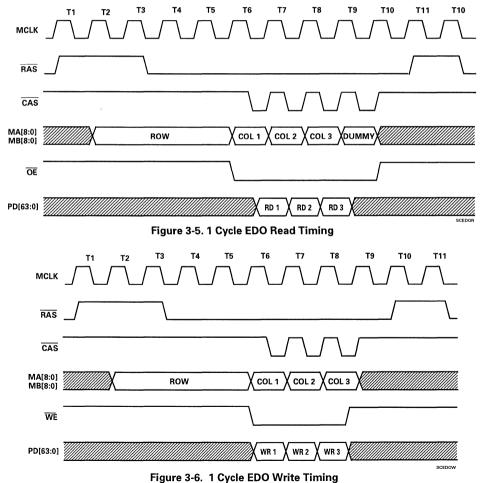

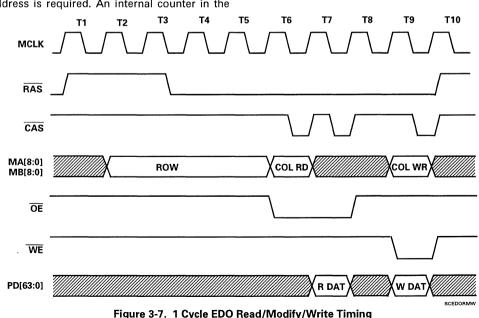

| 3.9     | 1 CYCLE EDO DRAM SUPPORT 3-       | -7 |

| 3.10    | BURST MODE DRAM SUPPORT 3-        | -7 |

|         |                                   |    |

| Section | on 4: Electrical Data 4-          | 1  |

| 4.1     | MAXIMUM RATINGS 4                 | -1 |

| 4.2     | DC SPECIFICATIONS 4               | -1 |

| 4.3     | AC SPECIFICATIONS 4               | -2 |

| 4.3     | 8.1 Clock Timing 4                | -3 |

| 4.3     | 3.2 Input/Output Timing 4         | -4 |

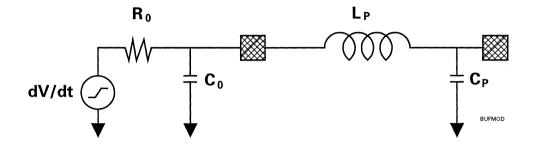

| 4.4     | OUTPUT BUFFER MODEL 4             | -7 |

#### Section 5: Enhanced Mode

| Programming 5-1                       |

|---------------------------------------|

| 5.1 MEMORY-MAPPED I/O 5-1             |

|                                       |

| 5.1.1 Backward-Compatible MMIO . 5-1  |

| 5.1.2 New MMIO 5-2                    |

| 5.1.2.1 Big/Little Endian Support 5-4 |

| 5.1.2.2 Packed MMIO Register          |

| Mapping 5-4                           |

| 5.2 DIRECT BITMAP ACCESSING—          |

| LINEAR ADDRESSING 5-4                 |

| 5.2.1 Backward-Compatible Linear      |

| Addressing 5-4                        |

| 5.2.2 New Linear Addressing 5-5       |

| 5.3 BITMAP ACCESS THROUGH THE         |

| GRAPHICS ENGINE 5-5                   |

| 5.4 PROGRAMMING 5-8                   |

| 5.4.1 Notational Conventions 5-9      |

| 5.4.2 Initial Setup 5-9               |

| 5.4.3 Programming Examples 5-10       |

| 5.4.3.1 Solid Line 5-11               |

| 5.4.3.2 Textured Line 5-12            |

|                                       |

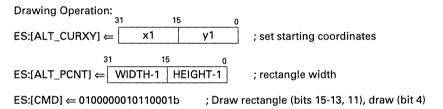

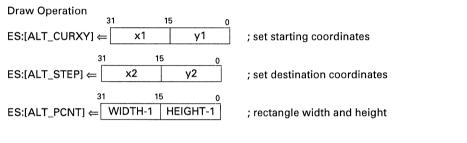

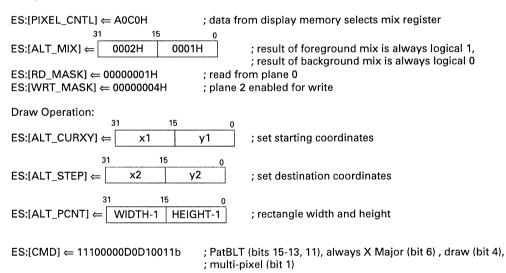

| 5.4.3.4       Image Transfer—Through<br>the Plane       5-15         5.4.3.5       Image Transfer—Across the<br>Plane       5-17         5.4.3.6       BitBLT—Through the Plane       5-19         5.4.3.7       BitBLT—Through the Plane       5-20         5.4.3.8       PatBLT—Pattern Fill<br>Through the Plane       5-22         5.4.3.9       PatBLT—Pattern Fill<br>Across the Plane       5-23         5.4.3.10       Short Stroke Vectors       5-24         5.4.3.11       Polyline/2-Point Line       5-25         5.4.3.12       Polygon Fill Solid       5-26         5.4.3.13       Polygon Fill Solid       5-26         5.4.3.14       4-Point Trapezoid Fill Solid       5-29         5.4.3.15       4-point Trapezoid Fill Solid       5-29         5.4.3.16       Bresenham Parameter<br>Trapezoid Fill Solid       5-31         5.4.3.17       Bresenham Parameter<br>Trapezoid Fill Solid       5-31         5.4.3.18       ROPBLTs       5-33         5.4.3.19       Programmable Hardware<br>Cursor       5-45         5.5       RECOMMENDED READING       5-46         Section 6: Video Engine       6-1         6.1       VIDEO ENGINE OVERVIEW       6-1         6.2       SCALING       6-2 <th>5</th> <th>5.4.3.3</th> <th>Rectangle Fill Solid 5-14</th> | 5     | 5.4.3.3             | Rectangle Fill Solid 5-14       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------|---------------------------------|

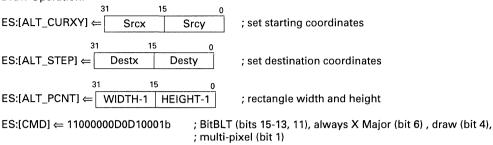

| 5.4.3.5       Image Transfer—Across the<br>Plane         Plane       5-17         5.4.3.6       BitBLT—Through the Plane       5-19         5.4.3.7       BitBLT—Across the Plane       5-20         5.4.3.8       PatBLT—Pattern Fill       5-22         5.4.3.9       PatBLT—Pattern Fill       5-22         5.4.3.9       PatBLT—Pattern Fill       5-23         5.4.3.10       Short Stroke Vectors       5-24         5.4.3.10       Short Stroke Vectors       5-26         5.4.3.11       Polygon Fill Solid       5-26         5.4.3.12       Polygon Fill Solid       5-26         5.4.3.13       Polygon Fill Solid       5-26         5.4.3.14       Polygon Fill Solid       5-29         5.4.3.15       4-point Trapezoid Fill Solid       5-29         5.4.3.16       Bresenham Parameter       5-30         5.4.3.16       Bresenham Parameter       5-31         5.4.3.17       Bresenham Parameter       5-33         5.4.3.18       ROPBLTs       5-33         5.4.3.19       Programmable Hardware       Cursor         Cursor       5-46       Section 6: Video Engine       6-1         6.1       VIDEO ENGINE OVERVIEW       6-1       6.2                                                                                                                       | 5     | 5.4.3.4             | Image Transfer—Through          |

| Plane       5-17         5.4.3.6       BitBLT—Through the Plane       5-19         5.4.3.7       BitBLT—Across the Plane       5-20         5.4.3.8       PatBLT—Pattern Fill       5-20         5.4.3.9       PatBLT—Pattern Fill       5-22         5.4.3.9       PatBLT—Pattern Fill       5-23         5.4.3.10       Short Stroke Vectors       5-23         5.4.3.10       Short Stroke Vectors       5-24         5.4.3.10       Short Stroke Vectors       5-25         5.4.3.10       Short Stroke Vectors       5-25         5.4.3.11       Polygon Fill Solid       5-26         5.4.3.12       Polygon Fill Solid       5-26         5.4.3.13       Polygon Fill Pattern       5-28         5.4.3.14       4-Point Trapezoid Fill Solid       5-29         5.4.3.15       4-point Trapezoid Fill Solid       5-29         5.4.3.16       Bresenham Parameter       5-30         5.4.3.17       Bresenham Parameter       5-33         5.4.3.18       ROPBLTs       5-33         5.4.3.19       Programmable Hardware       5-45         5.5       RECOMMENDED READING       5-46         Section 6: Video Engine       6-1                                                                                                                                                 |       |                     |                                 |

| Plane       5-17         5.4.3.6       BitBLT—Through the Plane       5-19         5.4.3.7       BitBLT—Across the Plane       5-20         5.4.3.8       PatBLT—Pattern Fill       5-20         5.4.3.9       PatBLT—Pattern Fill       5-22         5.4.3.9       PatBLT—Pattern Fill       5-23         5.4.3.10       Short Stroke Vectors       5-23         5.4.3.10       Short Stroke Vectors       5-24         5.4.3.10       Short Stroke Vectors       5-25         5.4.3.10       Short Stroke Vectors       5-25         5.4.3.11       Polygon Fill Solid       5-26         5.4.3.12       Polygon Fill Solid       5-26         5.4.3.13       Polygon Fill Pattern       5-28         5.4.3.14       4-Point Trapezoid Fill Solid       5-29         5.4.3.15       4-point Trapezoid Fill Solid       5-29         5.4.3.16       Bresenham Parameter       5-30         5.4.3.17       Bresenham Parameter       5-33         5.4.3.18       ROPBLTs       5-33         5.4.3.19       Programmable Hardware       5-45         5.5       RECOMMENDED READING       5-46         Section 6: Video Engine       6-1                                                                                                                                                 | Ę     | 5.4.3.5             | Image Transfer—Across the       |

| 5.4.3.7       BitBLT—Across the Plane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |                     |                                 |

| 5.4.3.8       PatBLT—Pattern Fill<br>Through the Plane       5-22         5.4.3.9       PatBLT—Pattern Fill<br>Across the Plane       5-23         5.4.3.10       Short Stroke Vectors       5-24         5.4.3.10       Short Stroke Vectors       5-24         5.4.3.10       Short Stroke Vectors       5-24         5.4.3.11       Polygon Fill Solid       5-25         5.4.3.12       Polygon Fill Solid       5-26         5.4.3.13       Polygon Fill Pattern       5-28         5.4.3.14       4-Point Trapezoid Fill Solid       5-29         5.4.3.15       4-point Trapezoid Fill Solid       5-30         5.4.3.16       Bresenham Parameter<br>Trapezoid Fill Solid       5-31         5.4.3.17       Bresenham Parameter<br>Trapezoid Fill Pattern       5-32         5.4.3.18       ROPBLTS       5-33         5.4.3.19       Programmable Hardware<br>Cursor       5-45         5.5       RECOMMENDED READING       5-46         Section 6: Video Engine       6-1         6.1       VIDEO ENGINE OVERVIEW       6-1         6.2       SCALING       6-2         6.3       COLOR SPACE CONVERSION       6-2                                                                                                                                                           | 5     | 5.4.3.6             | BitBLT—Through the Plane . 5-19 |

| Through the Plane       5-22         5.4.3.9       PatBLT—Pattern Fill         Across the Plane       5-23         5.4.3.10       Short Stroke Vectors       5-24         5.4.3.11       Polyline/2-Point Line       5-25         5.4.3.12       Polygon Fill Solid       5-26         5.4.3.13       Polygon Fill Pattern       5-28         5.4.3.14       4-Point Trapezoid Fill Solid       5-29         5.4.3.15       4-point Trapezoid Fill Solid       5-29         5.4.3.16       Bresenham Parameter       5-30         5.4.3.17       Bresenham Parameter       5-31         5.4.3.17       Bresenham Parameter       5-32         5.4.3.18       ROPBLTs       5-33         5.4.3.19       Programmable Hardware       5-33         5.4.3.19       Programmable Hardware       5-45         5.5       RECOMMENDED READING       5-46         Section 6: Video Engine       6-1         6.1       VIDEO ENGINE OVERVIEW       6-1         6.2       SCALING       6-2         6.3       COLOR SPACE CONVERSION       6-2                                                                                                                                                                                                                                                    | 5     | 5.4.3.7             | BitBLT—Across the Plane 5-20    |

| 5.4.3.9       PatBLT—Pattern Fill         Across the Plane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | - E   | 5.4.3.8             | PatBLT—Pattern Fill             |

| Across the Plane       5-23         5.4.3.10 Short Stroke Vectors       5-24         5.4.3.11 Polyline/2-Point Line       5-25         5.4.3.12 Polygon Fill Solid       5-26         5.4.3.13 Polygon Fill Pattern       5-28         5.4.3.14 4-Point Trapezoid Fill Solid       5-29         5.4.3.15 4-point Trapezoid Fill       5-30         5.4.3.16 Bresenham Parameter       5-30         5.4.3.17 Bresenham Parameter       7         Trapezoid Fill Solid       5-31         5.4.3.17 Bresenham Parameter       7         Trapezoid Fill Pattern       5-32         5.4.3.18 ROPBLTS       5-33         5.4.3.19 Programmable Hardware       2         Cursor       5-45         5.5       RECOMMENDED READING       5-46         Section 6: Video Engine         6.1       VIDEO ENGINE OVERVIEW       6-1         6.2       SCALING       6-2         6.3       COLOR SPACE CONVERSION       6-2                                                                                                                                                                                                                                                                                                                                                                          |       |                     | Through the Plane 5-22          |

| 5.4.3.10 Short Stroke Vectors       5-24         5.4.3.11 Polyline/2-Point Line       5-25         5.4.3.12 Polygon Fill Solid       5-26         5.4.3.13 Polygon Fill Pattern       5-28         5.4.3.14 4-Point Trapezoid Fill Solid       5-29         5.4.3.15 4-point Trapezoid Fill Pattern       5-30         5.4.3.16 Bresenham Parameter       5-31         5.4.3.17 Bresenham Parameter       5-31         5.4.3.18 ROPBLTS       5-33         5.4.3.19 Programmable Hardware       5-33         5.5       RECOMMENDED READING       5-46         Section 6: Video Engine         6.1       VIDEO ENGINE OVERVIEW       6-1         6.2       SCALING       6-2         6.3       COLOR SPACE CONVERSION       6-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5     | 5.4.3.9             | PatBLT—Pattern Fill             |

| 5.4.3.10 Short Stroke Vectors       5-24         5.4.3.11 Polyline/2-Point Line       5-25         5.4.3.12 Polygon Fill Solid       5-26         5.4.3.13 Polygon Fill Pattern       5-28         5.4.3.14 4-Point Trapezoid Fill Solid       5-29         5.4.3.15 4-point Trapezoid Fill Pattern       5-30         5.4.3.16 Bresenham Parameter       5-31         5.4.3.17 Bresenham Parameter       5-31         5.4.3.18 ROPBLTS       5-33         5.4.3.19 Programmable Hardware       5-33         5.5       RECOMMENDED READING       5-46         Section 6: Video Engine         6.1       VIDEO ENGINE OVERVIEW       6-1         6.2       SCALING       6-2         6.3       COLOR SPACE CONVERSION       6-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |                     | Across the Plane 5-23           |

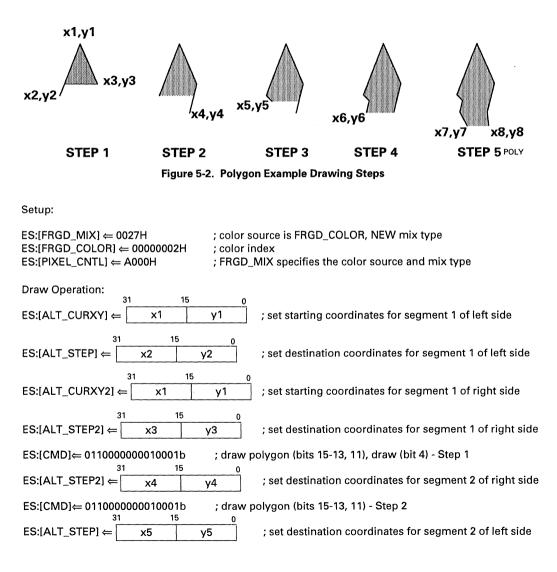

| 5.4.3.12       Polygon Fill Solid       5-26         5.4.3.13       Polygon Fill Pattern       5-28         5.4.3.14       4-Point Trapezoid Fill Solid       5-29         5.4.3.15       4-point Trapezoid Fill Solid       5-29         5.4.3.16       Bresenham Parameter       5-30         5.4.3.16       Bresenham Parameter       5-31         5.4.3.17       Bresenham Parameter       5-31         5.4.3.17       Bresenham Parameter       5-32         5.4.3.18       ROPBLTS       5-33         5.4.3.19       Programmable Hardware       Cursor         Cursor       5-45       5.5         Section 6: Video Engine       5-46         Section 6: Video Engine       6-1         6.1       VIDEO ENGINE OVERVIEW       6-1         6.2       SCALING       6-2         6.3       COLOR SPACE CONVERSION       6-2                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5     | 5.4.3.10            |                                 |

| 5.4.3.12       Polygon Fill Solid       5-26         5.4.3.13       Polygon Fill Pattern       5-28         5.4.3.14       4-Point Trapezoid Fill Solid       5-29         5.4.3.15       4-point Trapezoid Fill Solid       5-29         5.4.3.16       Bresenham Parameter       5-30         5.4.3.16       Bresenham Parameter       5-31         5.4.3.17       Bresenham Parameter       5-31         5.4.3.17       Bresenham Parameter       5-32         5.4.3.18       ROPBLTS       5-33         5.4.3.19       Programmable Hardware       Cursor         Cursor       5-45       5.5         Section 6: Video Engine       5-46         Section 6: Video Engine       6-1         6.1       VIDEO ENGINE OVERVIEW       6-1         6.2       SCALING       6-2         6.3       COLOR SPACE CONVERSION       6-2                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5     | 5.4.3.11            | Polyline/2-Point Line 5-25      |

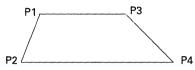

| 5.4.3.14 4-Point Trapezoid Fill Solid . 5-29<br>5.4.3.15 4-point Trapezoid Fill<br>Pattern 5-30<br>5.4.3.16 Bresenham Parameter<br>Trapezoid Fill Solid 5-31<br>5.4.3.17 Bresenham Parameter<br>Trapezoid Fill Pattern 5-32<br>5.4.3.18 ROPBLTs 5-33<br>5.4.3.19 Programmable Hardware<br>Cursor 5-45<br>5.5 RECOMMENDED READING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |                     |                                 |

| 5.4.3.15       4-point Trapezoid Fill<br>Pattern         Pattern       5-30         5.4.3.16       Bresenham Parameter<br>Trapezoid Fill Solid       5-31         5.4.3.17       Bresenham Parameter<br>Trapezoid Fill Pattern       5-32         5.4.3.18       ROPBLTs       5-33         5.4.3.19       Programmable Hardware<br>Cursor       5-45         5.5       RECOMMENDED READING       5-46         Section 6: Video Engine         6.1       VIDEO ENGINE OVERVIEW       6-1         6.2       SCALING       6-2         6.3       COLOR SPACE CONVERSION       6-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Ę     | 5.4.3.13            | Polygon Fill Pattern 5-28       |

| 5.4.3.15       4-point Trapezoid Fill<br>Pattern         Pattern       5-30         5.4.3.16       Bresenham Parameter<br>Trapezoid Fill Solid       5-31         5.4.3.17       Bresenham Parameter<br>Trapezoid Fill Pattern       5-32         5.4.3.18       ROPBLTs       5-33         5.4.3.19       Programmable Hardware<br>Cursor       5-45         5.5       RECOMMENDED READING       5-46         Section 6: Video Engine         6.1       VIDEO ENGINE OVERVIEW       6-1         6.2       SCALING       6-2         6.3       COLOR SPACE CONVERSION       6-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |                     |                                 |

| Pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |                     |                                 |

| 5.4.3.16 Bresenham Parameter         Trapezoid Fill Solid        5-31         5.4.3.17 Bresenham Parameter         Trapezoid Fill Pattern        5-32         5.4.3.18 ROPBLTs        5-33         5.4.3.19 Programmable Hardware       Cursor        5-45         5.5 RECOMMENDED READING        5-46         Section 6: Video Engine         6.1       VIDEO ENGINE OVERVIEW       6-1         6.2       SCALING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |                     | Pattern                         |

| 5.4.3.17 Bresenham Parameter<br>Trapezoid Fill Pattern       5-32         5.4.3.18 ROPBLTs       5-33         5.4.3.19 Programmable Hardware<br>Cursor       5-45         5.5 RECOMMENDED READING       5-46         Section 6: Video Engine         6.1       VIDEO ENGINE OVERVIEW       6-1         6.2       SCALING       6-2         6.3       COLOR SPACE CONVERSION       6-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Ę     | 5.4.3.16            |                                 |

| 5.4.3.17 Bresenham Parameter<br>Trapezoid Fill Pattern       5-32         5.4.3.18 ROPBLTs       5-33         5.4.3.19 Programmable Hardware<br>Cursor       5-45         5.5 RECOMMENDED READING       5-46         Section 6: Video Engine         6.1       VIDEO ENGINE OVERVIEW       6-1         6.2       SCALING       6-2         6.3       COLOR SPACE CONVERSION       6-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |                     | Trapezoid Fill Solid 5-31       |

| Trapezoid Fill Pattern       5-32         5.4.3.18 ROPBLTs       5-33         5.4.3.19 Programmable Hardware       Cursor         Cursor       5-45         5.5       RECOMMENDED READING         Section 6: Video Engine       6-1         6.1       VIDEO ENGINE OVERVIEW       6-1         6.2       SCALING       6-2         6.3       COLOR SPACE CONVERSION       6-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Ę     | 5.4.3.17            |                                 |

| 5.4.3.18 ROPBLTs       5-33         5.4.3.19 Programmable Hardware       Cursor         Cursor       5-45         5.5 RECOMMENDED READING       5-46         Section 6: Video Engine         6.1 VIDEO ENGINE OVERVIEW       6-1         6.2 SCALING       6-2         6.3 COLOR SPACE CONVERSION       6-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |                     |                                 |

| 5.4.3.19 Programmable Hardware<br>Cursor         5.4.3           5.5         RECOMMENDED READING         5.45           5.5         RECOMMENDED READING         5.46           Section 6: Video Engine           6.1         VIDEO ENGINE OVERVIEW         6-1           6.2         SCALING         6-2           6.3         COLOR SPACE CONVERSION         6-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Ę     | 5.4.3.18            | ROPBLTs                         |

| Cursor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |                     |                                 |

| 5.5         RECOMMENDED READING         5-46           Section 6: Video Engine         6-1         6-1           6.1         VIDEO ENGINE OVERVIEW         6-1           6.2         SCALING         6-2           6.3         COLOR SPACE CONVERSION         6-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |                     |                                 |

| Section 6: Video Engine         6-1           6.1         VIDEO ENGINE OVERVIEW         6-1           6.2         SCALING         6-2           6.3         COLOR SPACE CONVERSION         6-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5.5   | RECO                | MMENDED READING 5-46            |

| 6.2         SCALING         6-2           6.3         COLOR SPACE CONVERSION         6-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |                     |                                 |

| 6.2         SCALING         6-2           6.3         COLOR SPACE CONVERSION         6-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Secti | on 6 <sup>.</sup> \ | Video Engine                    |

| 6.2         SCALING         6-2           6.3         COLOR SPACE CONVERSION         6-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 61    | VIDEC               | FNGINE OVERVIEW 6-1             |

| 6.3 COLOR SPACE CONVERSION 6-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |                     |                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |                     | B SPACE CONVERSION 6-2          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6.4   |                     | RING 6-2                        |

# Appendix A: Listing of Raster

| 0 | pera | tions | • | • | • | • | • | • | • | • | • | • | • | • | A-1 |  |

|---|------|-------|---|---|---|---|---|---|---|---|---|---|---|---|-----|--|

|---|------|-------|---|---|---|---|---|---|---|---|---|---|---|---|-----|--|

STATUS . . . . . . . . . . . . . . . 6-3

6.5

# **List of Figures**

| #   | Title Page                            |

|-----|---------------------------------------|

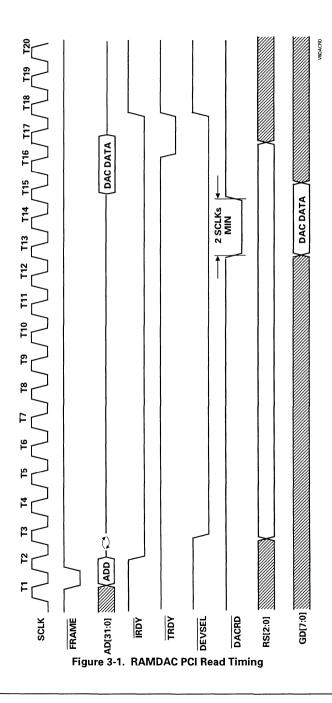

| 3-1 | RAMDAC PCI Read Timing 3-3            |

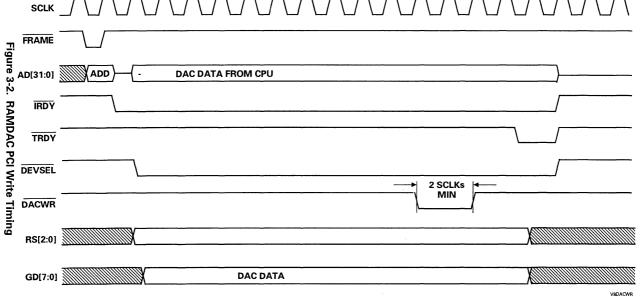

| 3-2 | RAMDAC PCI Write Timing 3-4           |

| 3-3 | Fast Page Mode Read/Modify            |

|     | Write Timing 3-5                      |

| 3-4 | EDO Mode Read/Modify Write            |

|     | Timing 3-5                            |

| 3-5 | 1 Cycle EDO Read Timing 3-6           |

| 3-6 | 1 Cycle EDO Write Timing 3-6          |

| 3-7 | 1 Cycle EDO Read/Modify/Write         |

|     | Timing 3-7                            |

| 3-8 | Burst Mode Read Timing 3-8            |

| 3-9 | Burst Mode Write Timing 3-8           |

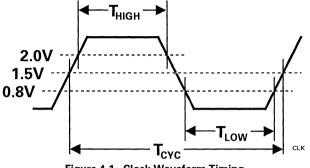

| 4-1 | Clock Waveform Timing 4-3             |

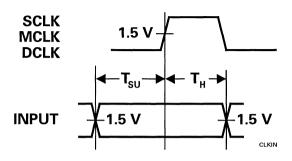

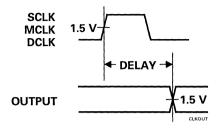

| 4-2 | Input Timing 4-4                      |

| 4-3 | Output Timing 4-5                     |

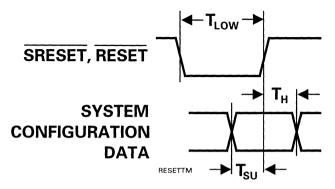

| 4-4 | Reset Timing 4-7                      |

| 4-5 | First Order Output Buffer Model . 4-8 |

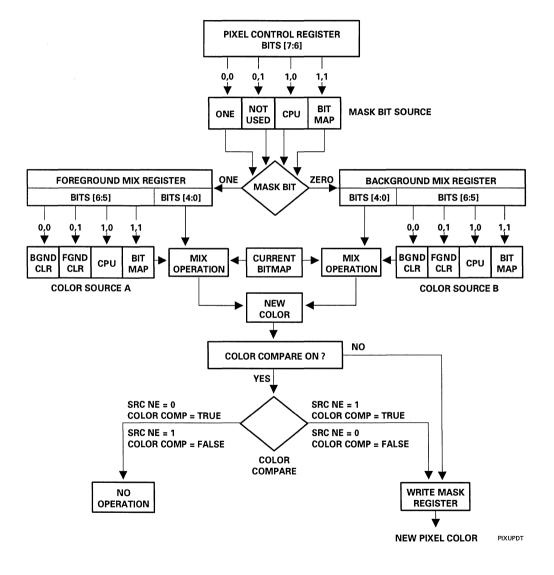

| 5-1 | Pixel Update Flowchart 5-6            |

| 5-2 | Polygon Example Drawing Steps 5-26    |

# **List of Tables**

| #    | Title Pa                         | ige |

|------|----------------------------------|-----|

| 1-1  | Video Resolutions Supported      | 1-2 |

| 2-1  | Register Differences Between the |     |

|      | Vision868 and Vision864          | 2-1 |

| 4-1  | Absolute Maximum Ratings         | 4-1 |

| 4-2  | DC Specifications                | 4-1 |

| 4-3  | Clock Waveform Timing            | 4-3 |

| 4-4  | SCLK-Referenced Input Timing .   | 4-4 |

| 4-5  | SCLK-Referenced Output Timing    | 4-5 |

| 4-6  | MCLK-Referenced Input Timing .   | 4-6 |

| 4-7  | MCLK-Referenced Output Timing    | 4-6 |

| 4-8  | DCLK-Referenced Output Timing    | 4-6 |

| 4-9  | Fast Page, 1 Cycle EDO, Burst    |     |

|      | Mode Memory Input Timing         | 4-6 |

| 4-10 | Reset Timing                     | 4-7 |

| 5-1  | Enhanced Registers Memory        |     |

|      | Mapping                          | 5-2 |

| 5-2  | New MMIO Addresses               | 5-3 |

| 5-3  | Big Endian Byte Swap Select      | 5-4 |

| 5-4  | Polygon Fill Example Summary . 5 | -27 |

| 6-1  | Video Engine Input/Output        |     |

|      | Combinations                     | 6-1 |

# **Section 1: Introduction**

#### 1.1 OVERVIEW OF THIS DATA BOOKLET

This data booklet largely describes the areas in which the S3<sup>®</sup> Vision868™ accelerator (hereinafter referred to as the Vision868) is different from the S3 Vision864™ (hereinafter referred to as the Vision864).

Although enhanced mode programming largely remains unchanged from the Vision864 data book description, the entire section is included in this data booklet because it has been extensively revised. Similarly, the entire electrical data section is included. For information on other common features between the Vision868 and Vision864, including most of the registers and the graphics acceleration functionality, see the *Vision864 Graphics Accelerator Data Book.* In particular, note that the pinout and pin descriptions are the same for both chips.

#### 1.2 PRODUCT OVERVIEW

In general, the Vision868 provides all the features found in the Vision864. The exception is that backward compatibility support for CGA, MDA and HGC is no longer provided in hardware.

The Vision868 provides a number of enhanced capabilities not found in the Vision864. These are summarized below and are described in detail in subsequent sections.

#### 1.3 ENHANCED DRAM SUPPORT

The Vision868 supports burst mode DRAMs and single cycle EDO operation at speeds up to 50 MHz. These are capable of sequential read or write data transfers at rates approaching twice that of convention fast page mode DRAMs.

#### 1.4 PACKED PIXEL ACCELERATION

The Vision868 provides packed 24 bits/pixel (true color) acceleration. This means that each pixel in 24 bits/pixel modes now occupies 3 bytes of memory instead of 4 for the Vision864. In addition, the graphics engine can process more pixels in a given number of clock cycles than for the Vision864.

#### 1.5 ENHANCED MEMORY-MAPPED I/O IMPLEMENTATION

The Vision864 provides memory-mapped I/O (MMIO) access to certain enhanced command registers at fixed memory addresses. The Vision868 provides the following enhancements to this scheme:

- The base address for MMIO is now the same as for linear addressing and is relocatable for plug and play support

- The new MMIO is enabled at power-on reset for PCI systems, allowing the PCI subsystem to configure the Vision868 without accessing the VGA registers through the I/O space

- All registers are now memory mapped

- Related 16-bit Enhanced command registers are packed into 32-bit registers to reduce the number of CPU cycles required to access them

- There are two apertures into the MMIO address space. One provides little endian (Intel<sup>©</sup>-style) access and the other provides big endian (Motorola<sup>©</sup>/ PowerPC<sup>™</sup>-style) access

#### 1.6 NEW DRAWING COMMANDS

The following drawing commands have been added to those available with the Vision864:

- polyline/2-point line

- polygon with solid or patterned fills

- trapezoid with solid or patterned fills (Bresenham parameters in hardware)

- trapezoid with solid or patterned fills (Bresenham parameters specified by programmer)

- ROPBLT Support is provided for the full set of 256 triadic raster operations for BitBLTs (as defined by Microsoft<sup>®</sup>)

#### 1.7 IMPROVED COPROCESSOR SUPPORT

During shared frame buffer operation, the coprocessor can now be guaranteed a specified amount of the memory bandwidth without being forced to return control of the memory bus.

#### 1.8 PCI SUPPORT ENHANCEMENTS

The following have been added to improve operation in PCI systems:

- New registers for interrupt handling

- Complete RAMDAC snooping capability

- PCI disconnect based on the command FIFO status

#### 1.9 VIDEO ENGINE

The Video Engine integrated into the Vision868 can convert a YUV data stream to an RGB data stream. The output of the color space converter is then sent through the scaling engine for scaling up or down. Additionally, a dithering engine converts 24 bits/pixel images to a 16- or 8- bit format (and 16-bit images to an 8-bit format) with little quality impact. To support image compression, the Video Engine can scale images down to the size required to meet disk drive bandwidth requirements.

#### 1.10 RESOLUTIONS SUPPORTED

Supported resolutions are shown in the following table. Extended VGA text modes up to 132 columns by 43 rows are possible as well.

#### Table 1-1. Video Resolutions Supported

| Resolution    | 1 MB<br>DRAM | 2 MBs<br>DRAM | 4 MBs<br>DRAM |

|---------------|--------------|---------------|---------------|

| 640x480x4     | ~            | ~             | ~             |

| 640x480x8     | ~            | ~             | ~             |

| 640x480x16    | ~            | ~             | ~             |

| 640x480x24    | ~            | ~             | ~             |

| 640x480x32    |              | ~             | ~             |

| 800x600x4     | ~            | ~             | ~             |

| 800x600x8     | ~            | ~             | ~             |

| 800x600x16    | ~            | ~             | ~             |

| 800x600x24/32 |              | ~             | ~             |

| 1024x768x4    | ~            | ~             | ~             |

| 1024x768x8    | ~            | ~             | ~             |

| 1024x768x16   |              | ~             | ~             |

| 1024x768x24   |              |               | ~             |

| 1152x864x8    | ~            | ~             | ~             |

| 1280x1024x4   | ~            | ~             | <b>v</b>      |

| 1280x1024x8   |              | ~             | <b>v</b>      |

| 1600x1200x4   | ~            | ~             | ~             |

| 1600x1200x8   |              | ~             | ~             |

# **Section 2: Register Changes**

#### 2.1 Vision868 REGISTER CHANGES

Most Vision868 registers operate exactly as their Vision864 counterparts. The exceptions are shown in Table 2-1. New Vision868 registers are described in Sections 3.2 through 3.6.

| Vision864 Register | Bit(s) | Vision868 Description                                                                                                                                                                                       |  |  |  |  |

|--------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CR30               | 7-0    | This is hardwired to E1H.                                                                                                                                                                                   |  |  |  |  |

| CR32               | 3-2    | Reserved                                                                                                                                                                                                    |  |  |  |  |

| CR36               | 3-2    | 00 = One cycle EDO DRAM (new)<br>01 = Burst mode DRAM (new)<br>10 = EDO DRAM<br>11 = Fast page mode DRAM                                                                                                    |  |  |  |  |

| CR40               | 3      | 0 = Normal SRDY operation<br>1 = SRDY delayed by one cycle (VL-Bus only)                                                                                                                                    |  |  |  |  |

| CR50               | 1      | 0 = DACRD, DACWR active pulse = 2 SCLKs<br>1 = DACRD, DACWR active pulse = 4 SCLKs                                                                                                                          |  |  |  |  |

| CR50               | 5-4    | 00 = 4/8 bits/pixel<br>01 = 16 bits/pixel<br>10 = 24 bits/pixel (new)<br>11 = 32 bits/pixel                                                                                                                 |  |  |  |  |

| CR53               | 0      | Reserved (write per bit no longer supported)                                                                                                                                                                |  |  |  |  |

| CR53               |        | The power-on default depends on the system bus type. See the description for bits 4-3 below                                                                                                                 |  |  |  |  |

| CR53               | 2-1    | Big endian data byte swap (linear addressing and Video Engine<br>transfers only)<br>00 = No swap<br>01 = Swap bytes within each word<br>10 = Swap all bytes in doubleword (bytes reversed)<br>11 = Reserved |  |  |  |  |

| Table 2-1. | <b>Begister Differences</b> | Between the | Vision868 and Vision864 |

|------------|-----------------------------|-------------|-------------------------|

|            | negister binerences         | Detween the |                         |

#### Table 2-1. Register Differences Between the Vision864 and Vision868 (Continued)

| Vision864 Register | Bit(s) | Vision868 Description                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CR53               | 4-3    | MMIO select<br>00 = MMIO disabled<br>01 = MMIO disabled<br>10 = Vision864-type MMIO (A0000H window)<br>11 = New MMIO (relocatable/packed) and Vision864-type MMIO<br>VL-Bus power-on default = 00<br>PCI bus power-on default = 11                                                                                                                                                                                                                                             |

| CR53               | 7      | Enable upper byte write protection in 32 bits/pixel mode<br>0 = CAS3 and CAS7 enabled during 32 bits/pixel memory writes<br>1 = CAS3 and CAS7 disabled during 32/bits/pixel memory writes                                                                                                                                                                                                                                                                                      |

| CR54               | 1-0    | Big endian data byte swap (not linear addressing, not image writes<br>and not Video Engine access)<br>00 = No swap<br>01 = Swap bytes within each word<br>10 = Swap all bytes in doubleword (bytes reversed)<br>11 = Swap according to BE[3:0] (VL-Bus ) or C/BE(3:0] (PCI bus)<br>BE[3:0]/C/BE[3:0]<br>0000 = Swap all bytes in doubleword (bytes reversed)<br>0011 = Swap bytes within selected word<br>1100 = Swap bytes within selected word<br>All other values = No swap |

| CR54               | 2      | This is the high order extension bit (bit 5) for the M parameter (bits 7-<br>3 of this register). This doubles the amount of memory bandwidth<br>that can be allocated for Graphics Engine/CPU access.                                                                                                                                                                                                                                                                         |

| CR58               |        | The power-on default depends on the system bus type. See the description for bit 4 below.                                                                                                                                                                                                                                                                                                                                                                                      |

| CR58               | 4      | VL-Bus power-on default = 0<br>PCI bus power-on default = 1                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CR59, CR5A         | 15-0   | VL-Bus power-on default = 000AH<br>PCI bus power-on default = 7000H                                                                                                                                                                                                                                                                                                                                                                                                            |

| CR61               | 6-5    | Big endian data byte swap (image writes)<br>00 = No swap<br>01 = Swap bytes within each word<br>10 = Swap all bytes in doubleword (bytes reversed)<br>11 = Reserved                                                                                                                                                                                                                                                                                                            |

| CR66               | 3      | <ul> <li>PCI disconnect enable (PCI bus only)</li> <li>0 = No effect</li> <li>1 = An attempt to write data with the Command FIFO full or to read data with the Command FIFO not empty generates a PCI bus disconnect cycle</li> <li>Bit 7 of this register must also be set to 1 to enable this feature.</li> </ul>                                                                                                                                                            |

| CR67               | 7-4    | 0111 = Mode 11: 32-bit color, 2 VCLKs/pixel<br>1001 = Mode 12: 24-bit packed color, 3 VCLKs/2 pixels                                                                                                                                                                                                                                                                                                                                                                           |

#### S3 Vision868 Multimedia Accelerator

#### Table 2-1. Register Differences Between the Vision864 and Vision868 (Continued)

| Vision864 Register | Bit(s)       | Vision868 Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|--------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Enhanced Registers |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 82E8H              | 11-0         | For polygons or trapezoids, this is the starting pixel vertical position for the first of two edges to be drawn.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 86E8H              | 11-0         | For polygons or trapezoids, this is the starting pixel horizontal position for the first of two edges to be drawn.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 8AE8H              | 11-0         | For polylines, this is the ending vertical position for each line<br>segment. For polygons and 4-point trapezoids, this is the ending<br>vertical position for the first of two edges to be drawn. For<br>Bresenham parameter trapezoids, this is the axial step constant for<br>the first of two edges to be drawn.                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 8EE8H              | 11-0         | For polylines, this is the ending horizontal position for each line<br>segment. For polygons and 4-point trapezoids, this is the ending<br>horizontal position for the first of two edges to be drawn. For<br>Bresenham parameter trapezoids, this is the diagonal step constant<br>for the first of two edges to be drawn.                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 92E8H              | 11-0         | For Bresenham parameter trapezoids, this is the error term for the first of two edges to be drawn.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 96E8H              | 11-0         | For Bresenham parameter trapezoids, this is the major axis length for the first of two edges to be drawn.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 9AE8H              | 10-9         | <ul> <li>Select image write (E2E8H, E2EAH) bus transfer width</li> <li>00 = 8 bits</li> <li>01 = 16 bits</li> <li>10 = 32 bits. All doubleword bits beyond the image rectangle width are discarded. Each line starts with a fresh doubleword. The current drawing position ends up one pixel below the lower left hand corner of the image rectangle</li> <li>11 = 32 bits. This setting applies only to image transfers across the plane. Only padding bits up to the start of the next byte are discarded. The current drawing position ends up one pixel to the right of the top right corner of the rightmost image rectangle.</li> </ul> |  |  |  |

| 9AE8H              | 11,<br>15-13 | Drawing Command<br>0000 = NOP<br>0001 = Draw line<br>0010 = Rectangle fill<br>0011 = Polygon fill solid (new)<br>0100 = 4-point trapezoid fill solid (new)<br>0101 = Bresenham parameter trapezoid fill solid (new)<br>0110 = BitBLT<br>0111 = Polyline/2-point line (new)<br>1011 = Polygon fill pattern (new)<br>1011 = Polygon fill pattern (new)<br>1100 = 4-point trapezoid fill pattern (new)<br>1101 = Bresenham parameter trapezoid fill pattern (new)<br>1110 = ROPBLT (new)<br>See the Enhanced Mode Programming section for a description of<br>each of these commands.                                                            |  |  |  |

#### Table 2-1. Register Differences Between the Vision864 and Vision868 (Continued)

| Vision864 Register | Bit(s) | Vision868 Description                                                                                  |

|--------------------|--------|--------------------------------------------------------------------------------------------------------|

| AEE8H              | 31-0   | Read mask for the ROPBLT pattern (same as previous Read Mask)                                          |

| BEE8H, Index E     | 6      | Reserved                                                                                               |

| BEE8H, Index E     | 10     | 0 = Allow burst mode/1 cycle EDO write operation<br>1 = Disable burst mode/1 cycle EDO write operation |

| PCI Registers      |        |                                                                                                        |

| PCI Index 02H      | 15-0   | The device ID is hardwired to 8880H.                                                                   |

| PCI Index 04H      | 7      | Hardwired to 1 to indicate that the device always does address/data stepping.                          |

| PCI Index 0AH      | 7-0    | Now included in new Class Code register.                                                               |

#### 2.2 NEW Vision868 SR REGISTERS

The SR registers described in this section have been added for the Vision868 and are not found in the Vision864.

#### Extended Sequencer Register 9 (SR9)

Read/Write A Power-On Default: 00H

Address: 3C5H, Index 09H

| 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|---|---|---|---|---|---|

| MMIO- |   |   |   |   |   |   |   |

| ONLY  | R | R | R | R | R | R | R |

#### Bits 6-0 Reserved

- Bit 7 MMIO-ONLY Memory-mapped I/O register access only

- 0 = If MMIO is enabled, both programmed I/O and memory-mapped I/O register accesses are allowed

- 1 = If MMIO is enabled, only memory-mapped I/O register accesses are allowed

#### External Bus Request Control Register (SRA)

Read/Write Power-On Default: 00H Address: 3C5H, Index 0AH

| 7    | 6 | 5 | 4 | 3    | 2   | 1 | 0 |

|------|---|---|---|------|-----|---|---|

| 2    |   |   |   | P VA | LUE |   |   |

| MCLK | R | 5 | 4 | 3    | 2   | 1 | 0 |

#### Bits 5-0 P VALUE

The integer equivalent of the binary value in this field is the number of MCLK units less one a secondary memory controller is allowed to retain control of the memory bus before the Vision864 drops its bus grant. See Section 3.2 for a detailed explanation.

- Bit 6 Reserved

- Bit 7 2MCLK 2 MCLK CPU writes to memory (linear addressing) 0 = 3 MCLK memory writes

- 1 = 2 MCLK memory writes

#### 2.3 NEW Vision868 CR REGISTERS

The CR registers described in this section have been added for the Vision868 and are not found in the Vision864.

#### Device ID High Register (CR2D)

Read Only Address: 3?5H, Index 2DH Power-On Default: 88H

This register contains the same value as the upper byte of the PCI Vendor ID (Index 00H) register.