# 3-phase spindle motor driver with servo for ODD BA6851AFP-Y

The BA6851AFP-Y is a one-chip IC for use as a spindle motor driver for optical disc drives. The IC consists of a digital servo and 3-phase, full-wave motor driver circuits. The IC also contains all the necessary functions for an optical/magnetic disk driver, including a reversal brake, a lock signal pin, and a power save pin for informing when the speed of rotation has stabilized.

#### Applications

Spindle motors for optical disk drives, LBP polygon mirror drivers

#### Features

- 3-phase, pseudo-linear drive system, which has shown positive achievements in ROHM FDD motor driver series, provides superb torque characteristics.

- 2) Built-in digital servo.

- 3) Reversal brake.

- 4) Hall elements bias switch ; current to the Hall elements controlled by a single resistor.

- 5) Power save circuit.

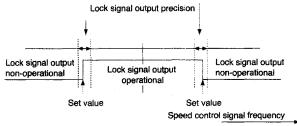

- Lock signal that indicates when the motor frequency is within a set range.

- 7) Switch to set the lock signal range to  $\pm$ 2.5%,  $\pm$  3.75%, or  $\pm$ 5.0%.

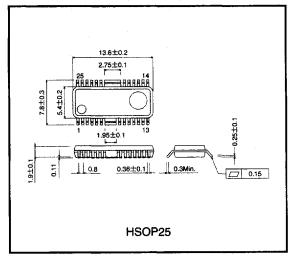

- 8) Available in a HSOP25 package with a small mounting area. Perfect for smaller motors.

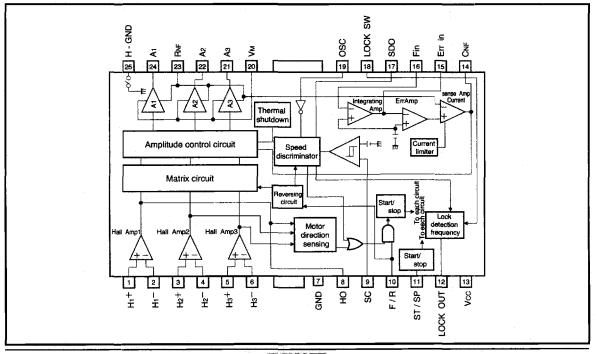

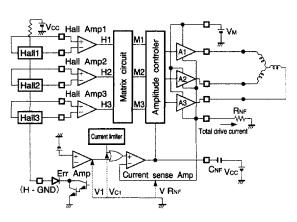

#### Block diagram (pin arrangement)

# BA6851AFP-Y

## ●Absolute maximum ratings (Ta=25℃)

| Parameter              | Symbol | Limits | Unit |

|------------------------|--------|--------|------|

| Power supply voltage 1 | Vcc    | 7.0    | V    |

| Power supply voltage 2 | Vм     | 13.5   | v    |

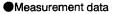

| Power dissipation      | Pd     | 1450*  | mW   |

| Operating temperature  | Topr   | -25~75 | Ĵ    |

| Storage temperature    | Tstg   |        | Ĵ    |

| Maximum output current | OMax.  | 1000   | mA   |

\* Mounted on a glass epoxy PCB (90 X 50 X 1.6 mm). Reduce power by 11.6 mW for each degree above 25°C

#### Recommended operating conditions (Ta=25°C)

| Parameter              | Symbol | Limits   | Unit |

|------------------------|--------|----------|------|

| Power supply voltage 1 | Vcc    | 4.2~6.5  | v    |

| Power supply voltage 2 | Vм     | 4.2~13.3 | V    |

# Pin descriptions

| Pin No. | Pin name         | Function                                                                  |

|---------|------------------|---------------------------------------------------------------------------|

| 1       | H1+              | Hall input amplifier 1 input (+)                                          |

| 2       | H1 -             | Hall input amplifier 1 input (-)                                          |

| 3       | H <sub>2</sub> + | Hall input amplifier 2 input (+)                                          |

| 4       | H2 -             | Hall input amplifier 2 input (-)                                          |

| 5       | H <sub>3</sub> + | Hall input amplifier 3 input (+)                                          |

| 6       | H3 -             | Hall input amplifier 3 input (-)                                          |

| 7       | GND              | GND                                                                       |

| 8       | но               | Hall signal output                                                        |

| 9       | SC               | Speed signal input                                                        |

| 10      | F/R              | Forward/reverse select switch                                             |

| 11      | ST / SP          | Start/stop pin; start when LOW                                            |

| 12      | LOCK OUT         | Lock signal pin                                                           |

| 13      | Vcc              | Signal power supply                                                       |

| 14      | CNF              | Capacitor connection pin for error amplifier<br>output phase compensation |

| 15      | Err in           | Error amplifier input; integrating amplifier output                       |

| 16      | Fin              | Integrating amplifier input (-)                                           |

| 17      | SDO              | Speed discriminator output                                                |

| 18      | LOCK SW          | Lock signal operating range select switch                                 |

| 19      | OSC              | Clock input pin                                                           |

| 20      | VM               | Driver power supply                                                       |

| 21      | A3               | Motor output 3                                                            |

| 22      | A2               | Motor output 2                                                            |

| 23      | RNF              | Driver ground pin; current sensing pin                                    |

| 24      | <b>A</b> 1       | Motor output 1                                                            |

| 25      | H - GND          | Hall device bias switch (ground side)                                     |

# BA6851AFP-Y

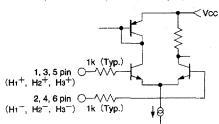

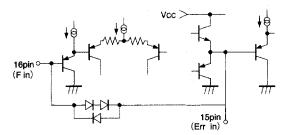

Input/output circuit

1) Holl input (H<sub>1</sub>+: 1 pin, H<sub>1</sub><sup>-</sup>: 2 pin, H<sub>2</sub>+: 3 pin, H<sub>2</sub><sup>-</sup>: 4 pin, H<sub>3</sub>+: 5 pin, H<sub>3</sub><sup>-</sup>: 6 pin)

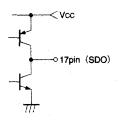

3) Speed discriminator output (SDD: 17 pin)

2) Integrating amplifier (Err in: 15 pin, Fin: 16 pin)

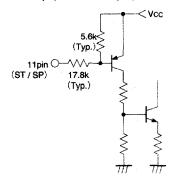

4) Start stop (ST/SP:11 pin)

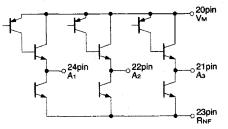

Motor output (A1: 24 pin, A2: 22 pin, A3: 21 pin, VM: 20 pin, RNF: 23 pin)

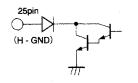

7) Hall elements bias switch (H-GND: 25 pin)

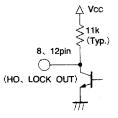

6) Hall signal output pin, lock output pin (HO: 8 pin, LOCK OUT: 12 pin)

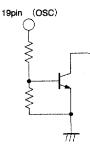

8) OSC pin (OSC: 19 pin)

a. 264 - 142

●Electrical characteristics (Unless otherwise noted, Ta=25℃, Vcc=5V, OSC frequency = 307.2kHz)

| Parameter                                          | Symbol | Min.  | Тур.  | Max.  | Unit              | Conditions                                            |

|----------------------------------------------------|--------|-------|-------|-------|-------------------|-------------------------------------------------------|

| Circuit current                                    | lcc    | 28    | 37    | 52    | mA                | ST/SP pin = GND                                       |

| Standby current 1                                  | Ist1   | 0     | -     | 5     | μA                | ST/SP pin = 5 V                                       |

| Standby current 2                                  | Ist2   | 1.7   | 2.3   | 3.3   | mA                | F/R =Vcc                                              |

| Hall in-phase input voltage range                  | VHB    | 1.5   |       | 4.0   | V                 |                                                       |

| Hall amplifier input sensitivity                   | VHin   | 60    | . —   |       | mV <sub>P-P</sub> | Differential input                                    |

| Output saturation voltage                          | Vsat   | 0.7   | 1.0   | 1.3   | V                 | lour= 350 mA, total of high and lo                    |

| Speed discriminator HIGH<br>level output voltage   | V⊳H    | 4.7   | 4.9   | -     | v                 | 500 µA source current                                 |

| Speed discriminator LOW level output voltage       | VoL    |       | 0.1   | 0.25  | v                 | 500 $\mu$ A sink current                              |

| Integrating amplifier HIGH level<br>output voltage | VeinH  | 2.4   | 3.0   | 3.75  | v                 | Ri pin ≈ 2.0 V                                        |

| Integrating amplifier LOW level<br>output voltage  | VEinL  | 1.1   | 1.4   | 1.7   | v                 | Rí pin ≈ 3.0 V                                        |

| Error amplifier reference voltage                  | VErr   | 2.0   | 2.5   | 3.0   | V                 | Err AMP pin voltage                                   |

| Control input gain                                 | GErr   | -15   | -12   | -9    | dB                | VR №vs. Err AMP pin voltage<br>R <sub>NF</sub> =0.56Ω |

| Current limiter voltage                            | Vcl    | 170   | 220   | 270   | mV                | GND vs. RNF pin, R №= 0.56 Ω                          |

| ST/SP pin HIGH level voltage                       | VssH   | 3.0   | -     | 5     | V                 | Standby state                                         |

| ST/SP pin LOW level voltage                        | VssL   | 0     | —     | 1.5   | V                 | Operating state                                       |

| Hall elements bias pin saturation<br>voltage       | VH-G   | 1.2   | 1.5   | 1.8   | V                 | 10 mA into the Hall elements bias pin                 |

| Hall signal output<br>saturation voltage           | VноL   | -     | 0.17  | 0.5   | V                 |                                                       |

| Hall signal output<br>pull-up resistance           | Rно    | 8     | 11    | 14    | kΩ                |                                                       |

| Reverse rotation input voltage                     | VF/RH  | 3.0   | -     | 5.0   | <u> </u>          |                                                       |

| Forward rotation input voltage                     | VF/RL  | 0     |       | 1.5   | V                 |                                                       |

| Clock input threshold                              | VthCK  | 1.2   | 1.75  | 2.5   | V                 |                                                       |

| Clock input operating frequency                    | fCK    |       | —     | 400   | kHz               |                                                       |

| Clock input sink current                           | VOSCB  | 250   | 380   | 600   | μA                | OSC pin = 5 V                                         |

| Lock signal output precision 1A                    | Διο1Α  | -2.58 | -2.42 | -2.25 | %                 | Lock SW = GND                                         |

| Lock signal output precision 1B                    | Δισ1Β  | 2.34  | 2.50  | 2.66  | %                 | Lock SW = GND                                         |

| Lock signal output precision 2A                    | Διο2Α  | -3.83 | -3.67 | -3.51 | %                 | Lock SW = 1/2 Vcc                                     |

| Lock signal output precision 2B                    | Διο2Β  | 3.59  | 3.75  | 3.91  | %                 | Lock SW = 1/2 Vcc                                     |

| Lock signal output saturation voltage              | VLL    |       | 0.15  | 0.5   | V                 | lo = 2 mA                                             |

| Lock signal output pull-up resistance              | RL     | 8     | 11    | 14    | kΩ                |                                                       |

| Speed signal input rising edge threshold           | VthVH  | 1.94  | 2.14  | 2.34  | v                 |                                                       |

| Speed signal input falling edge threshold          | VihvL  | 1.84  | 2.04  | 2.24  | v                 |                                                       |

| Speed signal input hysteresis width                | Vhis   | 50    | 100   | 150   | mV                |                                                       |

| Lock signal input switch input level 1             | VRS1   | 0     |       | 1.5   | V                 |                                                       |

| Lock signal input switch input level 2             | VRS2   | 2.0   |       | 3.0   | V                 |                                                       |

| Lock signal input switch input level 3             | VRS3   | 3.5   |       | 5.0   | V                 |                                                       |

#### Circuit operation

1. Motor drive circuits

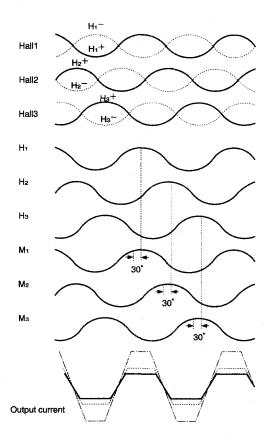

The motor drive employs a 3-phase, full-wave, pseudo-linear current drive system, in which the rotor position is sensed by Hall elements. The motor drive current is sensed by the  $R_{NF}$  resistor. The total drive current is controlled and limited by sensing the voltage developed across this resistor. The motor drive circuit consists of Hall amplifiers, a matrix circuit, an amplitude controller, a driver, an error amplifier, and a current sensing amplifier.

The waveforms of different steps along the signal path from the Hall elements to the motor driver output are shown in Fig. 1. The Hall amplifiers receive the Hall elements voltage signals as differential signals. The signals are amplified and output to the matrix circuit, which combines three voltage signals (H1, H2, and H3) to create three current signals (M1, M2, and M3). For instance, by deducting the output voltage signal of Hall amplifier 2 (H<sub>2</sub>) from the output voltage signal of Hall amplifier 1 (H<sub>1</sub>), current signal M1, which has a phase 30 degrees ahead of H1, is created. The amplitude control circuit then amplifies the M1 signal according to the current sensing amplifier signal. Then, a drive current signal is created at A1 by applying a constant magnification factor. With a "180-degree on" trapezoidal waveform, the drive current has low noise and a low total current ripple.

The total drive current is controlled by the error amplifier input voltage. The error amplifier has a voltage gain of about -12dB (a factor of 0.25). The error amplifier output voltage (V1) and the total drive current are controlled through the RNF pin (0.56  $\Omega$ ). If V1 exceeds the current limiter voltage (Vcl), the constant voltage Vcl takes precedence, and a current limit is applied at the level of Vcl / RNF. When setting the limit, note that the current limiter voltage and the control input gain vary with resistance.

Use adequate phase compensation to the feedback amplifier to reduce the high frequency gain. An external pin ( $C_{NF}$ ) is provided to connect a capacitor for this purpose.

Fig.2

Rehm

### BA6851AFP-Y

#### Circuit operation

2. Speed control circuit

The speed control circuit is a non-adjustable digital servo system that uses a frequency locked loop (FLL). The circuit consists of an integrating amplifier, an error amplifier, a current sensing amplifier, and a speed discriminator.

An external clock signal input from the OSC pin is processed in an internal frequency divider to produce a speed control reference frequency. A signal corresponding to the motor speed is input from the speed signal input pin (SC). The speed discriminator compares the frequency of this signal with the reference frequency, and outputs an error pulse according to the frequency difference between the two signals.

The integrator flattens out and amplifies the error pulse sent from the speed discriminator to form the motor drive circuit control signal. Key characteristics such as control system stability and transient characteristics are determined here. In normal use, input the Hall signal output (HO) signal to the SC pin.

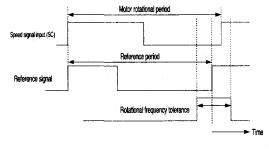

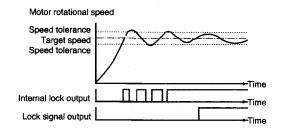

3. Motor frequency lock circuit

The lock output indicates whether the actual motor speed is within the tolerance of the target speed. The tolerance can be changed by using the LOCK SW pin. Figure 3 shows the relationship between the motor rotational period and the IC reference frequency period. The rotational frequency tolerance signal is created from the IC reference frequency period signal.

Fig. 4

The SC-pin input signal (motor rotational period) is compared with the rotational frequency tolerance signal, and an internal lock signal is generated if the former signal falls within the limits of the latter signal.

Before the motor speed is stabilized, the internal lock signal rises and falls a few times (Fig. 4). To prevent this, the BA6851AFP-Y has an internal counter, which allows the motor frequency to be compared with the tolerance only after a given time period. The lock output signal falls immediately when the motor frequency goes out of tolerance.

4. Reversal brake circuit

A reversal brake can be applied by using the forward/reverse switching input (F/R pin). The motor can be stopped more quickly than usual by generating an output opposite to the ongoing rotation. In the BA6851AFP-Y, the output is turned off when the motor speed is reversed or decreased to a certain level by reversal braking.

5. Other circuits

The following circuits are provided.

Start/stop circuit

During the stop mode, the circuit current is almost zero and the lock output is HIGH.

Hall bias switch

The operation of the Hall bias switch is linked to that of the start / stop circuit. In the stop mode, the bias switch is OFF and the currents flowing into the Hall elements are zero. This switch also functions at the end of reversal braking. Because the switch ON state voltage is high, only one resistor is needed to regulate the amount of current applied to the Hall elements.

Thermal shutdown circuit

This circuit shuts down all the IC circuits when the chip junction temperature is increased to about  $175^{\circ}$ C (typ.). The thermal shutdown circuit is deactivated when the temperature drops to about  $150^{\circ}$ C (typ.).

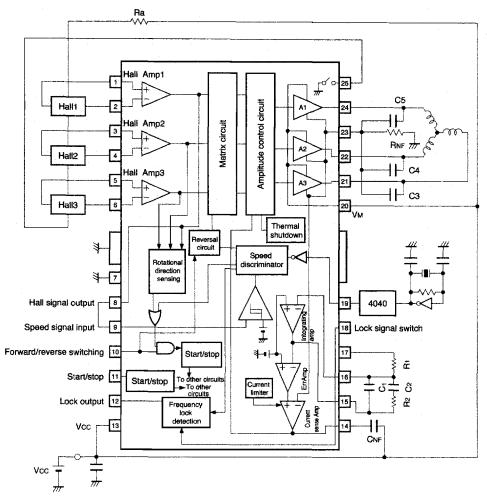

BA6851AFP-Y

Application example

#### External components

| Component | Function<br>Hall elements current regulation |  |  |  |

|-----------|----------------------------------------------|--|--|--|

| Ra        |                                              |  |  |  |

| CNF       | Output current phase compensation            |  |  |  |

| C1,C2     | Integration constants                        |  |  |  |

| R1, R2    | Integration constants                        |  |  |  |

| RNF       | Motor current sensing resistor               |  |  |  |

| C3,4,5    | Output waveform stabilizer                   |  |  |  |

#### Operation notes

1. Radiation fins

The radiation fins are connected to the IC substrate. Make sure to connect them to the ground.

Hall elements connection Hall elements bias pin can be connected in either series or parallel. When connecting in series, care must be taken not to allow the Hall output to exceed the Hall common-mode input range.

#### Operation notes

#### 3. Two standby modes

The BA6851AFP-Y has two standby modes : one is activated by setting the start / stop pin to HIGH, and the other is activated when a reversal brake is applied.

When the start/stop pin is set to HIGH, the circuit current is reduced almost to zero (standby current 1). When a reversal brake is applied, on the other hand, a full reversal torque is applied first, and the circuit current is partially reduced (standby current 2) when the motor speed is suddenly reversed or decreased to a certain level. This circuit does not operate when the motor is running at normal speed.

#### 4. Lock signal pin

The lock signal output pin rises when the frequency of the speed control input signal falls within the operating range of the lock signal output. The lock signal output precision indicates the range of switching point between the operational and nonoperational conditions of the lock signal output, as a relative error against the speed discriminator count.

The lock signal rises also in the following situations:

- The start/stop pin is HIGH (standby state),

- The forward / reverse pin is HIGH and the circuit current is partially cut off (standby state).

5. Package power dissipation

The IC power dissipation changes greatly with the supply voltage and the output current. Give full consideration to the power dissipation rating when setting the supply voltage and the output current.

6. ASO

Make sure that the output current and the supply voltage will not exceed the ASO values.

- Thermal shutdown circuit This circuit shuts down all the IC circuits when the chip junction temperature is increased to about 175°C (typical). The thermal shutdown circuit is deactivated when the temperature drops to about 150°C (typical).

- 8. Speed discriminator count The speed discriminator count is 1280 (typical).

- 9. OSC pin threshold voltage

The OSC pin threshold voltage has a temperature characteristics of about -6mV/C.

# BA6851AFP-Y

# Motor anyor K.

External dimensions (Units: mm)