Semiconductor Products Division

# MODEM PRODUCTS DATA BOOK

# MODEM PRODUCTS DATA BOOK

**Semiconductor Products Division**

©Rockwell International Corporation 1987 All Rights Reserved Printed in U.S.A.

Order No. 1 February, 1987 Rockwell Semiconductor Products Division is headquartered in Newport Beach, California with Field Sales Offices located throughout the United States, Canada, Europe and the Far East. Their listings, plus those of domestic and international representatives and distributors, appear in Appendix A.

| Document Type               | Product Status                | Definition                                                                                                                                                                                                                                                             |

|-----------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product Preview             | Formative or<br>Development   | The document type contains the general features and/or specifications for a product in definition or development. The features and/or specifications may change in any manner without notice.                                                                          |

| Product Summary             | Development or<br>Production  | This document type contains the general features and/or<br>specifications of a product in development or in production.<br>Additional information is usually available in a separate<br>document, not contained in this book, such as a Designer's<br>Guide.           |

| Data Sheet<br>(Preliminary) | Sampling or<br>Pre-Production | This document type contains preliminary or design-to<br>characteristic data for a product in pre-production. Additional<br>and/or refined characteristic data will be released in<br>subsequent revisions to the document.                                             |

| Data Sheet                  | Production                    | This document type contains final specification information resulting from measured characteristics. This document type is subject to revision if characteristics are further refined during production.                                                               |

| Product Description         | Production                    | This document type contains final specification information<br>resulting from measured characteristics along with additional<br>application aid information. This document type is subject<br>to revision if characteristics are further refined during<br>production. |

| Application Note            | Development or<br>Production  | This document type contains application aids in the use of<br>the subject product. Schematics included in an application<br>note are intended to convey system design concepts only.                                                                                   |

#### DEFINITION OF DOCUMENT TYPES

#### NOTICE

Information furnished by Rockwell International Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Rockwell International for its use, nor any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Rockwell International other than for circuitry embodied in a Rockwell product. Rockwell International reserves the right to change circuitry at any time without notice. All documents in this book are subject to change without notice.

# TABLE OF CONTENTS

,

| Par | t No./Data Book Page Index                                                        | iv    |

|-----|-----------------------------------------------------------------------------------|-------|

|     | lem Products—<br>etting Standards in Connectivity                                 | v     |

| Pro | duct Index                                                                        | vii   |

| 1   | 1200, 2400 bps Data Modems                                                        | 1-1   |

|     | Product Family Overview                                                           | 1-2   |

|     | R212DP Device Set Bell 212A Compatible<br>R212AT Device Set "AT" Command Set Bell | 1-3   |

|     | 212A Compatible                                                                   | 1-5   |

|     | R1212 1200 bps Full-Duplex Modem                                                  | 1-7   |

|     | R2424 2400 bps Full-Duplex Modem                                                  | 1-36  |

|     | R201/26DP 2400/1200 bps Data Pump Modem                                           | 1-65  |

|     | RC1212 V.22 1200 bps Modem                                                        | 1-82  |

|     | RC2424 V.22 bis 2400 bps Modem                                                    | 1-84  |

|     | RDAA Rockwell Data Access Arrangement                                             |       |

|     | Module                                                                            | 1-86  |

| 2   | 4800, 9600, 14400 bps Data Modems                                                 | 2-1   |

|     | Product Family Overview                                                           | 2-2   |

|     | R208/201 4800 bps Modem                                                           | 2-3   |

|     | R48DP/208 4800 bps Data Pump Modem                                                | 2-25  |

|     | R48DP 4800 bps Data Pump Modem                                                    | 2-47  |

|     | R96DP 9600 bps Data Pump Modem                                                    | 2-68  |

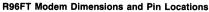

|     | R96FT 9600 bps Fast Train Modem                                                   | 2-90  |

|     | R96FT/SC 9600 bps Fast Train Modem with                                           |       |

|     | Forward Secondary Channel                                                         |       |

|     | R144DP V.33 Ultra High Speed Modem                                                |       |

|     | R9696DP V.32 Ultra High Speed Modem                                               | 2-122 |

|     | R1496MM V.33, V.32 Ultra High                                                     |       |

|     | Speed Modem                                                                       | 2-124 |

| 3   | Imaging Modems                                                                    | 3-1   |

|     | Product Family Overview                                                           | 3-2   |

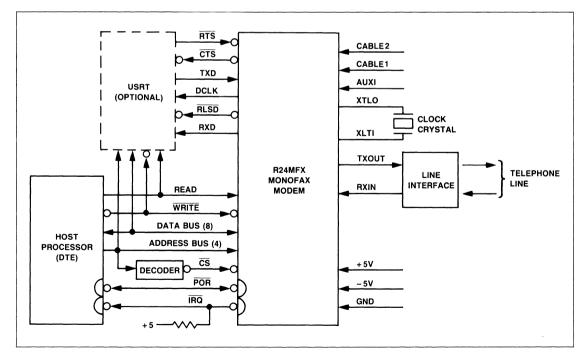

|     | R24MFX 2400 bps MONOFAX <sup>™</sup> Modem                                        | 3-3   |

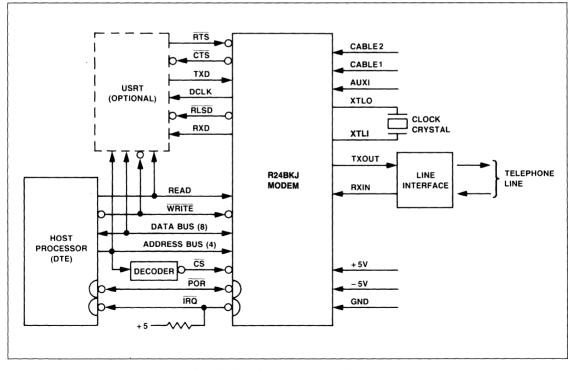

|     | R24BKJ 2400 bps V.26 bis Modem                                                    | 3-19  |

|     | R48MFX 4800 bps MONOFAX Modem                                                     | 3-35  |

|   | R48PCJ 4800 bps PC Communication Modem          | 3-51       |

|---|-------------------------------------------------|------------|

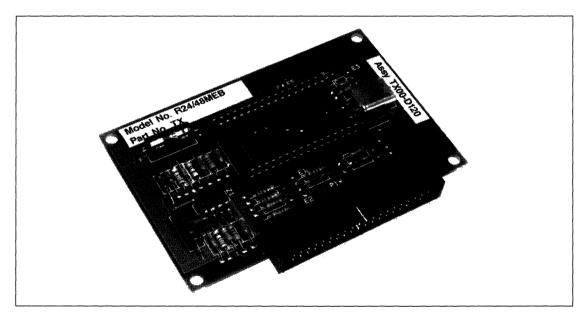

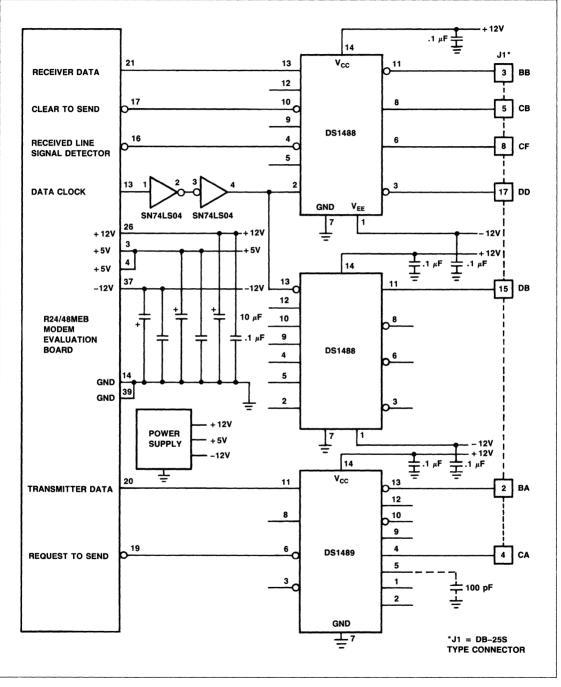

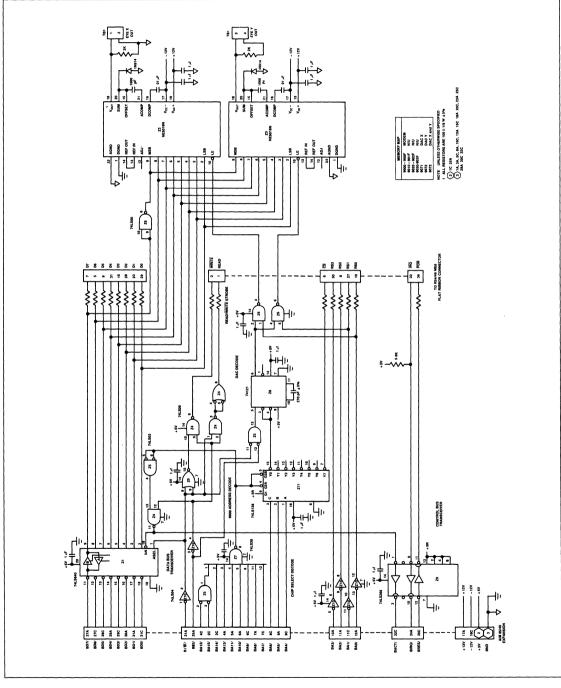

|   | R24/48MEB Modern Evaluation Board               | 3-67       |

|   | R96PCJ 9600 bps PC Communication Modem          | 3-80       |

|   | R96F 9600 bps Facsimile Modem                   | 3-93       |

|   | R96MD 9600 bps Facsimile Modem                  |            |

|   | R144HD 14400 bps Half-Duplex Modem              |            |

|   |                                                 |            |

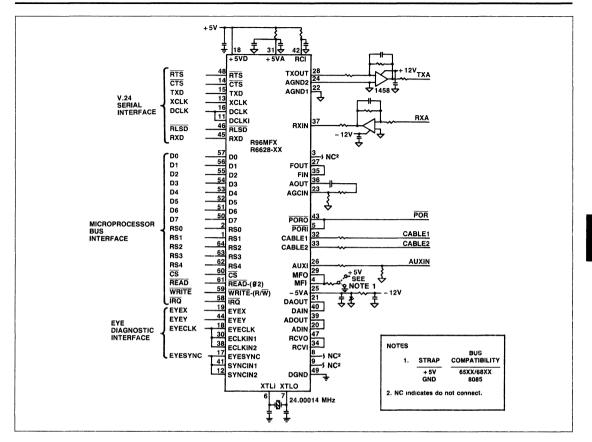

|   | R96MFX 9600 bps MONOFAX Modem                   | 3-144      |

|   |                                                 |            |

| 4 | Custom and Private Label Modems                 | 4-1        |

| 4 |                                                 | 4-1        |

|   | Product Line Overview                           |            |

|   | RG224EC 2400 bps Private Label Modem            | 4-3        |

|   | RG208 4800 bps Private Label Modem              | 4-5        |

|   | RGV29FT 9600 bps Private Label Modem            | 4-7        |

|   |                                                 |            |

| - | Anniliantian Matan                              | 5-1        |

| 5 | Application Notes                               |            |

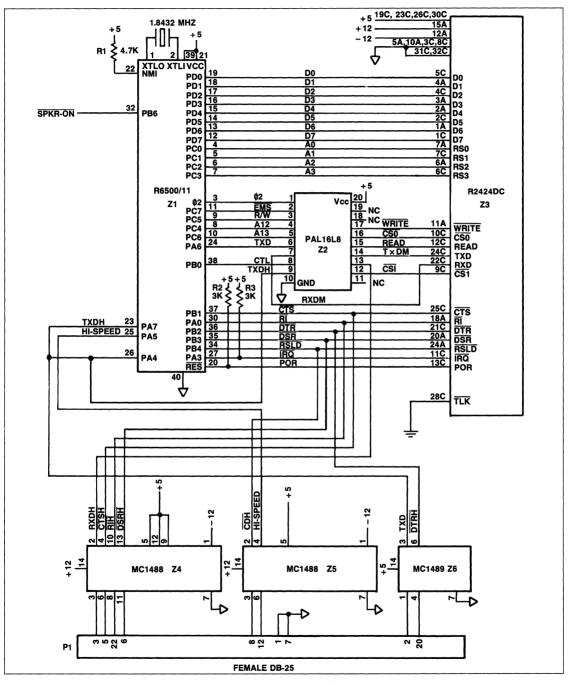

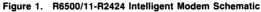

|   | An R6500/11-R2424 Intelligent Modem Design      | 5-3        |

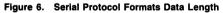

|   | Interfacing Rockwell Signal Processor-Based     |            |

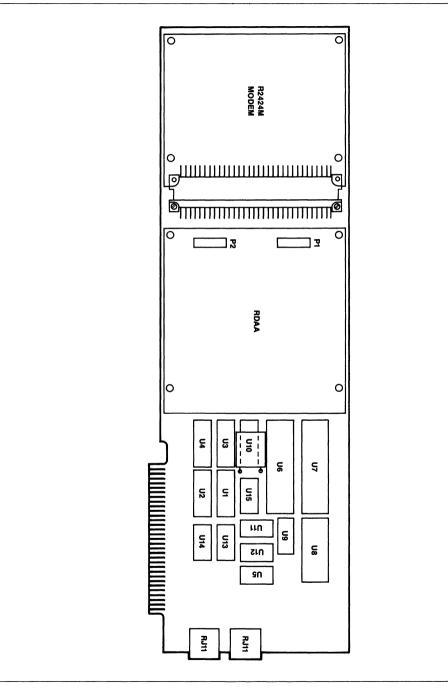

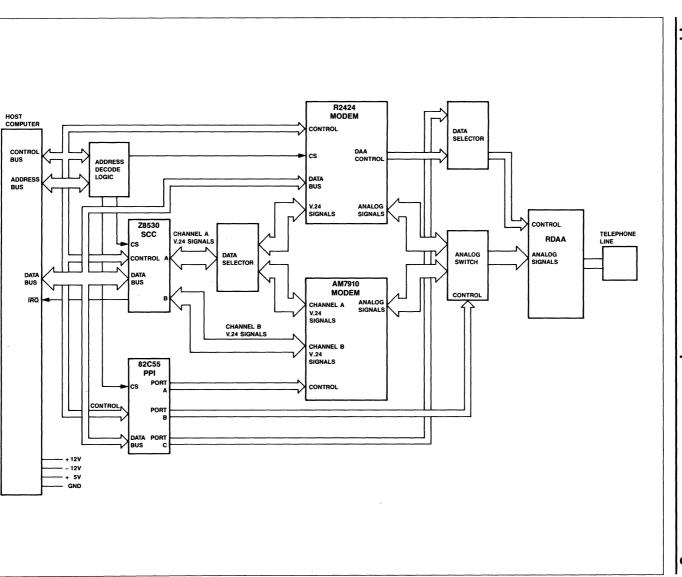

|   | Modems to an Apple Ile Computer                 | 5-46       |

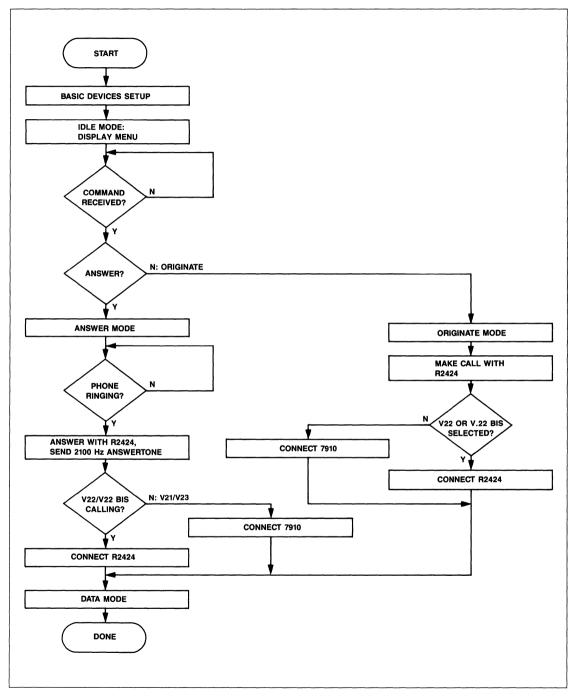

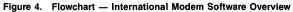

|   | 2400/1200/300 bps International Modern Design . | 5-50       |

|   | Quality of Received Data for Signal             |            |

|   | Processor-Based Modems                          | 5-83       |

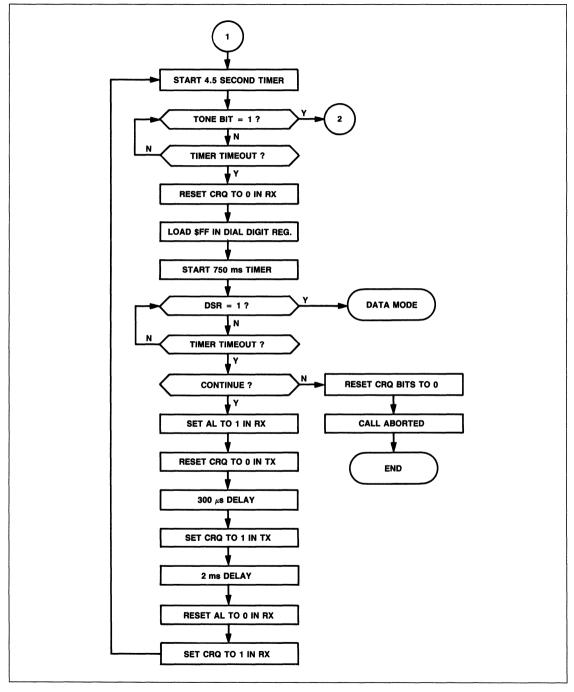

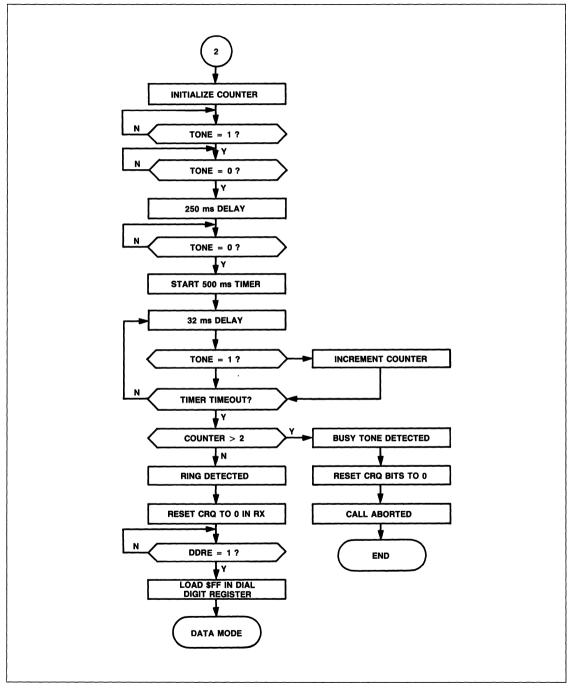

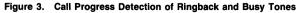

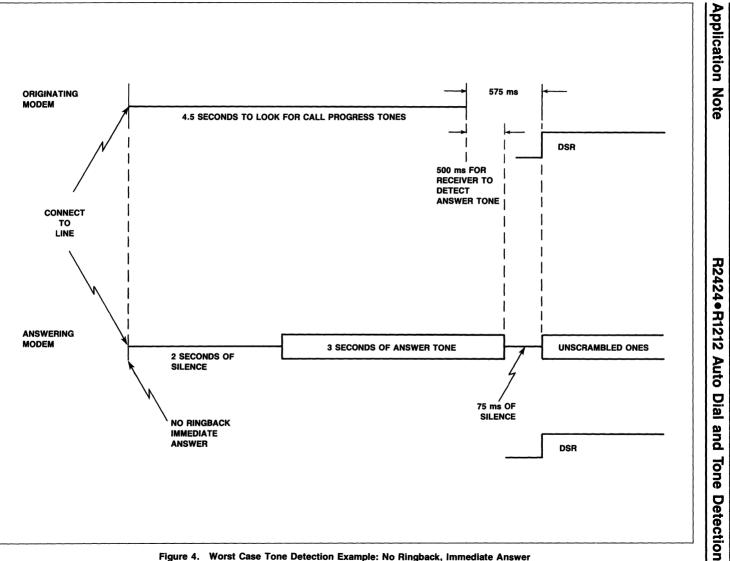

|   | R2424 and R1212 Modems Auto Dial and Tone       |            |

|   | Detection                                       | 5-104      |

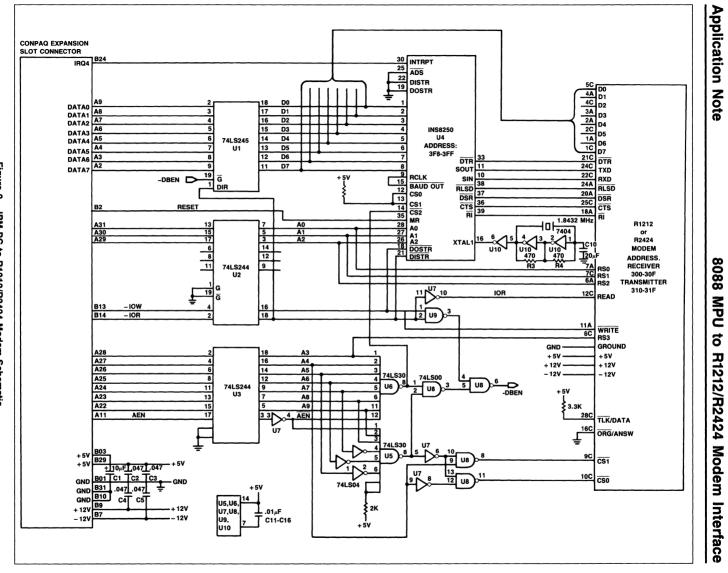

|   | 8088 Microprocessor to R1212/R2424 Modem        | 5-10-      |

|   | •                                               | E 114      |

|   | Interface                                       |            |

|   | High Speed Modems Filter Characteristics        |            |

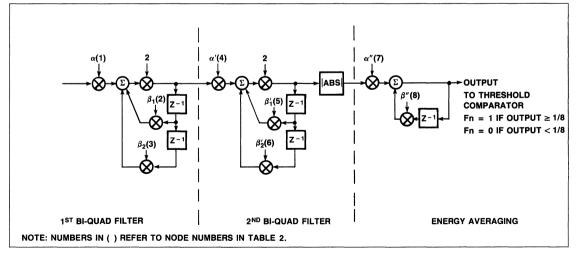

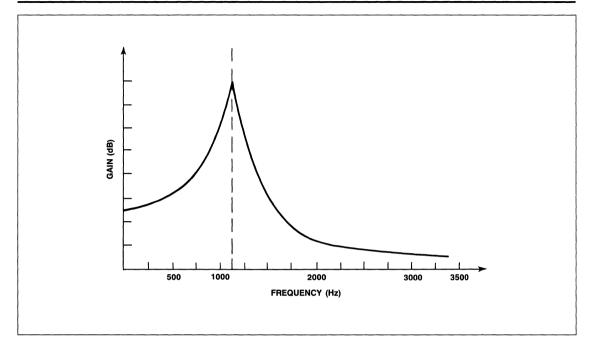

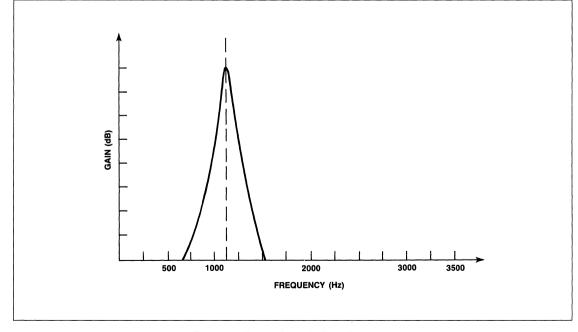

|   | R96F Modem Tone Detector Filter Tuning          | 5-121      |

|   | R96F Modem Recommended Receive                  |            |

|   | Sequence for Group 2 Facsimile                  | 5-127      |

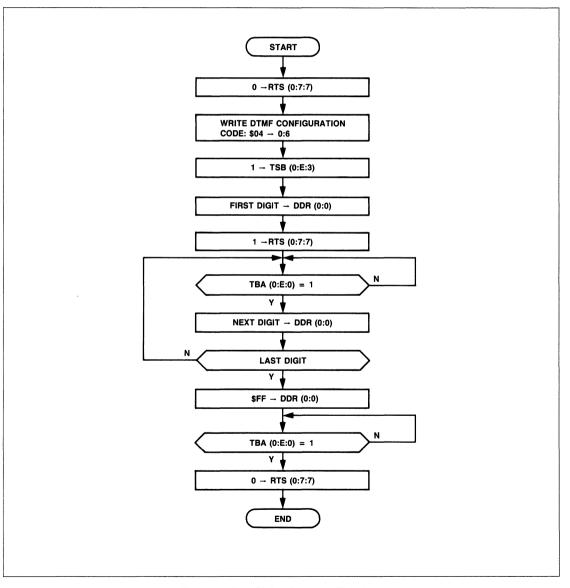

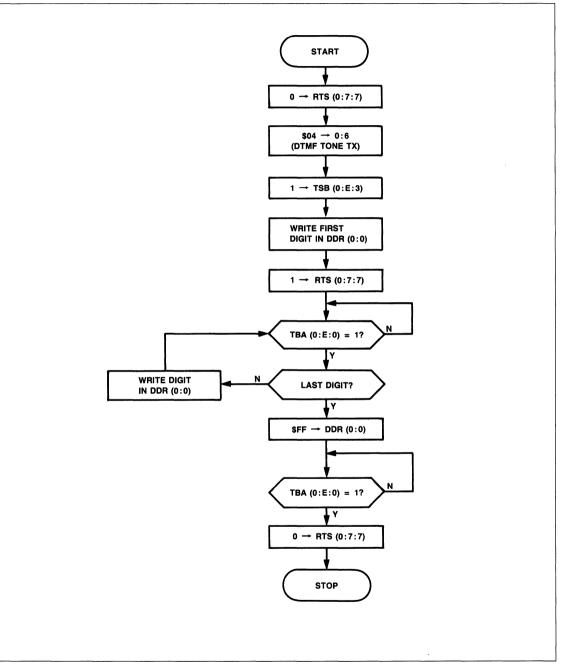

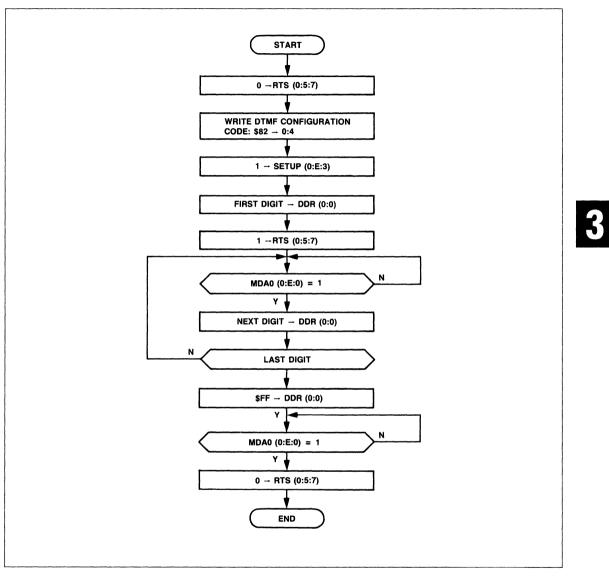

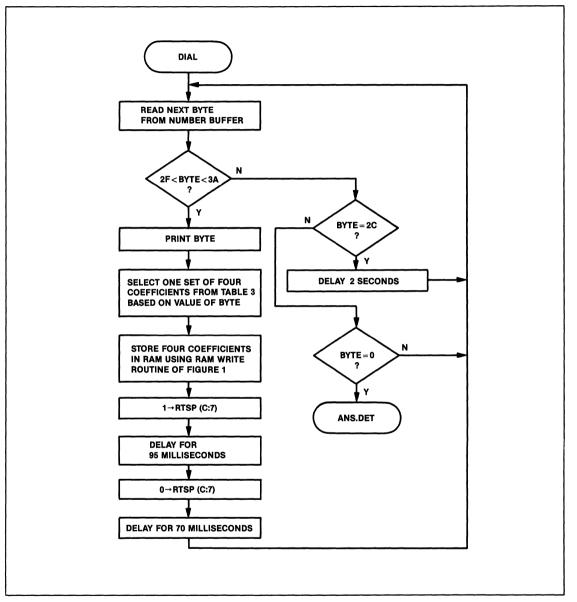

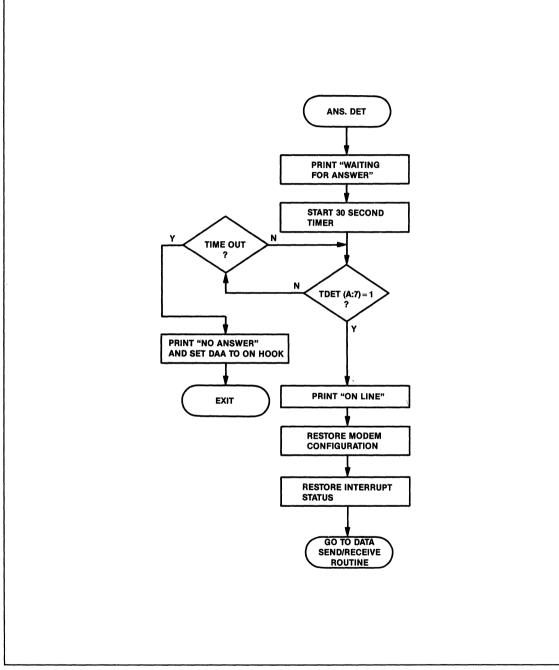

|   | DTMF Dialing for R24MFX, R48MFX, R24BKJ,        |            |

|   | or R48BKJ                                       | 5-130      |

|   |                                                 |            |

| - |                                                 |            |

| A | SPD Regional Offices and U.S./Canada            | <b>.</b> . |

|   | Sales Reps                                      | A-1        |

|   | SPD Industrial Distributers                     | A-3        |

|   | SPD International Distributers/Sales Reps       | A-5        |

|   | Notes                                           | A-6        |

# PART NO./DATA BOOK PAGE INDEX

Page

## Part No./Description

#### Part No./Description

Page

| R48PCJ 4800 bps PC Communication Modem       | 3-51  |

|----------------------------------------------|-------|

| R9696DP V.32 Ultra High Speed Modem          | 2-122 |

| R96DP 9600 bps Data Pump Modem               | 2-68  |

| R96F 9600 bps Facsimile Modem                | 3-93  |

| R96FT 9600 bps Fast Train Modem              | 2-90  |

| R96FT/SC 9600 bps Fast Train Modem with      |       |

| Forward Secondary Channel                    | 2-105 |

| R96MD 9600 bps Facsimile Modem               | 3-112 |

| R96MFX 9600 bps MONOFAX Modem                | 3-144 |

| R96PCJ 9600 bps PC Communication Modem       | 3-80  |

| RC1212 V.22 1200 bps Modem                   | 1-82  |

| RC2424 V.22 bis 2400 bps Modem               | 1-84  |

| RDAA Rockwell Data Access Arrangement Module | 1-86  |

| RG208 4800 bps Private Label Modem           | 4-5   |

| RG224EC 2400 bps Private Label Modem         | 4-3   |

| RGV29FT 9600 bps Private Label Modem         | 4-7   |

# Modem Products Setting Standards in Connectivity

Rockwell International's OEM modem products offer a highly reliable, cost effective solution for your modem needs. Rockwell has been a driving force behind data communications technology for over 30 years. In the early 1950's we introduced our first modem product. We later pioneered the development of many digital signal processing techniques such as automatic adaptive equalization, digital filtering carrier recovery, phase lock loop and quadrature amplitude modulation. In addition to advanced signal processing technology, Rockwell engineers have developed sophisticated analog filtering techniques.

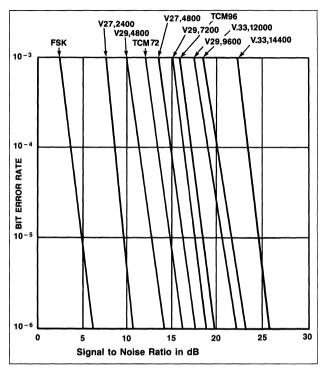

Today, Rockwell is a generation ahead of our competition with the first fully integrated VLSI modems. Whether communicating at 1200, 2400, 4800, 9600 or 14400 bps, we provide products for any dial-up or leased line modem requirement. High speed network control and multiplexers, personal computer and terminals, standalone and custom modems, facsimile and desktop publishing equipment are samples of end user equipment using Rockwell modems.

With the confidence borne of many years experience in the business, Rockwell offers a full five year warranty on all its standard modem modules and components. This guarantee to our customers reinforces Rockwell's commitment to quality and reliability.

Rockwell is the world's largest supplier of original equipment manufacturer (OEM) modems. We are uniquely positioned to provide the highest quality and performance at competitive prices. With extensive pre-and post-sale support from experienced application engineers, doing business with Rockwell combines the advantages of a large, stable supplier with the responsiveness and innovation of a small entrepreneurial firm.

MONOFAX is a trademark of Rockwell International. Microsoft is a registered trademark of Microsoft Corporation. HP and LaserJet are trademarks of Hewlett Packard. Smartcom II is a trademark of Hayes Microcomputer Products, Inc. Microcom Network Protocol and MNP are trademarks of Microcom, Inc CROSSTALK is a registered trademark of Digital Communications Associates, Inc

1200, 2400 bps Data Modems

4800, 9600, 14400 bps Data Modems

**Custom and Private Label Modems**

**Applications Notes**

| Imaging | Modems |  |

|---------|--------|--|

|---------|--------|--|

2

**PRODUCT INDEX**

3

Λ

5

.

# SECTION 1 1200, 2400 bps DATA MODEMS

|                                                         | гауе |

|---------------------------------------------------------|------|

| Product Family Overview                                 | 1-2  |

| R212DP Device Set Bell 212A Compatible                  | 1-3  |

| R212AT Device Set "AT" Command Set Bell 212A Compatible | 1-5  |

| R1212 1200 bps Full-Duplex Modem                        | 1-7  |

| R2424 2400 bps Full-Duplex Modem                        | 1-36 |

| R201/26DP 2400/1200 bps Data Pump Modem                 | 1-65 |

| RC1212 V.22 1200 bps Modem                              | 1-82 |

| RC2424 V.22 bis 2400 bps Modem                          | 1-84 |

| RDAA Rockwell Data Access Arrangement Module            | 1-86 |

# 1200, 2400 bps DATA MODEMS Experience Makes a Difference

Rockwell's line of 1200 and 2400 bit-per-second (bps) modem products can easily be incorporated into products requiring high performance, quality and reliability while maintaining a competitive cost advantage. Whether the modem application is internal to a personal computer, or for installation in remote monitoring equipment, Rockwell has a product with the features, form factor and price to meet your requirement.

With the medium speed modem market moving so quickly, time to market is critical. For designers not wishing to develop a custom product, Rockwell offers a Bell 212A and 103 compatible, two-chip set modem with an RS-232-C interface. It also includes the standard "AT" command set in firmware. With minimal external components, such as the FCC-required phone line protection circuitry, a complete modem can be developed within a few weeks. For product designs requiring more flexibility and control, Rockwell offers a standard microprocessor bus (8088 compatible) interface along with user accessible, dual port scratch pad RAM. Together, they allow you to treat the Rockwell modem as a microprocessor peripheral device thus speeding design time. Also, the scratch pad RAM allows the modem to be easily controlled and configured for a wide variety of applications in markets worldwide.

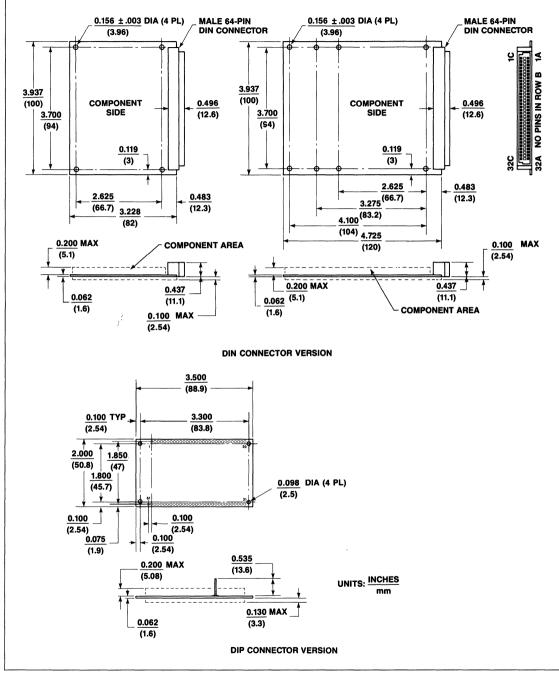

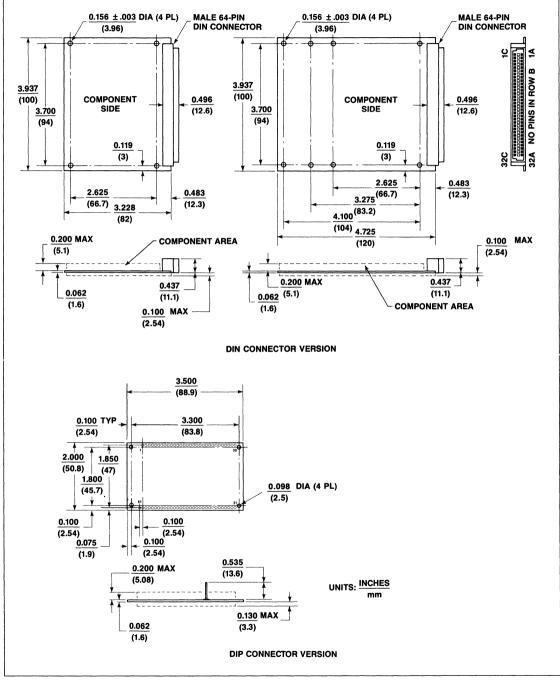

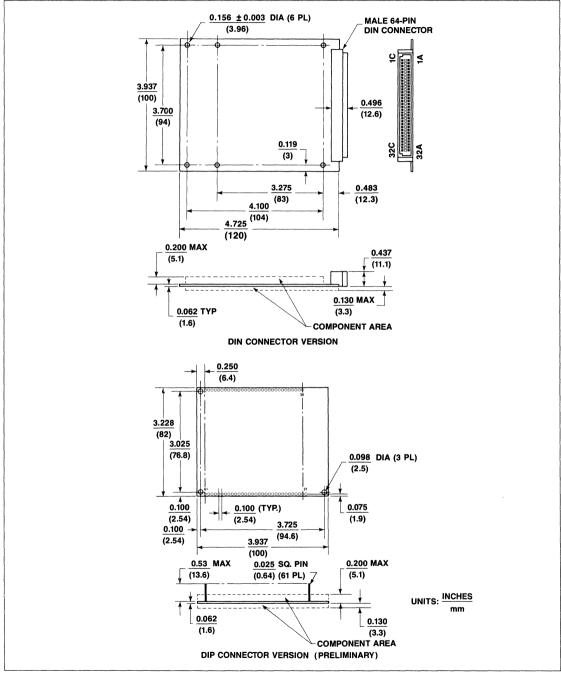

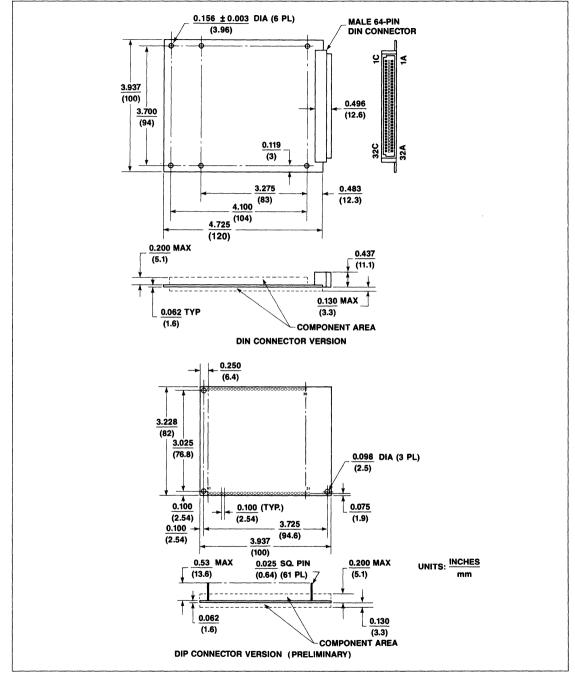

Rockwell also maximizes the design option to develop a single host board and, by plugging in different Rockwell device sets or modules, have a variety of full- or half-duplex, 1200 or 2400 bps modems. Rockwell pioneered this concept with Eurosized modules incorporating DIN connectors. Now, the next generation form factor is available — a module only seven inches square with dual-in-line pins. This DIP module can be handled as any DIP-type integrated circuit during board assembly and wave soldering. Its small size is ideal for extremely dense designs, such as "1/2 card" modems for personal computers. What's more, all medium speed DIP module products are pin compatible and have the same external dimensions. System designers thereby have a smooth, economical upgrade path from the current R1212 and R2424 products to the new RC1212 and RC2424 families.

| Model     | Data Speed<br>(bps)       | PSTN/<br>Leased<br>Line | 2/4-Wire<br>Half/Full-Duplex | Sync/Async  | Compliance                                                 |

|-----------|---------------------------|-------------------------|------------------------------|-------------|------------------------------------------------------------|

| R212AT    | 1200, 0-300               | Р                       | 2WFD                         | Async       | Bell 212A, 103<br>"AT" Command Set                         |

| R212DP    | 1200, 0-300               | Р                       | 2WFD                         | Async       | Bell 212A, 103                                             |

| R1212     | 1200, 600,<br>0-300       | P/L                     | 2WFD                         | Sync, Async | CCITT V.22 A/B;<br>Bell 212A, 103                          |

| R2424     | 2400, 1200,<br>600, 0-300 | P/L                     | 2WFD                         | Sync, Async | CCITT V.22 bis, V.22 A/B;<br>Bell 212A, 103                |

| R201/26DP | 2400, 1200                | P/L                     | 2WHD, 4WFD                   | Sync        | CCITT V.26, V.26 bis;<br>Bell 201B/C                       |

| RC1212    | 1200, 600,<br>0-300       | P/L                     | 2WFD                         | Sync, Async | CCITT V.22 A/B, V.21; V.23;<br>Bell 212A, 103              |

| RC2424    | 2400, 1200,<br>600, 0-300 | P/L                     | 2WFD                         | Sync, Async | CCITT V.22 bis, V.22 A/B,<br>V.21, V.23;<br>Bell 212A, 103 |

# R212DP/DS and R212DP/EB

# R212DP Modem Device Set Bell 212A Compatible

## INTRODUCTION

The R212DP/DS Data Pump device set is a high performance 1200/300 bps modem. Using state-of-the-art VLSI technology, the R212DP provides the entire modulation/demodulation process, high and low band filtering, and complete auto dialing function in only two devices.

The R212DP is ideal for data transmission over the 2-wire dial-up network. Bell 212A and 103 compatible, the R212DP can handle virtually all applications for full-duplex 1200 bps and 0 to 300 bps asynchronous data transmission over the public switched telephone network (PSTN).

The RS-232-C compatible interface integrates easily into a personal computer, box modem, terminal or any other communications product. The added feature of an integral asynchronous serial auto dialer capable of dialing with DTMF tones or pulses from its 40-byte character buffer offers the user added flexibility in creating a 1200 bps modem customized for specific packaging and functional requirements.

An R212DP/EB Evaluation Board is also available to aid modem system design and evaluation. Included on the printed circuit board are the R212DP/DS modem device set, RS-232-C connector, power connector, an RJ-11 phone jack, six LED indicators, and four configuration switches. The evaluation board comes with an in-depth R212DP Device Set Designer's Guide (Order No. 678) and a wall-mount power supply. All that is required to use the R212DP/EB is an RS-232-C cable connected to a terminal or computer, and a phone cord.

## **FEATURES**

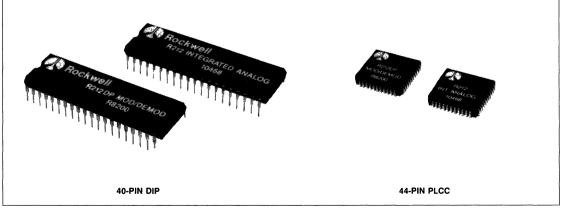

- 2 Device Implementation

- R8200 Modulator/Demodulator

10468 Integrated Analog

- Bell 212A and 103 Compatible (2-Wire Full-Duplex)

Asynchronous

1200 bps DPSK (+1%, -2.5%)

- 0-300 bps FSK Auto Fallback, Answer Mode

- DTE Interface

Functionally: RS-232-C Compatible

Electrically: TTI

- Electrically: TTL

- Auto/Manual Answer

- Auto/Manual Dial

- --- DTMF or Pulses --- 0-9 # \*, T P CR (ASCII)

- 40-Byte Character Buffer

- 10-Bit Character Length

- Break Generation/Detection

- Send/Receive Space Disconnect

- Automatic Adaptive Equalizer

- Analog Loopback

0 to 300 bps, 1200 bps

- Packaging Options

- 40-pin Plastic DIP

- 44-pin PLCC

R212DP/DS Modem Device Set

# R212DP

# **Data Pump Modem Device Set**

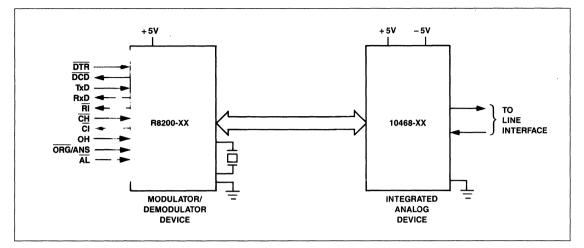

R212DP/DS Modem Device Set Interface Diagram

# **SPECIFICATIONS**

#### **Power Consumption**

+5 Vdc ±5% <300 mA -5 Vdc ±5% <40 mA 600 mW (typical)

#### Environmental

Temperature: Operating 0°C to 70°C Storage -55°C to +150°C Relative Humidity: Up to 90% noncondensing, or a wet bulb temperature up to 35°C, whichever is less.

# R212AT Modem Device Set "AT" Command Set Bell 212A Compatible

# 1

## INTRODUCTION

The R212AT/DS ("AT" Command Set Compatible) device set is a high performance 1200/300 bps modem. Using state-of-theart VLSI technology, the R212AT provides the entire modulation/ demodulation process, high and low band filtering, and an enhanced "AT" Command Set in only two devices.

The R212AT is ideal for data transmission over the 2-wire dial-up network. Bell 212A and 103 compatible, the R212AT can handle virtually all applications for full-duplex 1200 bps and 0 to 300 bps asynchronous data transmission over the public switched telephone network (PSTN).

The RS-232-C compatible interface integrates easily into a personal computer, box modem, terminal or any other communications product. The added features of the enhanced "AT" Command Set offer the user added flexibility in creating a 1200 bps modem customized for specific packaging and functional requirements. The R212AT can be readily used with industry standard communication software packages.

An R212AT/EB Evaluation Board is also available to aid modem system design and evaluation. Included on the printed circuit board are the R212AT/DS modem device set, RS-232-C connector, power connector, two RJ-11 phone jacks, 11 LED indicators, four configuration switches, and a speaker with volume control. The evaluation board comes with a detailed R212AT Device Set Designer's Guide (Order No. 686), and a wall-mount power supply. All that is required to use the R212AT/EB is an RS-232-C cable connected to a terminal or computer, and a phone cord.

## FEATURES

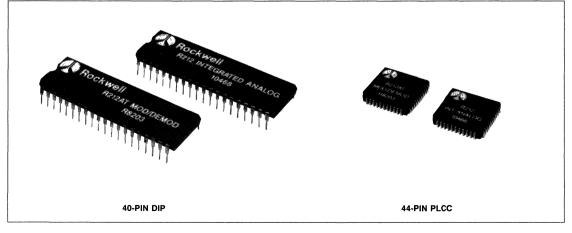

- 2 Device Implementation

- R8203 Modulator/Demodulator

- 10468 Integrated Analog

- · Bell 212A and 103 Compatible (2-Wire Full-Duplex)

- 1200 bps DPSK (+1%, -2.5%) asynchronous

- 0-300 bps FSK asynchronous

- Auto Fallback, Answer Mode

- Auto/Manual Answer

- Auto/Manual Dial

- "AT" Command Set (see reverse side)

- DTE Interface

- Functionally: RS-232-C Compatible

- Electrically: TTL

- Data Format

- 7 Data Bits; 1 or 2 Stop Bits; Even, Odd, or Fixed Parity

- 8 Data Bits; 1 or 2 Stop Bits; No Parity

- Automatic Adaptive Equalizer

- Packaging Options

- 40-pin Plastic DIP

- 44-pin PLCC

R212AT/DS Modem Device Set

Document No. 29220N83

Order No. 683 Rev. 2, February 1987

# **R212AT**

# "AT" Compatible Modem Device Set

| Command | Function            | Command | Function            | Command | Function             |

|---------|---------------------|---------|---------------------|---------|----------------------|

| AT      | Attention Code      | Sr=n    | Set Register        | н       | On/Off Hook          |

| A/      | Repeat Last Command | V V     | Verbal/Numeric      |         | Returns Product Code |

| Α       | Answer              |         | Result Code         | M       | Speaker On/Off       |

| D       | Dial                |         | Pause               | 0       | On Line              |

| R       | Reverse Dial        |         | Return to Command   | Q       | Quiet On/Off         |

| т       | Tone Dial           |         | State After Dialing | l z     | Reset                |

| Р       | Pulse Dial          | E       | Echo On/Off         | +++     | Escape Code          |

| Sr?     | Read Register       |         |                     |         |                      |

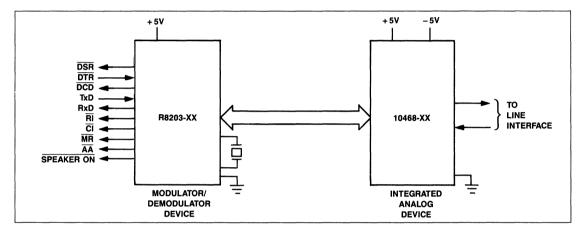

# R212AT/DS Modem Device Set Interface Diagram

# Environmental

SPECIFICATIONS Power Consumption +5 Vdc ±5% <300 mA

-5 Vdc  $\pm 5\%$  < 300 mA -5 Vdc  $\pm 5\%$  < 40 mA 600 mW (typical) Temperature: Operating 0°C to 70°C Storage - 55°C to + 150°C Relative Humidity: Up to 90% noncondensing, or a wet bulb temperature up to 35°C, whichever is less.

# R1212 Integral Modems

# R1212 1200 bps Full-Duplex Modem

# INTRODUCTION

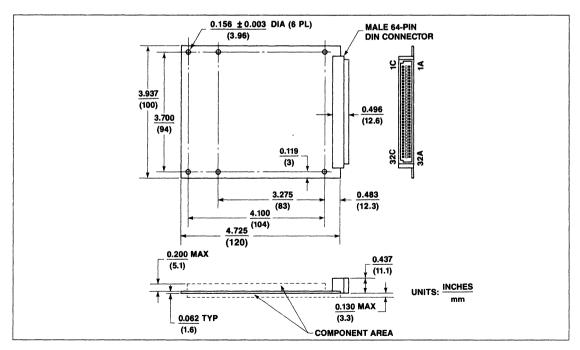

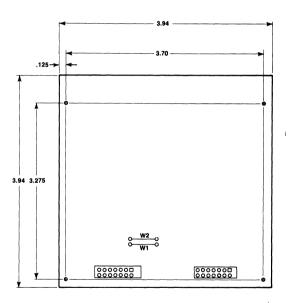

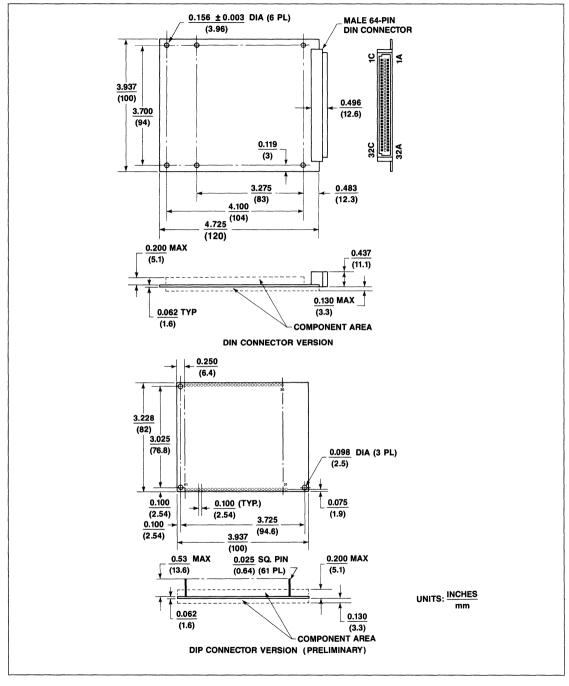

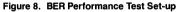

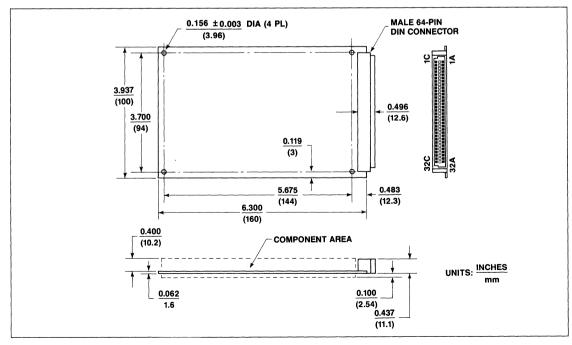

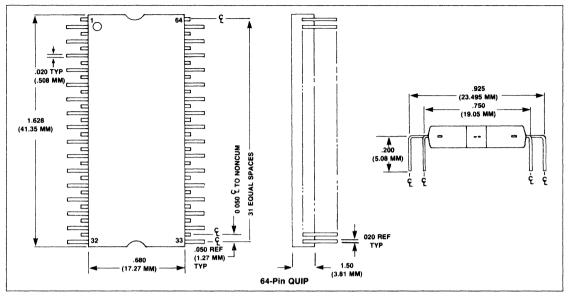

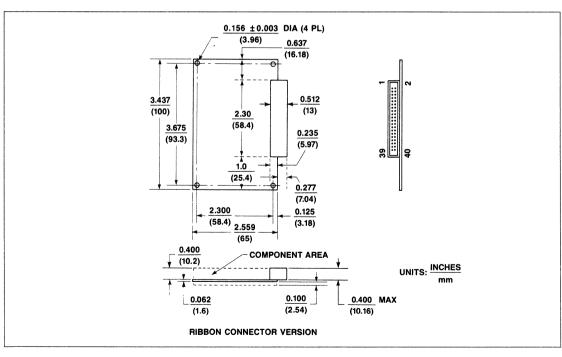

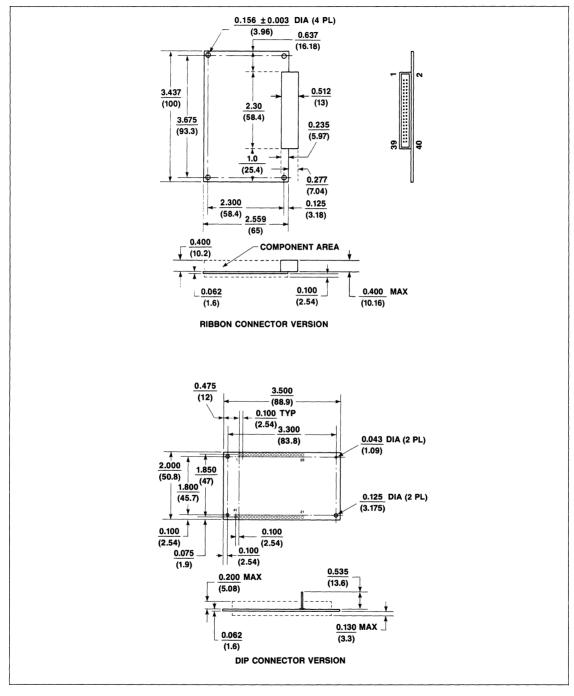

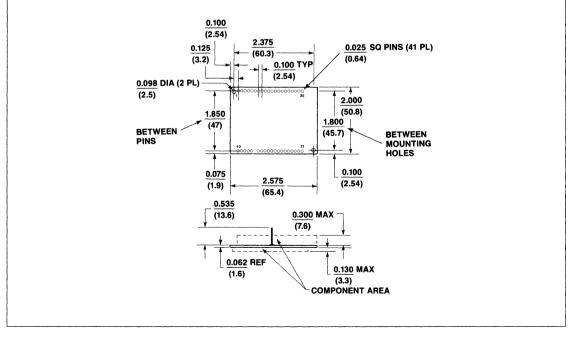

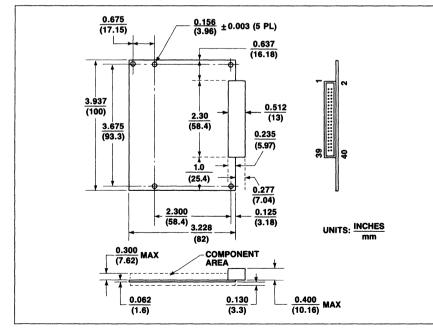

The Rockwell R1212 is a high performance full-duplex 1200 bps modem. Using state-of-the-art VLSI and signal processing technology, the R1212 provides enhanced performance and reliability. The modem is assembled as a small module with a DIN connector (R1212M and R1212DC) or a new, smaller module (seven square inches) with a dual-in-line pin (DIP) interface.

Being CCITT V.22 A, B compatible, as well as Bell 212A and 103 compatible, the R1212 fits most applications for full-duplex 1200 bps (synchronous and asynchronous) and 0 to 300 bps asynchronous data transmission over the general switched telephone network, and over point-to-point leased lines.

The direct-connect, auto dial/answer features are specifically designed for remote and central site computer applications. The bus interface allows easy integration into a personal computer, box modem, microcomputer, terminal or any other communications product that demands the utmost in reliability and performance.

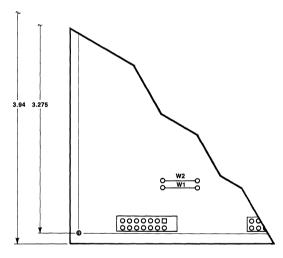

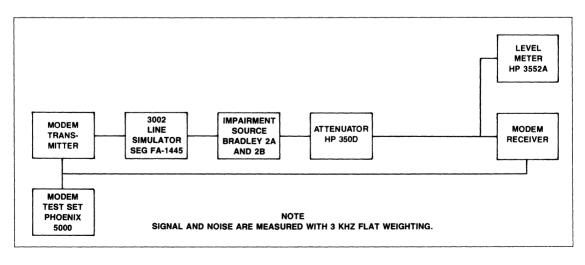

The R1212/DM, with its small form factor and DIP connection, can be automatically installed and soldered onto a host module. Its small size is ideal for internal "1/2-card" PC modem applications. Moreover, the R1212/DM is pin and firmware compatible with the R2424/DM and pin compatible with Rockwell's next generation of medium speed modems, the RC2424 and RC1212.

R1212M Modem

#### Document No. 29200N10

# FEATURES

- CCITT V.22 A, B Compatible

- Bell 212A and 103 Compatible

- Synchronous: 1200 bps, 600 bps ± 0.01%

- Asynchronous: 1200 bps, 600 bps + 1%, -2.5%, 0-300 bps

- Character Length 8, 9, 10, or 11 bits

- DTE Interface

- Functional: CCITT V.24 (RS-232-C) (Data/Control) and Microprocessor Bus (Data/Configuration/Control)

- Electrical: TTL Compatible

- 2-wire Full-Duplex Operation

- Adaptive and Fixed Compromise Equalization

- Test Configurations:

- Local Analog Loopback

- Remote Digital Loopback

- Self Test

- Auto/Manual Answer

- Auto/Manual Dial—DTMF Tone or Pulse Dial

- Power Consumption: 2.3 Watts Typical

- Power Requirements: +5 Vdc, ±12 Vdc

- Three Functional Configurations:

- R1212DC (Direct Connect): DIN connector module with FCC approved DAA Part 68 Interface

- R1212M: DIN connector module without DAA

- R1212/DM: DIP connection module without DAA

R1212/DM Modem

Order No. MD10 Rev. 4, February 1987

# **TECHNICAL SPECIFICATIONS**

# TRANSMITTER CARRIER AND SIGNALING FREQUENCIES

The transmitter and signaling frequencies supported in the R1212 are listed in Table 1.

Table 1. Transmitter Carrier and Signaling Frequencies Specifications

| Mode                                 | Frequency<br>(Hz ±0.01%) |

|--------------------------------------|--------------------------|

| V.22 low channel, Originate Mode     | 1200                     |

| V.22 high channel, Answer Mode       | 2400                     |

| Bell 212A high channel Answer Mode   | 2400                     |

| Bell 212A low channel Originate Mode | 1200                     |

| Bell 103/113 Originating Mark        | 1270                     |

| Bell 103/113 Originating Space       | 1070                     |

| Bell 103/113 Answer Mark             | 2225                     |

| Bell 103/113 Answer Space            | 2025                     |

#### TONE GENERATION

The specifications for tone generation are as follows:

- Answer Tones: The R1212 generates echo disabling tones for both the CCITT and Bell configurations, as follows:

a. CCITT: 2100 Hz ± 15 Hz.

- b. Bell: 2225 Hz ± 10 Hz.

- 2. Guard Tones: If GTS (see Interface Memory Definitions) is low, an 1800 Hz guard tone frequency is selected; if GTS is high, a 553.846 Hz tone is employed. In accordance with the CCITT V.22 Recommendation, the level of transmitted power for the 1800 Hz guard tone is  $6 \pm 1$  dB below the level of the data power in the main channel. The total power transmitted to the line is the same whether or not a guard tone is enabled. If a 553.846 Hz guard is used, its transmitted power is  $3 \pm 1$  dB below the level of the main channel power, and again the overall power transmitted to the line will remain constant whether or not a guard tone is enabled. The device accomplishes this by reducing the main channel transmit path gain by .97 dB and 1.76 dB for the cases of the 1800 Hz and 553.846 Hz guard tones respectively.

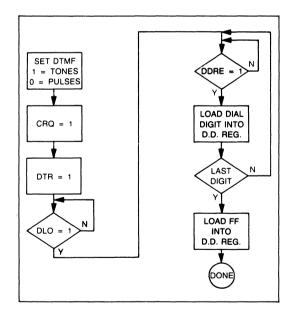

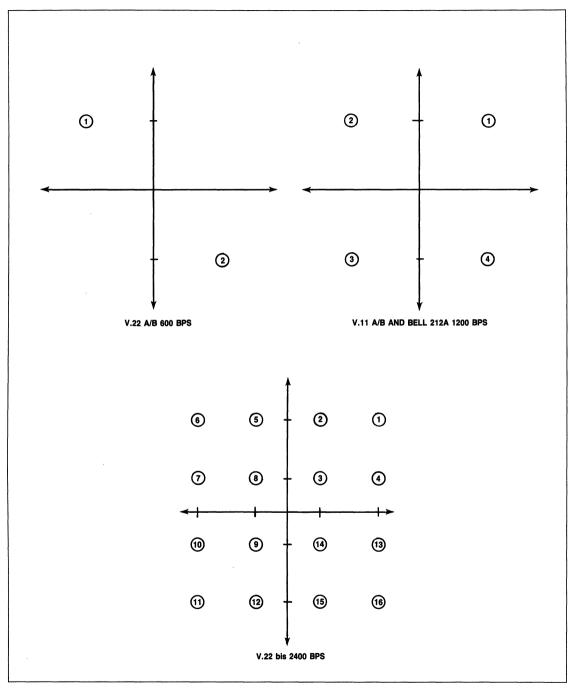

# 1200 bps Full-Duplex Modem

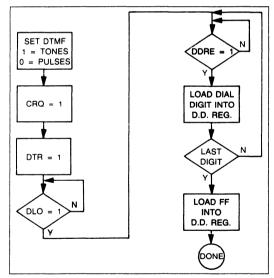

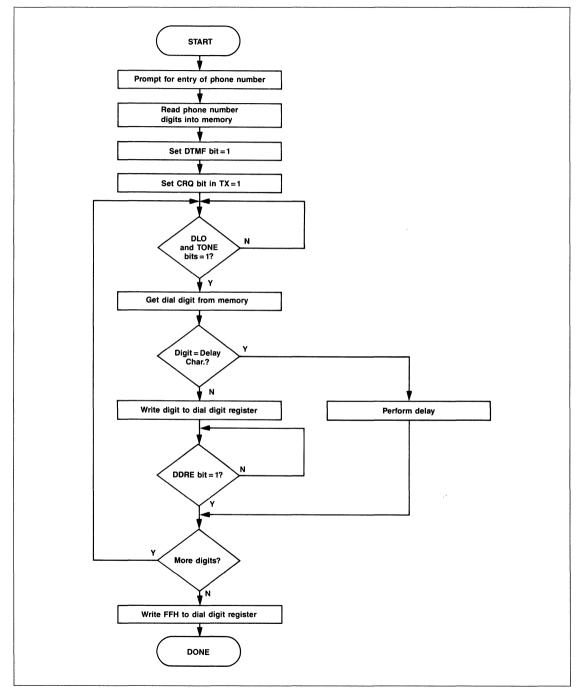

3. DTMF Tones: The R1212 generates dual tone multifrequency tones. When the transmission of DTMF tones are required, the CRQ and DTMF bits (see Interface Memory Definitions)must be set to a 1. When in this mode, the specific DTMF tones generated are decided by loading the dial digit register with the appropriate digit as shown in Table 2.

T-1-1- A

| Dial |                      |            |      |  |

|------|----------------------|------------|------|--|

| Hex  | Digits               | Tone Pairs |      |  |

| 00   | 0                    | 941        | 1336 |  |

| 01   | 1                    | 697        | 1209 |  |

| 02   | 2                    | 697        | 1336 |  |

| 03   | 3                    | 697        | 1477 |  |

| 04   | 4                    | 770        | 1209 |  |

| 05   | 5                    | 770        | 1336 |  |

| 06   | 6                    | 770        | 1477 |  |

| 07   | 7                    | 852        | 1209 |  |

| 08   | 8                    | 852        | 1336 |  |

| 09   | 9                    | 852        | 1477 |  |

| 0A   | *                    | 941        | 1209 |  |

| 0B   | Spare (B)            | 697        | 1633 |  |

| 0C   | Spare (C)            | 770        | 1633 |  |

| 0D   | Spare (D)            | 852        | 1633 |  |

| 0E   | #                    | 941        | 1477 |  |

| 0F   | Spare (F)            | 941        | 1633 |  |

| 10   | 1300 Hz Calling Tone |            |      |  |

#### TONE DETECTION

The R1212 detects tones in the 340  $\pm$ 5 Hz to 640  $\pm$ 5 Hz band. Detection Level. -10 dBm to -43 dBm Response Time: 17  $\pm$ 2 ms

#### SIGNALING AND DATA RATES

The signaling and data rates for the R1212 are defined in Table 3.

| Operating Mode                        | Signaling Rate (Baud) | Data Rate                                                              |

|---------------------------------------|-----------------------|------------------------------------------------------------------------|

| V.22<br>(Alternative A)               |                       |                                                                        |

| Mode i                                | 600                   | 1200 bps ±0.01% Synchronous                                            |

| Mode III                              | 600                   | 600 bps ±0.01% Synchronous                                             |

| (Alternative B)<br>Mode i<br>Mode III | 600<br>600            | 1200 bps ±0.01% Synchronous<br>600 bps ±0 01% Synchronous              |

| Mode ii                               |                       | 1200 bps Asynchronous, 8, 9, 10 or 11 Bits Per Character               |

| Mode iv                               |                       | 600 bps Asynchronous, 8, 9, 10 or 11 Bits Per Character                |

| Bell 212A;                            | 600<br>0 to 300       | 1200 bps ±0.01%, Synchronous/Asynchronous<br>0 to 300 bps Asynchronous |

Table 3. Signaling and Data Rates

# 1200 bps Full-Duplex Modem

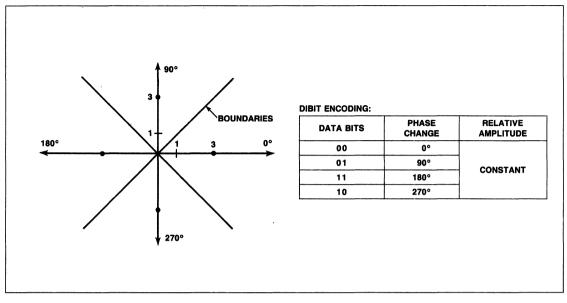

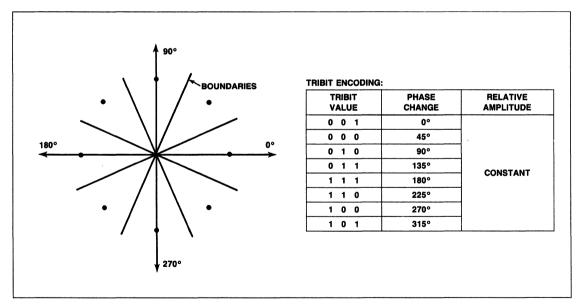

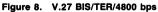

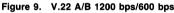

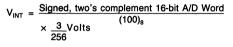

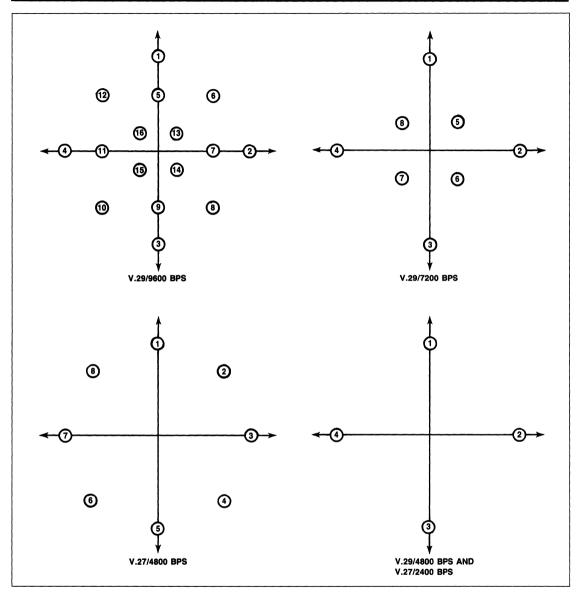

## DATA ENCODING

The specifications for data encoding are as follows:

- 1200 bps (V.22 and Bell 212A). The transmitted data is divided into groups of two consecutive bits (dibits) forming a four-point signal structure.

- 600 bps (V.22). Each bit is encoded as a phase change relative to the phase preceding signal elements.

#### EQUALIZERS

The R1212 provides equalization functions that improve performance when operating over low quality lines.

Automatic Adaptive Equalizer—An automatic adaptive equalizer is provided in the receiver circuit for V.22 and Bell 212A configurations.

**Fixed Compromise Equalizer**—A fixed compromise equalizer is provided in the transmitter.

#### TRANSMITTED DATA SPECTRUM

After making allowance for the nominal specified compromise equalizer characteristic, the transmitted line signal has a frequency spectrum shaped by the square root of a 75 percent raised cosine filter. Similarly, the group delay of the transmitter output is within  $\pm$  150 microseconds over the frequency range 900 to 1500 Hz (low channel) and 2100 to 2700 Hz (high channel).

#### SCRAMBLER/DESCRAMBLER

The R1212 incorporates a self-synchronizing scrambler-/descrambler. In accordance with the CCITT V.22 and the Bell 212A recommendations.

#### **RECEIVED SIGNAL FREQUENCY TOLERANCE**

The receiver circuit of the R1212 can adapt to received frequency errors of up to  $\pm$ 7 Hz with less than a 0.2 dBm degradation in BER performance.

#### **RECEIVE LEVEL**

The receiver circuit of the R1212 satisfies all specified performance requirements for the received line signals from  $-10 \, dBm$  to  $-48 \, dBm$ . The received line signal is measured at the receiver analog input RXA.

#### TRANSMIT LEVEL

The R1212M output control circuitry contains a variable gain buffer which reduces the modem output level. The R1212M can be strapped via the host interface memory to accomplish this.

## PERMISSIVE/PROGRAMMABLE CONFIGURATIONS

The R1212M transmit level is +6 dBm to allow a Data Access Arrangement (DAA) to be used. The DAA then determines the permissive or programmable configuration.

The R1212DC transmit level is strapped in the permissive mode so that the maximum output level is  $-10 \text{ dBm} \pm 1.0 \text{ dBm}$ .

#### AUTOMATIC RECONFIGURATION

The R1212 is capable of automatically configuring itself to the compatibility of a remote modern. The R1212 can be in either the answer or originate mode for this to occur. The R1212 adaptation compatibilities are limited to V.22 A/B (1200 bps), Bell 212, and Bell 103. If the R1212 is to originate in a specific configuration, the MODE bits (see Interface Memory Definitions) must be set.

## **MODEM OPERATION**

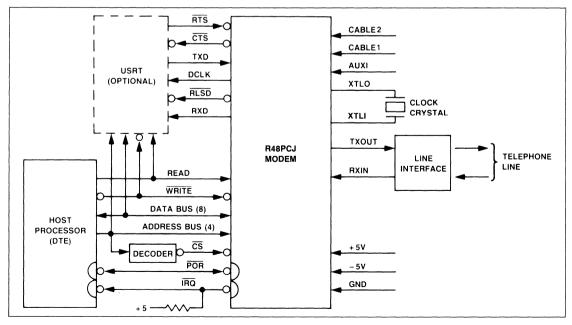

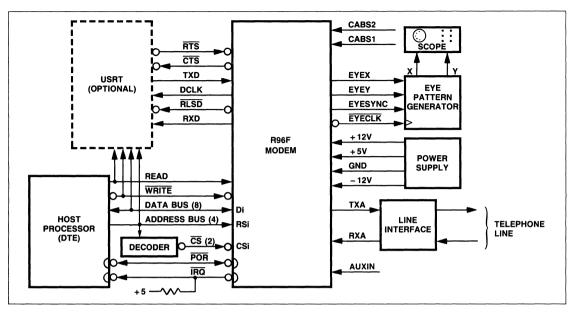

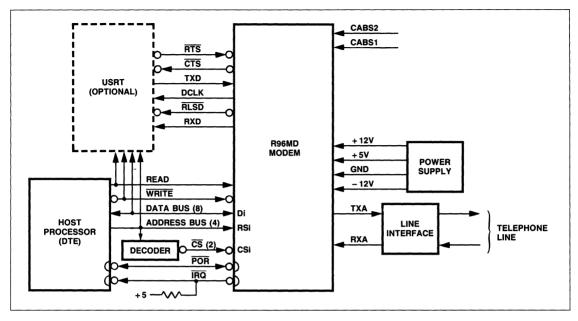

Because the modem is implemented in firmware executed by a specialized computer (the signal processor), operation can best be understood by dividing this section into hardware circuits and software circuits. Hardware circuits include all pins on the modem connector. Software circuits include configuration, control (soft strapping), status, and RAM access routines.

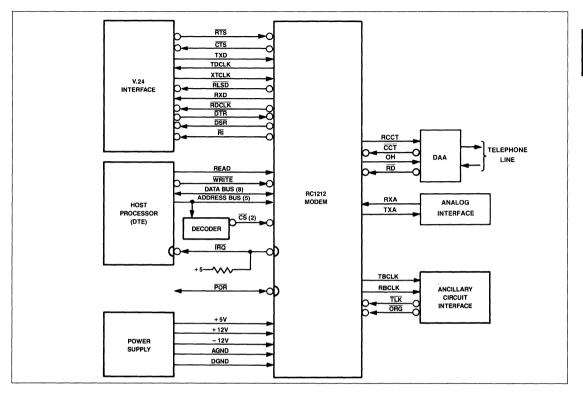

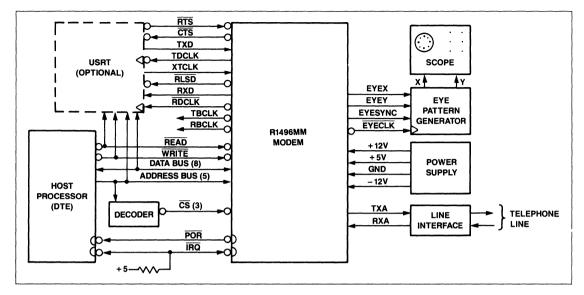

## HARDWARE CIRCUITS

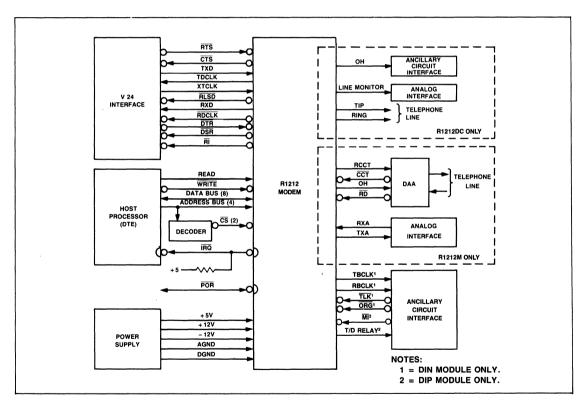

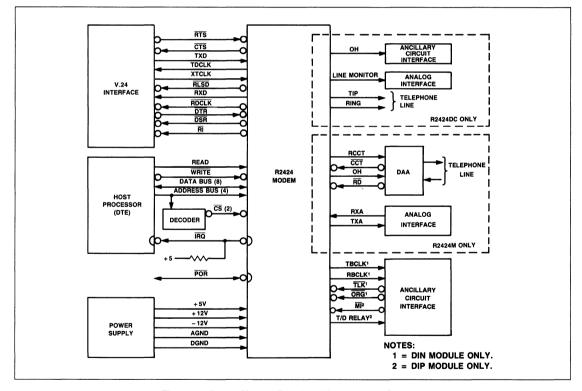

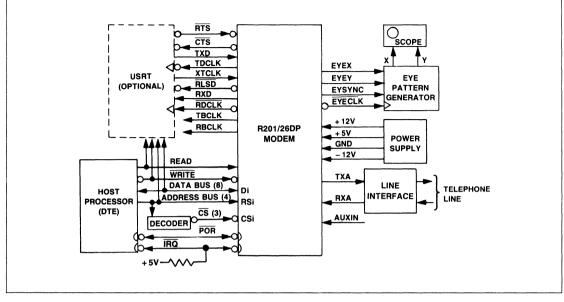

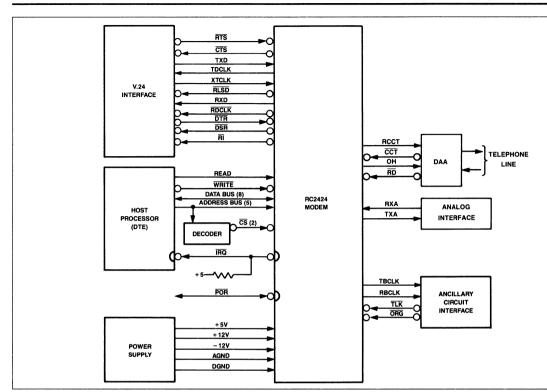

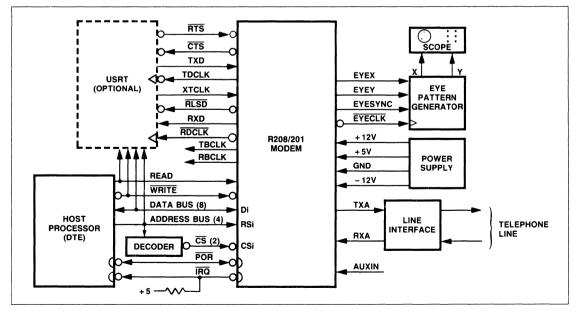

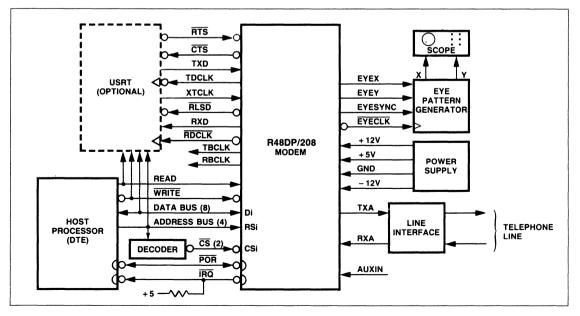

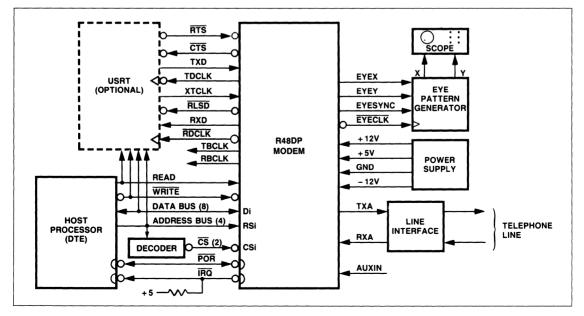

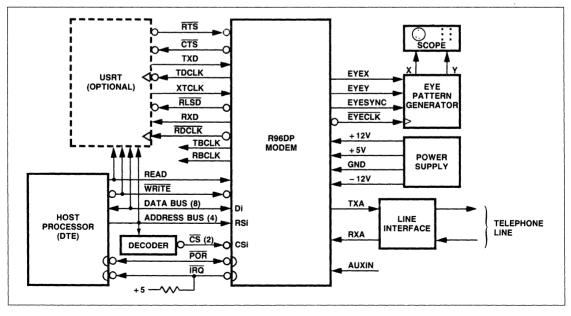

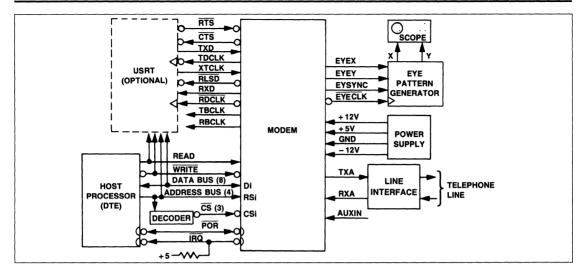

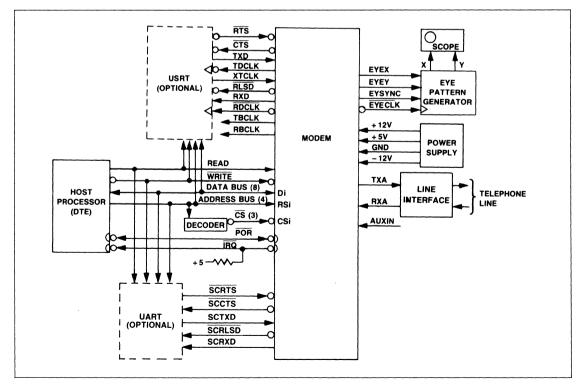

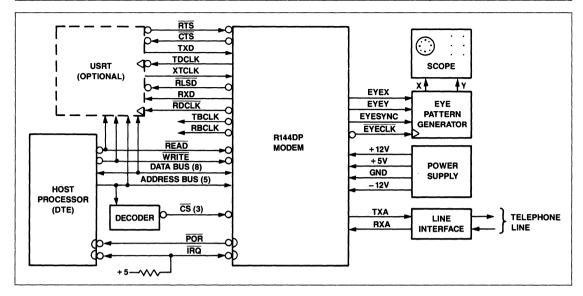

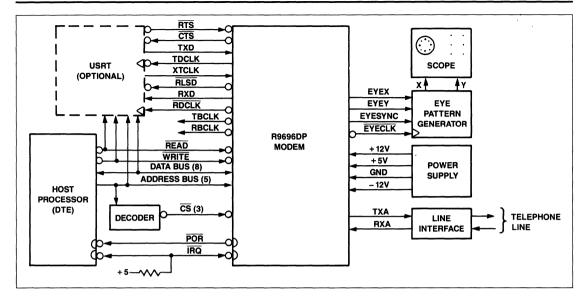

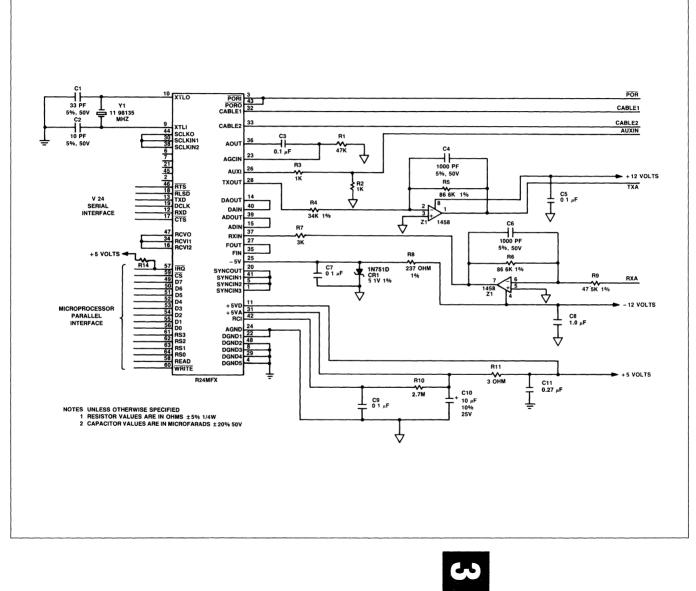

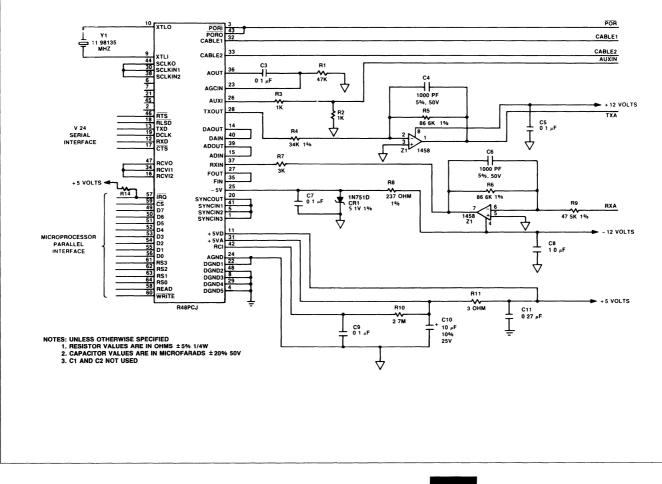

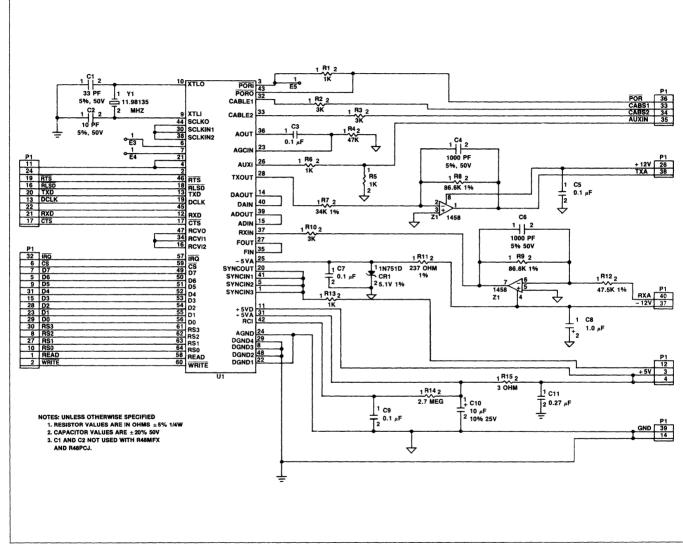

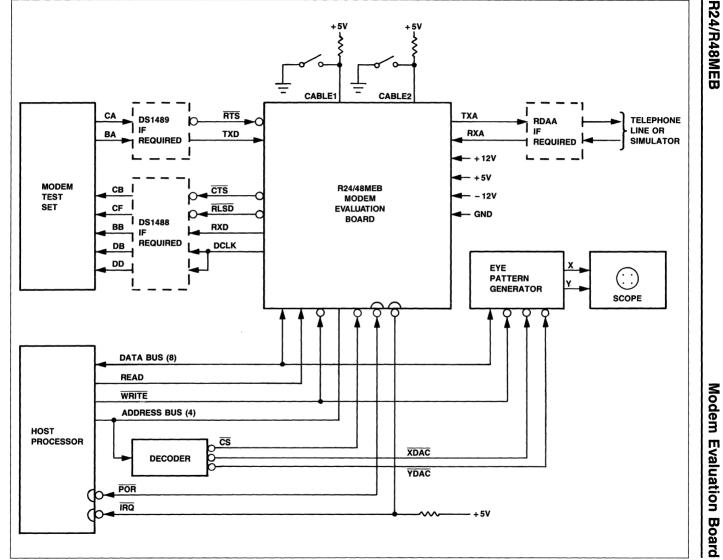

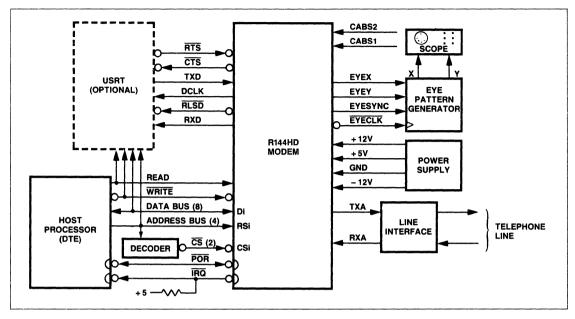

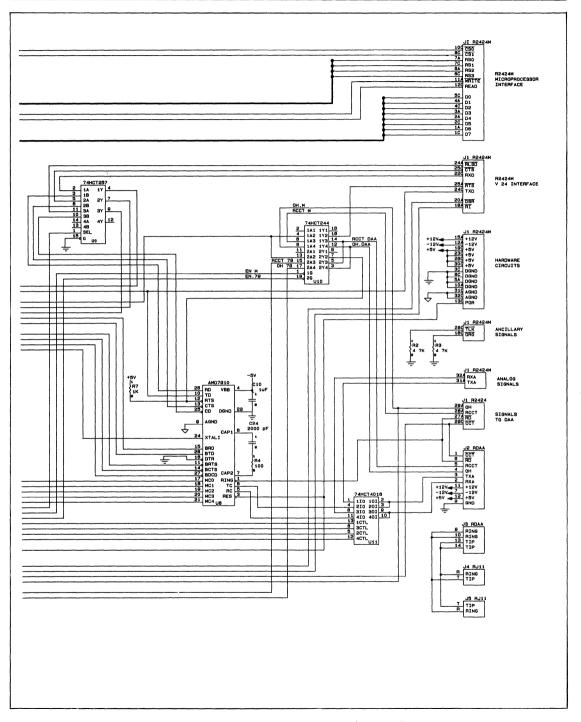

The functional interconnect diagram (Figure 1) shows the modem connected into a system. In this diagram, any point that is active when exhibiting the relatively more negative voltage of a two voltage system (e.g., 0 Vdc for TTL or -12 Vdc for RS-232-C) is called low active and is represented by association with a small circle at the signal point. The particular voltage levels used to represent the binary states do not change the logic symbol. Two types of I/O points that may cause confusion are edge-triggered inputs and open-collector (open-source or opendrain) outputs. These signal points include the additional notation of a small triangle or a small half-circle (see signal IRQ). respectively. Active low signals are named with an overscore (e.g., POR). In deciding whether a clock output is high active or low active, the convention followed is to assume that the clocking (activating) edge appropriate to the host hardware is a transition from the clocks active to its inactive state (i.e., a trailing edge trigger). A clock intended to activate logic on its rising edge is called low active while a clock intended to activate logic on its falling edge is called high active. When a clock input is associated with a small circle, the input activates on a falling edge. If no circle is shown, the input activates on a rising edge.

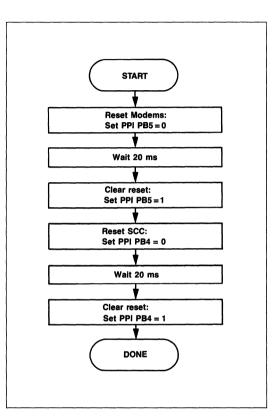

The interconnect signals on Figure 1 are organized into six groups of modem operation: overhead signals, V.24 interface signals, microprocessor interface signals, DAA signals, analog signals, and ancillary signals. Table 4 lists these groups along with their corresponding connector pin numbers. The column titled "Type" refers to designations found in the Hardware Circuits Interface Characteristics (Tables 5 and 6). The six groups of hardware circuits are described in the following paragraphs.

# 1200 bps Full-Duplex Modem

### **POWER-ON RESET**

Basic modem operation can be understood most easily by beginning with the modem configured to default conditions. When the modem is initially energized a signal called Power-On-Reset (POR) causes the modem to assume a valid operational state. The modem drives pin 13C to ground during the beginning of the POR sequence. Approximately 10 ms after the low to high transition of pin 13C, the modem is ready for normal use. The POR sequence is reinitiated anytime the  $\pm$ 5V supply drops below  $\pm$  3.5V for more than 30 ms, or an external device drives pin 13C low for at least 3  $\mu$ s. When an external low input is applied to pin 13C, the modem is ready for normal use approximately 10 ms after the low input is removed. Pin 13C is not driven low by the modem when the POR sequence is initiated externally. In all cases, the POR sequence requires 50 ms to 350 ms to com-

plete. The R1212 POR sequence leaves the modem configured as follows:

- 1200 bps

- Asynchronous

- 10-bit Character Length

- Constant Carrier

- Serial Mode

- Answer Mode

- Auto Answer Disabled

- RAM Access Code = 00

This configuration is suitable for performing high speed data transfer over the public switched telephone network using the serial data port. Individual features are discussed in subsequent paragraphs.

Figure 1. R1212 Modem Functional Interconnect Diagram

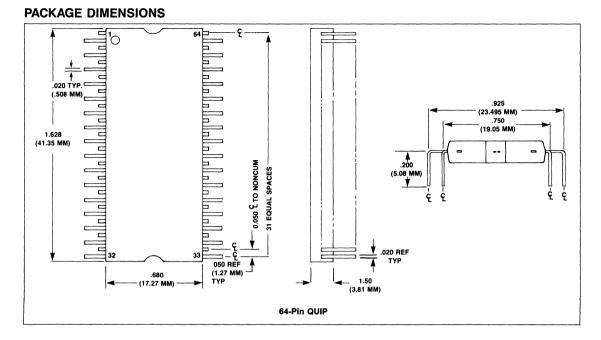

| Name       | Туре   | DIN<br>Pin No.        | DIP<br>Pin No.    | Description              |

|------------|--------|-----------------------|-------------------|--------------------------|

|            |        |                       | Fin NO.           | Description              |

| A. OVERHE  |        |                       | ·                 |                          |

| Ground (A) | AGND   | 31C, 32C              | 21, 26,<br>39     | Analog Ground<br>Return  |

| Ground (D) | DGND   | 3C, 8C,<br>5A, 10A    | 20, 40,<br>51, 60 | Digital Ground<br>Return |

| +5 volts   | PWR    | 19C, 23C,<br>26C, 30C | 1, 19,            | +5 volt supply           |

| + 12 volts | PWR    | 15A                   | 22                | + 12 volt supply         |

| - 12 volts | PWB    | 12A                   | 25                | - 12 volt supply         |

| POR        | I/OB   | 13C                   | 13                | Power-on-Reset           |

| B. MICROPF | OCESSO | R INTERFAC            | E SIGNALS         |                          |

| D7         | I/OA   | 1C                    | 52                | 4                        |

| D6         | I/OA   | 1A                    | 53                |                          |

| D5         | I/OA   | 2C                    | 54                |                          |

| D4         | I/OA   | 2A                    | 55                | •                        |

| D3         | I/OA   | 3A                    | 56                | Data Bus (8-Lines)       |

| D2         | I/OA   | 4C                    | 57                | +                        |

| D1         | I/OA   | 4A                    | 58                |                          |

| D0         | I/OA   | 5C                    | 59                | +                        |

| RS3        | IA     | 6C                    | 45                | Register Select          |

| RS2        | IA     | 6A                    | 44                | (4-Lines)                |

| RS1        | IA     | 7C                    | 43                | (+ Lines)                |

| RS0        | IA     | 7A                    | 42                |                          |

| CS0        | IA     | 10C                   | 48                | Chip Select              |

|            |        |                       |                   | Receiver (Baud           |

|            |        |                       |                   | Rate Device)             |

| CS1        | IA     | 9C                    | 41                | Chip Select              |

|            |        |                       |                   | Transmitter              |

|            |        |                       |                   | (Sample Rate             |

|            |        |                       |                   | Device)                  |

| READ       | IA     | 12C                   | 47                | Read Enable              |

| WRITE      | IA     | 11A                   | 49                | Write Enable             |

| IRQ        | OB     | 11C                   | 50                | Interrupt Request        |

|                                                      |           |                |                | r                                         |  |  |  |

|------------------------------------------------------|-----------|----------------|----------------|-------------------------------------------|--|--|--|

| Name                                                 | Туре      | DIN<br>Pin No. | DIP<br>Pin No. | Description                               |  |  |  |

|                                                      |           |                | Phi NO.        | Description                               |  |  |  |

| C. V.24 INTERI                                       | FACE S    | SIGNALS        |                |                                           |  |  |  |

| XTCLK                                                | IB        | 22A            | 3              | External Transmit                         |  |  |  |

|                                                      | {         |                |                | Clock                                     |  |  |  |

| TDCLK                                                | OC        | 23A            | 7              | Transmit Data Clock                       |  |  |  |

| RDCLK                                                | oc        | 21A            | 8              | Receive Data Clock                        |  |  |  |

| RTS                                                  | IB        | 25A            | 4              | Request-to-Send                           |  |  |  |

| CTS                                                  | OC        | 25C            | 5              | Clear-to-Send                             |  |  |  |

| TXD                                                  | IB        | 24C            | 6              | Transmit Data                             |  |  |  |

| RXD                                                  | 00        | 22C            | 9              | Receive Data                              |  |  |  |

| RLSD                                                 | oc        | 24A            | 10             | Received Line Signal<br>Detector          |  |  |  |

| DTR                                                  | в         | 21C            | 12             | Data Terminal Ready                       |  |  |  |

| DSR                                                  | oc        | 20A            | 11             | Data Set Ready                            |  |  |  |

| RI                                                   | oc        | 18A            | 2              | Ring Indicator                            |  |  |  |

| D. ANALOG SI                                         | GNALS     |                |                |                                           |  |  |  |

|                                                      | · · · · · |                |                |                                           |  |  |  |

| RXA (M)                                              | IB<br>OC  | 32A<br>31A     | 23             | Receive Analog Input                      |  |  |  |

| TXA (M)                                              | 00        | 31A            | 24             | Transmit Analog                           |  |  |  |

| TIP/RING (DC)                                        | AE        | RJ11 Jacks     |                | Output<br>Phone Line Interface            |  |  |  |

| LINE                                                 |           | HUTT Jacks     | _              | Filone Line Internace                     |  |  |  |

| MONITOR (DC)                                         | AD        | 30A            | _              | Analog Line Monitor                       |  |  |  |

| E. DAA INTER                                         | ACE S     | SIGNALS        |                |                                           |  |  |  |

| RD (M)                                               | IB        | 27A            | 35             | Ding Datast                               |  |  |  |

| RCCT (M)                                             | OC        | 27A<br>28A     | 35             | Ring Detect<br>Request Coupler Cut        |  |  |  |

|                                                      | 00        | 204            | _              | Through                                   |  |  |  |

| CCT (M)                                              | в         | 29C            | _              | Coupler Cut Through                       |  |  |  |

| OH (III)                                             | oc        | 29A            | 36             | Off-Hook Relay Status                     |  |  |  |

| T/D Relay                                            | oc        |                | 37             | Talk/Data Relay                           |  |  |  |

| MI                                                   | IC        | _              | 38             | Manual Input                              |  |  |  |

| F. ANCILLARY                                         | INTER     | FACE SIGNA     | LS             |                                           |  |  |  |

|                                                      | r         |                |                | Treasure in David Olasti                  |  |  |  |

| TBCLK<br>RBCLK                                       |           | 27C<br>26A     | _              | Transmit Baud Clock<br>Receive Baud Clock |  |  |  |

| TLK                                                  |           | 28A<br>28C     | _              | Talk (TLK = Data)                         |  |  |  |

| ORG                                                  | IB        | 26C<br>16C     | _              | Originate (ORG =                          |  |  |  |

| ond                                                  | 10        | 100            |                | Answer)                                   |  |  |  |

|                                                      |           |                | L              |                                           |  |  |  |

| (M) R1212M Only, (DC) R1212DC Only, = not applicable |           |                |                |                                           |  |  |  |

|                 |                               |        |           | Input/Ouput Type |           |                       |                          |                       |                       |                       |

|-----------------|-------------------------------|--------|-----------|------------------|-----------|-----------------------|--------------------------|-----------------------|-----------------------|-----------------------|

| Symbol          | Parameter                     | Units  | IA        | IB               | IC        | OA                    | OB                       | oc                    | 1/O A                 | I/OB                  |

| VIH             | Input Voltage, High           | V      | 2.0 min.  | 2.0 min.         | 2.0 min.  |                       |                          |                       | 2.0 min.              | 5.25 max.<br>2.0 min. |

| VIL             | Input Voltage, Low            | V      | 0.8 max.  | 0.8 max.         | 0.8 max.  |                       |                          |                       | 0.8 max.              | 0.8 max.              |

| V <sub>OH</sub> | Output Voltage, High          | V      |           |                  |           | 2.4 min.1             |                          |                       | 2.4 min. <sup>2</sup> | 2.4 min. <sup>3</sup> |

| VoL             | Output Voltage, Low           | V      |           |                  |           | 0.4 max. <sup>2</sup> | 0.4 max. <sup>2</sup>    | 0.4 max. <sup>2</sup> | 0.4 max. <sup>2</sup> | 0.4 max.⁵             |

| I <sub>IN</sub> | Input Current, Leakage        | μA     | ±2.5 max. |                  |           |                       |                          |                       | ±2.5 max.4            |                       |

| I <sub>OH</sub> | Output Current, High          | mA     |           |                  |           | -0.1 max.             |                          |                       |                       |                       |

| IOL             | Output Current, Low           | mA     |           |                  | }         | 16 max.               | 1.6 max.                 | 1.6 max.              |                       |                       |

| L L             | Output Current, Leakage       | μA     |           | ]                |           |                       | ±10 max.                 |                       |                       |                       |

| I <sub>PU</sub> | Pull-up Current               | μA     |           | – 240 max        | – 240 max | 1                     | [                        | - 240 max.            |                       | – 260 max.            |

|                 | (Short Circuit)               |        |           | – 10 min.        | – 10 min. |                       |                          | – 10 min.             |                       | – 100 min.            |

| CL              | Capacitive Load               | pF     | 5         | 5                | 20        |                       |                          |                       | 10                    | 40                    |

| C               | Capacitive Drive              | pF     |           |                  |           | 100                   | 100                      | 100                   | 100                   | 100                   |

| -               | Circuit Type                  |        | TTL       | TTL              | TTL       | TTL                   | Open-Drain               | Open-Drain            | 3 State               | Open-Drain            |

|                 |                               |        |           | w/Pull-up        | w/Pull-up |                       |                          | w/Pull-up             | Transceiver           | w/Pull-up             |

| Notes:          | 1. I load = $-100 \ \mu A$ 2. | I load | = 16 mA   | 3. I load =      | –40 μA 4. | $V_{\rm IN} = 0.4$ to | 2.4 Vdc, V <sub>CC</sub> | ; = 5.25 Vdc          | 5 I load =            | = 0.36 mA             |

# 1200 bps Full-Duplex Modem

Table 6. Analog Interface Characteristics

| Name            | Туре | Characteristics                                                                                                                                               |

|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ТХА             | AA   | The transmitter output impedance is $604\Omega \pm 1\%$ with an output level of + 6 dBm.<br>To obtain a 0 dBm output, a $600\Omega$ load to ground is needed. |

| RXA             | AB   | The receiver input impedance is 23.7 K $\Omega$ ±1%. The receive level at RXA must be no greater than -9 dBm (or -6 dBm with the 3DB bit enabled).            |

| LINE<br>MONITOR | AD   | The line monitor output impedance is 15 K $\Omega$ ±5%.                                                                                                       |

| TIP/RING        | AE   | The impedance of TIP with respect to RING is 600 $\ensuremath{\Omega}.$                                                                                       |

## V.24 INTERFACE

Eleven hardware circuits provide timing, data, and control signals for implementing a serial interface compatible with CCITT Recommendation V.24. These signals interface directly with circuits using TTL logic levels (0V, +5V). These TTL levels are suitable for driving the short wire lengths or printed circuitry normally found within stand-alone modem enclosures or equipment cabinets. For driving longer cables, the voltage levels and connector arrangement recommended by EIA standard RS-232-C are preferred.

The sequence of events leading to successful data transfer from transmitter to receiver is:

- 1. The transmitter is activated and a training sequence is sent.

- The receiver detects channel energy above the prescribed threshold level and synchronizes its operation to the transmitter.

- 3. Data transfer proceeds to the end of the message.

- 4. The transmitter turns off after insuring that all data has had time to be recovered at the receiver output.

#### Data Terminal Ready (DTR)

DTR prepares the modern to be connected to the communications channel, and maintains the connection established by the DTE (manual answering) or internal (automatic answering) means. DTR OFF places the modern in the disconnect state.

## Data Set Ready (DSR)

Data Set Ready  $(\overline{\text{DSR}})$  ON indicates that the modem is in the data transfer state. DSR OFF is an indication that the DTE is to

disregard all signals appearing on the interchange circuits except  $\overline{\text{RI}}$ .  $\overline{\text{DSR}}$  will switch to the OFF state when in test state. The ON condition of  $\overline{\text{DSR}}$  indicates the following:

- 1. The modem is not in the talk state, i.e., an associated telephone handset is not in control of the line.

- 2. The modem is not in the process of automatically establishing a call via pulse or DTMF dialing.

- 3. The modern has generated an answer tone or detected answer tone.

- After ring indicate (RI) goes ON, DSR waits at least two seconds before turning ON to allow the telephone company equipment to be engaged.

DSR will go OFF 50 ms after DTR goes OFF, or 50 ms plus a maximum of 4 seconds when the SSD bit is enabled.

## Request To Send (RTS)

$\overline{\text{RTS}}$  ON allows the modem to transmit data on TXD when  $\overline{\text{CTS}}$  becomes active. In constant carrier mode,  $\overline{\text{RTS}}$  can be wired to  $\overline{\text{DTR}}$ . In controlled carrier operation, independent operation of  $\overline{\text{RTS}}$  turns the carrier ON and OFF. The responses to  $\overline{\text{RTS}}$  are shown in Table 7 (assume the modem is in data mode).

| I | able | 7. | RTS | Responses |

|---|------|----|-----|-----------|

| TS OFF                                            | Carrier ON                                                         |

|---------------------------------------------------|--------------------------------------------------------------------|

|                                                   | 210 to 275 ms Scrambled<br><u>1 s</u> Transmitted<br><u>CTS</u> ON |

| TS OFF<br>arrier ON<br>crambled 1 s<br>ransmitted | CTS ON<br>Carrier ON<br>Data Transmitted                           |

| 1                                                 | rrier ON<br>rambled 1 s                                            |

# Clear To Send (CTS)

CTS ON indicates to the terminal equipment that the modern will transmit any data which are present on TXD. CTS response times from an ON or OFF condition of RTS are shown in Table 8.

#### Table 8. CTS Response Times

| <b>CTS</b> Transition  | Constant Carrier | Controlled Carrier       |

|------------------------|------------------|--------------------------|

| OFF to ON<br>ON to OFF | <2 ms<br><20 ms* | 210 to 275 ms<br><20 ms* |

| Note: *Programma       |                  | < 20 ms                  |

# 1200 bps Full-Duplex Modem

## Transmit Data Clock (TDCLK)

The modem provides a Transmit Data Clock (TDCLK) output with the following characteristics:

- 1. Frequency. Selected data rate of 1200 Hz or 600 Hz (±0.01%).

- 2. Duty Cycle. 50 ± 1%.

TDCLK is provided to the user in both asynchronous and synchronous communications. TDCLK is not necessary in asynchronous communication but it can be used to supply a clock for UART/USART timing (TDCLK is not valid in FSK). TDCLK is necessary for synchronous communication. In this case Transmit Data (TXD) must be stable during the one  $\mu$ s periods immediately preceding and following the rising edge of TDCLK.

#### External Transmit Clock (XTCLK)

In synchronous communication where the user needs to supply the transmit data clock, the input XTCLK can be used. The clock supplied at XTCLK must exhibit the same characteristics of TDCLK. The XTCLK input is then reflected at TDCLK.

#### Receive Data Clock (RDCLK)

The modem provides a Receive Data Clock (RDCLK) output in the form of a 50  $\pm$  1% duty cycle squarewave. The low-to-high transitions of this output coincide with the center of received data bits. The timing recovery circuit is capable of tracking a  $\pm$ .035% (relative) frequency error in the associated transmit timing source.

RDCLK is provided to the user in both asynchronous and synchronous communications. RDCLK is not necessary in asynchronous communication but it can be used to supply a clock for UART/USART timing (RDCLK is not valid in FSK). RDCLK is necessary for synchronous communication.

#### Received Line Signal Detector (RLSD)

The RLSD thresholds for both high and low channels are:

$\frac{\overline{\text{RLSD}}}{\overline{\text{RLSD}}} \text{ ON } \ge -43 \text{ dBm}$   $\overline{\text{RLSD}} \text{ OFF } \le -48 \text{ dBm}$

RLSD will not respond to guard tones or answer tones.

When RLSD is active, it indicates to the terminal equipment that valid data is available on RXD.

#### **Transmitted Data (TXD)**

The modem obtains serial data from the local DTE on this input.

## **Received Data (RXD)**

The modem presents received data to the local DTE on this output.

#### Ring Indicator (RI)

The modem provides a Ring Indicator ( $\overline{RI}$ ) output; its low state indicates the presence of a ring signal on the line. The low condition appears approximately coincident with the ON segment of the ring cycle (during rings) on the communication channel. (The ring signal cycle is typically two seconds ON, four seconds OFF.) The high condition of the  $\overline{RI}$  output is maintained during the OFF segment of the ring cycle (between rings) and at all other times when ringing is not being received. The operation of  $\overline{RI}$  is not disabled by an OFF condition on  $\overline{DTR}$ .

RI will respond to ring signals in the frequency range of 15.3 Hz to 68 Hz with voltage amplitude levels of 40 to 150 Vrms (applied across TIP and RING), with the response times given in Table 13.

This OFF-to-ON (ON-to-OFF) response time is defined as the time interval between the sudden connection (removal) of the ring signal across TIP and RING and the subsequent ON (OFF) transition of  $\overline{\text{RI}}$ .

Table 9. RI Response Time

| <b>RI</b> Transition                                                                                                             | Response Time                             |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|--|--|--|

| OFF-to-ON*<br>ON-to-OFF                                                                                                          | 110 ±50 ms (50% duty cycle)<br>450 ±50 ms |  |  |  |  |

| ON-to-OFF         450 ± 50 ms           Note: *The OFF-to-ON time is duty cycle dependent:<br>890 ms (15%) ≥ time ≥ 50 ms (100%) |                                           |  |  |  |  |

## MICROPROCESSOR INTERFACE

Seventeen hardware circuits provide address, data, control, and interrupt signals for implementing a parallel interface compatible with an 8080 microprocessor. With the addition of a few external logic gates, the interface can be made compatible with a wide variety of microprocessors such as 6500, 6800, or 68000.

The microprocessor interface allows a host microprocessor to change modem configuration, read or write channel data as well as diagnostic data, and supervise modem operation by means of soft strappable control bits and modem status bits. The significance of the control and status bits and methods of data interchange are discussed in a later section devoted to software circuits. This section describes the operation of the interface from a hardware standpoint.

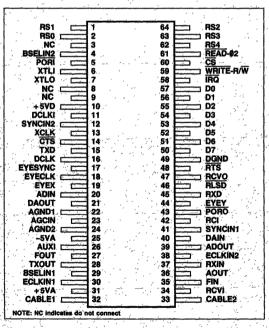

# Chip Select ( $\overline{CS0}$ and $\overline{CS1}$ ) and Register Selects (RS0-RS1)

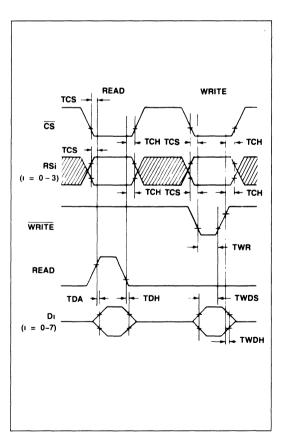

The signal processor to be accessed is selected by grounding one of two unique chip select lines,  $\overline{CS1}$  or  $\overline{CS0}$ . The selected chip decodes the four address lines, RS3 through RS0, to select one of sixteen internal registers. The most significant address bit ( $2^3$ ) is RS3 while the least significant address bit ( $2^0$ ) is RS0. Once the address bits have been decoded, the selected register can be read from or written into via an 8-bit parallel data bus, D7 through D0. The most significant data bit ( $2^7$ ) is D7 while the least significant data bit ( $2^0$ ) is D0.

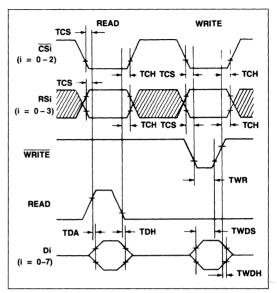

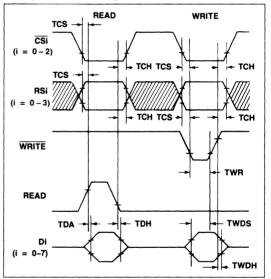

# Read Enable (READ) and Write Enable (WRITE)

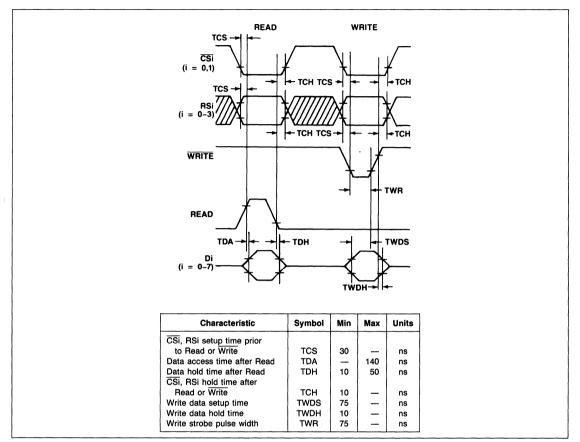

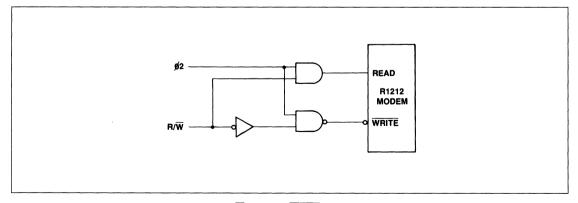

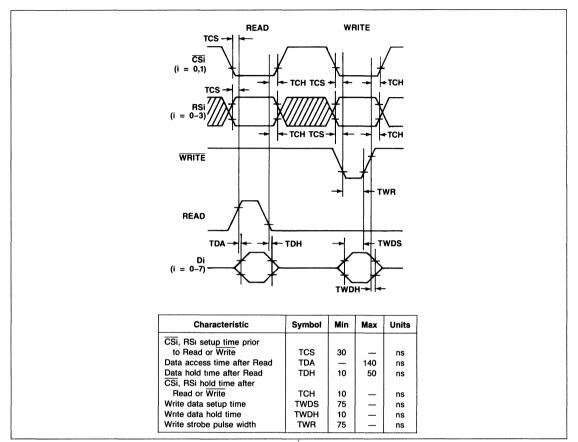

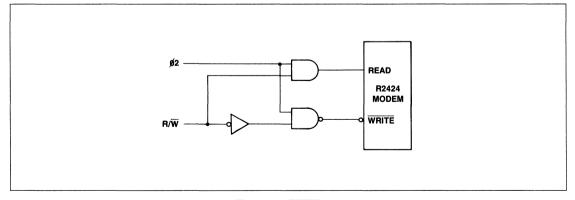

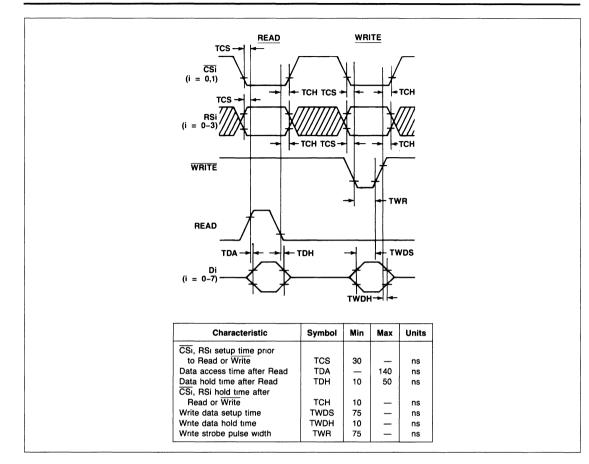

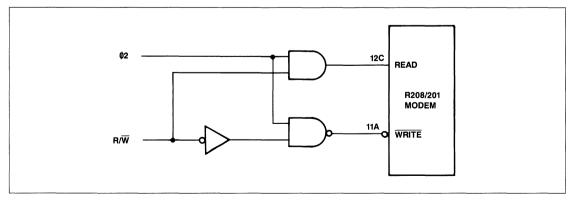

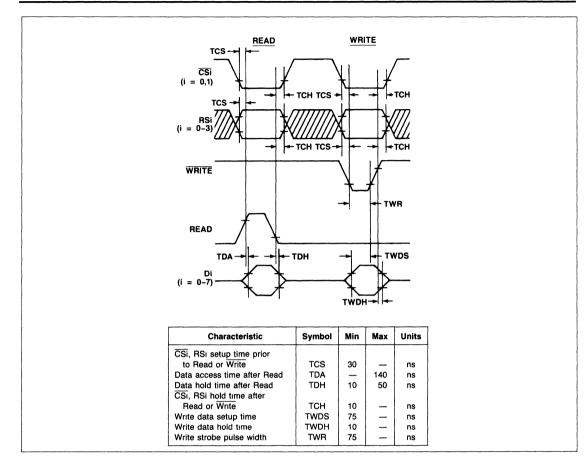

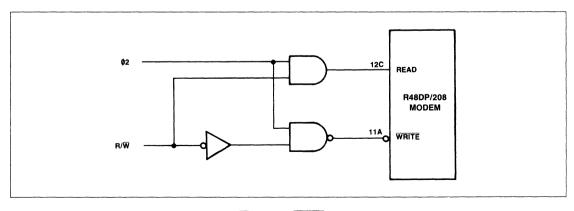

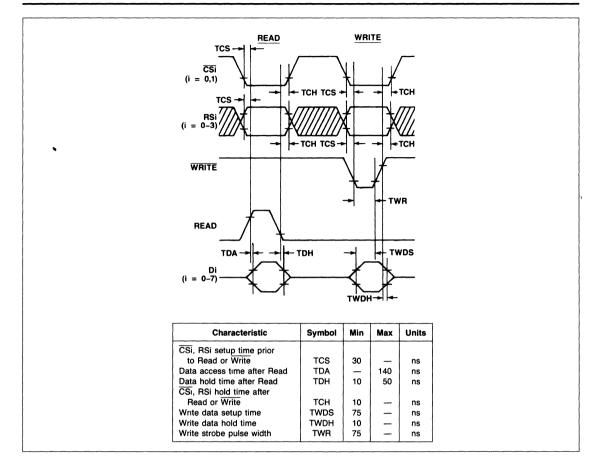

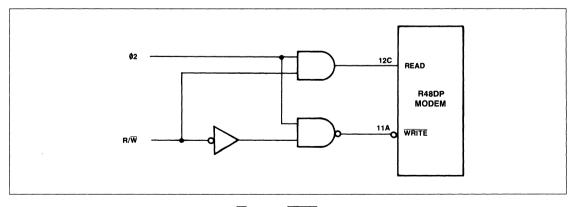

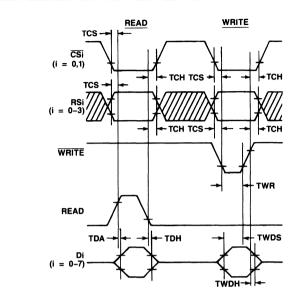

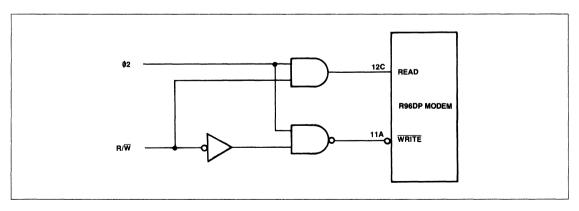

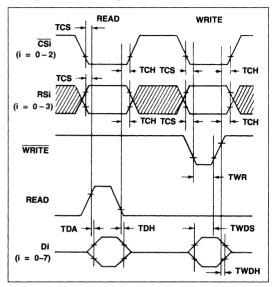

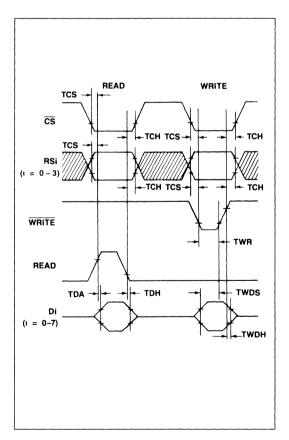

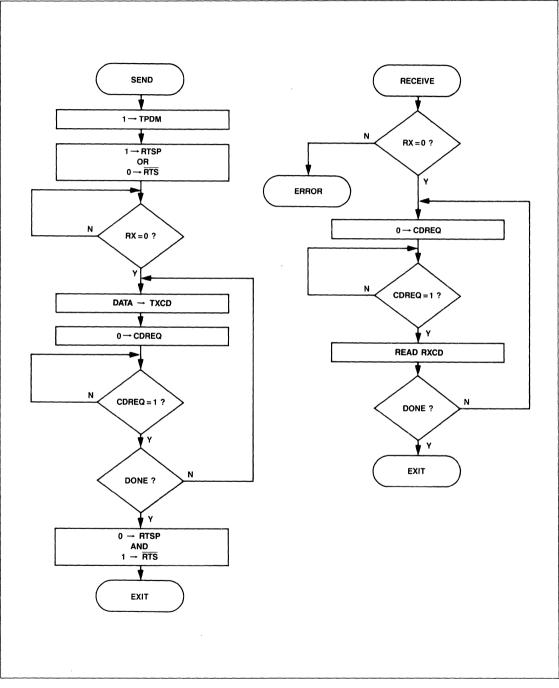

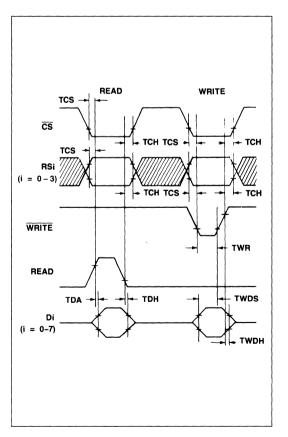

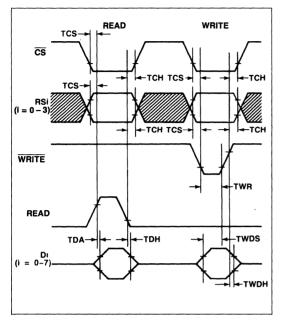

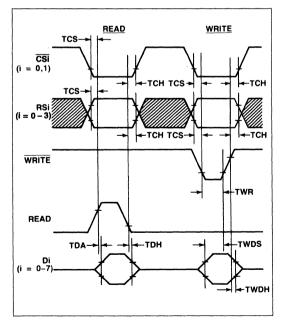

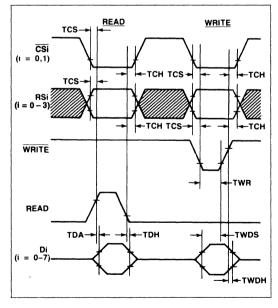

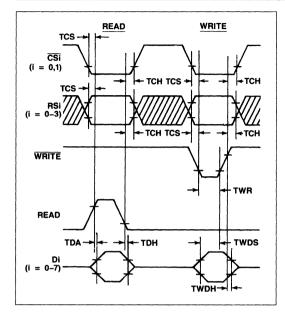

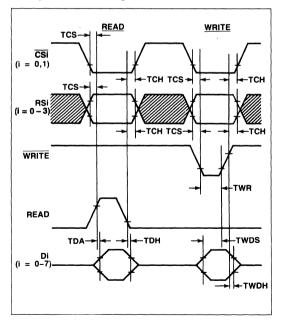

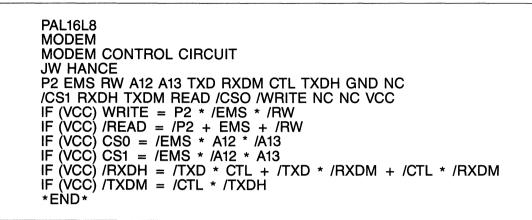

Reading or writing is activated by pulsing either the READ line high or the WRITE line low. During a read cycle, data from the selected register is gated onto the data bus by means of threestate drivers. These drivers force the data lines high for a one bit or low for a zero bit. When not being read, the three-state drivers assume their off, high-impedance, state. During a write cycle, data from the data bus is copied into the selected register, with high and low bus levels representing one bits and zero bits, respectively. The timing required for correct read/write cycles is illustrated in Figure 2. Logic necessary to convert the single RM output from a 65XX series microprocessor to the separate READ and WRITE signals required by the modem is shown in Figure 3.

## Interrupt Request (IRQ)

The final signal on the microprocessor interface is Interrupt Request (IRQ). This signal may be connected to the host microprocessor interrupt request input in order to interrupt host program execution for modem service. The use of IRQ is optional and the method of software implementation is described in a subsequent section, Software Circuits. The IRQ output structure is an open-drain field-effect-transistor (FET). This form of output allows IRQ to be connected in parallel to other sources of inter-

# 1200 bps Full-Duplex Modem

rupt. Any of these sources can drive the host interrupt input low, and the interrupt servicing process continues until all interrupts have been cleared and all IRQ sources have returned to their high impedance state. Because of the open-drain structure of IRQ, an external pull-up resistor to +5 volts is required at some point on the IRQ line. The resistor value should be small enough to pull the IRQ line high when all IRQ drivers are off (i.e., it must overcome the leakage currents). The resistor value should be large enough to limit the driver sink current to a level acceptable to each driver. For the case where only the modem IRQ driver is used, a resistor value of 5.6K ohms  $\pm 20\%$ , 0.25 watt, is sufficient.

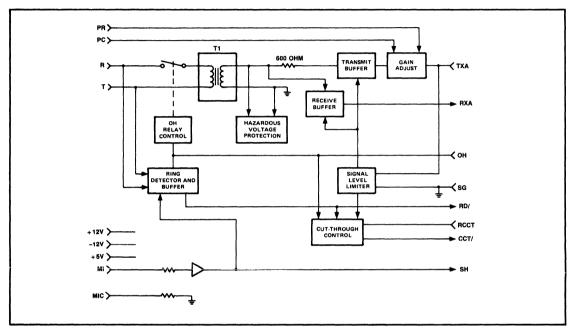

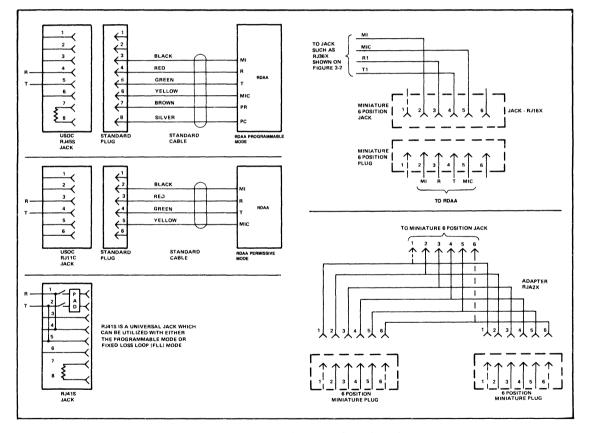

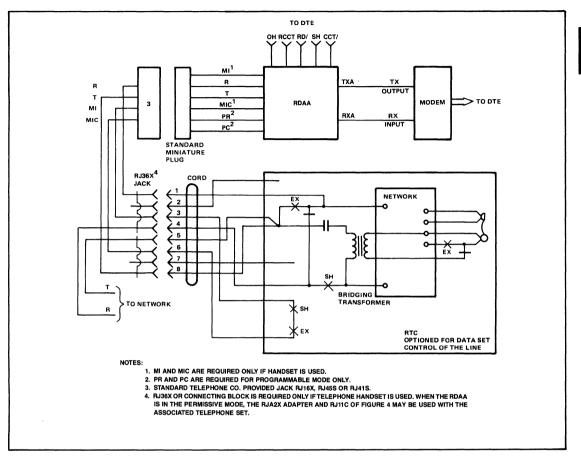

## DAA INTERFACE

The R1212M provides a Data Access Arrangement (DAA) interface that is directly hardware and software compatible with the RDAA. Manual/automatic originate and answer are then controlled via the appropriate R1212M hardware ancillary circuits or software control bits. The modem provides the only interface with the microprocessor (MPU) bus, i.e., no RDAA interface signals must be directly controlled from the MPU bus.

# Ring Detect (RD)

$\overline{\text{RD}}$  indicates to the modem by an ON (low) condition that a ringing signal is present. The signal (a 4N35 optoisolator compatible output) into the  $\overline{\text{RD}}$  input should not respond to momentary bursts of ringing less than 125 ms in duration, or to less than 40 Vrms, 15 to 68 Hz, appearing across TIP and RING with respect to ground. The ring is then reflected on  $\overline{\text{RI}}$ .

## **Request Coupler Cut Through (RCCT)**

RCCT is used to request that a data transmission path through the DAA be connected to the telephone line. When RCCT goes OFF (low), the cut-through buffers are disabled and  $\overline{\text{CCT}}$  should go OFF (high). RCCT should be OFF during dialing but ON for tone address signaling.

# Coupler Cut Through (CCT)

An ON (low) signal to the CCT lead indicates to the modem that the data transmission path through the DAA is connected. This input can always be grounded if the two second billing delay squelch is desired. If CCT is user controlled, the billing delay squelch can only be 2 seconds or greater.

## **Off-Hook Relay Status (OH)**

The modem provides an OH output which indicates the state of the OH relay. A high condition on OH implies the OH relay is closed and the modem is connected to the telephone line (offhook). A low condition on OH implies the OH relay is open (i.e., the modem is on-hook). The delay between the low-to-high or high-to-low transition of OH and the subsequent close-to-open or open-to-close transition of the OH relay is 8 ms maximum.

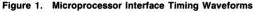

Figure 2. Microprocessor Interface Timing Diagram

Figure 3. R/W to READ WRITE Conversion Logic

## ANALOG SIGNALS (R1212M)

Two connections are devoted to analog audio signals: TXA and RXA.

### Transmit Analog (TXA)

The TXA output is suitable for driving a data access arrangement for connection to either leased lines or the public switched telephone network. The transmitter output impedance is 604 ohms  $\pm$  1% with an output level of +6 dBm  $\pm$ 1 dBm. To obtain a 0 dBm output, a 600 ohm load to ground is needed.

## **Receive Analog (RXA)**

RXA is an input to the receiver from a data access arrangement. The input impedance is 23.7K ohms  $\pm$  1%. The received level at RXA must be no greater than - 9 dBm (or - 6 dBm with the 3DB bit enabled).

## **ANALOG SIGNALS (R1212DC)**

Three analog signals are output by the R1212DC: LINE MONI-TOR, TIP and RING.

## Analog Line Monitor (LINE MONITOR)

The LINE MONITOR output is suitable for a speaker interface. It provides an output for all dialing signals, call progress signals, and the carrier signals. The output impedance is 15K ohms  $\pm$  1%. The signals which appear on LINE MONITOR are approximately the same level as the signals would appear on the network (assuming a 1 dB loss attributed to the audio transformer).

## Phone Line Interface (TIP and RING)

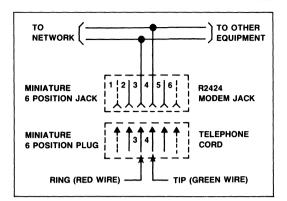

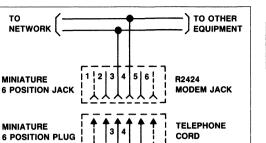

TIP and RING are the DAA analog outputs to the public switched telephone network. These outputs use two RJ11 jacks in parallel as the interface to the network (see Table 10 and Figure 4). The R1212DC, which contains the DAA TIP and RING interface, has been FCC Part 68 approved. The user need not apply for further Part 68 approval. The impedance of TIP with respect to RING is 600 ohms.

Table 10. R1212DC Network Interface

| Connector<br>Type | Pin<br>Number | Name | Function               |

|-------------------|---------------|------|------------------------|

| RJ11 Jack         | 3             | RING | One Side of TELCO Line |

|                   | 4             | TIP  | One Side of TELCO Line |

# 1200 bps Full-Duplex Modem

Figure 4. RJ11 Telephone Jack

# ANCILLARY CIRCUITS

# Transmit Baud Clock (TBCLK) and Received Baud Clock (RBCLK)

TBCLK and RBCLK are provided to the user at the baud rate (600 Hz).

## Talk (TLK) (DIN Module Only)

$\overline{TLK}$  is an input which manually places the modem on-hook (relay open,  $\overline{TLK} = 0$ ) or off-hook (relay closed,  $\overline{TLK} = 1$ ). The on-hook condition is referred to as TALK mode and the off-hook condition is referred to as DATA mode.  $\overline{TLK}$  is used with  $\overline{ORG}$  to manually originate or answer a call.  $\overline{TLK}$  should be 0 at power-on or reset to prevent the modem from inadvertently entering the data mode.

## Originate (ORG)

$\overline{ORG}$  is an input which manually places the modem in the originate mode ( $\overline{ORG} = 0$ ) or the answer mode ( $\overline{ORG} = 1$ ). To manually originate a call,  $\overline{ORG} = 0$  and  $\overline{TLK} = 0$ . Dial the number using the telephone. When the other modem answers and sends answer tone switch the  $\overline{TLK}$  input from 0 to 1 placing the modem off-hook.

To manually answer a call  $\overline{ORG}$  = 1 and  $\overline{TLK}$  = 0. When the phone rings switch the  $\overline{TLK}$  input from 0 to 1 placing the modem off-hook.

#### **Off-Hook Relay Status (OH)**

The modem provides an OH output which indicates the state of the OH relay. A high condition on OH implies the OH relay is closed and the modem is connected to the telephone line (offhook). A low condition on OH implies the OH relay is open (i.e., the modem is on-hook). The delay between the low-to-high or high-to-low transition of OH and the subsequent close-to-open or open-to-close transition of the OH relay is 8 ms maximum.

### T/D Relay. (DIP Module Only)

The T/D Relay signal may be used as a second relay control when the parallel control mode of operation is selected (BUS bits 0 and 1 = 1). If the serial control mode is selected (BUS bits 0 and 1 = 0) the T/D relay follows the status of the OH output signal which is controlled by the Mi signal. In the parallel control mode the OH output signal is controlled by the status of the DATA bit, while independent control of the T/D relay is provided by the Mi signal. During pulse dialing the OH signal reflects the pulse signals being dialed. It is therefore possible to use the T/D Relay signal to control the off-hook relay and use the OH signal to perform pulse dialing on a separate, independent relay.

## Manual Input (MI) (DIP Module Only)

$\overline{\text{MI}}$  is an input which manually places the modem on-hook (relay open,  $\overline{\text{MI}} = 0$ ) or off-hook (relay closed,  $\overline{\text{MI}} = 1$ ). The on-hook condition is referred to as TALK mode and the off-hook condition is referred to as DATA mode.  $\overline{\text{MI}}$  is used with  $\overline{\text{ORG}}$  to manually originate or answer a call.  $\overline{\text{MI}}$  should be 0 at power-on or reset to prevent the modem from inadvertently entering the data mode.

# SOFTWARE CIRCUITS

Operation of the microprocessor interface circuits was described in the hardware section from the standpoint of timing and load-/drive characteristics. In this section, operation of the microprocessor interface is described from a software standpoint.

The modem is implemented in firmware running on two special purpose signal processors. These signal processors share the computing load by performing tasks that are divided into two areas. These areas are partitioned into receiver and transmitter devices.

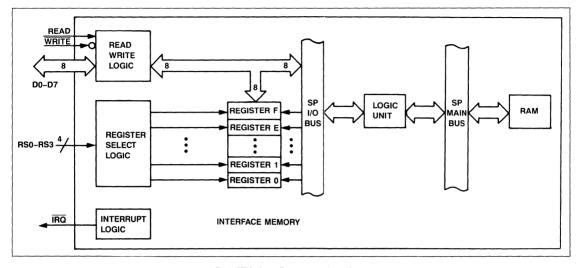

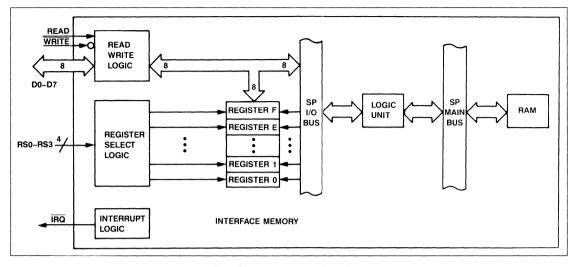

## INTERFACE MEMORY

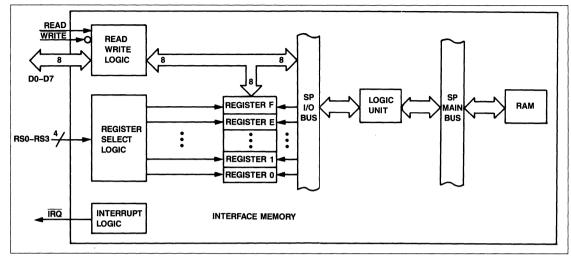

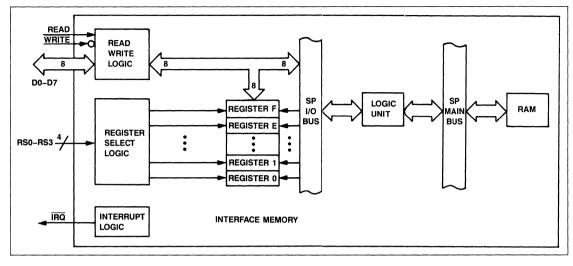

Each signal processor can communicate with the host processor by means of a specialized, dual-port, scratch-pad memory called

# 1200 bps Full-Duplex Modem

interface memory. A set of sixteen 8-bit registers, labeled register 0 through register F, can be read from or written into by either the host processor or signal processor. The host communicates via the microprocessor interface lines shared between the two signal processors. The signal processor communicates via its internal I/O bus. Information transfer from SP RAM to interface memory is accomplished by the signal processor logic unit moving data between the SP main bus and the SP I/O bus. Two of the 16 addressable interface memory registers (i.e., register 0 and register E) have unique hardware connections to the interrupt logic. It is possible to enable a bit in register E to cause an interrupt each time it sets. This interrupt can then be cleared by a read or write cycle from the host processor to register 0. This operation is discussed in detail later in this section.

Memory maps of the 32 addressable registers in the modem receiver (CS0) and transmitter (CS1) interface memory are shown in Figures 5 and 6, respectively. These registers may be read or written on any host read or write cycle, but all eight bits of that register are affected. In order to read a single bit or a group of bits in a register, the host processor must mask out unwanted data. When writing a single bit or group of bits in a register the host processor must perform a read-modify-write operation. That is, the entire register is read, the necessary bits are set or reset in the accumulator of the host, then the original unmodified bits and the modified bits are written back into the register of the interface memory.

Figures 7 and 8 show the registers according to the overall function they perform in the receiver and transmitter, respectively. Figures 9 and 10 show the power-on configuration for the R1212 modem receiver and transmitter devices, respectively.

Table 11 defines the individual bits in the interface memory. In the Table 11 descriptions, bits in the interface memory are referred to using the format Y:Z:Q. The chip number is specified by Y (0 or 1), the register number by Z (0 through F), and the bit number by Q (0 through 7, with 0 = LSB).

| Bit<br>Register | 7                                                  | 6    | 5     | 4       | 3       | 2    | 1   | 0    |

|-----------------|----------------------------------------------------|------|-------|---------|---------|------|-----|------|

| F               | RAM Access R                                       |      |       |         |         |      |     |      |

| Е               | IRQ                                                | ENSI | NEWS  | -       | NEWC    | -    | 1   | -    |

| D               | BUS                                                | CRQ  | -     | -       | -       | LCD  | RSD | -    |

| С               | 1                                                  | -    | -     | СН      | AR      | I    | -   | -    |

| В               | -                                                  | -    | -     | -       | -       | -    | -   | AL   |

| A               | ERDL                                               | RDL  | DL    | ST      |         | мо   | DE  |      |

| 9               | -                                                  | -    | SPE   | ED      | -       | I    | -   | —    |

| 8               | TONE                                               | ATD  | -     | —       | -       | -    | тм  | RLSD |

| 7               | -                                                  | -    | -     | -       | -       | —    | -   | +    |

| 6               | -                                                  |      | -     | -       | -       | -    | Ŀ   | -    |

| 5               |                                                    |      | RAM D | ata YR  | M (YRA  | MRM) |     |      |

| 4               |                                                    |      | RAM ( | Data YF | RL (YRA | MRL) |     |      |

| 3               |                                                    |      | RAM D | ata XR  | M (XRA  | MRM) |     |      |

| 2               |                                                    |      | RAM ( | Data XF | RL (XRA | MRL) |     |      |

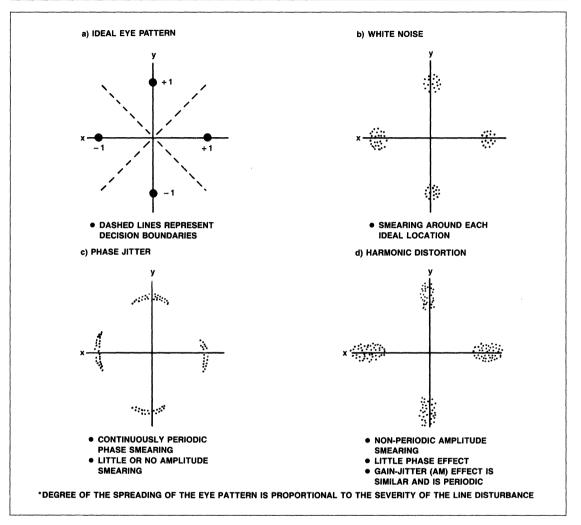

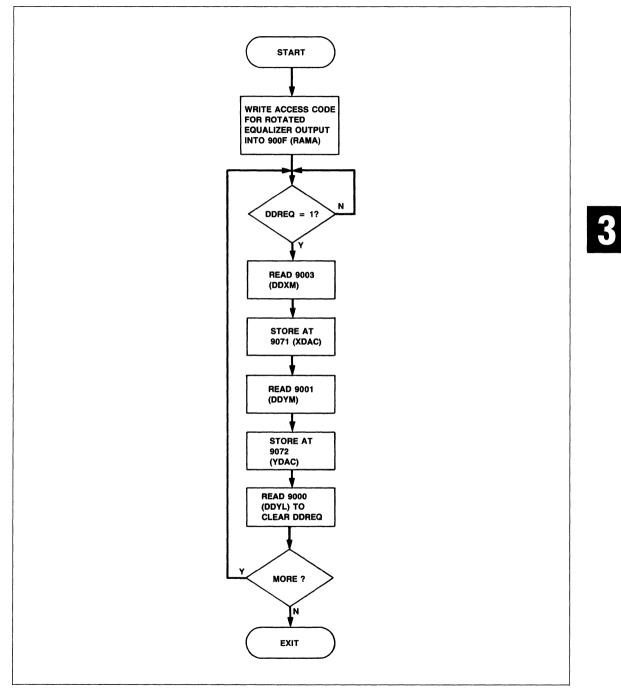

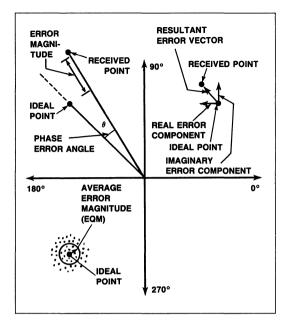

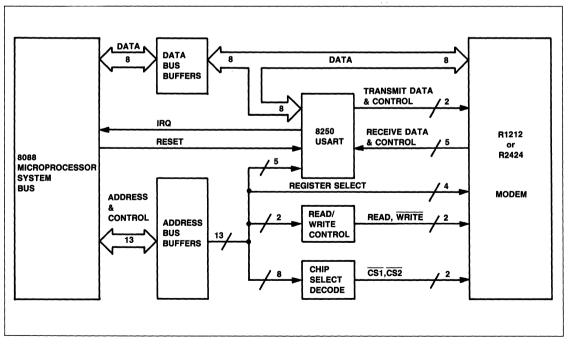

| 1               | -                                                  | _    | -     | -       | -       | -    | -   | —    |