**Rockwell International**

**Semiconductor Products Division**

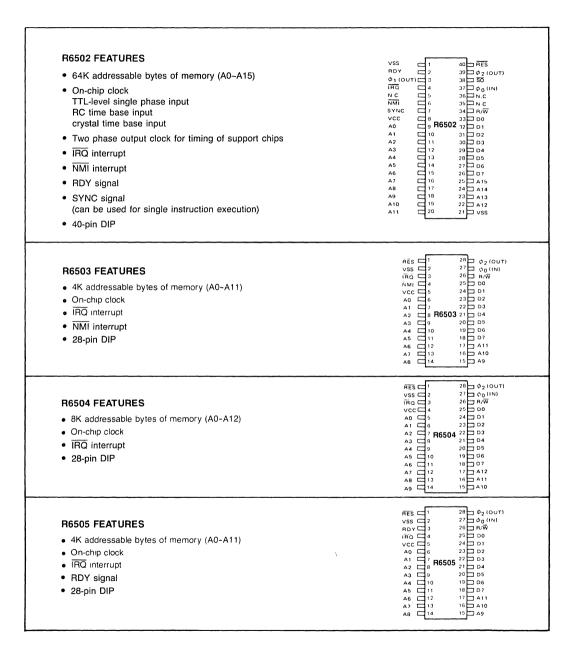

# CONTROLLER PRODUCTS DATA BOOK

Rockwell International

# 1987 CONTROLLER PRODUCTS DATA BOOK

**Semiconductor Products Division**

Rockwell Semiconductor Products Division is headquartered in Newport Beach, California with Field Sales Offices located throughout the United States, Canada, Europe and the Far East. Their listings, plus those of domestic and international representatives and distributors, appear in Appendix A.

#### **DEFINITION OF DOCUMENT TYPES**

| Document Type               | Product Status                | Definition                                                                                                                                                                                                                                                 |

|-----------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product Preview             | Formative or<br>Development   | The document type contains the general features and/or specifications for a product in definition or development. The features and/or specifications may change in any manner without notice.                                                              |

| Product Summary             | Development or<br>Production  | This document type contains the general features and/or specifications of a product in development or in production. Additional information is usually available in a separate document, not contained in this book, such as a Designer's Guide.           |

| Data Sheet<br>(Preliminary) | Sampling or<br>Pre-Production | This document type contains preliminary or design-to-characteristic data for a product in pre-production. Additional and/or refined characteristic data will be released in subsequent revisions to the document.                                          |

| Data Sheet                  | Production                    | This document type contains final specification information resulting from measured characteristics. This document type is subject to revision if characteristics are further refined during production.                                                   |

| Product Description         | Production                    | This document type contains final specification information resulting from measured characteristics along with additional application aid information. This document type is subject to revision if characteristics are further refined during production. |

| Application Note            | Development or<br>Production  | This document type contains application aids in the use of the subject product. Schematics included in an application note are intended to convey system design concept only.                                                                              |

#### NOTICE

Information furnished by Rockwell International Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Rockwell International for its use, nor any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Rockwell International other than for circuitry embodied in a Rockwell product. Rockwell International reserves the right to change circuitry at any time without notice. All document in this book are subject to change without notice.

#### **TABLE OF CONTENTS**

| Pa  | rt No./Data Book Page Index                                                                                                                                                                                                                                                                                                                  | iv                                                        |   | R6501 One-Chip Microprocessor                                                                                                                                                                                                                                                                                      | 3-103                                           |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

|     | ntroller Products — Providing Solutions for Your<br>SI Requirements                                                                                                                                                                                                                                                                          | v                                                         |   | One-Chip Microcomputer                                                                                                                                                                                                                                                                                             | 3-173                                           |

| Pre | oduct Index                                                                                                                                                                                                                                                                                                                                  | vii                                                       |   | Microcomputers                                                                                                                                                                                                                                                                                                     |                                                 |

| 1   | CMOS 8-Bit Microprocessors & Peripherals Product Family Overview                                                                                                                                                                                                                                                                             | 1-1<br>1-2<br>1-3<br>1-19<br>1-31<br>1-53                 | 5 | 16-Bit Microprocessors and Peripherals                                                                                                                                                                                                                                                                             | 4-1<br>4-2<br>4-3<br>4-62<br>4-83<br>5-1<br>5-2 |

|     | Adapter (ACIA) R65C52 Dual Asynchronous Communications Interface Adapter (DACIA)                                                                                                                                                                                                                                                             | 1-95<br>1-116                                             |   | Controller                                                                                                                                                                                                                                                                                                         | 5-3<br>5-11                                     |

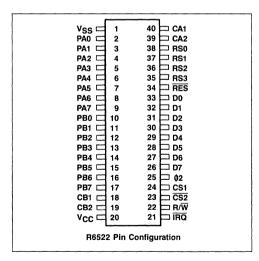

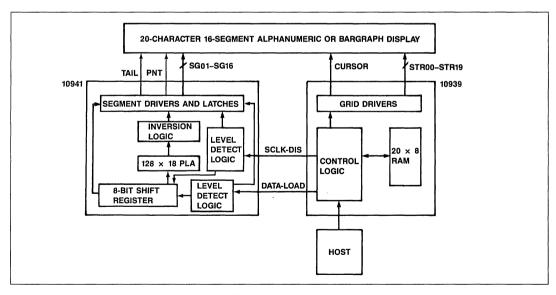

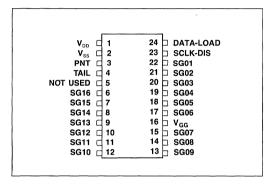

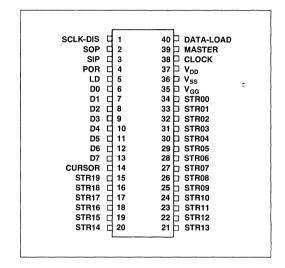

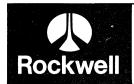

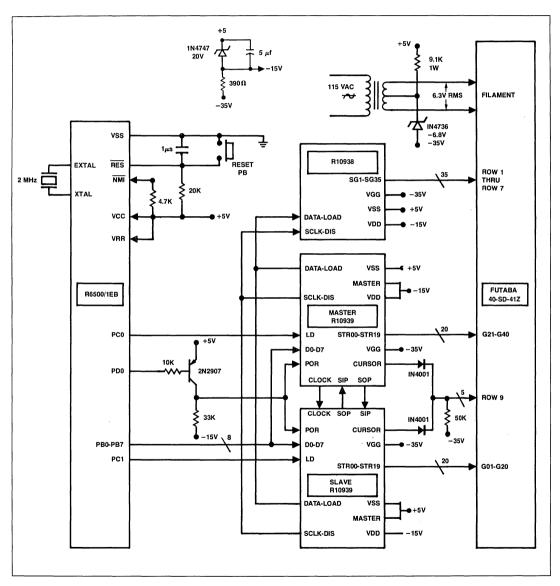

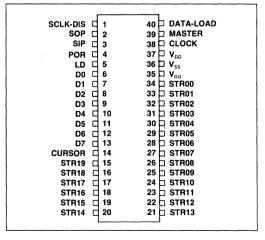

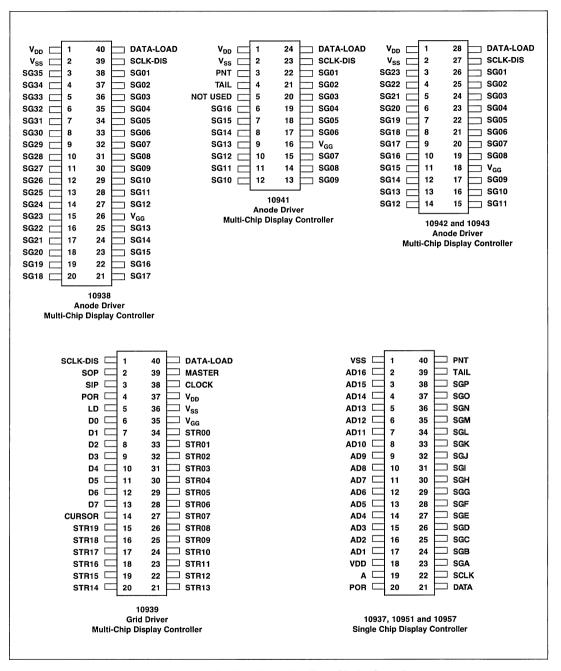

| 2   | NMOS 8-Bit Microprocessors & Peripherals Product Family Overview R650X and R651X Microprocessors (CPU) R6520 Peripheral Interface Adapter (PIA) R6522 Versatile Interface Adapter (VIA) R6532 RAM-I/O-Timer (RIOT) R6545/R6545E CRT Controller (CRTC) R6549 Color Video Display Generator (CVDG) R6551 Asynchronous Communications Interface | 2-1<br>2-2<br>2-3<br>2-18<br>2-30<br>2-52<br>2-62<br>2-81 | 6 | Controller 10941 and 10939 Alphanumeric and Bargraph Display Controller 10951 Bargraph and Numeric Display Controller 10955 Segmented Display Controller/Driver  Application Notes Low-Cost Crystal Oscillator for Clock Input R6500/R6532 Timer Interrupt Precautions A Dot Matrix Controller System Design Using | 5-21<br>5-31<br>5-41<br>5-51<br>6-1<br>6-3      |

| 3   | Adapter (ACIA)  8-Bit Microcomputers  Product Family Overview                                                                                                                                                                                                                                                                                | 3-1<br>3-2                                                |   | 10938/10939 Display Drivers and R6500/1EB<br>Microcomputer                                                                                                                                                                                                                                                         | 6-6<br>6-22                                     |

|     | R65C10 One-Chip Microcomputer                                                                                                                                                                                                                                                                                                                | 3-3<br>3-26<br>3-49<br>3-57<br>3-63<br>3-98               | A | SPD Regional Offices and U.S./Canada Sales Reps SPD Industrial Distributors SPD International Distributors/Sales Reps Notes                                                                                                                                                                                        | A-3                                             |

#### **PART NO./DATA BOOK PAGE INDEX**

| Part No./Description                                                                                  | Page  | Part No./Description                              | Page  |

|-------------------------------------------------------------------------------------------------------|-------|---------------------------------------------------|-------|

| 10937 and 10957 Alphanumeric Display Controller                                                       | 5-3   | R6545 CRT Controller (CRTC)                       | 2-62  |

| <b>10938 and 10939</b> Dot Matrix Display Controller <b>10939, 10942 and 10943</b> Dot Matrix Display | 5-11  | R6549 Color Video Display Generator (CVDG)        | 2-81  |

| Controller                                                                                            | 5-21  | Interface Adapter (ACIA)                          | 2-112 |

| 10941 and 10939 Alphanumeric and Bargraph                                                             |       | R65C02 Microprocessors (CPU)                      | 1-3   |

| Display Controller                                                                                    | 5-31  | R65C10 One-Chip Microcomputer                     | 3-3   |

| 10951 Bargraph and Numeric Display Controller                                                         | 5-41  | R65C21 Peripheral Interface Adapter (PIA)         | 1-19  |

| 10955 Segmented Display Controller/Driver                                                             | 5-51  | R65C22 Versatile Interface Adapter (VIA)          | 1-31  |

| R65/11EB Backpack Emulators                                                                           | 3-98  | R65C24 Peripheral Interface Adapter/Timer (PIAT)  | 1-75  |

| R6500/1 One-Chip Microcomputer                                                                        | 3-26  | R65C51 Asynchronous Communications Interface      |       |

| R6500/11, /12 and /15 One-Chip Microcomputer                                                          | 3-63  | Adapter (ACIA)                                    | 1-95  |

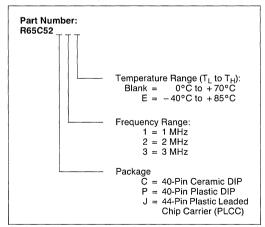

| R6500/1E Microprocessor Emulator Device                                                               | 3-49  | R65C52 Dual Asynchronous Communications Interface |       |

| R6500/1EB Backpack Emulator                                                                           | 3-57  | Adapter (DACIA)                                   | 1-116 |

| R6501 One-Chip Microprocessor                                                                         | 3-103 | R65F11 and R65F12 FORTH Based Microcomputers      | 3-203 |

| R650X Microprocessors (CPU)                                                                           | 2-3   | R65FRx FORTH Development and Kernel ROMs          | 3-235 |

| R6511Q One-Chip Microprocessor and                                                                    |       | R65NC22 Versatile Interface Adapter (VIA)         | 1-53  |

| R6500/13 One-Chip Microcomputer                                                                       | 3-138 | R68000 16-bit Microprocessing Unit (MPU)          | 4-3   |

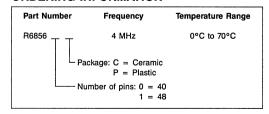

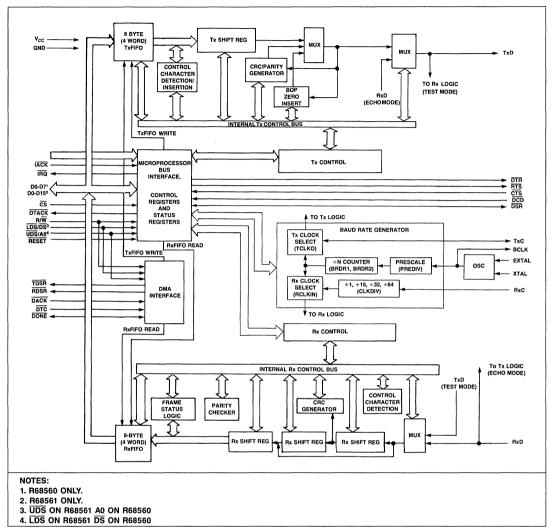

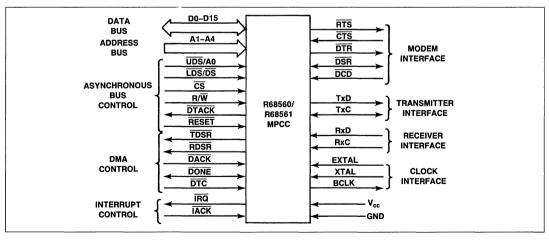

| R6518 One-Chip Microprocessor                                                                         | 3-173 | R68560 Multi-Protocol Communications Controller   |       |

| R6520 Peripheral Interface Adapter (PIA)                                                              | 2-18  | (MPCC)                                            | 4-83  |

| R6522 Versatile Interface Adapter (VIA)                                                               | 2-30  | R68C552 Dual Asynchronous Communications          |       |

| R6532 RAM-I/O-Timer (RIOT)                                                                            |       | Interface Adapter (DACIA)                         | 4-62  |

## CONTROLLER PRODUCTS Providing Solutions for Your VLSI Requirements

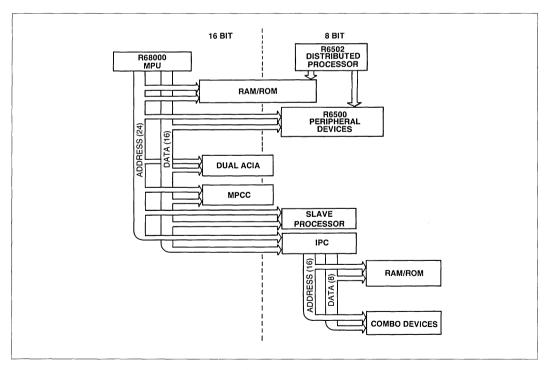

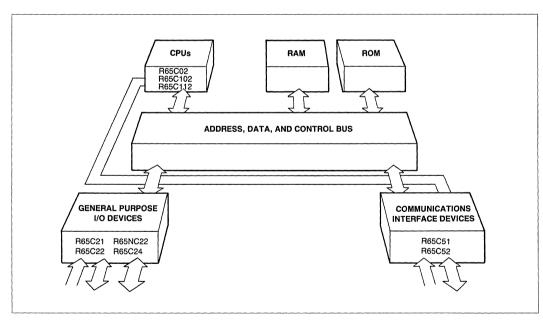

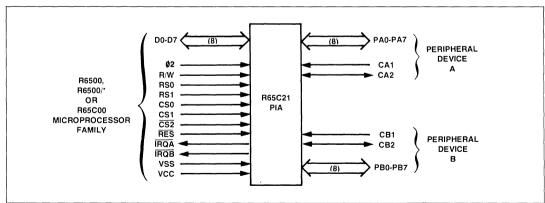

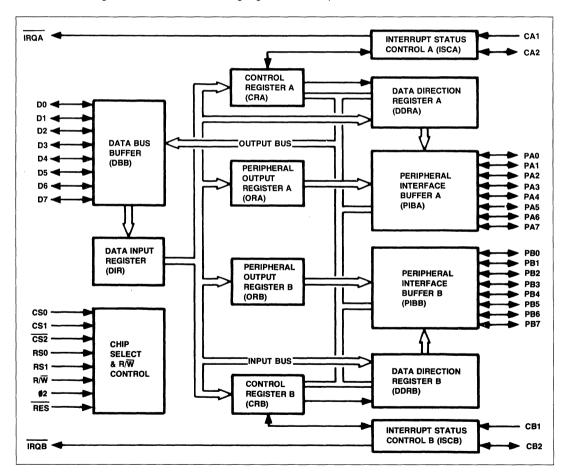

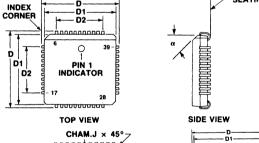

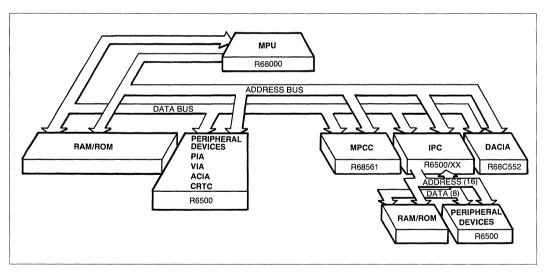

Rockwell International designs and manufactures a family of VLSI products to serve your system requirements. As shown in the diagram below, compatible controller products are available for a wide range of 16-bit and 8-bit applications. Peripheral devices operate on either the 68000 or the 6500 microprocessor bus structure. Many of the peripheral devices are now being used on additional bus structures such as 8085, 80286 and Z80, just to name a few.

The product line utilizing the R6502 processor, recognized world-wide for its high performance, was recently improved by redesigning it in a CMOS process. Enhancements include a 2000% improvement in speed and a 20 times reduction in power dissipation.

These products are produced in high volume at a modern state-of-the-art facility located in Newport Beach, California, and are packaged in a newly constructed, fully automated manufacturing facility in Mexicali, Mexico. The class 10,000 clean room environment produces devices to the most stringent industry standards. Rockwell has the organization, systems and support to manufacture products to existing and future quality levels.

In fact, Rockwell is the first and only semiconductor company to offer a 5 year warranty. You can rely on customer satisfaction and service when choosing a Rockwell semiconductor product.

Serving System Requirements

### **PRODUCT INDEX**

| CMOS 8-Bit Microprocessors & Peripherals |   |

|------------------------------------------|---|

| NMOS 8-Bit Microprocessors & Peripherals | 2 |

| 8-Bit Microcomputers                     | 3 |

| 16-Bit Microprocessors and Peripherals   | 4 |

| Intelligent Display Controllers          | 5 |

| Application Notes                        | 6 |

# Section 1 CMOS 8-Bit Microprocessors & Peripherals

|                                                                   | Page  |

|-------------------------------------------------------------------|-------|

| Product Family Overview                                           | 1-2   |

| R65C02, R65C102 and R65C112 Microprocessors (CPU)                 | 1-0   |

| R65C21 Peripheral Interface Adapter (PIA)                         | 1-19  |

| R65C22 Versatile Interface Adapter (VIA)                          | 1-3   |

| R65NC22 Versatile Interface Adapter (VIA)                         | 1-50  |

| R65C24 Peripheral Interface Adapter/Timer (PIAT)                  | 1-7   |

| R65C51 Asynchronous Communications Interface Adapter (ACIA)       | 1-9   |

| R65C52 Dual Asynchronous Communications Interface Adapter (DACIA) | 1-110 |

## CMOS 8-bit Microprocessors & Peripherals Fastest Executing — Low Power

There is no CMOS microprocessor family easier to implement than the R65CXX. It is the fastest instruction executing 8-bit family available. It's software compatible with a family of single-chip microcomputers and has three powerful CPUs and peripherals for parallel and serial I/O.

In the 8-bit range, nothing gives faster instruction execution (500  $\mu s)$  with most parts available in 1, 2, 3 and 4 MHz versions. Thirteen address modes provide the most efficient ways of addressing memory. R65CXX peripherals are system oriented, designed to implement systems with minimum device count.

Because of its inherent characteristics, advanced Rockwell CMOS provides low power consumption, high noise immunity and high speed operation. Its 2 MHz CPU dissipates only 40 mW (compared to 800 mW in NMOS) and requires only 10 mA standby current. Instruction memory requirements are 20% less due to added bit manipulation features.

The entire 8-bit R65CXX family is upward compatible with the 16-bit 68000 bus, software compatible with Rockwell's 8-bit microcomputers, and are the building blocks for a wide range of system applications. It's one of the world's highest performing and lowest cost microprocessors.

**CMOS R65CXX Microprocessor Family**

#### R65C02, R65C102 and R65C112 R65C00 Microprocessors (CPU)

#### DESCRIPTION

The 8-bit R65C00 microprocessor family of devices are produced using CMOS silicon gate technology which provides advanced system architecture for performance speed and system costeffectiveness enhancements over their NMOS counterparts, the R6500 family of microprocessor devices.

Three CPU devices are available. All are software-compatible and provide 64K bytes of memory addressing, two interrupt inputs, and on-chip clock oscillators and/or drivers. All are bus-compatible with the NMOS R6500 family devices.

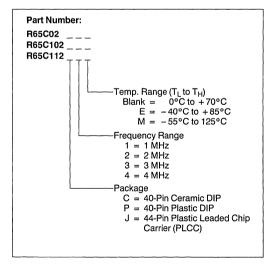

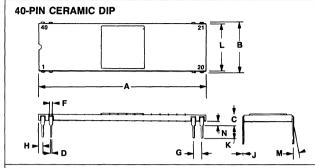

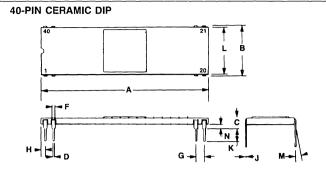

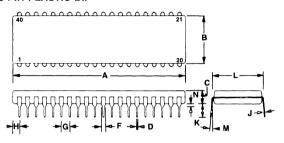

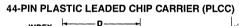

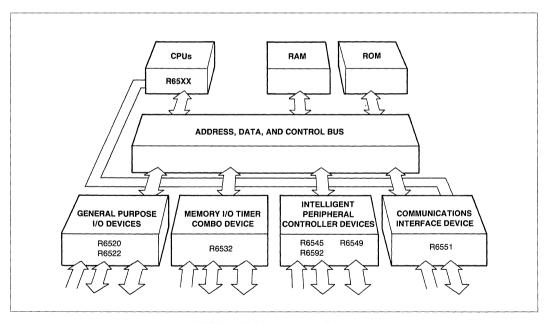

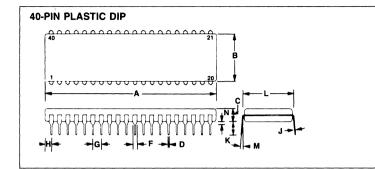

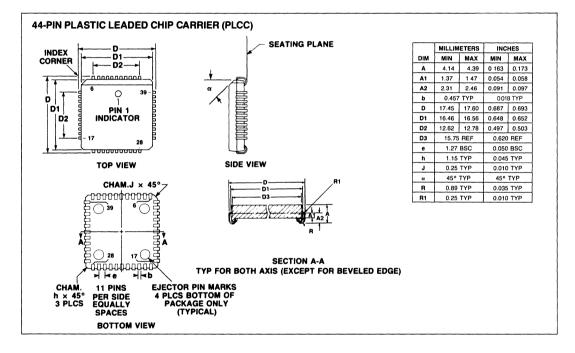

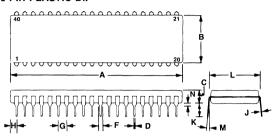

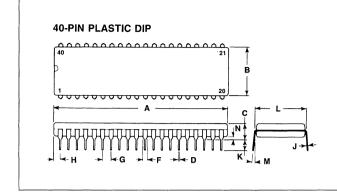

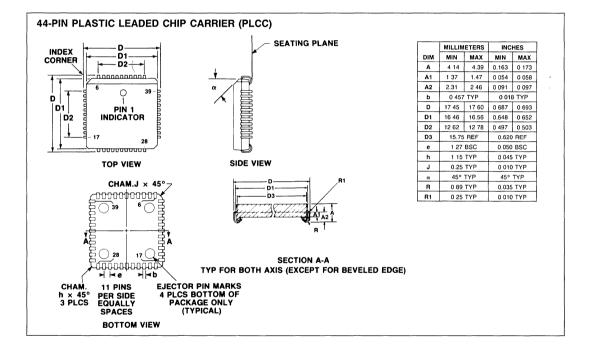

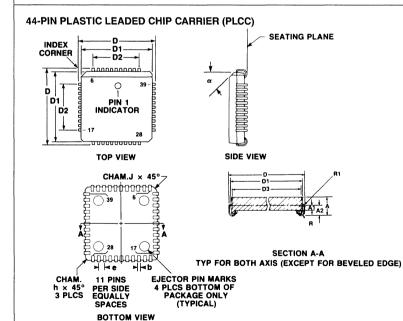

The CMOS family includes two microprocessors (R65C02 and R65C102) with on-board clock oscillators and drivers and one microprocessor (R65C112) driven by an external clock. The on-chip clock versions are aimed at high performance, low-cost applications where single phase inputs, crystal or RC inputs provide the time base. The slave processor version is geared for multiprocessor system applications where maximum timing control is mandatory. All R65C00 microprocessors are available in ceramic and plastic packaging, operating frequency of 1 MHz, 2 MHz, 3 MHz and 4 MHz, and commercial and industrial temperature versions. All three devices are available in 40-pin DIP or 44-pin PLCC packages.

#### **FEATURES**

- CMOS silicon gate technology

- Low Power (4 mA/MHz)

- Software compatible with R6502

- Single 5V ±5% power supply requirements

- Eight-bit parallel processing

- Decimal and binary arithmetic

- True indexing capability

- Programmable stack pointer

- Interrupt capability Non-maskable interrupt

- Eight-bit bidirectional data bus

- Memory address range of up to 64K bytes

- "Ready" input

- Direct memory access (DMA) capability

- Memory lock output

- 1 MHz. 2 MHz. 3 MHz. and 4 MHz versions

- · Choice of external or on-chip clocks

- · On-chip clock options

- -External single clock input

- -Direct crystal input ( ÷ 4)

- · Commercial and industrial temperature versions

- Pipeline architecture

- Slave processor version (R65C112)

#### MAJOR FEATURES AND DIFFERENCES

| Feature                             | R65C02 | R65C102 | R65C112 |

|-------------------------------------|--------|---------|---------|

| Pin compatible with NMOS R6502      | Х      |         |         |

| 64K addressable bytes of memory     | X      | X       | x       |

| IRQ interrupt                       | X      | X       | x       |

| On-chip clock oscillator            |        | Х       | 1       |

| External clock only                 | X      |         | x       |

| TTL level single phase clock input  | X      | Х       | ĺ       |

| RC time base clock input            | Х      | Х       | 1       |

| Crystal time base clock input       | Х      | х       | 1       |

| Single phase clock input            |        |         | x       |

| Two phase output clock              | X      | Х       | 1       |

| SYNC and RDY signals                | X      | X       | x       |

| Bus Enable (BE) signal              |        | X       | x       |

| Memory Lock (ML) output signal      |        | X       | x       |

| Direct Memory Access (DMA) capacity |        | X       | x       |

| NMI interrupt signal                | х      | X       | Х       |

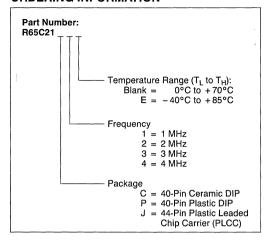

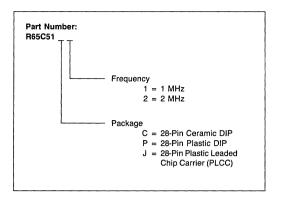

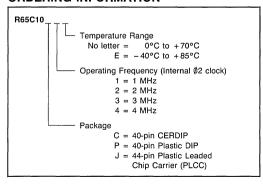

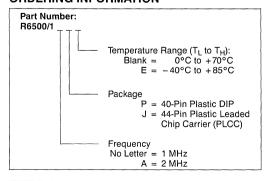

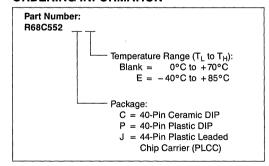

#### ORDERING INFORMATION

#### INTERFACE SIGNALS

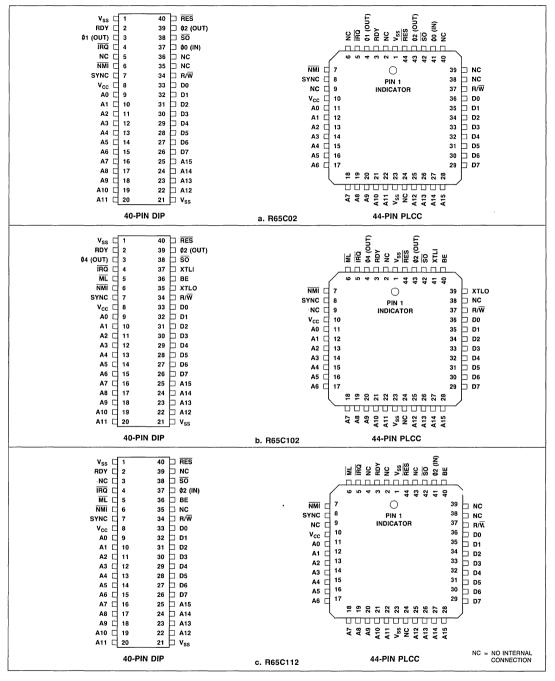

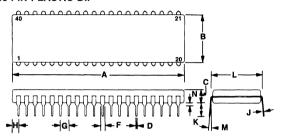

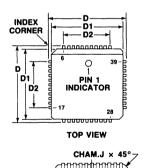

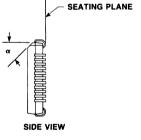

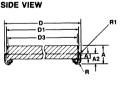

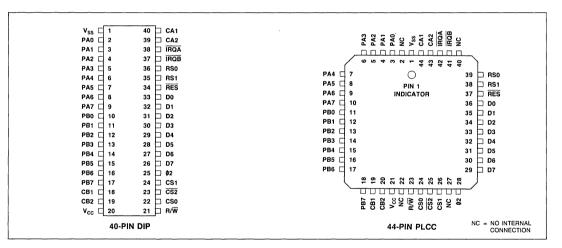

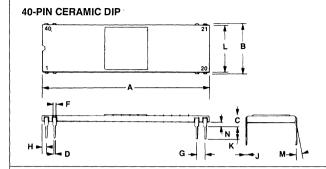

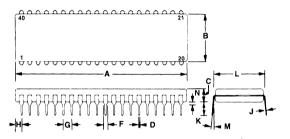

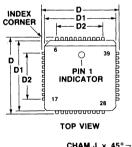

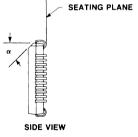

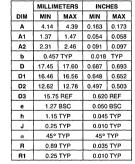

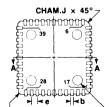

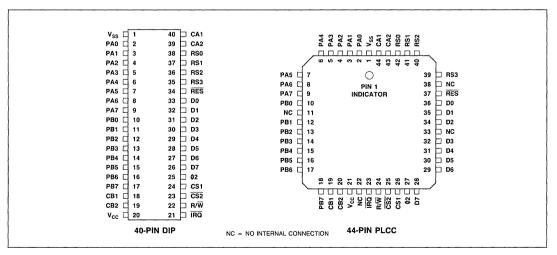

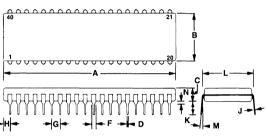

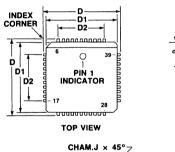

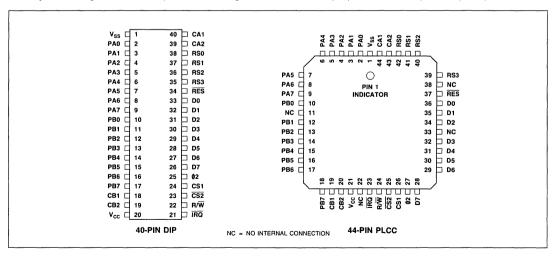

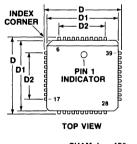

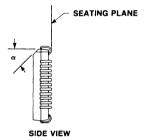

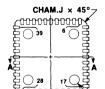

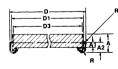

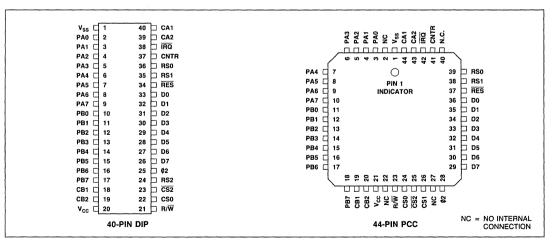

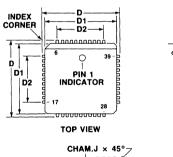

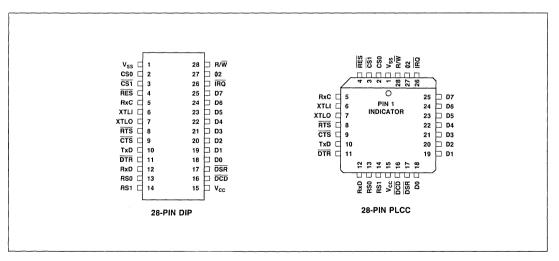

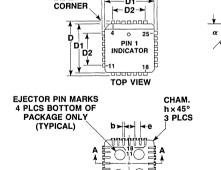

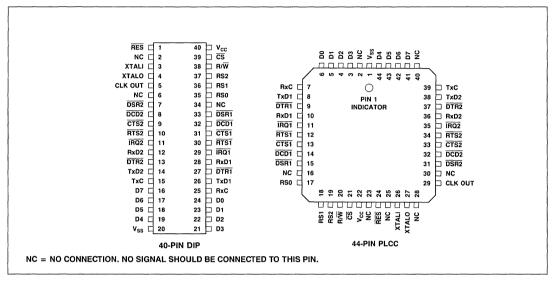

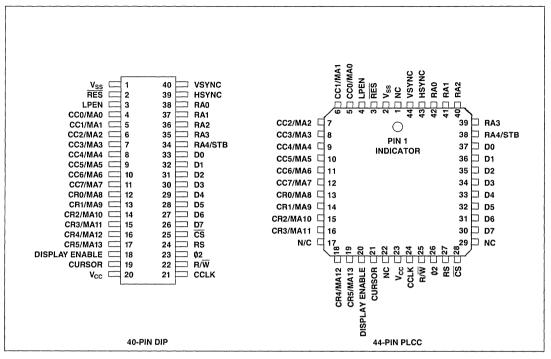

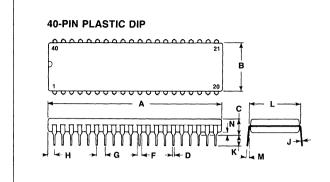

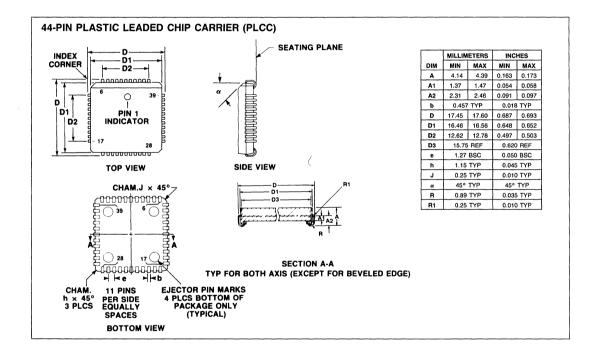

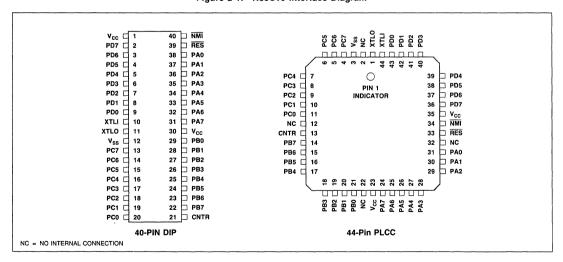

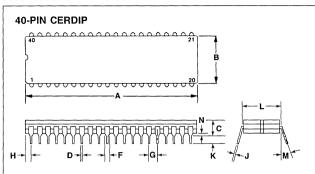

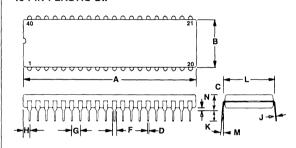

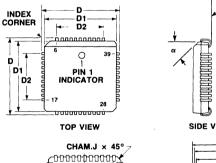

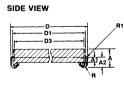

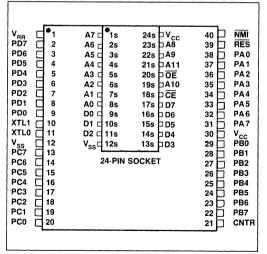

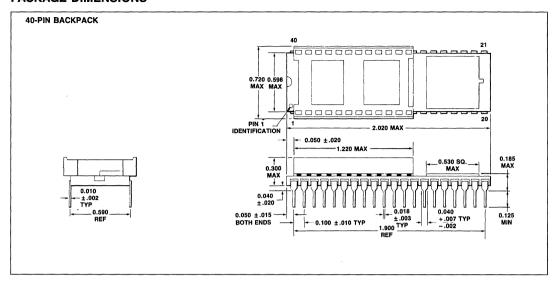

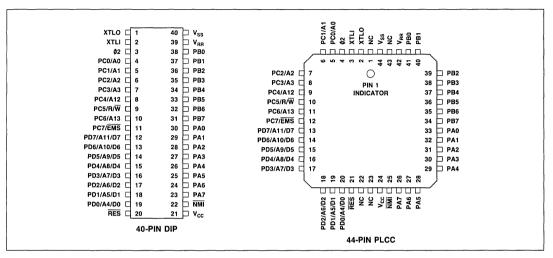

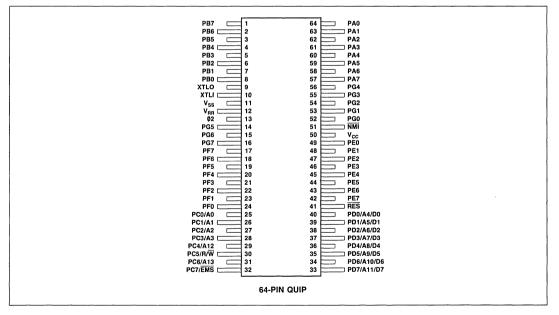

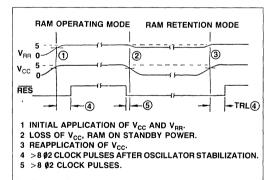

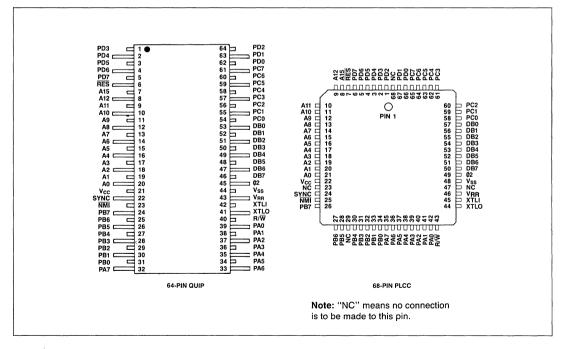

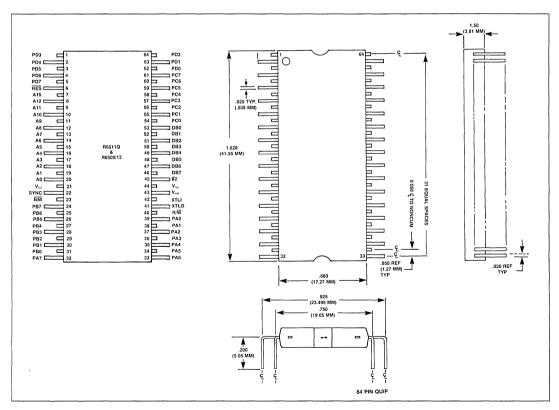

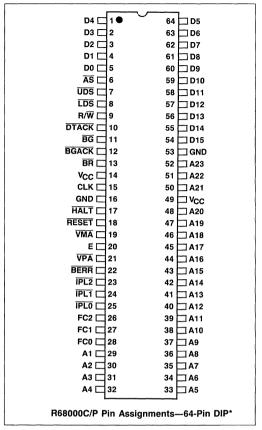

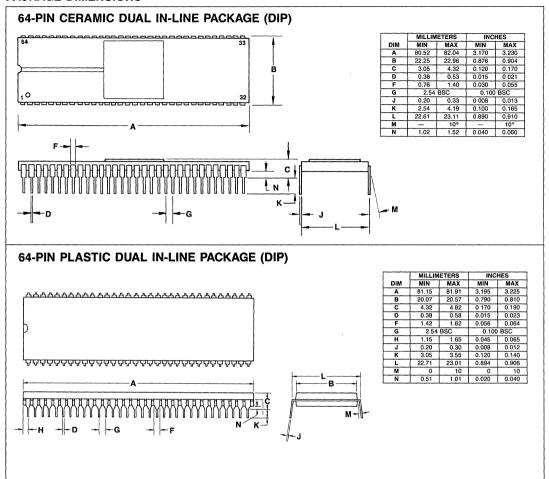

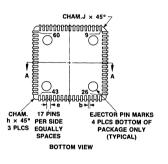

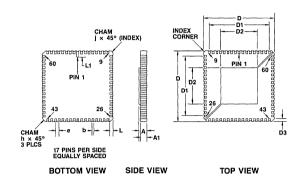

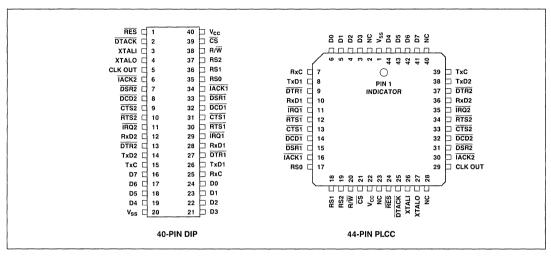

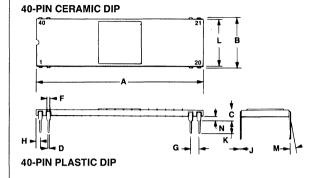

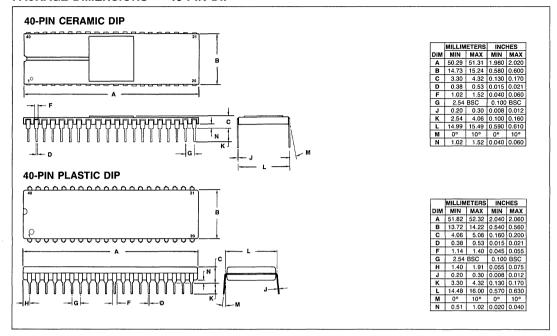

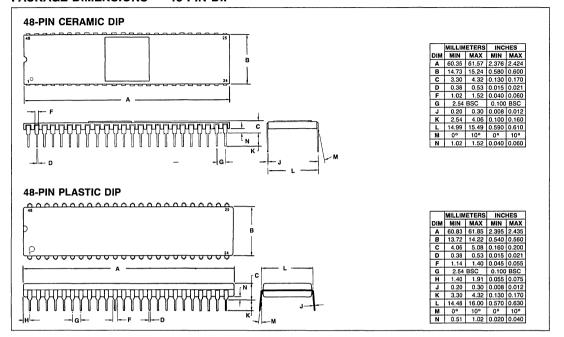

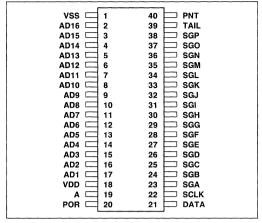

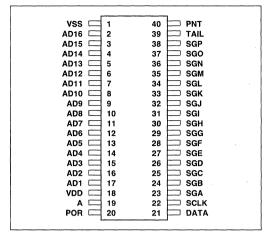

Figure 1 shows the pin assignments for the members of the R65C00 CPU family. All devices are housed in 40-pin ceramic or plastic dual-in-line (DIP) or 44-pin plastic leaded chip carrier (PLCC) packages.

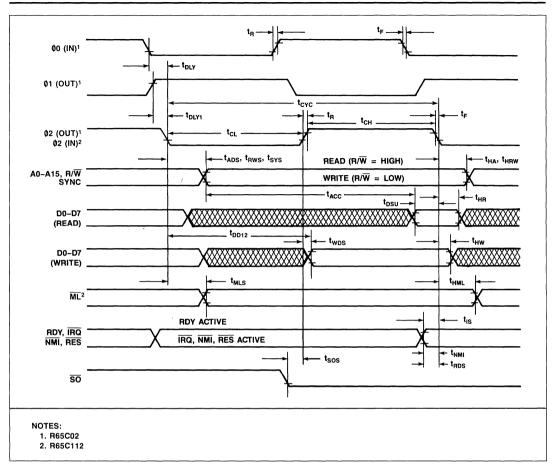

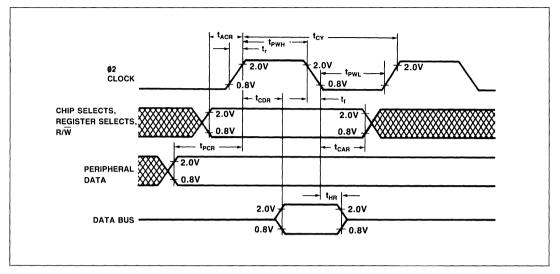

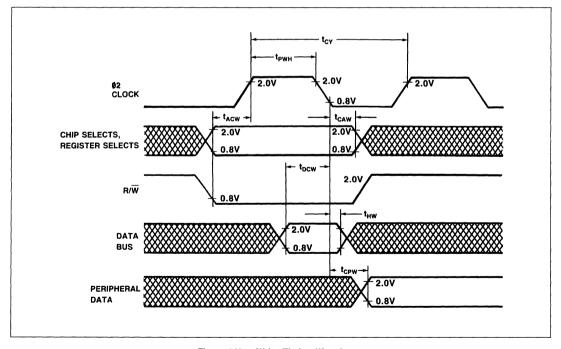

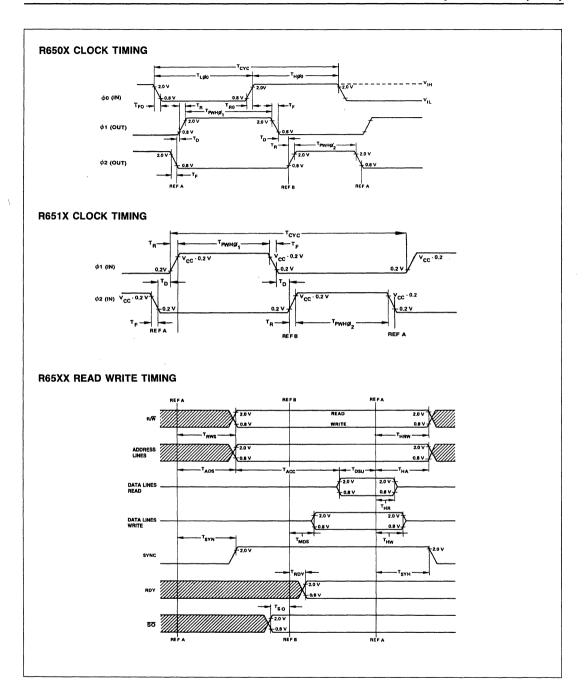

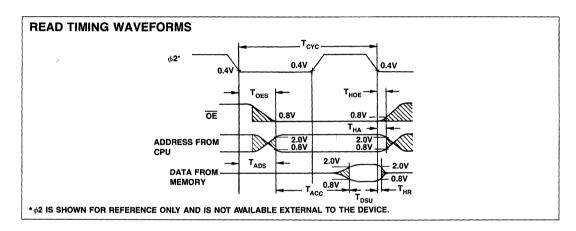

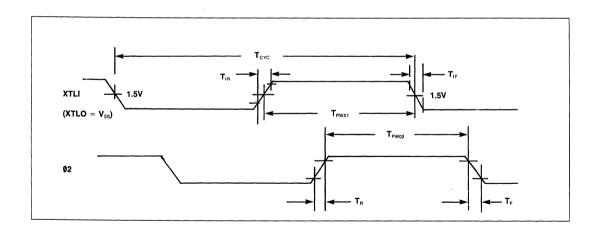

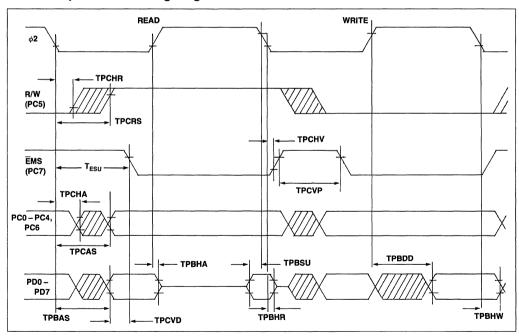

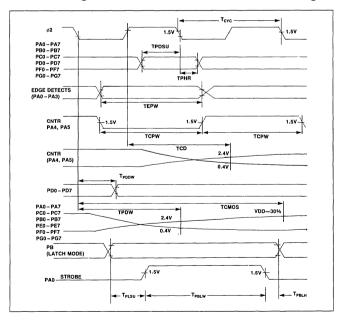

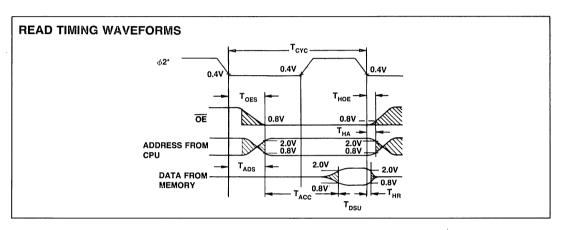

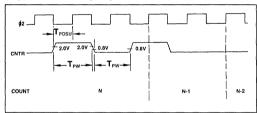

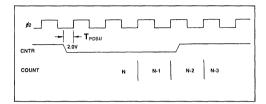

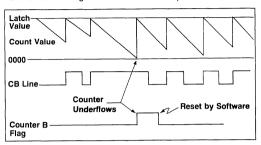

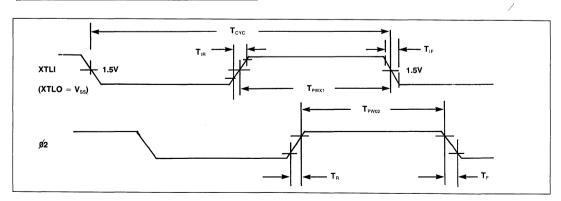

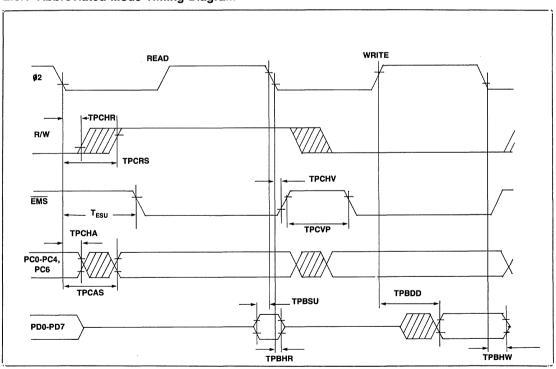

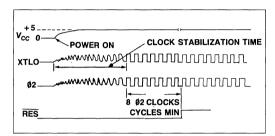

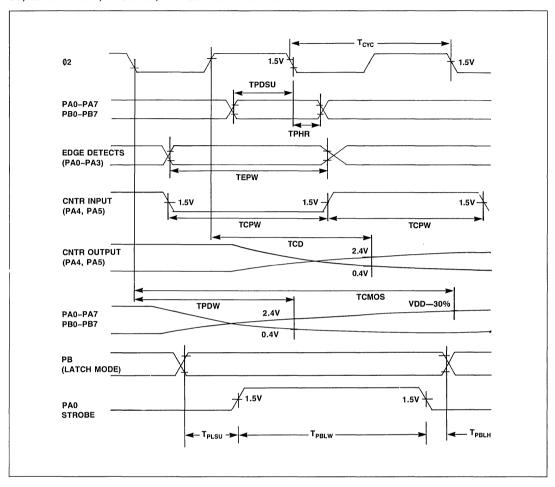

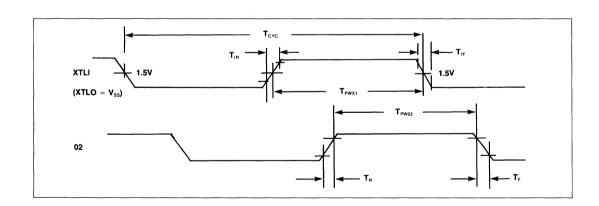

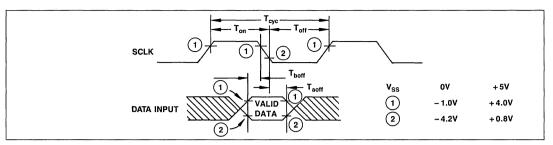

Refer to the timing diagrams (Figures 3, 4, and 5) for the particular device in the following discussion.

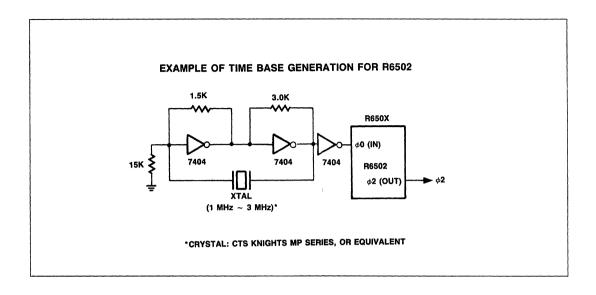

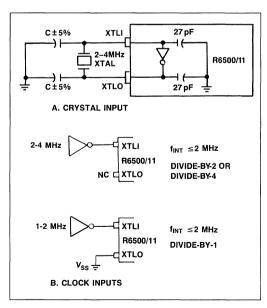

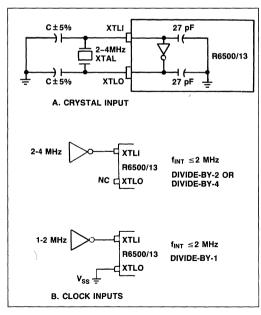

#### **CLOCK SIGNALS (R65C02)**

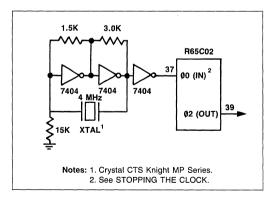

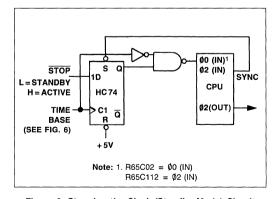

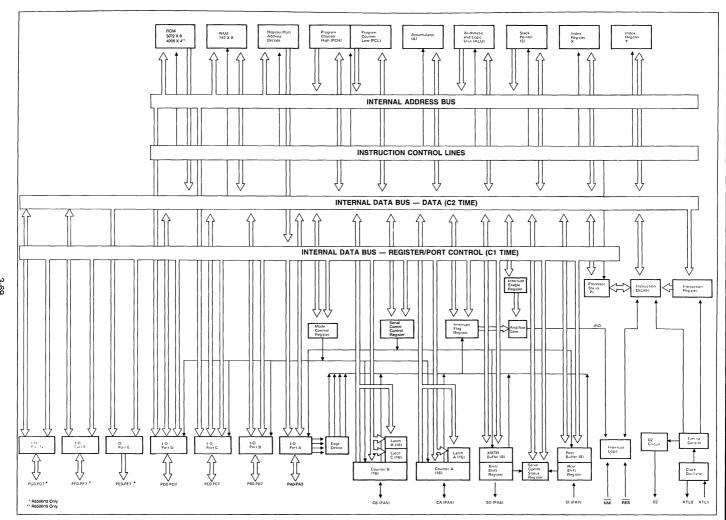

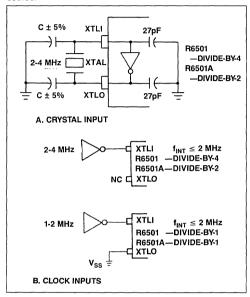

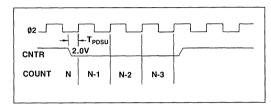

The R65C02 requires an external  $\emptyset$ 0 clock. See Figure 6 for an example clock circuit.  $\emptyset$ 0 is a TTL level input that is used to generate the internal clocks of the R65C02. Two full level output clocks are generated by the R65C02. The  $\emptyset$ 2 clock is in phase with  $\emptyset$ 0. The  $\emptyset$ 1 clock output is 180° out of phase with  $\emptyset$ 0. When the input clock is stopped, the CPU is in the standby mode. See Figure 8 for special standby mode considerations.

For non-critical timing configurations, a simple RC or crystal network may be strapped between  $\emptyset$ 0 (IN) and  $\emptyset$ 1 (OUT).

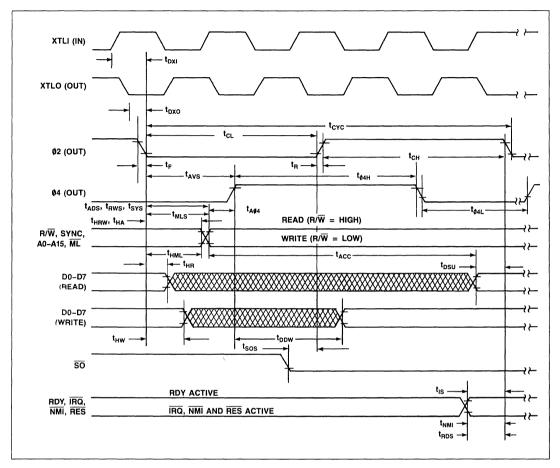

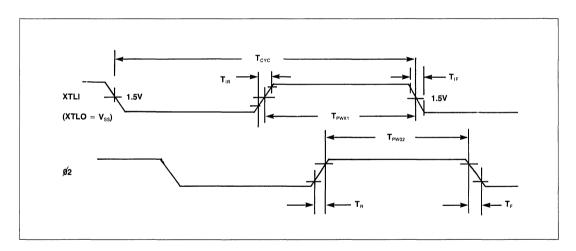

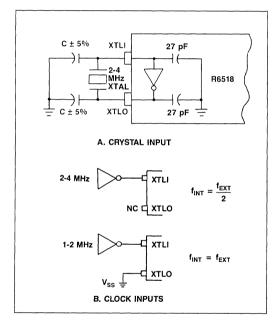

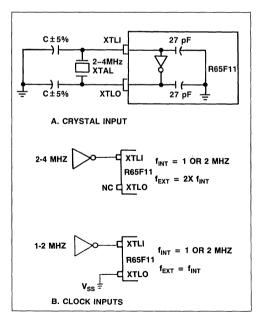

#### CLOCK SIGNALS (R65C102)

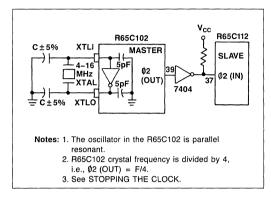

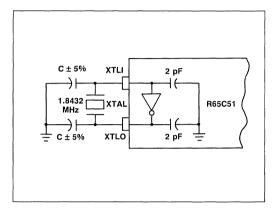

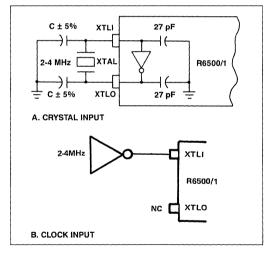

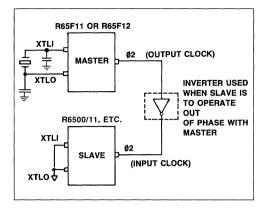

The R65C102 internal clocks may be generated by a TTL level single phase input, an RC time base input, or a crystal time base input ( $\div$ 4) using the XTLO and XTLI input pins. See Figure 7 for an example of a crystal time base circuit. Two full level output clocks are generated by the R65C102. The  $\emptyset$ 2 clock output provides timing for external  $R\overline{W}$  operations. Addresses are valid after the address delay time (t\_{ADS}) referenced to the falling edge of  $\emptyset$ 2 (OUT). The  $\emptyset$ 4 output is a quadrature output clock that is delayed from the falling edge of the  $\emptyset$ 2 clock by delay time t\_AVS. Using the  $\emptyset$ 4 clock, addresses are valid at the rising edge of  $\emptyset$ 4.

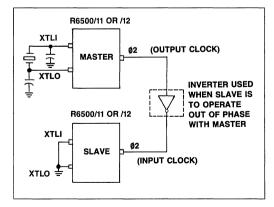

#### **CLOCK SIGNALS (R65C112)**

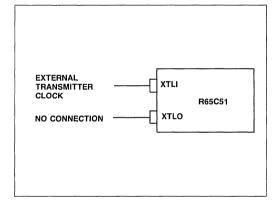

All internal clock signals for the R65C112 are generated by the input clock signal \$\psi\_2\$ (IN). Since this device is intended to be operated in the slave mode it does not have internal clock generation, but rather requires the external clock \$\psi\_2\$ (IN) from a host device. Figure 7 shows an example of a clock circuit for the R65C112 configured for slave mode.

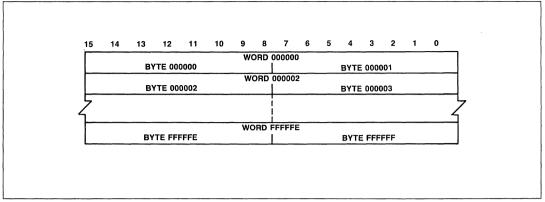

#### ADDRESS BUS (A0-A15)

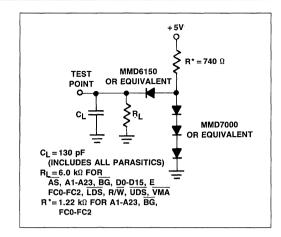

Address lines A0–A15 form a 16-bit address bus for memory and I/O exchanges on the data bus. The output of each address line is TTL compatible, capable of driving one standard TTL load and 130 pF.

#### DATA BUS (D0-D7)

The data lines (D0–D7) constitute an 8-bit bidirectional data bus used for data exchanges to and from the device and peripherals. The outputs are tri-state buffers capable of driving one TTL load and 130 pF.

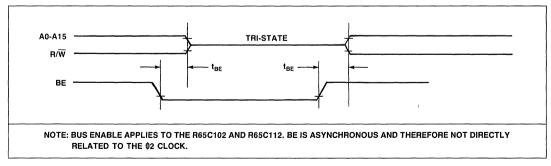

#### **BUS ENABLE (BE)**

This signal allows external control of the data and the address output buffers and  $R\overline{W}$ . For normal operation, BE is high causing the address buffers and  $R\overline{W}$  to be active and the data buffers to be active during a write cycle. For external control, BE is held low to disable the buffers. BE is an asynchronous signal and

therefore not related to, or controlled by the CPU internal clock signals. Figure 5 shows timing relationships of BE to  $R/\overline{W}$  and address output buffers.

#### INTERRUPT REQUEST (IRQ)

This TTL compatible input requests that an interrupt sequence begin within the microprocessor.  $\overline{\text{IRQ}}$  is sampled at the falling edge of  $\emptyset 2$  prior to the last cycle of the instruction; if the interrupt flag in the processor status register is zero, the current instruction is completed and the interrupt sequence begins during  $\emptyset 1.$  The program counter and processor status register are stored in the stack. The microprocessor will then set the interrupt mask flag high so that no further  $\overline{\text{IRQ}}$ s may occur. At the end of this cycle, the program counter low byte will be loaded from address FFFE, and program counter high byte from location FFFF, thus transferring program control to the memory vector located at these addresses. The RDY signal must be in the high state for any interrupt to be recognized. A 3K ohm external resistor should be used for proper wire OR operation.

#### MEMORY LOCK (ML)

In a multiprocessor system, the  $\overline{\text{ML}}$  output indicates the need to defer the rearbitration of the next bus cycle to ensure the integrity of read-modify-write instructions.  $\overline{\text{ML}}$  goes low during ASL, DEC, INC, LSR, ROL, ROR, RMB, SMB, TRB, TSB memory referencing instructions. This signal is low for the modify and write cycles.

#### NON-MASKABLE INTERRUPT (NMI)

A negative-going edge on this input requests that a non-maskable interrupt sequence be generated within the microprocessor. The  $\overline{NMI}$  is sampled during  $\emptyset 2$ ; the current instruction is completed and the interrupt sequence begins during  $\emptyset 1$ . The program counter is loaded with the interrupt vector from locations FFFA (low byte) and FFFB (high byte), thereby transferring program control to the non-maskable interrupt routine.

#### NOTE

Since this interrupt is non-maskable, another  $\overline{\text{NMI}}$  can occur before the first is finished. Care should be taken when using  $\overline{\text{NMI}}$  to avoid this.

#### READY (RDY)

This input allows the user to single-cycle the microprocessor on all cycles including write cycles. A negative transition to the low state, during or coincident with  $\emptyset$ 2, will halt the microprocessor with the output address lines reflecting the current address. This condition will remain through a subsequent  $\emptyset$ 2 in which the RDY signal is low. This feature allows microprocessor interfacing with low-speed memory as well as direct memory access (DMA).

#### READ/WRITE (R/W)

This signal is normally in the high state indicating that the microprocessor is reading data from memory or I/O bus. In the low state the data bus has valid data from the microprocessor to be stored at the addressed memory location.

#### SET OVERFLOW (SO)

A negative transition on this line sets the overflow bit (V) in the processor status register. The signal is sampled prior to the rising edge of  $\emptyset$ 2 by the  $\overline{SO}$  setup time (t<sub>SOS</sub>).

Figure 1. Pin Assignments

#### RESET (RES)

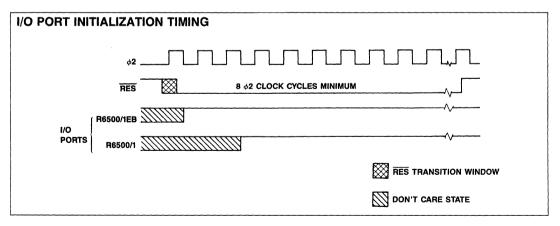

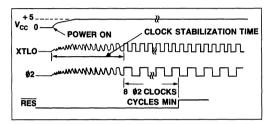

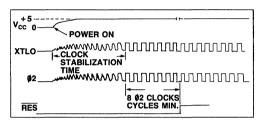

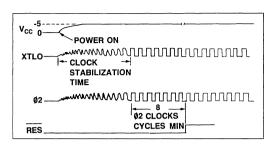

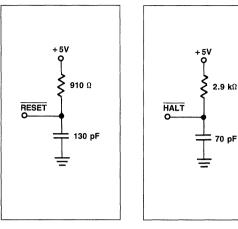

This input resets the microprocessor. Reset must be held low for at least two clock cycles after V<sub>CC</sub> reaches operating voltage from a power down. A positive transition on this pin will then cause an initialization sequence to begin. Likewise, after the system has been operating, a low on this line of at least two cycles will cease microprocessing activity, followed by initialization after the positive edge on RES.

When a positive edge is detected, there is an initialization sequence lasting seven clock cycles. Then the interrupt mask flag is set, the decimal mode is cleared, and the program counter is loaded with the restart vector from locations FFFC (low byte) and FFFD (high byte). This is the start location for program control. This input should be high in normal operation.

#### SYNCHRONIZE (SYNC)

This output line identifies those cycles during which the microprocessor is fetching the instruction operation code (OP CODE). The SYNC line goes high during  $\emptyset$ 1 of an OP CODE fetch and stays high for the remainder of that cycle. If the RDY line is pulled low during the clock cycle in which SYNC went high, the processor will stop in its current state and will remain in the state until the RDY line goes high. In this manner, the SYNC signal can be used to control RDY to cause single instruction execution.

#### **FUNCTIONAL DESCRIPTION**

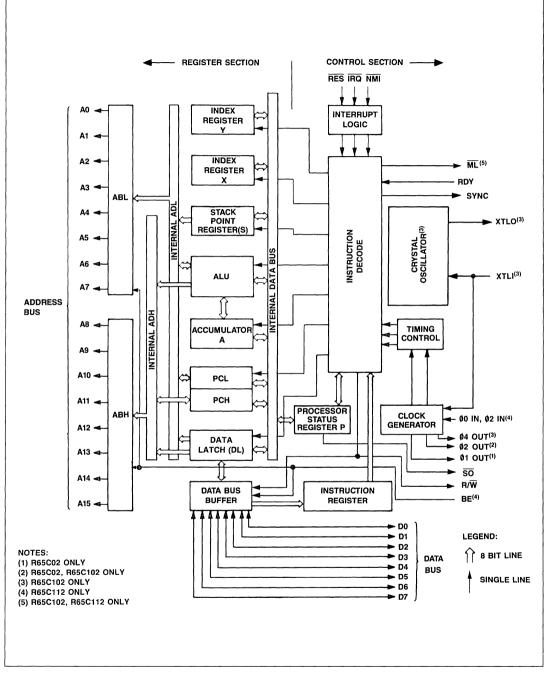

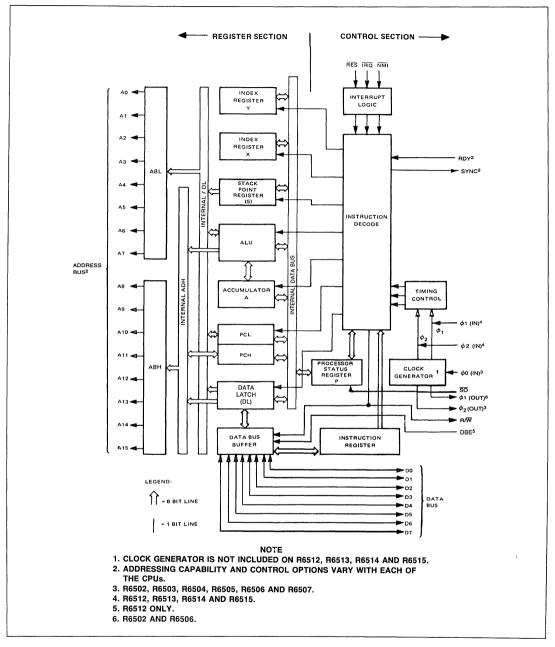

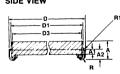

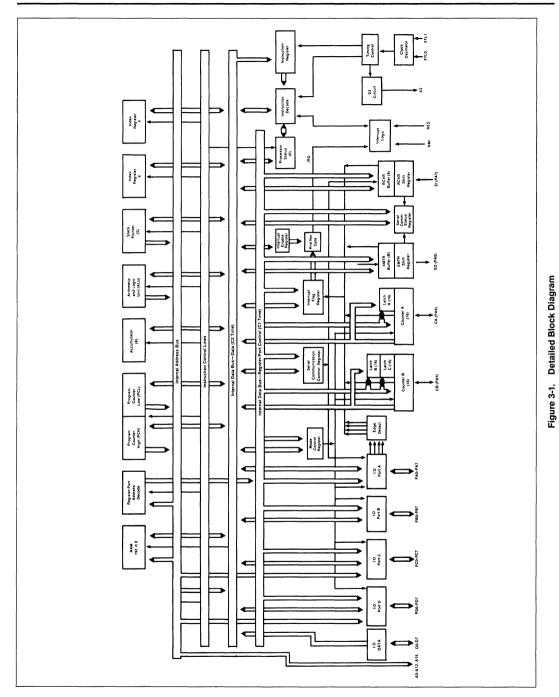

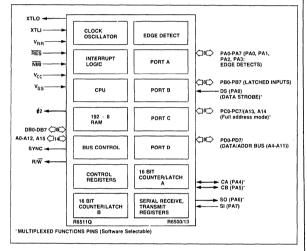

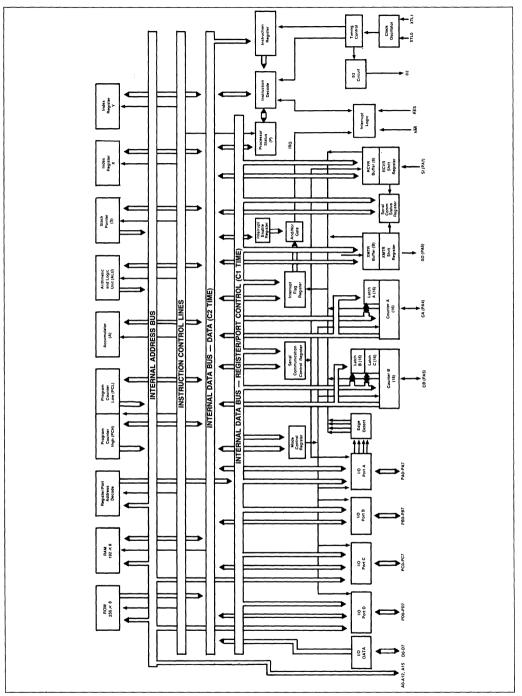

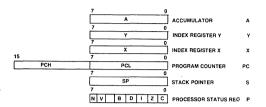

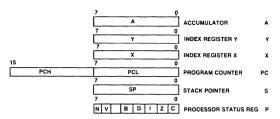

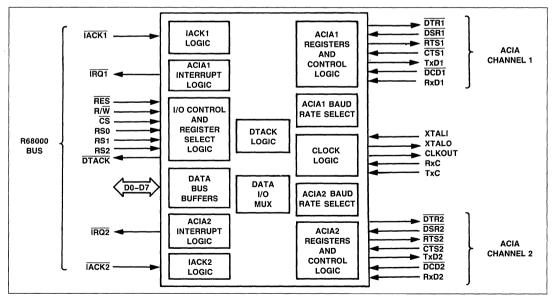

Figure 2 shows the block diagram of the R65C00 CPU internal architecture for all three devices. With the exception of the crystal oscillator, clock signals, Memory Lock (ML), and Bus Enable (BE) signals, the internal architecture of the three members of the R65C00 CPU of devices is identical. This block diagram supports the following text that describes the function of each of the device's major elements.

#### CRYSTAL OSCILLATOR (R65C102 Only)

The crystal oscillator, driven by a crystal across XTLO and XTLI, divides the crystal frequency by four to provide the basic \$2\$ clock signal that drives the internal clock generator.

#### **CLOCK GENERATOR**

The clock generator develops all internal clock signals, and (where applicable) external clock signals, associated with the device. It is the clock generator that drives the timing control unit and the external timing for slave mode operations.

#### **TIMING CONTROL**

The timing control unit keeps track of the instruction cycle being monitored. The unit is set to zero each time an instruction fetch is executed and is advanced at the beginning of each phase one clock pulse for as many cycles as is required to complete the instruction. Each data transfer which takes place between the registers depends upon decoding the contents of both the instruction register and the timing control unit.

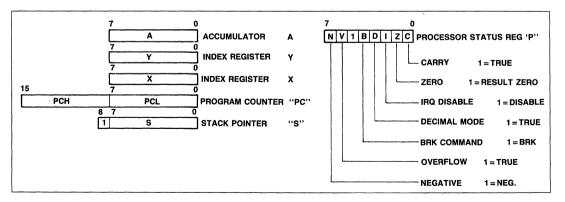

#### PROGRAM COUNTER

The 16-bit program counter provides the addresses which step the microprocessor through sequential instructions in a program.

Each time the microprocessor fetches an instruction from program memory, the lower byte of the program counter (PCL) is placed on the low-order bits of the address bus and the higher byte of the

program counter (PCH) is placed on the high-order 8 bits. The counter is incremented each time an instruction or data is fetched from program memory.

#### INSTRUCTION REGISTER AND DECODE

Instructions fetched from memory are gated onto the internal data bus. These instructions are latched into the instruction register, then decoded, along with timing and interrupt signals, to generate control signals for the various registers.

#### ARITHMETIC AND LOGIC UNIT (ALU)

All arithmetic and logic operations take place in the ALU including incrementing and decrementing internal registers (except the program counter). The ALU has no internal memory and is used only to perform logical and transient numerical operations.

#### ACCUMULATOR

The accumulator is a general purpose 8-bit register that stores the results of most arithmetic and logic operations, and in addition, the accumulator usually contains one of the two data words used in these operations.

#### INDEX REGISTERS

There are two 8-bit index registers (X and Y), which may be used to count program steps or to provide an index value to be used in generating an effective address.

When executing an instruction which specifies indexed addressing, the CPU fetches the op code and the base address, and modifies the address by adding the index register to it prior to performing the desired operation. Pre- or post-indexing of indirect addresses is possible (see addressing modes).

#### STACK POINTER

The stack pointer is an 8-bit register used to control the addressing of the variable-length stack on page one. The stack pointer is automatically incremented and decremented under control of the microprocessor to perform stack manipulations under direction of either the program or interrupts  $(\overline{\text{NMi}} \text{ and } \overline{\text{IRQ}})$ . The stack allows simple implementation of nested subroutines and multiple level interrupts. The stack pointer should be initialized before any interrupts or stack operations occur.

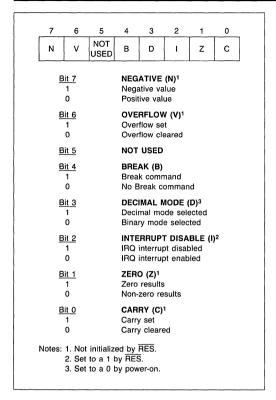

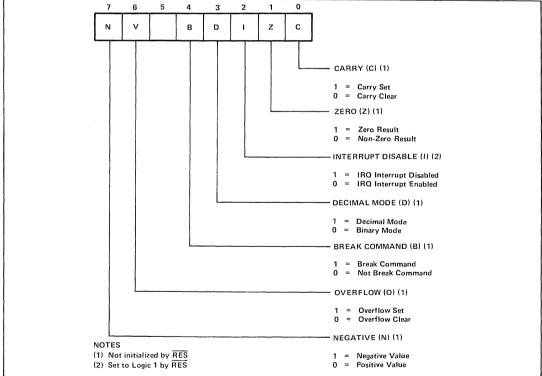

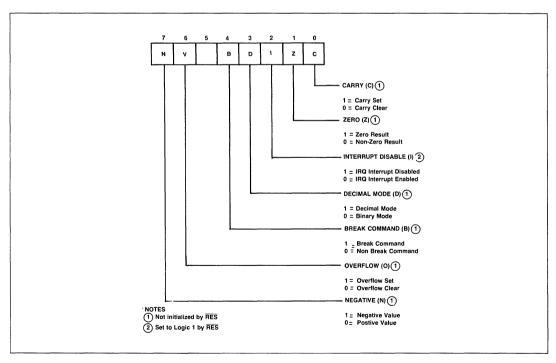

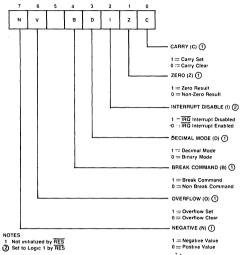

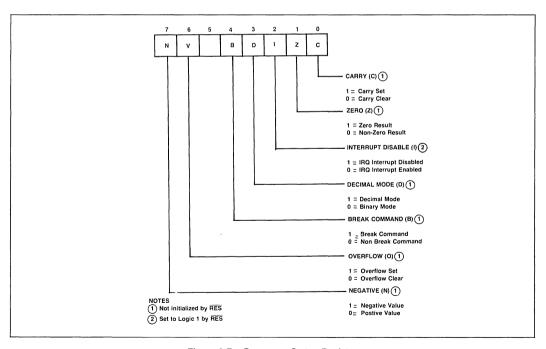

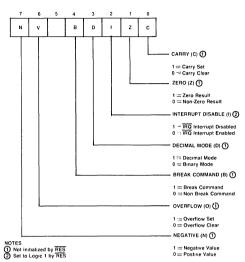

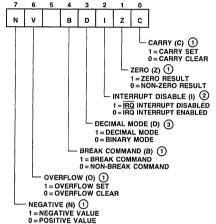

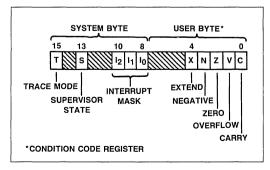

#### PROCESSOR STATUS REGISTER

The 8-bit processor status register contains seven status flags. Some of the flags are controlled by the program, others may be controlled both by the program and the CPU. The R65C00 instruction set contains a number of conditional branch instructions which are designed to allow testing of these flags.

#### HARDWARE ENHANCEMENTS

The R65C00 family of CPU devices have incorporated hardware enhancements over their NMOS counterpart, the R6502. These hardware enhancements are:

- The NMOS device would ignore the assertion of a Ready (RDY) during a write operation. The CMOS family will stop the processor during Ø2 clock if RDY is asserted during a write operation.

- On the NMOS device, unused input-only pins (IRQ, NMI, RDY, RES, and SO) must be connected to a low impedance signal to avoid noise problems. These unused pins on the CMOS devices are internally connected by a high impedance to V<sub>CC</sub> (approximately 250K ohms).

Figure 2. R65C00 Internal Architecture

#### ADDRESSING MODES

The R65C00 CPU family has 15 address modes (two more than the NMOS equivalent family). In the following discussion of these addressing modes, a bracketed expression follows the title of the mode. This expression is the term used in the Instruction Set Op Code Matrix table (later in this product description) to make it easier to identify the actual addressing mode used by the instruction.

**ACCUMULATOR ADDRESSING [Accum]** — This form of addressing is represented with a one byte instruction, implying an operation on the accumulator.

**IMMEDIATE ADDRESSING [IMM]** — In immediate addressing, the second byte of the instruction contains the operand, with no further memory addressing required.

ABSOLUTE ADDRESSING [ABS] — In absolute addressing, the second byte of the instruction specifies the eight low order bits of the effective address while the third byte specifies the eight high order bits. Thus the absolute addressing mode allows access to the entire 64K bytes of addressable memory.

**ZERO PAGE ADDRESSING [ZP]** — The zero page instructions allow for shorter code and execution times by fetching only the second byte of the instruction and assuming a zero high address byte. Careful use of the zero page can result in significant increase in code efficiency.

ZERO PAGE INDEXED ADDRESSING [ZP, X or Y] — (X, Y indexing) — This form of addressing is used with the index register and is referred to as "Zero Page, X" or "Zero Page, Y". The effective address is calculated by adding the second byte to the contents of the index register. Since this is a form of "Zero Page" addressing, the content of the second byte references a location in page zero. Additionally, due to the "Zero Page" addressing nature of this mode, no carry is added to the high order eight bits of memory and crossing of page boundaries does not occur.

ABSOLUTE INDEXED ADDRESSING [ABS, X or Y] — (X, Y indexing) — This form of addressing is used in conjunction with X and Y index register and is referred to as "Absolute, X" and "hosolute, Y". The effective address is formed by adding the contents of X or Y to the address contained in the second and third bytes of the instruction. This mode allows the index register to contain the index or count value and the instruction to contain the base address. This type of indexing allows any location referencing and the index to modify fields, resulting in reduced coding and execution time.

**INDEXED ABSOLUTE INDIRECT [(ABS, X)]\*** — The contents of the second and third instruction bytes are added to the X-register. The sixteen-bit result is a memory address containing the effective address. (JMP (ABS, X) only).

**IMPLIED ADDRESSING [Implied]** — In the implied addressing mode, the address containing the operand is implicitly stated in the operation code of the instruction.

**RELATIVE ADDRESSING [Relative]** — Relative addressing is used only with branch instructions and establishes a destination for the conditional branch.

The second byte of the instruction becomes the operand which is an "Offset" added to the contents of the lower eight bits of the program counter when the counter is set at the next instruction. The range of the offset is -128 to +127 bytes from the next instruction.

ZERO PAGE RELATIVE ADDRESSING [ZP REL]\* — This mode bit tests the zero page location specified for bit set/reset per the mask and performs a conditional relative branch based on the results of the bit test.

INDEXED INDIRECT ADDRESSING [(IND, X)] — In indexed indirect addressing (referred to as (Indirect, X)), the second byte of the instruction is added to the contents of the X index register, discarding the carry. The result of this addition points to a memory location on page zero whose contents are the low order eight bits of the effective address. The next memory location in page zero contains the high order eight bits of the effective address. Both memory locations specifying the high and low order bytes of the effective address must be in page zero.

INDIRECT INDEXED ADDRESSING [(IND), Y] — In indirect indexed addressing (referred to as (Indirect), Y), the second byte of the instruction points to a memory location in page zero. The contents of this memory location are added to the contents of the Y index register, the result being the low order eight bits of the effective address. The carry from this addition is added to the contents of the next page zero memory location, the result being the high order eight bits of the effective address.

ABSOLUTE INDIRECT [(ABS)] — The second byte of the instruction contains the low order eight bits of a memory location. The high order eight bits of that memory location are contained in the third byte of the instruction. The contents of the fully specified memory location are the low order byte of the effective address. The next memory location contains the high order byte of the effective address which is loaded into the sixteen bits of the program counter. (JMP (ABS) only.)

**INDIRECT** [(IND)]\* — The second byte of the instruction contains a zero page address serving as the indirect pointer.

#### **ENHANCEMENTS OVER R6502**

The CMOS family of microprocessor devices has been designed with many enhancements over the R6502 NMOS device while maintaining software compatibility. Besides the increased speed and lower power consumption inherent in CMOS technology, the R65C00 family has the following additional characteristics.

- 12 new instructions for a total of 68

- 59 new op codes, for a total of 210

- · Two new addressing modes

- · Seven software/operational enhancements

- Two hardware enhancements

<sup>\*</sup>These addressing modes are not available to the NMOS CPU family (e.g., the R6502).

Function

#### INSTRUCTION SET

Mnemonic

Table 1 lists the instruction set for the CMOS CPU family in alphabetic order according to mnemonic. Tabe 2 lists the hexadecimal codes for each of the instructions that are new to the CMOS family and were not available in the NMOS R6502 device family. Table 3 lists those instructions that were available on the

Function

NMOS family, but have been assigned new addressing modes in the CMOS CPU family.

#### OPERATIONAL ENHANCEMENTS

Table 4 lists the operational enhancements that have been added to the CMOS family of CPU devices and compares the results with their NMOS R6502 counterpart.

ADC Add Memory to Accumulator with Carry NOP No Operation (2)(2)AND "AND" Memory with Accumulator ASL Shift Left One Bit (Memory or Accumulator) (2) ORA "OR" Memory with Accumlator BBR Branch on Bit Reset PHA (1) Push Accumulator on Stack (1) **BBS** Branch on Bit Set PHP Push Processor Status on Stack Branch on Carry Clear PHX Push X Register on Stack BCC **BCS** Branch on Carry Set (1)PHY Push Y Register on Stack BEQ Branch on Result Zero PLA Pull Accumulator from Stack (2) BIT Test Bits in Memory with Accumulator PLP Pull Processor Status from Stack BMI Branch on Result Minus PLX Pull X Register from Stack (1) Branch on Result not Zero PLY Pull Y Register from Stack BNE (1) BPL. Branch on Result Plus (1) BRA Branch Always (1)**RMB** Reset Memory Bit ROL **BRK** Force Break Rotate One Bit Left (Memory or Accumulator) ROR **BVC** Branch on Overflow Clear Rotate One Bit Right (Memory or Accumulator) **BVS** Branch on Overflow Set RTI Return from Interrupt RTS Return from Subroutine CLC Clear Carry Flag CLD Clear Decimal Mode SBC Subtract Memory from Accumulator with Borrow Clear Interrupt Disable Bit SEC CLI Set Carry Flag CLV Clear Overflow Flag SED Set Decimal Mode (2) CMP Compare Memory and Accumulator SEI Set Interrupt Disable Status CPX Compare Memory and Index X (1) **SMB** Set Memory Bit CPY Compare Memory and Index Y STA Store Accumulator in Memory (2)Store Index X in Memory STX Decrement Memory by One (2) DEC STY Store Index Y in Memory DEX Decrement Index X by One (1) STZ Store Zero DEY Decrement Index Y by One TAX Transfer Accumulator to Index X (2)**EOR** "Exclusive-OR" Memory with Accumulator TAY Transfer Accumulator to Index Y (1)TRB Test and Reset Bits Test and Set Bits INC Increment Memory by One (1) TSB Transfer Stack Pointer to Index X TSX INX Increment Index X by One INY Increment Index Y by One TXA Transfer Index X to Accumulator TXS Transfer Index X to Stack Register

Table 1. Alphabetic Listing of the R65C00 Instruction Set

Mnemonic

#### Notes:

Jump to New Location

Load Accumulator with Memory

Load Index X with Memory

Load Index Y with Memory

(2)

(2)

**JMP**

**JSR**

LDA

LDX

LDY

LSR

(1) Instruction not available on the NMOS family.

Jump to New Location Saving Return Address

Shift One Bit Right (Memory or Accumulator)

(2) R6502 instruction with additional addressing mode(s).

TYA

Transfer Index Y to Accumulator

Table 2. Hexadecimal Codes For New Instructions in the R65C00 Microprocessors

| Hex                            | Mnemonic        | Description                                       |

|--------------------------------|-----------------|---------------------------------------------------|

| 80                             | BRA             | Branch relative always [Relative]                 |

| DA                             | PHX             | Push X on stack [Implied]                         |

| 5A                             | PHY             | Push Y on stack [Implied]                         |

| FA                             | PLX             | Pull X from stack [Implied                        |

| 7A                             | PLY             | Pull Y from stack [Implied]                       |

| 9C                             | STZ             | Store zero [Absolute]                             |

| 9E                             | STZ             | Store zero [ABS, X]                               |

| 64                             | STZ             | Store zero [ZP]                                   |

| 74                             | STZ             | Store zero [ZP, X]                                |

| 1C                             | TRB             | Test and reset memory bits with accumulator [ABS] |

| 14                             | TRB             | Test and reset memory bits with accumulator [ZP]  |

| 0C                             | TSB             | Test and set memory bits with accumulator [ABS]   |

| 04                             | TSB             | Test and set memory bits with accumulator [ZP]    |

| 0F-7F <sup>(1)</sup>           | BBR             | Branch on bit reset [Bit Manipulation, ZP, REL]   |

| 8F-FF(1)                       | BBS             | Branch on bit set [Bit Manipulation, ZP, REL]     |

| 07-77(1)                       | RMB             | Reset memory bit [Bit Manipulation, ZP]           |

| 87-F7 <sup>(1)</sup>           | SMB             | Set memory bit [Bit Manipulation, ZP]             |

| Note:  1. Most significant dic | it change only. |                                                   |

Table 3. Hexadecimal Codes For R65C00 Instructions With New Addressing Modes

| Hex | Mnemonic | Description                                          |

|-----|----------|------------------------------------------------------|

| 72  | ADC      | Add memory to accumulator with carry [(IND)]         |

| 32  | AND      | AND memory with accumulator [(IND)]                  |

| 3C  | BIT      | Test memory bits with accumulator [ABS, X]           |

| 34  | BIT      | Test memory bits with accumulator [ZP, X]            |

| 89  | BIT      | Test Immediate with accumulator [IMM]                |

| D2  | CMP      | Compare memory and accumulator [(IND)]               |

| 3A  | DEC      | Decrement accumulator [Accum]                        |

| 52  | EOR      | Exclusive Or memory with accumulator [(IND)]         |

| 1A  | INC      | Increment accumulator [Accum]                        |

| 7C  | JMP      | Jump (New addressing mode) [(ABS, X)]                |

| B2  | LDA      | Load accumulator with memory [(IND)]                 |

| 12  | ORA      | OR memory with accumulator [(IND)]                   |

| F2  | SBC      | Subtract Memory from accumulator with borrow [(IND)] |

| 92  | STA      | Store accumulator in memory [(IND)]                  |

Table 4. R65C00 Operational Enhancements

| Function                                             | NMOS R6502 Microprocessor                            | CMOS R65C00 Family Microprocessor                              |

|------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------|

| Indexed addressing across page boundary.             | Extra read of invalid address.                       | Extra read of last instruction byte.                           |

| Execution of invalid op codes.                       | Some terminate only by reset. Results are undefined. | All are NOPs (reserved for future use).                        |

| Jump Indirect, operand = XXFF.                       | Page address does not increment.                     | Page address increments and adds one additional cycle.         |

| Read/modify/write instructions at effective address. | One read and two write cycles.                       | Two read and one write cycle.                                  |

| Decimal flag.                                        | Indeterminate after reset.                           | Initialized to binary mode (D = 0) after reset and interrupts. |

| Flags after decimal operation.                       | Invalid N, V and Z flags.                            | Valid flag adds one additional cycle.                          |

| Interrupt after fetch of BRK instruction.            | Interrupt vector is loaded, BRK vector is ignored.   | BRK is executed, then interrupt is executed.                   |

#### **INSTRUCTION SET OP CODE MATRIX**

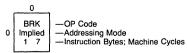

The following matrix shows the 210 Op Codes associated with the R65C00 family of CPU devices. The matrix identifies the hexadecimal code, the mnemonic code, the addressing mode,

the number of instruction bytes, and the number of machine cycles associated with each Op Code. Also, refer to the instruction set summary for additional information on these Op Codes.

| MSD | SD 0                     | 1                        | 2                    | 3 | 4                   | 5                    | 6                   | 7                 | 8                     | 9                      | Α                     | В | С                      | D                      | E                     | F                   |   |

|-----|--------------------------|--------------------------|----------------------|---|---------------------|----------------------|---------------------|-------------------|-----------------------|------------------------|-----------------------|---|------------------------|------------------------|-----------------------|---------------------|---|

| 0   | BRK<br>Implied<br>1 7    | ORA<br>(IND, X)<br>2 6   |                      |   | TSB<br>ZP<br>2 5    | ORA<br>ZP<br>2 3     | ASL<br>ZP<br>2 5    | RMB0<br>ZP<br>2 5 | PHP<br>Implied<br>1 3 | ORA<br>IMM<br>2 2      | ASL<br>Accum<br>1 2   |   | TSB<br>ABS<br>3 6      | ORA<br>ABS<br>3 4      | ASL<br>ABS<br>3 6     | BBR0<br>ZP<br>3 5** | 0 |

| 1   | BPL<br>Relative<br>2 2** | ORA<br>(IND), Y<br>2 5*  | ORA<br>(IND)<br>2 5  |   | TRB<br>ZP<br>2 5    | ORA<br>ZP, X<br>2 4  | ASL<br>ZP, X<br>2 6 | RMB1<br>ZP<br>2 5 | CLC<br>Implied<br>1 2 | ORA<br>ABS, Y<br>3 4*  | INC<br>Accum<br>1 2   |   | TRB<br>ABS<br>3 6      | ORA<br>ABS, X<br>3 4*  | ASL<br>ABS, X<br>3 7  | BBR1<br>ZP<br>3 5** | 1 |

| 2   | JSR<br>ABS<br>3 6        | AND<br>(IND, X)<br>2 6   |                      |   | BIT<br>ZP<br>2 3    | AND<br>ZP<br>2 3     | ROL<br>ZP<br>2 5    | RMB2<br>ZP<br>2 5 | PLP<br>Implied<br>1 4 | AND<br>IMM<br>2 2      | ROL<br>Accum<br>1 2   |   | BIT<br>ABS<br>3 4      | AND<br>ABS<br>3 4      | ROL<br>ABS<br>3 6     | BBR2<br>ZP<br>3 5** | 2 |

| 3   | BMI<br>Relative<br>2 2** | AND<br>(IND), Y<br>2 5*  | AND<br>(IND)<br>2 5  |   | BIT<br>ZP, X<br>2 4 | AND<br>ZP, X<br>2 4  | ROL<br>ZP, X<br>2 6 | RMB3<br>ZP<br>2 5 | SEC<br>Implied<br>1 2 | AND<br>ABS, Y<br>3 4*  | DEC<br>Accum<br>1 2   |   | BIT<br>ABS, X<br>3 4*  | AND<br>ABS, X<br>3 4*  | ROL<br>ABS, X<br>3 7  | BBR3<br>ZP<br>3 5** | 3 |

| 4   | RTI<br>Implied<br>1 6    | EOR<br>(IND, X)<br>2 6   |                      |   |                     | EOR<br>ZP<br>2 3     | LSR<br>ZP<br>2 5    | RMB4<br>ZP<br>2 5 | PHA<br>Implied<br>1 3 | EOR<br>IMM<br>2 2      | LSR<br>Accum<br>1 2   |   | JMP<br>ABS<br>3 3      | EOR<br>ABS<br>3 4      | LSR<br>ABS<br>3 6     | BBR4<br>ZP<br>3 5** | 4 |

| 5   | BVC<br>Relative<br>2 2** | EOR<br>(IND), Y<br>2 5*  | EOR<br>(IND)<br>2 5  |   |                     | EOR<br>ZP, X<br>2 4  | LSR<br>ZP, X<br>2 6 | RMB5<br>ZP<br>2 5 | CLI<br>Implied<br>1 2 | EOR<br>ABS, Y<br>3 4*  | PHY<br>Implied<br>1 3 |   |                        | EOR<br>ABS, X<br>3 4*  | LSR<br>ABS, X<br>3 7  | BBR5<br>ZP<br>3 5** | 5 |

| 6   | RTS<br>Implied<br>1 6    | ADC<br>(IND, X)<br>2 6†  |                      |   | STZ<br>ZP<br>2 3    | ADC<br>ZP<br>2 3†    | ROR<br>ZP<br>2 5    | RMB6<br>ZP<br>2 5 | PLA<br>Implied<br>1 4 | ADC<br>IMM<br>2 2†     | ROR<br>Accum<br>1 2   |   | JMP<br>(ABS)<br>3 6    | ADC<br>ABS<br>3 4†     | ROR<br>ABS<br>3 6     | BBR6<br>ZP<br>3 5** | 6 |

| 7   | BVS<br>Relative<br>2 2** | ADC<br>(IND), Y<br>2 5*† | ADC<br>(IND)<br>2 5† |   | STZ<br>ZP, X<br>2 4 | ADC<br>ZP, X<br>2 4† | ROR<br>ZP, X<br>2 6 | RMB7<br>ZP<br>2 5 | SEI<br>Implied<br>1 2 | ADC<br>ABS, Y<br>3 4*† | PLY<br>Implied<br>1 4 |   | JMP<br>(ABS, X)<br>3 6 | ADC<br>ABS, X<br>3 4*† | ROR<br>ABS, X<br>3 7  | BBR7<br>ZP<br>3 5** | 7 |

| 8   | BRA<br>Relative<br>2 3*  | STA<br>(IND, X)<br>2 6   |                      |   | STY<br>ZP<br>2 3    | STA<br>ZP<br>2 3     | STX<br>ZP<br>2 3    | SMB0<br>ZP<br>2 5 | DEY<br>Implied<br>1 2 | BIT<br>IMM<br>2 2      | TXA<br>Implied<br>1 2 |   | STY<br>ABS<br>3 4      | STA<br>ABS<br>3 4      | STX<br>ABS<br>3 4     | BBS0<br>ZP<br>3 5** | 8 |

| 9   | BCC<br>Relative<br>2 2** | STA<br>(IND), Y<br>2 6   | STA<br>(IND)<br>2 5  |   | STY<br>ZP, X<br>2 4 | STA<br>ZP, X<br>2 4  | STX<br>ZP, Y<br>2 4 | SMB1<br>ZP<br>2 5 | TYA<br>Implied<br>1 2 | STA<br>ABS, Y<br>3 5   | TXS<br>Implied<br>1 2 |   | STZ<br>ABS<br>3 4      | STA<br>ABS, X<br>3 5   | STZ<br>ABS, X<br>3 5  | BBS1<br>ZP<br>3 5** | 9 |

| Α   | LDY<br>IMM<br>2 2        | LDA<br>(IND, X)<br>2 6   | LDX<br>IMM<br>2 2    |   | LDY<br>ZP<br>2 3    | LDA<br>ZP<br>2 3     | LDX<br>ZP<br>2 3    | SMB2<br>ZP<br>2 5 | TAY<br>Implied<br>1 2 | LDA<br>IMM<br>2 2      | TAX<br>Implied<br>1 2 |   | LDY<br>ABS<br>3 4      | LDA<br>ABS<br>3 4      | LDX<br>ABS<br>3 4     | BBS2<br>ZP<br>3 5** | A |

| В   | BCS<br>Relative<br>2 2** | LDA<br>(IND), Y<br>2 5*  | LDA<br>(IND)<br>2 5  |   | LDY<br>ZP, X<br>2 4 | LDA<br>ZP, X<br>2 4  | LDX<br>ZP, Y<br>2 4 | SMB3<br>ZP<br>2 5 | CLV<br>Implied<br>1 2 | LDA<br>ABS, Y<br>3 4*  | TSX<br>Implied<br>1 2 |   | LDY<br>ABS, X<br>3 4*  | LDA<br>ABS, X<br>3 4°  | LDX<br>ABS, Y<br>3 4* | BBS3<br>ZP<br>3 5** | В |

| С   | CPY<br>IMM<br>2 2        | CMP<br>(IND, X)<br>2 6   |                      |   | CPY<br>ZP<br>2 3    | CMP<br>ZP<br>2 3     | DEC<br>ZP<br>2 5    | SMB4<br>ZP<br>2 5 | INY<br>Implied<br>1 2 | CMP<br>IMM<br>2 2      | DEX<br>Implied<br>1 2 |   | CPY<br>ABS<br>3 4      | CMP<br>ABS<br>3 4      | DEC<br>ABS<br>3 6     | BBS4<br>ZP<br>3 5** | С |

| D   | BNE<br>Relative<br>2 2** | CMP<br>(IND), Y<br>2 5*  | CMP<br>(IND)<br>2 5  |   |                     | CMP<br>ZP, X<br>2 4  | DEC<br>ZP, X<br>2 6 | SMB5<br>ZP<br>2 5 | CLD<br>Implied<br>1 2 | CMP<br>ABS, Y<br>3 4*  | PHX<br>Implied<br>1 3 |   |                        | CMP<br>ABS, X<br>3 4*  | DEC<br>ABS, X<br>3 7  | BBS5<br>ZP<br>3 5** | D |

| E   | CPX<br>IMM<br>2 2        | SBC<br>(IND, X)<br>2 6†  |                      |   | CPX<br>ZP<br>2 3    | SBC<br>ZP<br>2 3†    | INC<br>ZP<br>2 5    | SMB6<br>ZP<br>2 5 | INX<br>Implied<br>1 2 | SBC<br>IMM<br>2 2†     | NOP<br>Implied<br>1 2 |   | CPX<br>ABS<br>3 4      | SBC<br>ABS<br>3 4†     | INC<br>ABS<br>3 6     | BBS6<br>ZP<br>3 5** | E |

| F   | BEQ<br>Relative<br>2 2** | SBC<br>(IND), Y<br>2 5*† | SBC<br>(IND)<br>2 5† |   |                     | SBC<br>ZP, X<br>2 4† | INC<br>ZP, X<br>2 6 | SMB7<br>ZP<br>2 5 | SED<br>Implied<br>1 2 | SBC<br>ABS, Y<br>3 4*† | PLX<br>Implied<br>1 4 |   |                        | SBC<br>ABS, X<br>3 4*† | INC<br>ABS, X<br>3 7  | BBS7<br>ZP<br>3 5** | F |

|     | 0                        | 1                        | 2                    | 3 | 4                   | 5                    | 6                   | 7                 | 8                     | 9                      | Α                     | В | С                      | D                      | E                     | F                   | - |

†Add 1 to N if in decimal mode.

\*Add 1 to N if page boundary is crossed.

<sup>\*\*</sup>Add 1 to N if branch occurs to same page; Add 2 to N if branch occurs to different page.

N

# **INSTRUCTION SET SUMMARY**

PROCESSOR STATUS

| Bale (right)   Branch on M, =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |                                    |     |     |   |     |    |    |            |               |     |       |     |     |     |      |        |                |     |   |    | ADD | RES | SIN  | G M    | ODI   | ES   |       |       |     |    |   |    |     |       |       |     |     |     |    |     |     |    |     | PRC          |     | CO  | OR S<br>DES |     | ıus    | j |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------------------|-----|-----|---|-----|----|----|------------|---------------|-----|-------|-----|-----|-----|------|--------|----------------|-----|---|----|-----|-----|------|--------|-------|------|-------|-------|-----|----|---|----|-----|-------|-------|-----|-----|-----|----|-----|-----|----|-----|--------------|-----|-----|-------------|-----|--------|---|

| AMO A (1) (1) (2) (3) (4) (2) (2) (2) (2) (3) (4) (3) (3) (2) (4) (3) (4) (4) (3) (4) (4) (4) (4) (4) (4) (4) (4) (4) (4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MNEMONIC     | OPERATION                          |     |     |   |     |    |    | +-         | $\overline{}$ |     |       |     |     |     |      |        |                |     |   |    |     |     |      |        |       |      |       |       |     |    |   |    |     |       |       |     |     |     |    |     |     |    |     |              |     |     |             |     |        |   |

| SSL C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |                                    |     |     |   |     |    |    |            |               |     |       | n # | OP  | n   | *    | OP r   | . #            |     |   |    |     |     |      |        |       |      |       |       |     | Pn | - | -  | _   | _     | Р     | #   |     |     |    |     | P n | #  | _   | _            | _   |     |             |     |        | _ |

| SSL C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ADC          | A + M + C A(1) (5) (7)             | 69  | 2   | 2 | 6D  | 4  | 3  | 65         | 3             | 2   |       | - 1 | Į   | Ш   |      | -      |                | 61  | 6 | 2  | 71  | 5   | 2    | 75 4   | 4   3 | 2 7  |       | 4   3 | 3   |    |   | 79 | 4   | 3     |       |     | 72  | 5 5 | 2  | . 1 |     |    | N   | ٧            |     |     | ٠           | ٠   | Z      | С |

| BBR (#67) Branch on M, = f  BR (#67) Branch on M | ASL          |                                    | 29  | 1   | - | øΕ  | 6  | 3  | ø6         | 5             | 2   |       |     | ØΑ  | 2   | 1    |        |                | 16. | 1 | -  | 1   | ١١  | -    | 16     | 6     | 2 1  | Ĕ :   | 7   3 | 3   |    |   | 33 | 1   | ٦     |       |     | ٦   | "   | 1- |     |     |    | N   | :            | :   | :   | ÷           | :   | ž      | ċ |

| BBS [#47]  Branch on M = 1  BRS (#27)  Branch on C = 1 (2)  Branch on C = 2 (2)  Branch on C = 2 (2)  Branch on C = 3 (2)  Branch on C = 3 (2)  Branch on C = 4 (2)  Branch on C = 6 (2)  Branch on C  | BBR [#(Ø-7)] |                                    |     |     |   | Ì   |    |    |            |               | 1 1 | M2⊢-1 | 5 3 |     |     |      |        |                | 1   | 1 |    |     |     | 1    | -      |       | 1    | 1     |       | ı   |    | ĺ |    | 1   | 1     | 1     | 1   | 1   | 1   | 1  |     | 1   |    | 1.  |              |     |     |             |     |        |   |

| Banch on C = 9 (2) Binach on C = 1 (2) Binach  | DBS 1#/dL7\1 | Branch on M - 1                    | 11  |     |   |     |    | 1  | 1          |               | 1   | 8F-   | 5 3 |     |     |      |        |                | 1   |   |    |     |     | ١    |        |       | 1    | 1     | 1     | 1   |    | ĺ |    | 1   | Ì     | 1     | 1   | 1   | i   | 1  | 1   |     |    | ١.  |              |     |     |             |     |        |   |

| STATE SAME BRACH ON N = 1 (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |                                    | 1   | 1   |   | 1   |    | ļ  | 1          | 1             |     | FF    | 1   |     |     | 1    |        |                | 1   |   |    | 1   |     | - }  | -      |       | -    | 1     |       | ł   |    |   | 1  | 1   | 9     | ø 2   | 2   | 1   | 1   | 1  |     |     |    | ١.  |              |     |     |             |     |        |   |

| STATE SAME BRACH ON N = 1 (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | BCS          | Branch on C = 1 (2)                |     |     |   |     |    |    | 1          | 1             |     |       | - ( | 1   | П   |      |        |                | 1   |   |    | 1 1 |     | - (  | - 1    |       | -    | -     |       | ļ   |    |   | ١, |     | В     | 0 2   | 2   | 1   |     |    |     |     |    |     |              |     | ٠   |             |     | ٠      |   |

| MMC Branch on N = 1 (2) BRA Br | BIT          | A > M (6)                          | 89  | 2   | 2 | 2C  | 4  | 3  | 24         | 3             | 2   |       |     | 1   |     |      |        | İ              | 1   |   |    |     |     | - 1  | 34     | 4 :   | 2 3  | cl.   | 4 3   | 3   |    |   |    | 1   |       |       |     |     |     |    |     |     | 1  | M.  | . м <u>.</u> | . : | :   | :           | :   | ż      | : |

| BRK Break Dreak Break Dreak Break Dreak Break Dreak Break Dreak Break Dreak Dreak Break Dreak Dr | RMI I        | Branch on N = 1 (2)                |     |     |   | ı   |    |    | 1          |               |     |       |     | 1   |     |      |        |                | 1   |   |    |     | lÌ  | - 1  |        |       | Ì    |       |       |     | 1  | 1 |    | ì   | 3     | Ø   2 | 2   | 1   |     |    |     | 1   | 1  | 1:  |              | •   | •   | •           | •   | •      | • |

| BRK Break Dreak Break Dreak Break Dreak Break Dreak Break Dreak Break Dreak Dreak Break Dreak Dr | BPL          | Branch on N = Ø (2)                |     |     |   |     |    |    | 1          |               |     | 1     |     | ì   |     |      | - 1    |                | 1   | 1 |    |     |     | 1    | - 1    | 1     | ł    | 1     |       | 1   | İ  | 1 |    | 1   | 11    | 0 2   | 2   | 1   | 1   | 1  |     | 1   |    | 1 : |              |     |     |             |     |        |   |

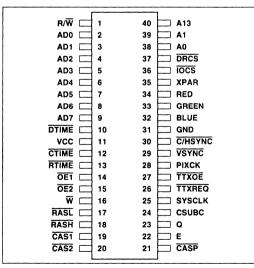

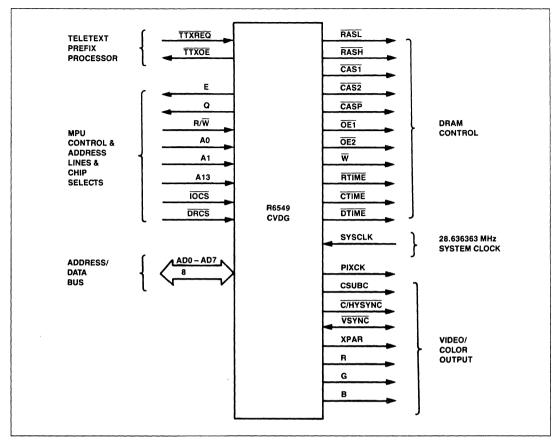

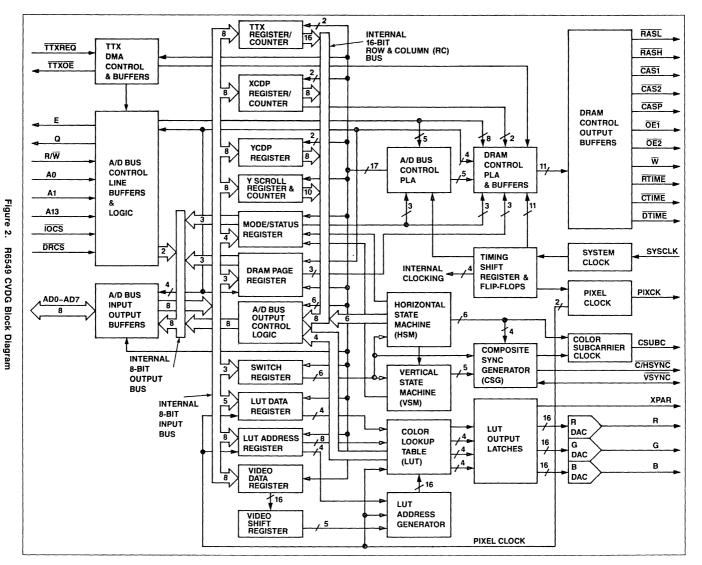

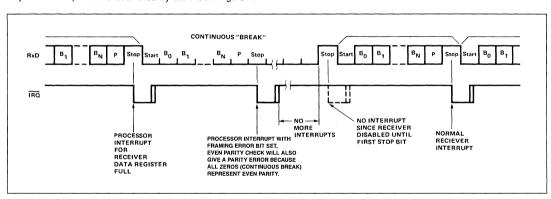

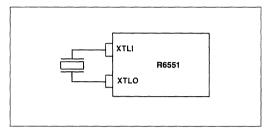

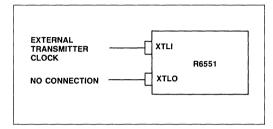

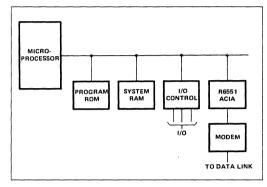

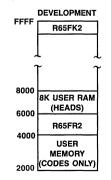

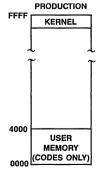

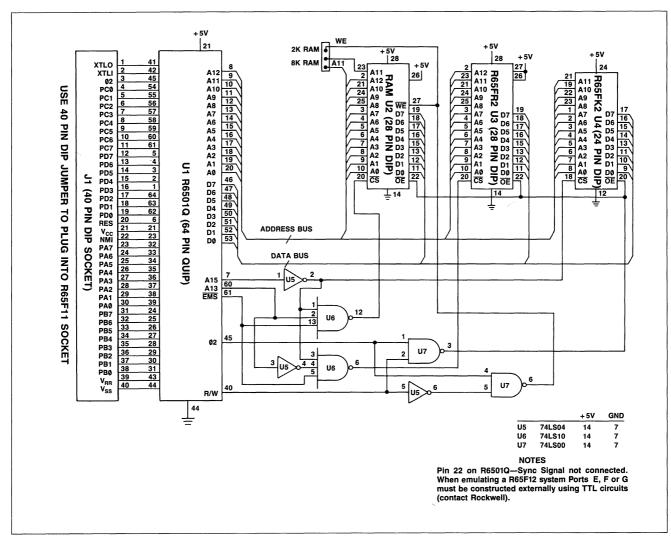

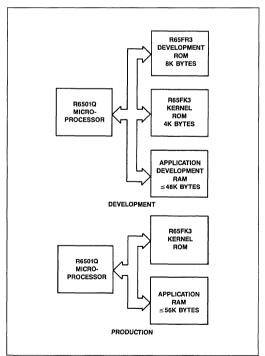

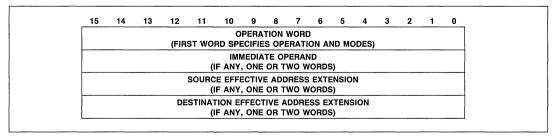

| Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch on V = 8 (2) Biranch o | BRA<br>BRK   |                                    | 1 1 | 1   |   |     |    |    |            |               |     | 1     | -   | 1   |     | - 1  | øø :   | 7 1            | 1   |   |    | 1   |     | - 1  | -      | 1     | 1    | 1     | -     |     | 1  | 1 |    | - { | - 1   | - 1   | - 1 | 1   | 1   |    | 1   | 1   | 1  | 1:  | :            | :   | i   | :           | i   | :      | : |