# Microprocessors • Memories • Peripherals

# RCA CMOS LSI Microprocessors, Memories, Peripherals

This DATABOOK contains full information on CMOS LSI products (microprocessors, memories, and peripherals) currently available from RCA Solid State Division. An Index to Products provides a complete listing of types.

The Index to Products is followed by several pages of general product information that includes photographs showing the package options available for RCA CMOS LSI products, a Product Overview that summarizes the basic features and complement of each category of products, and a Product Classification Chart that groups integrated circuits and systems according to product type and intended function. Next, a Cross-Reference Guide lists popular memory integrated circuits supplied by other manufacturers together with a recommended RCA replacement type. The DATABOOK then includes a general discussion of Operating and Handling Considerations for CMOS Integrated Circuits.

Five separate data sections provide definitive ratings, electrical characteristics, and user information for the (1) 1800 series of microprocessors and microcomputers, (2) 1800 series memories, (3) 1800 series peripherals, (4) general-purpose memories, and (5) 6805 series LSI products.

Within each data section, the data pages for individual integrated circuits are grouped in alphanumerical sequence of type numbers.

The DATABOOK also contains selected application note abstracts on RCA LSI products and dimensional outlines of all packages in which RCA LSI products are supplied.

# **Table of Contents**

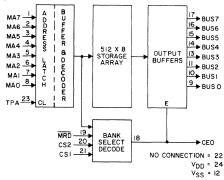

**General Guide to** RCA LSI Products

**1800-Series Microprocessors** and Microcomputers

1800-Series Memories

1800-Series Peripherals

**General-Purpose Memories**

6805-Series LSI Products

Supplementary Information

**RCA Sales Offices. Authorized Distributors and** Manufacturers' Representatives

Solid | Somerville, NJ • Brussels • Paris • London State | Hamburg • Sao Paulo • Hong Kong

Information furnished by RCA is believed to be accurate and reliable. However, no responsibility is assumed by RCA for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of RCA.

The device data shown for some types are indicated as preliminary, advance, or objective. **Preliminary data** are intended for guidance purposes in evaluating devices for equipment design. Such data are shown for types currently being designed for inclusion in our standard line of commercially available products. **Advance** or **Objective data** are intended for engineering evaluation of types in the initial stages of design. The type designations and data are subject to change, unless otherwise arranged. No obligations are assumed for notice of change or future manufacture of these devices. For current information on the status of preliminary or objective programs, please contact your local RCA sales office.

Copyright 1982 by RCA Corporation (All rights reserved under Pan-American Copyright Convention)

Trademark(s)®Registered Marca(s) Registrada(s)

Printed in USA/10-82

# General Guide to RCA LSI Products 1

| P | ag | 16 |

|---|----|----|

|   |    |    |

| Index to Products                     |  |

|---------------------------------------|--|

| Packages and Ordering Information     |  |

| Product Overview                      |  |

| Product Classification Chart          |  |

| Cross-Reference Guide                 |  |

| Operating and Handling Considerations |  |

# **Index to Products**

| Part<br>No.                                                         | Page<br>No. De                                                                             |                                                                                           | File<br>No.                          | Part<br>No.                                                        | Page<br>No.              | Description                                                                                                                           | File<br>No.                                  |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

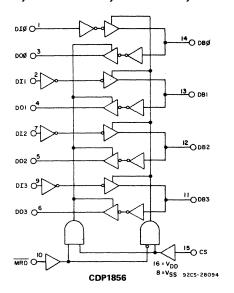

| CD4036A<br>CD4039A<br>CD4061A<br>CD40061<br>CD40061A                | 376 4 x 8 RAM<br>376 4 x 8 RAM<br>383 256 x 1 RAM<br>391 256 x 1 RAM<br>391 256 x 1 RAM    | 1<br>                                                                                     | 613<br>613<br>786<br>1188<br>1188    | CDP1854C<br>CDP1855<br>CDP1855C<br>CDP1856<br>CDP1856C             | 232<br>232<br>245        | UART<br>8-Bit Programmable MDU<br>8-Bit Programmable MDU<br>4-Bit Bus Buffer/Separator<br>4-Bit Bus Buffer/Separator                  | 1193<br>1053<br>1053<br>1192<br>1192         |

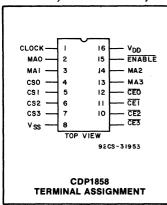

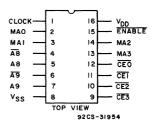

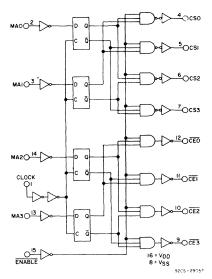

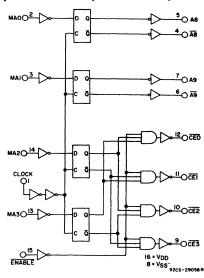

| CD40114B<br>CDM5332<br>CDM5333<br>CDM6116-1<br>CDM6116-2            | 396 16 x 4 RAM<br>401 4096 x 8 RO<br>401 4096 x 8 RO<br>407 2048 x 8 RA<br>407 2048 x 8 RA | M 1<br>M 1<br>M 1                                                                         | 1116<br>1366<br>1366<br>1372<br>1372 | CDP1857<br>CDP1857C<br>CDP1858<br>CDP1858C<br>CDP1859              | 245<br>250<br>250        | 4-Bit Bus Buffer/Separator<br>4-Bit Bus Buffer/Separator<br>4-Bit Latch/Decoder<br>4-Bit Latch/Decoder<br>4-Bit Latch/Decoder         | 1192<br>1192<br>1127<br>1127<br>1127         |

| CDP1802A<br>CDP1802AC<br>CDP1802BC<br>CDP1804AC                     | Ctr/Tmr                                                                                    | orocessor 1<br>processor 1<br>comp/ROM/RAM/                                               | 1305<br>1305<br>1342<br>1371         | CDP1859C<br>CDP1861C<br>CDP1862C<br>CDP1863                        | 258<br>266<br>271        | 4-Bit Latch/Decoder Video Display Controller Color Generator Controller 8-Bit Progr'ble Frequency Generator                           | 1127<br>1223<br>1181<br>1179                 |

| CDP1805C<br>CDP1805AC<br>CDP1806C                                   | 84 8-Bit Microp<br>103 8-Bit Microp<br>84 8-Bit Microp                                     |                                                                                           | 1349<br>1370<br>1349                 | CDP1863C<br>CDP1864C                                               |                          | 8-Bit Progr'ble Frequency<br>Generator<br>PAL Video Display Controller                                                                | 1179<br>1196                                 |

| CDP1806AC<br>CDP1821<br>CDP1821C                                    | 103 8-Bit Microp<br>128 1K x 1 RAM<br>128 1K x 1 RAM                                       | processor 1<br>1                                                                          | 1370<br>1200<br>1200                 | CDP1866<br>CDP1866<br>CDP1867<br>CDP1867                           | 286<br>286<br>286        | 4-Bit Latch/Decoder 4-Bit Latch/Decoder 4-Bit Latch/Decoder 4-Bit Latch/Decoder 4-Bit Latch/Decoder                                   | 1112<br>1112<br>1112<br>1112                 |

| CDP1822<br>CDP1822C<br>CDP1823<br>CDP1823C<br>CDP1824               | 134 256 x 4 RAM<br>134 256 x 4 RAM<br>141 128 x 8 RAM<br>141 128 x 8 RAM<br>147 32 x 8 RAM | 1 1<br>1 1                                                                                | 1074<br>1074<br>1198<br>1198<br>1103 | CDP1868<br>CDP1868C<br>CDP1869<br>CDP1869C                         | 286<br>286<br>295        | 4-Bit Latch/Decoder<br>4-Bit Latch/Decoder<br>Video Interface System<br>Video Interface System                                        | 1112<br>1112<br>1112<br>1197<br>1197         |

| CDP1824C<br>CDP1826C<br>CDP1831<br>CDP1831C<br>CDP1832              | 147 32 x 8 RAM<br>153 64 x 8 RAM<br>160 512 x 8 ROM<br>160 512 x 8 ROM<br>164 512 x 8 ROM  | 1<br>1<br>1                                                                               | 1103<br>1311<br>1104<br>1104<br>1145 | CDP1870<br>CDP1870C<br>CDP1871A<br>CDP1871AC<br>CDP1872C           | 295<br>312<br>312<br>320 | Video Interface System<br>Video Interface System<br>Keyboard Encoder<br>Keyboard Encoder<br>8-Bit Input Port                          | 1197<br>1197<br>1374<br>1374<br>1255         |

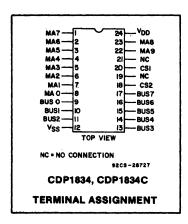

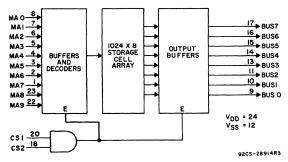

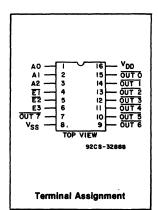

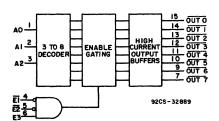

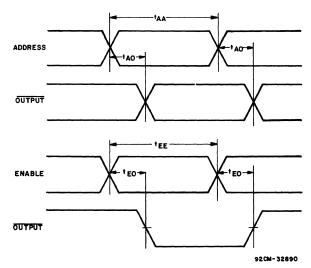

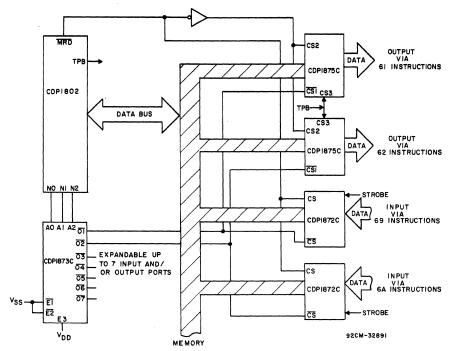

| CDP1832C<br>CDP1833<br>CDP1833BC<br>CDP1833C<br>CDP1834<br>CDP1834C | 168 Mask-Progr<br>168 Mask-Progr<br>174 Mask-Progr                                         | ble, 1K x 8 ROM 1 | 1145<br>1135<br>1135<br>1135<br>1143 | CDP1873C<br>CDP1874C<br>CDP1875C<br>CDP1876<br>CDP1876C<br>CDP1877 | 320<br>320<br>295<br>295 | 1 of 8 Binary Decoder 8-Bit Input Port 8-Bit Output Port Video Interface System Video Interface System Progr'ble Interrupt Controller | 1248<br>1255<br>1255<br>1197<br>1197<br>1319 |

| CDP1835C<br>CDP1837C<br>CDP1851<br>CDP1851C                         | 177 Mask-Progr<br>183 Mask-Progr<br>190 Programma<br>190 Programma                         | ble, 2K x 8 ROM<br>ble, 4K x 8 ROM<br>ble I/O<br>ble I/O                                  | 1267<br>1381<br>1056<br>1056         | CDP1877C<br>CDP1878<br>CDP1878C<br>CDP1879<br>CDP1879C             | 338<br>338<br>351        | Progr'ble Interrupt Controller Dual Counter-Timer Dual Counter-Timer Real-Time Clock Real-Time Clock                                  | 1319<br>1341<br>1341<br>1360<br>1360         |

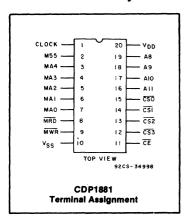

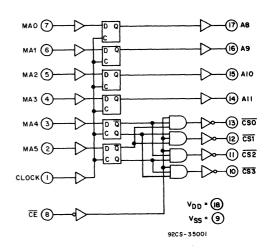

| CDP1852<br>CDP1852C<br>CDP1853<br>CDP1853C<br>CDP1854               | 203 Byte-Wide I<br>203 Byte-Wide I<br>210 N-Bit 1 of 8<br>210 N-Bit 1 of 8<br>214 UART     | O Port Decoder Decoder                                                                    | 1166<br>1166<br>1189<br>1189<br>1193 | CDP1881<br>CDP1881C<br>CDP1882<br>CDP1882C<br>CDP6402              | 365<br>365<br>365<br>365 | 6-Bit Latch/Decoder<br>6-Bit Latch/Decoder<br>6-Bit Latch/Decoder<br>6-Bit Latch/Decoder<br>UART                                      | 1367<br>1367<br>1367<br>1367<br>1328         |

# Index to Products (Cont'd)

| Part<br>No. | Page<br>No.         | Description          | File<br>No. | Part<br>No. | Page<br>No.    | Description | File<br>No. |

|-------------|---------------------|----------------------|-------------|-------------|----------------|-------------|-------------|

| CDP6402C    | 367 UART            | •                    | 1328        | MWS5101DL   | .3 412         | 256 x 4 RAM | 1106        |

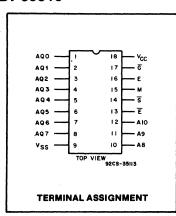

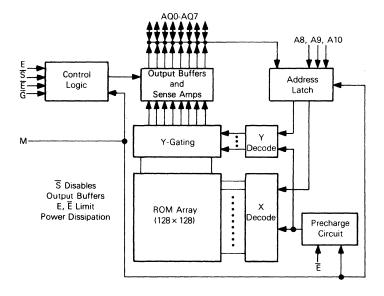

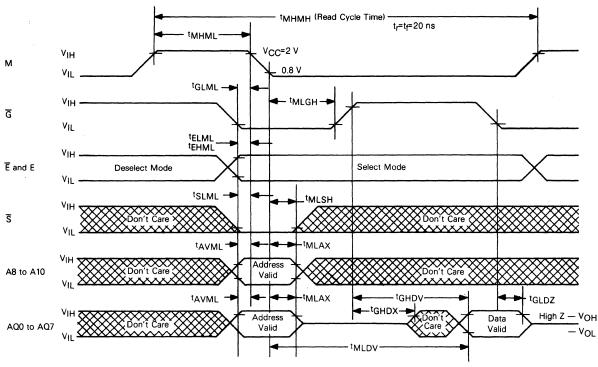

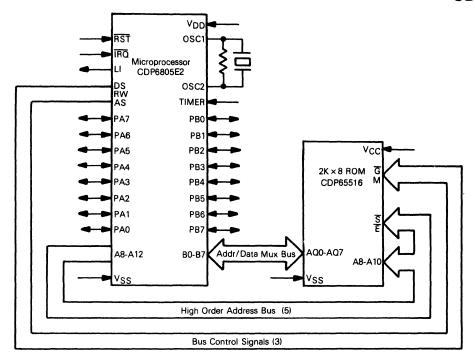

| CDP65516    | 434 2K x 8          | ROM                  | 1376        | MWS5101EL   | <b>2</b> 412   | 256 x 4 RAM | 1106        |

| CDP6805E2   | 442 8-Bit           | Micropro/RAM/Ctr/Tmr | 1363        | MWS5101EL   | <b>3</b> 412   | 256 x 4 RAM | 1106        |

| CDP6805F2   |                     | Microcomp/ROM/RAM/   |             | MWS5101AE   | L2 419         | 256 x 4 RAM | 1207        |

|             | Ctr/T               |                      | 1369        | MW\$5101AE  | <b>)L3</b> 419 | 256 x 4 RAM | 1207        |

| CDP6805G2   |                     | Microcomp/ROM/RAM/   | 4004        | MWS5101AE   | <b>L2</b> 419  | 256 x 4 RAM | 1207        |

|             | Ctr/T               | mr                   | 1364        | MWS5101AE   | <b>L3</b> 419  | 256 x 4 RAM | 1207        |

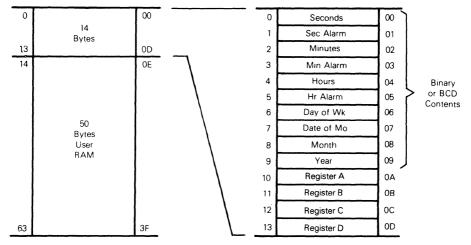

| CDP6818     |                     | Time Clock/RAM       | 1375        | MWS5114-1   | 426            | 1K x 4 RAM  | 1325        |

| CDP6823     |                     | el Interface         | 1377        | MWS5114-2   | 426            | 1K x 4 RAM  | 1325        |

| MWS5101DL   | <b>.2</b> 412 256 x | 4 RAM                | 1106        | MWS5114-3   | 426            | 1K x 4 RAM  | 1325        |

# **Package and Ordering Information**

## **Packages**

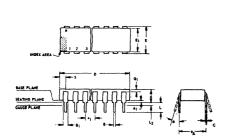

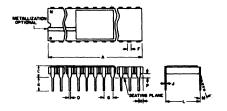

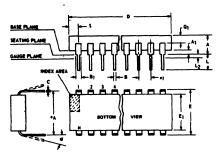

D Suffix

Dual-In-Line Size-Brazed Ceramic Packages

16-, 18-, 22-, 24-, 28-, and 40-lead versions

E Suffix Plastic Dual-In-Line Packages

16-, 18-, 22-, 24-, and 40-lead versions

H Suffix Chip

#### **Ordering Information**

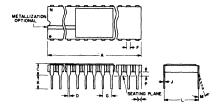

RCA CMOS microprocessor and memory integrated circuits are available in one or more of the following package styles and are identified by the Suffix Letters indicated: dual-in-line size-brazed ceramic, dual-in-line welded-seal ceramic, dual-in-line plastic, flat-pack ceramic, leadless chip-carrier ceramic and in chip form. The available package styles for any specific type are given in the technical data for that type.

When ordering CMOS devices, it is important that the appropriate suffix letter be affixed to the type number of the device required. For example a CDP1802A in a dual-in-line ceramic package will be identified as the CDP1802AD.

D Suffix

Dual-In-Line Welded-Seal Ceramic Packages

16- and 24-lead versions

K Suffix 24-Lead Ceramic Flat Pack

CD4036A and CD4039A only

L SUFFIX — LEADLESS-CHIP-CARRIER CERAMIC PACKAGE

| PACKAGE                                            | SUFFIX<br>LETTERS |

|----------------------------------------------------|-------------------|

| Dual-In-Line Welded-Seal or<br>Side-Brazed Ceramic | D                 |

| Dual-In-Line Plastic                               | E                 |

| Chip                                               | н                 |

| Ceramic Flat Pack<br>(CD4036A and CD4039A only)    | К                 |

| Ceramic Leadless Chip-Carrier                      | L                 |

# **Product Overview**

RCA offers an all CMOS line of microprocessor, memory and peripheral integrated circuits for use in a broad range of diverse industrial, consumer, and military applications. These devices offer the user all the advantages unique to CMOS technology, including:

- Low power drain—makes CMOS integrated circuits a natural choice for battery-operated systems, battery backed-up systems, and systems in which heat dissipation is a prime consideration.

- High noise immunity and wide operating temperature range (-55° C to +125° C)—allows CMOS integrated circuits to be used in the most demanding industrial environments.

- Wide operating voltage range—reduces the need for expensive regulated power supplies and thereby allows the design engineer greater freedom to concentrate on other aspects of system design.

#### CDP1800 Series

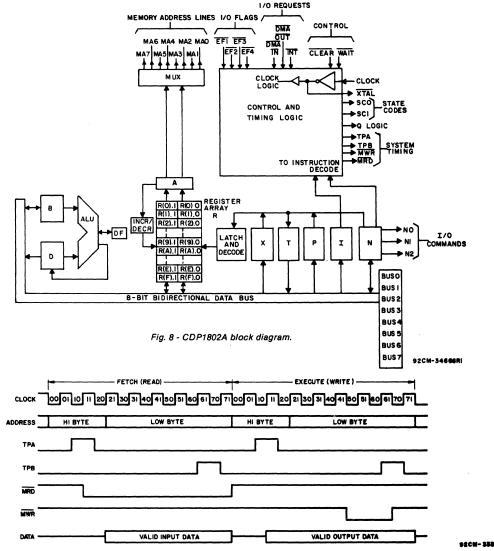

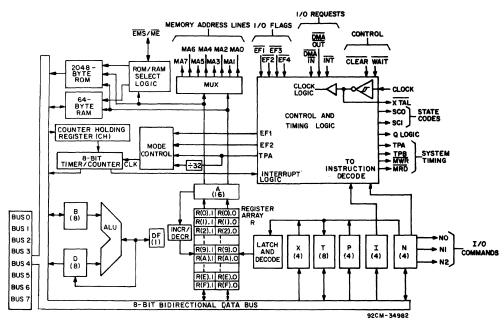

The RCA CDP1800 series offers the most complete line of CMOS microprocessor and associated memory and peripheral devices in the industry. The heart of the series is the CDP1802A central processing unit (CPU). This unit, which features CMOS register-based architecture, offers 16 internal registers to facilitate data manipulation and to reduce the need for additional devices. The need for external devices is even further reduced by use of an on-chip clock, DMA, and single-phase operation.

The CDP1804A microcomputer, currently under development, incorporates all the features of the CDP1802 augmented by additional hardware and increased performance capabilities. The additional hardware includes 2 kilobytes of ROM, a 64-byte RAM array, an 8-bit presettable down-counter, and 32 additional software instruction, which add subroutine call and return capability, enhance data transfer manipulation, control counter modes and interrupt arbitration, and provide BCD arithmetic capability.

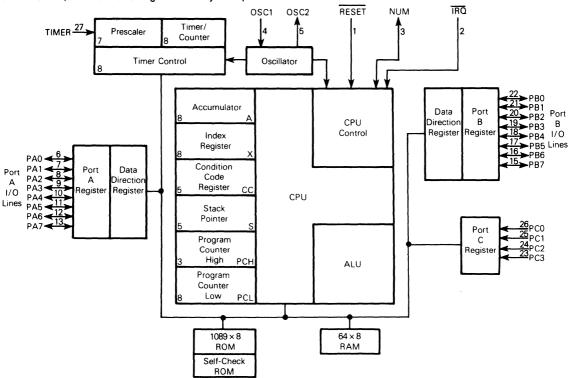

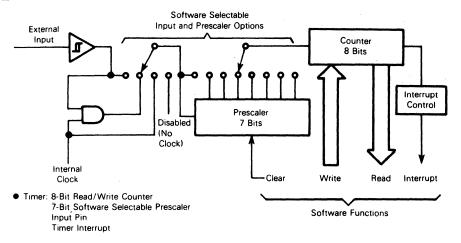

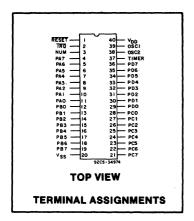

Also available, are four other 8-bit microprocessors that are functional and performance enhancements of the CDP1802. The CDP1805 and CDP1805A feature an onboard RAM and Counter/Timer. The CDP1806 and CDP1806A have all the features of the CDP1805 and CDP1805A, respectively, but contain no on-board RAM.

The microcomputer and microprocessor devices use the CMOS technology, designed on a single chip to maintain low power drain.

RCA's large and expanding CDP1800-series LSI product line offers the system designer exceptional flexibility in hardware/software tradeoffs. In addition to microprocessors and microcomputers, this product line includes a hardware multiply/divide unit (MDU), a programmable I/O, video and keyboard interface circuits, latches and decoders, a universal asynchronous receiver-transmitter (UART), buffers, separators, and a broad complement of directly interfaceable random-access memories (RAM's) and read-only memories (ROM's).

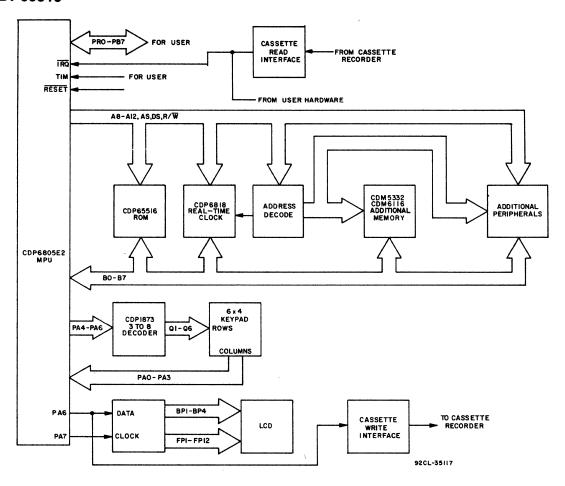

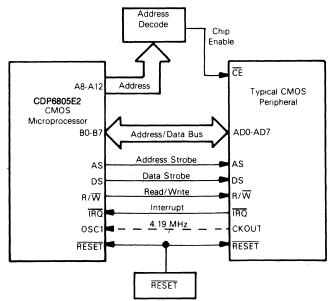

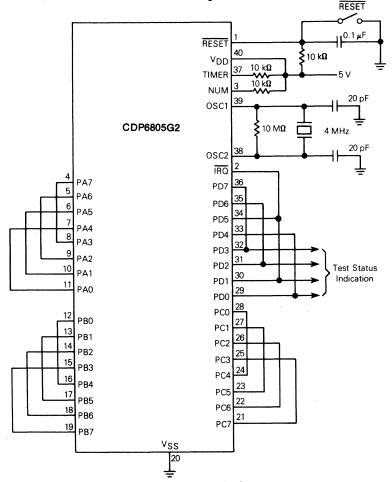

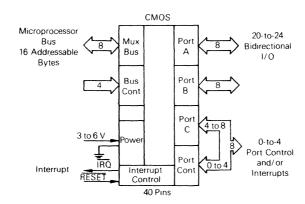

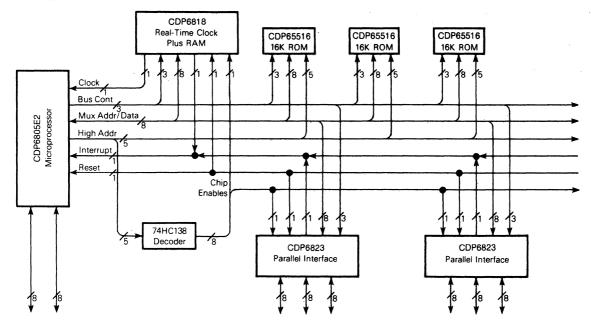

#### CDP6800 Series

RCA also offers the CDP6800 family, a new series of pinfor-pin replacements for the Motorola MC146805 Series of CMOS microprocessors and peripherals primarily intended for single-chip system applications. This family of parts includes the CDP6805E2 8-bit microprocessor; the CDP-6805F2 8-bit microcomputer (1K ROM); the CDP6805G2 8-bit microcomputer (2K ROM); the CDP6818 Real-Time

Clock plus RAM; the CDP6823 Parallel Interface I/O; and the CDP65516 2Kx8 Mask Programmable ROM. Additional types will be added as they become available.

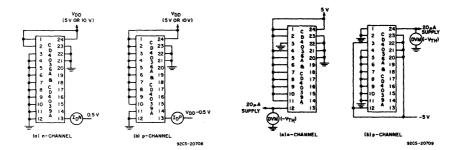

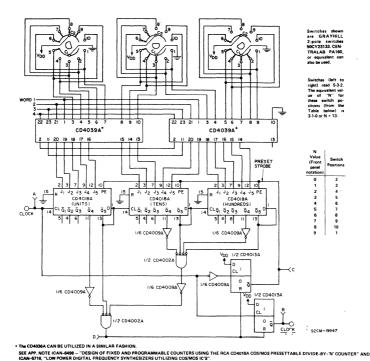

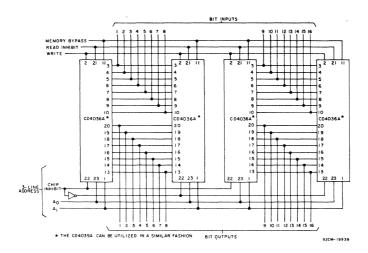

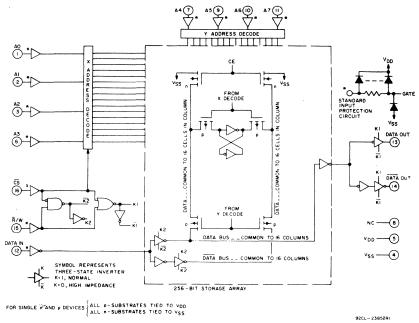

#### **General-Purpose Memories**

In addition to the memories designed to interface directly with CDP1800-series microprocessors, RCA also offers a line of general-purpose memories. These memories include small scratchpad types in the CD4000 series, and types in the MWS5000 and CDM series.

#### **Leadless Chip Carrier**

RCA's broad CMOS LSI product line now includes 12 standard CDP1800 series chips in leadless chip-carrier packages. This basic chip set will consist of 20, 28, and 44-lead packages on 50-mil lead centers.

#### **Extra-Value Product**

Most RCA CDP1800 series parts are offered with burn-in (EVP - Extra-Value Program) and are designated by an "X", "Y" or "Q" suffix added to the part number, e.g., CDM5332EX.

# Microprocessor Development Systems and Microboard Computer Modules

For the designers of microprocessor-based equipment and in support of the CDP1800-series microprocessors and associated memory and peripheral circuits, RCA provides a strong and extensive line of systems, system support components, system support software, system modules (including Microboard milliwatt computer systems), and other development aids. The support-system line includes development systems ranging from a minimum tape-based system to a full development system having floppy-disk mass memory storage and operating system software. This line also includes two evaluation systems that serve as convenient learning tools for design. hardware interfacing, and programming of microcomputer systems. These systems can also be used as the basis for breadboarding and prototyping user-designed microcomputer systems.

The RCA Microboard milliwatt computer systems form an extensive line of fully coordinated products based on a standard, simple-to-use 4.5 by 7.5 inch module. These modules feature the inherent CMOS advantages of low power consumption, wide operating voltage range, and excellent noise immunity. The microboard systems are all designed with the microboard universal backplane and are compatible with RCA Development Systems. User-developed systems, therefore, can be readily developed and easily modified.

As a convenient starting point for the user, two microboard prototyping systems are available. These systems include an expandable 5-card chassis, a microboard computersystem module, a microboard control-and-display module, ROM-based utility software, and ample room for user-designed expansion. These prototyping systems enable the user to reduce his hardware concerns to a minimum and to maximize his efforts in custom design and software development to meet the specific requirements of his application.

The RCA Microsystems DATABOOK SSD-270 provides detailed information on RCA Microprocessor-based development systems and Microboard computer modules and in the product description booklets and user manuals available on specific types. (A list of these publications are included at the end of this DATABOOK).

# **Product Classification Chart**

|             |                             |            |                    |                                                | 70-        |

|-------------|-----------------------------|------------|--------------------|------------------------------------------------|------------|

| Part Number | Description                 | Page No.   | Part Number        | Description                                    | Page No.   |

| Microproc   | cessors                     |            | ROMs (Co           | ont'd)                                         |            |

| CDP1802A    | 8-Bit                       | 14         | CDP1834            | Mask-programmable ROM                          |            |

| CDP1802A    | 8-Bit                       | 36         | 02                 | 1K x 8                                         | 174        |

| CDP1805C    | 8-Bit with RAM              | 84         | CDP1835            | Mask-programmable ROM                          |            |

|             | 8-Bit with RAM              | 103        |                    | 2K x 8                                         | 177        |

| CDP1806C    | 8-Bit with Counter-Timer    | 84         | CDP1837            | Mask-programmable ROM                          |            |

|             | 8-Bit with Counter-Timer    | 103        |                    | 4K x 8                                         | 183        |

|             | 8-Bit with RAM/I-O/Counter- |            | CDP65516           | Mask-programmable ROM                          |            |

|             | Timer                       | 442        |                    | 2K x 8                                         | 434        |

|             | • • •                       |            |                    |                                                |            |

| Microcom    | •                           |            | Input/Out          | put Circuits                                   |            |

| CDP1804A    | 8-Bit with RAM/ROM/Counter- |            | •                  |                                                | 190        |

|             | Timer                       | 56         | CDP1851            | Programmable I/O (PIO)                         | 203        |

| CDP6805F2   | 8-Bit with RAM/ROM/I-O/     | 477        | CDP1852<br>CDP1853 | Byte I/O - 8-Bit I/O Port<br>Decoder - 1 of 8  | 203        |

|             | Counter-Timer               | 477        | CDP1855            | Multiply/Divide Unit (MDU)                     | 323        |

| CDP6805G2   | 8-Bit with RAM/ROM/I-O/     | 500        | CDP1856            | Buffer - 4-Bit                                 | 245        |

|             | Counter-Timer               | 503        | CDP1857            | Buffer - 4-Bit                                 | 250        |

| RAMs        |                             |            | CDP1858            | Latch/Decoder - 4-Bit                          | 250<br>250 |

| CDP1821     | 1K x 1                      | 128        | CDP1859            | Latch/Decoder - 4-Bit                          | 250        |

| CDP1822     | 256 x 4                     | 134        | CDP1861            | Video Display, Controller                      | 200        |

| CDP1823     | 128 x 8                     | 141        | ODFIOOI            | (VDC)                                          | 258        |

| CDP1824     | 32 x 8                      | 147        | CDP1862            | Color Generator Circuit                        | 266        |

| CDP1826     | 64 x 8                      | 153        | CDP1863            | Programmable Frequency                         | 200        |

| CDM6116     | 2K x 8                      | 407        | 05. 1000           | Generator                                      | 271        |

|             |                             |            | CDP1864            | PAL Video Display Controller                   |            |

| MWS5101     | 256 x 4                     | 412<br>419 |                    | (VDC)                                          | 277        |

| MWS5101A    | 256 x 4                     | 419<br>426 | CDP1866            | Latch/Decoder - 4-Bit                          | 286        |

| MWS5114     | 1K x 4                      | 420        | CDP1867            | Latch/Decoder - 4-Bit                          | 286        |

| CD4036A     | 4 x 8                       | 376        | CDP1868            | Latch/Decoder - 4-Bit                          | 286        |

| CD4039A     | 4 x 8                       | 376        | CDP1869            | Video Interface System (VIS)                   | 295        |

| CD4061A     | 256 x 1                     | 383        | CDP1870            | Video Interface System (VIS)                   | 295        |

| CD40061A    | 256 x 1                     | 391        | CDP1871A           | Keyboard Encoder, ASCII/Hex                    | 312        |

| CD40114B    | 16 x 4                      | 396        | CDP1872            | High-Speed Input Port - 8-Bit                  | 320        |

|             |                             |            | CDP1873            | High-Speed Decoder - 1 of 8                    | 325        |

|             |                             |            | CDP1874            | High-Speed Input Port - 8-Bit                  | 320        |

|             |                             |            | CDP1875            | High-Speed Output Port                         | 320        |

| DOI:        |                             |            | CDP1876            | Video Interface System (VIS)                   | 295        |

| ROMs        |                             |            | CDP1877            | Programmable Interrupt                         | 200        |

| A-11777     | Mark and and the Both       |            | 0004070            | Controller                                     | 329        |

| CDM5332     | Mask-programmable ROM       |            | CDP1878            | Dual Counter-Timer<br>Real Time Clock          | 338<br>351 |

| 0.0117.000  | 512 x 8                     | 401        | CDP1879            |                                                |            |

| CDM5333     | Mask-programmable ROM       |            | CDP1881            | Latch/Decoder - 4-Bit<br>Latch/Decoder - 4-Bit | 365<br>365 |

|             | 512 x 8                     | 401        | CDP1882            | Real Time Clock with RAM                       | 529        |

| CDP1831     | Mask-programmable ROM       |            | CDP6818<br>CDP6823 | Parallel Interface                             | 529<br>547 |

|             | 512 x 8                     | 160        | CDF0023            | raianei iiitei iace                            | 547        |

| CDP1832     | Mask-programmable ROM       |            |                    |                                                |            |

|             | 512 x 8                     | 164        |                    |                                                |            |

| CDP1833     | Mask-programmable ROM       |            | <b>UARTs</b>       |                                                |            |

|             | 1K x 8                      | 168        |                    |                                                |            |

| CDP1833B    | Mask-programmable ROM       |            | CDP1854A           | UART                                           | 214        |

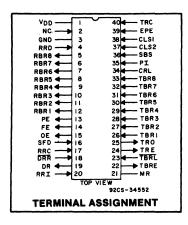

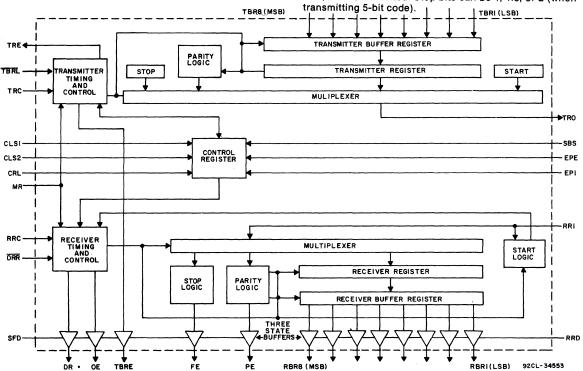

|             | 1K x 8                      | 168        | CDP6402            | Industry Standard UART                         | 367        |

|             |                             |            |                    |                                                |            |

# **Cross-Reference Guide**

**Note:** An RCA equivalent type may not be identical with other manufacturer's type in every detail. Refer to published data for further information.

|                        | J                  |                            |             |

|------------------------|--------------------|----------------------------|-------------|

| Manufact-<br>urer/Type | Description        | RCA Nearest<br>Equiv. Type | Pin-for-Pin |

| ulei/Type              | Description        | Equiv. Type                | Compatible  |

| AMI                    |                    |                            |             |

| S5614                  | 1K×4RAM            | MWS5114                    | Yes         |

| S5101                  | 256 x 4 RAM        | CDP1822/                   | Yes         |

|                        |                    | MWS5101                    |             |

| S6508                  | 1K x 1 RAM         | CDP1821                    | Yes         |

| FUJITSU                |                    |                            |             |

| MB8414E                | 1K x 4 RAM         | MWS5114                    | Yes         |

| HARRIS                 |                    |                            |             |

| 6402                   | UART               | CDP6402                    | Yes         |

| HM6551                 | 256 x RAM          | CDP1822/                   | Yes         |

|                        |                    | MWS5101                    |             |

| HM6508                 | 1K x 1 RAM         | CDP1821                    | Yes         |

| HM6514                 | 1K x 4 RAM         | MWS5114                    | Yes         |

| HITACHI                |                    |                            |             |

| HM435101               | 256 x 4 RAM        | CDP1822/                   | Yes         |

|                        |                    | MWS5101                    |             |

| HM4334                 | 1K x 4 RAM         | MWS5114                    | Yes         |

| HUGHES                 | OBU                | 0001000                    |             |

| HCMP1802<br>HCMP1822   | CPU<br>256 x 4 RAM | CDP1802                    | Yes         |

| HCMP1022               | 256 X 4 HAM        | CDP1822/                   | Yes         |

| HCMP1824               | 32 x 8 RAM         | MWS5101<br>CDP1824         | Yes         |

| HCMP1831               | 512 x 8 ROM        | CDP1824<br>CDP1831         | Yes<br>Yes  |

| HCMP1832               | 512 x 8 ROM        | CDP1831<br>CDP1832         | Yes         |

| HCMP1833               | 1K x 8 ROM         | CDP1832                    | Yes         |

| HCMP1834               | 1K x 8 ROM         | CDP1834                    | Yes         |

| HCMP1835               | 2K x 8 ROM         | CDP1835                    | Yes         |

| HCMP1851               | I/O Interface      | CDP1851                    | Yes         |

| HCMP1852               | I/O Port           | CDP1852                    | Yes         |

| HCMP1853               | N-Bit              | CDP1853                    | Yes         |

|                        | Decoder            |                            |             |

| HCMP1854               | UART               | CDP1854                    | Yes         |

| HCMP1855               | 8-Bit MDU          | CDP1855                    | Yes         |

| HCMP1856/              | Bus Buffer         | CDP1856/                   | Yes         |

| 1857                   |                    | CDP1857/                   |             |

| HCMP1858/              | Latch/             | CDP1858/                   | Yes         |

|                        | Decoder            |                            |             |

| 1859                   |                    | CDP1859                    |             |

| HCMP1861               | VDC                | CDP1861                    | Yes         |

| HCMP1871               | Keyboard           | CDP1871                    | Yes         |

|                        | Encoder            |                            |             |

|                        |                    |                            |             |

| UART        | CDP6402                                                                                                                                                                                                                                                        | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 256 x 4 RAM | CDP1822/                                                                                                                                                                                                                                                       | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             | MWS5101                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1K x 4 RAM  | MWS5114                                                                                                                                                                                                                                                        | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2K x 8 ROM  | CDP1835                                                                                                                                                                                                                                                        | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|             |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Decoder     | CDP1873C                                                                                                                                                                                                                                                       | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| I/O Port    | CDP1872C/                                                                                                                                                                                                                                                      | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|             | CDP1874C                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1K x 1 RAM  | CDP1821                                                                                                                                                                                                                                                        | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 256 x 4 RAM | CDP1822/                                                                                                                                                                                                                                                       | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             | MWS5101                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1K x 4 RAM  | MWS5114                                                                                                                                                                                                                                                        | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 256 x 4 RAM | CDP1822/                                                                                                                                                                                                                                                       | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|             | MWS5101                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1K x 1 RAM  | CDP1821                                                                                                                                                                                                                                                        | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 256 x 4 RAM | CDP1822/                                                                                                                                                                                                                                                       | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             | MWS5101                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1k x 4 RAM  | MWS5114                                                                                                                                                                                                                                                        | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1K x 4 RAM  | MWS5114                                                                                                                                                                                                                                                        | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 256 x 4 RAM | CDP1822/                                                                                                                                                                                                                                                       | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             | MWS5101                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1K x 4 RAM  | MWS5114                                                                                                                                                                                                                                                        | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2K x 8 ROM  | CDP1835                                                                                                                                                                                                                                                        | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|             |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2K x 8 ROM  | CDP1835                                                                                                                                                                                                                                                        | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|             |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1K x 4 RAM  | MWS5114                                                                                                                                                                                                                                                        | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 256 x 4 RAM | CDP1822/                                                                                                                                                                                                                                                       | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             | MWS5101                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1K x 1 RAM  | CDP1821                                                                                                                                                                                                                                                        | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1K x 4 RAM  | MWS5114                                                                                                                                                                                                                                                        | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|             |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             | 1K x 4 RAM 2K x 8 ROM  Decoder I/O Port  1K x 1 RAM 256 x 4 RAM 1K x 4 RAM 2K x 8 ROM 2K x 8 ROM 1K x 4 RAM 2K x 8 ROM 1K x 4 RAM 2K x 8 ROM 1K x 4 RAM 2K x 8 ROM | 1K x 4 RAM       MWS5101         2K x 8 ROM       CDP1835         Decoder I/O Port       CDP1873C         CDP1872C/CDP1874C         1K x 1 RAM       CDP1821         256 x 4 RAM       CDP1822/MWS5101         1K x 1 RAM       CDP1822/MWS5101         1K x 1 RAM       CDP1821         256 x 4 RAM       CDP1822/MWS5101         1K x 1 RAM       CDP1822/MWS5101         1k x 4 RAM       MWS5114         256 x 4 RAM       CDP1822/MWS5101         1K x 4 RAM       CDP1835         2K x 8 ROM       CDP1835         1K x 4 RAM       MWS5114         256 x 4 RAM       CDP1835         1K x 8 ROM       CDP1835         1K x 1 RAM       MWS5101         1K x 1 RAM       CDP1821 |

# Operating and Handling Considerations RCA CMOS Integrated Circuits

This Note summarizes important operating recommendations and precautions which should be followed in the interest of maintaining the high standards of performance of solid state devices.

The ratings included in RCA Solid State Devices data bulletins are based on the Absolute Maximum Rating System, which is defined by the following Industry Standard (JEDEC) statement:

Absolute-Maximum Ratings are limiting values of operating and environmental conditions applicable to any electron device of a specified type as defined by its published data, and should not be exceeded under the worst probable conditions.

The device manufacturer chooses these values to provide acceptable serviceability of the device, taking no responsibility for equipment variations, environmental variations, and the effects of changes in operating conditions due to variations in device characteristics.

The equipment manufacturer should design so that initially and throughout life no absolute-maximum value for the intended service is exceeded with any device under the worst probable operating conditions with respect to supply voltage variation, equipment component variation, equipment control adjustment, load variation, signal variation, environmental conditions, and variations in device characteristics.

It is recommended that equipment manufacturers consult RCA whenever device applications involve unusual electrical, mechanical or environmental operating conditions.

#### **General Considerations**

The design flexibility provided by these devices makes possible their use in a broad range of applications and under many different operating conditions. When incorporating these devices in equipment, therefore, designers should anticipate the rare possibility of device failure and make certain that no safety hazard would result from such an occurence.

The small size of most solid state products provides obvious advantages to the designers of electronic equipment. However, it should be recognized that these compact devices usually provide only relatively small insulation area between adjacent leads and the metal envelope. When these devices are used in moist or contaminated atmospheres, therefore, supplemental protection must be provided to prevent the development of electrical conductive paths across the relatively small insulating surfaces.

The metal shells of the TO-5 style package often used for integrated circuits usually has the substrate or most negative supply voltage connected to the case. Therefore, consideration should be given to the possibility of shock hazard if the shells are to operate at voltages appreciably above or below ground potential. In general, in any application in which devices are operated at voltages which may be dangerous to personnel, suitable

precautionary measures should be taken to prevent direct contact with these devices.

Devices should not be connected into or disconnected from circuits with the power on because high transient voltages may cause permanent damage to the devices.

#### **TESTING PRECAUTIONS**

In common with many electronic components, solidstate devices should be operated and tested in circuits which have reasonable values of current limiting resistance, or other forms of effective current overload protection. Failure to observe these precautions can cause excessive internal heating of the device resulting in destruction and/or possible shattering of the enclosure.

#### Mounting

Integrated circuits are normally supplied with lead-tin plated leads to facilitate soldering into circuit boards. In those relatively few applications requiring welding of the device leads, rather than soldering, the devices may be obtained with gold or nickel plated Kovar leads.\* It should be recognized that this type of plating will not provide complete protection against lead corrosion in the presence of high humidity and mechanical stress.

Trade Name: Westinghouse Corp.

\*Mil-M-38510A, paragraph 3.5.6.1(a), lead material

The aluminum-foil-lined cardboard "sandwich pack" employed for static protection of the flat-pack also provides some additional protection against lead corrosion, and it is recommended that the devices be stored in this package until used.

When integrated circuits are welded onto printed circuit boards or equipment, the presence of moisture between the closely spaced terminals can result in conductive paths that may impair device performance in high-impedance applications. It is therefore recommended that conformal coatings or potting be provided as an added measure of protection against moisture penetration.

In any method of mounting integrated circuits which involves bending or forming of the device leads, it is extremely important that the lead be supported and clamped between the bend and the package seal, and that bending be done with care to avoid damage to lead plating. In no case should the radius of the bend be less than the diameter of the lead, or in the case of rectangular leads, such as those used in RCA 14-lead and 16-lead flat-packages, less than the lead thickness. It is also extremely important that the ends of the bent leads be straight to assure proper insertion through the holes in the printed-circuit board.

#### Handling

All CMOS gate inputs have a resistor/diode gate protection network. All transmission gate inputs and all outputs have diode protection provided by inherent p-n junction diodes. These diode networks at input and

# Operating and Handling Considerations (Cont'd)

output interfaces protect CMOS devices from gate-oxide failure in handling environments where static discharge is not excessive. In low-temperature, low-humidity environments, improper handling may result in device damage. See ICAN-6525, "Handling and Operating Considerations for MOS Integrated Circuits", for proper handling procedures.

#### Operating

#### **Unused Inputs**

All unused input leads must be connected to either Vss or VDD, whichever is appropriate for the logic circuit involved. A floating input on a high-current type not only can result in faulty logic operation, but can cause the maximum power dissipation of 200 milliwatts to be exceeded and may result in damage to the device. Inputs to these types, which are mounted on printed-circuit boards that may temporarily become unterminated, should have a pull-up resistor to Vss or VDD. A useful range of values for such resistors is from 10 kilohms to 1 megohm.

#### **Input Signals**

Signals shall not be applied to the inputs while the device power supply is off unless the input current is limited to a steady state value of less than 10 milliamperes. Input currents of less than 10 milliamperes prevent device damage; however, proper operation may be impaired as a result of current flow through structural diode junctions.

#### **Output Short Circuits**

Shorting of outputs to VSS or VDD can damage many of the higher-output-current CMOS types. In general, these types can all be safely shorted for supplies up to 5 volts, but will be damaged (depending on type) at higher powersupply voltages. For cases in which a short-circuit load, such as the base of a p-n-p or an n-p-n bipolar transistor, is directly driven, the device output characteristics given in the published data should be consulted to determine the requirements for a safe operation below 200 milliwatts.

For detailed CMOS IC operating and handling considerations, refer to Application Note ICAN-6525 "Handling and Operating Considerations for MOS Integrated circuits".

#### IC Chips

Integrated-circuit chips, unlike packaged devices, are non-hermetic devices, normally fragile and small in physical size, and therefore, require special handling considerations as follows:

- Chips must be stored under proper conditions to insure that they are not subjected to a moist and/or contaminated atmosphere that could alter their electrical, physical, or mechanical characteristics. After the shipping container is opened, the chip must be stored under the following conditions:

- A. Storage temperature, 40° C.

- B. Relatively humidity, 50% max.

- C. Clean, dust-free environment.

- The user must exercise proper care when handling chips to prevent even the slightest physical damage to the chip.

- During mounting and lead bonding of chips the user must use proper assembly techniques to obtain proper electrical, thermal, and mechanical peformance.

- 4. After the chip has been mounted and bonded, any necessary procedure must be followed by the user to insure that these non-hermetic chips are not subjected to moist or contaminated atmosphere which might cause the development of electrical conductive paths across the realtively small insulating surfaces, In addition, proper consideration must be given to the protection of these devices from other harmful environments which could conceivably adversely affect their proper performance.

# 1800-Series Microprocessors and Microcomputers Technical Data

# **CMOS 8-Bit Microprocessor**

#### Features:

- Minimum instruction fetch-execute time of 5 μs or 7.5 μs at V<sub>DD</sub>=5 V: 2.5 μs or 3.75 μs at V<sub>DD</sub>=10 V

- Any combination of standard RAM and ROM up to 65,536 bytes

- Operates with slow memories, up to 1 µs access time at f<sub>CL</sub>=4 MHz

- 8-bit parallel organization with bidirectional data bus and multiplexed address bus

- 16 x 16 matrix of registers for use as multiple program counters, data pointers, or data registers

- On-chip DMA, interrupt, and flag inputs

- Programmable single-bit output port

- 91 easy-to-use instructions

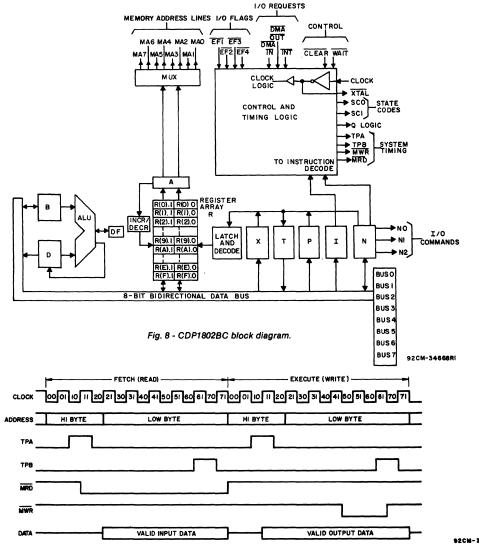

The RCA-CDP1802A LSI CMOS 8-bit register-oriented central-processing unit (CPU) is designed for use as a general-purpose computing or control element in a wide range of stored-program systems or products.

The CDP1802A includes all of the circuits required for fetching, interpreting, and executing instructions which have been stored in standard types of memories. Extensive input/output (I/O) control features are also provided to facilitate system design.

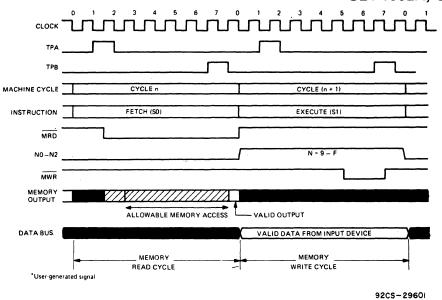

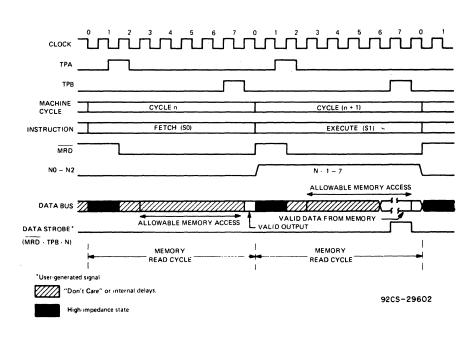

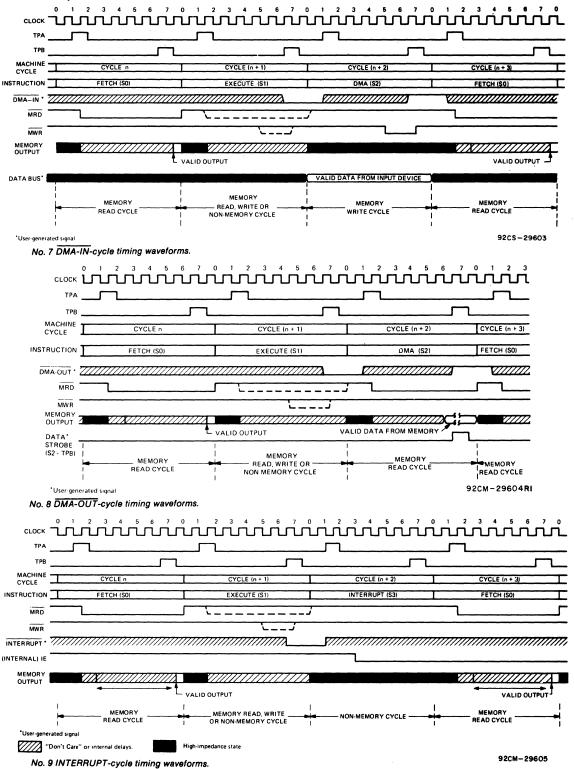

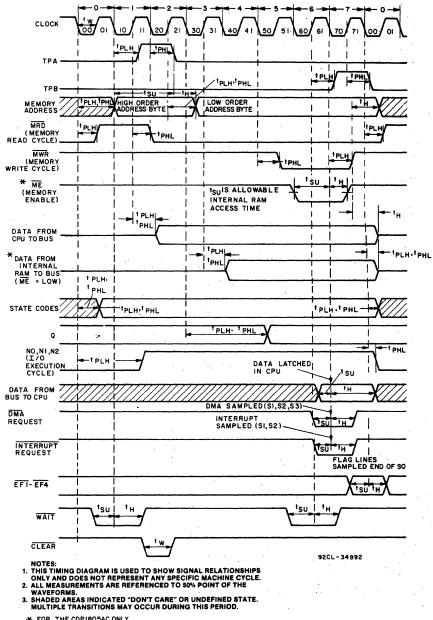

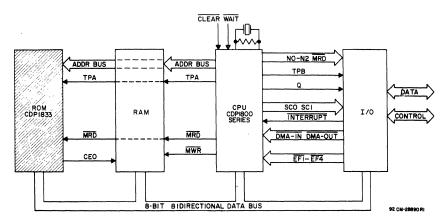

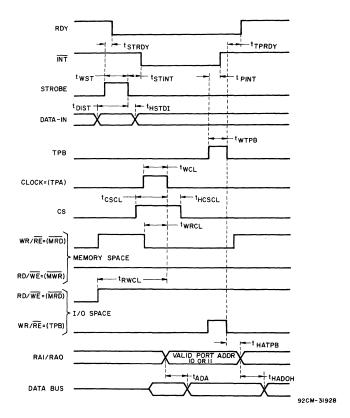

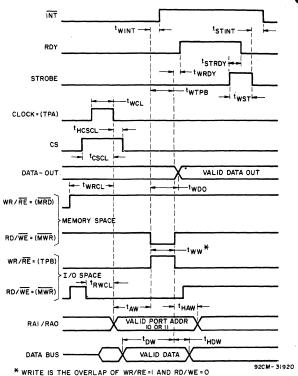

The 1800 series architecture is designed with emphasis on the total microcomputer system as an integral entity so that systems having maximum flexibility and minimum cost can be realized. The 1800 series CPU also provides a syn-

chronous interface to memories and external controllers for I/O devices, and minimizes the cost of interface controllers. Further, the I/O interface is capable of supporting devices operating in polled, interrupt-driven, or direct memory-access modes.

The CDP1802A and CDP1802AC are functionally identical. They differ in that the CDP1802A has a recommended operating voltage range of 4 to 10.5 volts, and the CDP1802AC a recommended operating voltage range of 4 to 6.5 volts.

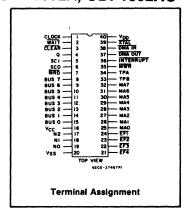

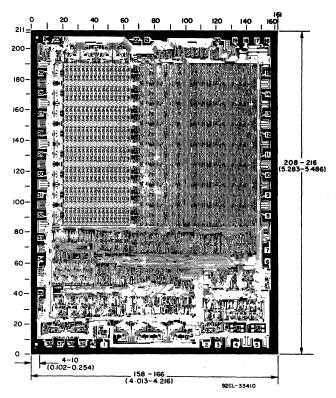

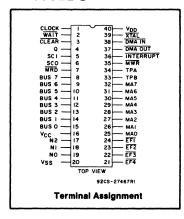

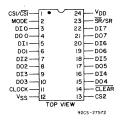

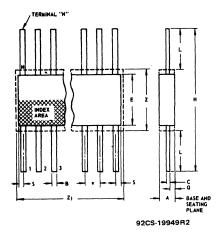

These types are supplied in 40-lead dual-in-line side-brazed ceramic packages (D suffix), and 40-lead dual-in-line plastic packages (E suffix). The CDP1802AC is also available in chip form (H suffix).

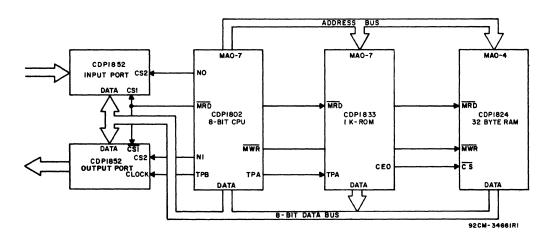

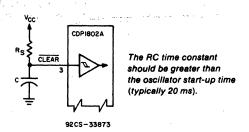

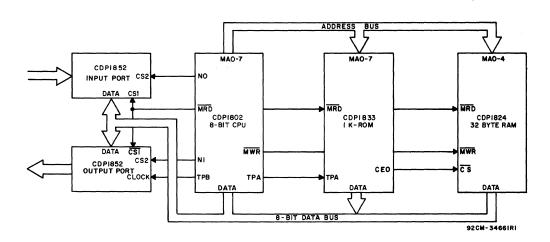

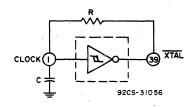

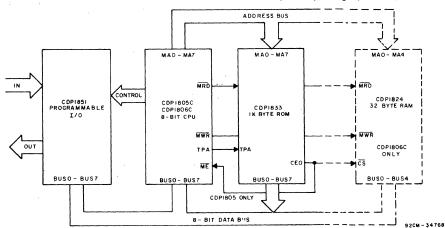

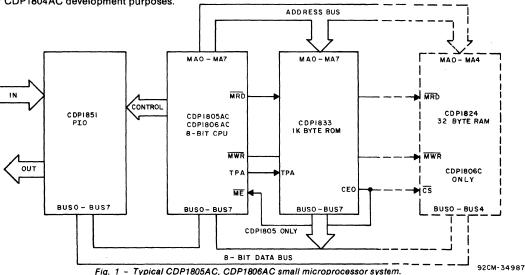

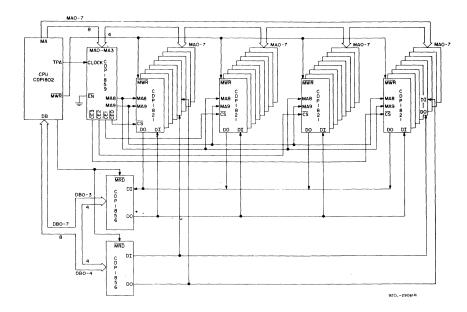

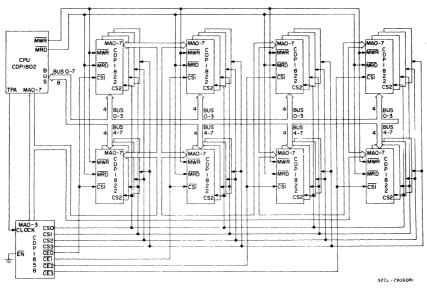

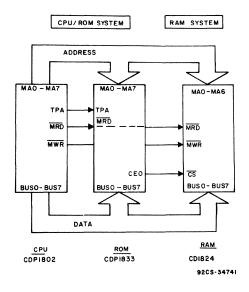

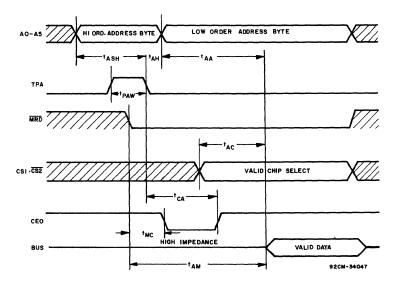

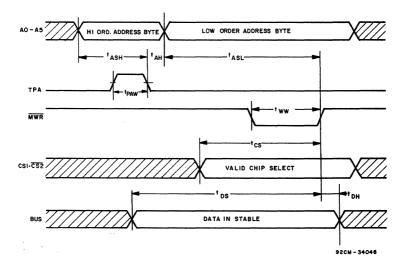

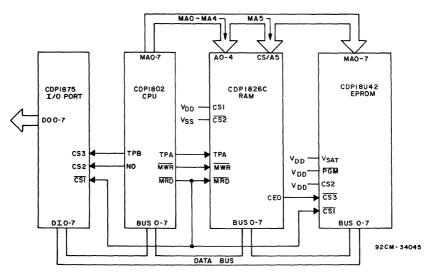

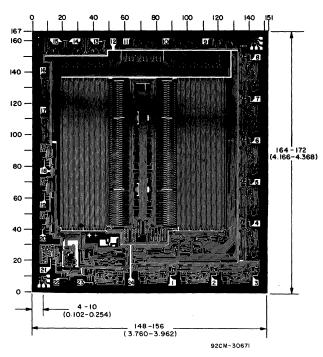

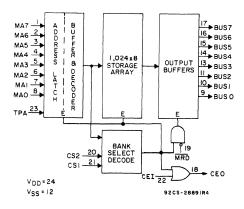

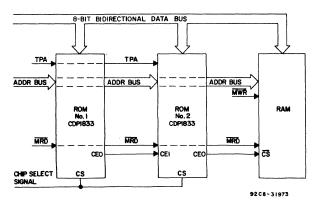

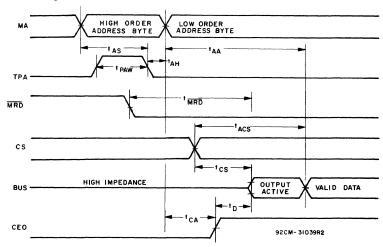

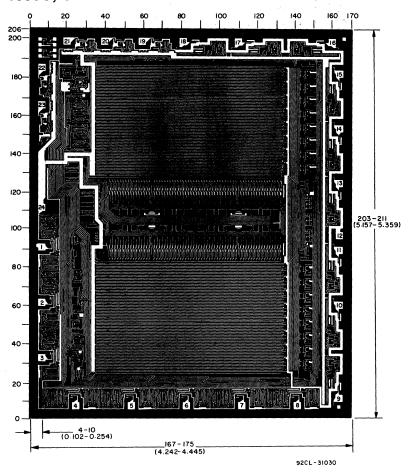

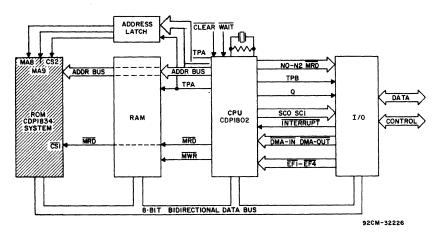

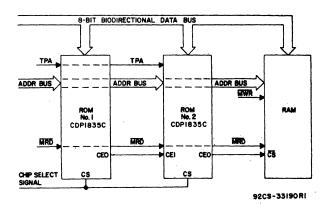

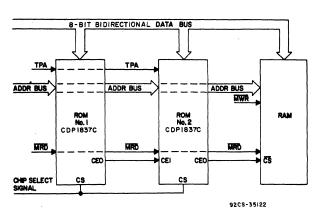

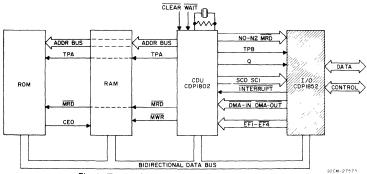

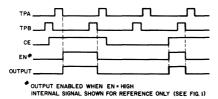

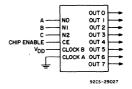

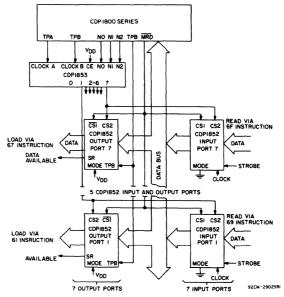

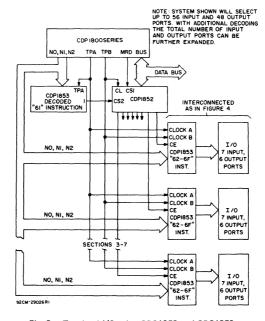

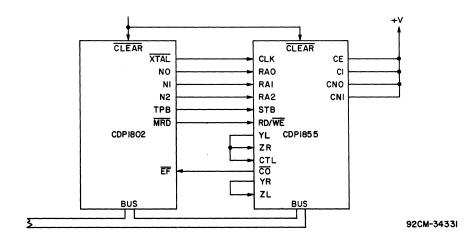

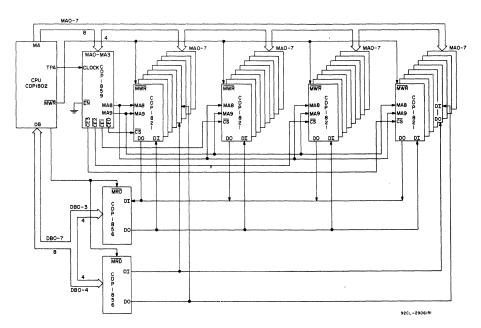

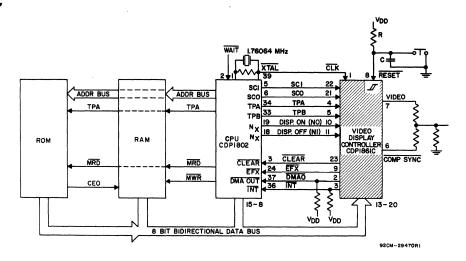

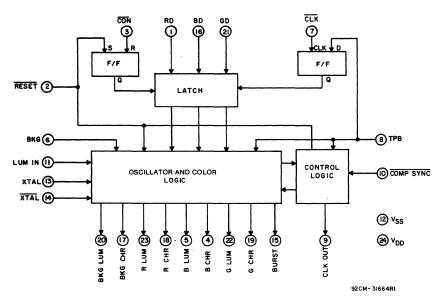

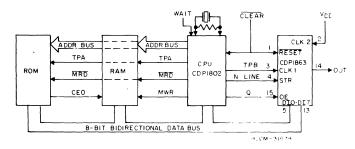

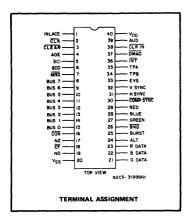

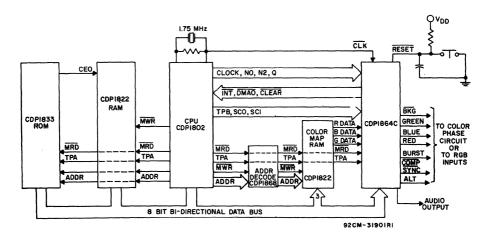

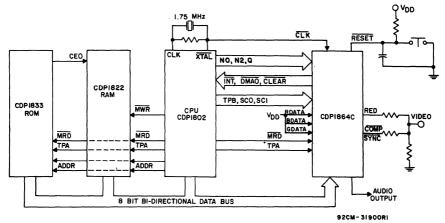

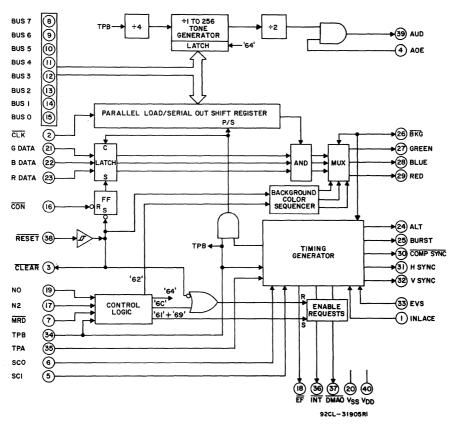

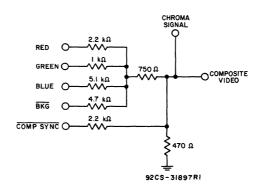

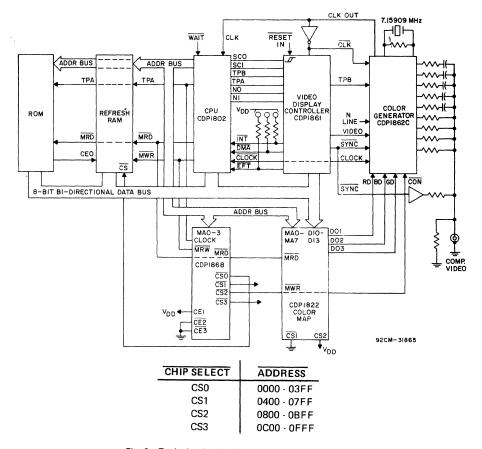

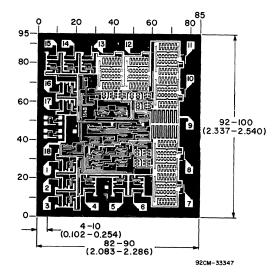

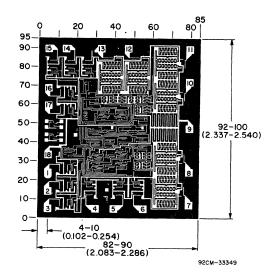

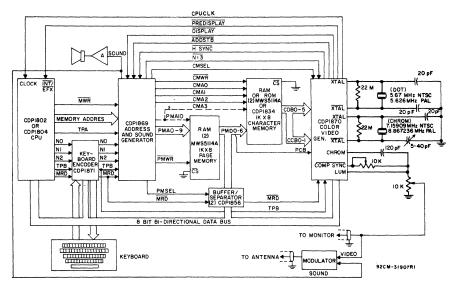

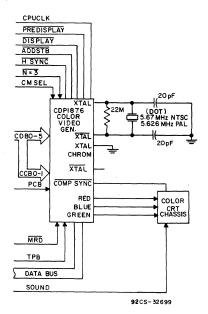

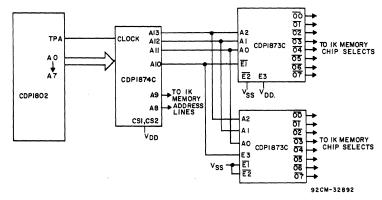

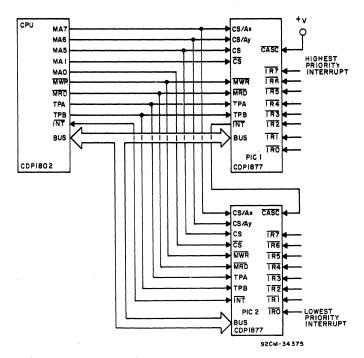

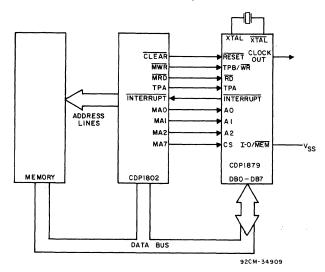

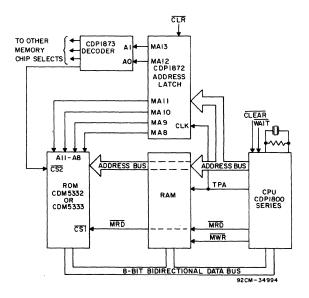

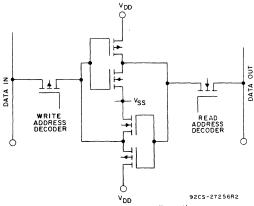

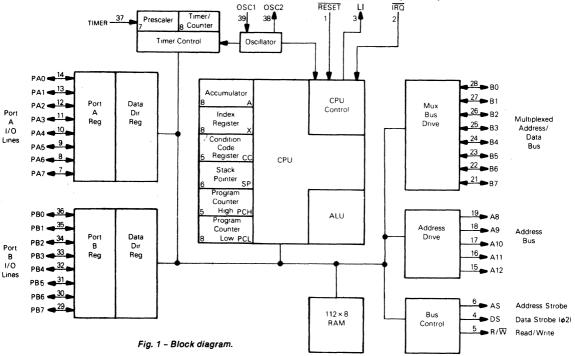

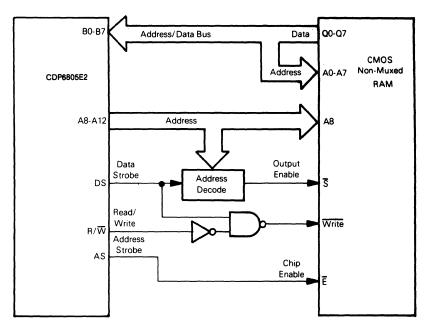

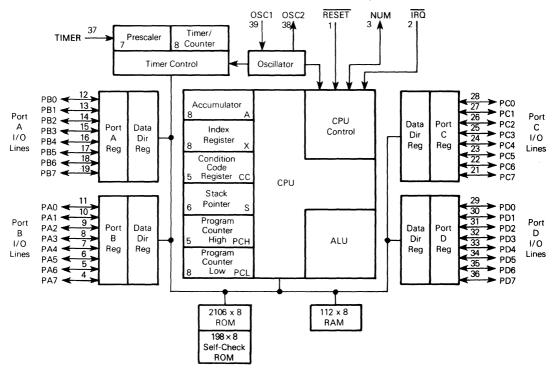

Fig. 1 - Typical CDP1802A small microprocessor system.

#### MAXIMUM RATINGS, Absolute-Maximum Values:

| DC SUPPLY-VOLTAGE RANGE, (V <sub>DD</sub> ): (All voltages referenced to V <sub>SS</sub> terminal) |                                        |

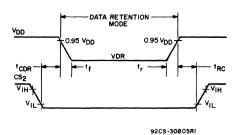

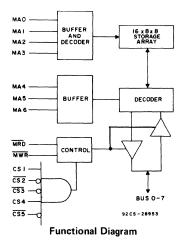

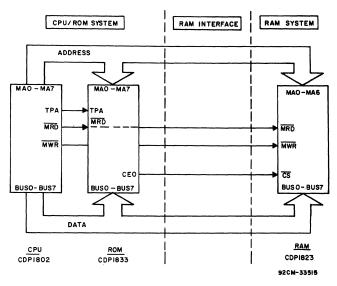

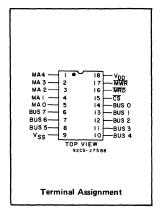

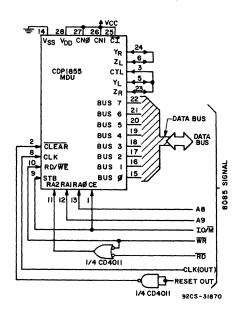

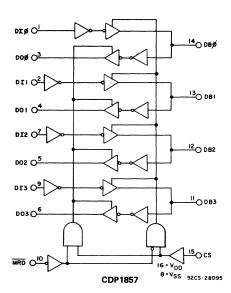

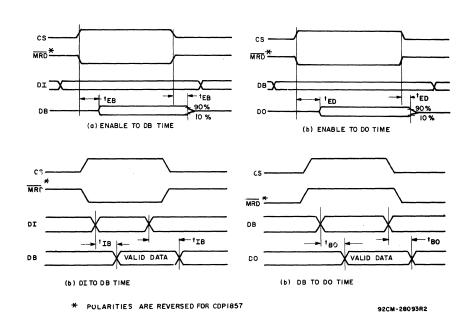

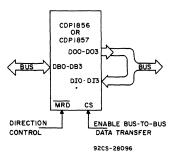

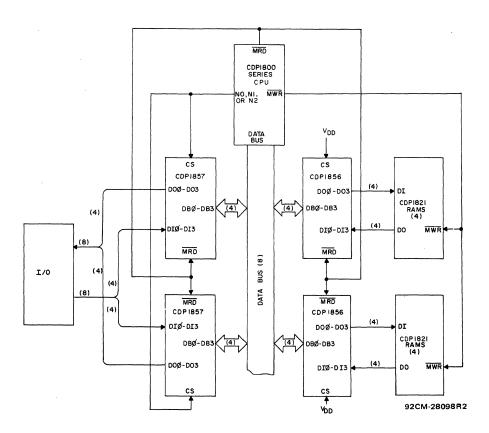

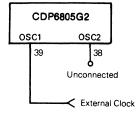

|----------------------------------------------------------------------------------------------------|----------------------------------------|