# **ExpressLane PEX 8114BA**PCI Express-to-PCI/PCI-X Bridge

# **Data Book**

Version 1.2

March 2007

Website www.plxtech.com

Technical Support www.plxtech.com/support

Phone 800 759-3735 408 774-9060 FAX 408 774-2169 Data Book PLX Technology, Inc.

#### **Revision History**

| Version | Date         | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0     | June, 2006   | Initial production release, Silicon Revision BA.                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.1     | August, 2006 | Added notes regarding NT mode errata. Revised Register 17-12, offset 30h Expansion ROM Base Address. Updated miscellaneous electrical specifications. Added pull-up information for JTAG_TCK, and removed pull-up information from EE_PR# and all Hot Plug outputs. Moved thermal resistance information to Chapter 20 (from Chapter 19) and added heat sink-related information. Miscellaneous corrections throughout the data book. |

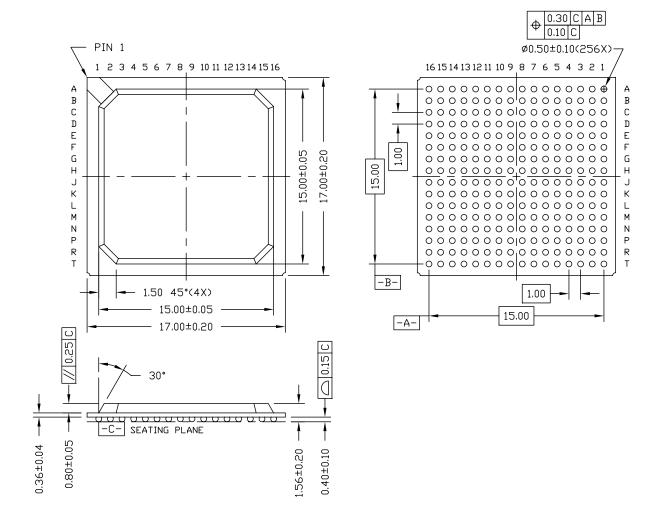

| 1.2     | March, 2007  | Corrected ball diameter and mechanical drawing in Chapter 20.<br>Removed Table 18-6 reference under Table 2-9.                                                                                                                                                                                                                                                                                                                        |

#### **Copyright Information**

Copyright © 2006 – 2007 PLX Technology, Inc. All rights reserved. The information in this document is proprietary to PLX Technology. No part of this document may be reproduced in any form or by any means or used to make any derivative work (such as translation, transformation, or adaptation) without written permission from PLX Technology.

PLX Technology provides this documentation without warranty, term or condition of any kind, either express or implied, including, but not limited to, express and implied warranties of merchantability, fitness for a particular purpose, and non-infringement. While the information contained herein is believed to be accurate, such information is preliminary, and no representations or warranties of accuracy or completeness are made. In no event will PLX Technology be liable for damages arising directly or indirectly from any use of or reliance upon the information contained in this document. PLX Technology may make improvements or changes in the product(s) and/or the program(s) described in this documentation at any time.

PLX Technology retains the right to make changes to this product at any time, without notice. Products may have minor variations to this publication, known as errata. PLX Technology assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of PLX Technology products.

PLX Technology and the PLX logo are registered trademarks and ExpressLane is a trademark of PLX Technology, Inc.

PCI Express is a trademark of the PCI Special Interest Group (PCI-SIG).

All product names are trademarks, registered trademarks, or servicemarks of their respective owners.

Order Number: 8114BA-SIL-DB-P1-1.2

March, 2007 Preface

#### **Preface**

The information contained in this document is subject to change without notice. This document is periodically updated as new information is made available.

#### **Audience**

This data book provides the functional details of the PLX ExpressLane PEX 8114BA PCI Express-to-PCI/PCI-X Bridge, for hardware designers and software/firmware engineers.

#### **Supplemental Documentation**

This data book assumes that the reader is familiar with the following documents:

• PCI Special Interest Group (PCI-SIG)

3855 SW 153rd Drive, Beaverton, OR 97006 USA

Tel: 503 619-0569, Fax: 503 644-6708, www.pcisig.com

- PCI Local Bus Specification, Revision 2.3

- PCI Local Bus Specification, Revision 3.0

- PCI 2.0 Card Electromechanical Specification, Revision 1.0a

- PCI to PCI Bridge Architecture Specification, Revision 1.1

- PCI Bus Power Management Interface Specification, Revision 1.2

- PCI Hot Plug Specification, Revision 1.1

- PCI Standard Hot Plug Controller and Subsystem Specification, Revision 1.0

- PCI-X Addendum to PCI Local Bus Specification, Revision 1.0b

- PCI-X Addendum to PCI Local Bus Specification, Revision 2.0a

- PCI Express Base Specification, Revision 1.0a

- PCI Express to PCI/PCI-X Bridge Specification, Revision 1.0

- The Institute of Electrical and Electronics Engineers, Inc. (IEEE)

445 Hoes Lane, PO Box 1331, Piscataway, NJ 08855-1331 USA

Tel: 800 678-4333 (domestic only) or 732 981-0060, Fax: 732 981-1721, www.ieee.org

- IEEE Standard 1149.1-1990, IEEE Standard Test Access Port and Boundary-Scan Architecture, 1990

- IEEE 1149.1a-1993, IEEE Standard Test Access Port and Boundary-Scan Architecture

- IEEE Standard 1149.1b-1994, Specifications for Vendor-Specific Extensions

- IEEE Standard 1149.6-2003, IEEE Standard Test Access Port and Boundary-Scan Architecture Extensions

Data Book PLX Technology, Inc.

# **Supplemental Documentation Abbreviations**

In this data book, shortened titles are provided to the previously listed documents. The following table delineates these abbreviations.

| Abbreviation                                           | Document                                                                      |

|--------------------------------------------------------|-------------------------------------------------------------------------------|

| PCI r3.0                                               | PCI Local Bus Specification, Revision 3.0                                     |

| PCI 2.0 CEM r1.0a                                      | PCI 2.0 Card Electromechanical Specification, Revision 1.0a                   |

| PCI 2.0 CEM r1.1                                       | PCI 2.0 Card Electromechanical Specification, Revision 1.1                    |

| PCI-to-PCI Bridge r1.1                                 | PCI to PCI Bridge Architecture Specification, Revision 1.1                    |

| PCI Power Mgmt. r1.2                                   | PCI Bus Power Management Interface Specification, Revision 1.2                |

| PCI Hot Plug r1.1                                      | PCI Hot Plug Specification, Revision 1.1                                      |

| PCI Standard Hot Plug Controller and<br>Subsystem r1.0 | PCI Standard Hot Plug Controller and Subsystem Specification,<br>Revision 1.0 |

| PCI-X r1.0b                                            | PCI-X Addendum to PCI Local Bus Specification, Revision 1.0b                  |

| PCI-X r2.0a                                            | PCI-X Addendum to PCI Local Bus Specification, Revision 2.0a                  |

| PCI Express r1.0a                                      | PCI Express Base Specification, Revision 1.0a                                 |

| PCI Express-to-PCI/PCI-X Bridge r1.0                   | PCI Express to PCI/PCI-X Bridge Specification, Revision 1.0                   |

| IEEE Standard 1149.1-1990                              | IEEE Standard Test Access Port and Boundary-Scan Architecture                 |

# **Data Assignment Conventions**

| Data Width        | PEX 8114 Convention |

|-------------------|---------------------|

| 1 byte (8 bits)   | Byte                |

| 2 bytes (16 bits) | Word                |

| 4 bytes (32 bits) | DWORD/DWord         |

March, 2007 Terms and Abbreviations

#### **Terms and Abbreviations**

The following table delineates common terms and abbreviations used in this document. Terms and abbreviations defined in the *PCI Express r1.0a* are not included in this table.

| Terms and Abbreviations | Definition                                                                                                                                                                                                                                                                                         |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| #                       | Active-Low signal.                                                                                                                                                                                                                                                                                 |

| ACK                     | Acknowledge Control Packet. A control packet used by a destination to acknowledge data packet receipt. A signal that acknowledges signal receipt.                                                                                                                                                  |

| ADB                     | Allowable Disconnect Boundary.                                                                                                                                                                                                                                                                     |

| ADQ                     | Allowable Disconnect Quantity. In the PCI Express interface, the ADQ is a buffer size, which is used to indicate memory requirements or reserves.                                                                                                                                                  |

| BAR                     | Base Address Register.                                                                                                                                                                                                                                                                             |

| BCR                     | Bridge Control Register of the Type 1 CSR space.                                                                                                                                                                                                                                                   |

| Cold Reset              | A "Fundamental Reset" following the application of power.                                                                                                                                                                                                                                          |

| Completer               | Device addressed by a requester.                                                                                                                                                                                                                                                                   |

| CPL                     | Completion Transaction.                                                                                                                                                                                                                                                                            |

| CRC                     | Cyclic Redundancy Check                                                                                                                                                                                                                                                                            |

| CSR                     | Configuration Status Register; Control and Status Register; Command and Status Register.                                                                                                                                                                                                           |

| DL_Down                 | Data Link Layer is down (a PCI Express link/port status).                                                                                                                                                                                                                                          |

| DLLP                    | Data Link Layer Packet (originate at the Data Link Layer); allow Flow Control (FCx DLLPs) to acknowledge packets (ACK and NAK DLLPs); and Power Management (PMx DLLPs).                                                                                                                            |

| DW                      | DWord.                                                                                                                                                                                                                                                                                             |

| ECC                     | Error Checking and Correction.                                                                                                                                                                                                                                                                     |

| EEPROM                  | Electrically Erasable Programmable Read-Only Memory.                                                                                                                                                                                                                                               |

| Endpoint                | Device, other than the Root Complex and switches that are requesters or completers of PCI Express transactions.  • Endpoints can be PCI Express endpoints or Conventional PCI endpoints.  • Conventional PCI endpoints support I/O and Locked transaction semantics. PCI Express endpoints do not. |

| FCP                     | Flow Control Packet devices on each link exchange FCPs, which carry <i>Header</i> and <i>Data Payload</i> credit information for one of three packet types – Posted requests, Non-Posted requests, and Completions.                                                                                |

| Fundamental Reset       | The mechanism of setting or returning all registers and state machines to default/initial conditions, as defined in all PCI Express, PCI, PCI-X and Bridge specifications. This mechanism is implemented by way of the PEX_PERST# Input ball/signal.                                               |

| Host                    | A Host computer provides services to computers that connect to it on a network. It is considered in charge over the remainder of devices connected on the bus.                                                                                                                                     |

| Hot Reset               | A reset propagated in-band across a Link using a Physical Layer mechanism (Training Sequence).                                                                                                                                                                                                     |

| I                       | CMOS Input.                                                                                                                                                                                                                                                                                        |

| I/O                     | CMOS Bi-Directional Input Output.                                                                                                                                                                                                                                                                  |

| INCH                    | Ingress Credit Handler.                                                                                                                                                                                                                                                                            |

| ITCH                    | Internal Credit Handler.                                                                                                                                                                                                                                                                           |

| Terms and<br>Abbreviations | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lane                       | Differential signal pair in each direction.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Layers                     | <ul> <li>PCI Express defines three layers:</li> <li>Transaction Layer – Provides assembly and disassembly of TLPs, the major components of which are Header, Data Payload, and an optional Digest Field.</li> <li>Data Link Layer – Provides link management and data integrity, including error detection and correction. Defines the data control for PCI Express.</li> <li>Physical Layer – Appears to the upper layers as PCI. Connects the lower protocols to the upper layers.</li> </ul> |

|                            | <ul> <li>Physical connection between two devices that consists of xN lanes.</li> <li>An x1 link consists of 1 Transmit and 1 Receive signal, where each signal is a differential pair. This is one lane. There are four lines or signals in an x1 link.</li> <li>An x4 link contains four lanes or four differential signal pairs for each direction, for a total of 16 lines or signals.</li> </ul>                                                                                            |

|                            | $V_1$ $V_2$ A Differential Pair                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Link                       | This is an x1 Link There are four signals  A Differential Pair in each direction = one Lane                                                                                                                                                                                                                                                                                                                                                                                                     |

|                            | A Differential Pair in each direction and four of them = four Lanes  This is an x4 Link There are 16 signals                                                                                                                                                                                                                                                                                                                                                                                    |

| LLIST                      | Link List.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| LVDSRn                     | Differential low-voltage, high-speed, LVDS negative Receiver Inputs.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| LVDSRp                     | Differential low-voltage, high-speed, LVDS positive Receiver Inputs.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| LVDSTn                     | Differential low-voltage, high-speed, LVDS negative Transmitter Outputs.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| LVDSTp                     | Differential low-voltage, high-speed, LVDS positive Transmitter Outputs.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| MAM                        | Master Abort Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MSI                        | Message Signaled Interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MWI                        | Memory Write and Invalidate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| NAK                        | Negative Acknowledge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

March, 2007 Terms and Abbreviations

| Terms and Abbreviations      | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Non-Posted<br>Request Packet | Packet transmitted by a requester that has a Completion packet returned by the associated completer.                                                                                                                                                                                                                                                                                                                                                                             |

| Non-Transparent Bridge       | Provides the capability of address isolation. Devices on both sides of the bridge contain their own independent Memory space, and data from one side of the bridge is forwarded to the other side, using an Address translation mechanism. The Non-Transparent bridge is used when there is more than one intelligent entity ( <i>such as</i> multiple processors) in the system. It is a common mechanism used for creating intelligent I/O boards and multi-processor systems. |

| NPR                          | Non-Posted Request.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| NS                           | No Snoop.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0                            | CMOS Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| OD                           | Open Drain Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Packet Types                 | There are three packet types:  • TLP, Transaction Layer Packet  • DLLP, Data Link Layer Packet  • PLP, Physical Layer Packet                                                                                                                                                                                                                                                                                                                                                     |

| PCI                          | Peripheral Component Interconnect. A PCI Bus is a high-performance, 32- or 64-bit bus. It is designed to use with devices that contain high-bandwidth requirements; <i>for example</i> , the display subsystem. A PCI Bus is an I/O bus that can be dynamically configured.                                                                                                                                                                                                      |

| PCI                          | PCI/PCI-X Compliant.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PCI-X                        | Peripheral Component Interconnect. An extension to PCI, designed to address the need for the increased bandwidth of PCI devices.                                                                                                                                                                                                                                                                                                                                                 |

| PEX                          | PCI Express.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Port                         | <ul> <li>Interface between a PCI Express component and the link, and consists of transmitters and receivers.</li> <li>An <i>ingress</i> port receives a packet.</li> <li>An <i>egress</i> port that transmits a packet.</li> </ul>                                                                                                                                                                                                                                               |

| Posted Request Packet        | Packet transmitted by a requester that does have a Completion packet returned by the associated completer.                                                                                                                                                                                                                                                                                                                                                                       |

| PR                           | Posted Request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PU                           | Signal is internally pulled up.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| QoS                          | Quality of Service.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RC                           | Root Complex. Device that connects the CPU and Memory subsystem to the PCI Express fabric, which supports one or more PCI Express ports.                                                                                                                                                                                                                                                                                                                                         |

| RCB                          | Read Completion Boundary.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Requester                    | Device that originates a transaction or places a transaction sequence into the PCI Express fabric.                                                                                                                                                                                                                                                                                                                                                                               |

| RO                           | Relaxed Ordering.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RoHS                         | Restrictions on the use of certain Hazardous Substances (RoHS) Directive.                                                                                                                                                                                                                                                                                                                                                                                                        |

| RX                           | Receiver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SOPS                         | Station Operations block.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Terms and<br>Abbreviations | Definition                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sticky bits                | Status bits that are reset to default on a fundamental reset. Sticky bits are not modified or initialized by a reset, except a fundamental reset. Devices that consume AUX power preserve register values when AUX power consumption is enabled (by way of AUX power or PME Enable). HwInit, ROS, R/WS. and R/W1CS CSR types. (Refer to Table 14-2 for CSR type definitions.)                                                            |

| STRAP                      | Strapping pads must be tied to H (VDD33) or L (VSS) on the board.                                                                                                                                                                                                                                                                                                                                                                        |

| STS                        | PCI-X Sustained Three-State Output, driven High for One CLK before Float.                                                                                                                                                                                                                                                                                                                                                                |

| Switch                     | Device that appears to software as two or more logical PCI-to-PCI bridges.                                                                                                                                                                                                                                                                                                                                                               |

| TC                         | Traffic Class.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TLP                        | Translation Layer Packet.                                                                                                                                                                                                                                                                                                                                                                                                                |

| TP                         | Totem Pole.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Transparent Bridge         | Provides connectivity from the Conventional PCI or PCI-X Bus system to the PCI Express hierarchy or subsystem. The bridge not only converts the physical bus to PCI Express point-to-point signaling, it also translates the PCI or PCI-X Bus protocol to PCI Express protocol. The Transparent bridge allows the Address domain on one side of the bridge to be mapped into the CPU system hierarchy on the primary side of the bridge. |

| TS                         | Three-State Bi-Directional.                                                                                                                                                                                                                                                                                                                                                                                                              |

| TX                         | Transceiver.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VC                         | Virtual Channel.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Warm Reset                 | "Fundamental Reset" without cycling the supplied power.                                                                                                                                                                                                                                                                                                                                                                                  |

# **Contents**

| Chapter 1 | Introduction                                                              | 1    |

|-----------|---------------------------------------------------------------------------|------|

|           | 1.1 Features                                                              | 1    |

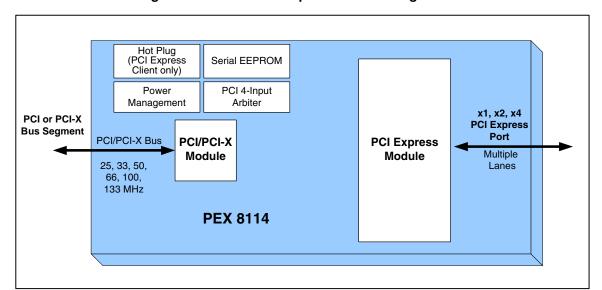

|           | 1.2 PEX 8114 Serial PCI Express to PCI/PCI-X Bridge                       | 3    |

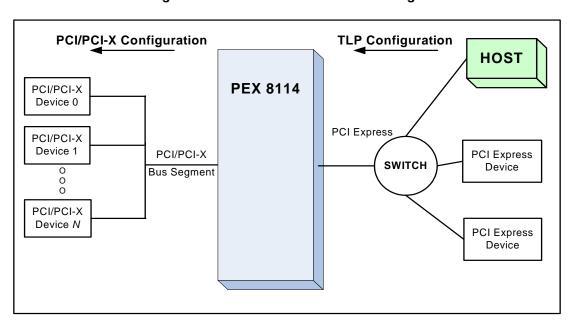

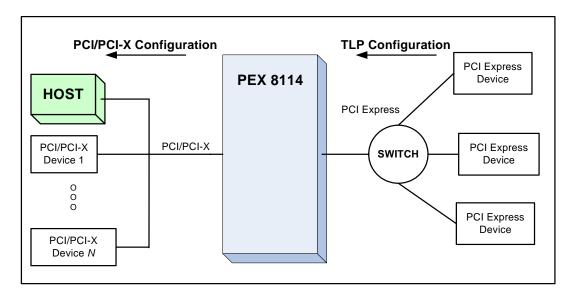

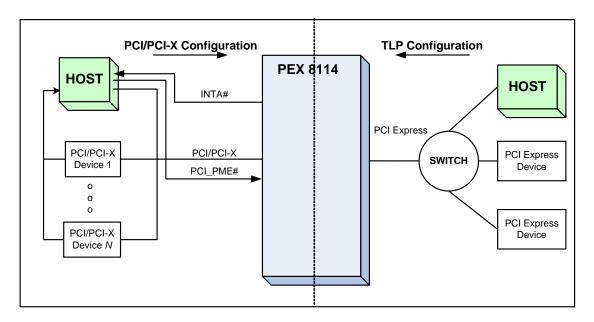

|           | 1.2.1 Introduction to PEX 8114 Operation                                  | 4    |

|           | 1.3 Detailed Block Diagram                                                | 5    |

|           | 1.3.1 Physical Layer – Layer 1                                            | 6    |

|           | 1.3.2 Data Link Layer – Layer 2                                           | 6    |

|           | 1.3.3 Transaction Layer – Layer 3                                         |      |

|           | 1.3.4 Sample Paths                                                        |      |

|           | 1.3.4.1 Forward Bridge Mode                                               |      |

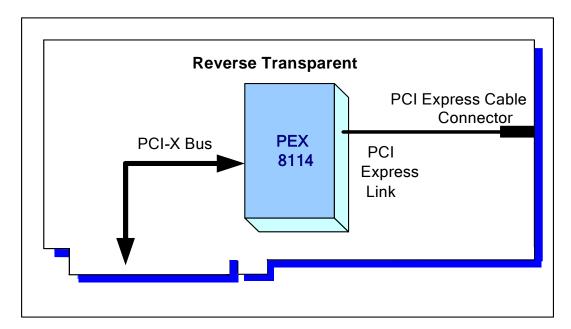

|           | 1.3.4.2 Reverse Bridge Mode                                               |      |

|           | 1.3.4.3 Non-Transparent Mode                                              |      |

|           | 1.4 PEX 8114 Applications                                                 |      |

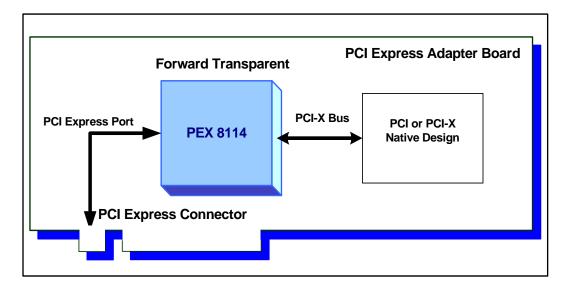

|           | 1.4.1 PCI Express Adapter Board                                           |      |

|           | 1.4.2 Intelligent PCI Express Adapter Board                               |      |

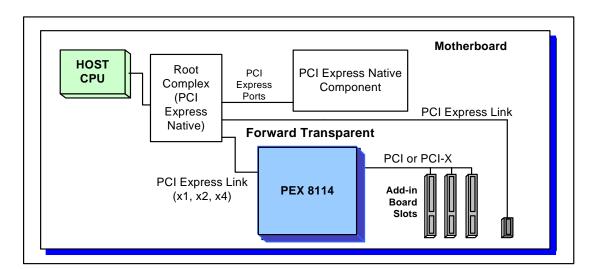

|           | 1.4.3 PCI Express Motherboard to PCI-X Expansion Slot                     |      |

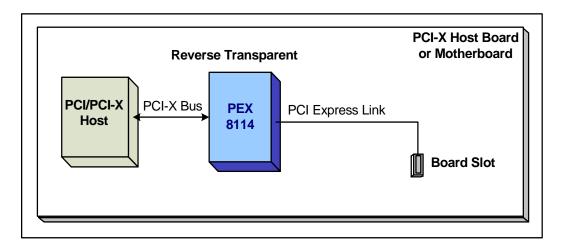

|           | 1.4.4 PCI-X Host Supporting a PCI Express Expansion Slot                  |      |

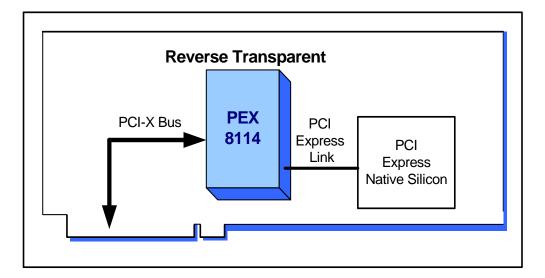

|           | 1.4.5 PCI-X Add-In Board Created from PCI Express Native Silicon          |      |

|           | 1.4.6 PCI-X Extender Board                                                |      |

|           | 1.4.0 FOI-A Exterider board                                               | . 10 |

| Chapter 2 | Signal Poll Description                                                   | 17   |

| Chapter 2 | Signal Ball Description                                                   |      |

|           | 2.1 Introduction                                                          |      |

|           | 2.2 Abbreviations                                                         |      |

|           | 2.2.1 Pull-Up Resistors                                                   |      |

|           | 2.3 PCI/PCI-X Bus Interface Signals                                       |      |

|           | 2.4 PCI Express Interface Signals                                         |      |

|           | 2.5 Hot Plug Signals                                                      |      |

|           | 2.6 Strapping Signals                                                     |      |

|           | 2.7 JTAG Interface Signals                                                |      |

|           | 2.8 Serial EEPROM Interface Signals                                       |      |

|           | 2.9 Power and Ground Signals                                              |      |

|           | 2.10 Ball Assignments by Location                                         |      |

|           | 2.11 Ball Assignments by Signal Name                                      | . 38 |

|           | 2.12 Physical Ball Assignment                                             | . 45 |

|           |                                                                           |      |

| Chapter 3 | Clock and Reset                                                           | . 47 |

|           | 3.1 PEX 8114 Clocking Introduction                                        | . 47 |

|           | 3.1.1 PCI-X Clock Generator                                               | . 47 |

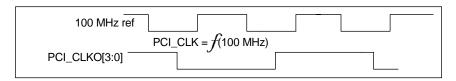

|           | 3.1.2 PCI-X Clocking of PCI-X Module                                      | . 48 |

|           | 3.1.2.1 Clocking the PCI Module when PEX 8114 Clock Generator Is Not Used | . 48 |

|           | 3.1.2.2 Clocking the PCI Module when PEX 8114 Clock Generator Is Used     | . 48 |

|           | 3.2 Determining PCI Bus and Internal Clock Initialization                 |      |

|           | 3.2.1 Determining Bus Mode Capability and Maximum Frequency               | . 50 |

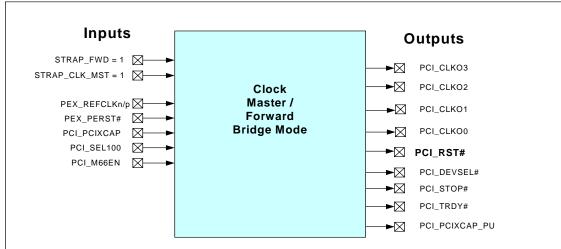

|           | 3.3 PCI Clock Master Mode                                                 |      |

|           | 3.3.1 Clock Master Mode Signals                                           |      |

|           | 3.4 PCI Clock Slave Mode                                                  |      |

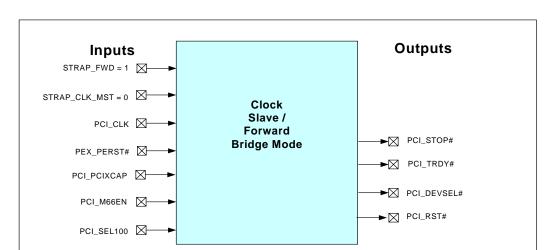

|           | 3.4.1 Clock Slave – Forward Bridge Mode                                   |      |

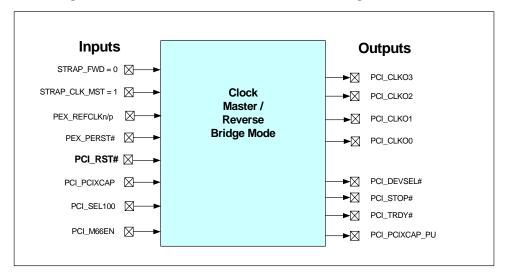

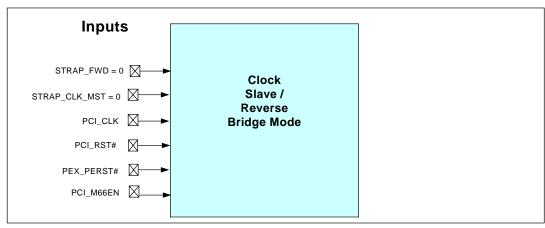

|           | 3.4.2 Clock Slave – Reverse Bridge Mode                                   |      |

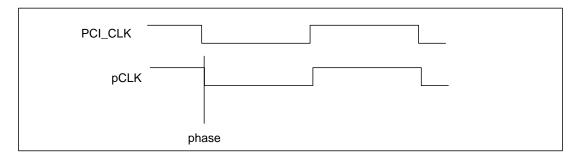

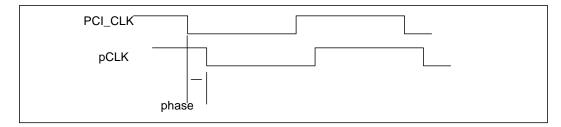

|           | 3.4.3 Timing Diagrams – Forward or Reverse Bridge Mode                    |      |

|           |                                                                           |      |

|           | 3.5 Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

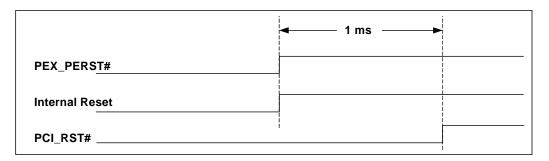

|           | 3.5.1 Level-0, Fundamental Reset (Power-On, Hard, Cold, Warm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|           | 3.5.1.1 PEX_PERST#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|           | 3.5.1.2 Level-0 Reset – Forward Bridge Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

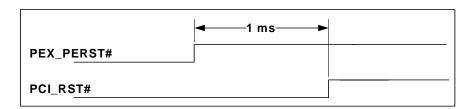

|           | 3.5.1.3 Level-0 Reset – Reverse Bridge Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

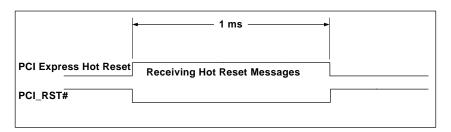

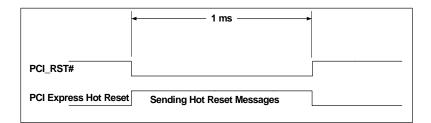

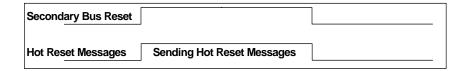

|           | 3.5.2 Level-1, Hot Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|           | 3.5.2.1 Level-1 Reset – Polward Bridge Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

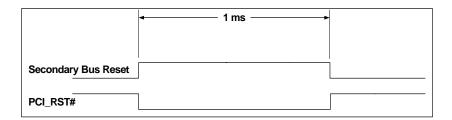

|           | 3.5.3 Secondary Bus Reset, Level-2 Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|           | 3.5.3.1 Level-2 Reset – Forward Bridge Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|           | 3.5.3.2 Level-2 Reset – Reverse Bridge Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

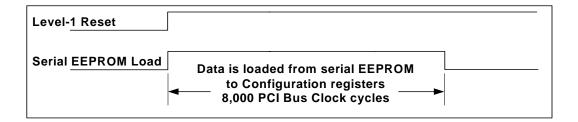

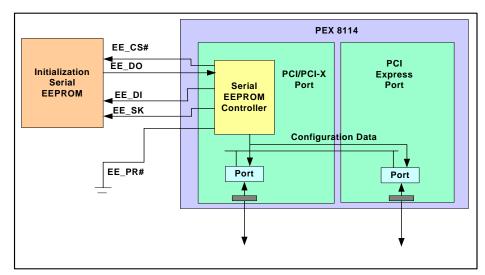

|           | 3.6 Serial EEPROM Load Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |