**DISTRIBUTED BY**

## Marshall

San Francisco Division

336 Los Coches Street Milpitas, California 95035

Electronics Group

Claude Michael Group

FAX

(408) 942-4600

(408) 942-4700 (408) 262-1224

## DATA HANDBOOK

Philips Semiconductors

PHILIPS

0

0

8

#### CONTENTS

|            |                                                  | page |

|------------|--------------------------------------------------|------|

|            | PREFACE                                          | . 3  |

| SECTION 1  | GENERAL INFORMATION                              | 5    |

| SECTION 2  | INTRODUCTION                                     | 15   |

| SECTION 3  | PAL DEVICES                                      | 35   |

| SECTION 4  | PROGRAMMABLE LOGIC ARRAY DEVICES                 | 177  |

| SECTION 5  | PROGRAMMABLE LOGIC SEQUENCER DEVICES             | 235  |

| SECTION 6  | LOW VOLT DEVICES                                 | 431  |

| SECTION 7  | PROGRAMMABLE MACRO LOGIC DEVICES                 | 489  |

| SECTION 8  | MILITARY SELECTION GUIDE                         | 453  |

| SECTION 9  | DEVELOPMENT SOFTWARE                             | 507  |

| SECTION 10 | PROGRAMMER/SOFTWARE SUPPORT                      | 511  |

| SECTION 11 | APPLICATION NOTES                                | 535  |

| SECTION 12 | PACKAGE OUTLINE DRAWINGS                         | 875  |

| SECTION 13 | SALES OFFICES, REPRESENTATIVES, AND DISTRIBUTORS | 893  |

| APPENDIX A | DATA HANDBOOK SYSTEM                             | 896  |

Philips Semiconductors and Philips Electronics North America Corporation reserve the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified. Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### LIFE SUPPORT APPLICATIONS

Philips Semiconductors and Philips Electronics North America Corporation Products are not designed for use in life support appliances, devices, or systems where malfunction of a Philips Semiconductors and Philips Electronics North America Corporation Product can reasonably be expected to result in a personal injury. Philips Semiconductors and Philips Electronics North America Corporation customers using or selling Philips Semiconductors and Philips Electronics North American Philips Corporation Products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors and Philips Electronics North America Corporation for any damages resulting from such improper use or sale.

Philips Semiconductors and Philips Electronics North America Corporation registers eligible circuits under the Semiconductor Chip Protection Act

© Copyright Philips Electronics North America Corporation 1993

#### **Preface**

The 1994 Philips Semiconductors Programmable Logic Devices Data Handbook contains all the information a designer needs to implement virtually any logic design in a PLD.

Philips offers a variety of programmable logic devices which have been tailored to implement a wide range of applications.

In addition to a full complement of industry standard PAL-type devices, Philips offers several application specific devices.

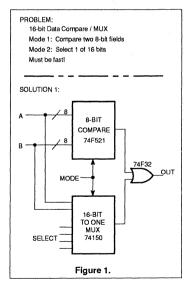

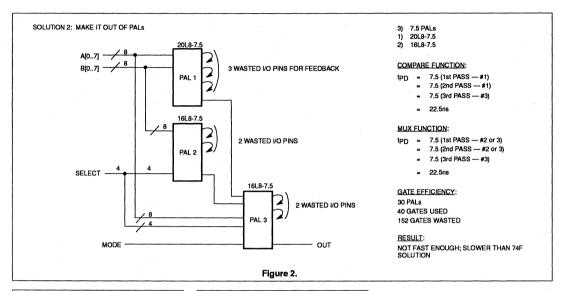

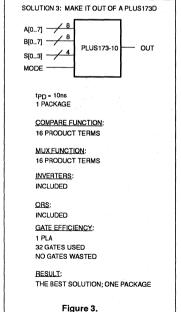

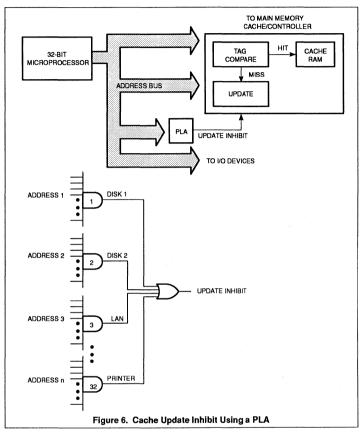

For ultra high speed applications, the Philips PLAs are the right solution. The logical power of two programmable arrays makes complex decoding easy. The PLUS153 and the PLUS173 offer 32 input wide AND-OR decoding, with a worst case  $T_{PD}$  of 10ns.

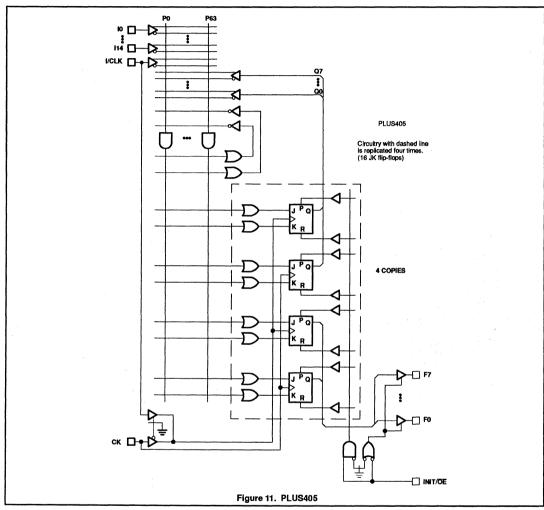

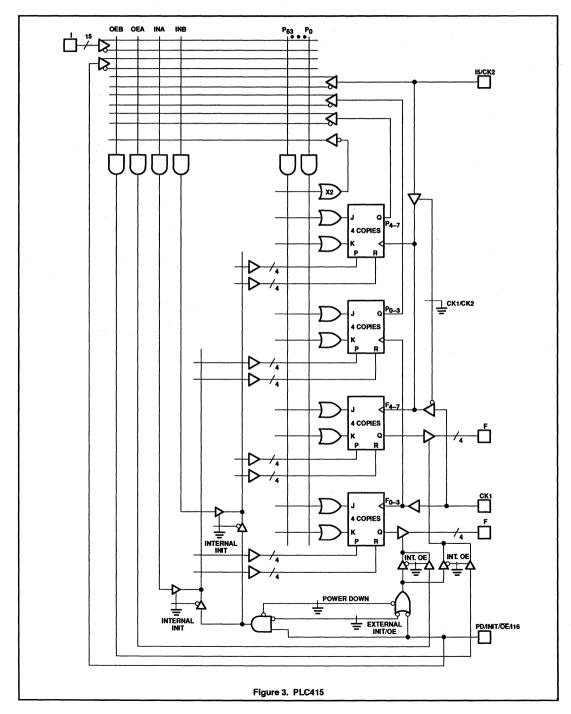

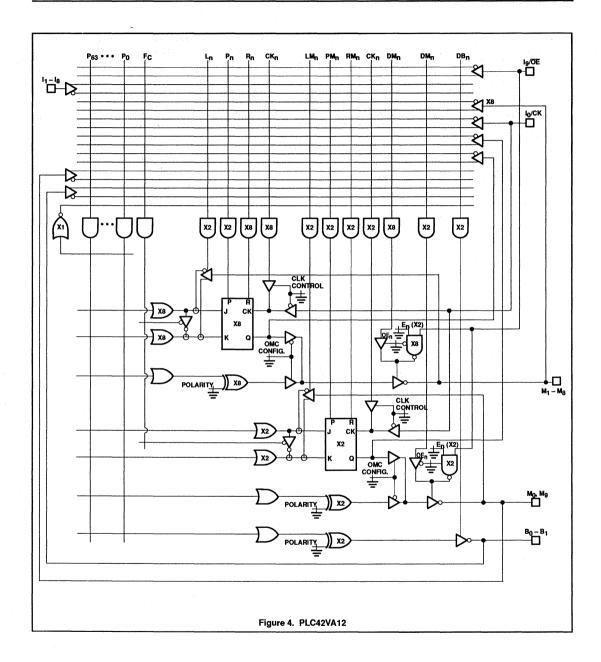

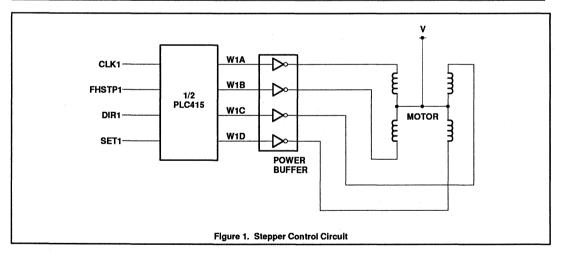

Designers using high performance DRAM, VRAM and graphics devices will appreciate the variety of complex state machines which include the PLC42VA12, PLC415, PLUS405 and the PLUS105. Check out the new 70 MHz PLUS105 in Section 5.

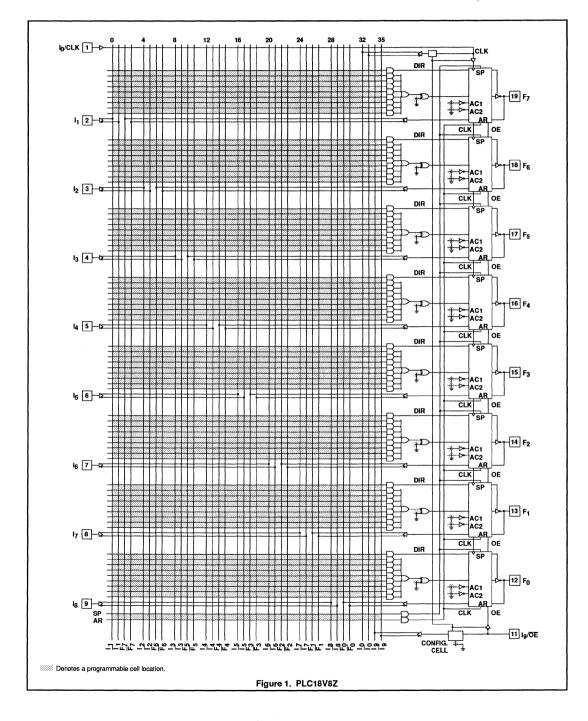

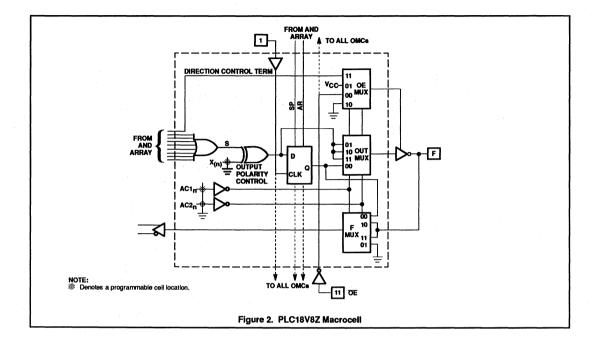

The PLC18V8Z can replace virtually all 20 PALs and GALs. The zero standby power of 20 micro amps is the lowest of any available PLD.

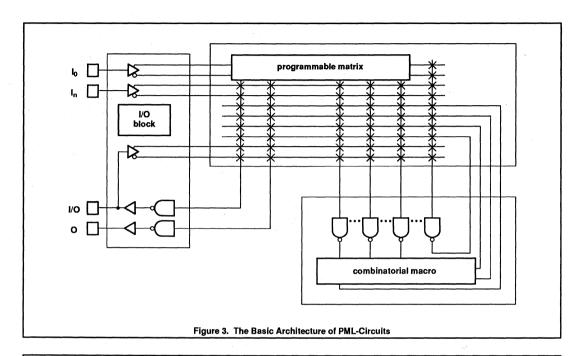

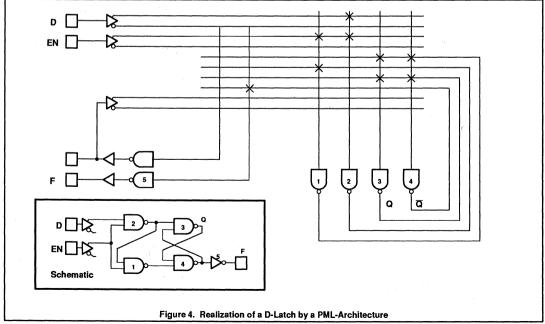

For maximum density in truly compact systems, the Programmable Macro Logic family is the right choice. These field programmable gate arrays are ideal for bus interface applications which require very wide gates.

The newest addition to the Philips PLD line is a family of low voltage devices (2.7 to 3.6 volts). Refer to Section 6 for details on the zero standby power P3C18V8Z Universal PAL device and the 3 very high speed BiCMOS devices.

Designing and programming of Philips PLDs is easy; many third party software and programmer vendors support the entire line of Philips devices. Section 10 details information on the approved software and programmer vendors, as well as all the latest software and firmware revisions.

For ideas on how to implement your designs, take a look at all the application notes in Section 11 of this manual.

Philips provides a high level of customer service via our 24-hour computer bulletin board and our staff of applications engineers who are ready to answer all your design and software related questions. The toll free bulletin board number (from the USA only) is (800) 451-6644. It may also be reached at (408) 991-2406.

# **Section 1**General Information

#### CONTENTS

| Table of Contents          |   |

|----------------------------|---|

| Alphanumeric index         | 1 |

| Product Status Definitions | 1 |

| Selection guide            | 1 |

| Ordering Information       | 1 |

## **Contents**

| Section 1 - General Information |                                                           |     |

|---------------------------------|-----------------------------------------------------------|-----|

| Table of Contents               |                                                           | 7   |

| Alphanumeric index              |                                                           | 10  |

| Product Status Definitions      |                                                           | 11  |

| Selection guide                 |                                                           | 12  |

| Ordering Information            |                                                           | 14  |

| Section 2 – Introduction        |                                                           |     |

| Introduction                    | Programmable logic                                        | 17  |

|                                 | riogiammable logic                                        |     |

| Section 3 – PAL Devices         | December would be high a consideration in (40 or 40 or 6) | 37  |

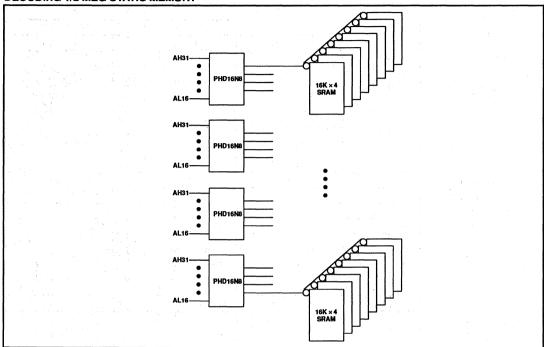

| PHD16N8-5                       | Programmable high-speed decoder logic (16 × 16 × 8)       |     |

| PLC18V8Z35/PLC18V8ZI            | Zero standby power CMOS versatile PAL devices             | 45  |

| PLC18V8Z25/PLC18V8ZIA           | Zero standby power CMOS versatile PAL devices             | 58  |

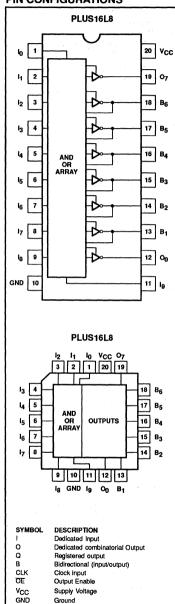

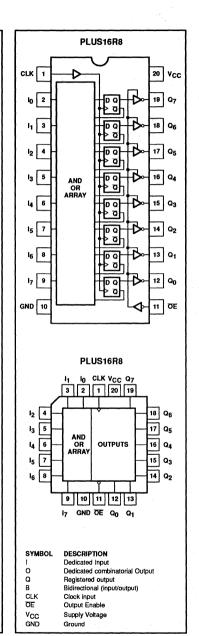

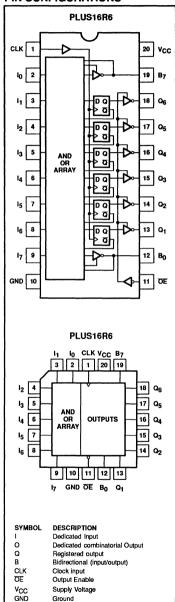

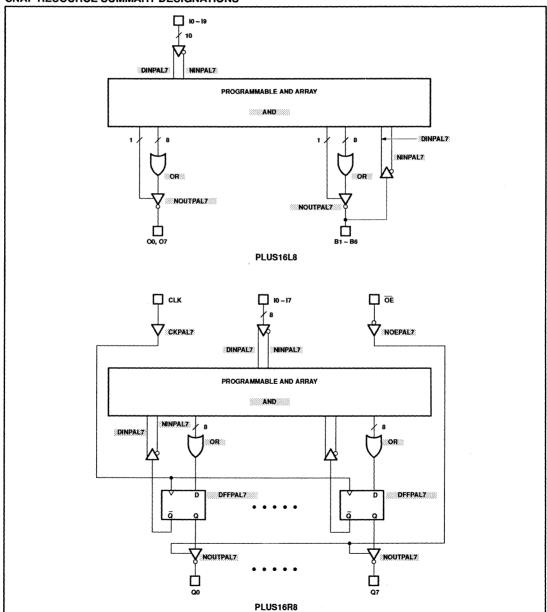

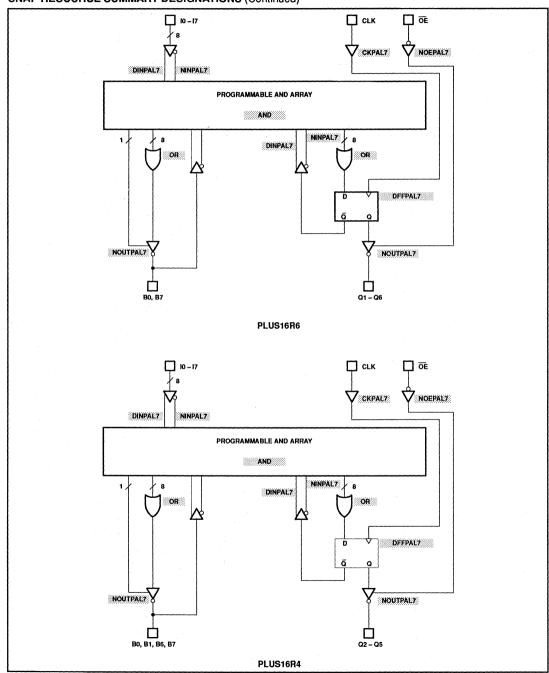

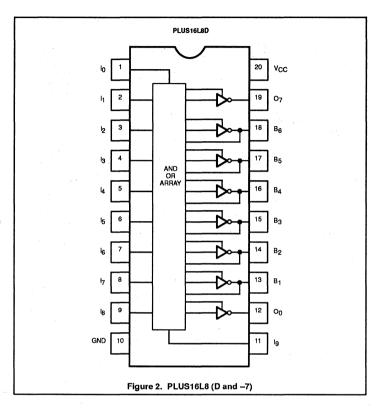

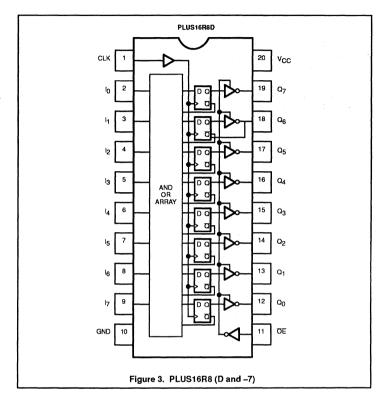

| PLUS16R8D/-7 Series             | PAL devices 16L8, 16R8, 16R6, 16R4                        | 71  |

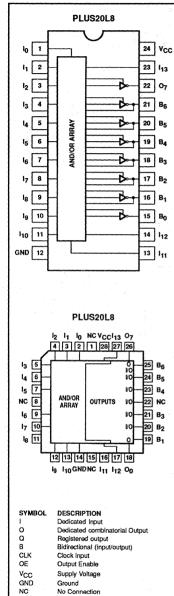

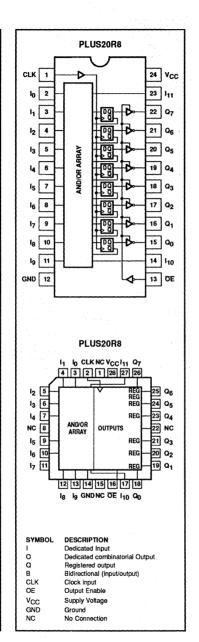

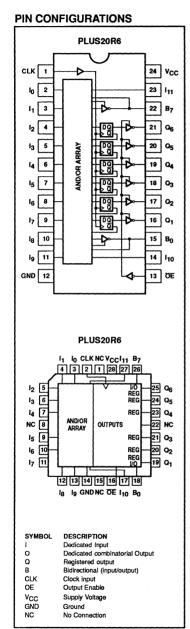

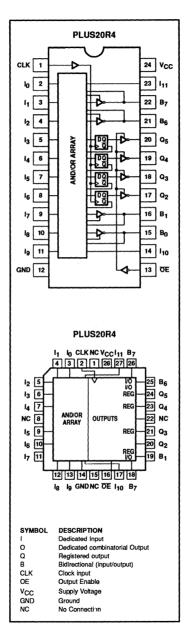

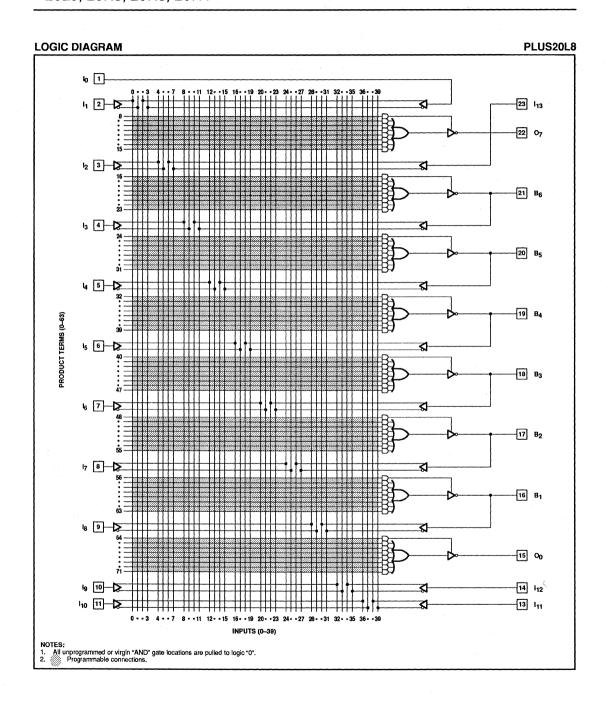

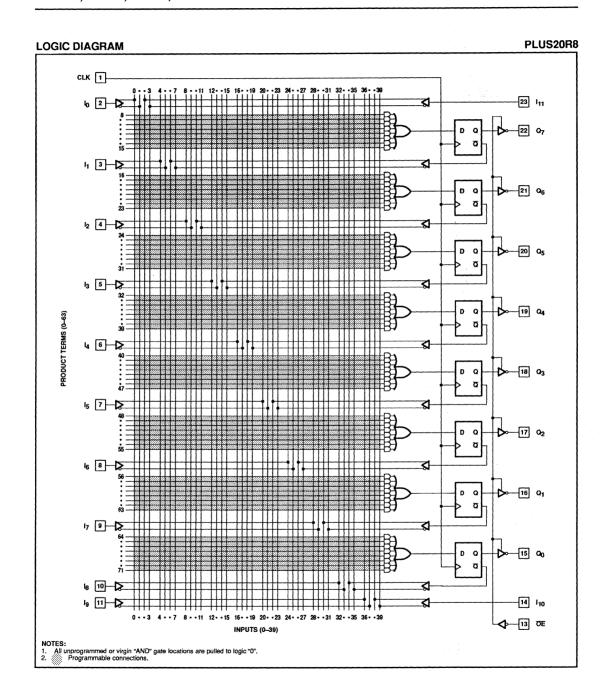

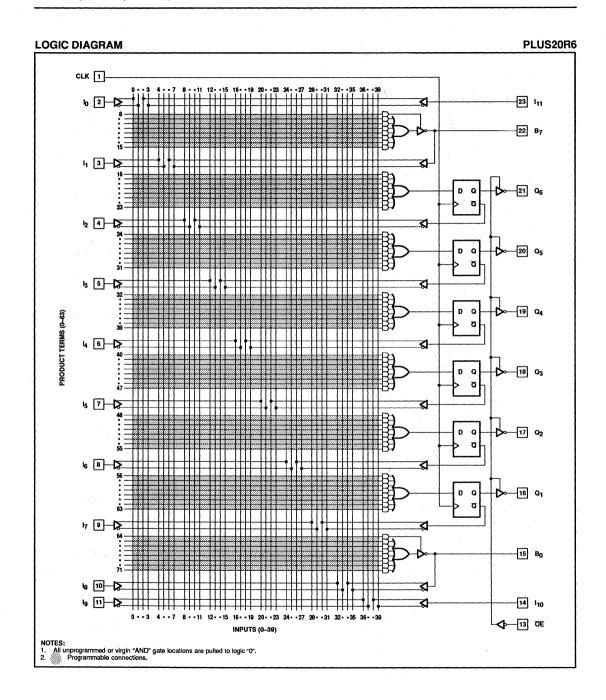

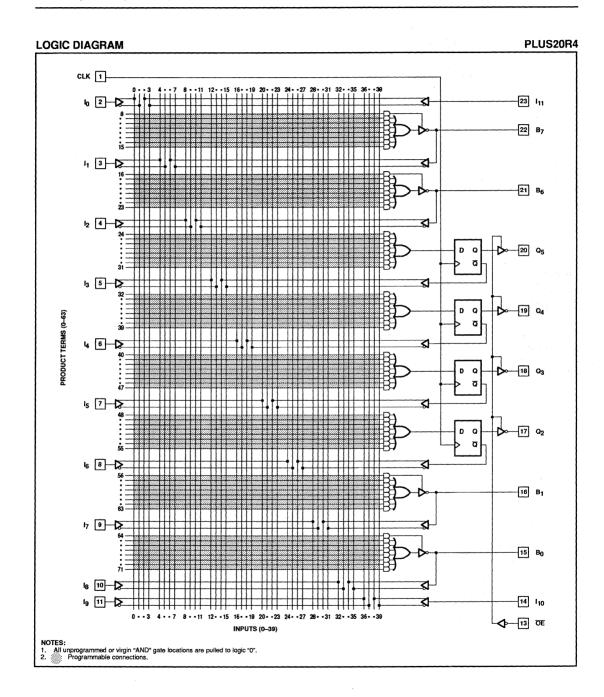

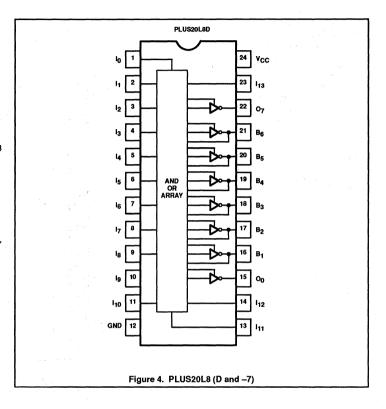

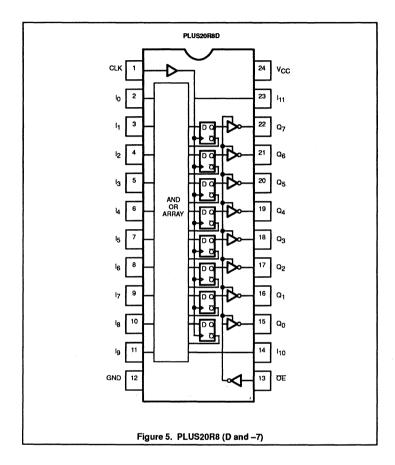

| PLUS20R8D/-7 Series             | PAL devices 20L8, 20R8, 20R6, 20R4                        | 87  |

| PL22V10-10                      | CMOS programmable electrically erasable logic device      | 103 |

| PL22V10-12/-15, PL22V10I15      |                                                           | 118 |

| ABT22V10-7                      | BiCMOS versatile PAL device                               | 133 |

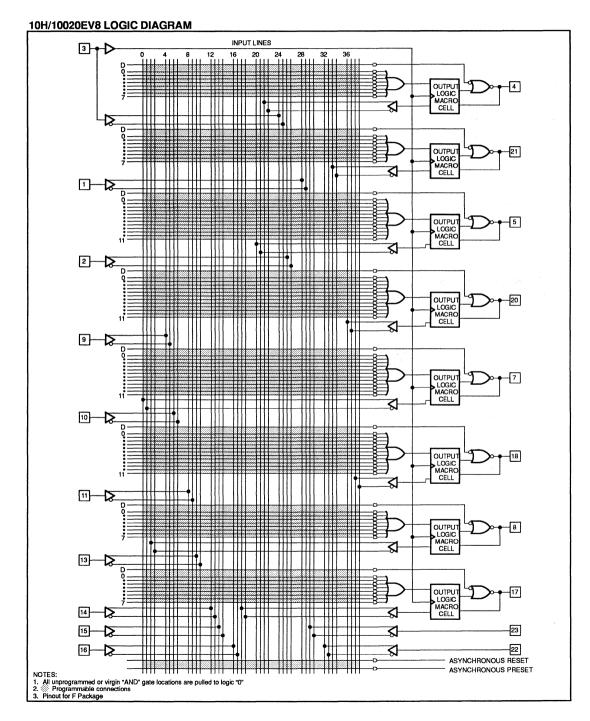

| 10H20EV8/10020EV8               | ECL programmable array logic                              | 148 |

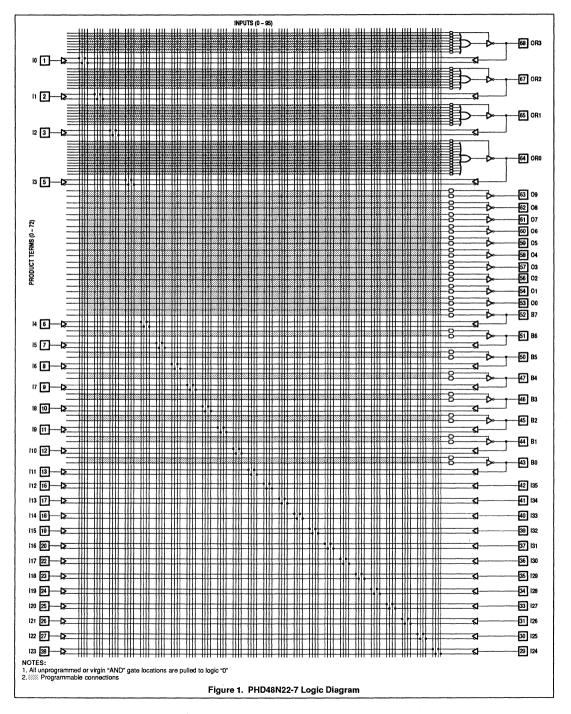

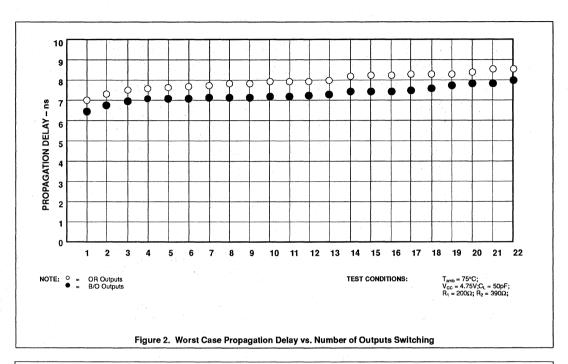

| PHD48N22-7                      | Programmable high-speed decoder logic (48 × 73 × 22)      | 165 |

| Section 4 – Programmable Logic  | Arrays Devices                                            |     |

| PLS153/A                        | Programmable logic arrays (18 × 42 × 10)                  | 179 |

| PLUS153B/D                      | Programmable logic arrays (18 × 42 × 10)                  | 187 |

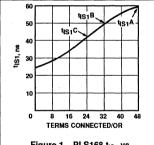

| PLUS153-10                      | Programmable logic array (18 × 42 × 10)                   | 195 |

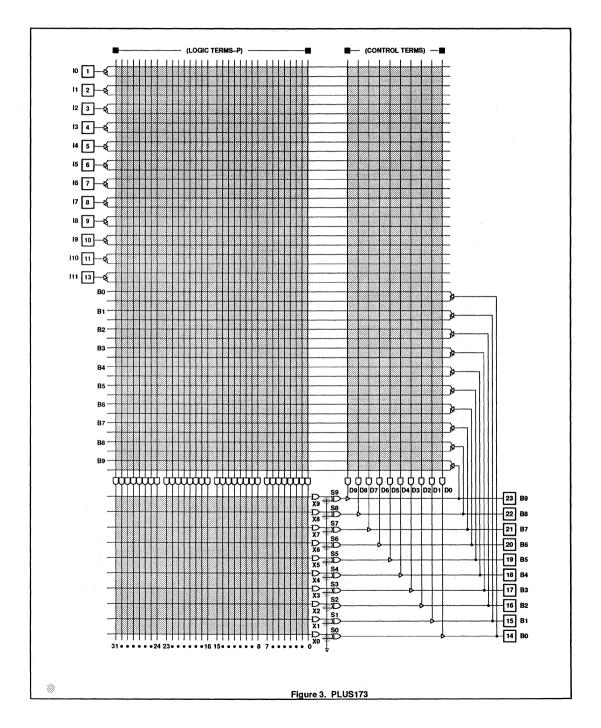

| PLS173                          | Programmable logic array (22 × 42 × 10)                   | 203 |

| PLUS173B/D                      | Programmable logic arrays (22 × 42 × 10)                  | 211 |

| PLUS17310                       | Programmable logic array (22 × 42 × 10)                   | 219 |

| PLS100/PLS101                   | Programmable logic arrays (16 × 48 × 8)                   | 227 |

| Section 5 – Programmable Logic  | Sequencers Devices                                        |     |

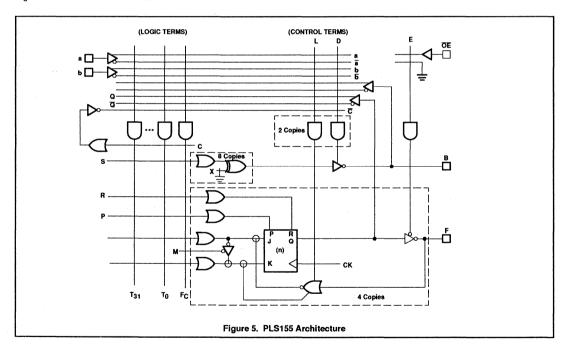

| PLS155                          | Programmable logic sequencer (16 × 45 × 12)               | 237 |

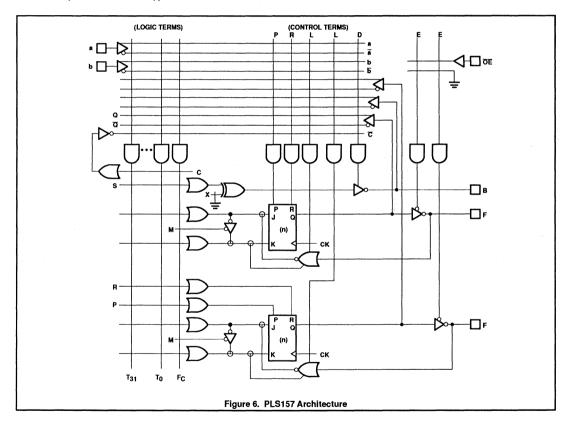

| PLS157                          | Programmable logic sequencer (16 × 45 × 12)               | 249 |

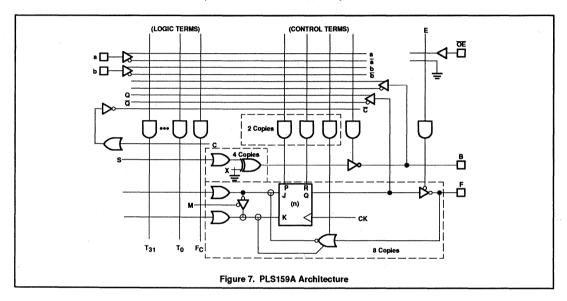

| PLS159A                         | Programmable logic sequencer (16 × 45 × 12)               | 261 |

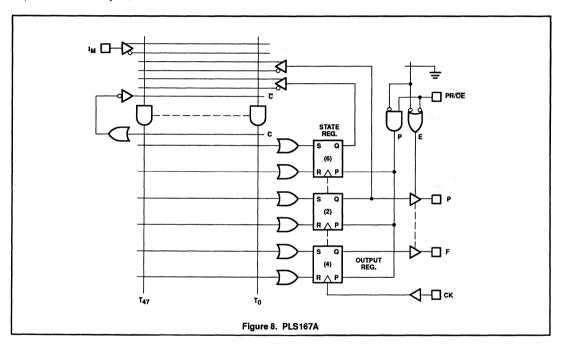

| PLS167/A                        | Programmable logic sequencers (14 × 48 × 6)               | 273 |

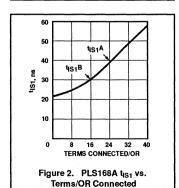

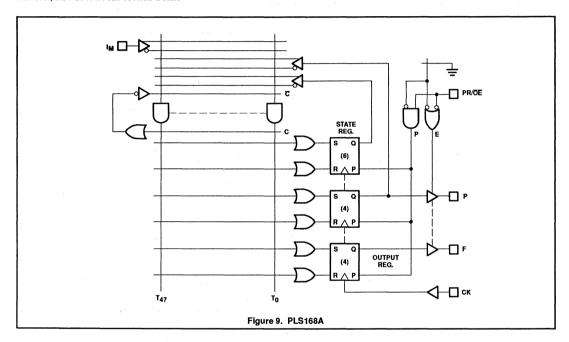

| PLS168/A                        | Programmable logic sequencers (12 × 48 × 8)               | 285 |

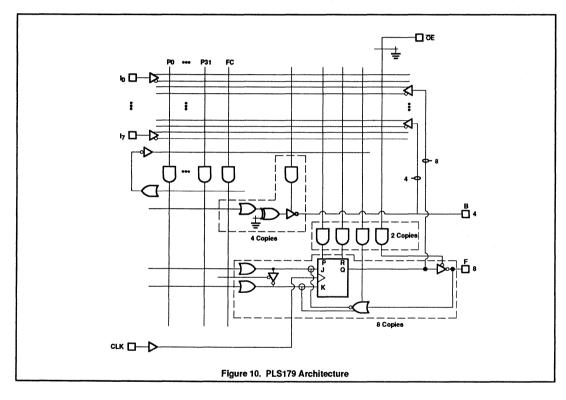

| PLS179                          | Programmable logic sequencer (20 × 45 × 12)               | 297 |

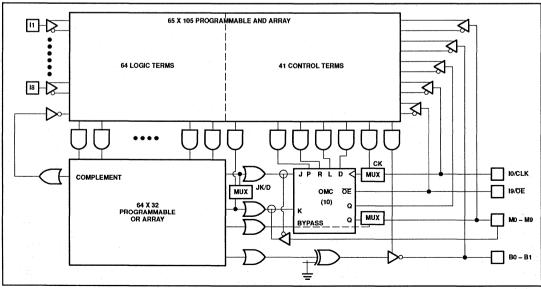

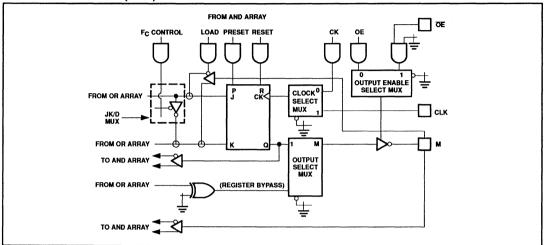

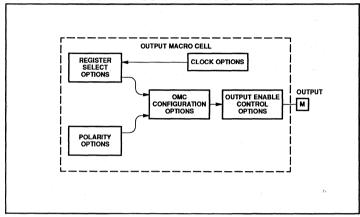

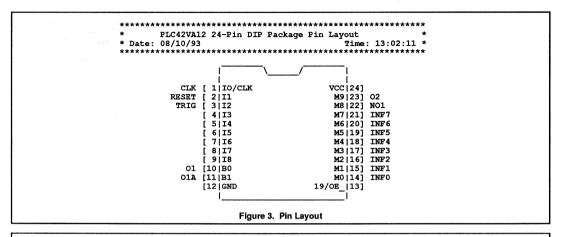

| PLC42VA12                       | CMOS programmable multi-function PLD (42 × 105 × 12)      | 309 |

| PLC415-16                       | CMOS programmable logic sequencer (17 × 68 × 8)           | 329 |

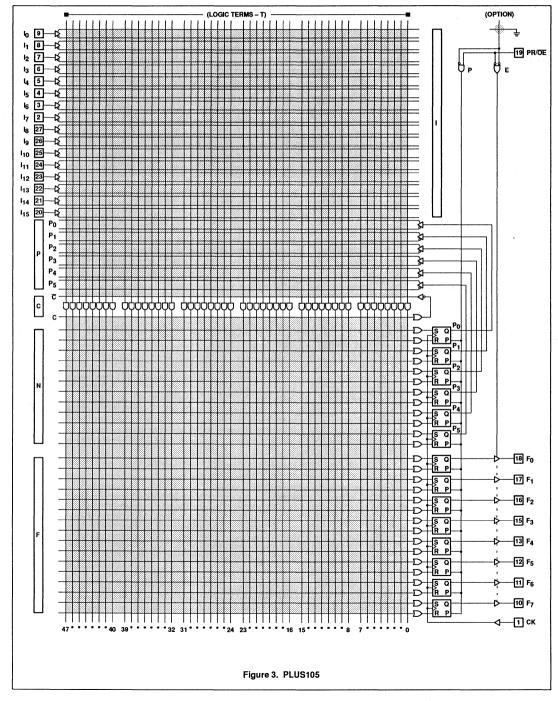

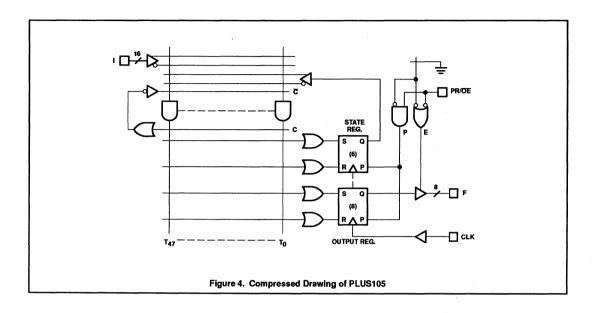

| PLS105/A                        | Programmable logic sequencers (16 × 48 × 8)               | 348 |

| PLUS105-45                      | Programmable logic sequencer (16 × 48 × 8)                | 360 |

| PLUS105-55                      | Programmable logic sequencer (16 × 48 × 8)                | 373 |

| PLUS105-35<br>PLUS105-70        | Programmable logic sequencer (16 × 48 × 8)                | 386 |

| PLUS105-70<br>PLUS405-37/-45    |                                                           | 399 |

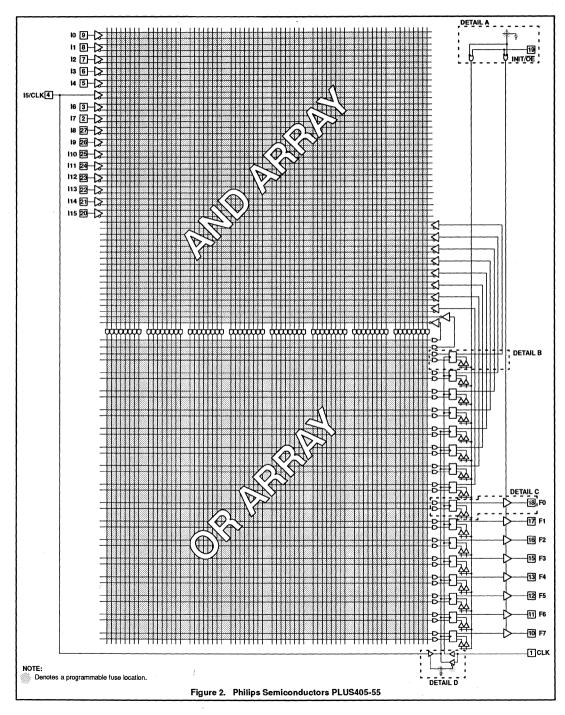

| PLUS405-37/-45<br>PLUS405-55    | Programmable logic sequencers (16 × 64 × 8)               | 415 |

| F LU3403-33                     | Programmable logic sequencer (16 × 64 × 8)                | 413 |

October 1993 7

## Contents

| Section 6 - Low Volt Devices          |                                                         |     |

|---------------------------------------|---------------------------------------------------------|-----|

| P3C18V8z35/P3C18V8ZI                  | 3 Volt zero standby power universal PAL devices         | 433 |

| LVT16V8-7                             | 3 Volt BiCMOS Versatile GAL-type PLD                    | 447 |

| LVT22V10-7                            | 3 Volt BiCMOS Versatile PAL                             | 449 |

| LVT20V8-7                             | 3 Volt BiCMOS Versatile GAL-type PLD                    | 451 |

| Section 7 - Programmable Mac          | ro Logic Devices                                        |     |

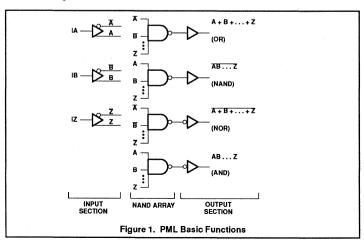

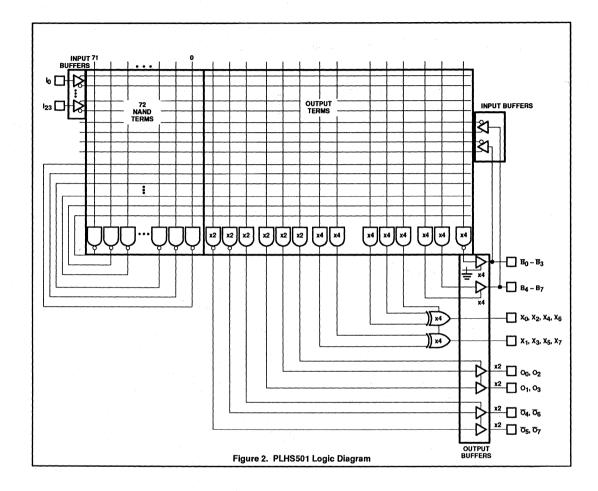

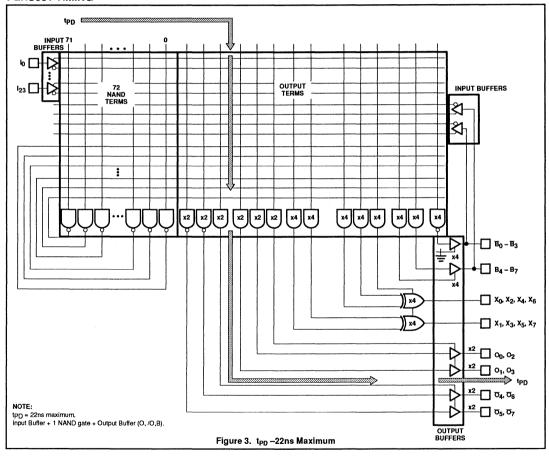

| PLHS501/PLHS501I                      | Programmable macro logic                                | 455 |

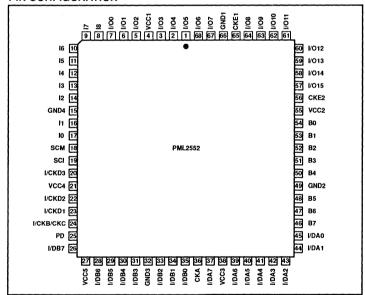

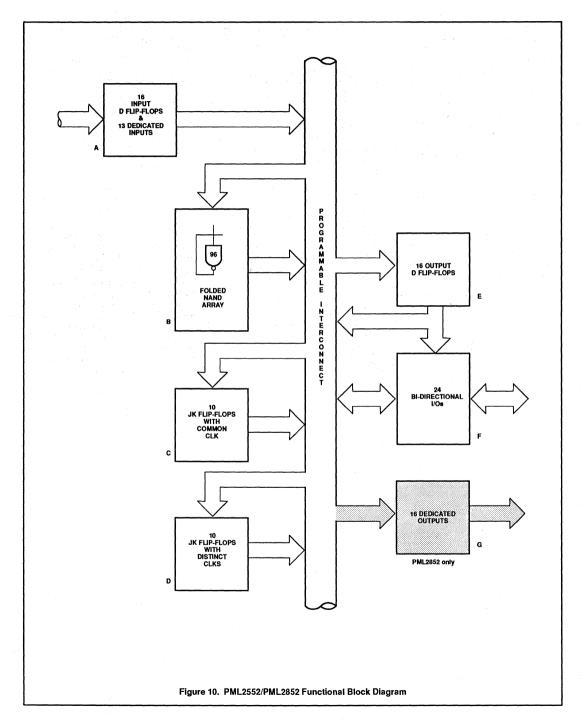

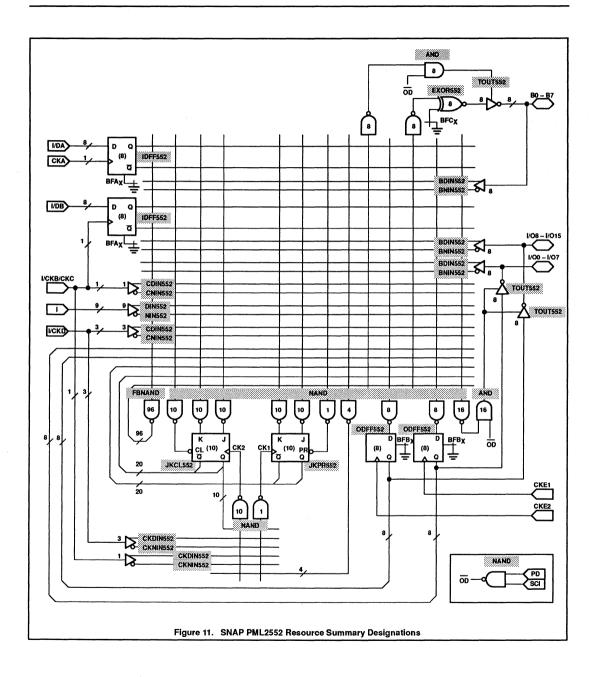

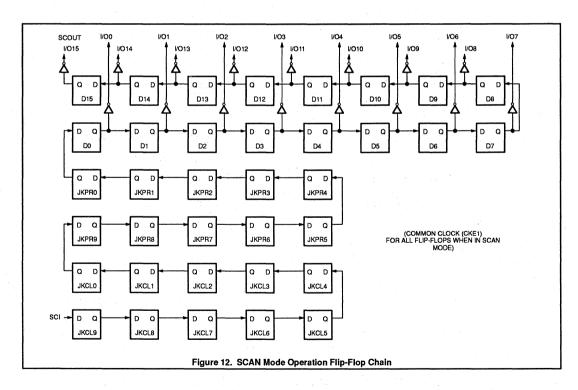

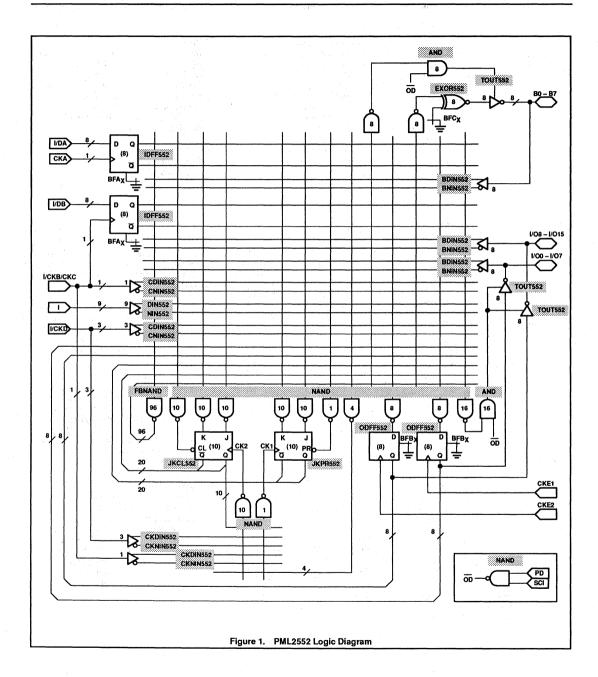

| PML2552                               | CMOS high density programmable macro logic              | 467 |

| PML2852                               | CMOS high density programmable macro logic              | 486 |

| Section 8 - Military selection or     | uide                                                    | 509 |

| Section 9 - Development Softw         |                                                         |     |

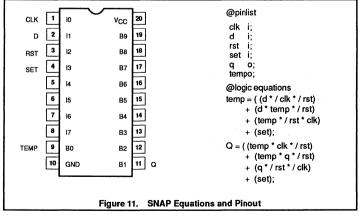

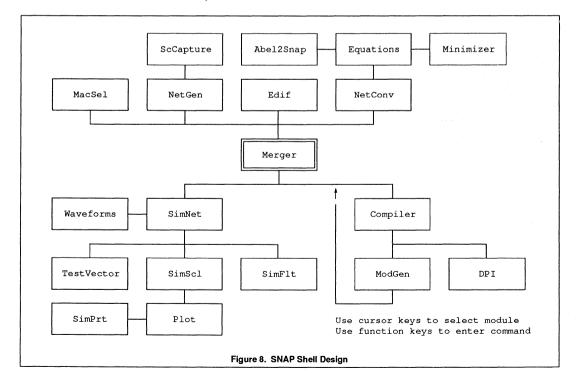

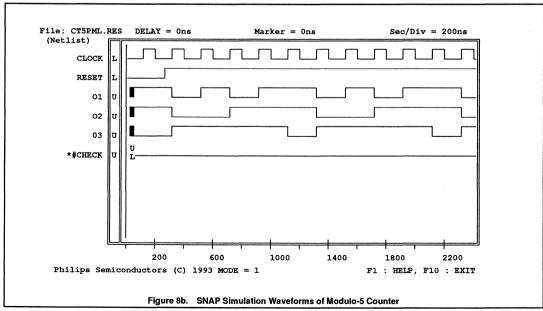

| SNAP 1.9                              |                                                         | 513 |

| SIVAF 1.9                             | Synthesis Netlist Analysis Program                      | 313 |

| Section 10 - Programmer/Softw         | vare Support                                            |     |

| Philips Semiconductors PLD            | programming guide                                       | 522 |

|                                       |                                                         |     |

|                                       |                                                         |     |

|                                       |                                                         |     |

|                                       |                                                         |     |

| · · · · · · · · · · · · · · · · · · · | guide — Data I/O Corporation                            | 524 |

| PLD programmer reference              | guide — Stag Micro Systems, Inc                         | 527 |

|                                       | ontact guide                                            | 528 |

|                                       |                                                         | 529 |

|                                       |                                                         | 530 |

|                                       |                                                         | 530 |

|                                       |                                                         |     |

| PLDesigner                            |                                                         | 533 |

| PLD software vendors conta            | ct guide                                                | 534 |

| Section 11 - Application Notes        |                                                         |     |

| PAL Devices                           |                                                         |     |

|                                       | Introduction                                            | 537 |

| AN043                                 | 10H/10020EV8 high-speed (4.4ns) ECL PLD                 | 542 |

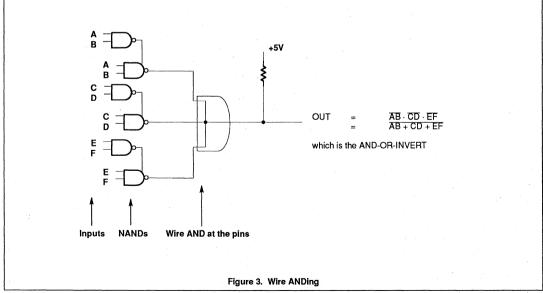

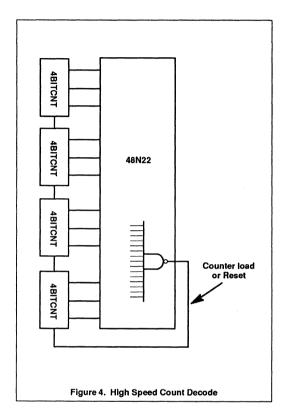

| AN031                                 | PHD48N22 high speed (7.5ns) 32-bit programmable decoder | 553 |

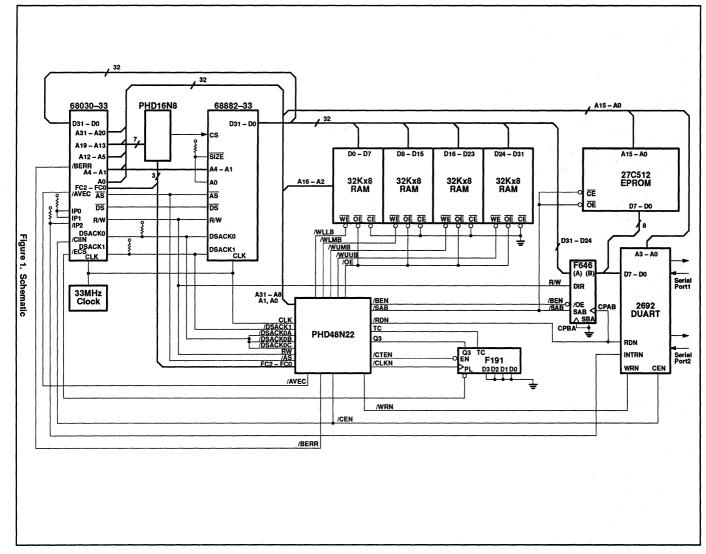

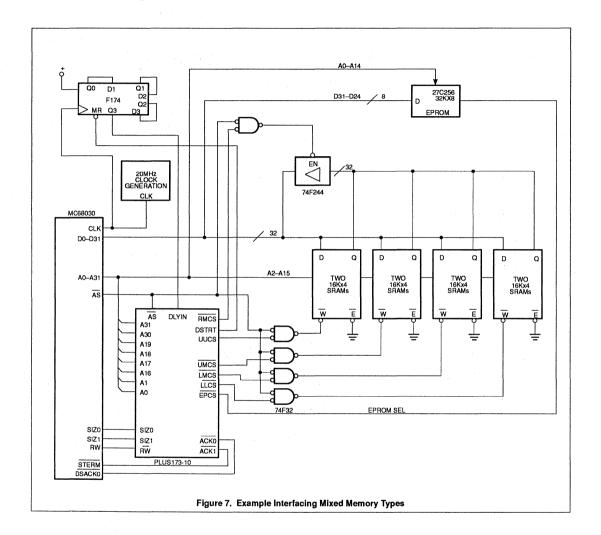

| AN044                                 | 68030 system decoding                                   | 559 |

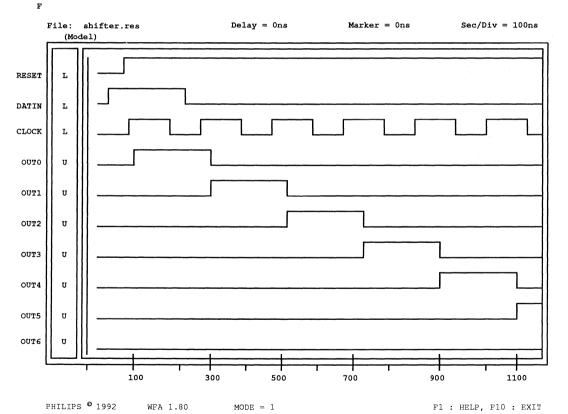

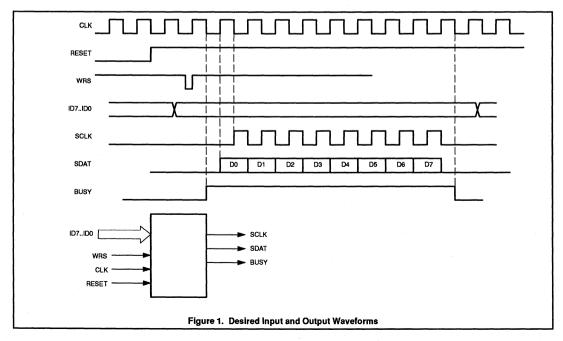

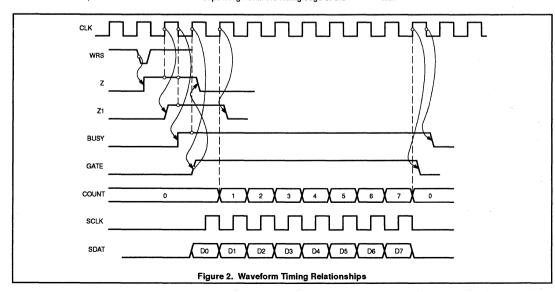

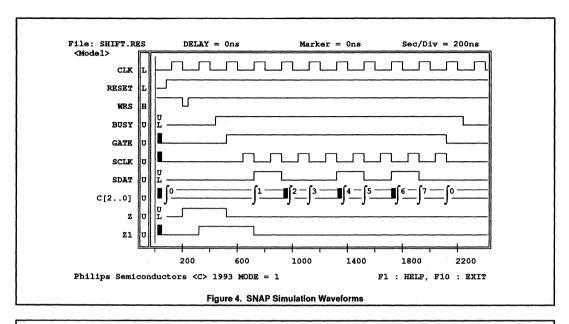

| AN045                                 | High speed 8-bit parallel to serial converter           | 564 |

| AN219                                 | A Metastability Primer                                  | 568 |

| PLA Devices                           |                                                         |     |

|                                       | Introduction                                            | 571 |

| AN046                                 | Quick PLA                                               | 575 |

| AN014                                 | Latches and flip-flops with PLS153                      | 580 |

| AN024                                 | PLS173 as a 10-bit comparator, 74LS460                  | 583 |

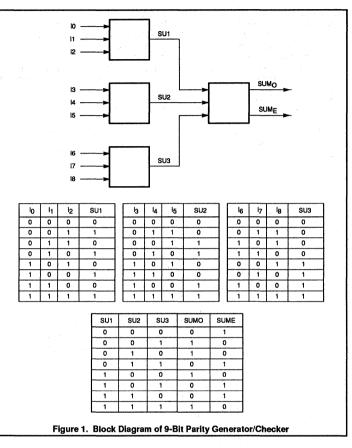

| AN021                                 | 9-Bit parity generator/checker with PLS153/153A         | 584 |

| Sequencer Devices                     |                                                         |     |

| · ·                                   | Introduction                                            | 590 |

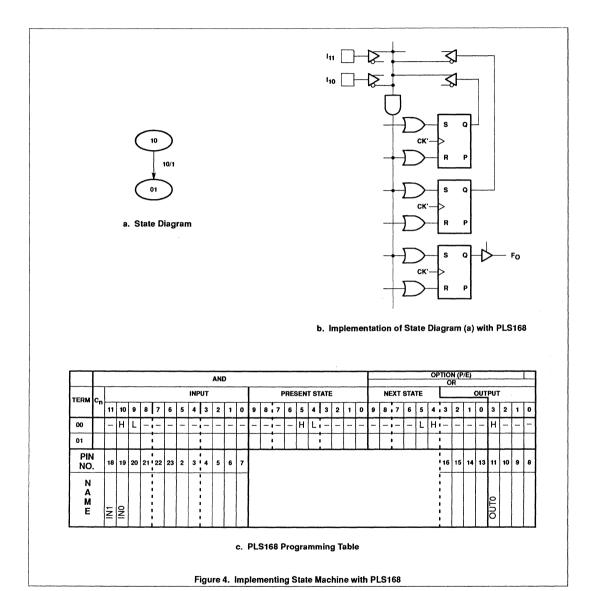

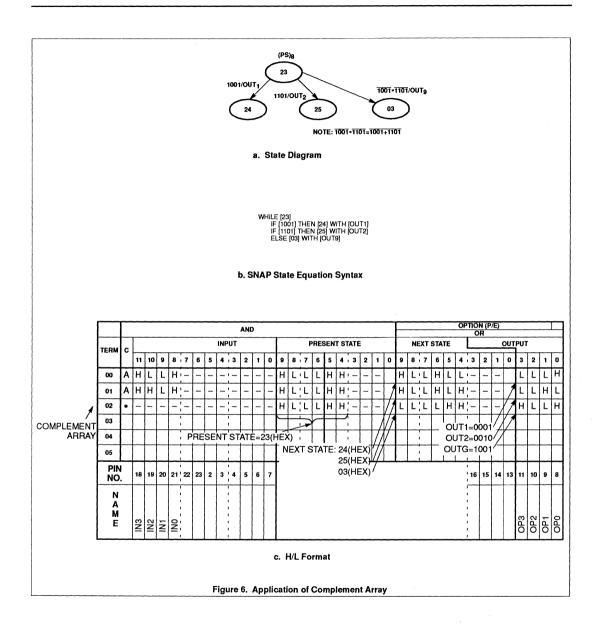

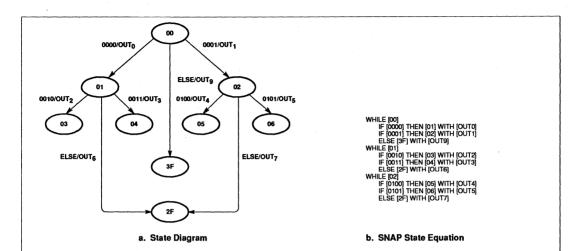

| AN023                                 | PLS168/168A Primer                                      | 602 |

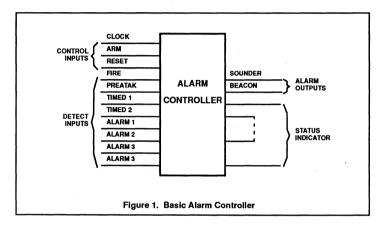

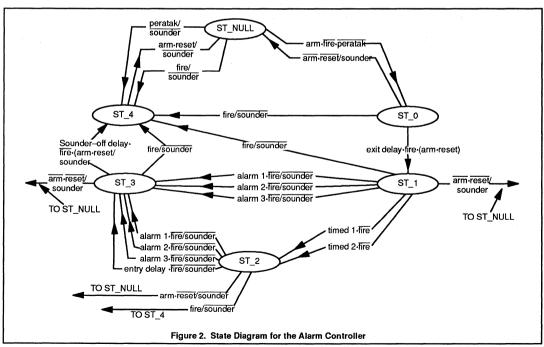

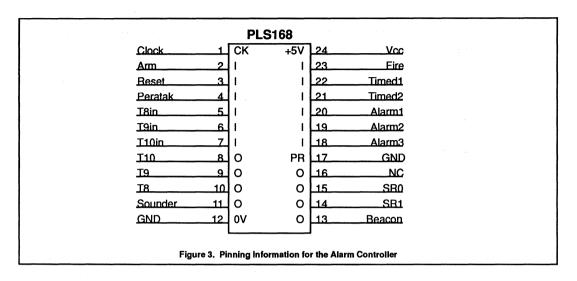

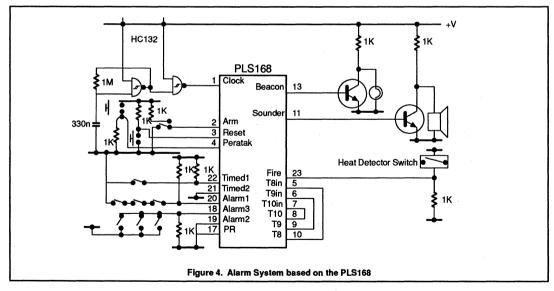

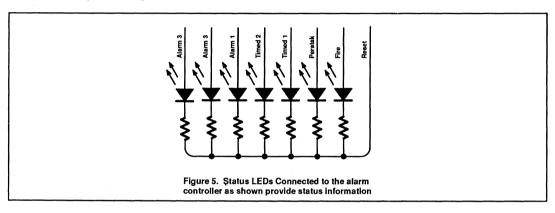

| AN047                                 | Alarm Controller                                        | 615 |

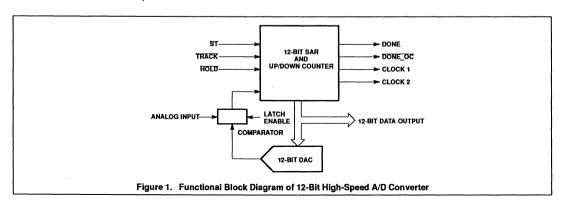

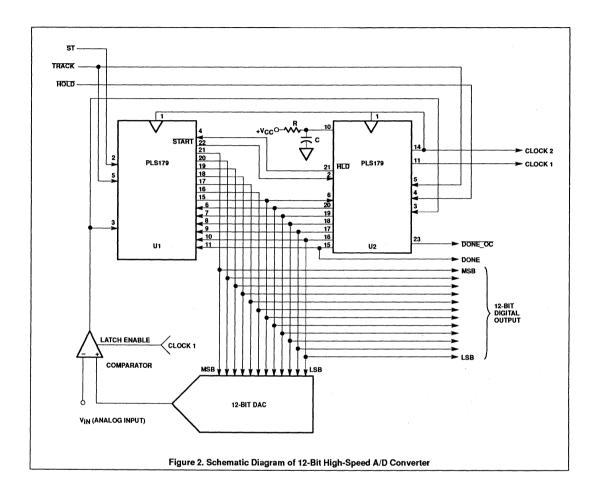

| AN028                                 | High-speed 12-bit tracking A/D converter using PLS179   | 622 |

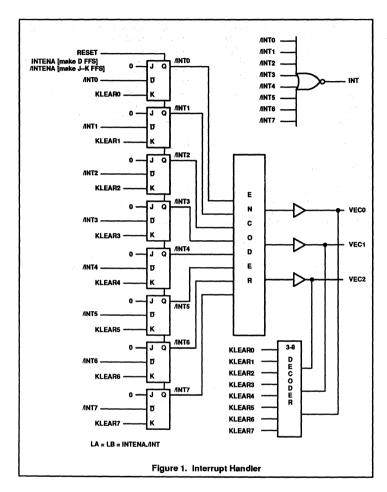

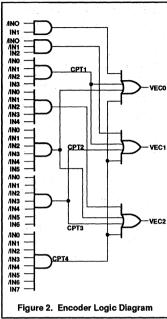

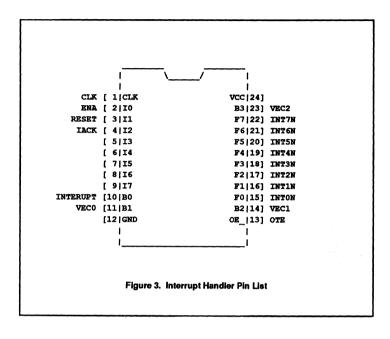

| AN048                                 | Interrupt Handler                                       | 633 |

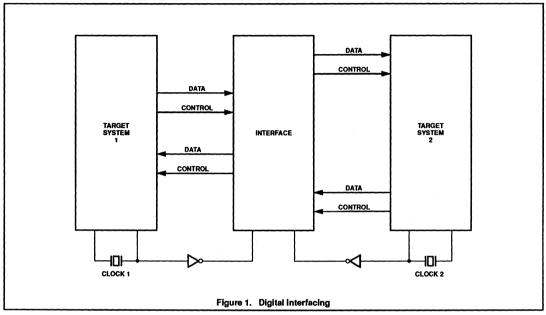

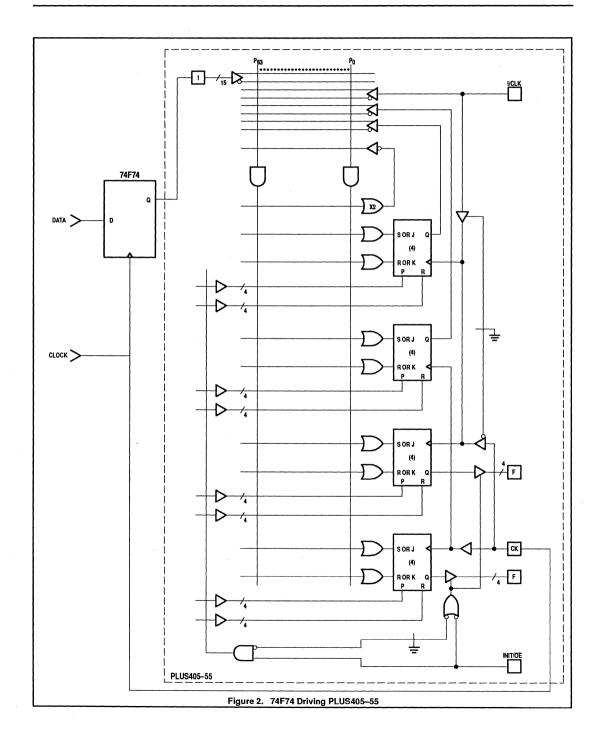

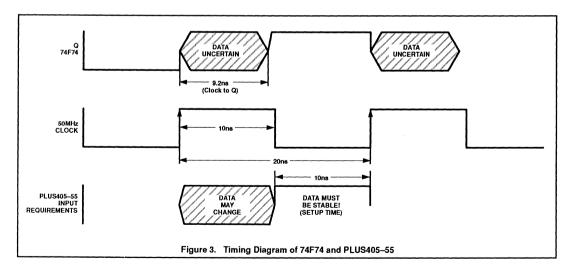

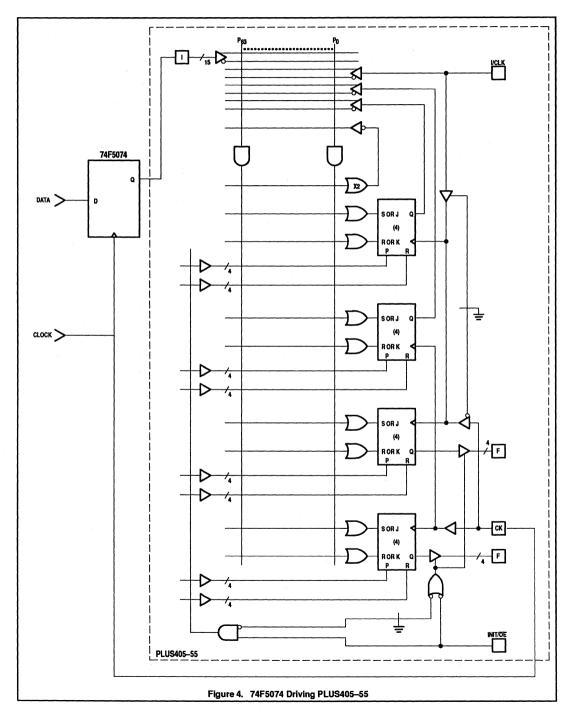

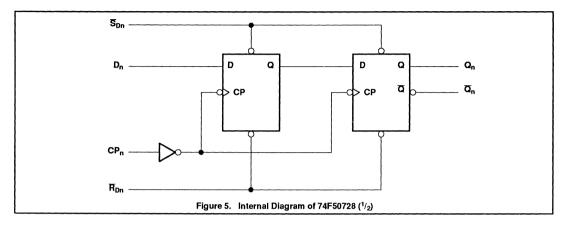

| AN034                                 | PLUS405-55 – the ideal high speed interface             | 637 |

| AN032                                 | Minimize metastability in 50MHz state machines          | 652 |

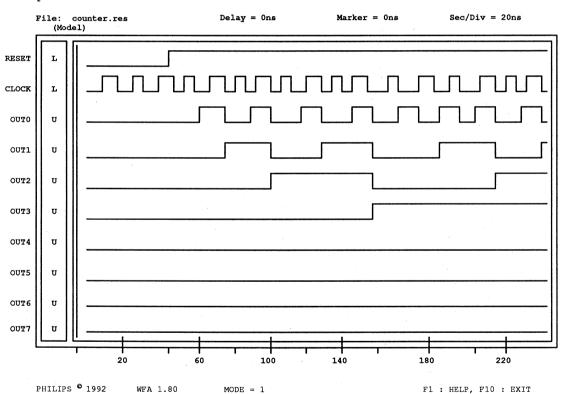

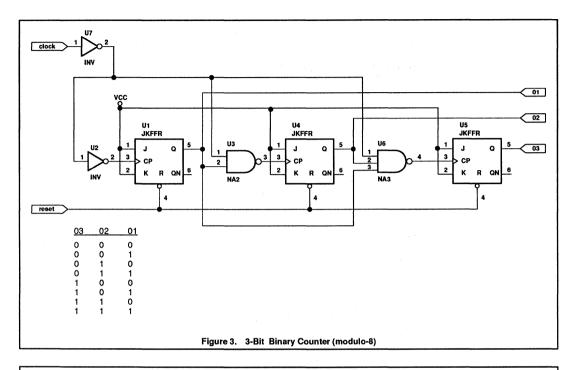

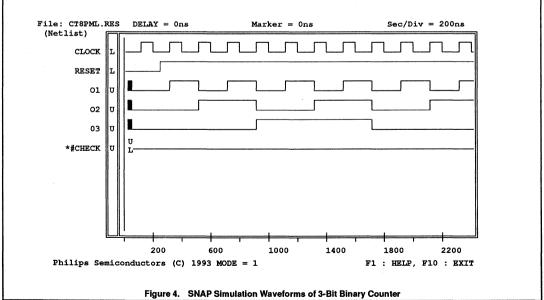

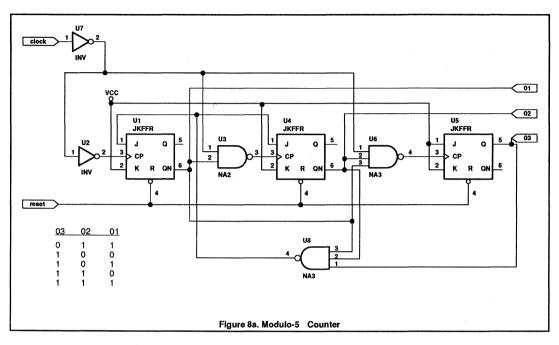

| AN050                                 | Implementing Counters in Sequencer Devices              | 660 |

| A14000                                | implementing counters in sequencer bevices              | 000 |

October 1993

## Contents

|      | CMOS Sequencers            |                                                                                    |            |

|------|----------------------------|------------------------------------------------------------------------------------|------------|

|      | ·                          | Introduction                                                                       | 666        |

|      | AN0301                     | CMOS power in PLDs                                                                 | 673        |

|      | AN0302                     | Microcontroller power management                                                   | 676        |

|      | AN0303                     | Motor controller                                                                   | 680        |

|      | AN0304                     | DMA controller                                                                     | 685        |

|      | AN036                      | I <sup>2</sup> C bus expander                                                      | 688        |

|      | AN037                      | ISDN peripheral control                                                            | 710        |

|      | PML Devices                |                                                                                    |            |

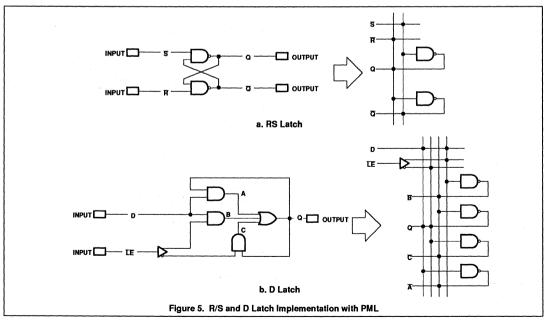

|      |                            | Introduction: Designing with programmable macro logic                              | 724        |

|      | AN029                      | Programmable macro logic primer                                                    | 737        |

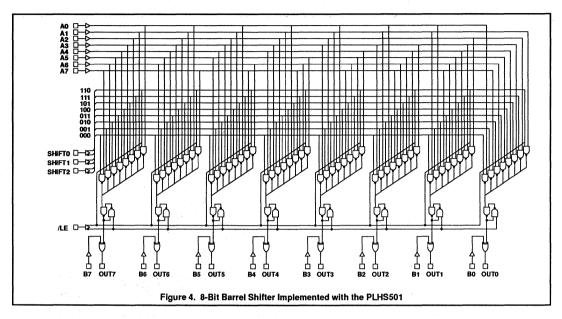

|      | AN049                      | PLHS501 design examples                                                            | 750        |

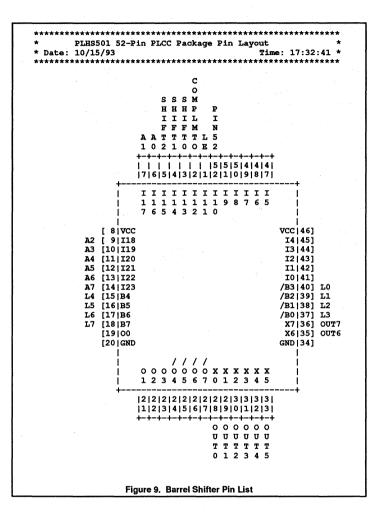

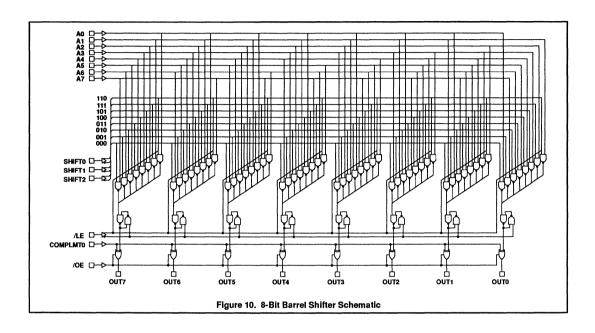

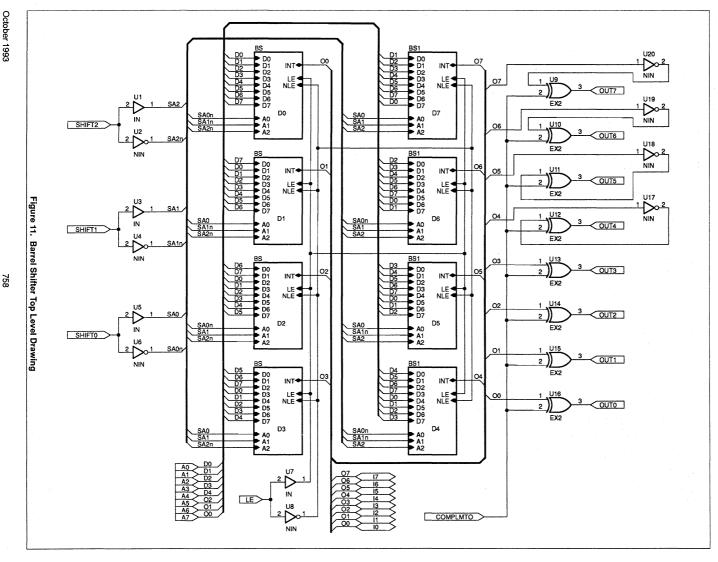

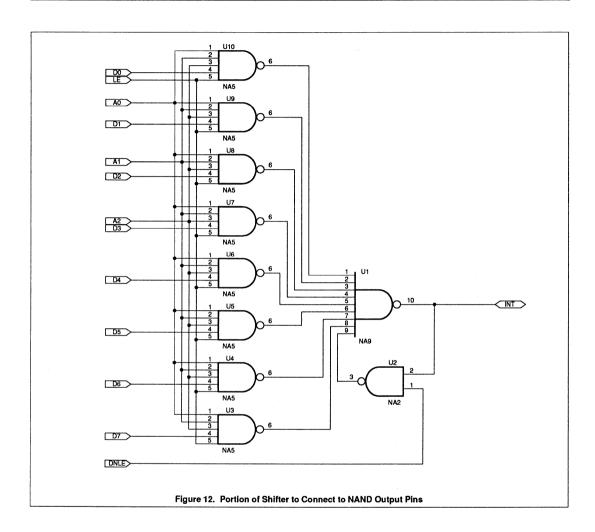

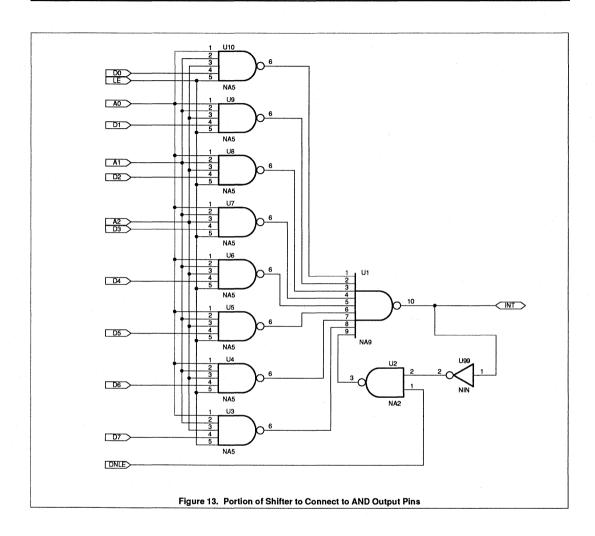

|      |                            | 8-Bit Barrel Shifter                                                               | 756        |

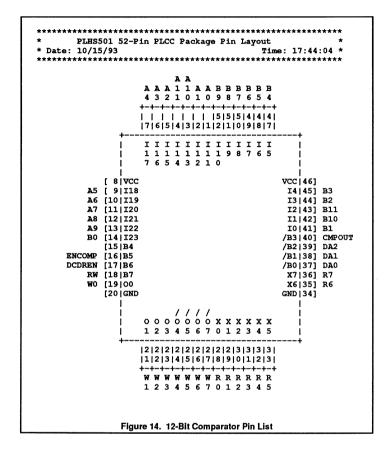

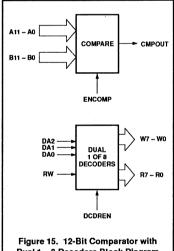

|      |                            | 12-Bit Comparator with Dual 1-of-8 Decoders                                        | 761        |

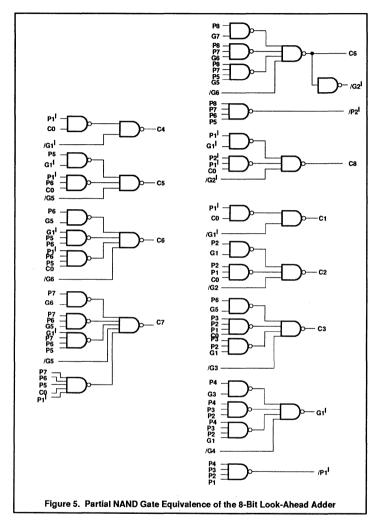

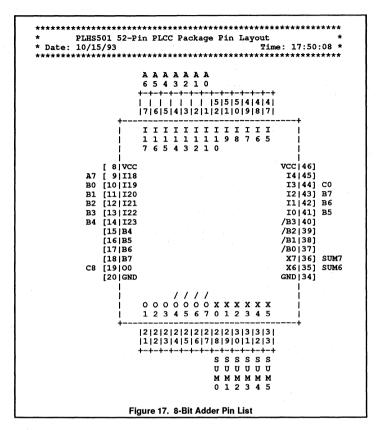

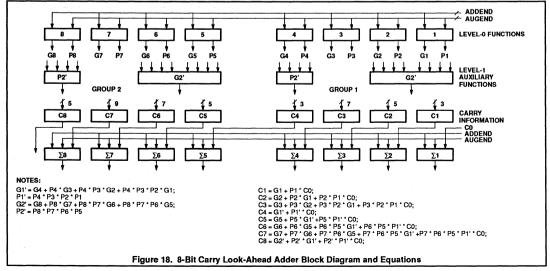

|      |                            | 8-Bit Carry Look-Ahead Adder                                                       | 764        |

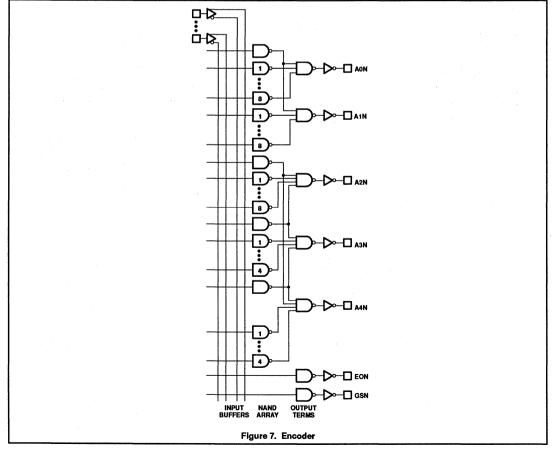

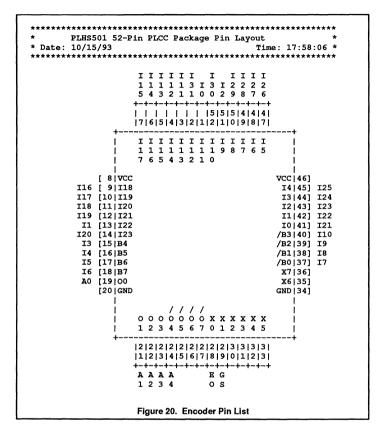

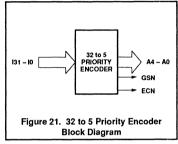

|      |                            | 32- to 5-Bit Priority Encoder                                                      | 767        |

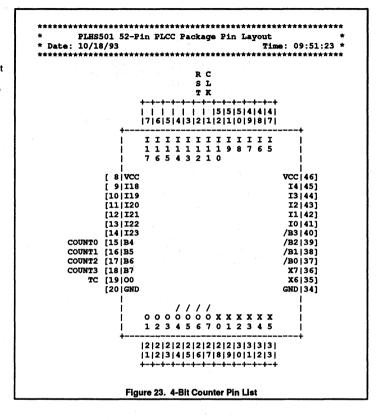

|      |                            | 4-Bit Synchronous Counter                                                          | 770        |

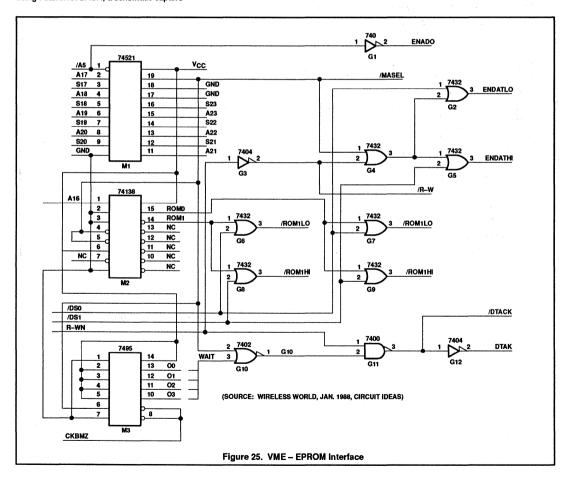

|      |                            | VME Bus EPROM Interface                                                            | 772        |

|      |                            | Micro Channel Interface                                                            | 779        |

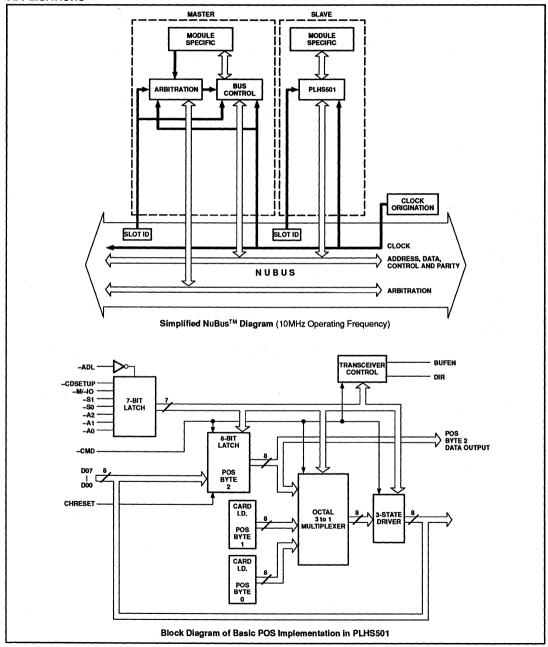

|      |                            | NuBus Interface                                                                    | 784        |

|      |                            | Data Bus Parity                                                                    | 791        |

|      |                            | 16-Bit Comparator                                                                  | 795        |

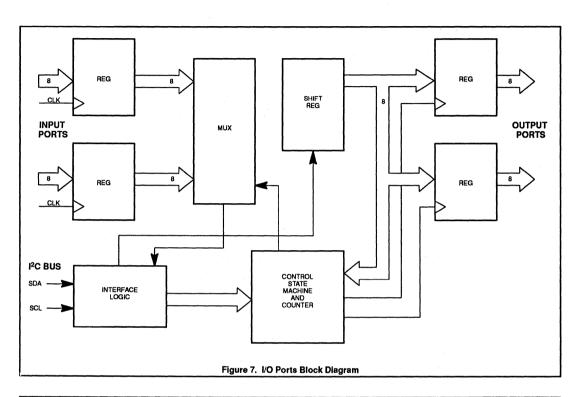

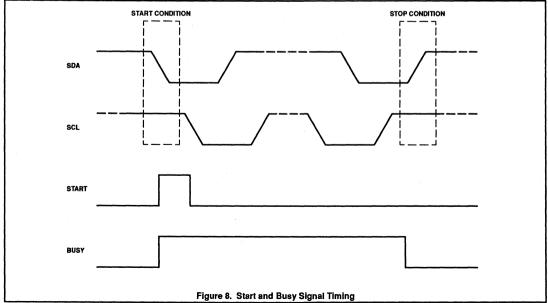

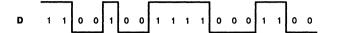

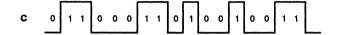

|      | AN038                      | I <sup>2</sup> C I/O ports                                                         | 797        |

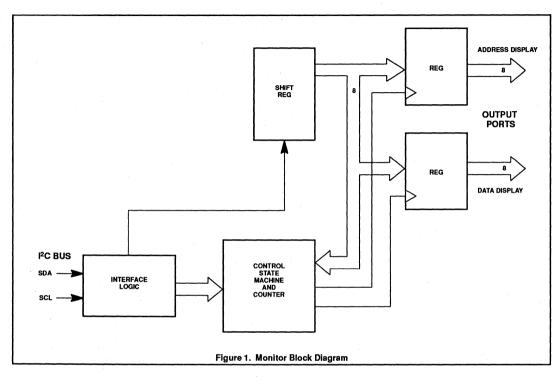

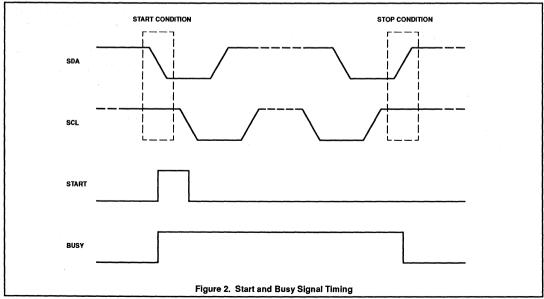

|      | AN039                      | I <sup>2</sup> C bus monitor                                                       | 813        |

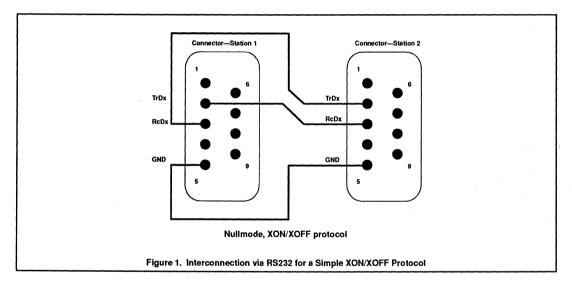

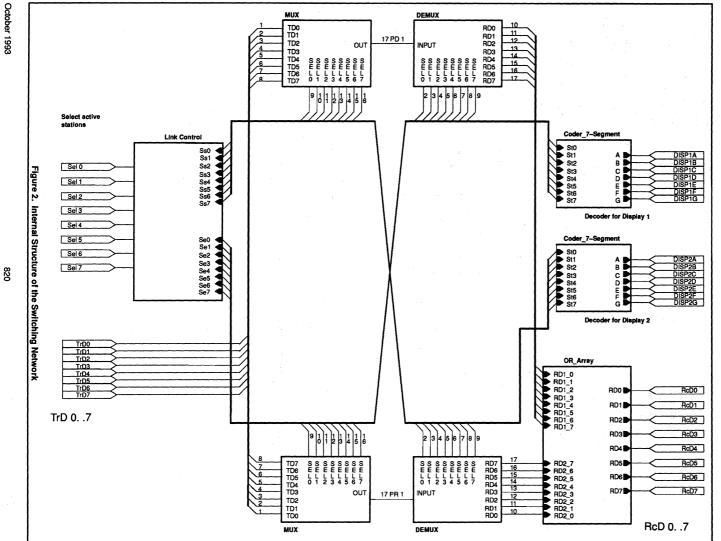

|      | AN040                      | Switching control unit for data communication via RS232                            | 819        |

|      | AN035                      | Microcontroller acceleration                                                       | 831        |

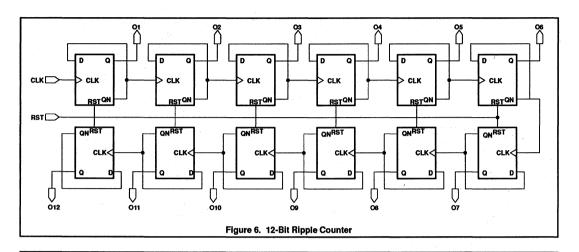

|      | AN042                      | Implementing counters in PML2X52 devices                                           | 845        |

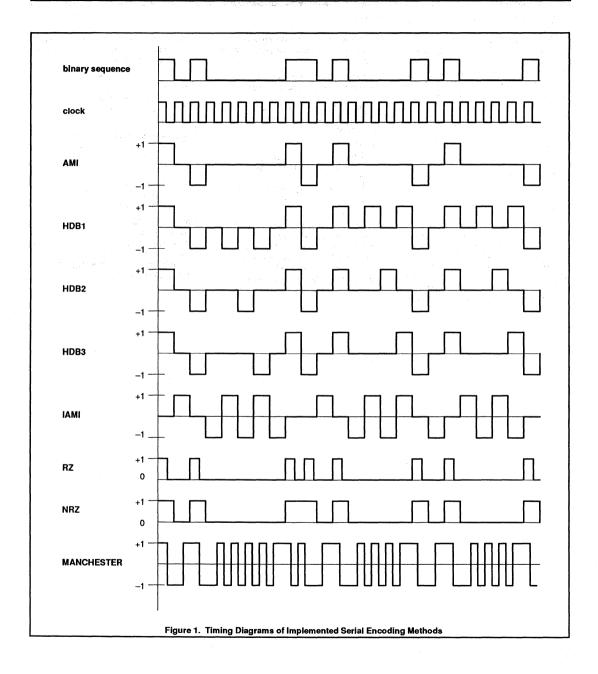

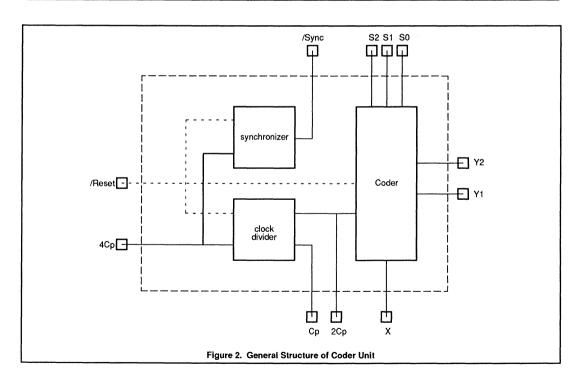

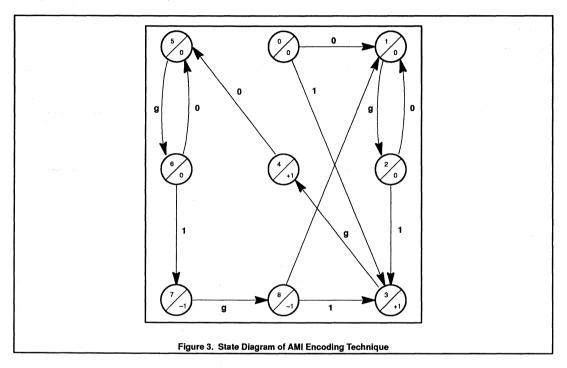

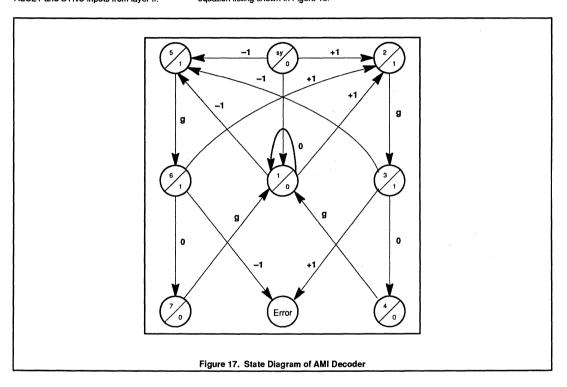

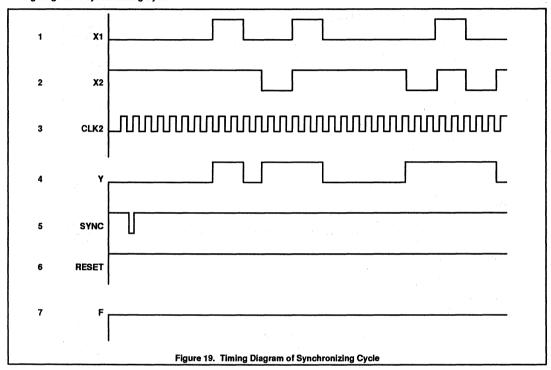

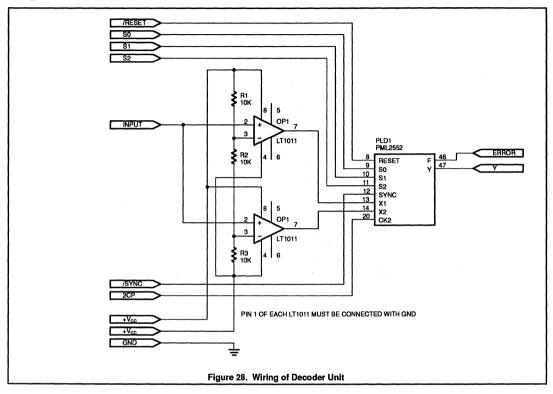

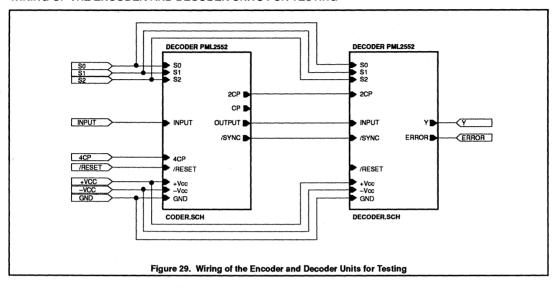

|      | AN041                      | Serial data encoder and decoder                                                    | 853        |

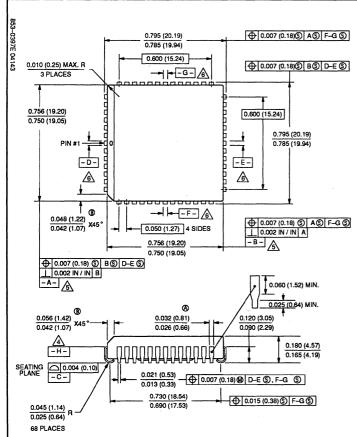

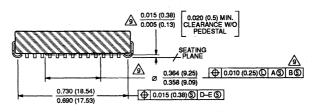

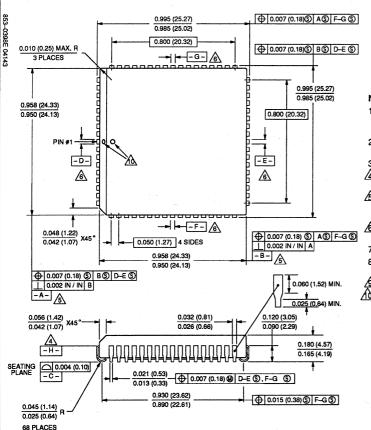

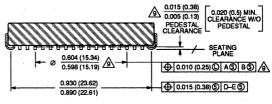

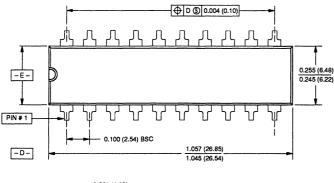

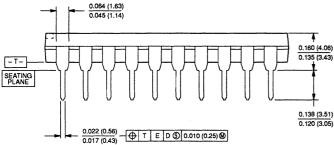

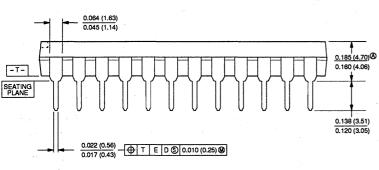

| Sect | ion 12 – Package Outline D | rawinge                                                                            |            |

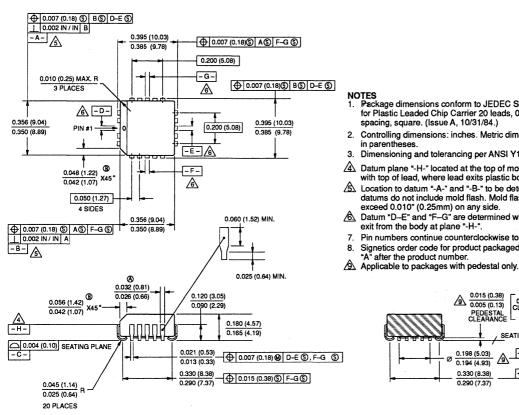

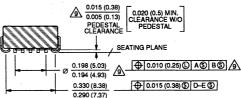

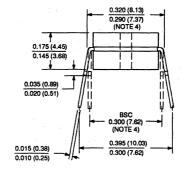

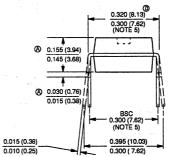

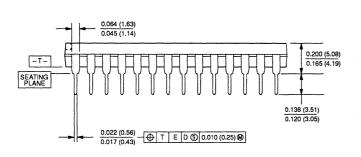

|      | 0400E                      | 20-Pin (350 mils wide) Plastic Leaded Chip Carrier (A) Package                     | 877        |

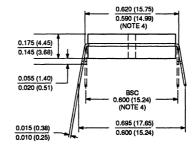

|      | 0400E                      | 28-Pin (300 mils wide) Plastic Leaded Chip Carrier (A) Package                     | 878        |

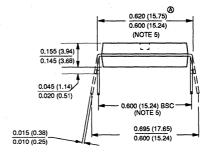

|      | 0397E                      | · · · · · · · · · · · · · · · · · · ·                                              | 879        |

|      | 0398E                      | 52-Pin Plastic Leaded Chip Carrier (A) Package                                     | 880        |

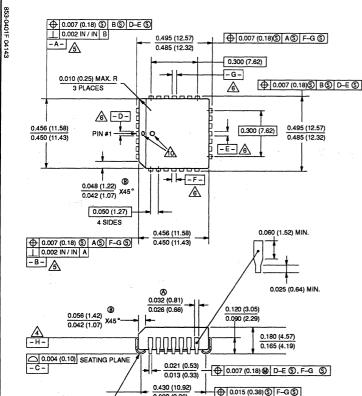

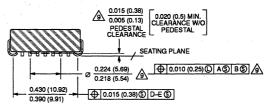

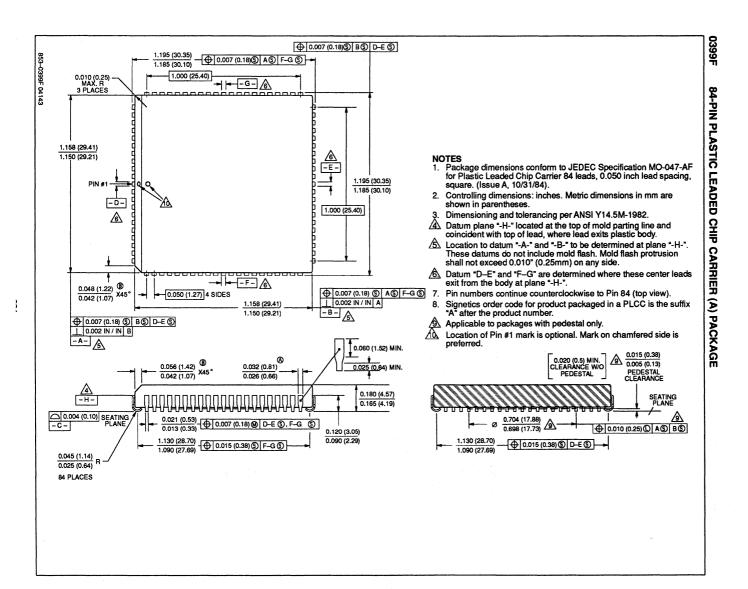

|      | 0399F                      | 68-Pin Plastic Leaded Chip Carrier (A) Package                                     |            |

|      | 0584B                      | 84-Pin Plastic Leaded Chip Carrier (A) Package                                     | 881<br>882 |

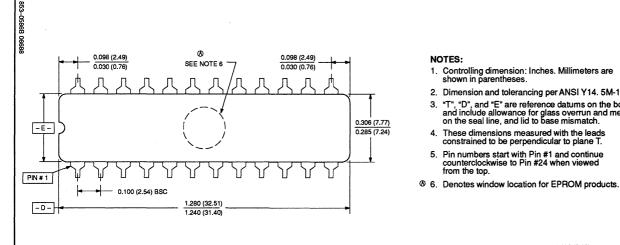

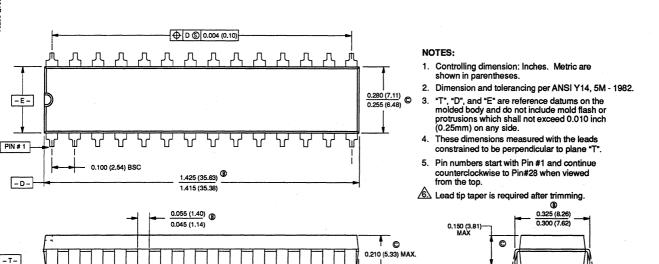

|      | 0586B                      | 20-Pin (300 mils wide) Ceramic Dual In-line (F) Package (with window (FA) Package) |            |

|      | 0589B                      | 24-Pin (300 mils wide) Ceramic Dual In-line (F) Package (with Window (FA) Package) | 883<br>884 |

|      | 1473A                      | 28-Pin (600 mils wide) Ceramic Dual In-line (F) Package (with Window (FA) Package) |            |

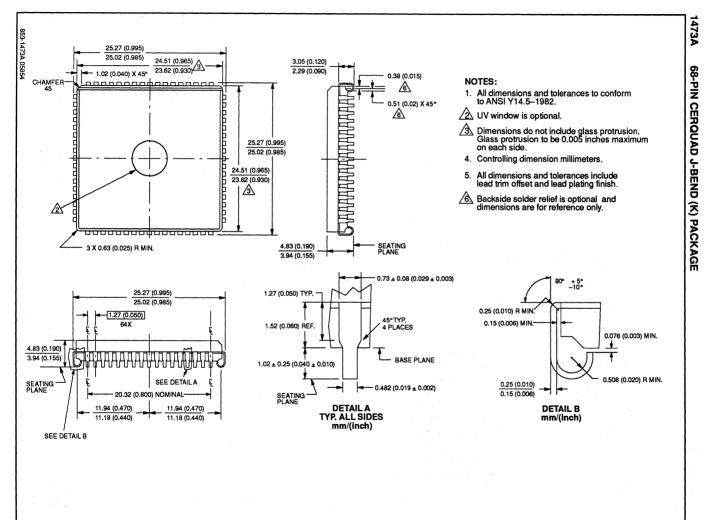

|      | 1551                       | 68-Pin CerQuad J-Bend (K) Package                                                  | 885        |

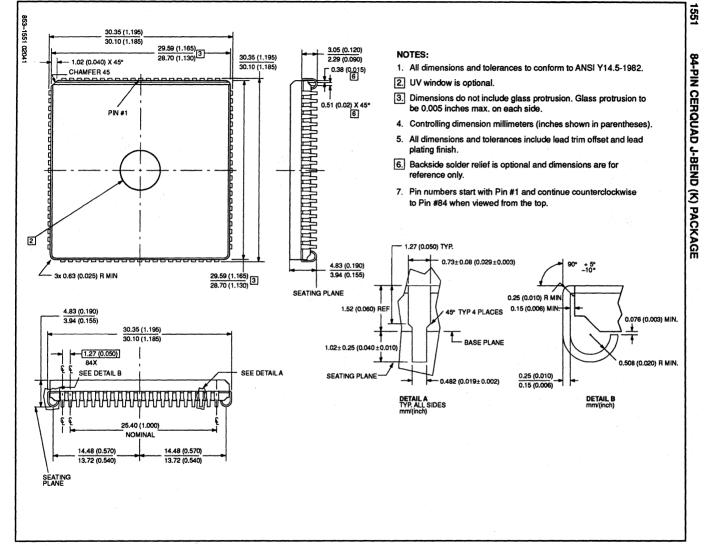

|      | 0408B                      | 84-Pin CerQuad J-Bend (K) package                                                  | 886        |

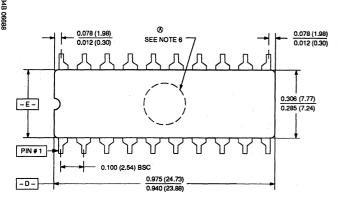

|      |                            | 20-Pin (300 mils wide) Plastic Dual In-Line (N) Package                            | 887        |

|      | 0410D                      | 24-Pin (300 mils wide) Plastic Dual In-Line (N) Package                            | 888        |

|      | 0413B                      | 28-Pin (600 mils wide) Plastic Dual In-Line (N) Package                            | 889        |

|      | 0864D                      | 28-Pin (300 mils wide) Plastic Dual In-Line (N) Package                            | 890        |

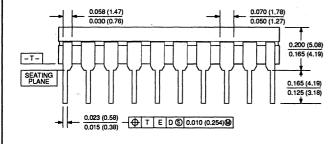

|      | 0172D                      | 20-Pin (300 mils wide) Plastic SOL (Small Outline Large) Dual In-Line (D) Package  | 891        |

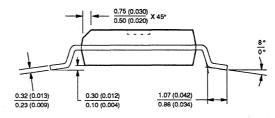

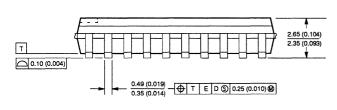

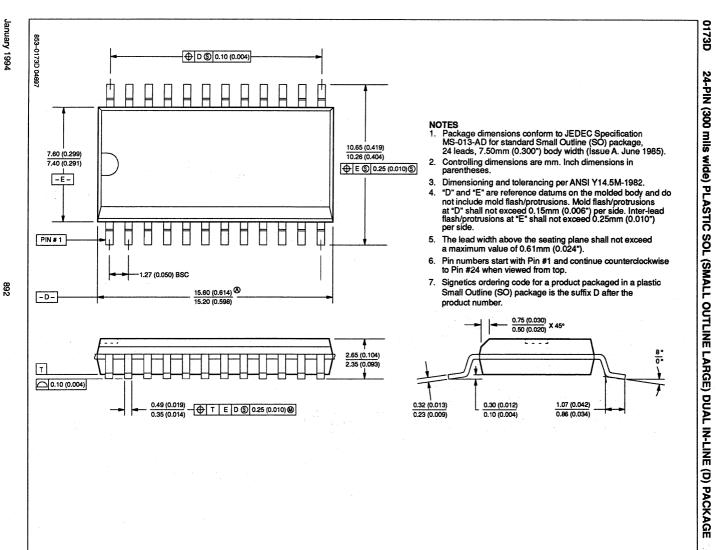

|      | 0173D                      | 24-Pin (300 mils wide) Plastic SOL (Small Outline Large) Dual In-Line (D) Package  | 892        |

| Sect | ion 13 – North American Sa | ales Offices, Representatives and Distributors                                     | 895        |

| Appe | endix A – Data Handbook S  | ystem                                                                              | 896        |

October 1993 9

## Alphanumeric index

| ABT22V10-7         | Series 24 | BiCMOS Versatile PLD Device; 7.5ns                          | 133 |

|--------------------|-----------|-------------------------------------------------------------|-----|

| LVT16V8-8          | Series 20 | 3 Volt BiCMOS Versatile GAL-type PLD                        | 447 |

| LVT20V8-8          | Series 24 | 3 Volt BiCMOS Versatile GAL-type PLD                        | 451 |

| LVT22V10-7         | Series 24 | 3 Volt BiCMOS Versatile PAL                                 | 449 |

| PHD16N8-5          | Series 20 | Programmable High-Speed Decoder (16 × 16 × 8); 5ns          | 37  |

| PHD48N22-7         | Series 68 | Programmable High-Speed Decoder (48 × 73 × 22); 7.5ns       | 165 |

| PLC18V8Z25/IA      | Series 20 | Zero Standby Power CMOS Versatile PAL Devices; 25, 40ns     | 58  |

| PLC18V8Z35/I       | Series 20 | Zero Standby Power CMOS Versatile PAL Devices; 35, 40ns     | 45  |

| PLC42VA12          | Series 24 | CMOS Programmable Multi-function PLD (42 × 105 × 12); 25MHz | 309 |

| PLC415-16          | Series 28 | CMOS Programmable Logic Sequencer (17 × 68 × 8); 16MHz      | 329 |

| PLHS501            |           | Programmable Macro Logic                                    | 455 |

| PLS100/101         | Series 28 | Programmable Logic Arrays (16 × 48 × 8); 50ns               | 227 |

| PLS105/A           | Series 28 | Programmable Logic Sequencers (16 × 48 × 8); 14, 20MHz      | 348 |

| PLS153/A           | Series 20 | Programmable Logic Arrays (18 × 42 × 10); 40/30ns           | 179 |

| PLS155             | Series 20 | Programmable Logic Sequencer (16 × 45 × 12); 14MHz          | 237 |

| PLS157             | Series 20 | Programmable Logic Sequencer (16 × 45 × 12); 14MHz          | 249 |

| PLS159A            | Series 20 | Programmable Logic Sequencer (16 × 45 × 12); 18MHz          | 261 |

| PLS167/A           | Series 24 | Programmable Logic Sequencers (14 × 48 × 6); 14, 20MHz      | 273 |

| PLS168/A           | Series 24 | Programmable Logic Sequencers (12 × 48 × 8); 14, 20MHz      | 285 |

| PLS173             | Series 24 | Programmable Logic Array (22 × 42 × 10); 30ns               | 203 |

| PLS179             | Series 24 | Programmable Logic Sequencer (20 × 45 × 12); 18MHz          | 297 |

| PLUS16R8D/-7       | Series 20 | PAL Devices (16L8, 16R4, 16R6 and 16R8); 7.5ns & 10ns       | 71  |

| PLUS20R8D/-7       | Series 24 | PAL Devices (20L8, 20R4, 20R6 and 20R8); 7.5ns & 10ns       | 87  |

| PLUS105-45         | Series 28 | Programmable Logic Sequencer (16 × 48 × 8); 45MHz           | 360 |

| PLUS105-55         | Series 28 | Programmable Logic Sequencer (16 × 48 × 8); 55MHz           | 373 |

| PLUS105-70         | Series 28 | Programmable Logic Sequencer (16 × 48 × 8); 70MHz           | 386 |

| PLUS153B/D         | Series 20 | Programmable Logic Arrays (18 × 42 × 10); 15/12ns           | 187 |

| PLUS153-10         | Series 20 | Programmable Logic Array (18 × 42 × 10); 10ns               | 195 |

| PLUS173B/D         | Series 24 | Programmable Logic Arrays (22 × 42 × 10); 15/12ns           | 211 |

| PLUS173-10         | Series 24 | Programmable Logic Array (22 × 42 × 10); 10ns               | 219 |

| PLUS405-37/-45     | Series 28 | Programmable Logic Sequencers (16 × 64 × 8); 37, 45MHz      | 399 |

| PLUS405-55         | Series 28 | Programmable Logic Sequencer (16 × 64 × 8); 55MHz           | 415 |

| PL22V10-10/-12/-15 |           |                                                             |     |

| PL22V10I15         | Series 24 | CMOS Programmable Electrically Erasable Logic Device        | 103 |

| PML2552-35/-50     |           | CMOS High Density Programmable Macro Logic                  | 467 |

| PML2852-35/-50     |           | CMOS High Density Programmable Macro Logic                  | 486 |

| P3C18V8Z35         | Series 20 | 3 Volt zero standby power universal PAL Devices             | 433 |

| 10H20EV8/10020EV8  | Series 24 | ECL Programmable Array Logic: 4 5ns                         | 148 |

April 1992 10

## **Product Status**

#### **DEFINITIONS**

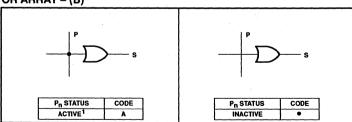

| Data Sheet<br>Identification | Product Status         | Definition                                                                                                                                                                                                                                    |

|------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective Specification      | Formative or in Design | This data sheet contains the design target or goal specifications for product development. Specifications may change in any manner without notice.                                                                                            |

| Preliminary Specification    | Preproduction Product  | This data sheet contains preliminary data, and supplementary data will be published at a later date. Signetics reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |

| Product Specification        | Full Production        | This data sheet contains Final Specifications. Signetics reserves the right to make changes at any time without notice, in order to improve design and supply the best possible product.                                                      |

## Selection guide

| PHILIPS<br>SEMICONDUCTORS<br>PART NUMBER | ARCHITECTURE<br>(Inputs × Terms*<br>× Outputs) | PACKAGE | TOTAL<br>INPUTS<br>(# Dedicated) | PRODUCT<br>TERMS PER<br>OR GATE | INTERNAL<br>STATE<br>REGISTERS<br>(# Dedicated) | OUTPUTS<br>C, I/O, R, R I/O | t <sub>PD</sub> (Max) | f <sub>MAX</sub> | I <sub>CC</sub> (Max) |

|------------------------------------------|------------------------------------------------|---------|----------------------------------|---------------------------------|-------------------------------------------------|-----------------------------|-----------------------|------------------|-----------------------|

| PAL DEVICES                              |                                                |         |                                  |                                 |                                                 |                             |                       |                  |                       |

| 10H20EV8-4/                              |                                                |         |                                  |                                 |                                                 |                             |                       |                  |                       |

| 10020EV8-4                               | 20 × 90 × 8                                    | 24-Pin  | 20 (12)                          | 8 to 12                         | 0                                               | 8 varied                    | 4.5ns                 | 208MHz           | -250mA                |

| PHD16N8-5                                | 16 × 16 × 8                                    | 20-Pin  | 16 (10)                          | 1♦                              | 0                                               | 2 C, 6 I/O                  | 5ns                   | i                | 180mA                 |

| PHD48N22-7                               | 48 × 73 × 22                                   | 68-Pin  | 48 (36)                          | 7 to 12                         | 0                                               | 10 C, 12 I/O                | 7.5ns                 | ł                | 420mA                 |

| PLUS16L8-7                               | 16 × 64 × 8                                    | 20-Pin  | 16 (10)                          | 7                               | 0                                               | 2 C, 6 I/O                  | 7.5ns                 |                  | 180mA                 |

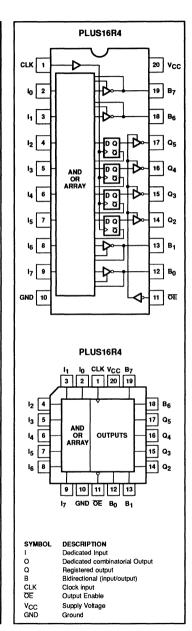

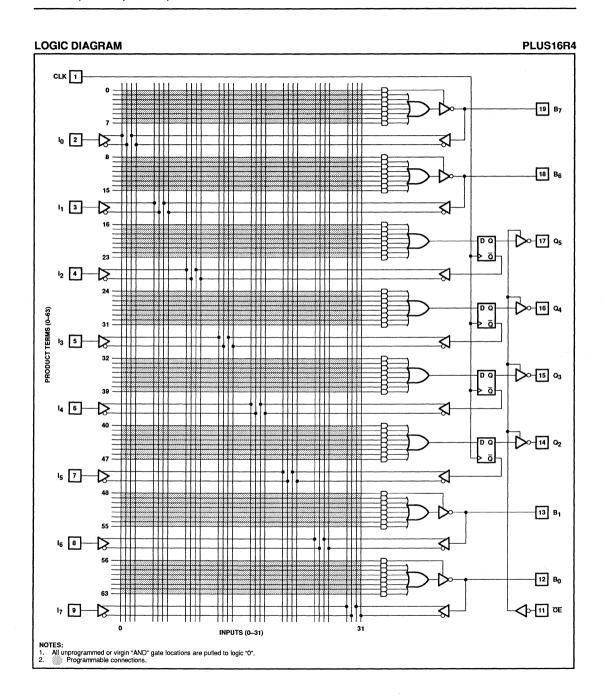

| PLUS16R4-7                               | 16 × 64 × 8                                    | 20-Pin  | 16 (8)                           | 7 to 8                          | 4 (0)                                           | 4 VO, 4 R                   | 7.5ns                 | 74MHz            | 180mA                 |

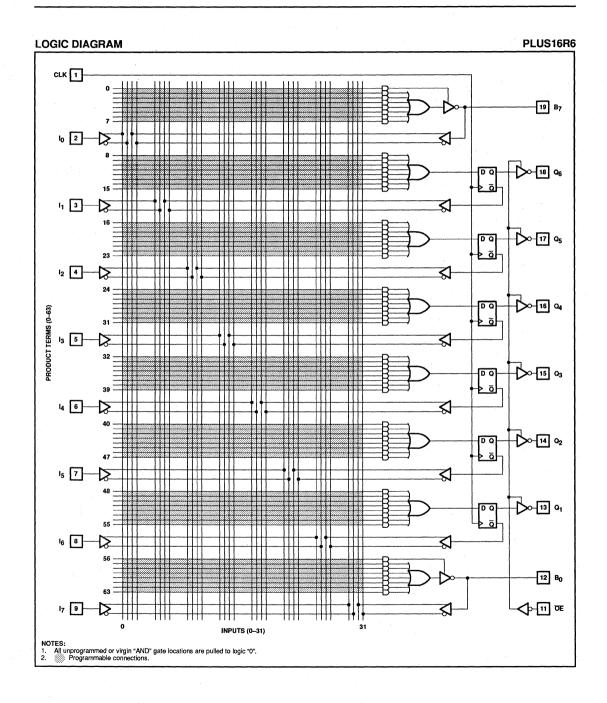

| PLUS16R6-7                               | 16 × 64 × 8                                    | 20-Pin  | 16 (8)                           | 7 to 8                          | 6 (0)                                           | 2 VO, 6 R                   | 7.5ns                 | 74MHz            | 180mA                 |

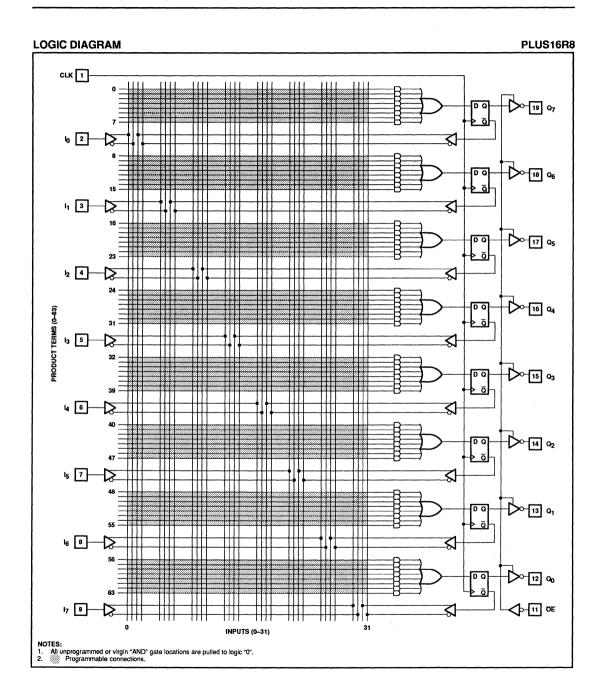

| PLUS16R8-7                               | 16 × 64 × 8                                    | 20-Pin  | 16 (8)                           | 8                               | 8 (0)                                           | 8 R                         | 1                     | 74MHz            | 180mA                 |

| PLUS16L8D                                | 16 × 64 × 8                                    | 20-Pin  | 16 (10)                          | . 7                             | , 0                                             | 2 C, 6 I/O                  | 10ns                  |                  | 180mA                 |

| PLUS16R4D                                | 16 × 64 × 8                                    | 20-Pin  | 16 (8)                           | 7 to 8                          | 4 (0)                                           | 4 VO, 4 R                   | 10ns                  | 60MHz            | 180mA                 |

| PLUS16R6D                                | 16 × 64 × 8                                    | 20-Pin  | 16 (8)                           | 7 to 8                          | 6 (0)                                           | 2 I/O, 6R                   | 10ns                  | 60MHz            | 180mA                 |

| PLUS16R8D                                | 16 × 64 × 8                                    | 20-Pin  | 16 (8)                           | 8                               | 8 (0)                                           | 8 R                         | 1                     | 60MHz            | 180mA                 |

| PLUS20L8-7                               | 20 × 64 × 8                                    | 24-Pin  | 20 (14)                          | 7                               | 0                                               | 2 C, 6 I/O                  | 7.5ns                 |                  | 210mA                 |

| PLUS20R4-7                               | 20 × 64 × 8                                    | 24-Pin  | 20 (12)                          | 7 to 8                          | 4 (0)                                           | 4 VO, 4 R                   | 7.5ns                 | 74MHz            | 210mA                 |

| PLUS20R6-7                               | 20 × 64 × 8                                    | 24-Pin  | 20 (12)                          | 7 to 8                          | 6 (0)                                           | 2 VO, 6 R                   | 7.5ns                 | 74MHz            | 210mA                 |

| PLUS20R8-7                               | 20 × 64 × 8                                    | 24-Pin  | 20 (12)                          | 8                               | 8 (0)                                           | 8 R                         |                       | 74MHz            | 210mA                 |

| PLUS20L8D                                | 20 × 64 × 8                                    | 24-Pin  | 20 (14)                          | 7                               | 0                                               | 2 C, 6 I/O                  | 10ns                  |                  | 210mA                 |

| PLUS20R4D                                | 20 × 64 × 8                                    | 24-Pin  | 20 (12)                          | 7 to 8                          | 4 (0)                                           | 4 I/O, 4R                   | 10ns                  | 60MHz            | 210mA                 |

| PLUS20R6D                                | 20 × 64 × 8                                    | 24-Pin  | 20 (12)                          | 7 to 8                          | 6 (0)                                           | 2 I/O, 6 R                  | 10ns                  | 60MHz            | 210mA                 |

| PLUS20R8D                                | 20 × 64 × 8                                    | 24-Pin  | 20 (12)                          | 8                               | 8 (0)                                           | 8 R                         | 1                     | 60MHz            | 210mA                 |

| ABT22V10-7                               | 22 × 130 × 10                                  | 24-Pin  | 22 (12)                          | 8 to 16                         | 10 (0)                                          | 10 varied                   | 7.5ns                 | 87MHz            | 210mA                 |

| PL22V10-15/I15                           | 22×130×10                                      | 24-Pin  | 22 (12)                          | 8 to 16                         | 10 (0)                                          | 10 varied                   | 15ns                  | 53MHz            | 90mA,<br>0.5mA/MHz    |

| PL22V10-12                               | 22 × 130 × 10                                  | 24-Pin  | 22 (12)                          | 8 to 16                         | 10 (0)                                          | 10 varied                   | 12ns                  | 67MHz            | 90mA,<br>0.5mA/MHz    |

| PL22V10-10                               | 22 × 130 × 10                                  | 24-Pin  | 22 (12)                          | 8 to 16                         | 10 (0)                                          | 10 varied                   | 10ns                  | 77MHz            | 110mA,<br>0.5mA/MHz   |

| PLC18V8Z35<br>PLC18V8ZI                  | 18 × 74 × 8                                    | 20-Pin  | 18 (8)                           | 8                               | 8 (0)                                           | 8 varied                    | 35, 40ns              | 21MHz            | 100μA,<br>1.5mA/MHz   |

| PLC18V8Z25<br>PLC18V8ZAI                 | 18 × 74 × 8                                    | 20-Pin  | 18 (8)                           | 8                               | 8 (0)                                           | 8 varied                    | 25ns                  | 30MHz            | 100μA,<br>1.5mA/MHz   |

| P3C18V8Z25 #<br>P3C18V8ZAI #             | 18 × 74 × 8                                    | 20-Pin  | 18 (8)                           | 8                               | 8 (0)                                           | 8 varied                    | 35ns<br>40ns          | 25MHz<br>20MHz   | 60μA,<br>0.8mA/MHz    |

| P3C16V8-7 + #                            | 18 × 64 × 8                                    | 20-Pin  | 18 (10)                          | 7                               | 8 (0)                                           | 8 varied                    | 7.5ns                 | 100MHz           | 150mA                 |

| P3C20V8-7 + #                            | 22×64×8                                        | 24-Pin  | 22 (14)                          | 7                               | 8 (0)                                           | 8 varied                    | 7.5ns                 | 100MHz           | 150mA                 |

| LVT22V10-7 + #                           | 22 × 130 × 10                                  | 28-Pin  | 22 (12)                          | 8 to 16                         | 10 (0)                                          | 10 varied                   | 7.5ns                 | 100MHz           | 150mA                 |

| PLA                                      |                                                |         |                                  |                                 |                                                 |                             |                       |                  |                       |

| PLS100/101                               | 16 × 48 × 8                                    | 28-Pin  | 16 (16)                          | Up to 48                        | 0                                               | 8 C                         | 50ns                  |                  | 170mA                 |

| PLS153                                   | 18 × 42 × 10                                   | 20-Pin  | 18 (8)                           | Up to 32                        | 0                                               | 10 I/O                      | 40ns                  |                  | 155mA                 |

| PLS153A                                  | 18 × 42 × 10                                   | 20-Pin  | 18 (8)                           | Up to 32                        | 0                                               | 10 I/O                      | 30ns                  |                  | 155mA                 |

| PLUS153B                                 | 18 × 42 × 10                                   | 20-Pin  | 18 (8)                           | Up to 32                        | 0                                               | 10 I/O                      | 15ns                  |                  | 200mA                 |

| PLUS153D                                 | 18 × 42 × 10                                   | 20-Pin  | 18 (8)                           | Up to 32                        | 0                                               | 10 I/O                      | 12ns                  |                  | 200mA                 |

| PLUS153-10                               | 18 × 42 × 10                                   | 20-Pin  | 18 (8)                           | Up to 32                        | 0                                               | 10 I/O                      | 10ns                  |                  | 200mA                 |

| PLS173                                   | 22 × 42 × 10                                   | 24-Pin  | 22 (12)                          | Up to 32                        | 0                                               | 10 I/O                      | 30ns                  |                  | 170mA                 |

| PLUS173B                                 | 22 × 42 × 10                                   | 24-Pin  | 22 (12)                          | Up to 32                        | 0                                               | 10 I/O                      | 15ns                  |                  | 200mA                 |

| PLUS173D                                 | 22 × 42 × 10                                   | 24-Pin  | 22 (12)                          | Up to 32                        | 0                                               | 10 I/O                      | 12ns                  |                  | 200mA                 |

| PLUS173-10                               | 22 × 42 × 10                                   | 24-Pin  | 22 (12)                          | Up to 32                        | 0                                               | 10 1/0                      | 10ns                  |                  | 210mA                 |

## Selection guide

| PHILIPS<br>SEMICONDUCTORS<br>PART NUMBER | ARCHITECTURE<br>(Inputs × Terms*<br>× Outputs) | PACKAGE | TOTAL<br>INPUTS<br>(# Dedicated) | PRODUCT<br>TERMS PER<br>OR GATE | INTERNAL<br>STATE<br>REGISTERS<br>(# Dedicated) | OUTPUTS<br>C, I/O, R, R I/O | t <sub>PD</sub> (Max) | fmax  | I <sub>CC</sub> (Max) |

|------------------------------------------|------------------------------------------------|---------|----------------------------------|---------------------------------|-------------------------------------------------|-----------------------------|-----------------------|-------|-----------------------|

| PLS                                      | <u></u>                                        |         |                                  |                                 |                                                 |                             |                       |       |                       |

| PLS105                                   | 22 × 48 × 8                                    | 28-Pin  | 22 (16)                          | Up to 48                        | 6 (6)                                           | 8 R                         |                       | 14MHz | 180mA                 |

| PLS105A                                  | 22 × 48 × 8                                    | 28-Pin  | 22 (16)                          | Up to 48                        | 6 (6)                                           | 8 R                         |                       | 20MHz | 180mA                 |

| PLUS105-45                               | 22 × 48 × 8                                    | 28-Pin  | 22 (16)                          | Up to 48                        | 6 (6)                                           | 8 R                         |                       | 45MHz | 200mA                 |

| PLUS105-55                               | 22 × 48 × 8                                    | 28-Pin  | 22 (16)                          | Up to 48                        | 6 (6)                                           | 8 R                         |                       | 55MHz | 200mA                 |

| PLUS405-37                               | 24 × 64 × 8                                    | 28-Pin  | 24 (16)                          | Up to 64                        | 8 (8)                                           | 8 R                         |                       | 37MHz | 225mA                 |

| PLUS405-45                               | 24 × 64 × 8                                    | 28-Pin  | 24 (16)                          | Up to 64                        | 8 (8)                                           | 8 R                         |                       | 45MHz | 225mA                 |

| PLUS405-55                               | 24 × 64 × 8                                    | 28-Pin  | 24 (16)                          | Up to 64                        | 8 (8)                                           | 8 R                         |                       | 55MHz | 225mA                 |

| PLS155                                   | 16 × 45 × 12                                   | 20-Pin  | 16 (4)                           | Up to 32                        | 4 (0)                                           | 8 I/O, 4 R I/O              | 50ns                  | 14MHz | 190mA                 |

| PLS157                                   | 16 × 45 × 12                                   | 20-Pin  | 16 (4)                           | Up to 32                        | 6 (0)                                           | 6 I/O, 6 R I/O              | 50ns                  | 14MHz | 190mA                 |

| PLS159A                                  | 16 × 45 × 12                                   | 20-Pin  | 16 (4)                           | Up to 32                        | 8 (0)                                           | 4 I/O, 8 R I/O              | 35ns                  | 18MHz | 190mA                 |

| PLS167                                   | 22 × 48 × 6                                    | 24-Pin  | 22 (14)                          | Up to 48                        | 8 (6)                                           | 6R                          |                       | 14MHz | 180mA                 |

| PLS167A                                  | 22 × 48 × 6                                    | 24-Pin  | 22 (14)                          | Up to 48                        | 8 (6)                                           | 6R                          |                       | 20MHz | 180mA                 |

| PLS168                                   | 22 × 48 × 8                                    | 24-Pin  | 22 (12)                          | Up to 48                        | 10 (6)                                          | 8 R                         |                       | 14MHz | 180mA                 |

| PLS168A                                  | 22 × 48 × 8                                    | 24-Pin  | 22 (12)                          | Up to 48                        | 10 (6)                                          | 8 R                         |                       | 20MHz | 180mA                 |

| PLS179                                   | 20 × 45 × 12                                   | 24-Pin  | 20 (8)                           | Up to 32                        | 8 (0)                                           | 4 I/O, 8 R I/O              | 35ns                  | 18MHz | 210mA                 |

| PLC42VA12/I                              | 42 × 105 × 12                                  | 24-Pin  | 42 (10)                          | Up to 64                        | 10 (0)                                          | 10 I/O or R I/O,<br>2 I/O   | 35ns                  | 25MHz | 135mA                 |

| PLC415-16                                | 25 × 68 × 8                                    | 28-Pin  | 25 (17)                          | Up to 64                        | 8 (8)                                           | 8 R                         |                       | 16MHz | 100μA/<br>80mA        |

| PML                                      |                                                |         |                                  |                                 |                                                 |                             |                       |       |                       |

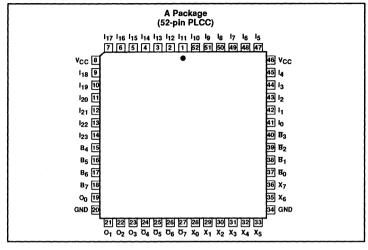

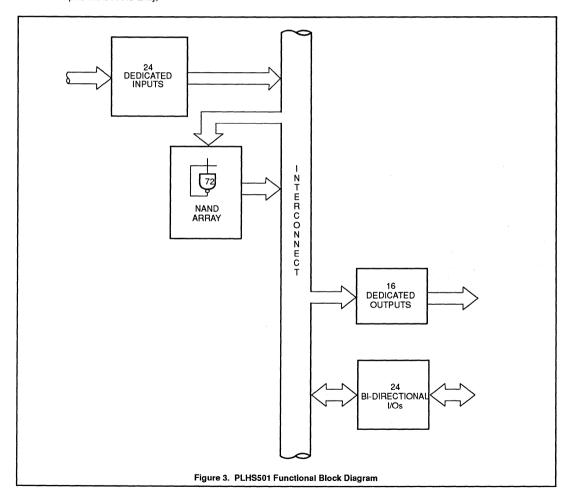

| PLHS501                                  | 104 × 116 × 24                                 | 52-Pin  | 32 (24)                          | Up to 136 •                     | 0                                               | 16 C, 8 I/O                 | 22ns                  |       | 295mA                 |

| PML2552-35                               | 205 × 210 × 24                                 | 68-Pin  | 53 (29)                          | Up to 258+                      | 36 (20)                                         | 8 I/O, 16 R I/O             | 35ns                  | 50MHz | 10mA/<br>100mA        |

| PML2552-50                               | 205 × 210 × 24                                 | 68-Pin  | 53 (29)                          | Up to 258•                      | 36 (20)                                         | 8 I/O, 16 R I/O             | 50ns                  | 35MHz | 10mA/<br>100mA        |

| PML2852-35                               | 205 × 210 × 40                                 | 84-Pin  | 53 (29)                          | Up to 258∙                      | 36 (20)                                         | 16 C, 8 I/O,<br>16 R I/O    | 35ns                  | 50MHz | 10mA/<br>100mA        |

| PML2852-50                               | 205 × 210 × 40                                 | 84-Pin  | 53 (29)                          | Up to 258∙                      | 36 (20)                                         | 16 C, 8 I/O,<br>16 R I/O    | 50ns                  | 35MHz | 10mA/<br>100mA        |

PAL Device = Programmable Array Logic (Fixed OR Array)-Type PHD = Programmable High-Speed Decoder PLA = Programmable Logic Array PLS = Programmable Logic Sequencer PML = Programmable Macro Logic

R I/O = Registered I/O

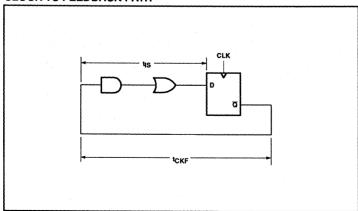

f<sub>MAX</sub> = 1/(t<sub>IS</sub> + t<sub>CKO</sub>) worst case \* Includes control product terms

R = Registered output

I/O = Combinatorial I/O

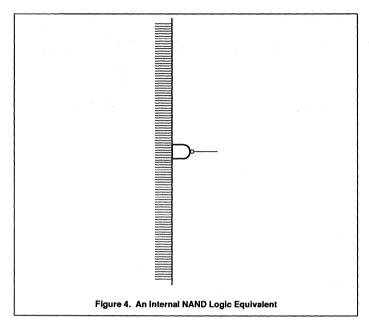

• Product terms per NAND gate PAL is a registered trademark of AMD.

PML is a trademark of Philips Semiconductors.

+ Under development

# 3 Volt devices

#### **OUTPUTS:**

C = Combinatorial output

All packages refer to DIP configurations except PHD48N22, PML2552 and PML2852, which are offered in PLCC only.

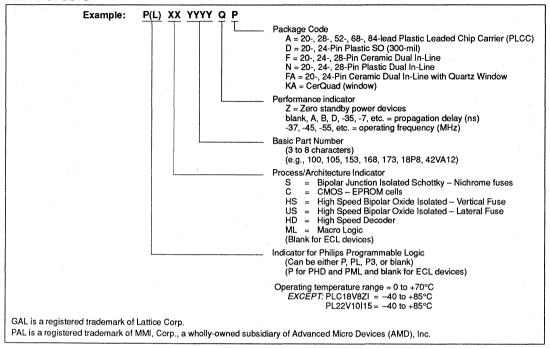

#### **Ordering Information**

#### **PLD PRODUCTS**

# Section 2 Introduction

| Introduction | Programmable logic | 1 |

|--------------|--------------------|---|

| Introduction | Programmable logic |   |

#### Introduction

## WHAT IS PROGRAMMABLE LOGIC?

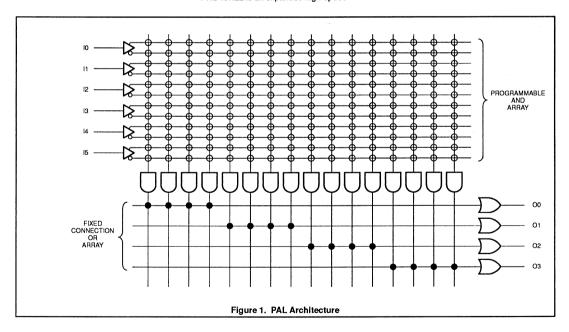

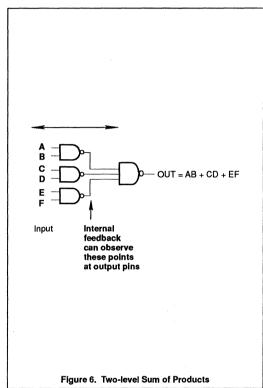

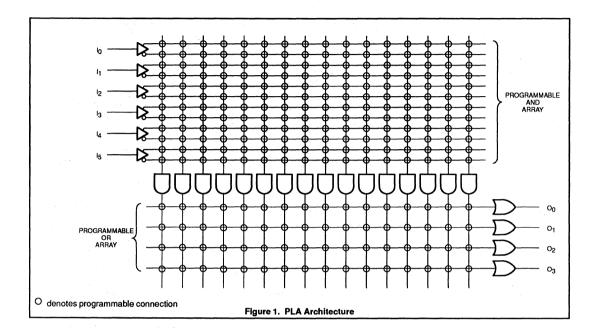

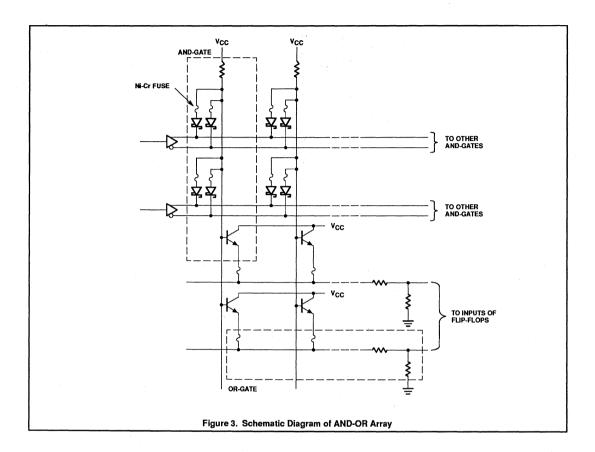

In 1975, Philips Semiconductors developed a new product family by combining its expertise in semi-custom gate array products and fuse-link Programmable Read Only Memories (PROMs). Out of this marriage came Philips Semiconductors Programmable Logic Family. The PLS100 Field-Programmable Logic Array (FPLA) was the first member of this family. The FPLA was an important industry first in two ways. First, the AND/OR/INVERT

architecture allowed the custom implementations of Sum of Product logic equations. Second, the three-level fusing allows complete flexibility in the use of this device family. All logic interconnections from input to output are programmable.

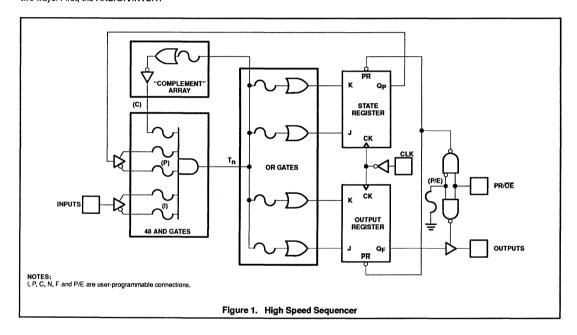

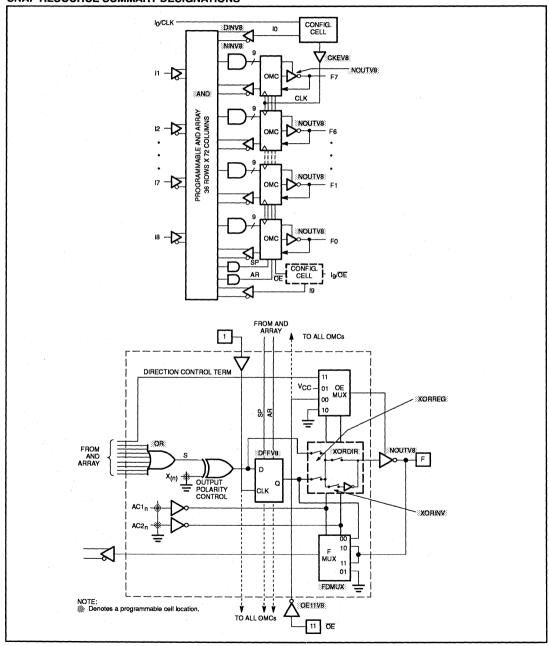

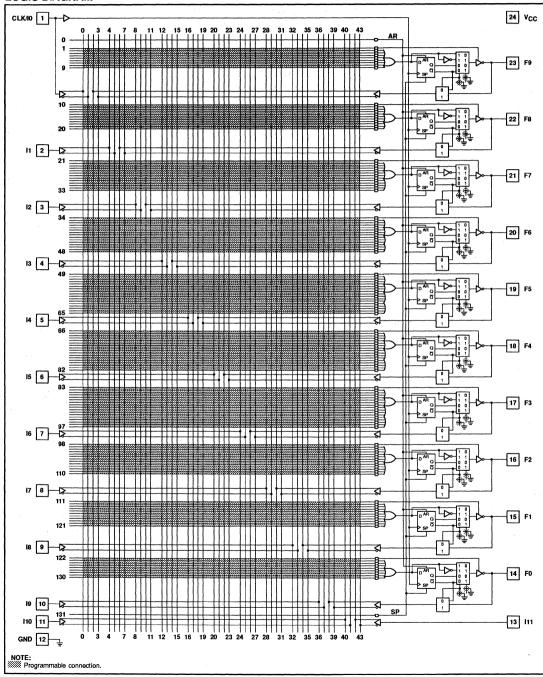

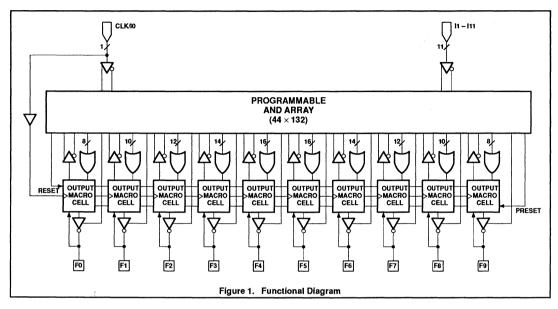

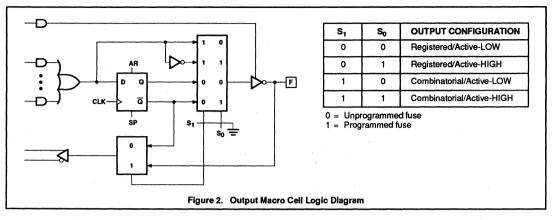

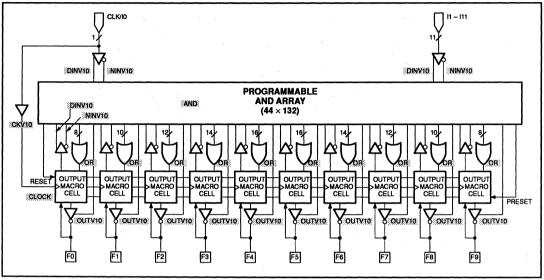

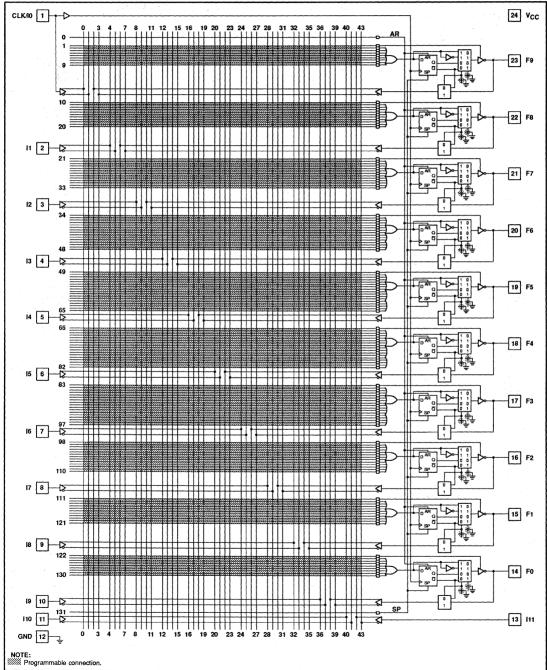

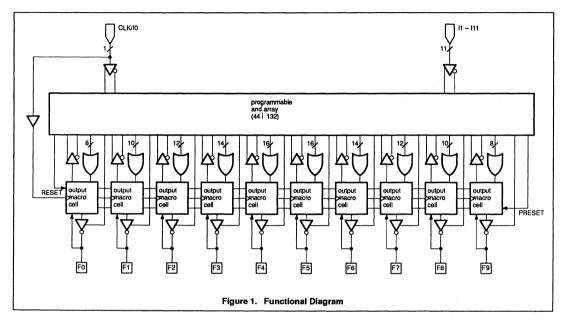

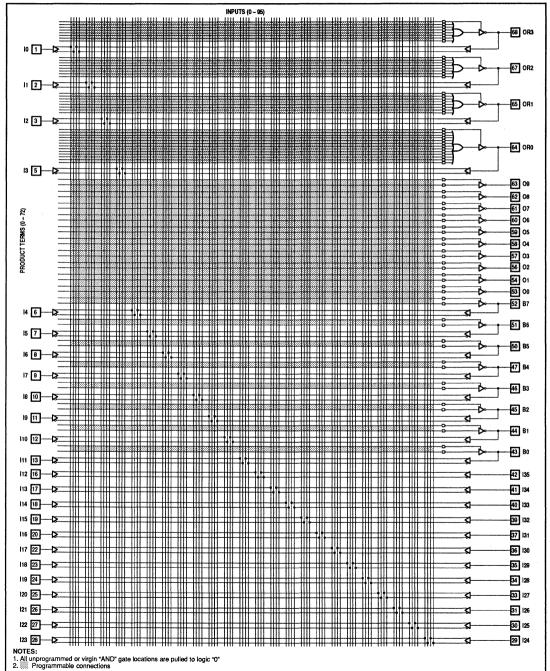

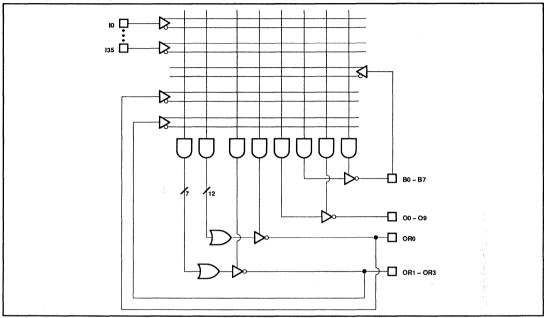

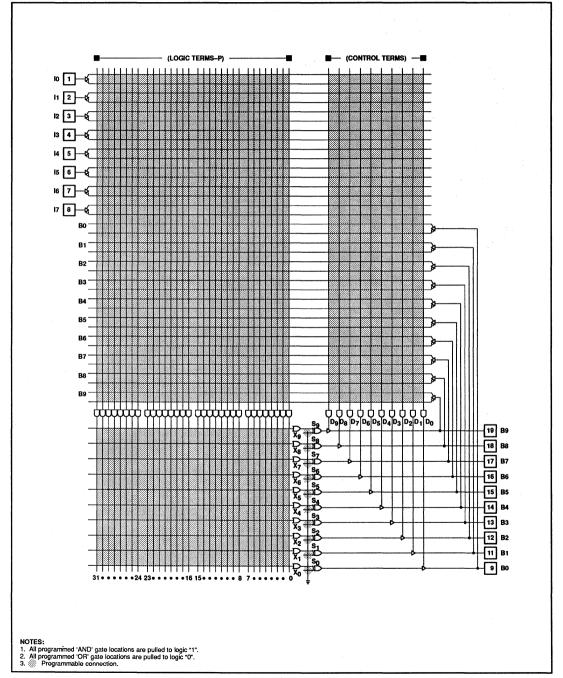

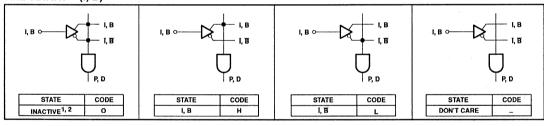

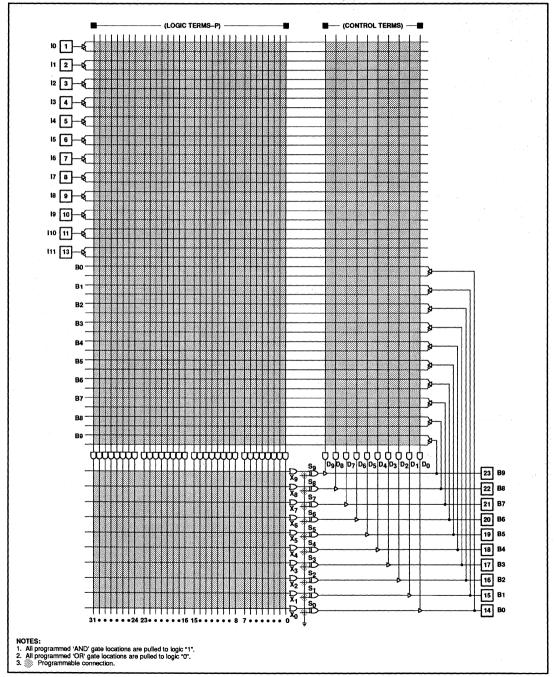

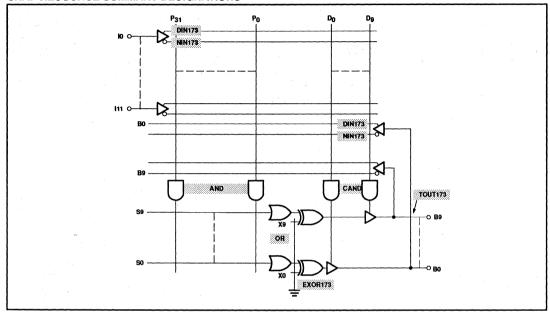

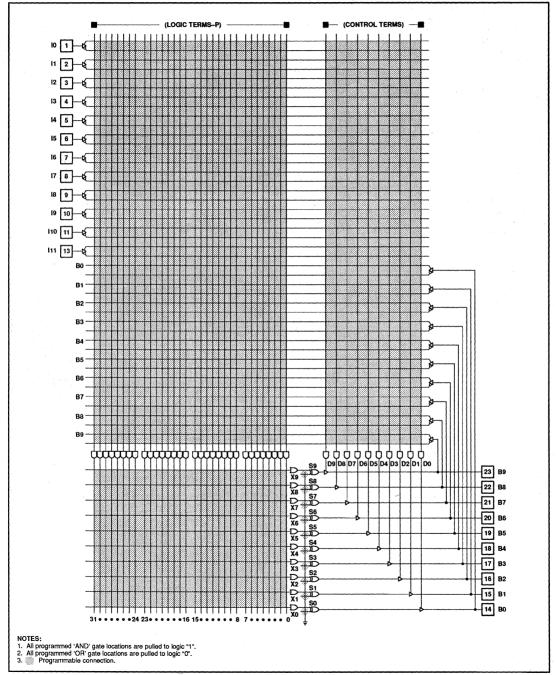

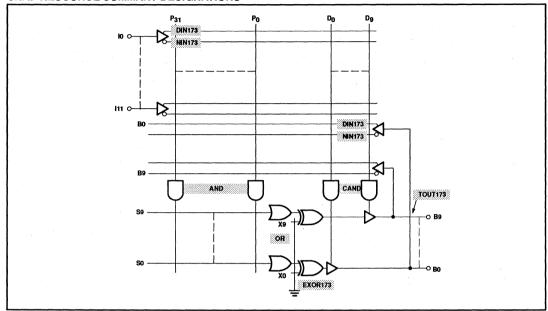

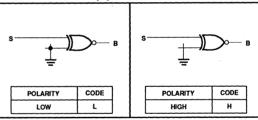

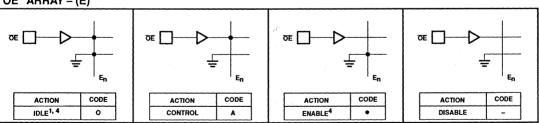

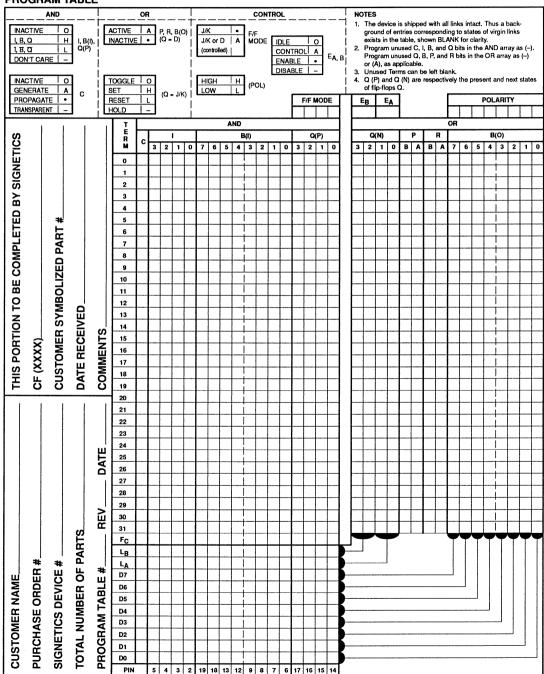

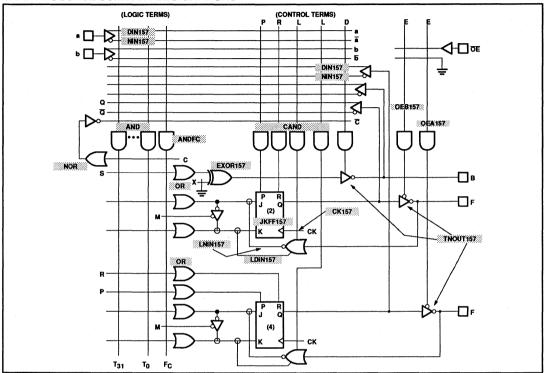

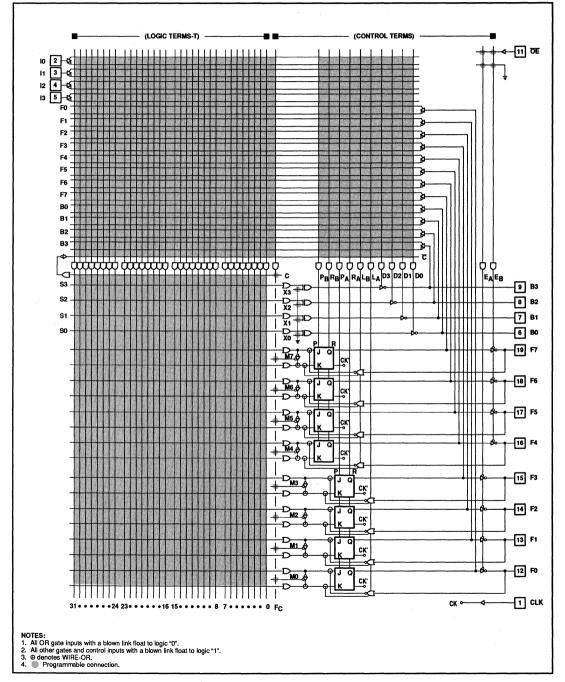

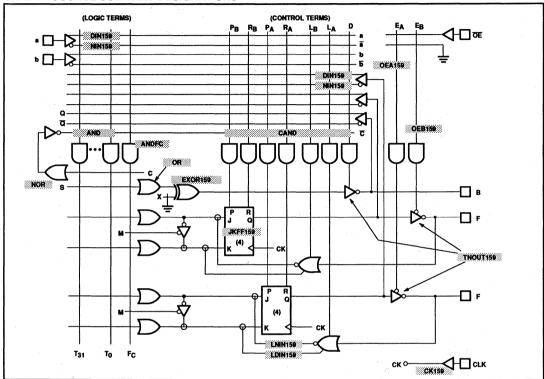

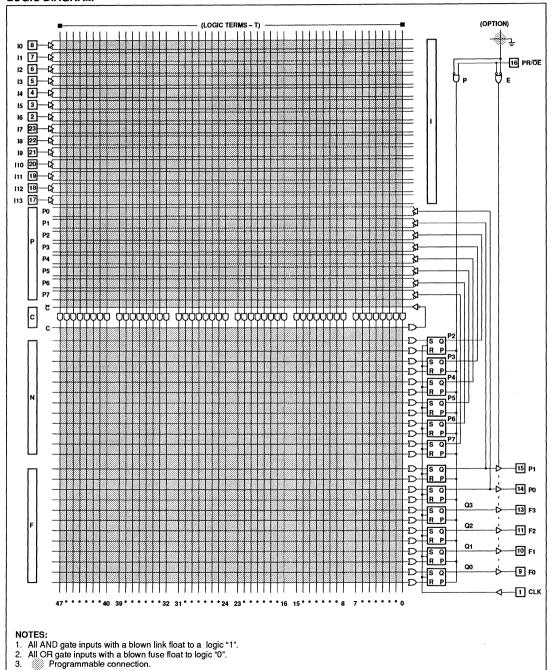

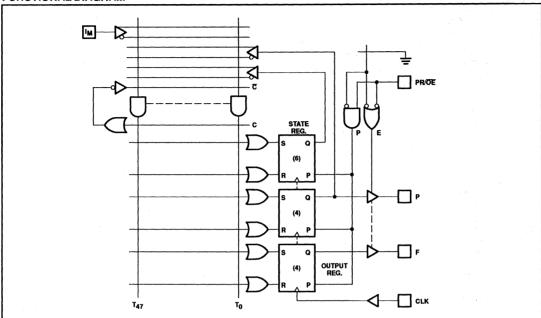

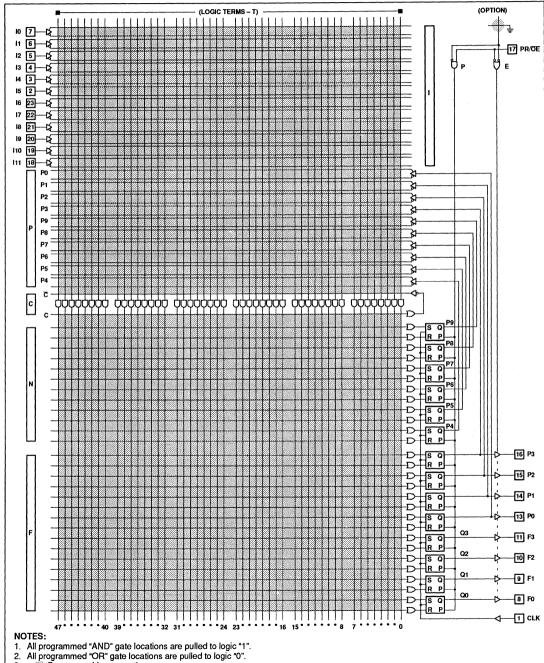

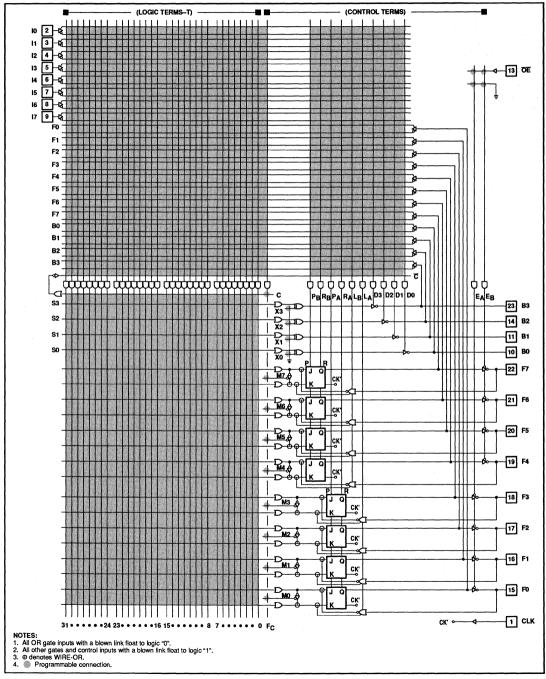

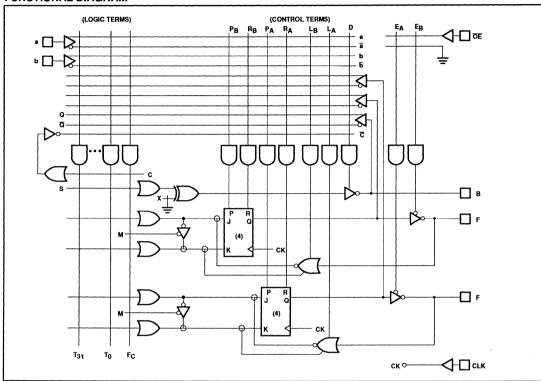

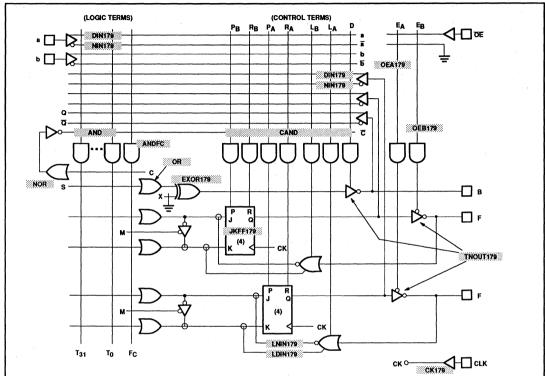

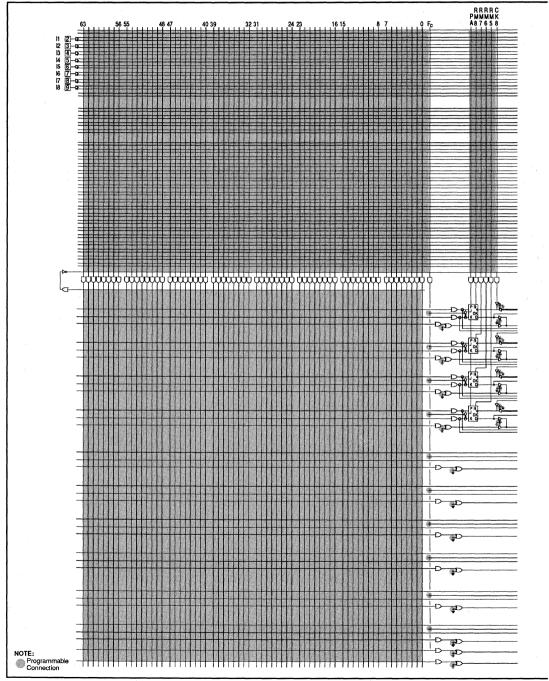

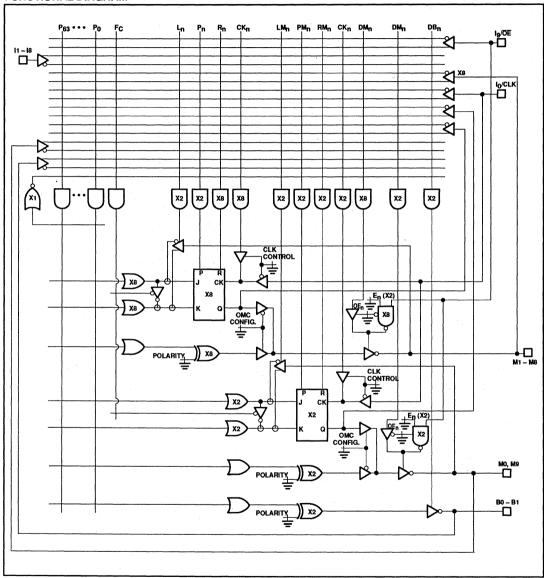

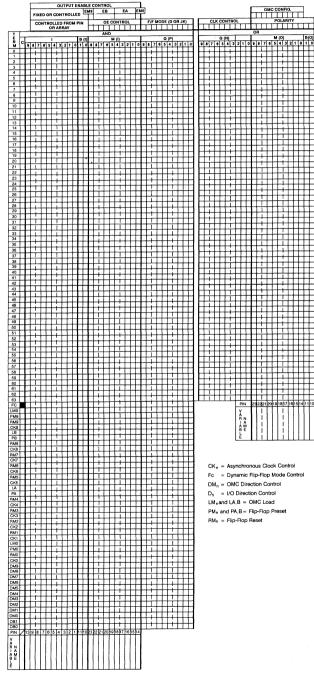

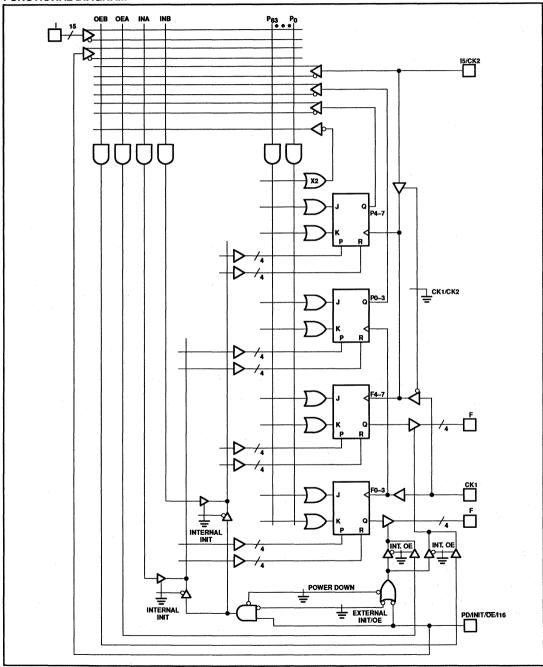

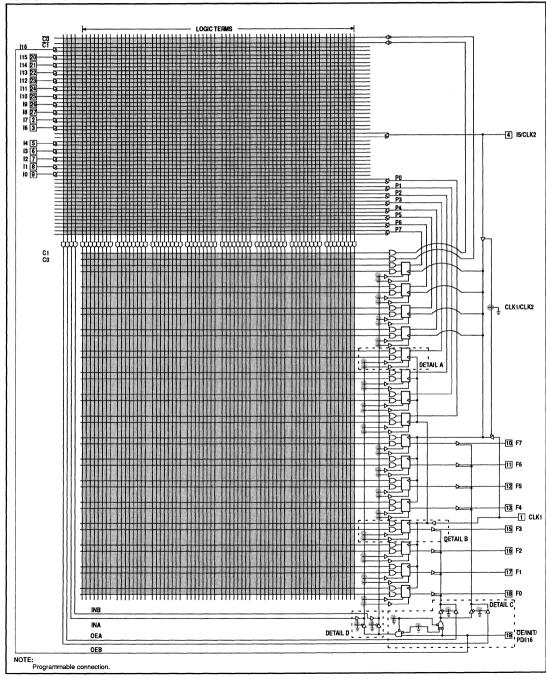

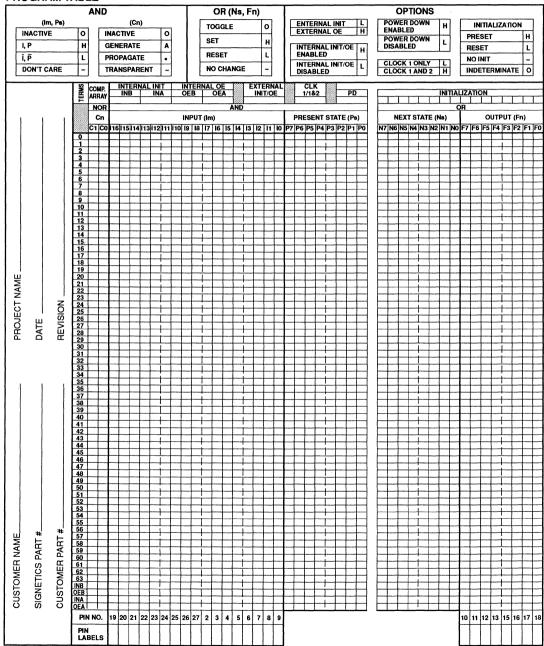

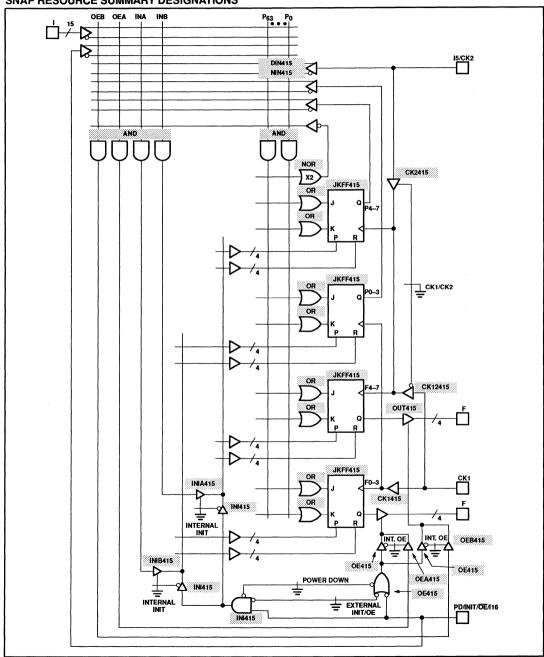

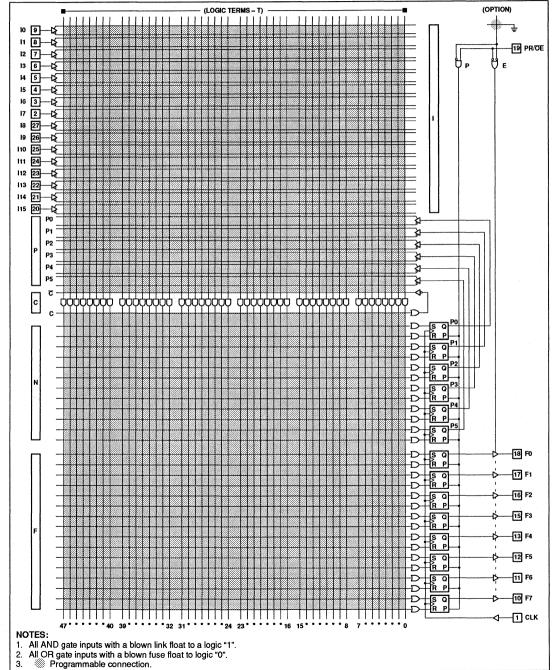

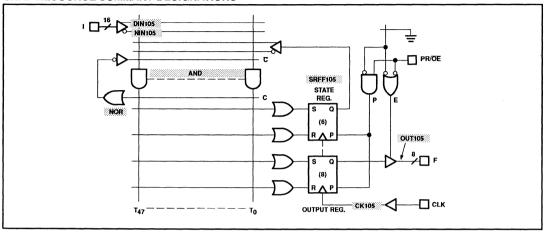

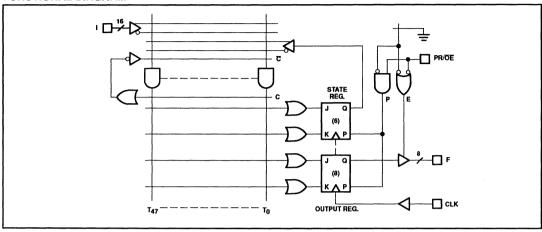

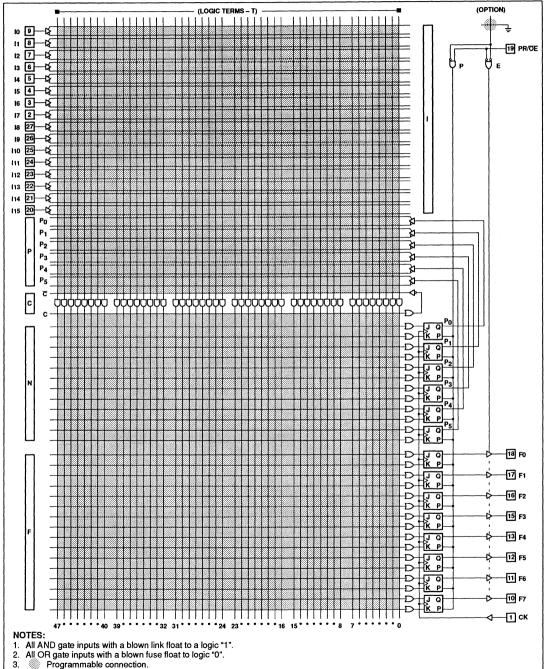

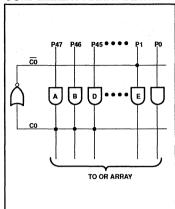

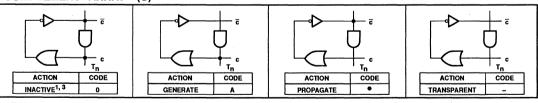

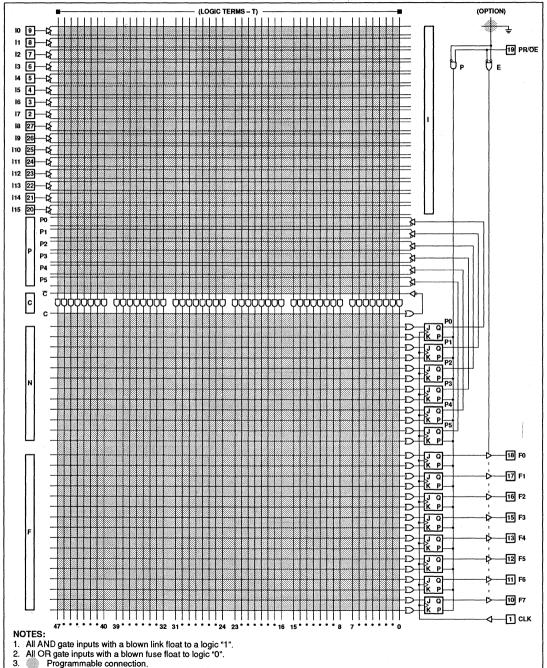

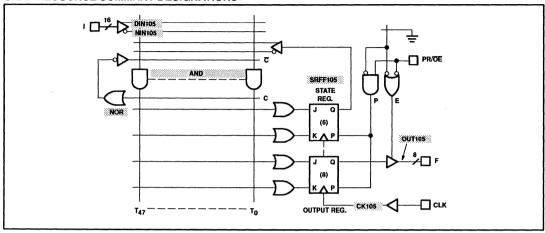

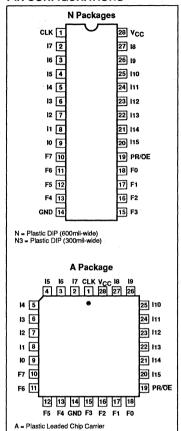

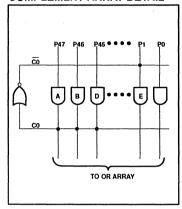

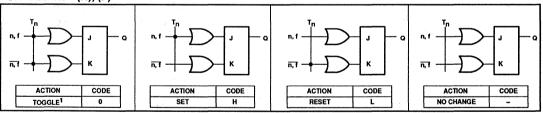

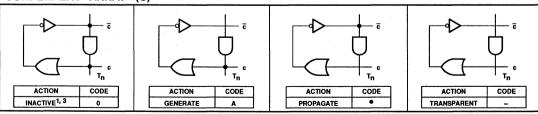

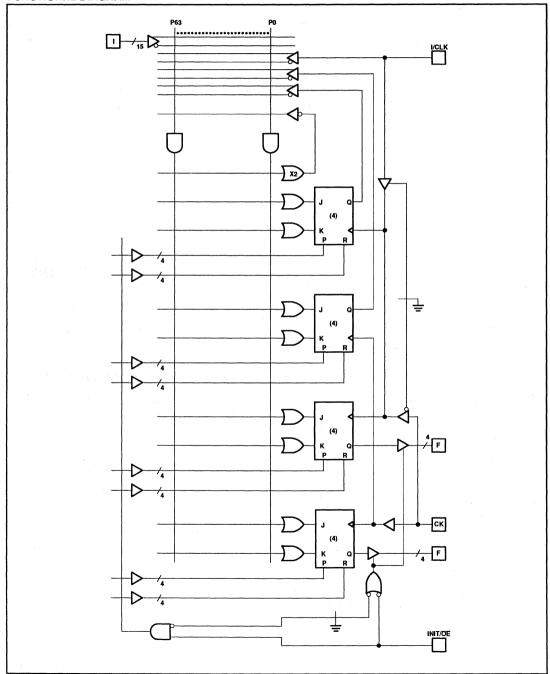

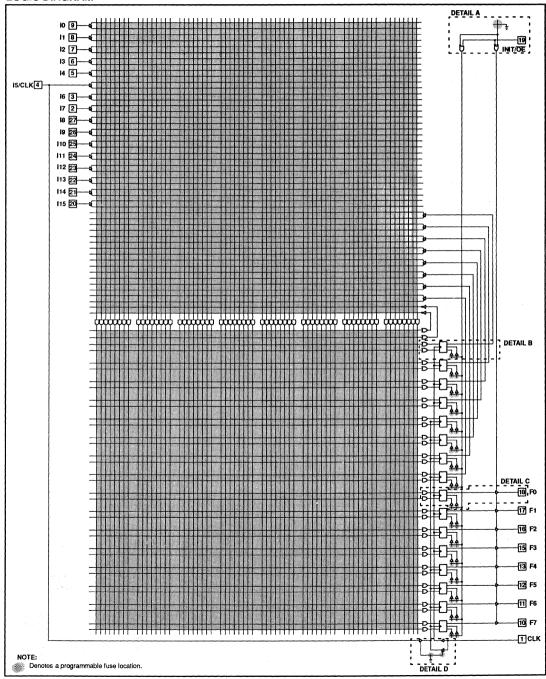

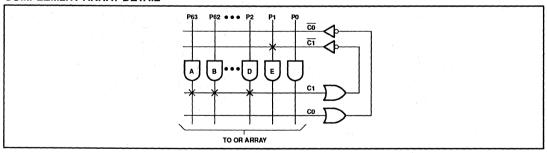

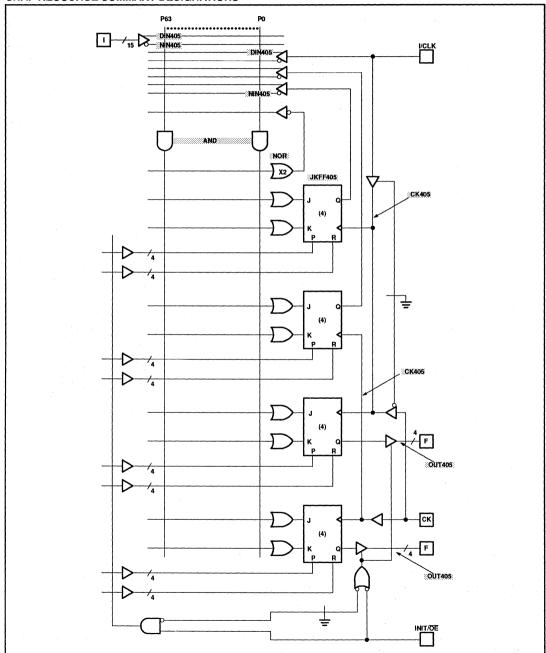

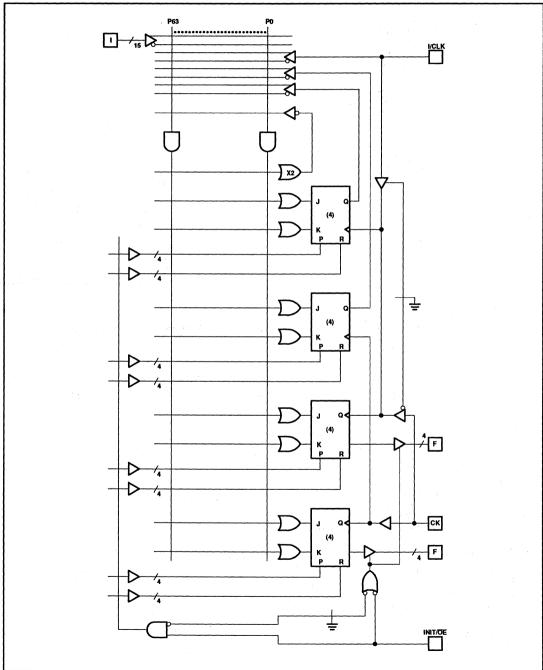

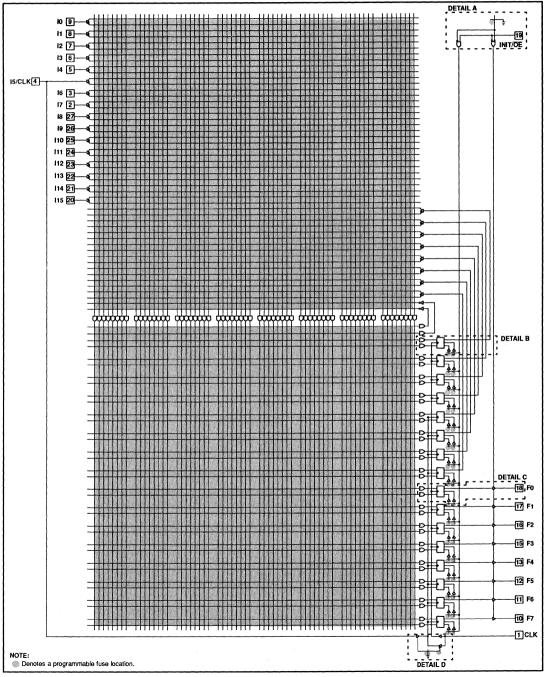

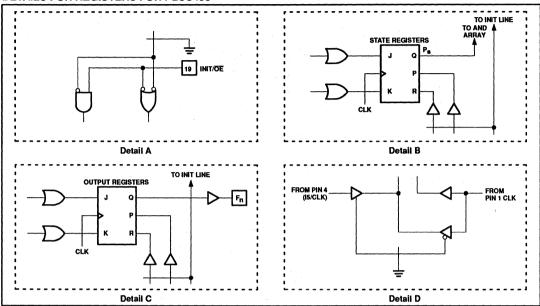

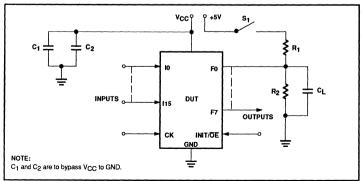

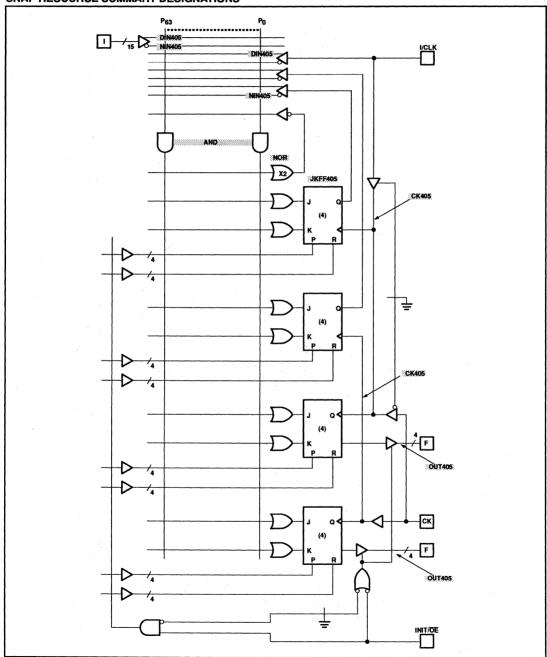

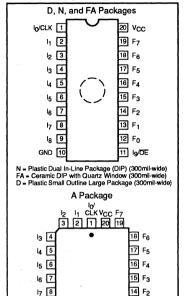

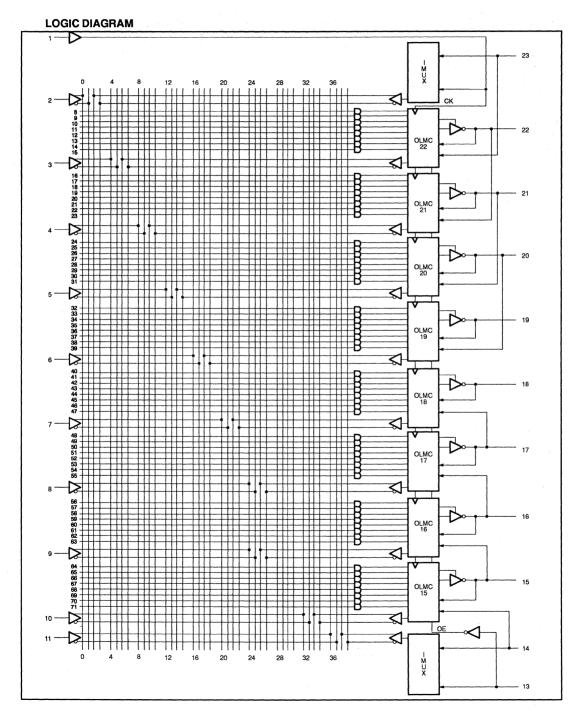

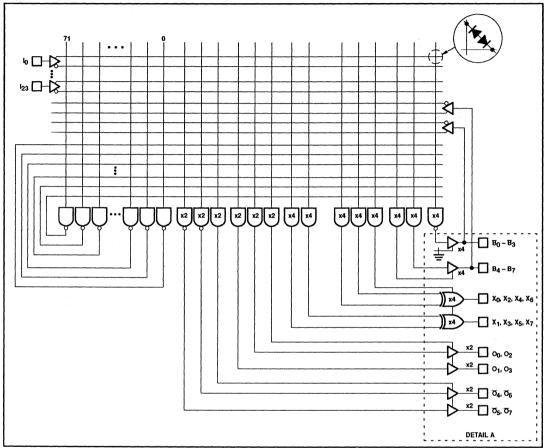

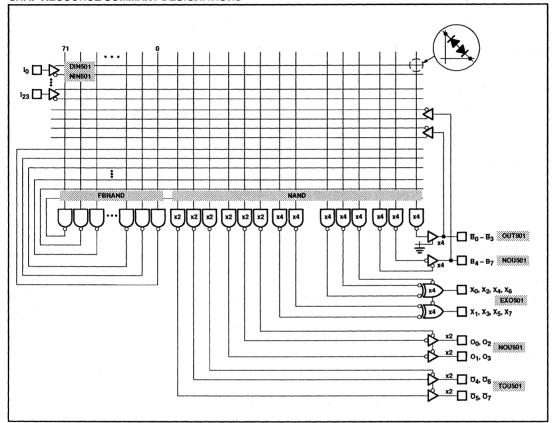

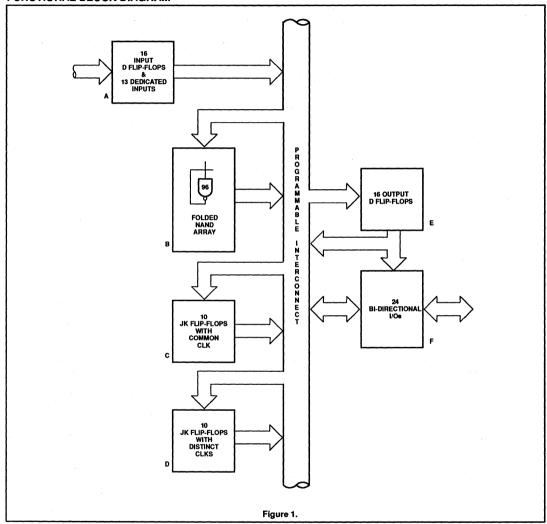

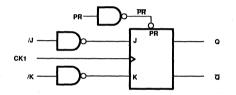

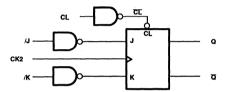

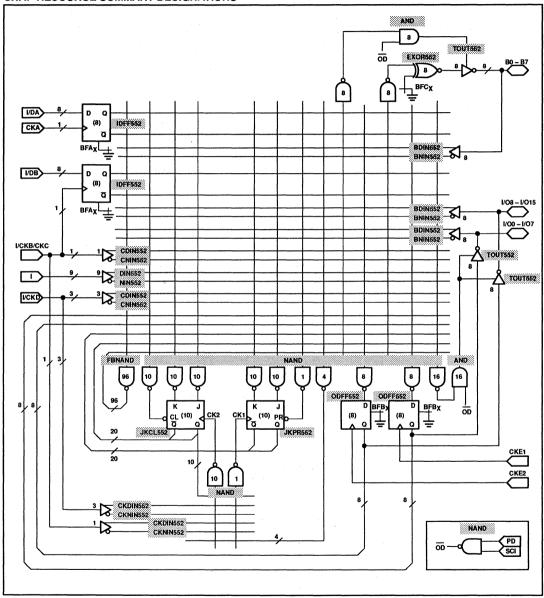

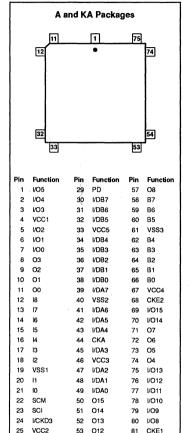

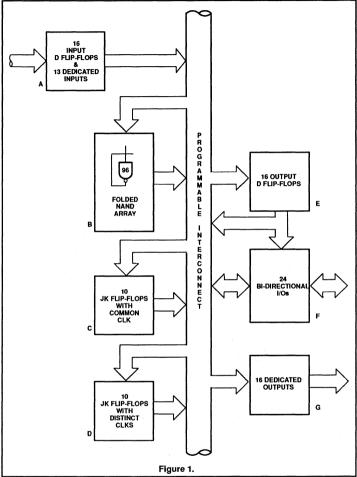

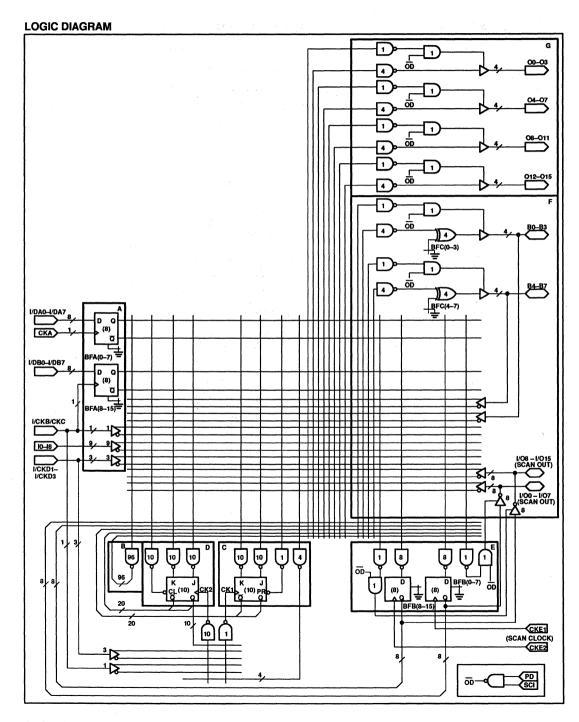

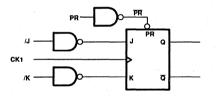

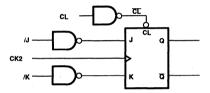

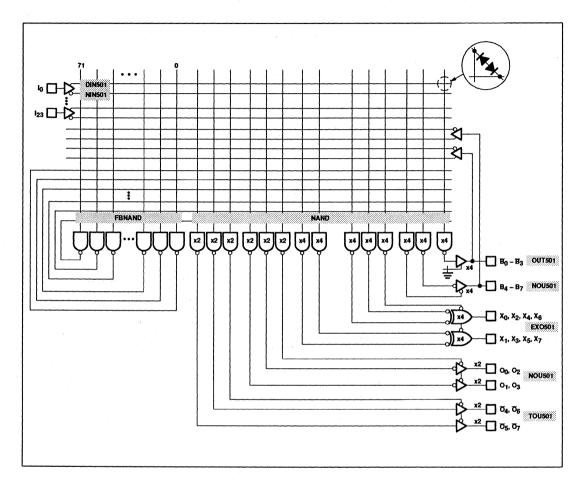

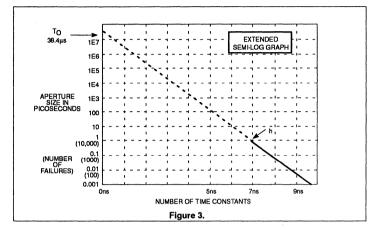

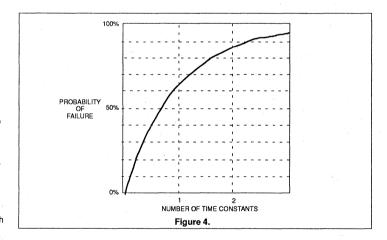

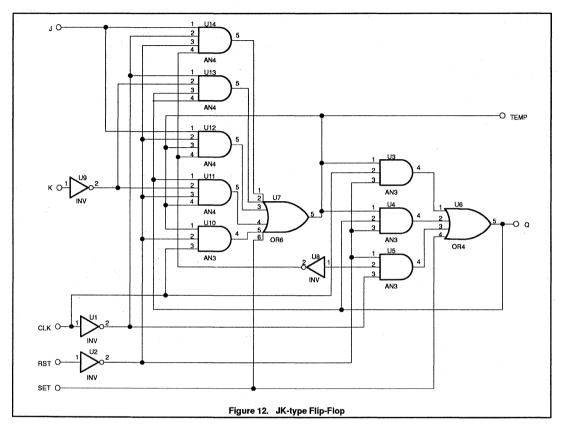

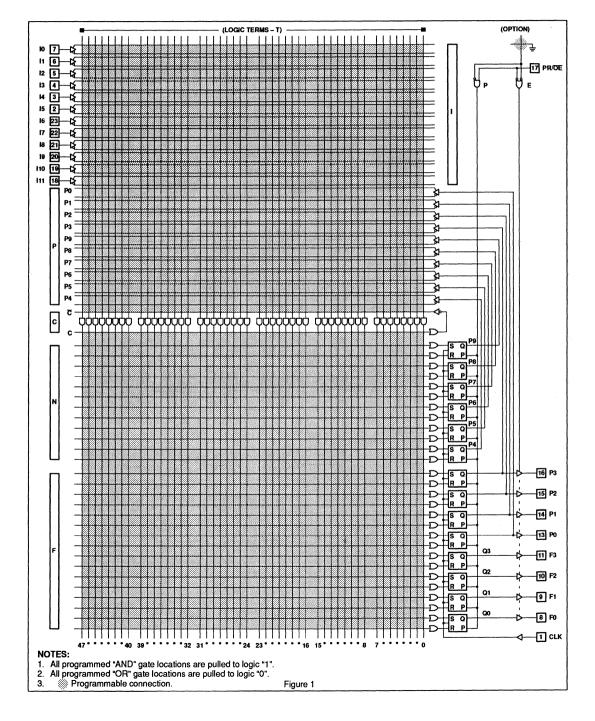

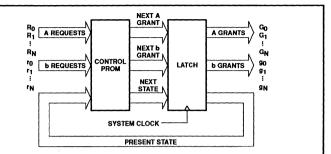

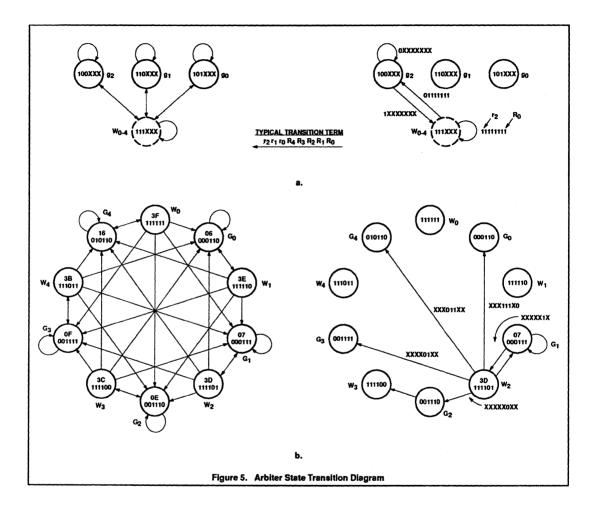

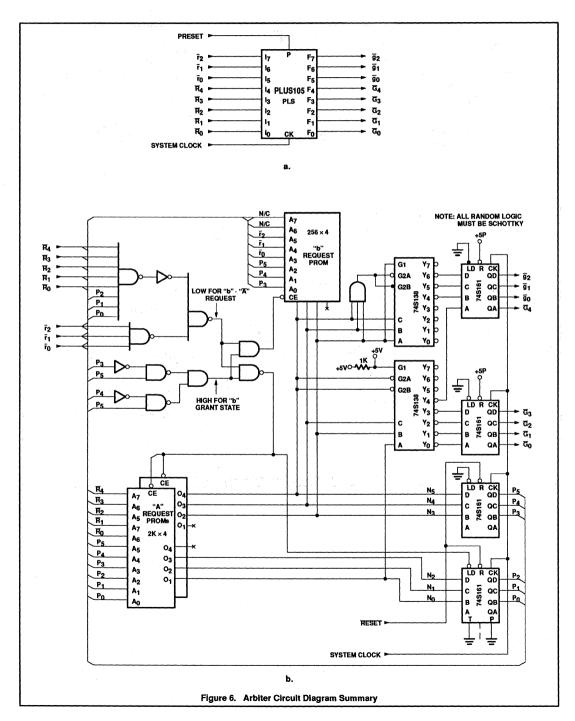

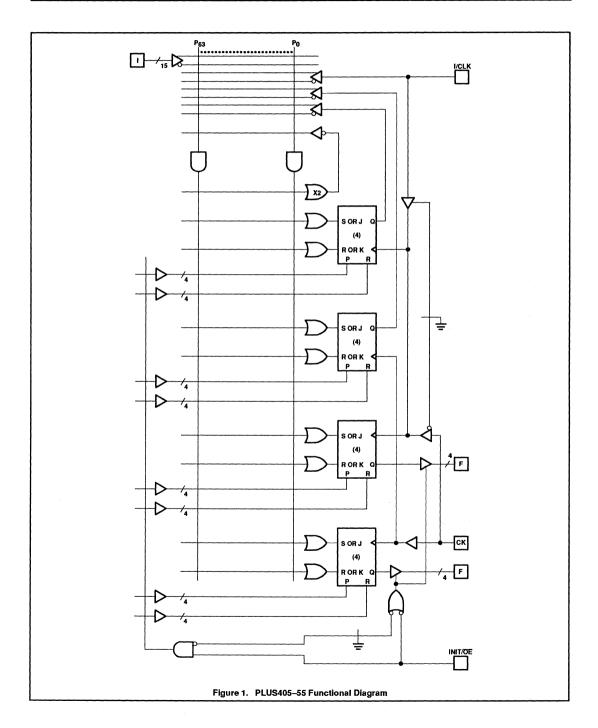

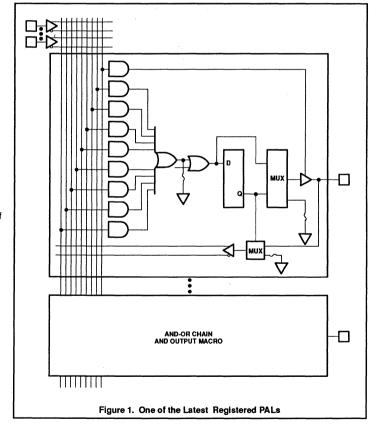

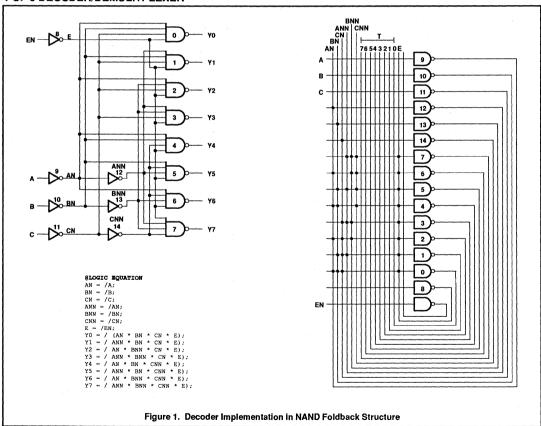

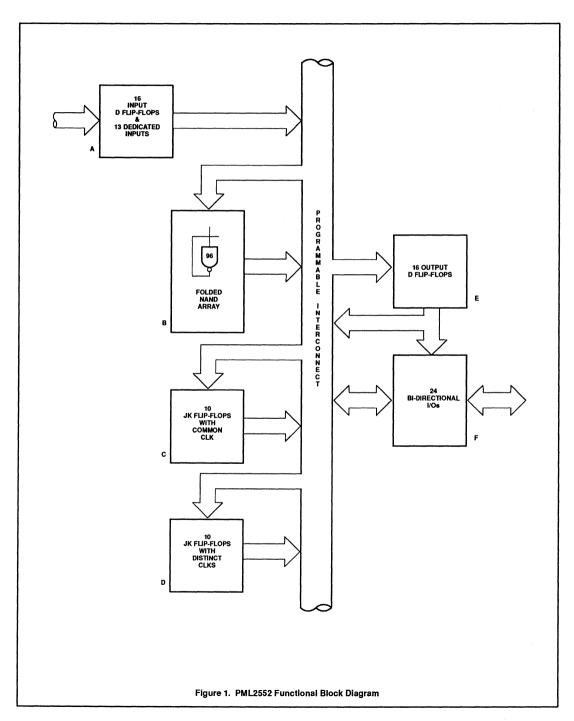

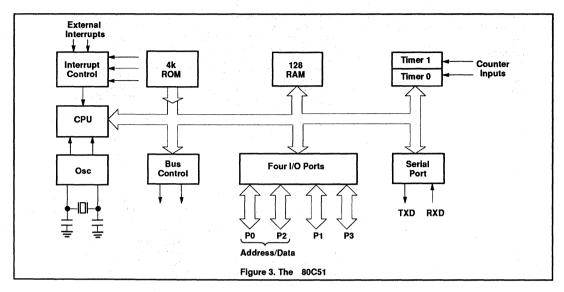

Figure 1 shows the architecture of a high performance sequencer combining a PLA architecture with JK flip-flops. The Selection Guide shown on pages 12 and 13 of this data handbook shows the current spectrum of

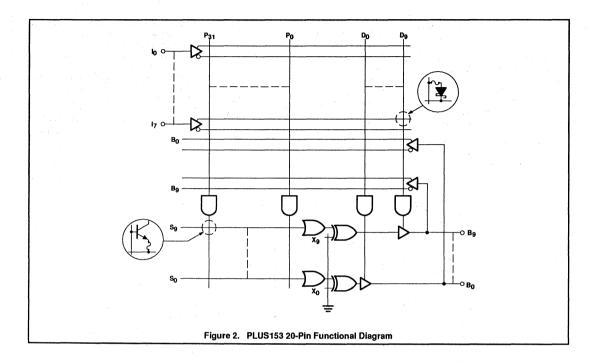

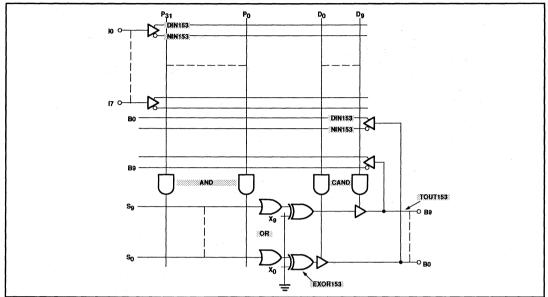

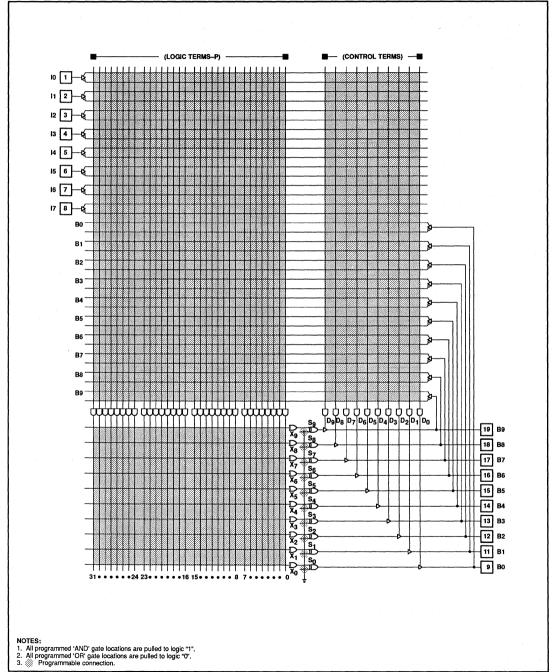

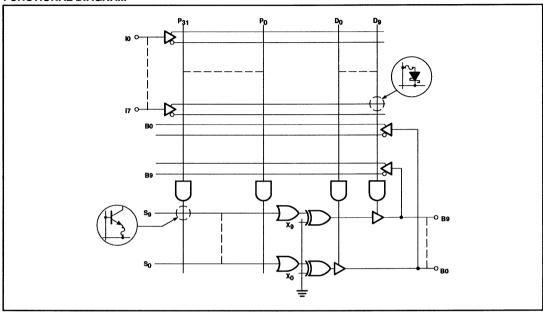

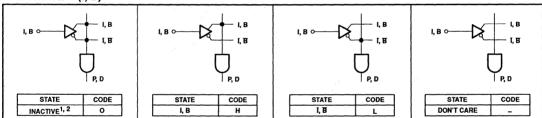

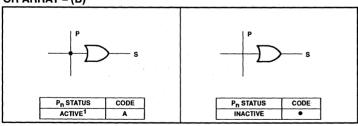

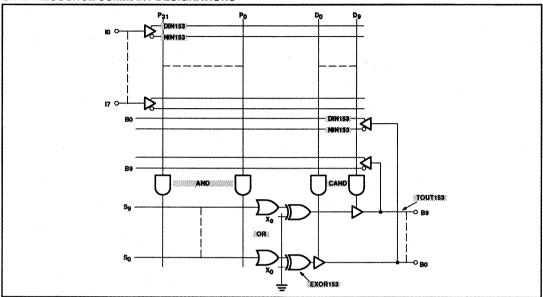

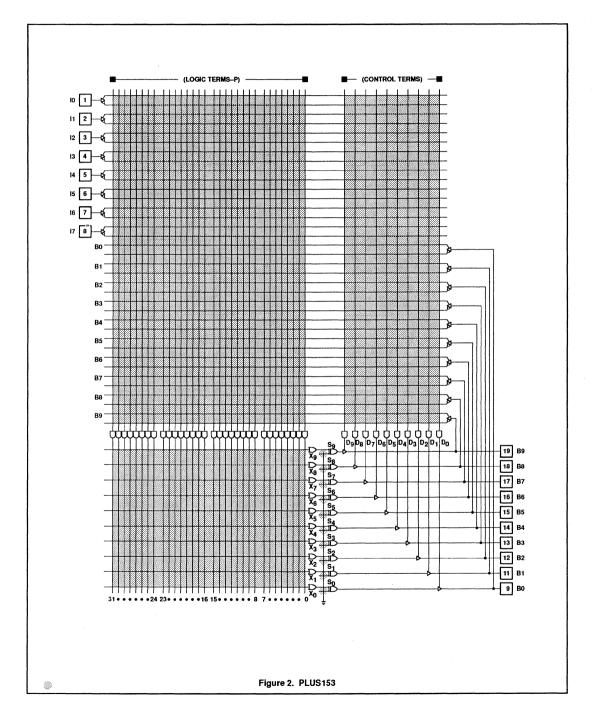

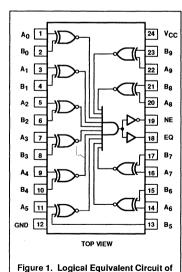

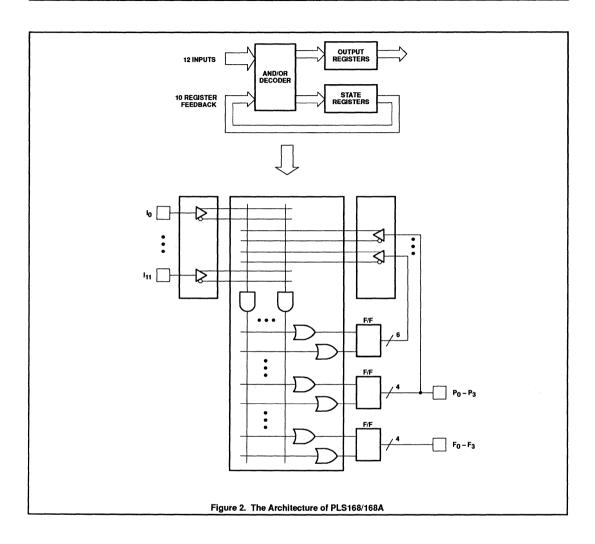

Philips Semiconductors PLDs. Parts for every need are available in nearly every architecture and across at least three technologies. The PLUS and PLHS prefixes describe bipolar parts, the PLC and P3C prefix describes EPLD (CMOS) parts and the PLQ and P3Q prefix refers to the new Philips Semiconductors QUBIC BICMOS process. Figure 2 shows a shorthand image of the PLUS153 programmable logic array (PLA), which was derived from the original PLS100.

#### Introduction

#### PLD LOGIC SYNTHESIS

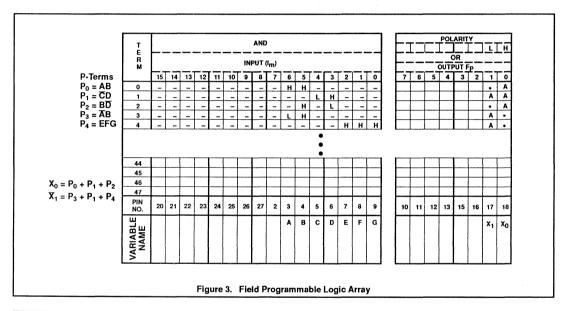

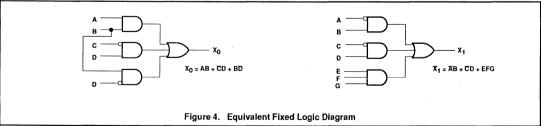

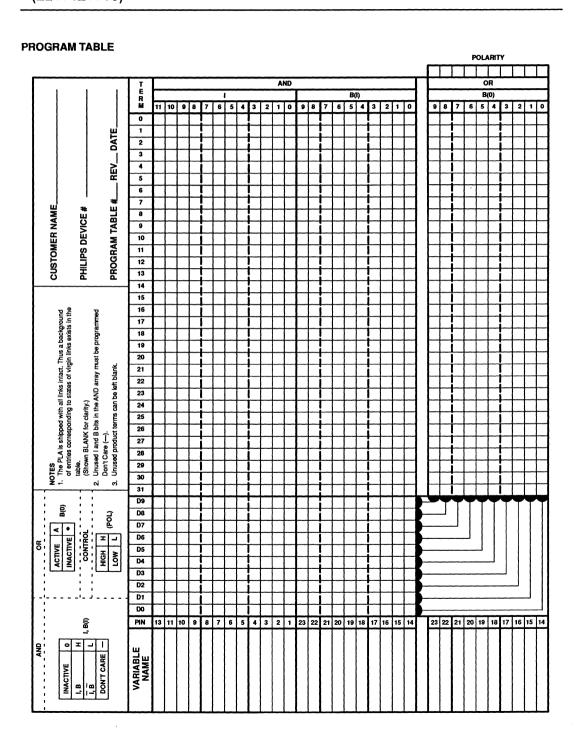

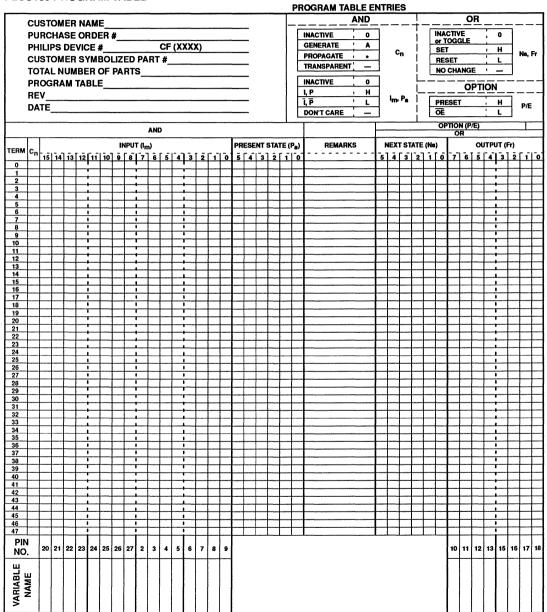

No intermediate step is required to implement Boolean Logic Equations with PLDs. Each term in each equation simply becomes a direct entry into the Logic Program Table. The following example illustrates this straightforward concept:

$$X_0 = AB + \overline{C}D + B\overline{D}$$

$$X_1 = \overline{A}B + \overline{C}D + EFG$$

Introduction

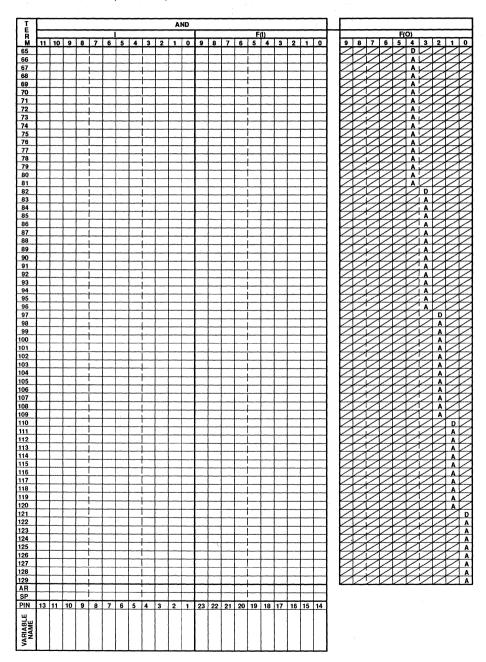

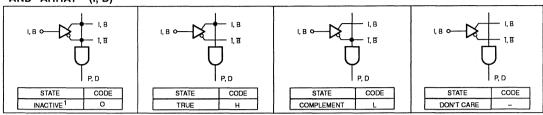

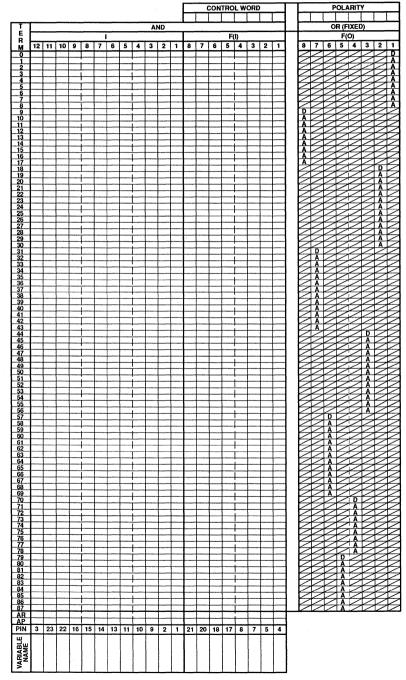

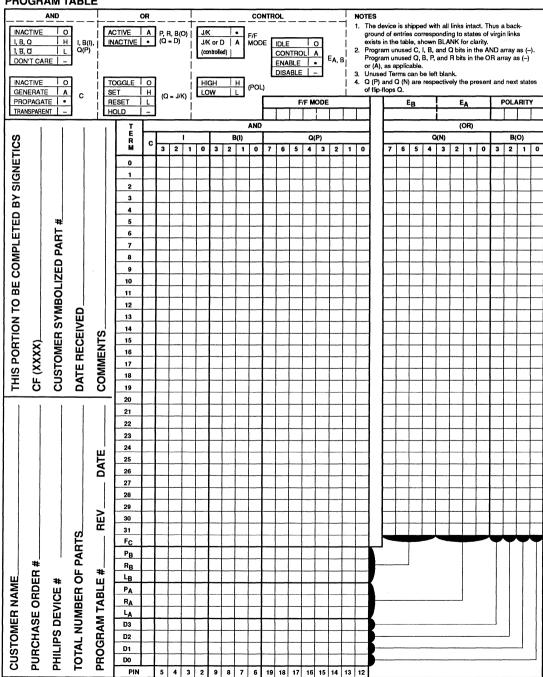

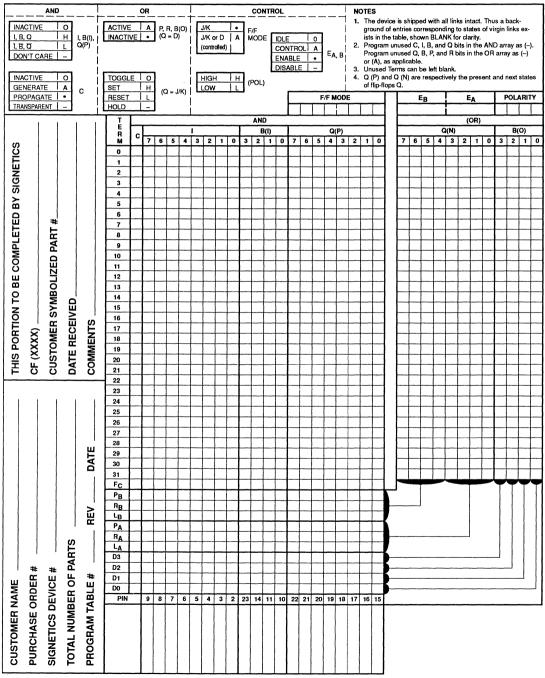

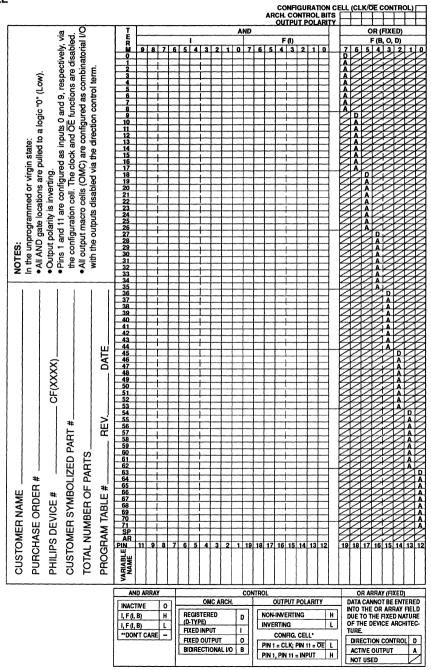

In the previous example, the two Boolean Logic equations were broken into Product terms. Each P-term was then programmed into the P-term section of the PLA Program Table. This was accomplished in the following manner:

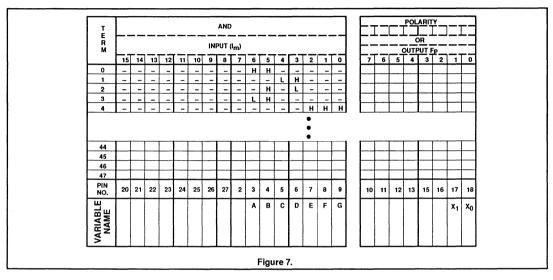

Step 1 Select which input pins  $I_0-I_{15}$  will correspond to the input variables. In this case A-G are the input variable names.  $I_6$  through  $I_0$  were selected to accept inputs A-G respectively.

Step 2

Transfer the Boolean Terms to the PLA

Program Table. This is done simply by

defining each term and entering it on the

Program Table.

e.g.,  $P_0 = AB$

This P-term translates to the Program Table by selecting  $A=I_6=H$  and  $B=I_5=H$  and entering the information in the appropriate column.

$P_1 = \overline{C}D$

This term is defined by selecting  $C=I_4=L$  and  $D=I_3=H$ , and entering the data into the Program Table. Continue this operation until all P-terms are entered into the Program Table.

|     | т                |             | AND |          |    |    |     |    |     |   |   |      |     |    |   |   | POL | ARIT | Υ  | -  |    |    |    |    |          |  |  |      |             |      |  |          |

|-----|------------------|-------------|-----|----------|----|----|-----|----|-----|---|---|------|-----|----|---|---|-----|------|----|----|----|----|----|----|----------|--|--|------|-------------|------|--|----------|

|     | E<br>R<br>M      | R INDUT ( ) |     |          |    |    |     |    | E R |   |   |      |     |    |   |   |     |      |    |    |    |    |    |    |          |  |  | OUTP | OR<br>OUT F | <br> |  | <u> </u> |

|     |                  | 15          | 14  | 13       | 12 | 11 | 10  | 9  | 8   | 7 | 6 | 5    | 4   | 3  |   | 1 | T 6 | 7    | 6  |    | 4  |    |    | 1  | 0        |  |  |      |             |      |  |          |

|     | 0                | -           | -   | _        | -  | _  | _   | _  | -   | - | Н | Н    | _   | _  | - | _ | -   |      |    |    |    |    |    |    |          |  |  |      |             |      |  |          |

| 1   | 1                | -           | _=  | _        | _  | -  | -   | -  | _   | - | _ | -    | L   | Н  | _ | _ | _   |      |    |    |    |    |    |    |          |  |  |      |             |      |  |          |

|     | 2                | _           | _   | -        | -  | -  |     | -  | 三   | _ | _ | Н    | -   | L  | _ | - | -   |      |    |    |    |    |    |    |          |  |  |      |             |      |  |          |

|     | 3                | -           | -   |          | -  | -  | -   |    | _   |   | L | Н    | -   | -  | - | - |     |      |    |    |    |    |    |    |          |  |  |      |             |      |  |          |

| - 1 | 4                |             |     | L=       |    | -  | لبا |    |     | - | - |      | -   |    | Н | Н | Н   |      |    |    |    |    |    |    |          |  |  |      |             |      |  |          |

|     |                  |             |     |          |    |    |     |    |     |   |   |      | :   |    | : |   |     |      |    | -  |    |    |    |    |          |  |  |      |             |      |  |          |

| - 1 | 44               |             |     |          |    |    |     |    |     |   |   |      |     |    |   |   |     |      |    |    |    |    |    |    |          |  |  |      |             |      |  |          |

|     | 45               |             |     | <u></u>  |    |    |     |    |     |   |   |      |     |    |   |   |     |      |    |    |    |    |    | L  |          |  |  |      |             |      |  |          |

| - 1 | 46               |             |     | <u> </u> |    |    |     |    |     |   |   |      |     |    |   |   |     |      | _  |    |    |    |    |    |          |  |  |      |             |      |  |          |

|     | 47               |             |     | _        | -  |    |     | -  |     |   |   |      |     | -  |   | - |     |      |    |    |    | -  |    | -  | <u> </u> |  |  |      |             |      |  |          |

|     | PIN<br>NO.       | 20          | 21  | 22       | 23 | 24 | 25  | 26 | 27  | 2 | 3 | 4    | 5   | 6  | 7 | 8 | 9   | 10   | 11 | 12 | 13 | 15 | 16 | 17 | 18       |  |  |      |             |      |  |          |

|     | VARIABLE<br>NAME |             |     |          |    |    |     |    |     |   | A | В    | С   | D  | E | F | G   |      |    |    |    |    |    |    |          |  |  |      |             |      |  |          |

|     |                  |             |     |          |    |    |     |    |     |   |   | Figu | ıre | 6. |   |   |     |      |    |    |    |    |    |    |          |  |  |      |             |      |  |          |

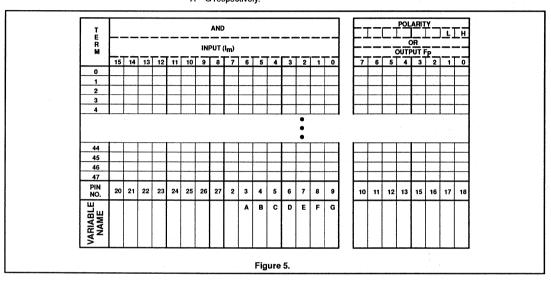

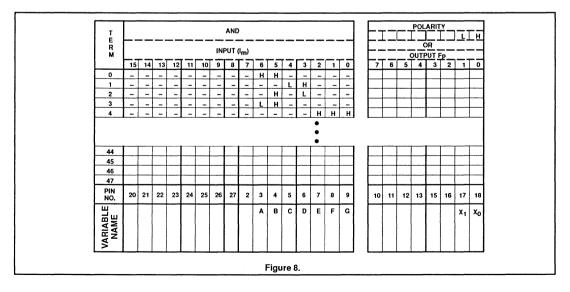

Step 3 Select which output pins correspond to each output function. In this case  $F_0 = Pin 18 = X_0$ , and  $F_1 = Pin 17 = X_1$ .

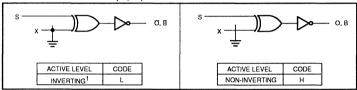

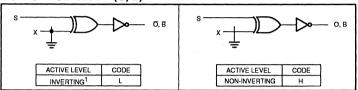

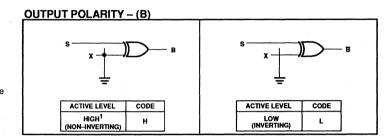

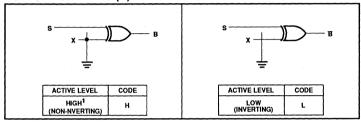

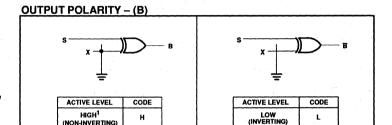

Step 4 Select the Output Active Level desired for each Output Function. For  $X_0$  the active level is high for a positive logic expression of

this equation. Therefore, it is only necessary to place an (H) in the Active Level box above Output Function 0, (F<sub>0</sub>). Conversely,  $X_1$  can

be expressed as  $X_1$  by placing an (L) in the Active Level box above Output Function 1, (F.)

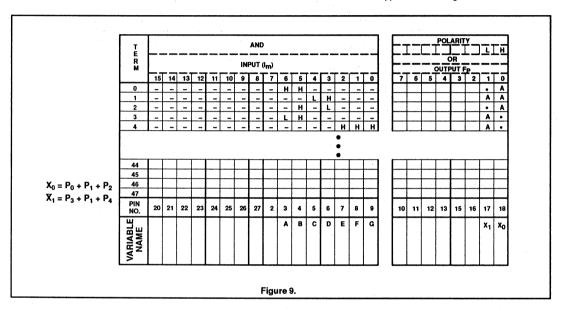

Introduction

#### Step 5

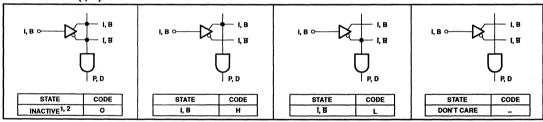

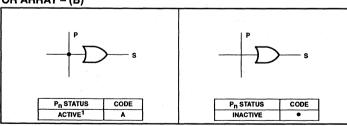

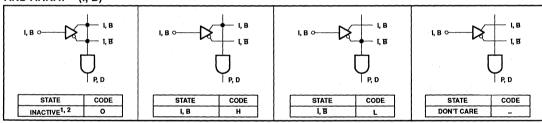

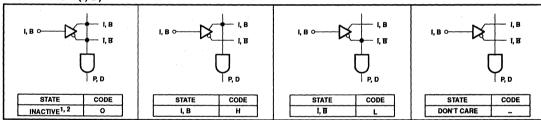

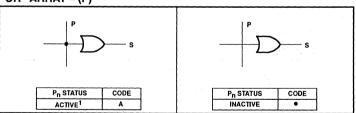

Select the P-Terms you wish to make active for each Output Function. In this case  $X_0 = P_0 + P_1 + P_2$ , so an A has been placed in the intersection box for  $P_0$  and  $X_0$ ,  $P_1$  and  $X_0$  and  $P_2$  and  $X_0$ .

Terms which are not active for a given output are made inactive by placing a (•) in the box under that P-term. Leave all unused P-terms unprogrammed.

Continue this operation until all outputs have been defined in the Program Table.

#### Step 6

Enter the data into a Philips Semiconductors approved programmer. The input format is identical to the Philips Semiconductors Program Table. You specify the P-terms, Output Active Level, and which P-terms are active for each output exactly the way it appears on the Program Table.

#### Introduction

#### PLD LOGIC SYNTHESIS

(Continued)

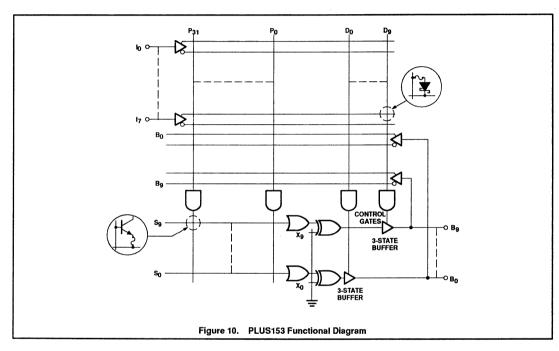

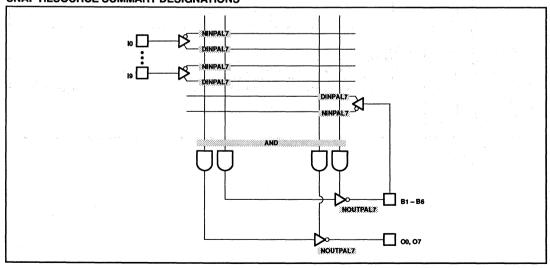

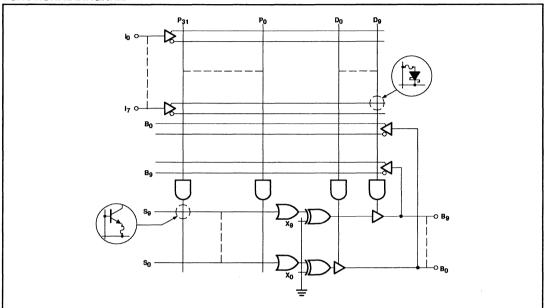

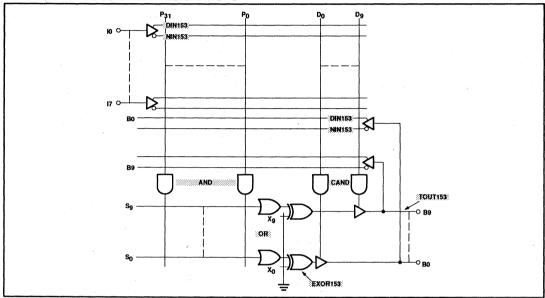

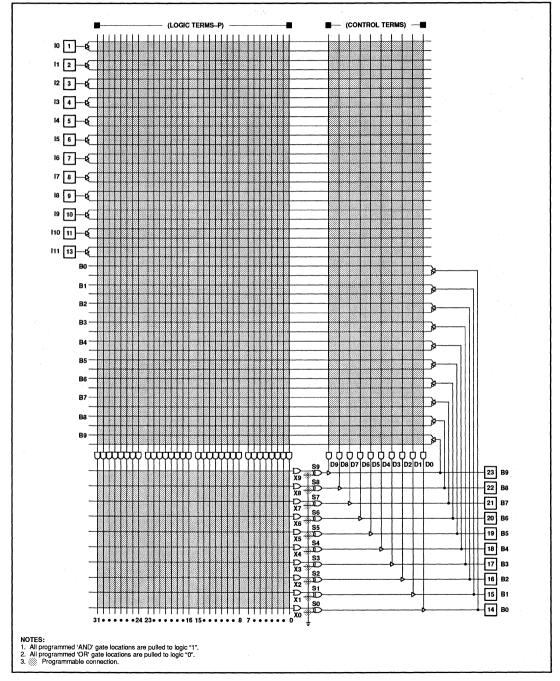

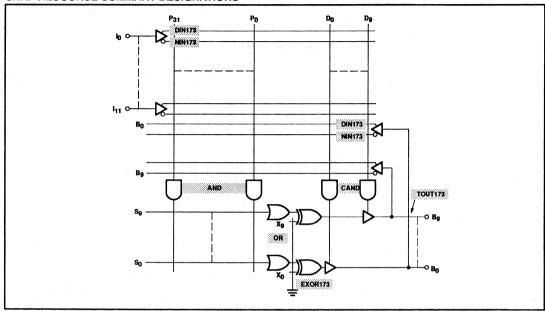

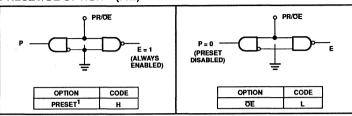

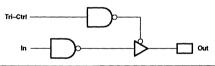

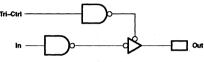

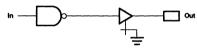

When fewer inputs and outputs are required in a logic design and low cost is most important, the Phillips Semiconductors 20-pin PLD should be considered first choice. The

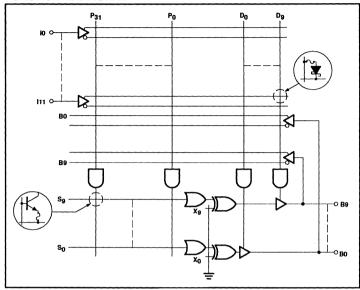

PLUS153 is a PLA with 8 inputs, 10 I/O pins, and 42 product terms. The user can configure the device by defining the direction of the I/O pins. This is easily accomplished by using the direction control terms  $D_0 - D_9$  to establish

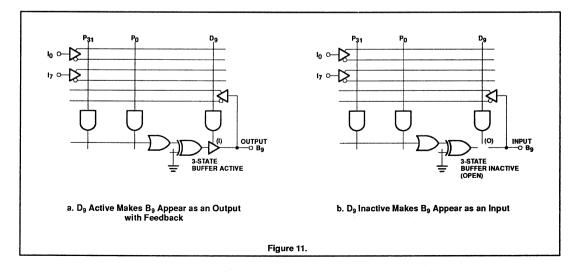

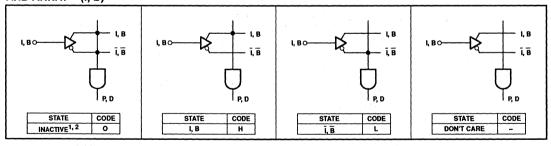

the direction of pins  $B_0-B_9$ . The D-terms control the 3-State buffers found on the outputs of the Ex-OR gates. Figures 10 and 11 show how the D-term configures each  $B_X$  pin.

#### Introduction

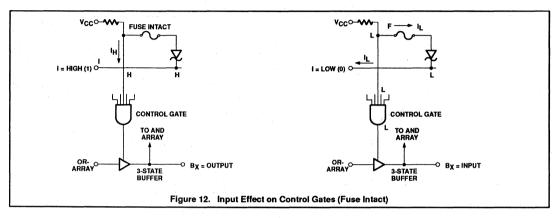

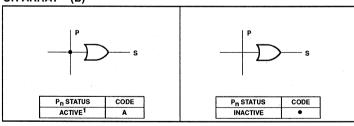

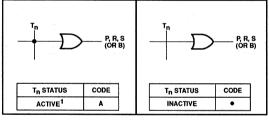

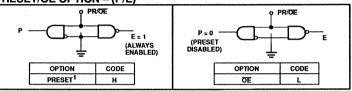

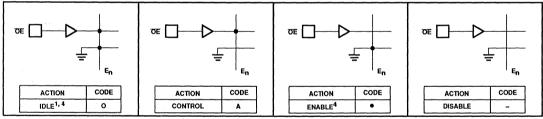

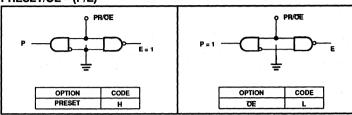

To control each D-term, it is necessary to understand that each control gate is a 36-input AND gate. To make the 3-State buffer active (B<sub>x</sub> pin an output), the output of the control gate must be at logic HIGH (1). This can be accomplished in one of two

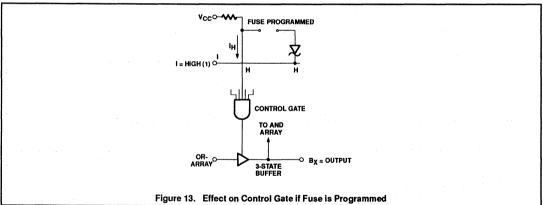

ways. A HIGH can be forced on all control gate input nodes, or fuses can be programmed. When a fuse is programmed, that control gate input node is internally pulled up to HIGH (1). See Figure 12 and Figure 13.

Programming the fuse permanently places a HIGH (1) on the input to the control gate. The input pin no longer has any effect on that state.

#### Introduction

#### DEDICATING B<sub>x</sub> PIN DIRECTION

Since each input to the D-terms is true and complement buffered (see Figure 11), when the device is shipped with all fuses intact, all control gates have half of the 36 input lines at logic low (0). The result of this is all Control Gate outputs are low (0) and the 3-State buffers are inactive. This results in all B<sub>X</sub> pins being in the input condition, the resultant device is, therefore, an 18-input, 0-output FPLA. While useful as a bit bucket or

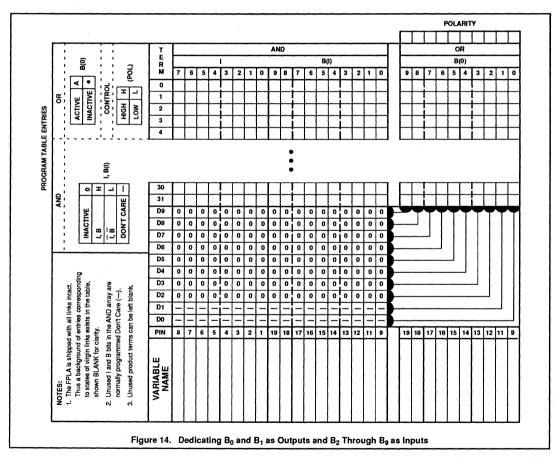

Write-Only-Memory (WOM), most applications require at least one output. Clearly, the first task is to determine which of the  $B_X$  pins are to be outputs. The next step is to condition the control gate to make the 3-State buffer for those gates active. To dedicate  $B_0$  and  $B_1$  as outputs, it is necessary to program all fuses to the inputs to Control Gates  $D_0$  and  $D_1$ . This internally pulls all inputs to those gates to HIGH (1) permanently. since all inputs to the Control

Gates are HIGH (1), the output is HIGH (1) and the 3-State buffers for  $B_0$  and  $B_1$  are active. This permanently enables  $B_0$  and  $B_1$  as outputs. Note that even though  $B_0$  and  $B_1$  are outputs, the output data is available to the AND array via the internal feedback (see Figure 11a).

To program this data, the PLUS153 Program Table is used as shown in Figure 14.

Introduction

By placing a (—) Don't Care in each input box you are specifying that the True and Complement fuses are programmed on each Control Gate, thus permanently dedicating the  $B_0$  and  $B_1$  pins as outputs. By placing a (0) in all input boxes for  $B_2$  -  $B_9$ , you are specifying that both True and Complement fuses are intact. This causes a low (0) to be forced on half of the Control Gate inputs, guaranteeing the output of the Control Gate will be low (0). When the Control Gate outputs are low (0), the 3-State buffer is

inactive and the  $B_2$  -  $B_9$  pins are enabled as inputs. All  $B_X$  pin directions can be controlled in this manner.

#### **ACTIVE DIRECTION CONTROL**

Sometimes it is necessary to be able to actively change the direction of the  $B_X$  pins without permanently dedicating them. Some applications which require this include 3-State bus enable, multi-function decoding, etc. This can easily be done by programming the

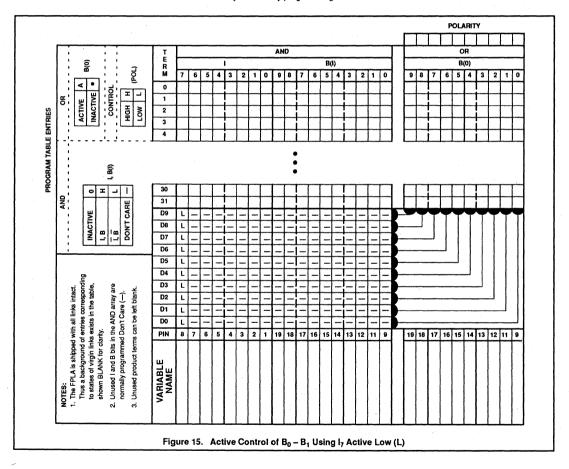

Control Gate to respond to one or more input pins. It is only necessary to select which  $I_X$  and  $B_X$  pins will control the pin directions and the active level HIGH (H) or LOW (L) that will be used. The PLUS153 Program Table in Figure 15 shows the method of controlling  $B_0-B_9$  with  $I_7$ . When  $I_7$  is LOW (L), pins  $B_0-B_9$  are outputs; when  $I_7$  is HIGH (H), pins  $B_0-B_9$  are inputs. Note that by programming all other  $I_X$  and  $B_X$  pins as DON'T CARE (—), they are permanently disconnected from control of  $B_X$  pin direction.

#### Introduction

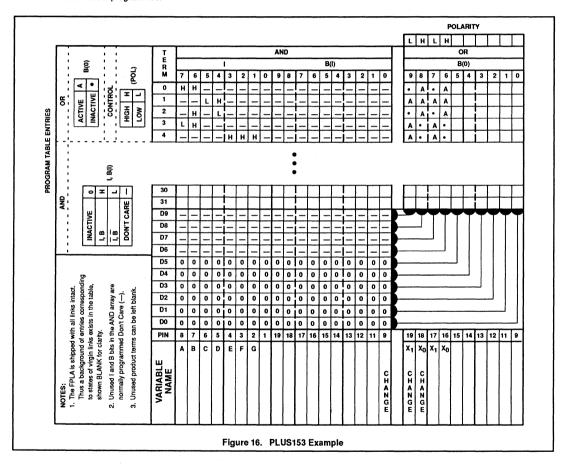

The previous 28-pin logic synthesis example could be done on the PLUS153 as follows:

$$X_0 = AB + \overline{C}D + B\overline{D}$$

$\overline{X}_1 = \overline{A}B + \overline{C}D + EFG$

Note that  $B_0$  was used as a CHANGE input. When  $B_0$  is HIGH (H) the outputs appear on  $B_8$  and  $B_9$ . When  $B_0$  is LOW (L), the outputs appear on  $B_6$  and  $B_7$ .  $B_1$  through  $B_5$  are not used and therefore left unprogrammed.

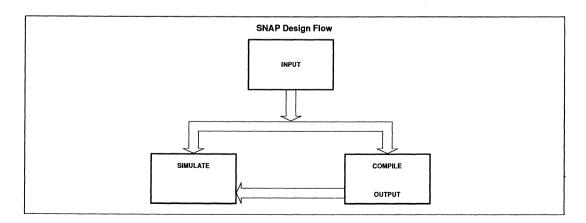

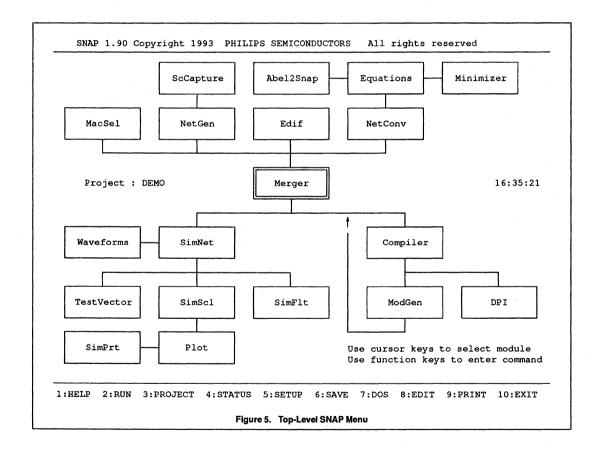

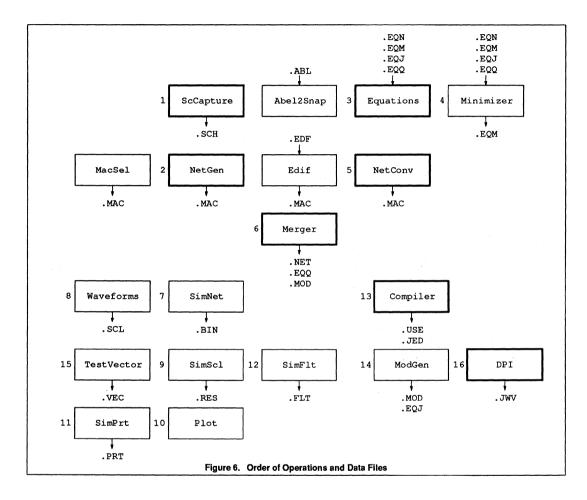

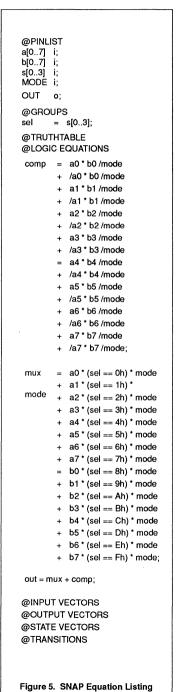

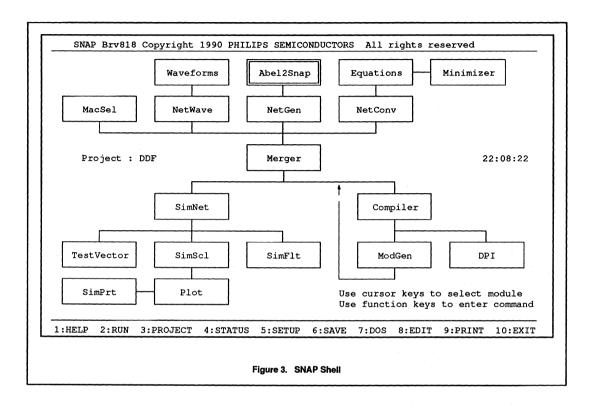

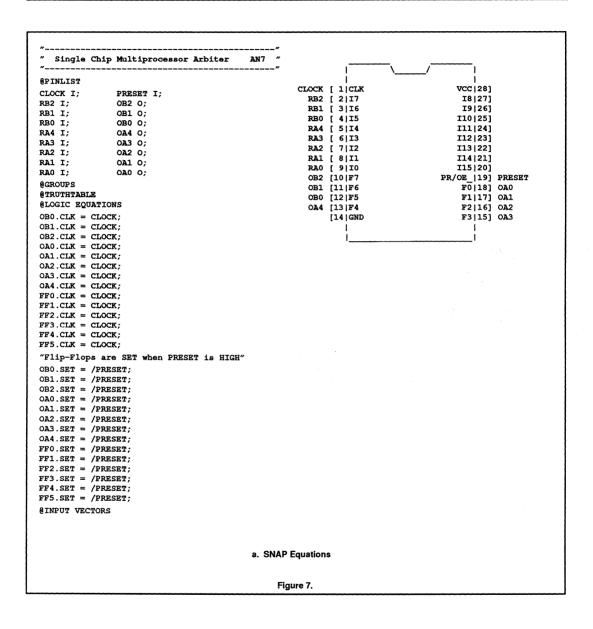

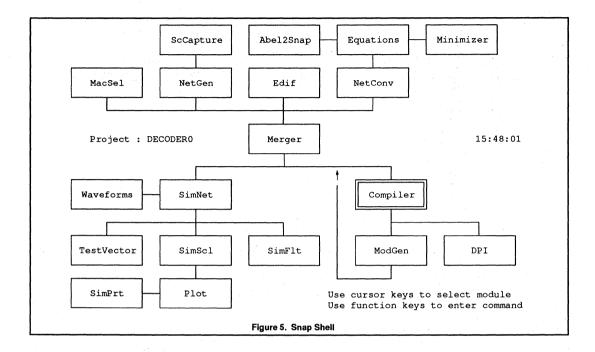

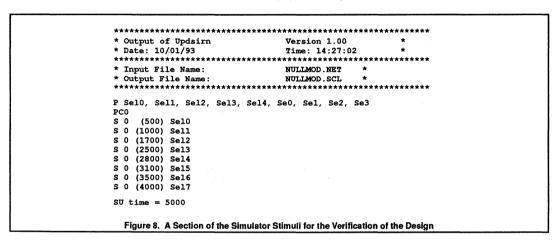

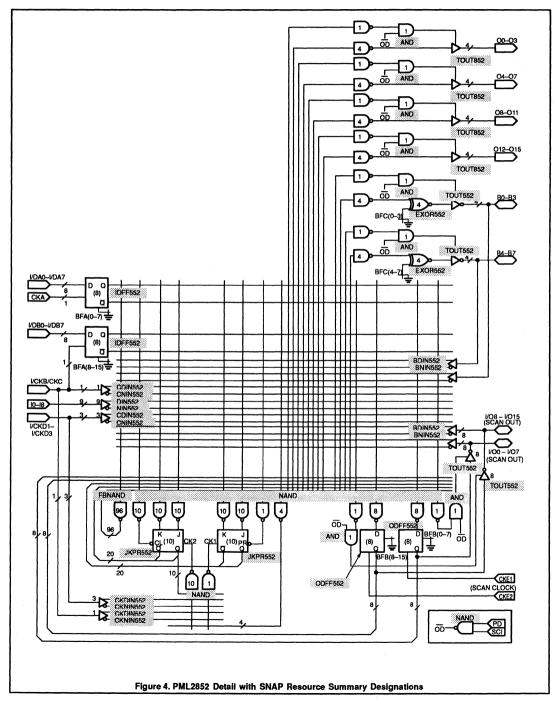

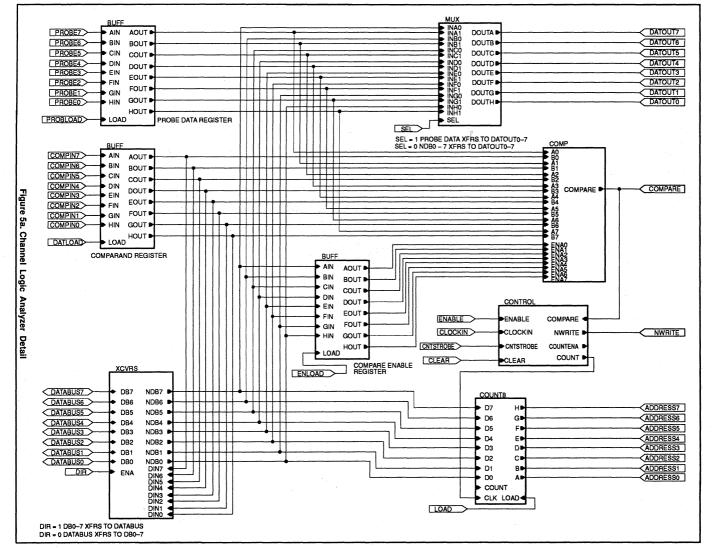

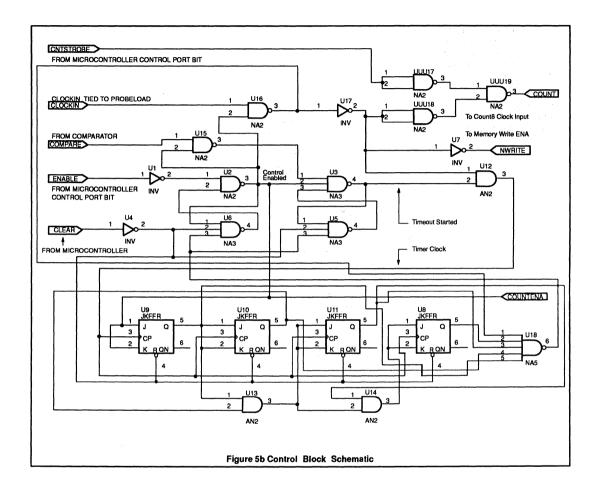

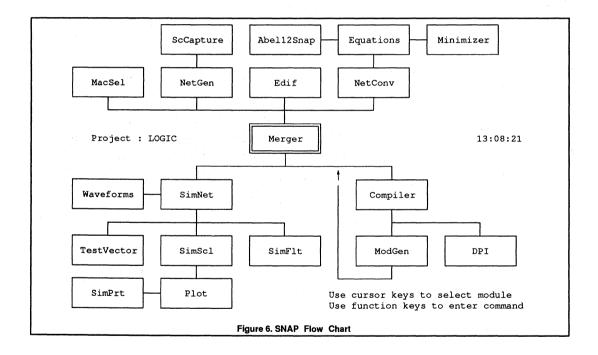

Philips Semiconductors offers two packages for user-friendly design assistance. The first package, AMAZE, has evolved over 10 years to support Philips Semiconductors programmable products with logic equation, state equation, and schematic entry. AMAZE can compile designs quite well for Philips Semiconductors lower density parts. However, to satisfy the needs of

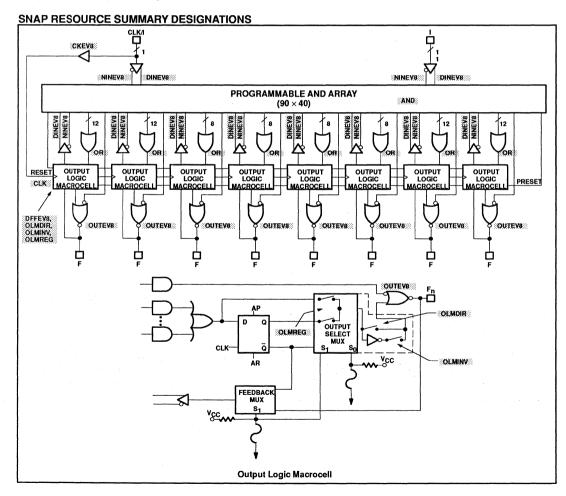

Programmable Macro Logic users, Philips Semiconductors developed an additional software package called SNAP. SNAP expands upon the capabilities of AMAZE in its approach to design implementation, more closely resembling a gate array methodology. Both of these products are described in more depth at a later point in this handbook.

#### Introduction

## SEQUENTIAL LOGIC CONSIDERATIONS

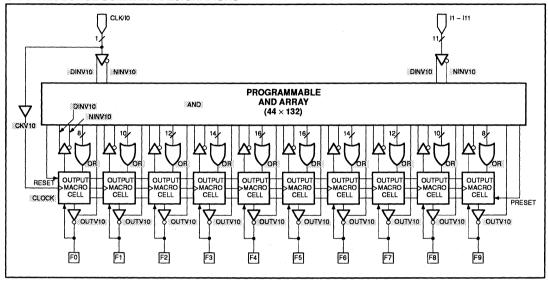

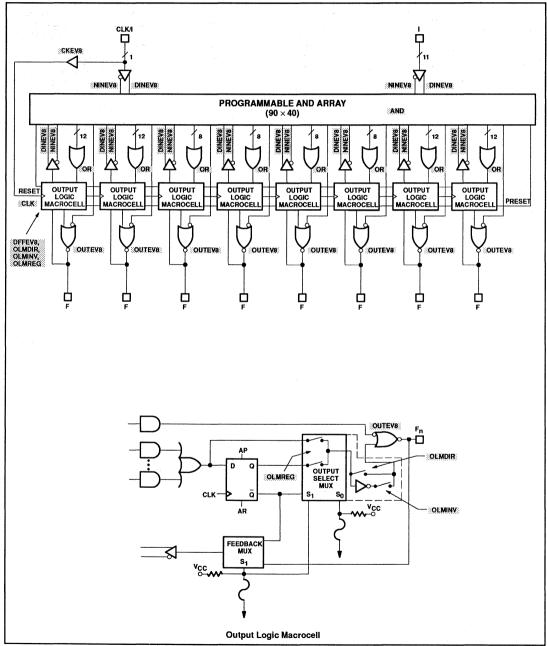

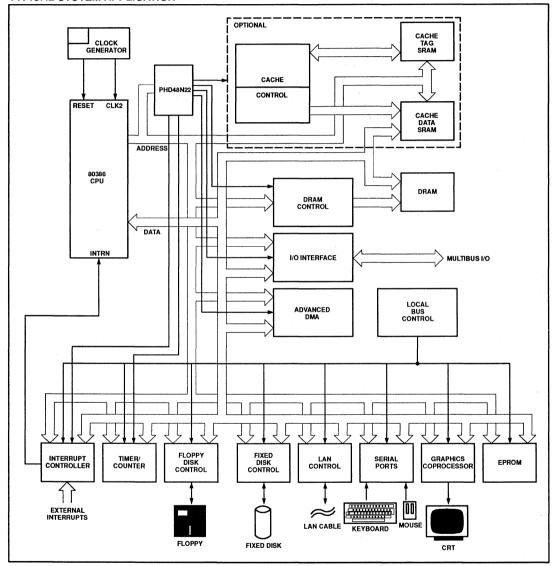

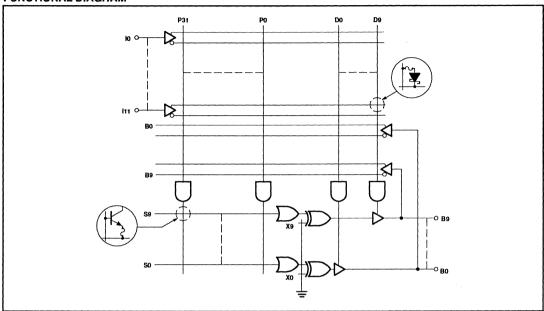

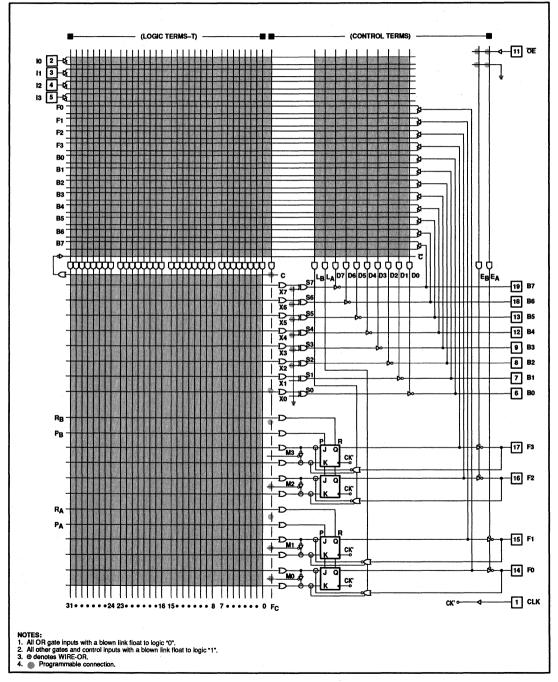

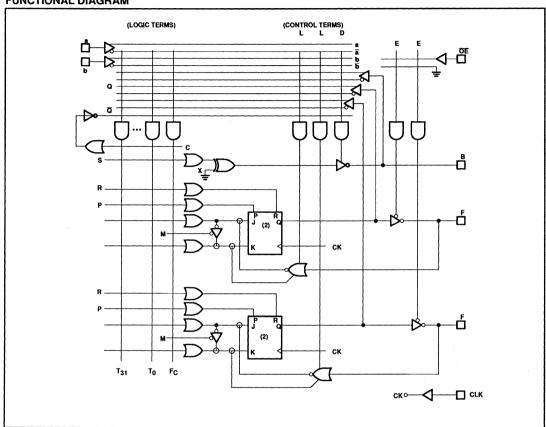

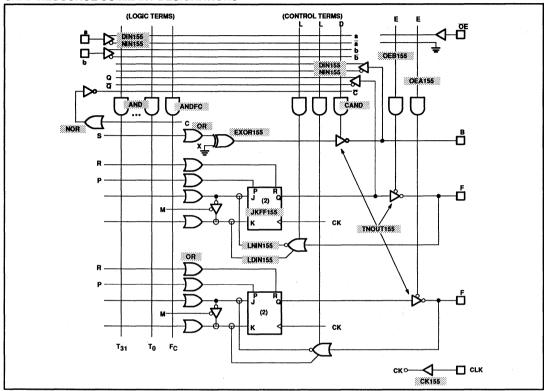

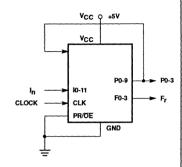

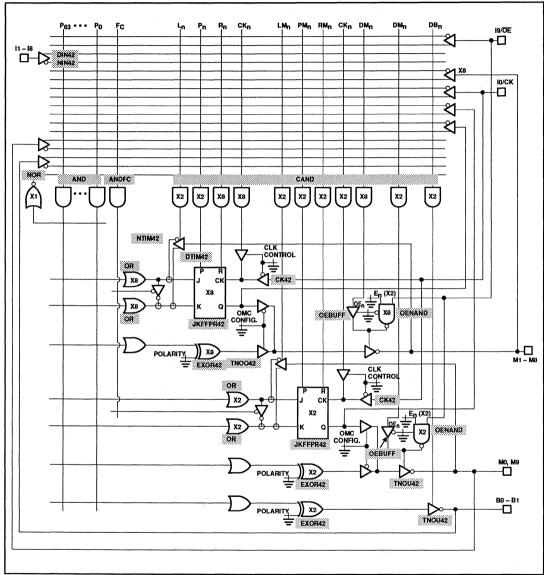

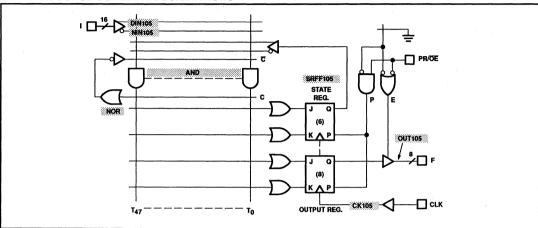

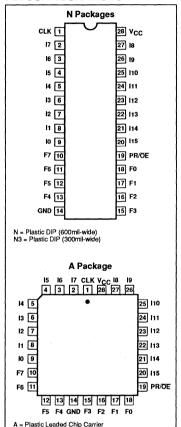

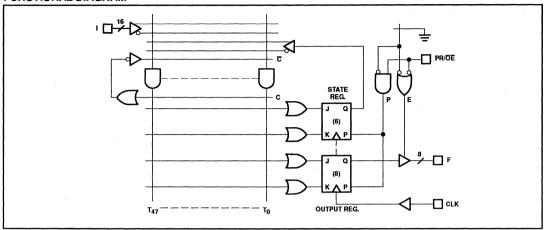

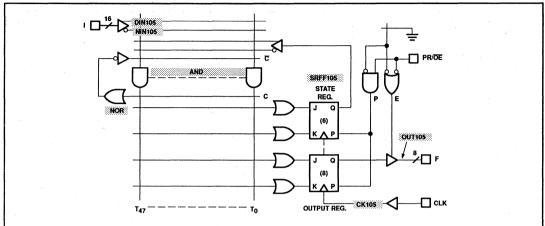

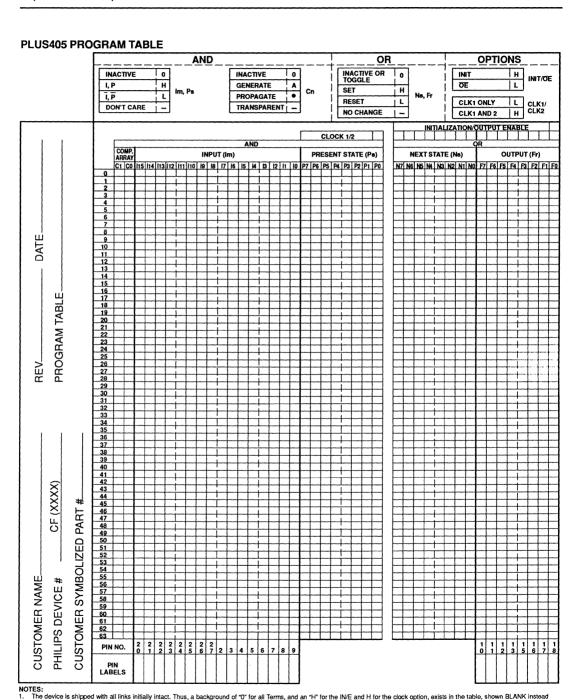

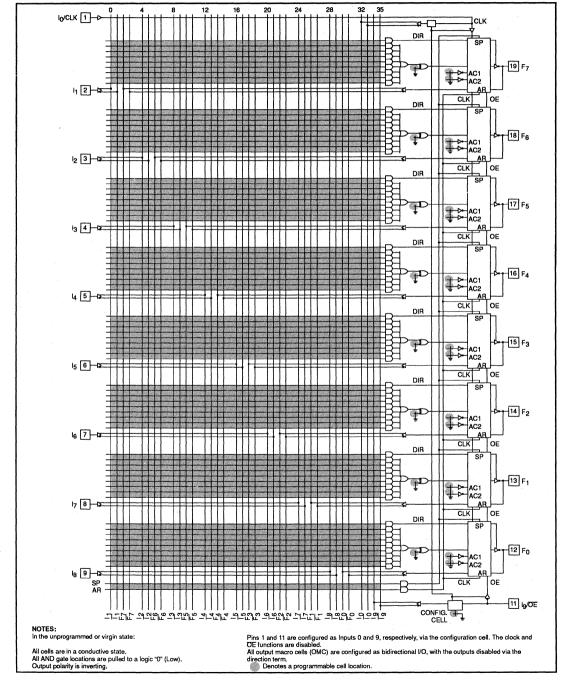

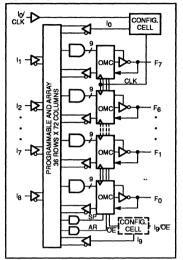

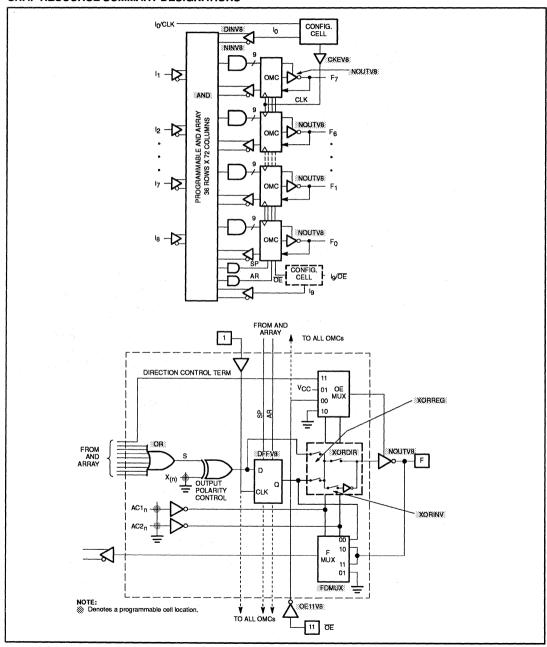

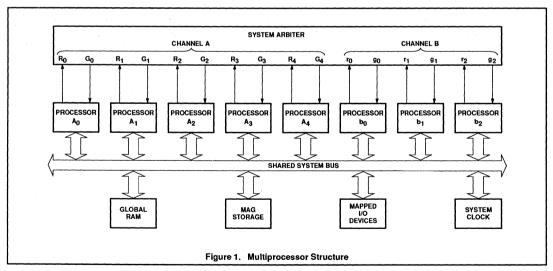

The PLUS405, PLUS105 and PLC42VA12 represent significant increases in complexity when compared to the combinatorial logic devices previously discussed. By combining the AND/OR combinatorial logic with clock output flip-flops and appropriate feedback, Philips Semiconductors has created the first family of totally flexible sequential logic machines.

The PLUS405 (Programmable Logic Sequencer) is an example of a high-order machine whose applications are many. Application areas for this device include VRAM, DRAM, Bus and LAN control. The PLUS405 is fully capable of performing fast

sequential operations in relatively high-speed processor systems. By placing repetitive sequential operations on the PLUS405, processor overhead is reduced.

The following pages summarize the PLUS405 architecture and features.

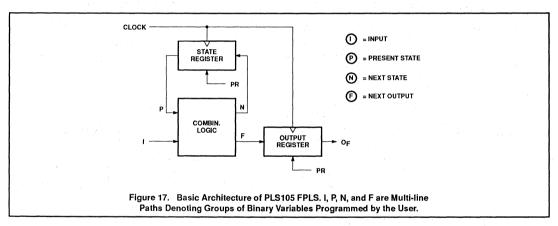

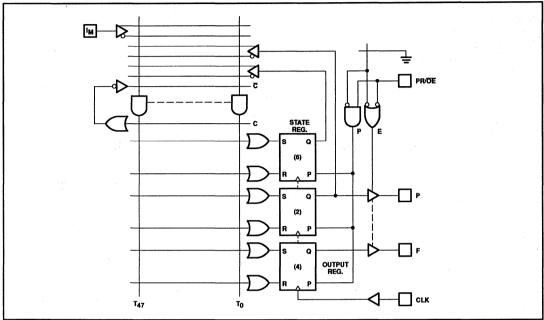

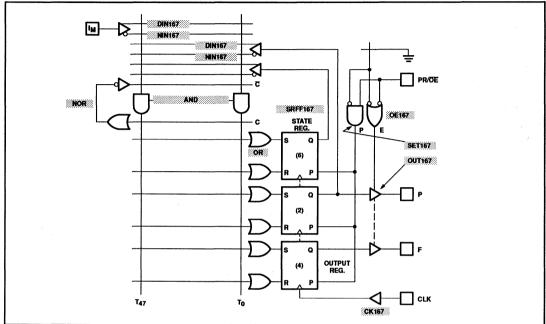

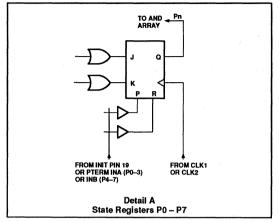

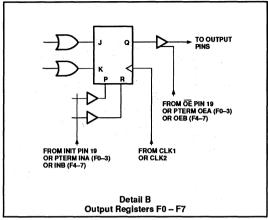

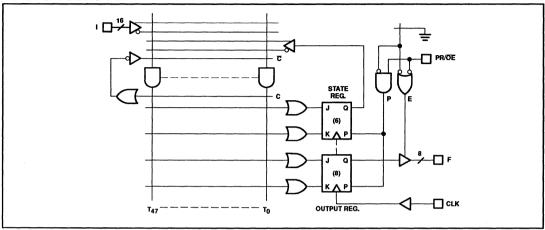

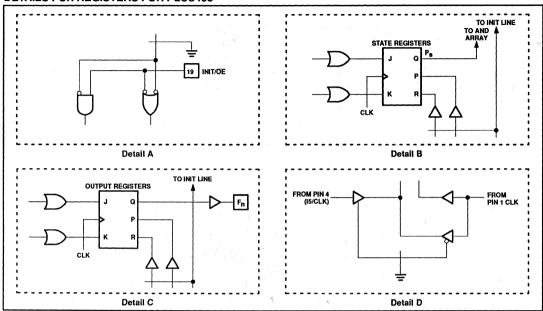

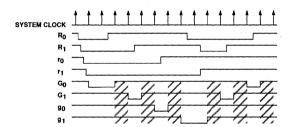

#### Sequencer Architecture

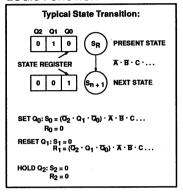

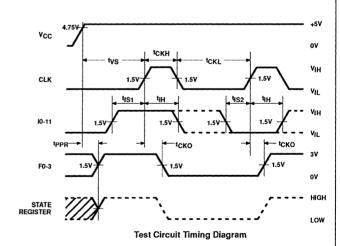

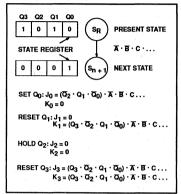

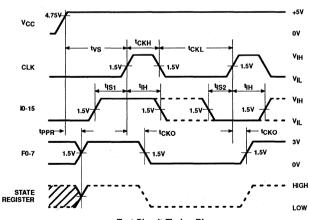

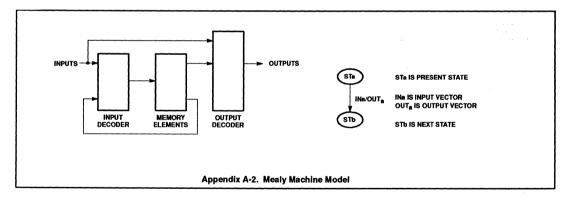

The PLUS405 Logic Sequencer is a programmable state machine, in which the output is a function of the present state and the present input.

With the PLUS405, a user can program any logic sequence expressed as a series of jumps between stable states, triggered by a valid input condition (I) at clock time (t). All stable states are stored in the State Register.

The logic output of the machine is also programmable, and is stored in the Output Register. The PLUS105 is a subset of the PLUS405.

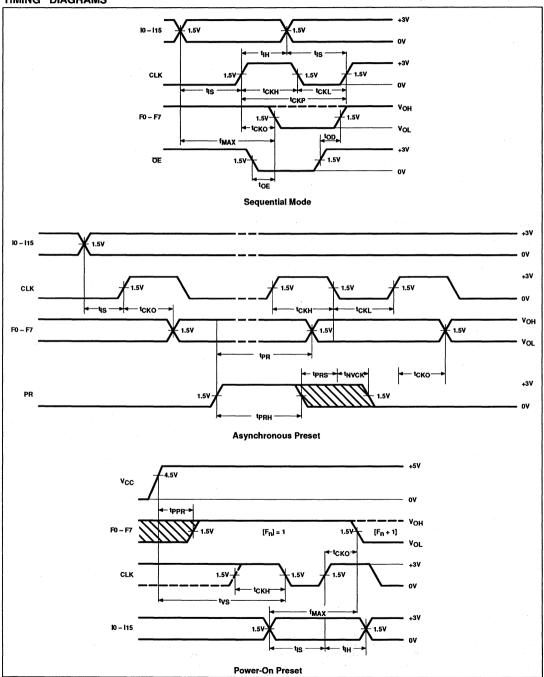

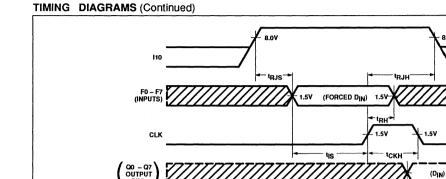

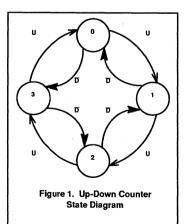

#### **Clocked Sequence**

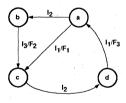

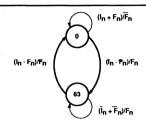

A synchronous logic sequence can be represented as a group of circles interconnected with arrows. The circles represent stable states, labeled with an arbitrary numerical code (binary, hex, etc.) corresponding to discrete states of a suitable register. The arrows represent state transitions, labeled with symbols denoting the jump condition and the required change in output. The number of states in the sequence depends on the length and complexity of the desired algorithm.

$I_{1-3}$  are jump conditions which must be satisfied before any transitions take place.

$F_{\rm r}$  are changes in output triggered by  $I_{\rm m}$ , and stored in the output register.

State transitions  $a \rightarrow b$  and  $c \rightarrow d$  involve no output change.

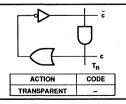

Figure 18. Typical State Diagram.

$$\begin{array}{c} P \\ \hline \\ \hline \\ N \end{array}$$

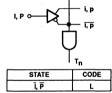

The arrow connecting the two states gives rise to a transition term  $\mathsf{T}_\mathsf{n}$ . I is the jump condition.

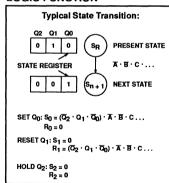

Figure 19. Typical State Transition Between Any Two States of Figure 18.

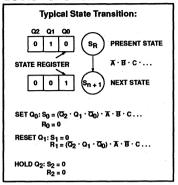

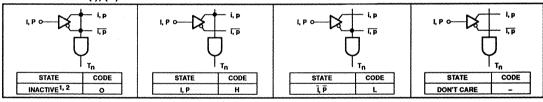

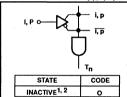

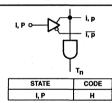

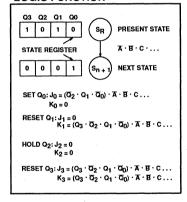

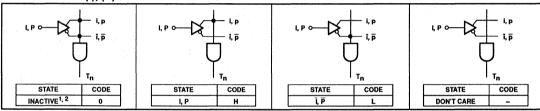

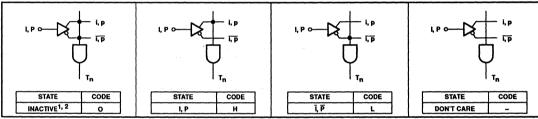

#### State Jumps

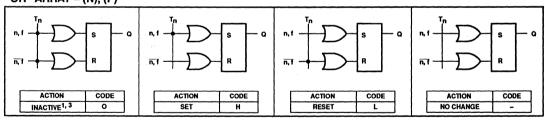

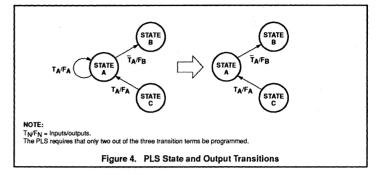

The state from which a jump originates is referred to as the Present state (P), and the state to which a jump terminates is defined as the Next state (N). A state jump always causes a change in state, but may or may not cause a change in machine output (F).

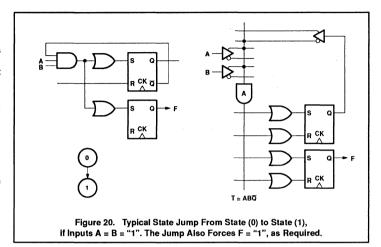

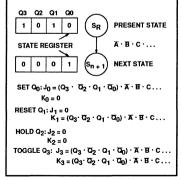

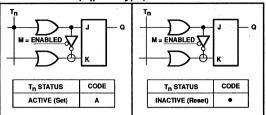

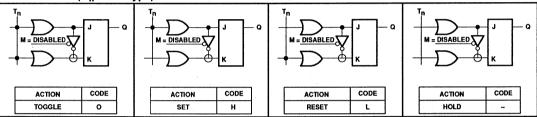

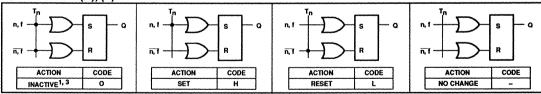

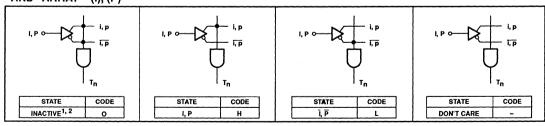

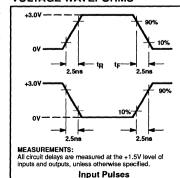

State jumps can occur only via "transition terms"  $T_n$ . These are logical AND functions of the clock (t), the Present state (P), and a valid input (I). Since the clock is actually applied to the State Register,  $T_n = I \bullet P$ . When  $T_n$  is "true", a control signal is generated and used at clock time (t) to force the contents of the State Register from (P) to (N), and to change the contents of the Output Register (if necessary). The simple state jump in Figure 20, involving 2 inputs, 1 state bit, and 1 output bit, illustrates the equivalence of discrete and programmable logic implementations.

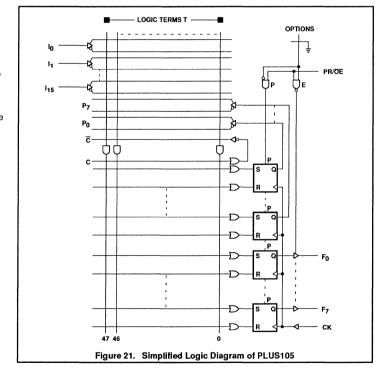

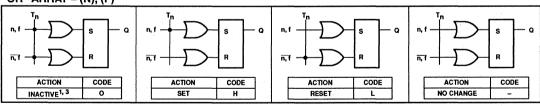

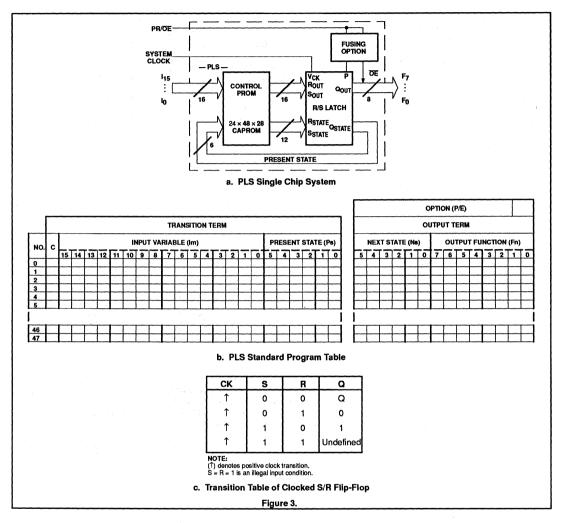

#### **Sequencer Logic Structure**

The Sequencer consists of programmable AND and OR gate arrays which control the Set and Reset inputs of a State Register, as well as monitor its output via an internal feedback path. The arrays also control an independent Output Register, added to store output commands generated during state transitions, and to hold the output constant during state sequences involving no output changes. If desired, any number of bits of the Output Register can be used to extend the width of the State Register, via external feedback.

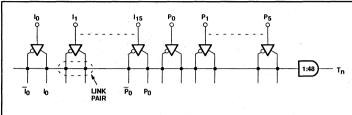

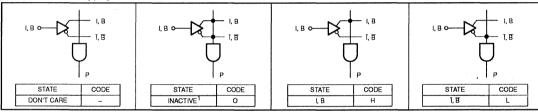

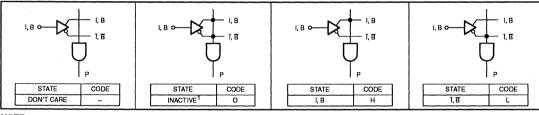

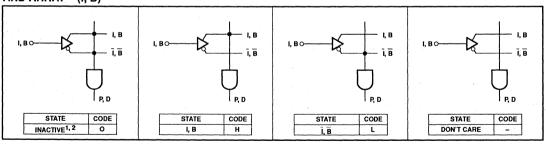

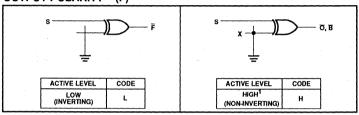

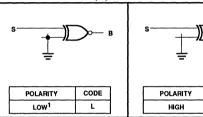

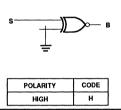

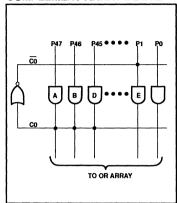

Figure 22. Typical AND Gate Coupled to (I) and (P) Inputs.

If at Least One Link Pair Remains Intact, T<sub>n</sub> is Unconditionally Forced Low.

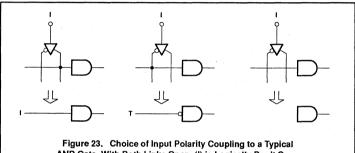

Figure 23. Choice of Input Polarity Coupling to a Typical AND Gate. With Both Links Open, (I) is Logically Don't Care.

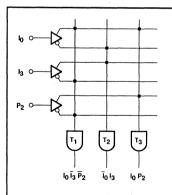

Figure 24. Typical Transition Terms Involving Arbitrary Inputs and State Variables. All Remaining Gate Inputs Are Programmed Don't Care. Note That T<sub>2</sub> Output is State Independent.

#### **Input Buffers**

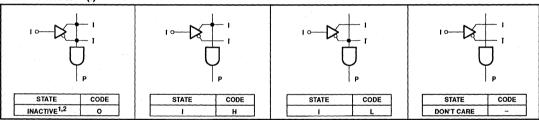

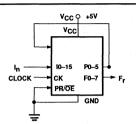

16 external inputs ( $I_m$ ) and 6 internal inputs ( $P_s$ ), fed back from the State Register, are combined in the AND array through two sets of True/Complement (T/C) buffers. There are a total of 22 T/C buffers, all connected to multi-input AND gates via fusible links which are initially intact.

Selective fusing of these links allows coupling either True, Complement, or Don't Care values of  $(I_m)$  and  $(P_n)$ .

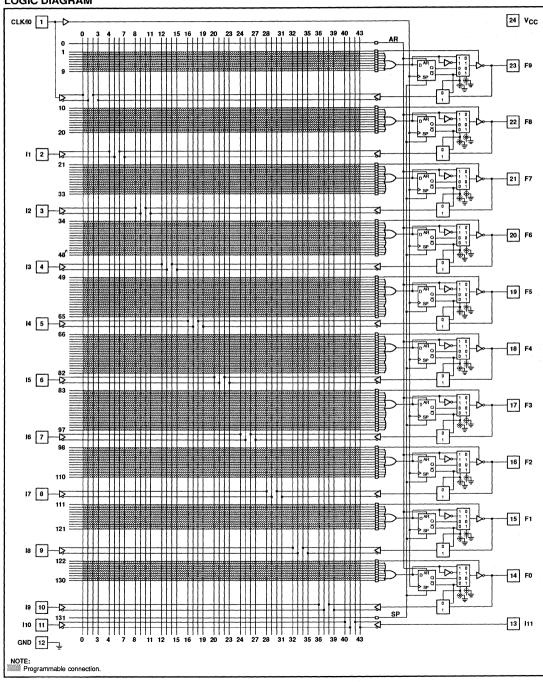

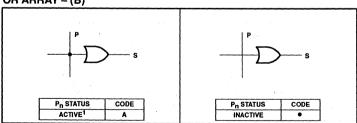

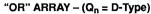

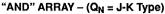

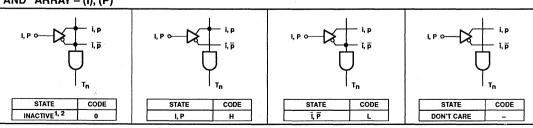

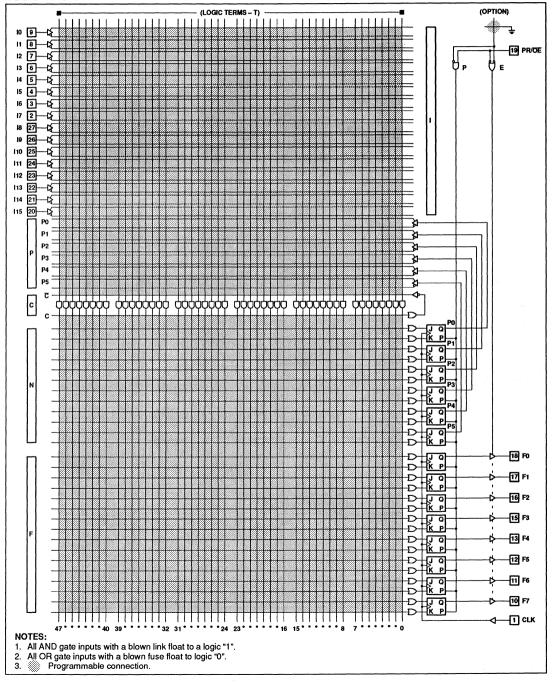

#### "AND" Array

State jumps and output changes are triggered at clock time by valid transition terms T<sub>n</sub>. These are logical AND functions of the present state (P) and the present input (I).

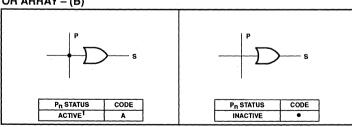

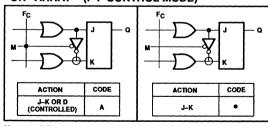

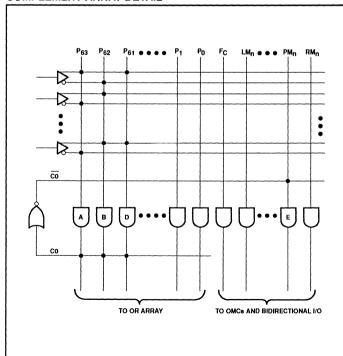

The PLUS105 AND Array contains a total of 48 AND gates. Each gate has 45 inputs – 44 connected to 22 T/C input buffers, and 1 dedicated to the Complement Array. The outputs of all AND gates are propagated through the OR Array, and used at clock time (t) to force the contents of the State Register from (P) to (N). they are also used to control the Output Register, so that the FPLS 8-bit output F<sub>r</sub> is a function of the inputs and the present state. The PLUS405 contains 64 AND gates in its' AND array.

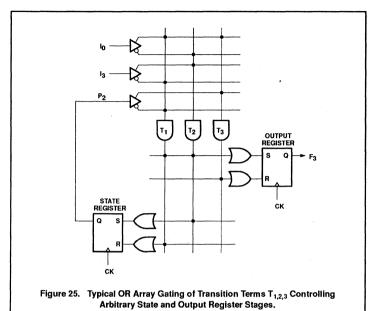

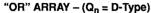

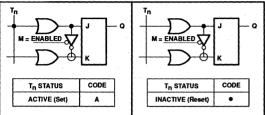

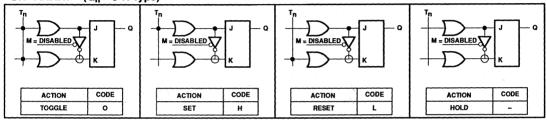

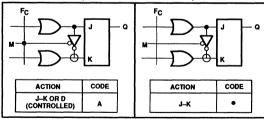

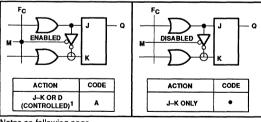

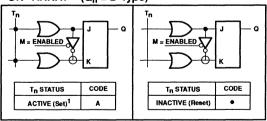

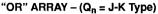

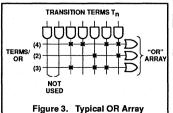

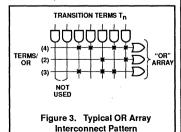

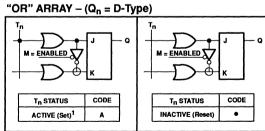

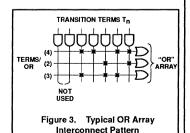

#### "OR" Array

In general, a clocked sequence will consist of several stable states and transitions, as determined by the complexity of the desired algorithm. All state and output changes in the state diagram imply changes in the contents of State and Output Registers.

Thus, each flip-flop in both registers may need to be conditionally set or reset several times with Tn commands. This is accomplished by selectively ORing through a programmable OR Array all AND gate outputs T<sub>n</sub> necessary to activate the proper flip-flop control inputs.

The PLUS105 OR Array consists of 14 pairs of OR gates, controlling the S/R inputs of 14 State and Output Register stages, and a single NOR gate for the Complement Array. All gates have 48 inputs for connecting to all 48 AND gates. The PLUS405 uses 64 input

The PLUS405 contains 16 pairs of OR gates controlling state transitions and output stages and two additional NOR gates for dual complement arrays.

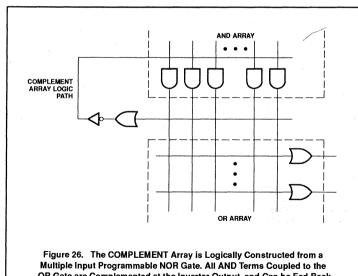

OR Gate are Complemented at the Inverter Output, and Can be Fed Back as Inputs to the AND Array.

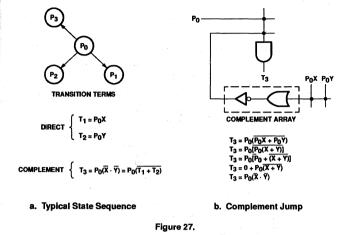

- a. X and Y Specify the Conditional Logic for Direct Jump Transition Terms  $T_1$  and  $T_2$ . The Complement Jump Term  $T_3$  is True Only When Both  $T_1$  and  $T_2$  are False.

- Note that the Complementary Logic Expression for T<sub>3</sub>, T<sub>1</sub> + T<sub>2</sub>, Corresponds Exactly to the Logic Structure of the Complement Array.

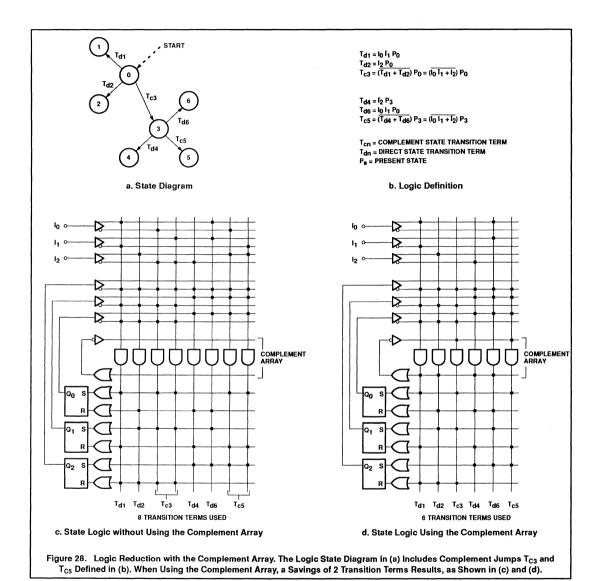

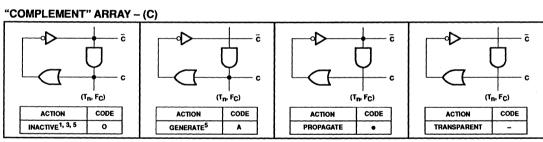

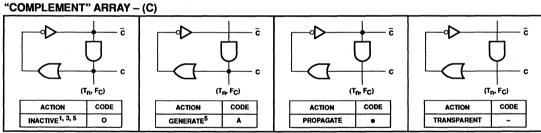

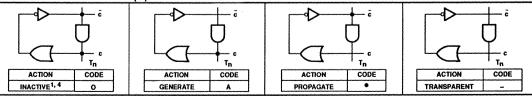

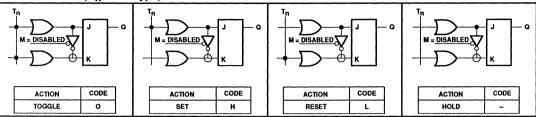

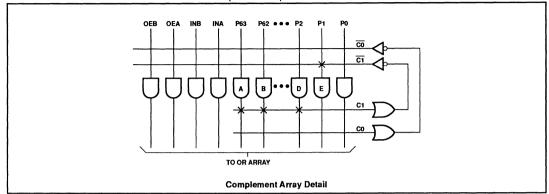

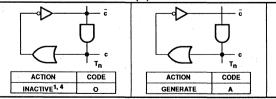

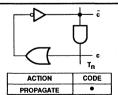

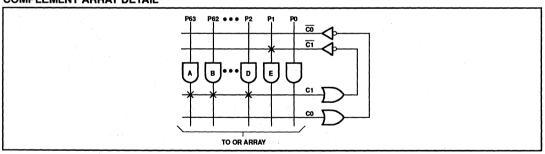

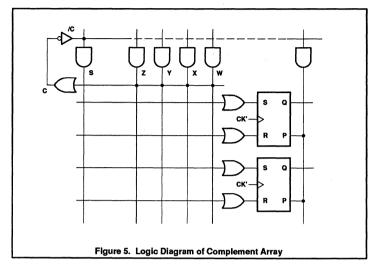

#### **Complement Array**

The Complement Array provides an asynchronous feedback path from the OR Array back to the AND Array.

This structure enables the sequencer to perform both direct and complement sequential state jumps with a minimum of transition (AND) terms.

Typically direct jumps, such as  $T_1$  and  $T_2$  in Figure 27 require only a single AND gate each.

But a complement jump such as T<sub>3</sub> generally requires many AND gates if implemented as a direct jump. However, by using the Complement Array, the logic requirements for this type of jump can be handled with just one more gate from the AND Array. Because it can be split into separate machines (2 clocks), the PLUS405 incorporates two Complement Arrays.

As indicated in Figure 28, the single Complement Array gate may be used for many states of the state diagram. This happens because all transition terms linked to the OR gate include the present state as a part of their conditional logic. In any particular state, only those transition terms which are a function of that state are enabled; all other terms coupled to different states are disabled and do not influence the output of the Complement Array. As a general rule of thumb, the Complement Array can be used as many times as there are states.

Additional features are available depending on a specific part. In particular, the PLC42VA12 has everything mentioned here, and more. More details on PLAs, PAL devices and Sequencers can be found in the application section later in the manual.

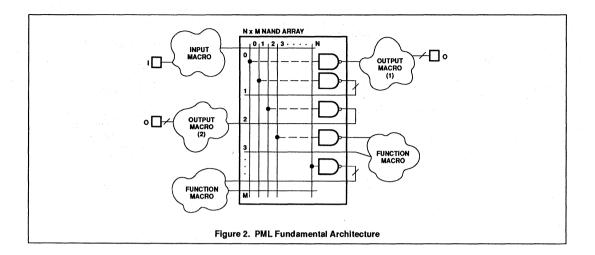

Programmable Macro Logic, Philips Semiconductors very high density logic is fully described in detail in its own section.

# Section 3 PAL Devices

#### CONTENTS

| PHD16N8-5                  | Programmable high-speed decoder logic ( $16 \times 16 \times 8$ ) 3   | 3 |

|----------------------------|-----------------------------------------------------------------------|---|

| PLC18V8z35/PLC18V8ZI       | Zero standby power CMOS versatile PAL devices                         | 4 |

| PLC18V8Z25/PLC18V8ZIA      | Zero standby power CMOS versatile PAL devices                         | 5 |

| PLUS16R8D/-7 Series        | PAL devices 16L8, 16R8, 16R6, 16R4                                    | 7 |

| PLUS20R8D/-7 Series        | PAL devices 20L8, 20R8, 20R6, 20R4                                    | 8 |

| PL22V10-10                 | CMOS programmable electrically erasable logic device . 10             | 0 |

| PL22V10-12/-15, PL22V10I15 | CMOS programmable electrically erasable logic device . 1              | 1 |

| ABT22V10-7                 | BiCMOS versatile PAL device                                           | 3 |

| 10H20EV8/10020EV8          | ECL programmable array logic                                          | 4 |

| PHD48N22-7                 | Programmable high-speed decoder logic ( $48 \times 73 \times 22$ ) 16 | 6 |

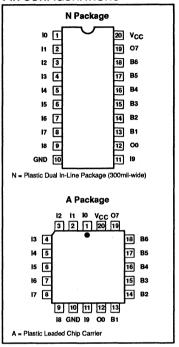

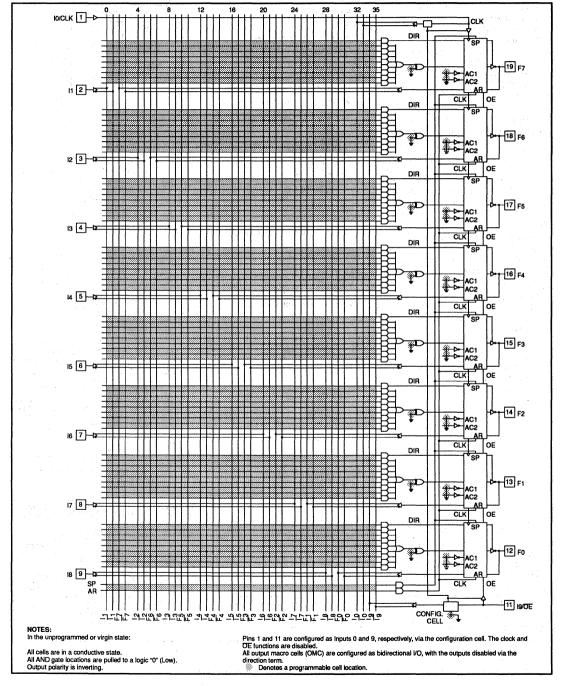

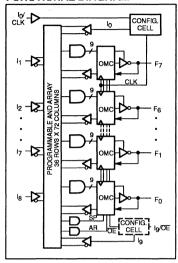

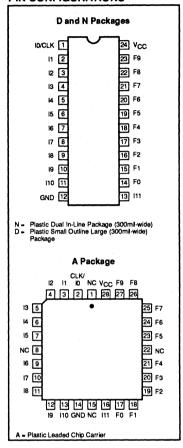

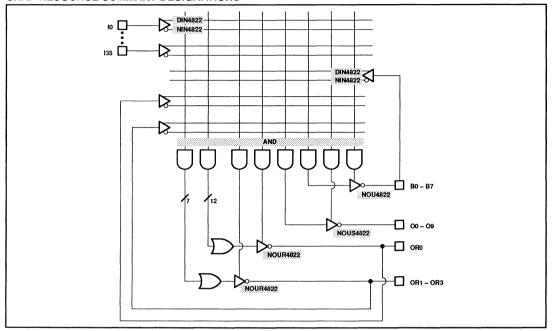

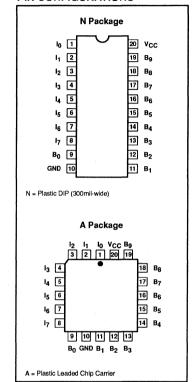

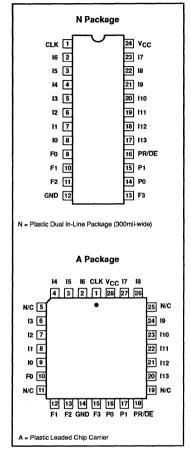

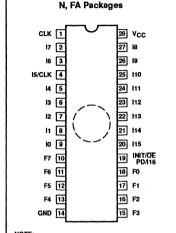

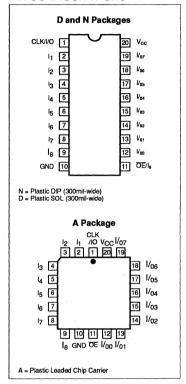

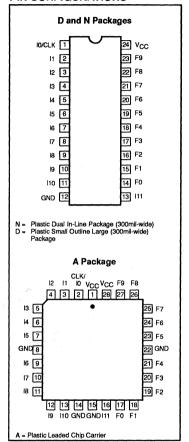

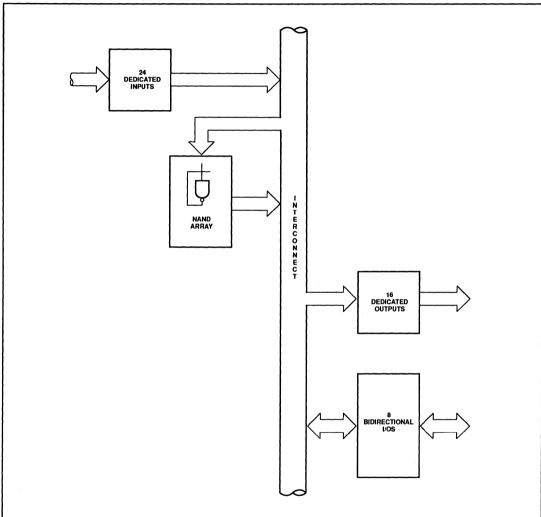

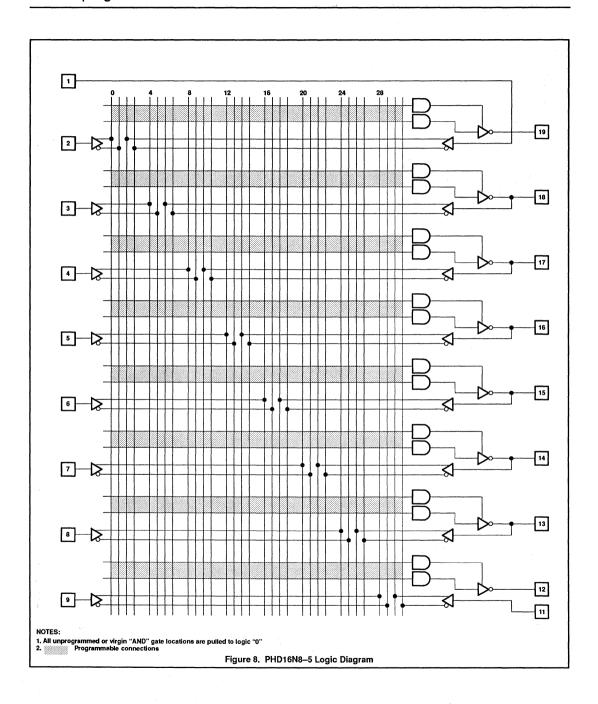

PHD16N8-5

### DESCRIPTION

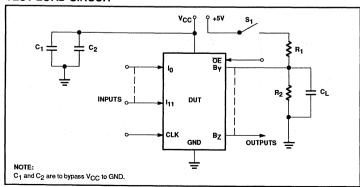

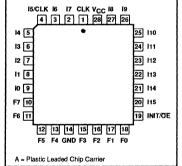

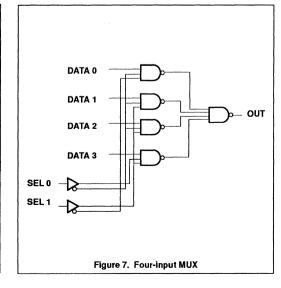

The PHD16N8-5 is an ultra fast Programmable High-speed Decoder featuring a 5ns maximum propagation delay. The architecture has been optimized using Philips Semiconductors state-of-the-art bipolar oxide isolation process coupled with titanium-tungsten fuses to achieve superior speed in any design.

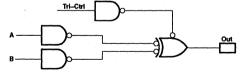

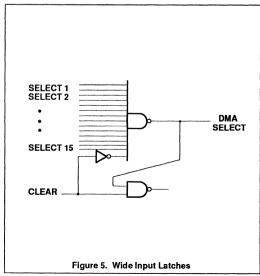

The PHD16N8-5 is a single level logic element comprised of 10 fixed inputs, 8 AND gates, and 8 outputs of which 6 are bidirectional. This gives the device the ability to have as many as 16 inputs. Individual 3-State control of all outputs is also provided.

The device is field-programmable, enabling the user to quickly generate custom patterns using standard programming equipment. Proprietary designs can be protected by programming the security fuse.

The SLICE software package from Philips Semiconductors supports easy design entry for the PHD16N8-5 as well as other PLD devices.

Order codes are listed below.

### **FEATURES**

- Ideal for high speed system decoding

- Super high speed at 5ns tpD

- 10 dedicated inputs

- 8 outputs

- 6 bidirectional I/O

- 2 dedicated outputs

- Security fuse to prevent duplication of proprietary designs.

- Individual 3-State control of all outputs

- Field-programmable on industry standard programmers

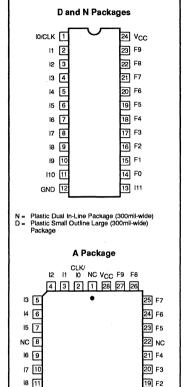

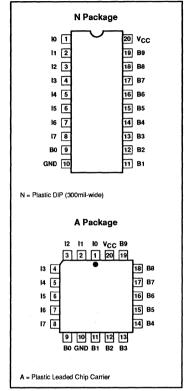

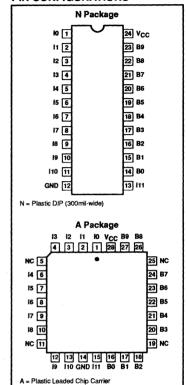

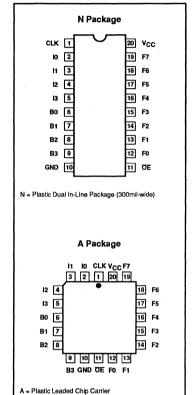

- Available in 20-pin Plastic Dual In-Line and 20-Pin PLCC

### **APPLICATIONS**

- High speed memory decoders

- High speed code detectors

- Random logic

- Peripheral selectors

- Machine state decoders

- Footprint compatible to 16L8

- Fuse/Footprint compatible to TIBPAD

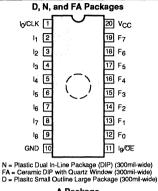

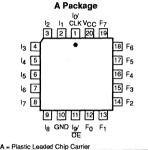

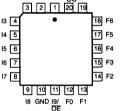

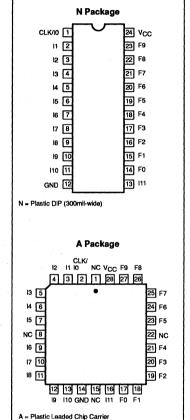

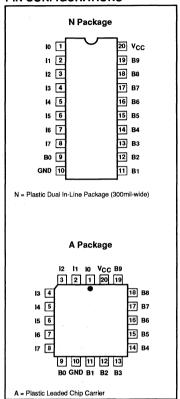

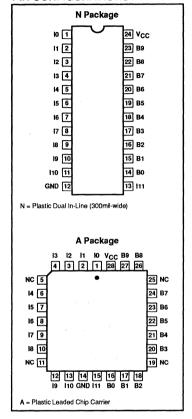

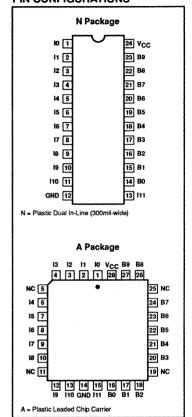

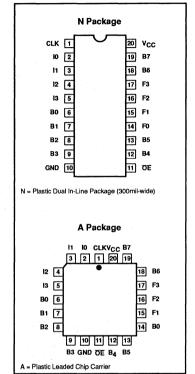

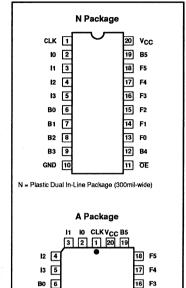

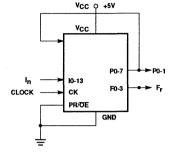

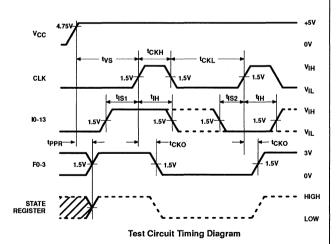

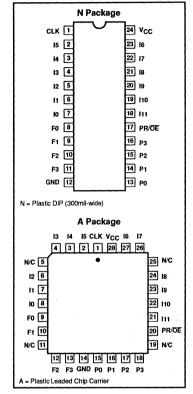

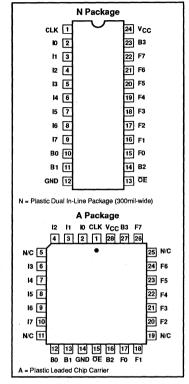

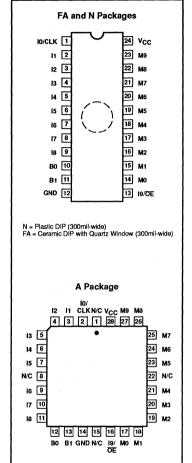

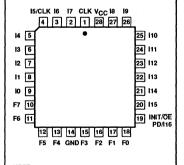

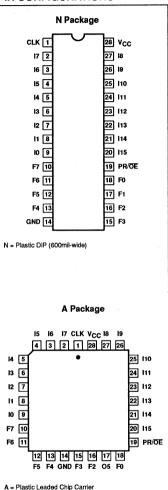

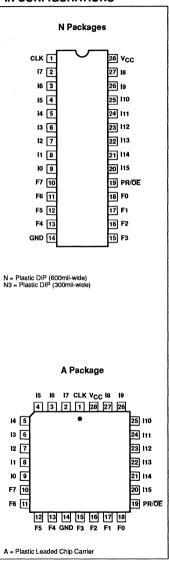

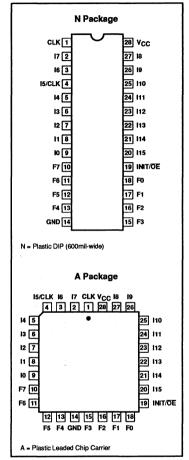

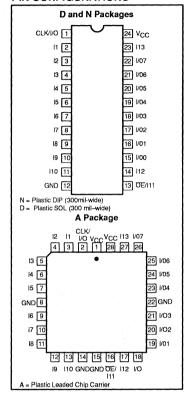

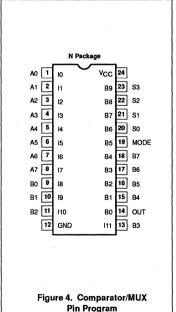

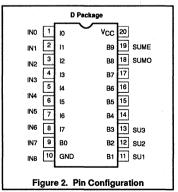

### **PIN CONFIGURATIONS**

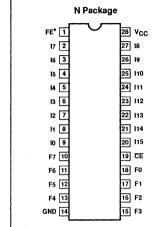

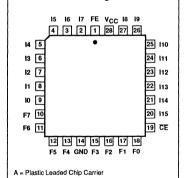

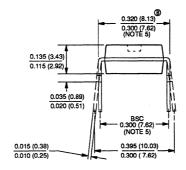

### ORDERING INFORMATION

| DESCRIPTION                                          | ORDER CODE | DRAWING NUMBER |

|------------------------------------------------------|------------|----------------|

| 20-Pin Plastic Dual In Line Package; (300 mil-wide)  | PHD16N8-5N | 0173D          |

| 20-Pin Plastic Leaded Chip Carrier; (350 mil square) | PHD16N8-5A | 0400E          |

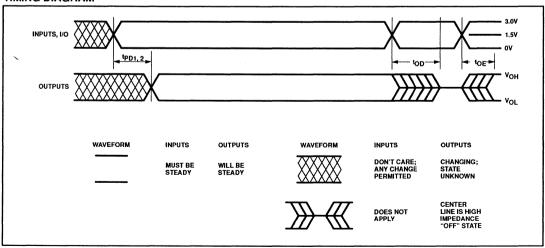

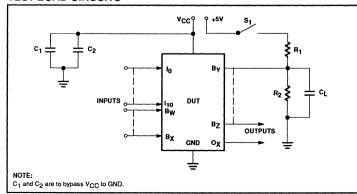

PHD16N8-5

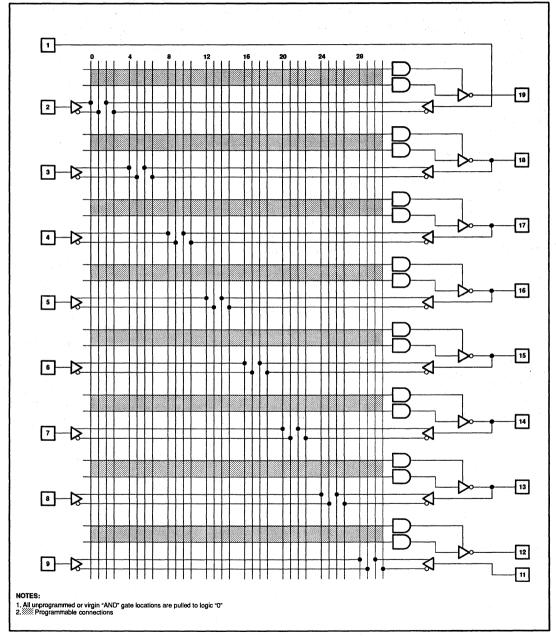

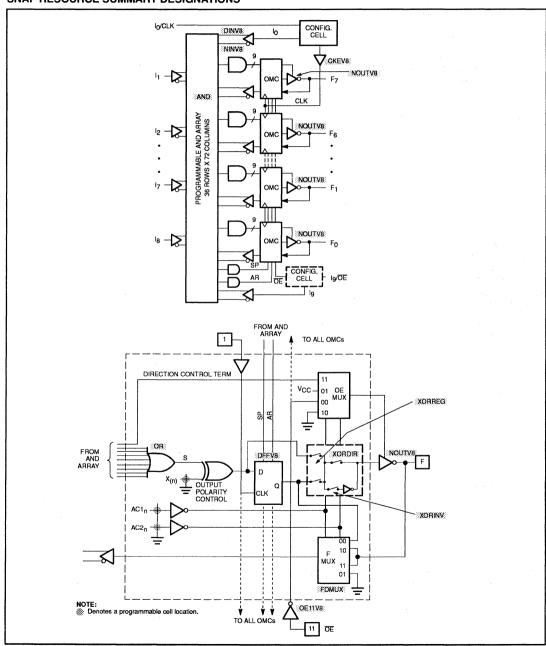

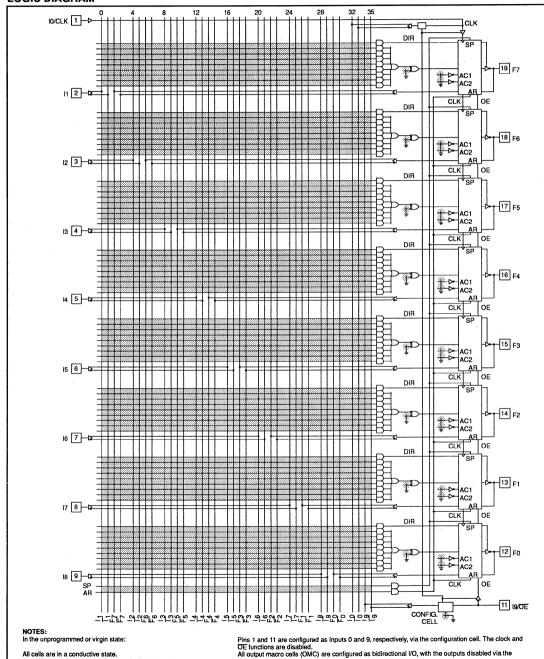

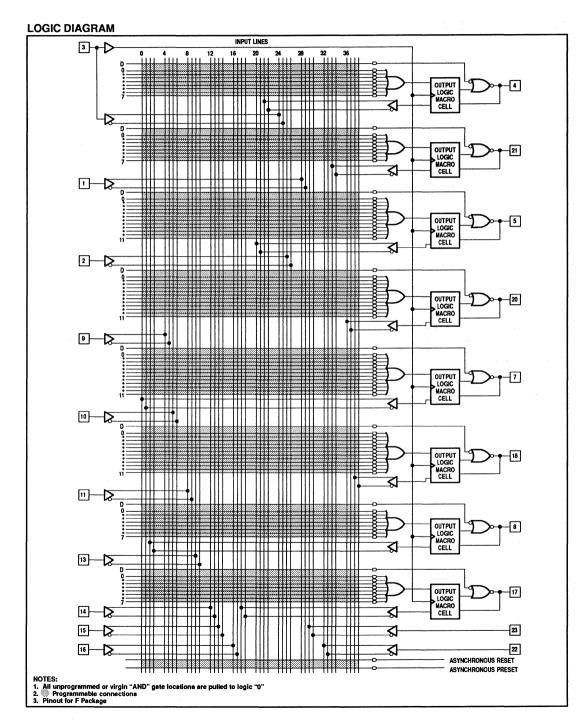

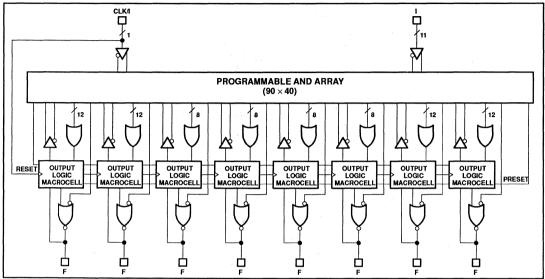

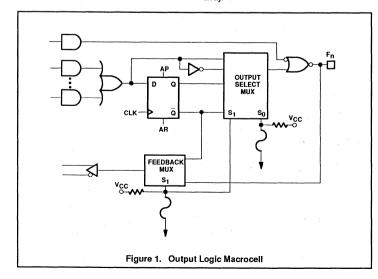

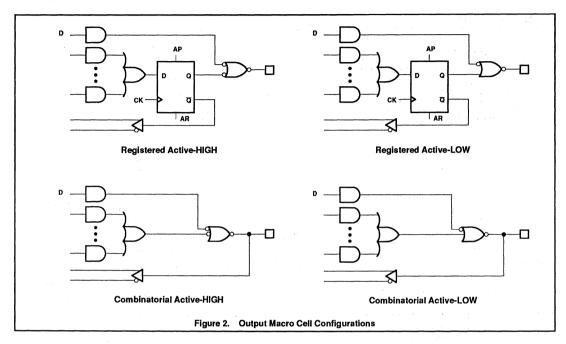

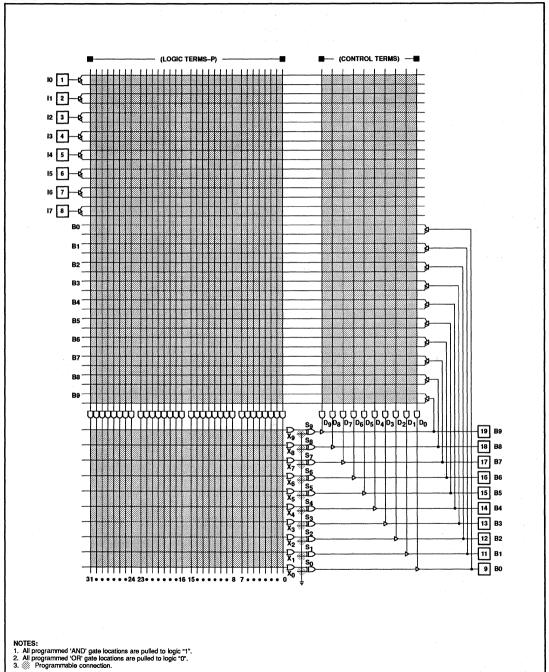

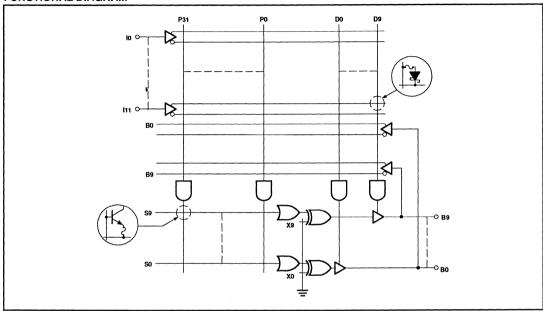

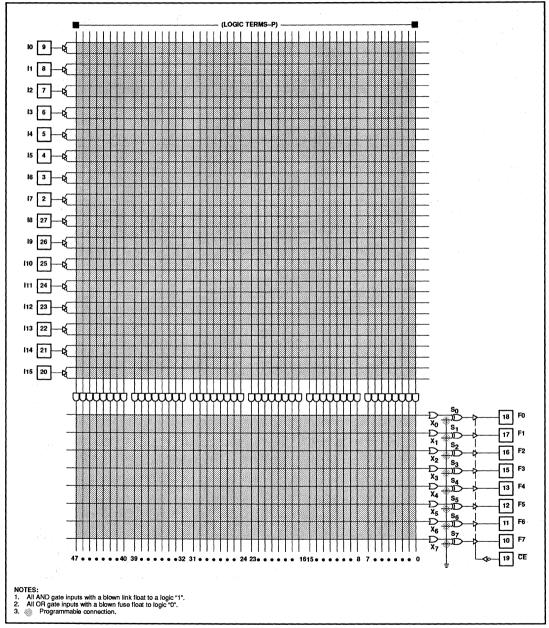

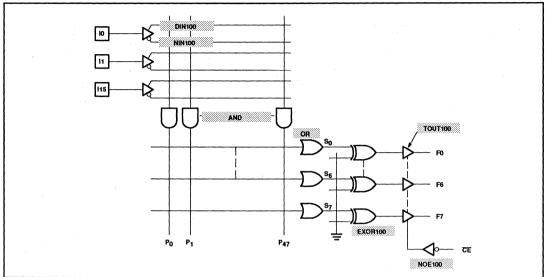

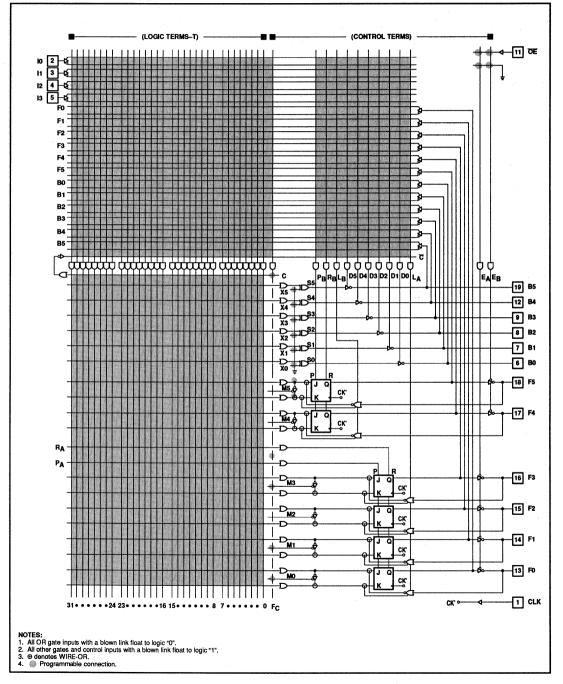

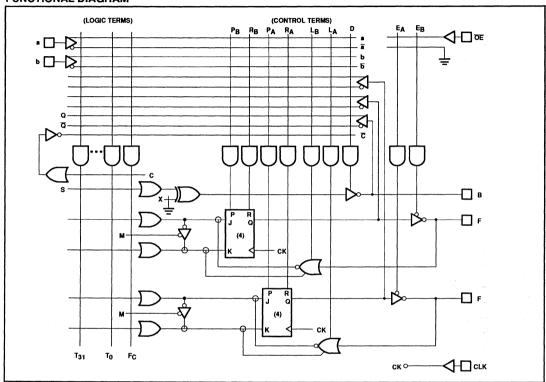

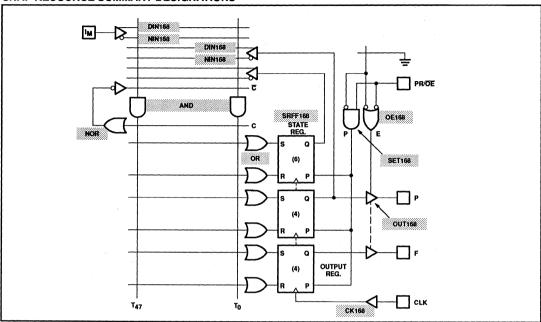

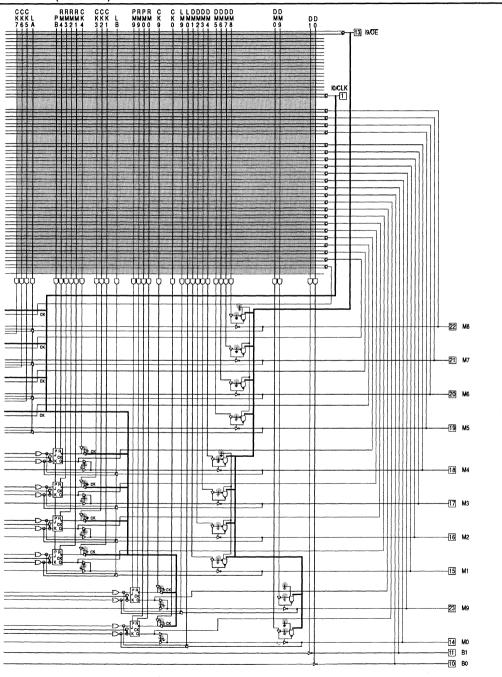

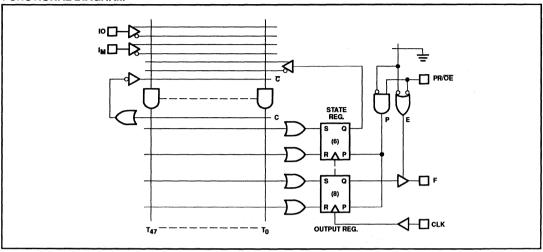

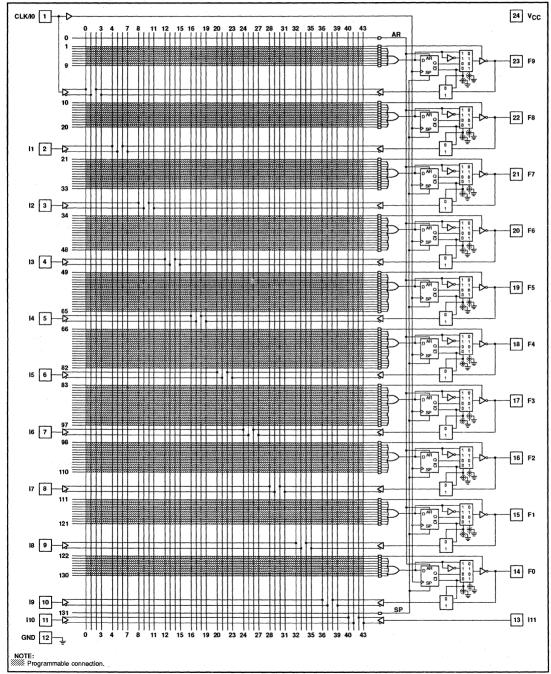

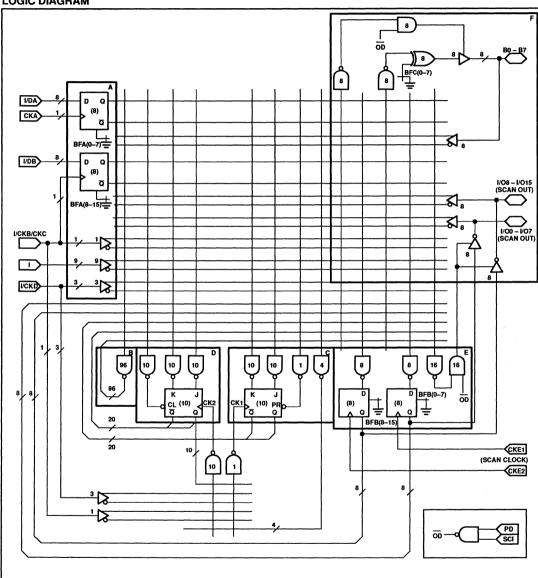

### **LOGIC DIAGRAM**

PHD16N8-5

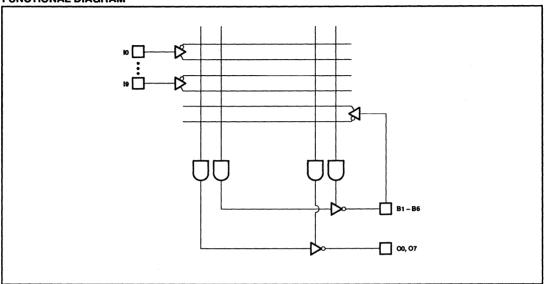

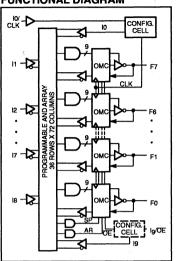

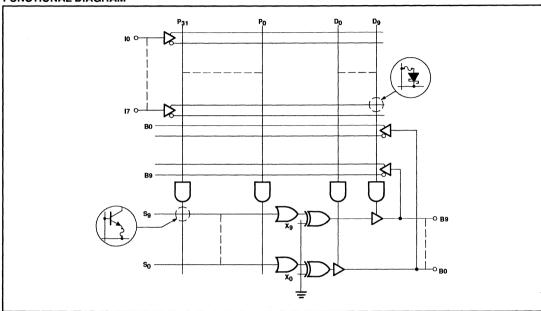

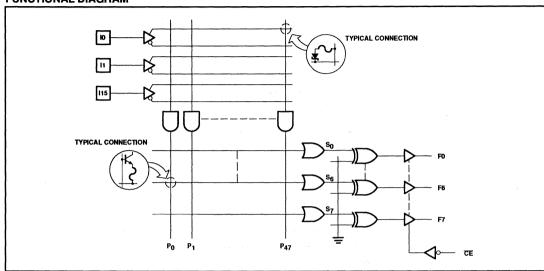

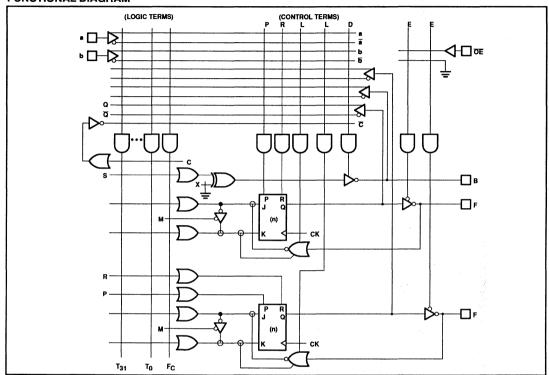

### **FUNCTIONAL DIAGRAM**

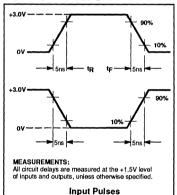

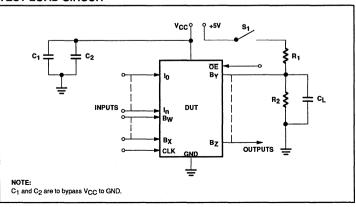

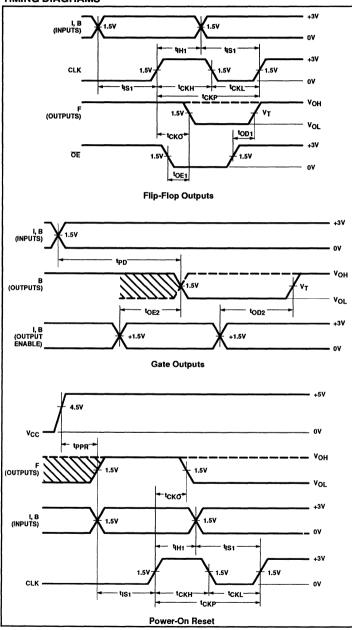

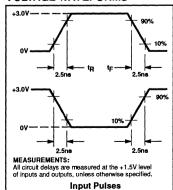

### **ABSOLUTE MAXIMUM RATINGS<sup>1</sup>**

|                  |                             | RATI |      |                 |

|------------------|-----------------------------|------|------|-----------------|

| SYMBOL           | PARAMETER                   | Min  | Max  | UNIT            |

| V <sub>CC</sub>  | Supply voltage              | -0.5 | +7   | V <sub>DC</sub> |

| V <sub>IN</sub>  | Input voltage               | -0.5 | +5.5 | V <sub>DC</sub> |

| V <sub>OUT</sub> | Output voltage              |      | +5.5 | V <sub>DC</sub> |

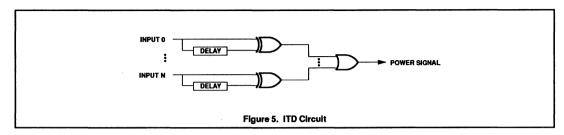

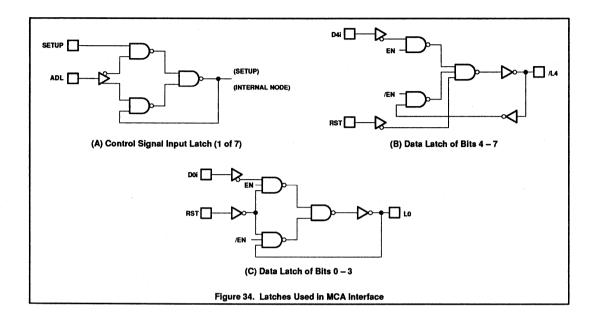

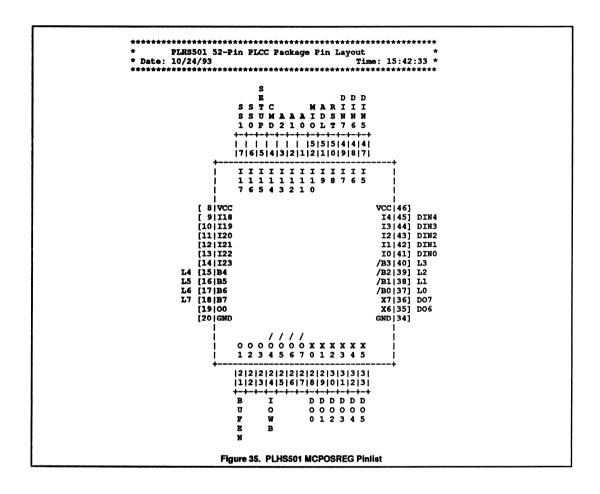

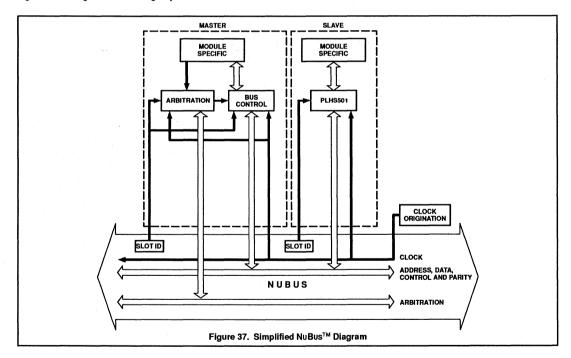

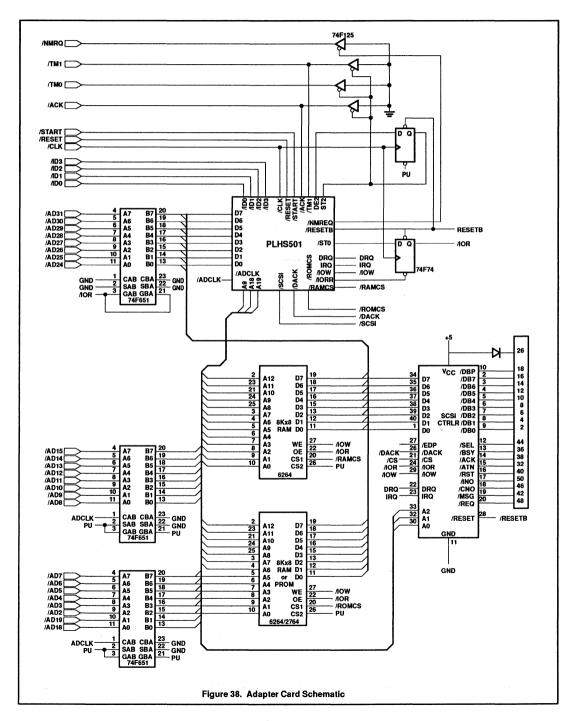

| I <sub>IN</sub>  | Input currents              | -30  | +30  | mA              |