#### INTEGRATED CIRCUITS

# **Desktop Video Data Handbook**

**Philips Semiconductors**

**PHILIPS**

# **Desktop Video Products**

**Philips Semiconductors**

**PHILIPS**

#### **DEFINITIONS**

| Data Sheet<br>Identification | Product Status         | Definition                                                                                                                                                                                                                                                 |

|------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective Specification      | Formative or in Design | This data sheet contains the design target or goal specifications for product development. Specifications may change in any manner without notice.                                                                                                         |

| Preliminary Specification    | Preproduction Product  | This data sheet contains preliminary data, and supplementary data will be published at a later date. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |

| Product Specification        | Full Production        | This data sheet contains Final Specifications. Philips<br>Semiconductors reserves the right to make changes at any time<br>without notice, in order to improve design and supply the best<br>possible product.                                             |

Philips Semiconductors and North American Philips Corporation reserve the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified. Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### LIFE SUPPORT APPLICATIONS

Philips Semiconductors and North American Philips Corporation Products are not designed for use in life support appliances, devices, or systems where malfunction of a Philips Semiconductors and North American Philips Corporation Product can reasonably be expected to result in a personal injury. Philips Semiconductors and North American Philips Corporation customers using or selling Philips Semiconductors and North American Philips Corporation Products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors and North American Philips Corporation for any damages resulting from such improper use or sale.

Philips Semiconductors and North American Philips Corporation register eligible circuits under the Semiconductor Chip Protection Act.

Our appreciation is extended to the following persons for their assistance in the publication of the Desktop Video Handbook:

To: all the Philips factory representatives who supplied updated data sheets at short notice.

also to:

Herb Kniess Application notes

Leo Warmuth Adam H. Barnett Layout

Celia Tippit Compilation and Editing

George Ellis Compilation, Editing, and Application notes

Steve Solari Concept

Joe Kelly Cover Art

© Copyright North American Philips Corporation, 1993

# **Table of Contents**

| Section 1         |                                                                                 |      |

|-------------------|---------------------------------------------------------------------------------|------|

| Digital video nov | w, an introduction                                                              | 1-4  |

|                   | figurations                                                                     |      |

| Pro electron type | e designation code for integrated circuits                                      | 1-1  |

| Handling MOS of   | devices                                                                         | 1-1: |

|                   |                                                                                 |      |

| Alphanumeric in   | ndex of products                                                                | 1-10 |

| Section 2         |                                                                                 |      |

| High-performane   | ce 8-bit video data converters                                                  | 2-   |

|                   | tal colour decoding                                                             |      |

| -                 | 26 Digital interfaces for component video signals                               |      |

|                   | -2 Encoding parameters of digital television for studios                        |      |

|                   | OMMENDATIONS OF THE CCIR, 1990                                                  |      |

|                   | n standards; colour systems                                                     |      |

| International TV  | / systems and standards                                                         | 2-5  |

|                   | al video evaluation module                                                      |      |

|                   | al Television Demonstration System                                              |      |

|                   | rational modes                                                                  |      |

|                   |                                                                                 |      |

|                   | uation Board                                                                    |      |

|                   | top video demo board                                                            |      |

|                   | ations                                                                          |      |

|                   | level and gain modulation circuit                                               |      |

|                   | g decoder application                                                           |      |

|                   | aluation board                                                                  |      |

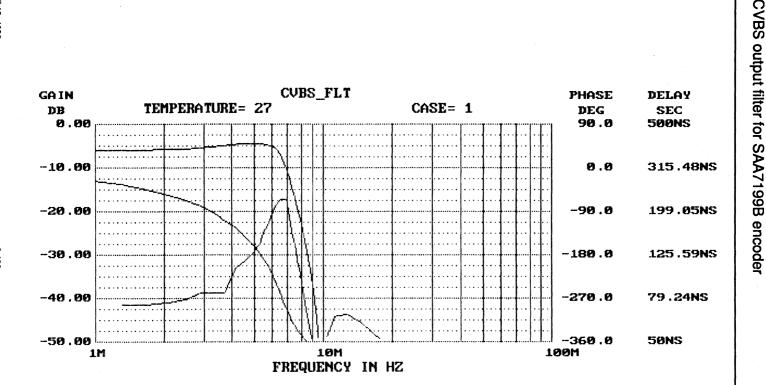

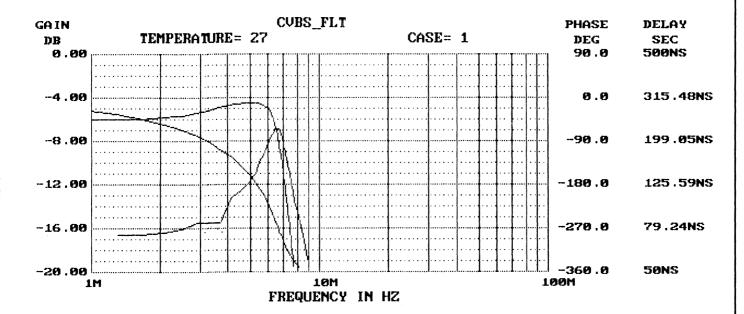

| -                 | ter for SAA7199B encoder                                                        |      |

| •                 | generator application                                                           |      |

|                   | ation (including fast-mode)                                                     |      |

| •                 | Ses                                                                             |      |

|                   | ter port adaptor                                                                |      |

|                   | ng the PCD8584 I <sup>2</sup> C-bus controller to 80C51 family microcontrollers |      |

|                   | ing the POD03041 C-bus controlled to 00031 family find occitationers            | 2-20 |

| Section 3         |                                                                                 |      |

| Analog-to-digita  |                                                                                 |      |

|                   | I converter selection guide                                                     |      |

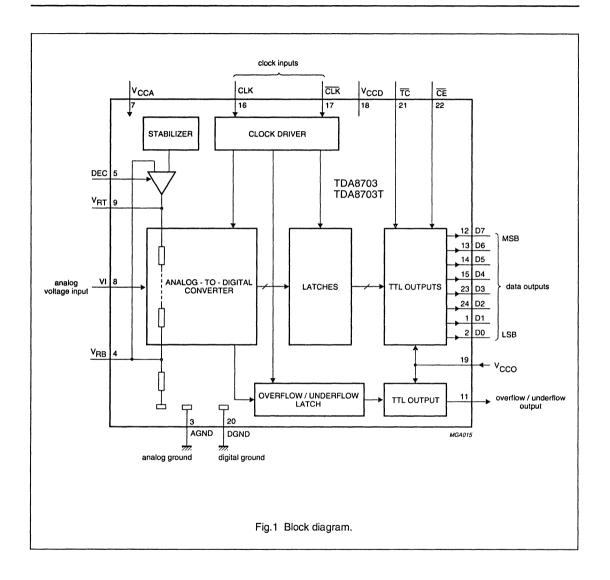

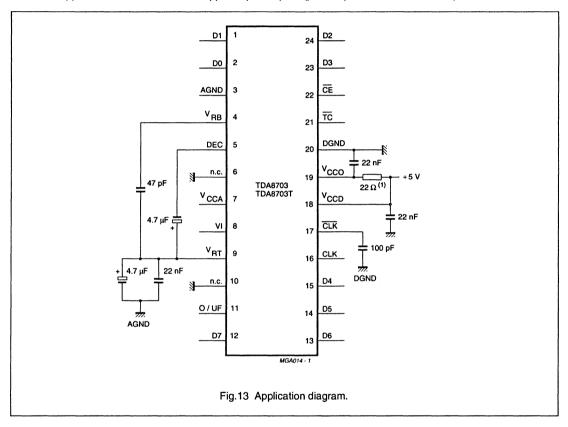

| TDA8703           | 8-bit high-speed analog-to-digital converter                                    |      |

| TDA8706           | 6-bit analog-to-digital converter with multiplexer and clamp                    |      |

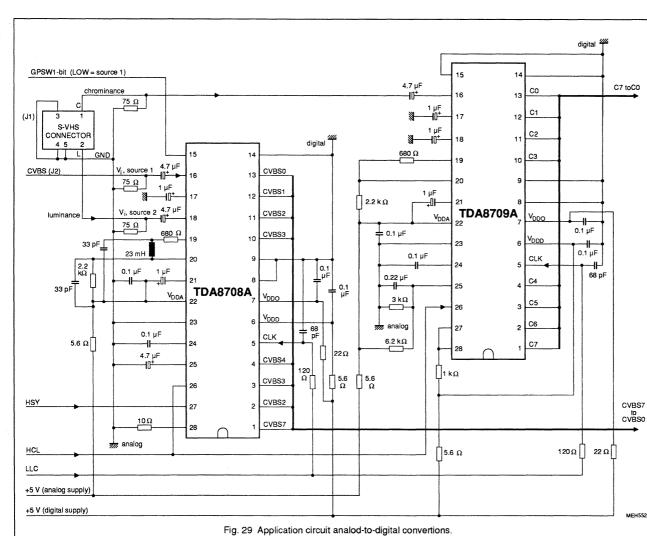

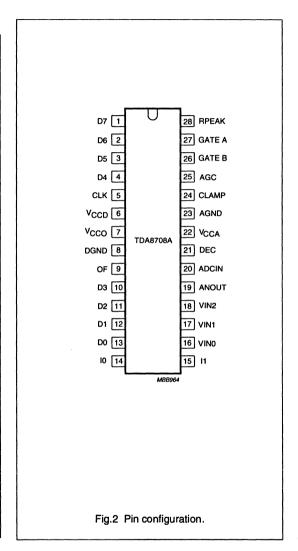

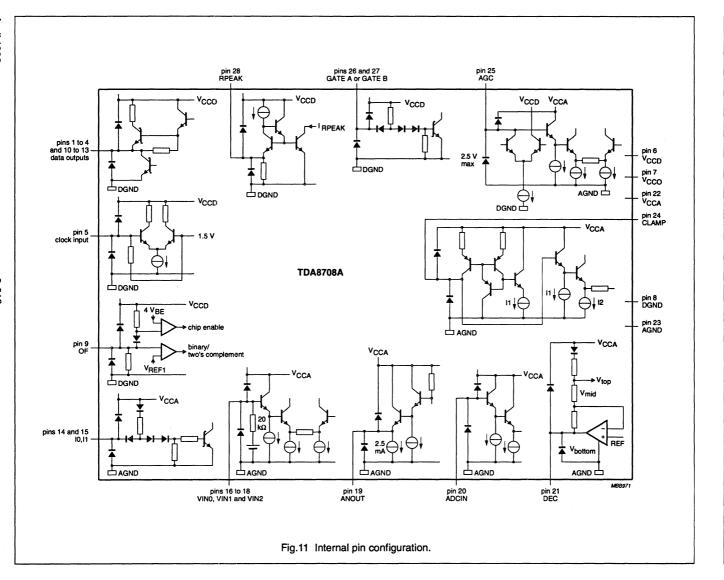

| TDA8708A          | Video analog input interface                                                    |      |

| TDA8708B          | Video analog input interface                                                    |      |

| TDA8709A          | Video analog input interface                                                    |      |

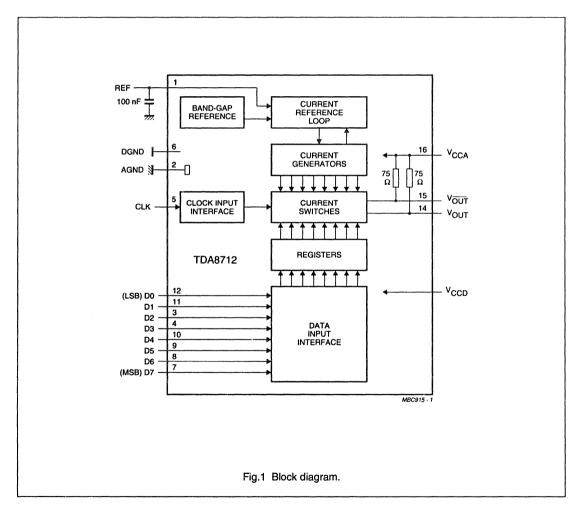

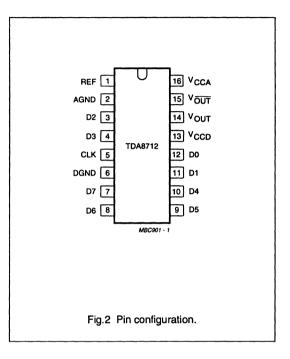

| TDA8712           | 8-bit video digital-to-analog converter                                         |      |

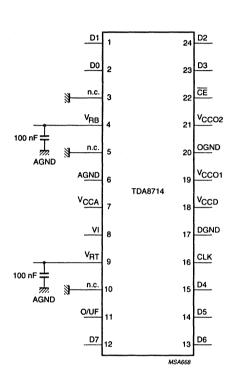

| TDA8714           | 8-bit high-speed analog-to-digital converter                                    |      |

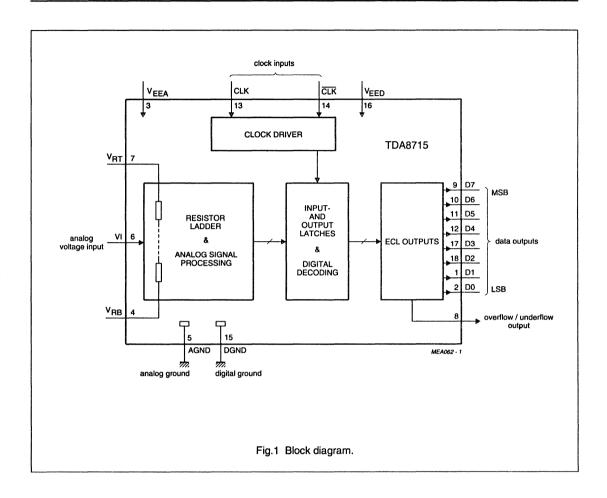

| TDA8715           | 8-bit high-speed analog-to-digital converter                                    |      |

| TDA8716           | 8-bit high-speed analog-to-digital converter                                    |      |

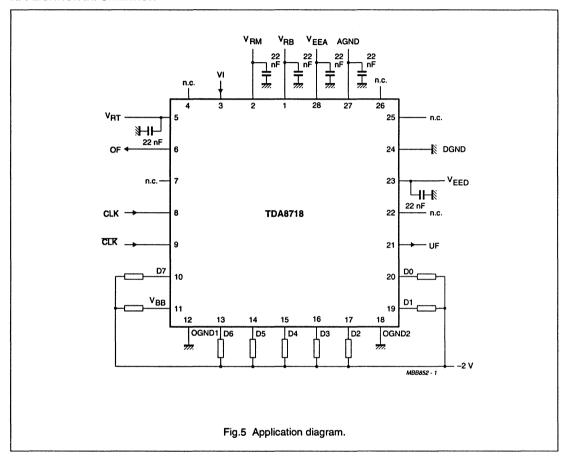

| TDA8718           | 8-bit high-speed analog-to-digital converter                                    |      |

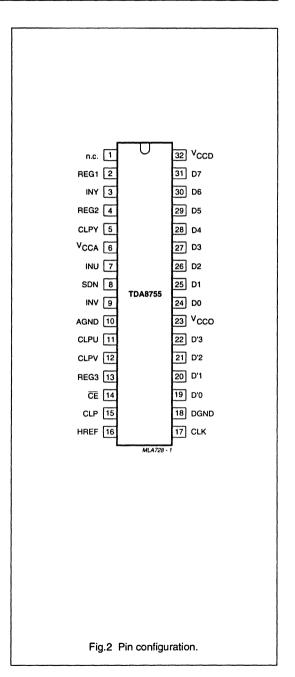

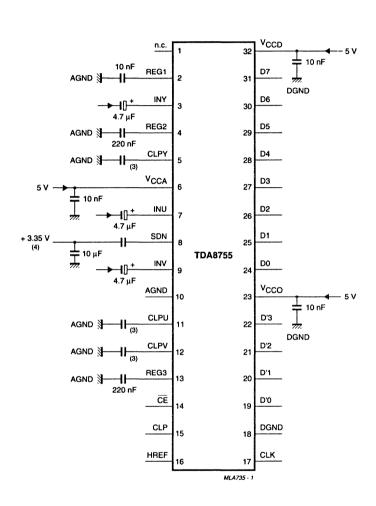

| TDA8755           | YUV 8-bit video low-power analog-to-digital interface                           |      |

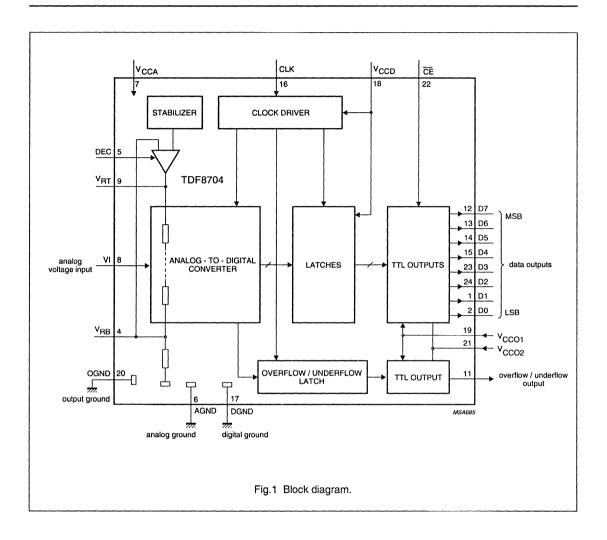

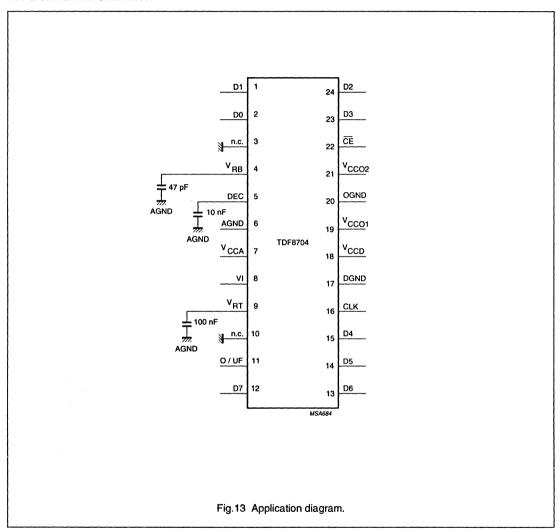

| TDF8704           | 8-bit high-speed analog-to-digital converter                                    | 3-77 |

#### **Auxiliary functions**

| PCD8584                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1 <sup>2</sup> C-bus controller                                         | -5                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| PCF8574/PCF8574A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Remote 8-bit I/O expander for I <sup>2</sup> C-bus                      | 27                                                                                          |

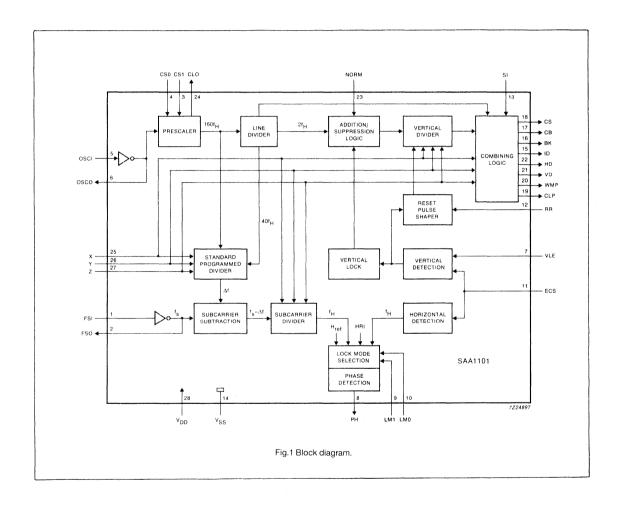

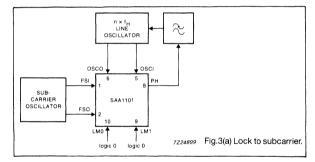

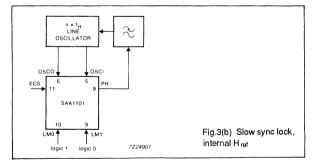

| SAA1101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Universal sync generator (USG)                                          |                                                                                             |

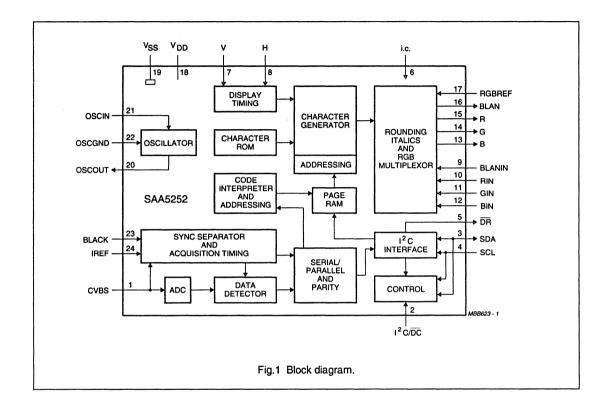

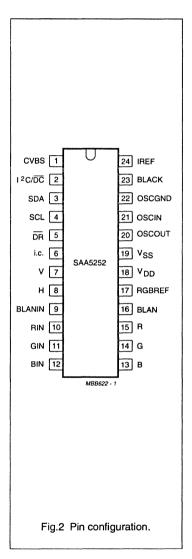

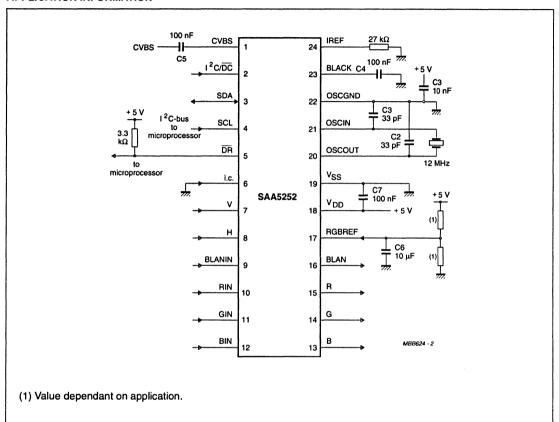

| SAA5252                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Line twenty-one acquisition and display (LITOD)                         | 49                                                                                          |

| TDA2595                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Horizontal combination                                                  | 28                                                                                          |

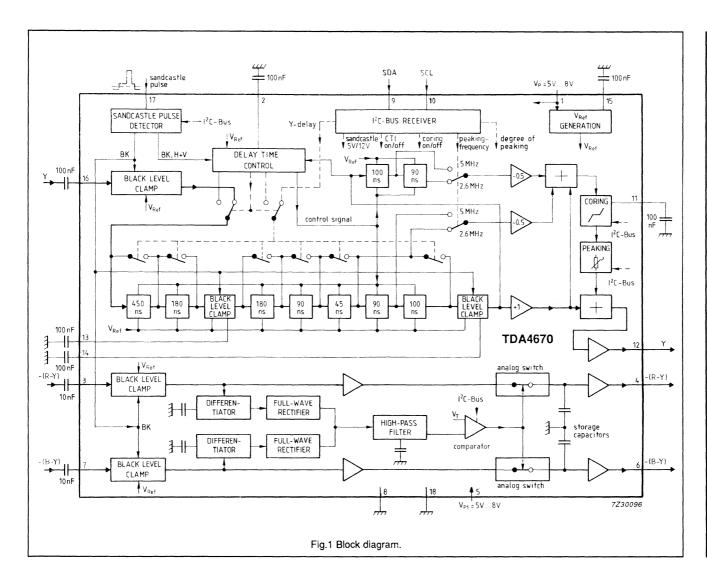

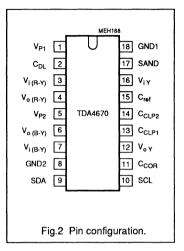

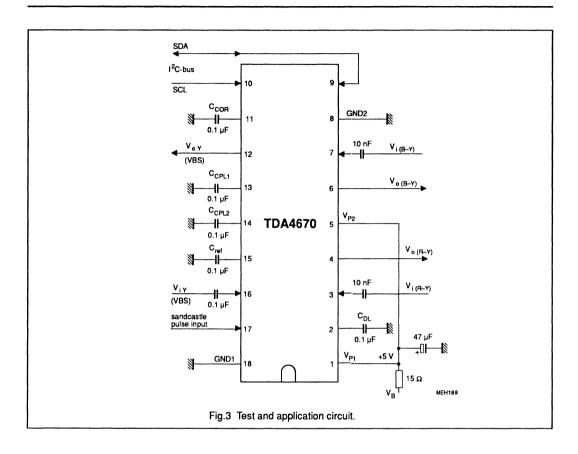

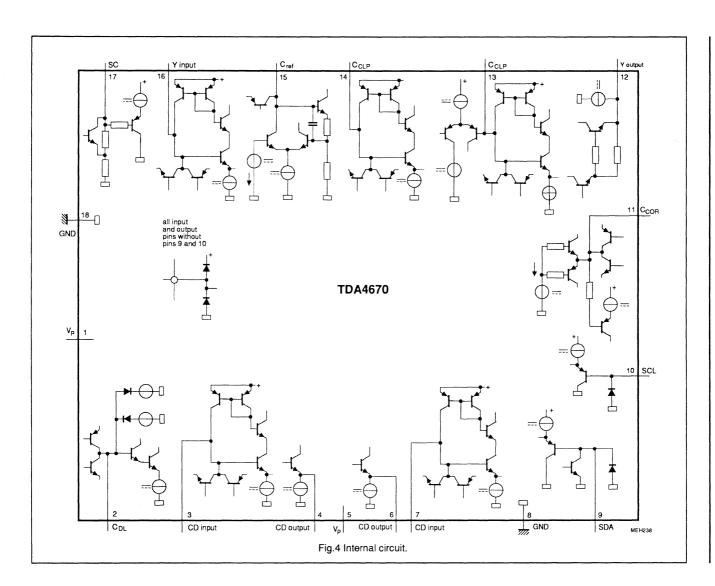

| TDA4670                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Picture signal improvement (PSI) circuit                                | 58                                                                                          |

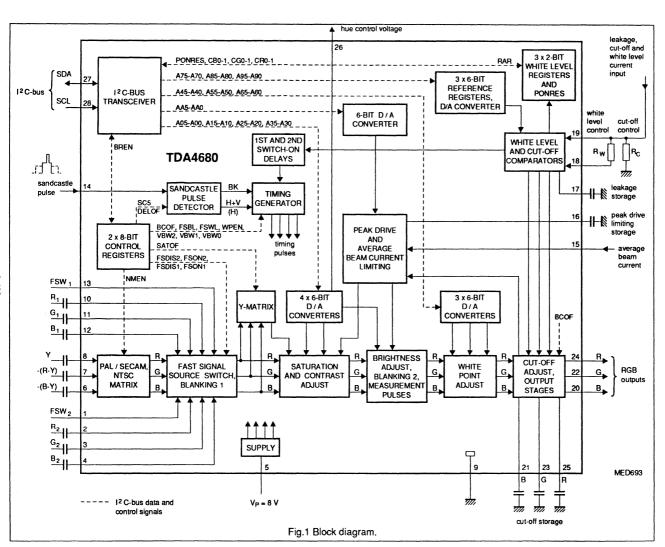

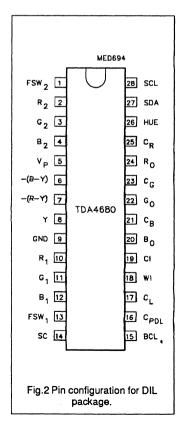

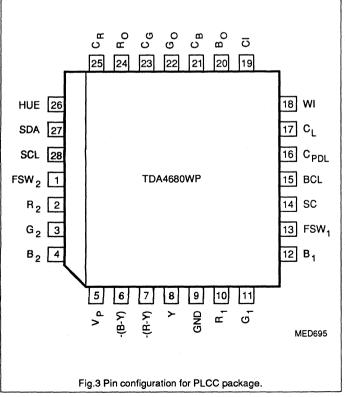

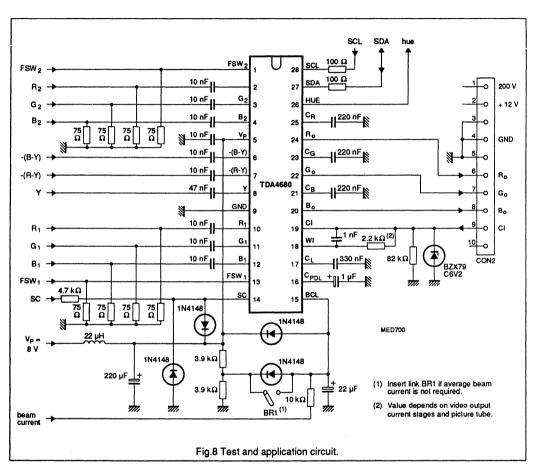

| TDA4680                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Video processor with automatic cut-off and white level control          | 68                                                                                          |

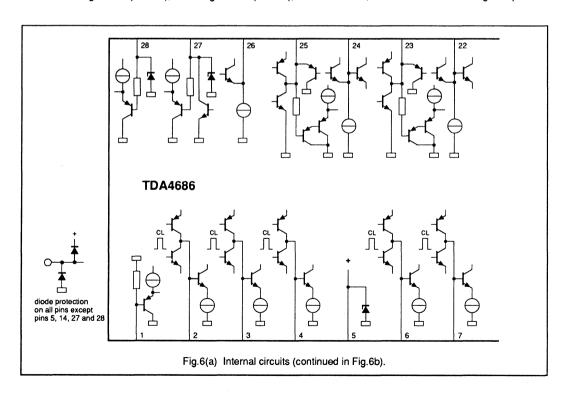

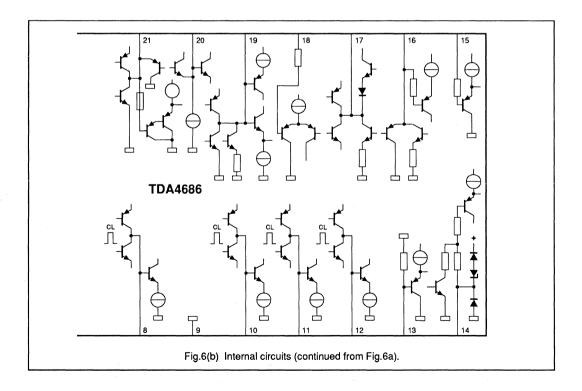

| TDA4686                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Video processor, with automatic cut-off control                         | 84                                                                                          |

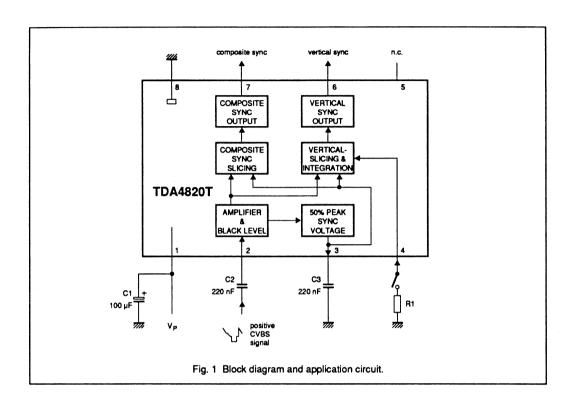

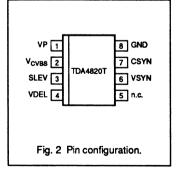

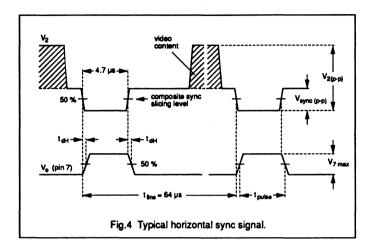

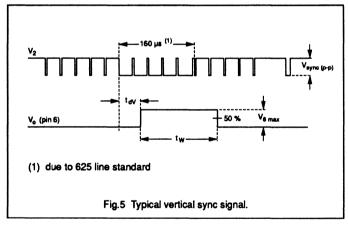

| TDA4820T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Sync separation circuit for video applications                          | 00                                                                                          |

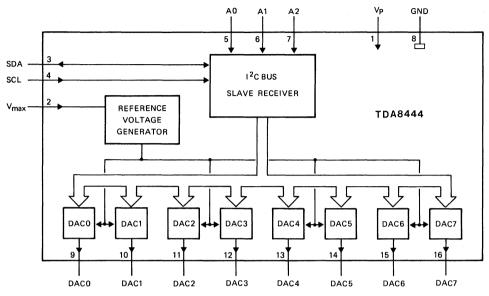

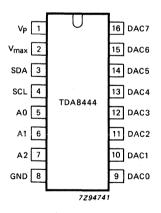

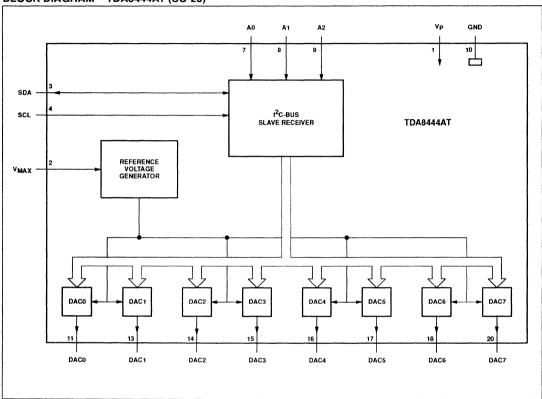

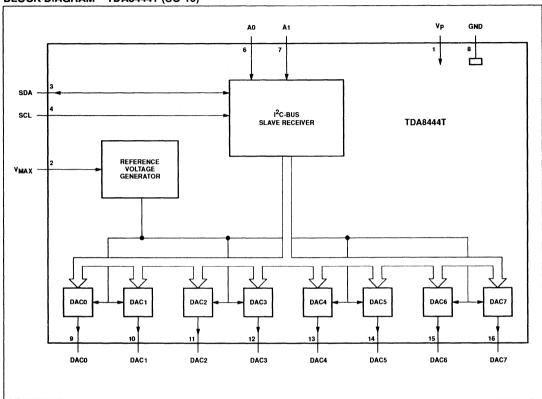

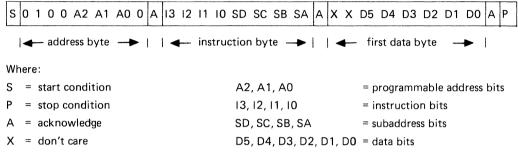

| TDA8444/AT/T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Octuple 6-bit digital-to-analog converter with I <sup>2</sup> C-bus     | )5                                                                                          |

| TDA8446                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Fast RGB/YC switch for digital decoding                                 | 14                                                                                          |

| TDA8540                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4 × 4 video switch matrix 3-54                                          | 46                                                                                          |

| Analog color decodi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ng                                                                      |                                                                                             |

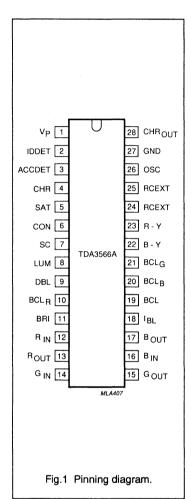

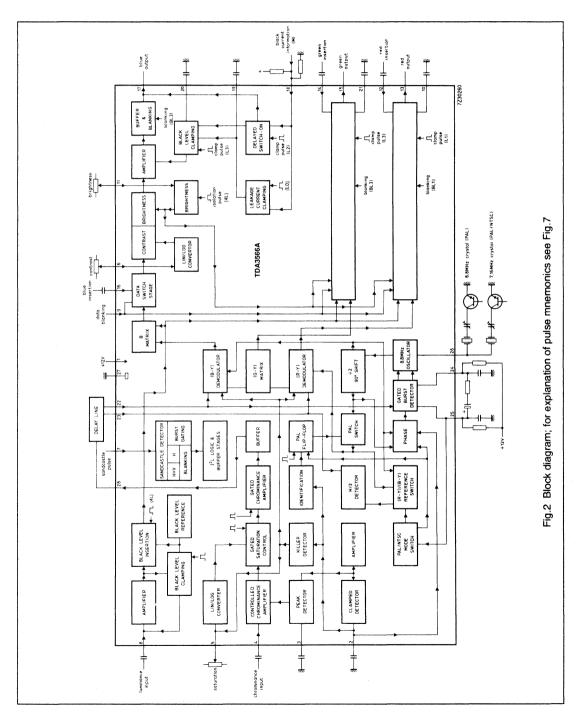

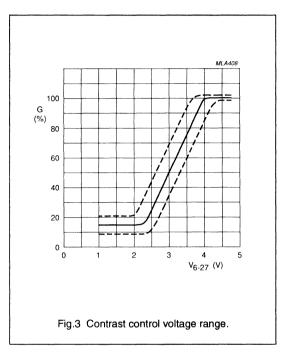

| TDA3566A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PAL/NTSC decoder                                                        | 35                                                                                          |

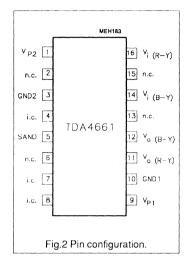

| TDA4661                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Baseband delay line 3-45                                                | 52                                                                                          |

| TDA8501                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PAL/NTSC encoder                                                        | 21                                                                                          |

| TDA9141                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PAL/NTSC/SECAM decoder/sync processor                                   | 48                                                                                          |

| Color decoding, enc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | oding and clock ICs (digital)                                           |                                                                                             |

| SAA7151B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Digital multistandard colour decoder with SCART interface (DMSD2-SCART) | 62                                                                                          |

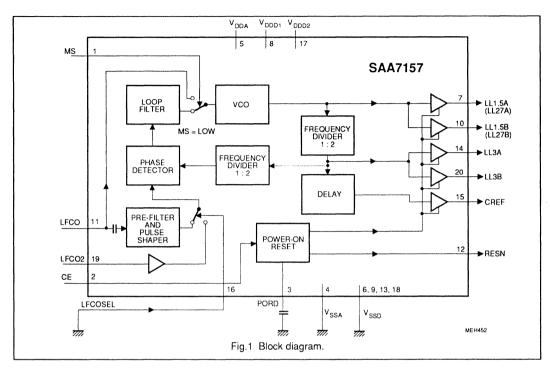

| SAA7157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Clock signal generator circuit for digital TV systems (SCGC)            |                                                                                             |

| SAA7191B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Digital multistandard colour decoder, square pixel (DMSD-SQP)           |                                                                                             |

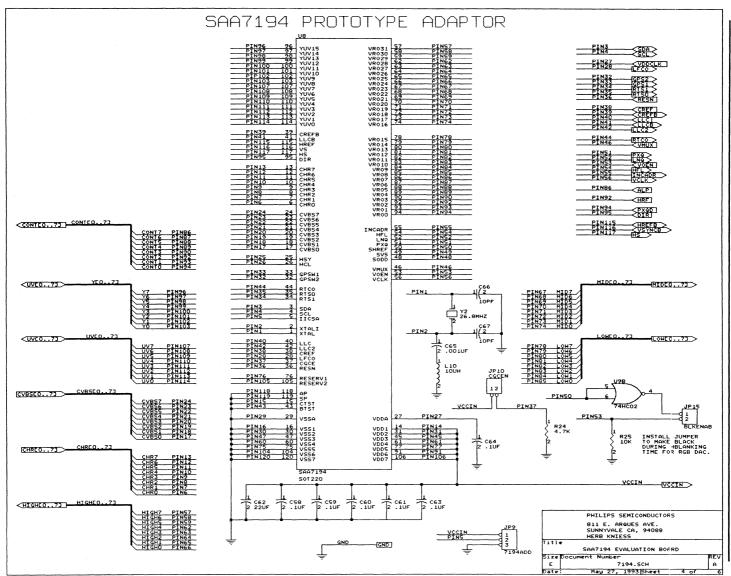

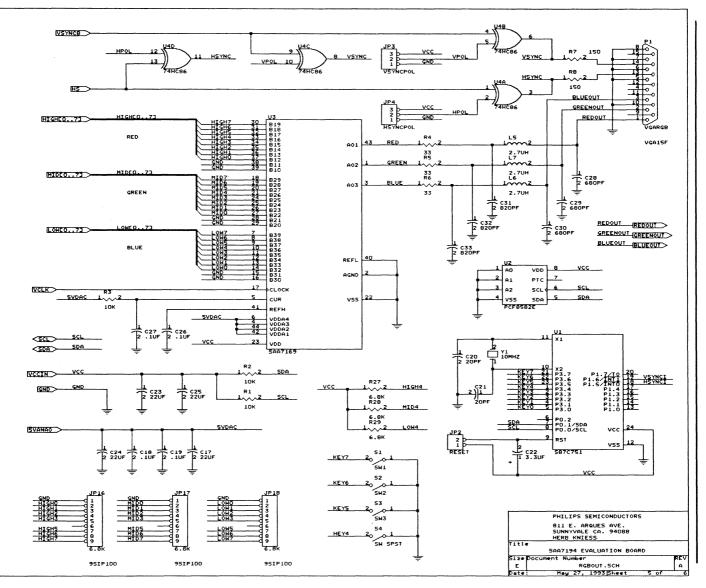

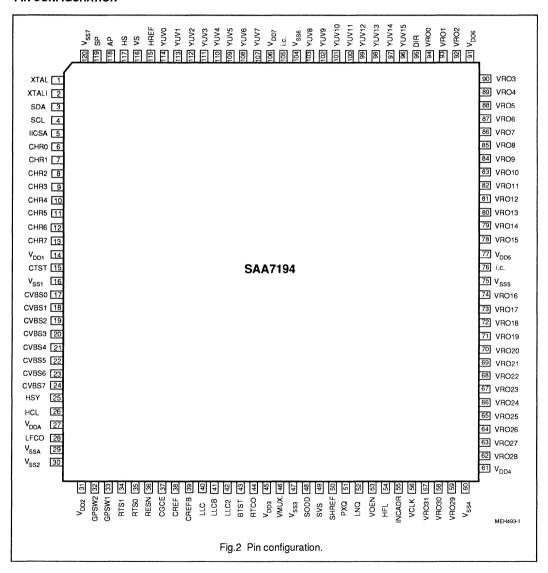

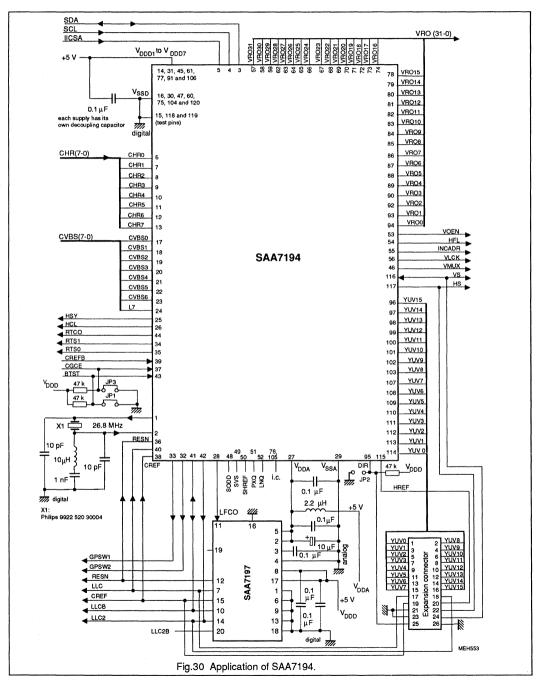

| SAA7194                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Digital video decoder and scaler circuit (DESC)                         |                                                                                             |

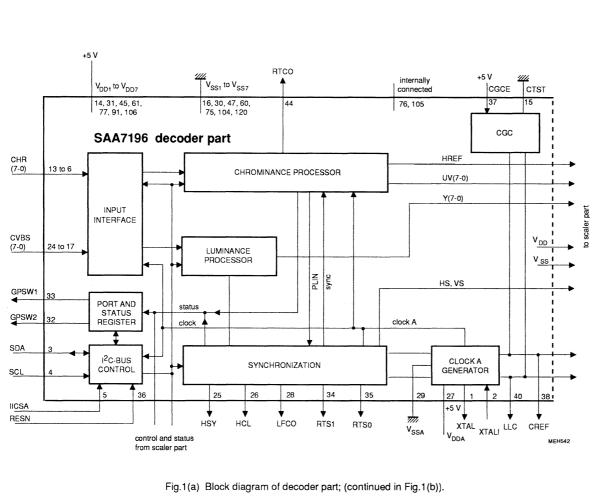

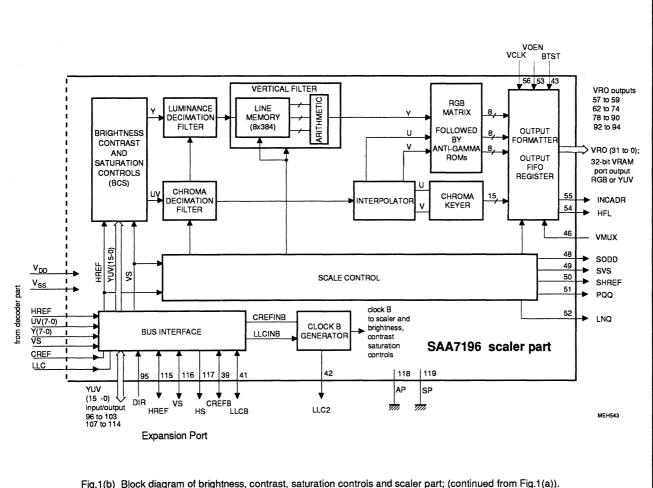

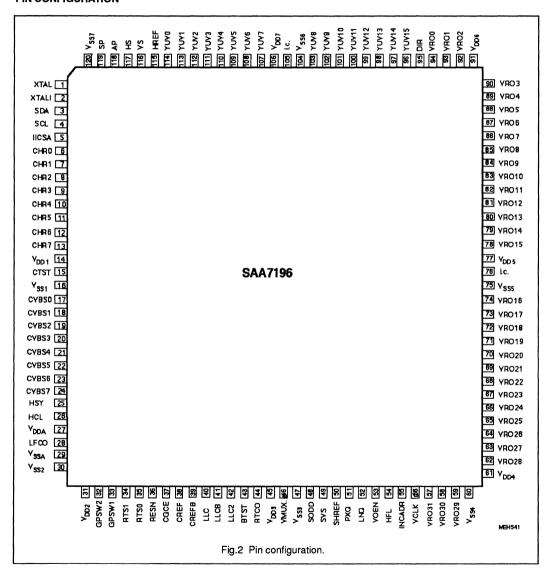

| SAA7196                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Digital video decoder, scaler, and clock generator (DESCPro)            |                                                                                             |

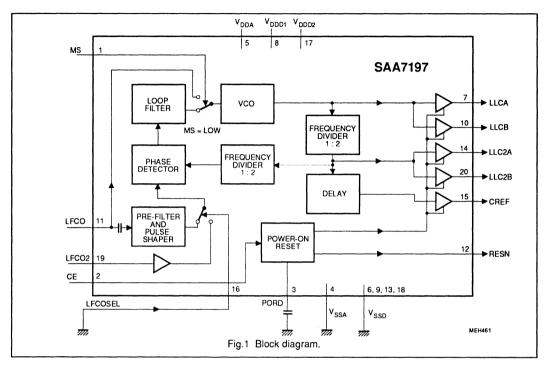

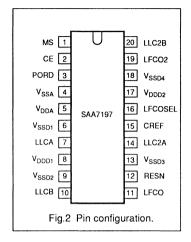

| SAA7197                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Clock signal generator circuit for Desktop Video systems (SCGC)         |                                                                                             |

| SAA7199B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Digital video encoder, GENLOCK-capable                                  |                                                                                             |

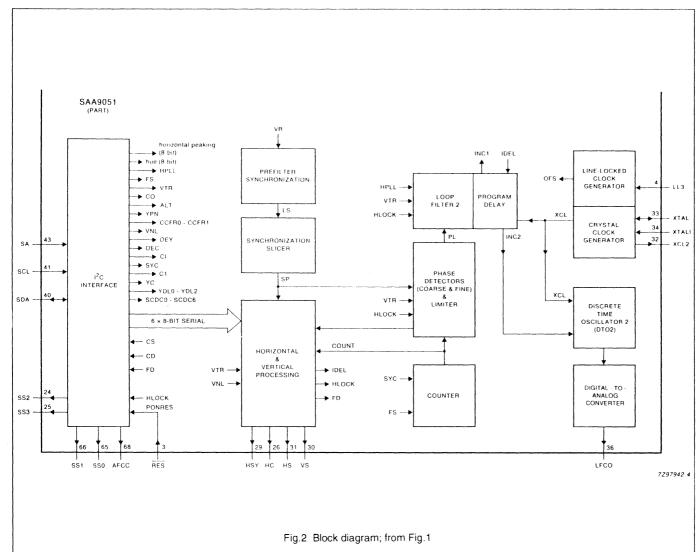

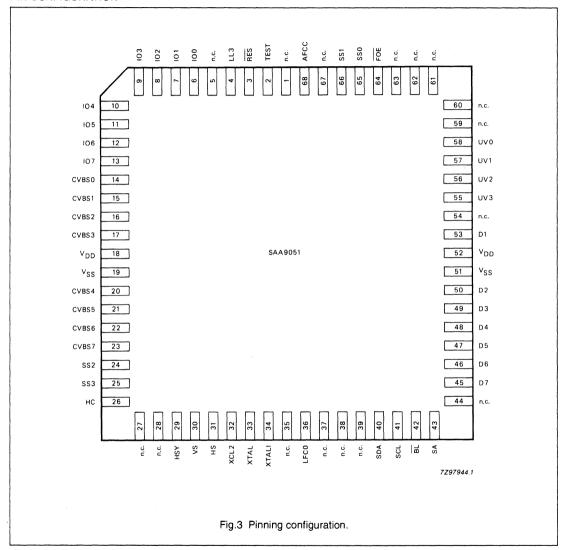

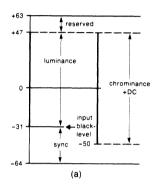

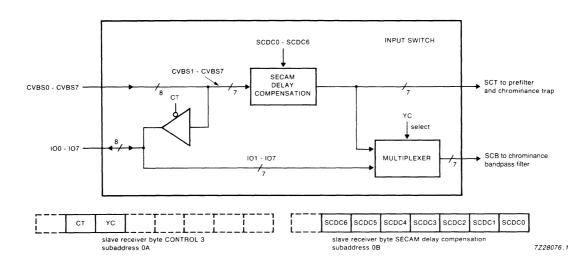

| SAA9051                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Digital multistandard TV decoder                                        |                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                         |                                                                                             |

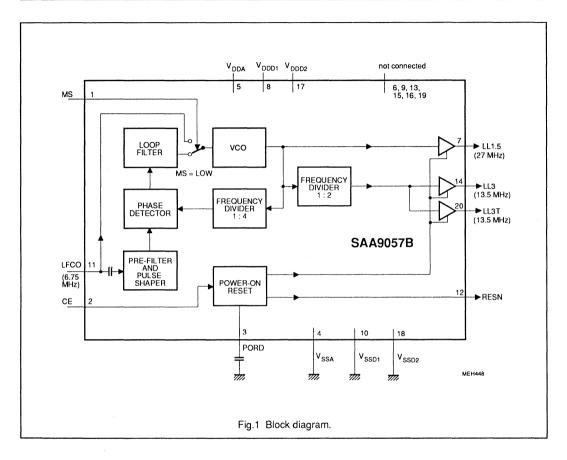

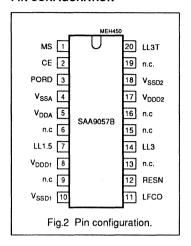

| SAA9057B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Clock signal generator circuit for Digital TV systems (CGC)             | us                                                                                          |

| SAA9057B  Digital-to-analog cor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Clock signal generator circuit for Digital TV systems (CGC)             | 03                                                                                          |

| Digital-to-analog cor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | nversion                                                                |                                                                                             |