# DATA HANDBOOK

# RF Communications

Signetics

**Philips Semiconductors**

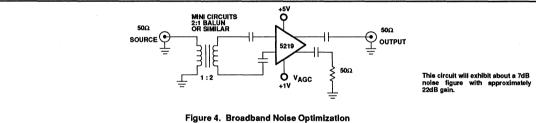

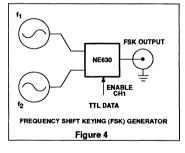

**PHILIPS**

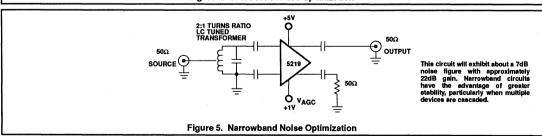

Signetics reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Signetics assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified. Applications that are described herein for any of these products are of illustrative purposes only. Signetics makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

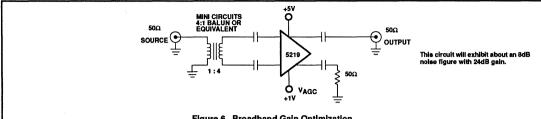

LIFE SUPPORT APPLICATIONS

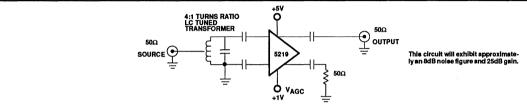

Signetics Products are not designed for use in life support appliances, devices, or systems where malfunction of a Signetics Product can reasonably be expected to result in a personal injury. Signetics customers using or selling Signetics' Products for use in such applications do so at their own risk and agree to fully indemnify Signetics for any damages resulting from such improper use or sale.

> Signetics registers eligible circuits under the Semiconductor Chip Protection Act.

Copyright 1991 Signetics Company a division of North American Philips Corporation

All rights reserved.

# **Product Status**

# **DEFINITIONS**

| Data Sheet<br>Identification                                                           | Product Status         | Definition                                                                                                                                                                                                                                    |  |

|----------------------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Objective Specification                                                                | Formative or in Design | This data sheet contains the design target or goal specifications for product development. Specifications may change in any manner without notice.                                                                                            |  |

| Preliminary Specification Preproduction Product  Product Specification Full Production |                        | This data sheet contains preliminary data, and supplementary data will be published at a later date. Signetics reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |  |

|                                                                                        |                        | This data sheet contains Final Specifications. Signetics reserves the right to make changes at any time without notice, in order to improve design and supply the best possible product.                                                      |  |

# RF Communications Handbook Contents

| Preface                 |                                                                 | iii |

|-------------------------|-----------------------------------------------------------------|-----|

| Product status          |                                                                 | iv  |

| Alphanumeric prod       | luct list                                                       | vii |

| Ordering information    | ncno                                                            | x   |

| Section 1 Amplifier     | rs                                                              | 1   |

| NE/SA5200               | RF dual gain-stage                                              | 3   |

| NE/SA5204               | Wide-band high-frequency amplifier                              | 15  |

| NE/SA5205               | Wide-band high-frequency amplifier                              | 25  |

| NE/SA5209               | Wideband variable gain amplifier                                | 35  |

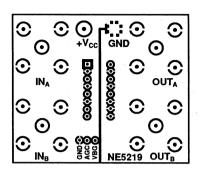

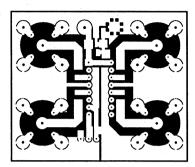

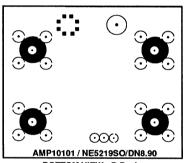

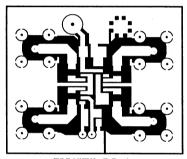

| NE/SA5219               | Wideband variable gain amplifier                                | 50  |

| NE/SA5234               | Matched quad high-performance low-voltage operational amplifier | 63  |

| AN1651                  | Using the NE/SA5234 amplifier                                   | 67  |

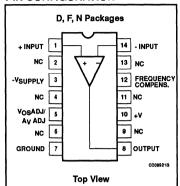

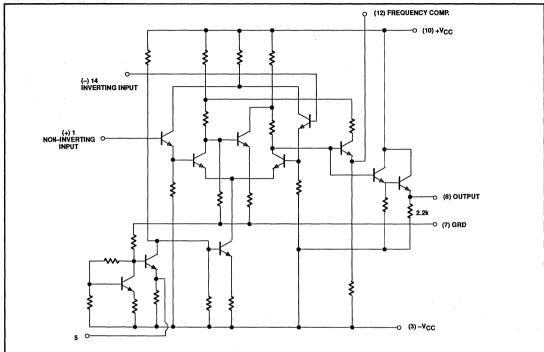

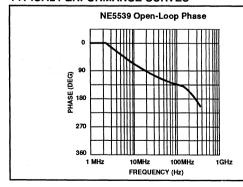

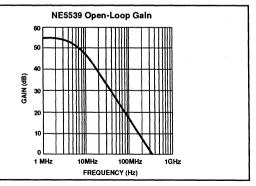

| NE/SE5539               | High frequency operational amplifier                            | 81  |

| NE5592                  | Video amplifier                                                 | 89  |

| NE/SA/SE592             | Video amplifier                                                 | 94  |

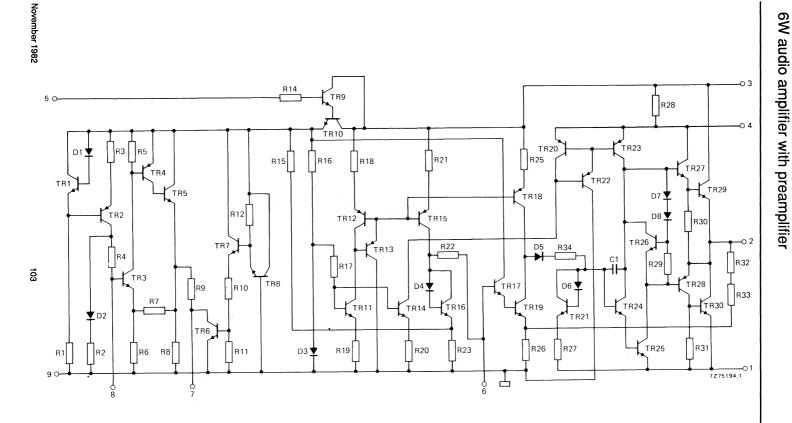

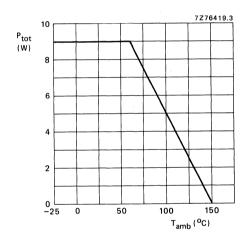

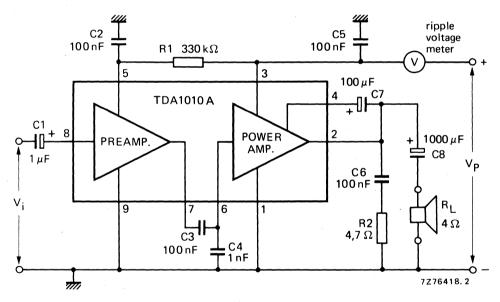

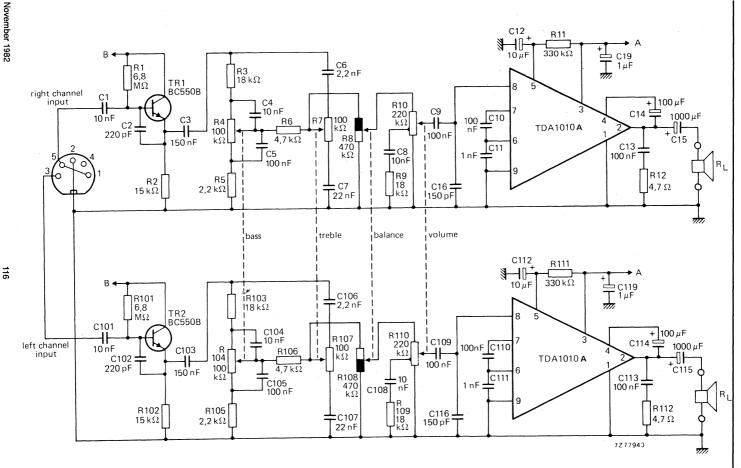

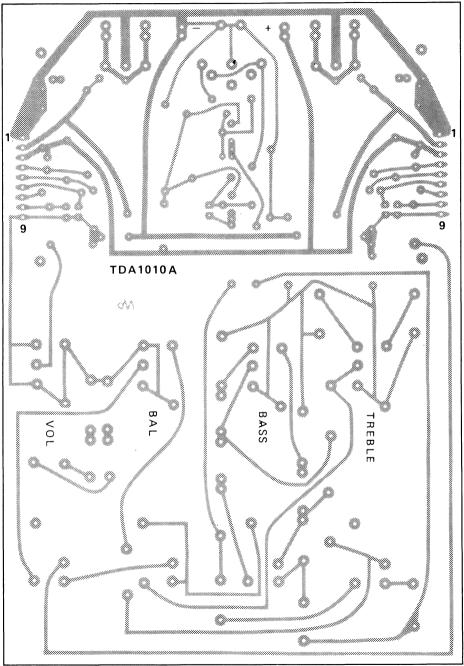

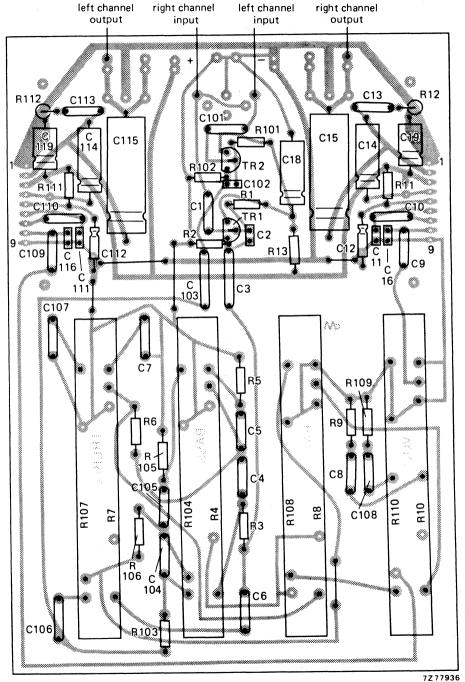

| TDA1010A                | 6W audio amplifier with preamplifier                            | 102 |

| TDA1015                 | 1 to 4W audio amplifier with preamplifier                       | 120 |

| TDA1011A                | 2 to 6W audio power amplifier with preamplifier                 | 130 |

| TDA1013B                | 4W amplifier with DC volume control                             | 138 |

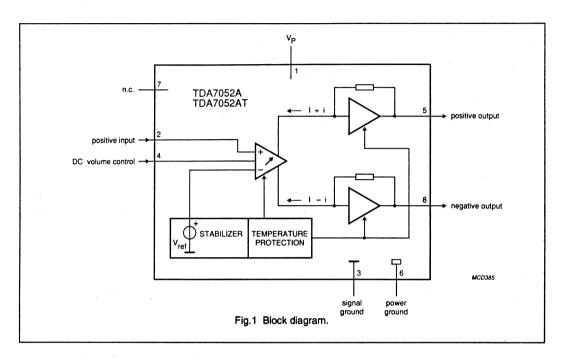

| TDA7052                 | 1 Watt low voltage audio power amplifier                        | 146 |

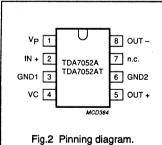

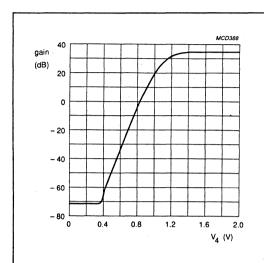

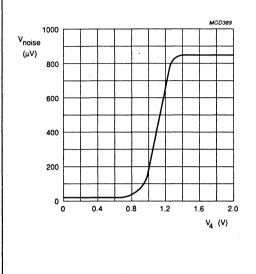

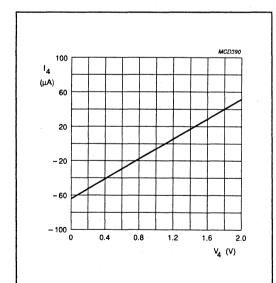

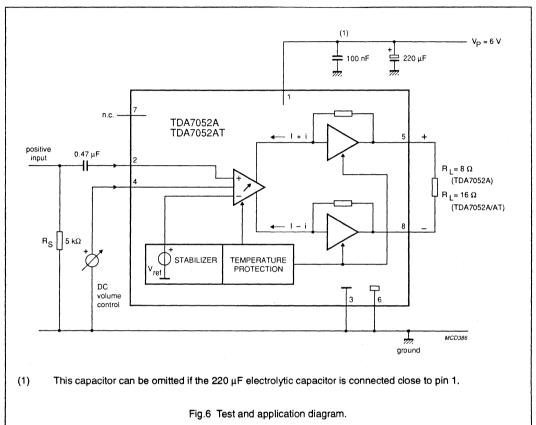

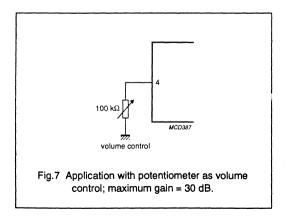

| TDA7052A/AT             | 1-Watt low voltage audio power amp with DC volume control       | 151 |

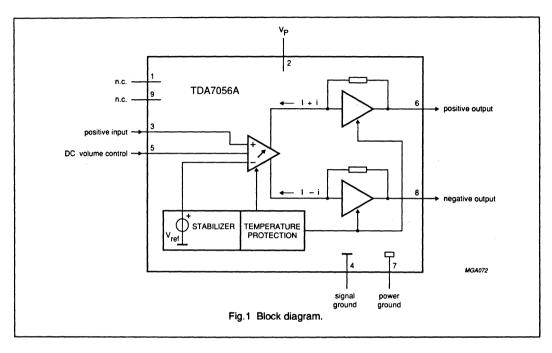

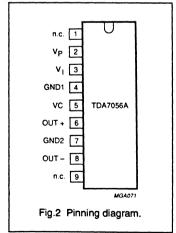

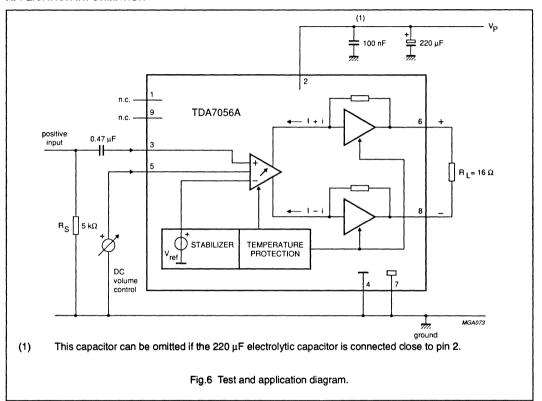

| TDA7056A                | 3-Watt mono BTL audio output amplifier                          | 158 |

| Section 2 Compan        | dors                                                            | 165 |

| •                       | otor Guide                                                      | 166 |

| •                       |                                                                 | 167 |

| NES70/S71/SAS7<br>AN174 | 1 Compandor                                                     | 174 |

| AN174<br>AN176          | Applications for compandors NE570/571/SA571                     | 183 |

|                         | Compandor cookbook                                              | 189 |

| NE/SA572<br>AN175       | Programmable analog compandor                                   | 197 |

|                         | Automatic level control using the NE572                         | 198 |

| NE/SA575                | Low voltage compandor                                           | 198 |

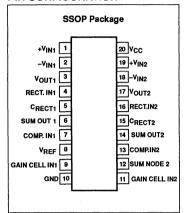

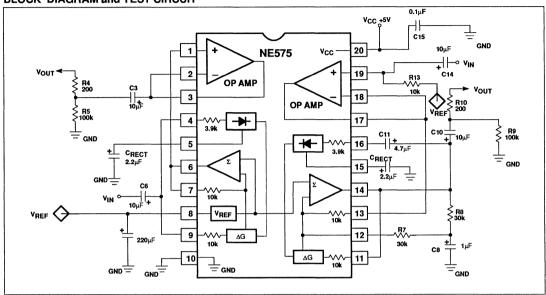

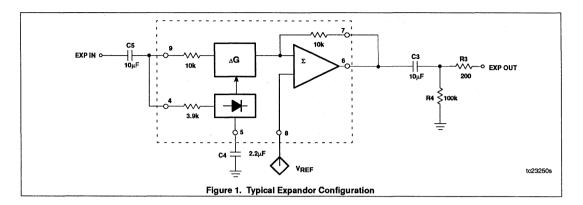

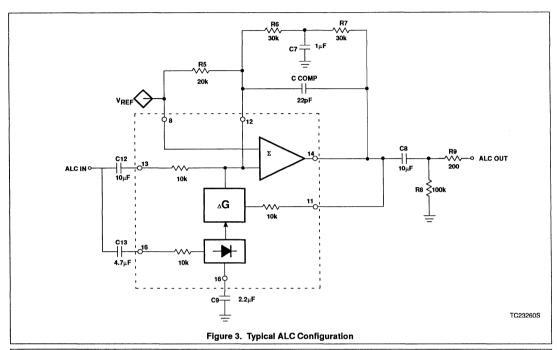

| NE/SA575SSOP            | Low voltage compandor in shrink small outline package           | 208 |

| NE/SA576                | Low power compandor                                             | 218 |

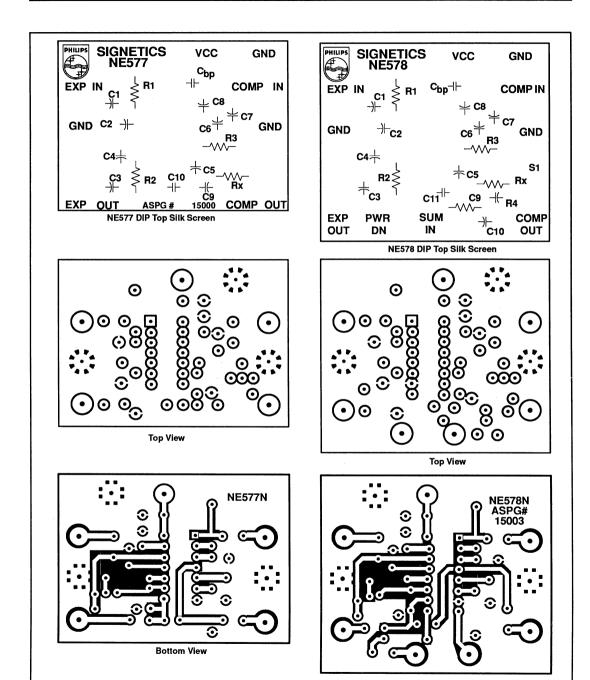

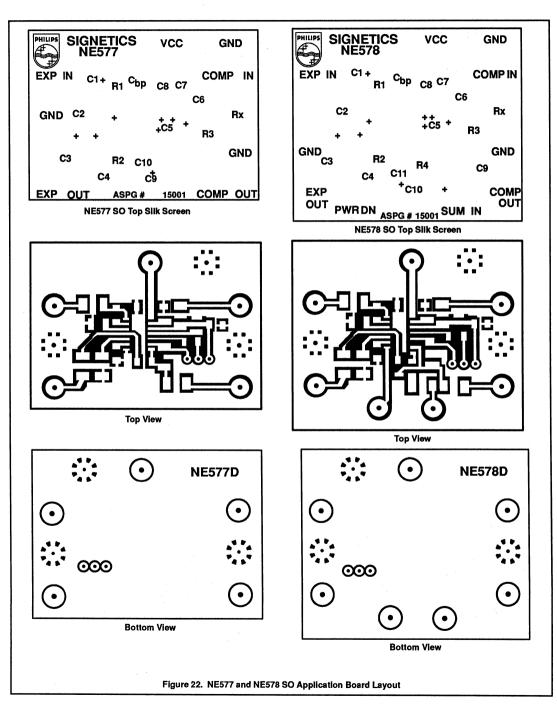

| NE/SA577                | Unity gain level programmable power compandor                   | 221 |

| NE/SA578                | Unity gain level programmable low power compandor               | 225 |

| AN1762                  | Companding with the NE577 and NE578                             | 229 |

| Section 3 FM IF Sy      | /stems                                                          | 241 |

|                         | elector Guide                                                   | 242 |

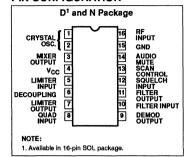

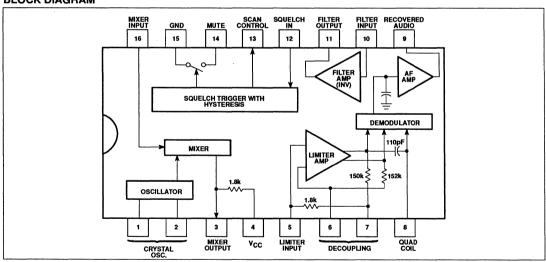

| MC3361                  | Low-power FM IF                                                 | 243 |

| *NE/SA604A              | High performance low power FM IF system                         | 246 |

| NE/SA614A               | Low power FM IF system                                          | 256 |

| AN1991                  | Audio decibel level detector with meter driver                  | 266 |

December 1991

# **RF Communications Handbook**

# Contents

| Section 3 FM IF Sy |                                                                                  |           |

|--------------------|----------------------------------------------------------------------------------|-----------|

| AN1993             | High sensitivity applications of low-power RF/IF integrated circuits             | 268       |

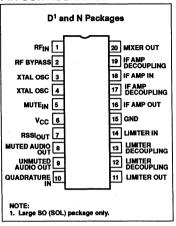

| NE/SA605           | High performance low power mixer FM IF system                                    | 28        |

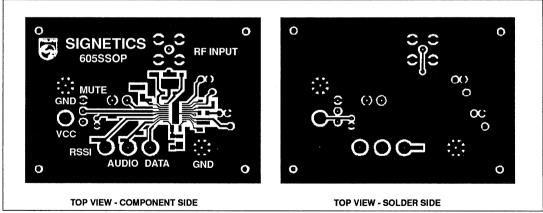

| NE/SA605SSOP       | High performance low power mixer FM IF system in shrink small outline package    | 29        |

| NE/SA615           | High performance low power mixer FM IF system                                    | 29        |

|                    | P) High performance low power mixer FM IF system in shrink small outline package | 30        |

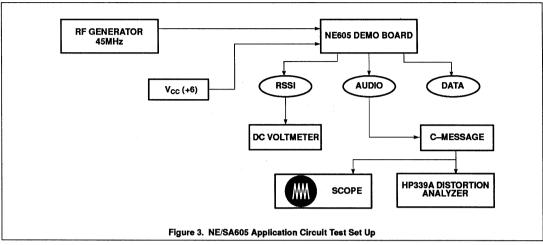

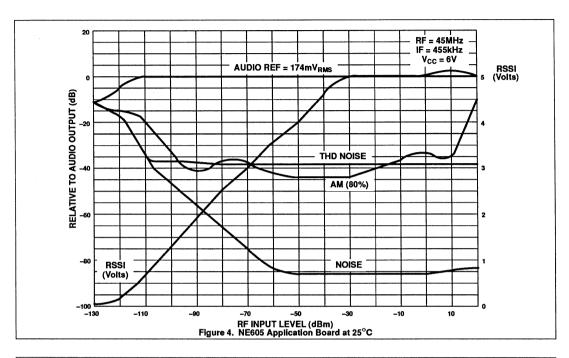

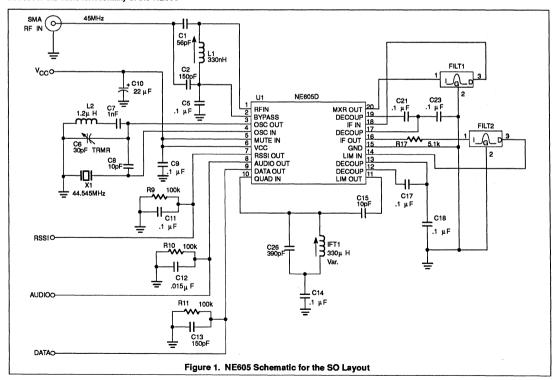

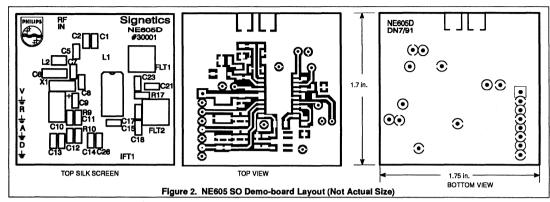

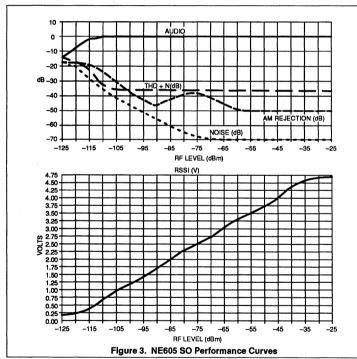

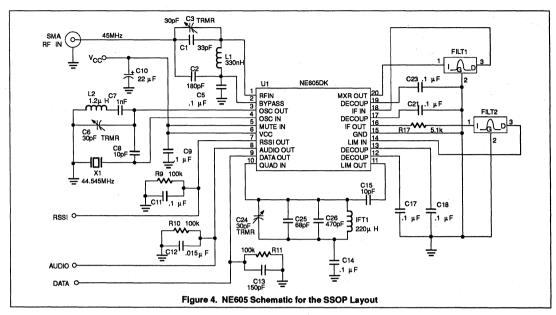

| AN1994             | Reviewing key areas when designing with the NE605                                | 31        |

| AN1995             | Evaluating the NE605 SO and SSOP demo-board                                      | 33        |

| NE/SA606           | Low-voltage high performance mixer FM IF system                                  | 34        |

| NE/SA616           | Low-voltage high performance mixer FM IF system                                  | 36        |

| NE/SA607           | Low voltage high performance mixer FM IF system                                  | 37        |

| NE/SA617           | Low-voltage high performance mixer FM IF system                                  | 39        |

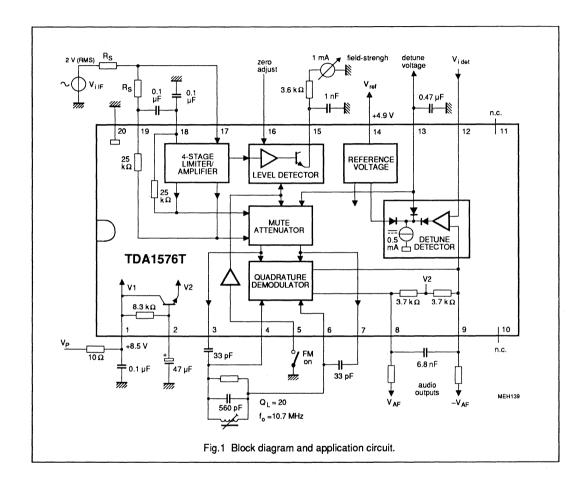

| TDA1576T           | FM/IF amplifier/demodulator circuit                                              | 40        |

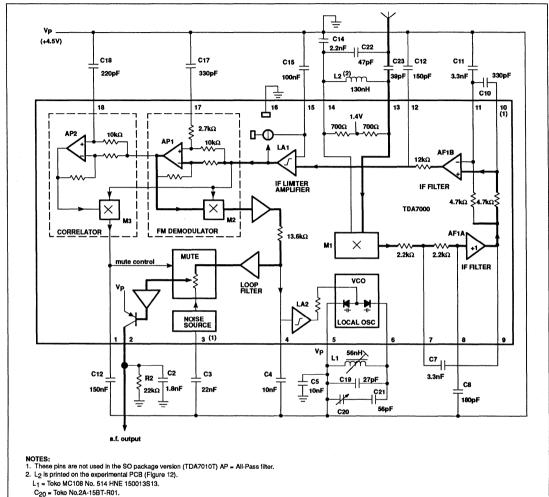

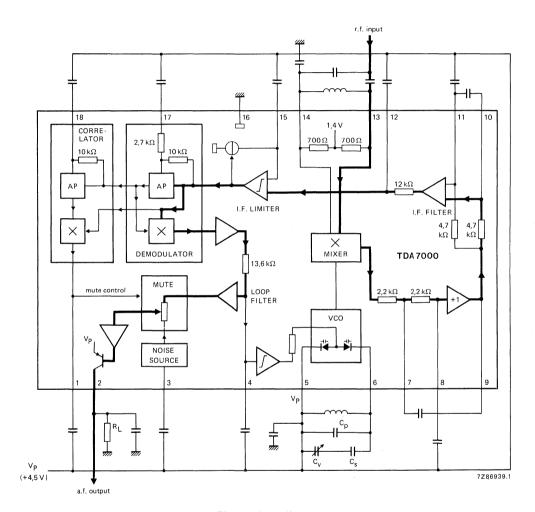

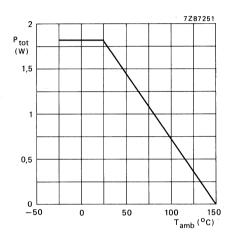

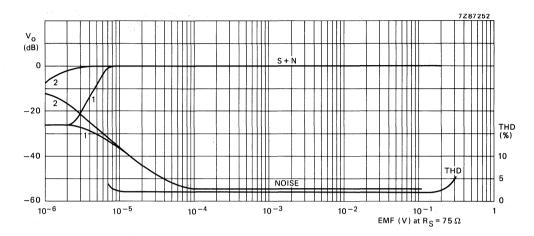

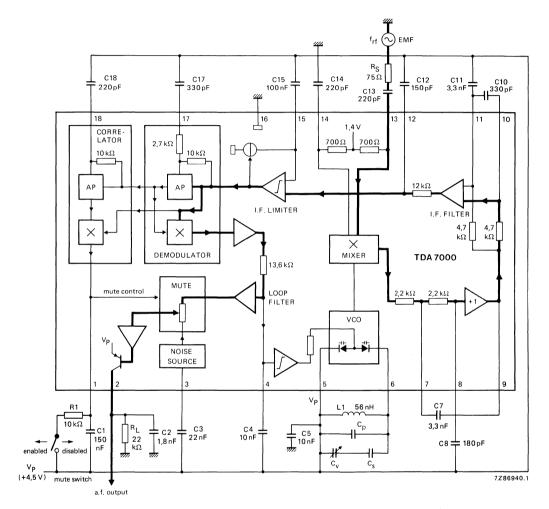

| AN192              | A complete FM radio on a chip                                                    | 41        |

| AN193              | TDA7000 for narrowband FM reception                                              | 42        |

| TDA7000            | Single-chip FM radio circuit                                                     | 44        |

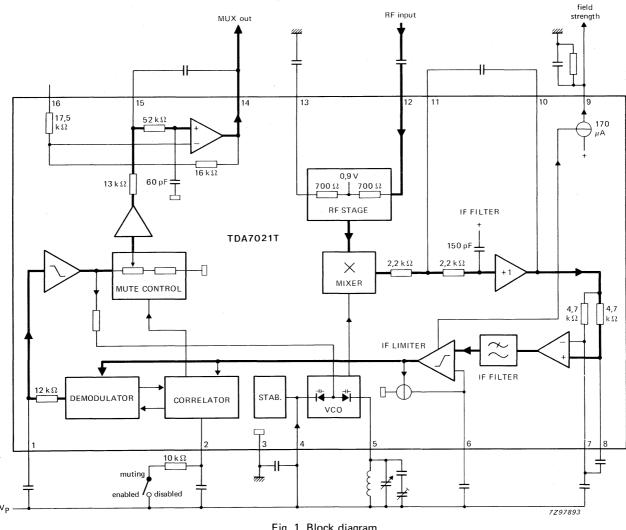

| TDA7021T           | Single-chip FM radio circuit                                                     | 44        |

| Castian 4 Missas   |                                                                                  |           |

|                    | 6 Balanced modulator/demodulator                                                 | <b>45</b> |

| AN189              | Balanced modulator/demodulator applications using the MC1496/1596                | 46        |

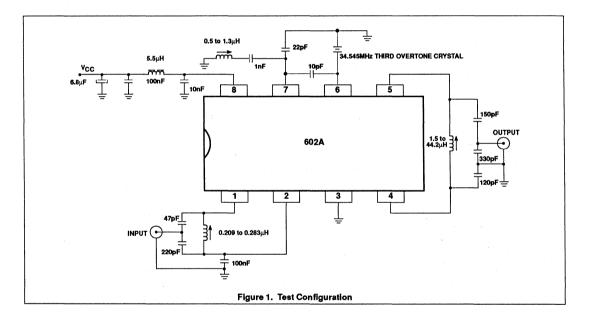

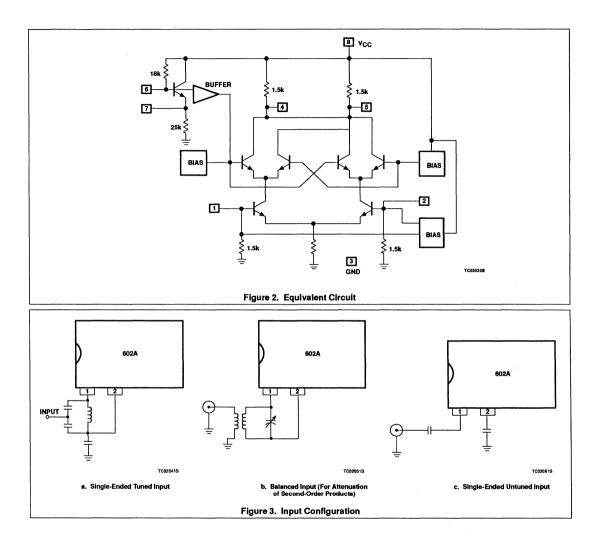

| NE/SA602A          | Double-balanced mixer and oscillator                                             | 47        |

| NE/SA612A          | Double-balanced mixer and oscillator                                             | 47        |

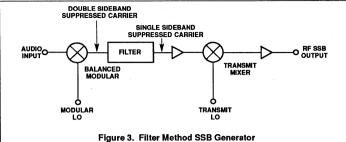

| AN1981             | New low-power single sideband circuits                                           | 48        |

| AN1982             | Applying the oscillator of the NE602 in low-power mixer applications             | 49        |

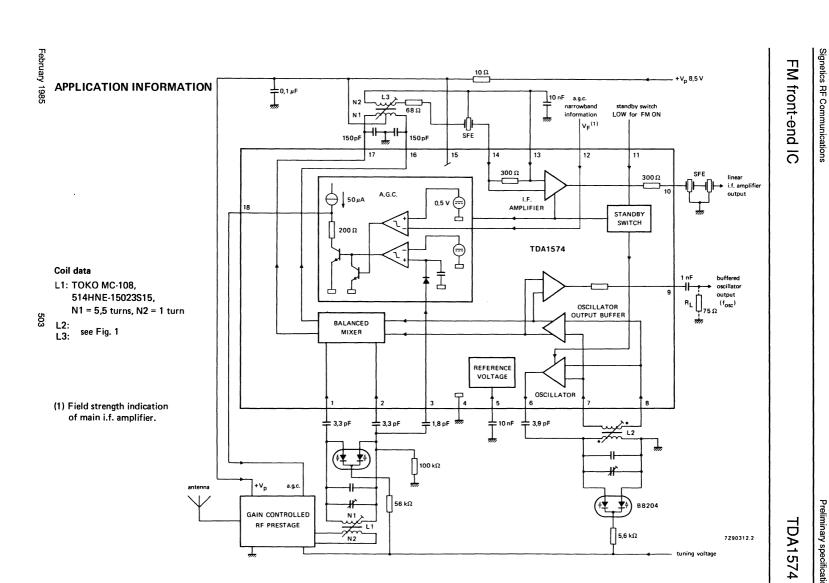

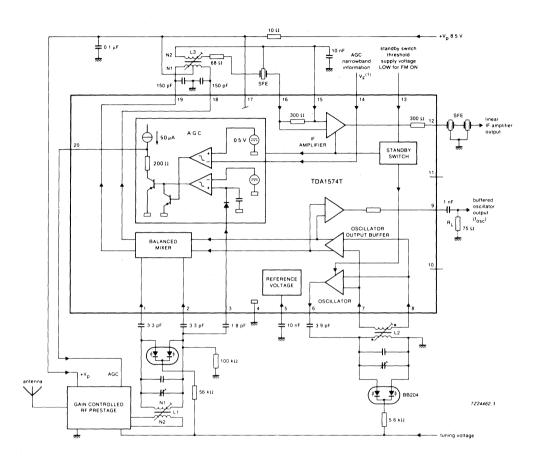

| TDA1574            | FM front-end IC                                                                  | 49        |

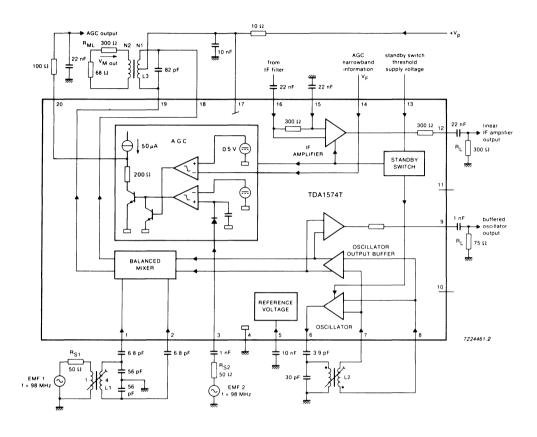

| TDA 1574T          | Integrated FM tuner for radio receivers                                          | 50        |

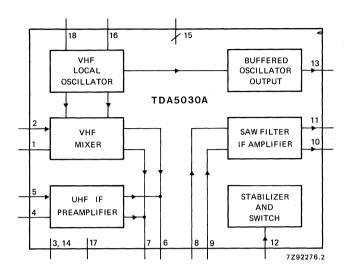

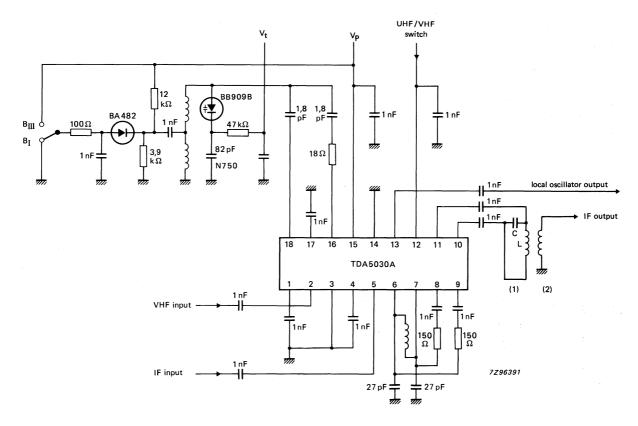

| TDA5030A           | TV VHF mixer/oscillator UHF preamplifier                                         | 51        |

| Section 5 Audio a  | nd Data Processors                                                               | 51        |

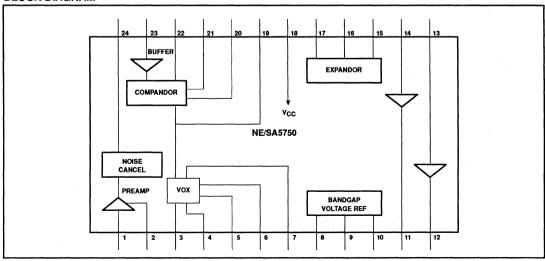

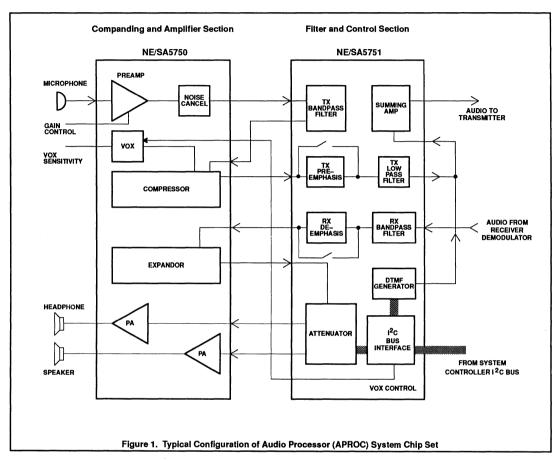

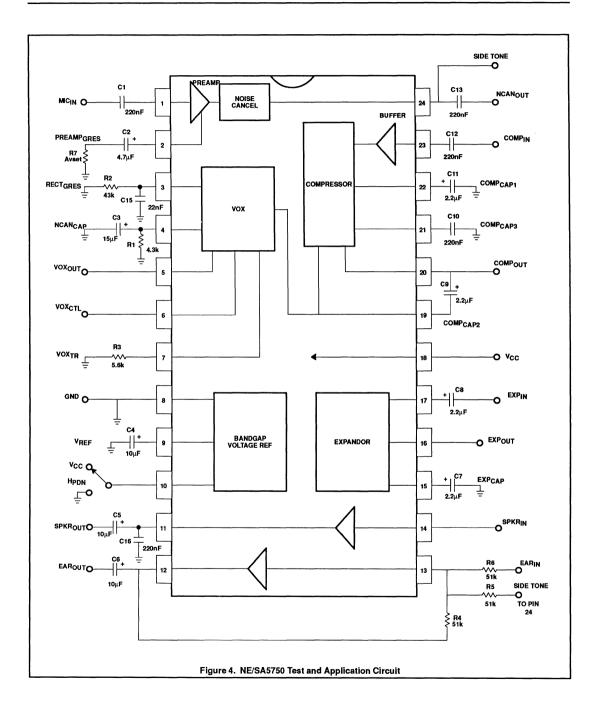

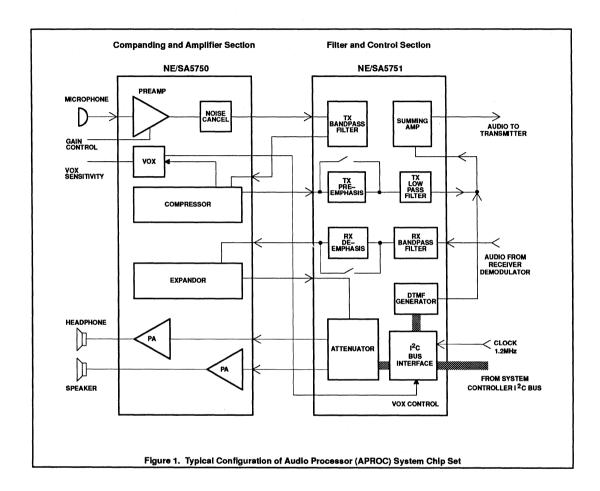

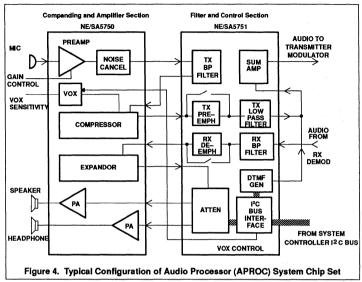

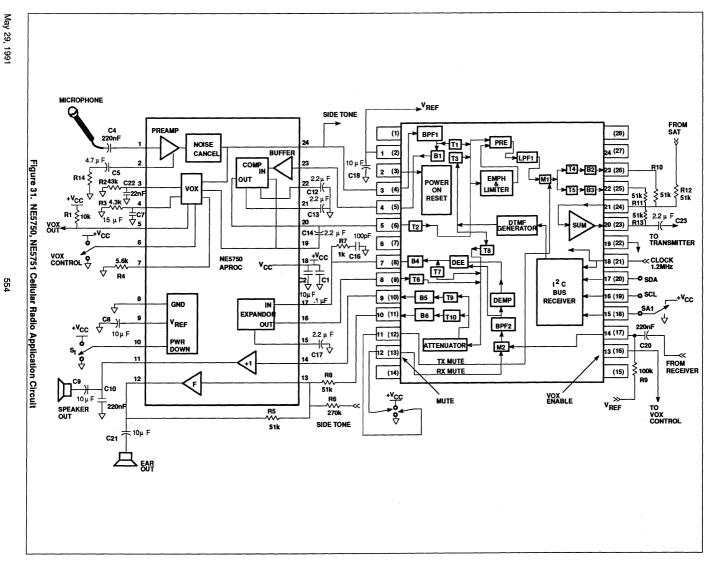

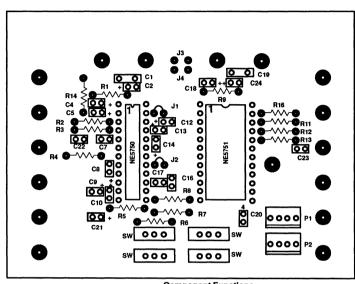

| NE/SA5750          | Audio processor - companding and amplifier section                               | 52        |

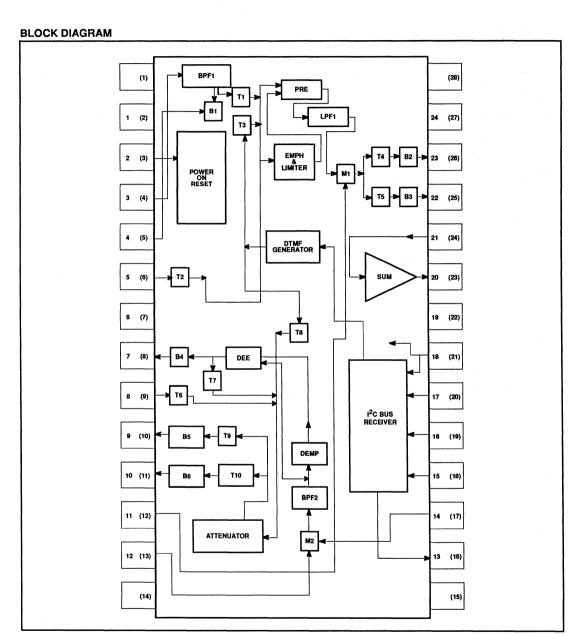

| NE/SA5751          | Audio processor - filter and control section                                     | 52        |

| AN1741             | Using the NE5750 and NE5751 for audio processing                                 | 53        |

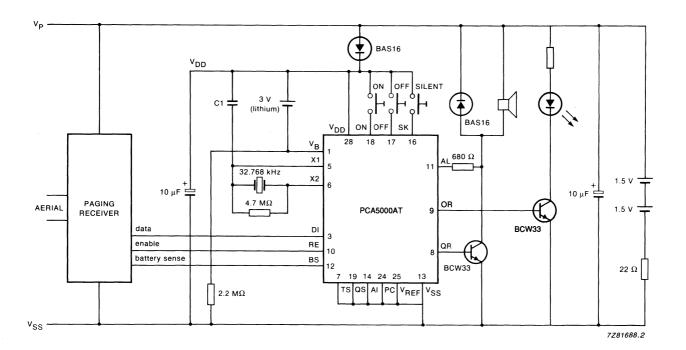

| PCA5000AT          | Paging decoder                                                                   | 55        |

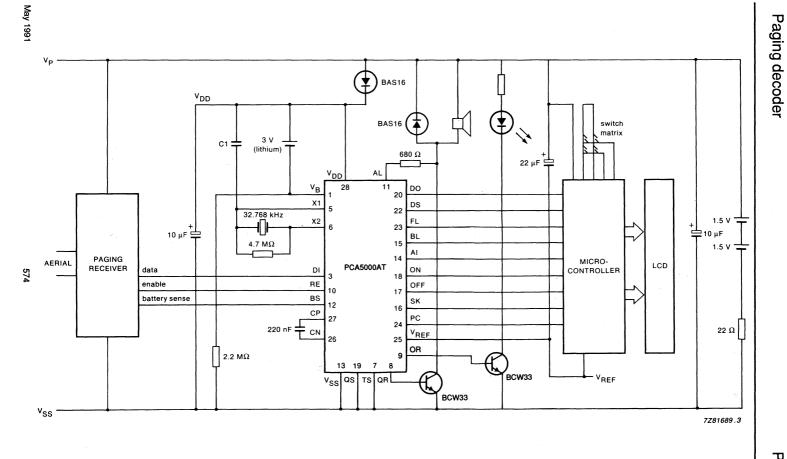

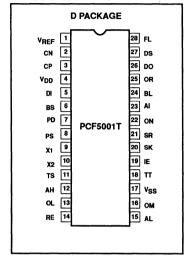

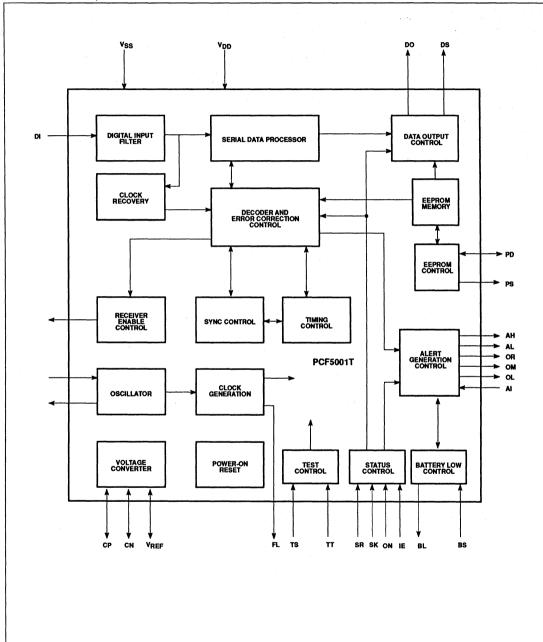

| PCF5001T           | POCSAG paging decoder with EEPROM storage                                        | 57        |

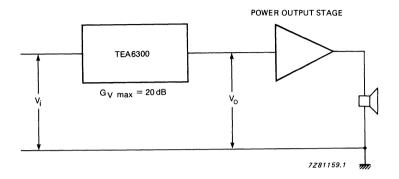

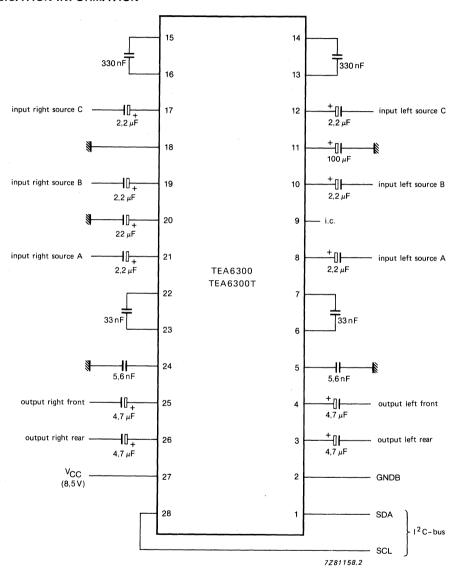

| TEA6300            | Sound fader control circuit                                                      | 57        |

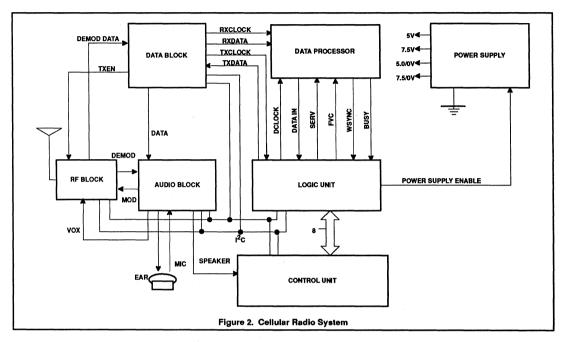

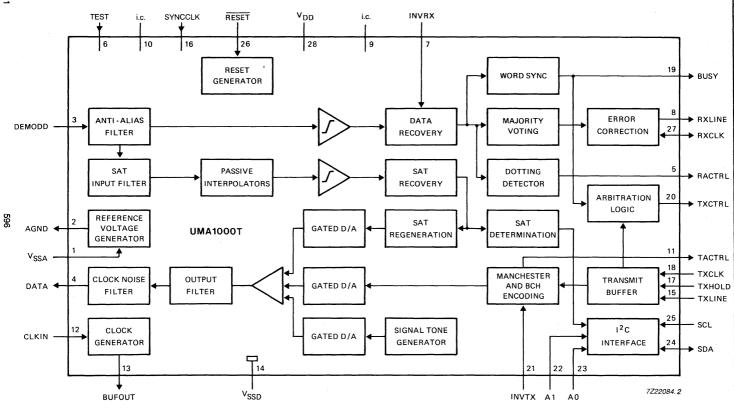

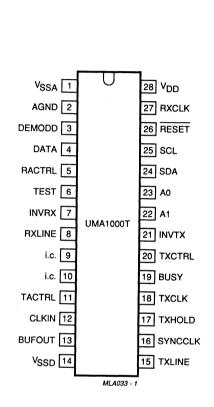

| UMF1000T           | Data processor for cellular radio (DPROC)                                        | 59        |

|                    | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                          | -         |

|                    | ncy Synthesizers, Pagers, and Data Receivers                                     | 62        |

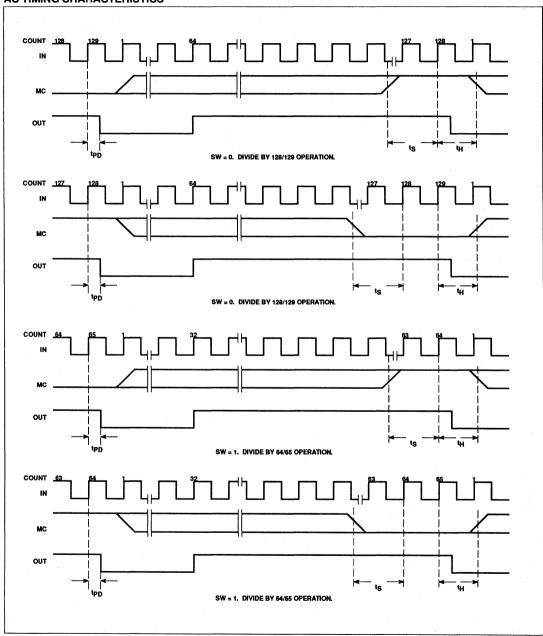

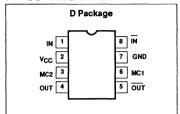

| NE/SA701           | Divide by: 128/129-64/65 dual modulus low power<br>ECL prescaler                 | 62        |

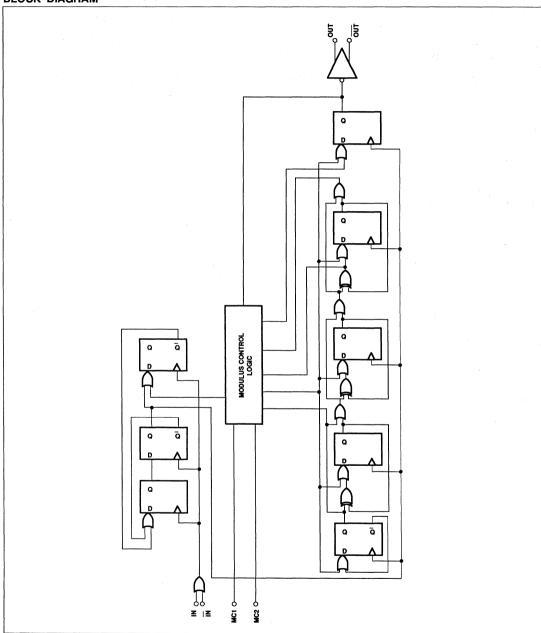

| NE/SA702           | Divide by: 64/65/72 triple modulus low power                                     |           |

| NE/SA703           | ECL prescaler                                                                    | 63        |

|                    | ECL prescaler                                                                    | 63        |

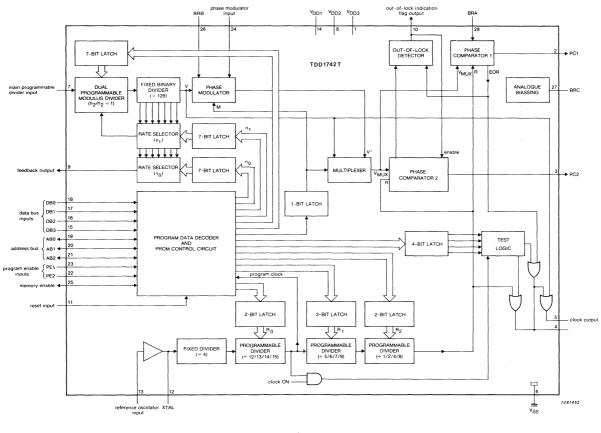

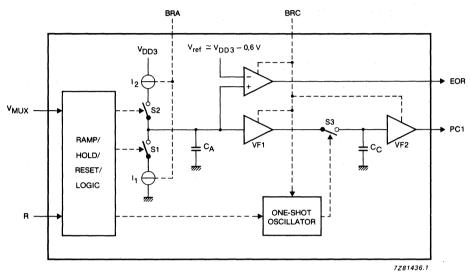

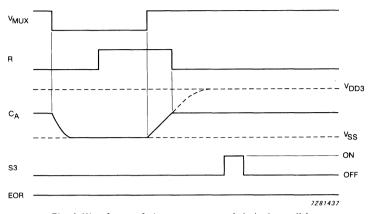

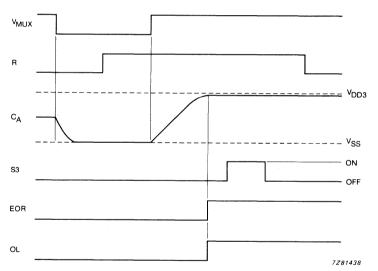

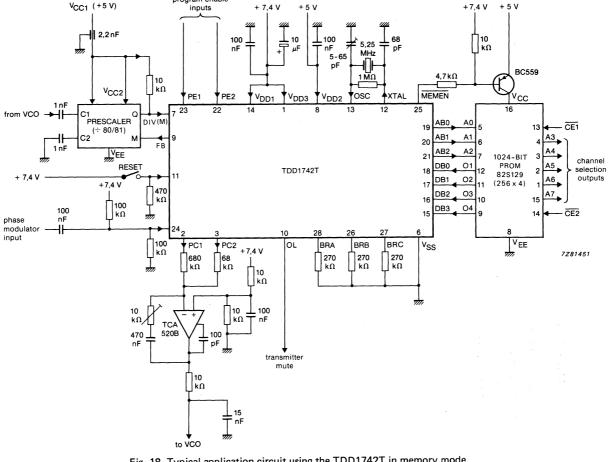

| TDD1742T           | CMOS frequency synthesizer                                                       | 64        |

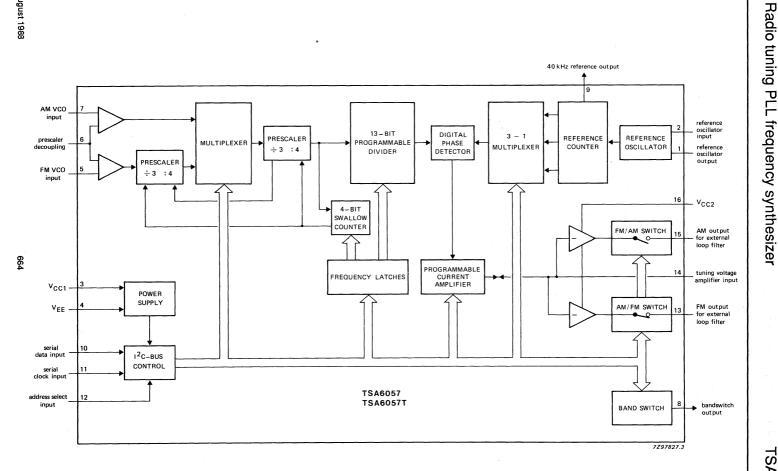

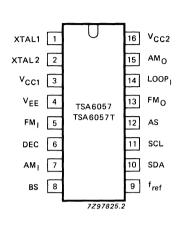

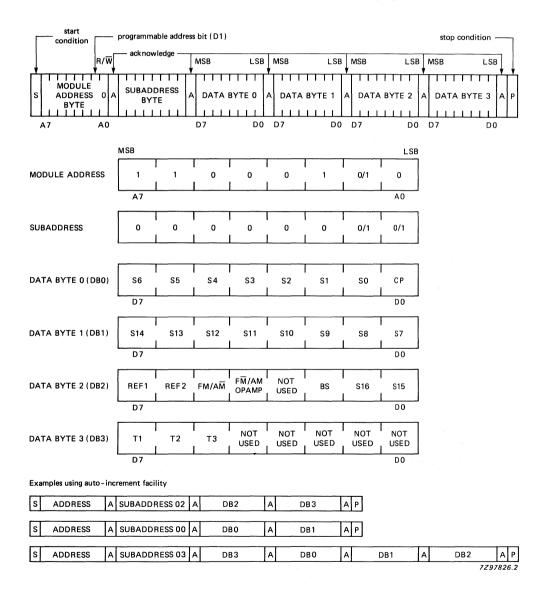

| TSA6057/T          | Radio tuning PLL frequency synthesizer                                           | 66        |

| TSA5511            | 1.3GHz bi-directional I2C bus controlled synthesizer                             | 67        |

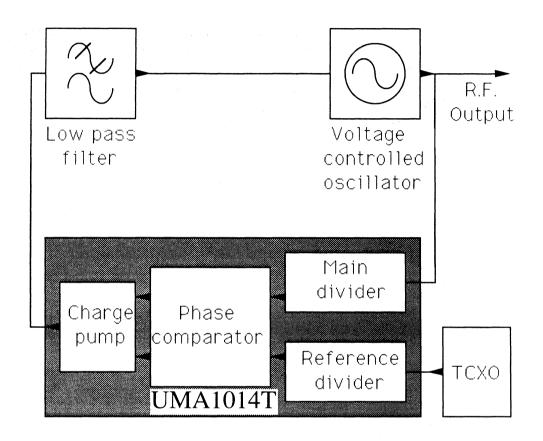

| UMA1014T           | Frequency synthesizer for cellular radio communication                           | 68        |

| UMF1005T           | Low-power frequency synthesizer                                                  | 69        |

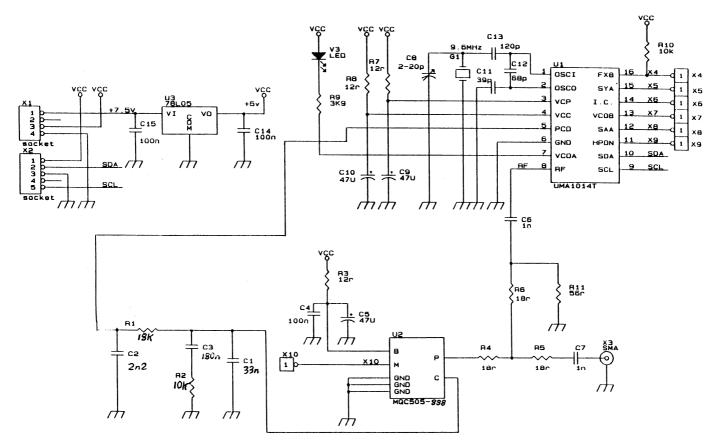

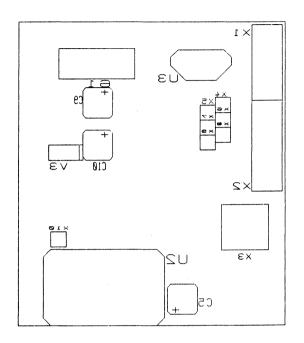

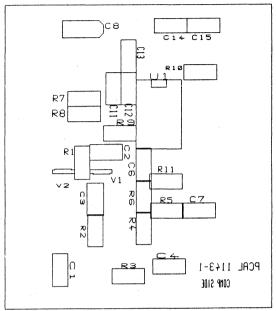

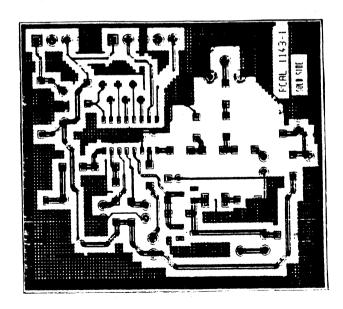

| SCO/AN91004        | Application report for the UMA1014T frequency synthesizer                        | 71        |

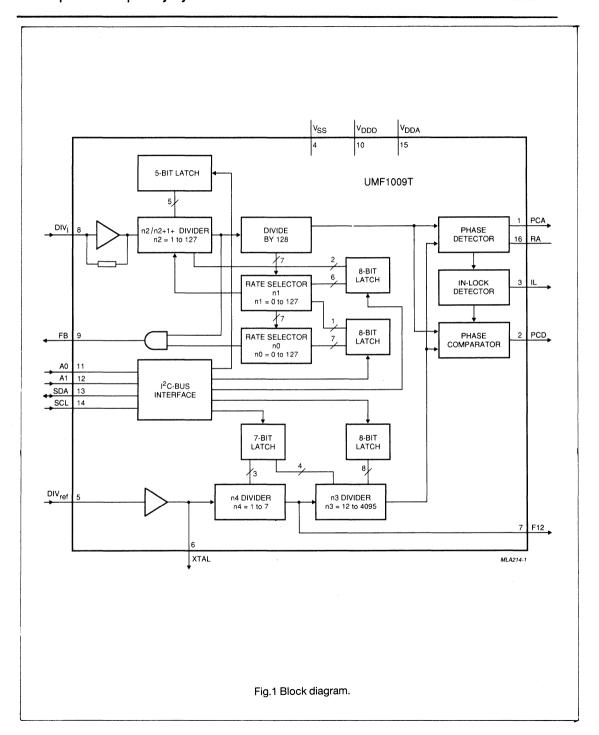

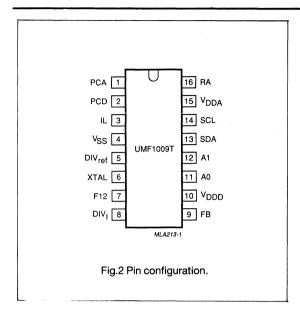

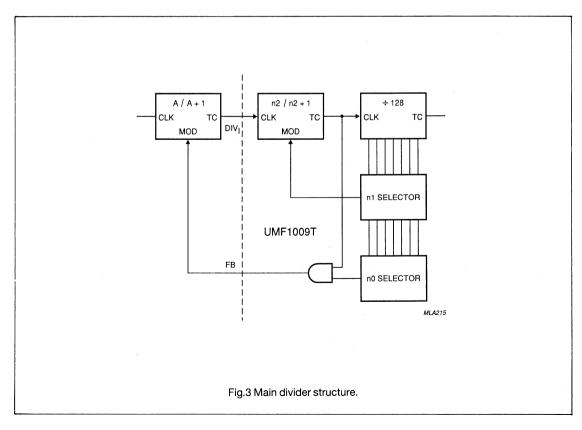

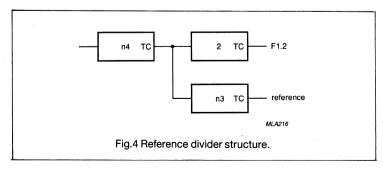

| UMF1009T           | Low power frequency synthesizer for radio communication                          | 74        |

| Section 7 Callular | chip set                                                                         | 70        |

|                    |                                                                                  | 76        |

|                    | design guide                                                                     | 76        |

|                    | tion                                                                             | 80        |

|                    |                                                                                  |           |

December 1991

# **RF Communications Handbook**

# **Contents**

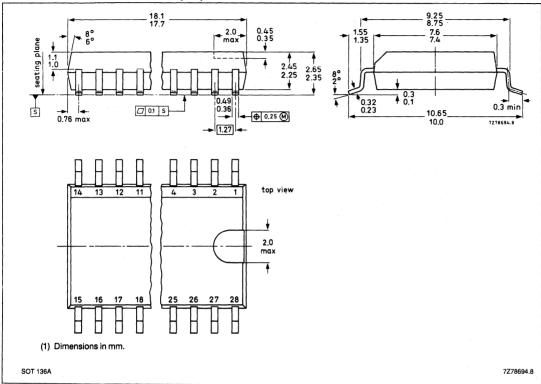

| Section 8 Packa  | ge outlines                                                          | 833 |

|------------------|----------------------------------------------------------------------|-----|

| NE/SA630         | Single pole double throw (SPDT) switch                               | 835 |

| Section 9 Packa  | ge outlines                                                          | 845 |

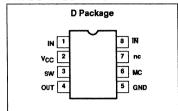

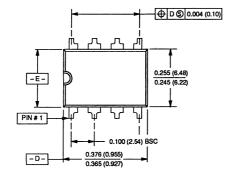

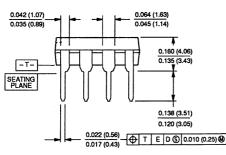

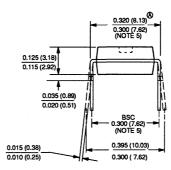

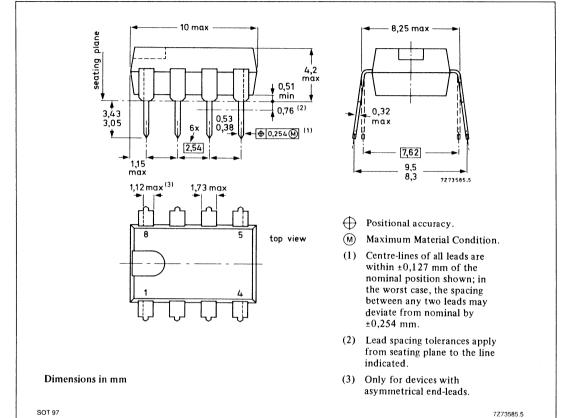

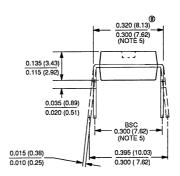

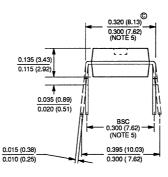

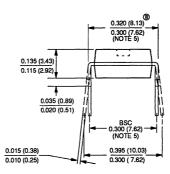

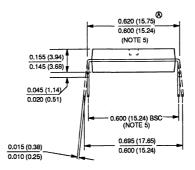

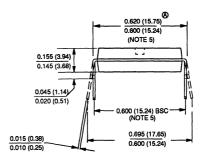

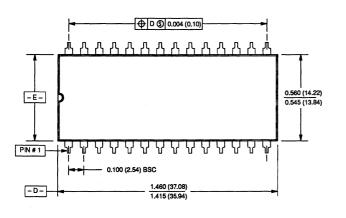

| 8-PIN (300 mils  | s wide) Plastic Dual In-Line (N) Package                             | 847 |

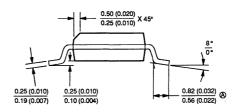

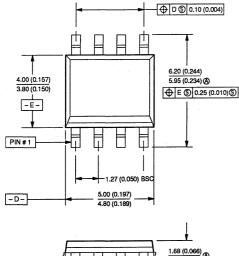

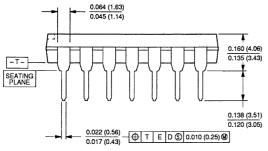

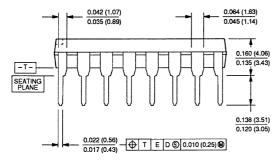

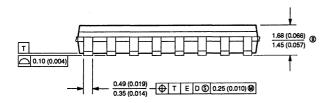

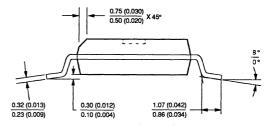

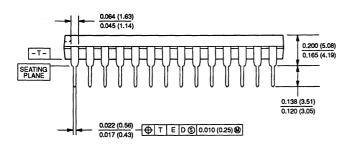

| 8-PIN (157 mils  | s wide) Plastic SO (Small Outline) Dual In-Line (D) Package          | 848 |

|                  | oual in-line (N/P) package                                           | 849 |

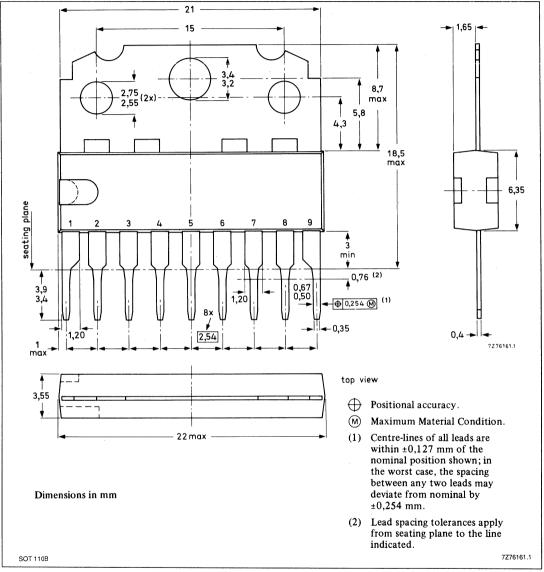

| 9-PIN Plastic S  | ingle in-line (U) package                                            | 850 |

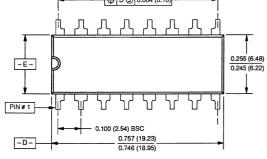

| 14-PIN (300 mi   | ils wide) Plastic Dual In-Line (N) package                           | 851 |

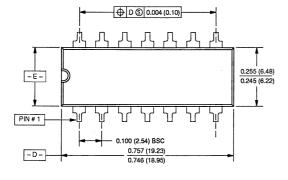

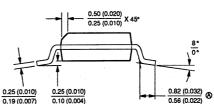

| 14-PIN (157 m    | ils wide) Plastic SO (Small Outline) Dual In-Line (D) Package        | 852 |

| 16-PIN (300 mi   | ils wide) Plastic Dual In-Line (N) Package                           | 853 |

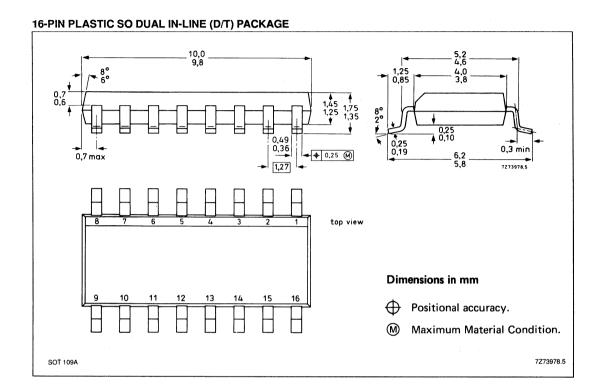

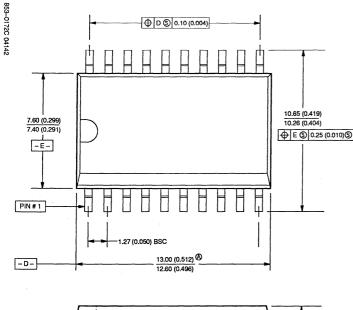

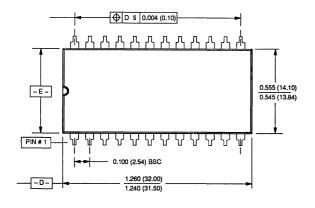

| 16-PIN (157 m    | ils wide) Plastic SO (Small Outline) Dual In-Line (D) Package        | 854 |

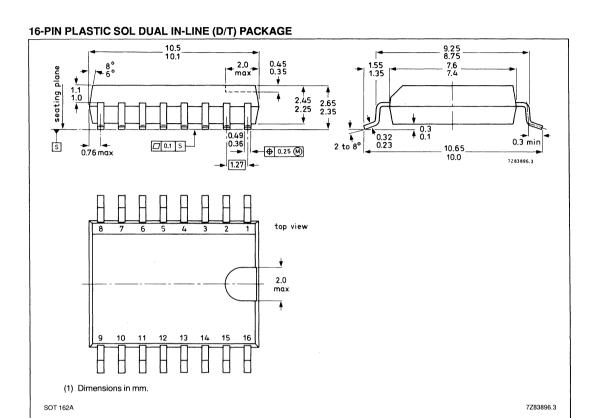

|                  | SO Dual In-Line (D/T) Package                                        | 855 |

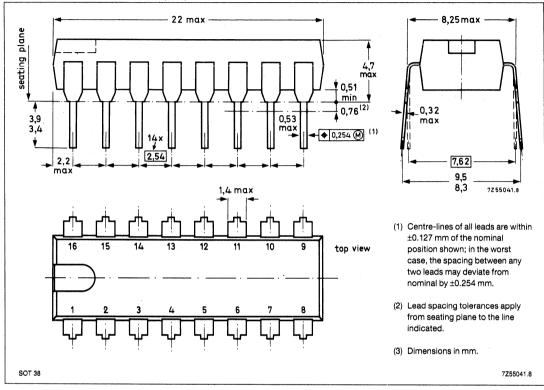

| 16-PIN Plastic   | Dual In-Line (N/P) Package                                           | 856 |

| 16-PIN Plastic   | SOL Dual In-Line (D/T) Package                                       | 857 |

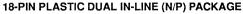

| 18-PIN Plastic   | Dual In-Line (N/P) Package                                           | 858 |

| 20-PIN (300 mi   | ils wide) Plastic Dual In-Line (N) Package                           | 859 |

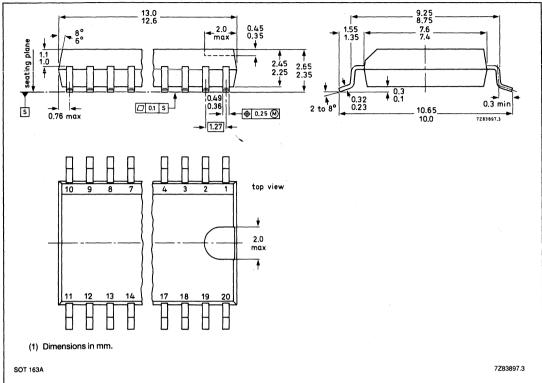

| 20-PIN (300 mi   | ils wide) Plastic SOL (Small Outline Large) Dual In-Line (D) Package | 860 |

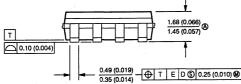

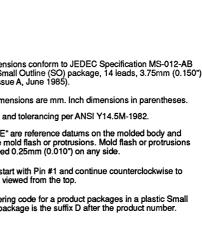

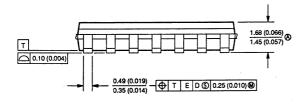

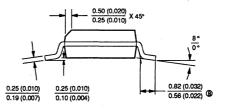

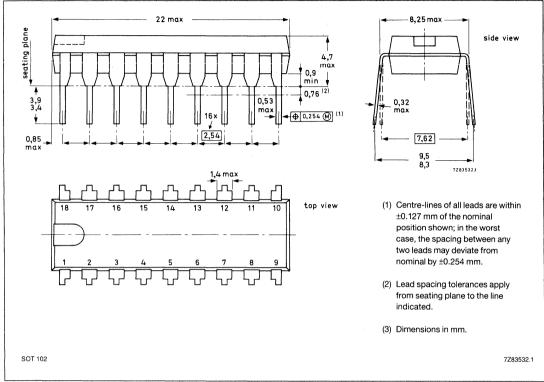

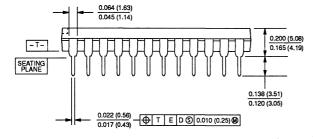

|                  | Shrink Small Outline Package (SSOP) (DK Package)                     | 861 |

| 20-PIN Plastic   | SO Dual In-Line (D/T) Package                                        | 862 |

| 24-PIN (600 m    | ils wide) Plastic Dual IN-Line Package                               | 863 |

| 24-PIN (300 m    | ils wide) Plastic SOL (Small Outline Large) Dual In-Line (D) Package | 864 |

| 28-PIN (600 m    | ils wide) Plastic Dual In-Line (N) Package                           | 865 |

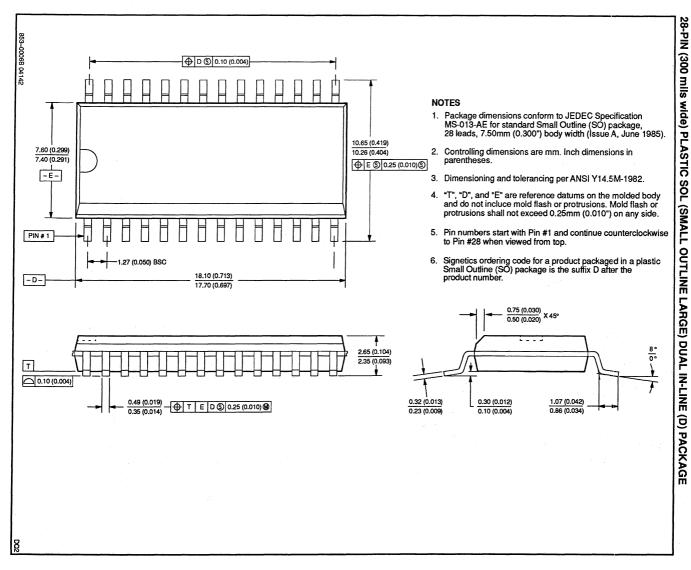

| 28-PIN (300 m    | ils wide) Plastic SOL (Small Outline Large) Dual In-Line (D) Package | 866 |

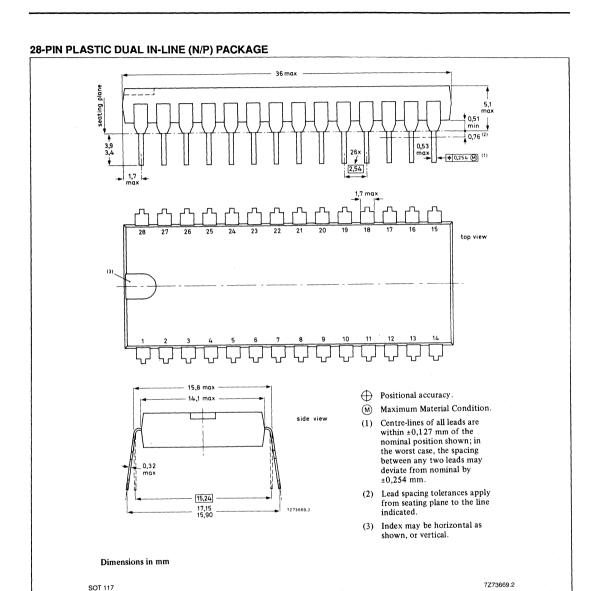

| 28-PIN Plastic   | Dual In-Line (N/P) Package                                           | 867 |

| 28-PIN Plastic   | SO Dual In-Line (D/T) Package                                        | 868 |

| Section 10 Sales | office listings                                                      | 869 |

December 1991 v

# RF Communications Handbook Alphanumeric product list

#### **RF Communications**

| MC1496/MC1596   | Balanced modulator/demodulator                                                | 461 |

|-----------------|-------------------------------------------------------------------------------|-----|

| MC3361          | Low-power FM IF                                                               | 243 |

| NE/SA5200       | RF dual gain-stage                                                            | 3   |

| NE/SA5204       | Wide-band high-frequency amplifier                                            | 15  |

| NE/SA5205       | Wide-band high-frequency amplifier                                            | 25  |

| NE/SA5209       | Wideband variable gain amplifier                                              | 35  |

| NE/SA5219       | Wideband variable gain amplifier                                              | 50  |

| NE/SA5234       | Matched quad high-performance low-voltage operational amplifier               | 63  |

| NE/SE5539       | High frequency operational amplifier                                          | 81  |

| NE5592          | Video amplifier                                                               | 89  |

| NE570/571/SA571 | Compandor                                                                     | 167 |

| NE/SA572        | Programmable analog compandor                                                 | 189 |

| NE/SA575        | Low voltage compandor                                                         | 198 |

| NE/SA575 SSOP   | Low voltage compandor in shrink small outline package                         | 208 |

| NE/SA5750       | Audio processor - companding and amplifier section                            | 521 |

| NE/SA5751       | Audio processor - filter and control section                                  | 528 |

| NE/SA576        | Low power compandor                                                           | 218 |

| NE/SA577        | Unity gain level programmable power compandor                                 | 221 |

| NE/SA578        | Unity gain level programmable low power compandor                             | 225 |

| NE/SA/SE592     | Video amplifier                                                               | 94  |

| NE/SA602A       | Double-balanced mixer and oscillator                                          | 470 |

| NE/SA604A       | High performance low power FM IF system                                       | 246 |

| NE/SA605        | High performance low power mixer FM IF system                                 | 280 |

| NE/SA605 (SSOP) | High performance low power mixer FM IF system in shrink small outline package | 290 |

| NE/SA606        | Low-voltage high performance mixer FM IF system                               | 346 |

| NE/SA607        | Low voltage high performance mixer FM IF system                               | 378 |

| NE/SA612A       | Double-balanced mixer and oscillator                                          | 478 |

| NE/SA614A       | Low power FM IF system                                                        | 256 |

| NE/SA615        | High performance low power mixer FM IF system                                 | 298 |

| NE/SA615 (SSOP) | High performance low power mixer FM IF system in shrink small outline package | 308 |

| NE/SA616        | Low-voltage high performance mixer FM IF system                               | 362 |

| NE/SA617        | Low-voltage high performance mixer FM IF system                               | 392 |

| NE630           | Single-pole doulbe-throw switch (SPDT)                                        | 835 |

| NE/SA701        | Divide by: 128/129-64/65 dual modulus low power ECL prescaler                 | 629 |

| NE/SA702        | Divide by: 64/65/72 triple modulus low power ECL prescaler                    | 633 |

| NE/SA703        | Divide by: 128/129/144 triple modulus low power ECL prescaler                 | 637 |

| PCA5000AT       | Paging decoder                                                                | 558 |

| PCF5001T        | POCSAG paging decoder with EEPROM storage                                     | 577 |

| TDA1010A        | 6W audio amplifier with preamplifier                                          | 102 |

| TDA1011A        | 2 to 6W audio power amplifier with preamplifier                               | 130 |

| TDA1013B        | 4W amplifier with DC volume control                                           | 138 |

| TDA1015         | 1 to 4W audio amplifier with preamplifier                                     | 120 |

| TDA1574         | FM front-end IC                                                               | 496 |

| TDA1574T        | Integrated FM tuner for radio receivers                                       | 504 |

| TDA1576T        | FM/IF amplifier/demodulator circuit                                           | 406 |

| TDA5030A        | TV VHF mixer/oscillator UHF preamplifier                                      | 513 |

| TDA7000         | Single-chip FM radio circuit                                                  | 442 |

# Alphanumeric product list

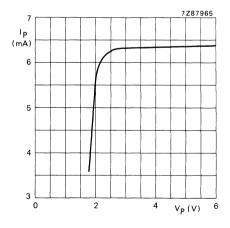

| TDA7021T  | Single-chip FM radio circuit                                      | 449 |

|-----------|-------------------------------------------------------------------|-----|

| TDA7052   | 1 Watt low voltage audio power amplifier                          |     |

| TDA7052A  | 1-Watt low voltage audio power amp with DC volume control         | 151 |

| TDA7056A  | 3-Watt mono BTL audio output amplifier                            | 158 |

| TDD1742T  | CMOS frequency synthesizer                                        | 641 |

| TEA6300   | Sound fader control circuit                                       | 579 |

| TSA5511   | 1.3GHz bi-directional I <sup>2</sup> C bus controlled synthesizer | 672 |

| TSA6057/T | Radio tuning PLL frequency synthesizer                            |     |

| UMF1000T  | Data processor for cellular radio (DPROC)                         | 595 |

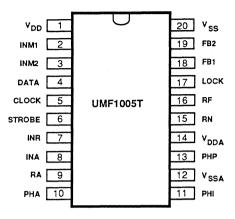

| UMF1005T  | Low-power frequency synthesizer                                   | 697 |

| UMF1009T  | Low power frequency synthesizer for radio communication           | 746 |

| UMA1014T  | Frequency synthesizer for cellular radio communication            |     |

December 1991 ix

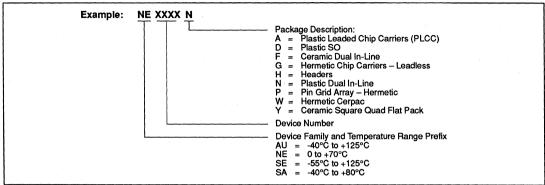

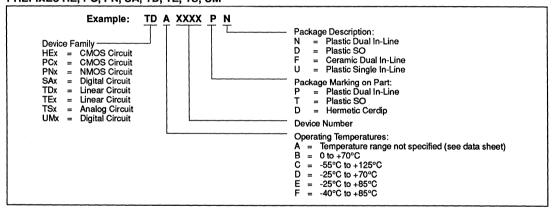

# **Ordering Information**

#### LINEAR PRODUCTS PART NUMBERING SYSTEM

# PHILIPS PRODUCTS PART NUMBERING SYSTEM PREFIXES HE, PC, PN, SA, TD, TE, TS, UM

# Signetics

# Section 1 Amplifiers

# **RF Communications**

# INDEX

| RF Amplifier Sel | ector Guide 2                                                   |

|------------------|-----------------------------------------------------------------|

| NE/SA5200        | RF dual gain-stage                                              |

| NE/SA5204        | Wide-band high-frequency amplifier                              |

| NE/SA5205        | Wide-band high-frequency amplifier                              |

| NE/SA5209        | Wideband variable gain amplifier                                |

| NE/SA5219        | Wideband variable gain amplifier 50                             |

| NE/SA5234        | Matched quad high-performance low-voltage operational amplifier |

| AN1651           | Using the NE/SA5234 amplifier 67                                |

| NE/SE5539        | High frequency operational amplifier 81                         |

| NE5592           | Video amplifier 89                                              |

| NE/SA/SE592      | Video amplifier                                                 |

| TDA1010A         | 6W audio amplifier with preamplifier                            |

| TDA1015          | 1 to 4W audio amplifier with preamplifier                       |

| TDA1011A         | 2 to 6W audio power amplifier with preamplifier                 |

| TDA1013B         | 4W amplifier with DC volume control                             |

| TDA7052          | 1 Watt low voltage audio power amplifier                        |

| TDA7052A         | 1-Watt low voltage audio power amp with DC volume control       |

| TDA7056A         | 3-Watt mono BTL audio output amplifier                          |

RF Communications

# RF AMPLIFIER FAMILY OVERVIEW

| 0 8 8 8                         | NE5200                                                                               | NE5204                                     | NE5205                                     | NE5209                                              | NE5219                                               |

|---------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------|-----------------------------------------------------|------------------------------------------------------|

| V <sub>cc</sub>                 | 4 – 9V                                                                               | 5 – 8V                                     | 5 – 8V                                     | 4.5 – 7.0V                                          | 4.5 – 7.0V                                           |

| l <sub>cc</sub>                 | 8mA / 95 μA                                                                          | 24mA                                       | 24mA                                       | 43mA                                                | 43mA                                                 |

| Bandwidth (3dB)                 | 1.2GHz                                                                               | 550MHz                                     | 550MHz                                     | 850MHz                                              | 700MHz                                               |

| Noise Figure                    | 3.6dB                                                                                | 6.0dB 50 Ω<br>4.8dB 75 Ω                   | 6.0dB 50 Ω<br>4.8dB 75 Ω                   | 9.3dB                                               | 9.3dB                                                |

| 1dB Compression<br>(output)     | 6dBm                                                                                 | +4dBm                                      | +4dBm                                      | -3dBm                                               | -3dBm                                                |

| 3rd Order Intercept<br>(output) | +4dBm                                                                                | +17dBm                                     | +17dBm                                     | +13dBm                                              | +13dBm                                               |

| Input Impedance                 | 50 Ω                                                                                 | 50 Ω                                       | 50 Ω                                       | 1.2kΩ                                               | 1.2k Ω                                               |

| Output Impedance                | 50 Ω                                                                                 | 50 Ω                                       | 50 Ω                                       | 60Ω                                                 | 60 Ω                                                 |

| Gain (per amplifier)            | 7.5dB/–13dB                                                                          | 19dB                                       | 19dB                                       | 25dB*                                               | 25dB*                                                |

| Package                         | SO8                                                                                  | DIP8<br>SO8                                | DIP8<br>SO8                                | DIP16<br>SO16                                       | DIP16<br>SO16                                        |

| Features                        | +Dual Gain Stage<br>+Enable Pin<br>+Good Noise Figure<br>+Low current<br>consumption | +Low-cost amp<br>+Simple<br>Implementation | +Low-cost amp<br>+Simple<br>Implementation | +Variable gain and attenuation +Excellent Linearity | +Variable gain and attentuation +Excellent Linearity |

<sup>\*</sup>Single in / Differential out

#### NE/SA5200

#### DESCRIPTION

The NE/SA5200 is a dual amplifier with DC to 1200MHz response. Low noise (NF = 3.6dB) makes this part ideal for RF front-ends, and a simple power-down mode saves current for battery operated equipment. Inputs and outputs are matched to  $50\Omega$ .

The enable pin allows the designer the ability to turn the amplifiers on or off, allowing the part to act as an amplifier as well as an attenuator. This is very useful for front-end buffering in receiver applications.

#### **FEATURES**

- Dual amplifiers

- DC 1200MHz operation

- Low DC power consumption (4.2mA per amplifier @ V<sub>CC</sub> = 5V)

- Power-Down Mode (I<sub>CC</sub> = 95μA typical)

- 3.6dB noise figure at 900MHz

- Unconditionally stable

- Fully ESD protected

- Low cost

- Supply voltage 4-9V

- Gain S21 = 7dB at f = 1GHz

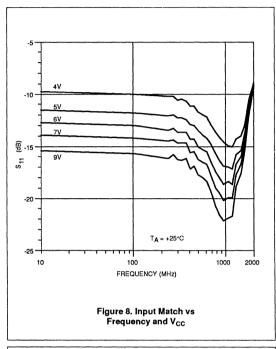

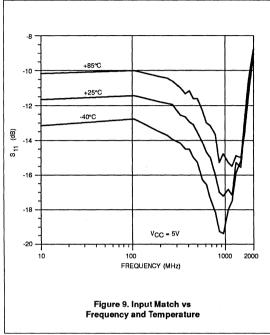

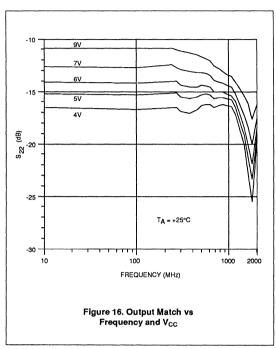

- Input and output match S<sub>11</sub>, S<sub>22</sub> typically

<−14dB</li>

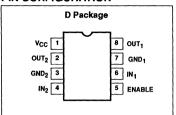

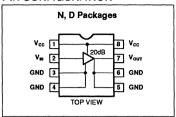

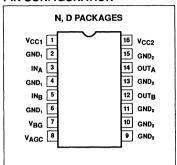

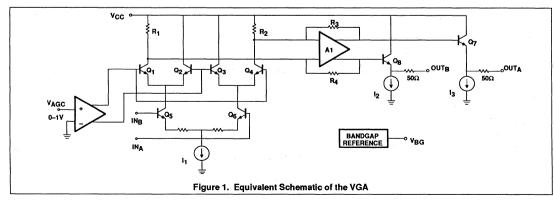

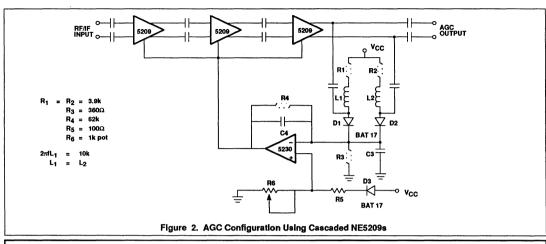

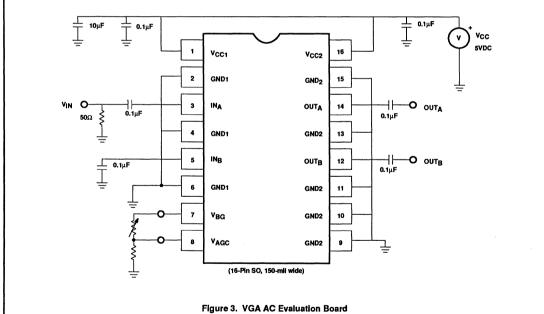

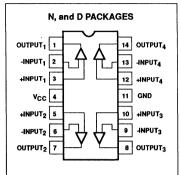

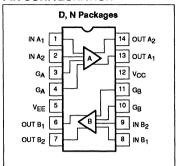

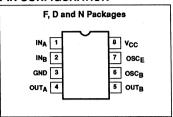

#### **PIN CONFIGURATION**

#### **APPLICATIONS**

- Cellular radios

- RF IF strips

- Portable equipment

#### ORDERING INFORMATION

| DESCRIPTION                      | TEMPERATURE RANGE | ORDER CODE |  |

|----------------------------------|-------------------|------------|--|

| 8-Pin Plastic SO (Surface-mount) | 0-70°C            | NE5200D    |  |

| 8-Pin Plastic SO (Surface-mount) | -40-+85°C         | SA5200D    |  |

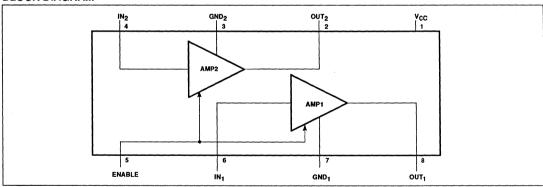

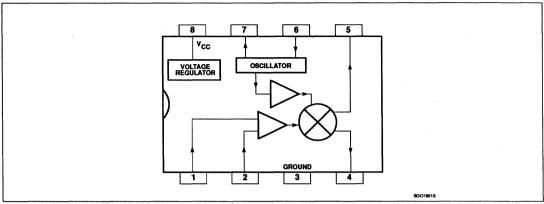

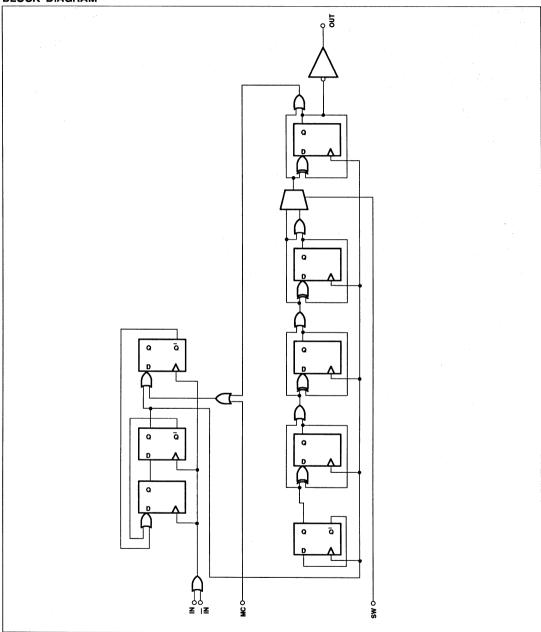

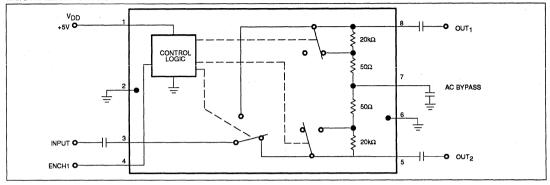

#### **BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL            | PARAMETER                                                                             | RATING      | UNITS |

|-------------------|---------------------------------------------------------------------------------------|-------------|-------|

| V <sub>CC</sub>   | Supply voltage <sup>1</sup>                                                           | -0.5 to +9  | V     |

| P <sub>D</sub>    | Power dissipation, T <sub>A</sub> = 25°C (still air) <sup>2</sup><br>8-Pin Plastic SO | 780         | mW    |

| T <sub>JMAX</sub> | Maximum operating junction temperature                                                | 150         | °C    |

| P <sub>MAX</sub>  | Maximum power input/output                                                            | +20         | dBm   |

| T <sub>STG</sub>  | Storage temperature range                                                             | -65 to +150 | °C    |

#### NOTE:

- 1. Transients exceeding 10.5V on V<sub>CC</sub> pin may damage product.

- 2. Maximum dissipation is determined by the operating ambient temperature and the thermal resistance,  $\theta_{JA}$ : 8-Pin SO:  $\theta_{JA} = 158^{\circ}\text{C/W}$

NE/SA5200

#### RECOMMENDED OPERATING CONDITIONS

| SYMBOL          | PARAMETER                                                   | RATING                  | UNITS     |

|-----------------|-------------------------------------------------------------|-------------------------|-----------|

| V <sub>CC</sub> | Supply voltage                                              | 4.0 to 9.0              | V         |

| TA              | Operating ambient temperature range<br>NE Grade<br>SA Grade | 0 to +70<br>-40 to +85  | o<br>o    |

| TJ              | Operating junction temperature<br>NE Grade<br>SA Grade      | 0 to +90<br>-40 to +105 | ို<br>ပို |

#### DC ELECTRICAL CHARACTERISTICS $V_{CC} = +5V$ , $T_A = 25$ °C; unless otherwise stated.

| SYMBOL               | PARAMETER                                     | TEST CONDITIONS                     |      | LIMITS |      |    |

|----------------------|-----------------------------------------------|-------------------------------------|------|--------|------|----|

|                      |                                               |                                     | MIN  | TYP    | MAX  | 1  |

| V <sub>CC</sub>      | Supply voltage                                |                                     | 4    | 5.0    | 9.0  | V  |

|                      |                                               | V <sub>CC</sub> = 5V, ENABLE = High | 6.4  | 8.4    | 10.4 | mA |

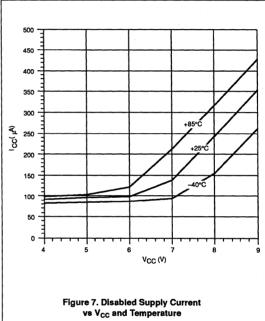

| lcc                  | Total supply current                          | V <sub>CC</sub> = 5V, ENABLE = Low  |      | 95     | 255  | μА |

|                      |                                               | V <sub>CC</sub> = 9V, ENABLE = High |      | 17.8   | 22.2 | mA |

|                      |                                               | V <sub>CC</sub> = 9V, ENABLE = Low  |      | 320    | 960  | μΑ |

| V <sub>T</sub>       | TTL/CMOS logic threshold voltage <sup>1</sup> |                                     |      | 1.25   |      | V  |

| VIH                  | Logic 1 level                                 | Power-up mode                       | 2.0  |        | Vcc  | V  |

| V <sub>IL</sub>      | Logic 0 level                                 | Power-down mode                     | -0.3 |        | 0.8  | V  |

| I <sub>IL</sub>      | Enable input current                          | Enable = 0.4V                       | -1   | 0      | 1    | μА |

| I <sub>IH</sub>      | Enable input current                          | Enable = 2.4V                       | -1   | 0      | 1    | μА |

| V <sub>IDC,ODC</sub> | Input and output DC levels                    |                                     | 0.6  | 0.83   | 1.0  | V  |

#### AC ELECTRICAL CHARACTERISTICS<sup>1</sup> V<sub>CC</sub> = +5V, T<sub>A</sub> = 25°C, either amplifier, enable = 5V; unless otherwise stated.

| SYMBOL          | PARAMETER                                     | TEST CONDITIONS |     | LIMITS |      |     |  |

|-----------------|-----------------------------------------------|-----------------|-----|--------|------|-----|--|

|                 |                                               |                 | MIN | TYP    | MAX  | 1   |  |

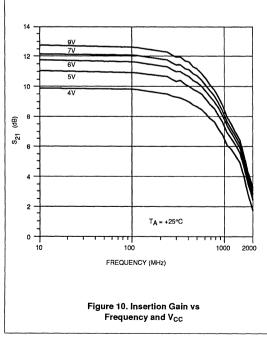

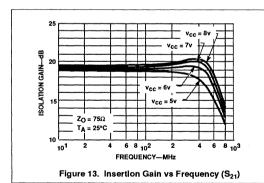

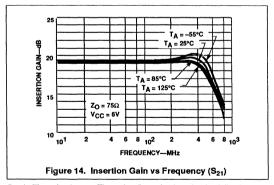

| S21             | Insertion gain                                | f = 100MHz      | 9.2 | 11     | 13.2 | dB  |  |

|                 |                                               | f = 900MHz      | 5.2 | 7.5    |      | dB  |  |

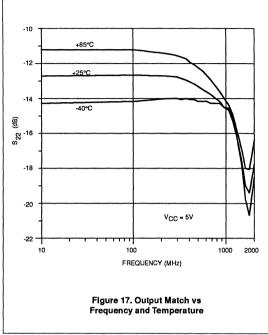

| S22             | Output return loss                            | f = 900MHz      |     | -14.3  |      | dB  |  |

| S12             | Reverse isolation                             | f = 900MHz      |     | -17.9  |      | dB  |  |

| S11             | Input return loss                             | f = 900MHz      |     | -16.5  |      | dB  |  |

| P-1             | Output 1dB compression point                  | f = 900MHz      |     | -4.3   |      | dBm |  |

| NF              | Noise figure in $50\Omega$                    | f = 900MHz      |     | 3.6    |      | dB  |  |

| IP <sub>2</sub> | Input second-order intercept point            | f = 900MHz      |     | +4.3   |      | dBm |  |

| IP <sub>3</sub> | Input third-order intercept point             | f = 900MHz      |     | -1.8   |      | dBm |  |

| ISOL            | Amplifier-to-amplifier isolation <sup>2</sup> | f = 900MHz      |     | -25    |      | dB  |  |

| Pout            | Saturated output power                        | f = 900MHz      |     | -1.7   |      | dBm |  |

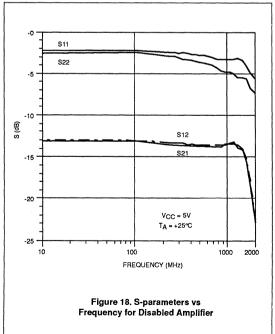

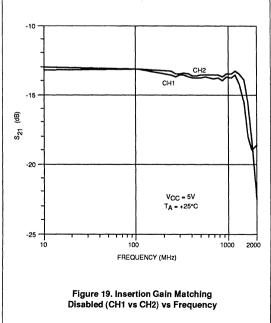

| S21             | Insertion gain when disabled                  | f = 100MHz      |     | -13    | 1    | dB  |  |

|                 |                                               | f = 900MHz      |     | -13.5  | 1    | dB  |  |

<sup>1.</sup> The ENABLE input must be connected to a valid logic level for proper operation of the NE/SA5200.

All measurements include the effects of the NE/SA5200 Evaluation Board (see Figure 2). Measurement system impedance is 50Ω.

Input applied to one amplifier, output taken at the other output. All ports terminated into 50Ω.

NE/SA5200

#### **APPLICATIONS**

NE/SA5200 is a user-friendly, wide-band, unconditionally stable, low power dual gain amplifier circuit. There are several advantages to using the NE/SA5200 as a high frequency gain block instead of a discrete implementation. First is the simplicity of use. The NE/SA5200 does not need any external biasing components. Due to the higher level of integration and small footprint (SO8) package it occupies less space on the printed circuit board and reduces the manufacturing cost of the system. Also the higher level of integration improves the reliability of the amplifier over a discrete implementation with several components. The power down mode in the NE/SA5200 helps reduce power consumption in applications where the amplifiers can be disabled. And last but not the least is the impedance matching at inputs and outputs. Only those who have toiled through discrete transistor implementations for  $50\Omega$  input and output impedance matching can truly appreciate the elegance and simplicity of the NE/SA5200 input and output impedance matching to  $50\Omega$ .

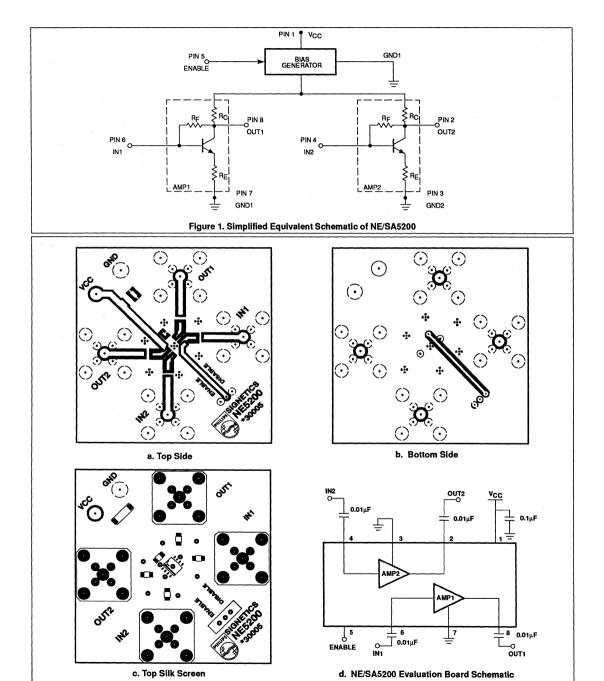

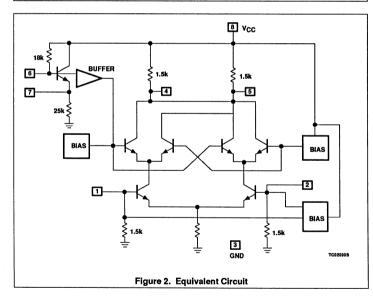

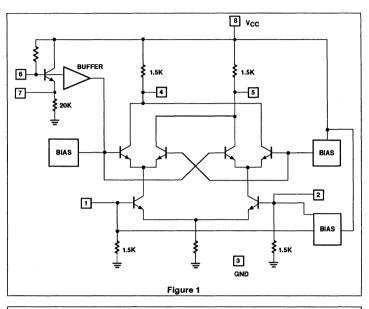

A simplified equivalent schematic is shown in Figure 1. Each amplifier is composed of an NPN transistor with an Ft of 13GHz in a classical series-shunt feedback configuration. The two wideband amplifiers are biased from the same bias generator. In normal operation each amplifier consumes about 4mA of quiescent current (at  $V_{CC} = 5V$ ). In the disable mode the device consumes about  $90\mu A$  of current, most of it is in the TTL enable buffer and the bias generator. The input impedance of the amplifiers is  $50\Omega$ . The amplifiers have typical gain of 11dB at 100MHz and 7dB of gain at 1.2GHz.

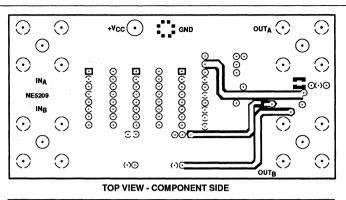

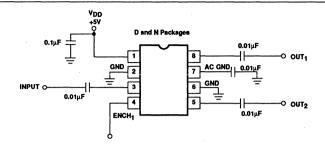

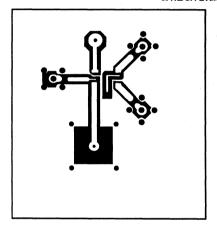

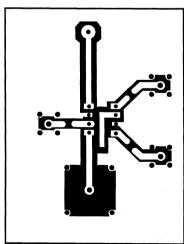

It can be seen from Figure 1 that any inductance between Pin 7, 3 and the ground plane will reduce the gain of the amplifiers at higher frequencies. Thus proper grounding of Pins 7 and 3 is essential for maximum gain and increased frequency response. Figure 2

shows the printed circuit board layout and the component placement for the NE/SA5200 evaluation board. The AC coupling capacitors should be selected such that at they are shorts at the desired frequency of operation. Since most low-cost large value surface mount capacitors cease to be simply capacitors in the UHF range and exhibit an inductive behavior, it is recommended that high frequency chip capacitors be utilized in the circuit. A good power supply bypass is also essential for the performance of the amplifier and should be as close to the device as practical.

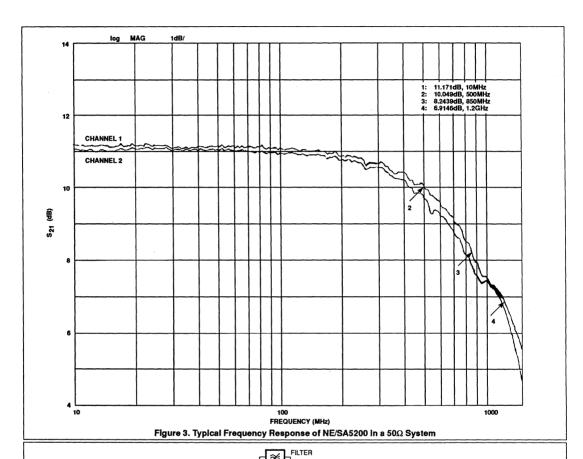

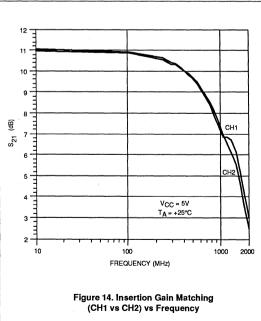

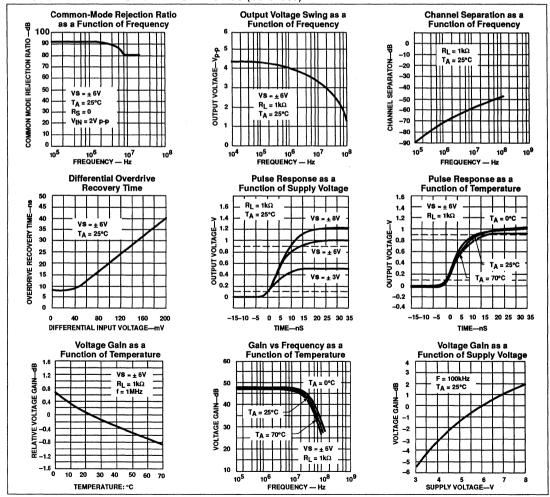

Figure 3 shows the typical frequency response of the two channels of NE/SA5200. The low frequency gain is about 11dB at 100MHz and slowly drops off to 10dB at 500MHz. The gain is about 8dB at 900MHz and 7dB at 1.2 GHz which is typical of NE/SA5200 with a good printed circuit board layout. It can also be seen that both channels have a very well matched frequency response and matched gain to within 0.1dB at 100MHz and 0.2dB at 900MHz.

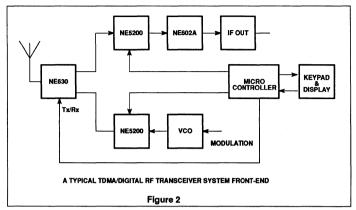

NE/SA5200 finds applications in many areas of RF communications. It is an ideal gain block for high performance, low cost, low power RF communications transceivers. A typical radio transceiver front-end is shown in Figure 4. This could be the front-end of a cellular phone, a VHF/ UHF hand-held transceiver, UHF cordless telephone or a spread spectrum system. The NE/SA5200 can be used in the receiver path of most systems as an LNA and pre-amplifier. The bandpass filter between the two amplifiers also minimize the noise into the first mixer. In the transmitter path, NE/SA5200 can be used as a buffer to the VCO and isolate the VCO from any load variations due to the power level changes in the power amplifier. This improves the stability of the VCOs. The NE/SA5200 can also be used as a pre-driver to the power amplifier modules.

The two amplifiers in NE/SA5200 can be easily cascaded to have a 13dB gain block at

900MHz. At 100MHz the gain will be 22dB and a noise figure of about 5.5dB. The NE/SA5200 can be operated at a higher voltage up to 9V for much improved 1dB output compression point and higher 3rd order intercept point.

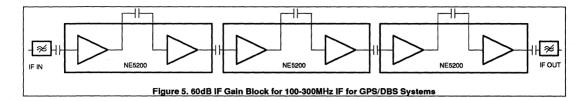

Several stages of NE/SA5200 can also be cascaded and be used as an IF amplifier strip for DBS/TV/GPS receivers. Figure 5 shows a 60dB gain IF strip at 180MHz. The noise figure for the cascaded amplifier chain is given by equation 1.

NF (total) = NF1 + NF2/G1 + NF3/G1\*G2 + NF4/G1\*G2\*G3 + ... (Equation. 1)

NOTE: The noise figure and gain should not be in dB in the above equation.

Since the noise figure for each stage is about 3.6dB and the gain is about 11dB, the noise figure for the 60dB gain IF strip will be about 6.4dB.

In applications where a single amplifier is required with a 7.5dB gain at 900MHz and current consumption is of paramount importance (battery powered receivers), the amplifier A1 can be used and amplifier A2 can be disabled by leaving GND2 (Pin 3) unconnected. This will reduce the total current consumption for the IC to a meager 4mA.

The ENABLE pin is useful for Time-Division-Duplex systems where the receiver can be disabled for a period of time. In this case the overall system supply current will be decreased by 8mA.

The ENABLE pin can also be used to improve the system dynamic range. For input levels that are extremely high, the NE/SA5200 can be disabled. In this case the input signal is attenuated by 13dB. This prevents the system from being overloaded as well as improves the system's overall dynamic range. In the disabled condition the NE/SA5200 IP3 increases to nearly +20dBm.

# NE/SA5200

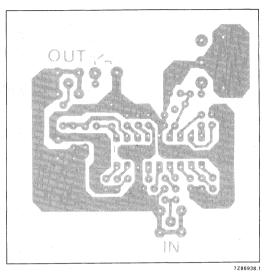

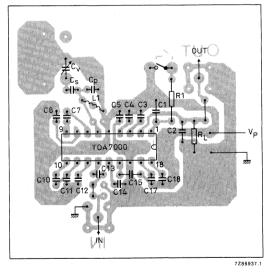

Figure 2. Printed Circuit Board Layout of the NE/SA5200 Evaluation Board

# NE/SA5200

ANTENNA

NES200

ENABLE

DUPLEX

FILTER

NE5200

VCO

ENABLE

ENABLE

VCO

Figure 4. Typical Radio Transceiver Front-End

MODULATION

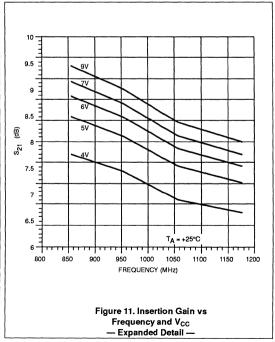

9.5 40°C 8.5 7 40°C 800 850 900 950 1000 1050 1100 1150 1200 FREQUENCY (MHz)

Figure 13. Insertion Gain vs Frequency and Temperature – Expanded Detail –

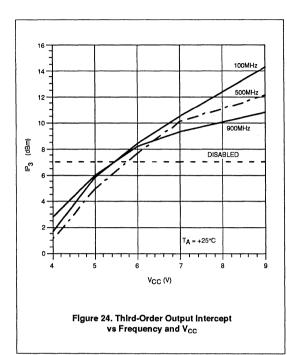

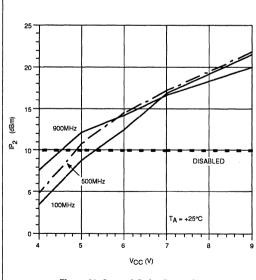

Figure 26. Second-Order Output Intercept vs Frequency and V<sub>CC</sub>

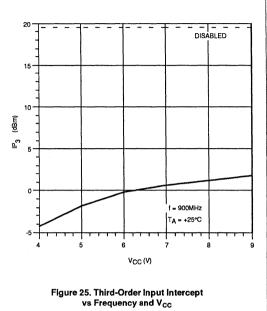

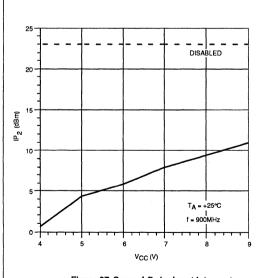

Figure 27. Second-Order Input Intercept vs Frequency and V<sub>CC</sub>

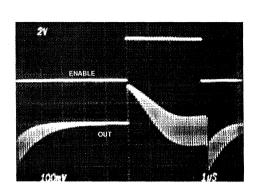

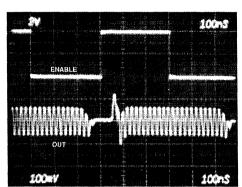

Figure 28. Switching Speed;  $f_{IN}$  = 10MHz at –26dBm,  $V_{DD}$  = 5V, Coupling Capacitors Set to  $0.01\mu F$

Figure 29. Switching Speed; f<sub>IN</sub> = 50MHz at -26dBm, V<sub>DD</sub> = 5V, Coupling Capacitors Set to 100pF

#### NE/SA5204

#### DESCRIPTION

The NE/SA5204 is a high-frequency amplifier with a fixed insertion gain of 20dB. The gain is flat to  $\pm 0.5$ dB from DC to 200MHz. The 3dB bandwidth is greater than 350MHz. This performance makes the amplifier ideal for cable TV applications. The NE/SA5204 operates with a single supply of 6V, and only draws 25mA of supply current, which is much less than comparable hybrid parts. The noise figure is 4.8dB in a  $75\Omega$  system and 6dB in a  $50\Omega$  system.

The NE/SA5204 is a relaxed version of the NE5205. Minimum guaranteed bandwidth is relaxed to 350MHz and the "S" parameter Min/Max limits are specified as typicals only.

Until now, most RF or high-frequency designers had to settle for discrete or hybrid solutions to their amplification problems. Most of these solutions required trade-offs that the designer had to accept in order to use high-frequency gain stages. These include high power consumption, large component count, transformers, large packages with heat sinks, and high part cost. The NE/SA5204 solves these problems by incorporating a wideband amplifier on a single monolithic chip.

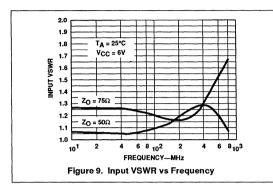

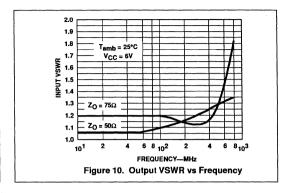

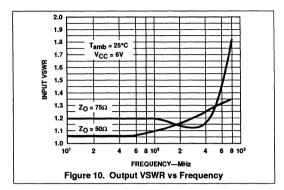

The part is well matched to 50 or  $75\Omega$  input and output impedances. The standing wave ratios in 50 and  $75\Omega$  systems do not exceed 1.5 on either the input or output over the entire DC to 350MHz operating range.

Since the part is a small, monolithic IC die, problems such as stray capacitance are minimized. The die size is small enough to fit into a very cost-effective 8-pin small-outline (SO) package to further reduce parasitic effects.

No external components are needed other than AC-coupling capacitors because the

# ORDERING INFORMATION

| DESCRIPTION              | TEMPERATURE RANGE          | ORDER CODE         |  |  |

|--------------------------|----------------------------|--------------------|--|--|

| 8-Pin Plastic DIP        | 0 to +70°C<br>-40 to +85°C | NE5204N<br>SA5204N |  |  |

| 8-Pin Plastic SO package | 0 to +70°C<br>-40 to +85°C | NE5204D<br>SA5204D |  |  |

NE/SA5204 is internally compensated and matched to 50 and 75Ω. The amplifier has very good distortion specifications, with second and third-order intermodulation intercepts of +24dBm and +17dBm, respectively, at 100MHz.

The part is well matched for  $50\Omega$  test equipment such as signal generators, oscilloscopes, frequency counters, and all kinds of signal analyzers. Other applications at  $50\Omega$  include mobile radio, CB radio, and data/video transmission in fiber optics, as well as broadband LANs and telecom systems. A gain greater than 20dB can be achieved by cascading additional NE/SA5204s in series as required, without any degradation in amplifier stability.

#### **FEATURES**

- Bandwidth (min.)

200 MHz, ±0.5dB

350 MHz, -3dB

- 20dB insertion gain

- 4.8dB (6dB) noise figure ZO=75Ω (ZO=50Ω)

- No external components required

- Input and output impedances matched to 50/75Ω systems

- Surface-mount package available

- Cascadable

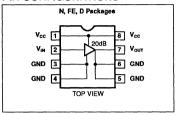

#### PIN CONFIGURATION

#### **APPLICATIONS**

- Antenna amplifiers

- Amplified splitters

- Signal generators

- Frequency counters

- Oscilloscopes

- Signal analyzers

- Broadband LANs

- Networks

- Modems

- Mobile radio

- Security systems

- Telecommunications

NE/SA5204

#### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL            | PARAMETER                                                                 | RATING      | UNIT             |

|-------------------|---------------------------------------------------------------------------|-------------|------------------|

| V <sub>CC</sub>   | Supply voltage                                                            | 9           | ٧                |

| V <sub>IN</sub>   | AC input voltage                                                          | 5           | V <sub>P-P</sub> |

| TA                | Operating ambient temperature range                                       |             |                  |

| <u>.</u>          | NE grade                                                                  | 0 to +70    | °C-              |

|                   | SA grade                                                                  | -40 to +85  | °C               |

| P <sub>DMAX</sub> | Maximum power dissipation <sup>1, 2</sup> T <sub>A</sub> =25°C(still-air) |             |                  |

|                   | N package                                                                 | 1160        | mW               |

|                   | D package                                                                 | 780         | mW               |

| TJ                | Junction temperature                                                      | 150         | °C               |

| T <sub>STG</sub>  | Storage temperature range                                                 | -55 to +150 | °C               |

| T <sub>SOLD</sub> | Lead temperature<br>(soldering 60s)                                       | 300         | ပံ               |

#### NOTES:

- Derate above 25°C, at the following rates

N package at 9.3mW/°C

D package at 6.2mW/°C

See "Power Dissipation Considerations" section.

# **EQUIVALENT SCHEMATIC**

#### DC ELECTRICAL CHARACTERISTICS

V<sub>CC</sub>=6V, Z<sub>S</sub>=Z<sub>L</sub>=Z<sub>O</sub>=50Ω and T<sub>A</sub>=25°C, in all packages, unless otherwise specified.

| SYMBOL          | PARAMETER                                       | TEST CONDITIONS            |     | LIMITS |     |     |

|-----------------|-------------------------------------------------|----------------------------|-----|--------|-----|-----|

|                 |                                                 |                            | Min | Тур    | Max |     |

| V <sub>CC</sub> | Operating supply voltage range                  | Over temperature           | 5   |        | 8   | ٧   |

| Icc             | Supply current                                  | Over temperature           | 19  | 24     | 31  | mA  |

| S21             | Insertion gain                                  | f=100MHz, over temperature | 16  | 19     | 22  | dB  |

| S11             | Input return loss                               | f=100MHz                   |     | 25     |     | dB  |

|                 |                                                 | DC –550MHz                 |     | 12     |     | dB  |

| S22             | Output return loss                              | f=100MHz                   |     | 27     |     | dB  |

| 022             |                                                 | DC –550MHz                 |     | 12     |     | dB  |

| S12             | Isolation                                       | f=100MHz                   |     | 25     |     | dB  |

|                 |                                                 | DC –550MHz                 |     | -18    |     | dB  |

| BW              | Bandwidth                                       | ±0.5dB                     | 200 | 350    |     | MHz |

| BW              | Bandwidth                                       | –3dB                       | 350 | 550    |     | MHz |

|                 | Noise figure (75Ω)                              | f=100MHz                   |     | 4.8    |     | dB  |

|                 | Noise figure (50Ω)                              | f=100MHz                   |     | 6.0    |     | dB  |

|                 | Saturated output power                          | f=100MHz                   |     | +7.0   |     | dBm |

|                 | 1dB gain compression                            | f=100MHz                   |     | +4.0   |     | dBm |

|                 | Third–order intermodulation intercept (output)  | f=100MHz                   |     | +17    |     | dBm |

|                 | Second–order intermodulation intercept (output) | f=100MHz                   |     | +24    |     | dBm |

| t <sub>R</sub>  | Rise time                                       |                            |     | 5      |     | ps  |

|                 | Propagation delay                               |                            |     | 5      |     | ps  |

#### NE/SA5204

#### THEORY OF OPERATION

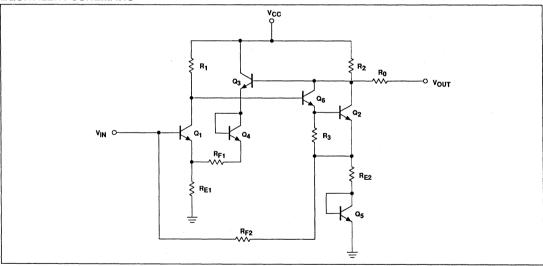

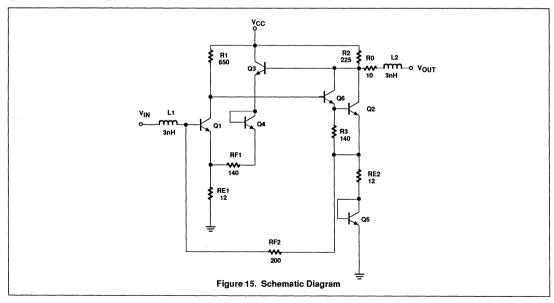

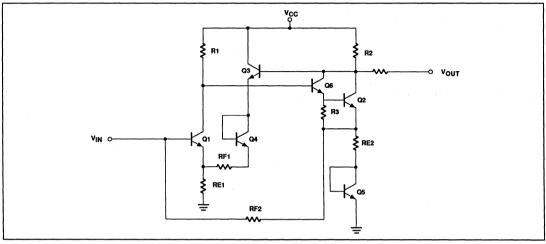

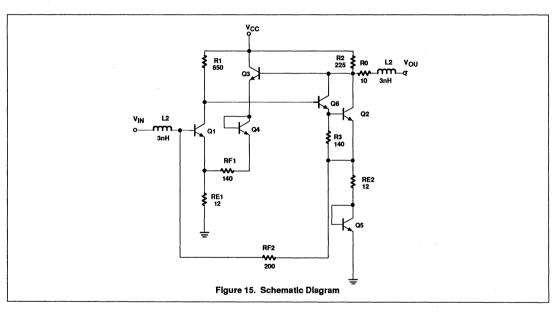

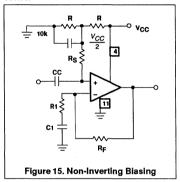

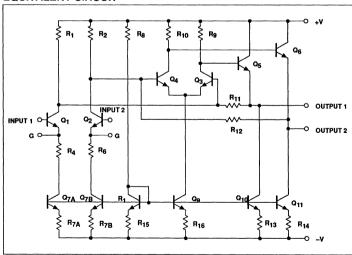

The design is based on the use of multiple feedback loops to provide wide-band gain together with good noise figure and terminal impedance matches. Referring to the circuit schematic in Figure 15, the gain is set primarily by the equation:

$$\frac{V_{OUT}}{V_{IN}} = (R_{F1} + R_{E1}) / R_{E1}$$

(1)

which is series-shunt feedback. There is also shunt-series feedback due to  $R_{\rm F2}$  and  $R_{\rm E2}$  which aids in producing wide-band terminal impedances without the need for low value input shunting resistors that would degrade the noise figure. For optimum noise performance,  $R_{\rm E1}$  and the base resistance of  $Q_1$  are kept as low as possible, while  $R_{\rm F2}$  is maximized.

The noise figure is given by the following equation:

$$NF = 10 Log \left( 1 + \frac{\left[ r_b + R_{E1} + \frac{KT}{2q|_{C1}} \right]}{R_O} \right) dB (2)$$

where I  $_{C1}$  =5.5mA, R  $_{E1}$  =12  $\Omega,$   $r_{b}$  =130  $\Omega,$  KT/q=26mV at 25°C and R  $_{0}$  =50 for a 50  $\Omega$  system and 75 for a 75  $\Omega$  system.

The DC input voltage level V<sub>IN</sub> can be determined by the equation:

where  $R_{E1}{=}12\Omega,~V_{BE}{=}0.8V,~I_{C1}{=}5\text{mA}$  and  $I_{C3}{=}7\text{mA}$  (currents rated at  $V_{CC}{=}6V$ ).

Under the above conditions, V<sub>IN</sub> is approximately equal to 1V.

Level shifting is achieved by emitter-follower  $Q_3$  and diode  $Q_4$ , which provide shunt feedback to the emitter of  $Q_1$  via  $R_{F1}$ . The use of an emitter-follower buffer in this feedback loop essentially eliminates problems of shunt-feedback loading on the output. The value of  $R_{F1}$ =140 $\Omega$  is chosen to give the desired nominal gain. The DC output voltage  $V_{OUT}$  can be determined by:

$$V_{OUT} = V_{CC} - (I_{C2} + I_{C6})R2,(4)$$

where  $V_{CC}{=}6V,\,R_2{=}225\Omega,\,I_{C2}{=}7mA$  and  $I_{C6}{=}5mA.$

From here, it can be seen that the output voltage is approximately 3.3V to give relatively equal positive and negative output swings. Diode  $Q_5$  is included for bias purposes to allow direct coupling of  $R_{F2}$  to the base of  $Q_1$ . The dual feedback loops stabilize the DC operating point of the amplifier.

The output stage is a Darlington pair ( $Q_6$  and  $Q_2$ ) which increases the DC bias voltage on

the input stage  $(\Omega_1)$  to a more desirable value, and also increases the feedback loop gain. Resistor  $R_0$  optimizes the output VSWR (Voltage Standing Wave Ratio). Inductors  $L_1$  and  $L_2$  are bondwire and lead inductances which are roughly 3nH. These improve the high-frequency impedance matches at input and output by partially resonating with 0.5pF of pad and package capacitance.

# POWER DISSIPATION CONSIDERATIONS

When using the part at elevated temperature, the engineer should consider the power dissipation capabilities of each package.

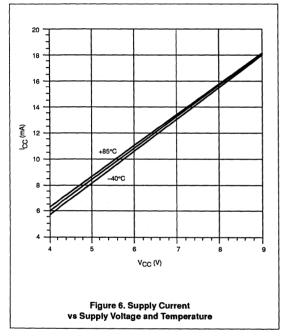

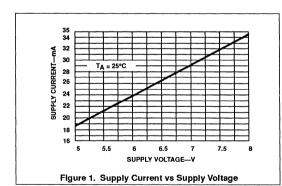

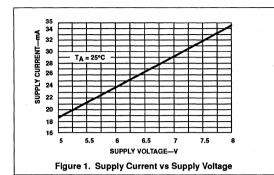

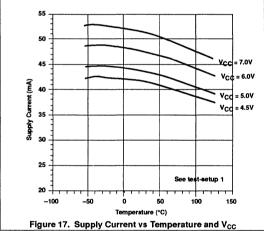

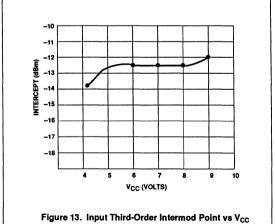

At the nominal supply voltage of 6V, the typical supply current is 25mA (30mA max). For operation at supply voltages other than 6V, see Figure 1 for I<sub>CC</sub> versus V<sub>CC</sub> curves. The supply current is inversely proportional to temperature and varies no more than 1mA between 25°C and either temperature extreme. The change is 0.1% per °C over the range.

The recommended operating temperature ranges are air-mount specifications. Better heat-sinking benefits can be realized by mounting the SO and N package bodies against the PC board plane.

#### NE/SA5204

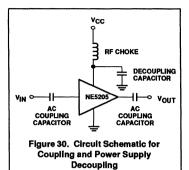

#### PC BOARD MOUNTING

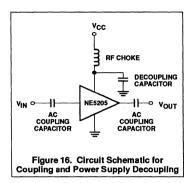

In order to realize satisfactory mounting of the NE5204 to a PC board, certain techniques need to be utilized. The board must be double-sided with copper and all pins must be soldered to their respective areas (i.e., all GND and V<sub>CC</sub> pins on the package). The power supply should be decoupled with a capacitor as close to the V<sub>CC</sub> pins as possible, and an RF choke should be inserted between the supply and the device. Caution should be exercised in the connection of input and output pins. Standard microstrip should be observed wherever possible. There should be no solder bumps or burrs or any obstructions in the signal path to cause launching problems. The path should be as straight as possible and lead lengths as short as possible from the part to the cable connection. Another important consideration is that the input and output should be

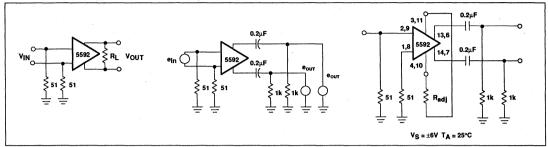

AC-coupled. This is because at  $V_{CC}$ =6V, the input is approximately at 1V while the output is at 3.3V. The output must be decoupled into a low-impedance system, or the DC bias on the output of the amplifier will be loaded down, causing loss of output power. The easiest way to decouple the entire amplifier is by soldering a high-frequency chip capacitor directly to the input and output pins of the device. This circuit is shown in Figure 16. Follow these recommendations to get the best frequency response and noise immunity. The board design is as important as the integrated circuit design itself.

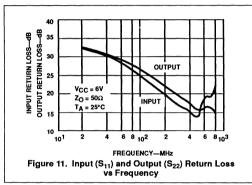

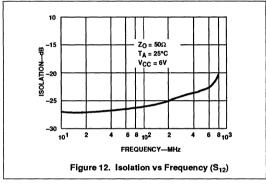

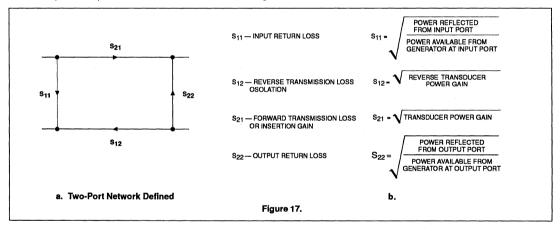

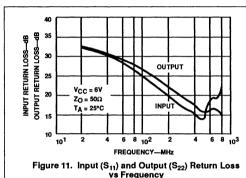

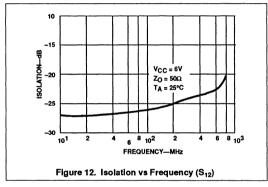

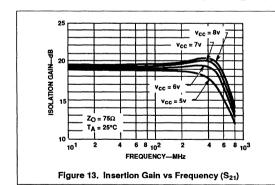

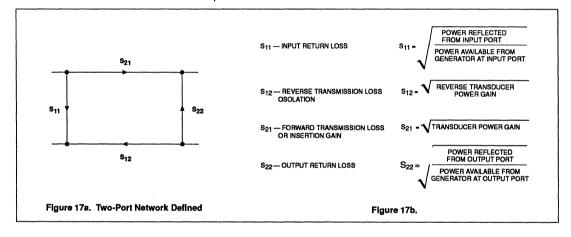

#### SCATTERING PARAMETERS

The primary specifications for the NE5204 are listed as S-parameters. S-parameters are measurements of incident and reflected currents and voltages between the source.

amplifier, and load as well as transmission losses. The parameters for a two-port network are defined in Figure 17.

NE/SA5204

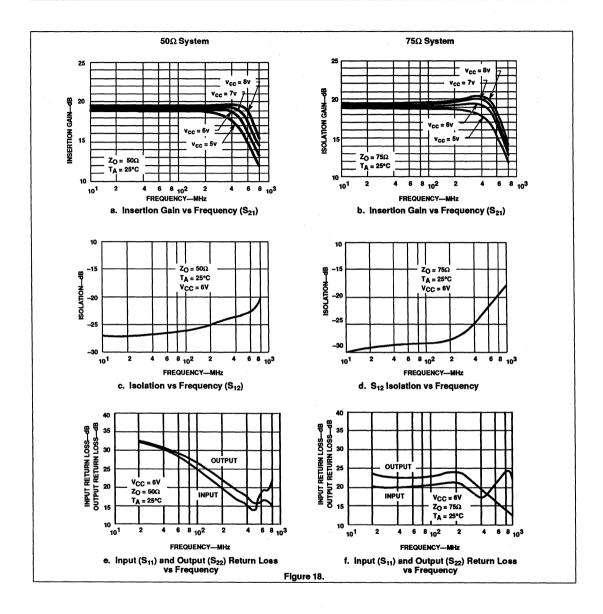

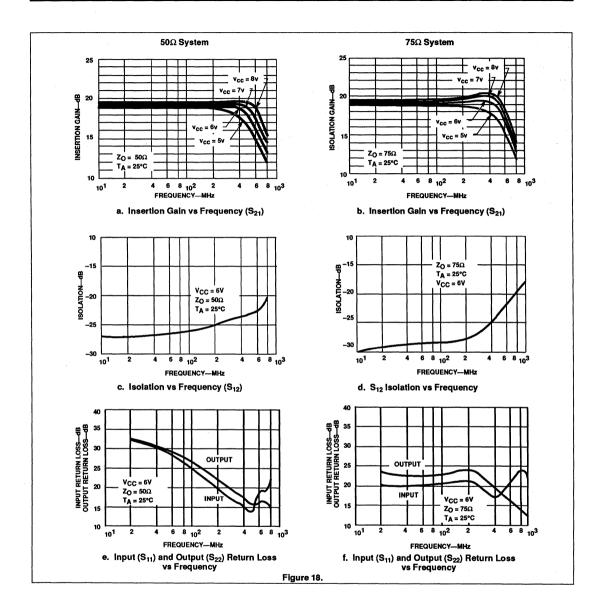

Actual S-parameter measurements using an HP network analyzer (model 8505A) and an HP S-parameter tester (models 8503A/B) are shown in Figure 18.

Values for the figures below are measured and specified in the data sheet to ease adaptation and comparison of the NE/SA/SE5205 to other high-frequency amplifiers.

The most important parameter is S21. It is defined as the square root of the power gain, and, in decibels, is equal to voltage gain as shown below:

Z<sub>D</sub>=Z<sub>IN</sub>=Z<sub>OUT</sub> for the NE/SA/SE5205

$$P_{IN} + \frac{V_{IN}^2}{Z_D} \circ \underbrace{\begin{array}{c} NE5204 \\ Z_D \end{array}} \circ \underbrace{\begin{array}{c} P_{OUT} + \frac{V_{OUT}^2}{Z_D} \end{array}$$

$$\therefore \frac{P_{OUT}}{P_{IN}} = \frac{\frac{V_{OUT}^2}{Z_D}}{\frac{V_{IN}^2}{Z_D}} = \frac{V_{OUT}^2}{V_{IN}^2} = P_I$$

P<sub>I</sub>=V<sub>I</sub><sup>2</sup>

P<sub>I</sub>=Insertion Power Gain

V<sub>i</sub>=Insertion Voltage Gain

Measured value for the  $NE/SA/SE5205 = |S_{21}|^2 = 100$

$$P_{I} = \frac{P_{OUT}}{P_{IN}} = |S_{21}|^{2} = 100$$

and  $V_{I} = \frac{V_{OUT}}{V_{OU}} = \sqrt{P_{I}} = S_{21} = 10$

In decibels:

$P_{I(dB)} = 10 \text{ Log } | S_{21} |^2 = 20 dB$  $V_{I(dB)} = 20 \text{ Log } S_{21} = 20 \text{dB}$ ∴ P<sub>I(dB)</sub> = V<sub>I(dB)</sub> = S<sub>21(dB)</sub> = 20dB

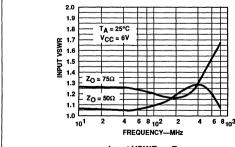

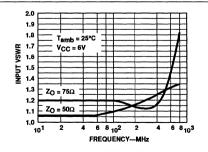

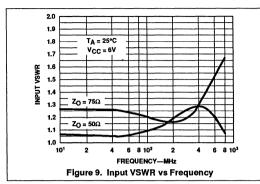

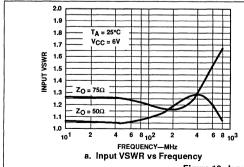

Also measured on the same system are the respective voltage standing wave ratios. These are shown in Figure 19. The VSWR

can be seen to be below 1.5 across the entire operational frequency range.

Relationships exist between the input and output return losses and the voltage standing wave ratios. These relationships are as follows:

INPUT RETURN LOSS=S<sub>11</sub>dB S<sub>11</sub>dB=20 Log | S<sub>11</sub> | OUTPUT RETURN LOSS=S22dB S22dB=20 Log | S22 | INPUT VSWR=≤1.5 OUTPUT VSWR=≤1.5

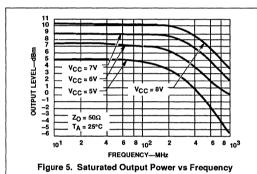

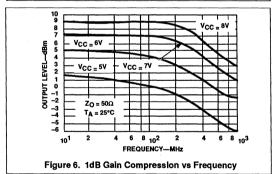

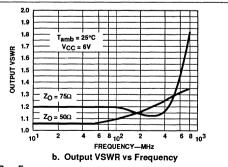

#### 1DB GAIN COMPRESSION AND SATURATED OUTPUT POWER

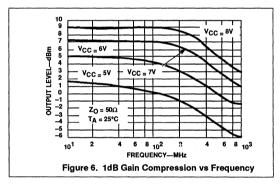

The 1dB gain compression is a measurement of the output power level where the small-signal insertion gain magnitude decreases 1dB from its low power value. The decrease is due to nonlinearities in the amplifier, an indication of the point of transition between small-signal operation and the large signal mode.

The saturated output power is a measure of the amplifier's ability to deliver power into an external load. It is the value of the amplifier's output power when the input is heavily overdriven. This includes the sum of the power in all harmonics.

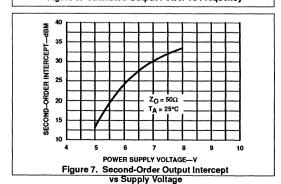

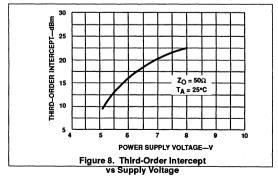

#### INTERMODULATION INTERCEPT **TESTS**

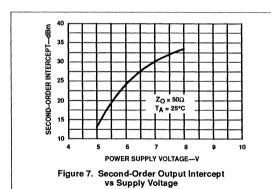

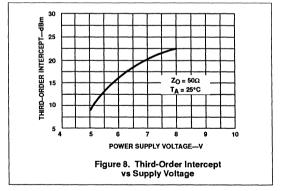

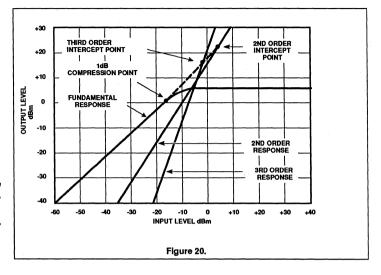

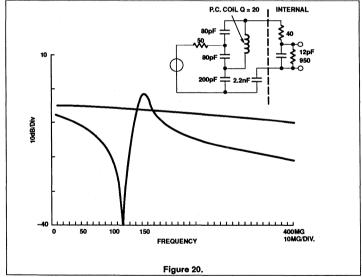

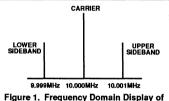

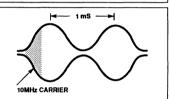

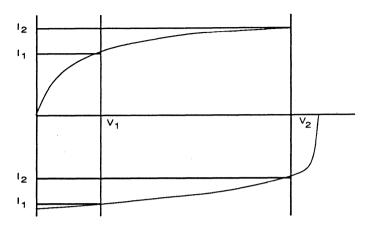

The intermodulation intercept is an expression of the low level linearity of the amplifier. The intermodulation ratio is the difference in dB between the fundamental output signal level and the generated distortion product level. The relationship between intercept and intermodulation ratio is illustrated in Figure 20, which shows product output levels plotted versus the level of the fundamental output for two equal strength

output signals at different frequencies. The upper line shows the fundamental output plotted against itself with a 1dB to 1dB slope. The second and third order products lie below the fundamentals and exhibit a 2:1 and 3:1 slope, respectively.

The intercept point for either product is the intersection of the extensions of the product curve with the fundamental output.

The intercept point is determined by measuring the intermodulation ratio at a single output level and projecting along the appropriate product slope to the point of intersection with the fundamental. When the intercept point is known, the intermodulation ratio can be determined by the reverse process. The second order IMR is equal to the difference between the second order intercept and the fundamental output level. The third order IMR is equal to twice the difference between the third order intercept and the fundamental output level. These are expressed as:

IP2=POUT+IMR2

IP<sub>3</sub>=P<sub>OUT</sub>+IMR<sub>3</sub>/2

where P<sub>OUT</sub> is the power level in dBm of each of a pair of equal level fundamental output signals, IP2 and IP3 are the second and third order output intercepts in dBm, and IMR2 and IMR<sub>3</sub> are the second and third order intermodulation ratios in dB. The intermodulation intercept is an indicator of intermodulation performance only in the small signal operating range of the amplifier. Above some output level which is below the 1dB compression point, the active device moves into large-signal operation. At this point the intermodulation products no longer follow the straight line output slopes, and the intercept description is no longer valid. It is therefore important to measure IP2 and IP3 at output levels well below 1dB compression. One

a. Input VSWR vs Frequency

Figure 19. Input/Output VSWR vs Frequency

b. Output VSWR vs Frequency

NE/SA5204

must be careful, however, not to select too low levels because the test equipment may not be able to recover the signal from the noise. For the NE/SA/SE5205 we have chosen an output level of –10.5dBm with fundamental frequencies of 100.000 and 100.01MHz, respectively. \*5COL

# ADDITIONAL READING ON SCATTERING PARAMETERS

For more information regarding S-parameters, please refer to High-Frequency Amplifiers by Ralph S. Carson of the University of Missouri, Rolla, Copyright 1985; published by John Wiley & Sons, Inc.

"S-Parameter Techniques for Faster, More Accurate Network Design", HP App Note 95-1, Richard W. Anderson, 1967, HP Journal.

"S-Parameter Design", HP App Note 154, 1972.

#### **NE/SA5205**

#### DESCRIPTION

The NE/SA/SE5205 is a high-frequency amplifier with a fixed insertion gain of 20dB. The gain is flat to  $\pm 0.5$ dB from DC to 450MHz, and the -3dB bandwidth is greater than 600MHz in the EC package. This performance makes the amplifier ideal for cable TV applications. For lower frequency applications, the part is also available in industrial standard dual in-line and small outline packages. The NE/SA/SE5205 operates with a single supply of 6V, and only draws 24mA of supply current, which is much less than comparable hybrid parts. The noise figure is 4.8dB in a 75 $\Omega$  system and 6dB in a 50 $\Omega$  system.

Until now, most RF or high-frequency designers had to settle for discrete or hybrid solutions to their amplification problems. Most of these solutions required trade-offs that the designer had to accept in order to use high-frequency gain stages. These include high-power consumption, large component count, transformers, large packages with heat sinks, and high part cost. The NE/SA/SE5205 solves these problems by incorporating a wide-band amplifier on a single monolithic chip.

The part is well matched to 50 or  $75\Omega$  input and output impedances. The Standing Wave Ratios in 50 and  $75\Omega$  systems do not exceed 1.5 on either the input or output from DC to the -3dB bandwidth limit.

Since the part is a small monolithic IC die, problems such as stray capacitance are minimized. The die size is small enough to fit into a very cost-effective 8-pin small-outline (SO) package to further reduce parasitic effects. A TO-46 metal can is also available that has a case connection for RF grounding which increases the -3dB frequency to 600MHz. The Cerdip package is hermetically sealed, and can operate over the full -55°C to +125°C range.

No external components are needed other than AC coupling capacitors because the NE/SA/SE5205 is internally compensated and matched to 50 and 75Ω. The amplifier has very good distortion specifications, with second and third-order intermodulation intercepts of +24dBm and +17dBm respectively at 100MHz.

The device is ideally suited for  $75\Omega$  cable television applications such as decoder boxes, satellite receiver/decoders, and front-end amplifiers for TV receivers. It is also useful for amplified splitters and antenna amplifiers.

The part is matched well for  $50\Omega$  test equipment such as signal generators, oscilloscopes, frequency counters and all kinds of signal analyzers. Other applications at  $50\Omega$  include mobile radio, CB radio and data/video transmission in fiber optics, as well as broad-band LANs and telecom systems. A gain greater than 20dB can be achieved by cascading additional NE/SA/SE5205s in series as required, without any degradation in amplifier stability.

#### **FEATURES**

- 600MHz bandwidth

- 20dB insertion gain

- 4.8dB (6dB) noise figure ZO=75Ω (ZO=50Ω)

- No external components required

- Input and output impedances matched to 50/75Ω systems

- Surface mount package available

- MIL-STD processing available

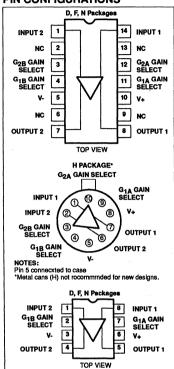

#### PIN CONFIGURATIONS

#### **APPLICATIONS**

- 75Ω cable TV decoder boxes

- Antenna amplifiers

- Amplified splitters

- Signal generators

- Frequency counters

- Oscilloscopes

- Signal analyzers

- Broad-band LANs

- Fiber-optics

- Modems

- Mobile radio

- Security systems

- Telecommunications

#### ORDERING INFORMATION

| DESCRIPTION       | TEMPERATURE RANGE | ORDER CODE |

|-------------------|-------------------|------------|

| 8-Pin Plastic SO  | 0 to +70°C        | NE5205D    |

| 8-Pin Cerdip      | 0 to +70°C        | NE5205FE   |

| 8-Pin Plastic DIP | 0 to +70°C        | NE5205N    |

| 8-Pin Plastic SO  | -40 to +85°C      | SA5205D    |

| 8-Pin Plastic DIP | -40 to +85°C      | SA5205N    |

| 8-Pin Cerdip      | -40 to +85°C      | SA5205FE   |

| 8-Pin Cerdip      | -55 to +125°C     | SE5205FE   |

| 8-Pin Plastic DIP | -55 to +125°C     | SE5205N    |

NE/SA5205

#### **EQUIVALENT SCHEMATIC**

#### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL            | PARAMETER                                                                      | RATING      | UNIT             |

|-------------------|--------------------------------------------------------------------------------|-------------|------------------|

| V <sub>CC</sub>   | Supply voltage                                                                 | 9           | ·V               |

| V <sub>AC</sub>   | AC input voltage                                                               | 5           | V <sub>P-P</sub> |

| TA                | Operating ambient temperature range                                            |             |                  |

|                   | NE grade                                                                       | 0 to +70    | °C               |

|                   | SA grade                                                                       | -40 to +85  | •€               |

|                   | SE grade                                                                       | -55 to +125 | •€               |

| P <sub>DMAX</sub> | Maximum power dissipation,<br>T <sub>A</sub> =25°C (still-air) <sup>1, 2</sup> |             |                  |

|                   | FE package                                                                     | 780         | mW               |

|                   | N package                                                                      | 1160        | mW               |

|                   | D package                                                                      | 780         | mW               |

#### NOTES:

1. Derate above 25°C, at the following rates:

FE package at 6.2mW/°C

N package at 9.3mW/°C

D package at 6.2mW/°C

2. See "Power Dissipation Considerations" section.

NE/SA5205

DC ELECTRICAL CHARACTERISTICS  $V_{CC} = 6V, Z_S = Z_L = Z_O = 50\Omega \text{ and } T_A = 25^{\circ}C \text{ in all packages, unless otherwise specified.}$

| SYMBOL           | PARAMETER                                       | TEST CONDITIONS                |            | SE5205 |            |            | NE/SA5205 |            |          |

|------------------|-------------------------------------------------|--------------------------------|------------|--------|------------|------------|-----------|------------|----------|

|                  |                                                 |                                | Min        | Тур    | Max        | Min        | Тур       | Max        |          |

|                  | Operating supply voltage range                  | Over temperature               | 5<br>5     |        | 6.5<br>6.5 | 5<br>5     |           | 8<br>8     | >>       |

| lcc              | Supply current                                  | Over temperature               | 20<br>19   | 24     | 30<br>31   | 20<br>19   | 24        | 30<br>31   | mA<br>mA |

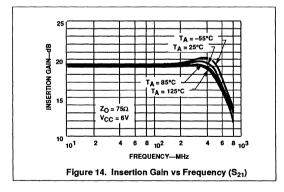

| S21              | Insertion gain                                  | f=100MHz<br>Over temperature   | 17<br>16.5 | 19     | 21<br>21.5 | 17<br>16.5 | 19        | 21<br>21.5 | dB       |

| S11              | Input return loss                               | f=100MHz D, N, FE              |            | 25     |            |            | 25        |            | dB       |

|                  | <u> </u>                                        | DC - f <sub>MAX</sub> D, N, FE | 12         |        | <u> </u>   | 12         |           |            | dB       |

| S11              | Input return loss                               | f=100MHz EC package            |            |        |            |            | 24        |            | dB       |

|                  | 1                                               | DC - f <sub>MAX</sub> EC       |            |        |            | 10         |           |            | dB       |

| S22              | Output return loss                              | f=100MHz D, N, FE              |            | 27     |            |            | 27        |            | dB       |

|                  |                                                 | DC - f <sub>MAX</sub>          | 12         |        |            | 12         |           |            | dB       |

| S22              | Output return loss                              | f=100MHz EC package            |            |        |            |            | 26        |            | dB       |

|                  |                                                 | DC - f <sub>MAX</sub>          |            |        |            | 10         |           |            | dB       |

| S12              | Isolation                                       | f=100MHz                       |            | -25    |            |            | -25       |            | dB       |

|                  |                                                 | DC - f <sub>MAX</sub>          | -18        |        |            | -18        |           |            | dB       |

| t <sub>R</sub>   | Rise time                                       |                                |            | 5      |            |            | 5         |            | ps       |

|                  | Propagation delay                               |                                |            | 5      |            |            | 5         |            | ps       |

| BW               | Bandwidth                                       | ±0.5dB D, N                    |            |        |            |            | 450       |            | MHz      |

| f <sub>MAX</sub> | Bandwidth                                       | ±0.5dB EC                      |            |        |            |            | 500       |            | MHz      |

| f <sub>MAX</sub> | Bandwidth                                       | ±0.5dB FE                      |            | 300    |            |            | 300       |            | MHz      |

| f <sub>MAX</sub> | Bandwidth                                       | -3dB D, N                      |            |        |            | 550        |           |            | MHz      |

| f <sub>MAX</sub> | Bandwidth                                       | -3dB EC                        |            | -      |            | 600        |           |            | MHz      |

| f <sub>MAX</sub> | Bandwidth                                       | -3dB FE                        | 400        |        | Ţ          | 400        |           |            | MHz      |

|                  | Noise figure (75Ω)                              | f=100MHz                       |            | 4.8    |            |            | 4.8       |            | dB       |

|                  | Noise figure (50Ω)                              | f=100MHz                       |            | 6.0    |            |            | 6.0       |            | dB       |

|                  | Saturated output power                          | f=100MHz                       |            | +7.0   |            |            | +7.0      |            | dBm      |

|                  | 1dB gain compression                            | f=100MHz                       |            | +4.0   |            |            | +4.0      |            | dBm      |

|                  | Third-order intermodulation intercept (output)  | f=100MHz                       |            | +17    |            |            | +17       |            | dBm      |

|                  | Second-order intermodulation intercept (output) | f=100MHz                       |            | +24    |            |            | +24       |            | dBm      |

### NE/SA5205

#### THEORY OF OPERATION

The design is based on the use of multiple feedback loops to provide wide-band gain together with good noise figure and terminal impedance matches. Referring to the circuit schematic in Figure 15, the gain is set primarily by the equation:

$$\frac{V_{OUT}}{V_{CM}} = \frac{\left(R_{F1} + R_{E1}\right)}{R_{E2}}$$

which is series-shunt feedback. There is also shunt-series feedback due to  $R_{\rm F2}$  and  $R_{\rm F2}$  which aids in producing wideband terminal impedances without the need for low value input shunting resistors that would degrade the noise figure. For optimum noise performance,  $R_{\rm E1}$  and the base resistance of  $Q_1$  are kept as low as possible while  $R_{\rm F2}$  is maximized.

The noise figure is given by the following equation:

NF =

$$10 \log \left\{ 1 + \left[ \frac{r_b + R_{E1} + \frac{KT}{2qlC_1}}{R_O} \right] \right\} dB \qquad (2)$$

NE/SA5205

where I<sub>C1</sub>=5.5mA, R<sub>E1</sub>=12 $\Omega$ , r<sub>b</sub>=130 $\Omega$ , KT/q=26mV at 25°C and R<sub>0</sub>=50 for a 50 $\Omega$  system and 75 for a 75 $\Omega$  system.

The DC input voltage level V<sub>IN</sub> can be determined by the equation:

VIN=VBE1+(IC1+IC3) RE1

where  $R_{E1}=12\Omega$ ,  $V_{BE}=0.8V$ ,  $I_{C1}=5mA$  and  $I_{C3}=7mA$  (currents rated at  $V_{CC}=6V$ ).

Under the above conditions, V<sub>IN</sub> is approximately equal to 1V.

Level shifting is achieved by emitter-follower  $Q_3$  and diode  $Q_4$  which provide shunt feedback to the emitter of  $Q_1$  via  $R_{F1}$ . The use of an emitter-follower buffer in this

feedback loop essentially eliminates problems of shunt feedback loading on the output. The value of  $R_{F1}$ =140 $\Omega$  is chosen to give the desired nominal gain. The DC output voltage  $V_{OUT}$  can be determined by:

where  $V_{CC}$ =6V,  $R_2$ =225 $\Omega$ ,  $I_{C2}$ =7mA and  $I_{C6}$ =5mA.

From here it can be seen that the output voltage is approximately 3.9V to give relatively equal positive and negative output swings. Diode  $Q_6$  is included for bias purposes to allow direct coupling of  $R_{\rm F2}$  to

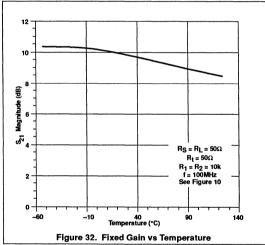

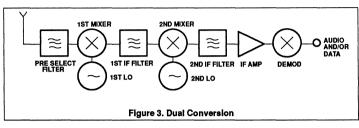

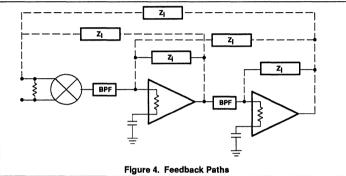

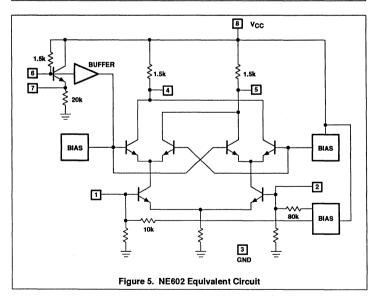

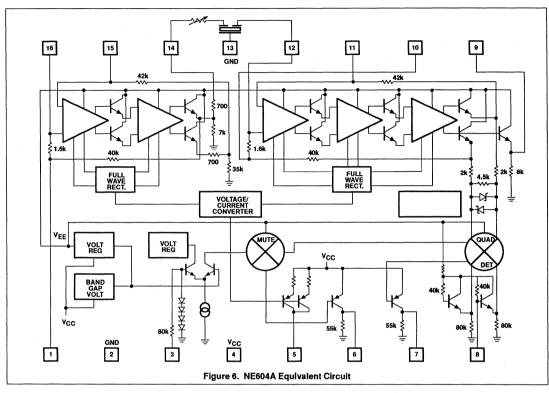

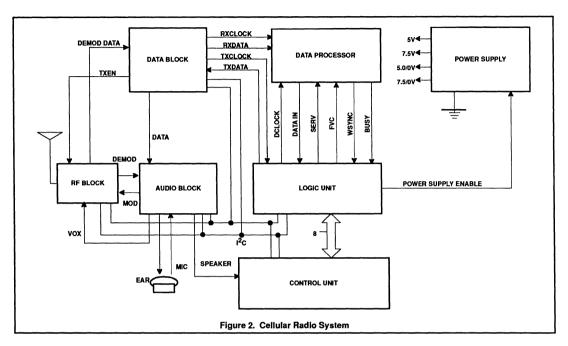

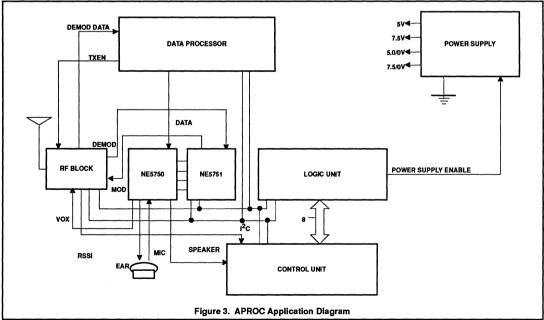

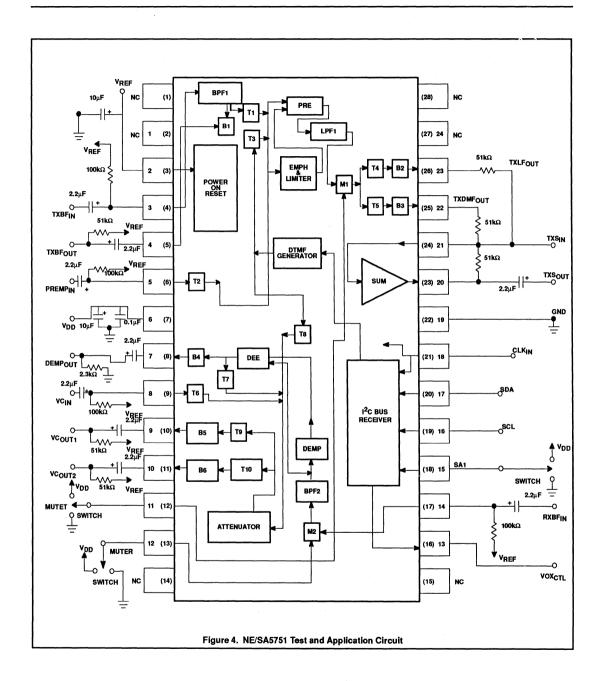

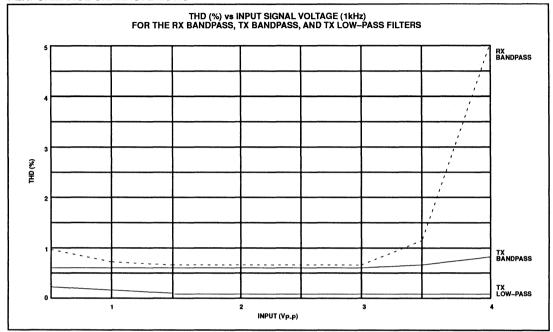

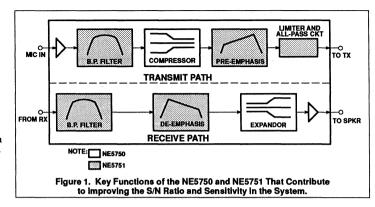

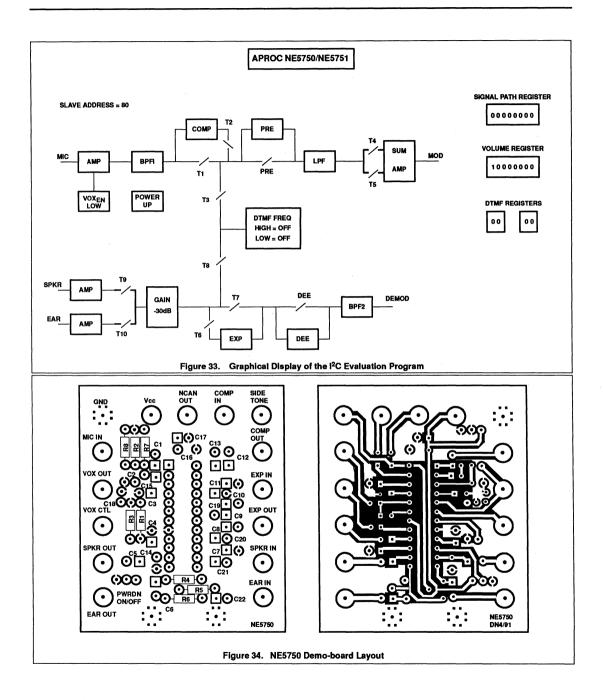

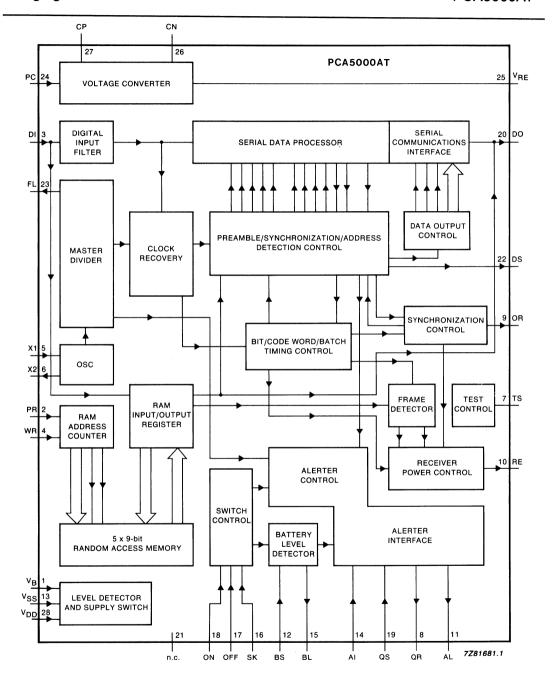

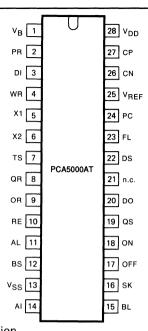

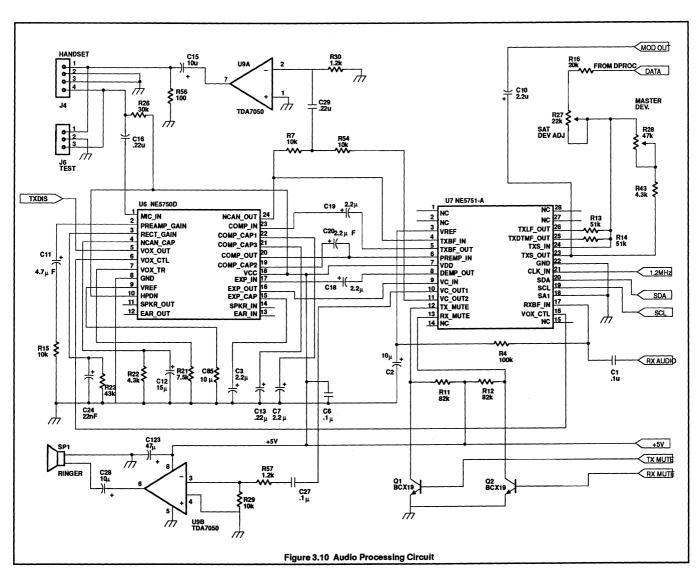

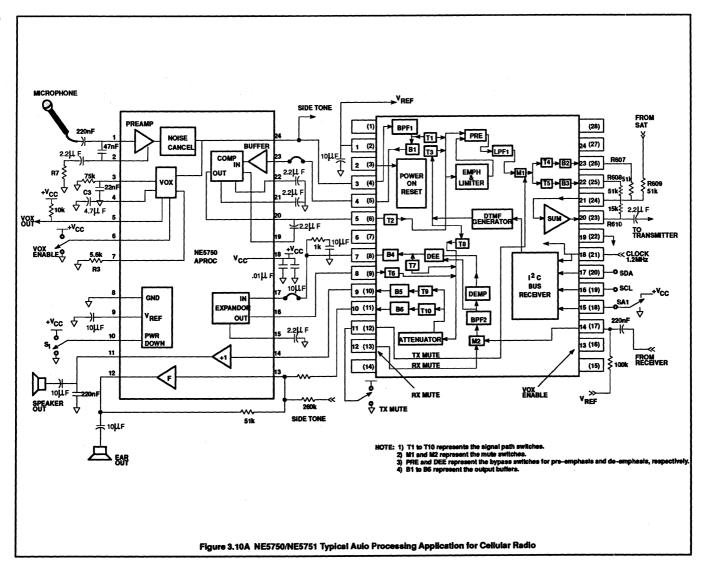

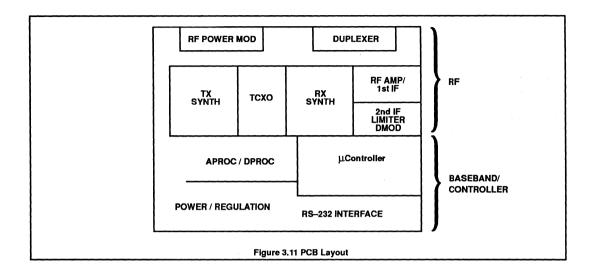

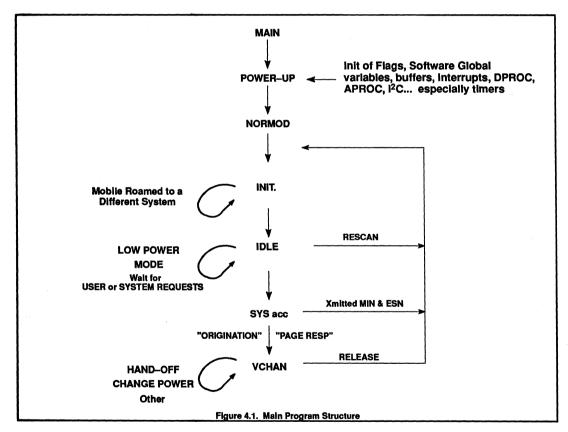

the base of Q<sub>1</sub>. The dual feedback loops stabilize the DC operating point of the amplifier.