### INTEGRATED CIRCUITS

# DATA HANDBOOK

### DISTRIBUTED BY

San Francisco Division

336 Los Coches Street Milpitas, California 95035

Electronics Group Claude Michael Group FAX (408) 942-4600 (408) 942-4700 (408) 262-1224

# Memories MOS, TTL, and ECL

Signetics Philips Components

### MEMORIES MOS, TTL, ECL

|                                                                | page  |

|----------------------------------------------------------------|-------|

| Selection guide .<br>Functional index                          | . 5   |

| Numerical index                                                | . 9   |

| Introduction                                                   |       |

| Introduction for type numbers with prefixes FCB, PCA, PCD, PCF |       |

| Rating systems                                                 |       |

| Handling MOS devices                                           | . 23  |

| Introduction for type numbers with numerical prefixes          | . 25  |

| Product status                                                 |       |

| Quality and reliability                                        |       |

| Bipolar reliability information                                | . 33  |

| EPROM reliability information                                  |       |

| Selection guide                                                |       |

| PROM cross reference guide                                     |       |

| EPROM cross reference guide                                    | . 51  |

| EPROM programming information                                  |       |

| Bipolar programming procedures                                 | . 55  |

| MOS Memories                                                   |       |

| CMOS static RAM                                                |       |

| CMOS EEPROM                                                    |       |

| 128K-bit CMOS EPROM                                            |       |

| 256K-bit CMOS EPROM                                            |       |

| 516K-bit CMOS EPROM                                            |       |

| 1M-bit CMOS EPROM                                              | . 271 |

| TTL Memories                                                   | . 281 |

| 64-bit RAM                                                     |       |

| 256-bit RAM                                                    |       |

| Byte-organized RAM                                             | . 321 |

| 4K-bit PROM                                                    |       |

| 8K-bit PROM                                                    |       |

| 16K-bit PROM                                                   |       |

| 32K-bit PROM                                                   |       |

| 128K-bit PROM                                                  |       |

|                                                                |       |

| ECL Memories                                                   |       |

| Low complexity PROM                                            |       |

|                                                                | . 541 |

| Package information                                            | . 537 |

ŧ

Signetics reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Signetics assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified. Applications that are described herein for any of these products are for illustrative purposes only. Signetics makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

### LIFE SUPPORT APPLICATIONS

Signetics Products are not designed for use in life support appliances, devices, or systems where malfunction of a Signetics Product can reasonably be expected to result in a personal injury. Signetics customers using or selling Signetics' Products for use in such applications do so at their own risk and agree to fully indemnify Signetics for any damages resulting from such improper use or sale.

Signetics registers eligible circuits under the Semiconductor Chip Protection Act.

© Copyright 1989 Signetics Company a division of North American Philips Corporation

All rights reserved.

### SELECTION GUIDE

Functional index Numerical index

# FUNCTIONAL INDEX

| pe number description |                                                               |     |  |  |

|-----------------------|---------------------------------------------------------------|-----|--|--|

| CMOS STATIC RAM       |                                                               |     |  |  |

| FCB51C64/65           | B51C64/65 8192 x 8-bit latched static RAM                     |     |  |  |

| FCB61C65(L/LL)        | L) 8192 x 8-bit static RAM                                    |     |  |  |

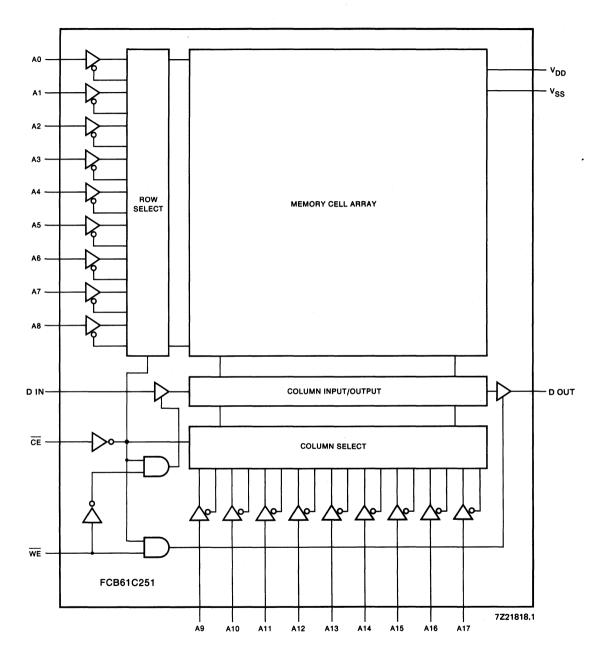

| FCB61C251             | 262 144 x 1-bit static RAM                                    | 75  |  |  |

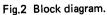

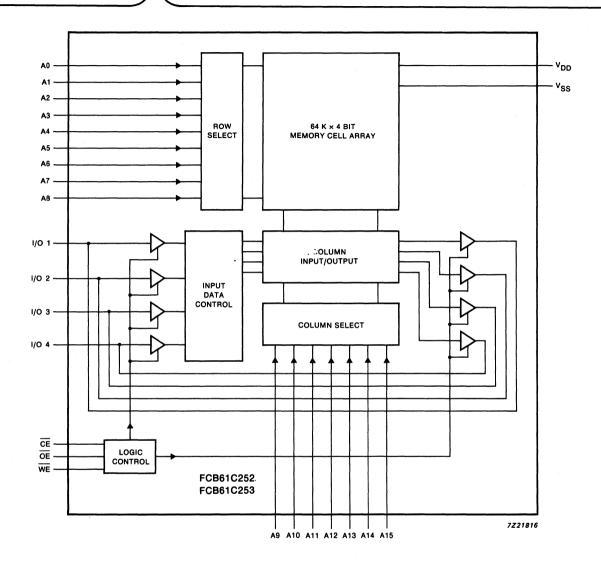

| FCB61C252/253         | 65 536 x 4-bit static RAM                                     | 79  |  |  |

| FCB61C257(L/LL)       | 32 768 x 8-bit static RAM                                     | 85  |  |  |

| FCB61C1025(L/LL)      | 131 072 x 8-bit static RAM                                    | 89  |  |  |

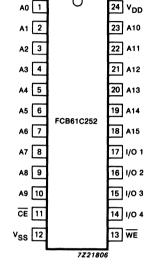

| PCD5101               | 256 x 4-bit static RAM                                        | 93  |  |  |

| PCD5114               | 1024 x 4-bit static RAM                                       | 101 |  |  |

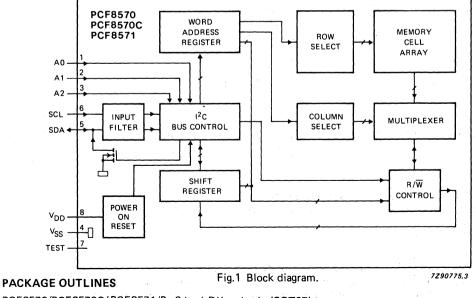

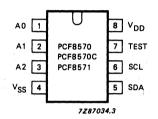

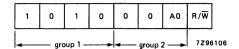

| PCF8570/70C/71        | 256 x 8-bit static RAM with I <sup>2</sup> C-bus interface    | 109 |  |  |

| PCF8583               | 256 x 8-bit static RAM with I <sup>2</sup> C-bus interface    | 119 |  |  |

| CMOS EEPROM           |                                                               |     |  |  |

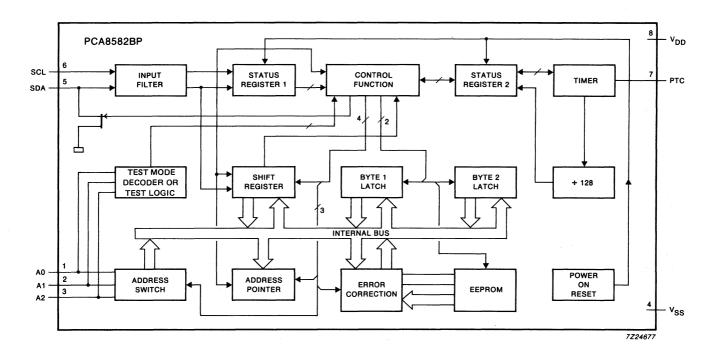

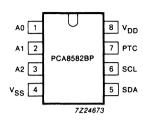

| PCA8582B              | 256 x 8-bit static EEPROM with I <sup>2</sup> C-bus interface |     |  |  |

|                       | for automotive applications                                   | 139 |  |  |

| PCF8581/81C           | 128 x 8-bit EEPROM with I <sup>2</sup> C-bus interface        | 151 |  |  |

| PCF8582A              | 256 x 8-bit static EEPROM with I <sup>2</sup> C-bus interface | 161 |  |  |

| PCF8582C              | 256 x 8-bit static EEPROM with I <sup>2</sup> C-bus interface |     |  |  |

|                       | for automotive applications                                   | 171 |  |  |

| 64K-bit CMOS EPROM    |                                                               |     |  |  |

| 27C64A-IND            | 64K-bit CMOS EPROMs (8K x 8) 150 ns; 200 ns                   | 185 |  |  |

| 27C64A O.T.P.         | 64K-bit CMOS EPROM (8K x 8) 100 ns                            | 189 |  |  |

| 27C64A O.T.P.         | 64K-bit CMOS EPROMs (8K x 8) 120 ns; 150 ns                   | 193 |  |  |

| 27C64A O.T.P.         | 64K-bit CMOS EPROM (8K x 8) 200 ns                            | 197 |  |  |

| 27C64A U.V.           | 64K-bit erasable CMOS EPROM (8K x 8) 100 ns                   | 201 |  |  |

| 27C64A U.V.           | 64K-bit erasable CMOS EPROMs (8K x 8) 120 ns; 150 ns          | 205 |  |  |

| 27C64A U.V.           | 64K-bit erasable CMOS EPROMs (8K x 8) 200 ns                  | 209 |  |  |

| 27HC641 O.T.P.        | 64K-bit CMOS EPROMs (8K x 8) 45 ns; 55 ns                     | 213 |  |  |

| 27HC641 U.V.          | 64K-bit erasable CMOS EPROMs (8K x 8) 35 ns; 45 ns; 55 ns     | 217 |  |  |

| 128K-bit CMOS EPRO    | Μ                                                             |     |  |  |

| 27HC128 O.T.P.        | 128K-bit CMOS EPROMs (16K x 8) 45 ns; 55 ns                   | 223 |  |  |

| 27HC128 U.V.          | 128K-bit erasable CMOS EPROMs (16K x 8) 45 ns; 55 ns          | 227 |  |  |

ķ

| type number          | description                                                    | page        |

|----------------------|----------------------------------------------------------------|-------------|

| 256K-bit CMOS EPROM  |                                                                |             |

| 27C256-IND           | 256K-bit EPROMs (32K x 8) 150 ns; 200 ns                       | 233         |

| 27C256 O.T.P.        | 256K-bit EPROM (32K x 8) 120 ns                                | 237         |

| 27C256 O.T.P.        | 256K-bit EPROMs (32K x 8) 150 ns; 170 ns                       | 241         |

| 27C256 O.T.P.        | 256K-bit EPROM (32K x 8) 200 ns                                | 245         |

| 27C256 U.V.          | 256K-bit erasable EPROM (32K x 8) 120 ns                       | 249         |

| 27C256 U.V.          | 256K-bit erasable EPROMs (32K x 8) 150 ns; 170 ns              | 253         |

| 27C256 U.V.          | 256K-bit erasable EPROM (32K x 8) 200 ns                       | 257         |

| 516K-bit CMOS EPRO   | Μ                                                              |             |

| 27C512 O.T.P.        | 512K-bit CMOS EPROMs (64K x 8) 150 ns; 170 ns; 200 ns          | 263         |

| 27C512 U.V.          | 512K-bit erasable CMOS EPROMs (64K x 8) 150 ns; 170 ns; 200 ns | 267         |

| 1M-bit CMOS EPROM    |                                                                |             |

| 27C210 O.T.P.        | 1M programmable EPROM (64K x 16) 150 ns; 200 ns                | 273         |

| 27C210 U.V.          | 1M erasable CMOS EPROM (64K x 16) 150 ns; 200 ns               | 277         |

| 64-bit TTL RAM       |                                                                |             |

| 82S25/3101A/         |                                                                |             |

| 74S189               | 64-bit TTL Bipolar RAM (16 x 4) 50 ns; 35 ns                   | 285         |

| 74F189A              | 64-bit TTL Bipolar RAM (16 x 4) 15 ns                          | 289         |

| 74F219A              | 64-bit TTL Bipolar RAM (16 x 4) 10 ns                          | 293         |

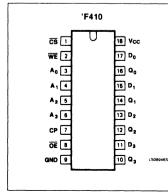

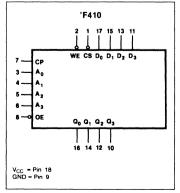

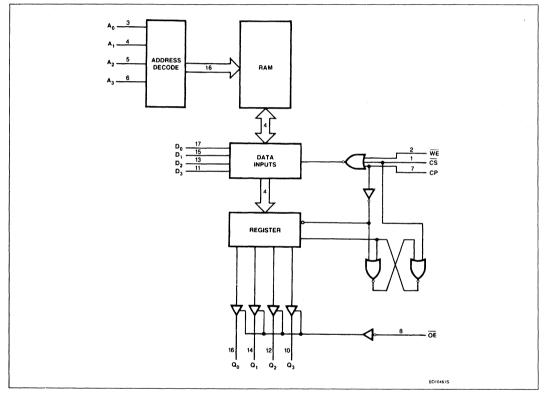

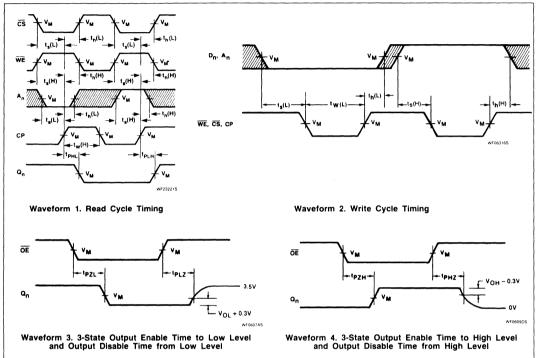

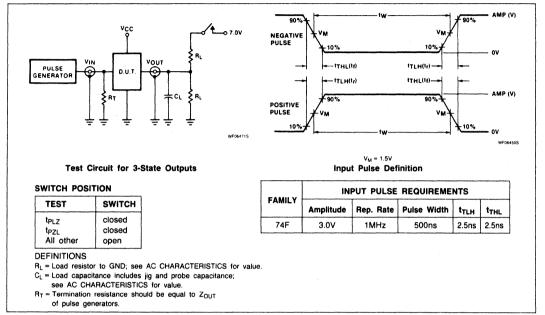

| 74F410               | 64-bit TTL Bipolar register stack (16 x 4) 19.5 ns             | 297         |

| 256-bit TTL RAM      |                                                                |             |

| 82S16                | 256-bit TTL Bipolar RAM (256 x 1) 50 ns                        | 305         |

| 82LS16               | 256-bit TTL Bipolar RAM (256 x 1) 40 ns                        | 309         |

| 74S301               | 256-bit TTL Bipolar RAM (256 x 1) 50 ns                        | 313         |

| 74LS301              | 256-bit TTL Bipolar RAM (256 x 1) 40 ns                        | 317         |

| Byte-Organized TTL R | AM                                                             |             |

| 82S09/82S09A         | 576-bit TTL Bipolar RAM (64 x 9) 45 ns; 35 ns                  | 323         |

| 82S19                | 576-bit TTL Bipolar RAM (64 x 9) 35 ns                         | 327         |

| 82S212/82S212A       | 2304-bit TTL Bipolar RAM (256 x 9) 45 ns; 35 ns                | 331         |

| 8X350                | 2048-bit TTL Bipolar RAM (256 x 8)                             | 335         |

| Low Complexity TTL   | PROM                                                           |             |

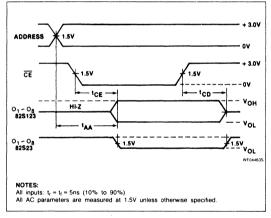

| 82S23/82S123A        | 256-bit TTL Bipolar PROM (32 x 8) 50 ns                        | 343         |

| 82S23A/82S123A       | 256-bit TTL Bipolar PROM (32 x 8) 25 ns                        | <b>3</b> 47 |

| 82US23/82US123       | 256-bit TTL Bipolar PROM (32 x 8) 13 ns; 10 ns                 | 351         |

| 82S126/82S129        | 1024-bit TTL Bipolar PROM (256 x 4) 50 ns                      | 355         |

| 82S126A/82S129A      | 1024-bit TTL Bipolar PROM (256 x 4) 30 ns; 27 ns               | 359         |

| 825130/825131        | 2048-bit TTL Bipolar PROM (512 x 4) 50 ns                      | 363         |

| 82S130A/82S131A      | 2048-bit TTL Bipolar PROM (512 x 4) 33 ns; 30 ns               | 367         |

| 82S135               | 2048-bit TTL Bipolar PROM (256 x 8) 45 ns                      | 371         |

| 82LS135              | 2048-bit TTL Bipolar PROM (256 x 8) 100 ns                     | 375         |

## FUNCTIONAL INDEX

| type number          | description                                                                                            | page |

|----------------------|--------------------------------------------------------------------------------------------------------|------|

| 4K-bit TTL PROM      |                                                                                                        |      |

| 82S115               | 4096-bit TTL Bipolar PROM (512 x 8) 60 ns                                                              | 38/  |

| 82S137               | 4096-bit TTL Bipolar PROM (1024 x 4) 60 ns                                                             | 385  |

| 82S137A/82S137B      | 4096-bit TTL Bipolar PROM (1024 x 4) 45 ns; 35 ns                                                      | 389  |

| 82S141/82S141A       | 4096-bit TTL Bipolar PROM (512 x 8) 60 ns; 45 ns                                                       | 393  |

| 82S147/82S147A       | 4096-bit TTL Bipolar PROM (512 x 8) 60 ns; 45 ns                                                       | 397  |

| 82S147B              | 4096-bit TTL Bipolar PROM (512 x 8) 25 ns                                                              | 40   |

| 8K-bit TTL PROM      |                                                                                                        |      |

| 82S181/82S181A       | 8192-bit TTL Bipolar PROM (1024 x 8) 70 ns; 55 ns                                                      | 407  |

| 82S181C              | 8192-bit TTL Bipolar PROM (1024 x 8) 35 ns                                                             | 41   |

| 82S183               | 8192-bit TTL Bipolar PROM (1024 x 8) 60 ns                                                             | 41   |

| 82S185               | 8192-bit TTL Bipolar PROM (2048 x 4) 100 ns                                                            | 41   |

| 82S185A              | 8192-bit TTL Bipolar PROM (2048 x 4) 50 ns                                                             | 42   |

| 82S185B              | 8192-bit TTL Bipolar PROM (2048 x 4) 35 ns                                                             | 42   |

| 82HS187/82HS187A     | 8192-bit TTL Bipolar PROM (1024 x 8) 55 ns; 45 ns                                                      | 43   |

| 82HS189/82HS189A     | 8192-bit TTL Bipolar PROM (1024 x 8) 55 hs, 45 hs<br>8192-bit TTL Bipolar PROM (1024 x 8) 55 hs; 45 hs | 43   |

| 16K-bit TTL PROM     |                                                                                                        |      |

| 82S191/82S191A       | 16 384-bit TTL Bipolar PROM (2048 x 8) 80 ns; 55 ns                                                    | 44   |

| 82S191/025191A       | 16 384-bit TTL Bipolar PROM (2048 x 8) 35 ns                                                           | 44   |

| 82HS191              | 16 384-bit TTL Bipolar PROM (2048 x 8) 25 ns                                                           | 44   |

| 82LHS191             | 16 384-bit TTL Bipolar PROM (2048 x 8) 35 ns                                                           | 45   |

| 82HS195/82HS195A/    |                                                                                                        | 40.  |

| 82HS195/82HS195A/    | 16 384-bit TTL Bipolar PROM (4096 x 4) 45 ns; 35 ns; 25 ns                                             | 45   |

| 32K-bit TTL PROM     |                                                                                                        |      |

|                      |                                                                                                        |      |

| 82HS321/82HS321A/    | 22 769 hit TTL Bingles BBOM (4006 x 9) 45 per 25 per 20 pe                                             | 46   |

| 82HS321B             | 32 768-bit TTL Bipolar PROM (4096 x 8) 45 ns; 35 ns; 30 ns                                             |      |

| 82HS321C             | 32 768-bit TTL Bipolar PROM (4096 x 8) 25 ns                                                           | 46   |

| 82LHS321             | 32 768-bit TTL Bipolar PROM (4096 x 8) 35 ns                                                           | 47   |

| 64K-bit TTL PROM     |                                                                                                        |      |

| 82HS641/82HS641A/    |                                                                                                        |      |

| 82HS641B             | 65 536-bit TTL Bipolar PROM (8192 x 8) 55 ns; 45 ns; 35 ns                                             | 47   |

| 82HS641C             | 65 536-bit TTL Bipolar PROM (8192 x 8) 25 ns                                                           | 48   |

| 128K-bit TTL PROM    |                                                                                                        |      |

| 82HS1281             | 131 072-bit TTL Bipolar PROM (16384 x 8) 45 ns                                                         | 48   |

| Low Complexity ECL P |                                                                                                        |      |

| 10P256               | 256-bit ECL Bipolar PROM (32 x 8) 3 ns                                                                 | 49   |

| 100P256              | 256-bit ECL Bipolar PROM (32 x 8) 3 ns                                                                 | 49   |

| 10149                | 1024-bit ECL Bipolar PROM (256 x 4) 20 ns                                                              | 50   |

| 100149               | 1024-bit ECL Bipolar PROM (256 x 4) 20 ns                                                              | 50   |

| 10149A               | 1024-bit ECL Bipolar PROM (256 x 4) 10 ns                                                              | 51   |

| 100149A              | 1024-bit ECL Bipolar PROM (256 x 4) 10 ns                                                              | 51   |

| 10149B               | 1024-bit ECL Bipolar PROM (256 x 4) 5 ns                                                               | 51   |

| 100149B              | 1024-bit ECL Bipolar PROM (256 x 4) 5 ns                                                               | 52   |

| F | JNCTIONAL<br>INDEX |                                              |      |

|---|--------------------|----------------------------------------------|------|

|   | type number        | description                                  | page |

|   | 16K-bit ECL PROM   | Λ                                            |      |

|   | 10P016             | 16 384-bit ECL Bipolar PROM (4096 x 4) 10 ns | 529  |

|   | 100P016            | 16 384-bit ECL Bipolar PROM (4096 x 4) 10 ns | 523  |

8

### NUMERICAL INDEX

| type number       | description                                        | page |

|-------------------|----------------------------------------------------|------|

| FCB51C64P         | 8192 x 8-bit latched static RAM                    | 61   |

| FCB51C64T         | 8192 x 8-bit latched static RAM                    | 61   |

| FCB51C65P         | 8192 x 8-bit latched static RAM                    | 61   |

| FCB51C65T         | 8192 x 8-bit latched static RAM                    | 61   |

| FCB61C65(L/LL)P   | 8192 x 8-bit static RAM                            | 63   |

| FCB61C65(L/LL)T   | 8192 x 8-bit static RAM                            | 63   |

| FCB61C251P        | 26 144 x 1-bit static RAM                          | 75   |

| FCB61C251T        | 26 144 x 1-bit static RAM                          | 75   |

| FCB61C252P        | 65 536 x 4-bit static RAM                          | 79   |

| FCB61C252T        | 65 536 x 4-bit static RAM                          | 79   |

| FCB61C253P        | 65 536 x 4-bit static RAM                          | 79   |

| FCB61C253T        | 65 536 x 4-bit static RAM                          | 79   |

| FCB61C257(L/LL)P  | 32 768 x 8-bit static RAM                          | 85   |

| FCB61C257(L/LL)T  | 32 768 x 8-bit static RAM                          | 85   |

| FCB61C1025(L/LL)P | 131 072 x 8-bit static RAM                         | 89   |

| FCB61C1025(L/LL)T | 131 072 x 8-bit static RAM                         | 89   |

| N3101A D          | 64-bit TTL Bipolar RAM (16 x 4) 35 ns              | 285  |

| N3101A N          | 64-bit TTL Bipolar RAM (16 x 4) 35 ns              | 285  |

| N74F189A D        | 64-bit TTL Bipolar RAM (16 x 4) 15 ns              | 289  |

| N74F189A N        | 64-bit TTL Bipolar RAM (16 x 4) 15 ns              | 289  |

| N74F219A D        | 64-bit TTL Bipolar RAM (16 x 4) 10 ns              | 293  |

| N74F219A N        | 64-bit TTL Bipolar RAM (16 x 4) 10 ns              | 293  |

| N74F410 N         | 64-bit TTL Bipolar register stack (16 x 4) 19.5 ns | 297  |

| N74LS301 D        | 256-bit TTL Bipolar RAM (256 x 1) 40 ns            | 303  |

| N74LS301 N        | 256-bit TTL Bipolar RAM (256 x 1) 40 ns            | 303  |

| N74S189 D         | 64-bit TTL Bipolar RAM (16 x 4) 35 ns              | 285  |

| N74S189 N         | 64-bit TTL Bipolar RAM (16 x 4) 35 ns              | 285  |

| N74S301 D         | 256-bit TTL Bipolar RAM (256 x 1) 50 ns            | 313  |

| N74S301 N         | 256-bit TTL Bipolar RAM (256 x 1) 50 ns            | 313  |

| N8X350 A          | 2048-bit TTL Bipolar RAM (256 x 8)                 | 335  |

| N8X350 N          | 2048-bit TTL Bipolar RAM (256 x 8)                 | 335  |

| N82LHS191 A       | 16 384-bit TTL Bipolar PROM (2048 x 8) 35 ns       | 453  |

| N82LHS191 N       | 16 384-bit TTL Bipolar PROM (2048 x 8) 35 ns       | 453  |

| N82LHS191 N3      | 16 384-bit TTL Bipolar PROM (2048 x 8) 35 ns       | 453  |

| N82LHS321 N       | 32 768-bit TTL Bipolar PROM (4096 x 8) 35 ns       | 471  |

| N82LHS321 N3      | 32 768-bit TTL Bipolar PROM (4096 x 8) 35 ns       | 471  |

| N82LHS321 A       | 32 768-bit TTL Bipolar PROM (4096 x 8) 35 ns       | 471  |

| N82HS187A A       | 8192-bit TTL Bipolar PROM (1024 x 8) 45 ns         | 431  |

| N82HS187A N       | 8192-bit TTL Bipolar PROM (1024 x 8) 45 ns         | 431  |

| N82HS187 A        | 8192-bit TTL Bipolar PROM (1024 x 8) 55 ns         | 431  |

| N82HS187 N        | 8192-bit TTL Bipolar PROM (1024 x 8) 55 ns         | 431  |

9

| type number  | number description                                                                           |  |     |

|--------------|----------------------------------------------------------------------------------------------|--|-----|

| N82HS189A A  | 8192-bit TTL Bipolar PROM (1024 x 8) 45 ns                                                   |  | 435 |

| N82HS189A N  | 8192-bit TTL Bipolar PROM (1024 x 8) 45 ns                                                   |  | 435 |

| N82HS189 A   | 8192-bit TTL Bipolar PROM (1024 x 8) 55 ns                                                   |  | 435 |

| N82HS189 N   | 8192-bit TTL Bipolar PROM (1024 x 8) 55 ns                                                   |  | 435 |

| N82HS191 A   | 16 384-bit TTL Bipolar PROM (2048 x 8) 25 ns                                                 |  | 449 |

| N82HS191 N   | 16 384-bit TTL Bipolar PROM (2048 x 8) 25 ns                                                 |  | 449 |

| N82HS191 N3  | 16 384-bit TTL Bipolar PROM (2048 x 8) 25 ns                                                 |  | 449 |

| N82HS195B A  | 16 384-bit TTL Bipolar PROM (4096 x 4) 25 ns                                                 |  | 457 |

| N82HS195B N  | 16 384-bit TTL Bipolar PROM (4096 x 4) 25 ns                                                 |  | 457 |

| N82HS195A A  | 16 384-bit TTL Bipolar PROM (4096 x 4) 35 ns                                                 |  | 457 |

| N82HS195A N  | 16 384-bit TTL Bipolar PROM (4096 x 4) 35 ns                                                 |  | 457 |

| N82HS195 A   | 16 384-bit TTL Bipolar PROM (4096 x 4) 45 ns                                                 |  | 457 |

| N82HS195 N   | 16 384-bit TTL Bipolar PROM (4096 x 4) 45 ns                                                 |  | 457 |

| N82HS321B A  | 32 768-bit TTL Bipolar PROM (4096 x 8) 30 ns                                                 |  | 463 |

| N82HS321B F  | 32 768-bit TTL Bipolar PROM (4096 x 8) 30 ns                                                 |  | 463 |

| N82HS321B N  | 32 768-bit TTL Bipolar PROM (4096 x 8) 30 ns                                                 |  | 463 |

| N82HS321A A  | 32 768-bit TTL Bipolar PROM (4096 x 8) 35 ns                                                 |  | 463 |

| N82HS321A F  | 32 768-bit TTL Bipolar PROM (4096 x 8) 35 ns                                                 |  | 463 |

| N82HS321A N  | 32 768-bit TTL Bipolar PROM (4096 x 8) 35 ns                                                 |  | 463 |

| N82HS321 A   | 32 768-bit TTL Bipolar PROM (4096 x 8) 45 ns                                                 |  | 463 |

| N82HS321 F   | 32 768-bit TTL Bipolar PROM (4096 x 8) 45 ns                                                 |  | 463 |

| N82HS321 N   | 32 768-bit TTL Bipolar PROM (4096 x 8) 45 ns                                                 |  | 463 |

| N82HS321C N  | 32 768-bit TTL Bipolar PROM (4096 x 8) 45 ns                                                 |  | 403 |

| N82HS321C N3 | 32 768-bit TTL Bipolar PROM (4096 x 8) 25 ns                                                 |  | 467 |

| N82HS321C F  | 32 768-bit TTL Bipolar PROM (4096 x 8) 25 ns                                                 |  | 467 |

| N82HS321C A  | 32 768-bit TTL Bipolar PROM (4096 x 8) 25 ns                                                 |  | 467 |

|              | 65 536-bit TTL Bipolar PROM (4030 x 8) 25 hs                                                 |  | 477 |

| N82HS641B F  | 65 536-bit TTL Bipolar PROM (8192 x 8) 35 ns                                                 |  | 477 |

| N82HS641B N  | •                                                                                            |  | 477 |

| N82HS641A F  | 65 536-bit TTL Bipolar PROM (8192 x 8) 45 ns                                                 |  | 477 |

| N82HS641A N  | 65 536-bit TTL Bipolar PROM (8192 x 8) 45 ns                                                 |  | 477 |

| N82HS641 N   | 65 536-bit TTL Bipolar PROM (8192 x 8) 55 ns                                                 |  | 477 |

| N82HS641 F   | 65 536-bit TTL Bipolar PROM (8192 x 8) 55 ns<br>65 536-bit TTL Bipolar PROM (8192 x 8) 25 ns |  | 481 |

| N82HS641C N  |                                                                                              |  | 481 |

| N82HS641C F  | 65 536-bit TTL Bipolar PROM (8192 x 8) 25 ns                                                 |  | 481 |

| N82HS641C A  | 65 536-bit TTL Bipolar PROM (8192 x 8) 25 ns                                                 |  |     |

| 82HS1281 N   | 131 072-bit TTL Bipolar PROM (16384 x 8) 45 ns                                               |  | 487 |

| N82LS16 D    | 256-bit TTL Bipolar RAM (256 x 1) 40 ns                                                      |  | 309 |

| N82LS16 N    | 256-bit TTL Bipolar RAM (256 x 1) 40 ns                                                      |  | 309 |

| N82S09A A    | 576-bit TTL Bipolar RAM (64 x 9) 35 ns                                                       |  | 323 |

| N82S09A N    | 576-bit TTL Bipolar RAM (64 x 9) 35 ns                                                       |  | 323 |

| N82S09 A     | 576-bit TTL Bipolar RAM (64 x 9) 45 ns                                                       |  | 323 |

| N82S09 N     | 576-bit TTL Bipolar RAM (64 x 9) 45 ns                                                       |  | 323 |

| N82S16 D     | 256-bit TTL Bipolar RAM (256 x 1) 50 ns                                                      |  | 305 |

| N82S16 N     | 256-bit TTL Bipolar RAM (256 x 1) 50 ns                                                      |  | 305 |

| N82S19 A     | 576-bit TTL Bipolar RAM (64 x 9) 35 ns                                                       |  | 327 |

| N82S19 N     | 576-bit TTL Bipolar RAM (64 x 9) 35 ns                                                       |  | 327 |

| N82S23 A     | 256-bit TTL Bipolar PROM (32 x 8) 50 ns                                                      |  | 343 |

| N82S23 N     | 256-bit TTL Bipolar PROM (32 x 8) 50 ns                                                      |  | 343 |

| N82S23A A    | 256-bit TTL Bipolar PROM (32 x 8) 25 ns                                                      |  | 347 |

| N82S23A D    | 256-bit TTL Bipolar PROM (32 x 8) 25 ns                                                      |  | 347 |

| N82S23A N    | 256-bit TTL Bipolar PROM (32 x 8) 25 ns                                                      |  | 347 |

September 1989

| type number | number description                               |     |

|-------------|--------------------------------------------------|-----|

| N82US23 A   | 256-bit TTL Bipolar PROM (32 x 8) 13 ns          | 351 |

| N82US23 D   | 256-bit TTL Bipolar PROM (32 x 8) 13 ns          | 351 |

| N82US23 N   | 256-bit TTL Bipolar PROM (32 x 8) 13 ns          | 351 |

| N82S25 D    | 64-bit TTL Bipolar RAM (16 x 4) 50 ns            | 285 |

| N82S25 N    | 64-bit TTL Bipolar RAM (16 x 4) 50 ns            | 285 |

| V82S115 N   | 4096-bit TTL Bipolar PROM (512 x 8) 60 ns        | 381 |

| N82S123 A   | 256-bit TTL Bipolar PROM (32 x 8) 50 ns          | 343 |

| N82S123 N   | 256-bit TTL Bipolar PROM (32 x 8) 50 ns          | 343 |

| N82S123A A  | 256-bit TTL Bipolar PROM (32 x 8) 25 ns          | 347 |

| V82S123A D  | 256-bit TTL Bipolar PROM (32 x 8) 25 ns          | 347 |

| N82S123A N  | 256-bit TTL Bipolar PROM (32 x 8) 25 ns          | 347 |

| N82US123 A  | 256-bit TTL Bipolar PROM (32 x 8) 10 ns          | 351 |

| N82US123 D  | 256-bit TTL Bipolar PROM (32 x 8) 10 ns          | 351 |

| V82US123 N  | 256-bit TTL Bipolar PROM (32 x 8) 10 ns          | 351 |

| N82S126 A   | 1024-bit TTL Bipolar PROM (256 x 4) 50 ns        | 355 |

| N82S126 N   | 1024-bit TTL Bipolar PROM (256 x 4) 50 ns        | 355 |

| 82S126A A   | 1024-bit TTL Bipolar PROM (256 x 4) 30 ns        | 359 |

| 82S126A D   | 1024-bit TTL Bipolar PROM (256 x 4) 30 ns        | 359 |

| 82S126A N   | 1024-bit TTL Bipolar PROM (256 x 4) 30 ns        | 359 |

| 82S129 A    | 1024-bit TTL Bipolar PROM (256 x 4) 50 ns        | 355 |

| 82S129 N    | 1024-bit TTL Bipolar PROM (256 x 4) 50 ns        | 355 |

| 82S129A A   | 1024-bit TTL Bipolar PROM (256 x 4) 27 ns        | 359 |

| 82S129A D   | 1024-bit TTL Bipolar PROM (256 x 4) 27 ns        | 359 |

| 82S129A N   | 1024-bit TTL Bipolar PROM (256 x 4) 27 ns        | 359 |

| 82S130 A    | 2048-bit TTL Bipolar PROM (512 x 4) 50 ns        | 363 |

| 82S130 N    | 2048-bit TTL Bipolar PROM (512 x 4) 50 ns        | 363 |

| 82S130A A   | 2048-bit TTL Bipolar PROM (512 x 4) 33 ns        | 367 |

| 82S130A D   | 2048-bit TTL Bipolar PROM (512 x 4) 33 ns        | 367 |

| 82S130A N   | 2048-bit TTL Bipolar PROM (512 x 4) 33 ns        | 367 |

| 82S131 A    | 2048-bit TTL Bipolar PROM (512 x 4) 50 ns        | 363 |

| 82S131 N    | 2048-bit TTL Bipolar PROM (512 x 4) 50 ns        | 363 |

| 82S131A A   | 2048-bit TTL Bipolar PROM (512 $\times$ 4) 30 ns | 367 |

| 82S131A D   | 2048-bit TTL Bipolar PROM (512 x 4) 30 ns        | 367 |

| 82S131A N   | 2048-bit TTL Bipolar PROM (512 $\times$ 4) 30 ns | 367 |

| N82LS135 A  | 2048-bit TTL Bipolar PROM (256 x 8) 100 ns       | 375 |

| 82LS135 D   | 2048-bit TTL Bipolar PROM (256 x 8) 100 ns       | 375 |

| 182LS135 N  | 2048-bit TTL Bipolar PROM (256 x 8) 100 ns       | 375 |

| 182S135 A   | 2048-bit TTL Bipolar PROM (256 x 8) 45 ns        | 371 |

| 182S135 D   | 2048-bit TTL Bipolar PROM (256 x 8) 45 ns        | 371 |

| 182S135 N   | 2048-bit TTL Bipolar PROM (256 x 8) 45 ns        | 371 |

| 82S137 A    | 4096-bit TTL Bipolar PROM (1024 x 4) 60 ns       | 385 |

| 182S137 N   | 4096-bit TTL Bipolar PROM (1024 x 4) 60 ns       | 385 |

| 182S137A A  | 4096-bit TTL Bipolar PROM (1024 x 4) 45 ns       | 389 |

| 182S137A A  | 4096-bit TTL Bipolar PROM (1024 x 4) 45 ns       | 389 |

| 182S137A N  | 4096-bit TTL Bipolar PROM (1024 x 4) 45 hs       | 389 |

| 182S137B A  | 4096-bit TTL Bipolar PROM (1024 x 4) 35 ns       | 389 |

|             | 4096-bit TTL Bipolar PROM (1024 x 4) 35 hs       | 393 |

| 182S141A A  |                                                  | 393 |

| 182S141A N  | 4096-bit TTL Bipolar PROM (512 x 8) 45 ns        |     |

| N82S141A N3 | 4096-bit TTL Bipolar PROM (512 x 8) 45 ns        | 393 |

| type number           | description                                                                                                      | page            |

|-----------------------|------------------------------------------------------------------------------------------------------------------|-----------------|

| N82S141 N             | 4096-bit TTL Bipolar PROM (512 x 8) 60 ns                                                                        | 393             |

| N82S141 N3            | 4096-bit TTL Bipolar PROM (512 x 8) 60 ns                                                                        | 393             |

| N82S147A A            | 4096-bit TTL Bipolar PROM (512 x 8) 45 ns                                                                        | 397             |

| N82S147A N            | 4096-bit TTL Bipolar PROM (512 x 8) 45 ns                                                                        | 397             |

| N82S147 A             | 4096-bit TTL Bipolar PROM (512 x 8) 60 ns                                                                        | 397             |

| N82S147 N             | 4096-bit TTL Bipolar PROM (512 x 8) 60 ns                                                                        | 397             |

| N82S147B A            | 4096-bit TTL Bipolar PROM (512 x 8) 25 ns                                                                        | 401             |

| N82S147B N            | 4096-bit TTL Bipolar PROM (512 x 8) 25 ns                                                                        | 401             |

| N82S181A A            | 8192-bit TTL Bipolar PROM (1024 x 8) 55 ns                                                                       | 407             |

| N82S181A N            | 8192-bit TTL Bipolar PROM (1024 x 8) 55 ns                                                                       | 407             |

| N82S181 A             | 8192-bit TTL Bipolar PROM (1024 x 8) 70 ns                                                                       | 407             |

| N82S181 N             | 8192-bit TTL Bipolar PROM (1024 x 8) 70 ns                                                                       | 407             |

| N82S181C A            | 8192-bit TTL Bipolar PROM (1024 x 8) 35 ns                                                                       | 411             |

| N82S181C N            | 8192-bit TTL Bipolar PROM (1024 x 8) 35 ns                                                                       | 411             |

| N82S181C N3           | 8192-bit TTL Bipolar PROM (1024 x 8) 35 ns                                                                       | 411             |

| N82S183 A             | 8192-bit TTL Bipolar PROM (1024 x 8) 60 ns                                                                       | 415             |

| N82S183 N             | 8192-bit TTL Bipolar PROM (1024 x 8) 60 ns                                                                       | 415             |

| N82S185A N            | 8192-bit TTL Bipolar PROM (2048 x 4) 50ns                                                                        | 423             |

| N82S185B N            | 8192-bit TTL Bipolar PROM (2048 x 4) 35 ns                                                                       | 427             |

| N82S185 N             | 8192-bit TTL Bipolar PROM (2048 x 4) 100 ns                                                                      | 419             |

| N82S191A A            | 16 384-bit TTL Bipolar PROM (2048 x 8) 55 ns                                                                     | 441             |

| N82S191A N            | 16 384-bit TTL Bipolar PROM (2048 x 8) 55 ns                                                                     | 441             |

| N82S191 A             | 16 384-bit TTL Bipolar PROM (2048 x 8) 80 ns                                                                     | 441             |

| N82S191 N             | 16 384-bit TTL Bipolar PROM (2048 x 8) 80 ns                                                                     | 441             |

| N82S191C A            | 16 384-bit TTL Bipolar PROM (2048 x 8) 35 ns                                                                     | 445             |

| N82S191C N            | 16 384-bit TTL Bipolar PROM (2048 x 8) 35 ns                                                                     | 445             |

| N82S191C N3           | 16 384-bit TTL Bipolar PROM (2048 x 8) 35 ns                                                                     | 445             |

| N82S212A A            | 2304-bit TTL Bipolar RAM (256 x 9) 35 ns                                                                         | 331             |

| N82S212A N            | 2304-bit TTL Bipolar RAM (256 x 9) 35 ns                                                                         | 331             |

| N82S212 A             | 2304-bit TTL Bipolar RAM (256 x 9) 45 ns                                                                         | 331             |

| N82S212 N             | 2304-bit TTL Bipolar RAM (256 x 9) 45 ns                                                                         | 331             |

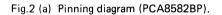

| PCA8582BP             | 256 x 8-bit static EEPROM with $1^{2}$ C-bus interface                                                           |                 |

| 04030201              | for automotive applications                                                                                      | 139             |

| PCA8582BT             | $256 \times 8$ -bit static EEPROM with I <sup>2</sup> C-bus interface                                            | 100             |

|                       | for automotive applications                                                                                      | 139             |

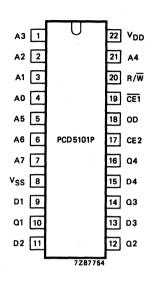

| PCD5101P              | 256 x 4-bit static RAM                                                                                           | 93              |

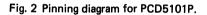

| PCD5101T              | 256 x 4-bit static RAM                                                                                           | 93              |

| PCD5114P              | 1024 x 4-bit static RAM                                                                                          | 10              |

| PCD5114T              | 1024 x 4-bit static RAM                                                                                          | 10 <sup>-</sup> |

| PCF8570P              | $256 \times 8$ -bit static RAM with $1^{2}$ C-bus interface                                                      | 109             |

| PCF8570T              | $256 \times 8$ -bit static RAM with 1 <sup>2</sup> C-bus interface                                               | 10              |

| PCF8570CP             | $256 \times 8$ -bit static RAM with 1 <sup>2</sup> C-bus interface                                               | 109             |

| PCF8570CF             | 256 x 8-bit static RAM with 1 <sup>2</sup> C-bus interface                                                       | 109             |

| PCF8570C1<br>PCF8571P | $128 \times 8$ -bit static RAM with 1 <sup>2</sup> C-bus interface                                               | 109             |

| PCF8571F<br>PCF8571T  | 128 x 8-bit static RAM with $1^{\circ}$ C-bus interface                                                          | 109             |

| PCF8581P              | 128 x 8-bit EEPROM with 1 <sup>2</sup> C-bus interface                                                           | 15              |

| PCF8581P<br>PCF8581T  | 128 x 8-bit EEPROM with 1 <sup>2</sup> C-bus interface<br>128 x 8-bit EEPROM with 1 <sup>2</sup> C-bus interface | 15<br>15        |

|                       |                                                                                                                  | 15              |

| PCF8581CP             | 128 x 8-bit EEPROM with I <sup>2</sup> C-bus interface                                                           | 15              |

| type number  | umber description                                                  |     |  |

|--------------|--------------------------------------------------------------------|-----|--|

| PCF8582AP    | 256 x 8-bit static CMOS EEPROM with I <sup>2</sup> C-bus interface | 161 |  |

| PCF8582AT    | 256 x 8-bit static CMOS EEPROM with I <sup>2</sup> C-bus interface | 161 |  |

| PCF8582CP    | 256 x 8-bit static EEPROM with I <sup>2</sup> C-bus interface      |     |  |

|              | for automotive applications                                        | 171 |  |

| PCF8582CT    | 256 x 8-bit static EEPROM with $I^2C$ -bus interface               |     |  |

|              | for automotive applications                                        | 171 |  |

| PCF8583P     | 256 x 8-bit static RAM with I <sup>2</sup> C-bus interface         | 119 |  |

| PCF8583T     | 256 x 8-bit static RAM with I <sup>2</sup> C-bus interface         | 119 |  |

| 10P016 F     | 16 384-bit ECL Bipolar PROM (4096 x 4) 10 ns                       | 529 |  |

| 100P016 F    | 16 384-bit ECL Bipolar PROM (4096 x 4) 10 ns                       | 533 |  |

| 10P256 F     | 256-bit ECL Bipolar PROM (32 x 8) 3 ns                             | 495 |  |

| 100P256 F    | 256-bit ECL Bipolar PROM (32 x 8) 3 ns                             | 499 |  |

| 10149B F     | 1024-bit ECL Bipolar PROM (256 x 4) 5 ns                           | 519 |  |

| 10149 F      | 1024-bit ECL Bipolar PROM (256 x 4) 20 ns                          | 503 |  |

| 100149B F    | 1024-bit ECL Bipolar PROM (256 x 4) 5 ns                           | 523 |  |

| 100149 F     | 1024-bit ECL Bipolar PROM (256 x 4) 20 ns                          | 507 |  |

| 10149A F     | 1024-bit ECL Bipolar PROM (256 x 4) 10 ns                          | 511 |  |

| 100149A F    | 1024-bit ECL Bipolar PROM (256 x 4) 10 ns                          | 515 |  |

| 27C64AI15 FA | 64K-bit CMOS EPROM (8K x 8) 150 ns                                 | 185 |  |

| 27C64A120 FA | 64K-bit CMOS EPROM (8K x 8) 200 ns                                 | 185 |  |

| 27C64A115 N  | 64K-bit CMOS EPROM (8K x 8) 150 ns                                 | 185 |  |

| 27C64A120 N  | 64K-bit CMOS EPROM (8K x 8) 200 ns                                 | 185 |  |

| 27C64A115 A  | 64K-bit CMOS EPROM (8K x 8) 150 ns                                 | 185 |  |

| 27C64A120 A  | 64K-bit CMOS EPROM (8K x 8) 200 ns                                 | 185 |  |

| 27C64A-10 N  | 64K-bit CMOS EPROM (8K x 8) 100 ns                                 | 189 |  |

| 27C64A-10 A  | 64K-bit CMOS EPROM (8K x 8) 100 ns                                 | 189 |  |

| 27C64A-12 N  | 64K-bit CMOS EPROM (8K x 8) 120 ns                                 | 193 |  |

| 27C64A-15 N  | 64K-bit CMOS EPROM (8K x 8) 150 ns                                 | 193 |  |

| 27C64A-12 A  | 64K-bit CMOS EPROM (8K x 8) 120 ns                                 | 193 |  |

| 27C64A-15 A  | 64K-bit CMOS EPROM (8K x 8) 150 ns                                 | 193 |  |

| 27C64A-20 N  | 64K-bit CMOS EPROM (8K x 8) 200 ns                                 | 197 |  |

| 27C64A-20 A  | 64K-bit CMOS EPROM (8K x 8) 200 ns                                 | 197 |  |

| 27C64A-10 FA | 64K-bit erasable CMOS EPROM (8K x 8) 100 ns                        | 201 |  |

| 27C64A-12 FA | 64K-bit erasable CMOS EPROM (8K x 8) 120 ns                        | 205 |  |

| 27C64A-15 FA | 64K-bit erasable CMOS EPROM (8K x 8) 150 ns                        | 205 |  |

| 27C64A-20 FA | 64K-bit erasable CMOS EPROM (8K x 8) 200 ns                        | 209 |  |

| 27C210-15 N  | 1M programmable EPROM (64K x 16) 150 ns                            | 273 |  |

| 27C210-20 N  | 1M programmable EPROM (64K $\times$ 16) 200 ns                     | 273 |  |

| 27C210-15 A  | 1M programmable EPROM ( $64K \times 16$ ) 150 ns                   | 273 |  |

| 27C210-20 A  | 1M programmable EPROM (64K $\times$ 16) 200 ns                     | 273 |  |

| 27C210-15 FA | 1M erasable CMOS EPROM (64K x 16) 150 ns                           | 277 |  |

| 27C210-20 FA | 1M erasable CMOS EPROM (64K x 16) 200 ns                           | 277 |  |

| 27C256I15 FA | 256K-bit EPROM (32K x 8) 150 ns                                    | 233 |  |

| 27C256I20 FA | 256K-bit EPROM (32K x 8) 200 ns                                    | 233 |  |

| 27C256I15 N  | 256K-bit EPROM (32K x 8) 150 ns                                    | 233 |  |

| 27C256I20 N  | 256K-bit EPROM (32K x 8) 200 ns                                    | 233 |  |

| 27C256I15 A  | 256K-bit EPROM (32K x 8) 150 ns                                    | 233 |  |

| 27C256120 A  | 256K-bit EPROM (32K x 8) 200 ns                                    | 233 |  |

| type number   | nber description                              |             |

|---------------|-----------------------------------------------|-------------|

| 27C256-12 N   | 256K-bit EPROM (32K x 8) 120 ns               | 237         |

| 27C256-12 A   | 256K-bit EPROM (32K x 8) 120 ns               | 237         |

| 27C256-15 N   | 256K-bit EPROM (32K x 8) 150 ns               | <b>24</b> 1 |

| 27C256-17 N   | 256K-bit EPROM (32K x 8) 170 ns               | 241         |

| 27C256-15 A   | 256K-bit EPROM (32K x 8) 150 ns               | 241         |

| 27C256-17 A   | 256K-bit EPROM (32K x 8) 170 ns               | 241         |

| 27C256-20 N   | 256K-bit EPROM (32K x 8) 200 ns               | 245         |

| 27C256-20 A   | 256K-bit EPROM (32K x 8) 200 ns               | 245         |

| 27C256-12 FA  | 256K-bit erasable EPROM (32K x 8) 120 ns      | 249         |

| 27C256-15 FA  | 256K-bit erasable EPROM (32K x 8) 150 ns      | 253         |

| 27C256-17 FA  | 256K-bit erasable EPROM (32K x 8) 170 ns      | 253         |

| 27C256-20 FA  | 256K-bit erasable EPROM (32K x 8) 200 ns      | 257         |

| 27C512-15 N   | 512K-bit CMOS EPROM (64K x 8) 150 ns          | 263         |

| 27C512-17 N   | 512K-bit CMOS EPROM (64K x 8) 170 ns          | 263         |

| 27C512-20 N   | 512K-bit CMOS EPROM (64K x 8) 200 ns          | 263         |

| 27C512-15 A   | 512K-bit CMOS EPROM (64K x 8) 150 ns          | 263         |

| 27C512-17 A   | 512K-bit CMOS EPROM (64K x 8) 170 ns          | 263         |

| 27C512-20 A   | 512K-bit CMOS EPROM (64K x 8) 200 ns          | 263         |

| 27C512-15 FA  | 512K-bit erasable CMOS EPROM (64K x 8) 150 ns | 267         |

| 27C512-17 FA  | 512K-bit erasable CMOS EPROM (64K x 8) 170 ns | 267         |

| 27C512-20 FA  | 512K-bit erasable CMOS EPROM (64K x 8) 200 ns | 267         |

| 27HC128-45 N  | 128K-bit CMOS EPROM (16K x 8) 45 ns           | 223         |

| 27HC128-55 N  | 128K-bit CMOS EPROM (16K x 8) 55 ns           | 223         |

| 27HC128-45 A  | 128K-bit CMOS EPROM (16K x 8) 45 ns           | 223         |

| 27HC128-55 A  | 128K-bit CMOS EPROM (16K x 8) 55 ns           | 223         |

| 27HC128-45 FA | 128K-bit erasable CMOS EPROM (16K x 8) 45 ns  | 227         |

| 27HC128-55 FA | 128K-bit erasable CMOS EPROM (16K x 8) 55 ns  | 227         |

| 27HC641-45 N  | 64K-bit CMOS EPROM (8K x 8) 45 ns             | 213         |

| 27HC641-55 N  | 64K-bit CMOS EPROM (8K x 8) 55 ns             | 213         |

| 27HC641-45 A  | 64K-bit CMOS EPROM (8K x 8) 45 ns             | 213         |

| 27HC641-55 A  | 64K-bit CMOS EPROM (8K x 8) 55 ns             | 213         |

| 27HC641-35 FA | 64K-bit erasable CMOS EPROM (8K x 8) 35 ns    | 213         |

| 27HC641-45 FA | 64K-bit erasable CMOS EPROM (8K x 8) 45 ns    | 217         |

| 27HC641-55 FA | 64K-bit erasable CMOS EPROM (8K x 8) 55 ns    | 217         |

# INTRODUCTION

| Introduction for type numbers with prefixes FCB, PCA, PCD and PCF | 17 |

|-------------------------------------------------------------------|----|

| Introduction for type numbers with numerical prefixes             | 25 |

# Introduction for type numbers with prefixes FCB, PCA, PCD and PCF

| page |

|------|

| 10   |

| Type designation     | 19 |

|----------------------|----|

| Rating systems       | 21 |

| Handling MOS devices | 23 |

### PRO ELECTRON TYPE DESIGNATION CODE FOR INTEGRATED CIRCUITS

This type nomenclature applies to semiconductor monolithic, semiconductor multi-chip, thin-film, thick-film and hybrid integrated circuits.

A basic number consists of:

THREE LETTERS FOLLOWED BY A SERIAL NUMBER

### FIRST AND SECOND LETTER

1. DIGITAL FAMILY CIRCUITS

The FIRST TWO LETTERS identify the FAMILY (see note 1).

2. SOLITARY CIRCUITS

The FIRST LETTER divides the solitary circuits into:

- S : Solitary digital circuits

- T : Analogue circuits

- U: Mixed analogue/digital circuits

The SECOND LETTER is a serial letter without any further significance except 'H' which stands for hybrid circuits.

3. MICROPROCESSORS

The FIRST TWO LETTERS identify microprocessors and correlated circuits as follows:

- MA : { Microcomputer

- Central processing unit

- MB : Slice processor (see note 2)

- MD : Correlated memories

- ME : Other correlated circuits (interface, clock, peripheral controller, etc.)

### 4. CHARGE-TRANSFER DEVICES AND SWITCHED CAPACITORS

The FIRST TWO LETTERS identify the following:

- NH : Hybrid circuits

- NL : Logic circuits

- NM : Memories

- NS : Analogue signal processing, using switched capacitors

- NT : Analogue signal processing, using CTDs

- NX : Imaging devices

- NY: Other correlated circuits

### Notes

- 1. A logic family is an assembly of digital circuits designed to be interconnected and defined by its basic electrical characteristics (such as: supply voltage, power consumption, propagation delay, noise immunity).

- 2. By 'slice processor' is meant: a functional slice of microprocessor.

### THIRD LETTER

TYPE

It indicates the operating ambient temperature range. The letters A to G give information about the temperature:

- A : temperature range not specified

- B : 0 to + 70 °C

- C : -55 to + 125 °C

- D : -25 to + 70 °C

- E : -25 to +85 °C

- F : -40 to +85 °C

- G: -55 to + 85 °C

If a circuit is published for another temperature range, the letter indicating a narrower temperature range may be used or the letter 'A'.

Example: the range 0 to + 75 °C can be indicated by 'B' or 'A'.

### SERIAL NUMBER

This may be either a 4-digit number assigned by Pro Electron, or the serial number (which may be a combination of figures and letters) of an existing company type designation of the manufacturer.

To the basic type number may be added:

### A VERSION LETTER

Indicates a minor variant of the basic type or the package. Except for 'Z', which means customized wiring, the letter has no fixed meaning. The following letters are recommended for package variants:

- C : for cylindrical

- D: for ceramic DIL

- F : for flat pack

- L : for chip on tape

- P : for plastic DIL

- Q: for QIL

- T : for miniature plastic (mini-pack)

- U: for uncased chip

Alternatively a TWO LETTER SUFFIX may be used instead of a single package version letter, if the manufacturer (sponsor) wishes to give more information.

### FIRST LETTER: General shape

- C : Cylindrical

- D : Dual-in-line (DIL)

- E: Power DIL (with external heatsink)

- F : Flat (leads on 2 sides)

- G : Flat (leads on 4 sides)

- K : Diamond (TO-3 family)

- M: Multiple-in-line (except Dual-, Triple-, Quadruple-in-line)

- Q : Quadruple-in-line (QIL)

- R : Power QIL (with external heatsink)

- S : Single-in-line

- T : Triple-in-line

A hyphen precedes the suffix to avoid confusion with a version letter.

### ie letters A to C

### SECOND LETTER: Material

- C : Metal-ceramic

- G: Glass-ceramic (cerdip)

- M : Metal

- P : Plastic

### RATING SYSTEMS

The rating systems described are those recommended by the International Electrotechnical Commission (IEC) in its Publication 134.

### DEFINITIONS OF TERMS USED

Electronic device. An electronic tube or valve, transistor or other semiconductor device.

Note

This definition excludes inductors, capacitors, resistors and similar components.

*Characteristic.* A characteristic is an inherent and measurable property of a device. Such a property may be electrical, mechanical, thermal, hydraulic, electro-magnetic, or nuclear, and can be expressed as a value for stated or recognized conditions. A characteristic may also be a set of related values, usually shown in graphical form.

*Bogey electronic device.* An electronic device whose characteristics have the published nominal values for the type. A bogey electronic device for any particular application can be obtained by considering only those characteristics which are directly related to the application.

*Rating.* A value which establishes either a limiting capability or a limiting condition for an electronic device. It is determined for specified values of environment and operation, and may be stated in any suitable terms.

#### Note

Limiting conditions may be either maxima or minima.

Rating system. The set of principles upon which ratings are established and which determine their interpretation.

### Note

The rating system indicates the division of responsibility between the device manufacturer and the circuit designer, with the object of ensuring that the working conditions do not exceed the ratings.

### ABSOLUTE MAXIMUM RATING SYSTEM

Absolute maximum ratings are limiting values of operating and environmental conditions applicable to any electronic device of a specified type as defined by its published data, which should not be exceeded under the worst probable conditions.

These values are chosen by the device manufacturer to provide acceptable serviceability of the device, taking no responsibility for equipment variations, environmental variations, and the effects of changes in operating conditions due to variations in the characteristics of the device under consideration and of all other electronic devices in the equipment.

The equipment manufacturer should design so that, initially and throughout life, no absolute maximum value for the intended service is exceeded with any device under the worst probable operating conditions with respect to supply voltage variation, equipment component variation, equipment control adjustment, load variations, signal variation, environmental conditions, and variations in characteristics of the device under consideration and of all other electronic devices in the equipment.

### DESIGN MAXIMUM RATING SYSTEM

Design maximum ratings are limiting values of operating and environmental conditions applicable to a bogey electronic device of a specified type as defined by its published data, and should not be exceeded under the worst probable conditions.

These values are chosen by the device manufacturer to provide acceptable serviceability of the device, taking responsibility for the effects of changes in operating conditions due to variations in the characteristics of the electronic device under consideration.

The equipment manufacturer should design so that, initially and throughout life, no design maximum value for the intended service is exceeded with a bogey device under the worst probable operating conditions with respect to supply voltage variation, equipment component variation, variation in characteristics of all other devices in the equipment, equipment control adjustment, load variation, signal variation and environmental conditions.

### DESIGN CENTRE RATING SYSTEM

Design centre ratings are limiting values of operating and environmental conditions applicable to a bogey electronic device of a specified type as defined by its published data, and should not be exceeded under normal conditions.

These values are chosen by the device manufacturer to provide acceptable serviceability of the device in average applications, taking responsibility for normal changes in operating conditions due to rated supply voltage variation, equipment component variation, equipment control adjustment, load variation, signal variation, environmental conditions, and variations in the characteristics of all electronic devices.

The equipment manufacturer should design so that, initially, no design centre value for the intended service is exceeded with a bogey electronic device in equipment operating at the stated normal supply voltage.

### HANDLING MOS DEVICES

Though all our MOS integrated circuits incorporate protection against electrostatic discharges, they can nevertheless be damaged by accidental over-voltages. In storing and handling them, the following precautions are recommended.

### Caution

Testing or handling and mounting call for special attention to personal safety. Personnel handling MOS devices should normally be connected to ground via a resistor.

### Storage and transport

Store and transport the circuits in their original packing. Alternatively, use may be made of a conductive material or special IC carrier that either short-circuits all leads or insulates them from external contact.

### Testing or handling

Work on a conductive surface (e.g. metal table top) when testing the circuits or transferring them from one carrier to another. Electrically connect the person doing the testing or handling to the conductive surface, for example by a metal bracelet and a conductive cord or chain. Connect all testing and hand-ling equipment to the same surface.

Signals should not be applied to the inputs while the device power supply is off. All unused input leads should be connected to either the supply voltage or ground.

### Mounting

Mount MOS integrated circuits on printed circuit boards *after* all other components have been mounted. Take care that the circuits themselves, metal parts of the board, mounting tools, and the person doing the mounting are kept at the same electric (ground) potential. If it is impossible to ground the printed-circuit board the person mounting the circuits should touch the board before bringing MOS circuits into contact with it.

### Soldering

Soldering iron tips, including those of low-voltage irons, or soldering baths should also be kept at the same potential as the MOS circuits and the board.

#### Static charges

Dress personnel in clothing of non-electrostatic material (no wool, silk or synthetic fibres). After the MOS circuits have been mounted on the board proper handling precautions should still be observed. Until the sub-assemblies are inserted into a complete system in which the proper voltages are supplied, the board is no more than an extension of the leads of the devices mounted on the board. To prevent static charges from being transmitted through the board wiring to the device it is recommended that conductive clips or conductive tape be put on the circuit board terminals.

### Transient voltages

To prevent permanent damage due to transient voltages, do not insert or remove MOS devices, or printed-circuit boards with MOS devices, from test sockets or systems with power on.

#### Voltage surges

Beware of voltage surges due to switching electrical equipment on or off, relays and d.c. lines.

HANDLING MOS DEVICES

•

# Introduction for type numbers with numerical prefixes

| page                          |

|-------------------------------|

| oduct Status                  |

| dering Information            |

| uality and Reliability        |

| polar Reliability Information |

| ROM Reliability Information   |

| lection Guide                 |

| AM Cross Reference Guide 40   |

| COM Cross Reference Guide 41  |

| ROM Cross Reference Guide 51  |

| ROM Programming Information53 |

| polar Programming Information |

# **Product Status**

**Memory Products**

| DEFINITIONS                  |                        |                                                                                                                                                                                                                                                       |  |

|------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Data Sheet<br>Identification | Product Status         | Definition                                                                                                                                                                                                                                            |  |

| Objective Specification      | Formative or In Design | This data sheet contains the design target or goal<br>specifications for product development. Specifications may<br>change in any manner without notice.                                                                                              |  |

| Preliminary Specification    | Preproduction Product  | This data sheet contains preliminary data and supplementary<br>data will be published at a later date. Signetics reserves the<br>right to make changes at any time without notice in order to<br>improve design and supply the best possible product. |  |

| Product Specification        | Full Production        | This data sheet contains Final Specifications. Signetics<br>reserves the right to make changes at any time without<br>notice in order to improve design and supply the best<br>possible product.                                                      |  |

## Ordering Information

#### **Memory Products**

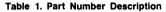

Signetics Memory integrated circuit products may be ordered by contacting either the local Signetics sales office, Signetics representatives and/or Signetics authorized distributors. A complete listing is located in the back of this manual. The tables shown below provide part number definitions for Signetics memory products. The Signetics part number system allows complete definition for ordering a device. The part number itself and the product description is defined on each data sheet. The suffix is a letter defining a package type. Additional or special processing is defined by adding the processing indicator when required.

The military qualification, Full MIL Signetics or Full JAN slash sheet status, can be determined by contacting Signetics Military Division or referring to the Signetics Military Data Book.

## Quality and Reliability

#### **Memory Products**

### SIGNETICS MEMORY QUALITY

Signetics has put together a winning process for manufacturing Memories. Our standard is zero defects, and current customer quality statistics demonstrate our commitment to this goal.

The memories produced in Signetics must meet rigid criteria as defined by our design rules and as evaluated with a thorough product characterization and quality process. The capabilities of our manufacturing process are measured and the results evaluated and reported through our corporate-wide QA05 data base system. The SURE (Systematic Uniform Reliability Evaluation) program monitors the performance of our product in a variety of accelerated environmental stress conditions. All of these programs and systems are intended to prevent product-related problems and to inform our customers and employees of our progress in achieving zero defects.

# RELIABILITY BEGINS WITH THE DESIGN

Quality and reliability must begin with design. No amount of extra testing or inspection will produce reliable ICs from a design that is inherently unreliable. Signetics follows very strict design and layout practices with its circuits. To eliminate the possibility of metal migration, current density in any path cannot exceed  $2 \times 10^5$  amps/cm<sup>2</sup>. Layout rules are followed to minimize the possibility of shorts, circuit anomalies, and SCR type latch-up effects. Numerous ground-to-substrate connections are required to ensure that the entire chip is at the same ground potential, thereby precluding internal noise problems.

### **PRODUCT CHARACTERIZATION**

Before a new design is released, the characterization phase is completed to insure that the distribution of parameters resulting from lot-to-lot variations is well within specified limits. Such extensive characterization data also provides a basis for identifying unique application-related problems which are not part of normal data sheet guarantees. Characterization takes place from  $-55^{\circ}$ C to  $+125^{\circ}$ C and at  $\pm 10\%$  supply voltage.

#### QUALIFICATION

Formal qualification procedures are required for all new or changed products, processes and facilities. These procedures ensure the high level of product reliability our customers expect. New facilities are qualified by corporate groups as well as by the quality organizations of specific units that will operate in the facility. After qualification, products manufactured by the new facility are subjected to highly accelerated environmental stresses to ensure that they can meet rigorous failure rate requirements. New or changed processes are similarly qualified.

### QA05 — QUALITY DATA BASE REPORTING SYSTEM

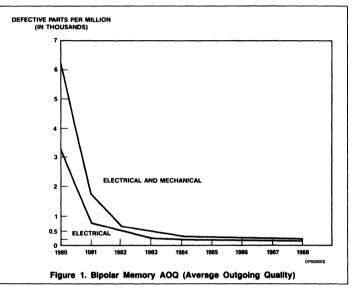

The QA05 data reporting system collects the results of product assurance testing on all finished lots and feeds this data back to concerned organizations where appropriate action can be taken. The QA05 reports EPQ (Estimated Process Quality) and AOQ (Average Outgoing Quality) results for electrical, visual/mechanical, hermeticity, and documentation audits. Data from this system is available upon request.

#### THE SURE PROGRAM

The SURE (Systematic Uniform Reliability Evaluation) program audits/monitors products from all Signetics' divisions under a variety of accelerated environmental stress conditions. This program, first introduced in 1964, has evolved to suit changing product complexities and performance requirements.

The SURE program has two major functions: Long-term accelerated stress performance audit and a short-term accelerated stress monitor. In the case of Memory products, samples are selected that represent all generic product groups in all wafer fabrication and assembly locations.

#### THE LONG-TERM AUDIT

One-hundred devices from each generic family are subjected to each of the following stresses every eight weeks:

- High Temperature Operating Life: T<sub>J</sub> = 150°C, 1000 hours, static biased or dynamic operation, as appropriate (worst case bias configuration is chosen)

- High Temperature Storage: T<sub>J</sub> = 150°C, 1000 hours

- Temperature Humidity Biased Life: 85°C, 85% relative humidity, 1000 hours, static biased

- Temperature Cycling (Air-to-Air): -65°C to +150°C, 1000 cycles

#### THE SHORT-TERM MONITOR

Every other week a 50-piece sample from each generic family is run to 168 hours of pressure pot (15psig, 121°C, 100% saturated steam) and 300 cycles of thermal shock (-65°C to +150°C)

In addition, each Signetics assembly plant performs SURE product monitor stresses weekly on each generic family and molded package by pin count and frame type. Fiftypiece samples are run on each stress, pressure pot to 96 hours, thermal shock to 300 cycles.

#### SURE REPORTS

The data from these test matrices provides a basic understanding of product capability, an indication of major failure mechanisms and an estimated failure rate resulting from each stress. This data is compiled periodically and is available to customers upon request.

Many customers use this information in lieu of running their own qualification tests, thereby eliminating time-consuming and costly additional testing.

### Quality and Reliability

#### **RELIABILITY ENGINEERING**

In addition to the product performance monitors encompassed in the memory SURE program, Signetics' Corporate and Division Reliability Engineering departments sustain a broad range of evaluation and qualification activities.

Included in the engineering process are:

- Evaluation and qualification of new or changed materials, assembly/wafer-fab processes and equipment, product designs, facilities and subcontractors

- Device or generic group failure rate studies

- Advanced environmental stress development

- Failure mechanism characterization and corrective action/prevention reporting

The environmental stresses utilized in the engineering programs are similar to those utilized for the SURE monitor; however, more highly-accelerated conditions and extended durations typify the engineering projects. Additional stress systems such as biased pressure pot, power-temperature cycling, and cycle-biased temperature-humidity, are also included in the evaluation programs.

### **FAILURE ANALYSIS**

The SURE Program and the Reliability Engineering Program both include failure analysis activities and are complemented by corporate, divisional and plant failure analysis departments. These engineering units provide a service to our customers who desire detailed failure analysis support, who in turn provide Signetics with the technical understanding of the failure modes and mechanisms actually experienced in service. This information is essential in our ongoing effort to accelerate and improve our understanding of product failure mechanisms and their prevention.

#### ZERO DEFECTS PROGRAM

In recent years, United States industry has increasingly demanded improved product quality. We at Signetics believe that the customer has every right to expect quality products from a supplier. The benefits which are derived from quality products can be summed up in the words, *lower cost of ownership*. Those of you who invest in costly test equipment and engineering to assure that incoming products meet your specifications have a special understanding of the cost of ownership. And your cost does not end there; you are also burdened with inflated inventories, lengthened lead times and more rework.

#### SIGNETICS UNDERSTANDS CUSTOMERS' NEEDS

Signetics has long had an organization of quality professionals, inside all operating units, coordinated by a corporate quality department. This broad decentralized organization provides leadership, feedback, and direction for achieving a high level of quality. Special programs are targeted on specific quality issues. For example, in 1978 a program to reduce electrically defective units for a major automotive manufacturer improved outgoing quality levels by an order of magnitude.

In 1980 we recognized that in order to achieve outgoing levels on the order of 100ppm (parts per million), down from an industry practice of 10,000ppm, we needed to supplement our traditional quality programs with one that encompassed all activities and all levels of the company. Such unprecedent-

ed low defect levels could only be achieved by contributions from all employees, from the R and D laboratory to the shipping dock. In short, from a program that would effect a total cultural change within Signetics in our attitude toward quality.

# QUALITY PAYS OFF FOR OUR CUSTOMERS

Signetics' dedicated programs in product quality improvement, supplemented by close working relationships with many of our customers, have improved outgoing product quality more than twenty-fold since 1980. Today, many major customers no longer test Signetics circuits. Incoming product moves directly from the receiving dock to the production line, greatly accelerating throughput and reducing inventories. Other customers have pared significantly the amount of sampling done on our products. Others are beginning tc adopt these cost-saving practices.

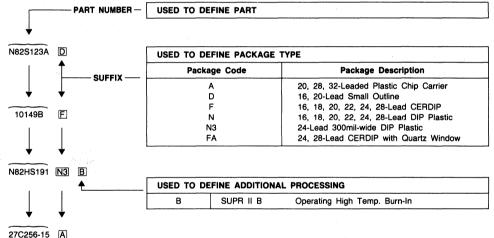

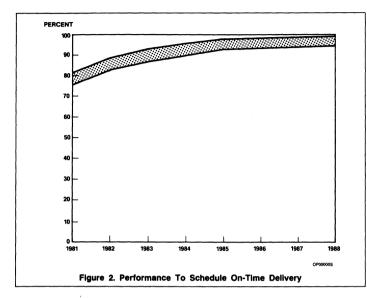

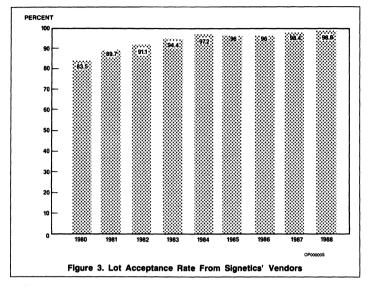

We closely monitor the electrical, visual, and mechanical quality of all our products and review each return to find and correct the cause. Since 1981, over 90% of our customers report a significant improvement in overall quality (see Figure 1).

### Quality and Reliability

At Signetics, quality means more than working circuits. It means on-time delivery of the right product at the agreed-upon price (see Figure 2).

### **ONGOING QUALITY PROGRAM**

The quality improvement program at Signetics is based on "Do it Right the First Time". The intent of this innovative program is to change the perception of Signetics' employees that somehow quality is solely a manufacturing issue where some level of defects is inevitable. This attitude has been replaced by one of acceptance of the fact that all errors and defects are preventable, a point of view shared by all technical and administrative functions equally.

This program extends into every area of the company, and more than 40 quality improvement teams throughout the organization drive its ongoing refinement and progress.

Key components of the program are the Quality College, the 'Make Certain' Program, Corrective Action Teams, and the Error Cause Removal System.

The core concepts of doing it right the first time are embodied in the four absolutes of quality:

1. The definition of quality is conformance to requirements.

- The system to achieve quality improvement is prevention.

- The performance standard is zero defects.

- 4. The measurement system is continuous improvement.

### QUALITY COLLEGE

Almost continuously in session, Quality College is a prerequisite for all employees. The intensive curriculum is built around the four absolutes of quality; colleges are conducted at company facilities throughout the world.

### "MAKING CERTAIN" — ADMINISTRATIVE QUALITY IMPROVEMENT

Signetics' experience has shown that the largest source of errors affecting product and service quality is found in paperwork and in other administrative functions. The "Make Certain" program focuses the attention of management and administrative personnel on error prevention, beginning with each employee's own actions.

This program promotes defect prevention in three ways: by educating employees as to the impact and cost of administrative errors, by changing attitudes from accepting occasional errors to one of accepting a personal work standard of zero defects, and by providing a formal mechanism for the prevention of errors.

### CORRECTIVE ACTION TEAMS

Employees with the perspective, knowledge, and necessary skills to solve a problem are formed into ad hoc groups called Corrective Action Teams. These teams, a major force within the company for quality improvement, resolve administrative, technical and manufacturing issues.

### ECR SYSTEM (ERROR CAUSE REMOVAL)

The ECR System permits employees to report to management any impediments to doing the job right the first time. Once such an impediment is reported, management is obliged to respond promptly with a corrective program. Doing it right the first time in all company activities produces lower cost of ownership through defect prevention.

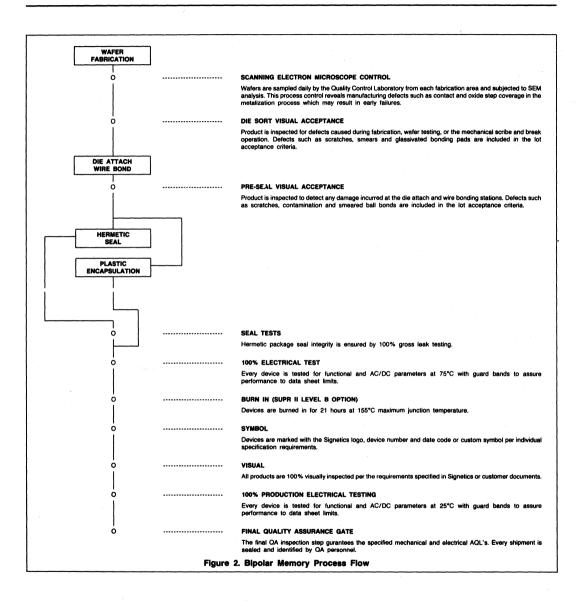

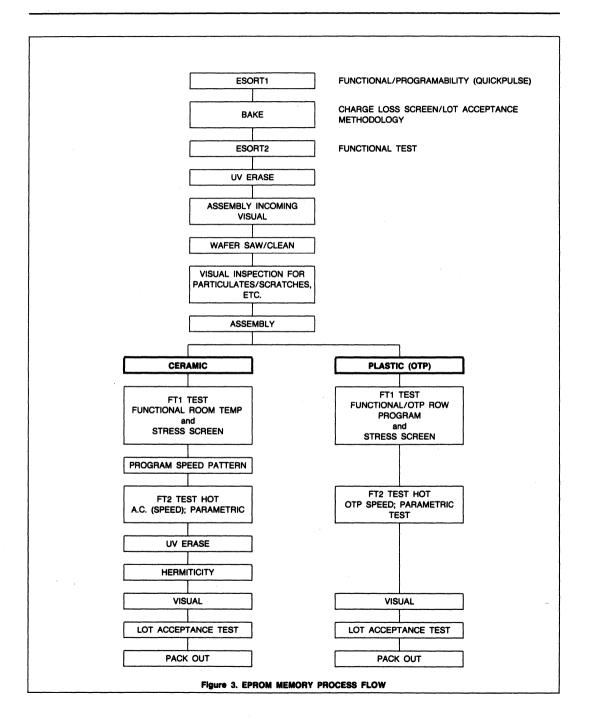

#### **PRODUCT QUALITY PROGRAM**