NTEGRATED CIRCUITS

# DATA HANDBOOK

Radio, audio and associated systems Bipolar, MOS CA3089 to TDA1510A

Philips Components

#### RADIO, AUDIO AND ASSOCIATED SYSTEMS BIPOLAR, MOS

| Part a                                                                                                                               |                |

|--------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Selection guide                                                                                                                      | page           |

| Functional index                                                                                                                     | 5<br>17<br>31  |

| General                                                                                                                              |                |

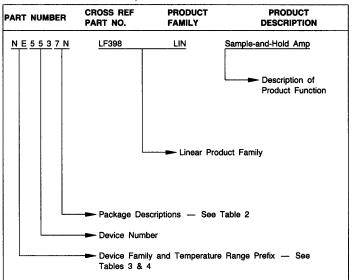

| Product status definition for type numbers<br>with prefixes CA, MC, NE, SA, SE and $\mu$ A                                           | 35             |

| prefixes CA, MC, NE, SA, SE and $\mu$ A<br>Type designation for type numbers with prefixes<br>HEF, MAB, MAF, OM, PCA, PCB, PCF, PNA, | 36             |

| SAA, SAD, SAF, TDA, TDB, TDD, TEA and TSA                                                                                            | 39<br>41<br>43 |

#### Device data

CA3089 to TDA1510A

#### Part b

|  | -2  |

|--|-----|

|  | - 5 |

| Selection guide       | page |

|-----------------------|------|

| Functional index      | 953  |

| Numerical index       | 965  |

| Maintenance type list | 979  |

#### Device data

TDA1512 to µA758N

#### Package information

| Package outlines for prefixes CA, MC, NE, SA, SE and $\mu$ A | 1839 |

|--------------------------------------------------------------|------|

| Package outlines for prefixes HEF, MAB, MAF, OM, PCA,        |      |

| PCB, PCF, PNA, SAA, SAD, SAF, TDA, TDB, TDD, TEA and TSA     | 1847 |

#### Soldering information

| For type numbers with prefixes HEF, MAB, MAF, OM, PCA,   |      |

|----------------------------------------------------------|------|

| PCB, PCF, PNA, SAA, SAD, SAF, TDA, TDB, TDD, TEA and TSA | 1887 |

### SELECTION GUIDE

Functional index Numerical index Maintenance type list

| type no.         | description                                                      | page |

|------------------|------------------------------------------------------------------|------|

| AMPLIFIERS       |                                                                  |      |

| NE542            | dual low-noise preamplifier                                      | 91   |

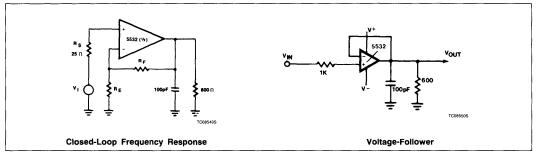

| NE5532           | internally-compensated dual low noise operational amplifier      | 129  |

| NE5532A          | internally-compensated dual low noise operational amplifier      | 129  |

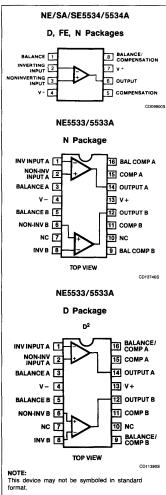

| NE5533           | dual and single low noise operational amplifier                  | 135  |

| NE5533A          | dual and single low noise operational amplifier                  | 135  |

| NE5534           | dual and single low noise operational amplifier                  | 135  |

| NE5534A          | dual and single low noise operational amplifier                  | 135  |

| SA5534           | dual and single low noise operational amplifier                  | 135  |

| SA5534A          | dual and single low noise operational amplifier                  | 135  |

| SE5532           | internally-compensated dual low noise operational amplifier      | 129  |

| SE5532A          | internally-compensated dual low noise operational amplifier      | 129  |

| SE5534           | dual and single low noise operational amplifier                  | 135  |

| SE5534A          | dual and single low noise operational amplifier                  | 135  |

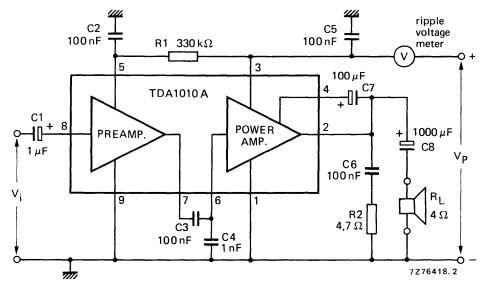

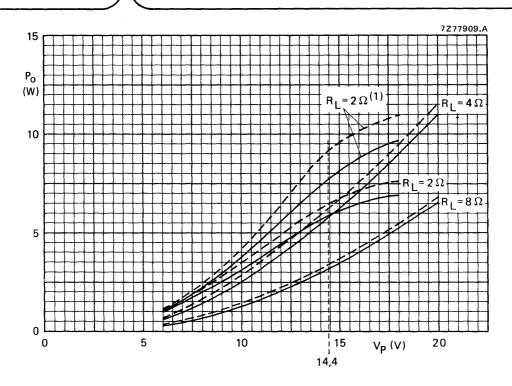

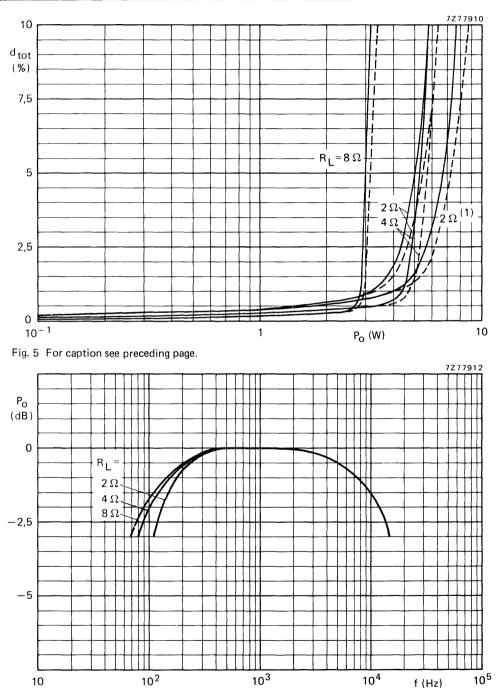

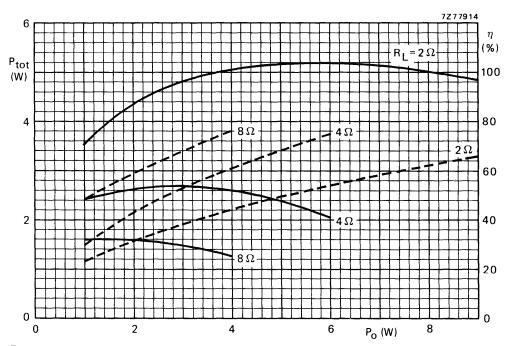

| TDA1010A         | 6 W audio power amplifier for in-car applications/10 W           |      |

|                  | audio power amplifier for mains-fed applications                 | 811  |

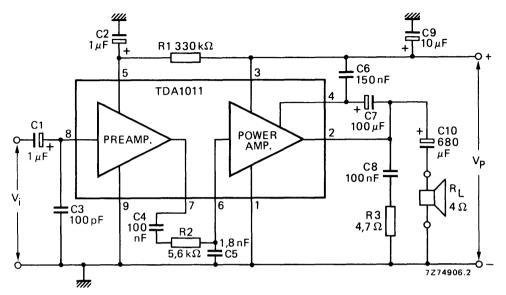

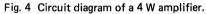

| TDA1011          | 2 to 6 W audio power amplifier with preamplifier                 | 829  |

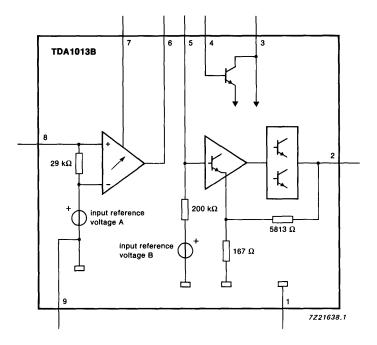

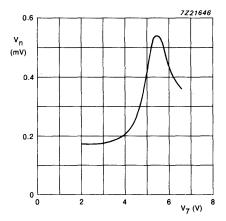

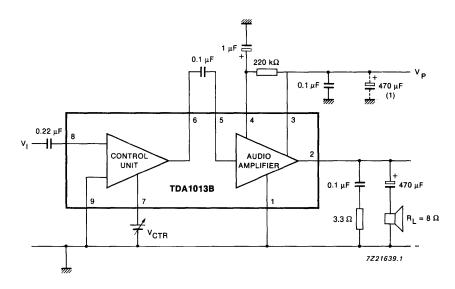

| TDA1013B         | 4 W audio power amplifier with DC volume control                 | 841  |

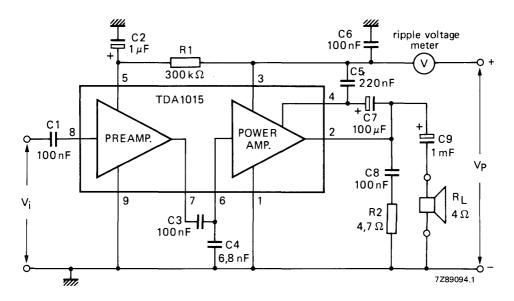

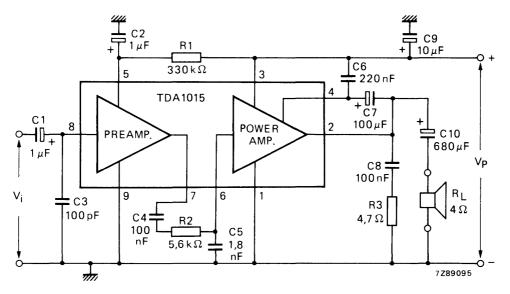

| TDA1015          | 1 to 4 W audio power amplifier with preamplifier                 | 849  |

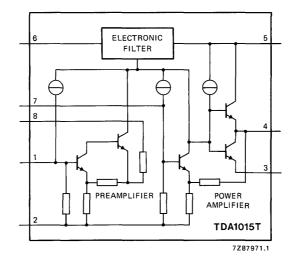

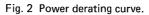

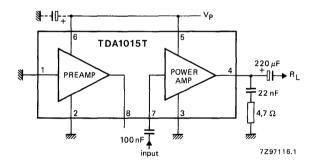

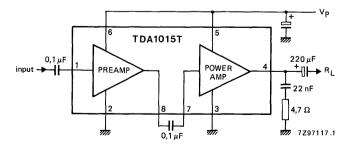

| TDA1015T         | 0.5 W audio power amplifier with preamplifier                    | 859  |

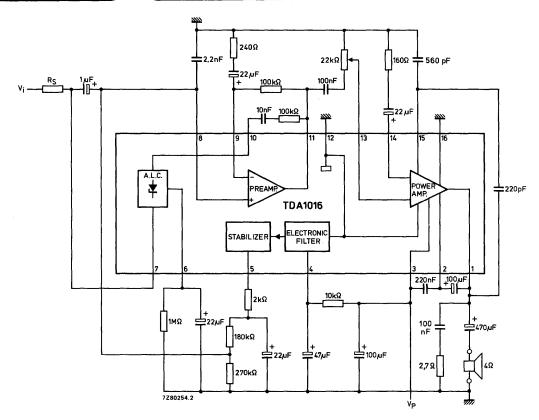

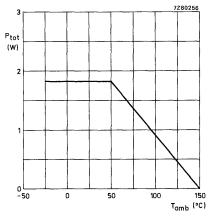

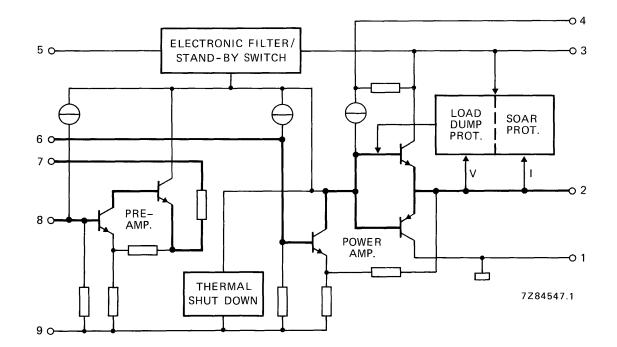

| TDA1016          | 2 W recording/playback audio power amplifier with                |      |

|                  | preamplifier, automatic level control, short-circuit             |      |

|                  | and thermal protection                                           | 865  |

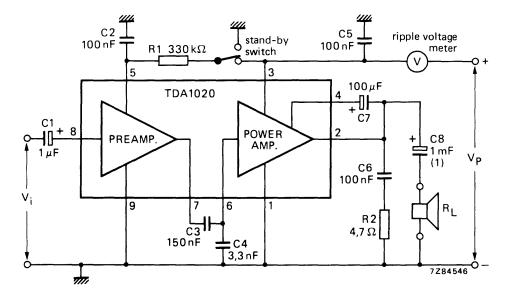

| TDA1020          | 12 W audio power amplifier with preamplifier for car radios      | 871  |

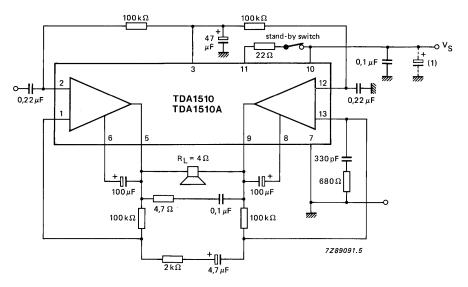

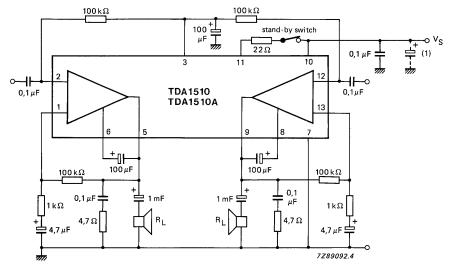

| TDA1510          | 24 W BTL or 2 x 12 W stereo car radio power amplifier            | 941  |

| TDA1510A         | 24 W BTL or 2 x 12 W stereo car radio power amplifier            | 941  |

| TDA1512          | 12 to 20 W hi-fi audio power amplifier                           | 983  |

| TDA1512Q         | 12 to 20 W hi-fi audio power amplifier                           | 983  |

| <b>F</b> DA1514A | 50 W hi-fi power amplifier for digital audio (e.g. Compact Disc) | 989  |

| TDA1515B         | 24 W BTL or 2 x 12 W stereo car radio power amplifier            | 997  |

| TDA1516Q         | 22 W BTL or 2 x 11 W stereo car radio power amplifier;           |      |

|                  | closed loop voltage gain 26 dB                                   | 1003 |

| TDA1517          | 2 x 6 W stereo car radio audio power amplifier (20 dB gain)      | 1011 |

| TDA1518Q         | 22 W BTL or 2 x 11 W stereo car radio power amplifier;           |      |

|                  | closed loop voltage gain 46 dB                                   | 1019 |

| TDA1519          | 2 x 6 W stereo car radio audio power amplifier (40 dB gain)      | 1027 |

| TDA1519A         | 22 W BTL or 2 x 11 W stereo car radio power amplifier            | 1035 |

| TDA1519B         | 12 W BTL or 2 x 6 W stereo car radio power amplifier             | 1045 |

| TDA1520B         | 20 W hi-fi audio power amplifier; complete SOAR protection       | 1055 |

| TDA1520BQ        | 20 W hi-fi audio power amplifier; complete SOAR protection       | 1055 |

| TDA1521          | 2 x 12 W hi-fi stereo audio power amplifier                      | 1061 |

| TDA1521A         | 2 x 6 W hi-fi stereo audio power amplifier                       | 1071 |

| TDA1521Q         | 2 x 12 W hi-fi stereo audio power amplifier                      | 1061 |

| type no.         | description                                                                                     | page    |

|------------------|-------------------------------------------------------------------------------------------------|---------|

| TDA1522          | stereo playback amplifier/equalizer with mute switch                                            | 1081    |

| TDA1535          | high-speed sample-and-hold amplifier                                                            | 1125    |

| TDA1579          | traffic warning decoder circuit (AM carriers); ARI system                                       | 1231    |

| TDA1579T         | traffic warning decoder circuit (AM carriers); ARI system                                       | 1231    |

| TDA1589          | traffic control message and warning tone circuit; ARI system                                    | 1241    |

| TDA2611A         | 5 W audio power amplifier                                                                       | 1305    |

| TDA2613          | 6 W hi fi audio power amplifier                                                                 | 1315    |

| TDA7050          | 150 mW BTL or 2 x 75 mW stereo audio power amplifier;                                           |         |

|                  | low voltage                                                                                     | 1423    |

| TDA7050T         | 150 mW BTL or 2 x 75 mW stereo audio power amplifier;                                           |         |

|                  | low voltage                                                                                     | 1423    |

| TDA7052          | 1 W BTL mono audio amplifier for portable applications                                          | 143     |

| TDA7053          | 2 x 1 W BTL stereo audio power amplifier for portable applications                              | 1437    |

| AUDIO ICs        |                                                                                                 |         |

| Bus-controlled   |                                                                                                 |         |

| TDA8420          | hi-fi stereo audio processor; l <sup>2</sup> C-bus                                              | 144     |

| TDA8 <b>4</b> 21 | hi-fi stereo audio processor; l <sup>2</sup> C-bus                                              | 146     |

| TDA8425          | hi-fi stereo audio processor; 1 <sup>2</sup> C-bus                                              | 148     |

| TEA6300          | car radio preamplifier and source selector with sound                                           |         |

|                  | and fader controls; I <sup>2</sup> C-bus                                                        | 178     |

| TEA6300T         | car radio preamplifier and source selector with sound                                           |         |

|                  | and fader controls: I <sup>2</sup> C-bus                                                        | 178     |

| TEA6310T         | sound fader control circuit; 1 <sup>2</sup> C-bus                                               | 180     |

| DC-controlled    |                                                                                                 |         |

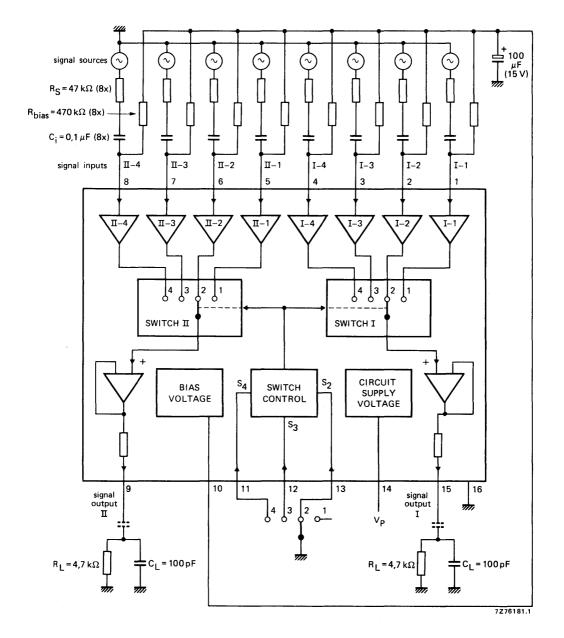

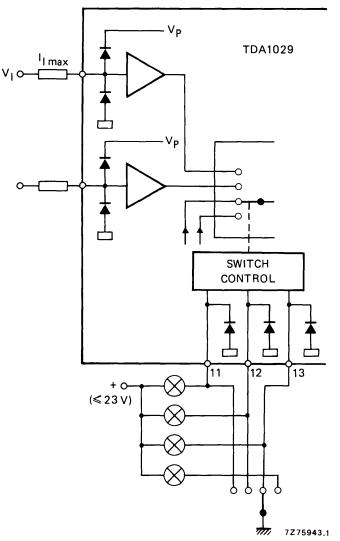

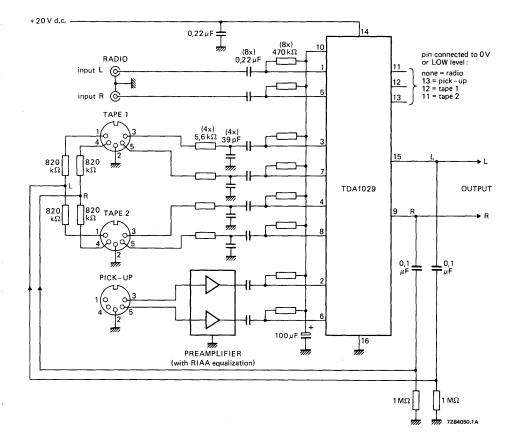

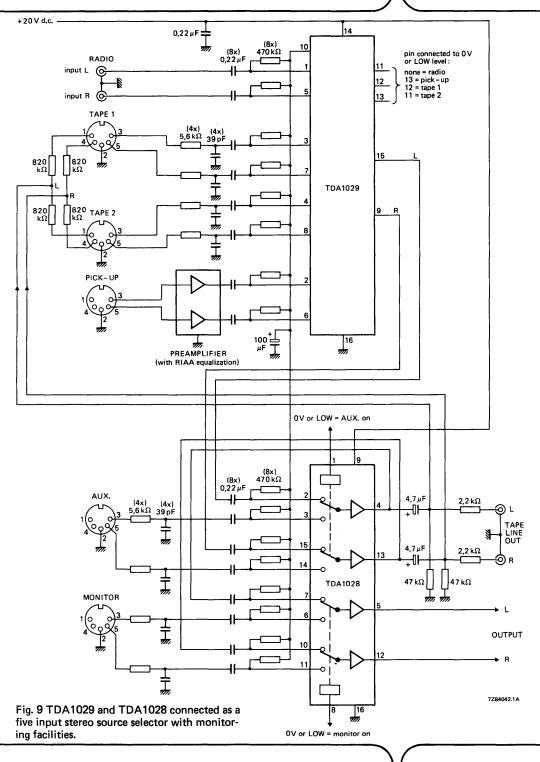

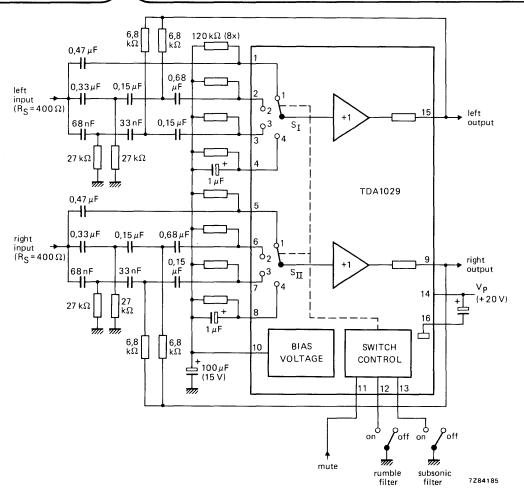

| TDA1029          | signal-source switch (4 x two channels)                                                         | 87      |

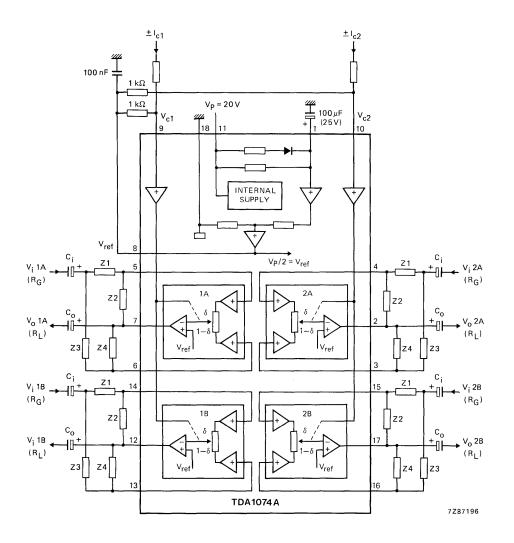

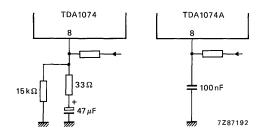

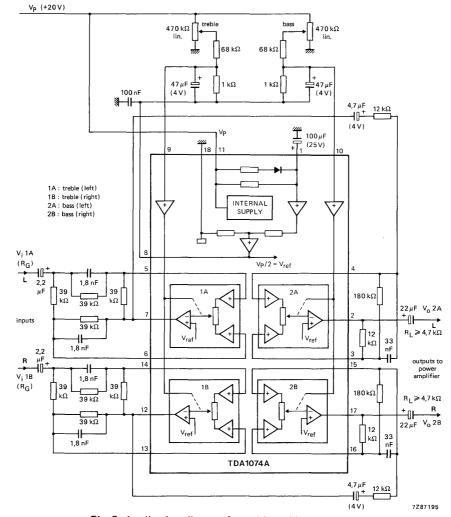

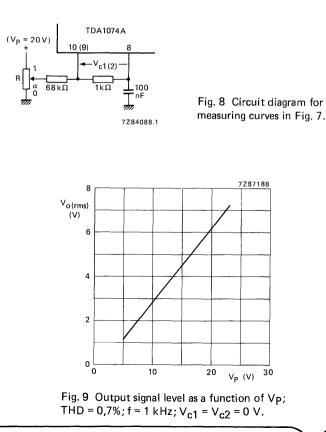

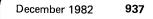

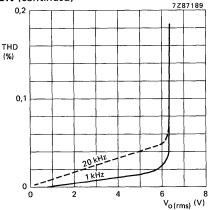

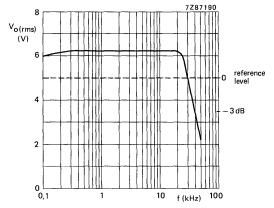

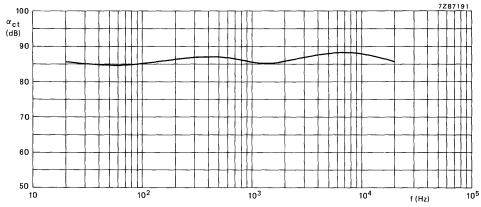

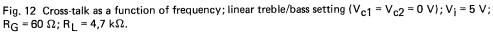

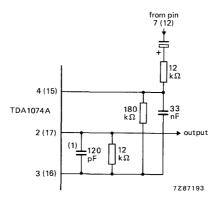

| TDA1074A         | dual tandem electronic potentiometer circuit                                                    | 93      |

| TDA1524A         | stereo tone/volume control circuit                                                              | 109     |

| TDA1525          | stereo tone/volume control circuit                                                              | 110     |

| TDA1600          | multi-function oscillator switch for audio cassette recorders                                   | 129     |

| TDA3810          | spatial, stereo and pseudo-stereo sound circuit                                                 | 133     |

| TDD1601          | equalizer for audio cassette recorders                                                          | 158     |

| CLOCK/CALENDA    | R                                                                                               |         |

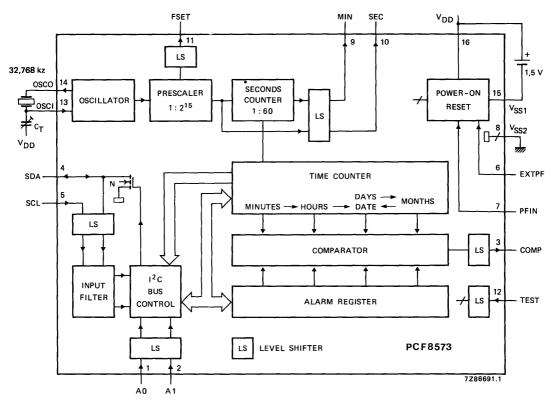

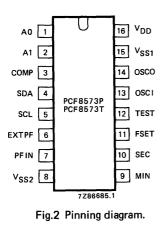

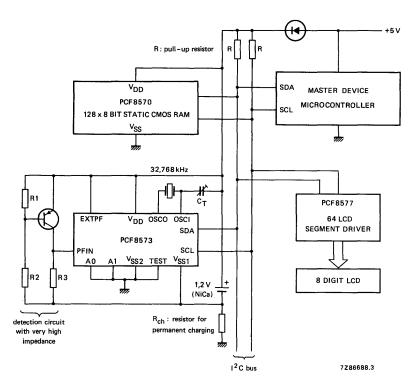

| PCF8573          | clock calendar; l <sup>2</sup> C-bus                                                            | 32      |

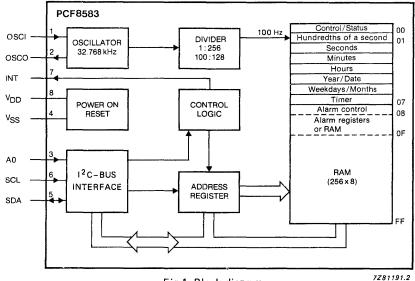

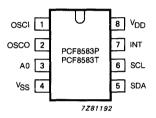

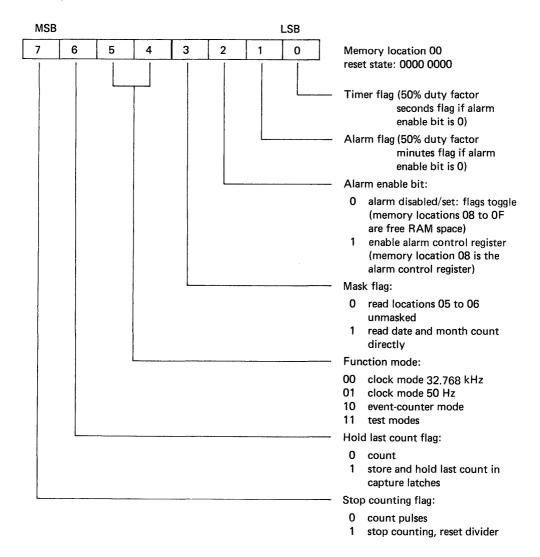

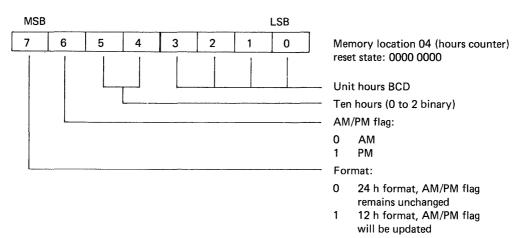

| PCF8583          | clock calendar, $1^{\circ}$ C-bus clock calendar with 256 x 8-bit static RAM; $1^{\circ}$ C-bus | 49      |

| COMPANDOR        |                                                                                                 |         |

| NE570            | compandor                                                                                       | 9       |

| NE571            | compandor                                                                                       | 9       |

| NE572            | programmable analogue compandor                                                                 | 10      |

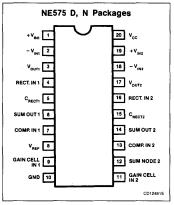

| NE575            |                                                                                                 | 11      |

|                  | low voltage compandor                                                                           | 9       |

| SA571            | compandor                                                                                       | 9<br>10 |

| SA572            | programmable analogue compandor                                                                 | 10      |

type no.

description

.

page

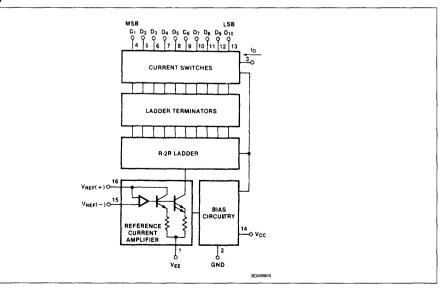

#### DATA CONVERSION

#### ADCs, DACs

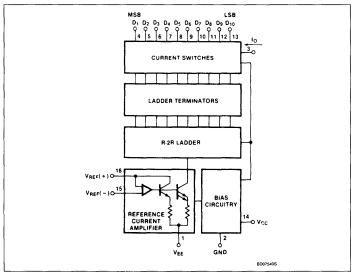

| MC3410   | 10-bit high-speed multiplying DAC                     | 83   |

|----------|-------------------------------------------------------|------|

| MC3410C  | 10-bit high-speed multiplying DAC                     | 83   |

| MC3510   | 10-bit high-speed multiplying DAC                     | 83   |

| NE5410   | 10-bit high-speed multiplying DAC                     | 119  |

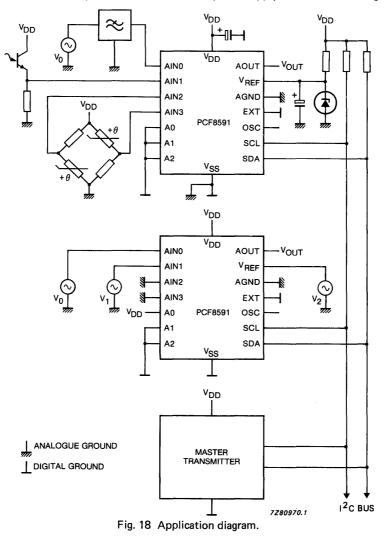

| PCF8591  | 8-bit ADC/DAC; I <sup>2</sup> C-bus                   | 509  |

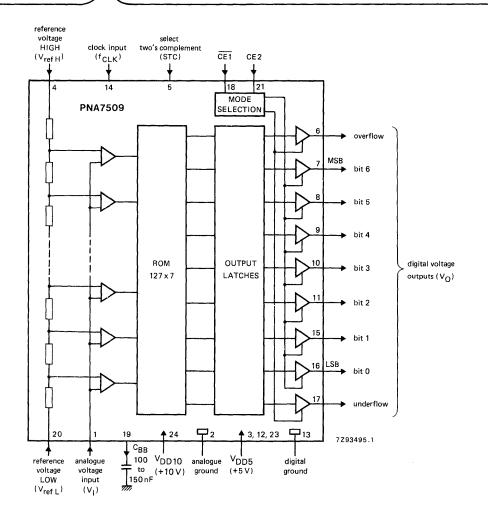

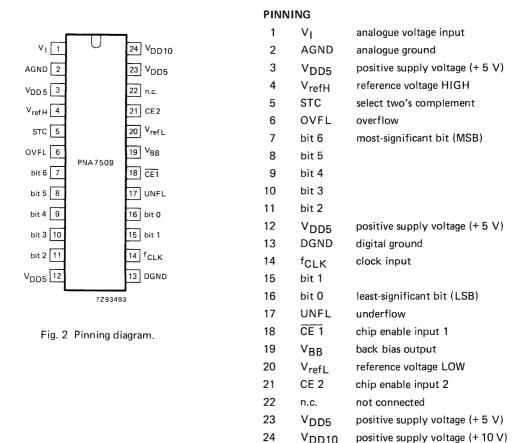

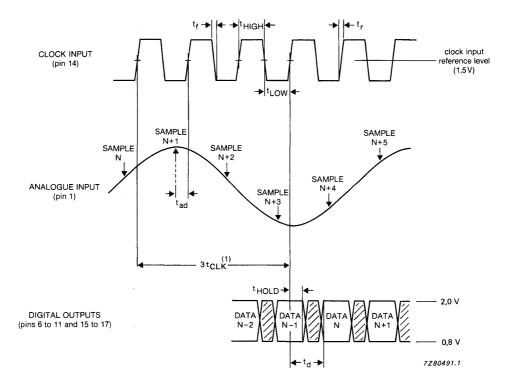

| PNA7509  | 7-bit ADC; 22 MHz; 3-state output                     | 527  |

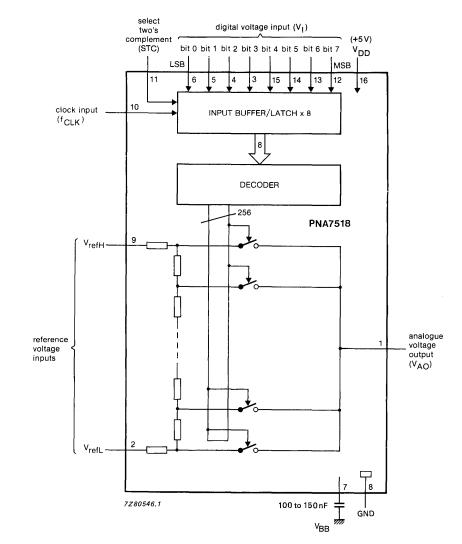

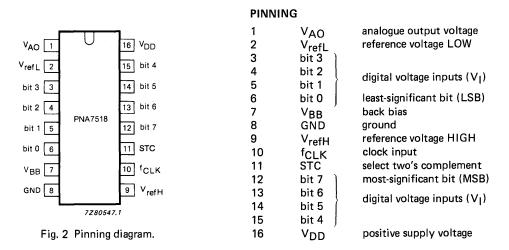

| PNA7518  | 8-bit multiplying DAC; 30 MHz                         | 539  |

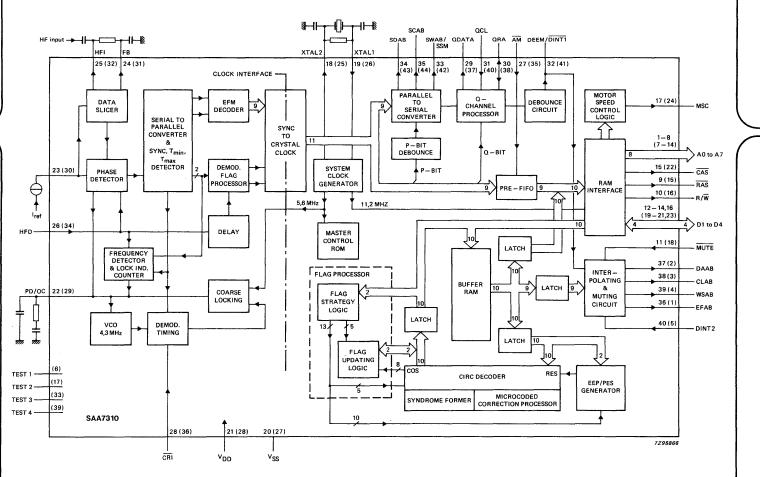

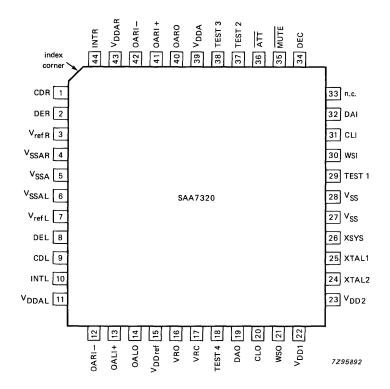

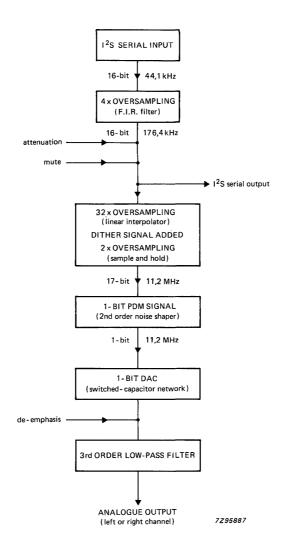

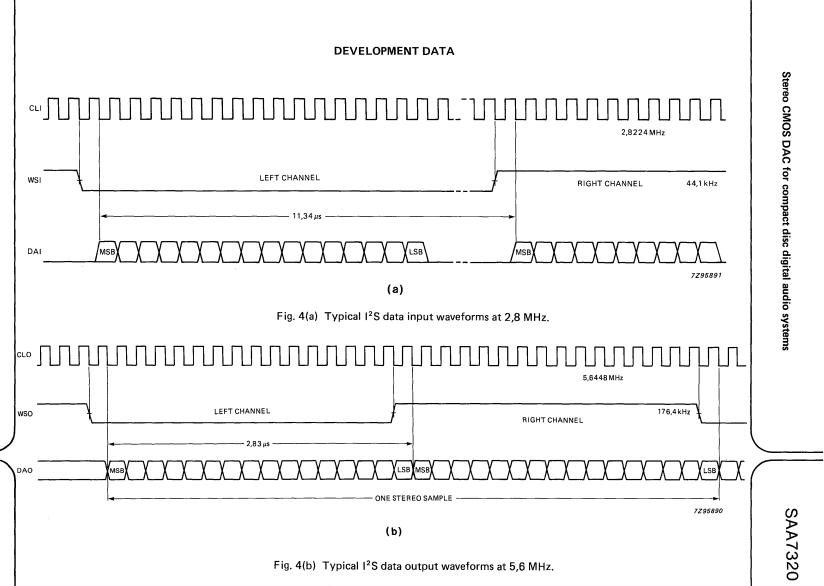

| SAA7320  | stereo DAC for Compact Disc                           | 757  |

| SE5410   | 10-bit high-speed multiplying DAC                     | 119  |

| TDA1534  | 14-bit ADC                                            | 1117 |

| TDA1541A | dual 16-bit DAC                                       | 1129 |

| TDA1543  | dual 16-bit economy DAC (I <sup>2</sup> S bus format) | 1145 |

| TDA8444  | octuple 6-bit DAC; 1 <sup>2</sup> C-bus               | 1511 |

#### DIGITAL AUDIO

#### Compact Disc

| •               |                                                                      |      |

|-----------------|----------------------------------------------------------------------|------|

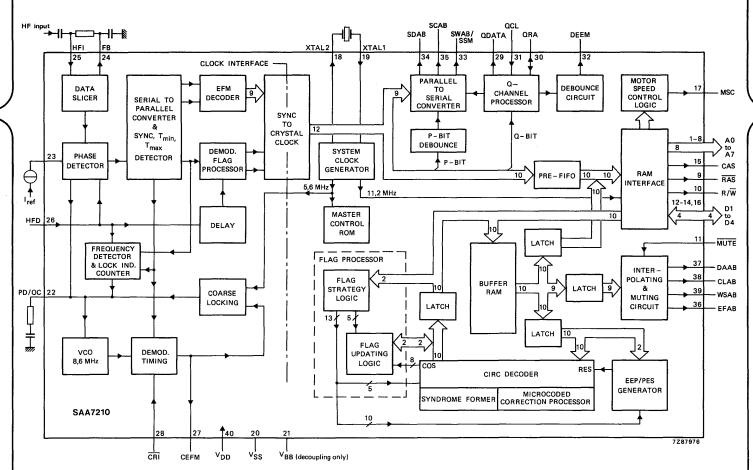

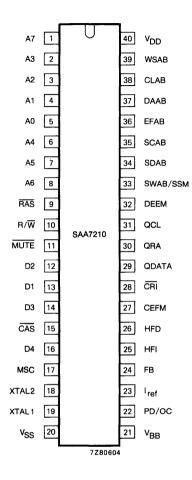

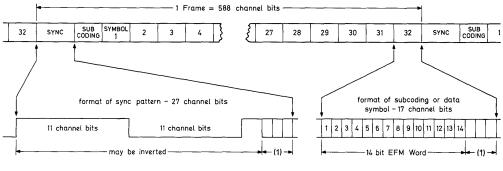

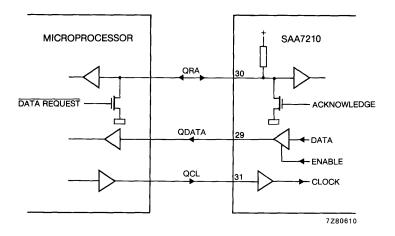

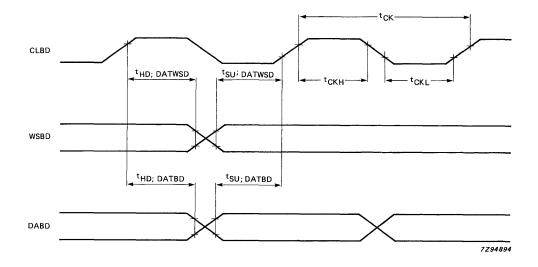

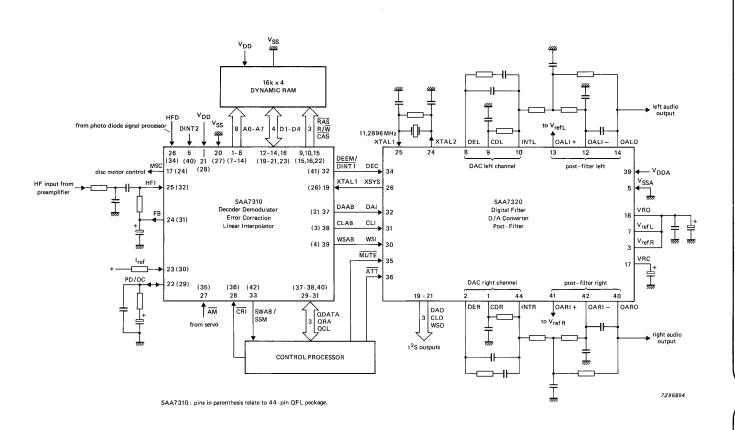

| SAA7210         | decoder for Compact Disc (second generation)                         | 671  |

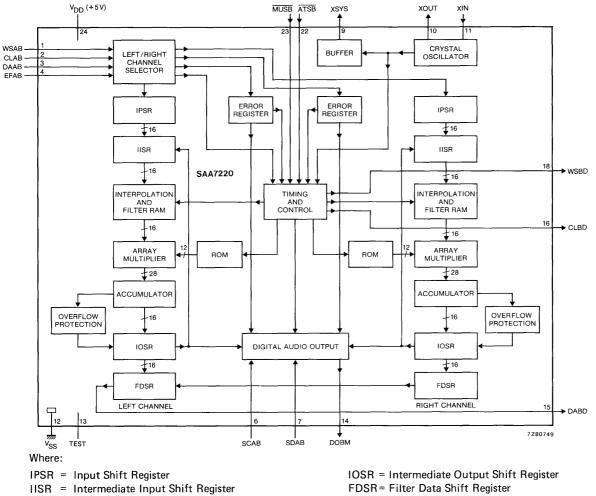

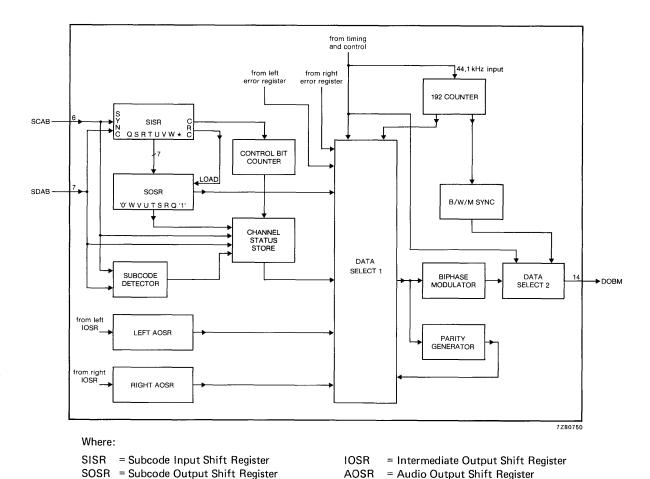

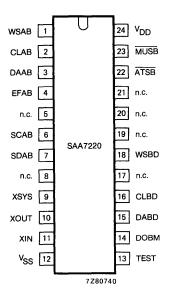

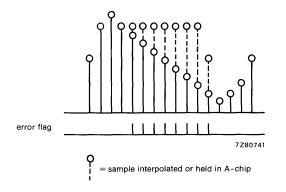

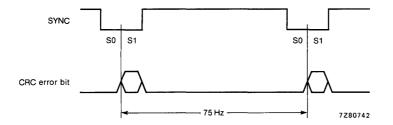

| SAA7220         | digital filter and interpolator for Compact Disc (second generation) | 693  |

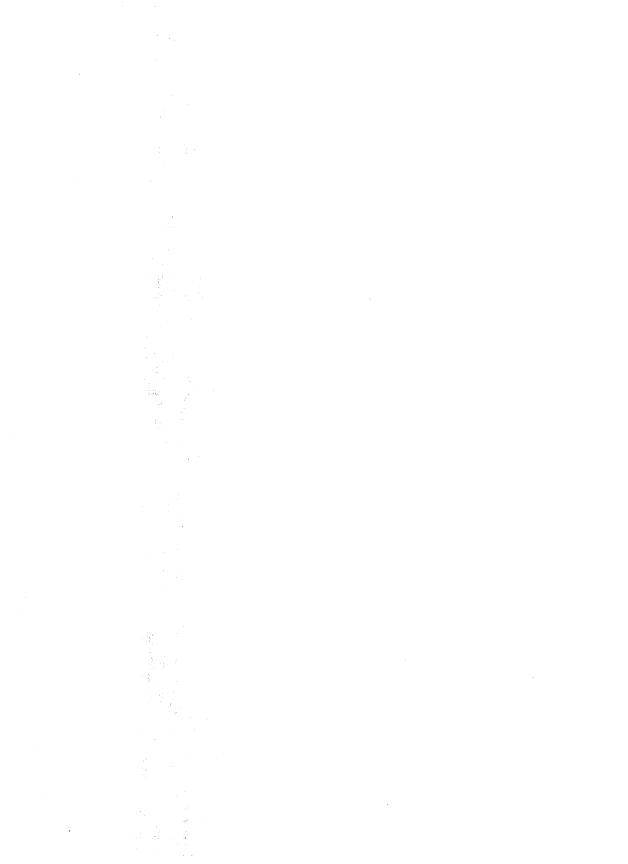

| SAA7310         | decoder for Compact Disc (third generation)                          | 727  |

| SAA7320         | stereo DAC for Compact Disc                                          | 757  |

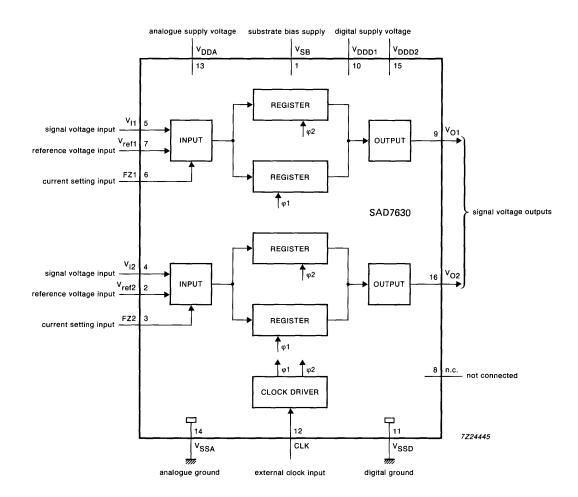

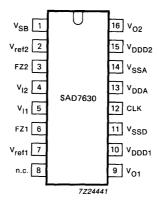

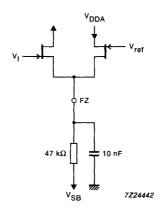

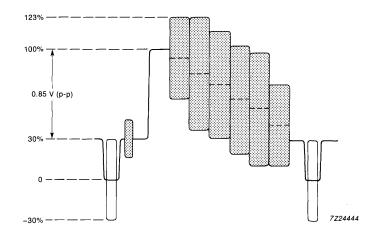

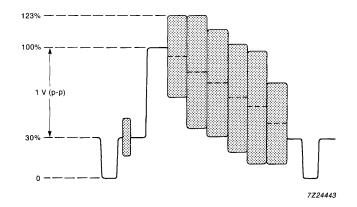

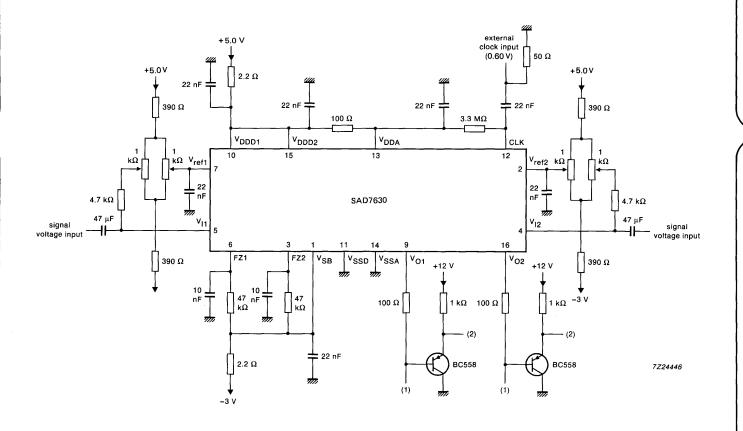

| SAD7630         | CCD delay line for error correction in video and sound               |      |

|                 | carrier timebases (laservision players)                              | 777  |

| TDA1514A        | 50 W hi-fi power amplifier for digital audio (e.g. Compact Disc)     | 989  |

| TDA1541A        | dual 16-bit DAC                                                      | 1129 |

| TDA15 <b>42</b> | active element for post filtering (dual channel)                     | 1137 |

| TDA1543         | dual 16-bit economy DAC (I <sup>2</sup> S bus format)                | 1145 |

| TDA5708         | photo diode signal processor for Compact Disc                        |      |

|                 | single-spot read-out systems                                         | 1347 |

| TDA5709         | radial error signal processor for Compact Disc                       | 1367 |

| TDA8808T        | photo diode signal processor for Compact Disc                        | 1519 |

| TDA8808AT       | photo diode signal processor for Compact Disc                        | 1519 |

| TDA8808T/AT     | transfer functions                                                   | 1539 |

| TDA8809T        | radial error signal processor for Compact Disc                       | 1559 |

| TDA8809T        | transfer functions                                                   | 1571 |

|                 |                                                                      |      |

| Input circuits  |                                                                      |      |

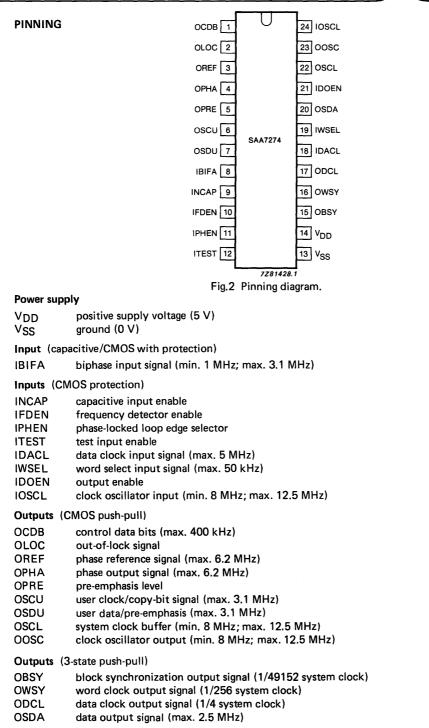

| SAA7274         | audio digital input circuit (ADIC)                                   | 715  |

| TDA1542         | active element for post filtering (dual channel)                     | 1137 |

|                 |                                                                      |      |

| type no.     | description                                                                                                      | page |

|--------------|------------------------------------------------------------------------------------------------------------------|------|

| DISPLAY DRIV | ERS                                                                                                              |      |

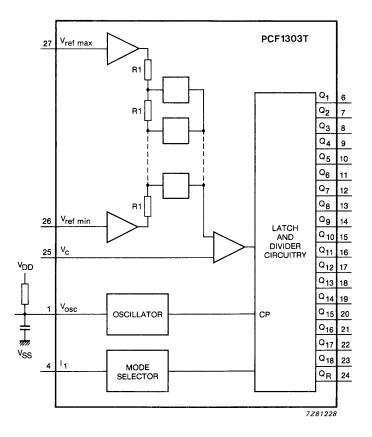

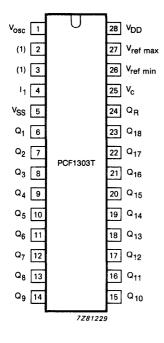

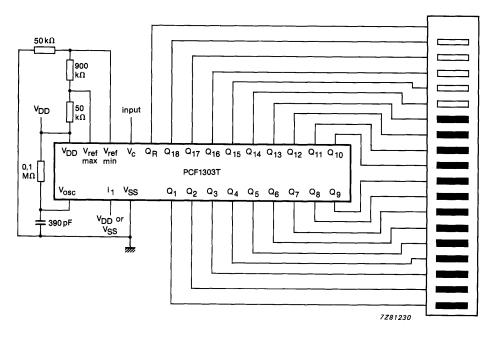

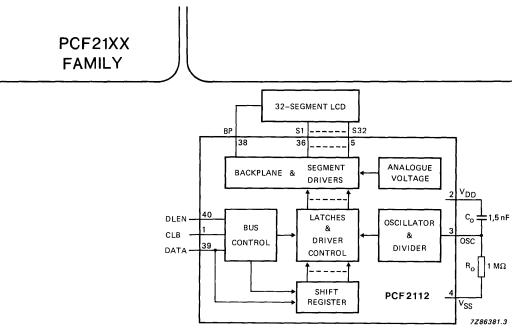

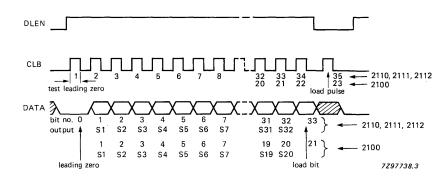

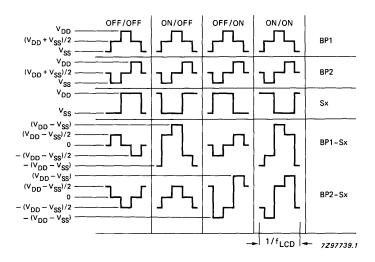

| PCF1303T     | 18-element bar graph LCD driver (with analogue input)                                                            | 223  |

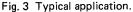

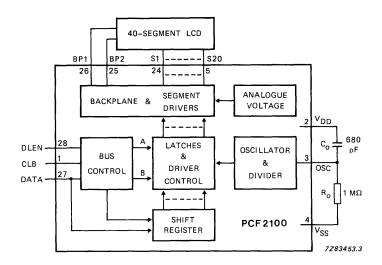

| PCF2100      | LCD duplex driver; 40 segments                                                                                   | 229  |

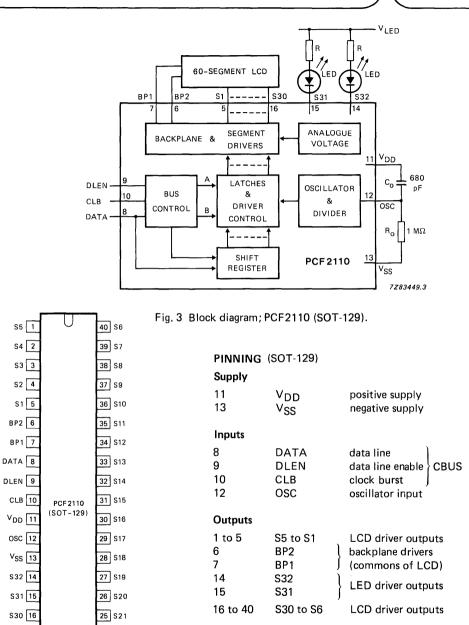

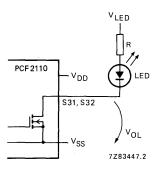

| PCF2110      | LCD duplex driver; 60 segments and 2 LEDs                                                                        | 229  |

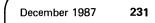

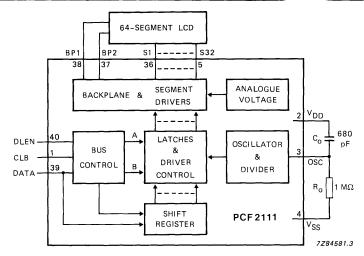

| PCF2111      | LCD duplex driver; 64 segments                                                                                   | 229  |

| PCF2112      | LCD driver; 32 segments                                                                                          | 229  |

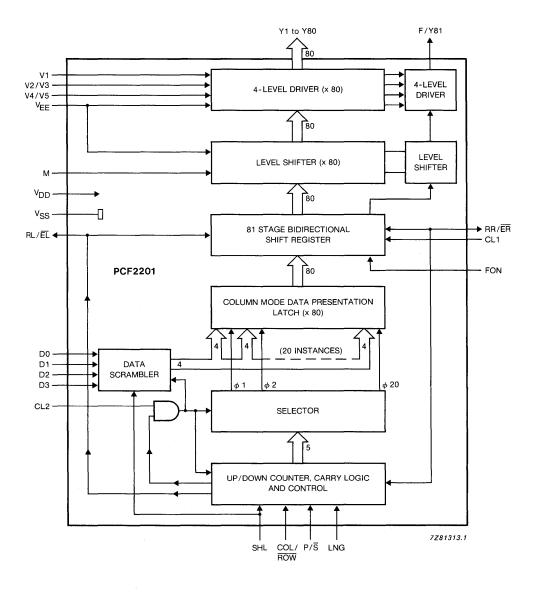

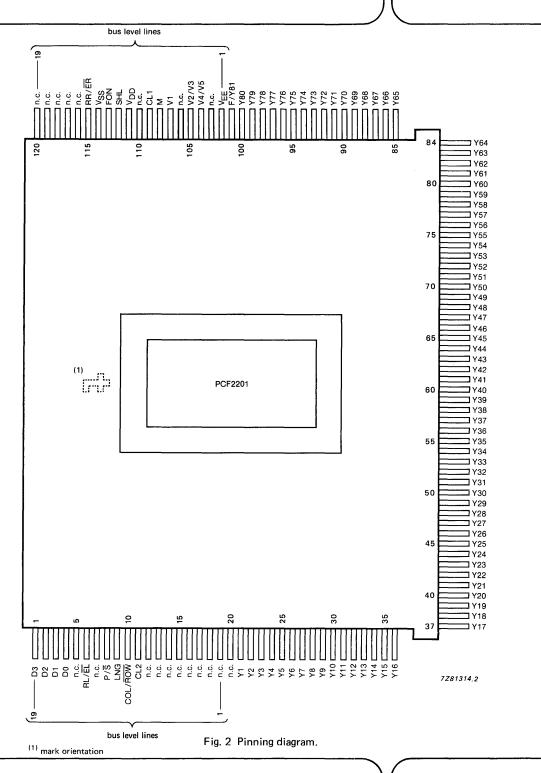

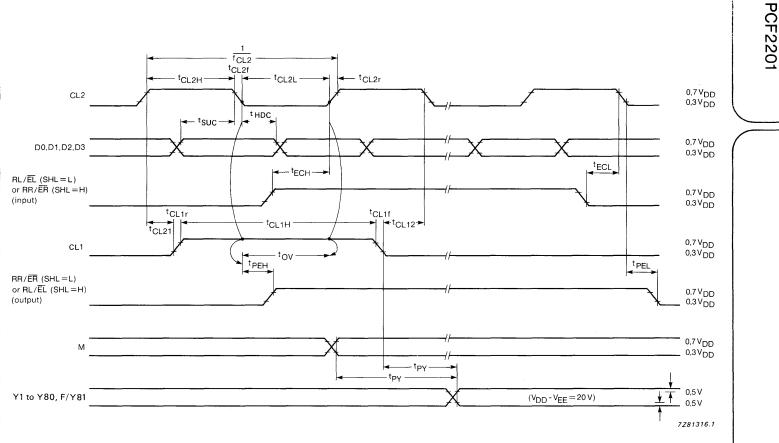

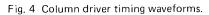

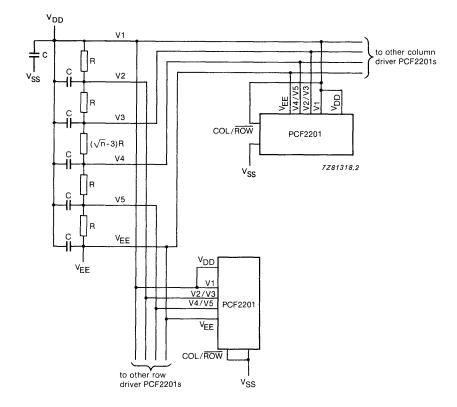

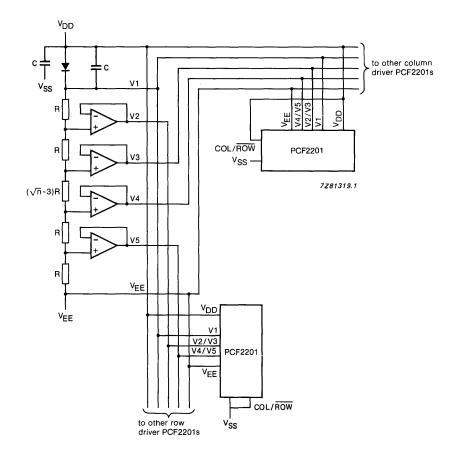

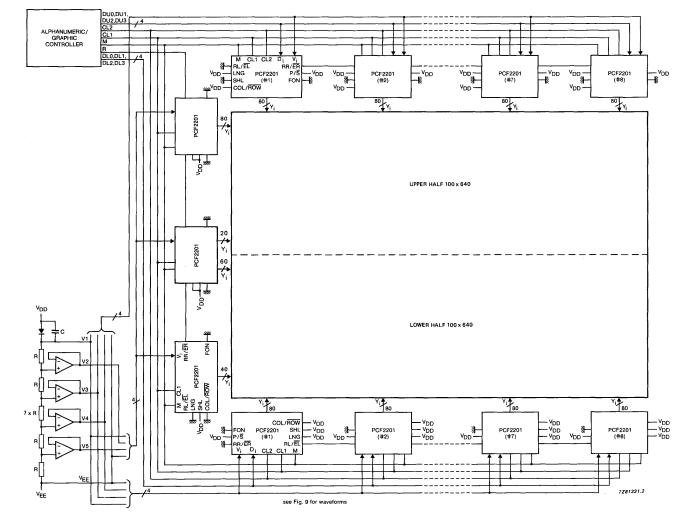

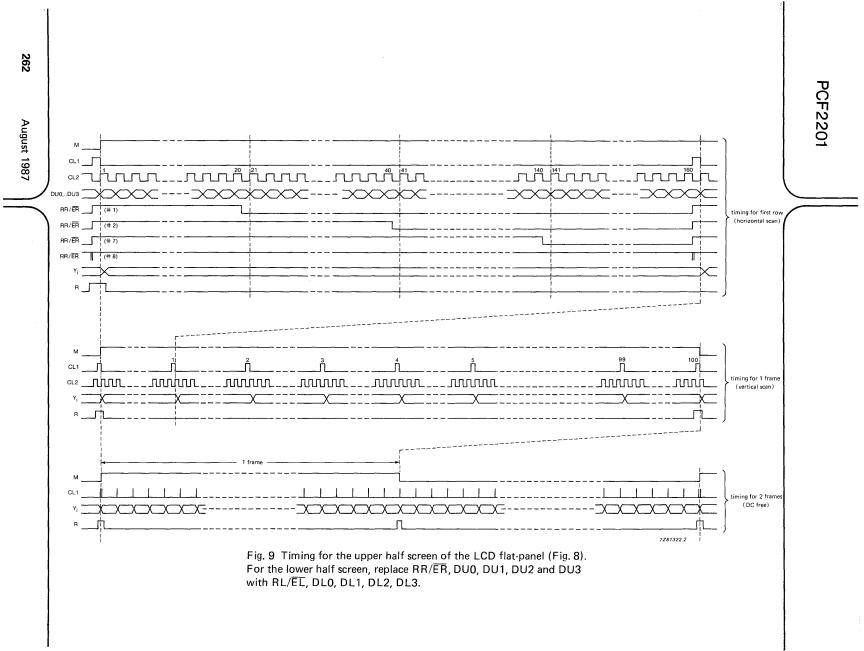

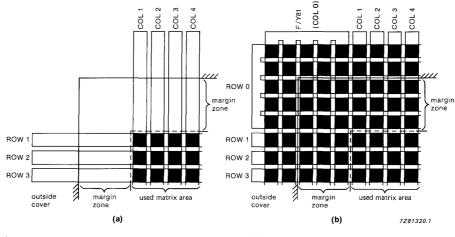

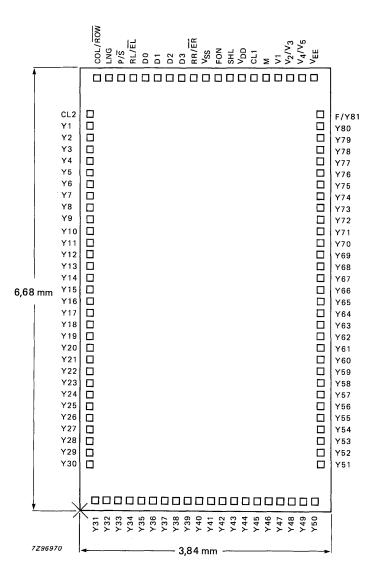

| PCF2201      | LCD flat panel row/column driver                                                                                 | 24   |

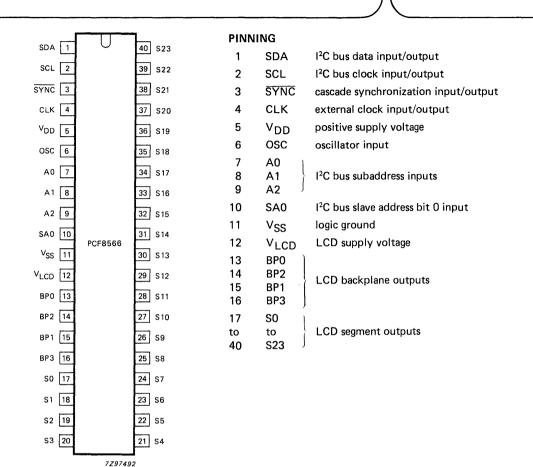

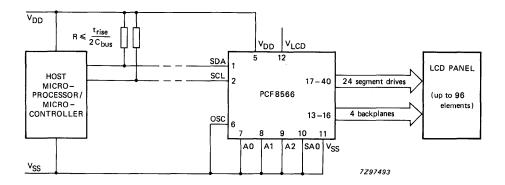

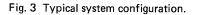

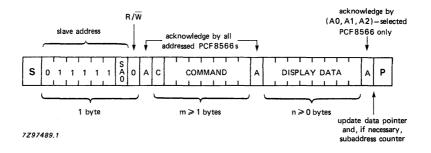

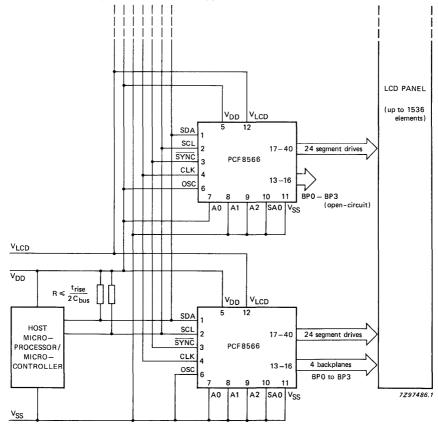

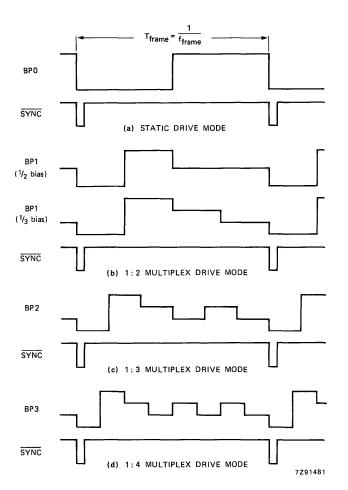

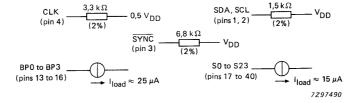

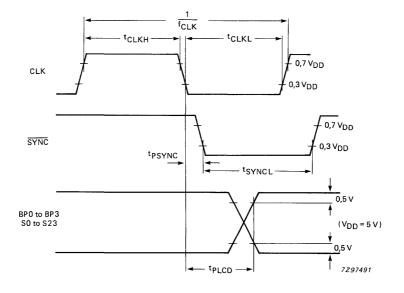

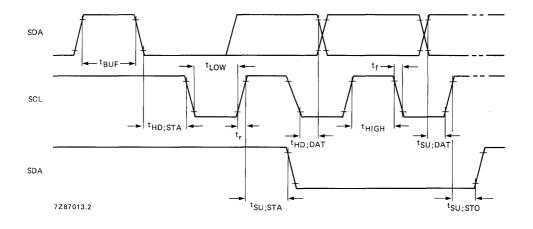

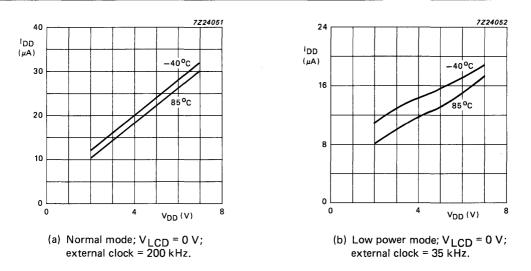

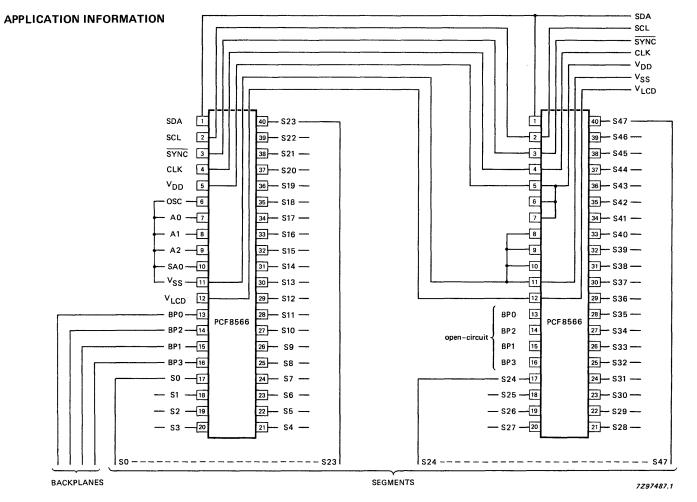

| PCF8566      | universal LCD driver for low multiplex rates                                                                     |      |

| 1010000      | (1:1 to 1:4); max. 96 elements; 1 <sup>2</sup> C-bus                                                             | 289  |

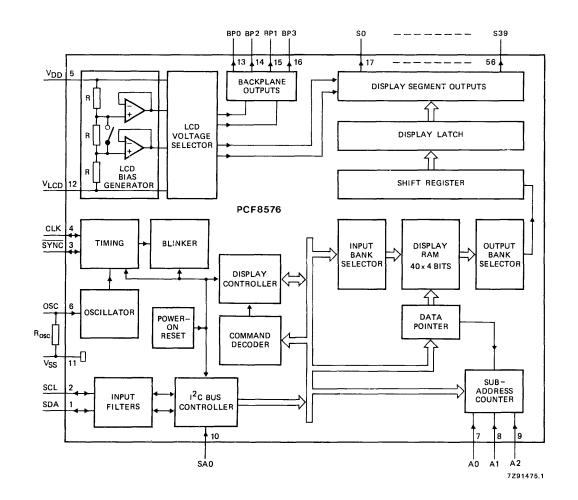

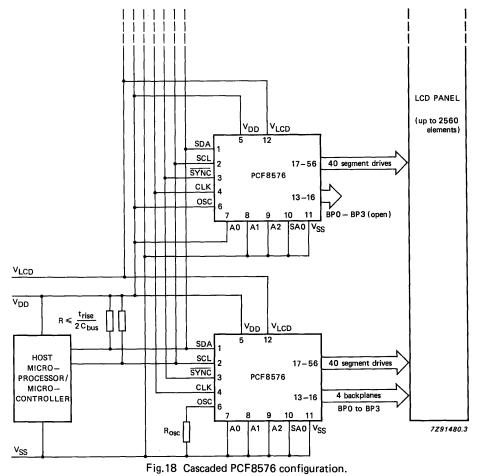

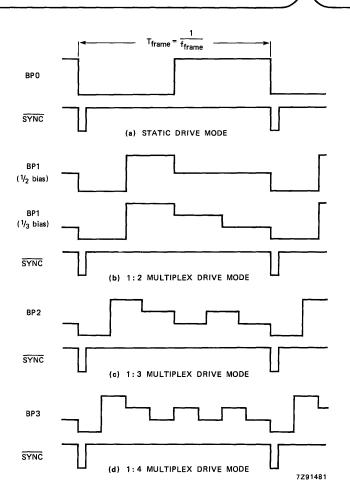

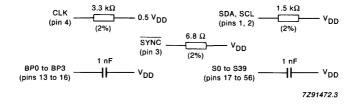

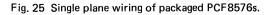

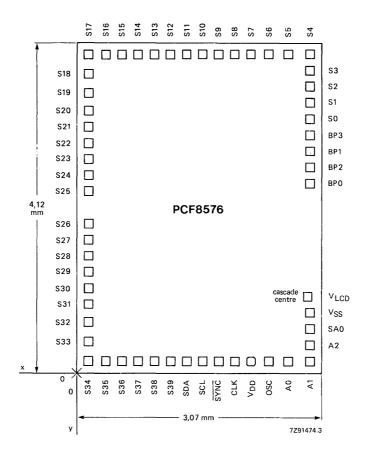

| PCF8576      | universal LCD driver for low multiplex rates                                                                     | 20   |

| 1010070      | (1:1 to 1:4); max. 160 segments; 1 <sup>2</sup> C-bus                                                            | 35   |

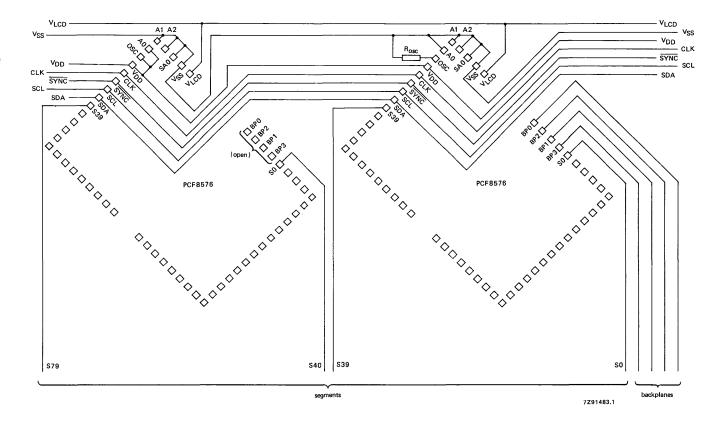

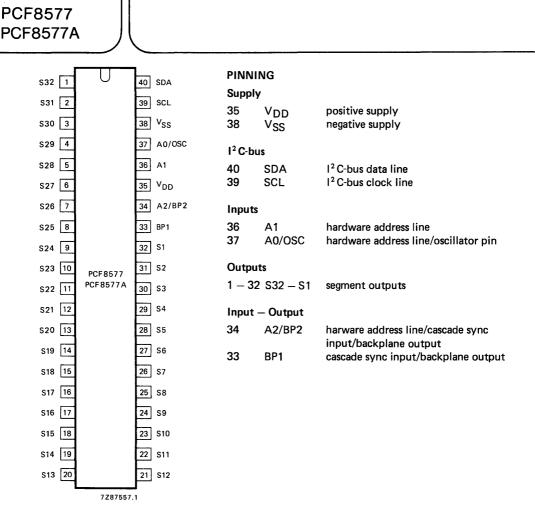

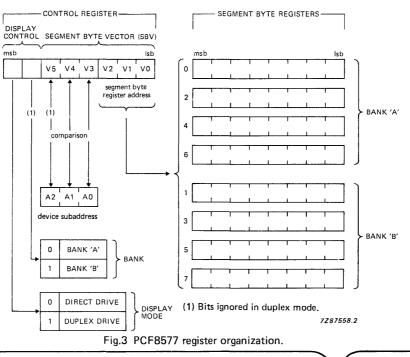

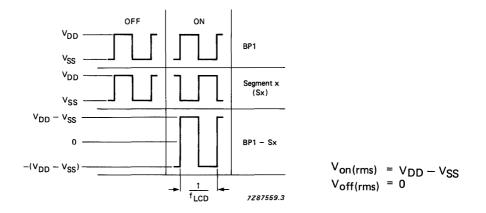

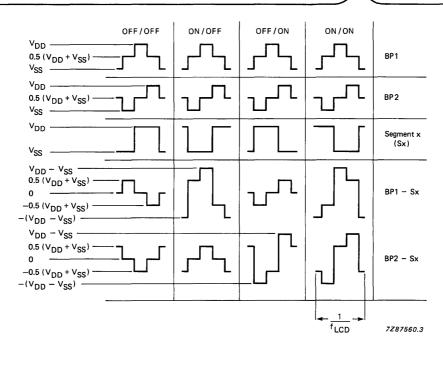

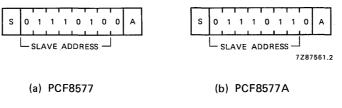

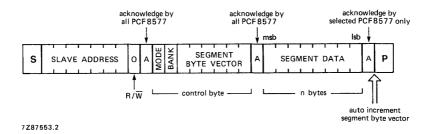

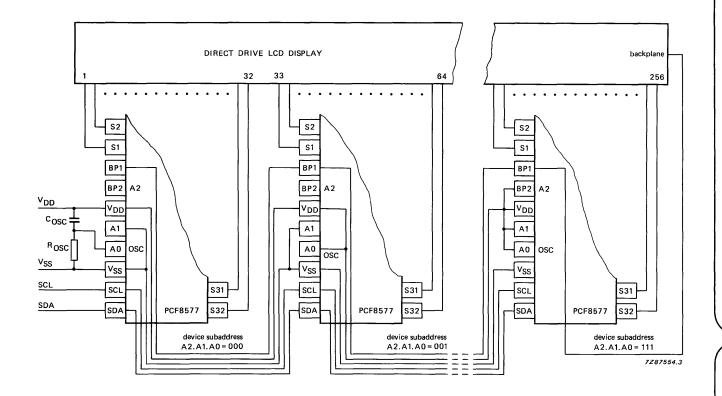

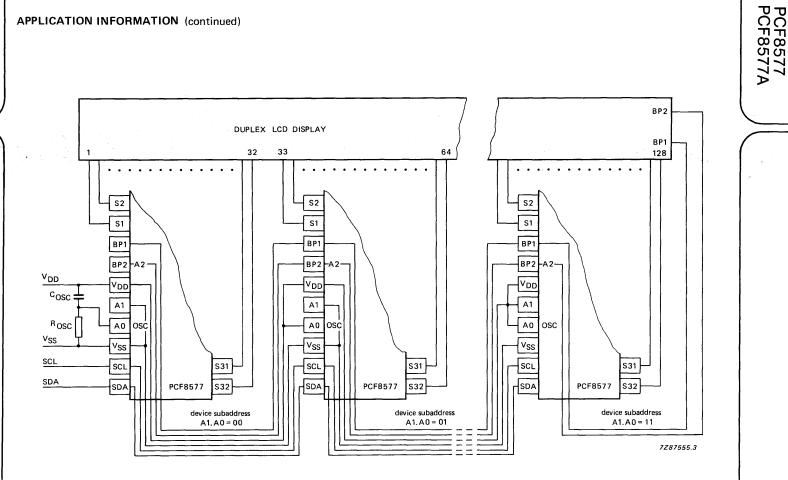

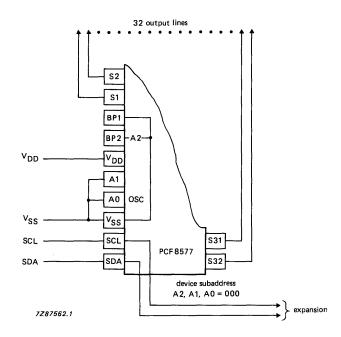

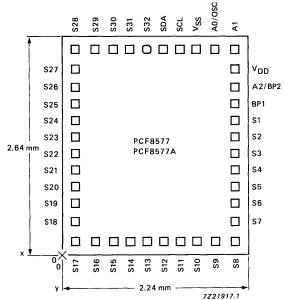

| PCF8577      | LCD direct driver (32 segments) or duplex driver                                                                 | 00.  |

| FCI 0077     | (64 segments); 1 <sup>2</sup> C-bus                                                                              | 39   |

| PCF8577A     |                                                                                                                  | 55   |

| FUF00//A     | LCD direct driver (32 segments) or duplex driver<br>(64 segments); l <sup>2</sup> C-bus; different slave address | 39   |

|              |                                                                                                                  | 39   |

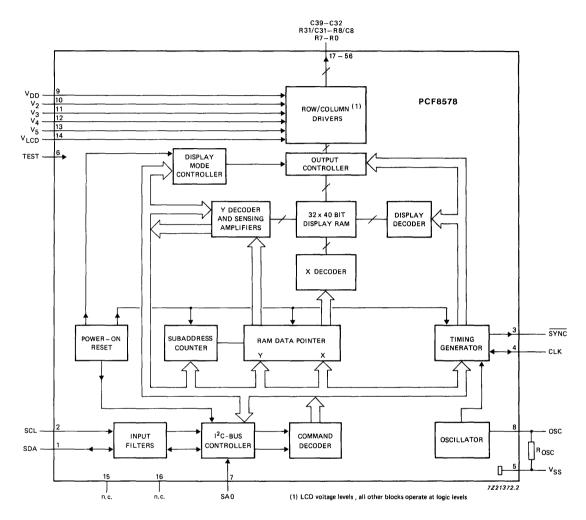

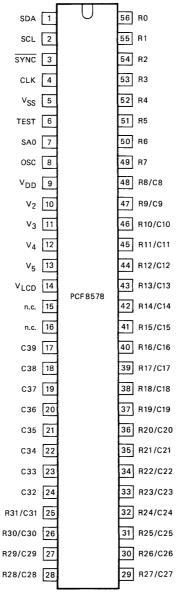

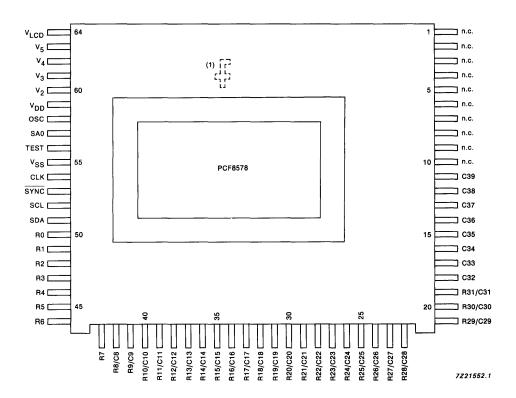

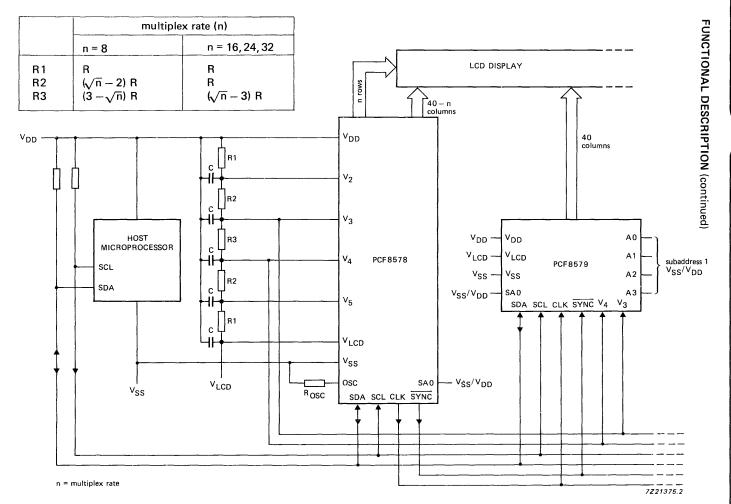

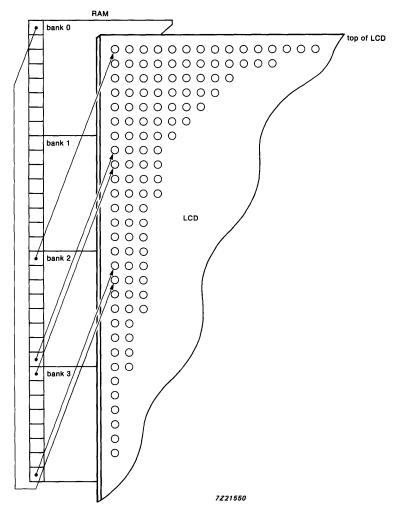

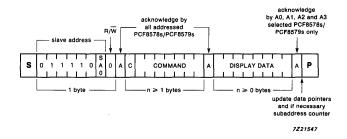

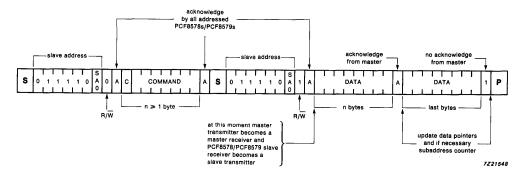

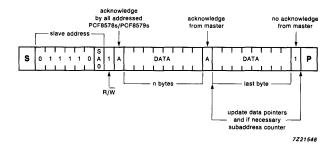

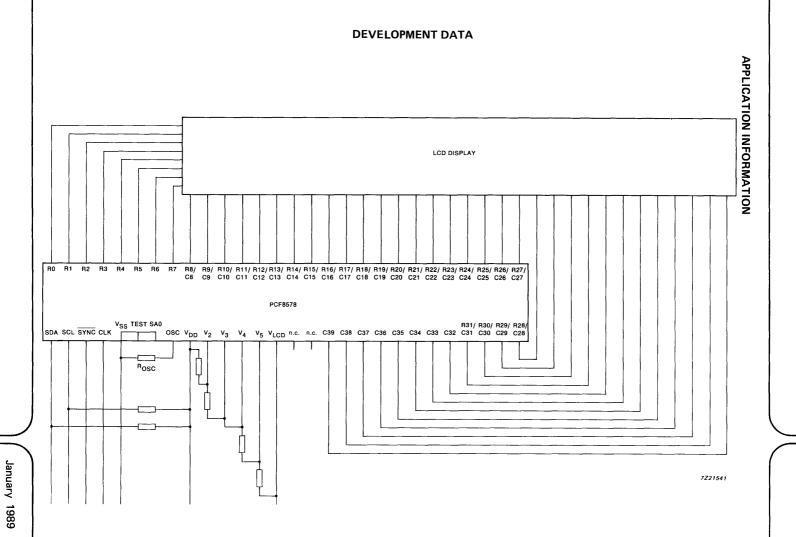

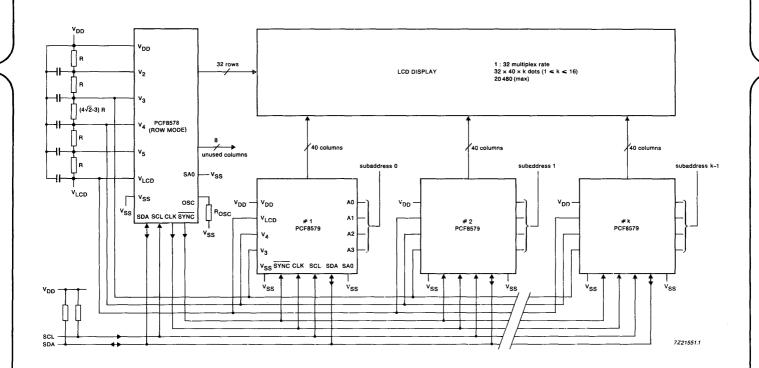

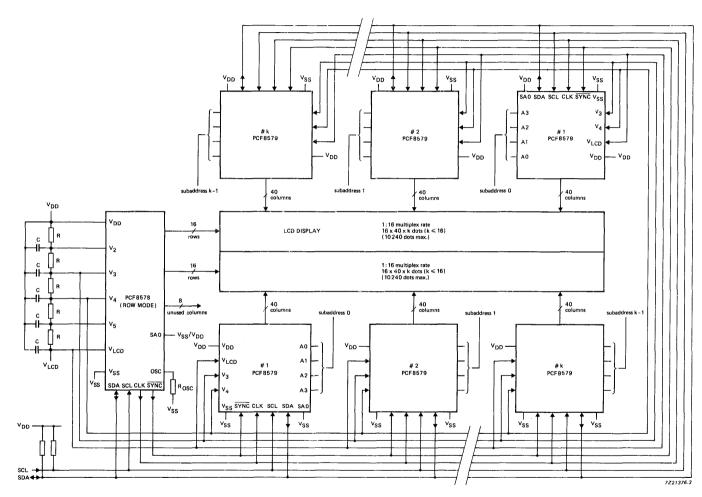

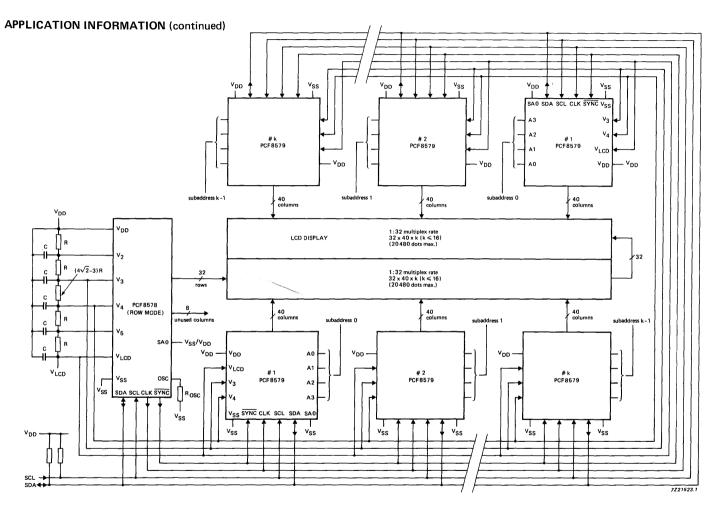

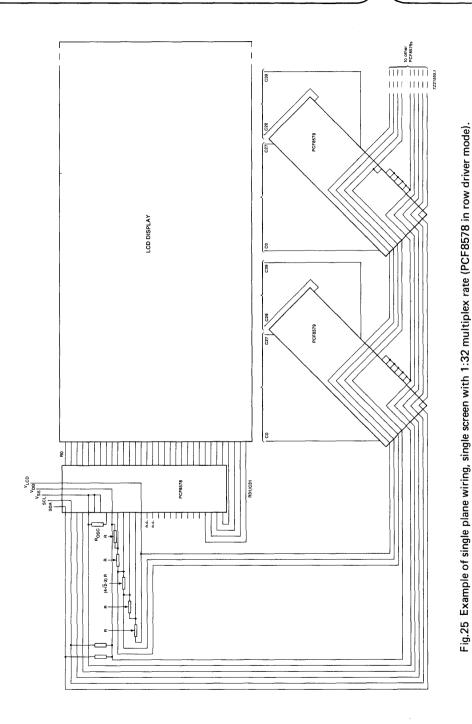

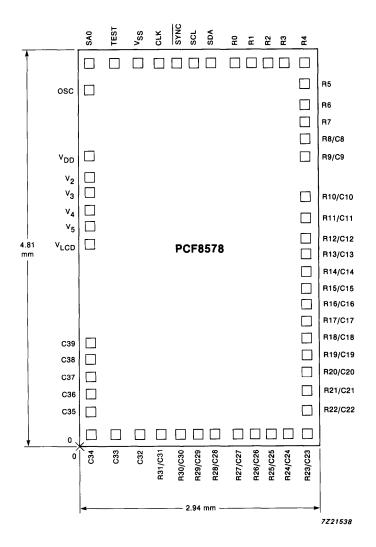

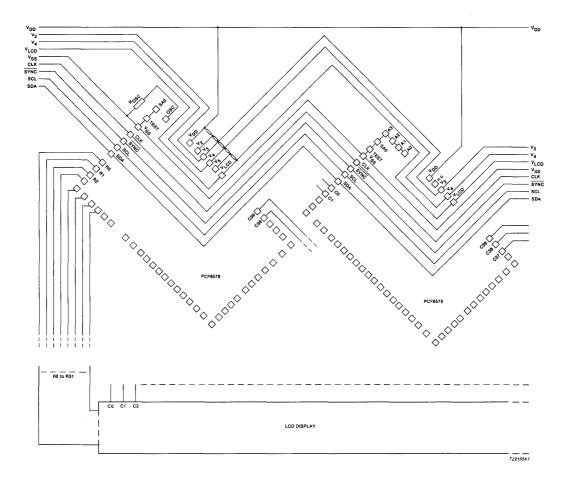

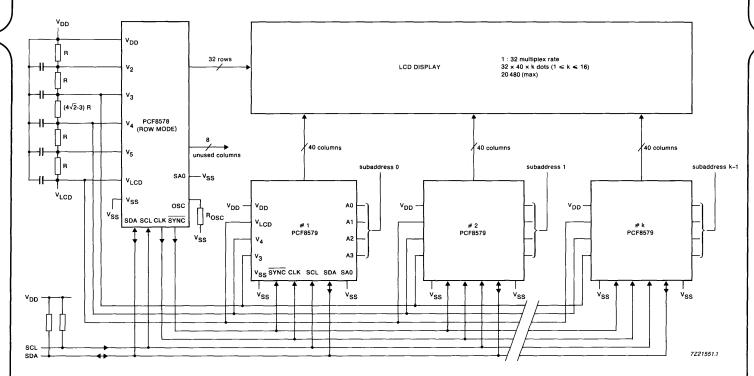

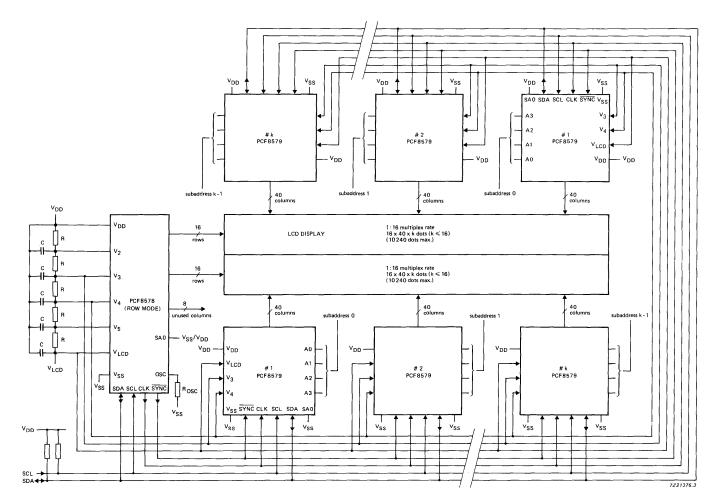

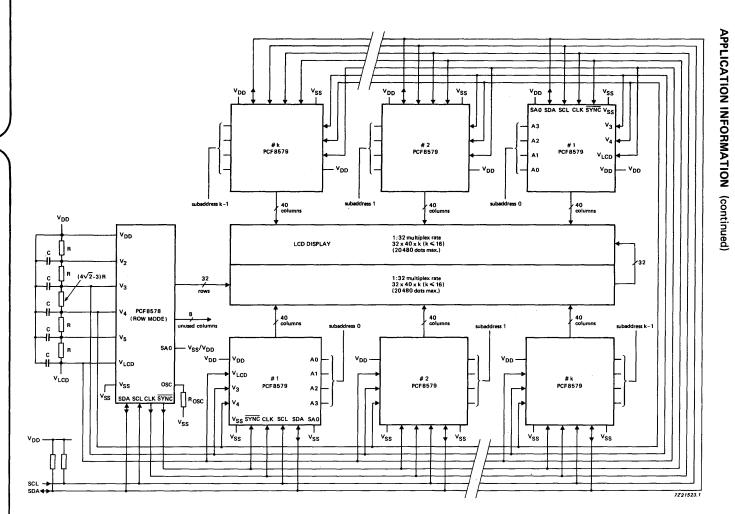

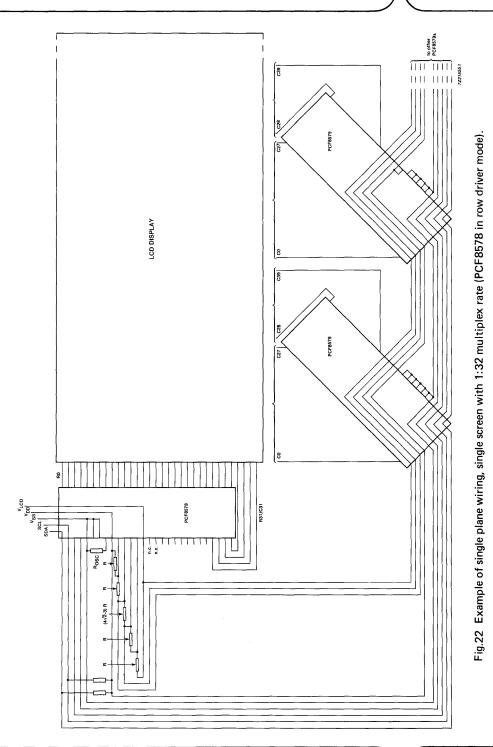

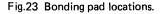

| PCF8578      | LCD row/column driver for dot matrix graphic displays;                                                           | 40   |

| 0050570      | 40 outputs, of which 24 are programmable; I <sup>2</sup> C-bus                                                   | 40   |

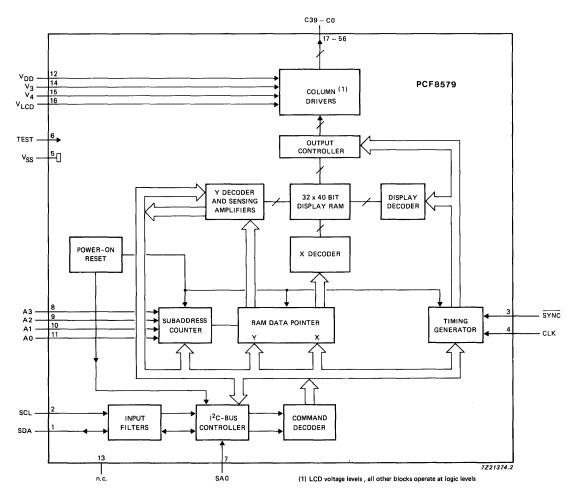

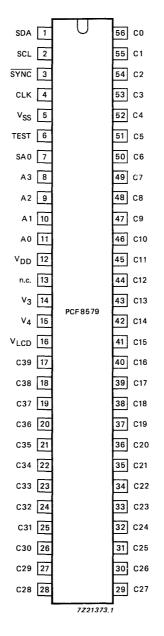

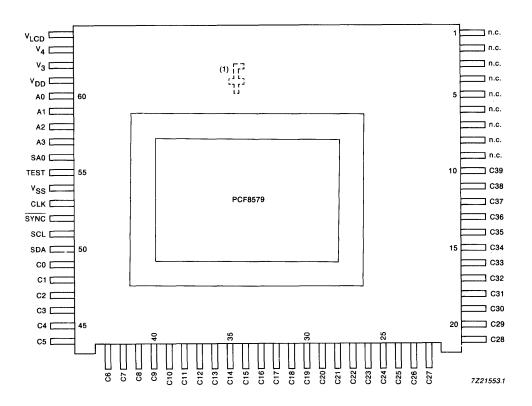

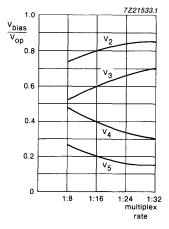

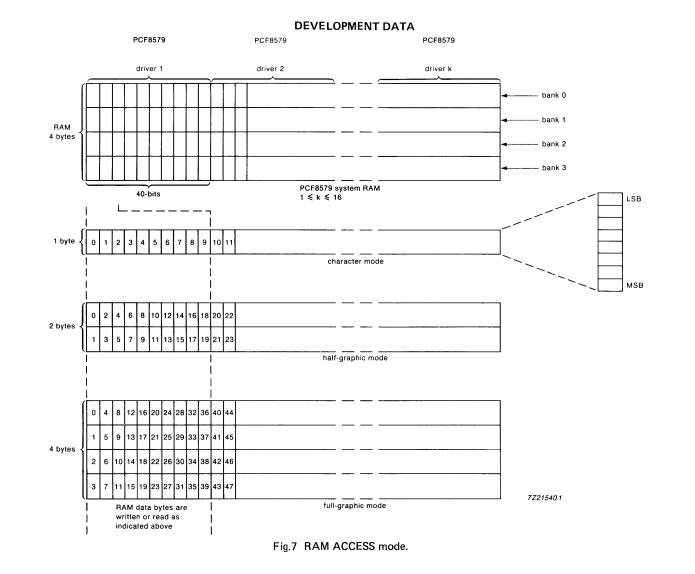

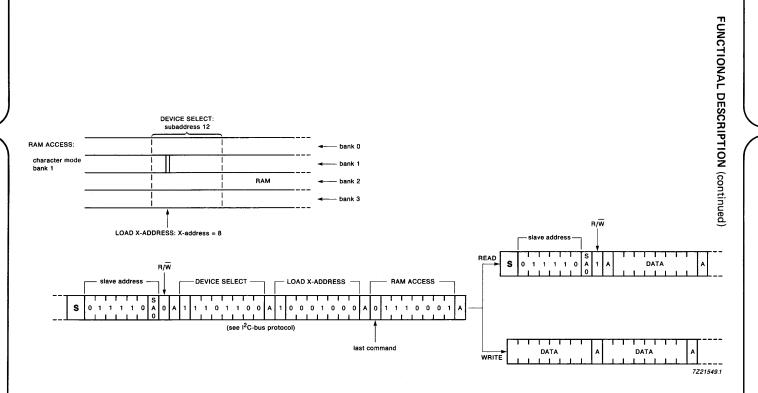

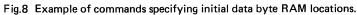

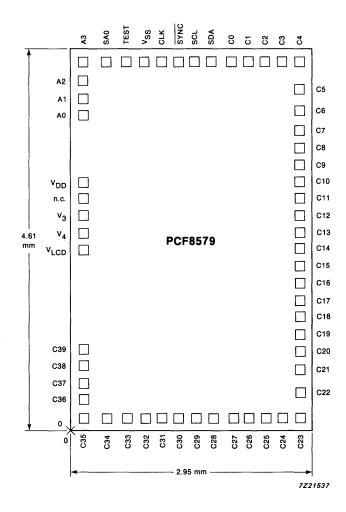

| PCF8579      | LCD column driver for dot matrix graphic displays;                                                               |      |

|              | 40 column outputs; l <sup>2</sup> C-bus                                                                          | 44   |

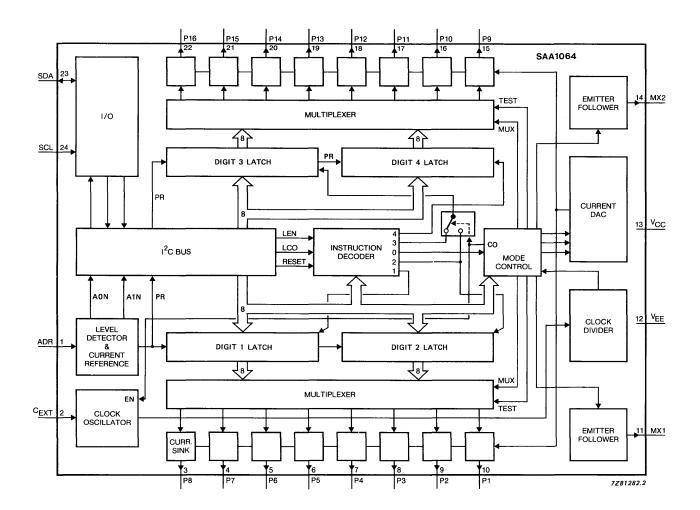

| SAA1064      | 4-digit LED driver; l <sup>2</sup> C-bus                                                                         | 55   |

| DOLBY CIRCUI | TS                                                                                                               |      |

| NE645        | Dolby B and C type noise reduction circuit                                                                       | 17   |

| NE646        | Dolby B and C type noise reduction circuit                                                                       | 17   |

| NE649        | low voltage Dolby B type noise reduction circuit                                                                 | 18   |

| NE650        | Dolby B type noise reduction circuit                                                                             | 19   |

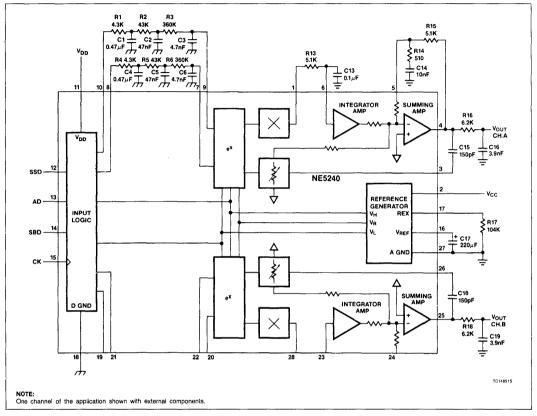

| NE5240       | Dolby digital audio decoder                                                                                      | 11   |

| TEA0651      | Dolby B & C noise reduction circuit                                                                              | 162  |

| TEA0652      | Dolby B & C noise reduction circuit                                                                              | 162  |

| TEA0653T     | stereo or 2-channel Dolby B noise reduction circuit                                                              | 164  |

| TEA0654      | preamplifier and electronic switch for Dolby B & C                                                               |      |

|              | noise reduction circuits                                                                                         | 162  |

| TEA0657      | dual Dolby B noise reduction circuit                                                                             | 165  |

| TEA0665      | Dolby B & C processor with preamplifier and electronic switch                                                    | 165  |

| TEA0665T     | Dolby B & C processor with preamplifier and electronic switch                                                    | 165  |

| TEA0666      | Dolby B & C processor with preamplifier and electronic switch;                                                   |      |

|              | changed frequency response in relation to TEA0665                                                                | 166  |

| TEA0666T     | Dolby B & C processor with preamplifier and electronic switch;                                                   |      |

|              | changed frequency response in relation to TEA0665                                                                | 166  |

| ТЕА0670Т     | Dolby B & C processor with preamplifier and electronic switch;                                                   |      |

|              | low voltage                                                                                                      | 167  |

| FREQUENCY S  | YNTHESIZERS                                                                                                      |      |

|              |                                                                                                                  | -    |

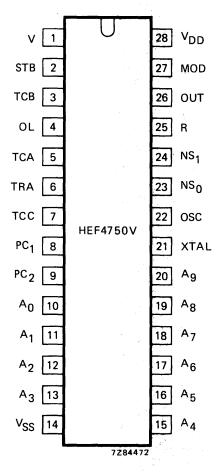

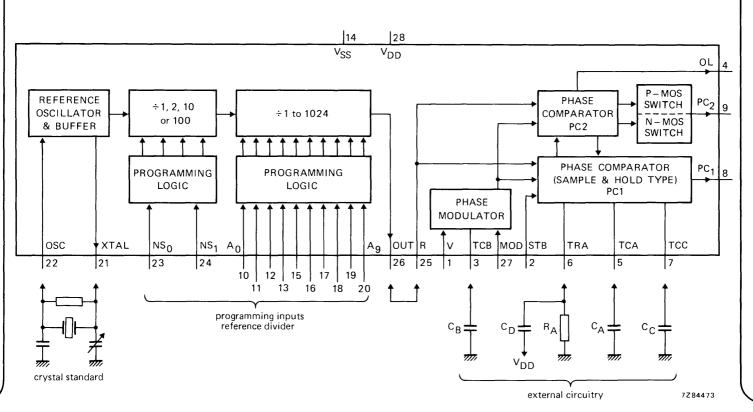

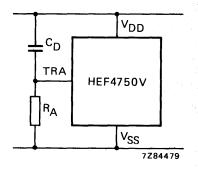

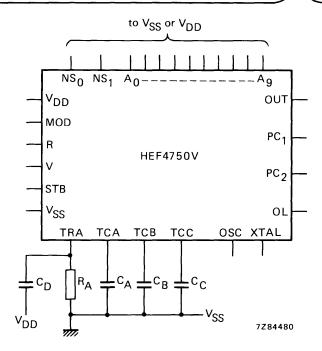

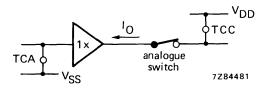

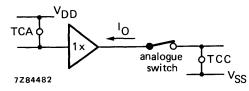

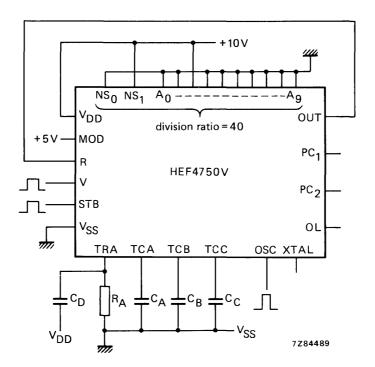

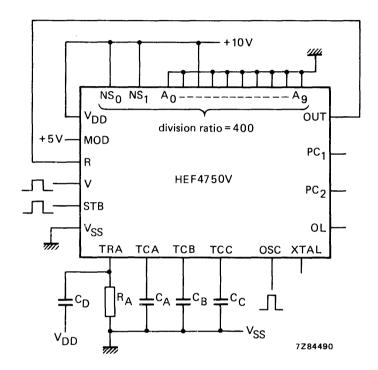

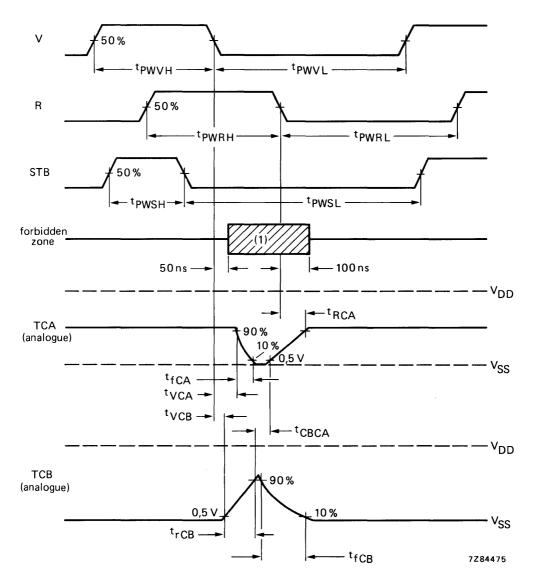

| HEF4750V     | frequency synthesizer                                                                                            | 5    |

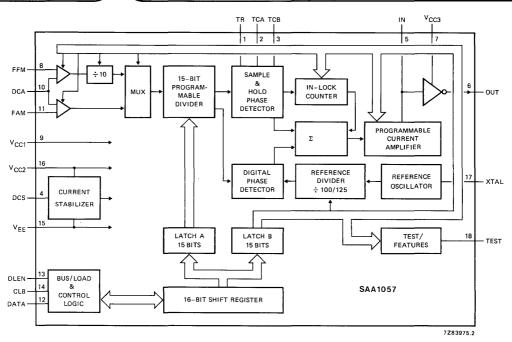

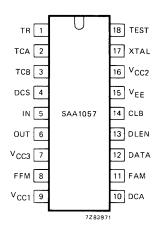

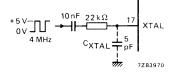

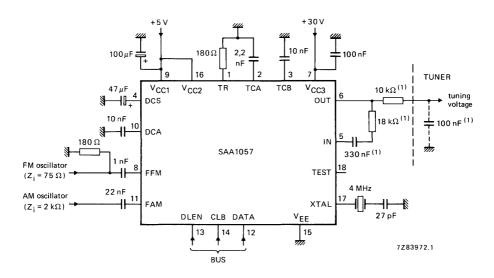

| SAA1057      | radio tuning PLL frequency synthesizer (SYMO II)                                                                 | 54   |

| TDD1742T     | low power frequency synthesizer (LOPSY)                                                                          | 160  |

| TSA6057      | radio tuning PLL frequency synthesizer; I <sup>2</sup> C-bus                                                     | 182  |

| TSA6057T     | radio tuning PLL frequency synthesizer; I <sup>2</sup> C-bus                                                     | 182  |

| type no.          | description                                                                                                | page |

|-------------------|------------------------------------------------------------------------------------------------------------|------|

| INTERFERENCE S    | SUPPRESSORS                                                                                                |      |

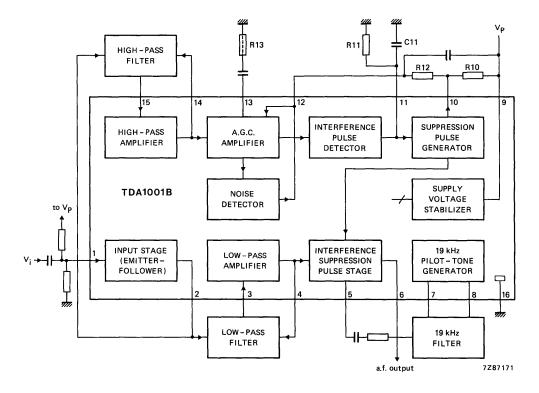

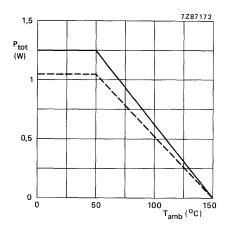

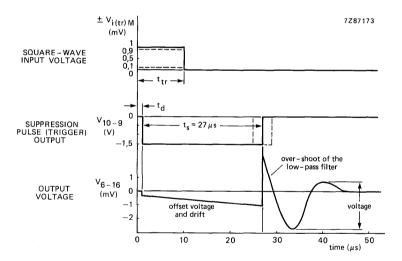

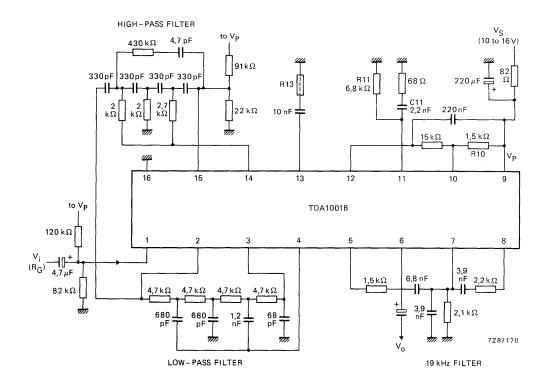

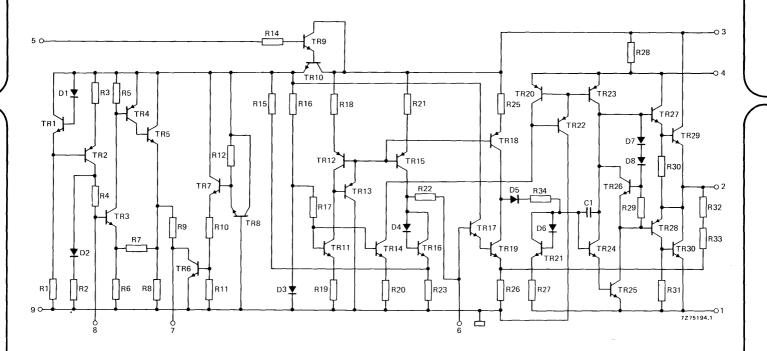

| TDA1001B          | interference and noise suppression circuit for FM receivers                                                | 80   |

| TDA1001BT         | interference and noise suppression circuit for FM receivers                                                | 80   |

| MEMORIES          |                                                                                                            |      |

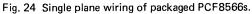

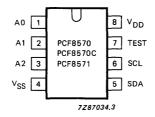

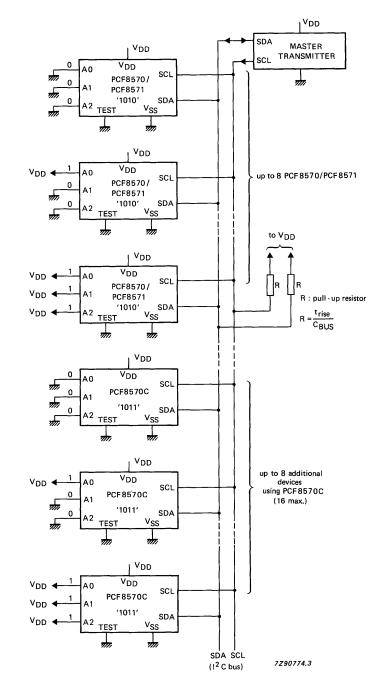

| PCF8570           | 256 x 8-bit static RAM; I <sup>2</sup> C-bus                                                               | 319  |

| PCF8570C          | 256 x 8-bit static RAM; $I^2$ C-bus; different slave address                                               | 319  |

| PCF8571           | 128 x 8-bit static RAM; I <sup>2</sup> C-bus                                                               | 31   |

| PCF8582A          | 256 x 8-bit EEPROM; I <sup>2</sup> C-bus; -40 to +85 °C                                                    | 48   |

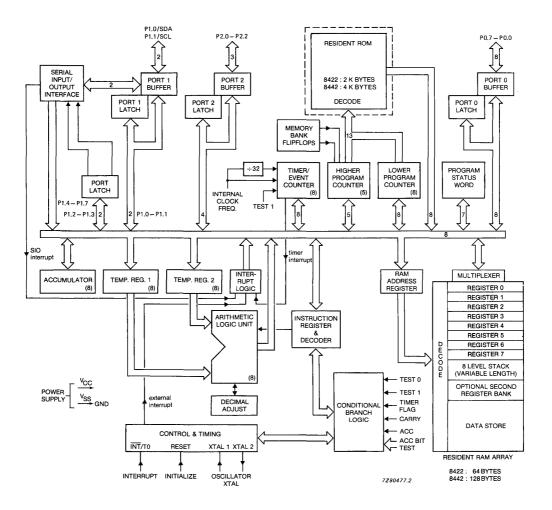

| MICROCONTROL      | LERS (8-bit)                                                                                               |      |

| 8051/80C51 family | CMOS                                                                                                       |      |

| PCA80C31BH-3      | microcontroller; 128 x 8 RAM; 1.2 to 12 MHz;                                                               |      |

|                   | 40 to + 125 °C                                                                                             | 20   |

| PCA80C51BH-3      | microcontroller; 128 x 8 RAM; 4K x 8 ROM;                                                                  |      |

|                   | 1.2 to 12 MHz; –40 to +125 <sup>o</sup> C                                                                  | 20   |

| PCA80C552         | microcontroller; 256 x 8 RAM; 80C31 CPU plus 16-bit                                                        |      |

|                   | capture/compare timer/counter; watch-dog timer;                                                            |      |

|                   | 2 pulse-width modulated signals; 10-bit ADC with                                                           |      |

|                   | 8 multiplexed input lines; I <sup>2</sup> C-bus; 1.2 to 12 MHz;                                            |      |

| BO 4 00 05 00     | -40 to + 125 °C                                                                                            | 21   |

| PCA80C562         | microcontroller; 256 x 8 RAM; 80C31 CPU plus 16-bit                                                        |      |

|                   | capture/compare timer/counter; watch-dog timer;                                                            |      |

|                   | 2-pulse-width modulated signals; 8-bit ADC with 8 multiplexed                                              | 21   |

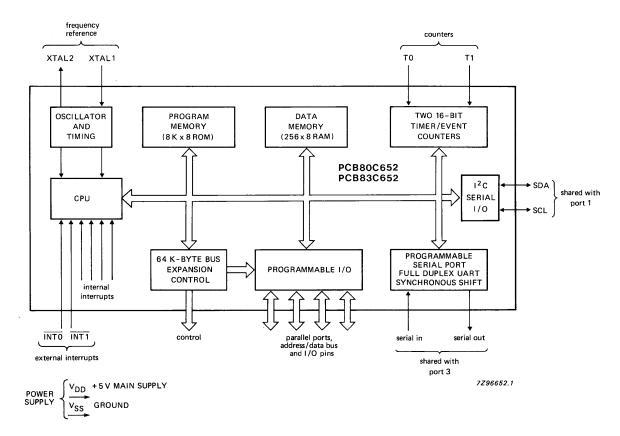

| PCA80C652         | input lines; 1.2 to 12 MHz; -40 to + 125 <sup>o</sup> C<br>microcontroller; 256 x 8 RAM; serial I/O; UART; | 21:  |

| rCAOUC052         | $1^{2}$ C-bus; 1.2 to 12 MHz; -40 to + 125 °C                                                              | 21   |

| PCA83C552         | microcontroller; 256 x 8 RAM; 8K x 8 ROM; 80C51 CPU                                                        | 21   |

| 1 0/00/002        | plus 16-bit capture/compare timer/counter; watch-dog timer;                                                |      |

|                   | 2 pulse-width modulated signals; 10-bit ADC with 8 multiplexed                                             |      |

|                   | input lines; $l^2$ C-bus; 1.2 to 12 MHz; -40 to + 125 oC                                                   | 21   |

| PCA83C562         | microcontroller; 256 x 8 RAM; 8K x 8 ROM; 80C51 CPU                                                        |      |

|                   | plus 16-bit capture/compare timer/counter; watch-dog timer;                                                |      |

|                   | 2-pulse-width modulated signals; 8 multiplexed input lines;                                                |      |

|                   | 1.2 to 12 MHz; –40 to + 125 °C                                                                             | 21   |

| PCA83C652         | microcontroller; 256 x 8 RAM; 8K x 8 ROM; serial I/O;                                                      |      |

|                   | UART; I <sup>2</sup> C-bus; 1.2 to 12 MHz;40 to + 125 <sup>O</sup> C                                       | 21   |

| PCA83C654         | microcontroller; 256 x 8 RAM; 16K x 8 ROM; serial I/O;                                                     |      |

|                   | UART; I <sup>2</sup> C-bus; 1.2 to 12 MHz; -40 to + 125 °C                                                 | 21   |

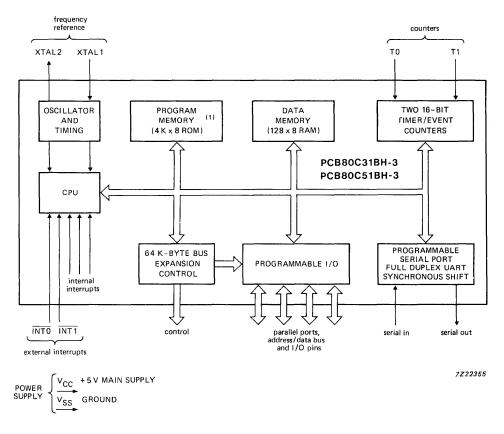

| PCB80C31BH-3      | microcontroller; 128 x 8 RAM; 0.5 to 12 MHz; 0 to +70 °C                                                   | 209  |

| PCB80C31BH-3      | microcontroller; 128 x 8 RAM; 1.2 to 16 MHz; 0 to +70 °C                                                   | 209  |

| PCB80C51BH-3      | microcontroller; 128 x 8 RAM; 4K x 8 ROM;                                                                  |      |

|                   | 0.5 to 12 MHz; 0 to + 70 <sup>o</sup> C                                                                    | 209  |

| PCB80C51BH-3      | microcontroller; 128 x 8 RAM; 4K x 8 ROM;                                                                  |      |

|                   | 1.2 to 16 MHz; 0 to + 70 <sup>o</sup> C                                                                    | 209  |

| type no.          | description                                                                                                                                    | page |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 8051/80C51 family | CMOS (continued)                                                                                                                               |      |

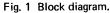

| PCB80C552         | microcontroller; 256 x 8 RAM; 80C31 CPU plus                                                                                                   |      |

|                   | 16-bit capture/compare timer/counter; watch-dog timer;                                                                                         |      |

|                   | two pulse-width modulated signals; 10-bit ADC with                                                                                             |      |

|                   | 8 multiplexed input lines; I <sup>2</sup> C-bus; 1.2 to 12 MHz;                                                                                |      |

|                   | 0 to + 70 °C                                                                                                                                   | 213  |

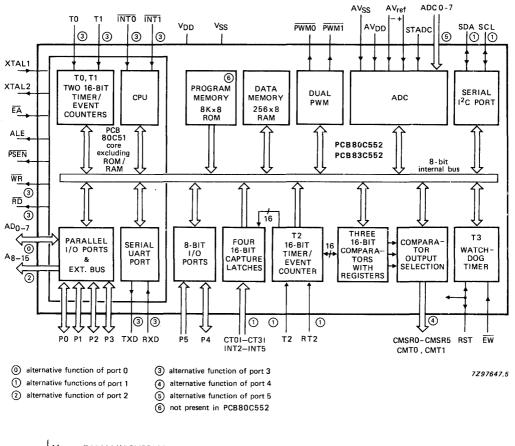

| PCB80C562         | microcontroller; 256 x 8 RAM; 80C31 CPU plus 16-bit                                                                                            |      |

|                   | capture/compare timer/counter; watch-dog timer;                                                                                                |      |

|                   | 2 pulse-width modulated signals; 8-bit ADC with                                                                                                |      |

|                   | 8 multiplexed input lines; 1.2 to 12 MHz; 0 to +70 °C                                                                                          | 215  |

| PCB80C652         | microcontroller; 256 x 8 RAM; serial I/O; UART; 1 <sup>2</sup> C-bus;                                                                          |      |

|                   | 1.2 to 12 MHz; 0 to +70 °C                                                                                                                     | 213  |

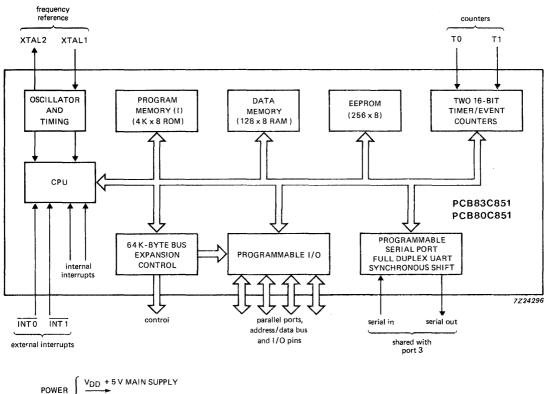

| PCB80C851         | microcontroller; 128 x 8 RAM; 256 x 8 EEPROM;                                                                                                  | 00   |

|                   | 1.2 to 12 MHz; 0 to +70 °C                                                                                                                     | 22   |

| PCB83C552         | microcontroller; 256 x 8 RAM; 8K x 8 ROM; 80C51 CPU                                                                                            |      |

|                   | plus 16-bit capture/compare timer/counter; watch-dog timer;                                                                                    |      |

|                   | two pulse-width modulated signals; 10-bit ADC with                                                                                             | 21   |

| PCB83C562         | 8 multiplexed input lines; I <sup>2</sup> C-bus; 1.2 to 12 MHz; 0 to +70 <sup>o</sup> C<br>microcontroller; 256 x 8 RAM; 8K x 8 ROM; 80C51 CPU | 21.  |

| CB03C302          | plus 16-bit capture/compare timer/counter; watch-dog timer;                                                                                    |      |

|                   | 2 pulse-width modulated signals; 8 multiplexed input lines;                                                                                    |      |

|                   | 1.2 to 12 MHz; 0 to $+70$ °C                                                                                                                   | 21   |

| PCB83C652         | microcontroller; 256 x 8 RAM; 8K x 8 ROM; serial I/O;                                                                                          | 21   |

| 0000002           | UART; $I^2$ C-bus; 1.2 to 12 MHz; 0 to +70 °C                                                                                                  | 21   |

| PCB83C654         | microcontroller; 256 x 8 RAM; 16K x 8 ROM; serial I/O;                                                                                         |      |

|                   | UART; I <sup>2</sup> C-bus; 1.2 to 12 MHz; 0 to +70 °C                                                                                         | 219  |

| PCB83C851         | microcontroller; 128 x 8 RAM; 4K x 8 ROM; 256 x 8 EEPROM;                                                                                      |      |

|                   | 1.2 to 12 MHz; 0 to + 70 °C                                                                                                                    | 22   |

| PCF80C31BH-3      | microcontroller; 128 x 8 RAM; 1.2 to 12 MHz;                                                                                                   |      |

|                   | -40 to +85 °C                                                                                                                                  | 209  |

| PCF80C51BH-3      | microcontroller; 128 x 8 RAM; 4K x 8 ROM;                                                                                                      |      |

|                   | 1.2 to 12 MHz; –40 to +85 °C                                                                                                                   | 20   |

| PCF80C552         | microcontroller; 256 x 8 RAM; 80C31 CPU plus 16-bit                                                                                            |      |

|                   | capture/compare timer/counter; watch-dog timer;                                                                                                |      |

|                   | 2 pulse-width modulated signals; 10-bit ADC with 8 multiplexed                                                                                 |      |

|                   | input lines; I <sup>2</sup> C-bus; 1.2 to 12 MHz;40 to +85 <sup>O</sup> C                                                                      | 21   |

| PCF80C562         | microcontroller; 256 x 8 RAM; 80C31 CPU plus 16-bit                                                                                            |      |

|                   | capture/compare timer/counter; watch-dog timer; 2 pulse-width                                                                                  |      |

|                   | modulated signals; 8-bit ADC with 8 multiplexed input lines;                                                                                   |      |

| 005000050         | 1.2 to 12 MHz; -40 to +85 °C                                                                                                                   | 21   |

| PCF80C652         | microcontroller; 256 x 8 RAM; serial I/O; UART; I <sup>2</sup> C-bus;                                                                          |      |

|                   | 1.2 to 12 MHz; -40 to +85 °C                                                                                                                   | 21   |

| PCF80C851         | microcontroller; 128 x 8 RAM; 256 x 8 EEPROM;                                                                                                  | ~~   |

|                   | 1.2 to 12 MHz; -40 to +85 °C                                                                                                                   | 22   |

| PCF83C552         | microcontroller; 256 x 8 RAM; 8K x 8 ROM; 80C51 CPU plus                                                                                       |      |

|                   | 16-bit capture/compare timer/counter; watch-dog timer;                                                                                         |      |

|                   | 2 pulse-width modulated signals; 10-bit ADC with 8 multiplexed                                                                                 | 0.1  |

|                   | input lines; I <sup>2</sup> C-bus; 1.2 to 12 MHz; -40 to +85 <sup>o</sup> C                                                                    | 213  |

| type no.        | description                                                             | page |

|-----------------|-------------------------------------------------------------------------|------|

| PCF83C562       | microcontroller; 256 x 8 RAM; 8K x 8 ROM; 80C51 CPU                     |      |

|                 | plus 16-bit capture/compare timer/counter; watch-dog timer;             |      |

|                 | 2 pulse-width modulated signals; 8 multiplexed input lines;             |      |

|                 | 1.2 to 12 MHz; -40 to +85 °C                                            | 215  |

| PCF83C652       | microcontroller; 256 x 8 RAM; 8K x 8 ROM; serial I/O; UART;             |      |

|                 | I <sup>2</sup> C-bus; 1.2 to 12 MHz; -40 to + 85 <sup>o</sup> C         | 217  |

| PCF83C654       | microcontroller; 256 x 8 RAM; 16K x 8 ROM; serial I/O;                  |      |

|                 | UART; I <sup>2</sup> C-bus; 1.2 to 12 MHz; —40 to +85 <sup>o</sup> C    | 219  |

| PCF83C851       | microcontroller; 128 x 8 RAM; 4K x 8 ROM; 256 x 8 EEPROM;               |      |

|                 | 1.2 to 12 MHz; –40 to +85 <sup>o</sup> C                                | 221  |

| 84CXX family CN | NOS                                                                     |      |

| PCF84C00        | microcontroller; 256 x 8 RAM; bond-out version                          |      |

|                 | PCF84CXX family; I <sup>2</sup> C-bus                                   | 283  |

| PCF84C12        | low cost microcontroller; 64 x 8 RAM; 1K x 8 ROM                        | 285  |

| PCF84C21        | microcontroller; 64 x 8 RAM; 2K x 8 ROM; plus 8-bit                     |      |

|                 | LED driver; I <sup>2</sup> C-bus; –40 to +85 <sup>o</sup> C             | 283  |

| PCF84C22        | low cost microcontroller; 64 x 8 RAM; 1K x 8 ROM                        | 285  |

| PCF84C41        | microcontroller; 128 x 8 RAM; 4K x 8 ROM; plus 8-bit                    |      |

|                 | LED driver; I <sup>2</sup> C-bus; –40 to +85 <sup>o</sup> C             | 283  |

| PCF84C42        | low cost microcontroller; 64 x 8 RAM; 4K x 8 ROM                        | 285  |

| PCF84C81        | microcontroller; 256 x 8 RAM; 8K x 8 ROM; plus 8-bit                    |      |

|                 | LED driver; I <sup>2</sup> C-bus; -40 to +85 <sup>o</sup> C             | 283  |

| PCF84C85        | microcontroller; 256 x 8 RAM; 8K x 8 ROM; 32 I/O;                       |      |

|                 | plus 8-bit LED driver; I <sup>2</sup> C-bus; -40 to + 85 <sup>o</sup> C | 287  |

| 84XX family NM  | os                                                                      |      |

| MAB8401         | microcontroller; 128 x 8 RAM; piggy-back version for                    |      |

|                 | MAB84XX family plus 8-bit LED driver; 1 <sup>2</sup> C-bus;             |      |

|                 | 1.0 to 6 MHz; 0 to +70 °C                                               | 79   |

| MAB8411         | microcontroller; 64 x 8 RAM; 1K x 8 ROM plus                            |      |

|                 | 8-bit LED driver; 20 I/O lines; 1 <sup>2</sup> C-bus;                   |      |

|                 | 1.0 to 6 MHz; 0 to +70 °C                                               | 79   |

| MAB8421         | microcontroller; 64 x 8 RAM; 2K x 8 ROM plus                            |      |

|                 | 8-bit LED driver; 20 I/O lines; I <sup>2</sup> C-bus;                   |      |

|                 | 1.0 to 6 MHz; 0 to +70 <sup>o</sup> C                                   | 79   |

| MAB8422         | microcontroller; 64 x 8 RAM; 2K x 8 ROM plus                            |      |

|                 | 8-bit LED driver; 15 I/O lines; I <sup>2</sup> C-bus;                   |      |

|                 | 1.0 to 6 MHz; 0 to +70 <sup>o</sup> C                                   | 81   |

| VAB8441         | microcontroller; 128 x 8 RAM; 4K x 8 ROM plus                           |      |

|                 | 8-bit LED driver; 20 I/O lines; I <sup>2</sup> C-bus;                   |      |

|                 | 1.6 to 6 MHz; 0 to +70 <sup>o</sup> C                                   | 79   |

| MAB8442         | microcontroller; 128 x 8 RAM; 4K x 8 ROM plus                           |      |

|                 | 8-bit LED driver; 15 I/O lines; I <sup>2</sup> C-bus;                   |      |

|                 | 1.6 to 6 MHz; 0 to +70 <sup>o</sup> C                                   | 81   |

| MAB8461         | microcontroller; 128 x 8 RAM; 6K x 8 ROM plus                           |      |

|                 | 8-bit LED driver; 20 I/O lines; I <sup>2</sup> C-bus                    |      |

|                 | 1.0 to 6 MHz; 0 to +70 <sup>o</sup> C                                   | 79   |

| type no.         | description                                                | page |

|------------------|------------------------------------------------------------|------|

| 84XX family NMOS | (continued)                                                |      |

| MAF84A11         | microcontroller; 64 x 8 RAM; 1K x 8 ROM;                   |      |

|                  | plus 8-bit LED driver; 20 I/O lines; I <sup>2</sup> C-bus; |      |

|                  | 1.0 to 5 MHz; -40 to + 110 °C                              | 79   |

| MAF84A21         | microcontroller; 64 x 8 RAM; 2K x 8 ROM plus               |      |

|                  | 8-bit LED driver; 20 I/O lines; I <sup>2</sup> C-bus;      |      |

|                  | 1.0 to 5 MHz;40 to + 110 <sup>o</sup> C                    | 79   |

| MAF84A22         | microcontroller; 64 x 8 RAM; 2K x 8 ROM plus               |      |

|                  | 8-bit LED driver; 15 I/O lines; I <sup>2</sup> C-bus;      |      |

|                  | 1.0 to 5 MHz; -40 to +110 °C                               | 81   |

| MAF84A41         | microcontroller; 128 x 8 RAM; 4K x 8 ROM plus              |      |

|                  | 8-bit LED driver; 20 I/O lines; I <sup>2</sup> C-bus;      |      |

|                  | 1.0 to 5 MHz; –40 to + 110 <sup>o</sup> C                  | 79   |

| MAF84A42         | microcontroller; 128 x 8 RAM; 4K x 8 ROM plus              |      |

|                  | 8-bit LED driver; 15 I/O lines; 1 <sup>2</sup> C-bus;      |      |

|                  | 1.0 to 5 MHz; -40 to + 110 °C                              | 81   |

| MAF84A61         | microcontroller; 128 x 8 RAM; 6K x 8 ROM plus              |      |

|                  | 8-bit LED driver; 20 I/O lines; I <sup>2</sup> C-bus;      |      |

|                  | 1.0 to 5 MHz; -40 to + 110 °C                              | 79   |

| MAF8411          | microcontroller; 64 x 8 RAM; 1K x 8 ROM plus               |      |

|                  | 8-bit LED driver; 20 I/O lines; I <sup>2</sup> C-bus;      |      |

|                  | 1.0 to 6 MHz; -40 to +85 °C                                | 79   |

| MAF8421          | microcontroller; 64 x 8 RAM; 2K x 8 ROM plus               |      |

|                  | 8-bit LED driver; 20 I/O lines; I <sup>2</sup> C-bus;      |      |

|                  | 1.0 to 6 MHz; -40 to +85 °C                                | 79   |

| MAF8422          | microcontroller; 64 x 8 RAM; 2K x 8 ROM plus               |      |

|                  | 8-bit LED driver; 15 I/O lines; I <sup>2</sup> C-bus       |      |

|                  | 1.0 to 6 MHz; -40 to +85 °C                                | 81   |

| MAF8441          | microcontroller; 128 x 8 RAM; 4K x 8 ROM plus              | 01   |

|                  | 8-bit LED driver; 20 I/O lines; 1 <sup>2</sup> C-bus;      |      |

|                  | 1.0 to 6 MHz; $-40$ to $+85$ °C                            | 79   |

| MAF8442          | microcontroller; 128 x 8 RAM; 4K x 8 ROM plus              | ,0   |

|                  | 8-bit LED driver; 15 I/O lines; I <sup>2</sup> C-bus;      |      |

|                  | 1.0 to 6 MHz; $-40$ to $+85$ °C                            | 81   |

| MAF8461          | microcontroller; 128 x 8 RAM; 6K x 8 ROM plus              | 01   |

|                  | 8-bit LED driver; 20 I/O lines; 1 <sup>2</sup> C-bus;      |      |

|                  | 1.0 to 6 MHz; $-40$ to $+85$ °C                            | 79   |

|                  |                                                            | 75   |

| 8048 family CMOS |                                                            |      |

| PCA80C39         | microcontroller; 128 x 8 RAM; 1.0 to 15 MHz;               |      |

|                  | -40 to + 110 °C                                            | 211  |

| PCA80C49         | microcontroller; 128 x 8 RAM; 2K x 8 ROM;                  | 211  |

| 10/100010        | 1.0 to 15 MHz; $-40$ to $+110$ °C                          | 211  |

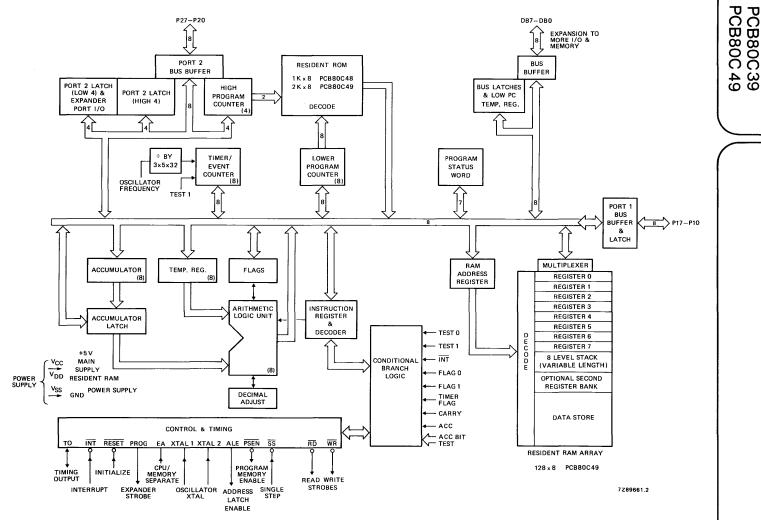

| PCB80C39         | microcontroller; 128 x 8 RAM; 1.0 to 15 MHz;               | 211  |

|                  | $0 \text{ to } + 70 ^{\circ}\text{C}$                      | 211  |

| PCB80C49         | microcontroller; 128 x 8 RAM; 2K x 8 ROM;                  | 211  |

| 1 000043         | 1.0 to 15 MHz; 0 to $+70 ^{\circ}\text{C}$                 | 011  |

| PCF80C39         | microcontroller; 128 x 8 RAM; 1.0 to 15 MHz;               | 211  |

| 1010003          | · · · ·                                                    | 011  |

| PCF80C49         | $-40 \text{ to } +85 ^{\circ}\text{C}$                     | 211  |

| F G F OU G 49    | microcontroller; 128 x 8 RAM; 2K x 8 ROM;                  | 014  |

|                  | 1.0 to 15 MHz;40 to +85 <sup>o</sup> C                     | 211  |

August 1989

| type no.     | description                                                        | page |

|--------------|--------------------------------------------------------------------|------|

| MOTOR CONTR  | OLLERS                                                             |      |

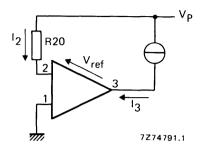

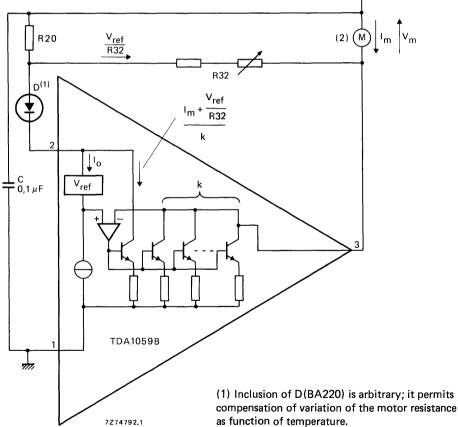

| TDA1059B     | motor speed regulator with thermal shut-down;                      |      |

|              | multiplication coefficient = 9; drop-out voltage = 1.8 V           | 891  |

| TDA5040T     | DC motor drive circuit with magnetic-field detector                | 1339 |

| PERSONAL RAI | DIO/AUDIO                                                          |      |

| TDA7000      | FM radio circuit; mono (in plastic DIL-18)                         | 1381 |

| TDA7010T     | FM radio circuit; mono (in SO-16 plastic mini-pack)                | 1389 |

| TDA7021T     | FM radio circuit; stereo/mono; for low voltage                     |      |

|              | micro tuning system (MTS)                                          | 1397 |

| TDA7030T     | low voltage micro tuning system (MTS)                              | 1407 |

| TDA7040T     | PLL stereo decoder; low voltage                                    | 1415 |

| TDA7050      | 150 mW BTL or 2 x 75 mW stereo audio power amplifier;              |      |

|              | low voltage                                                        | 1423 |

| TDA7050T     | 150 mW BTL or 2 x 75 mW stereo audio power amplifier;              |      |

|              | low voltage                                                        | 1427 |

| TDA7052      | 1 W BTL mono audio amplifier for portable applications             | 1431 |

| TDA7053      | 2 x 1 W BTL stereo audio power amplifier for portable applications | 1437 |

| TEA0670T     | Dolby B & C processor preamplifier and electronic switch;          | 1670 |

| TEAFE61T     | low voltage                                                        | 1679 |

| TEA5551T     | single-chip AM radio circuit, plus dual AF amplifier,              | 1685 |

|              | for pocket receivers with headphones                               | 1000 |

| RADIO RECEIV | ERS                                                                |      |

| АМ           |                                                                    |      |

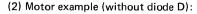

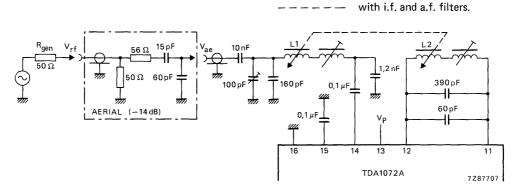

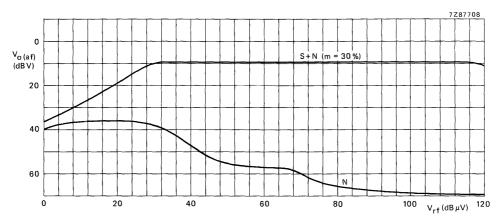

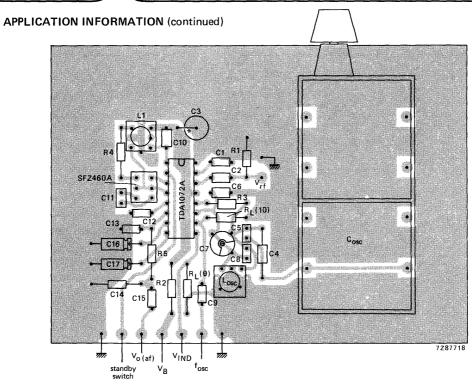

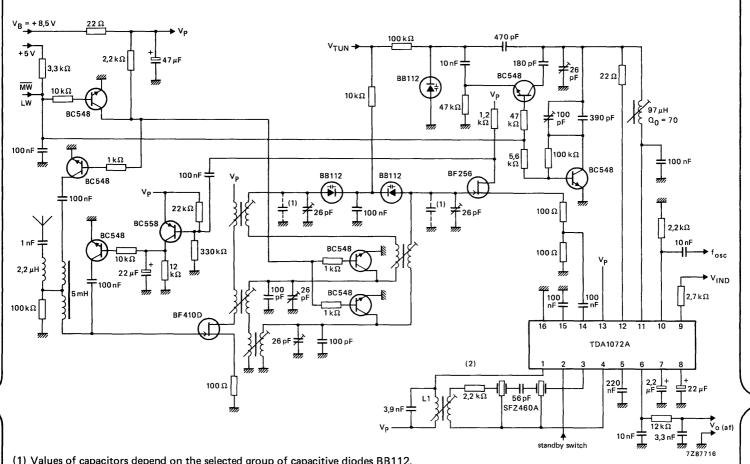

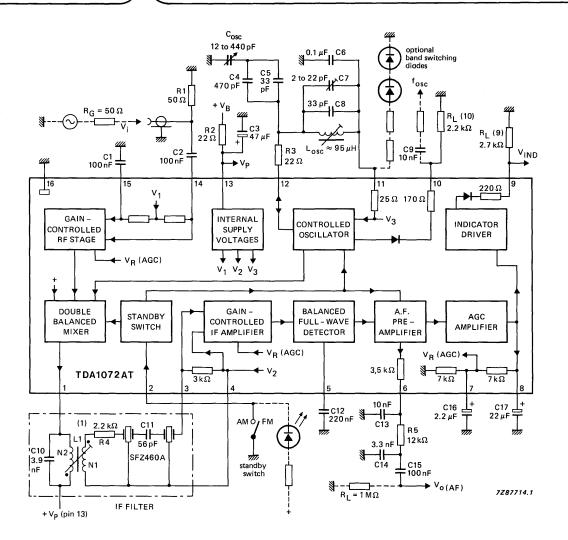

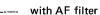

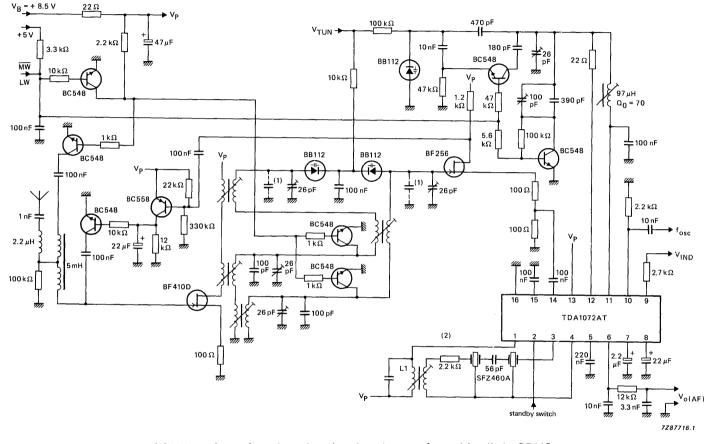

| TDA1072A     | AM receiver circuit for hi-fi and car radio                        | 897  |

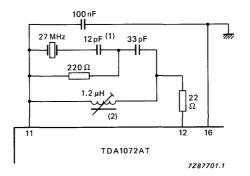

| TDA1072AT    | AM receiver circuit for hi-fi and car radio                        | 913  |

| TDA1572      | AM receiver circuit for stereo hi-fi and car radio                 | 1153 |

| TDA1572T     | AM receiver circuit for stereo hi-fi and car radio                 | 1171 |

| TDB1080      | IF limiting amplifier, FM detector and audio amplifier             | 1583 |

| TDB1080T     | IF limiting amplifier, FM detector and audio amplifier             | 1583 |

| TEA6200      | AM upconversion radio receiver; 10.7 MHz IF                        | 1775 |

#### AM/FM

| TEA5570 | AM/FM radio receiver circuit | 1697 |

|---------|------------------------------|------|

| TEA5591 | AM/FM radio receiver circuit | 1733 |

#### FM

| CA3089   | FM IF system                            | 47   |

|----------|-----------------------------------------|------|

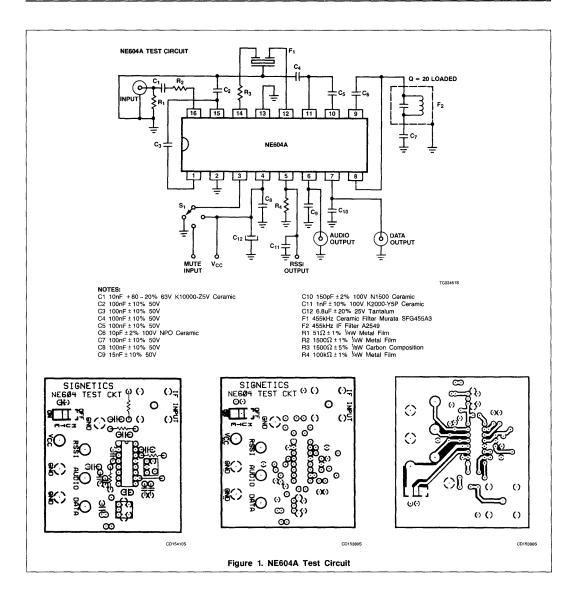

| NE604A   | high performance low-power FM IF system | 149  |

| NE605    | low-power FM IF system                  | 159  |

| NE614A   | low-power FM IF system                  | 169  |

| SA604A   | high performance low-power FM IF system | 149  |

| SA605    | low-power FM IF system                  | 159  |

| SA614A   | low-power FM IF system                  | 169  |

| TDA1574  | integrated FM tuner for radio receivers | 1187 |

| TDA1574T | integrated FM tuner for radio receivers | 1195 |

| TDA1576  | FM/IF amplifier and detector            | 1205 |

| type no.         | description                                                              | page       |

|------------------|--------------------------------------------------------------------------|------------|

| FM (continued)   | · · · · · · · · · · · · · · · · · · ·                                    |            |

| TDA1596          | FM/IF amplifier and detector                                             | 1249       |

| TDA1596T         | FM/IF amplifier and detector                                             | 1249       |

| TDA7000          | FM radio circuit; mono (in plastic D1L-18)                               | 1381       |

| TDA7000          | FM radio circuit; mono (in SO-16 plastic mini-pack)                      | 1389       |

| TDA7021T         | FM radio circuit; stereo/mono; for low voltage                           | 1309       |

|                  | micro tuning system (MTS)                                                | 1397       |

| TEA6100          | FM/IF system and microcomputer-based tuning                              |            |

|                  | interface; I <sup>2</sup> C-bus                                          | 1751       |

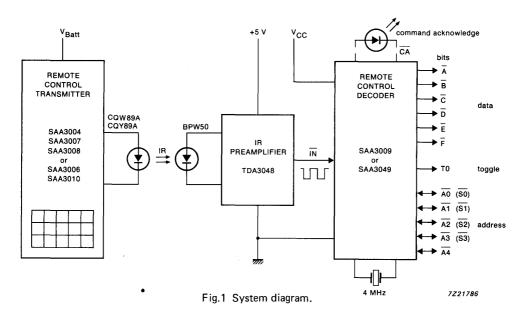

| REMOTE CONT      | ROLLERS                                                                  |            |

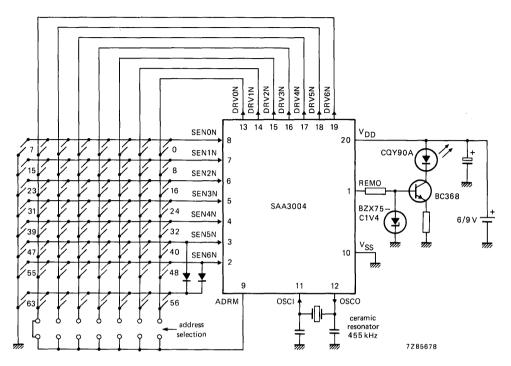

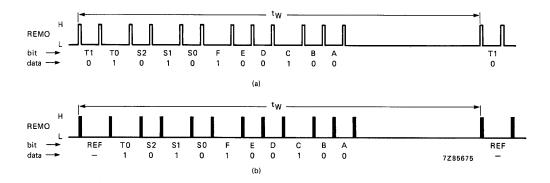

| SAA3004          | high performance transmitter (455 kHz) for infrared                      |            |

|                  | remote control; up to 448 commands                                       | 585        |

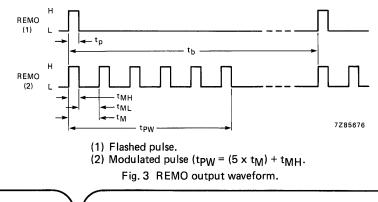

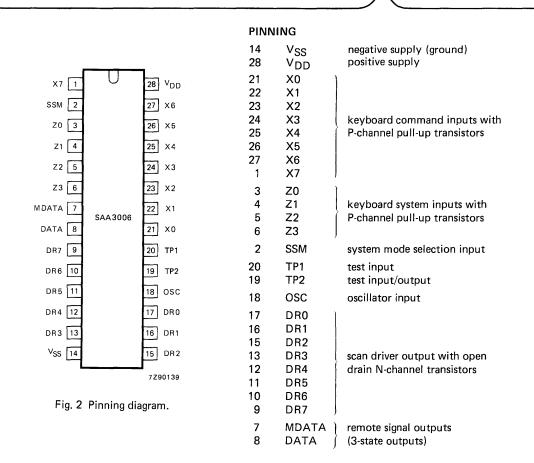

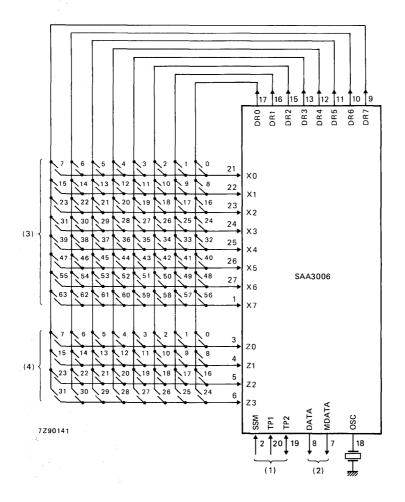

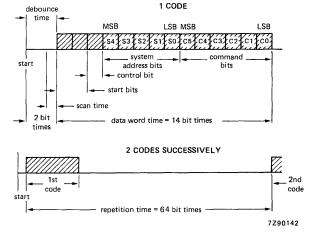

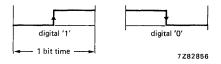

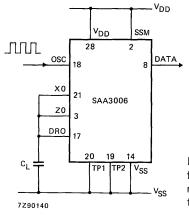

| SAA3006          | high performance transmitter (RC-5) for infrared                         |            |

|                  | remote control; up to 2048 commands                                      | 595        |

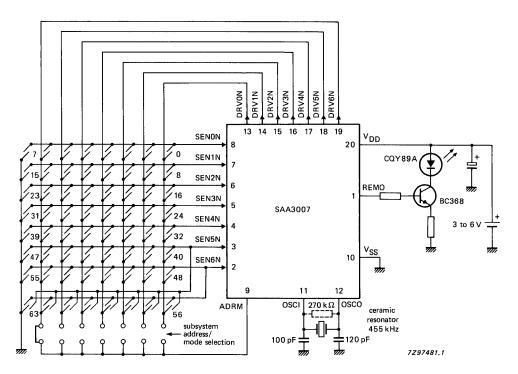

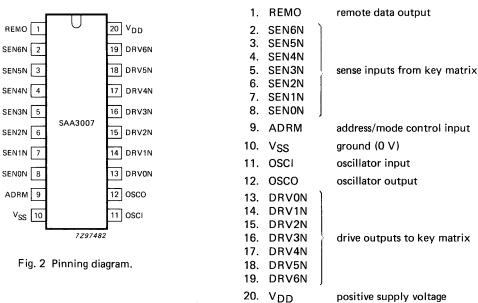

| SAA3007          | high performance transmitter (455 kHz) for infrared                      |            |

|                  | remote control; up to 1280 commands; low voltage                         | 609        |

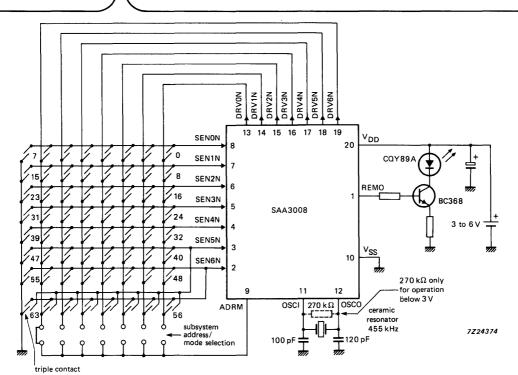

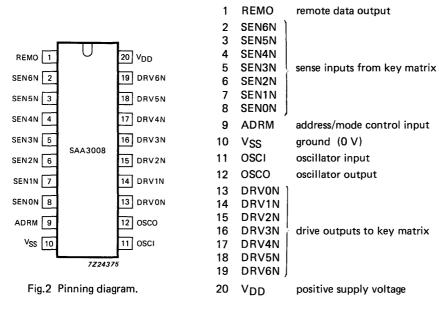

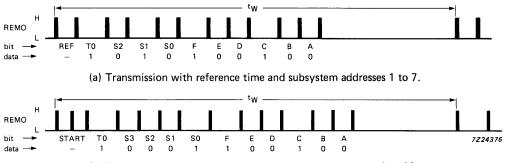

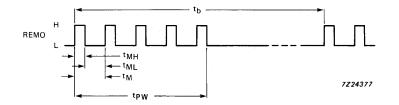

| SAA3008          | high performance transmitter (38 kHz) for infrared                       |            |

|                  | remote control; low voltage                                              | 623        |

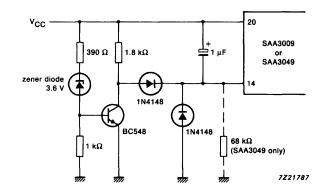

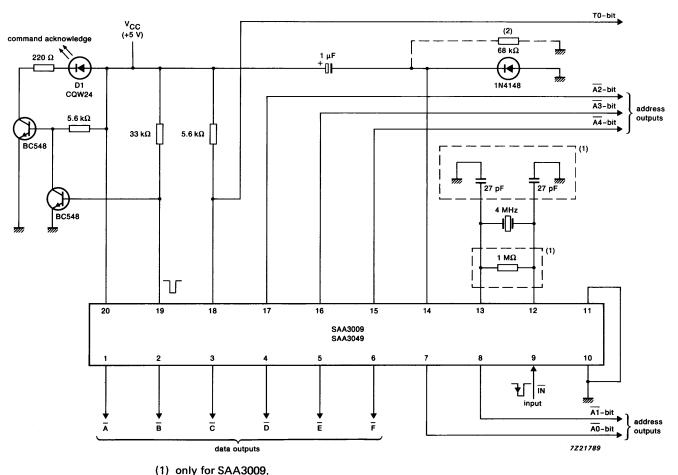

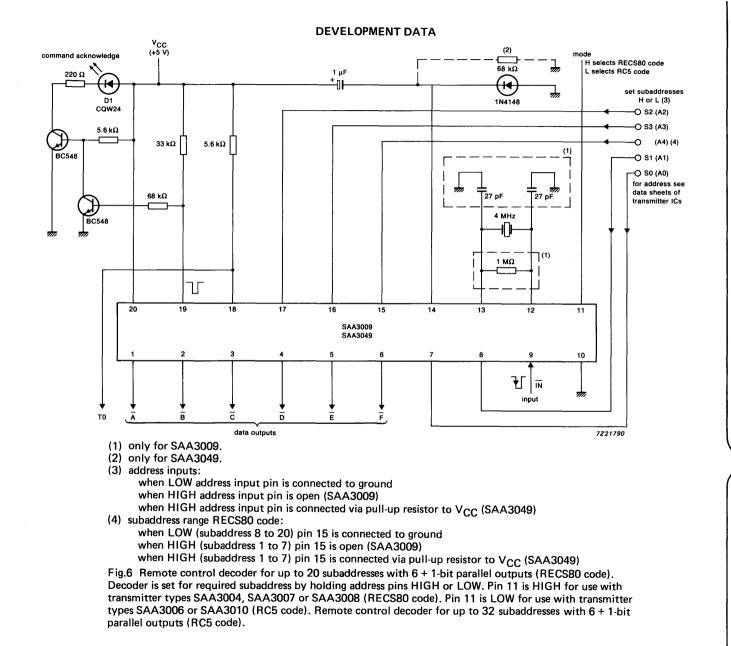

| SAA3009          | infrared remote control decoder; decodes 64 commands                     |            |

|                  | (RECS80/RC-5); up to 32 subaddresses; high current                       |            |

|                  | output capability for direct LED drive                                   | 637        |

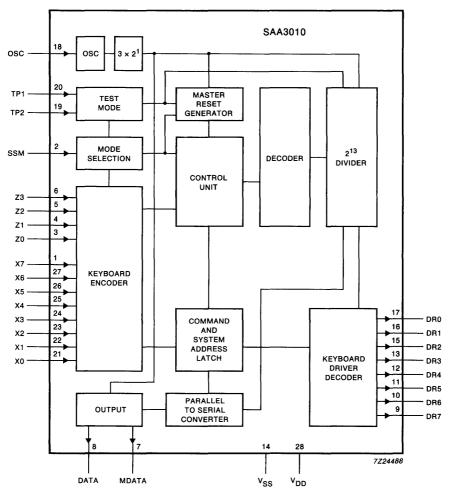

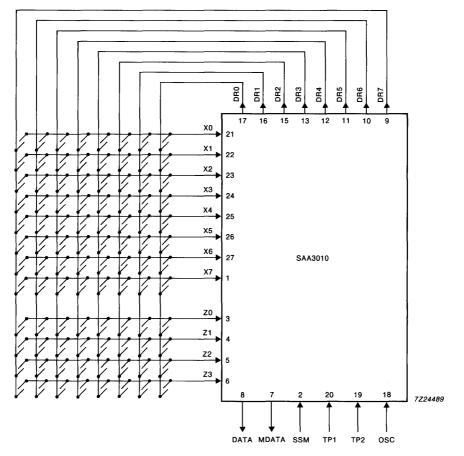

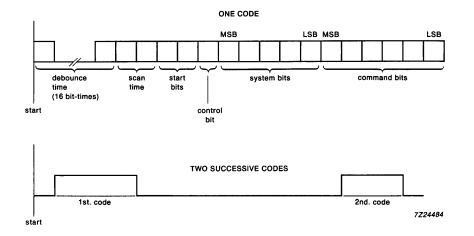

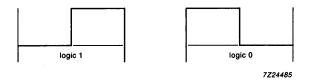

| SAA3010          | high-performance transmitter (RC-5) for infrared remote                  |            |

|                  | control; low voltage                                                     | 647        |

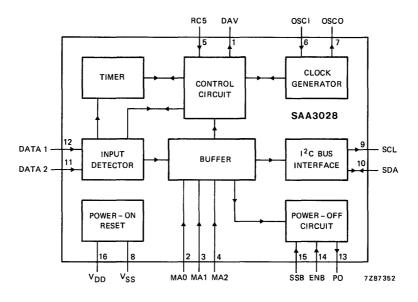

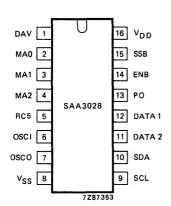

| SAA3028          | high performance transcoder (RC-5) for infrared remote                   |            |

|                  | control; l <sup>2</sup> C-bus                                            | 663        |

| SAA3049          | infrared remote control decoder, low current version                     |            |

|                  | of SAA3009                                                               | 637        |

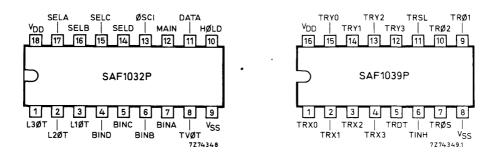

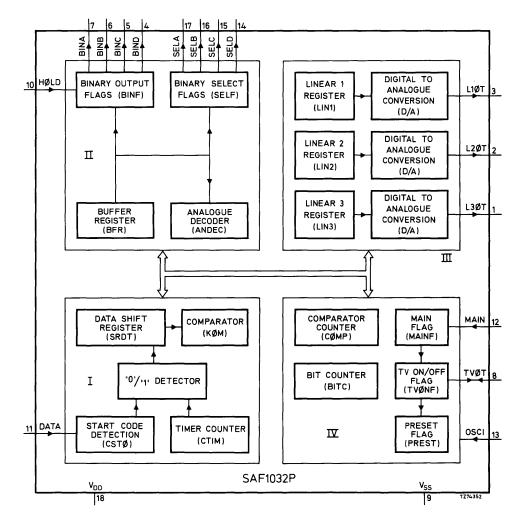

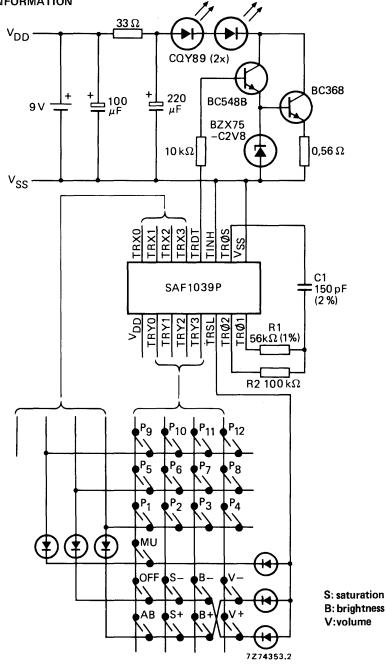

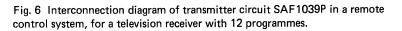

| SAF1032          | receiver/decoder for infrared remote control                             | 787        |

| SAF1039          | transmitter for infrared remote control                                  | 787        |

| TDA <b>3047</b>  | high performance receiver for infrared remote control;                   |            |

|                  | positive output voltage                                                  | 1323       |

| TDA <b>304</b> 8 | high performance receiver for infrared remote control;                   |            |

|                  | negative output voltage                                                  | 1329       |

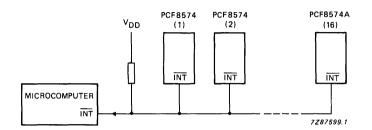

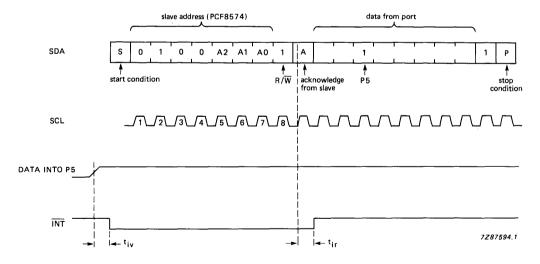

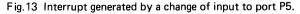

| REMOTE I/O EX    | PANDERS                                                                  |            |

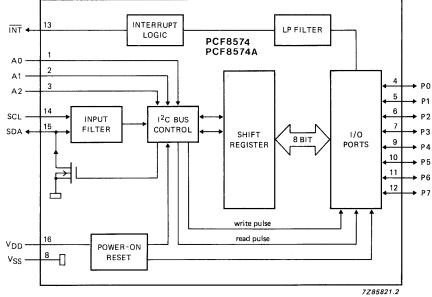

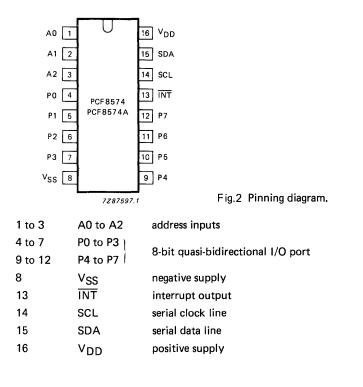

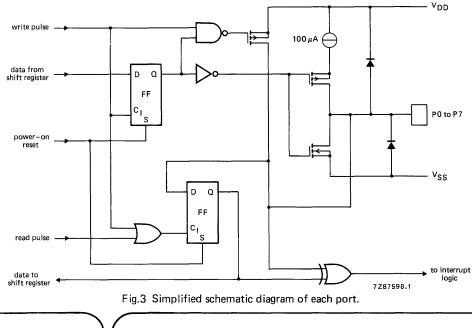

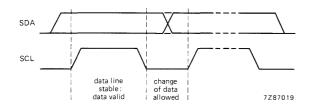

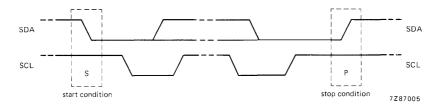

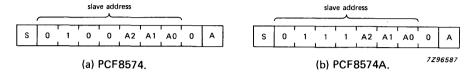

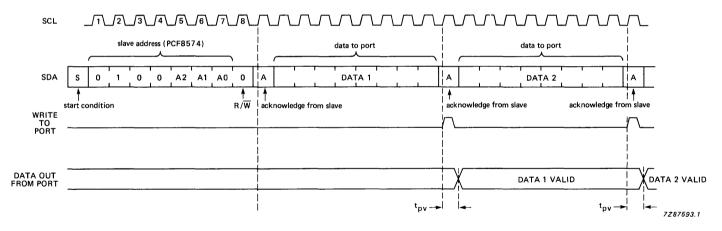

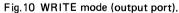

| PCF8574          | remote 8-bit I/O expander; I <sup>2</sup> C-bus                          | 347        |

| PCF8574A         | remote 8-bit I/O expander; I <sup>2</sup> C-bus; different slave address | 347        |

| SOUND GENERA     | ATOR                                                                     |            |

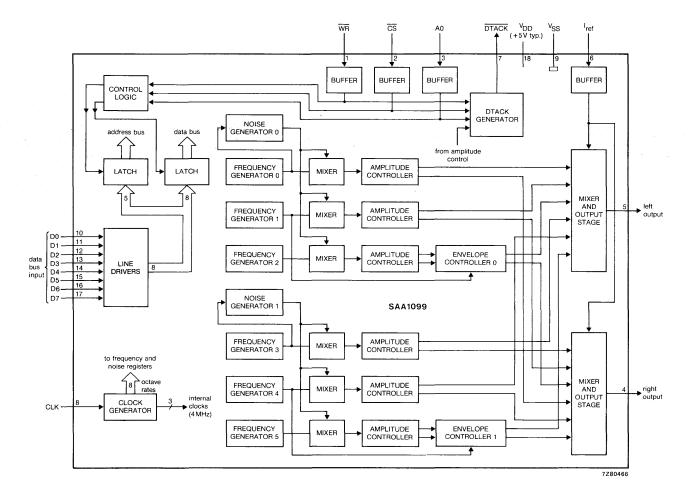

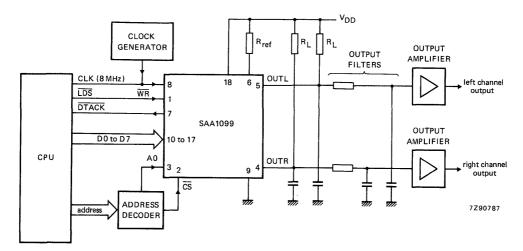

| SAA1099          | stereo sound generator for sound effects and music synthesis             |            |

|                  | $(\mu$ C-controlled)                                                     | 565        |

| SPEECH SYNTH     | ESIZERS                                                                  |            |

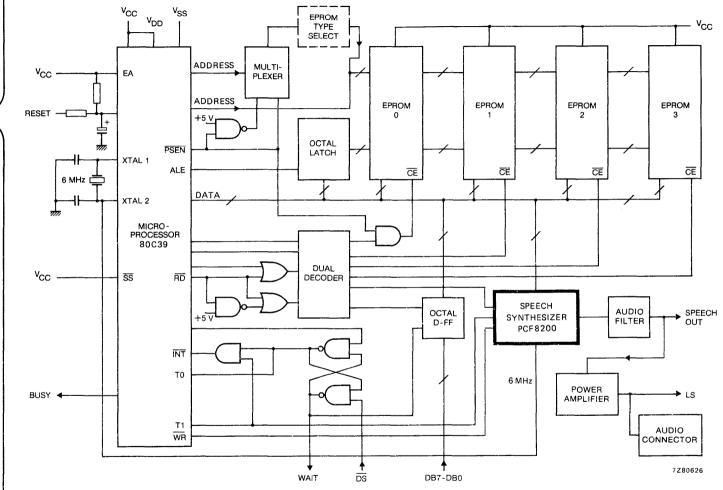

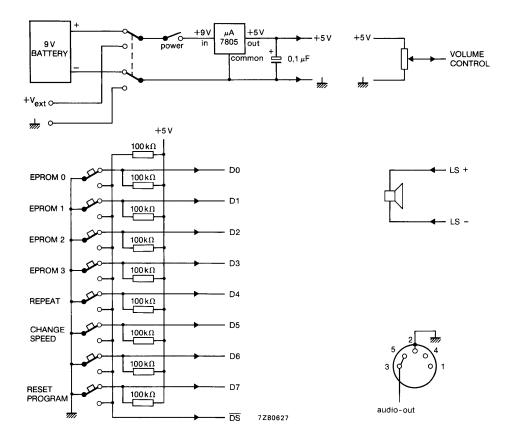

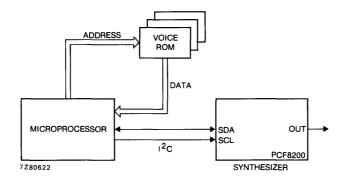

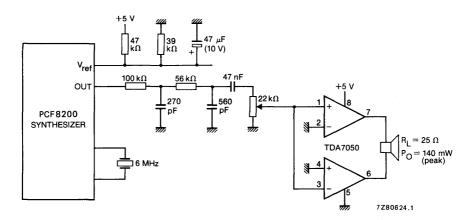

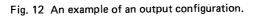

| OM8200           | speech demonstration board (PCF8200)                                     | 107        |

| OM8201           | speech demonstration box (PCF8200)                                       | 197<br>201 |

| OM8209           | update package for OM8010                                                | 201        |

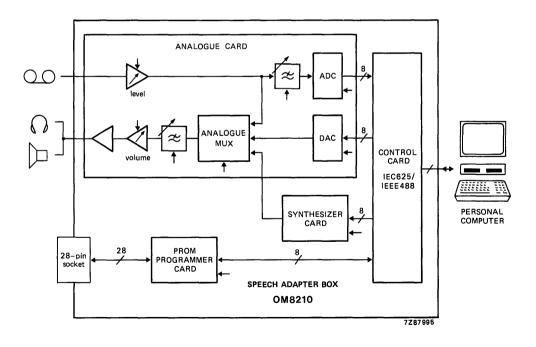

| OM8210           | speech analysis/editing system (PCF8200)                                 | 203        |

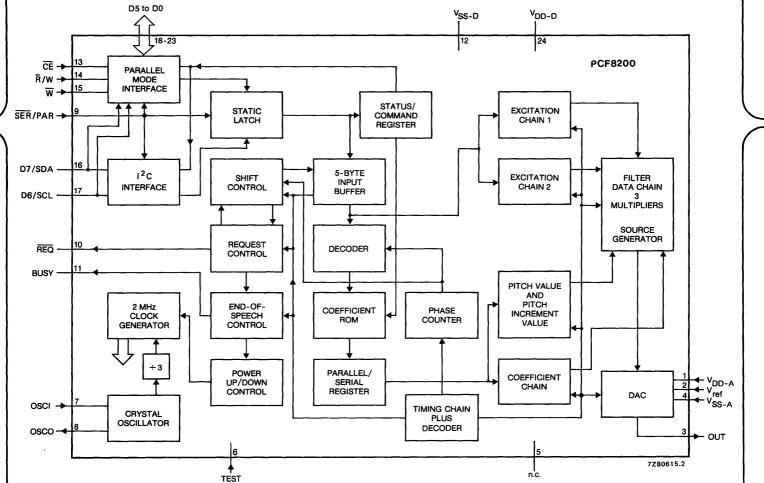

| PCF8200          | voice synthesizer (CMOS); 1 <sup>2</sup> C-bus                           | 205<br>267 |

| . 51 0200        | Voice synthesizer (CIVICO), r C-DUS                                      | 207        |

|                  |                                                                          |            |

| type no.     | description                                                  | page |

|--------------|--------------------------------------------------------------|------|

| STEREO DECOL | DERS                                                         |      |

| TDA1578A     | time multiplex PLL stereo decoder for hi-fi and car radios   | 1217 |

| TDA1598      | time multiplex PLL stereo decoder for hi-fi and car radios   | 1285 |

| TDA7040T     | PLL stereo decoder; low voltage                              | 1419 |

| TEA5580      | PLL stereo decoder for medium-fi and car radios              | 171  |

| TEA5581      | PLL stereo decoder with source selector switch for           |      |

|              | medium-fi and car radios                                     | 172  |

| TEA5581T     | PLL stereo decoder with source selector switch for           |      |

|              | medium-fi and car radios                                     | 172  |

| TSA6057      | radio tuning PLL frequency synthesizer; 1 <sup>2</sup> C-bus | 182  |

| TSA6057T     | radio tuning PLL frequency synthesizer; I <sup>2</sup> C-bus | 182  |

| μA758        | FM stereo multiplex decoder; PLL                             | 183  |

| TUNING CIRCU | ITS                                                          |      |

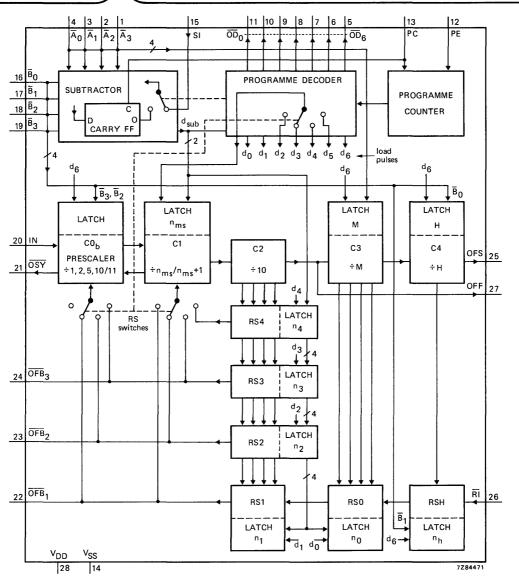

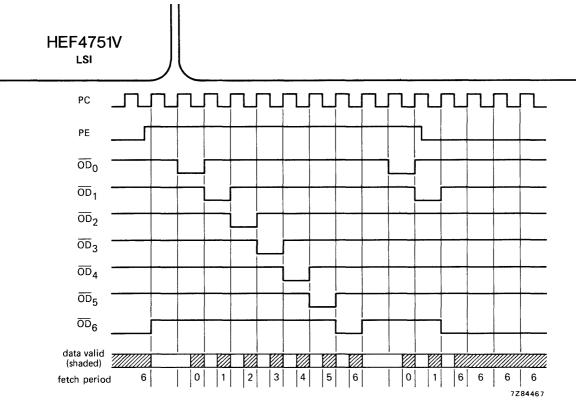

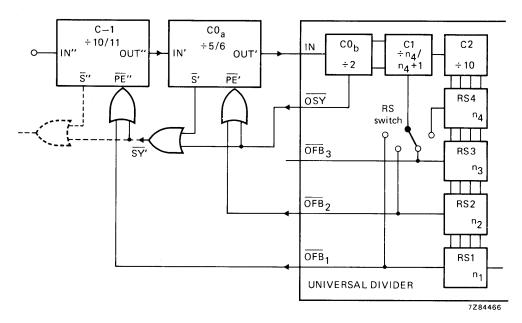

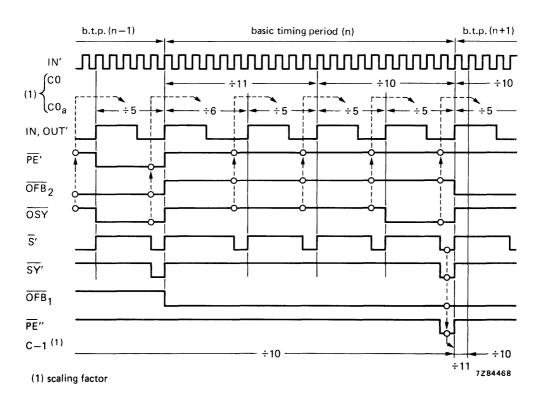

| HEF4750V     | frequency synthesizer                                        | 5    |

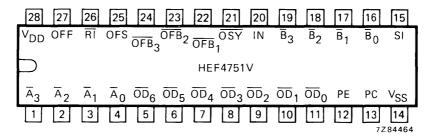

| HEF4751V     | universal divider                                            | 6    |

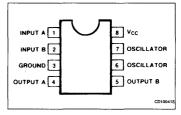

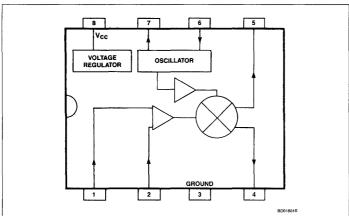

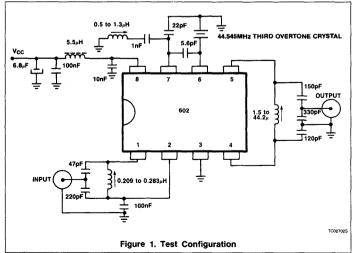

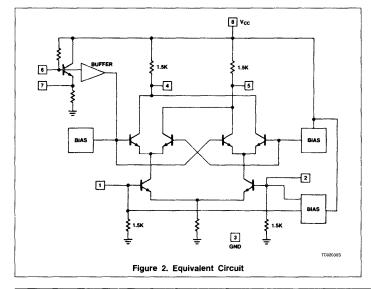

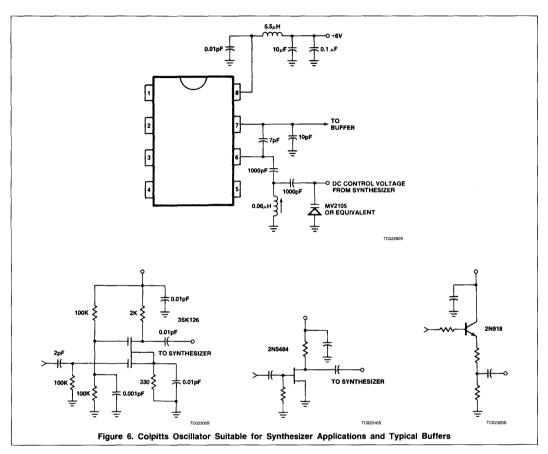

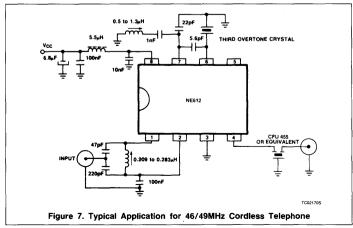

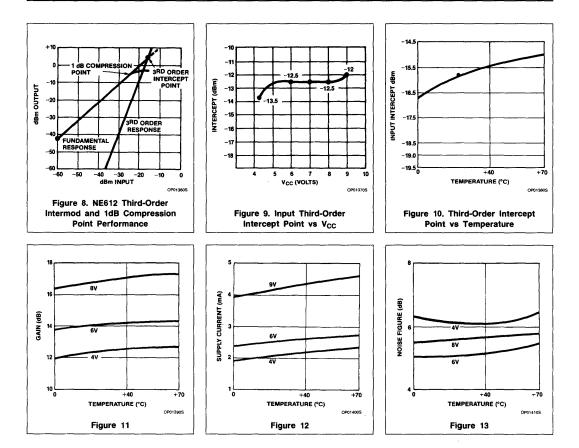

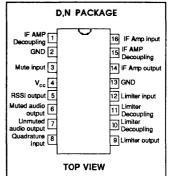

| NE602        | double-balanced mixer and oscillator                         | 14   |

| NE612        | double balanced mixer and oscillator                         | 16   |

| SA602        | double-balanced mixer and oscillator                         | 14   |

| SAA1057      | radio tuning PLL frequency synthesizer (SYMO II)             | 54   |

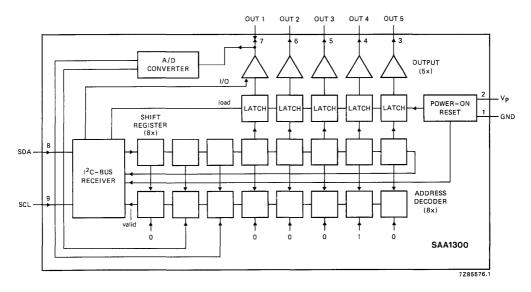

| SAA1300      | tuner switching circuit; 1 <sup>2</sup> C-bus                | 58   |

| TDA1574      | integrated FM tuner for radio receivers                      | 118  |

| TDA1574T     | integrated FM tuner for radio receivers                      | 119  |

|              |                                                              |      |

| SAA1300  | tuner switching circuit; 1 <sup>2</sup> C-bus | 581  |

|----------|-----------------------------------------------|------|

| TDA1574  | integrated FM tuner for radio receivers       | 1187 |

| TDA1574T | integrated FM tuner for radio receivers       | 1195 |

| TDA7030T | low voltage micro tuning system (MTS)         | 1407 |

| TDD1742T | low power frequency synthesizer (LOPSY)       | 1605 |

|          |                                               |      |

| type no.           | description                                                     | page |

|--------------------|-----------------------------------------------------------------|------|

| CA3089N            | FM IF system                                                    | 47   |

| HEF4750VD          | frequency synthesizer                                           | 53   |

| HEF <b>4750</b> VU | frequency synthesizer                                           | 53   |

| HEF4751VD          | universal divider                                               | 69   |

| HEF4751VP          | universal divider                                               | 69   |

| HEF4751VT          | universal divider                                               | 69   |

| HEF4751VU          | universal divider                                               | 69   |

| MAB8401B           | microcontroller; 128 x 8 RAM; piggy-back version                |      |

|                    | for MAB84XX family plus 8-bit LED driver; I <sup>2</sup> C-bus; |      |

|                    | 1.0 to 6 MHz; 0 to + 70 <sup>o</sup> C                          | 79   |

| MAB8401WP          | microcontroller; 128 x 8 RAM; piggy-back version                |      |

|                    | for MAB84XX family plus 8-bit LED driver; I <sup>2</sup> C-bus; |      |

|                    | 1.0 to 6 MHz; 0 to + 70 <sup>o</sup> C                          | 79   |

| MAB8411P           | microcontroller; 64 x 8 RAM; 1K x 8 ROM plus                    |      |

|                    | 8-bit LED driver; 20 I/O lines; I <sup>2</sup> C-bus;           |      |

|                    | 1.0 to 6 MHz; 0 to + 70 <sup>o</sup> C                          | 79   |

| MAB8411T           | microcontroller; 64 x 8 RAM; 1K x 8 ROM plus                    |      |

|                    | 8-bit LED driver; 20 I/O lines; I <sup>2</sup> C-bus;           |      |

|                    | 1.0 to 6 MHz; 0 to + 70 <sup>o</sup> C                          | 79   |

| MAB8421P           | microcontroller; 64 x 8 RAM; 2K x 8 ROM plus                    |      |

|                    | 8-bit LED driver; 20 I/O lines; I <sup>2</sup> C-bus;           |      |

|                    | 1.0 to 6 MHz; 0 to + 70 <sup>0</sup> C                          | 79   |

| MAB8421T           | microcontroller; 64 x 8 RAM; 2K x 8 ROM plus                    |      |

|                    | 8-bit LED driver; 20 I/O lines; I <sup>2</sup> C-bus;           |      |

|                    | 1.0 to 6 MHz; 0 to + 70 <sup>o</sup> C                          | 79   |

| MAB8422P           | microcontroller; 64 x 8 RAM; 2K x 8 ROM plus                    |      |

|                    | 8-bit LED driver; 15 I/O lines; I <sup>2</sup> C-bus;           |      |

|                    | 1.0 to 6 MHz; 0 to + 70 <sup>o</sup> C                          | 81   |

| MAB8441P           | microcontroller; 128 x 8 RAM; 4K x 8 ROM plus                   |      |

|                    | 8-bit LED driver; 20 I/O lines; I <sup>2</sup> C-bus;           |      |

|                    | 1.0 to 6 MHz; 0 to + 70 <sup>o</sup> C                          | 79   |

| MAB8441T           | microcontroller; 128 x 8 RAM; 4K x 8 ROM plus                   |      |

|                    | 8-bit LED driver; 20 I/O lines; I <sup>2</sup> C-bus;           |      |

|                    | 1.0 to 6 MHz; 0 to + 70 <sup>o</sup> C                          | 79   |

| MAB8442P           | microcontroller; 128 x 8 RAM; 4K x 8 ROM plus                   |      |

|                    | 8-bit LED driver; 15 I/O lines; I <sup>2</sup> C-bus;           |      |

|                    | 1.0 to 6 MHz; 0 to + 70 <sup>o</sup> C                          | 81   |

| MAB8461P           | microcontroller; 128 x 8 RAM; 6K x 8 ROM plus                   |      |

|                    | 8-bit LED driver; 20 I/O lines; I <sup>2</sup> C-bus;           |      |

|                    | 1.0 to 6 MHz; 0 to + 70 <sup>o</sup> C                          | 79   |

| MAB8461T           | microcontroller; 128 x 8 RAM; 6K x 8 ROM plus                   |      |

|                    | 8-bit LED driver; 20 I/O lines; I <sup>2</sup> C-bus;           |      |

|                    | 1.0 to 6 MHz; 0 to + 70 <sup>o</sup> C                          | 79   |

August 1989

| ype no.   | description                                           | page |

|-----------|-------------------------------------------------------|------|

| MAF84A11P | microcontroller; 64 x 8 RAM; 1K x 8 ROM plus          |      |

|           | 8-bit LED driver; 20 I/O lines; I <sup>2</sup> C-bus; |      |

|           | 1.0 to 5 MHz; –40 to + 110 <sup>o</sup> C             | 79   |

| /AF84A21P | microcontroller; 64 x 8 RAM; 2K x 8 ROM plus          |      |

|           | 8-bit LED driver; 20 I/O lines; I <sup>2</sup> C-bus; |      |

|           | 1.0 to 5 MHz; -40 to + 110 °C                         | 79   |

| AF84A22P  | microcontroller; 64 x 8 RAM; 2K x 8 ROM plus          |      |

|           | 8-bit LED driver; 15 I/O lines; I <sup>2</sup> C-bus; |      |

|           | 1.0 to 5 MHz; –40 to + 110 <sup>o</sup> C             | 81   |

| 1AF84A41P | microcontroller; 128 x 8 RAM; 4K x 8 ROM plus         |      |

|           | 8-bit LED driver; 20 I/O lines; I <sup>2</sup> C-bus; |      |

|           | 1.0 to 5 MHz; -40 to + 110 °C                         | 79   |

| 1AF84A42P | microcontroller; 128 x 8 RAM; 4K x 8 ROM plus         |      |

|           | 8-bit LED driver; 15 I/O lines; I <sup>2</sup> C-bus; |      |

|           | 1.0 to 5 MHz; -40 to + 110 °C                         | 81   |

| 1AF84A61P | microcontroller; 128 x 8 RAM; 6K x 8 ROM plus         |      |

|           | 8-bit LED driver; 20 I/O lines; I <sup>2</sup> C-bus; |      |

|           | 1.0 to 5 MHz; -40 to + 110 °C                         | 79   |

| 1AF8411P  | microcontroller; 64 x 8 RAM; 1K x 8 ROM plus          |      |

|           | 8-bit LED driver; 20 I/O lines; I <sup>2</sup> C-bus; |      |

|           | 1.0 to 6 MHz; -40 to +85 °C                           | 79   |

| 1AF8421P  | microcontroller; 64 x 8 RAM; 2K x 8 ROM plus          |      |

|           | 8-bit LED driver; 20 I/O lines; I <sup>2</sup> C-bus; |      |

|           | 1.0 to 6 MHz; -40 to + 85 °C                          | 79   |

| 1AF8422P  | microcontroller; 64 x 8 RAM; 2K x 8 ROM plus          |      |

|           | 8-bit LED driver; 15 I/O lines; I <sup>2</sup> C-bus; |      |

|           | 1.0 to 6 MHz; -40 to + 85 °C                          | 81   |

| 1AF8441P  | microcontroller; 128 x 8 RAM; 4K x 8 ROM plus         |      |

|           | 8-bit LED driver; 20 I/O lines; I <sup>2</sup> C-bus; |      |

|           | 1.0 to 6 MHz; -40 to + 85 °C                          | 79   |

| 1AF8442P  | microcontroller; 128 x 8 RAM; 4K x 8 ROM plus         |      |

|           | 8-bit LED driver; 15 I/O lines; I <sup>2</sup> C-bus; |      |

|           | 1.0 to 6 MHz; -40 to + 85 °C                          | 81   |

| /IAF8461P | microcontroller; 128 x 8 RAM; 6K x 8 ROM plus         |      |

|           | 8-bit LED driver; 20 I/O lines; I <sup>2</sup> C-bus; |      |

|           | 1.0 to 6 MHz; -40 to + 85 °C                          | 79   |

| 1C3410F   | 10-bit high-speed multiplying DAC                     | 83   |

| 1C3410CF  | 10-bit high-speed multiplying DAC                     | 83   |

| 1C3510F   | 10-bit high-speed multiplying DAC                     | 83   |

| IE542N    | dual low-noise preamplifier                           | 91   |

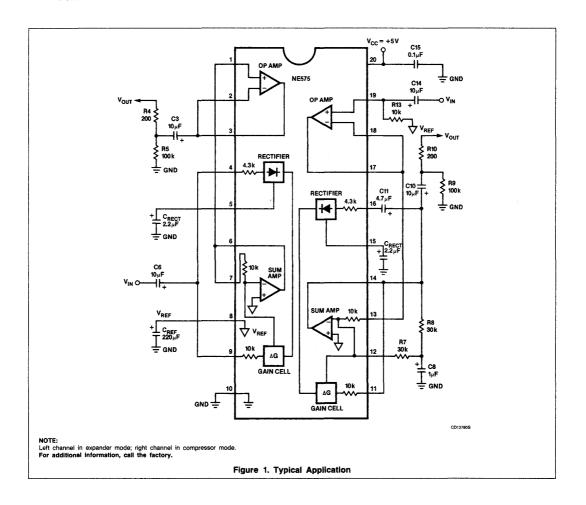

| IE570F    | compandor                                             | 95   |

| E570N     | compandor                                             | 95   |

| IE571D    | compandor                                             | 95   |

| E571F     | compandor                                             | 95   |

| IE571N    | compandor                                             | 95   |

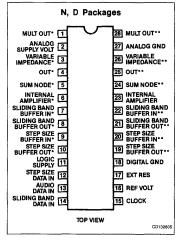

| IE572D    | programmable analogue compandor                       | 103  |

| E572N     | programmable analogue compandor                       | 103  |

| IE575D    | low voltage compandor                                 | 111  |

| IE575N    | low voltage compandor                                 | 111  |

| 1E5240D   | Dolby digital audio decoder                           | 115  |

18

| суре          | description                                                     | page |

|---------------|-----------------------------------------------------------------|------|

| NE5240N       | Dolby digital audio decoder                                     | 115  |

| NE5410F       | 10-bit high-speed multiplying DAC                               | 119  |

| NE5532D       | internally-compensated dual low noise operational amplifier     | 129  |

| NE5532N       | internally-compensated dual low noise operational amplifier     | 129  |

| NE5532FE      | internally compensated dual low noise operational amplifier     | 129  |

| 1E5532AN      | internally-compensated dual low noise operational amplifier     | 129  |

| NE5532AFE     | internally-compensated dual low noise operational amplifier     | 129  |

| E5533D        | dual and single low noise operational amplifier                 | 135  |

| 1E5533N       | dual and single low noise operational amplifier                 | 13   |

| 1E5533AD      | dual and single low noise operational amplifier                 | 139  |

| 1E5533AN      | dual and single low noise operational amplifier                 | 135  |

| VE5534D       | dual and single low noise operational amplifier                 | 13   |

| IE5534N       | dual and single low noise operational amplifier                 | 13   |

| E5534FE       | dual and single low noise operational amplifier                 | 13   |

| IE5534AD      | dual and single low noise operational amplifier                 | 13   |

| IE5534AN      | dual and single low noise operational amplifier                 | 13   |

| E5534AFE      | dual and single low noise operational amplifier                 | 13   |

| 1E602D        | double-balanced mixer and oscillator                            | 14:  |

| E602N         | double-balanced mixer and oscillator                            | 14   |

| E602FE        | double-balanced mixer and oscillatoe                            | 14   |

| IE604AD       | high performance low-power FM IF system                         | 14   |

| IE604AN       | high performance low-power FM IF system                         | 14   |

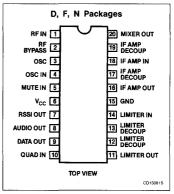

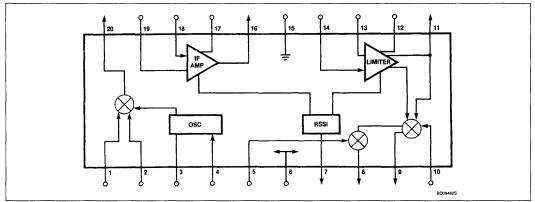

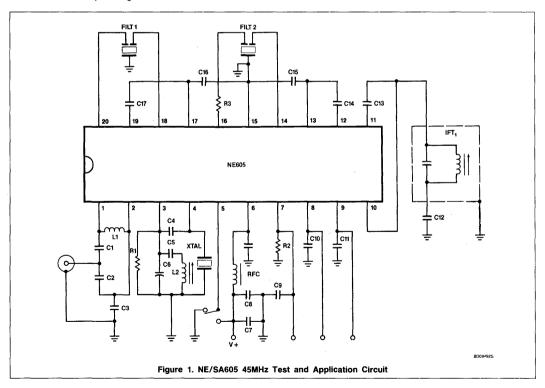

| 1E605D        | low-power FM IF system                                          | 15   |

| 1E605F        | low-power FM IF system                                          | 15   |

| 1E605N        | low-power FM IF system                                          | 15   |

| E612D         | double-balanced mixer and oscillator                            | 16   |

| 1E612N        | double-balanced mixer and oscillator                            | 16   |

| NE614AD       | low-power FM IF system                                          | 16   |

| IE614AN       | low-power FM IF system                                          | 16   |

| 1E645N        | Dolby B and C type noise reduction circuit                      | 17   |

| 1E646N        | Dolby B and C type noise reduction circuit                      | 17   |

| 1E649N        | low voltage Dolby B type noise reduction circuit                | 18   |

| 1E650N        | Dolby B type noise reduction circuit                            | 19   |

| DM8200        | speech demonstration board (PCF8200)                            | 19   |

| DM8201        | speech demonstration box (PCF8200)                              | 20   |

| DM8209        | update package for OM8010                                       | 20   |

| DM8210        | speech analysis/editing system (PCF8200)                        | 20   |

| CA80C31BH-3P  | microcontroller; 128 x 8 RAM; 1.2 to 12 MHz;                    |      |

| CABOCOTENTION | $-40 \text{ to } + 125 ^{\circ}\text{C}$                        | 20   |

| CA80C31BH-3WP | microcontroller; 128 x 8 RAM; 1.2 to 12 MHz;<br>-40 to + 125 °C | 20   |

| PCA80C39P     | microcontroller; 128 x 8 RAM; 1.0 to 15 MHz;<br>-40 to + 110 °C | 21   |

| PCA80C39WP    | microcontroller; 128 x 8 RAM; 1.0 to 15 MHz;<br>-40 to + 110 °C | 21   |

| PCA80C49P     | microcontroller; 128 x 8 RAM; 2K x 8 ROM;                       |      |

|               | 1.0 to 15 MHz; -40 to + 110 °C                                  | 21   |

| PCA80C49WP    | microcontroller; 128 x 8 RAM; 2K x 8 ROM;                       |      |

| type           | description                                                                   | page |

|----------------|-------------------------------------------------------------------------------|------|

| PCA80C51BH-3P  | microcontroller; 128 x 8 RAM; 4K x 8 ROM;                                     |      |

| -              | 1.2 to 12 MHz; -40 to + 125 °C                                                | 209  |

| CA80C51BH-3WP  | microcontroller; 128 x 8 RAM; 4K x 8 ROM;                                     |      |

|                | 1.2 to 12 MHz;40 to + 125 °C                                                  | 209  |

| CA80C552WP     | microcontroller; 256 x 8 RAM; 80C31 CPU plus                                  |      |

|                | 16-bit capture/compare timer/counter; watch-dog timer;                        |      |

|                | 2 pulse-width modulated signals; 10-bit ADC with                              |      |

|                | 8 multiplexed input lines; I <sup>2</sup> C-bus; 1.2 to 12 MHz;               |      |

|                | –40 to + 125 <sup>o</sup> C                                                   | 213  |

| CA80C562WP     | microcontroller; 256 x 8 RAM; 80C31 CPU plus                                  |      |

|                | 16-bit capture/compare timer/counter; watch-dog timer;                        |      |

|                | 2 pulse-width modulated signals; 8-bit ADC with                               |      |

|                | 8 multiplexed input lines; 1.2 to 12 MHz;                                     |      |

|                | –40 to + 125 °C                                                               | 215  |

| CA80C652P      | microcontroller; 256 x 8 RAM; serial I/O; UART;                               |      |

|                | l <sup>2</sup> C-bus; 1.2 to 12 MHz; –40 to + 125 <sup>o</sup> C              | 217  |

| CA80C652WP     | microcontroller; 256 x 8 RAM; serial I/O; UART;                               |      |

|                | I <sup>2</sup> C-bus; 1.2 to 12 MHz; –40 to + 125 <sup>o</sup> C              | 217  |

| PCA83C552WP    | microcontroller; 256 x 8 RAM; 8K x 8 ROM; 80C51 CPU                           |      |

|                | plus 16-bit capture/compare timer/counter; watch-dog timer;                   |      |

|                | 2 pulse-width modulated signals; 10-bit ADC with 8 multiplexed                |      |

|                | input lines; I <sup>2</sup> C-bus; 1.2 to 12 MHz; -40 to + 125 <sup>o</sup> C | 213  |

| PCA83C562WP    | microcontroller; 256 x 8 RAM; 8K x 8 ROM; 80C51 CPU                           |      |

|                | plus 16-bit capture/compare timer/counter; watch-dog timer;                   |      |

|                | 2 pulse-width modulated signals; 8 multiplexed input lines;                   |      |

|                | 1.2 to 12 MHz;40 to + 125 <sup>o</sup> C                                      | 215  |

| PCA83C652P     | microcontroller; 256 x 8 RAM; 8K x 8 ROM; serial I/O;                         |      |

|                | UART; I <sup>2</sup> C-bus; 1.2 to 12 MHz; –40 to + 125 <sup>o</sup> C        | 217  |

| PCA83C652WP    | microcontroller; 256 x 8 RAM; 8K x 8 ROM; serial I/O;                         |      |

|                | UART; I <sup>2</sup> C-bus; 1.2 to 12 MHz; –40 to + 125 <sup>o</sup> C        | 217  |

| PCA83C654P     | microcontroller; 256 x 8 RAM; 16K x 8 ROM; serial I/O;                        |      |

|                | UART; I <sup>2</sup> C-bus; 1.2 to 12 MHz; -40 to + 125 <sup>o</sup> C        | 219  |

| PCA83C654WP    | microcontroller; 256 x 8 RAM; 16K x 8 ROM; serial I/O;                        |      |

|                | UART; I <sup>2</sup> C-bus; 1.2 to 12 MHz; –40 to + 125 <sup>o</sup> C        | 219  |

| PCB80C31BH-3P  | microcontroller; 128 x 8 RAM; 0.5 to 12 MHz;                                  |      |

|                | 0 to + 70 <sup>o</sup> C                                                      | 209  |

| PCB80C31BH-3WP | microcontroller; 128 x 8 RAM; 0.5 to 12 MHz;                                  |      |