# MEMORY DATABOOK 1986

First Edition: July 1986

# MEMORY DATABOOK 1986

IC MEMORY LINE-UP AND TYPICAL CHARACTERISTICS

PACKAGING 2

RELIABILITY INFORMATION

MOS MEMORY

HANDLING PRECAUTIONS

EPROM WRITING AND ERASURE

MASK ROM CUSTOMER PROGRAM SPECIFICATIONS

MASK ROM DEVELOPMENT FLOWCHART

> TERMINOLOGY AND SYMBOLS

DATA SHEET

CROSS REFERENCE LIST

**APPLICATIONS**

## **CONTENTS**

|   | IC MEMORY LINE-UP AND TYPICAL CHARACTERISTICS       | 3  |

|---|-----------------------------------------------------|----|

|   | • DYNAMIC RAMS                                      | 5  |

|   | SIP/SIMM MODULE                                     | 6  |

|   | NMOS STATIC RAMS                                    | 7  |

|   | CMOS STATIC RAMS                                    | 7  |

|   | • MASK ROMS                                         | 8  |

|   | • EPROMS                                            | 9  |

|   | • E <sup>2</sup> P ROMS                             | 9  |

| 2 | PACKAGING                                           | 13 |

|   | • 16 PIN PLASTIC                                    | 15 |

|   | 16 PIN STACK PLASTIC                                | 16 |

|   | • 18 PIN PLCC                                       | 16 |

|   | • 18 PIN PLASTIC                                    | 17 |

|   | • 18 PIN SIDE-BRAZED                                | 17 |

|   | • 22 PIN PLCC                                       | 18 |

|   | • 22 PIN PLASTIC                                    | 18 |

|   | • 24 PIN PLASTIC                                    | 19 |

|   | • 24 PIN CERDIP                                     | 19 |

|   | 24 PIN PLASTIC FLAT                                 |    |

|   | • 26 PIN SOJ                                        |    |

|   | 28 PIN PLASTIC                                      |    |

|   | • 28 PIN CERDIP                                     |    |

|   | • 32 PIN PLCC                                       |    |

|   | 40 PIN SIDE-BRAZED                                  |    |

| 3 | RELIABILITY INFORMATION                             |    |

|   | 1. INTRODUCTION                                     |    |

|   | 2. QUALITY ASSURANCE SYSTEM AND UNDERLYING CONCEPTS |    |

|   | 3. EXAMPLE OF RELIABILITY TEST RESULTS              |    |

|   | 4. SEMICONDUCTOR MEMORY FAILURES                    |    |

| 4 | MOS MEMORY HANDLING PRECAUTIONS                     |    |

|   | 1. STATIC ELECTRICITY COUNTERMEASURES               |    |

|   | 2. POWER SUPPLY AND INPUT SIGNAL NOISE              |    |

|   | 3. CMOS MEMORY OPERATING PRECAUTIONS                |    |

| 5 | EPROM WRITING AND ERASURE                           |    |

|   | 1. EPROM WRITING ERASURE                            |    |

| _ | 2. EPROM HANDLING                                   |    |

| 6 | MASK ROM CUSTOMER PROGRAM SPECIFICATIONS            |    |

|   | 1. USABLE MEDIA                                     |    |

|   | 2. MAGNETIC TAPE SPECIFICATIONS                     |    |

|   | 3. EPROM SPECIFICATIONS                             |    |

|   | MASK ROM DEVELOPMENT FLOWCHART                      | 47 |

| 8 | TERM | IINOLOGY AND SYM | BOLS                                                    | 51  |

|---|------|------------------|---------------------------------------------------------|-----|

| _ |      |                  |                                                         |     |

|   | 2.   | ABSOLUTE MAXIMU  | IM RATINGS                                              | 52  |

|   | 3.   | RECOMMENDED OF   | ERATION CONDITIONS                                      | 53  |

|   |      |                  | ICS                                                     |     |

|   | 5.   | AC CHARACTERIST  | cs                                                      | 55  |

| 9 | DATA | SHEET            |                                                         |     |

|   | •    | MOS DYNAMIC RAM  | IS .                                                    |     |

|   |      | MSM 3732AS/RS    | 32,768-Word × 1-Bit RAM (NMOS)                          | 60  |

|   |      | MSM3764AS/RS     | 65,536-Word × 1-Bit RAM (NMOS)                          | 76  |

|   |      | MSM3764AAS/ARS   | 65,536-Word × 1-Bit RAM (NMOS)                          |     |

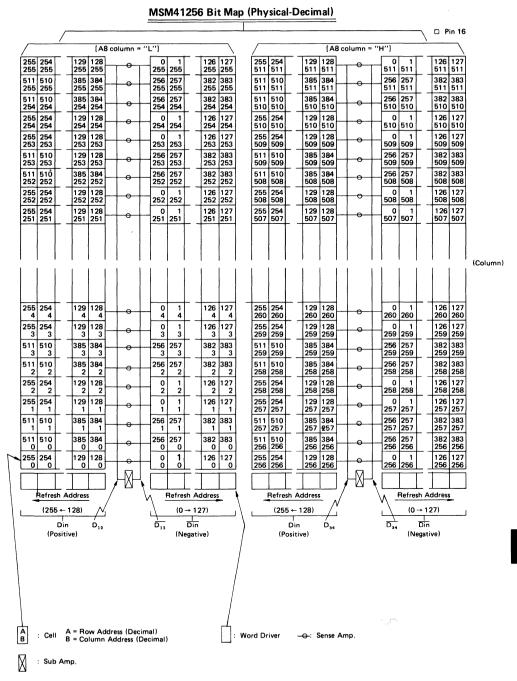

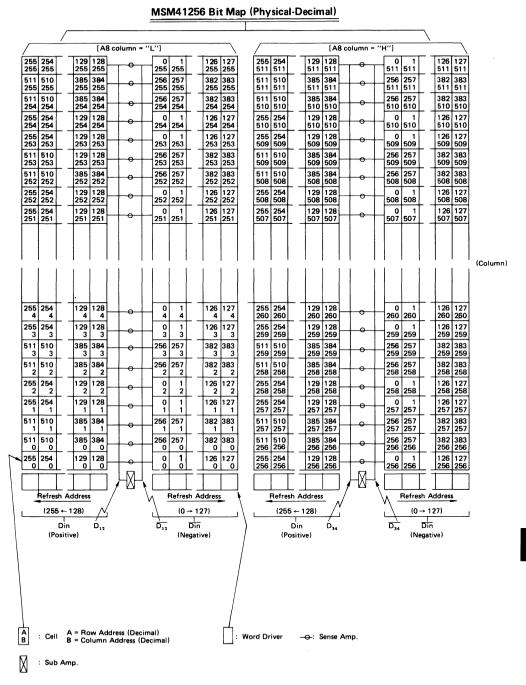

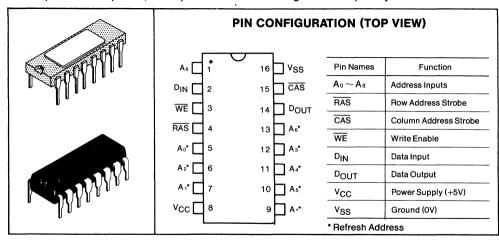

|   |      | MSM41256AS/RS    | 262,144-Word × 1-Bit RAM (NMOS) < Page Mode >           | 108 |

|   |      | MSM41256JS       | 262,144-Word × 1-Bit RAM (NMOS) < Page Mode >           |     |

|   |      | MSM41256AAS/RS   | 262,144-Word × 1-Bit RAM (NMOS) < Page Mode >           | 132 |

|   |      | MSM41257AAS/RS   | 262,144-Word × 1-Bit RAM (NMOS) < Nibble Mode >         | 147 |

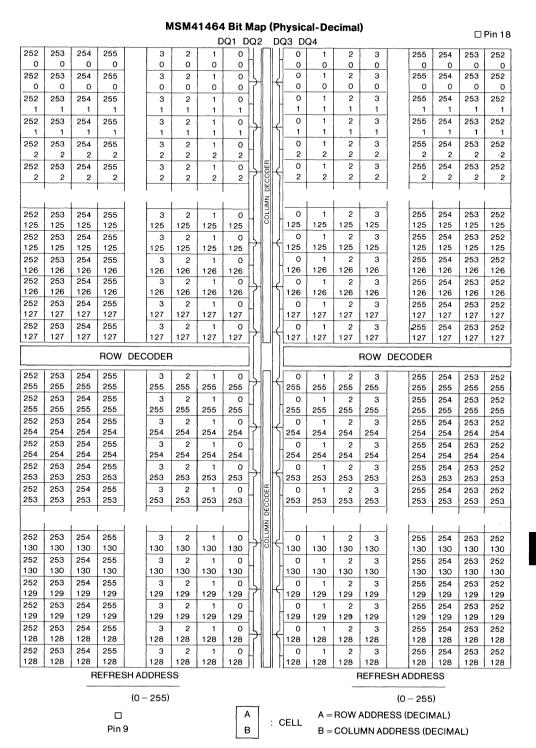

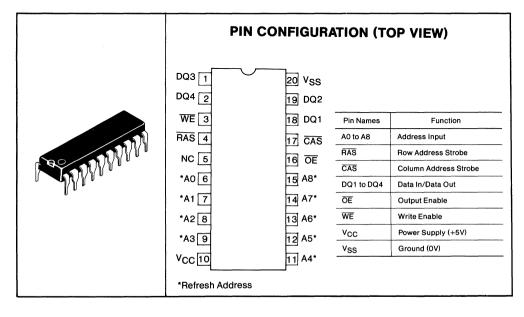

|   |      | MSM41464RS       | 65,536-Word × 4-Bit RAM (NMOS)                          |     |

|   |      | MSM414256RS      | 262,144-Word × 4-Bit RAM (NMOS)                         | 178 |

|   |      | MSM411000RS      | 1,048,576-Word × 1-Bit RAM (NMOS)                       | 191 |

|   |      | MSM411001RS      | 1,048,576-Word × 1-Bit RAM (NMOS) < Nibble Mode >       | 204 |

|   |      | MSM511000RS      | 1,048,576-Word × 1-Bit RAM (NMOS) <fast page=""></fast> | 217 |

|   |      | MSM511001RS      | 1,048,576-Word × 1-Bit RAM (NMOS) < Static Column >     | 218 |

|   |      | MSM514256RS      | 262,144-Word × 4-Bit RAM (CMOS) <fast page=""></fast>   | 219 |

|   |      | MSM514257RS      | 262,144-Word × 4-Bit RAM (CMOS) < Static Column >       | 220 |

|   |      | MSM37S64ARS/37   | S64RS 131,072-Word × 4-Bit RAM (NMOS)                   | 221 |

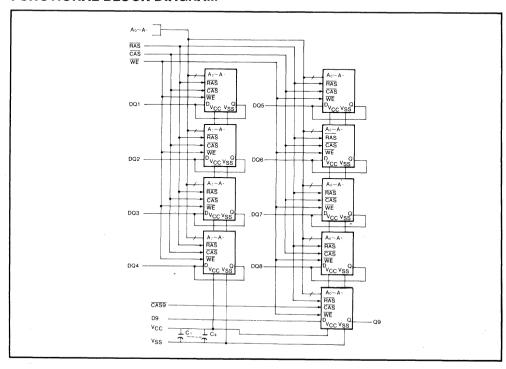

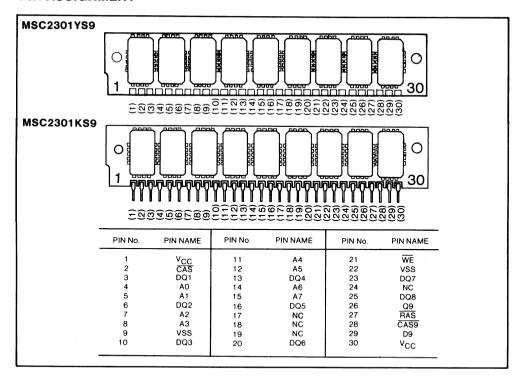

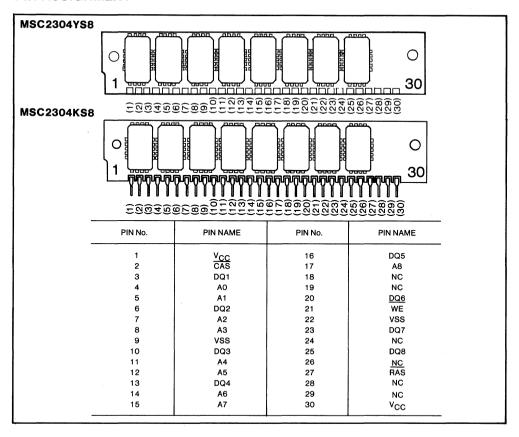

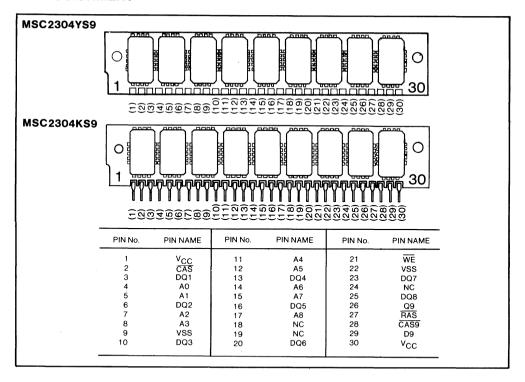

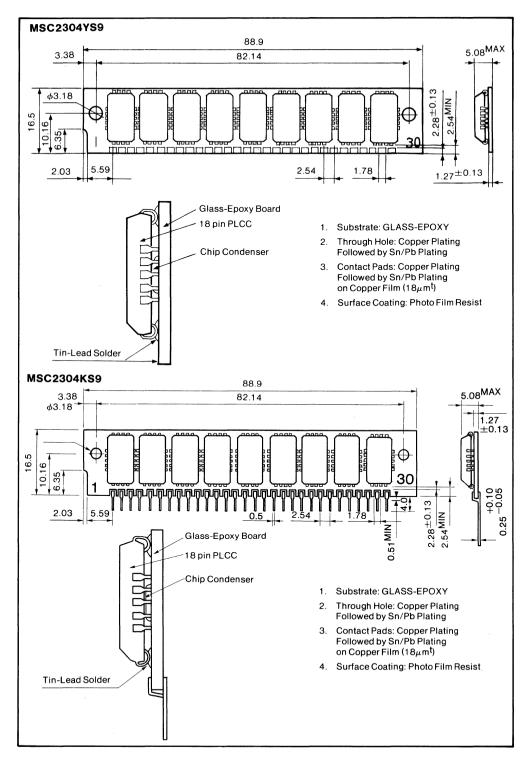

|   |      | MSC2301YS9/KS9   | 65,536-Word × 9-Bit RAM (NMOS)                          | 234 |

|   |      | MSC2304YS8/KS8   | 262,144-Word × 8-Bit RAM (NMOS)                         | 245 |

|   |      | MSC2304YS9/KS9   | 262,144-Word × 9-Bit RAM (NMOS)                         | 256 |

|   | •    | MOS STATIC RAMS  |                                                         |     |

|   |      | MSM5114RS        | 4,096-Word $\times$ 4-Bit RAM (CMOS)                    | 268 |

|   |      | MSM2128RS        | 2,048-Word $\times$ 8-Bit RAM (NMOS)                    | 273 |

|   |      | MSM5128RS        | 2,048-Word $\times$ 8-Bit RAM (CMOS)                    | 278 |

|   |      | MSM5128-20GSK    | 2,048-Word $\times$ 8-Bit RAM (CMOS)                    | 283 |

|   |      | MSM5126RS        | 2,048-Word $\times$ 8-Bit RAM (CMOS)                    | 289 |

|   |      | MSM5165RS/JS     | 8,192-Word $\times$ 8-Bit RAM (CMOS)                    | 294 |

|   |      | MSM5165LRS/JS    | 8,192-Word $\times$ 8-Bit RAM (CMOS)                    | 300 |

|   |      | MSM5188US        | 16,384-Word $\times$ 4-Bit RAM (CMOS)                   | 307 |

|   |      | MSM5127RS/JS     | 32,768-Word $\times$ 8-Bit RAM (CMOS)                   | 312 |

|   |      | MSM51257LRS/JS   | 32,768-Word $\times$ 8-Bit RAM (CMOS)                   | 318 |

|   | •    | MOS MASK ROMS    |                                                         |     |

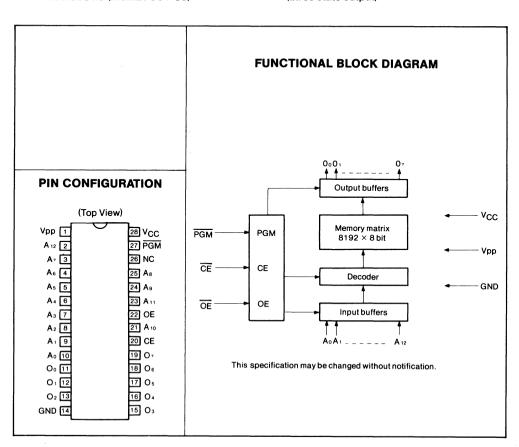

|   |      | MSM3864RS        | 8,192-Word $\times$ 8-Bit MASK ROM (NMOS)               | 326 |

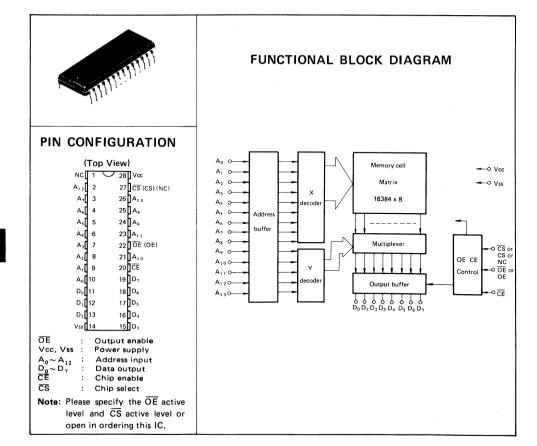

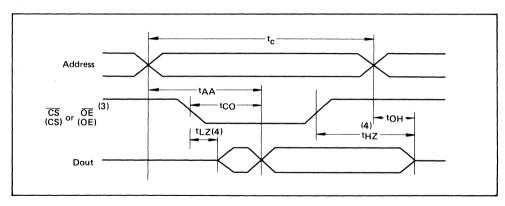

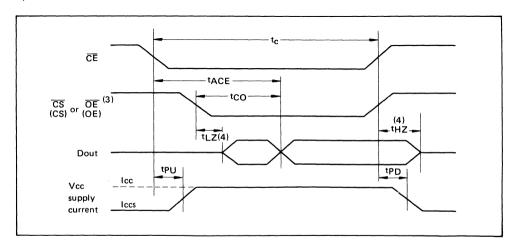

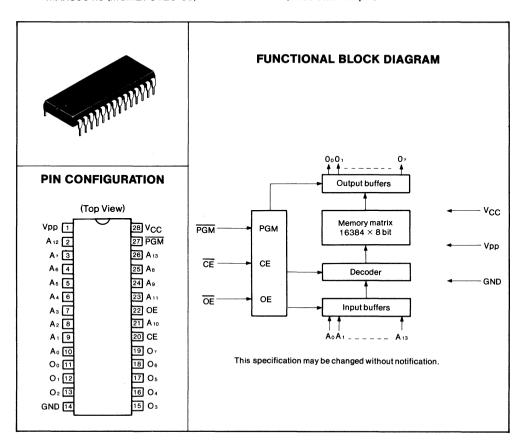

|   |      | MSM38128ARS      | 16,384-Word $\times$ 8-Bit MASK ROM (NMOS)              | 330 |

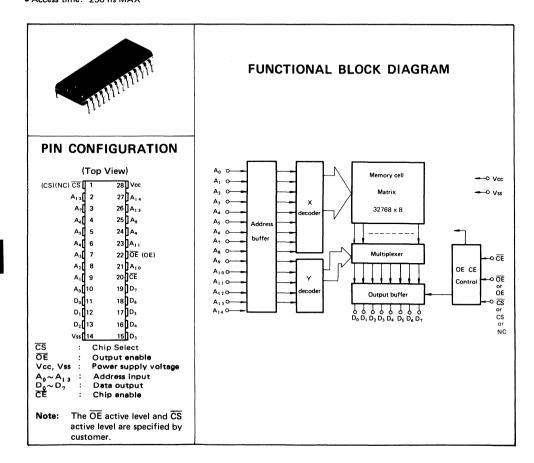

|   |      | MSM38256RS       | 32,768-Word $\times$ 8-Bit MASK ROM (NMOS)              |     |

|   |      | MSM38256ARS      | 32,768-Word $\times$ 8-Bit MASK ROM (NMOS)              | 338 |

|   |      | MSM38512RS       | 65,536-Word $\times$ 8-Bit MASK ROM (NMOS)              | 342 |

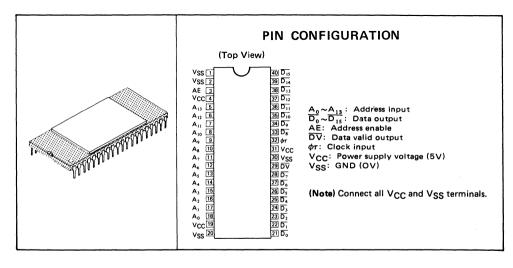

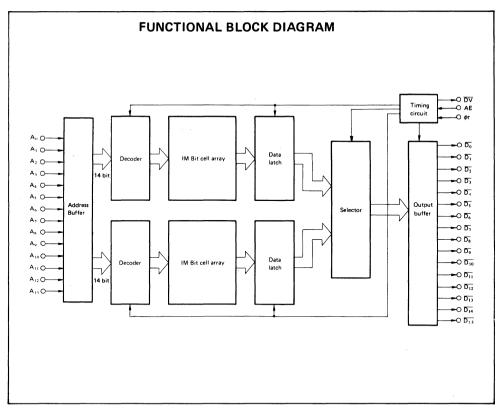

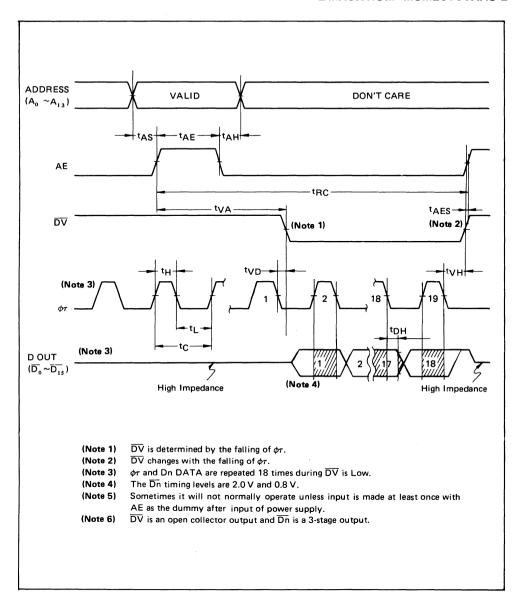

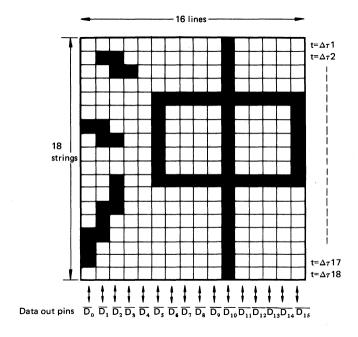

|   |      | MSM28101AAS      | 1 M Bit MASK ROM (NMOS)                                 | 346 |

|    |      | MSM28201AAS              | 1M Bit MASK ROM (NMOS)                        | 351   |

|----|------|--------------------------|-----------------------------------------------|-------|

|    |      | MSM53256RS               | 32,768-Word × 8-Bit MASK ROM (CMOS)           |       |

|    |      | MSK531000RS              | 131,072-Word × 8-Bit MASK ROM (CMOS)          |       |

|    | •    | MOS EPROMS               | Tot, or 2 Word A & Bit Miner (Total Contract) |       |

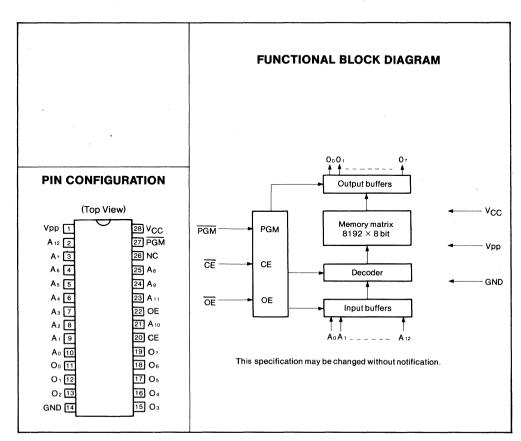

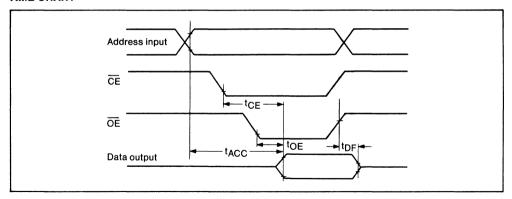

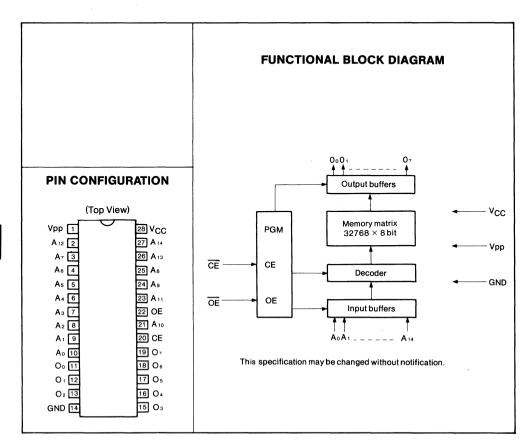

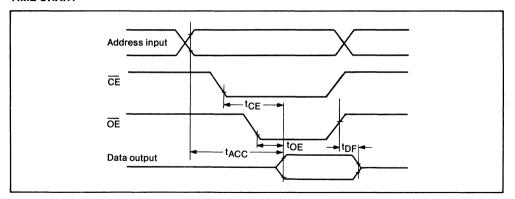

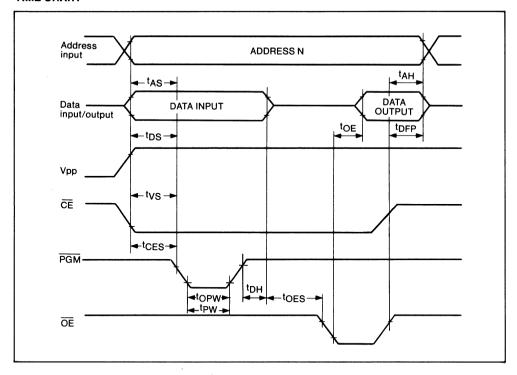

|    |      | MSM2764AS                | 8,192-Word × 8-Bit EPROM (NMOS)               | 366   |

|    |      | MSM27128AS               | 16.384-Word × 8-Bit EPROM (NMOS)              |       |

|    |      | MSM27256AS               | 32,768-Word × 8-Bit EPROM (NMOS)              |       |

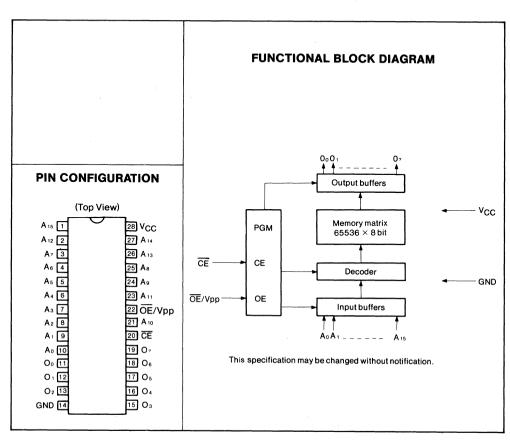

|    |      | MSM27512AS               | 65,536-Word × 8-Bit EPROM (NMOS)              |       |

|    |      | MSM271000AS              | 131,072-Word × 8-Bit EPROM (NMOS)             |       |

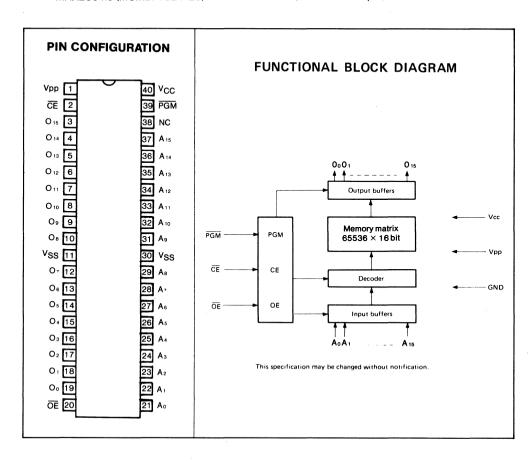

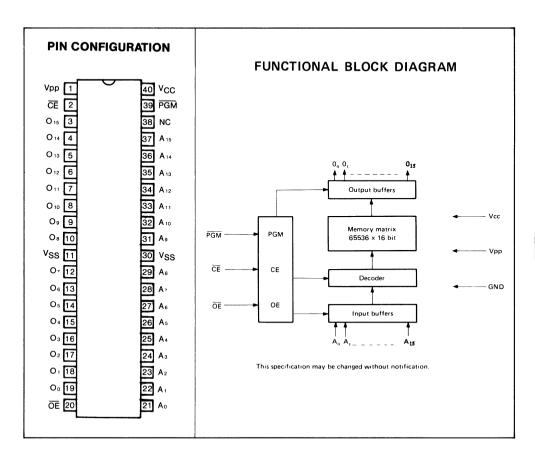

|    |      | MSM271024AS              | 65.536-Word × 16-Bit EPROM (NMOS)             |       |

|    |      | MSM27C64AS               | 8,192-Word × 8-Bit EPROM (CMOS)               |       |

|    |      | MSM27C128AS              | 16,384-Word × 8-Bit EPROM (CMOS)              |       |

|    |      | MSM27C1024AS             | 65,536-Word × 16-Bit EPROM (CMOS)             |       |

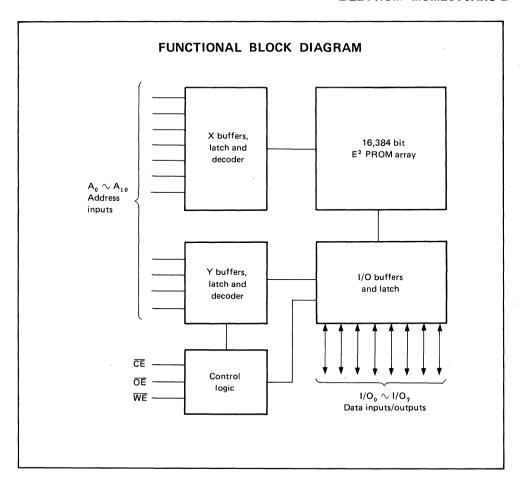

|    | •    | MOS E <sup>2</sup> PROMS | co,see word × 10 Bit El Helin (elinee),       |       |

|    |      | MSM2816ARS               | 2.048-Word × 8-Bit E <sup>2</sup> PROM        | 420   |

| Ti | CROS | SS REFERENCE LIST        | •                                             |       |

|    |      |                          |                                               | 431   |

|    |      |                          |                                               |       |

|    |      |                          |                                               |       |

|    |      |                          |                                               |       |

|    |      |                          |                                               |       |

| m  |      | ICATIONS                 |                                               |       |

|    |      |                          | PPLICATIONS NOTES                             | . 445 |

|    |      |                          |                                               |       |

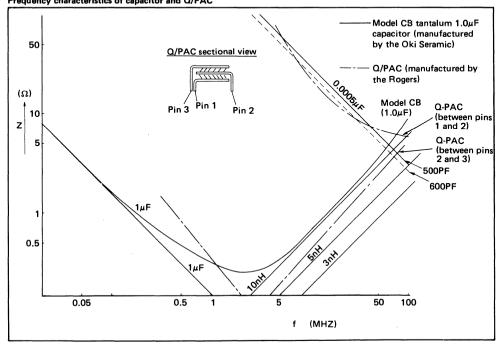

|    |      |                          | ACITORS                                       |       |

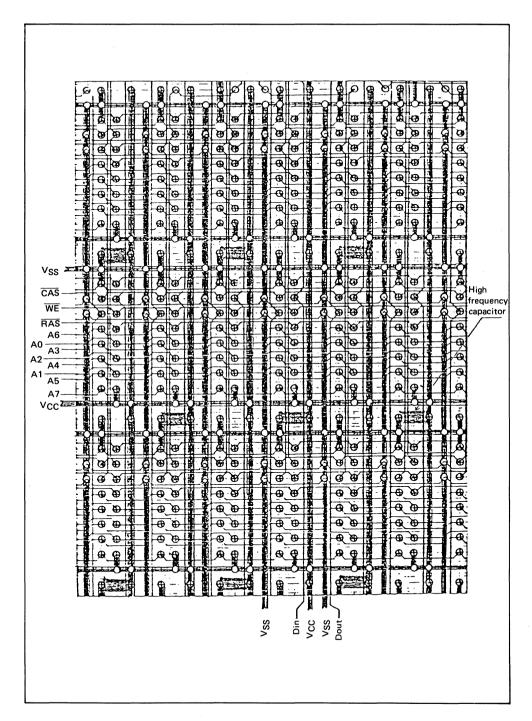

|    |      |                          | BOARD                                         |       |

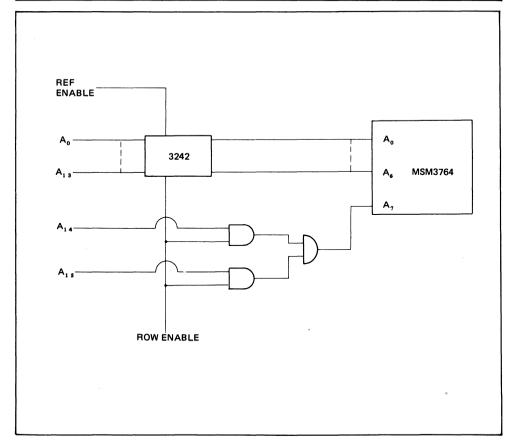

|    |      |                          | ROL CIRCUIT                                   |       |

|    |      |                          | ING 1MB MEMORY ON A BOARD                     |       |

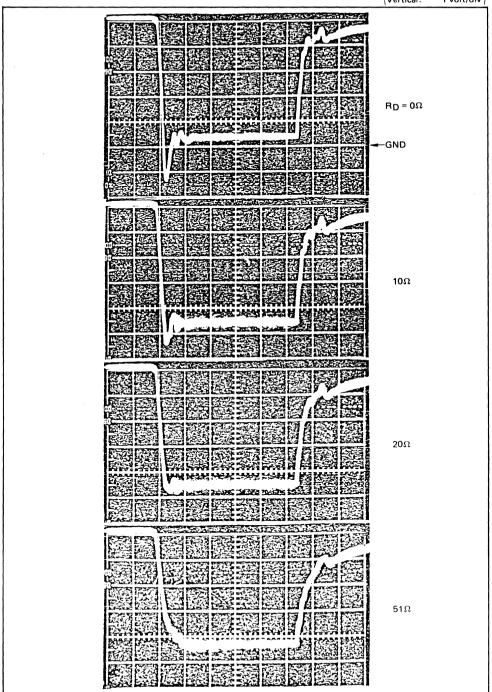

|    | 6.   | MEMORY SYSTEM            | RELIABILITY                                   | 449   |

|    | 7.   | MEMORY COMPAR            | ISON STANDARD                                 | 451   |

|    | СМО  | S RAM BATTERY BAG        | CK-UP                                         | 454   |

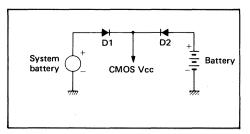

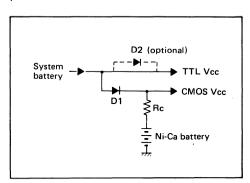

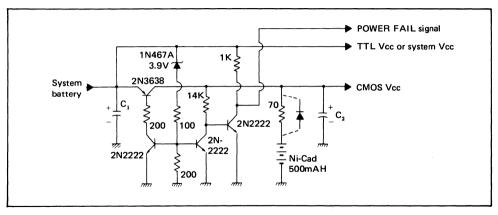

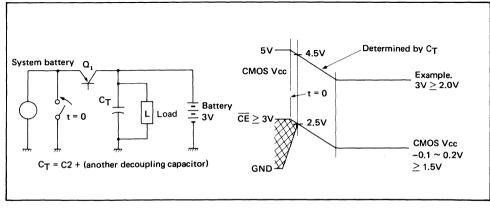

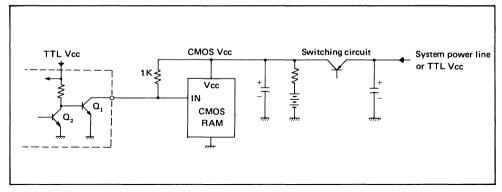

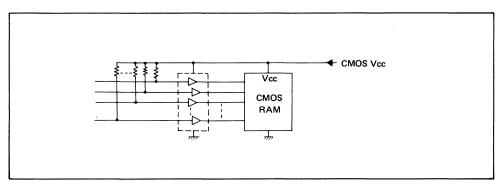

|    |      |                          | ND BATTERY SWITCHING CIRCUIT                  |       |

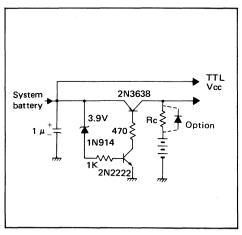

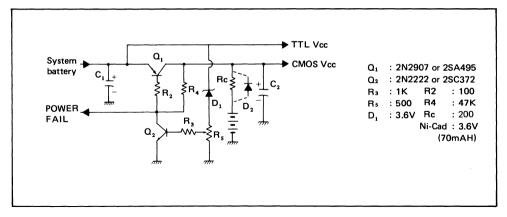

|    | 2.   | SWITCHING CIRCU          | IT MODIFICATIONS                              | 454   |

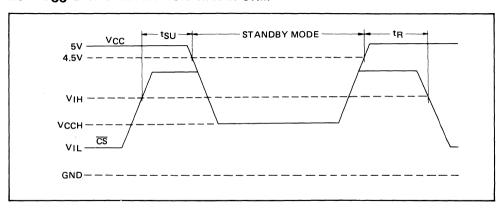

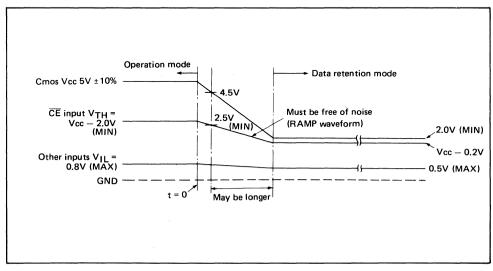

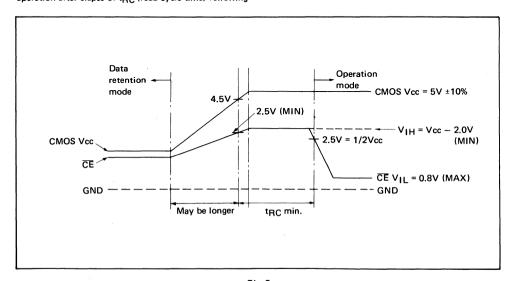

|    | 3.   | DATA RETENTION N         | MODE                                          | 456   |

|    |      |                          |                                               |       |

|    |      |                          |                                               |       |

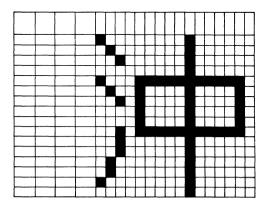

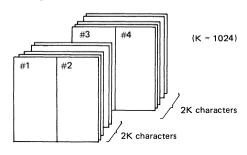

|    | MASH | K ROM KANJI GENER        | ATION MEMORY DESCRIPTION                      | 457   |

|    | 1.   | KANJI GENERATIOI         | N MEMORIES                                    | 458   |

|    |      | MCM20256 SEDIES          |                                               |       |

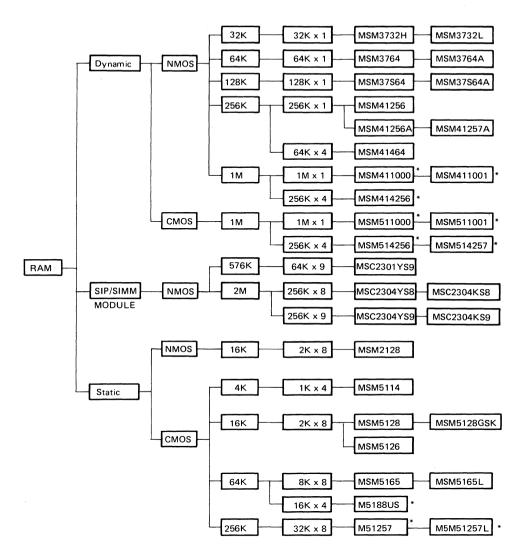

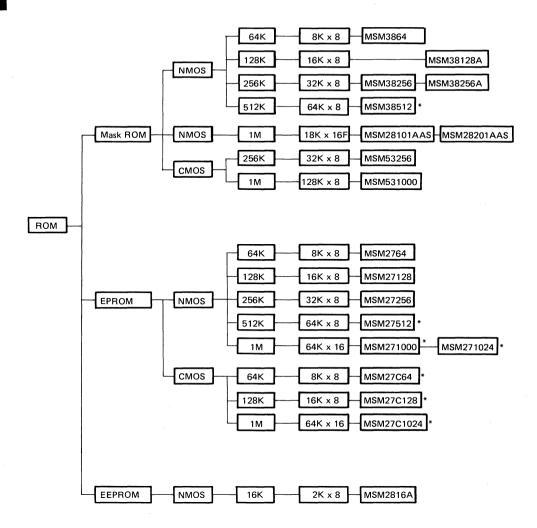

# IC MEMORY LINE-UP AND TYPICAL CHARACTERISTICS

| IC MEMORY LINE-UP AND TYPICAL CHARACTERISTICS | 3 |

|-----------------------------------------------|---|

| DYNAMIC RAMS                                  | 5 |

| SIP/SIMM MODULE                               | 6 |

| NMOS STATIC RAMS                              | 7 |

| CMOS STATIC RAMS                              | 7 |

| • MASK ROMS                                   | 8 |

| • EPROMS                                      | 9 |

| • E2D DOMS                                    | ٥ |

# IC MEMORY LINE-UP AND TYPICAL CHARACTERISTICS

<sup>\*</sup>Under development

\*Under development

#### • DYNAMIC RAMS

| Model Name   | Mem-<br>ory<br>Capac-<br>ity | Circuit Function | Memory<br>Configura-<br>tion | Num-<br>ber of<br>Pins<br>per<br>Pack-<br>age | Access<br>Time<br>MAX<br>(ns) | Cycle<br>Time<br>MIN<br>(ns) | Power<br>Consump-<br>tion<br>MAX<br>(mw)<br>Operating/<br>Standby | Power<br>Supply<br>Voltage<br>(V) | Equivalent<br>Device |  |

|--------------|------------------------------|------------------|------------------------------|-----------------------------------------------|-------------------------------|------------------------------|-------------------------------------------------------------------|-----------------------------------|----------------------|--|

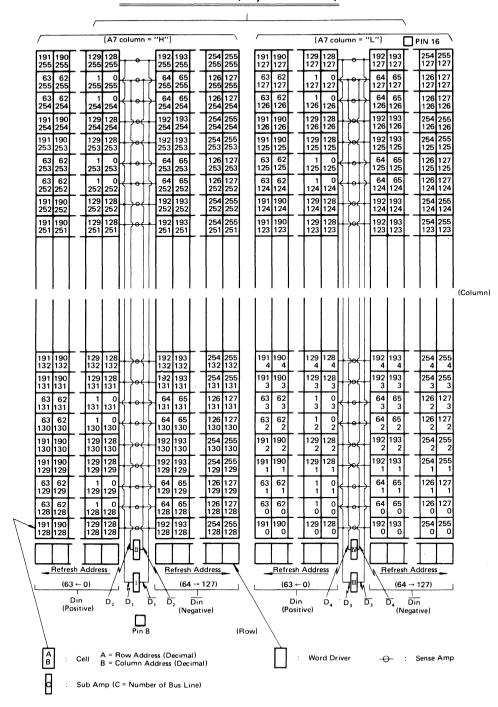

| MSM3732H-15  | 32k                          | 16 Pin Dynamic   | 32,768×1                     | 16                                            | 150                           | 270                          | 248/28                                                            | +5                                |                      |  |

| MSM3732H-20  | SZK                          | A7 (Column)=H    | 32,700x1                     | 10                                            | 200                           | 330                          | 248/28                                                            | 1.5                               |                      |  |

| MSM3732L-15  | 32k                          | 16 Pin Dynamic   | 32,768×1                     | 16                                            | 150                           | 270                          | 248/28                                                            | +5                                |                      |  |

| MSM3732L-20  | 32K                          | A7 (Column)=L    | 32,766X1                     | 16                                            | 200                           | 330                          | 248/28                                                            | +3                                |                      |  |

| MSM3764-15   | 64k                          | 16 Pin Dynamic   | 65,536×1                     | 16                                            | 150                           | 270                          | 248/28                                                            | +5                                | TMS4164-15           |  |

| MSM3764-20   | 04K                          | 16 FIN Dynamic   | 05,53681                     | 16                                            | 200                           | 330                          | 248/28                                                            | 75                                | TMS4164-20           |  |

| MSM3764A-12  |                              |                  |                              |                                               | 120                           | 230                          | 330/28                                                            |                                   |                      |  |

| MSM3764A-15  | 64k                          | 16 Pin Dynamic   | 65,536×1                     | 16                                            | 150                           | 260                          | 330/28                                                            | +5                                |                      |  |

| MSM3764A-20  |                              |                  |                              |                                               | 200                           | 330                          | 330/28                                                            |                                   |                      |  |

| MSM41256-15  | 0501                         | 40.0: 0          | 000 444 4                    | 4.0                                           | 150                           | 260                          | 385/28                                                            |                                   |                      |  |

| MSM41256-20  | 256k                         | 16 Pin Dynamic   | 262,144×1                    | 16                                            | 200                           | 330                          | 385/28                                                            | +5                                |                      |  |

| MSM41256A-10 |                              |                  |                              |                                               | 100                           | 200                          | 385/28                                                            |                                   |                      |  |

| MSM41256A-12 | 250k                         | 16 Pin Dynamic   | 262,144×1                    | 16                                            | 120                           | 220                          | 385/28                                                            | +5                                |                      |  |

| MSM41256A-15 |                              |                  |                              |                                               | 150                           | 260                          | 385/28                                                            |                                   |                      |  |

| MSM41257A-10 |                              |                  |                              |                                               | 100                           | 200                          | 385/28                                                            |                                   |                      |  |

| MSM41257A-12 | 256k                         | 256k             | 16 Pin Dynamic               | 262,144×1                                     | 16                            | 120                          | 220                                                               | 385/28                            | +5                   |  |

| MSM41257A-15 |                              |                  |                              |                                               | 150                           | 260                          | 385/28                                                            |                                   |                      |  |

| MSM41464-10  |                              |                  |                              |                                               | 100                           | 200                          | 385/28                                                            |                                   |                      |  |

| MSM41464-12  | 256k                         | 18 Pin Dynamic   | 65,536×4                     | 18                                            | 120                           | 230                          | 385/28                                                            | +5                                |                      |  |

| MSM41464-15  |                              |                  |                              |                                               | 150                           | 260                          | 385/28                                                            |                                   |                      |  |

| MSM414256-10 |                              |                  |                              |                                               | 100                           | 200                          | 413/28                                                            |                                   |                      |  |

| MSM414256-12 | 256k                         | 20 Pin Dynamic   | 262,144×4                    | 20                                            | 120                           | 230                          | 385/28                                                            | +5                                |                      |  |

| MSM411000-10 |                              |                  |                              |                                               | 100                           | 200                          | 413/28                                                            |                                   |                      |  |

| MSM411000-12 | 1M                           | 18 Pin Dynamic   | 1,048,576×1                  | 18                                            | 120                           | 230                          | 385/28                                                            | +5                                |                      |  |

| MSM411001-10 |                              |                  |                              |                                               | 100                           | 200                          | 413/28                                                            |                                   |                      |  |

| MSM411001-12 | 1M                           | 18 Pin Dynamic   | 1,048,576x1                  | 18                                            | 120                           | 230                          | 385/28                                                            | +5                                |                      |  |

| MSM511000-10 |                              |                  |                              |                                               | 100                           | 190                          | 385/11                                                            |                                   |                      |  |

| MSM511000-12 | 1M                           | 18 Pin Dynamic   | 1,048,576×1                  | 18                                            | 120                           | 220                          | 330/11                                                            | +5                                |                      |  |

| MSM511001-10 | 4                            | 40 B: B :        | 1040570                      | 10                                            | 100                           | 190                          | 385/11                                                            | , -                               |                      |  |

| MSM511001-12 | 1M                           | 18 Pin Dynamic   | 1,048,576×1                  | 18                                            | 120                           | 220                          | 330/11                                                            | +5                                |                      |  |

| MSM514256-10 | 111                          | 20 B:- D         | 262 444 4                    | 20                                            | 100                           | 190                          | 413/11                                                            | 15                                |                      |  |

| MSM514256-12 | 1M                           | 20 Pin Dynamic   | 262,144x4                    | 20                                            | 120                           | 220                          | 385/11                                                            | +5                                |                      |  |

| Model Name   | Mem-<br>ory<br>Capac-<br>ity | Circuit Function |           | Num-<br>ber of<br>Pins<br>per<br>Pack-<br>age | Access<br>Time<br>MAX<br>(ns) | Cycle<br>Time<br>MIN<br>(ns) | Power<br>Consump-<br>tion<br>MAX<br>(mw)<br>Operating/<br>Standby | Power<br>Supply<br>Voltage<br>(V) | Equivalent<br>Device |

|--------------|------------------------------|------------------|-----------|-----------------------------------------------|-------------------------------|------------------------------|-------------------------------------------------------------------|-----------------------------------|----------------------|

| MSM514257-10 | 1M                           | 20 Pin Dynamia   | 262.144×4 | 20                                            | 100                           | 190                          | 413/11                                                            | +5                                |                      |

| MSM514257-12 | IIVI                         | 20 Pin Dynamic   | 202.14484 |                                               | 120                           | 220                          | 385/11                                                            | 13                                |                      |

| MSM37S64-15  | 128k                         | k 16 Pin Dynamic | 131,072×1 | 16                                            | 150                           | 270                          | 360/55                                                            | +5                                |                      |

| MSM37S64-20  | 1288                         |                  |           |                                               | 200                           | 330                          | 360/55                                                            | +5                                |                      |

#### • SIP/SIMM MODULE

| Model Name            | Mem-<br>ory<br>Capac-<br>ity | Circuit Function  | Memory<br>Configura-<br>tion | Num-<br>ber of<br>Pins<br>per<br>Pack-<br>age | Access<br>Time<br>MAX<br>(ns) | Cycle<br>Time<br>MIN<br>(ns) | Power<br>Consump-<br>tion<br>MAX<br>(nw)<br>Operating/<br>Standby | Power<br>Supply<br>Voltage<br>(V) | Equivalent<br>Device |

|-----------------------|------------------------------|-------------------|------------------------------|-----------------------------------------------|-------------------------------|------------------------------|-------------------------------------------------------------------|-----------------------------------|----------------------|

| MSC2301-<br>12YS9/KS9 | 576k                         | 30 Pin Socket     | 65536×9                      | 30                                            | 120                           | 120                          | -                                                                 | +5                                |                      |

| MSC2301-<br>15YS9/KS9 | 376K                         | Insertable Module | 0333089                      |                                               | 150                           | 150                          | _                                                                 | , 0                               |                      |

| MSC2304-<br>12YS8/KS8 |                              | 30 Pin Socket     |                              | 30                                            | 120                           | 120                          | _                                                                 | ٠.                                |                      |

| MSC2304-<br>15YS8/KS8 | 2M                           | Insertable Module | 262144x8                     |                                               | 150                           | 150                          | _                                                                 | +5                                |                      |

| MSC2304-<br>12YS9/KS9 | 200                          | 30 Pin Socket     |                              | 20                                            | 120                           | 120                          | _                                                                 | +5                                |                      |

| MSC2304-<br>15YS9/KS9 | 2M                           | Insertable Module | 262144x9                     | 30                                            | 150                           | 150                          | _                                                                 | .5                                |                      |

#### • NMOS STATIC RAMS

| Model Name | Mem-<br>ory<br>Capac-<br>ity | Circuit Function                   | Memory<br>Configura-<br>tion | Num-<br>ber of<br>Pins<br>per<br>Pack-<br>age | Access<br>Time<br>MAX<br>(ns) | Cycle<br>Time<br>MIN<br>(ns) | Power<br>Consump-<br>tion<br>MAX<br>(mw)<br>Operating/<br>Standby | Power<br>Supply<br>Voltage<br>(V) | Equivalent<br>Device |

|------------|------------------------------|------------------------------------|------------------------------|-----------------------------------------------|-------------------------------|------------------------------|-------------------------------------------------------------------|-----------------------------------|----------------------|

| MSM2128-12 |                              |                                    |                              |                                               | 120                           | 120                          | 660/110                                                           |                                   |                      |

| MSM2185-15 | 16k                          | Static, Common I/O with Power Down | 2048×8                       | 24                                            | 150                           | 150                          | 550/110                                                           | +5                                | TMM2016<br>M58725    |

| MSM2128-20 |                              | Mode                               |                              |                                               | 200                           | 200                          | 550/110                                                           |                                   | 11100720             |

#### • CMOS STATIC RAMS

| Model Name    | Mem-<br>ory<br>Capac-<br>ity | Circuit Function            | Memory<br>Configura-<br>tion | Num-<br>ber of<br>Pins<br>per<br>Pack-<br>age | Access<br>Time<br>MAX<br>(ns) | Cycle<br>Time<br>MIN<br>(ns) | Power<br>Consump-<br>tion<br>MAX<br>(mw)<br>Operating/<br>Standby | Power<br>Supply<br>Voltage<br>(V) | Equivalent<br>Device |

|---------------|------------------------------|-----------------------------|------------------------------|-----------------------------------------------|-------------------------------|------------------------------|-------------------------------------------------------------------|-----------------------------------|----------------------|

| MSM5114-2     |                              |                             |                              |                                               | 200                           | 200                          | 192/0.04                                                          |                                   |                      |

| MSM5114-3     | 4k                           | Fully Static,<br>Common I/O | 1024×4                       | 18                                            | 300                           | 300                          | 192/0.04                                                          | +5                                | TC5514<br>μPD444     |

| MSM5114       |                              |                             |                              |                                               | 450                           | 450                          | 192/0.04                                                          |                                   |                      |

| MSM5128-12    |                              |                             |                              |                                               | 120                           | 120                          | 330/0.275                                                         |                                   | HM6116               |

| MSM5128-15    | 16k                          | Fully Static,<br>Common I/O | 2048x8                       | 24                                            | 150                           | 150                          | 300/0.275                                                         | +5                                | μPD446<br>TC5517     |

| MSM5128-20    |                              |                             |                              |                                               | 200                           | 200                          | 275/0.275                                                         |                                   |                      |

| MSM5126-20    |                              |                             | 2040.0                       |                                               | 150                           | 150                          | 385/0.165                                                         | _                                 |                      |

| MSM5126-25    | 16k                          | Fully Static<br>Common I/O  | 2048×8                       | 24                                            | 200                           | 200                          | 385/0.165                                                         | +5                                |                      |

| MSM5165-12    |                              |                             |                              |                                               | 120                           | 120                          | 248/5.5                                                           |                                   |                      |

| MSM5165-15    | 64k                          | Fully Static<br>Common I/O  | 8192x8                       | 28                                            | 150                           | 150                          | 248/5.5                                                           | +5                                |                      |

| MSM5165-20    |                              |                             |                              |                                               | 200                           | 200                          | 248/5.5                                                           |                                   |                      |

| MSM5165L-12   |                              |                             |                              |                                               | 120                           | 120                          | 248/0.55                                                          |                                   |                      |

| MSM5165L-15   | 64k                          | Fully Static<br>Common I/O  | 8192x8                       | 28                                            | 150                           | 150                          | 248/0.55                                                          | +5                                |                      |

| MSM5165L-20   |                              |                             |                              |                                               | 200                           | 200                          | 248/0.55                                                          |                                   |                      |

| MSM5188-45    |                              | ·                           |                              |                                               | 45                            | 45                           | 605/11                                                            |                                   | 1000                 |

| MSM5188-55    | 64k                          | Fully Static<br>Common I/O  | 16384×4                      | 22                                            | 55                            | 55                           | 605/11                                                            | +5                                |                      |

| MSM5188-70    |                              |                             |                              |                                               | 70                            | 70                           | 605/11                                                            |                                   |                      |

| MSM51257-85   |                              |                             |                              |                                               | 85                            | 85                           | 385/5.5                                                           |                                   |                      |

| MSM51257-100  | 256k                         | Fully Static<br>Common I/O  | 32768×8                      | 28                                            | 100                           | 100                          | 385/5.5                                                           | +5                                |                      |

| MSM51257-120  |                              |                             |                              |                                               | 120                           | 120                          | 385/5.5                                                           |                                   |                      |

| MSM51257L-85  |                              |                             |                              |                                               | 85                            | 85                           | 385/0.55                                                          |                                   |                      |

| MSM51257L-100 | 256k                         | Fully Static<br>Common I/O  | 32768x8                      | 28                                            | 100                           | 100                          | 385/0.55                                                          | +5                                |                      |

| MSM51257L-120 |                              |                             |                              |                                               | 120                           | 120                          | 385/0.55                                                          |                                   |                      |

#### ■ IC MEMORY LINE-UP AND TYPICAL CHARACTERISTICS ■-

#### • MASK ROMS

| Model Name | Mem-<br>ory<br>Capac-<br>ity | Circuit Function                      | Memory<br>Configura-<br>tion | Num-<br>ber of<br>Pins<br>per<br>Pack-<br>age | Access<br>Time<br>MAX<br>(ns) | Cycle<br>Time<br>MIN<br>(ns) | Power<br>Consump-<br>tion<br>MAX<br>(mw)<br>Operating/<br>Standby | Power<br>Supply<br>Voltage<br>(V) | Equivalent<br>Device                                          |

|------------|------------------------------|---------------------------------------|------------------------------|-----------------------------------------------|-------------------------------|------------------------------|-------------------------------------------------------------------|-----------------------------------|---------------------------------------------------------------|

| MSM3864    | 64k                          | Fully Static                          | 8192×8                       | 28                                            | 250                           | 250                          | 550/165                                                           | +5                                |                                                               |

| MSM38128A  | 128k                         | Fully Static                          | 16384×8                      | 28                                            | 250                           | 250                          | 550/165                                                           | +5                                |                                                               |

| MSM38256   | 256k                         | Fully Static                          | 32768×8                      | 28                                            | 250                           | 250                          | 660/165                                                           | +5                                |                                                               |

| MSM38256A  | 256k                         | Fully Static                          | 32768×8                      | 28                                            | 150                           | 150                          | 330/33                                                            | +5                                |                                                               |

| MSM38512   | 512k                         | Fully Static                          | 65536×8                      | 28                                            | 200                           | 200                          | _                                                                 | +5                                |                                                               |

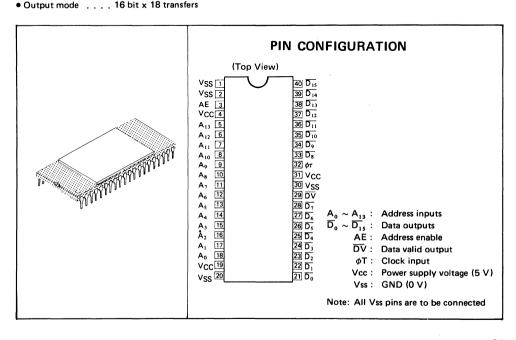

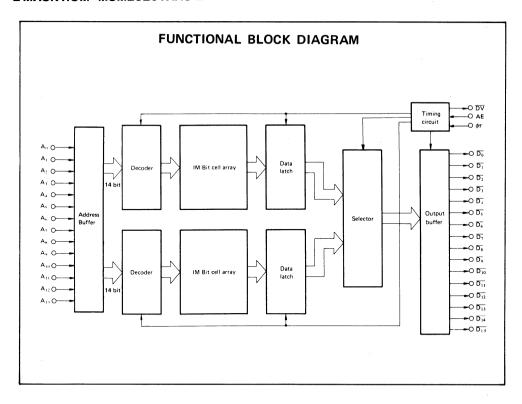

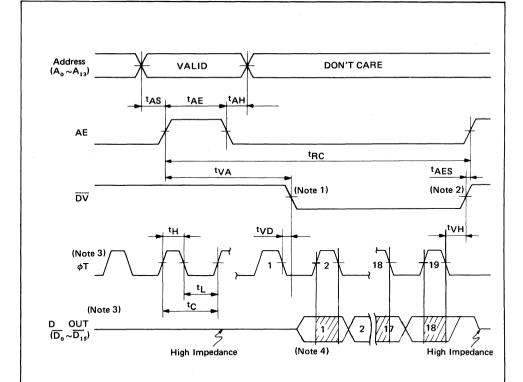

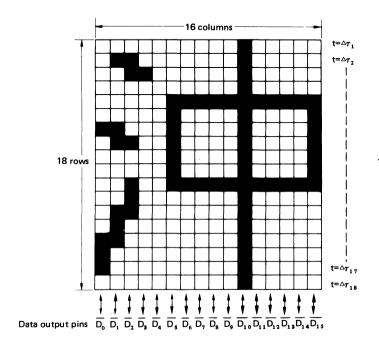

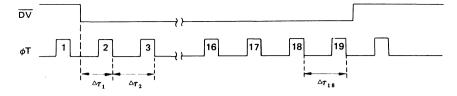

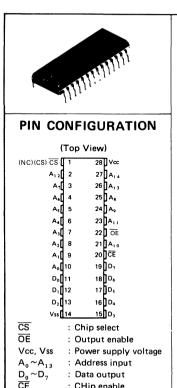

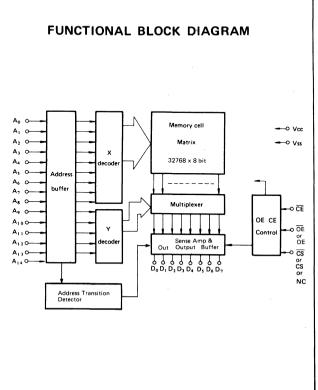

| MSM28101   | 1M                           | 40 Pin MASK RAM<br>18x16 Chinese-cha- | 3760×16                      | 40                                            | 10                            |                              |                                                                   | +5                                | JIS-Chinese-<br>character<br>coding sys-<br>tem 0~7,<br>16~47 |

| MSM28201   | T IVI                        | racter font output                    | x 18                         | 40                                            | 10μs                          | 22μs                         | 893                                                               |                                   | JIS-Chinese-<br>character<br>coding sys-<br>tem 48~87         |

| MSM53256   | 256k                         | Fully Static                          | 32768×8                      | 28                                            | 150                           | 150                          | 83/0.6                                                            | +5                                |                                                               |

| MSM531000  | 1M                           | Fully Static                          | 131072×8                     | 28                                            | 250                           | 250                          | 83/0.6                                                            | +5                                |                                                               |

#### • EPROMS

| Model Name | Mem-<br>ory<br>Capac-<br>ity | Circuit Function | Memory<br>Configura-<br>tion | Num-<br>ber of<br>Pins<br>per<br>Pack-<br>age | Access<br>Time<br>MAX<br>(ns) | Cycle<br>Time<br>MIN<br>(ns) | Power<br>Consump-<br>tion<br>MAX<br>(mw)<br>Operating/<br>Standby | Power<br>Supply<br>Voitage<br>(V) | Equivalent<br>Device |

|------------|------------------------------|------------------|------------------------------|-----------------------------------------------|-------------------------------|------------------------------|-------------------------------------------------------------------|-----------------------------------|----------------------|

| MSM2764    | 64k                          | 28 Pin EPROM     | 8192×8                       | 28                                            | 200                           | 200                          | 790/185                                                           | +5                                | 2764                 |

| MSM27128   | 128k                         | 28 Pin EPROM     | 16,384x8                     | 28                                            | 250                           | 250                          | 788/184                                                           | +5                                | 27128                |

| MSM27256   | 256k                         | 28 Pin EPROM     | 32,768×8                     | 28                                            | 150                           | 150                          | 525/184                                                           | +5                                | 27256                |

| MSM27512   | 512k                         | 28 Pin EPROM     | 65,536×8                     | 28                                            | 150                           | 150                          | 525/184                                                           | +5                                | 27512                |

| MSM271000  | 1M                           | 32 Pin EPROM     | 131,072x8                    | 32                                            | 120                           | 120                          | 525/184                                                           | +5                                | 271000               |

| MSM271024  | 1M                           | 40 Pin EPROM     | 65,536×16                    | 40                                            | 120                           | 120                          | 525/184                                                           | +5                                | 271024               |

| MSM27C64   | 64k                          | 28 Pin EPROM     | 8,192×8                      | 28                                            | 200                           | 200                          | 165/0.55                                                          | +5                                | 27C64                |

| MSM27C128  | 128k                         | 28 Pin EPROM     | 16,384×8                     | 28                                            | 200                           | 200                          | 165/0.55                                                          | +5                                | 27C128               |

| MSM27C1024 | 1M                           | 40 Pin EPROM     | 65,536×16                    | 40                                            | 100                           | 100                          | 175/0.55                                                          | +5                                | 27C1024              |

#### • E<sup>2</sup> P ROMS

| Model Name  | Mem-<br>ory<br>Capac-<br>ity | Circuit Function  | Memory<br>Configura-<br>tion | Num-<br>ber of<br>Pins<br>per<br>Pack-<br>age | Access<br>Time<br>MAX<br>(ns) | Cycle<br>Time<br>MIN<br>(ns) | Power<br>Consump-<br>tion<br>MAX<br>(nw)<br>Operating/<br>Standby | Power<br>Supply<br>Voltage<br>(V) | Equivalent<br>Device |

|-------------|------------------------------|-------------------|------------------------------|-----------------------------------------------|-------------------------------|------------------------------|-------------------------------------------------------------------|-----------------------------------|----------------------|

| MSM2816A-25 |                              | 24 Pin<br>E²P ROM | 2048×8                       |                                               | 250                           | 250                          |                                                                   |                                   |                      |

| MSM2816A-30 | 16k                          |                   |                              |                                               | 300                           | 300                          | _                                                                 | +5                                |                      |

| MSM2816A-35 | IBK                          |                   |                              | 24                                            | 350                           | 350                          | _                                                                 |                                   |                      |

| MSM2816A-45 |                              |                   |                              |                                               | 450                           | 450                          | _                                                                 | +5                                |                      |

2

PACKAGING

| 2 PACKAGIN | NG                | <br>13 |

|------------|-------------------|--------|

| ● 16 P     | PIN PLASTIC       | <br>15 |

| • 16 P     | PIN STACK PLASTIC | <br>16 |

| • 18 P     | PIN PLCC          | <br>16 |

| • 18 P     | PIN PLASTIC       | <br>17 |

| ● 18 P     | PIN SIDE-BRAZED   | <br>17 |

| • 22 P     | PIN PLCC          | <br>18 |

| • 22 P     | PIN PLASTIC       | <br>18 |

| ● 24 P     | PIN PLASTIC       | <br>19 |

| • 24 P     | PIN CERDIP        | <br>19 |

|            | PIN PLASTIC FLAT  |        |

| ● 26 P     | PIN SOJ           | <br>20 |

| • 28 P     | PIN PLASTIC       | <br>21 |

| • 28 P     | PIN CERDIP        | <br>21 |

| • 32 P     | PIN PLCC          | <br>22 |

| ● 40 P     | PIN SIDE-BRAZED   | <br>22 |

## **PACKAGING**

|                 | No.        | RS             | GS              | JS             | YS KS AS                                         |        |        |                 |  |  |

|-----------------|------------|----------------|-----------------|----------------|--------------------------------------------------|--------|--------|-----------------|--|--|

| Name            | of<br>Pins | PLASTIC<br>DIP | PLASTIC<br>FLAT | PLASTIC<br>LCC | PLASTIC<br>SKINNY                                | MODULE | MODULE | SIDE-<br>BRAZED |  |  |

| MSM3732         | 16         | 0              |                 |                |                                                  |        |        |                 |  |  |

| 3764            | 16         | 0              |                 |                |                                                  |        |        |                 |  |  |

| 3764A           | 16         | 0              |                 |                |                                                  |        |        |                 |  |  |

| 37S64           | 16         | 0              |                 |                |                                                  |        |        |                 |  |  |

| 37S64A          | 16         | 0              |                 | -              |                                                  |        | 1.00   |                 |  |  |

|                 | 16         | 0              |                 |                |                                                  |        |        |                 |  |  |

| 41256           | 18         |                |                 | 0              |                                                  |        |        |                 |  |  |

|                 | 16         | 0              |                 |                |                                                  |        |        |                 |  |  |

| 41256A          | 18         |                |                 | 0              |                                                  |        |        |                 |  |  |

| 41257A          | 16         | 0              |                 |                |                                                  |        |        | 1-2-11-21       |  |  |

| 41257A          |            | 0              |                 |                |                                                  |        |        |                 |  |  |

| 41464           | 18         |                |                 | 0              |                                                  |        |        |                 |  |  |

|                 | 22         |                |                 |                | -                                                |        |        |                 |  |  |

| 411000          | 18         | 0              |                 | -              |                                                  |        |        |                 |  |  |

|                 | 26         |                |                 | 0              | -                                                |        |        |                 |  |  |

| 411001          | 18         | 0              |                 |                |                                                  |        |        |                 |  |  |

|                 | 26         |                |                 | 0              |                                                  |        |        |                 |  |  |

| 414256          | 20         | 0              |                 | _              |                                                  |        |        |                 |  |  |

|                 | 26         |                |                 | 0              |                                                  |        |        |                 |  |  |

| 511000          | 18         | 0              |                 |                |                                                  |        |        |                 |  |  |

|                 | 26         |                |                 | 0              |                                                  |        |        |                 |  |  |

| 511001          | 18         | 0              |                 |                |                                                  |        |        |                 |  |  |

| 311001          | 26         |                |                 | 0              |                                                  |        |        |                 |  |  |

| 514256          | 20         | 0              |                 |                |                                                  |        |        |                 |  |  |

| 514250          | 26         |                |                 | 0              |                                                  |        |        |                 |  |  |

| E140E7          | 20         | 0              |                 |                |                                                  |        |        |                 |  |  |

| 514257          | 26         |                |                 | 0              |                                                  |        |        |                 |  |  |

| 2128            | 24         | 0              |                 |                |                                                  |        |        |                 |  |  |

| 5114            | 18         | 0              |                 |                |                                                  |        |        |                 |  |  |

| 5126            | 24         | 0              |                 |                |                                                  |        |        |                 |  |  |

| 5128            | 24         | 0              | 0               |                |                                                  |        |        |                 |  |  |

|                 | 28         | 0              |                 |                |                                                  |        |        |                 |  |  |

| 5165            | 32         |                |                 | 0              |                                                  |        |        |                 |  |  |

|                 | 28         | 0              |                 |                |                                                  |        |        |                 |  |  |

| 5165L           | 32         |                |                 | 0              |                                                  |        |        |                 |  |  |

| 5188            | 22         |                |                 |                | Ó                                                |        |        |                 |  |  |

|                 | 28         | 0              |                 |                |                                                  |        |        |                 |  |  |

| 51257           | 32         |                |                 | 0              | <del>                                     </del> |        |        |                 |  |  |

|                 | 28         | 0              |                 |                |                                                  |        |        |                 |  |  |

| 51257L          | 32         |                |                 | 0              | <del>                                     </del> |        |        |                 |  |  |

| 3864            | 28         | 0              |                 |                |                                                  |        |        |                 |  |  |

| 38128A          | 28         | 0              |                 |                |                                                  |        |        |                 |  |  |

| 38128A<br>38256 |            | 0              |                 |                | <del>                                     </del> |        |        |                 |  |  |

|                 | 28         | 0              |                 |                |                                                  |        |        |                 |  |  |

| 38256A          | 28         | 0              |                 |                |                                                  |        |        |                 |  |  |

| 28101A          | 40         |                |                 |                |                                                  |        |        | 0               |  |  |

| 28201A          | 40         |                |                 |                | <del>  </del>                                    |        |        | 0               |  |  |

| 38512           | 28         | 0              |                 |                |                                                  |        |        |                 |  |  |

| 531000          | 28         | 0              |                 |                |                                                  |        |        |                 |  |  |

| 53256           | 28         | 0              |                 |                |                                                  |        |        |                 |  |  |

| 2764            | 28         |                |                 |                |                                                  |        |        | 0               |  |  |

|         |      | PACKAGES       |                 |                |                   |        |        |                 |  |  |  |

|---------|------|----------------|-----------------|----------------|-------------------|--------|--------|-----------------|--|--|--|

| Name    | No.  | RS             | GS              | JS             | US                | YS     | KS     | AS              |  |  |  |

|         | Pins | PLASTIC<br>DIP | PLASTIC<br>FLAT | PLASTIC<br>LCC | PLASTIC<br>SKINNY | MODULE | MODULE | SIDE-<br>BRAZED |  |  |  |

| 27128   | 28   |                |                 |                |                   |        |        | 0               |  |  |  |

| 27256   | 28   |                |                 |                |                   |        |        | 0               |  |  |  |

| 27512   | 28   |                |                 |                |                   |        |        | 0               |  |  |  |

| 271000  | 32   |                |                 |                |                   |        |        | 0               |  |  |  |

| 271024  | 40   |                |                 |                |                   |        |        | 0               |  |  |  |

| 27C64   | 28   |                |                 |                |                   |        |        | 0               |  |  |  |

| 27C128  | 28   |                |                 |                |                   |        |        | 0               |  |  |  |

| 27C1024 | 40   |                |                 |                |                   |        |        | 0               |  |  |  |

| 2816A   | 24   | 0              |                 |                |                   |        |        |                 |  |  |  |

| 2301    | 30   |                |                 |                |                   | 0      | 0      |                 |  |  |  |

| 2304    | 30   |                |                 |                |                   | 0      | 0      |                 |  |  |  |

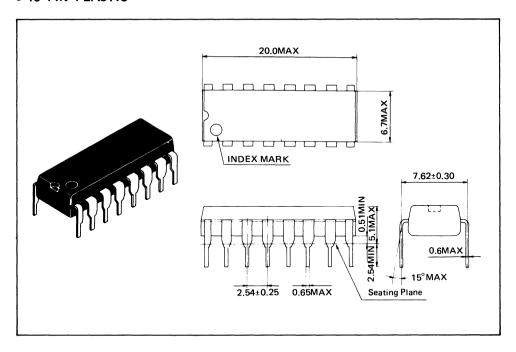

#### • 16 PIN PLASTIC

#### • 16 PIN PLASTIC

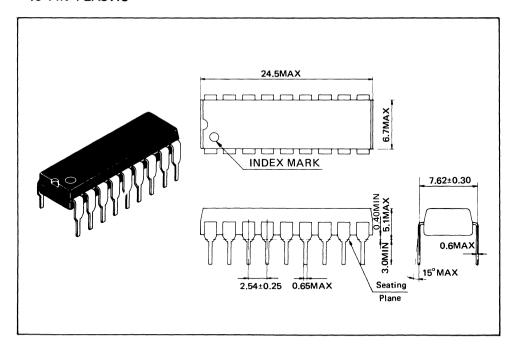

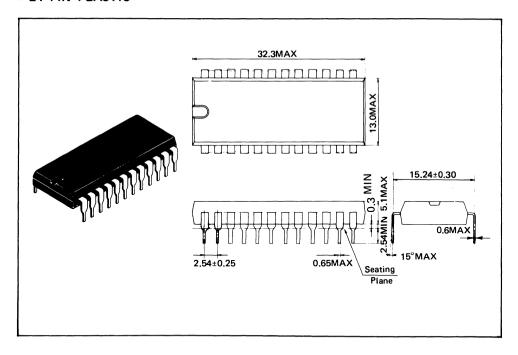

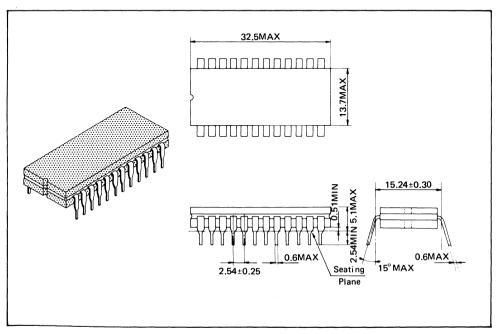

Note: All dimensions in millimeters.

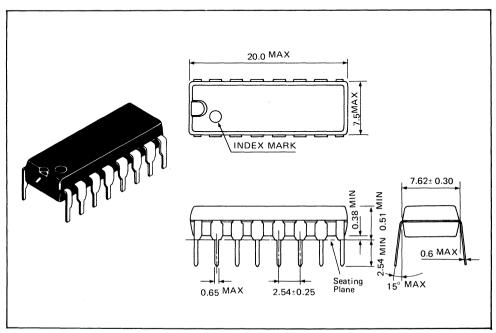

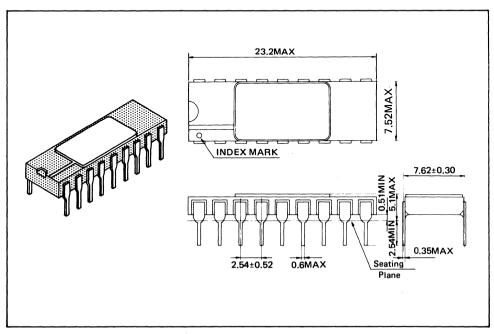

#### • 16 PIN STACK PLASTIC

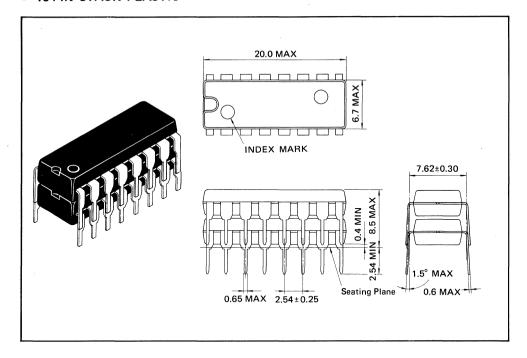

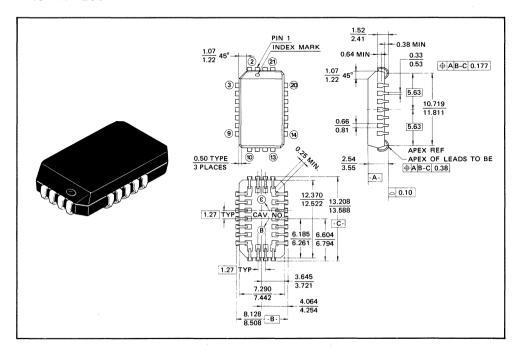

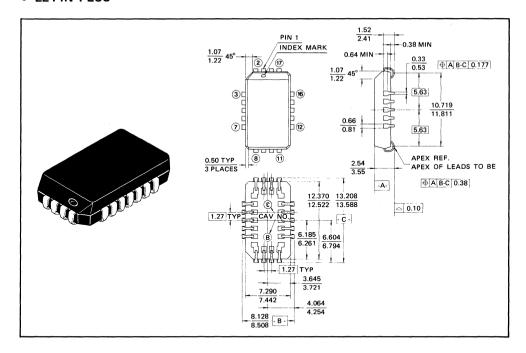

#### • 18 PIN PLCC

16

#### • 18 PIN PLASTIC

#### • 18 PIN SIDE-BRAZED

Note: All dimensions in millimeters.

#### • 22 PIN PLCC

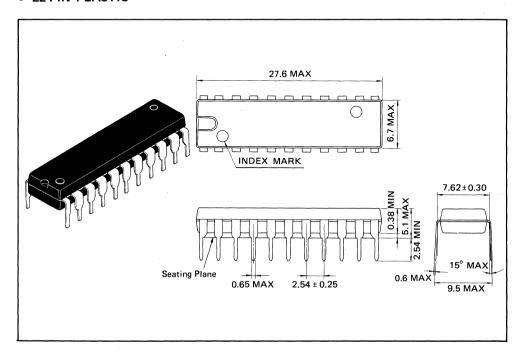

#### • 22 PIN PLASTIC

18

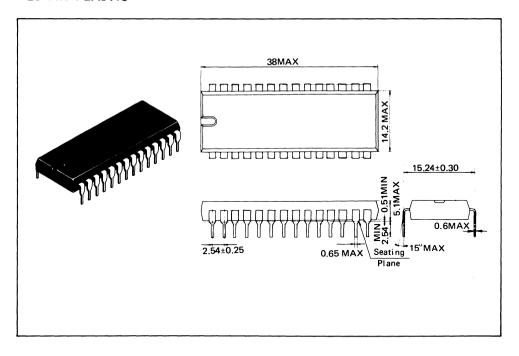

#### • 24 PIN PLASTIC

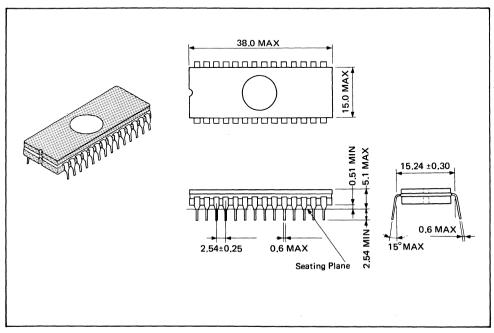

#### • 24 PIN CERDIP

Note: All dimensions in millimeters.

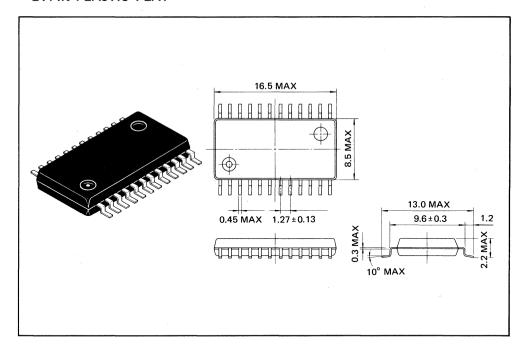

#### • 24 PIN PLASTIC FLAT

2

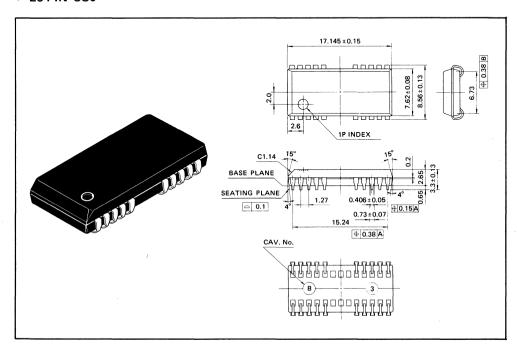

#### • 26 PIN SOJ

#### • 28 PIN PLASTIC

#### • 28 PIN CERDIP

Note: All dimensions in millimeters.

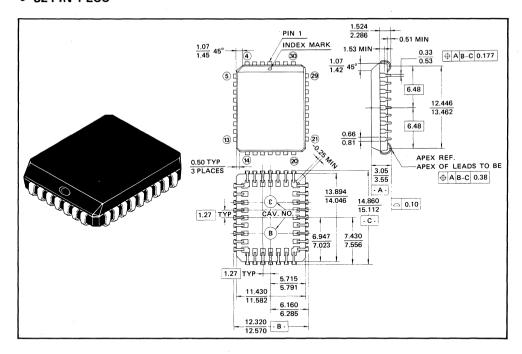

#### • 32 PIN PLCC

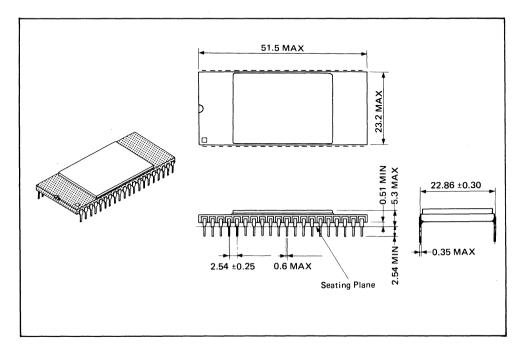

#### • 40 PIN SIDE-BRAZED

# 3

RELABILITY

INFORMATION

| 3 | RELIABILITY INFORMATION                             | 25 |

|---|-----------------------------------------------------|----|

|   | 1. INTRODUCTION                                     | 25 |

|   | 2. QUALITY ASSURANCE SYSTEM AND UNDERLYING CONCEPTS | 25 |

|   | 3. EXAMPLE OF RELIABILITY TEST RESULTS              | 27 |

|   | 4 SEMICONDUCTOD MEMODY FAILURES                     | 21 |

#### RELIABILITY INFORMATION

#### 1. INTRODUCTION

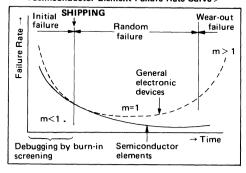

Semiconductor memories play a leading role in the explosive progress of semiconductor technology. They use some of the most advanced design and manufacturing technology developed to date. With greater integration, diversity and reliability, their applications have expanded enormously. Their use in large scale computers, control equipment, calculators, electronic games and in many other fields has increased at a fast rate.

A failure in electronic banking or telephone switching equipment, for example, could have far reaching effects and can cause incalculable losses. So, the demand, for stable high quality memory devices is strong.

We, at Oki Electric is fully aware of this demand. So we have adopted a comprehensive quality assurance system based on the concept of consistency in development, manufacturing and sales.

With the increasing demand for improvement in function, capability and reliability, we will expand our efforts in the future. Our quality assurance system and the underlying concepts are outlined briefy below.

## 2. QUALITY ASSURANCE SYSTEM AND UNDERLYING CONCEPTS

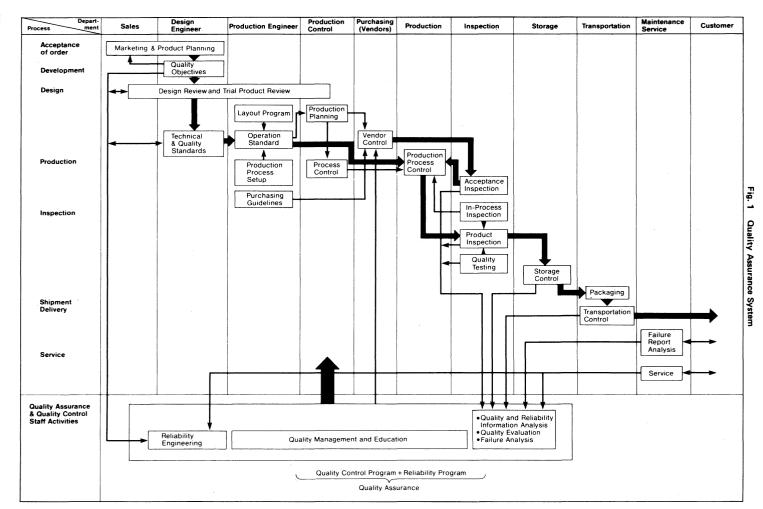

The quality assurance system employed by Oki Electric can be divided into 4 major stages: device planning, developmental prototype, production prototype, and mass production. This system is outlined in the following block diagram (Fig. 1-1).

#### 1) Device planning stage

To manufacture devices that meet the market demands and satisfy customer needs, we carefully consider functional and failure rate requirements, utilization form, environment and other conditions. Once we determine the proper type, material and structure, we check the design and manufacturing techniques and the line processing capacity. Then we prepare the development planning and time schedule.

#### 2) Developmental prototype stage

We determine circuits, pattern design, process settings, assembly techniques and structural requirements during this stage. At the same time, we carry out actual prototype reliability testing.

Since device quality is largely determined during the designing stage, Oki Electric pays careful attention to quality confirmation during this stage.

This is how we do it:

- (1) After completion of circuit design (or pattern design), personnel from the design, process technology, production technology, installation technology and reliability departments get together for a thorough review to ensure design quality and to anticipate problems that may occur during mass production. Past experience and know-how guide these discussions.

- (2) Since many semiconductor memories involve new concepts and employ high level manufacturing technology, the TEG evaluation test is often used during this stage.

- Note: TEG (Test Element Group) refers to the device group designed for stability evaluation of MOS transistors, diodes, resistors, capacitors and other circuit component element used in LSI memories.

- (3) Prototypes are subjected to repeated reliability and other special evaluation tests. In addition, the stability and capacity of the manufacturing process are checked.

#### 3) Production prototype stage

During this stage, various tests check the reliability and other special features of the production prototype at the mass production factory level. After confirming the quality of device, we prepare the various standards required for mass production, and then start production. Although reliability and other special tests performed on the production prototype are much the same as those performed on the developmental prototype, the personnel, facilities and production site differ for the two prototypes, necessitating repeated confirmation tests.

#### 4) Mass production

During the mass production stage, careful management of purchased materials, parts and facilities used during the manufacturing process, measuring equipment, manufacturing conditions and environment is necessary to ensure device quality first stipulated during the designing stages. The manufacturing process (including inspection of the completed device) is followed by a lot guarantee inspection to check that the specified quality is maintained under conditions identical to those under which a customer would actually use the device. This lot guarantee inspection is performed in 3 different forms as shown below.

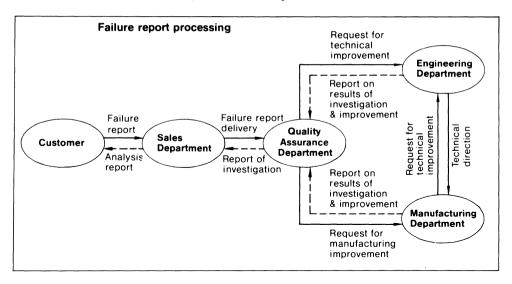

Fig. 2 Defect Processing Flowchart

1) Group A tests: appearance, labels, dimensions

and electrical characteristics in-

spection

(2) Group B tests:

check of durability under thermal and mechanical environmental stresses, and operating life charac-

(3) Group C tests:

performed periodically to check operational life etc on long term

basis.

teristics

Note: Like the reliability tests, the group B tests conform to the following standards.

MIL-STD-883B, JIS C 7022, EIAJ-IC-121

Devices which pass these lot guarantee inspections are stored in a warehouse awaiting shipment to customers. Standards are also set up for handling, storage and transportation during this period, thereby ensuring quality prior to delivery.

5) At Oki Electric, all devices are subjected to thorough quality checks. If, by chance, a failure does occur after delivery to the customer, defective devices are processed and the problem rectified immediately to minimize the inconvenience to the customer in accordance with the following flowchart.

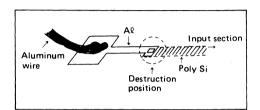

## 3. EXAMPLE OF RELIABILITY TEST RESULTS

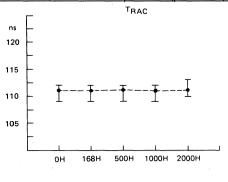

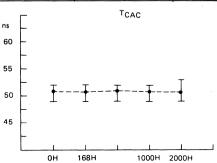

We have outlined the quality assurance system and the underlying concepts employed by Oki Electric. Now, we will give a few examples of the reliability tests performed during the developmental and production prototype stages. All reliability tests performed by Oki Electric conform with the following standards.

MIL-STD-883B, JIS C 7022, EIAJ-IC-121

Since these reliability tests must determine performance under actual working conditions in a short period of time, they are performed under severe test conditions. For example, the  $125^{\circ}$ C high temperature continuous operation test performed for 1000 hours is equivalent to testing device life from 2 to 300 years of use at Ta =  $40^{\circ}$ C.

By repeating these accelerated reliability tests, device quality is checked and defects analyzed. The resulting information is extremely useful in improving the manufacturing processes. Some of the more common defects in memory LSI elements and their analysis are described below.

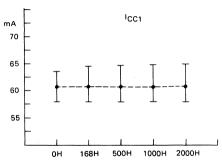

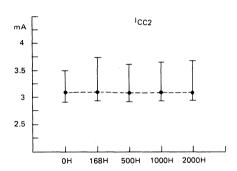

#### OKI MEMORY LSI LIFE TEST RESULTS

|                                | Device name                       | MSM41256-XXRS                        |                               | MSM      | 13764A-                              | XXRS                         | MSM5165-XXRS |                                      |                            |          |  |

|--------------------------------|-----------------------------------|--------------------------------------|-------------------------------|----------|--------------------------------------|------------------------------|--------------|--------------------------------------|----------------------------|----------|--|

|                                | Function                          |                                      | 262144 x 1 bit<br>DYNAMIC RAM |          |                                      | 65536 × 1 bit<br>DYNAMIC RAM |              |                                      | 8192 x 8 bit<br>STATIC RAM |          |  |

|                                | Structure                         | Si gate N-MOS<br>16P plastic package |                               |          | Si gate N-MOS<br>16P plastic package |                              |              | Si gate C-MOS<br>28P plastic package |                            |          |  |

| Test item                      | Test condition                    | Sample<br>size                       | Test<br>hours                 | Failures | Sample<br>Size                       | Test<br>hours                | Failures     | Sample<br>size                       | Test<br>hours              | Failures |  |

| Operating                      | Ta = 125°C<br>Vcc = 5.5V          | 300                                  | 2000                          | 0        | 300                                  | 2000                         | 0            | 88                                   | 2000                       | 0        |  |

| life test                      | Ta = 150° V<br>Vcc = 5.5V         | 40                                   | 6000                          | 0        | 50                                   | 2000                         | 0            | 50                                   | 2000                       | 0        |  |

| Temperature                    | 140°C 85%<br>Vcc = 5.5V           | 100                                  | 100                           | 0        | 100                                  | 100                          | 0            | 22                                   | 100                        | 0        |  |

| humidity test                  | 85° C 85%<br>Vcc = 5.5V           | 100                                  | 2000                          | 0        | 150                                  | 2000                         | 0            | 100                                  | 2000                       | 0        |  |

| Pressure<br>cooker test        | 121°C 100%<br>No bias             | 100                                  | 500                           | 0        | 100                                  | 500                          | 0            | 50                                   | 300                        | 0        |  |

| Low tempera-<br>ture life test | $Ta = -10^{\circ} C$ $Vcc = 7.0V$ | 22                                   | 2000                          | 0        | 22                                   | 2000                         | 0            | 22                                   | 2000                       | 0        |  |

| Temperature cycling test       | -55°C ~<br>150°C                  | 100                                  | 500<br>cycles                 | 0        | 100                                  | 500<br>cycles                | 0            | 100                                  | 500<br>cycles              | 0        |  |

|                                | Device name                        | MSM27256-AS    |                                     | MSN      | /38256->       | XXRS                      | MSM531000-XXRS |                                      |                            |          |  |

|--------------------------------|------------------------------------|----------------|-------------------------------------|----------|----------------|---------------------------|----------------|--------------------------------------|----------------------------|----------|--|

|                                | Function                           |                | 32768 x 8 bit<br>UV erasable EP ROM |          |                | 32768 x 8 bit<br>Mask ROM |                |                                      | MSM531000-XXRS<br>Mask ROM |          |  |

|                                | Structure                          | 11             | Si gate N-MOS<br>28P cerdip         |          |                | gate N-M<br>plastic pa    |                | Si gate C-MOS<br>28P plastic package |                            |          |  |

| Test item                      | Test condition                     | Sample<br>size | Test<br>hours                       | Failures | Sample<br>Size | Test<br>hours             | Failures       | Sample<br>size                       | Test<br>hours              | Failures |  |

| Operating                      | Ta = 125°C<br>Vcc = 5.5V           | 88             | 2000                                | 0        | 55             | 2000                      | 0              | 88                                   | 2000                       | 0        |  |

| life test                      | $Ta = 150^{\circ}C$ $Vcc = 5.5V$   | 40             | 2000                                | 0        |                |                           |                |                                      |                            |          |  |

| Temperature                    | 140°C 85%<br>Vcc = 5.5V            |                |                                     |          |                |                           |                | 22                                   | 100                        | 0        |  |

| humidity test                  | 85°C 85%<br>Vcc = 5.5V             | 50             | 1000                                | 0        | 50             | 2000                      | 0              | 25                                   | 2000                       | 0        |  |

| Pressure<br>cooker test        | 121°C 100%<br>No bias              | 22             | 48                                  | 0        | 22             | 500                       | 0              | 50                                   | 200                        | 0        |  |

| Low tempera-<br>ture life test | $Ta = -10^{\circ} C$<br>Vcc = 7.0V | 22             | 2000                                | 0        |                |                           |                | 22                                   | 2000                       | 0        |  |

| Temperature cycling test       | -55°C ∼<br>150°C                   | 100            | 500<br>cycles                       | 0        | 50             | 300<br>cycles             | 0              | 50                                   | 300                        | 0        |  |

#### OKI MEMORY LSI ENVIRONMENTAL TEST RESULTS

|                                     |                                    | Device name                                           | MSM41256-XXRS  |          | MSM376         | 4AXXRS   | MSM5165-XXRS   |          |

|-------------------------------------|------------------------------------|-------------------------------------------------------|----------------|----------|----------------|----------|----------------|----------|

| Test item                           |                                    | Test condition                                        | Sample<br>size | Failures | Sample<br>size | Failures | Sample<br>size | Failures |

|                                     | Soldering<br>heat                  | 260° C<br>10 sec                                      |                |          | 22             | O        | 22             |          |

| Thermal environmental               | Thermal shock                      | 0°C~100°C<br>5 min 5 min<br>10 cycles                 | 22             | 2 0      |                |          |                | 0        |

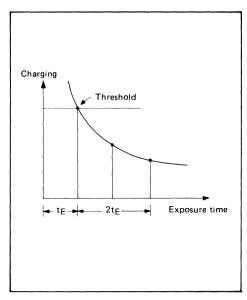

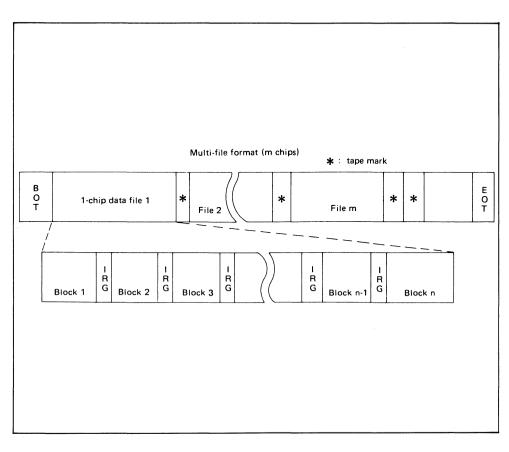

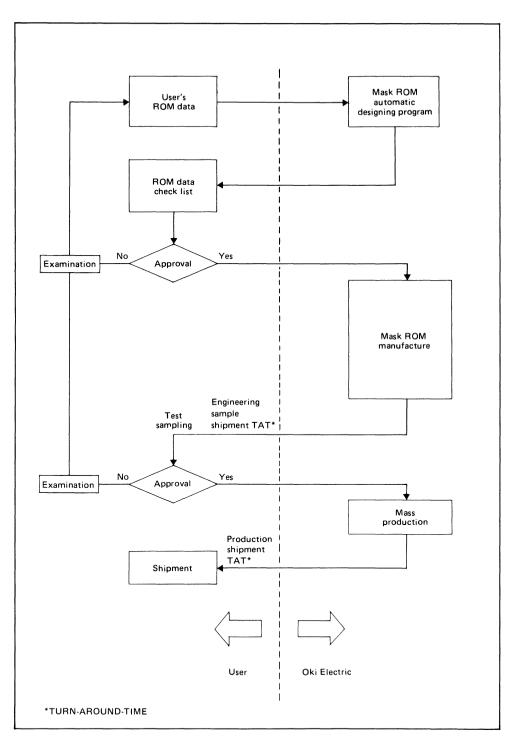

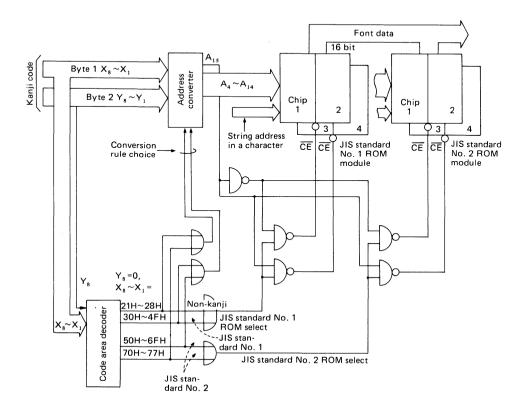

| test                                | Temperature cycling                | -55° C∼RT∼150° C<br>30 min 30 min<br>20 cycles        |                |          |                |          |                |          |