# **SPITFIRE**

64-bit Multimedia GUI Accelerator

OTI-64107/64105 Preliminary Specification

September 1994

# **SPITFIRE OTI-64107/64105**

# TABLE OF CONTENTS

| CHAPT | ER 1. OVERVIEW                        |      |

|-------|---------------------------------------|------|

| СНАРТ | ER 2. INTERFACE DESCRIPTION           |      |

| 2.1   | System Bus Interface                  |      |

| 2.2   | DAC Interface                         |      |

| 2.3   | Clock Interface                       | 2-8  |

| 2.4   | ROM BIOS Interface                    | 2-8  |

| 2.5   | Feature Connector Interface           |      |

| 2.6   | EEPROM/Dipswitch Interface            |      |

| СНАРТ | ER 3. DISPLAY MEMORY INTERFACE        | 3-1  |

| СНАРТ | ER 4. MULTIMEDIA INTERFACE            |      |

| 4.1   | Chroma-keying                         |      |

| 4.2   | Video Masking                         |      |

| 4.3   | Multimedia Input Port                 |      |

| 4.4   | Multimedia Output Port                | 4-5  |

| 4.5   | Support for External Video Chips      | 4-9  |

| 4.6   | Video Bandwidth                       | 4-11 |

| СНАРТ | ER 5. POWER MANAGEMENT SUPPORT.       | 5-1  |

| CHAPT | ER 6. PIN DESCRIPTION                 | 6-1  |

| СНАРТ | ER 7. OTI-64107 REGISTER DEFINITION   | 7-1  |

| СНАРТ | ER 8. VGA REGISTERS                   | 8-1  |

| CHAPT | ER 9. ELECTRICAL DATA                 | 9-1  |

| 9.1   | Maximum Ratings                       |      |

| 9.2   | DC Specifications                     |      |

| 9.3   | AC Specifications                     | 9-4  |

|       | ER 10. VIDEO BIOS                     |      |

| 10.1  | Overview                              | 10-1 |

| 10.2  | VGA Compatible Modes                  |      |

|       | OTI-64107 Extended Modes              |      |

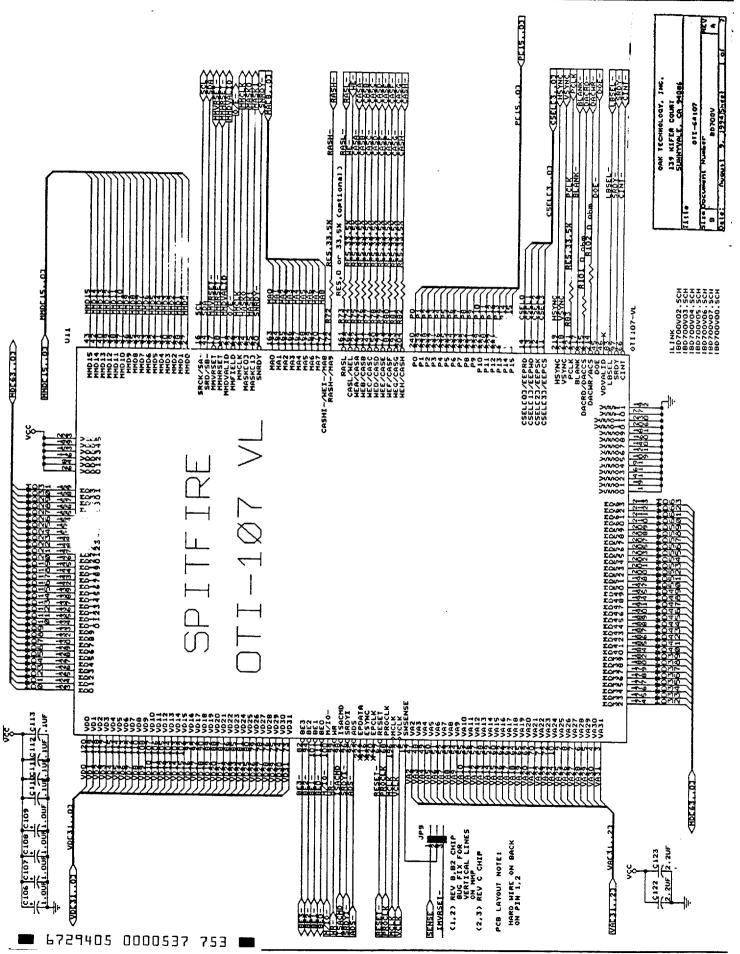

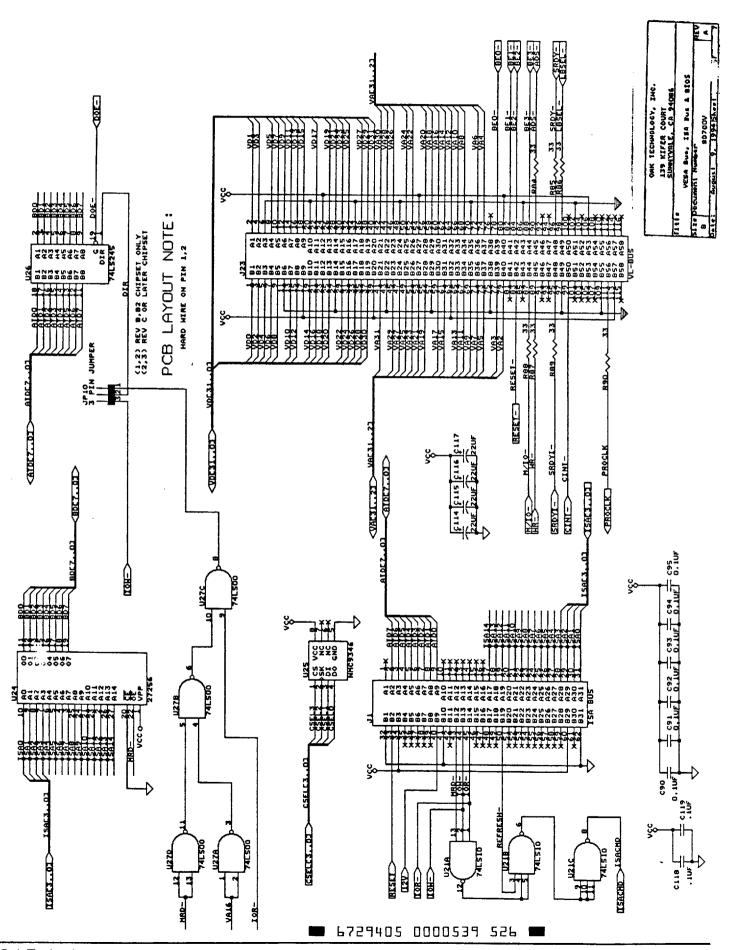

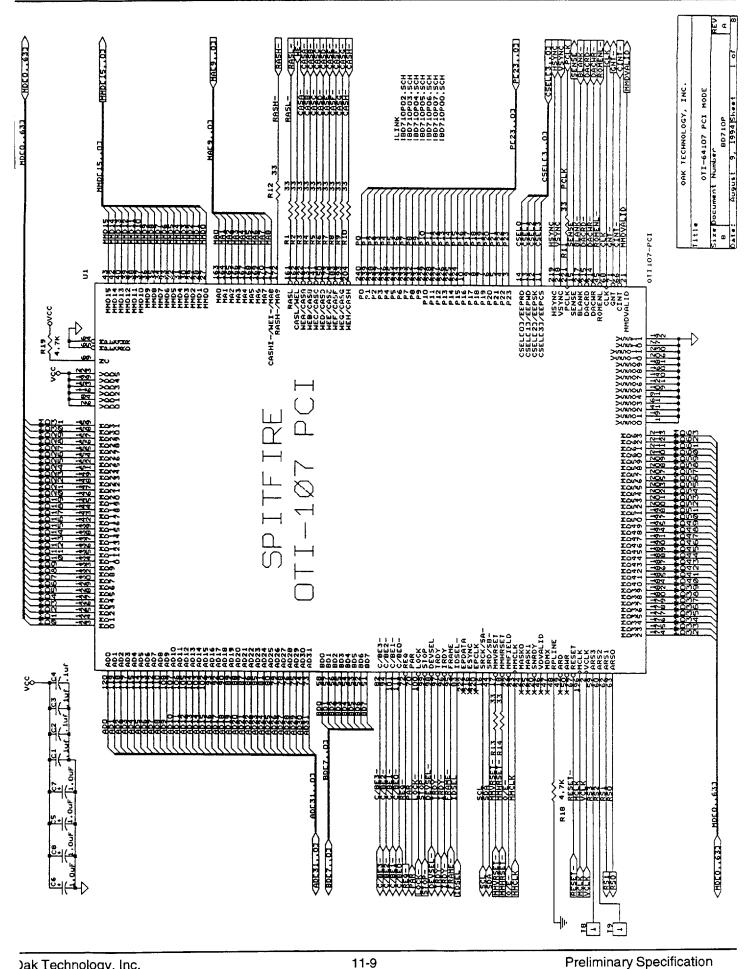

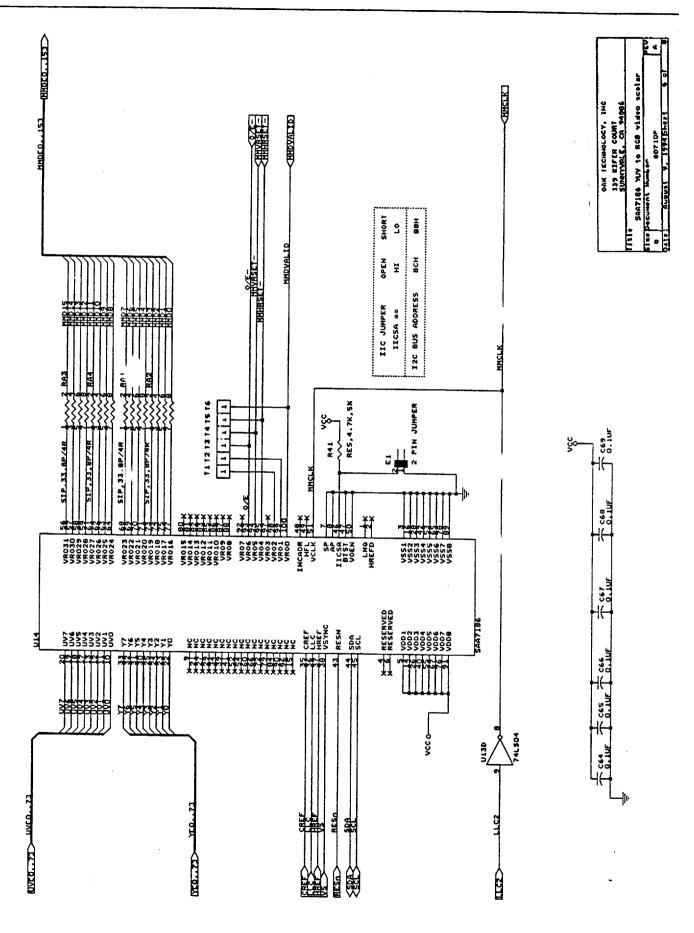

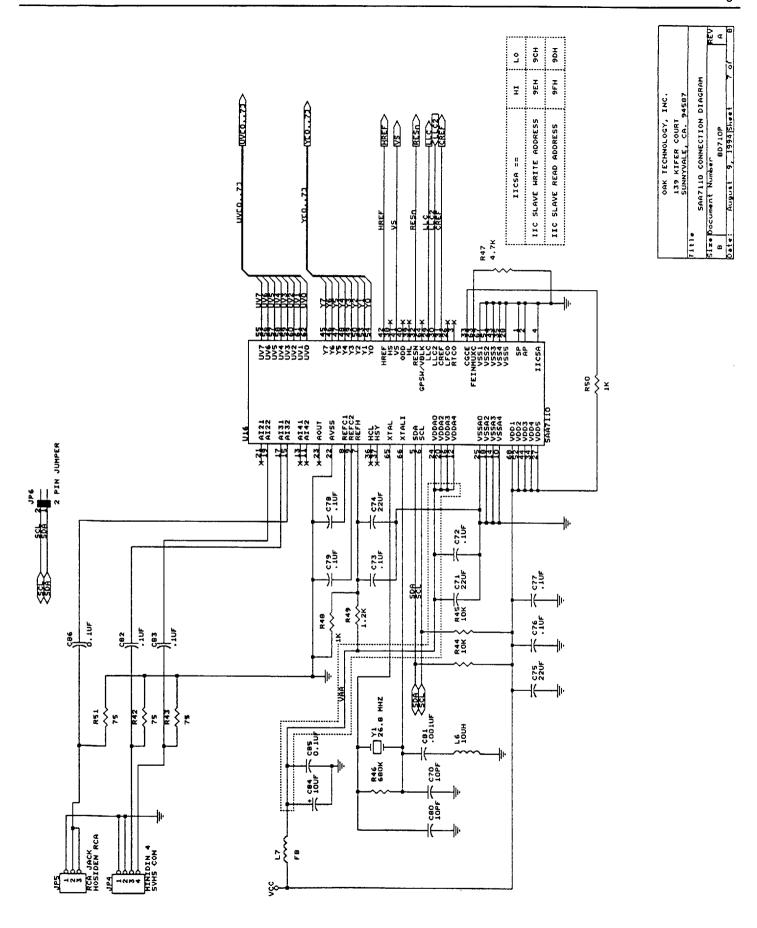

| СНАРТ | ER 11. REFERENCE DESIGN               | 11-1 |

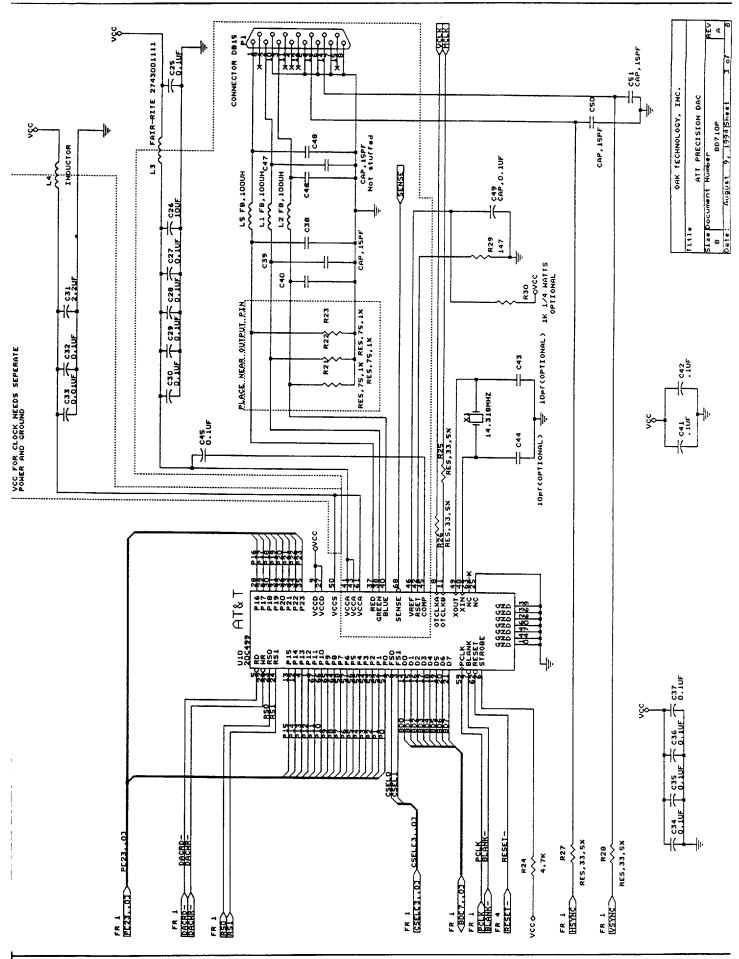

|       | OTI-64107 and ATT20C409 VL Bus Design |      |

| 11.2  | OTI64107 and ATT20C499 PCI-Bus Design |      |

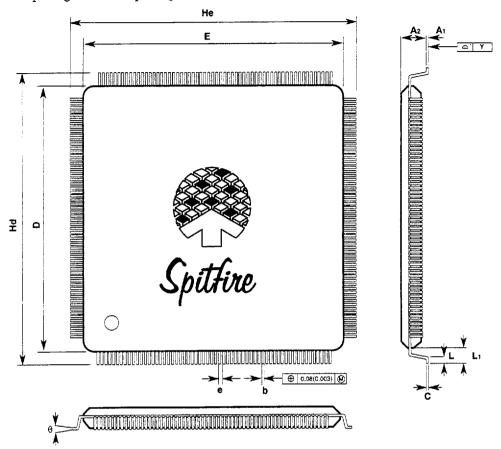

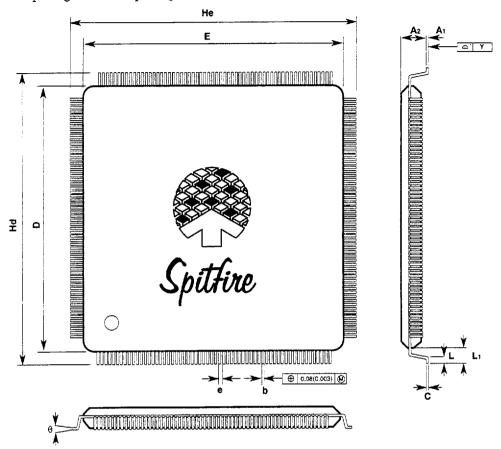

| СНАРТ | ER 12. PACKAGE DIMENSIONS             | 12-1 |

### **CHAPTER 1: OVERVIEW**

#### 1.1 FEATURES

- ◆ True 64-bit Architecture

- Screen resolutions:

- 1280 x 1024, 256 colors @ 75Hz Non-interlaced

- 1024 x 768, 16M colors @ 60Hz Non-interlaced

- ♦ 0.6-m CMOS technology

- 240-pin PQFP (0.5 mm lead pitch)

# TRUE MULTIMEDIA PORT (OTI-64107 only)

- 16-bit data path

- Shared DRAM frame buffer for graphics and video

- 33MHz transfer rate, 66Mbytes/sec data bandwidth

- Video Masking (using a standard inexpensive RAMDAC) allows:

- Text, Graphics, or Animation over video

- Live video does not freeze under a pull-down menu

- Arbitrarily shaped video windows

- Multiple video windows

- Supports chroma keying with a special RAMDAC

- · Hardware cursor on video

- ◆ Scaling: x 2, x 4, x 8

- Glueless live video support for the most popular video chips

- ◆ I<sup>2</sup>C interface built-in

- Modular upgradability, live video can be added as an option

## 1.2 GENERAL DESCRIPTION

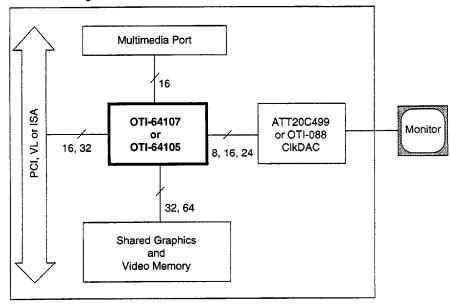

The Spitfire<sup>™</sup>, OTI-64107 and OTI-64105 are pin-compatible, high-performance 64-bit DRAM GUI Accelerators. The OTI-64107 also provides integrated multimedia support with a 16-bit interface and a shared display memory architecture. Spitfire's unique architecture allows the simultaneous display of multiple, overlapping video and graphics windows.

Both chips interface directly to the PCI bus as well as to the VL and ISA buses, with no external logic. Spitfire's 64-bit drawing engine and 64-bit DRAM interface provides high performance at a cost-effective price. Additionally, Spitfire supports Windows NT quaternary ROP's and Windows 3.x ternary ROP's providing dramatic performance improvement by executing typical software driver functions in hardware. On the PCI bus, Spitfire supports direct burst read from system memory and direct burst write to system memory for faster memory to screen and screen to memory transfers.

Combined with the OTI-088 Clock/DAC (24-bit pixel port) and DRAM, the Spitfire provides a complete, high-performance graphics solution with multimedia support. Using the OTI-64105, manufacturers can implement a cost effective GUI accelerator which can later be upgraded to add multimedia support by replacing the OTI-64105 with the OTI-64107 without the need for a board redesign.

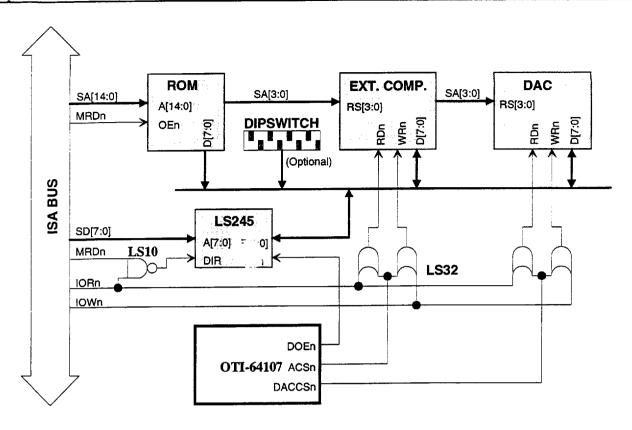

Spitfire System Block Diagram

(Features continued on next page)

# FEATURES (Cont.)

- High-Performance Drawing Engine:

- Bitblt engine with color expansion/conversion and chipping

- Supports four independent bitmaps (source, destination, pattern, mask)

- Supports Windows NT quaternary ROPs and Windows 3.1 ternary ROPs

- Line drawing, Area Fills, and CPU assisted drawing mode

- 1, 8, 16, 32 bits/pixel

- Hardware Cursor:

- 64 x 64 x 2 bits/pixel, at 16M colors

- Frequency of operation:

- Pclk=110MHz

- Mclk=66MHz

- Display Memory

- Typical 2Mbytes of DRAM

- Up to 8Mbytes

- Supports 256K x 16, 512K x 8, 1M x 4, 256K x 8, and 256K x 4 DRAMS

- 32/64-bit display memory data bus

- Programmable display memory timing

- ISA/VL/PCI buses supported

- Write buffer

- Memory mapped I/O

- 4Gbytes memory addressing capability

- Glueless 32-bit VL-bus interface

- PCI bus:

- Glueless 32-bit PCI bus interface

- Master Mode support

- Direct burst transfer to/from system memory

- 4Gbytes memory addressing capability

- Output pixel port:

- 8/16/24-bit

- Directly inputs to OTI-088 24-bit ClkDAC

- Allows multiple pixel packing

- Supports 1280 x 1024 x 256 colors at 75Hz (135-MHz clock) by multiple pixel packing out of the OTI-64107

- EEPROM support for switchless implementation

- Fully integrated Feature Connector support, compliant with VESA VAFC Proposal 1.0 p

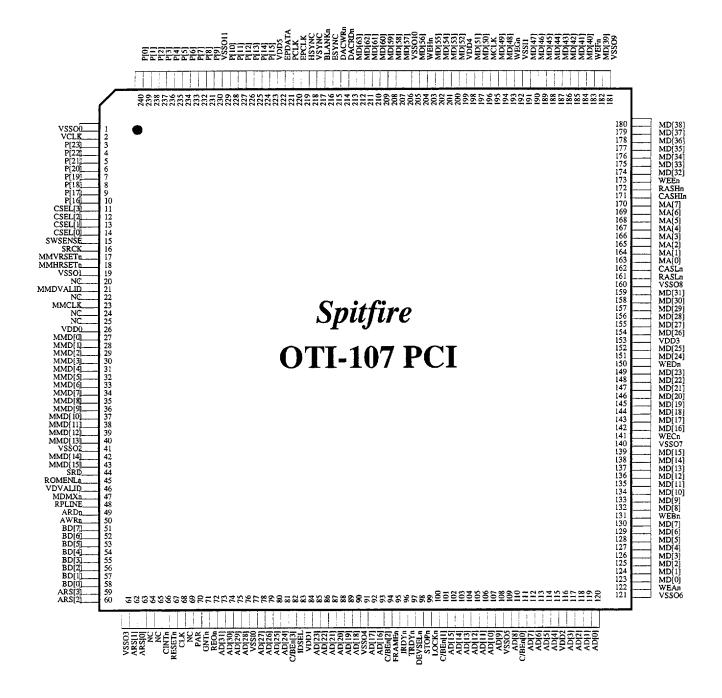

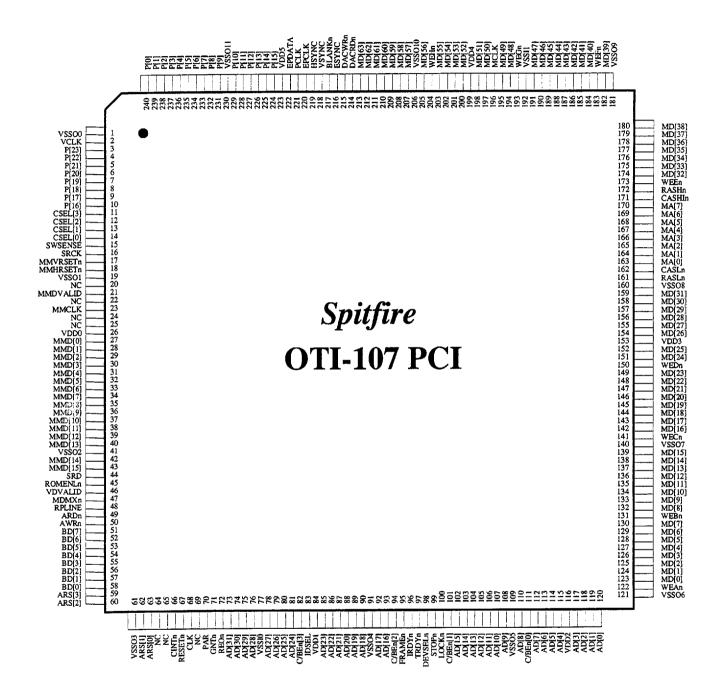

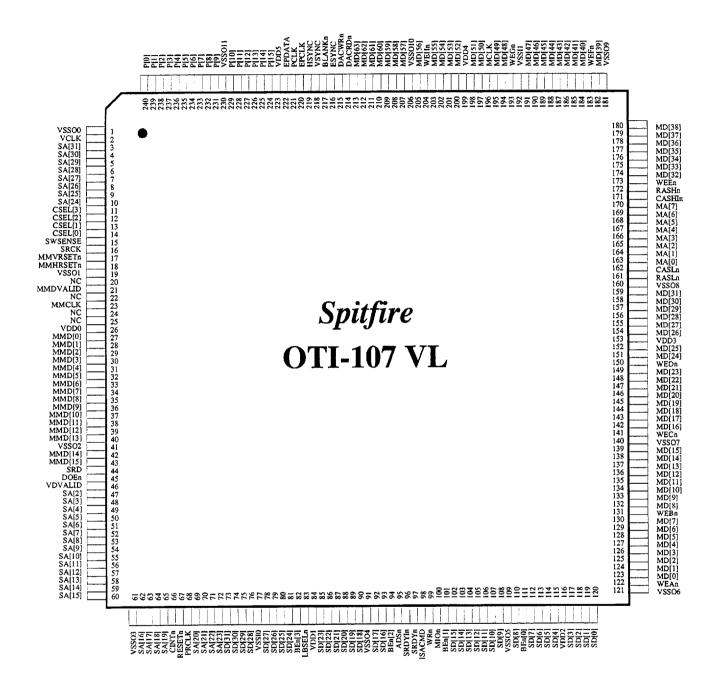

Spitfire Actual Package Size

# **CHAPTER 2: INTERFACE DESCRIPTION**

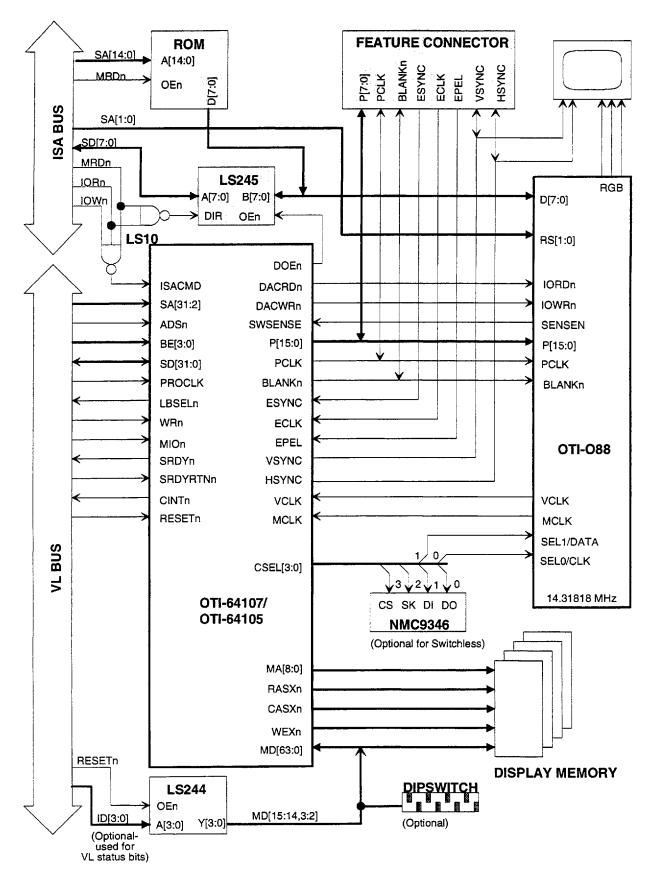

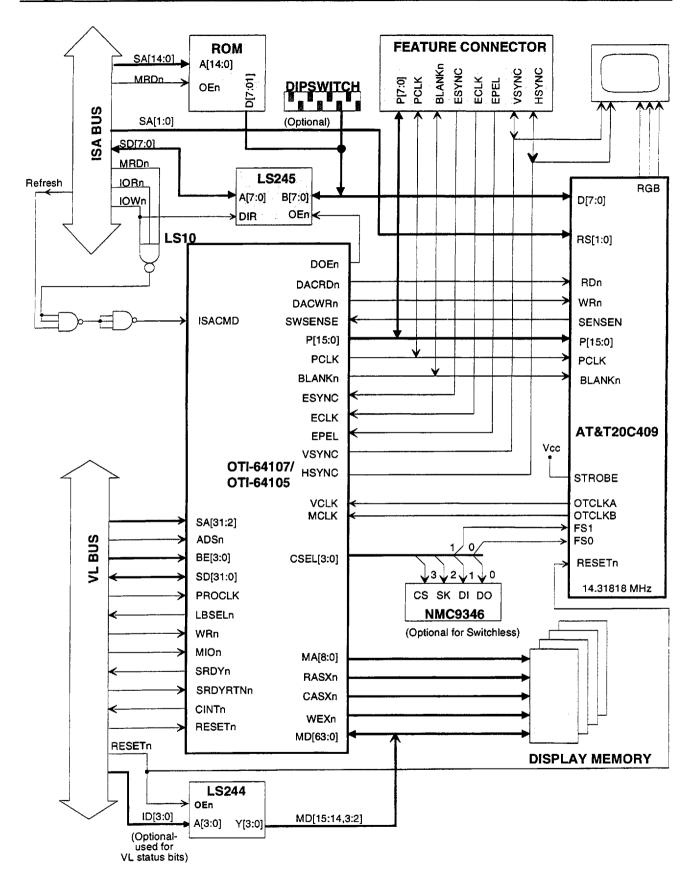

This section describes the interfaces of the OTI-64105/107 to the other components of the graphics subsystem. The Display Memory interface and the interface to the Multimedia Port are described in subsequent sections. The OTI-64105 and the OTI-64107 are pin-compatible parts, except the OTI-64105 does not have the Multimedia Port. The Multimedia Port pins are No-Connects for the OTI-64105. The OTI-64105/107 Interface Diagram is shown below:

In the rest of this document, these two pin-compatible parts are referred to as the OTI-64107 or 64107.

The following interfaces have been described in the following sections:

- 2.1 System bus interface

- 2.2 DAC interface

- 2.3 Clock interface

- 2.4 ROM BIOS interface

- 2.5 Feature connector interface

- 2.6 EEPROM/Dipswitch interface

# 2.1 System Bus Interface

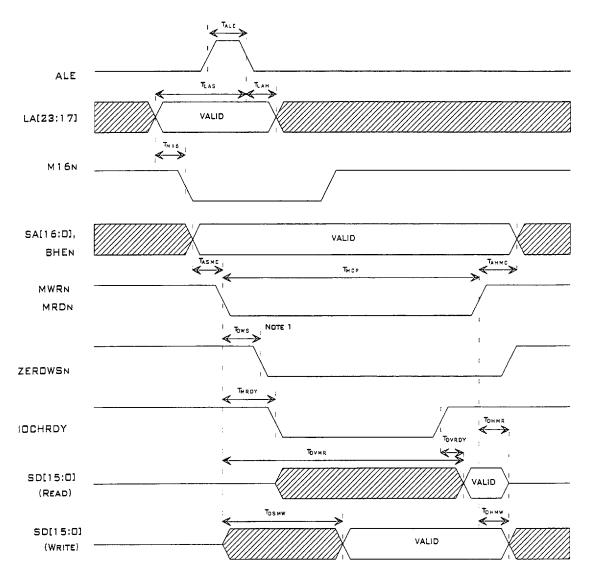

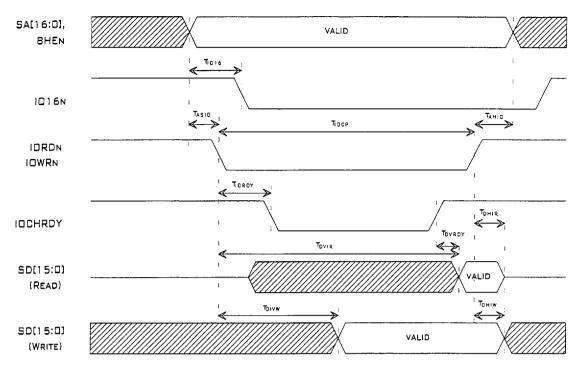

The OTI-64107 can be configured to interface directly to the three standard system buses in use today: VL, PCI and ISA. The chip configures itself to interface to a particular bus during hardware reset through the Hardware Configuration Register 1 (reg 3DF.07). The VL interface is compliant to the VESA VL-Bus Specification Version 2.0p, Revision 0.93p, dated 9/23/1993. The PCI interface is compliant to the PCI Local Bus Specification Revision 2.0, dated 4/30/1993. The ISA interface is compatible to the IEEE P996 standard for 8-bit and 16-bit ISA bus.

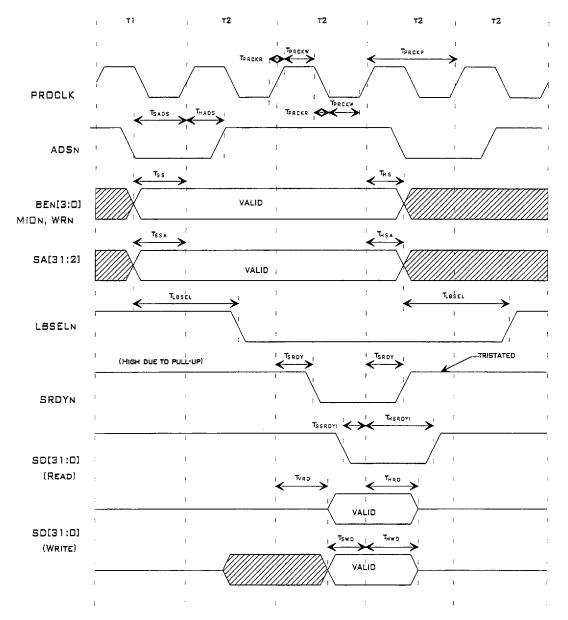

#### 2.1.1 VL-Bus

The OTI-64107 supports both I/O and memory cycles on the VL-bus up to 50MHz. I/O cycles are minimally one wait state and programmable up to five wait states. Memory write cycles are designed to run at 0-2 wait states on cache hit cycles, depending on the speed of the bus. Strictly following the VL-bus specification of 4 ns setup time for address and data would force the controller to run at a minimum of one wait. Memory mapped I/O write cycles are minimally one wait state and programmable up to five wait states, while memory mapped I/O read cycles are minimally two wait states and programmable up to six wait states. As a general rule of thumb, the memory write cycles are zero wait state at a 25MHz bus speed, and one wait state at 33-50MHz bus speeds.

32-bit I/O is supported for Extended System Interface registers (2xxx). Standard VGA and Oak Extended registers at 3DE/3DF can only be supported with word or byte cycles. DAC and Auxiliary registers can only be supported with byte cycle. BIOS and drivers must take care of this.

OTI-64107 does not support Bus Mastering or Burst mode on the VL-bus.

See VESA VL-Bus Specification for more operational information on the VL-bus.

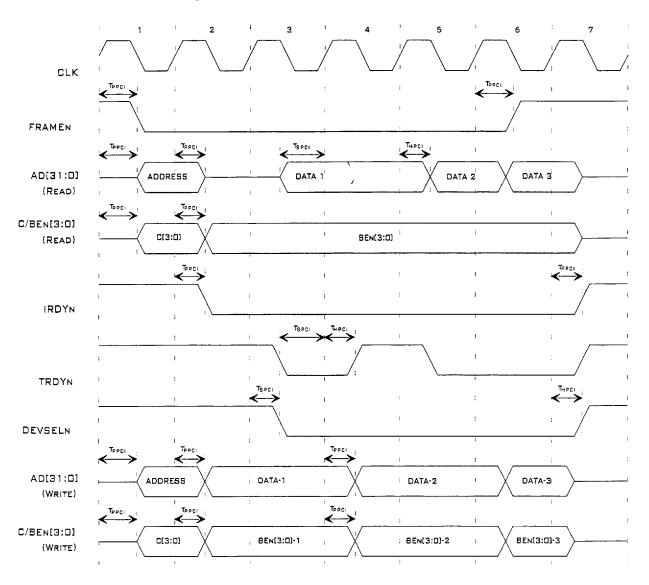

#### 2.1.2 **PCI Bus**

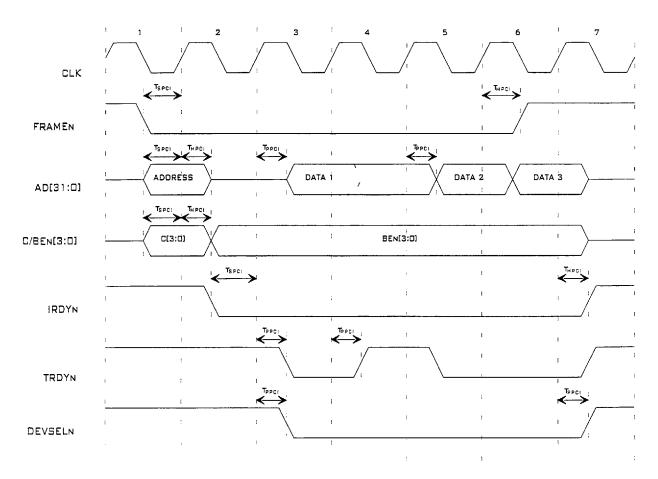

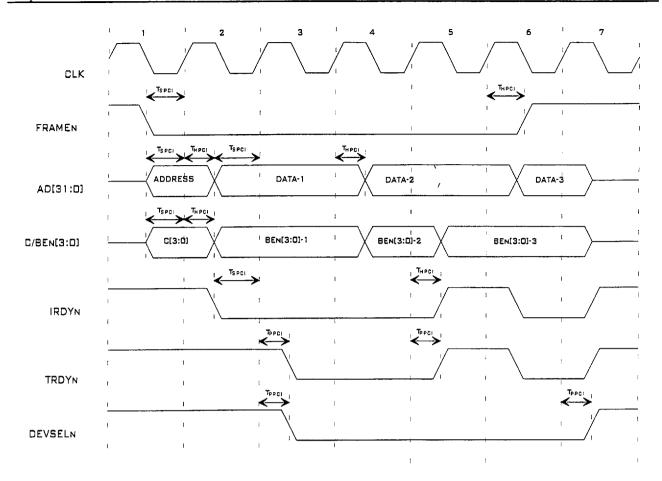

The 32-bit PCI bus is supported up to 33MHz. I/O and Configuration cycles are minimally one wait state and programmable up to five wait states. Memory cycles, both read and write, are minimally one wait state and maximally three wait states. Memory mapped I/O write cycles are minimally one wait state and programmable up to five wait states, while memory mapped I/O read cycles are minimally two wait states and programmable up to six wait states.

32-bit I/O is supported for Extended System Interface registers (2xxx). Standard VGA and Oak Extended registers at 3DE/3DF are only be supported with word or byte cycles. DAC and Auxiliary registers are only supported with byte cycles.

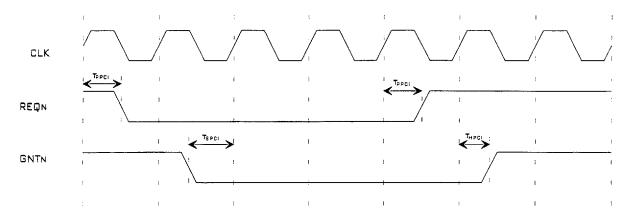

Bus mastering and burst mode are supported for the PCI bus. However, physical memory address must be used in order to use master mode. Parity generation is supported but there is no parity checking.

See PCI Local Bus Specification (Rev 2.0) for more details.

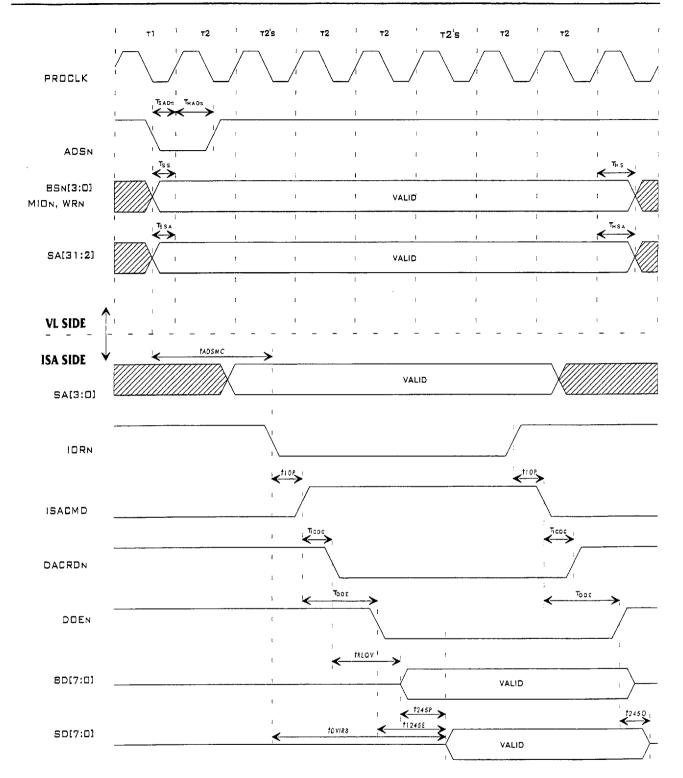

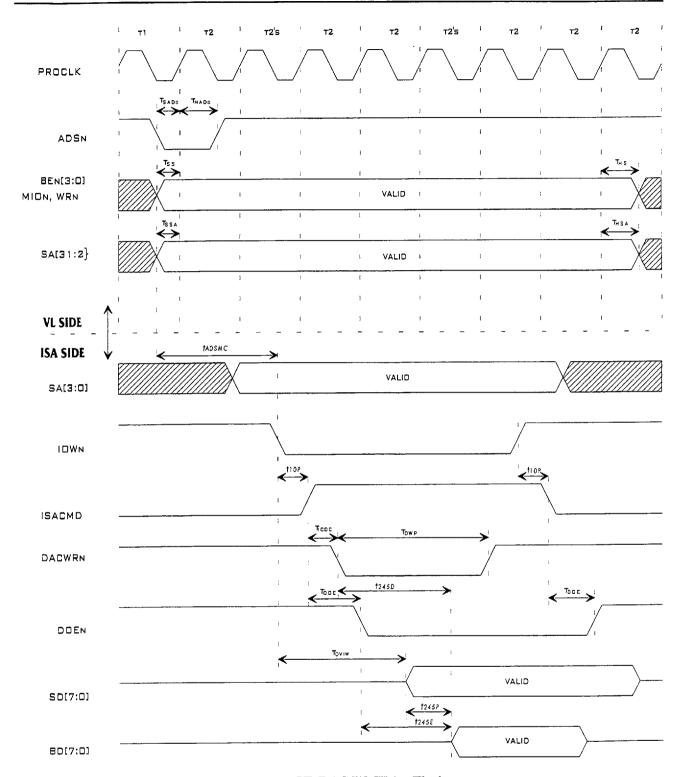

#### 2.1.3 **ISA Bus**

The OTI-64107 provides zero wait state memory operations and 1 wait I/O on ISA bus up to 12.5MHz. Faster bus systems should disable the zero wait state feature. DAC and Auxiliary registers can only be supported with byte cycle, IO16n will not be generated for these cycles.

Bus Mastering is not supported.

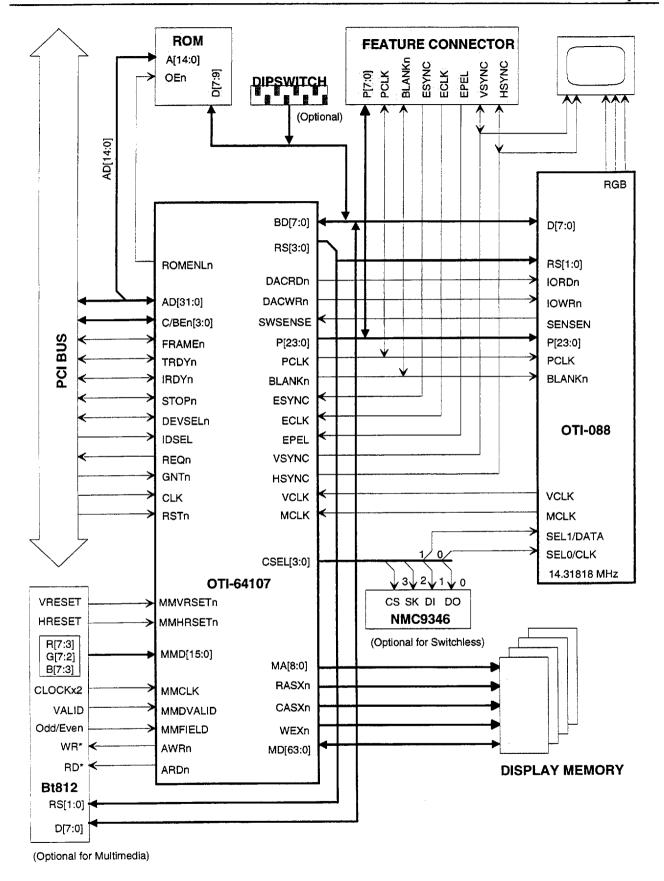

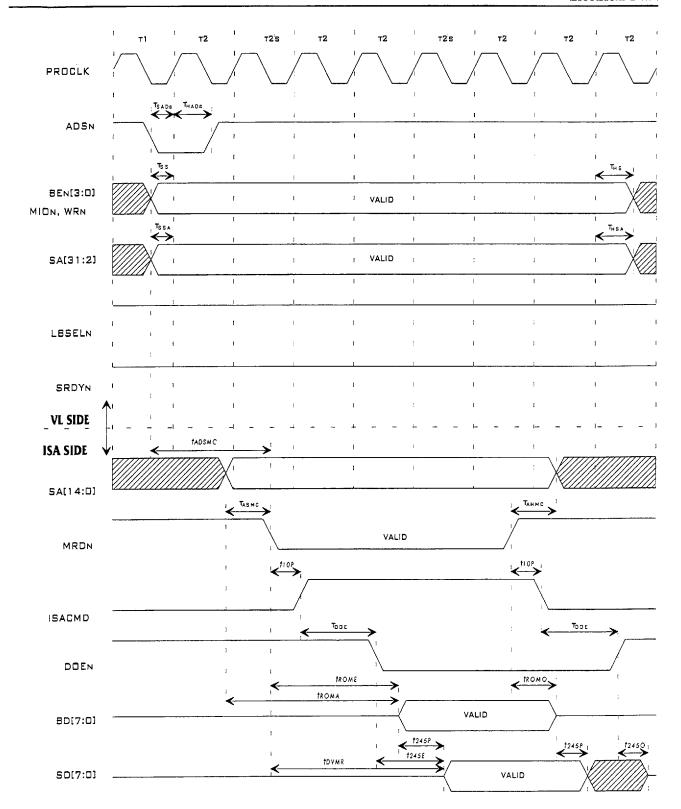

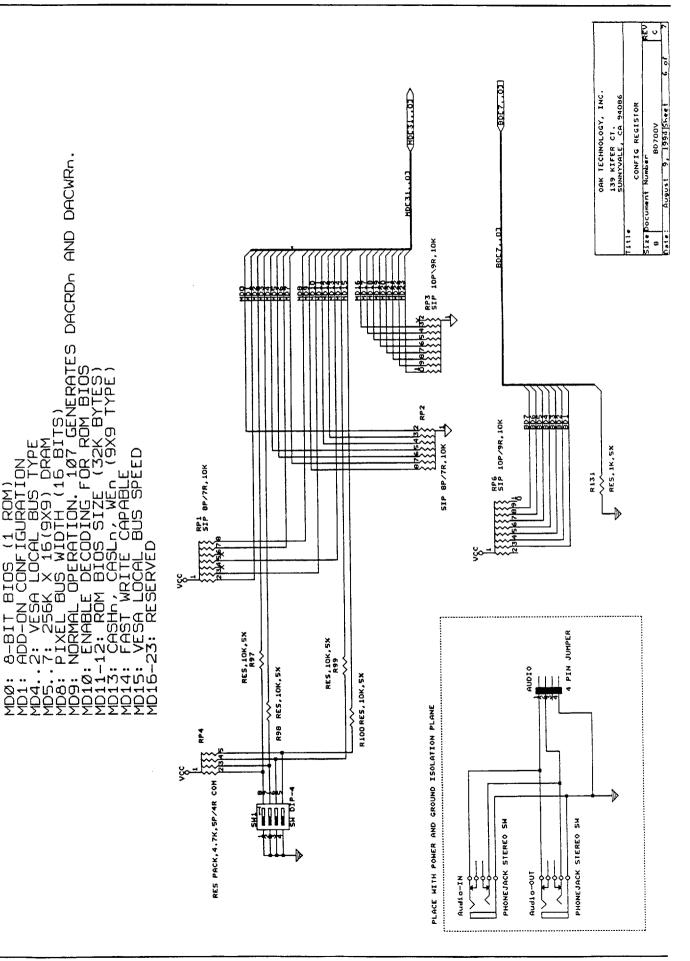

Figure 2.1 - VL Bus Block Diagram using OTI-088 ClkDAC

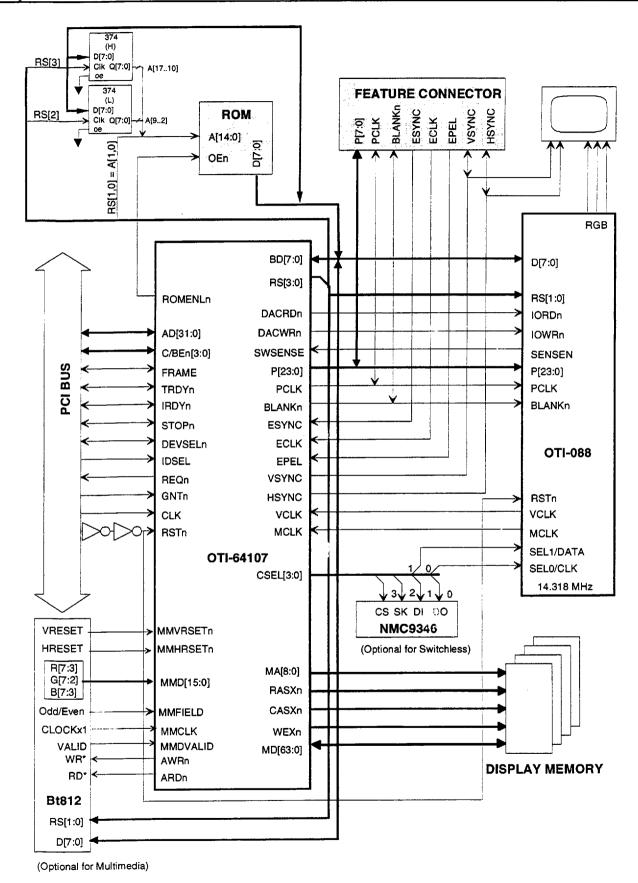

Figure 2.2 - VL Bus Block Diagram using AT&T20C409 Precision DAC™

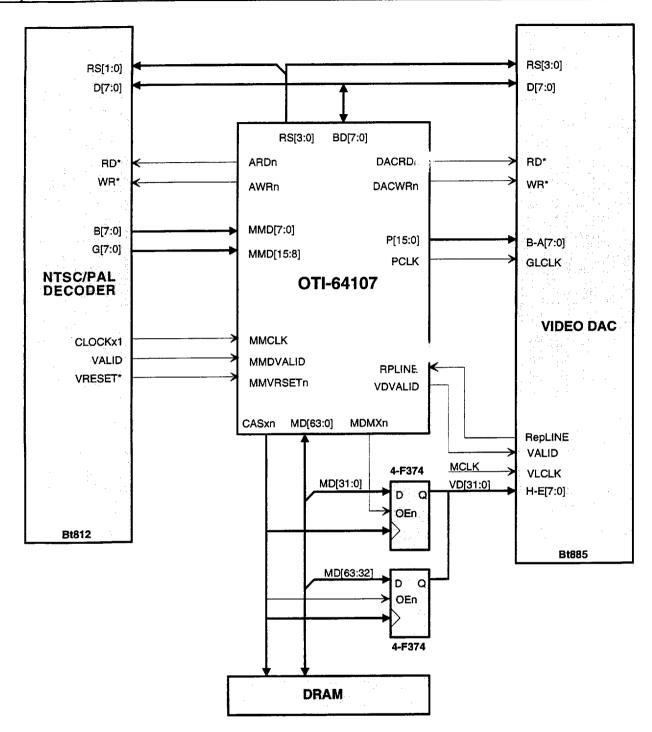

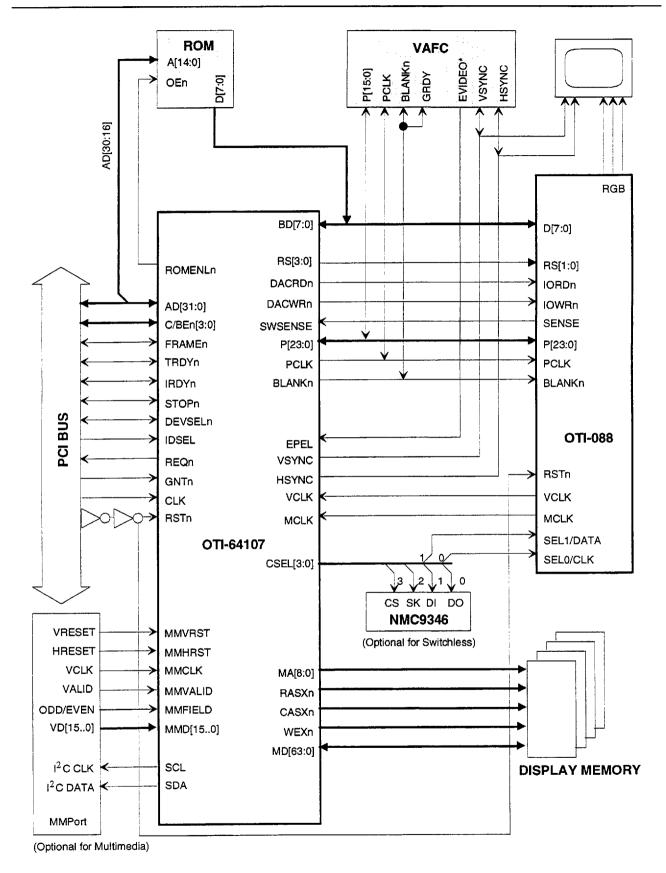

Figure 2.3 - PCI Bus Block Diagram (Glueless) with the Multimedia Port

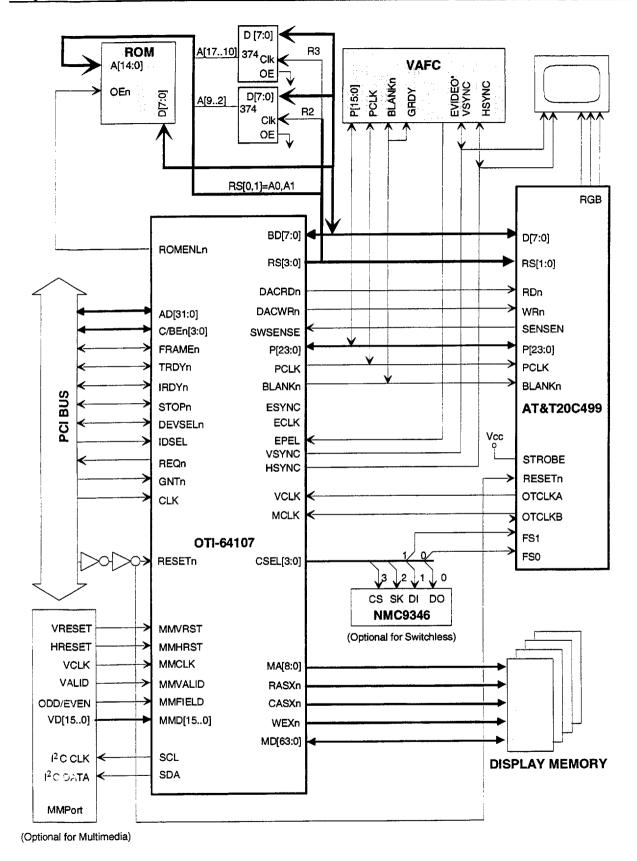

Figure 2.4 - PCI Bus Block Diagram (compliant) with the Multimedia Port

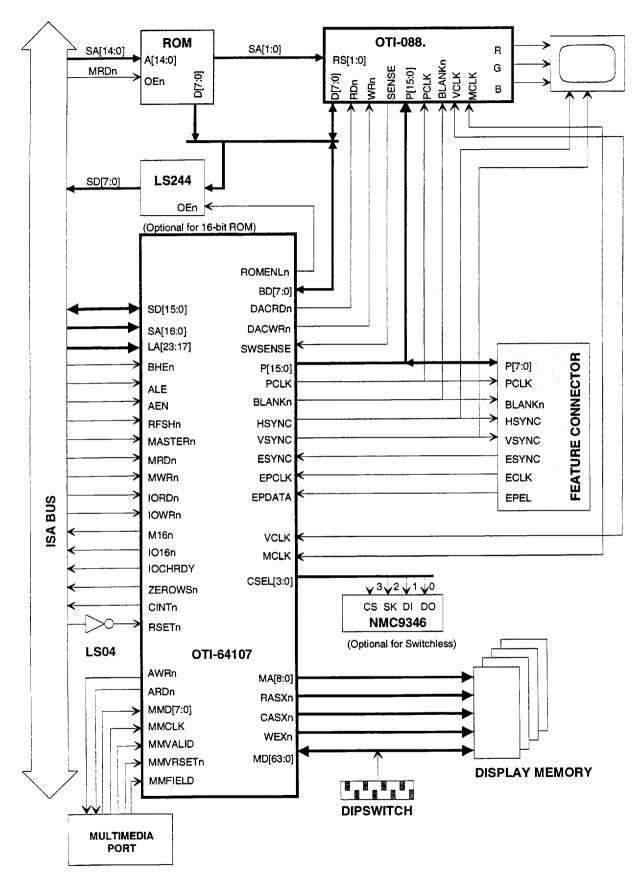

Figure 2.5 - ISA Bus Block Diagram

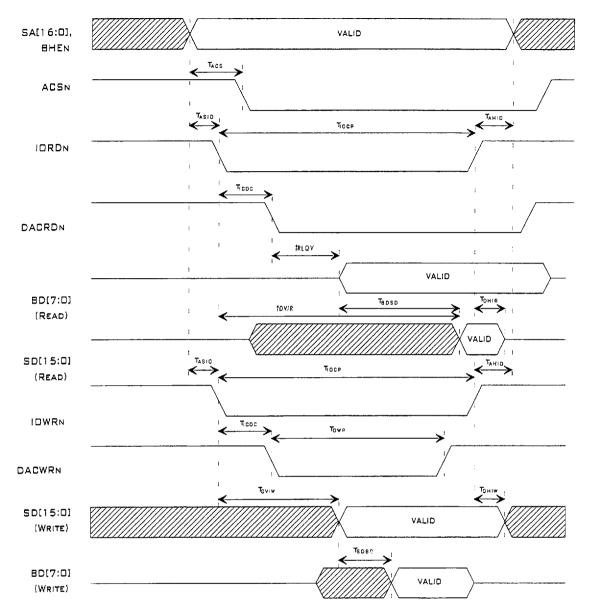

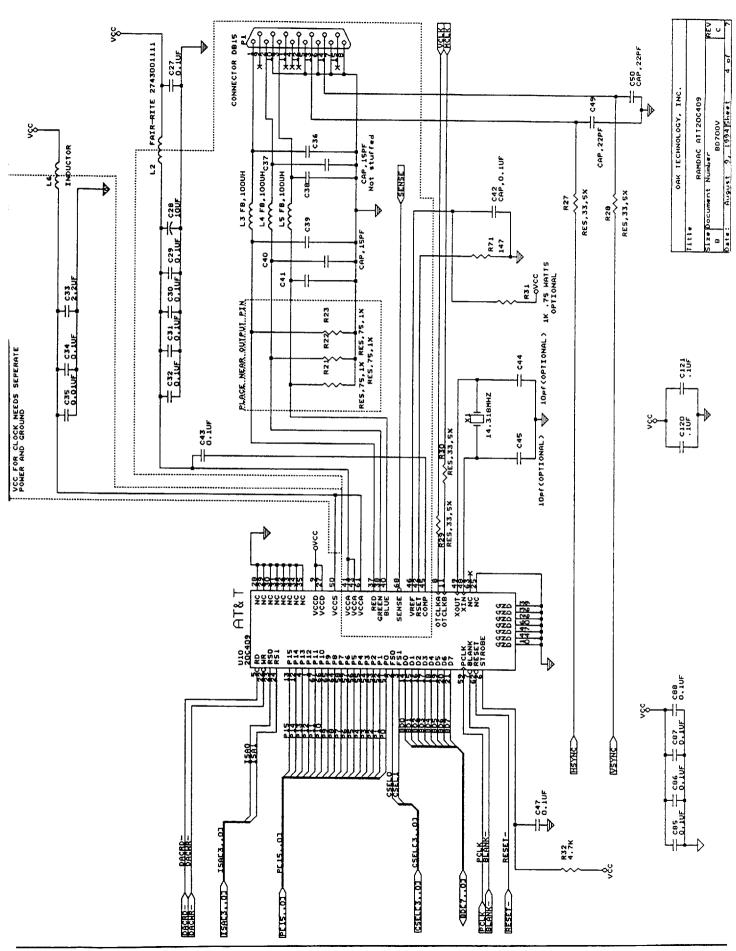

## 2.2 DAC Interface

DAC I/O only supports 8-bit transfers. For ISA or PCI bus implementation, DAC system data is routed through BD bus to the system bus. For VL bus implementation, DAC system data is routed to the ISA bus through external buffers. OTI-64107 will always decode address and status/command to generate DACRDn and DACWRn for the DAC I/O commands. DAC address space by default is 3C6-3C9. Extended DAC I/O space can be supported from 2x80-2x9F. The 'x' is programmable and defaults to 1. See system block diagrams for more information.

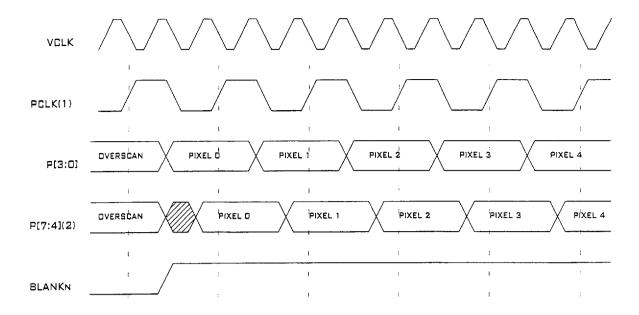

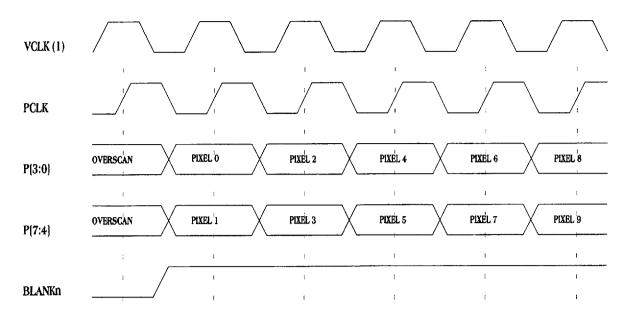

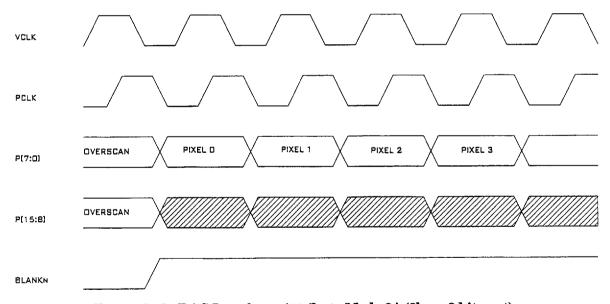

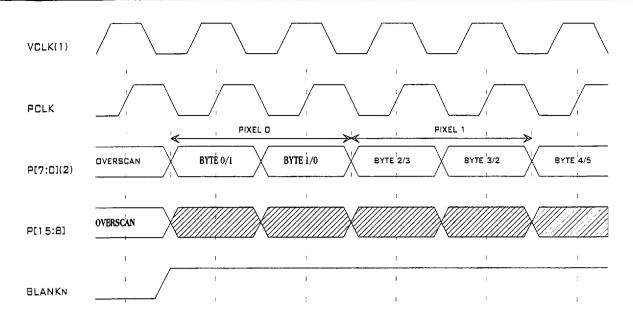

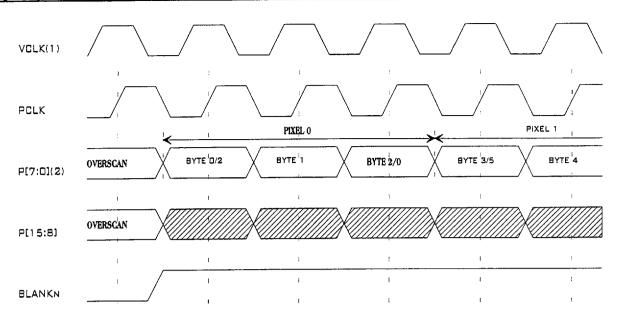

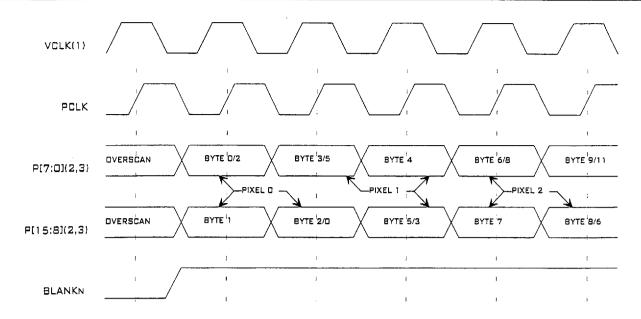

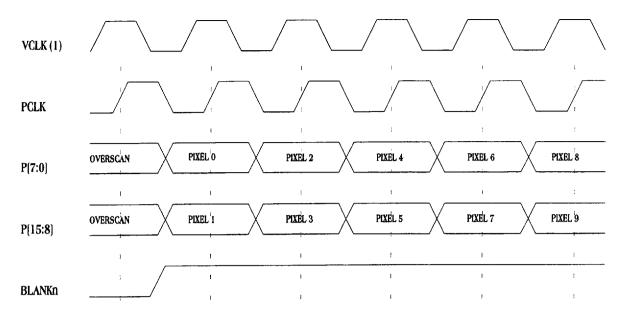

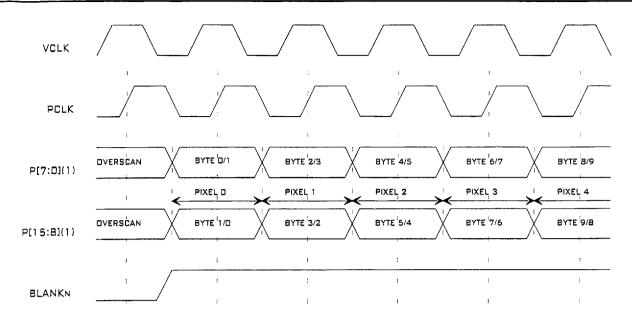

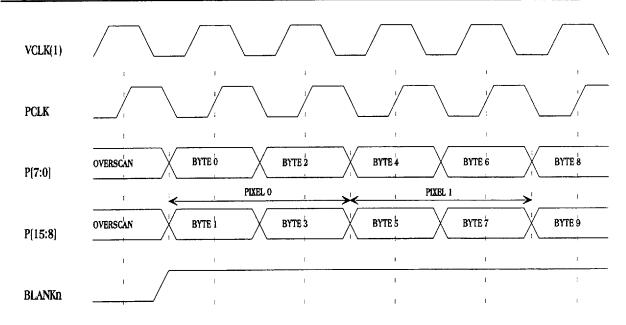

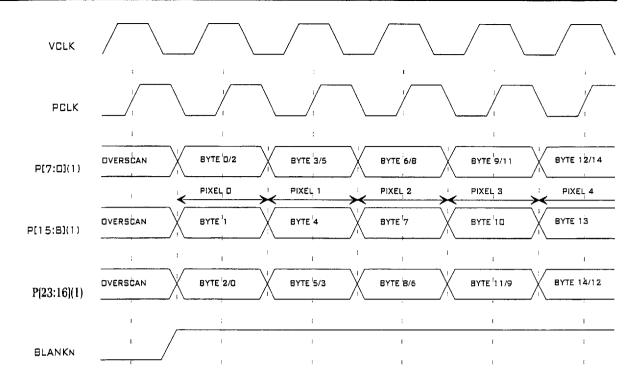

The OTI-64107 can be configured to be either 8-, 16-, or 24-bit pixel bus support. Hi-color and true-color support in 8-bit configuration is the same as 87X (double or triple frequency). Hi-color support in 16-bit pixel bus will allow the controller to run at regular frequency instead of doubling. True-color support in 16-bit pixel bus will require doubling frequency (with one byte wasted or with packed format), but not tripling the frequency. For high resolution (1280 x 1024) 256 color modes, there is an option to send two 8-bit pixels out at a time and consequently the pixel clock can be half the regular RAMDAC frequency.

24-bit pixel bus is supported for true color modes only. Due to pin limitations on the VL bus, pins P[23:16] are available only when the OTI-64107 is on either ISA or PCI buses. 24-bit pixel bus allows the OTI-64107 to support true color at higher resolution with all having to double or triple the pixel clock frequency. See Pixel Interface register for more information on various modes supported at different pixel bus widths.

# 2.3 Clock Interface

Up to 16 external video clock frequencies can be selected by four programmable clock select output pins. Video clock frequencies can be supported up to 110MHz. These programmable pins can also be used as clock and data pins for serially programmable clock sources, allowing the OTI-64107 to support both VESA and conventional video frequencies without any hardware switches.

Memory clock is selectable through either software if the clock chip is programmable, or by hardware through jumpers if the clock chip has fixed frequencies. Memory clock can be supported up to 66MFz

The dual clock synthesizers of the OTI-088 SynDAC have been designed for a glueless and flexible interface for the OTI-64107. The OTI-088 has two programmable pins which are used for clock and serial data inputs. The OTI-64107 sends out a 16-bit serial data stream to program each of the Video Clock and Memory Clock registers in the OTI-088. The register description of the Video Clock Select register (3DF index 6) explains how the OTI-64107 programs the OTI-088. Also refer to the Co-088 data sheet for more details on the clock interface.

The OTI-64107 can also be used with the AT&T *PrecisionDAC*'s AT&T20C409 (16-bit pixel port for VL bus) and AT&T20C499 (24-bit pixel port for PCI bus). The *PrecisionDAC*'s are programmed over the parallel 8-bit data bus. Please refer to the appropriate datasheet for more details on the clock interface.

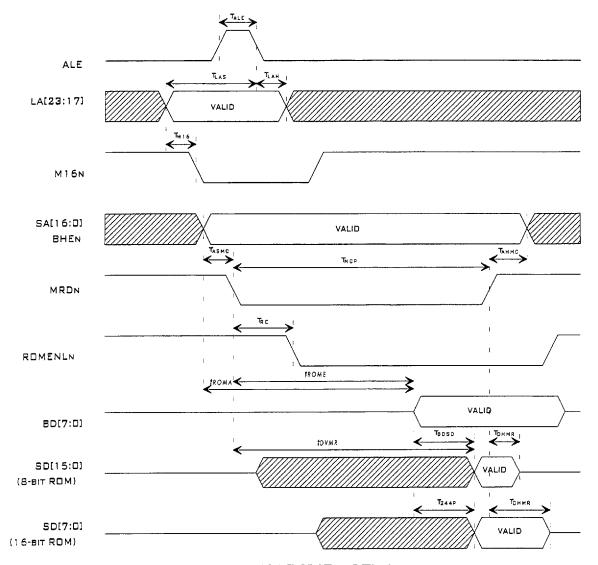

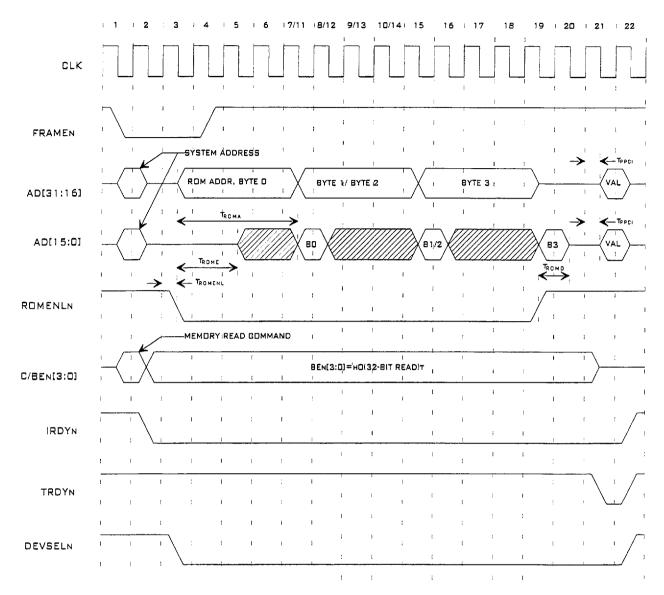

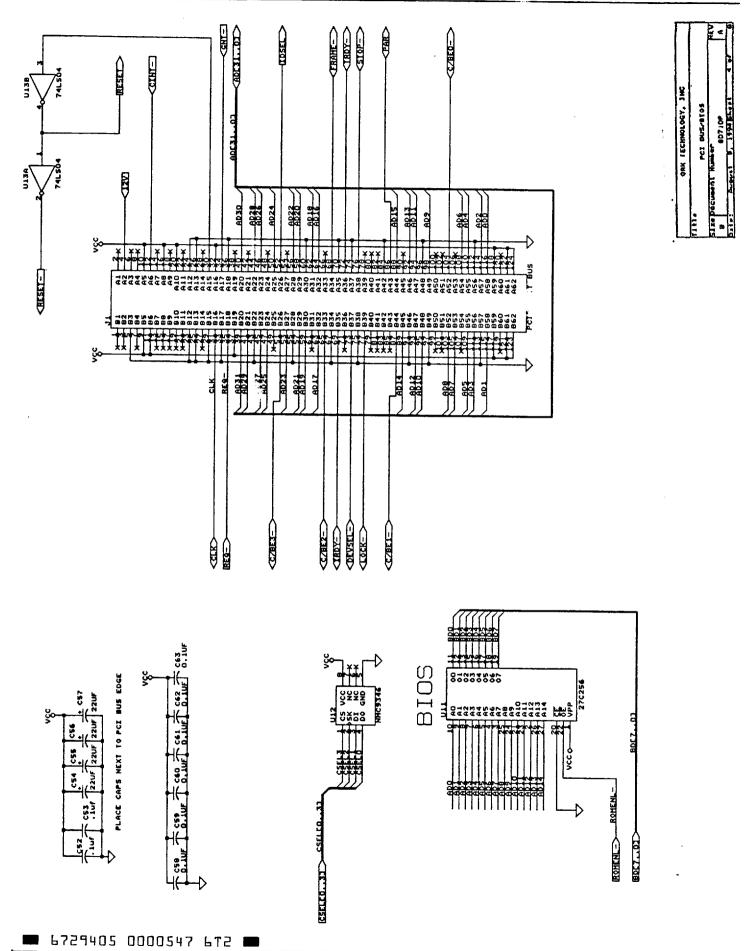

### 2.4 ROM BIOS Interface

For ISA 's configuration, the OTI-64107 can support either one (8-bit BIOS) or two ROMs (16-bit BIOS). The ROM does not routed back to the ISA bus through the BD bus and the external buffers if two ROM's are used.

For VL bus configuration, only a single ROM (8-bit BIOS) can be used. The BIOS ROM can only be on the ISA bus. ROM data is routed back to the ISA bus through an external buffer.

For PCI bus configuration, only a single ROM (8-bit BIOS) can be supported. The ROM address is connected to AD[14:0], while the data is connected to BD[7:0]. During ROM read cycles, the OTI-64107 latches the lower system address AD[14:0] to generate internal RA[14:0] and drives them out through AD[14:0], generates ROMENLn as a ROM output enable signal, and toggles the RA[1:0] appropriately depending on whether the current cycle is a byte, a word or a doubleword. If it is a word or a double word, the OTI-64107 toggles the RA[1:0] and latches in the ROM data through AD[7:0] bus, aligns the data, and sends it back out to AD[31:0]. Wait states are automatically asserted for the ROM access, assuming MCLK is 66MHz and the slowest ROM speed is 120ns.

ROM BIOS address space is assumed to be at C0000h. ROM BIOS support as described above can be enabled or disabled through the Hardware Configuration Register 2.

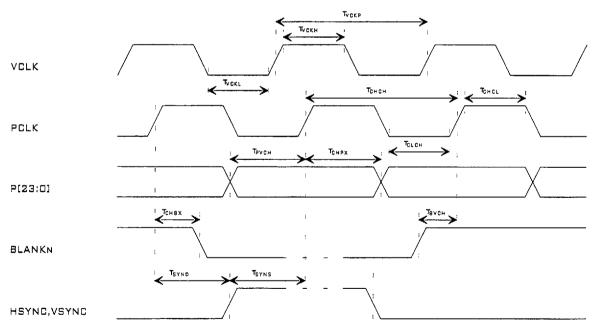

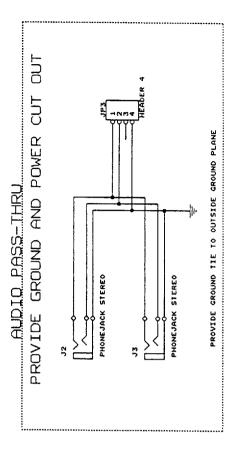

# 2.5 Feature Connector Interface

The OTI-64107 supports the feature connector in all configurations. The OTI-64107 feature connector support is compliant to the VESA Standard VGA Pass-Through Connector (VSVPC), and is compliant to the VESA Advanced Feature Connector (VAFC) with an appropriate DAC/Synthesizer like the OTI-088. For VAFC, base line compliance is readily achieved with OTI-64107 and any 16-bit pixel port DAC, with clock doubling modes, and 5:6:5 RGB format, such as the OTI-088. To be VAFC compliant in extended modes, a more advanced DAC such as the Bt885 is needed.

Pins EPDATA, EPCLK, and ESYNC are inputs to the chip to enable/disable P[23:0], PCLK, and BLANKn/HSYNC/VSYNC respectively. Pins HSYNC & VSYNC have AC timing requirements with respect to PCLK to meet the VAFC specification.

Although PCLK can operate up to 110MHz, it is not meant to drive the feature connector at this speed. Feature connector operation should be limited to 40MHz or less.

Pin GRDY is currently not generated from the OTI-64107, but with appropriate timing, BLANKn can be used to generate GRDY for the feature connector.

# 2.6 EEPROM/Dipswitch Interface

A small EEPROM (1024x1) can be supported to enable the add-on card or the graphics subsystem to be switchless. Because the control pins for the EEPROM interface are muxed with clock select pins, the EEPROM should be programmed or read during POST only. See EEPROM Control Register (3DF index E) description for more details. For cost saving purposes, an 8-bit dipswitch can be supported in place of the EEPROM. The dipswitch support does not need external buffers. Dipswitch can be read at anytime through extended register 3DF index D.

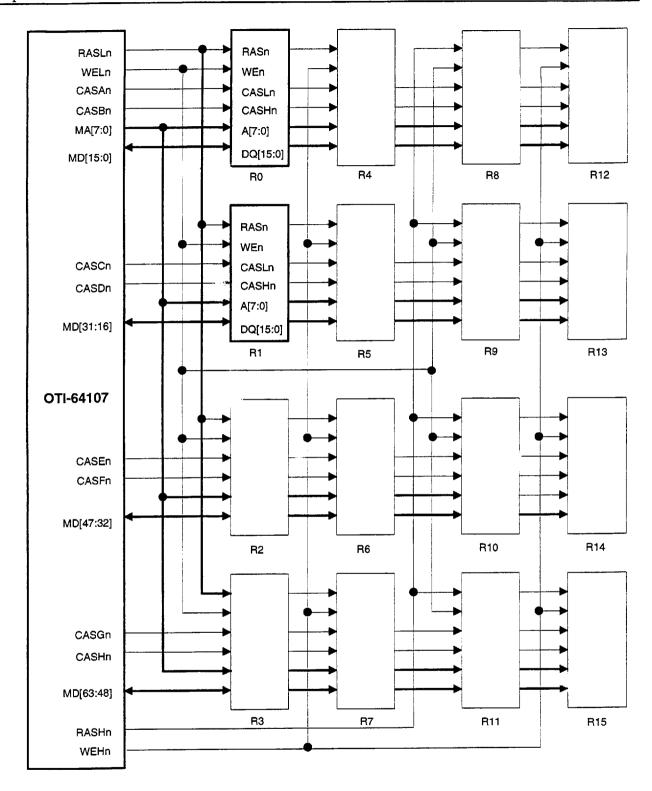

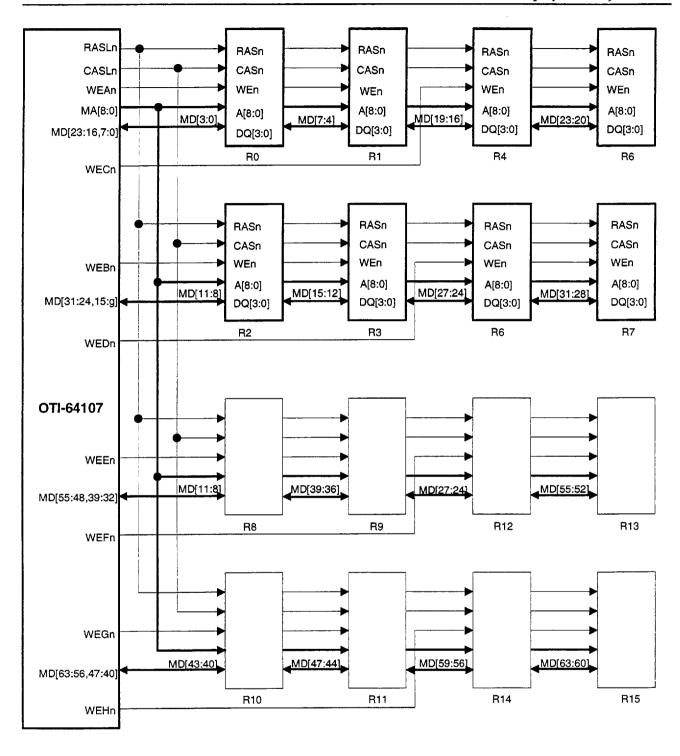

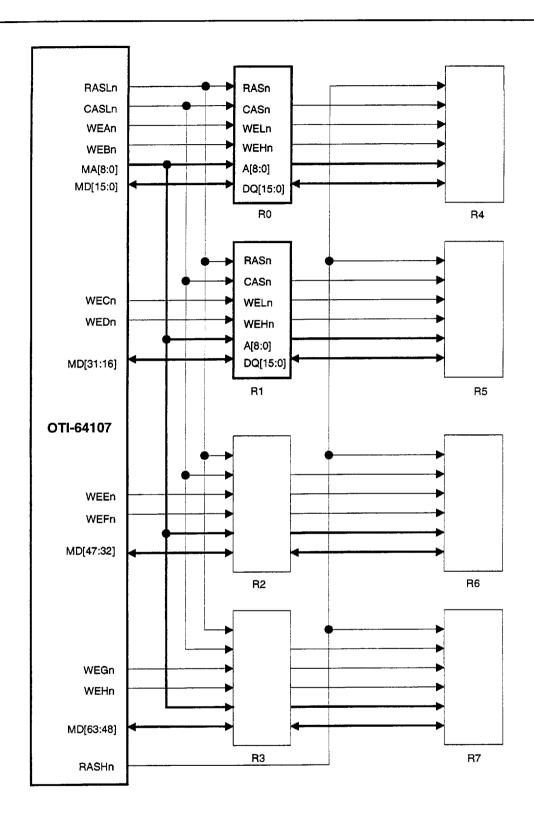

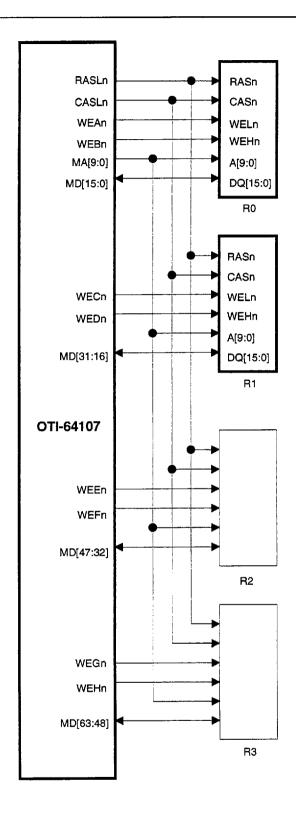

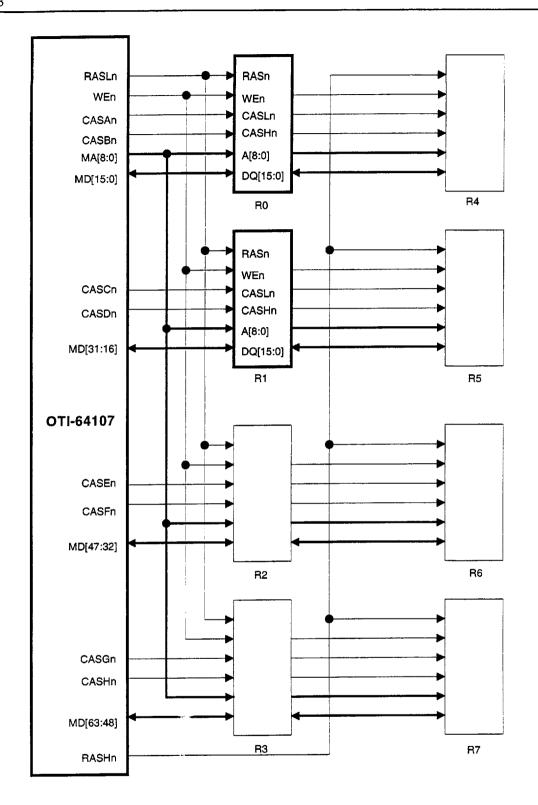

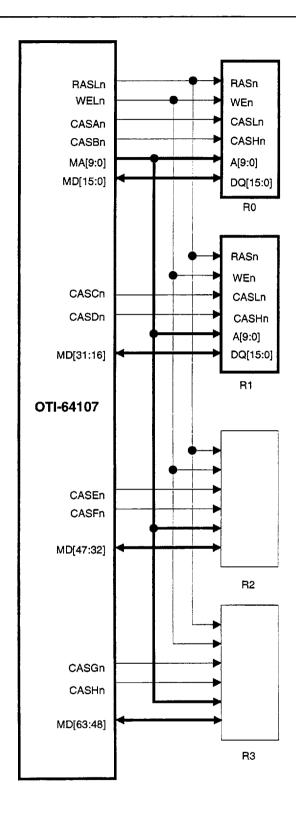

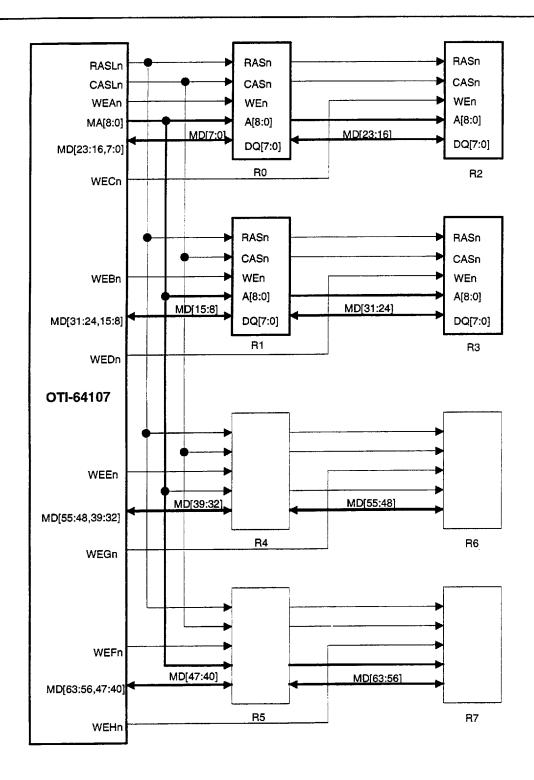

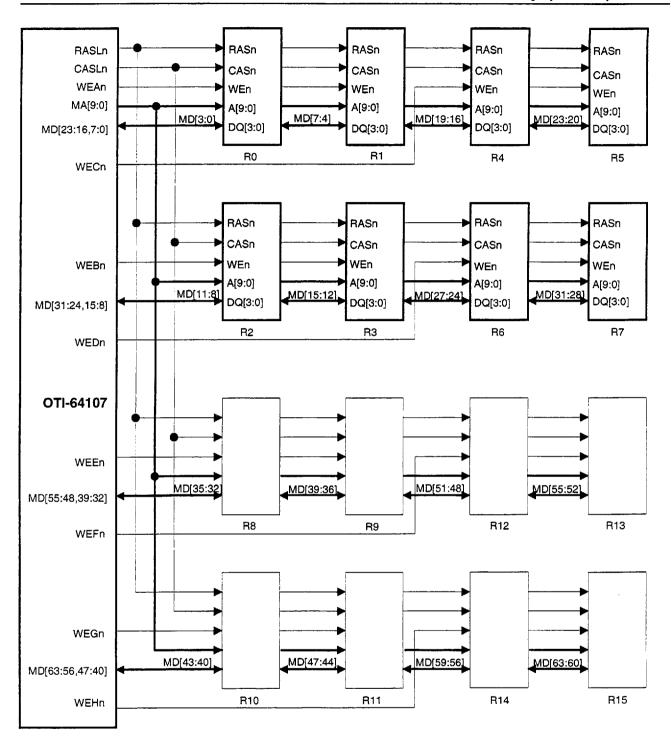

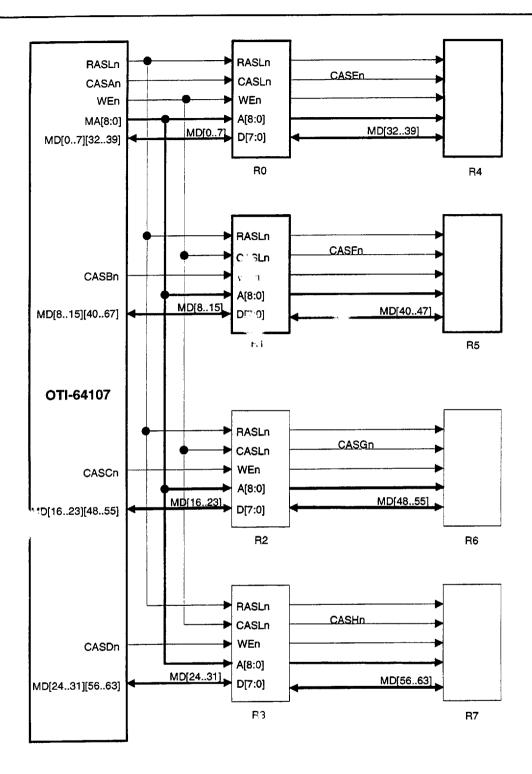

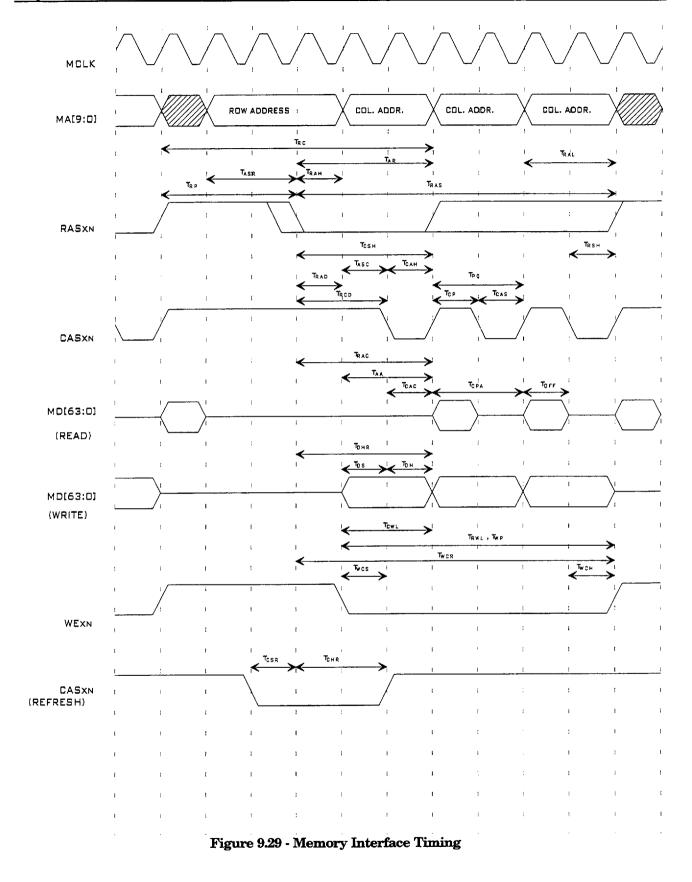

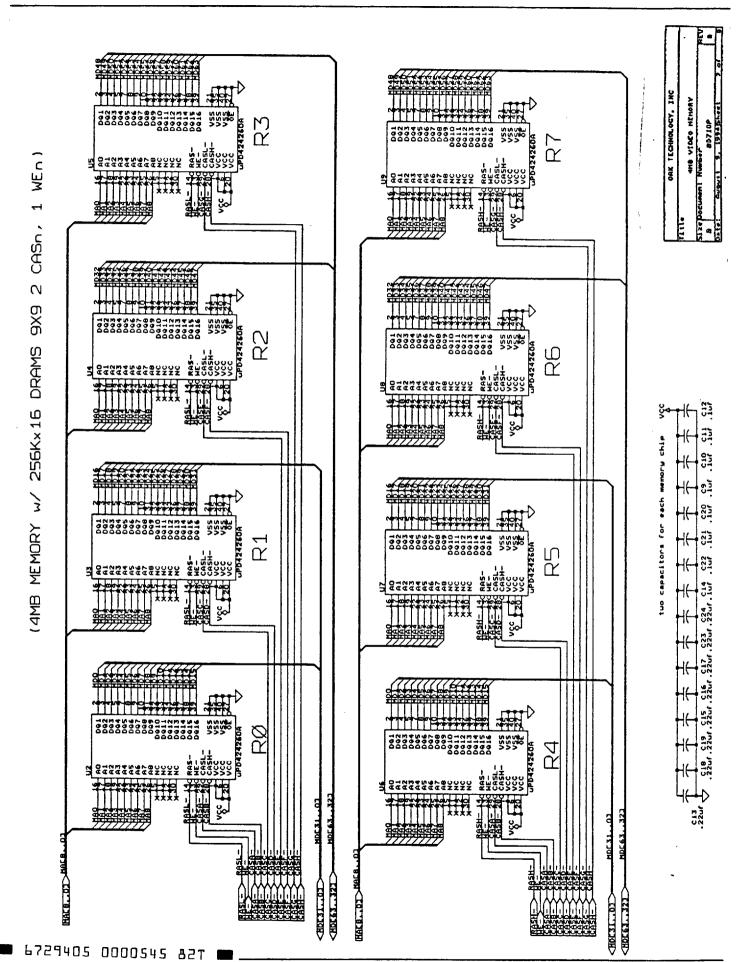

#### CHAPTER 3: DISPLAY MEMORY INTERFACE

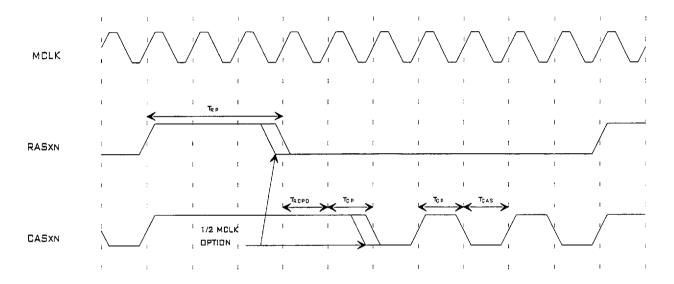

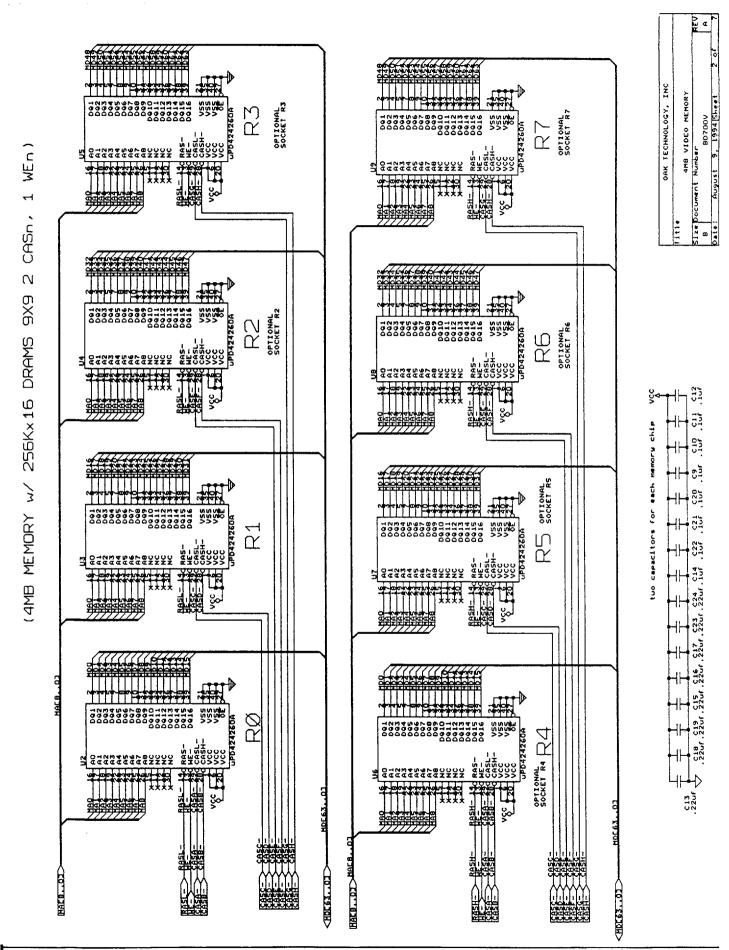

The OTI-64107 supports a wide variety of DRAM types. It supports 64K x 16, 256K x 4, 256K x 8, 256K x 16, 512K x 8, and 1M x 4 DRAMs. The OTI-64107 provides all the necessary control signals, address and data lines to access the display memory in fast page mode.

The wide variety of support for different DRAM types has been provided to take care of the contingency if availabilities of some DRAMs become scarce. The maximum display buffer size is 8Mbytes when used with 1M x 4 DRAMs, 4M bytes when used with 512K x 8 or symmetric 256K x 16 DRAMs, 2M when used with 64K x 16, 256K x 4 or asymmetric 256K x 16 DRAMs. The minimum configuration is 256Kbytes when used with 64K x 16 DRAM, 1Mbyte when used with 256K x XX or 512K x 8 DRAM, and 2Mbytes when used with 1M x 4 DRAM. See the table below for details on the different DRAMs supported.

Support for 256K x 16 includes the 10-bit row address, 8-bit column address type as well as the 9-bit row, 9-bit column address type. There is an option to convert WExn signals to CASxn signals, and vice versa, to support the myriad types of DRAMs available today.

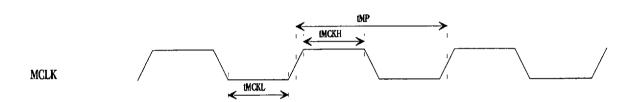

Memory cycles can be programmed to match the different types of DRAM. The RAS precharge and pulse, CAS pulse width, and RAS-to-CAS delay are all programmable. Matching memory cycles with a programmable memory clock would virtually guarantee the most efficient memory interface for a given memory type. Memory clock can be supported up to 66MHz. This can drive a 45ns fast page mode DRAM.

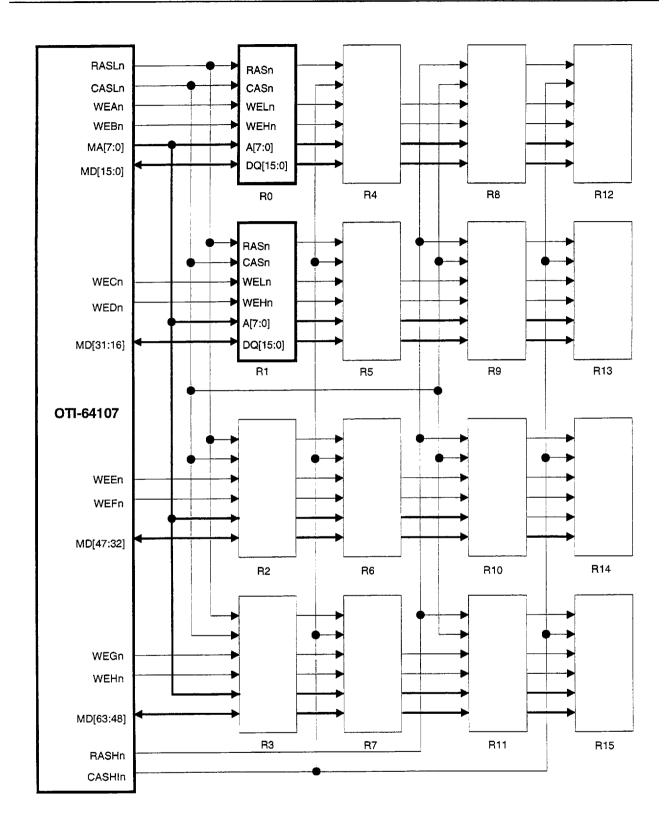

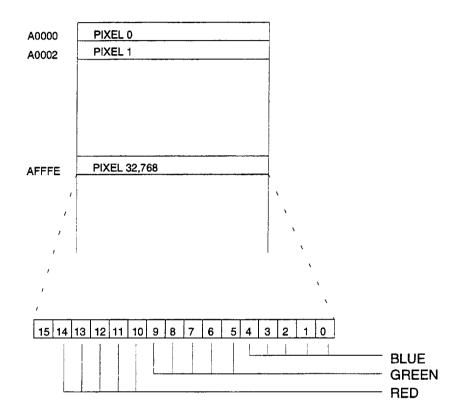

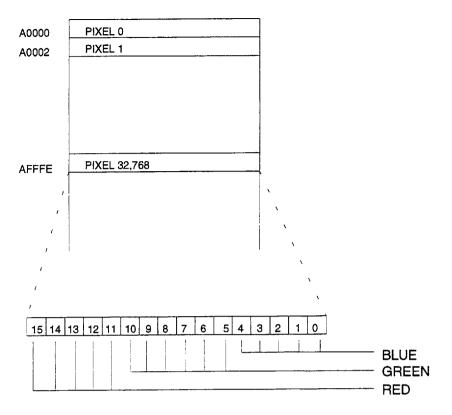

The display buffer can be addressed through either a programmable linear address range above 1M up to 4G on VL and PCI buses, and up to 16M on ISA bus, or through the conventional graphics address range (A0000 to BFFFF) with the segment registers. Depending on the type of memory used, and the amount of memory installed, the chip can be configured to have either 32-, or 64-bit memory data bus. See memory configuration block diagrams for more details.

# DRAM Types Supported

|                                                            | (for 64 bit data bus) |                         | Memory Size               |                           | Number of Control<br>Signal Lines |        |        |

|------------------------------------------------------------|-----------------------|-------------------------|---------------------------|---------------------------|-----------------------------------|--------|--------|

| DRAM Type<br>(address bits)<br>Control bits                | Memory<br>Size        | # of<br>Memory<br>Chips | Maximum<br>Memory<br>Size | Minimum<br>Memory<br>Size | RAS                               | CAS    | WE     |

| 256K x 16<br>(9 RAS, 9 CA.<br>1 CAS, 2 WE<br>2 CAS, 1 WE   | 2Mbytes               | 4                       | 4Mbytes                   | 1Mbyte                    | 2<br>2                            | 1<br>8 | 8<br>1 |

| 256K x 16<br>(10 RAS, 8 CAS)<br>1 CAS, 2 WE<br>2 CAS, 1 WE | 2Mbytes               | 4                       | 2Mbytes                   | 1Mbyte                    | 1<br>1                            | 1<br>8 | 8<br>1 |

| 64K x 16<br>1 CAS, 2 WE<br>2 CAS, 1 WE                     | 256Kbytes             | 4                       | 2Mbytes                   | 256Kbytes                 | 2<br>2                            | 2<br>8 | 8<br>2 |

| 256K x 4                                                   | 2Mbytes               | 16                      | 2Mbytes                   | 1Mbyte                    | 1                                 | 1      | 8      |

| 256K x 8                                                   | 2Mbytes               | 8                       | 4Mbytes                   | 1Mbyte                    | 1                                 | 8      | 1      |

| 512K x 8                                                   | 4Mbytes               | 8                       | 4Mbytes                   | 2Mbytes                   | 2                                 | 1      | 8      |

| 1M x 4                                                     | 8Mbytes               | 16                      | 8Mbytes                   | 4Mbytes                   | 1                                 | 1      | 8      |

Figure 3.1 - 64K x 16 DRAMs (1 CASn, 2 WEn), MD32 & 64, 256K - 2Mbytes

Figure 3.2 - 64K x 16 DRAMs (2 CASn, 1 WEn), MD32 & 64, 256K - 2Mbytes

Figure 3.3 - 256K x 4 DRAMs, MD32 & 64, 1M - 2Mbytes

Figure 3.4 - 256K x 16 DRAMs (10 x 8, 1 CASn, 2 WEn), MD32 & 64, 1M - 4Mbytes

Figure 3.5 - 256K x 16 DRAMs (10 x 8, 1 CASn, 2 WEn), MD32 & 64, 1M - 2M bytes

Figure 3.6 - 256K x 16 DRAMs (9 x 9, 2 CASn, 1 WEn), MD32 & 64, 1M - 4Mbytes

Figure 3.7 - 256K x 16 DRAMs  $(9 \times 9, 2$  CASn, 1 WEn), MD32 & 64, 1M - 2Mbytes

Figure 3.8 - 512K x 8 DRAMs, MD32 & 64, 2M - 4Mbytes

Figure  $3.9 - 1M \times 4$  DRAMs, MD32 & 64, 4M & 8Mbytes

Figure 3.10 - 256 x 8 DRAMs, MD32 & MD64, 1M or 2Mbytes

# CHAPTER 4: MULTIMEDIA INTERFACE

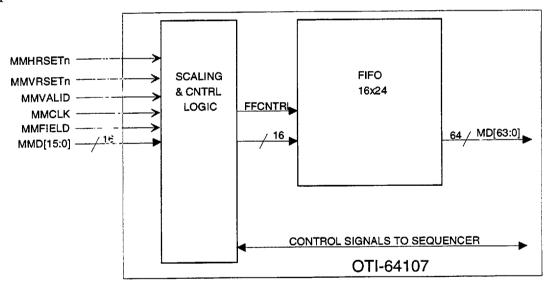

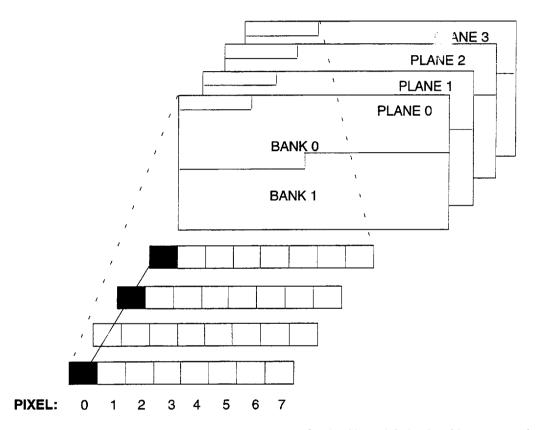

The Spitfire OTI-64107 has a 16-bit multimedia port which allows video data to be input to it's DRAM frame buffer. This multimedia interface consists of 5 control pins in addition to the 16-bit input data port. The multimedia section in OTI-64107 VGA chip consists of a multimedia input (MMI) port and a multimedia output (MMO) port pair connecting directly to the graphics frame buffer memory (also referred to as the display memory or video memory). The MMI port accepts live video data (i.e. a continuous input data stream from any external video source) and stores it into the graphics frame buffer, eliminating the need of a system bus data path and a dual-frame-buffer memory scheme. The video data coming into the MMI port can be either in an RGB or in a YUV data format. Once the video data is stored into the graphics frame buffer it can be displayed on the screen via the MMO port. The MMO port consists of a hardware window logic section that displays the stored video data (as opposed to graphics data) on the screen. The hardware window fetches the video data directly from the graphics frame buffer and sends the video data to the DAC.

There are two methods of displaying video data, which are described in the next two sections.

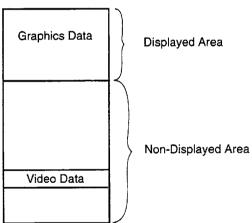

# 4.1 Chroma-keying

The first method called "chroma-keying" (also called color-keying) involves storing the video data into a non-displayed area of the graphics frame buffer. In this case, a 'key' code is placed in the display area of the graphics frame buffer at the point at which the video data is to be displayed on the screen. As the data from the graphics frame buffer is sent to the DAC, the DAC scans the incoming data for the key code. When this key code is encountered the DAC multiplexes the data between graphics data (displayed area) and video data (non-displayed area) on a pixel boundary each time the key code is encountered. Chroma-keying uses a predefined (programmable) byte for the key and a set of multiplexing logic to facilitate the switch between data types. The switch is done on a pixel boundary. The key code cannot be used for a color on the screen, as it will cause video to be displayed at that pixel. Figure 1 shows the memory map for chroma-keying.

Figure 1: Memory Map for Chroma-Keying

The 'window' size for the video data that is displayed on the screen is controlled in the following manner. For each scan line chroma-keys are placed in the graphics frame buffer to indicate the points at which the data multiplexing between the graphics and the video data is to occur. A key is placed in the display area to indicate the video image from begining to end, defining the window size of the video image. The advantage of chroma-keying is that the color depth of the video data (i.e. 4-, 8-, 16- or 24-bits per pixel) and format (RGB vs. YUV) can be different from that of the graphics data. While this scheme provides color depth flexibility it requires the use of an intelligent DAC such as Brooktree Bt885 and external support logic to multiplex between graphics and video data (the data bus to the frame buffer is 64-bits, whereas the video data port of the Bt885 is 32-bits).

As the Bt885 DAC performs the switch between displaying graphics data and ideo data, both data types must be transferred out of the graphics frame buffer. This requires a very high transfer ndwidth out of the graphics frame buffer memory; data must be fetched from two different places in the frame buffer, one from the graphics data area (the displayed area) and the other from the video data area (the non-displayed area). This is accomplished by sending the graphics data out during the display time and sending the video data out during the non-display time. This scheme effectively limits the size of the video window as the ratio of the non display time to the display time is typically only 20-25%. Another limit on the video window is the 800-byte video FIFO in the Bt885 (typically 400 pixels).

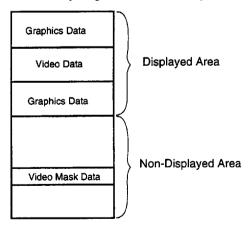

#### Video Masking 4.2

Another method called "Video Masking", or "Alpha Channel" is implemented in the OTI-64107 to eliminate these problems. It involves storing live video data into the graphics frame buffer at e location at which it will be displayed on the screen. This places two requirements on the system: the color depth of the video data must be the same as the color depth of the graphics data, and the input must be in RGB format, as the graphics and video data are both in RGB format.

There are several advantages of video-masking over chroma-keying. Any standard inexpensive DAC can be used which could result in significant cost savings. This scheme does not require additional graphics frame buffer memory bandwidth allowing the use of larger video windows. No external glue logic is required between the graphics DRAM memory and the DAC. Also, no special keying codes are required in video masking. This allows the use of all the colors, whereas in chroma-keying one color cannot be used as it is allocated to the key. The contents of the graphics frame buffer are sent to the DAC without regard of data type. In order to support overlapping windows a Multimedia Mask Map (not to be confused with the Coprocessor Mask Map) is utilized to mask the video data that is stored in the graphics frame buffer. The Multimedia Mask Map is a 1bpp map used to prevent the incoming video data from updating current graphics data on the screen, thus preserving the content of any graphics data that overlaps the video data. In this manner text, graphics, or animation can be displayed over the video data. Each bit in the mask corresponds to one pixel in the displayed area of the screen. Only incoming pixels of the video data corresponding to set bits in the mask will be stored into the graphics frame buffer. Because the video data occupies a portion of the displayed area, the video data is sent to the DAC in the same manner as graphics data. The driver must determine the size and shape requirements of the video window and setup the Multimedia Mask Map to simulate window overlap. A major advantage of video masking is that graphics or text data over video can be captured, unlike chroma-keying where text data or graphics annotated over the video cannot be captured. Video masking also allows arbitrarily shaped windows which can be used to create unique effects. Pull-down menus do not freeze the video. Figure 2 shows the memory map for video masking.

Figure 2: Memory Map for Video Masking

4-2

The Multimedia Mask Map is read and written as bytes in the graphics frame buffer memory address space; only whole bytes can be manipulated for each read or write to the mask. Since each bit in the mask corresponds to one pixel, and since the number of pixels that the mask operates on could be odd, the software driver must account for partial-byte reads or writes to the mask. A '1' would allow video data to update the screen, a '0' would prohibit updating. This map can be located anywhere in the non-displayed area and is programmable through the Multimedia Mask Map Start Address register. This map is assumed to be continuous and has no offset. There is no alignment hardware for this map. All unused bits should be filled with 0's, otherwise incorrect pixels might appear on the screen.

There are two sets of memory-mapped registers that affect this scheme. The first set of registers control the video data window: HW Start Address registers (offset[9C-9E]) and, HW Address Offset register (offset[9F]). The Start Address registers define the address within the graphics frame buffer at which the input video data will be stored. The Address Offset register defines the starting address of the next scan line of the video data. (The value in the Offset register is the scan line length of the displayed area of the screen which may not be the same as the total scan line length). Once these registers are setup, the video data is automatically written into the graphics frame buffer for each cycle on the MMI port. Or, in the case of the outputs, the video data is fetched from the frame buffer for each cycle on the MMO port.

A second set of registers control the Multimedia Mask Map: HW Mask Map Start Address registers 3DF[98-9A] and, HW Control register 3DF[96]. The Mask Map Start Address registers define the address within the frame buffer at which the Multimedia Mask Map begins. The Control register enables the use of the mask. In the case in which the video data is stored directly into the display area of the frame buffer, the Multimedia Mask Map, when enabled via the Control register, prevents live video data from updating the existing contents of the frame buffer whenever a 0 is encountered in the mask. The area defined by the video data window control registers must be greater than or equal to the area masked by the Multimedia Mask Map.

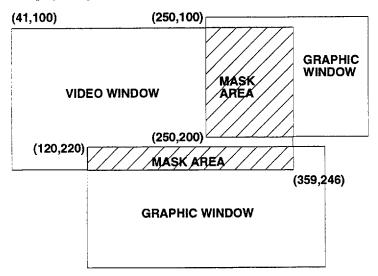

Figure 4.3 illustrates a display using the video masking scheme in the OTI-64107.

Figure 4.3 - Video Windows & Image Masking

Material Copyrighted By Its Respective Manufact

4-3

In the example, the display resolution is  $1024 \times 768$  and the color depth is eight bits/pixel. The absolute diagonal coordinates of the video windows are x1=41 pixels, y1=100 pixels and x2=359 pixels, y2=246 pixels. The Multimedia Mask Map is typically placed in the upper, non-displayed area of the graphics frame buffer. For this resolution 98,304 bytes are required to store the mask data.

The Multimedia Mask Map will contain 1's for the following areas: 41,100 to 250,200; 41,201 to 359,219; and 41,220 to 120,246. The mask will contain 0's in all other pixel positions.

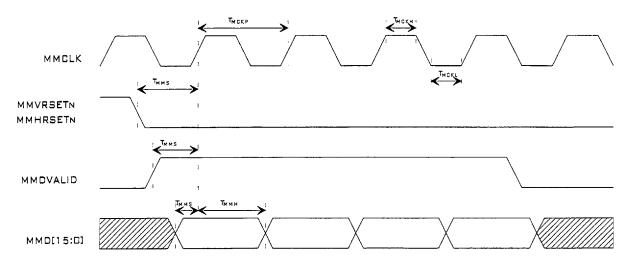

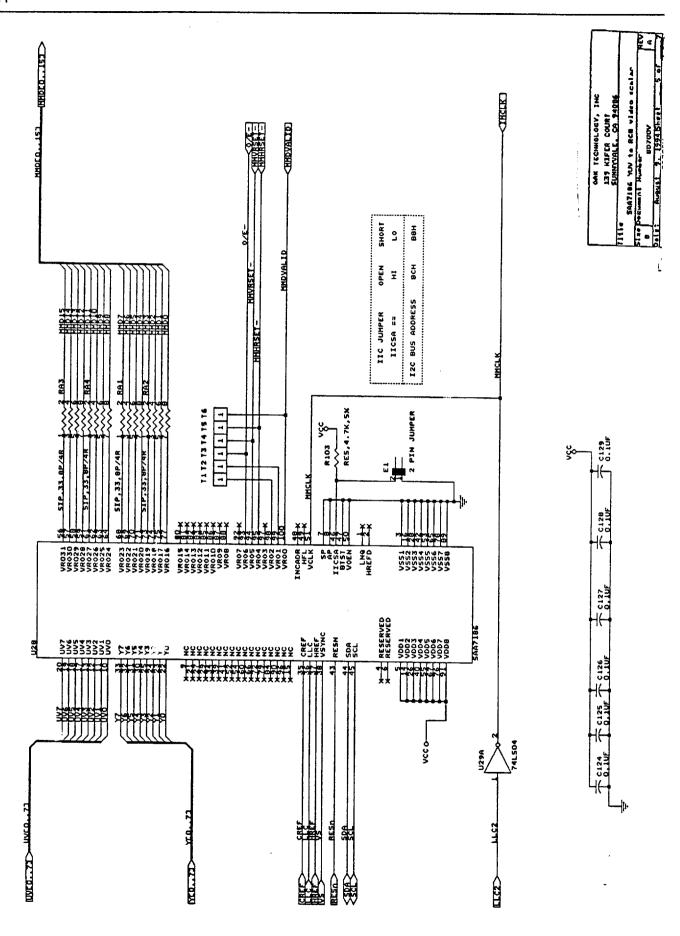

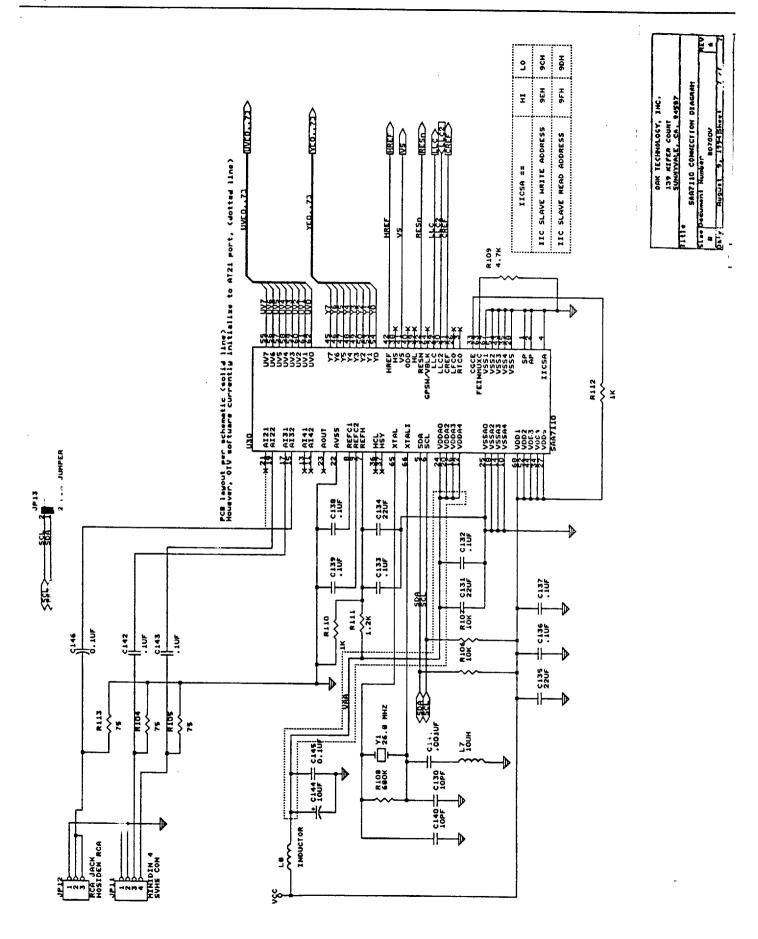

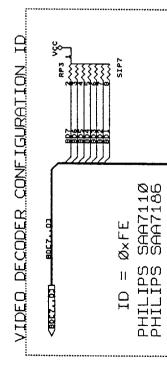

# 4.3 Multimedia Input (MMI) Port

The MMI port is an 16-bit synchronous data port that can receive data at rates up to 33MHz. In the Spitfire OTI-64107, this input port is designed to interface gluelessly to devices that support the I<sup>2</sup>C bus or directly to programmable video decoders or scalers. Devices that support the I<sup>2</sup>C protocol include video decoders and scalers from Philips (SAA7110, SAA7186, SAA7196, etc.), ITT, and Sony. Devices that have a programmable interface include video decoders from Brooktree (Bt812) and scalers from Thesys (Th6205). Almost all video chips that do not support the I<sup>2</sup>C bus, can be interfaced gluelessly with the OTI-64107 using the programmable interface. Support for the external video devices includes a chip select, system I/O command and system data control logic, and the I<sup>2</sup>C bus. In the future, the Spitfire family will be modified to interface directly to the VESA Media Channel, 16-bit mode and still maintain pin-to-pin compatibility with the current version. The MMI port takes video data into the OTI-64107 and stores it into the graphics frame buffer.

The input data can also be scaled down vertically and/or horizontally by the OTI-64107. Vertical scaling by displaying every 2, 4, or 8 lines is supported with an option to start skipping on odd or even scan lines. Horizontal scaling by displaying every 2, 4 or 8 pixels is supported in a similar manner. Scaling is particularly important to save memory space and bandwidth.

The input signals for the MMI Port are:

- MMVRSETn is used to indicate the beginning of a frame,

- MMHRSETn is used to indicate the end of a line,

- MMVALID is used to indicate that data is ready to be clocked in,

- MMFIELD is used to indicate even or odd fields,

- MMCLK is the input clock, and,

- MMD[15:0] is the 16-bit input data bus.

The registers that control the input port are:

- **HW Start Address** registers (offset[9C-9E]) define the address within the graphics frame buffer at which the input video data will be stored, and,

- HW Address Offset register (offset[9F]) defines the starting address of the next scan line of the video data. The value in the Offset register is the scan line length of the displayed area of the screen which may not be the same as the total scan line length.

Once these registers are setup,

- MMVRSETn would load the HW Start Address Register into the MMI address counter,

- MMHRSETn would add the HW Offset register to the current start address and load it into the MMI address counter, and.

- MMVALID active would initiate transferring data to the frame buffer.

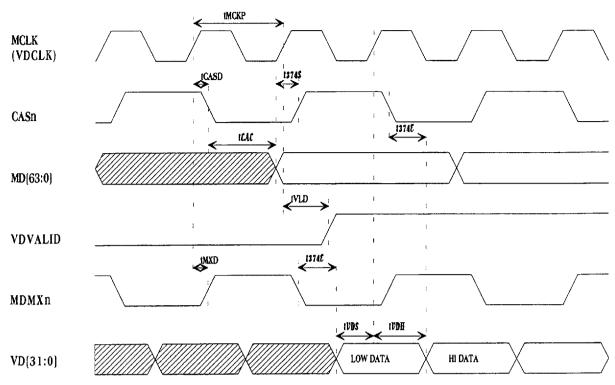

# 4.4 Multimedia Output (MMO) Port

The MMO port is supported as a hardware window (very similar to the hardware cursor) and is designed to interface with the Brooktree Bt885 with some additional logic (8 F374's when used with the 64-bit memory data bus, none with 32-bit memory data bus). The data path for the video data is connected to the Bt885 via MD[63:0]. A video window can be defined through the Vertical Position Start, Width and Height registers. In this case chroma-keying is selected. The MMO port as described above is used when video data is stored in the non-display area and a video DAC like the Bt885 is used. The Bt885 will display graphics data until it reads the chroma-key at which time it will start displaying video data in the window.

The hardware cursor is supported through the logic in the Bt885. A repeat line input signal is also available to assist the Bt885 to do vertical zooming. When this line is active, the memory controller would fetch the same video line again and cause zoom-in by pixel line replication.

The control signals for the MM Port are:

- VDVALID is use to indicate to the VideoDAC that the data is ready to be clocked in.

- MDMXn is used to mux MD(63:32) with MD(31:0)

- RPLINE is used to assist the Bt885 to do vertical zoom-in. The memory controller would fetch the same video line again and cause a zoom-in by pixel line replication.

The registers that control the output port are the Hardware Cursor control registers (registers 0-88).

When a standard ClkDAC like the OTI-088 or the AT&T20C499 are used, the hardware cursor logic is enabled in the OTI-64107 instead of the hardware window. In this case the video masking scheme must be used to display the video data window and the Multimedia Mask Map is used to control the size of the video window.

Video masking allows graphics (e.g., text or pull-down menus) to overwrite the video. It also allows arbitrarily shaped windows, and with some constraints, multiple video windows.

Figure 4.2 - Block Diagram of the Multi-Media Port with the Brooktree Bt885 Video DAC on the VL Bus

Figure 4.3 - Block Diagram of the Multi-Media Port and the VAFC using OTI-088 ClkDAC and PCI Bus (Glueless)

Figure 4.4 - Block Diagram of the Multi-Media Port and the VAFC using AT&T20C499 Precision DAC™ and PCI Bus (Glueless)

# 4.5 Support for External Video Chips

To save glue logic when external Video Chips (such as video decoders, image scalers, etc.) are required for the graphics subsystem, the OTI-64107 provides additional address decoding, address latching and data routing for these external components. For components that have an I<sup>2</sup>C interface (like Philips or ITT decoders and scalers) instead of the standard host interface, the OTI-64107 can also interface with them through a combination of hardware (through the Multimedia Port) and software. On the PCI bus, support for external Video chips normally requires fairly extensive circuitry (probably a custom gate array). This includes the configuration registers, address latches and decoders, data latches and buffers, address counters, etc. The OTI-64107 has all of this circuitry built-in, allowing a very low cost and convenient interface to external Video chips.

#### 4.5.1 **I**<sup>2</sup>C Bus

The I<sup>2</sup>C Bus is a serial data communications bus developed by Philips. It is a two-wire multi-master serial bus with a standard transfer rate of 100 Kbits/sec, and 400 Kbits/sec in fast-mode. The number of interfaces connected to the bus is solely dependent on the limiting bus capacitance of 400 pf.

The 2 wires, Serial Data (SDA) and Serial Clock (SCL), carry information between the devices connected to the bus. Each device is recognized by a unique address, and can operate as a **transmitter** or **receiver**, depending on the function of the device. A **master** is the device which initiates a data transfer and generates the clock signals to permit that transfer. Any device addressed is considered a **slave**. As the I<sup>2</sup>C bus is a multi-master bus, more than one device capable of controlling the bus can be connected to it.

More than one master could initiate a data transfer at the same time. An **arbitration** scheme using **wired-AND** connections on all I<sup>2</sup>C devices is used. Generation of the clock signals on the I<sup>2</sup>C bus is always the responsibility of the master device; each master generates its own clock signals when transferring data on the bus. Bus clock signals can only be altered when they are stretched by a slow-slave device holding down the clock line, or by another master when arbitration occurs.

The data on the SDA line must be stable during the HIGH period of the clock. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW. A HIGH to LOW transition on the SDA line when SCL is HIGH indicates a **start** condition. A LOW to HIGH transition of the SDA line defines a **stop** condition. Start and stop conditions are always generated by the master.

Data is transferred with the MSB first. The addressing procedure for the I<sup>2</sup>C bus is such that the first byte after the start condition usually determines which slave will be selected by the master. The first seven bits of the first byte make up the slave address, followed by the direction bit (R/Wn). Each data byte is followed by an acknowledge bit. See the I<sup>2</sup>C Bus Specification for more information.

#### 4.5.2 I<sup>2</sup>C Support

The OTI-64107 has the 2 programmable I<sup>2</sup>C bus pins, **SRCK** (Serial Clock line) and **SRD** (Serial Data line), to support the I<sup>2</sup>C bus. These two pins are controlled and can be read from the I<sup>2</sup>C **Control** register (3DF index C). Writing 0's will drive the pins low, and writing 1's will tristate the pins. Software can control and read these pins in accordance with the I<sup>2</sup>C bus protocol to program the external component's registers. A typical I<sup>2</sup>C (Philips decoder or scaler) bus to ISA interface needs to be designed to accept video in a PC system. This interface requires at least four TTL parts and three PALs to be implemented. The OTI-64107 has this interface built-in, saving the parts and time to implement the I<sup>2</sup>C bus interface.

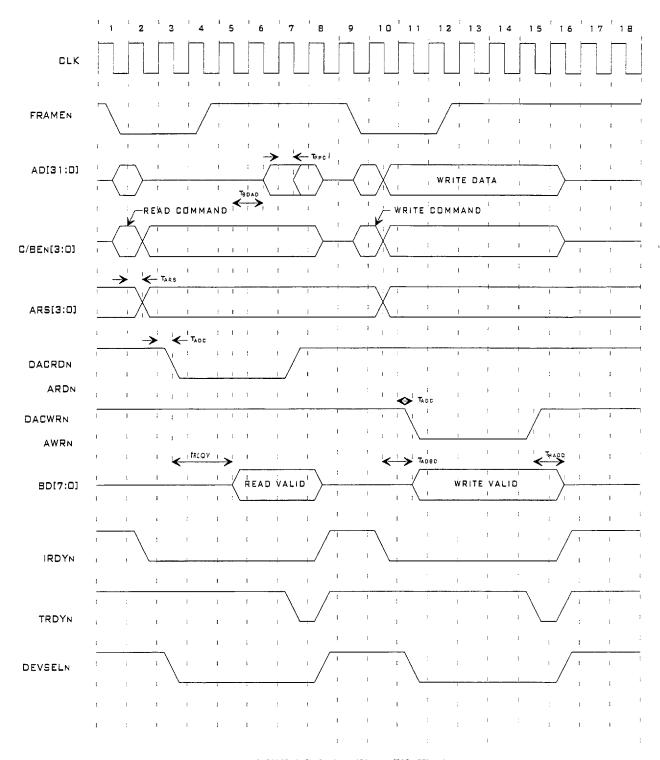

### 4.5.3 Auxiliary I/O Support

For non-I<sup>2</sup>C bus devices that have a 16-bit data bus, host read and host write signals (like the Bt812), the OTI-64107 provides all the necessary control signals to the address space to select and route data. The auxiliary I/O support is different for each system bus platform. On the VL-bus, auxiliary I/O can be supported by configuring the OTI-64107 to generate **DACCSn** (could be used by the Bt885) and **ACSn** (could be used by the Bt812) instead of DACRDn & DACWRn respectively. These chip select signals, can be ORed (LS32) with IOWRn and IORDn from the ISA bus to generate **DACRDn**, **DACWRn**, **ARDn**, and **AWRn**. The register select address can be connected directly to the SA bus of the ISA connector. Data routing is done through the same LS245 that is used for DAC & BIOS ROM routing.

Figure 4.5 - Auxi ry I/O on VL Bus (via ISA Bus)

On the PCI bus, ARDn and AWRn are generated from the OTI-64107. ARS[3:0] are latched from the system address and sent out to the external components. Up to 16 address pins can be supported using external address latches. Data is routed through the BD[7:0] bus. See the PCI Bus block diagram for more information.

On the ISA bus, ARDn and AWRn are also generated, BD[7:0] is used to route data, but ARS[3:0] are not generated and the register select lines should be connected directly to the system bus just like on the VL-bus.

## 4.6 Video Bandwidth

Maximum video resolution and refresh rate is a function of memory bandwidth available to the MM port after screen refresh has been satisfied. Total memory bandwidth is a function of memory clock, memory bus width, and the programmed memory timing. The memory controller of the OTI-64107 reserves first priority for screen refresh, then MM port, and then other sources. Thus, the maximum video resolution that can be supported for a given graphics mode can be defined by the maximum bandwidth available to the MM port for the mode. The only restriction is caused by the bandwidth of the 48-byte FIFO which recieves the input data from the 16-bit MMdata port. the Maximum Video Bandwidth numbers listed in the table below are extremely conservative. In actuality, the bandwidth should be significantly higher. The following tables show the video bandwidth that can be supported for a given graphics mode with 64-bit memory bus and 66MHz MClk.

Table 1. OTI-088 Video Bandwidth (or Equivalent DACs the AT&T 20C409/20C499)

| Graphics<br>Resolution | bpp | Vertical<br>Refresh | Maximum Video<br>Bandwidth | Maximum<br>MMClk | MClk  | MD |

|------------------------|-----|---------------------|----------------------------|------------------|-------|----|

| 1280 x 1024            | 8   | 75Hz                | 44Mbytes/sec               | 22MHz            | 66MHz | 64 |

| 1024 x 768             | 8   | 75Hz                | 70Mbytes/sec               | 35MHz            | 66MHz | 64 |

| 1024 × 768             | 16  | 75Hz                | 35Mbytes/sec               | 17MHz            | 66MHz | 64 |

| 1280 x 1024            | 8   | 60Hz                | 47Mbytes/sec               | 23MHz            | 66MHz | 64 |

| 1024 x 768             | 8   | 60Hz                | 70Mbytes/sec               | 35MHz            | 66MHz | 64 |

| 1024 x 768             | 16  | 60Hz                | 44Mbytes/sec               | 22MHz            | 66MHz | 64 |

#### Notes:

<sup>1.</sup> Standard Video Resolution is just an example of what standard resolution can be supported with the given available bandwidth. Standard Video Resolutions are 640 x 480, 320 x 240, and 160 x 120. The exact video resolution that can be supported is actually higher than the standard ones. For example, in the case of 1280 x 1024 8 bpp graphic mode, a video window of 640 x 480 at 30Hz and 8 bpp only requires 9.22Mbytes/sec, but the available bandwidth is 22Mbytes/sec.

<sup>2.</sup> Maximum MMClk is the maximum rate of transfer the MM port can sustain without losing any data. To run a higher rate than this, the internal scale down circuitry should be utilized.

<sup>3.</sup> Maximum video bandwidth is the maximum rate of updating the video screen.

For video windows using the Bt885 as the RAMDAC, the resolution that can be supported is limited not only by the bandwidth available to the MM port, but also the bandwidth available to MMO port, and the cache size (800 bites) of the Bt885.

Table 2. Bt855 (or equivalent RAMDAC) Video Bandwidth with the Bt885 DAC12

| Graphics<br>Resolution | bpp | Vertical<br>Refresh | Maximum Video<br>Bandwidth | Maximum Video<br>Resloution | Maximum<br>MMClk | MCLK  | MD |

|------------------------|-----|---------------------|----------------------------|-----------------------------|------------------|-------|----|

| 1280 × 1024            | 8   | 75Hz                | 35Mbytes/sec               | 256 x XX @ 16 bpp           | 17MHz            | 66MHz | 64 |

| 1024 × 768             | 8   | 75Hz                | 38Mbytes/sec               | 320 x XX @ 16 bpp           | 19MHz            | 66MHz | 64 |

| 800 × 600              | 8   | 75Hz                | 38Mbytes/sec               | 512 x XX @ 16 bpp*          | 19MHz            | 66MHz | 64 |

| 640 x 480              | 8   | 75Hz                | 38Mbytes/sec               | 640 x XX @ 16 bpp*          | 19MHz            | 66MHz | 64 |

| 1280 × 1024            | 8   | 60Hz                | 38Mbytes/sec               | 384 x XX @ 16 bpp           | 19MHz            | 66MHz | 64 |

| 1024 x 768             | 8   | 60Hz                | 38Mbytes/sec               | 512 x XX @ 16 bpp*          | 19MHz            | 66MHz | 64 |

| 800 x 600              | 8   | 60Hz                | 38Mbytes/sec               | 640 x XX @ 16 bpp*          | 19MHz            | 66MHz | 64 |

| 640 × 480              | 8   | 60Hz                | 38Mbytes/sec               | 640 x XX @ 16 bpp*          | 19MHz            | 66MHz | 64 |

#### Notes

2. Maximum Video Resolution - maximum video data that can be fetched to display per line.

<sup>1.</sup> Maximum Video Line Width is the maximum resolution that can be displayed by the MMO port at 16 bpp or 8 bpp video color depth.

<sup>3. \*</sup> Although 512 and 640 pixels can be fetched by the OTI-64107, only 400 pixels (800 bytes) can be handled by the Bt885 per line. Thus, the maximum resolution when used with Bt885 is 400 x XX.

#### **CHAPTER 5: POWER MANAGEMENT SUPPORT**

The OTI-64107 has power saving modes that are compliant to the VESA DPMS Proposal version 1.0p. The four modes of power management are as follows:

| State    | HSYNC     | VSYNC     | BLANKn  | P[23:0] | DPMS<br>Requirement | Power<br>Savings |

|----------|-----------|-----------|---------|---------|---------------------|------------------|

| On       | Pulses    | Pulses    | Active  | Active  | Mandatory           | None             |

| Stand-by | No Pulses | Pulses    | Blanked | Blanked | Optional            | Minimal          |

| Suspend  | Pulses    | No Pulses | Blanked | Blanked | Mandatory           | Substantial      |

| Off      | No Pulses | No Pulses | Blanked | Blanked | Mandatory           | Maximum          |

Active - means normal operation, signal is switching between active and inactive

No Pulses - signals remain at inactive state (HSYNC, VSYNC = 0)

Pulses - normal operation for HSYNC & VSYNC

Blanked - BLANKn is asserted (0), P[23:0] = 0

When in any of the power saving modes, the Memory Controller stops fetching data for display, but continues to refresh the DRAM. Power management is controlled by the Power Management Control register (3DF index F).

# **CHAPTER 6: PIN DESCRIPTION**

#### 6.1 ISABus Interface

| Pin Name  | Pin Number         | Type | Description                                                                                                                                                                                                                                    |

|-----------|--------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MASTERn   | 60                 | I    | MASTERn. This pin indicates that the current cycle is a master cycle when the controller is in add-on configuration. It enables the LA address to pass through during master cycle.                                                            |

| MWRn      | 62                 | I    | MEMORY WRITE. Active low memory write strobe.                                                                                                                                                                                                  |

| MRDn      | 63                 | I    | MEMORY READ. Active low memory read strobe.                                                                                                                                                                                                    |

| CINTn     | 66                 | Ood  | CRT INTERRUPT REQUEST. Interrupt is asserted when vertical retrace occurs if it is enabled by bit 5 of the Vertical Retrace End (3?5 index 11) register. It is an active low open drain output.                                                |

| RESETn    | 67                 | I    | RESET. Active low system reset signal. This input signal will reset the VGA controller and initialize the configuration register based on the logic level on MD[15:0] pins at power-up reset time. This signal is inverted from the bus reset. |

| LA[23:17] | 75-72,70,<br>65-64 | I    | UNLATCHED SYSTEM ADDRESS BITS 23:17. These bits are decoded to generate M16n. Bits 19:17 are latched by ALE to generate SA[19:17].                                                                                                             |

| M16n      | 68                 | Ood  | 16-BIT MEMORY. Active low, open drain output signal used to indicate to the system that the present cycle is a 16-bit data transfer to video memory. This signal is derived from the decoding of LA23:LA17.                                    |

| ZEROWSn   | 69                 | Ood  | ZERO WAIT STATE. This pin is used to indicate the current cycle is a 0 wait state cycle.                                                                                                                                                       |

| IO16n     | 71                 | Ood  | 16-BIT I/O. This active low, open drain output signal is used to indicate to the system that the present data transfer is a 16-bit I/O cycle. It is derived from the decode of system address bits SA19-SA0.                                   |

| BHEn      | 76                 | I    | BYTE HIGH ENABLE. This active low input indicates that there is valid data on SD[15:8] bus. This signal and SA[0] together indicate to the OTI-107 whether an 8 bit or 16 bit cycle is being executed by the system.                           |

| ALE       | 78                 | I    | ADDRESS LATCH ENABLE. This input is used to latch a valid address from the CPU in add-on configuration.                                                                                                                                        |

| RFSHn     | 79                 | I    | REFRESH. This input is used to qualify the video memory and I/O access from CPU. An active low indicates a system memory refresh cycle.                                                                                                        |

| IORn      | 80                 | I    | I/O READ. This is an active low I/O read strobe.                                                                                                                                                                                               |

| IOWn      | 81                 | I    | I/O WRITE. This is an active low I/O write strobe.                                                                                                                                                                                             |

| Pin Name | Pin Number                      | Type | Description                                                                                                                                                                                     |

|----------|---------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IOCHRDY  | 82                              | Ood  | IO CHANNEL READY. An open drain active high output to signal processor that it ready for memory access. This signal is used to add wait states to the bus cycle during display memory accesses. |

| SA[16:0] | 101-92,90-85,83                 | I    | LATCHED SYSTEM ADDRESS BITS 16:0.                                                                                                                                                               |

| SD[15:0] | 102-108,110,<br>112-115,117-120 | I/O  | SYSTEM DATA BUS BITS 15:0.                                                                                                                                                                      |

| AEN      | 111                             | I    | ADDRESS ENABLE. This input is used to qualify the video I/O access from CPU. When it is active high, the DMA controller has control of the add: s bus, data bus, and command lines.             |

Total: 55 pins

# 6.2 VL Bus Interface

| Pin Name | Pin Number                                                      | Type | Description                                                                                                                                                                                                                                                                                                                                                       |

|----------|-----------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SA[31:2] | 3-10,72-69,<br>65-62,60-47                                      | I    | SYSTEM ADDRESS BUS bits 31:2. This bus should be connected to the ADR[31:2] bus of the VL connector.                                                                                                                                                                                                                                                              |

| CINTn    | 66                                                              | Ood  | CRT INTERRUPT REQUEST. Interrupt is asserted when vertical retrace occurs if it is enabled by bit 5 of the Vertical Retrace End (register 3?5 index 11) register. It is an active low open drain output.                                                                                                                                                          |

| RESETn   | 67                                                              | I    | MASTER RESET. This reset signal is used to reset all internal state machines and some default registers. During Reset active, all bidirectional buses are tri-stated. This signal is also used to latch-in the configuration register values. This reset is active low and should be connected the VL bus RESETn signal instead of the ISA bus active high RESET. |

| PROCLK   | 68                                                              | I    | PROCESSOR CLOCK. Processor clock input used to sample CPU status and address. This clock is 1X for VL bus but can be configured to be 2X. This signal should be connected to the LCLK pin of the VL connector.                                                                                                                                                    |

| SD[31:0] | 73-76,78-81,<br>85-90,92-93,<br>102-108,110,<br>112-115,117-120 | I/O  | SYSTEM DATA BUS bits 31:0. This bus should be connected to the DAT[31:0] bus of the VL connector.                                                                                                                                                                                                                                                                 |

| BEn[3:0] | 82,94,101,111                                                   | I    | BYTE ENABLES. Used to indicate which of the 4 bytes of the 32-bit data bus are involved with the current transfer cycle. These signals should be connected to the BE[3:0] pins of the VL connector.                                                                                                                                                               |

| LBSELn   | 83                                                              | Ood  | LOCAL BUS SELECT. Active low simulated open drain output signal used to indicate to the system controller chipset that the current cycle is a video local bus cycle and the chipset should not respond to the CPU. This signal should be connected to the LDEVn pin of the VL connector.                                                                          |

| Pin Name | Pin Number | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADSn     | 95         | I    | ADDRESS STATUS. Active low input used to indicate a valid address is on the bus. This signal should be connected to the ADSn pin of the VL connector.                                                                                                                                                                                                                                                                                                             |

| SRDYIn   | 96         | I    | SYSTEM READY INPUT. Input from the chipset to indicate termination of a cycle. This signal should be connected to the RDYRTNn pin of the VL connector. For system without RDYRTNn signal, SRDYn should be routed back to SRDYIn.                                                                                                                                                                                                                                  |

| SRDYn    | 97         | Osod | SYSTEM READY. Tristateable active low output used to indicate the termination of a bus cycle. This signal should be driven high for one Proclk before being released. This signal should be driven during the first T2 state only when in Fast Write configuration. For regular write configuration and all read cycles, this signal should only be driven from the second T2 state onward. This signal should be connected to the LRDYn pin of the VL connector. |

| ISACMD   | 98         | I    | ISA COMMAND. This is a NAND of IORn, IOWn, MRDn. This signal is used to generate DACRDn, DACWRn, and DOEn.                                                                                                                                                                                                                                                                                                                                                        |

| WRn      | 99         | I    | WRITE/READ. Signal used to distinguish between a write (WRn high) or a read (WRn low) transfer. This signal should be connected to the W/Rn pin of the VL connector.                                                                                                                                                                                                                                                                                              |

| MIOn     | 100        | I    | MEMORY or I/O STATUS. Input from the bus to indicate the current cycle is a memory (MIOn high) transfer or an IO (MIOn low) transfer. This signal should be connected to the M/IOn pin of the VL connector.                                                                                                                                                                                                                                                       |

Total: 76 pins

# 6.3 PCI Bus Interface

| Pin Name | Pin Number | Туре | Description                                                                                                                                                                                                                                                |

|----------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CINTn    | 66         | Ood  | CRT INTERRUPT REQUEST. Interrupt is asserted when vertical retrace occurs if it is enabled by bit 5 of the Vertical Retrace End (register 3?5 index 11) register. It is an active low open drain output.                                                   |

| RESETn   | 67         | I    | RESET. This signal is used to reset all internal state machines and some default registers. During RST active, all bidirectional buses are tri-stated. RESET signal is also used to latch-in the configuration register values. This signal is active low. |

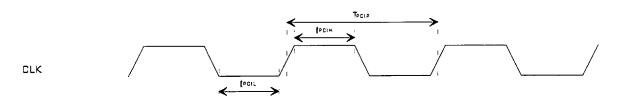

| CLK      | 68         | I    | CLOCK. Used to provide timing for all trasactions on PCI. ALL other PCI signals are sampled on the rising edge of CLK, and all other timing parameters are defined with respect to this edge.                                                              |

| Pin Name   | Pin Number                                                   | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|--------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAR        | 70                                                           | I/O    | PARITY. Active high even parity across AD[31:0] and C/BEn[3:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GNTn       | 71                                                           | I      | GRANT. Input from the bus arbiter to indicate that the request has been granted.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| REQn       | 72                                                           | 0      | REQUEST. Output to the bus arbiter to request for the bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AD[31:0]   | 73-76,78-81<br>85-90,92-93<br>102-108,110<br>112-115,117-120 | I/O    | ADDRESS/DATA BITS 31:0. Address and Data are multiplexed. During the first clock of transaction AD[31:00] contain a physical byte address (32-bits). During subsequent clocks, AD[31:0] contain data.                                                                                                                                                                                                                                                                                                                                   |

| C/BEn[3:0] | 82,94,101,111                                                | I/O    | BUS COMMAND/BYTE ENABLES. Bus Command and Byte Enables are multiplexed. During the address phase of transaction, C/BEn define the bus command. During the data phase C/BEn are used as Byte Enables. The Byte Enables determine which bytes carry meaningful data. This bus is an input during slave mode and an output during master mode.                                                                                                                                                                                             |

| IDSEL      | 83                                                           | I      | INITIALIZATION DEVICE SELECT. Active high chip select in lieu of the upper 24 address lines during configuration read and write transactions.                                                                                                                                                                                                                                                                                                                                                                                           |

| FRAMEn     | 95                                                           | ľO     | CYCLE FRAME. Used to indicate the beginning and duration of an access. This signal is an input during slave mode and an output during master mode.                                                                                                                                                                                                                                                                                                                                                                                      |

| IRDYn      | 96                                                           | I/Osod | INITIATOR READY. IRDYn used to indicate the initiating agent's ability to complete the current data phase of the transaction. It is used in conjunction with TRDYn. This signal is an input during slave mode and an output during master mode.                                                                                                                                                                                                                                                                                         |

| TRDYn      | 97                                                           | I/Osod | TARGET READY. Used to indicate the target agent's ability to complete the current data phase of the transaction. TRDYn is used in conjunction with IRDYn. A data phase is completed on any clock when both TRDYn and IRDYn are asserted. During a read TRDYn indicates that valid data is present on AD[31:0]. During a write it indicates the target is prepared to accept data. Wait cycles are inserted until both IRDYn and TRDY are asserted together. This signal is an output during slave mode and an input during master mode. |

| DEVSELn    | 98                                                           | I/Osod | DEVICE SELECT. When driven active, indicates the driving device has decoded its address as the target of the current access. As an input it indicates whether any device on the bus has been selected. This signal is an output during slave mode and an input during master mode.                                                                                                                                                                                                                                                      |

| STOPn      | 99                                                           | I/Osod | STOP. Active low signal used by the current slave to request the current Master to stop the current transaction. This signal is an output during slave mode and an input during master mode.                                                                                                                                                                                                                                                                                                                                            |

| LOCKn      | 100                                                          | I/Osod | LOCK. Active low signal used to indicate an atomic operation that may require multiple transactions to complete.                                                                                                                                                                                                                                                                                                                                                                                                                        |

Total: 49 pins

## 6.4 BIOS ROM Interface

| Pin Name         | Pin Number | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DOEn/<br>ROMENLn | 45         | 0    | DATA OUTPUT ENABLE. VL bus configuration, this is an active low signal to enable the low byte of BIOS data, DAC, and DIP SWITCH data to ISA data bus. Depending on the cycle, the selected device will drive the output data or will receive the input data. ROM ENABLE: PCI Bus configuration, this is an active low signal to enable the the ROM read. ISA bus 16-bit ROM configuration, this signal is used to enable the external buffer which routes the upper byte out to the system bus. |

Total: 1 pin

# 6.5 Clock Interface

| Pin Name | Pin Number | Туре | Description                                                                                                                                                                |

|----------|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCLK     | 2          | I    | VIDEO CLOCK. This is the master input pixel clock.                                                                                                                         |

| CSEL[3]  | 11         | 0    | CLOCK SELECT LINE 3. Clock select lines are used to select the appropriate video clock frequency. This pin can be programmed through register 3DF index 6.                 |

| CSEL[2]  | 12         | 0    | CLOCK SELECT LINE 2. Clock select lines are used to select the appropriate video clock frequency. This pin can be programmed through register 3DF index 6.                 |

| CSEL[1]  | 13         | 0    | CLOCK SELECT LINE 1. Clock select lines are used to select the appropriate video clock frequency. This pin can be programmed through register 3DF index 6 or register 3C2. |

| CSEL[0]  | 14         | 0    | CLOCK SELECT LINE 0. Clock select lines are used to select the appropriate video clock frequency. This pin can be programmed through register 3DF index 6 or register 3C2. |

| MCLK     | 196        | I    | MEMORY CLOCK. This is the input clock used for display memory timing.                                                                                                      |

Total: 6 pins

# 6.6 Feature Connector Interface

| Pin Name | Pin Number | Type | Description                                                                                       |

|----------|------------|------|---------------------------------------------------------------------------------------------------|

| ESYNC    | 216        | Ipu  | ENABLE SYNC. This active high input is used to enable the BLANKn, HSYNC and VSYNC output signals. |

| EPCLK    | 220        | Ipu  | ENABLE PCLK. This active high input is used to enable the PCLK output to the SynDAC.              |

| EPDATA   | 222        | Ipu  | ENABLE PDATA. This active high input is used to enable the P[23:0] Pixel Data output pins.        |

Total: 3 pins

## 6.7 DAC Interface

| Pin Name | Pin Number          | Туре | Description                                                                                                                                                                                                                                                                                                                                 |

|----------|---------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P[23:16] | 3-10                | 0    | PIXEL DATA. Upper 8-bits of pixel data. This bus exists on PCI & ISA buses only. It is not applicable for the VL-bus. These pins can be three-stated.                                                                                                                                                                                       |

| P[15:0]  | 224-229,<br>231-240 | 0    | PIXEL DATA. Output data bus interfaces to the external synDAC chip for color mapping during active CRT display time. These pins can be three-stated.                                                                                                                                                                                        |

| PCLK     | 221                 | 0    | PIXEL CLOCK. Pixel clock output to the SynDAC to latch the pixel data. It is derived from the dot clock of the operating mode.                                                                                                                                                                                                              |

| BLANKn   | 217                 | 0    | BLANK. Active low output signal to RAMDAC to blank the pixel data for the display monitor.                                                                                                                                                                                                                                                  |

| DACWRn   | 215                 | 0    | RAMDAC WRITE. An active low I/O write signal generated for writing external color palette registers. For VL bus configuration, this signal is also used to control data flow from ISA bus to and from the DAC, ROM, and DIP SWITCH. When DACWRn is high, data is output to the ISA bus, when DACRDn is low, data is input from the ISA bus. |