DATA BOOK Fall 1995

Application-Specific Memory

APPLICATION-SPECIFIC MEMORY DATA BOOK

### Application Specific Memory 1995 Data Book

Document No. M11002EU1V0DB00 ©1995 NEC Electronics Inc. All rights reserved. Printed in the United States of America.

No part of this document may be copied or reproduced in any form or by any means without the prior consent of NEC Electronics Inc. (NECEL). The information in this document is subject to change without notice. Devices sold by NECEL are covered by the warranty and patent indemnification provisions appearing in NECEL Terms and Conditions of Sale only. NECEL makes no warranty, express, statutory, implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. NECEL makes no warranty of merchantability or fitness for any purpose. NECEL assumes no responsibility for any errors that may appear in this document. NECEL makes no commitment to update or to keep current information contained in this document. The devices listed in this document are not suitable for use in applications such as, but not limited to, aircraft, aerospace equipment, submarine cables, nuclear reactor control systems and life support systems. If customers intend to use NEC devices in these applications or they intend to use "standard" quality grade devices are recommended for computers, office equipment, communication equipment, test and measurement equipment, machine tools, industrial robots, audio and visual equipment, and other consumer products. "Special" quality grade devices are recommended for automotive and transportation equipment, test for automotive and transportation equipment, test man measurement equipment, machine tools, industrial robots, audio and visual equipment, and other consumer products. "Special" quality grade devices are recommended for automotive and transportation equipment, test man measurement equipment, machine tools, industrial robots, audio and visual equipment, and other consumer products.

## Index

| Selection Guide           | ]1   |

|---------------------------|------|

| Dual Port Graphics Buffer | ]7   |

| Line Buffer               | ]189 |

| Field Buffer              | ]227 |

| Rambus <sup>™</sup> DRAM  | ]253 |

| Synchronous GRAM          | 357  |

#### NOTES FOR CMOS DEVICES -

#### **1** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note: Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

#### (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

Note: No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS device behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note: Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

## Contents

| Selection Guide                  | •••••         |                  |

|----------------------------------|---------------|------------------|

| Dual Port Graphics Buffer        | •••••         |                  |

| 4M 256K×16 5V±10%                | Fast Page     | — μPD482444      |

|                                  | Hyper Page    | — μPD482445      |

| 2M 256K×8 5V±10%                 | – Fast Page – | — μPD482234 107  |

|                                  | Hyper Page    | — μPD482235 107  |

| Line Buffer                      |               |                  |

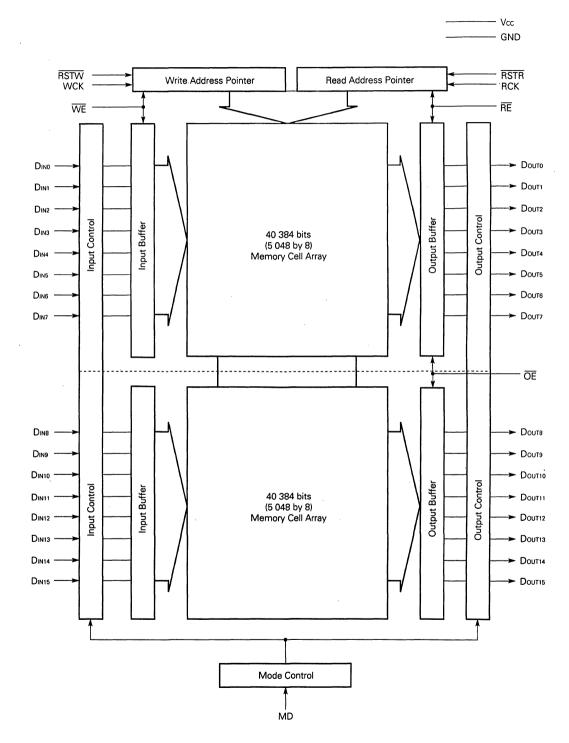

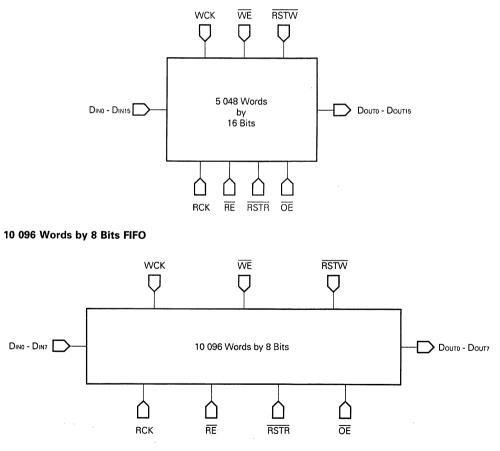

| 80K 5K × 16/10K × 8              | - 5V±10%      | — μPD485506 191  |

| 40K 5K × 8                       | 5V±10%        | — μPD485505 211  |

| Field Buffer                     |               |                  |

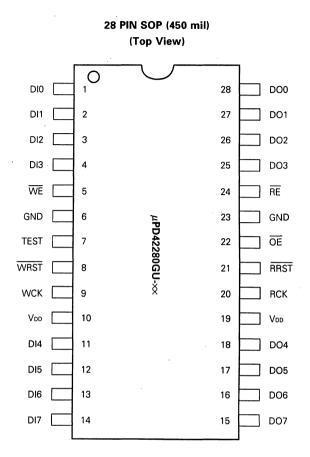

| 2M 256K × 8                      | 5V±10%        | — μPD42280 229   |

| Rambus DRAM                      | •••••         |                  |

| 18M $1M \times 9 \times 2$ banks | 3.3V±0.15V    | — μPD488170L 255 |

| 16M $1M \times 8 \times 2$ banks | 3.3V±0.15V    | — μPD488130L 305 |

| Synchronous GRAM                 |               |                  |

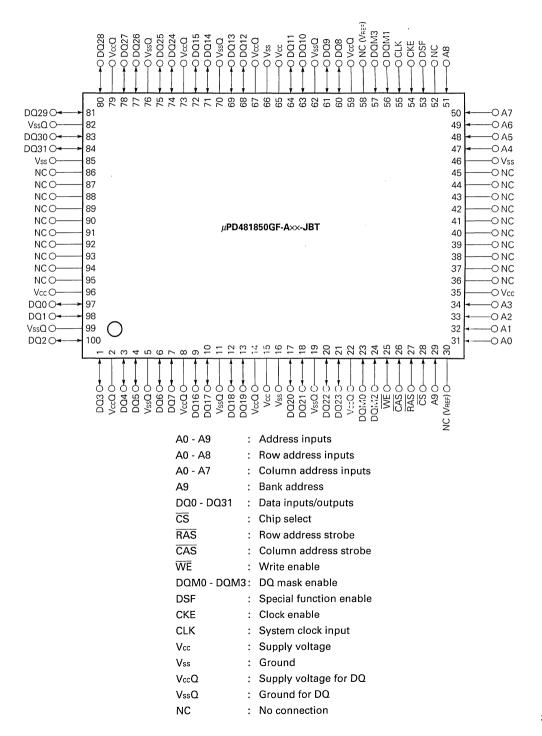

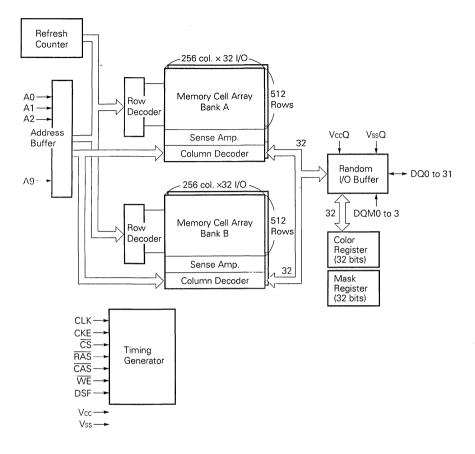

| 8M 128K × 32 × 2 banks           | - 3.3V±0.3V   | — μPD481850 359  |

·

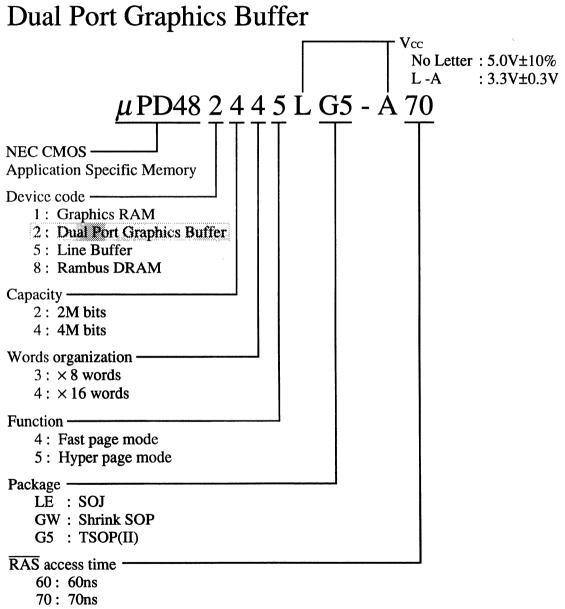

Selection Guide

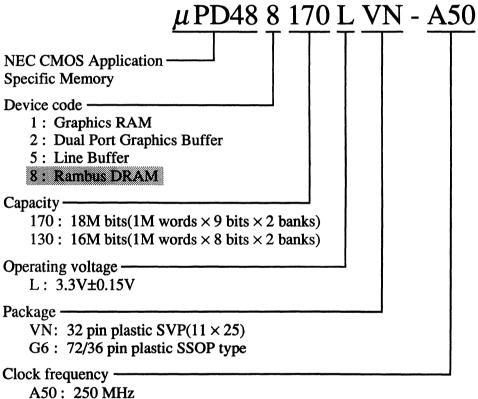

## Part Number

80: 80ns

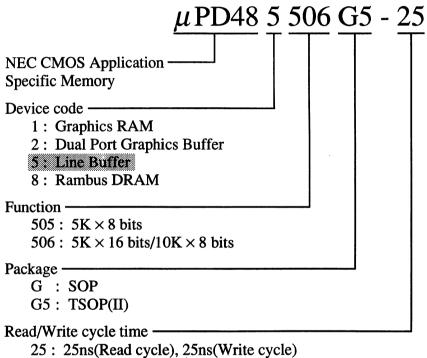

### Line Buffer

- 27 : 27ns(Read cycle), 25ns(Write cycle)

- 35: 35ns(Read cycle), 35ns(Write cycle)

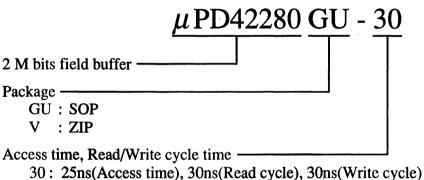

### Field Buffer

- 40: 30ns(Access time), 40ns(Read cycle), 40ns(Write cycle)

- 60: 40ns(Access time), 60ns(Read cycle), 60ns(Write cycle)

### Rambus DRAM

A30 : 230 MHz A45 : 225 MHz

## **Dual Port Graphics Buffer**

DATA SHEET

# MOS INTEGRATED CIRCUIT $\mu$ PD482444, 482445

#### 4M-Bit Dual Port Graphics Buffer

#### 256K WORDS BY 16 BITS

#### Description

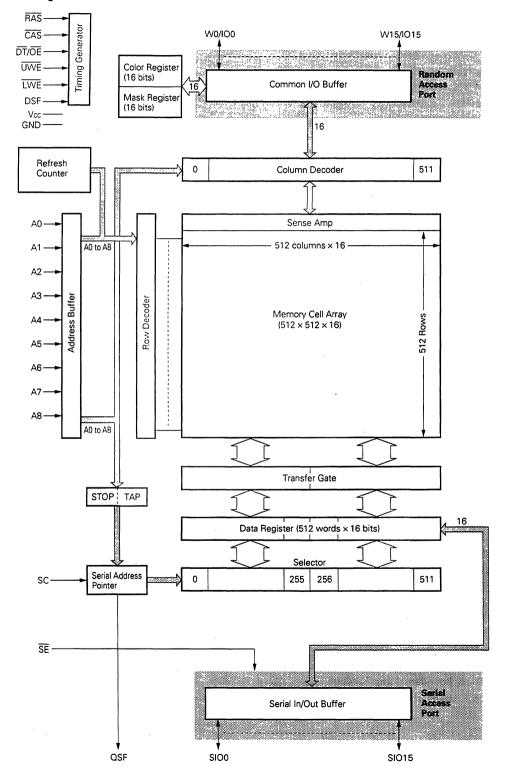

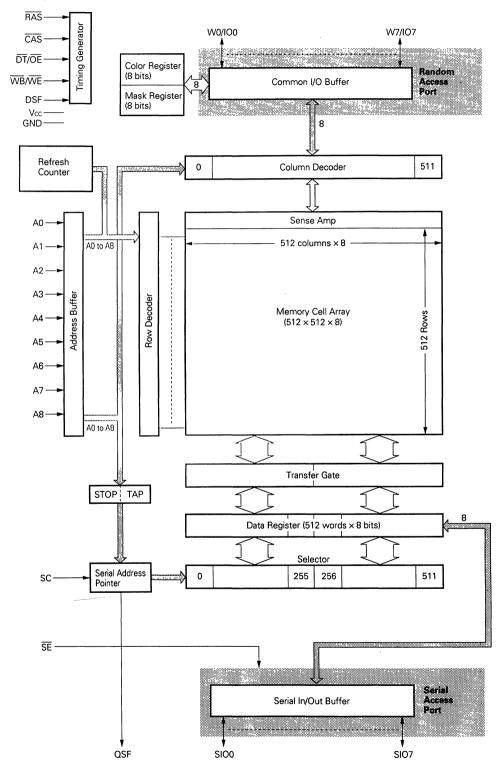

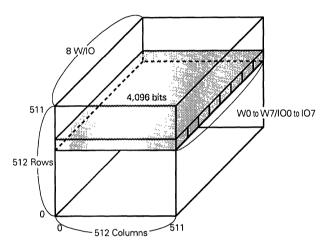

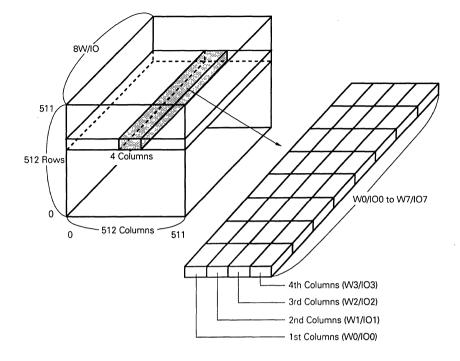

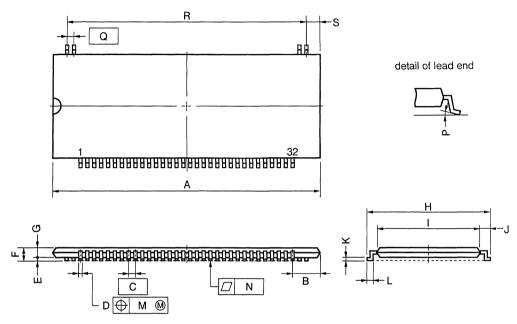

The  $\mu$ PD482444 and  $\mu$ PD482445 have a random access port and a serial access port. The random access port has a 4M-bit (262,144 words × 16 bits) memory cell array structure. The serial access port can perform clock operations of up to 50 MHz from the 8K-bit data register (512 words × 16 bits).

To simplify the graphics system design, the split data transfer function and binary boundary jump function have been adopted so that the number of split data registers can be programmed with the software during serial read/write operations.

The  $\mu$ PD482445 is provided with the hyper page mode, an improved version of the fast page mode of the  $\mu$ PD482444. The random access port can input and output data by  $\overline{CAS}$  clock operations of up to 33 MHz. The power supply voltage is 5 V ± 10 %.

#### Features

Dual port structure (Random access port, Serial access port)

Random access port (262,144-word × 16-bit structure)

#### μ**PD482444**

|                           | μPD482444-60 | μPD482444-70 |

|---------------------------|--------------|--------------|

| RAS access time           | 60 ns(MAX.)  | 70 ns(MAX.)  |

| Fast page mode cycle time | 35 ns(MIN.)  | 40 ns(MIN.)  |

#### μ**PD482445**

|                            | μPD482445-60 | μPD482445-70 |

|----------------------------|--------------|--------------|

| RAS access time            | 60 ns(MAX.)  | 70 ns(MAX.)  |

| Hyper page mode cycle time | 30 ns(MIN.)  | 35 ns(MIN.)  |

- Flash write function<sup>Note</sup>

- Block write function (8 columns)<sup>Note</sup>

- · Mask write (Write-per-bit function)

- 512 refresh cycles /8 ms

- CAS before RAS refresh, RAS only refresh, Hidden refresh

Note Write-per-bit can be specified.

The information in this document is subject to change without notice.

- Serial access port (512 words × 16 bits organization)

- · Serial read/write cycle time

| μPD482444-60 | μPD482444-70 |

|--------------|--------------|

| μPD482445-60 | μPD482445-70 |

| 20 ns(MIN.)  | 22 ns(MIN.)  |

- · Serial data read/write

- · Split buffer data transfer

- Binary boundary jump function

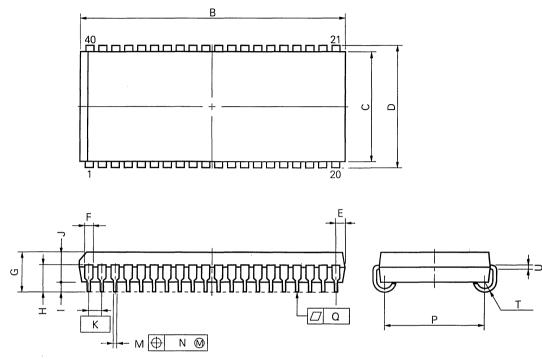

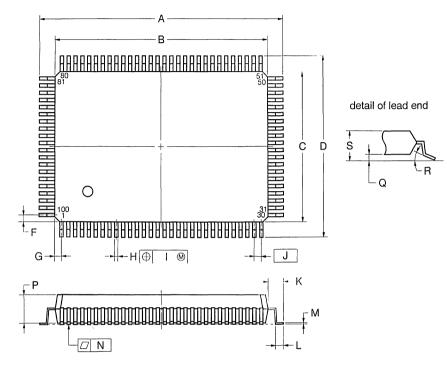

#### **Ordering Information**

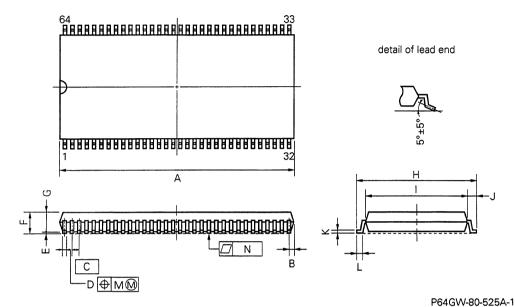

| Part Number    | RAS Access Time<br>ns (MAX.) | Package               | Power Supply<br>Voltage | Page Mode       |

|----------------|------------------------------|-----------------------|-------------------------|-----------------|

| μPD482444GW-60 | 60                           | 64-pin plastic shrink | 5 V ± 10 %              | Fast page mode  |

| μPD482444GW-70 | 70                           | SOP (525 mil)         |                         |                 |

| μPD482445GW-60 | 60                           | 64-pin plastic shrink | 5 V ± 10 %              | Hyper page mode |

| μΡD482445GW-70 | 70                           | SOP (525 mil)         |                         |                 |

|                |                              |                       |                         |                 |

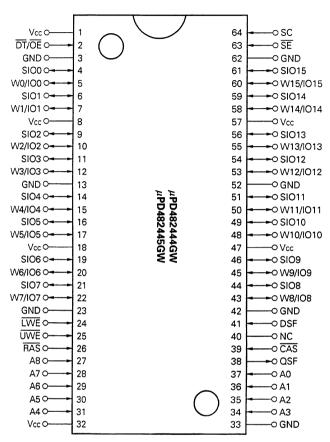

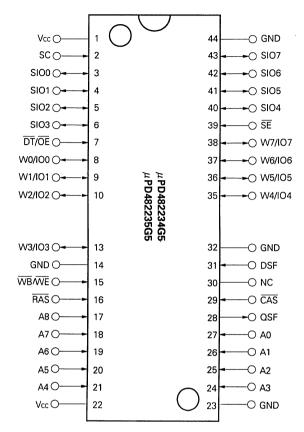

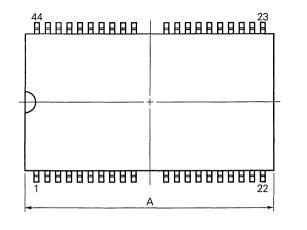

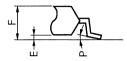

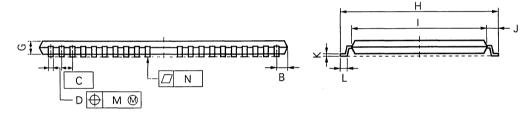

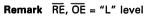

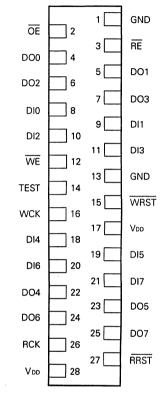

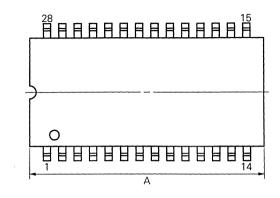

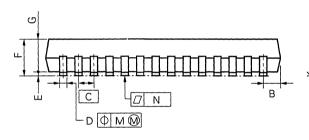

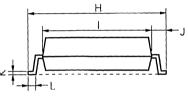

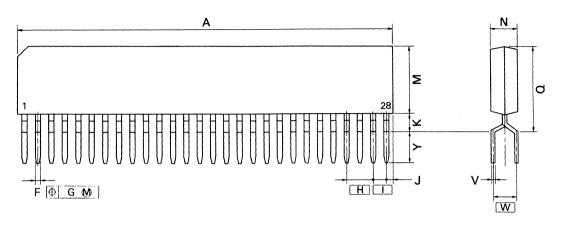

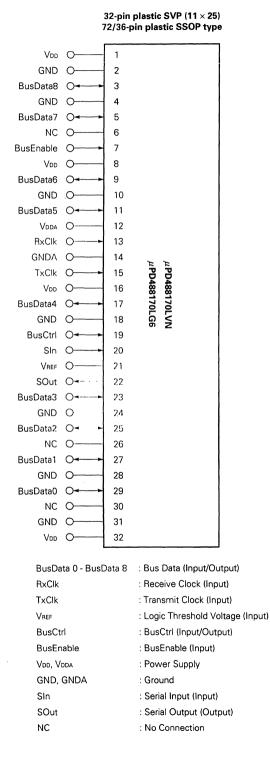

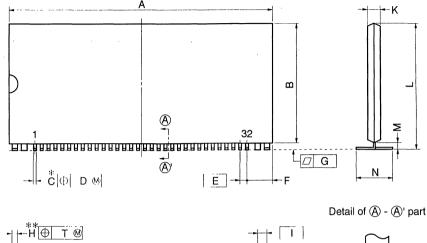

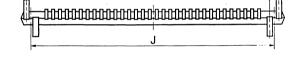

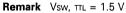

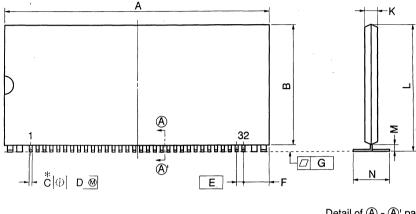

#### Pin Configurations (Marking Side)

64-Pin Plastic Shrink SOP (525 mil)

| A0 to A8              | : | Address inputs                            |

|-----------------------|---|-------------------------------------------|

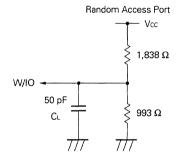

| W0 to W15/IO0 to IO15 | : | Mask data selects/Data inputs and outputs |

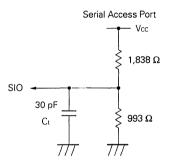

| SIO0 to SIO15         | : | Serial data inputs and outputs            |

| RAS                   | : | Row address strobe                        |

| CAS                   | : | Column address strobe                     |

| DT/OE                 | : | Data transfer/Output enable               |

| UWE, LWE              | : | Write-per-bit/Write enable                |

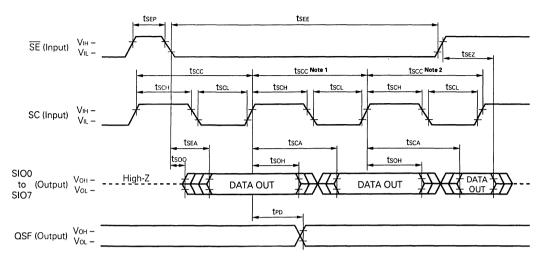

| SE                    | : | Serial data input/Output enable           |

| SC                    | : | Serial clock                              |

| QSF                   | : | Special function output                   |

| DSF                   | : | Special function enable                   |

| Vcc                   | : | Power supply voltage                      |

| GND                   | : | Ground                                    |

| NC <sup>Note</sup>    | : | No connection                             |

Note Some signals can be applied because this pin is not connected to the inside of the chip.

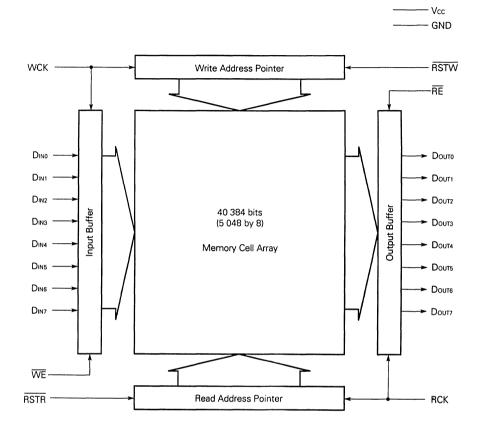

**Block Diagram**

#### 1. Pin Functions

This product is equipped with the RAS, CAS, UWE, LWE, DT/OE, A0 to A8, DSF, SC, SE inputs, QSF output, and W0 to W15/IO0 to IO15, SIO0 to SIO15 input/output pins.

(1/3)

| Pin Name                          | Input/<br>Output | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAS<br>(Row address strobe)       | Input            | This signal latches the row addresses (A0 to A8), selects the corresponding<br>word line, and activates the sense amplifier. It also refreshes the memory<br>cell array of the one line (8,192 bits) selected from the row addresses (A0<br>to A8).                                                                                                                                                                                                                |

|                                   |                  | It also serves as the signal which selects the following operations.         • Write-per-bit       • Flash write         • CAS before RAS refresh       • Split data transfer                                                                                                                                                                                                                                                                                      |

| CAS<br>(Column address<br>strobe) |                  | This signal latches the column addresses (A0 to A8), selects the digit line connecting the sense amplifier, and activates the output circuit which outputs data to the random access port.                                                                                                                                                                                                                                                                         |

|                                   |                  | It also serves as the signal which selects the following operations.• Read/write• Block write• Color register set• Mask register set                                                                                                                                                                                                                                                                                                                               |

| A0 to A8<br>(Address inputs)      |                  | These are the address input pins, TAP register input pins, and STOP register input pins.                                                                                                                                                                                                                                                                                                                                                                           |

|                                   |                  | Address input<br>This is a 9-bit address bus. It inputs a total of 18 bits of the address signal,<br>starting from the upper 9 bits (row address) and then followed by the lower<br>9 bits (column bits) (address multiplex method). Using these, one word<br>memory cells (16 bits) are selected from the 262, 144 words × 16 bits memory<br>cell array.                                                                                                          |

|                                   |                  | During use, specify the row address, activate the $\overline{RAS}$ signal, latch the row address, switch to the column address, and activate the $\overline{CAS}$ signal. After activating the $\overline{RAS}$ and $\overline{CAS}$ signals, each address signal is taken into the device. For this reason, the address input setup time (task, tasc) and hold time (trank, tcah) are specified for activating the $\overline{RAS}$ and $\overline{CAS}$ signals. |

|                                   |                  | TAP Register Input<br>In the data transfer cycle, this TAP register input pin functions as the<br>address input pin which selects the memory cell for transferring (9 bits are<br>latched at the falling edge of $\overline{RAS}$ ) and the TAP register data input pin<br>which specifies the start addresses of the serial read/write operation after<br>data transfer (9 bits are latched at the falling edge of the $\overline{CAS}$ ).                        |

|                                   |                  | STOP Register Input<br>This pin functions as the STOP register input pin when the STOP register<br>is set (STOP register data (9 bits) are latched at the falling edge of the RAS.)                                                                                                                                                                                                                                                                                |

NEC

(2/3)

| Pin Name                                                              | Input/<br>Output | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DT/OE<br>(Data transfer/<br>output enable)                            | Input            | These are the data transfer control signal and read operation control signa respectively. They have different functions in the data transfer cycle and read cycle.                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                       |                  | Data transfer control signal (in data transfer cycle)<br>The data transfer cycle is initiated when a low level is input to this pin a<br>the falling edge of $\overline{RAS}$ .                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                       |                  | Read operations control signal (in read cycle)<br>Read operation is performed when this signal, and the $\overline{RAS}$ and $\overline{CAS}$ signals are activated. The input/output pin is high impedance when this signal is not activated. When the $\overline{UWE}$ and $\overline{LWE}$ signals are activated while the $\overline{DT}/\overline{OE}$ signals are activated, the $\overline{DT}/\overline{OE}$ signals are invalid in the memory and read operations cannot be performed.                                                                   |

| UWE, <b>LWE</b><br>(Write enable)                                     |                  | These are the write operation control signal and mask write cycle (write per-bit function) mask data input control signal, respectively.<br>UWE controls the upper bytes (W8 to W15/IO8 to IO15) and LWE controls the lower bytes (W0 to W7/IO0 to IO7) of the input/output pins.<br>When this signal, RAS and CAS signals are activated, write operations o mask write can be performed. These mode are determined by the leve of UWE and LWE at the falling edge of RAS.<br>• High level8 or 16-bit write cycle<br>• Low level Mask write cycle (Write-per-bit) |

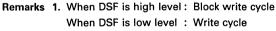

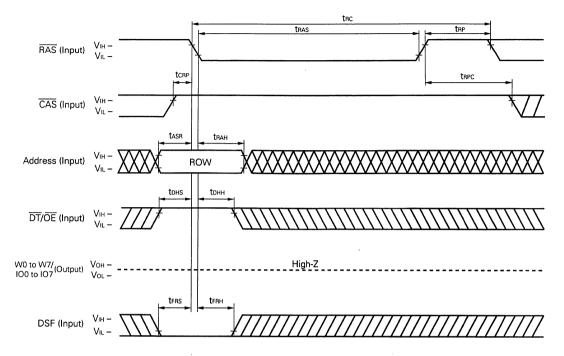

| DSF<br>(Special function<br>enable)                                   |                  | <ul> <li>This signal controls the selection of functions.</li> <li>The selection of functions is determined by the level of this signal at the falling edge of the RAS and CAS. The functions will change as follow when this signal is high level.</li> <li>The data transfer cycle changes to a split data transfer cycle.</li> <li>The read/write cycle of each RAS clock changes to the flash write cycle</li> <li>The write cycle of each CAS clock changes to the block write cycle</li> </ul>                                                              |

| W0 to W15/IO0 to IO15<br>(Mask data selects/<br>Data inputs, outputs) | Input/<br>Output | These are normally 16-bit data bus and are used for inputting an outputting data. (IO0 to IO15).<br>Function as the mask data input pins (W0 to W15) in the mask write cycl (write-per-bit function).<br>Write operations can be performed only for W0 to W15 that are input wit a high level at the falling edge of RAS (new mask data).<br>Functions as the column selection data input pin in the block write cycle                                                                                                                                            |

(3/3)

| Pin Name                                          | Input/<br>Output | Function                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

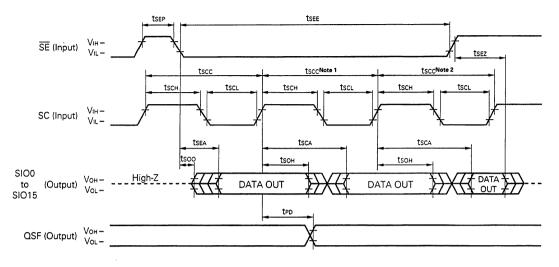

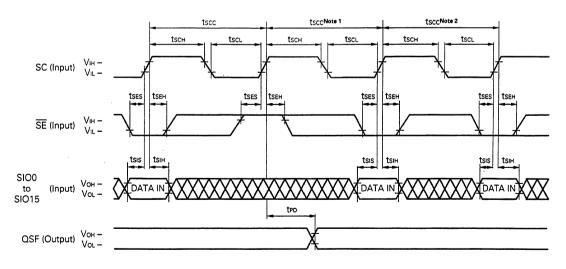

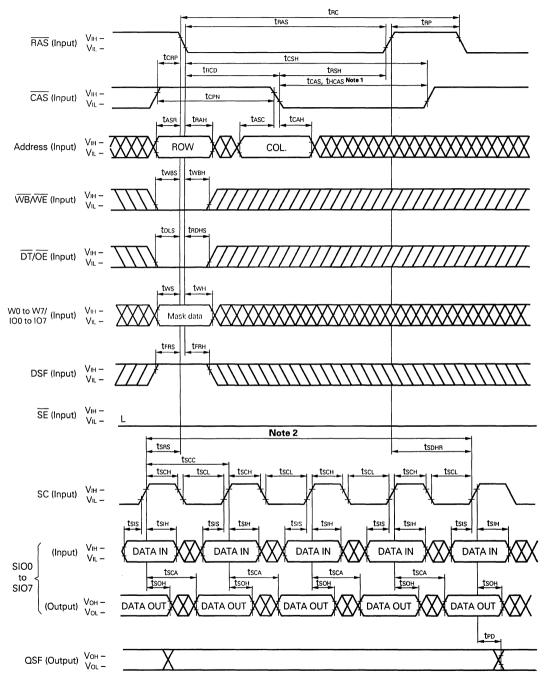

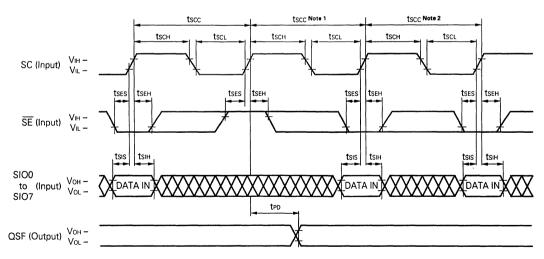

| SC<br>(Serial clock)                              | Input            | This pin inputs the clock which controls the serial access port operation. Serial Read The data of the data register which is synchronized with the rising edge of the SC are output from the SIO0 to SIO15 pins and kept until the next SC rising edge. Serial Write The data from the SIO0 to SIO15 pins are latched at the rising edge of the SC and written in the data register. |

| SE<br>(Serial data input/<br>output enable)       |                  | This is a control pin for the serial access port input/output buffer.<br>It controls data output during serial reading and controls data input during<br>serial writing.<br>By inputting the serial clock, the serial pointer will operate even if SE has<br>not been activated (high level input).                                                                                   |

| SIO0 to SIO15<br>(Serial data inputs/<br>outputs) | Input/<br>Output | These are the serial data input and output pins of the serial access port.                                                                                                                                                                                                                                                                                                            |

| QSF<br>(Special function<br>output)               | Output           | <ul> <li>This is a position discrimination pin of the serial pointer (upper side or lower side).</li> <li>Which side is being serial accessed (upper side or lower side) can be discriminated according to the output of this pin.</li> <li>High level Upper side (Addresses 256 to 511)</li> <li>Low level Lower side (Addresses 0 to 255)</li> </ul>                                |

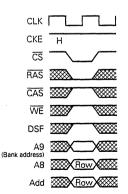

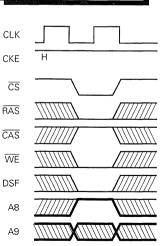

#### 2. Random Access Port Operations

The operation mode is determined by the  $\overline{CAS}$ ,  $\overline{DT}/\overline{OE}$ ,  $\overline{UWE}$ ,  $\overline{LWE}$ , and DSF level at the falling edge of  $\overline{RAS}$  and DSF level at the falling edge of  $\overline{CAS}$ .

|     | RAS Fa | lling I | Edge |     | CAS<br>Falling Edge |            | Operation Mode                                         |

|-----|--------|---------|------|-----|---------------------|------------|--------------------------------------------------------|

| CAS | DT/OE  | UWE     | LWE  | DSF | DSF                 |            |                                                        |

| н   | н      | Н       | н    | L   | L                   |            | Read/Write cycle                                       |

| н   | н      | н       | н    | L   | н                   |            | Block write cycle                                      |

| н   | Н      | L       | L    | L   | L                   |            | Mask write cycle <sup>Note 1</sup>                     |

| н   | н      | L       | н    | L   | L                   |            | Upper byte mask write cycle <sup>Note 1</sup>          |

| н   | Н      | Н       | L    | L   | L                   |            | Lower byte mask write cycleNote 1                      |

| н   | Н      | L       | L    | L   | н                   | e l        | Block mask write cycle <sup>Note 1</sup>               |

| н   | н      | L       | Н    | L   | Н                   | e Cycle    | Upper byte block mask write cycle <sup>Note 1</sup>    |

| н   | Н      | н       | L    | L   | н                   | Vrite      | Lower byte block mask write cycle <sup>Note 1</sup>    |

| н   | Н      | н       | Н    | Н   | Н                   | Read/Write | Color register set cycle                               |

| н   | н      | н       | Н    | H   | L                   | Re         | Write mask register set cycle                          |

| н   | Н      | L       | L    | н   | ×                   |            | Flash write cycle <sup>Note 1</sup>                    |

| н   | н      | L       | Н    | н   | ×                   |            | Upper byte flash write cycle <sup>Note 1</sup>         |

| н   | н      | н       | L    | н   | ×                   |            | Lower byte flash write cycle <sup>Note 1</sup>         |

| н   | L      | Н       | Н    | L   | ×                   | Cycle      | Single read data transfer cycle                        |

| н   | L      | Н       | н    | Н   | ×                   | Transfer ( | Split read data transfer cycle                         |

| н   | L      | L       | L    | L   | ×                   |            | Single write data transfer cycleNote 1                 |

| н   | L      | L       | L    | н   | ×                   | Data       | Split write data transfer cycle <sup>Note 1</sup>      |

| L   | ×      | ×       | ×    | L   | ×                   | Cycle      | CAS before RAS refresh cycle (Option reset)Note 1, 2   |

| L   | ×      | н       | н    | н   | ×                   |            | CAS before RAS refresh cycle (No reset)                |

| L   | ×      | L       | L    | н   | ×                   | Refresh    | CAS before RAS refresh cycle (STOP register set)Note 2 |

| Н   | н      | ×       | ×    | ×   | ×                   | Re         | RAS only refresh cycle                                 |

#### Table 2-1. Operation Mode

Notes 1. Observe the following conditions when using the new mask data or old mask data in these cycles. (1) Old mask data

Can be used after setting the mask data using the write mask register set cycle.

(2) New mask data

Can be used after selecting the new mask register using the write mask register set cycle (new mask selection) and after the optional reset cycle.

2. The STOP register is set to "FFH (1111111)" by the optional reset cycle.

Remark H: High level, L: Low level, X: High level or low level

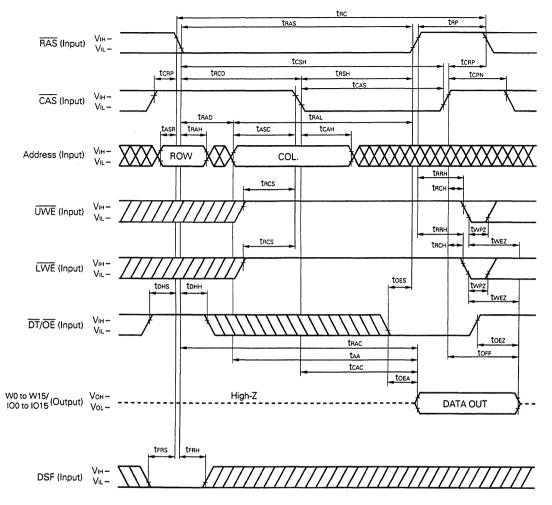

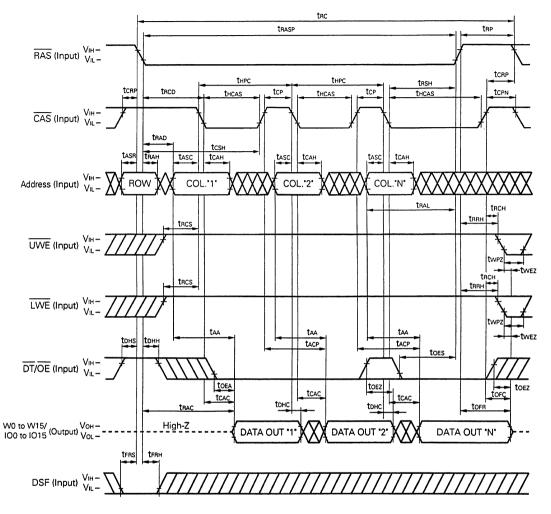

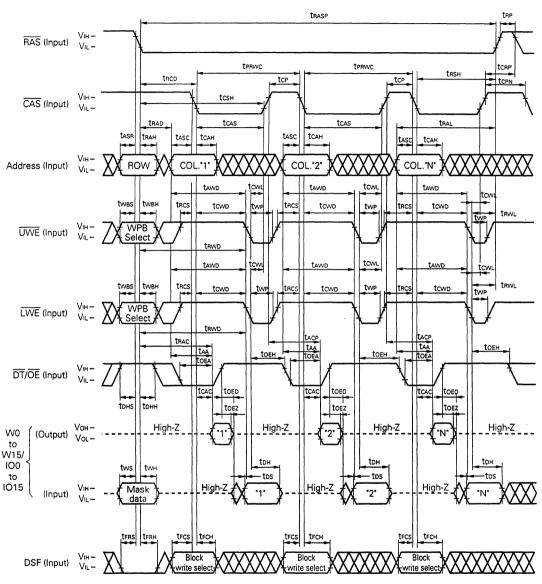

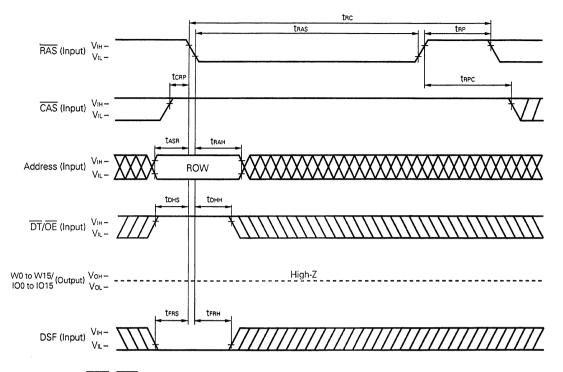

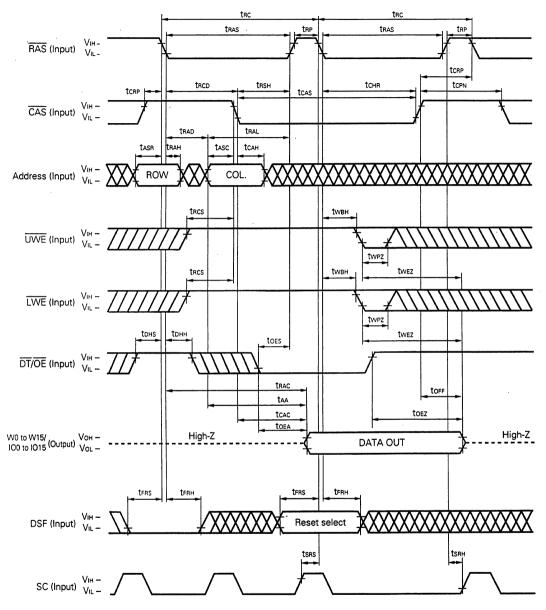

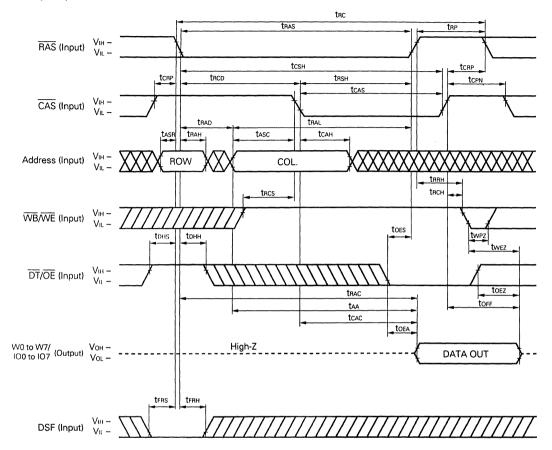

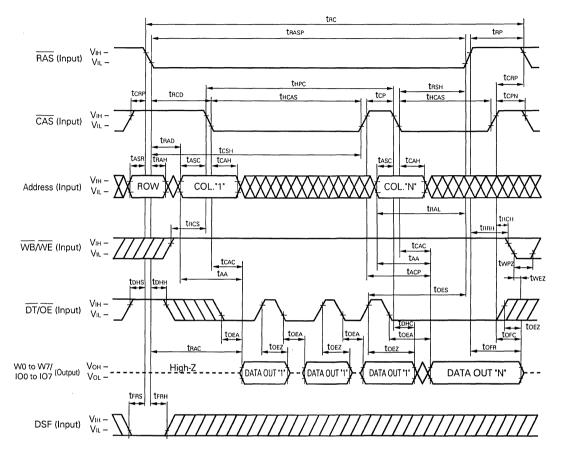

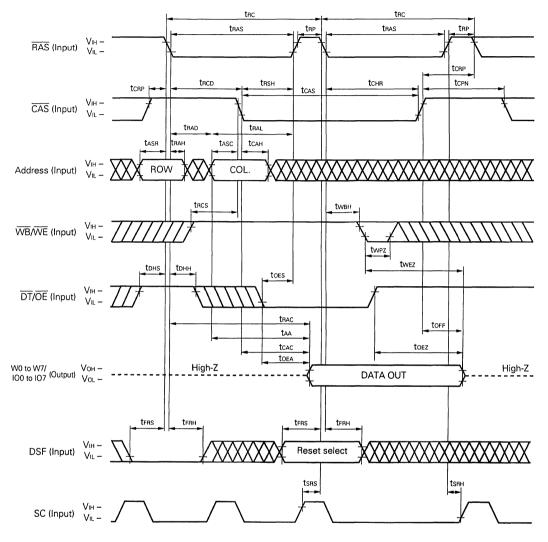

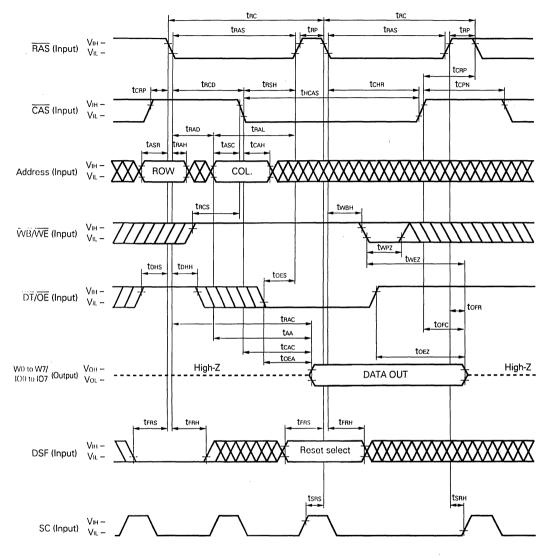

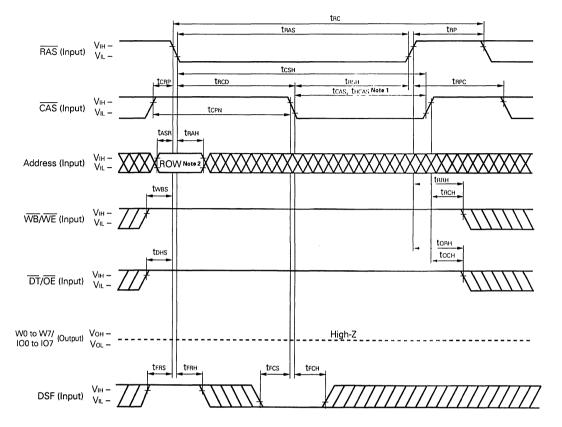

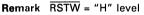

#### 2.1 Random Read Cycle

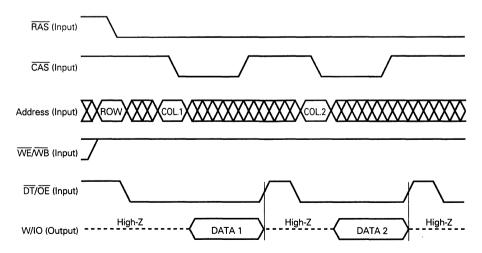

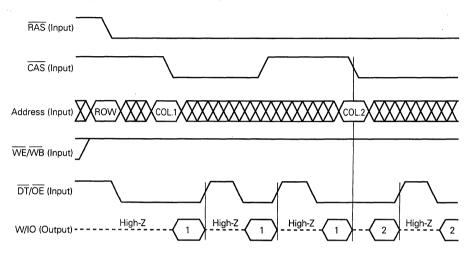

This product has a common 16-bit input/output pin. To output data, specify the address using the  $\overline{RAS}$  and  $\overline{CAS}$  clocks and then set  $\overline{DT/OE}$  to low level.

The data output will be kept until one of the following conditions is set.

- (1) Set RAS and CAS to high level

- (2) Set DT/OE to high level

- (3) Set UWE and LWE to low level (UWE controls the upper bytes, LWE controls the lower bytes)

The read cycle and data transfer cycle are differentiated according to the level of  $\overline{\text{DT}/\text{OE}}$  at the falling edge of the  $\overline{\text{RAS}}$  clock. If  $\overline{\text{DT}/\text{OE}}$  is set to low level at the falling edge of the  $\overline{\text{RAS}}$  clock, data transfer cycle operations will be initiated. Therefore, to set the read cycle, input a high level above tDHH (MIN.) to  $\overline{\text{DT}/\text{OE}}$  from the falling edge of the  $\overline{\text{RAS}}$  clock, and then input a low level.

### Caution Set the DSF to low level at the falling edge of RAS. If set to high level, the memory cell data cannot be output.

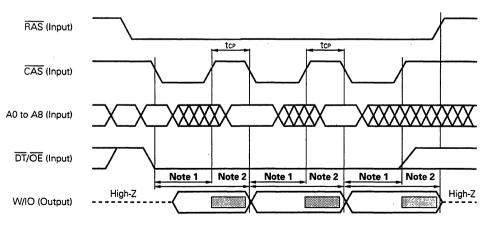

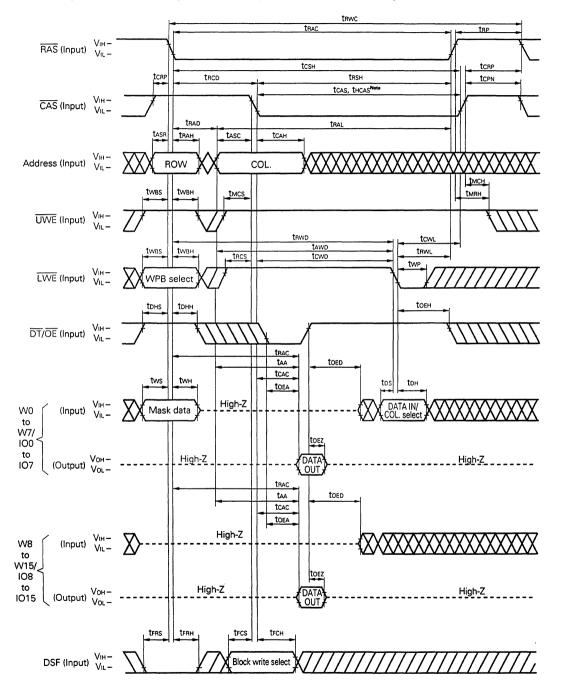

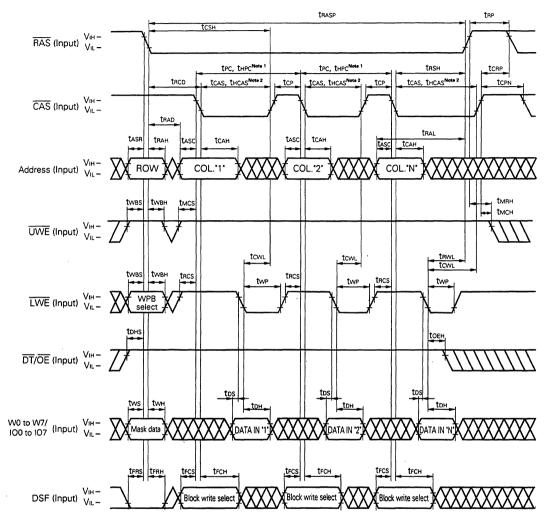

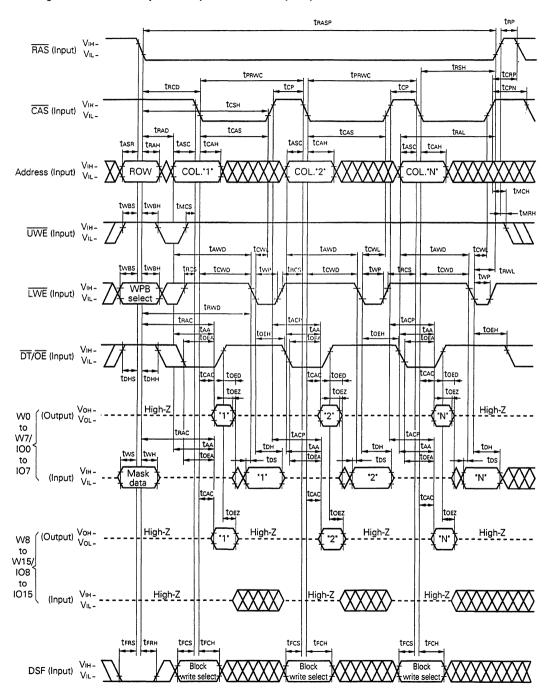

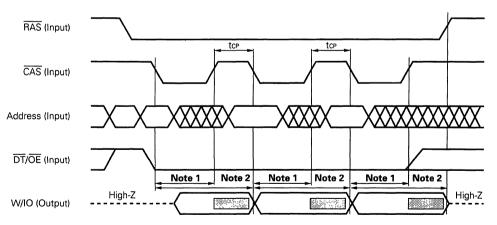

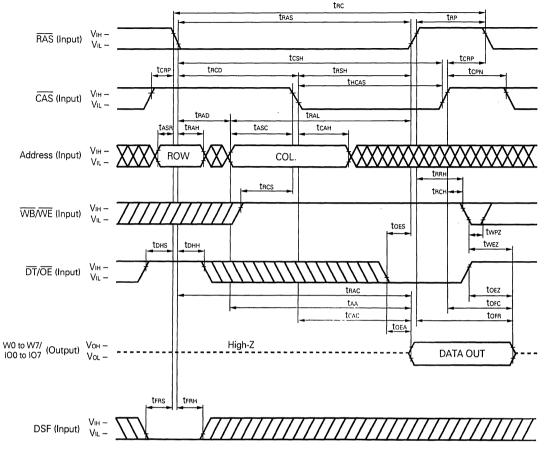

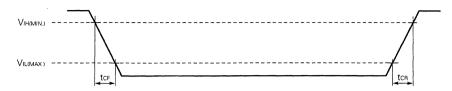

#### 2.1.1 Extended Read Data Output (µPD482445)

The  $\mu$ PD482445 adopts the hyper page mode cycle which is a faster resd/write cycle than the fast page mode of the  $\mu$ PD482444 (Hyper page mode cycle time: 30 ns (MIN.)).

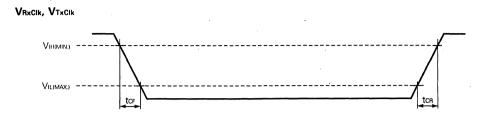

With this cycle, the read data output can be kept until the next  $\overline{CAS}$  cycle, and because the output is extended, the minimum cycle can easily be used. For example, by fixing  $\overline{DT}/\overline{OE}$  at low level after dropping  $\overline{RAS}$  and executing the hyper page read cycle, each time the column address is latched at the falling edge of  $\overline{CAS}$ , the data output will be updated and kept until the next falling edge of  $\overline{CAS}$ . As a result, the output will be extended only during  $\overline{CAS}$  precharge time (tcp) as compared to the normal fast page mode.

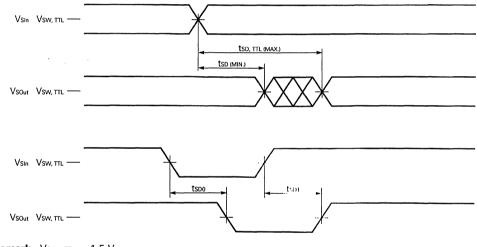

- Notes 1. Time during which the output data is kept in the fast page read cycle.

- 2. Time during which the output data is kept in the hyper page read cycle ( part: Extended data output).

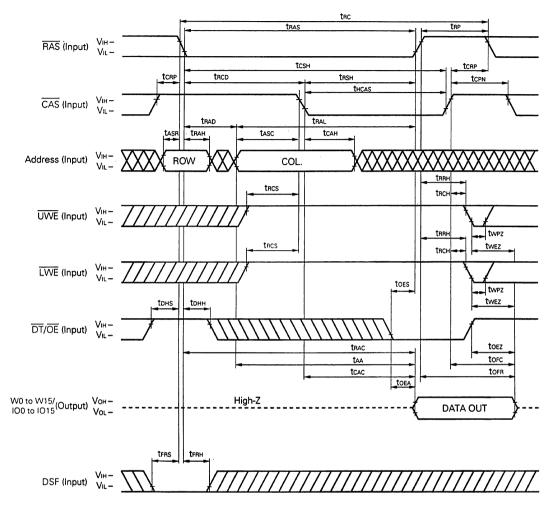

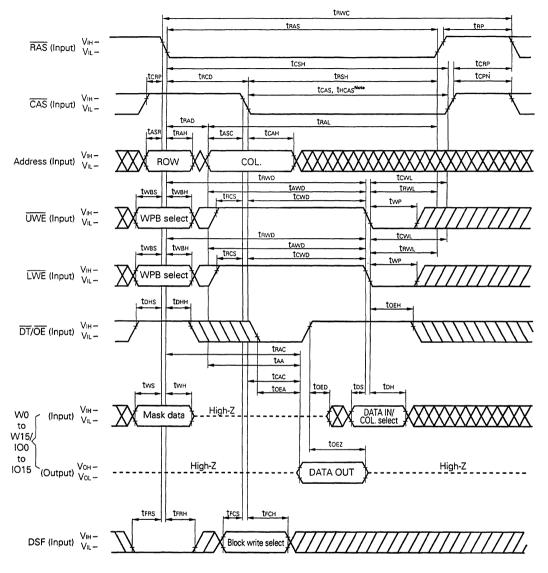

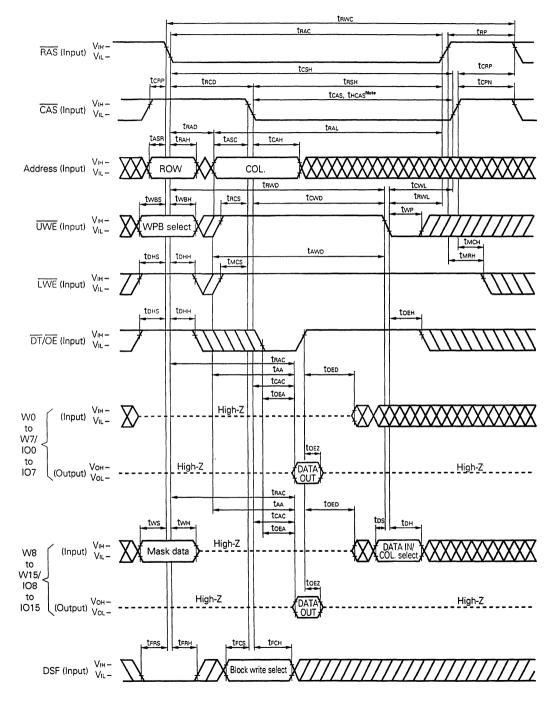

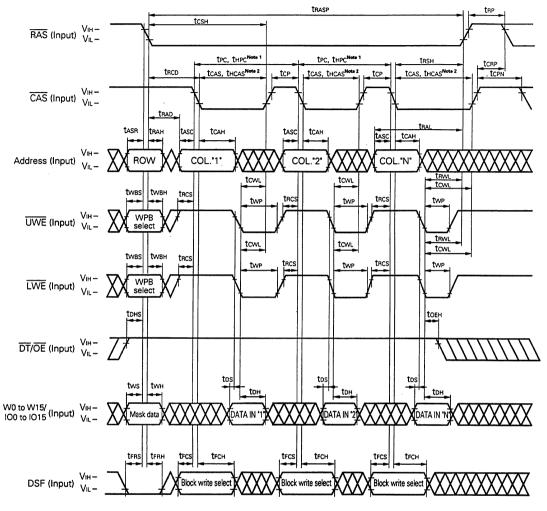

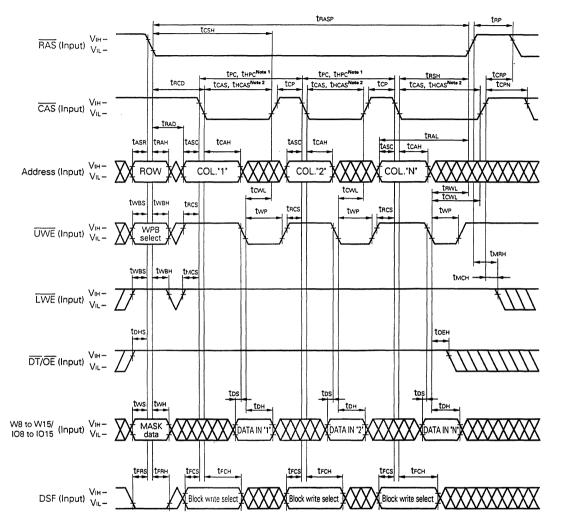

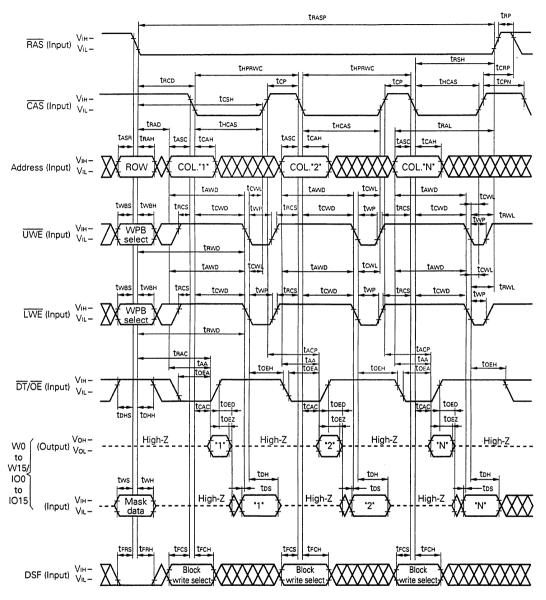

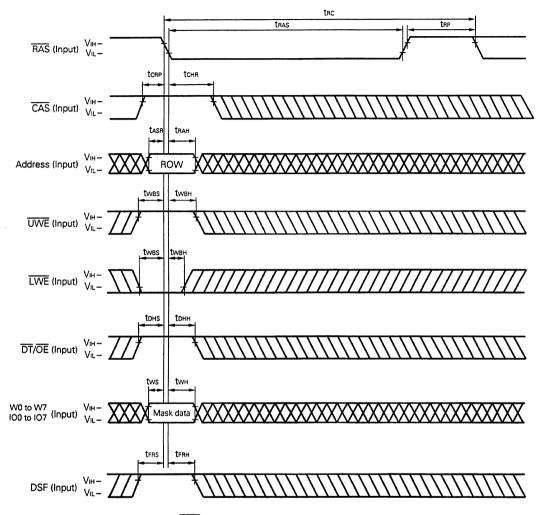

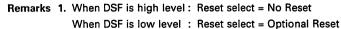

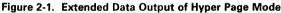

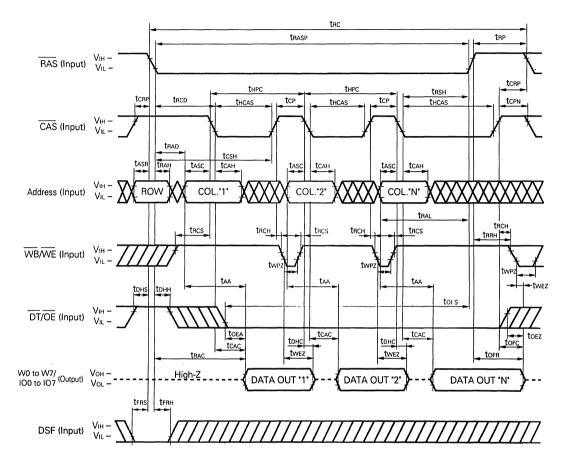

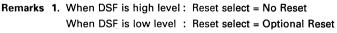

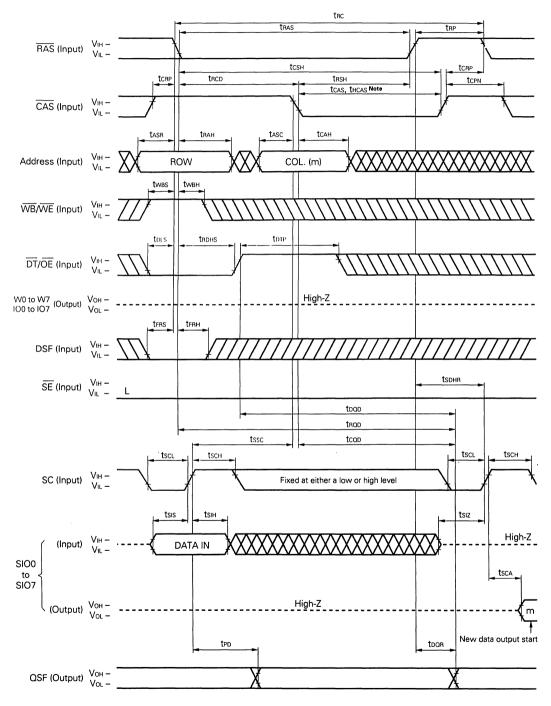

#### 2.2 Random Write Cycle (Early Write, Late Write, Read Modify Write)

There are three types of random write cycles-the early write, late write, and read modify write. To use these cycles, activate the RAS and CAS clocks and set  $\overline{UWE}$  and  $\overline{LWE}$  to low level. In addition, as this product has two write enables, data input can be controlled for every 8 bits (upper byte and lower byte).  $\overline{UWE}$  controls the upper bytes (W8 to W15/IO8 to IO15) while  $\overline{LWE}$  controls the lower bytes (W0 to W7/IO0 to IO7). Byte write cycle can therefore be performed by controlling  $\overline{UWE}$  and  $\overline{LWE}$ .

The random write cycle, regardless of the word/byte write cycle, latches the word data (16 bits) input to the data bus. By inputting a low level to  $\overline{\text{UWE}}$  (or  $\overline{\text{LWE}}$ ) during the byte write cycle, the latched word (16 bits) data will be written only in the upper byte (or lower byte) and the data of the unselected lower byte (or upper byte) will be ignored. In the same write cycle, by inputting a low level to  $\overline{\text{LWE}}$  (or  $\overline{\text{LWE}}$ ) later, the ignored lower byte (or upper byte) data can be written. By controlling the  $\overline{\text{UWE}}$  and  $\overline{\text{LWE}}$  pins, the word data (16 bits) in the same cycle can be written in one byte (8 bits).

The UWE and LWE also control the mask data for the write-per-bit function (mask write cycle). Therefore, when performing the normal write cycle which does not use the write-per-bit function, set these pins to high level at the falling edge of the RAS clock.

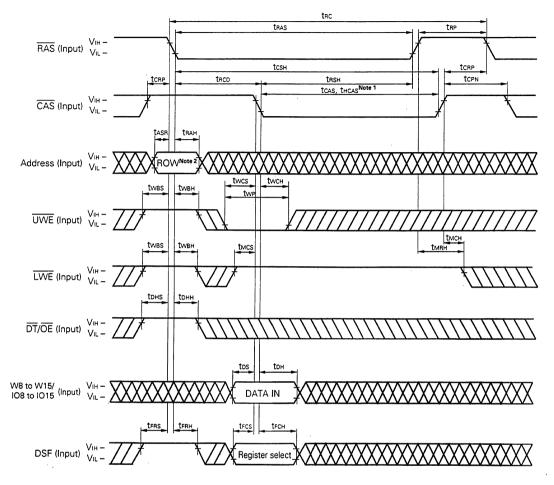

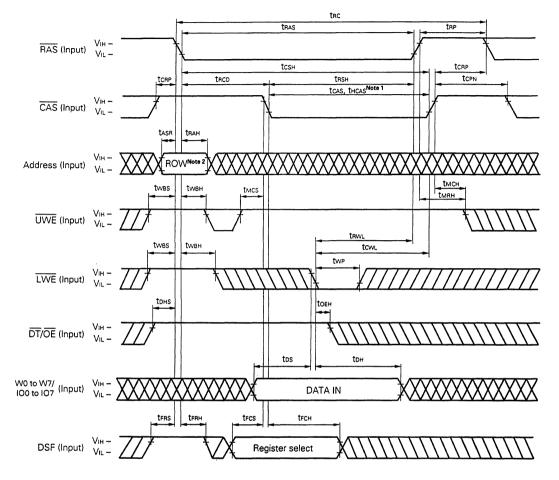

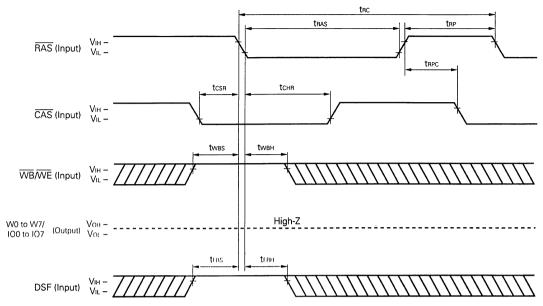

#### 2.2.1 Early Write Cycle

The early write cycle controls data writing according to the CAS clock.

To execute this cycle, set  $\overline{UWE}$  and  $\overline{LWE}$  to low level earlier than the  $\overline{CAS}$  clock. The write data is taken into the device at the falling edge of the  $\overline{CAS}$  clock.

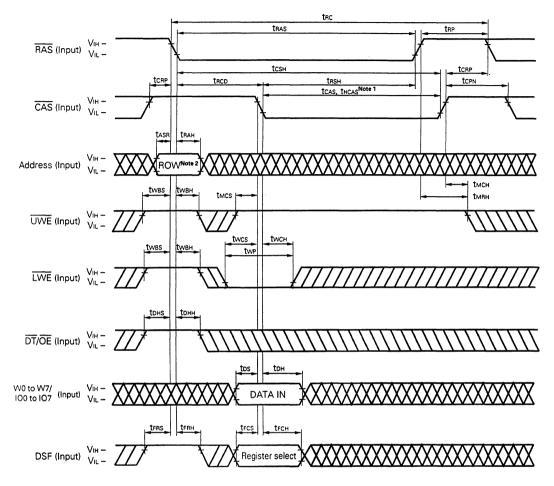

#### 2.2.2 Late Write Cycle

The late write cycle controls data writing according to the WE clock.

To execute this cycle, set  $\overline{\text{UWE}}$  and  $\overline{\text{LWE}}$  to low level later than the  $\overline{\text{CAS}}$  clock. The write data is taken into the device at the falling edge of  $\overline{\text{UWE}}$  and  $\overline{\text{LWE}}$ . To set the output to high impedance at this time, keep  $\overline{\text{DT/OE}}$  at high level until  $\overline{\text{UWE}}$  and  $\overline{\text{LWE}}$  are input.

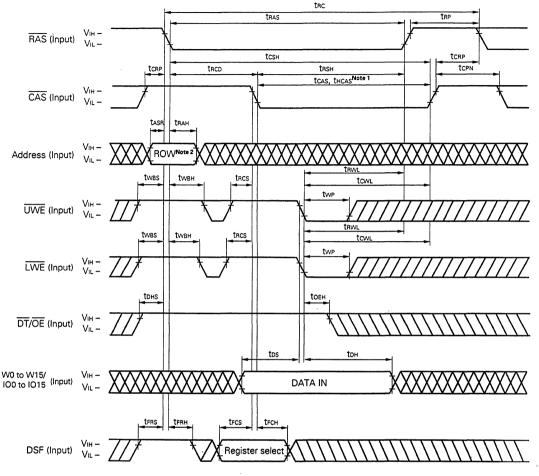

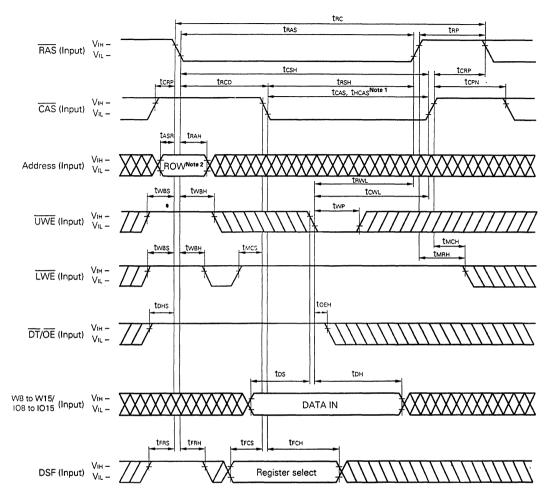

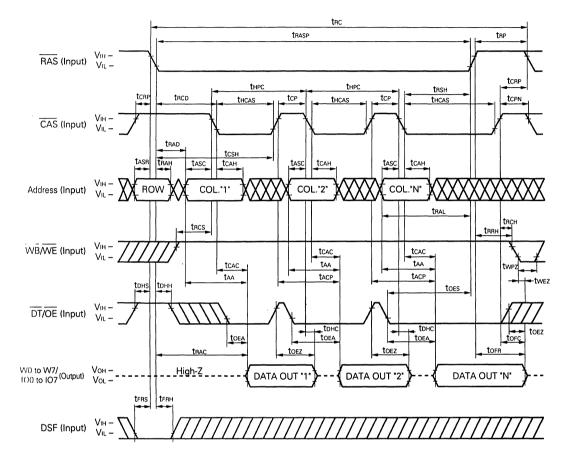

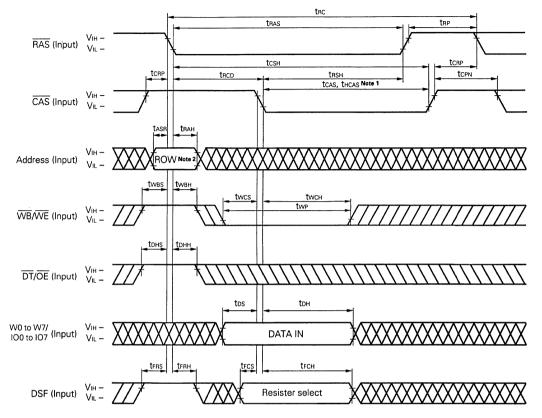

#### 2.2.3 Read Modify Write Cycle

The read modify write cycle performs data reading and writing in one RAS and CAS cycle.

To execute this cycle, delay UWE and LWE from the late write cycle by the (MIN.), tcwb (MIN.), and tawb (MIN.). Follow the toez and toeb specifications so that the output data and input data do not clash in the data bus. The data after modification can be input after more than toeb (MIN.) from the rising edge of DT/OE.

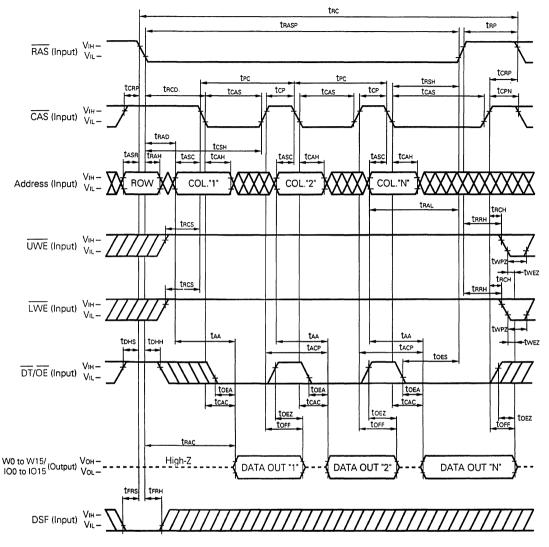

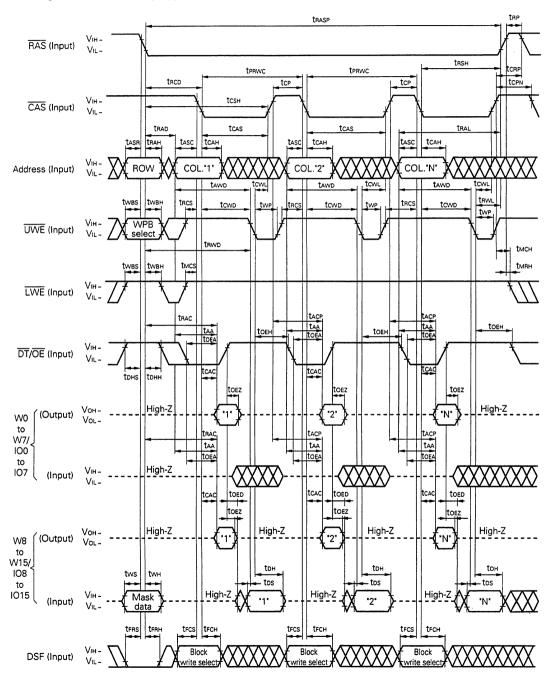

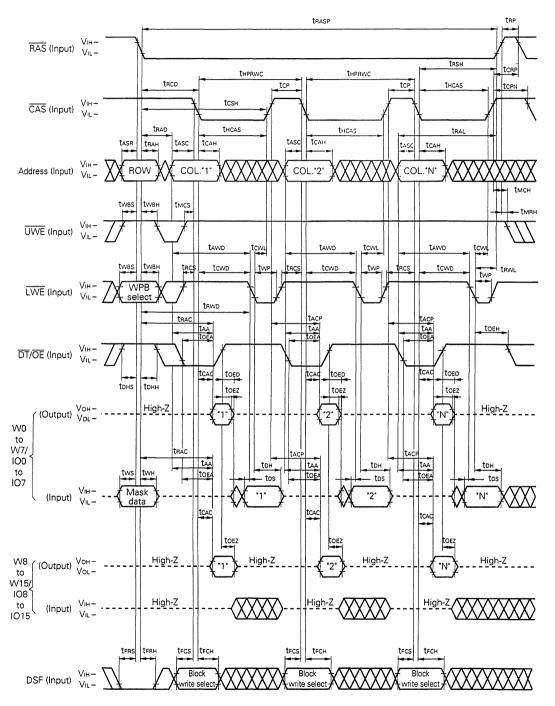

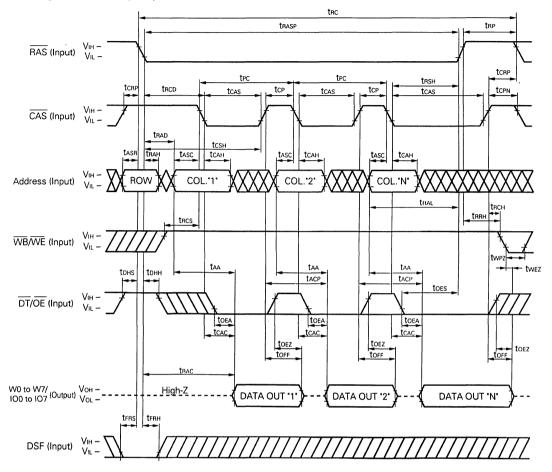

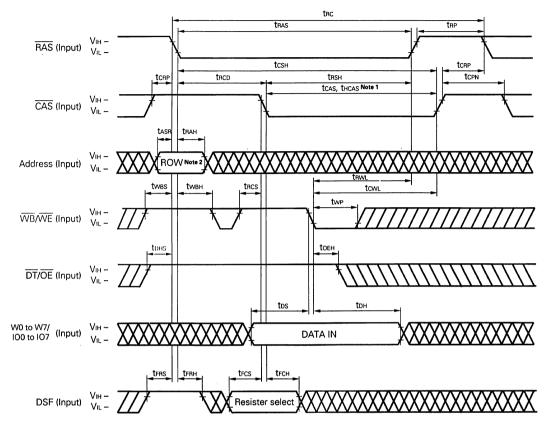

#### 2.3 Fast Page Mode Cycle (µPD482444)

The  $\mu$ PD482444 adopts the fast page mode. This mode accesses memory cells in the same row array in about 1/3 of the time taken by the normal random read/write cycle. This fast page mode cycle is executed by repeating the  $\overline{CAS}$  clock cycle more than two times while the  $\overline{RAS}$  clock is being activated. In this mode read, write and read modify write cycles are available for each of the consecutive  $\overline{CAS}$  cycles within the same  $\overline{RAS}$  cycle.

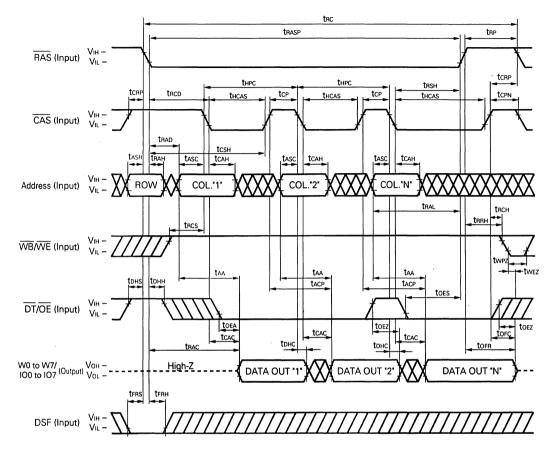

#### 2.4 Hyper Page Mode Cycle (µPD482445, 482445L)

The  $\mu$ PD482445 adopts a hyper page mode cycle which is a faster read/write cycle than the fast page mode of the  $\mu$ PD482444 (Hyper page mode cycle time: 30 ns (MIN.)).

In this cycle, because the read data output is kept until the following  $\overline{CAS}$  cycle and as a result, the output is extended, the minimum cycle can easily be used. The output is extended compared to the normal fast page mode of  $\mu$ PD482444. Refer to 2.1.1 Extended Read Data Output.

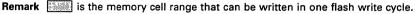

#### 2.5 Flash Write Cycle

This cycle writes the color register data in a 8,192-bit or 4,096-bit memory cell in one cycle. The memory cell range for one flash write cycle is 512 columns on the same row address (512-column  $\times$  16  $\cdot$  IO = 8,192 bits or 512-column  $\times$  8  $\cdot$  IO = 4,096 bits).

#### 2.5.1 Execution of Flash Write Cycle

(1) Execution of flash write for word (512-column  $\times$  16  $\cdot$  IO = 8,192 bits)

To execute the flash write cycle, set both UWE and LWE to low level at the falling edge of RAS. By using the write-per-bit function (new mask data/old mask data), only the required W/IO can be selected and written.

#### (2) Execution of flash write for byte (512-column $\times$ 8 $\cdot$ IO = 4,096 bits)

To execute the flash write cycle, set either  $\overline{UWE}$  or  $\overline{LWE}$  to low level at the falling edge of  $\overline{RAS}$ . By using the write-per-bit function (new mask data/old mask data), only the required W/IO can be selected and written.

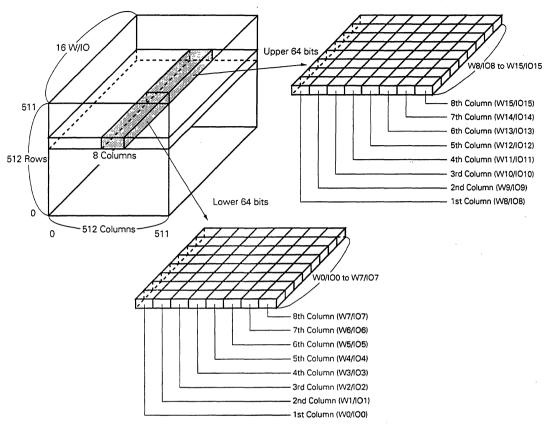

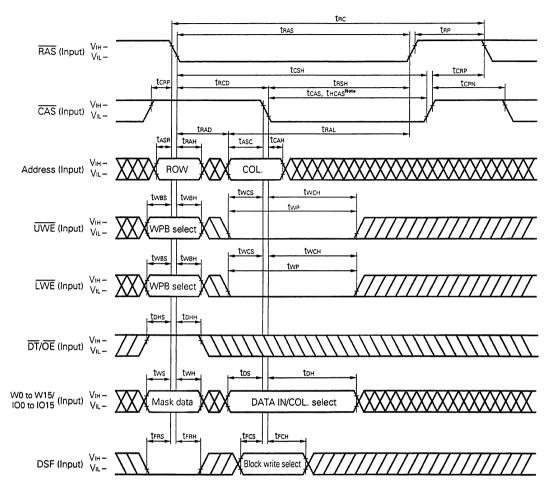

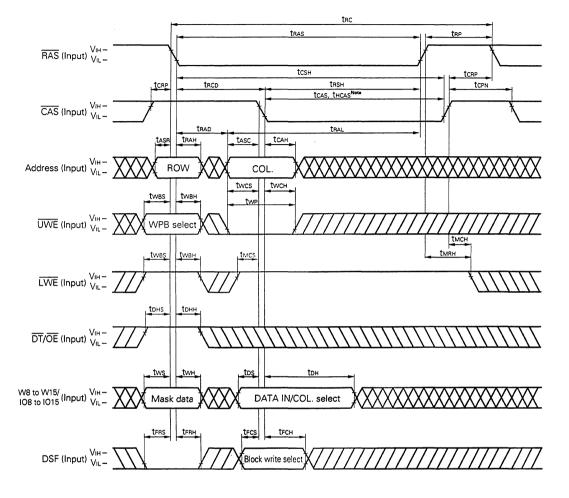

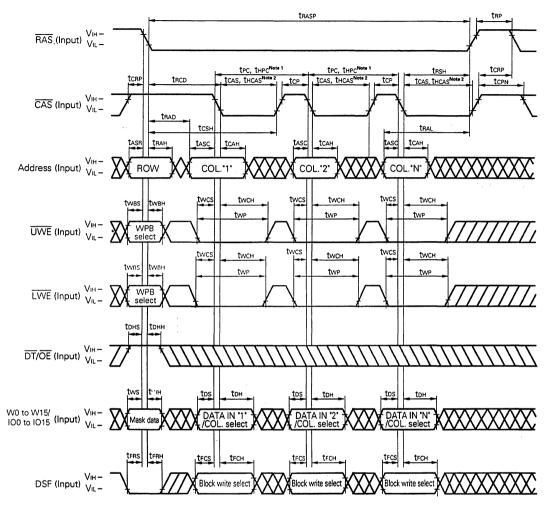

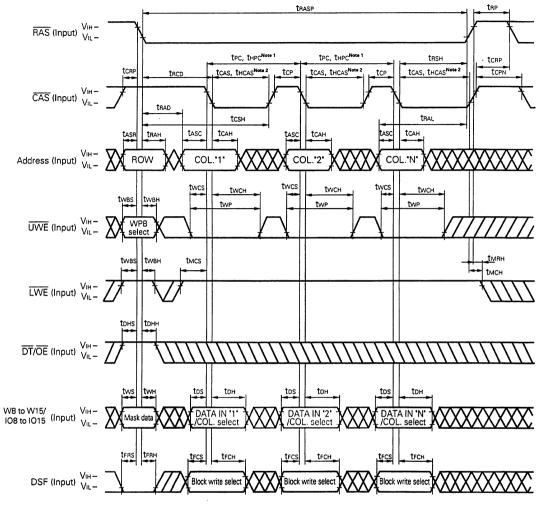

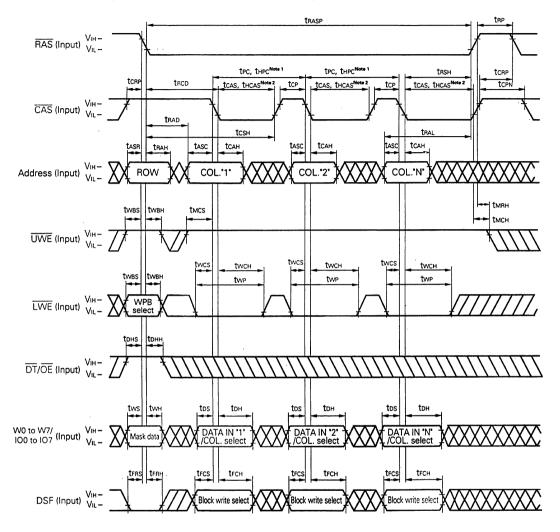

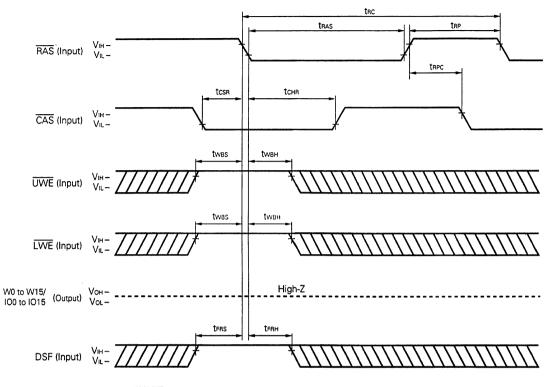

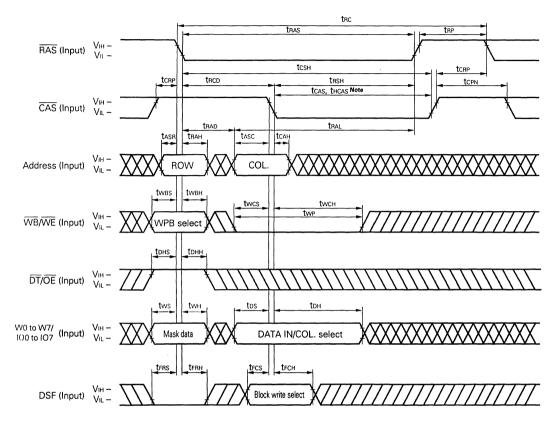

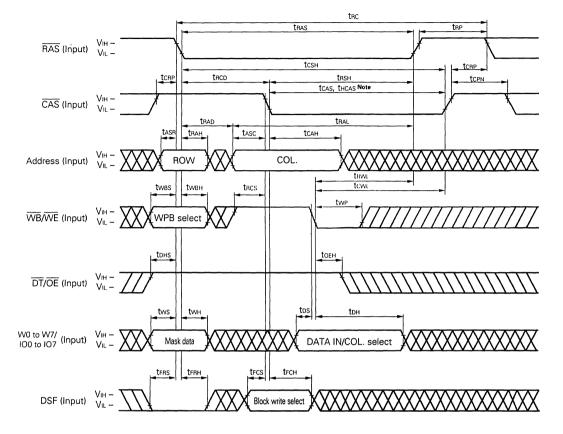

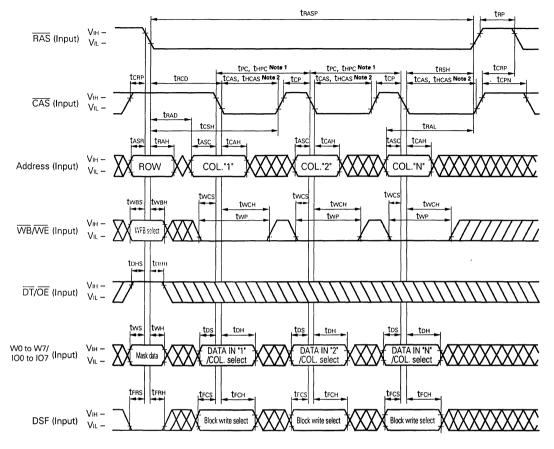

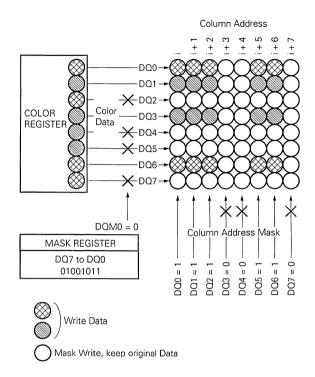

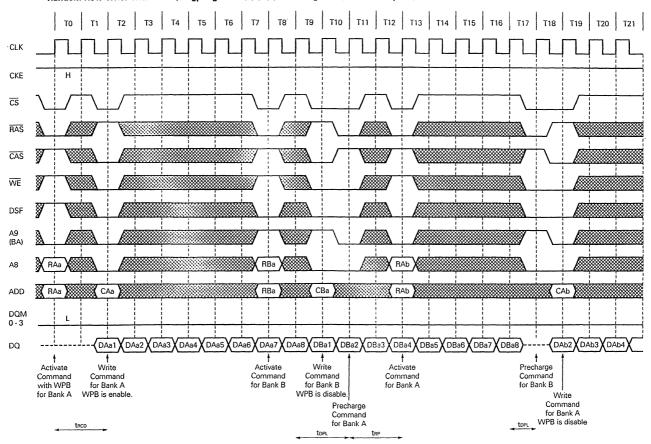

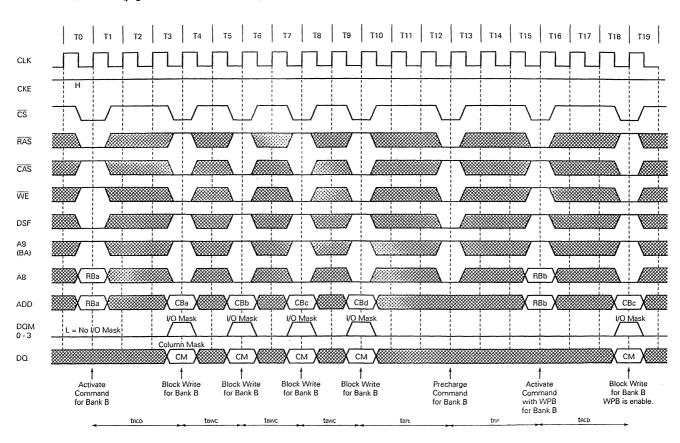

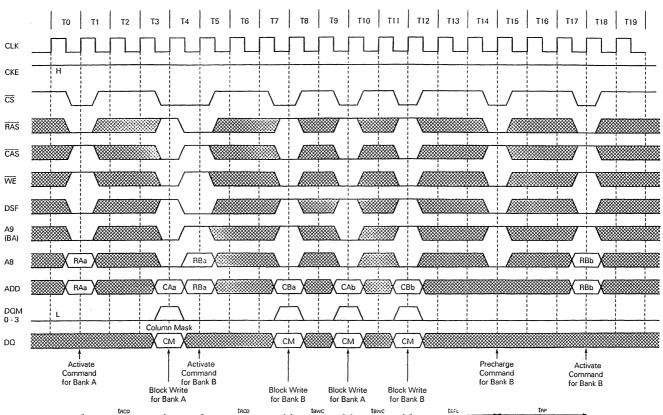

#### 2.6 Block Write Cycle

This cycle writes the color register data in 128-bit or 64-bit memory cell in one cycle. The memory cell range in which data can be written in one block write cycle is eight continuous columns on one row address (8-column  $\times$  16  $\cdot$  10 = 128 bits or 8-column  $\times$  8  $\cdot$  10 = 64 bits).

Any column of the eight columns can be selected and writing prohibited. Determine whether to write or prohibit writing according to the data selected for column.

#### 2.6.1 Free Column Selection

Determine which column to select according to the W/IO pin to which the data selected for the column is to be input.

The eight columns (1st to 8th) correspond to W0 to W15/IO0 to IO15 to which the data selected for column will be input (The following table shows the 1st to 8th columns specified by A0, A1, and A2 and the corresponding W/IO pins to which the data selected will be input.).

#### 2.6.2 Column Select Data

Input column select data for every eight columns at the upper 64 bits and lower 64 bits (a total of 16 columns). The data will be written if the column select data is "1". Writing will be prohibited if the column select data is "0".

#### 2.6.3 Execution of Block Write Cycle

At the falling edge of the slowest signal (CAS, UWE, or LWE), input the "1" column select data or "0" column select data to W0 to W15/IO0 to IO15 corresponding to columns 1st to 8th.

By using the write-per-bit (new mask data/old mask data) function, only the required W/IO can be selected and written.

#### Table 2-2. I/O Pins Input with Column Select Data Corresponding to Columns 1st to 8th

#### Column Select Data of Lower Byte (IO0 to IO7)

Column Select Data of Upper Byte (IO8 to IO15)

| Selected 8<br>Columns | and | Cor<br>W/ | resp<br>IO Pi |     | Column<br>Select<br>Data | Writing |

|-----------------------|-----|-----------|---------------|-----|--------------------------|---------|

|                       | A2  | A1        | A0            | 10  |                          |         |

| 1st column            | 0   | 0         | 0             | 100 | 1                        | Yes     |

|                       |     |           |               |     | 0                        | No      |

| 2nd column            | 0   | 0         | 1             | 101 | 1                        | Yes     |

|                       |     |           |               |     | 0                        | No      |

| 3rd column            | 0   | 1         | 0             | 102 | 1                        | Yes     |

|                       |     |           |               |     | 0                        | No      |

| 4th column            | 0   | 1         | 1             | 103 | 1                        | Yes     |

|                       |     |           |               |     | 0                        | No      |

| 5th column            | 1   | 0         | 0             | 104 | 1                        | Yes     |

|                       |     |           |               |     | 0                        | No      |

| 6th column            | 1   | 0         | 1             | 105 | 1                        | Yes     |

|                       |     |           |               |     | 0                        | No      |

| 7th column            | 1   | 1         | 0             | 106 | 1                        | Yes     |

|                       |     |           |               |     | 0                        | No      |

| 8th column            | 1   | 1         | 1             | 107 | 1                        | Yes     |

|                       |     |           |               |     | 0                        | No      |

| Selected 8<br>Columns | Column Address<br>and Corresponding<br>W/IO Pin |    |    |      | Column<br>Select<br>Data | Writing |  |

|-----------------------|-------------------------------------------------|----|----|------|--------------------------|---------|--|

|                       | A2                                              | A1 | A0 | 10   | Dala                     |         |  |

| 1st column            | 0                                               | 0  | 0  | 108  | 1                        | Yes     |  |

|                       |                                                 |    |    |      | 0                        | No      |  |

| 2nd column            | 0                                               | 0  | 1  | 109  | 1                        | Yes     |  |

|                       |                                                 |    |    |      | 0                        | No      |  |

| 3rd column            | 0                                               | 1  | 0  | 1010 | 1                        | Yes     |  |

|                       |                                                 |    |    |      | 0                        | No      |  |

| 4th column            | 0                                               | 1  | 1  | 1011 | 1                        | Yes     |  |

|                       |                                                 |    |    |      | 0                        | No      |  |

| 5th column            | 1                                               | 0  | 0  | 1012 | 1                        | Yes     |  |

|                       |                                                 |    |    |      | 0                        | No      |  |

| 6th column            | 1                                               | 0  | 1  | 1013 | 1                        | Yes     |  |

|                       |                                                 |    |    |      | 0                        | No      |  |

| 7th column            | 1                                               | 1  | 0  | 1014 | 1                        | Yes     |  |

|                       |                                                 |    |    |      | 0                        | No      |  |

| 8th column            | 1                                               | 1  | 1  | 1015 | 1                        | Yes     |  |

|                       |                                                 |    |    |      | 0                        | No      |  |

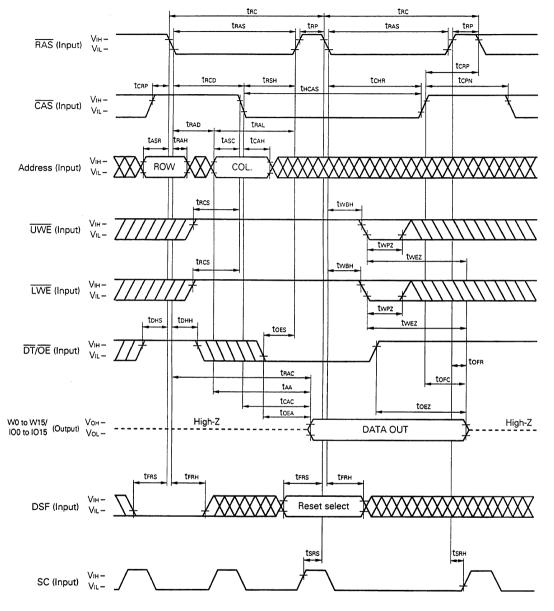

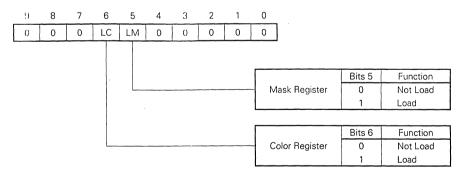

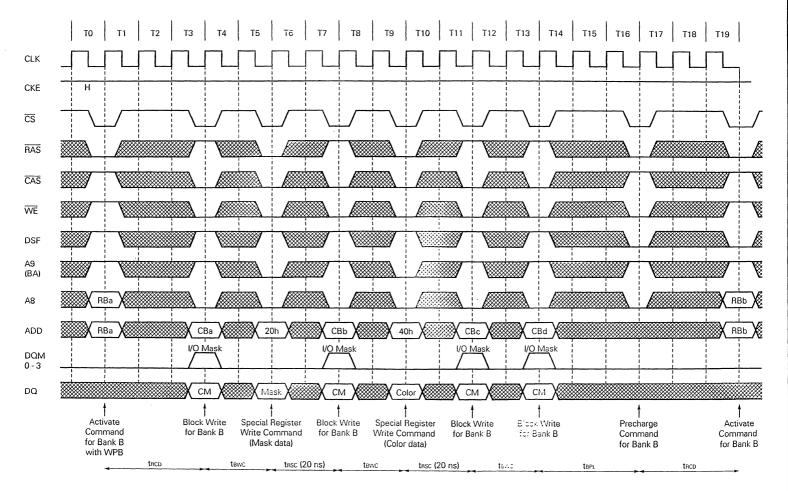

#### 2.7 Register Set Cycle (Color Register, Write Mask Register)

This cycle writes data in the color register and write mask register. To execute the register set cycle, set  $\overline{CAS}$ ,  $\overline{DT/OE}$ ,  $\overline{UWE}$ ,  $\overline{LWE}$  and DSF to high level at the falling edge of  $\overline{RAS}$ . Determine which register to select according to the DSF level at the falling edge of  $\overline{CAS}$ .

The register set cycle also serves as the RAS only refresh cycle.

| Table | 2-3. | Register | Selection |

|-------|------|----------|-----------|

|-------|------|----------|-----------|

| DSF level at $\overline{CAS}$ falling edge | Selected register   |

|--------------------------------------------|---------------------|

| High level                                 | Color register      |

| Low level                                  | Write mask register |

Caution After selecting the write mask register and writing the mask data, the write-per-bit function in the mask write cycle will be set for the old mask register. Refer to 2.8.1 Write-Per-Bit Function.

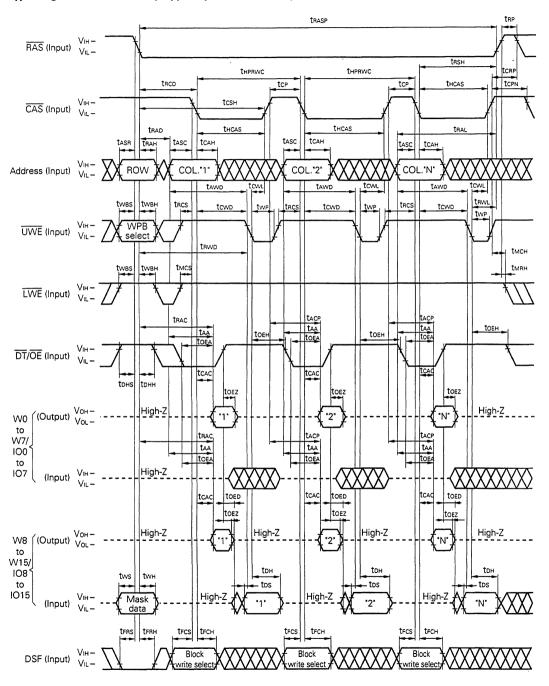

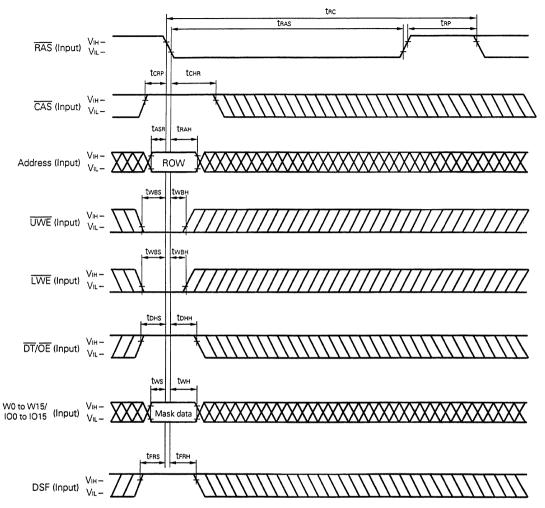

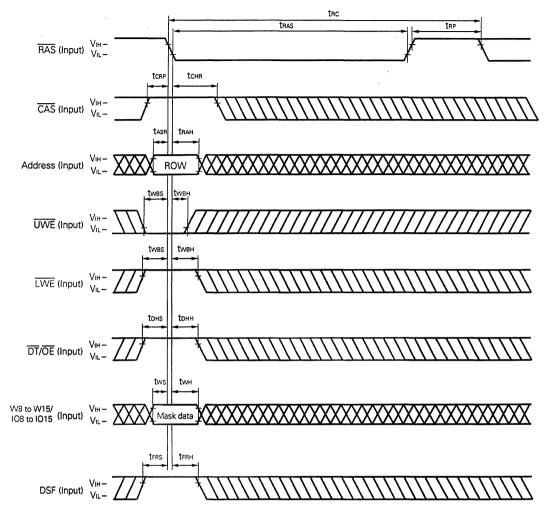

#### 2.8 Mask Write Cycle

Cycles that use the write-per-bit function during the random write cycle, flash write cycle, block write cycle, write data transfer cycle, are called mask write cycles. In the fast page/hyper page mode write cycle, the mask data cannot be changed during the TAS cycle.

#### 2.8.1 Write-Per-Bit Function

The write-per-bit function writes data using the mask data only in the required IO-pin. It writes when the mask data is "1" and prohibits writing when the data is "0".

| Table | 2-4. | Mask | Data | Selection |

|-------|------|------|------|-----------|

|       |      |      |      |           |

| W Pin     | Mask Data | Writing |  |

|-----------|-----------|---------|--|

| W0 to W15 | 1         | Yes     |  |

|           | 0         | No      |  |

#### 2.8.2 Selecting Mask Data

There are two ways of selecting mask data. One is the new mask data method and the other is the old mask data method.

With the new mask data method, new mask data is set in the cycle writing. With the old mask data, mask data set in the write mask register is used.

#### (1) New Mask Data Method

The new mask data method consists of the write mask register set cycle (new mask selection) method and  $\overline{CAS}$  before  $\overline{RAS}$  refresh cycle (optional reset cycle) method.

#### (a) Method Using Write Mask Register Set Cycle (New Mask Selection)

To switch to the mode using new mask data, keep the  $\overline{\text{DT}/\text{OE}}$ ,  $\overline{\text{UWE}}$ ,  $\overline{\text{LWE}}$  DSF to high level and set the  $\overline{\text{CAS}}$  and DSF to high level at the falling edge of  $\overline{\text{RAS}}$ , the DSF to low level at the falling edge of  $\overline{\text{CAS}}$ , and start up the next  $\overline{\text{RAS}}$  and  $\overline{\text{CAS}}$  after the tcas and tras.

As a result, the write-per-bit function can be used using the new mask data from the next mask write cycle.

#### (b) Method Using CAS Before RAS Refresh Cycle (Optional Reset Cycle)

To switch to the mode using new mask data, set the DSF to low level at the falling edge of  $\overline{CAS}$  in the  $\overline{CAS}$  before  $\overline{RAS}$  refresh cycle.

As a result, the write-per-bit function can be used using the old mask data from the next mask write cycle.

#### (2) Old Mask Data Method

To switch to the mode using old mask data, set the DSF to low level at the falling edge of  $\overline{CAS}$  in the write mask register set cycle, and write the mask data in the write mask register.

As a result, the write-per-bit function can be used using the old mask data from the next mask write cycle.

#### 2.8.3 Execution of Mask Write Cycle

To execute the write-per-bit function, select the new mask data method or old mask data method, and set  $\overline{\text{UWE}}$  and  $\overline{\text{LWE}}$  to low level at the falling edge of  $\overline{\text{RAS}}$  of each write cycle ( $\overline{\text{UWE}}$  controls the upper byte (W8 to W15/ IO8 to IO15) and  $\overline{\text{LWE}}$  controls the lower byte (W0 to W7/IO0 to IO7).). At this time, input the mask data to the W pin in the write cycle using the new mask data. In the write cycle using the old mask data, as the mask data set to the write mask register will be used, there is no need to input the mask data to the W pin.

This function is valid only at the falling edge of  $\overline{RAS}$ . In the fast page/hyper page mode write cycle, the mask data determined in the first  $\overline{RAS}$  cycle for moving onto the next fast page/hyper page mode will be valid while the fast page/hyper page mode write cycle continues.

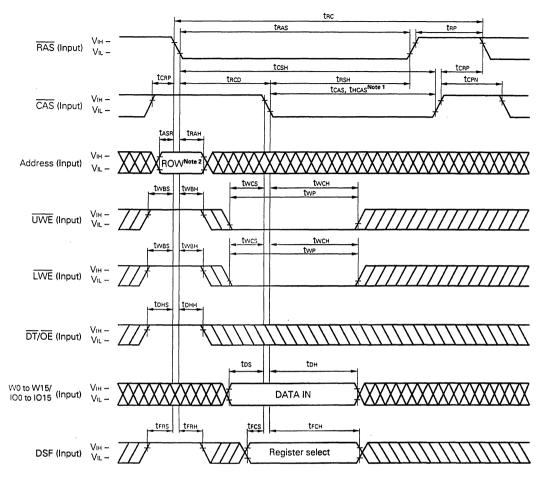

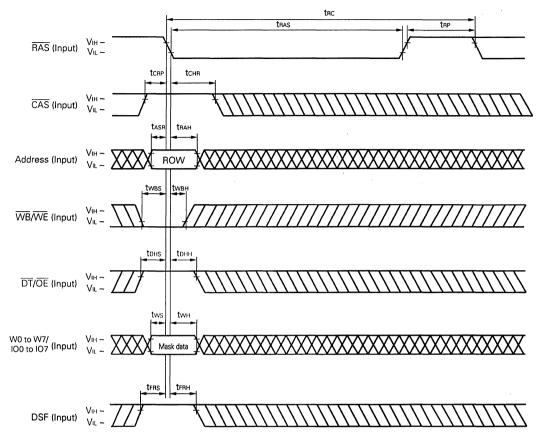

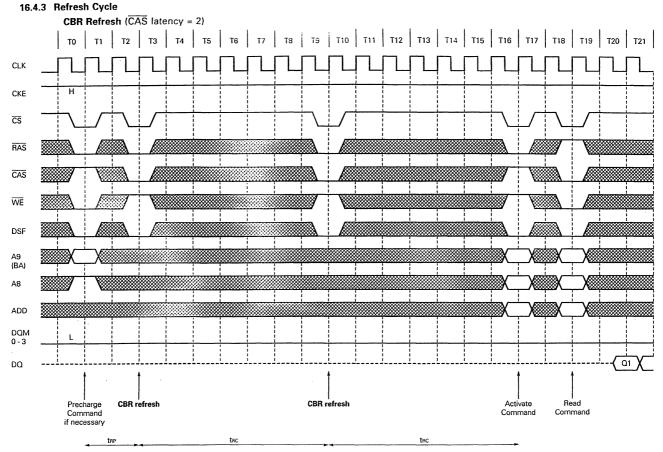

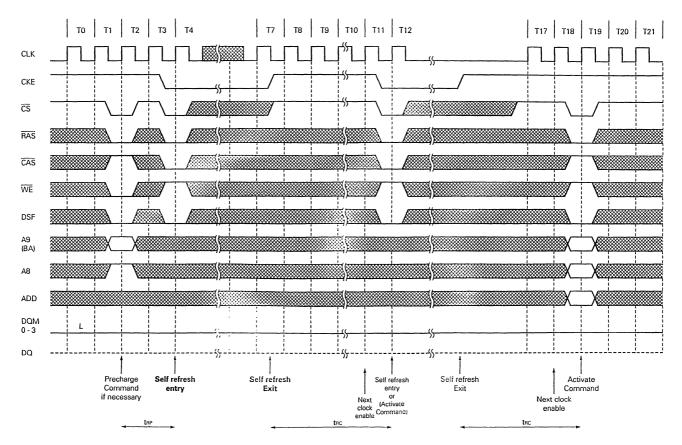

#### 2.9 Refresh Cycle

The refresh cycle of this product consists of the  $\overline{CAS}$  before  $\overline{RAS}$  refresh cycle and refresh cycle using external address inputs ( $\overline{RAS}$  only refresh and read/write refresh). The refresh period is the same as the 2M-bit dual port graphics buffer (× 8), 512 cycles/8 ms.

#### 2.9.1 Refresh Cycle Using External Address Input (RAS Only Refresh and Read/Write Refresh)

By specifying the row address using the 9 bits between A0 to A8 at the falling edge of  $\overline{RAS}$ , setting  $\overline{CAS}$  to high level, and keeping  $\overline{CAS}$  at high level while  $\overline{RAS}$  is low level, the memory cells on the specified row address (512 × 16 bits) can be refreshed. At this time, refresh is executed, W0 to W15/IO0 to IO15 pins are kept at high impedance, and information such as memory contents, register data, function settings, etc. are all also kept.

At the falling edge of RAS, all cycles whose CAS are high level input the external address. Therefore, in addition to the read/write cycle operations, etc. refresh operations similar to the RAS only refresh operations will be performed. For this reason, in systems in which addresses in the memory are always increased or decreased, it may not be necessary to perform refresh again.

When several devices exist on one bus, data will clash in the bus during the above read/write operations unless each device is equipped with a buffer. Consequently, as it is necessary to set the I/O line to high impedance beforehand during refresh, normally the RAS only refresh operation is used.

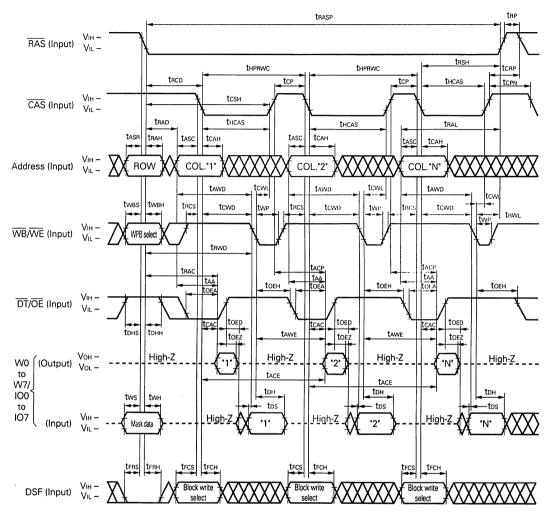

#### 2.9.2 CAS Before RAS Refresh Cycle (Including Hidden Refresh)

When CAS is set to low level at the falling edge of RAS, the refresh address is supplied from the internal refresh address counter. The internal refresh address counter is increased automatically each time this refresh cycle is executed.

During this refresh cycle, functions of random access port and serial access port are selected as follows according to the DSF,  $\overline{UWE}$ , and  $\overline{LWE}$  levels at the falling edge of  $\overline{RAS}$ .

#### (1) When DSF is low level: Optional reset

All STOP register data become "1" and the mask write cycle switches to the new mask data method.

(2) When DSF is high level and UWE, LWE are low level: STOP register set The STOP register data is input from the A0 to A8 pins at the falling edge of RAS.

#### (3) When DSF, $\overline{UWE}$ , and $\overline{LWE}$ are high level: No reset

Only refresh operations are performed and the function selection state is kept.

In all cases, the W/IO pin is kept at high impedance. When CAS and DT/OE are kept low level while the mode is changed to the CAS before RAS refresh cycle following the read cycle, and RAS is activated, the hidden refresh cycle will be initiated. In this cycle, the W/IO pin does not become high impedance and the data read in the former read cycle will be kept as it is.

Because internal memory operations are equivalent to CAS before RAS refresh, no external addresses are required.

Like  $\overline{CAS}$  before  $\overline{RAS}$  refresh, in the hidden cycle, functions will be selected according to the level of DSF,  $\overline{UWE}$ , and  $\overline{LWE}$  at the falling edge of  $\overline{RAS}$ . Operations are guaranteed when DSF is low level and when DSF,  $\overline{UWE}$ , and  $\overline{LWE}$  are high level.

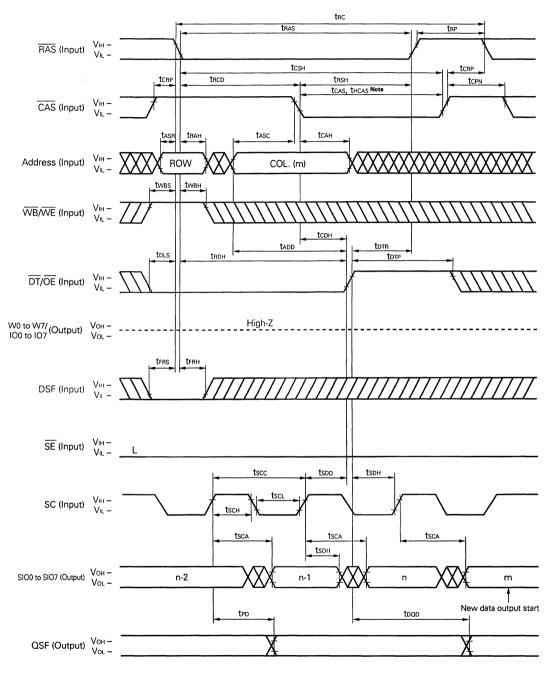

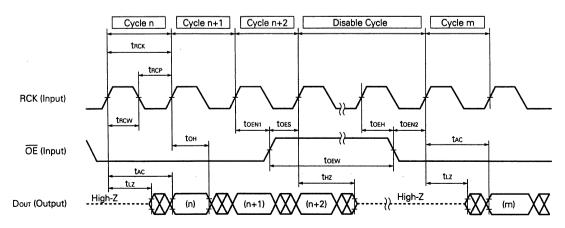

#### 3. Serial Access Port Operations

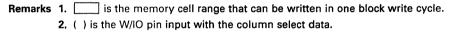

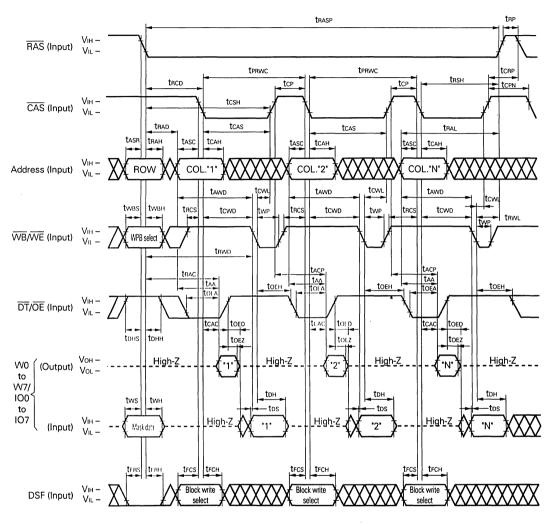

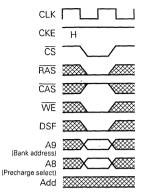

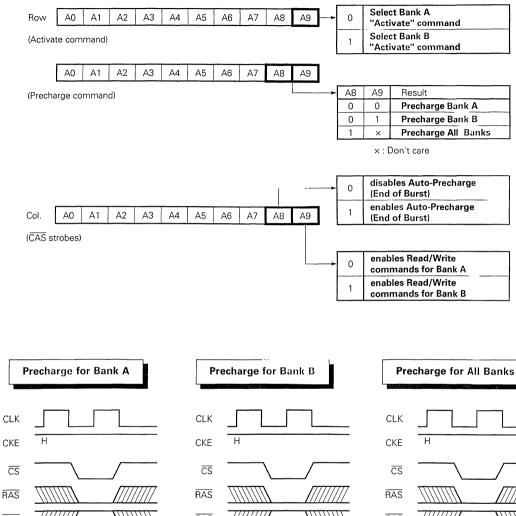

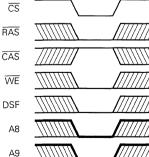

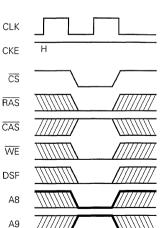

There are two types of data transfer cycles-data transfer from the random access port to the serial access port (read data transfer) and data transfer from the serial access port to the random access port (write data transfer). There are also two types of data transfer methods-single data transfer and split data transfer.

To set the data transfer cycle, input high level to  $\overline{CAS}$  and input low level to  $\overline{DT}/\overline{OE}$  at the falling edge of  $\overline{RAS}$ . The data transfer type differs according to the input levels of  $\overline{UWE}$ ,  $\overline{LWE}$ , and DSF at the falling edge of  $\overline{RAS}$ .

| At RAS Falling Edge |       |          |     | Transfer Direction                              |                 |                         |

|---------------------|-------|----------|-----|-------------------------------------------------|-----------------|-------------------------|

| CAS                 | DT/OE | UWE, IWE | DSF | Data Transfer Type                              | Transfer Source | Transfer<br>Destination |

| н                   | L     | н        | L   | Single read data transfer                       | Random access   | Serial access<br>port   |

| н                   | L     | н        | н   | Split read data transfer                        | port            |                         |

| н                   | L     | L        | L   | Single mask write data transfer <sup>Note</sup> | Serial access   | Random access<br>port   |

| н                   | L     | L        | н   | Split mask write data transfer <sup>Note</sup>  | port            |                         |

Table 3-1. Serial Access Port Operation Mode

Note Write-per-bit function can be specified.

Remark H: High level, L: Low level

#### 3.1 Single Data Transfer Method

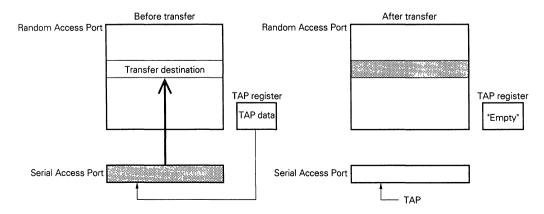

With this method, 512 words  $\times$  16 bits (whole memory range of serial access port) data is transferred at one time. This method can be used in both write data transfer and read data transfer.

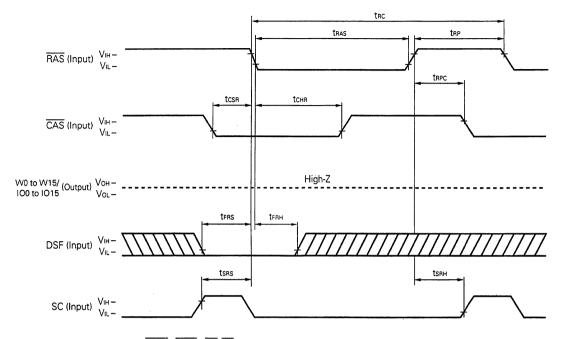

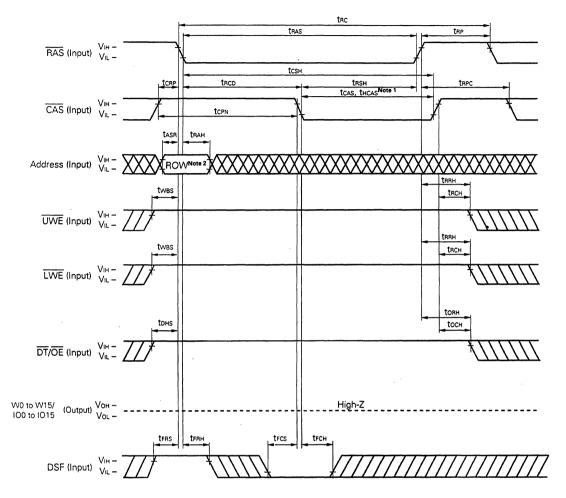

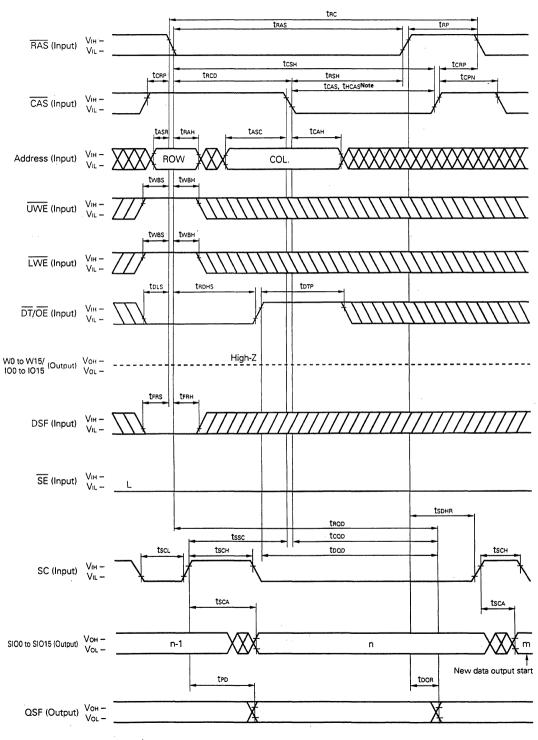

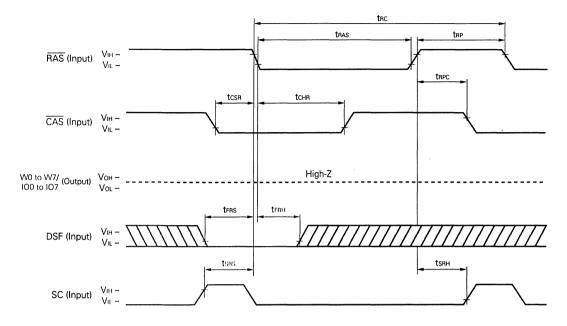

#### 3.1.1 Single Read Data Transfer Cycle

This cycle transfers the 8K-bit (512 words  $\times$  16 bits) data of the random access port to the serial access port in one cycle.

#### (a) Setting of Single Read Data Transfer Cycle

To set the data transfer cycle, input a high level to  $\overline{CAS}$ ,  $\overline{UWE}$ , and  $\overline{LWE}$  and low level to  $\overline{DT}/\overline{OE}$  and DSF at the falling edge of  $\overline{RAS}$ .

Using the row address input to A0 to A8 at the falling edge of  $\overline{RAS}$ , the memory cells (512 words × 16 bits) of the transfer source of the random access port can be selected. The address data input to A0 to A8 at the falling edge of  $\overline{CAS}$  will be latched as the TAP register data. Refer to **3.4 TAP Register**.

#### (b) Execution of Single Read Data Transfer Cycle

To execute the data transfer cycle, set the single read data transfer cycle and then input a high level to  $\overline{\text{DT/OE}}$  and  $\overline{\text{RAS}}$ .

When SC is active (edge control), data transfer will be executed at the rising edge of  $\overline{\text{DT}/\text{OE}}$ . When SC is inactive (self control), it will be executed at the rising edge of  $\overline{\text{RAS}}$ . At the same time, the serial address pointer jumps to the start column (TAP) of the next serial read cycle, and the TAP register will be set the empty state.

After the transfer is completed, the new serial access port data is output after tscA following the rise of the SC clock that occurs after tspH if the SC is active, and after tspHR if SC is inactive.

Caution When the single read data transfer cycle is executed while the serial access port is performing serial write operations, the serial access port will start serial read operations at the rising edge of RAS. Refer to 4. Electrical Characteristics Read Data Transfer Cycle (Serial Write → Serial Read Switching) Timings.

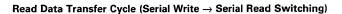

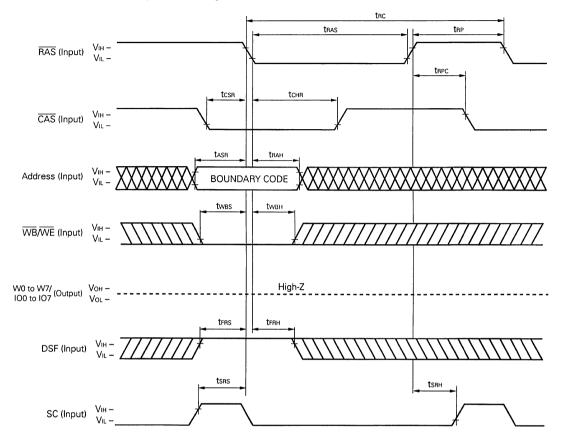

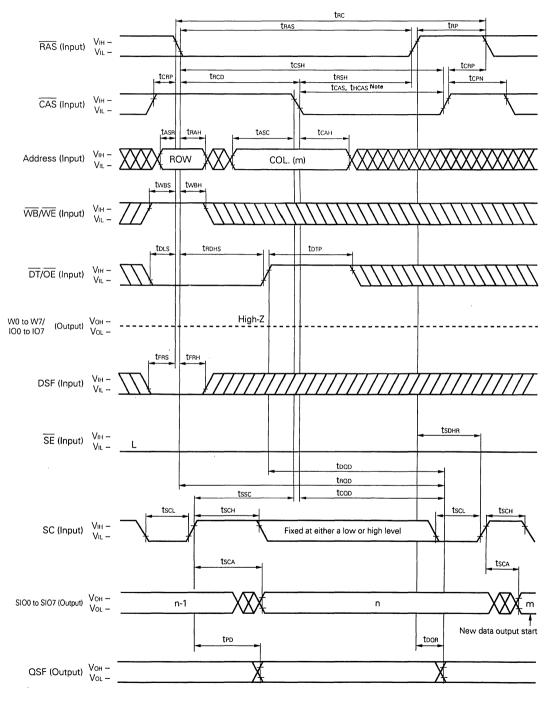

#### 3.1.2 Single Mask Write Data Transfer Cycle

This cycle transfers 8K-bit (512 word × 16 bits) data of the serial access port to the random access port in one cycle. Because  $\overline{\text{UWE}}$  and  $\overline{\text{LWE}}$  are low level at the falling edge of  $\overline{\text{RAS}}$ , the write-per-bit function always functions in this transfer cycle. Refer to **2.8 Mask Write Cycle**.

#### (a) Setting of Single Mask Write Data Transfer Cycle

To set this cycle, latch the data to be transferred to the serial access port, and then input a high level to  $\overline{CAS}$  and low level to  $\overline{DT/OE}$ ,  $\overline{UWE}$ ,  $\overline{LWE}$ , and DSF at the falling edge of  $\overline{RAS}$ . Because the write-per-bit function functions in this transfer operation, for the new mask data method, the mask data must be supplied to W0 to W15 at the falling edge of  $\overline{RAS}$ , and for the old mask data method, there is no need to control the mask data.

The memory cells (512 words  $\times$  16 bits) of the transfer destination of the random access port are selected using the row address input to A0 to A8 at the falling edge of  $\overline{RAS}$ . The address data input to A0 to A8 at the falling edge of  $\overline{CAS}$  is input as the TAP register data. Refer to **3.4 TAP Register**.

#### (b) Execution of Single Mask Write Data Transfer Cycle

To execute this cycle, set the single write data transfer cycle and then input high level to  $\overline{RAS}$ . Data will be transferred at the rising edge of  $\overline{RAS}$ . At the same time, the serial address pointer jumps to the start column (TAP) of the next serial write cycle, and the TAP register will be set the empty state. After the transfer is completed, the new serial access port data is latched at the rising edge of the SC clock that occurs after tsphe.

- Caution 1. When the single mask write data transfer cycle is executed while the serial access port is performing serial read operations, the serial access port will start serial write operations at the rising edge of RAS. Refer to 4. Electrical Characteristics Write Data Transfer Cycle (Serial Read → Serial Write Switching) Timings.

- 2. Always make CAS low level in the write data transfer cycle and latch TAP. If write data transfer is performed without setting TAP, serial access port operations cannot be ensured until either one of the following points. If the SC clock is input during this time, the serial register value also cannot be guaranteed.

- Until the falling edge of CAS during the write data transfer cycle

- Until the read data transfer cycle is executed again

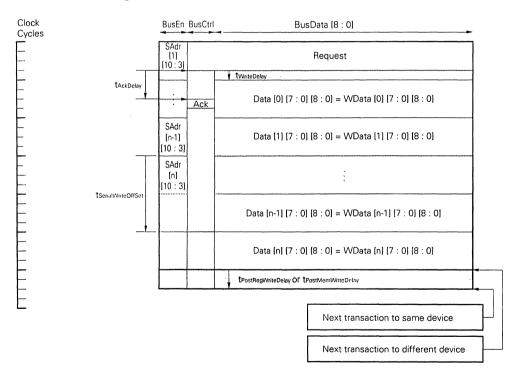

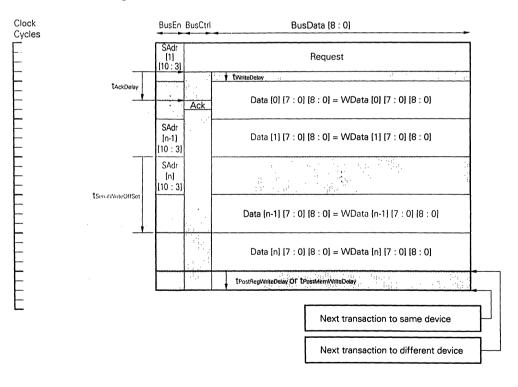

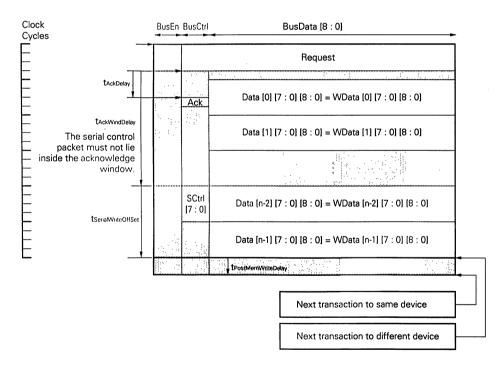

#### Figure 3-1. Single Write Data Transfer and TAP Operation

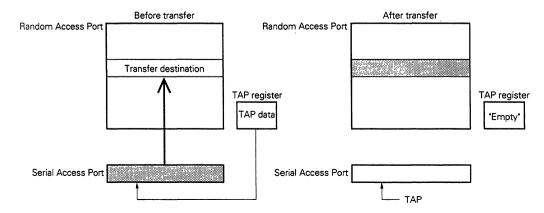

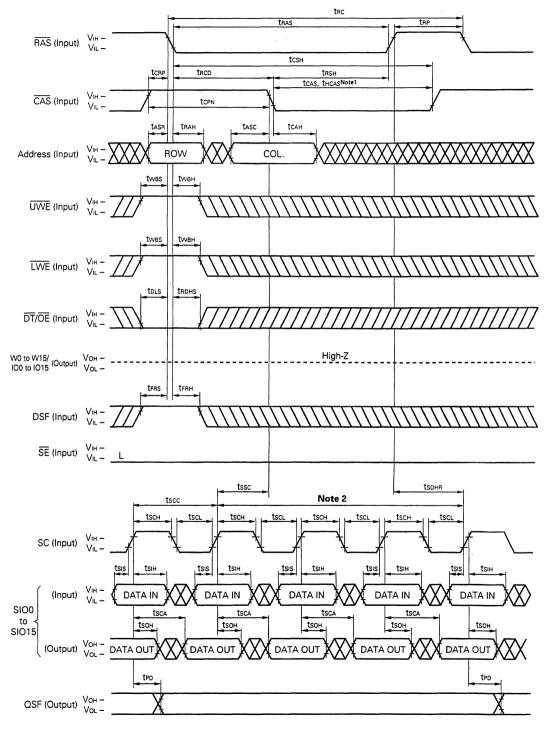

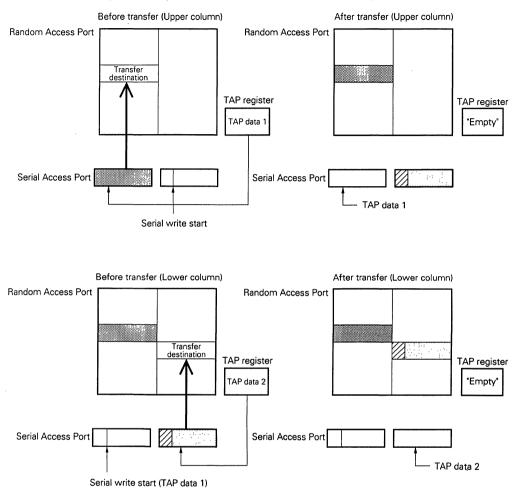

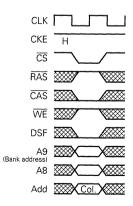

#### 3.2 Split Data Transfer Method

With this method, the 512 words  $\times$  16 bits (whole memory range of serial access port) data is divided into the lower column (0 to 255) and upper column (256 to 511), each consisting of 256 words  $\times$  16 bits.

Because the columns are divided into upper and lower columns with this method, data transfer can be performed on lower column (or upper column) while performing read/write operations in the upper column (or lower column). For this reason, transfer timing design is easy. This transfer method can be used in both write data transfer and read data transfer.

#### 3.2.1 Split Read Data Transfer Cycle

This cycle divides the 8K-bit (512 words  $\times$  16 bits) data of the random access port into the lower and upper columns and transfers them to the serial access port.

In this cycle, the serial read/write can be performed in the columns to which data is not transfer.

#### (a) Setting of Split Read Data Transfer Cycle

To set this cycle, input a high level to  $\overline{CAS}$ ,  $\overline{UWE}$ ,  $\overline{LWE}$  and DSF, and low level to  $\overline{DT}/\overline{OE}$  at the falling edge of  $\overline{RAS}$ .

The memory cells (512 words  $\times$  16 bits) of the transfer source of the random access port are selected using the row address input to A0 to A8 at the falling edge of  $\overline{RAS}$ . And the address data input to A0 to A7 at the falling edge of  $\overline{CAS}$  is latched as the TAP register data of serial access port. There is no need to control address data input to A8. Refer to 3.4 TAP Register.

#### (b) Execution of Split Read Data Transfer Cycle

To execute this cycle, set the split read data transfer cycle and then input the high level to RAS. Data will be transferred at the rising edge of RAS. Data is transferred from the random access port to the serial access port automatically at the column side where serial access port is inactive. To confirm the transferred column side, check the output state of the QSF pin. Refer to **3.3.3 QSF Pin Output**. When the serial address pointer comes to the jump source address specified by the STOP register, the serial address pointer jumps to the start column (TAP) of the serial read/write cycle at the inactive column side, and the TAP register will be set the empty state.

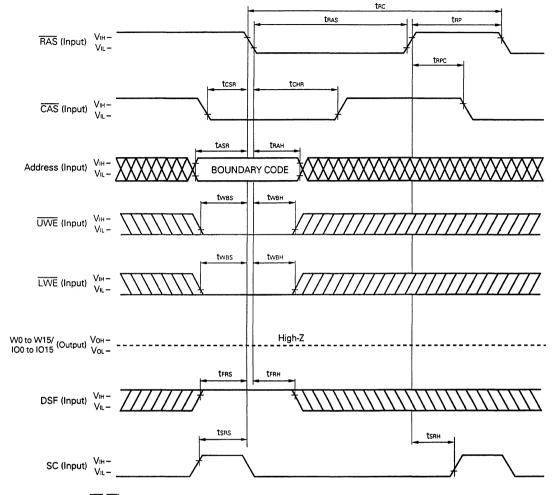

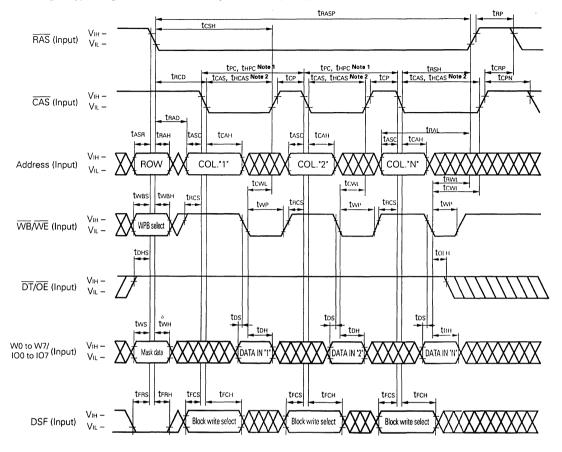

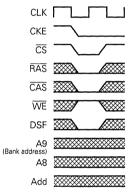

# 3.2.2 Split Mask Write Data Transfer Cycle

This cycle divides the 8K-bit (512 words × 16 bits) data of the serial access port into the lower and upper columns and transfers them to the random access port.

In this cycle, serial read/write can be performed for columns to which data is not transferred.

Because UWE and LWE are low level at the falling edge of RAS, the write-per-bit function always functions in this transfer cycle. Refer to 2.8 Mask Write Cycle.

# (a) Setting of Split Mask Write Data Transfer Cycle

To set this data transfer cycle, input a high level to  $\overline{CAS}$  and DSF and low level to  $\overline{DT/OE}$ ,  $\overline{UWE}$ , and  $\overline{LWE}$  at the falling edge of  $\overline{RAS}$ . Because the write-per-bit function functions in this transfer operation, for the new mask data method, the mask data must be supplied to W0 to W15 at the falling edge of  $\overline{RAS}$ , and for the old mask data method, there is no need to control the mask data.

The memory cells (512 words  $\times$  16 bits) of the transfer destination of the random access port are selected using the row address input to A0 to A8 at the falling edge of  $\overline{RAS}$ . The address data input to A0 to A7 at the falling edge of  $\overline{CAS}$  is input as the TAP register data. There is no need to control address data input to A8. Refer to 3.4 TAP Register.

# (b) Execution of Split Mask Write Data Transfer Cycle

To execute this cycle, set the split write data transfer cycle and then input high level to  $\overline{RAS}$ . Data will be transferred at the rising edge of  $\overline{RAS}$ . Data is transferred from the serial access port to the random access port automatically at the column side where the serial access port is inactive. To confirm the transferred column side, check the output state of the QSF pin. Refer to **3.3.3 QSF Pin Output**.

When the serial address pointer comes to the jump source address specified by the STOP register, the serial address pointer jumps to the start column (TAP) of the serial read/write cycle at the inactive column side, and the TAP register will be set the empty state.

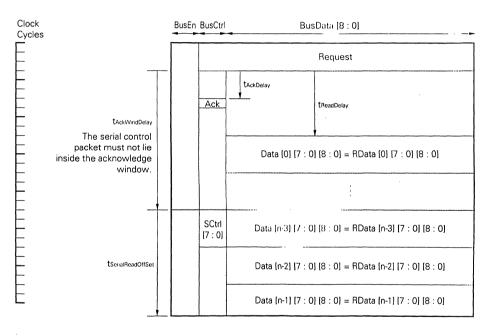

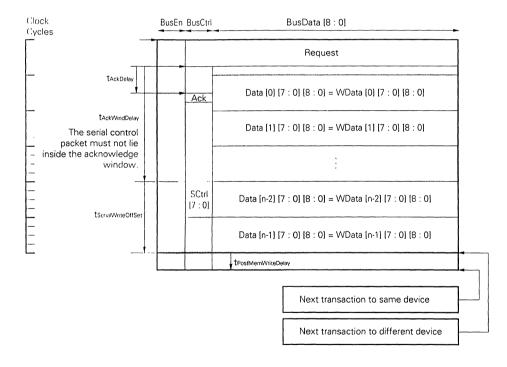

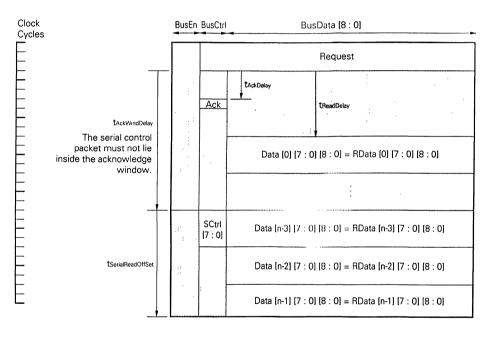

# Figure 3-2. Split Mask Write Data Transfer and TAP Operations

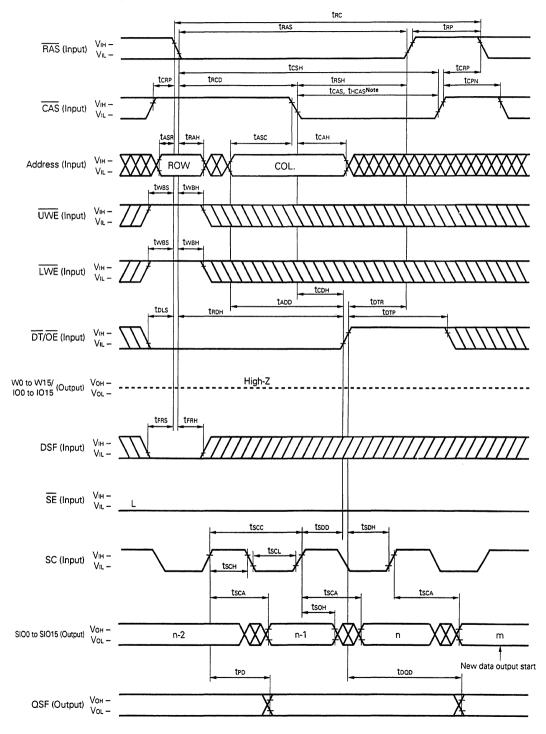

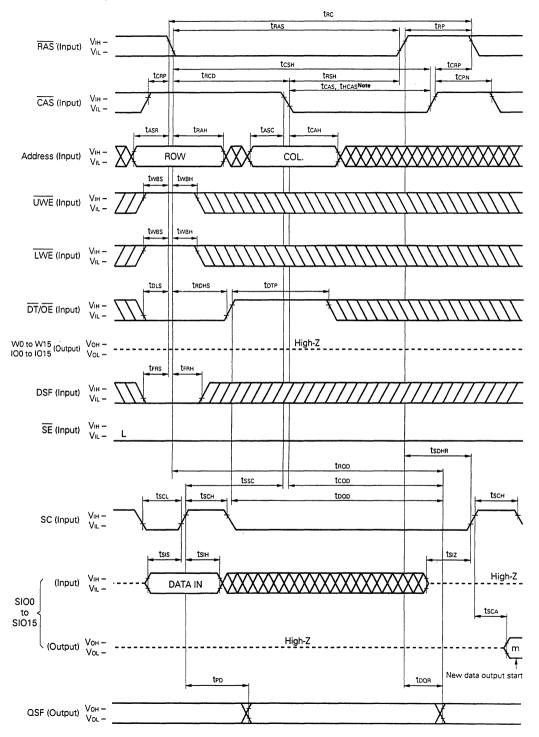

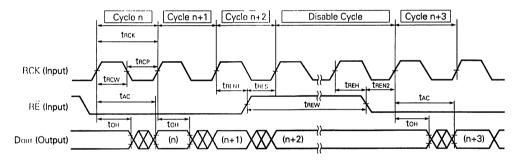

# 3.3 Serial Read/Write

The serial access port ( $512K \times 16$  bits) is independent from the random access port and can perform read and write operations. The serial access port performing single data transfer and split data transfer can not perform read and write operations independently.

# Caution When the power is turned on, the serial access port sets into the input (write) mode and the SIO pin is the high impedance state.

# 3.3.1 Serial Read Cycle

To set the serial read cycle, perform the single read data transfer cycle (The mode will not change in the split read data transfer cycle.).

Execute the single read data transfer cycle and latch the data and TAP data. By inputting a clock signal to the SC pin and inputting a low level to the  $\overline{SE}$  pin, data will be output from the serial address pointer specified by TAP register. The data synchronizes with the rising edge of the SC clock and is output from the SIO0 to SIO15 pin, and the data is kept until the next rising edge of the SC clock.

# (a) Reading-Jump

The SE pin controls the SIO pin output buffer independently from the SC clock. By setting the SE pin to high level even while inputting the SC clock, SIO0 to SIO15 pins become high impedance. But the operations of serial address pointer will be continued while the SC clock is being input even though reading has been prohibited from SE pin. Reading-jump of the column can be performed using this function.

# 3.3.2 Serial Write Cycle

To set the serial write cycle, perform the single write data transfer cycle (The mode will not change in the split write data transfer cycle.). To prevent the transfer data from being written in the memory cell of the random access port, set all bits of the mask data to "0" and control the mask data.

Execute the single write data transfer cycle and set the serial write cycle. By inputting the clock signal to the SC pin and inputting a low level to the  $\overline{SE}$  pin, data can be latched from the serial address pointer specified by TAP register. The data synchronizes with the rising edge of the SC clock and is input from SIO0 to SIO15 pins. Be sure to follow the specifications for the setup time (tses) and hold time (tseh) of  $\overline{SE}$  pin for the SC clock.

# (a) Writing-Jumps (Intermittent Writing)

The SE pin controls writing operations independently from the SC clock. By setting the SE pin to high level even while inputting the SC clock, writing will not be executed. But the operations of serial address pointer will be continued while the SC clock is being input even though writing has been prohibited from SE pin. These functions enable writing-jumps (intermittent writing) to be performed. The masked data is kept as the old data.

# 3.3.3 QSF Pin Output

QSF pin determines whether the serial address pointer is at the upper column side (addresses 256 to 511) or the lower column side (addresses 0 to 255) at the rising edge of the following SC clock during serial read or write. In other words, it outputs the uppermost bit (A8) of the column address of the serial address pointer. The following table shows the QSF pin output state and the access pointer of following SC clocks.

| Access Address of Following SC clock | QSF Output |

|--------------------------------------|------------|

| Addresses 0 to 255                   | Low level  |

| Addresses 256 to 511                 | High level |

# 3.4 TAP (Top Access Point) Register

The TAP register is a data register which specifies the start address (first serial address point = TAP) of the serial read or serial write.

Set data to this register each time a transfer cycle is executed.

# 3.4.1 Setting of TAP Register

The data input to A0 to A8 at the falling edge of  $\overline{CAS}$  during the setting of a transfer cycle is set as the TAP register data. By executing the transfer cycle, the start address of the following serial read (or write) operations is specified by the data of the TAP register and the TAP register will be kept in the empty state until the TAP register is set again.

In the split data transfer cycle, because the inactive serial access port column addresses are specified by the data of the TAP register automatically, there is no need to control the A8 data.

# Caution When the TAP register is empty, the address following the 511 serial address point will be 0. In addition, because the serial address pointer will not jump to the column specified by the STOP register, the binary boundary jump function cannot be used. Refer to 3.6 Binary Boundary Jump Function.

# 3.5 STOP Register

The STOP register is a data register which determines the column of the jump source when jumping to a different column side (lower column or upper column) in the split data transfer cycle. Five types of columns can be selected for starting jump (jumping is possible at 2, 4, 8, 16, and 32 points). The following table shows the correspondence between the column at the jump source and data of the STOP register.

Once set, the STOP register data is kept until it is set again.

### 3.5.1 Setting of STOP Register

To set the STOP register, set  $\overline{\text{UWE}}$  and  $\overline{\text{LWE}}$  to low level at the falling edge of RAS in the  $\overline{\text{CAS}}$  before  $\overline{\text{RAS}}$  refresh cycle. The data input to A0 to A7 will be input as the STOP register data.

| S  | тор | Reg      | iste | r Data   | Divi- | Bit                |                                                                                |

|----|-----|----------|------|----------|-------|--------------------|--------------------------------------------------------------------------------|

| A7 | A6  | A5       | A4   | A3 to A0 |       | Width              | Jump Source Bit Column (Decimal Number)                                        |

| 1  | 1   | 1        | 1    | 1        | 1/2   | 256                | 255                                                                            |

| Ľ  | •   |          | •    |          | 1/2   | 200                | 511                                                                            |

| 0  | 1   | 1        | 1    | 1        | 1/4   | 128                | 127, 255                                                                       |

| Ľ  |     | <u> </u> | •    |          | 1/4   | 120                | 383, 511                                                                       |

| 0  | 0   | 1        | 1    | 1        | 1/8   | 64                 | 63, 127, 191, 255                                                              |

| Ľ  | •   |          |      |          | 04    | 319, 383, 447, 511 |                                                                                |

| 0  | 0   | 0        | 1    | 1        | 1/16  | 32                 | 31, 63, 95, 127, 159, 191, 223, 255                                            |

| Ľ  | •   | Ů        | •    |          | 1/10  | 52                 | 287, 319, 351, 383, 415, 447, 479, 511                                         |

| 0  | 0   | 0        | 0    | 1        | 1/32  | 16                 | 15, 31, 47, 63, 79, 95, 111, 127, 143, 159, 175, 191, 207, 223, 239, 255       |

| Ľ  |     |          | 0    |          | .,52  |                    | 271, 287, 303, 319, 335, 351, 367, 383, 399, 415, 431, 447, 463, 479, 495, 511 |

Table 3-2. STOP Register Data and Jump Source Column

Remark A8: Don't care.

Caution When the power is supplied, all STOP register data will be set to all "1".

# 3.6 Binary Boundary Jump Function

This function causes the serial address pointer jump to the TAP specified by the TAP register when the pointer moves to a column specified by the STOP register (split data transfer).

This function cannot be used when the jump destination address is not set (TAP register is empty).

This function facilitates tile map application which divides the screen into tiles and manages data for each tile.

#### 3.6.1 Usage of Binary Boundary Jump Function

After setting the STOP register, execute the single read (or write) data transfer and initialize the serial access port. The initialization process will switch the serial access port read (or write) operations, set TAP, set the serial access port data, and set the TAP register to empty. By inputting the serial clock in this state, the serial access port will read (or write) operations from TAP in ascending order of address. Because the TAP register is in the empty state, the address at the jump source set by the STOP register will be ignored, and the serial address pointer will move on.

When the column to be jumped approaches, execute split data transfer and set new TAP data in the TAP register. The serial pointer will jump at the desired jump source address. Jump can be controlled freely by repeating these operations.

#### 3.7 Special Operations

#### 3.7.1 Serial Address Set Operations

Because the serial address counter is undefined when the power up, the serial access port operations when the SC clock is input are not guaranteed. Execute single read (or write) transfer after turning on the power. The serial access port will be initialized, enabling serial access port operations to be performed.

#### 3.7.2 Lap Around Operations

If all the data of the register is read (write) during data transfer while the serial read (write) cycle is being executed, the serial pointer will repeat 0 to 511.

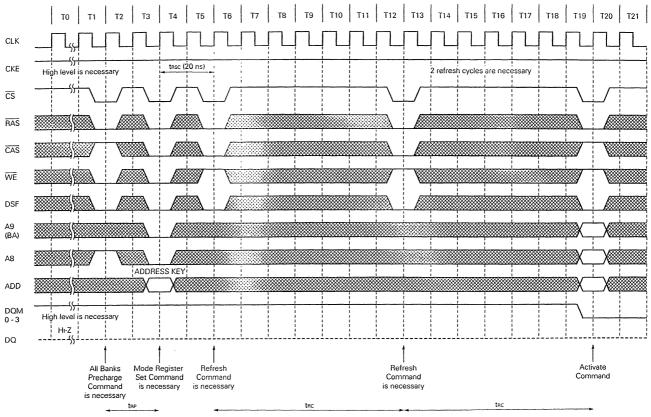

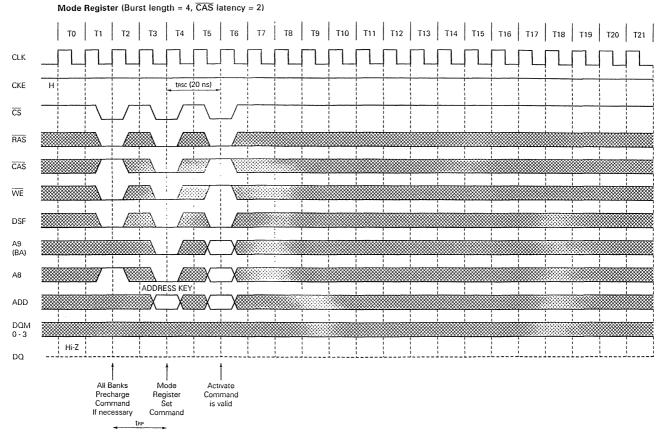

#### 3.7.3 Cycle After Power On

Execute the dummy cycle eight times more than 100  $\mu$ s after Vcc reaches the specified voltage in the recommended operation conditions.

If RAS, CAS, DT/OE, UWE, LWE are kept at high level when the power is turned on, the following will be set automatically.

- Serial access port ...... Input mode, SIO: High impedance

- Color register ..... Undefined

- Mask register ..... All "1"

- TAP register ...... Undefined

- STOP register ......All "1"

# 4. Electrical Characteristics

# 4.1 $\mu$ PD482444, 482445 (Power Supply Voltage Vcc = 5 V ± 10 %)

#### **Absolute Maximum Ratings**

| Parameter                     | Symbol | Rating       | Unit |

|-------------------------------|--------|--------------|------|

| Pin voltage                   | VT     | -1.0 to +7.0 | V    |

| Supply voltage                | Vcc    | -1.0 to +7.0 | v    |

| Output current                | lo     | 50           | mA   |

| Power dissipation             | Po     | 1.5          | w    |

| Operating ambient temperature | TA     | 0 to 70      | °C   |

| Storage temperature           | Tstg   | -55 to +125  | °C   |

Caution Exposing the device to stress above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits in the operational sections of this characteristics. Exposure to Absolute Maximum rating conditions for extended periods may affect device reliability.

# **Recommended Operating Conditions**

| Parameter                     | Symbol | MIN. | TYP. | MAX. | Unit |

|-------------------------------|--------|------|------|------|------|

| Supply voltage                | Vcc    | 4.5  | 5.0  | 5.5  | v    |

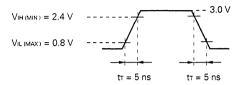

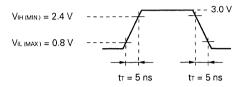

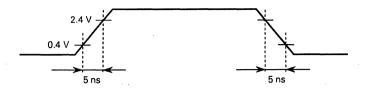

| High level input voltage      | Viн    | 2.4  |      | 5.5  | v    |

| Low level input voltage       | Vil    | -1.0 |      | +0.8 | v    |

| Operating ambient temperature | ΤA     | 0    |      | 70   | °C   |

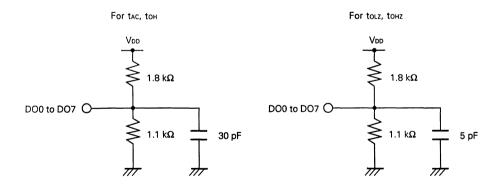

| Parameter                                       | Symbol  | Test conditions                                         | MIN. | TYP. | MAX. | Unit |

|-------------------------------------------------|---------|---------------------------------------------------------|------|------|------|------|

| Input leakage current                           | lı.     | V <sub>IN</sub> = 0 V to 5.5 V,<br>Other inputs are 0 V | -10  |      | +10  | μA   |

| Output leakage current                          | IOL .   | W/IO, SIO, QSF are inactive,<br>Vout = 0 V to 5.5 V     | -10  |      | +10  | μA   |

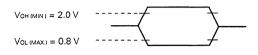

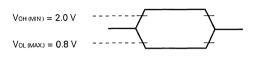

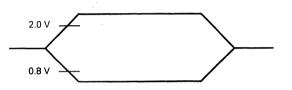

| Random access port<br>high level output voltage | Vон (R) | Іон (R) = -1.0mA                                        | 2.4  |      |      | V    |

| Random access port<br>low level output voltage  | Vol (R) | lol (R) = 2.1mA                                         |      |      | 0.4  | V    |

| Serial access port<br>high level output voltage | Vон (S) | lон (S) = -1.0mA                                        | 2.4  |      |      | V    |

| Serial access port<br>low level output voltage  | Vol (S) | lol (S) = 2.1mA                                         |      |      | 0.4  | V    |

# DC Characteristics 1 (Recommended operating conditions unless otherwise noted)

# Capacitance (TA = 25 °C, f = 1MHz)

| Parameter                | Symbol | Test conditions                        | MIN. | TYP. | MAX. | Unit |

|--------------------------|--------|----------------------------------------|------|------|------|------|

| Input Capacitance        | CI1    | RAS, CAS, UWE, LWE, DT/OE, DSF, SE, SC |      |      | 8    | pF   |

|                          | Cı2    | A0 to A8                               |      |      | 5    |      |

| Input/Output Capacitance | Сю     | W/IO (0 to 15), SIO (0 to 15)          |      |      | 7    | pF   |

| Output Capacitance       | Co     | QSF                                    |      |      | 7    | рF   |

| DC Characteristics 2 (Recommended operating conditions unless otherwise noted) <sup>Note 1</sup> |

|--------------------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------|

| Random Access Port                                                                | Serial<br>Access Port |        | Symbol |      |      | ) μPD482444-70<br>μPD482445-70 |      | Unit | Conditions |

|-----------------------------------------------------------------------------------|-----------------------|--------|--------|------|------|--------------------------------|------|------|------------|

|                                                                                   | Standby               | Active |        | MIN. | MAX. | MIN.                           | MAX. |      |            |

| Random Read/Write Cycle                                                           | 0                     |        | Icc1   |      | 110  |                                | 95   | mA   |            |

| $\overline{RAS}$ , $\overline{CAS}$ cycle,<br>trc = trc (MIN.), lo = 0mA          |                       | 0      | Icc7   |      | 130  |                                | 110  |      |            |

| Standby<br>RAS = CAS = VIII.                                                      | 0                     |        | lcc2   |      | 10   |                                | 10   | mA   | Note 2     |

| RAS = CAS = VIH,<br>Dout ≈ high impedance                                         |                       | 0      | Іссв   |      | 50   |                                | 45   | mA   | Note 2     |

| RAS only refresh cycle<br>RAS cycle, CAS = VIH,                                   | 0                     |        | Іссз   |      | 100  |                                | 85   | mA   | Note 3     |

| trc = trc (MIN.)                                                                  |                       | 0      | ါငင္ခ  |      | 140  |                                | 120  |      |            |

| Fast/Hyper page mode cycle<br>$\overline{RAS} = V_{IL}$ , $\overline{CAS}$ cycle, | 0                     |        | lcc₄   |      | 120  |                                | 105  | mA   | Note 4, 5  |

| $t_{PC} = t_{PC}$ (MIN.) or $t_{PPC} = t_{PPC}$ (MIN.)                            |                       | 0      | Icc10  |      | 150  |                                | 130  |      |            |

| CAS before RAS refresh cycle<br>trc = trc (MIN.)                                  | 0                     |        | lcc5   |      | 100  |                                | 95   | mA   |            |

|                                                                                   |                       | 0      | Icc11  |      | 130  |                                | 120  |      |            |