DIGITAL SIGNAL PROCESSOR (DSP) AND SPEECH PROCESSOR PRODUCTS DATA BOOK

NEC

200

# 1992 Digital Signal Processor (DSP) and Speech Processor Products Data Book

March 1992 Document No. 50052-1 ©1992 NEC Electronics Inc./Printed in the U.S.A.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics Inc. The information in this document is subject to change without notice. Devices sold by NEC Electronics Inc. are covered by the warranty and patent indemnification provisions appearing in NEC Electronics Inc. Terms and Conditions of Sale only. NEC Electronics Inc. makes no warranty, express, statutory, implied, or by description, regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. NEC Electronics Inc. makes no warranty of merchantability or fitness for any purpose. NEC Electronics Inc. assumes no responsibility for any errors that may appear in this document. NEC Electronics Inc. makes no commitment to update or to keep current the information contained in this document.

ii

# NEC

#### Section 1 Selection Guides

| Single-Chip Microcomputers                                                                                                                                                                      | 1-1                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| V-Series and RISC Microprocessors and Peripherals                                                                                                                                               | 1-8                          |

| Intelligent Peripheral Devices (IPD)                                                                                                                                                            | 1-11                         |

| DSP and Speech Products                                                                                                                                                                         | 1-13                         |

| Development Tools for Micro Products<br>V-Series Microprocessors<br>75xx Series Single-Chip Microcomputers<br>75xxx Series Single-Chip Microcomputers<br>78xx Series Single-Chip Microcomputers | 1-15<br>1-18<br>1-20<br>1-24 |

| K2 (782xx) Series Single-Chip<br>Microcomputers<br>K3 (783xx) Series Single-Chip<br>Microcomputers                                                                                              | 1-26<br>1-28                 |

| DSP and Speech Products<br>PG-1500 Programming Adapters                                                                                                                                         | 1-30<br>1-32                 |

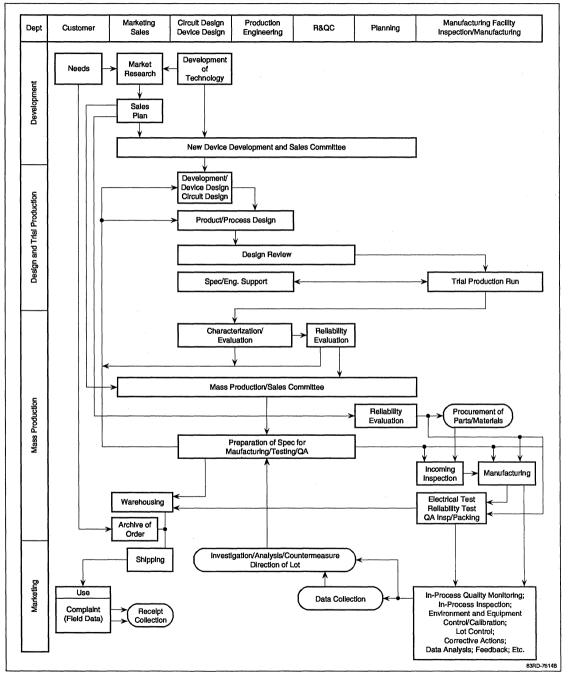

#### Section 2 Reliability and Quality Control

| Built-in TQC                                           | 2-1  |

|--------------------------------------------------------|------|

| Approaches to TQC                                      | 2-1  |

| Implementation of Quality Control                      | 2-3  |

| Reliability Theory                                     | 2-5  |

| Failure Analysis                                       | 2-9  |

| Summary                                                | 2-9  |

| Figure 1. NEC's Quality Control System                 | 2-2  |

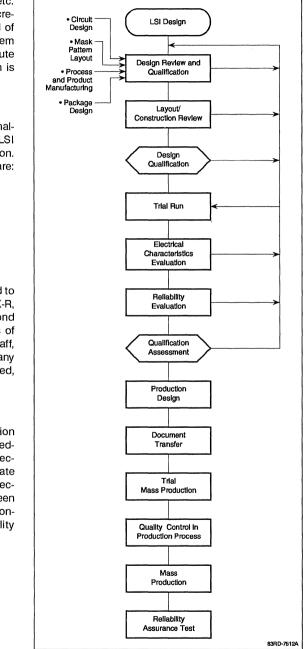

| Figure 2. New Product Development                      | 2-3  |

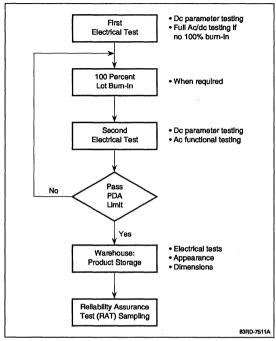

| Figure 3. Electrical Testing and Screening             | 2-5  |

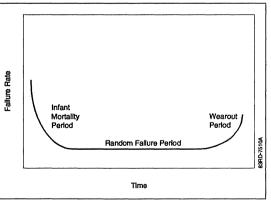

| Figure 4. Reliability Life (Bathtub) Curve             | 2-5  |

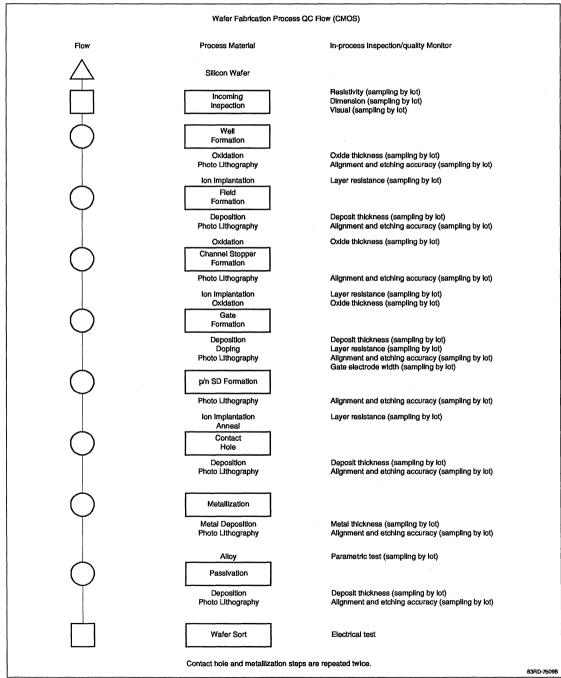

| Appendix 1A. Typical QC Flow for CMOS<br>Fabrication   | 2-10 |

| Appendix 1B. Typical QC Flow for PLCC<br>Assembly/Test | 2-11 |

| Appendix 2. Typical Reliability Assurance<br>Tests     | 2-13 |

| Appendix 3. New Product/Process Change<br>Tests        | 2-13 |

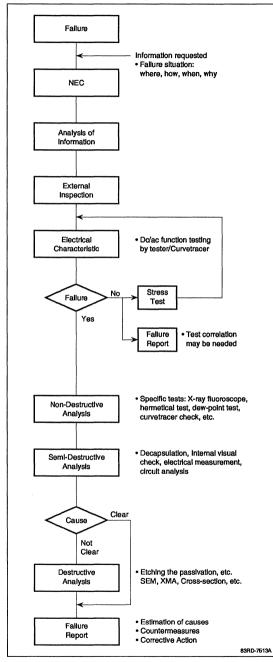

| Appendix 4. Failure Analysis Flowchart                 | 2-14 |

|                                                        |      |

| Section 3<br>Digital Signal Processors                                                             |    |

|----------------------------------------------------------------------------------------------------|----|

| μ <b>PD77C20A, 7720A, 77P20</b><br>Digital Signal Processors                                       | 3a |

| μ <b>PD77C25/77P25</b><br>Digital Signal Processor                                                 | 3b |

| μ <b>PD77220, 77P220</b><br>24-Bit Fixed-Point Digital Signal Processor                            | 30 |

| μ <b>PD77230A, 77P230</b><br>32-Bit Floating-Point Digital Signal Processor<br>(150 ns cycle time) | 3d |

| μ <b>PD77240</b><br>32-Bit Floating-Point Digital Signal Processor<br>(90 ns cycle time)           | 3e |

| μ <b>PD77810</b><br>Modem Digital Signal Processor                                                 | 3f |

| μ <b>PD7281</b><br>Image Pipelined Processor                                                       | 3g |

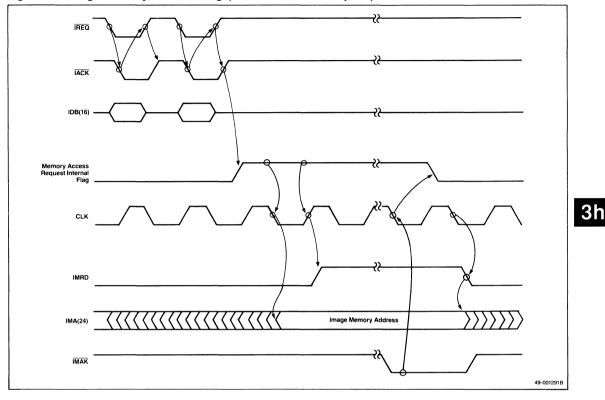

| $\mu$ PD9305<br>Memory Access and General Bus Interface for<br>the $\mu$ PD7281                    | 3h |

## Section 4

| Speech Processors                |    |

|----------------------------------|----|

| μPD77C30                         | 4a |

| ADPCM Speech Encoder/Decoder     |    |

| μPD7755/56/P56/57/58             | 4b |

| ADPCM Speech Processors          |    |

| μPD7759                          | 4c |

| ADPCM Speech Processor           |    |

| μPD77501                         | 4d |

| ADPCM Record and Playback Speech |    |

| Processor                        |    |

| μPD77522                         | 4e |

| ADPCM Codec                      |    |

## Contents

| Section 5<br>Development Tools                                       |     |

|----------------------------------------------------------------------|-----|

| Third-Party Development Tools                                        | 5-1 |

| μPD77C20A, 7720A, 77P20 Digital Signal<br>Processors                 |     |

| <b>EVAKIT-7720B</b><br>μPD7720 Standalone Emulator                   | 5a  |

| ASM77<br>μPD7720 Absolute Assembler                                  | 5b  |

| μPD77C25/77P25 Digital Signal Processor                              |     |

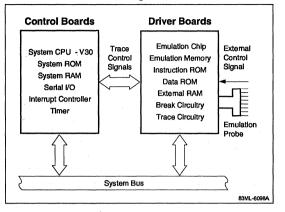

| <b>EVAKIT-77C25</b><br>μPD77C25 Standalone Emulator                  | 5c  |

| <b>RA77C25</b><br>μPD77C25 Relocatable Assembler Package             | 5d  |

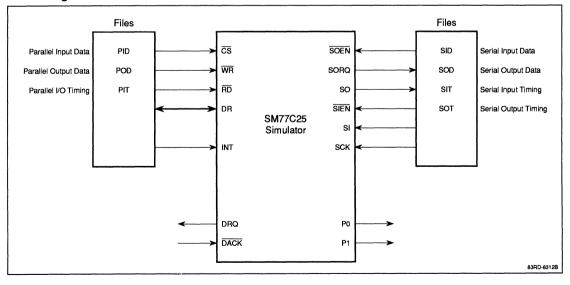

| SM77C25<br>PC-Based Simulator for μPD77C25 and<br>μPD77C20           | 5e  |

| μPD77220/P220, μPD77230/P230 Digital Signal<br>Processors            |     |

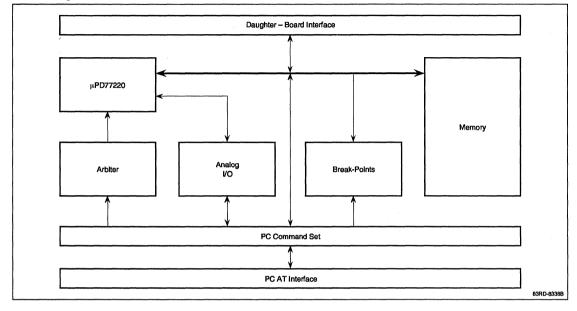

| <b>EVAKIT-77220</b><br>μPD77220 Standalone Emulator                  | 5f  |

| <b>EVAKIT-77230</b><br>μPD77230 Standalone Emulator                  | 5g  |

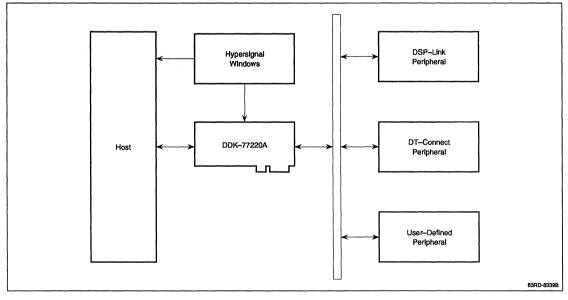

| <b>DDK-77220A</b><br>μPD77220 Evaluation Board                       | 5h  |

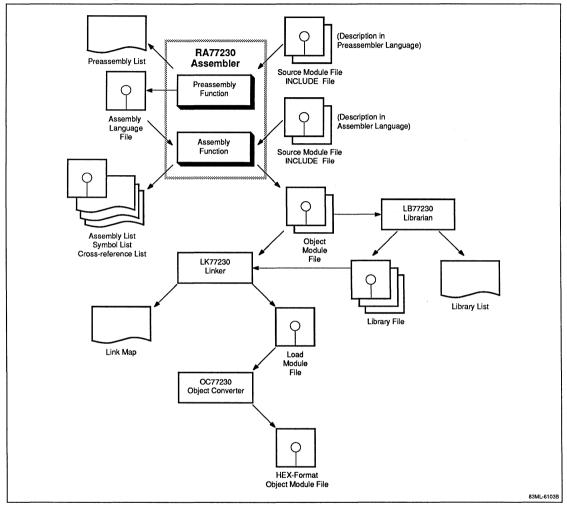

| <b>RA77230</b><br>μPD77220/μPD77230 Relocatable Assembler<br>Package | 5i  |

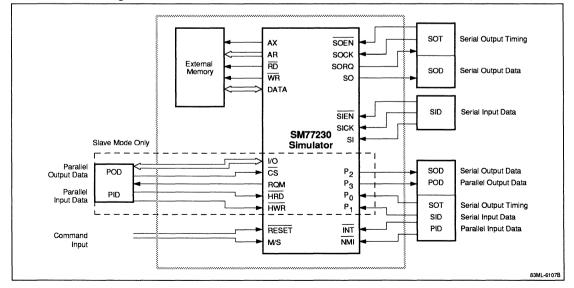

| SM77230<br>PC-Based Simulator for µPD77220/µPD77230                  | 5j  |

| μPD77240 Digital Signal Processor                                    |     |

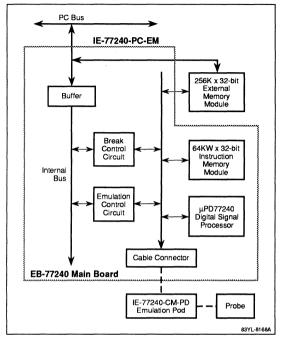

| IE-77240<br>In-Circuit Emulator for the µPD77240                     | 5k  |

| RA77240<br>Relocatable Assembler Package                             | 51  |

| μPD77810 Modem Digital Signal Processor                              |     |

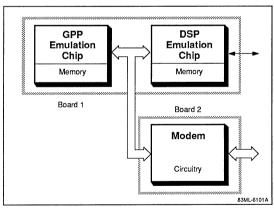

| <b>IE-77810</b><br>In-Circuit Emulator for the μPD77810              | 5m  |

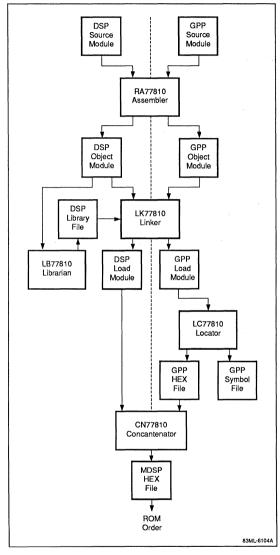

| <b>RA77810</b><br>Relocatable Assembler Package for the μPD77810     | 5n  |

#### Section 5 Development Tools

#### μPD775x ADPCM Speech Processors and μPD77501 ADPCM Record and Playback Speech Processor

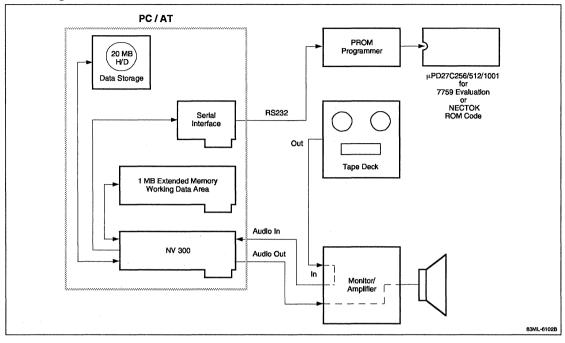

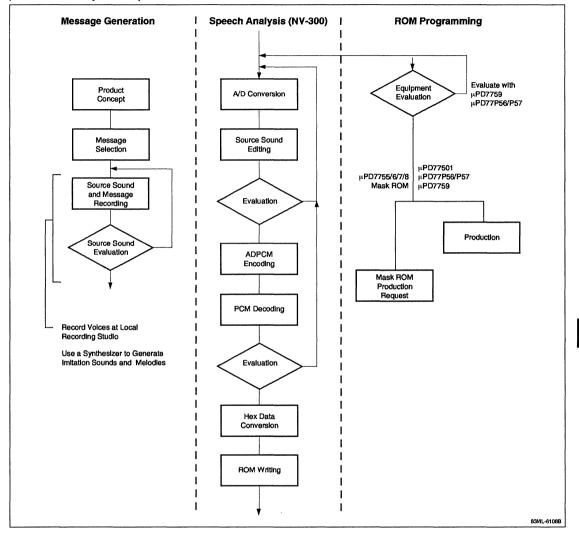

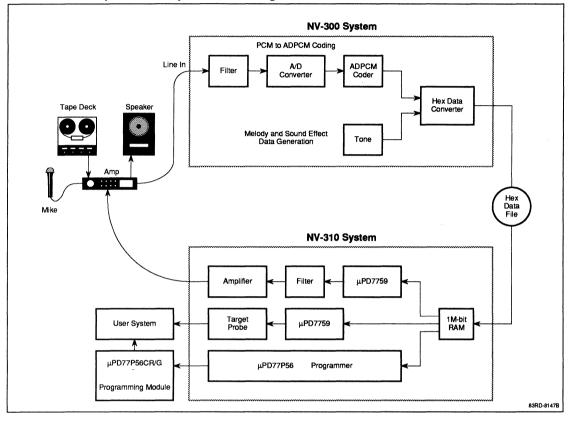

| <b>NV-300</b><br>Speech Analysis Tool for μPD775x and μPD77501      | 50 |

|---------------------------------------------------------------------|----|

| NV-310<br>Speech Analysis Tool for µPD775x                          | 5р |

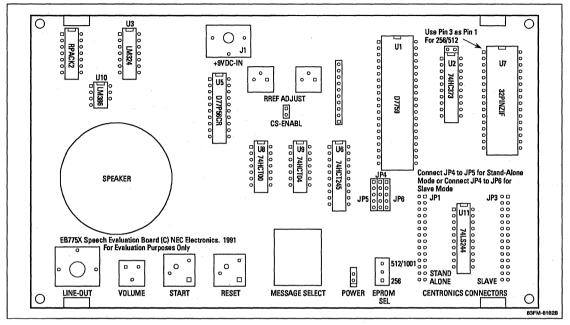

| <b>EB-775x</b><br>Demonstration and Evaluation Box for $\mu$ PD775x | 5q |

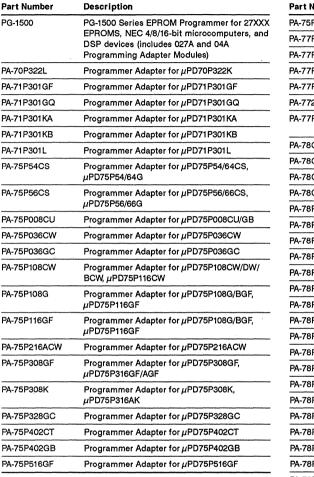

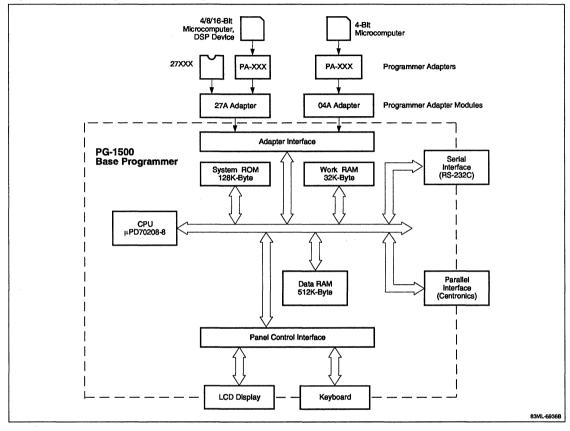

| PG-1500 Series<br>EPROM Programmer                                  | 5r |

#### Section 6 Package Drawings

| i ackage brawings                          |      |

|--------------------------------------------|------|

| Package/Device Cross Reference             | 6-1  |

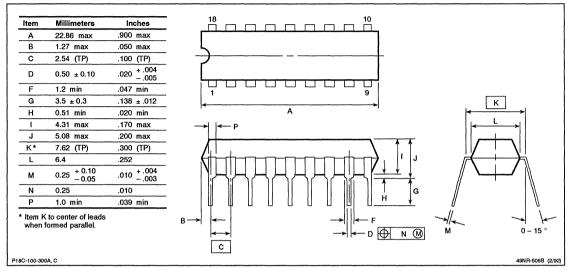

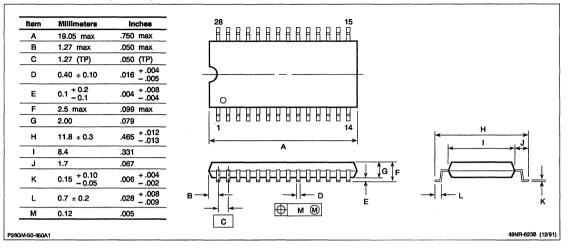

| 18-Pin Plastic DIP (300 mil) (A, C Outine) | 6-3  |

| 18-Pin Plastic DIP (300 mil) (SA Outline)  | 6-3  |

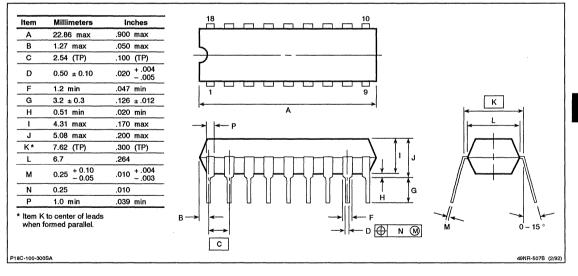

| 20-Pin Plastic DIP (300 mil)               | 6-4  |

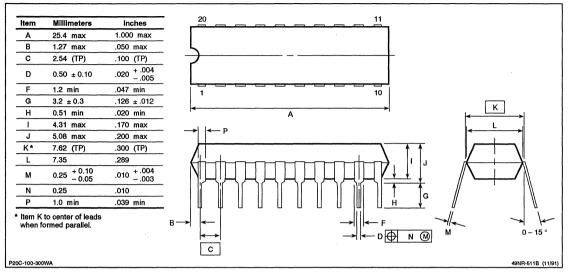

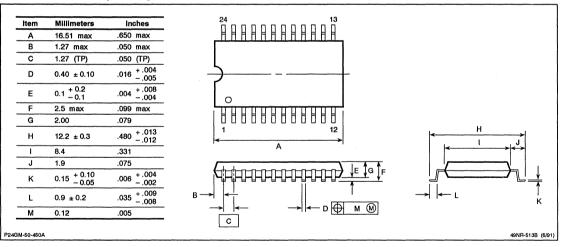

| 24-Pin Plastic SOP (450 mil)               | 6-4  |

| 28-Pin Plastic SOP (450 mil)               | 6-5  |

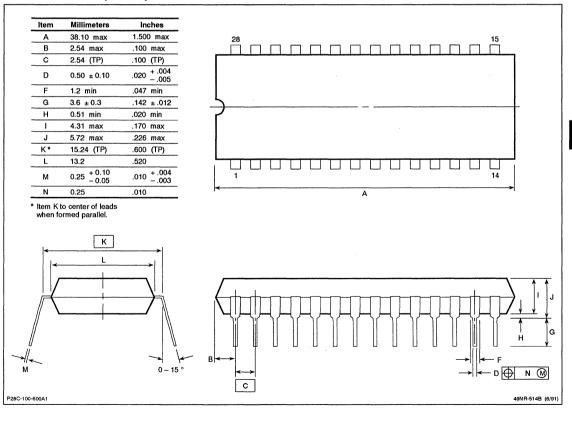

| 28-Pin Plastic DIP (600 mil)               | 6-5  |

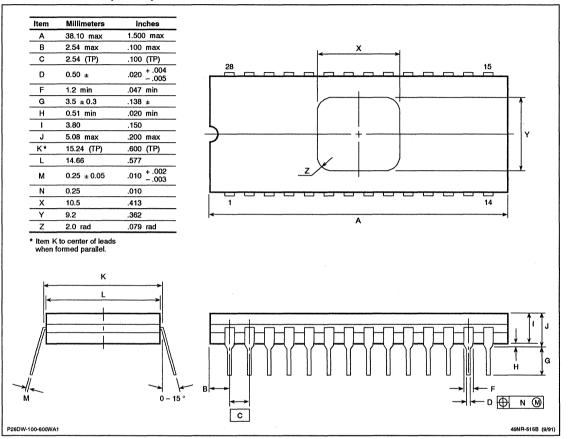

| 28-Pin Ceramic DIP (600 mil)               | 6-6  |

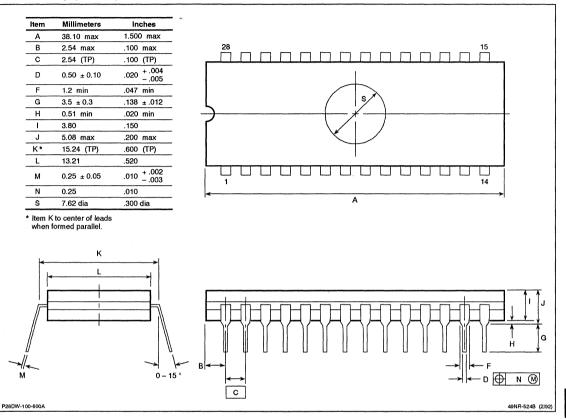

| 28-Pin Cerdip (600 mil)                    | 6-7  |

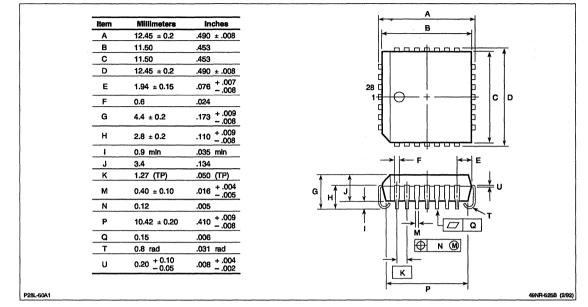

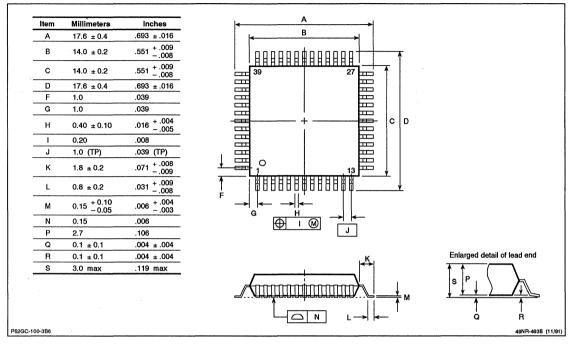

| 28-Pin PLCC                                | 6-8  |

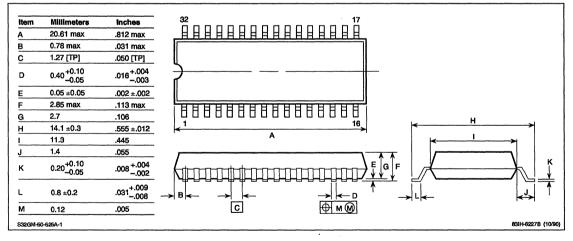

| 32-Pin SOP (525 mil)                       | 6-8  |

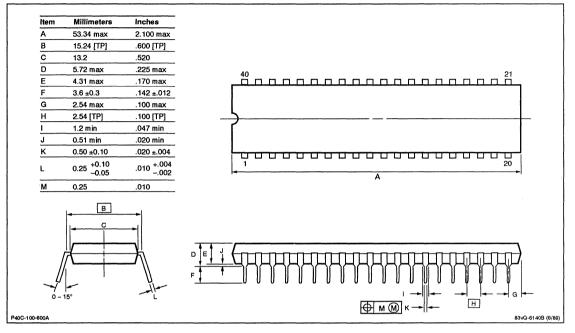

| 40-Pin Plastic DIP (600 mil)               | 6-9  |

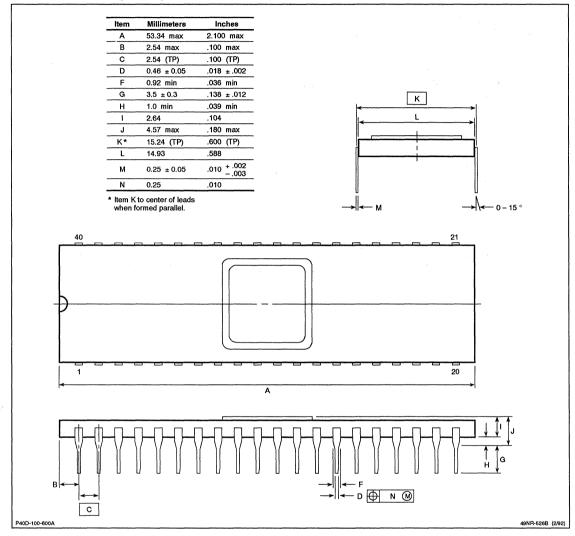

| 40-Pin Ceramic DIP (600 mil)               | 6-10 |

| 44-Pin PLCC                                | 6-11 |

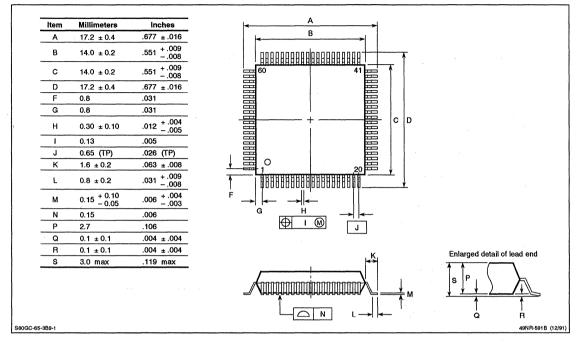

| 52-Pin Plastic QFP                         | 6-12 |

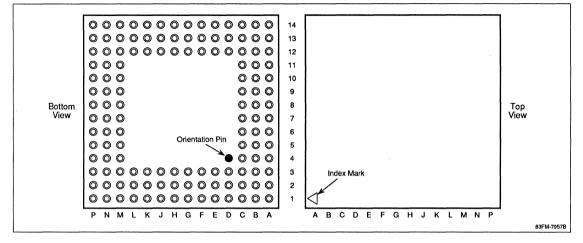

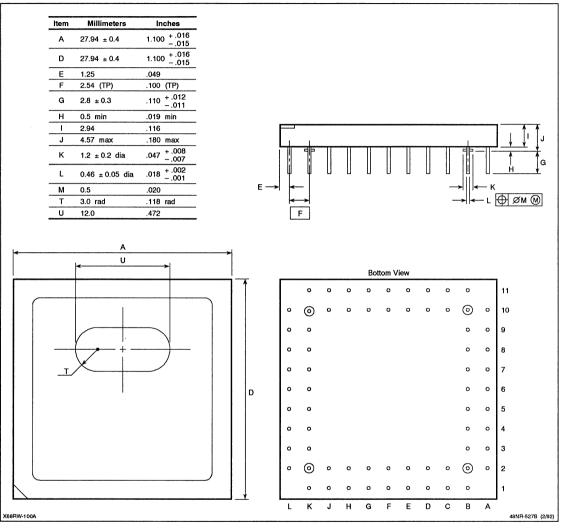

| 68-Pin Ceramic PGA (A Outline)             | 6-13 |

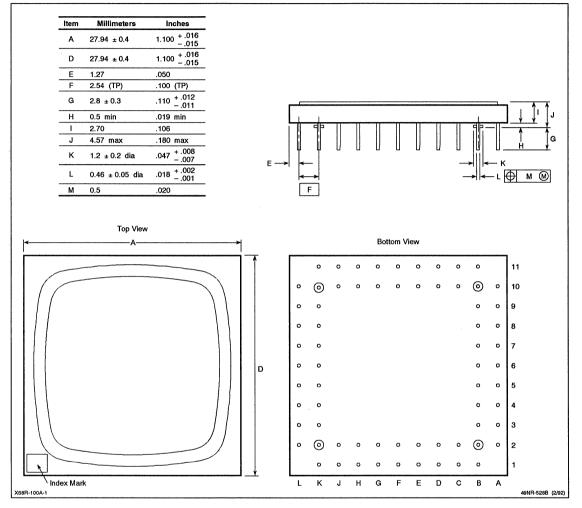

| 68-Pin Ceramic PGA (A-1 Outline)           | 6-14 |

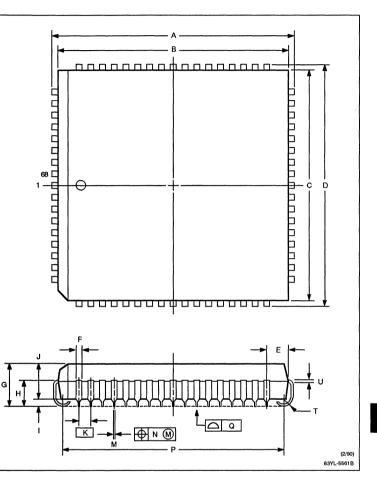

| 68-Pin PLCC                                | 6-15 |

| 80-Pin Plastic QFP                         | 6-16 |

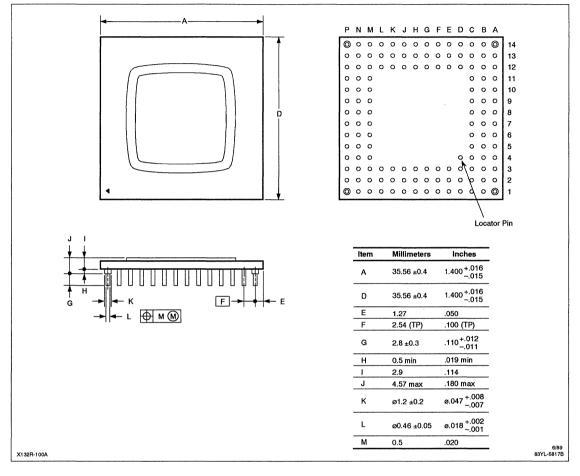

| 132-Pin Ceramic PGA                        | 6-17 |

|                                            |      |

# NEC

## Contents

#### Numerical Index

| Device, μPD | Section |

|-------------|---------|

| 7281        | 3g      |

| 7720A       | За      |

| 77220       | 30      |

| 77230A      | 3d      |

| 77240       | Зе      |

| 77501       | 4d      |

| 77522       | 4e      |

| 7755        | 4b      |

| 7756        | 4b      |

| 7757        | 4b      |

| 7758        | 4b      |

| 7759        | 4c      |

| 77810       | 3f      |

| 77C20A      | 3a      |

| 77C25       | 3b      |

| 77C30       | 4a      |

| 77P20       | 3a      |

| 77P25       | 3b      |

| 77P220      | 30      |

| 77P230      | 3d      |

| 77P56       | 4b      |

| 9305        | 3h      |

# **Selection Guides**

**Reliability and Quality Control**

**Digital Signal Processors**

**Speech Processors**

**Development Tools**

**Package Drawings**

1

#### Section 1 Selection Guides

| Single-Chip Microcomputers                                                                                                                            | 1-1                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| V-Series and RISC Microprocessors and<br>Peripherals                                                                                                  | 1-8                  |

| Intelligent Peripheral Devices (IPD)                                                                                                                  | 1-11                 |

| DSP and Speech Products                                                                                                                               | 1-13                 |

| Development Tools for Micro Products<br>V-Series Microprocessors<br>75xx Series Single-Chip Microcomputers<br>75xxx Series Single-Chip Microcomputers | 1-15<br>1-18<br>1-20 |

| 78xx Series Single-Chip Microcomputers<br>K2 (782xx) Series Single-Chip<br>Microcomputers<br>K3 (783xx) Series Single-Chip                            | 1-24<br>1-26<br>1-28 |

| Microcomputers<br>DSP and Speech Products<br>PG-1500 Programming Adapters                                                                             | 1-30<br>1-32         |

#### Part Numbering System

| μPD72001L | Typical microdevice part number           |

|-----------|-------------------------------------------|

| μP        | NEC monolithic silicon integrated circuit |

| D         | Device type (D = digital MOS)             |

- 72001 Device identifier (alphanumeric)

- L Package type (L = PLCC)

A part number may include an alphanumeric suffix that identifies special device characteristics; for example, µPD72001L-11 has an 11-MHz CPU clock rating.

#### 4-Bit, Single-Chip CMOS Microcomputers; 75xx Series

| Device<br>(μPD) | Features                                       | Clock<br>(MHz) | Supply<br>Voltage (V) | ROM (X8)  | RAM (X4) | I/O | Package †          | Pins           |

|-----------------|------------------------------------------------|----------------|-----------------------|-----------|----------|-----|--------------------|----------------|

| 7502A           | LCD controller/driver                          | 0.41           | 2.5 to 6.0            | 2K        | 128      | 23  | QFP                | 64             |

| 7503A           | LCD controller/driver                          | 0.41           | 2.5 to 6.0            | 4K        | 224      | 23  | QFP                | 64             |

| 7507B           | General-purpose                                | 0.5            | 2.2 to 6.0            | 2К        | 128      | 32  | SDIP<br>QFP        | 40<br>44       |

| 7508B           | General-purpose                                | 0.5            | 2.2 to 6.0            | 4K        | 224      | 32  | SDIP<br>QFP        | 40<br>44       |

| 7533            | A/D converter                                  | 0.51           | 2.7 to 6.0            | 4K        | 160      | 30  | DIP<br>SDIP<br>QFP | 42<br>42<br>44 |

| 75CG33          | Piggyback EPROM; A/D<br>converter              | 0.51           | 4.5 to 5.5            | 4K        | 160      | 30  | Ceramic DIP        | 42             |

| 7554            | Serial I/O; external<br>clock or RC oscillator | 0.71           | 2.5 to 6.0            | 1K        | 64       | 16  | SDIP<br>SOP        | 20<br>20       |

| 7554A           | Serial I/O; external<br>clock or RC oscillator | 0.71           | 2.0 to 6.0            | 1K        | 64       | 16  | SDIP<br>SOP        | 20<br>20       |

| 75P54           | Serial I/O; external<br>clock or RC oscillator | 0.71           | 4.5 to 6.0            | 1K OTPROM | 64       | 16  | SDIP<br>SOP        | 20<br>20       |

| 7564/7564A      | Serial I/O; ceramic<br>oscillator              | 0.71           | 2.7 to 6.0            | 1K        | 64       | 15  | SDIP<br>SOP        | 20<br>20       |

| 75P64           | Serial I/O; ceramic<br>oscillator              | 0.71           | 4.5 to 6.0            | 1K OTPROM | 64       | 15  | SDIP<br>SOP        | 20<br>20       |

| 7556            | Comparator; external<br>clock or RC oscillator | 0.71           | 2.5 to 6.0            | 1K        | 64       | 20  | SDIP<br>SOP        | 24<br>24       |

| 7556A           | Comparator; external<br>clock or RC oscillator | 0.71           | 2.0 to 6.0            | 1K        | 64       | 20  | SDIP<br>SOP        | 24<br>24       |

| 75P56           | Comparator; external<br>clock or RC oscillator | 0.71           | 4.5 to 6.0            | 1K OTPROM | 64       | 20  | SDIP<br>SOP        | 24<br>24       |

| 7566/7566A      | Comparator; ceramic<br>oscillator              | 0.71           | 2.7 to 6.0            | 1K        | 64       | 19  | SDIP<br>SOP        | 24<br>24       |

| 75P66           | Comparator; ceramic<br>oscillator              | 0.71           | 4.5 to 6.0            | 1K OTPROM | 64       | 19  | SDIP<br>SOP        | 24<br>24       |

† Plastic unless ceramic (or cerdip) is specified.

#### 4-Bit, Single-Chip CMOS Microcomputers; 75xxx Series

| Device (µPD) | Features                            | Clock<br>(MHz) | Supply<br>Voltage (V) | ROM (X8)   | RAM (X4) | I/O | Package †   | Pins     |

|--------------|-------------------------------------|----------------|-----------------------|------------|----------|-----|-------------|----------|

| 75004        | General-purpose                     | 4.19           | 2.7 to 6.0            | 4K         | 512      | 34  | SDIP<br>QFP | 42<br>44 |

| 75006        | General-purpose                     | 4.19           | 2.7 to 6.0            | 6K         | 512      | 34  | SDIP<br>QFP | 42<br>44 |

| 75008        | General-purpose                     | 4.19           | 2.7 to 6.0            | 8K         | 512      | 34  | SDIP<br>QFP | 42<br>44 |

| 75P008       | General-purposè; on-<br>chip OTPROM | 4.19           | 4.5 to 5.5            | 8K OTPROM  | 512      | 34  | SDIP<br>QFP | 42<br>44 |

| 75028        | A/D converter                       | 4.19           | 2.7 to 6.0            | 8K         | 512      | 48  | SDIP<br>QFP | 64<br>64 |

| 75P036       | A/D converter; on-chip<br>OTPROM    | 4.19           | 2.7 to 6.0            | 16K OTPROM | 1024     | 48  | SDIP<br>QFP | 64<br>64 |

.

## 4-Bit, Single-Chip CMOS Microcomputers; 75xxx Series (cont)

| Device (µPD) | Features                                                                           | Clock<br>(MHz) | Supply<br>Voltage (V) | ROM (X8)   | RAM (X4) | I/O | Package †     | Pins     |

|--------------|------------------------------------------------------------------------------------|----------------|-----------------------|------------|----------|-----|---------------|----------|

| 75048        | A/D converter; 1K x 4<br>EEPROM                                                    | 4.19           | 2.7 to 6.0            | 8K         | 512      | 48  | SDIP<br>QFP   | 64<br>64 |

| 75P048 *     | A/D converter; 1K x 4<br>EEPROM; on-chip<br>OTPROM                                 | 4.19           | 2.7 to 6.0            | 8K OTPROM  | 512      | 48  | SDIP<br>QFP   | 64<br>64 |

| 75104        | High-end with 8-bit<br>instruction                                                 | 4.19           | 2.7 to 6.0            | 4K         | 320      | 52  | SDIP<br>QFP   | 64<br>64 |

| 75104A       | High-end with 8-bit<br>instruction                                                 | 4.19           | 2.7 to 6.0            | 4K         | 320      | 52  | QFP           | 64       |

| 75106        | High-end with 8-bit<br>instruction                                                 | 4.19           | 2.7 to 6.0            | 6К         | 320      | 52  | SDIP<br>QFP   | 64<br>64 |

| 75108        | High-end with 8-bit<br>instruction                                                 | 4.19           | 2.7 to 6.0            | 8K         | 512      | 52  | SDIP<br>QFP   | 64<br>64 |

| 75108A       | High-end with 8-bit<br>instruction                                                 | 4.19           | 2.7 to 6.0            | 8K         | 512      | 52  | QFP           | 64       |

| 75108F       | High-end with 8-bit<br>instruction; high speed                                     | 4.19           | 2.7 to 5.0            | 8K         | 512      | 52  | QFP           | 64       |

| 75P108       | High-end with 8-bit<br>instruction; on-chip                                        | 4.19           | 4.5 to 5.5            | 8K OTPROM  | 512      | 52  | SDIP<br>QFP   | 64<br>64 |

|              | OTPROM or UVEPROM                                                                  |                |                       | 8K UVEPROM | 512      | 52  | Shrink cerdip | 64       |

| 75P108B      | High-end with 8-bit<br>instruction; on-chip<br>OTPROM                              | 4.19           | 2.7 to 6.0            | 8K OTPROM  | 512      | 52  | SDIP<br>QFP   | 64<br>64 |

| 75112        | High-end with 8-bit<br>instruction                                                 | 4.19           | 2.7 to 6.0            | 12K        | 512      | 52  | SDIP<br>QFP   | 64<br>64 |

| 75112F       | High-end with 8-bit<br>instruction; high speed                                     | 4.19           | 2.7 to 5.0            | 12K        | 512      | 52  | QFP           | 64       |

| 75116        | High-end with 8-bit<br>instruction                                                 | 4.19           | 2.7 to 6.0            | 16K        | 512      | 52  | SDIP<br>QFP   | 64<br>64 |

| 75116F       | High-end with 8-bit<br>instruction; high speed                                     | 4.19           | 2.7 to 5.0            | 16K        | 512      | 52  | QFP           | 64       |

| 75P116       | High-end with 8-bit<br>instruction; on-chip<br>OTPROM                              | 4.19           | 4.5 to 5.5            | 16K OTPROM | 512      | 52  | SDIP<br>QFP   | 64<br>64 |

| 75116H       | High-end with 8-bit<br>instruction; high<br>speed; low voltage                     | 4.19           | 1.8 to 5.0            | 16K        | 768      | 52  | QFP           | 64       |

| 75117H       | High-end with 8-bit<br>instruction; high<br>speed; low voltage                     | 4.19           | 1.8 to 5.0            | 24K        | 768      | 52  | QFP           | 64       |

| 75P117H*     | High-end with 8-bit<br>instruction; high<br>speed; low voltage; on-<br>chip OTPROM | 4.19           | 1.8 to 5.0            | 24K OTPROM | 768      | 52  | QFP           | 64       |

| 75206        | FIP controller/driver                                                              | 4.19           | 2.7 to 6.0            | 6K         | 369      | 28  | SDIP<br>QFP   | 64<br>64 |

| 75208        | FIP controller/driver                                                              | 4.19           | 2.7 to 6.0            | 8K         | 497      | 28  | SDIP          | 64       |

### 4-Bit, Single-Chip CMOS Microcomputers; 75xxx Series (cont)

| Device (µPD) | Features                                                   | Clock<br>(MHz) | Supply<br>Voltage (V) | ROM (X8)    | RAM (X4) | I/O | Package †   | Pins     |

|--------------|------------------------------------------------------------|----------------|-----------------------|-------------|----------|-----|-------------|----------|

| 75212A       | FIP controller/driver                                      | 4.19           | 2.7 to 6.0            | 12K         | 512      | 28  | SDIP<br>QFP | 64<br>64 |

| 75216A       | FIP controller/driver;<br>on-chip OTPROM                   | 4.19           | 2.7 to 6.0            | 16K         | 512      | 28  | SDIP<br>QFP | 64<br>64 |

| 75P216A      | FIP controller/driver;<br>on-chip OTPROM                   | 4.19           | 4.5 to 5.5            | 16K OTPROM  | 512      | 28  | SDIP        | 64       |

| 75217        | FIP controller/driver                                      | 4.19           | 2.7 to 6.0            | 24K         | 768      | 28  | SDIP<br>QFP | 64<br>64 |

| 75218        | FIP controller/driver                                      | 6.0            | 2.7 to 6.0            | 32K         | 1024     | 28  | SDIP<br>QFP | 64<br>64 |

| 75P218       | FIP controller/driver;<br>on-chip OTPROM or                | 6.0            | 2.7 to 6.0            | 32K OTPROM  | 1024     | 28  | SDIP<br>QFP | 64<br>64 |

|              | UVEPROM                                                    |                |                       | 32K UVEPROM | 1024     | 28  | Ceramic LCC | 64       |

| 75236        | FIP controller/driver;<br>A/D converter                    | 4.19           | 2.7 to 6.0            | 16K         | 768      | 40  | QFP         | 94       |

| 75237        | FIP controller/driver;<br>A/D converter                    | 6.0            | 2.7 to 6.0            | 24K         | 1024     | 40  | QFP         | 94       |

| 75238        | FIP controller/driver;<br>A/D converter                    | 6.0            | 2.7 to 6.0            | 32K         | 1024     | 40  | QFP         | 94       |

| 75P238       | FIP controller/driver;                                     | 6.0            | 2.7 to 6.0            | 32K OTPROM  | 1024     | 40  | QFP         | 94       |

|              | A/D converter; on-chip<br>OTPROM or UVEPROM                |                |                       | 32K UVEPROM | 1024     | 40  | Ceramic LCC | 94       |

| 75268        | FIP controller/driver                                      | 4.19           | 2.7 to 6.0            | 8K          | 512      | 28  | SDIP<br>QFP | 64<br>64 |

| 75304        | LCD controller/driver                                      | 4.19           | 2.7 to 6.0            | 4K          | 512      | 32  | QFP         | 80       |

| 75306        | LCD controller/driver                                      | 4.19           | 2.7 to 6.0            | 6К          | 512      | 32  | QFP         | 80       |

| 75308        | LCD controller/driver                                      | 4.19           | 2.7 to 6.0            | 8K          | 512      | 32  | QFP         | 80       |

| 75308B       | LCD controller/driver;<br>low voltage                      | 4.19           | 2.0 to 6.0            | 8K          | 512      | 32  | QFP         | 80       |

| 75P308       | LCD controller/driver;                                     | 4.19           | 4.75 to 5.25          | 8K OTPROM   | 512      | 32  | QFP         | 80       |

|              | on-chip OTPROM or<br>UVEPROM                               |                |                       | 8K UVEPROM  | 512      | 32  | Ceramic LCC | 80       |

| 75312        | LCD controller/driver                                      | 4.19           | 2.7 to 6.0            | 12K         | 512      | 32  | QFP         | 80       |

| 75316        | LCD controller/driver                                      | 4.19           | 2.7 to 6.0            | 16K         | 512      | 32  | QFP         | 80       |

| 75P316       | LCD controller/driver;<br>on-chip OTPROM                   | 4.19           | 4.75 to 5.25          | 16K OTPROM  | 512      | 32  | QFP         | 80       |

| 75P316A      | LCD controller/driver;                                     | 4.19           | 2.7 to 6.0            | 16K OTPROM  | 512      | 32  | QFP         | 80       |

|              | on-chip OTPROM or<br>UVEPROM                               |                |                       | 16K UVEPROM | 512      | 32  | Ceramic LCC | 80       |

| 75328        | LCD controller/driver;<br>A/D converter                    | 4.19           | 2.7 to 6.0            | 8K          | 512      | 36  | QFP         | 80       |

| 75P328       | LCD controller/driver;<br>A/D converter; on-chip<br>OTPROM | 4.19           | 4.5 to 5.5            | 8K OTPROM   | 512      | 36  | QFP         | 80       |

| 75336        | LLCD controller/driver;<br>A/D converter; high-end         | 4.19           | 2.7 to 6.0            | 16K         | 768      | 36  | QFP         | 80       |

### 4-Bit, Single-Chip CMOS Microcomputers; 75xxx Series (cont)

| Device (µPD) | Features                                                                      | Clock<br>(MHz) | Supply<br>Voltage (V) | ROM (X8)    | RAM (X4) | I/O | Package †          | Pine           |

|--------------|-------------------------------------------------------------------------------|----------------|-----------------------|-------------|----------|-----|--------------------|----------------|

| 75P336       | LCD controller/driver;<br>A/D converter; high-<br>end; on-chip OTPROM         | 4.19           | 2.7 to 6.0            | 16K OTPROM  | 768      | 36  | QFP                | 80             |

| 75348        | LCD controller/driver;<br>DTMF, high-end                                      | 4.19           | 2.0 to 6.0            | 8K          | 1024     | 32  | QFP                | 100            |

| 75352        | LCD controller/driver;<br>DTMF, high-end                                      | 4.19           | 2.0 to 6.0            | 12K         | 1024     | 32  | QFP                | 100            |

| 75402A       | Low-end                                                                       | 4.19           | 2.7 to 6.0            | 2K          | 64       | 22  | DIP<br>SDIP<br>QFP | 28<br>28<br>44 |

| 75P402       | Low-end; on-chip<br>OTPROM                                                    | 4.19           | 4.5 to 5.5            | 2K OTPROM   | 64       | 22  | DIP<br>SDIP<br>QFP | 28<br>28<br>44 |

| 75512        | High-end; A/D<br>converter                                                    | 4.19           | 2.7 to 6.0            | 12K         | 512      | 64  | QFP                | 80             |

| 75516        | High-end; A/D<br>converter                                                    | 4.19           | 2.7 to 6.0            | 16K         | 512      | 64  | QFP                | 80             |

| 75P516       | High-end; A/D                                                                 | 4.19           | 4.75 to 5.5           | 16K OTPROM  | 512      | 64  | QFP                | 80             |

|              | converter; on-chip<br>OTPROM or UVEPROM                                       |                |                       | 16K UVEPROM | 512      | 64  | Ceramic LCC        | 80             |

| 75517        | High-end; A/D<br>converter; high-speed                                        | 6.0            | 2.7 to 6.0            | 24K         | 1024     | 64  | QFP                | 80             |

| 75518        | High-end; A/D<br>converter; high-speed                                        | 6.0            | 2.7 to 6.0            | 32K         | 1024     | 64  | QFP                | 80             |

| 75P518       | High-end; A/D<br>converter; high-speed;                                       | 6.0            | 2.7 to 6.0            | 32K OTPROM  | 1024     | 64  | QFP                | 80             |

|              | on-chip OTPROM and UVEPROM                                                    |                |                       | 32K UVEPROM | 1024     | 64  | Ceramic LCC        | 80             |

| 75616        | LCD controller/driver;<br>DTMF, high-end; A/D<br>converter                    | 6.0            | 2.0 to 6.0            | 16K         | 1536     | 32  | QFP                | 100            |

| 75617        | LCD controller/driver;<br>DTMF, high-end; A/D<br>converter                    | 6.0            | 2.0 to 6.0            | 24K         | 1536     | 32  | QFP                | 100            |

| 75P618       | LCD controller/driver;<br>DTMF, high-end; A/D<br>converter; on-chip<br>OTPROM | 6.0            | 2.0 to 6.0            | 32K OTPROM  | 2048     | 32  | QFP                | 100            |

† Plastic unless ceramic (or cerdip) is specified.

#### 8-Bit, Single-Chip CMOS Microcomputers; 78xx Series

| Device (µPD) | Features            | Clock<br>(MHz) | Supply<br>Voltage (V) | ROM (X8) | RAM (X8) | I/O | Package † | Pins |

|--------------|---------------------|----------------|-----------------------|----------|----------|-----|-----------|------|

| 78C10A       | CMOS; A/D converter | 15             | 4.5 to 5.5            | External | 256      | 32  | QUIP      | 64   |

|              |                     |                |                       |          |          |     | SDIP      | 64   |

|              |                     |                |                       |          |          |     | QFP       | 64   |

|              |                     |                |                       |          |          |     | PLCC      | 68   |

| 78C11A       | CMOS; A/D converter | 15             | 4.5 to 5.5            | 4K       | 256      | 40  | QUIP      | 64   |

|              |                     |                |                       |          |          |     | SDIP      | 64   |

|              |                     |                |                       |          |          |     | QFP       | 64   |

|              |                     |                |                       |          |          |     | PLCC      | 68   |

#### 8-Bit, Single-Chip CMOS Microcomputers; 78xx Series (cont)

| Device (µPD) | Features             | Clock<br>(MHz) | Supply<br>Voltage (V) | ROM (X8)    | RAM (X8) | I/O | Package †     | Pins |

|--------------|----------------------|----------------|-----------------------|-------------|----------|-----|---------------|------|

| 78C12A       | CMOS; A/D converter  | 15             | 4.5 to 5.5            | 8K          | 256      | 40  | QUIP          | 64   |

|              |                      |                |                       |             |          |     | SDIP          | 64   |

|              |                      |                |                       |             |          |     | QFP           | 64   |

|              |                      |                |                       |             |          |     | PLCC          | 68   |

| 78C14/8C14A  | CMOS; A/D converter  | 15             | 4.5 to 5.5            | 16K         | 256      | 40  | QUIP          | 64   |

|              |                      |                |                       |             |          |     | SDIP          | 64   |

|              |                      |                |                       |             |          |     | QFP           | 64   |

|              |                      |                |                       |             |          |     | PLCC          | 68   |

| 78CP14       | CMOS; A/D converter; | 15             | 4.75 to 5.25          | 16K OTPROM  | 256      | 40  | QUIP          | 64   |

|              | on-chip OTPROM or    |                |                       |             |          |     | SDIP          | 64   |

|              | UVEPROM              |                |                       |             |          |     | QFP           | 64   |

|              |                      |                |                       |             |          |     | PLCC          | 68   |

|              |                      |                |                       | 16K UVEPROM | 256      | 40  | Ceramic QUIP  | 64   |

|              |                      |                |                       |             |          |     | Shrink cerdip | 64   |

| 78C17        | CMOS; A/D converter  | 15             | 4.5 to 5.5            | External    | 1024     | 40  | QUIP          | 64   |

|              |                      |                |                       |             |          |     | SDIP          | 64   |

|              |                      |                |                       |             |          |     | QFP           | 64   |

| 78C18        | CMOS; A/D converter  | 15             | 4.5 to 5.5            | 32K         | 1024     | 40  | QUIP          | 64   |

|              |                      |                |                       |             |          |     | SDIP          | 64   |

|              |                      |                |                       |             |          |     | QFP           | 64   |

| 78CP18       | CMOS; A/D converter; | 15             | 4.75 to 5.25          | 32K OTPROM  | 1024     | 40  | QUIP          | 64   |

|              | on-chip OTPROM or    |                |                       |             |          |     | SDIP          | 64   |

|              | UVEPROM              |                |                       |             |          |     | QFP           | 64   |

|              |                      |                |                       | 32K UVEPROM | 1024     | 40  | Ceramic LCC   | 64   |

† Plastic unless ceramic (or cerdip) is specified.

#### 8-Bit, Single-Chip CMOS Microcomputers; 782xx (K2) Series

| Device (µPD) | Features              | Clock<br>(MHz) | Supply<br>Voltage (V) | ROM (X8)    | RAM (X8) | I/O | Package †     | Pins |

|--------------|-----------------------|----------------|-----------------------|-------------|----------|-----|---------------|------|

| 78212        | CMOS; A/D converter;  | 12             | 4.5 to 5.5            | 8K          | 384      | 54  | SDIP          | 64   |

|              | advanced peripherals  |                |                       |             |          |     | QUIP          | 64   |

|              |                       |                |                       |             |          |     | QFP           | 64   |

|              |                       |                |                       |             |          |     | QFP           | 74   |

|              |                       |                |                       |             |          |     | PLCC          | 68   |

| 78213        | CMOS; A/D converter;  | 12             | 4.5 to 5.5            | External    | 512      | 36  | SDIP          | 64   |

|              | advanced peripherals  |                |                       |             |          |     | QUIP          | 64   |

|              |                       |                |                       |             |          |     | QFP           | 64   |

|              |                       |                |                       |             |          |     | QFP           | 74   |

|              |                       |                |                       |             |          |     | PLCC          | 68   |

| 78214        | CMOS; A/D converter;  | 12             | 4.5 to 5.5            | 16K         | 512      | 54  | SDIP          | 64   |

|              | advanced peripherals  |                |                       |             |          |     | QUIP          | 64   |

|              |                       |                |                       |             |          |     | QFP           | 64   |

|              |                       |                |                       |             |          |     | QFP           | 74   |

|              |                       |                |                       |             |          |     | PLCC          | 68   |

| 78P214       | CMOS; A/D converter;  | 12             | 4.5 to 5.5            | 16K OTPROM  | 512      | 54  | SDIP          | 64   |

|              | advanced peripherals; |                |                       |             |          |     | QUIP          | 64   |

|              | on-chip OTPROM or     |                |                       |             |          |     | QFP           | 64   |

|              | UVEPROM               |                |                       |             |          |     | QFP           | 74   |

|              |                       |                |                       |             |          |     | PLCC          | 68   |

|              |                       |                |                       | 16K UVEPROM | 512      | 54  | Shrink cerdip | 64   |

| 78217A       | CMOS; A/D converter;  | 12             | 4.5 to 5.5            | External    | 1024     | 36  | SDIP          | 64   |

|              | advanced peripherals  |                |                       |             |          |     | QFP           | 64   |

### 8-Bit, Single-Chip CMOS Microcomputers; 782xx (K2) Series (cont)

| Device (µPD) | Features                                                           | Clock<br>(MHz) | Supply<br>Voltage (V) | ROM (X8)    | RAM (X8)             | I/O | Package †          | Pins           |

|--------------|--------------------------------------------------------------------|----------------|-----------------------|-------------|----------------------|-----|--------------------|----------------|

| 78218A       | CMOS; A/D converter;<br>advanced peripherals                       | 12             | 4.5 to 5.5            | 32K         | 1024                 | 54  | SDIP<br>QFP        | 64<br>64       |

| 78P218A      | CMOS; A/D converter;<br>advanced peripherals;<br>on-chip OTPROM or | 12             | 4.5 to 5.5            | 32K OTPROM  | 1024                 | 54  | SDIP<br>QFP        | 64<br>64       |

|              | UVEPROM                                                            |                |                       | 32K UVEPROM | 1024                 | 54  | Shrink cerdip      | 64             |

| 78220        | CMOS; analog<br>comparator; large I/O                              | 12             | 4.5 to 5.5            | External    | 640                  | 53  | PLCC<br>QFP        | 84<br>94       |

| 78224        | CMOS; analog<br>comparator; large I/O                              | 12             | 4.5 to 5.5            | 16K         | 640                  | 71  | PLCC<br>QFP        | 84<br>94       |

| 78P224       | CMOS; analog<br>comparator; large I/O;<br>on-chip OTPROM           | 12             | 4.5 to 5.5            | 16K OTPROM  | 640                  | 71  | PLCC<br>QFP        | 84<br>94       |

| 78233        | CMOS; real-time<br>outputs; A/D and D/A<br>converters              | 12             | 4.5 to 5.5            | External    | 640                  | 46  | QFP<br>QFP<br>PLCC | 80<br>94<br>84 |

| 78234        | CMOS; real-time<br>outputs; A/D and D/A<br>converters              | 12             | 4.5 to 5.5            | 16K         | 640                  | 64  | QFP<br>QFP<br>PLCC | 80<br>94<br>84 |

| 78237        | CMOS; real-time<br>outputs; A/D and D/A<br>converters              | 12             | 4.5 to 5.5            | External    | 1024                 | 64  | QFP<br>QFP<br>PLCC | 80<br>94<br>84 |

| 78238        | CMOS; real-time<br>outputs; A/D and D/A<br>converters              | 12             | 4.5 to 5.5            | 32K         | 1024                 | 64  | QFP<br>QFP<br>PLCC | 80<br>94<br>84 |

| 78P238       | CMOS; real-time<br>outputs; A/D and D/A<br>converters; on-chip     | 12             | 4.5 to 5.5            | 32K OTPROM  | 1024                 | 64  | QFP<br>QFP<br>PLCC | 80<br>94<br>84 |

|              | OTPROM or UVEPROM                                                  |                |                       | 32K UVEPROM | 1024                 | 64  | Ceramic LCC        | 94             |

| 78243        | CMOS; A/D converter;<br>EEPROM                                     | 12             | 4.5 to 5.5            | External    | 512<br>512<br>EEPROM | 36  | SDIP<br>QFP        | 64<br>64       |

| 78244        | CMOS; A/D converter;<br>EEPROM                                     | 12             | 4.5 to 5.5            | 16K         | 512<br>512<br>EEPROM | 54  | SDIP<br>QFP        | 64<br>64       |

† Plastic unless ceramic (or cerdip) is specified.

#### 8/16-Bit, Single-Chip CMOS Microcomputers; 783xx (K3) Series

| Device<br>(µPD) | Features                | Clock<br>(MHz) | Supply<br>Voltage (V) | ROM (X8) | RAM (X8) | I/O | Package † | Pins |

|-----------------|-------------------------|----------------|-----------------------|----------|----------|-----|-----------|------|

| 78310A          | Real-time motor control | 12             | 4.5 to 5.5            | External | 256      | 48  | SDIP      | 64   |

|                 |                         |                |                       |          |          |     | QUIP      | 64   |

|                 |                         |                |                       |          |          |     | QFP       | 64   |

|                 |                         |                |                       |          |          |     | PLCC      | 68   |

| 78312A          | Real-time motor control | 12             | 4.5 to 5.5            | 8K       | 256      | 48  | SDIP      | 64   |

|                 |                         |                |                       |          |          |     | QUIP      | 64   |

|                 |                         |                |                       |          |          |     | QFP       | 64   |

|                 |                         |                |                       |          |          |     | PLCC      | 68   |

### 8/16-Bit, Single-Chip CMOS Microcomputers; 783xx (K3) Series

| Device<br>(µPD) | Features                                                                 | Clock<br>(MHz) | Supply<br>Voltage (V) | ROM (X8)    | RAM (X8) | I/O | Package †                     | Pins                 |

|-----------------|--------------------------------------------------------------------------|----------------|-----------------------|-------------|----------|-----|-------------------------------|----------------------|

| 78P312A         | Real-time motor<br>control; on-chip                                      | 12             | 4.5 to 5.5            | 8K UVEPROM  | 256      | 48  | Shrink cerdip<br>Ceramic QUIP | 64<br>64             |

|                 | OTPROM or UVEPROM                                                        |                |                       | 8K OTPROM   | 256      | 48  | SDIP<br>QUIP<br>QFP<br>PLCC   | 64<br>64<br>64<br>68 |

| 78320           | Real-time control; A/D<br>converter                                      | 16             | 4.5 to 5.5            | External    | 640      | 37  | QFP<br>PLCC                   | 74<br>68             |

| 78322           | Real-time control; A/D<br>converter                                      | 16             | 4.5 to 5.5            | 16K         | 640      | 55  | QFP<br>PLCC                   | 74<br>68             |

| 78P322          | Real-time control; A/D converter; on-chip                                | 16             | 4.5 to 5.5            | 16K OTPROM  | 640      | 55  | QFP<br>PLCC                   | 74<br>68             |

|                 | OTPROM or UVEPROM                                                        |                |                       | 16K UVEPROM | 640      | 55  | Ceramic LCC<br>Ceramic LCC    | 68<br>74             |

| 78323           | Real-time control; A/D<br>converter                                      | 16             | 4.5 to 5.5            | External    | 1024     | 37  | QFP<br>PLCC                   | 74<br>68             |

| 78324           | Real-time control; A/D converter                                         | 16             | 4.5 to 5.5            | 32K         | 1024     | 55  | QFP<br>PLCC                   | 74<br>68             |

| 78P324          | Real-time control; A/D<br>converter                                      | 16             | 4.5 to 5.5            | 32K OTPROM  | 1024     | 55  | QFP<br>PLCC                   | 74<br>68             |

|                 |                                                                          |                |                       | 32K UVEPROM | 1024     | 55  | Ceramic LCC<br>Ceramic LCC    | 68<br>74             |

| 78327           | Real-time control; A/D<br>converter; enhanced<br>real-time output        | 16             | 4.5 to 5.5            | External    | 512      | 34  | SDIP<br>QFP                   | 64<br>64             |

| 78328           | Real-time control; A/D<br>converter; enhanced<br>real-time output        | 16             | 4.5 to 5.5            | 16K         | 512      | 52  | SDIP<br>QFP                   | 64<br>64             |

| 78P328          | Real-time control; A/D<br>converter; enhanced<br>real-time output; on-   | 16             | 4.5 to 5.5            | 16K OTPROM  | 512      | 52  | SDIP<br>QFP                   | 64<br>64             |

|                 | chip OTPROM or<br>UVEPROM                                                |                |                       | 16K UVEPROM | 512      | 52  | Ceramic SDIP                  | 64                   |

| 78330           | Real-time control; A/D<br>converter, enhanced<br>real-time pulse unit    | 16             | 4.5 to 5.5            | External    | 1024     | 52  | QFP<br>PLCC                   | 94<br>84             |

| 78334           | Real-time control; A/D<br>converter, enhanced<br>real-time pulse unit    | 16             | 4.5 to 5.5            | 32K         | 1024     | 70  | QFP<br>PLCC                   | 94<br>84             |

| 78P334          | Real-time control; A/D<br>converter, enhanced                            | 16             | 4.5 to 5.5            | 32K OTPROM  | 1024     | 70  | QFP<br>PLCC                   | 94<br>84             |

|                 | real-time pulse unit;<br>on-chip OTPROM or<br>UVEPROM                    |                |                       | 32K UVEPROM | 1024     | 70  | Ceramic LCC<br>Ceramic LCC    | 94<br>84             |

| 78350           | High speed; multiply<br>and accumulate<br>instruction                    | 25             | 4.5 to 5.5            | External    | 640      | 30  | QFP                           | 64                   |

| 78P352          | High speed; multiply<br>and accumluate<br>instruction; on-chip<br>OTPROM | 25             | 4.5 to 5.5            | 32K OTPROM  | 640      | 50  | QFP                           | 64                   |

### **V-Series CMOS Microprocessors**

| Device,<br>μPD                | Features                                                                                             | Data Bits           | Clock (MHz) | Package †                         | Pins                 |

|-------------------------------|------------------------------------------------------------------------------------------------------|---------------------|-------------|-----------------------------------|----------------------|

| 70108 (V20)                   | 8088 compatible; enhanced                                                                            | 8/16                | 8 or 10     | DIP<br>Ceramic DIP<br>QFP<br>PLCC | 40<br>40<br>52<br>44 |

| 70108H (V20H)                 | Fully static; pin compatible with 80C88<br>enhanced microprocessor                                   | 8/16                | 10, 12, 16  | DIP<br>QFP<br>PLCC                | 40<br>52<br>44       |

| 70116 (V30)                   | 8086 compatible; enhanced                                                                            | 16                  | 8 or 10     | DIP<br>Ceramic DIP<br>QFP<br>PLCC | 40<br>40<br>52<br>44 |

| 70116H (V30H)                 | Fully static; pin compatible with 80C86<br>enhanced microprocessor                                   | 16                  | 10, 12, 16  | DIP<br>QFP<br>PLCC                | 40<br>52<br>44       |

| 70208 (V40)                   | MS-DOS, V20 compatible CPU with peripherals                                                          | 8/16                | 8 or 10     | Ceramic PGA<br>PLCC<br>QFP        | 68<br>68<br>80       |

| 70208H (V40H)                 | Fully static; low power; 80C88 compatible CPU<br>plus peripherals                                    | 8/16                | 10, 12, 16  | Ceramic PGA<br>PLCC<br>QFP        | 68<br>68<br>80       |

| 70216 (V50)                   | MS-DOS, V30 compatible CPU with peripherals                                                          | 16/16               | 8 or 10     | PGA<br>PLCC<br>QFP                | 68<br>68<br>80       |

| 70216H (V50H)                 | Fully static; low power; 80C88 compatible CPU<br>plus peripherals                                    | 16                  | 10, 12, 16  | Ceramic PGA<br>PLCC<br>QFP        | 68<br>68<br>80       |

| 70136 (V33)                   | Hardwired, enhanced V30                                                                              | 8 and 16<br>dynamic | 12 or 16    | PGA<br>PLCC                       | 68<br>68             |

| 70236 (V53)                   | V33 core-based; high-integration; DMA, serial I/O, interrupt controller, etc.                        | 8 and 16<br>dynamic | 10, 12, 16  | Ceramic PGA<br>QFP                | 132<br>120           |

| 70320 (V25)                   | MS-DOS compatible microcontroller; high-<br>integration; DMA, serial I/O, interrupt controller, etc. | 8/16                | 5 or 8      | PLCC<br>QFP                       | 84<br>94             |

| 70330 (V35)                   | MS-DOS compatible microcontroller; high-<br>integration; DMA, serial I/O, interrupt controller, etc. | 16                  | 8           | PLCC<br>QFP                       | 84<br>94             |

| 70325 (V25 Plus)              | MS-DOS compatible microcontroller; high-<br>integration; high-speed DMA                              | 8/16                | 8 or 10     | PLCC<br>QFP                       | 84<br>94             |

| 70335 (V35 Plus)              | MS-DOS compatible microcontroller; high-<br>integration; high-speed DMA                              | 16                  | 8 or 10     | PLCC<br>QFP                       | 84<br>94             |

| 70327 (V25<br>Software Guard) | MS-DOS compatible microcontroller; high-<br>integration; software protection                         | 8/16                | 8           | PLCC<br>QFP                       | 84<br>94             |

| 70337 (V35<br>Software Guard) | MS-DOS compatible microcontroller; high-<br>integration; software protection                         | 16                  | 8           | PLCC<br>QFP                       | 84<br>94             |

### V-Series CMOS System Support Products

| Device,<br>μPD | Features                                                    | Data Bits | Clock (MHz) | Package †                         | Pins                 |

|----------------|-------------------------------------------------------------|-----------|-------------|-----------------------------------|----------------------|

| 71011          | Clock Pulse Generator/Driver                                | _         | 20          | DIP<br>SOP                        | 18<br>20             |

| 71037          | Programmable DMA Controller                                 | 8         | 10          | DIP<br>QFP<br>PLCC                | 40<br>40<br>44       |

| 71051          | Serial Control Unit                                         | 8         | 8/10        | DIP<br>QFP<br>PLCC                | 28<br>44<br>28       |

| 71054          | Programmable Timer/Controller                               | 8         | 8/10        | DIP<br>QFP<br>PLCC                | 24<br>44<br>28       |

| 71055          | Parallel Interface Unit                                     | 8         | 8/10        | DIP<br>QFP<br>PLCC                | 40<br>44<br>44       |

| 71059          | Interrupt Control Unit                                      | 8         | 8/10        | DIP<br>QFP<br>PLCC                | 28<br>44<br>28       |

| 71071          | DMA Controller                                              | 8/16      | 8/10        | DIP<br>Ceramic DIP<br>QFP<br>PLCC | 48<br>48<br>52<br>52 |

| 71082          | Transparent Latch                                           | 8         | 8           | DIP<br>SOP                        | 20<br>20             |

| 71083          | Transparent Latch                                           | 8         | 8           | DIP<br>SOP                        | 20<br>20             |

| 71084          | Clock Pulse Generator/Driver                                |           | 25          | DIP<br>SOP                        | 18<br>20             |

| 71086          | Bus Buffer/Driver                                           | 8         | 8           | DIP<br>SOP                        | 18<br>20             |

| 71087          | Bus Buffer/Driver                                           | 8         | 8           | DIP<br>SOP                        | 20<br>20             |

| 71088          | System Bus Controller                                       |           | 8/10        | DIP<br>SOP                        | 20<br>20             |

| 71101          | Complex Peripheral Unit; serial, parallel, timer, interrupt | 8         | 10          | QFP                               | 120                  |

| 71641          | Cache Memory Controller                                     | 8/16/32   | 25          | PGA                               | 132                  |

| 72291          | Floating Point Coprocessor for V33/V53                      | 16        | 16          | PGA                               | 68                   |

| 9335           | Numeric Interface Adapter for V40/V50 ↔ i8087               |           | 8           | DIP                               | 20                   |

| Device                           | Name                     | Clock                      | Package      | Pins |

|----------------------------------|--------------------------|----------------------------|--------------|------|

| µPD30310 (V <sub>B</sub> 3000A)  | RISC Microprocessor      | 25 MHz                     | PQFP         | 160  |

|                                  |                          | 25, 33 MHz                 | PPGA or CPGA | 175  |

|                                  |                          | 40 MHz                     | CPGA         | 175  |

| μΡD30311 (V <sub>B</sub> 3010A)  | Floating-Point Processor | 25 MHz                     | PQFP         | 160  |

|                                  |                          | 25, 33 MHz                 | PPGA or CPGA | 84   |

|                                  |                          | 40 MHz                     | CPGA         | 84   |

| µPD30361 (V <sub>B</sub> 3600)   | RISC Microprocessor      | 25, 33 MHz                 | PPGA         | 175  |

|                                  |                          | 40 MHz                     | CPGA         | 175  |

| µPD30362 (V <sub>B</sub> 3600)   | RISC Microprocessor      | 25, 33 MHz                 | PPGA         | 175  |

|                                  | ·                        | 40 MHz                     | CPGA         | 175  |

| μPD31311                         | Bus Interface Unit       | 25, 33 MHz                 | PPGA         | 208  |

| μPD46710                         | 16K x 10-Bit x 2 SRAM    | Access time: 12, 15 20 ns  | PLCC         | 52   |

| μPD46741                         | 8K x 20-Bit x 2 SRAM     | Access time: 12, 15, 20 ns | PLCC         | 68   |

| µPD30400 (V <sub>R</sub> 4000PC) | RISC Microprocessor      | 50, 66, 75 MHz             | CPGA         | 179  |

| µPD30401 (V <sub>R</sub> 4000SC) | RISC Microprocessor      | 50, 66, 75 MHz             | CPGA or LGA  | 447  |

| µPD30402 (V <sub>B</sub> 4000MC) | RISC Microprocessor      | 50, 66, 75 MHz             | CPGA or LGA  | 447  |

NEC

## **RISC Microprocessors and Peripherals**

### **Communications Controllers**

| Device,<br>μPD | Name                                                                   | Description                                                                                                                                                                                            | Maximum<br>Data Rate | Package †           | Pins           |

|----------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------|----------------|

| 72001          | CMOS, Advanced<br>Multiprotocol Serial<br>Communications<br>Controller | Functional superset of 8530; 8086/V30<br>interface; two full-duplex serial channels; two<br>DPLLs; two baud-rate generators per channel;<br>loopback test mode; short frame and mark idle<br>detection | 2.5 Mb/s             | DIP<br>QFP<br>PLCC  | 40<br>52<br>52 |

| 72002          | CMOS, Advanced<br>Multiprotocol Serial<br>Communications<br>Controller | Low-cost, single-channel version of 72001;<br>software compatible; direct interface to 71071/<br>8237 DMA controllers                                                                                  | 2.5 Mb/s             | DIP<br>QFP<br>PLCC  | 40<br>44<br>44 |

| 72103          | CMOS, HDLC Controller                                                  | Single full-duplex serial channel; on-chip DMA controller                                                                                                                                              | 4 Mb/s               | SDIP<br>PLCC<br>QFP | 64<br>68<br>80 |

### **Graphics Controllers**

| Device,<br>μPD | Name                                               | Description                                                                                                                                                                    | Maximum<br>Drawing Rate | Package †   | Pins     |

|----------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------|----------|

| 7220A          | High-Performance<br>Graphics Display<br>Controller | General-purpose, high-integration controller;<br>hardwired support for lines, arc/circles,<br>rectangles, and graphics characters; 1024x1024<br>pixel display with four planes | 500 ns/dot              | Ceramic DIP | 40       |

| 72020          | Graphics Display<br>Controller                     | CMOS 7220A with 2M video memory; dual-port<br>RAM control; write-masking on any bit;<br>enhanced external sync                                                                 | 500 ns/dot              | DIP<br>QFP  | 40<br>52 |

| 72120          | Advanced Graphics<br>Display Controller            | High-speed graphics operations including paint,<br>area fill, slant, arbitrary angle rotate, up to 16x<br>enlargement and reduction; dual-port RAM<br>control; CMOS            | 500 ns/dot              | PLCC<br>QFP | 84<br>94 |

| 72123          | Advanced Graphics<br>Display Controller II         | Enhanced 72120; expanded command set;<br>improved painting performance; laser printer<br>interface controls; CMOS                                                              | 400 ns/dot              | PLCC<br>QFP | 84<br>94 |

#### Advanced Compression/Expansion Engine

| Device,<br>µPD | Name                                                   | Description                                                                                                                                                       | Package † | Pins |

|----------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|

| 72185          | Advanced Compression/                                  | High-speed CCITT Group 3/4 bit-map image compression/expansion                                                                                                    | SDIP      | 64   |

|                | Expansion Engine                                       | (A4 test chart, 400 PPI x 400 LPI in under 1 second); 32K-pixel line                                                                                              | PLCC      | 68   |

|                | (ACEE)                                                 | length; 32-megabyte image memory; on-chip DMA and refresh timing generator; CMOS                                                                                  | QFP       | 80   |

| 72186          | High-Speed Advanced<br>Compression/Expansion<br>Engine | High-speed upgrade of 72185 (A4 test chart, 400 PPI x 400 LPI in 0.5<br>second average); software compatible with 72185; separate image<br>address and data buses | QFP       | 100  |

### **Floppy-Disk Controllers**

| Device,<br>μPD | Name                                                     | Description                                                                                                                                                                                    | Maximum<br>Transfer<br>Rate | Package †          | Pins           |

|----------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------|----------------|

| 765A/B         | Floppy-Disk Controller                                   | Industry-standard controller supporting IBM<br>3740 and IBM System 34 double-density<br>format; enhanced 765B supports multitasking<br>applications                                            | 500 kb/s                    | DIP                | 40             |

| 72064          | Floppy-Disk Controller                                   | CMOS; all features of 72068 with complete AT<br>register set and 48-mA drivers. Pin compatible<br>with WD 37C65/A/B but with higher<br>performance DPLL and reliable multitasking<br>operation | 500 kb/s                    | PLCC<br>QFP        | 44<br>52       |

| 72065/65B      | CMOS Floppy-Disk Controller                              | 100% 765A/B microcode compatible;<br>compatible with 808x microprocessor families                                                                                                              | 500 kb/s                    | DIP<br>PLCC<br>QFP | 40<br>44<br>52 |

| 72070          | High-Capacity Universal<br>Floppy-Disk Controller (UFDC) | Single-chip FDC solution for high-capacity<br>FDDs of various types, conventional FDDs;<br>DPLL; 1.25 Mb/s data rate; perpendicular<br>recording format                                        | 24 MHz                      | QFP                | 64             |

#### **SCSI Controllers**

| Device,<br>μPD | Name                                                        | Description                                                                                                                                           | Maximum<br>Read/Write<br>Clock | Package †           | Pins           |

|----------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------------|----------------|

| 72111          | Small Computer System<br>Interface (SCSI)<br>Controller     | Selectable 8/16-bit data bus width; 16 high-level<br>commands for reduced CPU load; single-<br>command automatic execution; 4-Mb sync/<br>async; CMOS | 16 MHz                         | SDIP<br>PLCC<br>QFP | 64<br>68<br>74 |

| 72611          | Small Computer System<br>Interface-2 (SCSI-2)<br>Controller | 8/16/32-bit host data bus; supports fast SCSI,<br>command queuing, single and automatic<br>execution                                                  | 20 MHz                         | QFP                 | 100            |

#### **Digital Signal Processors**

| Device,<br>μPD | Description                                                   | Instruction<br>Cycle (ns) | Instruction<br>ROM (Bits) | Data ROM<br>(Bits)   | Data RAM<br>(Bits)   | Package †                  | Pine                 |

|----------------|---------------------------------------------------------------|---------------------------|---------------------------|----------------------|----------------------|----------------------------|----------------------|

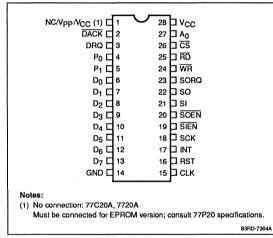

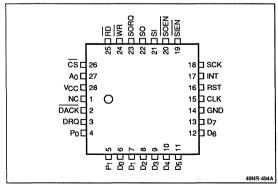

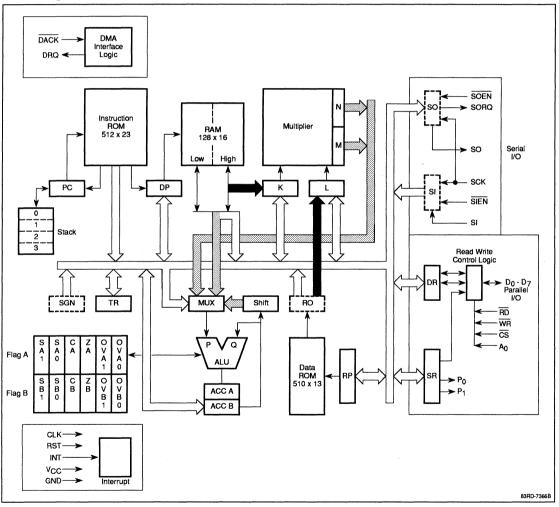

| 7720A          | 16-bit fixed point DSP; NMOS                                  | 240                       | 512 x 23                  | 510 x 13             | 128 x 16             | DIP                        | 28                   |

| 77C20A         | 16-bit fixed-point DSP; CMOS                                  | 244                       | 512 x 23                  | 510 x 13             | 128 x 16             | DIP<br>PLCC<br>SOP<br>PLCC | 28<br>28<br>32<br>44 |

| 77P20          | 16-bit fixed-point DSP; NMOS                                  | 244                       | 512 x 23<br>UVEPROM       | 510 x 13<br>UVEPROM  | 128 x 16             | Cerdip                     | 28                   |

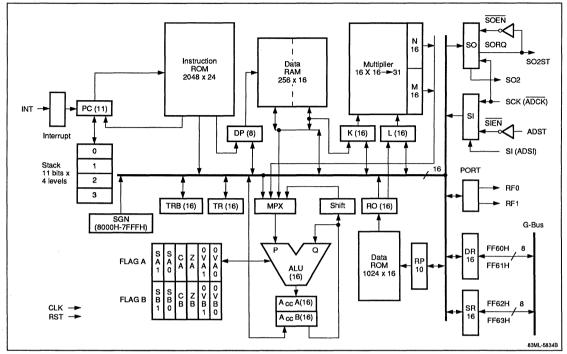

| 77C25          | 16-bit fixed-point DSP; CMOS                                  | 122/100                   | 2048 x 24                 | 1024 x 16            | 256 x 16             | DIP<br>SOP<br>PLCC         | 28<br>32<br>44       |

| 77P25          | 16-bit fixed-point DSP; CMOS                                  | 122/100                   | 2048 x 24<br>OTPROM       | 1024 x 16<br>OTPROM  | 256 x 16             | DIP<br>SOP<br>PLCC         | 28<br>32<br>44       |

|                |                                                               |                           | 2048 x 24<br>UVEPROM      | 1024 x 16<br>UVEPROM | 256 x 16             | Cerdip                     | 28                   |

| 77220          | 24-bit fixed-point DSP; CMOS                                  | 122/100                   | 2048 x 32                 | 1024 x 24            | 512 x 24             | Ceramic PGA<br>PLCC        | 68<br>68             |

| 77P220L        | 24-bit fixed-point DSP; CMOS                                  | 122/100                   | 2048 x 32<br>OTPROM       | 1024 x 24<br>OTPROM  | 512 x 24             | PLCC                       | 68                   |

| 77P220R        | 24-bit fixed-point DSP; CMOS                                  | 122/100                   | 2048 x 32<br>UVEPROM      | 1024 x 24<br>UVEPROM | 512 x 24             | Ceramic PGA                | 68                   |

| 77230AR        | 32-bit floating-point DSP; CMOS                               | 150                       | 2048 x 32                 | 1024 x 32            | 1024 x 32            | Ceramic PGA                | 68                   |

| 77230AR-003    | 32-bit floating-point DSP; CMOS;<br>standard library software | 150                       | n/a                       | n/a                  | n/a                  | Ceramic PGA                | 68                   |

| 77P230R        | 32-bit floating-point DSP; CMOS                               | 150                       | 2048 x 32<br>UVEPROM      | 1024 x 32<br>UVEPROM | 1024 x 32            | Ceramic PGA                | 68                   |

| 77240          | 32-bit floating-point DSP; CMOS                               | 90                        | 64K x 32<br>external      | n/a                  | 16M x 32<br>external | Ceramic PGA                | 132                  |

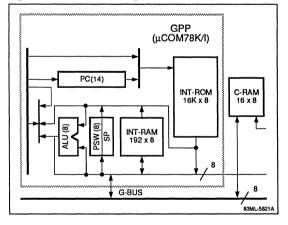

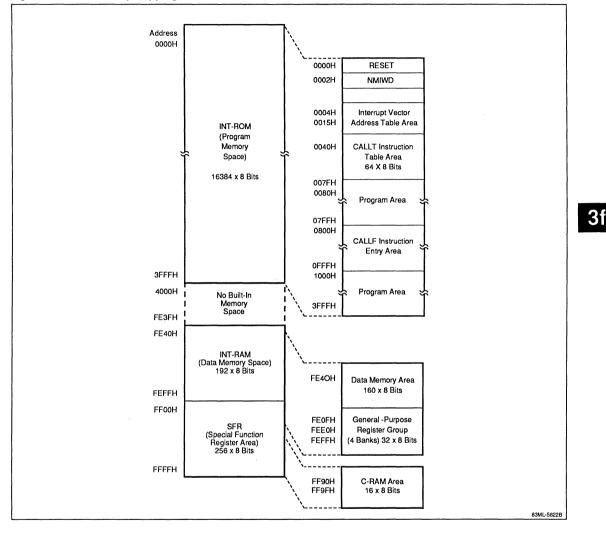

| 77810          | 16-bit fixed-point modem DSP;<br>CMOS                         | 181                       | 2048 x 24                 | 1024 x 16            | 256 x 16             | Ceramic PGA<br>PLCC        | 68<br>68             |

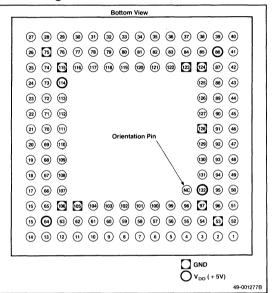

| 7281           | Image pipelined processor; NMOS                               | 5-MHz clock               | n/a                       | n/a                  | 512 x 18             | Ceramic DIP                | 40                   |

| 9305           | Support device for µPD7281 processors; CMOS                   | 10-MHz clock              | n/a                       | n/a                  | n/a                  | Ceramic PGA                | 132                  |

28

## **DSP and Speech Products**

#### Speech Processors

| Device,<br>μPD | Name                                       | Technology | Bit Rate<br>(kb/s) | Data ROM<br>(Bits)                    | Package †   | Pins     |

|----------------|--------------------------------------------|------------|--------------------|---------------------------------------|-------------|----------|

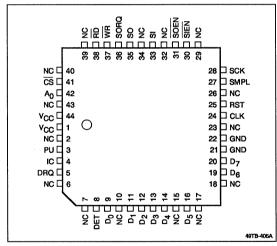

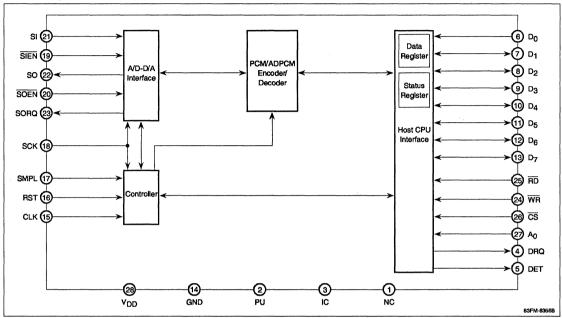

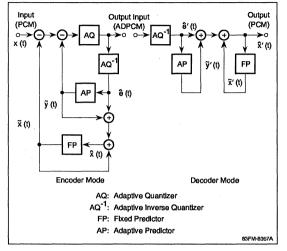

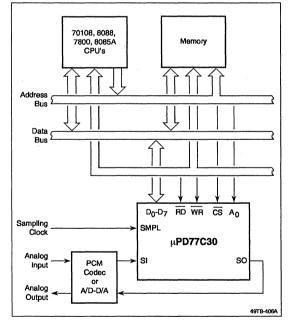

| 77C30          | ADPCM Speech Encoder/Decoder               | NMOS       | 32, 24             |                                       | DIP<br>PLCC | 28<br>44 |

| 7755           | ADPCM Speech Processor                     | CMOS       | 10-32              | 96K                                   | DIP<br>SOP  | 18<br>24 |

| 7756           | ADPCM Speech Processor                     | CMOS       | 10-32              | 256K                                  | DIP<br>SOP  | 18<br>24 |

| 77P56          | ADPCM Speech Processor                     | CMOS       | 10-32              | 256K<br>OTPROM                        | DIP<br>SOP  | 20<br>24 |

| 7757           | ADPCM Speech Processor                     | CMOS       | 10-32              | 512K                                  | DIP<br>SOP  | 18<br>24 |

| 7758           | ADPCM Speech Processor                     | CMOS       | 10-32              | 1M                                    | DIP<br>SOP  | 18<br>24 |

| 7759           | ADPCM Speech Processor                     | CMOS       | 10-32              | 1024K<br>External RAM                 | DIP<br>QFP  | 40<br>52 |

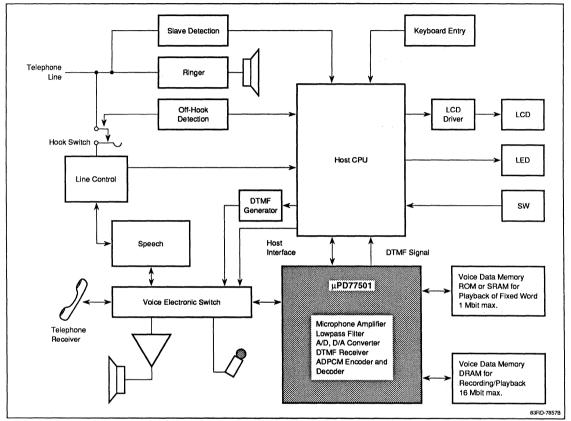

| 77501          | ADPCM Record and Playback Speech Processor | CMOS       | 12, 18, 24         | 16M DRAM<br>1M SRAM<br>External RAM   | QFP         | 80       |

| 77522          | ADPCM Codec                                | CMOS       | 32                 | · · · · · · · · · · · · · · · · · · · | SOP         | 28       |

### **V-Series Microprocessors**

| Device<br>(Note 1) | Full<br>Emulator  | Full<br>Emulator<br>Probe      | Mini-IE<br>Emulator | Mini-IE<br>Probe                 | Evaluation<br>Boards | EPROM<br>Device | Relocatable<br>Assembler<br>(Note 11) | C Compiler<br>(Note 12) |

|--------------------|-------------------|--------------------------------|---------------------|----------------------------------|----------------------|-----------------|---------------------------------------|-------------------------|

| μPD70136GJ-12      | IE-70136-<br>A016 | EP-70136L-A<br>(Note 2)        | IE-70136-PC         | EP-70136L-PC<br>(Note 2)         | DDK-70136            |                 | RA70136                               | CC70136                 |

| μPD70136GJ-16      | IE-70136-<br>A016 | EP-70136L-A<br>(Note 2)        | IE-70136-PC         | EP-70136L-PC<br>(Note 2)         | DDK-70136            |                 | RA70136                               | CC70136                 |

| μPD70136L-16       | IE-70136-<br>A016 | EP-70136L-A                    | IE-70136-PC         | EP-70136L-PC                     | DDK-70136            |                 | RA70136                               | CC70136                 |

| μPD70136L-12       | IE-70136-<br>A016 | EP-70136L-A                    | IE-70136-PC         | EP-70136L-PC                     | DDK-70136            |                 | RA70136                               | CC70136                 |

| µPD70136R-12       | IE-70136-<br>A016 | EP-70136L-A<br>(Note 3)        | IE-70136-PC         | EP-70136L-PC<br>(Note 3)         | DDK-70136            |                 | RA70136                               | CC70136                 |

| μPD70136R-16       | IE-70136-<br>A016 | EP-70136L-A<br>(Note 3)        | IE-70136-PC         | EP-70136L-PC<br>(Note 3)         | DDK-70136            | _               | RA70136                               | CC70136                 |

| μPD70208GF-8       | IE-70208-<br>A010 |                                | EB-V40MINI-<br>IE   |                                  | EB-70208             | —               | RA70116                               | CC70116                 |

| μPD70208GF-10      | IE-70208-<br>A010 |                                | EB-V40MINI-<br>IE   |                                  | EB-70208             |                 | RA70116                               | CC70116                 |

| μPD70208L-8        | IE-70208-<br>A010 | IE-70000 -<br>2958             | EB-V40MINI-<br>IE   | ADAPT68PGA<br>68PLCC<br>(Note 4) | EB-70208             | _               | RA70116                               | CC70116                 |

| μPD70208L-10       | IE-70208-<br>A010 | IE-70000 -<br>2958             | EB-V40MINI-<br>IE   | ADAPT68PGA<br>68PLCC<br>(Note 4) | EB-70208             | _               | RA70116                               | CC70116                 |

| μPD70208R-8        | IE-70208-<br>A010 | IE-70000-<br>2959              | EB-V40MINI-<br>IE   | (Note 4)                         | EB-70208             |                 | RA70116                               | CC70116                 |

| μPD70208R-10       | IE-70208-<br>A010 | IE-70000 -<br>2959             | EB-V40MINI-<br>IE   | (Note 4)                         | EB-70208             |                 | RA70116                               | CC70116                 |

| µPD70216GF-8       | IE-70216-<br>A010 | EP-70320J                      | EB-V50MINI-<br>IE   |                                  | EB70216              |                 | RA70116                               | CC70116                 |

| µPD70216GF-10      | IE-70216-<br>A010 | EP-70320J                      | EB-V50MINI-<br>IE   |                                  | EB70216              |                 | RA70116                               | CC70116                 |

| μPD70216L-8        | IE-70216-<br>A010 | IE-70000-<br>2958              | EB-V50MINI-<br>IE   | ADAPT68PGA<br>68PLCC<br>(Note 4) | EB70216              | _               | RA70116                               | CC70116                 |